# RAGE PRO and Derivatives Programmer's Guide

# Technical Reference Manual P/N: PRG-215R3-00-10 Rev 1.0

© 2000 ATI Technologies Inc.

#### **CONFIDENTIAL MATERIAL**

All information contained in this manual is confidential material of ATI Technologies Inc. Unauthorized use or disclosure of the information contained herein is prohibited.

You may be held responsible for any loss or damage suffered by ATI for your unauthorized disclosure hereof, in whole or in part. Please exercise the following precautions:

- Store all hard copies in a secure place when not in use.

- Save all electronic copies on password protected systems.

- Do not reproduce or distribute any portions of this manual in paper or electronic form (except as permitted by ATI).

- Do not post this manual on any LAN or WAN (except as permitted by ATI).

Your protection of the information contained herein may be subject to periodic audit by ATI. This manual is subject to possible recall by ATI.

The information contained in this manual has been carefully checked and is believed to be entirely reliable. No responsibility is assumed for inaccuracies. ATI reserves the right to make changes at any time to improve design and supply the best product possible.

#### ATI, mach64, 3D RAGE, RAGE THEATER, RAGE 128, and

**RAGE HDTV** are trademarks of ATI Technologies Inc. All other trademarks and product names are properties of their respective owners.

## **Record of Revisions**

| Release | Date     | Description of Changes                                                                                                          |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | March 00 | Formerly Mach64 Programmer's Guide.<br>Updated Chapters 1,3,7,8. Removed old<br>Appendices A-F and added new<br>Appendices A-K. |

### **Technical Reference Manuals**

- mach64 BIOS Kit (BIO-G01000)

- *mach64* Graphics Controller Specifications ATI-264CT/ET (GCS-C022001-00)

- mach64 Graphics Controller Specifications ATI-88800GX (GCS-C012001-00)

- *mach64* Graphics Controller Specifications ATI-264VT (GCS-C02500)

- mach64 Programmer's Guide (PRG-G01000)

- *mach64* Register Reference Guide (RRG-S022001-00)

- *mach64* Register Reference Guide ATI-264VT (RRG-C02500)

- mach64 VGA Register Guide (VGA-S022001-00)

# **Table of Contents**

## Chapter 1: Overview

| 1.1 | Introdu | ction                                           | 11 |

|-----|---------|-------------------------------------------------|----|

| 1.2 | Brief H | istory of ATI Graphics Products                 | 11 |

|     | 1.2.1   | VGAWONDER                                       |    |

|     | 1.2.2   | mach8                                           | 12 |

|     | 1.2.3   | mach32                                          | 12 |

|     | 1.2.4   | mach64                                          | 12 |

| 1.3 | mach64  | CT Family                                       | 15 |

|     | 1.3.1   | mach64VT                                        | 15 |

|     | 1.3.2   | mach64GT (3D RAGE, RAGE II, II+, IIC, RAGE PRO) | 15 |

|     | 1.3.3   | mach64LB (RAGE LT-PRO)                          | 15 |

|     | 1.3.4   | mach64GM (RAGE XL)                              | 16 |

|     | 1.3.5   | mach64LM (RAGE MOBILITY M/P/ M1)                |    |

| 1.4 | Feature | S                                               | 17 |

|     | 1.4.1   | mach64 Major Features                           | 17 |

|     | 1.4.2   | Functional Enhancements Relative To mach32      | 18 |

|     | 1.4.3   | Deletions Relative To mach32                    | 18 |

|     | 1.4.4   | Functional Differences From mach32              | 19 |

| 1.5 | Overvie | ew of the Manual                                | 19 |

|     | 1.5.1   | Chapter-By-Chapter Summary                      | 19 |

|     | 1.5.2   | Notations And Conventions Used In This Manual   |    |

## Chapter 2: Using the mach64

| 2.1 | Introdu | ction                  | 2-1 |

|-----|---------|------------------------|-----|

| 2.2 | Intel B | ased Architecture      | 2-1 |

|     | 2.2.1   | Memory Map             | 2-1 |

|     | 2.2.2   | BIOS Services          | 2-2 |

|     | 2.2.3   | Registers              | 2-3 |

| 2.3 | Non-In  | tel Based Architecture | 2-6 |

|     | 2.3.1   | Memory Map             | 2-6 |

|     | 2.3.2   | BIOS Services          | 2-7 |

|     | 2.3.3   | Registers              | 2-7 |

# Chapter 3: Getting Started

| 3.1 | Introdu | ction                                      | .3-1 |

|-----|---------|--------------------------------------------|------|

| 3.2 | Before  | you start                                  | .3-1 |

|     | 3.2.1   | Accelerator vs. VGA                        |      |

|     | 3.2.2   | Linear Aperture vs. VGA Aperture           | .3-2 |

|     | 3.2.3   | Protected Mode vs. Real Mode               |      |

| 3.3 | mach64  | Detection                                  | .3-5 |

|     | 3.3.1   | Card Detection                             | .3-5 |

|     | 3.3.2   | I/O Base                                   | .3-6 |

|     | 3.3.3   | Read/Write Test                            | .3-7 |

|     | 3.3.4   | CONFIG_CHIP_ID                             | .3-7 |

| 3.4 | Mode S  | witching                                   | .3-7 |

|     | 3.4.1   | BIOS Interface                             | .3-9 |

|     | 3.4.2   | Manual Mode Switching and Custom CRT Modes |      |

# Chapter 4: Linear Aperture

| 4.1 | Introduction                           | .4-1 |

|-----|----------------------------------------|------|

| 4.2 | Aperture Base Address                  | .4-1 |

| 4.3 | Convert Physical Address               | .4-2 |

| 4.4 | Enable the Aperture                    | .4-3 |

| 4.5 | Using the Linear Aperture              |      |

| 4.6 | Complete Example of Using the Aperture | .4-5 |

| 4.7 | VGA Interaction                        | .4-6 |

## **Chapter 5: Engine Initialization**

| 5.1 Introd | uction                                  | 5-1 |

|------------|-----------------------------------------|-----|

| 5.2 Backg  | round Information on the mach64 Engine  | 5-1 |

| 5.2.1      | Command FIFO Queue                      |     |

| 5.2.2      | Other Essentials                        |     |

| 5.3 Prelim | iinary Essentials                       | 5-3 |

| 5.3.1      | mach64 Detection                        |     |

| 5.3.2      | Hardware Query                          | 5-3 |

| 5.3.3      | Save/Restore Old Video Mode Information | 5-3 |

| 5.3.4      | Open Mode                               | 5-3 |

| 5.3.5     | Initializing The Engine                                 | 5-3                                              |

|-----------|---------------------------------------------------------|--------------------------------------------------|

| Openin    | g and Closing a Mode                                    | 5-4                                              |

| 5.4.1     | Opening                                                 | 5-4                                              |

| 5.4.2     | Reading from the Palette                                | 5-6                                              |

| 5.4.3     | Writing to the Palette                                  | 5-6                                              |

| Initializ | ing the Engine                                          | 5-7                                              |

| 5.5.1     | Setup Standard Engine Context                           | 5-7                                              |

| 5.5.2     | InitEngine Example                                      | 5-9                                              |

|           | Openin<br>5.4.1<br>5.4.2<br>5.4.3<br>Initializ<br>5.5.1 | <ul> <li>5.3.5 Initializing The Engine</li></ul> |

## Chapter 6: Engine Operations

| 6.1 | Introdu                                                                           | ction                                                                                                       | 6-1                                          |

|-----|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 6.2 | Backgr                                                                            | ound Information                                                                                            | 6-1                                          |

|     | 6.2.1                                                                             | Details About the Registers                                                                                 | 6-1                                          |

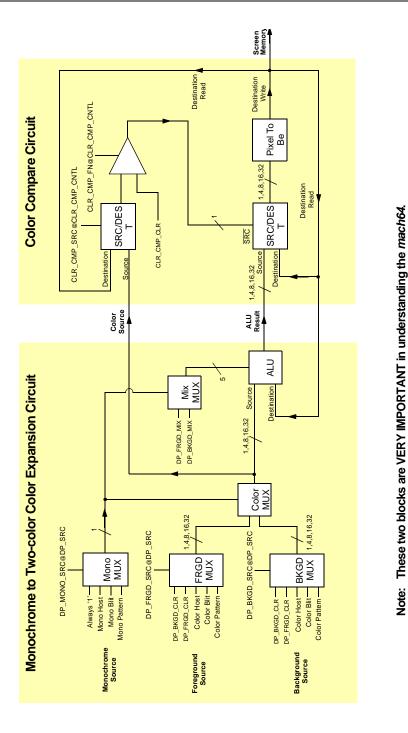

|     | 6.2.2                                                                             | Logical Pixel Data Path                                                                                     | 6-2                                          |

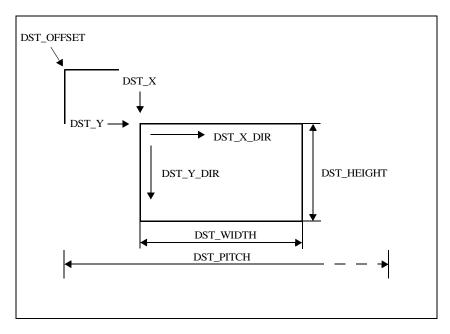

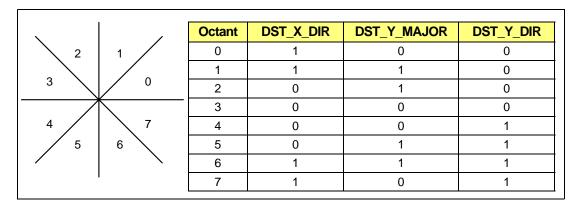

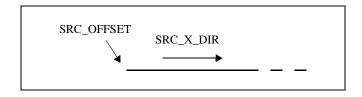

|     | 6.2.3                                                                             | Trajectories                                                                                                | 6-10                                         |

|     | 6.2.4                                                                             | Side Effects Of Trajectories                                                                                | 6-19                                         |

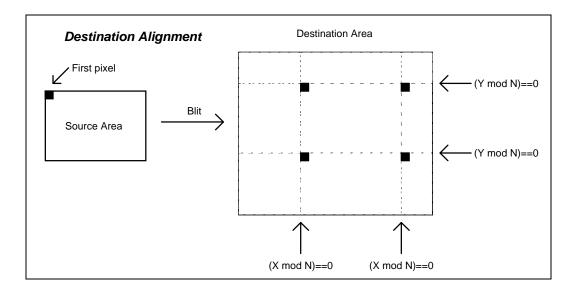

|     | 6.2.5                                                                             | Source And Destination Alignment                                                                            | 6-20                                         |

|     | 6.2.6                                                                             | Source and Destination Mixing Logic                                                                         | 6-22                                         |

|     | 6.2.7                                                                             | Remarks On Pixel Depth                                                                                      | 6-23                                         |

|     |                                                                                   |                                                                                                             |                                              |

| 6.3 | Draw C                                                                            | Dperations                                                                                                  | 6-24                                         |

| 6.3 | Draw C<br>6.3.1                                                                   | Dperations<br>Color Source                                                                                  |                                              |

| 6.3 |                                                                                   |                                                                                                             | 6-24                                         |

| 6.3 | 6.3.1                                                                             | Color Source                                                                                                | 6-24<br>6-31                                 |

| 6.3 | 6.3.1<br>6.3.2                                                                    | Color Source<br>Standard BitBlt Source                                                                      | 6-24<br>6-31<br>6-35                         |

|     | 6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                                  | Color Source<br>Standard BitBlt Source<br>Specialized BitBlt Source                                         | 6-24<br>6-31<br>6-35<br>6-38                 |

|     | 6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                                  | Color Source<br>Standard BitBlt Source<br>Specialized BitBlt Source<br>Pattern Source                       | 6-24<br>6-31<br>6-35<br>6-38<br>6-40         |

|     | <ul><li>6.3.1</li><li>6.3.2</li><li>6.3.3</li><li>6.3.4</li><li>Miscell</li></ul> | Color Source<br>Standard BitBlt Source<br>Specialized BitBlt Source<br>Pattern Source<br>laneous Operations | 6-24<br>6-31<br>6-35<br>6-38<br>6-40<br>6-40 |

## Chapter 7: Advanced Topics

| 7.1 | Introdu  | ction                                                   | 7-1 |

|-----|----------|---------------------------------------------------------|-----|

| 7.2 | Polygo   | ns                                                      | 7-1 |

| 7.3 | Scrollin | ng and Panning                                          | 7-5 |

| 7.4 |          | ynchronization and Animation                            |     |

|     |          | Double Buffering (Memory)<br>Double Buffering (Palette) |     |

|     |          | Single Buffering (Synchronized)                         |     |

|     | 7.4.4                                     | Single Buffering (Delta Framing)                                         | 7-7                                          |

|-----|-------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------|

| 7.5 | Manual                                    | Mode Switching And Custom CRT Modes                                      |                                              |

|     | 7.5.1                                     | Manual Mode Switching                                                    |                                              |

|     | 7.5.2                                     | Designing A Custom CRT Mode                                              | 7-9                                          |

| 7.6 | Interrup                                  | ots                                                                      | 7-13                                         |

|     |                                           | een Memory Management                                                    |                                              |

|     |                                           | ime Initialization                                                       |                                              |

|     |                                           |                                                                          |                                              |

| 7.9 | Perform                                   | nance Issues                                                             | 7-20                                         |

| 7.9 | Perform<br>7.9.1                          | nance Issues<br>Redundancy                                               |                                              |

| 7.9 |                                           | Redundancy                                                               | 7-20                                         |

| 7.9 | 7.9.1                                     | Redundancy<br>Draw Speed                                                 | 7-20<br>7-20                                 |

| 7.9 | 7.9.1<br>7.9.2                            | Redundancy<br>Draw Speed<br>Concurrency                                  |                                              |

| 7.9 | 7.9.1<br>7.9.2<br>7.9.3                   | Redundancy<br>Draw Speed                                                 |                                              |

| 7.9 | 7.9.1<br>7.9.2<br>7.9.3<br>7.9.4          | Redundancy<br>Draw Speed<br>Concurrency<br>Efficiency                    | 7-20<br>7-20<br>7-21<br>7-21<br>7-21         |

| 7.9 | 7.9.1<br>7.9.2<br>7.9.3<br>7.9.4<br>7.9.5 | Redundancy<br>Draw Speed<br>Concurrency<br>Efficiency<br>Expansion Buses | 7-20<br>7-20<br>7-21<br>7-21<br>7-21<br>7-22 |

# Chapter 8: mach64VT/GT Specific Features

| 8.1 | Introdu  | ction                             | 8-1  |

|-----|----------|-----------------------------------|------|

| 8.2 | Summa    | ry of Additional Features         | 8-1  |

| 8.3 | mach64   | VT/GT Register Access             | 8-2  |

|     | 8.3.1    | Memory Map                        | 8-2  |

|     | 8.3.2    | Determining Register Address      | 8-3  |

|     | 8.3.3    | Enabling Register Block 1         | 8-4  |

| 8.4 | Hardwa   | are Overlay/Scaler                | 8-4  |

|     | 8.4.1    | Overlay                           |      |

|     | 8.4.2    | Scaler                            |      |

|     | 8.4.3    | Color Keyer                       | 8-6  |

|     | 8.4.4    | Color Interpolator/ Alpha Blender | 8-6  |

|     | 8.4.5    | Color Space Converter             | 8-7  |

| 8.5 | Packed   | Pixel Modes                       | 8-8  |

| 8.6 | Planar I | Pixel Modes                       | 8-8  |

| 8.7 | Unpack   | er / Dynamic Range Corrector      | 8-10 |

| 8.8 | Overlay  | / Programming                     | 8-11 |

|     | 8.8.1    | Overlay Scaling                   |      |

|     | 8.8.2    | UV Interpolation                  |      |

| 8.9 | Front E  | nd Scaler Programming             | 8-13 |

| <ul><li>8.9.1 Front End Scaler Operation</li><li>8.9.2 Performing a Blt Using the Front End Scaler</li></ul> |      |

|--------------------------------------------------------------------------------------------------------------|------|

| 8.10 Bus Master Programming                                                                                  | 8-15 |

| 8.10.1 Bus Master Operation                                                                                  | 8-15 |

| 8.10.2 Creating a Descriptor Table                                                                           | 8-15 |

| 8.10.3 Setting up a System Bus Master Transfer                                                               | 8-17 |

| 8.10.4 Setting up a GUI Master Operation                                                                     | 8-17 |

# Appendix A: Video BIOS Functions Specification

| A.1 Calculating ROM Base Address                                                 |

|----------------------------------------------------------------------------------|

| A.2 Function Calls                                                               |

| A.3 Compatibility                                                                |

| A.4 Function 00h – Load Coprocessor CRTC Parameters                              |

| A.5 Function 01h – Set Display Mode                                              |

| A.6 Function 02h - Load Coprocessor CRTC Parameters and Set Display ModeA-3      |

| A.7 Function 03h – Read EEPROM Data                                              |

| A.8 Function 04h – Write EEPROM Data                                             |

| A.9 Function 05h – Memory Aperture Service                                       |

| A.10 Function 06h – Short Query Function                                         |

| A.11 Function 07h – Return Graphics Hardware Capability List                     |

| A.12 Function 08h – Return Query Device Data Structure in Bytes                  |

| A.13 Function 09h – Query Device                                                 |

| A.14 Function 0Ah – Return Clock Chip Frequency TableA-8                         |

| A.15 Function 0Bh – Program a Specified Clock EntryA-8                           |

| A.16 Function 0Ch – DPMS Service, Set DPMS Mode                                  |

| A.17 Function 0Dh – Return Current DPMS State in LCA-9                           |

| A.18 Function 0Eh – Set Graphics Controller Power Management State               |

| A.19 Function 0Fh – Return Current Graphics Controller Power Management StateA-9 |

| A.20 Function 10h – Set the DAC to Different StatesA-10                          |

| A.21 Function 11h – Return External Storage Device InformationA-10               |

| A.22 Function 12h – Short Query                                                  |

| A.23 Function 13h – Display Data Channel Support (DDC)A-11                       |

| A.24 Function 14h – Save and Restore Graphics Controller StatesA-14              |

| A.25 Function 15h – Refresh Rate Support                                         |

| A 26 Europian 16h Video Easture Support                       | A 17 |

|---------------------------------------------------------------|------|

| A.26 Function 16h – Video Feature Support                     | A-1/ |

| A.27 Function 17h – Enable / Disable Video Input Capture Mode |      |

| and Return Video Capture Capability                           | A-21 |

| A.28 Function 18h – Reserved for UMA                          | A-27 |

| A.29 Function 19h – TVOut Hooks (not supported in LT PRO)     | A-27 |

| A.30 Query Structure                                          | A-28 |

| A.31 Mode Table Structure                                     | A-32 |

| A.32 EEPROM Data Structure                                    | A-34 |

| A.33 CRT Parameter                                            | A-37 |

| A.34 Scratch Registers                                        | A-38 |

| A.35 ROM Header                                               | A-40 |

| A.35.1 TVOut Information                                      | A-41 |

| A.35.2 Hardware Information Table                             | A-42 |

| A.35.3 Multiple TV Standard Feature                           | A-44 |

| A.35.4 BIOS Driver Information Table                          | A-44 |

| A.35.5 Panel EDID Override Table                              | A-45 |

# Appendix B: 3D RAGE LT PRO and RAGE Mobility Specific Functions

| B.1 IntroductionB-1                                                                           |

|-----------------------------------------------------------------------------------------------|

| B.2 Function CallsB-1                                                                         |

| B.3 Extended ROM Services                                                                     |

| B.4 Function 80h - Return Panel Type and Controller Supported InformationB-2                  |

| B.5 Function 81h - Return Panel Identity InformationB-12                                      |

| B.6 Function 82h – VESA BIOS Extensions / Flat Panel Functions                                |

| B.7 Function 83h – LCD / Monitor / TV DetectionB-20                                           |

| B.8 Function 84h – Return / Select Active DisplayB-21                                         |

| B.9 Function 85h – Return / Select Power Management ModeB-22                                  |

| B.10 Function 86h – In and Out Of Suspend State<br>(not supported in LT PRO and Mobility)B-23 |

| B.11 Function 87h – Return / Select Refresh Rate                                              |

| B.12 Function 88h – Return / Select Dithering                                                 |

| B.13 Function 89h – Return / Select Cursor Blink Rate                                         |

| B.14 Function 8Ah – Hardware ICON SupportB-26                                                 |

| B.15 Function 8Bh – Set CMOS InformationB-30                                                  |

| B.16 Function 8Ch – Return / Select 475 Lines VGA ModeB-31                                    |

| B.17 Function 8Dh – Return Current Display Information     | B-32 |

|------------------------------------------------------------|------|

| B.18 Function 8Eh - LCD Display Data Channel Support (DDC) | B-33 |

| B.19 Function 8Fh – Get / Set Video BIOS Information       | B-34 |

| B.20 Function 04Exxh – System BIOS Int 15h                 | B-35 |

## Appendix C: RAGE XL Specific Functions

| C.1 IntroductionC-1                                                                                 |

|-----------------------------------------------------------------------------------------------------|

| C.2 Function CallsC-1                                                                               |

| C.3 Function 80h - Return Panel Type and Controller SupportedInformation (not supported in RAGE XL) |

| C.4 Function 81h - Return Panel Identity Information<br>(not supported in RAGE XL)C-2               |

| C.5 Function 82h – VESA BIOS Extensions / Flat Panel Functions (not supported in RAGE XL)           |

| C.6 Function 4F11h – VESA VBE / Flat Panel BIOSC-2                                                  |

| C.7 Function 83h – LCD / Monitor / TV DetectionC-4                                                  |

| C.8 Function 84h – Return / Select Active DisplayC-5                                                |

| C.9 Function 85h – Return / Select Power Management ModeC-6                                         |

| C.10 Function 87h – Return / Select Refresh RateC-8                                                 |

| C.11 Function 88h – Return / Select DitheringC-9                                                    |

| C.12 Function 89h – Return / Select Cursor Blink RateC-10                                           |

| C.13 Function 8Ah – Hardware ICON Support<br>(not supported in RAGE XL)C-11                         |

| C.14 Function 8Dh – Return Current Display InformationC-11                                          |

| C.15 Function 8Eh - LCD Display Data Channel Support (DDC)C-11                                      |

| C.16 Function 04Exxh – System BIOS Int 15h<br>(not supported in RAGE XL)C-13                        |

## Appendix D: TVOut Specific Functions

| D.1 Introduction                                          | D-1 |

|-----------------------------------------------------------|-----|

| D.2 Function 70h – Return / Select TVOut Configuration    | D-1 |

| D.3 Function 71h – Return TV Standard                     | D-3 |

| D.4 Function 72h – Re-initialize Digital Signal Processor | D-4 |

| D.5 Function 73h – Return / Select TVOut Auto-Display Switch                   | D-4 |

|--------------------------------------------------------------------------------|-----|

| D.6 Function 74h – Return TVOut Aligner Information For Slow Aligner Algorithm | D-4 |

| D.7 Function 75h – Return TVOut Aligner Group                                  | D-5 |

| D.8 Function 76h – Return TVOut Aligner Information For Fast Aligner Algorithm | D-6 |

# Appendix E: CRTC Parameters

| E.1 Introduction                  | E-1  |

|-----------------------------------|------|

| E.2 CRTC Parameters for 640x480   | E-1  |

| E.3 CRTC Parameters for 800x600   | E-4  |

| E.4 CRTC Parameters for 1024x768  | E-8  |

| E.5 CRTC Parameters for 1152x864  | E-11 |

| E.6 CRTC Parameters for 1280x1024 | E-14 |

| E.7 CRTC Parameters for 1600x1200 | E-17 |

# Appendix F: Parameter Table Format

| F.1 Table Description             |

|-----------------------------------|

| F.2 Spare Bits in Parameter Table |

# Appendix G: Pixel Clock Tables

| G.1 ATI-18811-1 Clock Chip | G- | 1 |

|----------------------------|----|---|

|----------------------------|----|---|

# Appendix H: Scratch Registers

| H.1 Scratch Registers and Their ContentsH-1 |

|---------------------------------------------|

|---------------------------------------------|

# Appendix I: ROM Header

| I.1 ROM HeaderI-1 |

|-------------------|

|-------------------|

# Appendix J: Programming PLL Registers in mach64 CT Family

| J.2 | PLL Registers                   | J-1  |

|-----|---------------------------------|------|

| J.3 | Clock Sources                   | J-4  |

| J.4 | External Clock Support          | J-4  |

| J.5 | Frequency Limits                | .J-5 |

| J.6 | Frequency Synthesis Description | .J-5 |

| J.7 | Duty Cycle Control              | J-8  |

| J.8 | PLL Gain Settings               | J-8  |

|     |                                 |      |

# Appendix K: Display Register Setting Calculations

| K.1 | Display Register Setting | Calculations | <b>K-</b> 1 | 1 |

|-----|--------------------------|--------------|-------------|---|

|-----|--------------------------|--------------|-------------|---|

## Appendix L: Bibliography

# 1.1 Introduction

This manual is a guide to understanding and programming the *mach64* accelerator. The *mach64* accelerator is a fixed-function, 2D graphics accelerator. It is function-compatible, but not register-compatible, with its predecessor – the *mach32* accelerator. It is not register compatible, yet it is function compatible, with *mach32*.

Those seeking a general understanding of the features and functions of the *mach64* only need to read *Chapter 2: Using the mach64*. Very specific examples and techniques are described in following chapters - *Chapter 3: Getting Started; Chapter 4: Linear Aperture; Chapter 5: Engine Initialization; Chapter 6: Engine Operations; Chapter 7: Advanced Topics* and *Chapter 8: mach64TV/GT Specific Features.*

The scope of this programmer's guide includes the *mach64* VT and GT (3D RAGE, RAGE PRO and its derivatives which include the LT-PRO, RAGE XL and RAGE MOBILITY) accelerator chips. Those wishing to obtain programming information on earlier *mach64* variants (GX and CT) should obtain the older version of the *mach64* Programmer's Guide (contact ATI Developer Relations).

# 1.2 Brief History of ATI Graphics Products

To understand how the mach64 relates to earlier ATI chips for compatibility, a short discussion of these earlier chips is necessary.

Although ATI did manufacture graphics boards prior to the introduction of the Video Graphics Array (VGA) by IBM in 1987, they will not be covered in the following discussion.

#### **1.2.1 VGAWONDER**

The VGAWONDER family (ATI18800 and ATI28800) were non-accelerated chips that fully implemented the IBM VGA standard. In addition, they also supported SuperVGA graphics modes of up to 1024x768 at 8bpp or 640x480 at 24bpp, depending on chip revision and amount of memory. These additional modes were supported with ATI-specific extended VGA registers.

VGAWONDER-based boards only came in ISA bus versions as it predates most of the extended bus architectures.

### 1.2.2 mach8

The *mach8* (ATI38800) was ATI's first true Graphics Accelerator, providing hardware assisted drawing capabilities for 2D primitives like lines, rectangles and polygons. It was register compatible with the IBM 8514/A Display Adapter. Thus any applications or drivers that supported the 8514/A would run on a *mach8* without any modification. The *mach8* also extended on the 8514/A specification.

The *mach8* did not have any VGA compatibility so a separate VGA controller was required for standard text and VGA modes. Some *mach8* boards, like the GRAPHICS VANTAGE and GRAPHICS ULTRA included a VGAWONDER controller on the same board as the *mach8* to provide this VGA support. The VGA controller had its own memory, completely separate from the *mach8* accelerator's memory.

mach8-based boards were produced in both ISA and Microchannel versions.

#### 1.2.3 mach32

The *mach32* chip (ATI68800) is the immediate predecessor to the current *mach64* family. The *mach32* was register compatible with both the IBM 8514/A and the *mach8*. The *mach32* also contained a VGA controller on the chip that was compatible with the VGAWONDER so a separate VGA controller was not needed. The memory on the *mach32* board was shared between the VGA controller and the *mach32* accelerator.

The *mach32* improved upon the *mach8* by providing a linear aperture to allow fast image data transfer by mapping the video memory to the system memory address space. Later revisions of the *mach32* also were able to memory map the *mach32* registers to overcome the performance penalty incurred in going through I/O port-mapped registers. Finally, the *mach32* contained a hardware cursor.

*mach32*-based boards were produced in five bus types: ISA, EISA, VESA Local Bus, Microchannel, and PCI.

## 1.2.4 mach64

The *mach64* represented a departure from the *mach32* in that it was no longer register compatible with previous ATI graphics accelerators or the 8514/A. (VGA register compatibility was retained, however.) This departure was necessary to resolve some design limitations that were a legacy of the older generation chips. Fortunately, almost all the functionality that was in the *mach32* was preserved in the *mach64* design, and some useful additions and enhancements were incorporated.

As indicated on the table below, the *mach64* can be divided into two major types, the GX family and the CT family. While applications that use the *mach64* should run on both types with little or no modification, there are some important differences between the two

families that are highlighted in the following sections.

Boards based on mach64 are produced in ISA, VESA Local Bus and PCI bus versions.

| mach64 Feature Set Variations                  |                     |       |                     |                     |                 |      |                                                         |                                              |                                            |

|------------------------------------------------|---------------------|-------|---------------------|---------------------|-----------------|------|---------------------------------------------------------|----------------------------------------------|--------------------------------------------|

|                                                | mach64GX Family     |       |                     |                     | mach64CT Family |      |                                                         |                                              |                                            |

| Feature                                        | GX-C/<br>D          | GX-E* | GX-F                | сх                  | СТ              | VT   | GT<br>(RAGE I,<br>RAGE II,<br>II+, IIC,<br>RAGE<br>PRO) | LB/GM<br>(RAGE<br>LT-<br>PRO,<br>RAGE<br>XL) | LM<br>(RAGE<br>MOBILI<br>TY<br>M/P/M1<br>) |

| Relocatable I/O (PCI only)†                    |                     |       | <b>√</b> †          |                     | <b>√</b> †      | ~    |                                                         | $\checkmark$                                 |                                            |

| Maximum Memory                                 | 8MB                 | 8MB   | 8MB                 | 4MB                 | 4MB             | 4MB  | 8/16 MB                                                 |                                              |                                            |

| Minimum Memory                                 | 512KB               | 1MB   | 1MB                 | 512KB               | 1MB             | 1MB  | IB 1MB                                                  |                                              |                                            |

| Standard Linear<br>Aperture (little<br>endian) | ✓                   | ✓     | ~                   | ~                   | ~               | ~    | ✓                                                       |                                              |                                            |

| Extended Linear<br>Aperture (big endian)       |                     | √     | $\checkmark$        |                     | $\checkmark$    | ~    |                                                         | $\checkmark$                                 |                                            |

| Linear Aperture<br>Boundary                    | 8MB <sup>‡</sup>    | 16MB  | 16MB                | 8MB                 | 16MB            | 16MB |                                                         | 16MB                                         |                                            |

| ATI SVGA Extended<br>Register Set              | ~                   | ~     | ~                   | ~                   |                 |      |                                                         |                                              |                                            |

| Supported bus types                            | ISA,<br>VLB,<br>PCI | PCI   | ISA,<br>VLB,<br>PCI | ISA,<br>VLB,<br>PCI | PCI             | PCI  | PCI, AGP                                                |                                              |                                            |

Table 1-1 mach64 Product Families

Revision E was a short-lived version that was only used in Apple Power Macintosh-based boards.

†Relocatable I/O requires a hardware strap to be enabled. If the feature is enabled, the standard I/O base addresses do not apply.

‡ A 4MB boundary is possible if the linear aperture size is set to 4MB.

$\Delta$  16 MB maximum on 3D RAGE PRO chips only.

C/DRevisions C and D.

#### 1.2.4.1 mach64GX Family

The *mach64*GX Family encompasses the *mach64*GX (ATI888GX00) and *mach64*CX (ATI888CX00) variants. The major distinguishing characteristics of this family are:

- Uses an external DAC

- Uses an external clock synthesizer

- Support for VRAM

- VGA controller is ATI VGAWONDER compatible

- VGA controller is independently programmable from the accelerator controller

From a very rough architectural perspective, the *mach64*GX family more resembles the *mach32* than it does the *mach64*CT family. However, from a functionality and register level perspective, the *mach64*GX is almost identical to the *mach64*CT.

# 1.3 mach64CT Family

The *mach64*CT Family encompasses the *mach64*CT (ATI264CT), *mach64*VT (ATI264VT) and *mach64*GT (3D RAGE) variants. The major distinguishing characteristics of this family are:

- Integrated DAC

- Integrated clock synthesizer

- No VRAM support

- VGA controller is "pure" VGA, not VGAWONDER compatible

- VGA controller is not independently programmable from the accelerator controller

#### 1.3.1 mach64VT

The *mach64*VT family of chips is built upon the previously mentioned CT. They have the same feature set as the CT, plus some additional video features such as:

- back end hardware overlay

- back end hardware scaler

## 1.3.2 mach64GT (3D RAGE, RAGE II, II+, IIC, RAGE PRO)

The *mach64*GT (commonly known as the 3D RAGE) introduces hardware support for 3D operations. While low level 3D operations are not discussed in this guide, we do demonstrate the usage of front and end scaler, which is part of the 3D pipeline. The 3D RAGE includes all *mach64*VT features with the addition of:

- hardware 3D acceleration

- improved video filtering

- integrates motion compensation (RAGE PRO only)

#### 1.3.3 mach64LB (RAGE LT-PRO)

The mach64LB (commonly known as the RAGE LT-PRO) provides the mach64GT core hardware support for 3D operations. The RAGE LT-PRO includes all mach64GT features with the addition of:

- integrates TV-Encoder, LVDS, and Dual CRT Controllers

- low graphics subsystem power

## 1.3.4 mach64GM (RAGE XL)

The mach64GM (commonly known as the RAGE XL) provides the mach64GT core hardware support for 3D operations. The RAGE XL includes all mach64GT features with the addition of:

- integrated TMDS for flat panels

- integrates motion compensation

## 1.3.5 mach64LM (RAGE MOBILITY M/P/ M1)

The mach64LM (commonly known as the RAGE MOBILITY) provides the mach64GT core hardware support for 3D operations. The RAGE MOBILITY includes all mach64GT features with the addition of:

- very low graphics subsystem power

- integrates TV-Encoder, LVDS, and Dual CRT Controllers

- TMDS LCD Panel Support

- hardware DVD decode via integrated iDCT

# **1.4 Features**

#### 1.4.1 mach64 Major Features

- Full draw capability at 1, 4, 8, 15, 16, and 32 bits per pixel color resolutions. Hardware-assisted draw functions are available for packed 24 bits per pixel draw modes.

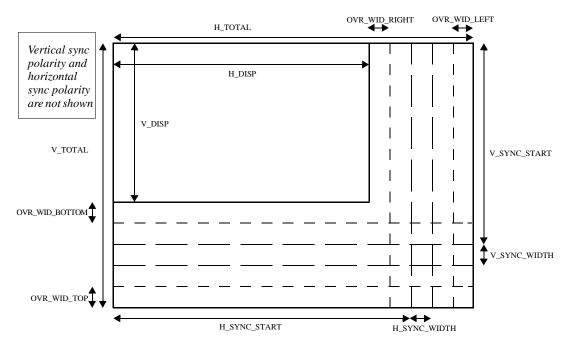

- Standard spatial resolution of 640x480, 800x600, 1024x768, and 1280x1024. Other resolutions with pixel clocks of up to 220 MHz can be supported, limited only by the DAC, memory size, and memory bandwidth.

- Full read/writable memory-mapped registers.

- Up to 8MB of memory (16 for 3D RAGE PRO).

- 32x32 command FIFO.

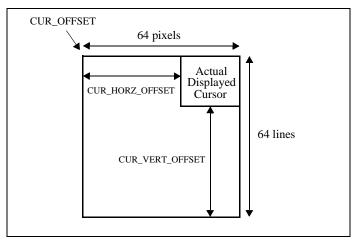

- Four-color (two fixed colors, complement, and transparent) hardware cursor of size up to 64x64.

- Overscan.

- Linear frame buffer is locatable on 16MB boundaries anywhere in a 4GB system memory address space.

- Paged frame buffer with two 32KB pages (independent read and write pages), pagable on 32KB boundaries anywhere in the 8MB video memory address space.

- Draw functions include rectangle fill, line draw, bitblt, polygon boundary lines, and polygon fill.

- Generalized 2D patterns with rotation.

- A linear memory mode for efficient memory management.

- Efficient monochrome expansion.

- Bit masking and scissoring capabilities.

- Seventeen-function ALU for full suite of logical ROPs.

- Source compare logic suitable for transparent blits.

- Destination compare logic suitable for alpha channel mixing.

- Scrolling and panning on a virtual desktop.

- Big endian support (*mach64*GX-E/F, *mach64*CT Family).

- EEPROM hardware support for non-volatile storage. (Certain controllers are EEPROM-less.)

- Four-level hardware Display Power Management System (DPMS) mode support.

- DAC power-down support.

- Diagnostic test modes.

## 1.4.2 Functional Enhancements Relative To mach32

- Full draw capability in 1 bpp and 32 bpp modes, and hardware assist in packed 24 bpp mode has been added.

- Full 32-bit registers. Some register pairs may be written in a single 32-bit write.

- Device coordinates have been expanded from -4096 to +4095 in the X direction, and from -16384 to +16383 in the Y direction.

- Bresenham parameters have been expanded from 12 bits to 18 bits.

- Packed monochrome expansion.

- The paged frame buffer is now pagable on 32KB boundaries instead of 64KB.

- The source trajectory types, strictly-linear, general-pattern, and general-pattern-with-rotation, have been added.

- Source compare.

- Four-level hardware Display Power Management System (DPMS) mode support.

- DAC power-down support.

- Diagnostic test modes.

## 1.4.3 Deletions Relative To mach32

- Point-to-point line draw.

- Line clip exception handling.

- VNIB and VPIX type rectangles.

- Short-stroke vectors.

- Scan line draw.

- Four compare functions.

- Bounds accumulators.

- CRTC shadow sets.

- Host reads; screen-to-host transfers can still be accomplished by aperture reads.

- Degree mode lines; Bresenham lines are still supported.

All the deleted functions listed above are redundant and may still be accomplished by other means.

#### 1.4.4 Functional Differences From *mach32*

- Monochrome blits are now packed instead of sparse.

- Host writes are packed to 32 bits. The 1 bpp and 4 bpp modes may be optionally aligned to a byte.

- Pixel consumption order from the host data register is only programmable in 1 bpp and 4 bpp modes.

- Polygon fills are always inclusive on both edges and optionally right edge exclusive on the mach64CT.

- Polygons derive their boundary data from an implicit polygon source instead of an explicit monochrome source.

- Rectangular trajectories are specified in width and height instead of start and end.

- The ALU carry chain mask is set explicitly instead of implicitly from the pixel depth.

- Line drawing options do not affect rectangular trajectories and rectangle options do not affect line drawing trajectories.

- Destination side effects (tiling) are now programmable.

- Source pointer always returns to the original SRC\_X, SRC\_Y position after draw completion.

- Pixel depths, pitches and offsets are independently specified for CRTC, source, destination, and host.

- Bresenham parameters have been expanded from 12 bits to 18 bits.

## **1.5** Overview of the Manual

#### 1.5.1 Chapter-By-Chapter Summary

*Chapters 1* to 7 cover the general functionality that is available in all variants of the *mach64*. In *Chapter 8*, the specific details of each particular variant will be covered in depth.

*Chapter 2* provides details of the features and basic programming model of the *mach64*.

*Chapter 3* demonstrates the fundamental steps that are necessary to use the *mach64* in accelerator mode. Issues such as card detection and setting a display mode are covered here. Programming considerations are also discussed.

*Chapter 4* covers the usage of the linear aperture, which provides immediate benefit to programs as they no longer have to deal with bank switching and the 64KB page limit.

*Chapter 5* goes into issues covering the accelerator engine itself, such as the command FIFO queue and engine initialization.

*Chapter 6* discusses general engine operation, and provides numerous examples of standard engine operations.

*Chapter 7* contains some advanced topics that highlight some of the special features and capabilities of the *mach64*.

*Chapter 8* covers some other advanced topics specific to the VT and 3D RAGE, including use of the hardware overlay/scaler, the front end scaler of the 3D RAGE, and the bus mastering capabilities of the 3D RAGE PRO

### 1.5.2 Notations And Conventions Used In This Manual

Mnemonics are used throughout this manual in place of hardware register names. The naming conventions for registers and/or bit fields within a register are as follows:

- Register\_Mnemonic

- Register\_Mnemonic[Bit\_Numbers]

- Field\_Name@Register\_Mnemonic

The following example is the mnemonic for the Configuration Chip ID register:

#### CONFIG\_CHIP\_ID

Continuing the above example, the Product Type Code field within the above register occupies bit positions 0 through 15. The examples below describe this field in two ways:

CONFIG\_CHIP\_ID[15:0]

CONFIG\_CHIP\_TYPE@CONFIG\_CHIP\_ID

The second convention will be the preferred one, with the first convention used mostly for describing unnamed fields.

Hexadecimal numbers will either be prefixed with "0x" (C-style) or appended with "h" (Intel assembly-style). Binary numbers will be appended with "b". All other numbers are in decimal.

Sample code and functions will be typeset in a **courier** font.

Sample Code Example

```

// Sample Function

void Sample_function (void)

{

printf ("This is a sample function\n");

} // Sample_function.

```

This page intentionally left blank.

# **Chapter 2** Using the mach64

# 2.1 Introduction

This chapter discusses the functionality of the *mach64*. The capabilities and features of the *mach64* are also summarized.

# 2.2 Intel Based Architecture

This section focuses on the features and services that are available on systems that have Intel and Intel-compatible CPUs as well as those systems that can emulate Intel CPUs.

## 2.2.1 Memory Map

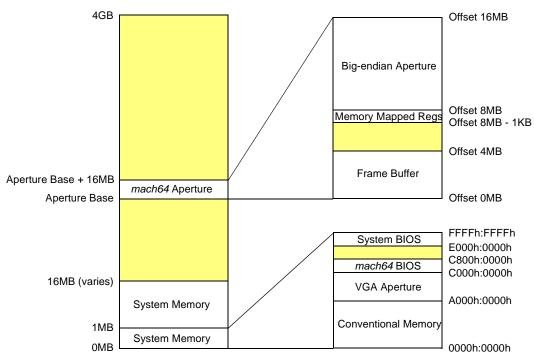

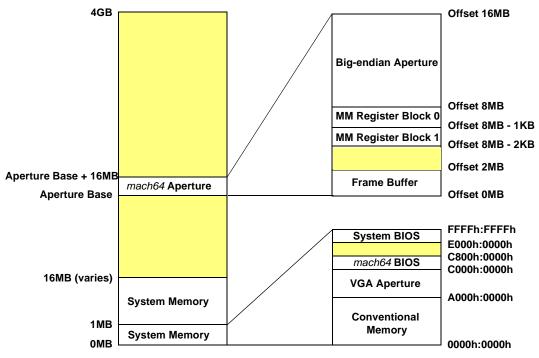

The *mach64* requires a memory aperture so that an application can access the frame buffer and the memory mapped registers. Normally, this aperture is located somewhere within the 4GB address space where it does not conflict with system (host) memory. Further, this aperture must be located on a 4MB, an 8MB, or a 16MB boundary, depending upon the particular *mach64* chip and configuration. The following diagram illustrates a typical memory organization for a *mach64* board with 4MB of display memory installed on system with 16MB of main memory:

# Typical Organization Of *mach64* Aperture Within Host Address Space (PC-compatible)

Aperture Base address can be located anywhere in the shaded region and is aligned to a multiple of 16 MB

#### Figure 2-1. Aperture Within Host Address Space (PC-compatible)

#### 2.2.2 BIOS Services

The BIOS Services provide a straightforward way of setting up and using the *mach64*. The BIOS Services also provide a way of querying the *mach64* hardware in order to determine its capabilities.

VGA modes are initialized with the standard INT 10h interface as described in the *mach64 Register Reference Guide*. For further information on using standard VGA BIOS Services, see *Programmer's Guide to the EGA, VGA, and Super VGA Cards*, by Richard Ferraro.

For accelerator BIOS services, either INT 10h (AH=A0h) or a far call to the ROM can be used. The key services that are provided include loading and setting a display mode, and the BIOS query functions. See *Appendix A*, *BIOS Services* for a complete definition of all accelerator BIOS services.

## 2.2.3 Registers

All of the *mach64* accelerator engine functions are performed through the use of the registers. There are 6 classes of registers that are available:

- VGA Registers are completely segregated from the accelerator registers. Their functions are mutually exclusive. They are addressed at I/O ports 3B0h-3BFh, 3C0h-3CFh, and 3D0h-3DFh. These are the registers that are provided for compatibility with the IBM VGA Display Adapter. Note that the ATI VGA extended registers at 1CEh-1CFh are only available on the *mach64*GX family in standard (non-relocatable) I/O mode. (*See mach64 Register Reference Guide for more details.*)

- Setup and Control Registers are usually initialized only once during boot time and are used for basic configuration of the *mach64* hardware and to report back hardware capabilities. The *mach64* diagnostic registers are also included in this category.

- Accelerator CRTC and DAC registers are used to program the resolution, refresh rate, and pixel depth of the display mode, and to provide hardware cursor services.

- **Draw Engine Control Registers** are used for manipulating *mach64* draw engine in terms of general data path setup and control.

- **Draw Engine Trajectory Control Registers** are used to set up and control specific engine drawing operations.

- Host Bus Dependent Registers are used for bus-specific information.

Registers must be accessed in order to be useful to the programmer. Most registers are memory mapped. Others are I/O mapped. Some are both. In general, the VGA registers are I/O mapped only, the *mach64* Draw Engine registers are memory mapped only, and the rest of the registers are both I/O and memory mapped. See *mach64 Register Reference Guide* for specifics and exceptions. The following sections demonstrate how to access these registers.

#### 2.2.3.2 Memory Mapping

All registers not associated with the draw engine are I/O mapped, and all have memory mapped register aliases (except for CONFIG\_CNTL on *mach64*GX-C/D). All registers are 32 bits wide, except for DAC\_REGS, which are 4x8 bit registers. All draw engine registers are memory mapped with DWORD offsets greater than or equal to 40h.

- If the small apertures are enabled, the memory mapped registers may be accessed through a 1KB area at a segment:offset of B000h:FC00h.

- If the big aperture is enabled, the memory mapped registers occupy the address space located at the base address of the aperture, plus an offset of 3FFC00h for a 4MB aperture, or 7FFC00h for an 8MB aperture configuration. A method of accessing extended memory is required to access the registers at this location.

On the *mach64*GX family, memory mapped registers may be read from and written to in 8-bit, 16-bit and 32-bit quantities.

On the *mach64*CT family, writes to the memory mapped registers must be performed in one 32-bit write. The memory mapped registers on the *mach64*CT family may be read in the same manner as on the *mach64*GX family.

Referring to the *mach64 Register Reference Guide*, the **DWORD Offset** or **Memory Map** (**MM**) **select** is given to describe the register's address. If access through the small apertures is desired, the physical address can be determined by the following equation:

physical memory address = (MM select << 2) + B000h:FC00h For example, if the **MM select** = 21h (SCRATCH\_REG1), the physical address would be B000h:FC84h.

If the big aperture is enabled, the equation becomes:

####

where **memmap offset** is either 3FFC00h or 7FFC00h. Using the example above, if the aperture base address is A0000000h, the aperture size is 8MB (offset 7FFC00h) and the **MM select** = 21h (SCRATCH\_REG1), the physical memory address would be A07FFC84h.

For some registers, it is necessary to access individual bytes within the 32-bit register (such as DAC\_REGS). The **MM select** must be converted to a byte offset before adding the individual byte offset (0, 1, 2, or 3). For example, to access the DAC\_MASK byte of DAC\_REGS through the small aperture the equation is:

byte offset = MM select << 2 = 30h << 2 = 00C0h (DAC\_REGS) individual byte offset = 2 (DAC\_MASK byte) physical memory address = byte offset + individual byte offset + B000h:FC00h = 00C0h + 2 + B000h:FC00h = B000h:FCC2h

For the big aperture, the equation is:

```

byte offset = MMselect << 2 = 30h << 2 = C0h (DAC_REGS)

individual byte offset = 2 (DAC_MASK byte)</pre>

```

#### 2.2.3.3 I/O Mapping

Since the I/O base address may be different depending on the card configuration, it cannot be assumed to be a specific value. The easiest way to obtain the I/O base address is to call *mach64* BIOS function 12h (*see Appendix A, BIOS Services for more information*). The BIOS services can be called in two ways: FAR CALL or INT 10h (it is recommended that the INT 10h method be used).

This function also returns the I/O base address type -- standard or relocatable. If it is standard, the I/O base address will typically be 2ECh. If it is relocatable (only on PCI), the I/O base address can be any value within a 64KB I/O space. The value is decided by the system to insure that no conflicts exist and is in accord with the "plug and play" specification of a PCI system.

In order to use the FAR CALL method, the *mach64* ROM segment is required. The ROM segment for a *mach64* card with the VGA enabled is always at C000h and is normally 32KB in size. To access the BIOS services in the ROM, the offset must be set to 64h. If the VGA is disabled, the ROM segment is usually at C000h or C800h but can be located at other segments. A VGA disabled ROM size is 2KB to 8KB.

Referring to the *mach64 Register Reference Guide*, the **I/O select** is given to describe the register's address. The physical address can be determined by the following equation:

physical I/O address = (I/O select << 10) + I/O base address For example, if the I/O base address = 2ECh and the I/O select = 11h (SCRATCH\_REG1), the physical I/O address would be 46ECh.

If the relocatable feature is enabled (PCI only), the DWORD Offset or Memory Map (MM) select is used to describe the register's address. For this case, the equation becomes:

physical I/O address = (MM select << 2) + I/O base address Using the example above, if the I/O base address = E000h and the **MM select** = 21h (SCRATCH\_REG1), the physical I/O address would be E084h.

For some I/O registers, it is necessary to access individual bytes within the 32-bit register (such as DAC\_REGS). The **I/O select** or **MM select** must be converted to a byte offset before adding the individual byte offset (0, 1, 2, or 3).

For example, to access the DAC\_MASK byte of DAC\_REGS, the equation is:

```

byte offset = I/O select << 10 = 17h << 10 = 5C00h (DAC_REGS)

individual byte offset = 2 (DAC_MASK byte)

I/O base address = 2ECh

physical I/O address = byte offset + individual byte offset + I/O base

address

= 5C00h + 2 + 2ECh = 5EEEh

For relocatable I/O, the equation is:

byte offset = MMselect << 2 = 30h << 2 = C0h (DAC_REGS)

individual byte offset = 2 (DAC_MASK byte)

I/O base address = E000h

physical I/O address = E000h

physical I/O address = byte offset + individual byte offset +

I/O base address

= C0h + 2 + E000h = E0C2h

```

# 2.3 Non-Intel Based Architecture

This section will focus on the features and services that are available on systems that cannot fully emulate Intel CPUs (such as the Apple Power Macintosh).

Note that the *mach64*GX-C/D cannot be used in non-Intel environments. Also, non-Intel platforms must conform to the PCI specification. Thus this section is restricted to PCI versions of the *mach64*GX-E/F and the *mach64*CT family.

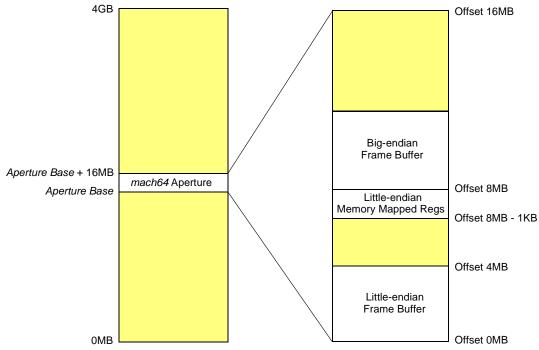

## 2.3.1 Memory Map

The *mach64* requires a memory aperture so that an application can access the frame buffer and the memory mapped registers. Normally, this aperture is located somewhere within the 4GB address space where it does not conflict with system (host) memory. Further, this aperture must be located on a 16MB boundary. The little endian aperture is located at offset 0MB of this aperture space, while the big endian aperture is located at offset 8MB The following diagram illustrates a typical memory organization for a *mach64* board with 4MB of display memory installed:

Typical Organization Of mach64 Aperture Within Host Address Space (non-Intel)

#### Figure 2-4. Aperture Within Host Address Space (non-Intel)

## 2.3.2 BIOS Services

BIOS Services are unavailable on non-Intel platforms. The BIOS is typically replaced with a ROM that conforms to the IEEE OpenBoot specification. Upon system powerup, the ROM will initialize the *mach64* board to a known state. The ROM image will disappear at the end of the boot process. All further access to the *mach64* must be done via the memory mapped registers. Setting modes, for example, must be done manually.

## 2.3.3 Registers

The VGA registers are normally not available, unless the non-Intel platform in question contains hardware support for an I/O address space that is distinct from Memory address space.

All registers are memory mapped and are 32 bits wide, except for DAC\_REGS, which are 4x8 bit registers.

• If the small apertures are enabled, the memory mapped registers may be accessed

Aperture Base address can be located anywhere in the shaded region and is aligned to a multiple of 16MB

through a 1KB area at a linear address 0x000BFC00.

• If the big aperture is enabled, the memory mapped registers occupy the address space located at the base address of the aperture, plus an offset of 0x003FFC00 for a 4MB aperture, or 0x007FFC00 for an 8MB aperture configuration. A method of accessing extended memory is required to access the registers at this location.

On the *mach64*GX family, memory mapped registers may be read from and written to in 8-bit, 16-bit and 32-bit quantities.

On the *mach64*CT family, writes to the memory mapped registers must be performed in one 32-bit write. The memory mapped registers on the *mach64*CT family may be read in the same manner as on the *mach64*GX family.

Referring to the *mach64 Register Reference Guide*, the **DWORD Offset** or **Memory Map** (**MM**) **select** is given to describe the register's address. If access through the small apertures is desired, the physical address can be determined by the following equation:

physical memory address = (MM select << 2) + 0x000BFC00For example, if the MM select = 0x21 (SCRATCH\_REG1), the physical address would be 0x000BFC84.

If the big aperture is enabled, the equation becomes:

####

where **memmap offset** is either 0x003FFC00 or 0x007FFC00. Using the example above, if the aperture base address is 0xA0000000, the aperture size is 8MB (offset 0x007FFC00) and the **MM select** = 0x21 (SCRATCH\_REG1), the physical memory address would be 0xA07FFC84.

For some registers, it is necessary to access individual bytes within the 32-bit register (such as DAC\_REGS). The **MM select** must be converted to a byte offset before adding the individual byte offset (0, 1, 2, or 3). For example, to access the DAC\_MASK byte of DAC\_REGS through the small aperture the equation is:

| byte offset             | = MM select << 2 = 0x30 << 2 = 0xC0 (DAC_REGS)                 |

|-------------------------|----------------------------------------------------------------|

| individual byte offset  | = 2 (DAC_MASK byte)                                            |

|                         |                                                                |

| physical memory address | <pre>= byte offset + individual byte offset + 0x000BFC00</pre> |

|                         | = 0xC0 + 2 + 0x000BFC00 = 0x000BFCC2                           |

For the big aperture, the equation is:

| byte offset             | = MMselect << 2 = $0x30$ << 2 = $0xC0$ (DAC_REGS)                                 |

|-------------------------|-----------------------------------------------------------------------------------|

| individual byte offset  | = 2 (DAC_MASK byte)                                                               |

| aperture base           | = 0xA0000000                                                                      |

| memmap offset (8MB)     | = 0x007FFC00                                                                      |

|                         |                                                                                   |

| physical memory address | <pre>= byte offset + individual byte offset + aperture base + memmap offset</pre> |

|                         | = 0xC0 + 2 + 0xA0000000 + 0x007FFC00<br>= 0xA07FFCC2                              |

I/O mapped registers may not be available on non-Intel platforms as this method of register access implicitly assumes Intel-style I/O port addressing capability. If I/O mapped registers are available, see section 2.2.3.3 for information on how to access these ports.

This page intentionally left blank.

# **Chapter 3** Getting Started

# 3.1 Introduction

This chapter discusses the basics of using the *mach64* and covers detection of the *mach64* and setting up a display mode.

# 3.2 Before you start

Before programming the *mach64* there are several issues that should be discussed as they will determine how the *mach64* will be used on the desired platform. These issues are discussed below.

## 3.2.1 Accelerator vs. VGA

The mach64 has two distinct operating modes:

#### • VGA mode

#### Accelerator mode

For more information on standard VGA programming, please refer to any of the texts that are mentioned in the Bibliography such as *Programmer's Guide to the EGA*, *VGA*, *and Super VGA Cards*, by Richard F. Ferraro.

Note that the *mach64* also supports the VESA VBE 1.2 programming interface. This interface was created by the Video Electronic Standards Association (VESA) to provide a standardized method for using SuperVGA display modes on non-accelerated hardware. Effectively, VBE 1.2 folded in VGA support for common high resolution modes such as 1024x768 with 256 colors. Contact VESA for further information on VBE.

The accelerator provides the ability to draw into screen memory concurrently with the operation of the host CPU. In accelerator mode, there are two ways of accessing the graphics memory:

#### Memory aperture

#### • Draw engine

The host application may read or write screen memory directly through a memory aperture (an **aperture** is an address space that maps directly to on-board memory).

Accesses through the aperture provide no acceleration, and the speed of these accesses is

generally bound by the speed of the host expansion bus.

The second way of accessing the memory is to use the draw engine to write to it. The draw engine can do two things:

- Rectangle fills

- Lines

These are known as **destination trajectories** (a **trajectory** defines a path through graphics memory which the draw engine reads or writes data). These trajectories may be filled with pixel data from various sources. If the source data comes from graphics memory, this is called a **bitblt** (or **blit**) and follows one of four different source trajectories.

A more detailed description of trajectories can be found in section 6.1.3: Trajectories.

### 3.2.2 Linear Aperture vs. VGA Aperture

Memory on the *mach64* may be directly accessed in one of three ways:

- Standard paged 64KB VGA aperture

- Small dual paged apertures

- Big aperture

Note that it is completely legitimate to have all three apertures simultaneously accessing framebuffer memory, but if the Big linear aperture is active there is typically no need to access memory through either the VGA or the small apertures.

#### 3.2.2.1 Standard Paged 64KB VGA Aperture

If the VGA is enabled and the *mach64* is in VGA mode, memory may be accessed through the **standard paged 64KB VGA aperture**. The segment base address of this aperture is either A000h or B000h depending on the video mode.

The *mach64*GX family also use this aperture to access the lower 1MB of memory in planar (16 color) SVGA modes. The ATI VGA extended registers are used to select the 64KB read or write page mapped to the aperture space. As the *mach64*CT family do not contain the VGA extended register set, the small dual paged apertures described in the next section are used to access video memory. Any memory writes via the VGA aperture are inhibited when the memory boundary is enabled.

For more information on how to page the 64KB aperture, see the *mach64 Register Reference Guide*.

#### **3.2.2.2 Small Dual Paged Apertures**

If the *mach64* is in an accelerator mode or a SVGA packed pixel mode, **two small 32KB apertures** may be enabled at segment base addresses A000h and A800h. The read and write pages are set independently on 32KB boundaries for each of the two apertures with the MEM\_VGA\_WP\_SEL and MEM\_VGA\_RP\_SEL registers. This aperture mode is a type of VGA aperture configuration that is not available in standard VGA modes. If the memory boundary is enabled, writes to these apertures are inhibited.

- These small apertures can access the full 8MB.

- These small apertures may be enabled only if the VGA is enabled on the chip; otherwise, a memory address conflict would exist between the accelerator and the existing VGA.

Some special initialization is required to enable the small apertures and the memory mapped registers in the VGA address space:

- The VGA must be put into packed pixel mode.

- The VGA must have a 128KB aperture enabled if both the small apertures and the memory mapped registers are addressed.

- The bit CFG\_MEM\_VGA\_AP\_EN@CONFIG\_CNTL must be set.

If access to the VGA memory mapped registers is not required, the setting of CFG\_MEM\_VGA\_AP\_EN@CONFIG\_CNTL is not necessary.

Because the small aperture page size is 32KB, programs which assume the page size to be 64KB need to double the page number within their page setting routine. When selecting the write page, for instance, the doubled page number must be written to MEM\_VGA\_WPS0@MEM\_VGA\_WP\_SEL to set the page number for the first 32KB aperture. This value plus one must then be written to MEM\_VGA\_WPS1@MEM\_VGA\_WP\_SEL to set the page number for the second 32KB aperture. A similar process may be used to set the read page in the MEM\_VGA\_RP\_SEL register. In this way, programs which assume a page size of 64KB can use the small apertures transparently.

The ATI VGA extended registers are used to change the display page in the *mach64*GX family. Because the *mach64*CT family does not include the VGA extended register set, they must use the small aperture to change the read or write page.

## 3.2.2.3 Big Aperture

If the *mach64* is in accelerator mode, a big linear aperture may be enabled to access the entire frame buffer. The size and location of the aperture depends on the *mach64* variant. For example, on the *mach64*GX-C/D, the aperture size may be set to 4MB or 8MB and require an 8MB boundary for the aperture location. The *mach64*GX-E/F and the

*mach64*CT family always require a 16MB boundary since enabling the big linear aperture also enables the 8MB big endian aperture (the big endian aperture starts at the standard linear aperture address plus 8MB). The *mach64*GX-E/F do allow 4MB or 8MB aperture sizing whereas the *mach64*CT family allows only an 8MB sized aperture. To produce code that works across all *mach64* variants, it is recommended that the aperture size be set to 8MB and located on a 16MB boundary.

The availability of this aperture is assured on all board configurations except ISA bus configurations. On an ISA system, the following two conditions must be met in order to use the big aperture:

- The aperture must fit within a 16MB address space.

- The aperture must not overlap host CPU memory.

An ISA system with greater than 12MB of host CPU memory cannot use a big aperture.

Given the restrictions imposed on using the linear aperture on ISA systems, it is recommended that the VGA dual paged aperture be used for ISA systems.

### 3.2.3 Protected Mode vs. Real Mode

Writing to and reading from the linear aperture can be done in several ways. Since the linear aperture is located in the "extended memory" space, a real mode application must use the extended memory services to access memory through the linear aperture. There are several services available:

- System BIOS INT 15h, function 87h.

- DOS Protected Mode Interface (DPMI).

- Virtual Control Program Interface (VCPI).

The last two points mentioned require protected mode memory managers that support these services. The first point mentioned will typically be available since it is supported by the system BIOS. This method is also the slowest and is not practical for performance applications. It should be noted that EMS (Expanded Memory Services) and XMS (eXtended Memory Services) are not practical for accessing graphics frame buffers.

If the application is in protected mode, the linear aperture can be accessed easily with virtually no overhead.

Before attempting to access the big aperture, the host application must enable it with BIOS services function 5 or by writing to the CONFIG\_CNTL register. (*See Appendix A, BIOS Services for more details.*)

# 3.3 mach64 Detection

There are several steps that are required in order to properly detect the *mach64*. Some of these steps may need to be performed differently on a non-Intel platform or if the BIOS is unavailable. The key steps to detection are:

- 1. Detect mach64 signatures.

- 2. Determining I/O base address.

- 3. Read/Write tests.

- 4. Determining specific *mach64* variant.

# 3.3.1 Card Detection

Find an ATI *mach64* ROM and its ROM segment by scanning through ROM segments C000h – FE00h, in 2KB steps. To match, the ROM ID, ATI product signature, and *mach64* product string must be found:

ROM ID = AA55h (PC compatibles) ATI product signature = "761295520" mach64 string2 = "MACH64" mach64 string1 = "GXCX" (older ROMs)

The ROM ID bytes will occur as the first two bytes in the segment. The ATI product signature will occur somewhere within the first 256 bytes of the segment and will identify the ROM as belonging to an ATI display adapter. One of the *mach64* strings will occur somewhere within the first 1024 bytes of the segment and will identify the ROM as belonging to a *mach64*-based product.

Only one the *mach64* strings will be present in a *mach64* ROM. Therefore, the ROM should be searched for string1 first. If it is not present, string2 should be searched for. If it is also not present, a *mach64* ROM is not present.

For non-Intel platforms, access to the PCI configuration space is required. Scan for a PCI card with a VendorID of 0x1002. This number is ATI's VendorID as registered with the PCI Special Interest Group, and all PCI-based products manufactured by ATI will have this VendorID. Once found, scan for the following DeviceID codes to identify a *mach64*:

| mach64 PCI DeviceID Codes |          |  |  |  |  |  |

|---------------------------|----------|--|--|--|--|--|

| Variant                   | DeviceID |  |  |  |  |  |

| mach64GX                  | 0x4758   |  |  |  |  |  |

| mach64CX                  | 0x4358   |  |  |  |  |  |

| mach64CT                  | 0x4354   |  |  |  |  |  |

| mach64VT                  | 0x5654   |  |  |  |  |  |

| mach64VTB                 | 0x5655   |  |  |  |  |  |

| mach64VT4                 | 0x5656   |  |  |  |  |  |

#### Table 3-1 PCI DeviceID Codes

| 3D RAGE PCI DeviceID Codes         |          |  |  |  |  |

|------------------------------------|----------|--|--|--|--|

| Variant                            | DeviceID |  |  |  |  |

| 3D RAGE (GT)                       | 0x4754   |  |  |  |  |

| 3D RAGE II+ (GTB)                  | 0x4755   |  |  |  |  |

| 3D RAGE IIC (PQFP, AGP)            | 0x475A   |  |  |  |  |

| 3D RAGE IIC (BGA, AGP)             | 0x4757   |  |  |  |  |

| 3D RAGE IIC (PQFP, PCI)            | 0x4756   |  |  |  |  |

| 3D RAGE PRO (BGA, AGP)             | 0x4742   |  |  |  |  |

| 3D RAGE PRO (BGA, AGP, 1X ONLY)    | 0x4744   |  |  |  |  |

| 3D RAGE PRO (BGA, PCI)             | 0x4749   |  |  |  |  |

| 3D RAGE PRO (PQFP, PCI)            | 0x4750   |  |  |  |  |

| 3D RAGE PRO (PQFP, limited 3D)     | 0x4751   |  |  |  |  |

| 3D RAGE LT PRO (BGA, PCI)          | 0x4C49   |  |  |  |  |

| 3D RAGE LT PRO (BGA, AGP)          | 0x4C42   |  |  |  |  |

| 3D RAGE LT PRO                     | 0x4C50   |  |  |  |  |

| 3D RAGE LT                         | 0x4C47   |  |  |  |  |

| RAGE XL (BGA, AGP)                 | 0x474D   |  |  |  |  |

| RAGE MOBILITY (M1, M, P, AGP, PCI) | 0x4C4D   |  |  |  |  |

On all systems that support multiple *mach64* cards installed the above procedure should be repeated until all *mach64* images have been located.

#### 3.3.2 I/O Base

Call the ROM (BIOS service 12h) to find the I/O base address and type (standard/relocatable). The CX register should be preloaded with zero before calling this BIOS function. This insures that CX is zero on return for older ROMs.

Standard (also known as Fixed or Sparse) I/O is the only I/O type available on ISA and VLB *mach64* boards. The lower 10 bits of the I/O port address are fixed and set to 0x2EC and the upper 6 bits are used to index the various *mach64* registers. Relocatable (also known as Block) I/O is available on PCI *mach64* boards with the exception of the *mach64*GX-C/D. The I/O base can be anywhere within the 64KB I/O address space and will occupy 256 consecutive registers.

For non-Intel platforms, the Base Addresses section of the PCI configuration space will indicate what the I/O base address is.

#### 3.3.3 Read/Write Test

Perform a write/read test on SCRATCH\_REG1 (its contents must be saved and restored since they are used by the BIOS services). This is done by writing the 32-bit value 55555555 to SCRATCH\_REG1 and then reading it back. If the value is different, a *mach64* is not present. If the value is the same, repeat this test with AAAAAAAA. Ensure that the register's contents are restored.

## 3.3.4 CONFIG\_CHIP\_ID

Read the CONFIG\_CHIP\_ID register for additional information such as the chip type, class, and revision.

Additional configuration information can be obtained with a BIOS query call (functions 6, 7, 8, 9, and Ah). (See *Appendix A, BIOS Services* for more information.).

# 3.4 Mode Switching

It is highly recommended that all mode switching be done by a BIOS service function call rather than by manually setting the CRT controller (CRTC). The main reasons for doing this are:

- Simplicity.

- The characteristics of the non-volatile storage device that stores mode and monitor information may not be known. Without monitor information, the only mode guaranteed to work on all analog monitors is 640x480 at 60 Hz non-interlaced.

- CRTC compatibility with future devices is not guaranteed.

On *mach64*GX family, there are separate CRTCs for the VGA and accelerator. The CRTC parameters may be set independently. On *mach64*CT family, both the VGA and accelerator share the same CRTC and therefore they cannot be set independently. For all *mach64* chips, the BIOS can be used to switch between VGA and accelerator modes.

The following table lists the VESA VBE modes that may be available on the *mach64*. These modes are set with the standard VESA VBE set mode call (INT 10h, AX=4F02h, BX=*mode*). Consult the VBE specification for further details.

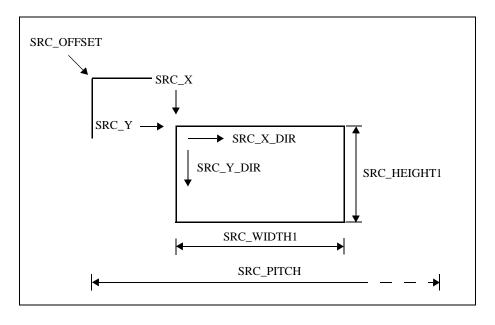

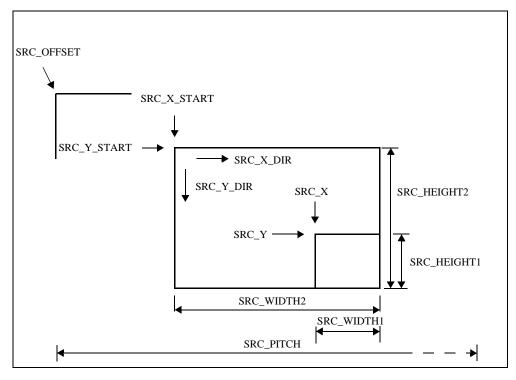

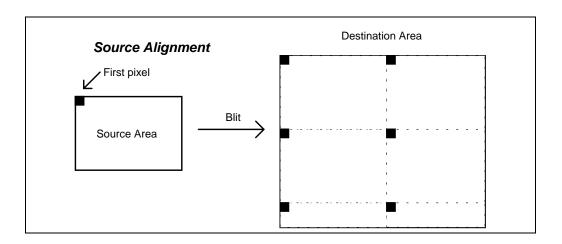

| VESA VB     | VESA VBE 1.2 Compatible Mode Support for mach64 |             |             |  |  |  |  |  |