# PALASM<sup>®</sup> 4 Reference Guide

Advanced Micro Devices

# PALASM® 4 USER'S MANUAL

VOLUME 2 - PALASM 4 REFERENCE GUIDE

© 1991 Advanced Micro Devices, Inc. 901 Thompson Place P.O. Box 3453 Sunnyvale, CA 94088

TEL: 408-732-2400 TWX: 910339-9280 TELEX: 34-6306 TOLL FREE: 800-538-8450

APPLICATIONS HOTLINE: 800-222-9323

i

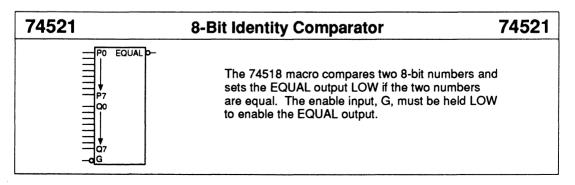

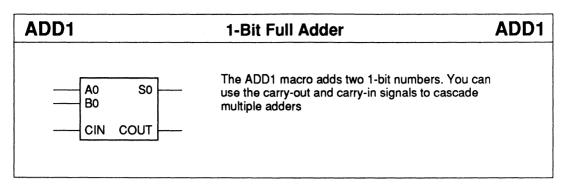

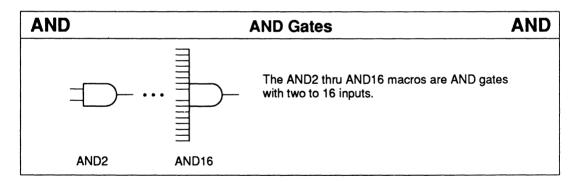

DocVer 2.0 May 1992 PALASM 4 USER'S MANUAL

Advanced Micro Devices reserves the right to make changes in specifications at any time and without notice. The information furnished by Advanced Micro Devices is believed to be accurate and reliable. However, no responsibility is assumed by Advanced Micro Devices for its use, nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Advanced Micro Devices.

IBM<sup>®</sup> is a registered trademark of International Business Machines Corporation.

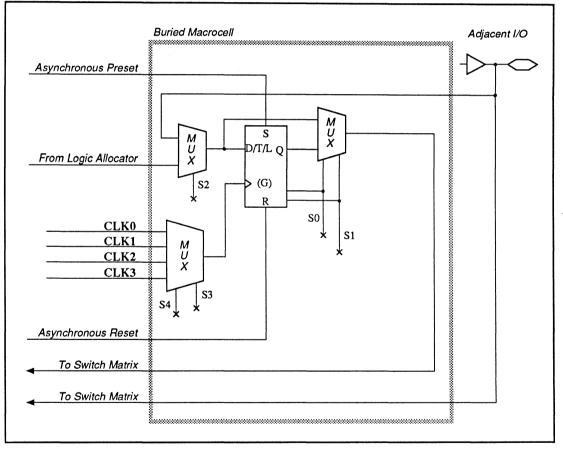

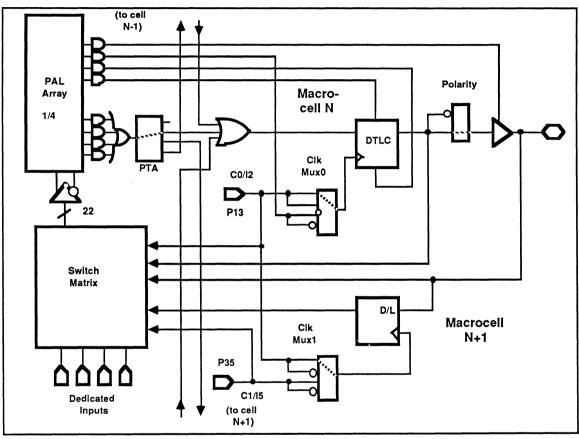

ABEL<sup>™</sup> is a trademark of Data I/O Corporation.

IBM PC<sup>™</sup>, PC AT<sup>™</sup>, PC AT<sup>™</sup>, and PS/2<sup>™</sup> are trademarks of International Business Machines Corporation.

MS-DOS<sup>™</sup> is a trademark of Microsoft Corporation.

PAL<sup>®</sup> and PALASM<sup>®</sup> are registered trademarks and MACH™ is a trademark of Advanced Micro Devices, Inc.

OrCAD<sup>®</sup> and OrCAD SDT/III<sup>®</sup> are registered trademarks of OrCAD.

# PALASM 4 USER'S MANUAL

# **VOLUME 1 - PALASM 4 Getting Started and MACH Workbook**

Preface

# Acknowledgements

- Section I:

Getting Started

Chapter 1:

Installation Guide

Chapter 2:

Design Entry Demonstration

Chapter 3:

Schematic-Based MACH Design Demonstration

- Section II: Designer's Guide

- Chapter 4: Entry

- Chapter 5: Compilation / Fitting

- Chapter 6: Simulation

# MACH Design Workbook

# VOLUME 2 - PALASM 4 Reference Guide

# Section III: Library Reference

Chapter Con Thirduction

PALASM 4 USER'S MANUAL

Chapter 8: Mache End Schematic Datasheets

# Section IV: Software Reference

Chapter 9: Menus and Commands

Chapter 10: Language Reference

Chapter 11: Device Programming Reference

## Section V: Appendices

Appendix A: PLD Text Editor

### Section VI: Glossary / Index

Glossary

Index

e d

# TABLE OF CONTENTS

# **VOLUME 1** - Getting Started and MACH Workbook

# SECTION I: GETTING STARTED

#### **CHAPTER 1: INSTALLATION GUIDE**

| 1.1 | REQUI   | REMENTS       | 1–2   |

|-----|---------|---------------|-------|

|     | 1.1.1   | HARDWARE      | . 1–2 |

|     | 1.1.2   | SOFTWARE      | 1–3   |

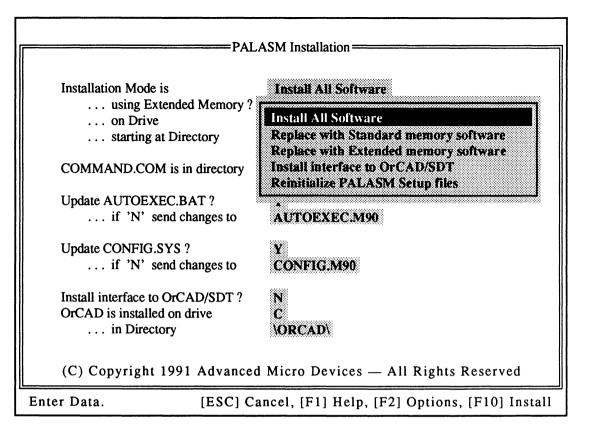

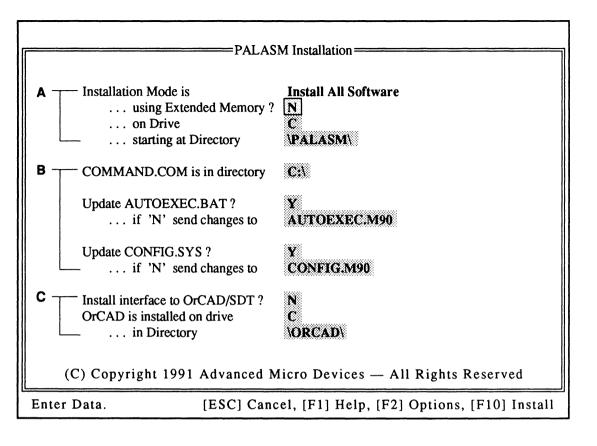

| 1.2 | STEPS   |               | 1–4   |

|     | 1.2.1   | INSTALLATION  | 1–4   |

|     | 1.2.2   | CONFIGURATION | 1–11  |

| 1.3 | FILE UF | PDATES        | 1–12  |

|     | 1.3.1   | AUTOEXEC      | 1–12  |

|     | 1.3.2   | CONFIG.SYS    | 1–12  |

#### **CHAPTER 2: DESIGN ENTRY**

| 2.1 CREA |       | TING A TEXT-BASED DESIGN                  |      |

|----------|-------|-------------------------------------------|------|

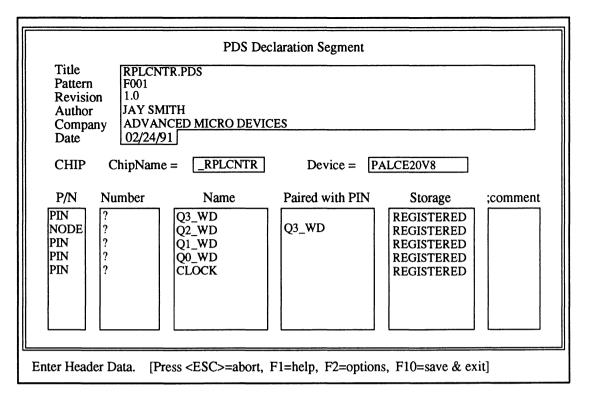

|          | 2.1.1 | BEGIN THE DESIGN                          | 2–5  |

|          | 2.1.2 | FILL IN THE PDS DECLARATION-SEGMENT FORM  | 2–7  |

|          | 2.1.3 | COMPLETE THE PDS FILE USING A TEXT EDITOR |      |

| 2.2      | SCHEM | IATIC-BASED DESIGN ENTRY                  | 2–17 |

|          | 2.2.1 | BEGIN THE DESIGN                          | 2–19 |

|          | 2.2.2 | FILL IN THE SCHEMATIC CONTROL-FILE FORM   | 2–22 |

|          | 2.2.3 | CREATE THE SCHEMATIC                      | 2–24 |

| 2.3      | MERGI | NG MULTIPLE PDS FILES                     | 2–30 |

|          | 2.3.1 | SET UP                                    | 2–31 |

|          | 2.3.2 | RETRIEVE FILES                            | 2–33 |

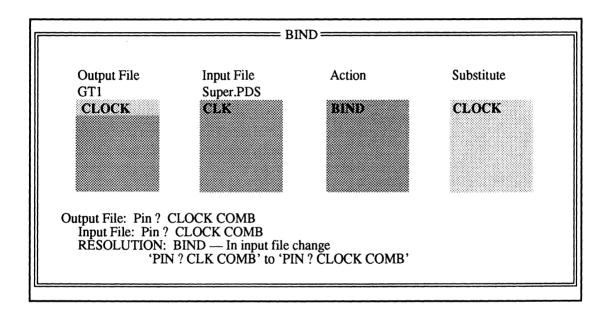

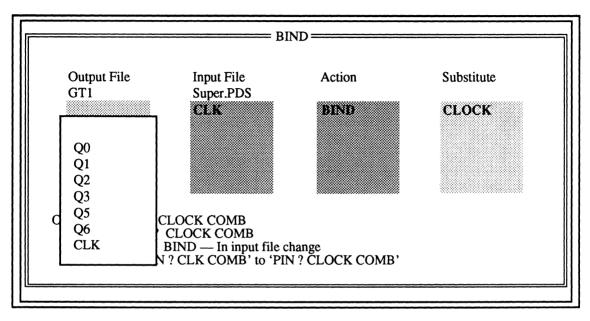

|          | 2.3.3 | RESOLVE CONFLICTS                         | 2–36 |

|          | 2.3.4 | MERGE FILES                               | 2–44 |

|          | 2.3.5 | RECOMPILE THE COMBINED DESIGN             | 2–48 |

#### CHAPTER 3: SCHEMATIC-BASED MACH DESIGN DEMONSTRATION

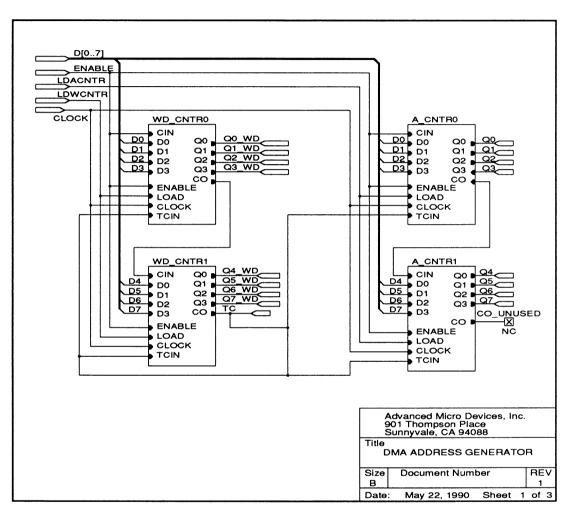

| 3.1 | DESIGN  | I EXAMPLE             | 3–2  |

|-----|---------|-----------------------|------|

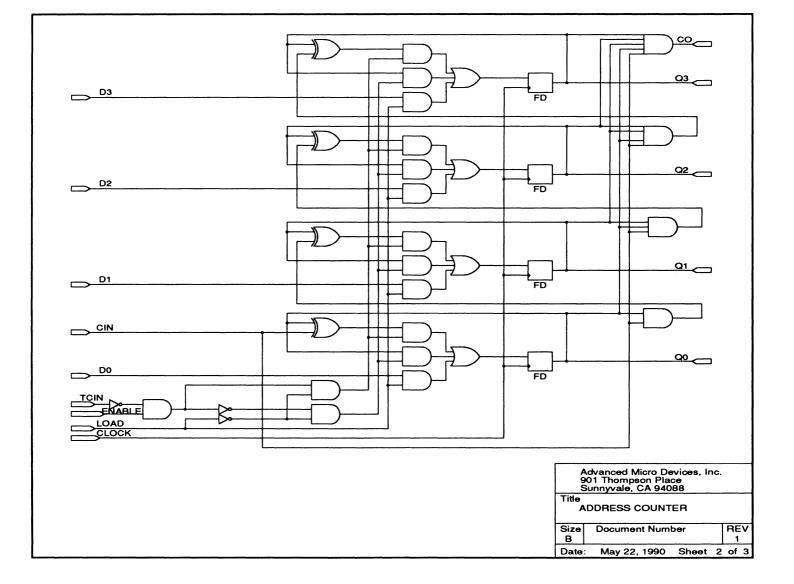

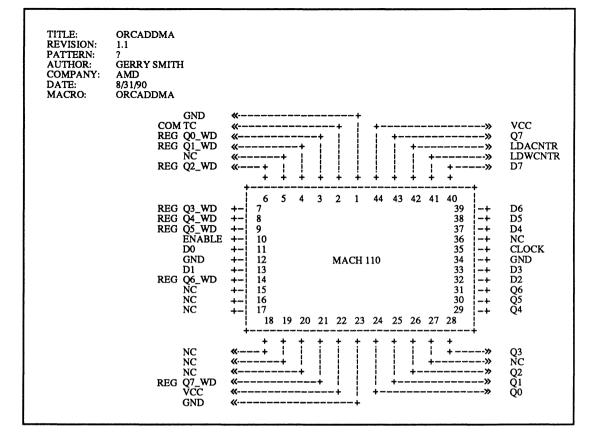

|     | 3.1.1   | ADDRESS COUNTER       | 3–4  |

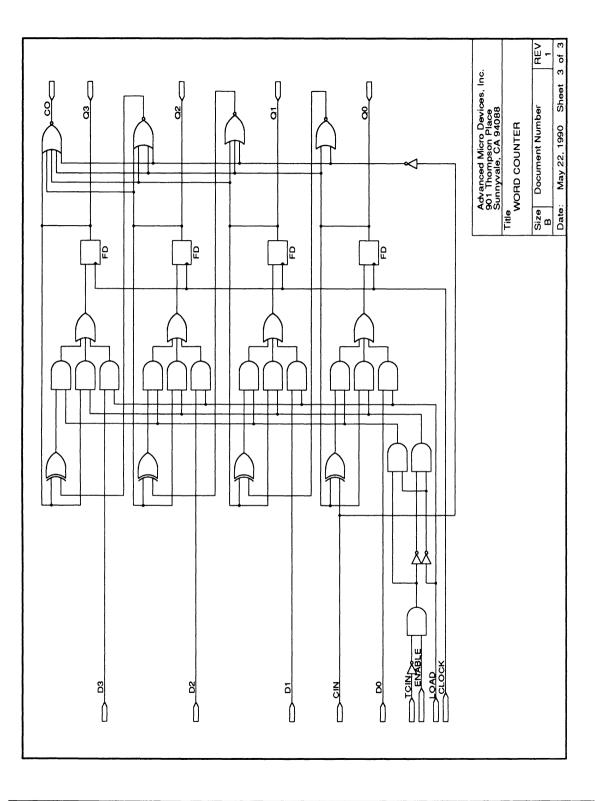

|     | 3.1.2   | WORD COUNTER          | 3–6  |

| 3.2 | CONFIF  | RM THE SETUP          | 3–8  |

|     |         | RETRIEVE THE DESIGN   |      |

|     |         |                       |      |

| 3.3 | VIEW D  | ESIGN FILES           | 3–14 |

|     | 3.3.1   | VIEW THE SCHEMATIC    | 3–14 |

|     | 3.3.2 💣 | VIEW THE CONTROL FILE | 3–19 |

| 3.4 | COMPIL  | ETHE DESIGN           | 3–21 |

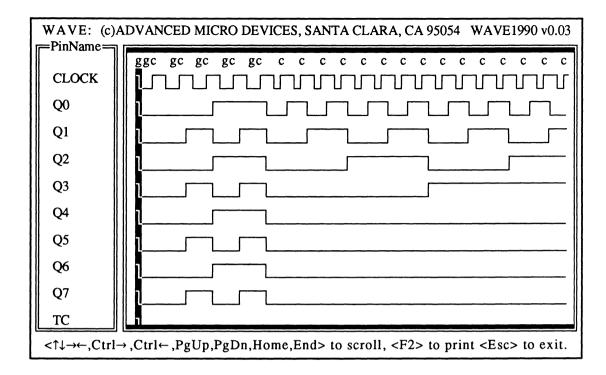

| 3.5 | SIMULA  | TE THE DESIGN         | 3–33 |

# SECTION II: DESIGNER'S GUIDE

#### CHAPTER 4: ENTRY

| 4.1 | OVER  | /IEW        | IEW                                                 |      |  |

|-----|-------|-------------|-----------------------------------------------------|------|--|

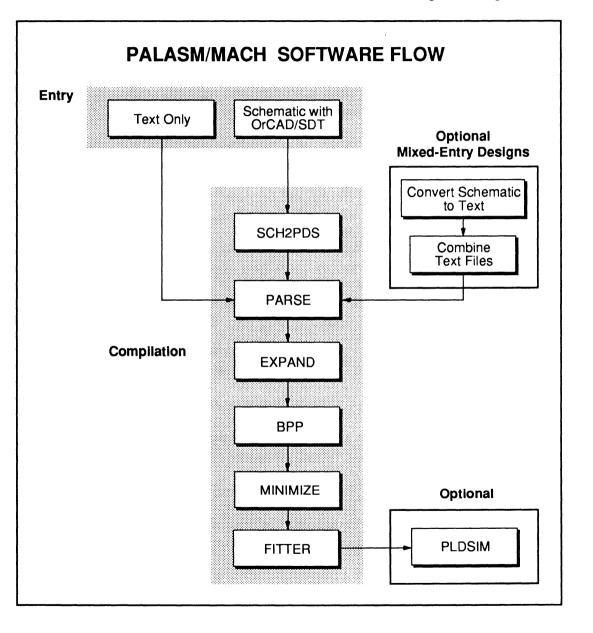

| 4.2 | DESIG | DESIGN FLOW |                                                     |      |  |

|     | 4.2.1 | TEXT EN     | ITRY                                                | 4–4  |  |

|     | 4.2.2 | SCHEMA      | ATIC ENTRY                                          | 4–4  |  |

|     | 4.2.3 | COMBIN      | ED ENTRY METHODS                                    | 4–6  |  |

| 4.3 | BOOLE | EAN DESIG   | IN STRATEGIES                                       | 4–7  |  |

|     | 4.3.1 | OUTPUT      | POLARITY                                            | 4–7  |  |

|     |       | 4.3.1.1     | The Two Components of Polarity                      | 4–7  |  |

|     |       | 4.3.1.2     | Controlling Polarity from the Equation              | 4–8  |  |

|     |       | 4.3.1.3     | Controlling Polarity from the Pin or Node Statement | 4–9  |  |

|     |       | 4.3.1.4     | Creating Equivalent Logic                           | 4–10 |  |

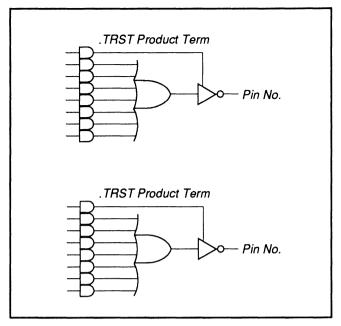

|     | 4.3.2 | CONTRO      | DLLING OUTPUT BUFFERS USING .TRST                   | 4–11 |  |

|     |       | 4.3.2.1     | Bank Output Enable                                  | 4–11 |  |

|     |       | 4.3.2.2     | Individual Output Enable                            | 4–12 |  |

|     |       | 4.3.2.3     | Grouped Output Enable                               | 4–14 |  |

|     | 4.3.3 |             | DLLING CLOCKS WITH .CLKF                            |      |  |

|     | 4.3.4 | CONTRO      | DLLING SET/RESET USING .SETF AND .RSTF              | 4–17 |  |

|     |       | 4.3.4.1     | Banking Set and Reset in MACH Devices               | 4–17 |  |

|     |       |             |                                                     |      |  |

|     | 4.3.5 | USING HI  | GH-LEVEL CONSTRUCTS                                     | 4–18 |

|-----|-------|-----------|---------------------------------------------------------|------|

|     |       | 4.3.5.1   | Vector Notation                                         | 4–18 |

|     |       | 4.3.5.2   | Radix Notation                                          | 4–20 |

|     |       | 4.3.5.3   | IF-THEN-ELSE Statement                                  | 4–21 |

|     |       | 4.3.5.4   | CASE Statement                                          | 4–22 |

|     | 4.3.6 | CONTRO    | LLING LOGIC REDUCTION                                   | 4–25 |

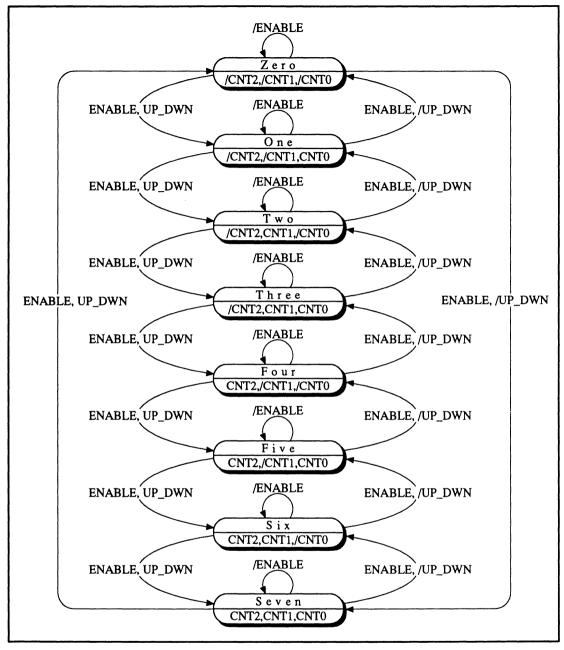

| 4.4 | STATE | MACHINE   | DESIGN STRATEGIES                                       | 4–26 |

|     | 4.4.1 | STATE SI  | EGMENT OVERVIEW                                         | 4–28 |

|     | 4.4.2 | DEFINING  | G MOORE AND MEALY MACHINES                              | 4–29 |

|     | 4.4.3 | CREATIN   | G STATE-MACHINE EQUATIONS                               | 4–30 |

|     |       | 4.4.3.1   | Condition Equations                                     | 4–31 |

|     |       | 4.4.3.2   | Transition Equations                                    | 4–31 |

|     |       | 4.4.3.3   | Output Equations                                        | 4–32 |

|     |       | 4.4.3.4   | State-Machine Example                                   | 4–32 |

|     | 4.4.4 | DEFAULT   | BRANCHES                                                | 4–34 |

|     |       | 4.4.4.1   | Global Defaults                                         | 4–35 |

|     |       | 4.4.4.2   | Local Defaults                                          | 4–35 |

|     |       | 4.4.4.3   | Example With Default Branches                           | 4–36 |

|     | 4.4.5 | ASSIGNI   | NG STATE BITS                                           | 4–38 |

|     |       | 4.4.5.1   | Automatic State-Bit Assignment                          | 4–38 |

|     |       | 4.4.5.2   | Manual State-Bit Assignment                             | 4–39 |

|     |       | 4.4.5.3   | Choosing State-Bit Assignments                          | 4–39 |

|     |       | 4.4.5.4   | Example Using Manual State-Bit Assignment               | 4–41 |

|     | 4.4.6 | USING S   | TATE BITS AS OUTPUTS                                    | 4–42 |

|     | 4.4.7 | INITIALIZ | ING A STATE MACHINE                                     | 4–43 |

|     | 4.4.8 | CLOCKIN   | IG A STATE MACHINE                                      | 4–44 |

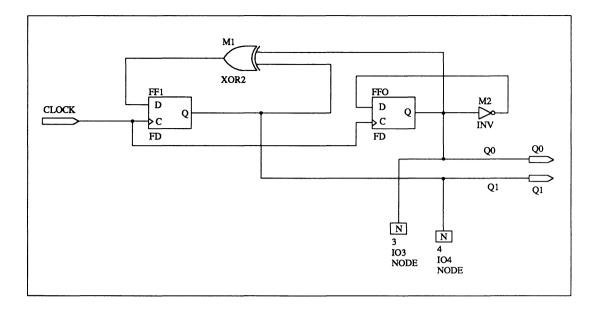

|     |       | 4.4.8.1   | Example Using State Bits as Outputs, Power-Up and Clock |      |

|     |       |           | Equations                                               |      |

| 4.5 | SCHEN |           | SUS TEXT ENTRY                                          |      |

|     | 4.5.1 |           | ANALYSIS                                                |      |

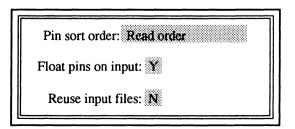

|     | 4.5.2 | SCHEMA    | TIC PARAMETERS                                          |      |

|     |       | 4.5.2.1   | Fixing Pin Locations                                    |      |

|     |       | 4.5.2.2   | Fixing Node Locations                                   |      |

|     |       | 4.5.2.3   | Assigning Logic to a Block                              |      |

|     |       | 4.5.2.4   | Controlling Minimization                                |      |

|     |       | 4.5.2.5   | Controlling Set/Reset                                   |      |

|     |       | 4.5.2.6   | Deleting Unused Logic                                   | 4–59 |

-----

|      | 4.5.3 | DESIGN D                                                                   | DESIGN DOCUMENTATION4-                                                                                                              |      |

|------|-------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|

|      | 4.5.4 | CONVERS                                                                    | ION, EXISTING SCHEMATICS TO MACH-DEVICE                                                                                             |      |

|      |       | DESIGNS                                                                    |                                                                                                                                     | 4–62 |

| 4.6. | COMBI | VING SCHE                                                                  | MATIC AND TEXT DESCRIPTIONS                                                                                                         |      |

| 4.7  | MERGI |                                                                            | LE PDS FILES                                                                                                                        |      |

|      | 4.7.1 | INPUT FIL                                                                  | ES                                                                                                                                  | 4–66 |

|      | 4.7.2 | DESIGN E                                                                   | VALUATION                                                                                                                           |      |

|      |       | 4.7.2.1                                                                    | Compatibility                                                                                                                       | 4–67 |

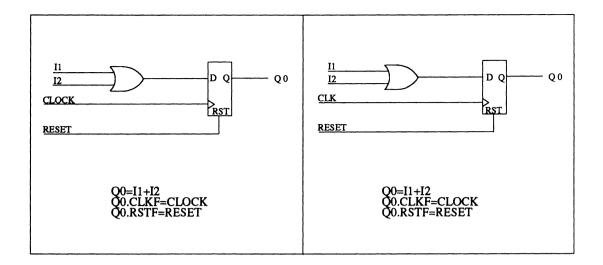

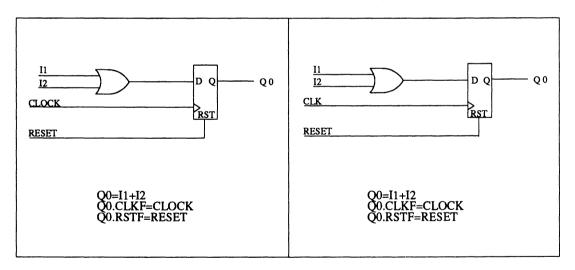

|      |       | 4.7.2.2                                                                    | Inputs, Clock Signals, and Set/Reset Control                                                                                        | 4–69 |

|      | 4.7.3 | GUIDELIN                                                                   | ES                                                                                                                                  | 4–69 |

|      |       | 4.7.3.1                                                                    | Set up                                                                                                                              |      |

|      |       | 4.7.3.2                                                                    | Retrieve Files                                                                                                                      | 4–72 |

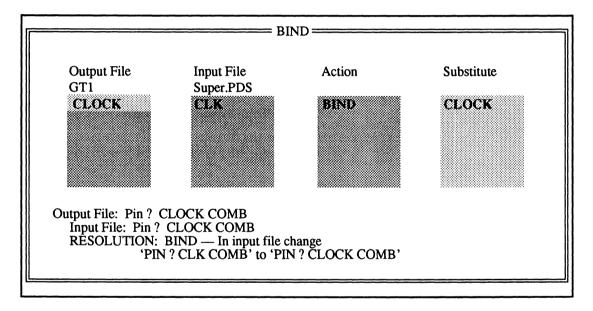

|      |       | 4.7.3.3                                                                    | Resolve Conflicts                                                                                                                   | 4–74 |

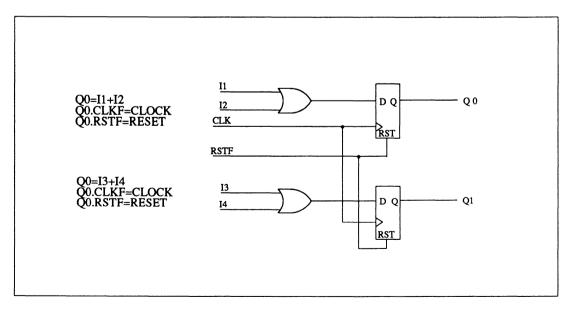

|      |       | 4.7.3.4                                                                    | Merge Files                                                                                                                         | 4–81 |

|      |       | 4.7.3.5                                                                    | Re-engineer the Combined Design                                                                                                     | 4–84 |

|      |       | 4.7.2.1<br>4.7.2.2<br>GUIDELIN<br>4.7.3.1<br>4.7.3.2<br>4.7.3.3<br>4.7.3.4 | Compatibility<br>Inputs, Clock Signals, and Set/Reset Control<br>ES<br>Set up<br>Retrieve Files<br>Resolve Conflicts<br>Merge Files |      |

### CHAPTER 5: COMPILATION / FITTING

| 5.1  | OVERV  | 'IEW      | EW 5–2                                |      |

|------|--------|-----------|---------------------------------------|------|

| 5.2. | THE FI | TTING PRO | DCESS                                 | 5–3  |

|      | 5.2.1  | INITIALIZ | ATION                                 | 5–3  |

|      | 5.2.2  | BLOCK P   | ARTITIONING                           | 5–3  |

|      | 5.2.3  | RESOUR    | CE ASSIGNMENT                         | 5–4  |

| 5.3  | DESIG  | NING TO F | IT                                    | 5–5  |

|      | 5.3.1  | METHOD    | OLOGY                                 | 5–6  |

|      | 5.3.2  | ANALYZE   | E DEVICE RESOURCES                    | 5–7  |

|      |        | 5.3.2.1   | Clock Signals                         | 5–8  |

|      |        | 5.3.2.2   | Set/Reset Signals                     | 5–8  |

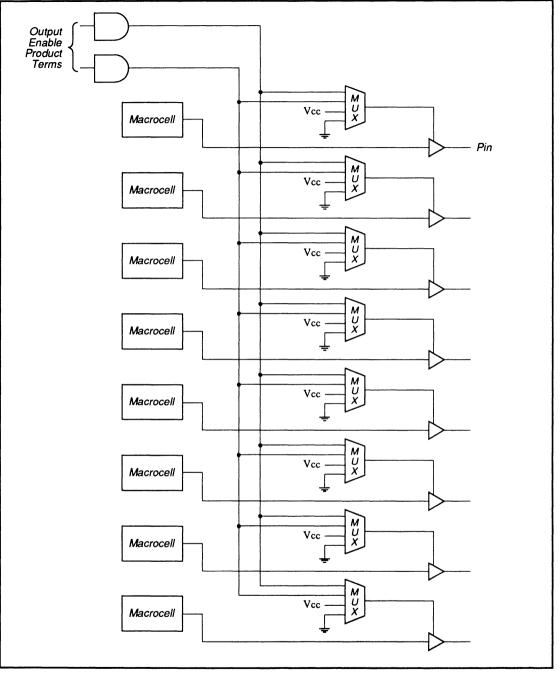

|      |        | 5.3.2.3   | Macrocells and I/O Pins               | 5–9  |

|      |        | 5.3.2.4   | Product Terms                         | 5–9  |

|      |        | 5.3.2.5   | Interconnection Resources             | 5–10 |

|      | 5.3.3  | ASSIGNI   | NG PIN AND NODE LOCATIONS             | 5–11 |

|      |        | 5.3.3.1   | Large Logic Functions                 | 5–13 |

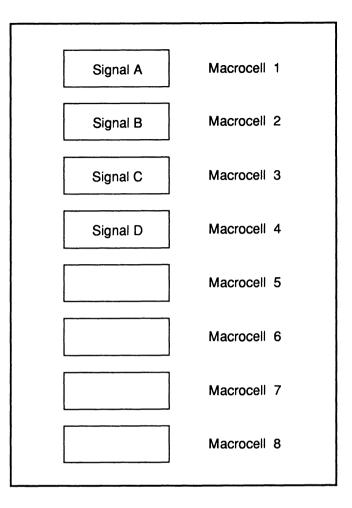

|      |        | 5.3.3.2   | Large Functions at the End of a Block |      |

|      |        | 5.3.3.3   | Adjacent Macrocell Use                |      |

|      | 5.3.4  | GROUPI    | NG LOGIC                              | 5–15 |

| 5–19<br>                           |

|------------------------------------|

|                                    |

| 5–21<br>5–21<br>5–22               |

| 5–21<br>                           |

|                                    |

|                                    |

| 5_23                               |

|                                    |

| Jsage Checks5–23                   |

|                                    |

|                                    |

| 5–25                               |

|                                    |

|                                    |

|                                    |

|                                    |

|                                    |

|                                    |

|                                    |

|                                    |

| rnings 5–35                        |

|                                    |

| Measure, Warning F120 5–37         |

| All Signals into Blocks, Error<br> |

| rror 6105–41                       |

| Connected, Error F6005–47          |

| Congested), Error F590 5–51        |

| sible Solution, Error F6205–54     |

| ogic Complexity 5–55               |

| 5–56                               |

| <u>=</u> 5–57                      |

|                                    |

|                                    |

|                                    |

|                                    |

#### **CHAPTER 6: SIMULATION**

| 6.1                            | OVERV  | ERVIEW    |                               |      |

|--------------------------------|--------|-----------|-------------------------------|------|

| 6.2 CREATING A SIMULATION FILE |        |           |                               | 6–3  |

|                                | 6.2.1  | SIMULATI  | ON COMMAND SUMMARY            | 6–3  |

|                                | 6.2.2  | SIMULATI  | ON SEGMENT VS. AUXILIARY FILE | 6–5  |

|                                | 6.2.3  | CONSIDE   | RATIONS                       |      |

|                                |        | 6.2.3.1   | Flip-Flops                    | 6–8  |

|                                |        | 6.2.3.2   | Internal Nodes                | 6–8  |

|                                |        | 6.2.3.3   | Latches                       | 6–9  |

|                                |        | 6.2.3.4   | Output Enable                 | 6–9  |

|                                |        | 6.2.3.5   | Preloaded Registers           | 6–9  |

|                                |        | 6.2.3.6   | Verified Signal Values        | 6–10 |

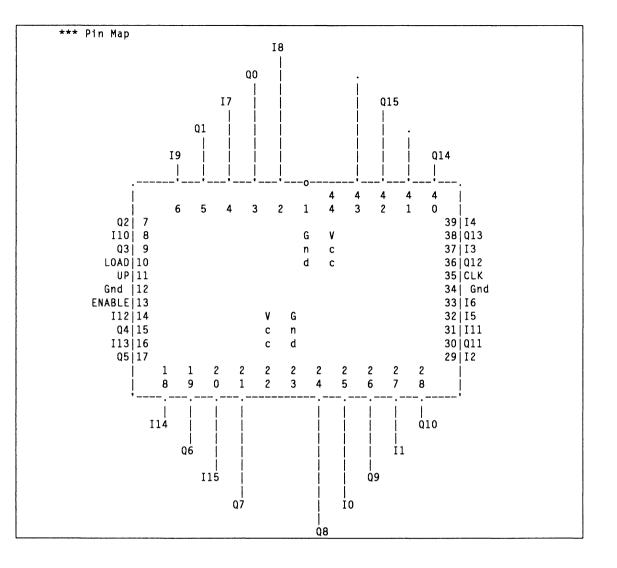

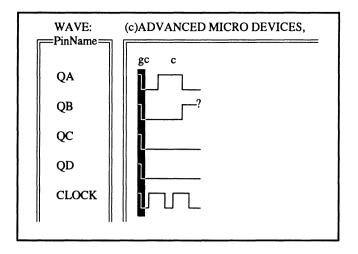

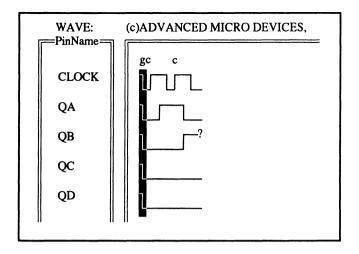

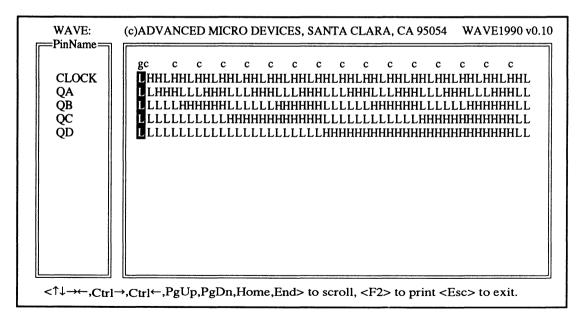

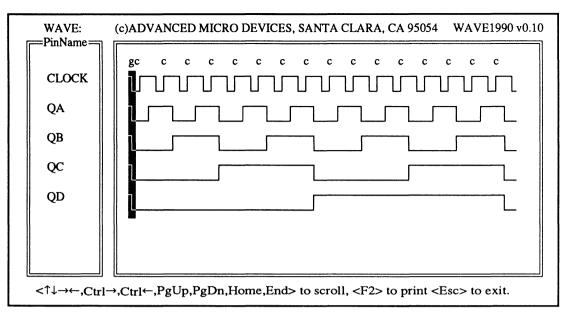

| 6.3                            | VIEWIN | G SIMULAT | TION RESULTS                  | 6–11 |

|                                | 6.3.1  | HISTORY   | FILE                          | 6–11 |

|                                | 6.3.2  | TRACE FI  | LE                            | 6–12 |

| 6.4                            | USING  | SIMULATIC | N CONSTRUCTS                  | 6–15 |

|                                | 6.4.1  | FOR LOO   | P                             | 6–15 |

|                                | 6.4.2  | WHILE LO  | OP                            | 6–15 |

|                                | 6.4.3  | IF-THEN-E | ELSE                          | 6–16 |

| 6.5                            | DESIGN | N EXAMPLE | S                             | 6–17 |

|                                | 6.5.1  | BOOLEAN   | EQUATION DESIGN               | 6–17 |

|                                | 6.5.2  | STATE-M/  | ACHINE DESIGN                 | 6–20 |

|                                |        |           |                               |      |

# **MACH Design Workbook**

### PREFACE

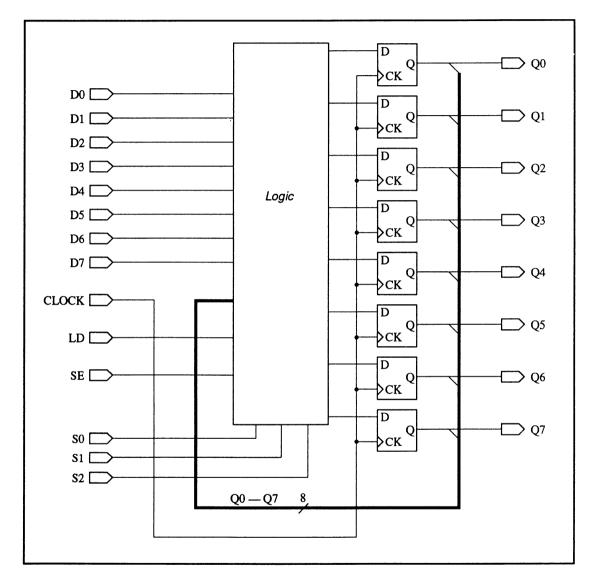

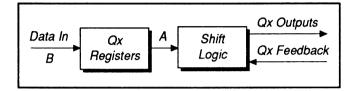

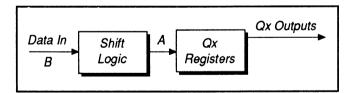

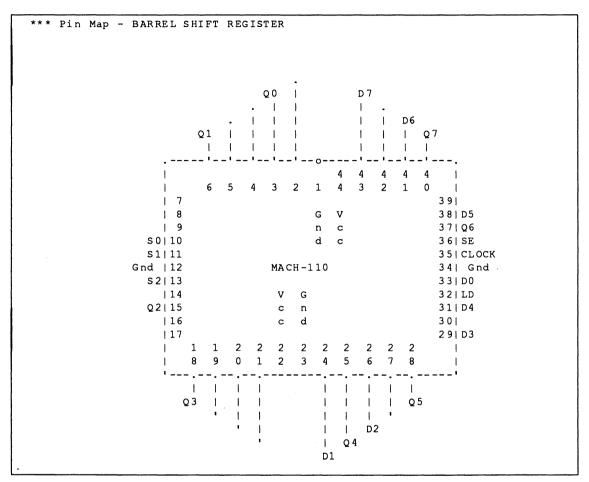

| 1     | 8-BIT BARREL SHIFT REGISTER:                        |

|-------|-----------------------------------------------------|

|       | A DESIGN WITH NUMEROUS INTERCONNECTS                |

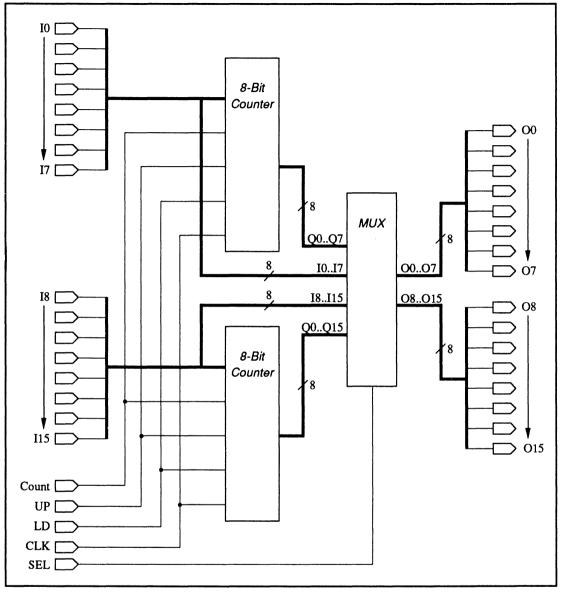

| 2     | TWO 8-BIT COUNTERS WITH A MUX:                      |

|       | A DESIGN WITH HIGH DEVICE-RESOURCE REQUIREMENTS 2-1 |

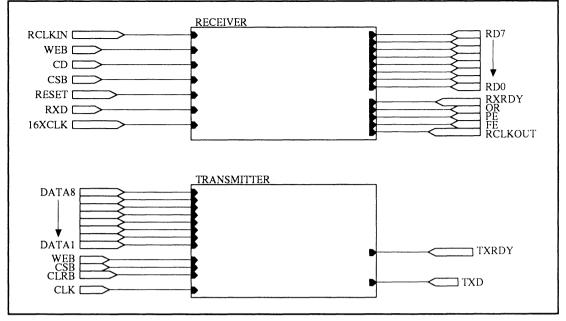

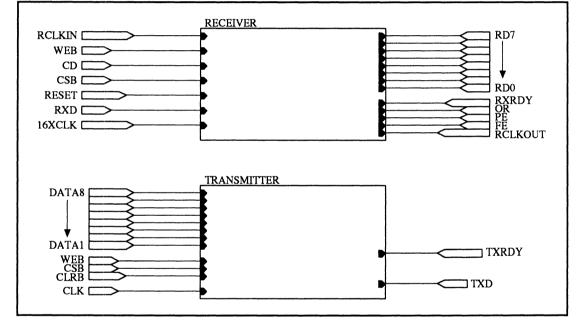

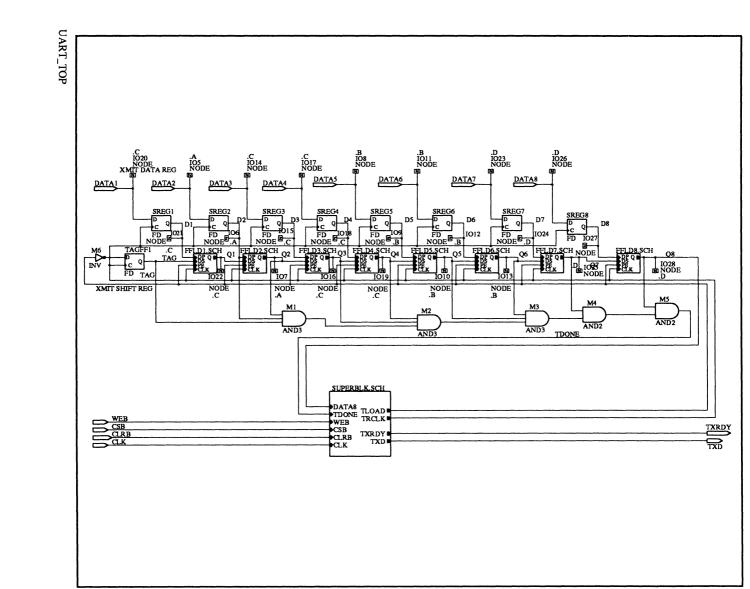

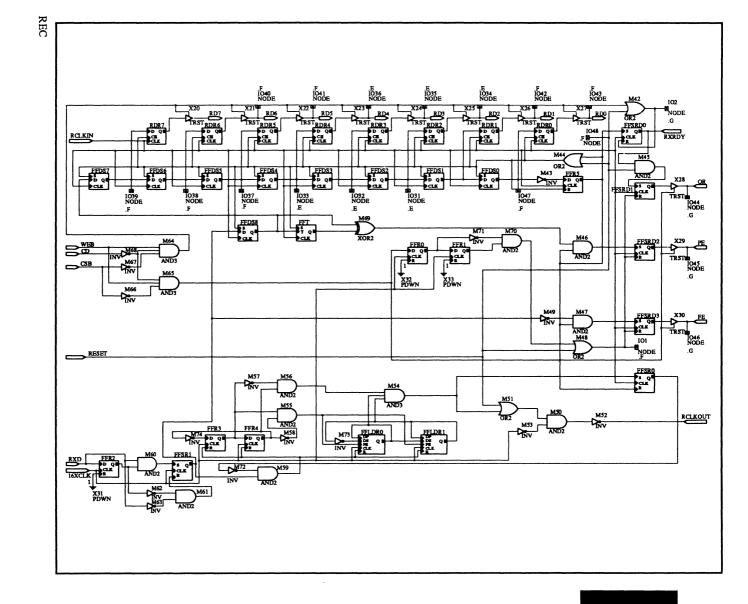

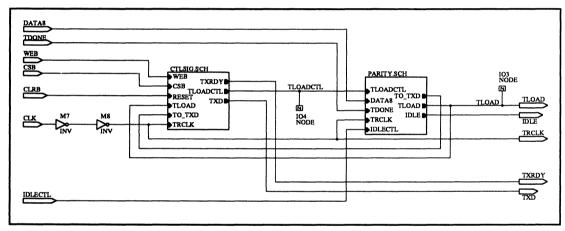

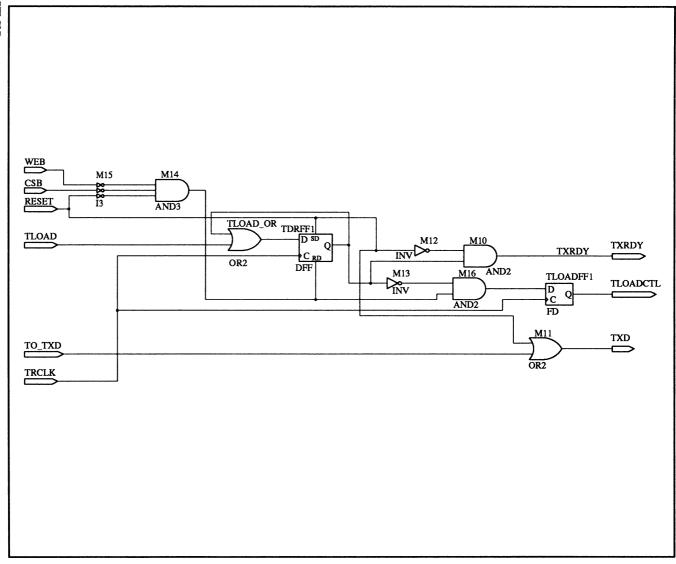

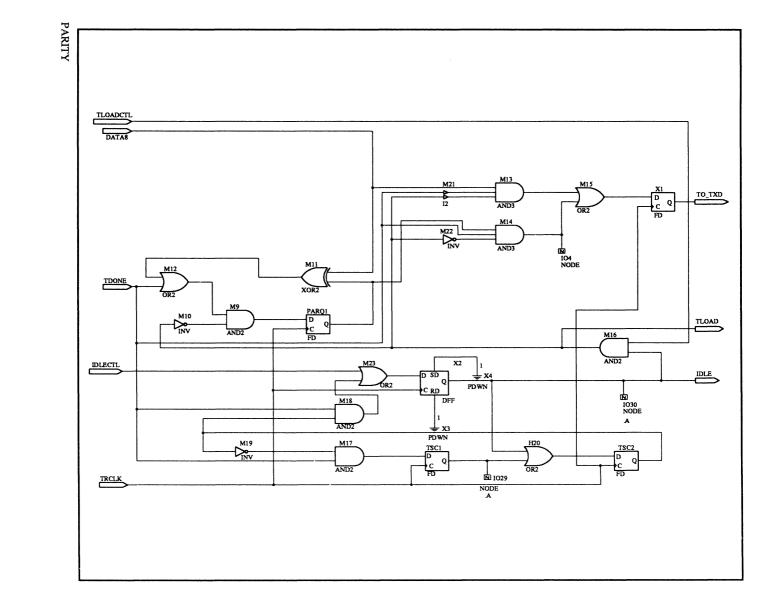

| 3     | UNIVERSAL ASYNCHRONOUS RECEIVER / TRANSMITTER:      |

|       | A DESIGN WITH SIGNAL GROUPING REQUIREMENTS          |

| INDEX | l-1                                                 |

# VOLUME 2 - Reference Guide

# SECTION III: LIBRARY REFERENCE

### **CHAPTER 7: INTRODUCTION**

| 7.1 | MACH I | LIBRARY OVERVIEW      | 7–2  |

|-----|--------|-----------------------|------|

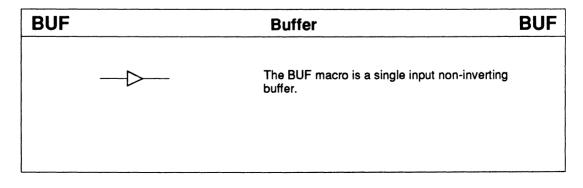

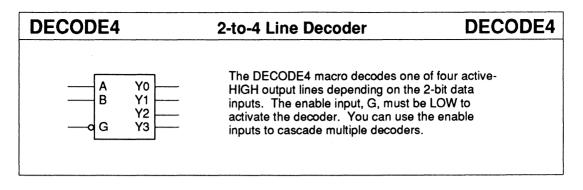

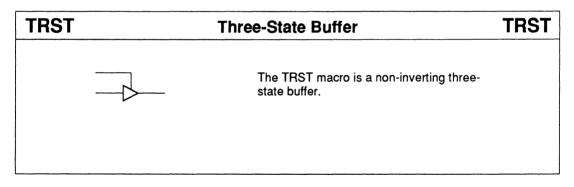

|     | 7.1.1  | BUFFER MACROS         | 7–2  |

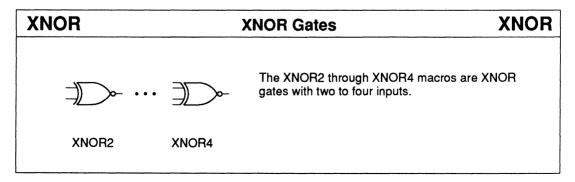

|     | 7.1.2  | COMBINATORIAL MACROS  | 7–4  |

|     | 7.1.3  | SINGLE-PIN MACROS     | 7–4  |

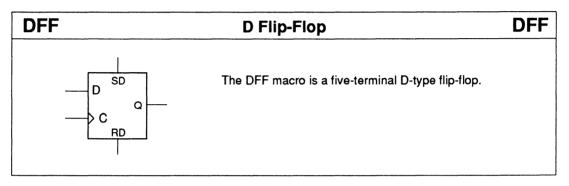

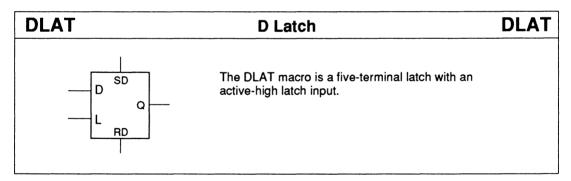

|     | 7.1.4  | STORAGE MACROS        | 7–6  |

|     | 7.1.5  |                       | 7–8  |

| 7.2 | LIBRAF | RY CONSIDERATIONS     | 7–9  |

|     | 7.2.1  | DESIGN EXAMPLES       | 7–9  |

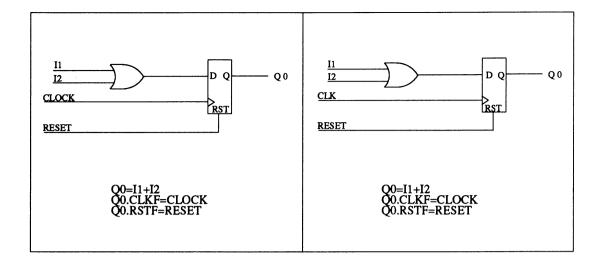

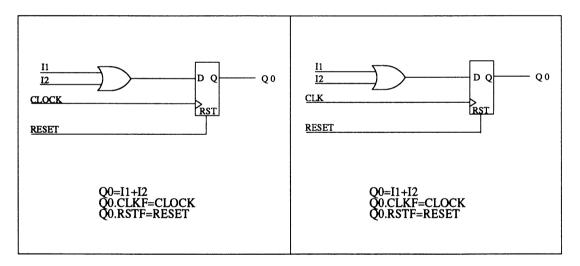

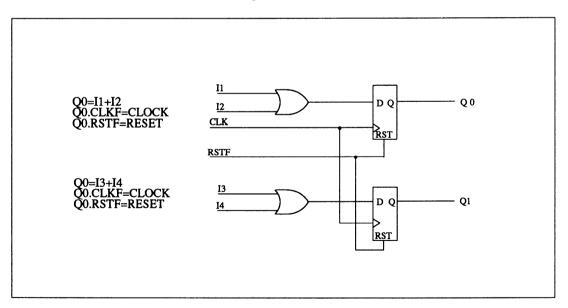

|     |        | 7.2.1.1 Example 1     | 7–10 |

|     |        | 7.2.1.2 Example 2     |      |

|     |        | 72.1.3 Example 3      |      |

|     | 7.2.2  | LATCH MACROS          | 7–15 |

|     | 7.2.3  | MINIMIZATION          | 7–15 |

|     | 7.2.4  | REFERENCE DESIGNATORS | 7–15 |

|     | 7.2.5  | SIGNAL NAMES          | 7–16 |

| 7.3 | ANNOT  | ATED DATASHEET        | 7–17 |

### CHAPTER 8: MACRO AND SCHEMATIC DATASHEETS

| QUICK REFERENCE |  |

|-----------------|--|

|                 |  |

| DISCO           |  |

# SECTION IV: SOFTWARE REFERENCE

### CHAPTER 9: MENUS AND COMMANDS

| OVERV | IEW                     |                                                                                 | 9-2      |

|-------|-------------------------|---------------------------------------------------------------------------------|----------|

| 9.1.1 | FEATURE                 | S                                                                               | 9–3      |

| 9.1.2 | CONVENT                 | IONS                                                                            | 95       |

|       |                         |                                                                                 |          |

|       |                         |                                                                                 |          |

|       |                         |                                                                                 |          |

|       |                         |                                                                                 |          |

|       | 9.1.1<br>9.1.2<br>COMMA | 9.1.1 FEATURES<br>9.1.2 CONVENT<br>COMMANDS AND 0<br>9.2.1 FILE MENU<br>9.2.1.1 | OVERVIEW |

PALASM 4 USER'S MANUAL

|       | 9.2.1.3  | Merge Design Files9-16                |

|-------|----------|---------------------------------------|

|       | 9.2.1.4  | Change Directory9-32                  |

|       | 9.2.1.5  | Delete Specified Files9-33            |

|       | ,9.2.1.6 | Set Up                                |

|       | 9.2.1.7  | Go To System                          |

|       | 9.2.1.8  | Quit                                  |

| 9.2.2 | EDIT MEI | NU                                    |

|       | 9.2.2.1  | Text File9-49                         |

|       | 9.2.2.2  | Schematic File9–50                    |

|       | 9.2.2.3  | Control File for Schematic Design9-50 |

|       | 9.2.2.4  | Auxiliary Simulation File9-51         |

|       | 9.2.2.5  | Other File                            |

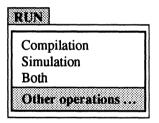

| 9.2.3 | RUN MEN  | NU                                    |

|       | 9.2.3.1  | Compile 9–53                          |

|       | 9.2.3.2  | Simulation                            |

|       | 9.2.3.3  | Both 9–55                             |

|       | 9.2.3.4  | Other Operations9-55                  |

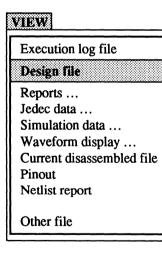

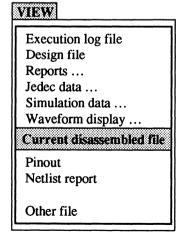

| 9.2.4 | VIEW ME  | NU                                    |

|       | 9.2.4.1  | Execution Log File9-61                |

|       | 9.2.4.2  | Design File9-61                       |

|       | 9.2.4.3  | Reports                               |

|       | 9.2.4.4  | JEDEC Data                            |

|       | 9.2.4.5  | Simulation Data                       |

|       | 9.2.4.6  | Waveform Display                      |

|       | 9.2.4.7  | Current Disassembled File             |

|       | 9.2.4.8  | Pinout                                |

|       | 9.2.4.9  | Netlist Report9–67                    |

|       | 9.2.4.10 | Other File                            |

| 9.2.5 | DOWNLC   | 0–68 MENU                             |

| 9.2.6 | DOCUME   | ENTATION MENU                         |

|       | 9.2.6.1  | Index of Topics                       |

|       | 9.2.6.2  | Language Reference9–70                |

|       | 9.2.6.3  | Help On Errors                        |

| 9.2.7 | [F1] FOR | HELP                                  |

|       |          |                                       |

### CHAPTER 10: LANGUAGE REFERENCE

| OVERVIEW 10                  | ⊢2        |

|------------------------------|-----------|

| BOOLEAN-EQUATION ELEMENTS 10 | <b></b> 4 |

| STATE-MACHINE CONSTRUCTS10   | ⊢5        |

#### PALASM 4 USER'S MANUAL

| SPECIFYING OUTPUTS IN IF-THEN-ELSE AND CASE STATEMENTS | 10–6   |

|--------------------------------------------------------|--------|

| SYNTAX AND EXAMPLES                                    | 10–12  |

| ASSIGNMENT OPERATOR                                    | 10–14  |

| AUTHOR                                                 | 10–18  |

| BOOLEAN EQUATION                                       | 10–20  |

| CASE                                                   | 10–24  |

| CHECK                                                  |        |

| CHECKQ                                                 | 10–34  |

| CHIP                                                   |        |

| .CLKF                                                  | 10–40  |

| CLKF                                                   | 10–44  |

| CLOCKF                                                 |        |

| .CMBF                                                  | 10–48  |

| COMBINATORIAL                                          |        |

| COMMENT                                                |        |

| COMPANY                                                |        |

| CONDITIONS                                             |        |

| DATE                                                   | 10–60  |

| DECLARATION SEGMENT                                    | 10–62  |

| DEFAULT_BRANCH                                         | 10–66  |

| DEFAULT_OUTPUT                                         | 10–70  |

| EQUATIONS SEGMENT                                      |        |

| EXPRESSION                                             |        |

| FLOATING PINS AND NODES                                |        |

| FOR-TO-DO                                              | 10–82  |

| FUNCTIONAL EQUATIONS                                   |        |

| GND                                                    |        |

| GROUP                                                  |        |

| IF-THEN-ELSE, EQUATIONS                                |        |

| IF-THEN-ELSE, SIMULATION                               |        |

| .J EQUATION                                            |        |

| .K EQUATION                                            |        |

| LATCHED                                                |        |

| LOCAL DEFAULT                                          |        |

| MACH_SEG_A                                             |        |

| MASTER_RESET                                           |        |

| MEALY_MACHINE                                          | 10–116 |

| MINIMIZE_OFF                                           |        |

| MOORE_MACHINE                                          | 10–120 |

| NODE 1                      | 0–122 |

|-----------------------------|-------|

| OPERATOR 1                  | 0–126 |

| .OUTF 1                     | 0–128 |

| OUTPUT_ENABLE 1             | 0–132 |

| OUTPUT_HOLD 1               | 0–134 |

| PAIR                        | 0–136 |

| PATTERN 1                   | 0–140 |

| PIN                         | 0–142 |

| PRELOAD1                    | 0–146 |

| .PRLD                       | 0–148 |

| PRLDF1                      | 0–150 |

| .R EQUATION                 | 0-152 |

| REGISTERED 1                | 0–154 |

| REVISION                    | 0–156 |

| .RSTF                       | 0–158 |

| .S EQUATION                 | 0–160 |

| .SETF 1                     | 0–162 |

| SETF                        | 0–164 |

| SIGNATURE                   | 0–166 |

| SIMULATION 1                | 0–170 |

| START_UP1                   | 0–172 |

| STATE1                      | 0–176 |

| STATE ASSIGNMENT EQUATION 1 | 0–180 |

| STATE EQUATIONS 1           | 0–184 |

| STATE OUTPUT EQUATION 1     | 0–188 |

| STATE TRANSITION EQUATION   | 0–192 |

| STRING 1                    | 0–194 |

| TEST1                       | 0–198 |

| .T EQUATION1                | 0–202 |

| .T1 EQUATION 1              | 0–204 |

| .T2 EQUATION 1              | 0–206 |

| TITLE 1                     | 0–208 |

| TRACE_OFF1                  | 0–210 |

| TRACE_ON 1                  | 0–212 |

| .TRST 1                     | 0–214 |

| VCC 1                       | 0–218 |

| VECTOR1                     | 0–220 |

| WHILE-DO 1                  | 0–222 |

.

| CHAPT | ER 11:  | DEVICE I   | PROGRAMMING REFERENCE                                  |

|-------|---------|------------|--------------------------------------------------------|

| 11.1  | PLD INT | RODUCTIC   | N                                                      |

|       | 11.1.1  | PLD NAMI   | NG CONVENTIONS                                         |

|       | 11.1.2  | STANDAR    | D PLD DEVICES VERSUS NON-STANDARD PLD                  |

|       |         | DEVICES    |                                                        |

| 11.2  | DEVICE  | FEATURE    | CROSS-REFERENCE 11-4                                   |

| 11.3  | GENER   | AL PLD LAN | IGUAGE SYNTAX 11–6                                     |

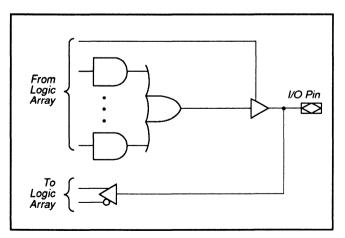

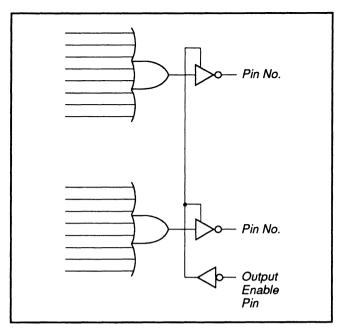

|       | 11.3.1  | OUTPUT-E   | NABLE CONTROL 11–7                                     |

|       |         | 11.3.1.1   | Common External Output-Enable Pin11-7                  |

|       |         | 11.3.1.2   | Individual Product Term Control 11-7                   |

|       |         | 11.3.1.3   | Common External Pin or Individual Product Term Control |

|       | 11.3.2  | CLOCK CC   | DNTROL11–10                                            |

|       |         | 11.3.2.1   | Common External Clock Control 11-10                    |

|       |         | 11.3.2.2   | Individual Product Term Clock Control 11-11            |

|       | 11.3.3  | PRESET C   | ONTROL 11–11                                           |

|       |         | 11.3.3.1   | Individual Product Term Control 11-12                  |

|       |         | 11.3.3.2   | Global Product Term Control 11–12                      |

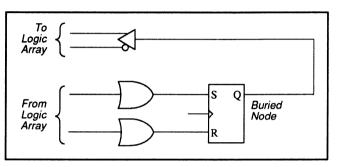

|       | 11.3.4  | RESET CC   | NTROL                                                  |

|       |         | 11.3.4.1   | Individual Product Term Control 11-13                  |

|       |         | 11.3.4.2   | Global Product Term Control 11–14                      |

|       | 11.3.5  | DEVICE PO  | OLARITY 11–15                                          |

|       |         | 11.3.5.1   | Active-Low Polarity 11-15                              |

|       |         | 11.3.5.2   | Active-High Polarity11-16                              |

|       |         | 11.3.5.3   | Programmable Polarity 11-18                            |

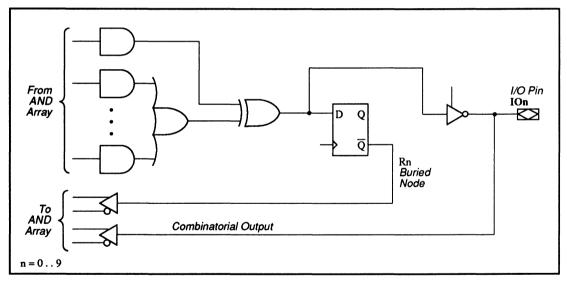

|       | 11.3.6  | COMBINA    | TORIAL LOGIC11–19                                      |

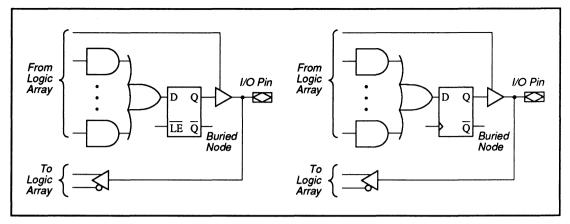

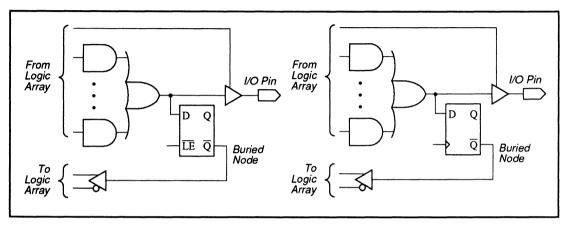

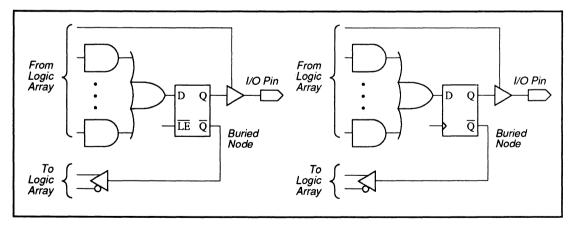

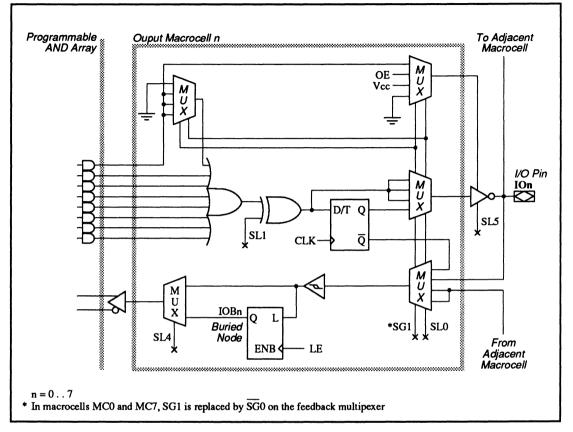

|       | 11.3.7  | REGISTER   | RED OR LATCHED LOGIC 11-20                             |

|       |         | 11.3.7.1   | D Flip-Flop 11-20                                      |

|       |         | 11.3.7.2   | SR Flip-Flop 11-21                                     |

|       |         | 11.3.7.3   | Latch                                                  |

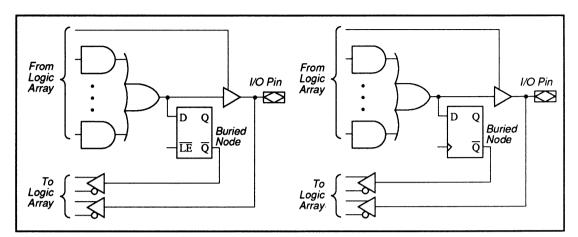

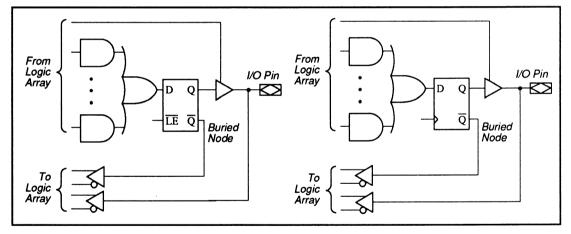

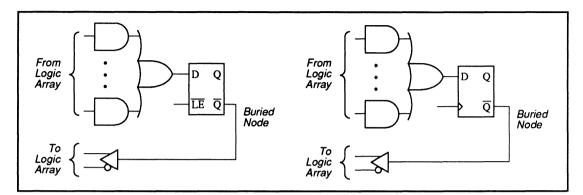

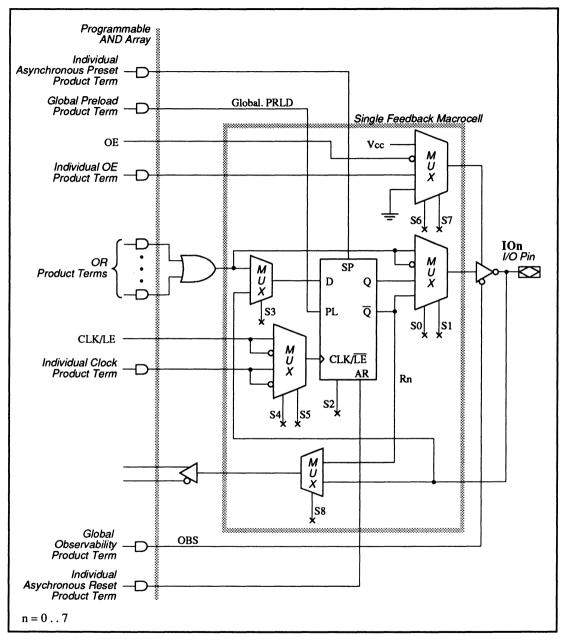

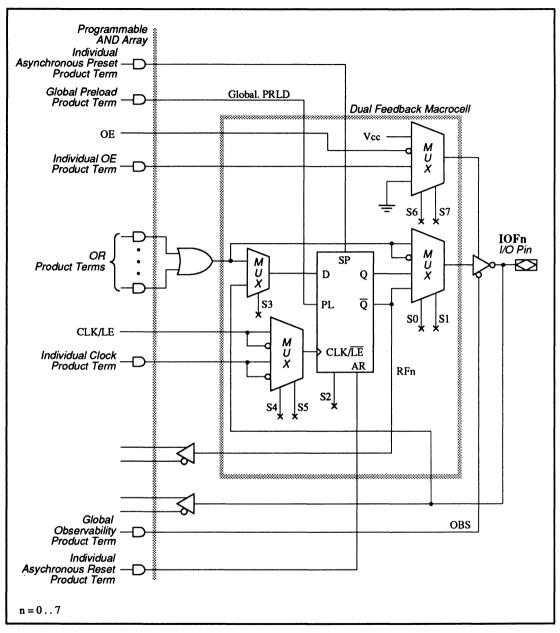

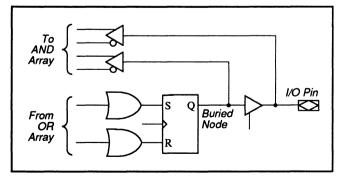

|       | 11.3.8  | FEEDBAC    | К 11–23                                                |

|       |         | 11.3.8.1   | Programmable Feedback 11-23                            |

|       |         | 11.3.8.2   | Non-Programmable Feedback 11-32                        |

|       | 11.3.9  | PRELOAD    | CONTROL 11-33                                          |

|       |         | 11.3.9.1   | Supervoltage11-33                                      |

|       |         | 11.3.9.2   | Product Term Control 11-33                             |

|       | 11.3.10 | OBSERVA    | BILITY PRODUCT TERM CONTROL 11-34                      |

|       | 11.3.11 | COMPLEN    | /ENT ARRAY 11–35                                       |

|       | 11.3.12 | ELECTRO    | NIC SIGNATURE 11–36                                    |

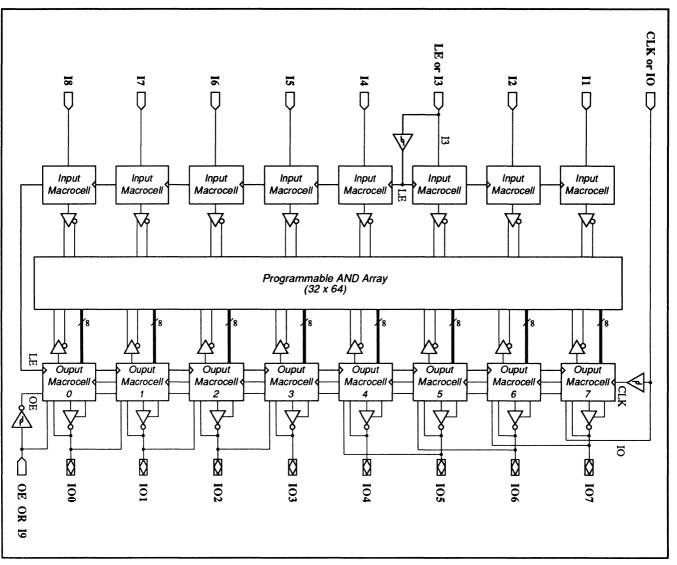

| 11.4  | PLD DE  | VICE SYNT  | TAX DATASHEETS 11–38                                   |

|      | 11.4.1 | PIN AND N | IODE DESCRIPTIONS             | 11–38  |

|------|--------|-----------|-------------------------------|--------|

|      | 11.4.2 | BLOCK AN  | ID MACROCELL DIAGRAM(S)       | 11–39  |

|      | 11.4.3 | SPECIAL F | PROGRAMMING FEATURES          |        |

|      |        | 105       |                               |        |

|      |        |           |                               |        |

|      |        |           |                               |        |

|      |        | 16V8HD    |                               |        |

|      |        | 20EG8     |                               |        |

|      |        | 20EV8     |                               |        |

|      |        | 20RA10    |                               | 11–70  |

|      |        | 22IP6     |                               | 11–74  |

|      |        | 22V10     |                               | 11–80  |

|      |        | 23S8      |                               |        |

|      |        | 26V12     |                               |        |

|      |        | 29M16     |                               | 11–96  |

|      |        | 29MA16    |                               | 11–104 |

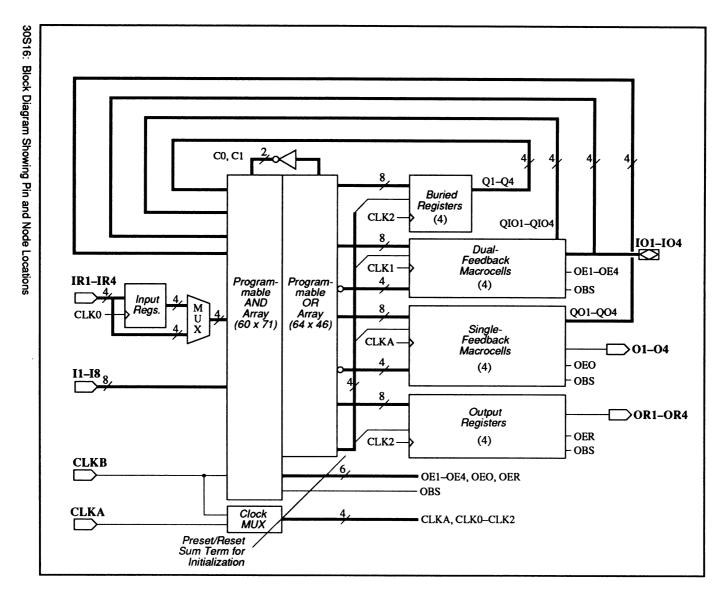

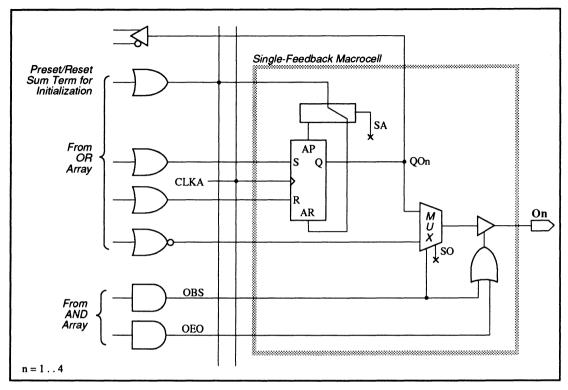

|      |        | 30S16     |                               |        |

|      |        | 32VX10    |                               | 11–130 |

|      |        | 610       |                               |        |

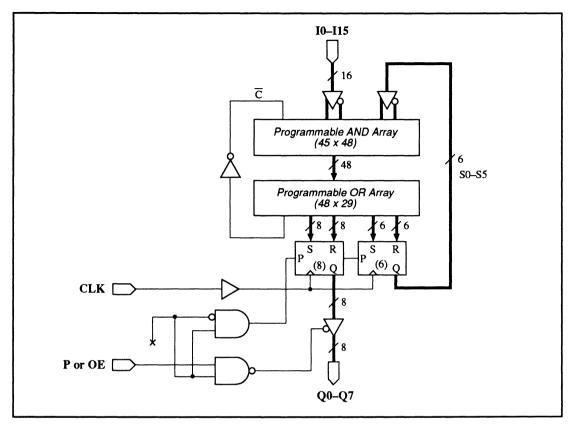

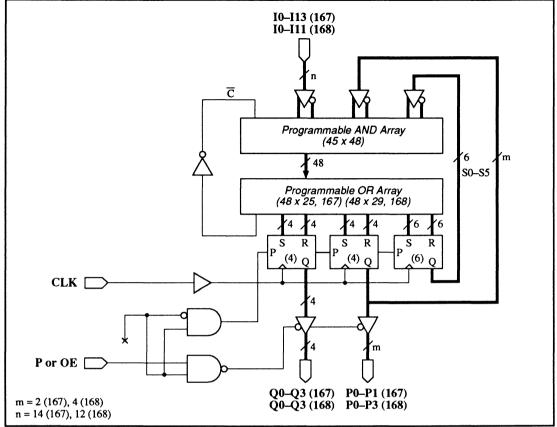

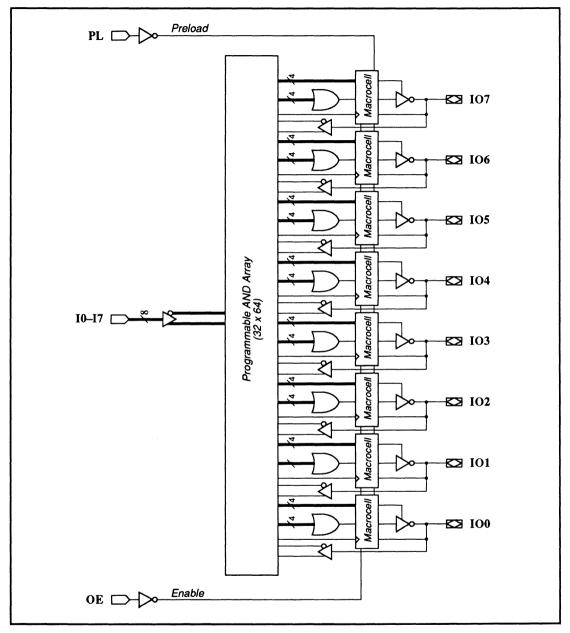

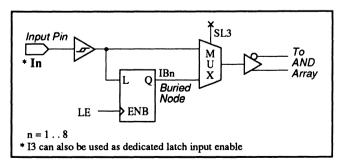

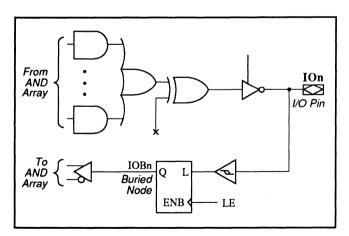

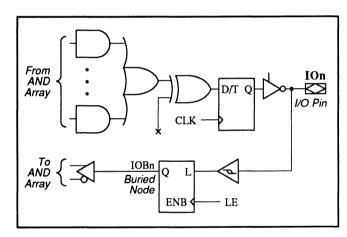

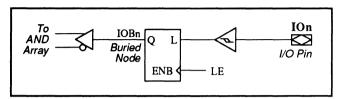

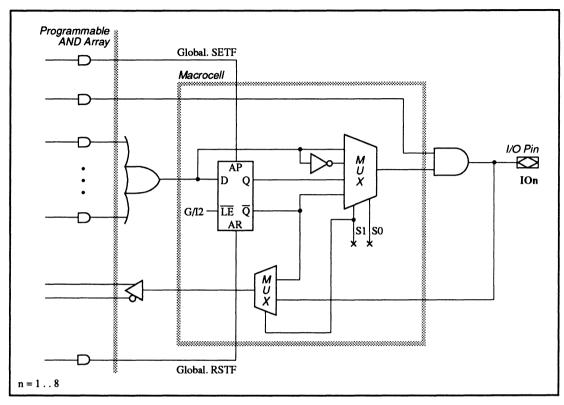

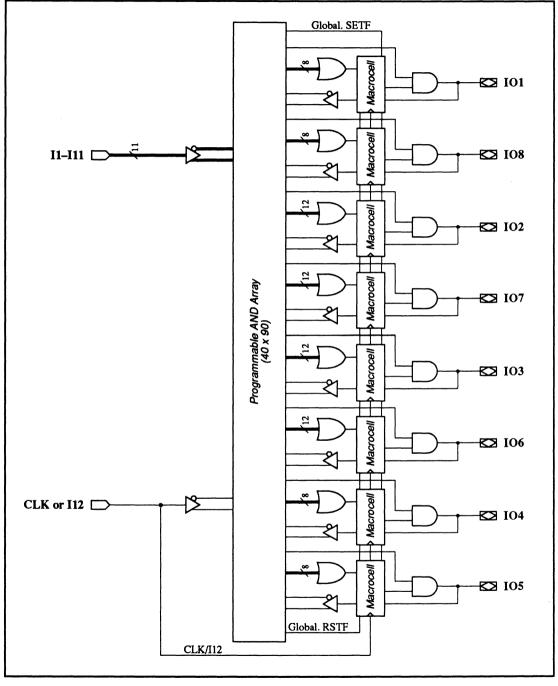

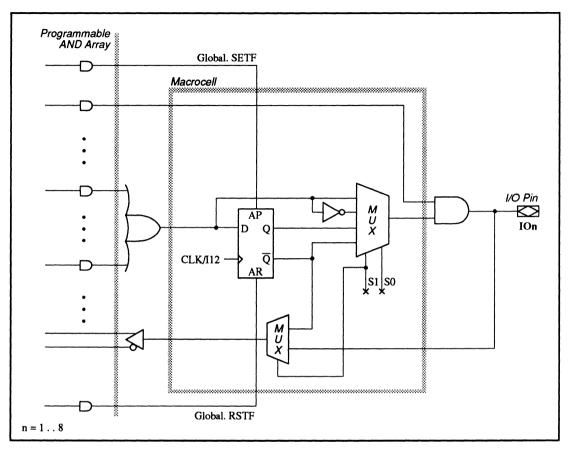

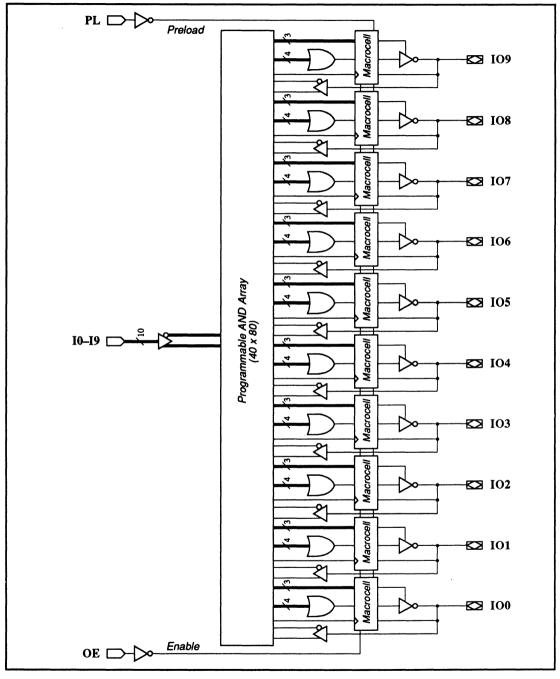

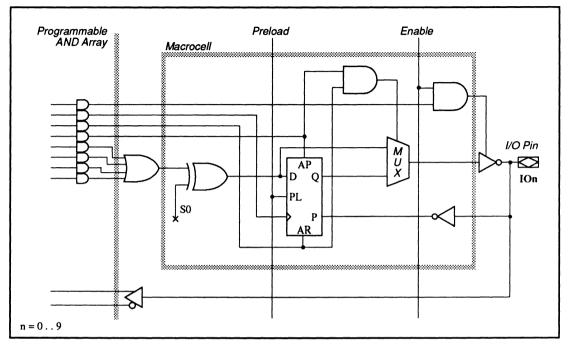

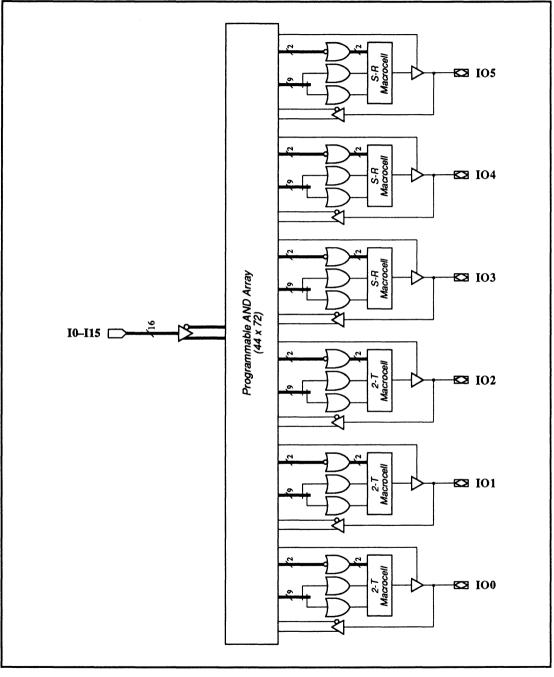

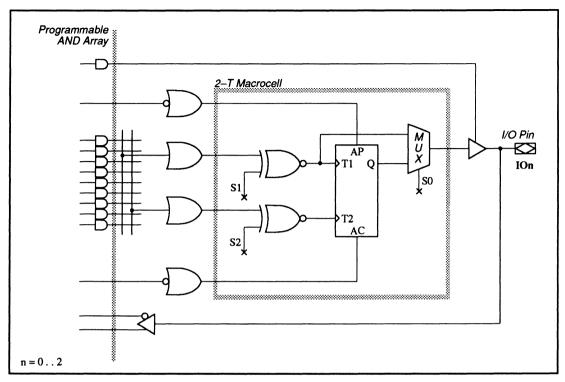

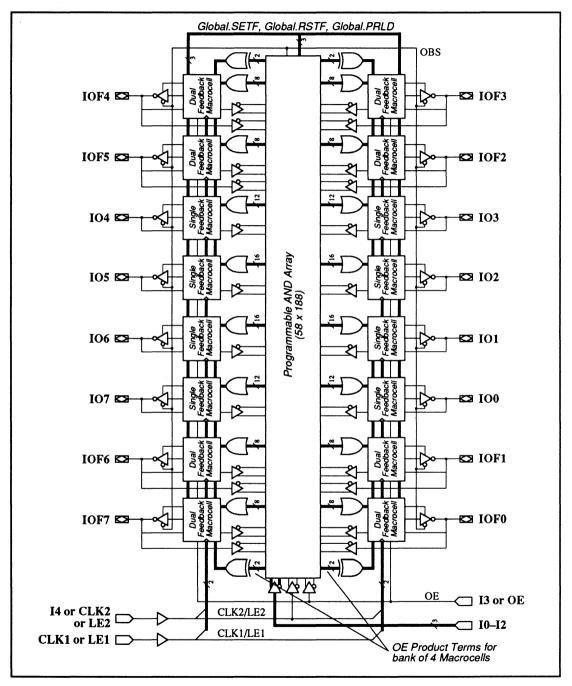

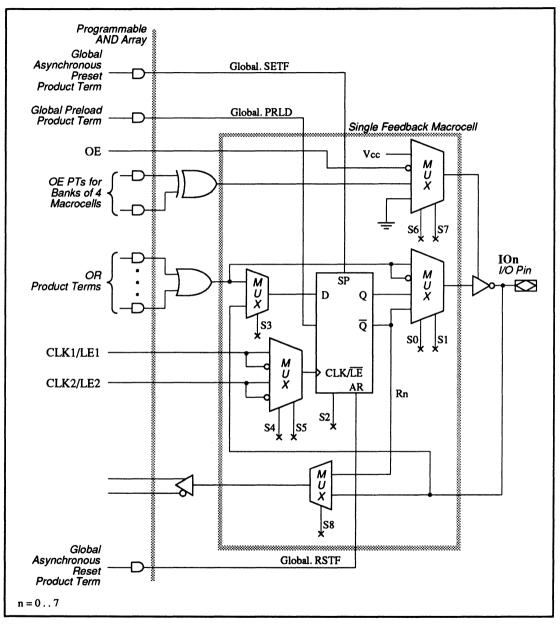

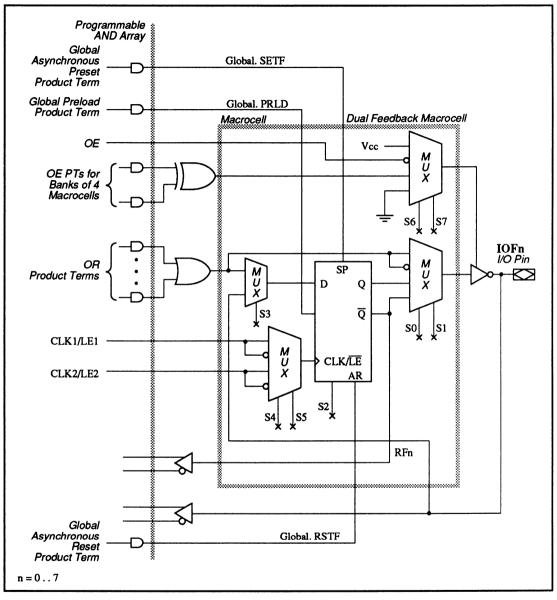

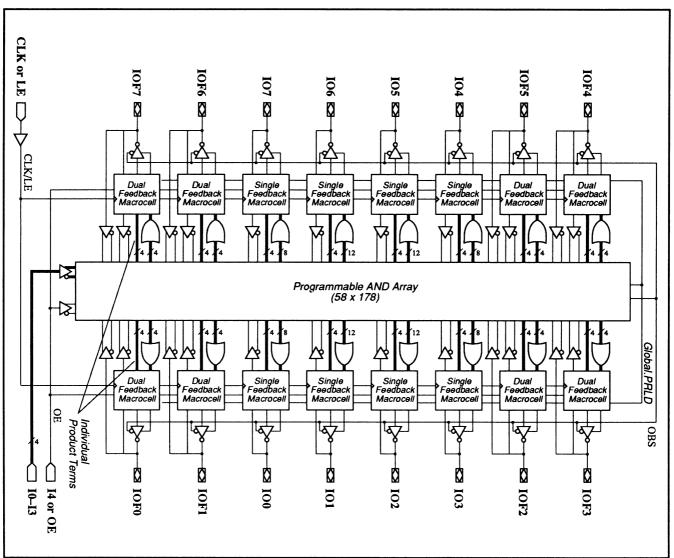

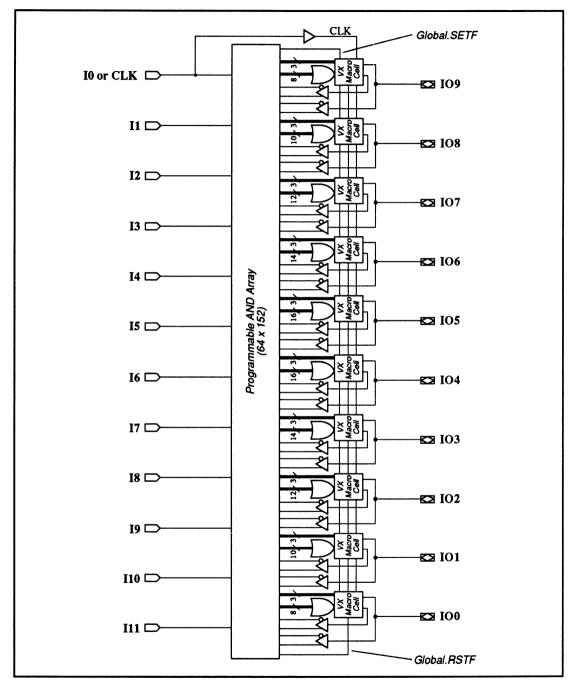

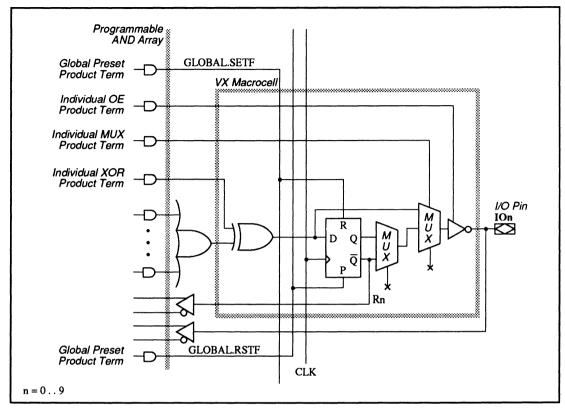

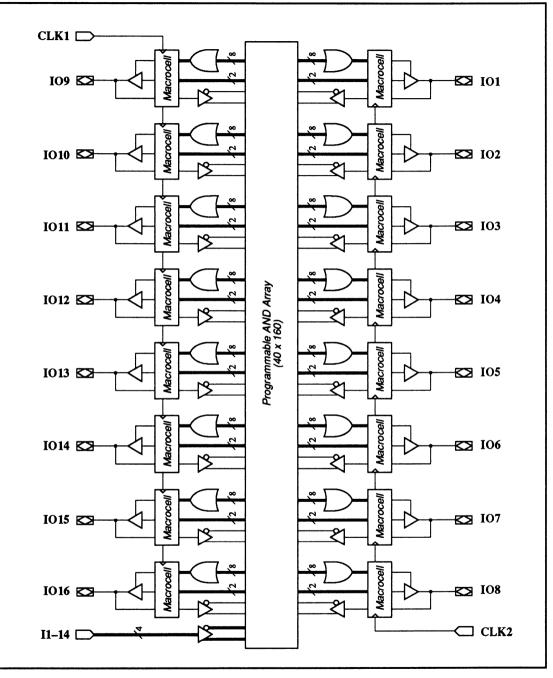

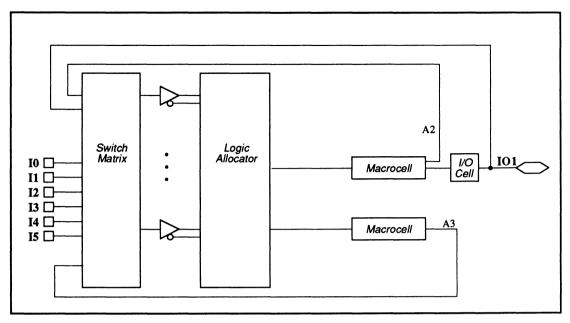

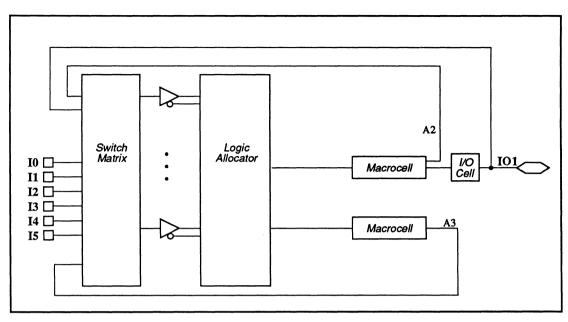

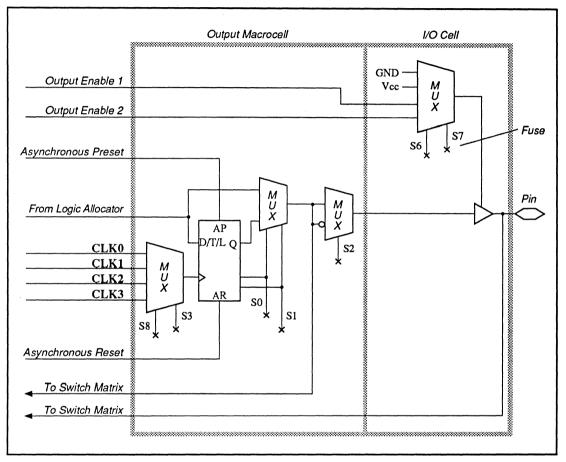

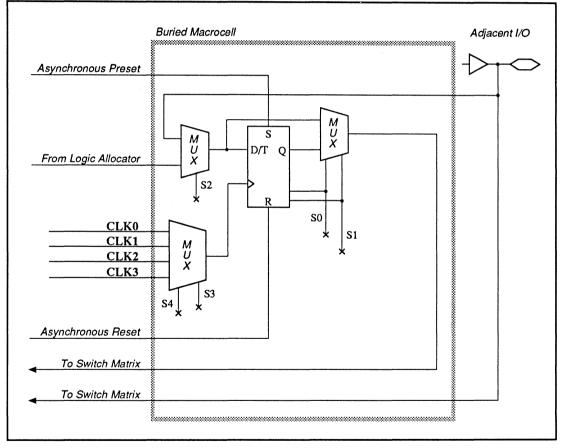

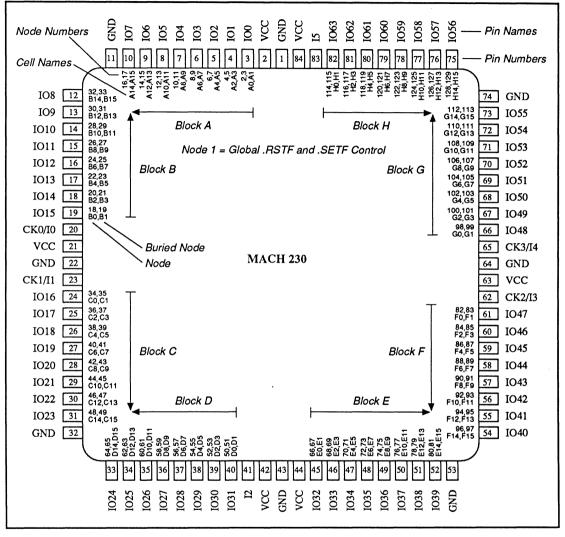

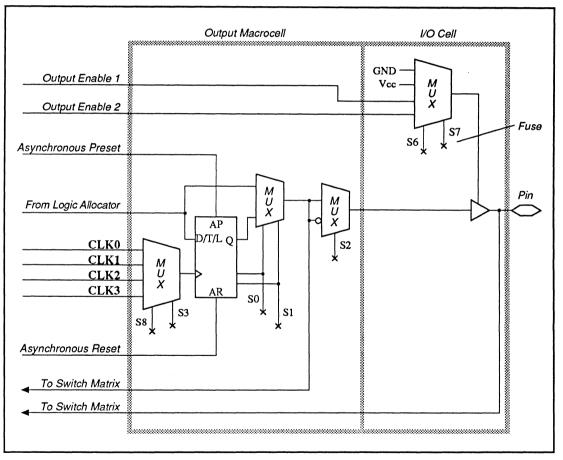

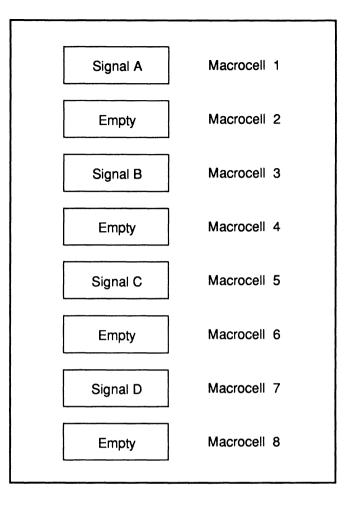

| 11.5 | MACH 1 | I AND MAC | H 2 SERIES DEVICES            | 11–156 |

|      | 11.5.1 | OVERVIE   | N                             | 11–156 |

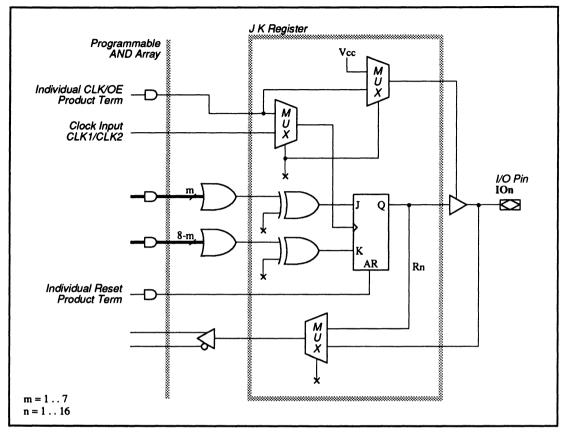

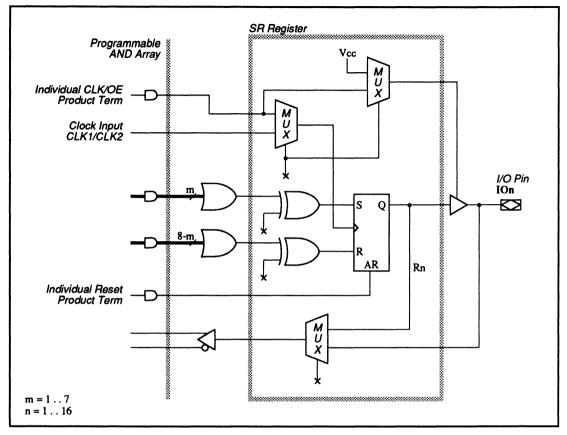

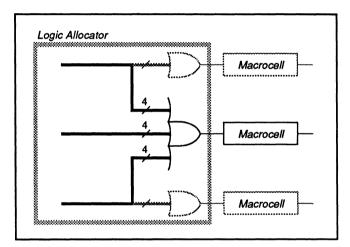

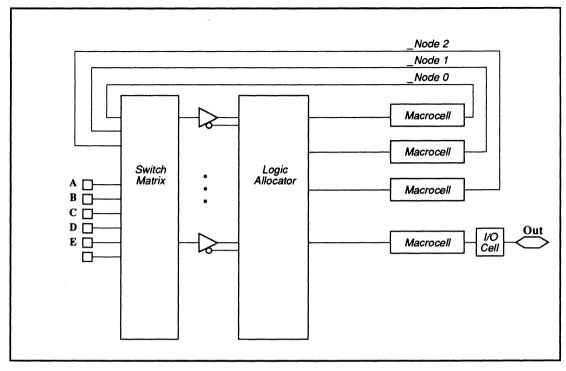

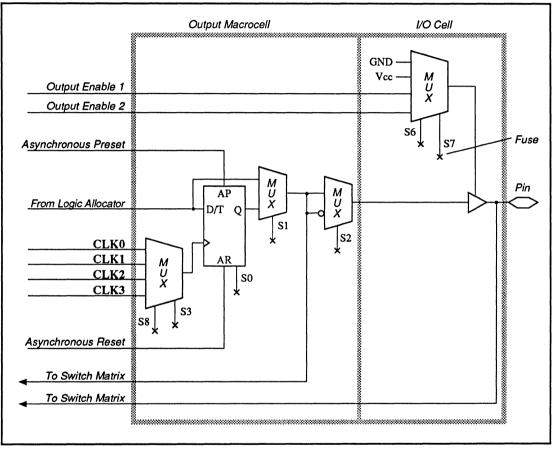

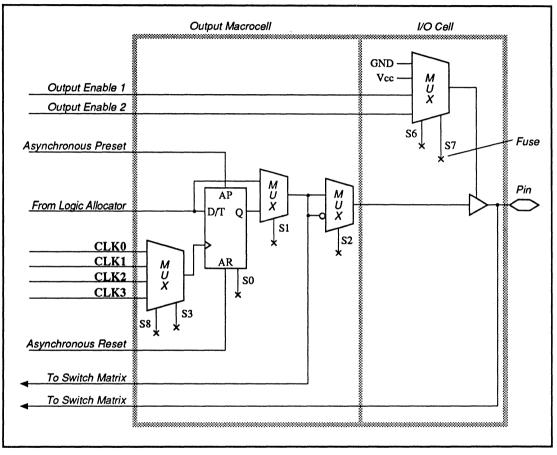

|      |        | 11.5.1.1  | Device Features               | 11–156 |

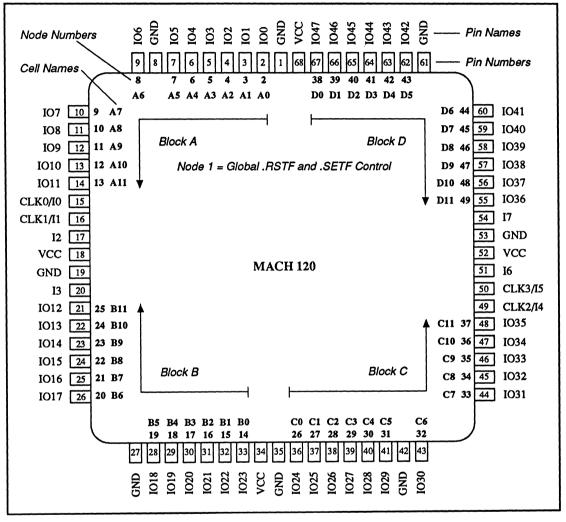

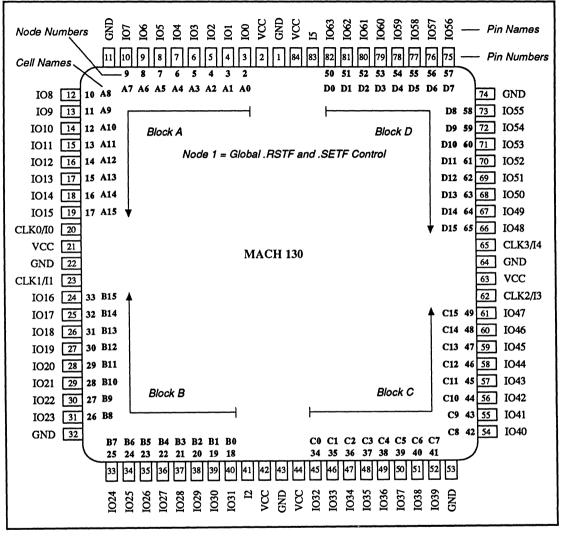

|      |        | 11.5.1.2  | Pin and Node Descriptions     | 11–157 |

|      |        | 11.5.1.3  | PALASM Programming Features   |        |

|      | 11.5.2 | SAMPLE E  | QUATIONS                      |        |

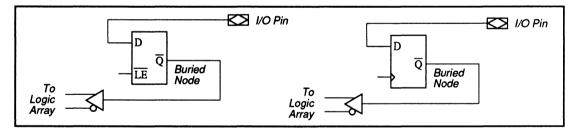

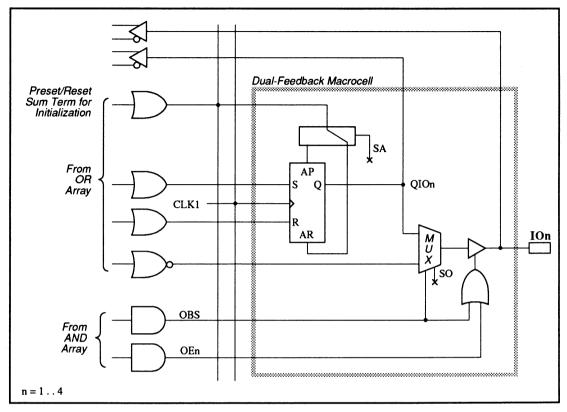

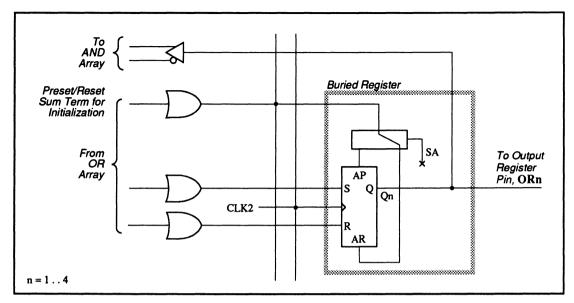

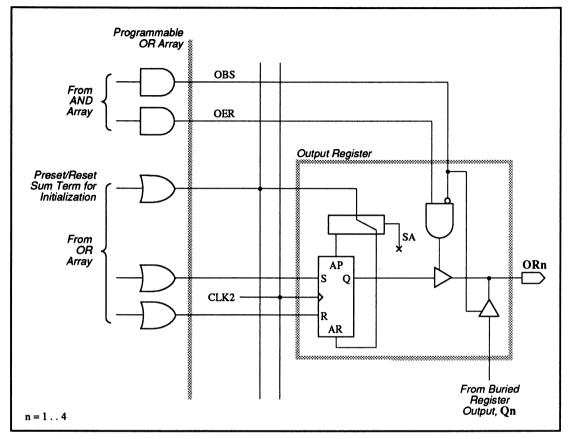

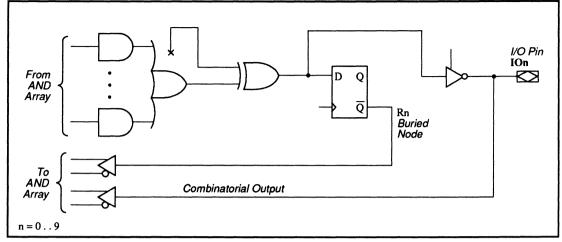

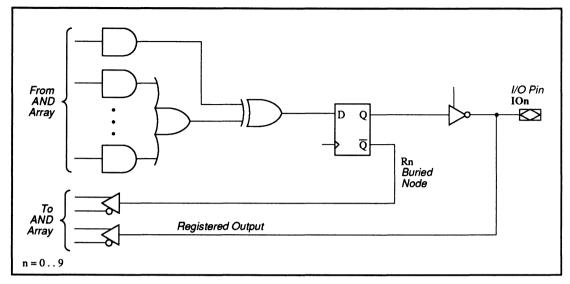

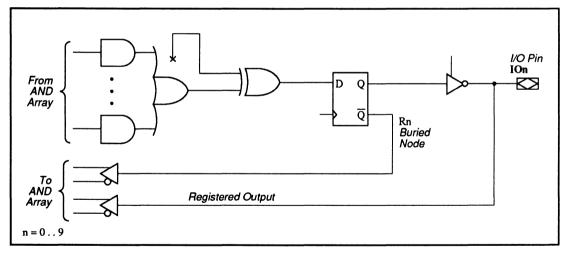

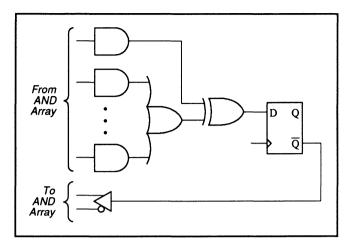

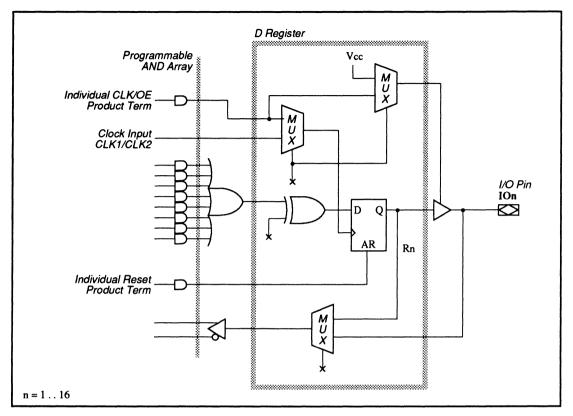

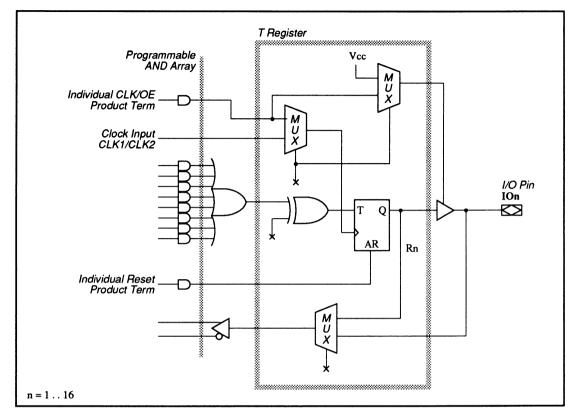

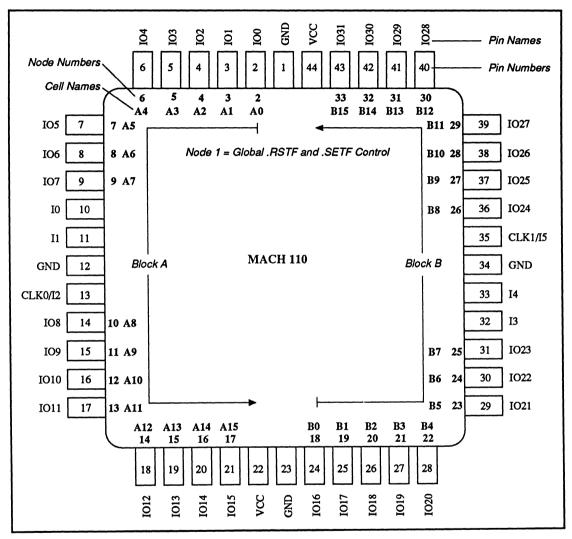

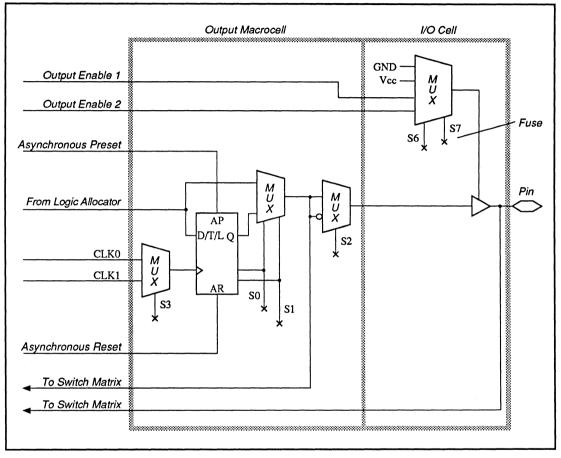

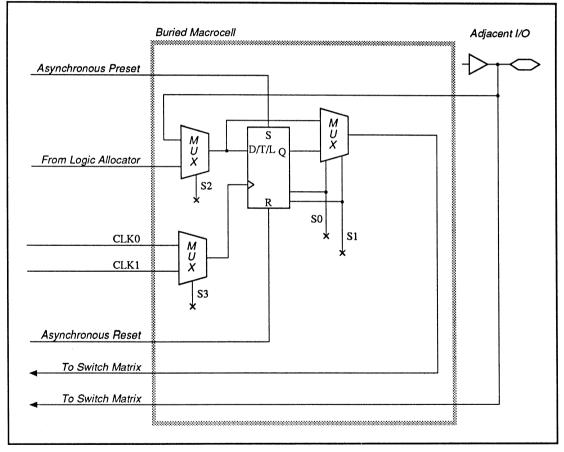

|      |        | 11.5.2.1  | I/O Cell and Macrocell        | 11–169 |

|      |        | 11.5.2.2  | Pin and Node Feedback         | 11–170 |

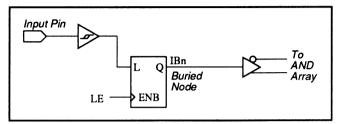

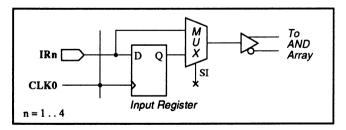

|      |        | 11.5.2.3  | Registered and Latched Inputs | 11–171 |

|      |        | MACH 110  | Device                        | 11–174 |

|      |        | MACH 120  | Device                        |        |

|      |        | MACH 130  | Device                        |        |

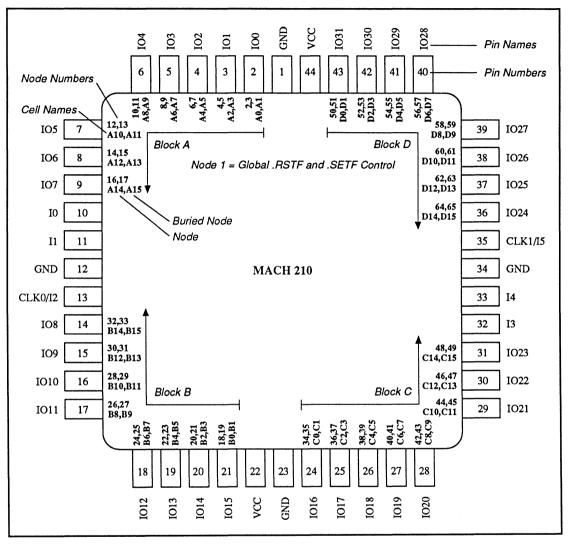

|      |        | MACH 210  | Device                        |        |

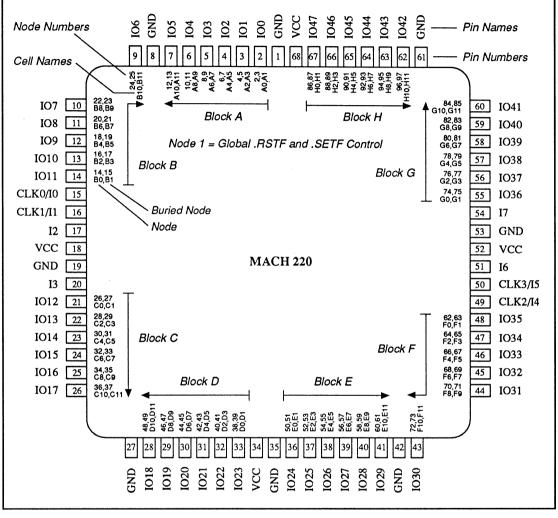

|      |        | MACH 220  | Device                        |        |

|      |        | MACH 230  | Device                        |        |

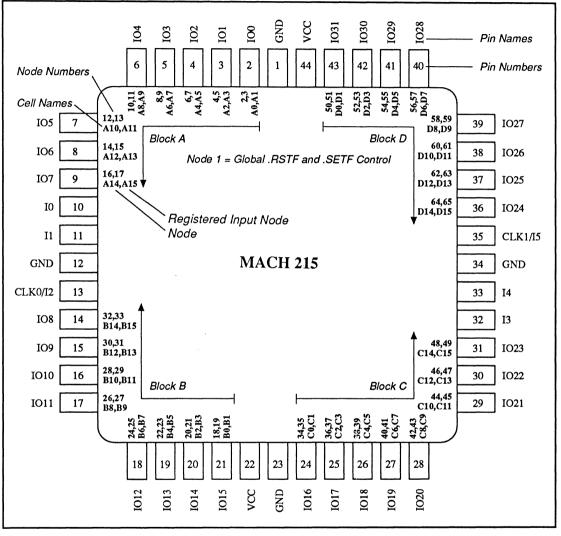

|      |        | MACH 215  | Device                        |        |

# SECTION V: APPENDICES

#### APPENDIX A: PLD TEXT EDITOR

| PLD TE | XT EDITOR    | A–1  |

|--------|--------------|------|

| A.1    | FILE MENU    | A–2  |

| A.2    | WINDOW MENU  |      |

| A.3    | BLOCK MENU   | A–4  |

| A.4    | SEARCH MENU  | A–5  |

| A.5    | PRINT MENU   |      |

| A.6    | MACRO MENU   | A–7  |

| A.7    | EDITING MENU | A–8  |

| A.8    | OTHER MENU   | A–9  |

| A.9    | QUIT MENU    | A–11 |

# SECTION VI: GLOSSARY / INDEX

#### GLOSSARY

#### INDEX

# SECTION III LIBRARY REFERENCE

- Chapter 7: Introduction

- Chapter 8: Macro and Schematic Datasheets

February 1991

# **CHAPTER 7**

# INTRODUCTION

DocVer 2.0 July 1991 PALASM 4 USER'S MANUAL SECTION III, LIBRARY REFERENCE, CHAPTER 7, INTRODUCTION

# CONTENTS

| INTF | IODUC. | TION                                  | 1  |

|------|--------|---------------------------------------|----|

| 7.1  | MACI   | H LIBRARY OVERVIEW                    | 2  |

| 7.2  | ANNO   | OTATED SCHEMATIC                      | 3  |

| 7.3  | CAPT   | FURING A SCHEMATIC                    | 6  |

|      | 7.3.1  | SPECIFYING PIN AND NODE NUMBERS       | 6  |

|      | 7.3.2  | GROUPING SIGNALS INTO A BLOCK         | 7  |

|      | 7.3.3  | TURNING MINIMIZATION OFF              |    |

|      | 7.3.4  | MANUALLY SPLITTING PRODUCT TERMS      | 8  |

|      | 7.3.5  | TERMINATING UNUSED INPUTS AND OUTPUTS | 8  |

|      | 7.3.6  |                                       |    |

|      | 7.3.7  | INTERPRETING REFERENCE DESIGNATORS    | 10 |

|      | 7.3.8  | NAMING SIGNALS                        | 10 |

| 7.4  | ANNO   | OTATED DATASHEET                      | 11 |

|      |        |                                       |    |

-

# INTRODUCTION

This chapter introduces the MACH library<sup>1</sup> and its functional elements, called macros, in four discussions.

- The overview, 7.1, introduces the categories of macros contained within the AMD-supplied library.

- The annotated schematic design discussion, 7.2, illustrates considerations for capturing a schematic and points to the corresponding descriptions in discussion 7.3.

- The capturing a schematic discussion, 7.3, describes how to use the library macros effectively to create a design using OrCAD/SDT III.

- The annotated datasheet, 7.4, provides a sample datasheet from Chapter 8, in this section, with a description of each information field.

<sup>&</sup>lt;sup>1</sup> Only the MACH family of devices is supported in the library. The library must be purchased separately from the PALASM 4 software.

# 7.1 MACH Library Overview

AMD provides over 100 commonly used logic functions as macros in the MACH library. A summary of the available macros is shown next.<sup>2</sup>

| BUFFER                      | COMBINATORIAL                           | OTHER                              | STORAGE                                              | TTL-EQUIVALENT |

|-----------------------------|-----------------------------------------|------------------------------------|------------------------------------------------------|----------------|

| MACROS                      | MACROS                                  | MACROS                             | MACROS                                               | MACROS         |

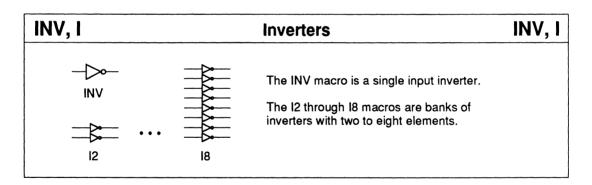

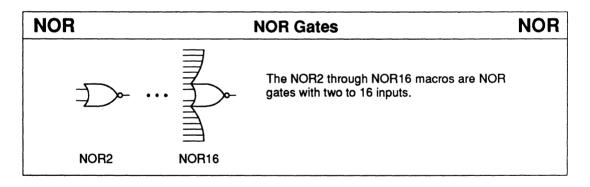

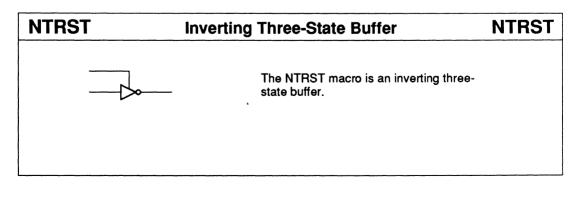

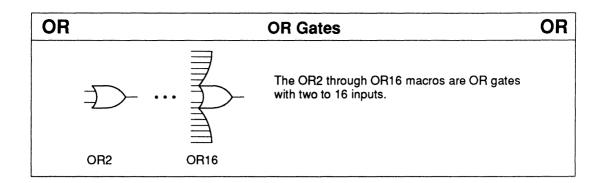

| BUF<br>INV<br>NTRST<br>TRST | AND<br>NAND<br>NOR<br>OR<br>XNOR<br>XOR | AINIT<br>NC<br>NODE<br>PDWN<br>PUP | FD<br>FT<br>LD<br>LDX<br>DFF<br>DLAT<br>DLATX<br>TFF | See Chapter 8  |

<sup>&</sup>lt;sup>2</sup> Refer to Chapter 8, in this section, for a complete list of macros, symbols, and datasheets.

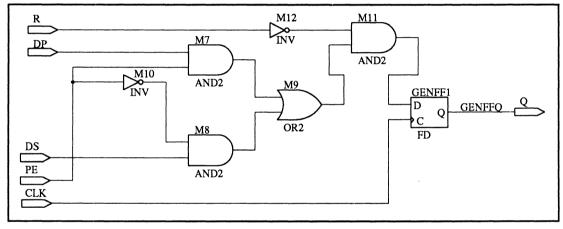

# 7.2 ANNOTATED Schematic

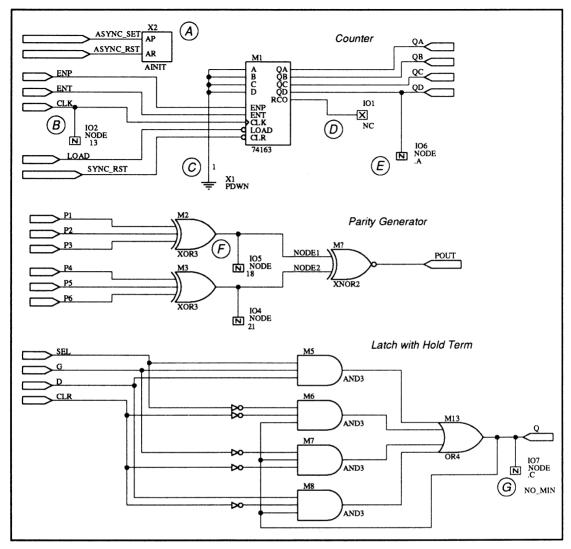

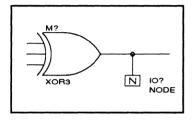

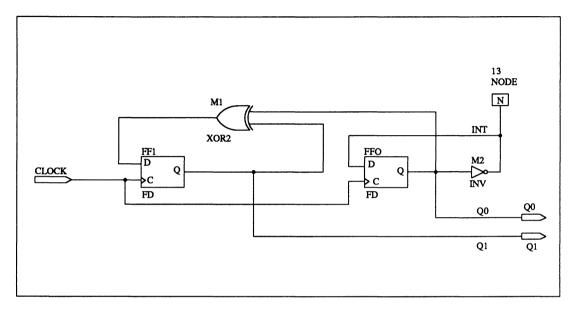

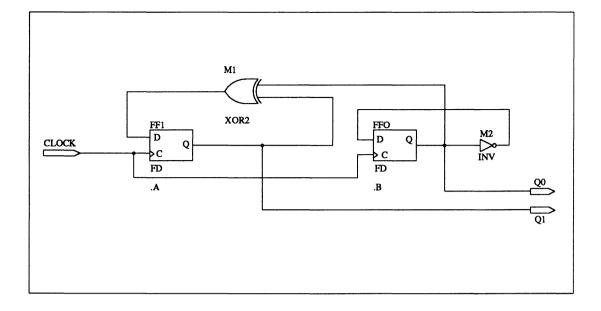

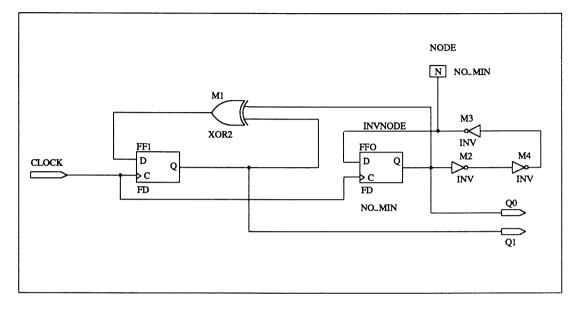

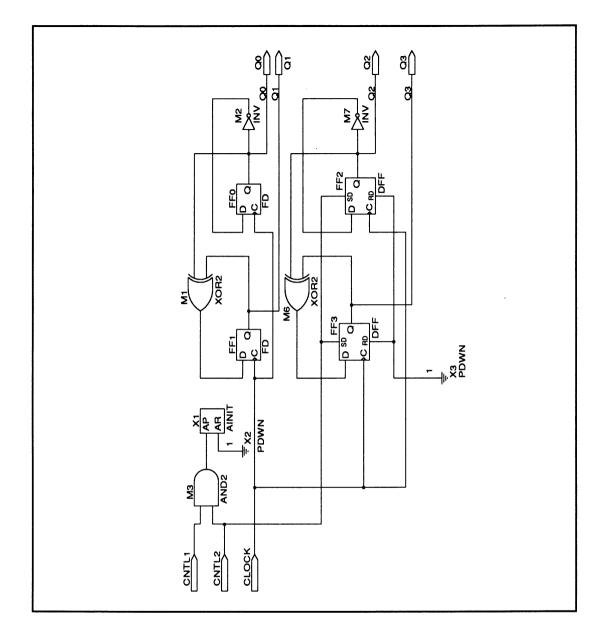

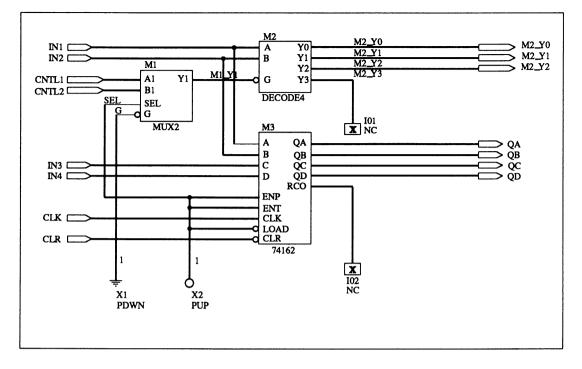

This discussion presents an annotated schematic to illustrate the features and considerations of capturing a MACH schematic design. Each lettered paragraph below corresponds to a circled letter in the next figure.

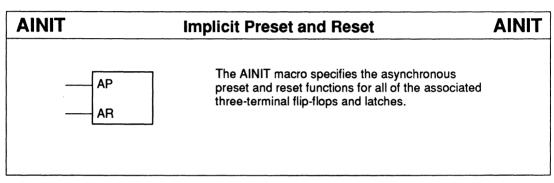

A. You use the AINIT macro to specify the asynchronous preset and reset for all three terminal storage macros in a design.

In this case, the T-type flip-flops in the 74163 are set and reset by the signals ASYNC\_SET and ASYNC\_RST. Use five-terminal storage macros to specify multiple asynchronous preset and reset functions.

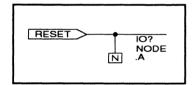

- B. You use the NODE macro on a wire connected to a module port to specify a package pin number. In this case, the clock is connected to pin 13.

- C. You use the PDWN and PUP macros to disable unused TTL-equivalent macro inputs, preventing the unused input signals from being connected to the package pins due to lower-level module ports.

Use the PDWN macro to disable an active-high input and the PUP macro to disable an active-low input.

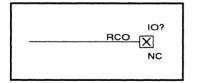

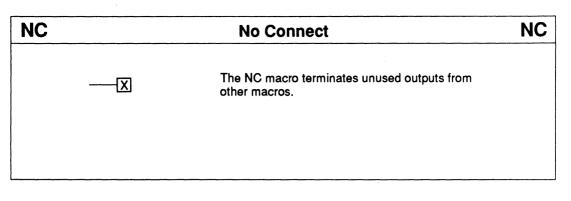

- D. You use the NC macro to terminate unused TTL-equivalent macro outputs. Any unused logic associated with the designated output is then removed during later processing.

- E. You use the NODE macro to assign logic to specific blocks in the MACH device. In this case, the equation driving QD is grouped into block A.

- F. You use the NODE macro to specify the node number of a buried node signal. In this case, the signal NODE1 is placed at location 18.<sup>3</sup>

- G. You use the NODE macro to prevent minimization of logic. In this case, inhibiting minimization preserves the redundant hold term of the latch design.

<sup>&</sup>lt;sup>3</sup> Refer to Section IV, Chapter 11, for details on node numbers for each MACH device.

Annotated Schematic

# 7.3 CAPTURING A SCHEMATIC

You capture a MACH schematic using OrCAD/SDT III and the optional MACH macro library. PALASM 4 provides an interface to the OrCAD/SDT III software.<sup>4</sup>

The features and considerations for capturing a MACH schematic design are presented in the following discussions.

- 7.3.1, Specifying Pin and Node Numbers

- 7.3.2, Grouping Signals into a Block

- 7.3.3, Turning Minimization Off

- 7.3.4, Manually Splitting Product Terms

- 7.3.5, Terminating Unused Inputs and Outputs

- 7.3.6, Defining Preset and Reset Functions

- 7.3.7, Interpreting Reference Designators

- 7.3.8, Naming Signals

7.3.1 SPECIFYING PIN AND NODE NUMBERS

I/O pins in a MACH design are automatically defined by unresolved module ports, ones that do not have a complementary connection. All module ports in the design above are unresolved.

**Note:** A module port is automatically linked to an I/O pin when it is unresolved.

To specify an I/O pin or a node location, you connect a NODE macro to the corresponding signal wire and edit part field 1 to indicate the desired number. You enter only the pin or node number; no alpha characters are allowed.

<sup>&</sup>lt;sup>4</sup> Refer to Section I, Chapter 1, for details on installing the interface to OrCAD/SDT III.

**Important:** Assign fixed I/O package pin locations only when necessary. Letting pins float allows more flexibility during the fitting process and results in a higher probability of success.

Also: You must connect the NODE macro to an individual signal wire; connections to bus wires are ignored.

To group the logic associated with a signal into a specific block, you can connect a NODE macro to the corresponding signal wire and edit part field 2. The block letter must be preceded by a period, for example, .A or .B.

**Important:** You must use the NODE macro to assign attributes to buffer, combinatorial, and module port nets. Storage and TTL-equivalent macros have inherent attribute fields.

7.3.3 TURNING MINIMIZATION OFF

During compilation, logic is replaced with its DeMorgan equivalent if the latter implementation requires fewer product terms.

**Important:** When DeMorganized equivalents are substituted for clocked macros, polarity inversion occurs after the storage element. As a result, the operation of the set/reset logic is reversed when viewed at the pin.

Inhibiting minimization also preserves the redundant hold used in latch designs to prevent timing glitches.

To prevent minimization for the logic associated with a signal, you connect a NODE macro to the corresponding signal wire and edit the name of part field 3 to NO\_MIN.

# 7.3.2 GROUPING SIGNALS INTO A BLOCK

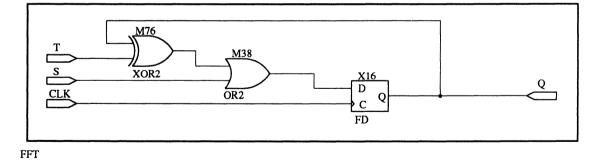

## 7.3.4 MANUALLY SPLITTING PRODUCT TERMS

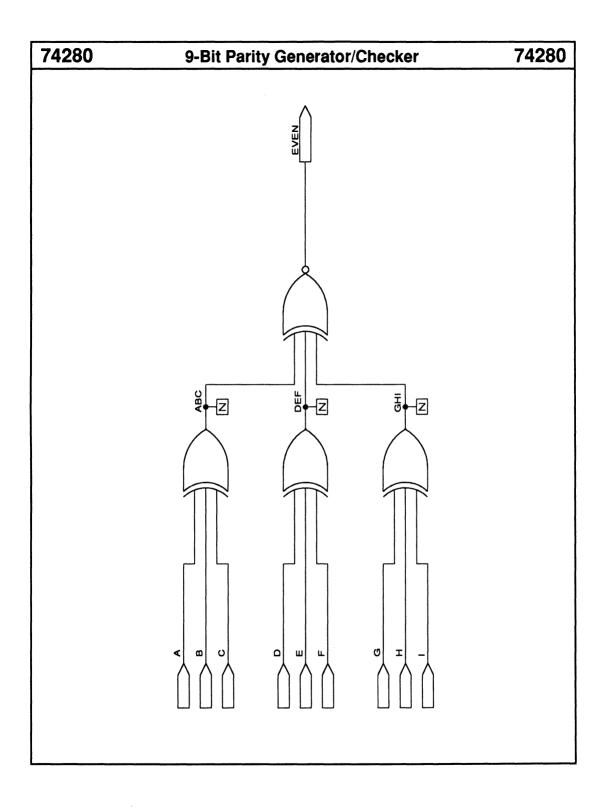

The 6-input parity generator, shown in the annotated schematic discussion, is an example of a circuit that requires gate splitting. To implement the complete function requires 32 product terms. However, a MACH 110 device can support only 12 product terms for a single macrocell.<sup>5</sup>

You can split the product terms of this function by placing a NODE macro at the output of each XOR3, thereby creating two buried nodes. The buried node results are fed back into the array to produce the result POUT. Each of the smaller XOR functions fits into a single macrocell; the final implementation of the parity generator fits into a MACH 110 device.

**Important:** Splitting product terms requires feedback through the array that introduces an additional unit of delay in the signal path. You must account for this added delay.

### 7.3.5 TERMINATING UNUSED INPUTS AND OUTPUTS

You must disable unused TTL-equivalent macro inputs by connecting them to supply or ground. This prevents the unused input signals from being connected to package pins due to lower-level module ports.

Similarly, you must terminate unused TTL-equivalent macro outputs with an NC macro. Any unused logic associated with the designated output is then removed during later processing.

<sup>&</sup>lt;sup>5</sup> Refer to Section IV, Chapter 11, for details on steering product terms.

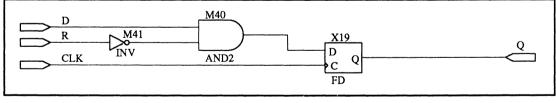

## 7.3.6 DEFINING PRESET AND RESET FUNCTIONS

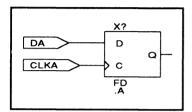

The MACH library contains storage macros with either implied or explicit asynchronous set and reset functions. You specify these functions to define when asynchronous set or reset signals are generated after the device powers up. All flip-flops and latches are automatically reset when the device powers up, independent of the asynchronous control logic.

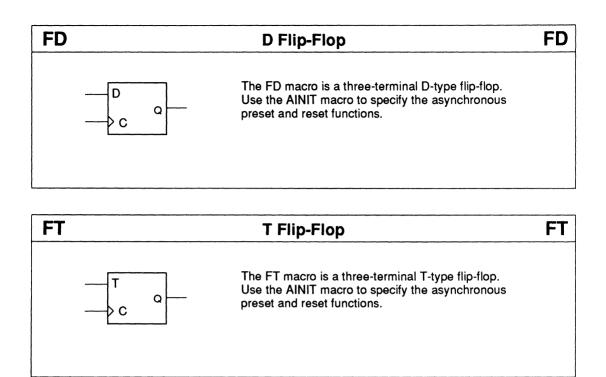

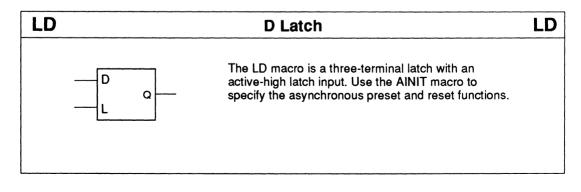

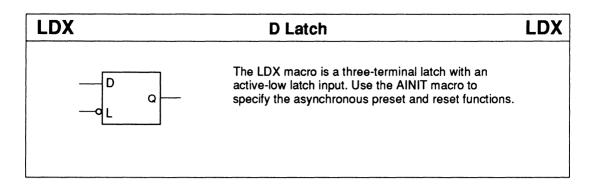

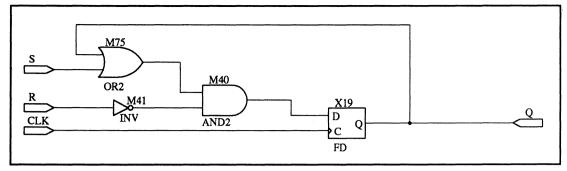

The AINIT macro represents the implied asynchronous set and reset functions for all of the three-terminal storage macros in a design. The following storage macros require the AINIT macro for asynchronous set and reset definition.

- FD

- FT

- LD

- LDX

**Note:** Only one AINIT macro can be specified per design. Any additional reset functions must be defined explicitly.

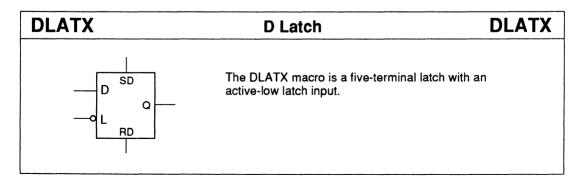

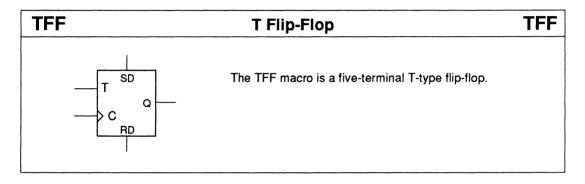

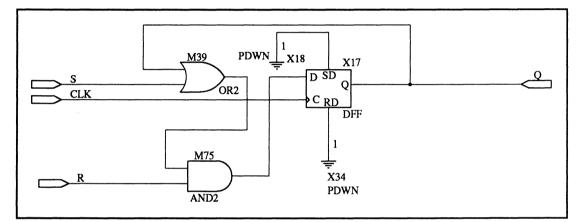

The following storage macros have five terminals, thereby allowing you to explicitly connect the appropriate asynchronous set and reset function.

- DFF

- DLAT

- DLATX

- TFF

**Important:** Only one asynchronous set and reset signal can be implemented in a single block within the MACH device. Each time you specify a unique set or reset function, the new logic is placed in a separate block.

## 7.3.7 INTERPRETING REFERENCE DESIGNATORS

Each instance of a macro in a schematic must have a unique reference designator. Reference designators are automatically assigned during the compilation process.

**Note:** Each reference designator must be unique across all levels of hierarchy, including the subsheets of MACH macros.

The following types of reference designators are used in the AMD-supplied macro libraries.

- **M?** appears with combinatorial, TTL-equivalent, and non-three-state buffer macros.

- X? appears with storage and three-state macros.

- IO? appears with the NODE and NC macros.

**Tip:** Error and warning messages include the reference designator and net name of the flagged logic; therefore, it is a good idea to name all nets in the design.

### 7.3.8 NAMING SIGNALS

Use an alphanumeric string no longer than nine characters for each signal name. Signal names are not case sensitive.

**Important:** A forward slash, /, does **not** affect the polarity in a schematic signal name.

**Note:** When a schematic-based design is compiled, a <design>.PDS file is generated. The signal names in this file may have prefixes or suffixes to guarantee uniqueness in the design hierarchy. For example, a forward slash is converted to a \_FS\_ prefix.

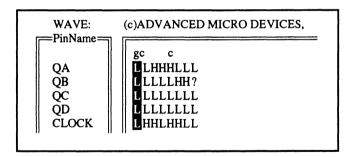

## 7.4 ANNOTATED Datasheet

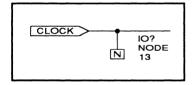

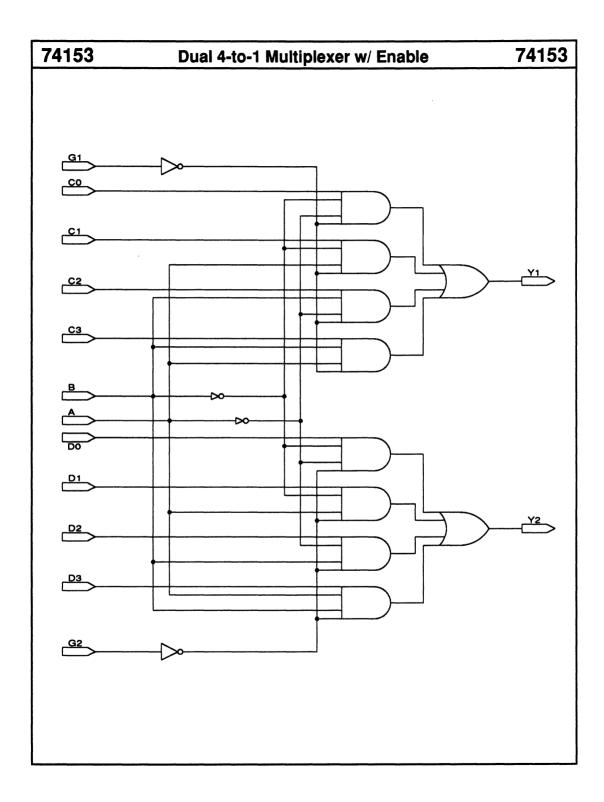

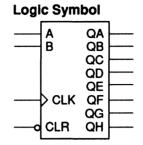

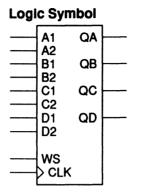

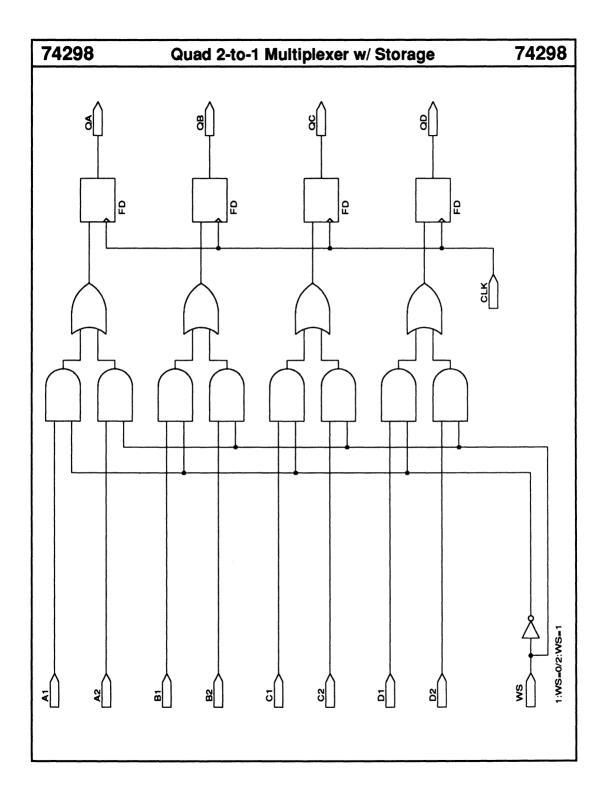

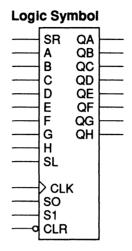

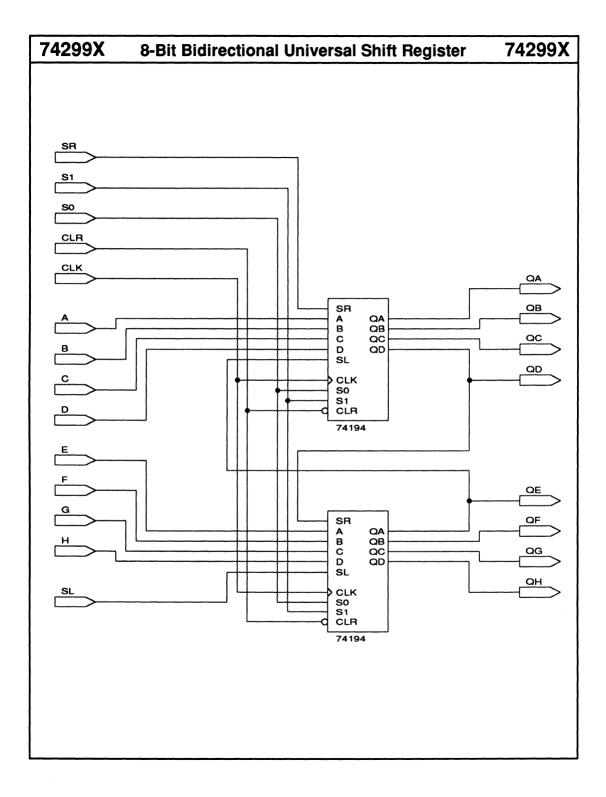

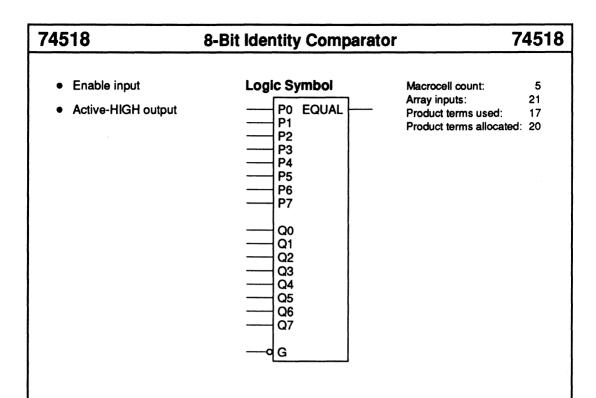

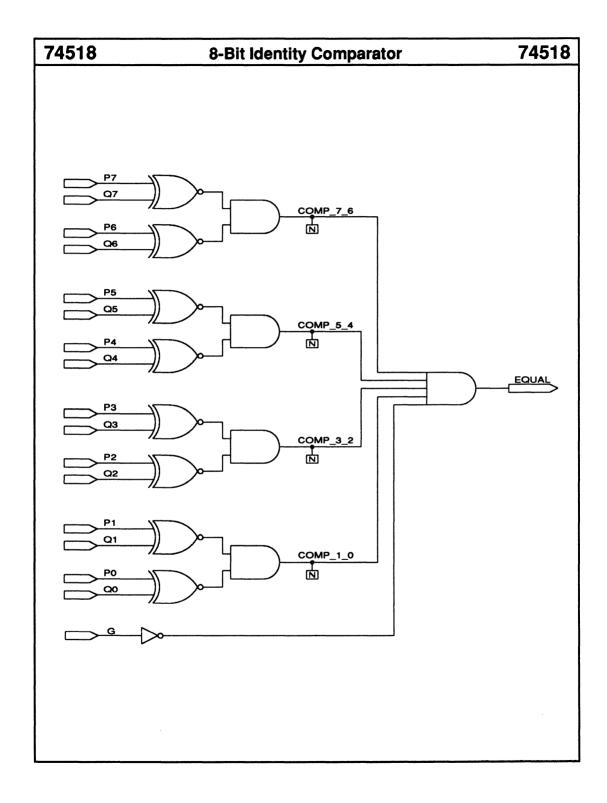

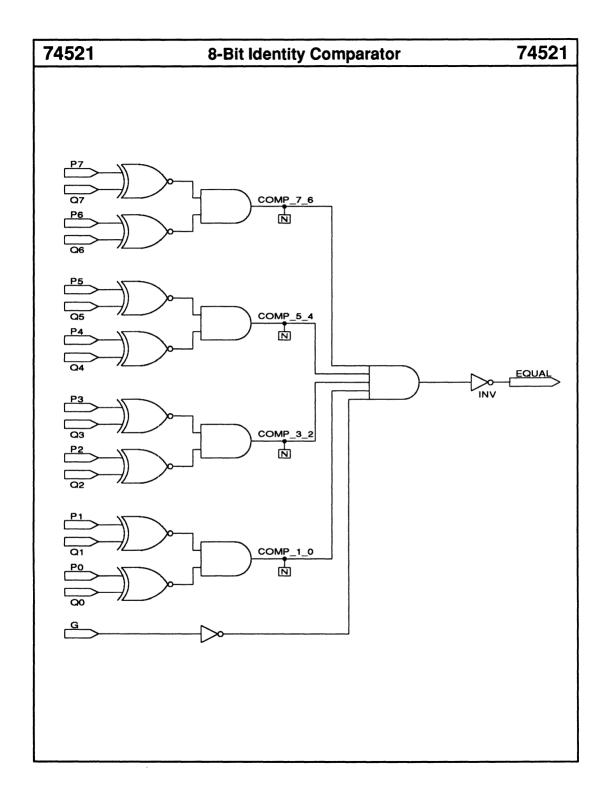

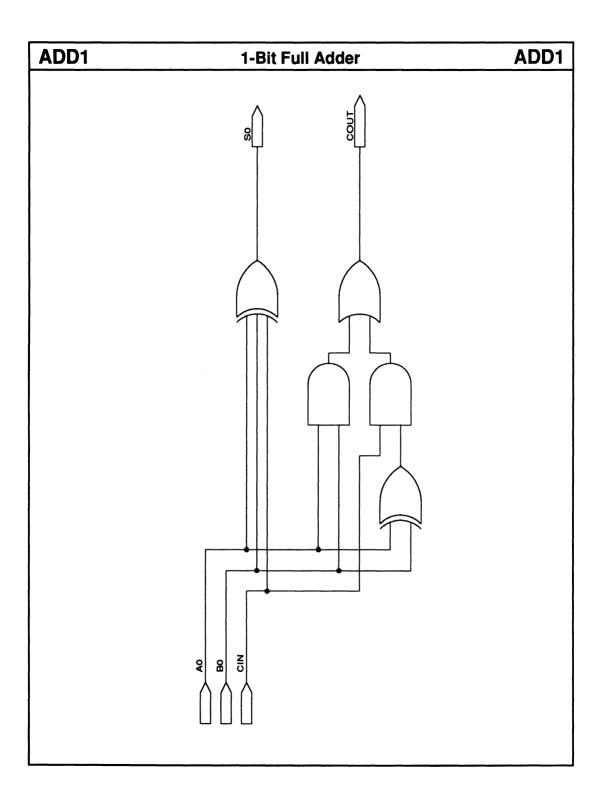

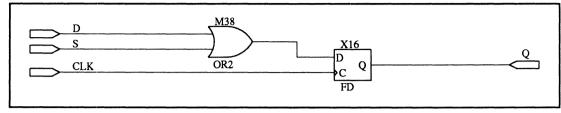

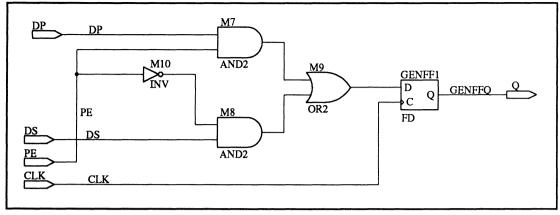

This discussion presents an annotated datasheet to illustrate the layout and information contained therein. Chapter 8, in this section, contains datasheets for each of the TTL-equivalent macros available in the MACH library. Each lettered paragraph below corresponds to a circled letter in the next two figures.

- A. The feature summary is a bulleted list that summarizes the logical features of the macro.

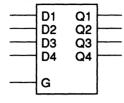

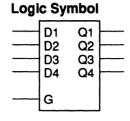

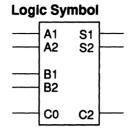

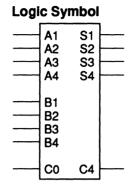

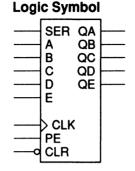

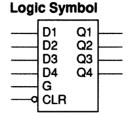

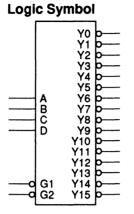

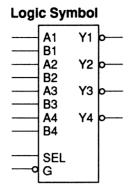

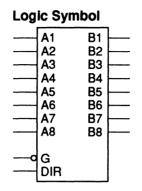

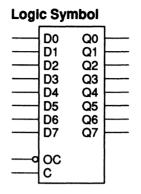

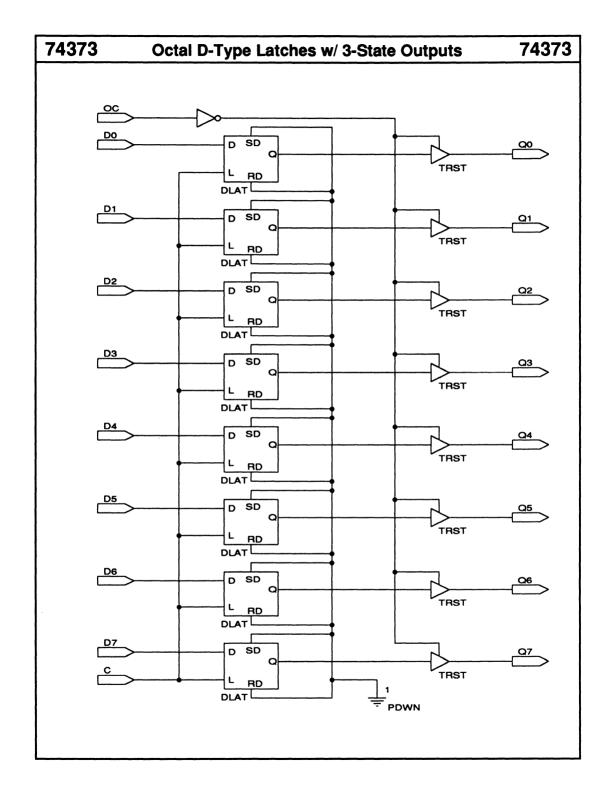

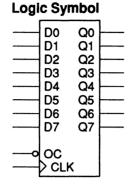

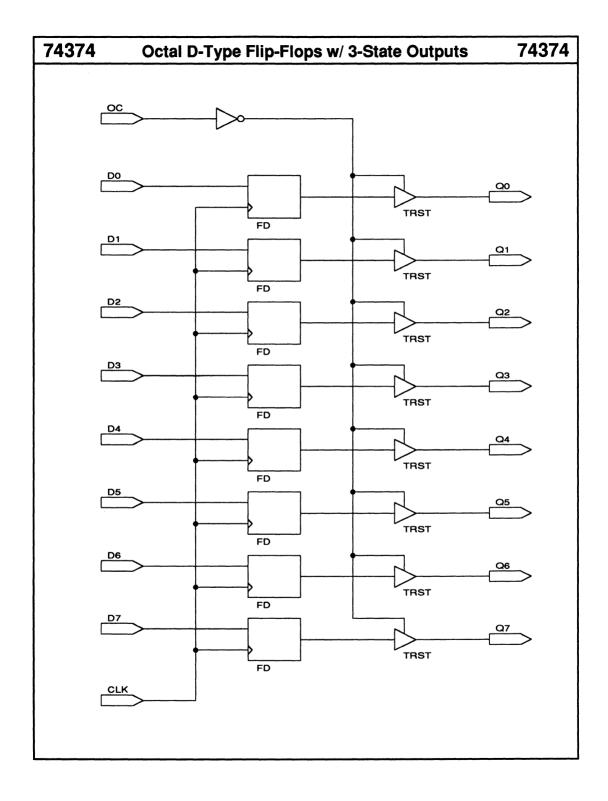

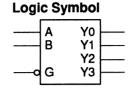

- B. The logic symbol illustrates the macro pin names and how they appear on the symbol.

- C. The MACH resource summary lists the number of resources consumed by a stand-alone macro. This summary does not account for potential minimization or conflicts with other logic in a design. The following utilized resources are listed.

- Macrocell count

- Array inputs

- Product terms used

- Product terms allocated

- MACH-family restrictions, if applicable

- D. The functional description explains the logical operation of the macro, and corresponds to the information presented in the function table. It also indicates if the macro is a non-standard TTL implementation.

- E. The sample PDS equivalent represents the PDS file generated when the macro schematic is processed as a stand-alone design.

- F. The function table illustrates the functional operation of the macro. Logic states are represented as follows.

- H represents a logical 1, or HIGH, state.

- L represents a logical 0, or LOW, state.

- X represents a don't-care condition.

- An up arrow represents a rising edge.

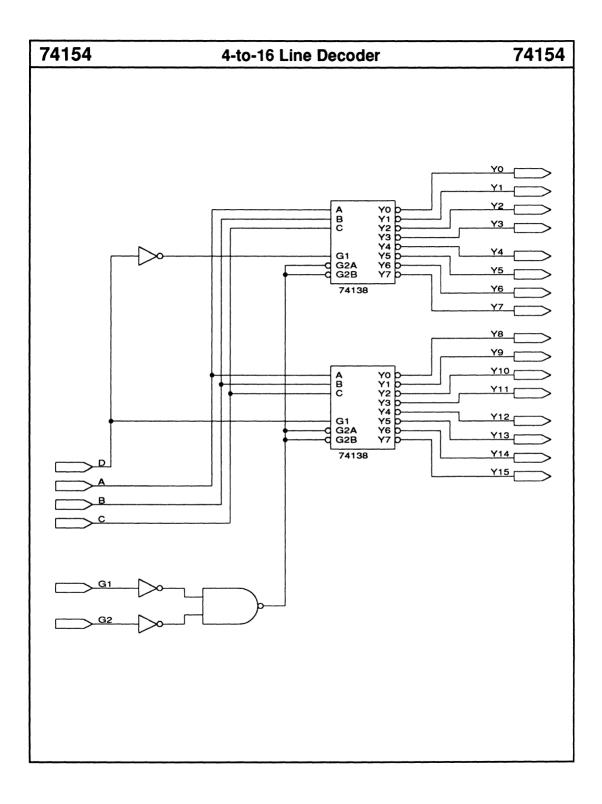

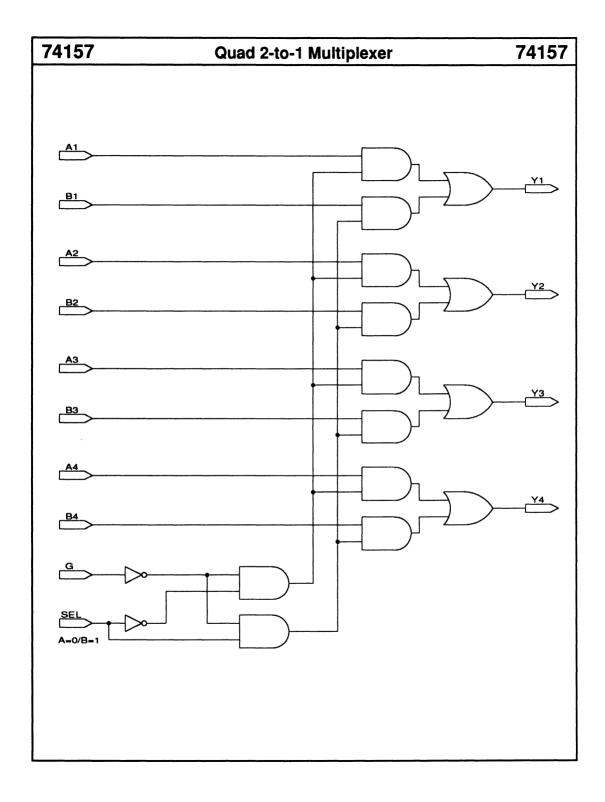

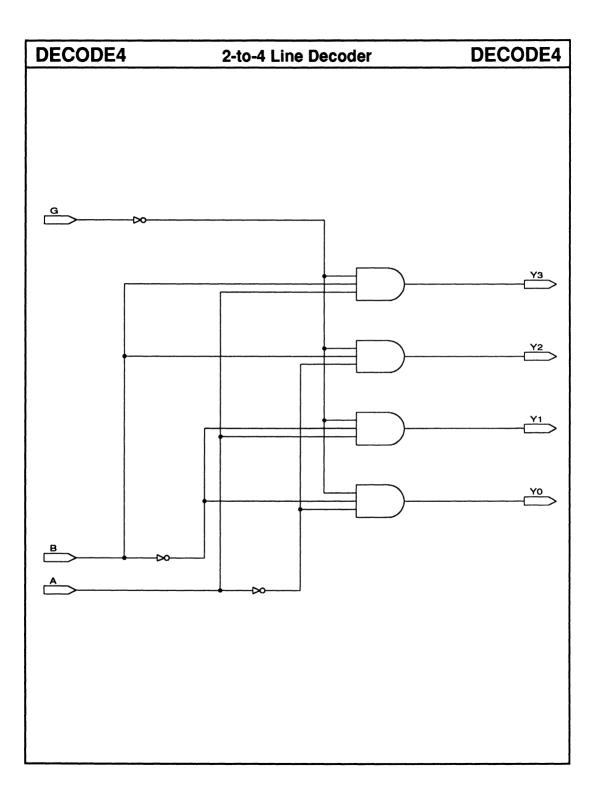

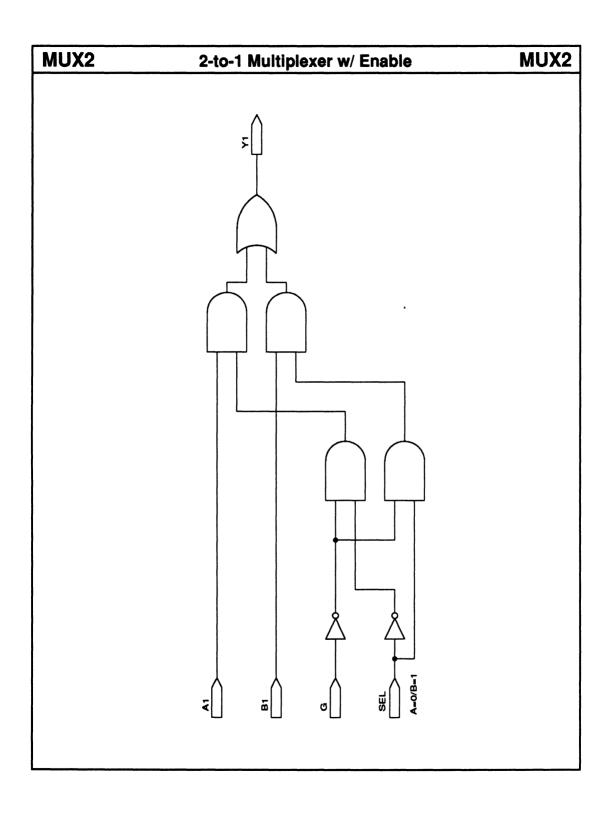

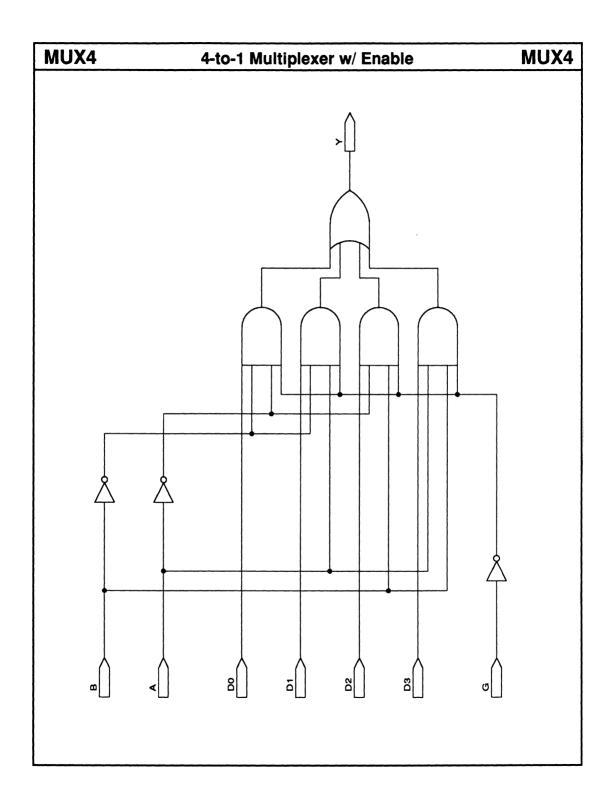

- G. The schematic is a logical representation of the macro circuit as created in OrCAD/SDT III. The following graphic changes have been made to enhance the clarity of the schematics. No changes have been made to the logic.

- Reference designators have been removed.

- Part values have been removed from nonstorage macros.

- Module-port names have been relocated to a position above the module-port symbol.

- Some pin names have been removed to prevent crowding.

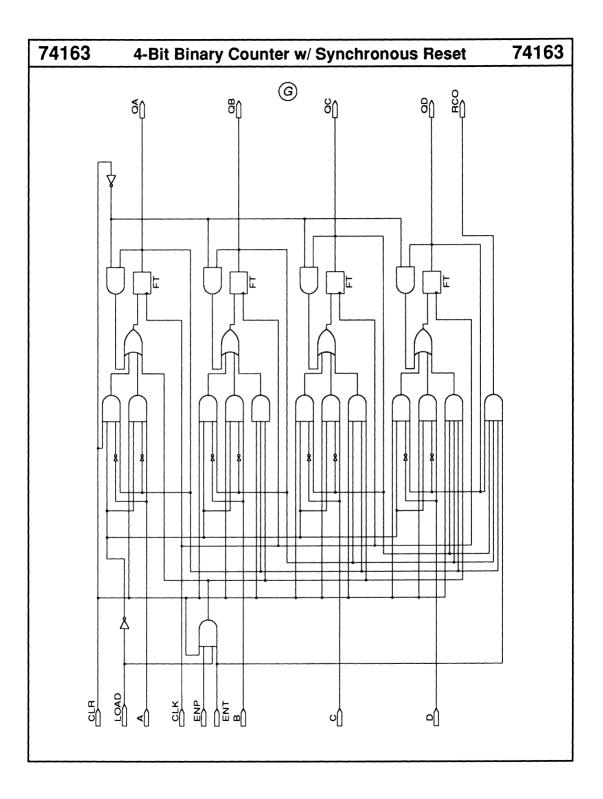

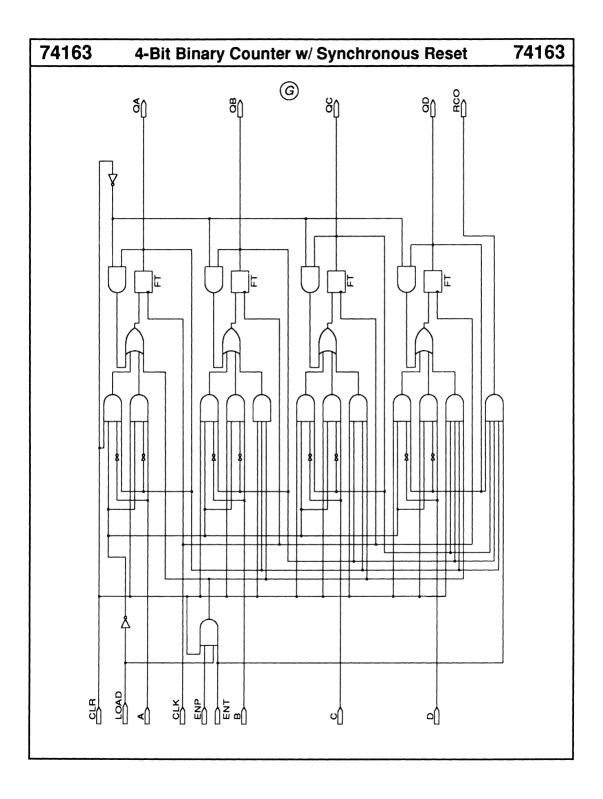

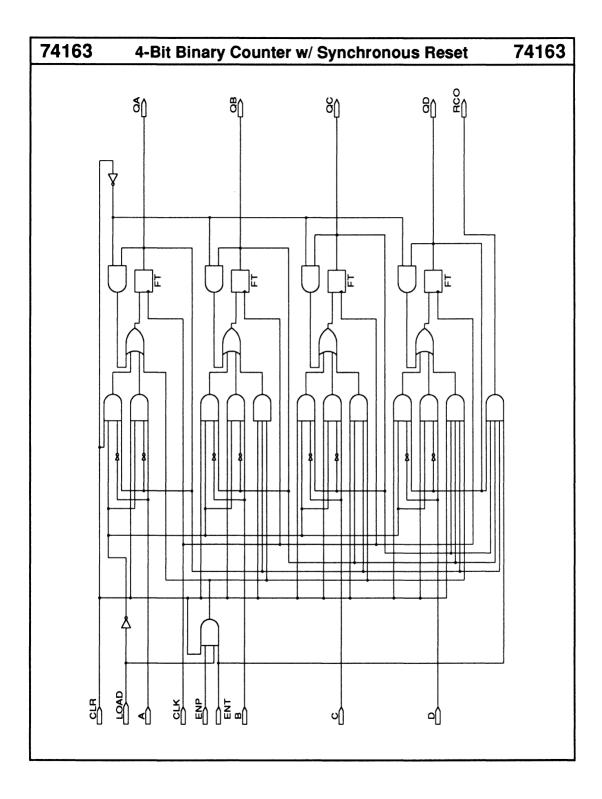

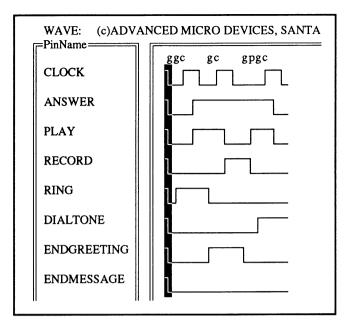

#### 74163 74163 4-Bit Binary Counter w/ Synchronous Reset $(\mathbf{A})$ B) С Synchronous 4-bit binary-Logic Symbol Macrocell count: 5 loadable up counter Array inputs: 12 Α QA Product terms used: 17 В QB Synchronous reset Product terms allocated: 20 С QC D QD Carry look-ahead output for RCO making wider counters ENP ENT ) CLK LOAD CLR Ď

### **Functional Description**

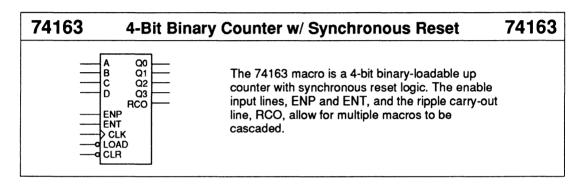

The 74163 macro is a 4-bit binary-loadable up counter with synchronous reset logic. The enable input lines, ENP and ENT, and the ripple carry-out line, RCO, allow for multiple macros to be cascaded. RCO goes HIGH when the maximum count of 15 has been reached and ENT is HIGH. To enable and increment the counter value, you feed the RCO output to the ENP and ENT inputs of the next counter stage. QD is the most significant counter bit.

QA.T = ((/CLR \* QA) + (CLR \* /LOAD)\*/A \* QA) + (CLR \* /LOAD \* /QA \* A) + (CLR \* ENP \* LOAD \* ENT)) QA.clkf = CLK QB.T = ((/CLR \* QB) + (CLR \* /LOAD)\*/B\*QB) + (CLR\*/LOAD\*/QB \* B) + (CLR \* QA \* (CLR \* ENP \* LOAD \* ENT))) QB.clkf = CLK QC.T = ((/CLR \* QC) + (CLR \* /LOAD)\*/C \* QC) + (CLR \* /LOAD \* /QC \* C) + (CLR \* QB \* QA \* (CLR \* ENP \* LOAD \* ENT))) QC.clkf = CLKQD.T = ((/CLR \* QD) + (CLR \* /LOAD)\*/D \* QD) + (CLR \* /LOAD \* /QD \* D) + (CLR \* QC \* QB \* QA \* (CLR \* ENP \* LOAD \* ENT))) QD.clkf = CLKRCO = (QD \* QC \* QB \* QA \* ENT)

## Function Table

|       | Inputs |     |      |     | Outputs |             |

|-------|--------|-----|------|-----|---------|-------------|

| Mode  | CLK    | CLR | Load | ENP | ENT     | QD QC QB QA |

| Clear | L      | L   | х    | Х   | Х       | QD QC QB QA |

| Clear | Ť      | L   | Х    | х   | Х       |             |

| Load  | Ť      | н   | L    | х   | Х       | DCBA        |

| Count | Î ↑    | н   | н    | н   | н       | Count Up    |

| Stop  | Ť      | н   | н    | L   | X       | QD QC QB QA |

| Stop  | Ť      | н   | н    | Х   | L       | QD QC QB QA |

The RCO is HIGH when the counter output is 15 and ENT is HIGH. Otherwise, it stays LOW.

## 7.2.2 LATCH Macros

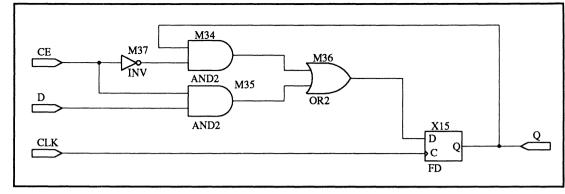

MACH 2 series devices have special resources to implement latch macros directly. MACH 1 series devices implement the latch macros as combinatorial functions.

## 7.2.3 MINIMIZATION

During compilation, logic is replaced with its DeMorgan equivalent if the latter implementation is more economical.

**Important:** When DeMorganized equivalents are substituted for clocked macros, polarity inversion occurs after the storage element. As a result, the operation of the Set/Reset logic is reversed when viewed at the pin.

To prevent this reversal, you use the NODE macro and specify the NO\_MIN attribute. Inhibiting minimization also preserves the redundant hold used in latch designs to prevent timing glitches.

# 7.2.4 REFERENCE DESIGNATORS

Each instance of a macro in a schematic must have a unique reference designator. Reference designators are automatically assigned during the compilation process.

**Note:** Each reference designator must be unique across all levels of hierarchy, including the subsheets of MACH macros.

The following types of reference designators are used in the AMD-supplied macro libraries.

- **M?** appears with combinatorial, TTL-equivalent, and non-three-state buffer macros.

- X? appears with storage and three-state macros.

• IO? appears with the NODE and NC macros.

**Tip:** Error and warning messages include the reference designator and net name of the flagged logic; therefore, it is a good idea to name all nets in the design.

# 7.2.5 SIGNAL NAMES

Use an alphanumeric string no longer than nine characters for each signal name. Signal names are not case sensitive.

**Important:** A slash, /, does **not** affect the polarity in a schematic signal name.

## 7.3 ANNOTATED Datasheet

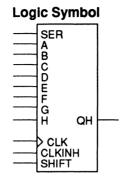

This discussion presents an annotated datasheet to illustrate the layout and information contained therein. Chapter 8 contains datasheets for each of the TTL-equivalent macros available in the MACH library. Each lettered paragraph below corresponds to a circled letter in the next two figures.

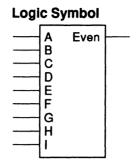

- A. The feature summary is a bulleted list that summarizes the logical features of the macro.

- B. The logic symbol illustrates the macro pin names and how they appear on the symbol.

- C. The MACH resource summary lists the number of resources consumed by a stand-alone macro. This summary does not account for potential minimization or conflicts with other logic in a design. The following utilized resources are listed.

- Macrocell count

- Array inputs

- Product terms used

- Product terms allocated

- MACH-family restrictions, if applicable

- D. The functional description explains the logical operation of the macro, and corresponds to the information presented in the function table. It also indicates if the macro is a non-standard TTL implementation.

- E. The sample PDS equivalent represents the PDS file that is generated when the macro schematic is processed as a stand-alone design.

- F. The function table illustrates the functional operation of the macro. Logic states are represented as follows.

- 1 represents a logical 1, or HIGH state

- 0 represents a logical 0, or LOW state

- X represents a don't-care condition

- An arrow represents a rising edge

- G. The schematic is a logical representation of the macro circuit as created in OrCAD/SDT III. The following graphic changes have been made to enhance the clarity of the schematics. No changes have been made to the logic.

- Reference designators have been removed.

- Part values have been removed from nonstorage macros.

- Module-port names have been relocated to a position above the module-port symbol.

- Some pin names have been removed to prevent crowding.

## 74163

## 4-Bit Binary Counter w/ Synchronous Reset

B)

## 74163

• Synchronous 4-bit binaryloadable up counter

$(\mathbf{A})$

- Synchronous reset

- Carry look-ahead output for making wider counters

|              | $\sim$                                               |  |  |  |  |

|--------------|------------------------------------------------------|--|--|--|--|

| Logic Symbol |                                                      |  |  |  |  |

| <b>0</b>     | A<br>B<br>C<br>D<br>ENP<br>ENT<br>CLK<br>LOAE<br>CLR |  |  |  |  |

## $(\mathcal{C})$

Macrocell count:5Array inputs:12Product terms used:17Product terms allocated:20

## (<u>D</u>)

#### **Functional Description**

The 74163 macro is a 4-bit binary-loadable up counter with synchronous reset logic. The enable input lines, ENP and ENT, and the ripple carry-out line, RCO, allow for multiple macros to be cascaded. RCO goes HIGH when the maximum count of 15 has been reached and ENT is HIGH. To enable and increment the counter value, you feed the RCO output to the ENP and ENT inputs of the next counter stage. QD is the most significant counter bit.

#### Sample PDS Equivalent

QA.T = ((/CLR \* QA) + (CLR \* /LOAD)\* /A \* QA) + (CLR \* /LOAD \* /QA \* A) + (CLR \* ENP \* LOAD \* ENT)) QA.clkf = CLK QB.T = ((/CLR \* QB) + (CLR \* /LOAD)\* /B \* QB) + (CLR \* /LOAD \* /QB \* B) + (CLR \* QA \* (CLR \* ENP \* LOAD \* ENT))) QB.clkf = CLK QC.T = ((/CLR \* QC) + (CLR \* /LOAD)\*/C \* QC) + (CLR \* /LOAD \* /QC \* C) + (CLR \* QB \* QA \* (CLR \* ENP \* LOAD \* ENT))) QC.clkf = CLK QD.T = ((/CLR \* QD) + (CLR \* /LOAD)\* /D \* QD) + (CLR \* /LOAD \* /QD \* D) + (CLR \* QC \* QB \* QA \* (CLR \* ENP \* LOAD \* ENT))) QD.clkf = CLKRCO = (QD \* QC \* QB \* QA \* ENT)

## F

### Function Table

|       | Inputs   |     |      | Outputs |     |             |

|-------|----------|-----|------|---------|-----|-------------|

| Mode  | CLK      | CLR | Load | ENP     | ENT | QD QC QB QA |

| Clear | L        | L   | X    | X       | Х   | QD QC QB QA |

| Clear | <b>↑</b> | L   | Х    | Х       | X   | LLLL        |

| Load  | <b>↑</b> | н   | L    | х       | Х   | DCBA        |

| Count | <b>↑</b> | н   | н    | н       | н   | Count Up    |

| Stop  | Î        | н   | н    | L       | Х   | QD QC QB QA |

| Stop  | <b>↑</b> | н   | н    | Х       | L   | QD QC QB QA |

The RCO is HIGH when the counter output is 15 and ENT is HIGH. Otherwise, it stays LOW.

## CHAPTER 8

## MACRO AND SCHEMATIC DATASHEETS

DocVer 1.0

PALASM 4 USER'S MANUAL

February 1991

SECTION III, LIBRARY REFERENCE, CHAPTER 8, MACRO AND SCHEMATIC DATASHEETS

## CONTENTS

| Quick Refe | erence                           | 1  |

|------------|----------------------------------|----|

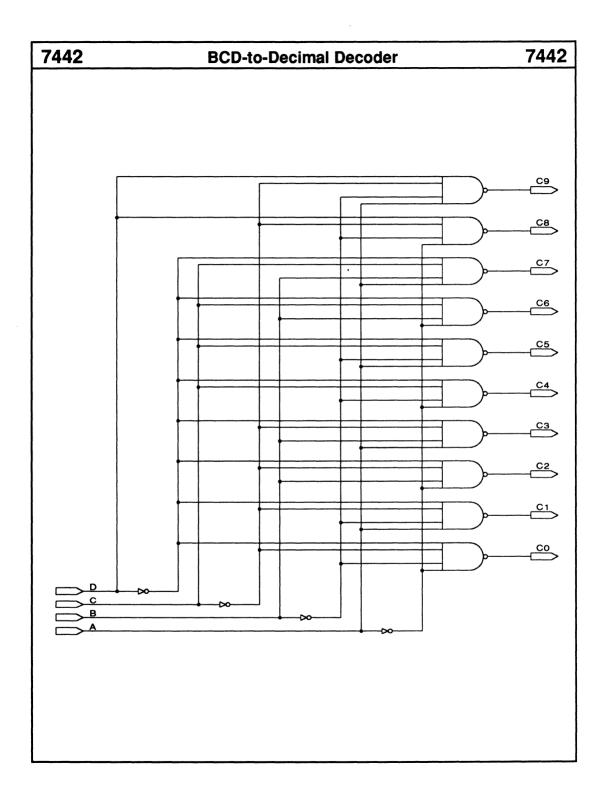

| 7442       | BCD-to-Decimal Decoder           |    |

|            | Schematic                        |    |

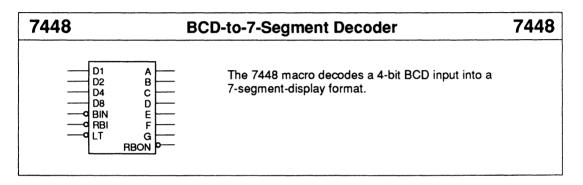

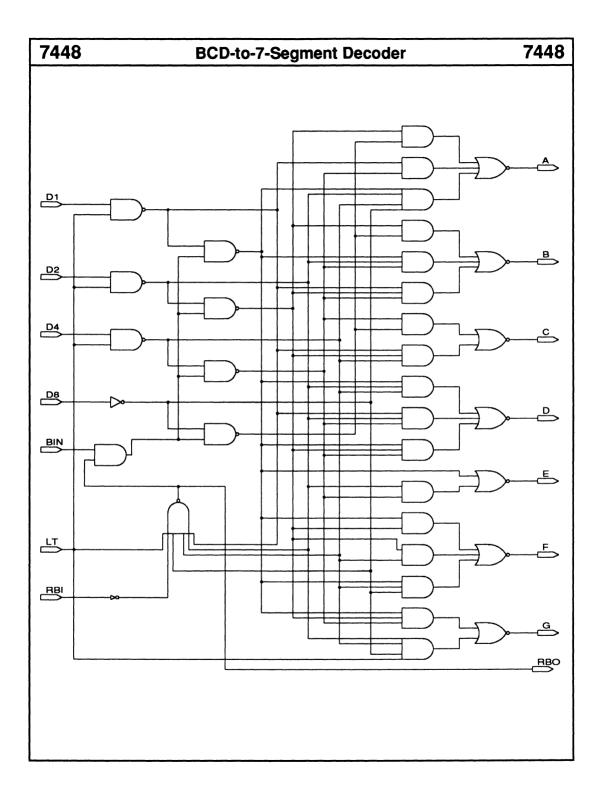

| 7448       | BCD-to-7-Segment Decoder         |    |

|            | Schematic                        | 21 |

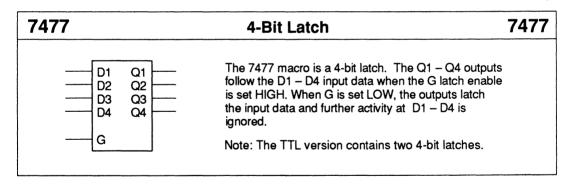

| 7477       | 4-Bit Latch                      |    |

|            | Schematic                        |    |

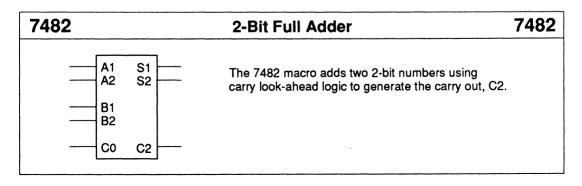

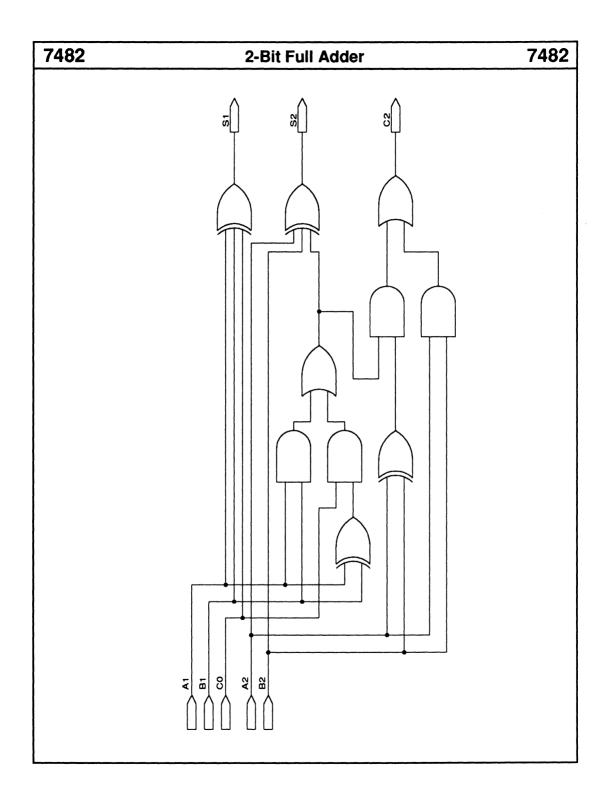

| 7482       | 2-Bit Full Adder                 |    |

|            | Schematic                        |    |

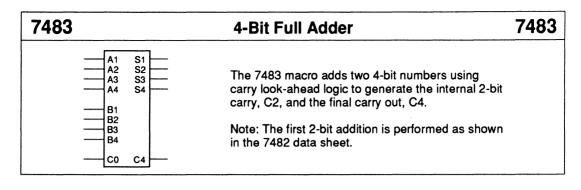

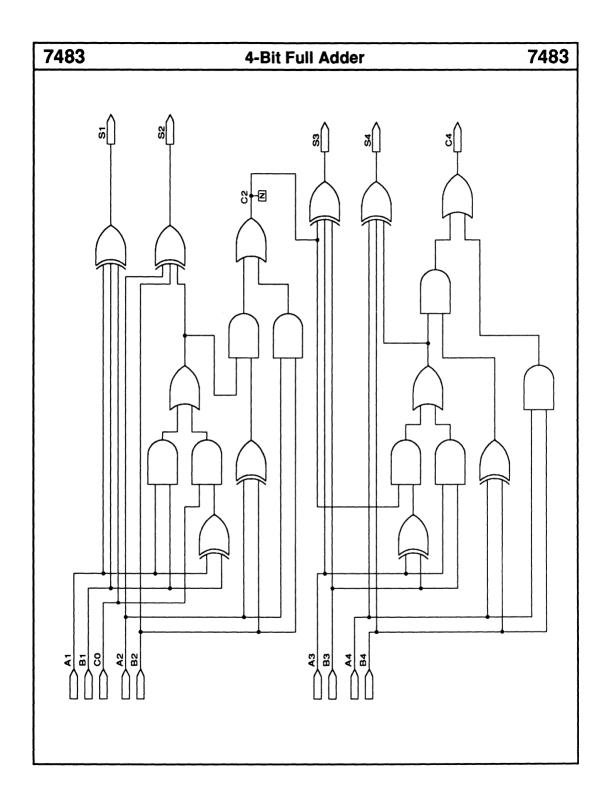

| 7483       | 4-Bit Full Adder                 |    |

|            | Schematic                        | 27 |

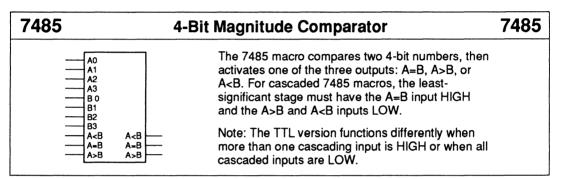

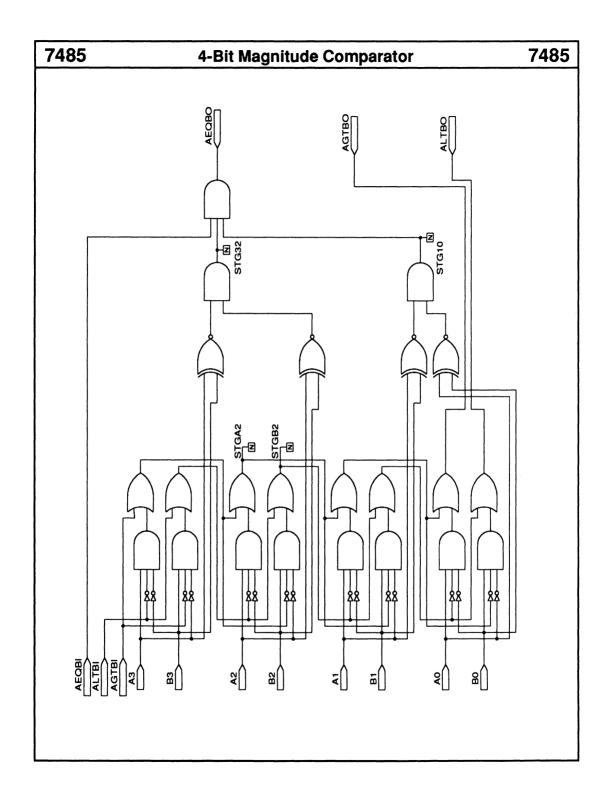

| 7485       | 4-Bit Magnitude Comparator       |    |

|            | Schematic                        | 29 |

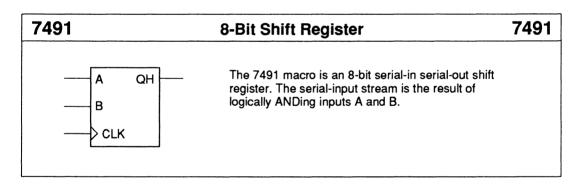

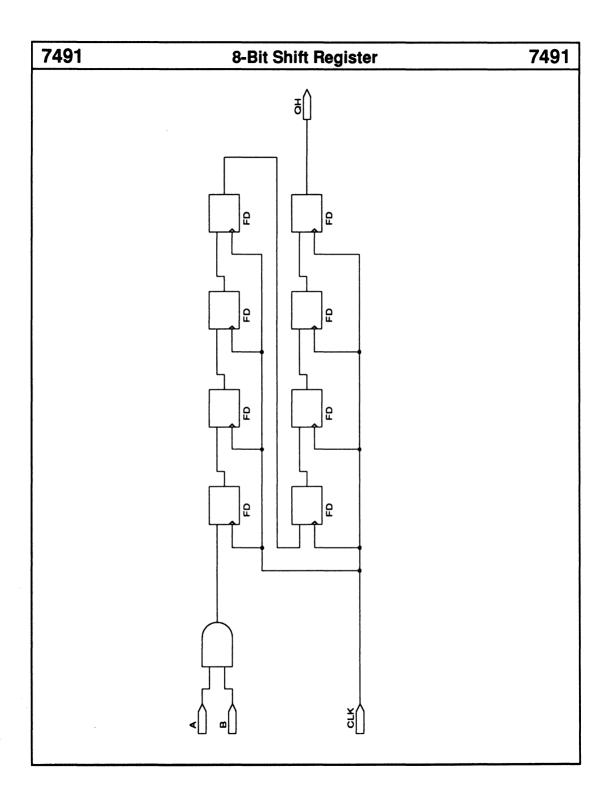

| 7491       | 8-Bit Shift Register             |    |

|            | Schematic                        |    |

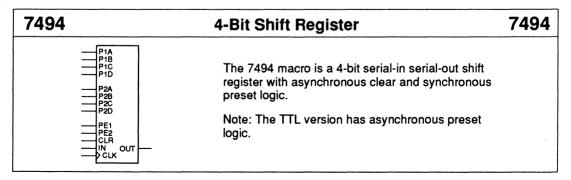

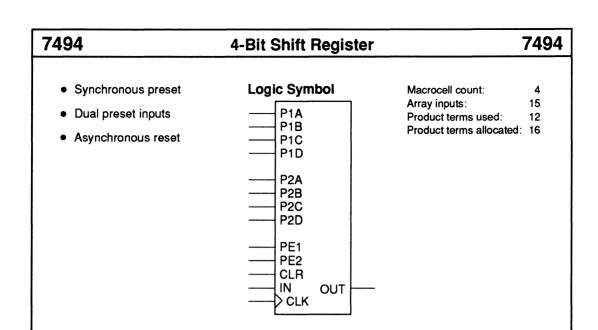

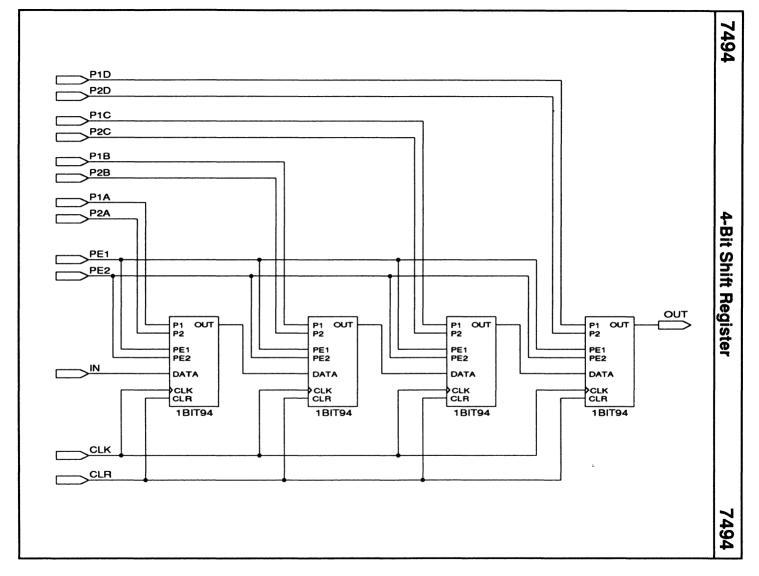

| 7494       | 4-Bit Shift Register             |    |

|            | Schematic                        |    |

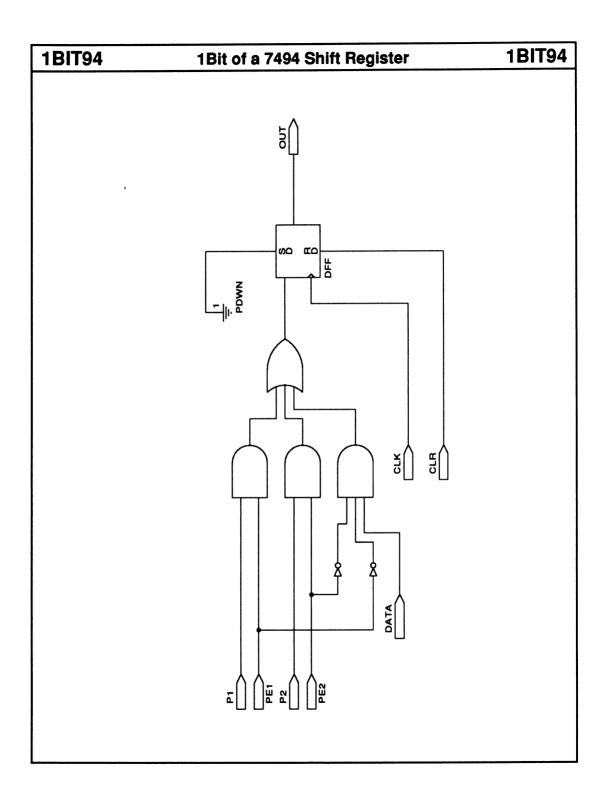

|            | 1 Bit of a 7494 Shift Register   |    |

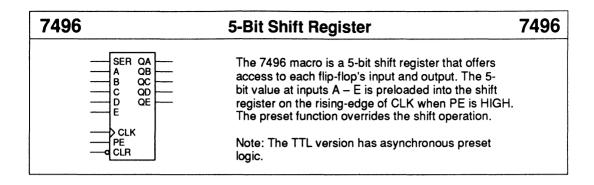

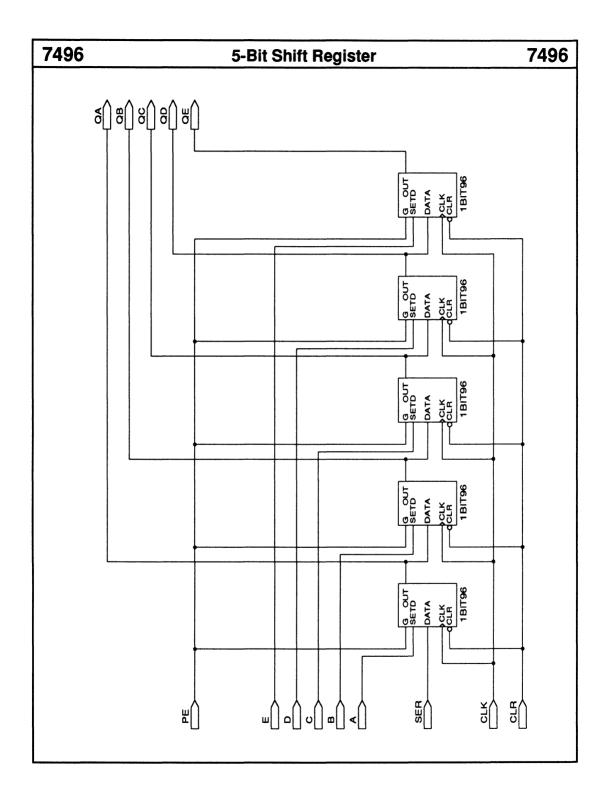

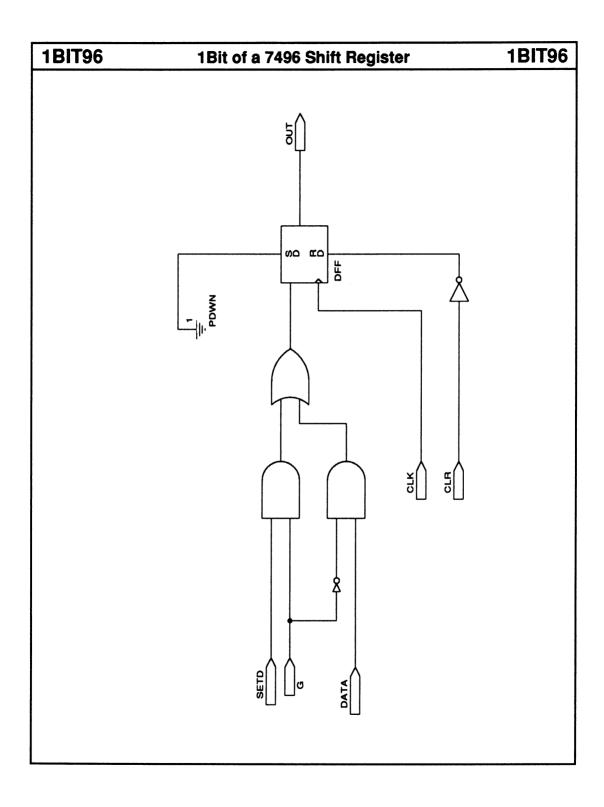

| 7496       | 5-Bit Shift Register             |    |

|            | Schematic                        |    |

|            | 1 Bit of a 7496 Shift Register   |    |

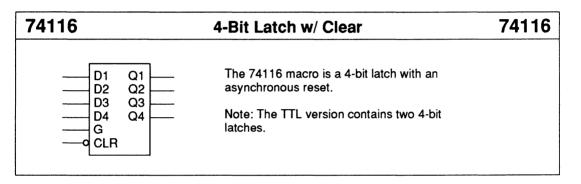

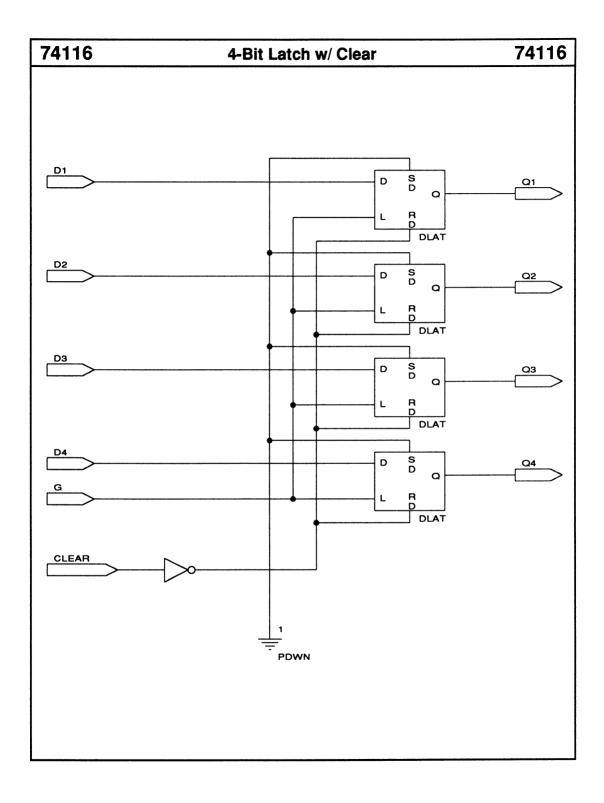

| 74116      | 4-Bit Latch w/Clear              | 40 |

|            | Schematic                        |    |

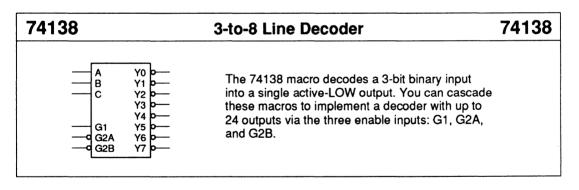

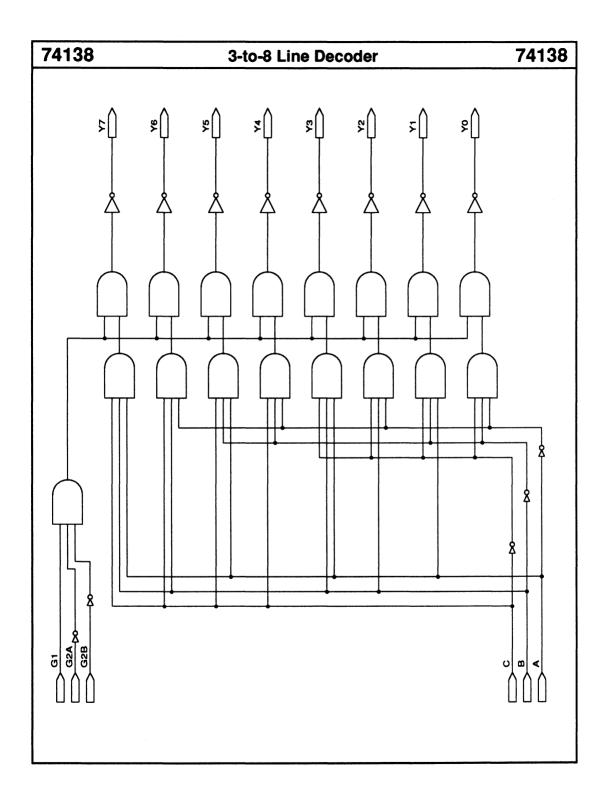

| 74138      | 3-to-8 Line Decoder              |    |

|            | Schematic                        |    |

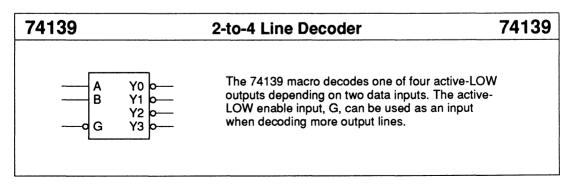

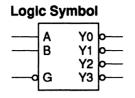

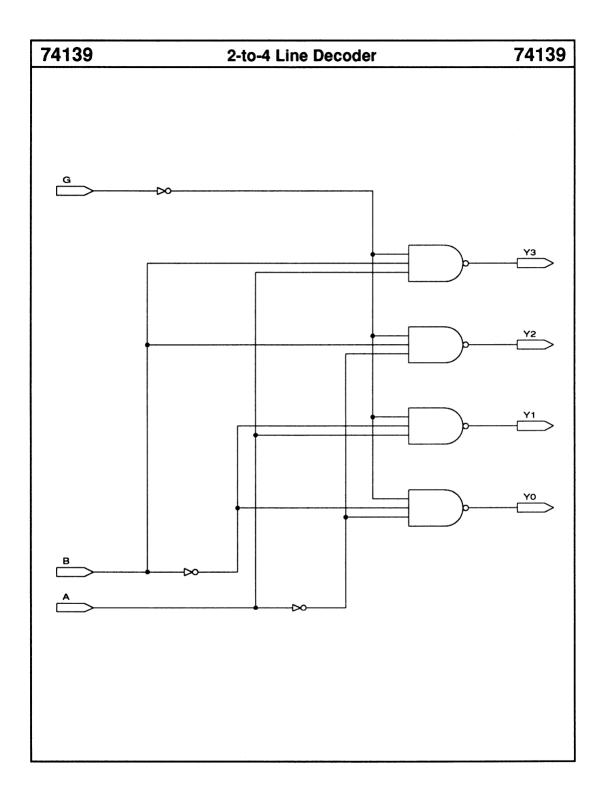

| 74139      | 2-to-4 Line Decoder              | 43 |

|            | Schematic                        |    |

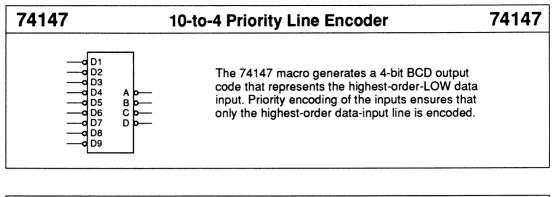

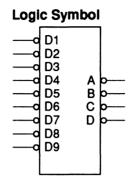

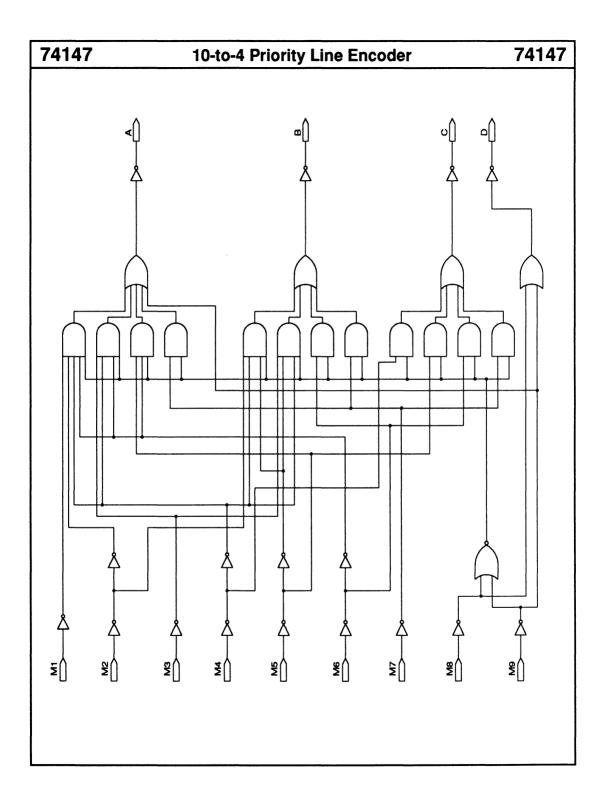

| 74147      | 10-to-4 Priority Line Encoder    |    |

|            | Schematic                        |    |

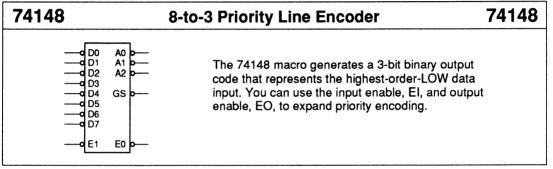

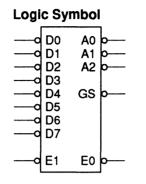

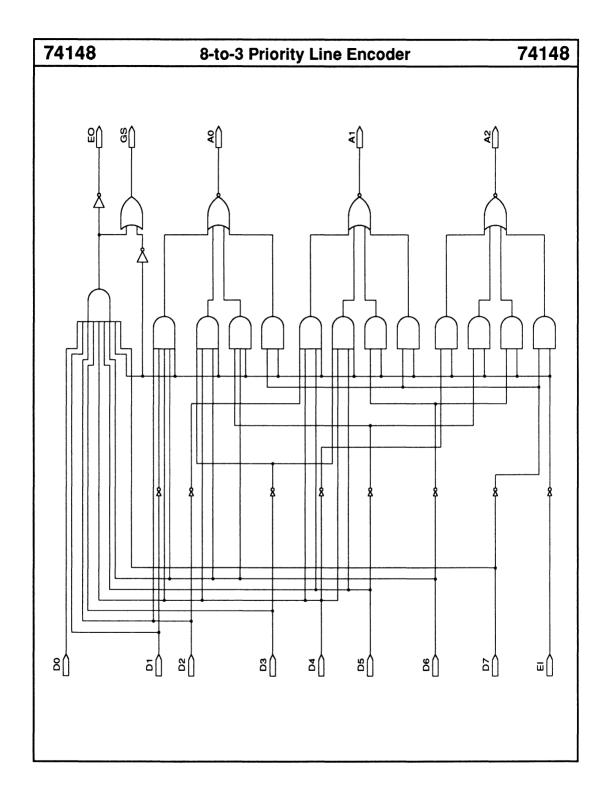

| 74148      | 8-to-3 Priority Line Decoder     |    |

|            | Schematic                        |    |

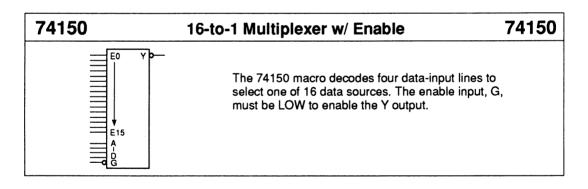

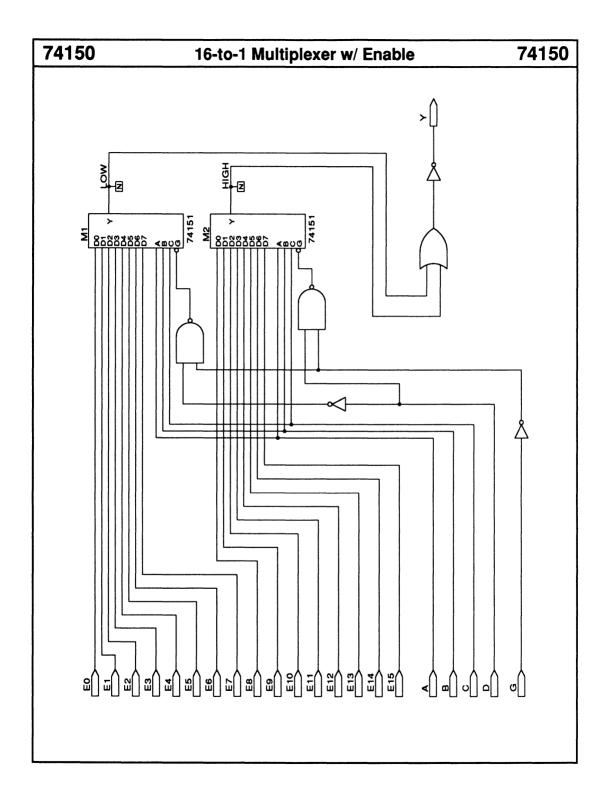

| 74150      | 16-to-1 Multiplexer w/Enable     |    |

|            | Schematic                        |    |

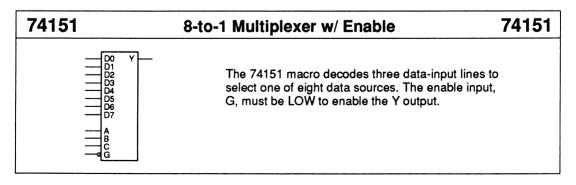

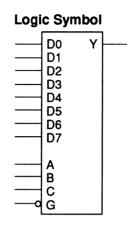

| 74151      | 8-to-1 Multiplexer w/Enable      |    |

|            | Schematic                        |    |

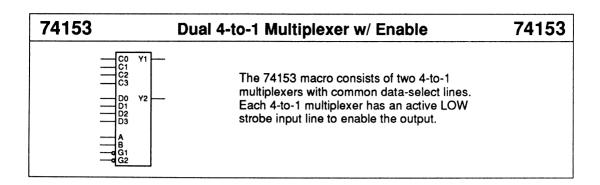

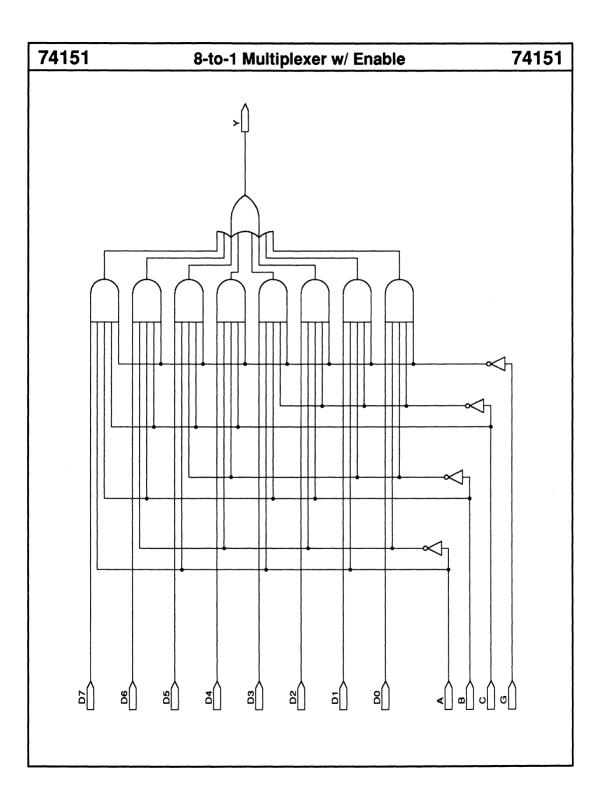

| 74153      | Dual 4-to-1 Multiplexer w/Enable |    |

|            | Schematic                        |    |

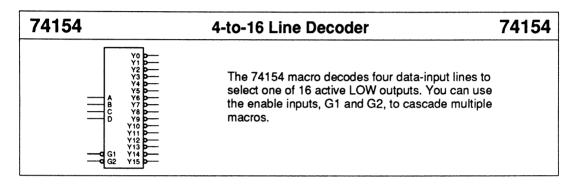

| 74154      | 4-to-16 Line Decoder             |    |

|            | Schematic                        |    |

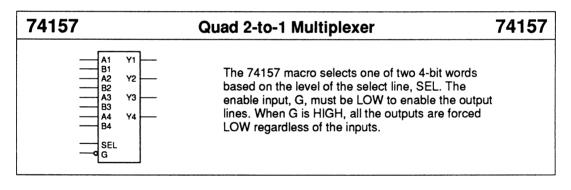

| 74157      | Quad 2-to-1 Multiplexer          |    |

|            | Schematic                        |    |

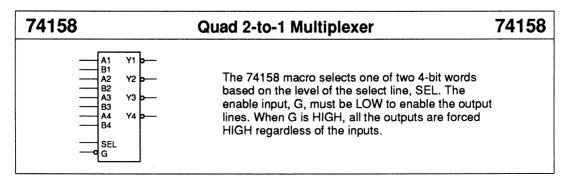

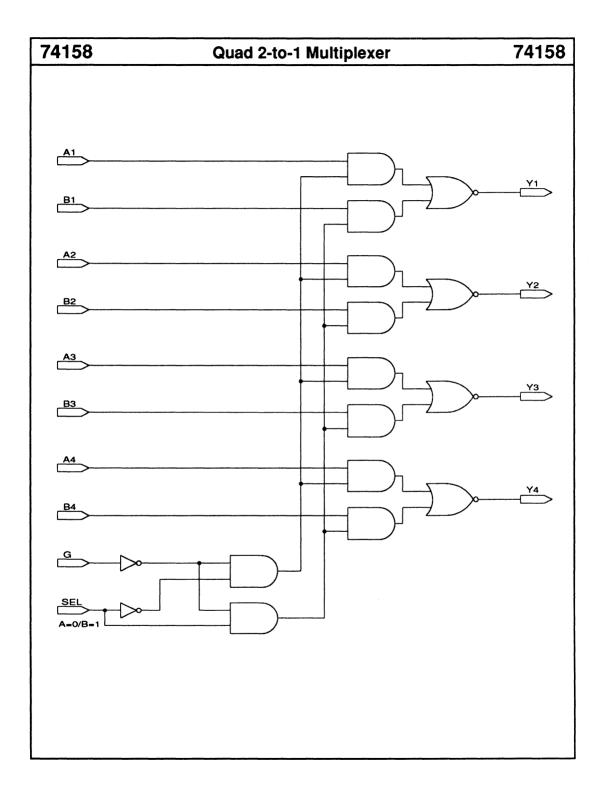

| 74158                                   | Quad 2-to-1 Multiplexer                       |                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | Schematic                                     | 61                                                                                                                                                                                                                                                                                                                                                                                          |

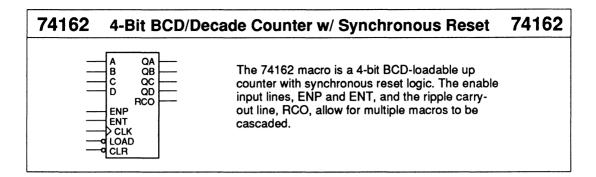

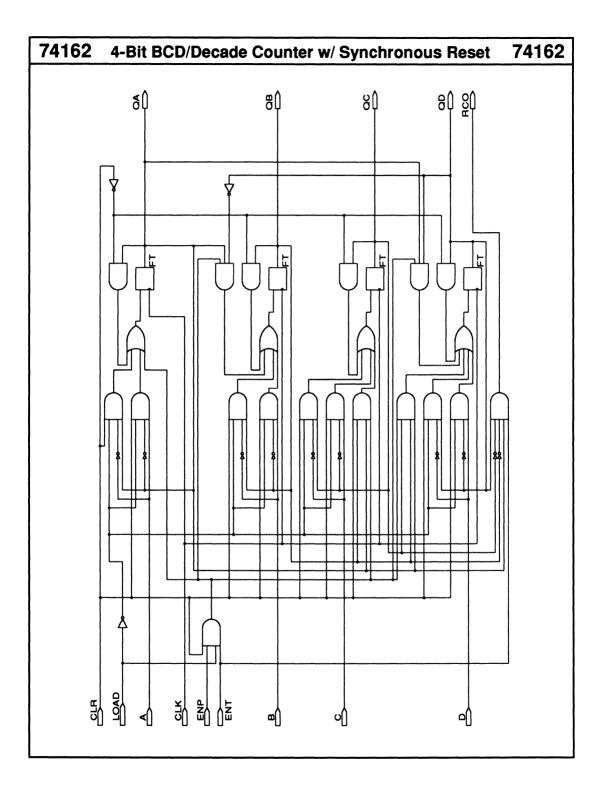

| 74162                                   | 4-Bit BCD/Decode Counter w/Synchronous Reset  | 62                                                                                                                                                                                                                                                                                                                                                                                          |

|                                         | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

| 74163                                   | 4-Bit Binary Counter w/Synchronous Reset      | 64                                                                                                                                                                                                                                                                                                                                                                                          |

|                                         | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

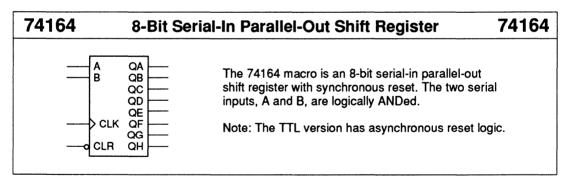

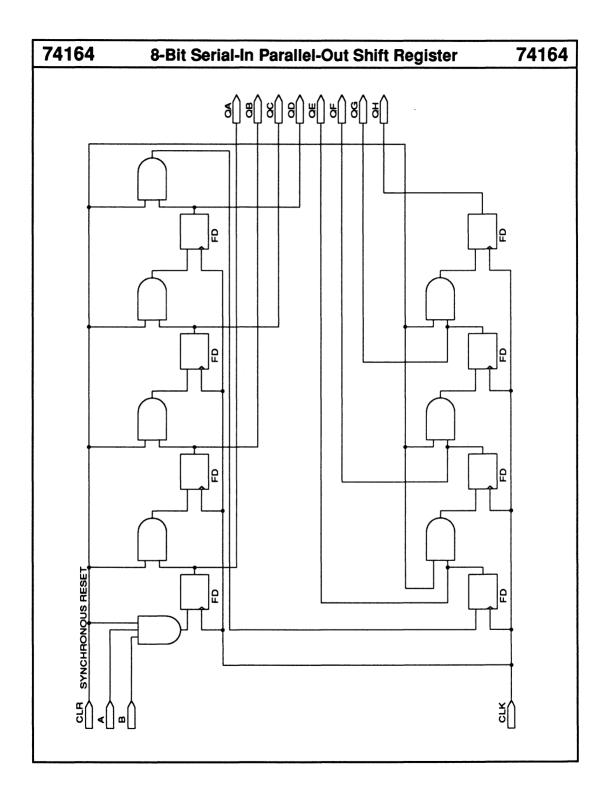

| 74164                                   | 8-Bit Serial-In Parallel-out Shift Register   |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

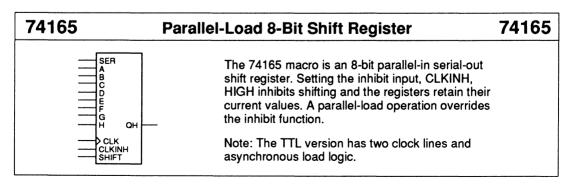

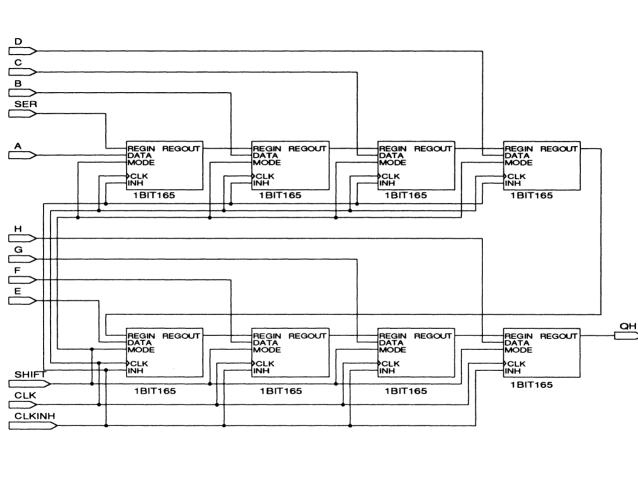

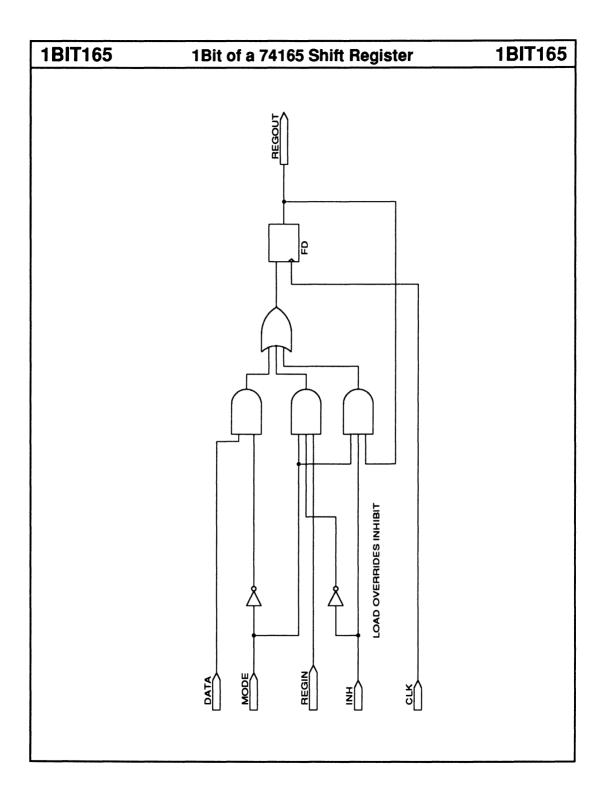

| 74165                                   | Parallel-Load 8-Bit Shift Register            |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         | 1 Bit of a 74165 Shift Register               |                                                                                                                                                                                                                                                                                                                                                                                             |

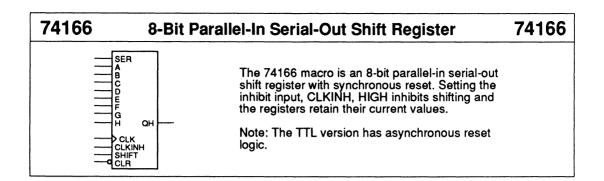

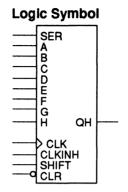

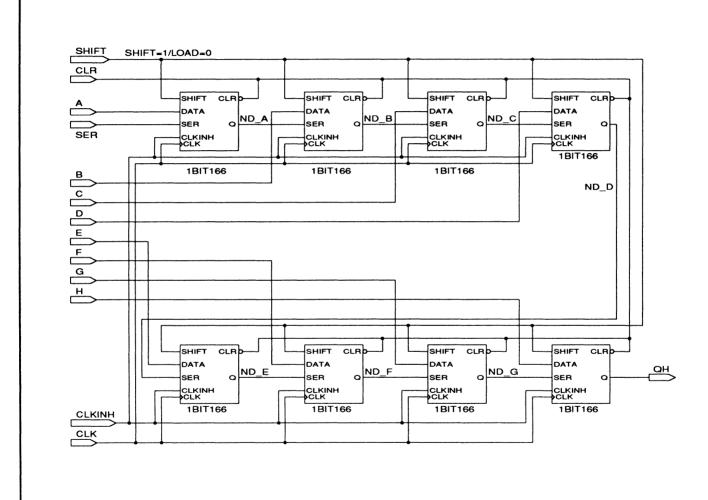

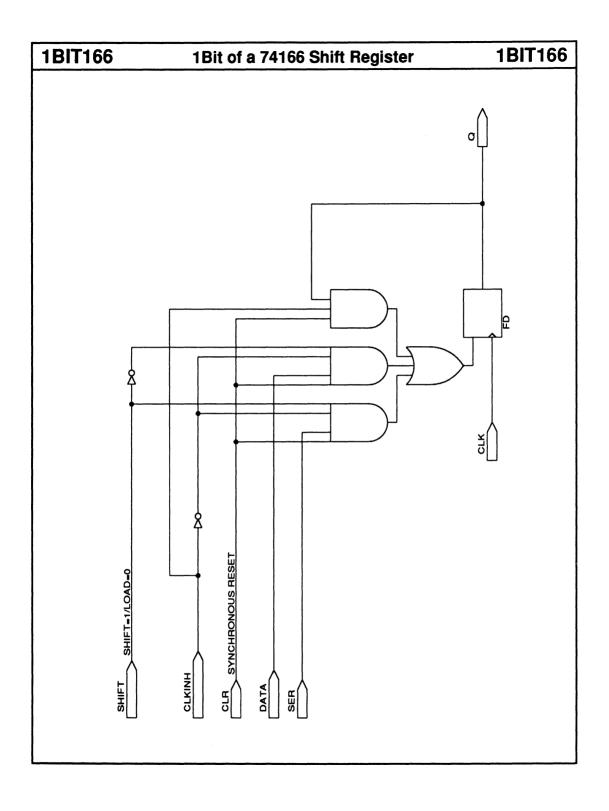

| 74166                                   | 8-Bit Parallel-In Serial-Out Shift Register   |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         | 1 Bit of a 74166 Shift Register               |                                                                                                                                                                                                                                                                                                                                                                                             |

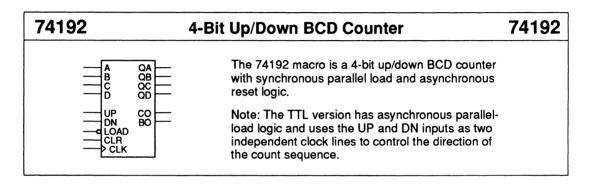

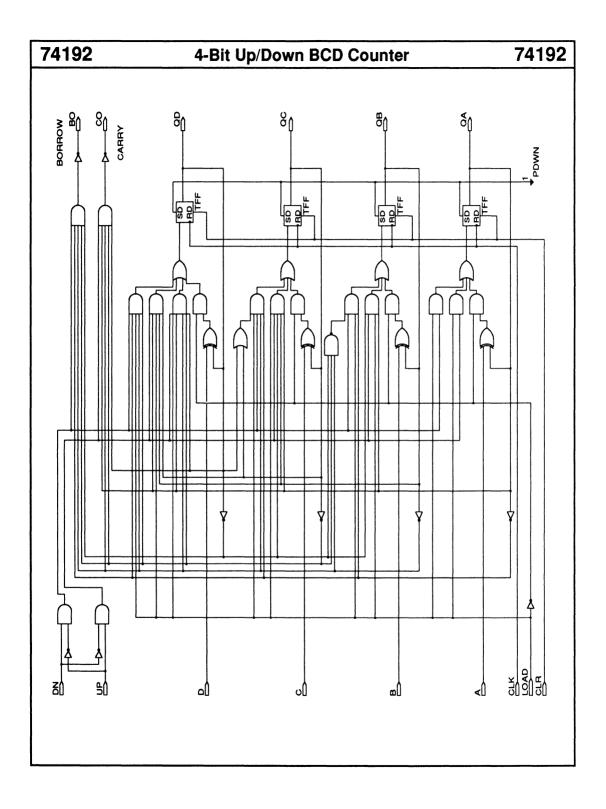

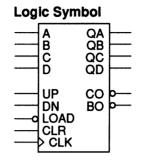

| 74192                                   | 4-Bit Up/Down BCD Counter                     |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

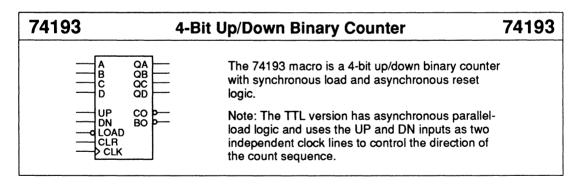

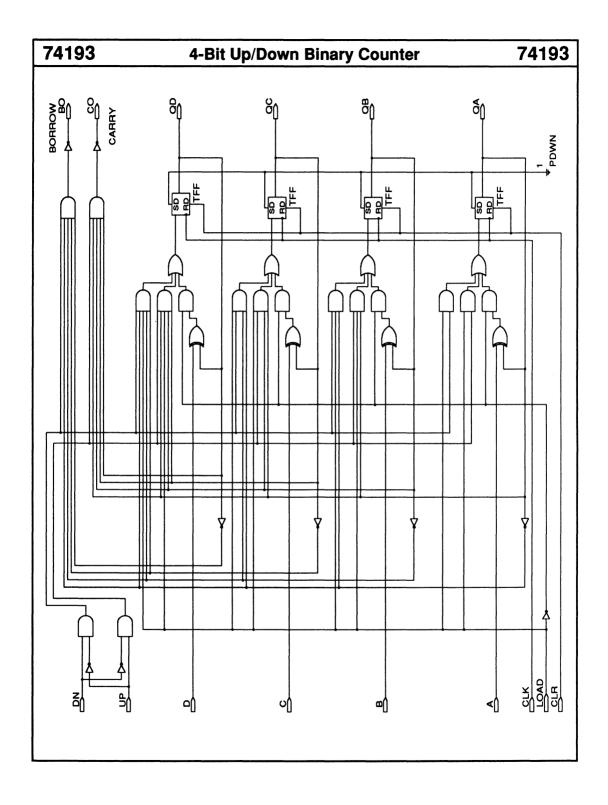

| 74193                                   | 4-Bit Up/Down Binary Counter                  |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

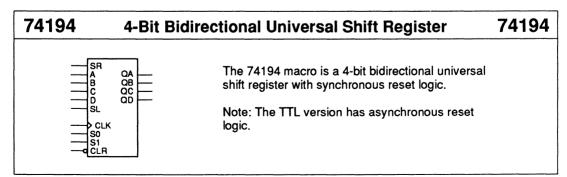

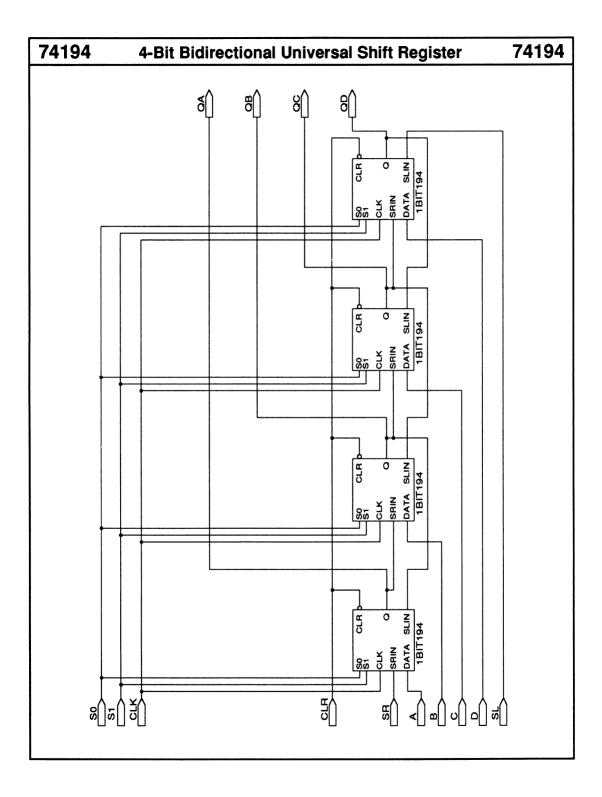

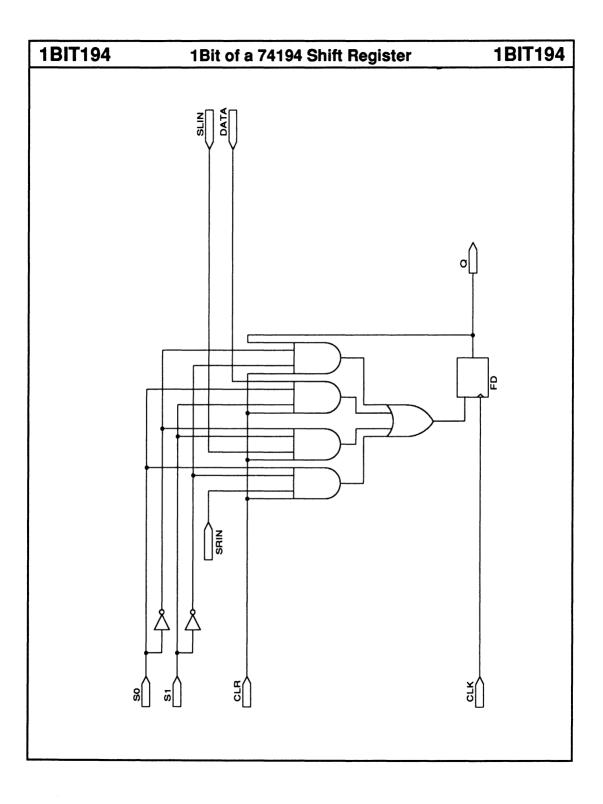

| 74194                                   | 4-Bit Bidirectional Universal Shift Register  |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         | 1 Bit of a 74194 Shift Register               |                                                                                                                                                                                                                                                                                                                                                                                             |

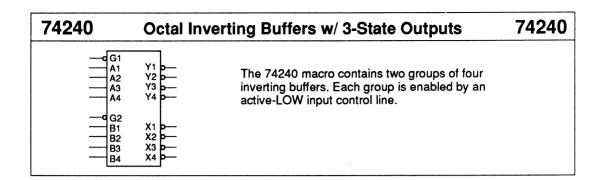

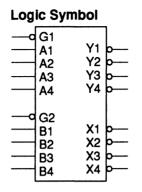

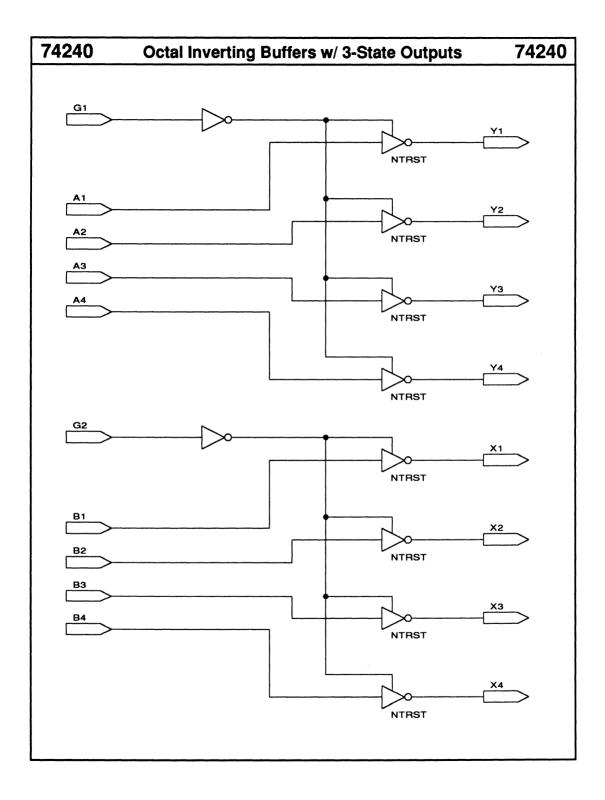

| 74240                                   | Octal Inverting Buffers w/3-State Outputs     |                                                                                                                                                                                                                                                                                                                                                                                             |

| 74240                                   | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

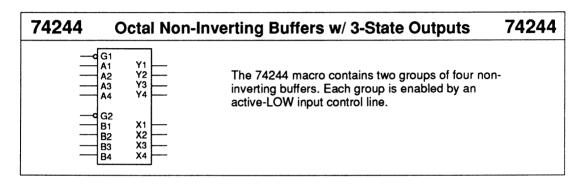

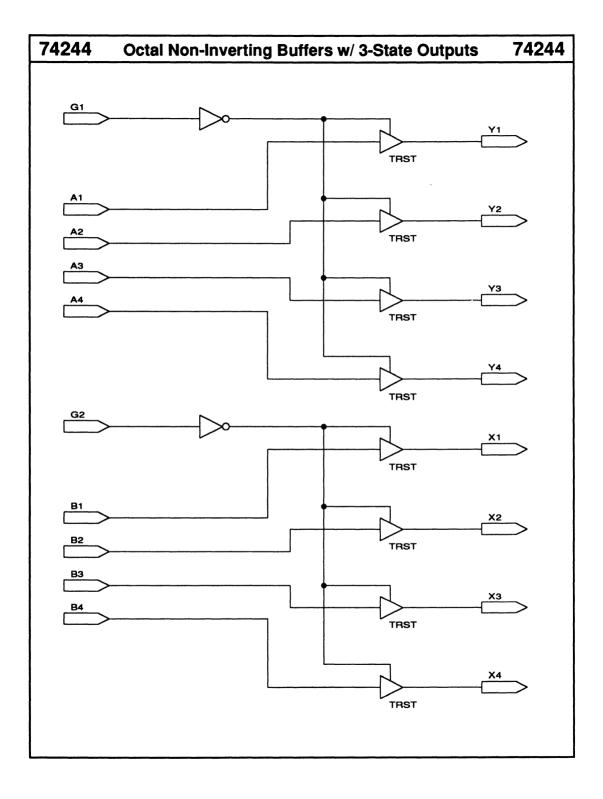

| 74244                                   | Octal Non-Inverting Buffers w/3-State Outputs |                                                                                                                                                                                                                                                                                                                                                                                             |

| , , , , , , , , , , , , , , , , , , , , | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

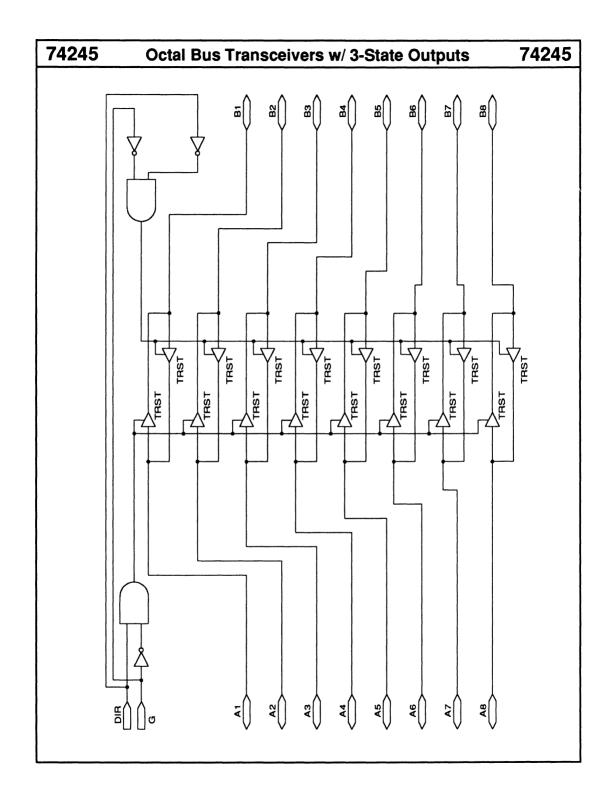

| 74245                                   | Octal Bus Transcribers w/3-State Outputs      |                                                                                                                                                                                                                                                                                                                                                                                             |

| , 1210                                  | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

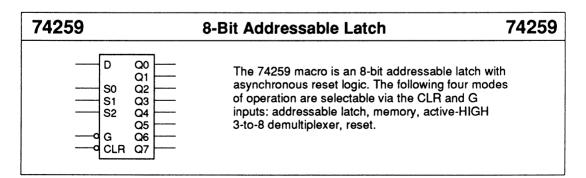

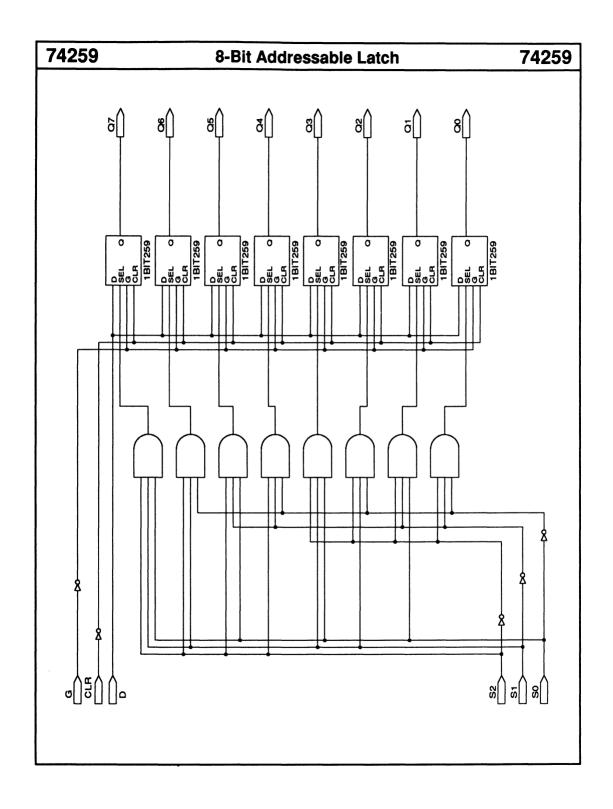

| 74259                                   | 8-Bit Addressable Latch                       |                                                                                                                                                                                                                                                                                                                                                                                             |

|                                         | Schematic                                     |                                                                                                                                                                                                                                                                                                                                                                                             |

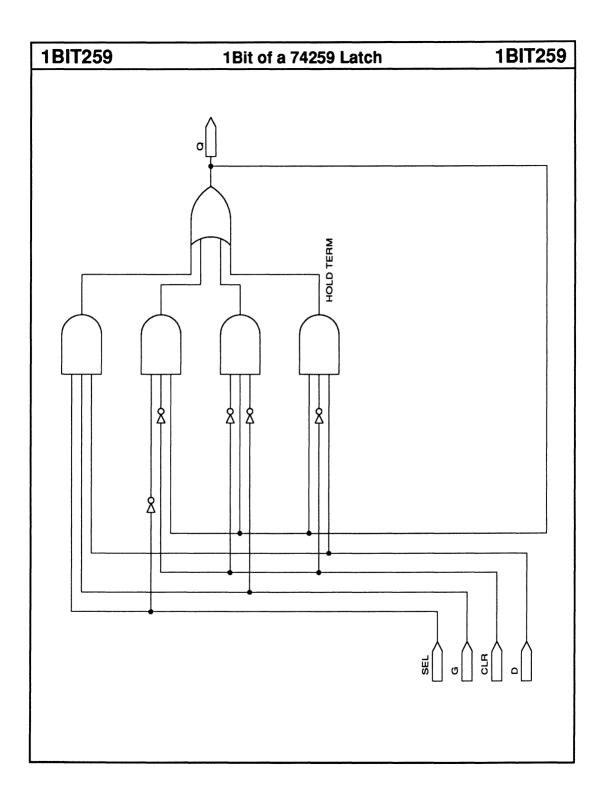

|                                         | 1 Bit of a 74259 Latch                        |                                                                                                                                                                                                                                                                                                                                                                                             |

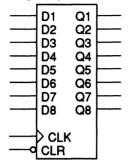

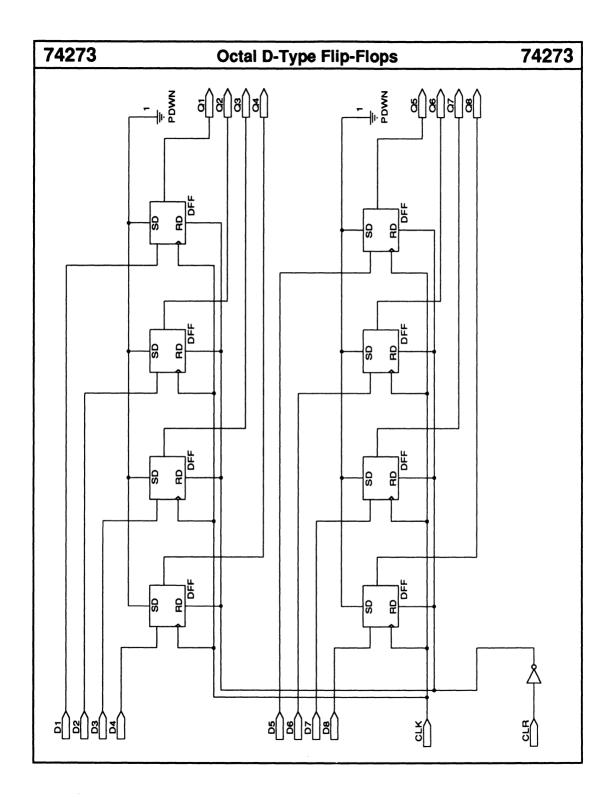

| 74273                                   | Octal D-Type Flip-Flops                       |                                                                                                                                                                                                                                                                                                                                                                                             |

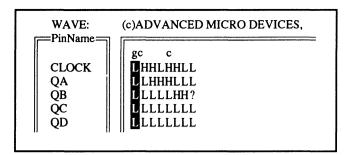

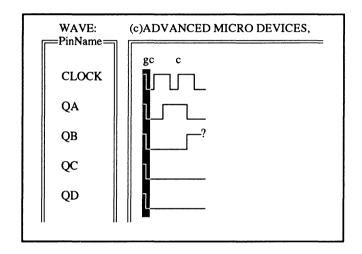

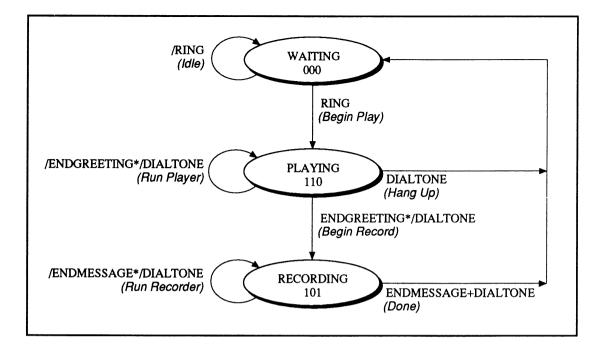

| 1 12/0                                  |                                               |                                                                                                                                                                                                                                                                                                                                                                                             |