## **Advanced Micro Devices**

# Schottky and Low-power Schottky Data Book Including Digital Signal Processing Handbook

Second Edition

First printing — November 1977 Second printing — July 1978

Copyright © 1978 by Advanced Micro Devices, Inc.

Advanced Micro Devices cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an Advanced Micro Devices' product.

901 Thompson Place, Sunnyvale, California 94086 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

#### **TABLE OF CONTENTS**

| IDEX SECTION                                                                                                                                                             |                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Application Note Index  Alpha Numeric Device Index  Functional Selector Guide                                                                                            | 1-                                              |

| TRODUCTION TO LOW-POWER SCHOTTKY                                                                                                                                         |                                                 |

| Comparison Between Am25LS and 54LS/74LS  Am25LS-54LS/74LS Low-Power Schottky Cross Reference  Designers Guide to High Performance Low-Power Schottky  Reliability Report | . 2-4                                           |

| DW-POWER SCHOTTKY DATA SHEETS                                                                                                                                            |                                                 |

| Definition of Standard Low-Power Schottky Terms Am25LS Am25LS-54LS/74LS Am26LS Am29                                                                                      | . 3-30<br>. 3-268                               |

|                                                                                                                                                                          |                                                 |

| GH SPEED SCHOTTKY DATA SHEETS                                                                                                                                            |                                                 |

| Definition of Standard Schottky Terms                                                                                                                                    |                                                 |

| Definition of Standard Schottky Terms                                                                                                                                    | . 4-3                                           |

| Definition of Standard Schottky Terms Am25S Am26S                                                                                                                        | . 4-3<br>. 4-51                                 |

| Definition of Standard Schottky Terms                                                                                                                                    | . 4-3<br>. 4-51<br>. 4-65                       |

| Definition of Standard Schottky Terms Am25S Am26S Am54S/74S                                                                                                              | . 4-3<br>. 4-51<br>. 4-65<br>. 4-123            |

| Definition of Standard Schottky Terms Am25S Am26S Am54S/74S Am8XXX                                                                                                       | . 4-3<br>. 4-5<br>. 4-65<br>. 4-123<br>. 4-148  |

| Definition of Standard Schottky Terms Am25S Am26S Am54S/74S Am8XXX Am93S  GITAL SIGNAL PROCESSING HANDBOOK                                                               | . 4-3<br>. 4-51<br>. 4-65<br>. 4-123<br>. 4-148 |

| Definition of Standard Schottky Terms Am25S Am26S Am54S/74S Am8XXX Am93S  GITAL SIGNAL PROCESSING HANDBOOK  ENERAL INFORMATION                                           | . 4-3<br>. 4-51<br>. 4-65<br>. 4-123<br>. 4-148 |

| Definition of Standard Schottky Terms Am25S Am26S Am54S/74S Am8XXX Am93S  GITAL SIGNAL PROCESSING HANDBOOK                                                               | . 4-3<br>. 4-51<br>. 4-65<br>. 4-123<br>. 4-148 |

## **Index Section**

| Application Note Index     | 1–1 |

|----------------------------|-----|

| Alpha Numeric Device Index | 1–2 |

| Functional Selector Guide  | 1-8 |

#### **APPLICATION NOTE INDEX**

|                                                              | Page  |

|--------------------------------------------------------------|-------|

| Designers Guide to High Performance                          |       |

| Low-Power Schottky                                           | 2-6   |

| Reliability Report Schottky and Low-Power                    |       |

| Schottky TTL Devices                                         | 2-20  |

| Understanding the Am25LS2517 and the                         |       |

| Am25LS381 Arithmetic Logic Units                             | 3-181 |

| The Am25LS2516 Eight-by-Eight LSI                            |       |

| Multiplier/Accumulator                                       | 3-211 |

| Use of the Am26LS29, 30, 31 and 32 Quad                      |       |

| Driver/Receiver Family in RS-422/423 Applications            | 3-283 |

| Schottky TTL MSI Registers                                   | 4-13  |

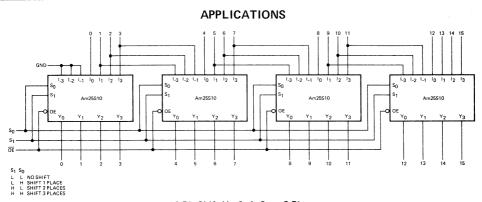

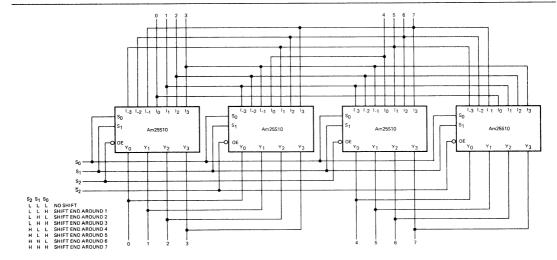

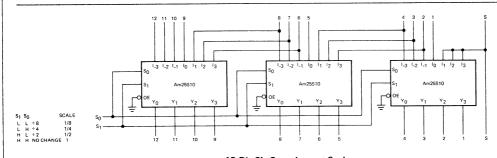

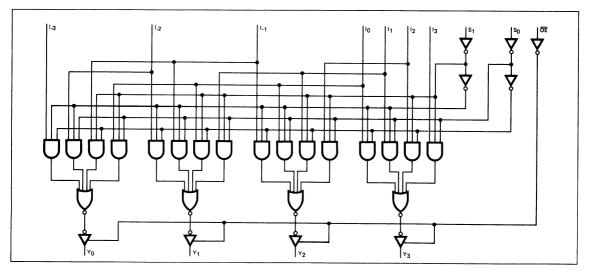

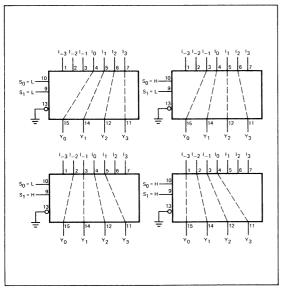

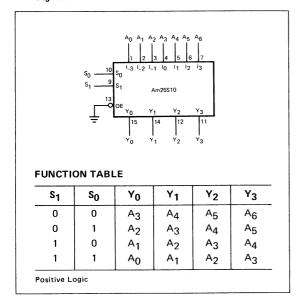

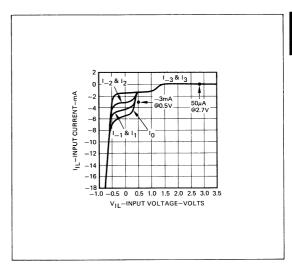

| Am25S10 Four-Bit Shifter                                     | 4-37  |

| Digital Signal Processing Handbook                           |       |

| Basic Digital Filter Theory                                  | 5-3   |

| Digital Filter Design                                        | 5-12  |

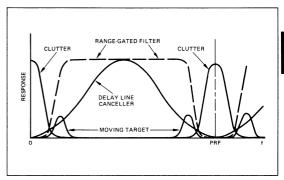

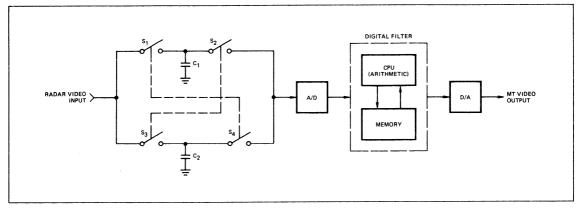

| Airborne MTI Radar — A Digital<br>Filter Application Example | 5-19  |

| Understanding Booth's Algorithm in Two's                     | 0.10  |

| Complement Digital Multiplication                            | 5-23  |

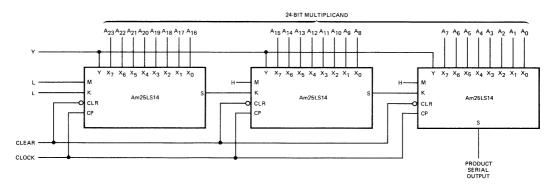

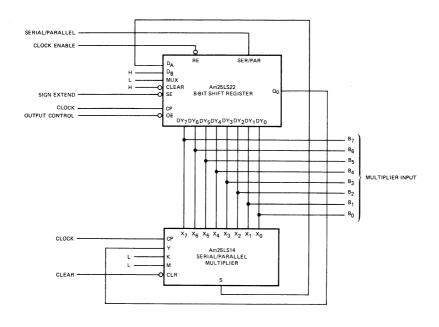

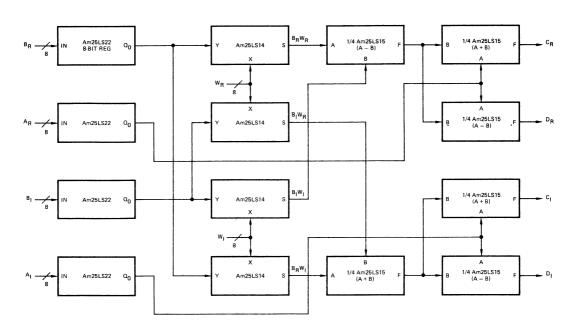

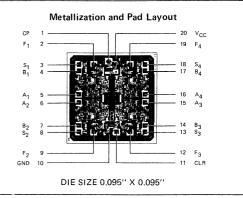

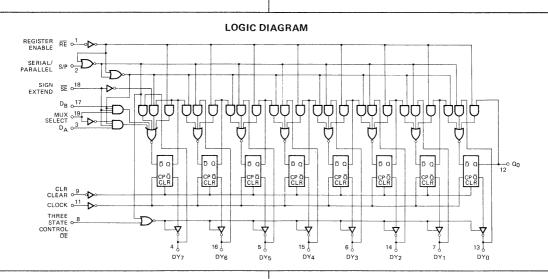

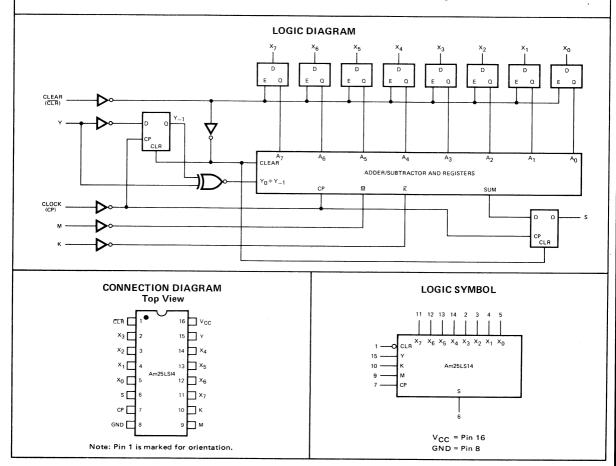

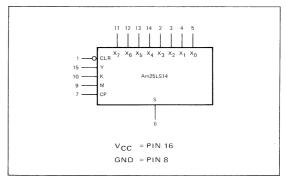

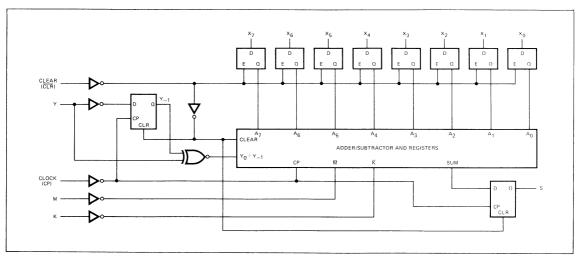

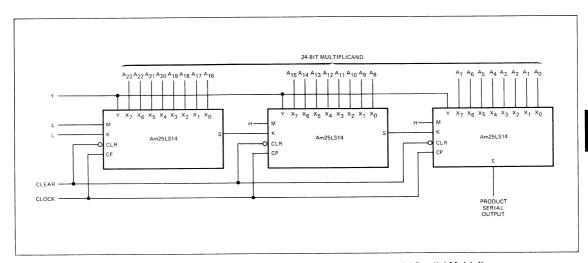

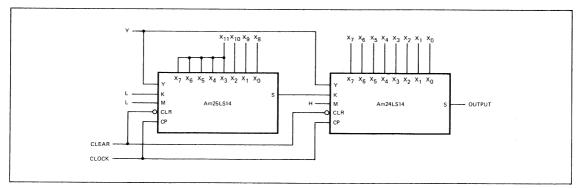

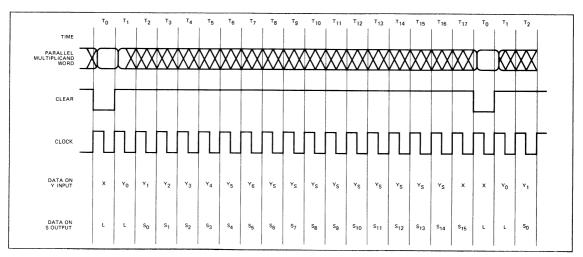

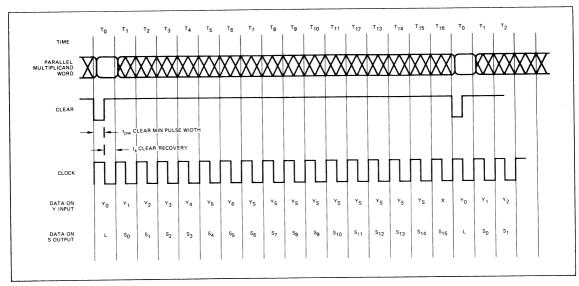

| A High-Speed Serial/Parallel<br>Multiplier – The Am25LS14    | 5-28  |

| Mechanization of the Am25LS14                                | 5-37  |

| How to Multiply and Divide in Two's Complement Hardware      | 5-41  |

| The Am25S05 Two's Complement Digital Multiplier              | 5-49  |

|                                                              |       |

#### **ALPHA-NUMERIC INDEX**

|   | Product                 | Description                                                    | Page    |

|---|-------------------------|----------------------------------------------------------------|---------|

|   | Am25LS07                | Six-Bit Register; Common Enable                                | 3-3     |

|   |                         | Four-Bit Register; Common Enable                               |         |

|   |                         | Four-Bit Register; Multiplexer Inputs                          |         |

|   |                         | Eight-Bit Serial/Parallel Two's Complement Multiplier          |         |

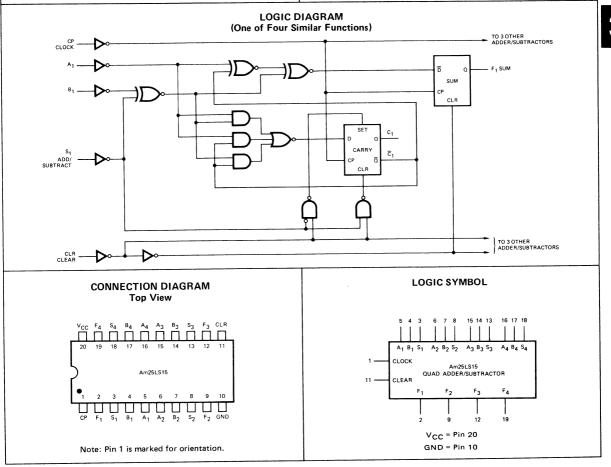

|   |                         | Four-Bit Serial/Parallel Adder Subtracter                      |         |

|   |                         | Eight-Bit Serial/Parallel Register; Sign Extend                |         |

|   |                         | Eight-Bit Universal Shift Register; Synchronous Clear          |         |

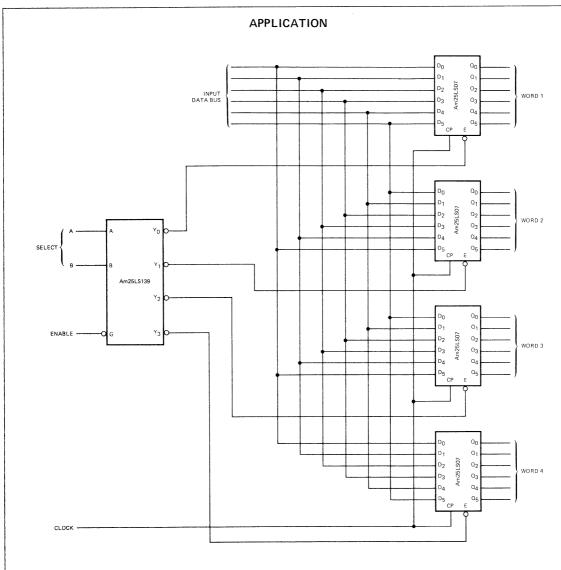

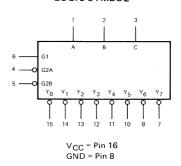

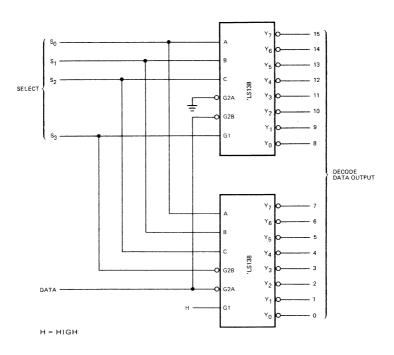

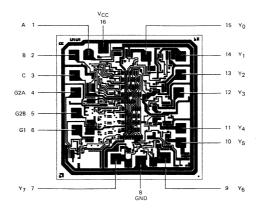

|   | Am25LS138               | One-of-Eight Decoder/Demultiplexer                             |         |

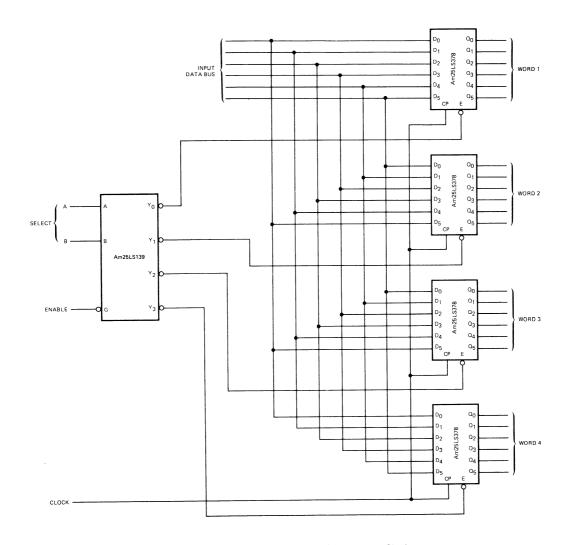

|   | Am25LS139               | Dual One-of-Four Decoder/Demultiplexer                         |         |

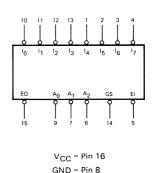

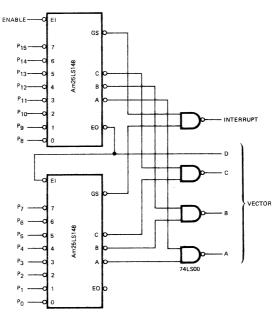

|   | Am25LS148               | Priority Encoder; Eight-Line to Three-Line                     |         |

|   | Am25LS151               | Eight-Input Multiplexer                                        |         |

| ٠ | Am25LS153               | Dual-Four-Input Multiplexer                                    |         |

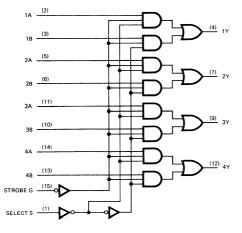

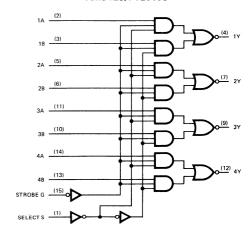

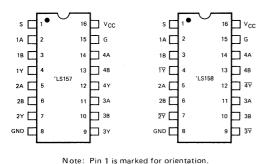

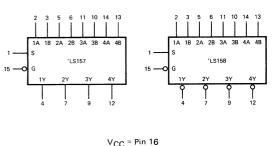

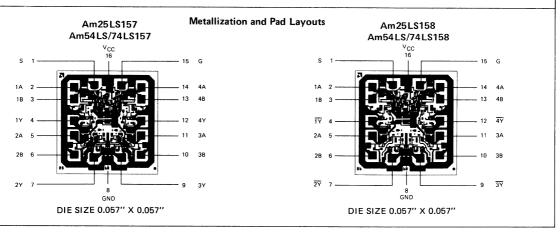

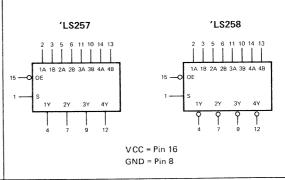

| ~ | Am25LS157               | Quad Two-Input Multiplexer; Non-Inverting                      |         |

|   | Am25LS158               | Quad Two-Input Multiplexer; Inverting                          |         |

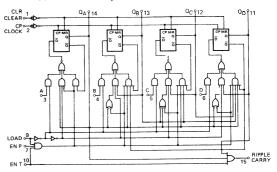

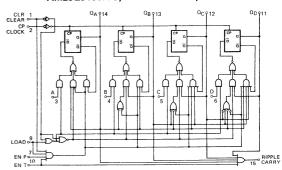

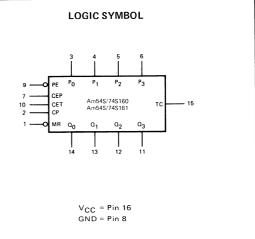

|   | Am25LS160A              | Synchronous BCD Decade Counter; Asynchronous Clear             | 3-59    |

|   | Am25LS161A              | Synchronous Four-Bit Binary Counter; Asynchronous Clear        |         |

|   | Am25LS162A              | Synchronous BCD Decade Counter; Synchronous Clear              | 3-59    |

|   | Am25LS163A              | Synchronous Four-Bit Binary Counter; Synchronous Clear         |         |

|   | Am25LS164               | Eight-Bit Serial-In, Parallel-Out Shift Register               |         |

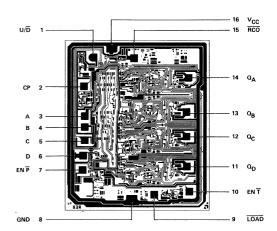

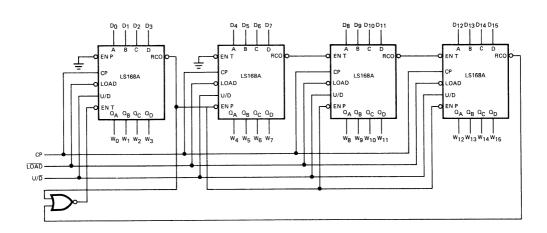

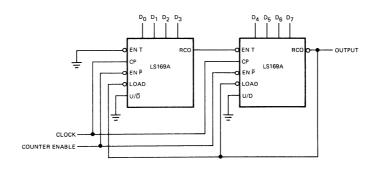

|   | Am25LS168A              | Synchronous BCD Decade Up-Down Counter; Programmable           |         |

|   | Am25LS169A              | Synchronous Four-Bit Binary Up-Down Counter; Programmable      |         |

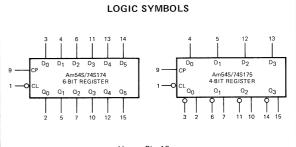

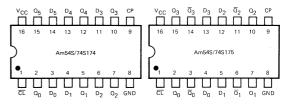

|   | Am25LS174               | Six-Bit Register; Common Clear                                 |         |

|   | Am25LS175               | Quad Register; Common Clear                                    |         |

|   | Am25LS181               | Four-Bit ALU/Function Generator                                |         |

|   | Am25LS190               | BCD Decade Up-Down Counter; Down-Up Mode Control               |         |

|   | Am25LS191               | Four-Bit Binary Up-Down Counter; Down-Up Mode Control          |         |

|   | Am25LS192               | BCD Decade Up-Down Counter; Dual Clocks                        | 3-99    |

|   | Am25LS193               | Four-Bit Binary Up-Down Counter; Dual Clocks                   | 3-99    |

|   | Am25LS194A              | Four-Bit Register; Shift Right, Left or Parallel Load          |         |

|   | Am25LS194A              | Four-Bit Register; Shift Right or Parallel Load                |         |

|   | Am25LS240               | Octal Bus Driver; Inverting, Three-State Outputs               |         |

|   |                         | Octal Bus Driver; Non-Inverting, Three-State Outputs           |         |

|   | Am25LS241               | Octal Three-State Bus Transceiver                              |         |

|   | Am25LS242               | Octal Three-State Bus Transceiver                              |         |

|   | Am25LS243               | Octal Three-State Buffer                                       |         |

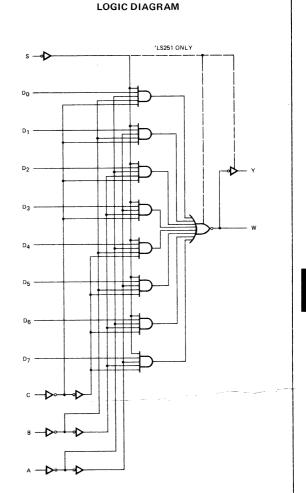

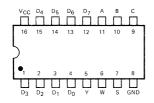

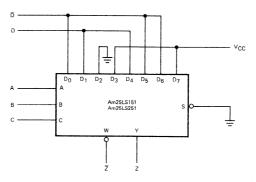

|   | Am25LS244               | Eight-Input Multiplexer; Three-State Outputs                   |         |

|   | Am25LS251               | Dual Four-Input Multiplexer; Three-State Outputs               |         |

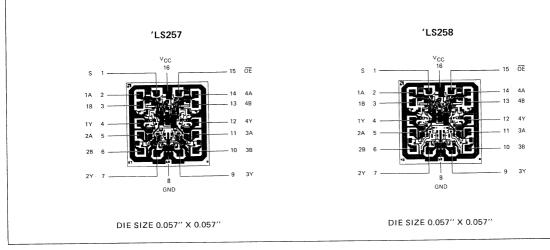

|   | Am25LS253               | Quad Two-Input Multiplexer; Non-Inverting, Three-State Outputs |         |

|   | Am25LS257               | Quad Two-Input Multiplexer; Inverting, Three-State Outputs     |         |

|   | Am25LS258               | Octal D-Register; Common Clear (Buffered Outputs)              |         |

|   | Am25LS273B              | Four-Bit Parallel Accumulator                                  |         |

|   | Am25LS281               | Eight-Bit Universal Shift Register; Asynchronous Clear         | . 3-145 |

|   | Am25LS299               | See Am25LS22                                                   |         |

|   | Am25LS322               | See Am25LS23                                                   |         |

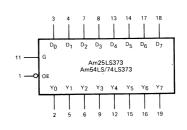

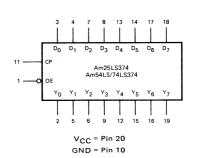

|   | Am25LS323               | Octal Transparent Latch; Three-State Outputs                   |         |

|   | Am25LS373               | Octal D-Register; Three-State Outputs                          |         |

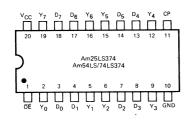

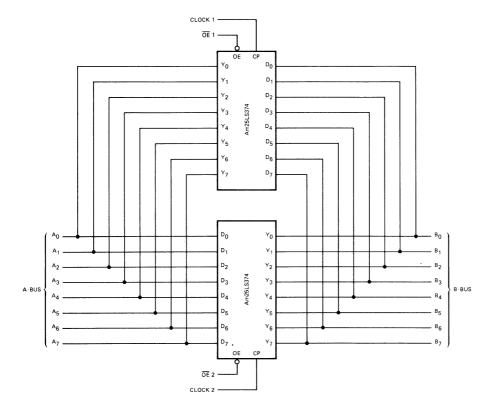

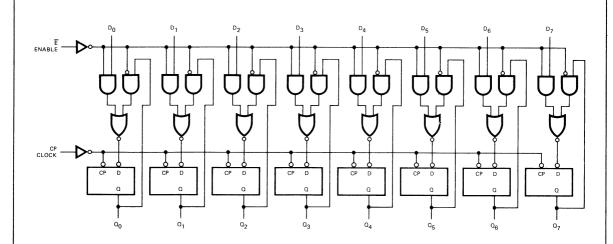

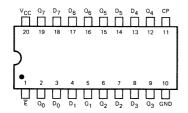

|   | Am25LS374<br>Am25LS377B | Octal D-Register; Common Enable (Buffered Outputs)             | 3-163   |

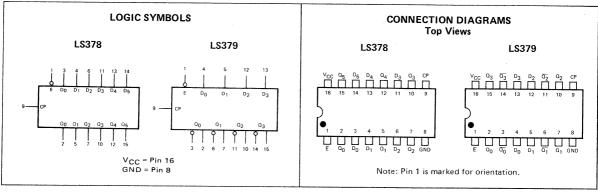

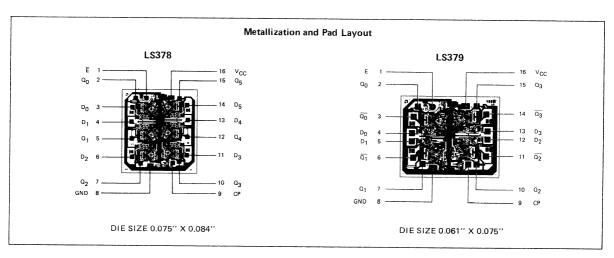

|   |                         | Six-Bit Register, Common Enable                                | 3-168   |

|   | Am25LS378<br>Am25LS379  | Four-Bit Register, Common Enable                               | . 3-168 |

|   |                         | Four-Bit ALU/Function Generator (20 pin 25LS181)               | . 3-173 |

|   | Am25LS381               | See Am25LS14                                                   | 3-11    |

|   | Am25LS384               | See Am25LS15                                                   |         |

|   | Am25LS385               | OCC AMEDIO IO                                                  |         |

| Product    | Description                                                     | Page  |

|------------|-----------------------------------------------------------------|-------|

| Am25LS388  | See Am25LS2518                                                  | 3-21  |

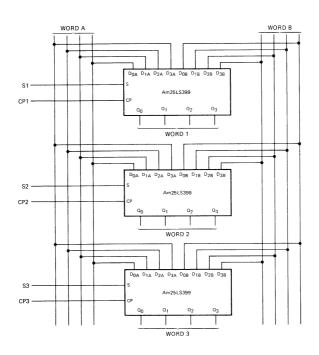

| Am25LS399  | Four-Bit Register, Multiplexed Inputs                           | 3-190 |

| Am25LS533  | Octal Transparent Latch; Three-State Outputs (Inv.)             |       |

| Am25LS534  | Octal D-Register;Three-State Outputs (Inv.)                     | 3-15  |

| Am25LS668  | See Am25LS168A                                                  |       |

| Am25LS669  | See Am25LS169A                                                  |       |

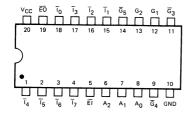

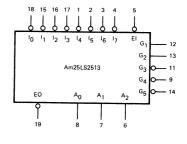

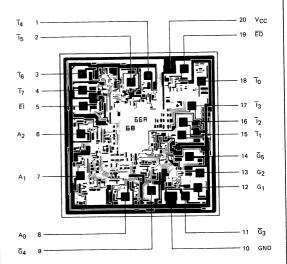

| Am25LS2513 | Priority Encoder; Three-State Outputs, Eight-Line to Three-Line |       |

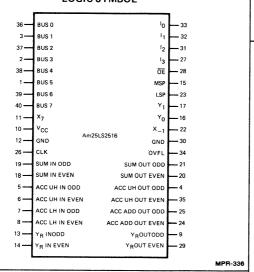

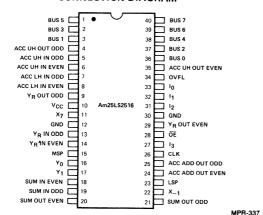

| Am25LS2516 | Eight-Bit by Eight-Bit Multiplier Accumulator                   |       |

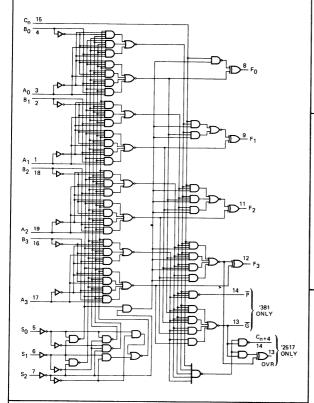

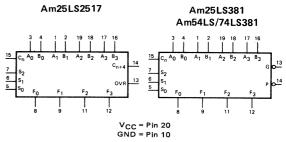

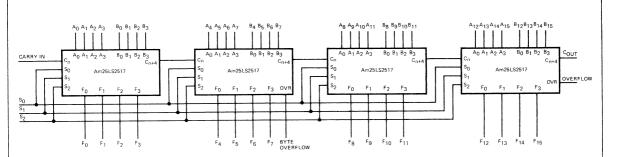

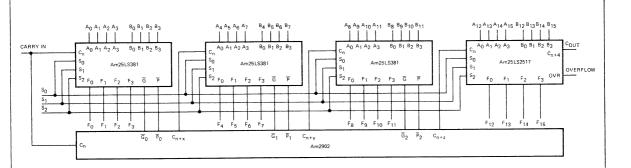

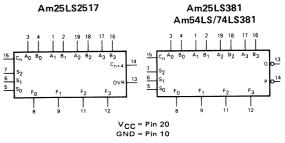

| Am25LS2517 | Four-Bit ALU/Function Generator; Overflow Detection             |       |

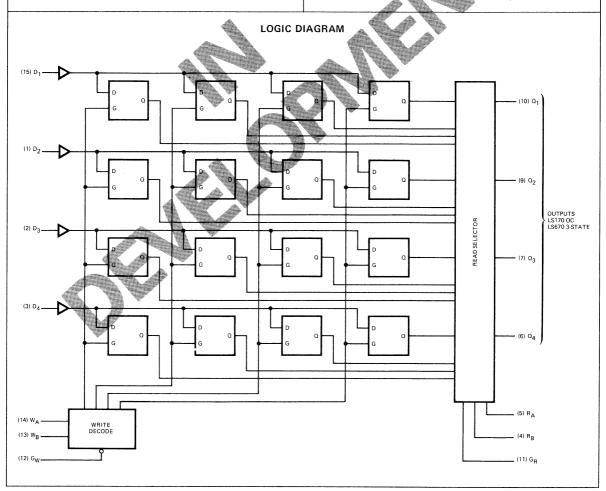

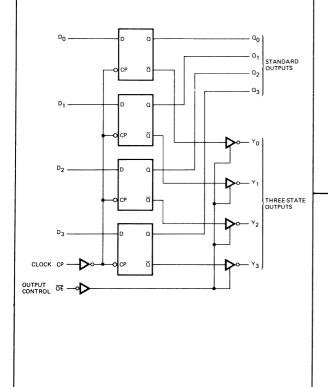

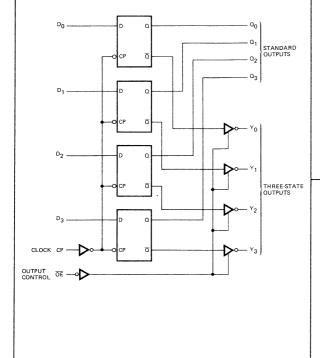

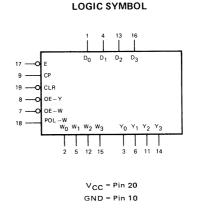

| Am25LS2518 | Quad Register with Standard and Three-State Outputs             |       |

| Am25LS2519 | Quad Register with Dual Three-State Outputs                     |       |

| Am25LS2520 | Octal D-Register; Common Clear and Enable, Three-State Outputs  |       |

| Am25LS2521 | Eight-Bit Comparator                                            |       |

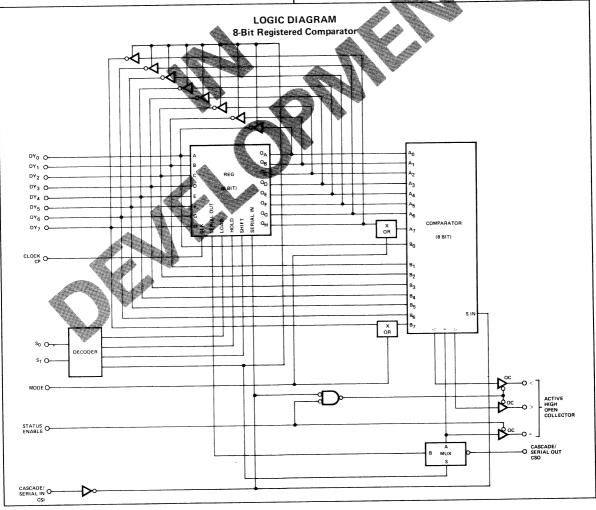

| Am25LS2524 | Registered Comparator                                           |       |

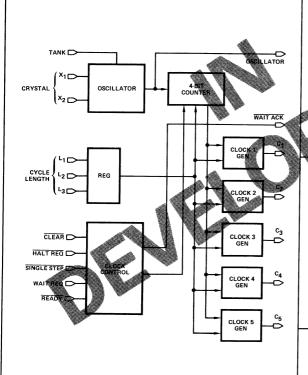

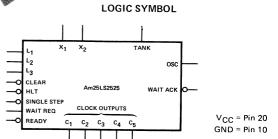

| Am25LS2525 | System Clock Generator and Driver                               |       |

| Am25LS2535 | Eight-Bit Multiplexer, Control Storage                          |       |

| Am25LS2536 | Eight-Bit Decoder; Control Storage                              |       |

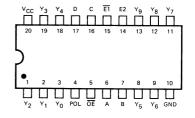

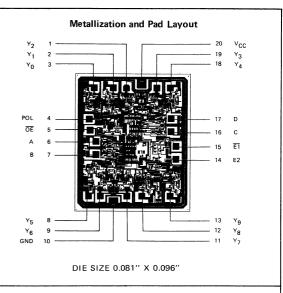

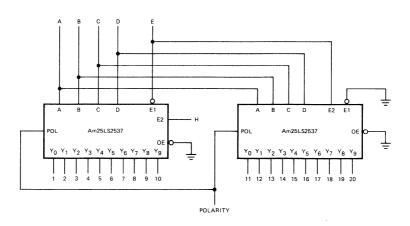

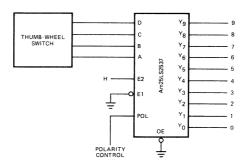

| Am25LS2537 | One-of-Ten Decoder; Three-State Outputs                         |       |

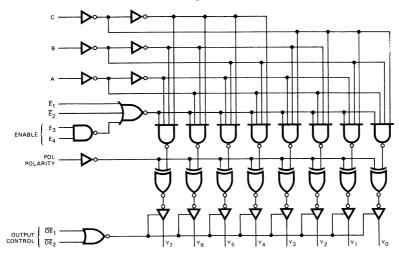

| Am25LS2538 | One-of-Eight Decoder; Three-State Outputs                       |       |

| Am25LS2539 | Dual One-of-Four Decoder; Three-State Outputs                   |       |

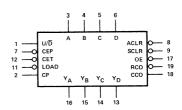

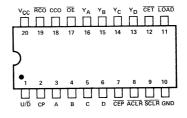

| Am25LS2568 | BCD Decade Up-Down Counter; Three-State Outputs                 |       |

| Am25LS2569 | Four-Bit Binary Up-Down Counter; Three-State Outputs            |       |

| Am26LS29   | Quad Driver RS-423, Three State                                 |       |

| Am26LS30   | Quad Driver RS-422/423                                          |       |

| Am26LS31   | Quad Driver RS-422, High-Speed                                  |       |

| Am26LS32   | Quad Differential Line Receiver RS-422/423                      |       |

| Am26LS33   | Quad Differential Line Receiver, High Common Mode               |       |

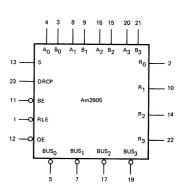

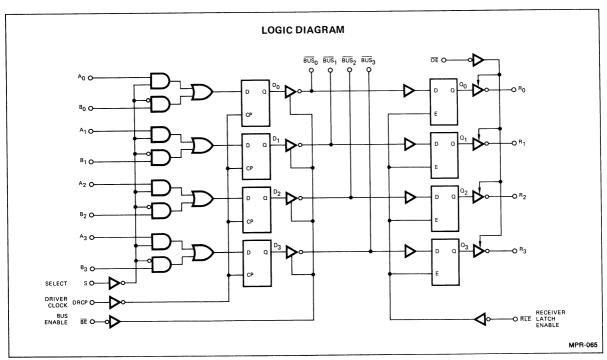

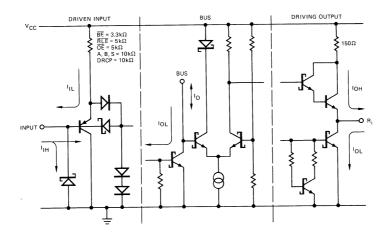

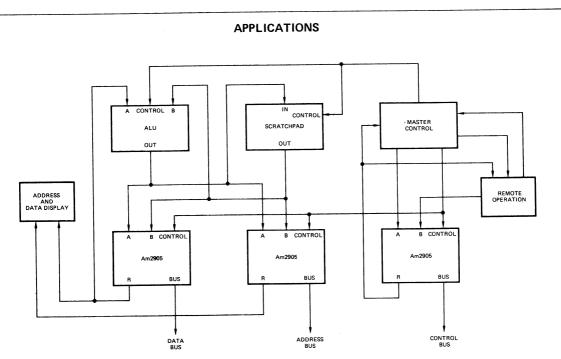

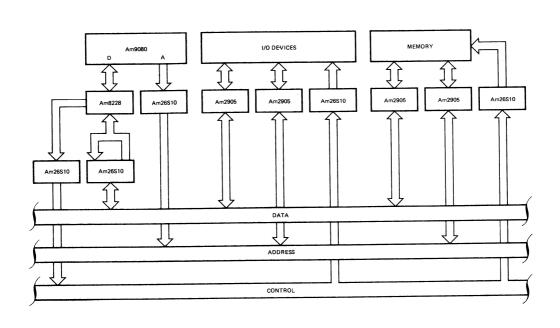

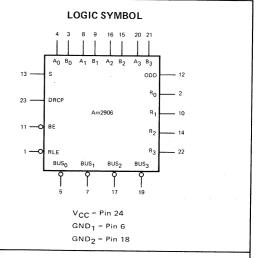

| Am2905     | Quad Two-Input OC Bus Transceiver with Three-State Receiver     |       |

| Am2906     | Quad Two-Input OC Bus Transceiver with Parity                   |       |

| Am2907     | Quad Bus Transceiver with Three-State Receiver and Parity       |       |

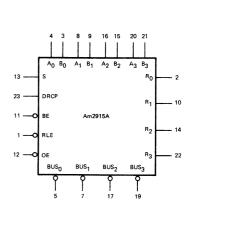

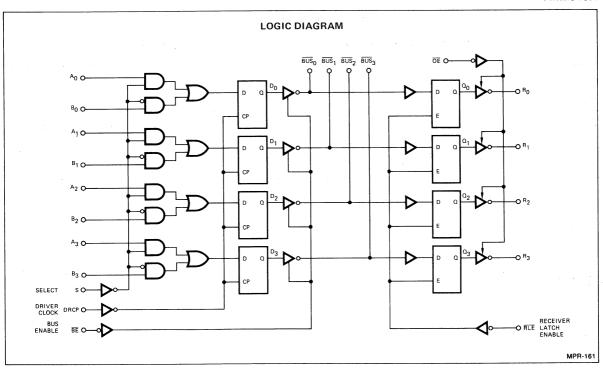

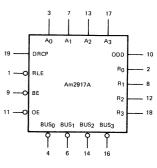

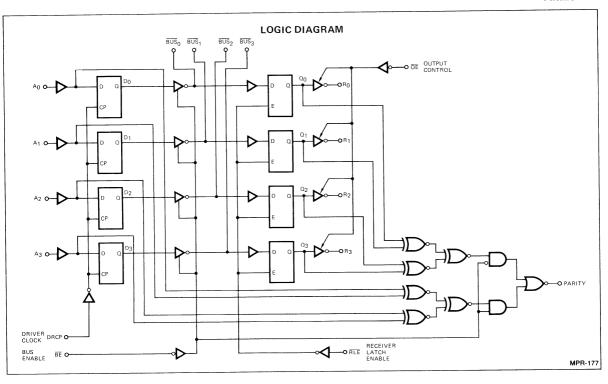

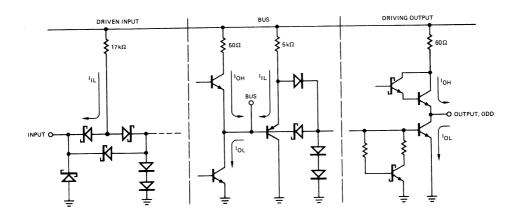

| Am2915A    | Quad Three-State Bus Transceiver with Interface Logic           |       |

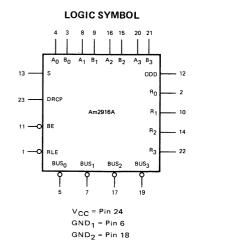

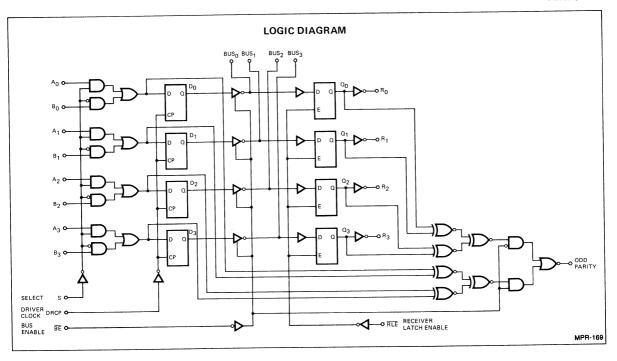

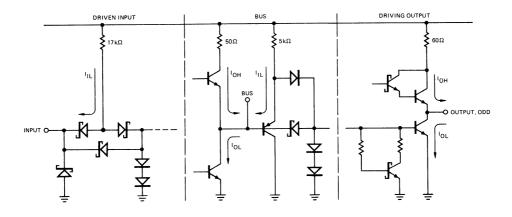

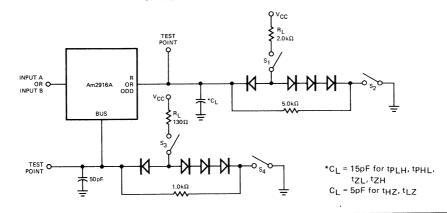

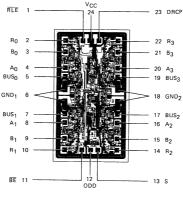

| Am2916A    | Quad Three-State Bus Transceiver with Interface Logic           |       |

| Am2917A    | Quad Three-State Bus Transceiver with Interface Logic           |       |

| Am54LS138  | One-of-Eight Decoder/Demultiplexer                              |       |

| Am54LS139  | Dual One-of-Four Decoder/Demultiplexer                          |       |

| Am54LS148  | Priority Encoder; Eight-Line to Three-Line                      |       |

| Am54LS151  | Eight-Input Multiplexer                                         |       |

| Am54LS153  | Dual-Four-Input Multiplexer                                     |       |

| Am54LS157  | Quad Two-Input Multiplexer; Non-Inverting                       |       |

| Am54LS158  | Quad Two-Input Multiplexer; Inverting                           |       |

| Am54LS160A | Synchronous BCD Decade Counter; Asynchronous Clear              |       |

| Am54LS161A | Synchronous Four-Bit Binary Counter; Asynchronous Clear         |       |

| Am54LS162A | Synchronous BCD Decade Counter; Synchronous Clear               |       |

| Am54LS163A | Synchronous Four-Bit Binary Counter; Synchronous Clear          |       |

| Am54LS164  | Eight-Bit Serial-In, Parallel-Out Shift Register                |       |

| Am54LS168A | Synchronous BCD Decade Up-Down Counter; Programmable            |       |

| Am54LS169A | Synchronous Four-Bit Binary Up-Down Counter; Programmable       |       |

| Am54LS174  | Six-Bit Register; Common Clear                                  |       |

| Am54LS175  | Quad Register; Common Clear                                     |       |

| Am54LS181  | Four-Bit ALU/Function Generator                                 |       |

| Am54LS190  | BCD Decade Up-Down Counter; Down-Up Mode Control                |       |

| Am54LS191  | Four-Bit Binary Up-Down Counter; Down-Up Mode Control           |       |

| Product    | Description                                                    | Page    |

|------------|----------------------------------------------------------------|---------|

| Am54LS192  | BCD Decade Up-Down Counter; Dual Clocks                        | . 3-99  |

| Am54LS193  | Four-Bit Binary Up-Down Counter; Dual Clocks                   | . 3-99  |

| Am54LS194A | Four-Bit Register; Shift Right, Left or Parallel Load          |         |

| Am54LS195A | Four-Bit Register; Shift Right or Parallel Load                |         |

| Am54LS240  | Octal Bus Driver; Inverting, Three-State Outputs               | . 3-110 |

| Am54LS241  | Octal Bus Driver; Non-Inverting, Three-State Outputs           | . 3-114 |

| Am54LS242  | Octal Three State Bus Transceiver                              |         |

| Am54LS243  | Octal Three-State Bus Transceiver                              |         |

| Am54LS244  | Octal Three-State Buffer                                       |         |

| Am54LS245  | Octal Bus Transceiver (Alternate recommendation)               |         |

| Am54LS251  | Eight-Input Multiplexer; Three-State Outputs                   | , 3-124 |

| Am54LS253  | Dual Four-Input Multiplexer; Three-State Outputs               |         |

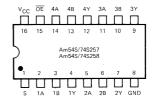

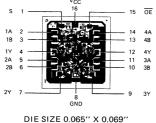

| Am54LS257  | Quad Two-Input Multiplexer; Non-Inverting, Three State Outputs | . 3-126 |

| Am54LS258  | Quad Two-Input Multiplexer; Inverting, Three-State Outputs     | . 3-126 |

| Am54LS273B | Octal D-Register; Common Clear (Buffered Outputs)              | . 3-131 |

| Am54LS281  | Four-Bit Parallel Accumulator                                  | . 3-126 |

| Am54LS299  | Eight-Bit Universal Shift Register; Asynchronous Clear         | . 3-145 |

| Am54LS322  | See Am25LS22                                                   |         |

| Am54LS323  | See Am25LS23                                                   | 3-26    |

| Am54LS348  | Three-State Priority Encoder (Alternate Recommendation)        | . 3-153 |

| Am54LS373  | Octal Transparent Latch; Three-State Outputs                   | . 3-154 |

| Am54LS374  | Octal D-Register; Three-State Outputs                          | . 3-158 |

| Am54LS377B | Octal D-Register; Common Enable (Buffered Outputs)             | . 3-163 |

| Am54LS378  | Six-Bit Register, Common Enable                                | . 3-168 |

| Am54LS379  | Four-Bit Register, Common Enable                               | . 3-168 |

| Am54LS381  | Four-Bit ALU/Function Generator (20 pin 25LS181                | . 3-173 |

| Am54LS382  | Four-Bit ALU/Function Generator (See Am25LS2517)               | . 3-173 |

| Am54LS384  | See Am25LS14                                                   |         |

| Am54LS385  | See Am25LS15                                                   |         |

| Am54LS388  | See Am25LS2518                                                 |         |

| Am54LS399  | Four-Bit Register, Multiplexed Input                           |         |

| Am54LS424  | See Am8224                                                     |         |

| Am54LS533  | Octal Transparent Latch; Three-State Outputs (Inv.)            | . 3-154 |

| Am54LS534  | Octal D-Register; Three-State Outputs (Inv.)                   | . 3-158 |

| Am54LS568  | See Am25LS2568                                                 | 3-262   |

| Am54LS569  | See Am25LS2569                                                 |         |

| Am54LS668  | Synchronous BCD Decade Up-Down Counter; Programmable           |         |

| Am54LS669  | Synchronous Four-Bit Binary Up-Down Counter; Programmable      |         |

| Am74LS138  | One-of-Eight Decoder/Demultiplexer                             |         |

| Am74LS139  | Dual One-of-Four Decoder/Demultiplexer                         |         |

| Am74LS148  | Priority Encoder; Eight-Line to Three-Line                     | 3-39    |

| Am74LS151  | Eight-Input Multiplexer                                        |         |

| Am74LS153  | Dual-Four-Input Multiplexer                                    | 3-50    |

| Am74LS157  | Quad Two-Input Multiplexer; Non-Inverting                      |         |

| Am74LS158  | Quad Two-Input Multiplexer; Inverting                          |         |

| Am74LS160A | Synchronous BCD Decade Counter; Asynchronous Clear             | 3-59    |

| Am74LS161A | Synchronous Four-Bit Binary Counter; Asynchronous Clear        |         |

| Am74LS162A | Synchronous BCD Decade Counter; Synchronous Clear              |         |

| Am74LS163A | Synchronous Four-Bit Binary Counter; Synchronous Clear         | 3-59    |

| Am74LS164  | Eight-Bit Serial-In, Parallel-Out Shift Register               | 3-64    |

| Am74LS168A | Synchronous BCD Decade Up-Down Counter; Programmable           |         |

| Am74LS169A | Synchronous Four-Bit Binary Up-Down Counter; Programmable      | 3-69    |

|            |                                                                |         |

| Product    | Description                                                    | Page    |

|------------|----------------------------------------------------------------|---------|

| Am74LS174  | Six-Bit Register; Common Clear                                 | 3-81    |

| Am74LS175  | Quad Register; Common Clear                                    | 3-81    |

| Am74LS181  | Four-Bit ALU/Function Generator                                |         |

| Am74LS190  | BCD Decade Up-Down Counter; Down-Up Mode Control               |         |

| Am74LS191  | Four-Bit Binary Up-Down Counter, Down-Up Mode Control          | . 3-93  |

| Am74LS192  | BCD Decade Up-Down Counter; Dual Clocks                        |         |

| Am74LS193  | Four-Bit Binary Up-Down Counter; Dual Clocks                   | . 3-99  |

| Am74LS194A | Four-Bit Register; Shift Right, Left or Parallel Load          | . 3-105 |

| Am74LS195A | Four-Bit Register; Shift Right or Parallel Load                | 3-105   |

| Am74LS240  | Octal Bus Driver; Inverting, Three-State Outputs               |         |

| Am74LS241  | Octal Bus Driver; Non-Inverting, Three-State Outputs           |         |

| Am74LS242  | Octal Three-State Bus Transceiver                              | . 3-118 |

| Am74LS243  | Octal Three-State Bus Transceiver                              | . 3-118 |

| Am74LS244  | Octal Three-State Buffer                                       | . 3-114 |

| Am74LS245  | Octal Bus Transceiver (Alternate Recommendation)               |         |

| Am74LS251  | Eight-Input Multiplexer; Three-State Outputs                   | . 3-124 |

| Am74LS253  | Dual Four-Input Multiplexer; Three-State Outputs               |         |

| Am74LS257  | Quad Two-Input Multiplexer; Non-Inverting, Three-State Outputs | . 3-126 |

| Am74LS258  | Quad Two-Input Multiplexer; Inverting, Three-State Outputs     | . 3-126 |

| Am74LS273B | Octal D-Register; Common Clear (Buffered Outputs)              |         |

| Am74LS281  | Four-Bit Parallel Accumulator                                  | . 3-136 |

| Am74LS299  | Eight-Bit Universal Shift Register, Asynchronous Clear         | . 3-145 |

| Am74LS322  | See Am25LS22                                                   | 3-20    |

| Am74LS323  | See Am25LS23                                                   | 3-26    |

| Am74LS348  | Three-State Priority Encoder                                   | . 3-153 |

| Am74LS373  | Octal Transparent Latch; Three-State Outputs                   | . 3-154 |

| Am74LS374  | Octal D-Register; Three-State Outputs                          | . 3-158 |

| Am74LS377B | Octal D-Register; Common Enable (Buffered Outputs)             | . 3-163 |

| Am74LS378  | Six-Bit Register, Common Enable                                | . 3-168 |

| Am74LS379  | Four-Bit Register, Common Enable                               | . 3-168 |

| Am74LS381  | Four-Bit ALU/Function Generator (20 pin 25LS181)               |         |

| Am74LS382  | Four-Bit ALU/Function Generator (See Am25LS2517)               | . 3-173 |

| Am74LS384  | See Am25LS14                                                   | 3-11    |

| Am74LS385  | See Am25LS15                                                   | 3-16    |

| Am74LS388  | See Am25LS2518                                                 | . 3-217 |

| Am74LS399  | Four-Bit Register, Multiplexed Inputs                          | . 3-190 |

| Am74LS424  | See Am8224                                                     | . 3-195 |

| Am74LS533  | Octal Transparent Latch; Three-State Outputs (Inv.)            |         |

| Am74LS534  | Octal D-Register; Three-State Outputs (Inv.)                   | . 3-158 |

| Am74LS568  | See Am25LS2568                                                 |         |

| Am74LS569  | See Am25LS2569                                                 | . 3-196 |

| Am74LS668  | Synchronous BCD Decade Up-Down Counter; Programmable           |         |

| Am74LS669  | Synchronous Four-Bit Binary Up-Down Counter; Programmable      | . 3-197 |

#### LOW-POWER SCHOTTKY MSI/LSI AND INTERFACE PRODUCTS

#### HIGH SPEED SCHOTTKY MSI AND INTERFACE CIRCUITS

| Product  | Description                                                                                            | raye           |

|----------|--------------------------------------------------------------------------------------------------------|----------------|

| Am25S05  | Four-Bit by Two-Bit 2's Complement Muliplier                                                           |                |

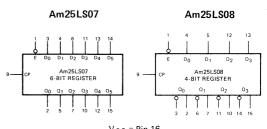

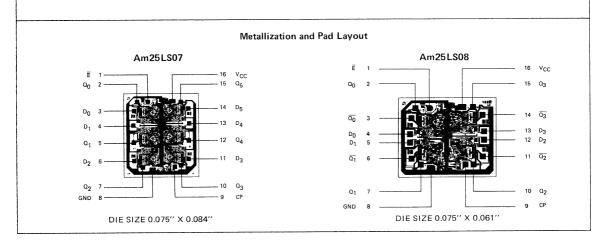

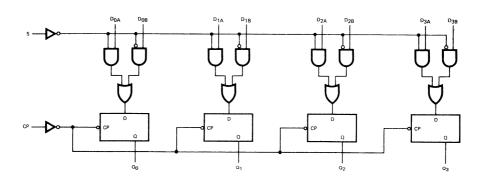

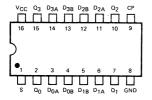

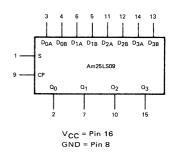

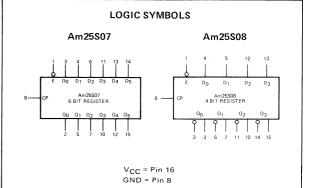

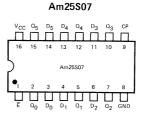

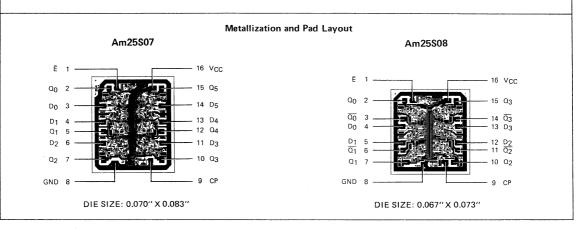

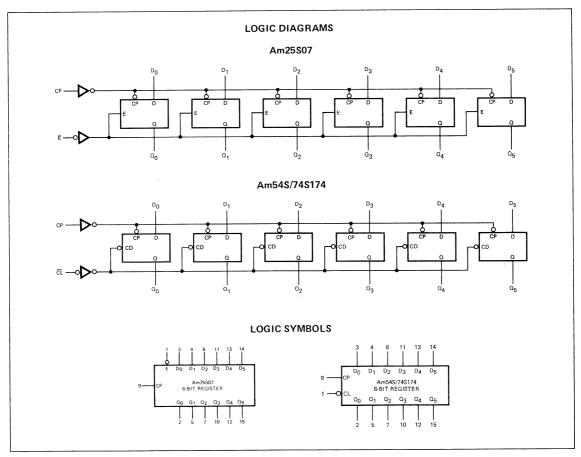

| Am25S07  | Hex/Quad Parallel D Register with Register Enable                                                      |                |

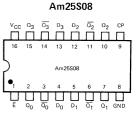

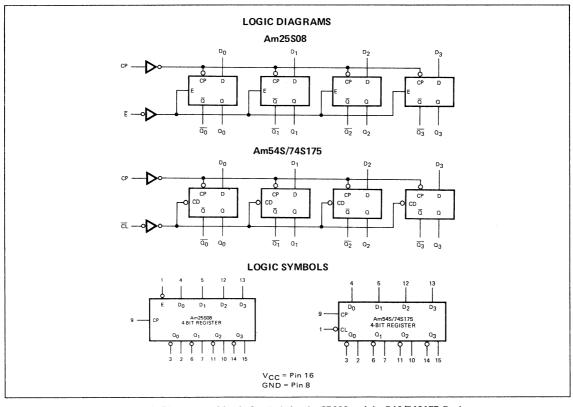

| Am25S08  | Hex/Quad Parallel D Register with Register Enable                                                      | 4-9            |

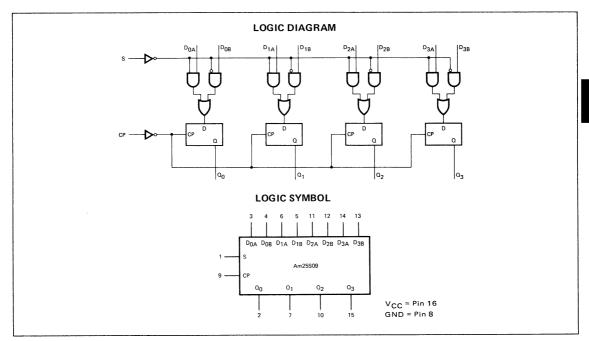

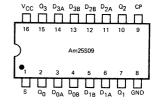

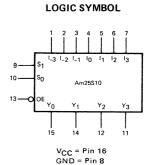

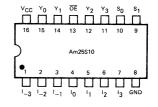

| Am25S09  | Quad Two-Input, High-Speed Register                                                                    | 4-29           |

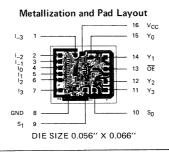

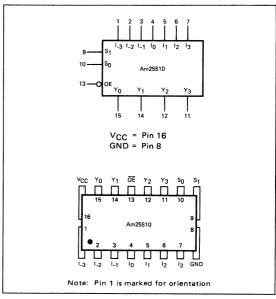

| Am25S10  | Four-Bit Shifter with Three-State Outputs                                                              | 4-33           |

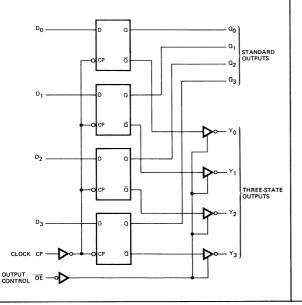

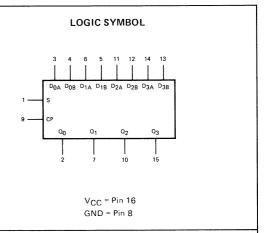

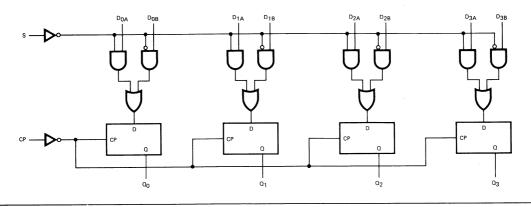

| Am25S18  | Quad D Register with Standard and Three-State Outputs                                                  | 4-47           |

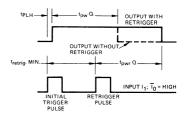

| Am26S02  | Schottky Dual Retriggerable, Resettable Monostable Multivibrator                                       | 4-51           |

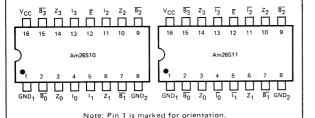

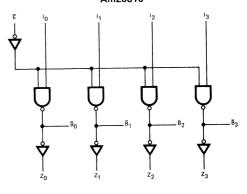

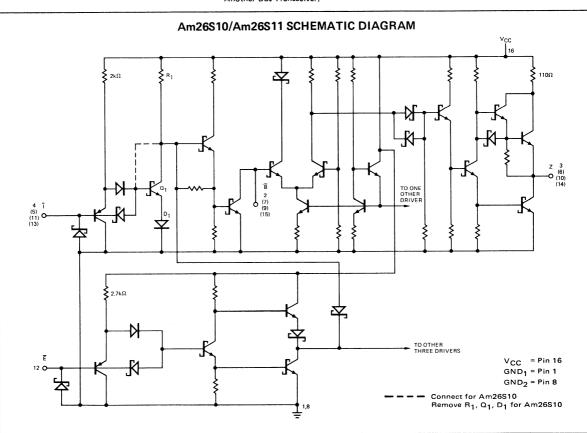

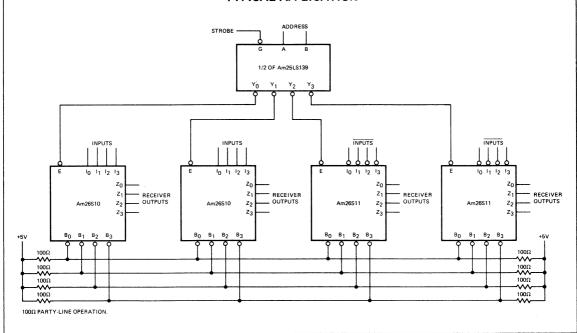

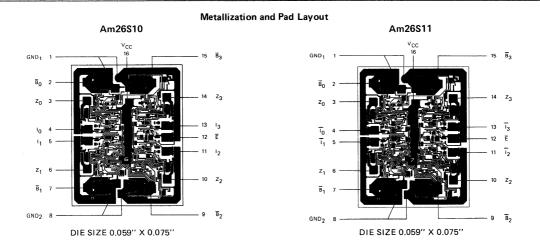

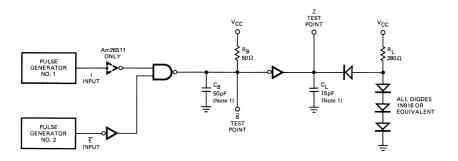

| Am26S10  | Quad Bus Transceiver                                                                                   |                |

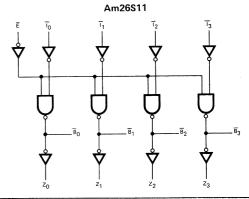

| Am26S11  | Quad Bus Transceiver                                                                                   |                |

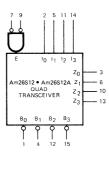

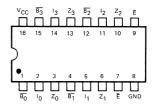

| Am26S12  | Quad Bus Transceiver                                                                                   | 4-60           |

| Am26S12A | Quad Bus Transceiver                                                                                   | 4-60           |

| Am54S138 | 3-Line to 8-Line Decoder/Demultiplexer                                                                 | 4-65           |

| Am54S139 | Dual 2-Line to 4-Line Decoder/Multiplexer                                                              | 4-69           |

| Am54S151 | Eight-Input Multiplexer                                                                                | 4-73           |

| Am54S153 | Dual 4-Line to 1-Line Data Selectors/Multiplexer                                                       | 4-77           |

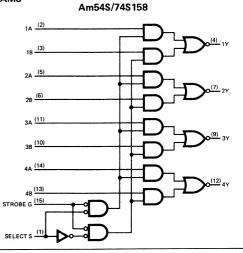

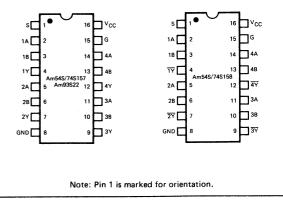

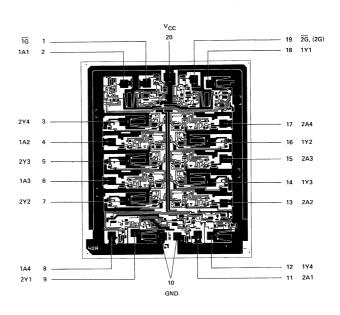

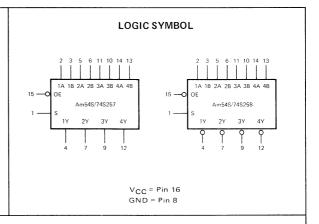

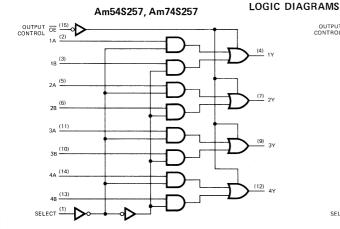

| Am54S157 | Quadruple 2-Line to 1-Line Data Selector/Multiplexer                                                   | 4-81           |

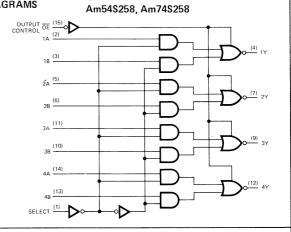

| Am54S158 | Quadruple 2-Line to 1-Line Data Selector/Multiplexer                                                   | 4-81           |

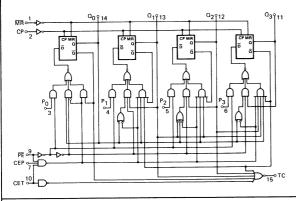

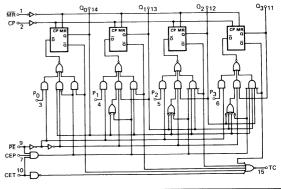

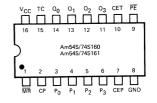

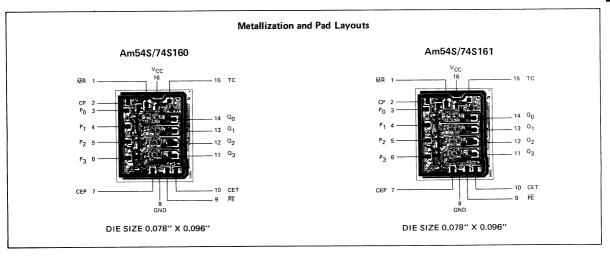

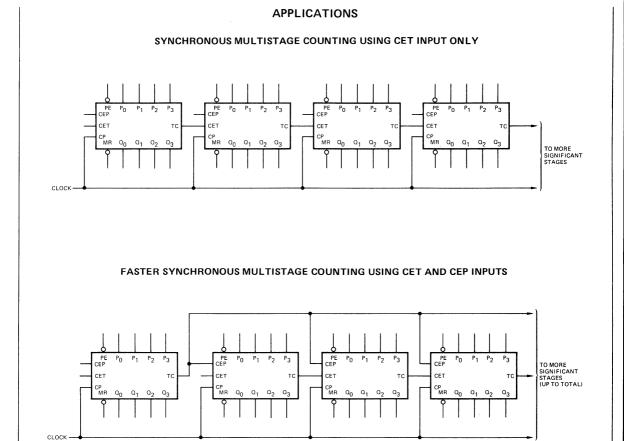

| Am54S160 | BCD Decade/Four-Bit Binary Counter                                                                     | 4-85           |

| Am54S161 | BCD Decade/Four-Bit Binary Counter                                                                     | 4-85           |

| Am54S174 | Hex Quadruple D-Type Flip-Flop with Clear                                                              | 4-89           |

| Am54S175 | Hex Quadruple D-Type Flip-Flop with Clear                                                              | 4-89           |

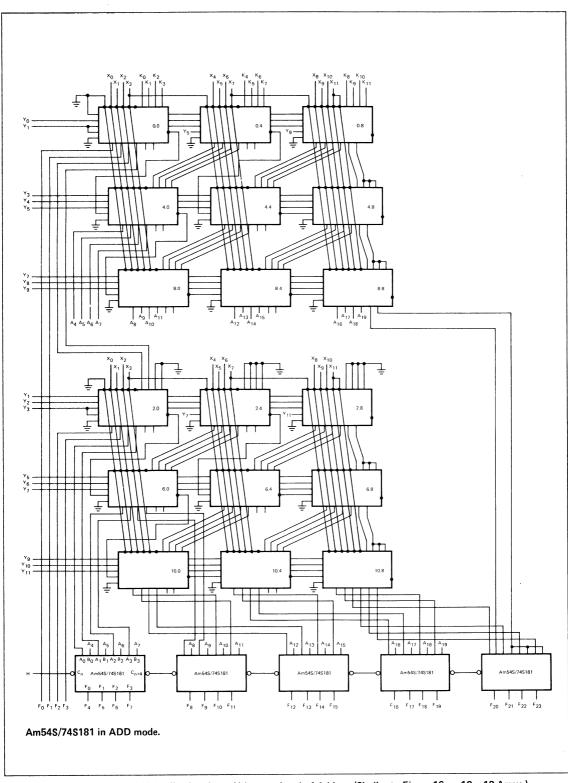

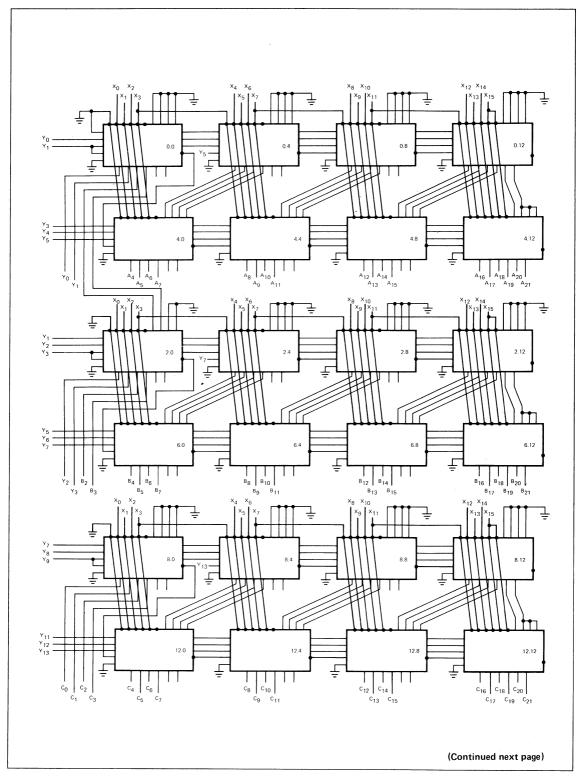

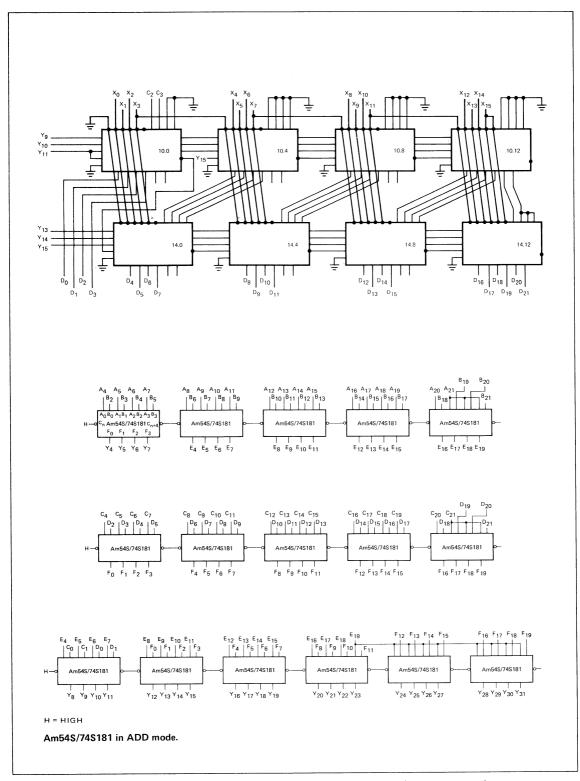

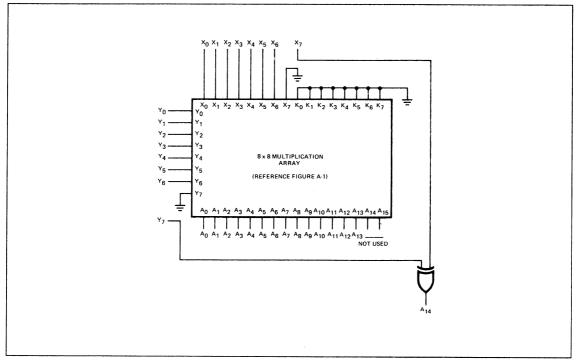

| Am54S181 | Four-Bit Arithmetic Logic Unit/Function Generator                                                      | 4-93           |

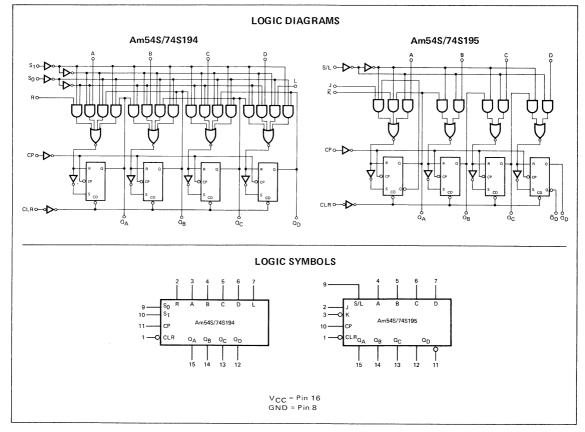

| Am54S194 | Four-Bit High-Speed Shift Register                                                                     | 4-99           |

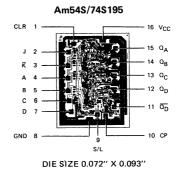

| Am54S195 | Four-Bit High-Speed Shift Register                                                                     | 4-99           |

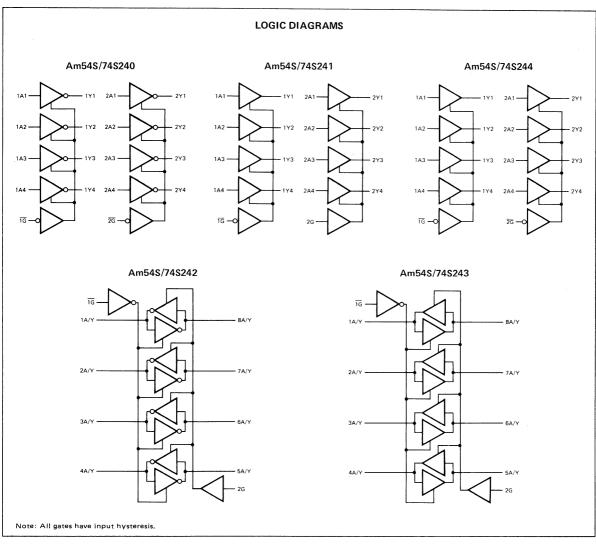

| Am54S240 | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs                                        | 4-103          |

| Am54S241 | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs                                        |                |

| Am54S242 | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs                                        |                |

| Am54S243 | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs                                        | 4-103          |

| Am54S244 | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs                                        |                |

| Am54S251 | Eight-Input Multiplexers                                                                               | 4-73           |

| Am54S253 | Dual 4-Line to 1-Line Data Selector/Multiplexer                                                        | 4-77           |

| Am54S257 | Quadruple 2-Line to 1-Line Data                                                                        | 4 100          |

| Am54S258 | Quadruple 2-Line to 1-Line Data                                                                        | 4 110          |

| Am54S350 | Four-Bit Shifter with Three-State Outputs                                                              | 4-112          |

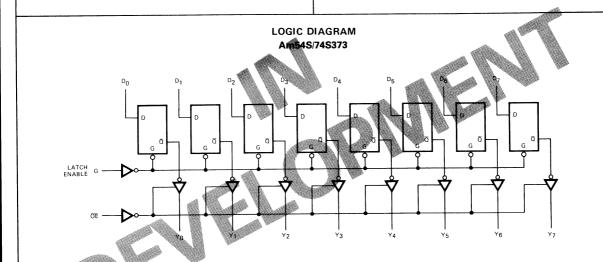

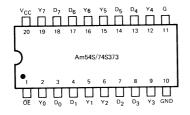

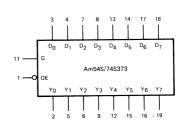

| Am54S373 | Octal Latch with Three-State Outputs                                                                   | 4-114<br>4-115 |

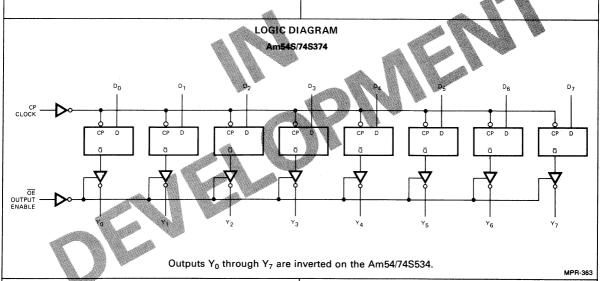

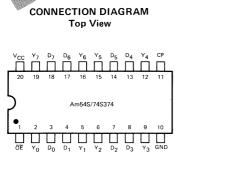

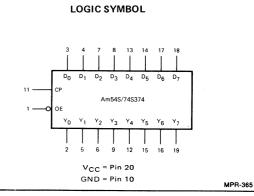

| Am54S374 | 8-Bit Register with Three-State Outputs                                                                | 4-116          |

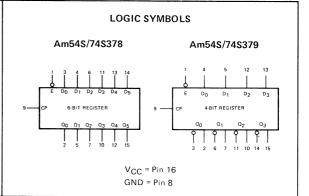

| Am54S378 | Hex/Quad Parallel D Registers with Register Enable  Hex/Quad Parallel D Registers with Register Enable | 4-116          |

| Am54S379 | Quad D Register with Standard and Three-State Outputs                                                  | 4-118          |

| Am54S388 | Quad Two-Input, High-Speed Register                                                                    | 4-120          |

| Am54S399 | See Am8212                                                                                             | 4-122          |

| Am54S412 | Octal Latch with Three-State Outputs (Inv.)                                                            | 4-114          |

| Am54S533 | Octal Register with Three-State Outputs (Inv.)                                                         | 4-115          |

| Am54S534 | 3-Line to 8-Line Decoder/Demultiplexer                                                                 | 4-65           |

| Am74S138 | Dual 2-Line to 4-Line Decoder/Demultiplexer                                                            | 4-69           |

| Am74S139 | Eight-Input Multiplexers                                                                               | 4-73           |

| Am74S151 | Dual 4-Line to 1-Line Data Selector/Multiplexer                                                        | 4-77           |

| Am74S153 | Quadruple 2-Line to 1-Line Data Selector/Multiplexer                                                   | 4-81           |

| Am74S157 | Quadruple 2-Line to 1-Line Data Selector/Multiplexer                                                   | 4-81           |

| Am74S158 | Quadruple 2-Line to 1-Line Bata Gelector/Hataplexes 1111111111111                                      |                |

1 0

| Product  | Description                                                     | Page  |

|----------|-----------------------------------------------------------------|-------|

| Am74S160 | BCD Decade/Four-Bit Binary Counter                              | _     |

| Am74S161 | BCD Decade/Four-Bit Binary Counter                              | 4-85  |

| Am74S174 | Hex/Quadruple D-Type Flip-Flop with Clear                       | 4-80  |

| Am74S175 | Hex/Quadruple D-Type Flip-Flop with Clear                       |       |

| Am74S181 | Four-Bit Arithmetic Logic Unit/Function Generator               | 4-03  |

| Am74S194 | Four-Bit High-Speed Shift Register                              |       |

| Am74S195 | Four-Bit High-Speed Shift Register                              | 4-00  |

| Am74S240 | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs | 4-103 |

| Am74S241 | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs | 4-103 |

| Am74S242 | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs | 4-103 |

| Am74S243 | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs | 4-103 |

| Am74S244 | Octal Buffer/Line Driver/Line Receiver with Three-State Outputs | 4-103 |

| Am74S251 | Eight-Input Multiplexers                                        | 4-73  |

| Am74S253 | Dual 4-Line to 1-Line Data Selector/Multiplexer                 |       |

| Am74S257 | Quadruple 2-Line to 1-Line Data                                 |       |

| Am74S258 | Quadruple 2-Line to 1-Line Data                                 | 4-108 |

| Am74S350 | Four-Bit Shifter with Three-State Output                        | 4-112 |

| Am74S373 | Octal Latch with Three-State Outputs                            |       |

| Am74S374 | 8-Bit Register with Three-State Outputs                         | 4-115 |

| Am74S378 | Hex/Quad Parallel D Registers with Register Enable              | 4-116 |

| Am74S379 | Hex/Quad Parallel D Registers with Register Enable              | 4-116 |

| Am74S388 | Quad D Register with Standard and Three-State Outputs           | 4-118 |

| Am74S399 | Quad Two-Input, High-Speed Register                             | 4-120 |

| Am74S412 | See Am8212                                                      |       |

| Am74S533 | Octal Latch with Three-State Outputs (Inv.)                     |       |

| Am74S534 | Octal Register with Three-State Outputs (Inv.)                  | 4-115 |

| Am3212   | Eight-Bit Input/Output Port                                     |       |

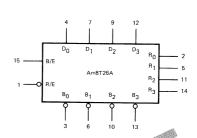

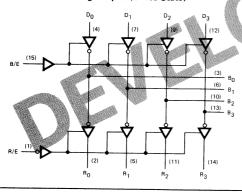

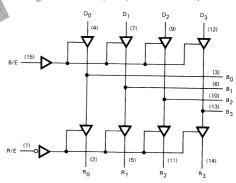

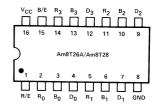

| Am8T26   | Schottky Three-State Quad Bus Driver/Receiver                   | 4-130 |

| Am8T26A  | Schottky Three-State Quad Bus Driver/Receiver                   | 4-135 |

| Am8T28   | Schottky Three-State Quad Bus Driver/Receiver                   | 4-135 |

| Am8212   | Eight-Bit Input/Output Port                                     | 4-123 |

| Am82S62  | Nine-Input Parity Checker/Generator                             | 4-140 |

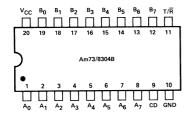

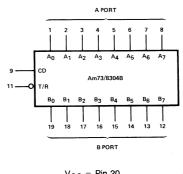

| Am8304B  | Octal Bidirectional Transceiver                                 | 4-144 |

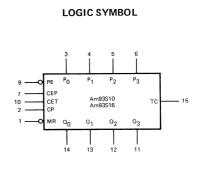

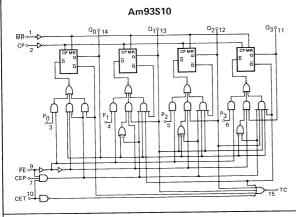

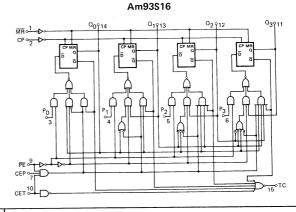

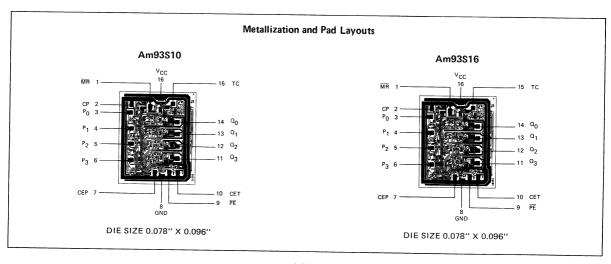

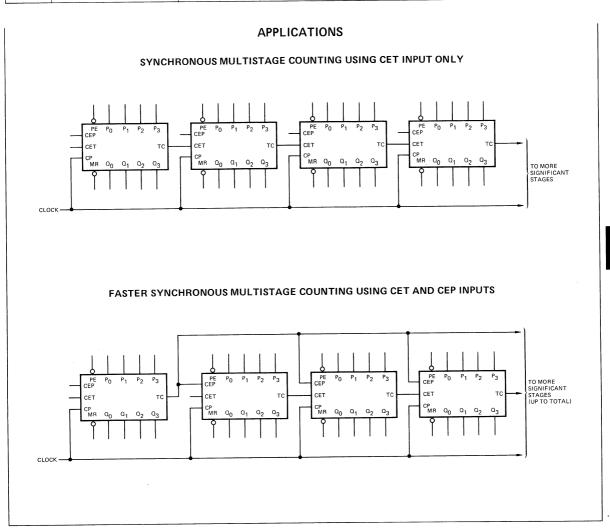

| Am93S10  | BCD Decade/Four-Bit Binary Counter                              | 4-148 |

| Am93S16  | BCD Decade/Four-Bit Binary Counter                              | 4-148 |

| Am93S21  | Dual 2-Line to 4-Line Decoder/Demultiplexer                     | 4-69  |

| Am93S22  | Quadruple 2-Line to 1-Line Data Selector/Multiplexer            | 4-81  |

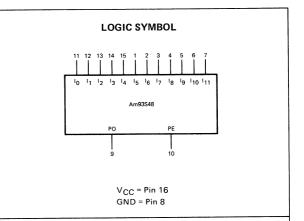

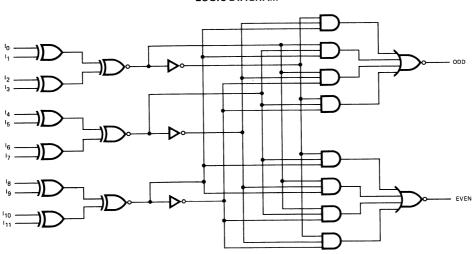

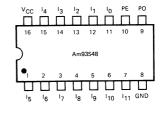

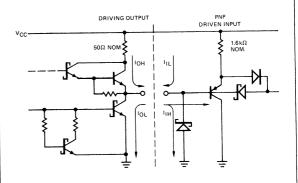

| Am93S48  | Twelve-Input Parity Checker/Generator                           | 4-152 |

#### SCHOTTKY AND LOW-POWER SCHOTTKY FUNCTIONAL SELECTOR GUIDE

This guide divides the AMD Low-Power Schottky and Schottky TTL Product Line by function into three basic performance categories indicated by the examples below.

- 1. High-Performance, Low-Power Schottky Ex. 25LS174 Six Bit Register.  $f_{max} = 40 \text{MHz}$  (Min.)

- 2. Standard Low-Power Schottky Ex. 74LS174 Six Bit Register.  $f_{max} = 30MHz$  (Min.)

- 3. High-Speed Schottky Ex. 74S174 Six Bit Register. f<sub>max</sub> = 75MHz (Min.)

|                                                          | HIGH-PERFORMANCE                 | STANDARD              | HIGH-SPEED          |

|----------------------------------------------------------|----------------------------------|-----------------------|---------------------|

| DESCRIPTION                                              | LOW-POWER<br>SCHOTTKY            | LOW-POWER<br>SCHOTTKY | SCHOTTKY            |

|                                                          |                                  |                       |                     |

| DECADE (BCD) COUNTERS                                    |                                  |                       | 5.4/7.404.00/0004.0 |

| Asynchronous Clear, Synchronous Preset                   | 25LS160A                         | 54/74LS160A           | 54/74S160/93S10     |

| Synchronous Clear, Synchronous Preset                    | 25LS162A                         | 54/74LS162A           |                     |

| Jp-Down, Synchronous Preset                              | 25LS168A                         | 54/74LS168A           |                     |

| Jp-Down, Asynchronous Preset, Single Clock               | 25LS190                          | 54/74LS190            |                     |

| Up-Down, Asynchronous Preset, Dual Clock                 | 25LS192                          | 54/74LS192            |                     |

| Jp-Down, Synchronous Preset, Three-State                 | 25LS2568                         |                       |                     |

| BINARY HEXADECIMAL COUNTERS                              |                                  |                       |                     |

| Asynchronous Clear, Synchronous Preset                   | 25LS161A                         | 54/74LS161A           | 54/74S161/93S16     |

| Synchronous Clear, Synchronous Preset                    | 25LS163A                         | 54/74LS163A           |                     |

| Up-Down, Synchronous Preset                              | 25LS169A                         | 54/74LS169A           |                     |

| Up-Down, Asynchronous Preset, Single Clock               | 25LS191                          | 54/74LS191            |                     |

| Up-Down, Asynchronous Preset, Dual Clock                 | 25LS193                          | 54/74LS193            |                     |

| Up-Down, Synchronous Preset, Three-State                 | 25LS2569                         |                       |                     |

| DECODER/DEMULTIPLEXERS                                   |                                  |                       |                     |

| One-of-Ten Decoder/Demultiplexer, Polarity Control       | 25LS2537                         |                       |                     |

| One-of-Eight Decoder/Demultiplexer                       | 25LS138                          | 54/74LS138            | 54/74S138           |

| One-of-Eight Decoder/Demultiplexer with Control Storage  | 25LS2536                         |                       |                     |

| Dual One-of-Four Decoder/Demultiplexer                   | 25LS139                          | 54/74LS139            | 54/74S139/93S21     |

| One-of-Eight Decoder/Demultiplexer, Polarity Control     | 25LS2538                         |                       |                     |

| Dual One-of-Four Decoder/Demultiplexer, Polarity Control | 25LS2539                         |                       |                     |

| Dual One-of-Four Decoder/Demantplexer, Folamy Control    | 2020200                          |                       |                     |

| MULTIPLEXERS                                             |                                  |                       | 5.4/7.404.54        |

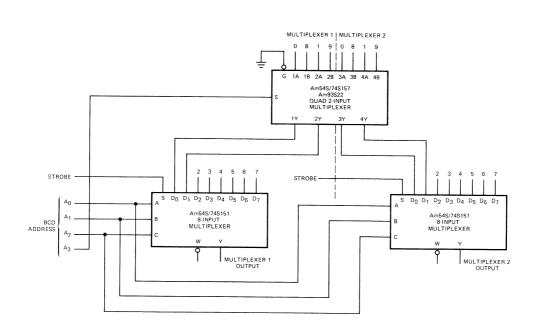

| Eight-Input Multiplexer                                  | 25LS151                          | 54/74LS151            | 54/74S151           |

| Eight-Input Multiplexer with Control Storage             | 25LS2535                         |                       |                     |

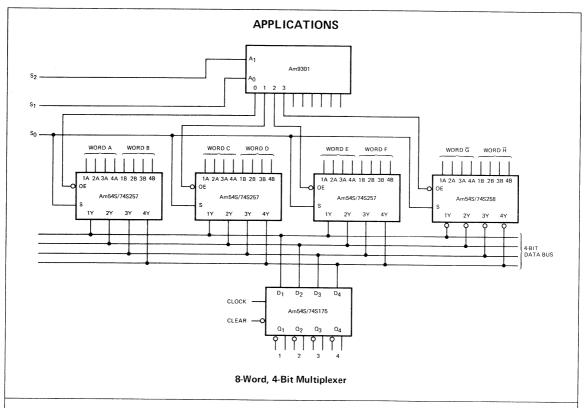

| Three-State Eight-Input Multiplexer                      | 25LS251                          | 54/74LS251            | 54/74S251           |

| Dual Four-Input Multiplexer                              | 25LS153                          | 54/74LS153            | 54/74S153           |

| Three-State Dual Four-Input Multiplexer                  | 25LS253                          | 54/74LS253            | 54/74S253           |

| Quad Two-Input Multiplexer; Non-Inverting                | 25LS157                          | 54/74LS157            | 54/74S157/93S22     |

| Three-State Quad Two-Input Multiplexer; Non-Inverting    | 25LS257                          | 54/74LS257            | 54/74S257           |

| Quad Two-Input Multiplexer; Inverting                    | 25LS158                          | 54/74LS158            | 54/74S158           |

| Three-State Quad Two-Input Multiplexer; Inverting        | 25LS258                          | 54/74LS258            | 54/74S258           |

| MONOSTABLE (ONE-SHOT)                                    |                                  |                       |                     |

| Dual Retriggerable, Resettable Monostable Multivibrator  |                                  |                       | 26S02               |

| OPERATORS (ALU, MULTIPLIER, PRIORITY ENCODER             | , etc.)                          |                       |                     |

| Four by Two Two's Complement Multiplier                  |                                  |                       | 25\$05              |

| Four-Bit, Four-Way Shifter                               |                                  |                       | 25S10/54/74S350     |

| Four-Bit ALU/Function Generator                          | 25LS181                          | 54/74LS181            | 54/74S181           |

| Four-Bit ALU/Function Generator                          | 25LS2517                         |                       |                     |

| Four-Bit ALU/Function Generator                          | 25LS381                          | 54/74LS381            |                     |

| Four-Bit Parallel Accumulator                            | 25LS281                          | 54/74LS281            |                     |

| Priority Encoder, Eight Line to Three Line               | 25LS148                          | 54/74LS148            |                     |

| Four-Bit Serial Adder/Subtractor                         | 25LS15                           |                       |                     |

| Priority Encoder, Three State                            | 25LS2513                         |                       |                     |

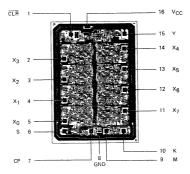

| Eight by One Serial/Parallel Two's Complement Multiplier | 25LS14                           |                       |                     |

| Eight-Bit by Eight-Bit Multiplier/Accumulator            | 25LS2516                         |                       |                     |

| EIGHT-DIL DY EIGHT-DIL WIGHTPHEI/ACCUMULATOL             |                                  |                       |                     |

|                                                          | 25  S2521                        |                       |                     |

| Eight-Bit Comparator                                     | 25LS2521<br>25LS2524             |                       |                     |

| • •                                                      | 25LS2521<br>25LS2524<br>25LS2525 |                       |                     |

#### **FUNCTIONAL SELECTOR GUIDE (Cont.)**

| DESCRIPTION                                                               | HIGH-PERFORMANCE<br>LOW-POWER<br>SCHOTTKY | STANDARD<br>LOW-POWER<br>SCHOTTKY | HIGH-SPEED<br>SCHOTTKY |

|---------------------------------------------------------------------------|-------------------------------------------|-----------------------------------|------------------------|

| PARITY CHECKER/GENERATORS                                                 |                                           |                                   |                        |

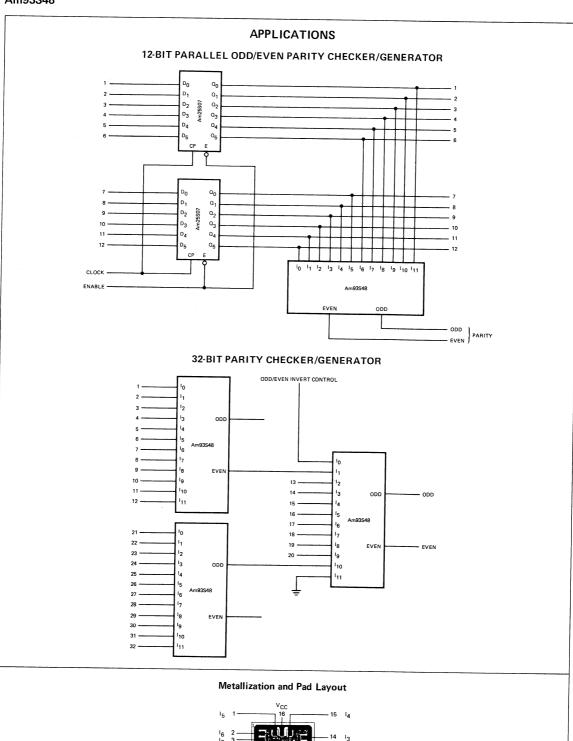

| Nine-Input Parity Checker/Generator Twelve-Input Parity Checker/Generator |                                           |                                   | 82S62<br>93S48         |

| REGISTERS                                                                 |                                           |                                   |                        |

| Four-Bit Register with Common Clock Enable                                | 25LS08                                    | 54/74LS379                        | 25S08/54/74S379        |

| Four-Bit Register with Two-Input Multiplexers on Inputs                   | 25LS09                                    | 54/74LS399                        | 25S09/54/74S388        |

| Four-Bit Register with Standard and Three-State Outputs                   | 25LS2518                                  |                                   | 25S18/54/74S388        |

| Four-Bit, Two-Output Three-State Register                                 | 25LS2519                                  |                                   |                        |

| Four-Bit Register with Common Clear                                       | 25LS175                                   | 54/74LS175                        | 54/74S175              |

| Four-Bit Register; Shift Right, Left or Parallel Load                     | 25LS194A                                  | 54/74LS194A                       | 54/74S194              |

| Four-Bit Register; Shift Right or Parallel Load                           | 25LS195A                                  | 54/74LS195A                       | 54/74S195              |

| Six-Bit Register with Common Clock Enable                                 | 25LS07                                    | 54/74LS378                        | 25S07/54/74S378        |

| Six-Bit Register with Common Clear                                        | 25LS174                                   | 54/74LS174                        | 54/74S174              |

| Eight-Bit, Serial-In, Parallel-Out Register                               | 25LS164                                   | 54/74LS164                        |                        |

| Eight-Bit Shift/Storage Register; Synchronous Clear                       | 25LS23                                    |                                   |                        |

| Eight-Bit Shift/Storage Register; Asynchronous Clear                      | 25LS299                                   | 54/74LS299                        |                        |

| Eight-Bit Shift-Storage Register with Sign Extend                         | 25LS22                                    |                                   |                        |

| Octal D-Type Register, Common Clear                                       | 25LS273B                                  | 54/74LS273B                       |                        |

| Octal Transparent Latch (Three State, non-inverting)                      | 25LS373                                   | 54/74LS373                        | *54/74S373             |

| Octal Transparent Latch (Three-state, inverting)                          | *25LS533                                  | *54/74LS533                       | *54/74S533             |

| Octal D-Type Register (Three State, non-inverting)                        | 25LS374                                   | 54/74LS374                        | *54/74S374             |

| Octal D-Type Register (Three-state, inverting)                            | *25LS534                                  | *54/74LS534                       | *54/74S534             |

| Octal D-Type Register, Common Enable                                      | 25LS377B                                  | 54/74LS377B                       | 5 .,. 1 <b>555</b> ?   |

| Octal D-Type Register, Common Enable and Clear,                           |                                           |                                   |                        |

| Three-State                                                               | 25LS2520                                  |                                   |                        |

| BUS INTERFACE                                                             |                                           |                                   |                        |

| Quad Bus Transceiver, Inverting (100mA)                                   |                                           |                                   | 26S10                  |

| Quad Bus Transceiver, Non-Inverting (100mA)                               |                                           |                                   | 26S11                  |

| Quad Bus Transceiver, Inverting                                           | 25LS242                                   | 54/74LS242                        | 54/74S242              |

| Quad Bus Transceiver, Non-Inverting                                       | 25LS243                                   | 54/74LS243                        | 54/74S243              |

| Quad Open-Collector Bus Transceiver                                       |                                           |                                   | 26S12/12A              |

| Quad Three-State Bus Transceiver (Inverting)                              |                                           |                                   | 8TS12/12A              |

| Quad Three-State Bus Transceiver (Non-Inverting)                          |                                           |                                   | 8T28                   |

| Quad Two I/P Transceiver with Three-State Receiver (O.C.)                 | 2905                                      |                                   |                        |

| Quad Two I/P Transceiver with Parity (O.C.)                               | 2906                                      |                                   |                        |

| Quad Two I/P Transceiver with Parity (O.C.)                               | 2907                                      |                                   |                        |

| Quad Two I/P Transceiver with Three-State Receiver                        |                                           |                                   |                        |

| (Three-State)                                                             | 2915A                                     |                                   |                        |

| Quad Two I/P Transceiver with Parity (Three-State)                        | 2916A                                     |                                   |                        |

| Quad Two I/P Transceiver with Parity (Three-State)                        | 2917A                                     |                                   |                        |

| Octal Bus Driver, Inverting                                               | 25LS240                                   | 54/74LS240                        | 54/74S240              |

| Octal Bus Driver, Non-Inverting                                           |                                           |                                   |                        |

| (Complementary G, G inputs)                                               | 25LS241                                   | 54/74LS241                        | 54/74S241              |

| Octal Bus Driver, Non-Inverting                                           | 25LS244                                   | 54/74LS244                        | 54/74S244              |

| Octal Bus Driver, Low-Power.                                              | 71/81LS95                                 |                                   |                        |

| Octal Bus Driver, Low-Power, Inv.                                         | 71/81LS96                                 |                                   |                        |

| Octal Bus Driver, Low-Power.                                              | 71/81LS97                                 |                                   |                        |

| Octal Bus Driver, Low-Power, Inv.                                         | 71/81LS98                                 |                                   |                        |

| Octal Bidirectional Bus Transceiver                                       | 8304                                      |                                   |                        |

<sup>\*</sup>In development.

## Introduction to Low-Power Schottky

| Comparison between Am25LS and 54LS/74LS                    | 2-2  |

|------------------------------------------------------------|------|

| Am25LS-54LS/74LS Low-Power Schottky Cross Reference        | 2-4  |

| Designers Guide to High Performance     Low-Power Schottky | 2-6  |

| Reliability Report                                         | 2-20 |

#### ADVANCED MICRO DEVICES SCHOTTKY AND LOW-POWER SCHOTTKY MSI

Advanced Micro Devices offers a complete line of Schottky and Low-Power Schottky MSI products. On the following pages are a selector guide for these products and brief data on several of the most useful parts. For complete data refer to our Schottky and Low-Power Schottky Data Book.

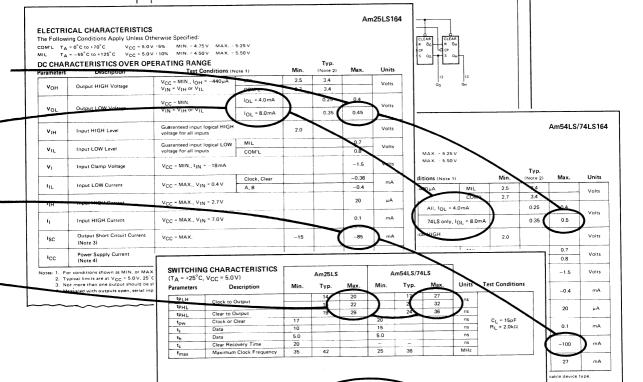

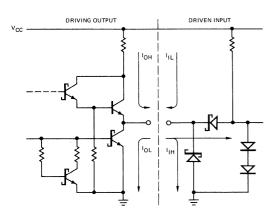

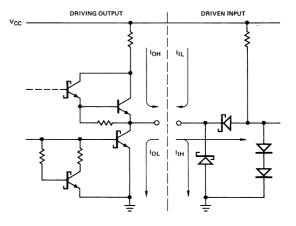

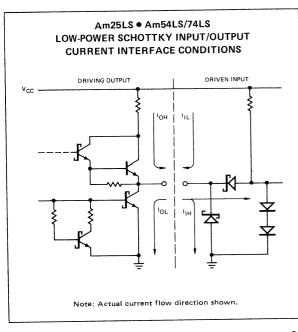

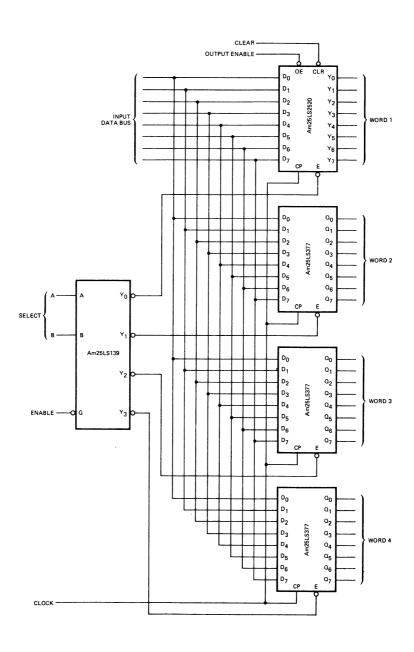

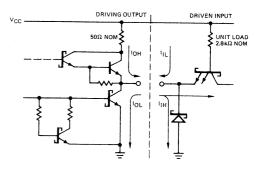

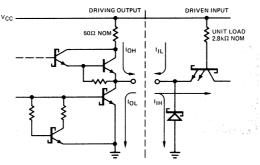

Advanced Micro Devices offers two LS Logic families. 10X • Am25LS – High Performance MORE RELIABLE Am54/74LS — Standard Performance Similar elements of both families are described on the same data sheet. Key parameters are compared below. All Advanced Micro Devices' products are manufactured to the quality assurance requirements of MIL-STD-883, Level C. According to Handbook 217B published by the Rome Air Development Center, the Air Force's principal authority on component reliability, Level C integrated circuits are up to ten times more reliable than normal industry commercial parts. Even if you don't need the performance features of Am25LS, you can buy our versions of 50mV MORE 54/74LS devices with the assurance that they are manufactured to the stringent quality NOISE MARGIN standards of MIL-STD-883. Am25LS IMPROVED PERFORMANCE Noise Margin TWICE THE-At  $I_{OL} = 8mA$ , Am25LS guarantees  $V_{OL} = 0.45V$  compared to 0.50V for 54/74LS. **FAN-OUT** • Fan Out Over the military temperature range, Am25LS is specified \( I\_{OL} = 8mA, \) (8mA/0.36mA). 54LS is guaranteed at  $I_{OL} = 4\text{mA}$  only, for F.O. = 11 (4 mA/0.36 mA).REDUCED SUPPLY Isc (Max.) CURRENT SPIKING Am25LS has I<sub>SC</sub> upper limit controlled to 85mA (Nax.). In this example, Am25LS164 has worst case clock to output delay specified tup to 45% faster and fMAX at more than 40% faster than 54/74LS164: Most Am25LS devices offer similar improvements. FASTER. SWITCHING SPEED SPECIFIED AT TEMPERATURE AND POWER SUPPLY EXTREMES The switching speeds of all new Am25LS devices are now being specified at: Full 50pF load • Over the operating temperature range - Military -55°C to +125°C - Commercial 0°C to +70°C

#### PRICE

Most Am25LS device list prices are the same or less than the equivalent 54/74LS standard performance device.

• Over the operating power supply range

- Military 5.0V ± 10%

- Commercial 5.0V ± 5%

MORE FULLY

SPECIFIED

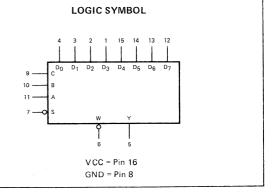

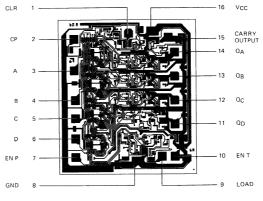

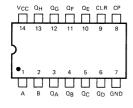

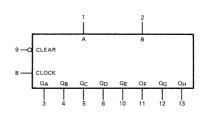

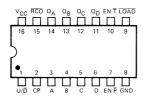

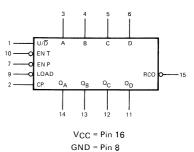

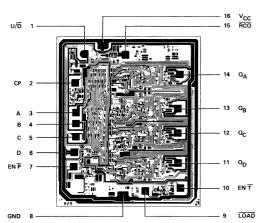

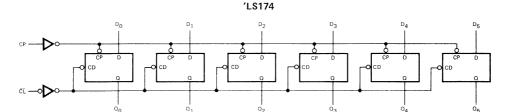

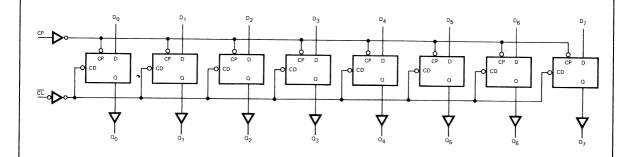

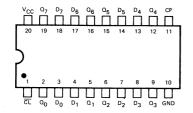

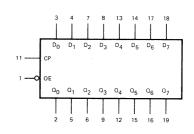

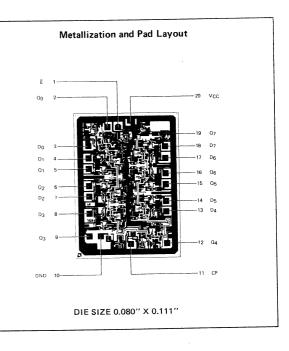

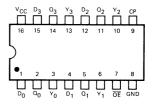

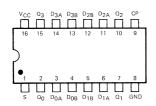

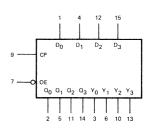

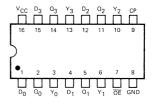

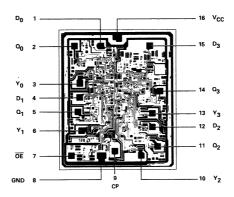

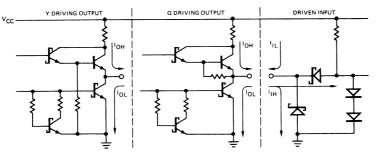

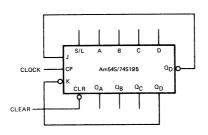

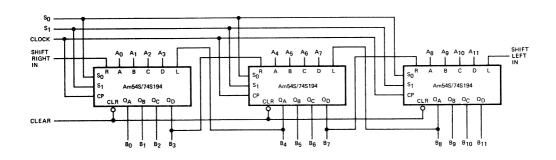

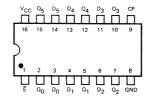

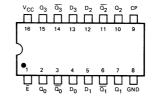

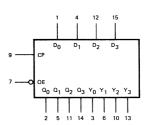

## Am25LS164 • Am54LS/74LS164 8-Bit Serial-In, Parallel-Out Shift Register

#### DISTINCTIVE CHARACTERISTICS

- Gated serial inputs

- Asynchronous clear

- Am25LS devices offer the following improvements over Am54/74LS

- Higher speed 50mV lower VOL at IOL = 8mA

- 440μA source current at HIGH output

- 100% product assurance testing to MIL-STD-883 requirements

#### FUNCTIONAL DESCRIPTION

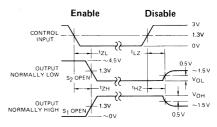

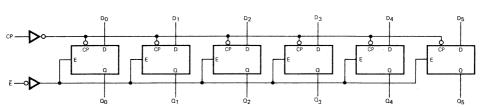

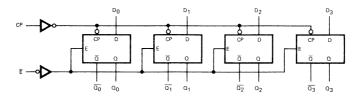

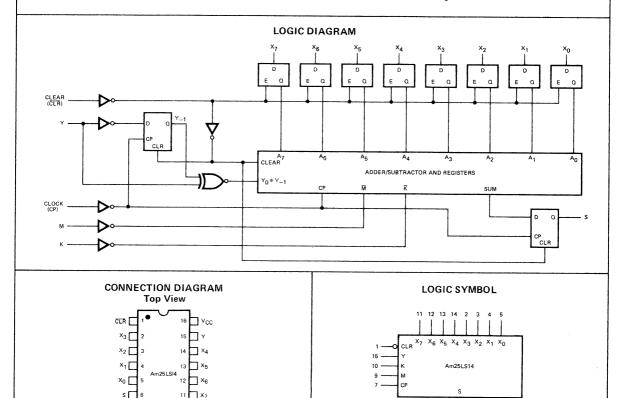

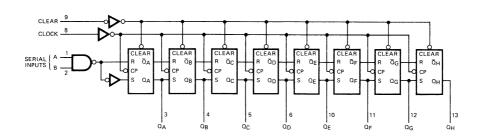

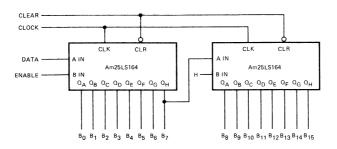

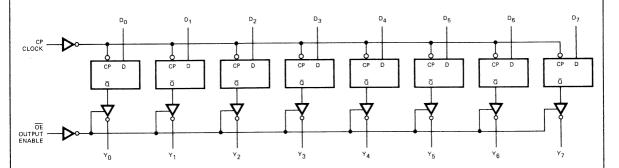

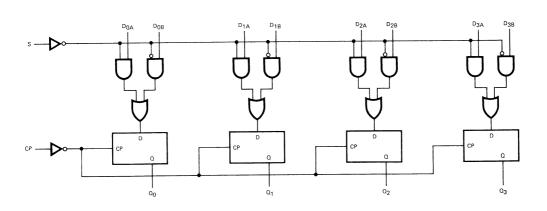

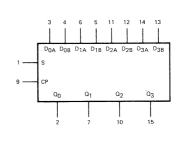

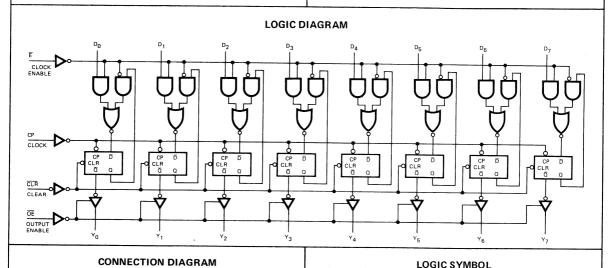

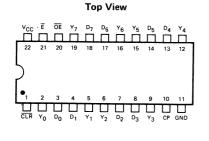

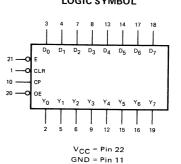

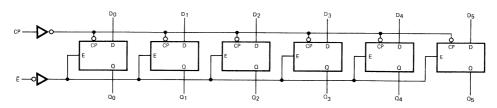

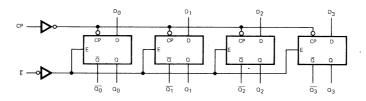

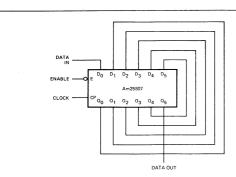

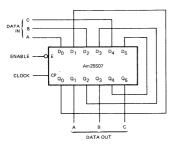

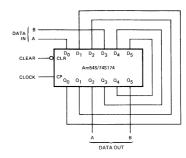

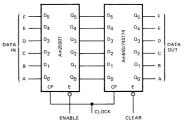

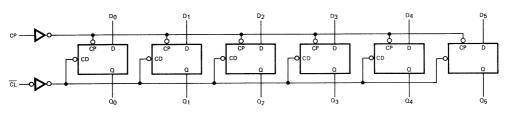

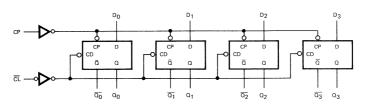

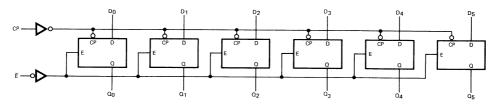

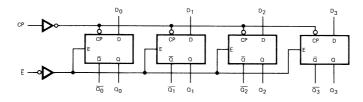

The Am25LS164 and Am54LS/74LS164 are eight-bit, serial in/parallel out shift registers built using advanced Low-Power Schottky processing. A gated input provides enable/disable control over incoming data such that the data can be entered or logic zeros can be entered into the register.

An asynchronous clear input can be used to simultaneously clear the eight flip-flops in the device. When the clear input is LOW, all internal flip-flops are forced LOW independent of the clock input. An incoming data bit is entered into the Q<sub>a</sub> flip-flop and the data in all internal flip-flops is shifted right on the LOW-to-HIGH transition of the clock input.

The Am54LS/74LS164 is a standard performance version of the Am25LS164. See appropriate electrical characteristic tables for detailed Am25LS improvements.

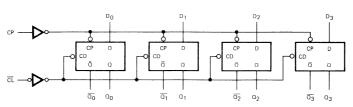

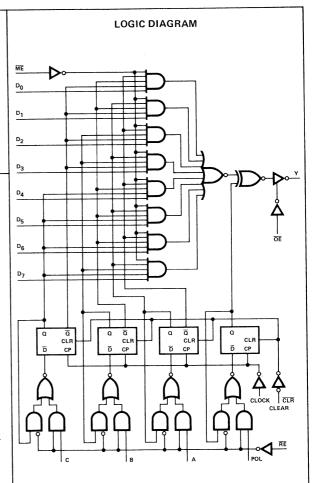

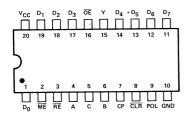

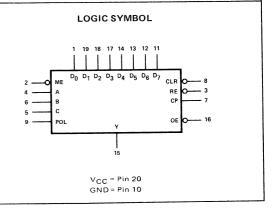

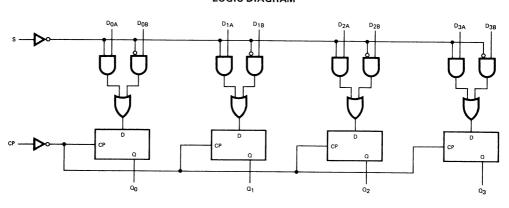

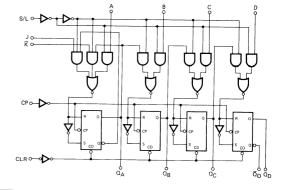

LOGIC DIAGRAM

Am25LS COM'L Am251 S MH SWITCHING CHARACTERISTICS T<sub>A</sub> = -55°C to +125°C V<sub>CC</sub> = 5.0V ±10% T<sub>A</sub> = 0°C to +70°C V<sub>CC</sub> = 5.0V ±5% OVER OPERATING RANGE Unit Test Conditions Max Min Max Description Parameters 26 tp: H ns Clock to Output tPHL 42 Clear to Output †PHL 25 C<sub>L</sub> = 50pF R<sub>L</sub> = 2.0kΩ 22 Clock or Clear tpw 15 ns 13 Data ts 5 ns Data 25 ts Maximum Clock Frequency 25

rmance over the operating temperature range is guaranteed by testing defined in Group A, Subgroup 9

#### Am25LS•Am54LS/74LS CROSS REFERENCE GUIDE

Advanced Micro Devices offers both Am25LS, High Performance, and 54LS/74LS Standard Performance, low-power Schottky families. Am25LS devices may be substituted for 54LS/74LS devices as shown in the table below.

Products with different numbers corresponding to the similar Am25LS and 54LS/74LS functions are Texas Instruments second source part numbers to Advanced Micro Devices products.

| Am25LS<br>HIGH PERFORMANCE<br>LS | Am54/74LS<br>STANDARD<br>LS  | DESCRIPTION                                                            | PACKAGE<br>PINS |

|----------------------------------|------------------------------|------------------------------------------------------------------------|-----------------|

| AM25LS07                         | AM54/74LS378                 |                                                                        |                 |

| AM25LS08                         | AM54/74LS378<br>AM54/74LS379 | Six-Bit Register; Common Enable                                        | 16              |

| AM25LS09                         | AM54/74LS379<br>AM54/74LS399 | Four-Bit Register; Common Enable Four-Bit Register; Multiplexed Inputs | 16              |

| AM25LS14                         | AM54/74LS384                 |                                                                        | 16              |

| AM25LS15                         | AM54/74LS385                 | Eight-Bit Serial/Parallel Two's Complement Multiplier                  | 16              |

| AM25LS22                         | AM54/74LS365                 | Four-Bit Serial/Parallel Adder Subtracter                              | 20              |

| AM25LS23                         | AM54/74LS322<br>AM54/74LS323 | Eight-Bit Serial/Parallel Register; Sign Extend                        | 20              |

| AM25LS138                        |                              | Eight-Bit Universal Shift Register; Synchronous Clear                  | 20              |

| AM25LS138                        | AM54/74LS138<br>AM54/74LS139 | One-of-Eight Decoder/Demultiplexer                                     | 16              |

| AM25LS139<br>AM25LS148           |                              | Dual One-of-Four Decoder/Demultiplexer                                 | 16              |

| AM25LS146<br>AM25LS151           | AM54/74LS148                 | Priority Encoder; Eight-Line to Three-Line                             | 16              |

|                                  | AM54/74LS151                 | Eight-Input Multiplexer                                                | 16              |

| AM25LS153<br>AM25LS157           | AM54/74LS153                 | Dual-Four-Input Multiplexer                                            | 16              |

| AM25LS157<br>AM25LS158           | AM54/74LS157                 | Quad Two-Input Multiplexer; Non-Inverting                              | 16              |

|                                  | AM54/74LS158                 | Quad Two-Input Multiplexer; Inverting                                  | 16              |

| AM25LS160A                       | AM54/74LS160A                | Synchronous BCD Decade Counter; Asynchronous Clear                     | 16              |

| AM25LS161A                       | AM54/74LS161A                | Synchronous Four-Bit Binary Counter; Asynchronous Clear                | 16              |

| AM25LS162A                       | AM54/74LS162A                | Synchronous BCD Decade Counter; Synchronous Clear                      | 16              |

| AM25LS163A                       | AM54/74LS163A                | Synchronous Four-Bit Binary Counter; Synchronous Clear                 | 16              |

| AM25LS164                        | AM54/74LS164                 | Eight-Bit Serial-In, Parallel-Out Shift Register                       | 14              |

| AM25LS168A                       | AM54/74LS168A                | Synchronous BCD Decade Up-Down Counter; Programmable                   | 16              |

| AM25LS169A                       | AM54/74LS169A                | Synchronous Four-Bit Binary Up-Down Counter; Programmable              | 16              |

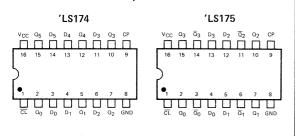

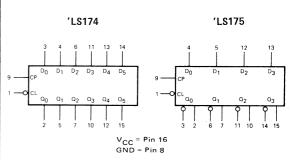

| AM25LS174                        | AM54/74LS174                 | Six-Bit Register; Common Clear                                         | 16              |

| AM25LS175                        | AM54/74LS175                 | Quad Register; Common Clear                                            | 16              |

| AM25LS181                        | AM54/74LS181                 | Four-Bit ALU/Function Generator                                        | 24              |

| AM25LS190                        | AM54/74LS190                 | BCD Decade Up-Down Counter; Down-Up Mode Control                       | 16              |

| AM25LS191                        | AM54/74LS191                 | Four-Bit Binary Up-Down Counter; Down-Up Mode Control                  | 16              |

| AM25LS192                        | AM54/74LS192                 | BCD Decade Up-Down Counter; Dual Clocks                                | 16              |

| AM25LS193                        | AM54/74LS193                 | Four-Bit Binary Up-Down Counter; Dual Clocks                           | 16              |

| AM25LS194A                       | AM54/74LS194A                | Four-Bit Register; Shift Right, Left or Parallel Load                  | 16              |

| AM25LS195A                       | AM54/74LS195A                | Four-Bit Register; Shift Right or Parallel Load                        | 16              |

| AM25LS240                        | AM54/74LS240                 | Octal Bus Driver; Inverting, Three State Outputs                       | 20              |

| AM25LS241                        | AM54/74LS241                 | Octal Bus Driver; Non-Inverting, Three State Outputs (G, G inputs)     | 20              |

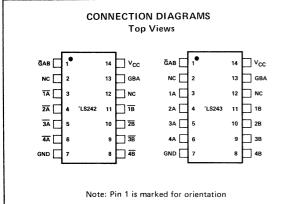

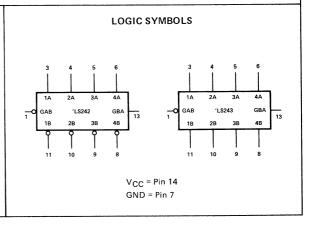

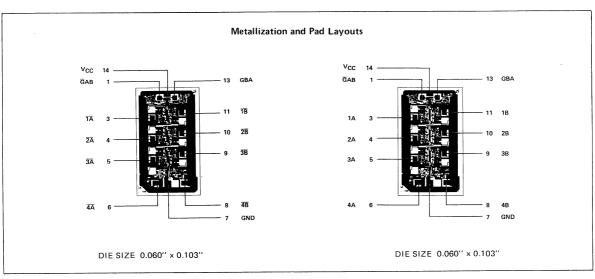

| AM25LS242                        | AM54/74LS242                 | Quad Bus Transceiver; Inverting                                        | 14              |

| AM25LS243                        | AM54/74LS243                 | Quad Bus Transceiver; Non-Inverting                                    | 14              |

| AM25LS244                        | AM54/74LS244                 | Octal Bus Driver; Non-Inverting, Three State Outputs                   | 20              |

| AM25LS251                        | AM54/74LS251                 | Eight-Input Multiplexer; Three State Outputs                           | 16              |

| AM25LS253                        | AM54/74LS253                 | Dual Four-Input Multiplexer; Three State Outputs                       | 16              |

| AM25LS257                        | AM54/74LS257                 | Quad Two-Input Multiplexer; Non-Inverting, Three State Outputs         | 16              |

| AM25LS258                        | AM54/74LS258                 | Quad Two-Input Multiplexer; Inverting, Three State Outputs             | 16              |

| AM25LS273                        | AM54/74LS273                 | Octal D-Register; Common Clear                                         | 20              |

| *AM25LS281                       | *AM54/74LS281                | Four-Bit Parallel Accumulator                                          | 24              |

| AM25LS299                        | AM54/74LS299                 | Eight-Bit Universal Shift Register, Asynchronous Clear                 | 20              |

| <del>-</del>                     | AM54/74LS322                 | See Am25LS22                                                           | 20              |

| <del>.</del>                     | AM54/74LS323                 | See Am25LS23                                                           | 20              |

| AM25LS373                        | AM54/74LS373                 | Octal Transparent Latch; Three State Outputs                           | 20              |

| AM25LS374                        | AM54/74LS374                 | Octal D-Register; Three State Outputs                                  | 20              |

| AM25LS377                        | AM54/74LS377                 | Octal D-Register; Common Enable                                        | 20              |

| AM25LS378                        | AM54/74LS378                 | Six-Bit Register, Common Enable (25LS07)                               | 16              |

| AM25LS379                        | AM54/74LS379                 | Four-Bit Register, Common Enable (25LS08)                              | 16              |

| AM25LS381                        | AM54/74LS381                 | Four-Bit ALU/Function Generator (20 pin 25LS181)                       | 20              |

<sup>\*</sup>In development.

#### Am25LS•Am54LS/74LS CROSS REFERENCE GUIDE (Cont.)

| Am25LS<br>HIGH PERFORMANCE<br>LS | Am54/74LS<br>STANDARD<br>LS | DESCRIPTION                                                     | PACKAGE<br>PINS |

|----------------------------------|-----------------------------|-----------------------------------------------------------------|-----------------|

|                                  | AM54/74LS382                | See Am25LS2517                                                  | 20              |

|                                  | AM54/74LS384                | See Am25LS14                                                    | 16              |

| _                                | AM54/74LS385                | See Am25LS15                                                    | 20              |

|                                  | AM54/74LS388                | See Am25LS2518                                                  | 16              |

| AM25LS399                        | AM54/74LS399                | Four-Bit Register, Multiplexed Inputs (25LS09)                  | 16              |

| AIVIZGEGGGG                      | *AM54/74LS533               | Inverting version of Am25/54/74LS373                            | 20              |

| _                                | *AM54/74LS534               | Inverting version of Am25/54/74LS374                            | 20              |

| _                                | AM54/74LS568                | See Am25LS2568                                                  | 20              |

| _                                | AM54/74LS569                | See Am25LS2569                                                  | 20              |

|                                  | AM54/74LS668                | Slow Version of Am25/54/74LS168A                                | 16              |

| _                                | AM54/74LS669                | Slow Version of Am25/54/74LS169A                                | 16              |

| AM25LS2513                       | -                           | Priority Encoder; Three State Outputs, Eight-Line to Three-Line | 20              |

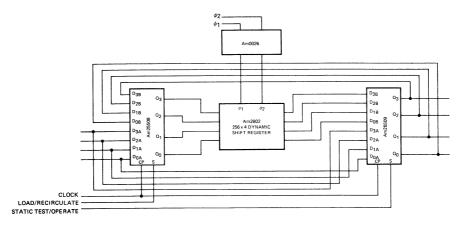

| AM25LS2516                       | _                           | Eight-Bit by Eight-Bit Serial/Parallel Multiplier/Accumulator   | 40              |

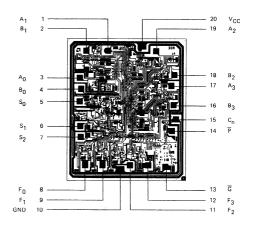

| AM25LS2517                       | _                           | Four-Bit ALU/Function Generator; Overflow Detection             | 20              |

| AM25LS2517<br>AM25LS2518         | AM54/74LS388                | Quad Register with Standard and Three State Outputs             | 16              |

| AM25LS2510                       | -                           | Quad Register with Dual Three State Outputs                     | 20              |

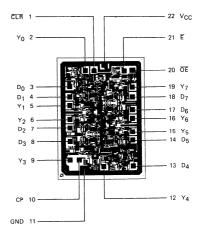

| AM25LS2519<br>AM25LS2520         | _                           | Octal D-Register; Common Clear and Enable, Three State Outputs  | 22              |

| AM25LS2520<br>AM25LS2521         | _                           | Eight-Bit Comparator                                            | 20              |

| *AM25LS2524                      | _                           | Registered Comparator                                           | 20              |

| *AM25LS2525                      | _                           | System Clock Generator and Driver                               | 20              |

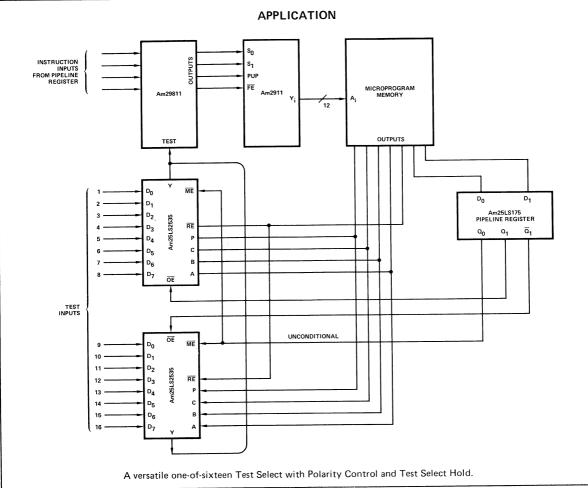

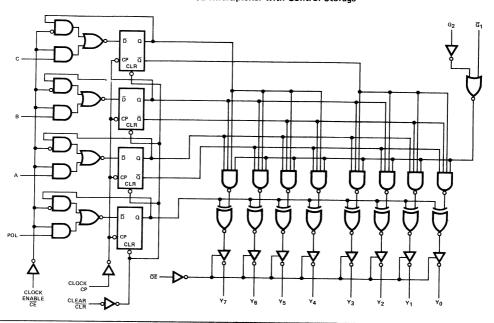

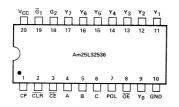

| AM25LS2525<br>AM25LS2535         | -                           | Eight-Bit Multiplexer; Control Storage                          | 20              |

| AM25LS2536                       |                             | Eight-Bit Decoder; Control Storage                              | 20              |

| AM25LS2537                       | _                           | One-of-Ten Decoder; Three State Outputs                         | 20              |

| AM25LS2537<br>AM25LS2538         | _                           | One-of-Eight Decoder; Three State Outputs                       | 20              |

| AM25LS2539                       | _                           | Dual One-of-Four Decoder; Three State Outputs                   | 20              |

| AM25LS2568                       |                             | BCD Decade Up-Down Counter; Three State Outputs                 | 20              |

| AM25LS2569                       | -                           | Four-Bit Binary Up-Down Counter; Three State Outputs            | 20              |

<sup>\*</sup>In development.

## DESIGNER'S GUIDE TO HIGH PERFORMANCE LOW-POWER SCHOTTKY LOGIC

By David A. Laws and Roy J. Levy.

#### 1\_

#### THE NEW STANDARD LOGIC

Low-power Schottky TTL integrated circuits are now firmly established as the standard logic configuration for new high performance system designs. They have essentially entirely replaced standard "gold-doped" TTL devices in all applications. In addition, they have relegated the other logic families to specialized needs where the ultimate in high speed (ECL) or low power for battery operated operation (CMOS) is mandatory.

This wide acceptance has been achieved because LS offered all of the important features of the earlier TTL families with two significant advantages:

- LS circuits provide performance equal to that of standard TTL at between 20% and 50% of the power requirements. As a result, considerable system cost savings have been made in bulky power supplies and fans.

- LS technology allows more complex designs to be fabricated on a given die size. A far wider selection of systems oriented MSI and LSI functions have therefore been developed in the LS family.

Additional factors in their popularity is that the devices are implemented with the same technology, and are therefore totally compatible with the LSI bit-slice processors and supporting memories which today form the heart of most new high speed designs. Users of LS devices have been able to exploit these features to improve the performance and enhance the functional capability of their systems. In many cases this has been achieved at a lower total cost.

Advanced Micro Devices is a leading supplier of low-power Schottky MSI and LSI devices. Two basic families of product are offered:

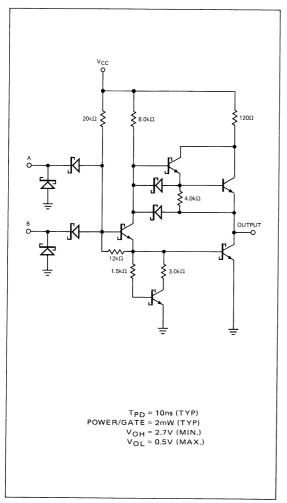

#### AM54/74LS Series

- Typical tpd 10ns/gate at 2mW

- Typical Register fmax = 40MHz

Pin for pin and electrical alternate source devices to the standard performance LS logic family.

#### AM25LS Series

- Typical tpd 5ns/gate at 2mW

- Typical Register fmax = 65MHz

Advanced Micro Devices' proprietary high performance LS logic family. This includes both original designs and enhanced specification versions of the AM54/74LS devices. Improvements include twice the fan-out over the military temperature range, higher noise margin and faster switching speeds.

The AM25LS improved performance devices are offered by Raytheon Semiconductor and identified by 25LS part numbers. Equivalent Fairchild and Motorola 9LS functions will come close to meeting AM25LS switching speeds on certain products.

The AM25LS proprietary designs have been carefully chosen to improve operation and reduce the cost of building high performance digital systems. A good example is the set of AM25LS14, 15 and 22 digital signal processing elements. Fairchild, Motorola and Texas Instruments have announced plans to alternate source many of the new Advanced Micro Devices' designs.

Both the Am25LS and the Am54LS/74LS families can be freely intermixed. Together with the Am2900 series of bipolar microprocessor functions they will satisfy most of the design requirements of today's advanced systems.

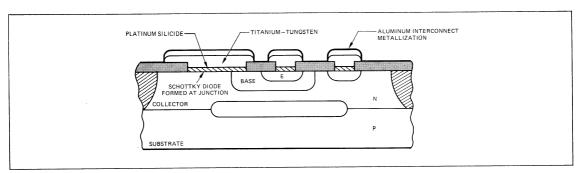

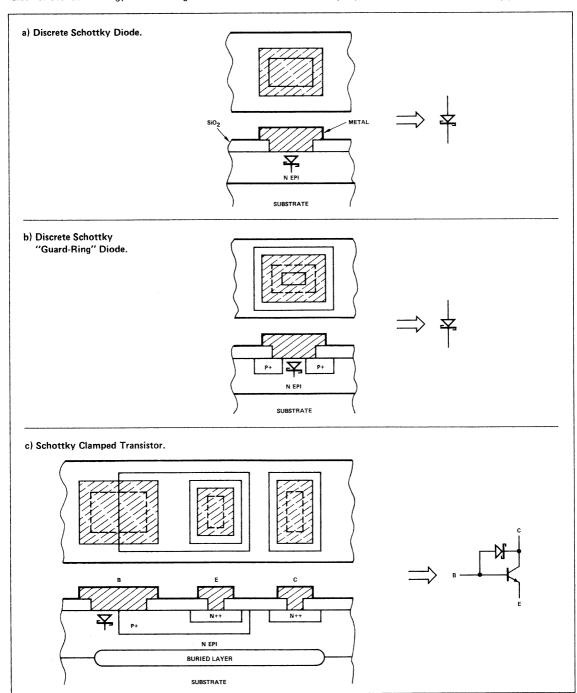

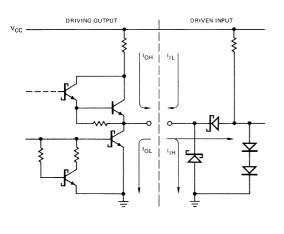

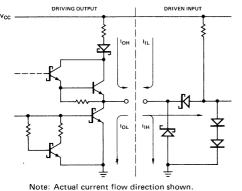

#### THE SCHOTTKY DIODE STRUCTURE

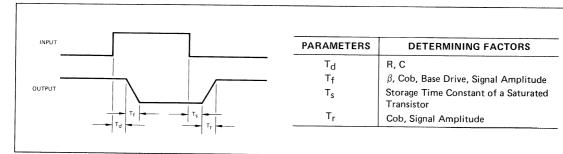

The major components of switching delays in digital integrated circuits are listed in Figure 1. One of the most significant of these is the storage time constant of a transistor driven into saturation Ts. Standard TTL circuits minimize this parameter with a process technique known as gold doping. This increases the rate of recombination of charge stored in the base region.

Figure 1. Major Causes of Propagation Delay.

The desired result of improved speed is achieved. Unfortunately it also reduces available design  $\beta$  at low temperatures and is marginally effective when hot. This results in lowered performance over the full military temperature range.

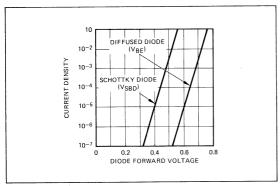

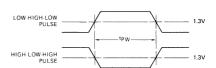

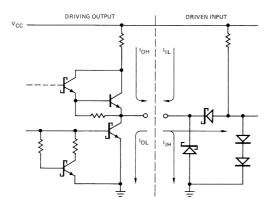

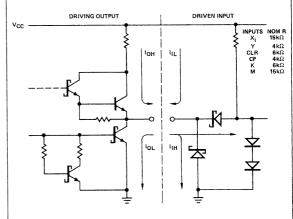

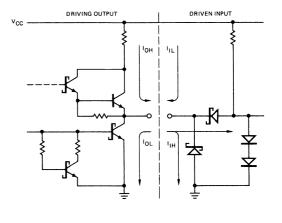

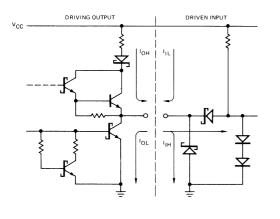

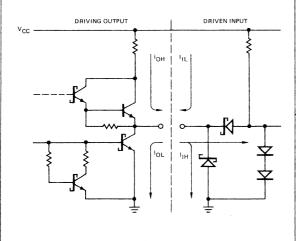

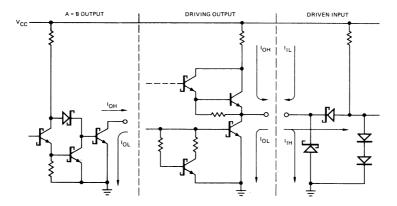

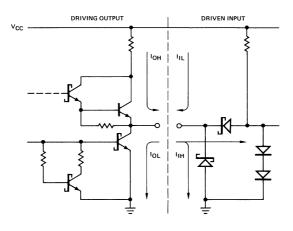

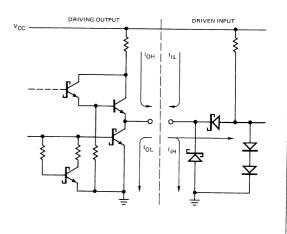

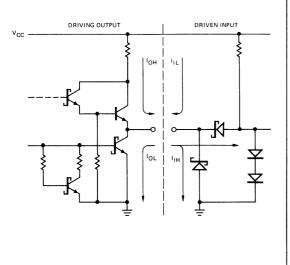

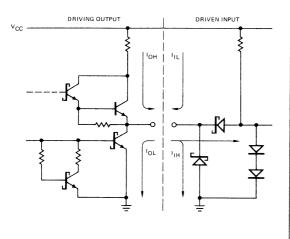

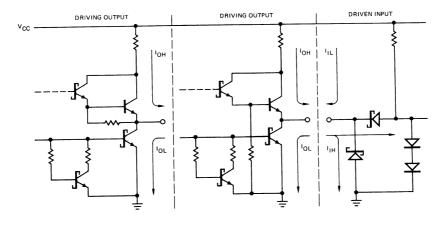

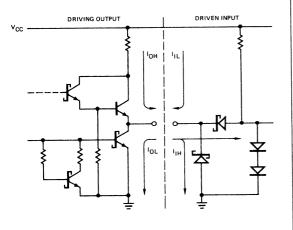

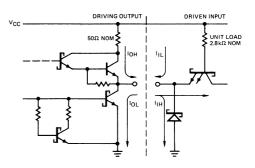

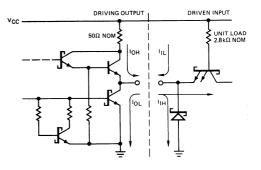

The development of the Schottky diode provides a more effective solution. A feature of the Schottky diode is its lower forward voltage at a given current level compared to a diffused (P-N) diode of the same area, Figure 2. Connecting a Schottky diode between the base and collector of a transistor, Figure 3, will shunt excess base current drive from the base to the collector, once the collector drops to a low enough voltage to forward bias the Schottky. This prevents the build up of stored charge and eliminates the Ts component of the delay.

Figure 2. Comparison of V<sub>F</sub> for Schottky and Diffused Diodes.

Figure 3. Schottky Clamped Transistor and its Conventional Circuit Symbol.