# 91A04A, 91AE04A, AND P6453 SERVICE MANUAL ADDENDUM

TO THE DAS 9100 SERIES SERVICE MANUAL (PART NUMBER 062-5848-00, -01, AND UP)

This Tektronix Manual Addendum supports the following products

91A04A Data Acquisition Module 91AE04A Data Acquisition Module P6453 Data Acquisition Probe

The 062-5848-00 manual set is a package consisting of loose leaf binders with manuals and addenda. Each manual and addendum in the set has its own part number starting with the prefix 070.

This addendum contains service information specific to the 91A04A and 91AE04A Data Acquisition Modules and the P6453 Data Acquisition Probe.

Refer to the DAS 9100 Series Service Manual for information on other DAS products, including mainframes, instrument modules, probes, and options.

**How To Use This Addendum.** This addendum is organized similarly to the DAS 9100 Series Service Manual: sections in the addendum correspond to the sections in the service manual. You can either leave the addendum whole and place it in one of the service manual binders, or you can separate the sections and insert them after the corresponding section in the main manual.

NOTE: You can order an extra service manual binder (Vol. III) by using P/N 016-0769-00.

## PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL

070-4298-00 Product Group 57

**FIRST PRINTING JANUARY 1984**

## WARNING

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO.

Copyright © 1984 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

Printed in U.S.A. Specification and price change privileges are reserved.

Tektronix, Inc. Walker Road Industial Park P.O. Box 4600 Beaverton,Oregon 97075

SERIAL NUMBER

Page

Page

# TABLE OF CONTENTS

## Section 1 -- INTRODUCTION AND SPECIFICATIONS

|                                                | •            |

|------------------------------------------------|--------------|

| DESCRIPTION                                    | 1-1          |

| MODES OF OPERATION                             | 1-1          |

| Data Acquisition Mode                          | 1-1          |

| High-Resolution Mode                           | 1-2          |

| Arms Trigger Mode                              | 1-2          |

| STANDARD AND OPTIONAL ACCESSORIES              | 1-2          |

| 91A04A Data Acquisition Modules                | 1-2          |

| 91AE04A High Speed Acquisition Expander Module | 1-3          |

| P6453 Data Acquistion Probe                    | 1-3          |

| SPECIFICATIONS                                 | 1-3          |

| Installation Requirements                      | 1-3          |

| 91A04A/91AE04A Electrical Specifications       | 1-4          |

| P6453 Electrical Specifications                | 1-11         |

| Environmental Specifications                   | 1-11         |

| 91A04A/91AE04A Physical Specifications         | 1-12<br>1-12 |

| P6453 Physical Specifications                  | 1-12         |

## Section 2 -- OPTIONS

## Section 3 -- OPERATING INSTRUCTIONS

| Description                                                                                                                                                                                              | 3-1                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Modes of Operation                                                                                                                                                                                       | 3-2                                                                  |

| Module Installation                                                                                                                                                                                      | 3-2                                                                  |

| Firmware Compatibility                                                                                                                                                                                   | 3-3                                                                  |

| Configuration Requirements                                                                                                                                                                               | 3-3                                                                  |

| Connecting the P6453 Probe                                                                                                                                                                               | 3-7                                                                  |

| P6453 Probe Operation                                                                                                                                                                                    | 3-8                                                                  |

| Module Deskewing         Trigger Specification Menu         91A04A Sub-Menu         ARMS 91A04 Sub-Menu         Clocking         Triggering         Clock Qualification         Arms Acquisition Display | 3-10<br>3-11<br>3-14<br>3-18<br>3-19<br>3-19<br>3-20<br>3-20<br>3-20 |

| MODULE ADJUSTMENT PROCEDURES | 3-24 |

|------------------------------|------|

| 91A04A Adjustment Procedure  |      |

| 91AE04A Adjustment Procedure | 3-27 |

| 91AE04 Adjustment Procedure  | 3-30 |

## Section 4 -- THEORY OF OPERATION

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-1                                                                    |

| LOGIC CONVENTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-1                                                                    |

| OVERVIEW: FUNCTIONS AND ACQUISITION CYCLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-1<br>4-2                                                             |

| INTERFACE BETWEEN MODULES AND THE DAS MAINFRAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-2                                                                    |

| INTERFACE BETWEEN THE 91A04A and 91AE04A MODULES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-2                                                                    |

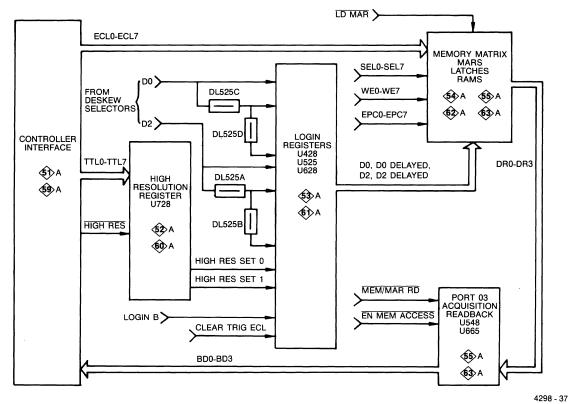

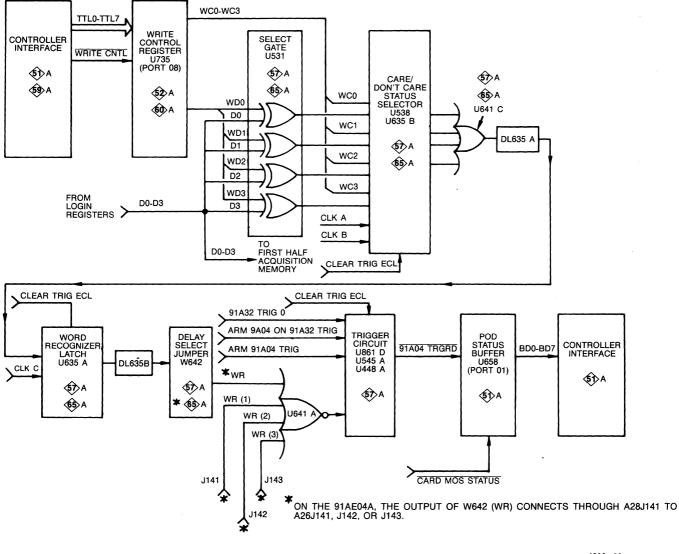

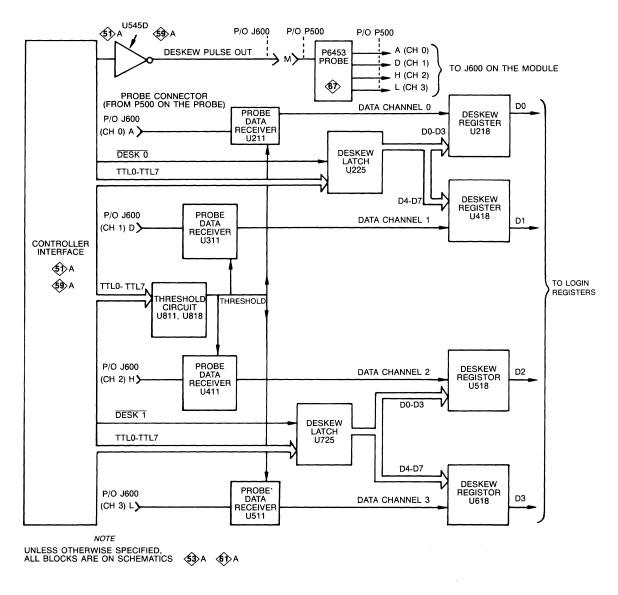

| GENERAL DESCRIPTION         P6453 Data Acquisition Probe         91A04A Data Acquisition Module         91A04A Controller Interface and ROM         Probe Receivers         Deskew Circuits         Clock Select and Control         Login Registers         Eight-Phase Clock Generator         Memory Address Registers         Write Enable Generator         3 ns and 5 ns Clock Generator         Acquisition Memory and Clock Array RAMs         Word Recognizer         Trigger         Delay Counter         Difference Counter         91AE04A Data Acquisition Module         91AE04A Controller Interface         Probe Receivers         Deskew Circuits         Login Registers         Wite Enable Generator         Memory Address Registers         Word Recognizer         Trigger         Delay Counter         Difference Counter         91AE04A Data Acquisition Module         91AE04A Controller Interface         Probe Receivers         Deskew Circuits         Login Registers         Eight-Phase Clock Generator         Memory Address Registers         Write Enable Generator         C | $\begin{array}{c} 4-3\\ 4-3\\ 4-3\\ 4-3\\ 4-3\\ 4-3\\ 4-3\\ 4-4\\ 4-4$ |

| Module to P6453 Interface         P6453 Data Acquisition Probe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-7<br>4-7                                                             |

#### Page

| DETAILED CIRCUIT DESCRIPTION Introduction 91A04A Data Acquisition Module 91AE04A Data Acquisition Module | 4-8<br>4-8<br>4-9<br>4-9 |

|----------------------------------------------------------------------------------------------------------|--------------------------|

| 91A04A and 91AE04A Circuit Description                                                                   | 4-9                      |

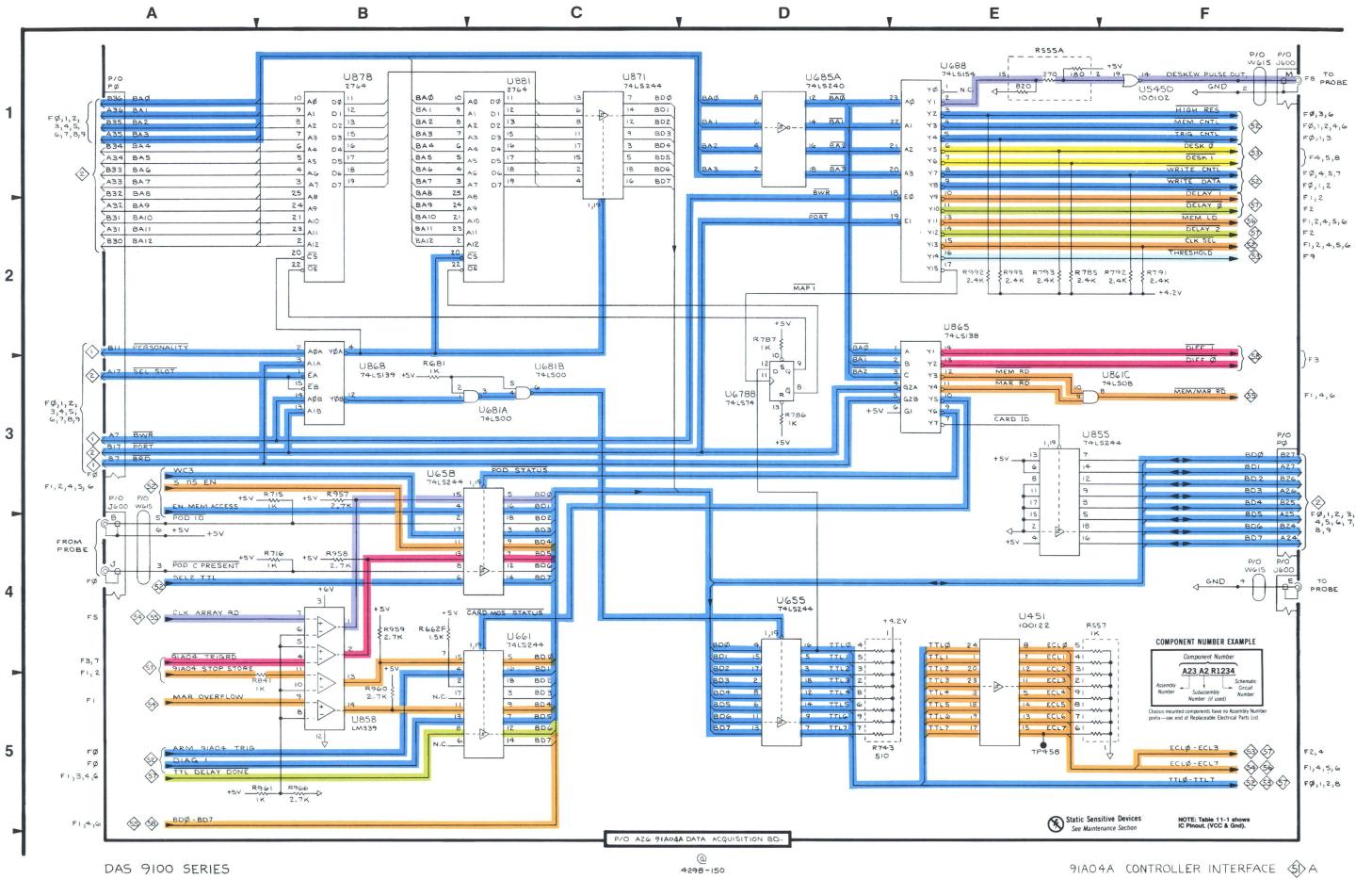

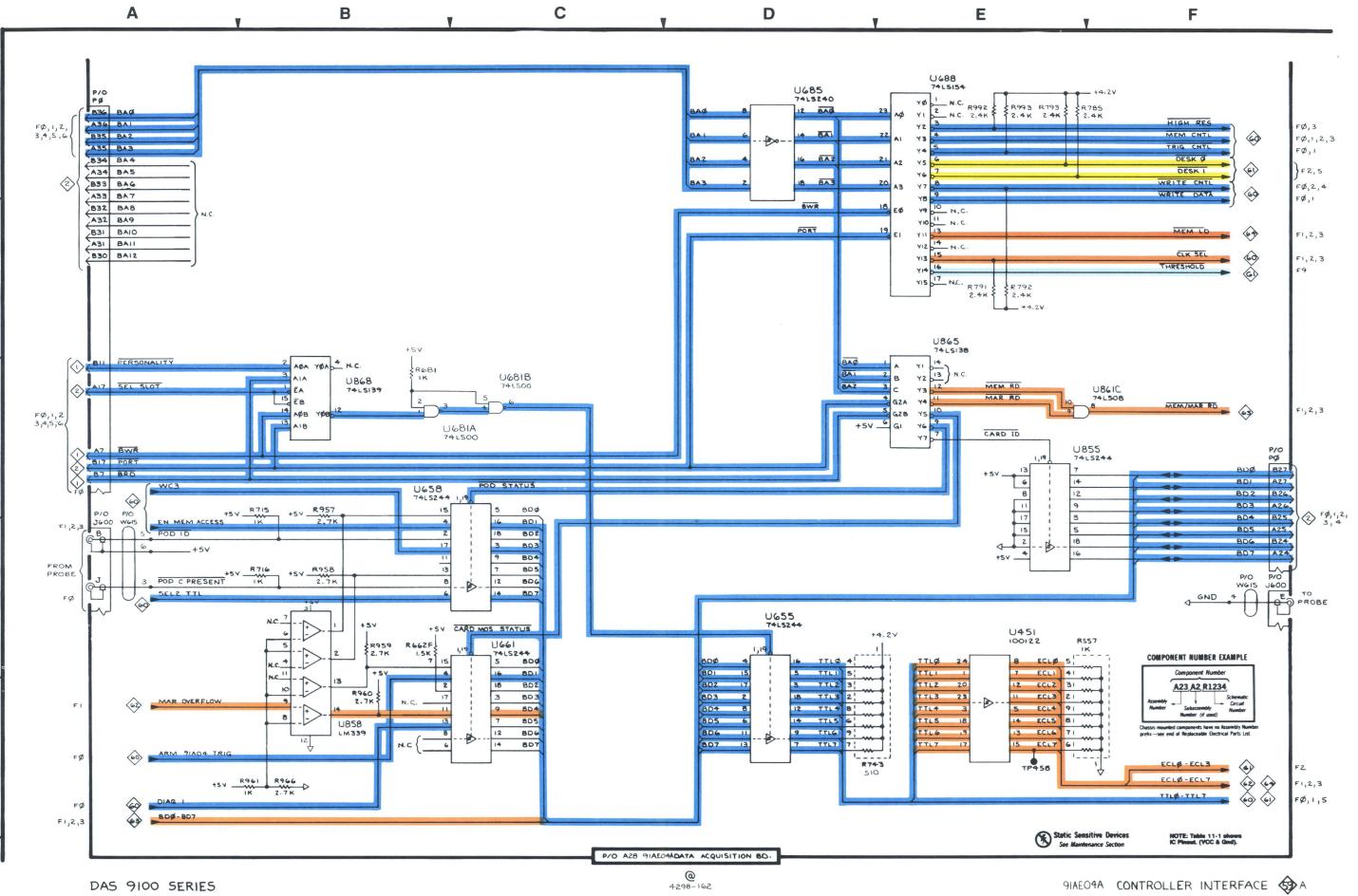

| Controller Interface 51 A/ 59 A                                                                          | 4-9                      |

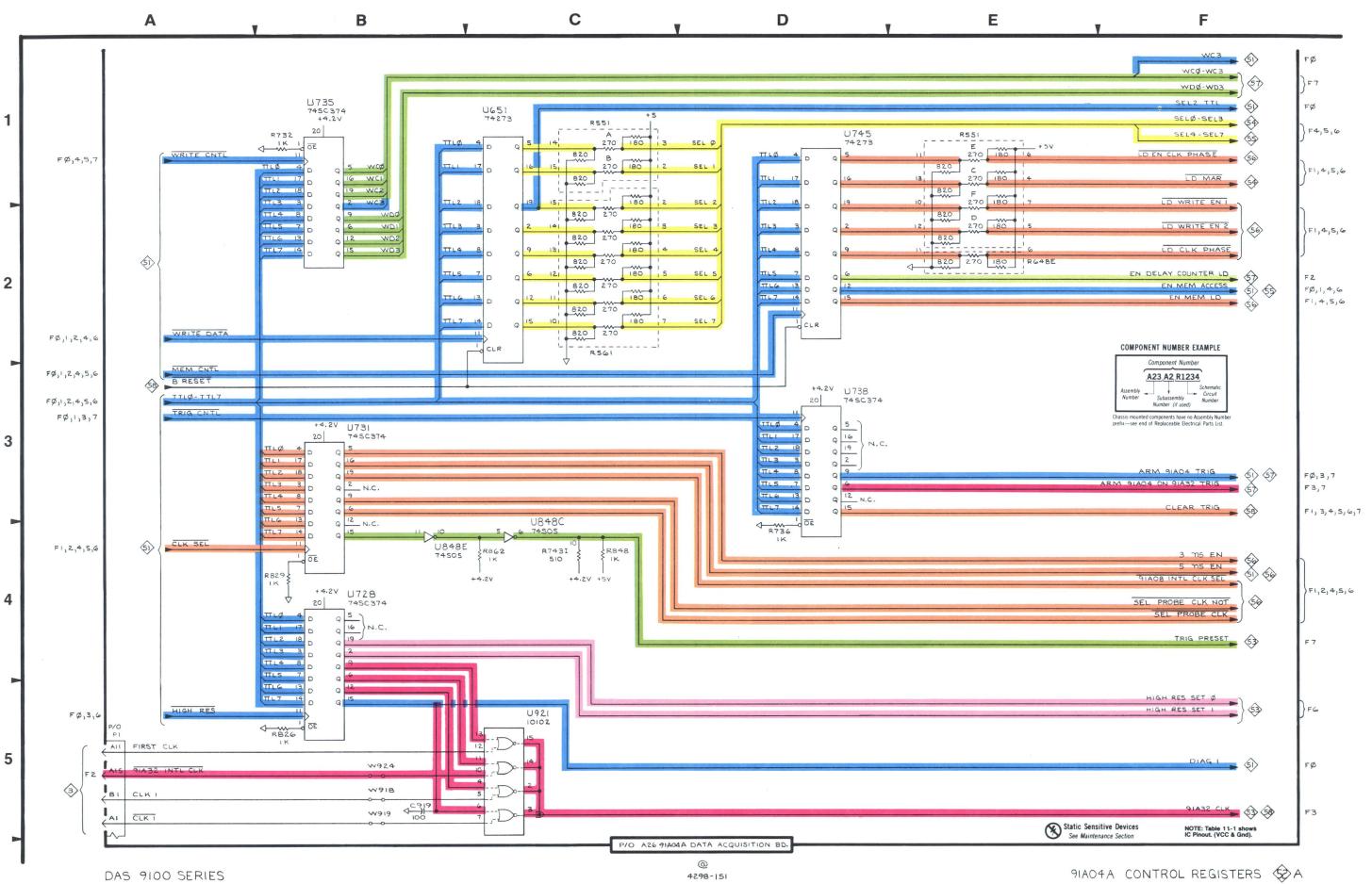

| Control Registers 52 A/ 60 A                                                                             | 4-10                     |

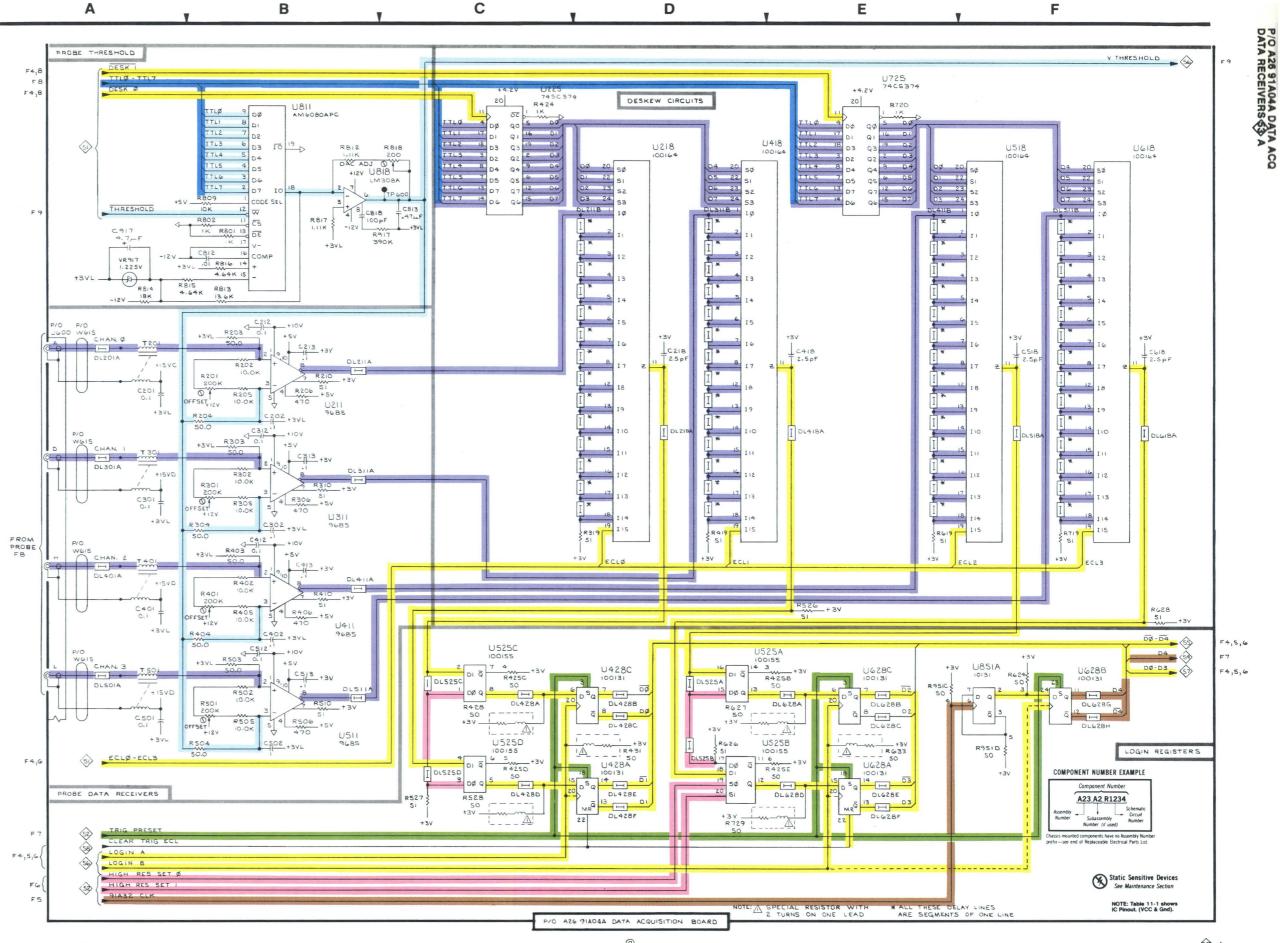

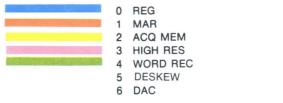

| Data Receivers 53 A/ 61 A                                                                                | 4-13                     |

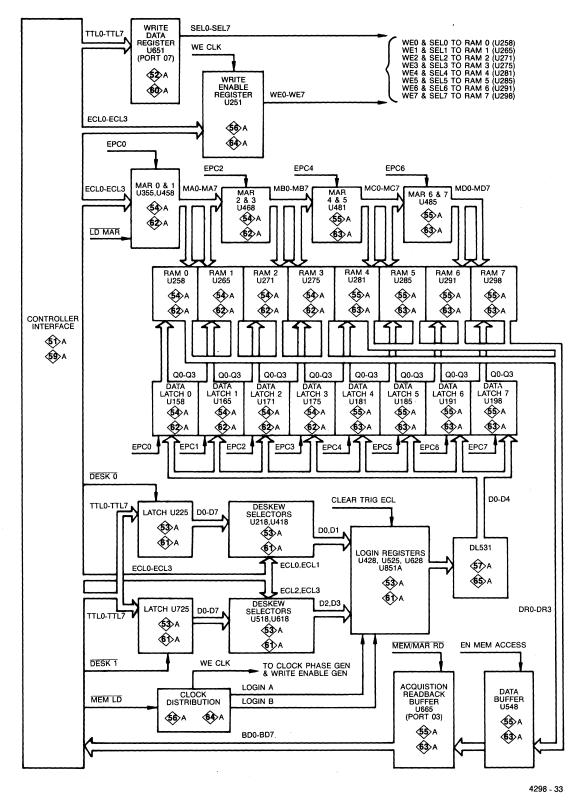

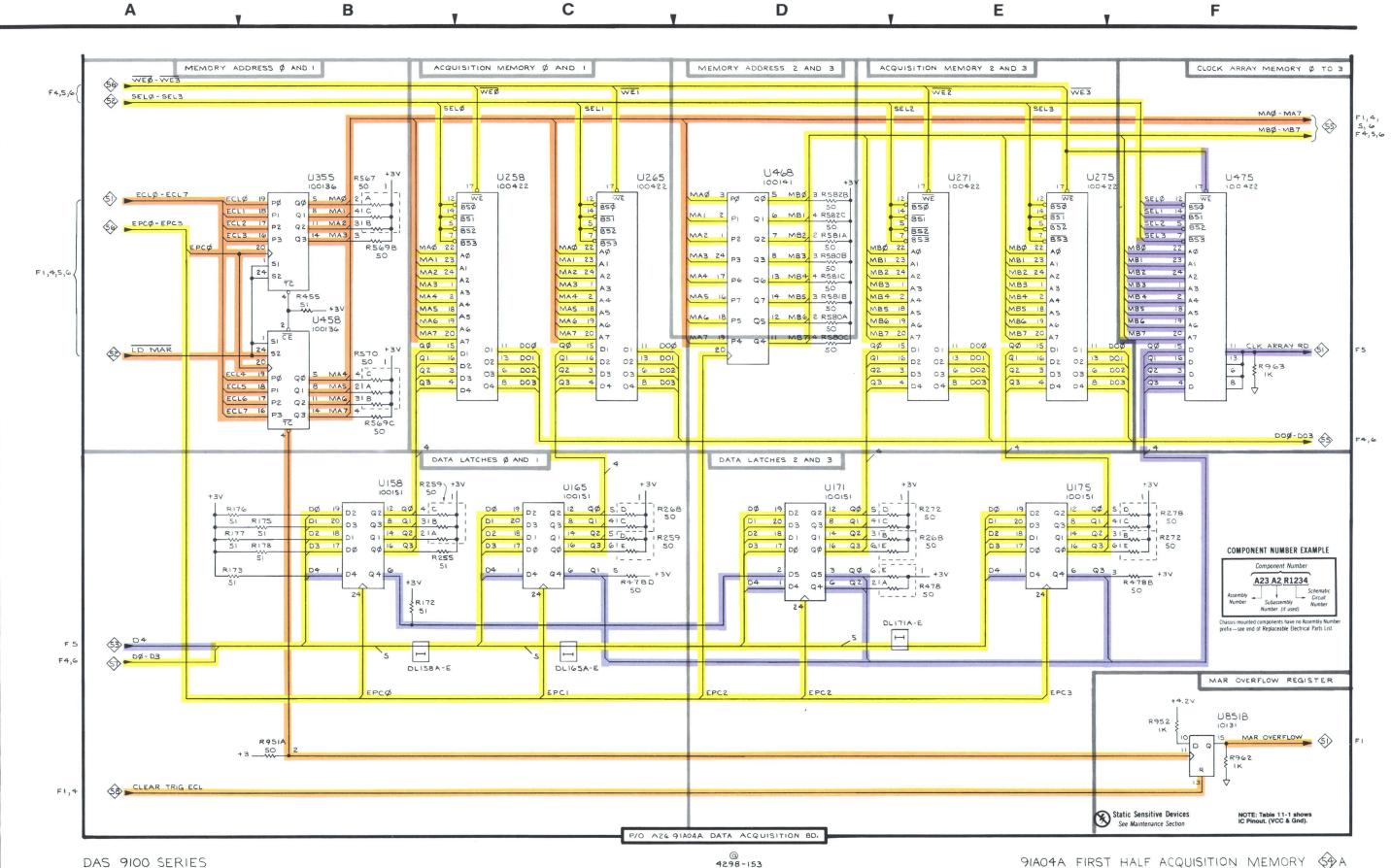

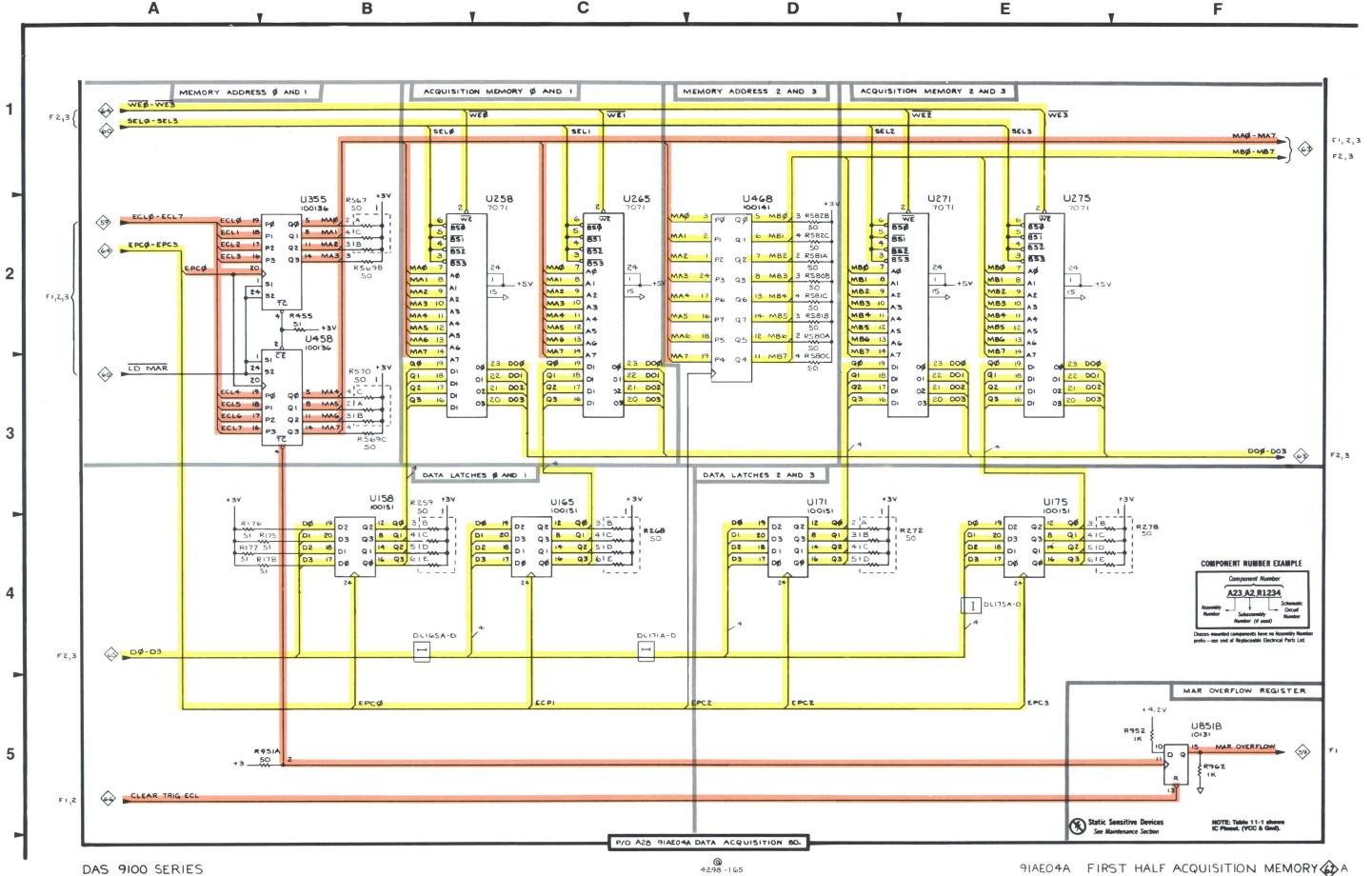

| First Half Acquisition Memory 54 A/ 62 A                                                                 | 4-15                     |

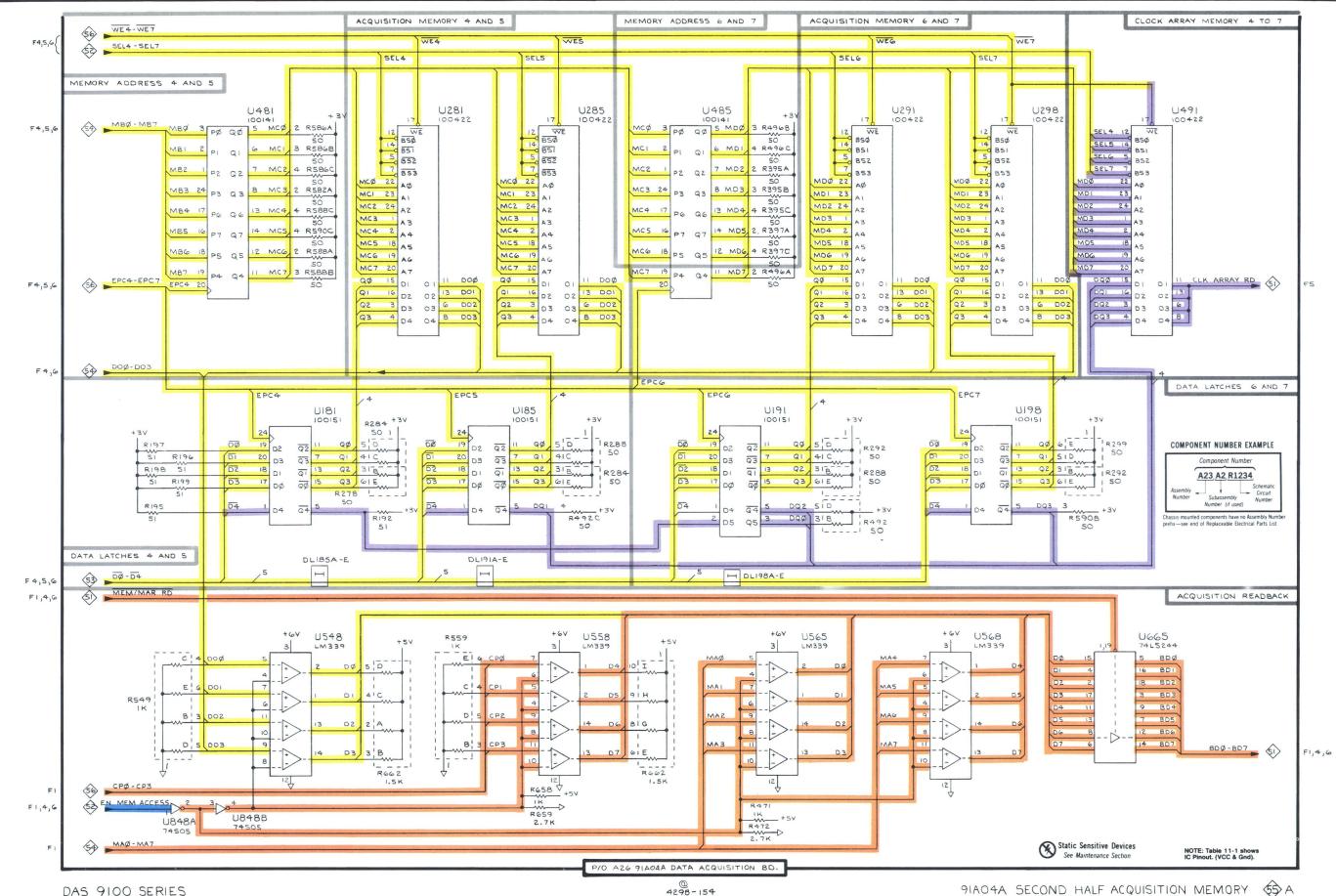

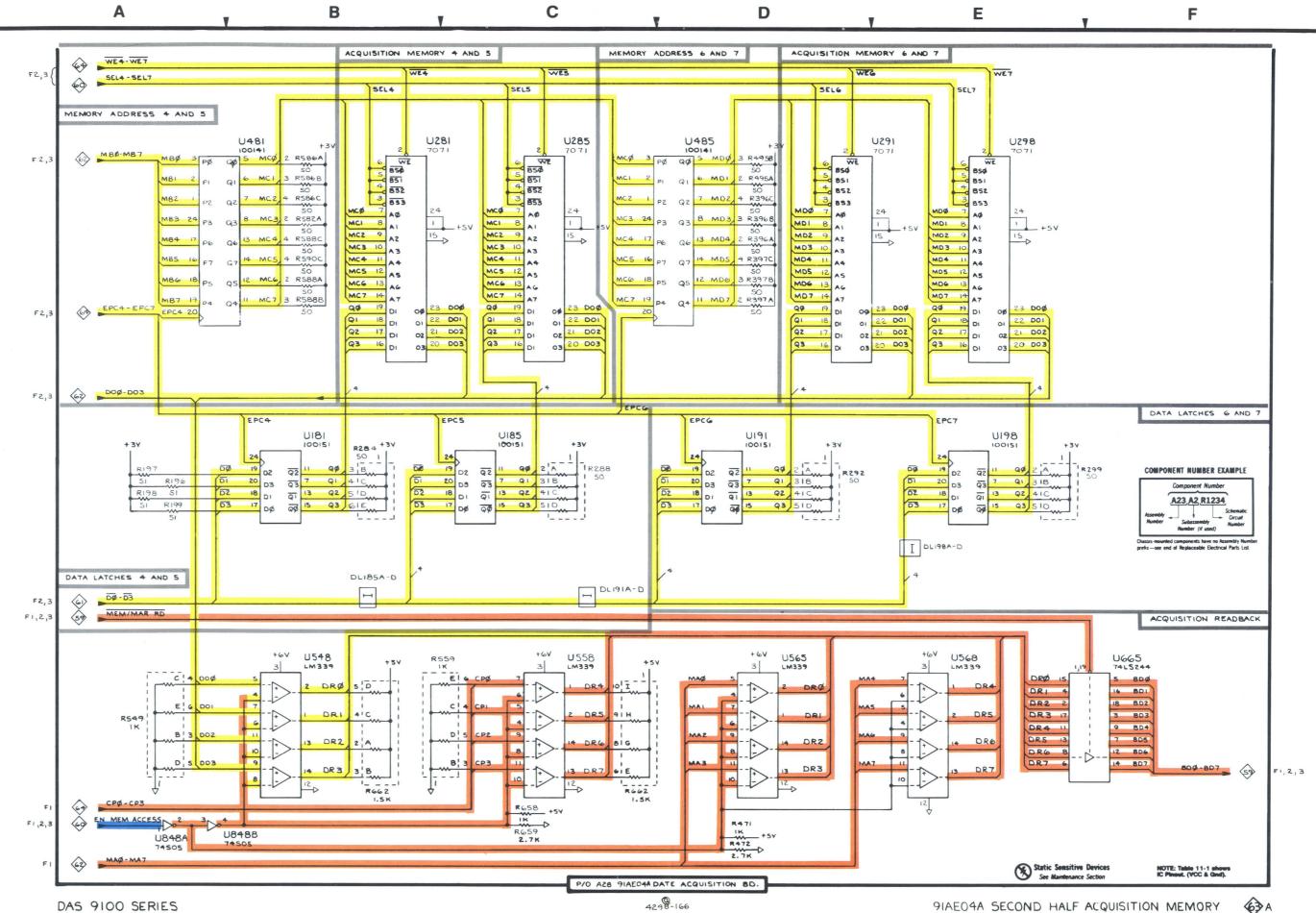

| Second Half Acquisition Memory 55 A/ 63 A                                                                | 4-16                     |

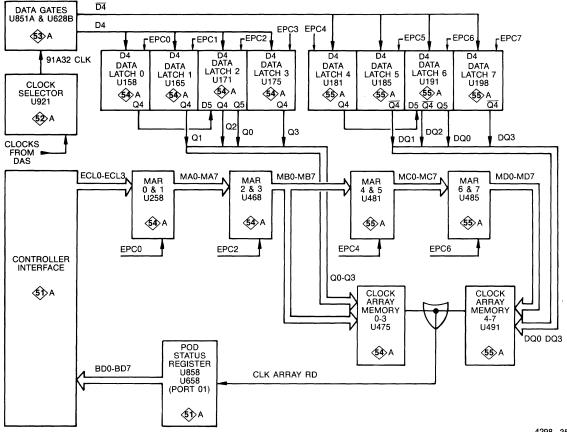

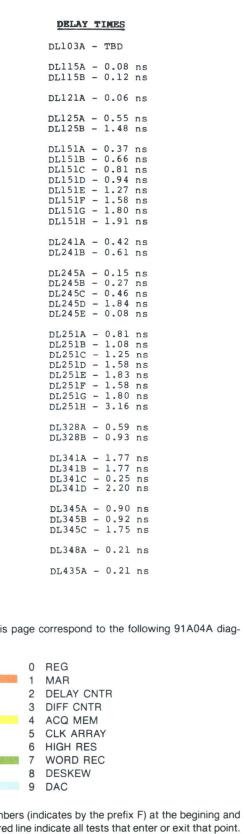

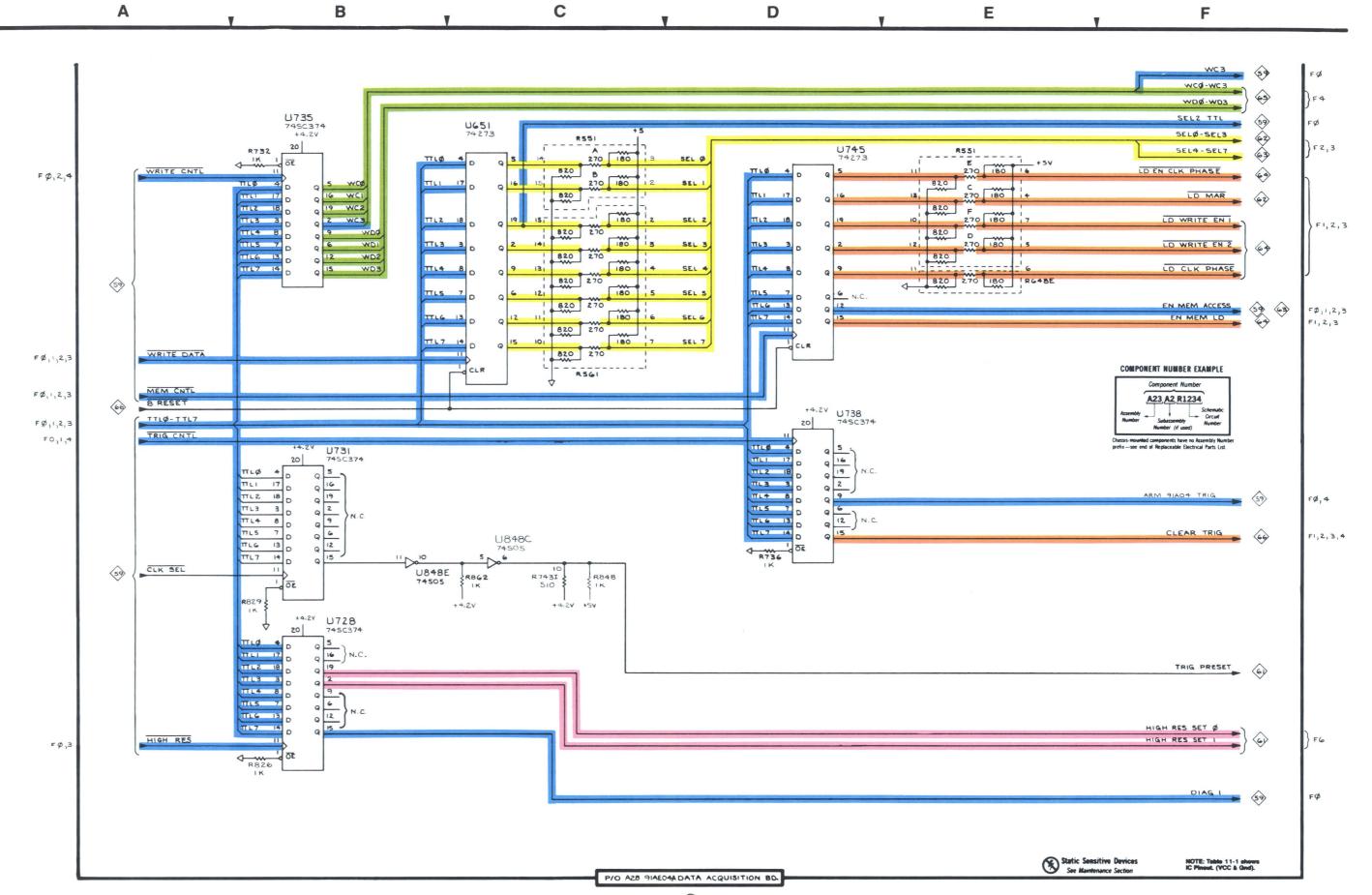

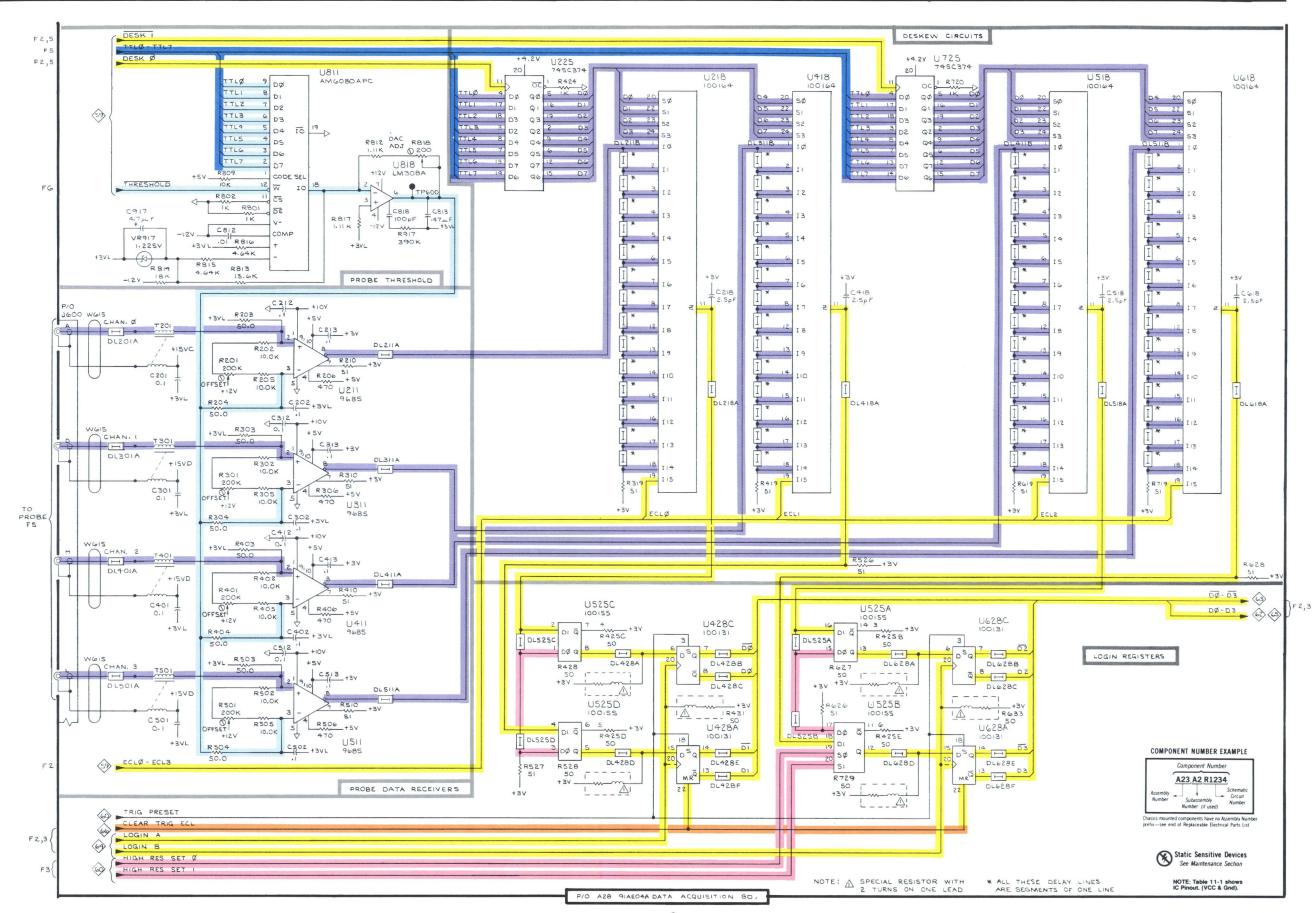

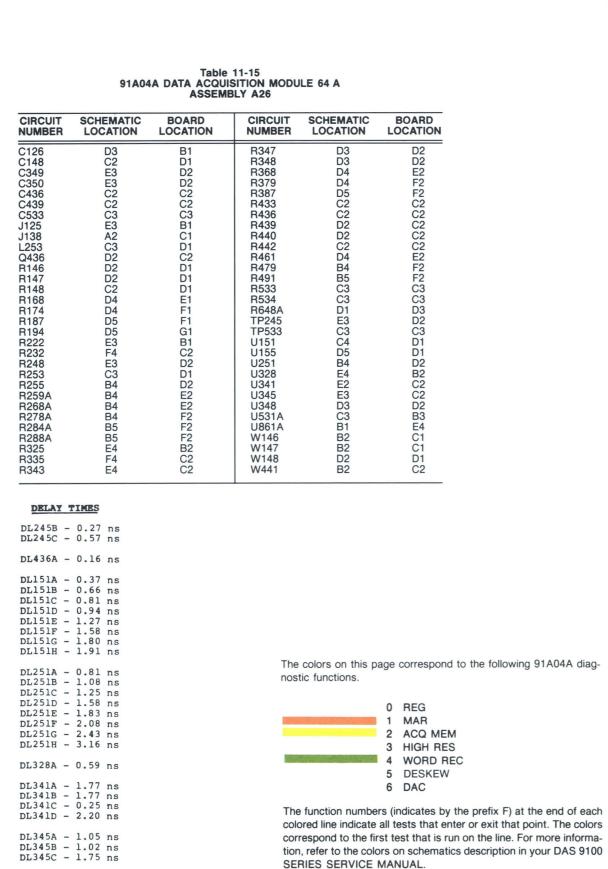

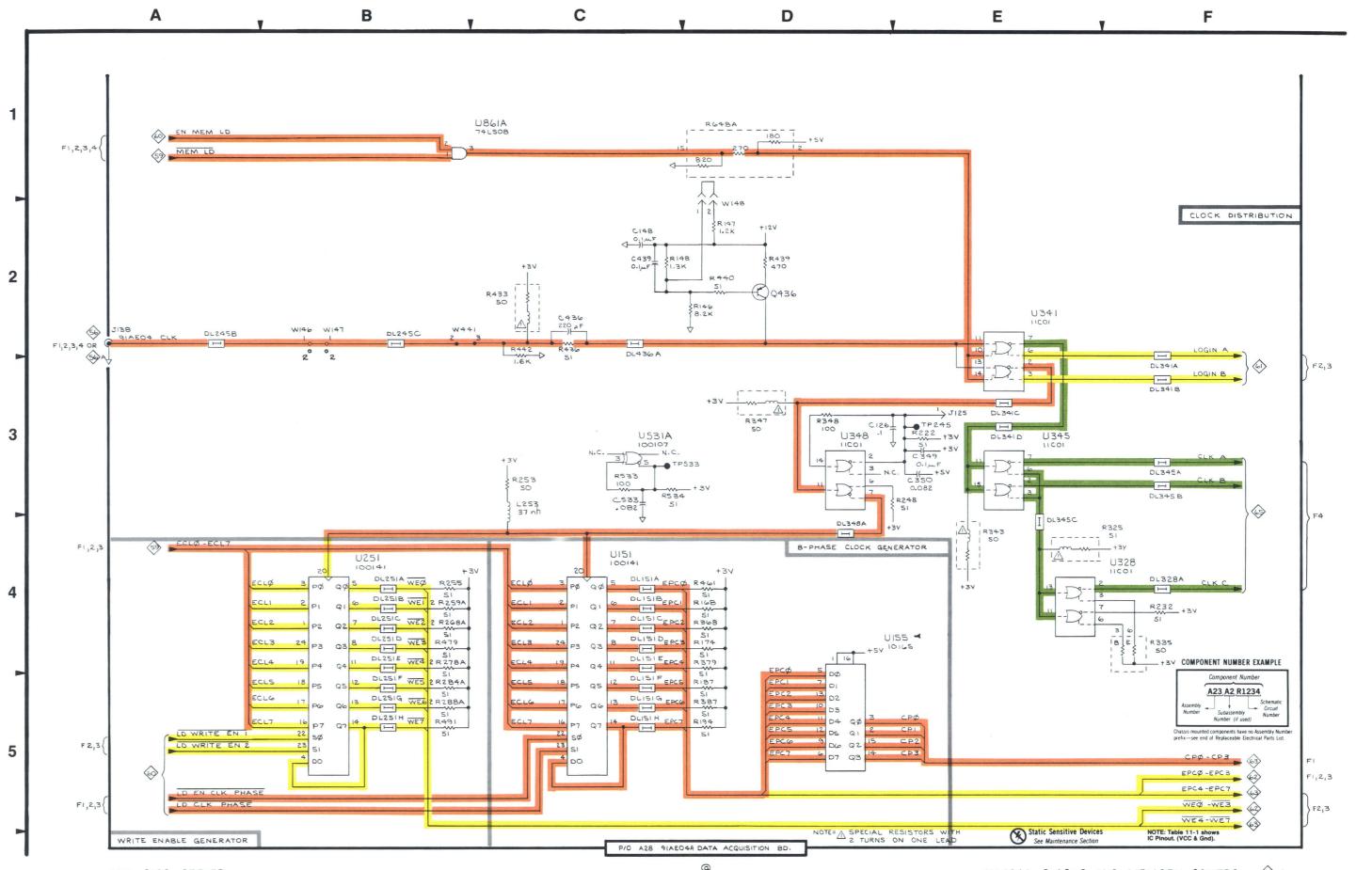

| Clocks and Memory Control 56 A/ 64 A                                                                     | 4-17                     |

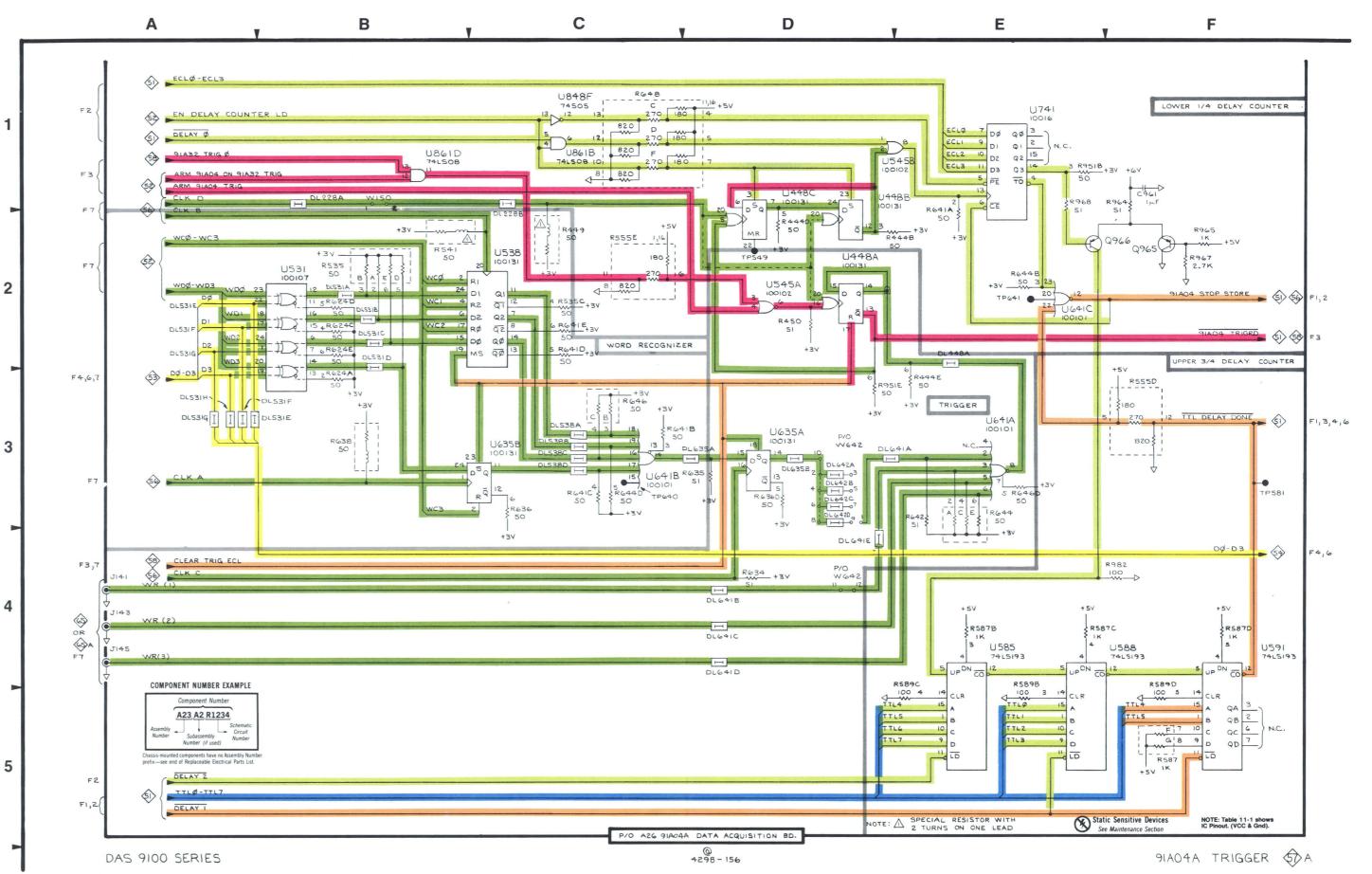

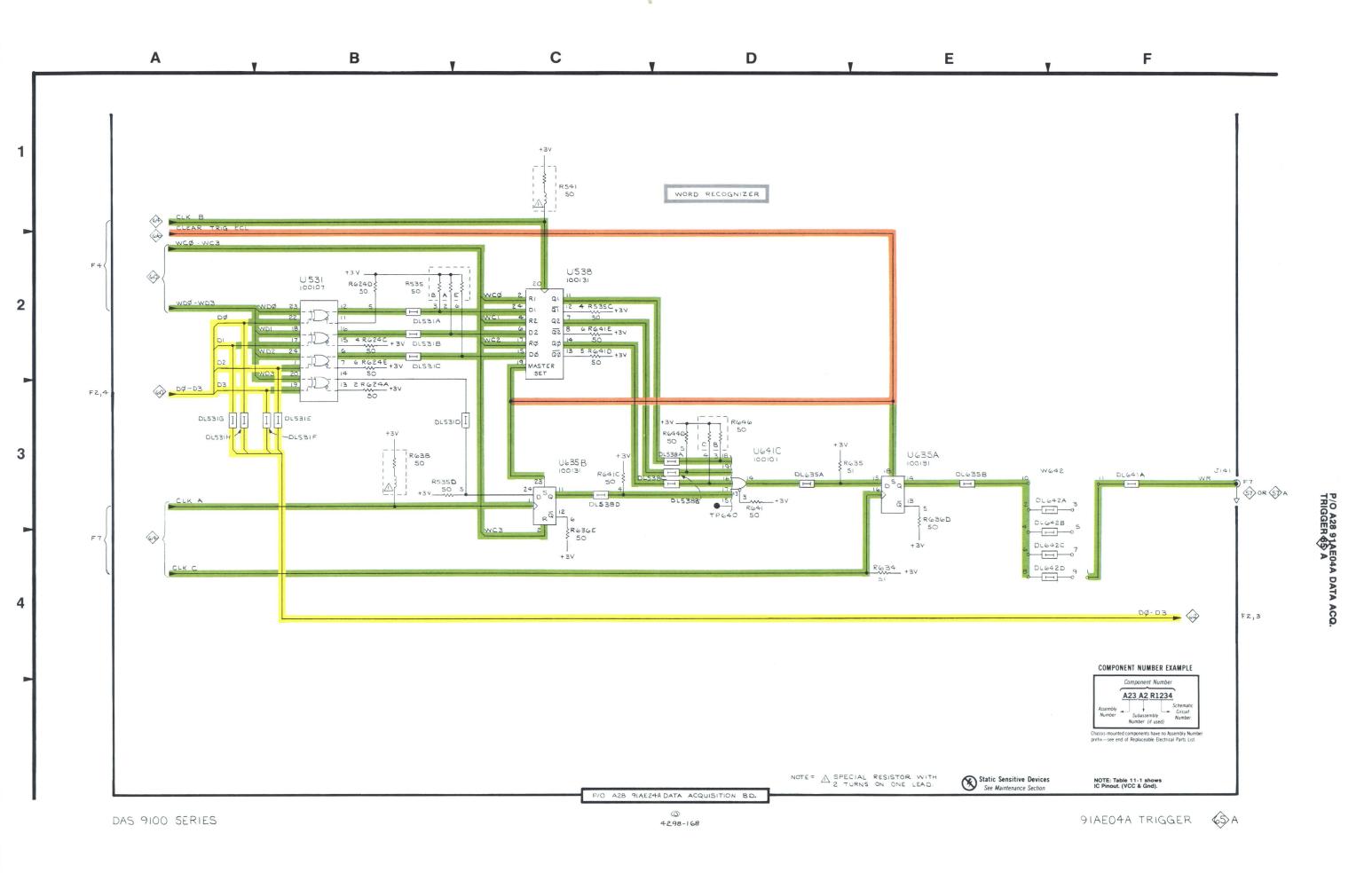

| Trigger 57 A/ 65 A                                                                                       | 4-21                     |

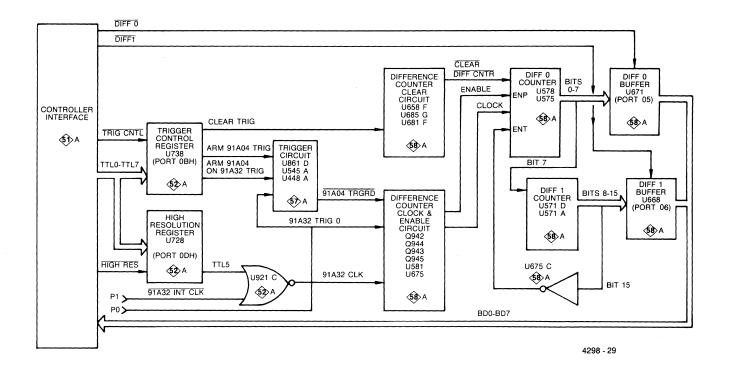

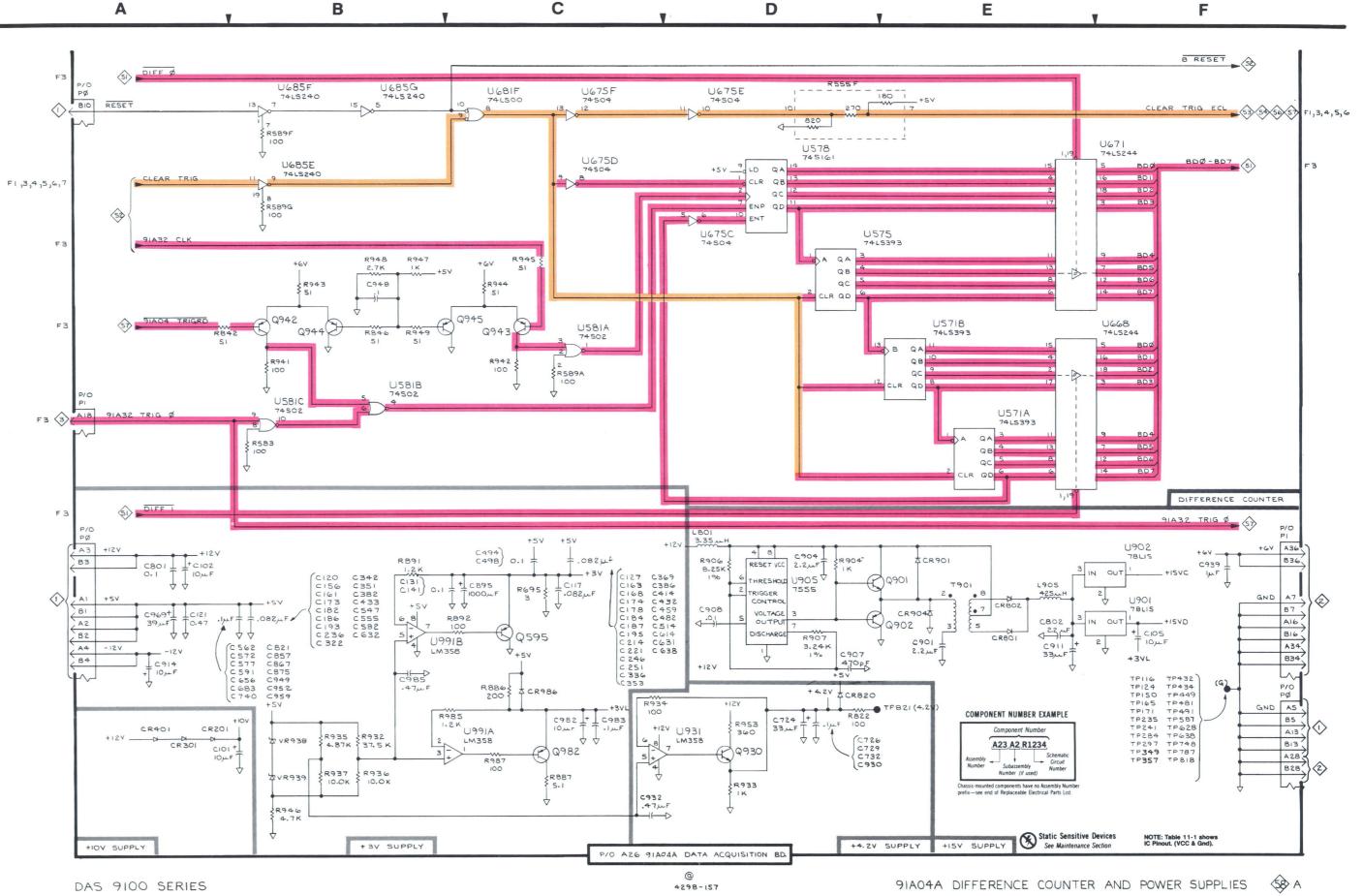

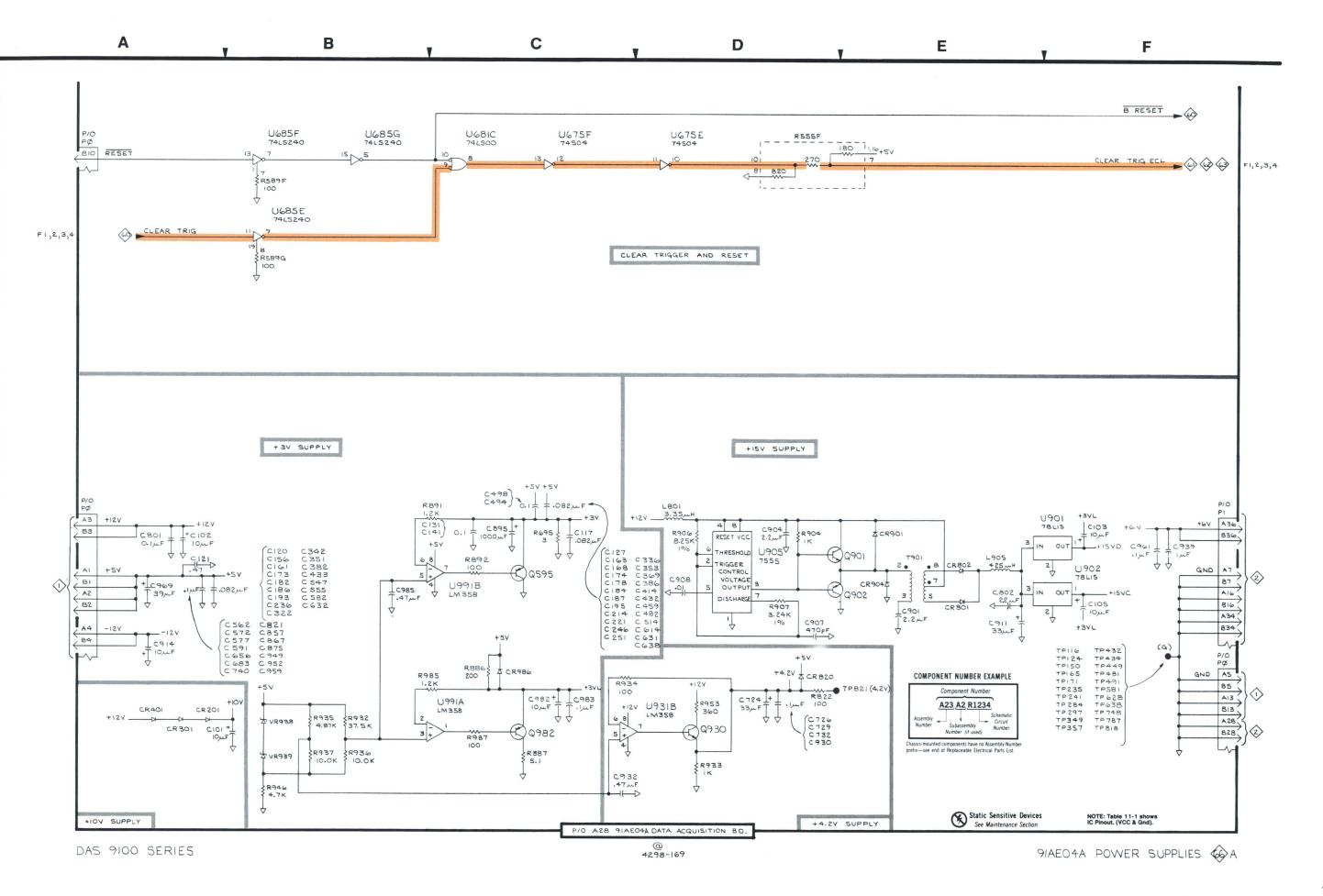

| Difference Counter and Power Supplies 58 A/66 A                                                          | 4-23                     |

## Section 5 -- VERIFICATION AND ADJUSTMENT PROCEDURES

|                                                     | Page |

|-----------------------------------------------------|------|

| INTRODUCTION                                        | 5-1  |

| TEST SETUP INFORMATION                              | 5-1  |

| Suggested Test Instruments                          | 5-1  |

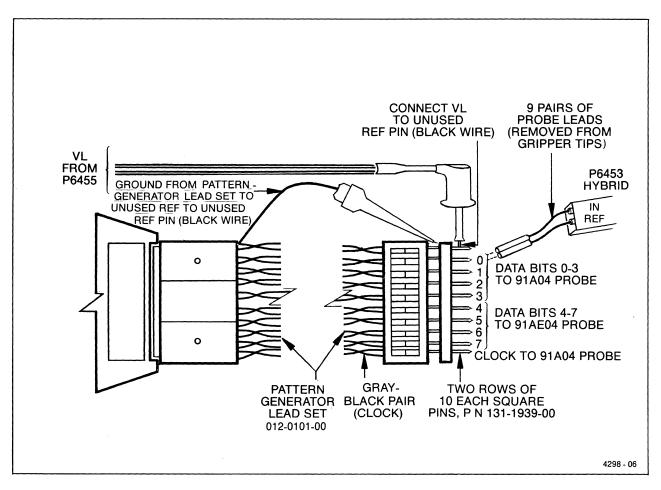

| Connecting a P6453 Probe to a P6455 Probe           | 5-5  |

| FUNCTIONAL CHECKS                                   | 5-7  |

| 91A04A and 91AE04A Data Acquisition Modules         |      |

| Functional Check                                    | 5-7  |

| Mainframe Setup for the Functional Check            | 5-7  |

| Executing the Diagnostic Self Test                  | 5-8  |

| Verifying Deskew Operation                          | 5-9  |

| Probe Setup for the Functional Check of the Module  | 5-9  |

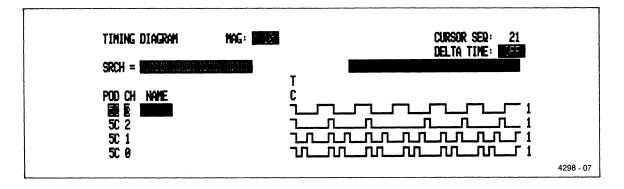

| Verifying Pod Connector C                           | 5-10 |

| Verifying the Acquisition Memory Cycle              | 5-11 |

| Verifying Triggering on 1s and Slow Internal Clocks | 5-11 |

| Verifying Triggering on Xs                          | 5-12 |

| Verifying the High-Speed Internal Clocks            | 5-13 |

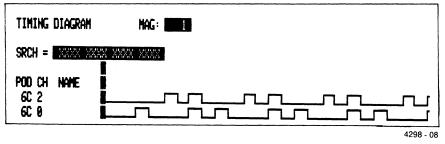

| Verifying High-Resolution Mode                      | 5-14 |

| Verifying 91A32 (slow card) ARMS 91A04 mode         | 5-15 |

|                                                     |      |

| P6453 Data Acquisition Probe Functional Check       | 5-16 |

| Mainframe Setup for the Functional Check            | 5-17 |

| Verifying Deskew Operation                          | 5-17 |

| Optional Probe Checks                               | 5-18 |

|                                                     |      |

| ADJUSTMENTS                                         | 5-18 |

| DAC (Digital-to-Analog-Converter) Adjustment        | 5-18 |

| Test Equipment Required                             | 5-19 |

| Equipment Setup Procedure                           | 5-19 |

| DAC Adjustment Procedure                            | 5-19 |

|                                                       | raye |

|-------------------------------------------------------|------|

| Adjusting Comparator Offsets Using the Fluke 5101B    |      |

| Multimeter Calibrator as a Current Source             | 5-20 |

| Test Equipment Required                               |      |

|                                                       |      |

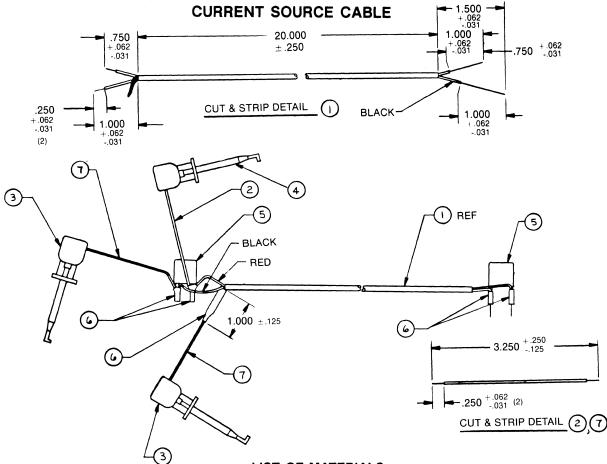

| Fabricating the Current Source Cable                  |      |

| Equipment Setup Procedure                             |      |

| Comparator Offset Adjustment Procedure                | 5-22 |

| Adjusting Comparator Offsets Using a Tektronix        |      |

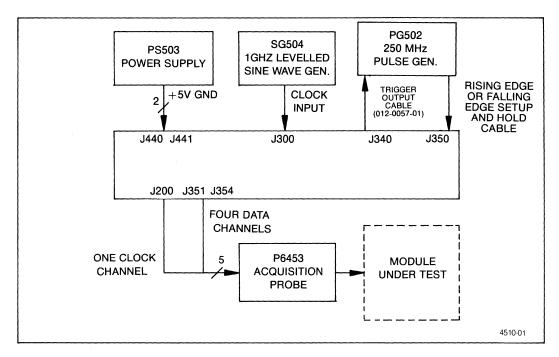

| PG502 250 MHz Pulse Generator as a Signal Source      | 5-24 |

| Test Equipment Required                               |      |

| Equipment Setup Procedure                             |      |

| Comparator Offset Adjustment Procedure                | -    |

|                                                       | 5-25 |

| Internal Oscillator Adjustments                       | 5-26 |

| 3 ns Oscillator Adjustment                            | 5-26 |

| 5 ns Oscillator Adjustment                            | 5-27 |

|                                                       |      |

| J600 Replacement and Calibration                      |      |

| Positioning Word Recognizer Timing Jumper W642        | 5-29 |

|                                                       |      |

| PERFORMANCE CHECK                                     | 5-33 |

| 91A04A and 91AE04A Data Acquisition Modules           |      |

| Performance Check                                     | 5-33 |

| What These Procedures Test                            |      |

| Test Equipment Setup for the Performance Checks       |      |

| Mainframe Setup for the Performance Checks            |      |

| Internal Power Supply Test                            |      |

| Internal Clock Accuracy Test (91A04A Only)            |      |

| Functional Tests                                      |      |

| DAS Mainframe Setup                                   |      |

| 660 MHz Asynchronous Word Recognition Test, Channel 0 |      |

| 660 MHz Asynchronous Word Recognition Test, Channel 2 |      |

|                                                       |      |

| 330 MHz Asynchronous Word Recognition Test, Channel 1 |      |

|                                                       |      |

| 1.5 ns Data Acquisition Test                          |      |

| Setup-and-Hold-Time Test Setup                        |      |

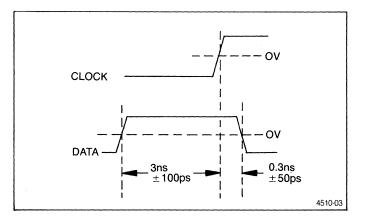

| 300 MHz Rising-Edge Clock Setup-and-Hold-Time Test    |      |

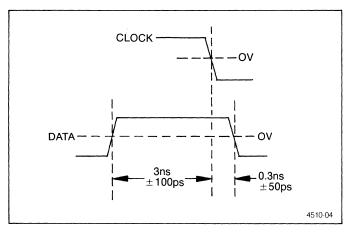

| 300 MHz Falling-Edge Clock Setup-and-Hold-Time Test   |      |

| High Speed Word Recognizer Timing Check (91A04A Only) |      |

| 91AE04A to 91A04A High Speed Word Recognizer Timing   | 5-47 |

| Data Acquisition Probe Performance Check              | 5-48 |

Page

## Section 6 -- MAINTENANCE: GENERAL INFORMATION

|                                               | Page |

|-----------------------------------------------|------|

| MAINTENANCE PRECAUTIONS                       | 6-1  |

| Installing and Removing Instrument Modules    | 6-1  |

| Installation Slot Restrictions                | 6-1  |

| PREVENTIVE AND CORRECTIVE MAINTENANCE         | 6-2  |

| Cleaning 91A04A and 91AE04A Modules           | 6-2  |

| Repairing a 91A04A Series Module              | 6-2  |

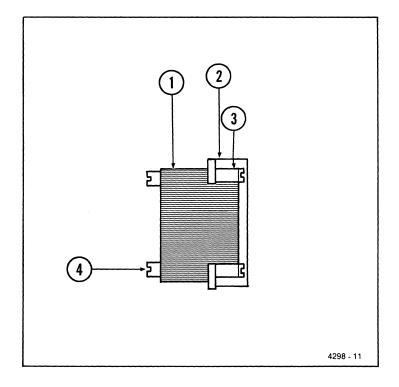

| Replacing the Probe Connector Bracket         | 6-2  |

| Replacing J600                                | 6-3  |

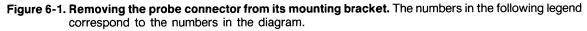

| Extending the Modules                         | 6-4  |

| Connecting Jumper Cables for Extended Modules | 6-5  |

| Air Core Inductors                            | 6-6  |

| Repairing P6453 Data Acquisition Probes       | 6-6  |

| REPACKAGING INFORMATION                       | 6-7  |

## Section 7 -- MAINTENANCE: TROUBLESHOOTING

#### Page

|                                                | 7-1  |

|------------------------------------------------|------|

| How to Use this Section                        | 7-1  |

| Troubleshooting Precautions                    | 7-2  |

| Internal Instrument Access                     | 7-2  |

| Soldering                                      | 7-2  |

| Static Discharge Damage                        | 7-2  |

| Troubleshooting Equipment                      | 7-3  |

| Troubleshooting Aids                           | 7-4  |

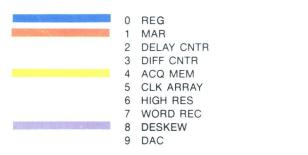

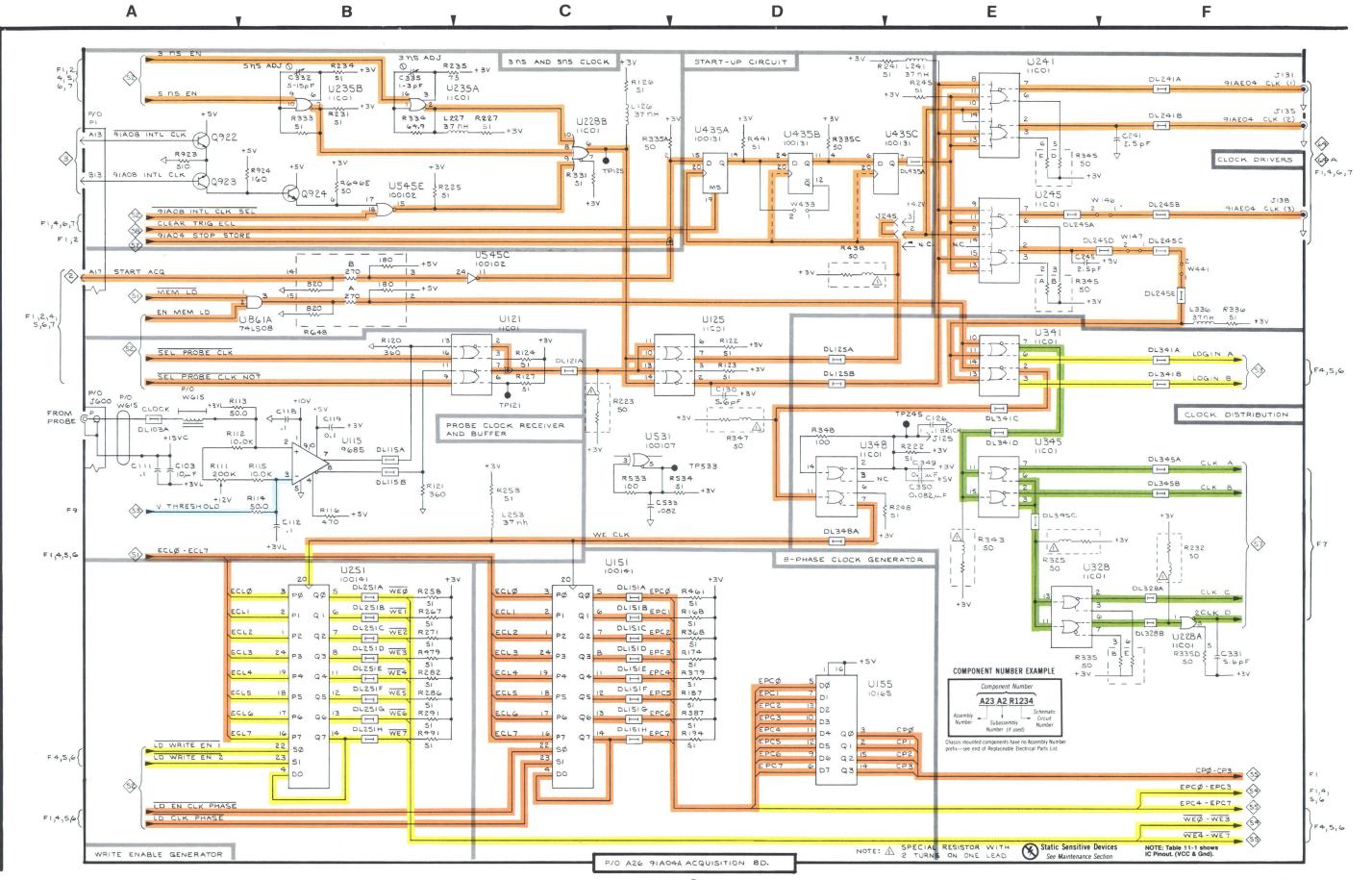

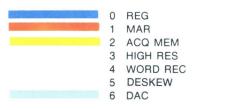

| Color-Coded Schematics                         | 7-4  |

| The Diagnostics Menu                           | 7-4  |

|                                                | 7-9  |

|                                                | 7-11 |

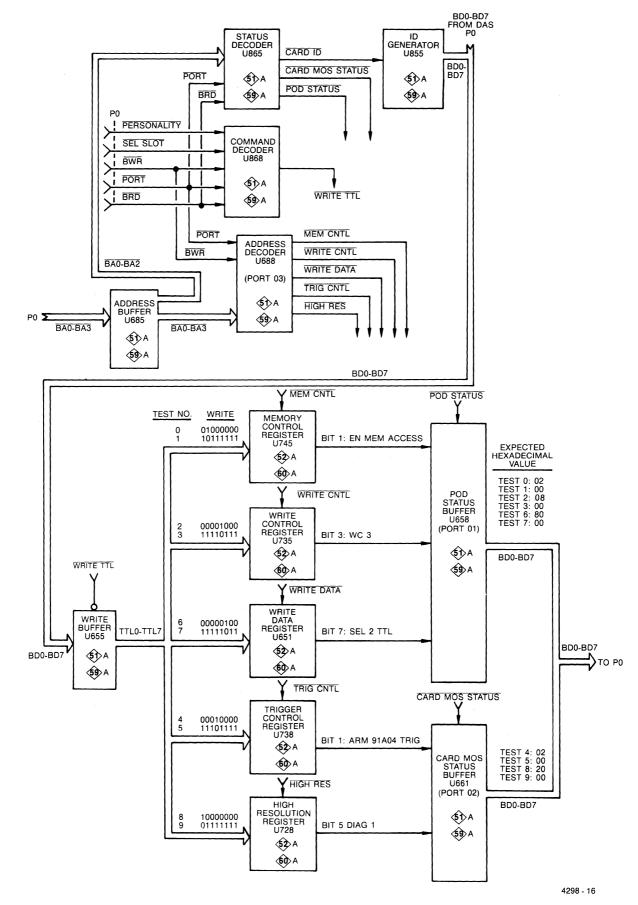

| 91A04A/91AE04A FUNCTION 0, REGISTER TESTS      | 7-13 |

|                                                | 7-13 |

| Function 0 Description                         | 7-13 |

|                                                | 7-13 |

|                                                | 7-13 |

|                                                | 7-13 |

|                                                | 7-13 |

| ······································         | 7-14 |

| ······································         | 7-15 |

| •                                              | 7-17 |

| Troubleshooting Undiagnosed Register Functions |      |

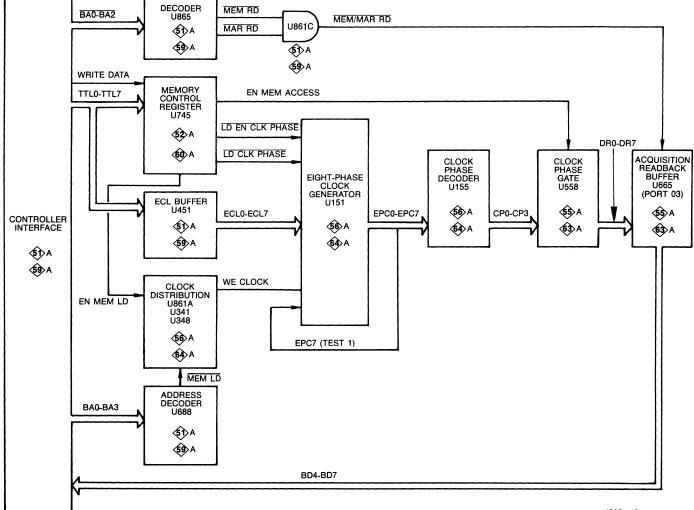

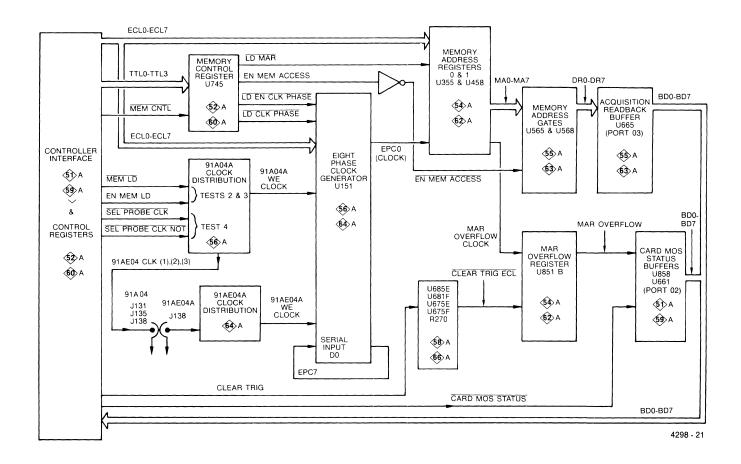

| 91A04A/91AE04A FUNCTION 1, MEMORY ADDRESS TESTS      | 7-19 |

|------------------------------------------------------|------|

| Circuit Overview                                     | 7-19 |

| Function 1 Description                               | 7-19 |

| Loading the Data                                     | 7-19 |

| Reading the Results                                  | 7-20 |

| 91A04A/91AE04A Memory Address Test 0 Troubleshooting | 7-20 |

| Reading the Test 0 Error Codes                       | 7-20 |

| Analyzing the Test Indications                       | 7-21 |

| 91A04A/91AE04A Memory Test 0 Description             | 7-23 |

| Circuit Conditions                                   | 7-23 |

| 91A04A/91AE04A Memory Address Test 1 Troubleshooting | 7-26 |

| Reading the Test 1 Error Codes                       | 7-26 |

| Analyzing the Test Indications                       | 7-26 |

| 91A04A/91AE04A Memory Address Test 1 Description     | 7-27 |

| Circuit Conditions                                   | 7-27 |

| 91A04A/91AE04A Memory Address Test 2 Troubleshooting | 7-27 |

| Reading the Test 2 Error Codes                       | 7-27 |

| Analyzing the Test Indications                       | 7-27 |

|                                                      | 7-28 |

| 91A04A/91AE04A Memory Address Test 2 Description     | 7-20 |

|                                                      | 7-30 |

| 91A04A/91AE04A Memory Address Test 3 Troubleshooting |      |

| Reading the Test 3 Error Codes                       | 7-32 |

| Analyzing the Test Indications                       | 7-32 |

| 91A04A/91AE04A Memory Address Test 3 Description     | 7-32 |

| Circuit Conditions                                   | 7-33 |

| 91A04A/91AE04A Memory Address Test 4 Troubleshooting | 7-33 |

| Reading the Test 4 Error Codes                       | 7-33 |

| Analyzing the Test Indications                       | 7-34 |

| 91A04A/91AE04A Memory Address Test 4 Description     | 7-34 |

| Circuit Conditions                                   | 7-35 |

|                                                      |      |

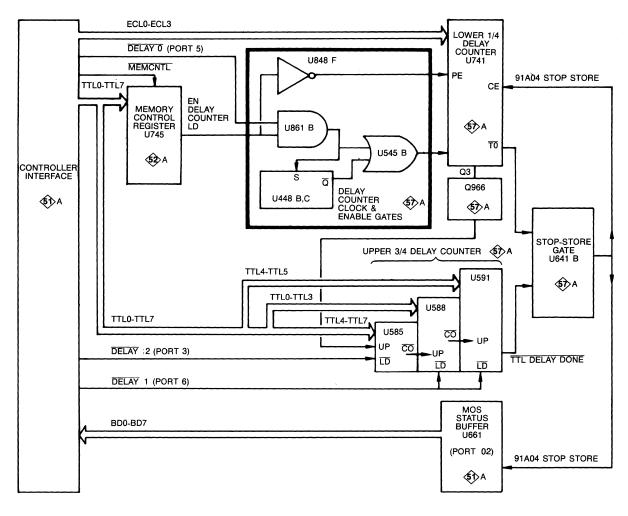

| 91A04A FUNCTION 2, DELAY COUNTER                     | 7-36 |

| Circuit Overview                                     | 7-36 |

| Function 2 Description                               | 7-36 |

| Loading the Data                                     | 7-37 |

| Reading the Results                                  | 7-37 |

| 91A04A Delay Counter Test 0 Troubleshooting          | 7-39 |

| Reading the Test 0 Error Codes                       | 7-39 |

| Analyzing the Test Indications                       | 7-39 |

| 91A04A Delay Counter Test 0 Description              | 7-39 |

| Circuit Conditions                                   | 7-40 |

| 91A04A Delay Counter Test 1 Troubleshooting          | 7-40 |

| Reading the Test 1 Error Codes                       | 7-40 |

| Analyzing the Test Indications                       | 7-41 |

| 91A04A Delay Counter Test 1 Description              | 7-41 |

| Circuit Conditions                                   | 7-41 |

|                                                      |      |

|                                                          | Page         |

|----------------------------------------------------------|--------------|

| 91A04A Delay Counter Test 2 Troubleshooting              | 7-42         |

| Reading the Test 2 Error Codes                           | 7-42         |

| Analyzing the Test Indications                           | 7-43         |

| 91A04A Delay Counter Test 2 Description                  | 7-43         |

| Circuit Conditions                                       | 7-43         |

| 91A04A Delay Counter Test 3 Troubleshooting              | 7-44         |

| Reading the Test 3 Error Codes                           | 7-44         |

| Analyzing the Test Indications                           | 7-45         |

| 91A04A Delay Counter Test 3 Description                  | 7-45         |

| Circuit Conditions                                       | 7-45         |

|                                                          | 7 45         |

| 91A04A FUNCTION 3 DIFFERENCE COUNTER                     | 7-45         |

|                                                          | 7-45         |

| Function 3 Description                                   | 7-46         |

| Loading the Difference Counter                           | 7-46<br>7-47 |

| Reading the Results                                      | 7-47         |

| 91A04A Difference Counter Tests 0 and 1 Troubleshooting  | 7-47         |

| Reading the Tests 0 and 1 Error Codes                    | 7-47         |

| Analyzing the Test Indications                           | 7-47         |

| Circuit Conditions                                       | 7-48         |

| 91A04A Difference Counter Test 2 Troubleshooting         | 7-40         |

| Reading the Test 2 Error Codes                           | 7-48         |

| Analyzing the Test Indications                           | 7-40         |

| 91A04A Difference Counter Test 2 Description             | 7-49         |

| Circuit Conditions                                       | 7-49         |

|                                                          | 7-40         |

| 91A04A FUNCTION 4/91AE04A FUNCTION 2, ACQUISITION MEMORY | 7-50         |

| Circuit Overview                                         | 7-50         |

| Function Description                                     | 7-51         |

| Loading the Data                                         | 7-52         |

| Reading the Results                                      | 7-52         |

| 91A04A/91AE04A Acquisition Memory Tests 0-7              |              |

| Troubleshooting                                          | 7-53         |

| Reading the Tests 0-7 Error Codes                        | 7-53         |

| Analyzing the Test Indications                           | 7-53         |

| 91A04A/91AE04A Acquisition Memory Tests 0-7 Description  | 7-53         |

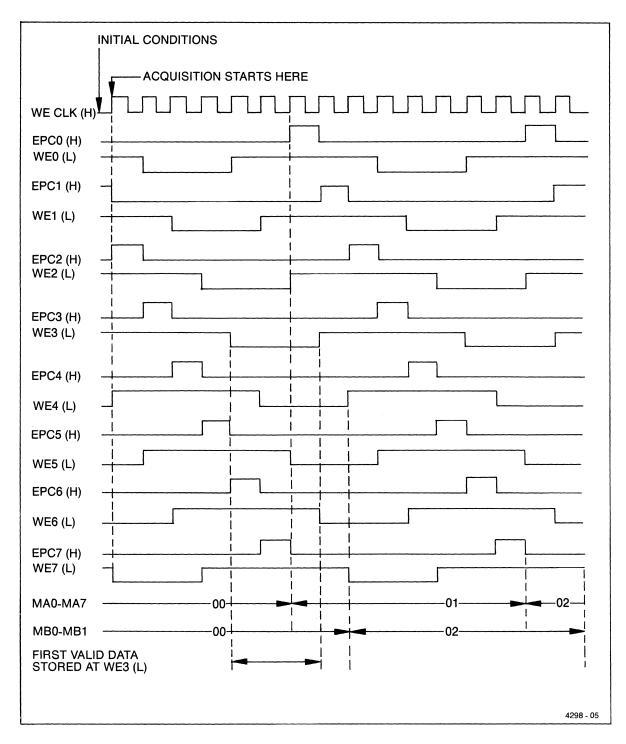

| Initial Conditions                                       | 7-55         |

| Test Sequence                                            | 7-55         |

| Circuit Conditions                                       | 7-55         |

| 91A04A/91AE04A Acquisition Memory Test 8 Troubleshooting | 7-57         |

| Reading the Test 8 Error Codes                           | 7-57         |

| Analyzing the Test Indications                           | 7-58         |

| 91A04A/91AE04A Acquisition Memory Test 8 Description     | 7-59         |

| Initial Conditions                                       | 7-59         |

| Test Sequence                                            | 7-59         |

| Circuit Conditions                                       | 7-59         |

|                                                                                 | Page         |

|---------------------------------------------------------------------------------|--------------|

| 91A04A FUNCTION 5, CLOCK ARRAY                                                  | 7-60         |

| Circuit Overview                                                                | 7-60         |

| Function 5 Description                                                          | 7-60         |

| Loading the Data                                                                | 7-60         |

| Reading the Results                                                             | 7-60         |

| 91A94A Clock Array Test 0 Troubleshooting                                       | 7-61         |

| Reading the Test 0 Error Codes                                                  | 7-61         |

| Analyzing the Test Indications                                                  | 7-62         |

| 91A04A Clock Array Test 0 Description                                           | 7-62         |

|                                                                                 | 7-64         |

|                                                                                 | 7-64         |

| Circuit Conditions                                                              | 7-64         |

| ATAAAA FUNATION COTAFOAA FUNATION A LUGU BEOOLUTION                             | 7 05         |

| 91A04A FUNCTION 6/91AE04A FUNCTION 3, HIGH RESOLUTION                           | 7-65         |

| Circuit Overview                                                                | 7-65         |

| High Resolution Function Description                                            | 7-65         |

| Loading the Data                                                                | 7-65         |

| Reading the Results       91A04A/91AE04A High Resolution Test 0 Troubleshooting | 7-66<br>7-66 |

| Reading the Test 0 Error Codes                                                  | 7-66         |

| Analyzing the Test Indications                                                  | 7-66         |

| 91A04A/91AE04A High Resolution Test 0 description                               | 7-67         |

| Initial Conditions                                                              | 7-68         |

| Test Sequence                                                                   | 7-68         |

| Circuit Conditions                                                              | 7-68         |

|                                                                                 | 7-00         |

| 91A04A FUNCTION 7/91AE04A FUNCTION 4, WORD RECOGNIZER                           | 7-68         |

| Circuit Overview                                                                | 7-68         |

| Word Recognizer Test Description                                                | 7-69         |

| Loading the Data                                                                | 7-69         |

| Reading the Results                                                             | 7-70         |

| 91A04A/91AE04A Word Recognizer Test 0 Troubleshooting                           | 7-70         |

| Reading the Test 0 Error Codes                                                  | 7-70         |

| Analyzing the Test Indications                                                  | 7-70         |

| 91A04A/91AE04A Word Recognizer Test 0 Description                               | 7-71         |

| Initial Conditions                                                              | 7-71         |

| Test Sequence                                                                   | 7-71         |

| Circuit Conditions                                                              | 7-73         |

| 91A04A/91AE04A Word Recognizer Test 1 Troubleshooting                           | 7-74         |

| Reading the Test 1 Error Codes                                                  | 7-74         |

| Analyzing the Test Indications                                                  | 7-74         |

| 91A04A/91AE04A Word Recognizer Test 1 Description                               | 7-74         |

|                                                                                 | 7-74         |

|                                                                                 | 7-74         |

| Circuit Conditions                                                              | 7-75         |

Page

| FUNCTION 8 91A04A/FUNCTION 5 91AE04A, DESKEW TEST         Circuit Overview         Deskew Test Description         Deskew Test Troubleshooting         Analyzing the Test Indications         91A04A/91AE04A Deskew Test Description         Circuit Conditions                                                                                                                                                                                                       | 7-75<br>7-75<br>7-75<br>7-76<br>7-76<br>7-76<br>7-78                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| FUNCTION 9 91A04A/FUNCTION 6 91AE04A, DAC THRESHOLD         Circuit Overview         DAC Threshold Test Description         Loading the Data         DAC Threshold Troubleshooting         DAC Threshold Function Description         Circuit Conditions                                                                                                                                                                                                              | 7-78<br>7-78<br>7-79<br>7-79<br>7-79<br>7-80<br>7-81                          |

| DETECTING AND ISOLATING HIGH-SPEED PROBLEMS<br>Circuitry Targeted by Functional or Performance Checks<br>High-Speed Problems                                                                                                                                                                                                                                                                                                                                          | 7-81<br>7-81<br>7-82                                                          |

| Section 8 MAINTENANCE: DIAGNOSTIC TEST DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |

| Section 9 REFERENCE INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                          |

| Section 9 REFERENCE INFORMATION GENERAL INFORMATION Loading the 91A04A and 91AE04A Acquisition Memory Error Codes and Indicators ROM Checksum Codes 91A04A and 91AE04A Error and Prompter Messages                                                                                                                                                                                                                                                                    | <b>Page</b><br>9-1<br>9-1<br>9-1<br>9-1<br>9-1                                |

| GENERAL INFORMATION<br>Loading the 91A04A and 91AE04A Acquisition Memory<br>Error Codes and Indicators<br>ROM Checksum Codes                                                                                                                                                                                                                                                                                                                                          | 9-1<br>9-1<br>9-1<br>9-1                                                      |

| GENERAL INFORMATION<br>Loading the 91A04A and 91AE04A Acquisition Memory<br>Error Codes and Indicators<br>ROM Checksum Codes<br>91A04A and 91AE04A Error and Prompter Messages                                                                                                                                                                                                                                                                                        | 9-1<br>9-1<br>9-1<br>9-1<br>9-1                                               |

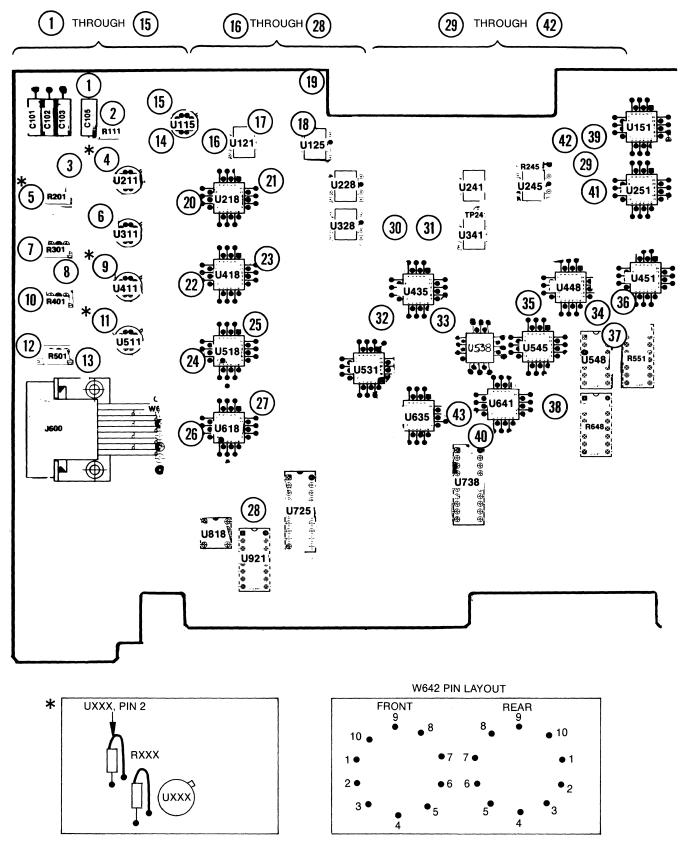

| GENERAL INFORMATION         Loading the 91A04A and 91AE04A Acquisition Memory         Error Codes and Indicators         ROM Checksum Codes         91A04A and 91AE04A Error and Prompter Messages         TEST POINT, JUMPER AND ADJUSTMENT LOCATIONS                                                                                                                                                                                                                | 9-1<br>9-1<br>9-1<br>9-1<br>9-1<br>9-2                                        |

| GENERAL INFORMATION         Loading the 91A04A and 91AE04A Acquisition Memory         Error Codes and Indicators         ROM Checksum Codes         91A04A and 91AE04A Error and Prompter Messages         TEST POINT, JUMPER AND ADJUSTMENT LOCATIONS         I/O MAPS                                                                                                                                                                                               | 9-1<br>9-1<br>9-1<br>9-1<br>9-1<br>9-2<br>9-8                                 |

| GENERAL INFORMATION         Loading the 91A04A and 91AE04A Acquisition Memory         Error Codes and Indicators         ROM Checksum Codes         91A04A and 91AE04A Error and Prompter Messages         TEST POINT, JUMPER AND ADJUSTMENT LOCATIONS         I/O MAPS         OSCILLOSCOPE TECHNIQUES FOR HIGH-FREQUENCY MEASUREMENTS         CALIBRATING THE OSCILLOSCOPE         High-Speed Measurement Tips                                                      | 9-1<br>9-1<br>9-1<br>9-1<br>9-2<br>9-2<br>9-8<br>9-12<br>9-12<br>9-12         |

| GENERAL INFORMATION         Loading the 91A04A and 91AE04A Acquisition Memory         Error Codes and Indicators         ROM Checksum Codes         91A04A and 91AE04A Error and Prompter Messages         TEST POINT, JUMPER AND ADJUSTMENT LOCATIONS         I/O MAPS         OSCILLOSCOPE TECHNIQUES FOR HIGH-FREQUENCY MEASUREMENTS         CALIBRATING THE OSCILLOSCOPE         High-Speed Measurement Tips         Signal Integrity and Solutions to Violations | 9-1<br>9-1<br>9-1<br>9-1<br>9-2<br>9-2<br>9-8<br>9-12<br>9-12<br>9-12<br>9-13 |

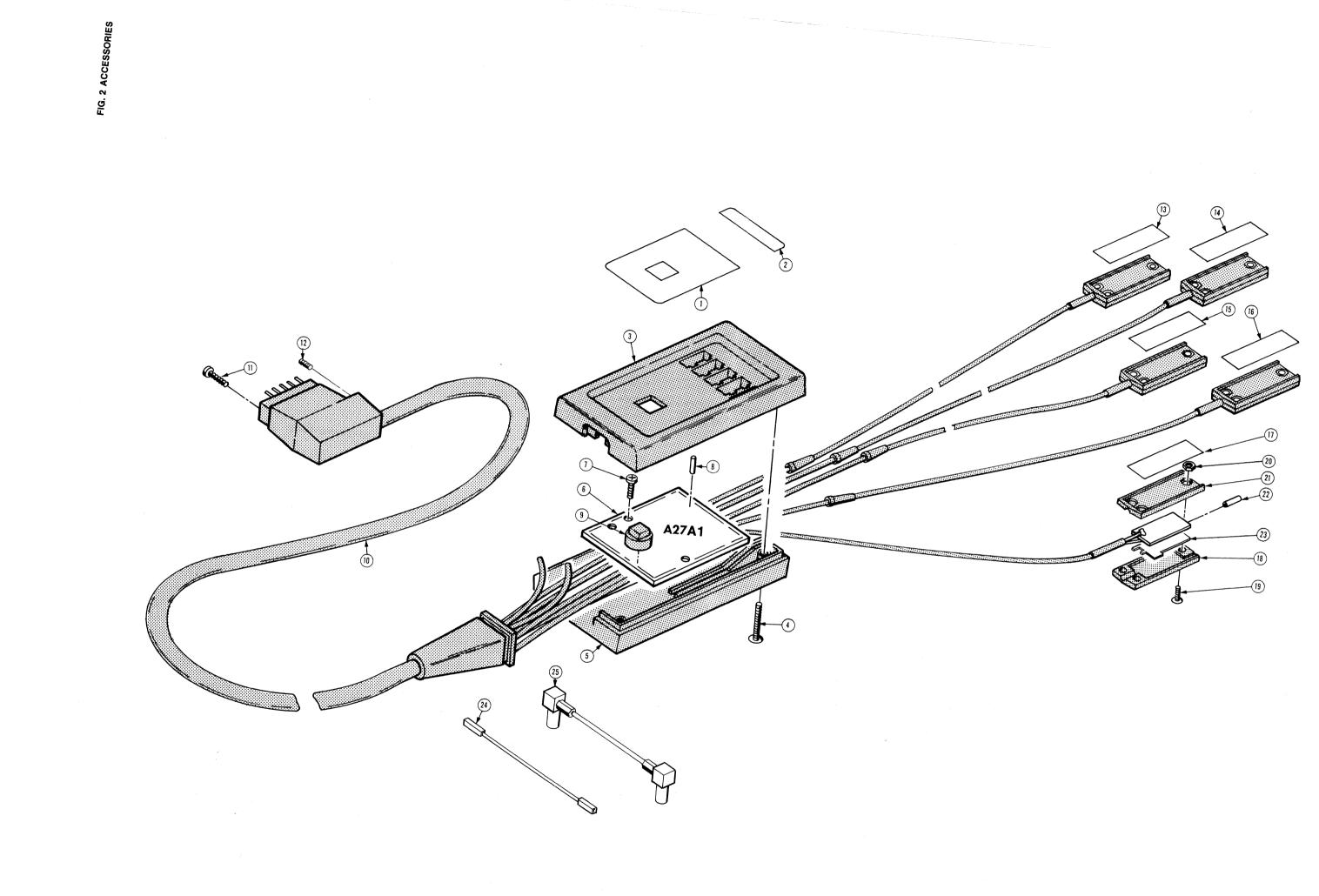

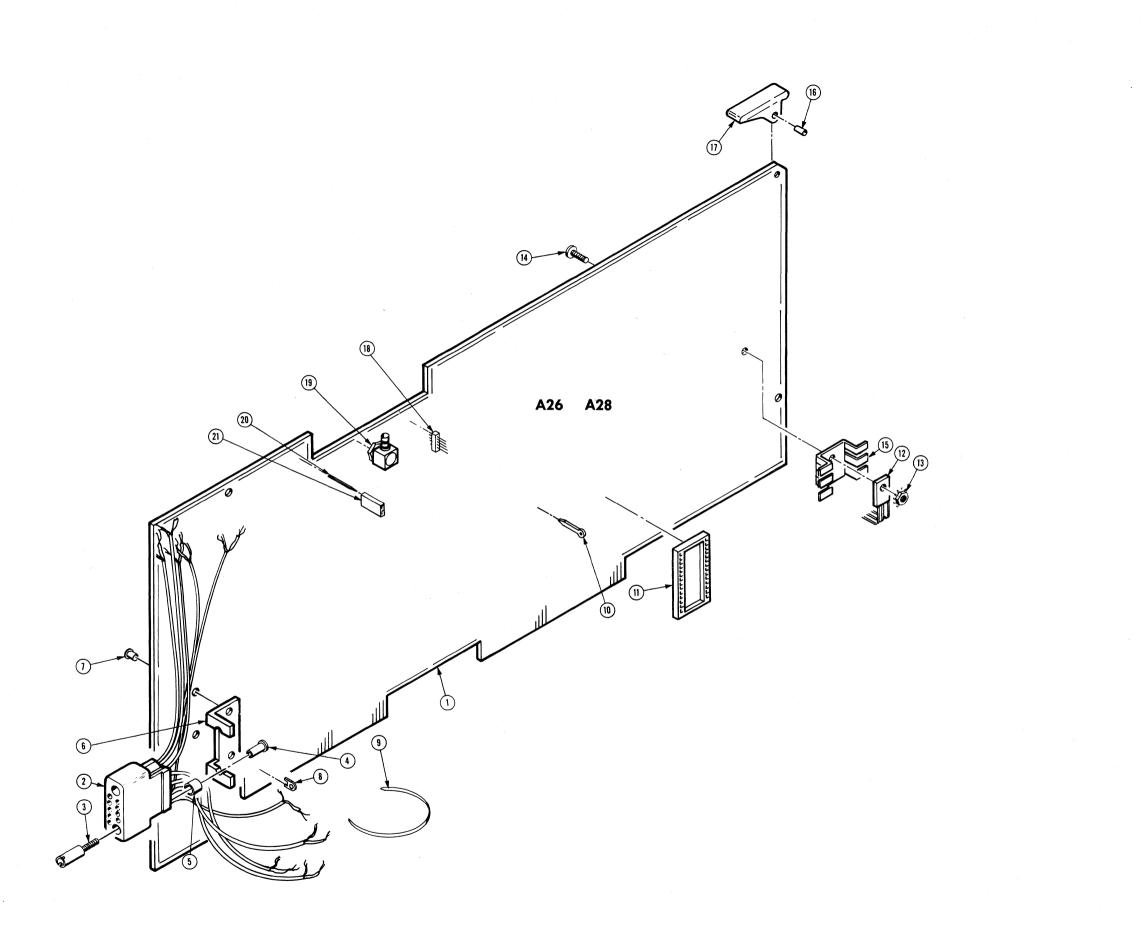

- Section 12 -- REPLACEABLE MECHANICAL PARTS

# LIST OF ILLUSTRATIONS

| Figur                                                                               | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                                     |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

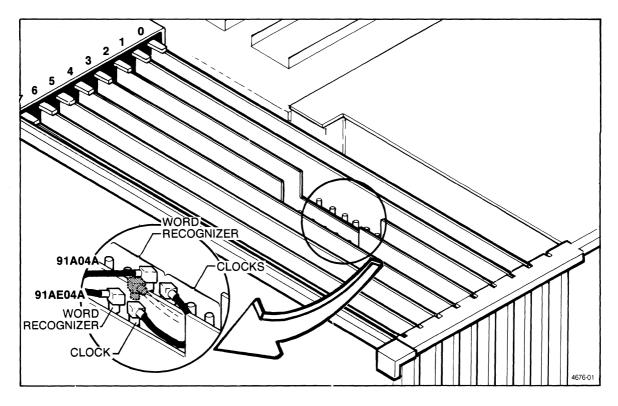

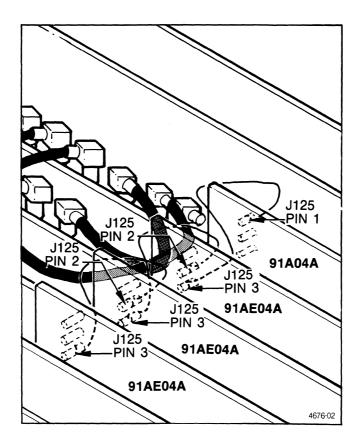

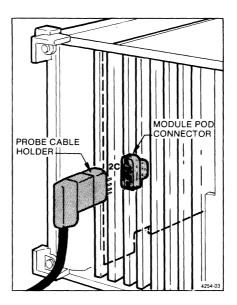

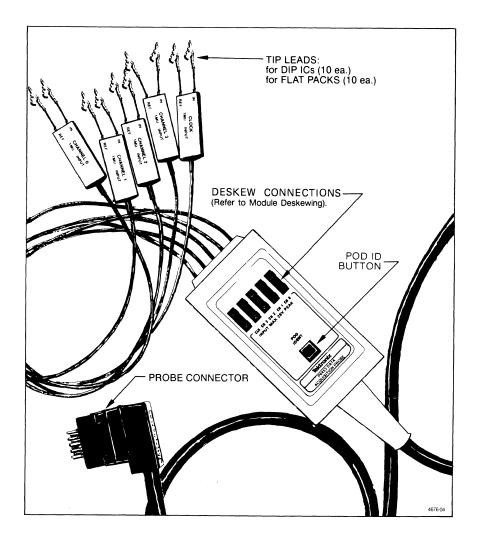

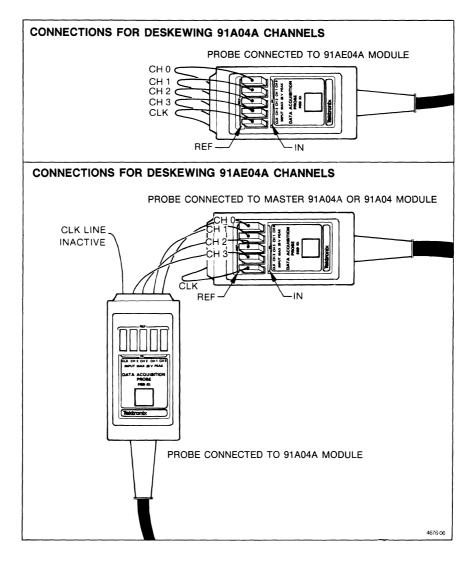

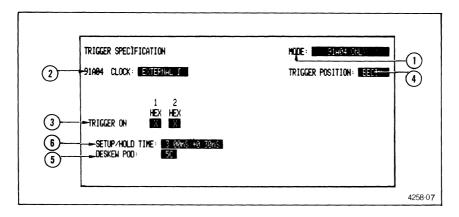

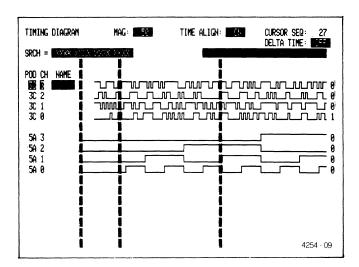

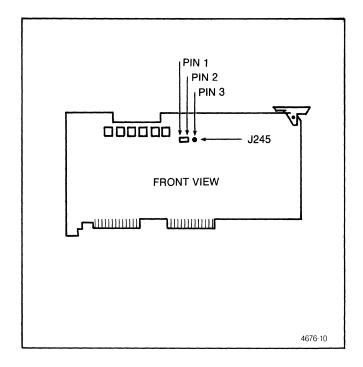

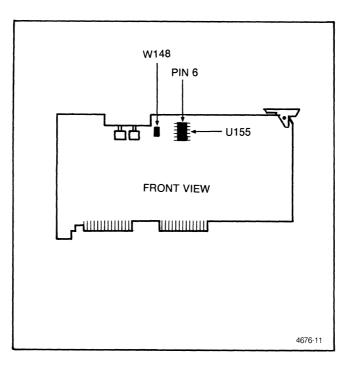

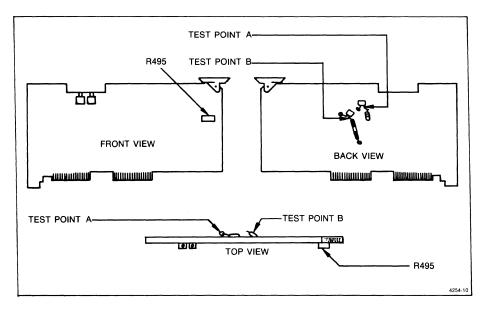

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12 | Connecting the word recognizer and clock cables between the 91A04A and<br>91AE04A modules<br>Connecting the threshold jumper cables<br>Connecting the P6453 probe<br>The P6453 Data Acquisition Probe parts<br>Setting up the Trigger Specification menu for the probe deskew operation<br>Connecting the probe channels for the deskew operation<br>The 91A04 ONLY sub-menu and its fields<br>Typical 91A32 ARMS 91A04 menu<br>91A32 ARMS 91A04 display in the Timing Diagram menu<br>Location of jumper J245 on 91A04A modules<br>Location of jumper W148 and IC U155 pin 16 on 91AE04A modules<br>Location of trimmer potentiometer R495 and test points on 91AE04A modules | 3-5<br>3-6<br>3-8<br>3-9<br>3-12<br>3-13<br>3-14<br>3-18<br>3-23<br>3-26<br>3-28<br>3-31 |

| 4-1                                                                                 | Acquisition pulse timing for 3 ns or slower acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-20                                                                                     |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9                         | How to connect a P6453 Data Acquisition Probe to a P6455 Pattern Generator<br>Probe<br>Initial test data acquired by 91A04A and 91AE04A modules<br>High resolution test data<br>Worst case timing for the 91A32 ARMS 91A04 test<br>Current-source cable details<br>91A04A and 91AE04A performance check test equipment connections<br>Rising-edge setup and hold time waveforms<br>Falling-edge setup and hold time waveforms<br>91A04A high-speed clock setup and hold times                                                                                                                                                                                                  | 5-6<br>5-10<br>5-15<br>5-16<br>5-21<br>5-35<br>5-43<br>5-43<br>5-45<br>5-47              |

| 6-1<br>6-2                                                                          | Removing the probe connector from its mounting bracket                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6-3<br>6-5                                                                               |

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6<br>7-7<br>7-8                                | Failure in the power-up self test         Diagnostics menu         Example of test readback display for a DAS diagnostic function         91A04A/91AE04A typical register-test display         Blocks of the 91A04A/91AE04A tested by register function 0         91A04A/91AE04A memory address function, typical test 0 readback display         91A04A/91AE04A blocks tested by memory address tests 0 and 1         91A04A/91AE04A memory address function, typical test 1 readback display                                                                                                                                                                                 | 7-5<br>7-6<br>7-10<br>7-14<br>7-16<br>7-20<br>7-22<br>7-26                               |

| 7-9<br>7-10<br>7-11<br>7-12<br>7-13<br>7-14<br>7-15<br>7-16                         | 91A04A/91AE04A memory address function, typical test 2 readback display<br>91A04A/91AE04A blocks tested by memory tests 2, 3, and 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-27<br>7-29<br>7-32<br>7-33<br>7-38<br>7-39<br>7-40<br>7-42                             |

# LIST OF ILLUSTRATIONS (cont.)

| Figu | Ire                                                                           | Page |

|------|-------------------------------------------------------------------------------|------|

| 7-17 | 91A04A delay counter function, typical test 3 display                         | 7-44 |

| 7-18 | Blocks tested by difference counter tests 0, 1, and 2                         | 7-46 |

| 7-19 | 91A04A difference counter function, typical tests 0 and 1 display             | 7-47 |

| 7-20 | 91A04A difference counter function, typical test 2 display                    | 7-48 |

| 7-21 | 91A04A/91AE04A acquisition memory function, typical test 0-7 readback display | 7-53 |

| 7-22 | Blocks tested by acquisition memory tests 0-8                                 | 7-54 |

| 7-23 | 91A04A/91AE04A acquisition memory function, typical test 8 readback display   | 7-58 |

| 7-24 | 91A04A clock array function, typical test 0 readback display                  | 7-61 |

| 7-25 | 91A04A blocks tested by clock array test 0                                    | 7-63 |

| 7-26 | 91A04A/91AE04A high resolution function, typical test 0 readback display      | 7-66 |

| 7-27 | 91A04A/91AE04A blocks tested by high resolution test 0                        | 7-67 |

| 7-28 | 91A04A/91AE04A word recognizer function, typical test 0 readback display      | 7-70 |

| 7-29 | 91A04A/91AE04A blocks tested by word recognizer tests 0 and 1                 | 7-72 |

| 7-30 | 91A04A/91AE04A word recognizer function, typical test 1 readback display      | 7-74 |

| 7-31 | 91A04A/91AE04A blocks tested by the deskew test                               | 7-77 |

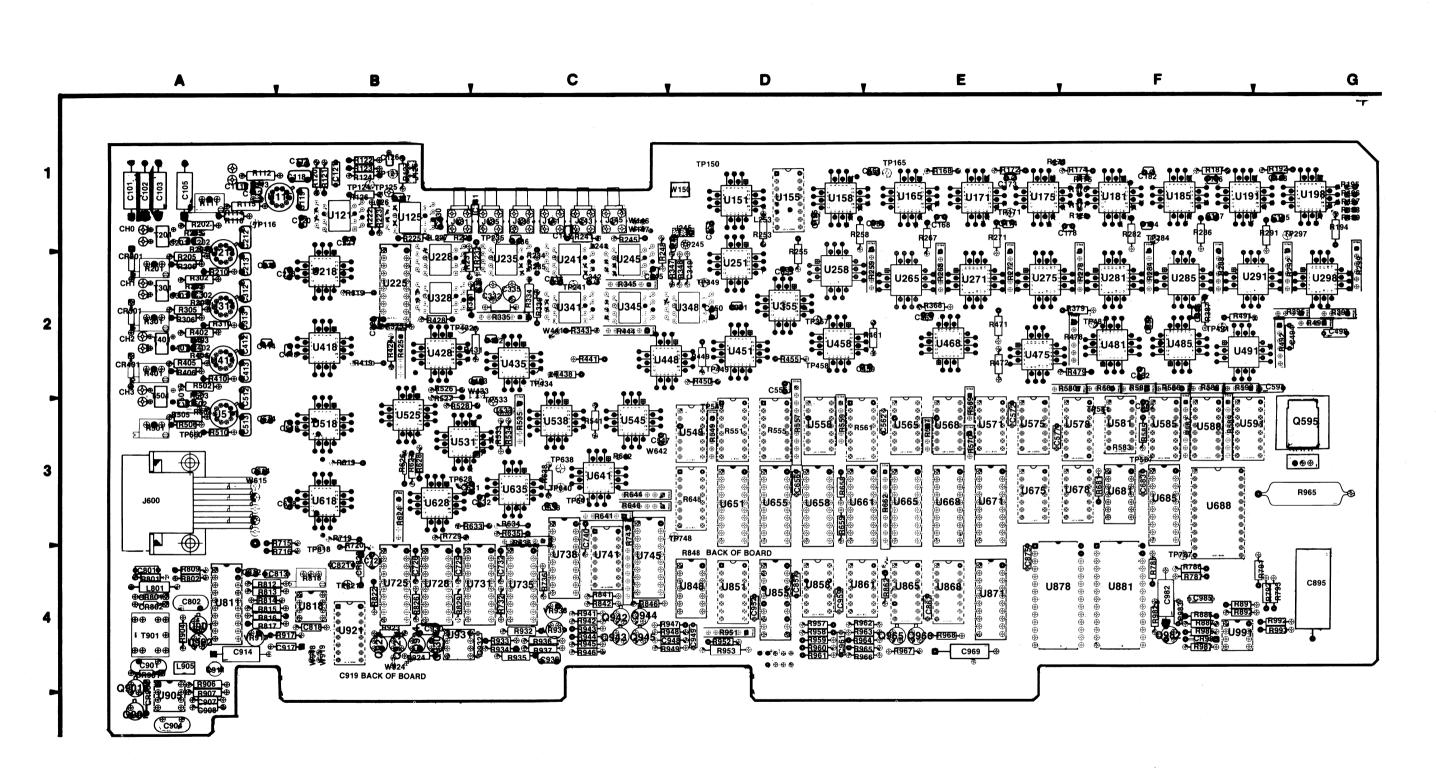

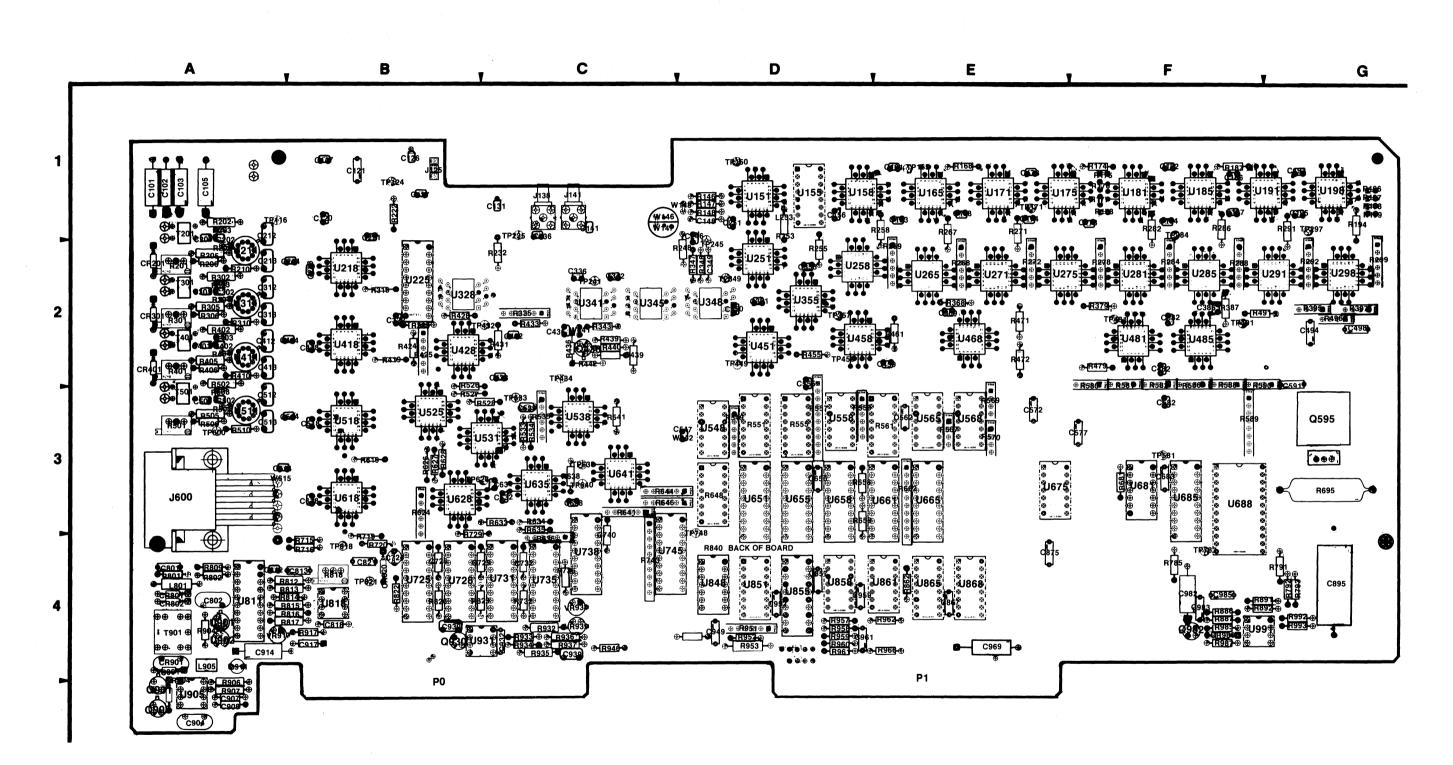

| 9-1  | Test-point, jumper, and adjustment locations                                  | 9-3  |

# LIST OF TABLES

| Table      |                                                                             | Page         |

|------------|-----------------------------------------------------------------------------|--------------|

| 1-1<br>1-2 | 91A04A/91AE04A Electrical Specifications: Power                             | 1-4<br>1-5   |

| 1-2        | 91A04A/91AE04A Electrical Specifications: Asynchronous Data Acquisition     | 1-5          |

| 1-3        | 91A04A/91AE04A Electrical Specifications: Asynchronous Data Acquisition     | 1-7          |

| 1-5        | 91A04A/91AE04A Electrical Specifications: Interconnection Between Modules   | 1-0          |

| 1-6        | 91A04A/91AE04A Electrical Specifications: Probe Interface and Support       | 1-10         |

| 1-7        | P6453 Electrical Specifications: Operating Characteristics                  | 1-11         |

| 1-8        | P6453 Physical Specifications                                               | 1-12         |

| 3-1        | +5 V Power Supply Restrictions                                              | 3-3          |

| 3-2        | 91A04A and 91AE04A Sample Bus Slot Placement                                | 3-4          |

| 3-3        | Module Adjustment Conditions                                                | 3-7          |

| 3-4        | Power-up Error Conditions                                                   | 3-10         |

| 3-5        | Equipment Required for 91A04A Adjustment                                    | 3-28         |

| 3-6        | Equipment Required for 91AE04A Adjustment                                   | 3-30         |

| 4-1        | Assembly Numbers                                                            | 4-8          |

| 4-2        | Controller Interface Map                                                    | 4-10         |

| 4-3        | Control Register Functions                                                  | 4-11         |

| 4-4        | Menu Setting Versus Threshold Output                                        | 4-13         |

| 5-1        | Equipment Needed for the Functional Check Procedures                        | 5-2          |

| 5-2        | Equipment Needed for the Adjustment Procedures                              | 5-3          |

| 5-3        | Equipment Needed for the Performance Check Procedures                       | 5-4          |

| 5-4        | Equipment Required for the DAC Adjustment Procedure                         | 5-19         |

| 5-5        | Equipment Required for the Comparator Offset Adjustment Procedure using the |              |

|            | Fluke 5101B                                                                 | 5-20         |

| 5-6        | Channels, Test Points, and Offset Adjustments for Fluke 5101B Method        | 5-23         |

| 5-7        | Equipment Required for the Comparator Offset Adjustment using the Tektronix | 5.04         |

| 5-8        | PG502 Internal Power Supply Measurements                                    | 5-24<br>5-37 |

| <b>J-0</b> |                                                                             | 5-37         |

| 7-1        | Relative Susceptibility of Semiconductors to Static Discharge Damage        | 7-2          |

| 7-2        | Equipment Needed for Troubleshooting                                        | 7-3          |

| 7-3        | Diagnostic Function Descriptions                                            | 7-9          |

| 7-4        | 91A04A/91AE04A Function 0 Write-Read Matrix                                 | 7-14         |

# LIST OF TABLES (cont.)

| Table |                                                 | Page |

|-------|-------------------------------------------------|------|

| 7-5   | Conditions for Register Tests                   | 7-17 |

| 7-6   | 91A04A/91AE04A Memory Address Function,         |      |

|       | Test 0 Expected Readback                        | 7-21 |

| 7-7   | Conditions for MAR Test 0                       | 7-24 |

| 7-8   | Conditions for MAR Test 1                       | 7-27 |

| 7-9   | 91A04A/91AE04A Memory Address Function,         |      |

|       | Test 2 Expected Readback                        | 7-28 |

| 7-10  | Conditions for MAR Test 2                       | 7-31 |

| 7-11  | Conditions for MAR Test 3 - 91A04A Only         | 7-33 |

| 7-12  | Conditions for MAR Test 4 - 91A04A Only         | 7-35 |

| 7-13  | Conditions for MAR Test 4 - 91AE04A Only        | 7-36 |

| 7-14  | Conditions for Delay Counter Test 0             | 7-40 |

| 7-15  | Load Sequence for Delay Counter Test 1          | 7-41 |

| 7-16  | Conditions for Delay Counter Test 1             | 7-42 |

| 7-17  | Load Sequence for Delay Counter Test 2          | 7-43 |

| 7-18  | Conditions for Delay Counter Test 2             | 7-44 |

| 7-19  | Load Sequence for Delay Counter Test 3          | 7-44 |

| 7-20  | Conditions for Delay Counter Test 3             | 7-45 |

| 7-21  | Conditions for Difference Counter Tests 0 and 1 | 7-48 |

| 7-22  | Conditions for Difference Counter Test 2        | 7-50 |

| 7-23  | Acquisition Memory Tests 0-7, Load Sequence     | 7-51 |

| 7-24  | Acquisition Memory Test 8 Load Patterns         | 7-51 |

| 7-25  | Conditions for Acquisition Memory Tests 0-7     | 7-56 |

| 7-26  | Conditions for Acquisition Memory Test 8        | 7-59 |

| 7-27  | Clock Array Test 0: Loaded and Expected Values  | 7-61 |

| 7-28  | Conditions for Clock Array Test 0               | 7-65 |

| 7-29  | High Resolution Function Test 0:                |      |

|       | Written and Expected Readback Values            | 7-66 |

| 7-30  | Conditions for High Resolution Test 0           | 7-68 |

| 7-31  | Values Written for Word Recognizer Test 1       | 7-69 |

| 7-32  | Conditions for Word Recognizer Test 0           | 7-73 |

| 7-33  | Conditions for Word Recognizer Test 1           | 7-75 |

| 7-34  | Conditions for the Deskew Test                  | 7-78 |

| 7-35  | Circuit Conditions for the DAC Test             | 7-81 |

| 9-1   | ROM Checksum Error Codes                        | 9-1  |

| 9-2   | Error and Prompter Messages                     | 9-2  |

| 9-3   | 91A04A/91AE04A I/O Maps                         | 9-8  |

# DAS9100 Series 91A04A-91AE04A Service

## **OPERATOR'S SAFETY SUMMARY**

The general safety information in this summary is for both operator and service personnel. Specific cautions and warnings are found throughout the manual where they apply but may not appear in this summary.

#### TERMS IN THIS MANUAL

**CAUTION** statements identify conditions or practices that could result in damage to the equipment or other property.

**WARNING** statements identify conditions or practices that could result in personal injury or loss of life.

#### TERMS AS MARKED ON EQUIPMENT

**CAUTION** indicates a personal injury hazard not immediately accessible as one reads the marking, or a hazard to property, including the equipment itself.

DANGER indicates a personal injury hazard immediately accessible as one reads the marking.

#### SYMBOLS AS MARKED ON EQUIPMENT

DANGER — High voltage.

Protective ground (earth) terminal.

ATTENTION — refer to manual.

#### **GROUNDING THE PRODUCT**

The mainframe in which this product is installed is intended to operate from a power source that does not apply more than 250 V rms between the supply conductors or between either supply conductor and ground.

This product is grounded through the mainframe in which it is operating. To avoid electrical shock, plug the power cord of the mainframe into a properly wired receptacle before connecting to the product. A protective-ground connection by way of the grounding conductor in the power cord is essential for safe operation.

#### DANGER ARISING FROM LOSS OF GROUND

Upon loss of the protective-ground connection, all accessible conductive parts (including keys and controls that may appear to be insulated) can render an electric shock.

### DO NOT OPERATE WITHOUT COVERS

To avoid personal injury, do not operate this product without mainframe covers or panels installed. Circuit boards and components can become very hot during operation.

### DO NOT OPERATE IN EXPLOSIVE ATMOSPHERES

To avoid explosion, do not operate this product in an explosive atmosphere unless it has been specifically certified for such operation.

# SERVICE SAFETY SUMMARY

FOR QUALIFIED SERVICE PERSONNEL ONLY Refer also to the preceding Operator's Safety Summary.

#### DO NOT SERVICE ALONE

Do not perform service or adjustment of this product unless another person capable of rendering first aid and resuscitation is present.

### USE CARE WHEN SERVICING WITH POWER ON

Dangerous voltages exist at several points in this product. To avoid personal injury, do not touch exposed connections and components while power is on.

Disconnect power before soldering or replacing components.

## DO NOT WEAR JEWELRY

Remove jewelry prior to servicing. Rings, necklaces, and other metallic objects could come into contact with dangerous voltages.

NOTE

Observe safety precautions stated in the DAS 9100 Series Service Manual concerning CRT safety, X-ray emission, and loose objects.

## Section 1 INTRODUCTION AND SPECIFICATIONS

This section provides a general description of the electrical and physical attributes of the 91A04A and 91AE04A High Speed Acquisition Modules, and lists their electrical and environmental specifications.

### DESCRIPTION

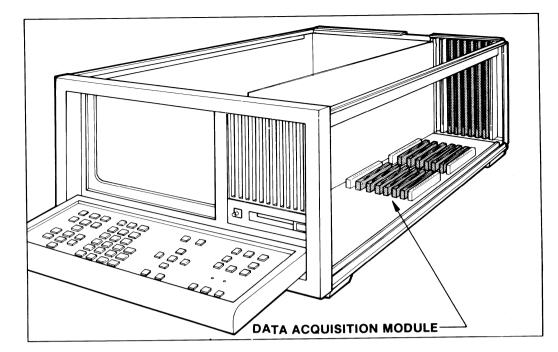

The 91A04A Series Data Acquisition Modules are plug-in circuit board assemblies compatible with any DAS 9100 Series mainframe. They feature acquisition rates of 330 MHz (3 ns) with four data channels, or 660 MHz (1.5 ns) with two data channels. Each module uses one P6453 Data Acquisition Probe.

The 91A04 and 91A04A master modules are functionally identical, as are the 91AE04 and 91AE04A expander modules. Therefore, pre-A and A version modules can be used in the same DAS mainframe in any combination provided the following criteria are observed:

- Only one master module is installed.

- No more than three expander modules are installed.

- All expander modules are installed on the same side of the master module.

A maximum of one master module may be installed in a DAS mainframe. Up to three expander modules may also be installed to increase the channel width. The expander modules can only be used if a master module is installed.

## MODES OF OPERATION

#### DATA ACQUISITION MODE

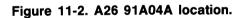

Each 91A04 Series module provides four incoming data channels supplied by a P6453 Data Acquisition Probe. Special deskew procedures are provided to correct any propagation delays between data channels and clocks. Deskewing ensures accurate setup and hold times, and minimizes channel-to-channel skew.

The 91AE04A Data Acquisition Expander Module is an etched circuit board assembly that is slaved to a 91A04A or 91A04 master module. 91AE04A and 91AE04 modules are functionally interchangeable. Each 91AE04A allows an additional four channels of 2048-word-deep data acquisition with word recognition for triggering. Clocks are distributed to all 91AE04A modules from the master module. Word recognizer signals from all expander modules in the system are sent to the master module.

The 91A04 Series modules can acquire data using the DAS internal clock at intervals ranging from 5 ms to 3 ns, or using an external clock's rising or falling edge (300 MHz maximum). The maximum memory depth in this mode is 2048 words.

The 91A04 Series modules have a one-word trigger. Triggering can be positioned in the beginning, center, or end of acquisition memory; or it may be delayed for up to 32,767 clock cycles.

Data may be displayed in either the DAS State Table or Timing Diagram menus.

#### **HIGH-RESOLUTION MODE**

The 91A04 Series modules can be operated in a 1.5 ns high-resolution mode, each module acquiring two channels of data instead of four, for a maximum of eight parallel channels. The memory depth is increased to 4096 words.

Data acquired in the high-resolution mode can only be displayed in the Timing Diagram menu.

#### ARMS TRIGGER MODE

The 91A04 series of data acquisition modules can be used in an ARMS TRIGGER mode with the 91A32 or 91A24 Data Acquisition Modules (slow cards) provided the following conditions are met:

- If the 91A04 series module has V2 software, it must reside in the DAS mainframe with V1.11 firmware.

- If the 91A04 series module has V1 software, it must reside in a DAS mainframe with V1.09 or lower firmware.

#### NOTE

DAS mainframes that are shipped with a 91A04A and/or a 91A24 have V1.11 firmware.

In this mode, the arming module and the armed module run simultaneously, but at different clock rates. The 91A24 trigger enables the 91A04 Series modules to begin looking for a trigger.

If the 91A04 Series acquisition rate is  $\leq$ 330 MHz, the resulting time-aligned display can be viewed in either the DAS State Table or Timing Diagram menus. If the 91A04 Series 660 MHz highresolution clock is used, the resulting time-aligned data can only be viewed in the Timing Diagram menu.

In the ARMS mode, the 91A04 Series data display is limited to the last 512 words acquired.

## STANDARD AND OPTIONAL ACCESSORIES

#### 91A04A DATA ACQUISITION MODULES

The following lists include the standard and optional accessories for 91A04A modules.

#### Standard Accessories

- 1

- P6453 Data Acquisition Probe

- 1 070-4678-00 91A04A Instructions

- 1 070-4676-00 91A04A, 91AE04A, and P6453 Operator's Manual Addendum (to the DAS 9100 Series Operator's Manual)

#### **Optional Accessories**

The following optional accessories are used for service and adjustment procedures.

| 070-4298-00 | 91A04A Series Service Manual Addendum (to the DAS 9100 Series Service Manual) |

|-------------|-------------------------------------------------------------------------------|

| 175-7322-00 | 10-inch Extender Cable                                                        |

| 195-0995-00 | 12-inch Threshold VBB Cable                                                   |

The remaining optional accessory is used for reference when 91A04A or 91AE04A Data Acquisition Modules are used with 91A04 or 91AE04 modules.

070-4254-00 91A04, 91AE04, and P6453 Operator's Manual Addendum (to the DAS 9100 Series Operator's Manual)

#### 91AE04A HIGH SPEED ACQUISITION EXPANDER MODULE

The following lists include the standard and optional accessories for the 91AE04A Data Acquisition Expander Module. There are no optional accessories to this module.

#### **Standard Accessories**

| 1 |             | P6453 Data Acquisition Probe    |

|---|-------------|---------------------------------|

| 1 | 195-0693-00 | 3.5-inch Threshold Jumper Cable |

| 2 | 175-6425-00 | 3-inch Coaxial Cables           |

| 1 | 070-4677-00 | 91AE04A Instructions            |

## P6453 DATA ACQUISITION PROBE

The following list includes the standard accessories for the P6453 Data Acquisition Probe.

#### **Standard Accessories**

- 1 195-2234-06 Package of 10 leads (probe tip leads for DIP IC packages)

- 1 195-1943-06 Package of 10 leads (miniature probe tips for flat packs)

- 1 070-3704-00 P6453 Instructions

#### **Optional Accessories**

195-3659-00 Package of 2 leads with grabber tips

## **SPECIFICATIONS**

#### **INSTALLATION REQUIREMENTS**

The 91A04A or 91AE04A may not meet specifications unless the modules are installed in the DAS mainframe in accordance with the *Module Installation* instructions in the *Operating Instructions* section of this addendum.

| CHARACTERISTICS                                               | PERFORMANCE<br>REQUIREMENTS                     | SUPPLEMENTAL<br>INFORMATION                                                                                                                                                |

|---------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 91A04A Input Power<br>(from mainframe)                        |                                                 | +12 V ±3%, 0.45 A max.<br>+6 V ±3%, 0.4 A max.<br>+5 V ±3%, 11 A max. (see <i>Installa-</i><br><i>tion Requirements)</i><br>-5 V ±3%, 0.2 A max.<br>-12 V ±10%, 0.4 A max. |

| 91AE04A Input Power<br>(from mainframe)                       |                                                 | +12 V ±3%, 0.4 A max.<br>+6 V ±3%, 0.4 A max.<br>+5 V ±3%, 9.0 A max.<br>-5 V ±3%, 0.2 A max.<br>-12 V ±10%, 0.4 A max.                                                    |

| Output Power from any<br>91A04A or 91AE04A<br>Module to Probe |                                                 | +15 VC and D $\pm$ 5%, 75 mA max.<br>ea., 150 mA max. total<br>+5 V $\pm$ 3%, 150 mA max.                                                                                  |

| Internal Supply Voltages<br>+4.2 V Supply                     | Supply Voltage = Vcc -<br>0.80 V ±50 mV         |                                                                                                                                                                            |

| +3 V Supply                                                   | Supply voltage = Vcc - $1.92 \pm 50 \text{ mV}$ |                                                                                                                                                                            |

| +15 V Supply Switch-<br>ing Frequency                         | 160 kHz ±30%                                    |                                                                                                                                                                            |

Table 1-1

91A04A/91AE04A ELECTRICAL SPECIFICATIONS: POWER

| CHARACTERISTICS                                                        | PERFORMANCE<br>REQUIREMENTS                                                                         | SUPPLEMENTAL<br>INFORMATION                                                                                                                                                       |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Minimum Data Amplitude                                                 | 600 mV p-p                                                                                          |                                                                                                                                                                                   |

| Minimum Data Slew Rate<br>at Probe Tip                                 |                                                                                                     | 0.05 V/ns                                                                                                                                                                         |

| Trigger                                                                |                                                                                                     |                                                                                                                                                                                   |

| Trigger Types                                                          |                                                                                                     | Single-level word recognition                                                                                                                                                     |

| Word Recognition                                                       |                                                                                                     | Single-level data word, externally armable                                                                                                                                        |

| Word Recognition with<br>1.5 ns Internal Clock<br>(async)              | To guarantee triggering,<br>the trigger word must be<br>present for 1 sample peri-<br>od $+2.5$ ns. |                                                                                                                                                                                   |

| Word Recognition with<br>Internal Clocks Slower<br>than 1.5 ns (async) | To guarantee triggering,<br>the trigger word must be<br>present for 1 sample peri-<br>od $+2$ ns.   |                                                                                                                                                                                   |

| Word Width                                                             |                                                                                                     | Same as memory width                                                                                                                                                              |

| Bit Specification                                                      |                                                                                                     | Logic 1, or 0, or X (don't care)                                                                                                                                                  |

| Trigger Position                                                       |                                                                                                     | Begin, center, end, or delay                                                                                                                                                      |

| Stop-store Delay                                                       |                                                                                                     | In 91A04 ONLY mode, selectable<br>from 1 to 32,767 sample periods after<br>trigger. In ARMS mode, the maximum<br>91A04A delay is 500 as set in the<br>Trigger Specification menu. |

| Pattern-sequence<br>Comparison                                         |                                                                                                     | Compare until equal and compare un-<br>til not equal                                                                                                                              |

| Comparison Sequence<br>Length                                          | From 1 to 2048 words with V2 firmware                                                               |                                                                                                                                                                                   |

| ARMS Mode<br>Characteristics                                           |                                                                                                     | The 91A04A trigger will be armed<br>within ten slow-card clock cycles after<br>the occurence of the slow-card<br>trigger.                                                         |

| Time Alignment<br>Requirements                                         |                                                                                                     | The DAS will not display time-aligned<br>ARMS data unless the following con-<br>ditions are met:                                                                                  |