## DAS 9100 SERIES

## SERVICE MANUAL WITH OPTIONS VOL. I

This Tektronix manual supports all products listed below. It revises the original manual (issued October 1982, part numbers 070-3625-00 and 070-3836-00) by incorporating service information for the DAS9129 Color Mainframe throughout all sections.

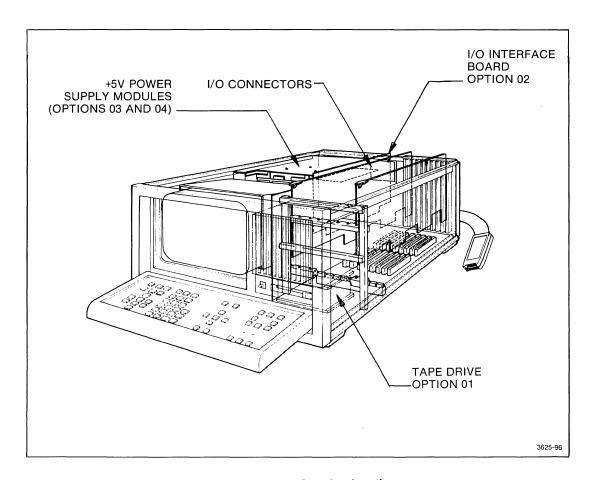

#### **MAINFRAMES**

DAS9129 - Color DAS9109 - Basic DAS9119 - ATE

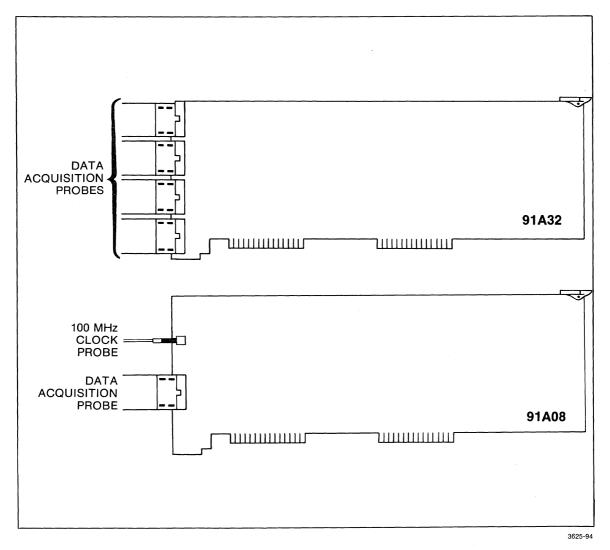

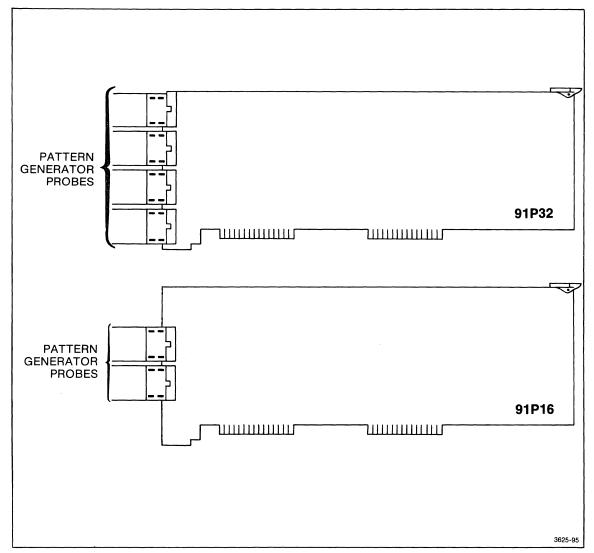

#### **INSTRUMENT MODULES**

91A32 - Data Acquisition 91A08 - Data Acquisition 91P16 - Pattern Generator 91P32 - Pattern Generator

#### **OPTIONS**

Option 01 - Tapedrive

Option 02 - I/O Interface

Option 03, 04 - +5 V Power Supply

Option 05 - Rackmount

## PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL.

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon

97077

Serial Number \_\_\_\_\_

070-3625-01 Product Group 57

FIRST PRINTING AUGUST 1982 REVISED PRINTING FEBRUARY 1984

#### **WARNING**

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO.

Copyright <sup>15</sup> 1982 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and are registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

## **MANUAL REVISION STATUS**

PRODUCT: DAS 9100 SERIES SERVICE MANUAL VOL. I

This manual supports the following versions of this product: All

| REV DATE   | DESCRIPTION                                                                                   |

|------------|-----------------------------------------------------------------------------------------------|

|            |                                                                                               |

| AUG 1982   | Original Issue                                                                                |

| APRIL 1983 | Revised Printing                                                                              |

| MAY 1983   | Revised Printing                                                                              |

| OCT 1983   | Revised Printing: Sections; 1, 4 and 5<br>Pages; iii and Tab 1, INTRODUCTION & SPECIFICATIONS |

| JAN 1984   | Revised Printing: Pages; i and 1-11                                                           |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|            |                                                                                               |

|  |  | 1<br>1<br>1<br>1                        |

|--|--|-----------------------------------------|

|  |  | 1<br>1<br>1<br>1                        |

|  |  | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|  |  | 1                                       |

|  |  | 1                                       |

|  |  | 1                                       |

|  |  |                                         |

|  |  |                                         |

|  |  |                                         |

|  |  |                                         |

|  |  |                                         |

|  |  | (                                       |

|  |  |                                         |

#### PREFACE

The DAS 9100 Series Service Manual is organized in two volumes. The first volume contains the specifications, the theory of operation, and other instrument familiarization information. The second volume contains the information most likely to be used directly while repairing or maintaining a DAS module or system. Note, however, that both of the volumes are required to complete a repair because the Verification and Adjustment Procedures are contained in the first volume.

This manual is designed for use by a qualified service technician with moderate experience with high-speed digital circuitry. Familiarity with both the TTL and ECL logic families is assumed. Familiarity with, and the ability to operate, standard test instruments used on digital circuitry, like high-speed oscilloscopes and logic analyzers, is also assumed.

The DAS 9100 Series contains some complicated and/or non-standard circuits. For most effective use of repair time, it is wise to become familiar with the operation of the instrument, both the hardware and the firmware. The Theory of Operation is organized as a learning guide to the structure and function of the instrument.

Since in many cases familiarity with the instrument is not feasible, the Maintenance: General Information and the Maintenance: Troubleshooting sections in volume two give the required information to complete most repairs in a short time. This will prove useful to the technician who does not often have occasion to repair a DAS 9100 Series instrument.

#### WHAT THIS MANUAL CONTAINS

The Service Manual is divided into twelve sections that are located in two binders. The third binder is available for Addenda to the Service Manual.

#### VOLUME 1

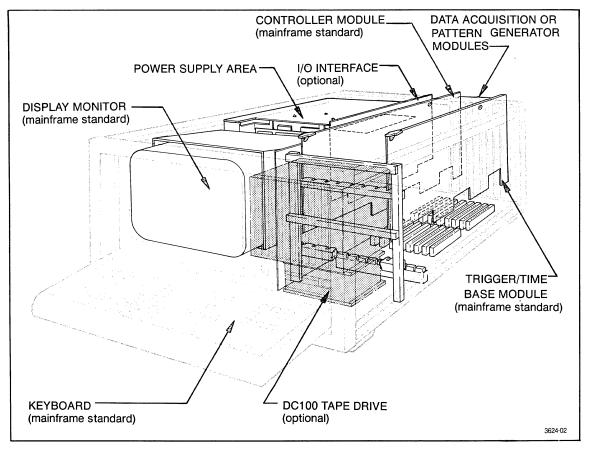

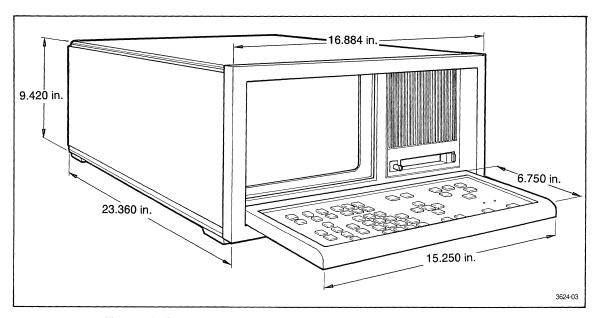

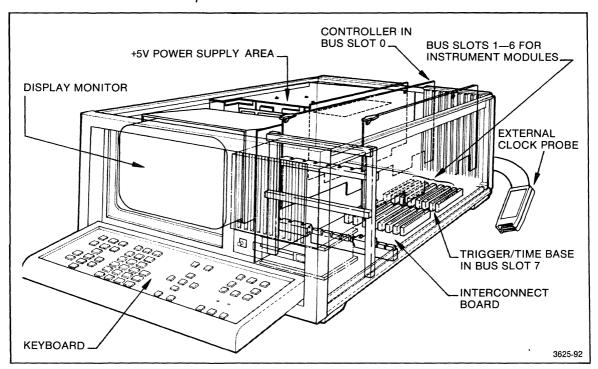

**Section 1 - Introduction and Specifications.** This section describes the DAS 9100, its modes of operation, products and options, standard and optional accessories, and electrical and physical specifications.

**Section 2 - Options.** This section lists the options that are available with the DAS 9100 Series of instruments.

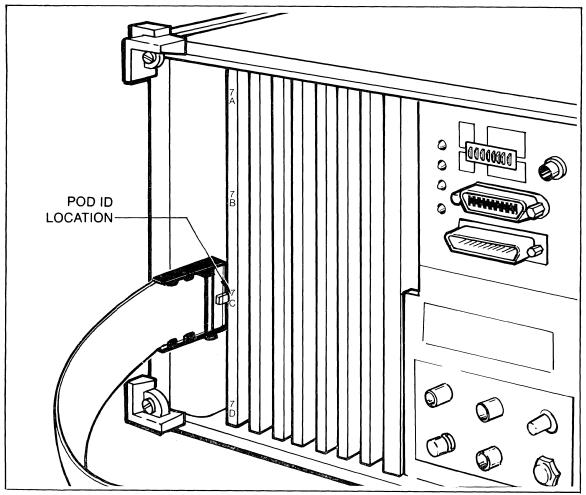

**Section 3 - Operating Instructions.** This section describes the DAS 9100 power requirements, module installation procedures, probe connections, and the keyboard. There is also an overview of the menus used by the operator to control the system. Refer to the DAS 9100 Series Operator's Manual for complete operating instructions.

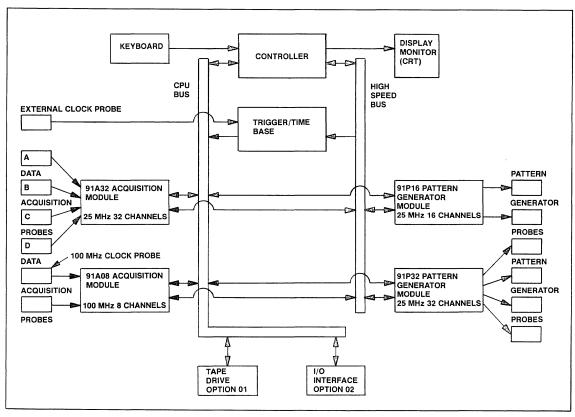

**Section 4 - Theory of Operation.** This section contains a discussion of the basic operation of the DAS 9100 Series instruments, a block diagram description of the DAS, and detailed circuit descriptions of all parts of the mainframe, modules, probes, and options.

**Section 5 - Verification and Adjustment Procedures.** This section contains the functional check procedures, the adjustment procedures and the performance check procedures for all parts of the DAS.

REV FEB 1984

#### **VOLUME 2**

**Section 6 - Maintenance: General Information.** This section of the manual contains information necessary to maintain the DAS. General precautions, disassembly procedures, and general maintenance information is included in this section.

**Section 7 - Maintenance: Troubleshooting.** This section contains troubleshooting trees and information.

**Section 8 - Maintenance: Diagnostic Test Descriptions.** This section gives detailed instructions for using the Diagnostics menu. It also provides detailed descriptions of the operation of each test used by the diagnostics.

**Section 9 - Reference Material.** This section provides quick reference material for use while troubleshooting or adjusting any part of the DAS.

**Section 10 - Replaceable Electrical Parts.** This section contains a list (including Tektronix part numbers) of all replaceable electrical parts in the DAS.

**Section 11 - Diagrams.** This section contains all schematics for the DAS as well as board and component locator diagrams and tables.

**Section 12 - Replaceable Mechanical Parts.** This section contains lists (including part numbers) of all replaceable mechanical parts in the DAS and provides illustration to show the location of each of these parts.

## TABLE OF CONTENTS

#### SECTION 1—INTRODUCTION AND SPECIFICATIONS

|                                                                                                                                                                                                                                                                                                                           | Page                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| DESCRIPTION                                                                                                                                                                                                                                                                                                               | 1-1                                                                  |

| MODES OF OPERATION  Data Acquisition  Acquisition and Reference Memory Display  Pattern Generation  GPIB, RS-232, and Hard Copy Interface  Tape Drive                                                                                                                                                                     | 1-1<br>1-2<br>1-2<br>1-3                                             |

| MAINFRAME STANDARD COMPONENTS                                                                                                                                                                                                                                                                                             | 1-4                                                                  |

| INSTRUMENT MODULES                                                                                                                                                                                                                                                                                                        | 1-6                                                                  |

| MAINFRAME OPTIONS                                                                                                                                                                                                                                                                                                         | 1-7                                                                  |

| STANDARD AND OPTIONAL ACCESSORIES  Mainframe  91A32 Data Acquisition Module  91A08 Data Acquisition Module  91P16 Pattern Generator Module  91P32 Pattern Generator Expander Module  P6452 Data Acquisition Probe  P6454 100 MHz Clock Probe  P6455 TTL/MOS Pattern Generator Probe  P6456 ECL Pattern Generator Probe    | 1-8<br>1-9<br>1-9<br>1-10<br>1-10<br>1-10                            |

| SPECIFICATIONS  Mainframes  91A32 Data Acquisition Module  91A08 Data Acquisition Module  Pattern Generator Modules  P6452 Data Acquisition Probe  P6454 100 MHz Clock Probe  P6455 TTL/MOS Pattern Generator Probe  P6456 ECL Pattern Generator Probe  Option 01, Tape Drive Assembly  Option 02, I/O Interface Assembly | 1-12<br>1-22<br>1-27<br>1-31<br>1-36<br>1-39<br>1-41<br>1-44<br>1-47 |

REV OCT 1983

#### **SECTION 2—OPTIONS**

|                                                                                                                                                                                                                                                                                                                                               | Page                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| OPTION 01, TAPE DRIVE                                                                                                                                                                                                                                                                                                                         | 2-1                                          |

| OPTION 02, I/O INTERFACE                                                                                                                                                                                                                                                                                                                      | 2-1                                          |

| OPTION 03, +5 V POWER SUPPLY                                                                                                                                                                                                                                                                                                                  | 2-1                                          |

| OPTION 04, TWO +5 V POWER SUPPLIES                                                                                                                                                                                                                                                                                                            | 2-2                                          |

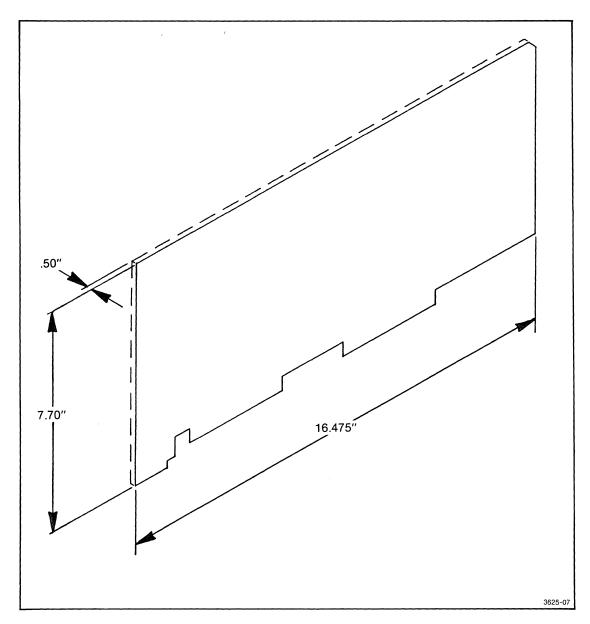

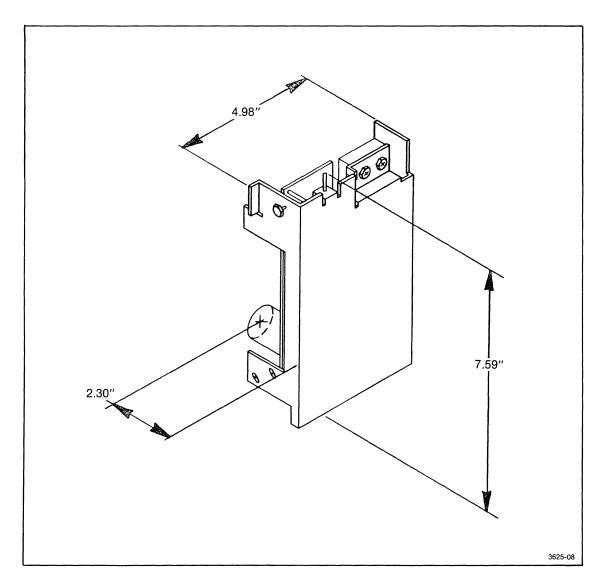

| OPTION 05, RACKMOUNT HARDWARE                                                                                                                                                                                                                                                                                                                 | 2-2                                          |

| SECTION 3—OPERATING INSTRUCTIONS                                                                                                                                                                                                                                                                                                              |                                              |

|                                                                                                                                                                                                                                                                                                                                               | Page                                         |

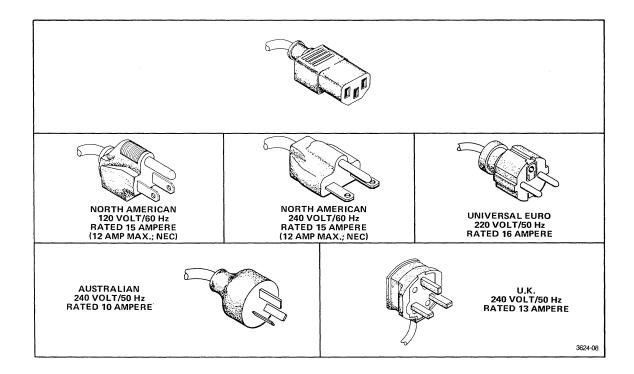

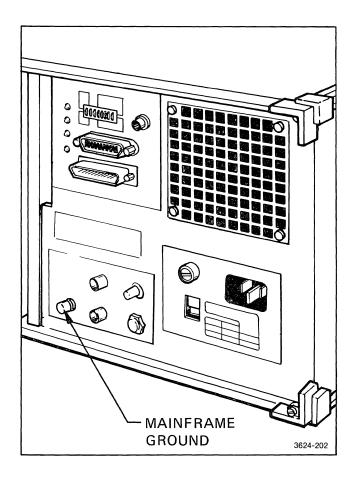

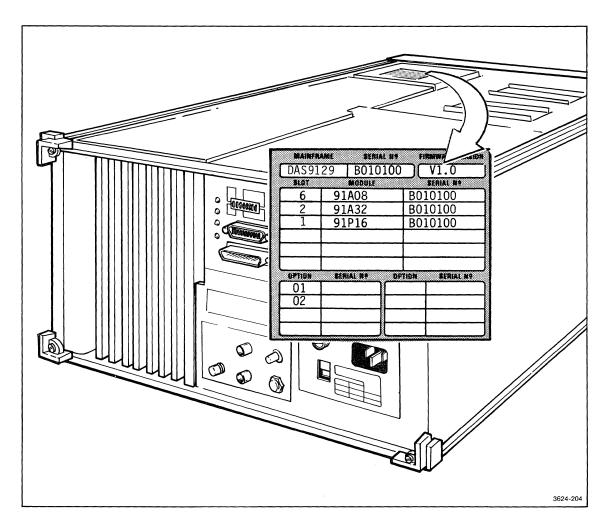

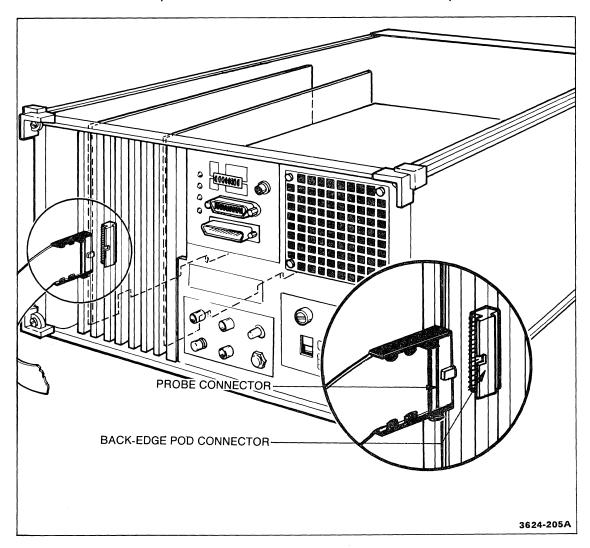

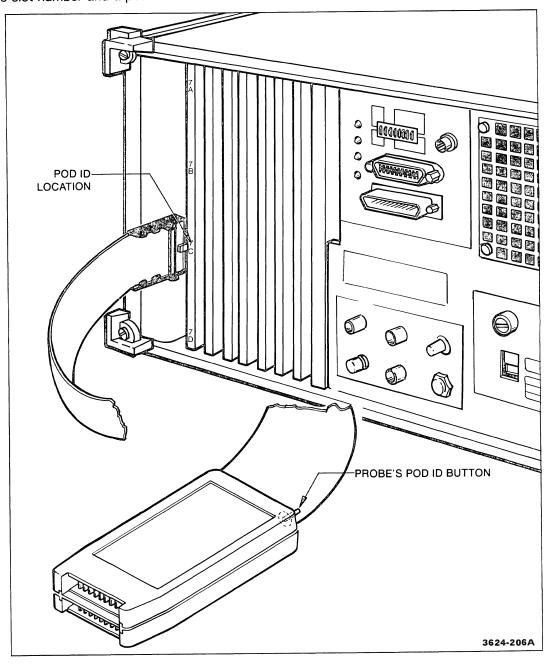

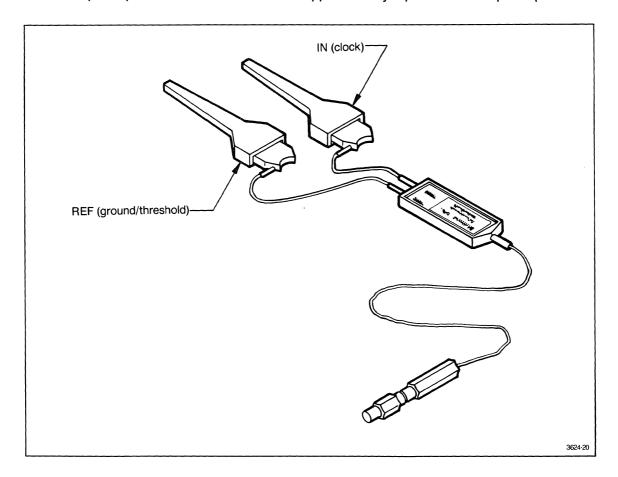

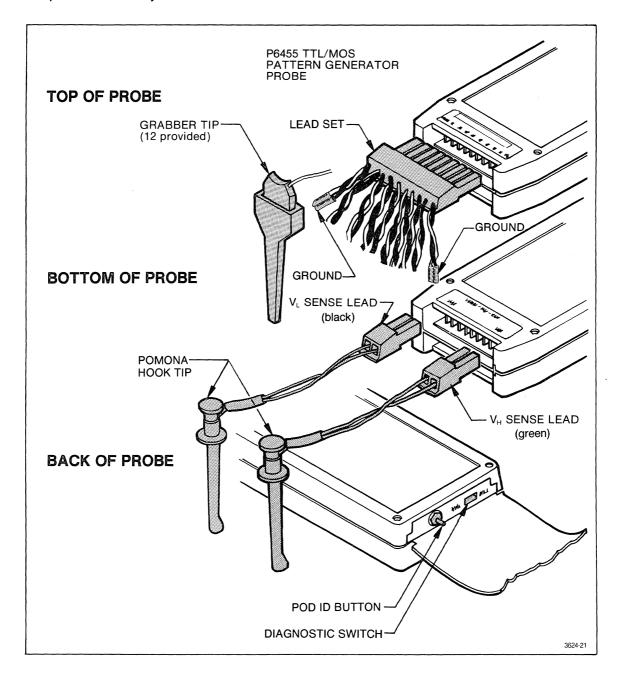

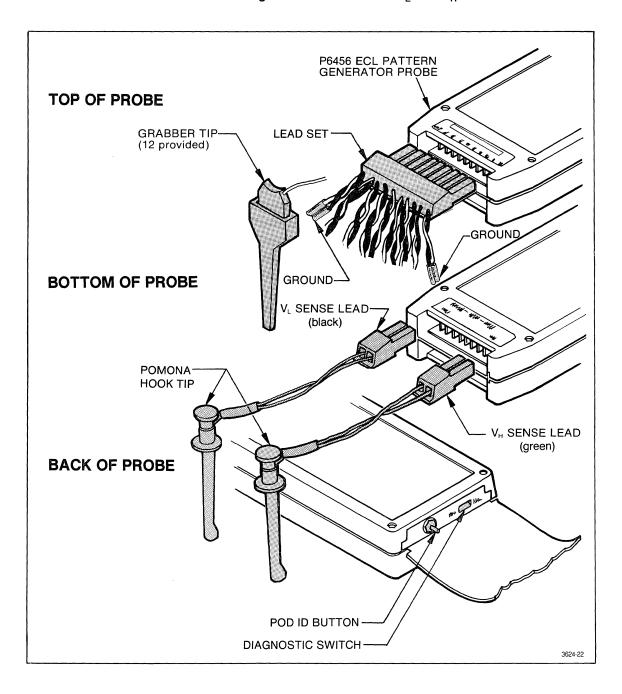

| MAINFRAME CONFIGURATION Power Requirements Power Cords Mainframe Ground Configuration Guidelines Module Configuration Label  PROBE CONNECTIONS Connecting a Probe to the DAS POD ID P6452 External Clock Probe P6452 Data Acquisition Probe P6454 100 MHz Clock Probe P6455 TTL/MOS Pattern Generator Probe P6456 ECL Pattern Generator Probe | 3-1<br>3-2<br>3-3                            |

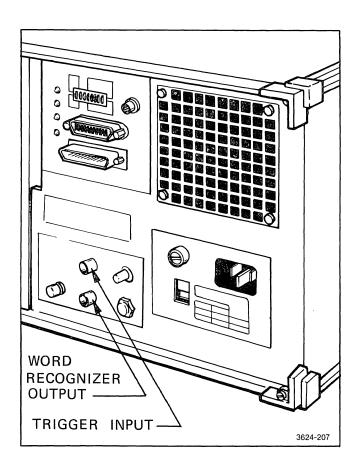

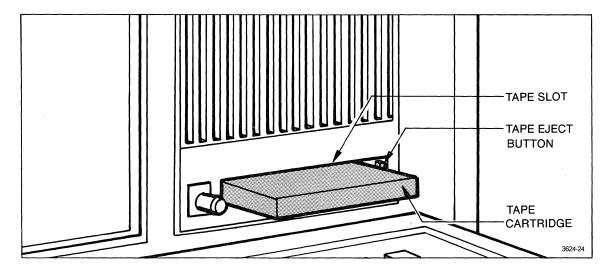

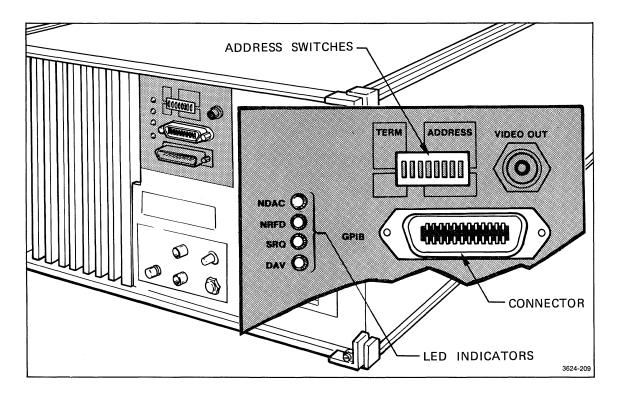

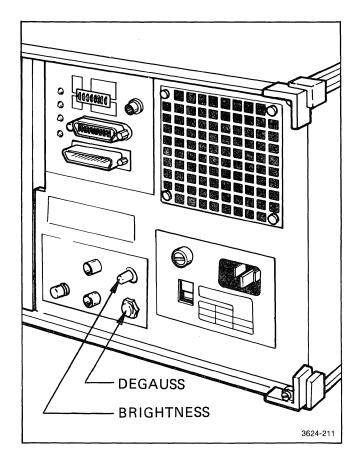

| STANDARD AND OPTIONAL I/O CONNECTORS  Word Recognizer Output and Trigger Input Connectors  Tape Drive Controls  RS-232 Interface  General Purpose Interface Bus (GPIB)  Video Composite Output                                                                                                                                                | 3-19<br>3-19<br>3-20<br>3-20<br>3-21<br>3-23 |

| COLOR MONITOR CONTROLS (DAS 9129 COLOR MAINFRAME ONLY)                                                                                                                                                                                                                                                                                        | 3-23                                         |

|                                                                                                                                                                                                                                                            | Page                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

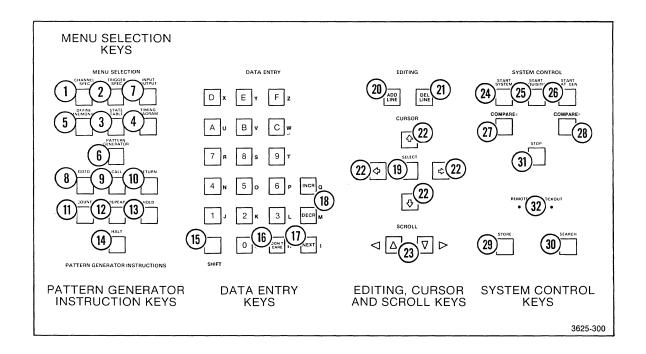

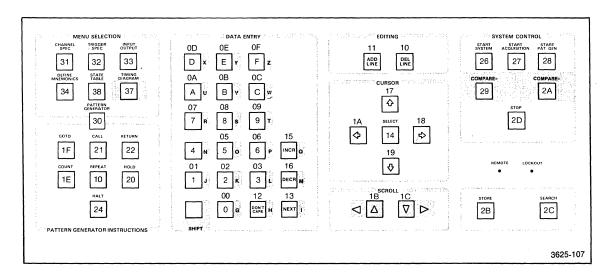

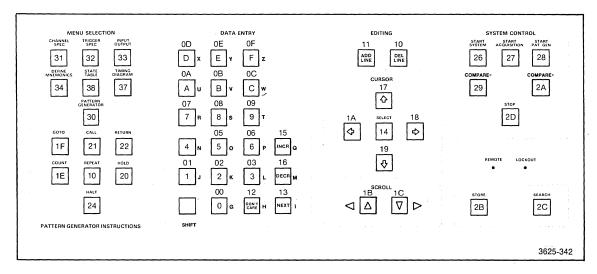

| KEYBOARD CONTROLS AND INDICATORS                                                                                                                                                                                                                           | 3-24                                                                      |

| Menu Selection                                                                                                                                                                                                                                             | 3-25                                                                      |

| Pattern Generator Instructions                                                                                                                                                                                                                             | 3-26                                                                      |

| Data Entry                                                                                                                                                                                                                                                 | 3-27                                                                      |

| Editing, Cursor, and Scroll                                                                                                                                                                                                                                | 3-28                                                                      |

| System Control                                                                                                                                                                                                                                             | 3-28                                                                      |

| Cyclem Condict                                                                                                                                                                                                                                             | 0-20                                                                      |

| MENU FAMILIARIZATION                                                                                                                                                                                                                                       | 3-30                                                                      |

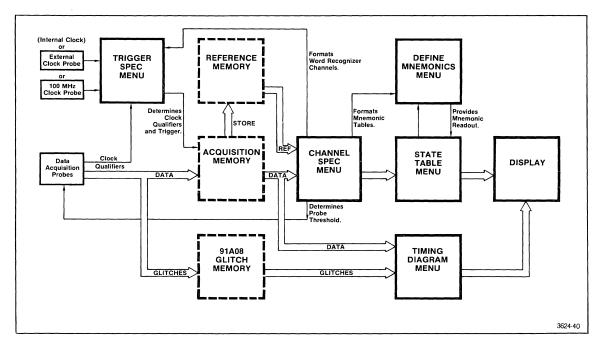

| Data Acquisition                                                                                                                                                                                                                                           | 3-30                                                                      |

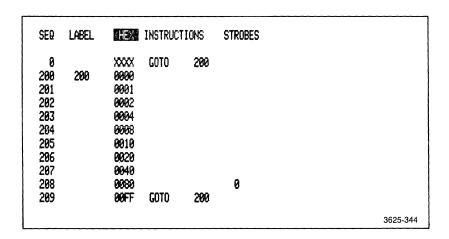

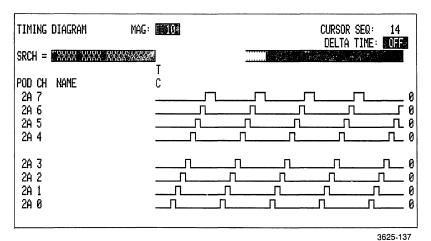

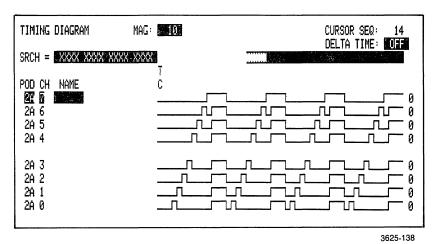

| Pattern Generator                                                                                                                                                                                                                                          | 3-31                                                                      |

| I/O Functions                                                                                                                                                                                                                                              | 3-32                                                                      |

| Menu Characteristics                                                                                                                                                                                                                                       | 3-32                                                                      |

|                                                                                                                                                                                                                                                            |                                                                           |

| OPERATOR'S CHECKOUT PROCEDURE                                                                                                                                                                                                                              | 3-33                                                                      |

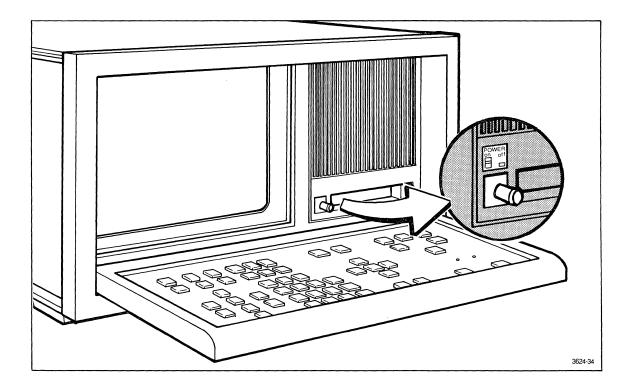

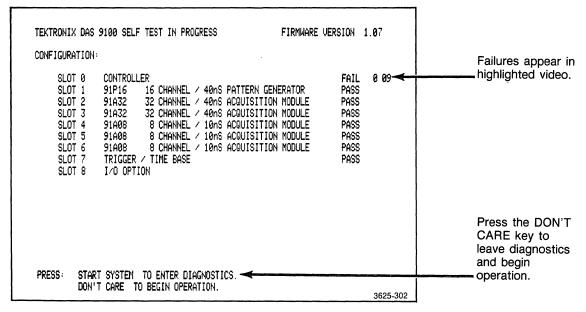

| Power-up Self-test                                                                                                                                                                                                                                         | 3-33                                                                      |

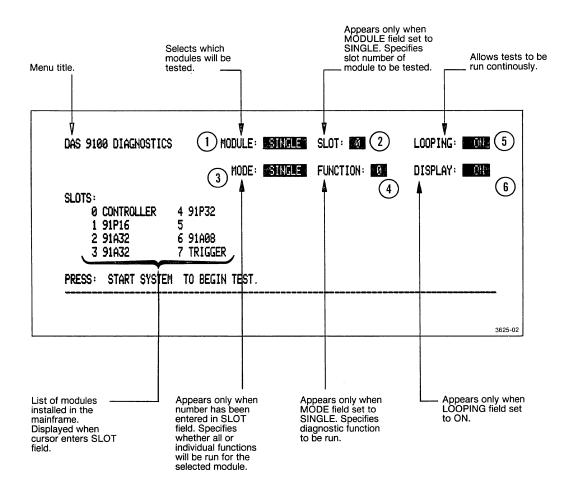

| Diagnostics Menu                                                                                                                                                                                                                                           | 3-37                                                                      |

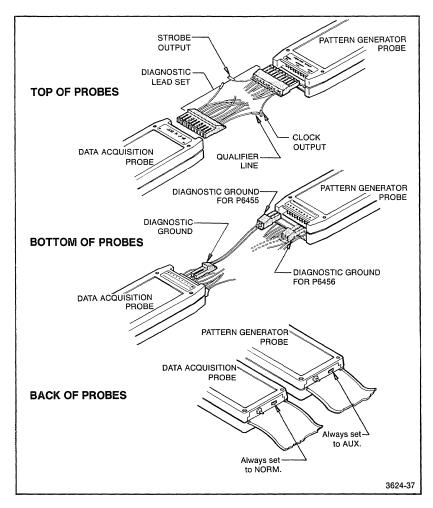

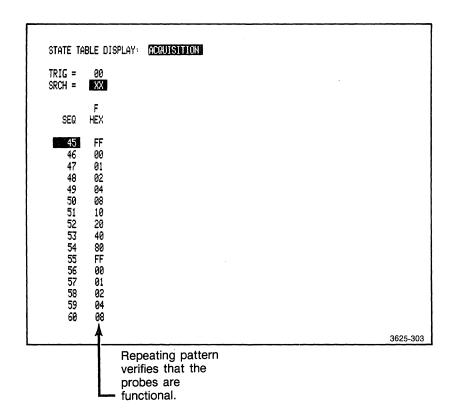

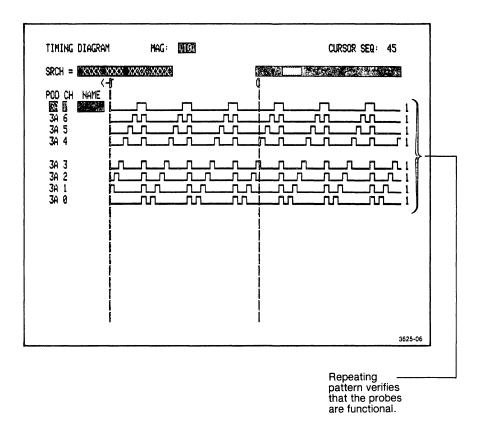

| Probe Self-test                                                                                                                                                                                                                                            | 3-39                                                                      |

|                                                                                                                                                                                                                                                            |                                                                           |

| COLOR DISPLAY (DAS 9129 MAINFRAME ONLY)                                                                                                                                                                                                                    | 3-43                                                                      |

| SECTION 4—THEORY OF OPERATION                                                                                                                                                                                                                              | Page                                                                      |

| Section Organization                                                                                                                                                                                                                                       | 4-1                                                                       |

| Logic Conventions                                                                                                                                                                                                                                          | 4-1                                                                       |

| Logio Gonvontiono                                                                                                                                                                                                                                          |                                                                           |

| SYSTEM ARCHITECTURE                                                                                                                                                                                                                                        |                                                                           |

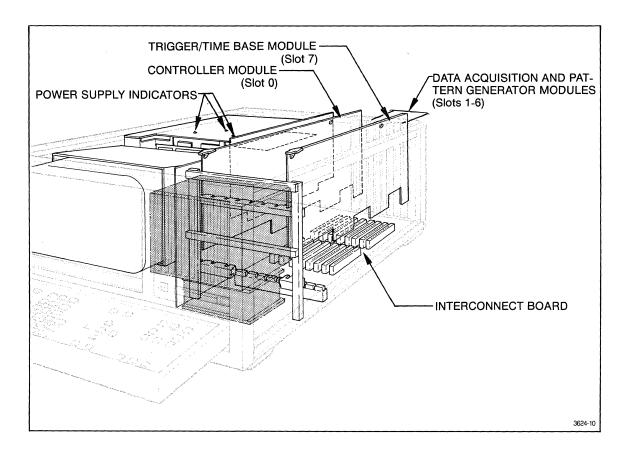

| DAS Mainframe                                                                                                                                                                                                                                              | 4-2                                                                       |

| Keyboard                                                                                                                                                                                                                                                   | 4-2<br>4-2                                                                |

| Nevboard                                                                                                                                                                                                                                                   |                                                                           |

| ·                                                                                                                                                                                                                                                          | 4-2                                                                       |

| Display Monitor                                                                                                                                                                                                                                            | 4-2<br>4-3                                                                |

| Display Monitor                                                                                                                                                                                                                                            | 4-2<br>4-3<br>4-3<br>4-3                                                  |

| Display Monitor  Main Power Supply  +5 V Power Supplies                                                                                                                                                                                                    | 4-2<br>4-3<br>4-3                                                         |

| Display Monitor  Main Power Supply  +5 V Power Supplies  Interconnect                                                                                                                                                                                      | 4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-4                                    |

| Display Monitor  Main Power Supply  +5 V Power Supplies  Interconnect  Controller                                                                                                                                                                          | 4-2<br>4-3<br>4-3<br>4-3<br>4-4                                           |

| Display Monitor  Main Power Supply  +5 V Power Supplies  Interconnect  Controller  Trigger/Time Base                                                                                                                                                       | 4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-4<br>4-5                             |

| Display Monitor  Main Power Supply +5 V Power Supplies Interconnect Controller Trigger/Time Base P6452 External Clock Probe                                                                                                                                | 4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-4<br>4-5<br>4-5                      |

| Display Monitor  Main Power Supply  +5 V Power Supplies  Interconnect  Controller  Trigger/Time Base  P6452 External Clock Probe  Data Acquisition Modules (With Probes)                                                                                   | 4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-4<br>4-5<br>4-5<br>4-6               |

| Display Monitor  Main Power Supply  +5 V Power Supplies Interconnect Controller Trigger/Time Base P6452 External Clock Probe Data Acquisition Modules (With Probes) 91A32 Data Acquisition Module                                                          | 4-2<br>4-3<br>4-3<br>4-4<br>4-4<br>4-5<br>4-5<br>4-6<br>4-7               |

| Display Monitor Main Power Supply +5 V Power Supplies Interconnect Controller Trigger/Time Base P6452 External Clock Probe Data Acquisition Modules (With Probes) 91A32 Data Acquisition Module P6452 Data Acquisition Probe                               | 4-2<br>4-3<br>4-3<br>4-4<br>4-4<br>4-5<br>4-5<br>4-6<br>4-7<br>4-7        |

| Display Monitor Main Power Supply +5 V Power Supplies Interconnect Controller Trigger/Time Base P6452 External Clock Probe Data Acquisition Modules (With Probes) 91A32 Data Acquisition Module P6452 Data Acquisition Probe 91A08 Data Acquisition Module | 4-2<br>4-3<br>4-3<br>4-4<br>4-4<br>4-5<br>4-5<br>4-6<br>4-7<br>4-7        |

| Display Monitor Main Power Supply +5 V Power Supplies Interconnect Controller Trigger/Time Base P6452 External Clock Probe Data Acquisition Modules (With Probes) 91A32 Data Acquisition Module P6452 Data Acquisition Probe                               | 4-2<br>4-3<br>4-3<br>4-4<br>4-4<br>4-5<br>4-5<br>4-6<br>4-7<br>4-7<br>4-7 |

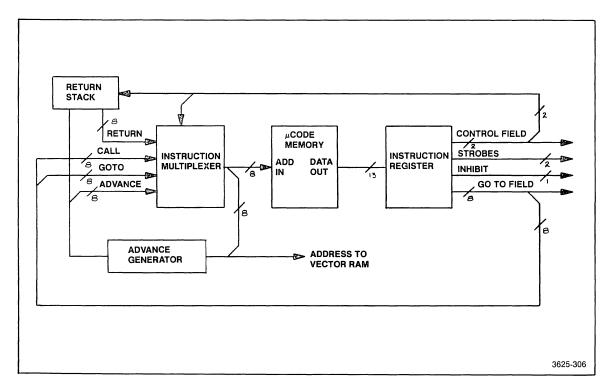

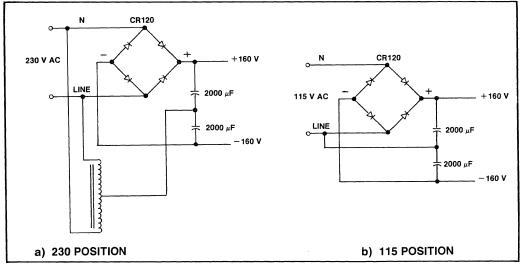

| DAS Mainframe       4-14         Keyboard       4-14         Controller       4-15         Keyboard Interface and Control Circuitry       4-15         Interrupt Logic       4-15         Microprocessor       4-16         ROM and System RAM       4-16         Address Buffer       4-16         DMA (Direct Memory Access)       4-16         CRT Controller       4-17         Display Generator       4-17         Timing Diagram Decoding       4-17         Display Monitor       4-17         High Speed Bus (P1)       4-17         CPU Bus (P0)       4-18         Trigger/Time Base and Probe       4-18         Trigger/Time Base Controller Interface and System ROM       4-18         External Clock Probe       4-18         Frequency Divider       4-18         91A08 Clock Select       4-18         91A08 Clock Select       4-19         91A32 Clock Select       4-19         Pipelined Internal Timing Sequencer       4-19         Event Conditioner       4-19         Arm Trigger       4-19         Arm Trigger       4-19         Arm Trigger       4-20         Trigger                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| P6455 TTL/MOS Pattern Generator Probe         4.9           P6456 ECL Pattern Generator Probe         4.9           91P32 Pattern Generator Expander Module         4.9           P6455 TTL/MOS Pattern Generator Probe         4.9           P6456 ECL Pattern Generator Probe         4.9           Options         4.10           Option 02 (I/O Interface)         4.10           Option 03 (+5 V Power Supply Module)         4.12           Option 04 (Two +5 V Power Supply Modules)         4.12           Option 05 (Rackmount Hardware)         4.12           Option 05 (Rackmount Hardware)         4.12           Optional Accessories         4.12           Service Maintenance Kit (067-0980-00)         4.12           Service Maintenance Kit (067-0980-00)         4.12           Service Maintenance Kit (067-1037-00)         4.12           GENERAL SYSTEM DESCRIPTION         4.12           DAS Mainframe         4.14           Keyboard         4.14           Keyboard Interface and Control Circuitry         4.15           Interrupt Logic         4.15           Interrupt Logic         4.15           Microprocessor         4.16           ROM and System RAM         4.16           Address Buffer         4.16 | 91P16 Pattern Generator Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-9  |

| 91P32 Pattern Generator Expander Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P6455 TTL/MOS Pattern Generator Probe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-9  |

| 91P32 Pattern Generator Expander Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P6456 ECL Pattern Generator Probe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-9  |

| P6455 TTL/MOS Pattern Generator Probe       4-9         P6456 ECL Pattern Generator Probe       4-9         Options       4-10         Option 02 (I/O Interface)       4-10         Option 03 (1+5 V Power Supply Module)       4-12         Option 04 (Two +5 V Power Supply Modules)       4-12         Option 05 (Rackmount Hardware)       4-12         Optional Accessories       4-12         Service Maintenance Kit (067-0980-00)       4-12         Setup/Hold Test Fixture (067-1037-00)       4-12         GENERAL SYSTEM DESCRIPTION       4-12         DAS Mainframe       4-14         Keyboard       4-14         Controller       4-15         Keyboard Interface and Control Circuitry       4-15         Keyboard Interface and Control Circuitry       4-15         Microprocessor       4-16         Address Buffer       4-16         DMA and System RAM       4-16         Address Buffer       4-16         DMA (Direct Memory Access)       4-16         CRT Controller       4-17         Display Generator       4-17         Ting Diagram Decoding       4-17         Display Monitor       4-17         High Speed Bus (P1)       4-17                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-9  |

| Options         4-10           Option 01 (Tape Drive for DC100-Type Cartridges)         4-10           Option 02 (I/O Interface)         4-11           Option 03 (+5 V Power Supply Module)         4-12           Option 05 (Rackmount Hardware)         4-12           Optional Accessories         4-12           Service Maintenance Kit (067-0980-00)         4-12           Service Maintenance Kit (067-1037-00)         4-12           GENERAL SYSTEM DESCRIPTION         4-12           DAS Mainframe         4-14           Keyboard         4-14           Controller         4-15           Keyboard Interface and Control Circuitry         4-15           Interrupt Logic         4-15           Microprocessor         4-16           ROM and System RAM         4-16           Address Buffer         4-16           DMA (Direct Memory Access)         4-16           CHT Controller         4-17           Display Generator         4-17           Timing Diagram Decoding         4-17           Tinger/Time Base and Probe         4-18           Trigger/Time Base and Probe         4-18           Trigger/Time Base and Probe         4-18           Trigger         4-18                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-9  |

| Option 01 (Tape Drive for DC100-Type Cartridges)         4-10           Option 02 (I/O Interface)         4-11           Option 03 (+5 V Power Supply Module)         4-12           Option 04 (Two +5 V Power Supply Modules)         4-12           Option 05 (Rackmount Hardware)         4-12           Optional Accessories         4-12           Service Maintenance Kit (067-0980-00)         4-12           Setup/Hold Test Fixture (067-1037-00)         4-12           GENERAL SYSTEM DESCRIPTION         4-12           DAS Mainframe         4-14           Keyboard         4-14           Controller         4-15           Keyboard Interface and Control Circuitry         4-15           Interrupt Logic         4-16           Microprocessor         4-16           ROM and System RAM         4-16           Address Buffer         4-16           DAA (Direct Memory Access)         4-16           CRT Controller         4-17           Display Generator         4-17           Timing Diagram Decoding         4-17           Display Monitor         4-17           Finger/Time Base and Probe         4-18           Trigger/Time Base Controller Interface and System ROM         4-18           E                    | P6456 ECL Pattern Generator Probe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-9  |

| Option 01 (Tape Drive for DC100-Type Cartridges)         4-10           Option 02 (I/O Interface)         4-11           Option 03 (+5 V Power Supply Module)         4-12           Option 04 (Two +5 V Power Supply Modules)         4-12           Option 05 (Rackmount Hardware)         4-12           Optional Accessories         4-12           Service Maintenance Kit (067-0980-00)         4-12           Setup/Hold Test Fixture (067-1037-00)         4-12           GENERAL SYSTEM DESCRIPTION         4-12           DAS Mainframe         4-14           Keyboard         4-14           Controller         4-15           Keyboard Interface and Control Circuitry         4-15           Interrupt Logic         4-16           Microprocessor         4-16           ROM and System RAM         4-16           Address Buffer         4-16           DAA (Direct Memory Access)         4-16           CRT Controller         4-17           Display Generator         4-17           Timing Diagram Decoding         4-17           Display Monitor         4-17           Finger/Time Base and Probe         4-18           Trigger/Time Base Controller Interface and System ROM         4-18           E                    | Ontions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4 10 |

| Option 02 (I/O Interface)         4-11           Option 03 (+5 V Power Supply Modules)         4-12           Option 04 (Two +5 V Power Supply Modules)         4-12           Option 05 (Rackmount Hardware)         4-12           Optional Accessories         4-12           Service Maintenance Kit (067-0980-00)         4-12           Setup/Hold Test Fixture (067-1037-00)         4-12           GENERAL SYSTEM DESCRIPTION         4-12           DAS Mainframe         4-14           Keyboard         4-14           Controller         4-15           Keyboard Interface and Control Circuitry         4-15           Interrupt Logic         4-15           Microprocessor         4-16           Address Buffer         4-16           Address Buffer         4-16           DMA (Direct Memory Access)         4-16           CRT Controller         4-17           Display Generator         4-17           Timing Diagram Decoding         4-17           Display Monitor         4-17           High Speed Bus (P1)         4-17           CPU Bus (P0)         4-18           Trigger/Time Base and Probe         4-18           Trigger/Time Base Controller Interface and System ROM         4-                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Option 03 (+5 V Power Supply Module)         4-12           Option 04 (Two +5 V Power Supply Modules)         4-12           Option 05 (Rackmount Hardware)         4-12           Optional Accessories         4-12           Service Maintenance Kit (067-0980-00)         4-12           Setup/Hold Test Fixture (067-1037-00)         4-12           GENERAL SYSTEM DESCRIPTION         4-12           DAS Mainframe         4-14           Keyboard         4-14           Controller         4-15           Keyboard Interface and Control Circuitry         4-15           Interrupt Logic         4-15           Microprocessor         4-16           ROM and System RAM         4-16           Address Buffer         4-16           DAMA (Direct Memory Access)         4-16           CRT Controller         4-17           Display Generator         4-17           Timing Diagram Decoding         4-17           Pisplay Monitor         4-17           Trigger/Time Base and Probe         4-18           Trigger/Time Base Controller Interface and System ROM         4-18           External Clock Probe         4-18           Frequency Divider         4-18           91A08 Clock Select <td< td=""><td></td><td></td></td<> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Option 04 (Two +5 V Power Supply Modules)         4-12           Option 05 (Rackmount Hardware)         4-12           Optional Accessories         4-12           Service Maintenance Kit (067-0980-00)         4-12           Setup/Hold Test Fixture (067-1037-00)         4-12           GENERAL SYSTEM DESCRIPTION         4-12           DAS Mainframe         4-14           Keyboard         4-14           Controller         4-15           Keyboard Interface and Control Circuitry         4-15           Interrupt Logic         4-15           Microprocessor         4-16           ROM and System RAM         4-16           Address Buffer         4-16           DMA (Direct Memory Access)         4-16           CRT Controller         4-17           Display Generator         4-17           Timing Diagram Decoding         4-17           Display Monitor         4-17           High Speed Bus (P1)         4-17           CPU Bus (P0)         4-18           Trigger/Time Base and Probe         4-18           Trigger/Time Base and Probe         4-18           Frequency Divider         4-18           91A02 Clock Select         4-18           91A08 Cloc                                                       | Option 03 (±5 V Power Supply Module)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| Option 05 (Rackmount Hardware)       4-12         Optional Accessories       4-12         Service Maintenance Kit (067-0980-00)       4-12         Setup/Hold Test Fixture (067-1037-00)       4-12         GENERAL SYSTEM DESCRIPTION       4-12         DAS Mainframe       4-14         Keyboard       4-14         Controller       4-15         Keyboard Interface and Control Circuitry       4-15         Interrupt Logic       4-15         Microprocessor       4-16         ROM and System RAM       4-16         Address Buffer       4-16         DMA (Direct Memory Access)       4-16         CRT Controller       4-17         Display Generator       4-17         Timing Diagram Decoding       4-17         Display Monitor       4-17         High Speed Bus (P1)       4-17         CPU Bus (P0)       4-18         Trigger/Time Base and Probe       4-18         Trigger/Time Base and Probe       4-18         Frequency Divider       4-18         91A08 Clock Probe       4-18         Frequency Divider       4-18         91A08 Clock Select       4-19         91A08 Clock Select       4-19                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Optional Accessories         4-12           Service Maintenance Kit (067-0980-00)         4-12           Setup/Hold Test Fixture (067-1037-00)         4-12           GENERAL SYSTEM DESCRIPTION         4-12           DAS Mainframe         4-14           Keyboard         4-14           Controller         4-15           Keyboard Interface and Control Circuitry         4-15           Interrupt Logic         4-15           Microprocessor         4-16           ROM and System RAM         4-16           Address Buffer         4-16           DATA (Direct Memory Access)         4-16           CRT Controller         4-17           Display Generator         4-17           Timing Diagram Decoding         4-17           Display Monitor         4-17           High Speed Bus (P1)         4-17           CPU Bus (P0)         4-18           Trigger/Time Base and Probe         4-18           Trigger/Time Base Controller Interface and System ROM         4-18           External Clock Probe         4-18           Frequency Divider         4-18           91A08 Clock Select         4-19           91A08 Clock Select         4-19           Pipelined Intern                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |