۰.

The Central Processor (CP) emulates the Mesa Processor as defined by the Mesa Processor Principles of Operation, and provides ALU service for the integral I/O controllers. The central processor is modeled almost exactly after the architecture of the Dandelion, but executes a slightly different version of the Dandelion microinstruction set. In addition, a small part of the Dandelion Mesa Emulator has been modified.

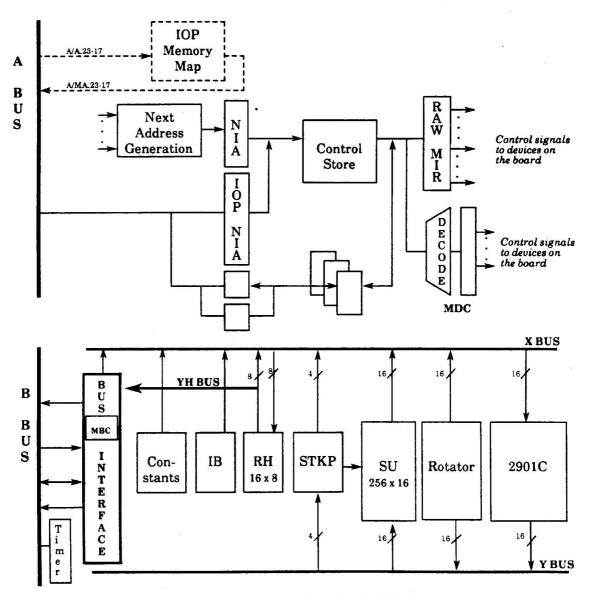

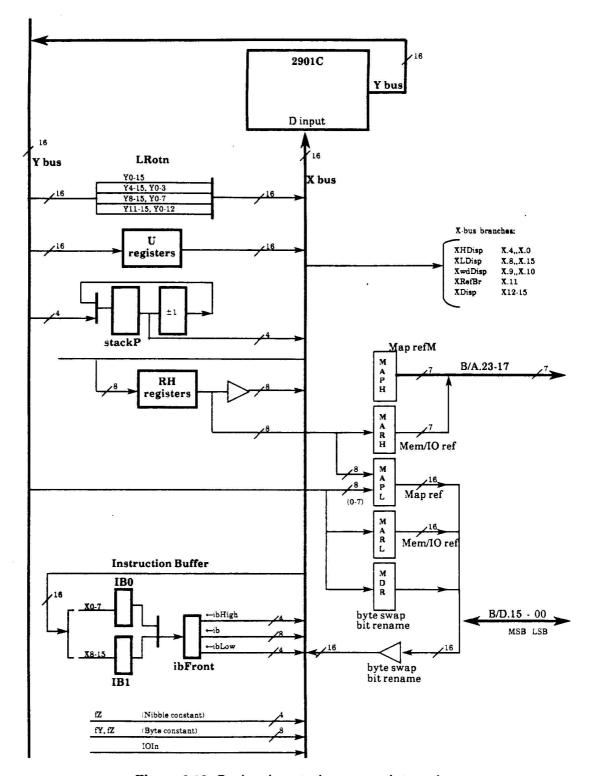

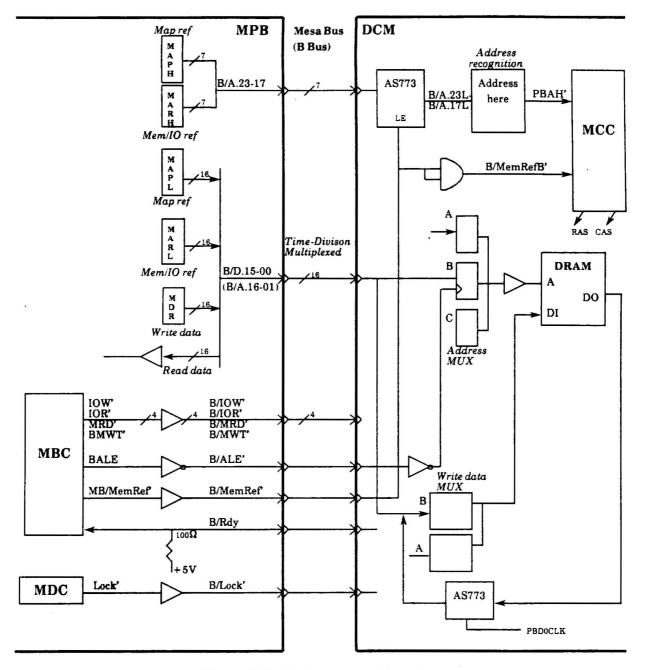

Figure 1.1 in Section 1 illustrates the relationship of the Mesa Processor Board (MPB) to the rest of the system. Figure 2.1 illustrates the MPB functional blocks that are described in this section.

Figure 2.1. Mesa processor board logical blocks

÷

İ

2 - 1

# 2.1 General Board Hardware

The central processor is a microprogrammed, 16-bit general purpose computer consisting of approximately 170 ICs of various sizes and complexity. It resides on a 10.9-inch by 16-inch printed wiring board assembly (PWBA), referred to as the Mesa Processor Board (MPB), located in slot 3 of the backplane.

The MPB contains:

- 4K by 48-bit writable control store and associated registers for loading and decoding microinstructions. Control store is expandable to 8K by 48 bits. An 84-pin gate array provides look-ahead decoding of certain microinstructions; the raw microinstruction register (RAW MIR) stores microinstructions.

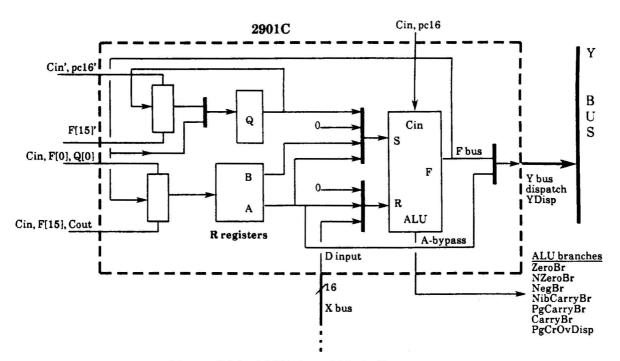

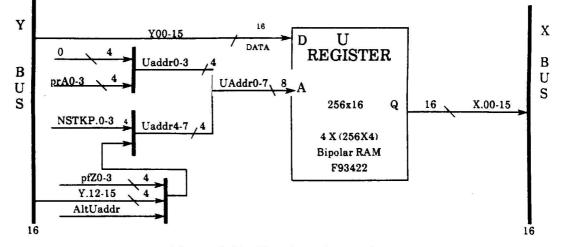

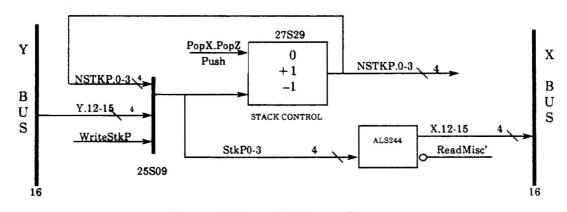

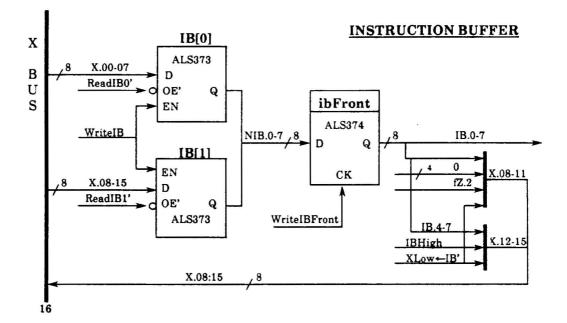

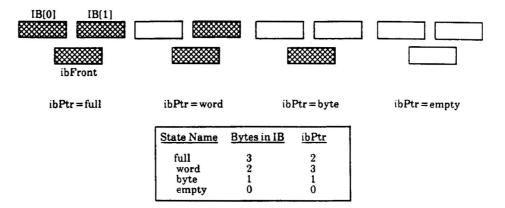

- Four 2901C LSI chips that make up the core of the central processor. The 2901C is a 4-bit processor; the four chips are cascaded to provide a 16-bit processor. Supporting the 2901C are four register sets (U, RH, IB, and Link), a four-bit rotator, and four emulator registers (stackP, ibPtr, pc16, and MInt).

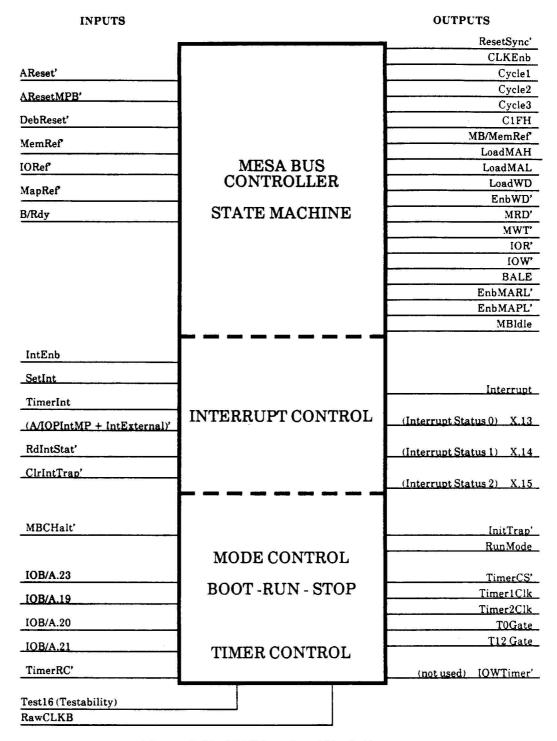

- The 68-pin gate array that serves as the Mesa bus controller, and the logic that interfaces the controller to internal buses (X and Y) and to the Mesa bus and backplane.

- Support devices, such as the process timer and trap machine.

- A 16 MHz clock generator which distributes a clock signal across the backplane.

- IOP address mapping, which is part of the I/O subsystem, and is not discussed in this manual.

Note: Not all devices are shown in Figure 2.1.

Most devices are described in detail in the appropriate subsections of Section 2. This subsection describes the overall MPB; that is, board layout, interfaces, power requirements, and internal clock generation.

### 2.1.1 Mesa Processor Board (MPB)

Figure 2.2 illustrates the layout of the Mesa Processor board.

# Figure 2.2. Mesa Processor Board layout

# 2.1.2 Backplane Interface

Table 2.1 lists the Mesa processor board interface to the backplane. On the backplane, pins are grouped in six rows of three columns each. The table reflects the grouping.

The board interfaces to the Mesa processor or B bus and the 80186 or A bus. Two interrupt lines connects the Mesa processor with the IOP.

Tables 2.2 and 2.3 list the pins and signals for the interfaces to the Mesa bus and 80186 bus, respectively.

į.

.

# Table 2.1. MPB Backplane Pin Assignment (Front View)

# <u>Outmost</u>

<u>Inmost</u>

| Spare-1 J3.001                         | GND                             | J3.002        | Spare-2                              | J3.003             |

|----------------------------------------|---------------------------------|---------------|--------------------------------------|--------------------|

| A/AD.07 (bi) J3.004                    | A/DT/R'(i)                      | J3.005        | A/AD.15 (                            | bi) J3.006         |

| A/AD.06 (bi) J3.007                    | <u>A/DEN' (i)</u>               | J3.008        | A/AD.14 ()                           | bi) J3.009         |

| A/AD.05 (bi) J3.010                    | GND                             | J3.011        | A/AD.13 (                            | bi) J3.012         |

| A/AD.04 (bi) J3.013                    | A/MemRdy                        | (i) J3.014    | A/AD.12 (                            | bi) J3.015         |

| A/AD.03 (bi) J3.016                    | <u>A/ALE' (i)</u>               | J3.017        | A/AD.11 (                            | bi) J3.018         |

| A/AD.02 (bi) J3.019                    | A/IOPMem                        | Wr'(i) J3.020 | A/AD.10 (                            | bi) J3.021         |

| A/AD.01 (bi) J3.022                    | Spare-3                         | J3.023        | A/AD.09 (                            | bi) J3.024         |

| A/AD.00 (bi) J3.025                    | GND                             | J3.026        | A/AD.08 (                            | bi) J3.027         |

| GND J3.028                             | A/CLK(i)                        | J3.029        | VCC                                  | J3.030             |

| J3.031 GND<br>J3.034 (i) A/AA.19       | J3.032<br>J3.035 (i)            | GND<br>A/S2'  | J <u>3.033</u><br>J <u>3.036 (i)</u> | GND<br>A/AA.23     |

| 3.034 (i) A/AA.19<br>3.037 (i) A/AA.18 | $\frac{J3.035 (i)}{J3.038 (i)}$ | A/S2<br>A/S1' | $J_{3.039}^{(i)}$ (i)                | A/AA.23<br>A/AA.22 |

| 3.040 (i) A/AA.17                      | $\frac{J3.038}{J3.041}$ (i)     | A/S0'         | $J_{3.042}$ (i)                      | A/AA.22<br>A/AA.21 |

| 3.043 (i) A/AA.16                      | J3.044 (i)                      | A/BHE'        | J3.045 (i)                           | A/AA.20            |

| 3.046 A/UCS'                           | J3.047                          | GND           | J3.048 (i)                           | A/IOR'             |

| 3.049 (o) Reserved-0                   | J3.050 (i)                      | A/LocRamCS'*  | J3.051                               | Spare-4            |

| 3.052 (i) A/IOPLock'                   | *J3.053                         | GND           | J3.054 (i)                           | A/IOW'             |

| 3.055 A/PCHoldAToArb*                  | J3.056 (o)                      | A/IOPMemRd'   | J3.057                               | Spare-5            |

| 3.058 -5V                              | J3.059                          | -5V           | J3.060                               | -5V                |

|                                        |                                 |               |                                      |                    |

| J3.061  |

|---------|

| J3.064  |

| J3.067  |

| J3.070  |

| J3.073  |

| *J3.076 |

| J3.079  |

| J3.082  |

| J3.085  |

| J3.088  |

|         |

|                       | 2) MPB-DCM                                                                                                      |                             |          |

|-----------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------|----------|

| GND                   | J3.062                                                                                                          | GND                         | J3.063   |

| A/MA.23 (0)           | J3.065                                                                                                          | A/MA.22 (0)                 | J3.066   |

| A/MA.21(0)            | J3.068                                                                                                          | A/MA.20 (0)                 | J3.069   |

| A/MA.19 (0)           | J3.071                                                                                                          | A/MA.18 (0)                 | J3.072   |

| A/MA.17 (0)           | J3.074                                                                                                          | A/AA.16B (0)                | J3.075   |

| GND                   | J3.077                                                                                                          | MPB-DCM-spare               | 1 J3.078 |

| MPB-DCM-spare1        | _ <u>J3.080</u>                                                                                                 |                             |          |

|                       |                                                                                                                 | 3) Mesa                     | Bus      |

|                       |                                                                                                                 |                             |          |

| GND                   | J3.083                                                                                                          | B/MWT' (0)                  | J3.081   |

| GND<br>MPB-DCM-spare3 | J3.083<br>J3.086                                                                                                | B/MWT' (o)<br>Dawn-Mp-spare |          |

|                       | and an |                             |          |

÷

÷,

\* not used

- more-

|                                                                                                                          | most                                                                                                                  | _                                                                                                                           |                                                                                                         | Ir                                                                                                             | nmost                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| IOP-Mesa                                                                                                                 |                                                                                                                       |                                                                                                                             |                                                                                                         | <br>3) MesaBus (con                                                                                            | ntinued)                                                                                                    |

| J3.091                                                                                                                   | GND                                                                                                                   | J3.092                                                                                                                      | GND                                                                                                     | _J3.093                                                                                                        | GND                                                                                                         |

| J3.094 (i)                                                                                                               | A/IOPIntMP'                                                                                                           | J3.095                                                                                                                      | CSWREN*                                                                                                 | J3.096                                                                                                         | (reserved)                                                                                                  |

| J3.097 (o)                                                                                                               | A/MPIntIOP                                                                                                            | J3.098                                                                                                                      | CSLOAD/SHIFT**                                                                                          | J3.099 (o)                                                                                                     | B/Lock'                                                                                                     |

| J3.100                                                                                                                   | A/IOPRdNIA                                                                                                            | J3.101                                                                                                                      | CSBUFFEREN*                                                                                             | J3.102 (o)                                                                                                     | B/IOR'                                                                                                      |

| J3.103 (o)                                                                                                               | A/Halt'                                                                                                               | J3.104                                                                                                                      | CSDATAIN*                                                                                               | J3.105 (o)                                                                                                     | B/MemRef                                                                                                    |

| J3.106                                                                                                                   | IOP-S-spare1                                                                                                          | J3.107                                                                                                                      | CSSHIFTCLK*                                                                                             | J3.108 (o)                                                                                                     | B/IOW                                                                                                       |

| J3.109 (o)                                                                                                               | A/ResetMPB'                                                                                                           | J3.110                                                                                                                      | CSDATAOUT*                                                                                              | J3.111 (i)                                                                                                     | B/Rdy                                                                                                       |

| J3.112                                                                                                                   | VCC                                                                                                                   | J3.113                                                                                                                      | VCC                                                                                                     | J3.114                                                                                                         | VCC                                                                                                         |

| J3.115                                                                                                                   | VCC                                                                                                                   | J3.116                                                                                                                      | VCC                                                                                                     | J3.117 (i)                                                                                                     | VCC                                                                                                         |

| J3.118                                                                                                                   | VCC                                                                                                                   | J3.119                                                                                                                      | VCC                                                                                                     | J3.120                                                                                                         | VCC                                                                                                         |

| GND<br>GND                                                                                                               | <u>J3.121</u><br>J3.124                                                                                               | GND<br>GND                                                                                                                  | J3.122<br>J3.125                                                                                        | GND<br>GND                                                                                                     | J3.123<br>J3.126                                                                                            |

| GND<br>GND<br>INTDIS'                                                                                                    | J3.124<br>J3.127<br>J3.130                                                                                            | GND<br>GND<br>B/A.18 (0)                                                                                                    | J3.125<br>J3.128<br>J3.131                                                                              | GND<br>GND<br>B/ALE' (0)                                                                                       | J3.126<br>J3.129<br>J3.132                                                                                  |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)                                                                                      | J3.124<br>J3.127<br>J3.130<br>J3.133                                                                                  | GND<br>GND<br>B/A.18 (o)<br>B/A.17 (o)                                                                                      | J3.125<br>J3.128<br>J3.131<br>J3.134                                                                    | GND<br>GND<br>B/ALE' (0)<br>Dawn-Mp-Sp                                                                         | J3.126<br>J3.129<br>J3.132<br>are3J3.135                                                                    |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)<br>B/A.22 (0)                                                                        | J3.124<br>J3.127<br>J3.130<br>J3.133<br>J3.133<br>J3.136                                                              | GND<br>GND<br>B/A.18 (0)<br>B/A.17 (0)<br>GND                                                                               | J3.125<br>J3.128<br>J3.131<br>J3.134<br>J3.137                                                          | GND<br>GND<br>B/ALE' (0)<br>Dawn-Mp-Sp<br>B/D.11 (bi)                                                          | J3.126<br>J3.129<br>J3.132<br>are3J3.135<br>J3.138                                                          |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)<br>B/A.22 (0)<br>B/A.21 (0)                                                          | J3.124<br>J3.127<br>J3.130<br>J3.133<br>JJ3.136<br>JJ3.139                                                            | GND<br>GND<br>B/A.18 (o)<br>B/A.17 (o)<br>GND<br>B/D.15 (bi)                                                                | J3.125<br>J3.128<br>J3.131<br>J3.134<br>J3.137<br>J3.140                                                | GND<br>GND<br>B/ALE' (0)<br>Dawn-Mp-Sp<br>B/D.11 (bi)<br>B/D.10 (bi)                                           | J3.126<br>J3.129<br>J3.132<br>are3J3.135<br>J3.138<br>J3.141                                                |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)<br>B/A.22 (0)<br>B/A.21 (0)<br>B/A.20 (0)                                            | J3.124<br>J3.127<br>J3.130<br>J3.133<br>JJ3.133<br>JJ3.136<br>JJ3.139<br>JJ3.142                                      | GND<br>GND<br>B/A.18 (o)<br>B/A.17 (o)<br>GND<br>B/D.15 (bi)<br>B/D.14 (bi)                                                 | J3.125<br>J3.128<br>J3.131<br>J3.134<br>J3.137<br>J3.140<br>J3.143                                      | GND<br>GND<br>B/ALE' (o)<br>Dawn-Mp-Sp<br>B/D.11 (bi)<br>B/D.10 (bi)<br>B/D.09 (bi)                            | J3.126<br>J3.129<br>J3.132<br>are3J3.135<br>J3.138<br>J3.141<br>J3.144                                      |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)<br>B/A.22 (0)<br>B/A.21 (0)<br>B/A.20 (0)<br>B/A.19                                  | J3.124<br>J3.127<br>J3.130<br>J3.133<br>JJ3.133<br>JJ3.136<br>JJ3.139<br>JJ3.142<br>J3.145                            | GND<br>GND<br>B/A.18 (o)<br>B/A.17 (o)<br>GND<br>B/D.15 (bi)<br>B/D.14 (bi)<br>B/D.13 (bi)                                  | J3.125<br>J3.128<br>J3.131<br>J3.134<br>J3.137<br>J3.140<br>J3.143<br>J3.146                            | GND<br>GND<br>B/ALE' (o)<br>Dawn-Mp-Sp<br>B/D.11 (bi)<br>B/D.10 (bi)<br>B/D.09 (bi)<br>B/D.08 (bi)             | J3.126<br>J3.129<br>J3.132<br>are3J3.135<br>J3.138<br>J3.141<br>J3.144<br>J3.144                            |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)<br>B/A.22 (0)<br>B/A.21 (0)<br>B/A.20 (0)                                            | J3.124<br>J3.127<br>J3.130<br>J3.133<br>JJ3.133<br>JJ3.136<br>JJ3.139<br>JJ3.142                                      | GND<br>GND<br>B/A.18 (o)<br>B/A.17 (o)<br>GND<br>B/D.15 (bi)<br>B/D.14 (bi)                                                 | J3.125<br>J3.128<br>J3.131<br>J3.134<br>J3.137<br>J3.140<br>J3.143                                      | GND<br>GND<br>B/ALE' (o)<br>Dawn-Mp-Sp<br>B/D.11 (bi)<br>B/D.10 (bi)<br>B/D.09 (bi)                            | J3.126<br>J3.129<br>J3.132<br>are3J3.135<br>J3.138<br>J3.141<br>J3.144                                      |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)<br>B/A.22 (0)<br>B/A.21 (0)<br>B/A.20 (0)<br>B/A.19                                  | J3.124<br>J3.127<br>J3.130<br>J3.133<br>JJ3.133<br>JJ3.136<br>JJ3.139<br>JJ3.142<br>J3.145                            | GND<br>GND<br>B/A.18 (o)<br>B/A.17 (o)<br>GND<br>B/D.15 (bi)<br>B/D.14 (bi)<br>B/D.13 (bi)                                  | J3.125<br>J3.128<br>J3.131<br>J3.134<br>J3.137<br>J3.140<br>J3.143<br>J3.146                            | GND<br>GND<br>B/ALE' (o)<br>Dawn-Mp-Sp<br>B/D.11 (bi)<br>B/D.10 (bi)<br>B/D.09 (bi)<br>B/D.08 (bi)             | J3.126<br>J3.129<br>J3.132<br>are3J3.135<br>J3.138<br>J3.141<br>J3.144<br>J3.144                            |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)<br>B/A.22 (0)<br>B/A.21 (0)<br>B/A.20 (0)<br>B/A.19                                  | J3.124<br>J3.127<br>J3.130<br>J3.133<br>JJ3.133<br>JJ3.136<br>JJ3.139<br>JJ3.142<br>J3.145                            | GND<br>GND<br>B/A.18 (o)<br>B/A.17 (o)<br>GND<br>B/D.15 (bi)<br>B/D.14 (bi)<br>B/D.13 (bi)                                  | J3.125<br>J3.128<br>J3.131<br>J3.134<br>J3.137<br>J3.140<br>J3.143<br>J3.146                            | GND<br>GND<br>B/ALE' (o)<br>Dawn-Mp-Sp<br>B/D.11 (bi)<br>B/D.10 (bi)<br>B/D.09 (bi)<br>B/D.08 (bi)             | J3.126<br>J3.129<br>J3.132<br>are3J3.135<br>J3.138<br>J3.141<br>J3.144<br>J3.144                            |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)<br>B/A.22 (0)<br>B/A.21 (0)<br>B/A.20 (0)<br>B/A.19<br>-12V                          | J3.124<br>J3.127<br>J3.130<br>J3.133<br>JJ3.133<br>JJ3.136<br>JJ3.139<br>JJ3.142<br>J3.145<br>J3.148                  | GND<br>GND<br>B/A.18 (o)<br>B/A.17 (o)<br>GND<br>B/D.15 (bi)<br>B/D.14 (bi)<br>B/D.13 (bi)<br>-12V                          | J3.125<br>J3.128<br>J3.131<br>J3.134<br>J3.137<br>J3.140<br>J3.143<br>J3.146<br>J3.149                  | GND<br>GND<br>B/ALE' (o)<br>Dawn-Mp-Sp<br>B/D.11 (bi)<br>B/D.10 (bi)<br>B/D.09 (bi)<br>B/D.08 (bi)<br>-12V     | J3.126<br>J3.129<br>J3.132<br>are3J3.135<br>J3.138<br>J3.141<br>J3.144<br>J3.147<br>J3.150                  |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)<br>B/A.22 (0)<br>B/A.21 (0)<br>B/A.20 (0)<br>B/A.19<br>-12V<br>J3.151<br>J3.154 (bi) | J3.124<br>J3.127<br>J3.130<br>J3.133<br>JJ3.136<br>JJ3.139<br>JJ3.142<br>J3.145<br>J3.148<br>GND                      | GND<br>GND<br>B/A.18 (o)<br>B/A.17 (o)<br>GND<br>B/D.15 (bi)<br>B/D.14 (bi)<br>B/D.13 (bi)<br>-12V                          | J3.125<br>J3.128<br>J3.131<br>J3.134<br>J3.137<br>J3.140<br>J3.143<br>J3.146<br>J3.149<br>GND           | GND<br>GND<br>B/ALE' (o)<br>Dawn-Mp-Sp<br>B/D.11 (bi)<br>B/D.09 (bi)<br>B/D.08 (bi)<br>-12V<br>J3.153          | J3.126<br>J3.129<br>J3.132<br>are3J3.135<br>J3.138<br>J3.141<br>J3.144<br>J3.147<br>J3.150<br>GND           |

| GND<br>GND<br>INTDIS'<br>B/A.23 (0)<br>B/A.22 (0)<br>B/A.21 (0)<br>B/A.20 (0)<br>B/A.19<br>-12V                          | J3.124<br>J3.127<br>J3.130<br>J3.133<br>JJ3.133<br>JJ3.136<br>JJ3.139<br>JJ3.142<br>J3.145<br>J3.148<br>GND<br>B/D.07 | GND<br>GND<br>B/A.18 (o)<br>B/A.17 (o)<br>GND<br>B/D.15 (bi)<br>B/D.14 (bi)<br>B/D.13 (bi)<br>-12V<br>J3.152<br>J3.155 (bi) | J3.125<br>J3.128<br>J3.131<br>J3.134<br>J3.137<br>J3.140<br>J3.143<br>J3.146<br>J3.149<br>GND<br>B/D.12 | GND<br>GND<br>B/ALE' (o)<br>Dawn-Mp-Sp<br>B/D.11 (bi)<br>B/D.09 (bi)<br>B/D.09 (bi)<br>B/D.08 (bi)<br>-12V<br> | J3.126<br>J3.129<br>J3.132<br>are3J3.135<br>J3.138<br>J3.141<br>J3.144<br>J3.147<br>J3.150<br>GND<br>B/D.06 |

# Table 2-1. MPB Backplane Pin Assignment (continued)

\* Not used

### Central Processor

2 - 5

۲

£,

| Pin Signal<br>(Connector J1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Signal Description                                            | Pin<br>(Connecto                                                                                                                                                         | Signal<br>or J1)                                                                                                                                                                        | Signal Description                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1.140         B/D.15           J1.143         B/D.14           J1.146         B/D.13           J1.155         B/D.12           J1.138         B/D.11           J1.141         B/D.10           J1.144         B/D.09           J1.144         B/D.09           J1.154         B/D.07           J1.156         B/D.06           J1.157         B/D.06           J1.159         B/D.04           J1.160         B/D.03           J1.162         B/D.02           J1.163         B/D.01           J1.165         B/D.00 | B-Bus multiplexed<br>Address/Data line,<br>bidirectional data | $\begin{array}{c} J1.133\\ J1.136\\ J1.139\\ J1.142\\ J1.142\\ J1.145\\ J1.131\\ J1.134\\ \\ J1.087\\ J1.087\\ J1.081\\ J1.008\\ J1.099\\ J1.132\\ J1.111\\ \end{array}$ | B/A.23 }<br>B/A.22 }<br>B/A.21 }<br>B/A.20 }<br>B/A.19 }<br>B/A.18 }<br>B/A.17 }<br>B/MemRef'<br>B/MRD'<br>B/MRD'<br>B/IOR'<br>B/IOR'<br>B/IOR'<br>B/IOW'<br>B/Lock'<br>B/ALE'<br>B/Rdy | <b>B-Bus Address line</b><br>B-bus Mesa memory reference<br>B-bus Memory Read<br>B-bus Memory Write<br>B-bus I/O read<br>B-bus I/O write<br>B-bus lock request to memory<br>Address Latch Enable<br>Ready |

| <b>Table 2.2.</b> I | Mesa (B) | <b>Bus Inte</b> | rface |

|---------------------|----------|-----------------|-------|

|---------------------|----------|-----------------|-------|

÷

Table 2.3. 80186 (A) Bus Interface

| Pin<br>(Connector J1) | Signal                | Signal Description | Pin<br>(Connecto | Signal            | Signal Description                     |

|-----------------------|-----------------------|--------------------|------------------|-------------------|----------------------------------------|

|                       |                       |                    |                  |                   |                                        |

| J1.065<br>J1.066      | A/MA23 }<br>A/MA.22 } |                    | J1.088<br>J1.029 | A/RawCLK<br>A/CLK | 16 MHz clock<br>8 MHz clock (not used) |

| J1.068                | A/MA.22 }             | A-bus              | J1.029<br>J1.161 | A/CLK<br>A/Reset' | System reset                           |

| J1.069                | A/MA.20               | Mapped Address     | J1.101           | A/Reset MPB'      | System reset                           |

| J1.071                | A/MA.19 }             | mapped Address     | J1.103           | A/Halt'           |                                        |

| J1.072                | A/MA.18 }             |                    | J1.041           | A/S0'             | A-bus status line                      |

| J1.074                | A/MA.17               |                    | J1.038           | A/S1'             | A-bus status line                      |

| J1.075                | A/A.16B               |                    | J1.035           | A/S2'             | A-bus status line                      |

| 01.010                | 1211100 1             |                    | J1.017           | A/ALE'            | Address Latch Enable                   |

|                       |                       |                    | J1.005           | A/DT/R'           | A Bus Data                             |

|                       |                       |                    | 01.000           |                   | Transmit/Receive                       |

| J1.036                | A/A.23 }              |                    |                  |                   |                                        |

| J1.039                | A/A.22                |                    | J1.008           | A/DEN'            | Data Enable                            |

| J1.042                | A/A.21                | A-bus              | J1.020           | A/IOPMemWr'       | Memory Write                           |

| J1.045                | A/A.20                | Address line       | J1.054           | A/IOW             | IO Write                               |

| J1.034                | A/A.19                |                    | J1.056           | A/IOPMemRd'       | Memory Read                            |

| J1.037                | A/A.18                | 2                  | J1.048           | A/IOR'            | IO Read                                |

| J1.040                | A/A.17                |                    | J1.044           | A/BHE'            | Byte High Enable                       |

| J1.043                | A/A.16 }              |                    | J1.097           | A/MPIntIOP'       | Mesa processor interrupts              |

|                       | ,                     |                    |                  |                   | IOP, A-bus←Mesa                        |

| J1.006                | A/AD.15 }             |                    | J1.094           | A/IOPIntMP'       | IOP interrupts Mesa.                   |

| J1.009                | A/AD.14               | Multiplexed        |                  |                   | Mesa ← A-bus                           |

| J.1012                | A/AD.13               | Address/Data       | J1.046           | A/UCS'            | Upper Chip Select                      |

| J1.015                | A/AD.12               | line, A-bus        |                  |                   | Edu • • Electron Electron (1997)       |

| J1.018                | A/AD.11               | Address line,      |                  |                   |                                        |

| J1.021                | A/AD.10               | bidirectional data |                  |                   |                                        |

| J1.024                | A/AD.09 }             |                    |                  |                   |                                        |

| J1.027                | A/AD.08 }             |                    |                  |                   |                                        |

| J1.004                | A/AD.07 }             |                    |                  |                   |                                        |

| J1.007                | A/AD.06 }             |                    |                  |                   |                                        |

| J1.010                | A/AD.05 }             | 1                  |                  |                   |                                        |

| J1.013                | A/AD.04 }             |                    |                  |                   |                                        |

| J1.016                | A/AD.03 }             |                    |                  |                   |                                        |

| J1.019                | A/AD.02 }             |                    |                  |                   |                                        |

| J1.022                | A/AD.01 }             |                    |                  |                   |                                        |

| J1.025                | A/AD.00 }             |                    |                  |                   |                                        |

\_\_\_\_\_

ī.

-

ţ

2

# 2.1.3 Power

Power consumption estimates for the Mesa Processor Board are: Typical 8.187 A (40.94 W) max. 12.318 A (61.59 W) Average = <u>Typical + Max</u>

$$= 10.253 \text{ A} (51.26 \text{ W})$$

Table 2.4 lists power interface connections.

Note: For detailed dc power distribution, please see Section 1.3.

| RAW 5v | J1.030 | GND J1.002 | GND J1.092 |  |

|--------|--------|------------|------------|--|

|        | J1.090 | J1.011     | J1.093     |  |

|        | J1.112 | J1.026     | J1.121     |  |

|        | J1.113 | J1.028     | J1.122     |  |

|        | J1.114 | J1.031     | J1.123     |  |

|        | J1.115 | J1.032     | J1.124     |  |

|        | J1.116 | J1.033     | J1.125     |  |

|        | J1.117 | J1.047     | J1.126     |  |

|        | J1.118 | J1.061     | J1.127     |  |

|        | J1.119 | J1.062     | J1.128     |  |

|        | J1.120 | J1.063     | J1.129     |  |

|        |        | J1.077     | J1.137     |  |

|        |        | J1.083     | J1.151     |  |

|        |        | J1.085     | J1.152     |  |

|        |        | J1.089     | J1.153     |  |

|        |        | J1.091     | J1.158     |  |

|        |        |            | J1.164     |  |

Table 2.4. Power Interface

# 2.1.4 Clock Generation

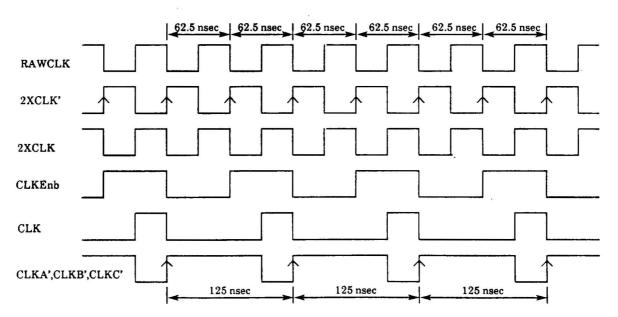

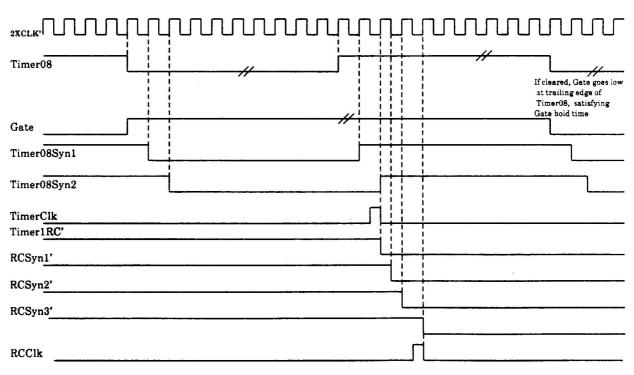

Figure 2.3 illustrates the relationship of the generated clocks to the system clock.

Figure 2.3. Internally generated clocks

2.044

¥

# 2.2 Microinstructions

Dove microcode implements Mesa bytecodes, as defined by the Mesa Processor Principles of Operation. The microcode does not control I/O devices, which are controlled by the IOP, an Intel 80186 microprocessor.

The microcode resides in RAM control store. The Mesa processor interprets control store through one of two devices: a microinstruction decoder gate array chip (MDC), and a microinstruction register (MIR). Control store is written by the IOP; the IOP also reads control store, but only the next instruction and only 8 bits at a time. During booting or debugging, the IOP can load microcode into control store, initialize the microcode program counter, and start and stop Mesa processor execution.

Microcode source files consist of lists of microinstructions, assembler macros, and comments. Microinstructions consist of a list of one or more phrases. (Refer to the examples at the end of this subsection.)

In this and subsequent sections discussing microinstructions, the following symbols are used:

- $\sim$  logical complement

- $\leftarrow$  assignment

- " (double comma) concatenation.

# 2.2.1 Hardware

Microinstruction hardware is described in section 2.3 titled "Control Architecture."

### 2.2.2 Theory of Operations

Up to 8K microinstructions can be written into (or read from) the control store RAM by the IOP.

Each microinstruction is decoded and executed in 125 nanoseconds, or one cycle. Microinstructions are not pipelined over several cycles, except that while one microinstruction is being executed, its successor is being read from control store.

Cycles are enumerated in c1, c2, and c3 order, and then c1 again. The sequence is never interrupted or altered. Consequently, both targets of a two-way branch must be specified with the same cycle number. (Strictly speaking, this is necessary only if the target microinstructions contain cycle-dependent operations.)

Three successful cycles, c1, c2, and c3, are grouped into one click. Five consecutive clicks (numbered 0..4) are grouped into a round. Each click of a round is permanently allocated to one or more of the I/O controllers. If an I/O controller does not request the service of its corresponding task microcode, the emulator microcode task runs during that click instead.

Microinstruction alignment, so that microinstructions execute in successful cycles, is, therefore, a necessary outcome of the fixed-task click structure. Moreover, when one desires code which is speed

÷

1

optimized, this structure requires the elimination of three microinstructions instead of one.

Look-ahead decoding of microinstructions is done in the MDC for the function fields fS, fX, fY, and fZ. The raw MIR stores the entire microinstruction except the Immediate Next Instruction Address (pINIA) field and the fS field.

The pINIA field, together with the branching logic, generates the Next Instruction Address inputs (pNIA) to the Next Instruction Address register.

### 2.2.3 Programmer Interface

Microinstructions are executed from a 4K by 48-bit, writable control store. Each 48-bit microinstruction contains the 12-bit address of the next instruction. Throughout this section, the subsections titled "Programmer Interface" are described in terms of microinstructions. Microinstruction examples in subsection 2.2.3.2 illustrate how certain elementary functions are accomplished.

Refer to <u>Daybreak Microcode Reference Manual</u> for detailed microcode instructions.

# 2.2.3.1

# Microinstruction

Format

Frequently applied operations are encoded in the smallest number of bits, and most of the important Mesa Emulator operations execute in one click.

The three major parts of a 48-bit microinstruction are: 1) the 2901 control bits (bits 0 through 15); miscellaneous function bits (bits 16-35); and the 'goto' address field (bits 36-47).

<u>2901 control bits</u> occupy the first word. They control the R register ports A and B, and specify ALU source address, function, and destination address.

<u>Miscellaneous function</u> fields control carry input, enable the stack and U registers, specify a memory operation, and specify functions (fX, fY, and fZ).

The fS field controls the decoding of the fY and fZ function fields:

Depending on fS0-1, fY field can

• specify a miscellaneous function (fYNorm)

• name a branch or multi-way dispatch (DispBr)

• name an I/O register to be loaded (IOOut)

• equal the high nibble of an 8-bit constant (Byte)

Depending on fS3-4, fZ field can

• specify a miscellaneous function (fZNorm)

- equal the low half of a U register address (Uaddr)

- name an I/O register to be read (IOXIn)

- equal a 4-bit constant or the low half of an 8-bit constant (Nibble)

The <u>'Goto' address</u>, INIA, occupies 12 bits and specifies a control store address unless the previous microinstruction specifies condition bits. Condition bits are ORed into INIA, resulting in a branch or dispatch. Thus, every microinstruction is a potential jump instruction. Figure 2.4 illustrates the microinstruction format and describes the fields and subfields.

| 00                                       | 04                                                                          | 4 0                                                                                                                                                                                        | 8 1                                                                                   | 1                                                        | 14                     | 16 20                              | 0                                      | 24                                                                                   | 2                                      | 8 ;        | 32                                                               | 36                                                                        | -                                                                    | 47                                                   |

|------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------|------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------|------------|------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------|

| rA                                       |                                                                             | rB                                                                                                                                                                                         | aS                                                                                    | aF                                                       | aD                     | <del>eP</del> ,Cin,<br>enU,<br>mem | เร                                     |                                                                                      | fX                                     | fY         | f                                                                | Z                                                                         | INIA                                                                 |                                                      |

| eP<br>Cin<br>mem<br>fS<br>fX<br>fY<br>fZ | 290<br>290<br>290<br>290<br>Eve<br>290<br>MA<br>Fun<br>X fu<br>Y fu<br>Z fu | <u>Descri</u><br>1 A reg add<br>1 B reg add<br>1 ALU sou<br>1 ALU sou<br>1 ALU des<br>mparity<br>1 Carry in,<br>$R \leftarrow (if c1),$<br>ction field<br>inction<br>nction<br>t instructi | dr, U ad<br>lr, RH a<br>rce oper<br>ction<br>ination/<br>shift er<br>MDR←<br>selector | addr<br>rand pai<br>shift con<br>nds, writ<br>(if c2), s | ir<br>ntrol<br>te U(if |                                    | A,Q<br>A,B<br>0,Q<br>0,B<br>0,A<br>D,A | II     aF       II     0       II     1       II     3       II     5       II     6 | R+S<br>S-R<br>0,Q<br>0,B<br>0,A<br>D,A | 11         | ntrol B<br><u>sh.,aD</u><br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | its<br>r[rB]<br>no write<br>no write<br>F<br>F/2<br>F/2<br>2F<br>2F<br>2F | Q←<br>F<br>no write<br>no write<br>Q/2<br>no write<br>2Q<br>no write | <u>Ybus←</u><br>F<br>F<br>F<br>F<br>F<br>F<br>F<br>F |

|                                          |                                                                             |                                                                                                                                                                                            |                                                                                       |                                                          |                        |                                    | D,Q<br>D,0                             | اا <sub>7</sub><br>_اد _                                                             | D,Q<br>D,0                             | <br>       |                                                                  |                                                                           |                                                                      |                                                      |

|                                          |                                                                             |                                                                                                                                                                                            |                                                                                       |                                                          | F                      | unction Fi                         | eld Sele                               | ector a                                                                              | and Fu                                 | nction Fie | elds                                                             |                                                                           |                                                                      |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             | $\frac{fY}{DispBr}$ $\frac{fYNorm}{fQUut}$ $Byte^{*}$ $11] \leftarrow 0.$ $15] \leftarrow fY, fZ$                                                                                                                                                                                                                                                           | 3 IOXI<br>• X[0-11]←0,                                                                                                                                                                        | rm 0,,st<br>le* 0,,st<br>lr[4-7] rA,,<br>n rA,, | fZ   rA,,                                                                                                                                                                                                                                                | Y[12-15]** if fZ<br>Y[12-15]** if fZ                                                                                                                         | Z = AltUaddr**<br>Z = AltUaddr**<br>us µinstruction                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| $\begin{array}{rcrc} \underline{fXNorm} \\ 0 & pCall/Ret0^{\bullet} \\ 1 & pcall/Ret1^{\bullet} \\ 2 & pCall/Ret2^{\bullet} \\ 3 & pCall/Ret3^{\bullet} \\ 4 & pCall/Ret3^{\bullet} \\ 4 & pCall/Ret5^{\bullet} \\ 5 & pCall/Ret6^{\bullet} \\ 7 & pCall/Ret7^{\bullet} \\ 8 & Noop \\ 9 & RH \leftarrow \\ A & shift(shiftX) \\ B & cycle(cycleX) \\ C & Cin \leftarrow pc16 \\ D & Map \leftarrow, or \\ (MapRefX) \\ E & pop(popX) \\ F & push(pushX) \\ \end{array}$ | 0112<br>  123456789 ABCD EF | $\begin{array}{l} \underline{fYNorm} \\ \underline{fYNorm} \\ ClrMPIntIOP \\ SetMPIntIOP \\ ClrIntErr \\ (ClrIntTrap) \\ IBDisp \\ MesaIntRq \\ stackP \leftarrow \\ IB \leftarrow \\ cycle (cycle Y) \\ Noop \\ Map \leftarrow , or \\ (MapRefY) \\ MAPA \leftarrow \\ push (push Y) \\ IO \leftarrow \\ Bank \leftarrow \\ ClrIE \\ SetIE \\ \end{array}$ | DispBr<br>NegBr<br>ZeroBr<br>NZeroBr<br>MesaIntBr<br>PgCarryBr<br>CarryBr<br>XRefBr<br>NibCarryBr<br>XDisp<br>YDisp<br>XC2npcDisp<br>XWt0KDisp<br>XWt0KDisp<br>XHDisp<br>XLDisp<br>PgDr0vDisp | I0 <b>←</b>                                     | I 1<br>I 2<br>I 3<br>I 4<br>I 5<br>I 6<br>I 7<br>I 8<br>I 7<br>I 8<br>I 6<br>I 7<br>I 8<br>I 7<br>I 8<br>I 7<br>I 8<br>I 7<br>I 8<br>I 7<br>I 8<br>I 7<br>I 8<br>I 7<br>I 7<br>I 8<br>I 7<br>I 8<br>I 7<br>I 7<br>I 7<br>I 7<br>I 7<br>I 7<br>I 7<br>I 7 | <u>fZNorm</u><br>IBPtr←1<br>IBPtr←0<br>Cin←pc16<br>pop (popZ)<br>push (pushZ)<br>AltUaddr<br>Noop<br>ClrLOCK<br>SetLOCK<br>LRot0<br>LRot12<br>LRot8<br>LRot4 | IOXIn<br>←ExtStat<br>IO←<br>←DebB<br>←IntStat<br>←ErrnIBnStkp (Misc)<br>←RH<br>←ibNA<br>←ib<br>←ib<br>HIgh |

Figure 2.4. Microinstruction format and subfield formats

2

1

--

Central Processor

2-10

# 2.2.3.2 Microinstruction Examples

The Central Processor hardware should be viewed in light of its corresponding microcode. The following four examples of microcode illustrate how and in what time frame certain elementary functions are accomplished. See the <u>Daybreak Microcode Reference Manual</u> for a description of the microcode format.

(1) The Mesa Emulator Load Local 1 (LL1) macroinstruction indexes the local frame pointer and then pushes the addressed word from memory onto the Stack. If the indexing operation does not cross a page boundary, then the microinstruction executes in one click. If a page cross occurs, then the microinstruction executes in three clicks. If the Map flags must be updated (RMapFix), then another two clicks are required.

@LL1: MAR  $\leftarrow Q \leftarrow [rhL, L+1], L1 \leftarrow L1.PopDec, push, c1, opcode(1'b);LLn:STK <math>\leftarrow$  TOS, PC  $\leftarrow$  PC + PC16, IBDisp, L2  $\leftarrow$  L2.LL, BRANCH(LLa, LLb, 1), c2;LLa:TOS  $\leftarrow$  MD, push, fZpop, DISPNI(OpTable), c3;LLb:Rx  $\leftarrow$  UvL, c3;

LSMap: Noop, c1;  $Q \leftarrow Q \cdot Rx$ , L2Disp, c2;  $Q \leftarrow Q$  and 0FF, RET(LSRtn), c3;

LLMap: Map  $\leftarrow Q \leftarrow [rhMDS, Rx + Q], c1, at[3,10,LSRtn];$ Noop, c2;  $Rx \leftarrow rhRx \leftarrow MD, XRefBr, c3;$ MAR  $\leftarrow [rhRx, Q + 0], L0 \leftarrow L0.R, BRANCH[RMUD,$], c1;$

IBDisp, GOTO[LLa], c2; RMUD: CALL[RMapFix], c2;

(2) The Mesa Emulator Read 1 (R1) macroinstruction indexes the virtual address on the top of stack and then pushes the addressed word from memory onto the stack. The microinstruction executes in two clicks. If the page has been read for the first time, then four clicks are required; that is, the Map flags must be updated.

@R1: Map ← Q ← [rhMDS, TOS + 1], L1 ← L1.Dec, pop, c1, opcode[101'b]; push, PC ← PC + PC16,c2; Rx ← rhRx ← MD, XRefBr, c3;

Į,

٢

$MAR \leftarrow [rhRx, Q + 0], L0 \leftarrow L0.R, BRANCH[RMUD, \$], \quad c1;$ IBDisp, GOTO[LLa], c2; (3) The Mesa Emulator Jump 2 (J2) macroinstruction increments the program counter by 2 bytecodes and then refills the instruction buffer. The microinstruction executes in two clicks. If the jump crosses a page boundary, then five clicks are required.

@J2: MAR ← PC ← [rhPC, PC + 1], push, c1,opcode[201b]; STK ← TOS, L2 ← L2.Pop0IncrX, Xbus←0, XC2npcDisp, DISP2[jnPNoCross], c2;

jnPNoCross:  $IB \leftarrow MD$ , pop, DISP4[JPtr1Pop0, 2], c3, at[0,4,jnPNoCross]; jnP1Cross:  $Q \leftarrow 0FF + 1$ ,  $L0 \leftarrow L0.JRemap$ , CANCELBR[UpdatePC, 0F], c3, at[2,4,jnPNoCross];

(4) The Mesa Emulator instruction buffer <u>refill</u> code executes in one click if the buffer was not empty. If the buffer was empty, then two clicks are required. If the refill occurs across a page boundary, then four to six clicks are required

{Buffer Empty Refill. Control goes from NoRCross to RefillNE since RefillE + 1 does not contain an IBDisp.}

RefillE: MAR  $\leftarrow$  [rhPC, PC], PC  $\leftarrow$  PC-1, L0  $\leftarrow$  L0.ERefill, c1, at[400]; PC  $\leftarrow$  PC + 1, DISP2[NoRCross], c2;

{Buffer Not Empty Refill.}

OpTable: {"Noop" location of Instruction Dispatch table} RefillNE:MAR ← [rhPC, PC + 1], c1, at[500]; AlwaysIBDisp, L0 ← L0.NERefill.Set, DISP2[NoRCross], c2;

NoRCross:  $IB \leftarrow MD$ , uPCCross  $\leftarrow 0$ , DISPNI[OpTable], c3, at[0,4,NoRCross]; RCross:  $Q \leftarrow 0FF + 1$ , GOTO[UpdatePC], c3, at[2,4,NoRCross];

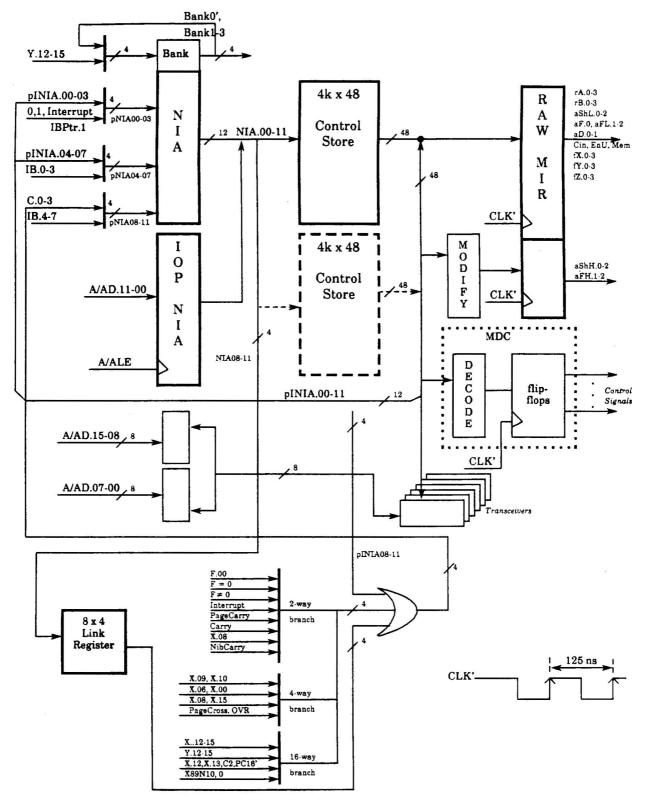

# 2.3 Microinstruction Control Architecture

Microinstructions are loaded into control store from the IOP via data transfer on the 80186 bus. During the execution of a program, microinstructions are read from control store RAM and stored in the Raw Microinstruction register, except for the pINIA field and the pfS field.

The pINIA field, together with the branching logic, generates the pNIA inputs to the Next Instruction Address register.

The encoded pfS, pfX, pfY, and pfZ fields are fed to the MDC, decoded into instruction commands, and stored in corresponding command registers in the MDC.

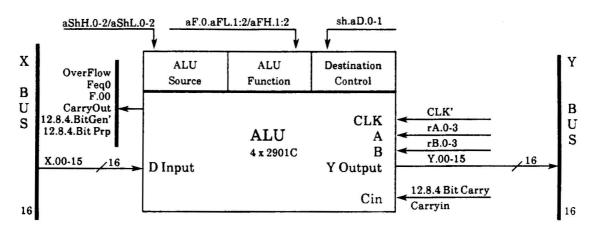

Because the Mesa processor is split into lower and upper bytes with no propagated carry, the paS and paF fields are modified to provide separate aShL and aFL for the low byte and aShH and aFH for the high byte.

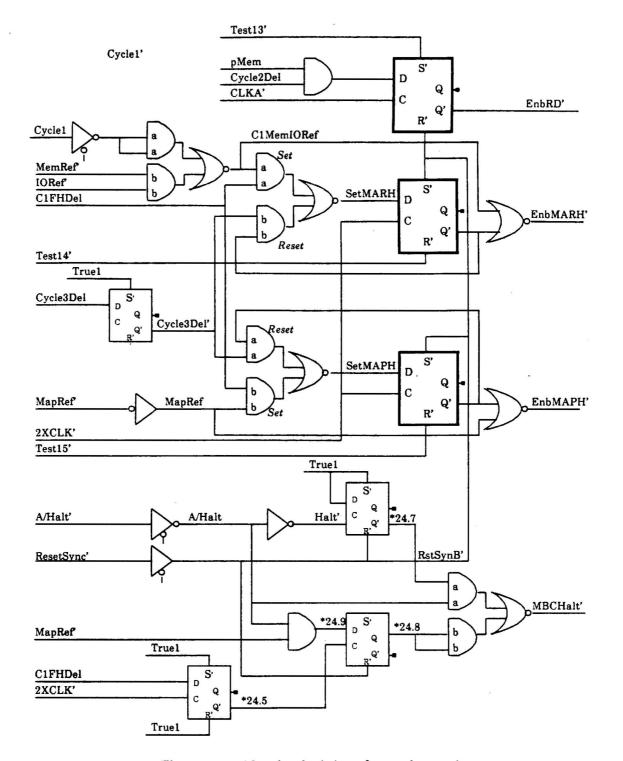

Figure 2.5 illustrates microinstruction control architecture.

ł

3

### 2.3.1 Hardware

Control hardware described below consists of the control store, the control store interface, the Microinstruction Decoder Chip (MDC), and the MicroInstruction Register (MIR). Other control hardware, consisting of the interface to the IOP, miscellaneous support logic, the trap machine, and MInt and Link registers, is described elsewhere.

### 2.3.1.1 **Control Store**

Two banks, each consisting of twelve 4K x 4 static RAM chips with a 55 ns access time, make up the 4K x 48 writable control store, expandable to 8K x 48. Figure 2.6 illustrates the control store pins and signals. For signal functions, refer to Figure 2.4, illustrating microinstruction format.

|        | 1                             | ÷  |                                                                      |                                                                                    |                                                                   |                                                                                                     |                                                                                           |                                                                                            |                      |

|--------|-------------------------------|----|----------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------|

| NIA.00 |                               | 16 | A11                                                                  | I/04                                                                               | 12                                                                | (CSnn)*                                                                                             | • (•                                                                                      | •)                                                                                         |                      |

| NIA.01 |                               | 17 | A10                                                                  | L/O3                                                                               | 13                                                                | (CS nn)                                                                                             | (*                                                                                        | *)                                                                                         |                      |

| NIA.02 |                               | 18 | A9                                                                   | I/O2                                                                               | 14                                                                | (CS nn)                                                                                             | (*                                                                                        | *)                                                                                         |                      |

| NIA.03 |                               | 19 | A8                                                                   | I/O1                                                                               | 15                                                                | (CS nn)                                                                                             | (*                                                                                        | *)                                                                                         |                      |

| NIA.04 |                               | 1  | A7                                                                   |                                                                                    |                                                                   |                                                                                                     |                                                                                           | ÷                                                                                          |                      |

| NIA.05 |                               | 2  | A6                                                                   |                                                                                    |                                                                   |                                                                                                     |                                                                                           |                                                                                            |                      |

| NIA.06 |                               | 3  | A5                                                                   | WE'                                                                                | 11                                                                |                                                                                                     | C                                                                                         | ntStWE                                                                                     | n <i>n'**</i>        |

| NIA.07 |                               | 4  | A4                                                                   | CS'                                                                                | 9                                                                 |                                                                                                     | B                                                                                         | ank0' (c                                                                                   | )r                   |

| NIA.08 |                               | 5  | A3                                                                   |                                                                                    |                                                                   |                                                                                                     | B                                                                                         | anki')                                                                                     |                      |

| NIA.09 |                               | 6  | A2                                                                   |                                                                                    |                                                                   |                                                                                                     | _                                                                                         | _                                                                                          |                      |

| NIA.10 |                               | 7  | A1                                                                   |                                                                                    |                                                                   | here nn =<br>n 00-47 se                                                                             |                                                                                           |                                                                                            |                      |

| NIA.11 |                               | 8  | A0                                                                   |                                                                                    | exa                                                               | mple, 12 i<br>s CS02, 15                                                                            | s CS00,                                                                                   | 13 is CS                                                                                   | 501,                 |

|        | As above (NIA.00:1<br>for all | 1) | II<br>CS<br>0-3<br>4-7<br>8-1<br>12-<br>20-3<br>24-3<br>28-3<br>32-4 | 7 I/<br>is I/<br>is P<br>7 P<br>11 pa<br>15 pa<br>19 pl<br>23 pf<br>31 pf<br>35 pf | 04<br>s<br>rA.0<br>rB.0<br>aF.1<br>EP<br>S.0<br>X.0<br>Y.0<br>Z.0 | L/O3<br>is<br>prA.1<br>prB.1<br>paS.1<br>paS.1<br>paF.2<br>pCin<br>pfS.1<br>pfX.1<br>pfY.1<br>pfZ.1 | rHEN<br>J/O2<br>is<br>prA.2<br>prB.2<br>psS.2<br>paD.0<br>pEnU<br>pfS.2<br>pfY.2<br>pfY.2 | I/O1<br>is<br>prA.3<br>prB.3<br>paF.0<br>paD.1<br>pMem<br>pfS.3<br>pfX.3<br>pfX.3<br>pfZ.3 | 2'<br>3'<br>3'<br>4' |

|        |                               |    |                                                                      | 35 pf                                                                              | <b>Z</b> .0                                                       |                                                                                                     | •                                                                                         | •                                                                                          | •                    |

|        |                               |    | 10                                                                   |                                                                                    | **** *                                                            | A 4 A #                                                                                             | ~ ~                                                                                       | ~ -                                                                                        |                      |

Figure 2.6. Writable control store pins and signals

40-43

44-47

p.INIA.04 .05

Y

p.INIA.08' .09'

.06

.10'

.07 5' 5'

.11'

# 2.3.1.2 **Control Store** Interface

The control store interface consists of a bank register, address registers, and supporting logic. Table 2.5 summarizes control store interface signals.

| Interface to:                  | Signal                                                                                                                                                                                                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Store                  | 1. CntStWE0'/1'<br>2. Bank0'/1/2/3<br>3. NIA.00-11                                                                                                                                                                   | <ol> <li>Control store Write Enable 0 (byte 0) and 1 (byte 1).</li> <li>Control store RAM bank select 0, 1, 2, 3.</li> <li>Next Instruction Address 00-11 - Control store RAM address.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Control store 00-03<br>04-07   | 4. prA.0-3<br>5. prB.0-3                                                                                                                                                                                             | <ol> <li>Pipelined microinstruction rA field.</li> <li>Pipelined microinstruction rB field.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 14-15                          | 6. paD.0-1                                                                                                                                                                                                           | 6. Pipelined microinstruction aD field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11-13                          | 7. paF.0-2                                                                                                                                                                                                           | 7. Pipelined microinstruction aF field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 08-10                          | 8. paS.0-2                                                                                                                                                                                                           | 8. Pipelined microinstruction aS field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

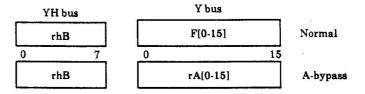

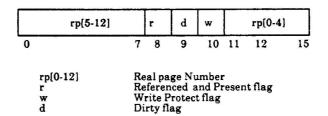

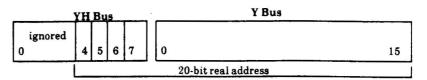

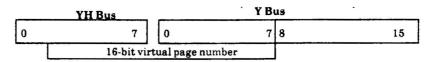

|                                | 9. CntStWE2'/3'                                                                                                                                                                                                      | 9. Control store Write Enable2 (byte 2) and 3 (byte 3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17                             | 10. pCin                                                                                                                                                                                                             | 10. Pipelined microinstruction CarryIn bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 18                             | 11. pEnU                                                                                                                                                                                                             | 11. Pipelined microinstruction Enable U register bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

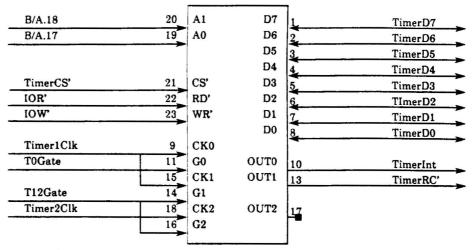

| 16                             | 12. pEP                                                                                                                                                                                                              | 12. Pipelined microinstruction Enable Parity bit (not used).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |