# **UNIX<sup>™</sup> MICROSYSTEM**

# WE® 32100 MICROPROCESSOR INFORMATION MANUAL

# MAXICOMPUTING IN MICROSPACE

451-000

## **UNIX<sup>™</sup> MICROSYSTEM**

# WE® 32100 MICROPROCESSOR INFORMATION MANUAL

451-000

#### ACKNOWLEDGEMENTS

Prepared and published by Document Development Organization – Microelectronics Projects Group AT&T Technologies, Inc., Morristown

for the

Microsystem Product Management AT&T Technologies, Inc.

and the

4516 Microsystems Laboratory AT&T Bell Laboratories, Holmdel

### A WORD ABOUT TRADEMARKS ...

The following trademarks are mentioned in this manual:

WE® 32100 Microprocessor

WE® 32101 Memory Management Unit

WE® 32102 Clock

WE® 321AP Microprocessor Analysis Pod

WE® 321DS Microprocessor Development System

WE® 321EB Microprocessor Evaluation Board

WE® 321SD Development Software Programs

WE® 321SE Software Evaluation Program

WE® 321SG Software Generation Programs

are registered trademarks of AT&T Technologies, Inc.

AT&T 3B20S Computers is a trademark of AT&T.

UNIX<sup>TM</sup> Operating System is a trademark of AT&T Bell Laboratories.

*PDP*<sup>TM</sup> 11/70 Computer and *VAX*<sup>TM</sup> 11/780 Computer are trademarks of Digital Equipment Corporation.

IBM<sup>®</sup> 370 Computer is a registered trademark of the IBM Corporation.

AT&T Technologies, Inc., reserves the right to make changes to the products(s) or circuit(s) described herein without notice. No liability is assumed as a result of their use or application. No right under any patent accompany the sale of any such product or circuit.

© 1985 AT&T Technologies, Inc. All Rights Reserved. Printed in the United States of America 104287958 IM232100CPU0115

January 1985

### WE® 32100 Microprocessor

### Information Manual

The information contained herein is subject to change.

•

#### FOREWORD

This manual contains information on the WE 32100 Microprocessor that is essential to computer designers, software architects, and system design engineers. The support software and development tools available simplify system integration for this complex 32-bit microprocessor. This issue contains a description of the version SVR2.0 of the WE 321SG Software Generation Programs.

Additional information is available in the form of data sheets, application notes, and on-line documentation from the UNIX Operating System.

For additional information contact your Sales Account Representative or call:

<sup>□</sup> AT&T and Associated Company sales: (215) 770-3204 or (CORNET) 8+624-3204.

To obtain additional copies of this manual, Select Code 451-000, call:  $\Box$  1-800-432-6600.

#### WE 32100 MICROPROCESSOR INFORMATION MANUAL

#### CONTENTS

#### **CHAPTER 1. INTRODUCTION**

| 1. I | Introduction                 | 1-1 |

|------|------------------------------|-----|

| 1.1  | Overview                     | 1-1 |

| 1.2  | Architecture                 | 1-2 |

| 1.3  | Instruction Set              | 1-4 |

| 1.4  | Operating System Support     | 1-4 |

| 1.5  | Software Generation Programs | 1-5 |

#### CHAPTER 2. ARCHITECTURE AND BUS OPERATION

| 2. WE 32100 MICROPROCESSOR OVERVIEW                                     | 2-1  |

|-------------------------------------------------------------------------|------|

| 2.1 USER REGISTERS                                                      | 2-3  |

| 2.1.1 General-Purpose Registers (r0-r8)                                 | 2-4  |

| 2.1.2 Frame Pointer                                                     |      |

| 2.1.3 Argument Pointer                                                  | 2-4  |

| 2.1.4 Processor Status Word                                             |      |

| 2.1.5 Stack Pointer                                                     | 2-7  |

| 2.1.6 Process Control Block Pointer                                     | 2-7  |

| 2.1.7 Interrupt Stack Pointer                                           | 2-7  |

| 2.1.8 Program Counter                                                   |      |

| 2.2 DATA HANDLING                                                       | 2-8  |

| 2.2.1 Data Types                                                        | 2-8  |

| 2.2.2 Data in Memory                                                    | 2-10 |

| 2.2.3 Memory Management                                                 | 2-10 |

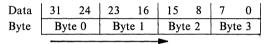

| 2.3 SIGNAL SAMPLING POINTS                                              | 2-11 |

| 2.4 READ AND WRITE OPERATIONS                                           | 2-12 |

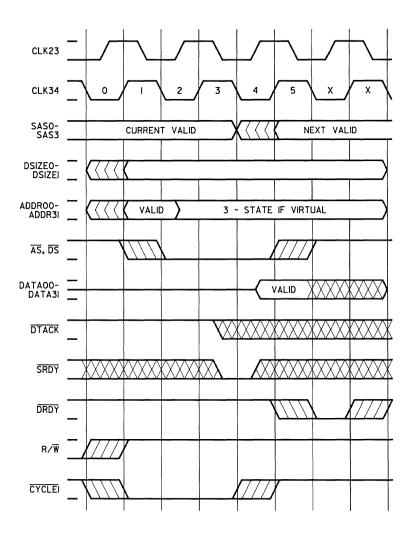

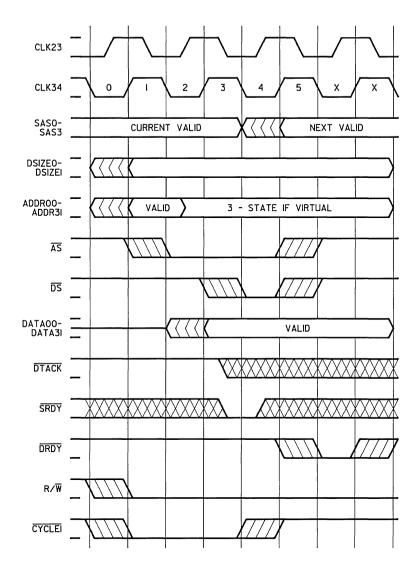

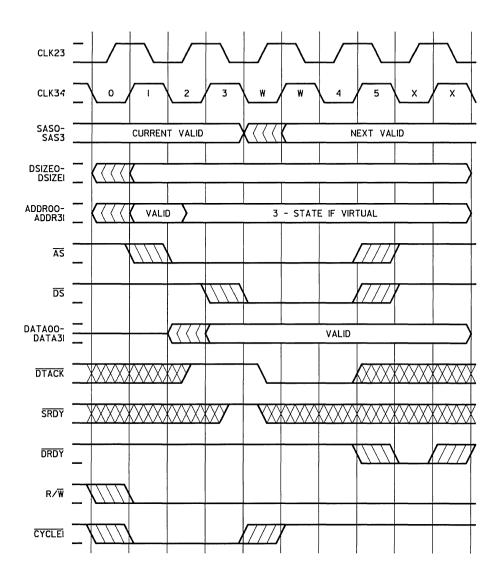

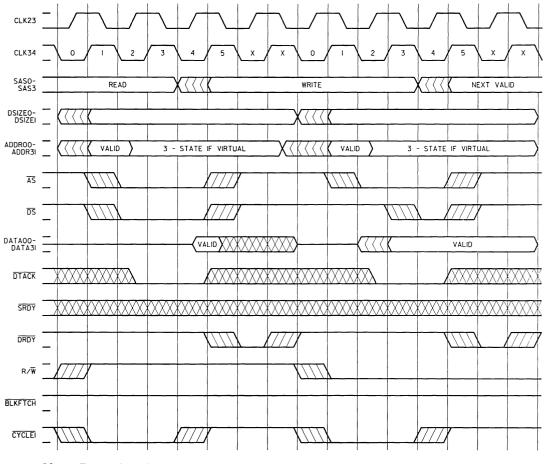

| 2.4.1 Read Transaction Using SRDY                                       | 2-13 |

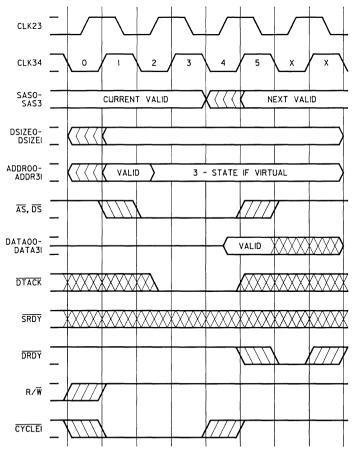

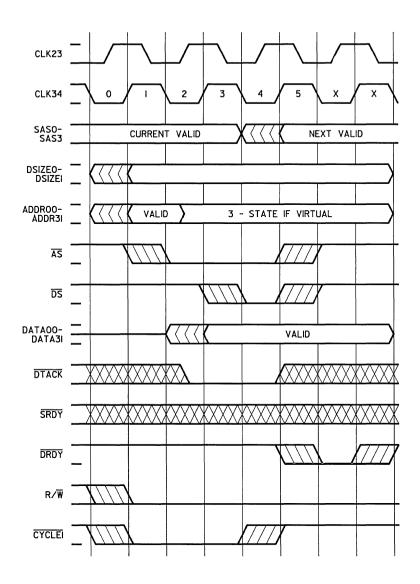

| 2.4.2 Read Transaction Using DTACK                                      | 2-15 |

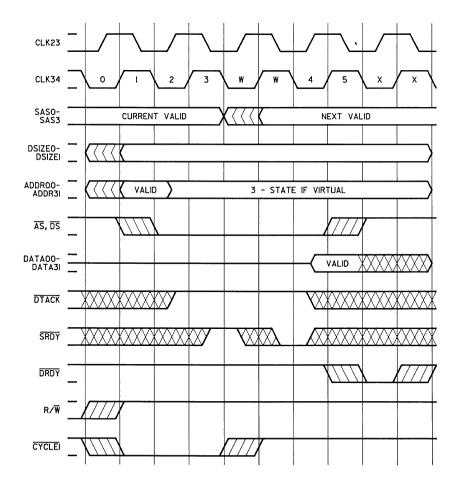

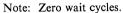

| 2.4.3 Read Transaction With Wait Cycle Using SRDY                       | 2-16 |

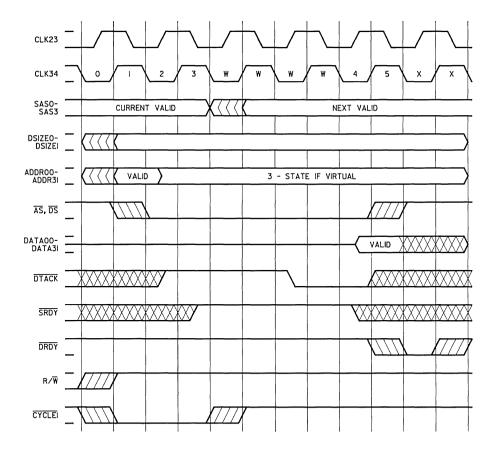

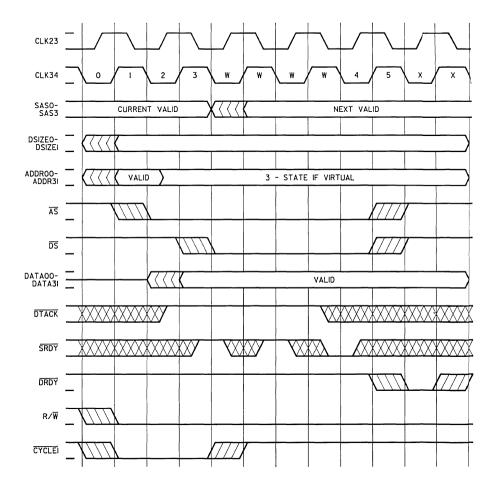

| 2.4.4 Read Transaction With Two Wait Cycles Using DTACK                 | 2-17 |

| 2.4.5 Write Transaction Using SRDY                                      |      |

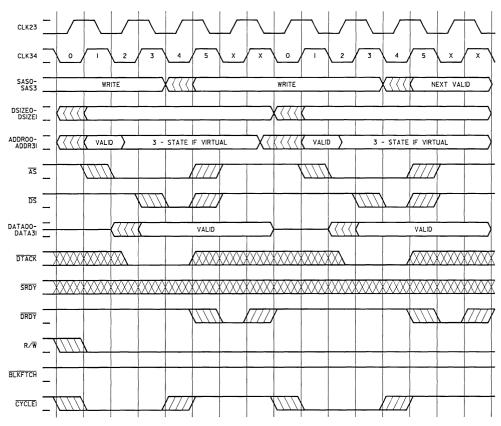

| 2.4.6 Write Transaction Using DTACK                                     | 2-18 |

| 2.4.7 Write Transaction With Wait Cycle Using SRDY                      | 2-18 |

| 2.4.8 Write Transaction With Wait Cycle Using DTACK                     | 2-22 |

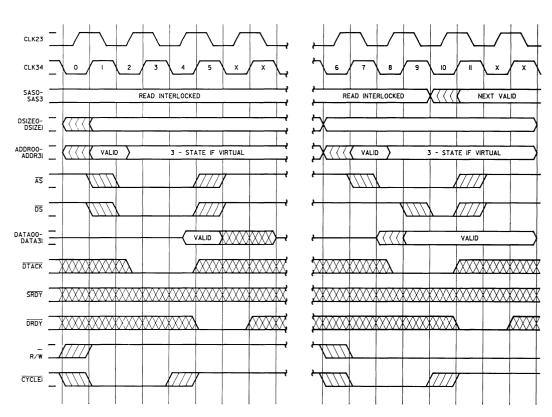

| 2.5 READ INTERLOCKED OPERATION                                          | 2-22 |

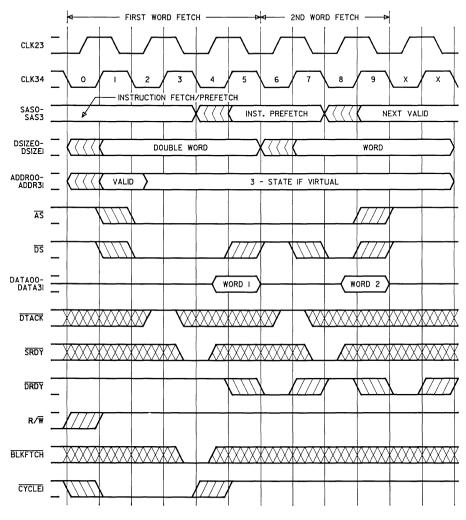

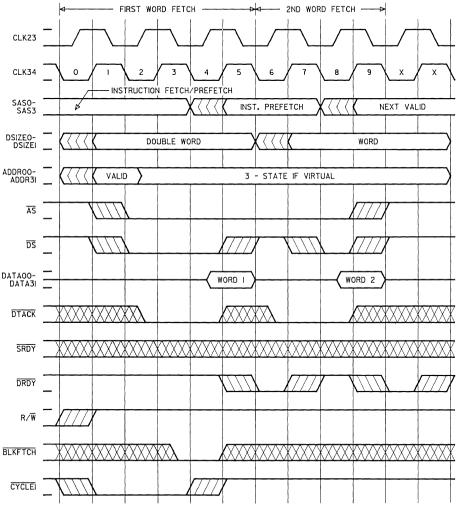

| 2.6 BLOCKFETCH OPERATION                                                | 2-25 |

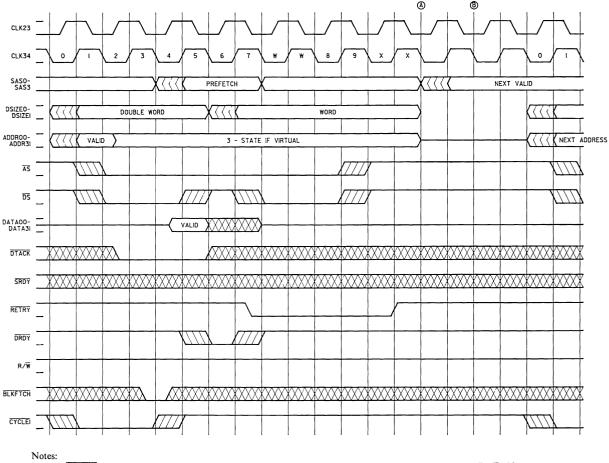

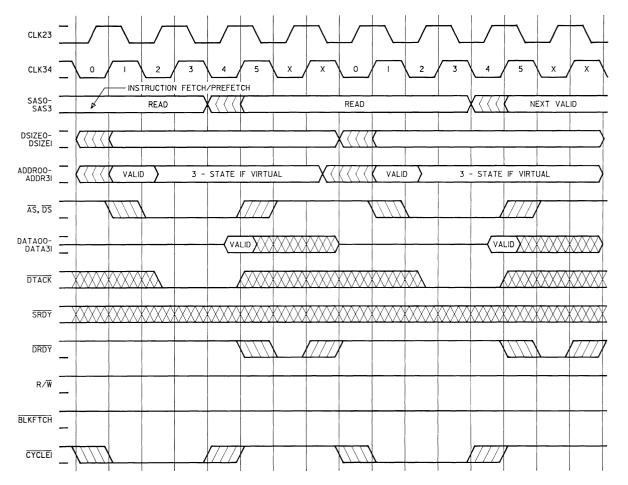

| 2.6.1 Blockfetch Transaction Using SRDY                                 | 2-25 |

| 2.6.2 Blockfetch Transaction Using DTACK                                | 2-27 |

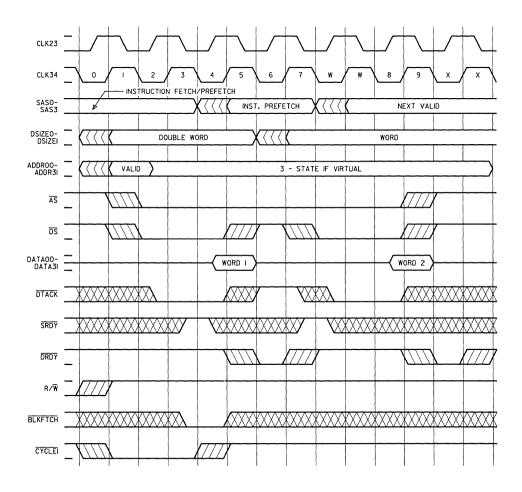

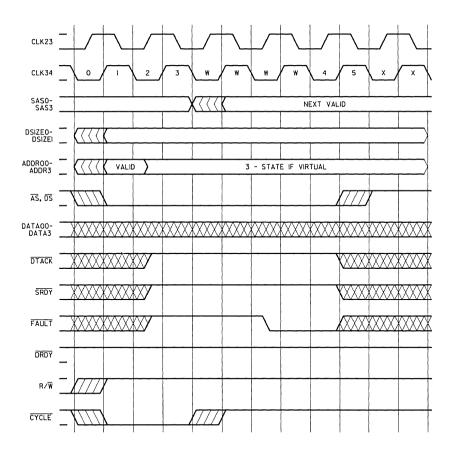

| 2.6.3 Blockfetch Transaction Using DTACK With Wait Cycle On Second Word | 2-28 |

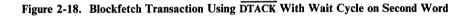

| 2.6.4 Blockfetch Transaction Using SRDY With Wait Cycles On Both Words  | 2-29 |

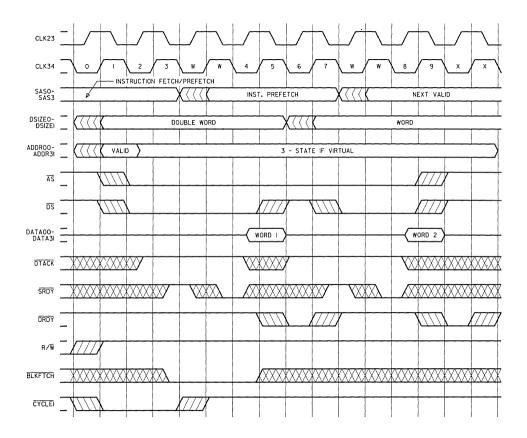

| 2.7 BUS EXCEPTIONS                                                      | 2-30 |

| 2.7.1 Faults                                                                 | 2-30   |

|------------------------------------------------------------------------------|--------|

| Fault With SRDY                                                              | 2-32   |

| Fault After DTACK                                                            |        |

| 2.7.2 Retry                                                                  | 2-34   |

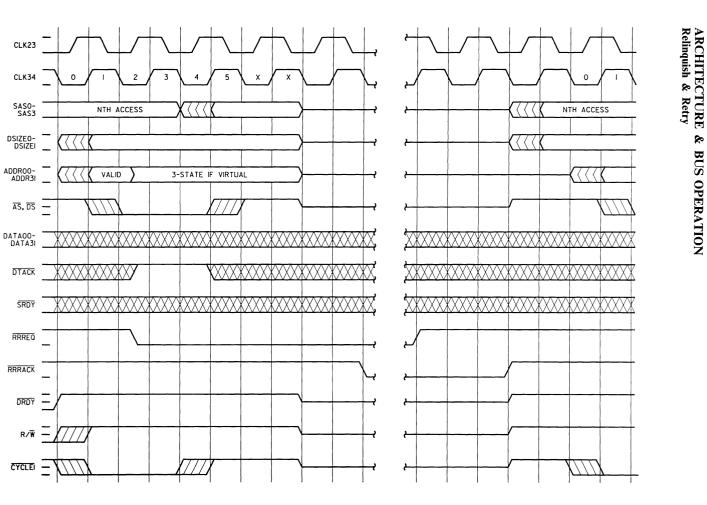

| 2.7.3 Relinquish and Retry                                                   | 2-34   |

| 2.8 BLOCKFETCH SPECIAL CASES                                                 | 2-37   |

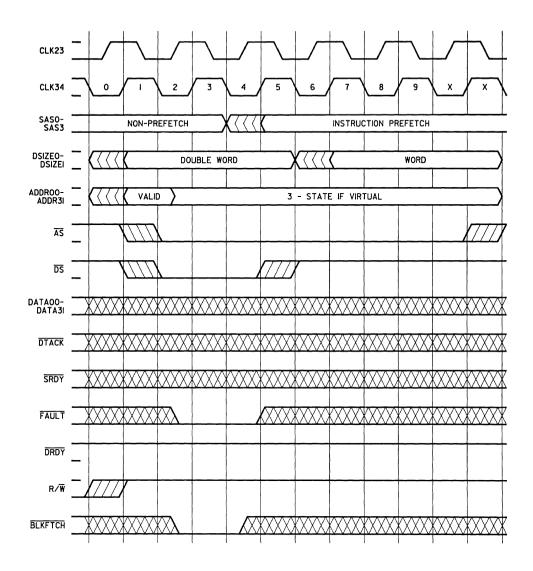

| 2.8.1 Fault on First Word of Blockfetch With Status Code Other Than Prefetch | 2-37   |

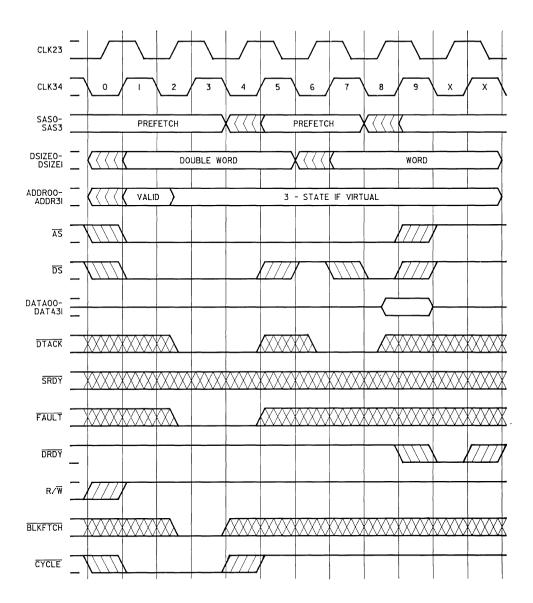

| 2.8.2 Fault on First Word of Blockfetch With Status of Prefetch              | 2-37   |

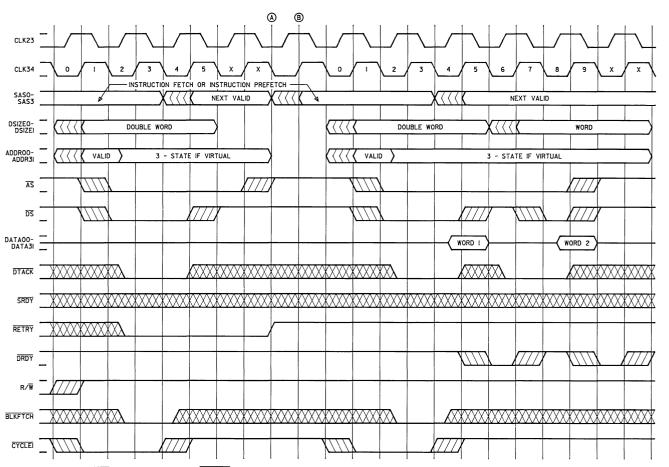

| 2.8.3 Retry on First Word of Blockfetch                                      | 2-37   |

| 2.8.4 Retry on Second Word of Blockfetch                                     | 2-37   |

| 2.8.5 Relinquish and Retry of Blockfetch                                     | 2-42   |

| 2.9 INTERRUPTS                                                               |        |

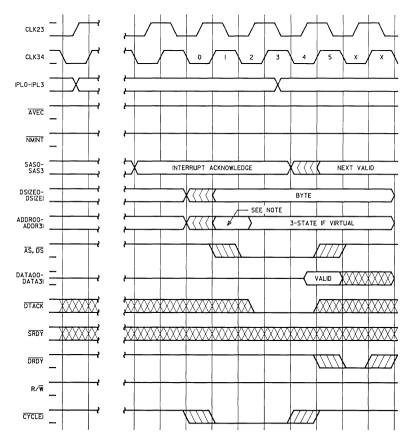

| 2.9.1 Interrupt Acknowledge                                                  | 2-42   |

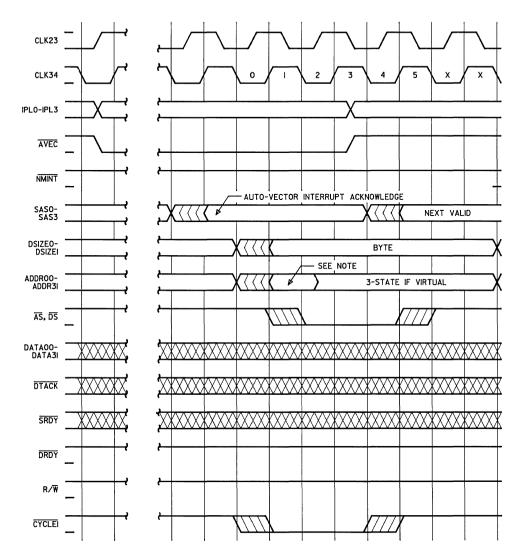

| 2.9.2 Auto-vector Interrupt                                                  | 2-45   |

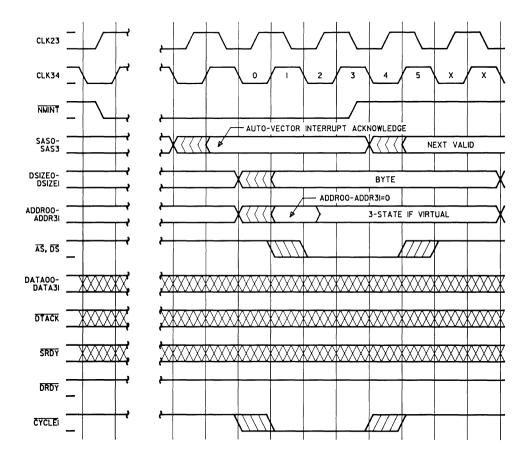

| 2.9.3 Nonmaskable Interrupt                                                  | 2-45   |

| 2.9.4 Quick Interrupt                                                        | 2-48   |

| 2.10 BUS ARBITRATION                                                         | 2-48   |

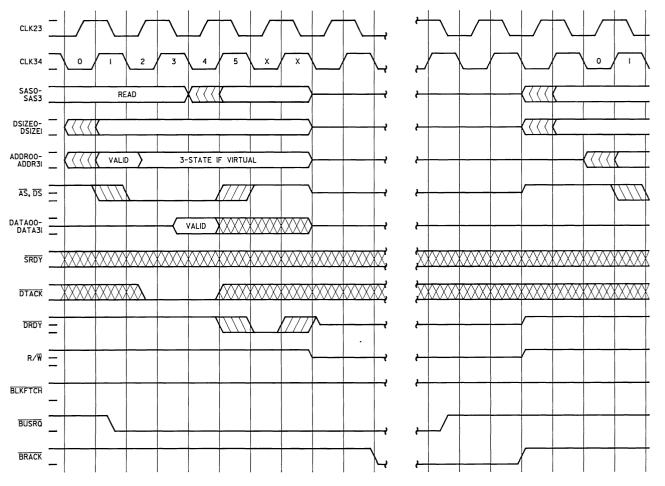

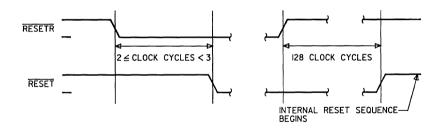

| 2.10.1 Bus Request During a Bus Transaction                                  | 2-48   |

| 2.10.2 DMA Operation                                                         | 2-51   |

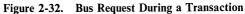

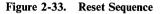

| 2.11 RESET                                                                   | 2-52   |

| 2.11.1 System Reset                                                          | 2-52   |

| 2.11.2 Internal Reset                                                        | 2-52   |

| 2.11.3 Reset Sequence                                                        | 2-54   |

| 2.12 ABORTED MEMORY ACCESSES                                                 | 2-54   |

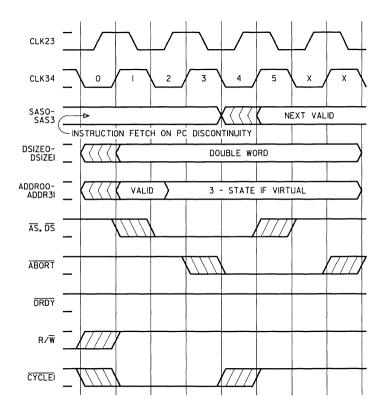

| 2.12.1 Aborted Access on PC Discontinuity With Instruction Cache Hit         | 2-55   |

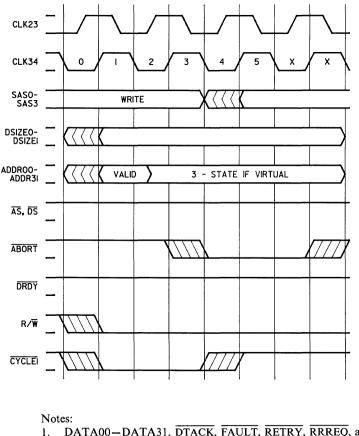

| 2.12.2 Alignment Fault Bus Activity                                          | 2-56   |

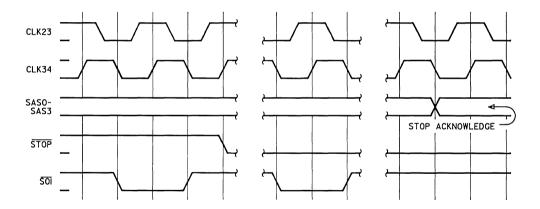

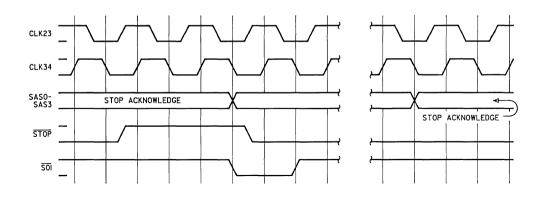

| 2.13 SINGLE-STEP OPERATION                                                   | 2-57   |

| 2.14 COPROCESSOR OPERATIONS                                                  | 2-58   |

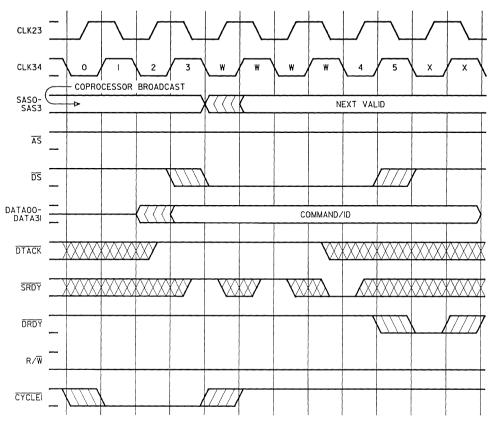

| 2.14.1 Coprocessor Broadcast                                                 | 2-58   |

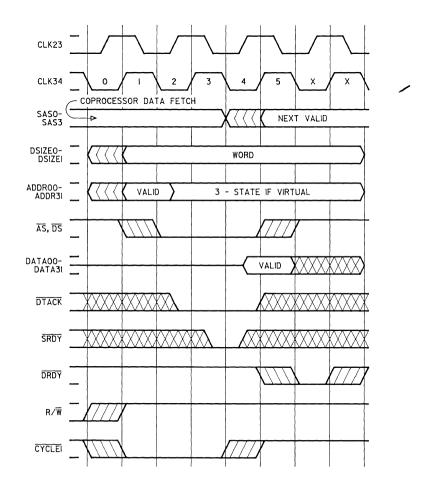

| 2.14.2 Coprocessor Operand Fetch                                             | 2-63 - |

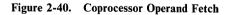

| 2.14.3 Coprocessor Status Fetch                                              | 2-64   |

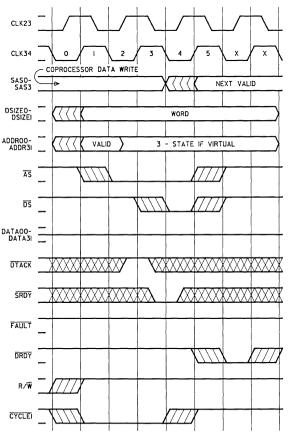

| 2.14.4 Coprocessor Data Write                                                | 2-65   |

| 2.15 EXCEPTIONAL CONDITIONS                                                  |        |

| 2.16 TRACE MECHANISM                                                         | 2-69   |

| 2.17 PIN ASSIGNMENTS                                                         |        |

| 2.18 MICROPROCESSOR OPERATING REQUIREMENTS                                   | 2-83   |

| 2.18.1 Electrical Requirements                                               | 2-84   |

| 2.18.2 Clocking Requirements                                                 | 2-85   |

| 2.18.3 Thermal Requirements                                                  | 2-85   |

| 2.19 SUPPLEMENTARY PROTOCOL DIAGRAMS                                         | 2-87   |

#### CHAPTER 3. INSTRUCTION SET AND ADDRESSING MODES

| 3. INSTRUCTION SET                  | 3-1 |

|-------------------------------------|-----|

| 3.1 DATA TYPES                      | 3-1 |

| 3.1.1 Sign and Zero Extension       | 3-3 |

| 3.2 REGISTERS                       | 3-3 |

| 3.2.1 Writing and Reading Registers | 3-6 |

| 3.3 INSTRUCTION FORMAT              | 3-6 |

| 3.3.1 Data Embedded in Operands     | 3-6 |

| 3.4 ADDRESS MODES                   | 3-6 |

|                                     |     |

| 3.4.1 | Absolute Address Modes                       |      |

|-------|----------------------------------------------|------|

|       | Absolute                                     | 3-10 |

|       | Absolute Deferred                            | 3-11 |

| 3.4.2 | Displacement Modes                           | 3-11 |

|       | Byte Displacement                            | 3-11 |

|       | Byte Displacement Deferred                   | 3-12 |

|       | Halfword Displacement                        | 3-12 |

|       | Halfword Displacement Deferred               | 3-13 |

|       | Word Displacement                            | 3-14 |

|       | Word Displacement Deferred                   | 3-14 |

|       | AP Short Offset                              | 3-15 |

|       | FP Short Offset                              |      |

| 3.4.3 | Immediate Modes                              | 3-16 |

|       | Byte Immediate                               | 3-16 |

|       | Halfword Immediate                           | 3-17 |

|       | Word Immediate                               | 3-17 |

|       | Positive Literal                             |      |

|       | Negative Literal                             | 3-18 |

| 344   | Register Modes                               |      |

| 5.1.1 | Register Mode                                | 3-19 |

|       | Register Mode Deferred                       |      |

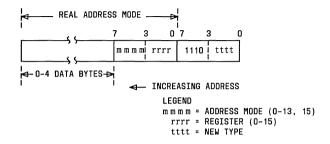

| 315   | Expanded-Operand Type Mode                   | 3-20 |

| 350   | CONDITION FLAGS                              | 3-20 |

| 26 5  | FUNCTIONAL GROUPS                            | 3-22 |

| 261   | Data Transfer Instructions                   | 3-23 |

| 262   | Arithmetic Instructions                      | 3-25 |

| 3.0.2 | Arithmetic Instructions                      | 3-23 |

| 3.0.3 | Logical Instructions                         | 3-26 |

| 3.6.4 | Program Control Instructions                 | 3-28 |

|       | Subroutine Transfer                          |      |

|       | Procedure Transfer                           |      |

| 3.6.5 | Coprocessor Instructions                     | 3-32 |

| 3.6.6 | Stack and Miscellaneous Instructions         | 3-32 |

|       | NSTRUCTION SET LISTINGS                      |      |

| 3.7.1 | Notation                                     |      |

|       | Assembler Syntax                             |      |

|       | Opcodes                                      |      |

|       | Operation                                    |      |

|       | Address Modes                                | 3-34 |

|       | Condition Flags                              | 3-34 |

|       | Exceptions                                   | 3-34 |

|       | Examples                                     | 3-34 |

|       | Notes (Optional)                             | 3-34 |

| 3.7.2 | Instruction Set Descriptions                 | 3-36 |

|       | Add (ADDB2, ADDH2, ADDW2)                    | 3-37 |

|       | Add, 3 Address (ADDB3, ADDH3, ADDW3)         | 3-38 |

|       | Arithmetic Left Shift (ALSW3)                | 3-39 |

|       | AND (ANDB2, ANDH2, ANDW2)                    | 3-40 |

|       | AND. 3 Address (ANDB3, ANDH3, ANDW3)         | 3-41 |

|       | Arithmetic Right Shift (ARSB3, ARSH3, ARSW3) | 3-42 |

|       | Branch on Carry Clear (BCCB, BCCH)           | 3-43 |

|       | Branch on Carry Set (BCSB, BCSH)             | 3-44 |

|       | Branch on Equal (BEB, BEH)                   | 3-45 |

|       | Standa on Equal (BEB, BEH)                   | 2-12 |

| Branch on Greater Than (Signed) (BGB, BGH)                   | 3-46 |

|--------------------------------------------------------------|------|

| Branch on Greater Than or Equal (Signed) (BGEB, BGEH)        | 3-47 |

| Branch on Greater Than or Equal (Unsigned) (BGEUB, BGEUH)    | 3-48 |

| Branch on Greater Than (Unsigned) (BGUB, BGUH)               | 3-49 |

| Bit Test (BITB, BITH, BITW)                                  | 3-50 |

| Branch on Less Than (Signed) (BLB, BLH)                      | 3-51 |

| Branch on Less Than or Equal (Signed) (BLEB, BLEH)           | 3-52 |

| Branch on Less Than or Equal (Unsigned) (BLEUB, BLEUH)       | 3-53 |

| Branch on Less Than (Unsigned) (BLUB, BLUH)                  | 3-54 |

| Branch on Not Equal (BNEB, BNEH)                             | 3-55 |

| Dialicii oli ivot Equal (DIVED, DIVEII)                      | 3-56 |

| Breakpoint Trap (BPT)<br>Branch (BRB, BRH)                   | 3-30 |

| Branch (BKB, BKH)                                            | 3-57 |

| Branch to Subroutine (BSBB, BSBH)                            |      |

| Branch on Overflow Clear (BVCB, BVCH)                        | 3-59 |

| Branch on Overflow Set (BVSB, BVSH)                          | 3-60 |

| Call Procedure (CALL)                                        | 3-61 |

| Cache Flush (CFLUSH)                                         | 3-62 |

| Clear (CLRB, CLRH, CLRW)                                     | 3-63 |

| Compare (CMPB, CMPH, CMPW)                                   | 3-64 |

| Decrement (DECB, DECH, DECW)                                 | 3-65 |

| Divide (DIVB2, DIVH2, DIVW2)                                 |      |

| Divide, 3 Address (DIVB3, DIVH3, DIVW3)                      | 3-67 |

| Extract Field (EXTFB, EXTFH, EXTFW)                          | 3-68 |

| Extract Field (EXTFD, EXTFH, EXTFW)                          | 3-69 |

| Extended Opcode (EXTOP)                                      | 3-09 |

| Increment (INCB, INCH, INCW)                                 |      |

| Insert Field (INSFB, INSFH, INSFW)                           | 3-71 |

| Jump (JMP)                                                   | 3-72 |

| Jump to Subroutine (JSB)                                     | 3-73 |

| Logical Left Shift (LLSB3, LLSH3, LLSW3)                     | 3-74 |

| Logical Right Shift (LRSW3)                                  | 3-75 |

| Move Complemented (MCOMB, MCOMH, MCOMW)                      | 3-76 |

| Move Negated (MNEGB, MNEGH, MNEGW)                           | 3-77 |

| Modulo (MODB2 MODH2 MODW2)                                   | 3-78 |

| Modulo, 3 Address (MODB3, MODH3, MODW3)                      | 3-79 |

| Move (MOVB, MOVH, MOVW)                                      | 3-80 |

| Move Address, Word (MOVAW)                                   | 3-82 |

| Move Block (MOVBLW)                                          | 3-83 |

| Multiply (MULB2, MULH2, MULW2)                               | 3-85 |

| Multiply, 3 Address (MULB3, MULH3, MULW3)                    | 2 06 |

| More Version Number (MVERNO)                                 | 3-87 |

| Nove version Number (MVERNO)                                 | 3-8/ |

| No Operation (NOP, NOP2, NOP3)                               | 3-88 |

| OR (ORB2, ORH2, ORW2)<br>OR, 3 Address (ORB3, ORH3, ORW3)    | 3-89 |

| OR, 3 Address (ORB3, ORH3, ORW3)                             | 3-90 |

| Pop (Word) (POPW)                                            | 3-91 |

| Push Address (Word) (PUSHAW)                                 | 3-92 |

| Push (Word) (PUSHW)                                          | 3-93 |

| Return on Carry Clear (RCC)                                  | 3-94 |

| Return on Carry Set (RCS)                                    | 3-95 |

| Return on Equal (REOL, REOLU)                                | 3-96 |

| Return on Equal (REQL, REQLU)<br>Restore Registers (RESTORE) | 3-97 |

|                                                              |      |

|                                                              |      |

|       | Return from Procedure (RET)                               | 3-98  |

|-------|-----------------------------------------------------------|-------|

|       | Return on Greater Than or Equal (Signed) (RGEQ)           |       |

|       | Return on Greater Than or Equal (Unsigned) (RGEQU)        | 3-100 |

|       | Return on Greater Than (Signed) (RGTR)                    | 3-101 |

|       | Return on Greater Than (Unsigned) (RGTRU)                 | 3-102 |

|       | Return on Less Than or Equal (Signed) (RLEQ)              | 3-103 |

|       | Return on Less Than or Equal (Unsigned) (RLEQU)           | 3-104 |

|       | Return on Less Than (Signed) (RLSS)                       | 3-105 |

|       | Return on Less Than (Unsigned) (RLSSU)                    | 3-106 |

|       | Return on Not Equal (RNEQ, RENQV))                        | 3-107 |

|       | Rotate (ROTW)                                             | 3-108 |

|       | Return from Subroutine (RSB)                              | 3-109 |

|       | Return on Overflow Clear (RVC)                            | 3-110 |

|       | Return on Overflow Set (RVS)                              | 3-111 |

|       | Save Registers (SAVE)                                     | 3-112 |

|       | Coprocessor Operation (no operands) (SPOP)                | 3-113 |

|       | Coprocessor Operation Read (SPOPRS, SPOPRD, SPOPRT)       | 3-114 |

|       | Coprocessor Operation, 2-Address (SPOPS2, SPOPD2, SPOPT2) | 3-115 |

|       | Coprocessor Operation Write (SPOPWS, SPOPWD, SPOPWT)      | 3-116 |

|       | String Copy (STRCPY)                                      | 3-117 |

|       | String End (STREND)                                       | 3-119 |

|       | Subtract (SUBB2, SUBH2, SUBW2)                            | 3-120 |

|       | Subtract, 3 Address (SUBB3, SUBH3, SUBW3)                 | 3-121 |

|       | Swap (Interlocked) (SWAPBI, SWAPHI, SWAPWI)               | 3-122 |

|       | Test (TSTB, TSTH, TSTW)                                   | 3-123 |

|       | Exclusive Or (XORB2, XORH2, XORW2)                        | 3-124 |

|       | Exclusive Or, 3 Address (XORB3, XORH3, XORW3)             | 3-125 |

| 3.7.3 | Instruction Set Summary by Function                       |       |

|       | Instruction Set Summary by Mnemonic                       |       |

| 3.7.5 | Instruction Set Summary by Opcode                         | 3-136 |

|       |                                                           |       |

#### CHAPTER 4. OPERATING SYSTEM CONSIDERATIONS

.

1

| 4. OPERATING SYSTEM CONSIDERATIONS 4                                | <b>-</b> 1  |

|---------------------------------------------------------------------|-------------|

| 4.1 FEATURES OF THE OPERATING SYSTEM 4                              | <b>-</b> 1  |

| 4.1.1 Memory Management Considerations for Virtual Memory Systems 4 | 1-4         |

| 4.2 STRUCTURE OF A PROCESS                                          | 1-4         |

| 4.2.1 Execution Privilege 4                                         | <b>I-</b> 5 |

|                                                                     | 1-5         |

| 4.2.3 Process Control Block 4                                       | 1-6         |

| Initial Context for a Process 4                                     | 1-9         |

| Saved Context for a Process 4                                       | 1-9         |

| Memory Specifications 4                                             | 1-9         |

|                                                                     | 4-10        |

| 4.3 SYSTEM CALL 4                                                   | 4-10        |

|                                                                     | 4-13        |

| Pointer Table 4                                                     | 4-13        |

|                                                                     | 4-13        |

| 4.3.2 | GATE Instruction                                         | 4-14   |

|-------|----------------------------------------------------------|--------|

|       | First Entry Point                                        | 4-14   |

|       | Second Entry Point – The Gate Mechanism                  | 4-15   |

|       | Return-From-Gate Instruction                             |        |

| 4.4 P | ROCESS SWITCHING                                         | 4-16   |

| 4.4.1 | Context Switching Strategy                               | 4-17   |

|       | R Bit                                                    | 4-17   |

|       | I Bit                                                    |        |

| 4.4.2 | Call Process Instruction                                 | 4-20   |

| 4.4.3 | Return-to-Process Instruction                            | 4-22   |

|       | NTERRUPTS                                                |        |

| 4.5.1 | Interrupt-Handler Model                                  | 4-23   |

| 4.5.2 | Interrupt Mechanism                                      | 4-24   |

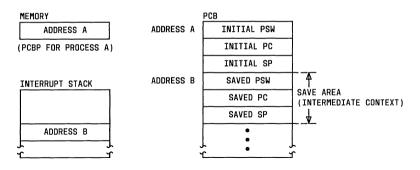

|       | Full-Interrupt Handler's PCB                             | 4-25   |

|       | Interrupt Stack and ISP                                  | 4-26   |

|       | Interrupt-Vector Table                                   | 4-27   |

| 4.5.3 | On-Interrupt Microsequence                               | 4-28   |

| 4.5.4 | Returning From an Interrupt                              | 4-29   |

|       | Full Interrupts                                          | 4-29   |

|       | Quick Interrupts                                         |        |

| 4.6 E | XCEPTIONS                                                | 4-29   |

| 4.6.1 | Levels of Exception Severity                             | 4-30   |

| 4.6.2 | Exception Handler                                        | 4-30   |

| 4.6.3 | Exception Microsequences                                 | 4-32   |

| 11015 | Normal Exceptions.                                       |        |

|       | Stack Exceptions                                         |        |

|       | Process Exceptions                                       | 4-35   |

|       | Reset Exceptions                                         |        |

| 4.7 N | MEMORY MANAGEMENT FOR VIRTUAL MEMORY SYSTEMS             | 4-36   |

| 471   | Initializing the Memory Management Unit                  | 4-40   |

|       | Defining Virtual Memory                                  | 4-40   |

|       | Peripheral Mode                                          | 4-40   |

| 472   | MMU Interactions                                         | 4-40   |

| 1.7.2 | MMU Exceptions                                           |        |

|       | Flushing                                                 |        |

| 473   | Efficient Mapping Strategies                             | 4-41   |

| 474   | Object Traps                                             | 4-42   |

| 475   | Indirect Segment Descriptors                             | 4-42   |

| 476   | Using the Cacheable Bit                                  | 4-42   |

| 4.7.7 | Using the Page-Write Fault                               | 4-42   |

| 478   | Access Protection                                        | 4-43   |

| 479   | Using the Software Bits                                  | 4-43   |

| 48 (  | Using the Software Bits<br>DPERATING SYSTEM INSTRUCTIONS | 4-43   |

| 4.81  | Notation                                                 | 4-43   |

| 482   | Privileged Instructions                                  | 4-44   |

| 4.0.2 | Nonprivileged Instructions                               | 4-56   |

|       | Microsequences                                           |        |

| r.u.T | TITLET OPAG RATIAAD                                      | -T-U-T |

#### CHAPTER 5. SOFTWARE GENERATION PROGRAMS

| 5. INTRODUCTION TO THE SOFTWARE GENERATION                   |      |

|--------------------------------------------------------------|------|

|                                                              | 5-1  |

| Distinctive SGP Features                                     | 5-1  |

| Host Computers                                               | 5-2  |

| 5.1 COMPILER AND THE C LANGUAGE                              | 5-3  |

| 5.1.1 Compiler                                               | 5-3  |

| Compiler Options                                             | 5-4  |

| Register Usage                                               | 5-6  |

| 5.1.2 C Language                                             | 5-7  |

| Flexnames                                                    | 5-7  |

| Enumerations                                                 | 5-7  |

| Structure Assignment                                         | 5-9  |

| Nonunique Structure Member Names                             | 5-9  |

| Former Member Name Restrictions                              | 5-10 |

| New Flexibility for Member Names                             | 5-10 |

| Complete Structure and Union Member Reference Qualifications | 5-11 |

| Nonunique Tag Names Allowed                                  |      |

| Vertical Tab Character Literal                               |      |

| In-Line Procedure Expansion                                  |      |

| 5.2 ASSEMBLER AND ASSEMBLY LANGUAGE                          | 5-13 |

| 5.2.1 Assembler                                              |      |

| Assembled Files                                              | 5-15 |

| Diagnostics                                                  | 5-15 |

| Macro Processing Facilities                                  | 5-16 |

| Interface Macros                                             | 5-17 |

| Function Interface Macros                                    | 5-18 |

| Scratch Register Macros                                      | 5-19 |

| Stack Frame Macros                                           | 5-19 |

| Restrictions                                                 | 5-19 |

| Using Predefined Macros                                      | 5-20 |

| Examples                                                     | 5-21 |

| M4 Reserved Words                                            | 5-22 |

| 5.2.2 Assembly Language                                      | 5-22 |

| Statements                                                   | 5-23 |

| Symbols                                                      | 5-23 |

| Values and Types                                             | 5-24 |

| Assigning Values and Types to Symbols                        | 5-25 |

| Constants                                                    | 5-25 |

| Location Counter                                             | 5-25 |

| Registers                                                    | 5-25 |

| Executable Instructions                                      | 5-20 |

| Operands                                                     | 5-28 |

| Expressions                                                  | 5-20 |

| Assembler Directives                                         | 5-30 |

| Assembler Directives                                         |      |

| Section Control Pseudo Operations                            | 5 22 |

| Pseudo Operations Dealing with Symbols                       | 5-33 |

| Assignment Pseudo Operation                                  |      |

| Assignment to Dot                                            | 5-34 |

| Alignment Pseudo Operation                                   |      |

| Data Generation Pseudo Operations                            | 5-35 |

| Symbolic Debugging Pseudo Operations            | 5-36 |

|-------------------------------------------------|------|

| File Name Pseudo Operation                      | 5-37 |

| Line Number Pseudo Operation                    | 5-37 |

| Function Calling Sequence                       |      |

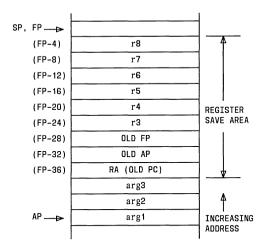

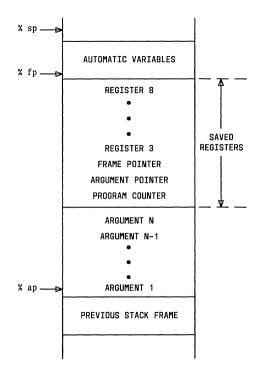

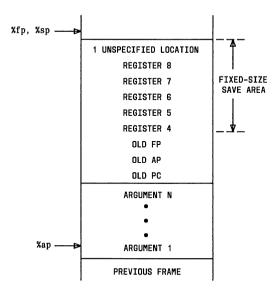

| Stack Frame                                     | 5-38 |

| Actions of Calling Function                     | 5-39 |

| Actions of Called Function                      |      |

| 5.2.3 Exception Conditions                      | 5-43 |

| 5.2.4 Programming Example                       | 5-43 |

| 5.2.5 Machine Independent Instruction Set       | 5-45 |

| 5.3 LINK EDITOR                                 | 5-48 |

| 5.3.1 Link Editor Command                       |      |

| Command Line Options                            |      |

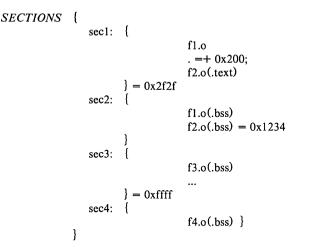

| 5.3.2 Link Editor Command Language              | 5-51 |

| Expressions                                     | 5-52 |

| Assignment Statements                           | 5-53 |

| Memory Configurations                           | 5-53 |

| Section Definition Directives                   | 5-55 |

| Virtual Address and Bindings                    | 5-56 |

| File Specifications                             | 5-56 |

| Load a Section at a Specified Address           | 5-57 |

| Aligning an Output Section                      | 5-57 |

| Grouping Sections Together                      | 5-58 |

| Creating Holes Within Output Sections           |      |

| Creating And Defining Symbols at Link-Edit Time | 5-60 |

| Allocating a Section Into Named Memory          | 5 61 |

| Initialized Section Holes or BSS Sections       | 5 61 |

| Notes on the Use of m32ld                       |      |

|                                                 |      |

| Changing the Entry Point                        |      |

| Use of Archive Libraries                        | 5-05 |

| Dealing With Holes In Physical Memory           | 5-04 |

| Allocation Algorithm                            | 5-65 |

| Subsystems (Incremental) Link Editing           | 5-66 |

| Nonrelocatable Input Files                      | 5-67 |

| DSECT, COPY and NLOAD Sections                  | 5-67 |

| Output File Blocking                            | 5-68 |

| 5.3.3 Error Messages                            | 5-68 |

| Corrupt Input Files                             | 5-68 |

| Errors During Output                            | 5-69 |

| Internal Errors                                 |      |

| Allocation Errors                               |      |

| Misuse of Link Editor Directives                |      |

| Misuse of Expressions                           | 5-72 |

| Misuse of Options                               | 5-72 |

| Space Restraints                                | 5-73 |

| Miscellaneous Errors                            | 5-73 |

| 5.3.4 Syntax Diagram for Input Directives       | 5-74 |

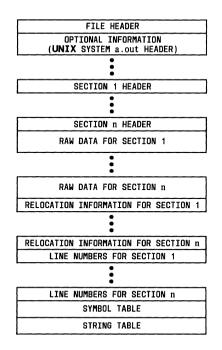

| 5.4 OBJECT FILE FORMAT                          | 5-77 |

| 5.4.1 Definitions                               |      |

| 5.4.2 File Header                               |      |

| Flags                                           |      |

| Optional Header Information                     |      |

| Standard UNIX System a.out Header               | 5-80 |

| · · · · · · · · · · · · · · · · · · ·           |      |

| 5.4.2. Constant II. and a model                         | 5 0 1 |

|---------------------------------------------------------|-------|

| 5.4.3 Section Header Table                              |       |

|                                                         | 5-82  |

| bss Section Header                                      |       |

|                                                         | 5-82  |

| 5.4.5 Relocation Information                            | 5-83  |

|                                                         | 5-84  |

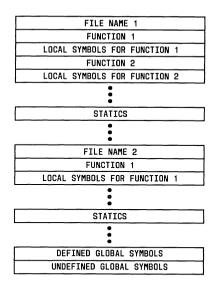

| 5.4.7 Symbol Table                                      | 5-84  |

| Special Symbols                                         | 5-84  |

|                                                         | 5-86  |

| Symbols For Functions                                   | 5-89  |

| Symbol Table Entries                                    |       |

| Symbol Name Field (n_name)                              | 5-90  |

| Symbol Value Field And Storage Classes (n_value)        | 5-90  |

| Section Number Field (n_scnum)                          | 5 02  |

| True Cield (n. seruin)                                  | 5-95  |

| Type Field (n_type)                                     | 5-94  |

| Structure for Symbol Table Entry                        | 5-97  |

| Auxiliary Table Entries                                 |       |

|                                                         | 5-98  |

|                                                         | 5-98  |

| Tag Names                                               | 5-99  |

| End of Structures                                       | 5-99  |

| Functions                                               | 5-99  |

| Arrays                                                  | 5-99  |

|                                                         | 5-100 |

|                                                         | 5-100 |

| Names Related to Structures, Unions, and Enumerations   |       |

|                                                         | 5-101 |

| 5.5 UTILITIES AND LIBRARY ROUTINES                      |       |

|                                                         | 5-102 |

| , ,                                                     | 5-103 |

|                                                         |       |

|                                                         | 5-105 |

|                                                         | 5-107 |

|                                                         | 5-108 |

|                                                         | 5-111 |

| m32list                                                 | 5-113 |

| m32lorder                                               | 5-114 |

| m32nm                                                   | 5-114 |

| m32size                                                 | 5-116 |

| m32strip                                                | 5-116 |

|                                                         | 5-117 |

|                                                         | 5-117 |

|                                                         |       |

|                                                         | 5-118 |

|                                                         | 5-120 |

|                                                         | 5-120 |

|                                                         |       |

| Function That Returns the Index of a Symbol Table Entry |       |

|                                                         | 5-121 |

| 5.5.3 General-Purpose Library                           | 5-121 |

| Use of the General Purpose Library                      | 5-121 |

| Routines in the General Purpose Library                 | 5-122 |

| Routines Required When Using printf and scanf           | 5-123 |

| 5.6 SGP MANUAL PAGES                                    | 5-124 |

#### **GLOSSARY AND ACRONYMS**

#### INDEX

#### LIST OF FIGURES

| Figure 1-1.  | The WE 32100 Microprocessor                                  | 1-1  |

|--------------|--------------------------------------------------------------|------|

| Figure 1-2.  | WE 321AP Microprocessor Analysis Pod                         |      |

| Figure 1-3.  | WE 321EB Microprocessor Evaluation Board                     |      |

|              |                                                              |      |

| Figure 2-1.  | WE 32100 Microprocessor Block Diagram                        | 2-2  |

| Figure 2-2.  | Programmer's Model for User Registers                        |      |

| Figure 2-3.  | Processor Status Word                                        |      |

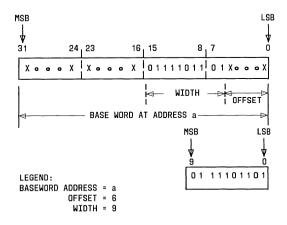

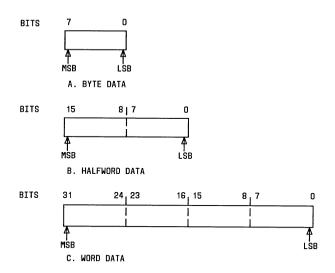

| Figure 2-4.  | Bit Order of Data                                            | 2-9  |

| Figure 2-5.  | Bit Field Data Type                                          | 2-9  |

| Figure 2-6.  | Signal Sampling Points                                       | 2-11 |

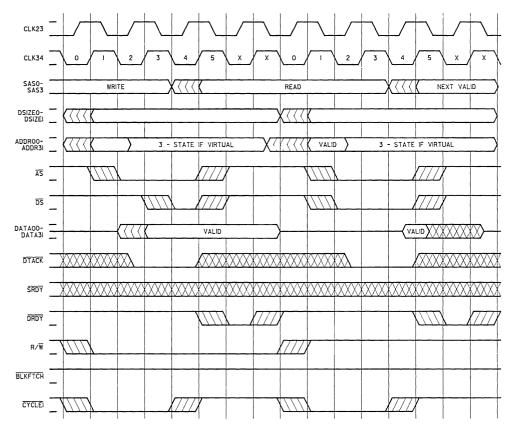

| Figure 2-7.  | Read Transaction (Using SRDY)                                | 2-14 |

| Figure 2-8.  | Read Transaction (Using DTACK)                               | 2-15 |

| Figure 2-9.  | Read Transaction with One Wait Cycle (Using SRDY)            |      |

| Figure 2-10. | Read Transaction With Two Wait Cycles (Using DTACK)          |      |

|              | Write Transaction (Using SRDY)                               |      |

|              | Write Transaction (Using DTACK)                              |      |

|              | Write Transaction With Two Wait Cycles (Using SRDY)          |      |

|              | Write Transaction With One Wait Cycle (Using DTACK)          |      |

| Figure 2-15. | Read Interlocked Transaction (Using DTACK)                   | 2-24 |

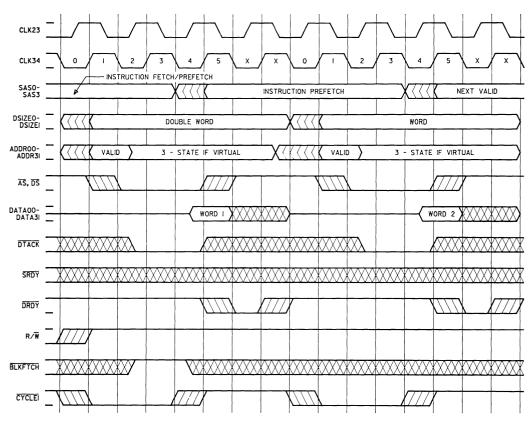

|              | Blockfetch Transaction (Using SRDY)                          |      |

| Figure 2-17. | Blockfetch Transaction (Using DTACK)                         | 2-27 |

|              | Blockfetch Transaction (Using DTACK)                         |      |

|              | Blockfetch Transaction (Using SRDY)                          |      |

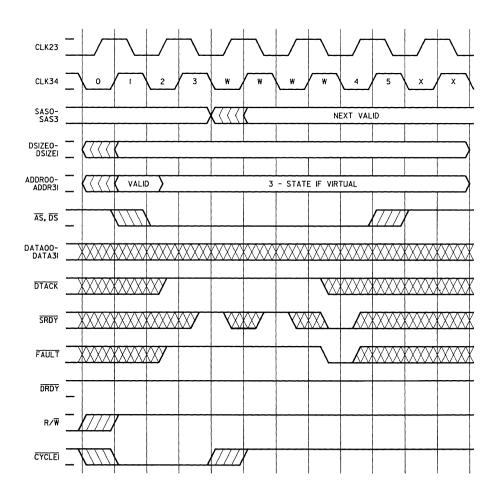

|              | Asynchronous Fault Without DTACK and SRDY (Read Transaction) |      |

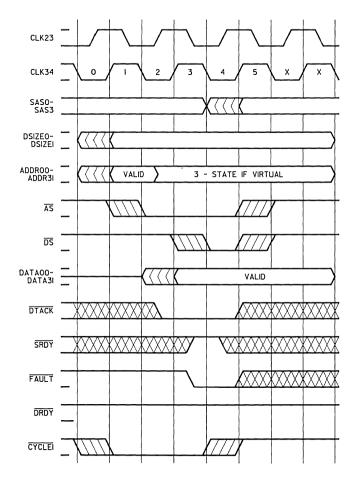

|              | Fault with Synchronous Ready (SRDY); i.e., Synchronous Fault |      |

|              | Fault After Assertion of DTACK (Write Transaction is Shown)  |      |

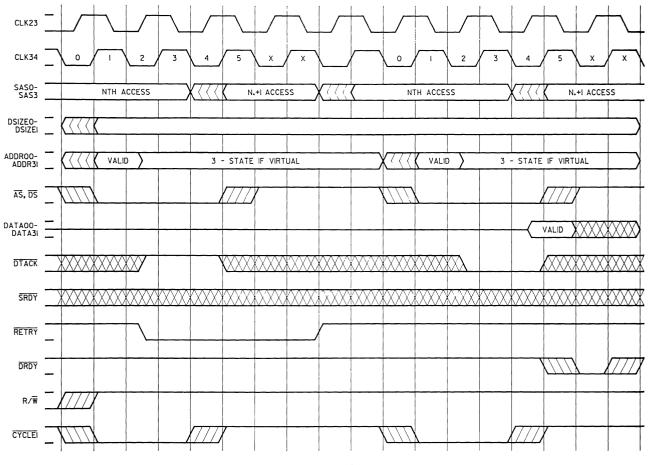

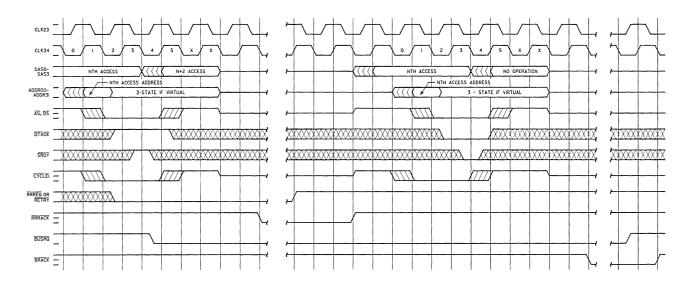

|              | Retry of Transaction (Read Transaction is Shown)             |      |

|              | Relinquish and Retry                                         |      |

|              | Fault on First Word of Blockfetch Transaction                |      |

| -            | With Access Status Code (Not Instruction Prefetch)           | 2-38 |

| Figure 2-26. | Fault on First Word of Blockfetch Transaction                |      |

| -            | With Access Status Code of Prefetch                          | 2-39 |

| Figure 2-27. | Retry on First Word of Blockfetch Transaction                |      |

| Figure 2-28. | Retry on Second Word of Blockfetch                           | 2-41 |

|              | Interrupt Acknowledge                                        |      |

| Figure 2-30. | Auto-Vector Interrupt Acknowledge                            | 2-46 |

|              | Nonmaskable Interrupt Acknowledge                            |      |

| Figure 2-32. | Bus Request During a Transaction                             | 2-49 |

|              | Reset Sequence                                               |      |

|              | Aborted Access on I-Cache Hit with PC Discontinuity          |      |

|              | Alignment Fault Bus Activity (Write Transaction is Shown)    |      |

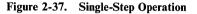

|              | Start of Single-Step Operation                               |      |

|              | Single-Step Operation                                        |      |

|              |                                                              |      |

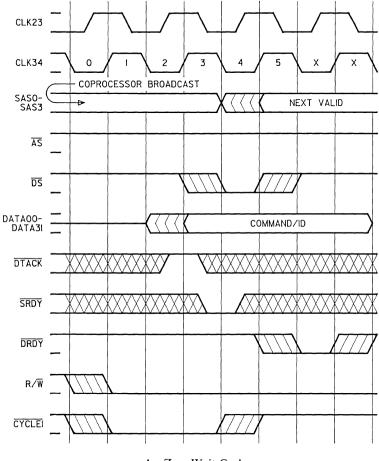

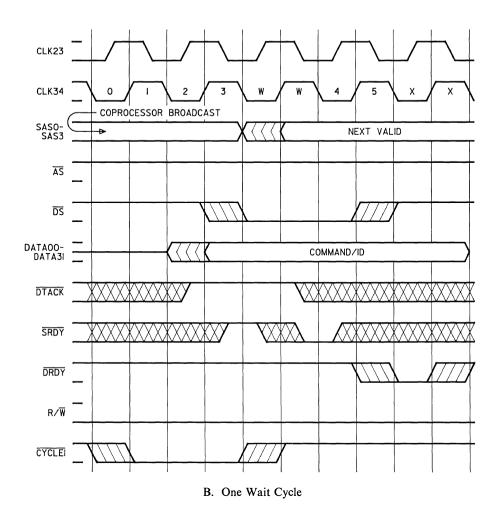

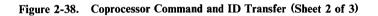

| Figure 2-38.   | Coprocessor Command and ID Transfer                     | 2-59 |

|----------------|---------------------------------------------------------|------|

|                | Coprocessor Command and ID Transfer                     |      |

| -              | (No Coprocessor Present)                                | 2-62 |

| Figure 2-40.   | Coprocessor Operand Fetch                               |      |

|                | Coprocessor Status Fetch (Using SRDY)                   |      |

|                | Coprocessor Data Write                                  |      |

|                | WE 32100 Microprocessor Pin Configuration               |      |

|                | Read Transaction Followed by a Read Transaction         |      |

|                | Read Transaction Followed by a Write Transaction        |      |

| U              | (Using DTACK)                                           | 2-89 |

| Figure 2-46.   | Write Transaction Followed by a Write Transaction       |      |

|                | Write Transaction Followed by a Read Transaction        |      |

|                | Double-Word Program Fetch Without Blockfetch            |      |

| e              | Transaction (using DTACK)                               | 2-92 |

| Figure 2-49.   | Bus Arbitration During Relinquish and Retry             |      |

| 8              |                                                         |      |

| Figure 3-1.    | Bit Order of Data                                       | 3-2  |

| Figure 3-2.    | Bit Order in a Bit Field                                |      |

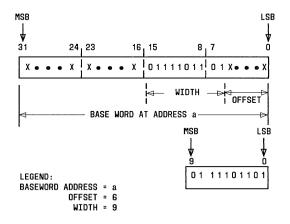

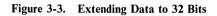

| Figure 3-3.    | Extending Data to 32 Bits                               |      |

| Figure 3-4.    | Register as a Source Operand                            |      |

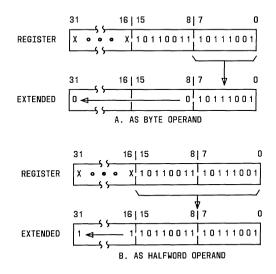

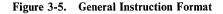

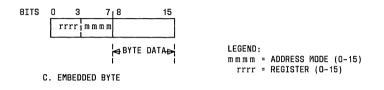

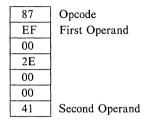

| Figure 3-5.    | General Instruction Format                              |      |

| Figure 3-6.    | Data Embedded in an Operand                             |      |

| Figure 3-7.    | Expanded-Operand Type Descriptor                        |      |

| Figure 3-8.    | Condition Flags                                         |      |

| Figure 3-9.    | Stack After CALL-SAVE Sequence                          |      |

| I IBui e e >i  |                                                         |      |

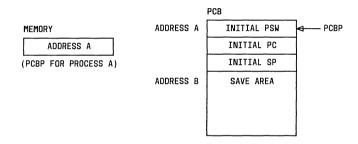

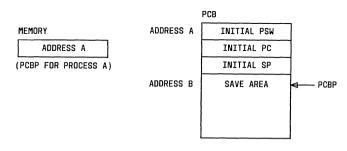

| Figure 4-1.    | A Typical Process Control Block                         | 4-8  |

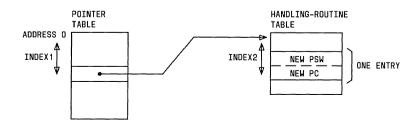

| Figure 4-2.    | Tables for the Gate Mechanism                           |      |

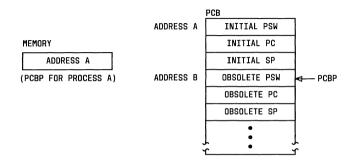

| Figure 4-3.    | A PCB on an Initial Process Switch to a Process         |      |

| Figure 4-4.    | A PCB on a Process Switch During Execution of a Process |      |

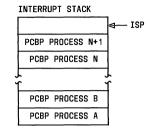

| Figure 4-5.    | An Interrupt Stack                                      |      |

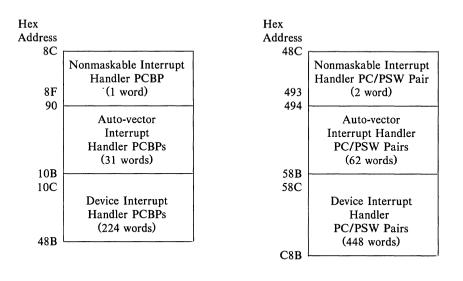

| Figure 4-6.    | Interrupt Vector Tables                                 |      |

| Figure 4-7.    | Exception-Vector Table                                  |      |

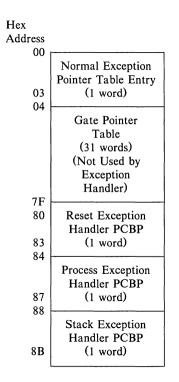

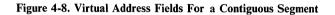

| Figure 4-8.    | Virtual Address Fields for a Contiguous Segment         |      |

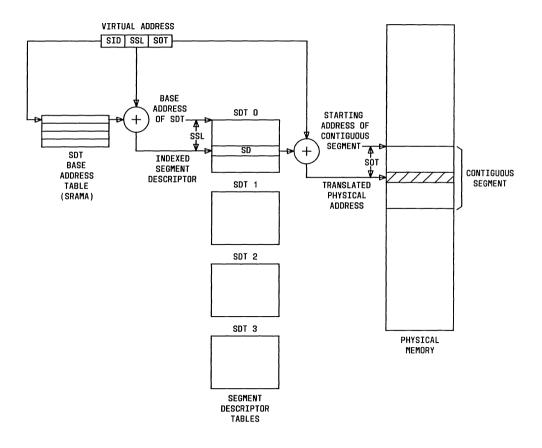

| Figure 4-9.    | Virtual Address Fields for a Paged Segment              |      |

|                | Virtual to Physical Translation for Contiguous Segments |      |

|                | Virtual to Physical Translation for Paged Segments      |      |

| 1 iguite 4-11. | Virtual to Thysical Translation for Taged Segments      | 4-J7 |

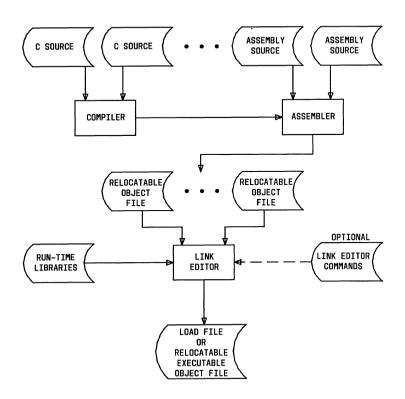

| Figure 5-1.    | Major Steps in the SGP                                  | 5-2  |

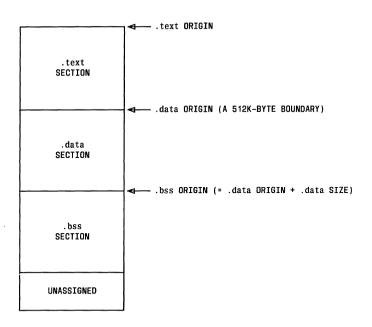

| Figure 5-2.    | Mapping Program Sections                                |      |

| Figure 5-3.    | Typical Stack Frame for a Function Call                 |      |

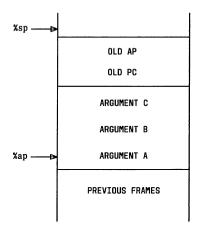

| Figure 5-4.    | Stack Frame Following a Call Instruction                | 5-42 |

| Figure 5-5.    | Stack Frame After Three Registers are Saved             | 5-42 |

| Figure 5-6.    | Object File Format                                      |      |

| Figure 5-0.    | COFF Symbol Table                                       |      |

| riguie J*/.    |                                                         | 5-05 |

#### LIST OF TABLES

| Table 2-1.  | Processor Status Word Fields                           | 2-5   |

|-------------|--------------------------------------------------------|-------|

| Table 2-2.  | Memory Write Summary                                   | 2-10  |

| Table 2-3.  | Simultaneously Asserted Exception Conditions           | 2-30  |

| Table 2-4.  | Interrupt Level Code Assignments                       | 2-44  |

| Table 2-5.  | Interrupt Acknowledge Summary                          | 2-50  |

| Table 2-6.  | Output Signal States after DMA Request is Acknowledged | 2-51  |

| Table 2-7.  | Output States on Reset                                 | 2-53  |

| Table 2-8.  | Exception Conditions                                   | 2-66  |

| Table 2-9.  | Truth Table for Trace Trap                             | 2-69  |

| Table 2-10. | WE 32100 Microprocessor Pin Descriptions               | 2-72  |

| Table 2-11. | Address and Data Signals                               | 2-75  |

| Table 2-12. | Interface and Control Signals                          | 2-76  |

| Table 2-13. | Access Status Signals                                  | 2-77  |

| Table 2-14. | Interrupt Signals                                      | 2-79  |

| Table 2-15. | Arbitration Signals                                    | 2-80  |

| Table 2-16. | Bus Exception Signals                                  | 2-81  |

| Table 2-17. | Development System Support Signals                     | 2-83  |

| Table 2-18. | Clock Signals                                          | 2-83  |

| Table 2-19. | Operating Requirements                                 | 2-85  |

| Table 2-20. | Output Electrical Specifications                       | 2-86  |

| Table 2-21. | Input Electrical Specifications                        | 2-86  |

|             |                                                        |       |

| Table 3-1.  | Register Set                                           | 3-4   |

| Table 3-2.  | Addressing Modes                                       | 3-9   |

| Table 3-3.  | Options for type in Expanded-Operand Mode              | 3-21  |

| Table 3-4.  | Data Transfer Instruction Group                        | 3-24  |

| Table 3-5.  | Arithmetic Instruction Group                           | 3-25  |

| Table 3-6.  | Logical Group                                          | 3-27  |

| Table 3-7.  | Program Control Instructions                           | 3-29  |

| Table 3-8.  | Coprocessor Instructions                               | 3-33  |

| Table 3-9.  | Stack and Miscellaneous Instructions                   | 3-33  |

| Table 3-10. | Condition Flag Code Assignments                        | 3-34  |

| Table 3-11. | Assembly Language Operators and Symbols                | 3-36  |

| Table 3-12. | Data Transfer Instruction Group                        | 3-126 |

| Table 3-13. | Arithmetic Instruction Group                           | 3-126 |

| Table 3-14. | Logical Group                                          | 3-128 |

| Table 3-15. | Program Control Instructions                           | 3-129 |

| Table 3-16. | Coprocessor Instructions                               | 3-131 |

| Table 3-17. | Stack and Miscellaneous Instructions                   | 3-131 |

| Table 3-18. | Instruction Set Summary by Mnemonic                    | 3-132 |

| Table 3-19. | Instruction Set Summary by Opcode                      | 3-136 |

|             |                                                        |       |

| Table 4-1.  | Operating System Instructions                          | 4-2   |

| Table 4-2.  | PCBP Locations                                         | 4-7   |

| Table 4-3.  | Processor Status Word Fields                           | 4-11  |

| Table 4-4.  | Severity Levels for Exceptions           | 4-30  |

|-------------|------------------------------------------|-------|

| Table 4-5.  | Normal Exceptions (ET=3)                 | 4-33  |

| Table 4-6.  | Stack Exceptions (ET=2)                  | 4-34  |

| Table 4-7.  | Process Exceptions (ET=1)                | 4-35  |

| Table 4-8.  | Reset Exceptions (ET=0)                  | 4-36  |

|             |                                          |       |

| Table 5-1.  | SGP Tools                                | 5-3   |

| Table 5-2.  | m32cc Command Line Options               | 5-5   |

| Table 5-3.  | m32as Command Line Options               | 5-16  |

| Table 5-4.  | Address Modes                            | 5-29  |

| Table 5-5.  | Alphabetical List of Pseudo-Operations   | 5-32  |

| Table 5-6.  | Machine Independent Instruction Set      | 5-46  |

| Table 5-7.  | m32ld Command Line Options               | 5-50  |

| Table 5-8.  | File Header Contents                     | 5-79  |

| Table 5-9.  | File Header Flags                        | 5-80  |

| Table 5-10. | Optional Header Contents                 | 5-80  |

|             | Section Header Contents                  | 5-81  |

| Table 5-12. | Section Types                            | 5-82  |

|             | Special Symbols in the Symbol Table      | 5-85  |

|             | Symbol Table Entry Format                | 5-89  |

|             | n_name Entry Formats                     | 5-90  |

| Table 5-16. | Symbol Values                            | 5-91  |

| Table 5-17. | Dummy Storage Classes                    | 5-92  |

|             | Restricted Special Symbols               | 5-92  |

|             | Restricted Storage Classes               | 5-92  |

|             | Section Numbers                          | 5-93  |

|             | Restricted Storage Classes               | 5-94  |

|             | Fundamental Types                        | 5-95  |

|             | Derived Types                            | 5-95  |

|             | Storage Class Type Entries               | 5-96  |

|             | Auxiliary Symbol Table Entries           | 5-98  |

| Table 5-26. | Section Format                           | 5-98  |

|             | Tag Name Format                          | 5-99  |

|             | End of Structure Format                  | 5-99  |

|             | Function Format                          | 5-99  |

|             | Array Format                             | 5-100 |

|             | End of Block and Function Format         | 5-100 |

|             | Beginning of Block and Function Format   | 5-100 |

|             | Structure, Union, and Enumeration Format | 5-101 |

|             | m32ar Command Line Keys                  | 5-104 |

|             | m32convert Target Machines               | 5-107 |

|             | m32dis Command Line Options              | 5-109 |

| Table 5-37. | m32dump Command Line Options             | 5-112 |

|             | m32nm Command Line Options               | 5-115 |

|             | SGP Manual Pages                         | 5-124 |

|             |                                          |       |

Chapter 1

Introduction

#### **CHAPTER 1. INTRODUCTION**

#### CONTENTS

| 1. I | ntroduction                  | 1-1 |

|------|------------------------------|-----|

|      | Overview                     |     |

| 1.2  | Architecture                 | 1-2 |

| 1.3  | Instruction Set              | 1-4 |

| 1.4  | Operating System Support     | 1-4 |

|      | Software Generation Programs |     |

#### 1. INTRODUCTION

This chapter introduces the WE 32100 Microprocessor and summarizes the support products available for it. The chapters describing the WE 32100 Microprocessor architecture, instruction set, operating system considerations, and software generation programs are also introduced.

#### 1.1 Overview

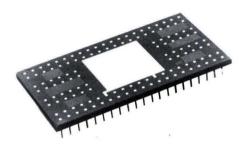

The WE 32100 Microprocessor is a high-performance, single-chip, 32-bit central processing unit designed for efficient operation in a high-level language environment. The WE 32100 Microprocessor represents a state-of-the-art concept in microprocessor architecture, providing one of the most powerful and extensive instruction sets available with any microprocessor. The WE 32100 Microprocessor, packaged in a 132-pin ceramic pin array, is shown on Figure 1-1.

Figure 1-1. The WE 32100 Microprocessor

The system memory space is addressed over a full 32-bit address bus using either physical or virtual addresses. The 32-bit address bus produces a vast memory space of more than four billion bytes which increases the flexibility of memory organization and provides ample space for the storage of software and data. Data can be read or written over the separate 32-bit data bus in byte (8-bit), halfword (16-bit), or word (32-bit) lengths.

The WE 32100 Microprocessor is an efficient execution vehicle for operating systems and high-level languages. The operating system instructions included in the instruction set establish an environment that permits process switching and interrupt handling with a minimum of operating system support. Other instructions allow the use of coprocessors and provide the necessary signals for interfacing with the WE 32101 Memory Management Unit for virtual memory systems.

Software support for the WE 32100 Microprocessor is available through the WE 321SG Software Generation Programs (SGP). This collection of programs and utilities provides everything necessary for rapid development of software. The high-level development language is the C language, and the entire SGP resides in the UNIX Operating System. The SGP includes a C compiler, an assembler, a link editor, and various utility programs.

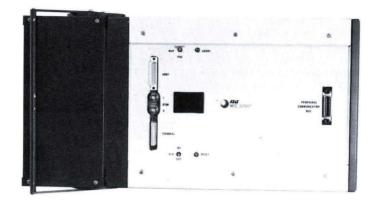

Development support is available through the WE 321DS Microprocessor Development System. The development system is a powerful development tool that can expedite the integration of hardware and software into a finished application. It permits the debugging of hardware and software to occur in parallel. The development system components include the WE 321AP Microprocessor Analysis Pod, the WE 321SD Development Software Programs, a UNIX System Host, and a logic analyzer. The modular design of the development system enables the user to configure the system for maximum productivity from initial hardware debug through the final stage of hardware and software integration. The WE 321AP Microprocessor Analysis Pod is shown on Figure 1-2.

Prototyping and performance evaluation support is available through the WE 321EB Microprocessor Evaluation Board. The evaluation board is a single-board microcomputer evaluation system that provides a prototyping vehicle to evaluate the hardware and software capabilities and performance of the WE 32100 Microprocessor in an application environment. The board is supplied with a WE 32100 Microprocessor as the CPU, a WE 32101 Memory Management Unit, a WE 32102 Clock, a ROM-based monitor, read/write memory (RAM), and sockets for additional memory. Also included are address decoding circuitry, RS-232C ports, programmable parallel I/O lines, programmable interval timers, and an interrupt controller. The WE 321EB Microprocessor Evaluation Board is shown on Figure 1-3.

#### 1.2 Architecture

The WE 32100 Microprocessor performs all the system address generation, control, memory access, and processing functions required in a 32-bit microcomputer system. Execution speed is enhanced by its unique pipelined architecture. Using this architecture, the microprocessor overlaps the execution of instructions while tracking each separately. In addition, as each instruction is fetched from memory it is cached in an internal instruction cache, resulting in even greater operating efficiency.

The CPU utilizes a combination of address and data strobes and interface and control signals to provide the bus protocol required for efficient transfer of data. The protocol facilitates interfacing to commercial memories and peripherals, as well as providing wait-state generation for handshaking with slow peripherals. In addition, the CPU also provides special coprocessor signals for a high throughput coprocessing environment.

The architecture and a bus protocol for the WE 32100 Microprocessor is discussed in Chapter 2. ARCHITECTURE AND BUS OPERATION.

Figure 1-2. WE 321AP Microprocessor Analysis Pod

Figure 1-3. WE 321EB Microprocessor Evaluation Board

#### 1.3 Instruction Set

The WE 32100 Microprocessor supports a powerful instruction set that includes standard data transfer, arithmetic, and logical operations for microprocessors, plus several unique operations. Its many program control instructions (branch, jump, return) provide flexibility for altering the sequence of execution. Other instructions are designed to aid in process switching for operating systems by manipulating the context of the processor with a minimum of code. In addition, special coprocessor instructions are included in the instruction set to implement a high-speed interface with special purpose coprocessors planned for the WE 32100 Microprocessor.

Eighteen addressing modes are provided that include special high-level language support modes such as frame pointer short offset and argument pointer short offset. These modes are designed for referring to local variables of high-level functions and function arguments.

Chapter 3. INSTRUCTION SET AND ADDRESSING MODES contains a detailed description of the WE 32100 Microprocessor Instruction Set.

#### 1.4 Operating System Support

The WE 32100 Microprocessor is designed for high-level language and operating system support. To aid in the design of process-oriented systems, it provides:

- four execution privilege levels: kernel, executive, supervisor, and user

- flexible transfer of execution control between privilege levels

- capability to have the operating system contained within the address space of every process

- support of explicit process switching by a scheduler

- implicit switching of processes through the interrupt structure

- layered exception handling structure, with different mechanisms used for different exceptions.

The processor groups all of the switchable process context into a compact area in memory called the process control block. This feature, plus the use of the special operating system instructions and microsequences, provides the programmer with an excellent tool for the creation and support of process-oriented systems.

**Chapter 4. OPERATING SYSTEM CONSIDERATIONS** discusses the techniques for efficient operating system design using the WE 32100 Microprocessor and also describes the use of the WE 32101 Memory Management Unit in a virtual memory operating system.

#### 1.5 Software Generation Programs

The WE 321SG Software Generation Programs (SGP) is a package of support tools used to create and test programs for the WE 32100 Microprocessor. The SGP runs under the UNIX Operating System and uses many features of the UNIX System shell. The SGP allows the programmer to generate code in the high-level C language and test programs at the source level. This improves productivity and program accuracy by freeing programmers from the details of the hardware architecture associated with assembly language programming.

The SGP contains a C compiler that converts C language programs into assembly language programs. The assembly language programs are ultimately translated into object files by the SGP assembler for the *WE* 32100 Microprocessor and link-edited into executable load modules by the link editor (also contained in the SGP). Each of these tools preserves all symbolic information necessary for meaningful symbolic testing at the source level. The SGP also provides a variety of utilities that read and manipulate object files.

The SGP is described in detail in Chapter 5. SOFTWARE GENERATION PROGRAMS.

Chapter 2

Architecture and Bus Operation

#### CHAPTER 2. ARCHITECTURE & BUS OPERATION

#### CONTENTS

| 2. WE 32100 MICROPROCESSOR                                            |       |

|-----------------------------------------------------------------------|-------|

| OVERVIEW                                                              | 2-1   |

| 2.1 USER REGISTERS                                                    | 2-3   |

| 2.1.1 General-Purpose Registers                                       |       |

| (r0-r8)                                                               | 2-4   |

| 2.1.2 Frame Pointer                                                   | 2-4   |

| 2.1.3 Argument Pointer                                                | 2-4   |

| 2.1.4 Processor Status Word                                           | 2-4   |

| 2.1.5 Stack Pointer                                                   | 2-7   |

| 2.1.6 Process Control Block Pointer                                   | 2-7   |

| 2.1.7 Interrupt Stack Pointer                                         | 2-7   |

| 2.1.8 Program Counter                                                 | 2-8   |

| 2.2 DATA HANDLING                                                     | 2-8   |

| 2.2.1 Data Types                                                      | 2-8   |

| 2.2.2 Data in Memory                                                  | 2-10  |

| <ul><li>2.2.3 Memory Management</li><li>2.3 SIGNAL SAMPLING</li></ul> | 2-10  |

| 2.3 SIGNAL SAMPLING                                                   |       |

| POINTS                                                                | 2-11  |

| 2.4 READ AND WRITE                                                    |       |

| OPERATIONS                                                            | 2-12  |

| 2.4.1 Read Transaction                                                |       |

| Using SRDY                                                            | 2-13  |

| 2.4.2 Read Transaction<br>Using DTACK                                 |       |

| Using DTACK                                                           | 2-15  |

| 2.4.3 Read Transaction With Wait                                      |       |

| Cycle Using SRDY                                                      | 2-16  |

| 2.4.4 Read Transaction With Two                                       |       |

| Wait Cycles Using DTACK                                               | 2-17  |

| 2.4.5 Write Transaction                                               |       |

| 2.4.5 Write Transaction<br>Using SRDY                                 | 2-18  |

| 2.4.6 Write Transaction                                               |       |

| Using DTACK                                                           | 2-18  |

| 2.4.7 Write Transaction With                                          |       |

| Wait Cycle Using SRDY                                                 | 2-18  |

| 2.4.8 Write Transaction With Wait<br>Cycle Using DTACK                |       |

| Cycle Using DTACK                                                     | 2-22  |

| 2.5 READ INTERLOCKED                                                  |       |

| OPERATION                                                             | 2-22  |

| 2.6 BLOCKFETCH OPERATION                                              | 2-25  |

| 2.6.1 Blockfetch Transaction                                          | 0.05  |

| Using SRDY                                                            | 2-25  |

| 2.6.2 Blockfetch Transaction                                          | ~ ~ ~ |

| Using DTACK                                                           | 2-27  |

| 2.6.3 <u>Blockfetch</u> Transaction Using<br>DTACK With Wait          |       |

| Cycle On Second Word                                                  | 2 20  |

| Cycle Un Second word                                                  | 2-28  |

| 2.6.4   | Blockfetch Transaction Using   |      |

|---------|--------------------------------|------|

|         | SRDY With Wait                 |      |

|         | Cycles On Both Words           | 2-29 |

| 2.7 B   | US EXCEPTIONS                  | 2-30 |

| 2.7.1   | Faults<br>Fault With SRDY      | 2-30 |

|         | Fault With SRDY                | 2-32 |

|         | Fault After DTACK              | 2-33 |

| 2.7.2   | Retry<br>Relinquish and Retry  | 2-34 |

| 2.7.3   | Relinquish and Retry           | 2-34 |

| 2.8 B   | LOCKFETCH SPECIAL              |      |

| C       | CASES                          | 2-37 |

| 2.8.1   | Fault on First Word of         |      |

|         | Blockfetch With Status         |      |

|         | Code Other Than Prefetch       | 2-37 |

| 2.8.2   | Fault on First Word            |      |

|         | of Blockfetch With             |      |

|         | Status of Prefetch             | 2-37 |

| 2.8.3   | Retry on First Word of         |      |

|         | Blockfetch                     | 2-37 |

| 2.8.4   | Retry on Second Word of        |      |

|         | Blockfetch                     | 2-37 |

| 2.8.5   | Relinquish and Retry of        |      |

|         | Blockfetch                     | 2-42 |

| 2.9 T   | NTERRUPTS                      | 2-42 |

|         | Interrupt Acknowledge          | 2-42 |

|         | Auto-vector Interrupt          | 2-45 |

|         | Nonmaskable Interrupt          | 2-45 |

| 2.9.4   | Quick Interrupt                | 2-48 |

| 2.10    | BUS ARBITRATION                | 2-48 |

|         | Bus Request During a           |      |

|         | Bus Transaction                | 2-48 |

| 2.10.2  | 2 DMA Operation                | 2-51 |

| 2.11    | RESET                          | 2-52 |

| 2.11.   | System Reset                   | 2-52 |

|         | 2 Internal Reset               | 2-52 |

| 2.11.3  | Reset Sequence                 | 2-54 |

| 2.12    | ABORTED MEMORY                 |      |

| 2.12    | ACCESSES                       | 2-54 |

| 2.12    | Aborted Access on PC           | 201  |

| 2.1 2.  | Discontinuity With             |      |

|         | Instruction Cache Hit          | 2-55 |

| 2.12    | 2 Alignment Fault Bus Activity |      |

| 2.13    | SINGLE-STEP OPERATION          | 2-57 |

|         | COPROCESSOR                    | 1    |

| ~,<br>( | OPERATIONS                     | 2-58 |

|         |                                |      |

#### CONTENTS

2.14.1 Coprocessor Broadcast2-582.14.2 Coprocessor Operand Fetch2-632.14.3 Coprocessor Status Fetch2-642.14.4 Coprocessor Data Write2-652.15 EXCEPTIONAL2-66CONDITIONS2-662.16 TRACE MECHANISM2-69

2.17 PIN ASSIGNMENTS ...... 2-70

| 2.18 MICROPROCESSOR            |      |

|--------------------------------|------|

| OPERATING                      |      |

| REQUIREMENTS                   | 2-83 |

| 2.18.1 Electrical Requirements | 2-84 |

| 2.18.2 Clocking Requirements   | 2-85 |

| 2.18.3 Thermal Requirements    | 2-85 |

| 2.19 Supplementary Protocol    |      |

| Diagrams                       | 2-87 |

|                                |      |

#### 2. WE 32100 MICROPROCESSOR OVERVIEW

The WE 32100 Microprocessor is the first 32-bit microprocessor with separate 32-bit address and data buses. Using either physical or virtual addresses, the 32-bit address bus can access over four billion  $(2^{32})$  bytes of system memory or peripherals. Data is read or written over the 32-bit bidirectional data bus in either byte (8-bit), halfword (16-bit), or word (32-bit) lengths and is processed internally over 32-bit internal data paths.

The execution speed of the microprocessor is enhanced by an internal instruction queue and an internal instruction cache that store prefetched instructions. Also, the microprocessor's extensive use of pipelining allows overlapping of the execution of instructions while tracking each one individually. Should a fault or interrupt occur during instruction execution, the instruction that caused it can be easily determined and execution restarted. This feature is essential for systems with demand-paged memory management.

Using a group of address and data strobes and interface and control signals, the microprocessor controls information flow over the address and data buses. These signals provide the timing required for transfer of data and facilitate interfacing to commercial memories and peripherals. The microprocessor also accommodates wait-state generation to allow handshaking with slow peripherals.

The WE 32100 Microprocessor consists of the four major sections shown on Figure 2-1. These are the main controller, the fetch unit, the execute unit, and the bus interface control. The main controller is responsible for acquiring and decoding instruction opcodes and directing the action of the fetch and execute controllers as the specified instruction is executed. The main controller also has the responsibility of responding to and directing the handling of interrupts and exception conditions.

The fetch unit handles the instruction stream and performs memory-based operand accesses. It consists of a fetch controller, an instruction cache, an instruction queue, an immediate and displacement extractor, and an address arithmetic unit (AAU). The fetch controller directs the action of the elements in the fetch unit. The instruction cache is a 64 by 32-bit on-chip cache which is used to increase the microprocessor's performance by reducing external memory reads for instruction fetches. When an instruction fetch from memory occurs, instruction data is placed in the cache and in the instruction queue. If that instruction data is needed again, it is fetched from the cache rather than from external memory, which improves performance. The instructions are taken from the queue for execution, and the fetch controller fills it asynchronously with respect to instruction execution data to the AAU for its use in calculating 32-bit addresses.

The execute unit performs all arithmetic and logic operations, performs all shift and rotate operations, and computes condition flags. It consists of:

• an execute controller that directs the actions of the elements in the execute unit

### ARCHITECTURE & BUS OPERATION Overview

- sixteen 32-bit registers that are user-accessible and include:

- $\Box$  nine general-purpose registers (r0-r8)

- $\Box$  seven dedicated registers (r9-r15)

- working registers that are used exclusively by the microprocessor and are not useraccessible

- a 33-bit ALU that performs arithmetic operations on 32-bit data, with an extra bit that is used whenever an operation requires a carry or borrow beyond 32 bits.

The bus interface control provides all the strobes and control signals necessary to implement the interface with peripherals.

The WE 32100 Microprocessor pin assignments are summarized in 2.17 Pin Assignments.

Figure 2-1. WE 32100 Microprocessor Block Diagram

#### ARCHITECTURE & BUS OPERATION User Registers

#### 2.1 USER REGISTERS

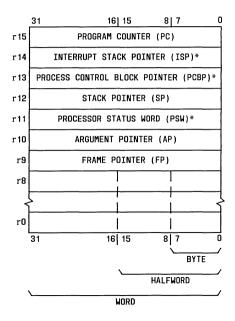

Figure 2-2 shows the programming model for the microprocessor's sixteen 32-bit registers (r0-r15). This register set is designed for efficient support of high-level language program execution. All of these registers, except for the program counter (r15) and the processor status word (r11), may be accessed in any addressing mode. The processor status word (r11), process control block pointer (r13), and interrupt stack pointer (r14) are privileged registers. These may be read at any time, but may be written only when the microprocessor is in kernel mode (i.e., the operating system is in control). The other registers may be read or written in any of the four execution levels.

<sup>\*</sup> KERNEL LEVEL PRIVILEGED

Figure 2-2. Programmer's Model for User Registers

## 2.1.1 General-Purpose Registers (r0-r8)

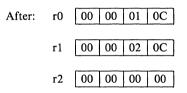

The nine general-purpose registers may be used for high-speed accumulation, for addressing, or for temporary data storage. The first three registers (r0-r2) are the microprocessor's *scratch* registers. These three registers are used by the C compiler to store temporary values during expression evaluation. They also pass and return specific values during procedure calls. For example, r0 should always be used to return the value of a procedure. If a floating point double value is returned from a procedure, it is stored in r0 and r1. If a procedure returns a structure, then the pointer to that structure should be returned to r2. In addition, registers r0-r2 are implicitly used by the data transfer instructions MOVBLW (move block of words), STRCPY (string copy), and STREND (string end) and also by the MVERNO (move version number), INTACK (interrupt acknowledge), ENBVJMP (enable virtual pin and jump), DISVJMP (disable virtual pin and jump), GATE (system-call), and CALLPS (call process) operating system instructions.

#### 2.1.2 Frame Pointer

The frame pointer (FP), r9, points to the beginning location in the stack of a function's local variables. It is affected implicitly only by the save register (SAVE) and the restore register (RESTORE) instructions.

#### 2.1.3 Argument Pointer

The argument pointer (AP), r10, points to the beginning location in the stack where a set of arguments for a function has been pushed. The AP is affected implicitly only by the procedure call (CALL) and return (RET) instructions.

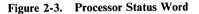

#### 2.1.4 Processor Status Word

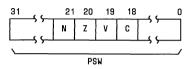

The processor status word (PSW), r11, contains status information about the microprocessor and the current process. It is divided into 14 fields, as shown on Figure 2-3. Although the PSW is a privileged register, the microprocessor may alter some of its fields at any execution level. Most instructions alter the N, Z, V, and C bits (condition flags) in the PSW. In general, the PSW changes as a whole *only* when a process switch occurs. The final values of the PSW bits are based on the result of the last calculation and are latched into the PSW at the end of the instruction. The PSW may not be referenced in some addressing modes.

Table 2-1 contains a description of each of the processor status word fields.

| Bit   | 31 | 26   | 25  | 24  | 23 | 22 | 21 1 | 8   17 | 16 13 | 12 11 | 10 9 | 8 | 7 | 3   | 2  | 10 |  |

|-------|----|------|-----|-----|----|----|------|--------|-------|-------|------|---|---|-----|----|----|--|

| Field | Un | used | CFD | QIE | CD | OE | NZV  | TE     | IPL   | CM    | PM   | R | Ι | ISC | ΤМ | ET |  |

# ARCHITECTURE & BUS OPERATION Processor Status Word

|        | Table 2-1. Processor Status Word Fields |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |