If you require further information or other technical support, please contact your authorized dealer:

#### IBM PC, PC XT, and PC AT are trademarks of International Business Machines Corporation. MS-DOS is a registered trademark of MicroSoft Corporation. Compaq is a registered trademark of Compaq Computer Corporation.

#### COPYRIGHT © 1987 WESTERN DIGITAL CORPORATION ALL RIGHTS RESERVED

This document is protected by copyright, and contains information proprietary to Western Digital Corporation. Any copying, adaptation, distribution, public performance, or public display of this document without the express written consent of Western Digital Corporation is strictly prohibited. The receipt or possession of this document does not convey any rights to reproduce or distribute its contents, or to manufacture, use or sell anything that it may describe, in whole or in part, without the specific written consent of Western Digital Corporation.

Document Number: 79-000141

Western Digital 2445 McCabe Way Irvine, California 92714 (800) 847-6181

W1107S 4/87 50M

÷

# WD1005-WAH ESDI Winchester Disk Controller

## USER'S GUIDE

IMPORTANT USER INFORMATION DO NOT DISCARD Making the leading edge work for you.

## WESTERN DIGITAL

#### uctions for nt'd.)

anced Diagnostics. ibed in the previous if necessary. After System Checkout. ne action desired"

m the Fixed Disk

ve with the Format

et Entry table.

ting the drive, press the system normally.

or other technical rized dealer.

roblems.

it" message appears he drive.

Initiate formatting

to press "y".

rtition.

Note that the drive  $\Lambda T$  and Compaq

xed Disk" appears a hard drive.

active.

LED continuously

is normal operation

vo controllers, both y LEDs light at the

ect or termination. cables. If the data

## **Description and Document Scope**

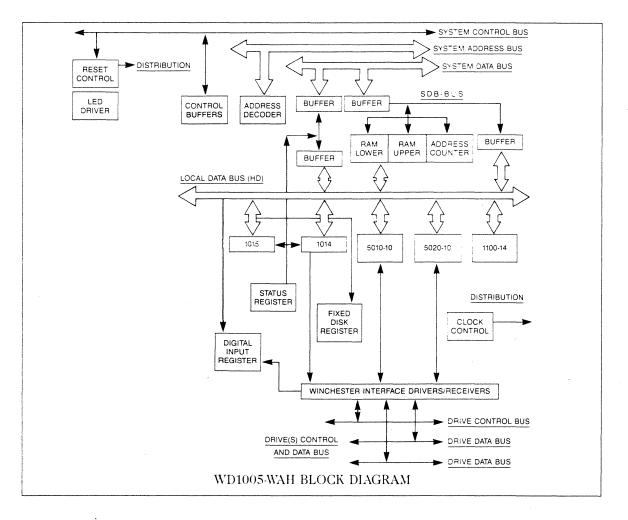

The WD1005-WAH Winchester Disk Controller is an IBM Personal Computer AT bus compatible module designed to interface one or two disk drives. The WD1005-WAH's drive interface conforms to the ESDI specification. Drives need not be of the same capacity or configuration. All necessary receivers and drivers are included on the board for direct connection to the drives(s).

The ESDI drives used with this controller generally have two modes of operation, soft sector and hard sector. The WD1005-WAH is designed to operate in the hard sector mode only. In the hard sector mode, the drive must be configured properly for the mode of operation and the number of desired sectors per track. The WD1005-WAH uses 34 sectors per track.

This document describes installation in the IBM Personal Computer AT. Therefore, all examples in this document use the AT as a "standard." Installation of the WD1005-WAH in AT compatibles may be outside the scope of this document. Refer to your system manuals or contact your dealer for information outside the scope of this document.

#### Hardware Installation Instructions

This section briefly describes installation of the WD1005-WAH. If the disk drives(s) is (are) being installed internally, it is best to locate the controller in the closest available expansion slot relative to the drive.

#### CAUTION

Handle the controller board by the ends of the board. Some of the chips are static sensitive and damage may occur if the board is incorrectly handled.

Integrating this controller into a system that does not have floppy support built in requires the use of a stand alone floppy controller such as the WD1002-FOX. It is not acceptable to change the primary/secondary address jumpers on the AT combination card, WD1003-WA2.

#### **Step Instruction**

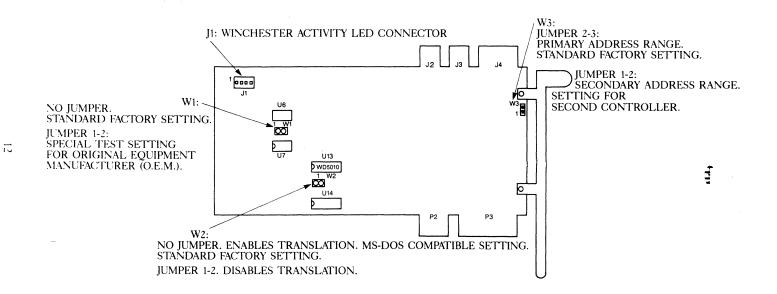

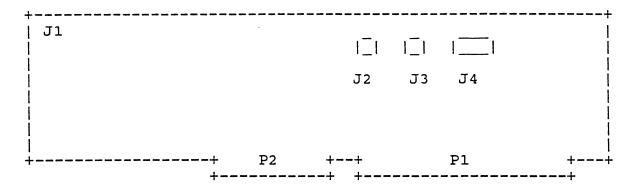

1. Verify controller jumper settings. Only verify the settings. Modification of the standard factory settings on the controller is rarely necessary. Modify the jumpers only under the direction of a qualified individual; i.e., your dealer. Figure 1 illustrates the jumper settings and locations.

- **2.** Verify termination on last drive. Verify proper setting of drive select switches on drive. Do NOΓ use the drive's radial select option. Refer to the drive owner's manual for information about proper drive termination and select switches.

- **3.** Remove the blank expansion slot bracket. Put the bracket away and save it for possible future use. The screw will be used to hold the controller board in place.

- **4.** Attach the 34-pin control cable connector pin 1 to J4. Keyed connectors prevent reversal of the cables.

- 5. Connect control cable to drive.

- 6. Attach drive 0's 20-pin data cable to J2. Data connectors are also keyed.

- 7. Attach drive 1's 20-pin data cable to J3.

- 8. Connect the cable(s) to the proper drives(s).

- **9.** Attach the Winchester activity LED connector to J1. J1 is a reversible connector.

- **10.** Install the controller board into the expansion slot. Ensure that the board is seated properly by pressing down on both ends of the board. Secure the board with the bracket screw.

#### **Software Installation Instructions**

This section contains instructions for preparing (low level format) the drive to be recognized by the operating system. Formatting the drive uses one of two software programs, the Advanced Diagnostics (or equivalent in AT compatibles) and the WDFMT.EXE or both programs. Use of the programs depends on the controller configuration. Configuring the controller to use the translation feature requires running the Advanced Diagnostics program, Setup, and WDFMT.EXE. Setup defines the drive type for the system and WDFMT.EXE low level formats the drive. Without translation, Advanced Diagnostics can low level format the drive if the system BIOS recognizes the 34 sector ESDI format. Run the DOS programs. FORMAT and FDISK, after performing the low level format, regardless of the controller configuration.

# Software Installation Installation for Translation Mode

#### Step Instruction

1. Insert the Diagnostics diskette, and turn on the power. After the system test, the program displays the following:

The IBM Personal Computer ADVANCE DIAGNOSTICS Version 1.04

© Copyright IBM Corp. 1981, 1982, 1983, 1984

#### SELECT AN OPTION

- 0 SYSTEM CHECKOUT

- **1 FORMAT DISKETTE**

- 2 COPY DISKETTE

- **3 PREPARE SYSTEM FOR MOVING**

- 4 SETUP

- 9 END DIAGNOSTICS

SELECT THE ACTION DESIRED ?

**2.** Enter 4 followed by a CARRIAGE RETURN or ENTER. The program displays:

Use the information on the following screens to set or verify Time, Date, and Options.

**Press** "ENTER" to continue . . . ?

**3.** Press CARRIAGE RETURN or ENTER. Key in the current date and time, if necessary, at the following displays:

Current date is:

If the current date is correct, press "ENTER".

If the current date is incorrect, type the new date MM-DD-YYYY. Then, press "ENTER". ?

#### Current time is:

If the current time is correct, press "ENTER".

If the current time is incorrect, type the new time HH:MM:SS. Then, press "ENTER".

24 hour format is required. (Example 1:00 - ... pm is equal to 13:00:00 in 24 hour format.)

4. After entering the current date and time, enter "n" at the following display prompt:

2

-4

#### Software Installion Instructions for Translation Mode (Cont'd.)

Your system may have other options installed. They are not required for Setup and are not displayed.

The following options have been set:

Diskette Drive A - High Capacity Diskette Drive B - Double Sided Fixed Disk Drive C - Type 4 Fixed Disk Drive D - Not Installed Base Memory size - 512KB Expansion memory size - 0KB Primary display is attached to: - Monochrome Display Adapter

Are these options correct (Y/N) ?n

Entering "n" at this point allows changing the drive type. The program continues:

System options information is required to answer the following questions.

Press "ENTER" continue . . . ?

**5.** After pressing ENTER, the program requests information regarding the system diskette drives as in the following example:

Your diskette drive types are set to the following: Diskette Drive A - High Capacity Diskette Drive B - Double Sided

Are diskette drive types correct (Y/N) ?y

6. The next displays define the drive type as follows: Your fixed disk drive types are set to the following: Fixed Disk Drive C - Type 4

Fixed Disk Drive D - Not Installed

Is this correct (Y/N)

?n

How many fixed disks are installed?

Enter 0, 1, or 2 for the number of fixed disk drives installed.

?1

At this point, the drive type must be entered. When using the translation mode, double the

# Software Installation Instructions for Translation Mode (Cont'd.)

number of physical head's but use the actual number of cylinders. In the following example, the drive contained four physical heads and 940 cylinders. Therefore, drive type 4 (8 heads, 940 cylinders) is chosen in this example. Refer to the appropriate technical manual when determining the drive types for AT compatibles.

Enter fixed disk type (1-15) for Fixed Disk Drive C.

\* \* WARNING \* \*

Entering the wrong drive type causes improper operation of the fixed disk. 24

You have set your fixed disk drive types to the following:

Fixed Disk Drive C - Type 4 Fixed Disk Drive - Not Installed

Is this correct (Y/N)

?у

The primary display comes on when you turn on the system power switch.

The primary display is attached to the Monochrome Display adapter.

Is this correct (Y/N) ?y

Base memory is composed of:

- 256KB on the system board or,

- 512KB on the system board or,

- 640KB of Base memory consisting of 512KB on the system board, and 128KB on the 128KB Memory Expansion Option.

Base memory size is 512KB

Is this correct (Y/N)

?y

The Expansion Memory size is composed of additional memory adapters not including the 128KB Memory Expansion option. Expansion memory size is 0KB

Is this correct (Y/N) ?y

Your system may have other options installed. They are not required for Setup and are not displayed.

# Software Installation Instructions for Translation Mode (Cont'd.)

The following options have been set:

Diskette Drive A - High Capacity Diskette Drive B - Double Sided Fixed Disk Drive C - Type 4 Fixed Disk Drive D - Not Installed Base memory size - 512KB Expansion memory size - 0KB Primary display is attached to: - Monochrome Display Adapter Are these options correct (Y/N) ?y Press "ENTER" and stand by while system resets . . .

7. Insert the DOS Diskette in drive A and boot the system normally.

#### CAUTION EXECUTION OF THE WD FORMAT PROGRAM IN STEP 8 DESTROYS ALL DATA ON THE TARGET DRIVE.

8. Remove the DOS diskette and insert the WD Format diskette into drive A. Type in the following command line if the drive configuration matches the default description of 500 physical cylinders, 4 physical heads, 34 sectors/track and 3 to 1 interleave:

#### A> WDFMT.EXE

If the drive configuration does NOT match the default values, type in the following command line:

#### A>WDFMT.EXE ccc hss i

Where:

ccc is the number of physical cylinders (2048 physical cylinders, maximum). h is the number of physical heads (1 to 16). ss is the sectors per track. (Must be 34 since the WD1005-WAH only supports hard sectored drives.)

i is the interleave factor.

Separate each command line parameter by a space.

The WD Format program displays the following menu:

\*\*\* Western Digital Corporation \*\*\* Disk Format Utility Rev. 1.00

## Software Inst Translation N

Current par

Cylinders: Sectors:

To enter nev enter a new

WDFMT -

<interlea

Warning!!!! . destroyed. P start format

Verifying cy

Separate the entered. Not cylinder and

9. WD Format information block inform drive manufa

> You may nov marked bad

> Enter cylind spaces) at th ENTER at th

> Enter <cylii

After enterin program disp

Format com

A>

10. Run the FOI

11. Operate the

#### Software Inst Non-Translati

Formatting<sup>1</sup>d operational n with a 34 sec

# Software Installation Instructions for Translation Mode (Cont'd.)

Current parameters are:

| Cylinders: | 940 | Heads:      | 4 |

|------------|-----|-------------|---|

| Sectors:   | 34  | Interleave: | 3 |

To enter new parameters, return to DOS and enter a new command line as follows:

WDFMT <#cvls> < #heads> <#sectors> <interleave>

Warning!!!! All data on drive C will be destroyed. Press ESC to return to DOS, F to start format.

Verifying cylinder: XXX head: y

Separate the new parameters with a space, if entered. Note that the XXX and Y in Verifying cylinder and head line constantly up counts.

**9.** WD Format program requests bad block information with the following menu. (Bad block information must be supplied from the drive manufacturer.)

You may now enter additional blocks to be marked bad.

Enter cylinder and head info (separated by spaces) at the prompt. To end entry, press ENTER at the prompt.

Enter <cylinder#> <head#>:

After entering the bad blocks, the format program displays the following message:

1 :

Format complete . . . Bad block marked A>

10. Run the FORMAT and FDISK utilities.

11. Operate the system normally.

# Software Installation Instructions for Non-Translation Mode

#### NOTE

Formatting disk media with this operational mode requires a host system with a 34 sector BIOS.

#### Software Installation Instructions for Non-Translation Mode (Cont'd.)

#### **Step Instruction**

- 1. Boot the system with the Advanced Diagnostics. Define the drive types as described in the previous section, steps 1 through 6, if necessary. After defining the drive types, run System Checkout. Enter 0 after the "Select the action desired" prompt.

- 2. Select fixed disk option 17.

- 3. Select the Format Menu from the Fixed Disk Diagnostic Menu.

- **4.** Unconditionally format the drive with the Format Selection Menu.

- 5. Enter bad blocks in the Defect Entry table.

- 6. Formatting begins. After formatting the drive, press "ENTER." Boot and operate the system normally.

If you require further information or other technical support, please contact your authorized dealer.

#### If You Have a Problem...

Listed below are some common problems.

| PROBLEM: | "Nothing Done Exit" message appears<br>when formatting the drive.                             |

|----------|-----------------------------------------------------------------------------------------------|

| COMMENT: | "y" was not pressed. Initiate formatting<br>procedure. Be sure to press "y".                  |

| PROBLEM: | Drive does not partition.                                                                     |

| COMMENT: | Check drive types. Note that the drive types for the AT and Compaq machines differ.           |

| PROBLEM: | "Error Reading Fixed Disk" appears<br>when booting from hard drive.                           |

| COMMENT: | DOS partition not active.                                                                     |

| PROBLEM: | Winchester activity LED continuously lit.                                                     |

| COMMENT: | No problem! This is normal operation for ATs.                                                 |

| PROBLEM: | For systems with two controllers, both<br>Winchester activity LEDs light at the<br>same time. |

| COMMENT: | Improper drive select or termination.<br>Inspect the drive cables. If the data                |

## Software Installation Instructions for Non-Translation Mode (Cont'd.)

cables are straight, then set both drives' select switches for drive select 2. If the data cables have a twist, set drive C's drive select switches for drive select 1 and drive D's drive select switches for drive select 2. Consult your drive manuals or dealer for drive switch settings. Finally, under no circumstance, use twisted floppy cables for the Winchester drive. Floppy and Winchester drive interface connections differ significantly.

PROBLEM: Error code 1701.

- COMMENT: Power supply is overloaded.

- PROBLEM: Error code 20.

- COMMENT: Controller component malfunction. Controller plugged in incorrectly. Cables reversed. For controller failures, contact your dealer.

- PROBLEM: Error code 40.

- COMMENT: Wrong drive type. Not enough drive power.

- PROBLEM: Error code 80.

- COMMENT: Not enough drive power. Bad cables. Improper drive select or termination. Bad drive.

This list is by no means exhaustive. For example, error codes differ for many  $A\Gamma$  compatibles and their operating systems. If your solution was not listed, then contact your dealer for further information.

#### For Those of You Who Want to Know More...

#### Translation

Some versions of MS-DOS are unable to function when the physical number of sectors per track is greater than 17. This becomes a problem when integrating ESDI hard sector encoded drives. The problem can be overcome by letting the controller "translate" the extra sectors per track above 17 into information that the system can recognize. In the case of the WD1005, the controller firmware changes these extra sectors to a "logical" head value that is double the physical heads used. Because of physical limitations of the controller and the system BIOS, this logical value cannot be

10

### Software,\_\_\_\_tallation Instructions for Non-Translation Mode (Cont'd.)

greater than 16, thus limiting the physical head usage to 8. When selecting a drive type during installation, the above limitations must be taken into account. The standard drive tables in most AT type machines limit the usage of most ESDI type drives. The use of software that allows the drive parameters to be changed allows full use of the drive.

1

In the non-translation mode, the controller uses the actual physical characteristics of the drive. The system BIOS drive tables will not support this feature unless changed to meet the physical requirements of the drive. Software utilities that can change parameter information overcomes this need.

#### **Low-Level Formatting**

Regardless of the mode of operation selected, translation or non-translation, the drive must be formatted with 34 sectors per track. A formatting utility called WDFMT, available from Western Digital, allows the drive to be formatted in this manner. Other utilities such as AT Advanced Diagnostics will not function properly because they are designed to work with 17 sectors per track only.

When formatting in the translation mode, the physical number of heads are formatted at 34 sectors per track. not the logical number of heads. For example, if a drive with 4 heads is being used in the translation mode, the logical head will be 8, but the 4 physical heads are formatted at 34 sectors per track.

When using the controller in the non-translation mode, the drive may be formatted to its full physical characteristics, with limits of 16 heads and 2048 cylinders.

#### DOS Usage/Partitioning

Most ESDI drives will have capacities beyond the DOS 32 megabyte limit. The use of third party software that will allow the drive to be split into multiple partitions can be used to get past the DOS limit. Compaq DOS and its associated FDISK and ENHDISK.SYS programs have the ability to create multiple partitions. New products available from Ontrack Computer Systems and Storage Dimensions have such capabilities. The Disk Manager program from Ontrack and Compaq DOS are the only ones that have been tested at this time. Both work well, providing full usage of the ESDI capacities. Finally, the SpeedStor 286 BIOS contains 34 sectors per track drive parameter tables and supports a 17 sector per track translation mode for extended (more than 16 physical head) drives. SpeedStor also provides a disketter for installation.

# WESTERN DIGITAL

## WD1005-SCS WINCHESTER DISK CONTROLLER

#### FEATURES

- CONTROLS FOUR SERIAL MODE ESDI COMPATIBLE DRIVES

- 10 MBITS/SEC

- SOFT/HARD SECTOR DRIVE

- AUTO CONFIGURATION FOR EACH DRIVE

- SUPPORTS DRIVES WITH UP TO 16 HEADS, AND 2048 CYLINDERS

- SCSI HOST TRANSFER RATE UP TO 1.67

MBYTE/SEC

- FULL FIRMWARE COMPLIANCE WITH ANSI SCSI X3T9.2 REV. 4A COMMON COMMAND SET

- MULTITHREADED OPERATIONS (MULTIPLE INITIATOR COMMAND QUEUING)

- USER SELECTABLE DEVICE ADDRESS

- LOGICAL UNIT ADDRESSING

- RESERVATIONS SUPPORTED

- PROGRAMMABLE DISCONNECT OPTIONS:

- IMMEDIATELY UPON RECEIPT OF A COMMAND

- IMMEDIATELY UPON THE START OF A

FORMAT OPERATION

- SEEKS FOR ONE OR MORE CYLINDERS

- WHEN A SECTOR OF DATA HAS BEEN TRANSFERRED FROM THE HOST TO THE DATA BUFFER

- WHEN DATA FROM THE HOST FILLS THE DATA BUFFER

- PROGRAMMABLE RECONNECT OPTIONS:

- RECONNECTS TIME-OUT

- THE DISK TRANSFERS ONE SECTOR OF DATA TO THE DATA BUFFER AND THE DATA HAS BEEN VERIFIED

- THE DISK FILLS THE DATA BUFFER (UP TO TWO SECTORS) AND THE DATA IS VERIFIED

- RECONNECT A PROGRAMMABLE NUMBER OF SECTORS PRIOR TO THE START OF DATA TRANSFER FROM THE DISK TO THE DATA BUFFER

- PROGRAMMABLE DEFECT HANDLING OPTIONS:

- AUTOMATIC DEFECT MAPPING

- A REASSIGN BLOCK COMMAND FOR POST FORMAT DEFECTS

- SPARE ALLOCATION ON SECTOR AND/OR TRACK BASIS

- SPARE SECTORS LOCATED ON SAME CYLINDER

- PROGRAMMABLE NUMBER OF SPARE SEC-TORS SPREAD EVENLY OVER THE DISK

- SUPPORTS A DEFECT LIST IN CYL/HD/SEC, CYL/HD/OFFSET FROM INDEX, OR LOGICAL SECTOR NUMBER FORMAT

- PROGRAMMABLE SECTOR SIZES (128, 256, 512, AND 1024 BYTES PER SECTOR)

- PROGRAMMABLE GAP SIZES

- PROGRAMMABLE INTERLEAVE (INCLUDING 1:1)

- 56-BIT ECC FOR WINCHESTER DATA ERROR DETECTION AND CORRECTION

- EXTENDED SENSE CAPABILITY

- SCSI BUS PARITY OPTION

- SCSI COMPATIBLE BUS HOST INTERFACE

- FULL HARDWARE COMPLIANCE WITH ANSI SCSI X3T9.2 SPECIFICATIONS

- SELF-TEST DIAGNOSTICS

#### DOCUMENT SCOPE

The intent of this document is to provide the reader with an overview of the WD1005-SCS. Following is a list of documents that will provide the reader with all necessary information:

- WD1005-SCS Winchester Disk Controller OEM Manual (DOC. 79-000062)

- SCSI Specification ANSI X3T9.2

- SCSI Commond Command Set Specification ANSI X3T9.2/85-82 REV. 4A

- Enhanced Small Device Interface Specification Rev. D July 1, 1984

- WD5010-10 Winchester Controller.....Data Sheet

- WD11C00-14 56-Bit ECC Support Device.....Data

Sheet

- WD11C00-19 SCSI Protocol Support Device...Data Sheet

- WD50C20-10 ESDI Adapter Device .... Data Sheet

#### DESCRIPTION

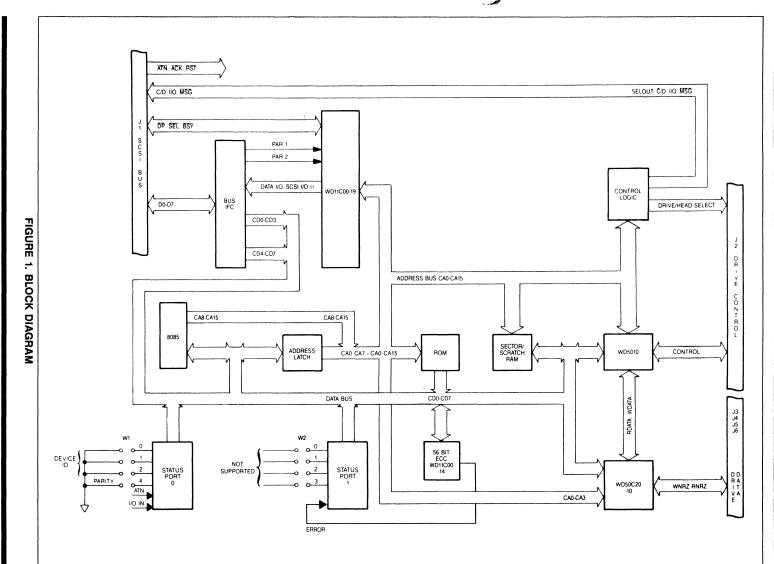

The WD1005-SCS is a single-board Winchester Disk Controller, designed to support up to four Enhanced Small Device Interface (ESDI) compatible disk drives and to interface with the Small Computer System Interface (SCSI) bus. Bus operation is in compliance with the ANSI X3T9.2 SCSI Specification.

Commands directed to the drives are executed by the WD1005-SCS. All communications and data transfers to and from the Host take place via the SCSI bus, in accordance with SCSI protocol.

The WD1005-SCS functions only as a Target device in the SCSI environment. The WD1005-SCS supports disconnect/reconnect operations, allowing for more efficient SCSI bus utilization. SCSI bus arbitration is provided allowing for multiple initiator operation. In addition, the WD1005-SCS Controller board supports one-to-one disk interleave, i.e., fully sustained operations on sequential disk access.

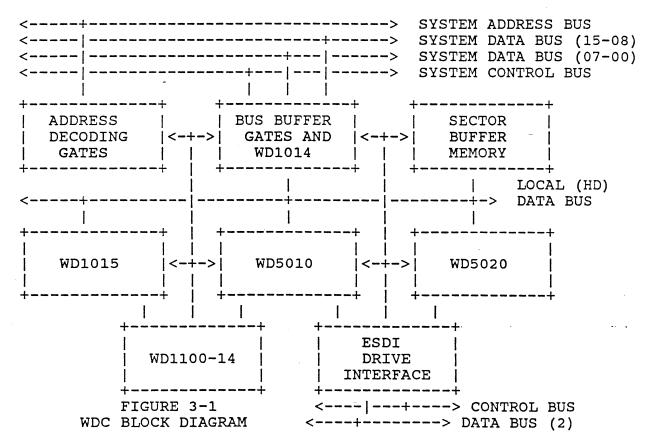

The WD1005-SCS is based on a proprietary chip set, consisting of the WD5010-10, WD11C00-14, WD50C20-10, and WD11C00-19 LSI devices, designed specifically for Winchester/SCSI interface. Extensive error detection and correction, as well as data recovery techniques for disk errors, are incorporated within the controller's design. The 56-Bit error correction circuitry resides in the WD11C00-14. The WD11C00-19 is used to control all communications and data transfer.

#### ARCHITECTURE

The WD1005-SCS architecture allows an optimum amount of design functions to reside within the board. This is accomplished by creating a unified internal bus

structure, whereby all major LSI devices share the same buses.

As illustrated in Figure 1, the WD1005-SCS contains five major VLSI devices:

- 8085 microprocessor

- WD5010-10 Winchester Controller

- WD50C20-10 ESDI Adapter Device

- WD11C00-14 56-Bit ECC Support Device

- WD11C00-19 SCSI Protocol Support Device

#### **Control Processor**

The Control Processor is an 8085 microprocessor used for the main board control and is supported by a 27128 (16K X 8) EPROM and a (2K X 8) 2016 static RAM device. The WD1005-SCS Controller's unique architecture facilitates two major functions:

- Support of the SCSI bus application

- 1:1 interleave capability

#### WD5010-10 Winchester Disk Controller

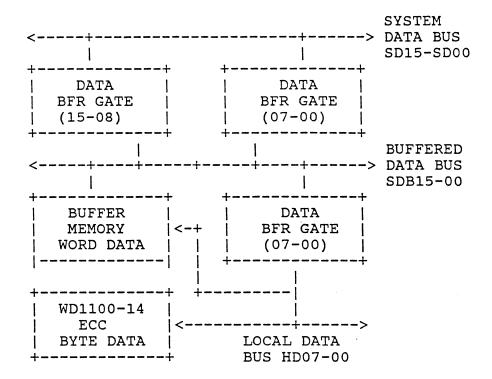

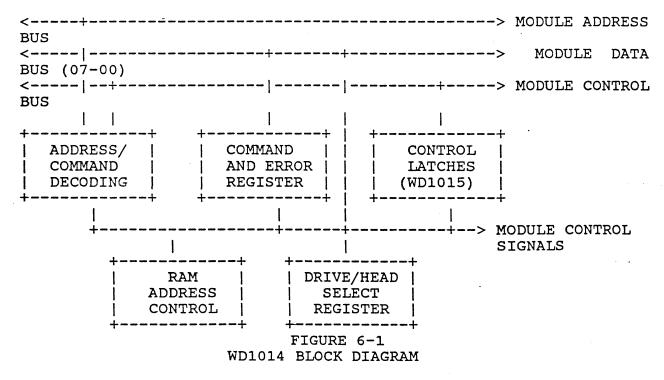

The primary function of the WD5010-10 is to control data transfer between the disk and the Sector Buffer, after the on-board control processor has positioned the selected head over the desired track. The WD5010-10 receives the parameters and commands from the control processor via the CD0 through CD7 bus.

In addition, the WD11C00-14 assists the WD5010-10 in performing the 56-Bit error detection and correction on all data transfers from the disk.

#### WD50C20 ESDI Adapter Device

The WD50C20 is an LSI device, implemented in a 3-micron, high-speed CMOS process. It converts the MFM Read and Write Data presented by the WD5010 Interface into NRZ Read and Write Data for use by the ESDI Drive. The WD50C20 also controls communications to serial mode ESDI drives. A serial communication transfer error is reported to the on board 8085 which will make a maximum of 3 attempts to correct the error.

#### WD11C00-19 SCSI Protocol Support Device

The WD11C00-19 is a 40-pin LSI device designed to provide five major support functions:

- Memory address generation

- Data transfer (read/write) control

- Arbitration

- Parity checker/generator

- · SCSI Bus control

All SCSI commands are read, format converted, and then issued to the WD5010-10 for execution.

.

ω

.

#### SPECIFICATION

**Host Interface**

Туре Cable length Termination all signals

Addressing

#### Dri

| Drive Interface           |                                                                                              |

|---------------------------|----------------------------------------------------------------------------------------------|

| Cylinders per drive       | Programmable up to 2048                                                                      |

| Bytes per sector          | Programmable (128, 256, 512, 1024)                                                           |

| Sectors per track         | Programmable                                                                                 |

| Heads per cylinder        | Programmable up to 16                                                                        |

| Drives                    | 4                                                                                            |

| Data transfer rate        | 10 Mbps                                                                                      |

| Sectoring                 | Soft and hard                                                                                |

| CRC polynomial            | $X^{16} + X^{12} + X^5 + 1$                                                                  |

| ECC polynomial - 56-Bit   | $X^{56} + X^{52} + X^{50} + X^{43} + X^{41} + X^{34} + X^{30} + X^{26} + X^{24} + X^8 + X^0$ |

| Cable length:             |                                                                                              |

| Control (daisy-chained)   | 10 ft (3 m) max.                                                                             |

| Data (radially connected) | 10 ft (3 m) max.                                                                             |

| Termination:              | All signals 220 ohms to +5 Volts, 330 ohms to ground                                         |

| Control                   | On last drive in chain                                                                       |

| Data                      | On WD1005-SCS                                                                                |

Socketed 220/330 ohm resistor pack

Jumper selectable (0 through 7)

#### Electrical

Voltage and Current

+5 Vdc ±5% @ 2.0 amps nominal 2.5 amps max

#### SCSI electrical description

When measured at the SCSI bus device connection, each signal driven by an SCSI device has the following output characteristics:

Signal assertion = 0 to 0.5 Vdc

Minimum driver output capability = 48 mA (sinking) @ 0.5 Vdc

SCSI

20 ft (6 m) max.

Default = 0

220 ohms to +5 Volts, 330 ohms to ground

Measured at the connector, each signal has the following input characteristics: 0 to 0.8 Vdc

2.0 to 5.00 Vdc

-0.4 mA @ 0.4 Vdc

8 inches (20.3 cm)

Signal asserted Maximum total input load Signal de-asserted

**Physical Dimensions**

Length Width Height (including board, components and leads)

5.75 inches (14.6 cm) 0.75 inches (1.9 cm)

#### Environment

Airflow

Temperature: Operating range Storage range Relative Humidity: Operating range Storage range Maximum wet bulb Altitude: Operating range

0°C (32°F) to 55°C (131°F) -40°C (-40°F) to 60°C (140°F)

8% to 80% non-condensing 5% to 95% non-condensing 24°C (75°F)

0 to 10,000 ft (3000 m) 150 linear ft/min @ 0.25 inches from component surfaces

#### INTERFACE ORGANIZATION

The WD1005-SCS is designed to be mounted directly onto a 5.25" Winchester-type hard disk drive. It contains six vertical-header connectors, a 34-pin edge connector, and one power connector located along the peripheral edges of the board:

- Four Winchester drive data connectors J3, J4, J5, J6

- Two Winchester drive control connectors, one verticalheader and one edge connector. These connectors are mutually exclusive and are both referred to as J2.

- Power connector J7

- Host interface connector J1

The WD1005-SCS accommodates up to four Winchester hard disk drives. The control cable is daisy-chained to each of the four drives; and the drive data cables, which carry differential signals, are radially connected. Table 1 defines the WD1005-SCS connectors and a source for the mating connectors on the associated cables.

| CONNECTOR        | ONNECTOR INTERFACE FUNCTION EQUIVALE |                            |  |  |

|------------------|--------------------------------------|----------------------------|--|--|

| J3, J4<br>J5, J6 | Drive Data<br>(Radially-connected)   | Burndy #FRS20BS            |  |  |

| J2               | Drive Control<br>(Daisy-chained)     | Burndy #FRS34BS or #FRE34B |  |  |

| J7               | Power                                | AMP 1-4840424-0            |  |  |

| J1               | Host Interface<br>(SCSI Bus )        | Burndy #FRS50BS            |  |  |

#### TABLE 1. CONNECTOR NUMBERS

#### HOST INTERFACE CONNECTOR

The WD1005-SCS interfaces with the Host via J1, a 50-pin vertical header connector mounted on 0.1 inch centers. The cable used should be a flat ribbon or twisted pair cable of not more than 20 feet in length. Cable termina-

tion is via 220/330 ohm resistor packs in position Z1 and Z2. Each signal is terminated to +5 volts, via 220 ohms and 330 ohms to ground. Table 2 provides the connector pin descriptions and its bus signals.

| SIG.<br>GND.    | SIG.<br>PIN     | MNEMONIC                      | SIGNAL<br>NAME                                         | 1/O<br>* | FUNCTION                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|-----------------|-------------------------------|--------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>thru<br>17 | 2<br>thru<br>18 | DB0<br>thru<br>DB7 and<br>DBP | DATA BUS 0<br>thru<br>DATA BUS 7<br>DATA BUS<br>PARITY | I/O      | These signals comprise the SCSI tri-state,<br>bi-directional data bus used to transfer commands,<br>status, and data. $\overline{DB0}$ through $\overline{DB7}$ are used for<br>Target device selection and arbitration. $\overline{DBP}$ is odd<br>parity for $\overline{DB0}$ through $\overline{DB7}$ and is not valid during<br>the arbitration process. |

| 19              | 20              | GND                           | GROUND                                                 |          |                                                                                                                                                                                                                                                                                                                                                              |

| 21              |                 | GND                           | GROUND                                                 |          |                                                                                                                                                                                                                                                                                                                                                              |

|                 | 22              | NOT CON                       |                                                        |          |                                                                                                                                                                                                                                                                                                                                                              |

| 23              | 24              | GND                           | GROUND                                                 |          |                                                                                                                                                                                                                                                                                                                                                              |

| 25              |                 | GND                           | GROUND                                                 |          |                                                                                                                                                                                                                                                                                                                                                              |

|                 | 26              | NOT CON                       |                                                        |          |                                                                                                                                                                                                                                                                                                                                                              |

| 27              | 28              | GND                           | GROUND                                                 |          |                                                                                                                                                                                                                                                                                                                                                              |

| 29              | 30              | GND                           | GROUND                                                 |          |                                                                                                                                                                                                                                                                                                                                                              |

\* The I/O column is in relation to the WD1005-SCS and not the Host.

| SIG.<br>GND. | SIG.<br>PIN | MNEMONIC | SIGNAL<br>NAME                                                                                                                                    | 1/O<br>*                                                                                       | FUNCTION                                                                                                                                                                                                                                                     |  |  |

|--------------|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 31           | 32          | ATN      | ATTENTION                                                                                                                                         | I                                                                                              | Asserted by the Host to indicate that a message is ready for the WD1005-SCS. This message is read by the WD1005-SCS at its convenience by performing a Message Out Phase.                                                                                    |  |  |

| 33           | 34          | GROUND   |                                                                                                                                                   |                                                                                                |                                                                                                                                                                                                                                                              |  |  |

| 35           | 36          | BSY      | BUSY                                                                                                                                              | 1/O                                                                                            | When asserted as an output, BSY indicates to the<br>Host that the WD1005-SCS is busy executing a com-<br>mand. When asserted as an input, BSY indicates<br>to the WD1005-SCS that the bus is busy with another<br>device and must wait to reselect the Host. |  |  |

| 37           | 38          | ACK      | ACKNOWLEDGE I ACK is the Host's acknowledgment of REC<br>a data transfer handshake. It sign<br>WD1005-SCS that the Host has accepted<br>transfer. |                                                                                                | ACK is the Host's acknowledgment of REQ during<br>a data transfer handshake. It signals the<br>WD1005-SCS that the Host has accepted the data<br>transfer.                                                                                                   |  |  |

| 39           | 40          | RST      | RESET                                                                                                                                             | RESET I When asserted at least 25 usec, RST plac<br>WD1005-SCS into its initial power-up state |                                                                                                                                                                                                                                                              |  |  |

| 41           | 42          | MSG      | MESSAGE         O         Asserted during the Message Byte Transfe           Used with Ī/O and C/D to indicate the type of                        |                                                                                                |                                                                                                                                                                                                                                                              |  |  |

| 43           | 44          | SEL      | SELECT         I/O         Used by the Host to select the WD1005-SCS the WD1005-SCS to reselect the Host.                                         |                                                                                                |                                                                                                                                                                                                                                                              |  |  |

| 45           | 46          | C/D      | CONTROL/DATA                                                                                                                                      | 0                                                                                              | $\overline{C}/D$ along with $\overline{I}/O$ and $\overline{MSG}$ Indicates to the Host whether control or data is on the bus.                                                                                                                               |  |  |

|              |             |          |                                                                                                                                                   |                                                                                                | $\overline{C}/D - 0 = Control$<br>- 1 = Data                                                                                                                                                                                                                 |  |  |

|              |             |          |                                                                                                                                                   |                                                                                                | Control is defined as command, status, or message.                                                                                                                                                                                                           |  |  |

| 47           | 48          | REQ      | REQUEST                                                                                                                                           |                                                                                                |                                                                                                                                                                                                                                                              |  |  |

| 49           | 50          | Ī/Ο      | INPUT/OUTPUT                                                                                                                                      | 0                                                                                              | Indicates the direction of transfer between the Host and the WD1005-SCS.                                                                                                                                                                                     |  |  |

|              |             |          |                                                                                                                                                   |                                                                                                | $\overline{I}/O - 0 =$ Input to the Host<br>- 1 = Output from the Host                                                                                                                                                                                       |  |  |

TION (Continued)

\* The I/O column is in relation to the WD1005-SCS and not Host.

#### WINCHESTER DRIVE CONTROL CONNECTOR

The WD1005-SCS supports the Serial Mode ESDI Drive control protocol. The drive control signals may be con-nected to either the 34-pin vertical header mounted on a 0.1 inch center, or the 34-pin edge connector. Control signals are common to all drives and are daisy-chained on a single connector J2. The cable used should be a flat ribbon or twisted-pair not more than 10 feet in length.

The control signals are to be terminated at the last drive in the daisy-chain with a 220/330 ohm resistor pack. Each control signal is connected to +5 volts with the 220 chm resistor and to ground with 330 ohms.

The drive control connector J2 pin description is provided in Table 3.

| SIG.<br>GND. | SIG.<br>PIN | MNEMONIC | SIGNAL<br>NAME                                                                                 | 1/0                                                                                                                                                                                                         | FUNCTION                                                                                                                                                                       |  |  |  |

|--------------|-------------|----------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1            | 2           | HS3      | HEAD<br>SELECT 3                                                                               | 0                                                                                                                                                                                                           | HS3 is one of four Head Select signals decoded the drive to select one of 16 R/W heads.                                                                                        |  |  |  |

| 3            | 4           | HS2      | HEAD<br>SELECT 2                                                                               | 0                                                                                                                                                                                                           | One of four Head Select signals decoded by t drive to select one of 16 R/W heads.                                                                                              |  |  |  |

| 5            | 6           | WG       | WRITE GATE                                                                                     | 0                                                                                                                                                                                                           | WG is asserted when valid data is to be written<br>the disk. WD1005-SCS de-asserts this signal wh<br>a ATN is detected.                                                        |  |  |  |

| 7            | 8           | CSD      | CONFIG DATA<br>STATUS                                                                          | STATUS       tion Data or Status plus a Parity bit re         the WD1005-SCS. The transfer of this of control of the XREQ/XACK handshake         TRANSFER       I         XACK/XREQ form the transfer hands |                                                                                                                                                                                |  |  |  |

| 9            | 10          | XACK     | TRANSFER<br>ACKNOWLEDGE                                                                        | RANSFER I XACK/XREQ form the transfer handshake                                                                                                                                                             |                                                                                                                                                                                |  |  |  |

| 11           | 12          | ATN      | ATTENION                                                                                       | 1                                                                                                                                                                                                           | ATN informs the WD1005-SCS of a fault conditi                                                                                                                                  |  |  |  |

| 13           | 14          | HSO      | HEAD<br>SELECT 0                                                                               | 0                                                                                                                                                                                                           | One of four Head Select signals decoded by drive to select one of 16 R/W heads.                                                                                                |  |  |  |

| 15           | 16          | SCT/AMF  | SECTOR/<br>ADDRESS<br>MARK FOUND                                                               | RESS of a sector.                                                                                                                                                                                           |                                                                                                                                                                                |  |  |  |

| 17           | 18          | HS1      | HEAD<br>SELECT 1                                                                               | O One of four Head Select signals decoded drive to select one of 16 R/W heads.                                                                                                                              |                                                                                                                                                                                |  |  |  |

| 19           | 20          | INDEX    | INDEX PULSE I Indicates the start of a track and is us synchronization point during formatting |                                                                                                                                                                                                             | Indicates the start of a track and is used both a synchronization point during formatting and a tir out mechanism for retries. This signal pulses or for each disk revolution. |  |  |  |

| 21           | 22          | DRDY     | DRIVE READY                                                                                    | 1                                                                                                                                                                                                           | Informs the WD1005-SCS that the drive motor to speed.                                                                                                                          |  |  |  |

| 23           | 24          | XREQ     | TRANSFER<br>REQUEST                                                                            | 0                                                                                                                                                                                                           | XREQ/XACK form the transfer handshake for CSD and CMD transfers between the drive and WD1005-SCS.                                                                              |  |  |  |

| 25           | 26          | DSEL 1   | DRIVE<br>SELECT 1                                                                              | 0                                                                                                                                                                                                           | DSEL 1 is one of three signals encoded for de selection.                                                                                                                       |  |  |  |

| 27           | 28          | DSEL 2   | DRIVE<br>SELECT 2                                                                              | 0                                                                                                                                                                                                           | DSEL 2 is one of three signals encoded for de selection.                                                                                                                       |  |  |  |

| 29           | 30          | DSEL 3   | DRIVE<br>SELECT 3                                                                              | 0                                                                                                                                                                                                           | DSEL 3 is one of three signals encoded for dr selection.                                                                                                                       |  |  |  |

| 31           | 32          | RG       | READ GATE                                                                                      | 0                                                                                                                                                                                                           | When asserted, RG enables data to be read fr the disk.                                                                                                                         |  |  |  |

| 33           | 34          | CMD      | COMMAND                                                                                        | 0                                                                                                                                                                                                           | The CMD signal transmits the 16 command bits p<br>a parity bit to the drive. This transfer is control<br>by the XREQ/XACK handshake.                                           |  |  |  |

č., 1

A second

#### WINCHESTER DRIVE DATA CONNECTOR

The data is differential in nature and must be radially connected to each drive with its own cable, drive 0 to J3 and drive 1 to J4 etc. It should be a flat ribbon cable, or twisted pair, not more than 10 ft. in length. The connector is a 20-pin vertical header on .1 inch center.

#### TABLE 4. DRIVE DATA CONNECTORS - J3, J4, J5, J6

| SIG.<br>GND. | SIG.<br>PIN | 1/0 | SIGNAL<br>NAME                      |

|--------------|-------------|-----|-------------------------------------|

|              | 1           |     | Drive Selected                      |

| 2            |             |     | NC                                  |

|              | 3           |     | Command Complete                    |

|              | 4           |     | Address Mark Enable                 |

|              | 5           |     | NC                                  |

| 6            |             |     | GND                                 |

|              | 7           |     | + Write Clock                       |

|              | 8           |     | <ul> <li>Write Clock</li> </ul>     |

|              | 9           |     | NC                                  |

|              | 10          |     | + Read/Ref. Clock                   |

|              | 11          |     | <ul> <li>Read/Ref. Clock</li> </ul> |

| 12           |             |     | GND                                 |

|              | 13          | 0   | + Write Data                        |

|              | 14          | 0   | – Write Data                        |

| 15           |             |     | GND                                 |

| 16           |             |     | GND                                 |

|              | 17          | I   | + Read Data                         |

|              | 18          | 1   | <ul> <li>Read Data</li> </ul>       |

| 19           |             |     | GND                                 |

| 20           |             |     | NC                                  |

#### POWER CONNECTOR

A 4-pin connector (J7) is provided for power input to the WD1005-SCS board.

| PIN         | VOLTAGE            |

|-------------|--------------------|

| 1<br>2<br>3 | NC<br>GND.<br>GND. |

| 4           | +5 V               |

#### **COMMAND DESCRIPTION**

The commands are separated into three Groups, group 0 standard commands, group 1 extended commands, and group 7 diagnostic commands. Commands in group 0 and 7 are received from the Host in a six-byte Command Descriptor Block format, while commands in group 1 are received in a 10-byte format.

A list of the commands supported by the WD1005-SCS, along with the two Command Description Block formats, follows. A detailed description of the commands is provided in the OEM Manual.

#### TABLE 5. COMMAND LIST

| COMMAND                                                                                                                                                                                                                                      | OP<br>CODE                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| TEST DRIVE READY<br>REZERO UNIT<br>REQUEST SENSE<br>FORMAT UNIT<br>REASSIGN BLOCKS<br>READ<br>WRITE<br>SEEK<br>INQUIRY<br>MODE SELECT<br>RESERVE UNIT<br>RELEASE UNIT<br>RELEASE UNIT<br>MODE SENSE<br>RECEIVE DIAGNOSTIC<br>SEND DIAGNOSTIC | 00<br>01<br>03<br>04<br>07<br>08<br>0A<br>0B<br>12<br>15<br>16<br>17<br>1A<br>1C<br>1D |

| READ CAPACITY                                                                                                                                                                                                                                | 25                                                                                     |

| READ EXTENDED                                                                                                                                                                                                                                | 28                                                                                     |

| WRITE EXTENDED                                                                                                                                                                                                                               | 2A                                                                                     |

| SEEK EXTENDED                                                                                                                                                                                                                                | 2B                                                                                     |

| VERIFY                                                                                                                                                                                                                                       | 2F                                                                                     |

| READ DEFECT DATA                                                                                                                                                                                                                             | 37                                                                                     |

| WRITE BUFFER                                                                                                                                                                                                                                 | 3B                                                                                     |

| READ BUFFER                                                                                                                                                                                                                                  | 3C                                                                                     |

| READ LONG                                                                                                                                                                                                                                    | E5                                                                                     |

| WRITE LONG                                                                                                                                                                                                                                   | E6                                                                                     |

#### **GROUP 0 AND 7 COMMAND DESCRIPTION BLOCK**

The Command Description Block format used by the Group 0 and 7 commands is provided in Figure 2.

| BYTE |                                                                                    |                                                                                                                 |   | BIT        | rs       |    |   |   |  |  |  |

|------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---|------------|----------|----|---|---|--|--|--|

|      | 7                                                                                  | 6                                                                                                               | 5 | 4          | 3        | 2  | 1 | 0 |  |  |  |

| 0    |                                                                                    | OPERATION CODE                                                                                                  |   |            |          |    |   |   |  |  |  |

| 1    | LUN LOGICAL BLOCK ADDRESS (MSB), FORMAT<br>DATA, COMPLETE LIST, DEFECT LIST FORMAT |                                                                                                                 |   |            |          | π  |   |   |  |  |  |

| 2    |                                                                                    |                                                                                                                 | L | OGICAL BLO | CK ADDRE | SS |   |   |  |  |  |

| 3    |                                                                                    | LOGICAL BLOCK ADDRESS (LSB) OR INTERLEAVE (MSB)                                                                 |   |            |          |    |   |   |  |  |  |

| 4    | N                                                                                  | NUMBER OF BLOCKS, NUMBER OF REQUEST SENSE BYTES,<br>NUMBER OF BYTES, INTERLEAVE (LSB), OR PARAMETER LIST LENGTH |   |            |          |    |   |   |  |  |  |

| 5    | ERTY                                                                               | 0                                                                                                               | 0 | 0          | 0        | 0  | 0 | 0 |  |  |  |

#### FIGURE 2. GROUP 0 AND 7 COMMAND DESCRIPTION BLOCK

|  | Operation Code                                          | Bits 7-5 designate the command Group, 0 or 7.                                                                                                |                                                                                               | value indicates the number of blocks to be transferred.                                                                                                                                      |  |

|--|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|  |                                                         | Bits 4-0 identify the command func-<br>tion within Group 0 or 7, e.g., Read<br>or Write.                                                     | Requested Sense<br>Bytes                                                                      | The number of bytes indicates the<br>length of data allocated by the Hos<br>for the returned sense information<br>The WD1005-SCS only returns<br>sense data in the Extended Sense<br>format. |  |

|  | LUN                                                     | Specifies the Logical Unit Number<br>of the attached drive. May be any<br>quantity 0 through 3.                                              |                                                                                               |                                                                                                                                                                                              |  |

|  | Logical Block<br>Address                                | Specifies the Logical Block Address (LBA) where an operation is to begin.                                                                    |                                                                                               | A requested sense byte count of zer<br>defaults to a data transfer of four<br>bytes. A requested count greater                                                                               |  |

|  | Format Data,<br>Complete List,<br>Defect List<br>Format | Used in conjunction with the Format<br>Commands:                                                                                             |                                                                                               | than zero results in a data transi<br>equal to the request, but never mo                                                                                                                     |  |

|  |                                                         | <ul> <li>Format Data. Bit 4 of byte 1.</li> <li>Complete List. Bit 3 of byte 1.</li> <li>Defect List. Bits 2, 1, and 0 of byte 1.</li> </ul> | Number of Bytes                                                                               | than eighteen bytes.<br>Used by the Inquiry Command, the<br>Number of Bytes indicates the data                                                                                               |  |

|  | Interleave                                              | The interleave factor is used by For-<br>mat Commands. The disk may be                                                                       |                                                                                               | length allocated by the Host for th<br>Returned Sense data.                                                                                                                                  |  |

|  |                                                         | formatted at a 1:1 ratio with the max-<br>imum interleave equal to the number<br>of sectors-per-track minus one.                             | Parameter List<br>Length                                                                      | The only valid length for proper<br>operation is 30 (decimal). Zero<br>represents a No-Operation                                                                                             |  |

|  |                                                         | Byte 3 must be zero, byte 4 can be<br>any interleave number from 0                                                                           |                                                                                               | condition.                                                                                                                                                                                   |  |

|  |                                                         | through 128. If an interleave factor of<br>0 is used, the WD1005-SCS uses a<br>default interleave value of 2.                                | ERTY                                                                                          | Disk error retry bit. When reset, in-<br>dicates a request for a retry opera-<br>tion. (Used if retries are supported<br>by a specific command.)                                             |  |

|  | Number of Blocks                                        | Indicates the number of contiguous<br>logical data blocks to be transferred                                                                  | GROUP 1 COMMAND DESCRIPTION BLOCK                                                             |                                                                                                                                                                                              |  |

|  |                                                         | by an operation. When zero, 256 blocks are transferred. Any other                                                                            | The Command Description Block format used by the<br>Group 1 commands is provided in Figure 3. |                                                                                                                                                                                              |  |

|  |                                                         |                                                                                                                                              |                                                                                               |                                                                                                                                                                                              |  |

¢

|      |                                                                               | BITS                        |   |   |   |   |   |   |

|------|-------------------------------------------------------------------------------|-----------------------------|---|---|---|---|---|---|

| BYTE | 7                                                                             | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

| 0    |                                                                               | OPERATION CODE              |   |   |   |   |   |   |

| 1    |                                                                               | LUN                         |   | 0 | 0 | 0 | 0 | 0 |

| 2    |                                                                               | LOGICAL BLOCK ADDRESS (MSB) |   |   |   |   |   |   |

| 3    | LOGICAL BLOCK ADDRESS                                                         |                             |   |   |   |   |   |   |

| 4    | LOGICAL BLOCK ADDRESS                                                         |                             |   |   |   |   |   |   |

| 5    | LOGICAL BLOCK ADDRESS (LSB)                                                   |                             |   |   |   |   |   |   |

| 6    | 0                                                                             | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |

| 7    | BUFFER TRANSFER LENGTH, NUMBER OF BLOCKS (MSB)                                |                             |   |   |   |   |   |   |

| 8    | BUFFER TRANSFER LENGTH, NUMBER OF BLOCKS (LSB)<br>OR PARTIAL MEDIUM INDICATOR |                             |   |   |   |   |   |   |

|      |                                                                               |                             |   |   |   |   |   |   |

| 9    | ERTY                                                                          | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |

FIGURE 3. GROUP 1 COMMAND DESCRIPTION BLOCK FORMAT

| Operation Code            | Bits 7-5 designate command Group 1.<br>Bits 4-0 identify the function of a<br>command within Group 1, e.g., Read                                                                                                                    | РМІ                                                                                                                                              | Partial Medium Indicator. Bit 0 of byte 8 used in the Read Capacity Command.                                                                                                                          |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                           | Extended, Write Extended, or Seek<br>Extended to be performed.                                                                                                                                                                      |                                                                                                                                                  | 0 = Controller returns address of<br>the last block on the LUN                                                                                                                                        |  |

| LUN                       | Specifies the Logical Unit Number<br>of the attached drive. May be any<br>quantity 0 through 3.                                                                                                                                     |                                                                                                                                                  | device.<br>1 = Controller returns the address<br>of the last block, prior to a<br>cylinder boundary following the                                                                                     |  |

| Logical Block<br>Address  | Specifies the Logical Block Address where an operation is to begin.                                                                                                                                                                 |                                                                                                                                                  | Block Address given by the<br>Host. For example, Block Ad-                                                                                                                                            |  |