| <b>ж. ж</b> | • |                                          |

|-------------|---|------------------------------------------|

|             |   | PUBLICATIONS<br>UDPATE                   |

|             |   | Operating System/3 (OS/3)                |

|             |   | Assembler<br>Programmer Reference        |

|             |   | (System 80)                              |

|             |   | (System 80)<br>For Series 90 see UP-8227 |

|             |   | UP-8914-D                                |

This Library Memo announces the release and availability of Updating Package A to "SPERRY® Operating System/3 (OS/3) Assembler Programmer Reference", UP-8914.

The Operating System/3 (OS/3) assembler translates a symbolic language into computer instructions such as how to store data and how to retrieve it. This manual provides a quick-reference guide for the experienced assembler programmer, summarizing the use of basic assembly language (BAL) instructions.

This update documents a change to the ICM instruction.

110

Copies of Updating Package A are now available for requisitioning. Either the updating package only or the complete manual with the updating package may be requisitioned by your local Sperry representative. To receive only the updating package, order UP-8914–D. To receive the complete manual, order UP-8914.

ŧ

|       | LIBRARY MEMO ONLY               | LIBRARY MEMO AND ATTACHMENTS                                                          | THIS SHEET IS                 |

|-------|---------------------------------|---------------------------------------------------------------------------------------|-------------------------------|

|       | Mailing Lists<br>BZ, CZ, and MZ | Mailing Lists BOO, B18, 28U, and 29U.<br>(Package A to UP-8914,<br>5 pages plus Memo) | Library Memo for<br>UP-8914–D |

|       |                                 |                                                                                       | RELEASE DATE:                 |

| 11261 | Rev. 11/83                      |                                                                                       | January, 1985                 |

| • • , • |  | and has been had been |  |

|---------|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         |  | PUBLICATIONS<br>UPDATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|         |  | Operating System/3 (OS/3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|         |  | Assembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|         |  | Programmer Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|         |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|         |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|         |  | UP-8914-C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

This Library Memo announces the release and availability of Updating Package C to "SPERRY Operating System/3 (OS/3) Assembler Programmer Reference", UP-8914.

This update contains corrections or clarifications applicable to features present in the OS/3 Assembler prior to the 8.2 release.

Copies of Updating Package C are now available for requisitioning. Either the updating package only or the complete manual with the updating package may be requisitioned by your local Sperry representative. To receive only the updating package, order UP-8914–C. To receive the complete manual, order UP-8914.

| LIBRARY MEMO ONLY              | LIBRARY MEMO AND ATTACHMENTS                                                         | THIS SHEET IS                 |

|--------------------------------|--------------------------------------------------------------------------------------|-------------------------------|

| Mailing Lists<br>BZ, CZ and MZ | Mailing Lists B00, B18, 28U, and 29U<br>(Package C to UP-8914<br>27 pages plus Memo) | Library Memo for<br>UP-8914–C |

|                                |                                                                                      | RELEASE DATE:                 |

This Library Memo announces the release and availability of Updating Package B to "SPERRY UNIVAC Operating System/3 (OS/3) Assembler Programmer Reference", UP-8914.

This update documents the following enhancements to the assembler for release 8.0:

- The display of final error messages on the console

- The addition of two privileged instructions (Get IORB, Put IORB)

- An additional warning message when using continuation characters with macroinstructions

This update also includes minor technical corrections to material applicable to the assembler prior to release 8.0.

Copies of Updating Package B are now available for requisitioning. Either the updating package only, or the complete manual with the updating package may be requisitioned by your local Sperry Univac representative. To receive only the updating package, order UP-8914–B. To receive the complete manual, order UP-8914.

LIBRARY MEMO ONLY LIBRARY MEMO AND ATTACHMENTS THIS SHEET IS

Mailing Lists BZ, CZ and MZ Mailing Lists B00, B18, 28U, and 29U (Package B to UP-8914, 98 pages plus Memo) Library Memo for UP-8914-B

RELEASE DATE:

September, 1982

. .

## UNISYS OS/3

Assembler **Programming Reference Manual**

**Relative to Release** Level 9.0

Priced Item

August 1987

Printed in U S America UP-8914

.

## UNISYS

# OS/3

Assembler

**Programming Reference Manual**

Copyright© 1987 Unisys Corporation All Rights Reserved Unisys is a trademark of Unisys Corporation. Previous Title: OS/3 Assembler Programmer Reference

Relative to Release Level 9.0

August 1987

Printed in U S America UP-8914

Priced Item

NO WARRANTIES OF ANY NATURE ARE EXTENDED BY THE DOCUMENT. Any product and related material disclosed herein are only furnished pursuant and subject to the terms and conditions of a duly executed Program Product License or Agreement to purchase or lease equipment. The only warranties made by Unisys, if any, with respect to the products described in this document are set forth in such License or Agreement. Unisys cannot accept any financial or other responsibility that may be the result of your use of the information in this document or software material, including direct, indirect, special or consequential damages.

You should be very careful to ensure that the use of this information and/or software material complies with the laws, rules, and regulations of the jurisdictions with respect to which it is used.

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

FASTRAND, SPERRY, SPERRY, UNIVAC, SPERRY, SPERRY UNIVAC, UNISCOPE, UNISERVO, UNIS, UNIVAC, and A are registered trademarks of Unisys Corporation. ESCORT, PAGEWRITER, PIXIE, PC/IT, PC/HT, PC/microIT, SPERRYLINK, and USERNET are additional trademarks of Unisys Corporation. MAPPER is a registered trademark and service mark of Unisys Corporation. CUSTOMCARE is a service mark of Unisys Corporation.

PSS 1 Update E

#### PAGE STATUS SUMMARY

ISSUE: Update E – UP-8914 RELEASE LEVEL: 9.0 Forward

| Part/Section         | Page<br>Number         | Update<br>Level | Part/Section | Page<br>Number                 | Update<br>Level             | Part/Section     | Page<br>Number          | Update<br>Level |

|----------------------|------------------------|-----------------|--------------|--------------------------------|-----------------------------|------------------|-------------------------|-----------------|

| Cover                |                        | E               | Section 2    | 90                             | В                           | Appendix A       | Title Page<br>1 thru 9  | Orig.           |

| Title Page/Disclaime | -                      | E*              | (cont)       | 91 thru 94<br>95<br>96 thru 98 | Orig <i>.</i><br>B<br>Orig. |                  | 10<br>11                | B<br>A<br>B     |

| PSS                  | 1                      | E               |              | 99<br>100 thru 109             | B<br>Orig.                  |                  | 12 thru 14<br>15        | Orig.<br>B      |

| Preface              | 1                      | Orig.           |              | 110<br>111 thru 116            | B<br>Orig.                  |                  | 16, 17                  | Orig.           |

| Contents             | 1, 2<br>3              | Orig.<br>B      |              | 117<br>118 thru 138            | A<br>Orig.                  | Appendix B       | Title Page<br>1 thru 5  | Orig.<br>Orig.  |

|                      | 4<br>5                 | A<br>B          |              | 138a<br>139                    | B<br>Orig.                  |                  | 6, 7                    | С               |

|                      | 6                      | Orig.           |              | 140                            | A                           | Appendix C       | Title Page<br>1 thru 13 | Orig.           |

|                      | 7<br>8 thru 10         | A<br>Orig.      |              | 141, 142<br>143                | Orig.<br>B                  |                  | 1 thru 13               | Orig.           |

|                      | 11                     | С               |              | 144 thru 157<br>158            | Orig.<br>B                  | Appendix D       | Title Page<br>1, 2      | Orig.<br>Orig.  |

| Section 1            | Title Page<br>1        | Orig.<br>C      |              | 159, 160<br>161                | Orig.<br>B                  |                  | 3 thru 5<br>6 thru 8    | B<br>Orig.      |

|                      | 2<br>3                 | Orig.<br>B      |              | 162<br>163                     | Orig.<br>B                  | Appendix E       |                         |                 |

|                      | 4, 5                   | Orig.           | i            | 164 thru 170<br>171            | Orig.<br>B                  |                  | Title Page<br>1 thru 5  | Orig.<br>Orig.  |

| Section 2            | Title Page<br>1 thru 5 | Orig.<br>Orig.  |              | 172 thru 174<br>175, 176       | Orig.<br>B                  | Appendix F       | Title Page              | Orig.           |

|                      | 6                      | B               |              | 177, 178                       | Orig.                       |                  | 1 thru 6                | Orig.           |

|                      | 7 thru 9<br>10, 11     | Orig.<br>B      |              | 179<br>180 thru 182            | A<br>Orig.                  | Glossary         | Title Page              | Orig.           |

|                      | 10, 11<br>12 thru 19   | Drig.           |              | 183                            | в                           | Glossary         | 1 thru 9                | Orig.           |

|                      | 20 thru 25<br>26       | C<br>B          |              | 184 thru 187<br>188            | Orig.<br>B                  |                  | 10, 11<br>12 thru 17    | B<br>Orig.      |

|                      | 20                     | Б<br>Orig.      |              | 189                            | Orig.                       |                  | 12 (INU 17              | Ong.            |

|                      | 28 thru 31             | С               |              | 190                            | A                           | User Comment For | m                       |                 |

|                      | 32 thru 40<br>41, 42   | Orig.<br>B      |              | 190a<br>191                    | A<br>Orig.                  |                  |                         |                 |

|                      | 43, 44                 | Orig.           |              | 192                            | B                           |                  |                         |                 |

|                      | 45                     | в               |              | 192a                           | В                           |                  |                         |                 |

|                      | 46 thru 52             | Orig.           |              | 193 thru 196                   | Orig.<br>B                  |                  |                         |                 |

|                      | 53<br>54 thru 65       | A<br>Orig.      |              | 197<br>198 thru 204            | в<br>Orig.                  |                  |                         |                 |

|                      | 66                     | A               |              |                                | 9.                          |                  |                         |                 |

|                      | 67                     | В               | Section 3    | Title Page                     | Orig.                       |                  |                         |                 |

|                      | 68                     | Orig.           |              | 1                              | Orig.                       |                  |                         |                 |

|                      | 69, 70<br>70           | В               |              | 2<br>3 thru 14                 | B<br>Orig.                  |                  |                         |                 |

|                      | 70a<br>71, 72          | B<br>B          |              | 15                             | B                           |                  |                         |                 |

|                      | 73                     | C               |              | 16                             | Orig.                       |                  |                         |                 |

|                      | 74                     | Orig.           |              | 17                             | в                           |                  |                         |                 |

|                      | 75                     | D               |              | 18 thru 31                     | Orig.                       |                  |                         |                 |

|                      | 76                     | А               |              |                                |                             |                  |                         |                 |

|                      | 76a                    | А               | Section 4    | Title Page                     | Orig.                       |                  |                         |                 |

|                      | 77 thru 80             | Orig.           |              | 1 thru 10<br>11, 12            | Orig.<br>B                  |                  |                         |                 |

|                      | 81<br>92 thru 89       | B<br>Orig       |              | 11, 12<br>13 thru 20           | в<br>Orig.                  |                  |                         |                 |

|                      | 82 thru 89             | Orig.           |              | 21                             | B                           |                  |                         |                 |

|                      |                        |                 | 1            | 22 thru 29                     | Orig.                       |                  |                         |                 |

\*New pages

All the technical changes are denoted by an arrow  $(\Longrightarrow)$  in the margin. A downward pointing arrow  $(\Downarrow)$  next to a line indicates that technical changes begin at this line and continue until an upward pointing arrow (\$) is found. A horizontal arrow (⇔) pointing to a line indicates a technical change in only that line. A horizontal arrow located between two consecutive lines indicates technical changes in both lines or deletions.

#### Preface

This programmer reference manual is one in a series designed to be used as a quick-reference document for programmers familiar with the SPERRY UNIVAC Operating System/3 (OS/3). This particular manual describes the basic assembly language (BAL) instructions, directives, and macro definition statements that allow the user to write assembly language programs and procedure definitions (procs).

No extensive introductory information or examples of use are provided. This type of information is presented in the current versions of two other assembler manuals: an introduction to the assembler, UP-8030, and an assembler user guide, UP-8913.

The information contained in this manual is presented as follows:

#### SECTION 1. GENERAL INFORMATION

Provides a brief overview of the assembler, the job control stream requirements of the assembler, and the conventions that must be observed when reading and writing assembler code.

#### SECTION 2. BAL APPLICATION INSTRUCTIONS

Describes each of the BAL application instructions recognized by the OS/3 assembler. These descriptions are presented in alphabetic order by their operation code mnemonic.

#### SECTION 3. BAL DIRECTIVES

Describes each of the directives that are used to control the operation of the assembler. These directives are also presented in alphabetic order by their operation code mnemonic.

#### SECTION 4. BAL MACRO DEFINITION STATEMENTS

Describes the macro definition statements used to write and call procedure definitions. These statements are presented in alphabetic order.

#### APPENDIXES

Contain assembler references, character set code references, math references, source corrections, and system variable symbols helpful to the BAL programmer.

#### GLOSSARY

Defines the terms, expressions, and abbreviations peculiar to the assembler.

.

#### Contents

#### PAGE STATUS SUMMARY

PREFACE

#### CONTENTS

#### 1. **GENERAL INFORMATION** ASSEMBLER OVERVIEW 1-1 JOB CONTROL REQUIREMENTS 1-1 ASSEMBLER CODING FORM 1-1 Symbol Field 1-2 **Operation Field** 1-2 **Operand Field** 1-2 **Comment Field** 1-2 **Continuation Column** 1-3 **Sequence Field** 1-3 **READING INSTRUCTION NOTATIONS** 1-3 Assembler Application Instruction Notations 1-3 Notation Rules and Meanings . 1-4

#### 2. BAL APPLICATION INSTRUCTIONS

| Α   | 2-1 |

|-----|-----|

| AD  | 2-2 |

| ADR | 2-3 |

| AE  | 2-4 |

| AER | 2-5 |

| АН  | 2-6 |

| AI   |   |   |   | 2-7              |

|------|---|---|---|------------------|

| AL   |   |   |   | 2-8              |

| ALR  |   |   |   | 2-10             |

| AP   |   |   |   | 2-11             |

| AR   |   |   |   | 2-13             |

| AU   |   |   |   | 2-14             |

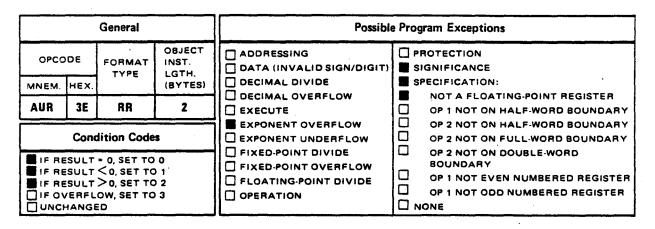

| AUR  |   |   |   | 2-15             |

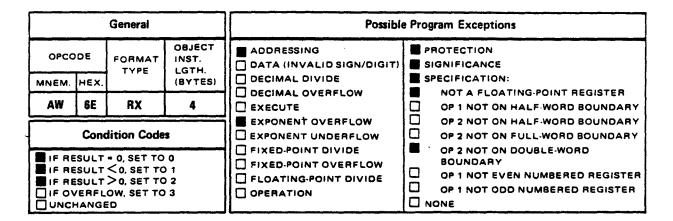

| AW   |   |   |   | 2-16             |

| AWR  |   |   |   | 2-17             |

| BAL  |   |   |   | 2-18             |

| BALR |   |   |   | 2-19             |

| BC   | • |   |   | 2-20             |

| BCR  |   |   |   | 2-22             |

| ВСТ  |   |   |   | 2-23             |

| BCTR |   |   |   | 2-24             |

| вхн  |   |   | • | 2-25             |

| BXLE |   | · |   | 2-26             |

| C    |   |   |   | 2-27             |

| CD   |   |   |   | 2-28             |

| CDR  |   |   |   | 2-2 <del>9</del> |

| CE   |   |   |   | 2-30             |

| CER  |   |   | · | 2-31             |

| сн   |   |   |   | 2-32             |

| CL   |   |   |   | 2-33             |

| CLC  |   |   |   | 2-34             |

| CLCL |   |   |   | 2-35             |

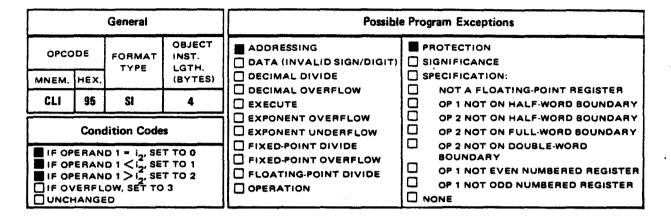

| CLI  |   |   |   | 2-36             |

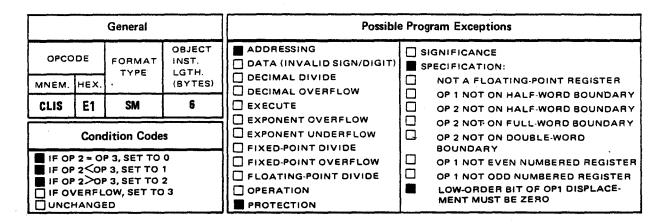

| CLIS |   |   |   | 2-37             |

UP-8914

Contents 2

|                  | ASSEIVIDLEN | Opuate D                           |

|------------------|-------------|------------------------------------|

|                  |             |                                    |

| CLM              |             | 2-38                               |

| CLR              |             | 2-40                               |

| CLRCH            |             | 2-41                               |

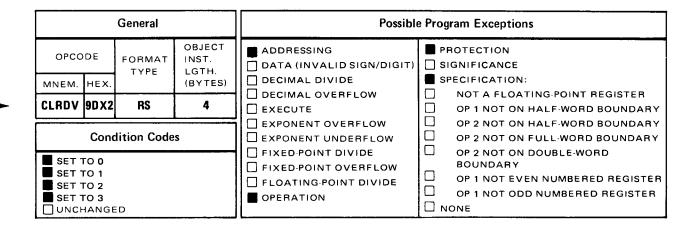

| CLRDV            |             | 2-42                               |

| СР               |             | 2-43                               |

| CR               |             | 2–44                               |

| CSM              |             | 2-45                               |

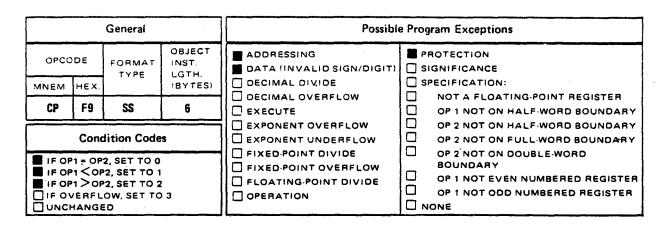

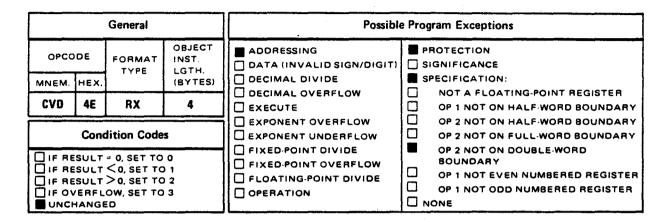

| СVВ              |             | 2–46                               |

| CVD              |             | 2-48                               |

| D                |             | 2–49                               |

| DD               |             | 2-50                               |

| DDR              |             | 2-51                               |

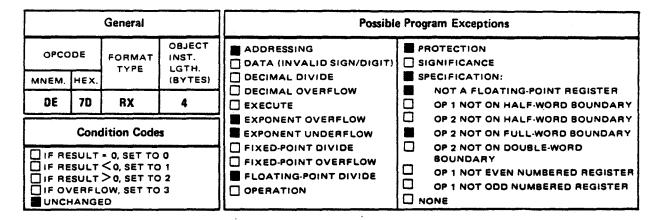

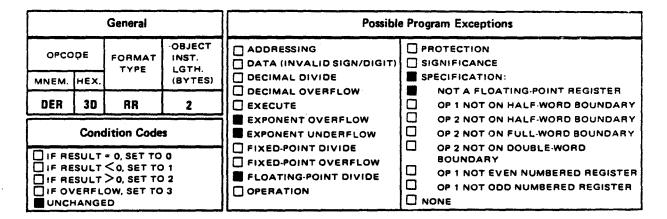

| DE<br>DEQ<br>DER |             | <b>2-52</b><br>2-53<br><b>2-54</b> |

| DP               |             | 2-55                               |

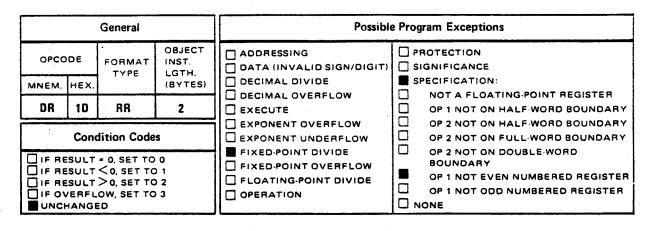

| DR               |             | 2-57                               |

| ED               |             | 2-58                               |

| EDMK             |             | 2-63                               |

| EIO<br>EN9<br>EX |             | 2-65<br>2-66<br>2-67               |

| EXD              |             | 2-69                               |

| GRB              |             | 2-70                               |

| HDR              |             | <b>2</b> -70a                      |

| HDV              |             | 2-71                               |

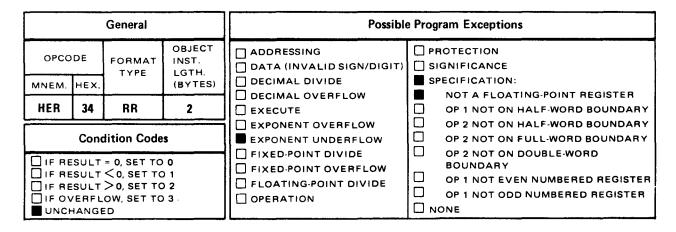

| HER              |             | 2-72                               |

| HPR              |             | 2-73                               |

| IC               |             | 2-74                               |

SPERRY UNIVAC OS/3

ASSEMBLER

Contents 3 Update B

•

· •

| ICM  | 2-75  |

|------|-------|

| IPL  | 2-76  |

| ISK  | 2–76a |

| L    | 2-77  |

| LA   | 2-78  |

| LCDR | 2-79  |

| LCER | 2-80  |

| LCHR | 2-81  |

| LCR  | 2-82  |

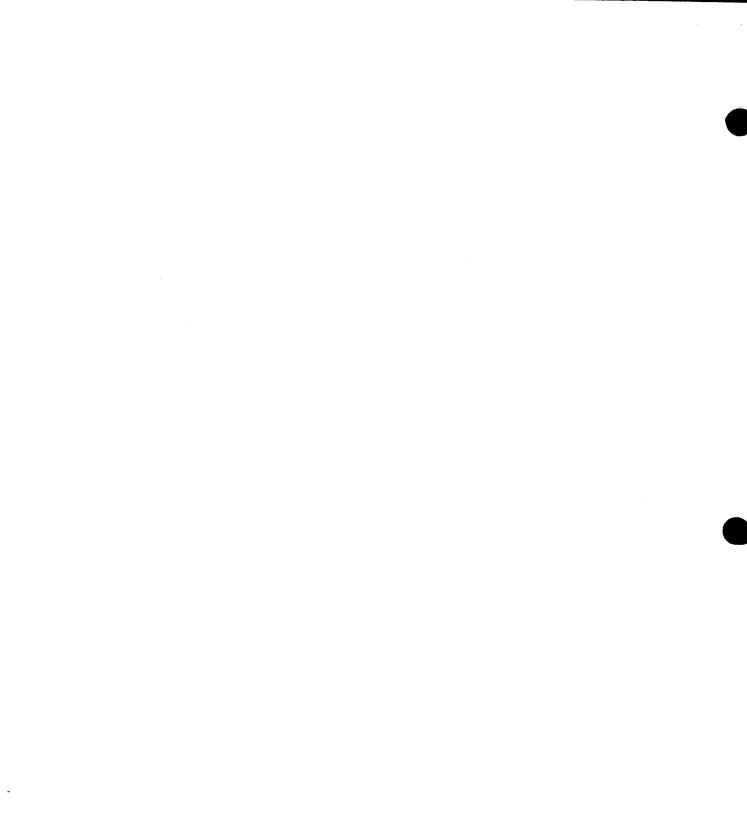

| LCTL | 2-83  |

| LD   | 2-84  |

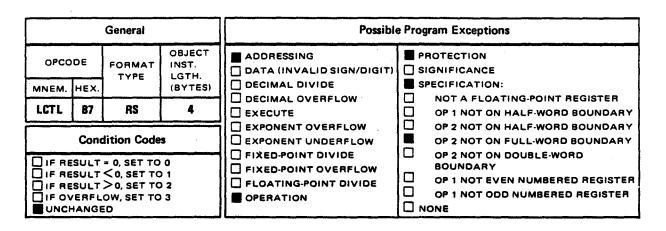

| LDA  | 2-85  |

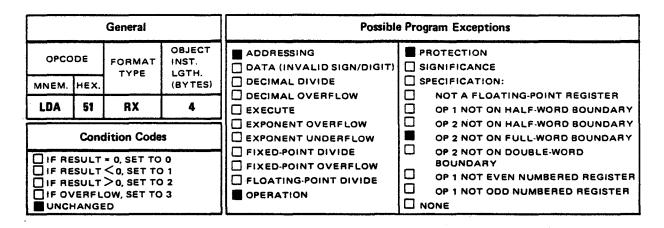

| LDR  | 2-86  |

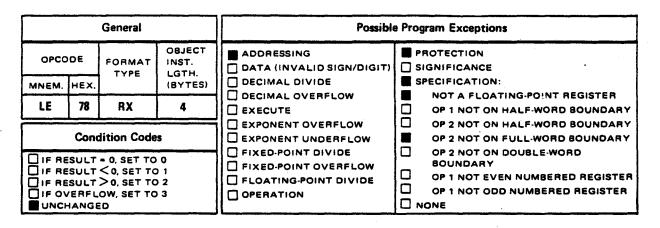

| LE   | 2-87  |

| LER  | 2-88  |

| LH   | 2-89  |

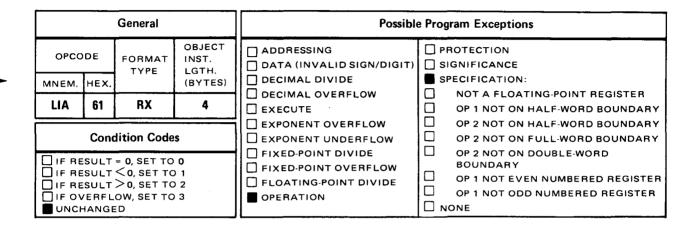

| LIA  | 2-90  |

| LM   | 2-91  |

| LNDR | 2-93  |

| LNER | 2–94  |

| LNR  | 2-95  |

| LPDR | 2-96  |

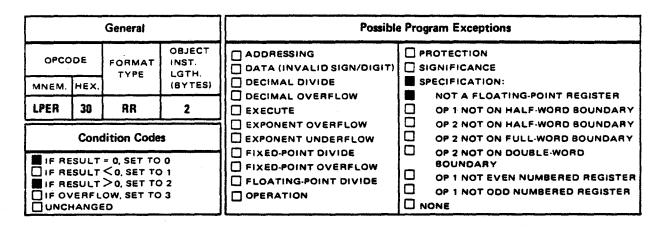

| LPER | 2-97  |

| LPR  | 2–98  |

| LPSW | 2–99  |

| LR   | 2-100 |

| LRC  | 2-101 |

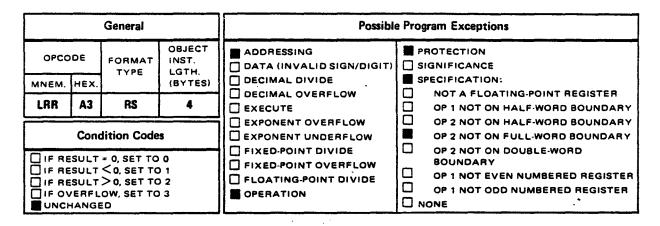

| LRR  | 2-102 |

| LTDR | 2-103 |

.

.

| LTER             | 2-104                   |

|------------------|-------------------------|

| LTR              | 2-105                   |

| Μ                | 2-106                   |

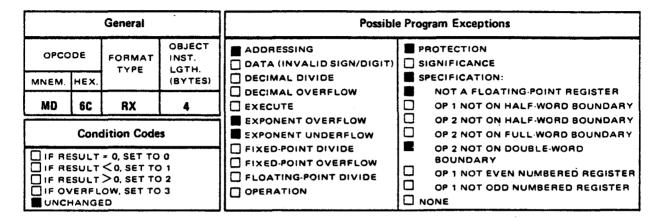

| MD               | 2–108                   |

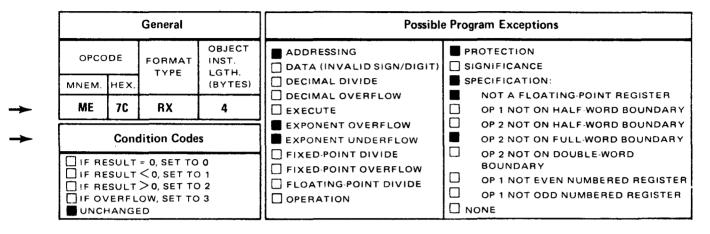

| MDR .            | 2–109                   |

| 1E               | 2–110                   |

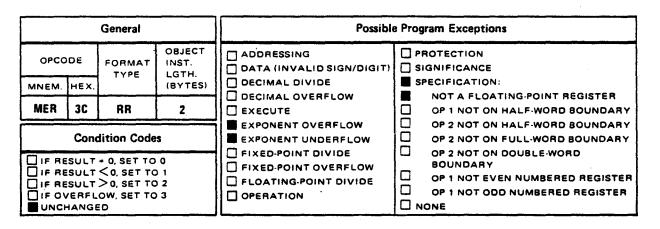

| /IER             | 2-111                   |

| лн               | 2-112                   |

| ΛΙΟ              | 2–113                   |

| ЛР               | 2-114                   |

| MR<br>MSS<br>MVC | 2-116<br>2-1/7<br>2-118 |

| MVCL             | 2–119                   |

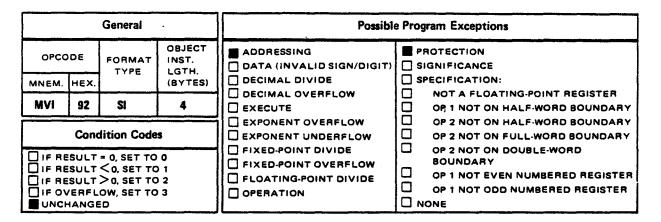

| MVI              | 2–120                   |

| MVN              | 2-121                   |

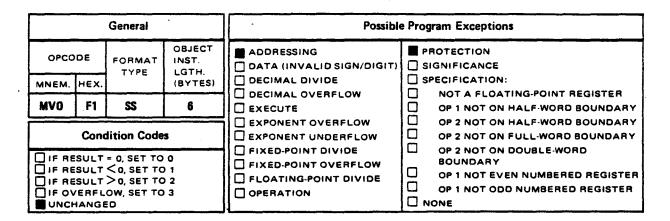

| MVO              | 2-122                   |

| ۸vz              | 2-123                   |

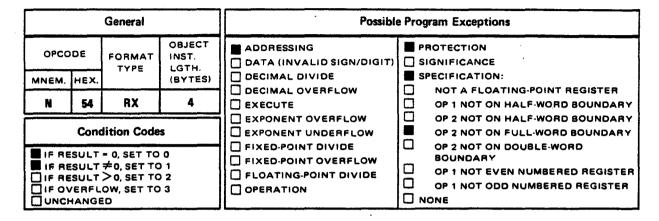

| N                | 2–124                   |

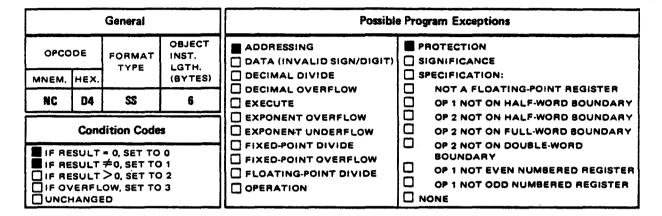

| NC               | 2–126                   |

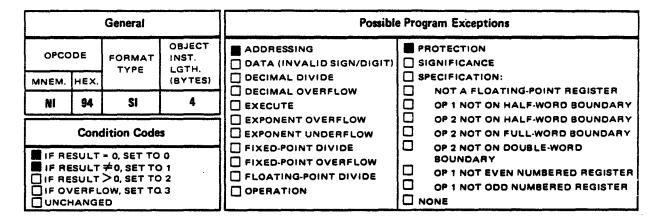

| 41               | 2-128                   |

| NR               | 2-130                   |

| 0                | 2-131                   |

| oc               | 2–133                   |

| וס               | 2-135                   |

| OR               | 2-137                   |

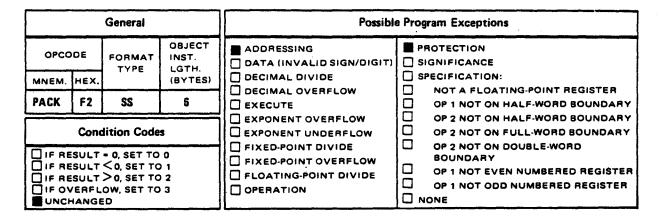

| РАСК             | 2–138                   |

| PRB              | 2-138a                  |

| RESET            | 2–139                   |

• •

+

| S    | 2-140 |

|------|-------|

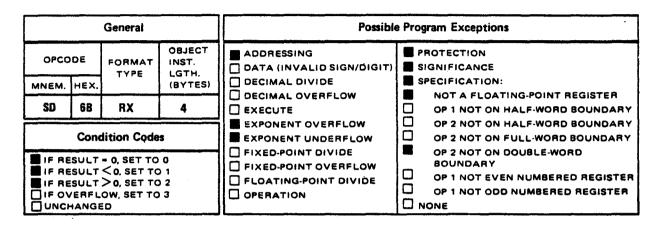

| SD   | 2-141 |

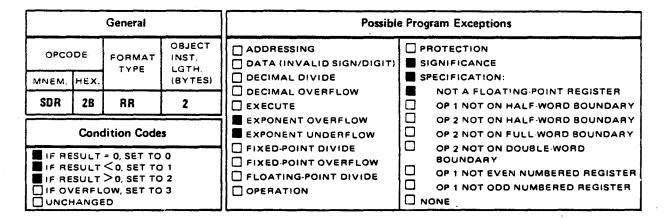

| SDR  | 2–142 |

| SDV  | 2–143 |

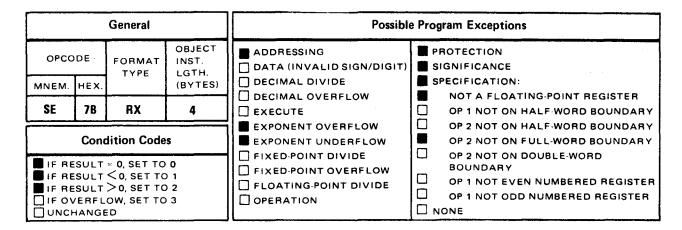

| SE   | 2-144 |

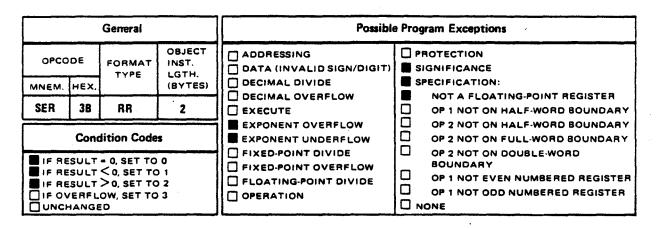

| SER  | 2-145 |

| SH   | 2–146 |

| SHL  | 2–147 |

| SL   | 2-149 |

| SLA  | 2-151 |

| SLDA | 2-153 |

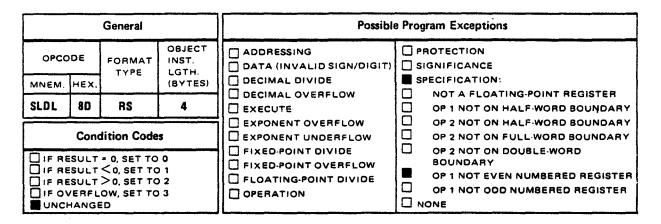

| SLDL | 2-155 |

| SLL  | 2-156 |

| SLM  | 2-157 |

| SLR  | 2-158 |

| SP   | 2–159 |

| SPM  | 2-161 |

| SR   | 2-162 |

| SRA  | 2–163 |

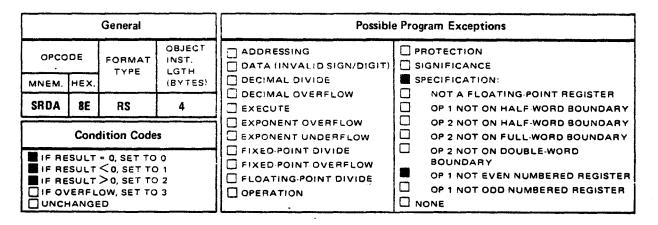

| SRDA | 2-165 |

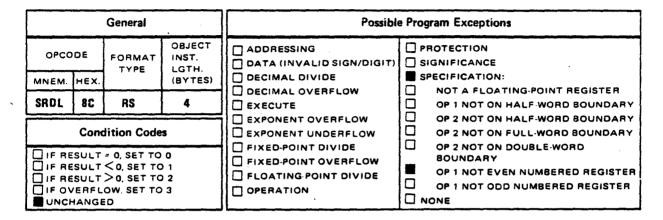

| SRDL | 2-166 |

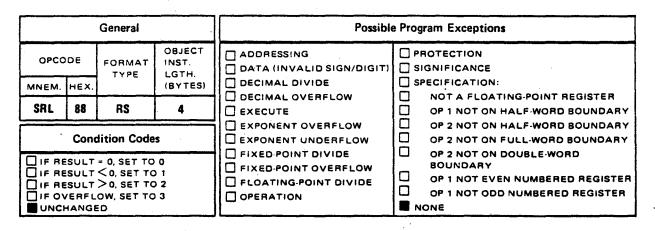

| SRL  | 2–167 |

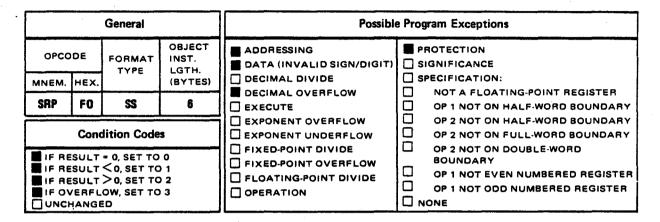

| SRP  | 2-168 |

| SSK  | 2-170 |

| SSM  | 2-171 |

| SSTM | 2-172 |

| ST   | 2-173 |

| STC  | 2-174 |

.

.

| STCM  |   | 2-175              |

|-------|---|--------------------|

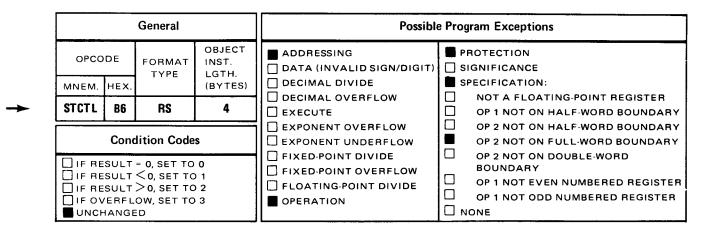

| STCTL |   | 2–176              |

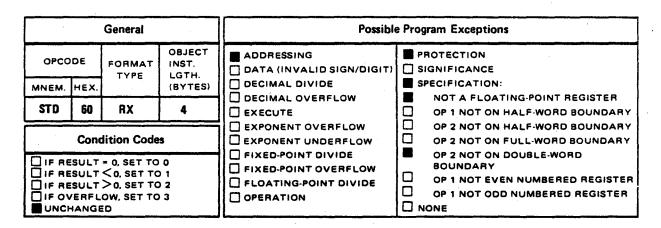

| STD   |   | 2-177              |

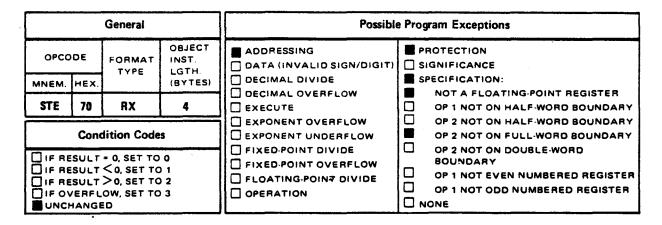

| STE   |   | 2-178              |

| STEP  | · | 2-179              |

| STH   |   | 2-180              |

| STM   |   | 2-181              |

| STR   |   | 2-183              |

| STRR  |   | 2–184              |

| STS . |   | 2-185              |

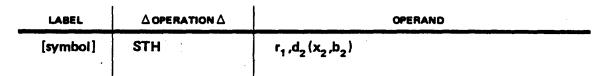

| SU    |   | 2-186              |

| SUR   |   | 2-187              |

| SVC   |   | 2-188              |

| SW    |   | 2-189              |

| SWR   |   | 2-1 <del>9</del> 0 |

| ТМ    |   | 2-191              |

| TMS   |   | 2–192              |

| TR    |   | 2–193              |

| TRT   |   | 2–195              |

| TS    |   | 2–197              |

| UNPK  |   | 2-198              |

| x     |   | 2-199              |

| xc    |   | 2-200              |

| XI    |   | 2-202              |

| XR    |   | 2-203              |

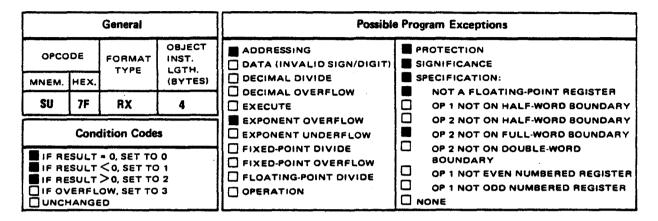

| ZAP   |   | 2-204              |

•

3. BAL DIRECTIVES

| ccw                  |   |   | 3-1    |

|----------------------|---|---|--------|

| CNOP                 |   |   | 3-2    |

| СОМ                  |   |   | 3-3    |

| СОРҮ                 |   |   | 3-5    |

| CSECT                |   |   | 3-6    |

| DC (Floating Point)  |   |   | 3-7    |

| DC (Standard Format) |   |   | 3–9    |

| DROP                 |   |   | 3-10   |

| DS                   |   | • | 3-11   |

| DSECT                |   | • | 3-12   |

| EJECT                |   |   | 3-13   |

| END                  |   |   | 3-14   |

| ENTRY                |   |   | 3-15   |

| EQU                  |   |   | 3-16   |

| EXTRN                |   |   | 3-17   |

| ICTL                 |   |   | 3-18   |

| ISEQ                 | • |   | 3-19   |

| LTORG                |   |   | 3–20   |

| OPSYM                |   |   | . 3-21 |

| ORG                  |   |   | 3-23   |

| PRINT                |   |   | 3-24   |

| PUNCH                |   | • | 3-25   |

| REPRO                |   |   | 3-26   |

| SPACE                |   |   | 3-27   |

| START                |   |   | 3-28   |

| TITLE                |   |   | 3–29   |

| USING                |   |   | 3–30   |

.

### 4. BAL MACRO DEFINITION STATEMENTS

| ACTR                   |   | 4-1  |

|------------------------|---|------|

| AGO                    |   | 4-2  |

| AIF                    |   | 4-3  |

| ANOP                   |   | 4-4  |

| DO                     |   | 4-5  |

| END                    |   | 4–6  |

| ENDO                   |   | 4-7  |

| GBL                    |   | 4-8  |

| GBLA                   |   | 4-8  |

| GBLB                   |   | 48   |

| GBLC                   |   | 4-8  |

| LCL                    |   | 4-9  |

| LCLA                   |   | 4-9  |

| LCLB                   | • | 4–9  |

| LCLC                   |   | 4–9  |

| MACRO                  |   | 4–10 |

| Macro Call Instruction |   | 4-11 |

| MEND                   |   | 4-13 |

| MEXIT                  |   | 4-14 |

| MNOTE                  |   | 4-15 |

| Model Statement        |   | 4–16 |

| NAME                   |   | 4-17 |

| PNOTE                  |   | 4–18 |

| PROC                   |   | 4–19 |

| Prototype Statement    |   | 4–21 |

| SET                    |   | 4-22 |

| SETA                   |   | 4-25 |

#### SPERRY UNIVAC OS/3 ASSEMBLER

| SETB |  |  | 4-26 |

|------|--|--|------|

| SETC |  |  | 4-29 |

#### **APPENDIXES**

#### A. ASSEMBLER REFERENCES

#### **B. CHARACTER SET CODE REFERENCES**

#### C. MATH REFERENCES

| FLOATING-POINT MATH           | C-10 |

|-------------------------------|------|

| Floating-Point Addition       | C-11 |

| Floating-Point Division       | C-12 |

| Floating-Point Multiplication | C-13 |

#### D. SOURCE CORRECTIONS

| GENERAL |  | D-1 |

|---------|--|-----|

| PARAM   |  | D-2 |

| REC     |  | D-6 |

| SEQ     |  | D-7 |

| SKI     |  | D-8 |

#### E. SYSTEM VARIABLE SYMBOLS

#### F. ATTRIBUTE REFERENCES

| Count Attributes<br>Number Attributes | F-5 |

|---------------------------------------|-----|

| Integer Attributes                    | F~5 |

| Scale Attributes                      | F-5 |

| Length Attributes                     | F-4 |

| Type Attributes                       | F-2 |

#### GLOSSARY

#### **USER COMMENT SHEET**

•

#### TABLES

| A-1. | Instruction Formats                                           | A-1  |

|------|---------------------------------------------------------------|------|

| A-2. | Instruction Repertoire                                        | A-3  |

| A-3. | Extended Mnemonic Branch Codes                                | A-12 |

| A-4. | Summary of Operators                                          | A–13 |

| A-5. | Comparison of Terms                                           | A-13 |

| A-6. | Characteristics of Constant and Storage Definition Type Codes | A-14 |

| A-7. | PROC, MACRO, and Call Instruction Comparison                  | A–15 |

| A-8. | Check-off Table Terms                                         | A–16 |

| B-1. | Punched-Card, ASCII, and EBCDIC Codes                         | B-1  |

| B–2. | EBCDIC Chart                                                  | B–6  |

| B3.  | ASCII Character Code Chart                                    | B7   |

| C-1. | Comparison of Numeric Expressions                             | C-1  |

| C–2. | Hexadecimal-Decimal Integer Conversion                        | C-2  |

| C-3. | Hexadecimal-Decimal Fraction Conversion                       | C-6  |

| C-4. | Hexadecimal Addition and Subtraction Table                    | C-7  |

| C5.  | Powers of 16                                                  | C-8  |

| C-6. | Powers of 2                                                   | C-9  |

| F-1. | Valid Attribute Reference Applications                        | F–2  |

| F-2. | Attributes of Symbols                                         | F–3  |

### 1. General Information

Ŧ

#### ASSEMBLER OVERVIEW

The SPERRY UNIVAC Operating System/3 (OS/3) assembler permits highly efficient, machine-instruction programs to be written in symbolic form. The assembler consists of an instruction translator and a macro facility. The instruction translator converts symbolic instructions to machine instructions on a one-to-one basis. The macro facility allows a subroutine to be coded, assigned a name, stored in a permanent library, and then to be included in a source program by a simple reference to the subroutine name in a single instruction. The macro facility greatly reduces the amount of repetitive coding required for routines used frequently within a program or in many different programs.

The assembler accepts source-image input from punched cards, magnetic tape, and disk. It reads source statements and produces a relocatable object module. The object module can then be linked to other object modules to form one load module that is suitable for loading and execution on your SPERRY system.

A set of assembler directives is provided to aid the user in program organization and in directing the course of an assembly. All assembly runs produce a printed listing of source code, object code, label cross-references, cross-references, and (when necessary) error diagnostics. The final error statement message, which gives the total number of statements flagged in the assembly, is also displayed on the console upon completion of the assembly.

#### **JOB CONTROL REQUIREMENTS**

| LAB<br>1    | EL     |            | 16       | DPERAND        | Δ                                            | COMMENTS                                     |

|-------------|--------|------------|----------|----------------|----------------------------------------------|----------------------------------------------|

| // J        | OIB ;  | obin,a,m,e |          |                |                                              | NAME J.O.B.                                  |

| /./. A      | SIMLO  |            | <u></u>  |                |                                              | ASSEMBLE, LINK, EXECUTIE,                    |

| /\$         | لللبيل |            |          |                |                                              | , , START OF DATA                            |

| <u>}</u>    |        |            |          |                |                                              |                                              |

| <u>huu</u>  |        |            | LING     |                | <u></u>                                      |                                              |

|             | SiovR  |            | DE PROGI | 2AM CLARKE     |                                              |                                              |

| i fi u u    | للبل   |            |          |                |                                              |                                              |

|             | للعب   |            |          | <u></u>        |                                              |                                              |

| <u>/*</u>   | للبل   |            |          |                | <u> </u>                                     | I IENO OF DATA                               |

| 18          |        |            | <u></u>  | <u>uluu</u> du | <u> </u>                                     | I I IENIO OF JOB                             |

| <u>11 E</u> | LIN.   | ┟┟┶┶╍┙┠    | +        | <u></u>        | <u></u>                                      | I GLOSE CARD READER                          |

|             |        |            |          |                | <u>, ,                                  </u> |                                              |

|             |        |            | <u>_</u> |                |                                              |                                              |

|             | للبل   |            |          |                |                                              | <u>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,</u> |

| ىبىت        | للللل  |            | <u></u>  |                | <u></u>                                      |                                              |

|             | ччч    |            | <u></u>  |                |                                              | <u>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,</u> |

The job control statements required to assemble, linkage edit, and execute are:

#### ASSEMBLER CODING FORM

Using an assembler coding form eases the job of writing the program, for the programmer and for the keypunch operator, who must prepare the punched card deck from the written program. Columns 9 and 15 are ruled to remind the programmer that the symbol and operation fields must be terminated by at least one blank.

#### Symbol Field

The first eight columns of the assembler coding form may contain a symbol. An asterisk (\*) indicates that this coding line does not contain instructions and that it contains only comments. The rules for using the symbol field are:

- 1. The symbol must start in column 1.

- 2. The symbol must begin with an alphabetic character or special letter.

- 3. The symbol must not exceed eight characters in length.

- 4. The symbol must not contain embedded blanks or other special characters.

- 5. The field must be terminated by a blank.

#### **Operation Field**

The operation code is written in the operation field (columns 10 through 14). These codes specify the operation to be performed. The rules for using this field are:

- 1. The operation code must not contain embedded blanks.

- 2. The operation code must be written exactly as shown in the list of mnemonics for instructions, directives, and procs or macroinstructions.

- 3. The operation field must be terminated by a blank.

- 4. The operation code must not start in column 1.

#### **Operand Field**

The operand field begins in column 16 and usually ends in or before column 71. The operands that form part of the assembler statements are written in this field. The rules for using this field are:

- 1. The operand field is terminated by a blank that is not enclosed by apostrophes.

- 2. Operands may be continued onto the next line by placing a nonblank character in column 72. Up to two continuation lines are permitted.

- 3. Continuation lines start in column 16.

#### **Comment Field**

Operand specification is usually completed by column 40, thus leaving columns 41 through 71 free for comments. There must be at least one blank between the end of the operand specification and the start of the comments. Long comments can be entered by coding an \* in column 1.

#### **Continuation Column**

When the operand specification is continued onto the next line, a nonblank character must be written in column 72. Do not confuse this with continuing a comment. An operand specification can be continued for a total of three lines. The second and third continuation lines start in column 16.

#### **Sequence Field**

Columns 73 through 80 may be used for entering sequence numbers. This is done by assigning consecutive numbers to each line of coding and is useful for reassembling the card deck if it should be dropped.

#### **READING INSTRUCTION NOTATIONS**

Throughout this manual, notations are used to describe the general forms of programmer-written and computergenerated formats. A complete consolidated listing of all the notations is given in Appendix A.

#### **Assembler Application Instruction Notations**

There are eight forms of assembler application instructions:

- RR Register to register

- RX Register to indexed storage or storage to indexed register

- RS Register to nonindexed storage or storage to nonindexed register

- SI Storage immediate

- SS Storage to storage (type SS1)

- SS Storage to storage (type SS2)

- S Storage

- SM Storage mask

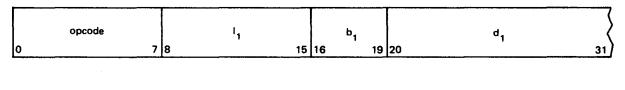

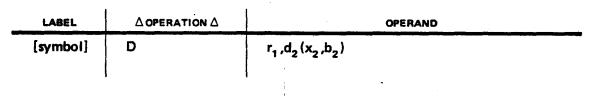

All of the assembler application instructions and other information are explained in formats that the user can write and in the assembler format that generates the machine coding. The following assembler application move instruction (MVC) is an SS1 type:

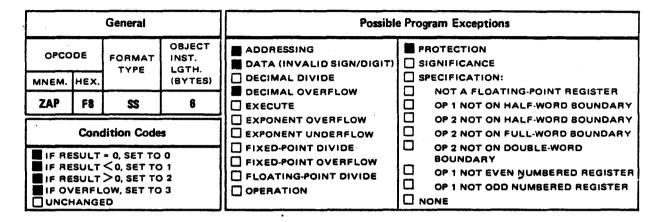

**Explicit Format:**

| LABEL    | $\Delta$ operation $\Delta$ | OPERAND                                                                           |

|----------|-----------------------------|-----------------------------------------------------------------------------------|

| [symbol] | MVC                         | d <sub>1</sub> (l <sub>1</sub> ,b <sub>1</sub> ),d <sub>2</sub> (b <sub>2</sub> ) |

Implicit Format:

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                                         |

|----------|-----------------------------|-------------------------------------------------|

| [symbol] | MVC                         | s <sub>1</sub> (I <sub>1</sub> ),s <sub>2</sub> |

After this application instruction is assembled, it is in the following form:

Table A—1 shows the six formats as generated by the assembler in machine code, as well as the explicit and implicit formats for the programmer coding.

#### **Notation Rules and Meanings**

The following conventions are used in application instruction, assembler directive, macroinstruction, proc, and control statement formats:

Optional information is enclosed in brackets [] and may be specified or omitted.

For example:

[symbol]

Braces { } indicate multiple options, at least one of which must be chosen.

For example:

Braces within brackets signify that one of the options must be chosen if that operand is specified.

For example:

When given a choice of multiple options, the option that is shaded is the default option and indicates the choice that is made by the system if the user does not specify one of the options.

For example:

Uppercase letters, terms, and punctuation marks indicate information that must be coded exactly as shown.

For example:

Mnemonic codes MVN, PACK, and CLC are uppercase.

Lowercase letters and terms indicate variables that are supplied by the user.

For example:

[symbol]

An ellipsis, a series of three periods, indicates that a series of entries may be coded.

For example:

r,[,r<sub>2</sub>,...,r<sub>n</sub>]

Keyword parameters may be coded in any order.

For example:

#### IOROUT=LOAD,BLKSIZE=512,RECFORM=FIXBLK BLKSIZE=512,IOROUT=LOAD,RECFORM=FIXBLK

Positional parameters must be coded in the order shown. Commas are required after each positional parameter except the last. When a positional parameter is omitted from a series of positional parameters, the comma must be retained to indicate the omission.

For example:

// JOB Q003,,30,8000,C000 // JOB Q003,,30,8000

Throughout this book, the register notations R0 through R15 represent the registers 0 through 15.

For example:

BALR R2,R3

• · · . . • . • •

### 2. BAL Application Instructions

|        |                                                                                                                     | General        |                          | Possible                                                                   | e Program Exceptions                                                                                    |

|--------|---------------------------------------------------------------------------------------------------------------------|----------------|--------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| OPCODE |                                                                                                                     | FORMAT<br>TYPE | OBJECT<br>INST.<br>LGTH. | ADDRESSING<br>DATA (INVALID SIGN/DIGIT)                                    | PROTECTION                                                                                              |

| MNEM.  | HEX.                                                                                                                |                | (BYTES)                  | DECIMAL DIVIDE                                                             | SPECIFICATION:                                                                                          |

| A      | 5A                                                                                                                  | RX             | 4                        |                                                                            | OP 1 NOT ON HALF-WORD BOUNDARY                                                                          |

|        | Condition Codes                                                                                                     |                |                          | EXPONENT OVERFLOW                                                          | OP 2 NOT ON HALF WORD BOUNDARY<br>OP 2 NOT ON FULL WORD BOUNDARY<br>OP 2 NOT ON DOUBLE WORD             |

|        | IF RESULT = 0, SET TO 0<br>IF RESULT < 0, SET TO 1<br>IF RESULT > 0, SET TO 2<br>IF OVERFLOW, SET TO 3<br>UNCHANGED |                |                          | FIXED-POINT DIVIDE  FIXED-POINT OVERFLOW  FLOATING-POINT DIVIDE  OPERATION | OP 2 NOT ON DOUBLE-WORD<br>BOUNDARY OP 1 NOT EVEN NUMBERED REGISTER OP 1 NOT ODD NUMBERED REGISTER NONE |

Function:

Causes the value of operand 2, a full word in main storage, to be algebraically added to operand 1, a general register; the results are placed in operand 1.

**Explicit Format:**

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND              |

|----------|-----------------------------|----------------------|

| [symbol] | A                           | $r_1, d_2(x_2, b_2)$ |

|          | · · · ·                     |                      |

**Implicit Format:**

| LA   | BEL   | $\Delta$ OPERATION $\Delta$ | OPERAND               |  |

|------|-------|-----------------------------|-----------------------|--|

| [syr | nbol] | A                           | $r_{1}, s_{2}(x_{2})$ |  |

|      |       |                             |                       |  |

**Operational Considerations:**

- Operand 2 must be on a full-word boundary address.

- Operand 2 must contain data in fixed-point binary format.

- A fixed-point overflow condition is produced when a value greater than 2<sup>31</sup>—1 or —2<sup>31</sup> is reached in operand 1 (r<sub>1</sub>). After overflow, the sign and value of the result are incorrect.

- The contents of operand 2 remain unchanged.

А

#### SPERRY UNIVAC OS/3 ASSEMBLER

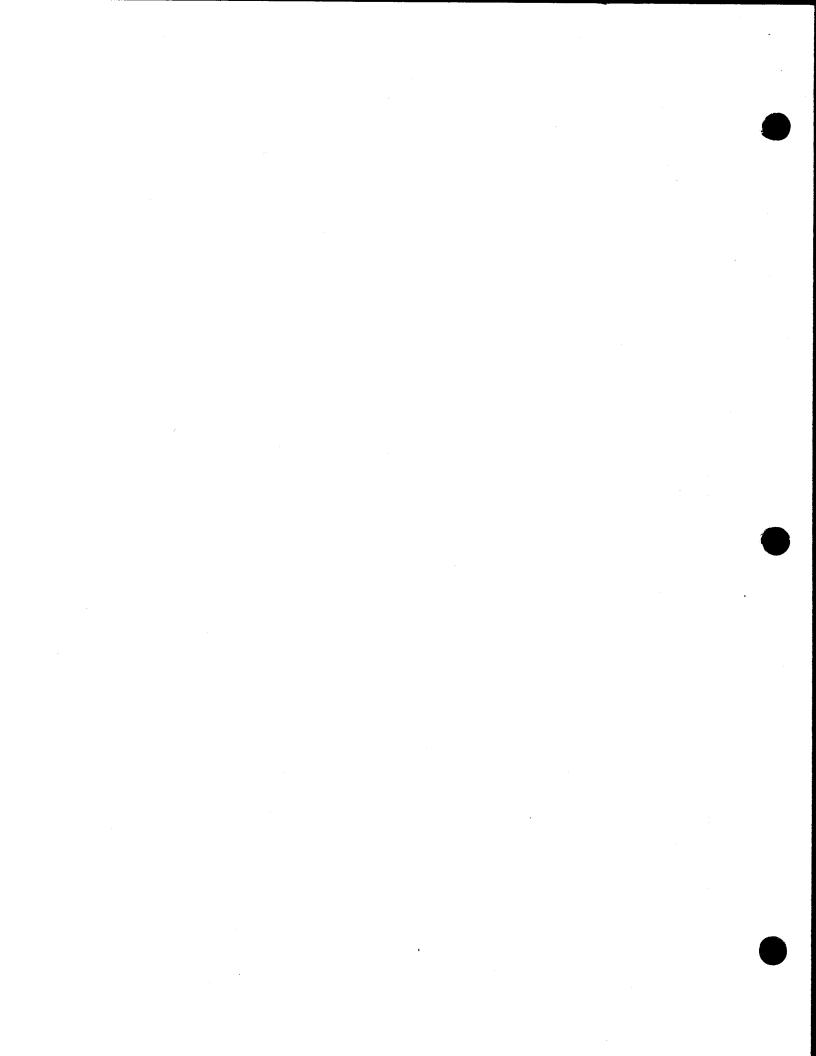

### AD

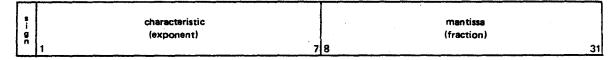

### **Floating Point**

### Function:

Causes the contents of the double word in storage specified by operand 2 to be algebraically added to the contents of the double-word register specified by operand 1 ( $r_1$ ). The sum is normalized and placed in the operand 1 ( $r_1$ ) register.

**Explicit Format:**

| LASEL    | $\Delta$ operation $\Delta$ | c                                                                | PERAND |

|----------|-----------------------------|------------------------------------------------------------------|--------|

| [symbol] | AD                          | r <sub>1</sub> ,d <sub>2</sub> (x <sub>2</sub> ,b <sub>2</sub> ) |        |

### **Implicit Format:**

|          | $\Delta$ OPERATION $\Delta$ | OPERAND                                          |

|----------|-----------------------------|--------------------------------------------------|

| [symbol] | AD                          | r <sub>1</sub> ,s <sub>2</sub> (x <sub>2</sub> ) |

|          |                             |                                                  |

ADR

Floating Point

|                                                                                                                     |                 | General        |                                         | Possible Program Exceptions                                                |                                                                                                         |  |

|---------------------------------------------------------------------------------------------------------------------|-----------------|----------------|-----------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

| OPCO                                                                                                                | DE              | FORMAT<br>TYPE | OBJECT<br>INST.<br>LGTH.                | ADDRESSING     DATA (INVALID SIGN/DIGIT)                                   |                                                                                                         |  |

| MNEM.                                                                                                               | HEX.            | 1176           | (BYTES)                                 |                                                                            | SPECIFICATION:                                                                                          |  |

| ADR                                                                                                                 | 2A              | RR             | 2                                       |                                                                            | OP 1 NOT ON HALF-WORD BOUNDARY                                                                          |  |

|                                                                                                                     | Condition Codes |                |                                         | EXPONENT OVERFLOW                                                          | OP 2 NOT ON HALF-WORD BOUNDARY                                                                          |  |

| IF RESULT = 0, SET TO 0<br>IF RESULT < 0, SET TO 1<br>IF RESULT > 0, SET TO 2<br>IF OVERFLOW, SET TO 3<br>UNCHANGED |                 |                | ) 1 · · · · · · · · · · · · · · · · · · | FIXED-POINT DIVIDE  FIXED-POINT OVERFLOW  FLOATING-POINT DIVIDE  OPERATION | OP 2 NOT ON DOUBLE-WORD<br>BOUNDARY OP 1 NOT EVEN NUMBERED REGISTER OP 1 NOT ODD NUMBERED REGISTER NONE |  |

#### Function:

Causes the contents of the double-word register specified by operand 2 ( $r_2$ ) to be algebraically added to the contents of the double-word register specified by operand 1 ( $r_1$ ). The sum is normalized and placed in the operand 1 ( $r_1$ ) register.

**Explicit and Implicit Format:**

| LABEL    | $\triangle$ OPERATION $\triangle$ |                                | OPERAND |             |

|----------|-----------------------------------|--------------------------------|---------|-------------|

| [symbol] | ADR                               | r <sub>1</sub> ,r <sub>2</sub> |         | · · · · · · |

|          |                                   |                                |         |             |

#### SPERRY UNIVAC OS/3 ASSEMBLER

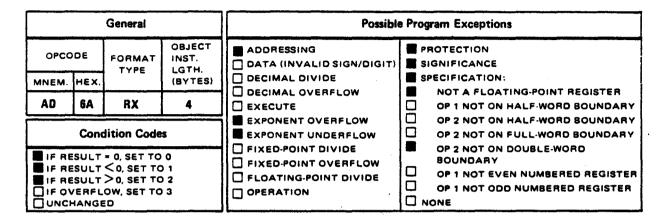

### AE

**Floating Point**

### Function:

Causes the contents of the full word in storage specified by operand 2 to be algebraically added to the contents of a full word in the register specified by operand 1 ( $r_1$ ). The sum is normalized and placed in the full word in the operand 1 ( $r_1$ ) register.

**Explicit Format:**

| LABEL    | $\Delta$ operation $\Delta$ | OPERAND              |

|----------|-----------------------------|----------------------|

| [symbol] | AE                          | $r_1, d_2(x_2, b_2)$ |

|          |                             |                      |

#### Implicit Format:

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                                          |

|----------|-----------------------------|--------------------------------------------------|

| [symbol] | AE                          | r <sub>1</sub> ,s <sub>2</sub> (x <sub>2</sub> ) |

|          |                             |                                                  |

2-4

.

#

**Floating Point**

|      |                                                                                                                     | General        |                                     | Possible                                                                   | Program Exceptions                                                                                                  |

|------|---------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| OPCO |                                                                                                                     | FORMAT<br>TYPE | OBJECT<br>INST.<br>LGTH.<br>(BYTES) | ADDRESSING DATA (INVALID SIGN/DIGIT) DECIMAL DIVIDE                        | PROTECTION     SIGNIFICANCE     SPECIFICATION:                                                                      |

| AER  | 3A                                                                                                                  | RR             | 2                                   | DECIMAL OVERFLOW     EXECUTE                                               | NOT A FLOATING-POINT REGISTER OP 1 NOT ON HALF-WORD BOUNDARY                                                        |

|      | Condition Codes                                                                                                     |                |                                     | EXPONENT OVERFLOW                                                          | OP 2 NOT ON HALF-WORD BOUNDARY OP 2 NOT ON FULL-WORD BOUNDARY OP 2 NOT ON DOUBLE-WORD                               |

|      | IF RESULT = 0, SET TO 0<br>IF RESULT < 0, SET TO 1<br>IF RESULT > 0, SET TO 2<br>IF OVERFLOW, SET TO 3<br>UNCHANGED |                |                                     | FIXED-POINT DIVIDE  FIXED-POINT OVERFLOW  FLOATING-POINT DIVIDE  OPERATION | OP 2 NOT ON DOUBLE-WORD<br>BOUNDARY     OP 1 NOT EVEN NUMBERED REGISTER     OP 1 NOT ODD NUMBERED REGISTER     NONE |

Function:

Causes the contents of a full word in the register specified by operand 2 ( $r_2$ ) to be algebraically added to a full word in the register specified by operand 1 ( $r_1$ ). The sum is normalized and placed in the operand 1 ( $r_1$ ) register.

Explicit and Implicit Format:

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                        |

|----------|-----------------------------|--------------------------------|

| [symbol] | AER                         | r <sub>1</sub> ,r <sub>2</sub> |

|          |                             |                                |

# AH

|       |                                                                                                                     | General        |                          | Possible                                                                                                                       | e Program Exceptions                                                                                                        |

|-------|---------------------------------------------------------------------------------------------------------------------|----------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| орсо  | DE                                                                                                                  | FORMAT<br>TYPE | OBJECT<br>INST.<br>LGTH. | ADDRESSING                                                                                                                     | PROTECTION<br>SIGNIFICANCE                                                                                                  |

| MNEM. | HEX.                                                                                                                |                | (BYTES)                  |                                                                                                                                | SPECIFICATION:                                                                                                              |

| AH    | 4A                                                                                                                  | RX             | 4                        | DECIMAL OVERFLOW     EXECUTE                                                                                                   | <ul> <li>NOT A FLOATING-POINT REGISTER</li> <li>OP 1 NOT ON HALF-WORD BOUNDARY</li> </ul>                                   |

|       | Conc                                                                                                                | lition Code    | S                        | EXPONENT OVERFLOW     EXPONENT UNDERFLOW     EXPONENT UNDERFLOW                                                                | <ul> <li>OP 2 NOT ON HALF-WORD BOUNDARY</li> <li>OP 2 NOT ON FULL-WORD BOUNDARY</li> <li>OP 2 NOT ON DOUBLE-WORD</li> </ul> |

| IF RE | IF RESULT = 0, SET TO 0<br>IF RESULT ≤ 0, SET TO 1<br>IF RESULT ≥ 0, SET TO 2<br>IF OVERFLOW, SET TO 3<br>UNCHANGED |                |                          | <ul> <li>☐ FIXED POINT DIVIDE</li> <li>■ FIXED POINT OVERFLOW</li> <li>☐ FLOATING POINT DIVIDE</li> <li>☐ OPERATION</li> </ul> | OP 2 NOT ON DOUBLE-WORD<br>BOUNDARY     OP 1 NOT EVEN NUMBERED REGISTER     OP 1 NOT ODD NUMBERED REGISTER     NONE         |

Function:

Causes the value of operand 2, a half word in main storage, to be algebraically added to operand 1, a general register; the results are placed in operand 1.

Explicit Format:

| LABEL    | $\Delta$ operation $\Delta$ | OPERAND              |

|----------|-----------------------------|----------------------|

| [symbol] | АН                          | $r_1, d_2(x_2, b_2)$ |

|          |                             |                      |

Implicit Format:

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND               |  |  |

|----------|-----------------------------|-----------------------|--|--|

| [symbol] | АН                          | $r_{1}, s_{2}(x_{2})$ |  |  |

|          |                             |                       |  |  |

- Operand 2 must be on a half-word boundary address.

- Operand 2 must contain data in fixed-point binary format.

- A fixed-point overflow condition is produced when a value greater than 2<sup>31</sup>—1 or —2<sup>31</sup> is reached in operand 1 (r<sub>1</sub>). After overflow, the sign and value of the result are incorrect.

- The contents of operand 2 remain unchanged.

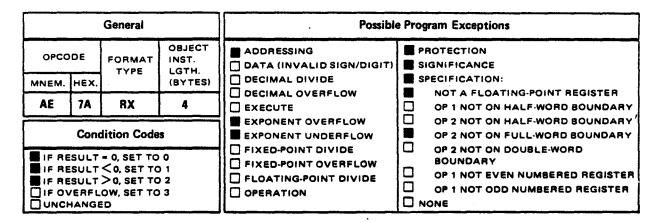

Function:

Causes the value of operand 2, immediate data, to be algebraically added to operand 1, a half word in main storage; the results are placed in operand 1.

**Explicit Format:**

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                                         |

|----------|-----------------------------|-------------------------------------------------|

| [symbol] | AI                          | d <sub>1</sub> (b <sub>1</sub> ),i <sub>2</sub> |

|          |                             |                                                 |

Implicit Format:

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                         |

|----------|-----------------------------|---------------------------------|

| [symbol] | AI                          | \$ <sub>1</sub> ,i <sub>2</sub> |

|          |                             |                                 |

**Operational Considerations:**

- Operand 1 must be on a half-word boundary address.

- Operand 1 must contain data in fixed-point binary format.

- A fixed-point overflow condition is produced when a value greater than 2<sup>15</sup>—1 or —2<sup>15</sup> is reached in operand 1. After overflow, the sign and value of the result are incorrect.

- The maximum value for operand 2 (i<sub>2</sub>) is +127 or --128.

2-7

| 1 | iD | -89 | ٦.1 | л |

|---|----|-----|-----|---|

| L |    | -03 | 7 I | 4 |

#### SPERRY UNIVAC OS/3 ASSEMBLER

AL

|            | General                                                                    |                |                                     | Possible Program Exceptions                               |                                                                                       |

|------------|----------------------------------------------------------------------------|----------------|-------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|

|            | DE<br>HEX.                                                                 | FORMAT<br>TYPE | OBJECT<br>(NST.<br>LGTH.<br>(BYTES) | ADDRESSING<br>DATA (INVALID SIGN/DIGIT)<br>DECIMAL DIVIDE | PROTECTION SIGNIFICANCE SPECIFICATION:                                                |

| AL         | 5E                                                                         | RX             | 4                                   |                                                           | OP 1 NOT ON HALF-WORD BOUNDARY                                                        |

|            | Condition Codes                                                            |                |                                     |                                                           | OP 2 NOT ON HALF-WORD BOUNDARY OP 2 NOT ON FULL-WORD BOUNDARY OP 2 NOT ON DOUBLE-WORD |

| SET<br>SET | SET TO 0<br>SET TO 1<br>SET TO 2<br>SET TO 3 -<br>SEE OPER. CONSIDERATIONS |                |                                     | FIXED-POINT DIVIDE                                        | BOUNDARY OP 1 NOT EVEN NUMBERED REGISTER OP 1 NOT ODD NUMBERED REGISTER NONE          |

Function:

Causes the contents of operand 2, a full word in storage, to be logically added to the contents of the full word in the operand 1  $(r_1)$  register. The sum is placed in operand 1  $(r_1)$ .

**Explicit Format:**