Operating System/3 (OS/3)

Assembler (Series 90)

For System 80 see UP-8914

**Programmer Reference**

This Library Memo announces the release and availability of "SPERRY UNIVAC<sup>®</sup> Operating System/3 (OS/3) Assembler Programmer Reference", UP-8227 Rev. 2.

This revision documents the following enhancements to the assembler for release 8.0:

- The display of error messages on the console

- An additional warning message when using continuation characters with macroinstructions

This revision also includes minor technical corrections to material applicable to the assembler prior to release 8.0.

<u>Destruction Notice</u>: If you are going to OS/3 release 8.0, use this revision and destroy all previous copies. If you are not going to OS/3 release 8.0, retain the copy you are now using and store this revision for future use.

Copies of UP-8227 Rev. 1, UP-8227 Rev. 1—A, UP-8227 Rev. 1—B, UP-8227 Rev. 1—C, UP-8227 Rev. 1—D and UP-8227 Rev. 1—E will be available for 6 months after the release of 8.0. Should you need additional copies of these editions, you should order them within 90 days of the release of 8.0. When ordering the previous edition of a manual, be sure to identify the exact revision and update packages desired and indicate that they are needed to support an earlier release.

Additional copies may be ordered by your local Sperry Univac representative.

| LIBRARY MEMO ONLY              | LIBRARY MEMO AND ATTACHMENTS                                | THIS SHEET IS:                     |

|--------------------------------|-------------------------------------------------------------|------------------------------------|

| Mailing Lists BZ,<br>CZ and MZ | Mailing Lists A00, A18, 75, and 76<br>(Cover and 345 pages) | Library Memo for<br>UP-8227 Rev. 2 |

|                                |                                                             | RELEASE DATE:                      |

|                                |                                                             | September, 1982                    |

# **Assembler**

Environment: 90/25, 30, 30B, 40 Systems

This document contains the latest information available at the time of preparation. Therefore, it may contain descriptions of functions not implemented at manual distribution time. To ensure that you have the latest information regarding levels of implementation and functional availability, please consult the appropriate release documentation or contact your local Sperry Univac representative.

Sperry Univac reserves the right to modify or revise the content of this document. No contractual obligation by Sperry Univac regarding level, scope, or timing of functional implementation is either expressed or implied in this document. It is further understood that in consideration of the receipt or purchase of this document, the recipient or purchaser agrees not to reproduce or copy it by any means whatsoever, nor to permit such action by others, for any purpose without prior written permission from Sperry Univac.

Sperry Univac is a division of the Sperry Corporation.

FASTRAND, SPERRY UNIVAC, UNISCOPE, UNISERVO, and UNIVAC are registered trademarks of the Sperry Corporation. ESCORT, MAPPER, PAGEWRITER, PIXIE, and UNIS are additional trademarks of the Sperry Corporation.

This document was prepared by Systems Publications using the SPERRY UNIVAC UTS 400 Text Editor. It was printed and distributed by the Customer Information Distribution Center (CIDC), 555 Henderson Rd., King of Prussia, Pa., 19406.

#### **PAGE STATUS SUMMARY**

UP-8227 Rev. 2 ISSUE: **RELEASE LEVEL:** 8.0 Forward

| Part/Section     | Page<br>Number                                                                                                                                                           | Update<br>Level | Part/Section | Page<br>Number         | Update<br>Level | Part/Section | Page<br>Number | Update<br>Level |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|------------------------|-----------------|--------------|----------------|-----------------|

| Cover/Disclaimer |                                                                                                                                                                          |                 | Appendix E   |                        |                 |              |                |                 |

| PSS              | 1                                                                                                                                                                        | _               |              | Title Page<br>1 thru 5 |                 |              |                |                 |

| Preface          | 1                                                                                                                                                                        |                 | Appendix F   |                        |                 |              |                |                 |

| Contents         | 1 thru 10                                                                                                                                                                | -               |              | Title Page<br>1 thru 6 |                 |              |                |                 |

| Section 1        |                                                                                                                                                                          |                 | Glossary     | 1 thru 17              |                 |              |                |                 |

|                  | Title Page<br>1 thru 5                                                                                                                                                   |                 | User Comment |                        |                 |              |                |                 |

| Section 2        | Title Page 1 thru 48 48a 49 thru 62 62a, 62b 63 thru 68 68a 69 thru 80 80a 81 thru 120 120a 121 thru 128 128a 129 thru 138 138a thru 138e 139 thru 146 146a 147 thru 163 |                 | Sheet        |                        |                 |              |                |                 |

| Section 3        | Title Page<br>1 thru 31                                                                                                                                                  |                 |              |                        |                 |              |                |                 |

| Section 4        | Title Page<br>1 thru 29                                                                                                                                                  |                 |              |                        |                 |              |                |                 |

| Appendix A       | Title Page<br>1 thru 24                                                                                                                                                  |                 |              |                        |                 |              |                |                 |

| Appendix B       | Title Page<br>1 thru 7                                                                                                                                                   |                 | !            |                        |                 |              |                |                 |

| Appendix C       | Title Page<br>1 thru 13                                                                                                                                                  |                 |              |                        |                 |              |                |                 |

| Appendix D       | Title Page<br>1 thru 8                                                                                                                                                   |                 |              |                        | :               |              |                |                 |

| , |   |  |  |  |

|---|---|--|--|--|

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   | · |  |  |  |

|   |   |  |  |  |

### **Preface**

This programmer reference manual is one in a series designed to be used as a quick-reference document for programmers familiar with the SPERRY UNIVAC Operating System/3 (OS/3). This particular manual describes the basic assembly language (BAL) instructions, directives, and macro definition statements that allow you to write your own assembly language programs and procedure definitions (procs).

No extensive introductory information or examples of use are provided. This type of information is presented in two other assembler manuals: an introduction to the assembler, UP-8030, and an assembler user guide, UP-8061.

The information contained in this manual is presented as follows:

#### Section 1. General Information

Provides a brief overview of the assembler, the job control stream requirements of the assembler, and the conventions that must be observed when reading and writing assembler code.

#### Section 2. BAL Application Instructions

Describes each of the BAL application instructions recognized by the OS/3 assembler. These descriptions are presented in alphabetic order by their operation code mnemonic.

#### Section 3. BAL Directives

Describes each of the directives that are used to control the operation of the assembler. These directives are also presented in alphabetic order by their operation code mnemonic.

#### Section 4. BAL Macro Definition Statements

Describes the macro definition statements used to write and call procedure definitions. These statements are presented in alphabetic order.

#### Appendixes

Contain assembler references, character set code references, math references, source corrections, and system variable symbols helpful to the BAL programmer.

#### Glossary

Defines the terms, expressions, and abbreviations peculiar to the assembler.

## **Contents**

1-1

#### **PAGE STATUS SUMMARY**

### **PREFACE**

#### **CONTENTS**

#### 1. GENERAL INFORMATION

ASSEMBLER OVERVIEW

|    | JOB CONTROL REQUIREMENTS                    | 11  |

|----|---------------------------------------------|-----|

|    | ASSEMBLER CODING FORM                       | 1-1 |

|    | Symbol Field                                | 1–2 |

|    | Operation Field                             | 1–2 |

|    | Operand Field                               | 1–2 |

|    | Comment Field                               | 1–2 |

|    | Continuation Column                         | 1-3 |

|    | Sequence Field                              | 13  |

|    | READING INSTRUCTION NOTATIONS               | 1–3 |

|    | Assembler Application Instruction Notations | 1–3 |

|    | Notation Rules and Meanings                 | 1–4 |

| 2. | BAL APPLICATION INSTRUCTIONS                |     |

|    | .A                                          | 2–1 |

|    | AD                                          | 2–2 |

|    | ADR                                         | 2–3 |

|    | AE                                          | 2–4 |

|    | AER                                         | 2–5 |

|    | АН                                          | 2–6 |

|    | AI                                          | 2–7 |

### SPERRY UNIVAC Operating System/3

UPDATE LEVEL

Contents 2 PAGE

| AL   |     | 2-8  |

|------|-----|------|

| ALR  |     | 2-10 |

| AP   |     | 2–11 |

| AR   |     | 2–13 |

| AU   |     | 2-14 |

| AUR  |     | 2–15 |

| AW   |     | 2-16 |

| AWR  |     | 2–17 |

| BAL  |     | 2–18 |

| BALR |     | 2-19 |

| BAS  |     | 2-20 |

| BASR |     | 2-20 |

| вс   |     | 2–21 |

| BCR  |     | 2–23 |

| вст  |     | 2-24 |

| BCTR |     | 2-25 |

| вхн  |     | 2–26 |

| BXLE |     | 2–27 |

| c    | * 1 | 228  |

| CD   |     | 2–29 |

| CDR  |     | 2-30 |

| CE   |     | 2–31 |

| CER  |     | 2-32 |

| СН   |     | 2–33 |

| CL   |     | 2–34 |

| CLC  |     | 2–35 |

| CLI  |     | 2–36 |

### SPERRY UNIVAC Operating System/3

UPDATE LEVEL

Contents 3 PAGE

| CLR  | 2–37          |

|------|---------------|

| СР   | 2–38          |

| CR   | 2–39          |

| CVB  | 2–40          |

| CVD  | 2–42          |

| D    | 2–43          |

| DD   | 2–44          |

| DDR  | 2–45          |

| DE   | 2–46          |

| DER  | 2–47          |

| DIAG | 2–48          |

| DP   | <b>2–48</b> a |

| DR   | 2–50          |

| ED   | 2–51          |

| EDMK | 2-56          |

| EX   | 2-58          |

| HDR  | 2–60          |

| HER  | 2–61          |

| HPR  | 262           |

| IC   | 2-62a         |

| ISK  | 2-62b         |

| L    | 2–63          |

| LA   | 2-64          |

| LCDR | 265           |

| LCER | 2-66          |

| LCR  | 2–67          |

| LCS  | 2–68          |

|      |               |

### SPERRY UNIVAC Operating System/3

UPDATE LEVEL

Contents 4

PAGE

| LD   | 2-68 |

|------|------|

| LDR  | 2–69 |

| LE   | 2-70 |

| LER  | 2–71 |

| LH   | 2–72 |

| LM   | 2–73 |

| LNDR | 2–75 |

| LNER | 2–76 |

| LNR  | 2–77 |

| LPDR | 2-78 |

| LPER | 2–79 |

| LPR  | 2-80 |

| LPSW | 2–80 |

| LR   | 2–81 |

| LTDR | 2–82 |

| LTER | 2–83 |

| LTR  | 2-84 |

| M    | 2-85 |

| MD   | 2–87 |

| MDR  | 2–88 |

| ME   | 2–89 |

| MER  | 2-90 |

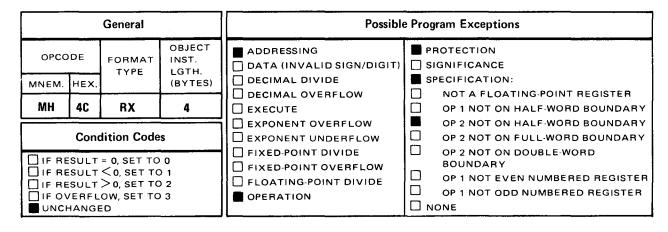

| мн   | 2–91 |

| MP   | 2-92 |

| MR   | 2–94 |

| MVC  | 2–95 |

| MVI  | 2–96 |

| MVN  | 2–97 |

8227 Rev. 2

UP-NUMBER

SPERRY UNIVAC Operating System/3

UPD

Contents 5

UPDATE LEVEL PAGE

2-134

| MVO  | 2–98   |

|------|--------|

| MVZ  | 2-99   |

| N    | 2-100  |

| NC   | 2-102  |

| NI   | 2-104  |

| NR   | 2-106  |

| 0    | 2-107  |

| ос   | 2-109  |

| OI   | 2–111  |

| OR   | 2–113  |

| PACK | 2-114  |

| S    | 2–115  |

| SD   | 2-116  |

| SDR  | 2–117  |

| SE   | 2–118  |

| SER  | 2–119  |

| SH   | 2-120  |

| SIO  | 2-120a |

| SL   | 2–121  |

| SLA  | 2-123  |

| SLDA | 2–125  |

| SLDL | 2–127  |

| SLL  | 2–128  |

| SLM  | 2-128a |

| SLR  | 2–129  |

| SP   | 2-130  |

| SPM  | 2–132  |

| SR   | 2–133  |

SRA

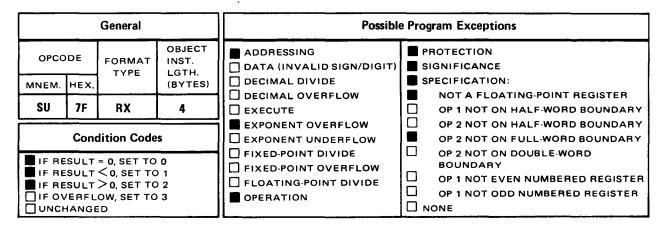

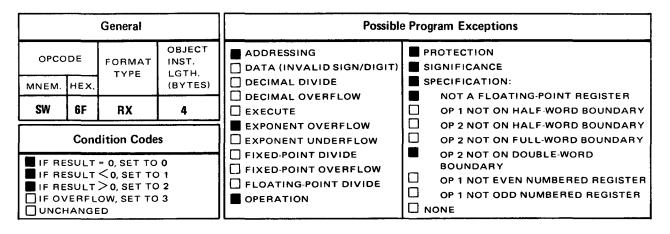

Contents 6 8227 Rev. 2 SPERRY UNIVAC Operating System/3 UPDATE LEVEL PAGE UP-NUMBER **SRDA** 2-136 **SRDL** 2-137 SRL 2-138 2-138a **SSFS** 2-138b SSK 2-138c SSM **SSRS** 2-138d 2-138e **SSTM** 2-139 ST 2-140 STC 2-141 STD 2-142 STE 2-143 STH 2-144 STM **STR** 2-146 SU 2-146a **SUR** 2-147 2-148 **SVC** SW 2-149 2-150 **SWR** TM 2-151 2-152 TR TRT 2-154

2-156

2-157

2-158

2-159

2-161

2-162

TS

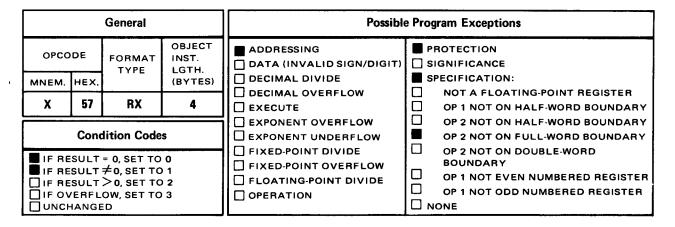

Χ

XC

ΧI

XR

UNPK

3.

### SPERRY UNIVAC Operating System/3

UPDATE LEVEL

Contents 7

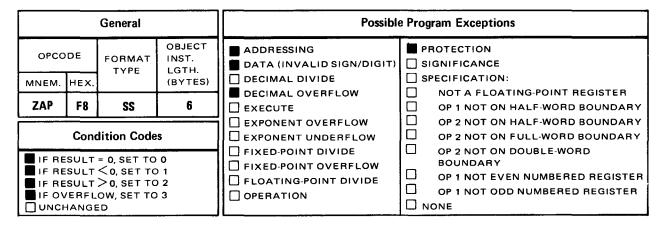

| ZAP                  | 2–163 |

|----------------------|-------|

| BAL DIRECTIVES       |       |

| CCW                  | 3–1   |

| CNOP                 | 3–2   |

| СОМ                  | 3–3   |

| COPY                 | 3–5   |

| CSECT                | 3–6   |

| DC (Floating Point)  | 3–7   |

| DC (Standard Format) | 3–9   |

| DROP                 | 3–10  |

| DS                   | 3–11  |

| DSECT                | 3–12  |

| EJECT                | 3–13  |

| END                  | 3–14  |

| ENTRY                | 3–15  |

| EQU                  | 3–16  |

| EXTRN                | 3–17  |

| ICTL                 | 3–18  |

| ISEQ                 | 3–19  |

| LTORG                | 3–20  |

| OPSYM                | 3–21  |

| ORG                  | 3–23  |

| PRINT                | 3–24  |

| PUNCH                | 3–25  |

| REPRO                | 3–26  |

| SPACE                | 3–27  |

| START                | 3–28  |

| TITLE                | 3–29  |

SET

4-22

USING 3-30 **BAL MACRO DEFINITION STATEMENTS ACTR** 4-1 AGO 4-2 AIF 4-3 **ANOP** 4-4 DO 4-5 **END** 4-6 **ENDO** 4-7 **GBL** 4-8 **GBLA** 4-8 **GBLB** 4-8 **GBLC** 4-8 LCL 4-9 **LCLA** 4-9 **LCLB** 4-9 **LCLC** 4-9 **MACRO** 4-10 **Macro Call Instruction** 4-11 MEND 4-13 **MEXIT** 4-14 **MNOTE** 4-15 **Model Statement** 4-16 **NAME** 4-17 **PNOTE** 4-18 **PROC** 4-19 **Prototype Statement** 4-21

|     | SETA                                                                                                     | 425                                    |

|-----|----------------------------------------------------------------------------------------------------------|----------------------------------------|

|     | SETB                                                                                                     | 4-26                                   |

|     | SETC                                                                                                     | 4–29                                   |

| APP | PENDIXES                                                                                                 |                                        |

| A.  | ASSEMBLER REFERENCES                                                                                     |                                        |

|     | CHECK-OFF TABLE TERMS                                                                                    | A-20                                   |

| B.  | CHARACTER SET CODE REFERENCES                                                                            |                                        |

| C.  | MATH REFERENCES                                                                                          |                                        |

|     | FLOATING-POINT MATH Floating-Point Addition Floating-Point Division Floating-Point Multiplication        | C-10<br>C-11<br>C-12<br>C-13           |

| D.  | SOURCE CORRECTIONS                                                                                       |                                        |

|     | GENERAL                                                                                                  | D-1                                    |

|     | PARAM                                                                                                    | D-2                                    |

|     | SEQ .                                                                                                    | D-6                                    |

|     | REC                                                                                                      | D-7                                    |

|     | SKI                                                                                                      | D-8                                    |

| E.  | SYSTEM VARIABLE SYMBOLS                                                                                  |                                        |

| F.  | ATTRIBUTE REFERENCES                                                                                     |                                        |

|     | Type Attributes Length Attributes Scale Attributes Integer Attributes Count Attributes Number Attributes | F-2<br>F-4<br>F-5<br>F-5<br>F-5<br>F-6 |

**GLOSSARY**

**USER COMMENT SHEET**

### **TABLES**

| A-1. | Instruction Formats                                           | A-1  |

|------|---------------------------------------------------------------|------|

| A-2. | Instruction Repertoire                                        | A-3  |

| A-3. | Extended Mnemonic Branch Codes                                | A-19 |

| A-4. | Summary of Operators                                          | A-20 |

| A-5. | Comparison of Terms                                           | A-20 |

| A6.  | Characteristics of Constant and Storage Definition Type Codes | A-2  |

| A-7. | Macro and Proc Format Comparison                              | A-22 |

| A-8. | Check-off Table Terms                                         | A-23 |

| B–1. | Punched Card, ASCII, and EBCDIC Codes                         | B-1  |

| B-2. | 90/30 EBCDIC Code Chart                                       | B-6  |

| B-3. | ASCII Character Code Chart                                    | B-7  |

| C-1. | Comparison of Numeric Expressions                             | C-1  |

| C-2. | Hexadecimal-Decimal Integer Conversion                        | C-2  |

| C-3. | Hexadecimal-Decimal Fraction Conversion                       | C-6  |

| C-4. | Hexadecimal Addition and Subtraction Table                    | C-7  |

| C-5. | Powers of 16                                                  | C-8  |

| C-6. | Powers of 2                                                   | C-9  |

| F–1. | Valid Attribute Reference Applications                        | F-2  |

| F2   | Type Attributes of Symbols                                    | F3   |

1. General Information

#### ASSEMBLER OVERVIEW

The SPERRY UNIVAC Operating System/3 (OS/3) assembler permits highly-efficient, machine-instruction programs to be written in symbolic form. The assembler consists of an instruction translator and a macro facility. The instruction translator converts symbolic instructions to machine instructions on a one-to-one basis. The macro facility allows a subroutine to be coded, assigned a name, stored in a permanent library, and then to be included in a source program by a simple reference to the subroutine's name in a single instruction. The macro facility greatly reduces the amount of repetitive coding required for routines used frequently within a program or in many different programs.

The assembler accepts source-image input from punched cards, magnetic tape, and disc. It reads source statements and produces a relocatable object module. The object module can then be linked to other object modules to form one load module that is suitable for loading and execution on a SPERRY UNIVAC 90/30 System.

A set of assembler directives is provided to aid you in your program organization and in directing the course of an assembly. All assembly runs produce a printed listing that lists source code, object code, label cross-references, cross-references, and, when necessary, error diagnostics. The final error statement message, which gives the total number of statements flagged in the assembly, is also displayed on the console upon completion of the assembly.

#### JOB CONTROL REQUIREMENTS

The job control statements required to assemble, linkage edit, and execute are:

| /./. JOBjo<br>/./. A.S.ML.O<br>/\$               | bin,a,m,e                                        |             |             | NAME JOB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------|--------------------------------------------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  | 1                                                |             | <u> </u>    | ASSEMBLE LITNE FIXECUTIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                  | 1 [                                              |             |             | THE PERSON NAMED IN THE PE |

|                                                  | <del>                                     </del> | <del></del> |             | START OF DIATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1                                                |                                                  |             |             | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                  |                                                  |             | <u>L </u>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| >, , S10,U,RC                                    | E. Co                                            | DE PROGRAM  | <del></del> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4-1-1-1-1                                        | 1111                                             |             | <del></del> | <del> </del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                  |                                                  |             |             | <del></del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| /*                                               |                                                  |             | <del></del> | - END OF DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18                                               |                                                  |             | <u> </u>    | END OF JOB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| /./F.I IN                                        |                                                  |             |             | , GLOSE CARO READER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                  |                                                  |             |             | <del> </del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <del></del>                                      | <del>┠┺┵┸┸</del> ╂┪                              | <del></del> | <u> </u>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <del>                                     </del> |                                                  | <del></del> | <u> </u>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                  |                                                  |             | <u> </u>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### ASSEMBLER CODING FORM

Using an assembler coding form eases the job of writing the program, both for yourself and for the keypunch operator, who must prepare the punched card deck from your written program. Columns 9 and 15 are ruled to remind you that the symbol and operation fields must be terminated by at least one blank.

#### Symbol Field

The first eight columns of the assembler coding form may contain a symbol. An asterisk (\*) indicates that this coding line does not contain instructions and that it contains only comments. The rules for using the symbol field are:

- 1. The symbol must start in column 1.

- 2. The symbol must begin with an alphabetic character or special letter.

- 3. The symbol must not exceed eight characters in length.

- 4. The symbol must not contain embedded blanks or other special characters.

- 5. The field must be terminated by a blank.

#### **Operation Field**

The operation code is written in the operation field (columns 10 through 14). These codes specify the operation to be performed. The rules for using this field are:

- 1. The operation code must not contain embedded blanks.

- 2. The operation code must be written exactly as shown in the list of mnemonics for application instructions, directives, and macro or proc instructions.

- 3. The operation field must be terminated by a blank.

- 4. The operation code must not start in column 1.

#### Operand Field

The operand field begins in column 16 and usually ends in or before column 71. The operands that form part of the assembler statements are written in this field. The rules for using this field are:

- 1. The operand field is terminated by a blank that is not enclosed by apostrophes.

- 2. Operands may be continued onto the next line by placing a nonblank character in column 72. Up to two continuation lines are permitted.

- 3. Continuation lines start in column 16.

#### **Comment Field**

Operand specification is usually completed by column 40, thus leaving columns 41 through 71 free for comments. There must be at least one blank between the end of the operand specification and the start of the comments. Long comments can be entered by coding an \* in column 1.

#### **Continuation Column**

When the operand specification is continued onto the next line, a nonblank character must be written in column 72. Do not confuse this with continuing a comment. An operand specification can be continued for a total of three lines. The second and third continuation lines start in column 16.

#### Sequence Field

Columns 73 through 80 may be used for entering sequence numbers. This is done by assigning consecutive numbers to each line of coding and is useful for reassembling the card deck if it should be dropped.

#### **READING INSTRUCTION NOTATIONS**

Throughout this manual, notations are used to describe the general forms of programmer-written and computergenerated formats. A complete consolidated listing of all the notations is given in A.1.

#### **Assembler Application Instruction Notations**

There are six forms of assembler application instructions:

| RR | _ | Register-to-register                                             |

|----|---|------------------------------------------------------------------|

| RX | _ | Register-to-indexed-storage or storage-to-indexed-register       |

| RS |   | Register-to-nonindexed-storage or storage-to-nonindexed-register |

| SI | _ | Storage immediate                                                |

| SS | _ | Storage-to-storage (type SS1)                                    |

| ss |   | Storage-to-storage (type SS2)                                    |

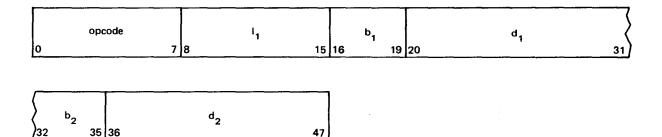

All of the assembler application instructions and other information are explained in formats that you can write and in the assembler format that generates the machine coding. The following assembler application move instruction (MVC) is an SS1 type:

#### **Explicit Format:**

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                                                                           |  |  |

|----------|-----------------------------|-----------------------------------------------------------------------------------|--|--|

| [symbol] | MVC                         | d <sub>1</sub> (I <sub>1</sub> ,b <sub>1</sub> ),d <sub>2</sub> (b <sub>2</sub> ) |  |  |

Implicit Format:

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                                         |

|----------|-----------------------------|-------------------------------------------------|

| [symbol] | MVC                         | s <sub>1</sub> (I <sub>1</sub> ),s <sub>2</sub> |

After this application instruction is assembled, it is in the following form:

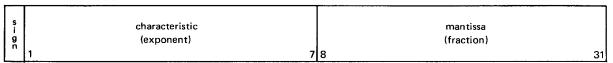

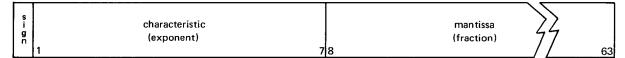

Table A—1 shows the six formats as generated by the assembler in machine code, as well as the explicit and implicit formats for the programmer coding.

#### **Notation Rules and Meanings**

The following conventions are used in application instruction, assembler directive, macro instruction, proc, and control statement formats:

Optional information is enclosed in brackets [] and may be specified or omitted.

For example:

[symbol]

Braces { } indicate multiple options, at least one of which must be chosen.

For example:

PRINT

$$\left\{ \begin{array}{c} ON \\ OFF \end{array} \right\}$$

Braces within brackets signify that one of the options must be chosen if that operand is specified.

For example:

When given a choice of multiple options, the option that is shaded is the default option and indicates the choice that is made by the system if you do not specify one of the options.

For example:

Uppercase letters, terms, and punctuation marks indicate information that must be coded exactly as shown.

For example:

Mnemonic codes MVN, PACK, and CLC are uppercase.

Lowercase letters and terms indicate variables that are supplied by you.

For example:

[symbol]

An ellipsis, a series of three periods, indicates that a series of entries may be coded.

For example:

$$r,[,r_2,...,r_n]$$

Keyword parameters may be coded in any order.

For example:

```

IOROUT=LOAD,BLKSIZE=512,RECFORM=FIXBLK BLKSIZE=512,IOROUT=LOAD,RECFORM=FIXBLK

```

Positional parameters must be coded in the order shown. Commas are required after each positional parameter except the last. When a positional parameter is omitted from a series of positional parameters, the comma must be retained to indicate the omission.

For example:

```

// JOB Q003,,30,8000,C000

// JOB Q003,,30,8000

```

Throughout this book, the register notations R0 through R15 represent the registers 0 through 15.

For example:

BALR R2,R3

2. BAL Application Instructions

A

|        |                                                                                                             | General        |                          | Possible                                                                | e Program Exceptions                                                                                 |  |

|--------|-------------------------------------------------------------------------------------------------------------|----------------|--------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| OPCODE |                                                                                                             | FORMAT<br>TYPE | OBJECT<br>INST.<br>LGTH. | ADDRESSING DATA (INVALID SIGN/DIGIT)                                    | PROTECTION SIGNIFICANCE                                                                              |  |

| MNEM.  | HEX.                                                                                                        | .,,,_          | (BYTES)                  | DECIMAL DIVIDE                                                          | SPECIFICATION:                                                                                       |  |

| Α      | 5A                                                                                                          | RX             | 4                        | DECIMAL OVERFLOW  EXECUTE                                               | NOT A FLOATING-POINT REGISTER OP 1 NOT ON HALF-WORD BOUNDARY                                         |  |

|        | Condition Codes                                                                                             |                |                          | EXPONENT OVERFLOW  EXPONENT UNDERFLOW                                   | OP 2 NOT ON HALF-WORD BOUNDAR' OP 2 NOT ON FULL-WORD BOUNDAR'                                        |  |

| IF RE  | IF RESULT = 0, SET TO 0  IF RESULT < 0, SET TO 1  IF RESULT > 0, SET TO 2  IF OVERFLOW, SET TO 3  UNCHANGED |                |                          | FIXED-POINT DIVIDE FIXED-POINT OVERFLOW FLOATING-POINT DIVIDE OPERATION | OP 2 NOT ON DOUBLE WORD BOUNDARY OP 1 NOT EVEN NUMBERED REGISTER OP 1 NOT ODD NUMBERED REGISTER NONE |  |

#### Function:

Causes the value of operand 2, a full word in main storage, to be algebraically added to operand 1, a general register; the results are placed in operand 1.

#### **Explicit Format:**

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                                                          |

|----------|-----------------------------|------------------------------------------------------------------|

| [symbol] | Α                           | r <sub>1</sub> ,d <sub>2</sub> (x <sub>2</sub> ,b <sub>2</sub> ) |

|          |                             |                                                                  |

#### Implicit Format:

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                                          |

|----------|-----------------------------|--------------------------------------------------|

| [symbol] | Α                           | r <sub>1</sub> ,s <sub>2</sub> (x <sub>2</sub> ) |

|          |                             |                                                  |

- Operand 2 must be on a full-word boundary address.

- Operand 2 must contain data in fixed-point binary format.

- A fixed-point overflow condition is produced when a value greater than 2<sup>31</sup>—1 or —2<sup>31</sup> is reached in operand 1 (r<sub>1</sub>). After overflow, the sign and value of the result are incorrect.

- The contents of operand 2 remain unchanged.

### AD\*

#### Floating Point

|       |                                                                                                                              | General           |                                     | Possible                                                                        | e Program Exceptions                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| OPCO  |                                                                                                                              | FORMAT<br>TYPE    | OBJECT<br>INST.<br>LGTH.<br>(BYTES) | ADDRESSING DATA (INVALID SIGN/DIGIT) DECIMAL DIVIDE                             | SPECIFICATION:                                                                                                                |

| AD    | 6A<br>Conc                                                                                                                   | RX<br>lition Code | 4<br>s                              | DECIMAL OVERFLOW EXECUTE EXPONENT OVERFLOW EXPONENT UNDERFLOW                   | NOT A FLOATING-POINT REGISTER  OP 1 NOT ON HALF-WORD BOUNDARY  OP 2 NOT ON HALF-WORD BOUNDARY  OP 2 NOT ON FULL-WORD BOUNDARY |

| IF RE | Condition Codes  IF RESULT = 0, SET TO 0  IF RESULT < 0, SET TO 1  IF RESULT > 0, SET TO 2  IF OVERFLOW, SET TO 3  UNCHANGED |                   |                                     | ☐ FIXED-POINT DIVIDE ☐ FIXED-POINT OVERFLOW ☐ FLOATING-POINT DIVIDE ■ OPERATION | OP 2 NOT ON DOUBLE-WORD BOUNDARY OP 1 NOT EVEN NUMBERED REGISTER OP 1 NOT ODD NUMBERED REGISTER NONE                          |

#### Function:

Causes the contents of the double word in storage specified by operand 2 to be algebraically added to the contents of the double-word register specified by operand 1  $(r_1)$ . The sum is normalized and placed in the operand 1  $(r_1)$  register.

#### **Explicit Format:**

| LABEL    | $\Delta$ operation $\Delta$ | OPERAND              |

|----------|-----------------------------|----------------------|

| [symbol] | AD                          | $r_1, d_2(x_2, b_2)$ |

|          |                             |                      |

#### Implicit Format:

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                                          |  |  |  |

|----------|-----------------------------|--------------------------------------------------|--|--|--|

| [symbol] | AD                          | r <sub>1</sub> ,s <sub>2</sub> (x <sub>2</sub> ) |  |  |  |

|          |                             |                                                  |  |  |  |

AD is a featured instruction. If you attempt to issue this instruction to a processor which does not have the control feature installed, you cause an operation program exception.

**ADR\***

Floating Point

|        |                       | General                                                       |            | Possible                                                                | Program Exceptions                                                                                   |  |

|--------|-----------------------|---------------------------------------------------------------|------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| OPCODE |                       | OBJECT FORMAT INST. TYPE LGTH.                                |            | ☐ ADDRESSING ☐ DATA (INVALID SIGN/DIGIT)                                | PROTECTION SIGNIFICANCE                                                                              |  |

| MNEM.  | HEX.                  | ,,,,                                                          | (BYTES)    | DECIMAL DIVIDE                                                          | SPECIFICATION:                                                                                       |  |

| ADR    | 2A                    | RR                                                            | 2          | ☐ EXECUTE                                                               | NOT A FLOATING-POINT REGISTER OP 1 NOT ON HALF-WORD BOUNDARY                                         |  |

|        | Conc                  | lition Code                                                   | s          | EXPONENT OVERFLOW  EXPONENT UNDERFLOW                                   | OP 2 NOT ON HALF-WORD BOUNDARY OP 2 NOT ON FULL-WORD BOUNDARY OP 2 NOT ON DOUBLE-WORD                |  |

| IF RE  | SULT<br>SULT<br>/ERFL | = 0, SET TO<br>< 0, SET TO<br>> 0, SET TO<br>OW, SET TO<br>ED | ) 1<br>) 2 | FIXED-POINT DIVIDE FIXED-POINT OVERFLOW FLOATING-POINT DIVIDE OPERATION | OP 2 NOT ON DOUBLE-WORD BOUNDARY OP 1 NOT EVEN NUMBERED REGISTER OP 1 NOT ODD NUMBERED REGISTER NONE |  |

#### Function:

Causes the contents of the double-word register specified by operand 2 ( $r_2$ ) to be algebraically added to the contents of the double-word register specified by operand 1 ( $r_1$ ). The sum is normalized and placed in the operand 1 ( $r_1$ ) register.

#### **Explicit and Implicit Format:**

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                        |  |  |

|----------|-----------------------------|--------------------------------|--|--|

| [symbol] | ADR                         | r <sub>1</sub> ,r <sub>2</sub> |  |  |

<sup>\*</sup> ADR is a featured instruction. If you attempt to issue this instruction to a processor which does not have the control feature installed, you cause an operation program exception.

#### AE\*

#### Floating Point

|       |                                                                                                             | General        |                                     | Possible                                                                | e Program Exceptions                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| OPCO  |                                                                                                             | FORMAT<br>TYPE | OBJECT<br>INST.<br>LGTH.<br>(BYTES) | ADDRESSING DATA (INVALID SIGN/DIGIT) DECIMAL DIVIDE                     | PROTECTION SIGNIFICANCE SPECIFICATION:                                                               |

| AE    | 7A                                                                                                          | RX             | 4                                   | DECIMAL OVERFLOW EXECUTE                                                | NOT A FLOATING-POINT REGISTER  OP 1 NOT ON HALF-WORD BOUNDARY                                        |

|       | Condition Codes                                                                                             |                |                                     | EXPONENT OVERFLOW  EXPONENT UNDERFLOW                                   | OP 2 NOT ON HALF-WORD BOUNDARY OP 2 NOT ON FULL-WORD BOUNDARY OP 2 NOT ON DOUBLE-WORD                |

| IF RE | IF RESULT = 0, SET TO 0  IF RESULT < 0, SET TO 1  IF RESULT > 0, SET TO 2  IF OVERFLOW, SET TO 3  UNCHANGED |                |                                     | FIXED-POINT DIVIDE FIXED-POINT OVERFLOW FLOATING-POINT DIVIDE OPERATION | OP 2 NOT ON DOUBLE-WORD BOUNDARY OP 1 NOT EVEN NUMBERED REGISTER OP 1 NOT ODD NUMBERED REGISTER NONE |

#### Function:

Causes the contents of the full word in storage specified by operand 2 to be algebraically added to the contents of a full word in the register specified by operand 1  $(r_1)$ . The sum is normalized and placed in the full word in the operand 1  $(r_1)$  register.

#### **Explicit Format:**

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND            |

|----------|-----------------------------|--------------------|

| [symbol] | AE                          | $r_1,d_2(x_2,b_2)$ |

|          |                             |                    |

#### Implicit Format:

| LABEL    | $\Delta$ OPERATION $\Delta$ | OPERAND                                          |

|----------|-----------------------------|--------------------------------------------------|

| [symbol] | AE                          | r <sub>1</sub> ,s <sub>2</sub> (x <sub>2</sub> ) |

|          |                             |                                                  |