PUBLICATIONS REVISION Operating System/3 (OS/3)

Assembler

**User Guide**

September, 1982

This Library Memo announces the release and availability of "SPERRY UNIVAC<sup>®</sup> Operating System/3 (OS/3) Assembler User Guide", UP-8061 Rev. 3.

This revision provides the 8.0 release enhancements to the OS/3 Assembler. The enhancements include:

- An additional UPSI byte setting for diagnostic errors.

- The addition of STXIT island code (providing the capacity to continue job streams when program checks occur).

- The display of error messages on the console.

- An additional warning message when using continuation characters with macroinstructions. (A comma after the last operand is checked.)

Appendix A was also expanded to include the job control to execute the sample program. In addition, other technical changes were made throughout the document.

Destruction Notice: If you are going to OS/3 release 8.0, use this revision and destroy all previous copies. If you are not going to OS/3 release 8.0, retain the copy you are now using and store this revision for future use.

Copies of UP-8061 Rev. 2, UP-8061 Rev. 2–A, UP-8061 Rev. 2–B and UP-8061 Rev. 2–C will be available for 6 months after the release of 8.0. Should you need additional copies of this edition, you should order them within 90 days of the release of 8.0. When ordering the previous edition of a manual, be sure to identify the exact revision and update packages desired and indicate that they are needed to support an earlier release.

Additional copies may be ordered by your local Sperry Univac representative.

| LIBRARY MEMO ONLY              | LIBRARY MEMO AND ATTACHMENTS                                                                     | THIS SHEET IS                      |

|--------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------|

| Mailing Lists<br>BZ, CZ and MZ | Mailing Lists A00,A18,18,18U,19,19U,20,20U,21,21U,75,<br>75U,76 and 76U<br>(Cover and 710 pages) | Library Memo for<br>UP-8061 Rev. 3 |

|                                |                                                                                                  | RELEASE DATE:                      |

# Assembler

Environment: 90/25, 30, 30B, 40 Systems

UP-8061 Rev. 3

This document contains the latest information available at the time of preparation. Therefore, it may contain descriptions of functions not implemented at manual distribution time. To ensure that you have the latest information regarding levels of implementation and functional availability, please consult the appropriate release documentation or contact your local Sperry Univac representative.

Sperry Univac reserves the right to modify or revise the content of this document. No contractual obligation by Sperry Univac regarding level, scope, or timing of functional implementation is either expressed or implied in this document. It is further understood that in consideration of the receipt or purchase of this document, the recipient or purchaser agrees not to reproduce or copy it by any means whatsoever, nor to permit such action by others, for any purpose without prior written permission from Sperry Univac.

Sperry Univac is a division of the Sperry Corporation.

FASTRAND, SPERRY UNIVAC, UNISCOPE, UNISERVO, and UNIVAC are registered trademarks of the Sperry Corporation. ESCORT, MAPPER, PAGEWRITER, PIXIE, and UNIS are additional trademarks of the Sperry Corporation.

This document was prepared by Systems Publications using the SPERRY UNIVAC UTS 400 Text Editor. It was printed and distributed by the Customer Information Distribution Center (CIDC), 555 Henderson Rd., King of Prussia, Pa., 19406.

#### PAGE STATUS SUMMARY

ISSUE: RELEASE LEVEL:

UP-8061 Rev. 3 8.0 Forward

| Part/Section     | Page<br>Number | Update<br>Level | Part/Section          | Page<br>Number | Update<br>Level | Part/Section | Page<br>Number | Update<br>Level |

|------------------|----------------|-----------------|-----------------------|----------------|-----------------|--------------|----------------|-----------------|

| Cover/Disclaimer |                |                 | 19                    | 1 thru 13      |                 |              |                | 1               |

| PSS              | 1              |                 | 20                    | 1 thru 6       |                 |              |                |                 |

| Preface          | 1, 2           |                 | 21                    | 1 thru 9       |                 |              |                |                 |

| Contents         | 1 thru 17      |                 | PART 5                |                |                 |              |                |                 |

| PART 1           | Title Dama     |                 | 22                    | Title Page     |                 |              |                |                 |

| _                | Title Page     |                 | 22                    | 1 thru 4       |                 |              |                |                 |

| 1                | 1 thru 19      |                 | 23                    | 1 thru 10      |                 |              |                |                 |

| 2                | 1 thru 10      |                 | 24                    | 1 thru 11      |                 |              |                |                 |

| 3                | 1 thru 3       |                 | 25                    | 1 thru 11      |                 |              |                |                 |

| 4                | 1 thru 19      |                 | 26                    | 1 thru 7       |                 |              |                |                 |

| PART 2           | Title Page     |                 | 27                    | 1 thru 30      |                 |              |                |                 |

| 5                | 1 thru 19      |                 | PART 6                | Title Page     |                 |              |                |                 |

| 6                | 1 thru 4       |                 | 28                    | 1 thru 5       |                 |              |                |                 |

| PART 3           | Title Page     |                 | PART 7                | Title Page     |                 |              |                |                 |

| 7                | 1 thru 6       |                 | 29                    | 1 thru 21      |                 |              |                |                 |

| 8                | 1 thru 19      |                 | 30                    | 1 thru 5       |                 |              |                |                 |

| 9                | 1 thru 52      |                 | PART 8                |                |                 |              |                |                 |

| 10               | 1 thru 63      |                 |                       | Title Page     |                 |              |                |                 |

| 11               | 1 thru 94      |                 | Appendix A            | 1 thru 4       |                 |              |                |                 |

| 12               | 1 thru 72      |                 | Appendix B            | 1 thru 7       |                 |              |                |                 |

| 13               | 1 thru 20      |                 | Appendix C            | 1 thru 9       |                 |              |                |                 |

| 14               | 1 thru 53      |                 | Appendix D            | 1 thru 3       |                 |              |                |                 |

| PART 4           |                |                 | Appendix E            | 1 thru 15      |                 |              |                |                 |

|                  | Title Page     |                 | Appendix F            | 1 thru 8       |                 |              |                |                 |

| 15               | 1              |                 | Appendix G            | 1 thru 5       | ļ               |              |                |                 |

| 16               | 1 thru 3       |                 | Index                 | 1 thru 28      |                 |              |                |                 |

| 17               | 1 thru 8       |                 | User Comment<br>Sheet |                |                 |              |                |                 |

| 18               | 1 thru 4       |                 |                       |                |                 |              |                |                 |

All the technical changes are denoted by an arrow  $(\rightarrow)$  in the margin. A downward pointing arrow  $(\ \ )$  next to a line indicates that technical changes begin at this line and continue until an upward pointing arrow  $(\ \ )$  is found. A horizontal arrow  $(\rightarrow)$  pointing to a line indicates a technical change in only that line. A horizontal arrow located between two consecutive lines indicates technical changes in both lines or deletions.

PSS 1

. .

# Preface

This manual is one of a series designed to instruct and guide the programmer in the use of the SPERRY UNIVAC Operating System/3 (OS/3). This manual specifically describes the OS/3 assembler and its effective use. Its intended audience is the novice programmer with a basic knowledge of data processing, but with limited programming experience, and the assembler programmer whose experience is limited to non-UNIVAC systems.

Two other manuals are available that cover OS/3 assembler; one is an introductory manual and the other is a programmer reference. The introductory manual briefly describes OS/3 assembler and its facilities. The programmer reference provides the characteristics of OS/3 assembler in skeletal form and is intended as a quick-reference document for the programmer experienced in the use of OS/3 assembler.

This user guide is divided into the following parts:

PART 1. BASIC DATA AND CONVENTIONS

Introduces you to what basic assembly language (BAL) is, how the computer stores information (data), how to locate the data required, and what forms mathematic notations assume in computer manipulations. The general rules that a programmer must understand to solve simple BAL problems are stated in this part. Where the content may seem out of context to the more experienced user, he can find such material repeated in greater detail in the following parts of this manual. As the manual progresses, the problems and examples become increasingly complex.

PART 2. STORAGE AND SYMBOL DEFINITIONS

Describes and illustrates the use of storage assignments, the constants, and the rules for symbol designations.

PART 3. BAL APPLICATION INSTRUCTIONS

Presents the explicit and implicit formats for all the assembly language application instructions, the rules of their use and illustrative examples.

PART 4. BAL DIRECTIVES

Describes and illustrates the use of all the assembler control directives.

■ PART 5. BAL MACROS

Explains the macro facility for writing and using this time-saving feature of the assembler.

PART 6. ASSEMBLY LISTING

Describes what an assembly listing is, what it means, and how it is of use to the programmer.

PART 7. PROGRAMMING TECHNIQUES

A series of programming techniques are presented in this part.

PART 8. APPENDIXES

The appendixes contain figures and tables for use in explaining the text and for general programmer reference.

Each of the foregoing parts consists of one or more sections that cover the different aspects of the subject matter covered in each part.

# Contents

#### PAGE STATUS SUMMARY

PREFACE

CONTENTS

# PART 1. BASIC DATA AND CONVENTIONS

# 1. INTRODUCTION TO ASSEMBLER LANGUAGE PROGRAMMING

|    | 1.1.   | CODING AN ASSEMBLER PROGRAM | 1–1  |

|----|--------|-----------------------------|------|

|    | 1.1.1. | Operation Field             | 1–4  |

|    | 1.1.2. | Operand Field               | 1–5  |

|    | 1.1.3. | Label Field                 | 1–6  |

|    | 1.1.4. | Comments Field              | 1–8  |

|    | 1.1.5. | Sequence Numbers            | 1-9  |

|    | 1.1.6. | Column 72                   | 1–10 |

|    | 1.1.7. | Additional Coding Rules     | 1-10 |

|    | 1.2.   | ASSEMBLING A PROGRAM        | 1-12 |

|    | 1.3.   | CREATING A LOAD MODULE      | 1–16 |

|    | 1.4.   | PROGRAM EXECUTION           | 1–17 |

| 2. | DATA   | FORMS                       |      |

|    | 2.1.   | DATA REPRESENTATION         | 2-1  |

|    | 2.2.   | BINARY REPRESENTATION       | 2-2  |

|    | 2.3.   | HEXADECIMAL REPRESENTATION  | 2-3  |

UP-8061 Rev. 3

3.

4.

| 2.4.             | CHARACTER REPRESENTATION                             |       | 2–5    |

|------------------|------------------------------------------------------|-------|--------|

| 2.4.1.           | Alphabetic Characters                                |       | 2–5    |

| 2.4.2.           | Special Letters                                      |       | 2-6    |

| 2.4.3.           | Numeric                                              |       | 2-6    |

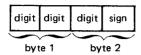

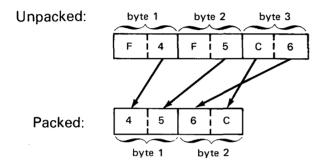

| 2.4.3.1.         | Unpacked Format                                      |       | 2-6    |

| 2.4.3.2.         | Packed Format                                        |       | 2–7    |

| 2.4.4.           | Special Characters                                   |       | 2–8    |

| 2.5.             | FIXED-POINT NUMBERS                                  |       | 2–9    |

| <b>2.6</b> .     | FLOATING-POINT NUMBERS                               |       | 2–9    |

| ADDRE            | SSING                                                |       |        |

| 3.1.             | MAIN COMPUTER STORAGE ADDRESSING                     |       | 3–1    |

| 3.1.1.           | Instruction Addressing                               |       | 3–1    |

| 3.1.2.           | Data Field Addressing                                |       | 3–2    |

|                  |                                                      |       |        |

| 3.2.             | REGISTER ADDRESSING                                  |       | 3–3    |

| RULES            | AND CONVENTIONS                                      |       |        |

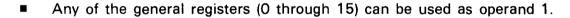

| 4.1.             | READING INSTRUCTION NOTATION                         |       | 4-1    |

| 4.1.1.           | Assembler Application Instruction Notations          |       | 4-1    |

| 4.1.2.           | Notation Rules and Meanings                          |       | 4-4    |

| 4.2.             | TERMS                                                |       | 4-8    |

| 4.2.1.           | Self-Defining Terms                                  | (SDT) | 4–9    |

| 4.2.2.           | Literals                                             |       | 4–10   |

| 4.2.3.           | Symbols                                              |       | 4-11   |

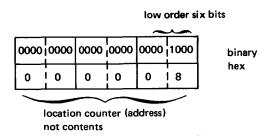

| 4.2.4.           | Location Counter References                          |       | 4–12   |

| 4.2.5.           | Length Attribute Reference                           |       | 4-13   |

| 4.3.             | OPERATORS                                            |       | 4-13   |

| 4.3.1.           | Arithmetic Operators                                 |       | 4-14   |

| 4.3.2.           | Logical Operators                                    |       | 4-14   |

| 4.3.3.           | Relational Operators                                 |       | 4–15   |

| 4.4.             | EXPRESSIONS                                          |       | 4-15   |

| 4.4.1.           | Absolute Expressions                                 |       | . 4–16 |

| 4.4.2.           | Relocatable Expressions                              |       | 4–17   |

| 4.4.3.           | Complex Relocatable Expressions                      |       | 4-17   |

| 4.4.4.<br>4.4.5. | Character Expressions                                |       | 4-18   |

| 4.4.5.<br>4.4.6. | Length Attribute of Expressions<br>Character Strings |       | 4-18   |

| <b></b>          | Character Strings                                    |       | 4–18   |

UP-8061 Rev. 3

# PART 2. STORAGE AND SYMBOL DEFINITIONS

# 5. STORAGE DEFINITIONS

|    | 5.1.           | STORAGE USAGE                      |                   | 5–1  |

|----|----------------|------------------------------------|-------------------|------|

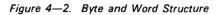

|    | 5.1.1.         | Define Constant                    | (DC)              | 5–4  |

|    | 5.1.2.         | Define Storage                     | (DS)              | 5-5  |

|    | 5.1.3.         | Duplication Factor                 |                   | 5-5  |

|    | 5.1.4.         | Definition Type                    |                   | 5-6  |

|    | 5.1.5.         | Length Factor                      | (L <sub>n</sub> ) | 5–6  |

|    | 5.1.6.         | Constant Specification             |                   | 5–7  |

|    | 5.1.7.         | Alignment                          | N                 | 5-8  |

|    | <b>5.2</b> .   | DEFINITION TYPES                   |                   | 5-8  |

|    | 5.2.1.         | Character Constants                | (C)               | 5-8  |

|    | 5.2.2.         | Hexadecimal Constants              | (X)               | 5-9  |

|    | 5.2.3.         | Binary Constants                   | (B)               | 5-9  |

|    | 5.2.4.         | Packed Decimal Constants           | (P)               | 5-10 |

|    | 5.2.5.         | Zoned Decimal Constants            | (Z)               | 5-10 |

|    | 5.2.6.         | Half-Word Fixed-Point Constants    | (H)               | 5-11 |

|    | 5.2.7.         | Full-Word Fixed-Point Constants    | (F)               | 5–12 |

|    | <b>5.2.8</b> . | Half-Word Address Constants        | (Y)               | 5-12 |

|    | <b>5.2.9</b> . | Full-Word Address Constants        | (A)               | 5–13 |

|    | 5.2.10.        | Base and Displacement Constants    | (S)               | 5–13 |

|    | 5.2.11.        | External Address Constants         | (V)               | 5-14 |

|    | 5.2.12.        | Floating-Point Constants           | (E and D)         | 5-15 |

|    | 5.3.           | LITERALS                           |                   | 5–18 |

| 6. | SYMBC          | DL DEFINITIONS                     |                   |      |

|    | 6.1.           | EQUIVALENT SYMBOLS                 |                   | 6-2  |

|    | 6.2.           | SYMBOL APPLICATIONS                |                   | 6-3  |

|    |                | PART 3. BAL APPLICATION IN         | STRUCTIONS        |      |

| 7  |                | UCTION TO APPLICATION INSTRUCTI    | ONS               |      |

|    |                |                                    |                   |      |

|    | 7.1.           | INSTRUCTION AND FORMAT CONVENTIONS | 5                 | 7–1  |

| 7.2. | EXPLICIT FORMS | 7-5 |

|------|----------------|-----|

| 7.3. | IMPLICIT FORMS | 7-6 |

7-6 **DEFINITIONS OF FORMAT TERMS** 7.4.

# 8. BRANCHING INSTRUCTIONS

|    | 8.1.           | USE OF BRANCHING INSTRUCTIONS                                            |                    | 8–1        |

|----|----------------|--------------------------------------------------------------------------|--------------------|------------|

|    | 8.2.           | EXTENDED MNEMONIC CODES                                                  |                    | 8–2        |

|    | 8.3.           | BRANCH AND STORE                                                         | (BAS, BASR)        | 8-5        |

|    | 8.4.<br>8.4.1. | BRANCH AND LINK<br>Use of the BALR Instruction in Base Register Assignme | (BAL, BALR)<br>ent | 8–6<br>8–8 |

|    | 8.5.           | BRANCH ON CONDITION                                                      | (BC, BCR)          | 8-10       |

|    | 8.6.           | BRANCH ON COUNT                                                          | (BCT, BCTR)        | 8-14       |

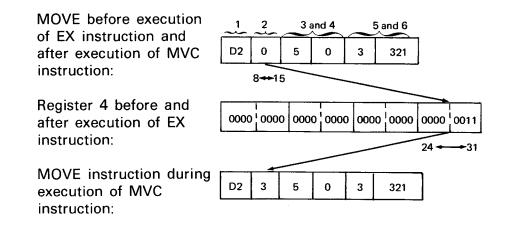

|    | 8.7.           | EXECUTE                                                                  | (EX)               | 8–16       |

| 9. | DECIM          | AL AND LOGICAL INSTRUCTIONS                                              |                    |            |

|    | 9.1.           | USING DECIMAL INSTRUCTIONS                                               |                    | 9–1        |

|    | 9.2.           | DEFINING PACKED AND UNPACKED CONSTANTS<br>AND MAIN STORAGE AREAS         |                    | 9-3        |

|    | 9.2.1.         | Packed Decimal Constants and Main Storage Areas                          |                    | 9-3<br>9-4 |

|    | 9.2.2.         | Unpacked Decimal Constants and Main Storage Areas                        |                    | 9–4<br>9–6 |

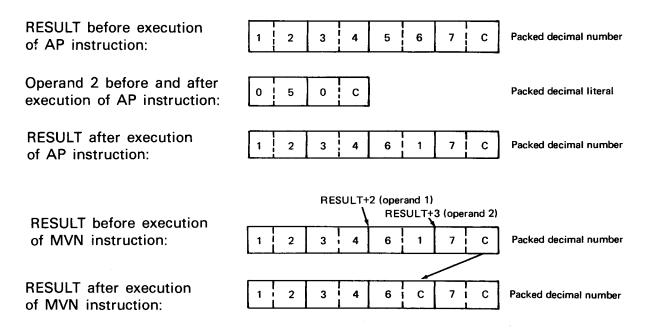

|    | 9.3.           | ADD DECIMAL                                                              | (AP)               | 9–8        |

|    | 9.4.           | COMPARE DECIMAL                                                          | (CP)               | 9–10       |

|    | 9.5.           | DIVIDE DECIMAL                                                           | (DP)               | 9–12       |

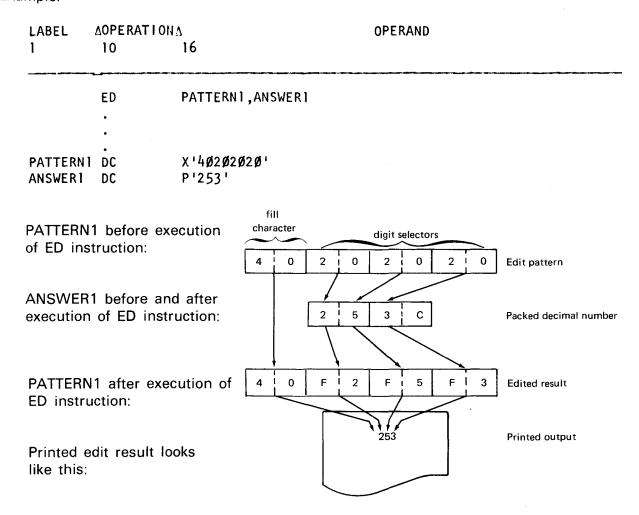

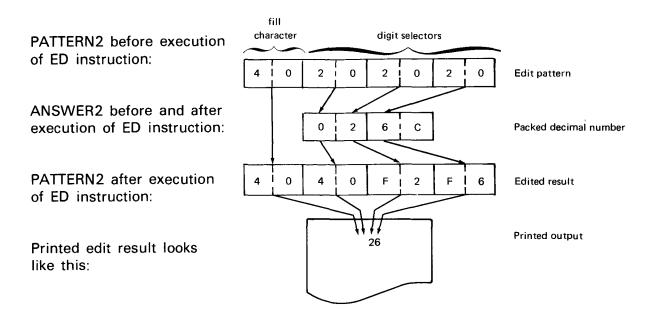

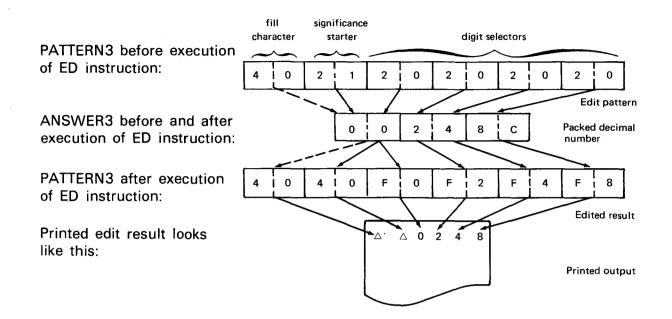

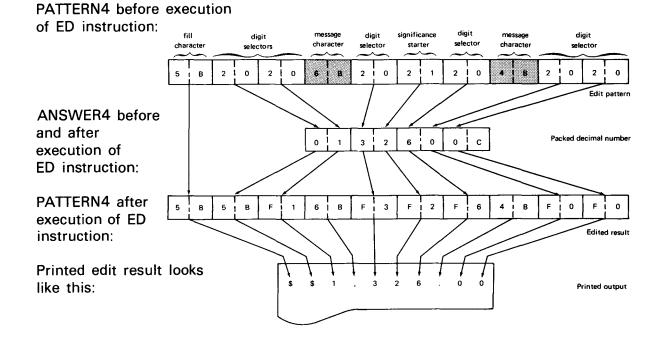

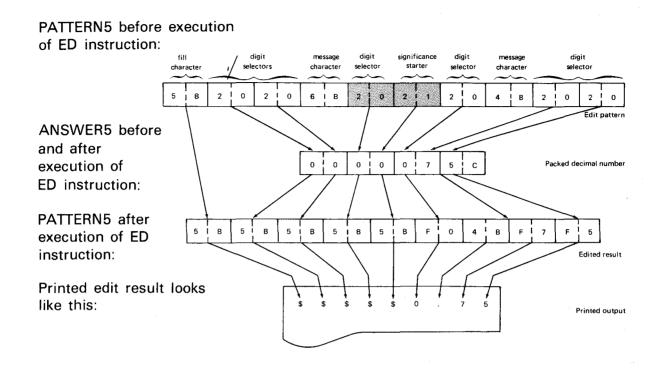

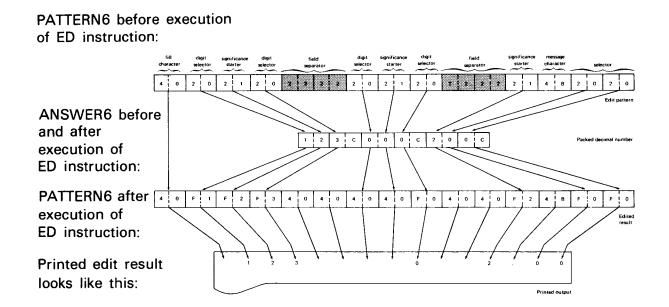

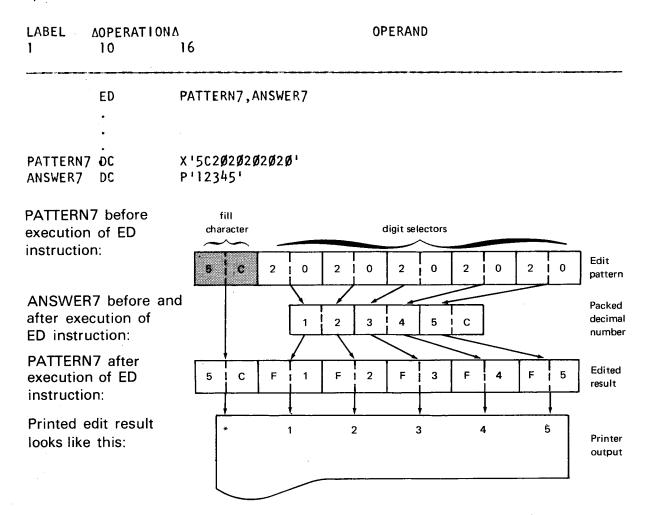

|    | 9.6.           | EDIT                                                                     | (ED)               | 9-15       |

|    | 9.6.1.         | The Edit Pattern                                                         |                    | 9–16       |

|    | 9.6.2.         | The Resulting Condition Code                                             |                    | 9-22       |

|    | 9.6.3.         | Examples of General Usage                                                |                    | 9-23       |

|    | 9.6.4.         | Summary                                                                  |                    | 9-25       |

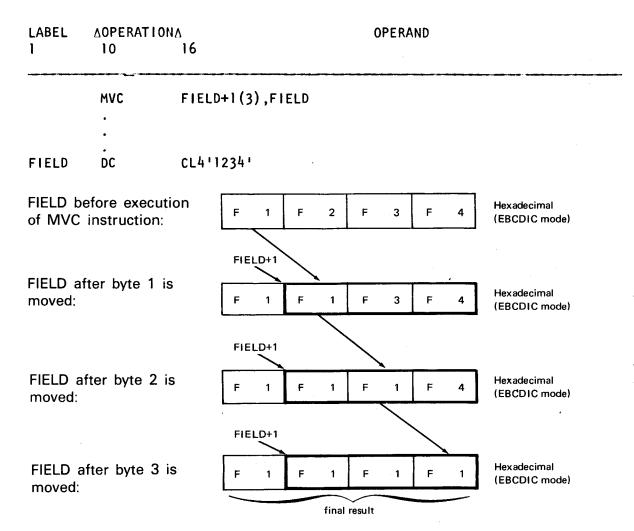

|    | <b>9</b> .7.   | MOVE CHARACTER                                                           | (MVC)              | 9–26       |

|    | 9.8.           | MOVE NUMERICS                                                            | (MVN)              | 9-30       |

|    | 9.9.           | MOVE WITH OFFSET                                                         | (MVO)              | 9–33       |

|    | 9.10.          | MOVE ZONES                                                               | (MVZ)              | 9–36       |

|    | 9.11.          | MULTIPLY DECIMAL                                                         | (MP)               | 9-38       |

|    | 9.12.          | PACK DECIMAL                                                             | (PACK)             | 9-40       |

|    | 9.13.          | SUBTRACT DECIMAL                                                         | (SP)               | 9–44       |

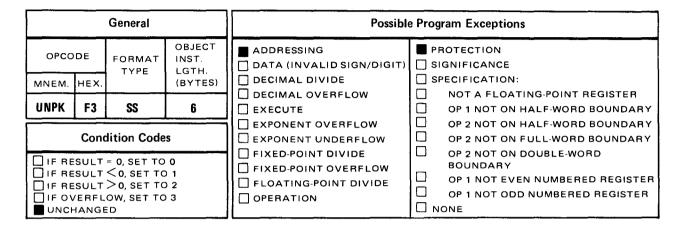

|    | 9.14.          | UNPACK DECIMAL                                                           | (UNPK)             | 9-47       |

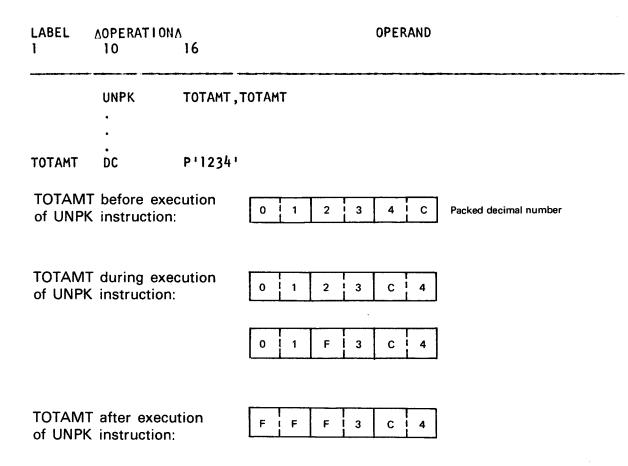

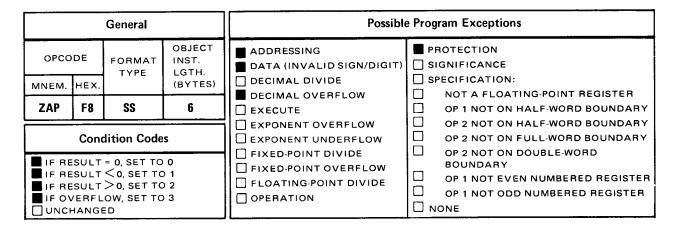

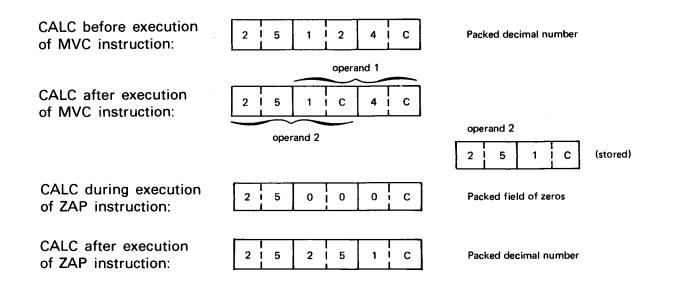

|    | 9.15.          | ZERO AND ADD DECIMAL                                                     | (ZAP)              | 9–50       |

# **10. FIXED-POINT BINARY INSTRUCTIONS**

| <b>10.1.3.</b><br>10.1.3.1<br>10.1.3.2 | Full-Word Fixed-Point Constants         Address Constants         Full-Word Address Constants         Half-Word Address Constants         Representation of Positive and Negative |       | 10-1<br>10-3<br>10-3<br>10-4<br>10-4<br>10-5 |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------|

|                                        | Fixed-Point Binary Numbers                                                                                                                                                        |       | 10–5                                         |

| 10.2.                                  | ADD                                                                                                                                                                               | (A)   | 10-7                                         |

| 10.3.                                  | ADD                                                                                                                                                                               | (AR)  | 10–9                                         |

| 10.4.                                  | ADD HALF WORD                                                                                                                                                                     | (AH)  | 10-11                                        |

| 10.5.                                  | ADD IMMEDIATE                                                                                                                                                                     | (AI)  | 10-13                                        |

| 10.6.                                  | COMPARE                                                                                                                                                                           | (C)   | 10-15                                        |

| 10.7.                                  | COMPARE                                                                                                                                                                           | (CR)  | 10–17                                        |

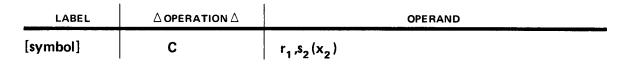

| 10.8.                                  | COMPARE HALF WORD                                                                                                                                                                 | (CH)  | 10–19                                        |

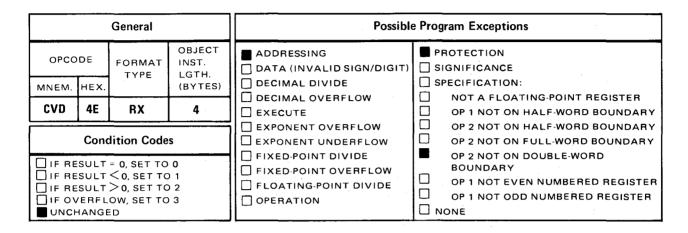

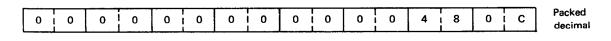

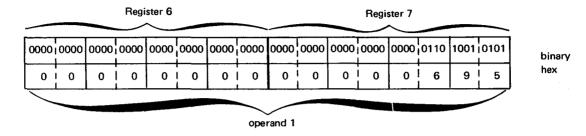

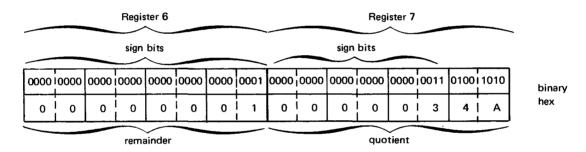

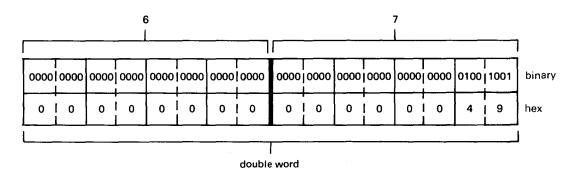

| 10.9.                                  | CONVERT TO BINARY                                                                                                                                                                 | (CVB) | 10-21                                        |

| 10.10.                                 | CONVERT TO DECIMAL                                                                                                                                                                | (CVD) | 10–24                                        |

| 10.11.                                 | DIVIDE                                                                                                                                                                            | (D)   | 10–27                                        |

| 10.12.                                 | LOAD                                                                                                                                                                              | (L)   | 10–31                                        |

| 10.13.                                 | LOAD                                                                                                                                                                              | (LR)  | 10–33                                        |

| 10.14.                                 | LOAD AND TEST                                                                                                                                                                     | (LTR) | 10–35                                        |

| 10.15.                                 | LOAD HALF WORD                                                                                                                                                                    | (LH)  | 10–37                                        |

| 10.16.                                 | LOAD MULTIPLE                                                                                                                                                                     | (LM)  | 10-39                                        |

| 10.17.                                 | MULTIPLY                                                                                                                                                                          | (M)   | 10–45                                        |

| 10.18.                                 | STORE                                                                                                                                                                             | (ST)  | 10–49                                        |

| 10.19.                                 | STORE HALF WORD                                                                                                                                                                   | (STH) | 10-51                                        |

| 10.20.                                 | STORE MULTIPLE                                                                                                                                                                    | (STM) | 10–53                                        |

| 10.21.                                 | SUBTRACT                                                                                                                                                                          | (S)   | 10–56                                        |

| 10.22.                                 | SUBTRACT                                                                                                                                                                          | (SR)  | 10–58                                        |

| 10.23.                                 | SUBTRACT HALF WORD                                                                                                                                                                | (SH)  | 10–61                                        |

## **11. FLOATING-POINT INSTRUCTIONS**

| 11.1.         | INTRODUCTION                   |        | 11-1  |

|---------------|--------------------------------|--------|-------|

| 11.2.         | ADD NORMALIZED, LONG FORMAT    | (AD)   | 11-3  |

| 11.3.         | ADD NORMALIZED, LONG FORMAT    | (ADR)  | 11–6  |

| 11.4.         | ADD NORMALIZED, SHORT FORMAT   | (AE)   | 11-9  |

| 11.5.         | ADD NORMALIZED, SHORT FORMAT   | (AER)  | 11-12 |

| <b>11.6</b> . | ADD UNNORMALIZED, SHORT FORMAT | (AU)   | 11–15 |

| 11.7.         | ADD UNNORMALIZED, SHORT FORMAT | (AUR)  | 11-17 |

| 11.8.         | ADD UNNORMALIZED, LONG FORMAT  | (AW)   | 11–19 |

| 11.9.         | ADD UNNORMALIZED, LONG FORMAT  | (AWR)  | 11–21 |

| 11.10.        | COMPARE, LONG FORMAT           | (CD)   | 11-23 |

| 11.11.        | COMPARE, LONG FORMAT           | (CDR)  | 11-25 |

| 11.12.        | COMPARE, SHORT FORMAT          | (CE)   | 11–27 |

| 11.13.        | COMPARE, SHORT FORMAT          | (CER)  | 11-29 |

| 11.14.        | DIVIDE, LONG FORMAT            | (DD)   | 11–31 |

| 11.15.        | DIVIDE, LONG FORMAT            | (DDR)  | 11-33 |

| 11.16.        | DIVIDE, SHORT FORMAT           | (DE)   | 11-35 |

| 11.17.        | DIVIDE, SHORT FORMAT           | (DER)  | 11-37 |

| 11.18.        | HALVE, LONG FORMAT             | (HDR)  | 11–39 |

| 11.19.        | HALVE, SHORT FORMAT            | (HER)  | 11-41 |

| 11.20.        | LOAD COMPLEMENT, LONG FORMAT   | (LCDR) | 11-43 |

| 11.21.        | LOAD COMPLEMENT, SHORT FORMAT  | (LCER) | 11–45 |

| 11.22.        | LOAD, LONG FORMAT              | (LD)   | 11–47 |

| 11.23.        | LOAD, LONG FORMAT              | (LDR)  | 11-49 |

| 11.24.        | LOAD, SHORT FORMAT             | (LE)   | 11-51 |

| 11.25.        | LOAD, SHORT FORMAT             | (LER)  | 11-53 |

| 11.26.        | LOAD NEGATIVE, LONG FORMAT     | (LNDR) | 11-55 |

| 11.27.        | LOAD NEGATIVE, SHORT FORMAT    | (LNER) | 11-57 |

| UP-8061 | Rev. | 3 |

|---------|------|---|

|---------|------|---|

| Contents | 7 |

|----------|---|

|----------|---|

|     | 11.28. | LOAD POSITIVE, LONG FORMAT          | (LPDR) | 11–59 |

|-----|--------|-------------------------------------|--------|-------|

|     | 11.29. | LOAD POSITIVE, SHORT FORMAT         | (LPER) | 11–61 |

|     | 11.30. | LOAD AND TEST, LONG FORMAT          | (LTDR) | 11-63 |

|     | 11.31. | LOAD AND TEST, SHORT FORMAT         | (LTER) | 11–65 |

|     | 11.32. | MULTIPLY, LONG FORMAT               | (MD)   | 11–67 |

|     | 11.33. | MULTIPLY, LONG FORMAT               | (MDR)  | 11–69 |

|     | 11.34. | MULTIPLY, SHORT FORMAT              | (ME)   | 11-71 |

|     | 11.35. | MULTIPLY, SHORT FORMAT              | (MER)  | 11-73 |

|     | 11.36. | SUBTRACT NORMALIZED, LONG FORMAT    | (SD)   | 11-75 |

|     | 11.37. | SUBTRACT NORMALIZED, LONG FORMAT    | (SDR)  | 11-77 |

|     | 11.38. | SUBTRACT NORMALIZED, SHORT FORMAT   | (SE)   | 11-79 |

|     | 11.39. | SUBTRACT NORMALIZED, SHORT FORMAT   | (SER)  | 11-81 |

|     | 11.40. | STORE, LONG FORMAT                  | (STD)  | 11-83 |

|     | 11.41. | STORE, SHORT FORMAT                 | (STE)  | 11-85 |

|     | 11.42. | SUBTRACT UNNORMALIZED, SHORT FORMAT | (SU)   | 11–87 |

|     | 11.43. | SUBTRACT UNNORMALIZED, SHORT FORMAT | (SUR)  | 11–89 |

|     | 11.44. | SUBTRACT UNNORMALIZED, LONG FORMAT  | (SW)   | 11–91 |

|     | 11.45. | SUBTRACT UNNORMALIZED, LONG FORMAT  | (SWR)  | 11-93 |

| 12. | LOGIC  | AL INSTRUCTIONS                     |        |       |

|     | 12.1.  | THE USE OF LOGICAL INSTRUCTIONS     |        | 12-1  |

|     | 12.2.  | AND                                 | (N)    | 12-2  |

|     | 12.3.  | AND                                 | (NC)   | 12–5  |

|     | 12.4.  | AND                                 | (NI)   | 12-8  |

|     | 12.5.  | AND                                 | (NR)   | 12-11 |

|     | 12.6.  | COMPARE LOGICAL                     | (CL)   | 12–14 |

|     | 12.7.  | COMPARE LOGICAL CHARACTERS          | (CLC)  | 12–17 |

|     | 12.8.  | COMPARE LOGICAL IMMEDIATE           | (CLI)  | 12–20 |

|     |        |                                     |        |       |

| UP-8061 | Rev. | 3 |

|---------|------|---|

|---------|------|---|

| SPERRY | UNIVAC OS/3 |

|--------|-------------|

| AS     | SEMBLER     |

Contents 8

| 12.9.          | COMPARE LOGICAL            | (CLR) | 12-25 |

|----------------|----------------------------|-------|-------|

| 12.10.         | EXCLUSIVE OR               | (X)   | 12–27 |

| 12.11.         | EXCLUSIVE OR               | (XC)  | 12–30 |

| 12.12.         | EXCLUSIVE OR               | (XI)  | 12–33 |

| 12.13.         | EXCLUSIVE OR               | (XR)  | 12-36 |

| 12.14.         | INSERT CHARACTER           | (IC)  | 12–39 |

| 12.15.         | LOAD ADDRESS               | (LA)  | 12-41 |

| 12.16.         | MOVE IMMEDIATE             | (MVI) | 12-43 |

| 12.17.         | OR                         | (O)   | 12-45 |

| 12.18.         | OR                         | (OC)  | 12-48 |

| <b>12.19</b> . | OR                         | (OI)  | 12-51 |

| 12.20.         | OR                         | (OR)  | 12-54 |

| 12.21.         | SHIFT LEFT SINGLE LOGICAL  | (SLL) | 12–57 |

| 12.22.         | SHIFT RIGHT SINGLE LOGICAL | (SRL) | 12-60 |

| 12.23.         | STORE CHARACTER            | (STC) | 12–62 |

| 12.24.         | TEST UNDER MASK            | (TM)  | 12–64 |

| 12.25.         | TRANSLATE                  | (TR)  | 12-67 |

| 12.26.         | TRANSLATE AND TEST         | (TRT) | 12–70 |

|                |                            |       |       |

# **13. PRIVILEGED AND STATUS SWITCHING INSTRUCTIONS**

|        | 13-1                              |

|--------|-----------------------------------|

|        | 13-1                              |

| (HPR)  | 13-2                              |

| (ISK)  | 13-3                              |

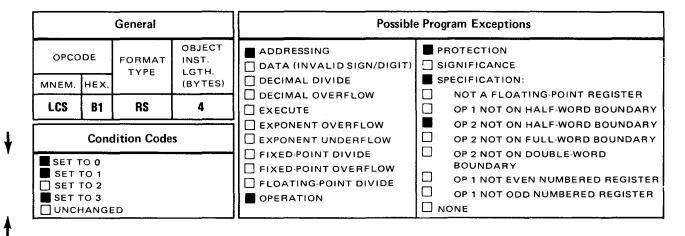

| (LCS)  | 13-4                              |

| (LPSW) | 13-5                              |

| (SSK)  | 13–6                              |

| (SSM)  | 13-7                              |

|        | (ISK)<br>(LCS)<br>(LPSW)<br>(SSK) |

14.

Contents 9

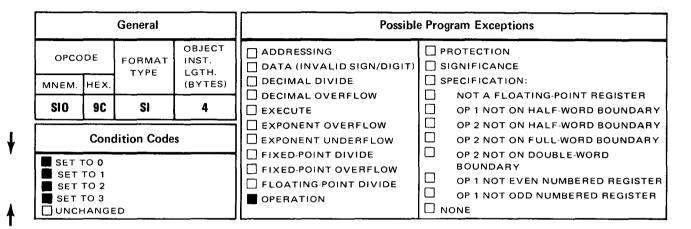

| 13.3.<br>13.3.1. | INPUT/OUTPUT PRIVILEGED INSTRUCTION<br>Start I/O                                                                          | (SIO)                      | 13-7<br>13-8                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------|

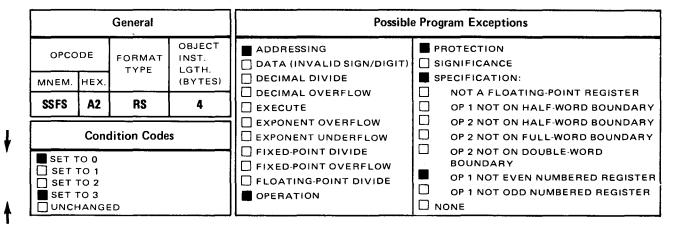

|                  | DIAGNOSTIC PRIVILEGED INSTRUCTIONS<br>Diagnose<br>SOFTSCOPE Forward Scan<br>SOFTSCOPE Reverse Scan                        | (DIAG)<br>(SSFS)<br>(SSRS) | 13–8<br>13–9<br>13–10<br>13–11 |

| 13.5.<br>13.5.1. | INTERNAL TIMER PRIVILEGED INSTRUCTION<br>Service Timer Register                                                           | (STR)                      | 13–11<br>13–12                 |

|                  | GENERAL REGISTER PRIVILEGED INSTRUCTIONS<br>Supervisor Load Multiple Instruction<br>Supervisor Store Multiple Instruction | (SLM)<br>(SSTM)            | 13-13<br>13-13<br>13-14        |

| 13.7.            | SET PROGRAM MASK STATUS-SWITCHING                                                                                         | (SPM)                      | 13–15                          |

| 13.8.            | SUPERVISOR CALL STATUS-SWITCHING                                                                                          | (SVC)                      | 13–17                          |

| 13.9.            | TEST AND SET STATUS-SWITCHING                                                                                             | (TS)                       | 13–19                          |

| FEATU            | RED INSTRUCTIONS                                                                                                          |                            |                                |

| 14.1.            | FEATURED BRANCHING INSTRUCTIONS                                                                                           |                            | 14-1                           |

|                  | Branch on Index High                                                                                                      | (BXH)                      | 14–2                           |

|                  | Branch on Index Low or Equal                                                                                              | (BXLE)                     | 14–5                           |

| 14.2.            | FEATURED FIXED-POINT INSTRUCTIONS                                                                                         |                            | 14–6                           |

| 14.2.1.          |                                                                                                                           | (DR)                       | 14–7                           |

| 14.2.2.          | Load Complement                                                                                                           | (LCR)                      | 14-9                           |

|                  | Load Negative                                                                                                             | (LNR)                      | 14–11                          |

| 14.2.4.          | Load Positive                                                                                                             | (LPR)                      | 14–14                          |

| 14.2.5.          | Multiply                                                                                                                  | (MR)                       | 14–17                          |

| 14.2.6.          | Multiply Half Word                                                                                                        | (MH)                       | 14–19                          |

| 14.2.7.          |                                                                                                                           | (SLDA)                     | 14-22                          |

| 14.2.8.          | -                                                                                                                         | (SLA)                      | 14-25                          |

|                  | Shift Right Double                                                                                                        | (SRDA)                     | 14-28                          |

| 14.2.10          | ). Shift Right Single                                                                                                     | (SRA)                      | 14–31                          |

| 14.3.            | FEATURED LOGICAL INSTRUCTIONS                                                                                             |                            | 14-33                          |

| 14.3.1.          | -                                                                                                                         | (AL)                       | 14–34                          |

| 14.3.2.          | -                                                                                                                         | (ALR)                      | 14-37                          |

| 14.3.3.          |                                                                                                                           | (EDMK)                     | 14-39                          |

| 14.3.4.          | -                                                                                                                         | (SLDL)                     | 14-42                          |

| 14.3.5.          |                                                                                                                           | (SRDL)<br>(SL)             | 14–45<br>14–48                 |

|                  | Subtract Logical<br>Subtract Logical                                                                                      | (SL)<br>(SLR)              | 14-48                          |

| 14.3.7.          | Subtract Logical                                                                                                          |                            |                                |

17.

### PART 4. BAL DIRECTIVES

## **15. INTRODUCTION TO DIRECTIVES**

### **16. EQUATE AND DELETE OPERATION CODE DIRECTIVES**

| 16.1. | EQUATE                  | (EQU)   | 16–1 |

|-------|-------------------------|---------|------|

| 16.2. | DELETE OPERATION CODE   | (OPSYM) | 16–3 |

| ASSEM | BLER CONTROL DIRECTIVES |         |      |

| 17.1. | CONDITION NO OPERATION  | (CNOP)  | 17–2 |

| 17.2. | PROGRAM END             | (END)   | 17–4 |

| 17.3. | GENERATE LITERALS        | (LTORG) | 17–5 |

|-------|--------------------------|---------|------|

| 17.4. | SPECIFY LOCATION COUNTER | (ORG)   | 17–6 |

| 17.5. | PROGRAM START            | (START) | 17-8 |

#### **18. BASE REGISTER ASSIGNMENT DIRECTIVES**

| 18.1. | UNASSIGN BASE REGISTER | (DROP)  | 18–2 |

|-------|------------------------|---------|------|

| 18.2. | ASSIGN BASE REGISTER   | (USING) | 18-3 |

#### **19. PROGRAM LINKING AND SECTIONING DIRECTIVES**

| 19.1. | COMMON STORAGE DEFINITION                | (COM)   | 19–2          |

|-------|------------------------------------------|---------|---------------|

| 19.2. | CONTROL SECTION IDENTIFICATION           | (CSECT) | 1 <b>9</b> –5 |

| 19.3. | DUMMY CONTROL SECTION IDENTIFICATION     | (DSECT) | 19–7          |

| 19.4. | EXTERNALLY REFERENCED SYMBOL DECLARATION | (ENTRY) | 19–9          |

| 19.5. | EXTERNALLY DEFINED SYMBOL DECLARATION    | (EXTRN) | 19-10         |

| 19.6. | SUBROUTINE LINKAGE                       |         | 19–11         |

## **20. LISTING CONTROL DIRECTIVES**

| 20.1. | ADVANCE LISTING              | (EJECT) | 20–2 |

|-------|------------------------------|---------|------|

| 20.2. | LISTING CONTENT CONTROL      | (PRINT) | 20–3 |

| 20.3. | LEAVE BLANK LINES ON LISTING | (SPACE) | 20–5 |

| 20.4. | LISTING TITLE DECLARATION    | (TITLE) | 20-6 |

#### **21. INPUT AND OUTPUT CONTROL DIRECTIVES**

| 21.1. | INPUT FORMAT CONTROL        | (ICTL)  | 21-2 |

|-------|-----------------------------|---------|------|

| 21.2. | INPUT SEQUENCE CONTROL      | (ISEQ)  | 21-4 |

| 21.3. | REPRODUCE FOLLOWING RECORD  | (REPRO) | 21–5 |

| 21.4. | PRODUCE A RECORD            | (PUNCH) | 21–6 |

| 21.5. | INCLUDE CODE FROM A LIBRARY | (COPY)  | 21-7 |

| 21.6. | CHANNEL COMMAND WORD        | (CCW)   | 21-8 |

#### PART 5. BAL MACROS

#### 22. MACRO FACILITY

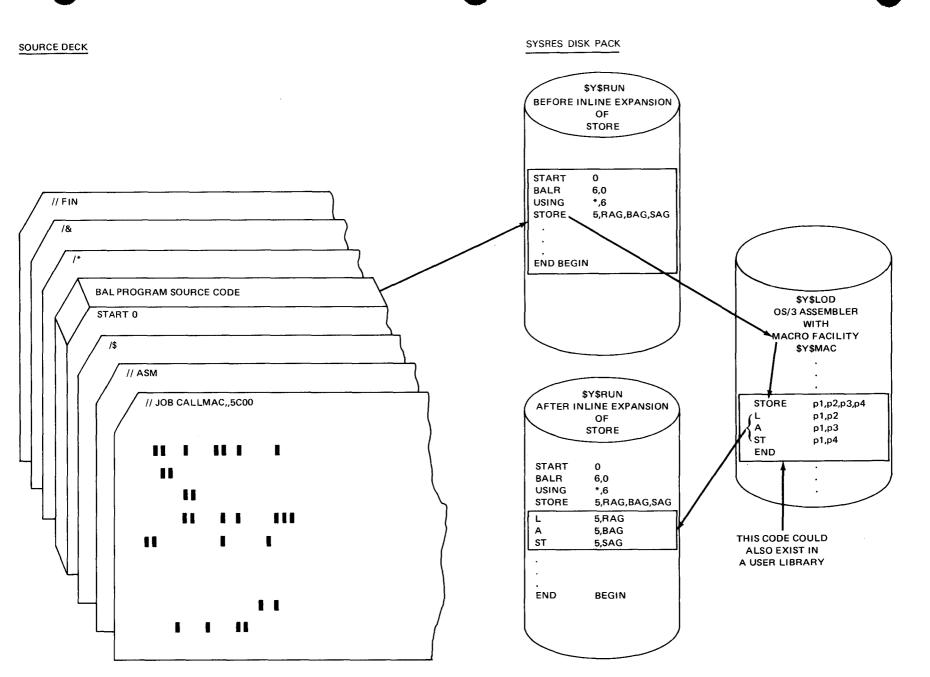

|     | 22.1. | THE MACRO PROCESSOR            | 22-1 |

|-----|-------|--------------------------------|------|

|     | 22.2. | MACRO SOURCE CODE              | 22-3 |

| 23. | MACRO | DESIGN                         |      |

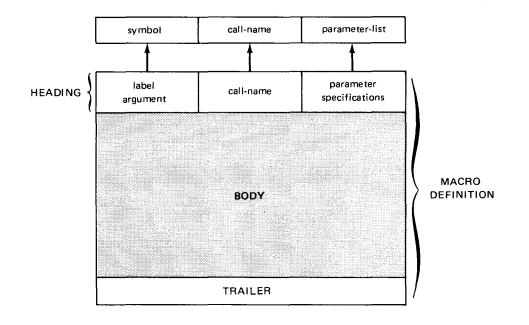

|     | 23.1. | THE MACRO DEFINITION           | 23–1 |

|     | 23.2. | MACRO DEFINITION STORAGE       | 23-3 |

|     | 23.3. | THE MACRO CALL INSTRUCTION     | 23-6 |

| 24. | тwo т | YPES OF MACRO DEFINITIONS      |      |

|     | 24.1. | PROCS AND MACROS               | 24–1 |

|     | 24.2. | CALL INSTRUCTION DESIGN        | 24–2 |

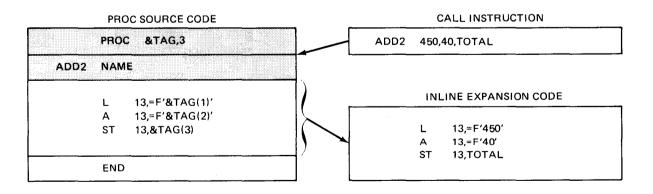

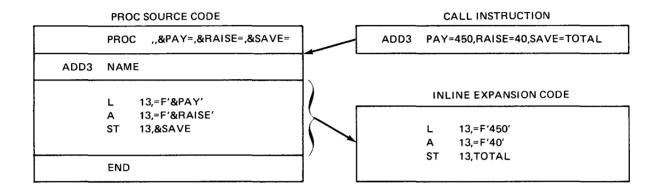

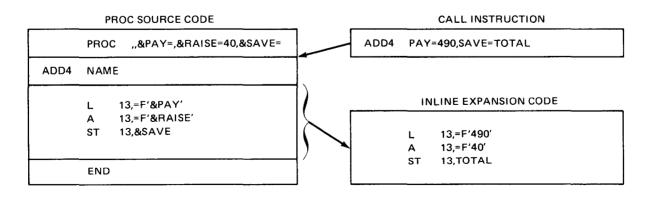

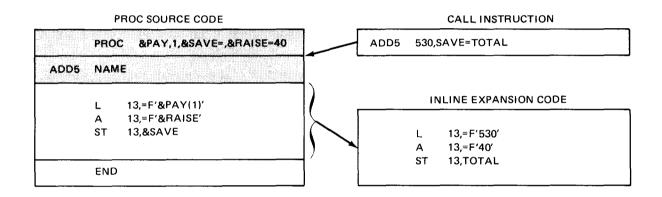

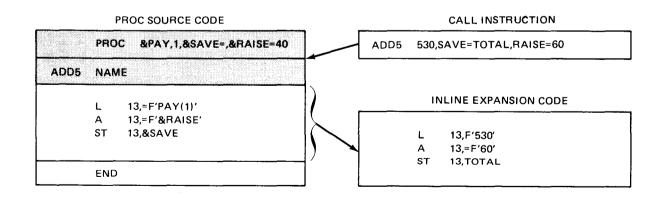

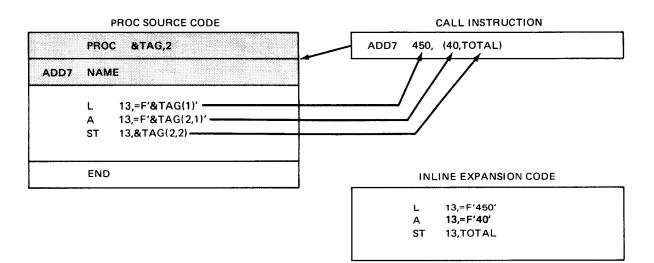

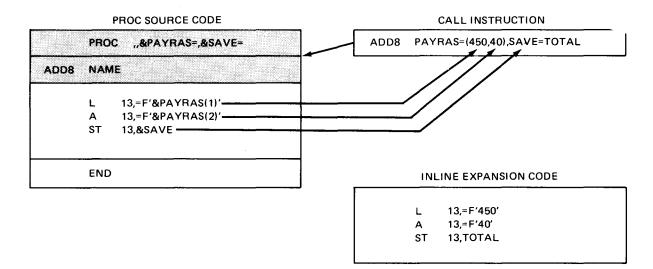

|     | 24.3. | PASSING PARAMETERS TO THE BODY | 24-6 |

27-12

27-13

27-13

27-14

27-14

27-14

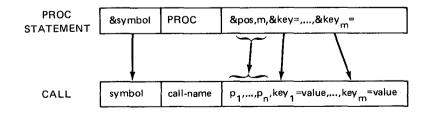

# 25. PROC FORMAT

|             | 25.1.         | BASIC PROC DESIGN                                 | 25-1  |

|-------------|---------------|---------------------------------------------------|-------|

|             | 25.2.         | REFERENCING POSITIONAL PARAMETERS IN<br>THE CALL  | 25-3  |

|             | 25.3.         | REFERENCING KEYWORD PARAMETERS IN THE<br>CALL     | 25-4  |

|             | 25.4.         | REFERENCING SUBPARAMETERS IN THE CALL             | 25-7  |

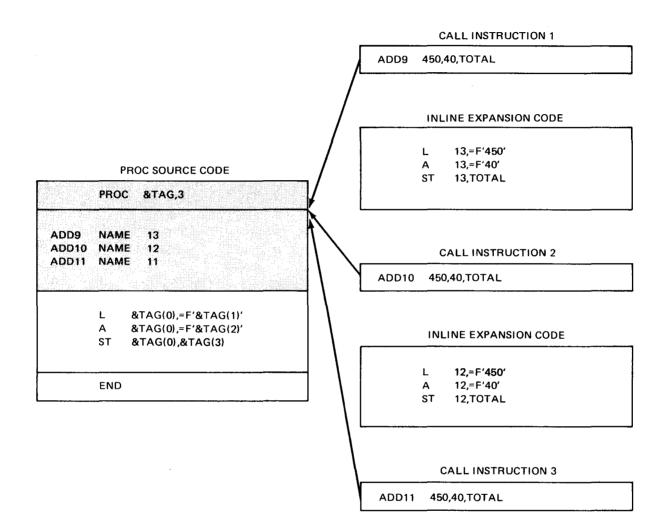

|             | 25.5.         | MULTIPLE PROC NAMES AND POSITIONAL<br>PARAMETER 0 | 25-9  |

|             | <b>25.6</b> . | THE LABEL ARGUMENT                                | 25-11 |

| <b>26</b> . | MACRO         | D FORMAT                                          |       |

|             | 26.1.         | BASIC MACRO DESIGN                                | 26-1  |

|             | 26.2.         | REFERENCING POSITIONAL PARAMETERS IN THE CALL     | 26-2  |

|             | 26.3.         | REFERENCING KEYWORD PARAMETERS IN<br>THE CALL     | 26-4  |

|             | 26.4.         | REFERENCING SUBPARAMETERS IN THE CALL             | 26-5  |

|             | 26.5.         | THE LABEL ARGUMENT                                | 266   |

| 27.         | CONDI         | TIONAL ASSEMBLY                                   |       |

|             |               | SET SYMBOLS                                       | 27-2  |

|             |               | Local Set Symbols                                 | 27-3  |

|             |               | Global Set Symbols                                | 27-4  |

|             |               | Set Symbol Value Assignment                       | 27-6  |

|             |               | SET Statement                                     | 27-6  |

|             |               | SETA Statement                                    | 27–9  |

|             | 27.1.6.       | SETB Statement                                    | 27-10 |

| <b>27</b> .1.7.    | SETC Statement                   |       |

|--------------------|----------------------------------|-------|

| 27.1.8.            | Character Expressions            |       |

| 27.1.9.            | Subscripted SET Symbols          |       |

| 27.1. <b>9</b> .1. | Defining Subscripted SET Symbols |       |

| 27.2.              | BRANCHING                        |       |

| 27.2.1.            | Sequence Symbols                 |       |

| 27.2.2.            | Unconditional Branch             | (AGO) |

| 0700               |                                  |       |

27.2.2.

Unconditional Branch

(AGO)

27-15

27.2.3.

Conditional Branch

(AIF)

27-16

27.2.4.

Define Branch Destination

(ANOP)

27-17

27.2.5.

Macro Definition Exit

(MEXIT)

27-18

| 27.3.   | ERROR MESSAGES AND COMMENTS          |         | 27–18 |

|---------|--------------------------------------|---------|-------|

| 27.3.1. | MNOTE Message Statements             | (MNOTE) | 27–19 |

| 27.3.2. | PNOTE Message Statements             | (PNOTE) | 27–20 |

| 27.3.3. | Comments Statement                   |         | 27–20 |

| 27.4.   | REPETITIVE CODE GENERATION           |         | 2721  |

| 27.4.1. | Define Start of Range                | (DO)    | 27–21 |

| 27.4.2. | Define End of Range                  | (ENDO)  | 27–22 |

| 27.4.3. | Conditional Assembly Control Counter | (ACTR)  | 27–23 |

| 27.5.   | ATTRIBUTE REFERENCES                 |         | 27-23 |

| 27.5.1. | Type Attributes                      |         | 27–25 |

| 27.5.2. | Length Attributes                    |         | 27-27 |

| 27.5.3. | Scale Attributes                     |         | 27-28 |

| 27.5.4. | Integer Attributes                   |         | 27–28 |

| 27.5.5. | Count Attributes                     |         | 27–29 |

| 27.5.6. | Number Attributes                    |         | 27-30 |

|         |                                      |         |       |

#### PART 6. ASSEMBLY LISTING

### **28. ORGANIZATION OF LISTING**

| 28.1. | HEADER LINES                       | 28–1 |

|-------|------------------------------------|------|

| 28.2. | PREFACE                            | 28-1 |

| 28.3. | CODEDIT                            | 28–2 |

| 28.4. | EXTERNAL SYMBOL DICTIONARY LISTING | 28-3 |

| 28.5. | CROSS-REFERENCE LISTING            | 28-4 |

| 28.6. | DIAGNOSTIC LISTING                 | 28–5 |

| 28.7. | EXAMPLE OF ASSEMBLY LISTING        | 28–5 |

### PART 7. PROGRAMMING TECHNIQUES

#### **29. JOB CONTROL PROCEDURES**

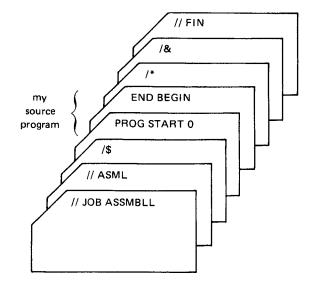

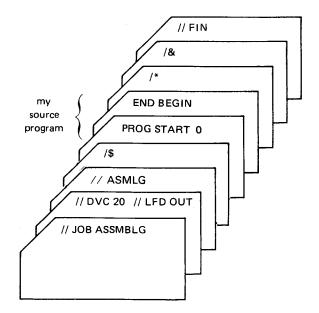

| 29.1.   | HOW TO RUN A JOB             | 29-1 |

|---------|------------------------------|------|

| 29.2.   | INTRODUCING THE SOURCE DECK  | 29-1 |

| 29.2.1. | JOB Control Statement        | 29-2 |

| 29.2.2. | OPTION Job Control Statement | 29–2 |

| 29.3.     | ASSEMBLE; ASSEMBLE AND LINK-EDIT;         |                   |

|-----------|-------------------------------------------|-------------------|

|           | OR ASSEMBLE LINK-EDIT AND EXECUTE         | 29-3              |

| 29.3.1.   | Assemble (ASM)                            | 2 <del>9</del> -3 |

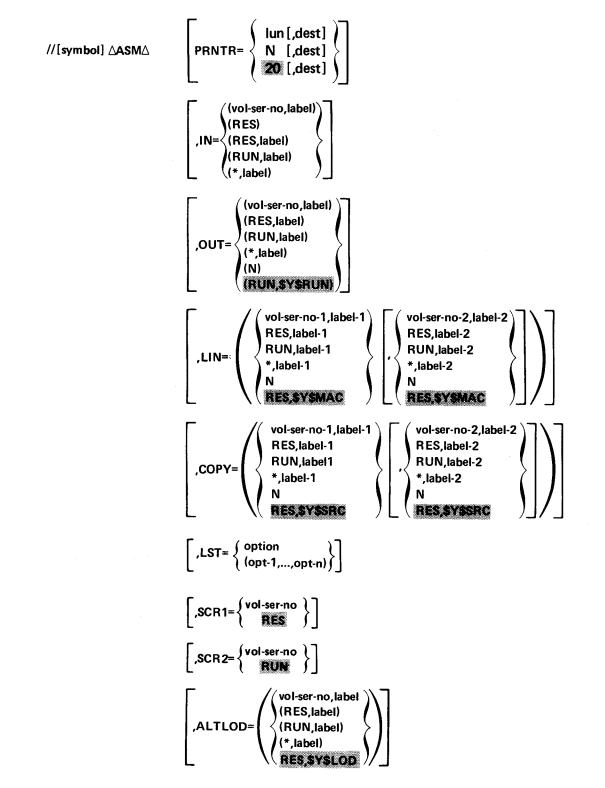

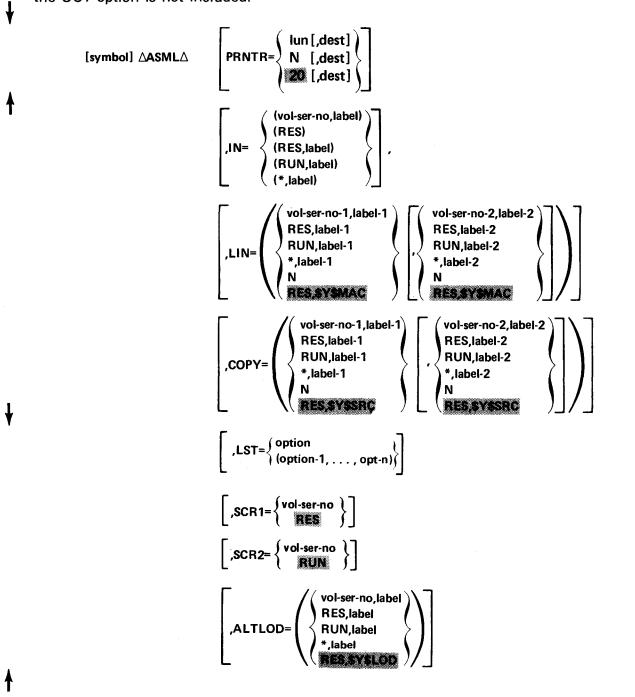

| 29.3.1.1. | ASM Jproc Call Statement                  | 29-4              |

| 29.3.2.   | Assemble and Link-Edit (ASML)             | 29-11             |

| 29.3.2.1. | ASML Jproc Call Statement                 | <b>29</b> -12     |

| 29.3.3.   | Assemble, Link-Edit, and Execute (ASMLG)  | 29-13             |

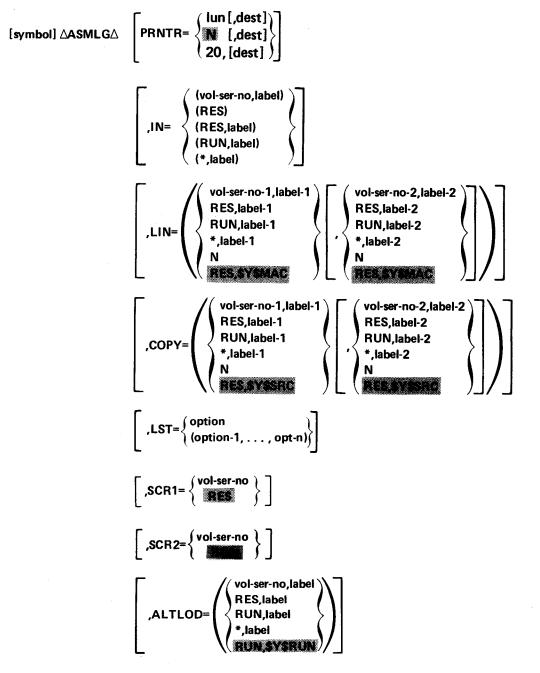

| 29.3.3.1  | ASMLG Jproc Call Statement                | 29-14             |

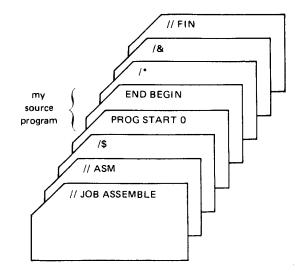

| 29.4.     | START-OF-DATA JOB CONTROL STATEMENT (/\$) | 29-15             |

| 29.5.     | FOLLOWING THE SOURCE DECK                 | 29–15             |

| 29.5.1.   | End-of-Data Job Control Statement (/*)    | 29-15             |

| 29.5.2.   | End-of-Job Control Statement (/&)         | 29-16             |

| 29.5.3.   | Terminate-the-Card-Reader Job Control     |                   |

|           | Statement (// FIN)                        | 29-16             |

| 29.5.4.   | Setting the UPSI Byte                     | 29-16             |

| 29.6.     | SUMMARY OF JOB CONTROL PROCEDURE          | 29-17             |

| 29.6.1.   | Assembly                                  | 29-17             |

| 29.6.2.   | Assembly and Link-Edit                    | 29-19             |

| 29.6.3.   | Assembly, Link-Edit, and Execution        | 29-21             |

#### **30. EXAMPLE MACRO DEFINITIONS**

| 30.1. | SMALR/LARGR PROC (POSITIONAL PARAMTER 0)     | 30-1 |

|-------|----------------------------------------------|------|

| 30.2. | SMALL6/LARGE6 PROC (DO LOOP)                 | 30-2 |

| 30.3. | BLANK MACRO (VARIABLE INLINE EXPANSION CODE) | 30-4 |

# PART 8. APPENDIXES

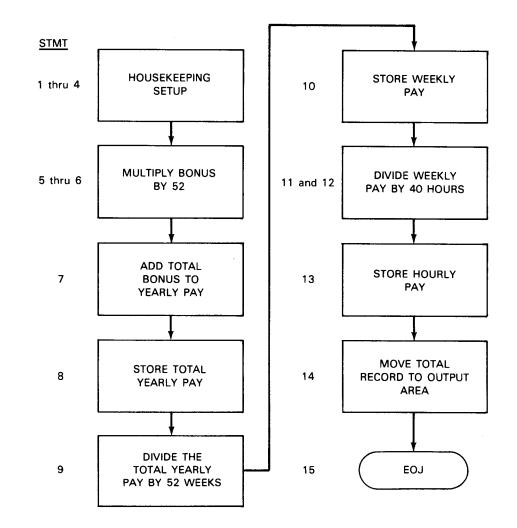

#### A. SAMPLE PROGRAM

#### **B. CHARACTER CONVERSION CODES**

### C. MATH TABLES

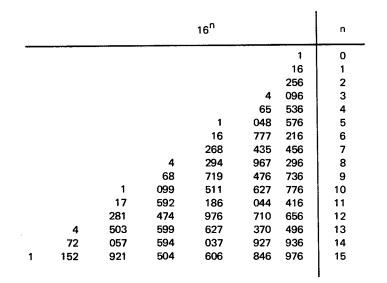

| C.1. | HEXADECIMAL-DECIMAL INTEGER CONVERSION     | C-1 |

|------|--------------------------------------------|-----|

| C.2. | HEXADECIMAL FRACTIONS (APPROXIMATE VALUES) | C-7 |

| C.3. | POWERS OF 2                                | C-8 |

| C.4. | POWERS OF 16                               | C-9 |

.

| D.  | CHECK            | -OFF TABLE TERMS                                                      |                          |

|-----|------------------|-----------------------------------------------------------------------|--------------------------|

| Ε.  | INSTRU           | ICTION LISTINGS                                                       |                          |

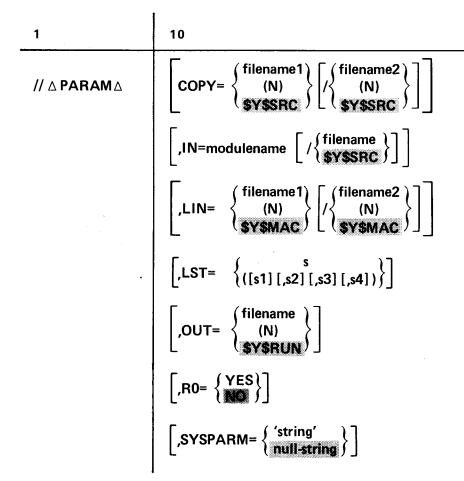

| F.  | USE OF           | PARAM STATEMENT                                                       |                          |

|     | F.1.             | PARAM STATEMENT                                                       | F-1                      |

|     | F.2.1.<br>F.2.2. | SOURCE CORRECTIONS<br>SEQ Statement<br>REC Statement<br>SKI Statement | F-5<br>F-6<br>F-7<br>F-7 |

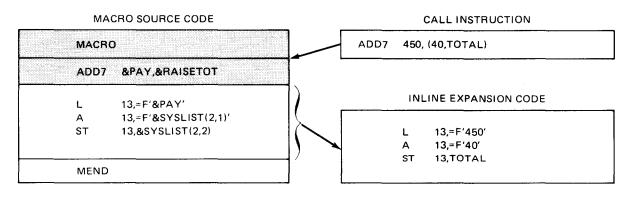

| G.  | SYSTE            | M VARIABLE SYMBOLS                                                    |                          |

|     | G.1.             | &SYSECT                                                               | G-1                      |

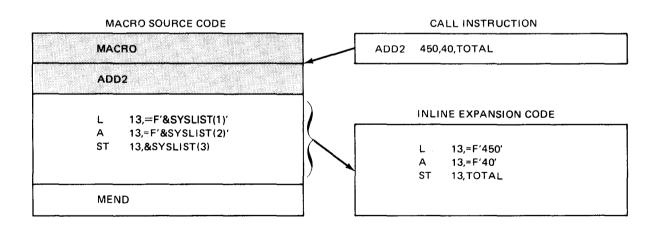

|     | G.2.             | &SYSLIST                                                              | G-1                      |

|     | G.3.             | &SYSNDX                                                               | G-2                      |

|     | G.4.             | &SYSDATE                                                              | G-2                      |

|     | G.5.             | &SYSTIME                                                              | G-3                      |

|     | G.6.             | &SYSJDATE                                                             | G-4                      |

|     | G.7.             | &SYSPARM                                                              | G-4                      |

| US  | ER COM           | IMENT SHEET                                                           |                          |

| FIG | GURES            |                                                                       |                          |

| 1-1.  | Writing and Submitting a Program             | 1–1  |

|-------|----------------------------------------------|------|

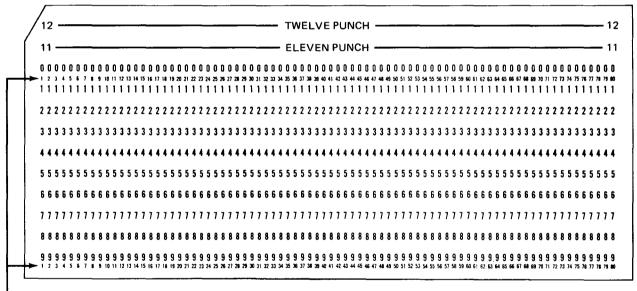

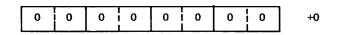

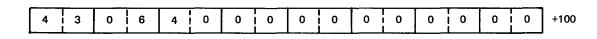

| 1-2.  | Punched Card                                 | 1–2  |

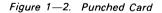

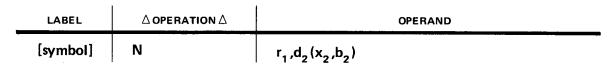

| 1–3   | Assembler Coding Form                        | 1–3  |

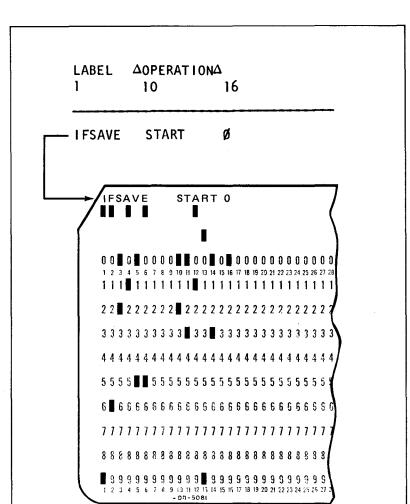

| 1–4.  | Coding Form and Punched Card Relationship    | 1–4  |

| 1–5.  | Example of Proper Coding Techniques          | 1–11 |

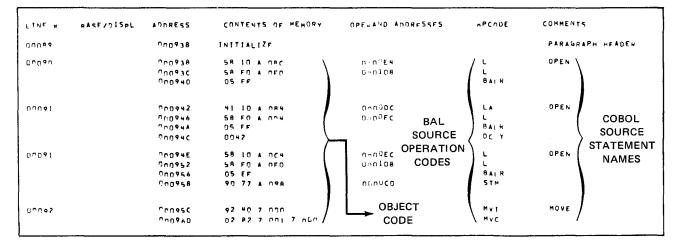

| 1–6.  | COBOL Source Code                            | 1–13 |

| 1-7.  | Object Code Generated from COBOL Source Code | 1–13 |

| 1–8.  | Assembly Listing                             | 1–14 |

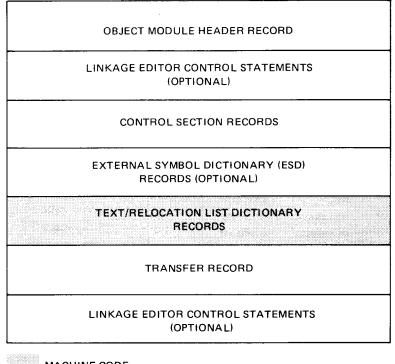

| 1-9.  | OS/3 Object Module Format                    | 1–16 |

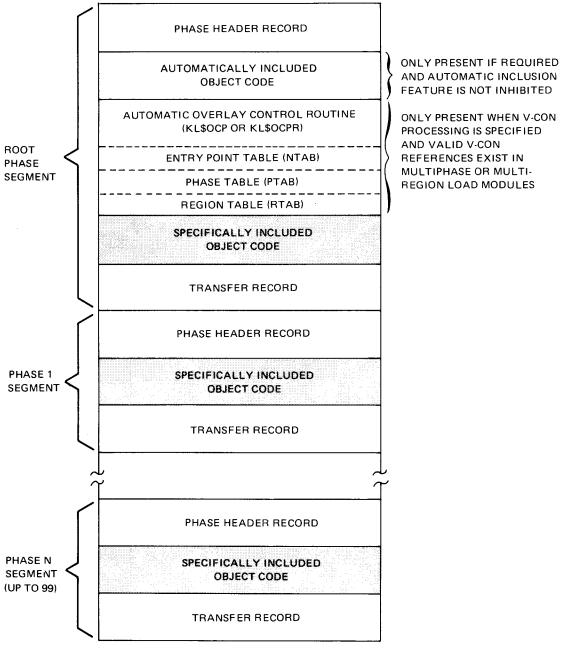

| 1-10. | OS/3 Load Module Format                      | 1–18 |

| 1-11. | Assemble, Link, and Go Operation             | 1–19 |

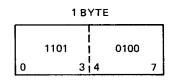

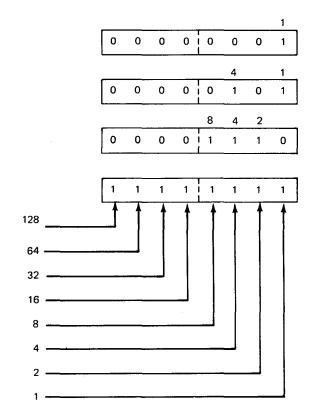

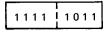

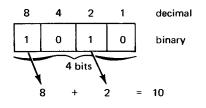

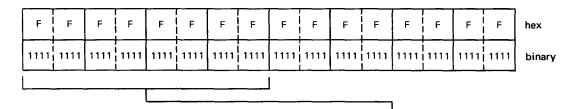

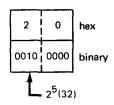

| 2-1.  | Determining Binary Values                    | 2–3  |

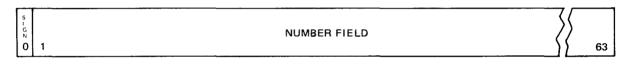

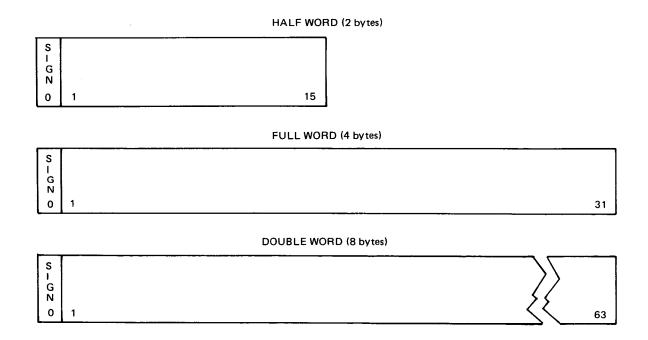

| 2–2.  | Fixed-Point Number Formats                   | 2-9  |

| 4-1.  | Assembler Format Relationships               | 4–5  |

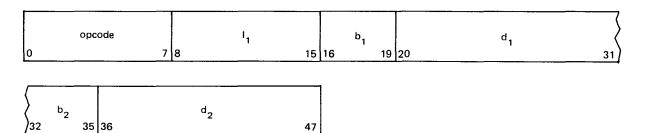

| 4-2.  | Byte and Word Structure                      | 4-7  |

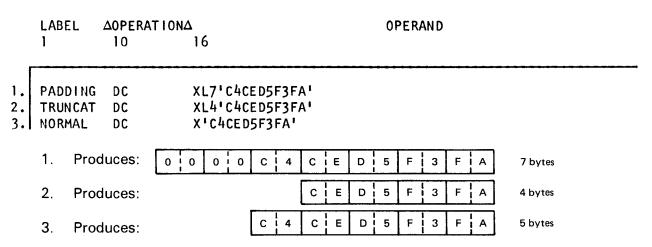

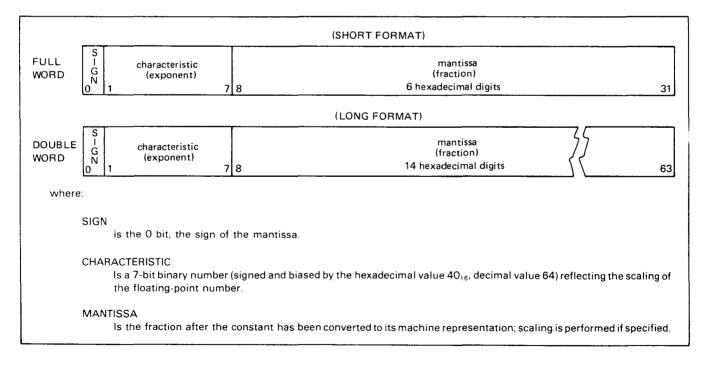

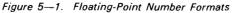

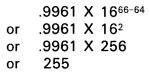

Floating-Point Number Formats

5-1.

5-16

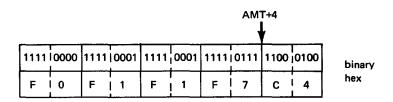

| 7–1.  | Instruction Formats                                                        | 7–2   |

|-------|----------------------------------------------------------------------------|-------|

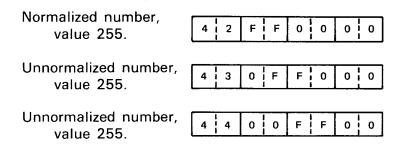

| 8-1.  | Program Status Word Diagram                                                | 8-1   |

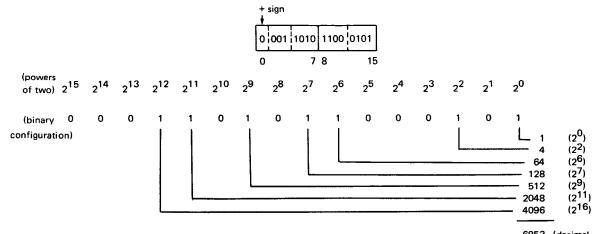

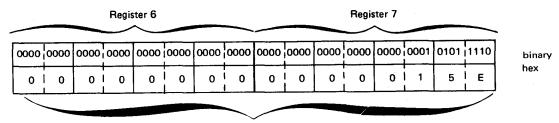

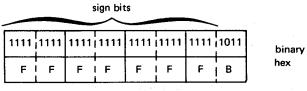

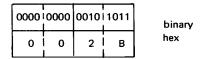

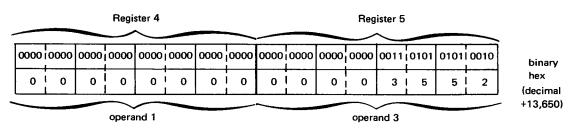

| 10-1. | Comparison of Binary Numbers and Values Expressed in Powers of 2           | 10–5  |

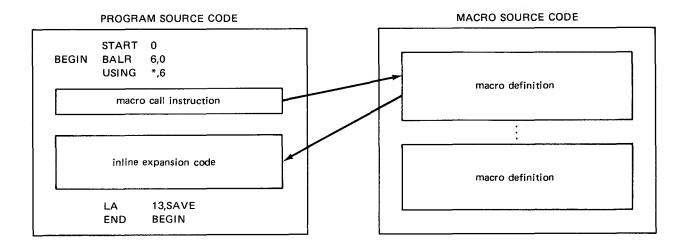

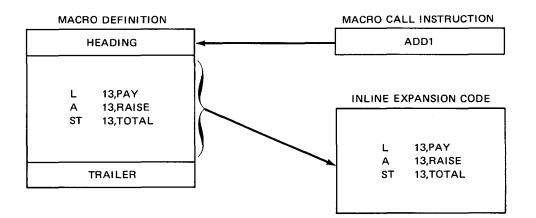

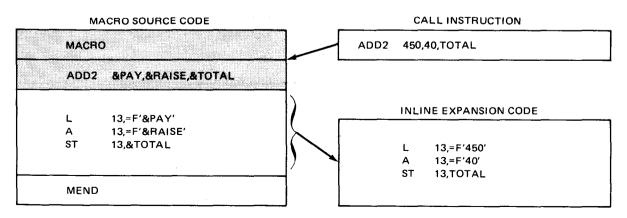

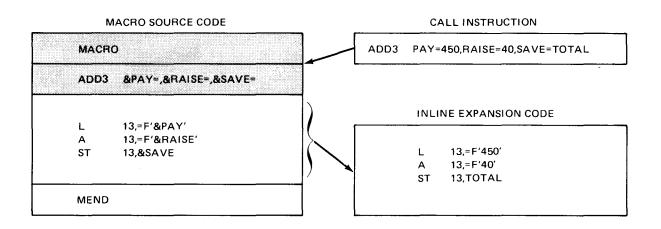

| 22-1. | Example of Inline Macro Expansion                                          | 22-2  |

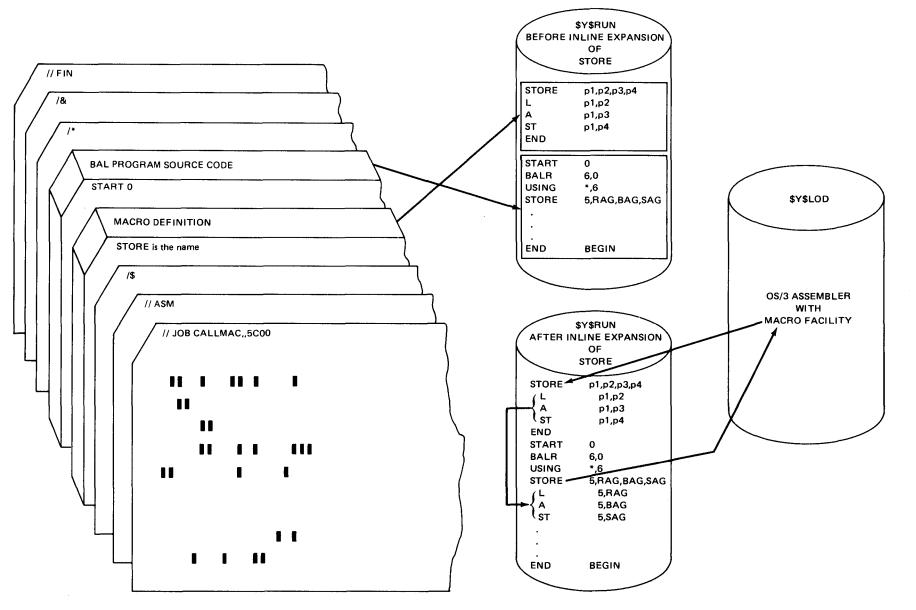

| 23–1. | Accessing a Macro Definition Submitted in the Source Deck                  | 23-4  |

| 23–2. | Accessing a Macro Definition Stored in a Library                           | 23-5  |

| 24-1. | PROC and MACRO Heading                                                     | 24-1  |

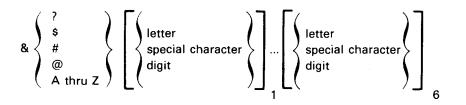

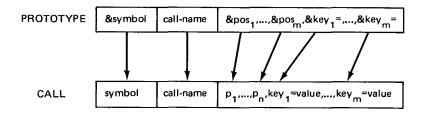

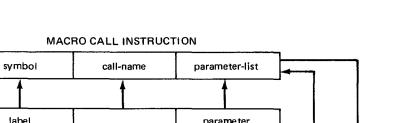

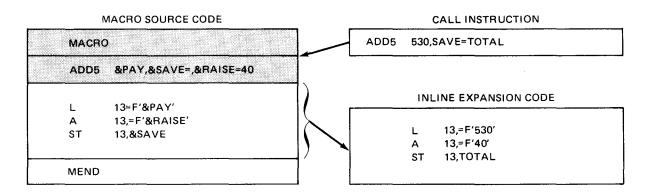

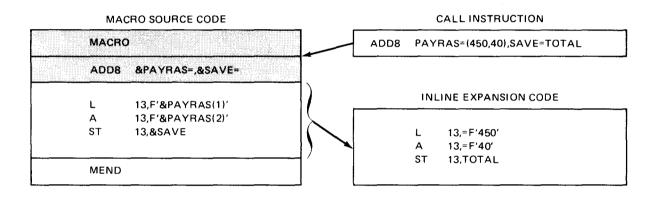

| 24-2. | PROC, MACRO, and Call Instruction Comparison                               | 24-6  |

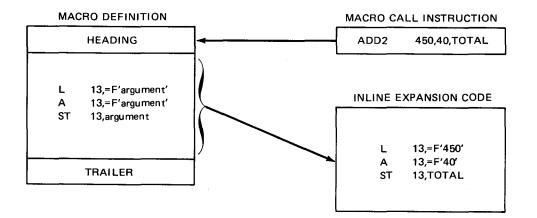

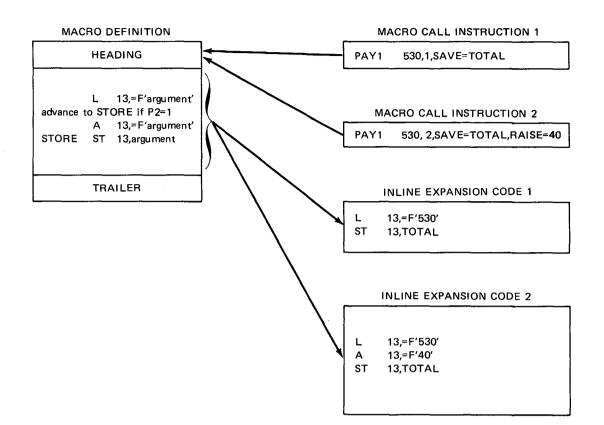

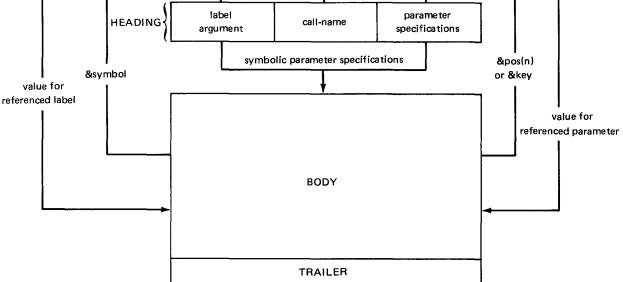

| 24-3. | Communication between Macro Instruction and Macro Definition               | 24-8  |

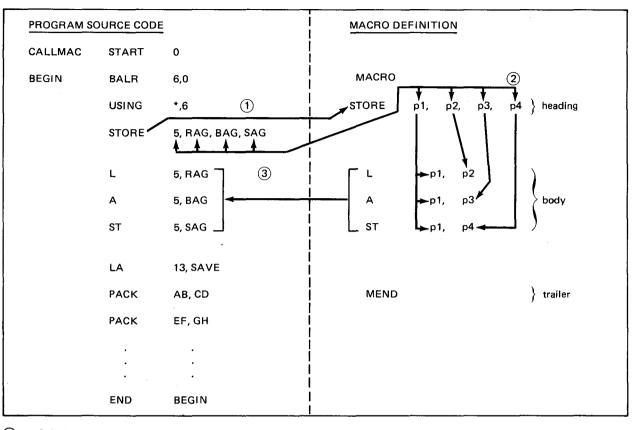

| 24-4. | Example MACRO and PROC Definitions                                         | 24-11 |

| TABL  | ES                                                                         |       |

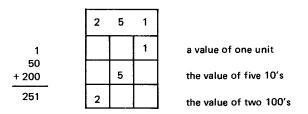

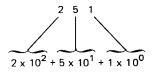

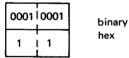

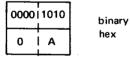

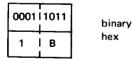

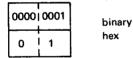

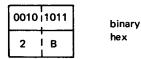

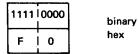

| 2-1.  | Comparison of Numeric Expressions                                          | 2-2   |

| 2-2.  | Hexadecimal Notation                                                       | 2-4   |

| 4-1.  | Comparison of Terms                                                        | 4-9   |

| 4-2.  | Summary of Operators                                                       | 4-13  |

| 5-1.  | Characteristics of Constant and Storage Definition Types                   | 5–2   |

| 5-2.  | Zero Duplication Area Examples                                             | 5–6   |

| 8–1.  | Extended Mnemonics and Functions                                           | 8-3   |

| 8–2.  | Operand 1 Mask Combinations                                                | 8-11  |

| 8–3.  | Branch-on-Condition Instruction by Usage                                   | 8-12  |

| 9-1.  | Edit Instruction Operation                                                 | 9–25  |

| 15–1. | Assembler Directives                                                       | 15–1  |

| 17–1. | Assembler Control Directives                                               | 17-1  |

| 20-1. | Listing Control Directives                                                 | 20-1  |

| 27–1. | Conditional Assembly Language Statements                                   | 27-1  |

| 27–2. | Operator Priority                                                          | 27-8  |

| 27–3. | Valid Attribute Reference Applications                                     | 27-24 |

| 27–4. | Type Attributes of Symbols                                                 | 27-25 |

| 28–1. | CODEDIT Listing Content                                                    | 28-2  |

| 28–2. | External Symbol Dictionary (ESD) Listing Content                           | 28-3  |

| 28–3. | Cross-Reference Content                                                    | 28-4  |

| 28–4. | Diagnostic Listing Content                                                 | 28-5  |

| B-1.  | ASCII (American Standard Code for Information Interchange) Character Codes | B-1   |

| B-2.  | EBCDIC (Extended Binary Coded Decimal Interchange Code) Character Codes    | B-2   |

| B-3.  | Punched Card, ASCII, and EBCDIC Codes                                      | B-3   |

•

| E-1. | Mnemonic List of Instructions        | E-1  |

|------|--------------------------------------|------|

| E-2. | Alphabetic Listing of Instructions   | E-5  |

| E-3. | List of Instructions by Machine Code | E-10 |

.

-

# PART 1. BASIC DATA AND CONVENTIONS

# 1. Introduction to Assembler Language Programming

#### 1.1. CODING AN ASSEMBLER PROGRAM

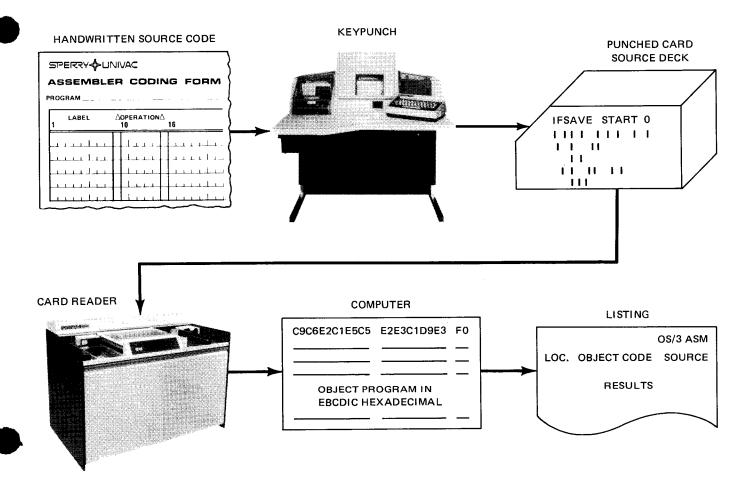

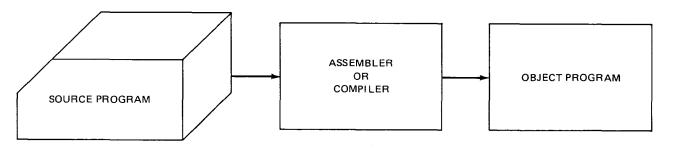

An assembler language program goes through several transformations before it is actually inside the computer and operating (Figure 1—1). The first change is from handwritten form to punched card form. This conversion takes code that is decipherable by people and changes it to data that can be processed by the computer. Although an assembler source program may exist on other media, such as disk or tape, the deck of cards is almost always the artifact of the basic assembly language (BAL) programmer. An assembler program is built with a punched card deck.

Figure 1—1. Writing and Submitting a Program

The punched card deck is a biform storage medium that is common to the programmer and the computer. It contains a copy of a computer program that can be interpreted by both man and machine. This is unlike your handwritten program, which can only be deciphered by you and is meaningless to a digital computer. The punched card is in a form that can be converted to computer data.

The data converter for the computer is the card reader. It is an electromechanical device designed to read information from punched cards by detecting the presence and absence of holes in a card. The card reader converts the holes punched in cards on a column-by-column basis to data that can be processed by the computer. Each column on a punched card is used to represent a single unit of information and the card reader converts each column to the character it represents.

A blank card is shown in Figure 1—2. From this figure, you can see that a card has 80 vertical columns (numbered at the bottom and near the top of the card) and each column has 12 punch positions called rows. Rows 0 through 9 are numbered on the card, and 12 and 11 are not numbered; the 12 position is at the top of the card, and the 11 position immediately follows it and is before the 0 row.

- COLUMN NUMBERS

Different combinations of holes in a column represent different characters and numbers. For instance, each of the decimal numbers 0 through 9 are represented by the respective punch positions on a card. If a column has a hole punched only in row 0, then the card reader detects a 0. If a punch is only in row 1, then the card reader detects a 1, and so on through row 9. Everything you code in assembly language is based on the 80-column card.

The cards that make up an assembler language program are punched on a keypunch machine from code that is handwritten on an assembler coding form. (The Sperry Univac assembler coding form is shown in Figure 1—3.) Each line on the assembler coding form has 80 positions that correspond to the 80 columns on a punched card. One card is keypunched for every line of code on the assembler coding form (Figure 1—4). The lines of code on the assembler coding form and the cards keypunched from the form are called source code lines. Collectively, these source lines make a source program.

A BAL source program is written with instructions, directives, conditional statements, and macros. They are the elements of the assembler language and each is usually written on one source line. (Sometimes it may take more than one source line to write a single element, but most of the time it takes only one source line for one instruction, directive, statement, or macro.) The assembler ignores the presence of any blank cards in the source deck. A blank line will not be printed nor terminate a sequence of continuation lines. The rules for coding assembler language source lines are reflected on the assembler coding form. Each source line has five fields and the assembler expects specific information to be coded in each field.

|                                                 |                   | ASSE                                          | ASSEMBLER CODING FORM                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |                          |

|-------------------------------------------------|-------------------|-----------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------|

| LABEL                                           | AOPERATIONA<br>10 | OPERAND<br>16                                 | Δ                                     | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       | 72                       |

|                                                 |                   |                                               |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |                          |

| <u>ki ki k</u> |                   | +++++++++++++++++++++++++++++++++++++++       | يتعيده ليتحد بتطريط                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | للتربية فالمتصلية فالمتصلي            | للبيا بالتا بالبيا       |