## **TECHNICAL MANUAL**

### **SYSTEMS 32 SERIES**

### **TLC Controller Model 9005**

June 1979

# **REVISION INSTRUCTIONS AND MANUAL HISTORY**

#### UIPMENT: TLC Controller Model 9005

### PUBLICATION NO. 303-329005-000

**RPOSE:** To provide a general description, operation and programming information, and theory of operation for the Teletypewriter, Line Printer, and Card Reader Controller (TLC), Model 9005.

### EVISION INSTRUCTIONS: Delete and add pages as shown on the following table.

| DELETE | , ADD |

|--------|-------|

|        |       |

|        |       |

|        |       |

| NA     | NA    |

|        |       |

|        |       |

|        |       |

### **MANUAL HISTORY**

| REV.    | REV.<br>NO. | DATE<br>ISSUED | CONTROL<br>DOC. NO. | ECL |

|---------|-------------|----------------|---------------------|-----|

| 1st Ptg | Original    | 6-79           | 180-103160          | 4   |

| REV.<br>TYPE | REV.<br>NO. | DATE<br>ISSUED | CONTROL<br>DOC. NO. | ECL |

|--------------|-------------|----------------|---------------------|-----|

|              |             |                |                     |     |

|              |             |                |                     |     |

|              |             |                |                     |     |

|              |             |                |                     |     |

R= INTERIM REVISION

F= FORMAL REVISION

### LIST OF EFFECTIVE PAGES

The total number of pages in this book is 81, consisting of the following:

| Page                                                                                                                                          | Issue                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Title<br>iii through ix/x<br>1-1 through 1-4<br>2-1 through 2-22<br>3-1 through 3-38<br>A-1 through A-2<br>B-1 through B-2<br>C-1 through C-2 | Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original |

| D-1 through D-2                                                                                                                               | Original                                                                                     |

|                                                                                                                                               |                                                                                              |

4

iv

# TABLE OF CONTENTS

# SECTION I GENERAL DESCRIPTION

Page

۷

| 1-1 | Introduction                           | .1-1 |

|-----|----------------------------------------|------|

| 1-2 | Model Numbers                          |      |

| 1-3 | Physical Description                   |      |

| 1-4 | Functional Description                 |      |

| 1-5 | Specifications and Leading Particulars | .1-2 |

### SECTION II OPERATION AND PROGRAMMING

| 2-1  | Introduction                           | .2-3 | 1  |

|------|----------------------------------------|------|----|

| 2-2  | Controls and Indicators                | .2-3 | 1  |

| 2-3  | Off-Line Switch                        |      |    |

| 2-4  | TLC Physical Address Jumpers           | .2-3 | 1  |

| 2-5  | Multiple Controller Controller (MCC)   | .2-3 | 1  |

| 2-6  | SelBUS Priority Recognition Jumpers    | .2-3 | 1  |

| 2-7  | SelBUS Priority Generation Jumpers     | .2-  | 1  |

| 2-8  | SelBUS Priority Enable Switches        |      |    |

| 2-9  | Baud Rate Jumpers                      |      |    |

| 2-10 | Power On/Off Procedures                | .2-2 | 2  |

| 2-11 | Operating Procedures                   |      |    |

| 2-12 | Programming                            |      |    |

| 2-13 | I/O Instructions                       | .2-3 | 3  |

| 2-14 | Command Device (CD) Instruction        | .2-3 | 3  |

| 2-15 | Transfer Control Word (TCW)            | .2-3 | 3  |

| 2-16 | Input/Output Command Doubleword (IOCD) | .2-3 | 3  |

| 2-17 | Test Device (TD) Instruction           | .2-4 | 4  |

| 2-18 | Interrupt Control Instruction          | .2-! | 5  |

| 2-19 | CPU Initiated Program Load (IPL)       | .2-3 | 7  |

| 2-20 | SelBUS Transfers                       | .2-3 | 7  |

| 2-21 | I/O Microcommands                      | .2-3 | 7  |

| 2-22 | Teletypewriter (TTY)                   | .2-8 | 8  |

| 2-23 | CD Instruction                         | .2-8 | B  |

| 2-24 | TD Instruction                         | .2-8 | 8  |

| 2-25 | Line Printer                           | .2-3 | 14 |

| 2-26 | CD Instruction                         | .2-2 | 14 |

| 2-27 | TD Instruction                         | .2-1 | 14 |

| 2-28 | Card Reader                            |      |    |

| 2-29 | CD Instruction                         | .2-1 | 18 |

| 2-30 | TD Instruction                         |      |    |

| 2-31 | TD Level 8000 <sub>H</sub>             | .2-1 | 18 |

| 2-32 | TD Level 4000 <sub>H</sub>             | .2-  | 18 |

### TABLE OF CONTENTS (Cont'd)

### SECTION III THEORY OF OPERATION

Page

| 3-1  | Introduction                                               | 3-1  |

|------|------------------------------------------------------------|------|

| 3-2  | General Theory                                             |      |

| 3-3  | Purpose                                                    |      |

| 3-4  | TLC Basic Organization                                     |      |

| 3-5  | Overall Operation                                          |      |

| 3-6  | Peripheral Device Control                                  |      |

| 3-7  | Detailed Theory                                            |      |

| 3-8  | SelBUS Interface                                           |      |

| 3-9  | SelBUS Transfer Classification                             |      |

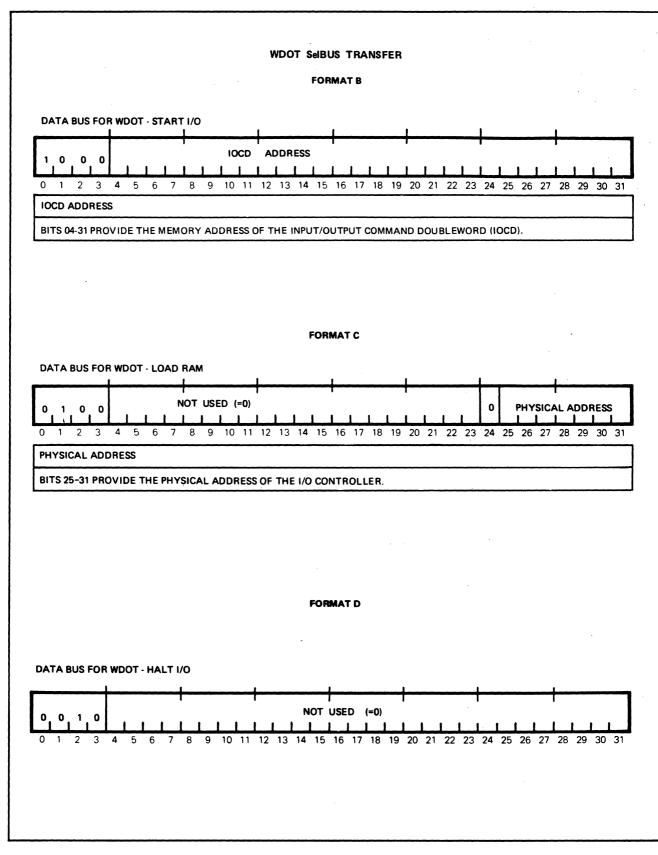

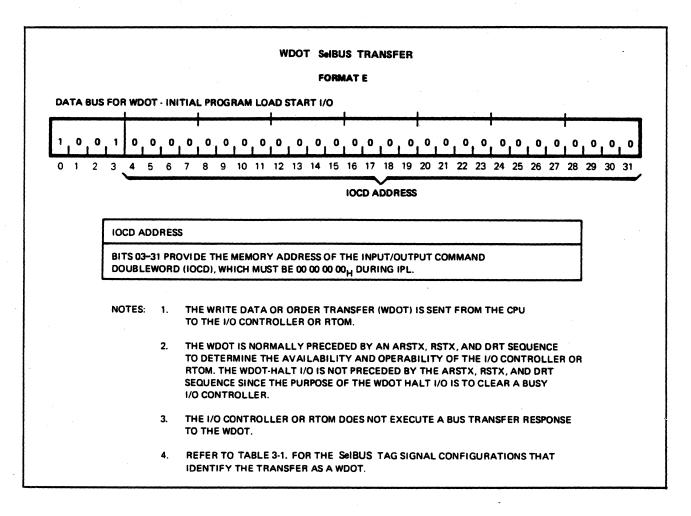

| 3-10 | Write Data or Order Transfer (WDOT)                        |      |

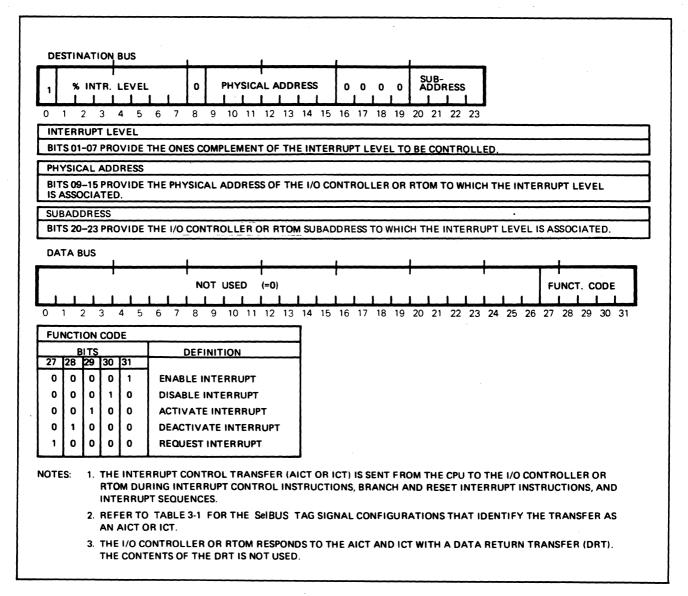

| 3-11 | Advance Interrupt Control Transfer (AICT)                  |      |

| 3-12 | Interrupt Control Transfer (ICT)                           |      |

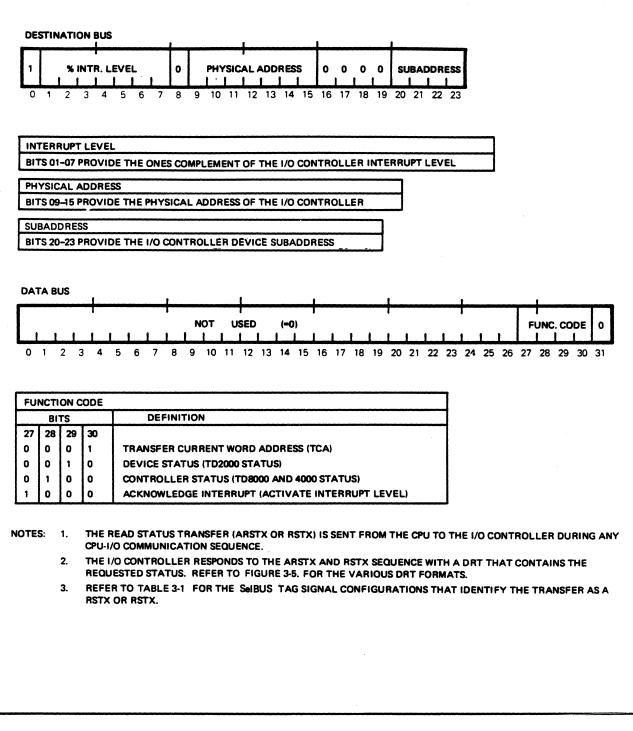

| 3-13 | Advance Read Status Transfer (ARSTX)                       | 3-11 |

| 3-14 | Read Status Transfer (RSTX)                                |      |

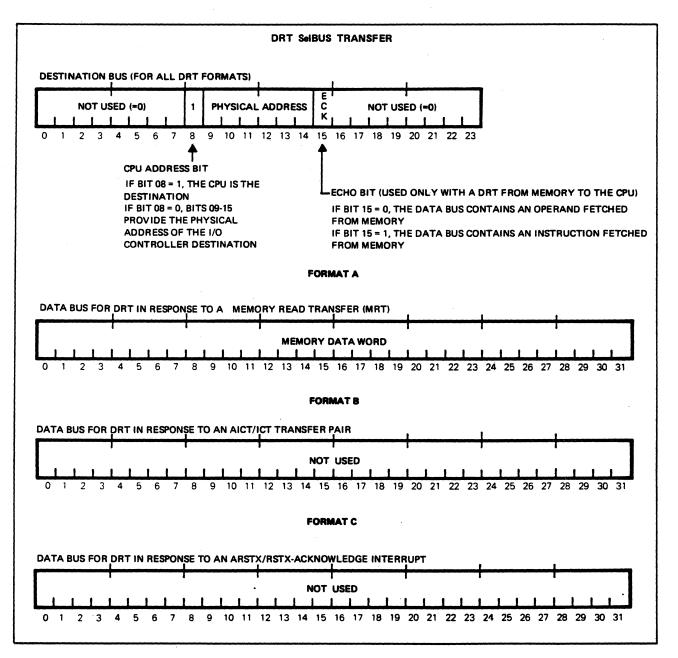

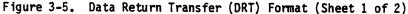

| 3-15 | Data Return Transfer (DRT)                                 |      |

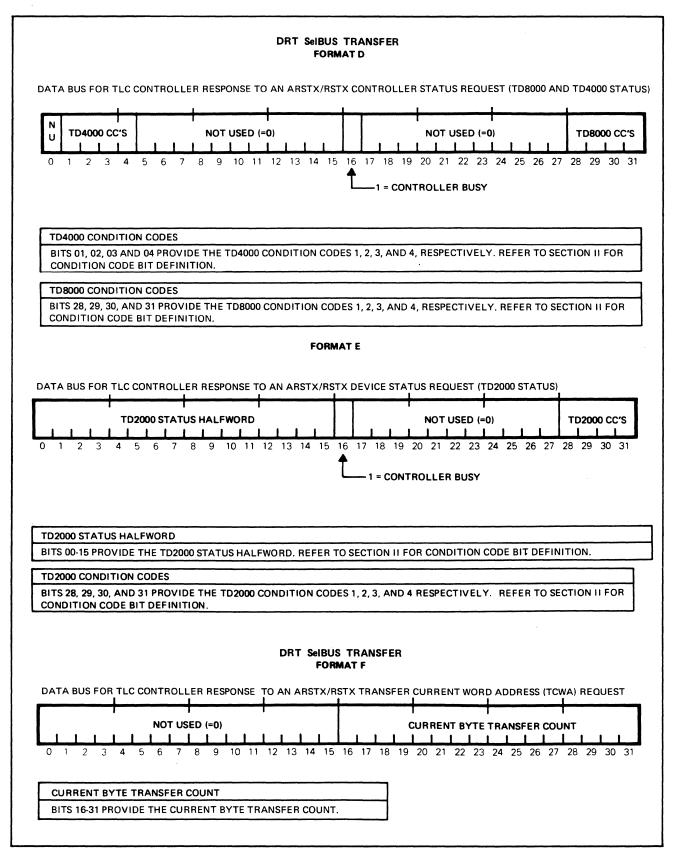

| 3-16 | Error Transfer (ET)                                        |      |

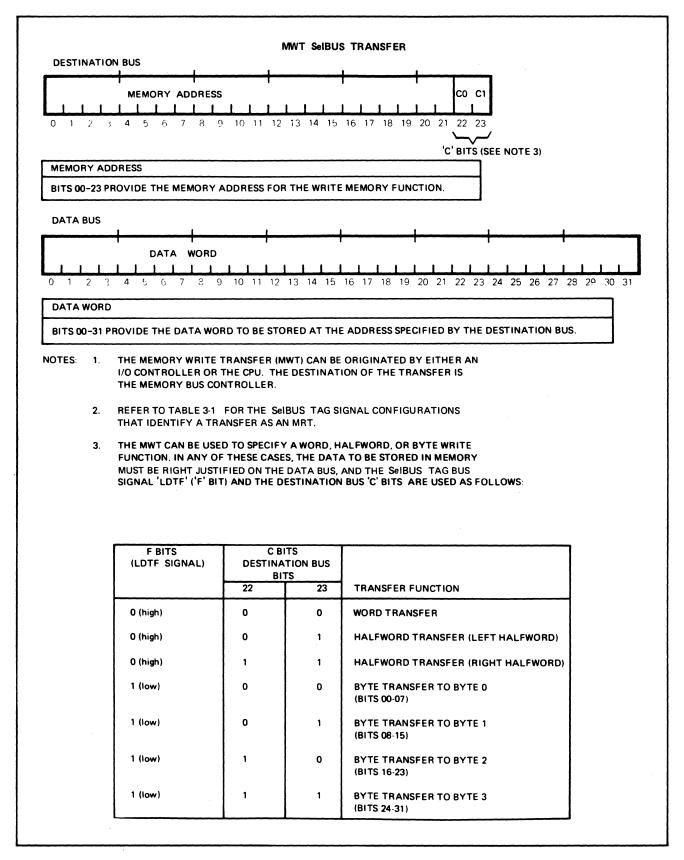

| 3-17 | Memory Write Transfer (MWT)                                |      |

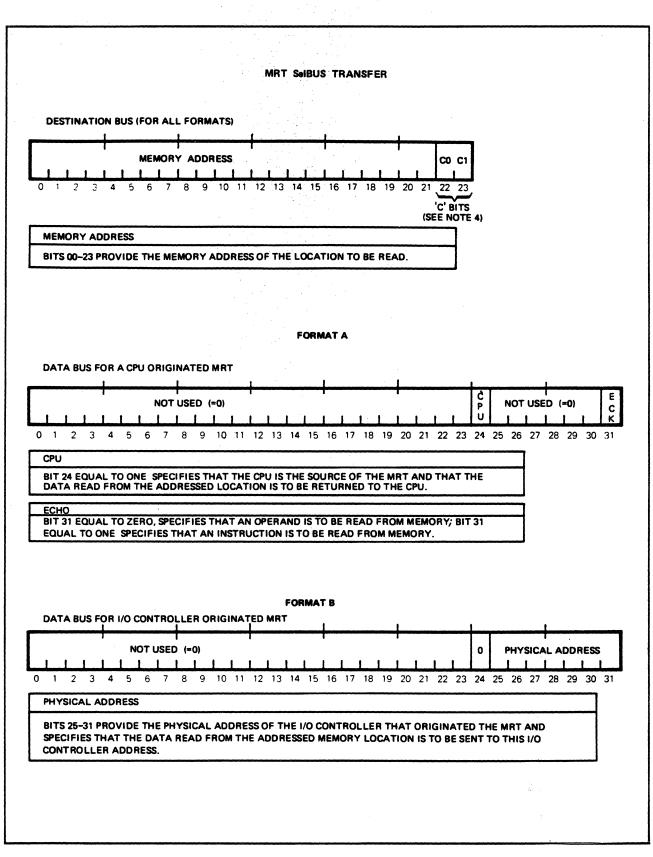

| 3-18 | Memory Read Transfer (MRT)                                 |      |

| 3-19 | Microprogrammable Processor (MP)                           | 3-19 |

| 3-20 | Peripheral Device Controller Interface                     |      |

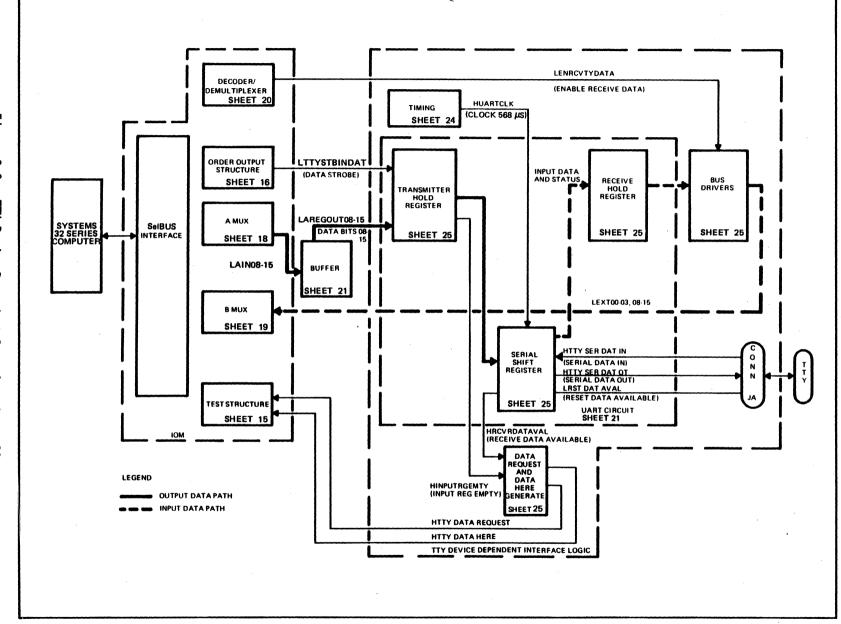

| 3-21 | Teletypewriter (TTY) Device Dependent Interface Controller |      |

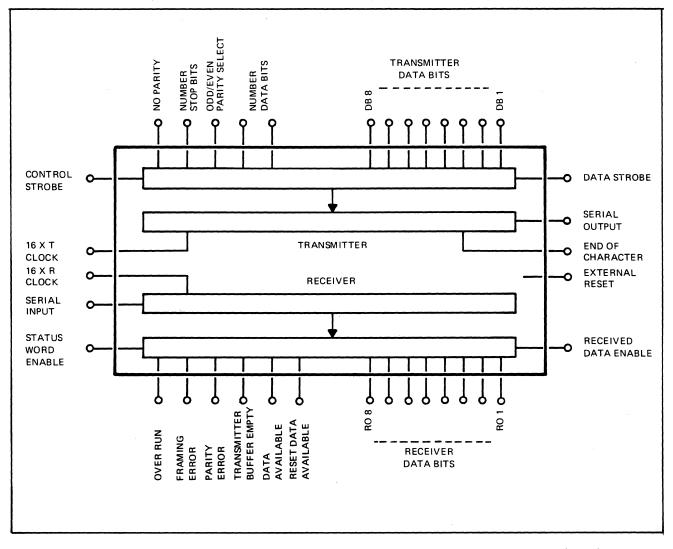

| 3-22 | Universal Asynchronous Receiver/Transmitter (UART)         |      |

| 3-23 | Transmitter Operation                                      |      |

| 3-24 | Receiver Operation                                         |      |

| 3-25 | Output Data Transfer (TTY)                                 |      |

| 3-26 | Input Data Transfer (TTY)                                  |      |

| 3-27 | Line Printer (LP) Device Dependent Interface Controller    |      |

| 3-28 | Card Reader Device Dependent Interface                     |      |

### APPENDIXES

| Appendix A | Teletypewriter Mnemonic List |

|------------|------------------------------|

| Appendix B | Line Printer Mnemonic List   |

| Appendix C | Card Reader Mnemonic List    |

| Appendix D | TLC Jumper ChartD-1          |

8

Figure

| Ρ | a | q | e |

|---|---|---|---|

|   |   |   |   |

| 1-1          | Copper TLC Controller1-2                                                        |

|--------------|---------------------------------------------------------------------------------|

| 1-2          | Block Diagram - TLC Controller1-3                                               |

| 2-1          | Command Device (CD) Instruction Format2-3                                       |

| 2-2          | Transfer Control Word (TCW) Format2-4                                           |

| 2 <b>-</b> 3 | Input/Output Command Doubleword (IOCD) Format2-6                                |

| 2-4          | IPL Basic Input/Output Command Doubleword (IOCD) Format2-7                      |

| 2-5          | Test Device (TD) Instruction Format2-9                                          |

| 2-6          | Interrupt Control Instruction Format                                            |

| 2-7          | TLC Microcommand Format                                                         |

| 2-8          | Command Device Format TTY System                                                |

| 2-9          | Test Device Format and Function Code TTY System                                 |

| 2-10         | Line Printer Command Device Instruction Format2-15                              |

| 2-11         | Line Printer Test Device Instruction Format2-16                                 |

| 2-12         | Card Reader Command Device Instruction Format2-19                               |

| 2-13         | Card Reader Test Device Instruction Format2-20                                  |

| 3-1          | Block Diagram - SYSTEMS 32 SERIES Computer                                      |

| 3-2          | Write Data or Order Transfer (WDOT) Format                                      |

| 3-3          | Advance Interrupt Control Transfer (AICT) and Interrupt                         |

|              | Control Transfer (ICT) Formats                                                  |

| 3-4          | Advance Read Status Transfer (ARSTX) and Read Status Transfer<br>(RSTX) Formats |

| 3-5          | Data Return Transfer (DRT) Format                                               |

| 3-6          | Error Transfer (ET) Format                                                      |

| 3-7          | Memory Write Transfer (MWT) Format                                              |

| 3-8          | Memory Read Transfer (MRT) Format                                               |

| 3-9          | TTY Device Dependent Interface Controller                                       |

| 3-10         | Block Diagram - Universal Asynchronous Receiver/Transmitter                     |

| 3-10         | (UART)                                                                          |

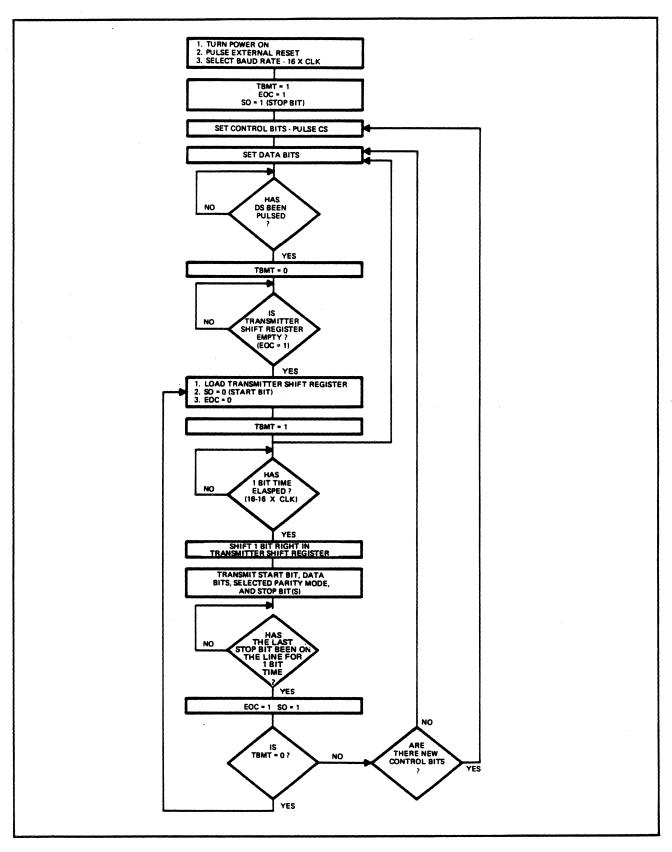

| 3-11         | UART – Transmitter Flow Diagram                                                 |

| 3-12         | UART - Transmitter riow Diagram                                                 |

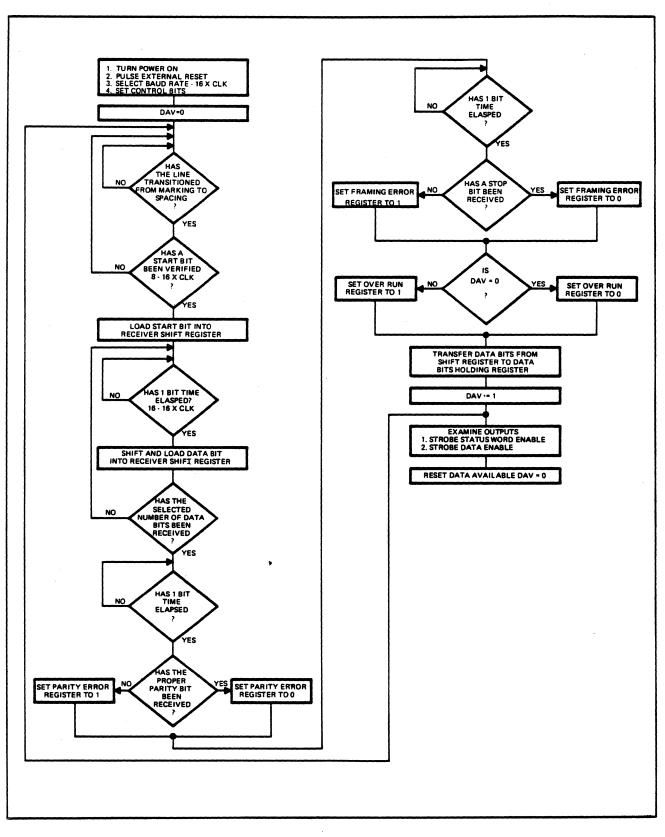

| 3-12         | UART - Receiver Flow Diagram                                                    |

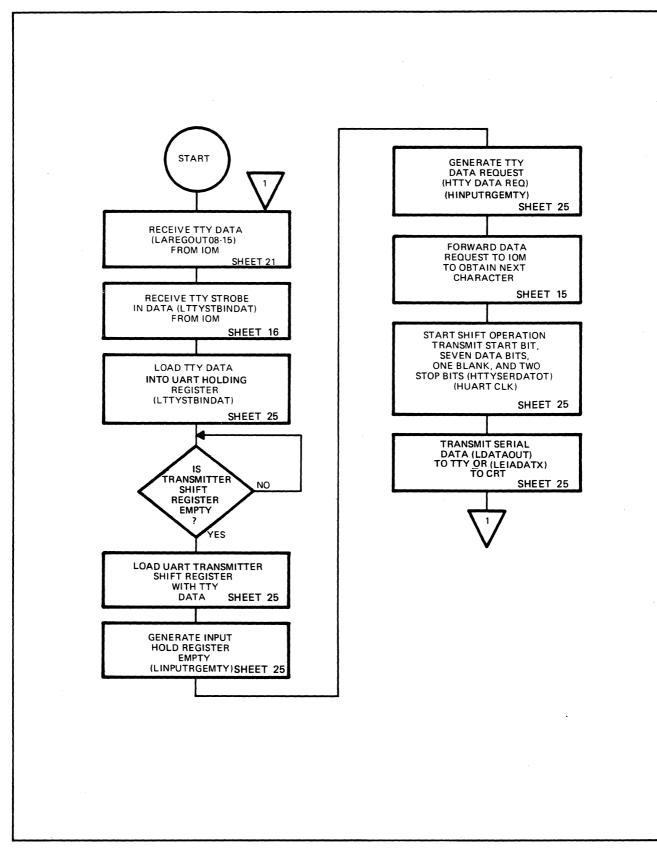

| 3-13         | Output Data Transfer (TTY)                                                      |

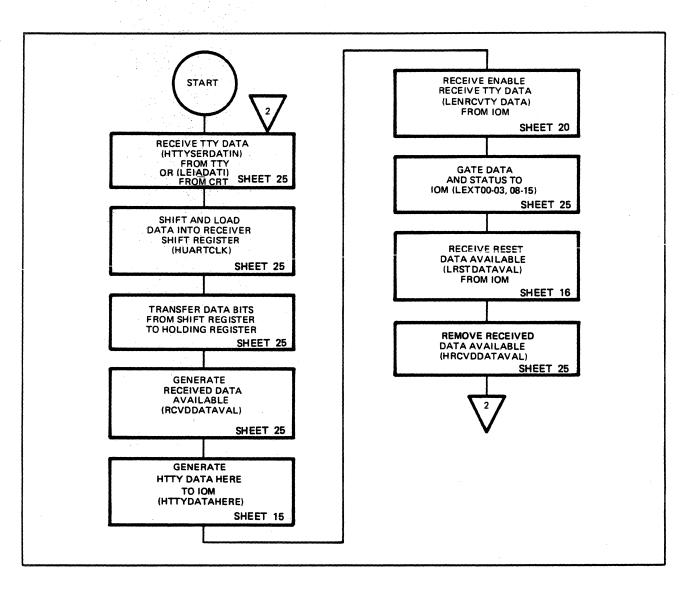

|              | Input Data Transfer (TTY)                                                       |

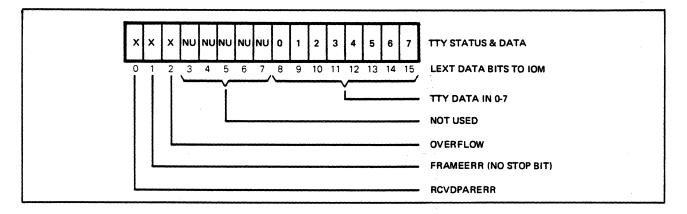

| 3-15         | TTY DRT Format                                                                  |

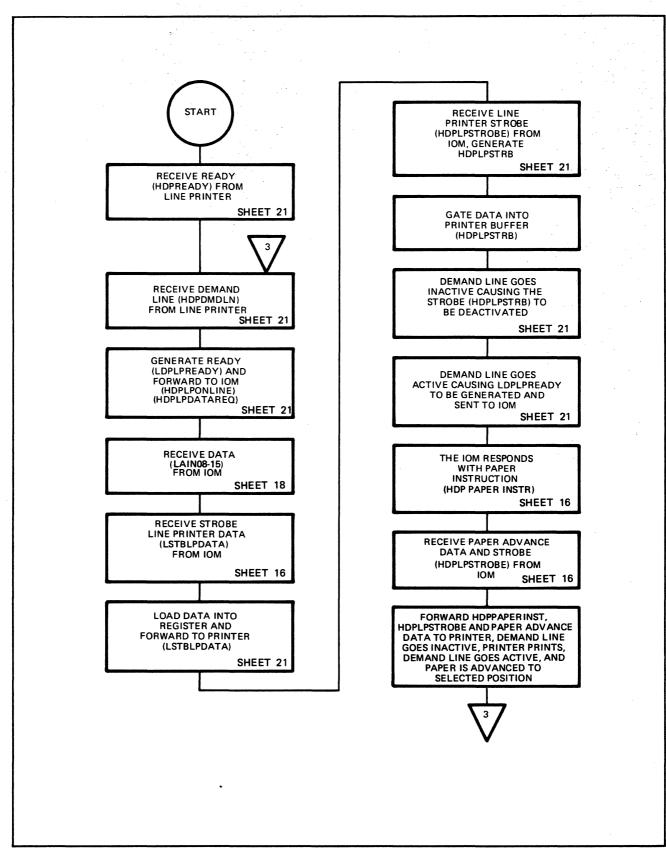

| 3-16         | Print and Paper Advance Operation                                               |

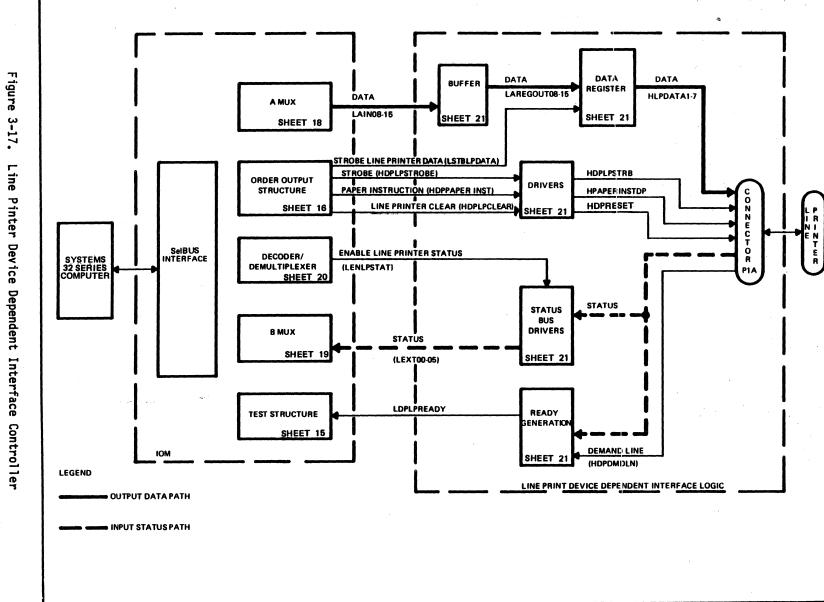

| 3-17         | Line Printer Device Dependent Interface Controller                              |

| 3-18         | IOM to LP WDOT Format                                                           |

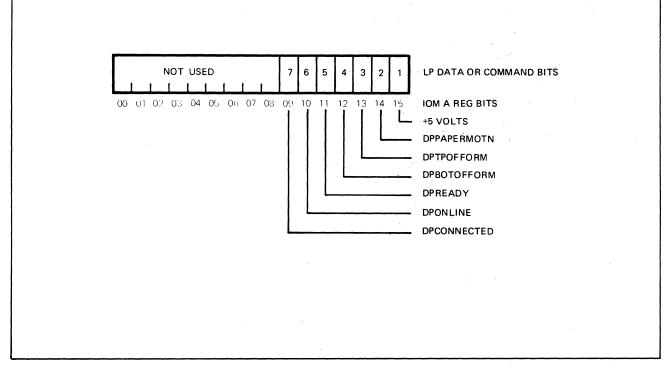

| 3-19         | LP to IOM DRT (Status) Format                                                   |

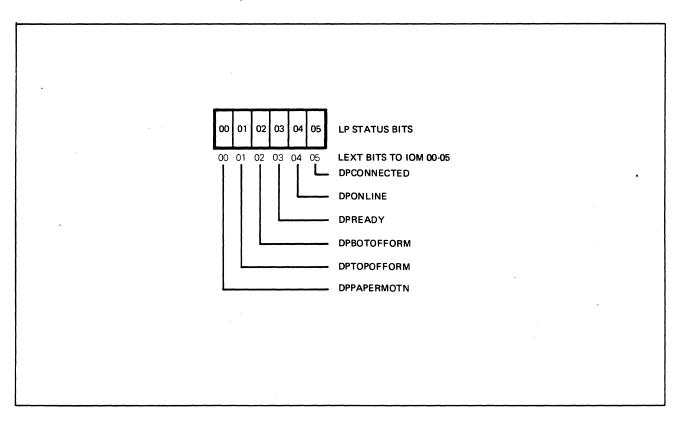

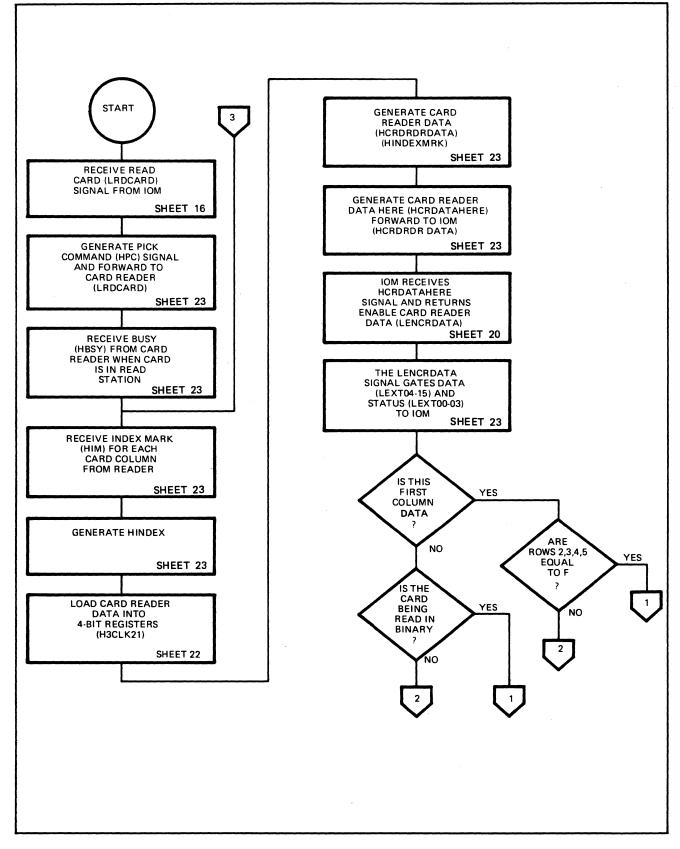

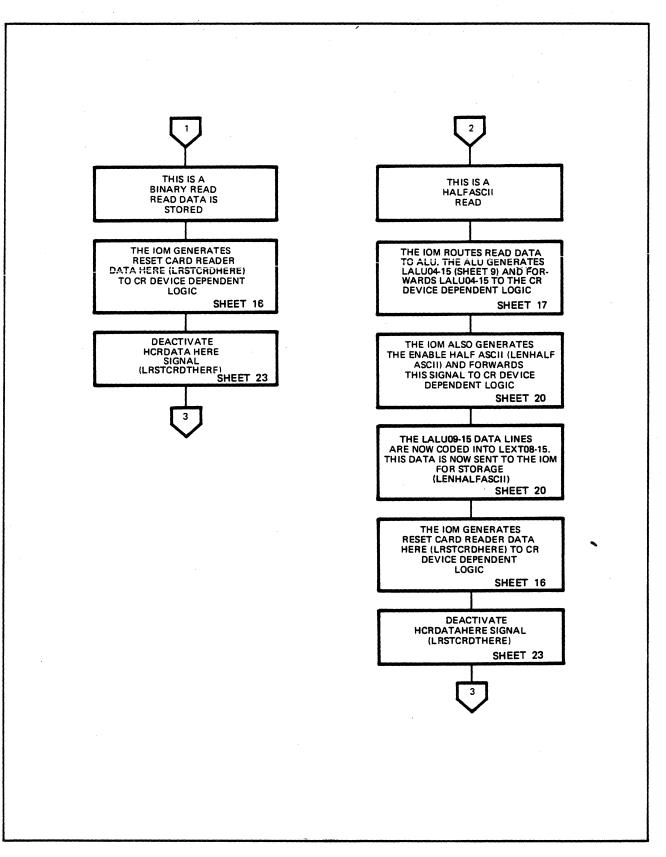

| 3-20         | Card Reader Operation3-35                                                       |

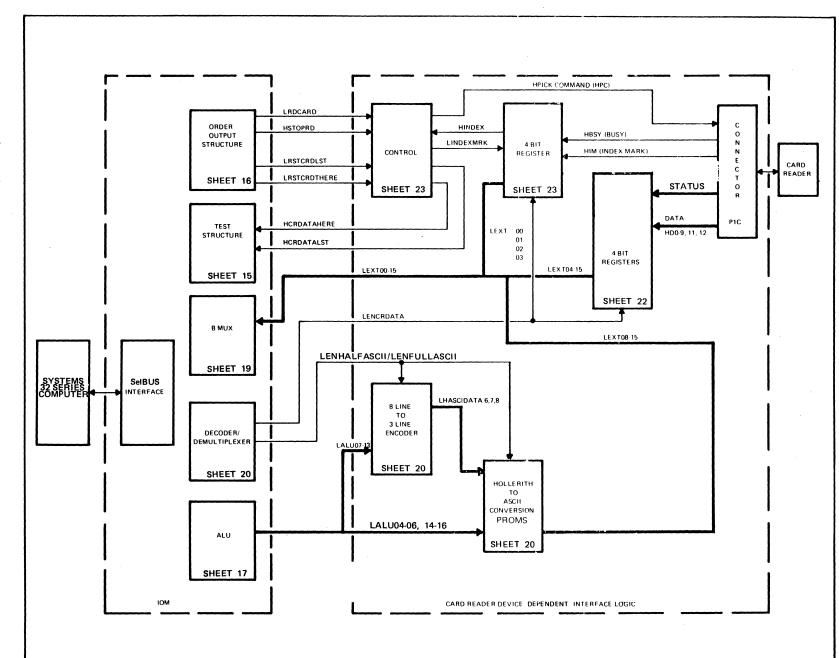

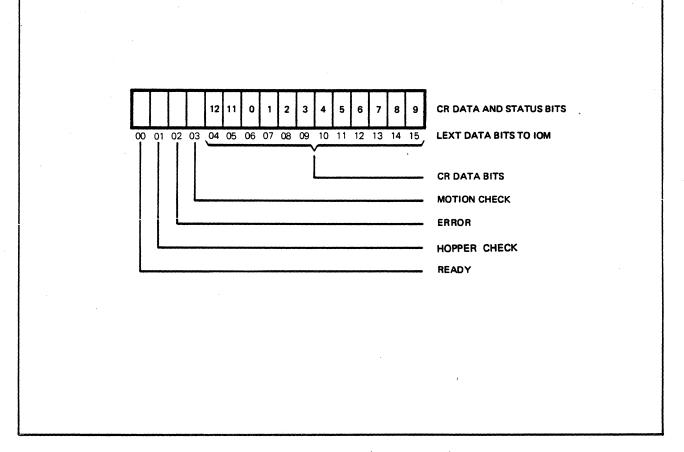

| 3-21         | Card Reader Device Dependent Interface Controller                               |

| 3-22         | CR to IOM DRT (Data/Status) Format                                              |

### LIST OF TABLES

| Table        |                                                         | Page |

|--------------|---------------------------------------------------------|------|

| 1-1          | Specifications and Leading Particulars                  | 1-3  |

| 2-1          | Baud Rate Switch Settings                               |      |

| 2 <b>-</b> 2 | Transfer Interrupt (TCW) Dedicated Memory Locations     |      |

| 2-3          | Input/Output Command Doubleword (IOCD) Dedicated Memory |      |

|              | Locations                                               | 2-8  |

| 2-4          | Priority Interrupt Dedicated Memory Locations           | 2-10 |

| 2-5          | Command Device Function Codes (TTY)                     |      |

| 2-6          | Test Device Results, Level 8000 <sub>H</sub>            |      |

| 2-7          | Test Device Results, Level 4000 <sub>H</sub>            | 2-14 |

| 2-8          | 8000 Level Condition Code Definitions                   | 2-16 |

| 2-9          | 4000 Level Condition Code Definitions                   | 2-17 |

| 2-10         | 2000 Level Status Bit Definitions                       | 2-17 |

| 2-11         | Line Printer DCC/Device Condition Code Bit Assignment   | 2-18 |

| 2-12         | Line Printer Device Status Bit Assignment               |      |

| 2-13         | Command Device Function Codes (CR)                      |      |

| 2-14         | Test Device Condition Codes - Level 8000H               |      |

| 2-15         | Test Device Condition Codes - Level 4000H               | 2-21 |

| 3-1          | SelBUS Input/Output Transfer Identifications            | 3-7  |

| 3-2          | P1A Connector Pin and Signal List                       | 3-21 |

| 3-3          | P1C Connector Pin and Signal List                       | 3-21 |

| 3-4          | Description of Pin Functions (UART)                     |      |

Table

| Title                                                                           | Publication Number |

|---------------------------------------------------------------------------------|--------------------|

| Drawings Manual - SYSTEMS 32 SERIES<br>TLC Controller Model 9005                | 304-329005         |

| Firmware Manual - SYSTEMS 32 SERIES<br>TLC Controller Model 9005                | 305-329005         |

| Technical Manual - SYSTEM 32 SERIES Input/Output<br>Microprogrammable Processor | 325-329000         |

| SYSTEMS 32 SERIES Circuit Registration Manual                                   | 313-325000         |

#### SECTION I

#### GENERAL DESCRIPTION

#### 1-1 INTRODUCTION

This manual contains or references information concerning the maintenance and installation of the SYSTEMS 32 SERIES Computer TLC Controller, Model 9005, shown in Figure 1-1. The TLC Controller is designed and manufactured by Systems Engineering Laboratories, Fort Lauderdale, Florida.

The information contained in this manual is presented in the following order:

| Section | I   | - | General Description |

|---------|-----|---|---------------------|

| Section | II  | - | Programming         |

| Section | III | - | Theory of Operation |

The Drawings Manual (Publication Number 304-329005) provides the assembly drawings, circuit card drawings, and logic diagrams used with the SYSTEMS 32 SERIES Computer. The Firmware Manual (Publication Number 305-329005) contains the microprogram listings for the Input/Output Microprogrammable Processor (IOM) used for control of the SYSTEMS 32 SERIES Computer peripheral devices.

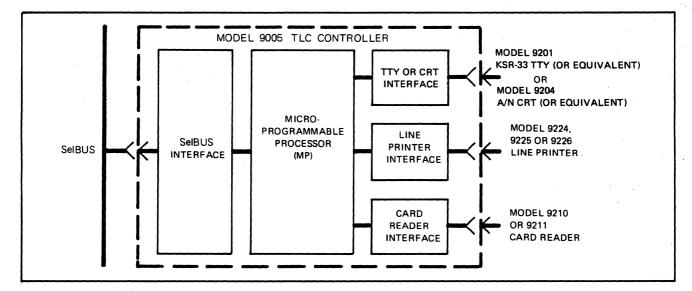

The TLC Controller is an optional feature for SYSTEMS 32 SERIES Computers and provides the capability to output data to a teletypewriter or line printer and input data from a teletypewriter or card reader. The TLC Controller also provides the capability to input data from the teletypewriter and output it to the line printer.

#### 1-2 MODEL NUMBERS

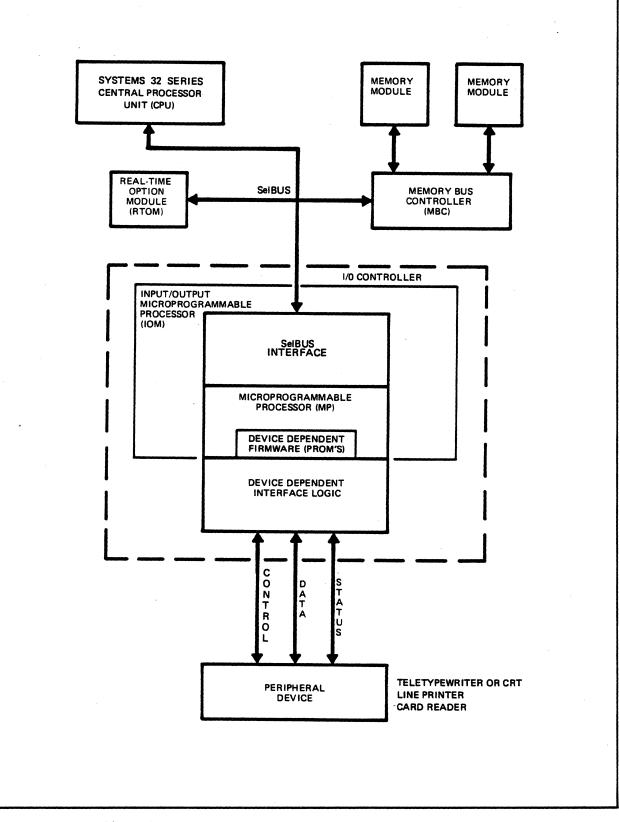

SYSTEMS Model 9005 TLC Controller includes an IOM, Teletypewriter, Line Printer, and Card Reader Device Dependent Interface logic. The The IOM consists of a SelBUS interface and a Microprogrammable Processor (MP).

The SYSTEMS Model 9005 TLC Controller is designed to operate with the following compatible input/output peripheral devices:

1. Teletypewriter (TTY) Interface

Model 9201 TTY (10 cps) Model 9202 TTY (30 cps) Model 9203 A/N CRT (95 char) Model 9204 A/N CRT (64 char) 2. Line Printer (LP) Interface

Model 9223 Matrix Printer Model 9225 LP (300 1pm) Model 9245 LP (260 1pm) Model 9226 LP (600 1pm) Model 9226 LP (436 1pm) Model 9237 LP (900 1pm) Model 9247 LP (660 1pm)

3. Card Reader (CR) Interface

Model 9209 CR (200 cpm) Model 9210 CR (300 cpm) Model 9211 CR (1000 cpm)

#### 1-3 PHYSICAL DESCRIPTION

The TLC Controller, Model 9005, consists of an IOM, teletypewriter, line printer, and card reader device plug-in module. The Model 9005 plugs directly into the SelBUS like all other standard IOMs for the SYSTEMS 32 SERIES Computers. The TLC Controller circuit card is 15 inches x 17.90 inches, installs in the CPU logic chassis or an I/O extender logic chassis, and requires one SelBUS slot.

#### 1-4 FUNCTIONAL DESCRIPTION

The Model 9005 TLC Controller is a multidevice IOM for the SYSTEMS 32 SERIES Computers. The TLC, contained on a single plug-in module, provides I/O control for a teletypewriter, line printer, and card reader.

The TLC Controller consists of the five functional parts listed below:

- 1. SelBUS Interface

- 2. Microprogrammable Processor (MP)

- 3. Teletypewriter Interface

- 4. Line Printer Interface

- 5. Card Reader Interface

The SelBUS interface includes drivers and receivers for data and control lines on the SelBUS, a 32-bit buffer register, and a toggle switch for logically disconnecting the TLC Controller from the SelBUS.

| · . |                   |  |

|-----|-------------------|--|

|     | <image/> <image/> |  |

|     |                   |  |

Figure 1-1. Copper TLC Controller

The firmware in the microprocessor has been designed to respond to the Command Device (CD), Test Device (TD), and other SYSTEMS 32 SERIES I/O instructions. Any of the three interfaces in the TLC Controller can be conditioned for a block transfer by the CPU executing a single CD instruction. Once the block transfer has been initialized, the TLC Controller takes full control over the operation, and the CPU is free to perform other tasks.

When the block transfer is completed, the TLC Controller signals the CPU with an interrupt. The CPU then executes a TD instruction to determine whether the transfer was successful and, if not, what errors were encountered.

Concurrent operation of the Teletypewriter, Line Printer, and Card Reader interfaces in the TLC Controller is accomplished by using individual buffers and I/0 interrupts for each device.

Figure 1-2 is a block diagram for the TLC Controller and related input/output devices.

#### 1-5 SPECIFICATIONS AND LEADING PARTICULARS

Table 1-1 lists the specifications and leading particulars of the TLC Controller.

Figure 1-2. Block Diagram - TLC Controller

| Table 1-1. | Specifications | and Leading | Particulars |

|------------|----------------|-------------|-------------|

|------------|----------------|-------------|-------------|

| Characteristic           | Specification                                                                 |

|--------------------------|-------------------------------------------------------------------------------|

| IOM Thruput (Max)        | 1.2M bytes/second                                                             |

| Number of Devices        | 1 each; TTY, LP, and CR                                                       |

| Compatible Devices       |                                                                               |

| TTY Channel              | Model 9201 KSR-33, or Model 9204 A/N CRT<br>or equivalent devices             |

| LP Channel               | Model 9224 LP (125 lpm)<br>Model 9225 LP (300 lpm)<br>Model 9226 LP (600 lpm) |

| CR Channel               | Model 9210 CR (285 cpm)<br>Model 9211 CR (1000 cpm)                           |

| Dimensions               | 15 in. x 17.90 in. (plug-in board)                                            |

| Weight                   | 3 1ь                                                                          |

| SelBUS Slot Requirement  | 2 slots                                                                       |

| SelBUS Electrical Load   | 1 load                                                                        |

| Power Requirements       | Provided by SelBUS                                                            |

| Temp/Humidity            | Same as CPU                                                                   |

| Maximum Cable Length To: |                                                                               |

| TTY or CRT               | 30 ft                                                                         |

| LP                       | 20 ft                                                                         |

| CR                       | 60 ft                                                                         |

| Prerequisite             | SYSTEMS 32 SERIES Computer                                                    |

**,**

An and the second s

#### SECTION II

#### OPERATION AND PROGRAMMING

#### **2-1 INTRODUCTION**

This section of the manual contains the operating and programming instructions for the TLC Controller; however, specific operating instructions for the related peripheral devices not contained in this manual may be found in the vendor's manual associated with the device.

#### 2-2 CONTROLS AND INDICATORS

#### 2-3 OFF-LINE SWITCH

The TLC Controller circuit card is provided with an Off-Line switch on the front edge of the circuit card. This switch must be placed in the On-Line (right-hand) position to enable the TLC controller to communicate with the SelBUS and the CPU.

#### 2-4 TLC PHYSICAL ADDRESS JUMPERS

The TLC Controller circuit card has a set of jumpers that selects the physical address (SelBUS address) of the TLC. The address selected by these jumpers must correspond to the TLC physical address associated with the TLC I/O instruction address (CD, Device Address field) during the SYSTEMS 32 SERIES CPU Initial Program Load (IPL) of the Initial Configuration List (ICL).

The Physical Address jumpers are shown on Logic Drawing 130-103175 (sheet 6) contained in the Drawings Manual. The Physical Address jumpers are referenced by logic callouts X7-1 through X7-7 and must be set to reflect the Low true physical address of the TLC. Switch X7-1 selects the most significant address bit, and X7-7 selects the least significant address bit.

#### 2-5 MULTIPLE CONTROLLER CONTROLLER (MCC)

In an MCC configuration, the IOM acts as several types of controllers, such as the TLC Controller, which controls a teletype, line printer, and card reader which are contained on one logic card.

#### 2-6 Selbus PRIORITY RECOGNITION JUMPERS

The TLC circuit card has a set of 21 Priority Recognition jumpers used to assign priorities to all system modules that have a SelBUS transfer priority higher than this TLC. The TLC's request for transfer is inhibited if any controller with a higher priority wishes to transfer data at the same time. The Priority Recognition jumpers are shown on Logic Drawing 130-103175 (sheet 10) and are referenced by logic callouts X4-2 through X4-8, X5-1 through X5-8, and X6-1 through X6-6. To assign higher priority transfer levels, the jumpers corresponding to the specific higher priority levels must be placed in the CLOSED (ON) position, and the jumpers corresponding to the priority level assigned to this TLC and all lower priorities must be placed in the OPEN (OFF) position.

#### 2-7 Selbus PRIORITY GENERATION JUMPERS

The TLC circuit card has a set of 22 Priority Generation jumpers used to assign the bus transfer priority of this TLC. The Priority Generation jumpers are shown on Logic Drawing 130-103175 (sheet 10) and are referenced by logic callouts X1-1 through X1-8, X2-1 through X2-8, and X3-1 through X3-6. To assign a bus transfer priority level to this TLC, the jumper controlling the priority level must be placed in the CLOSED (ON) position, and all remaining jumpers must be placed in the OPEN (OFF) position. The priority level chosen by this procedure must correspond to the priority level used for this TLC in the Priority Recognition jumpers.

#### 2-8 Selbus PRIORITY ENABLE SWITCHES

The SYSTEMS 32 SERIES CPU logic chassis backplane has a SelBUS terminator circuit card that contains a set of 22 Priority Enable switches. Those switches associated with priority levels assigned to modules on the SelBUS must be in the OPEN (OFF) position, and switches associated with the unassigned priority levels must be in the

CLOSED (ON) position. The SYSTEMS 32 SERIES Computer Technical Manual applicable to the system being used provides a system level discussion of all switches that must be set to communicate with the SelBUS.

#### 2-9 BAUD RATE JUMPERS

The TLC circuit card has a set of 21 jumpers that selects the Baud Rate for the desired operation when the Teletypewriter Device Dependent interface is used to interface with a CRT unit. Under normal operating conditions, the Baud Rate jumpers are configured for 110 Baud.

Table 2-1 shows the settings of the Baud Rate jumpers for the 12 different Baud Rates available in the TLC Controller.

The Baud Rate jumpers are shown on Logic Diagram 130-103175 (sheet 24), contained in the drawings manual. The Baud Rate switches are referenced by logic callouts X8-1 through X8-7, X9-1 through X9-8, and X10-2 through X10-6.

The TLC circuit card has no indicators that monitor TLC or system operation.

#### 2-10 POWER ON/OFF PROCEDURES

DC power is supplied to the TLC circuit card by the logic chassis in which the TLC circuit card is installed. The Power On/Off procedures for the logic chassis are normally covered by the CPU Power On/Off procedures. These procedures are described in the applicable SYSTEMS 32 SERIES Computer Technical Manual.

#### 2-11 OPERATING PROCEDURES

There are no special operating procedures for the TLC; however, the technical manual for the I/O devices attached to the TLC should be consulted before the TLC is operated.

#### 2-12 PROGRAMMING

The following discussions are intended to provide a brief description of the software instructions used to control and obtain

| Baud<br>Rate | Hex Code<br>X8 X9 X10 | X8<br>1234 5678 | X9<br>1234 5678 | X10<br>1 2 3 4 5 6 7 8 |

|--------------|-----------------------|-----------------|-----------------|------------------------|

| 110          | 10 17 2C              | 0001 000X       | 0001 0111       | X01X 11XX              |

| 150          | 10 67 24              | 0001 000X       | 0110 0111       | X O 1 X O 1 X X        |

| 300          | 20 9E 48              | 0010 000X       | 1001 1110       | X 1 0 X 1 0 X X        |

| 600          | 40 79 20              | 0100 000X       | 0111 1001       | X01X 00XX              |

| 900          | 80 D7 40              | 1000 000X       | 1101 0111       | X 1 0 X 0 0 X X        |

| 1200         | 80 E6 40              | 1000 000X       | 1110 0110       | X 1 0 X 0 0 X X        |

| 1800         | 02 DB 00              | 0000 001 X      | 1101 1011       | хоох оохх              |

| 2400         | 02 5D 00              | 0000 001 X      | 0101 1101       | x o o x x o o x x      |

| 3600         | 04 3A 00              | 0000 010X       | 0011 1010       | x o o x x o o x x      |

| 4800         | 04 F2 00              | 0000 010X       | 1111 0010       | хоох оохх              |

| 7200         | 08 6C 00              | 0000 100X       | 0110 1100       | XOOX OOXX              |

| 9600         | 00 22 80              | 0000 100X       | 1100 1100       | хоох оохх              |

Table 2-1. Baud Rate Switch Settings

|         | X7 . 10 |

|---------|---------|

| EIA     | 0       |

| Current | 1       |

status from the TLC. A more complete description of the software I/O instructions is provided in the SYSTEMS 32 SERIES Computer Technical Manual applicable to the user's particular system.

#### 2-13 I/O INSTRUCTIONS

#### 2-14 COMMAND DEVICE (CD) INSTRUCTION

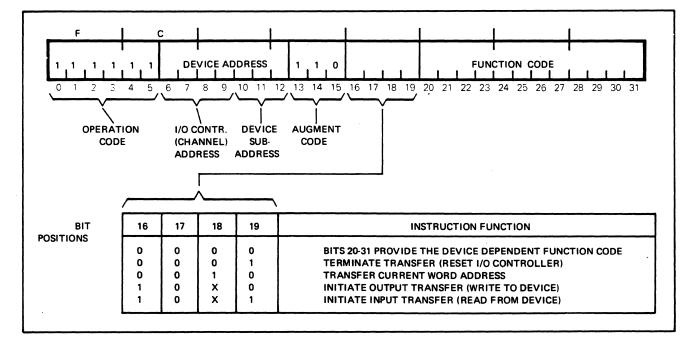

The TLC is controlled by the CD software instruction. Figure 2-1 shows the basic format of the CD instruction and lists the basic decodes of the instruction. The specific operations that can be controlled by the CD instruction are defined in subsequent discussions under the individual peripheral devices.

#### 2-15 Transfer Control Word (TCW)

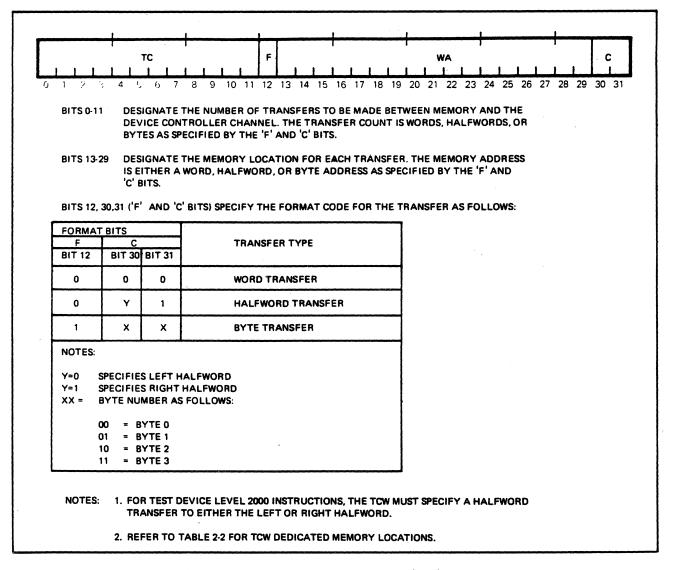

The TCW is a 32-bit word used with the CD Initialize Data Transfer instruction. The TCW provides the memory data transfer address and the data transfer count as shown in Figure 2-2. The TCW is stored in a dedicated memory location for the TLC Controller. Table 2-2 lists the dedicated memory locations (transfer interrupt addresses) used by the CPU.

The controlling software system must program the TCW with the memory data address, data transfer count, and the F- and C-bits before the CD Initialize Data Transfer instruction is initiated.

#### 2-16 Input/Output Command Doubleword (IOCD)

The CPU firmware formats the CD instruction and either the TCW address or the contents of the TCW into a 64-bit word called the Input/ Output Command Doubleword (IOCD). This doubleword is stored in memory locations dedicated to the TLC Controller being operated by the CD instruction. Remember that the IOCD is a firmware format and has no relationship to the system software.

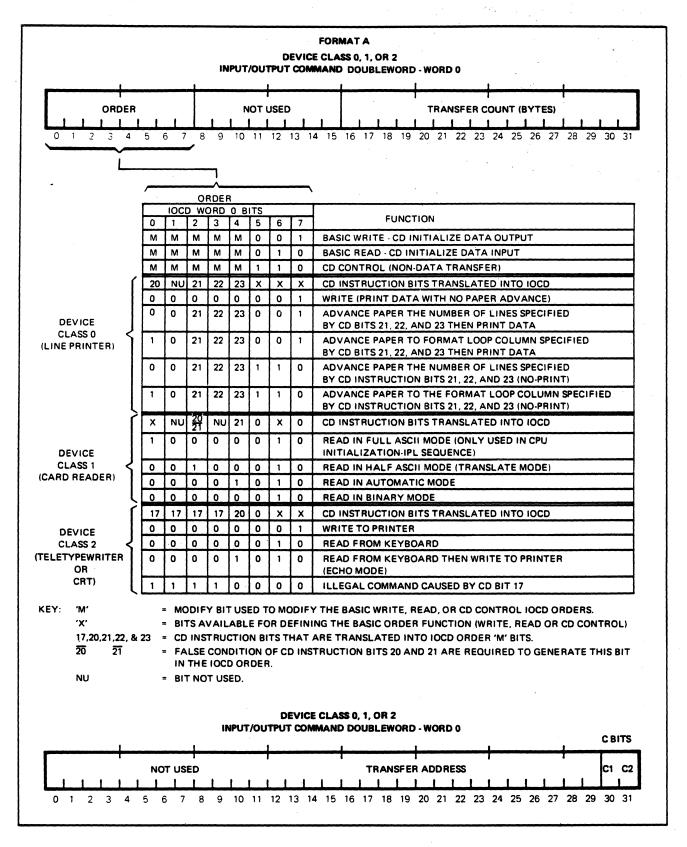

The specific IOCD format is a function of the class of device or controller being operated by the CD instruction and the type of I/O operation being initiated. Figure 2-3 shows the format for the IOCD used with Class O, 1, and 2 devices controlled by the TLC Controller. The Class O device is the line printer, the Class 1 device is the card reader, and the Class 2 device is the teletypewriter. In this format, the CD instruction function code is translated into the Order byte in the first IOCD word, and the contents of the TCW are formatted into the remaining portions of the IOCD as shown in Figure 2-3.

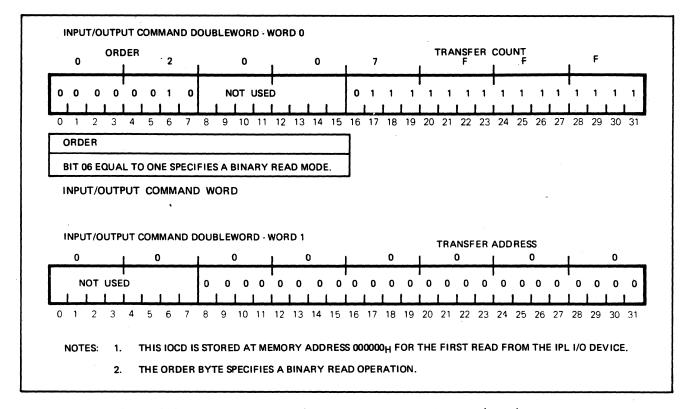

Figure 2-4 shows the IOCD format of an IPL initiated by the IPL switch on the CPU Turnkey Panel. This specific IOCD format is only used for the first Read from the IPL device; however, the basic IOCD format remains true for all subsequent reads from the IPL device during the CPU IPL firmware sequence.

Figure 2-1. Command Device (CD) Instruction Format

When the CPU generates the IOCD, it stores the IOCD at a dedicated memory address for the TLC Controller being operated. Table 2-3 lists the dedicated memory locations used with the 16 I/O controllers that can be controlled by the CPU.

#### 2-17 TEST DEVICE (TD) INSTRUCTION

The TD instruction is used by system software to obtain status from the TLC. The system software can program the TD instruction at the 8000, 4000, or 2000 levels. The 8000 level obtains basic I/O controlled (channel) status, which is returned to the CPU and software as four software testable condition codes. The 4000 level obtains TLC status, which is returned as four software testable condition codes. The 2000 level obtains the specific status of the TLC device dependent interface and the I/O device. The status is returned as a 16-bit status halfword and/or four condition codes. The bit definitions of the status halfword and three of the four condition codes are device dependent, and the fourth condition code indicates that the status halfword transfer was not performed. When the CPU receives the status halfword from the TLC, it stores the halfword at the memory location addressed by the contents of the TCW for TLC Controller addressed by the TD instruction.

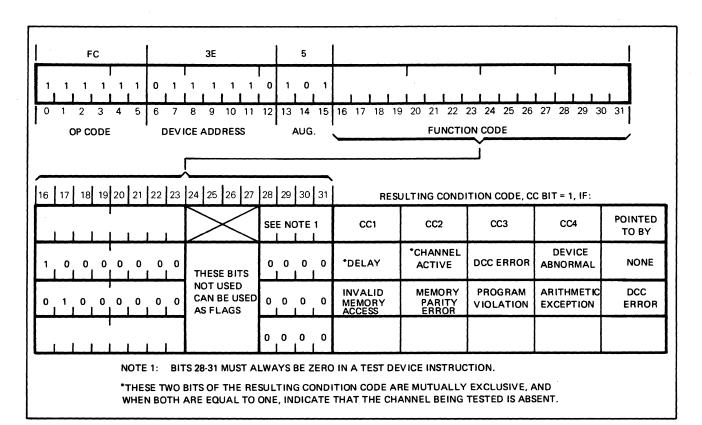

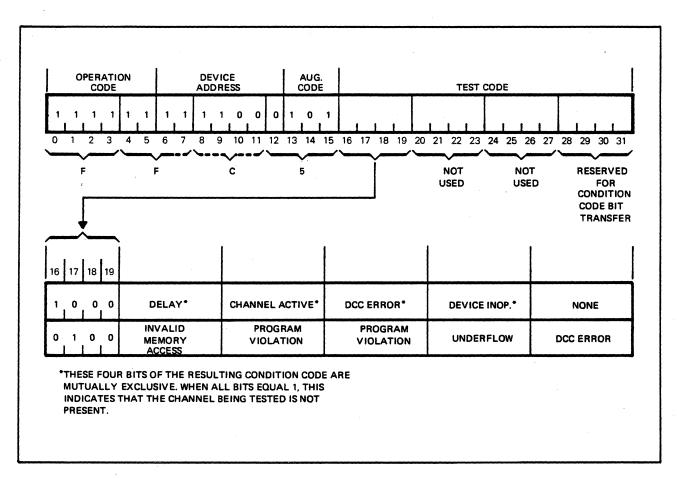

Figure 2-5 shows the format of the TD instruction and lists the condition code response for each of the three levels of the TD instruction.

Figure 2-2. Transfer Control Word (TCW) Format

| Memory<br>Dedicated<br>Address (H)                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Typical<br>CD or TD<br>Address (H)<br>(See Note 1) | Function     |               | I/O Controller<br>Service Interrupt<br>Level (H) |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|---------------|--------------------------------------------------|--|--|

| 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00                                                 | Input/Output | Controller O  | 14                                               |  |  |

| 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 04                                                 |              | 1             | 15                                               |  |  |

| 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 08                                                 |              | 2             | 16                                               |  |  |

| 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | OC                                                 |              | 3             | 17                                               |  |  |

| 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                                 |              | 4             | 18                                               |  |  |

| 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                 |              | 5             | 19                                               |  |  |

| 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                 |              | 6             | 1A                                               |  |  |

| 11C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30                                                 |              | 7             | 1B                                               |  |  |

| 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                 |              | 8             | 10                                               |  |  |

| 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50                                                 |              | 9             | 1D                                               |  |  |

| 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60                                                 |              | 10            | 1E                                               |  |  |

| 12C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70                                                 |              | 11            | 1F                                               |  |  |

| 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78                                                 |              | 12            | 20                                               |  |  |

| 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7A                                                 |              | 13            | 21                                               |  |  |

| 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7C                                                 |              | 14            | 22                                               |  |  |

| 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7E                                                 | Input/Output | Controller 15 | 23                                               |  |  |

| Notes: 1. Typical CD and TD Device addresses refer to the address configurations most commonly<br>used to address the respective I/O controller. The Typical CD and TD addresses are<br>CD or TD instructions bits 06-12 which are configured as follows:<br>a. Hex digit 1 represents instruction bits 06-08.<br>b. Hex digit 2 represents instruction bits 09-12.<br>2. The TD memory location is used to hold the Transfer Control Word (TCW) for the<br>corresponding I/O controller. |                                                    |              |               |                                                  |  |  |

#### Table 2-2. Transfer Interrupt (TCW) Dedicated Memory Locations

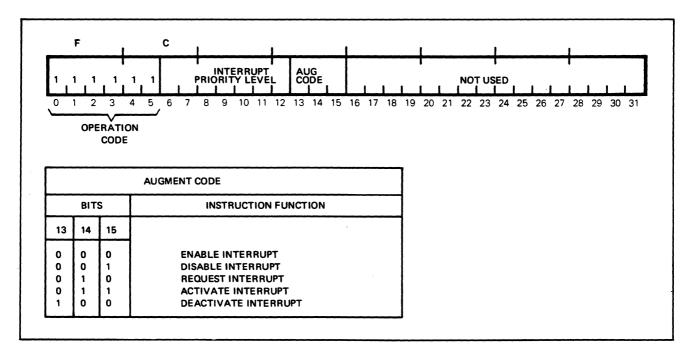

#### 2-18 INTERRUPT CONTROL INSTRUCTIONS

The software Interrupt Control instructions control the interrupt level provided by the TLC. Figure 2-6 shows the format of the Interrupt Control instructions and lists the Interrupt Control functions that can be commanded by the instruction. Each of the 128 priority interrupts in the CPU has a dedicated memory location that contains the address of a software program that handles the interrupt. This memory location is accessed whenever an interrupt occurs from the corresponding interrupt level. If the interrupt level is enabled and the level has the highest priority, the program addressed by the dedicated memory location is initiated. Table 2-4 lists the priority levels available to the CPU and the dedicated memory location (Service Interrupt address) for each level. Note that only levels 14<sub>H</sub> through 23<sub>H</sub> are applicable to the I/O controllers. Interrupt levels 02 through 11 are dedicated to transfer interrupts, and the contents of these locations is the TCW for the corresponding I/O controller.

Figure 2-3. Input/Output Command Doubleword (IOCD) Format

The Branch and Reset Interrupt (BRI) instruction is also used by software to clear the active condition of the TLC controller interrupt level, although the BRI is not one of the Interrupt Control instructions. A description of the format and functions of the BRI instruction can be found in any SYSTEMS 32 SERIES Computer Reference Manual.

#### 2-19 CPU INITIAL PROGRAM LOAD (IPL)

The CPU IPL sequence is entirely controlled by the CPU and is used to load software and hardware parameters that describe the system configuration into the CPU firmware control logic. The IPL sequence also loads a bootstrap software program into memory and initiates the execution of the bootstrap. The execution of the bootstrap causes the operating system program to be loaded into memory.

A complete and more detailed description of the IPL sequence can be found in the IOM Technical Manual, Publication Number 325-329000.

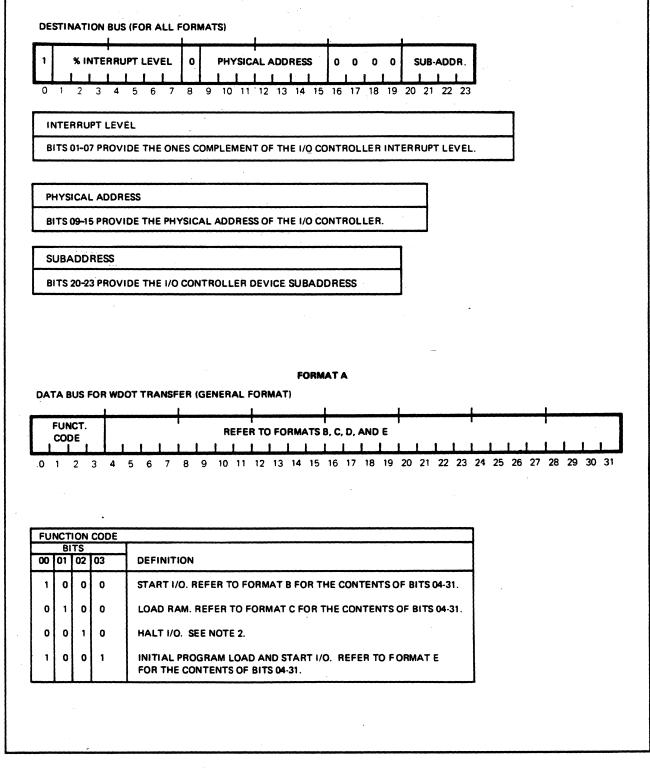

#### 2-20 SelBUS TRANSFERS

During the execution of the I/O command, a series of SelBUS transfers occurs. The SelBUS

can handle a total of 12 types of transfers; these are:

- 1. Write Data or Order Transfer (WDOT)

- 2. Read Data Transfer (RDT)

- 3. Interrupt Control Transfer (ICT)

- 4. Read Status Transfer (RSTX)

- 5. Advance Read Status Transfer (ARSTX)

- 6. Advance Interrupt Control Transfer (AICT)

- 7. Data Return Transfer (DRT)

- 8. Error Transfer (ET)

- 9. Memory Write Transfer (MWT)

- 10. Memory Read Transfer (MRT)

- 11. Memory Read and Lock Transfer (MRLT)

- 12. Memory Instruction Read Transfer (MIRT)

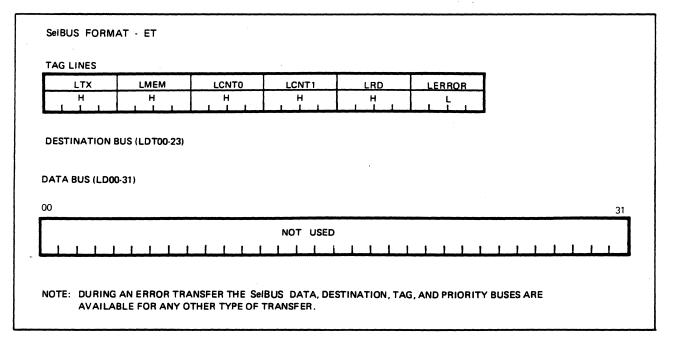

- 2-21 I/O MICROCOMMANDS

The TLC firmware, which is implanted in the control memory (PROM), uses a 32-bit microcommand word format (Figure 2-7). As data

Figure 2-4. IPL Basic Input/Output Command Doubleword (IOCD) Format

and control signals are received by the MP from the SelBUS or the external device, the MP sequences through its program at a rate of 6.66 million microcommands per second. The MP interprets all incoming control signals, generates its own control signals, and passes data to and from the external device and the SelBUS.

Since the machine language instructions and their macro instruction components are processed by the CPU, they are not discussed here. The remainder of this discussion describes in more detail the operation of the SelBUS interface which responds to SelBUS transfers, and the MP which processes the 32-bit microcommands.

#### 2-22 TELETYPEWRITER (TTY)

#### 2-23 CD INSTRUCTION

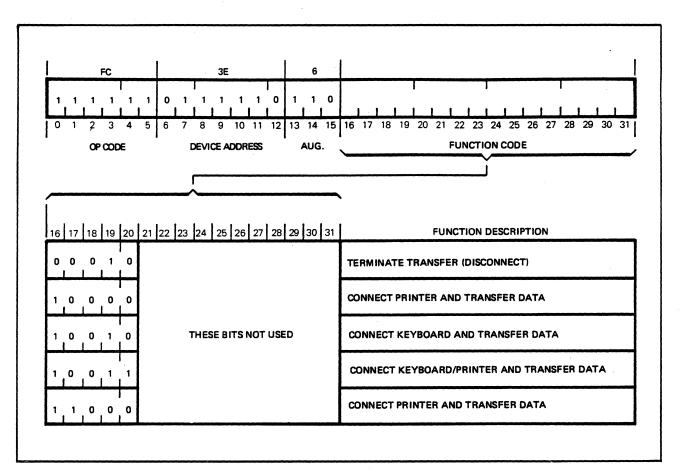

The TTY system can operate on eight command functions. These function codes are unique to the TTY system and should not be confused with those for other devices. Figure 2-8 shows the CD instruction, and Table 2-5 defines the CD function codes in hexadecimal format.

#### 2-24 TD INSTRUCTION

The initial status level of the TTY is obtained by executing a TD  $8000_{\rm H}$  instruction. This instruction tests for Channel Active, Device Controller Channel Error, and Device Abnormal. If any of these conditions are found, an associated bit is returned to the condition code field of the Program Status Word Register (PSWR).

If testing at this level returns a Device Controller Channel Error, further testing by execution of a TD  $4000_{\rm H}$  instruction determines the specific error. Execution of a TD at this level returns the following information: Invalid Memory Access, Memory Parity Error, Program Violation, Overflow, or Underflow. Figure 2-9 and Tables 2-6 and 2-7 support the preceding discussion on TD instructions.

| Table 2-3. | Input/Output | Command | Doubleword ( | (IOCD) | ) Dedicated | Memory | Locations |

|------------|--------------|---------|--------------|--------|-------------|--------|-----------|

|------------|--------------|---------|--------------|--------|-------------|--------|-----------|

| I/O Controller<br>Service Interrupt<br>Level (H) | IOCD Memory<br>Dedicated<br>Address (H)         | Used With                                           |

|--------------------------------------------------|-------------------------------------------------|-----------------------------------------------------|

| 14                                               | 700                                             | Input/Output Controller O                           |

| 15                                               | 708                                             | 1                                                   |

| 16                                               | 710                                             | 2                                                   |

| 17                                               | 718                                             | 3                                                   |

| 18                                               | 720                                             | 4                                                   |

| 19                                               | 728                                             | 5                                                   |

| 1A                                               | 730                                             | 6                                                   |

| 1B                                               | 738                                             | . 7                                                 |

| 1C                                               | 740                                             | 8                                                   |

| 1D                                               | 748                                             | 9                                                   |

| 1E                                               | 750                                             | 10                                                  |

| 1F                                               | 758                                             | 11                                                  |

| 20                                               | 760                                             | 12                                                  |

| 21                                               | 768                                             | 13                                                  |

| 22                                               | 770                                             | 14                                                  |

| 23                                               | 778                                             | Input/Output Controller 15                          |

| <br>Note: During the CPU<br>device are sto       | Firmware IPL sequence<br>res at memory location | all IOCD's for the IPL I/O<br>000000 <sub>H</sub> . |

| OPERATION<br>CODE | I/O CONTR. DEV                  | ICE AUGMENT<br>IB- CODE          | TD LEVEL                  | 4000                          |

|-------------------|---------------------------------|----------------------------------|---------------------------|-------------------------------|

| TD LEVEL          |                                 | CONDITION COD                    | E RESPONSE                |                               |

|                   | CC1                             | CC2                              | CC3                       | CC4                           |

| TD 8000           | DELAY                           | I/O CHANNEL<br>ACTIVE (BUSY)     | TD 4000<br>STATUS PRESENT | TD 2000<br>STATUS PRESENT     |

| TD 4000           | NON-PRESENT<br>MEMORY<br>ACCESS | MEMORY PARITY<br>ERROR           | PROGRAM<br>VIOLATION      | DATA UNDERFLOW<br>OR OVERFLOW |

| TD 2000           |                                 | STATUS TRANSFER<br>NOT PERFORMED | **                        | ••                            |

| NOTE: 1 **        |                                 |                                  |                           |                               |

|                   |                                 | OLLER DEPENDENT COM              |                           | ITROLLER                      |

| Figure 2-5. | Test Device | (TD) | Instruction | Format |

|-------------|-------------|------|-------------|--------|

|-------------|-------------|------|-------------|--------|

Figure 2-6. Interrupt Control Instruction Format

| Table 2-4. | Priority | Interrupt | Dedicated | Memory | Locations |

|------------|----------|-----------|-----------|--------|-----------|

|------------|----------|-----------|-----------|--------|-----------|

| Priority<br>Level (H) | Memory<br>Dedicated<br>Address (H) | Function                                             |

|-----------------------|------------------------------------|------------------------------------------------------|

| 00#                   | 050                                |                                                      |

| 00*                   | 0F0                                | Power Fail Safe - Auto Start Interrupt               |

| 00*                   | 0F4                                | Power Fail Safe - Auto Start Trap                    |

| 01*                   | 0F8                                | System Override Interrupt                            |

| 01*                   | OFC                                | System Override Trap                                 |

| 02**                  | 100                                | Input/Output Controller O Transfer Interrupt         |

| 03**                  | 104                                | Input/Output Controller 1 Transfer Interrupt         |

| 04**                  | 108                                | Input/Output Controller 2 Transfer Interrupt         |

| 05**                  | 100                                | Input/Output Controller 3 Transfer Interrupt         |

| 06**                  | 110                                | Input/Output Controller 4 Transfer Interrupt         |

| 07**                  | 114                                | Input/Output Controller 5 Transfer Interrupt         |

| 08**                  | 118                                | Input/Output Controller 6 Transfer Interrupt         |

| 09**                  | 11C                                | Input/Output Controller 7 Transfer Interrupt         |

| 0A**                  | 120                                | Input/Output Controller 8 Transfer Interrupt         |

| 0B**                  | 124                                | Input/Output Controller 9 Transfer Interrupt         |

| 0C**                  | 128                                | Input/Output Controller 10 Transfer Interrupt        |

| 0D**                  | 120                                | Input/Output Controller 11 Transfer Interrupt        |

| 0E**                  | 130                                | Input/Output Controller 12 Transfer Interrupt        |

| 0F**                  | 134                                | Input/Output Controller 13 Transfer Interrupt        |

| 10**                  | 138                                | Input/Output Controller 14 Transfer Interrupt        |

| 11**                  | 130                                | Input/Output Controller 15 Transfer Interrupt        |

| 12*                   | 0E8                                | Memory Parity Trap                                   |

| 13*                   | OEC                                | Console Interrupt (Turnkey Panel Attention)          |

| 14                    | 140                                | Input/Output Controller O Service Interrupt          |

| 14                    | 140                                | Input/Output Controller 1 Service Interrupt          |

| 16                    | 144                                | Input/Output Controller 2 Service Interrupt          |

|                       | 148                                |                                                      |

| 17                    | 140                                |                                                      |

| 18                    | 150                                |                                                      |

| 19                    |                                    |                                                      |

| 1A                    | 158                                |                                                      |

| 1B                    | 150                                | Input/Output Controller 7 Service Interrupt          |

| 10                    | 160                                | Input/Output Controller 8 Service Interrupt          |

| 1D                    | 164                                | Input/Output Controller 9 Service Interrupt          |

| 1E                    | 168                                | Input/Output Controller 10 Service Interrupt         |

| 1F                    | 160                                | Input/Output Controller 11 Service Interrupt         |

| 20                    | 170                                | Input/Output Controller 12 Service Interrupt         |

| 21                    | 174                                | Input/Output Controller 13 Service Interrupt         |

| 22                    | 178                                | Input/Output Controller 14 Service Interrupt         |

| 23                    | 170                                | Input/Output Controller 15 Service Interrupt         |

| 24*                   | 190                                | Nonpresent Memory Trap                               |

| 25*                   | 194                                | Undefined Instruction Trap                           |

| 26*                   | 198                                | Privilege Violation Trap                             |

| 27*                   | 190                                | Call Monitor Interrupt                               |

| 28*                   | 1A0                                | Real-Time Clock Interrupt                            |

| 29*                   | 1A4                                | Arithmetic Exception Interrupt                       |

| 2A*                   | 1A8                                | External Interrupt                                   |

| 2B*                   | 1AC                                | External Interrupt                                   |

| 2C*                   | 1B0                                | External Interrupt                                   |

| 2D*                   | 1B4                                | External Interrupt                                   |

| 2E*                   | 188                                | External Interrupt                                   |

| 2F*                   | 1BC                                | External Interrupt (Last PI in standard RTOM)        |

| 30                    | 100                                | External Interrupt                                   |

| <b>₩</b>              |                                    |                                                      |

|                       | 1 ∳ 1                              |                                                      |

| 7F                    | 2FC                                | External Interrupt                                   |

| + D                   |                                    |                                                      |

|                       | in first RTOM.                     | reserved for Transfer Control Words (TCW) and cannot |

27 28 18 10 INST RE ADDR REG CONTROL ALU FUNCTION ORDER COMPLEMENT OF LITERAL (MS BITS) LITERAL (LS HITS) LONG BRANCH ADDR TEST FUNCTION SHORT BRANCH ADDR ALU FUNCTION (BITS 00 & 01 - (00)2) DO NOT SAVE ALU STATUS (BIT 31=0) SAVE ALU STATUS (BIT 31=1) ORDER BIT 02 = 1 TEST FUNCTION BITS 00 & 01-(10, 11, OR 01); FUNCTION FUNCTION INST L/H LEVEL REG CONTROL CODE CARR CODE PULSE SINCE BINOO NORMAL MICRORETRY ACTIVE CLEARS PC16 CLR.HALTIO ..... A-1 01 A.1 01/81 12/83 20/A0 0/00 MICROBUSY NORMAL TEST 3 STELPDATA LBRANCH-SEL PEOIN BIN01 PC TO A FILE 80 . 09 . 11/91 21/A1 11/01 NORMAL ENB ORDER TEST1 DPLPCLEAR LCLRINT RDCARD **BIN 10** BIN02 EXT DEV TO B FILE 30 -1 F 31 -1 F 21/A1 2/A2 22/A2 2/C2 NORMAL ENB INT & ORDER TTYSTBINDAT DPPAPERINST RSTCRDTHERE RSTCRDLST BIN11 BIN03 3/C3 т 32 32 ZERO ZERO т 31/81 2/82 23/A3 SEL DATA TO . BING4 WAIT RSTDATAVAL STOPRD LREGINT BIN 12 58 в 59 . 1/C1 42/C2 24/44 . LMICROACK BIN 13 BINOS WAIT ENBINT MICRORST LMICRODATALD 60 A-8-1 F 61 F A-8-1 51/D1 28/45 105 WAIT ENINBUSA DPLPSTROBE LMICROTRANS LMICRODESTLD BIN14 BIN05 т 62 A-B 63 Ŧ A-B 61/E1 C ENINBUSB ENINBUSC WAIT BIN 15 BIN07 . LMICROREADY 90 F 91 F A+8 A+B 71/F1 72/F2 27/A7 SHORT BRANCH AMSB-FF AEQB-FF 92 т A+8+1 93 A+8+1 Ŧ -/C8 SHORT BRANCH MEMDATAHERE NONPRISMEM DEST TO A FILE 94 A+8+CARRY LAST 95 A+B+CARRY AST 29/ 49 I/C9 LITERAL TO RDIN PBEIN INDIRECT 98 AIB 98 AIB 24/44 N/CA CNTOIN A8 MICROINPUT **A9** 8 8 28/A8 VCB ALU TO A & B LONG BRANCH CNTIIN P2EIN 96 A:8 ... A:B C/AC /CC LONG BRANCH ALU TO A FILE PIEIN SYNC C0 A+A (SHIFT LEFT) A+A (SHIFT LEFT) C1 ENB INT A+A+MSB (SHIFT CIRCULAR) A+A+MSB (SHIFT CIRCULAR) INDIRECT CTRL2 UNCONDITIONAL ALU TO B FILE C7 cs MSB LONG BRANCH ZE/AR E/CE BRANCH (+V) ERRORIN CPU DATA HERE CHECK ALU **C8** ZERO **C9** ZERO F/CF OUTPUT 2F/AF E8 EØ RA00 RA06 A & B A & B 30/90 0/00 RA07 RA05 F8 . FØ . b1/81 1/D1 **\*AVAILABLE FOR THE DEVICE DEPENDENT INTERFACE** RAOS CRBUSY 32/82 2/D2 NOTE: THIS FORMAT DOES NOT PROVIDE THE 'LOAD LITERAL INTO A FILE' FUNCTION. CRDATALST CTRL4 LEGEND 33/83 ALU CARRY CRDATAHERE CTRL3 + - ADD - - SUBTRACT - LOGICAL AND - LOGICAL AND - LOGICAL OR - EXCLUSIVE OR A - ONES COMPLEMENT F - FALSE T - TRUE MSB- GENERATE FROM MOST SIGNIFICANT INPUT BIT LAST - GENERATE FROM CARRY STATUS THAT WAS SAVED DPLPREADY . TTYDATAREQ RA04 / TTYDATAHERE RA03 37/87 7/07

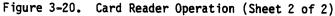

Figure 2-7. TLC Microcommand Format

Figure 2-8. Command Device Format TTY System

Table 2-5. Command Device Function Codes (TTY)

| 16-Bit<br>Function Code (H) | Function      | Definition                                                                                                                                                                                      |

|-----------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1000                        | Control       | Execution of a Command Device with this<br>function code causes a Terminate Transfer<br>(disconnect). This aborts the data transfer and<br>shuts down the device in an orderly manner.          |

| 8000                        | Data Transfer | Execution of a Command Device with this func-<br>tion code connects the Page Printer to the<br>Device Controller Channel and transfers data.                                                    |

| 9000                        | Data Transfer | Execution of a Command Device with this func-<br>tion code connects the Keyboard to the Device<br>Controller Channel and transfers keyed data.                                                  |

| 9800                        | Data Transfer | Execution of a Command Device with this func-<br>tion code connects the Keyboard and Page Printer<br>to the Device Controller Channel for transfer of<br>keyed data with Character Turn-Around. |

| C000                        | Data Transfer | Execution of a Command Device with this func-<br>tion code connects the Page Printer to the<br>Device Controller Channel and transfers data.                                                    |

Figure 2-9. Test Device Format and Function Code TTY System

| -                               |                                          |                                          |                                                                                                                                                                                                                               |

|---------------------------------|------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function<br><sup>Code</sup> (H) | Condition<br>Code                        | Designation                              | Definition                                                                                                                                                                                                                    |

| 8000                            | CC1 = 1                                  | Delay                                    | Not applicable to this device.                                                                                                                                                                                                |

| 8000                            | CC2 = 1                                  | Channel<br>Active                        | Indicates that the Device Controller<br>Channel is performing a Data Transfer.                                                                                                                                                |

| 8000                            | CC3 = 1                                  | Device<br>Controller<br>Channel<br>Error | Indicates that an error condition was<br>detected within the Device Controller<br>Channel during the previous operation.<br>The specific error can be determined by<br>executing a Test Device at level 4000 <sub>(H)</sub> . |

| 8000                            | CC4 = 1                                  | Device<br>Abnormal                       | Indicates that an abnormal condition<br>has been detected. In the keyboard/<br>printer the presence of this bit indi-<br>cates that the device is Inoperable:<br>Power Off, in Local Modes, etc.                              |

| 8000                            | CC1 = 1<br>CC2 = 1<br>CC3 = 1<br>CC4 = 1 | Nonexistent                              | Indicates that the channel to which the<br>Test was directed is nonexistent.                                                                                                                                                  |

| 8000                            | CC1 = 1<br>CC2 = 1<br>CC3 = 0<br>CC4 = 0 | Device<br>Not Available                  | Not applicable to this device.                                                                                                                                                                                                |

Table 2-6. Test Device Results, Level 8000(H)

| P                               |                   |                             |                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------|-------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function<br>Code <sub>(H)</sub> | Condition<br>Code | Designation                 | Definition                                                                                                                                                                                                                                                                                                                                                              |

| 4000                            | CC1 = 1           | Invalid<br>Memory<br>Access | Indicates that the Device Controller<br>Channel has addressed a memory module<br>that is either not present in the CPU<br>or, in a Multiprocessor Configuration,<br>to which the Device Controller Channel<br>is denied access.                                                                                                                                         |

| 4000                            | CC2 = 1           | Memory<br>Parity<br>Error   | Indicates that a Memory Parity Error<br>was detected while the Device Controller<br>Channel was fetching data or a Transfer<br>Control Word from memory.                                                                                                                                                                                                                |

| 4000                            | •CC3 = 1          | Program<br>Violation        | Indicates that a Command Device was<br>executed that could not be performed by<br>the device. This can occur when a<br>command is issued before the Device<br>Controller Channel has completed a<br>current operation. The Service Interrupt<br>is generated when the current operation<br>is completed, and this bit is provided<br>to indicate the Program Violation. |

| 4000                            | CC4 = 1           | Overflow<br>or<br>Underflow | Indicates that data was lost while<br>being transferred from the Device<br>Controller Channel or memory to the<br>peripheral device (Overflow) or from<br>the Peripheral Device to the Device<br>Controller Channel or memory (Underflow).                                                                                                                              |

# Table 2-7. Test Device Results, Level 4000(H)

#### 2-25 LINE PRINTER

#### 2-26 CD INSTRUCTION

The CD instruction causes the transfer of an 8-bit instruction command code to the TLC Controller. The CD instruction command codes are shown in Figure 2-10. The bit assignments for the CD command codes are as follows:

- Bit 16 equals One Initialize Output Data Transfer

- Bit 17 equals One Reserved for future expansion.

- 3. Bit 19 equals One Terminate Operation

- Bits 20 through 23 Paper Line Advance Control bits

- 5. Bits 24 through 31 These bits are not used with the line printer

2-27 TD INSTRUCTION

The TD instruction tests the status information to determine the condition of the line printer Device Controller Channel (DCC) and the line printer device. The TD instruction format is shown in Figure 2-11.

- Bit 16 equals One Select Test Level 8000 (Initial Conditions)

- 2. Bit 17 equals One Select Test Level 4000 (DCC Errors)

- 3. Bit 18 equals One Select Test Level 2000 (Device Status)

The initial condition of the line printer is obtained by executing a TD 8000 instruction. This instruction tests for Channel Active, DCC Error, and Device Abnormal. If any of these conditions are found, an associated bit is returned to the condition code field of the PSWR.

If an 8000 level test shows an error in the DCC, a TD 4000 instruction is used to determine the specific error.

If an 8000 level test shows an abnormal status in the device, a TD 2000 instruction is used to determine the fault within the device. Tables 2-8 through 2-12 support the previous discussion.

:0  $\overline{\mathbf{C}}$ 9000 :0 OPERATION DEVICE AUG-COMMAND CODE ADDRESS CODE MENT COMMAND DEVICE (CD) 011 0 INSTRUCTION 111111 11 0 2 3 4 5 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 1 6 7 NOT USED WITH F С 6 THIS DEVICE 16 17 18 19 20 21 22 23 н H COMMAND FUNCTION COMMAND FUNCTION 0 0 0 0 0 ADVANCE PAPER ONLY 0 0 0 0 0 NO PAPER ADVANCE 0 0 0 1 1 TERMINATE 0 1 0 0 1 ADVANCE SINGLE LINE 2 ADVANCE DOUBLE LINE 2 0 0 1 0 3 3 ADVANCE TRIPLE LINE 0 0 1 1 4 4 5 5 6 6 7 7 8 OUTPUT INITIALIZE 8 1 0 0 0 0 0 0 CHANNEL 0 ADVANCE TO TOP OF FORM 9 CHANNEL 1 ADVANCE TO BOTTOM OF FORM 0 0 1 9 0 1 0 Α Α CHANNEL 2 в CHANNEL 3 В 0 1 1 С CHANNEL 4 0 0 С 1 OPERATOR SELECTION D CHANNEL 5 1 0 1 D Ε 1 0 Ε CHANNEL 6 1 F 1 1 F CHANNEL 7 1

Figure 2-10. Line Printer Command Device Instruction Format

| ro)                              |              |           |                                          | n an an Araba an Araba<br>An Araba an Araba<br>An Araba an Araba                                                                                                                                                                  |

|----------------------------------|--------------|-----------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NSTRUCTION                       |              | 1         |                                          |                                                                                                                                                                                                                                   |

| OPERATION DEVICE<br>CODE ADDRESS | AUG-<br>MENT |           | TEST C                                   | ODE                                                                                                                                                                                                                               |

|                                  | T            |           | 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1 |                                                                                                                                                                                                                                   |

|                                  | 1 10 11      | XIXIXI    |                                          |                                                                                                                                                                                                                                   |

| 0 1 2 3 4 5 6 7 8 9 10 11        |              |           | 20 21 22 23 2                            | 24 25 26 27 28 29 30 31                                                                                                                                                                                                           |

| F C                              | <u> </u>     | ~         | NO                                       | RESERVED                                                                                                                                                                                                                          |

|                                  |              | NOT USED  | USE                                      | D FOR                                                                                                                                                                                                                             |

|                                  |              |           | · .                                      | CONDITION<br>CODE BIT                                                                                                                                                                                                             |