# Gould CONCEPT 32/67

# Reference Manual

April 1983

Publication: 301-000410-000

This manual is supplied without representation or warranty of any kind. Gould Inc., S.E.L. Computer Systems Division therefore assumes no responsibility and shall have no liability of any kind arising from the supply or use of this publication or any material contained herein.

Copyright 1983 Gould Inc., S.E.L. Computer Systems Division Printed in the U.S.A.

#### HISTORY

The Gould CONCEPT 32/67 Reference Manual, Publication Order Number 301-000410-000, was printed April, 1983.

This manual contains the following pages:

Title page Copyright page iii/iv through xi/xii 1-1 through 1-4 2-1 through 2-17/2-18 3-1 through 3-6 4-1 through 4-26 5-1 through 5-22 6-1 through 5-22 6-1 through 6-428 A-1 through A-7/A-8 B-1 through A-7/A-8 B-1 through B-8 C-1 through C-5/C-6 D-1 through D-2 •

## CONTENTS

# Chapter

# Page

# **1 GENERAL DESCRIPTION**

| 1.1 | Introduct | tion                                         |

|-----|-----------|----------------------------------------------|

| 1.2 | System C  | Dverview                                     |

|     | 1.2.1     | General Information 1-1                      |

|     | 1.2.2     | 32/67 Characteristics 1-2                    |

| 1.3 | 32/67 Ce  | entral Processing Unit (CPU) 1-2             |

|     | 1.3.1     | Operating Mode 1-2                           |

|     | 1.3.2     | Nonbase and Base Register Modes 1-3          |

|     | 1.3.3     | General Purpose Register 1-3                 |

|     | 1.3.4     | Memory Management and Address Generation 1-3 |

|     | 1.3.5     | Interrupts 1-3                               |

|     | 1.3.6     | Traps 1-3                                    |

|     | 1.3.7     | Input/Output (I/O) Operations 1-4            |

| 1.4 | 32/67 Int | ernal Processing Unit (IPU) 1-4              |

|     | 1.4.1     | Operating Mode 1-4                           |

## 2 CENTRAL PROCESSOR

| 2.1 | Introduc  | tion                                        |

|-----|-----------|---------------------------------------------|

| 2.2 | CPU Cor   | ntrol Modes                                 |

|     | 2.2.1     | Program Status Doubleword 2-1               |

|     | 2.2.2     | Condition Codes                             |

|     | 2.2.3     | Privileged/Unprivileged Operations 2-1      |

| 2.3 | Instructi | on Repertoire and Formats 2-3               |

| 2.4 | Memory    | Boundaries 2-4                              |

|     | 2.4.1     | Instructions                                |

|     | 2.4.2     | Operands                                    |

|     | 2.4.3     | Instruction Formats 2-6                     |

|     | 2.4.4     | Program Counter                             |

| 2.5 | Memory    | Reference Instructions 2-6                  |

|     | 2.5.1     | Nonbase Register Mode 2-6                   |

|     |           | 2.5.1.1 F and C Bits 2-6                    |

|     |           | 2.5.1.2 Direct Addressing 2-7               |

|     |           | 2.5.1.3 Indexed Addressing 2-7              |

|     |           | 2.5.1.4 Indirect Addressing 2-8             |

|     |           | 2.5.1.5 Indirect and Indexed Addressing 2-8 |

|     | 2.5.2     | Base Register Mode 2-9                      |

|     |           | 2.5.2.1 Address Alignment 2-9               |

|     |           | 2.5.2.2 Base Register Format 2-9            |

| 2.6 | Memory    | Address Generation 2-10                     |

|     | 2.6.1     | Mapped Environment 2-10                     |

|     | 2.6.2     | Unmapped Environment 2-10                   |

|     | 2.6.3     | Nonextended Addressing Option 2-14          |

|     | 2.6.4     | Extended Addressing Option 2-14             |

|     | 2.6.5     | Write Protection                            |

Contents

## **3 MEMORY MANAGEMENT**

| 3.1 | Hardware Memory Management     | 3-1 |

|-----|--------------------------------|-----|

| 3.2 | Memory Mapping Scheme          | 3-1 |

| 3.3 | Memory Mapping Data Structures | 3-1 |

| 3.4 | Current Process Index          | 3-1 |

| 3.5 | Master Process List            | 3-1 |

| 3.6 | MAP Image Descriptor List      | 3-2 |

| 3.7 | MAP Image Descriptor           | 3-2 |

| 3.8 | MAP Initializaton              | 3-5 |

| 3.9 | The Look-Aside Buffer          | 3-5 |

# **4 INTERRUPTS AND TRAPS**

| 4.1 | Introduc  | tion • • • • • • |                                                                        | -1  |

|-----|-----------|------------------|------------------------------------------------------------------------|-----|

| 4.2 | Interrupt | ts               |                                                                        | -1  |

| 4.3 |           |                  | struction                                                              |     |

|     | 4.3.1     | Interrupt C      | ontrol Instructions for Non-Extended I/O, RTOM,                        | _   |

|     | 10201     |                  | eal-Time Interrupts 4-                                                 | -2  |

|     |           | 4.3.1.1          | Enable Interrupt Instruction (EI) 4-                                   | -2  |

|     |           | 4.3.1.2          | Disable Interrupt Instruction (DI) 4-                                  | _2  |

|     |           | 4.3.1.3          | Request Interrupt Instruction (RI)                                     | -2  |

|     |           | 4.3.1.4          | Activate Interrupt Instruction (AI)                                    | -4  |

|     |           | 4.3.1.5          | Descriver Interrupt Instruction (DAI)                                  | -4  |

|     | 4.3.2     |                  | Deactivate Interrupt Instruction (DAI) 4-                              | -4  |

|     | 4.3.2     |                  | ontrol Instructions for Extended                                       |     |

|     |           |                  | els                                                                    |     |

|     |           | 4.3.2.1          | Enable Channel Interrupt (ECI) 4-                                      |     |

|     |           | 4.3.2.2          | Disable Channel Interrupt (DCI)                                        |     |

|     |           | 4.3.2.3          | Activate Channel Interrupt (ACI)                                       |     |

|     |           | 4.3.2.4          | Deactivate Channel Interrupt (DACI) 4-                                 |     |

|     |           | 4.3.2.5          | Deferment 4-                                                           |     |

|     | 4.3.3     |                  | elated Instructions 4-                                                 |     |

|     |           | 4.3.3.1          | Block External Interrupt<br>Instruction (BEI) 4-                       | _   |

|     |           |                  | Instruction (BEI)                                                      | -5  |

|     |           | 4.3.3.2          | Unblock External Interrupt                                             |     |

|     |           |                  | Instruction (UEI).                                                     | -5  |

|     |           | 4.3.3.3          | Load Program Status Doubleword (LPSD) 4-                               | -5  |

|     |           | 4.3.3.4          | Load Program Status Doubleword and Change                              |     |

|     |           |                  | MAP (LPSDCM) 4                                                         |     |

| 4.4 | Interrup  |                  | ritching                                                               |     |

|     | 4.4.1     | CPU Scrate       | chpad                                                                  | -7  |

|     | 4.4.2     | Interrupt V      | ector Table (IVT)                                                      | -7  |

|     | 4.4.3     | Interrupt C      | ontext Block (ICB) 4                                                   | -7  |

| 4.5 | Traps     |                  | 4-1                                                                    | 12  |

|     | 4.5.1     | Trap Types.      |                                                                        | 12  |

|     |           | 4.5.1.1          | Power Fail Trap 4-1                                                    | 13  |

|     |           | 4.5.1.2          | Power-On Trap 4-1                                                      |     |

|     |           | 4.5.1.3          | Memory Parity Trap 4-1                                                 |     |

|     |           | 4.5.1.4          | Nonpresent Memory Trap 4-:                                             |     |

|     |           | 4.5.1.5          | Undefined Instruction Trap 4-                                          |     |

|     |           | 4.5.1.6          | Privileged Violation Trap 4-                                           |     |

|     |           | 4.5.1.7          | Supervisor Call Trap 4-                                                |     |

|     |           | 4.5.1.8          | Machine Check Trap 4-                                                  |     |

|     |           | 4.5.1.9          | System Check Trap 4-                                                   |     |

|     |           | 2 • 1 • 2        | 4.5.1.9.1 System Check Trap-Group 1 4-                                 |     |

|     |           |                  | Tiperior Oystem oncer righ-group I + + + + + + + + + + + + + + + + + + | * 4 |

Gould CONCEPT 32/67 Reference Manual

| 4.5.1.9.4System Check Trap-Group 44-4.5.1.10MAP Fault Trap4-4.5.1.11IPU Undefined Instruction Trap4-4.5.1.12Signal CPU/Signal IPU Trap4-4.5.1.13Address Specification Trap4-4.5.1.14Console Attention Trap4-4.5.1.15Privileged Mode Halt Trap4-4.5.1.16Arithmetic Exception Trap4-4.5.2Trap Halts4-4.5.3Trap Halt Implementation4-4.5.4Supervisor Call4-4.5.4.1Supervisor Call4-4.5.4.3Disable Arithmetic Exception Trap4-4.5.4.4SETCPU Mode4-4.5.5.1CPU Scratchpad4-4.5.5.2Trap Vector Table (TVT)4-4.5.5.3Trap Context Block (TCB)4-                                                                                        | System Check Trap-Group 2 4-15 | 4.5.1.9.2                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------|

| 4.5.1.10MAP Fault Trap4-4.5.1.11IPU Undefined Instruction Trap4-4.5.1.12Signal CPU/Signal IPU Trap4-4.5.1.13Address Specification Trap4-4.5.1.14Console Attention Trap4-4.5.1.15Privileged Mode Halt Trap4-4.5.1.16Arithmetic Exception Trap4-4.5.3Trap Halts4-4.5.4Trap Related Macroinstructions4-4.5.4.1Supervisor Call4-4.5.4.2Enable Arithmetic Exception Trap4-4.5.4.3Disable Arithmetic Exception Trap4-4.5.4.4SETCPU Mode4-4.5.5.1CPU Scratchpad4-4.5.5.2Trap Vector Table (TVT)4-4.5.6.4ICB/TCB Formats4-                                                                                                            | System Check Trap-Group 3 4-16 | 4.5.1.9.3                    |

| 4.5.1.11IPU Undefined Instruction Trap4-4.5.1.12Signal CPU/Signal IPU Trap4-4.5.1.13Address Specification Trap4-4.5.1.14Console Attention Trap4-4.5.1.15Privileged Mode Halt Trap4-4.5.1.16Arithmetic Exception Trap4-4.5.2Trap Halts4-4.5.3Trap Halt Implementation4-4.5.4Supervisor Call4-4.5.4.1Supervisor Call4-4.5.4.2Enable Arithmetic Exception Trap4-4.5.5.3Trap Context Switching4-4.5.5.2Trap Vector Table (TVT)4-4.5.5.3Trap Context Block (TCB)4-                                                                                                                                                                 | System Check Trap-Group 4 4-16 | 4.5.1.9.4                    |

| 4.5.1.12Signal CPU/Signal IPU Trap4-4.5.1.13Address Specification Trap4-4.5.1.14Console Attention Trap4-4.5.1.15Privileged Mode Halt Trap4-4.5.1.16Arithmetic Exception Trap4-4.5.2Trap Halts4-4.5.3Trap Halt Implementation4-4.5.4Trap Related Macroinstructions4-4.5.4.1Supervisor Call4-4.5.4.2Enable Arithmetic Exception Trap4-4.5.4.3Disable Arithmetic Exception Trap4-4.5.4.4SETCPU Mode4-4.5.5.1CPU Scratchpad4-4.5.5.2Trap Vector Table (TVT)4-4.5.5.3Trap Context Block (TCB)4-4.5.6ICB/TCB Formats4-                                                                                                              | p                              | 4.5.1.10 MAP Faul            |

| 4.5.1.12Signal CPU/Signal IPU Trap4-4.5.1.13Address Specification Trap4-4.5.1.14Console Attention Trap4-4.5.1.15Privileged Mode Halt Trap4-4.5.1.16Arithmetic Exception Trap4-4.5.2Trap Halts4-4.5.3Trap Halt Implementation4-4.5.4Trap Related Macroinstructions4-4.5.4.1Supervisor Call4-4.5.4.2Enable Arithmetic Exception Trap4-4.5.4.3Disable Arithmetic Exception Trap4-4.5.4.4SETCPU Mode4-4.5.5.1CPU Scratchpad4-4.5.5.2Trap Vector Table (TVT)4-4.5.5.3Trap Context Block (TCB)4-4.5.6ICB/TCB Formats4-                                                                                                              | Instruction Trap 4-16          | 4.5.1.11 IPU Undef           |

| <ul> <li>4.5.1.13 Address Specification Trap</li> <li>4.5.1.14 Console Attention Trap</li> <li>4.5.1.15 Privileged Mode Halt Trap</li> <li>4.5.1.16 Arithmetic Exception Trap</li> <li>4.5.2 Trap Halts</li> <li>4.5.3 Trap Halt Implementation</li> <li>4.5.4 Trap Related Macroinstructions</li> <li>4.5.4.1 Supervisor Call</li> <li>4.5.4.2 Enable Arithmetic Exception Trap</li> <li>4.5.4.3 Disable Arithmetic Exception Trap</li> <li>4.5.4.4 SETCPU Mode</li> <li>4.5.5.1 CPU Scratchpad</li> <li>4.5.5.2 Trap Vector Table (TVT)</li> <li>4.5.5.3 Trap Context Block (TCB)</li> <li>4.5.6 ICB/TCB Formats</li> </ul> | nal IPU Trap 4-17              | 4.5.1.12 Signal CP           |

| 4.5.1.14Console Attention Trap.4-4.5.1.15Privileged Mode Halt Trap4-4.5.1.16Arithmetic Exception Trap4-4.5.2Trap Halts4-4.5.3Trap Halt Implementation4-4.5.4Trap Related Macroinstructions4-4.5.4.1Supervisor Call4-4.5.4.2Enable Arithmetic Exception Trap4-4.5.4.3Disable Arithmetic Exception Trap4-4.5.4.4SETCPU Mode4-4.5.5.1CPU Scratchpad4-4.5.5.2Trap Vector Table (TVT)4-4.5.5.3Trap Context Block (TCB)4-4.5.6ICB/TCB Formats4-                                                                                                                                                                                     |                                |                              |

| 4.5.1.15Privileged Mode Halt Trap4-4.5.1.16Arithmetic Exception Trap4-4.5.2Trap Halts4-4.5.3Trap Halt Implementation4-4.5.4Trap Related Macroinstructions4-4.5.4.1Supervisor Call4-4.5.4.2Enable Arithmetic Exception Trap4-4.5.4.3Disable Arithmetic Exception Trap4-4.5.4.4SETCPU Mode4-4.5.5.1CPU Scratchpad4-4.5.5.2Trap Vector Table (TVT)4-4.5.5.3Trap Context Block (TCB)4-4.5.6ICB/TCB Formats4-                                                                                                                                                                                                                      |                                |                              |

| <ul> <li>4.5.1.16 Arithmetic Exception Trap</li> <li>4.5.2 Trap Halts</li> <li>4.5.3 Trap Halt Implementation</li> <li>4.5.4 Trap Related Macroinstructions</li> <li>4.5.4.1 Supervisor Call</li> <li>4.5.4.2 Enable Arithmetic Exception Trap</li> <li>4.5.4.3 Disable Arithmetic Exception Trap</li> <li>4.5.4.4 SETCPU Mode</li> <li>4.5.5.1 CPU Scratchpad</li> <li>4.5.5.2 Trap Vector Table (TVT)</li> <li>4.5.5.3 Trap Context Block (TCB)</li> <li>4.5.6 ICB/TCB Formats</li> </ul>                                                                                                                                   |                                |                              |

| <ul> <li>4.5.2 Trap Halts</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                |                              |

| <ul> <li>4.5.4 Trap Related Macroinstructions.</li> <li>4.5.4.1 Supervisor Call.</li> <li>4.5.4.2 Enable Arithmetic Exception Trap</li> <li>4.5.4.3 Disable Arithmetic Exception Trap</li> <li>4.5.4.4 SETCPU Mode</li> <li>4.5.5 Trap Context Switching</li> <li>4.5.5.1 CPU Scratchpad</li> <li>4.5.5.2 Trap Vector Table (TVT)</li> <li>4.5.5.3 Trap Context Block (TCB)</li> <li>4.5.6 ICB/TCB Formats</li> </ul>                                                                                                                                                                                                         |                                |                              |

| <ul> <li>4.5.4 Trap Related Macroinstructions.</li> <li>4.5.4.1 Supervisor Call.</li> <li>4.5.4.2 Enable Arithmetic Exception Trap</li> <li>4.5.4.3 Disable Arithmetic Exception Trap</li> <li>4.5.4.4 SETCPU Mode</li> <li>4.5.5 Trap Context Switching</li> <li>4.5.5.1 CPU Scratchpad</li> <li>4.5.5.2 Trap Vector Table (TVT)</li> <li>4.5.5.3 Trap Context Block (TCB)</li> <li>4.5.6 ICB/TCB Formats</li> </ul>                                                                                                                                                                                                         |                                | 4.5.3 Trap Halt Implementati |

| 4.5.4.2Enable Arithmetic Exception Trap4-4.5.4.3Disable Arithmetic Exception Trap4-4.5.4.4SETCPU Mode4-4.5.5Trap Context Switching4-4.5.5.1CPU Scratchpad4-4.5.5.2Trap Vector Table (TVT)4-4.5.5.3Trap Context Block (TCB)4-4.5.6ICB/TCB Formats4-                                                                                                                                                                                                                                                                                                                                                                            |                                |                              |

| 4.5.4.3Disable Arithmetic Exception Trap4-4.5.4.4SETCPU Mode4-4.5.5Trap Context Switching4-4.5.5.1CPU Scratchpad4-4.5.5.2Trap Vector Table (TVT)4-4.5.5.3Trap Context Block (TCB)4-4.5.6ICB/TCB Formats4-                                                                                                                                                                                                                                                                                                                                                                                                                     |                                | 4.5.4.1 Supervisor           |

| 4.5.4.4SETCPU Mode4-4.5.5Trap Context Switching4-4.5.5.1CPU Scratchpad4-4.5.5.2Trap Vector Table (TVT)4-4.5.5.3Trap Context Block (TCB)4-4.5.6ICB/TCB Formats4-                                                                                                                                                                                                                                                                                                                                                                                                                                                               | etic Exception Trap 4-20       | 4.5.4.2 Enable Ar            |

| 4.5.5Trap Context Switching4-4.5.5.1CPU Scratchpad4-4.5.5.2Trap Vector Table (TVT)4-4.5.5.3Trap Context Block (TCB)4-4.5.6ICB/TCB Formats4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | etic Exception Trap 4-20       | 4.5.4.3 Disable Ar           |

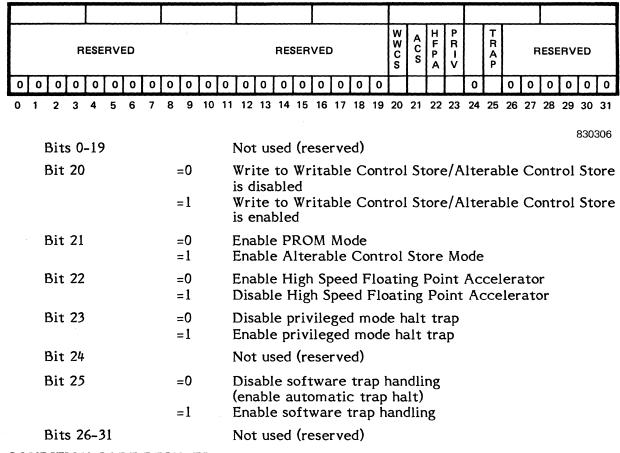

| 4.5.5.1       CPU Scratchpad       4-         4.5.5.2       Trap Vector Table (TVT)       4-         4.5.5.3       Trap Context Block (TCB)       4-         4.5.6       ICB/TCB Formats       4-                                                                                                                                                                                                                                                                                                                                                                                                                             |                                | 4.5.4.4 SETCPU N             |

| 4.5.5.2       Trap Vector Table (TVT)       4-         4.5.5.3       Trap Context Block (TCB)       4-         4.5.6       ICB/TCB Formats       4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                | 4.5.5 Trap Context Switching |

| 4.5.5.3Trap Context Block (TCB)4-4.5.6ICB/TCB Formats4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | d                              | 4.5.5.1 CPU Scra             |

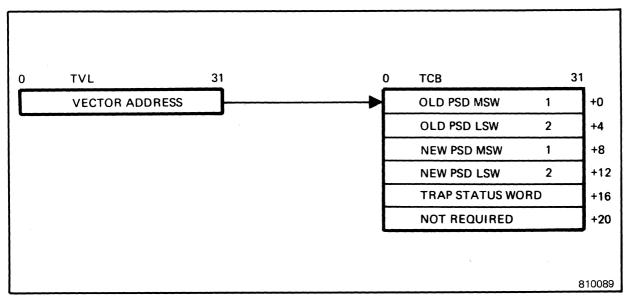

| 4.5.6 ICB/TCB Formats 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ble (TVT) 4-21                 | 4.5.5.2 Trap Vect            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | olock (TCB)                    | 4.5.5.3 Trap Cont            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |                              |

| 4.5.6.1 Old and New PSD 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SD 4-23                        | 4.5.6.1 Old and N            |

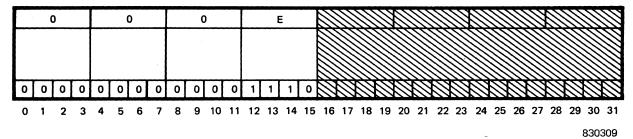

| 4.5.6.2 External and Nonextended Format 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |                              |

| 4.5.6.3 Trap Format 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                | 4.5.6.3 Trap Form            |

| 4.5.6.4 Class F I/O Format 4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | mat 4-26                       | 4.5.6.4 Class F I/           |

| 4.5.6.5 Supervisor Call Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Format 4-26                    | 4.5.6.5 Supervisor           |

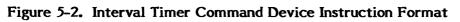

# 5 INPUT/OUTPUT SYSTEM

| 5.1 | Introdu | ction        |                                       |

|-----|---------|--------------|---------------------------------------|

| 5.2 | I/O Org | anization    |                                       |

| 5.3 |         |              | · · · · · · · · · · · · · · · · · · · |

|     | 5.3.1   | Operation of | Class 3 or B I/O Devices 5-3          |

|     |         | 5.3.1.1      | Interrupt Level                       |

|     |         | 5.3.1.2      | Subaddress                            |

|     |         | 5.3.1.3      | Interval Timer                        |

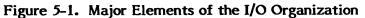

|     |         | 5.3.1.4      | Command Device Instruction            |

|     |         | 5.3.1.5      | Test Device Instruction               |

|     |         | 5.3.1.6      | Read the Interval Timer 5-5           |

|     |         | 5.3.1.7      | Program the Interval Timer 5-5        |

|     | 5.3.2   | Operation of | Class E or 6 Devices 5-5              |

|     |         | 5.3.2.1      | Interrupt Level                       |

|     |         | 5.3.2.2      | Subaddress 5-5                        |

|     |         | 5.3.2.3      | Command Device Instruction 5-7        |

|     |         | 5.3.2.4      | Transfer Control Word 5-7             |

|     |         | 5.3.2.5      | Input/Output Command                  |

|     |         |              | Doubleword (IOCD)                     |

|     |         | 5.3.2.6      | Address of the IOCD and TCW 5-9       |

|     |         | 5.3.2.7      | Test Device Instruction 5-9           |

|     | 5.3.3   | Operation of | Class F or 7 I/O Processors 5-13      |

|     |         | 5.3.3.1      | Interrupt Level                       |

|     |         | 5.3.3.2      | Subaddresses 5-15                     |

|     |         | 5.3.3.3      | Input/Output Instructions 5-15        |

|     |         | 5.3.3.4      | Input/Output Initiation 5-16          |

|     |         |              |                                       |

Gould CONCEPT 32/67 Reference Manual

Contents

|     | 5.3.3.5             | Input/Output Command List       |

|-----|---------------------|---------------------------------|

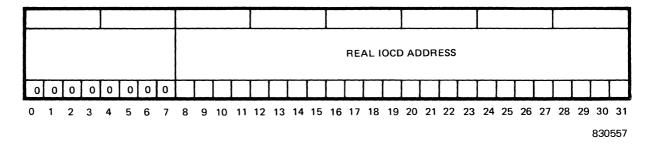

|     |                     | Address (IOCLA) 5-17            |

|     | 5.3.3.6             | Input/Output Memory Addressing  |

|     | 5.3.3.7             | Input/Output Command Doubleword |

|     |                     | Format 5-17                     |

|     | 5.3.3.8             | Input/Output Commands 5-19      |

|     | 5.3.3.9             | Input/Output Termination 5-20   |

|     | 5.3.3.10            | Input/Output Status Words 5-20  |

| 5.4 | Input/Output Interr | upts                            |

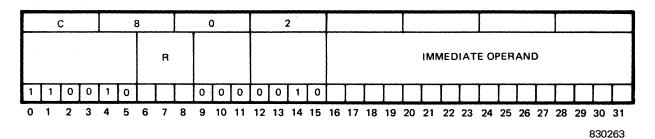

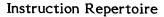

# **6** INSTRUCTION REPERTOIRE

| 6.1 | Introduct |                    |                                               |

|-----|-----------|--------------------|-----------------------------------------------|

|     | 6.1.1     |                    |                                               |

|     | 6.1.2     | Formats            |                                               |

|     | 6.1.3     | Definition         |                                               |

|     | 6.1.4     |                    |                                               |

|     | 6.1.5     | Summary E          | xpressions 6-3                                |

|     | 6.1.6     |                    | Code                                          |

|     | 6.1.7     |                    | Coding Conventions 6-8                        |

| 6.2 |           |                    |                                               |

|     | 6.2.1     |                    | Instructions                                  |

|     |           | 6.2.1.1            | Instruction Format 6-9                        |

|     |           | 6.2.1.2            | Condition Code                                |

|     |           | 6.2.1.3            | Memory to Register Transfers 6-9              |

|     | 6.2.2     |                    | ransfer Instructions 6-85                     |

|     |           | 6.2.2.1            | Instruction Format                            |

|     |           | 6.2.2.2            | Condition Code 6-85                           |

|     | 6.2.3     |                    | anagement Instructions                        |

|     | 6.2.4     |                    | ructions                                      |

|     |           | 6.2.4.1            | Instruction Format                            |

|     |           | 6.2.4.2            | Condition Code                                |

|     | 6.2.5     |                    | nstructions                                   |

|     |           | 6.2.5.1            | Instruction Format                            |

|     |           | 6.2.5.2            | Condition Code                                |

|     | 6.2.6     |                    | tructions                                     |

|     |           | 6.2.6.1            | Instruction Format                            |

|     |           | 6.2.6.2            | Condition Code                                |

|     | 6.2.7     |                    | ation Instructions                            |

|     |           | 6.2.7.1            | Instruction Format                            |

|     | (         | 6.2.7.2            | Condition Code                                |

|     | 6.2.8     |                    | lation Instructions                           |

|     |           | 6.2.8.1            | Instruction Format                            |

|     |           | 6.2.8.2            | Condition Code                                |

|     |           | 6.2.8.3            | Shared Memory Configurations                  |

|     |           | 6.2.8.4<br>6.2.8.5 | Interprocessor Semaphores                     |

|     | 6.2.9     |                    | Interprocessor Semaphore Considerations       |

|     | 6.2.7     | 6.2.9.1            | Instruction Format                            |

|     |           | 6.2.9.2            |                                               |

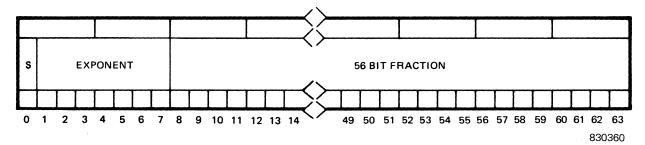

|     |           | 6.2.9.2            | Data Formats                                  |

|     |           | 0.2.7.5            | Handling Logical and Arithmetic<br>Operations |

|     |           | 6.2.9.4            | Condition Code                                |

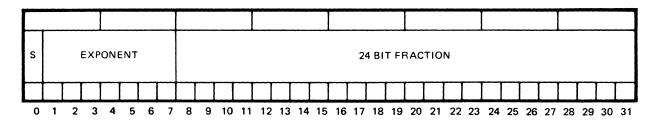

|     | 6.2.10    |                    | oint Arithmetic Instructions                  |

|     | 0.2.10    | r ioating-r        |                                               |

|        | 6.2.10.1          | Instruction Format                 |

|--------|-------------------|------------------------------------|

|        | 6.2.10.2          | Condition Codes                    |

|        | 6.2.10.3          | Floating-Point Arithmetic Operands |

| 6.2.11 | Floating-P        | Point Conversion Instructions.     |

|        | 6 <b>.2.</b> 11.Ĭ | Instruction Format                 |

|        | 6.2.11.2          | Condition Code                     |

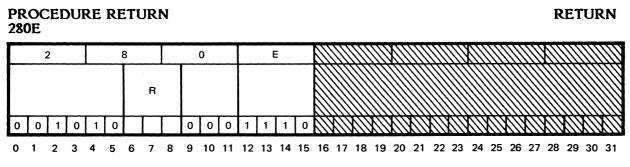

| 6.2.12 | Control In        | structions                         |

|        | 6.2.12.1          | Instruction Format                 |

|        | 6.2.12.2          | Condition Code                     |

| 6.2.13 | Interrupt (       | Control Instructions               |

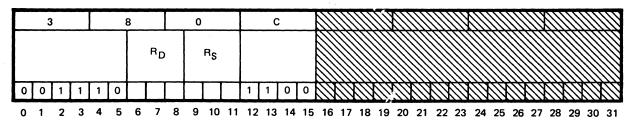

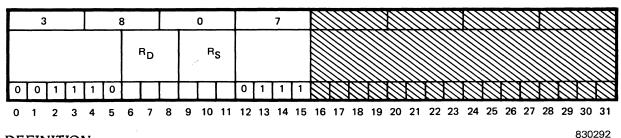

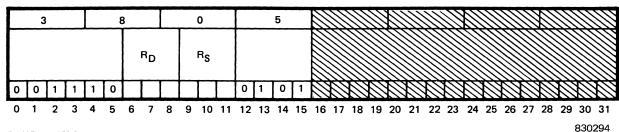

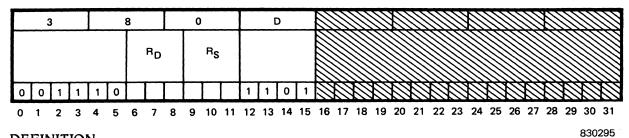

|        | 6.2.13.1          | Instruction Format                 |

|        | 6.2.13.2          | Condition Code                     |

| 6.2.14 | Input/Outp        | but Instructions                   |

|        | 6.2.14.1          | Command Device and Test Device     |

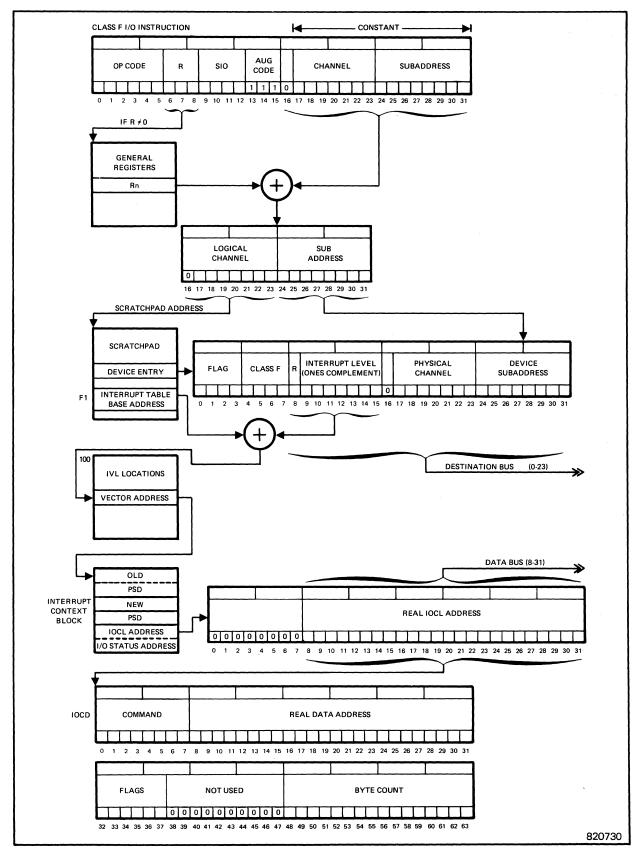

| 6.2.15 | Class F I/C       | D Instructions                     |

| 6.2.16 | Alterable         | Control Storage/Writable Control   |

|        | Storage I         | nstructions                        |

|        | 6.2.16.1          | Instruction Format                 |

|        | 6.2.16.2          | Condition Code                     |

|        | 6.2.16.3          | ACS/WCS Programming                |

## APPENDIX A

| 32/67 CPU Instruction Set Functionally Grouped by |       |

|---------------------------------------------------|-------|

| Sequential Page Number                            | A-1/8 |

### **APPENDIX B**

| 32/67 CPU Instruction Set Grouped by Mnemonic in |

|--------------------------------------------------|

| Alphabetical Order                               |

# APPENDIX C

| 32/67 CPU Instruction Set Grouped by Op Code in |      |

|-------------------------------------------------|------|

| Hexadecimal Order C                             | -1/6 |

# APPENDIX D

| 32/67 CPU Instruction Set as Compared to the 32 Series |       |

|--------------------------------------------------------|-------|

| Instructions                                           | D-1/2 |

## **ILLUSTRATIONS**

Title

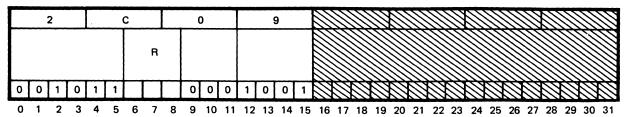

| 2-1  | Program Status Doubleword Format 2-2                    |

|------|---------------------------------------------------------|

| 2-2  | Information Boundaries in Memory 2-5                    |

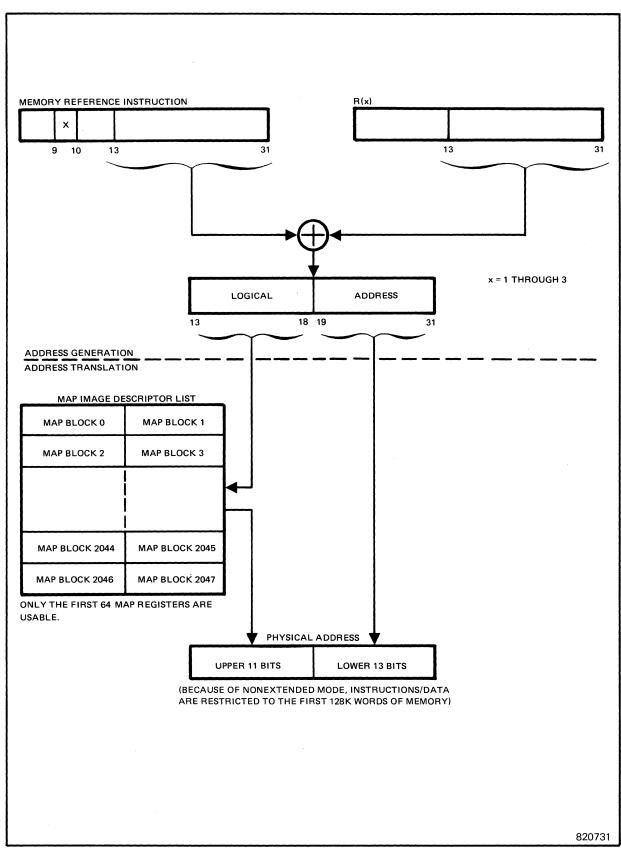

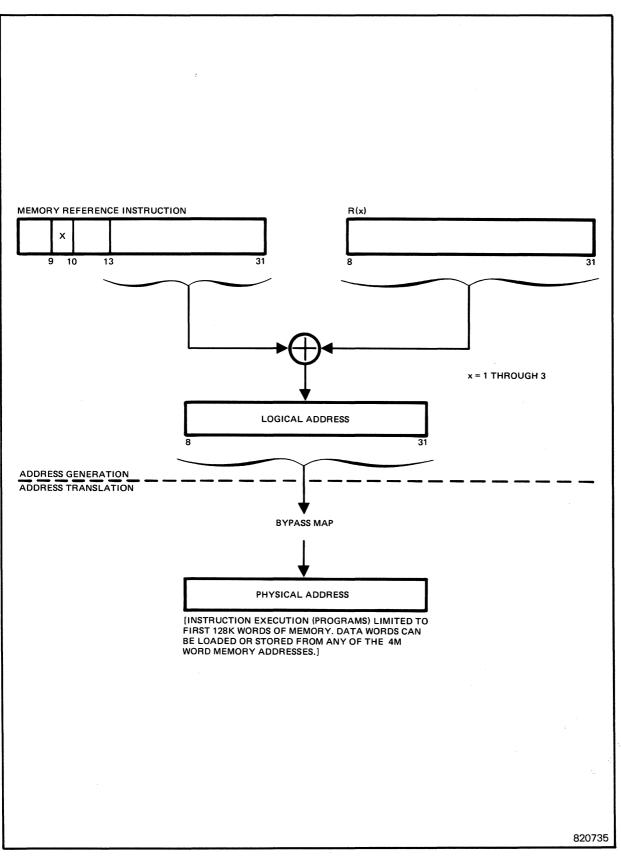

| 2-3  | Mapped Environment for Nonbase Nonextended Mode 2-11    |

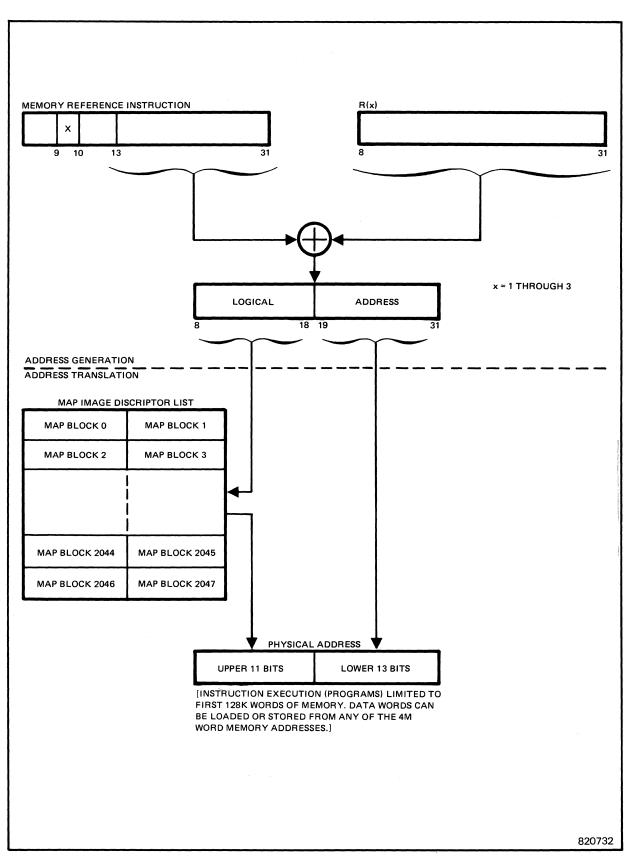

| 2-4  | Mapped Environment for Nonbase Extended Mode 2-12       |

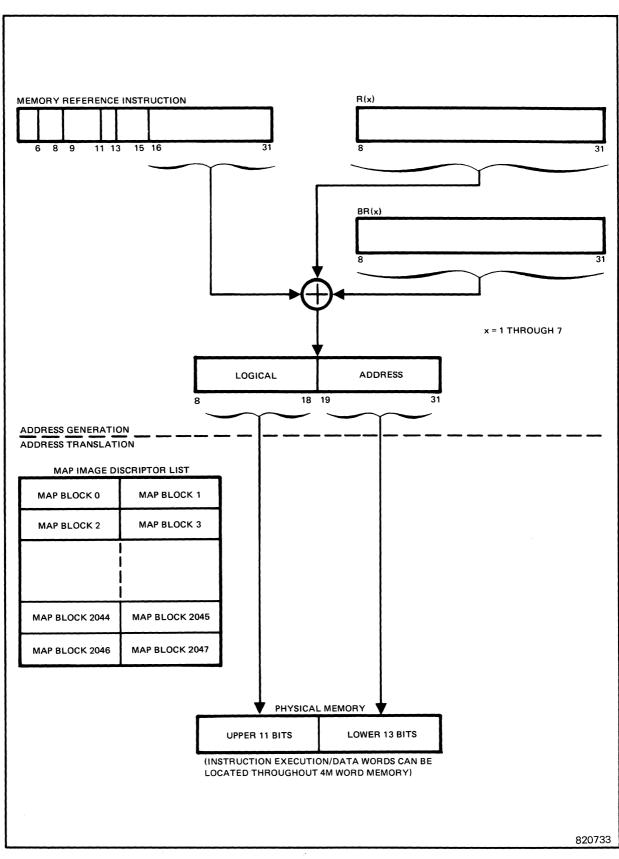

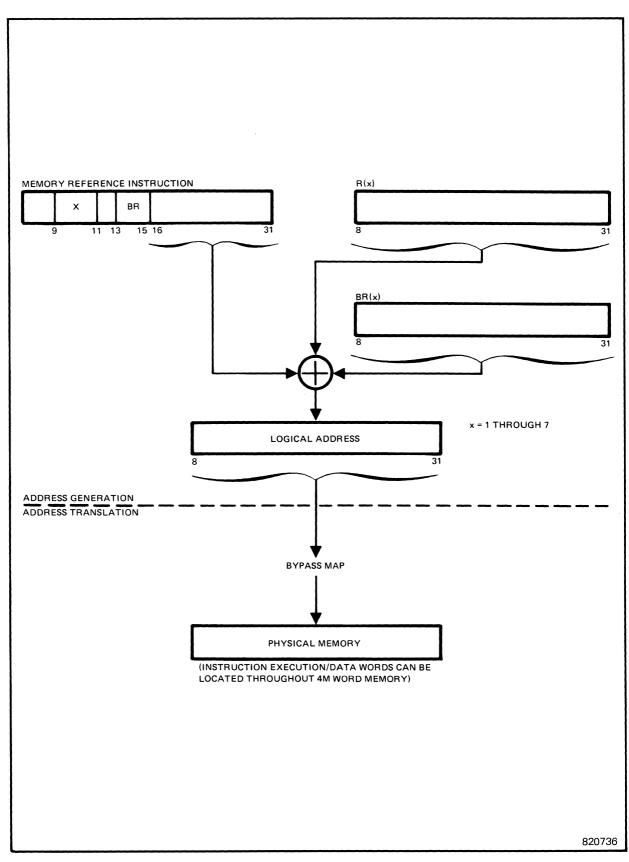

| 2-5  | Mapped Environment for Base Register Mode 2-13          |

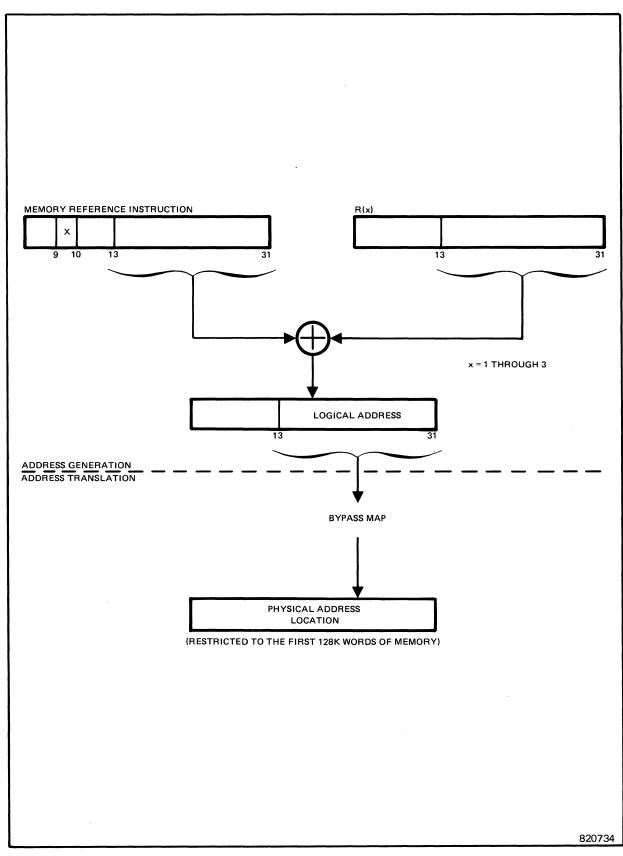

| 2-6  | Unmapped Environment for Nonbase Nonextended Mode 2-15  |

| 2-7  | Unmapped Environment for Nonbase Extended Mode 2-16     |

| 2-8  | Unmapped Environment for Base Register Mode 2-17        |

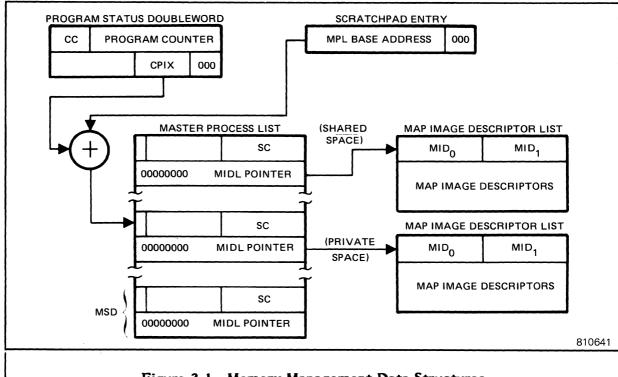

| 3-1  | Memory Management Data Structures                       |

| 3-2  | MAP Segment Descriptor (MSD) 3-3                        |

| 3-3  | MAP Image Descriptor List                               |

| 3-4  | MAP Image Descriptor (MID)                              |

| 4-1  | Interrupt Structure                                     |

| 4-2  | Scratchpad I/O Device Entry Format 4-9                  |

| 4-3  | Scratchpad Interrupt Entry Format 4-10                  |

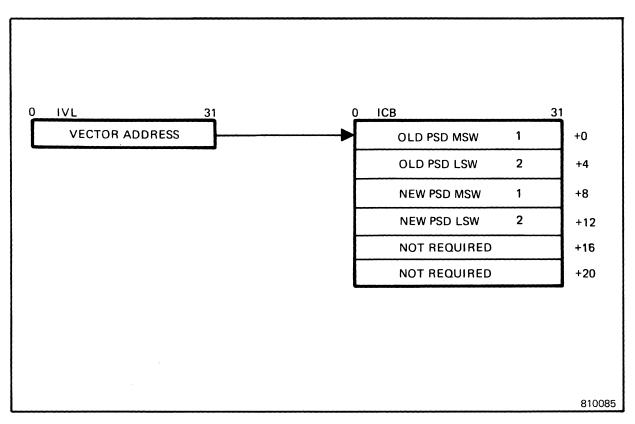

| 4-4  | Interrupt Context Block Format-External and Nonextended |

|      | I/O Interrupt                                           |

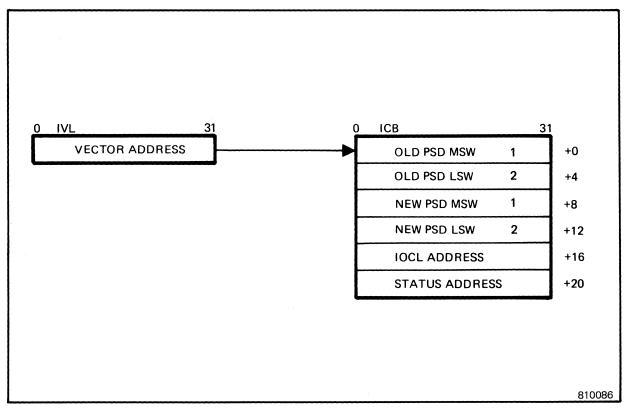

| 4-5  | Interrupt Context Block Format-Class F (Extended)       |

|      | I/O Interrupts 4-11                                     |

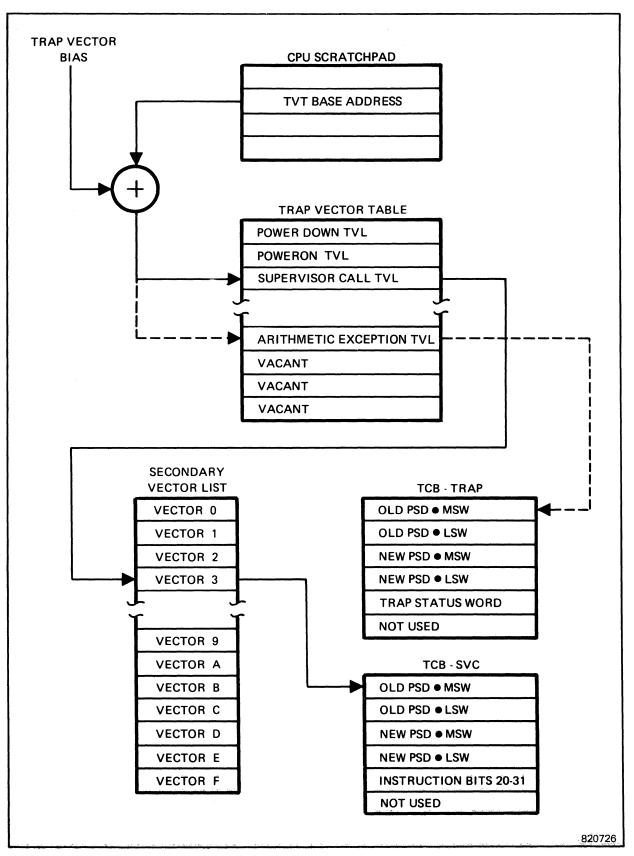

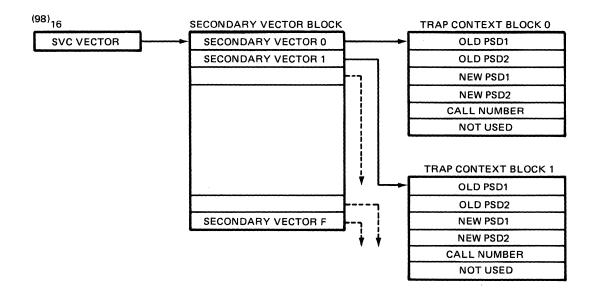

| 4-6  | Trap Structure                                          |

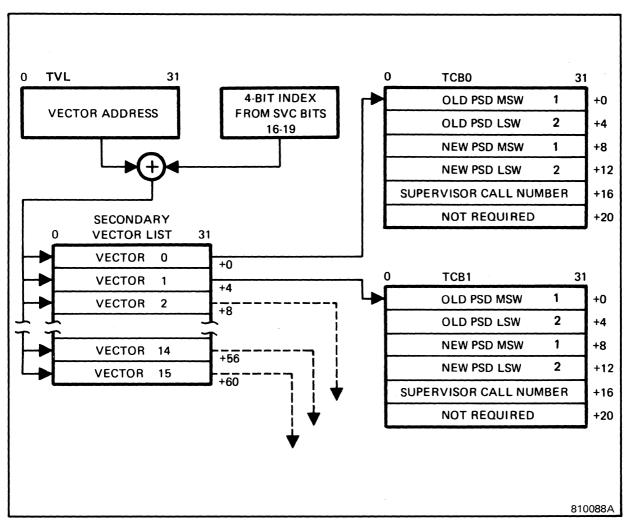

| 4-7  | Trap Context Block Format-Supervisor Call (SVC) 4-24    |

| 4-8  | Trap Context Block Format 4-24                          |

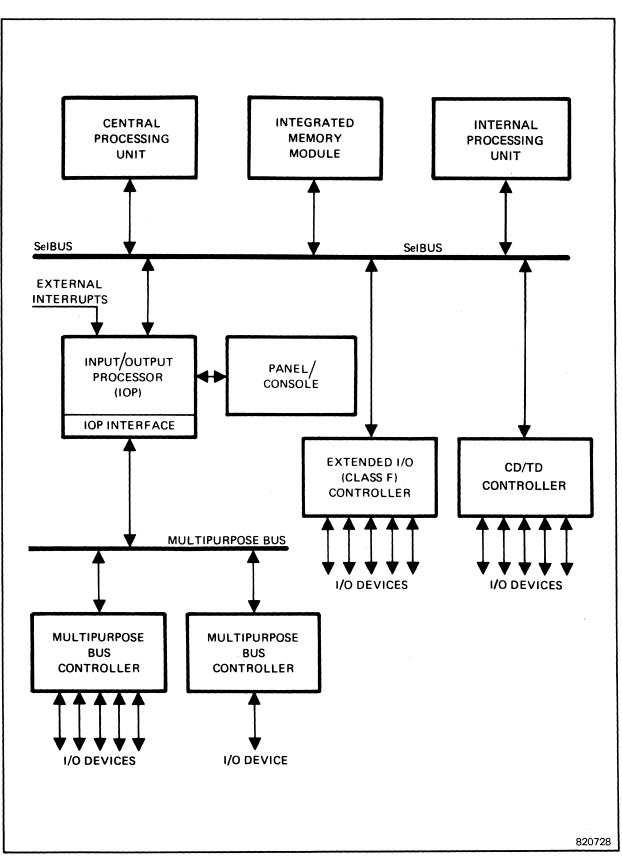

| 5-1  | Major Elements of the I/O Organization 5-2              |

| 5-2  | Interval Timer Command Device Instruction Format        |

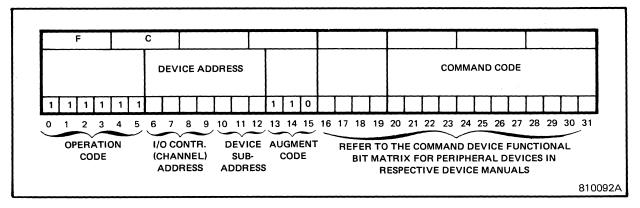

| 5-3  | Class E Command Device Instruction Format               |

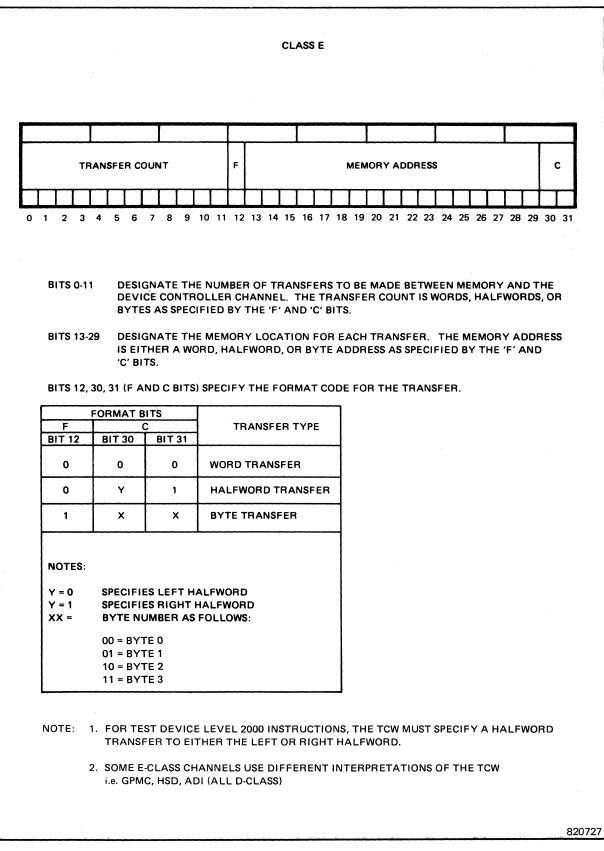

| 5-4  | Transfer Control Word Format 5-8                        |

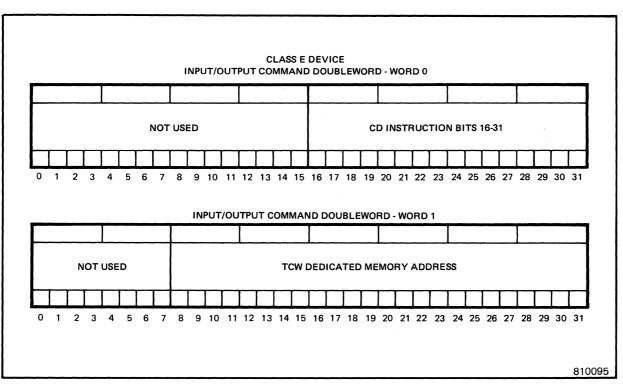

| 5-5  | Class E Devices, IOCD Format 5-10                       |

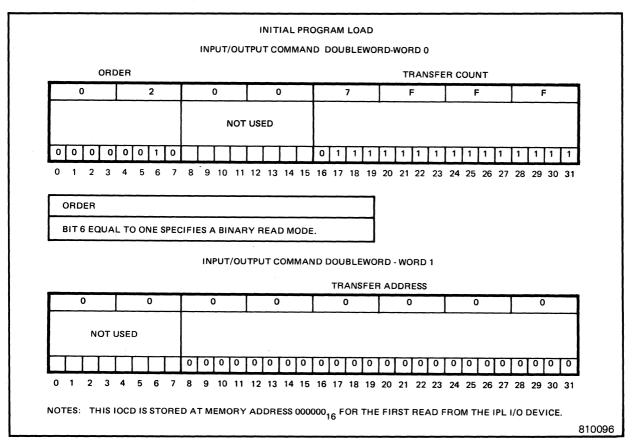

| 5-6  | Initial Program Load, IOCD Format                       |

| 5-7  | Test Device Instruction Format                          |

| 5-8  | I/O Control Words (Class F) 5-14                        |

| 5-9  | Class F Devices IOCD Format                             |

| 5-10 | Input/Output Status Words Format                        |

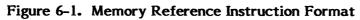

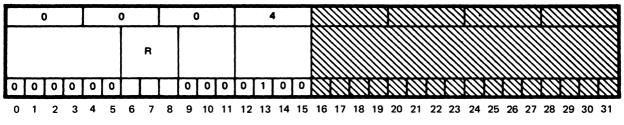

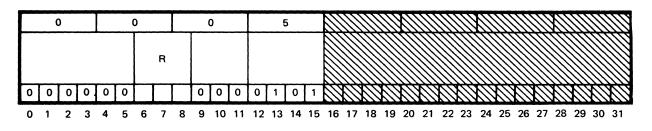

| 6-1  | Memory Reference Instruction Format                     |

| 6-2  | Immediate Instruction Format                            |

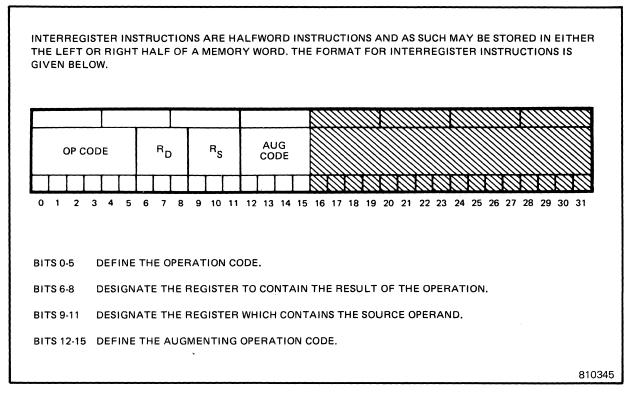

| 6-3  | Interregister Instruction Format                        |

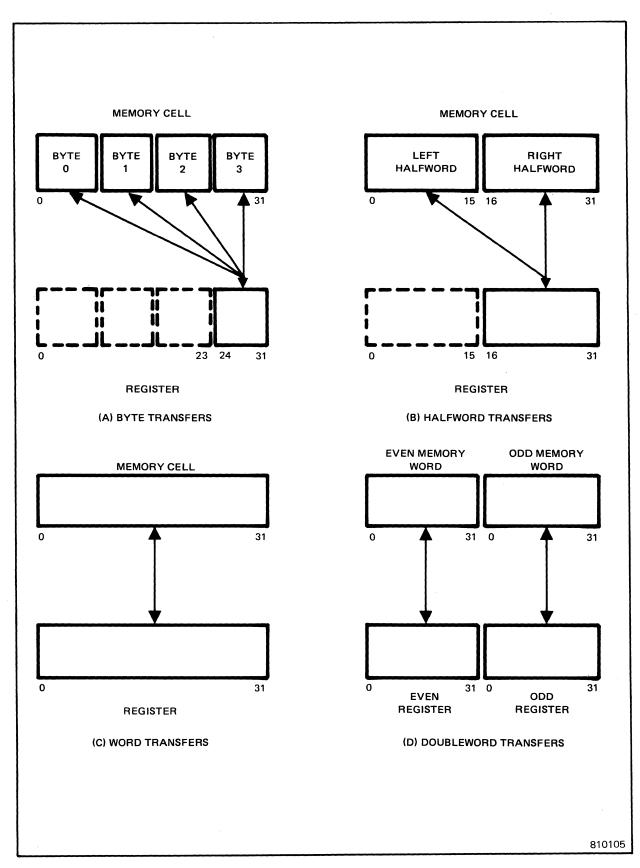

| 6-4  | Positioning of Information Transferred Between Memory   |

|      | and Registers 6-11                                      |

|      | ×                                                       |

Page

x

Figure

# TABLES

# Title

| P | age  |

|---|------|

| 1 | arc. |

| 4-1<br>4-2<br>4-3<br>4-4<br>5-1<br>5-2 | Default Interrupt Vector Locations |

|----------------------------------------|------------------------------------|

| 5-2<br>6-1                             | Symbol Definitions (3 Sheets)      |

| 6-2                                    | Assembler Coding Symbols           |

Table

## CHAPTER 1

#### GENERAL DESCRIPTION

#### **1.1 INTRODUCTION**

Chapter 1 provides a general description of the Gould CONCEPT 32/67 Central Processing Unit (CPU) and the Internal Processing Unit (IPU).

#### **1.2 SYSTEM OVERVIEW**

### 1.2.1 General Information

The 32/67 is a high performance computer, designed with high speed transistor to transistor logic (TTL) and large machine architecture. The combination of CPU with IPU permits a higher system throughput as two programs may be run simultaneously.

The CPU and IPU have equal computational abilities but the CPU retains control of the I/O and interrupt operations. Should the CPU fail the IPU may be converted to a CPU and operation may be re-initialized.

The CPU is provided with a combination of hardwired and microprogrammed control. The microprogram resides in a programmable read only memory (PROM) bank, known as the control read only memory (CROM), from where the required microwords are accessed and sent to the CPU's control structure. The PROM cannot be dynamically changed or modified.

Alternatively the microprogram may reside in the alterable control store (ACS) or the writable control store (WCS). The primary function of the ACS is to provide a mechanism to dynamically modify or "patch" CPU microcode under software control. This obviates the necessity to field replace the PROM. The primary function of the WCS is to provide an add-on control store for the scientific accelerator (SA) option or custom microcode implementation.

Another option available with the 32/67 CPU and IPU is the floating point accelerator (FPA) which substantially improves the performance times for single and double precision floating point instructions. The FPA also enhances the performance of the fixed multiply instructions.

Processors 1 and 2 are identified by the presence or absence of a jumper on the cache SelBUS (CS) board. The absence of the jumper identifies Processor #1. The presence of the jumper identifies Processor #2. Each processor may function as a CPU or IPU selected at the turnkey panel. Processor #1 does not poll for the SelBUS (pseudo priority 23). Processor #2 uses SelBUS priority 22. The 32/67 CPU has a 150 nanosecond machine cycle time which is further enhanced by hardware logic that permits multiple CPU functions to be performed in one machine cycle. The precise instruction times are dependent upon the nature of the operation and the characteristics of the data involved. Typical instruction execution times are provided in Appendix B.

### 1.2.2 32/67 Characteristics

The 32/67 system includes the following characteristics:

- CPU with high speed TTL logic

- 8KW Cache memory

- 256KW Main Memory (minimum)

- Hardware memory management

- Instruction and operand prefetch

- Base register support

- Overlapped instruction prefetch, decode, vector, execution and operand put away

- Interface with standard 32 SERIES SelBUS

- Compatible with Class F I/O devices

The 32/67 system may include the following characteristics:

- IPU with high speed TTL

- Concurrent CPU/IPU operations

- 4MW Main Memory (maximum)

- High speed floating point accelerator

- Interleaved storage facilities

#### NOTES

- 1. Gould S.E.L. software does not support all the standard Class E I/O devices on the 32/67 computer systems. References to Class E operation in this document are for informational purposes only.

- 2. Gould S.E.L. software manuals refer to a Class D I/O device. This nomenclature is for software referencing only since Class D is in reality Class E protocol with an IOCD format for all hardware/firmware uses. These are the only Class E I/O devices that are supported by Gould S.E.L. software.

#### 1.3 32/67 CENTRAL PROCESSING UNIT (CPU)

#### 1.3.1 Operating Mode

The 32/67 CPU operates under control of the program status doubleword (PSD) and is capable of either privileged or unprivileged operation. During privileged operation, the CPU is permitted to perform control functions and input/output (I/O) instructions. Unprivileged operation is the normal user execution mode.

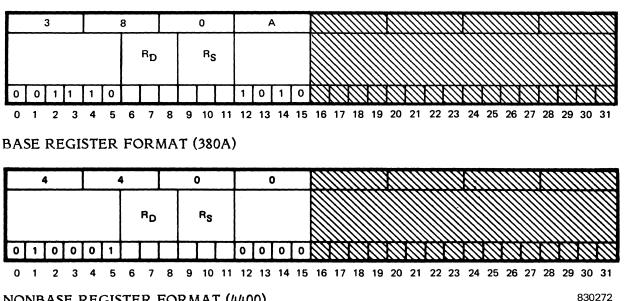

## 1.3.2 Nonbase And Base Register Modes

The 32/67 CPU hardware supports two instruction sets: one for nonbase register mode and one for base register mode. The mode is controlled by bit 6 in the PSD (0 = nonbase register mode, 1 = base register mode). Nonbase register mode is used to maintain software compatibility with previous Gould CONCEPT 32 SERIES computer systems. It is more restrictive than base register mode because software programs are limited to the first 128K words of logical address space. In base register mode, software programs can occupy the entire logical address space (4M words). The 32/67 CPU is provided with a set of eight high speed base registers. These registers are used in base register mode instructions to calculate the logical address.

## 1.3.3 General Purpose Register

The 32/67 CPU is provided with a set of eight high speed general purpose registers (GPR). These registers are used in most instructions, such as arithmetic, logical, and shift operations. Register R0 is also used as a link register between software subroutines; Register R4 is used as the mask register. In the nonbase register mode, registers R1 through R3 may be used as index registers. In the base register mode, registers R1 through R7 may be used as index registers.

## 1.3.4 Memory Management and Address Generation

The memory management of the 32/67 CPU permits full utilization of all available memory. This feature includes hardware memory allocation and protection (MAP). The memory management scheme of the CPU comprises the following:

- 2K word MAP block

- 512 word write protect granularity

- 2048 entry hardware MAP

- 4M word (16M byte) maximum logical address space

- 4M word (16M byte) maximum physical space

There are two memory addressing environments: mapped and unmapped. Under each, there are two options (when in nonbase register mode): extended and nonextended. The user controls the selection of the options under each environment, and it is these options which determine the rules for logical address generation.

## 1.3.5 Interrupts

Interrupts are the means by which real-time events, external to the CPU, are reported to software. Interrupts are events that are prioritized, scheduled and, in some cases deferrable.

## 1.3.6 Traps

Traps are exceptional conditions that are identified and reported to software by the CPU or IPU. All traps have the same priority, with the exception of the power fail trap. This trap overrides all other traps. Additionally, all traps are non-deferrable.

### 1.3.7 Input/Output (I/O) Operations

I/O operations consist of transferring data in blocks of bytes, halfwords, or words between peripheral devices and main memory. Once initiated, such transfers occur automatically, which leaves the CPU free for other tasks.

#### 1.4 32/67 INTERNAL PROCESSING UNIT (IPU)

#### 1.4.1 Operating Mode

The 32/67 IPU is functionally identical to the CPU. The CPU or IPU can be selected as the system CPU through turnkey panel switch selection. The IPU has the same capabilities as the CPU with the following exceptions:

- The IPU traps all class 3, E and F instructions

- The IPU traps all BEI instructions

The IPU is an option for the 32/6750 computer system. The IPU is a part of the 32/6780 computer system. The 32/6705 is a CPU only computer system.

Because the IPU is identical to the CPU, all information contained in this reference manual pertains to both the CPU and the IPU except where specifically noted.

## CHAPTER 2

#### CENTRAL PROCESSOR

#### 2.1 INTRODUCTION

This chapter includes basic information concerning the Gould CONCEPT 32/67 Central Processing Unit (CPU) control modes, followed by a discussion of the instruction repertoire, the memory reference instruction format, and addressing modes. Brief descriptions of the program status doubleword (PSD), condition codes, and privileged/unprivileged operation are given. The instruction repertoire portion includes an accounting of the instruction set with a discussion of memory word boundaries. The memory reference instruction is compared for base register mode and nonbase register mode, followed by the direct, indirect, and indexed addressing techniques.

#### 2.2 CPU CONTROL MODES

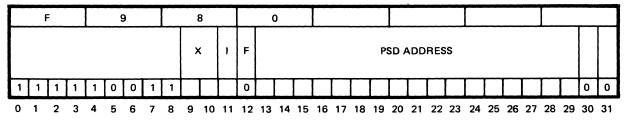

#### 2.2.1 Program Status Doubleword

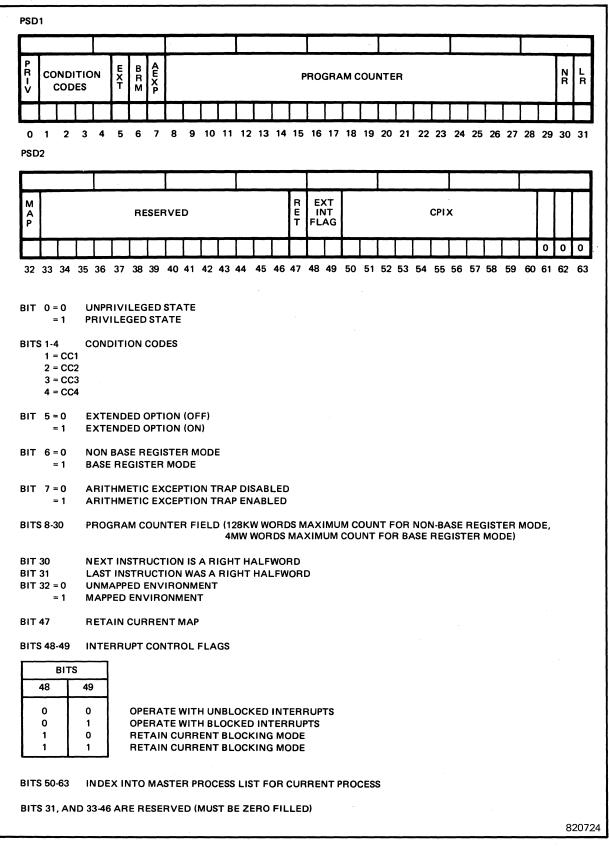

The CPU operates under the control of the program status doubleword (PSD). The PSD records machine conditions that must be preserved prior to the context switching. The format of the PSD is shown in Figure 2-1.

#### 2.2.2 Condition Codes

The four condition code bits in the PSD (bits 1 through 4) are set upon execution of most instructions. For arithmetic operations, the condition codes are set as follows:

- CC1 is set if an arithmetic exception occurs.

- CC2 is set if the result is greater than zero.

- CC3 is set if the result is less than zero.

- CC4 is set if the result is equal to zero.

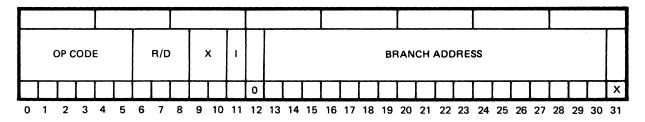

The branch condition true (BCT), branch condition false (BCF), and the branch function true (BFT) instructions allow testing and branching on the condition codes.

#### 2.2.3 Privileged/Unprivileged Operations

The CPU is capable of either privileged or unprivileged operation. During privileged operation, the CPU is permitted to perform control functions and input/output (I/O) instructions. Unprivileged operation is the normal user execution mode. In this mode, memory protection is in effect and all privileged operations are prohibited.

Bit 0 in the PSD is the privileged state bit. If the privileged state bit is set, privileged instructions can be executed and a privileged user may write to protected memory. If the privileged state bit is reset, any attempt to execute a privileged instruction will cause a privileged violation trap. The following instructions are privileged:

- 1. All interrupt related instructions such as enable interrupt or request interrupt.

- 2. All instructions that can modify the memory mapping registers.

- 3. All input/output instructions.

- 4. All instructions that can place the machine in a state that requires operator intervention to continue processing, such as HALT, or change the machine operating environment.

Certain events can change the CPU from the unprivileged to the privileged state by loading a new program status doubleword. These events are as follows:

- 1. An interrupt from an external event or the I/O system.

- 2. A hardware trap caused by addressing nonpresent memory, executing an undefined instruction, executing a privileged instruction by a nonprivileged program, or writing to protected memory.

- 3. A hardware trap caused by a nonrecoverable condition such as an uncorrectable error on a memory read, or an arithmetic exception.

- 4. The execution of the supervisor call instruction by a user requesting monitor services.

- 5. System reset sets the privileged state bit.

The execution of either a load program status doubleword (LPSD) or a load program status doubleword and change MAP (LPSDCM) instruction can cause the system to change from the privileged to the unprivileged state.

## **2.3 INSTRUCTION REPERTOIRE AND FORMATS**

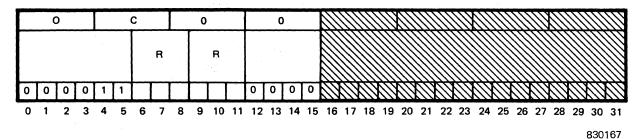

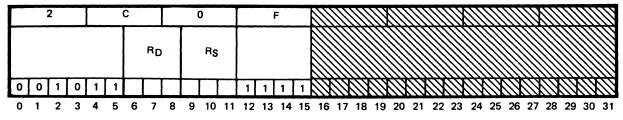

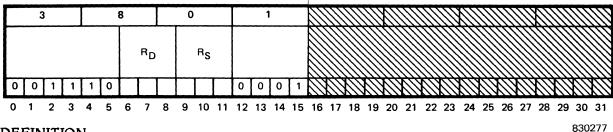

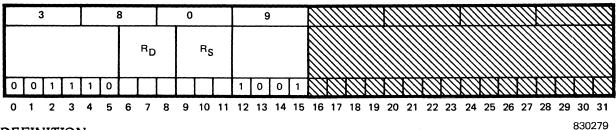

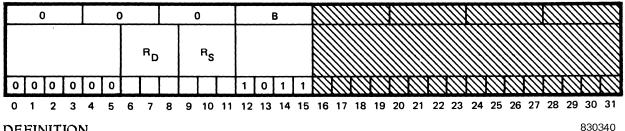

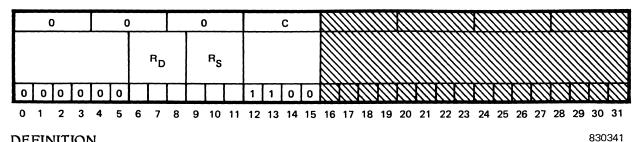

The functional classifications and corresponding number of instructions for the 32/67 CPU are as follows:

| Classification            | Number of Instructions |

|---------------------------|------------------------|

| Fixed-point arithmetic    | 30                     |

| Floating-point arithmetic | 16                     |

| Boolean (logical)         | 17                     |

| Load/store                | 37                     |

| Bit manipulation          | 8                      |

| Shift                     | 13                     |

| Interrupt                 | 7                      |

| Compare                   | 11                     |

| Branch                    | 10                     |

| Register transfer         | 15                     |

| Input/output              | 2                      |

| Control                   | 20                     |

| Memory management         | 4                      |

| Floating-point conversion | 4                      |

| Class F I/O               | 13                     |

| Writable control storage  | 3                      |

| Total                     | 210                    |

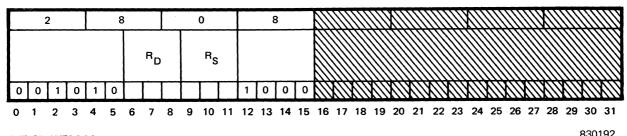

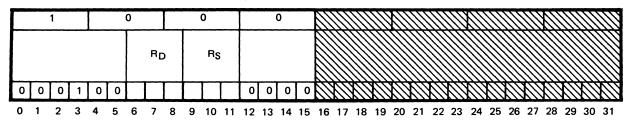

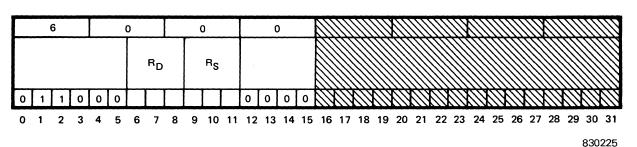

The instructions are classified as either word instructions (32 bits) or halfword instructions (16 bits). The word instructions primarily refer to memory operands; the halfword instructions primarily deal with register operands. Program memory can be conserved by packing two consecutive halfword instructions into one memory location (word).

The instruction lookahead technique allows for fast instruction execution. Instruction fetches are made concurrently with instruction execution and the decoding of a previously fetched instruction.

Of particular significance are the bit manipulation instructions because they provide the capability to selectively set, zero, add, or test any bit in memory or in a register.

## 2.4 MEMORY BOUNDARIES

#### 2.4.1 Instructions

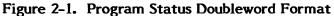

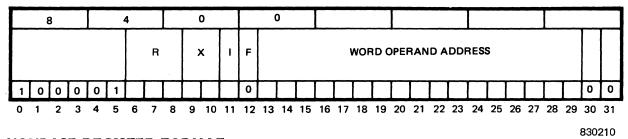

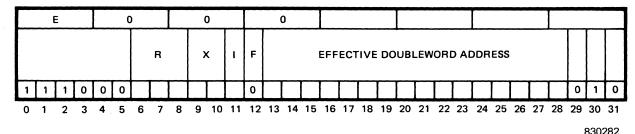

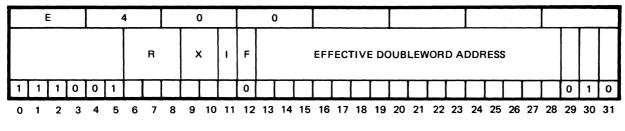

Each fullword instruction (32 bits) must be stored in memory on a word boundary (address with bits 30 and 31 equal to zero). Memory information boundaries are illustrated in Figure 2-2.

Halfword instructions may be stored two per word. However, when a halfword is followed by a word instruction, the assembler positions the halfword instruction in the left half of the word and stores a no operation (NOP) instruction in the right half of the word. This maintains the word boundary discipline.

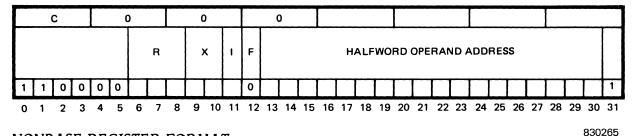

Memory reference instructions which address a byte in memory do not alter the other three bytes in the memory word containing the specified byte. Memory instructions which address a halfword do not alter the other halfword of the memory location. The exception to the preceding is the add bit in memory instruction. This is actually a 32-bit add; therefore, it may propagate a carry as far as the most-significant bit of the word containing the specified bit.

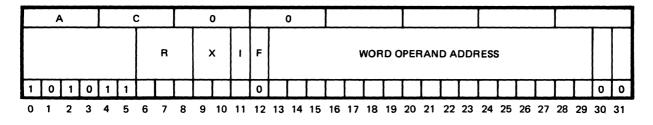

#### 2.4.2 Operands

Word operands must be stored in memory on a word boundary. The most significant word of a doubleword operand must be stored in a memory location having an even word address with the least significant word stored in the next sequentially higher (i.e., odd word) location. Some examples of memory addressing follow:

| Byte           | Halfword | Word  | Doubleword |

|----------------|----------|-------|------------|

| 00000          | 00000    | 00000 | 00000      |

| 00001<br>00002 | 00002    |       |            |

| 00002          | 00002    |       |            |

| 00004          | 00004    | 00004 |            |

| 00005          |          |       |            |

| 00006          | 00006    |       |            |

| 00007          |          |       |            |

| 00008          | 00008    | 00008 | 00008      |

| 00009          |          |       |            |

| 0000A          | 0000A    |       |            |

| 0000B          |          |       |            |

| 0000C          | 0000C    | 0000C |            |

| 0000D          |          |       |            |

| 0000E          | 0000E    |       |            |

| 0000F          |          |       |            |

| 00010          | 00010    | 00010 | 00010      |

|                |          |       |            |

Gould CONCEPT 32/67 Reference Manual

Figure 2-2. Information Boundaries in Memory

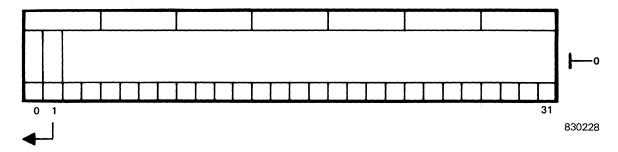

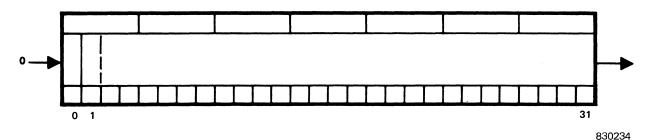

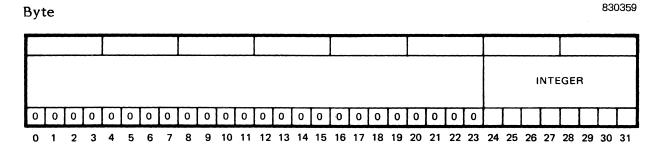

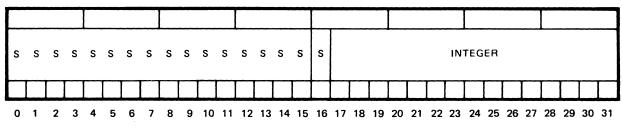

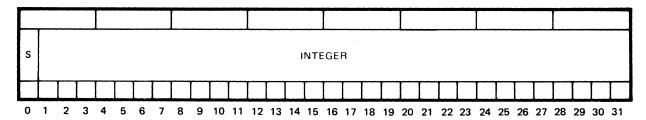

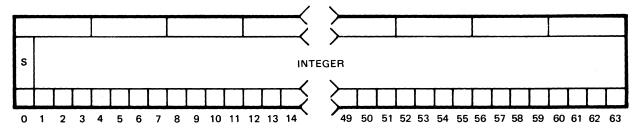

Byte, halfword, or word operands are always right justified when handled in the 32/67 32bit data structure. Doublewords are processed as two single words (LSW processed first then MSW) with carry and zero detect transmission between LSW and MSW if applicable.

#### 2.4.3 Instruction Formats

The 32/67 CPU supports two instruction sets: one when utilizing the base register mode, and the other when operating with the nonbase register mode. The mode is controlled by bit 6 in the PSD (0= nonbase register mode, 1= base register mode).

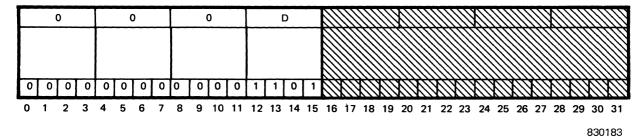

#### 2.4.4 Program Counter

The program counter contains the logical address of the instruction about to be executed. The PC field occupies bits 8 through 30 of the PSD (see Figure 2-1). In the base register mode, the maximum PC value is 16M bytes and in the nonbase register mode, the maximum PC value allowed is 512 K bytes.

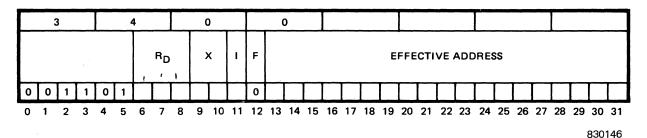

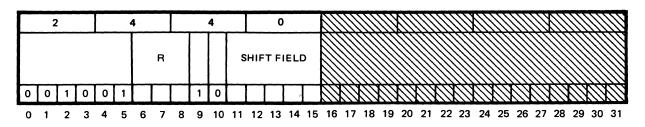

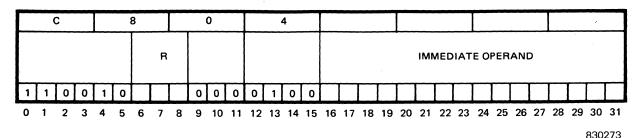

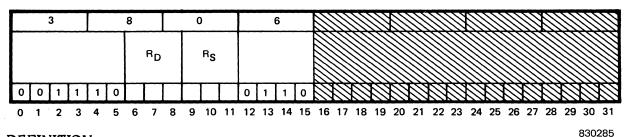

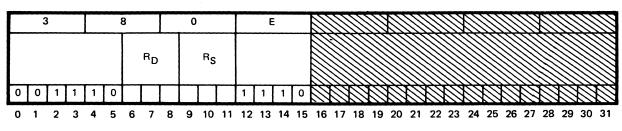

#### 2.5 MEMORY REFERENCE INSTRUCTIONS

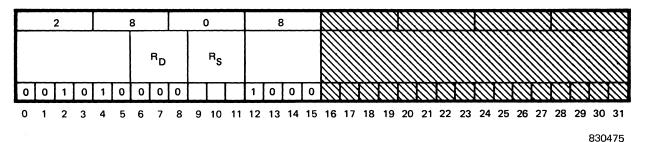

With the implementation of the base register mode, the application of memory reference instructions requires two distinct formats. The operation code (bits 0 through 5) in both formats is identical for recognition of each separate instruction. Also, bits 6 through 8 identify the GPR to be used as an operand source or destination.

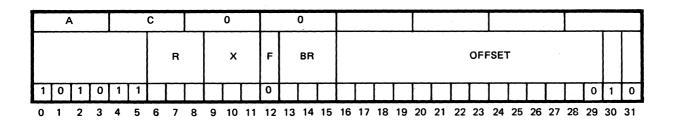

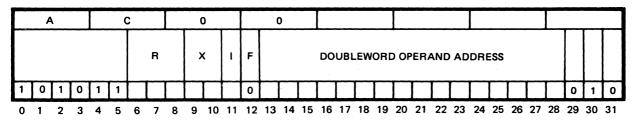

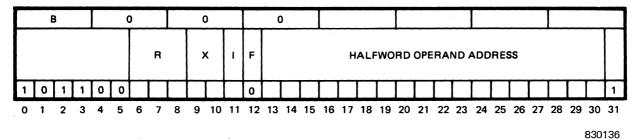

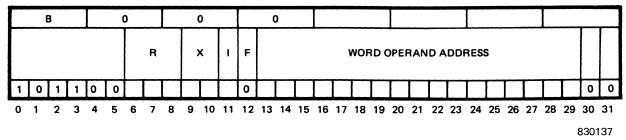

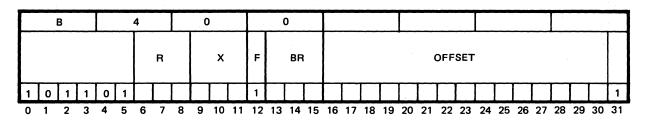

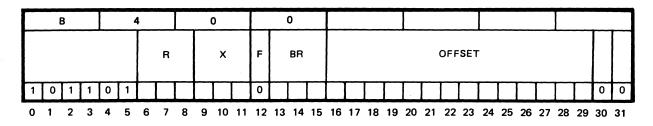

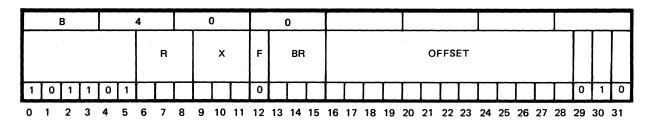

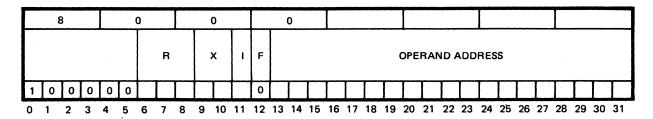

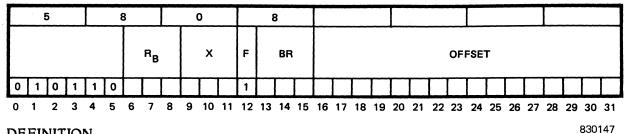

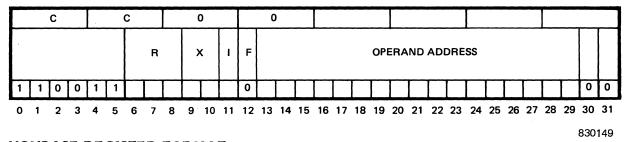

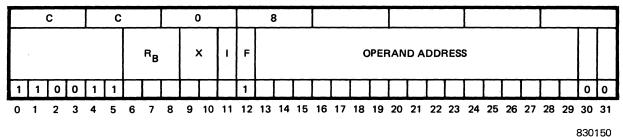

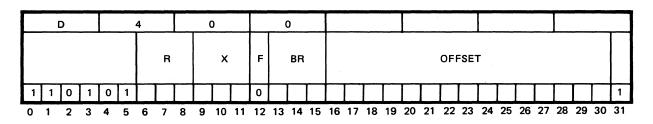

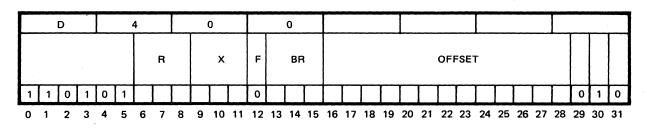

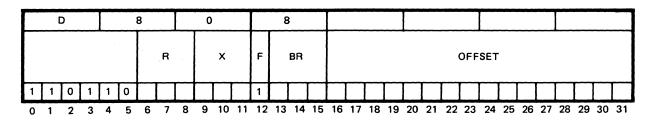

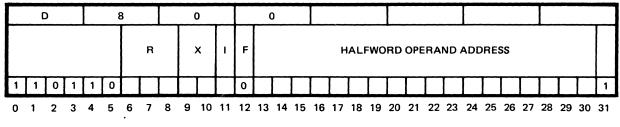

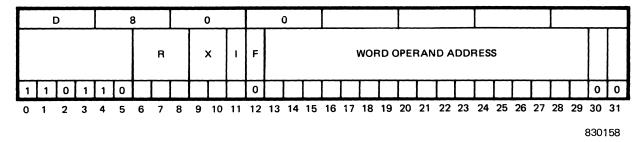

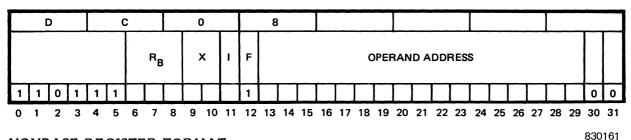

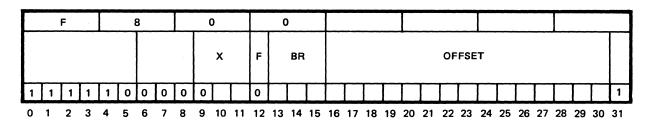

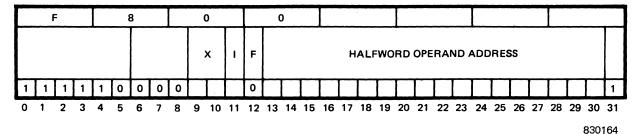

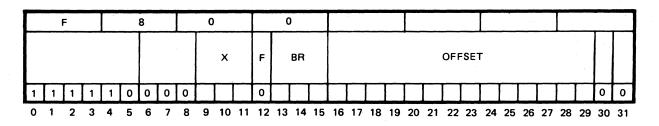

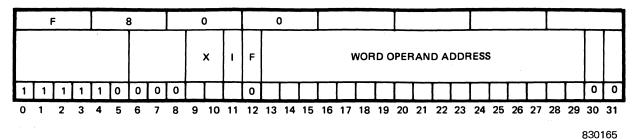

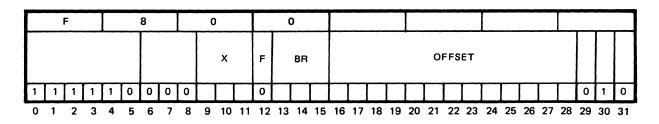

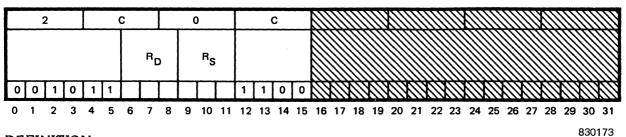

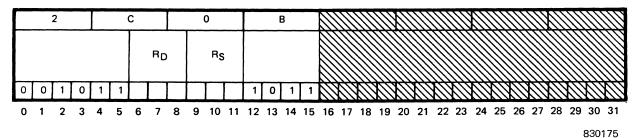

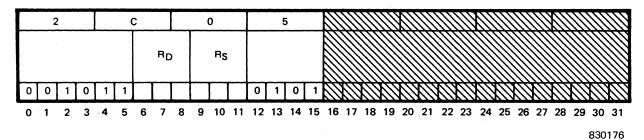

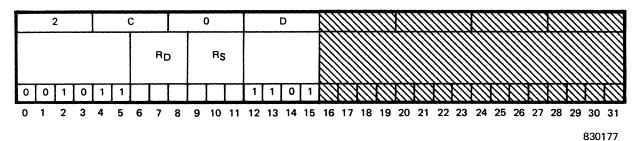

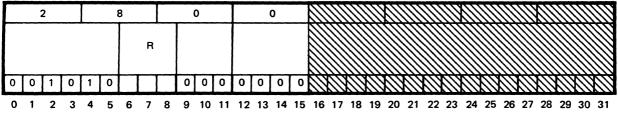

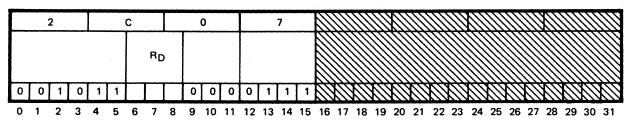

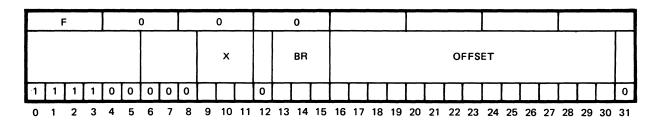

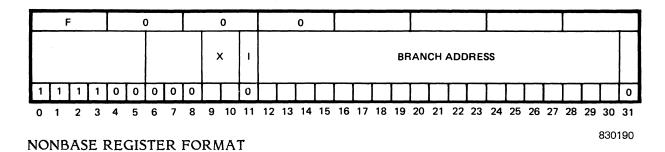

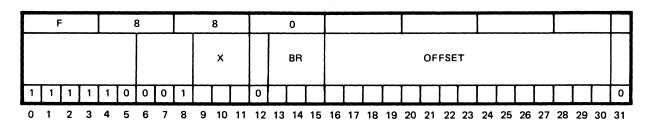

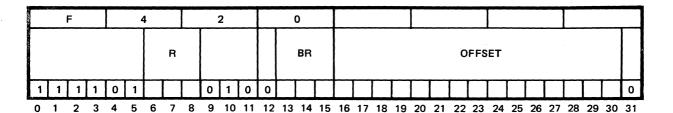

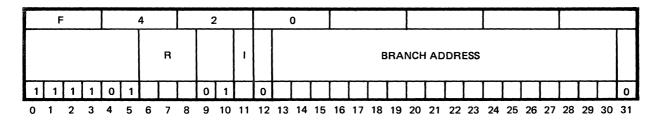

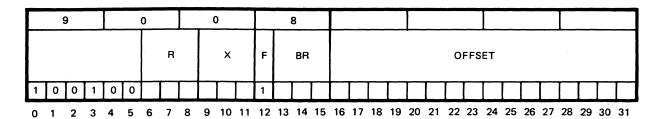

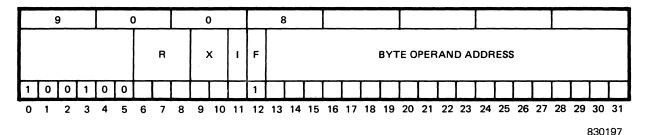

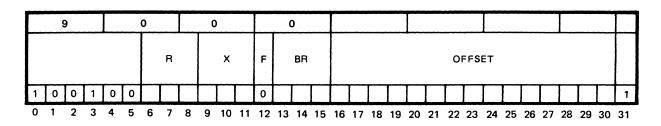

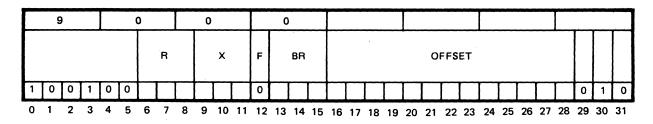

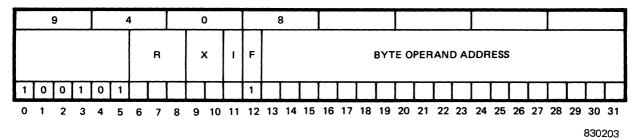

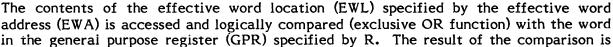

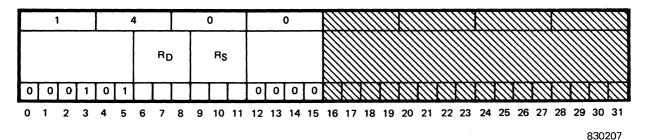

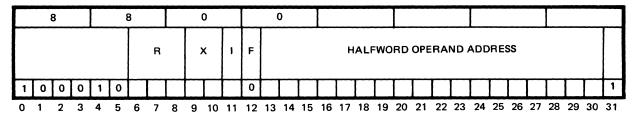

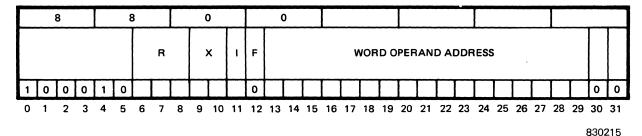

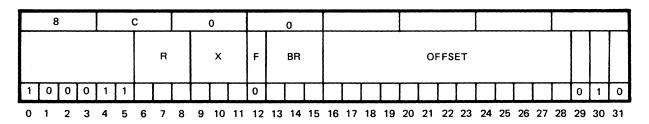

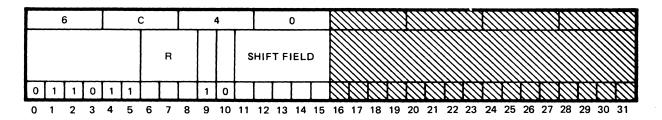

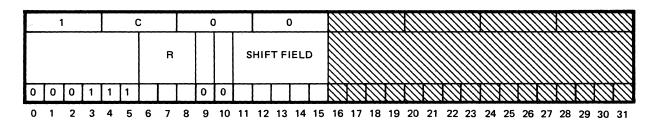

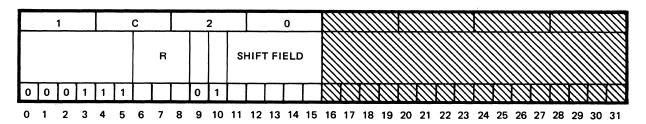

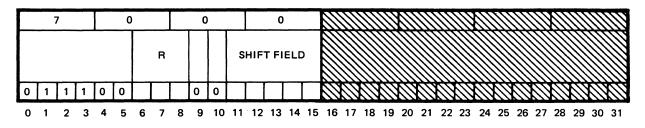

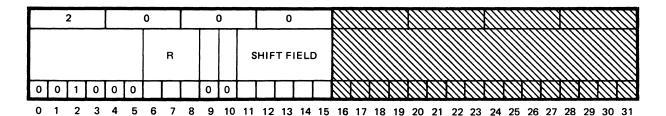

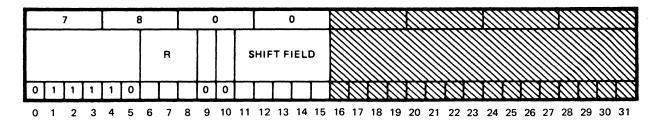

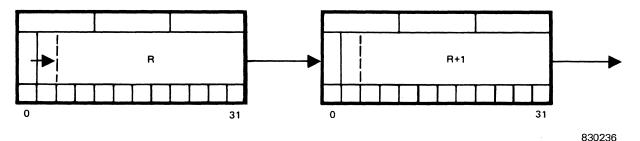

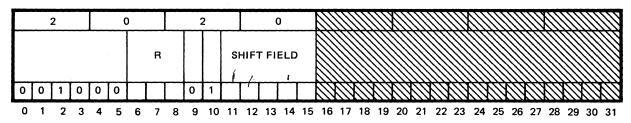

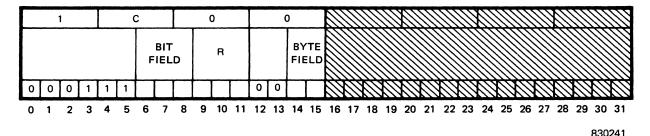

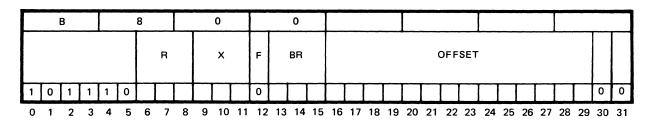

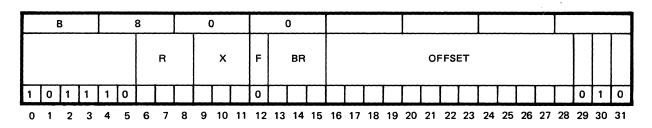

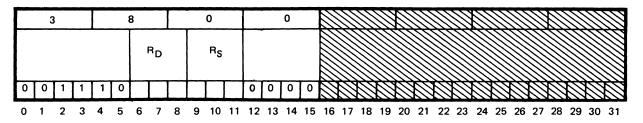

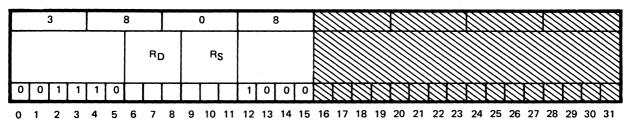

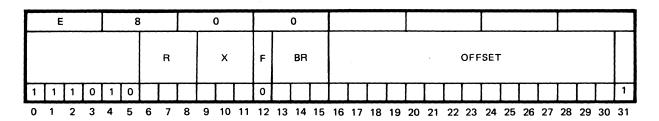

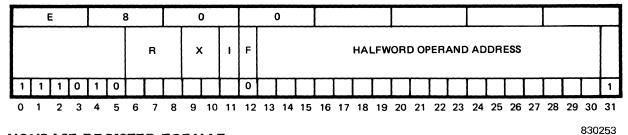

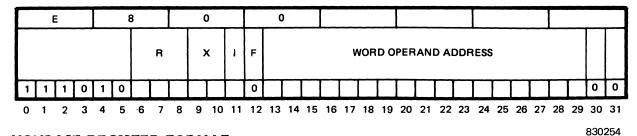

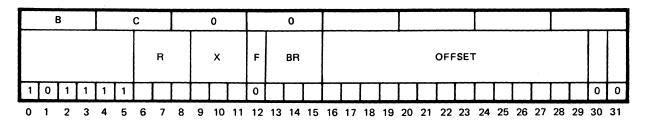

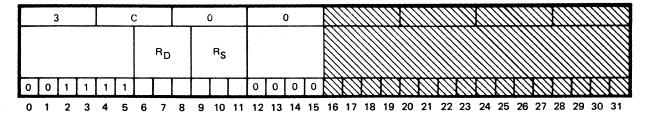

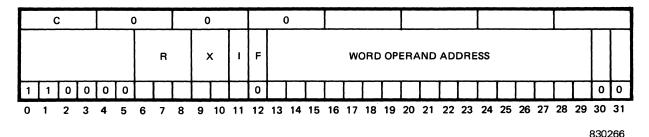

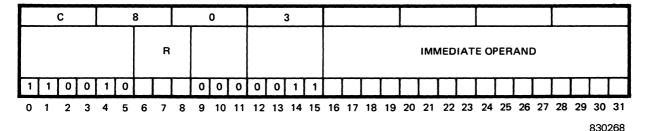

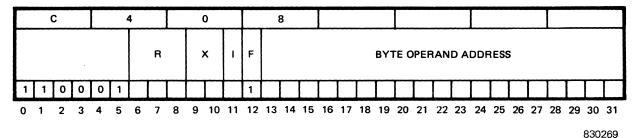

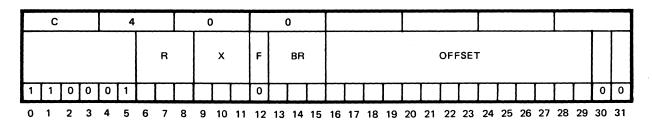

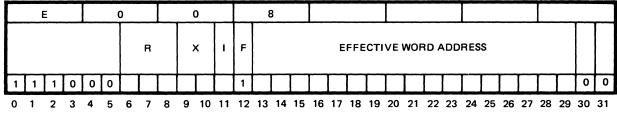

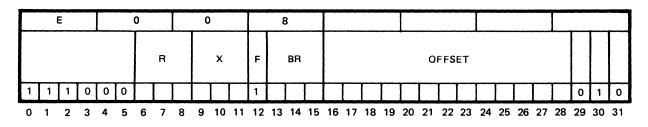

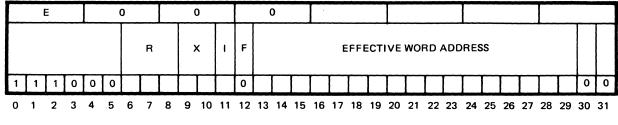

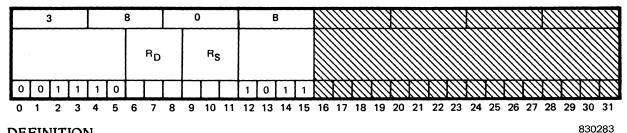

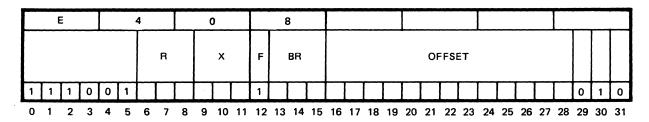

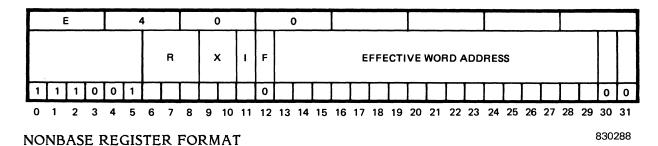

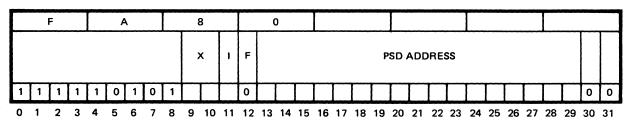

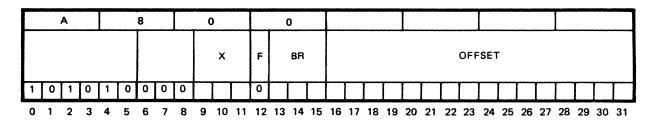

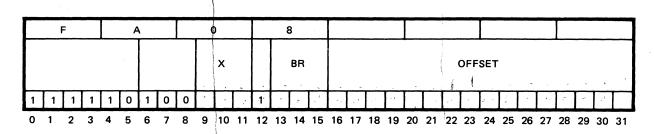

#### 2.5.1 Nonbase Register Mode

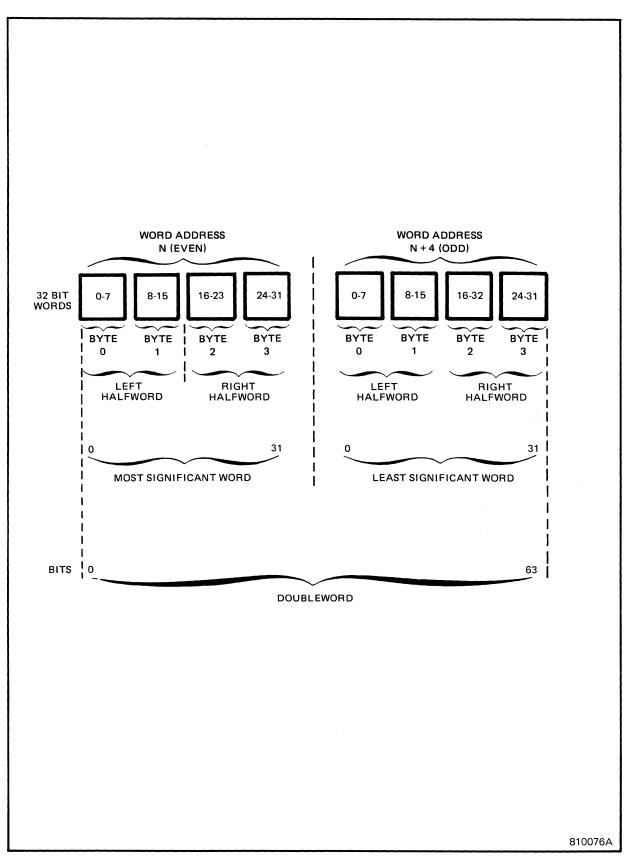

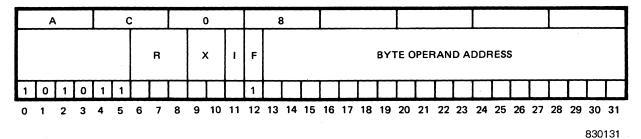

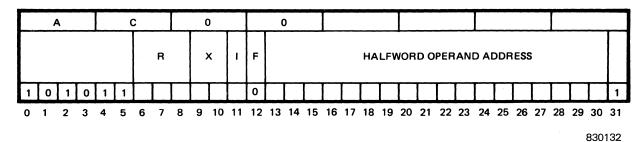

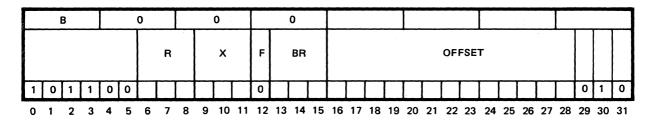

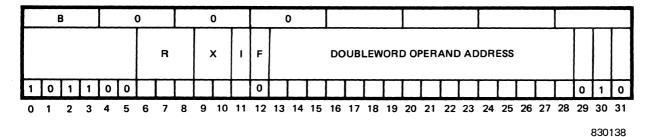

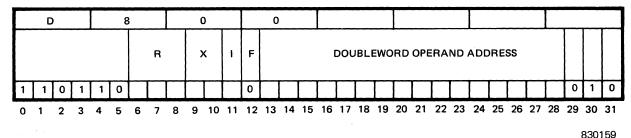

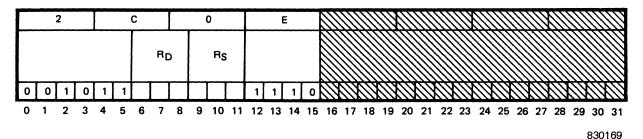

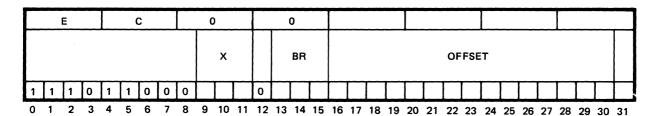

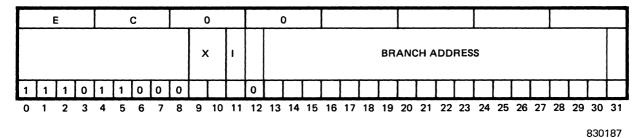

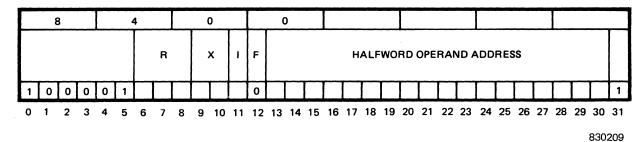

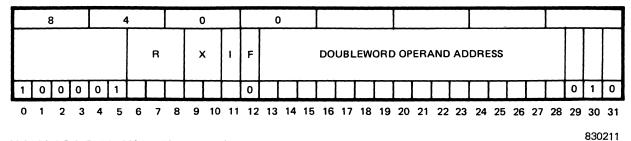

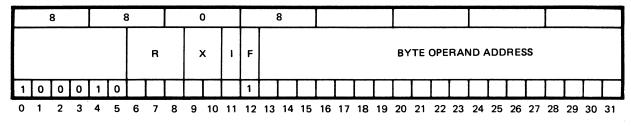

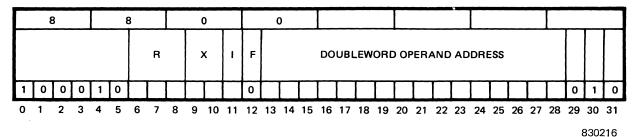

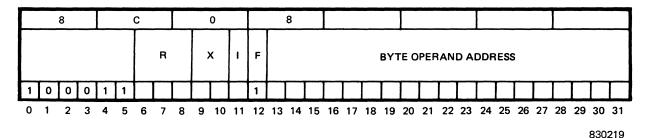

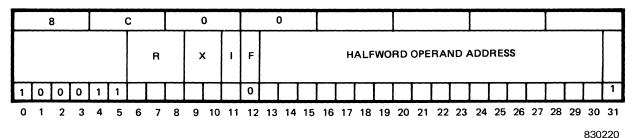

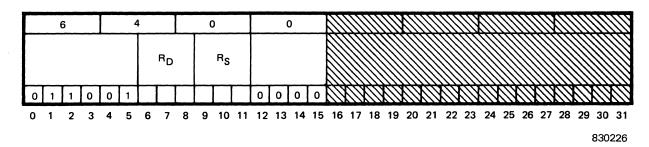

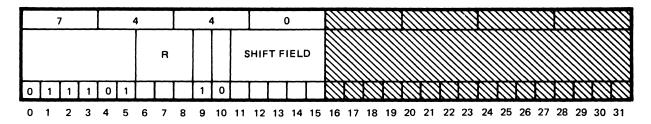

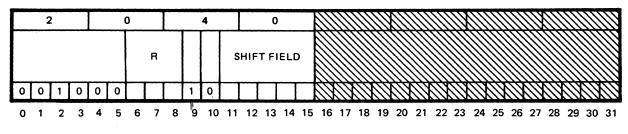

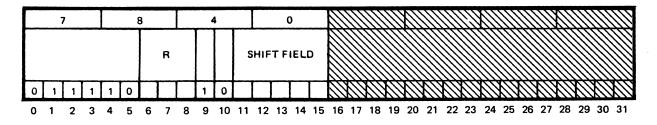

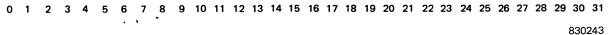

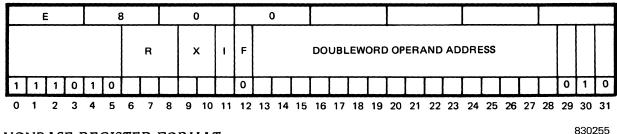

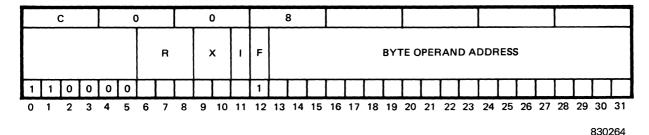

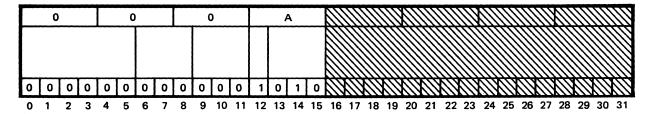

In the nonbase register mode, bits 9 and 10 specify the GPR to be used as an index register, bit 11 is the indirect bit, and bits 12-31 define the operand address and data type. The effective address of the operand depends on the values of I, X, and bits 12-31.

| OP CODE     | R >     | X I F   | OPERAND ADDRESS      |                            |          |  |  |  |  |  |  |

|-------------|---------|---------|----------------------|----------------------------|----------|--|--|--|--|--|--|

|             |         |         |                      |                            |          |  |  |  |  |  |  |

| 0 1 2 3 4 5 | 6 7 8 9 | 10 11 1 | 13 14 15 16 17 18 19 | 20 21 22 23 24 25 26 27 28 | 29 30 31 |  |  |  |  |  |  |

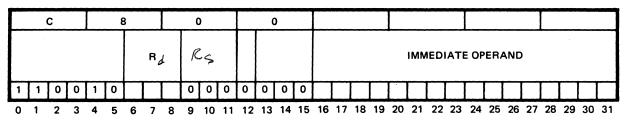

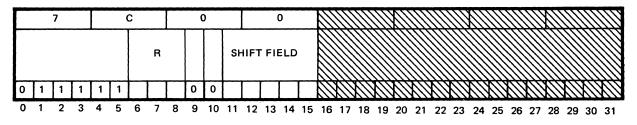

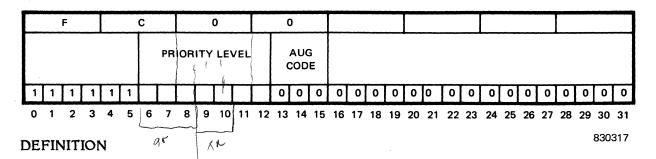

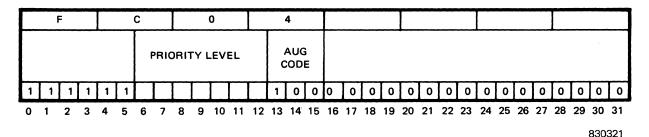

### 2.5.1.1 F AND C BITS

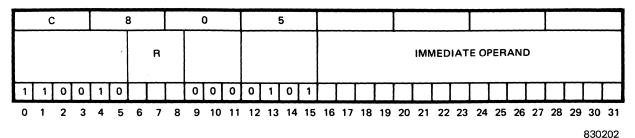

The format of the F and C bits is designed so that any selected data type (byte, halfword, word, or doubleword) can be conveniently specified by combinations of the F and C bits as follows:

| F | <u>C</u> | Data Type                   |  |

|---|----------|-----------------------------|--|

| 0 | 00       | 32-bit word                 |  |

| 0 | 01       | Left halfword (bits 0-15)   |  |

| 0 | 10       | 64-bit doubleword           |  |

| 0 | 11       | Right halfword (bits 16-31) |  |

| 1 | 00       | Byte 0 (bits 0-7)           |  |

| 1 | 01       | Byte 1 (bits 8-15)          |  |

| 1 | 10       | Byte 2 (bits 16-23)         |  |

| 1 | 11       | Byte 3 (bits 24-31)         |  |

|   |          |                             |  |

830555

### NOTE

For restrictions of the F and C bits refer to indirect addressing and address specification traps in chapters 2 and 4 respectively.

### 2.5.1.2 DIRECT ADDRESSING

When bits 9 and 10 (X field) are zero (no indexing), and bit 11 (I field) is zero (no indirect), the effective memory address is taken directly from bits 13 through 29 of the memory reference instruction.

For example, the store word instruction is coded: STW 0,0 and is assembled as hexadecimal D4000000. When executed, this instruction stores the contents of GPR0 directly into memory word location 0.

Likewise, the store byte instruction is coded: STB 0,1 and is assembled as hexadecimal D4080001. Note that the F and C fields of this instruction have been altered. When executed, this instruction stores the least significant byte of GPR0 directly into memory byte location 1.

### 2.5.1.3 INDEXED ADDRESSING

When bits 9 and 10 (X field) are nonzero, indexed addressing is in effect. Bits 13 through 31 of the instruction are used to produce a memory address by adding to these bits the contents of the GPR, bits 12 through 31, specified by the X field. Only GPRs 1, 2, and 3 function as index registers.

Any data type may be indexed in sequential fashion by adjusting the index value by the size of the data type. This can be done by adding the bit position that corresponds to the displacement value for the applicable data type to the index register. These are as follows:

| Data Type  | Bit Position | Displacement Value |

|------------|--------------|--------------------|

| Byte       | 31           | 1                  |

| Halfword   | 30           | 2                  |

| Word       | 29           | 4                  |

| Doubleword | 28           | 8                  |

For indexed addressing, except for extended indexing, the displacement value is a twos complement integer within one of the GPRs used for indexing. For word indexing, bit 29 of the index register is the least significant bit of the address. If bit 29 of GPR3 is set to one to provide a displacement of one word, the indexed store word instruction is coded as: STW 0, 0, 3. This now stores the contents of GPR0 in the memory location indexed by the contents of GPR3. The instruction would assemble as D4600000. The calculated logical effective word operand address (after indexing) is 00004. Therefore, the contents of GPR0 are stored in memory location 0004.

During indexing, only the C bits may change; the F bit is unaffected. If the original mode of addressing was the byte mode, indexing may only specify which particular byte is being addressed. If the mode was not originally a byte attribute, indexing can select a halfword, word, or doubleword attribute, depending on which C bits are set.

For example, the load word instruction for indexing is coded: LW 5, X'1000', 2. The contents of register 2 contain X'0000 2000'. The word from memory location 3000 will be loaded into register 5.

## 2.5.1.4 INDIRECT ADDRESSING

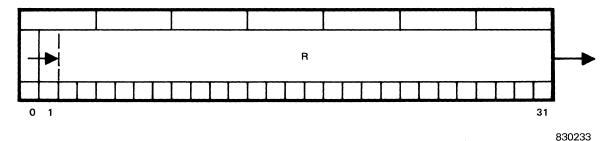

When bit 11 (I field) is one, addressing is indirect, and the CPU retrieves an indirect word specified by the operand address. In this indirect word, bits 9 and 10 select the index register, bit 11 is the indirect bit, and bits 12 through 31 specify an operand address.

For example, to use the indirect addressing capability, the store word instruction would be coded: STW 0,\*0. This causes bit 11, the indirect bit, to be set to one. When this instruction is executed, it stores the contents of GPR0 into the location specified by the address found in memory location 0.

Multilevel indirect addressing can be performed when each new address taken from memory has the indirect bit set to one. The process of fetching indirect addresses continues until a memory address has bit 11 set to zero. This address is the logical effective operand address.

An indirect fetch is always a word fetch, and an indirect word can specify a byte, halfword, or doubleword attribute. An indirect word can specify new F and C bits, or if the indirect word has F bit equal to 0 and C bits equal to 00, then the previous addressing attribute will be used. Indirect addressing is the only way to change the F and C bits.

For example, to use indirect addressing, the load word instruction is coded: LW 5,\*X'1000'. Memory location X'1000' contains X'0008 3000'; therefore, byte 0 from memory location 3000 is loaded, right justified and zero filled, into register 5.

### 2.5.1.5 INDIRECT AND INDEXED ADDRESSING

Indirect addressing can be combined with indexing at any indirect level. An example of indirect addressing with indexing follows.

| Location<br>Counter                                                          | Machine<br>Instruction                                                           | Byte<br>Address                      | Label                        | Operation                                                       | Operand                                                       |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------|------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------|

| P00000<br>P00000<br>P00004<br>P00008<br>P0000C<br>P00010<br>P00014<br>P00018 | C9800004<br>AC90000C<br>C8061055<br>00100010<br>00700014<br>00000000<br>0000001C | P0000C<br>P00010<br>P00014<br>P0001C | STRT<br>LOC1<br>LOC2<br>LOC3 | PROGRAM<br>REL<br>LI<br>LW<br>SVC<br>ACW<br>ACW<br>DATAW<br>ACW | R3,4<br>R1,*LOC1<br>1,X'55'<br>*LOC2<br>*LOC3,R3<br>0<br>LOC4 |

| P0001C<br>P00020                                                             | 0000FFFF                                                                         | P00000                               | LOC4                         | DATAW<br>END                                                    | X'0000FFFF'<br>STRT                                           |

Gould CONCEPT 32/67 Reference Manual The first executable instruction is the load immediate (LI) to load a value of 4 into GPR3. The next instruction to be executed is the load word (LW). The indirect bit of this instruction is set; therefore, the operand address in the LW points to an indirect word at location P0000C (LOC1). Since the indirect bit is set in the indirect word at LOC1, the indirect addressing chain is continued. The next indirect word at label LOC2 has the indirect bit set and also specifies GPR3 as the index register. So, the contents of the address word field of this indirect word are added to the contents of GPR3 to form the address of the third indirect word in the indirect bit in the indirect word at this location is not set, indicating that the contents of the indirect word is the effective address of the target operand. The effective address points to label LOC4. The contents at this location are loaded into GPR1. At this point in the execution of the instructions, GPR1 contains the hexadecimal value 0000FFFF.

The ACW statement is a macro assembler directive used to generate an address constant. The DATAW is also a macro assembler directive, and the SVC 1,X'55' is a call to the monitor exit service in MPX.

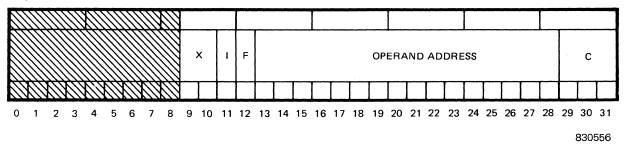

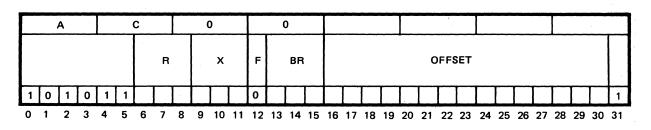

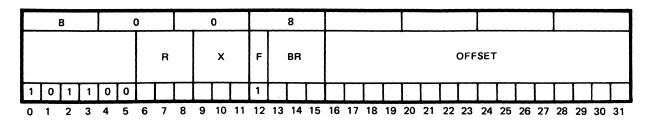

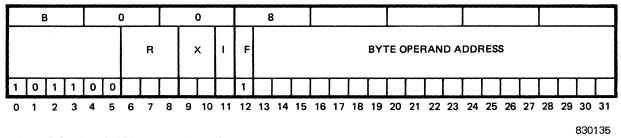

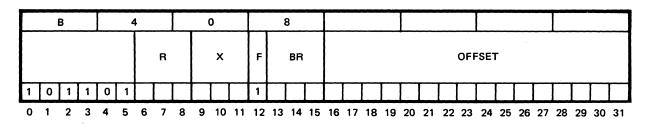

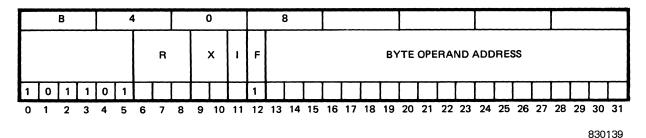

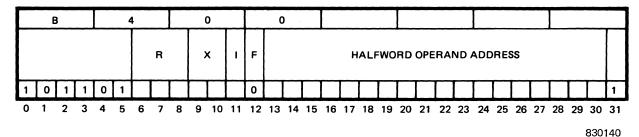

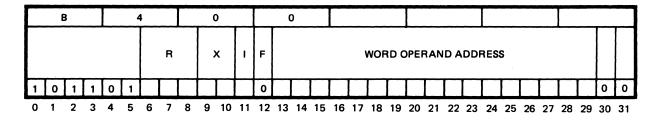

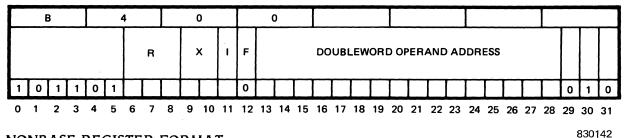

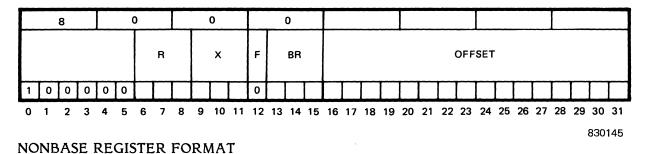

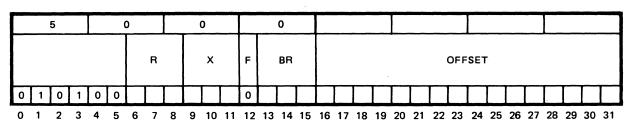

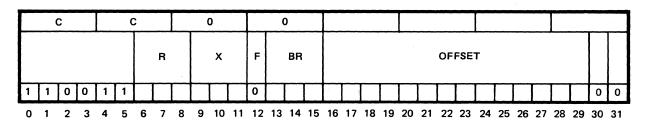

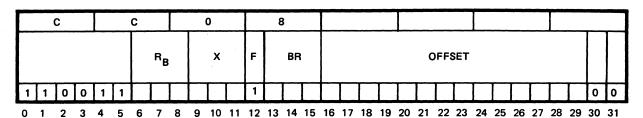

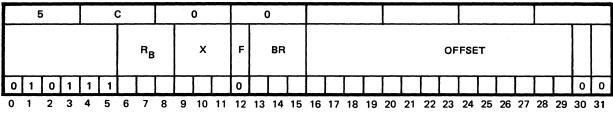

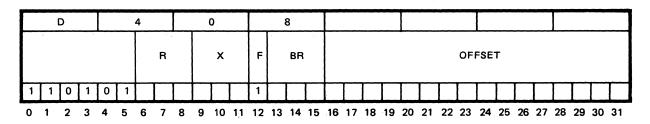

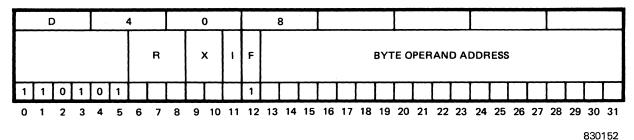

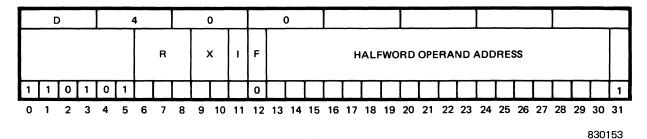

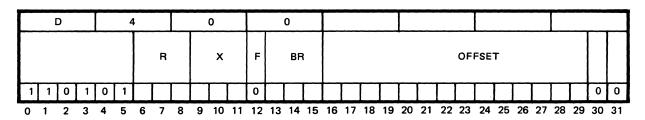

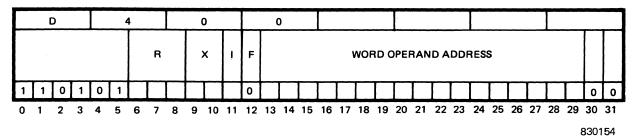

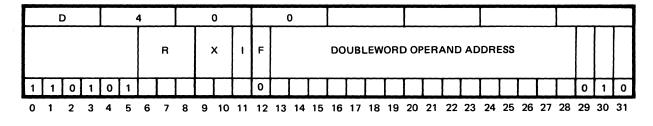

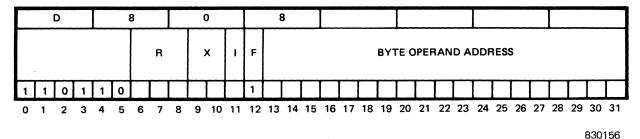

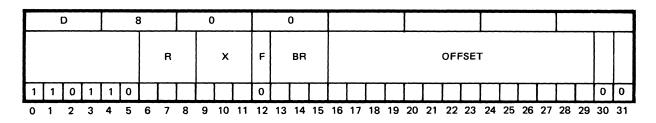

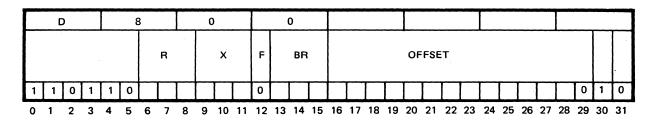

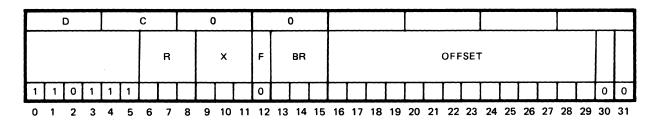

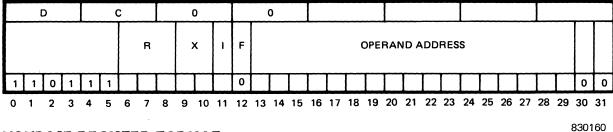

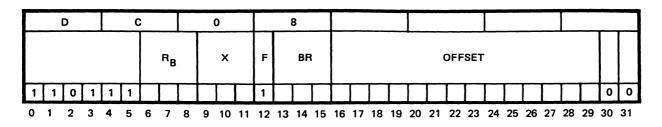

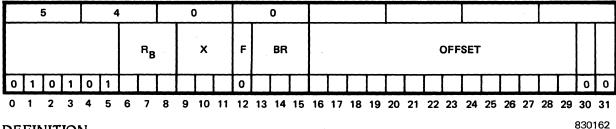

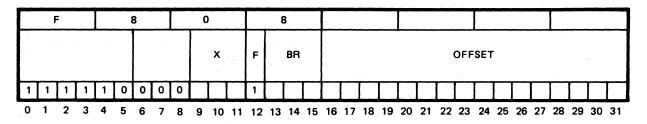

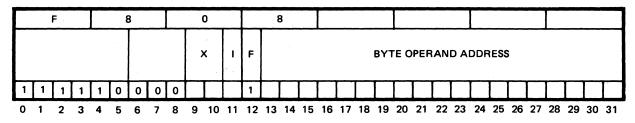

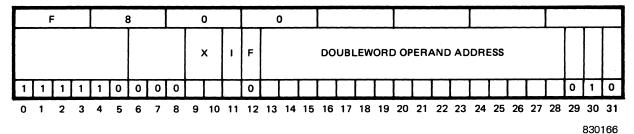

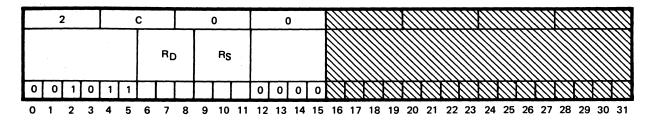

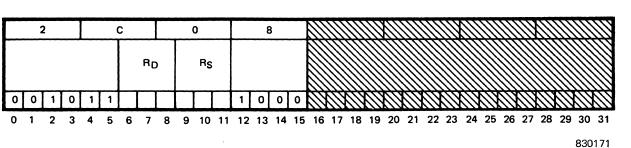

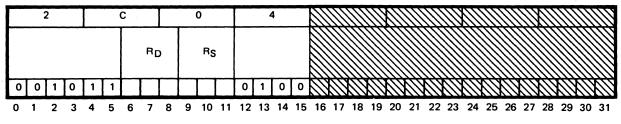

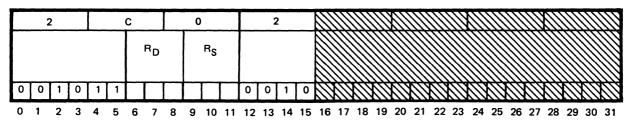

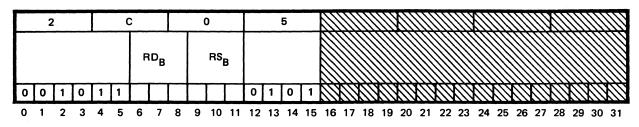

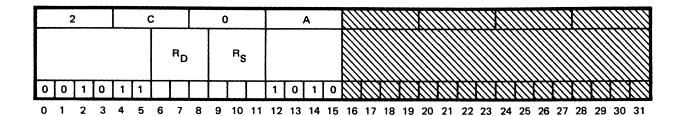

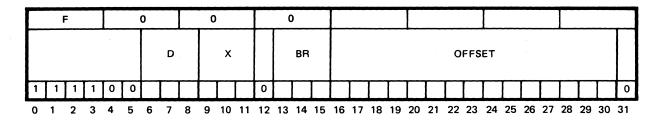

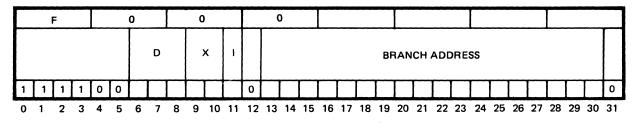

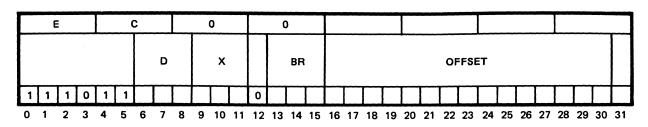

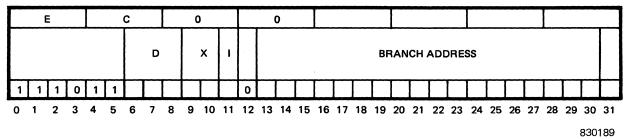

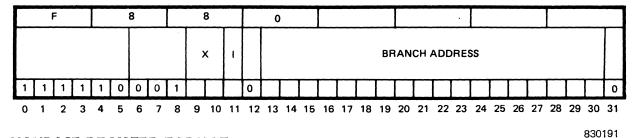

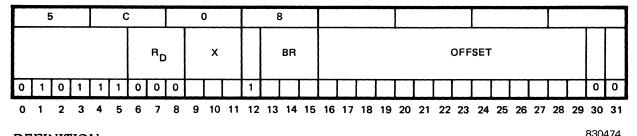

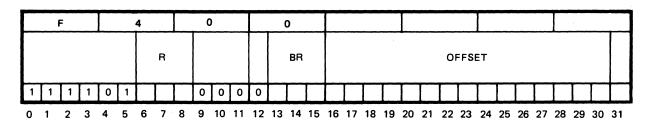

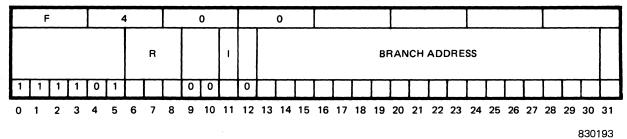

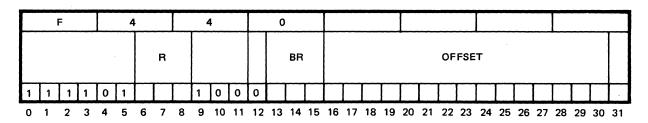

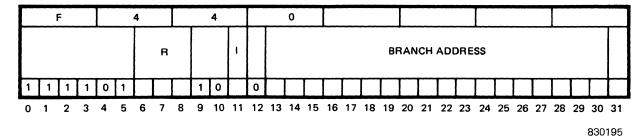

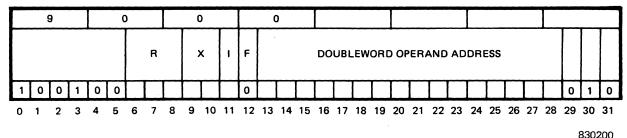

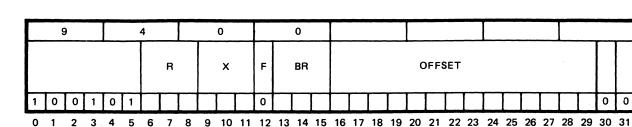

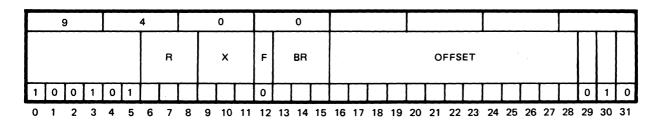

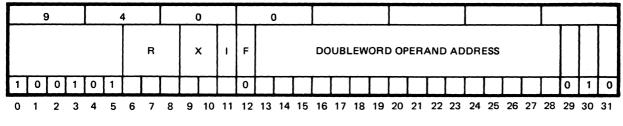

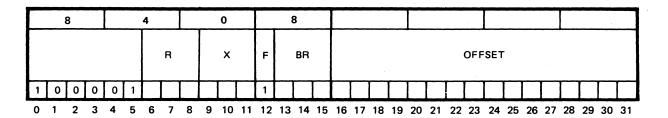

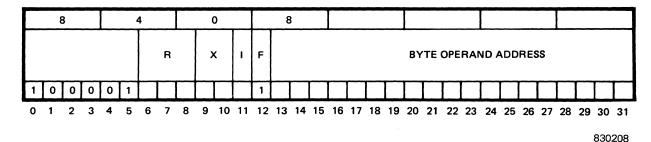

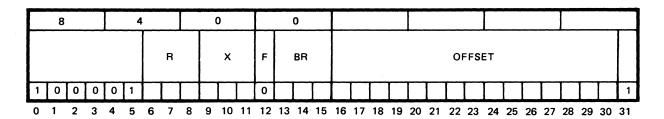

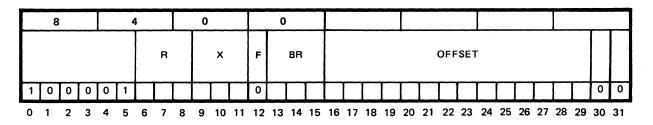

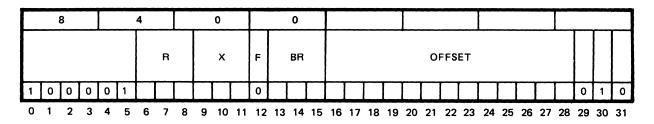

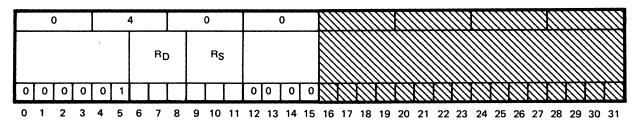

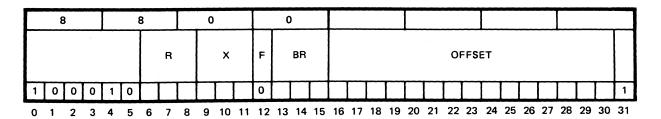

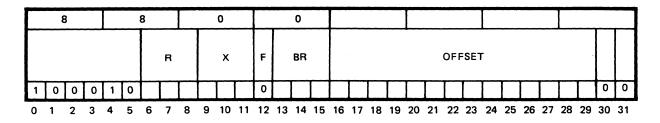

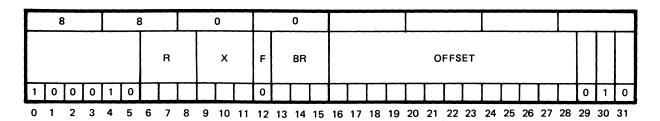

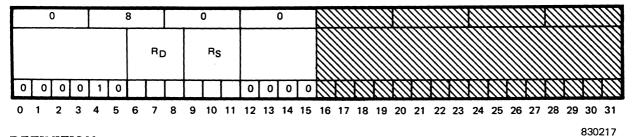

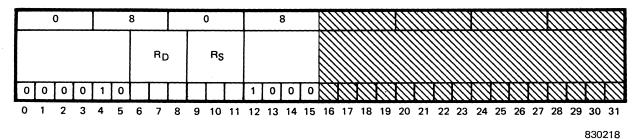

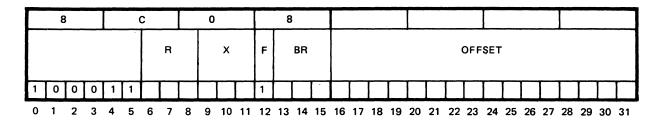

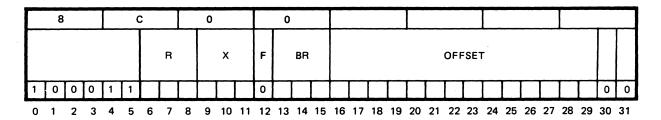

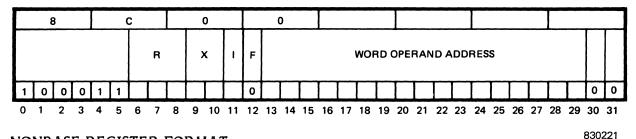

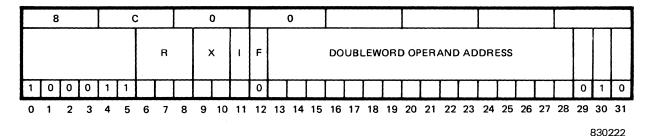

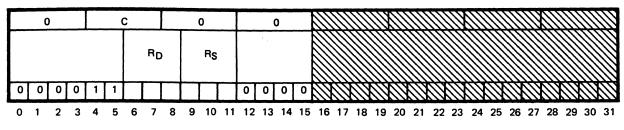

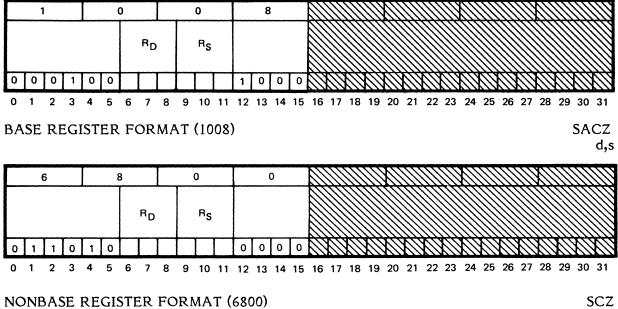

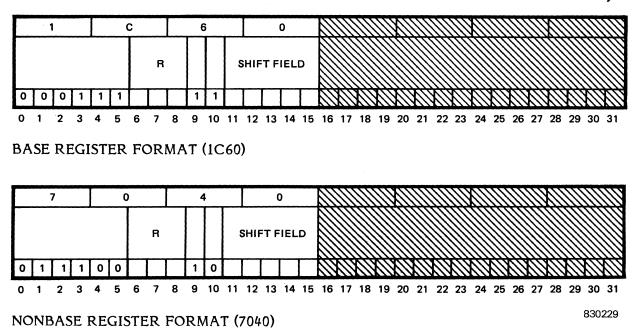

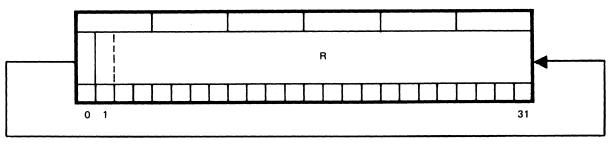

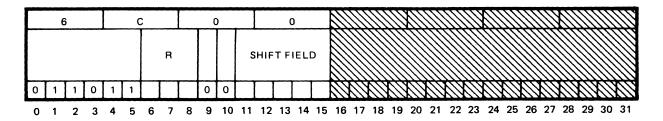

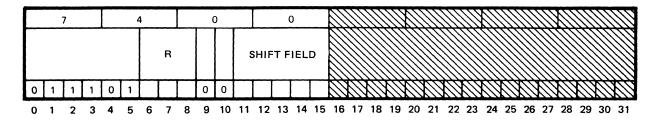

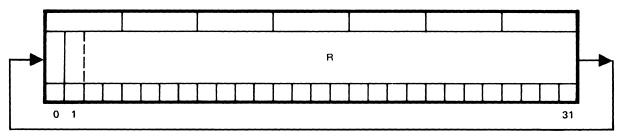

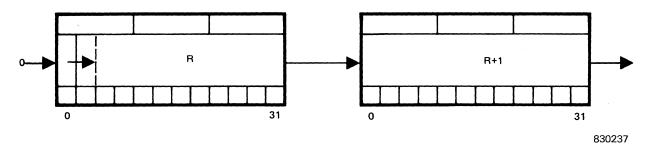

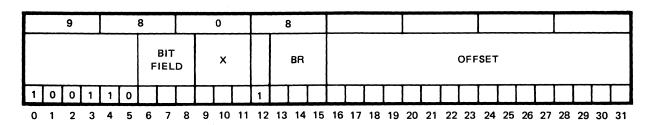

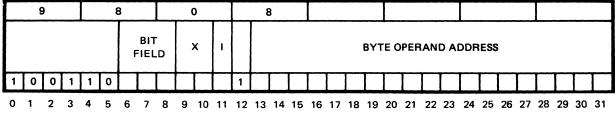

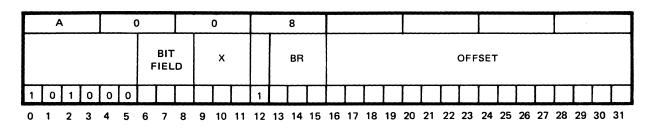

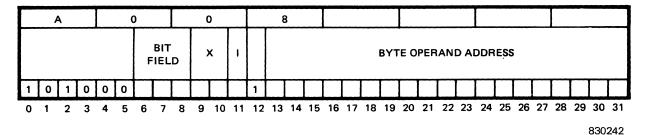

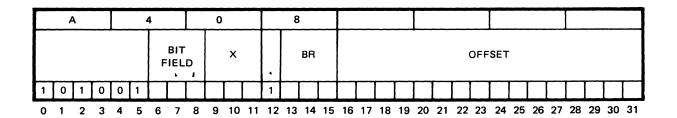

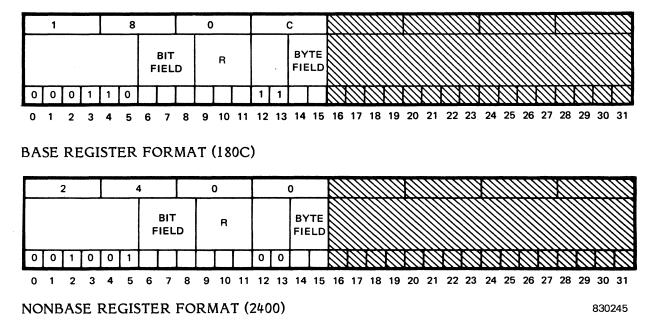

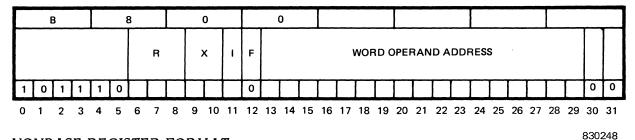

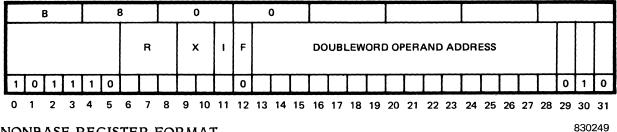

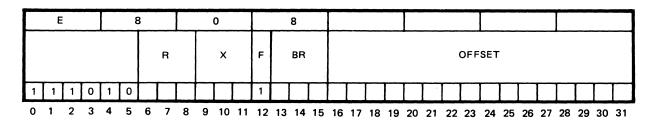

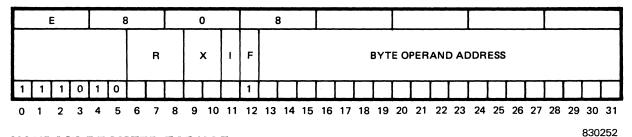

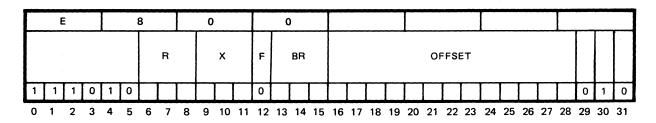

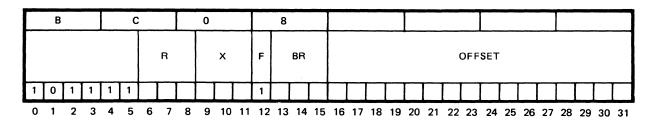

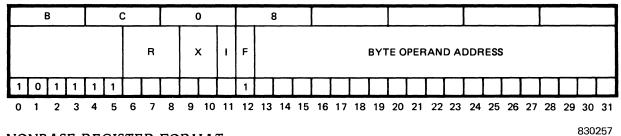

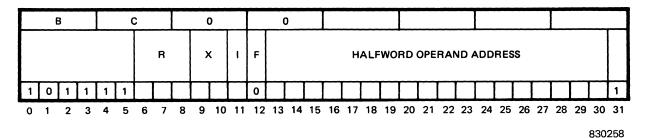

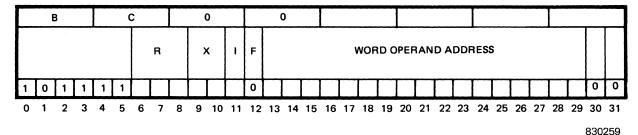

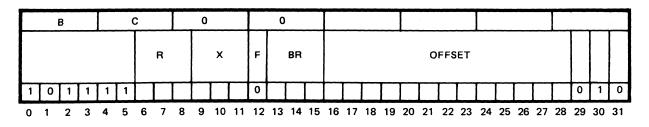

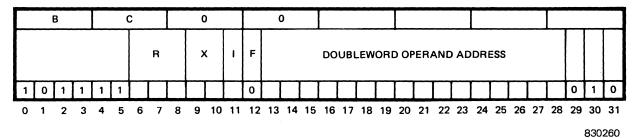

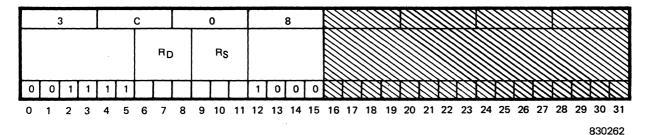

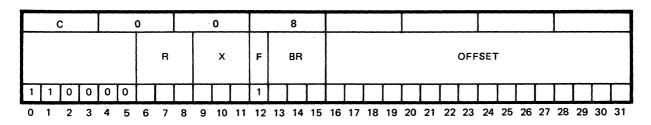

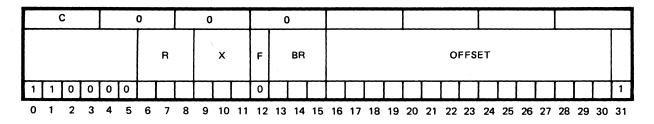

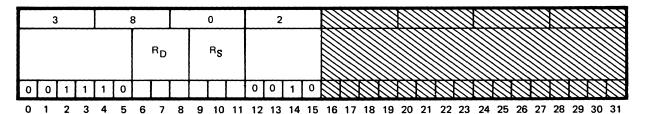

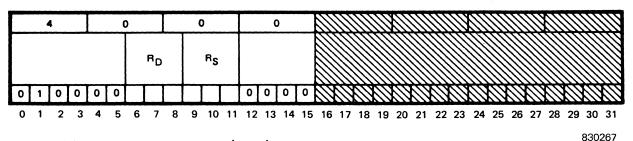

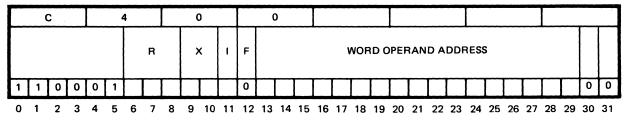

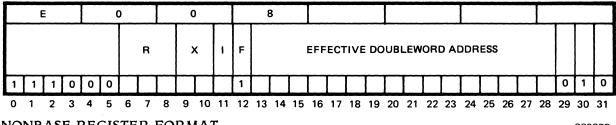

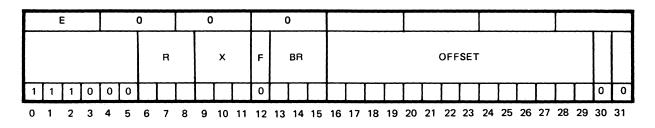

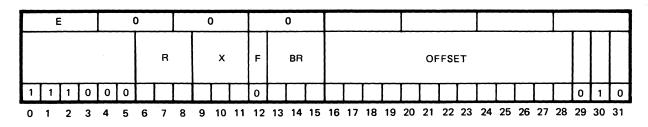

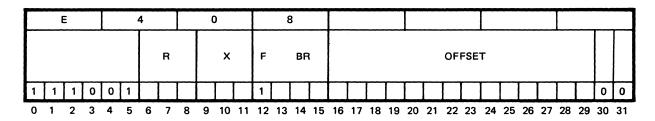

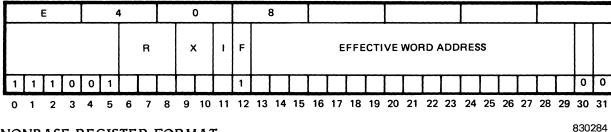

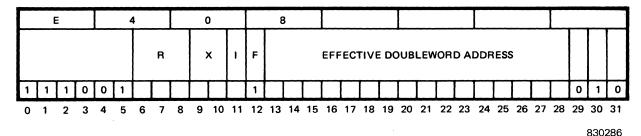

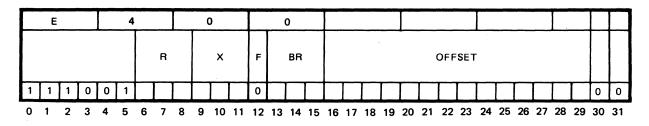

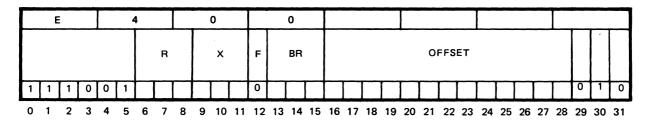

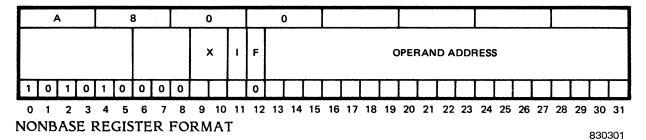

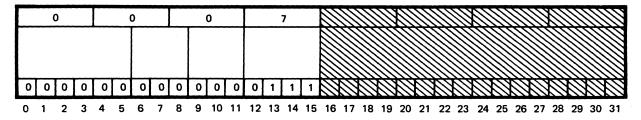

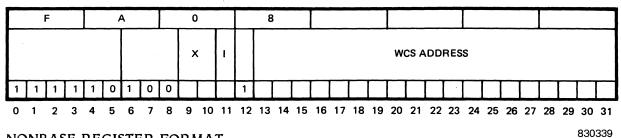

#### 2.5.2 Base Register Mode

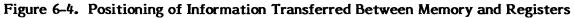

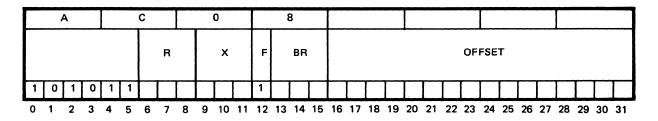

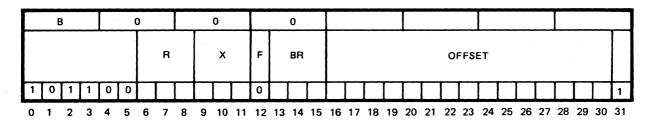

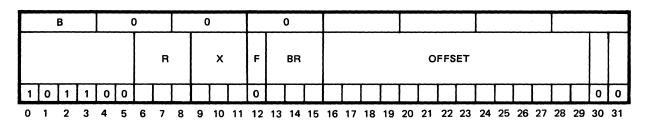

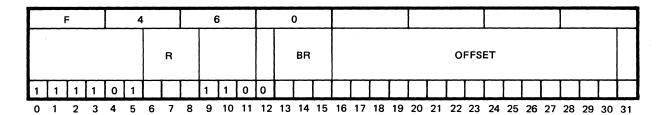

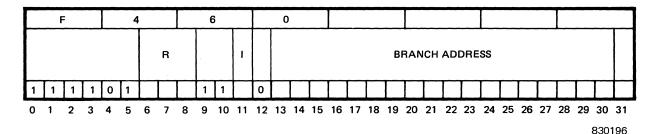

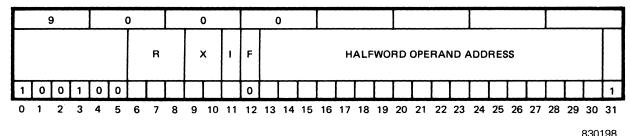

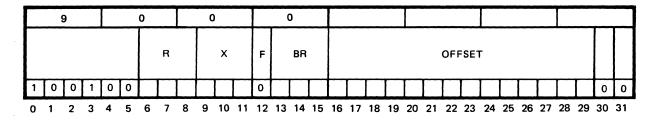

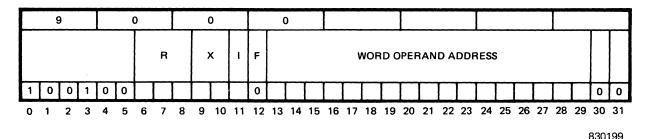

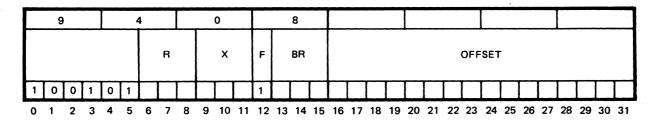

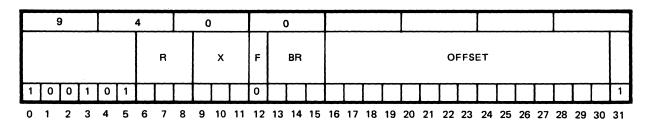

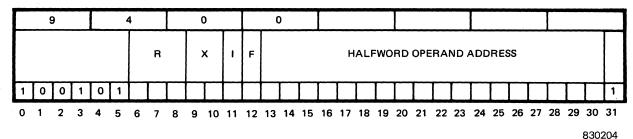

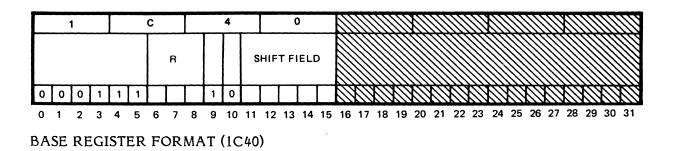

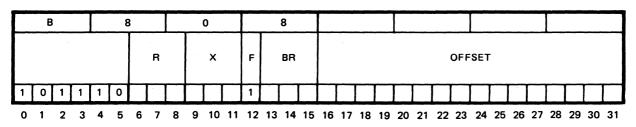

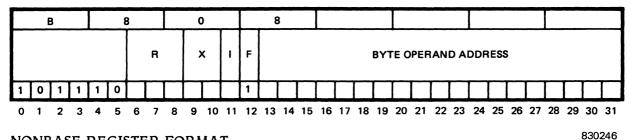

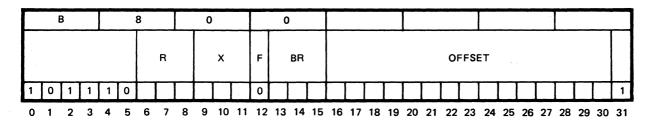

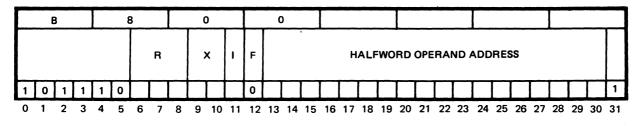

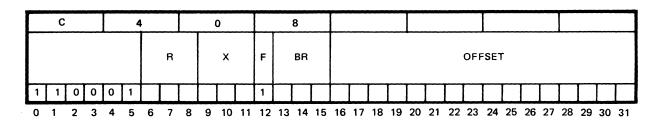

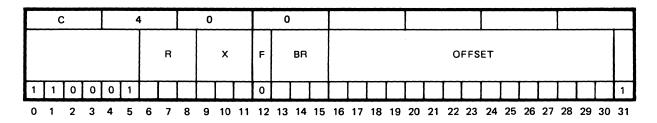

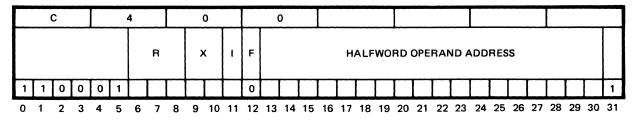

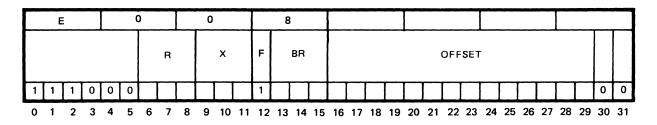

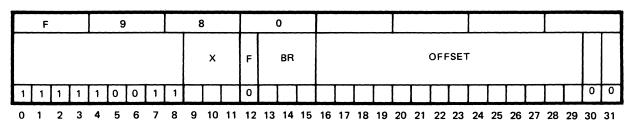

In the base register mode the 32/67 CPU allows GPRs 1 through 7 to be used as index registers. Bits 9 through 11 of the memory reference instruction represent the index register field. The F bit (bit 12) is a part of the operation code.

|   |   |   | OP | со | Dŧ | E |   |   | R |   |   | x  |    | F  |    | BR |    | •  |    |    |    | OFFSET |    |    |    |    |    |    |    |    | (  | с   |     |

|---|---|---|----|----|----|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|--------|----|----|----|----|----|----|----|----|----|-----|-----|

|   |   |   |    |    |    |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |        |    |    |    |    |    |    |    |    |    |     |     |

| ( | ) | 1 | 2  | 3  |    | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20     | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30  | 31  |

|   |   |   |    |    |    |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |        |    |    |    |    |    |    |    |    |    | 820 | 430 |

The contents of the base register field (bits 13 through 15) identify one of the seven registers to be used as a reference address within the program address space. The offset field contains the positive displacement value that is added to the contents of the specified base register to form the address of the operand. If the base register field contains all zeros, a 32-bit value of zero is used as the base address in the logical address calculation.

### 2.5.2.1 ADDRESS ALIGNMENT

The 32/67 CPU checks the alignment of the effective address of the operand against the alignment specified in the instruction. If the compare does not agree, the hardware will generate the address specification trap.

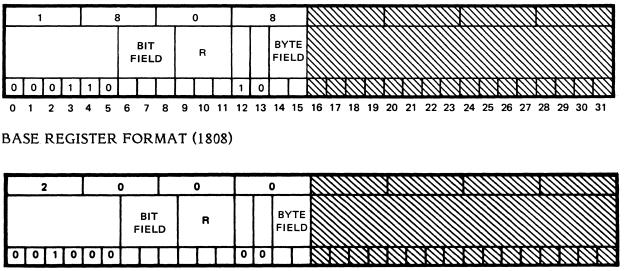

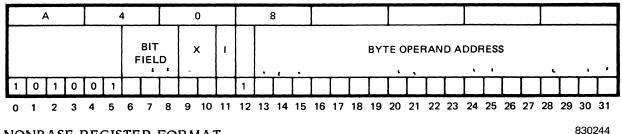

#### 2.5.2.2 BASE REGISTER FORMAT

Base address field of the base register format is 24 bits.

## 2.6 MEMORY ADDRESS GENERATION

There are two memory addressing environments: mapped and unmapped. There are two options when in nonbase register mode: extended and nonextended. The user controls the selection of the options under each environment, and it is these options which determine the rules for logical address generation.

The memory environment is controlled by the software operating system which determines the rules for transposing logical addresses into physical addresses.

When the user's task is loaded into memory, it may be dispersed into noncontiguous map blocks throughout physical memory. All of the MAP blocks used for a specific user's task are considered the physical (real) space of that task.

Physical blocks of memory can be common to many logical address spaces. Thus, multiple users may have access to some of the same physical address space and share those common blocks of memory.

### 2.6.1 Mapped Environment

The memory management hardware is used to convert a task's address space to the assigned physical MAP blocks. The set of valid addresses is known as the logical address space of the task. Figures 2-3 through 2-5 illustrate how the memory management hardware uses a memory MAP (random access memory) to transform logical space (addresses) into physical space (addresses) for nonbase-nonextended (Figure 2-3), nonbase-extended (Figure 2-4) and base register mode (Figure 2-5).

The CPU is operating in the mapped environment when bit 32 of the PSD2 is set. The mapped environment specifies that the user's program has been partitioned into MAP blocks of 2K words per block and the blocks may be distributed throughout physical memory. In the mapped environment, the CPU loads the physical MAP registers through a table called the MAP image descriptor list (MIDL). Each MAP image descriptor of the MIDL defines a unique MAP register image. Thus, all MAP entries may be linked together contiguously in the logical memory space. Consecutive entries in the MIDL will produce a contiguous logical address space.

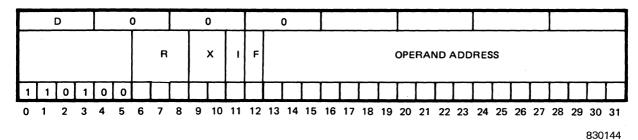

#### 2.6.2 Unmapped Environment

When the CPU is operating in the unmapped environment, the MAP registers are not used. No address transformation takes place; therefore, the logical address is identical to the physical address. The CPU is in the unmapped environment when bit 32 of the PSD2 is zero. No memory protection is provided in this environment. Figures 2-6 through 2-8 illustrate the translation of a logical address to a physical address for nonbase-nonextended (Figure 2-6), nonbase-extended (Figure 2-7), and base register mode (Figure 2-8).

Figure 2-3. Mapped Environment for Nonbase Nonextended Mode

Figure 2-4. Mapped Environment for Nonbase Extended Mode

Figure 2-5. Mapped Environment for Base Register Mode

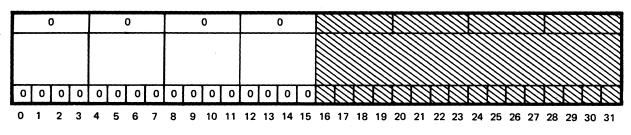

## 2.6.3 Nonextended Addressing Option

The nonextended option is in effect when bits 5 and 6 of the PSD1 are zero.

In the nonbase register mode, the nonextended option allows the CPU to access only those instructions and operands (bit, byte, halfword, word, or doubleword) in the primary address space. A 19-bit address field is provided in all memory reference instructions for this purpose. Refer to Figures 2-3 and 2-6 for the nonextended addressing calculation.

When bit 6 is set to one, bit 5 has no relevancy and the system is in the base register mode, which provides a 24-bit address field. Refer to Figures 2-5 and 2-8 for the base register mode address calculation.

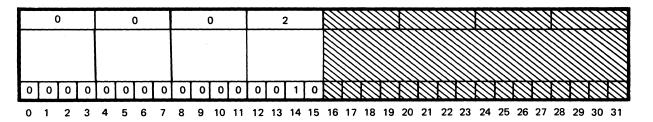

#### 2.6.4 Extended Addressing Option

Refer to Figures 2-4 and 2-7 for the extended addressing calculation. The logical address space beyond the first 128K words in the nonbase register mode may be used for operands only.

The upper limit of the extended space is 4M words.

In the nonbase register mode, indexed addressing is necessary to achieve addressing above 128K words. In each memory reference instruction, bits 9 and 10 designate one of three general purpose registers to be used as an index register. The extended option is in effect when bit 5 of the PSD1 is set to one and bit 6 is zero. Only bits 8 through 31 of the index register are used.

In the base register mode, the extended addressing option is not required, therefore not used.

### 2.6.5 Write Protection

The memory protection system provides write protection for individual memory map blocks. However, write protection is overridden when the CPU is operating in the privileged state.

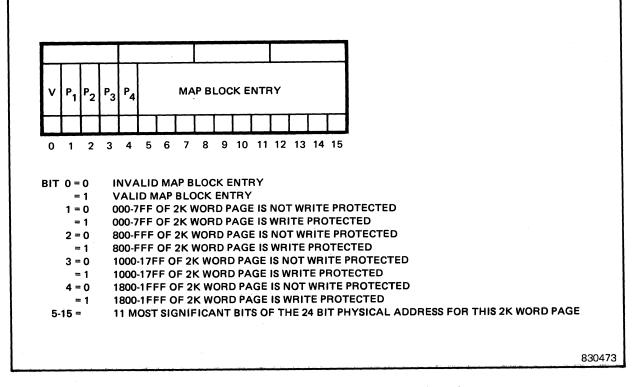

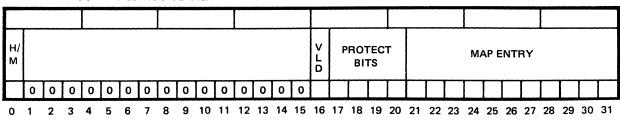

When the CPU is operating in the mapped environment, each map block of logical program address space can be write-protected for any quarter (512W) of any MAP block. This is done by the setting of the appropriate protect/unprotect bit in the MAP image descriptor for that particular map block. Details of the MAP image descriptor are provided in CHAPTER 3.

If a task attempts to read or write to a location which is not defined in its logical address space, a MAP fault trap will occur. This prevents one task from accessing memory that is not part of its address space. If a task attempts to write to an area within its own address space and the operating system has defined that location as protected, a privilege violation trap will occur. This prevents the task from destroying critical locations within its own logical address space.

No protection is provided in the unmapped environment; direct access to all available physical address space is attainable, through extended indexing.

Figure 2-6. Unmapped Environment for Nonbase Nonextended Mode

Figure 2-8. Unmapped Environment for Base Register Mode

## CHAPTER 3

### MEMORY MANAGEMENT

## 3.1 HARDWARE MEMORY MANAGEMENT

The hardware memory management of the Gould CONCEPT 32/67 CPU permits full utilization of all available memory. This feature includes hardware memory allocation and protection (MAP). The hardware memory management allows user programs to be loaded into and executed from anywhere in physical memory.

### 3.2 MEMORY MAPPING SCHEME

The memory mapping scheme for the 32/67 CPU consists of the following principal parameters:

- 2048 MAP blocks each of 2KW length

- 512 word write protect granularity.

- 4M word (16M byte) maximum logical address space.

- 4M word (16M byte) maximum physical space.

## 3.3 MEMORY MAPPING DATA STRUCTURES

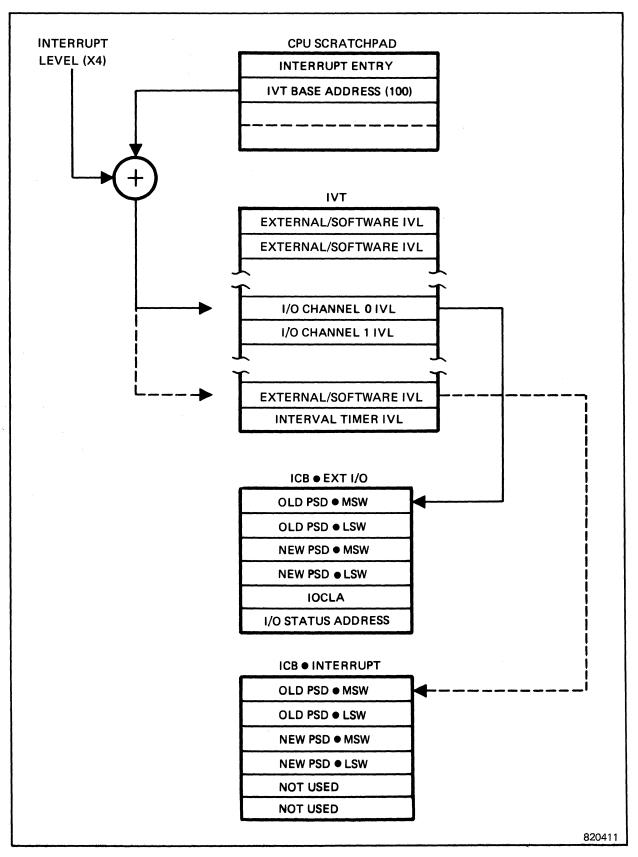

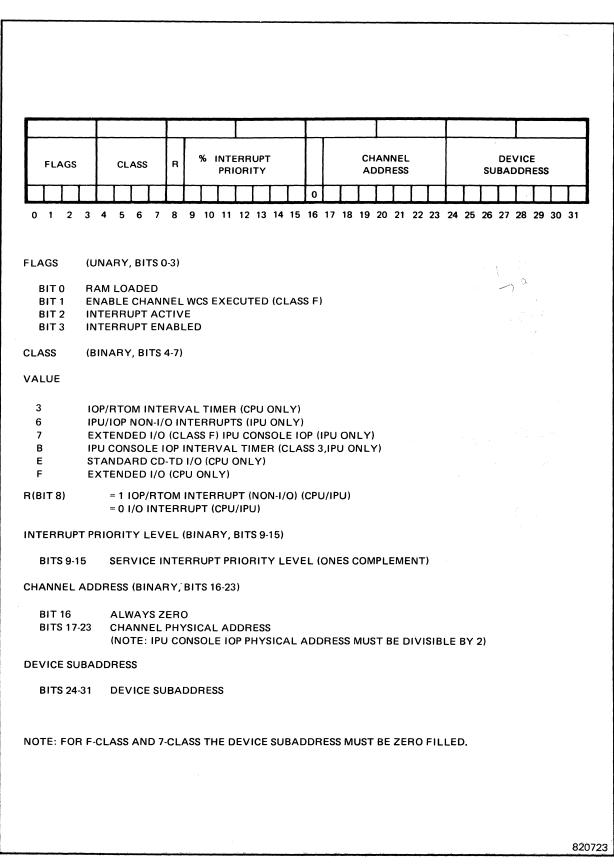

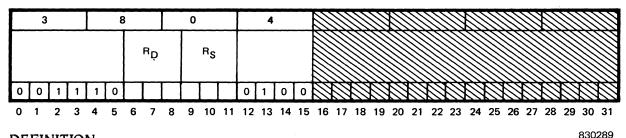

Figure 3-1 depicts the software memory mapping data structures used by the CPU to load its MAP. The master process list (MPL) and the MAP image descriptor list (MIDL) must be kept in memory on doubleword boundaries. These contain the information for the CPU to initialize the MAP. MPL 0 is normally reserved for the operating system (OS). The remaining MPSs are used for tasks (programs) within the OS.

#### 3.4 CURRENT PROCESS INDEX

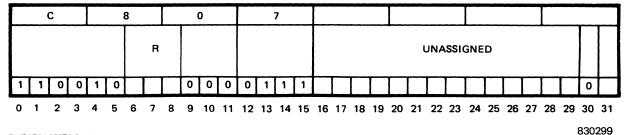

The second word of the program status doubleword (PSD) contains the 14-bit current process index (CPIX) field. The CPIX is the index that locates the MAP segment descriptors (MSDs) in the master process list (MPL) in order to provide a link from the PSD to the MAP image descriptors (MIDs). As the CPIX must point to a doubleword boundary, the three least-significant bits of the 14-bit CPIX field are always zero.

## 3.5 MASTER PROCESS LIST

The MAP segment descriptors (MSDs) are contained in the MPL. The address of the MPL is set at system reset time by loading a predetermined scratchpad cell (F3-hex) with the 24-bit physical MPL address. This location points to MSD 0. Therefore, when the CPIX equals 0, the MIDs for MSD 0 are used. If the CPIX is not equal to 0, then the CPIX and location F3 (hex) are added together and the resultant points to an MSD entry other than zero (on a doubleword boundary).

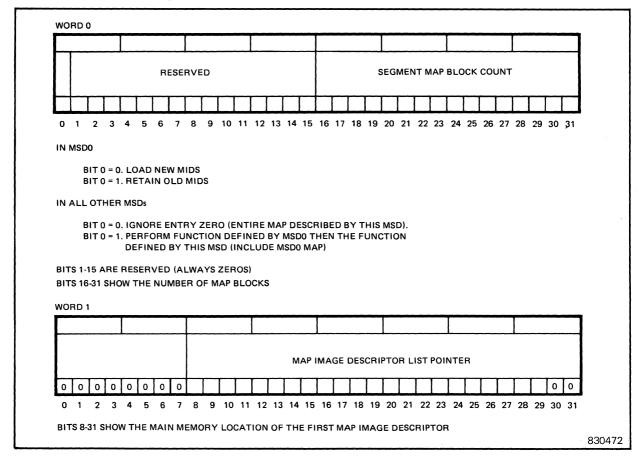

Gould CONCEPT 32/67 Reference Manual The format of an MSD entry is illustrated in Figure 3-2. Bit 0 of word 0 in an MSD is interpreted one way for MSD 0 and another way for all other MSDs. For MSD 0, bit 0 is called the retain bit, and for any other MSD, this bit is called the include bit. When a MAP change is required as a result of a Load Program Status Doubleword and Change MAP (LPSDCM) instruction or a context switch, the firmware determines the appropriate MSD to retrieve by adding the CPIX portion of PSD word 2 to the MPL base address located in scratchpad (location F3-hex). The resultant MSD is retrieved. Firmware analyzes bit 0 (include bit) of the retrieved MSD. If bit 0 is equal to zero, then all maps described by the CPIX are used. The hit RAM is zeroed and the lookaside buffer pointer points to the CPIX MSD.

If bit 0 of the selected MSD is equal to one, then firmware retrieves MSD 0. Bit 0 (retain bit) of MSD 0 is analyzed. If bit 0 is equal to zero which occurs once during system initialization and after any changes to the MSD 0 MAP blocks, then an absolute load of all MAPs described by MSD 0 occurs and the CPIX offset is computed.

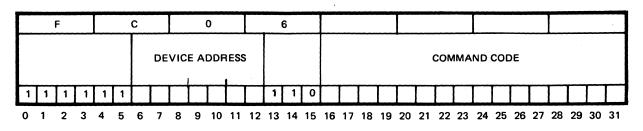

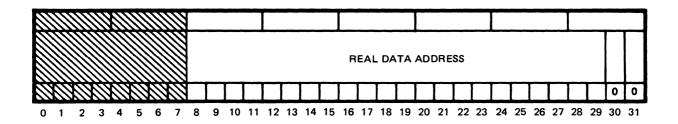

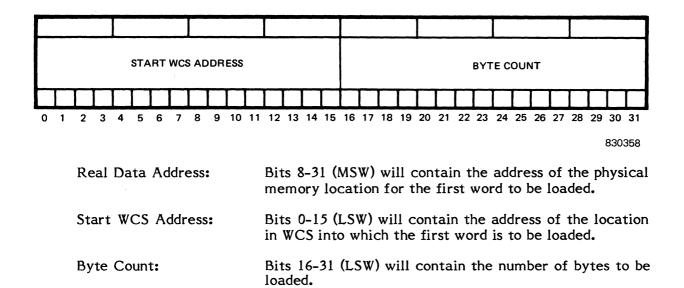

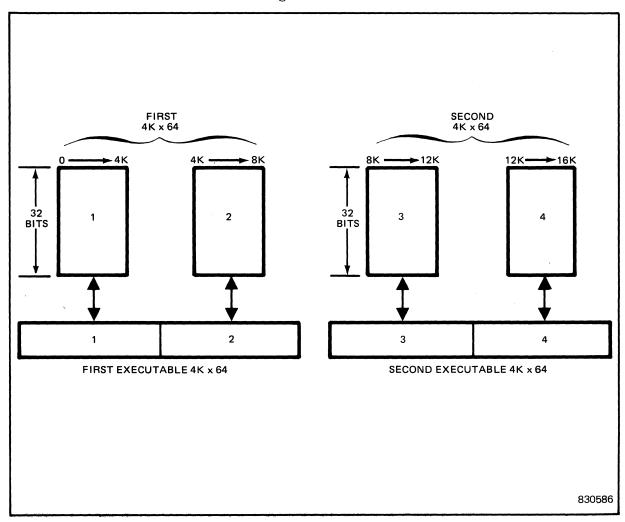

If bit 0 of MSD 0 is equal to one, then the MAP blocks of MSD 0 should be retained and the computed CPIX offset used. Therefore, the user task executing uses the MAP blocks defined by the computed CPIX offset MSD to translate the logical address of the instruction/operand into a physical memory address while retaining the MAP blocks of the OS (MSD 0).