Xerox Data Systems 701 South Aviation Blvd., El Segundo, California 90245 (213) 772-4511, 679-4511

# Effective Pages SDS 901172 LIST OF EFFECTIVE PAGES Total number of pages is 860, as follows: Page No. Issue Page No. Issue Title . . . . . . . . . . . . . . . . Original A.OriginalA.Originali thru xivOriginal1-1 thru 1-12Original2-1 thru 2-20Original3-1 thru 3-758Original4-1 thru 4-54Original

#### TABLE OF CONTENTS

| Section |        | Title                                          | Page |

|---------|--------|------------------------------------------------|------|

| I       | GENER  | AL DESCRIPTION                                 | 1-1  |

|         | 1-1    | Introduction                                   | 1-1  |

|         | 1-2    | Physical Description.                          | 1-1  |

|         | 1-3    | Basic Computer.                                | 1-1  |

|         | 1-4    |                                                | 1-1  |

|         |        | Equipment Breakdown                            |      |

|         | 1-5    | Computer Configuration                         | 1-2  |

|         | 1-6    | Optional Features                              | 1-2  |

|         | 1-7    | Functional Description                         | 1-2  |

|         | 1-8    | Basic Computer Description                     | 1-2  |

|         | 1-9    | Computer Optional                              | 1-8  |

|         | 1-10   | Two Additional Real-Time Clocks                | 1-8  |

|         | 1-11   | Power Fail–Safe Feature                        | 1-8  |

|         | 1-12   | Memory Protection                              | 1-8  |

|         | 1-13   | Private Memory Register Extension              | 1-8  |

|         | 1-14   | Floating Point                                 | 1-8  |

|         | 1-15   | External Interrupts                            | 1-9  |

|         | 1-16   | Memory Expansion                               | 1-9  |

|         | 1-17   | Port Expansion                                 | 1-9  |

|         | 1-18   | Multiplexing Input/Output Processor            | 1-9  |

|         | 1-19   | Additional Eight Subchannels (IOP)             | 1-9  |

|         | 1-20   | Selector Input/Output Processor                | 1-9  |

|         | 1-21   | Six Internal Interrupt Levels                  | 1-9  |

|         | 1-22   | Maximum Computer System                        | 1-9  |

|         | 1-23   | Specifications and Leading Particulars         | 1-9  |

|         |        |                                                |      |

| II      | OPERAI | IION AND PROGRAMMING                           | 2-1  |

|         | 2-1    | General                                        | 2-1  |

|         | 2-2    | Operation                                      | 2-1  |

|         | 2-3    | Controls and Indicators                        | 2-1  |

|         | 2-4    | Operating Procedures                           | 2-1  |

|         | 2-5    | Applying Power                                 | 2-1  |

|         | 2-6    | Displaying Contents of Memory Location         | 2-1  |

|         | 2-7    | Storing Into Memory                            | 2-1  |

|         | 2-8    | Clearing the Program Status Words              | 2-9  |

|         | 2-9    | Altering the Current Program Status Doubleword | 2-9  |

|         | 2-10   | Branching From the PCP                         | 2-10 |

|         | 2-11   | Stepping Through a Program                     | 2-10 |

|         | 2-12   | Single Clocking an Instruction                 | 2-10 |

|         | 2-13   | Single Instruction Repetition                  | 2-10 |

|         | 2-14   | Loading a Program.                             | 2-10 |

|         | 2-15   | Programming                                    | 2-11 |

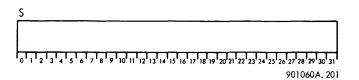

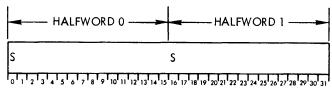

|         | 2-16   | Word Formats                                   | 2-11 |

|         | 2-18   |                                                | 2-11 |

|         |        | Data Word Formats                              |      |

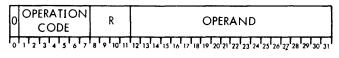

|         | 2-18   | Instruction Formats                            | 2-13 |

|         | 2-19   | Memory Addressing                              | 2-14 |

|         | 2-20   | Reference Address                              | 2-14 |

|         | 2-21   | Effective Address                              | 2-14 |

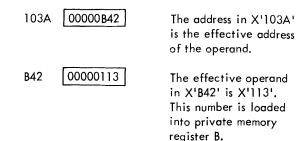

|         | 2-22   | Indirect Address                               | 2-14 |

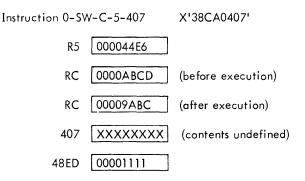

|         | 2-23   | Indexed Addressing                             | 2-14 |

i

#### TABLE OF CONTENTS (Cont.)

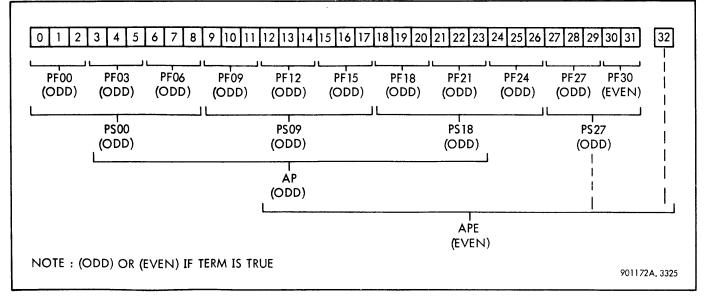

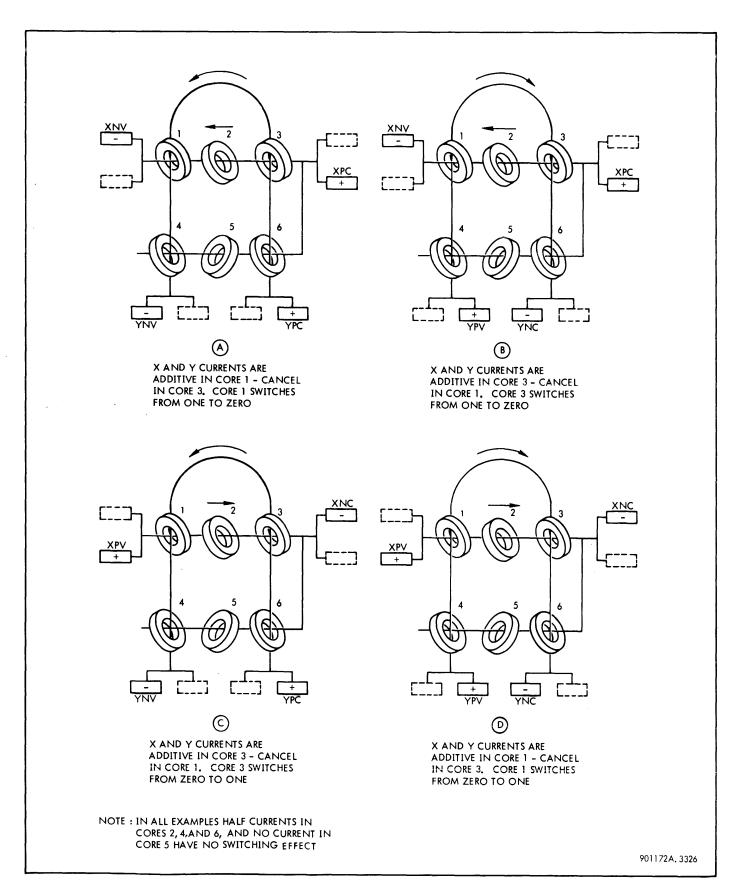

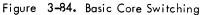

#### Title Page Section 2 - 142-24 Indirect Indexed Addressing..... 2 - 152-25 2-26 2 - 152 - 152-27 Halfword Addressing 2-28 2 - 16Byte Addressing ..... 2-17 2-29 Basic Instructions PRINCIPLES OF OPERATION..... 3-1 Ш 3-1 3-1 3-2 General Principles of Operation ..... 3 - 13-3 3-1 3-1 3-4 Arithmetic, Control, and Address Functions ..... 3-5 3-5 3-7 3-6 Interrupt/Trap Functions...... 3-7 Private Memory Organization ..... 3-8 3-8 3-8 Processor Control Panel ..... 3-9 3-8 3-10 3-8 3-9 3-11 3-10 3-12 3-10 3-13 3-14 Memory Input-Output 3-11 3-15 3-11 3-16 3-13 3-17 3 - 14Integral IOP 3-16 3-18 Chaining ..... 3-19 3-16 3-20 3-16 3-21 Detailed Principles of Operation 3-16 3-22 3-21 3-23 3-21 3-24 3 - 503-25 CPU Phases and Timing 3-61 3-26 Real-Time Clock.... 3-61 3-27 3-62 3-28 Memory Protection ...... 3-65 3-29 3-71 3-30 3 - 793-31 Memory..... 3 - 953 - 953-32 3-95 3-33 3-99 3-34 3-35 3-99 3-36 3-101 3-37 3 - 101Memory Configuration 3-38 3 - 101Interleave Transformation ...... 3-39 3 - 109Memory Access Request..... 3-40 3-109 3-41 Address Release..... 3-109 3-42 3-109 3-43 Memory Delay Lines. 3-113 3-44 3-118 3-45 Memory Reset..... 3-119 3-46 3-119

3-121

3-47

#### TABLE OF CONTENTS (Cont.)

#### Section

#### Title

| 3-48         | Read Timing and Data Flow                                            | 3-121          |

|--------------|----------------------------------------------------------------------|----------------|

| 3-49         | Full Write Timing and Data Flow                                      | 3-121          |

| 3-50         | Partial Write Timing and Data Flow                                   | 3-121          |

| 3-51         | Parity Checking and Parity Generation                                | 3-125          |

| 3-52         | Sigma 5 Core Selection.                                              | 3-127          |

| 3-53         | Core Characteristics                                                 | 3-127          |

| 3-54         | Basic Core Switching                                                 | 3-127          |

| 3-55         | Reading From Memory                                                  | 3-127          |

| 3-56         | Writing Into Memory                                                  | 3-130          |

| 3-57         | Core Diode Module                                                    | 3-130          |

| 3-58         | Operation Code Implementation                                        | 3-130          |

| 3-59         |                                                                      |                |

|              | Preparation Phases                                                   | 3-174          |

| 3-60         | Family of Load Instructions (FALOAD)                                 | 3-204          |

| 3-61         | Family of Load Absolute Instructions (FALOAD/A)                      | 3-224          |

| 3-62         | Family of Store Instructions (FASTORE)                               | 3-235          |

| 3-63         | Family of Selective Instructions (FASEL) LOAD SELECTIVE (LS; 4A, CA) | 3-249          |

| 3-64         | Family of Analyze Instructions                                       | 3-261          |

| <b>3-6</b> 5 | Interpret (INT; 6B, EB)                                              | 3-270          |

| 3-66         | Family of Arithmetic Instructions (FAARITH)                          | 3-274          |

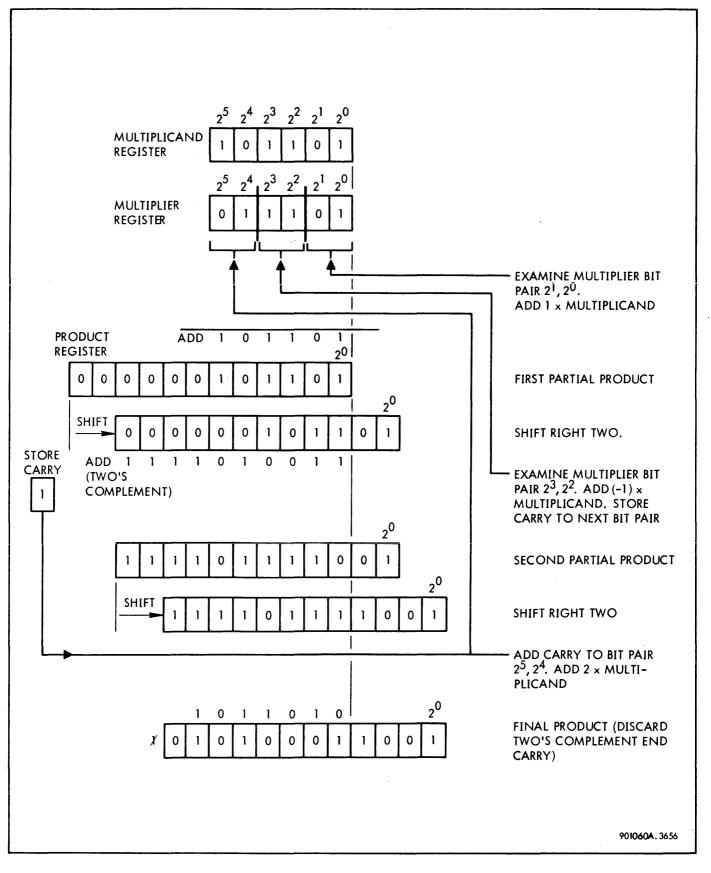

| 3-67         | Family of Multiply Instructions (FAMUL)                              | 3-286          |

| 3-68         | Family of Divide Instructions (FADIV)                                | 3-301          |

| 3-69         | Family of Modify and Test Instructions                               | 3-317          |

| 3-70         | Family of Compare Instructions                                       | 3-330          |

| 3-71         | Family of Compare With Limits Instructions (FACOMP/L).               | 3-340          |

| 3-72         | Family of Logical Instructions (FALOGIC)                             | 3-349          |

| 3-73         | Family of Shift Instructions (FASH)                                  | 3-353          |

| 3-74         | Family of Floating Point Instructions                                | 3-378          |

|              |                                                                      |                |

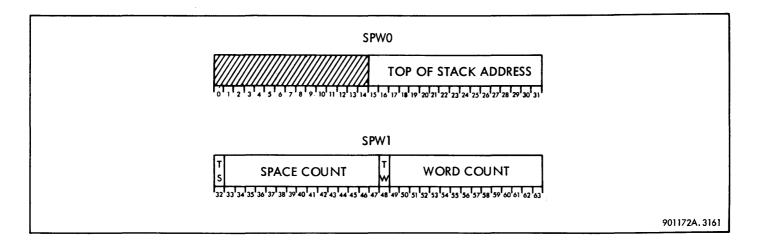

| 3-75         | Family of Stack and Multiple Instructions (FAST)                     | 3-438          |

| 3-76         | Family of Branch Instructions (FABRANCH)                             | 3-508          |

| 3-77         | Family of Call Instructions (FACAL)                                  | 3-522          |

| 3-78         | Family of Program Status Doubleword Instructions (FAPSD)             | 3-524          |

| 3-79         | Move to Memory Control (MMC; 6F, EF)                                 | 3-538          |

| 3-80         | Wait (WAIT; 2E, AE)                                                  | 3-551          |

| 3-81         | Family of Direct Instructions (FARWD)                                | 3-553          |

| 3-82         | Family of Input/Output Instructions (FAIO)                           | 3-564          |

| 3-83         | Glossary of Terms                                                    | 3-600          |

| 3-84         | Power Fail–Safe                                                      | 3-624          |

| 3-85         | General                                                              | 3-624          |

| 3-86         | Interrupts                                                           | 3-624          |

| 3-87         | Power Monitor Assembly                                               | 3-624          |

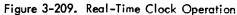

| 3-88         | Floating Point Unit                                                  | 3-638          |

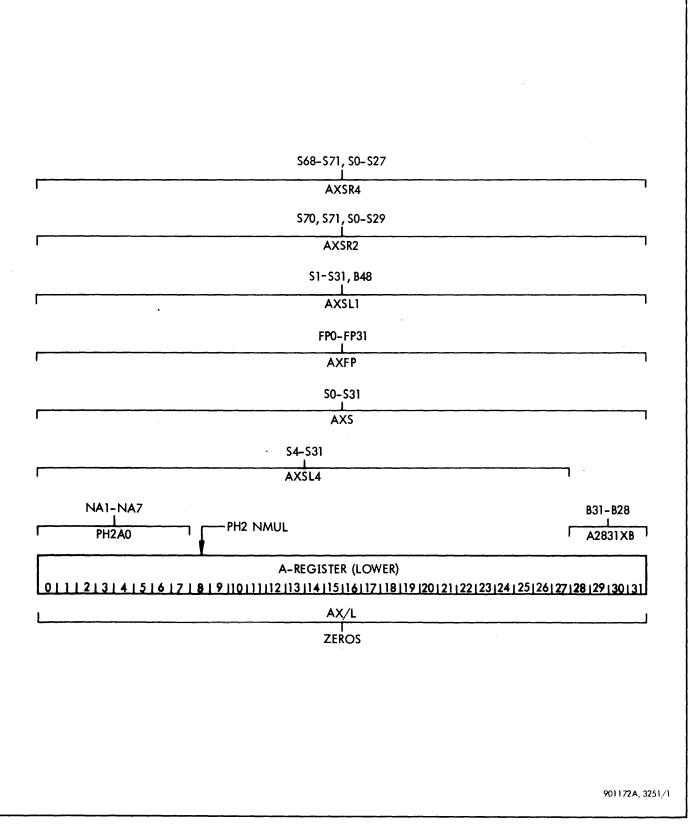

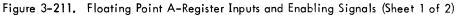

| 3-89         | A-Register                                                           | 3-638          |

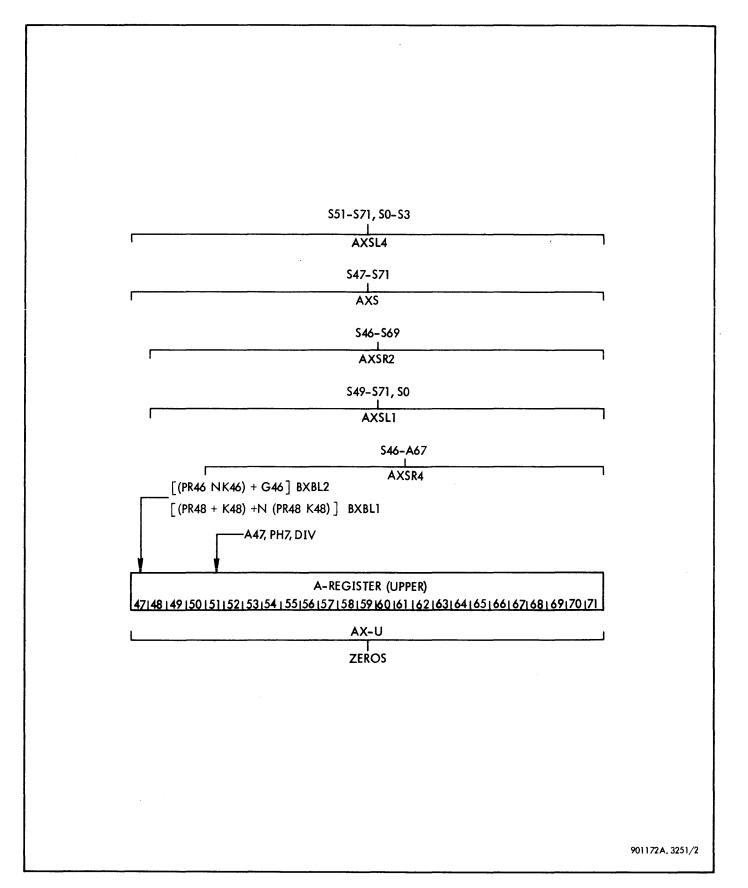

| 3-90         | B-Register                                                           | 3-638          |

| 3-91         | D-Register                                                           | 3-638          |

| 3-92         | F-Register                                                           | 3-644          |

| 3-93         | -                                                                    | 3-644          |

|              | E-Register                                                           | 3-644          |

| 3-94         | Adder                                                                | 3-644<br>3-644 |

| 3-95         | Floating Point Display                                               | -              |

| 3-96         | Processor Control Panel (PCP)                                        | 3-648          |

| 3-97         | Control Switches                                                     | 3-648          |

| 3-98         | Indicators                                                           | 3-648          |

| 3-99         | PCP Phase Sequencing                                                 | 3-648          |

| 3-100        | CLOCK MODE Switch                                                    | 3-648          |

| 3-101        | CONTROL MODE Switch                                                  | 3-648          |

| 3-102        | WATCHDOG TIMER Switch                                                | 3-655          |

.

## TABLE OF CONTENTS (Cont.)

#### Section

#### Title

| Page |

|------|

|------|

| 3-103        | INTERLEAVE SELECT Switch                 | 3-655          |

|--------------|------------------------------------------|----------------|

| 3-104        | AUDIO Switch                             | 3 <b>-6</b> 55 |

| 3-105        | SENSE Switches                           | <b>3-6</b> 55  |

| 3-106        | REGISTER DISPLAY Switch                  | 3-655          |

| 3-107        | REGISTER SELECT Switch                   | 3-655          |

| 3-108        | I/O RESET Switch                         | 3-656          |

| 3-109        | UNIT ADDRESS Switches                    | 3-656          |

| 3-110        | INTERRUPT Switch                         | 3-656          |

| 3-111        | SELECT ADDRESS Switches.                 | 3-656          |

| 3-112        | DATA Switches                            | 3-656          |

| 3-113        | Entering PCP Phases.                     | 3-656          |

| 3-114        | Reset Function                           | 3-658          |

| 3-115        | Clear PSW1, PSW2 Function                | 3-658          |

| 3-116        | STEP or RUN from Idle Operation          | 3-658          |

| 3-117        | INSERT Function.                         | 3-662          |

| 3-118        | DATA ENTER/CLEAR Function                | 3-662          |

| 3-119        | STORE INSTR ADDR/SELECT ADDR Function.   | 3-666          |

| 3-119        | DISPLAY INSTRADDR/SELECT ADDR Function   | 3-666          |

|              |                                          |                |

| 3-121        | INSTR ADDR HOLD/INCREMENT Function       | 3-666          |

| 3-122        | Clear Memory Function                    | 3-666          |

| 3-123        | LOAD Function                            | 3-672          |

| 3-124        | PARITY ERROR MODE Function               | 3-672          |

| 3-125        | Indicator Lamp Drive Operation           | 3-672          |

| 3-126        | Integral Input/Output Processor          | 3-680          |

| 3-127        | General                                  | 3-680          |

| 3-128        | Address and Priority Assignment          | 3-680          |

| 3-129        | Capabilities                             | 3-680          |

| 3-130        | I/O Fast Memory IOFM                     | 3-680          |

| 3-131        | I/O Address Register IOFR                | 3-685          |

| 3-132        | I/O Data Register IODA                   | 3-685          |

| 3-133        | Address Conversion Circuits              | 3-686          |

| 3-134        | Instructions, Commands, Orders           | 3-686          |

| 3-135        | Integral IOP/Device Controller Interface | 3-686          |

| 3-136        | Service Cycles                           | 3-686          |

| 3-137        | I/O Phase Sequencing                     | 3-686          |

| 3-138        | Power Distribution                       | 3-748          |

| 3-139        | Main Power Distribution Box              | 3-748          |

| 3-140        | Power Junction Box                       | 3-749          |

| 3-141        | Power Supplies                           | 3-749          |

|              |                                          |                |

| MAINTE       | NANCE AND PARTS LIST                     | 4-1            |

| 4-1          | Maintenance                              | 4-1            |

| 4-2          | Special Tools and Test Equipment         | 4-1            |

| 4-3          | Preventive Maintenance.                  | 4-1            |

| 4-4          | Diagnostic Testing.                      | 4-1            |

| 4-5          |                                          | 4-1            |

| 4-6          | Electronic Testing                       | 4-1            |

| 4-0<br>4-7   | Switch Settings                          | 4-2<br>4-8     |

| 4-7<br>4-8   | Corrective Maintenance                   |                |

| 4-0<br>4-9   | Wirewrap Techniques                      | 4-8            |

| 4-9<br>4-10  | Power Supplies                           | 4-8            |

| 4-10<br>4-11 | Parts Lists                              | 4-8            |

|              | Tabular Listings                         | 4-8            |

| 4-12         | Illustrations                            | 4-8            |

IV

#### TABLE OF CONTENTS (Cont.)

| Section | Title        |                   |            |  |

|---------|--------------|-------------------|------------|--|

|         | 4-13<br>4-14 | Parts List Tables | 4-8<br>4-8 |  |

#### LIST OF ILLUSTRATIONS

| Figure | Title                                                         | Page |

|--------|---------------------------------------------------------------|------|

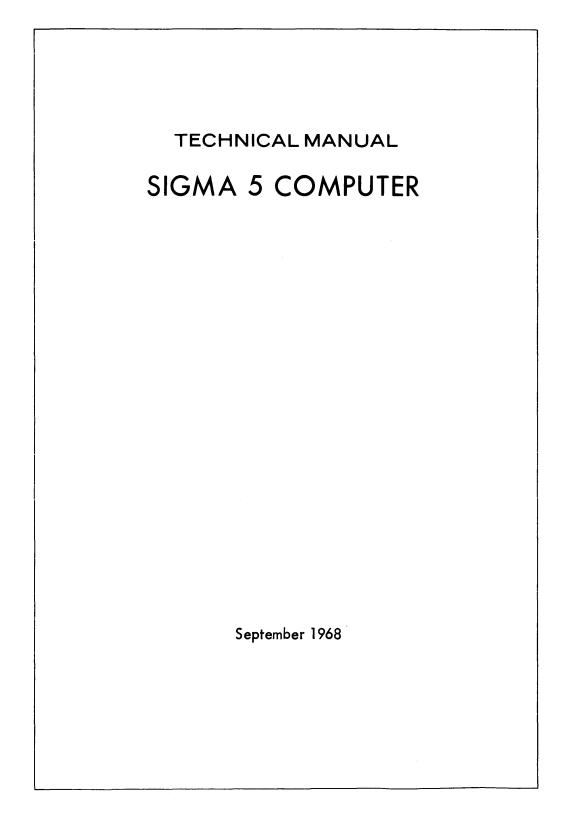

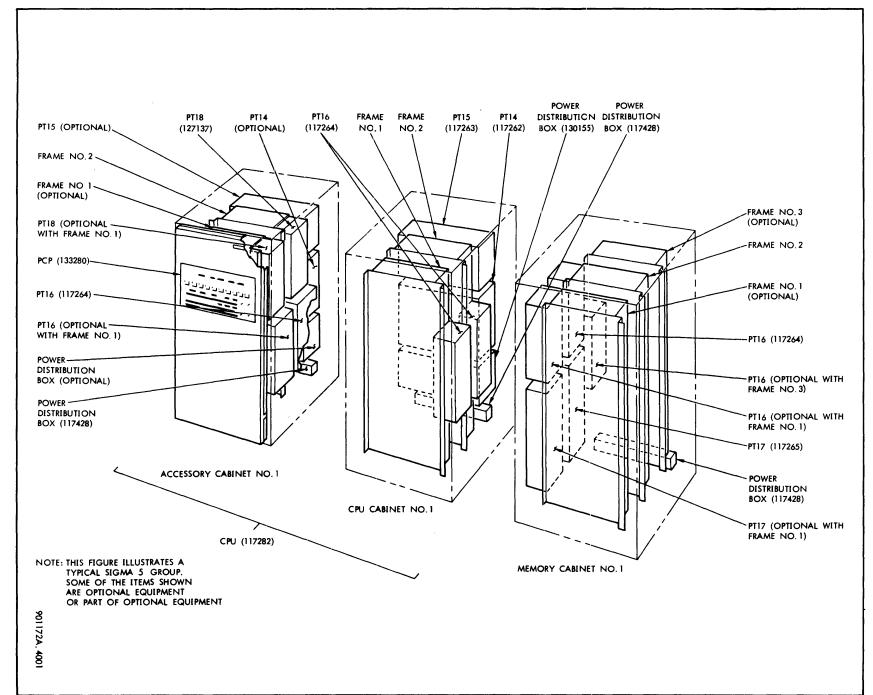

| 1-1    | Sigma 5 Computer (Typical Configuration)                      | 1-1  |

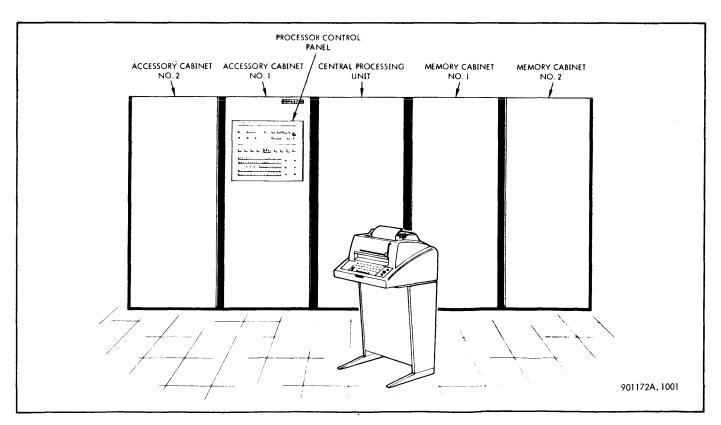

| 1-2    | Equipment Breakdown                                           | 1-3  |

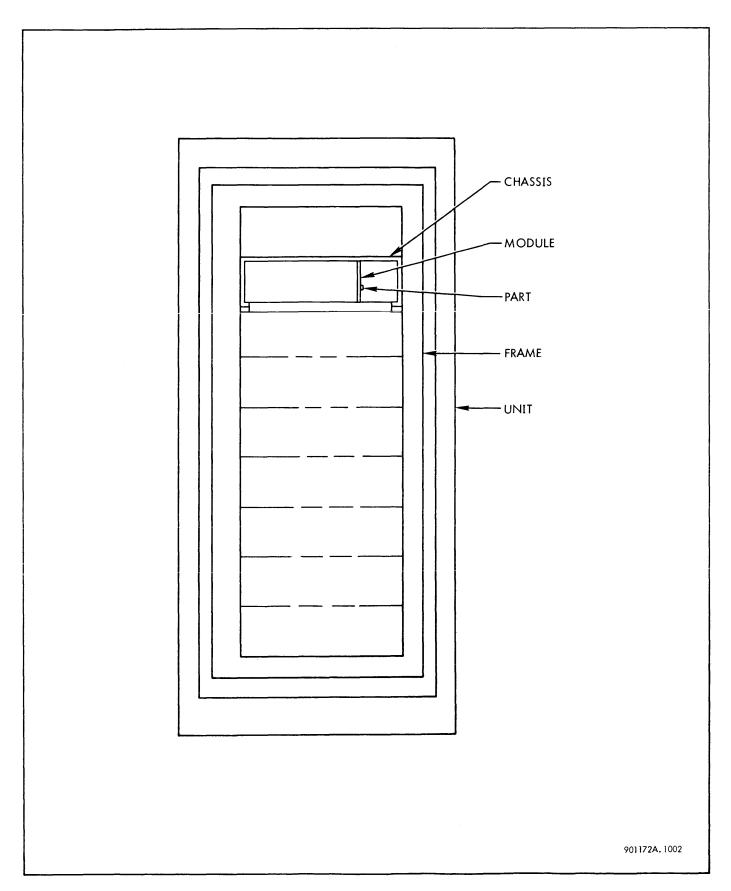

| 1-3    | CPU Cabinet                                                   | 1-4  |

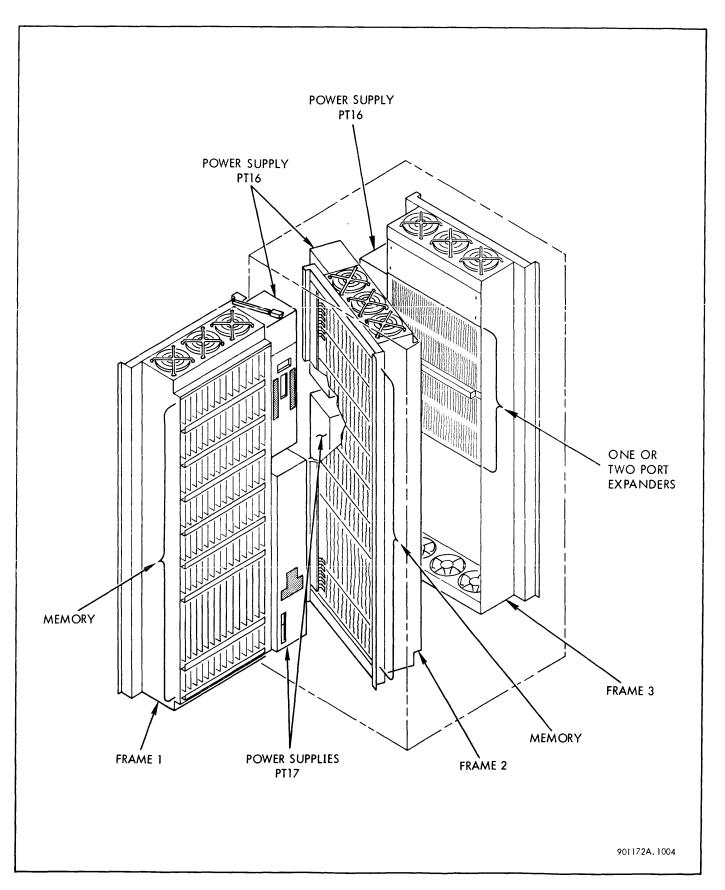

| ī-4    | Memory Cabinet (Typical)                                      | 1-5  |

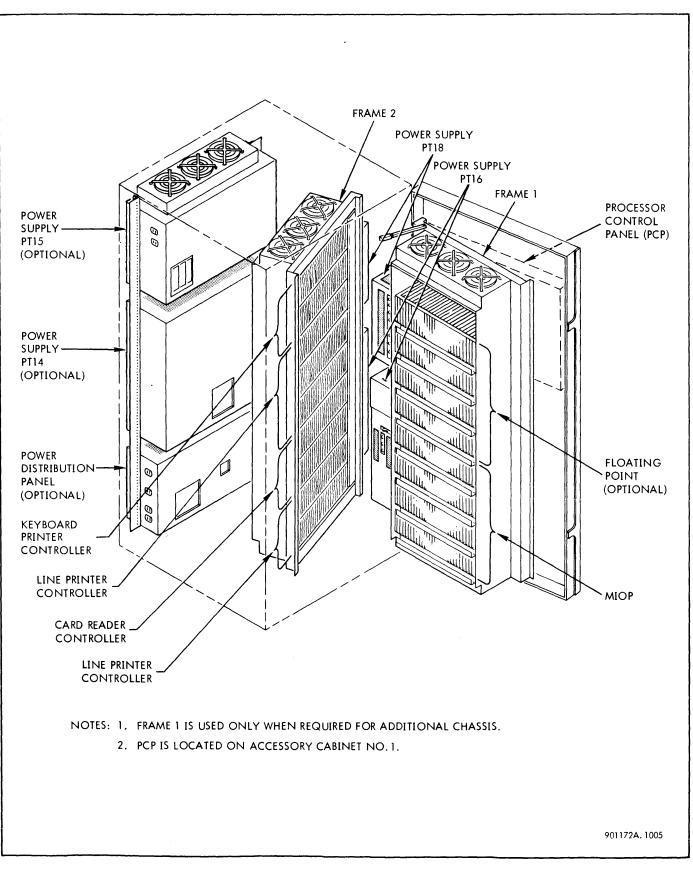

| 1-5    | Accessory Cabinet No. 1 (Typical)                             | 1-6  |

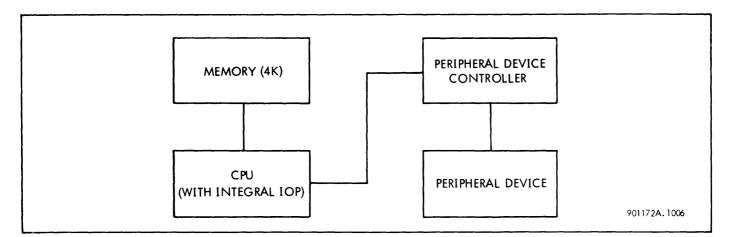

| 1-6    | Sigma 5 Minimum System With Integral IOP                      | 1-8  |

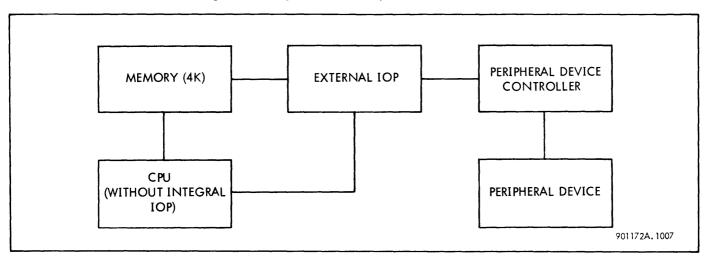

| 1-7    | Sigma 5 Minimum System Without Integral IOP                   | 1-8  |

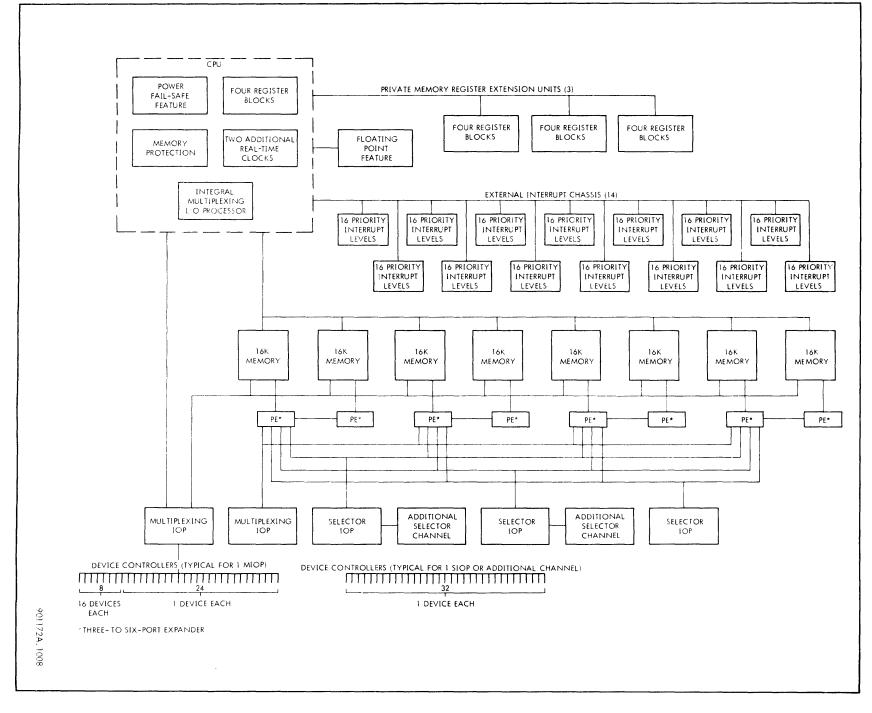

| 1-8    | Sigma 5 Maximum System (Typical)                              | 1-10 |

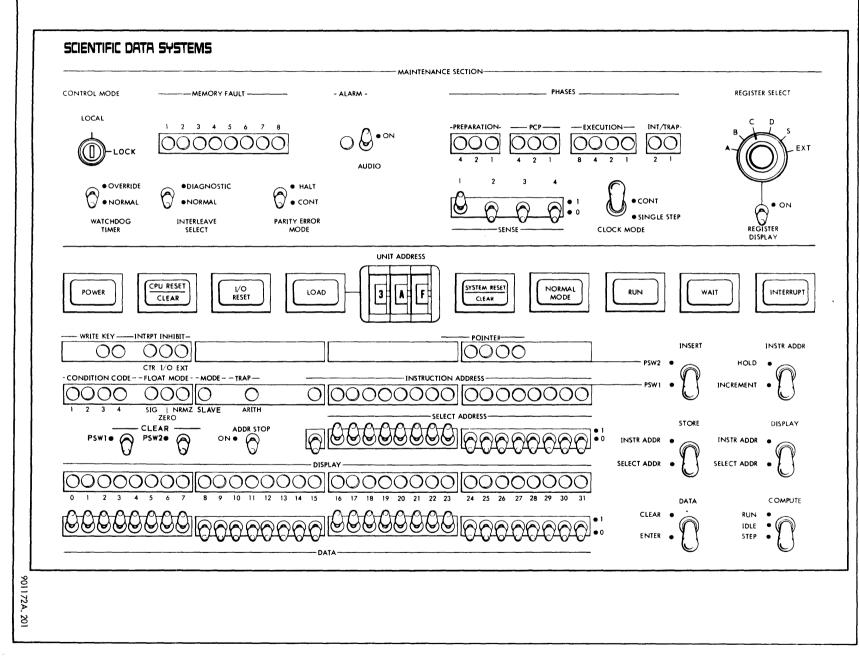

| 2-1    | Sigma 5 Processor Control Panel (PCP)                         | 2-2  |

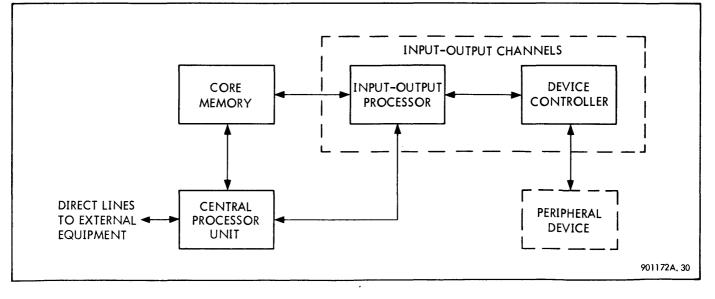

| 3-1    | Sigma 5 Major Elements                                        | 3-1  |

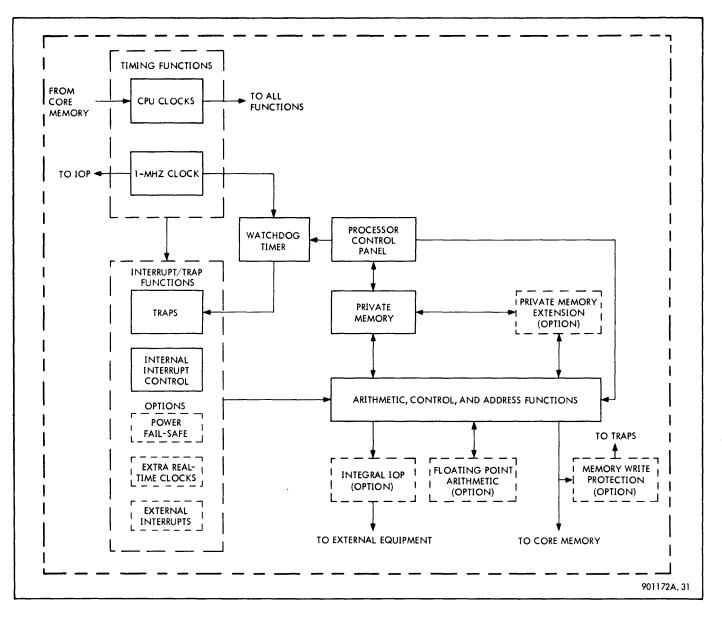

| 3-2    | Central Processing Unit, Functional Block Diagram             | 3-2  |

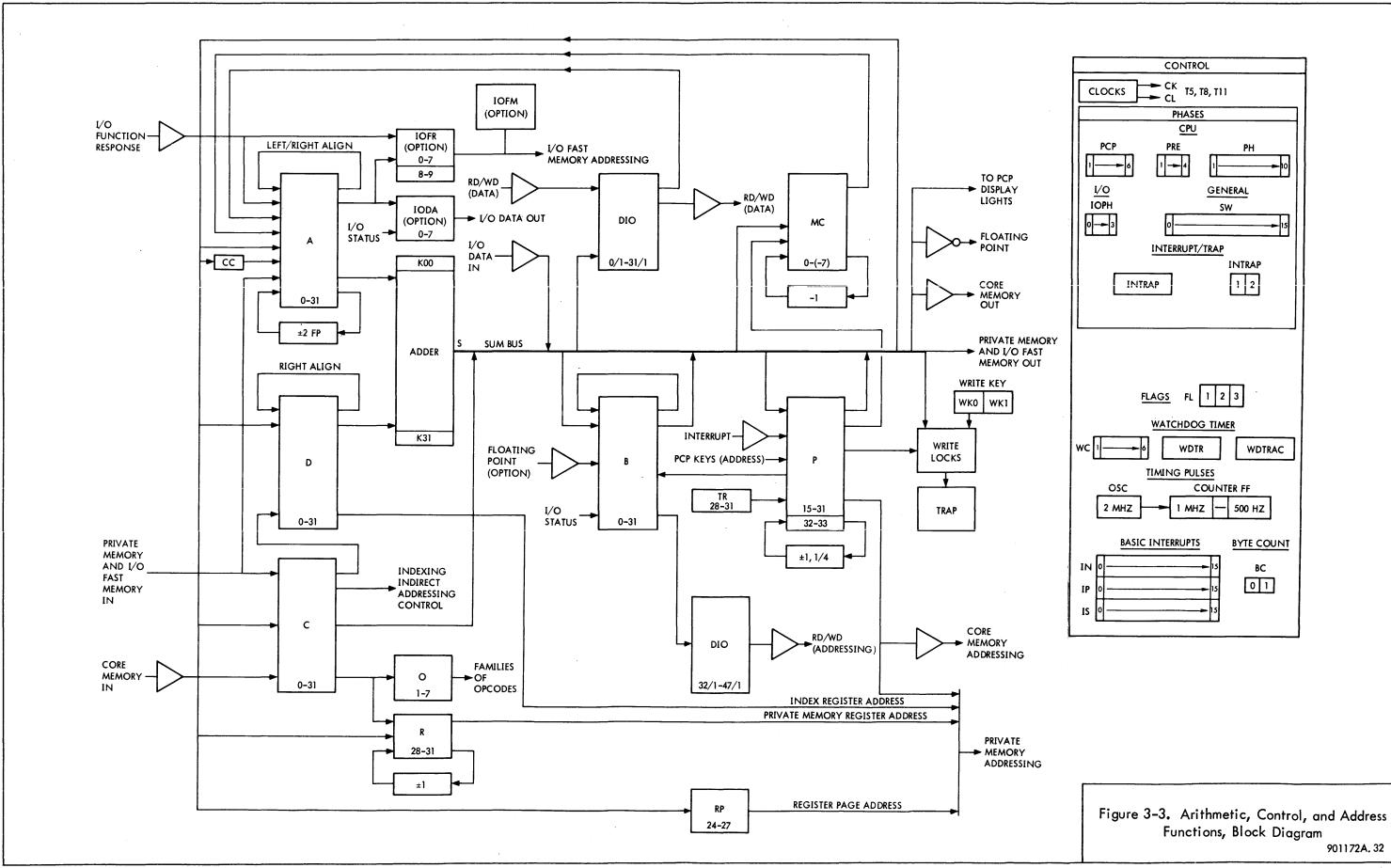

| 3-3    | Arithmetic, Control, and Address Functions, Block Diagram     | 3-3  |

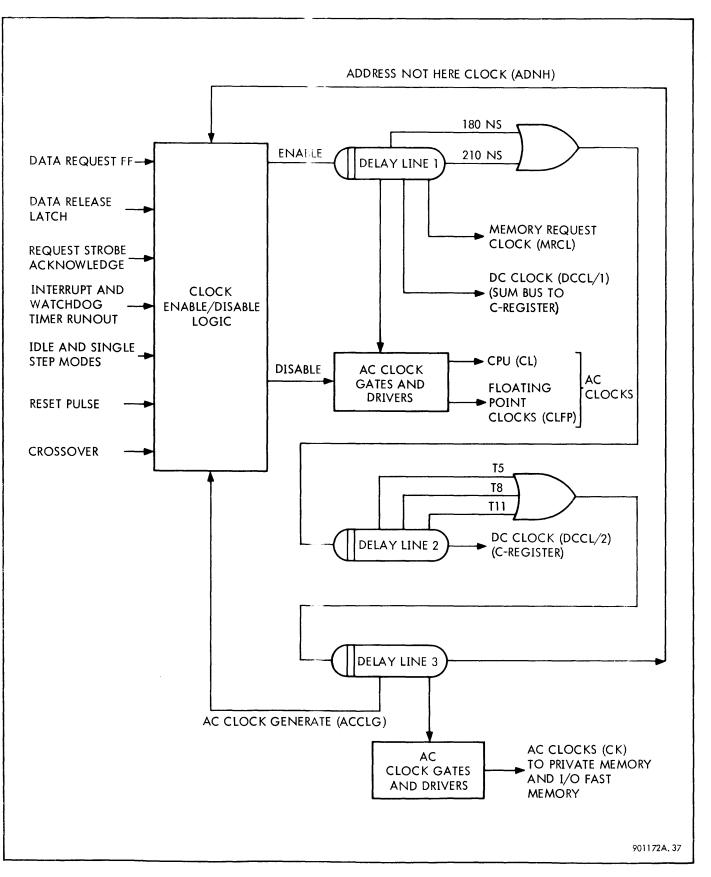

| 3-4    | CPU Clock Generator, Simplified Block Diagram                 | 3-6  |

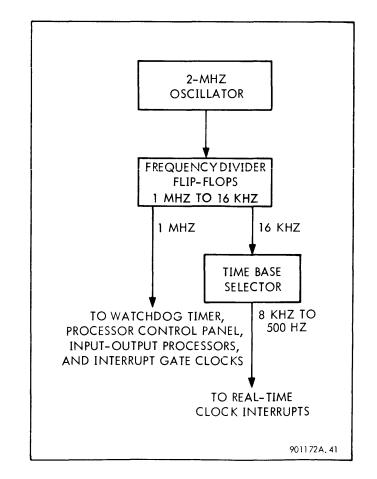

| 3-5    | Oscillator Clock Generator, Simplified Block Diagram          | 3-7  |

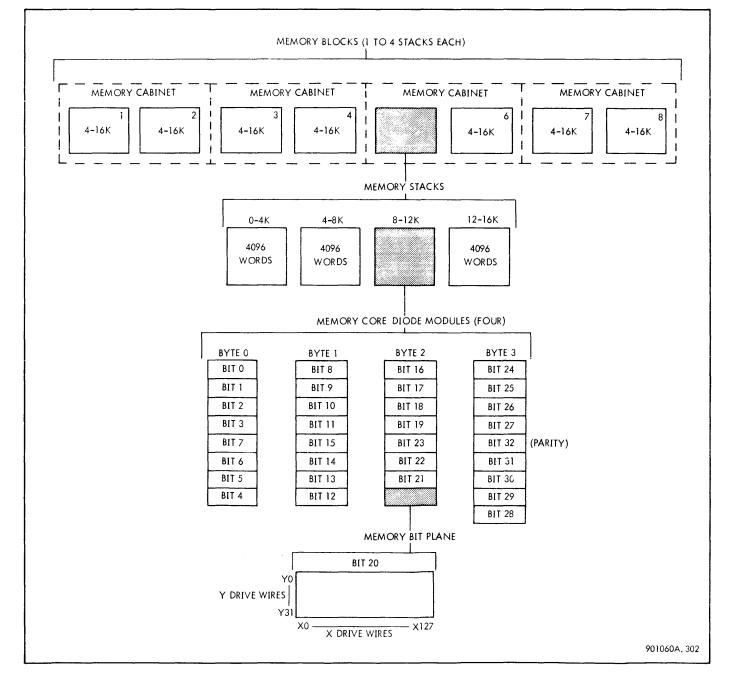

| 3-6    | Core Memory Organization                                      | 3-9  |

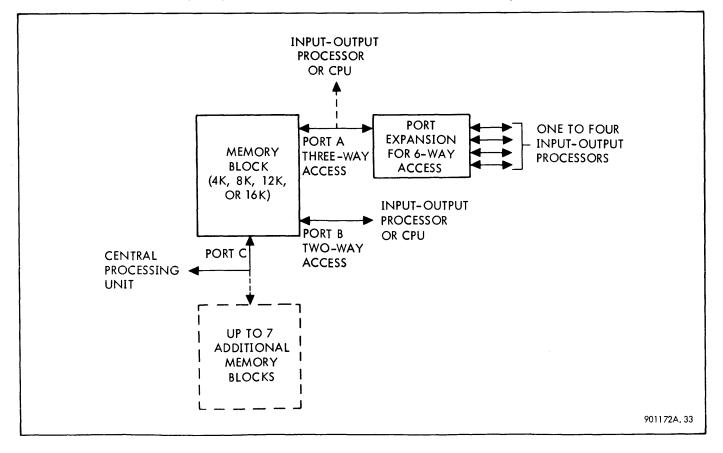

| 3-7    | Memory Connections and Port Expansion                         | 3-10 |

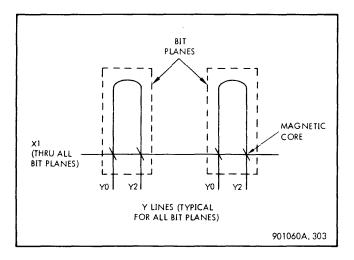

| 3-8    | Typical X and Y Core Wiring                                   | 3-11 |

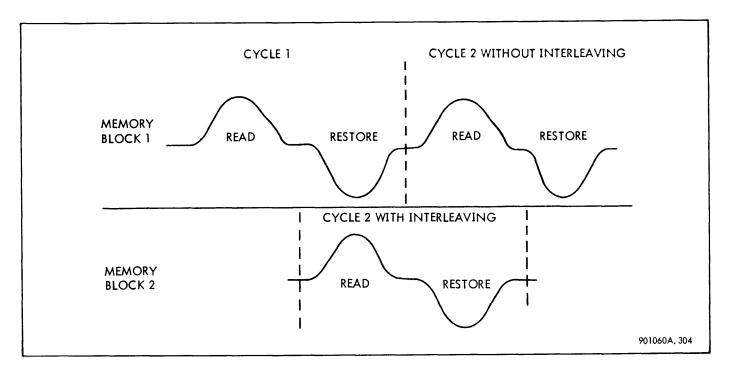

| 3-9    | Example of Interleaving in Read-Restore Mode                  | 3-12 |

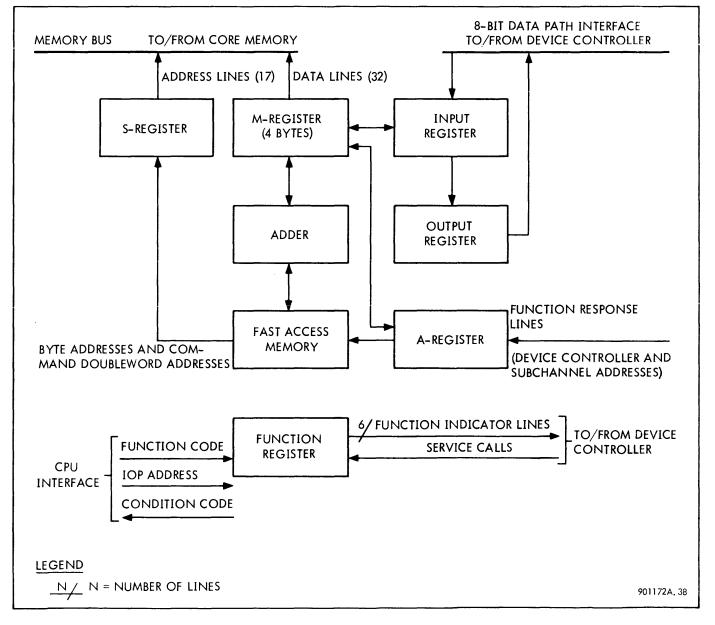

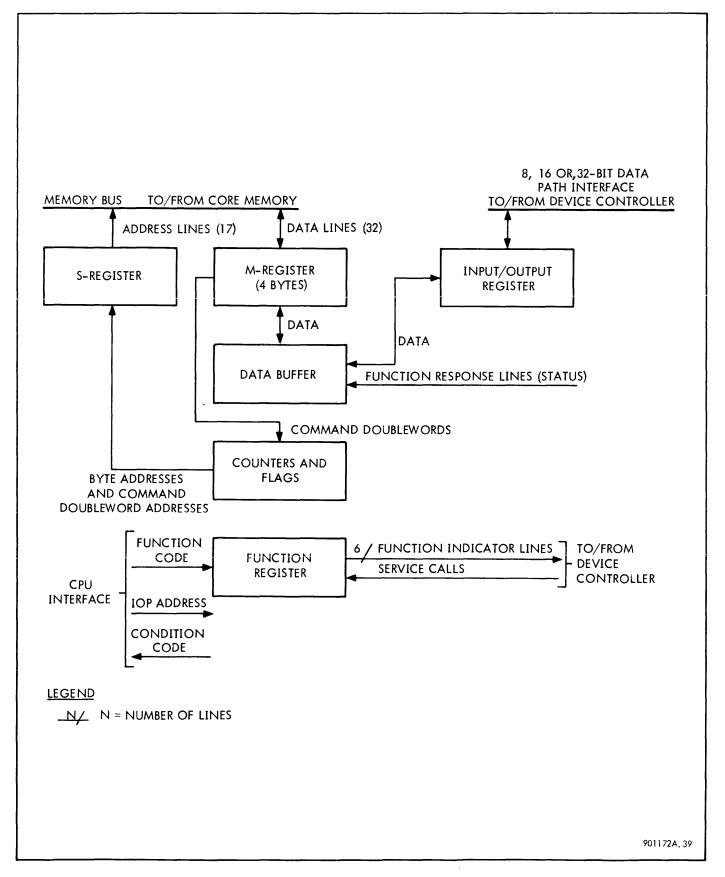

| 3-10   | Multiplexing IOP, Simplified Block Diagram                    | 3-13 |

| 3-11   | Selector IOP, Simplified Block Diagram                        | 3-15 |

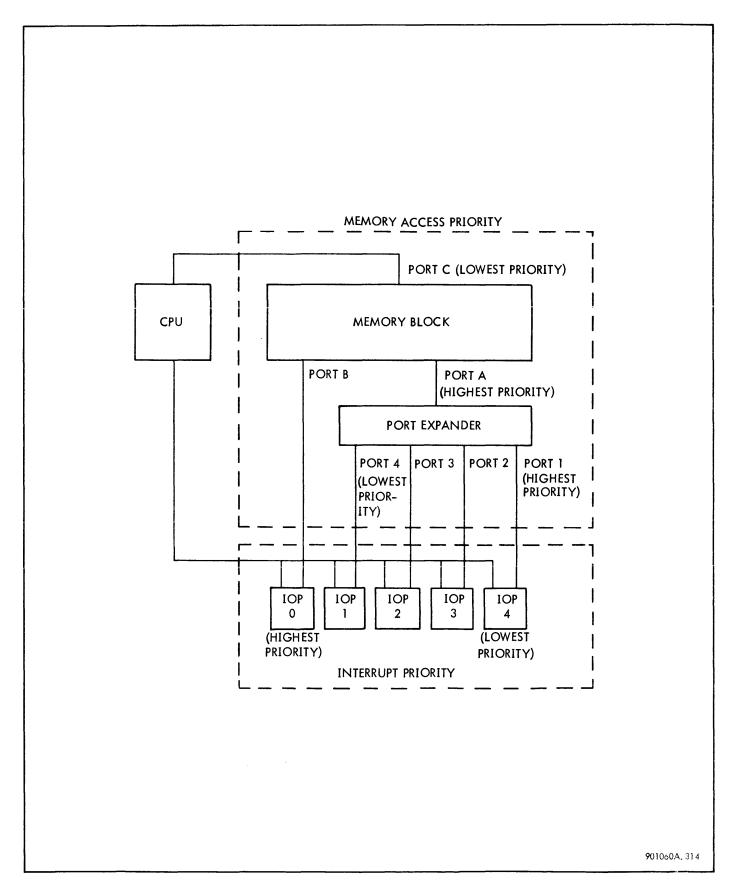

| 3-12   | Typical IOP Priority Arrangement                              | 3-17 |

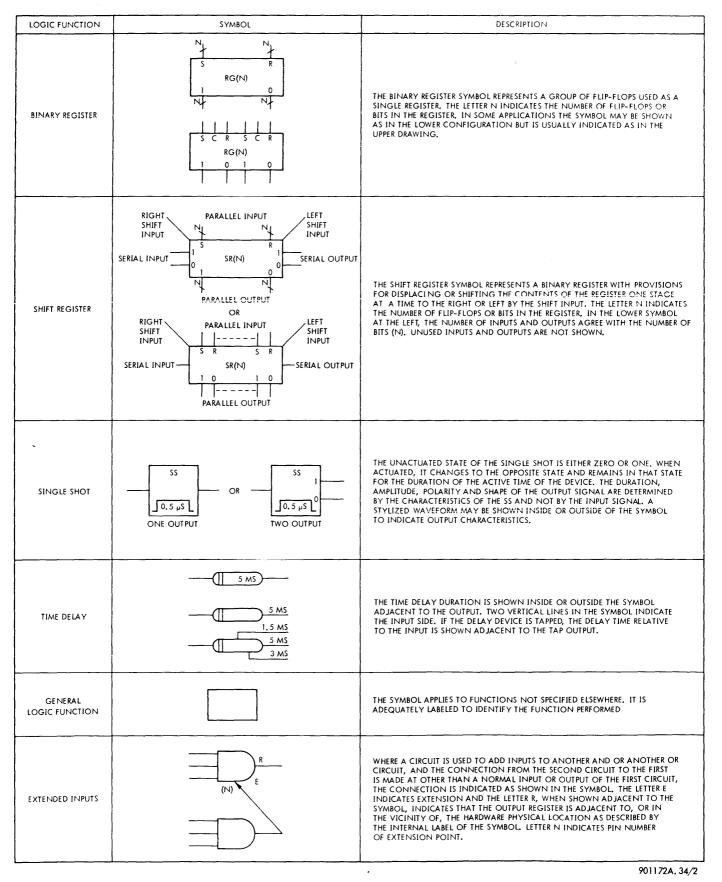

| 3-13   | Basic Logic Symbols Chart                                     | 3-18 |

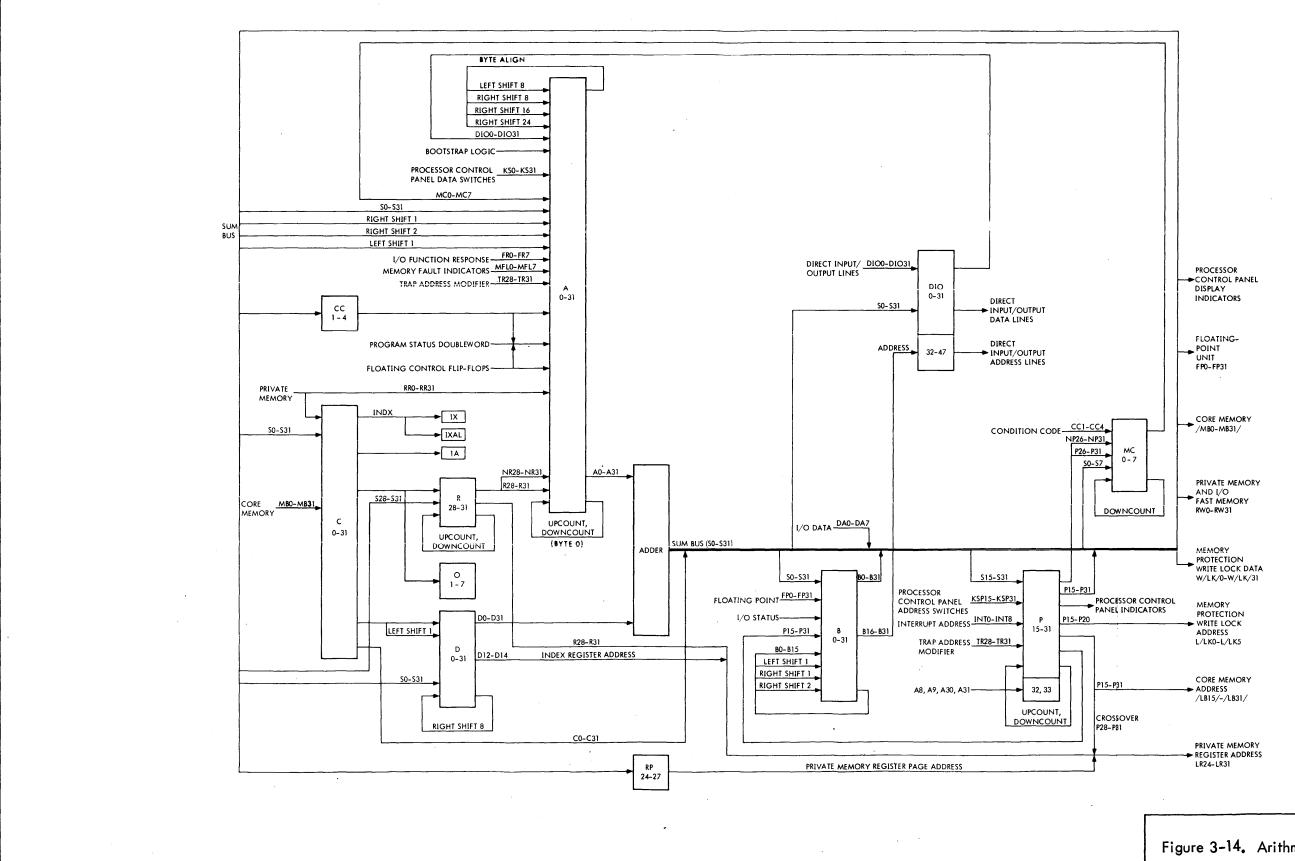

| 3-14   | Arithmetic and Control Circuits                               | 3-23 |

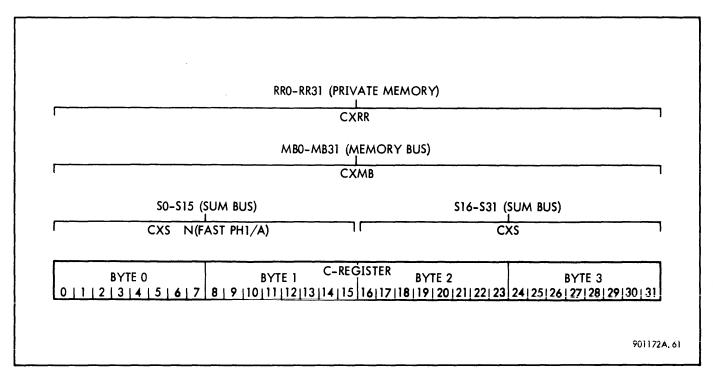

| 3-15   | C–Register Inputs and Enabling Signals                        | 3-25 |

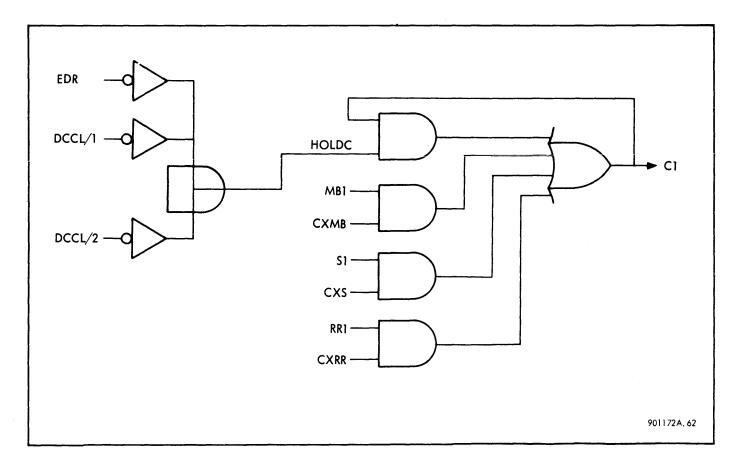

| 3-16   | C-Register Bit 1 Logic Diagram                                | 3-25 |

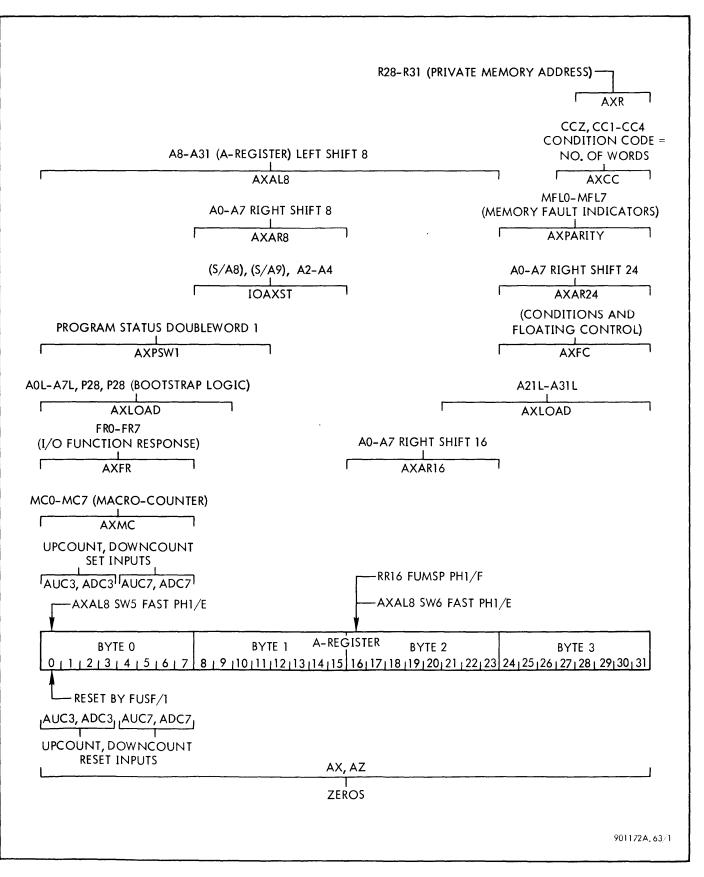

| 3-17   | A–Register Inputs and Enabling Signals.                       | 3-26 |

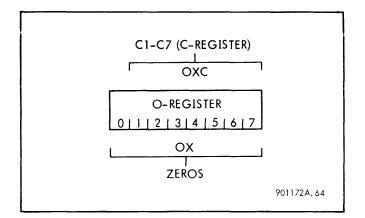

| 3-18   | O–Register Inputs and Enabling Signals                        | 3-28 |

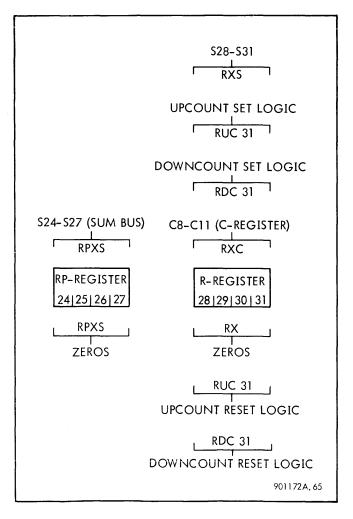

| 3-19   | RP-Register and R-Register Inputs and Enabling Signals        | 3-28 |

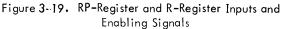

| 3-20   | D–Register Inputs and Enabling Signals                        | 3-29 |

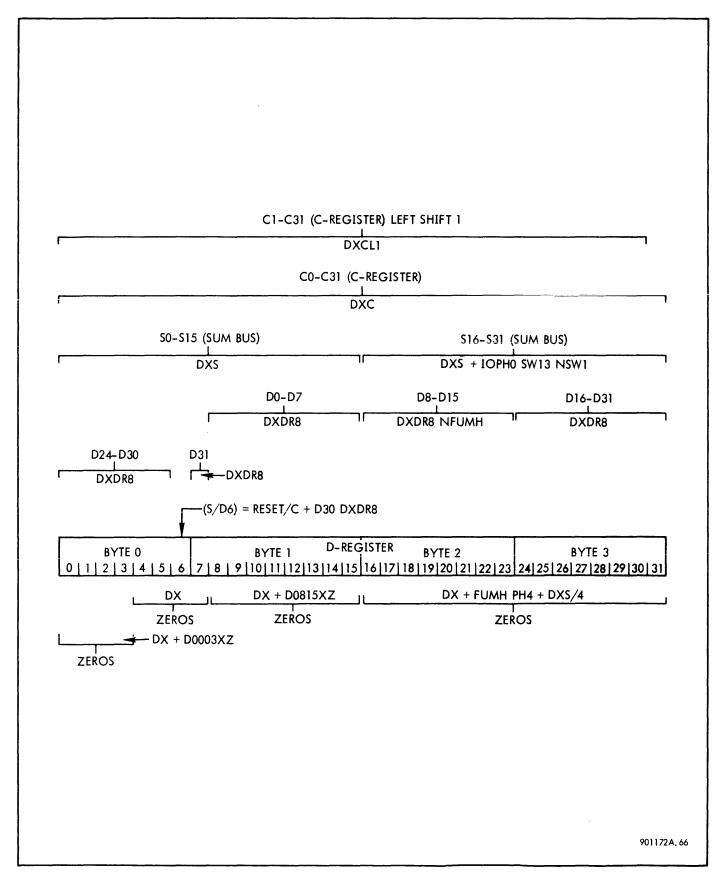

| 3-21   | B-Register Inputs and Enabling Signals                        | 3-30 |

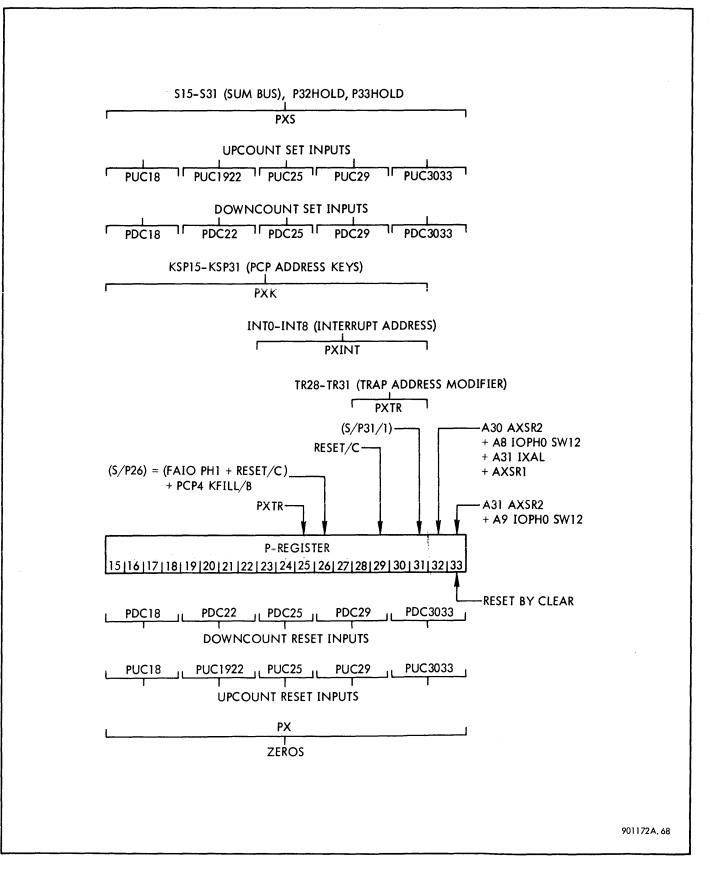

| 3-22   | P-Register Inputs and Enabling Signals                        | 3-31 |

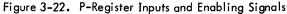

| 3-23   | DIO-Register Inputs and Enabling Signals                      | 3-32 |

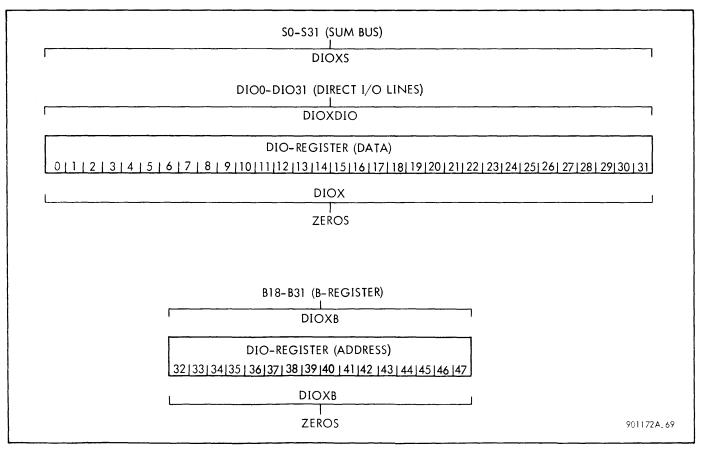

| 3-24   | Macro-Counter Inputs and Enabling Signals                     | 3-33 |

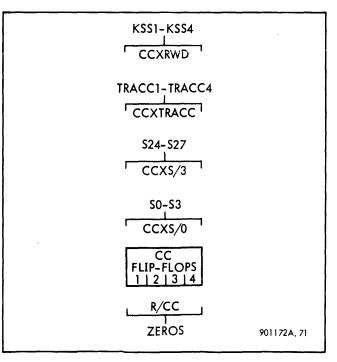

| 3-25   | Condition Code Flip-Flop Register Inputs and Enabling Signals | 3-33 |

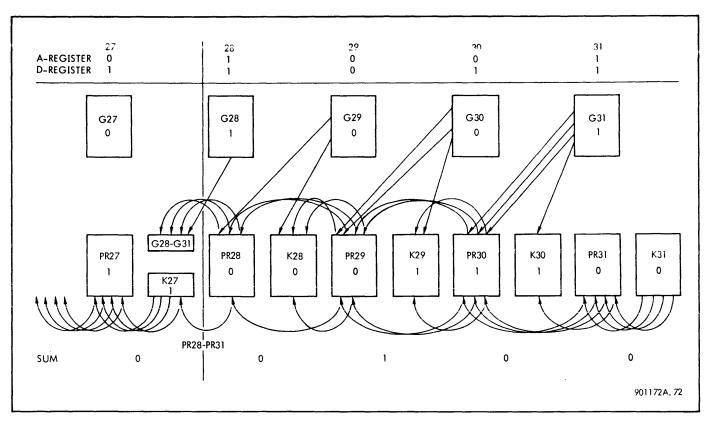

| 3-26   | A Plus D Adder Logic.                                         | 3-34 |

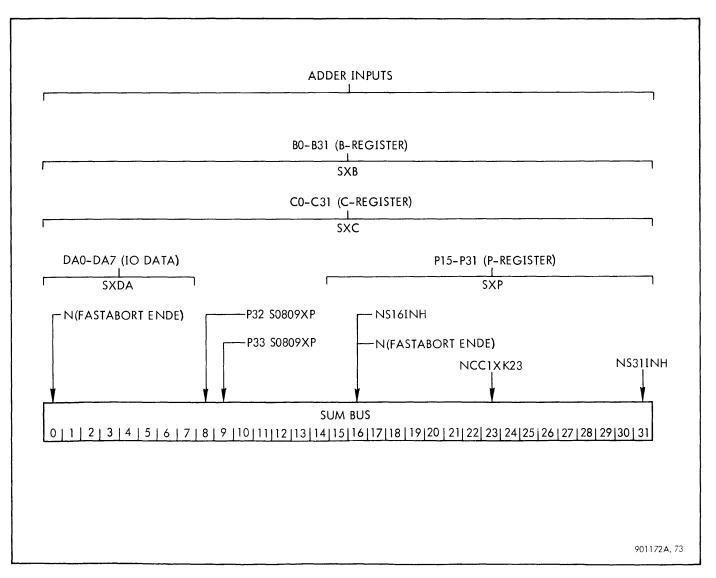

| 3-27   | Sum Bus Inputs and Enabling Signals                           | 3-38 |

| 3-28   | Private Memory Register Block                                 | 3-43 |

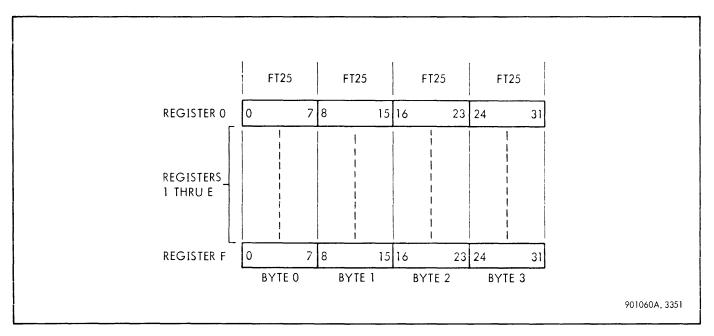

| 3-29   | Word Distribution in Private Memory Block                     | 3-44 |

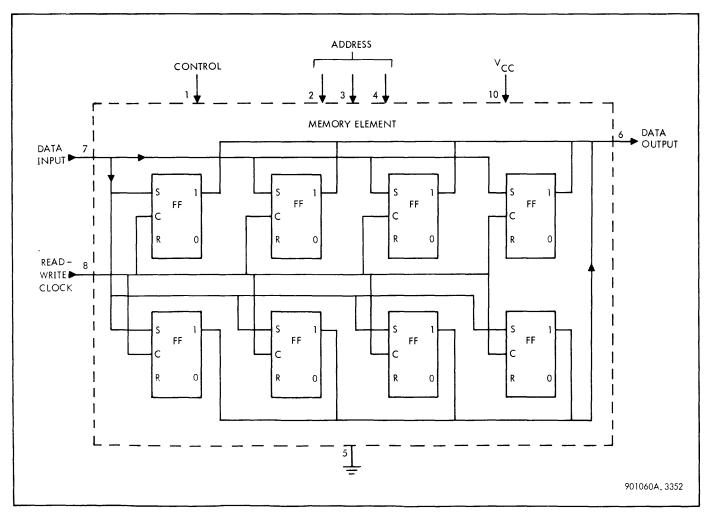

| 3-30   | SDS 304 Memory Element, Simplified Diagram                    | 3-44 |

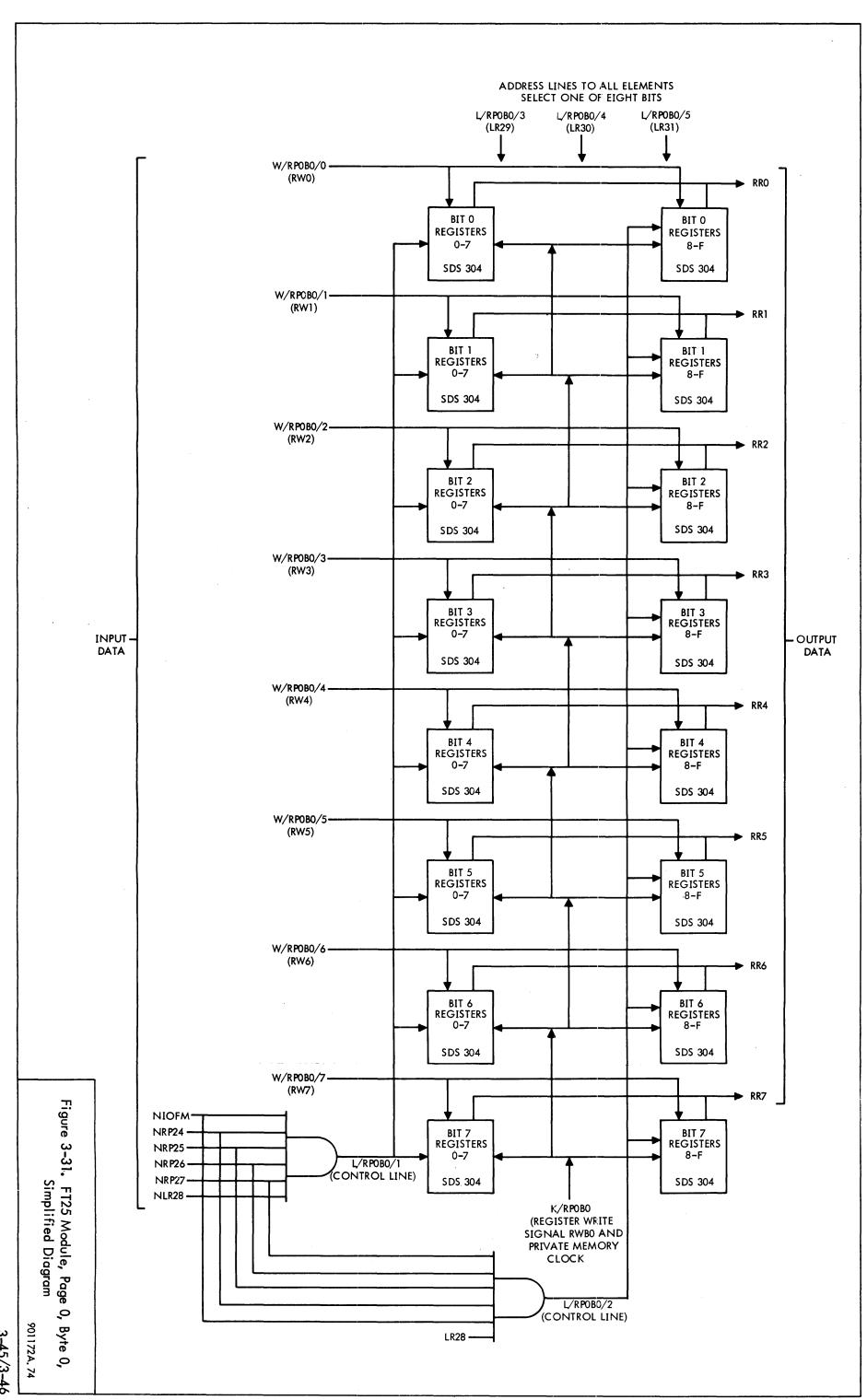

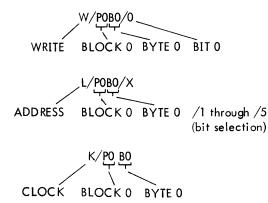

| 3-31   | FT25 Module, Page 0, Byte 0, Simplified Program               | 3-45 |

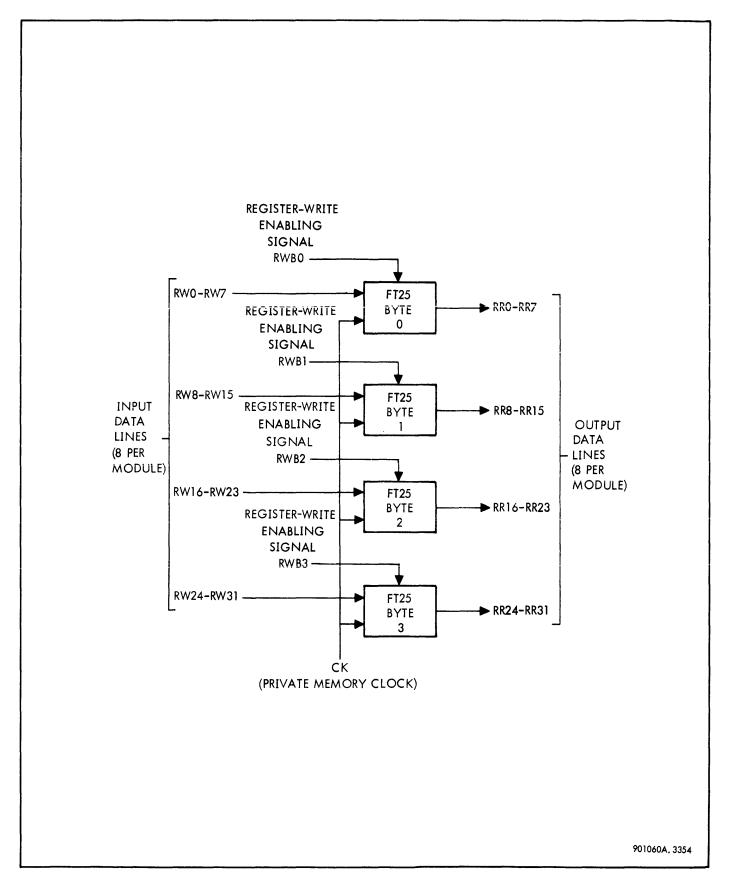

| 3-32   | Private Memory Data Organization                              | 3-47 |

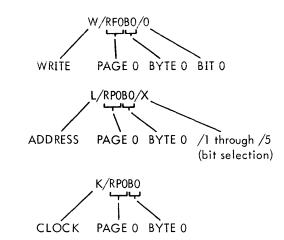

| 3-33   | Bit Addressing on FT25 Module.                                | 3-48 |

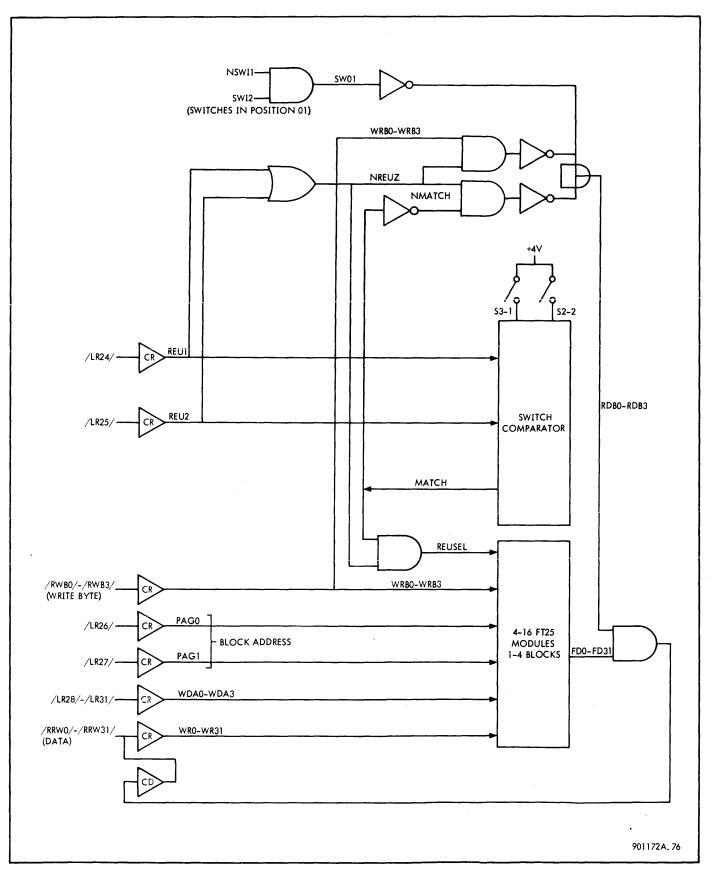

| 3-34   | Register Extension Chassis, Simplified Logic Diagram          | 3-49 |

|        |                                                               |      |

### LIST OF ILLUSTRATIONS (Cont.)

| Figure        | Title                                                                            | Page           |

|---------------|----------------------------------------------------------------------------------|----------------|

| 3-35          | Register Extension FT25 Module, Page 0, Byte 0, Simplified Diagram               | 3-51           |

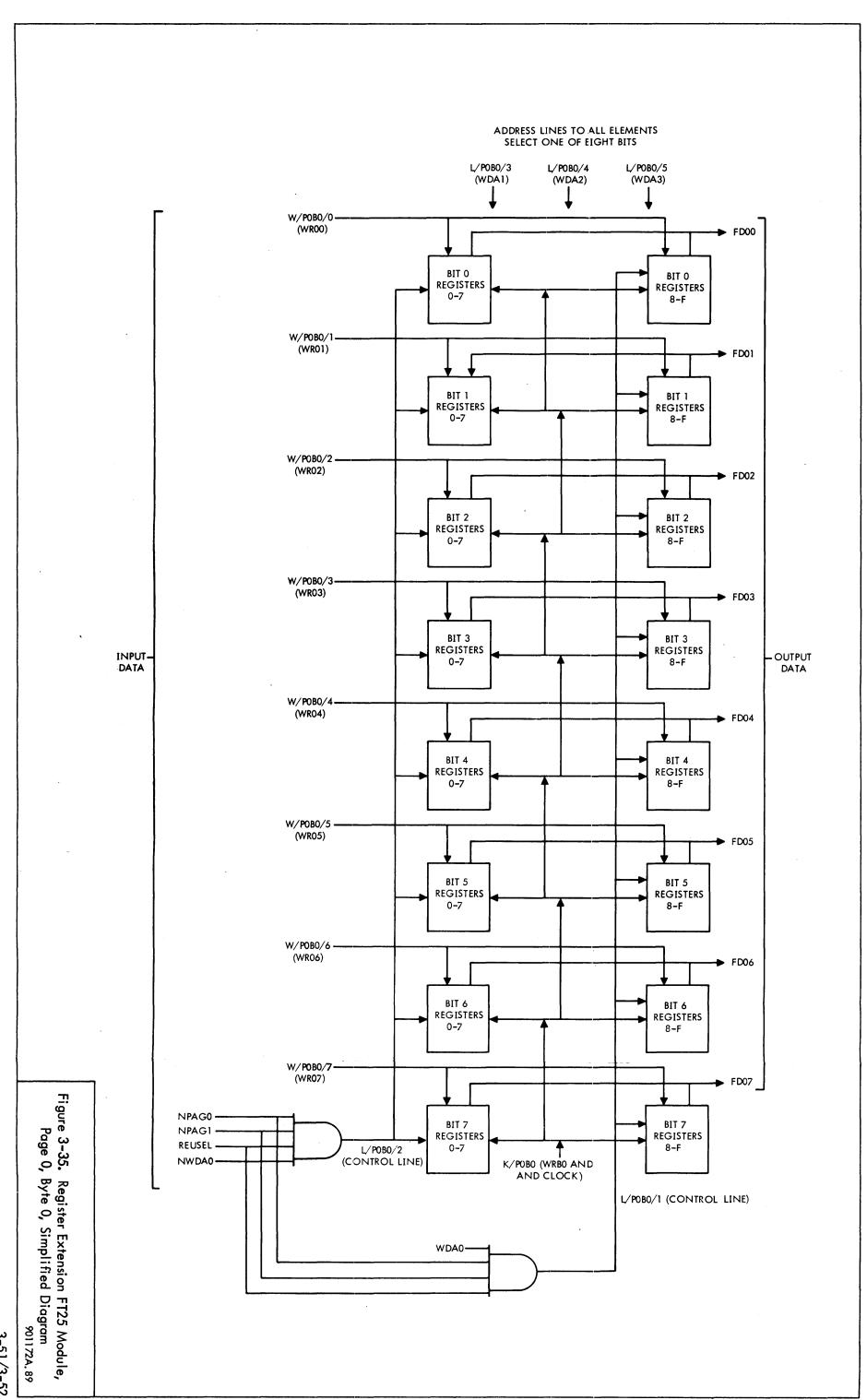

| 3 <b>-36</b>  | Clock Generator, Simplified Block Diagram                                        | 3-54           |

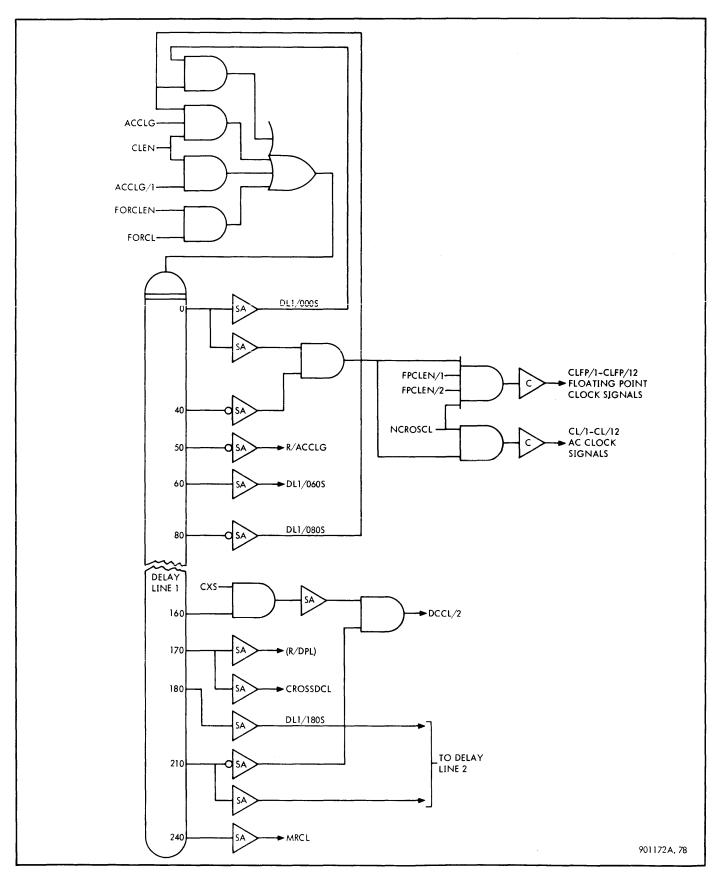

| 3-37          | Delay Line 1, Logic Diagram                                                      | 3-55           |

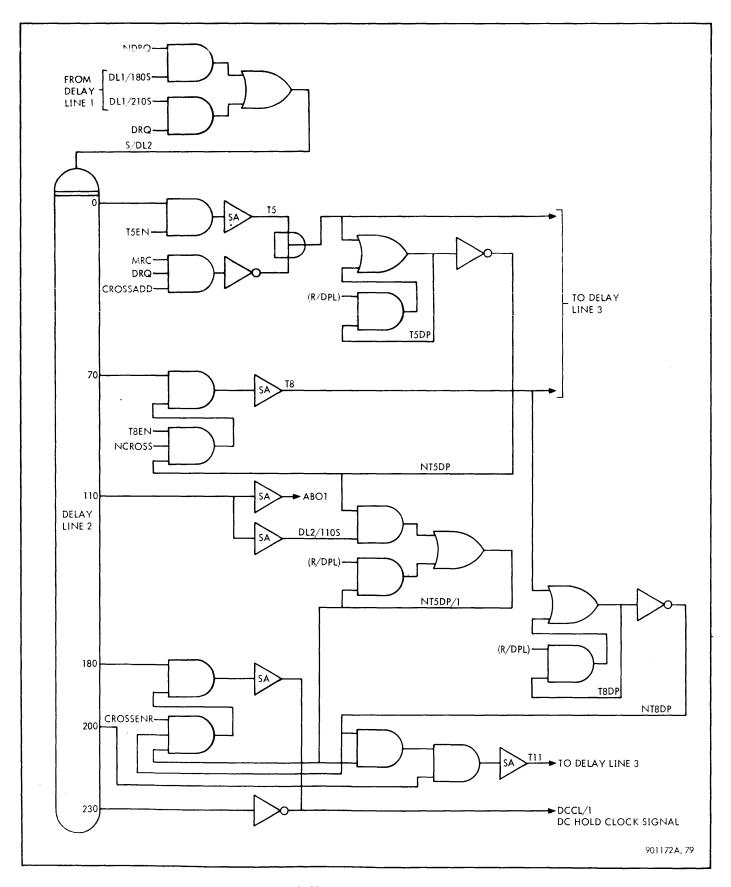

| 3-38          | Delay Line 2, Logic Diagram                                                      | 3-56           |

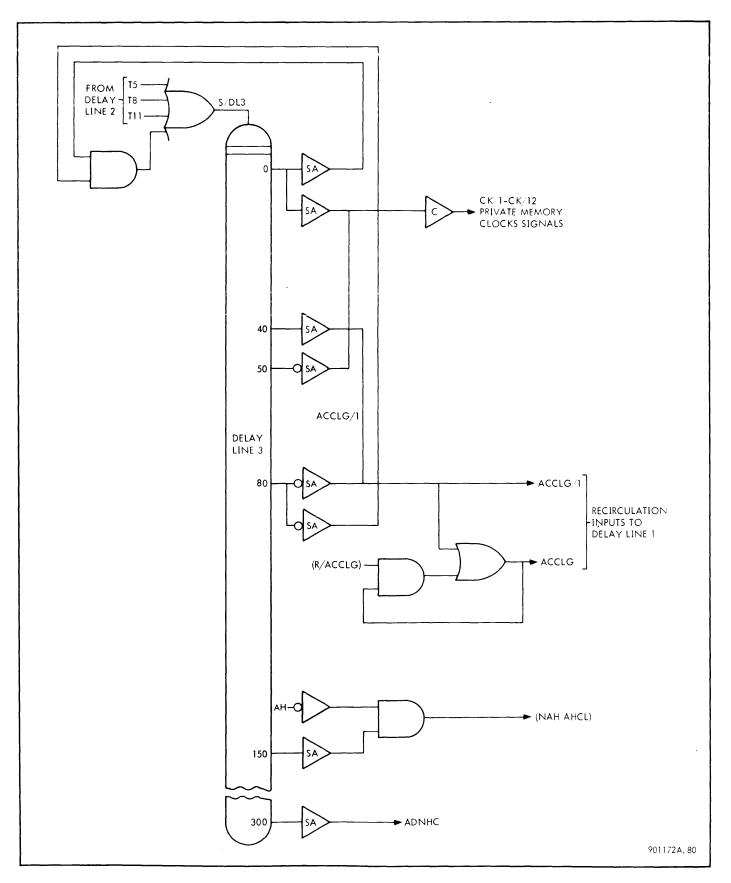

| 3-39          | Delay Line 3, Logic Diagram                                                      | 3-58           |

| 3-40          | Clock Enabling Gates                                                             | 3-59           |

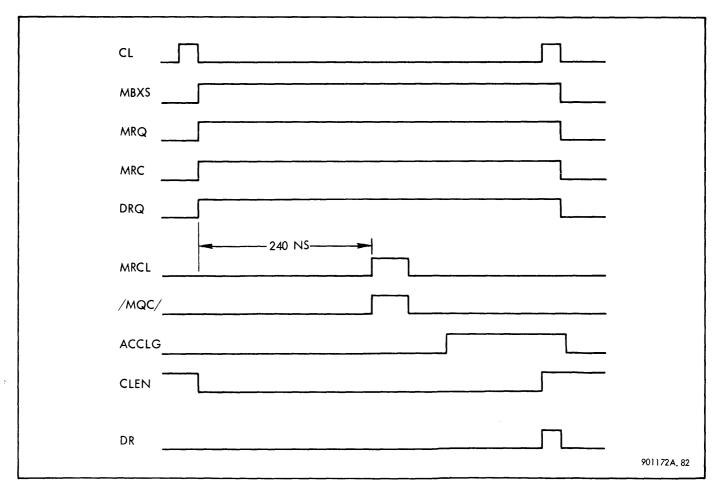

| 3-41          | Store Operation Timing Diagram                                                   | 3-59           |

| 3-42          | Data Release Latch, Logic Diagram                                                | 3-60           |

| 3-43          | Single Clock Generation                                                          | 3-61           |

| 3-44          | Oscillator Clock Generator, Block Diagram                                        | 3-62           |

| 3-45          | Real-Time Clock, Simplified Diagram                                              | 3-63           |

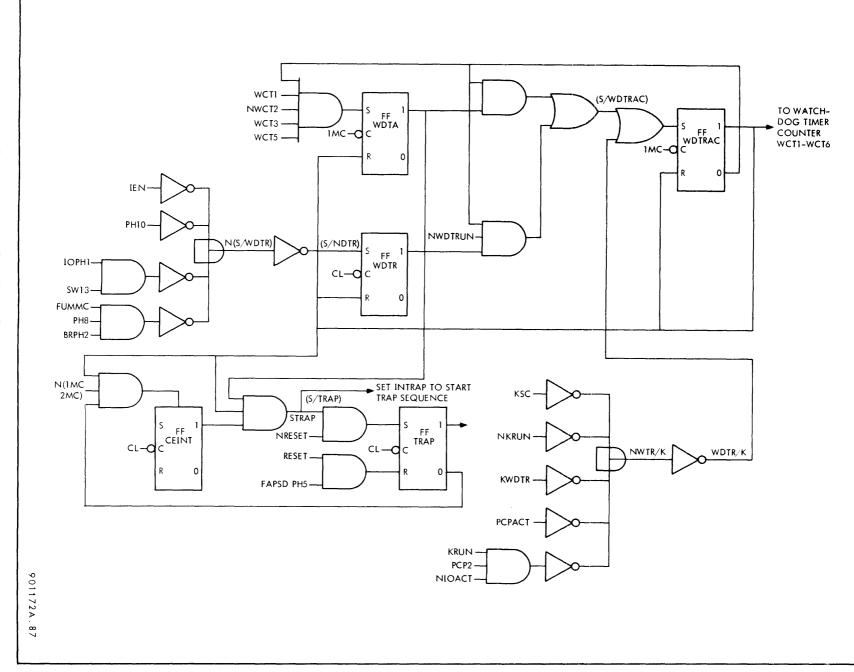

| 3-46          | Watchdog Timer Control Circuits, Logic Diagram                                   | 3-64           |

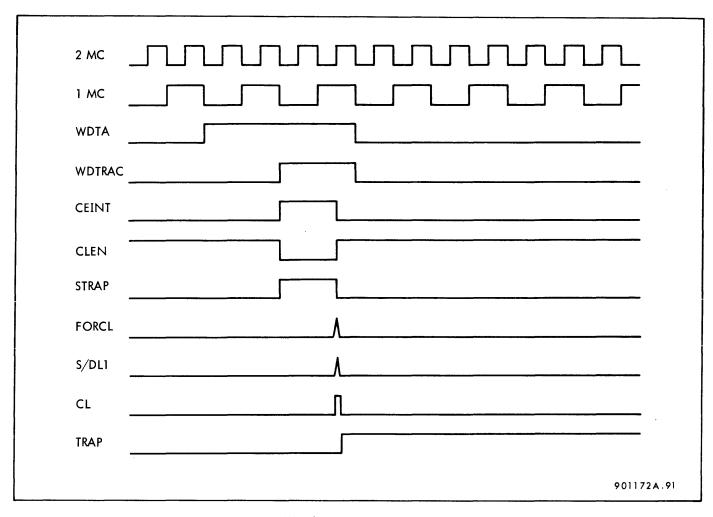

| 3-47          | Watchdog Timer Runout, Timing Diagram                                            | 3-65           |

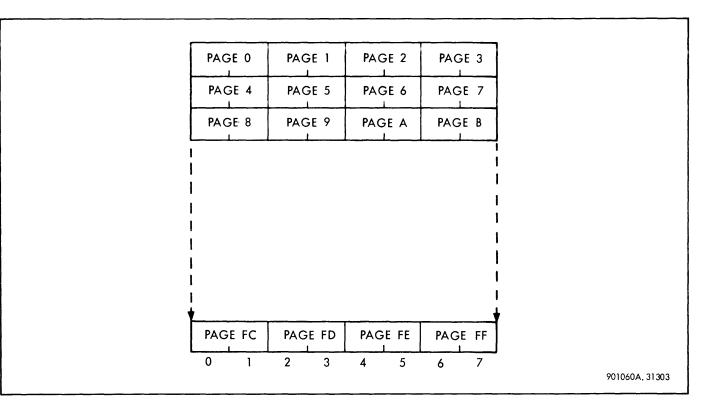

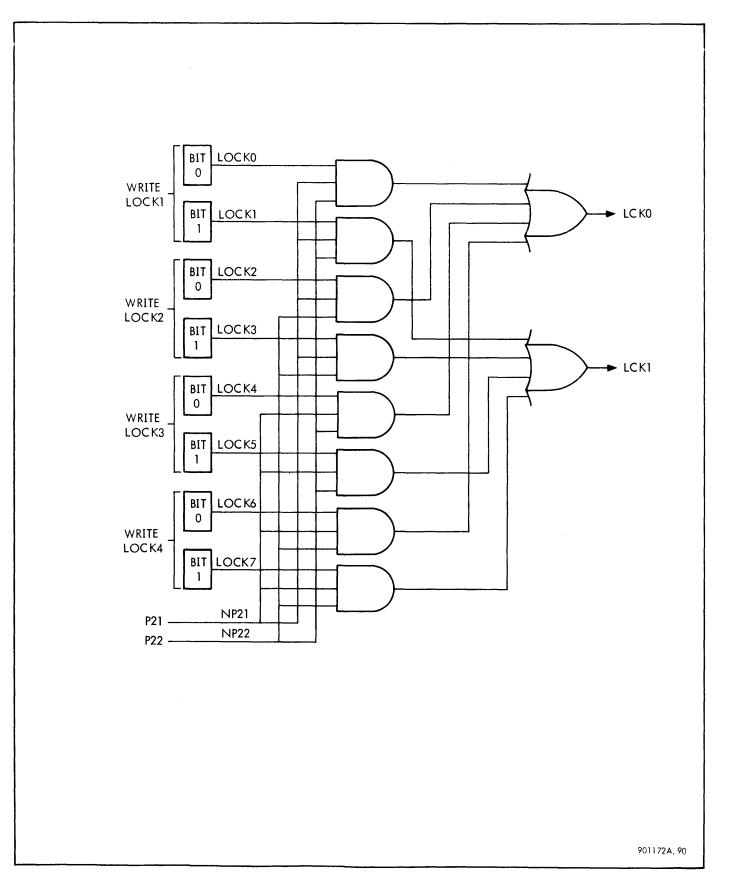

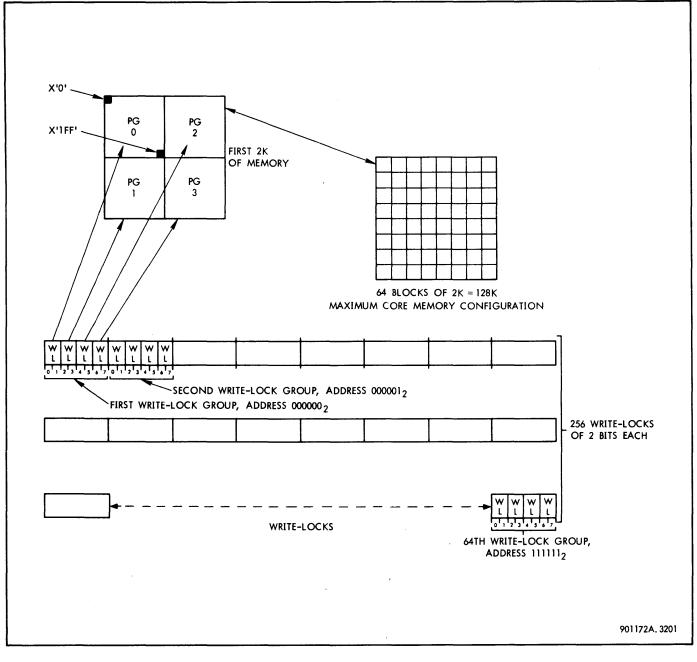

| 3-48          | Write Lock Registers                                                             | 3-66           |

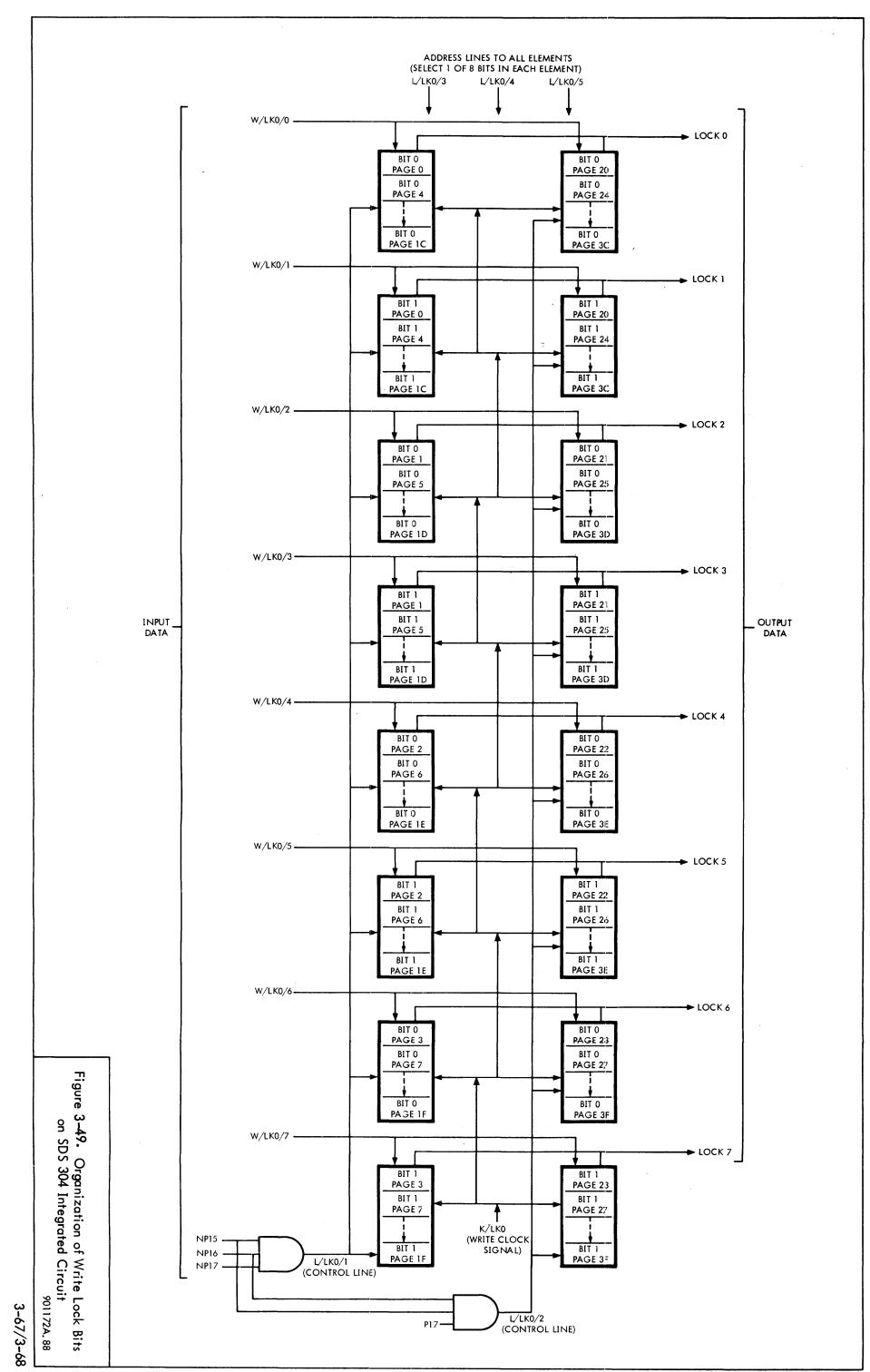

| 3-49          | Organization of Write Lock Bits on SDS 304 Integrated Circuit                    | 3-67           |

| 3-50          | Write Lock Addressing                                                            | 3-70           |

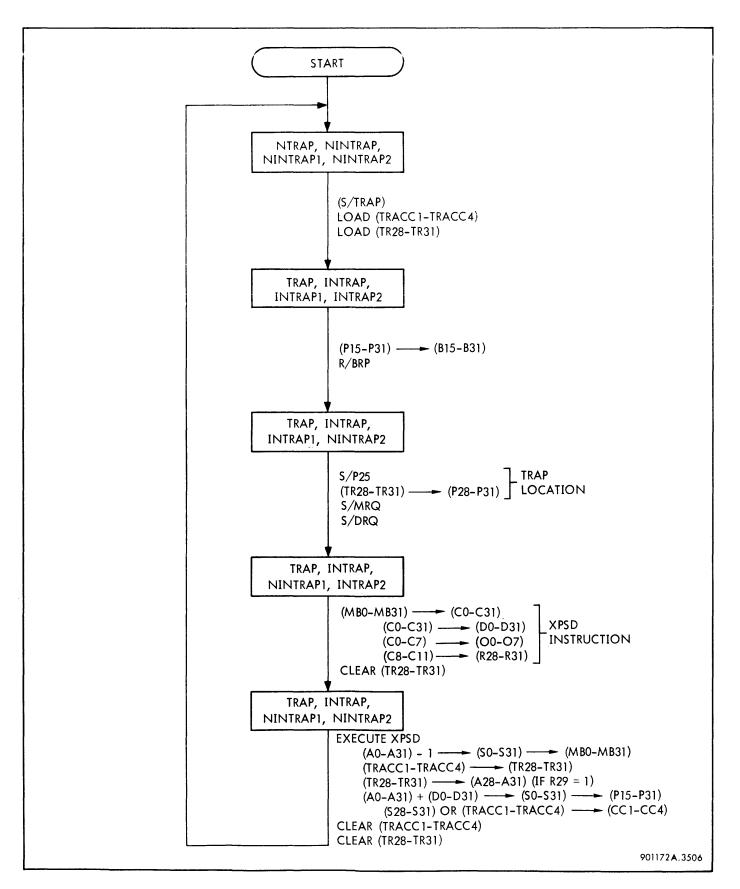

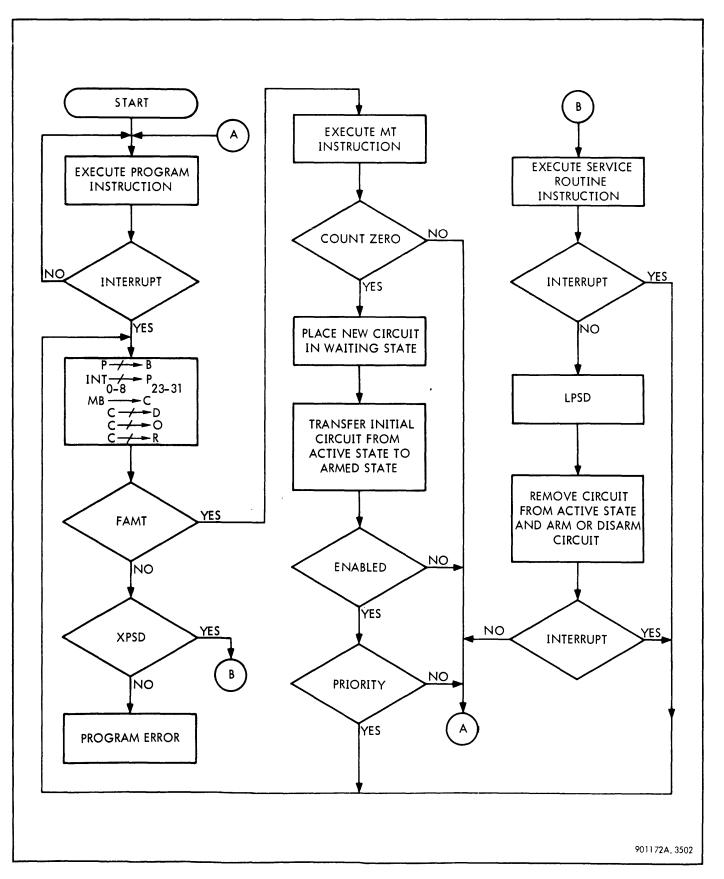

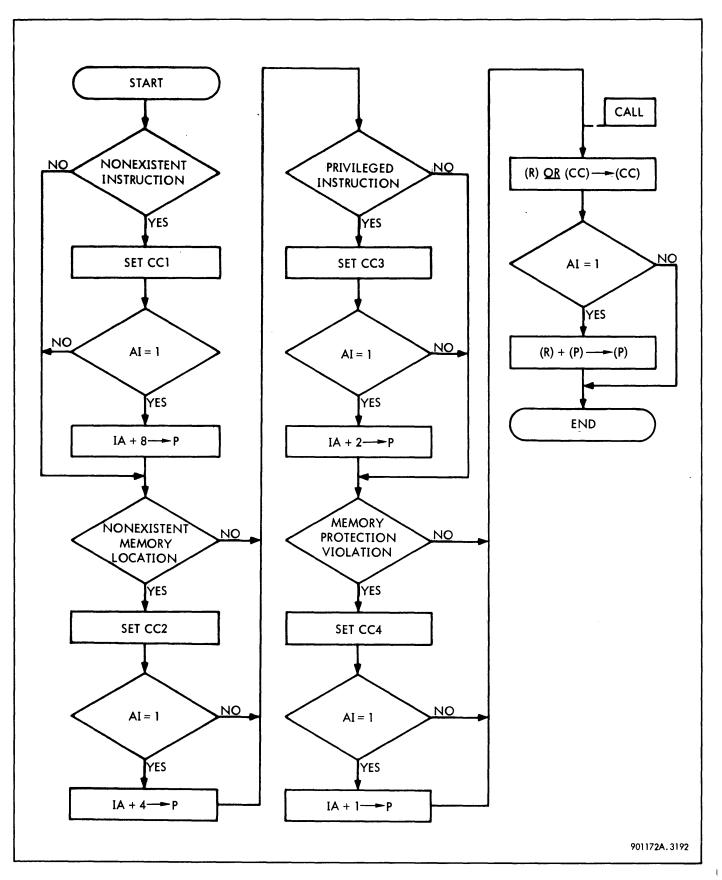

| 3-51          | Trap Sequence, Flow Diagram                                                      | 3-74           |

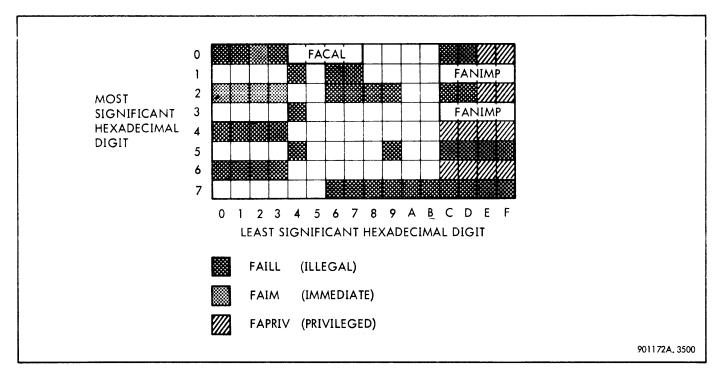

| 3-52          | Operation Codes Resulting in Trap                                                | 3-76           |

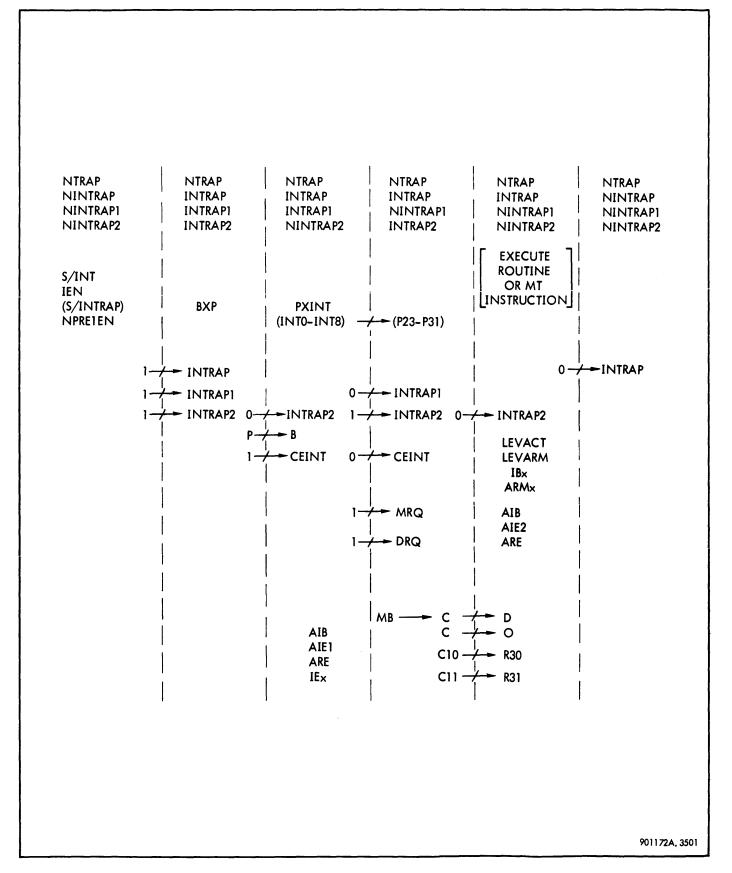

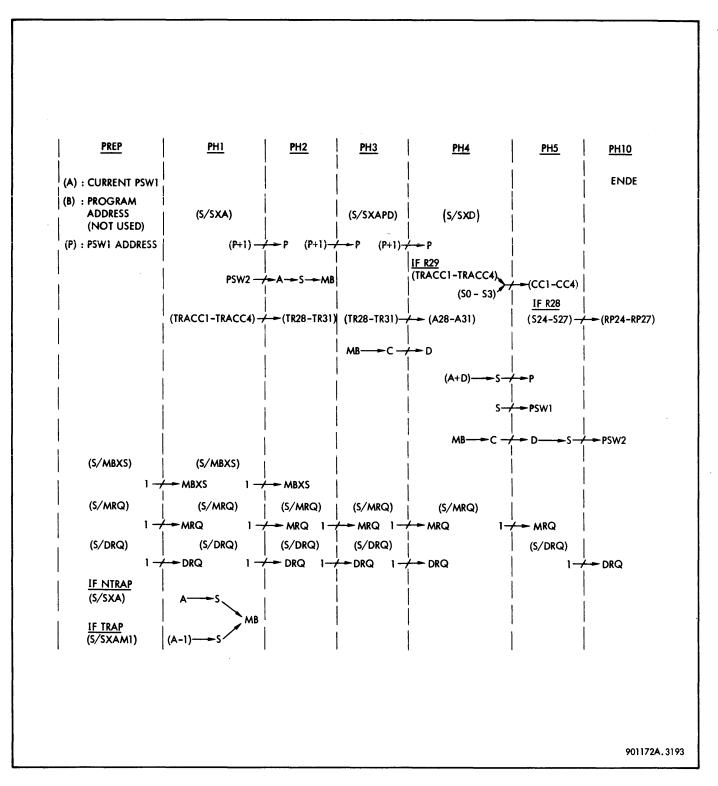

| 3-53          | Interrupt Phases                                                                 | 3-83           |

| 3-54          | Interrupt Sequence, Flow Diagram                                                 | 3-84           |

| 3-55          | Power-On and Power-Off Interrupt Circuits, Cycle of Operation                    | 3-85           |

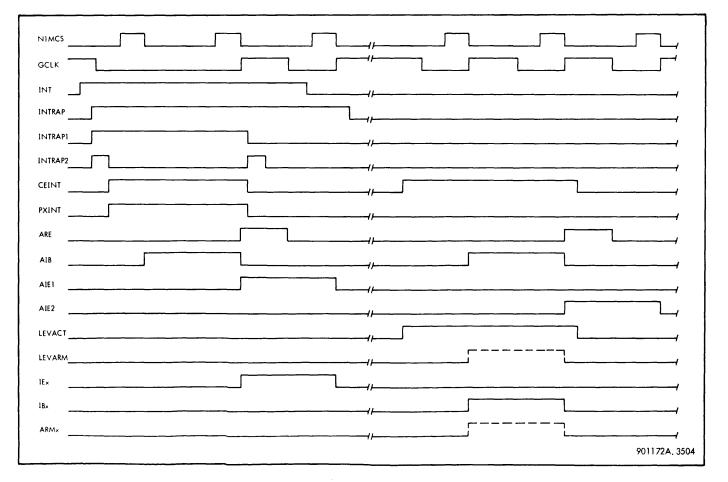

| 3-56          | Service Routine, Timing Diagram                                                  | 3-90           |

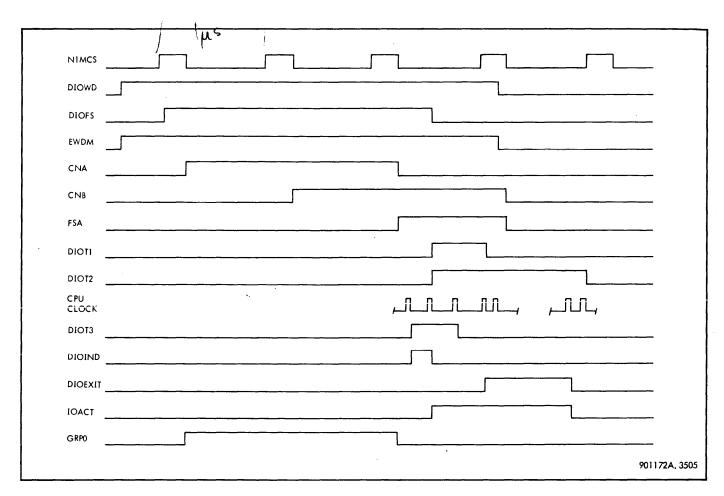

| 3-57          | Write Direct Sequence, Timing Diagram                                            | 3-93           |

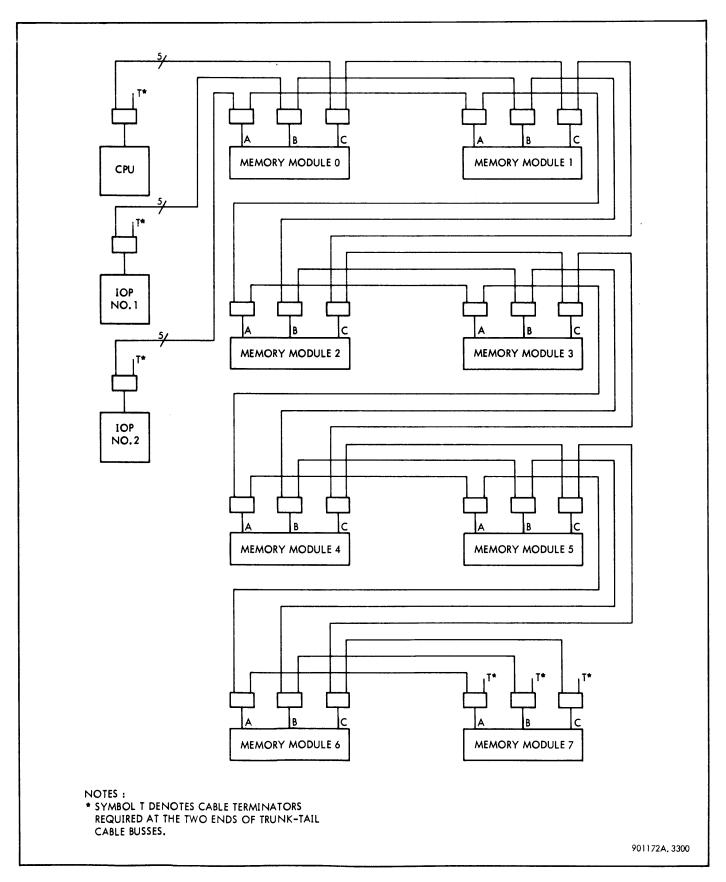

| 3-58          | Memory System Interconnection for Eight Memory Modules, One CPU, and Three IOP's | 3-96           |

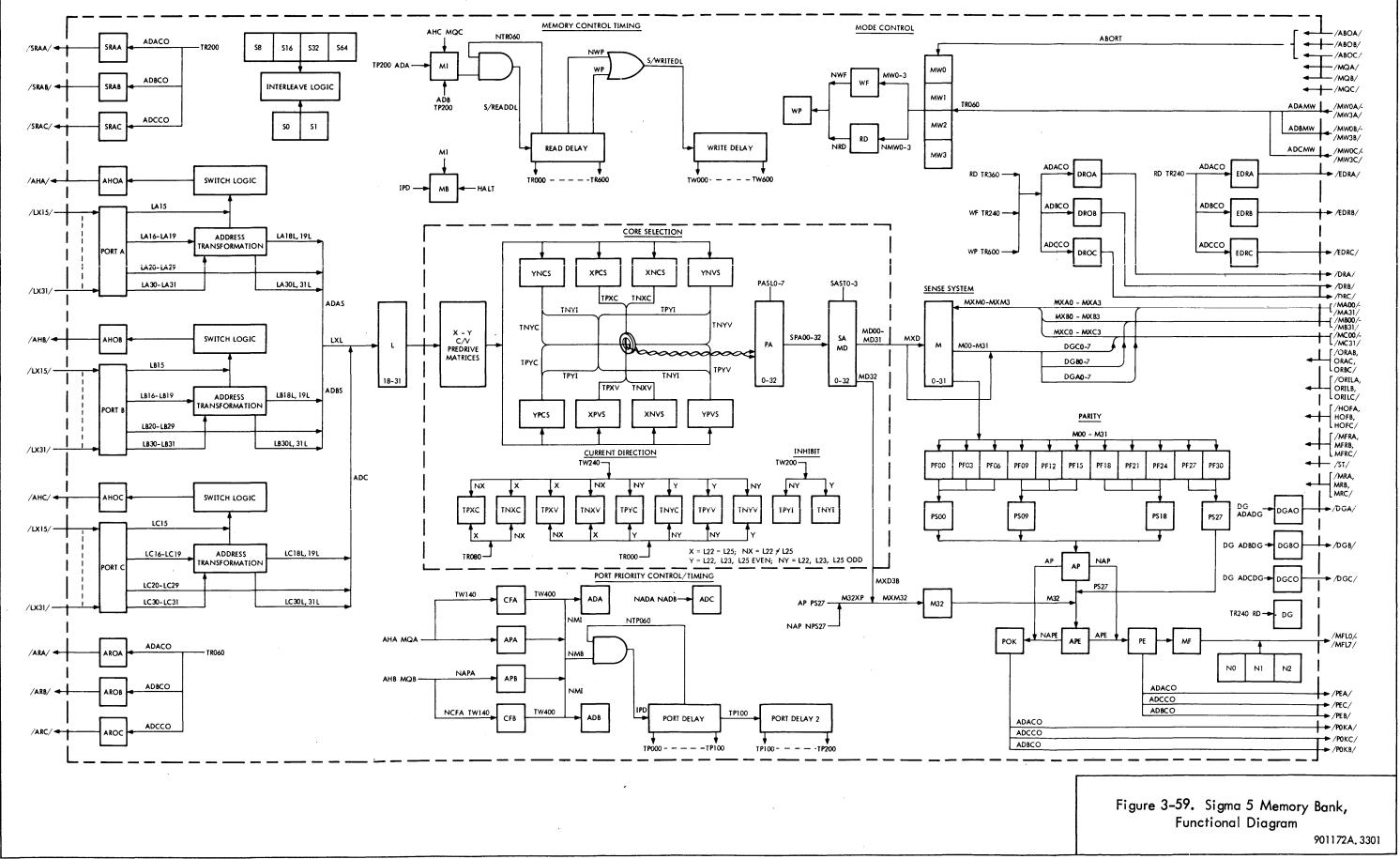

| 3-59          | Sigma 5 Memory Bank, Functional Diagram                                          | 3-97           |

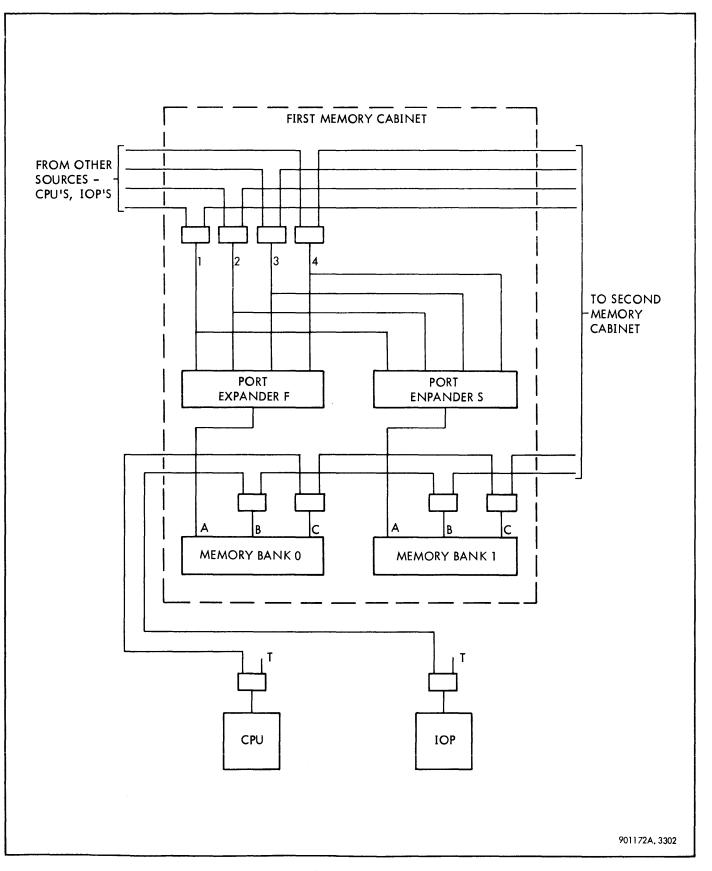

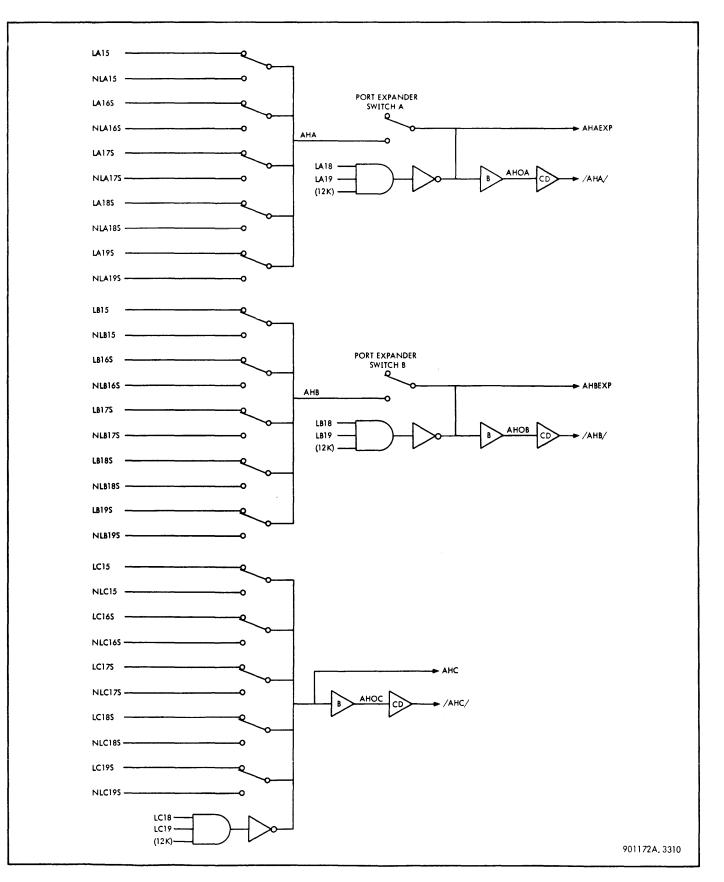

| 3-60          | Port Expanders F and S (First and Second)                                        | 3-100          |

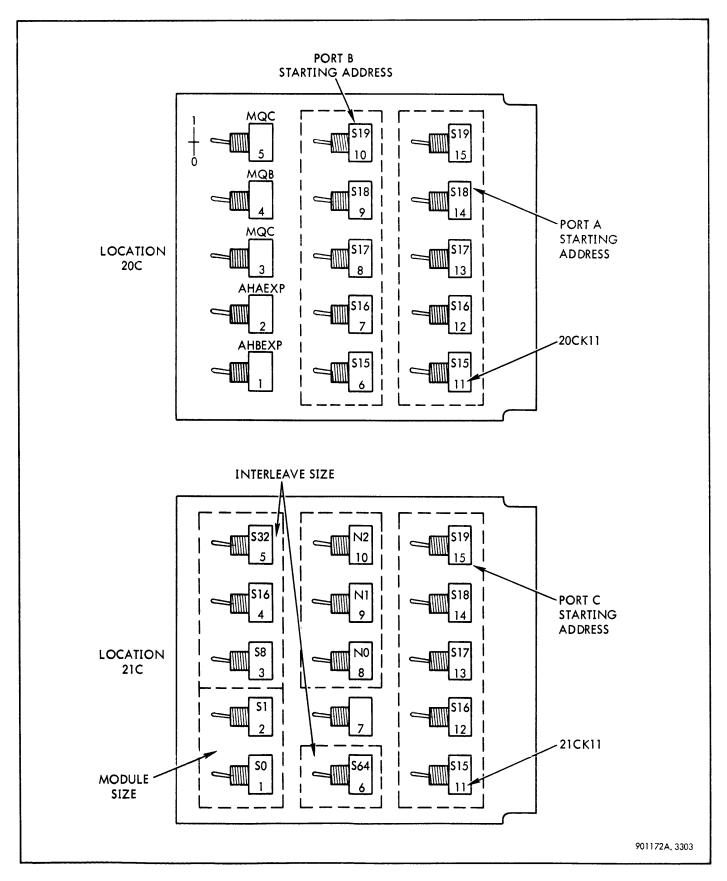

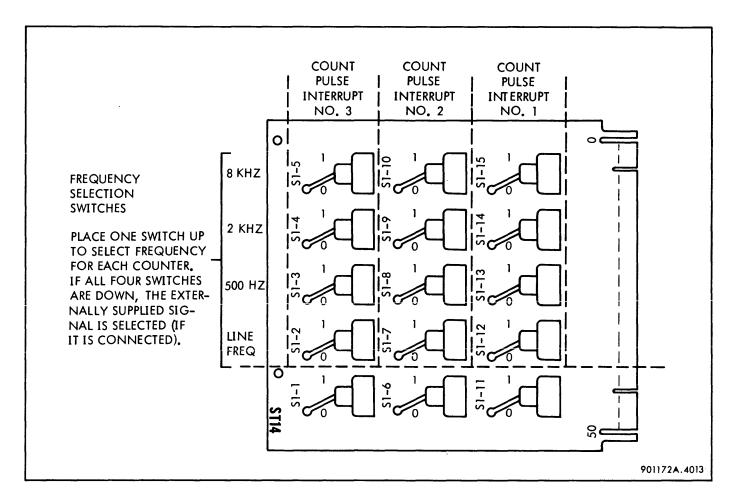

| 3-61          | Toggle Switch Modules (ST14)                                                     | 3-102          |

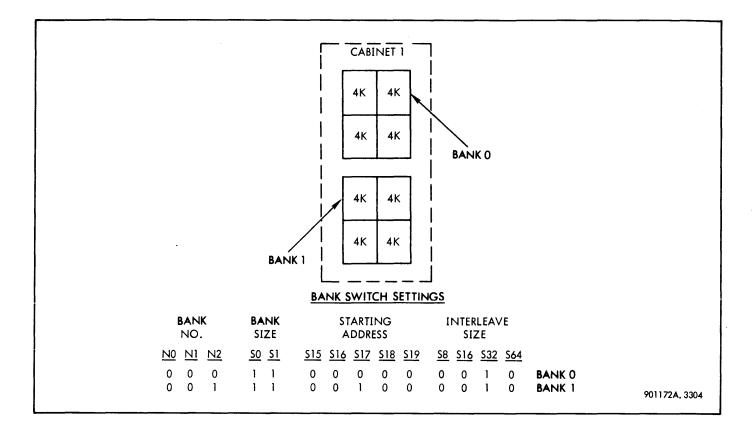

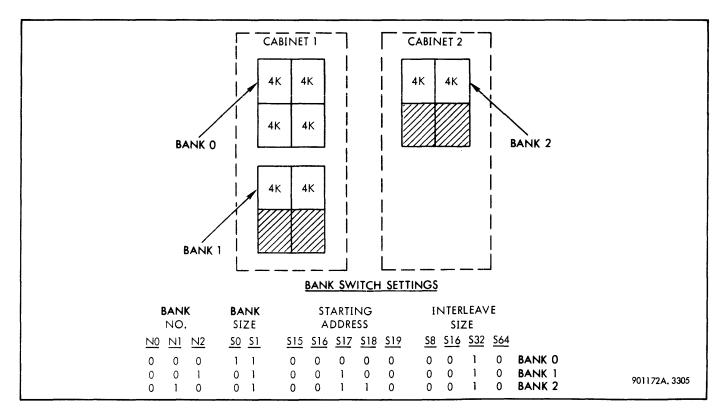

| 3-62          | 32K Interleaved Memory, Example 1                                                | 3-103          |

| 3-63          | 32K Interleaved Memory, Example 2                                                | 3-103          |

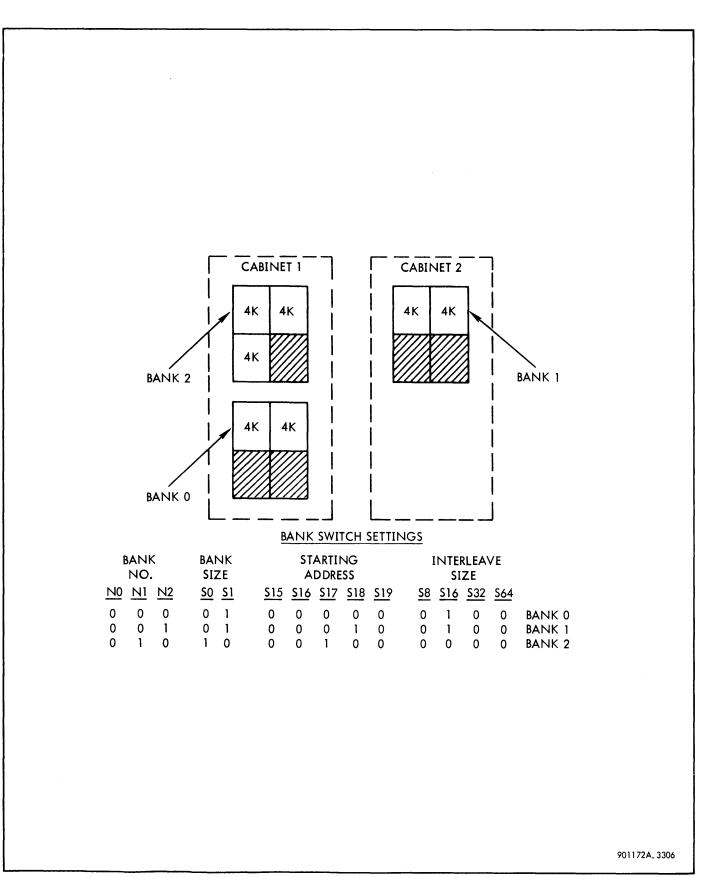

| 3-64          | 32K Interleaved Memory, Example 3                                                | 3-104          |

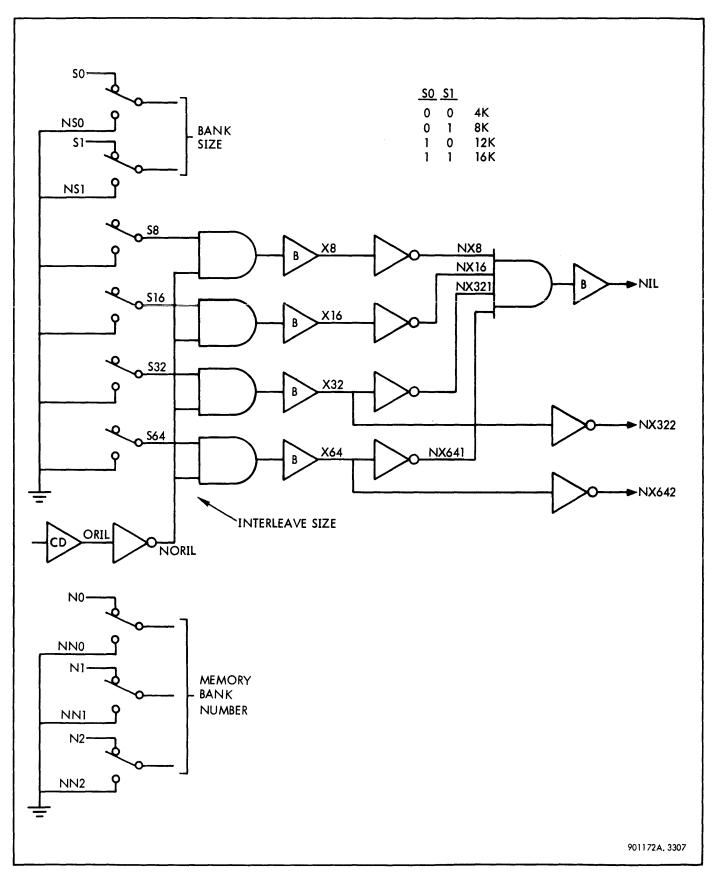

| 3-65          | Bank Size, Interleave Size, and Bank Number Switches                             | 3-105          |

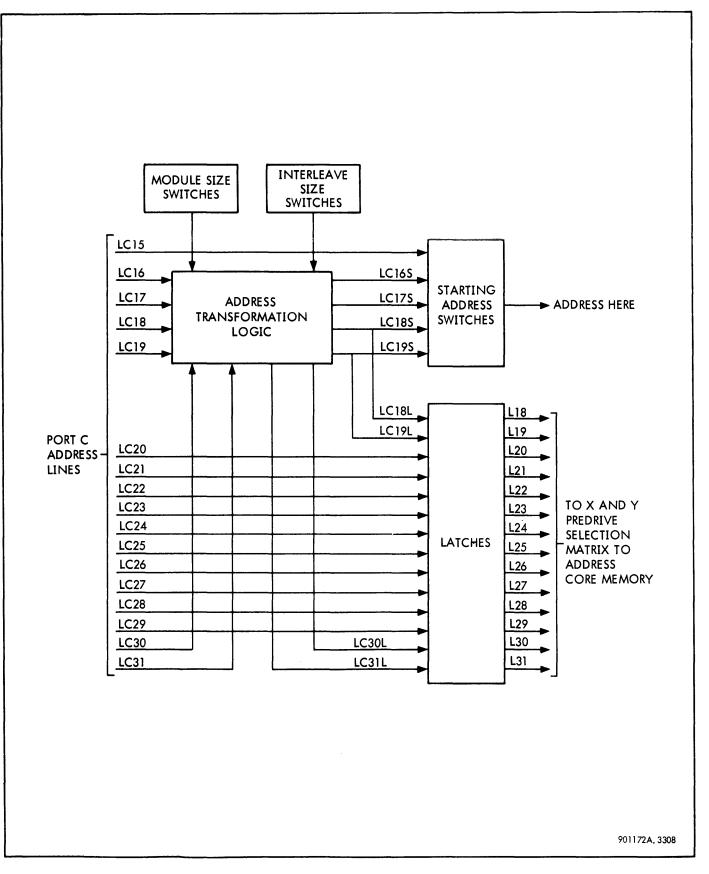

| 3-66          | Address Transformation for Interleaving (Port C), Simplified Diagram             | 3-106          |

| 3-67          | Memory Address Register and Interleave Transformation Logic                      | 3-107          |

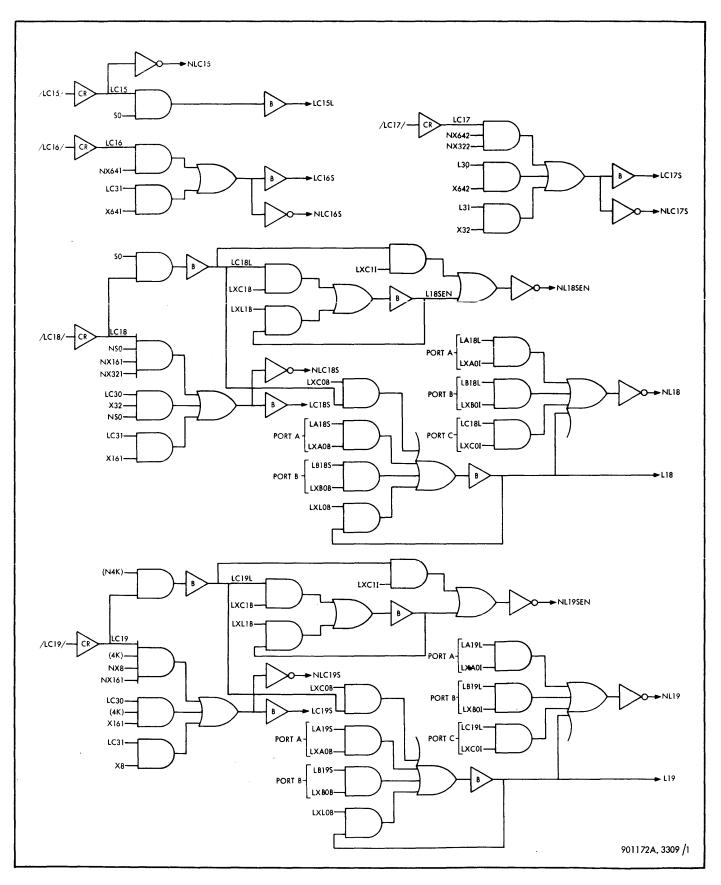

| 3-68          | Address Here Logic, Ports A, B, and C                                            | 3-110          |

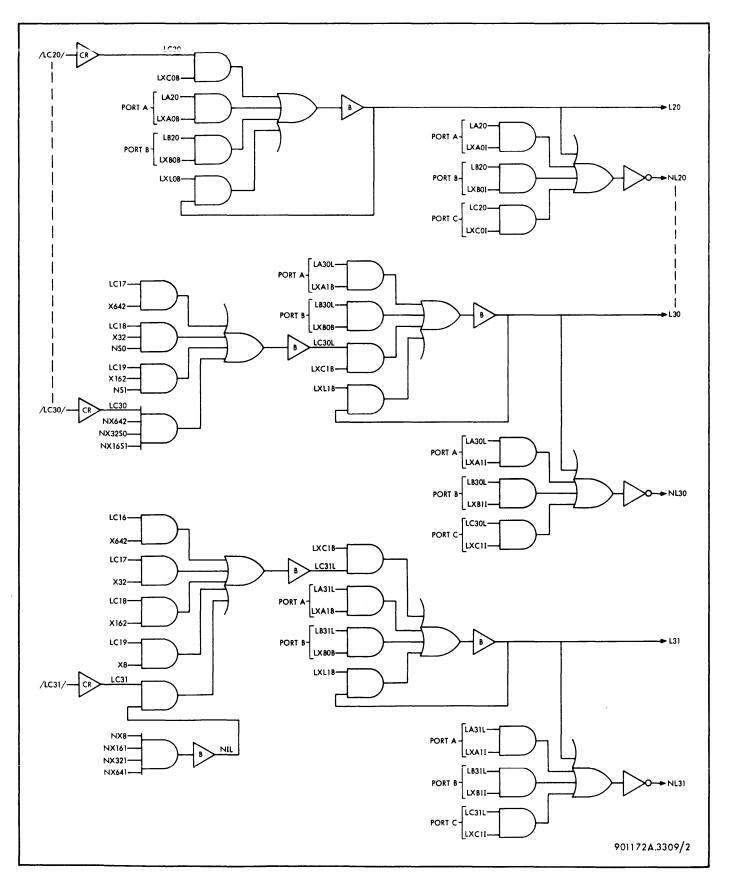

| 3-69          | Memory Request and Port Override Logic                                           | 3-111          |

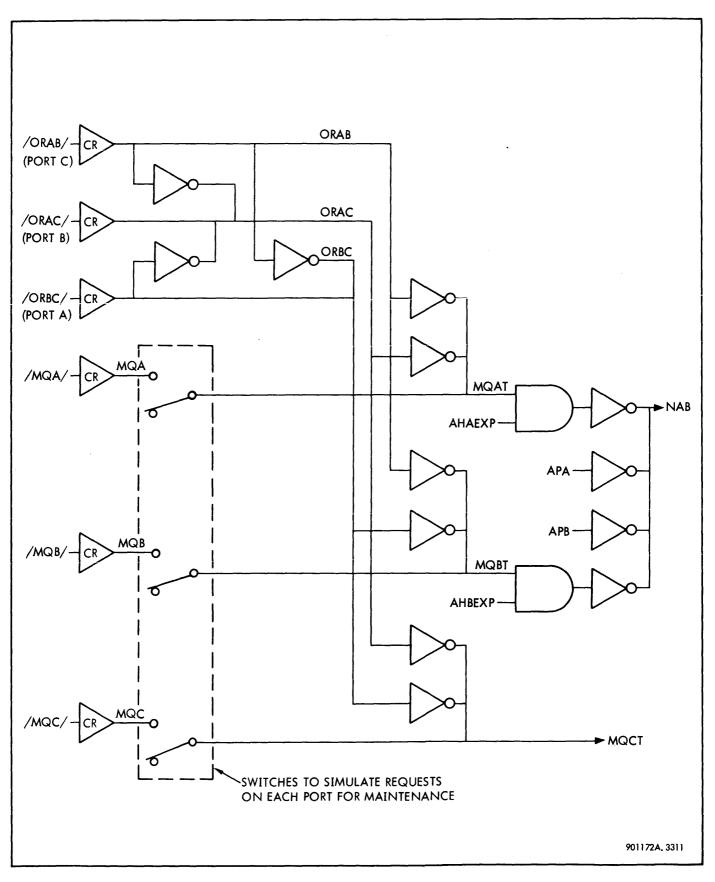

| 3-70          | Port Priority and Address Release Logic                                          | 3-112          |

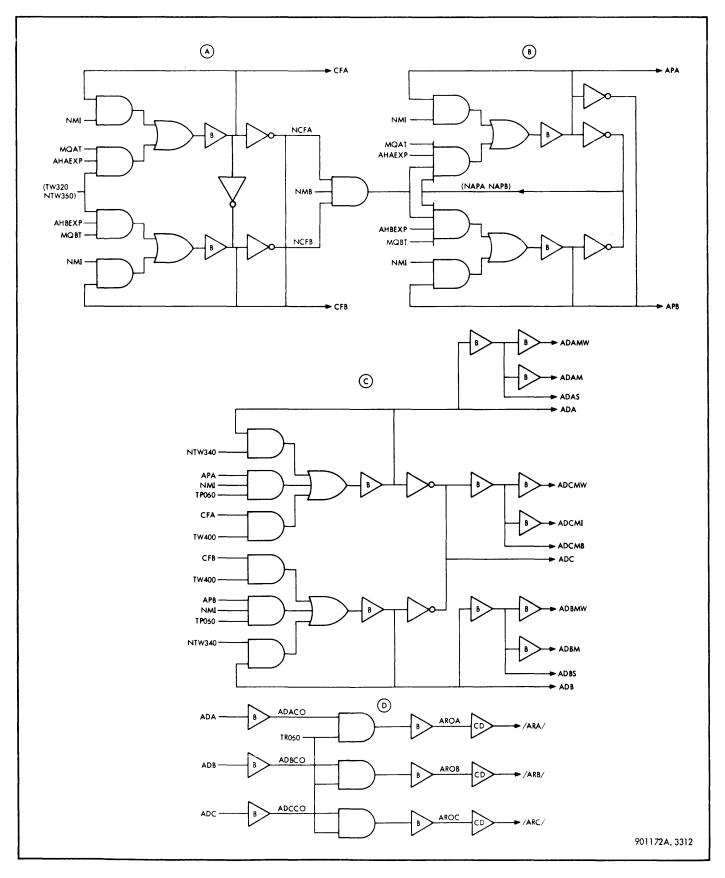

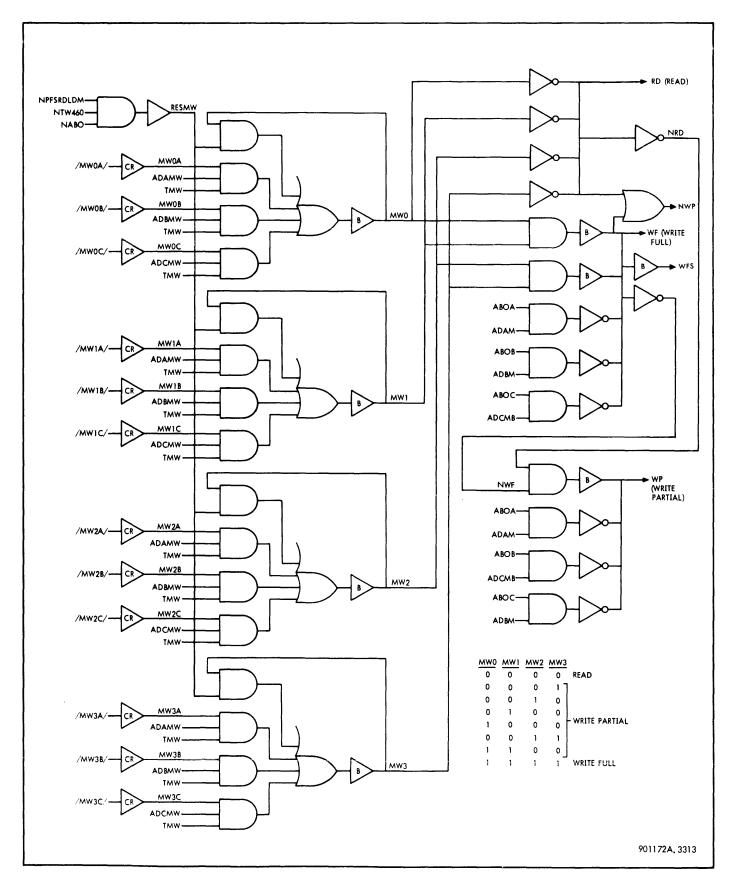

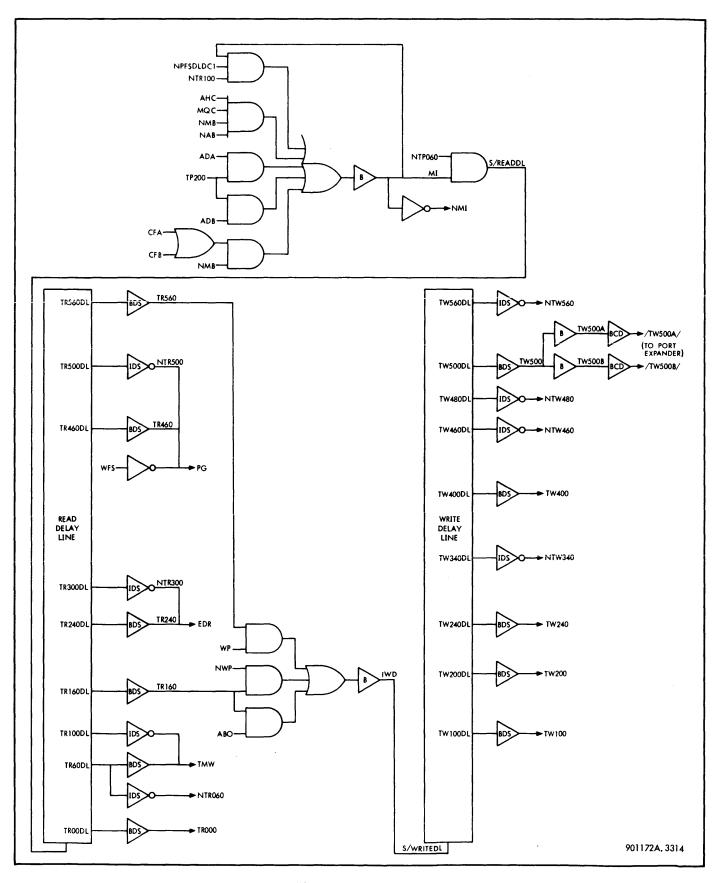

| 3-71          | Read, Full Write, and Partial Write Logic Diagram                                | 3-114          |

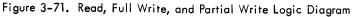

| 3-72          | Read and Write Delay Lines                                                       | 3-115          |

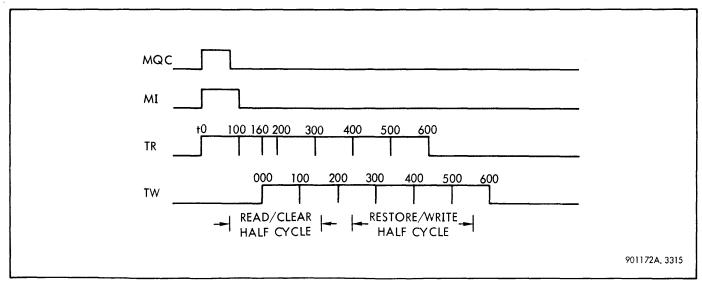

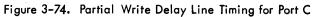

| 3 <b>-</b> 73 | Read–Restore and Full Write Delay Line Timing for Port C                         | 3-116          |

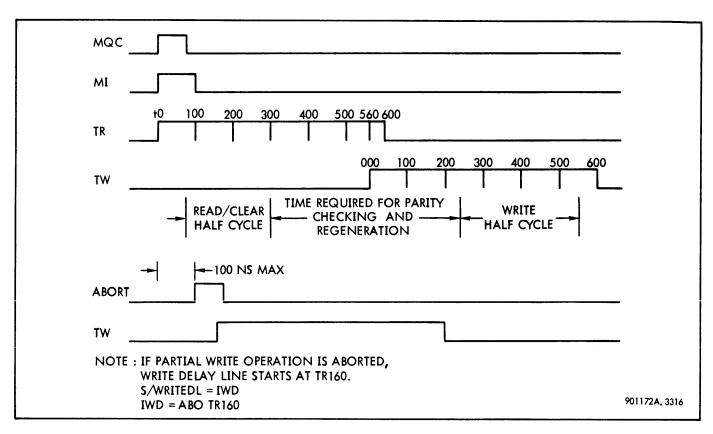

| 3-74          | Partial Write Delay Line Timing for Port C                                       | 3-117          |

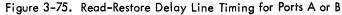

| 3-75          | Read–Restore Delay Line Timing for Ports A or B                                  | 3-117          |

| 3-76          | Ports A and B Delay Line                                                         | 3-118          |

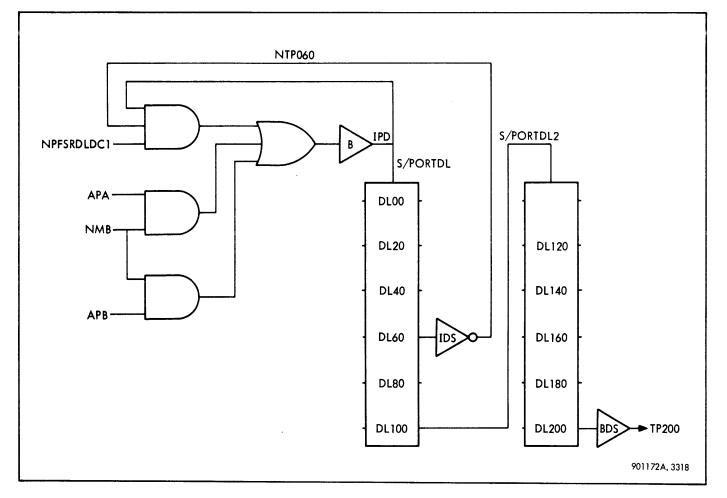

| 3 <b>-</b> 77 | Memory Busy (MB), Logic Diagram                                                  | 3-119          |

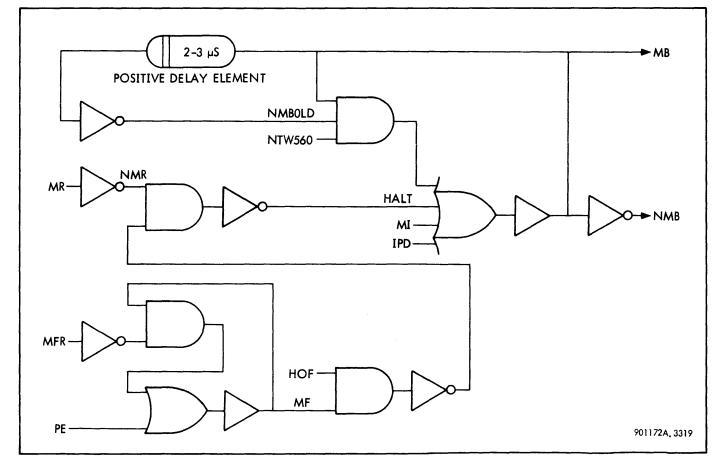

| 3-78          | Power Fail–Safe, Reset, and Memory Fault, Logic Diagram                          | 3-120          |

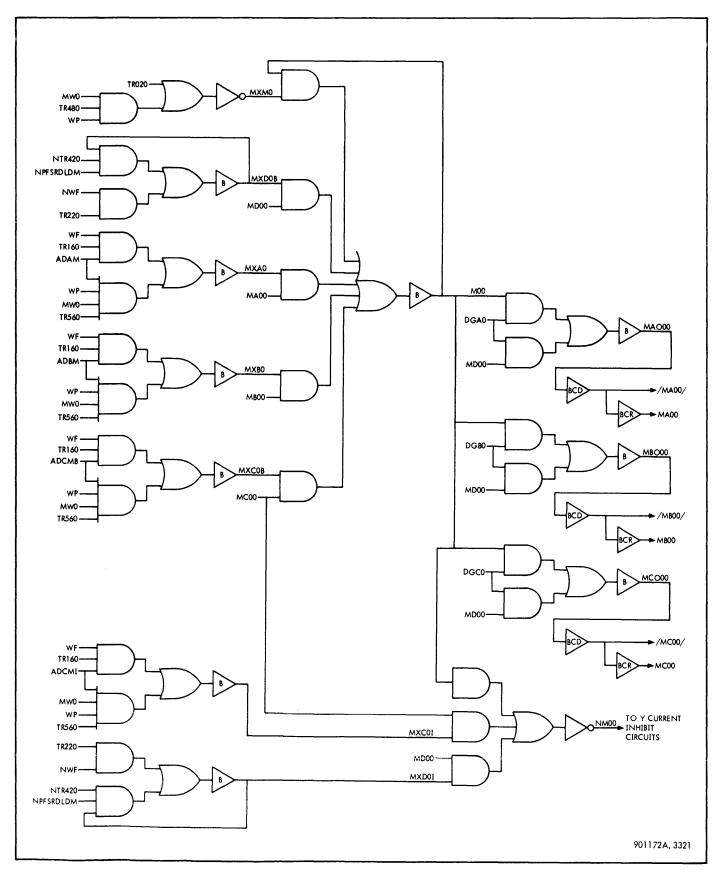

| 3-79          | M-Register (M00, Typical of M00–M31)                                             | 3-122          |

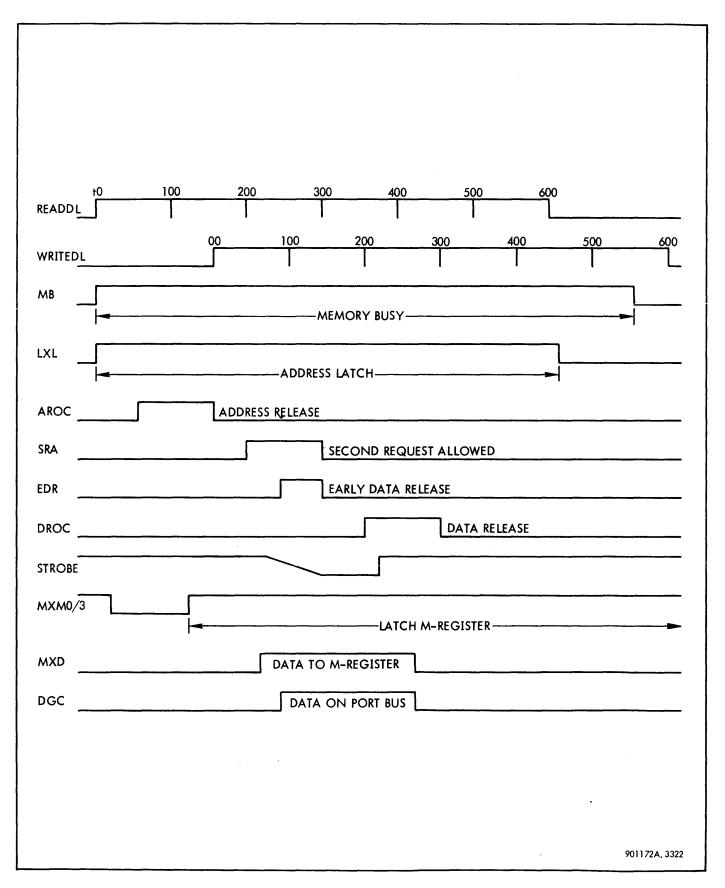

| 3-80          | Read Timing Diagram                                                              | 3-123          |

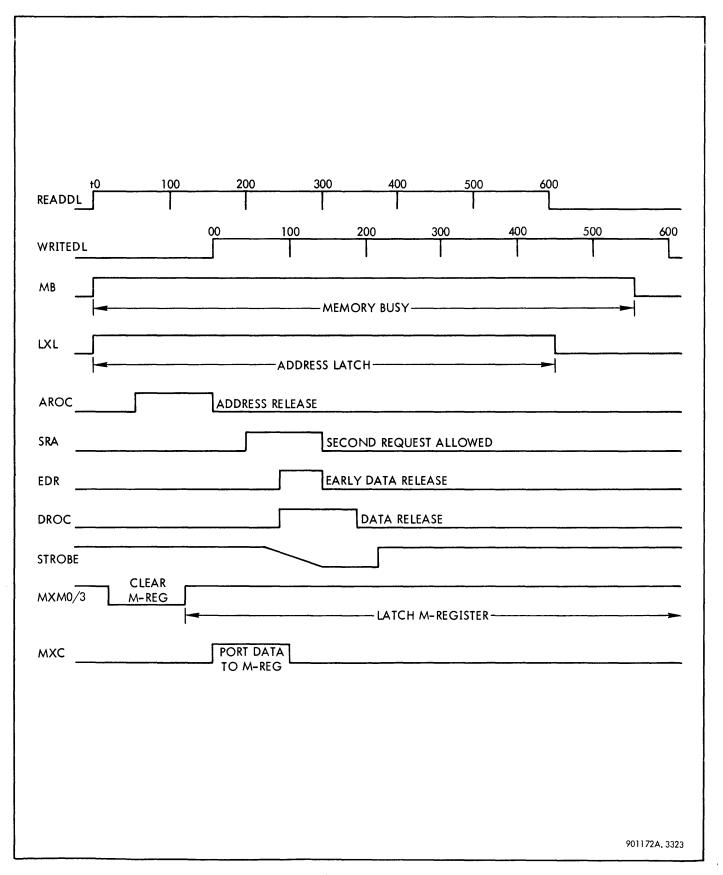

| 3-81          | Full Write Timing Diagram                                                        | 3-124          |

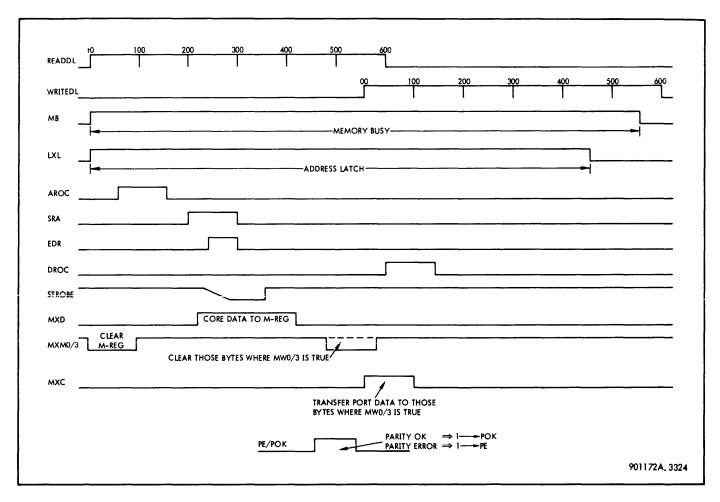

| 3-82          | Partial Write Timing Diagram                                                     | 3 <b>-</b> 125 |

| 3-83          | Parity Determination Logic Scheme                                                | 3-126          |

| 3-84          | Basic Core Switching                                                             | 3-128          |

| 3-85          | Simplified Memory, Read–Restore Operation                                        | 3-129          |

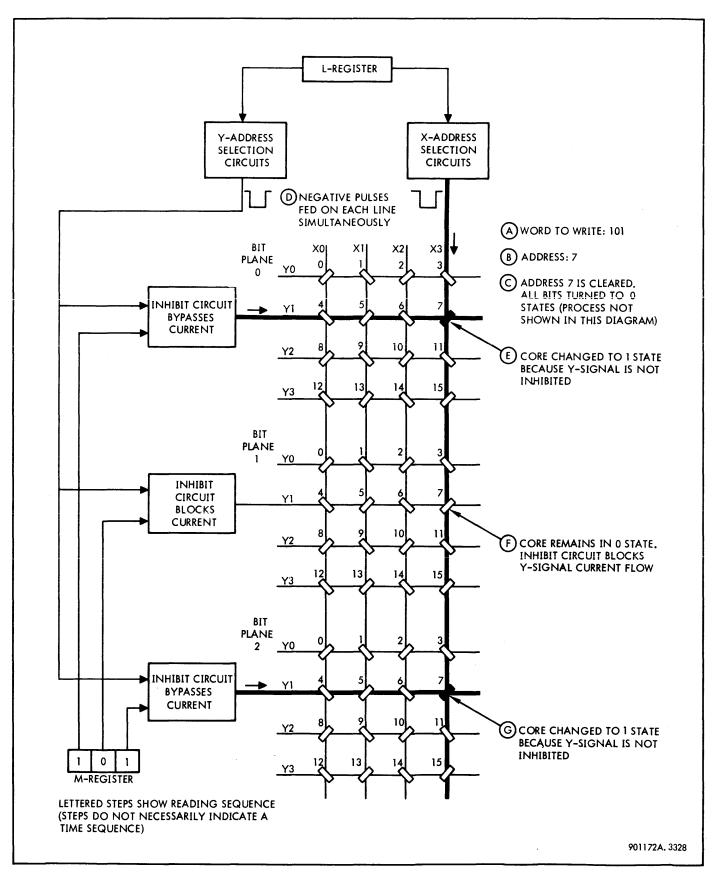

| 3-86          | Simplified Memory, Clear Write Operation                                         | 3-131          |

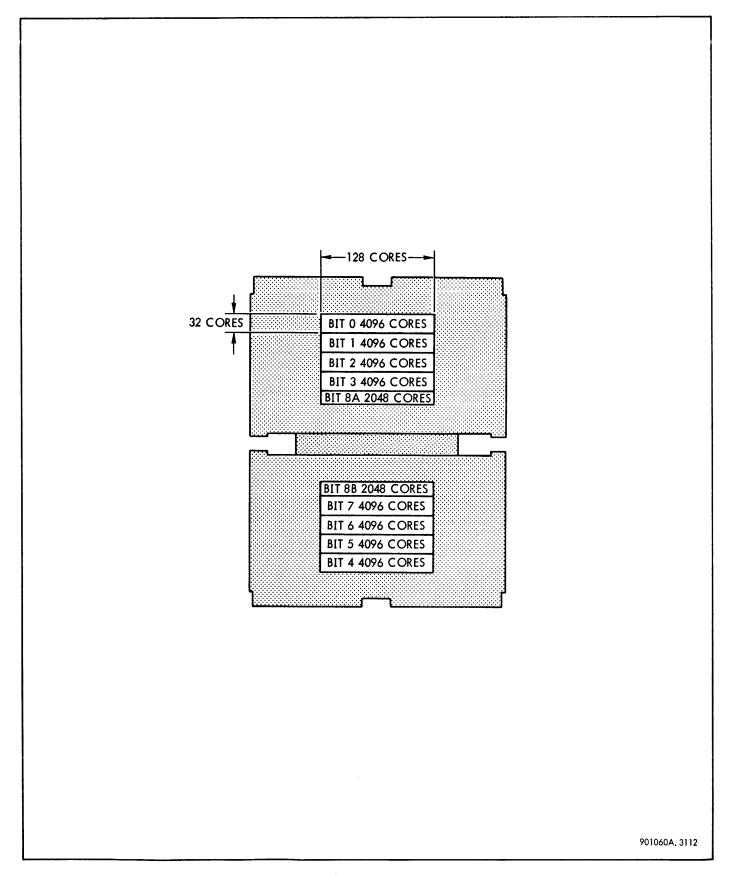

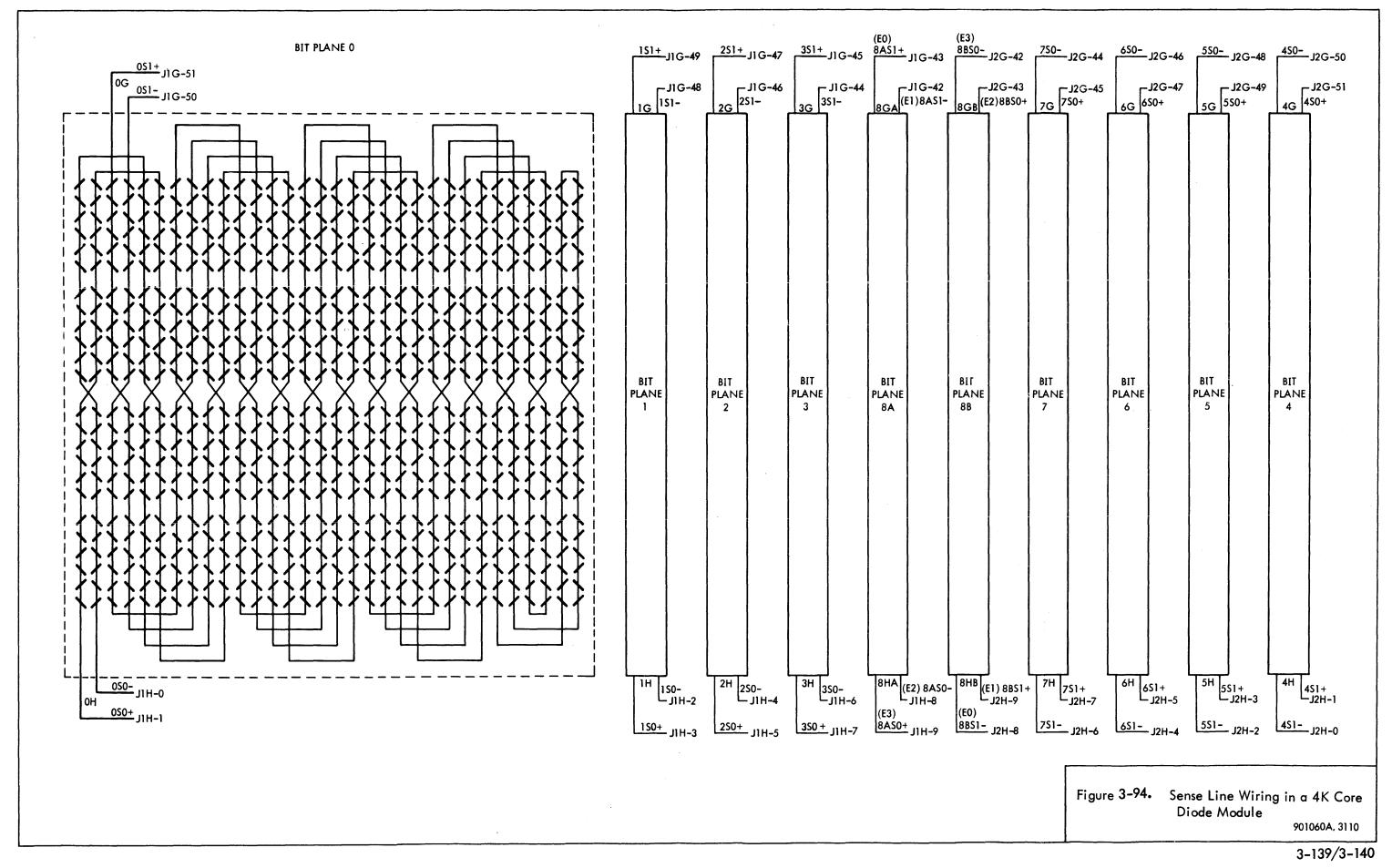

| 3-87          | Bit Plane Layout in a Core Diode Module                                          | 3-132          |

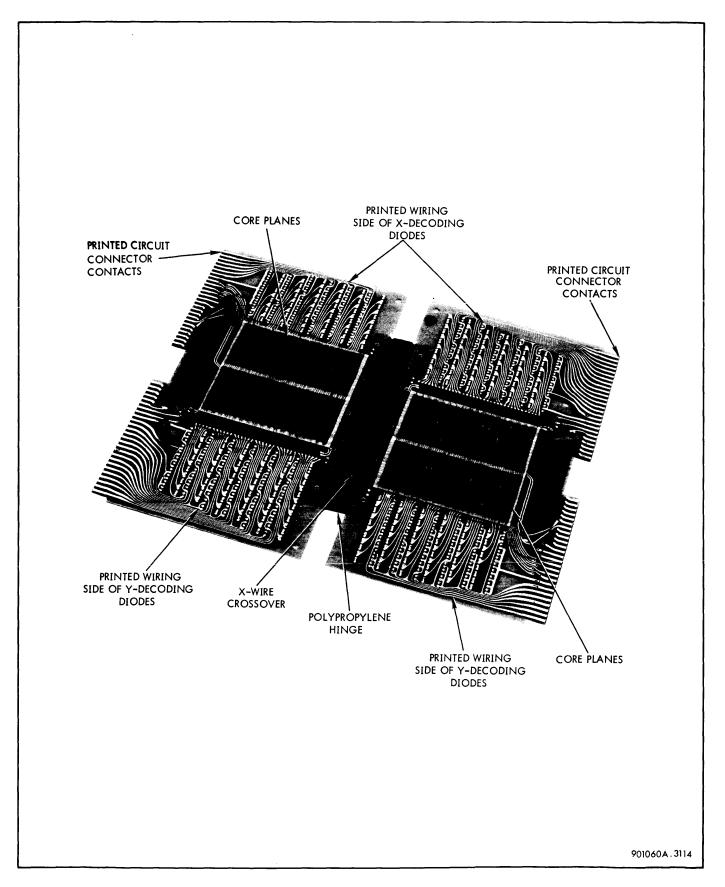

| 3-88          | Core Diode Module, Open to Expose Bit Planes                                     | 3-133          |

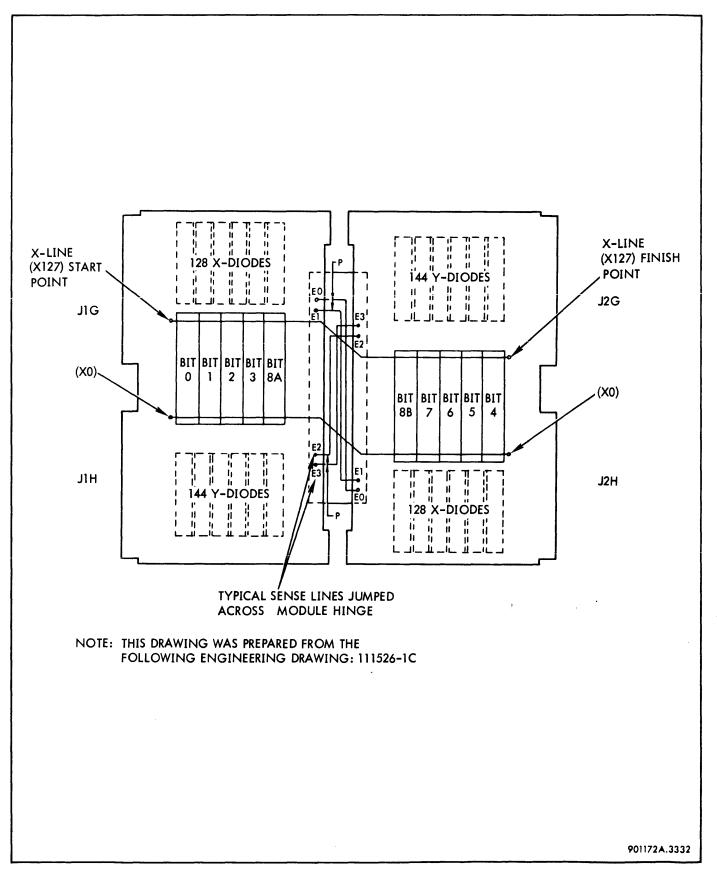

| 3-89          | Core Diode Module, Closed, as Inserted                                           | 3-134          |

### Illustrations

#### SDS 901172

### LIST OF ILLUSTRATIONS (Cont.)

### Figure

#### Title

| 3-90  | Core Diode Module, Bit Planes, X Wire Crossover                                    | 3-135         |

|-------|------------------------------------------------------------------------------------|---------------|

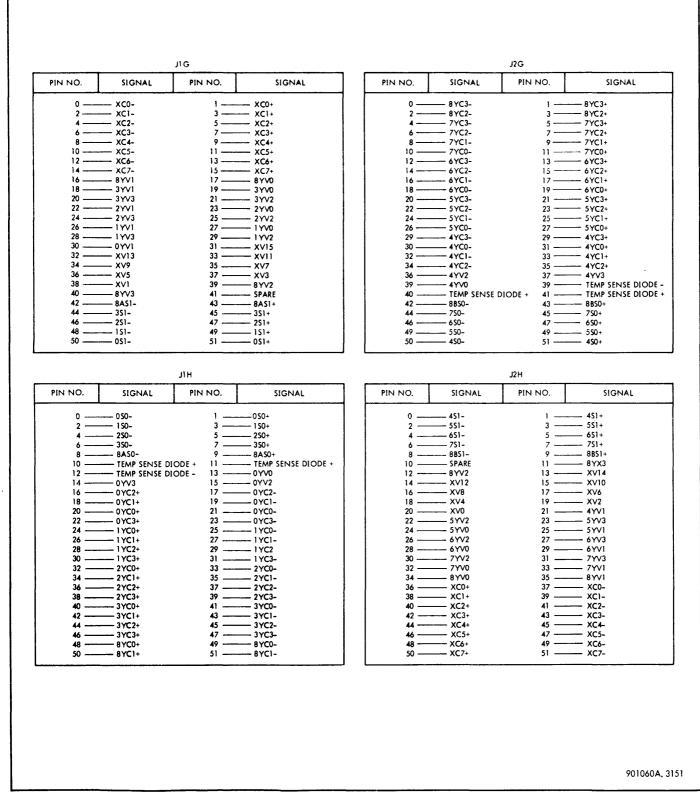

| 3-91  | Core Diode Module, Jack Pins and Signals                                           | 3-136         |

| 3-92  | Core Diode Module, Left Half Wiring Details                                        | 3-137         |

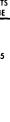

| 3-93  | Core Diode Module, Right Half Wiring Details                                       | 3-138         |

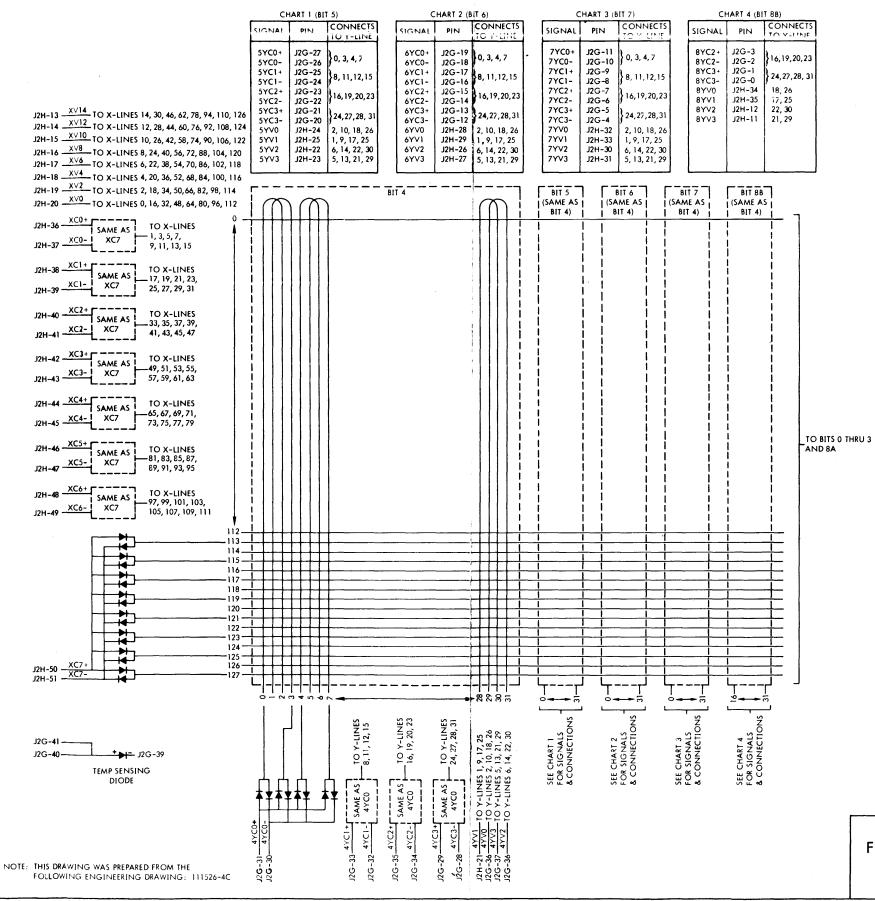

| 3-94  | Sense Line Wiring in a 4K Core Diode Module                                        | 3-139         |

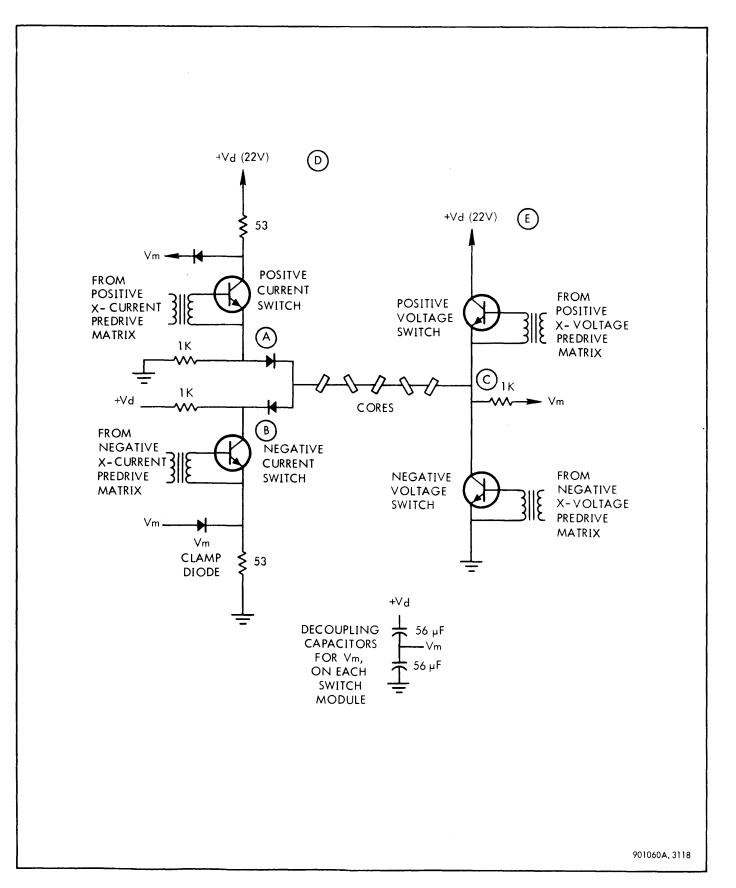

| 3-95  | Memory Core Drive System, Simplified Schematic                                     | 3-142         |

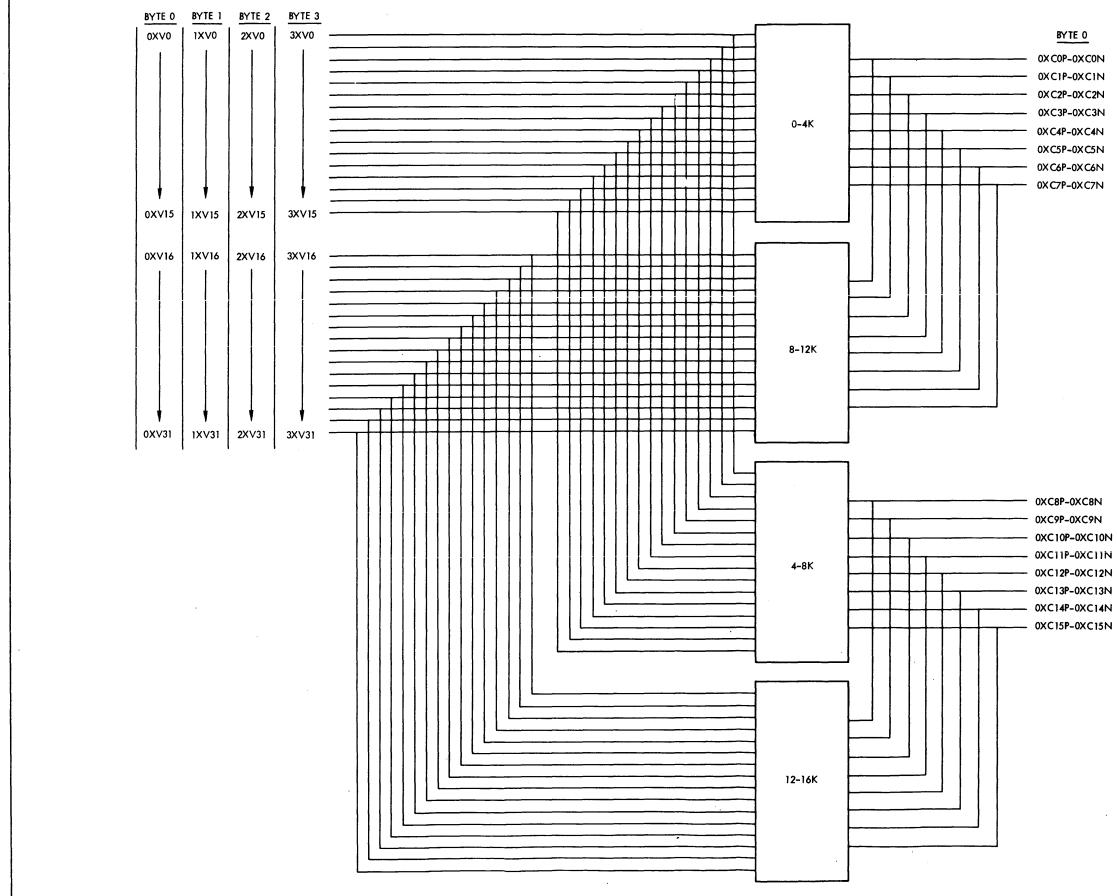

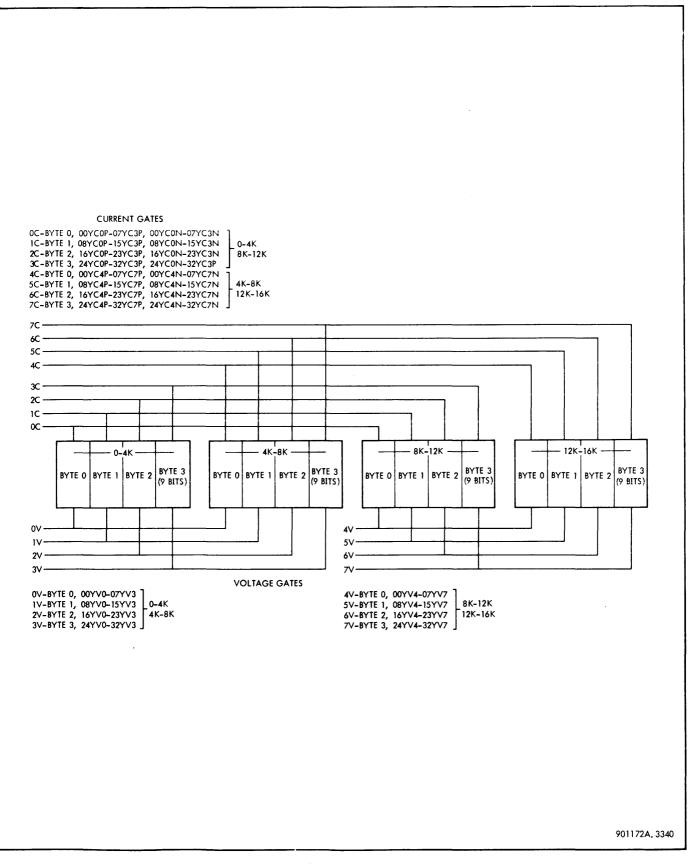

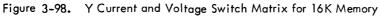

| 3-96  | X Current and Voltage Switch Matrix for 16K Memory.                                | 3-145         |

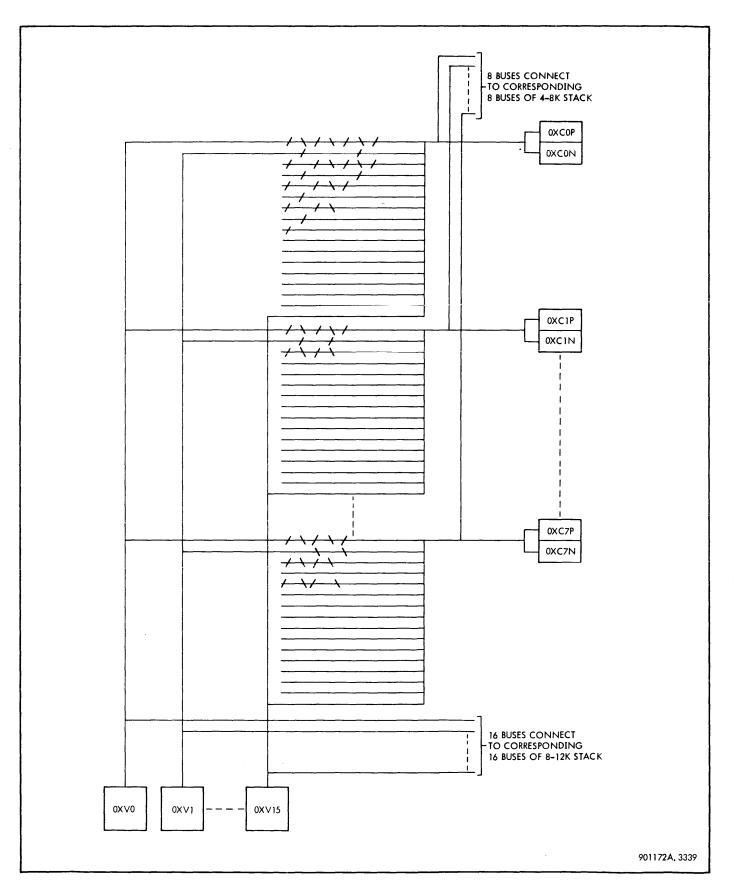

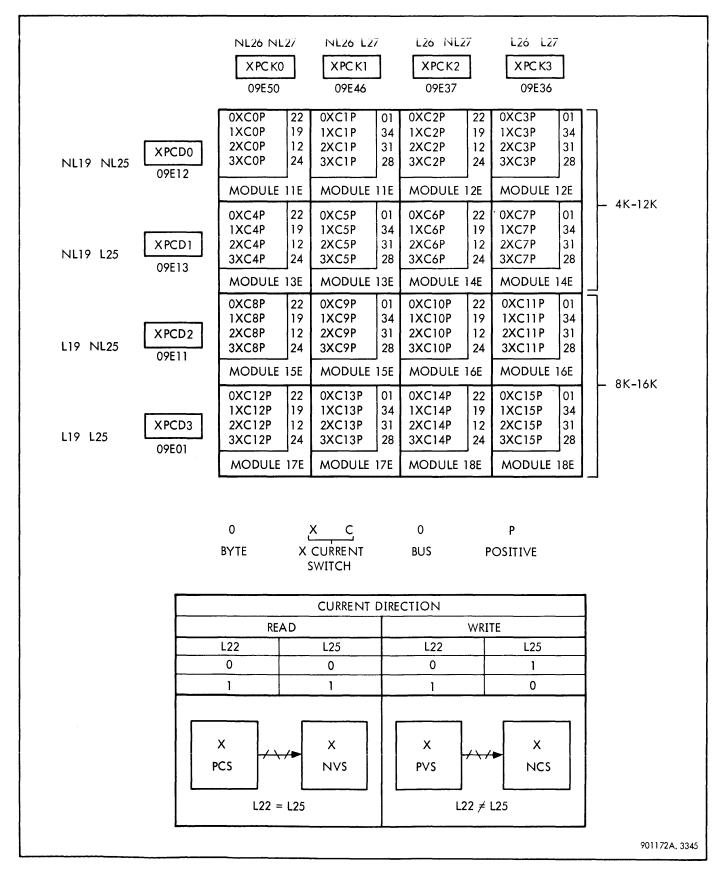

| 3-97  | X Current and Voltage Switch Matrix, Byte 0, 4K Stack                              | 3-147         |

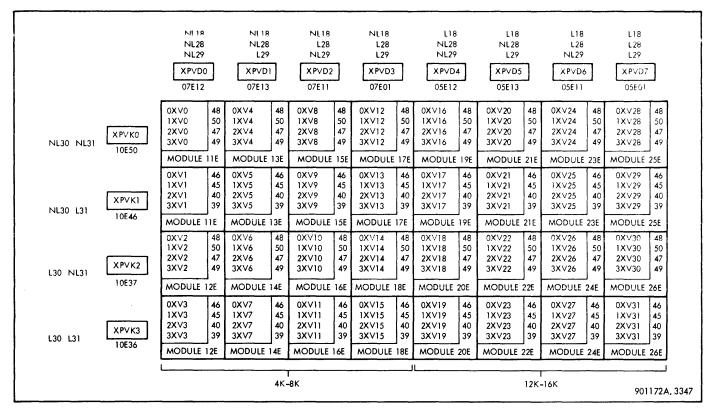

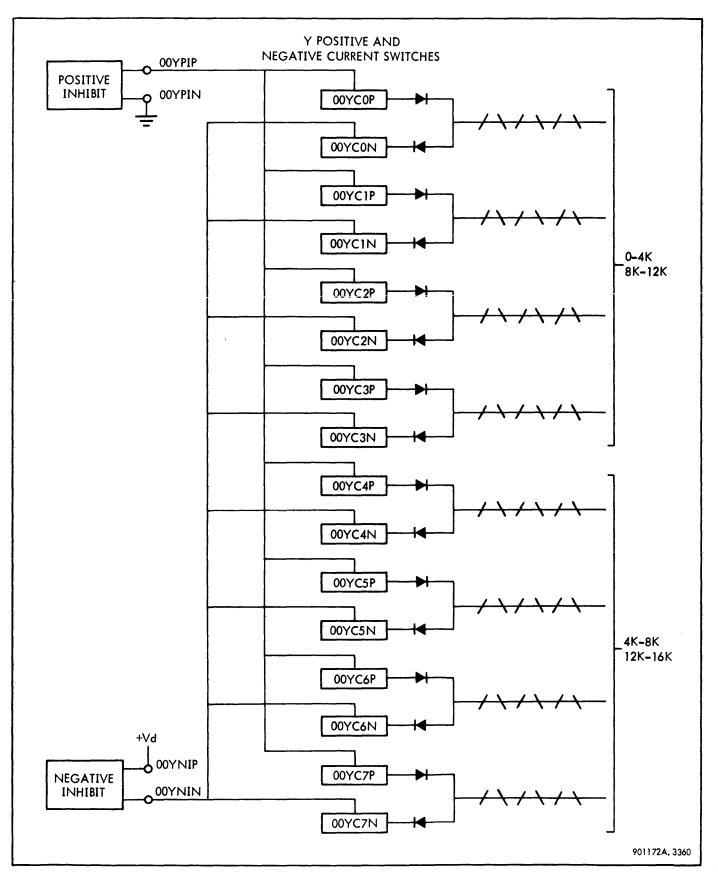

| 3-98  | Y Current and Voltage Switch Matrix for 16K Memory.                                | 3-148         |

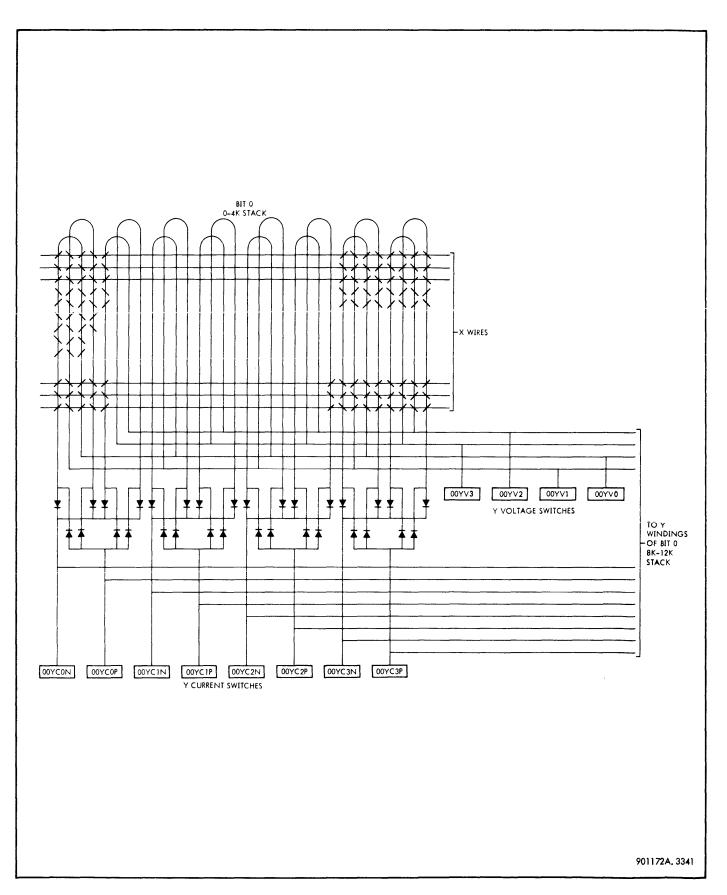

| 3-99  | Y Current and Voltage Switch Matrix for Bit 0.                                     | 3-149         |

| 3-100 | Y Positive Current Predrive/Drive Coupling, Simplified Schematic                   | 3-150         |

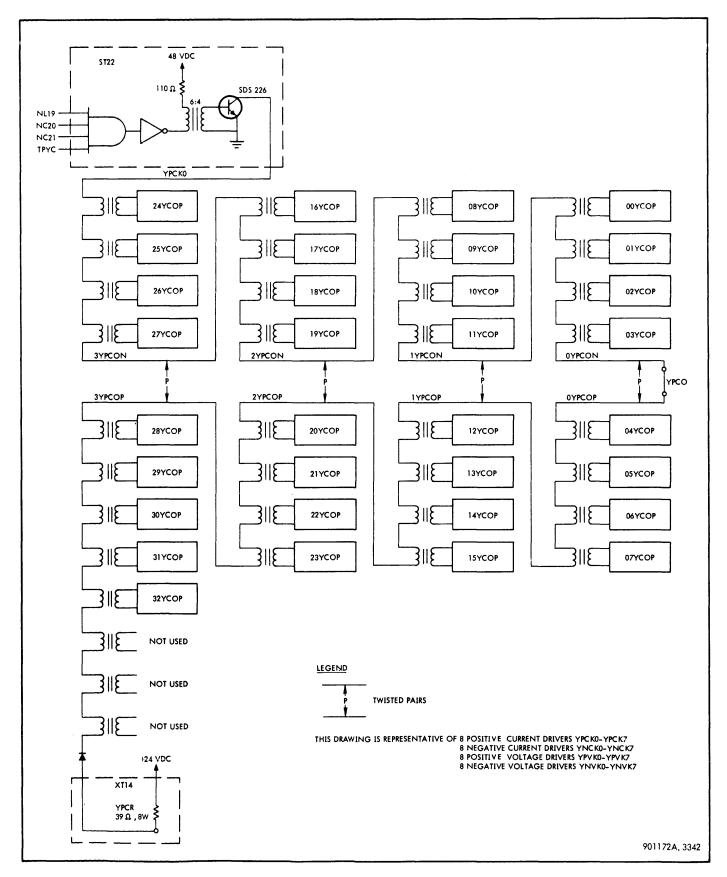

| 3-101 | X Positive Current Predrive Matrix, Simplified Schematic                           | 3-151         |

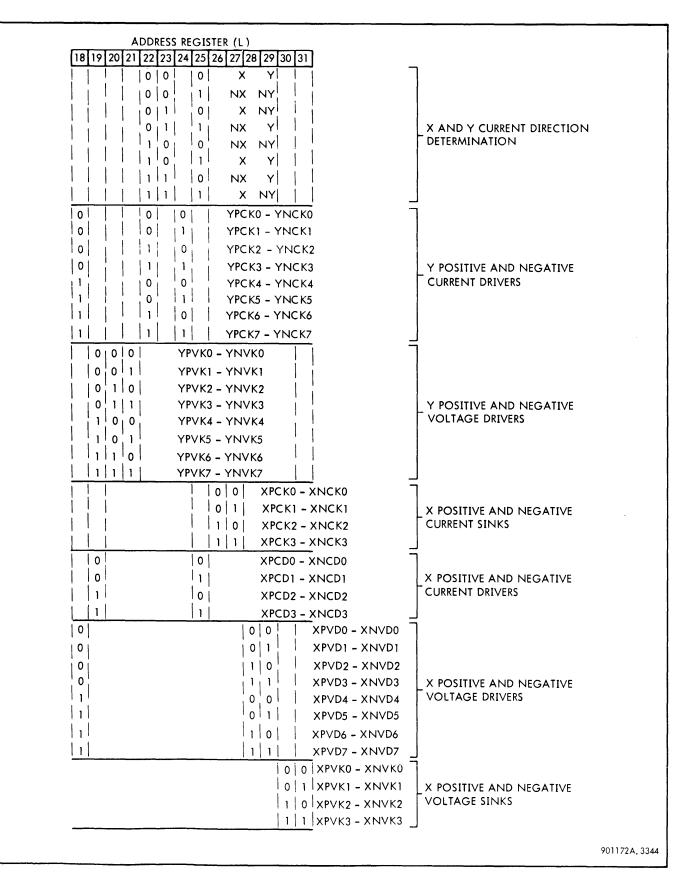

| 3-102 | X and Y Predrive Selection Relative to Memory Address.                             | 3-152         |

| 3-103 | X Positive Current Predrive Matrix                                                 | 3-154         |

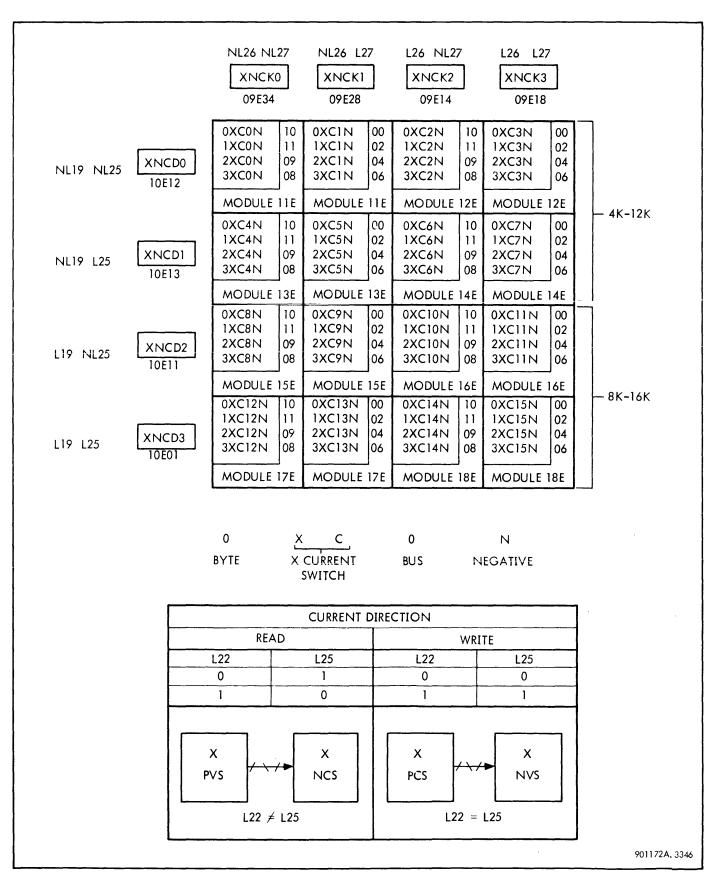

| 3-104 | X Negative Current Predrive Matrix                                                 | 3-155         |

| 3-105 | X Positive Voltage Predrive Matrix                                                 | 3-156         |

| 3-106 | X Negative Voltage Predrive Matrix                                                 | 3-156         |

| 3-107 | Y Positive Current Predrive/Drive Coupling System                                  | 3-157         |

| 3-108 | Y Negative Current Predrive/Drive Coupling System                                  | 3-158         |

| 3-109 | Y Positive/Negative Predrive/Drive Coupling System                                 | 3-159         |

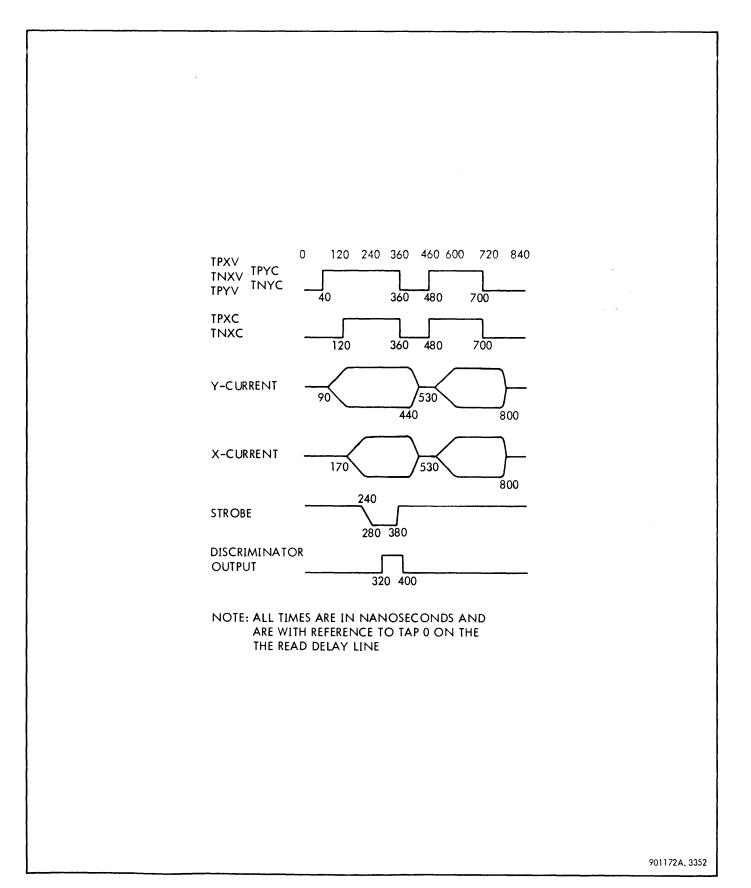

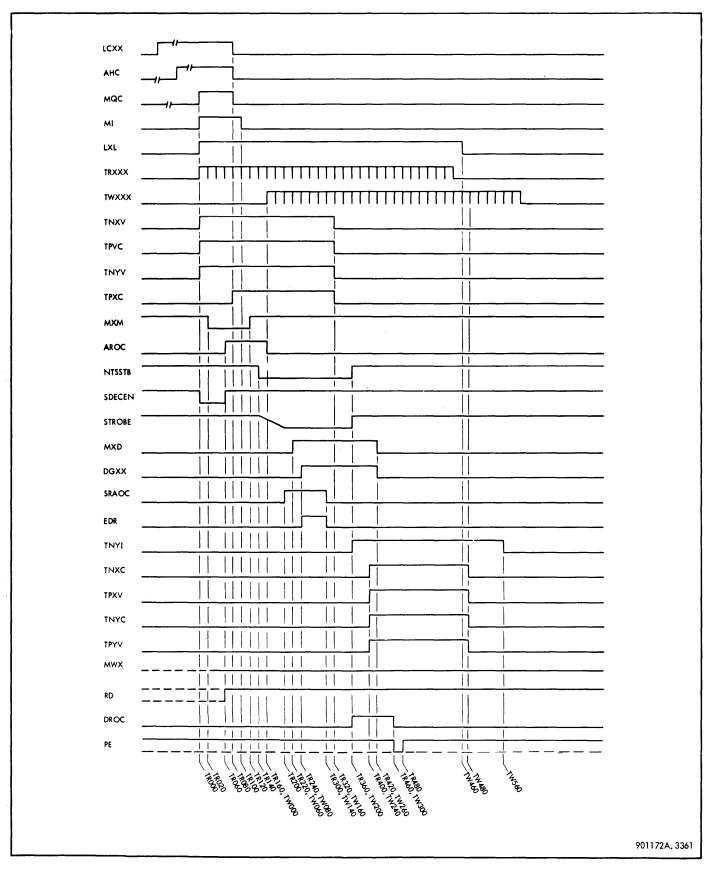

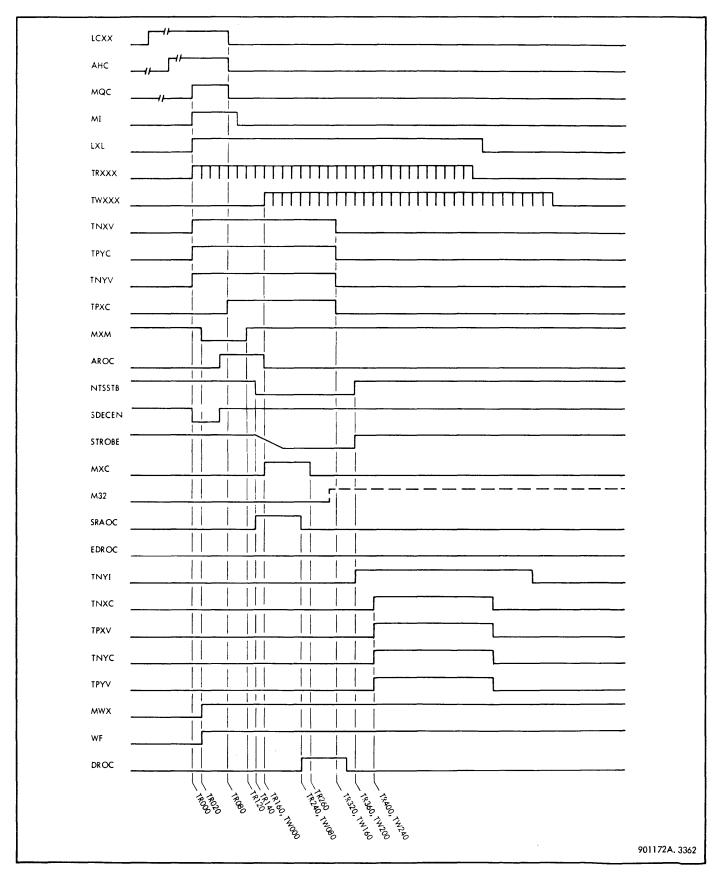

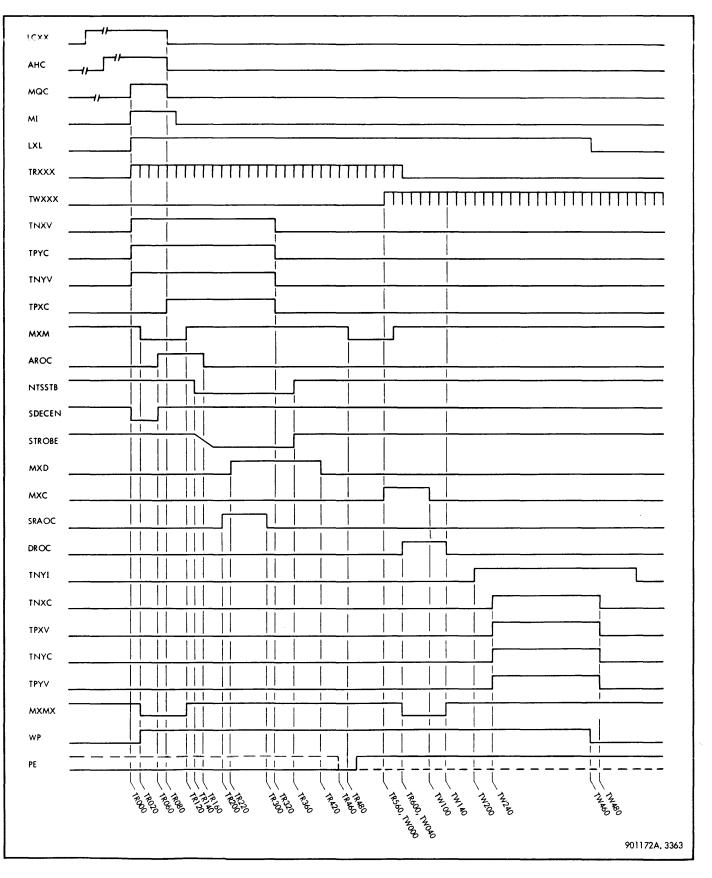

| 3-110 | Magnetics Timing Diagram                                                           | 3-160         |

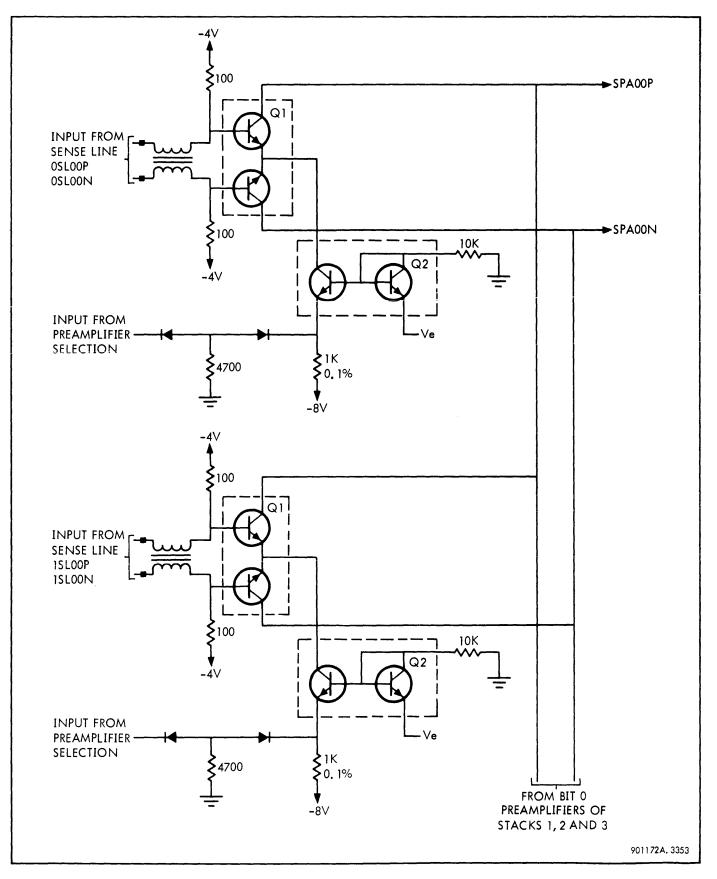

| 3-111 | Sense Preamplifier (HT26) Simplified Schematic, Bit 0, Stack 0                     | 3-161         |

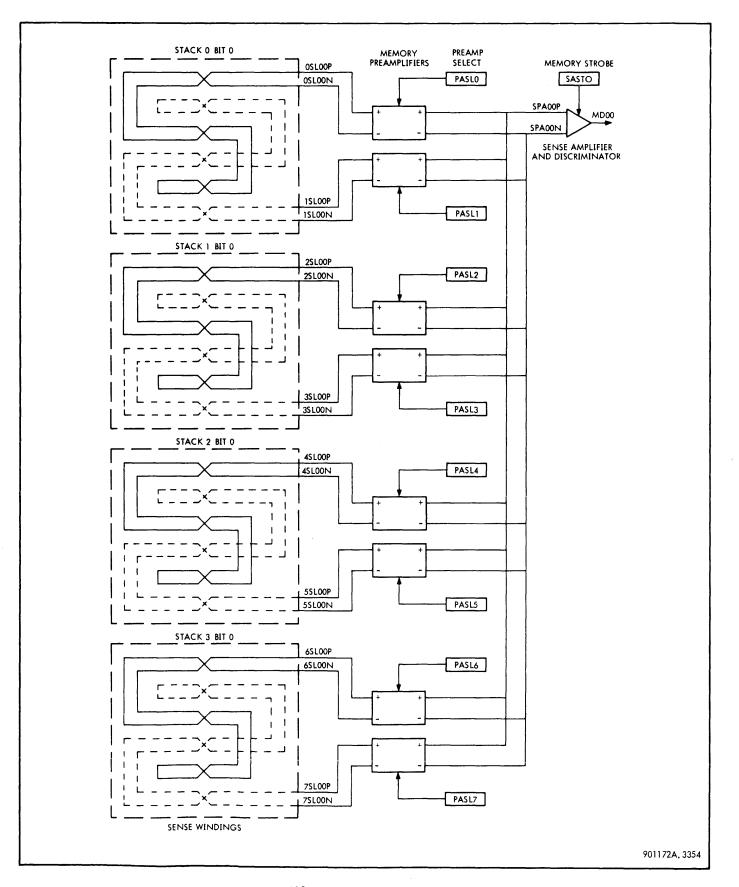

| 3-112 | Sensing System for Bit 0 (Typical)                                                 | 3-162         |

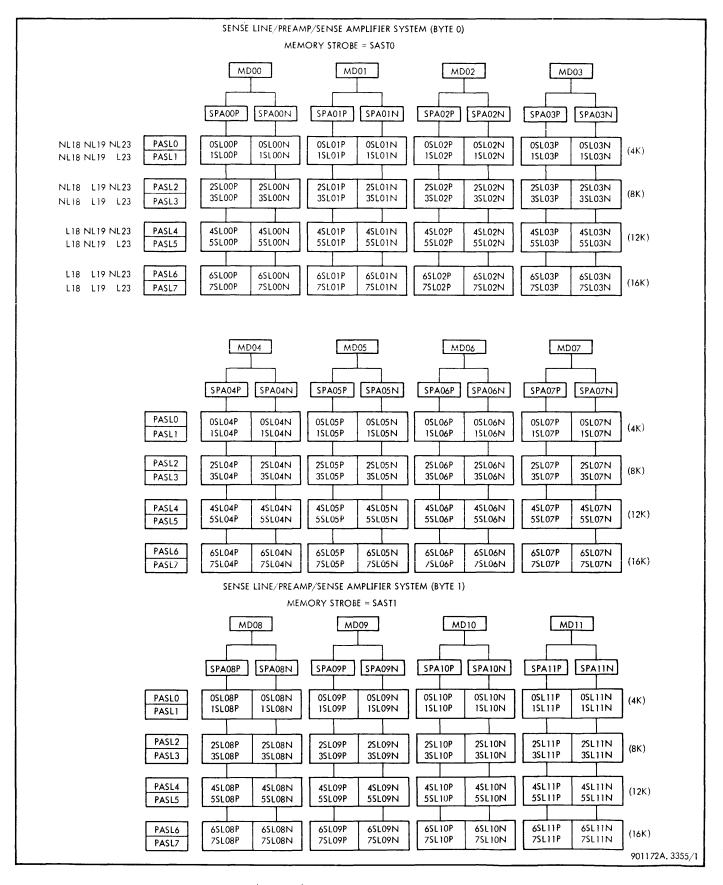

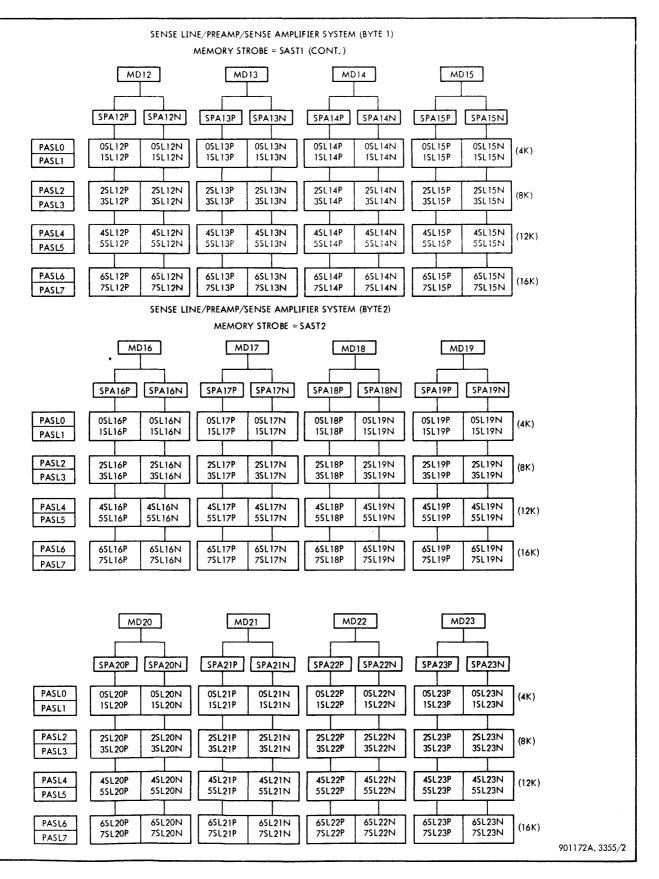

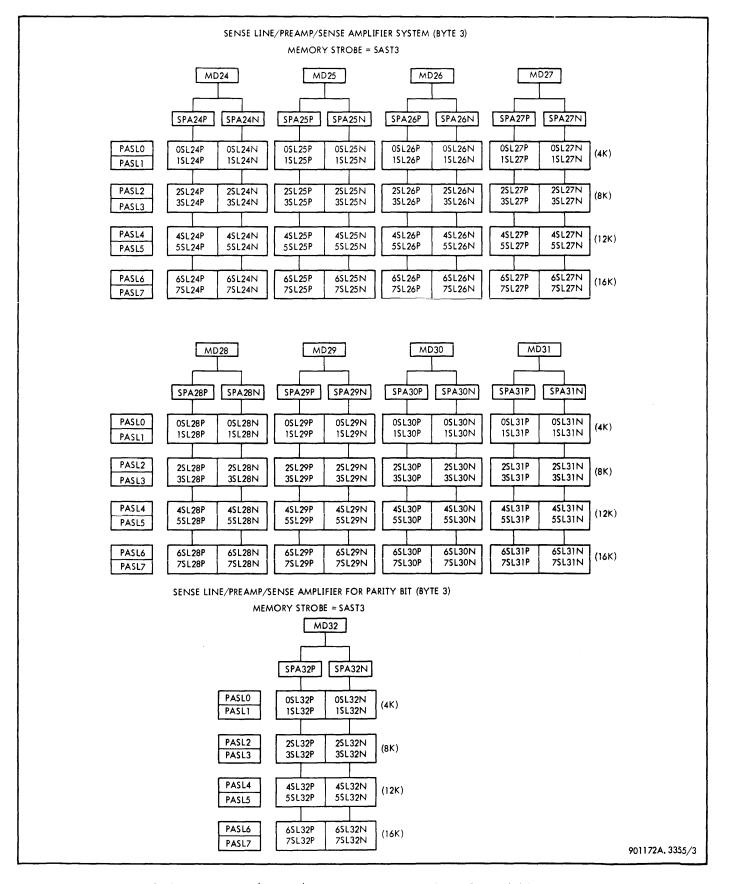

| 3-113 | Sense Line/Preamp/Sense Amplifier System (Bytes 0 and 1)                           | 3-163         |

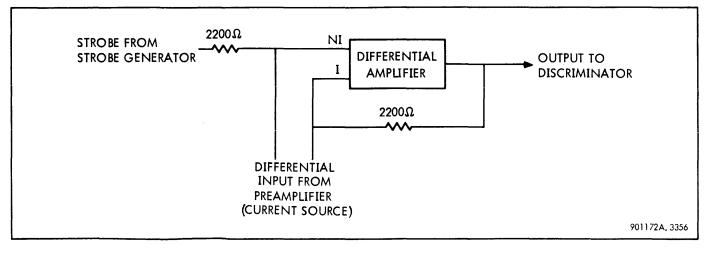

| 3-114 | Basic Sense Amplifier, Logic Diagram                                               | 3-166         |

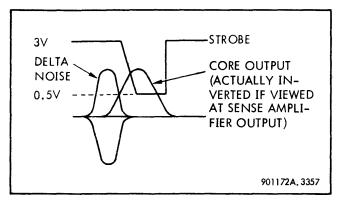

| 3-115 | Sense Waveforms                                                                    | 3-167         |

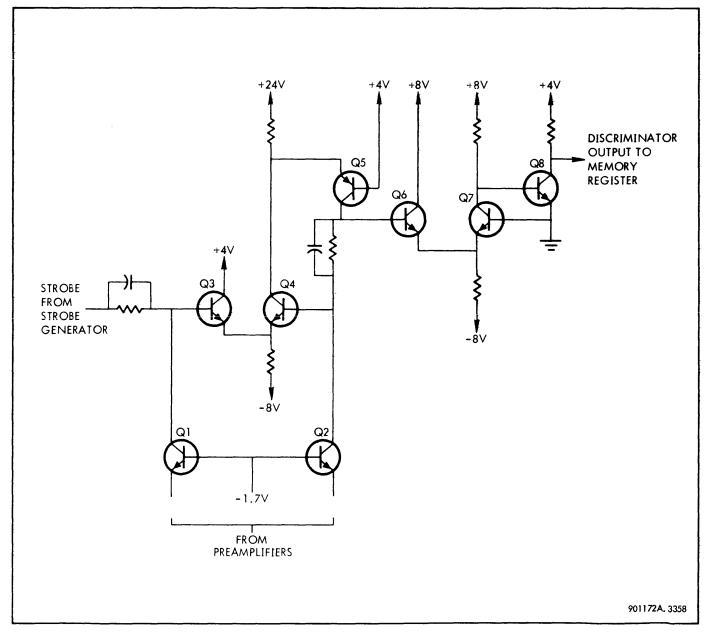

| 3-116 | Sense Amplifier, Simplified Schematic                                              | 3-167         |

| 3-117 | Y Current Inhibit Circuits, Simplified Diagram                                     | 3-168         |

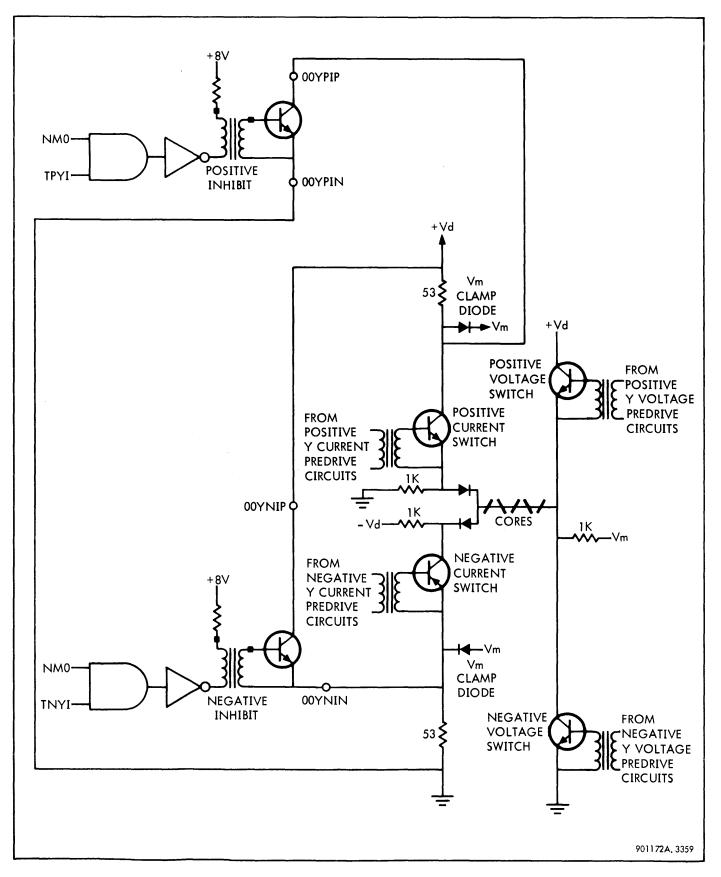

| 3-118 | Positive and Negative Y Current Inhibit, Bit 0                                     | 3-169         |

| 3-119 | Read-Restore, Timing Diagram                                                       | 3-170         |

| 3-120 | Full Clear Write, Timing Diagram                                                   | 3-171         |

| 3-121 | Partial Write, Timing Diagram                                                      | 3-172         |

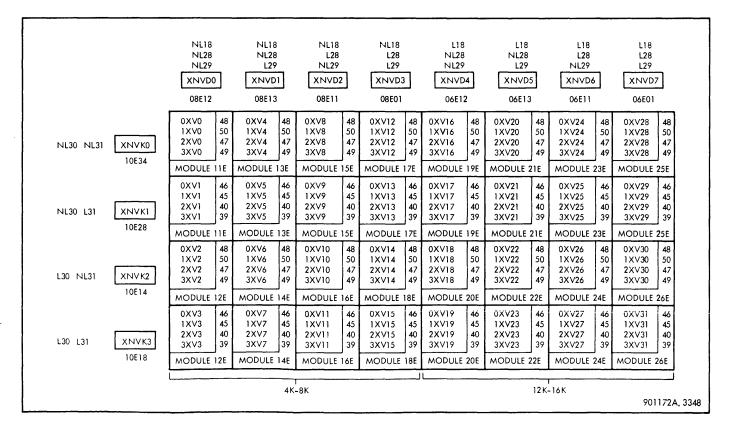

| 3-122 | Memory Module Location Chart                                                       | 3-173         |

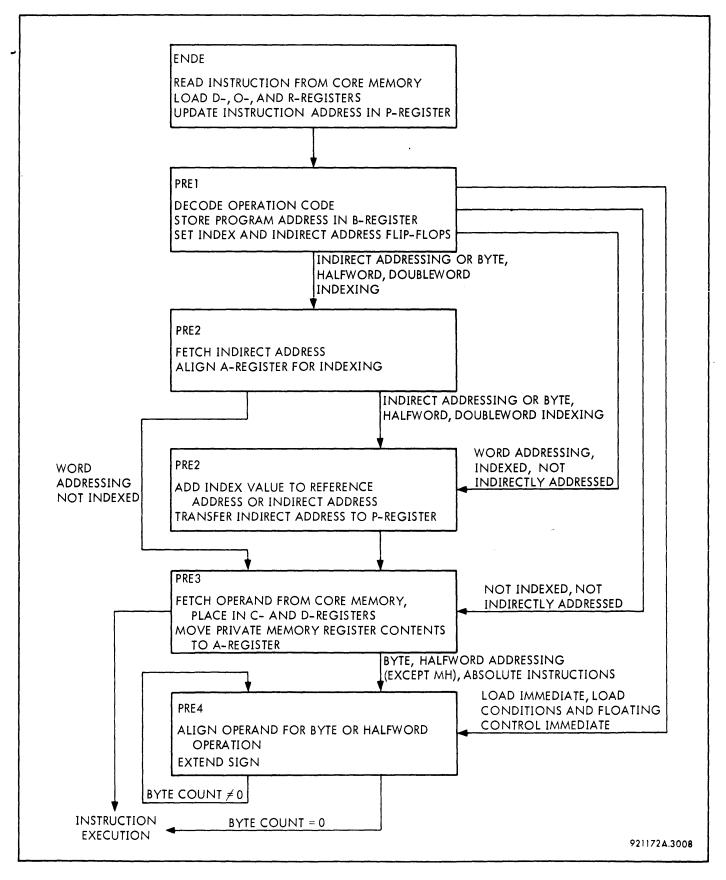

| 3-123 | Preparation Phases General Functions, Block Diagram                                | 3-177         |

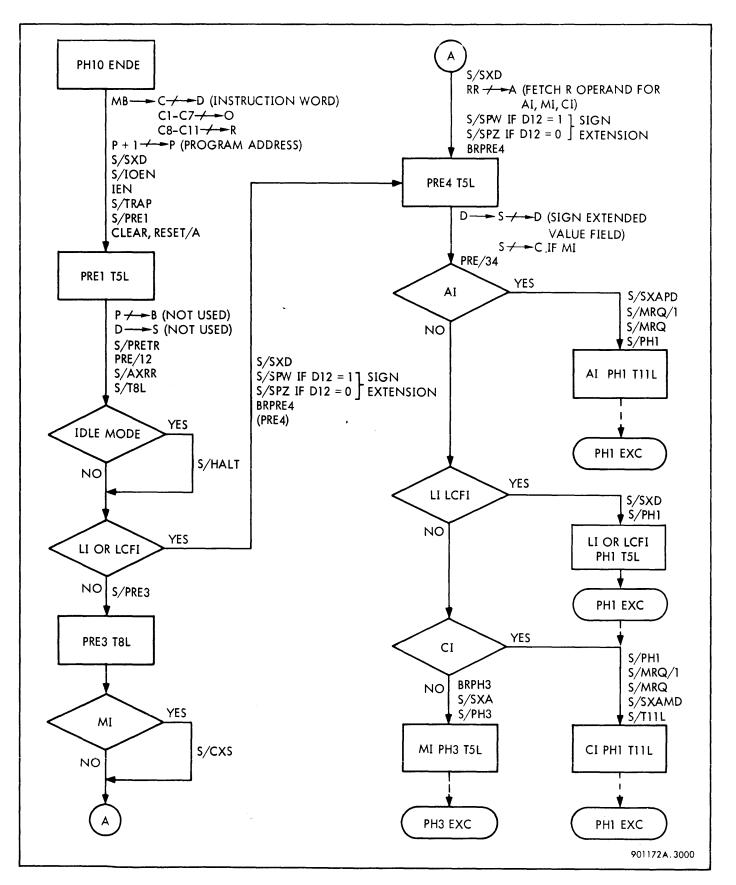

| 3-124 | Immediate Instruction Preparation Phases, Flow Diagram                             | 3-194         |

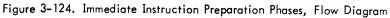

| 3-125 | Preparation Phase PRE1, Flow Diagram                                               | 3-195         |

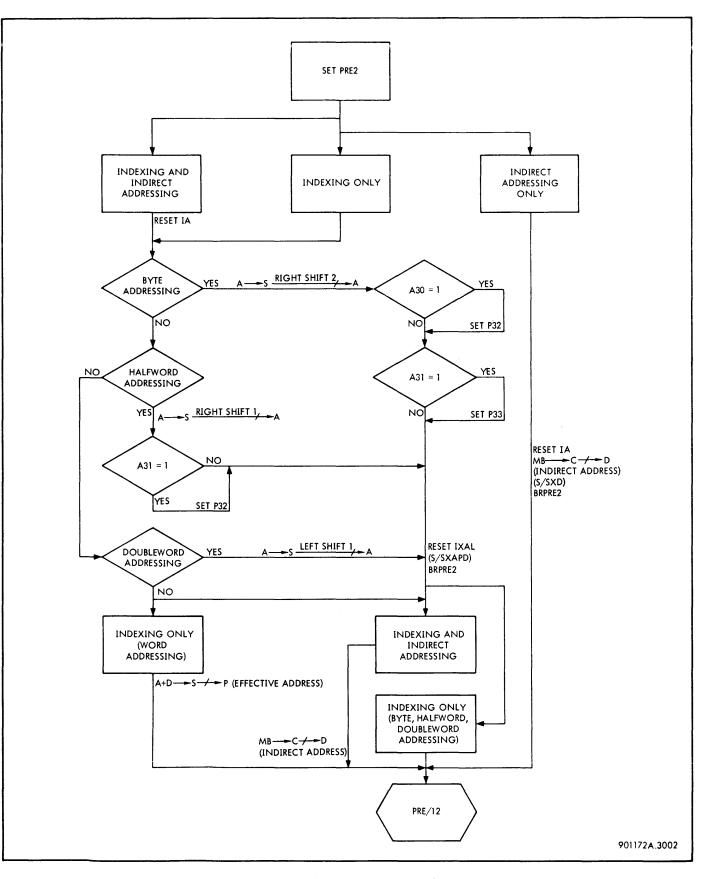

| 3-126 | Preparation Phase PRE2 (Not PRE/12), Flow Diagram                                  | 3-196         |

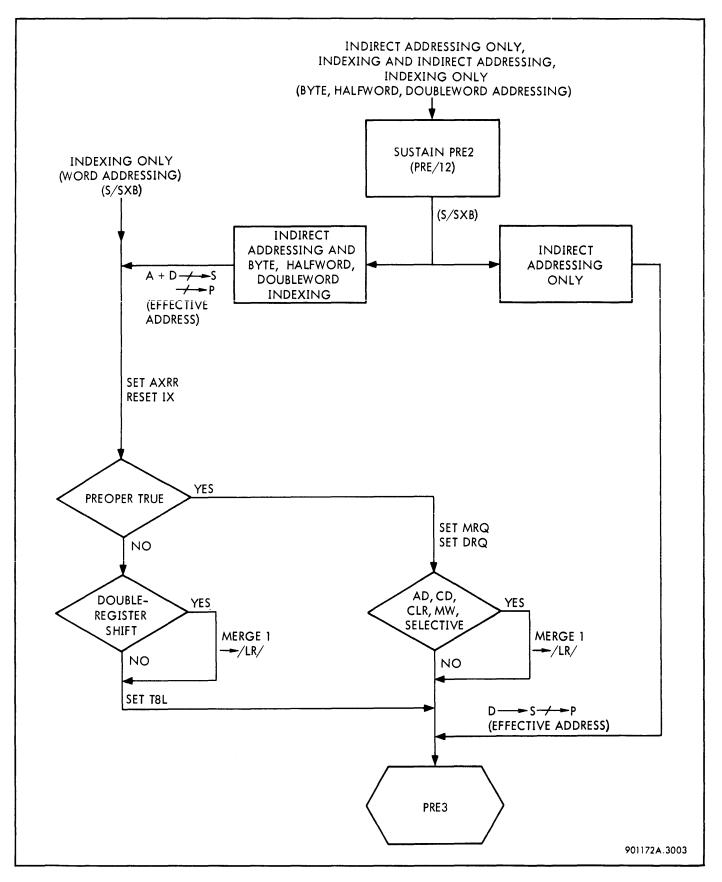

| 3-127 | Preparation Phase PRE2 (PRE/12 Time), Flow Diagram                                 | 3-197         |

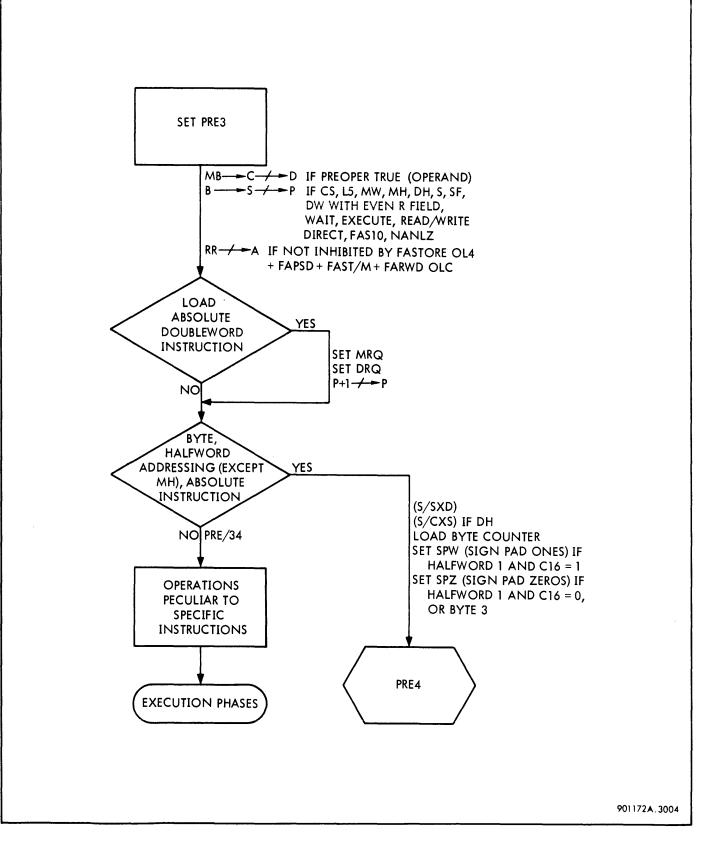

| 3-128 | Preparation Phase PRE3, Flow Diagram                                               | 3-198         |

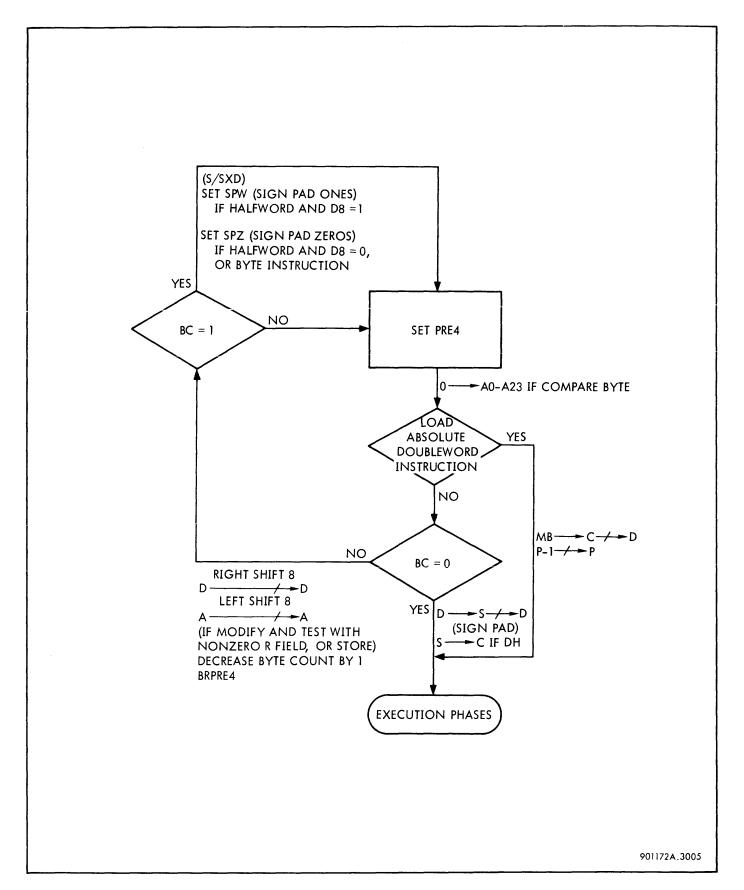

| 3-129 | Preparation Phase PRE4, Flow Diagram                                               | 3-199         |

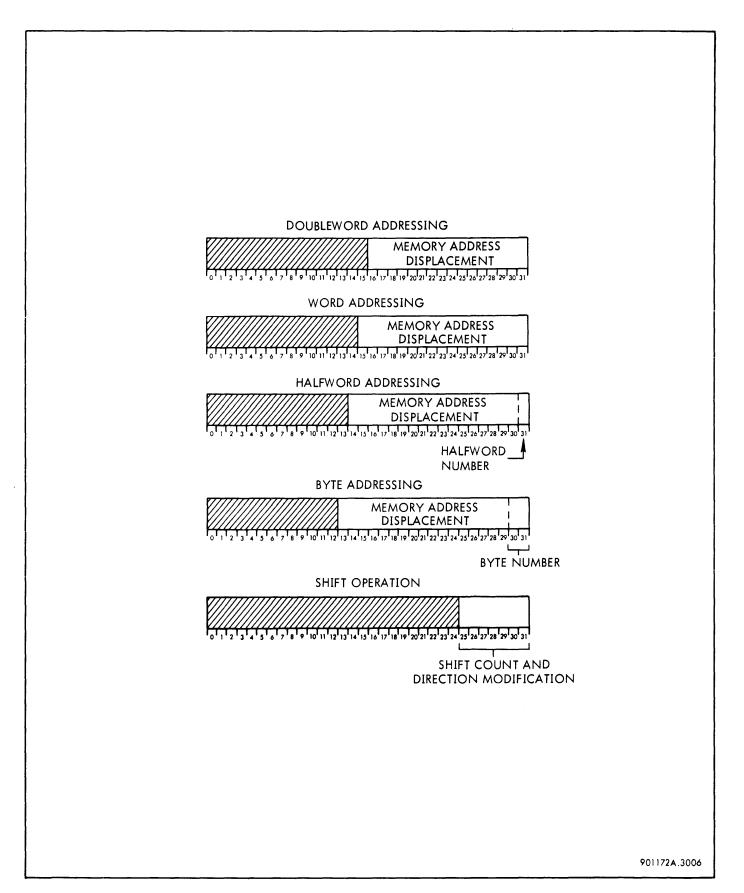

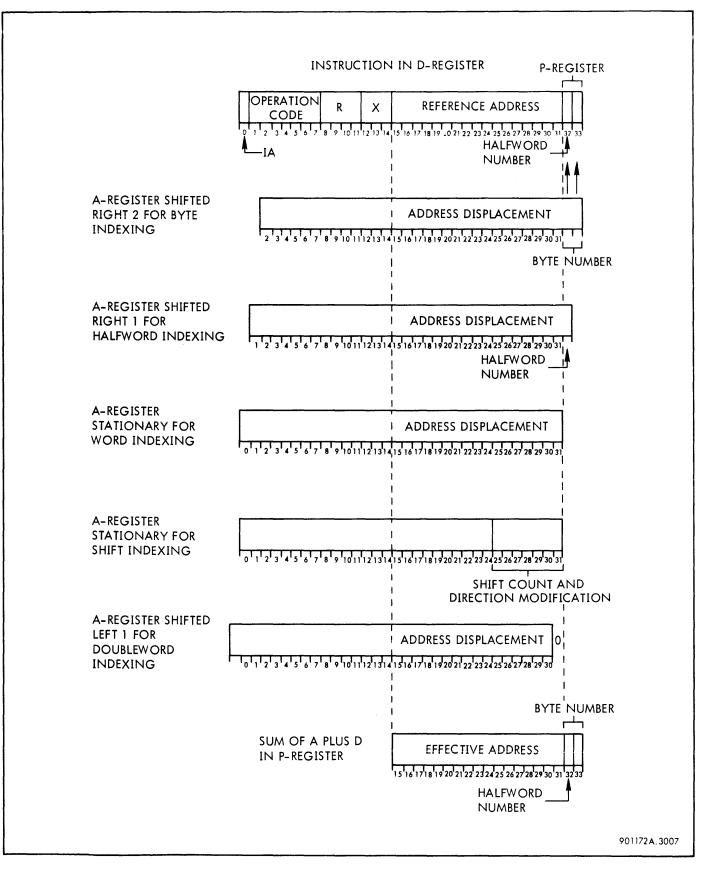

| 3-130 | Index Register Contents for Byte, Halfword, Word, Doubleword, and Shift Operations | 3-201         |

| 3-131 | Index Register Alignment for Effective Address Computation                         | 3-202         |

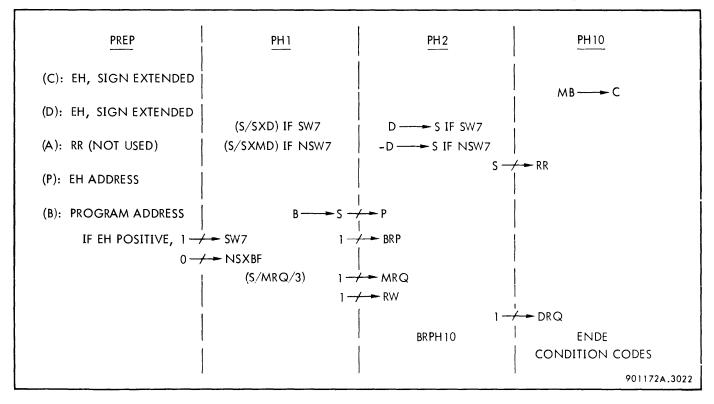

| 3-132 | Load Absolute Halfword Phases                                                      | 3-224         |

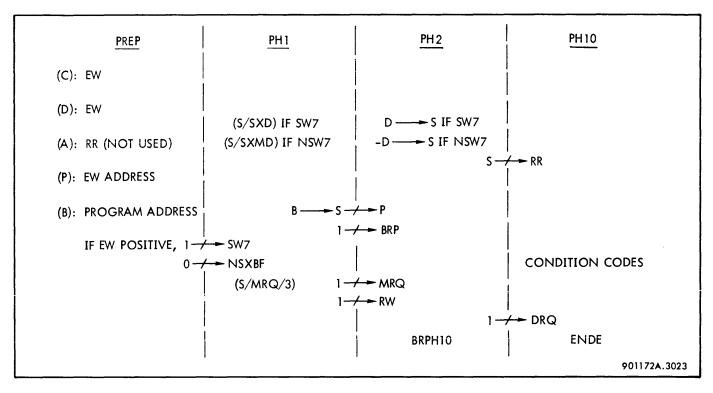

| 3-133 | Load Absolute Word Phases                                                          | 3-227         |

| 3-134 | Load Absolute Doubleword Phases                                                    | 3-230         |

| 3-135 | Store Doubleword Phases                                                            | 3-240         |

| 3-136 | Load Selective Phases                                                              | 3-250         |

| 3-137 | Store Selective Phases                                                             | 3-254         |

| 3-138 | Compare Selective Phases                                                           | 3-258         |

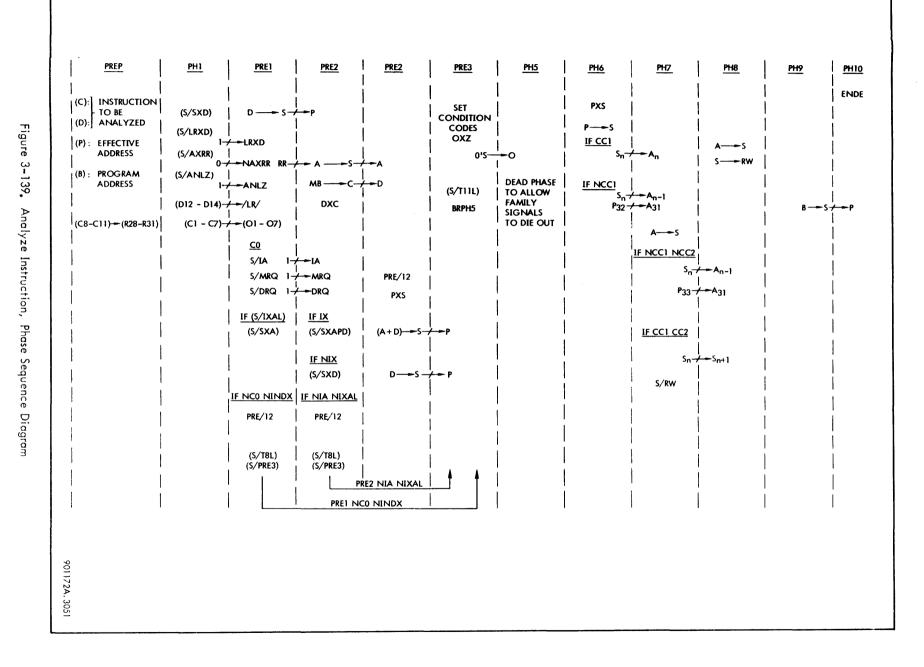

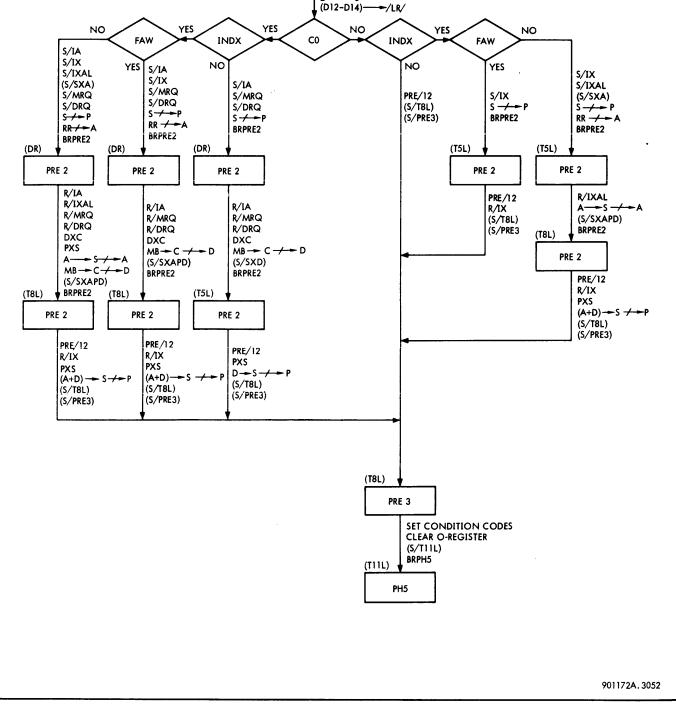

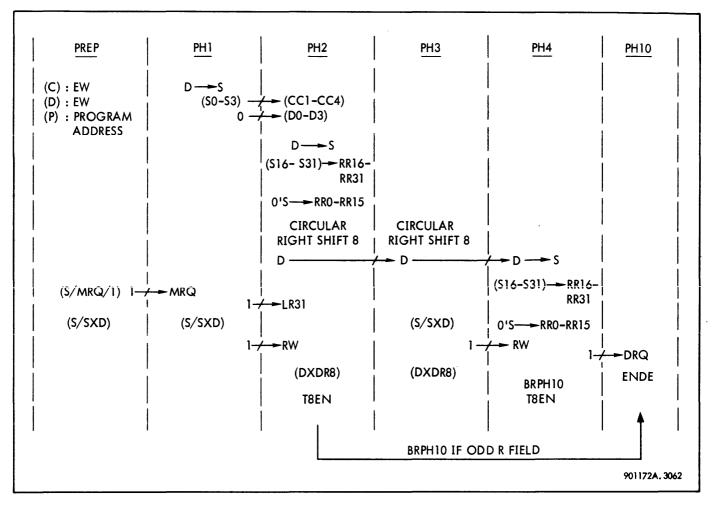

| 3-139 | Analyze Instruction, Phase Sequence Diagram                                        | 3 <b>-262</b> |

| 3-140 | Analyze Instruction, Preparation Phases Flow Diagram.                              | 3-263         |

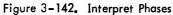

| 3-141 | Interpret Examples                                                                 | 3-270         |

| 3-142 | Interpret Phases                                                                   | 3-271         |

| 3-143 | Add Doubleword and Subtract Doubleword Instruction, Phase Diagram.                 | 3-280         |

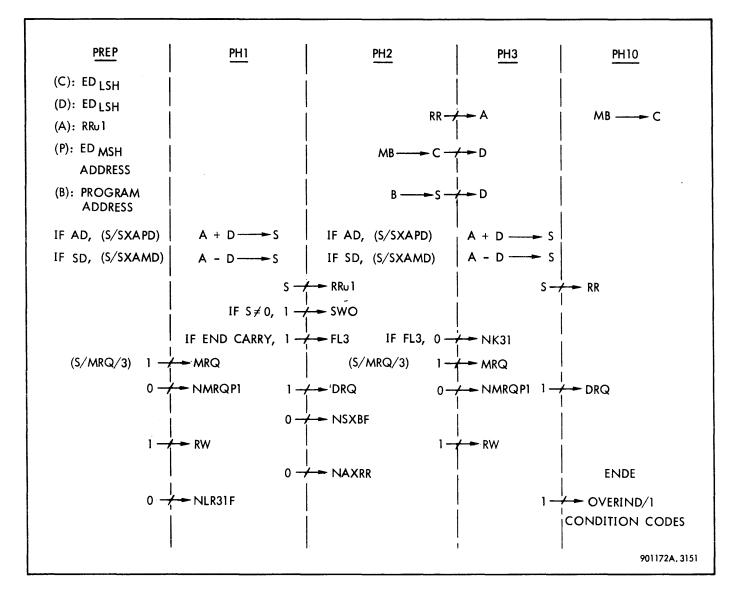

| 3-144 | Bit-Pair Multiplication                                                            | 3-287         |

|       | · · · · · · · · · · · · · · · · · · ·                                              |               |

#### LIST OF ILLUSTRATIONS (Cont.)

| Figure | Title                                                                                              | Page           |

|--------|----------------------------------------------------------------------------------------------------|----------------|

| 3-145  | Multiply Immediate and Multiply Word Instructions, Phase Sequence Diagram                          | 3-289          |

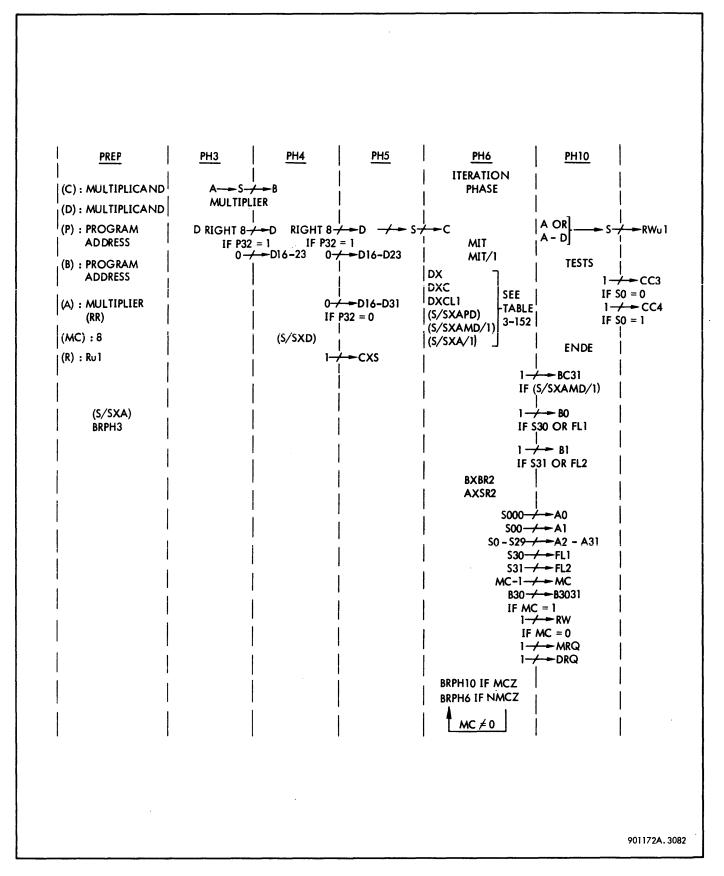

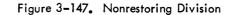

| 3-146  | Multiply Halfword Instruction, Phase Sequence Diagram                                              | 3-295          |

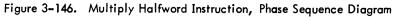

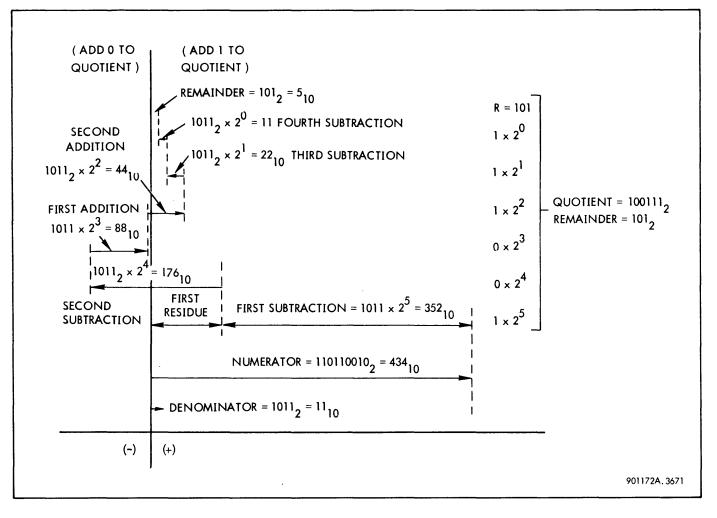

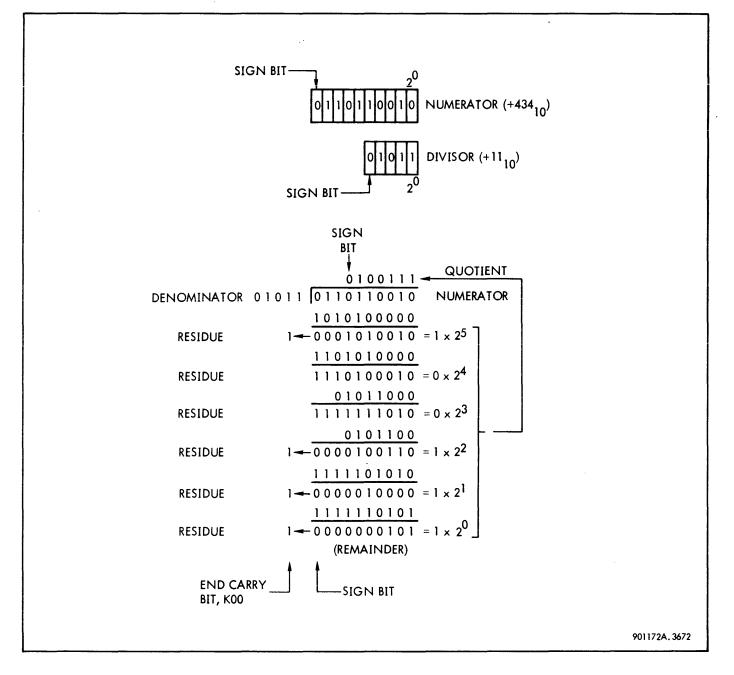

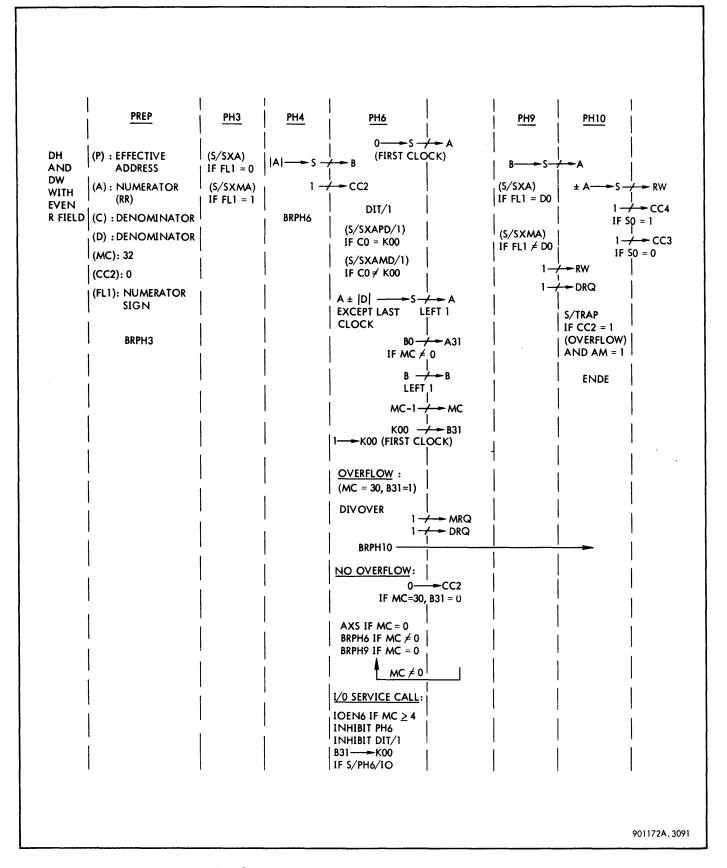

| 3-147  | Nonrestoring Division                                                                              | 3-301          |

| 3-148  | Nonrestoring Division, Graphic Representation                                                      | 3-302          |

| 3-149  | Nonrestoring Division With Two's Complement Addition                                               | 3-303          |

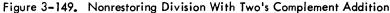

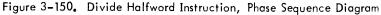

| 3-150  | Divide Halfword Instruction, Phase Sequence Diagram                                                | 3-304          |

| 3-151  | Divide Word Instruction, Phase Sequence Diagram                                                    | 3-310          |

| 3-152  | Modify and Test Byte and Modify and Test Halfword Instructions, Phase Sequence Diagram             | 3-317          |

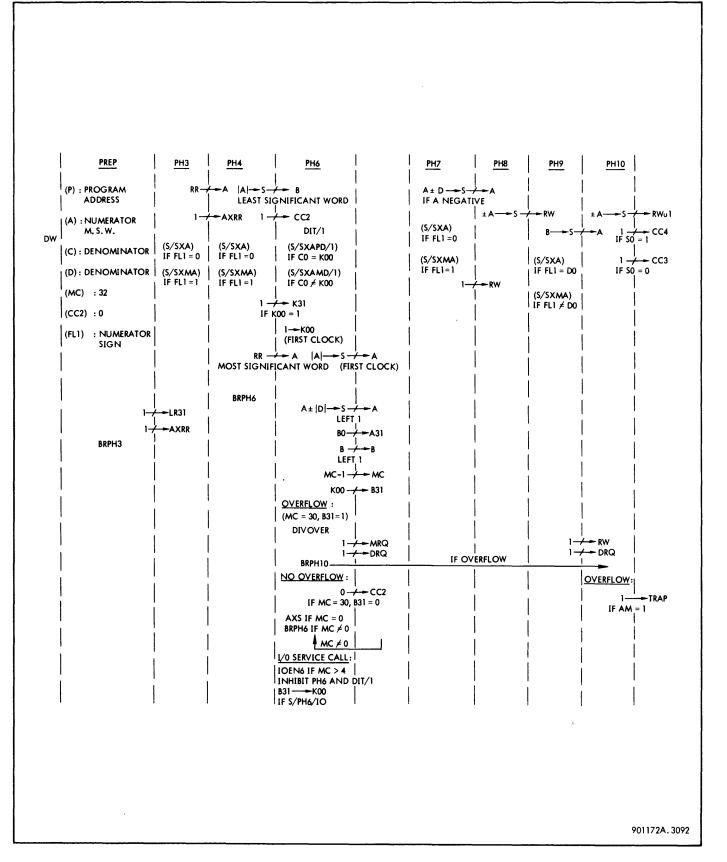

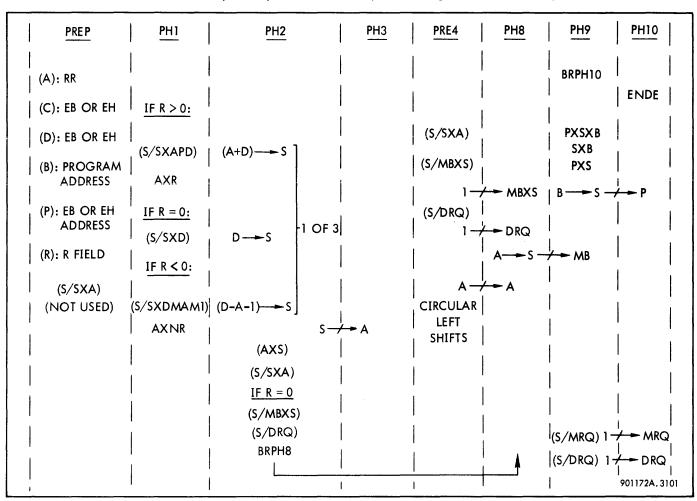

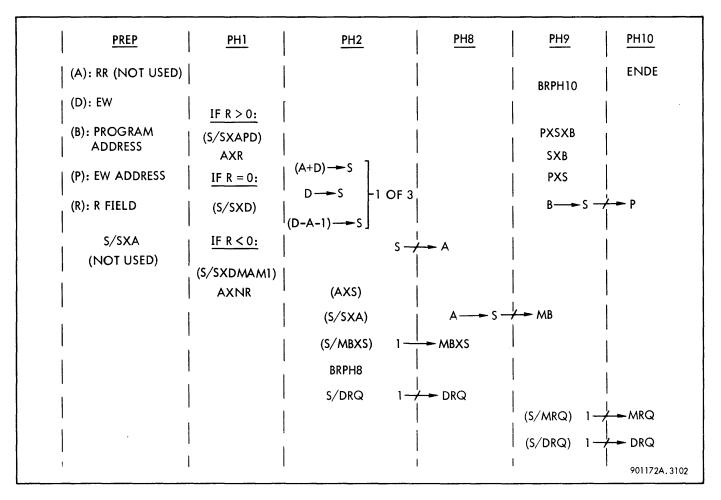

| 3-153  | Modify and Test Word Instruction, Phase Sequence Diagram                                           | 3-326          |

| 3-154  | Compare Immediate, Compare Byte, Compare Halfword, and Compare Word Instructions,<br>Phase Diagram | 3-335          |

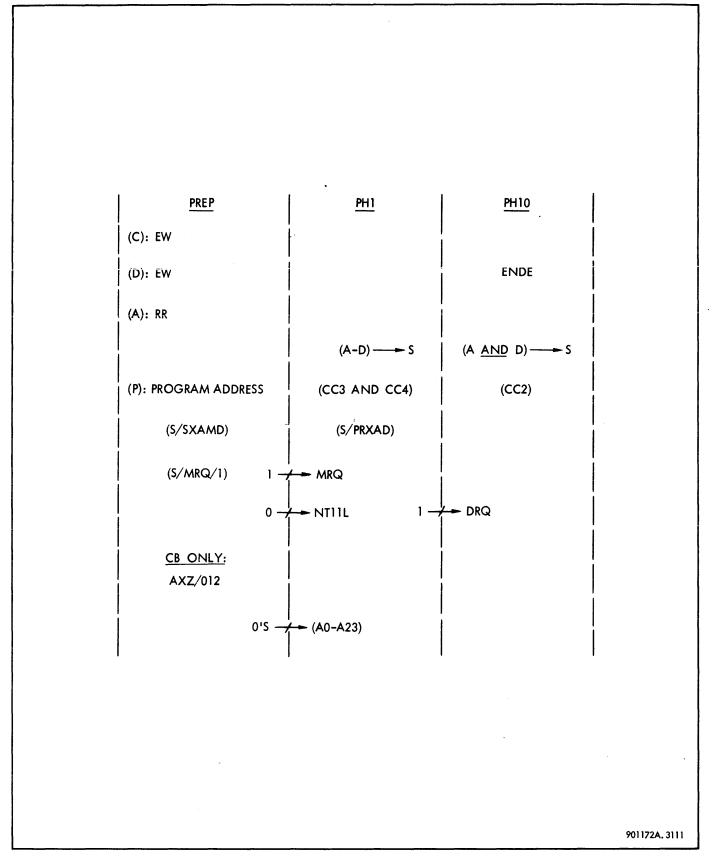

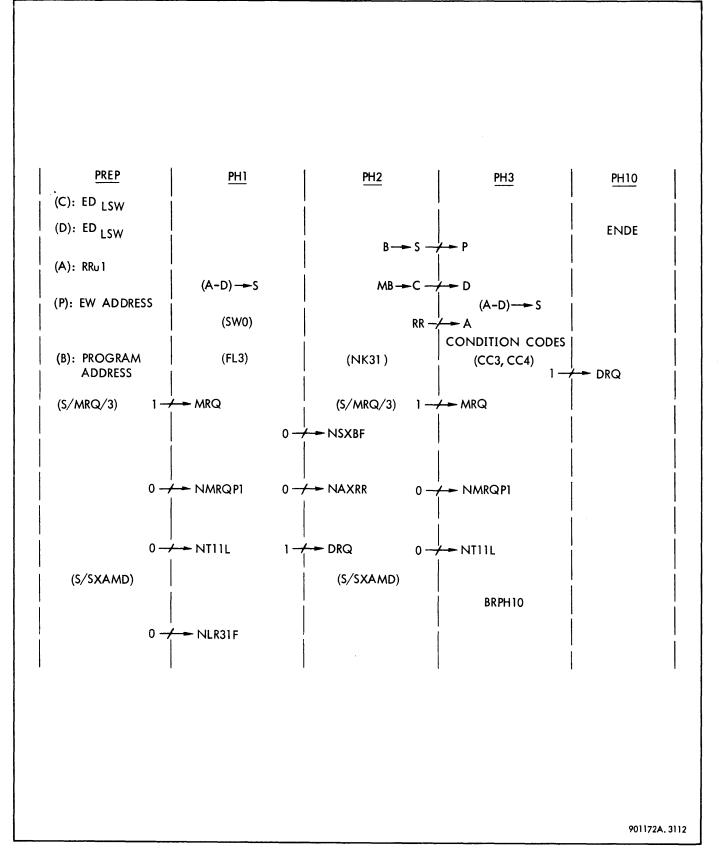

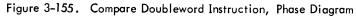

| 3-155  | Compare Doubleword Instruction, Phase Diagram                                                      | 3-336          |

| 3-156  | Compare With Limits in Register, Phase Diagram                                                     | 3-341          |

| 3-157  | Compare With Limits in Memory, Phase Diagram.                                                      | 3-345          |

| 3-158  | AND Instruction Phase Sequence.                                                                    | 3-350          |

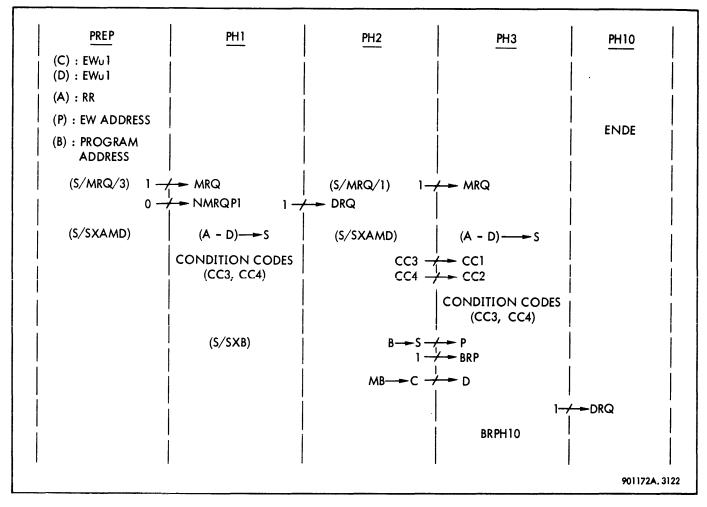

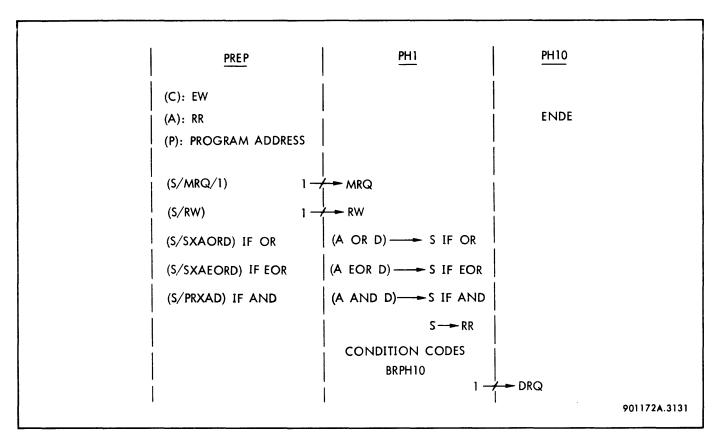

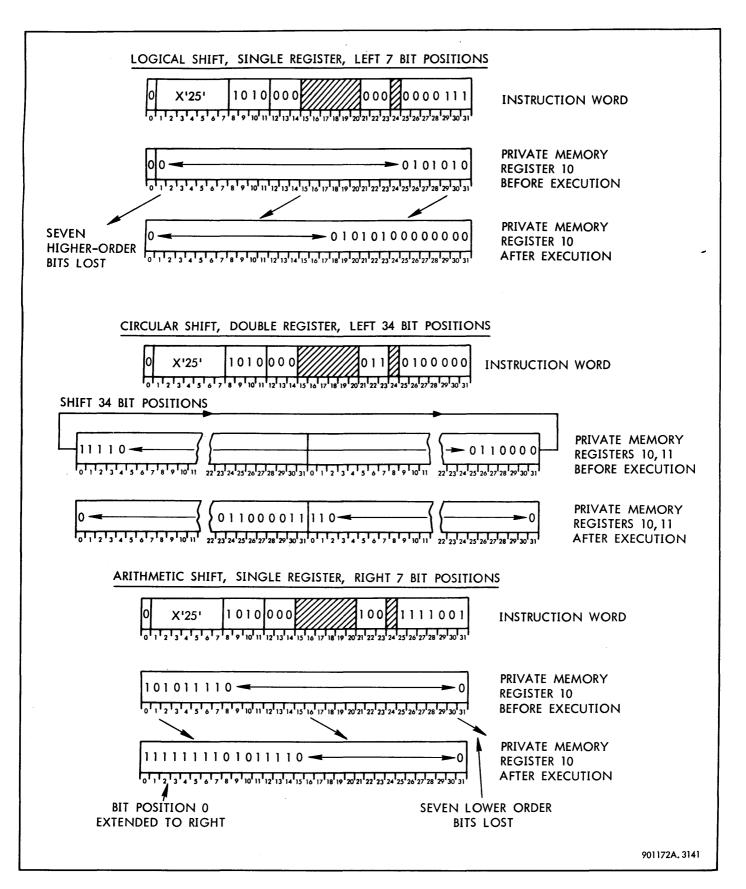

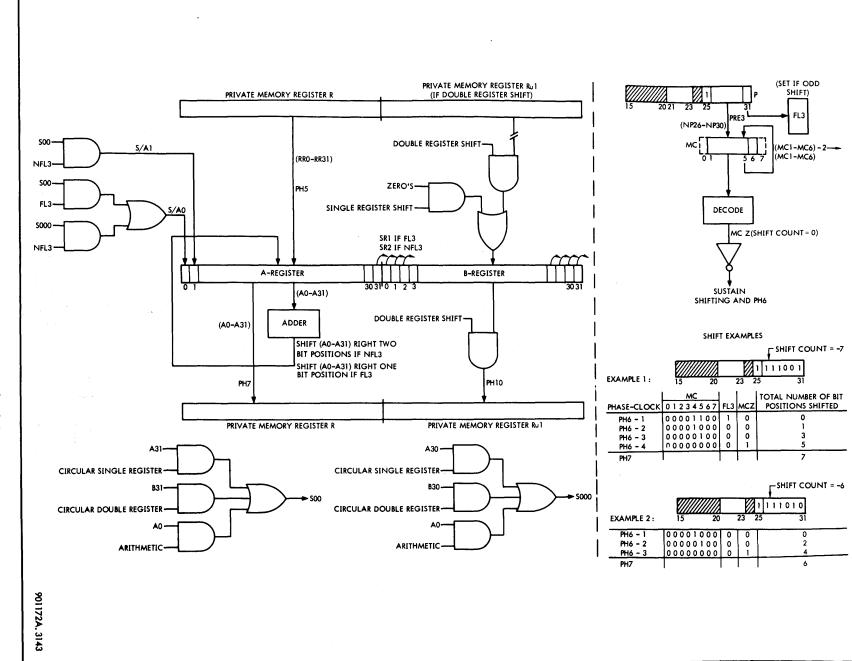

| 3-159  | Shift Examples                                                                                     | 3-354          |

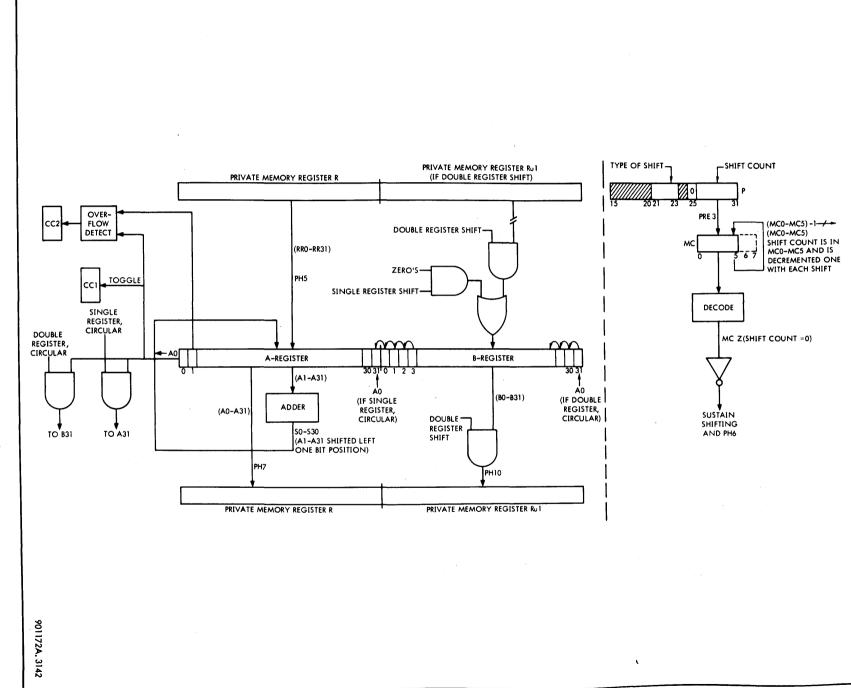

| 3-160  | Implementation of Left Shift                                                                       | 3-355          |

| 3-161  | Implementation of Right Shift.                                                                     | 3-356          |

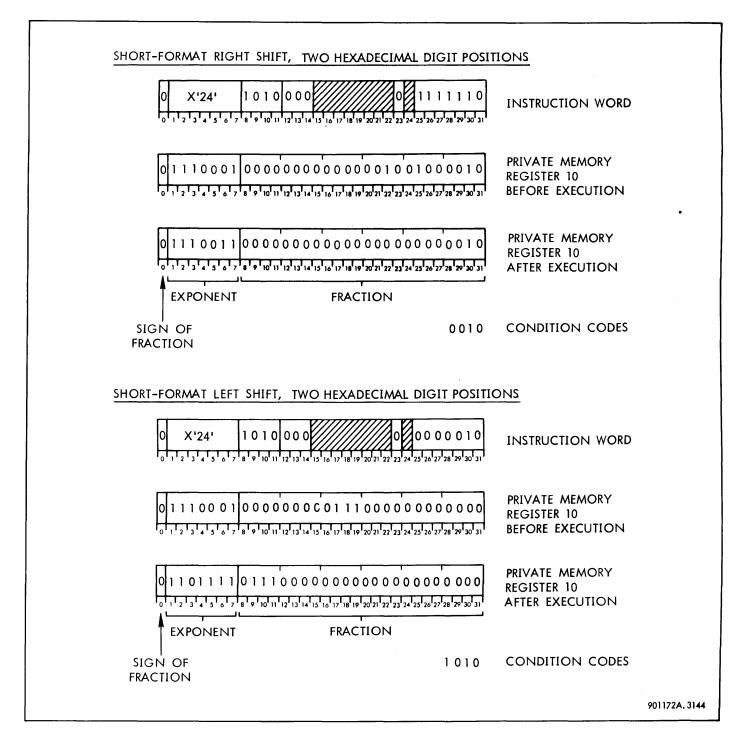

| 3-162  | Shift Floating Examples.                                                                           | 3-365          |

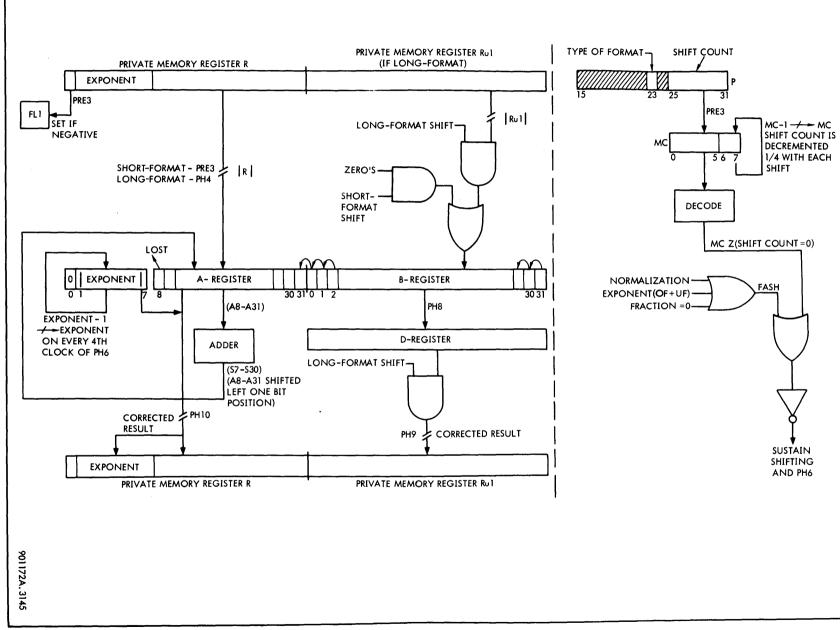

| 3-163  | Implementation of Left Shift Floating.                                                             | 3-366          |

| 3-164  | Implementation of Right Shift Floating                                                             | 3-367          |

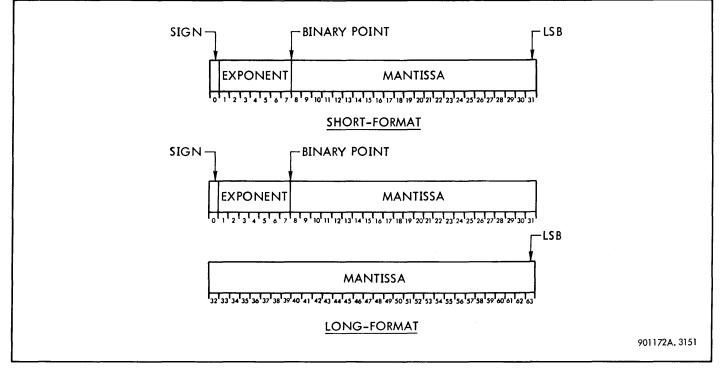

| 3-165  | Floating Point Number Formats.                                                                     | 3-378          |

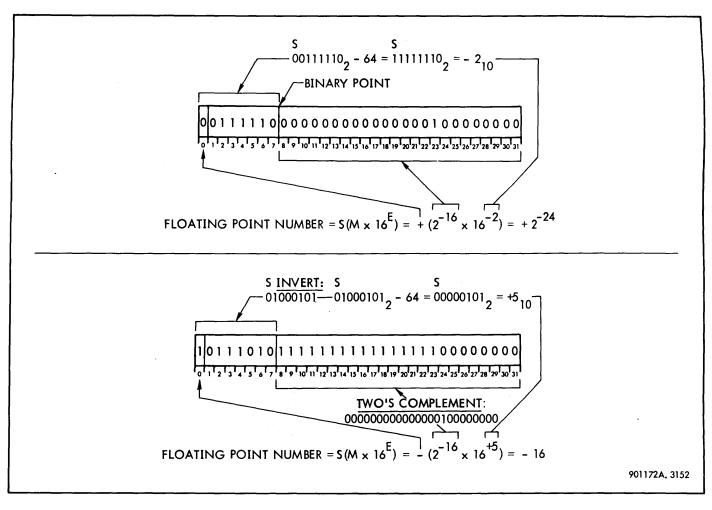

| 3-166  | Floating Point Number Example                                                                      | 3-379          |

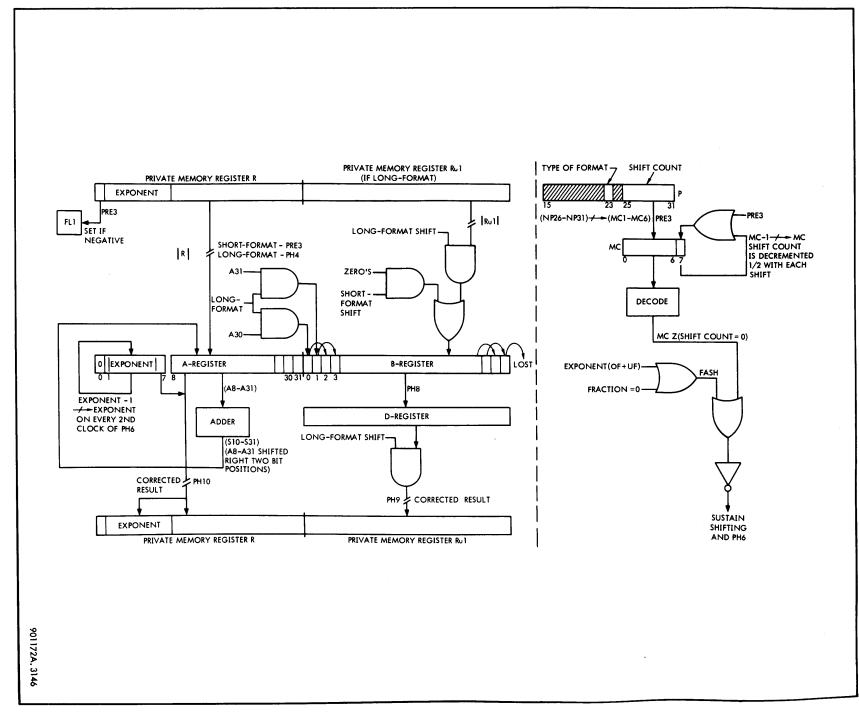

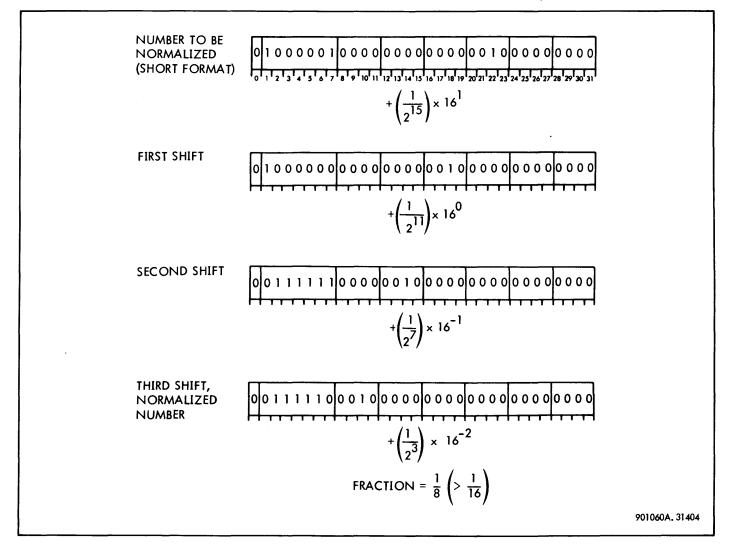

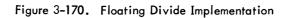

| 3-167  | Normalization of Floating Point Numbers                                                            | 3-380          |

| 3-168  | Floating Add and Subtract Implementation                                                           | 3-382          |

| 3-169  | Floating Multiply Implementation                                                                   | 3-401          |

| 3-170  | Floating Divide Implementation                                                                     | 3-401          |

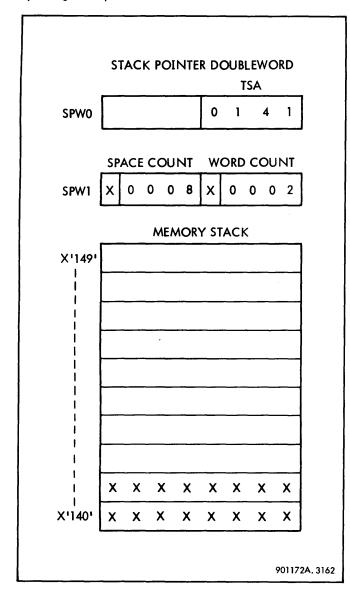

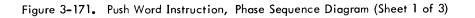

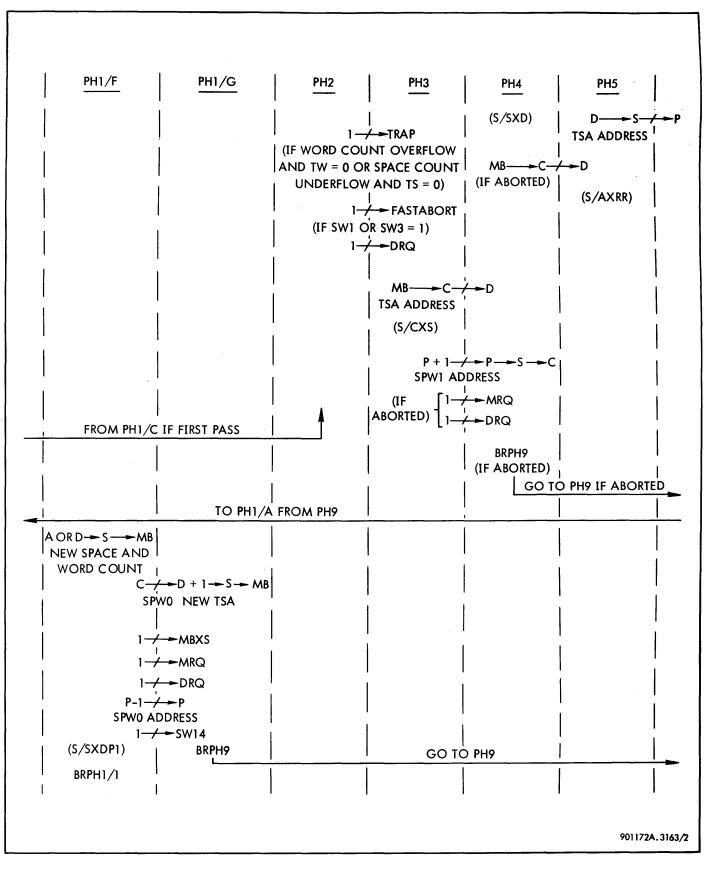

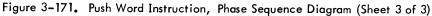

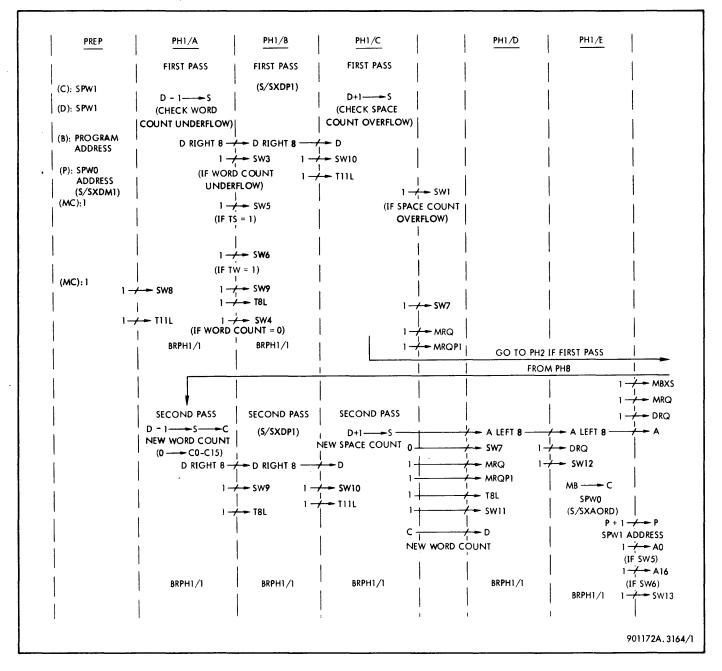

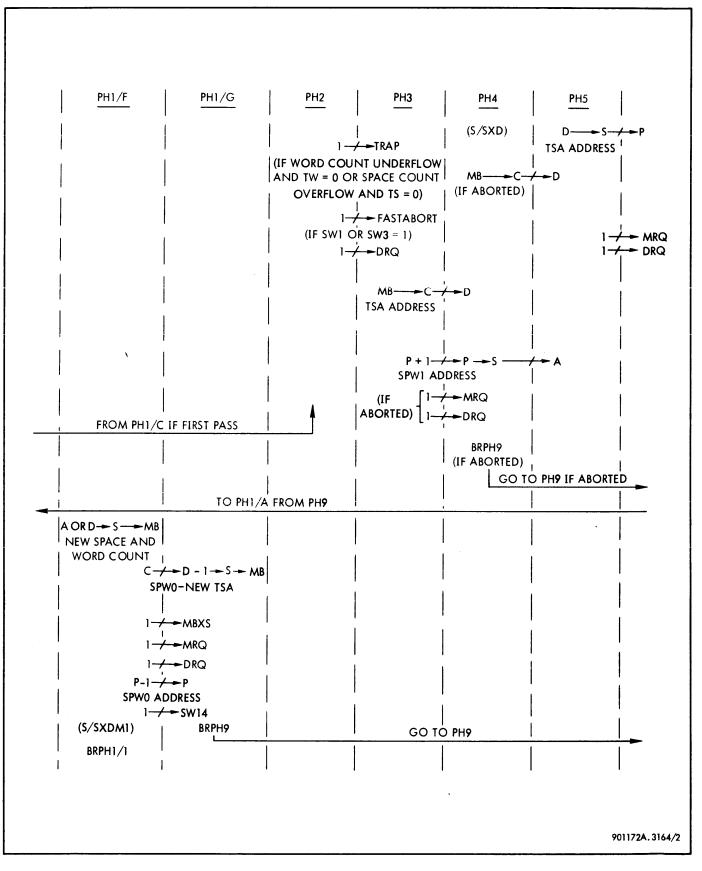

| 3-171  | Push Word Instruction, Phase Sequence Diagram.                                                     | 3-440          |

| 3-172  | Pull Word Instruction, Phase Sequence Diagram                                                      | 3-440          |

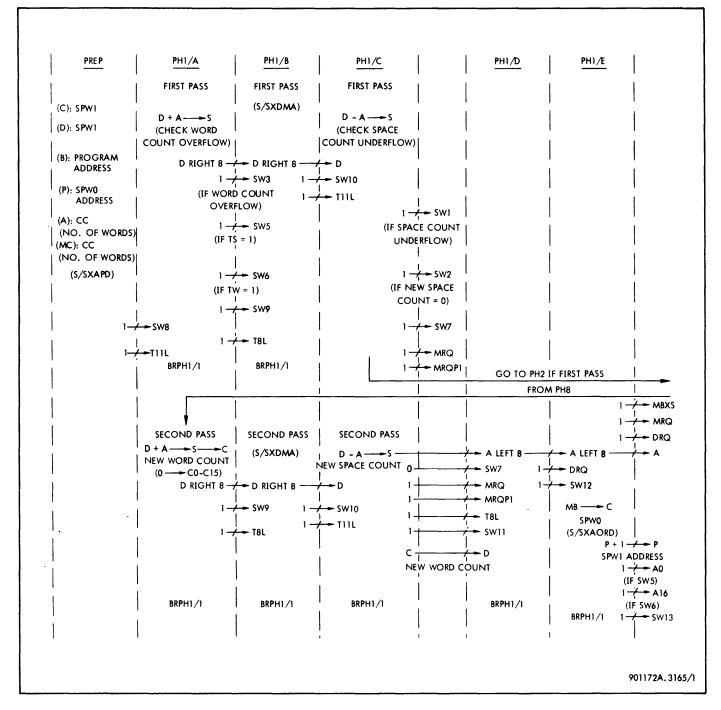

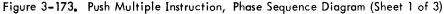

| 3-172  | Push Multiple Instruction, Phase Sequence Diagram                                                  | 3-452          |

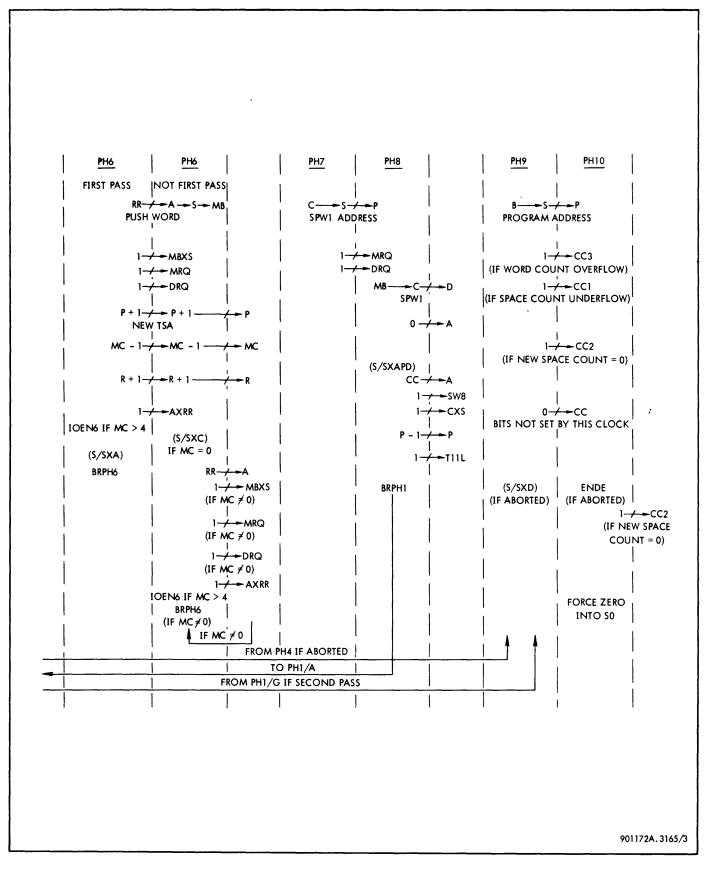

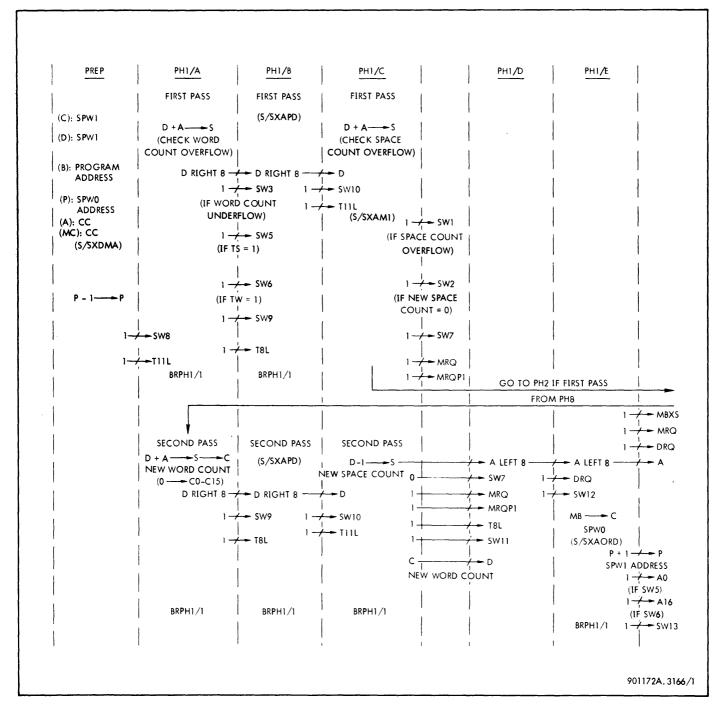

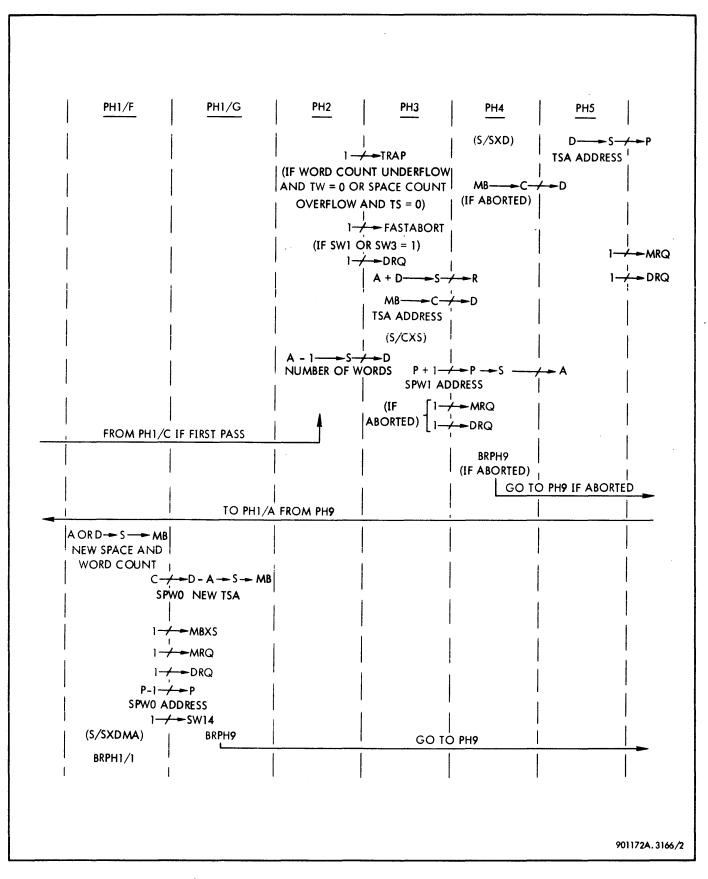

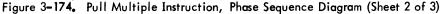

| 3-173  | Pull Multiple Instruction, Phase Sequence Diagram                                                  | 3-404          |

| 3-174  | Modify Stack Pointer Instruction, Phase Sequence Diagram                                           | 3-478          |

| 3-175  | Load Multiple Instruction, Phase Sequence Diagram                                                  | 3-501          |

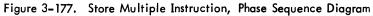

| 3-170  | Store Multiple Instruction, Phase Sequence Diagram                                                 | 3-505          |

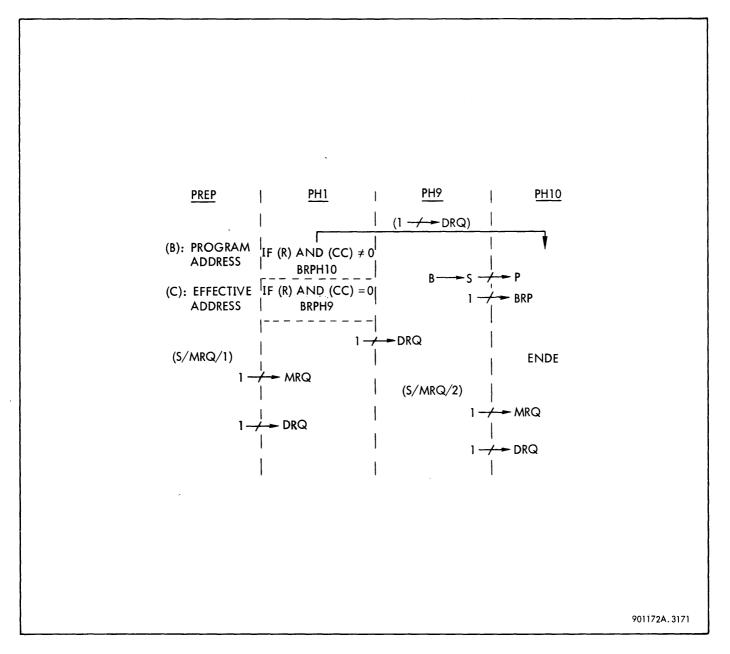

| 3-178  | BCS Instruction, Phase Sequence Diagram                                                            | 3-508          |

| 3-179  | BCR Instruction, Phase Sequence Diagram                                                            | 3 <b>-</b> 511 |

| 3-177  | BAL Instruction, Phase Sequence Diagram                                                            | 3-513          |

| 3-180  | BDR Instruction, Phase Sequence Diagram                                                            | 3-515          |

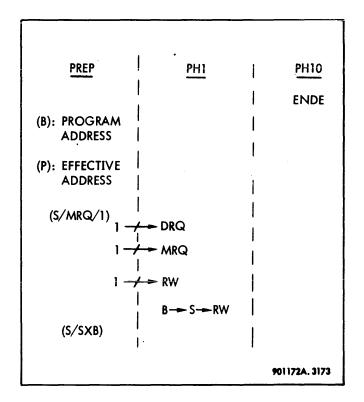

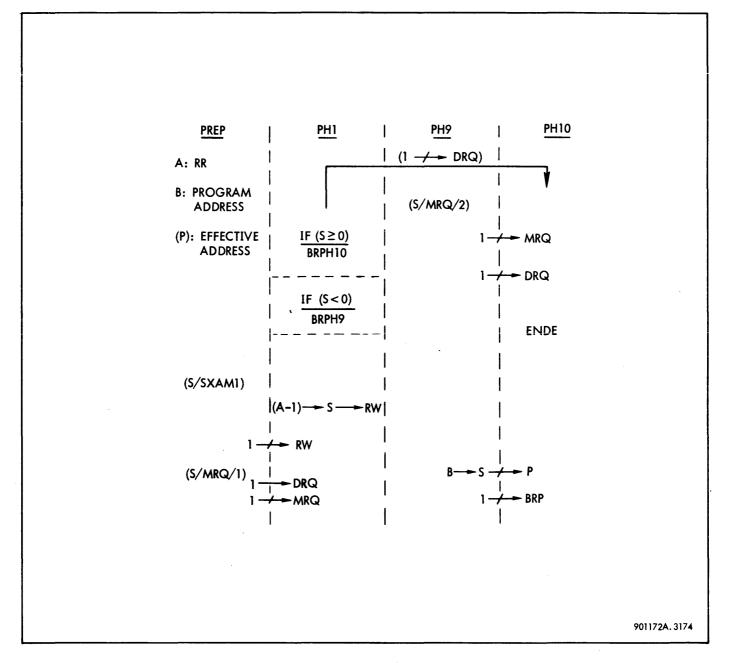

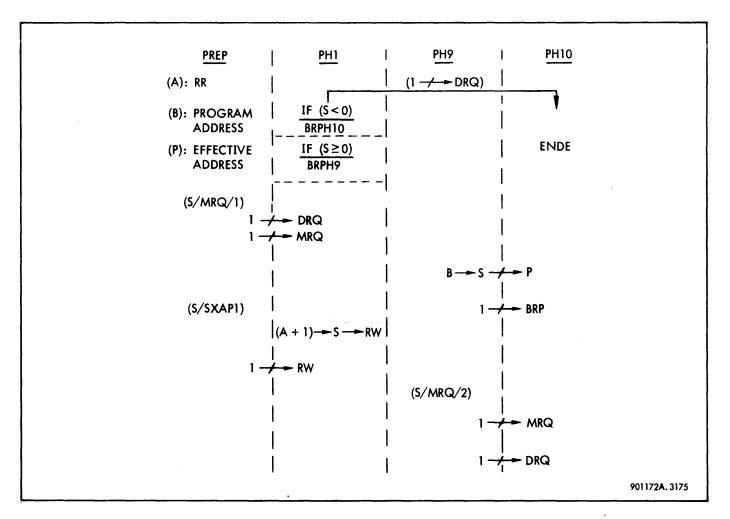

| 3-182  | BIR Instruction, Phase Sequence Diagram                                                            | 3-515          |

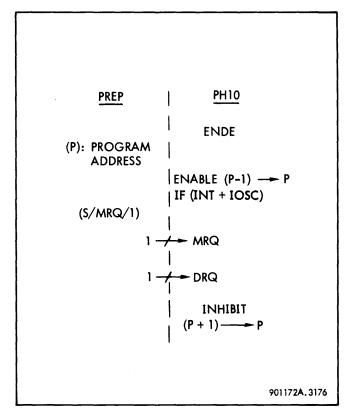

| 3-182  | EXU Instruction, Phase Sequence Diagram.                                                           | 3-520          |

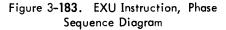

| 3-183  | Load Program Status Doubleword Instruction, Phase Sequence Diagram                                 | 3-525          |

| 3-185  | Exchange Program Status Doubleword Instruction, Flow Diagram                                       | 3-530          |

| 3-186  | Exchange Program Status Doubleword Instruction, Phase Sequence Diagram                             | 3-531          |

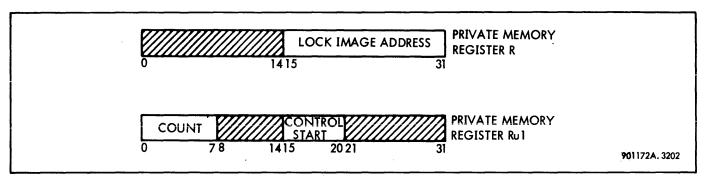

| 3-187  | Write-Lock Configuration                                                                           | 3-538          |

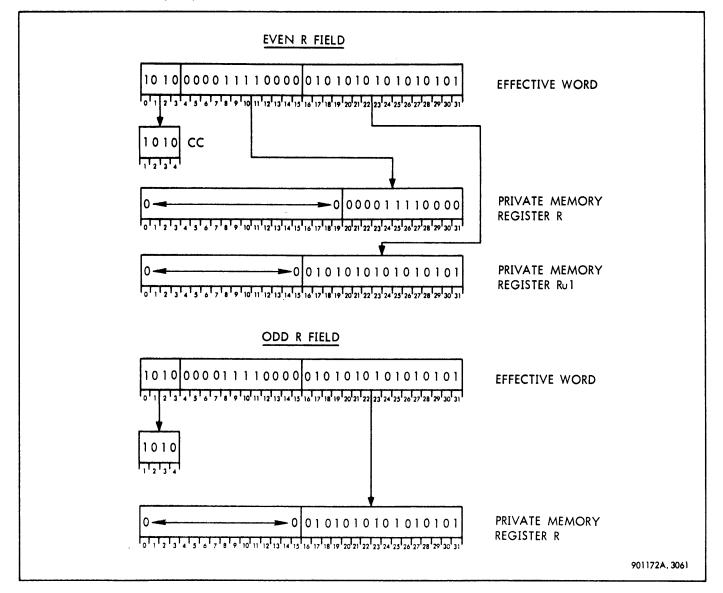

| 3-188  | Contents of Private Memory Registers R and Rul                                                     | 3-539          |

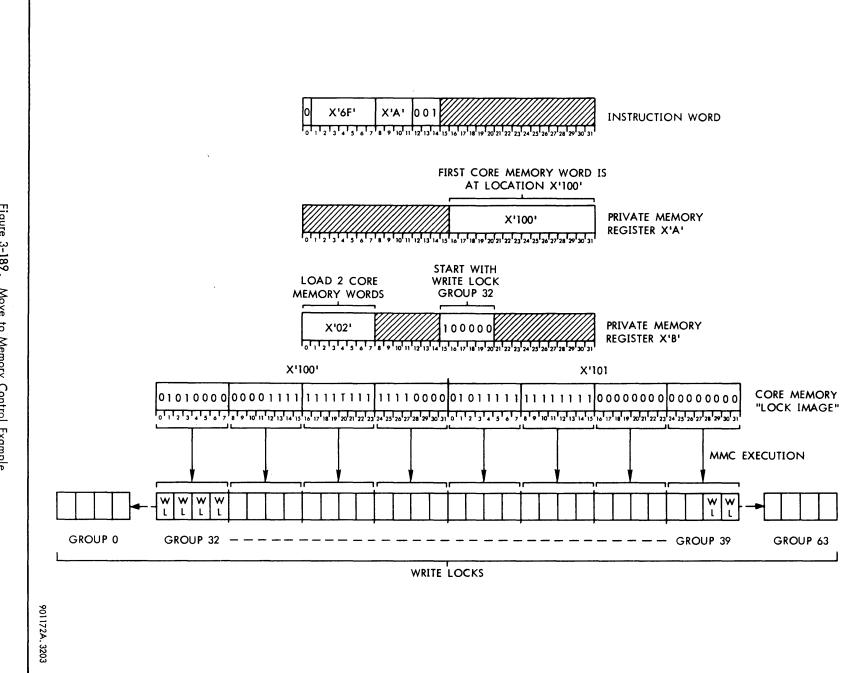

| 3-189  | Move to Memory Control Example                                                                     | 3-540          |

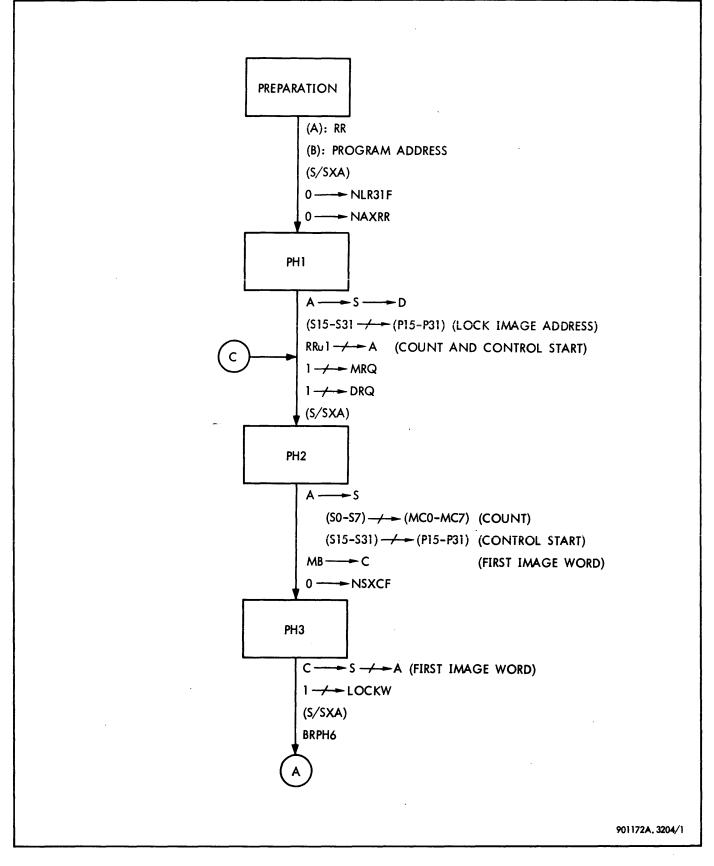

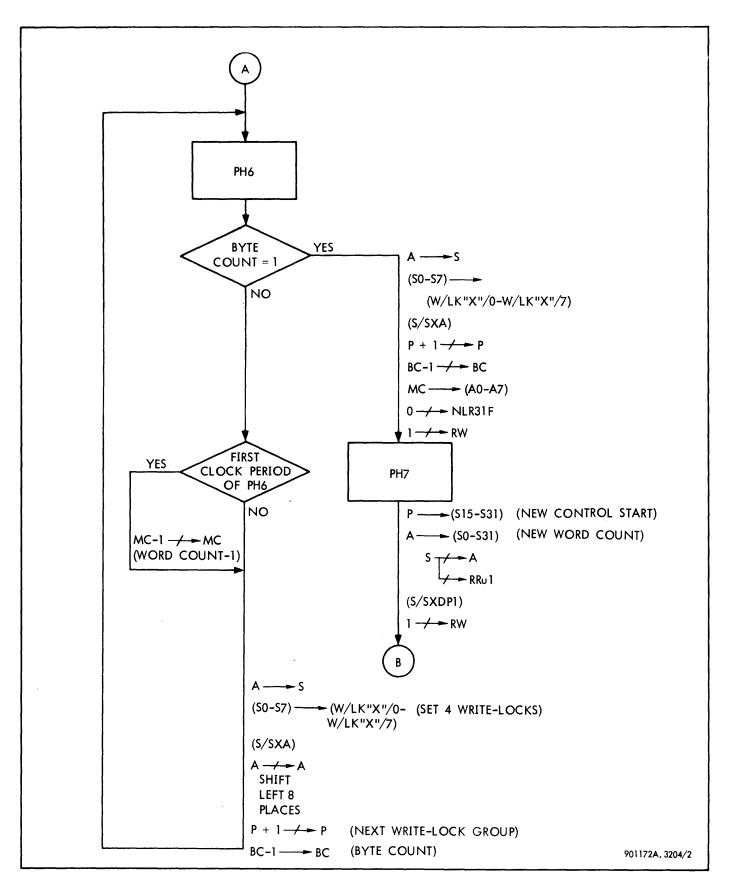

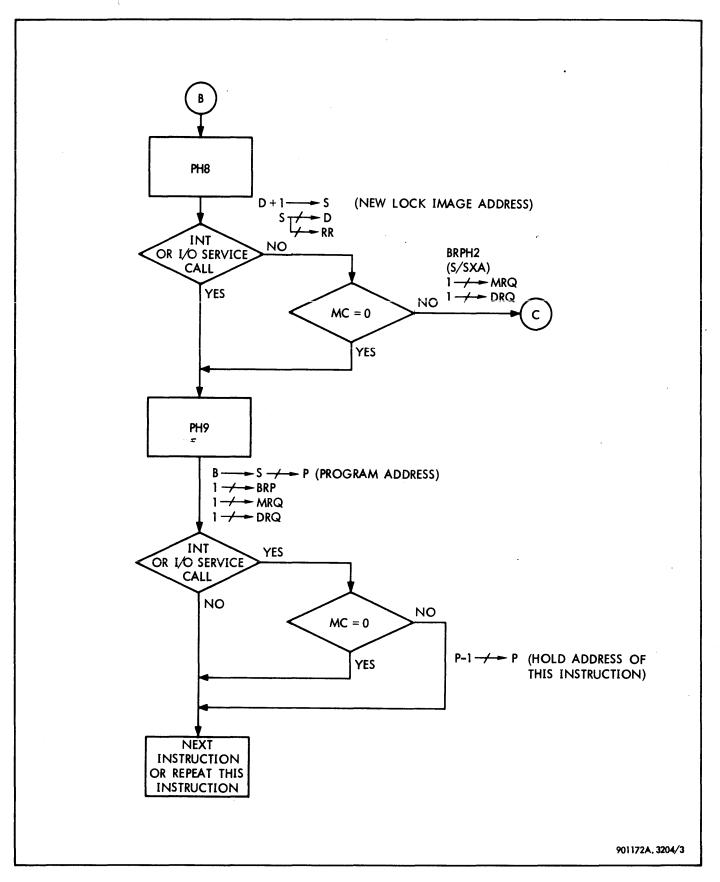

| 3-190  | Move to Memory Control, Flow Diagram                                                               | 3-541          |

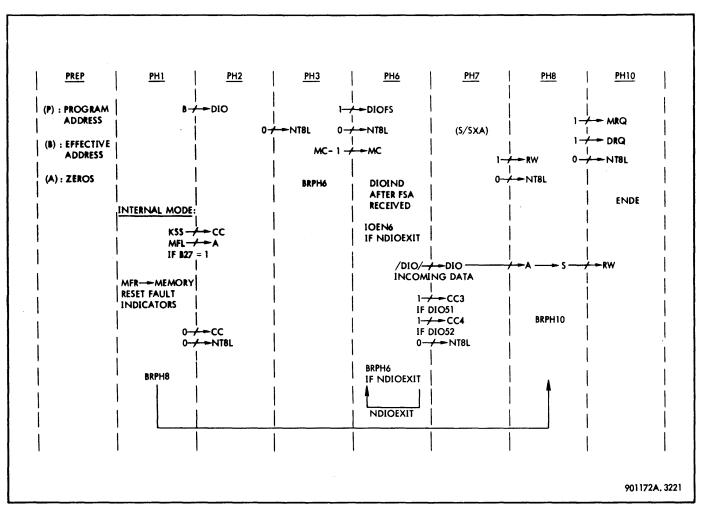

| 3-191  | Read Direct Instruction, Phase Sequence Diagram                                                    | 3-554          |

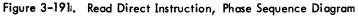

| 3-192  | DIO Timing Flip-Flops, Simplified Logic Diagram                                                    | 3-557          |

| 3-193  | Write Direct Instruction, Phase Sequence Diagram                                                   | 3-559          |

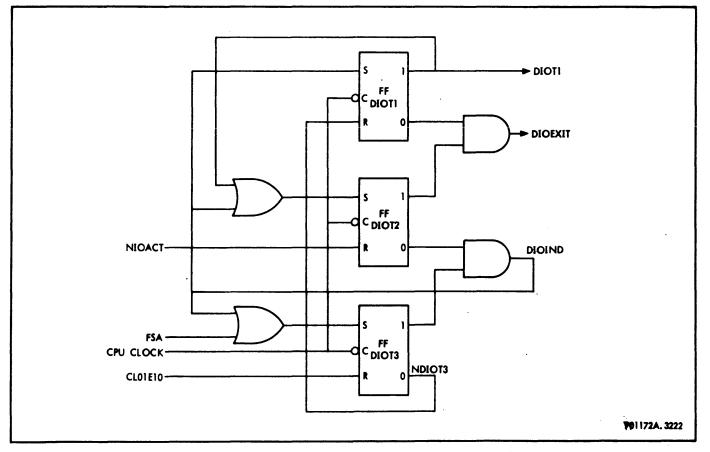

| 3-194  | Start Input/Output Instruction Format.                                                             | 3-565          |

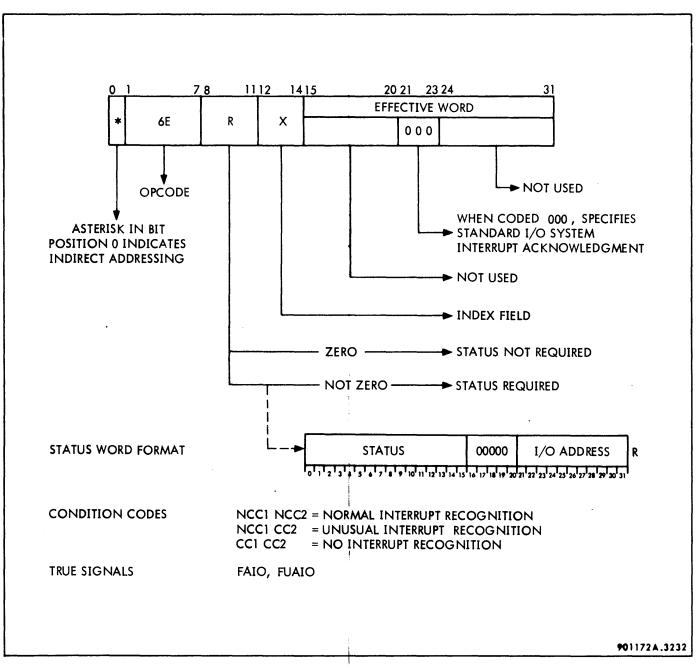

| 3-195  | Acknowledge Input/Output Interrupt Instruction Format                                              | 3-566          |

| 3-196  | SIO, HIO, TIO, TDV, Flow Diagram for MIOP                                                          | 3-567          |

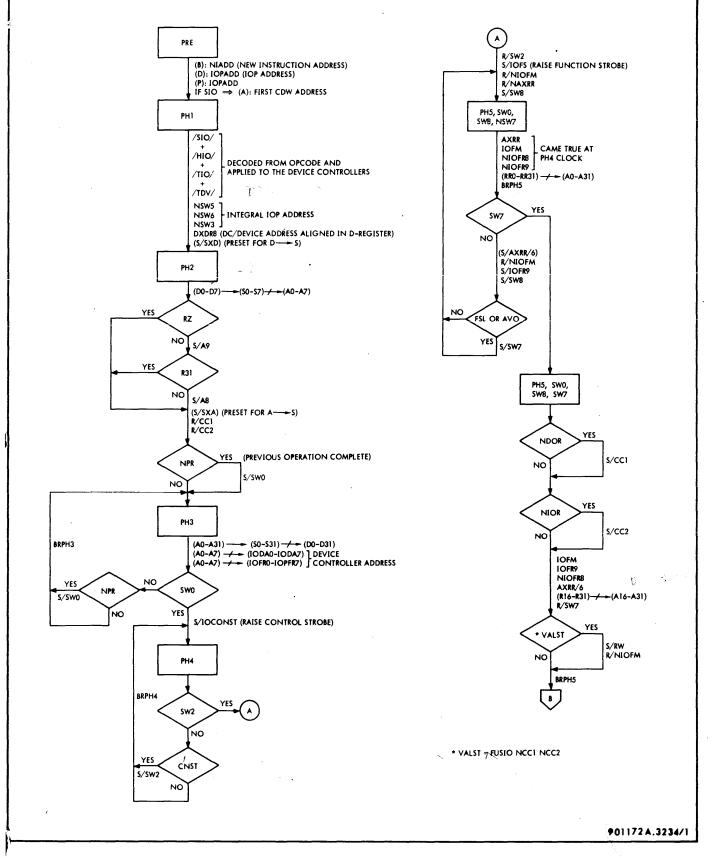

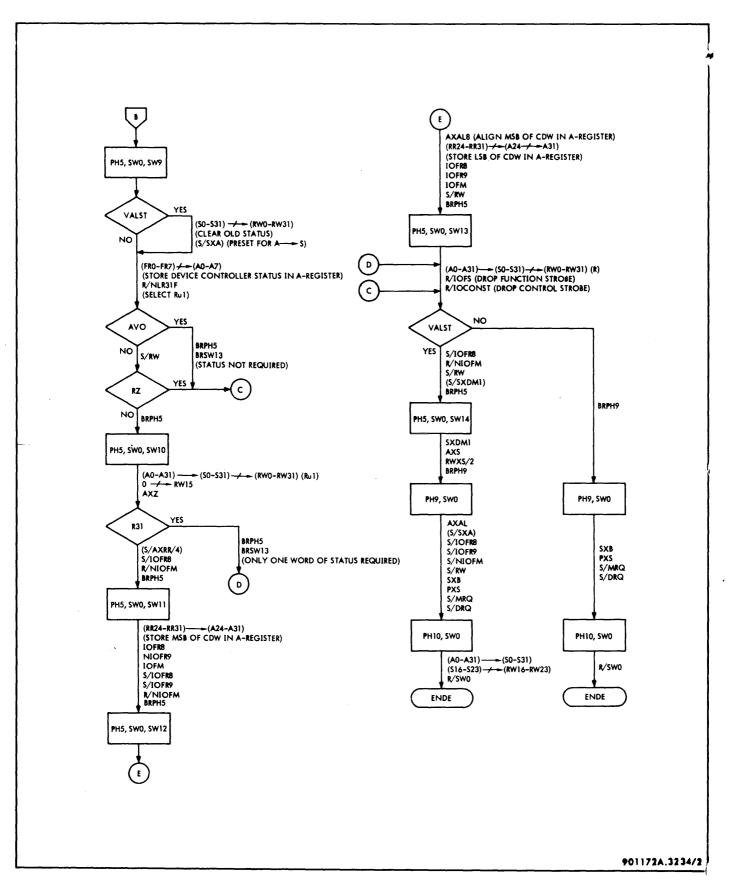

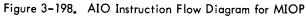

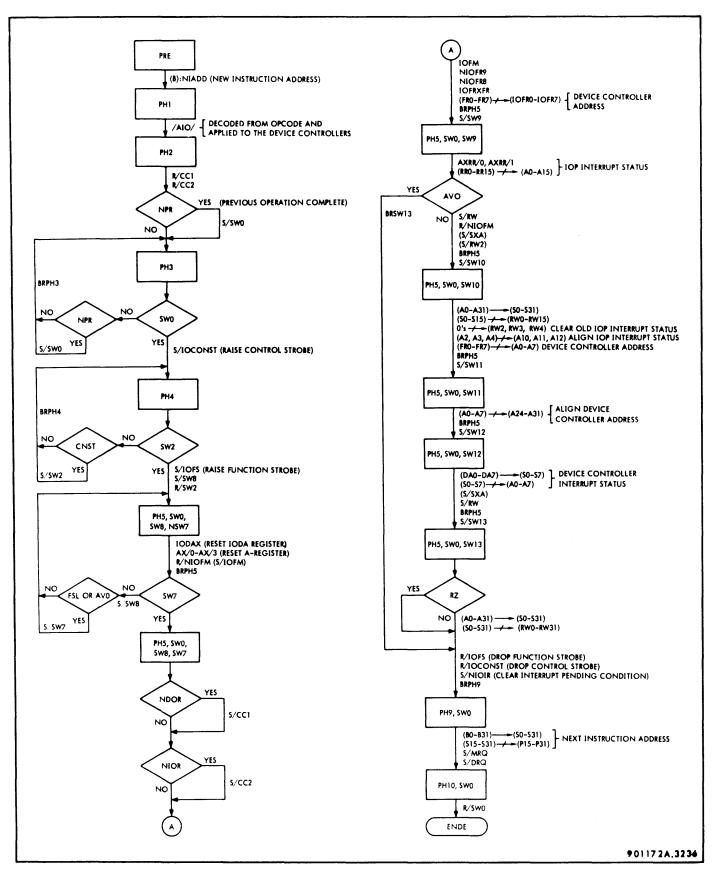

| 3-197  | SIO, HIO, TIO, TDV Flow Diagram for Integral IOP                                                   | 3-575          |

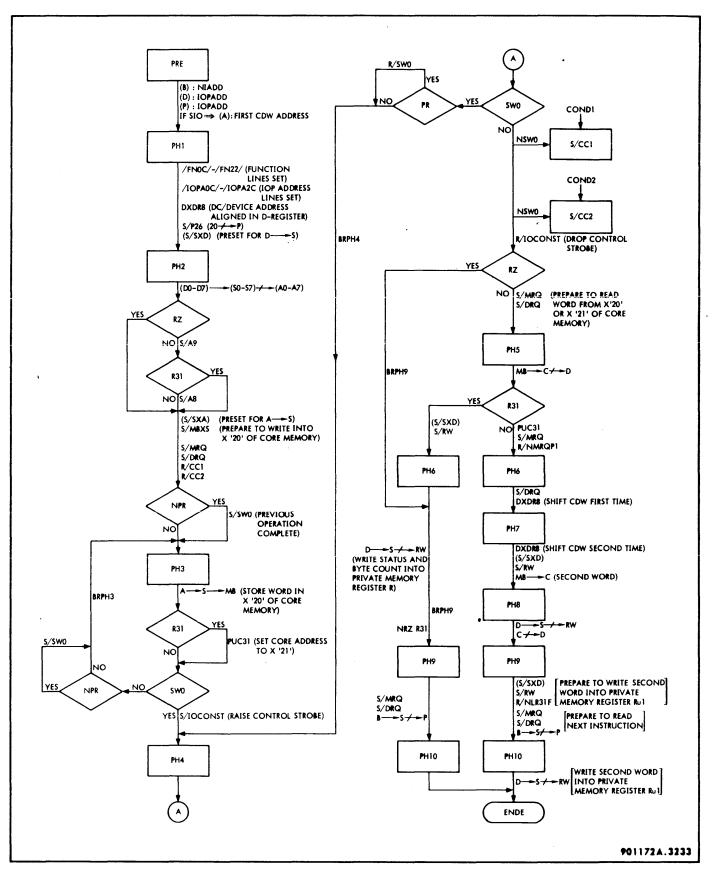

| 3-198  | AIO Instruction Flow Diagram for MIOP                                                              | 3-588          |

|        |                                                                                                    |                |

٠

#### LIST OF ILLUSTRATIONS (Cont.)

| Figure | Title                                                                                  | Page           |

|--------|----------------------------------------------------------------------------------------|----------------|

| 3-199  | AIO Instruction Flow Diagram for Integral IOP                                          | 3-592          |

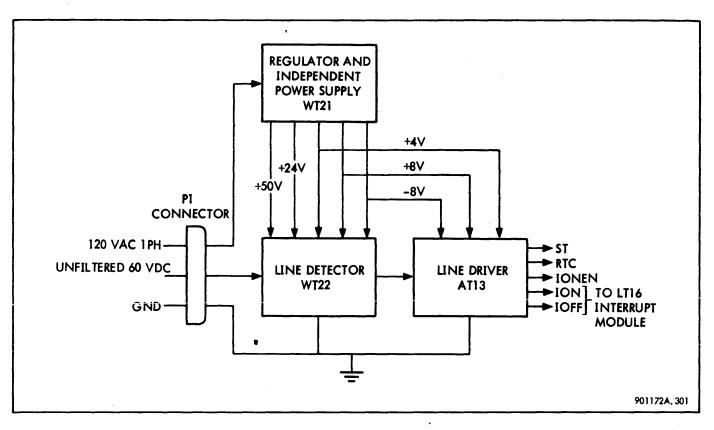

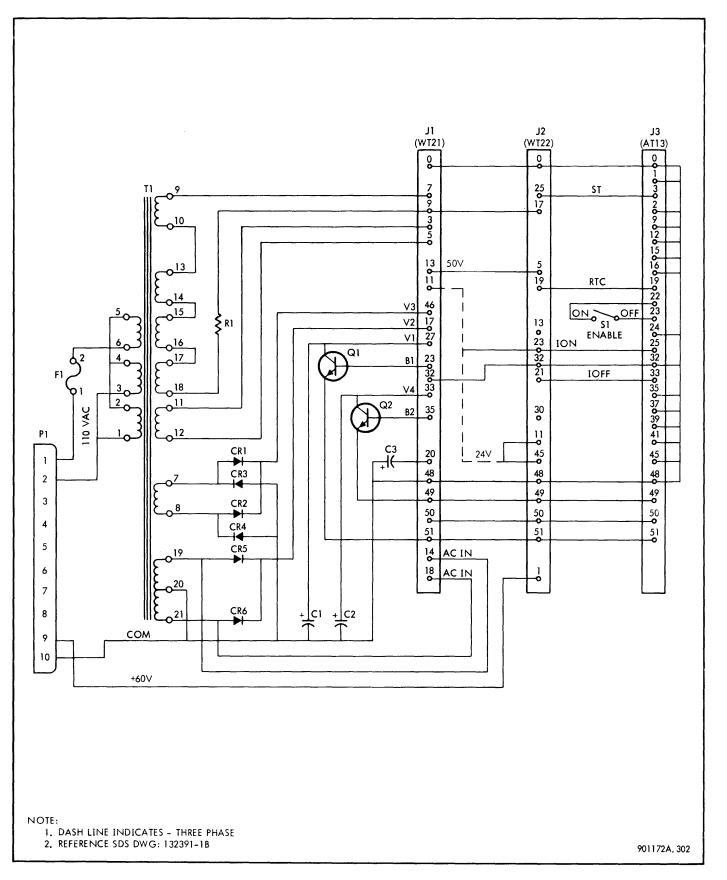

| 3-200  | Power Monitor Assembly, Simplified Block Diagram                                       | 3-625          |

| 3-201  | Power Monitor, Functional Schematic Diagram                                            | 3-626          |

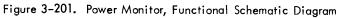

| 3-202  | WT21 Regulator, Schematic Diagram                                                      | 3-627          |

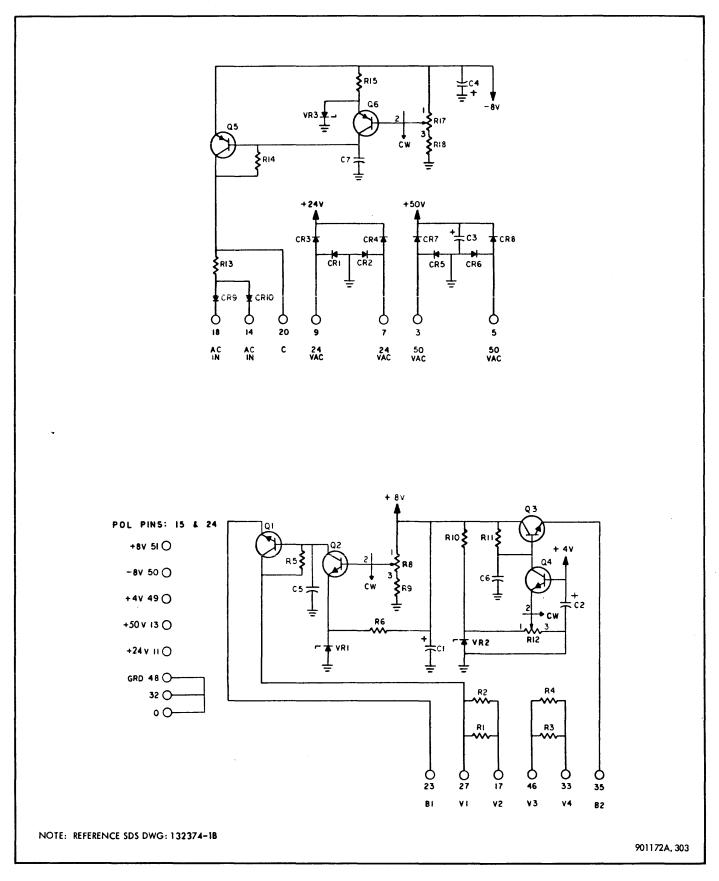

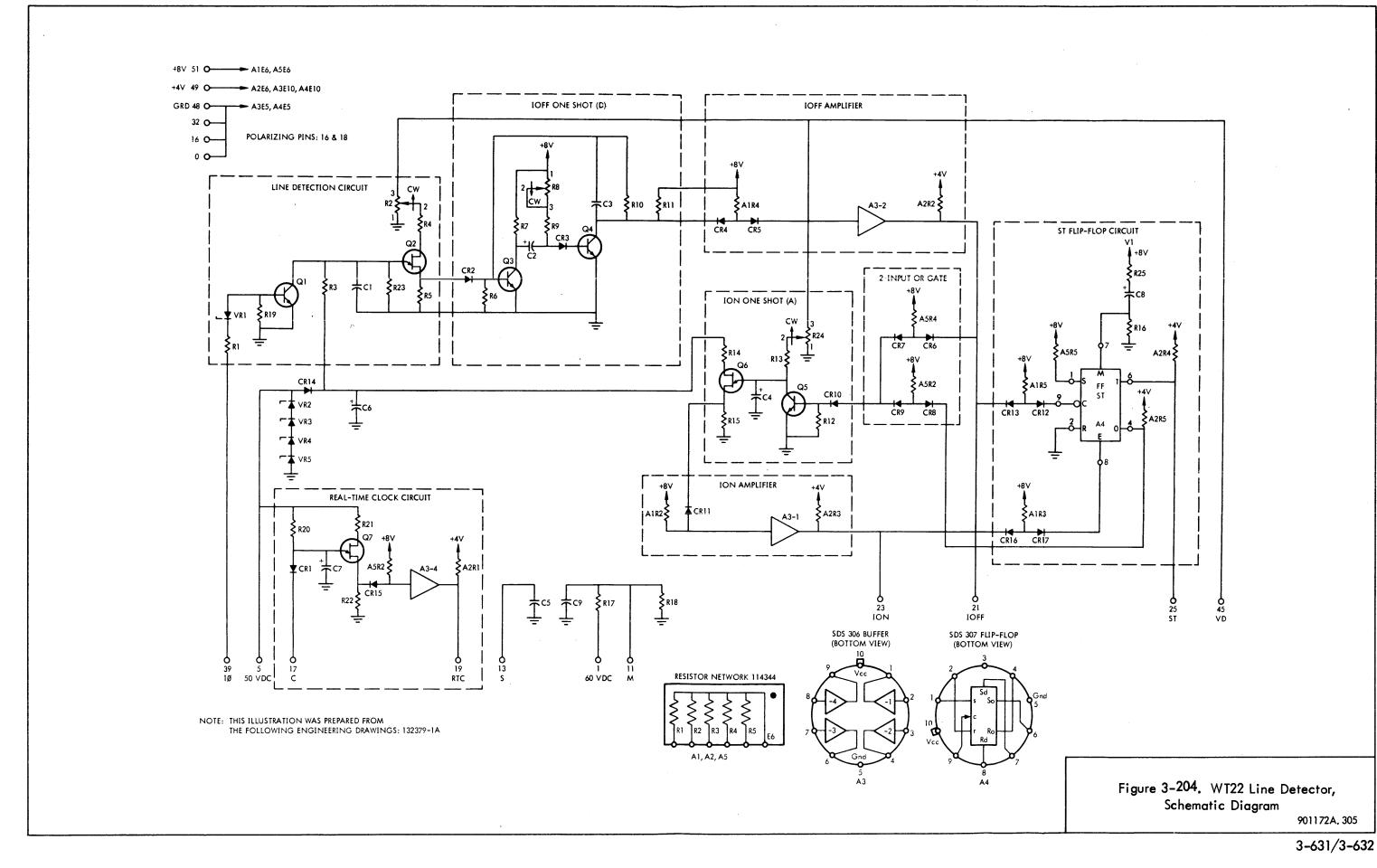

| 3-203  | WT22 Line Detector, Block Diagram                                                      | 3-629          |

| 3-204  | WT22 Line Detector, Schematic Diagram                                                  | 3-631          |

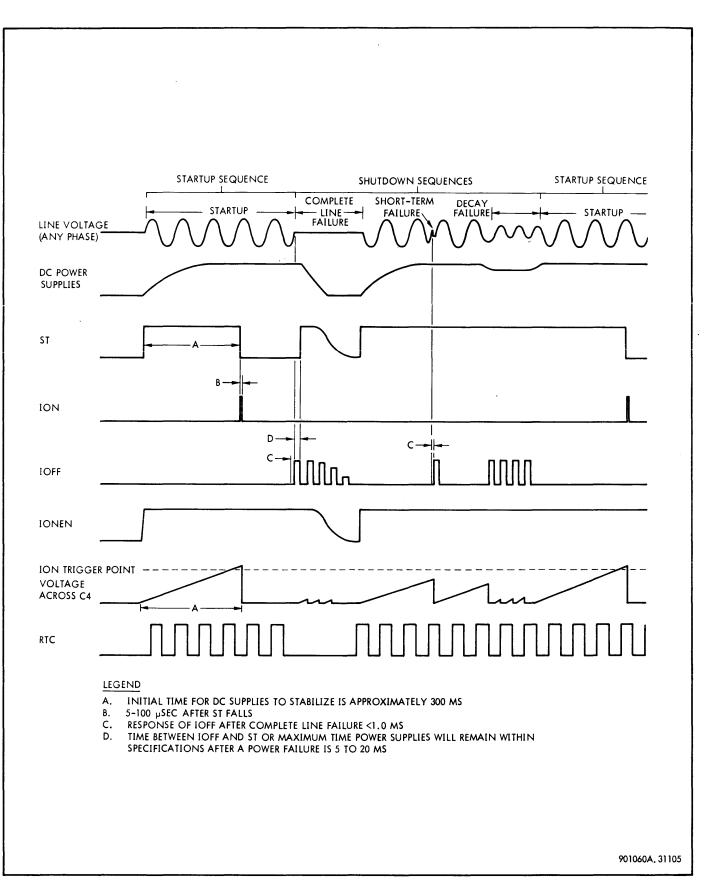

| 3-205  | Power Fail-Safe Waveforms                                                              | 3-633          |

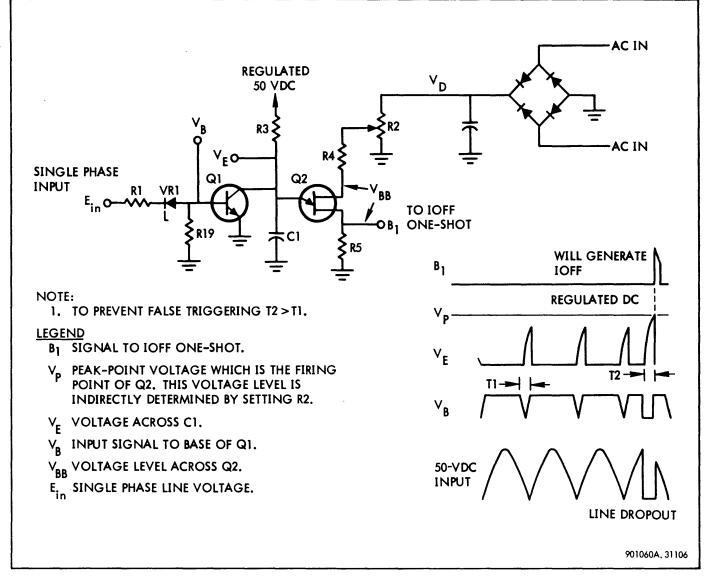

| 3-206  | Single-Phase Detection                                                                 | 3-634          |

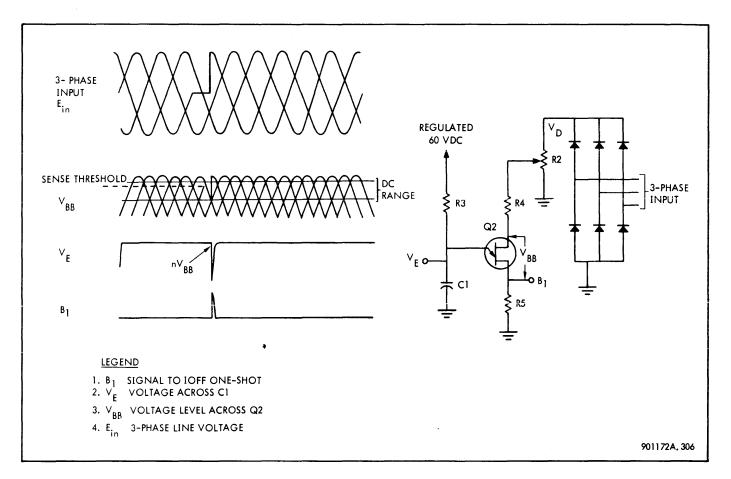

| 3-207  | Three-Phase Detection                                                                  | 3-635          |

| 3-208  | ION One-Shot Operation                                                                 | 3-636          |

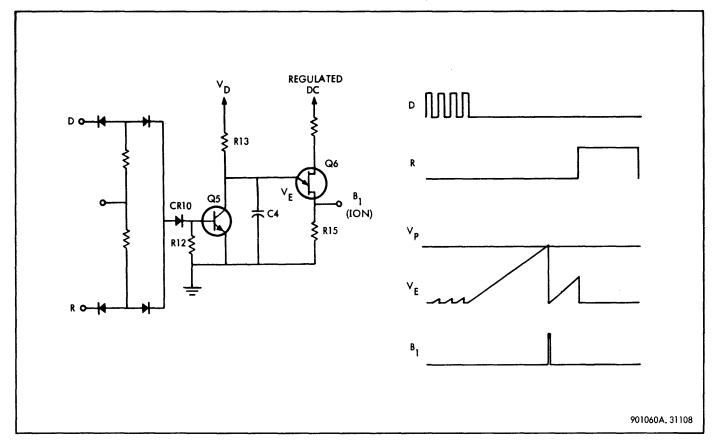

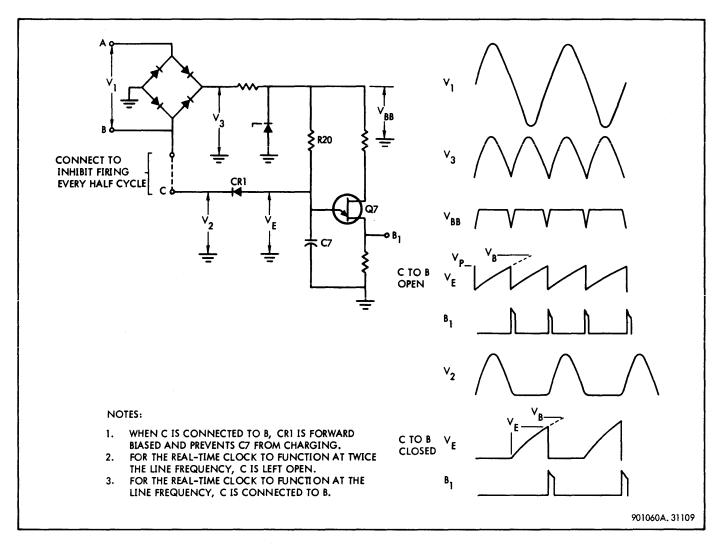

| 3-209  | Real-Time Clock Operation                                                              | 3-637          |

| 3-210  | Floating Point Unit, Block Diagram                                                     | 3-639          |

| 3-211  | Floating Point A-Register Inputs and Enabling Signals                                  | 3-640          |

| 3-212  | Floating Point B-Register Inputs and Enabling Signals                                  | 3-642          |

| 3-213  | Floating Point D-Register Inputs and Enabling Signals                                  | 3-643          |

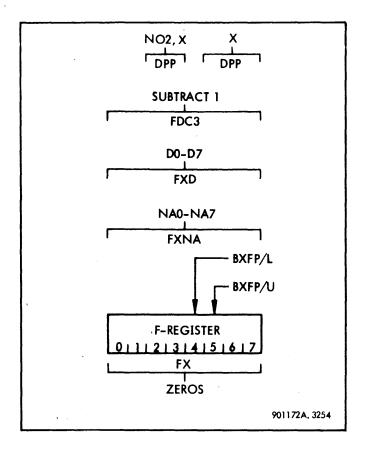

| 3-214  | Floating Point F-Register Inputs and Enabling Signals                                  | 3-644          |

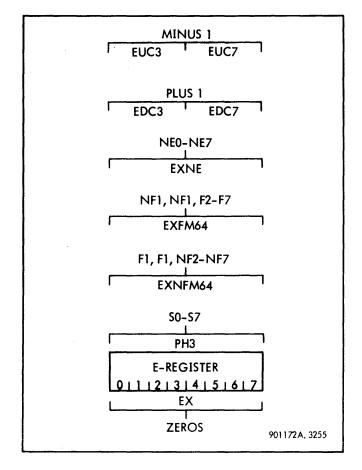

| 3-215  | Floating Point E-Register Inputs and Enabling Signals                                  | 3-644          |

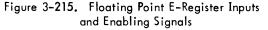

| 3-216  | Data on Floating Point Lines and Gating Terms                                          | 3-645          |

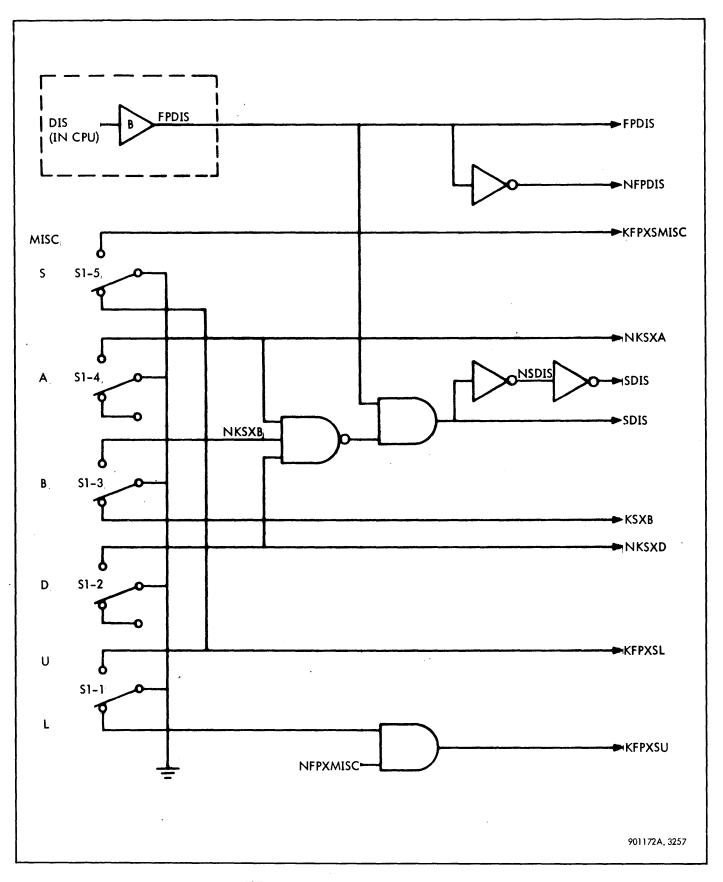

| 3-217  | Floating Point Display Switches, Logic Diagram                                         | 3-646          |

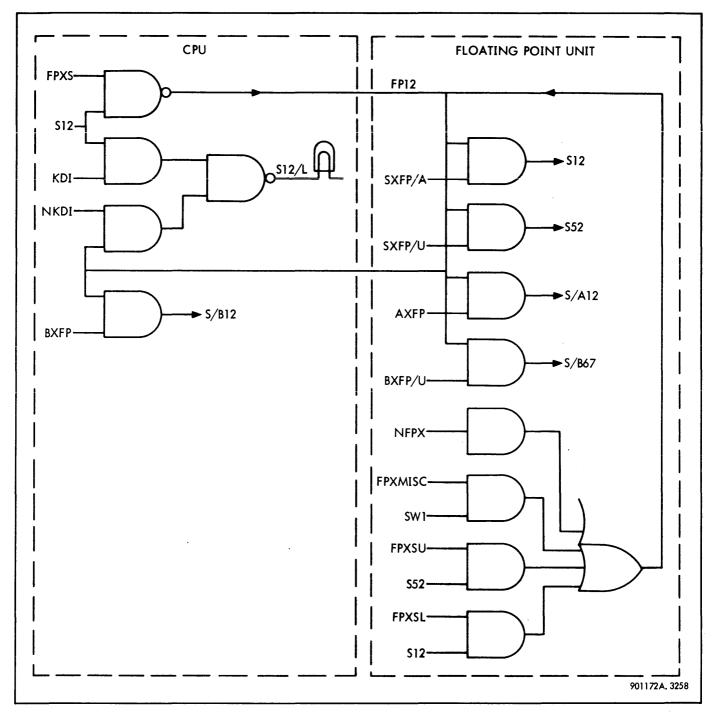

| 3-218  | Floating Point Bit 12, Logic Diagram                                                   | 3-647          |

| 3-219  | Entering PCP Phases                                                                    | 3-657          |

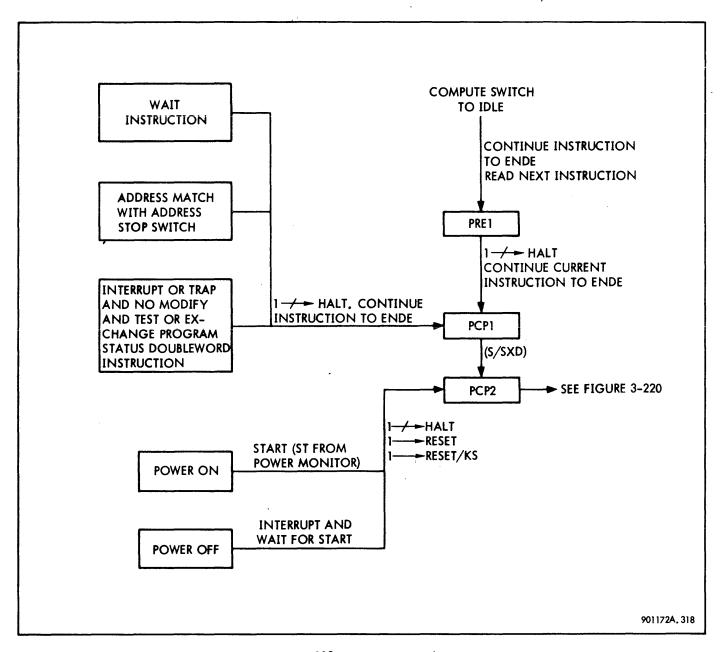

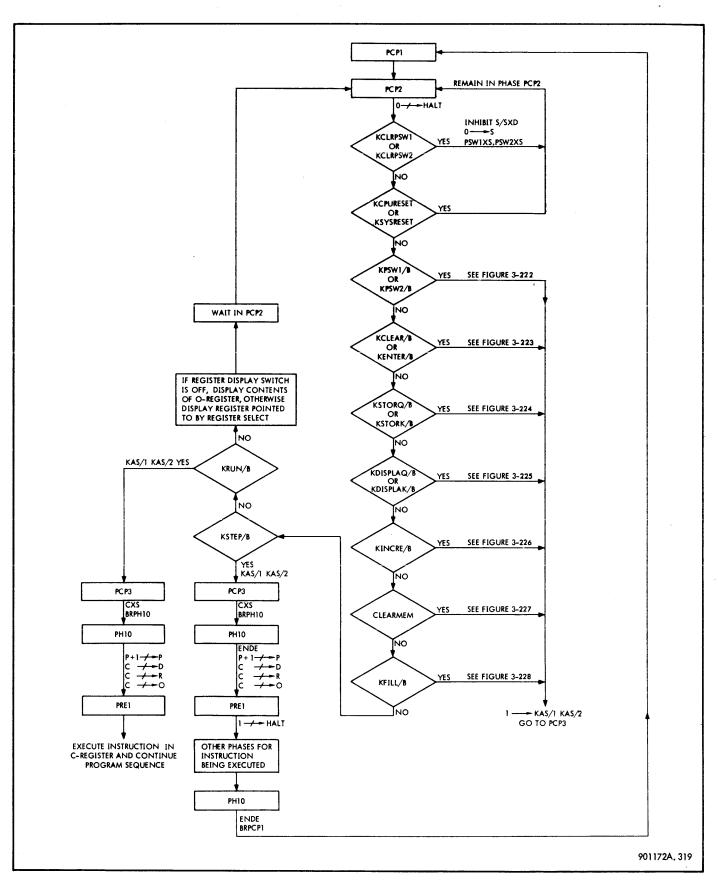

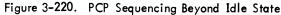

| 3-220  | PCP Sequencing Beyond Wait State                                                       | 3-661          |

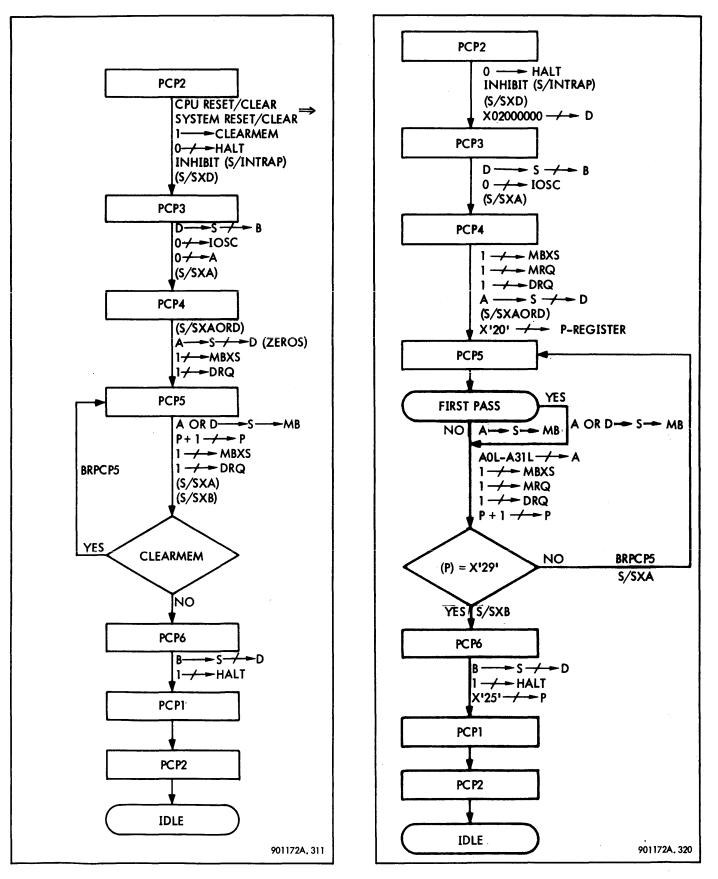

| 3-221  | CPU RESET/CLEAR and SYSTEM RESET/CLEAR, Flow Diagram                                   | 3-662          |

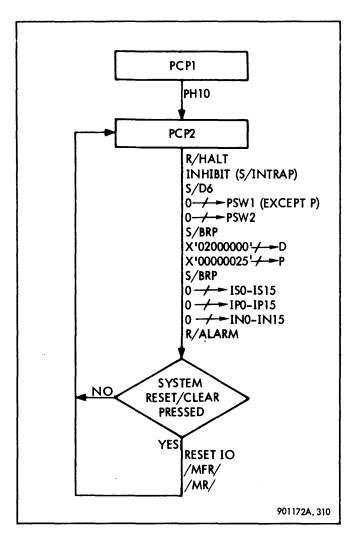

| 3-222  | Insert PSW1/Insert PSW2, Flow Diagram                                                  | 3-662          |

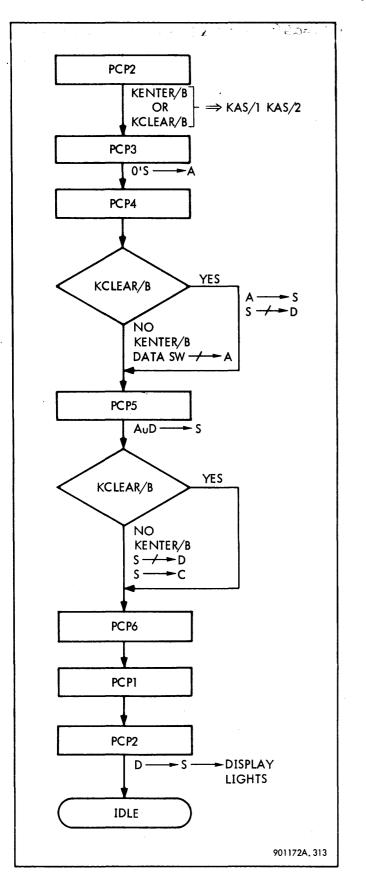

| 3-223  | DATA ENTER/DATA CLEAR, Flow Diagram                                                    | 3-666          |

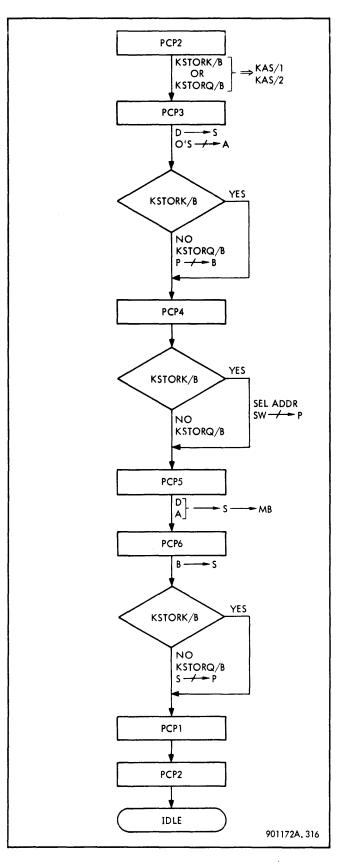

| 3-224  | STORE INSTR ADDR/STORE SELECT ADDR, Flow Diagram                                       | 3-668          |

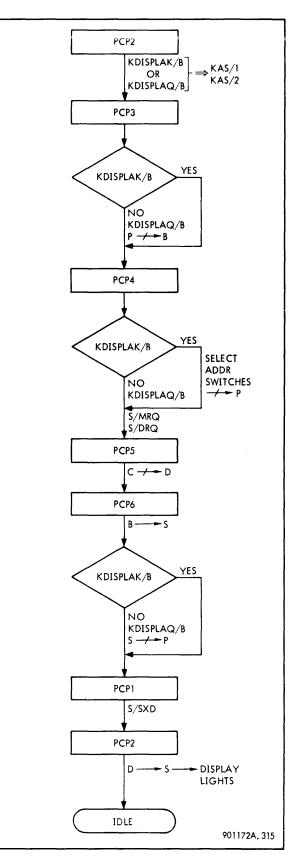

| 3-225  | DISPLAY SELECT ADDR/DISPLAY INSTR ADDR, Flow Diagram                                   | 3 <b>-66</b> 8 |

| 3-226  | INSTR ADDR INCREMENT, Flow Diagram                                                     | 3-671          |

| 3-227  | Clear Memory, Flow Diagram                                                             | 3-679          |

| 3-228  | Load, Flow Diagram                                                                     | 3-679          |

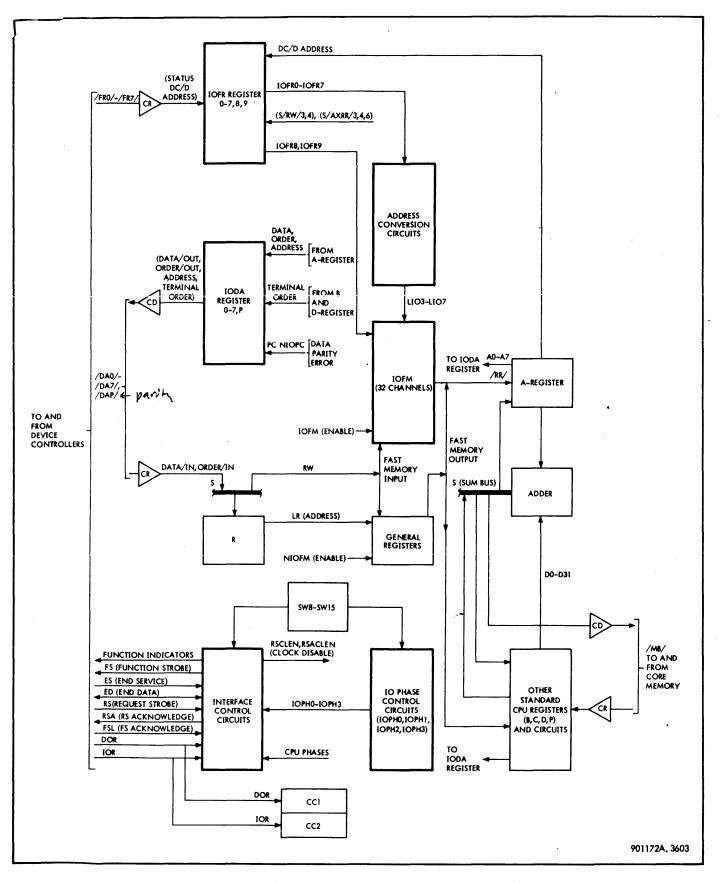

| 3-229  | Integral IOP, Functional Block Diagram                                                 | 3-681          |

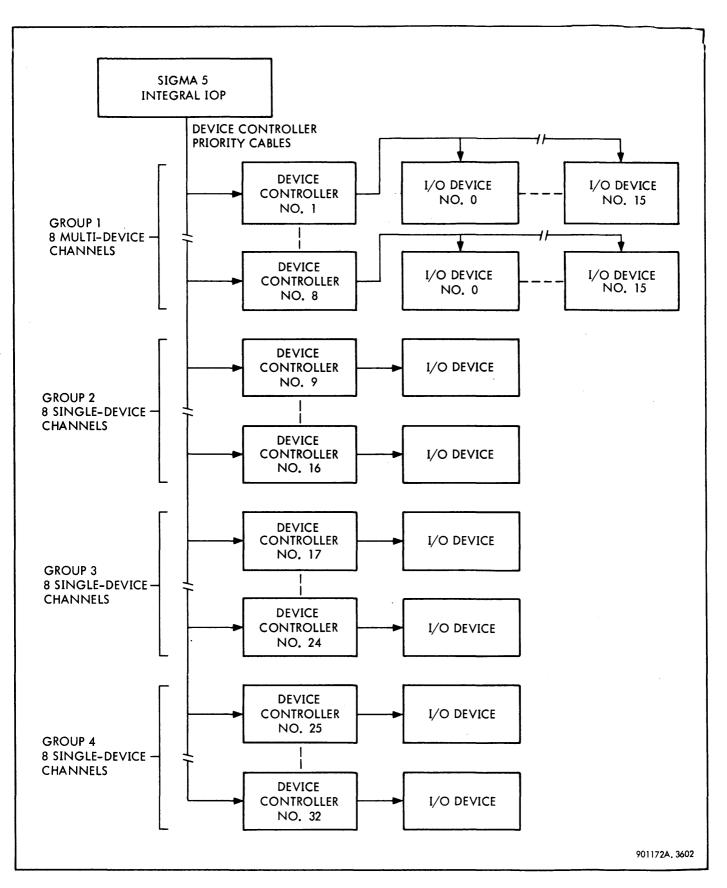

| 3-230  | Integral IOP, Device Controller/Device Configuration                                   | 3-682          |

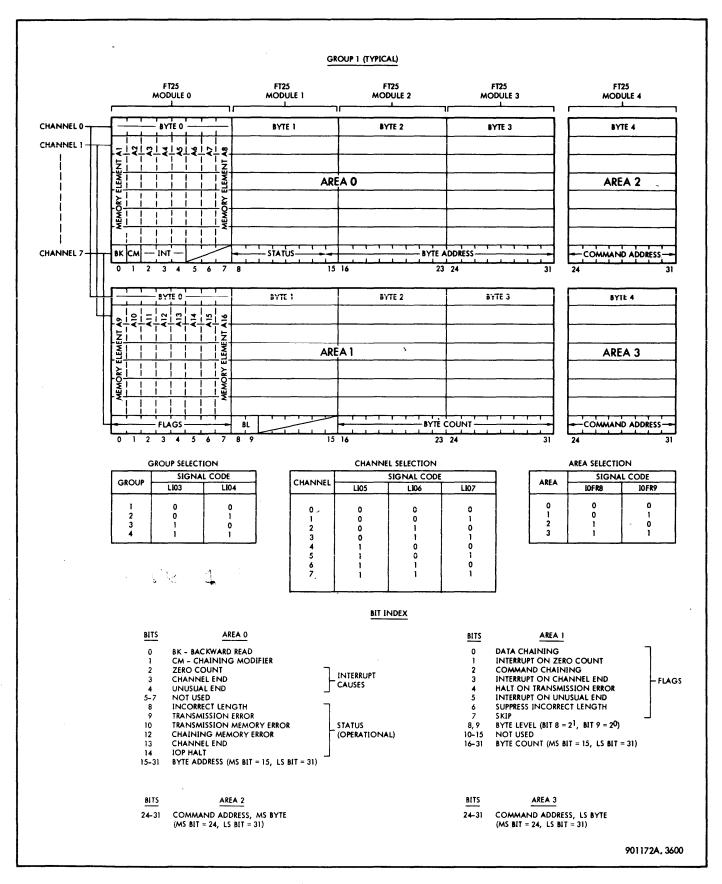

| 3-231  | I/O Fast Memory, Group Organization                                                    | 3 <b>-6</b> 83 |

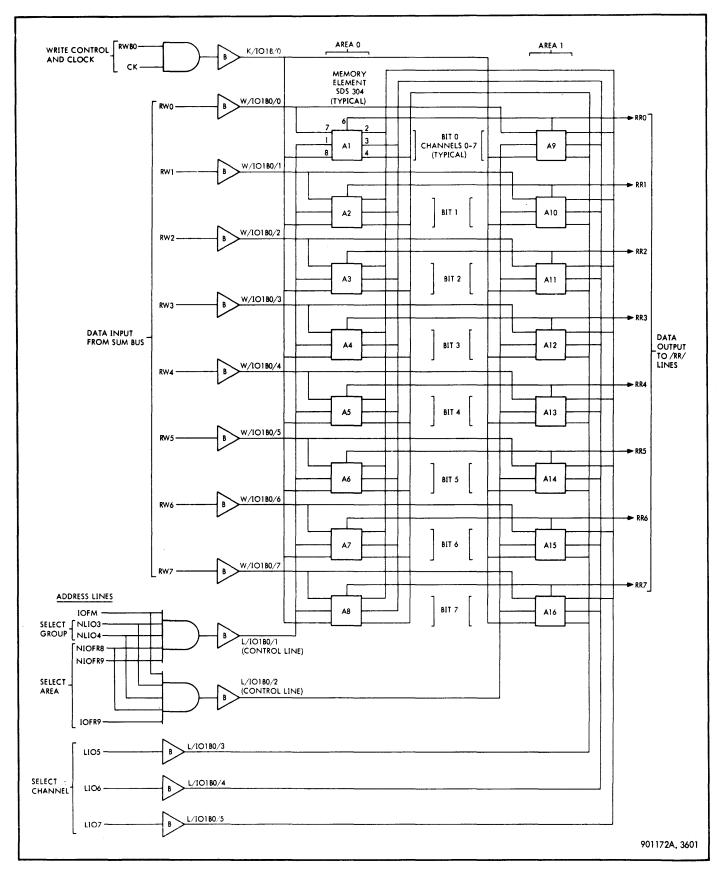

| 3-232  | Fast Memory Module FT25, Logic Diagram                                                 | 3 <b>-6</b> 84 |

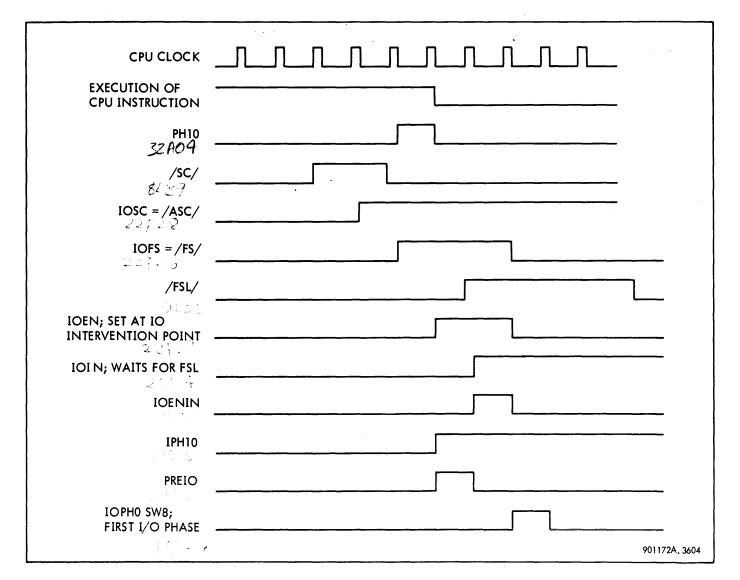

| 3-233  | Service Call Connect Phases, Typical Timing Sequence                                   | 3-688          |

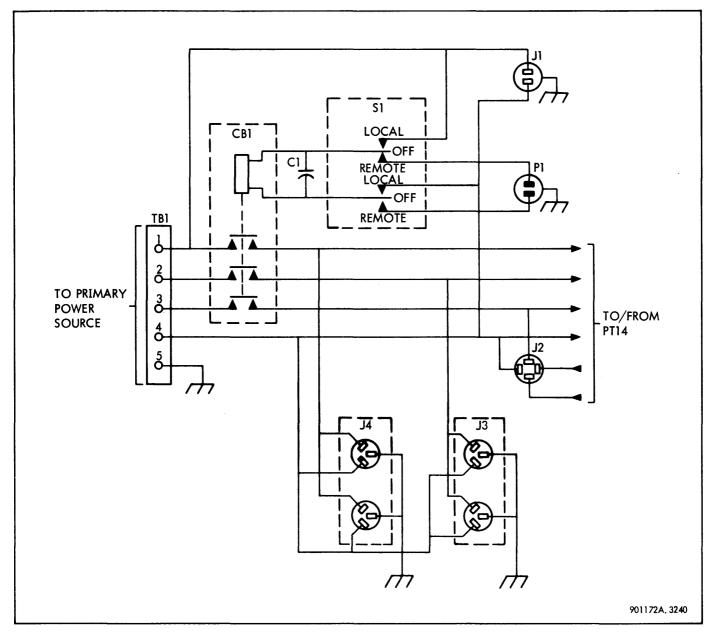

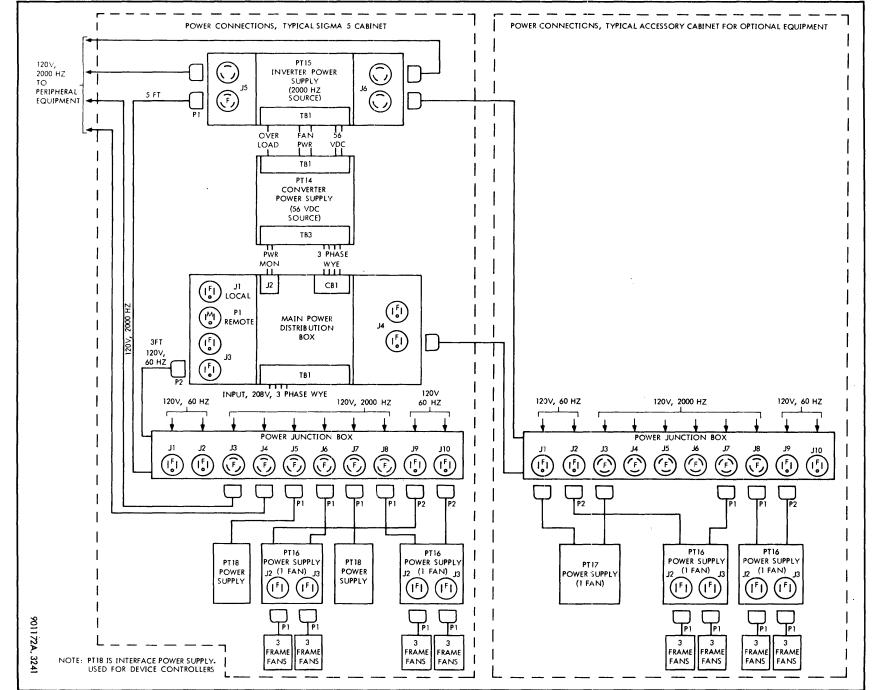

| 3-234  | Main Power Distribution Box, Schematic Diagram                                         | 3-748          |

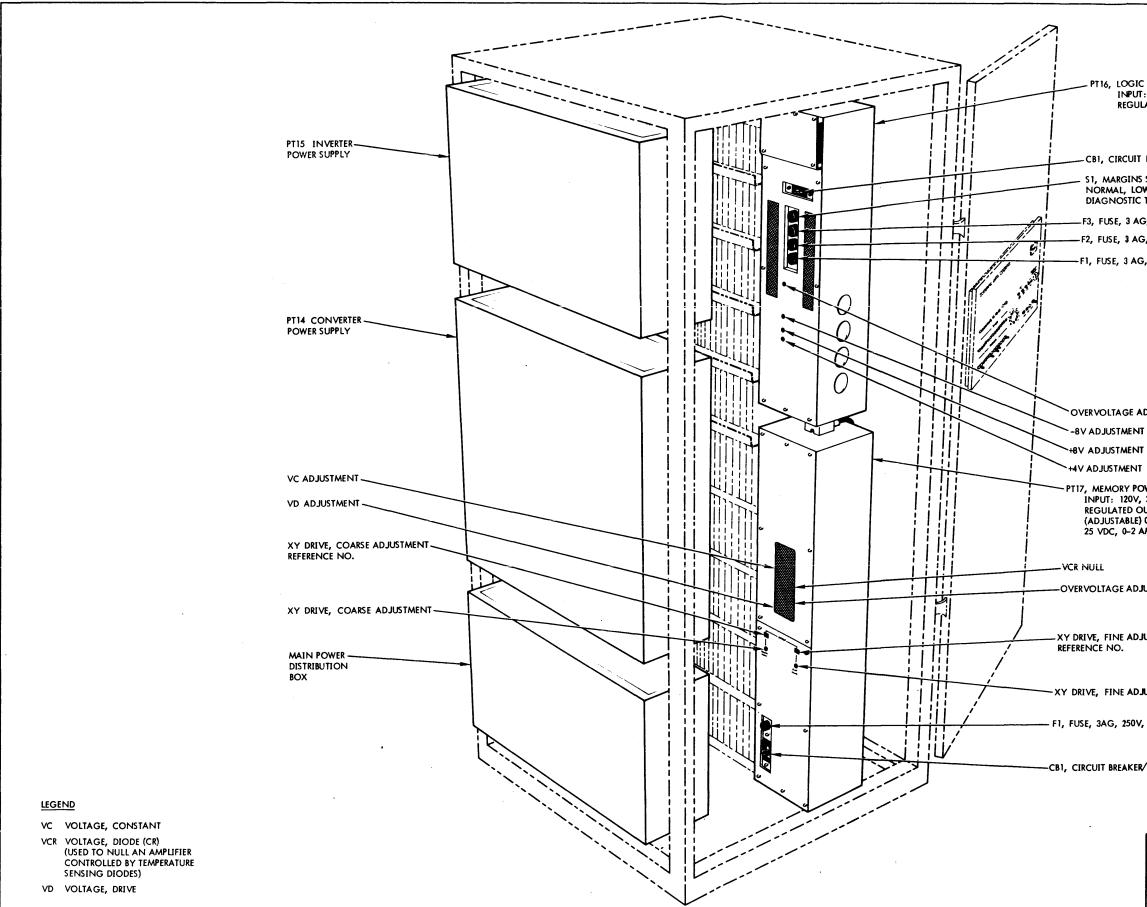

| 3-235  | Physical Details of Sigma 5 PT16 and PT17 Power Supplies                               | 3-751          |

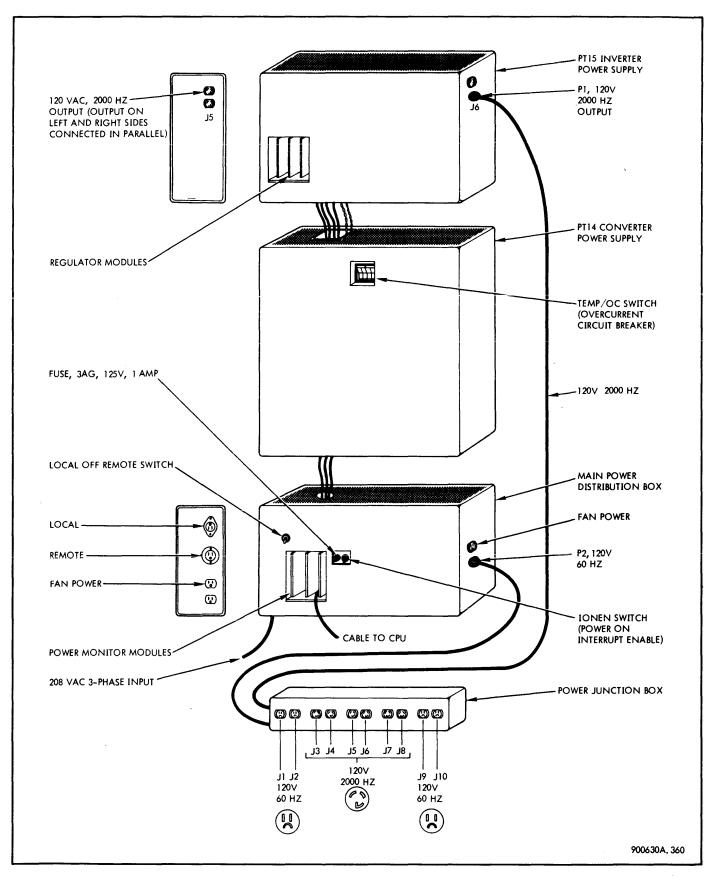

| 3-236  | Physical Details of PT14 and PT15 Power Supplies, Main Power Distribution Box, and     |                |

|        | Power Junction Box                                                                     | 3-753          |

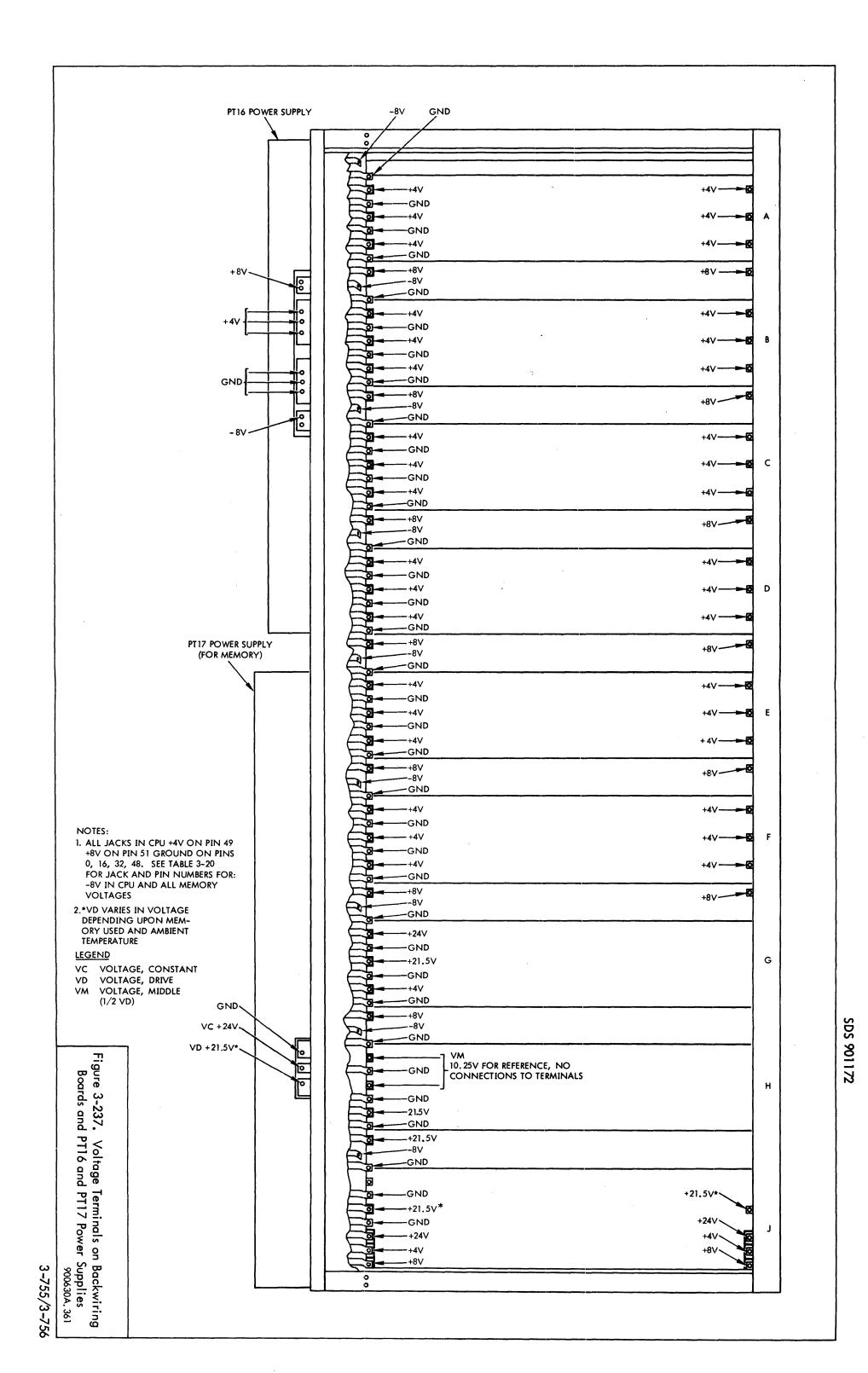

| 3-237  | Voltage Terminals on Backwiring Boards and PT16 and PT17 Power Supplies                | 3-755          |

| 3-238  | Typical Power Distribution Diagram                                                     | 3-757          |

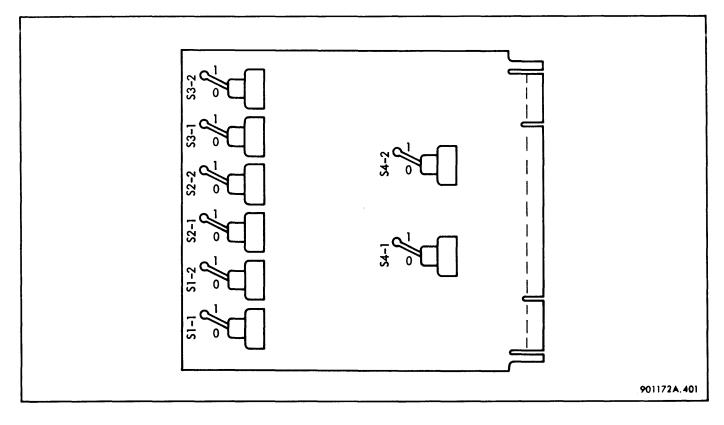

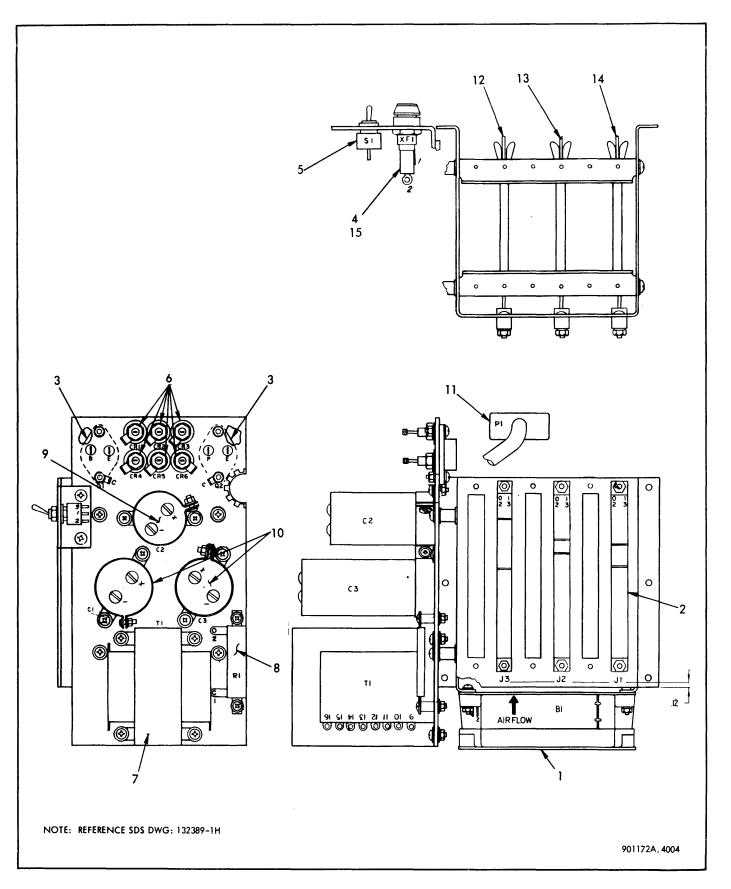

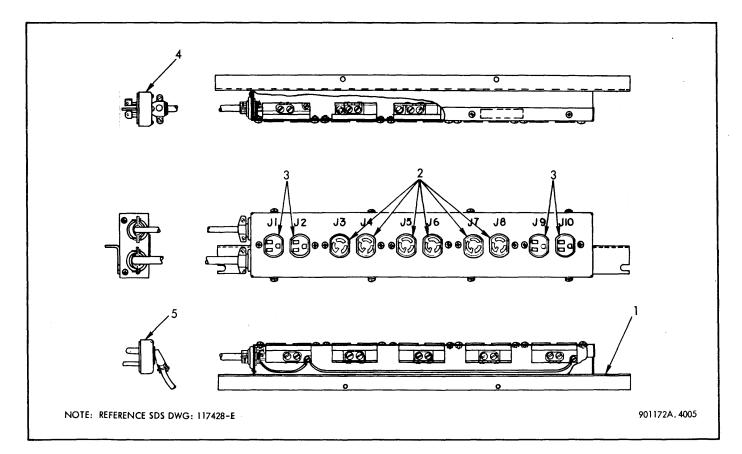

| 4-1    | Address Selector Module ST14                                                           | 4-3            |

| 4-2    | Switch Comparator LT26                                                                 | 4-4            |

| 4-3    | Sigma 5 Computer Group                                                                 | 4-9            |

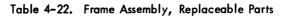

| 4-4    | Frame Assembly With Fan Arrangement                                                    | 4-13           |

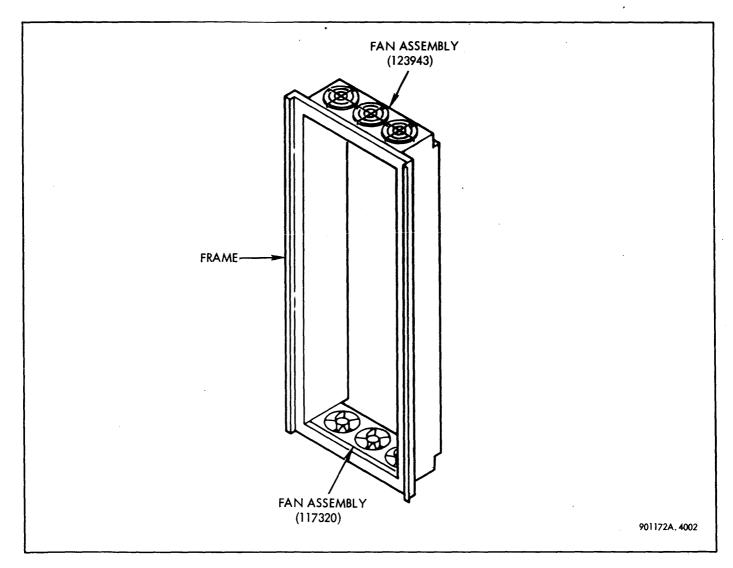

| 4-5    | Power Distribution Assembly                                                            | 4-16           |

| 4-6    | Power Monitor Assembly                                                                 | 4-18           |

| 4-7    | Power Distribution Box Assembly                                                        | 4-19           |

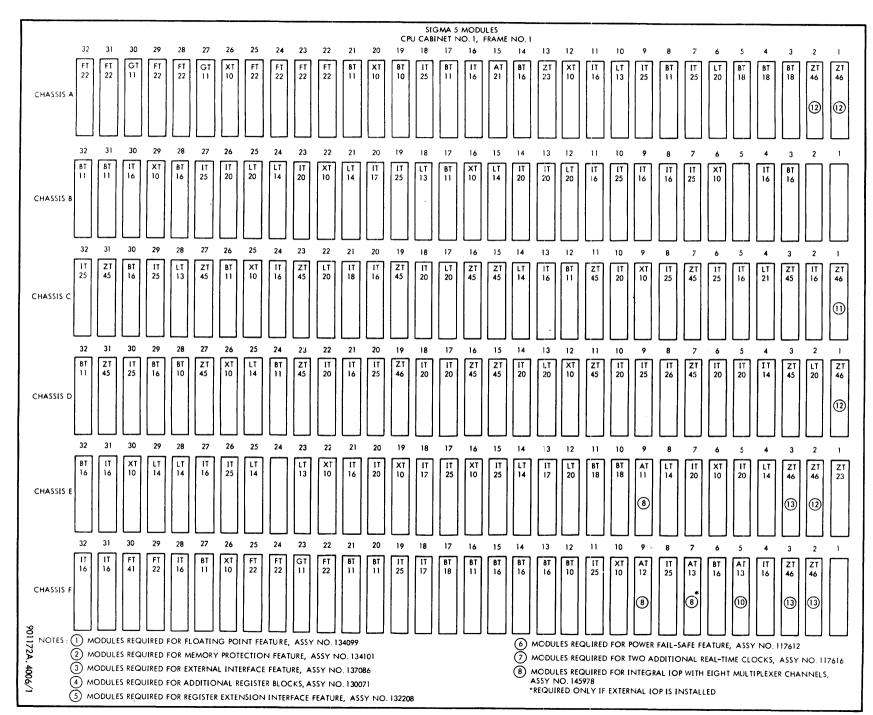

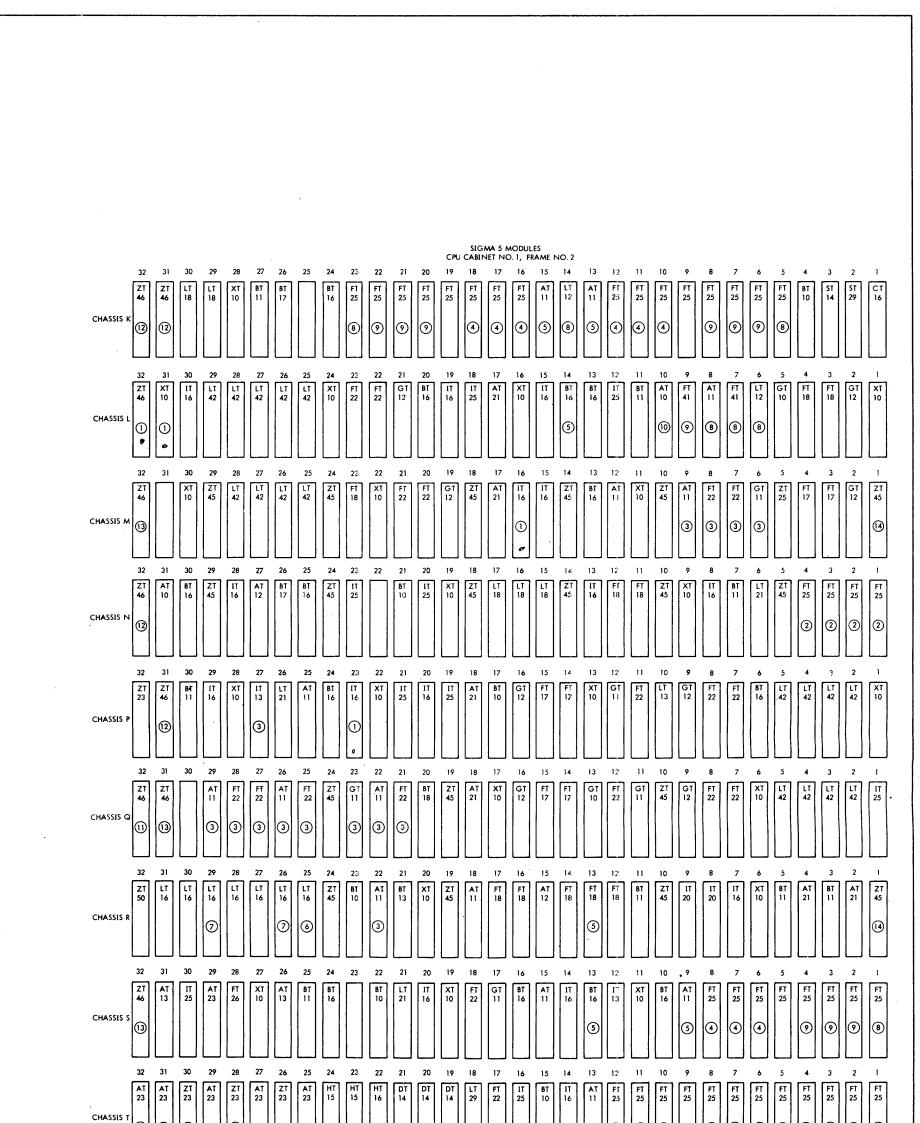

| 4-8    | Module Assembly, CPU Cabinet No. 1, Frame 1                                            | 4-23           |

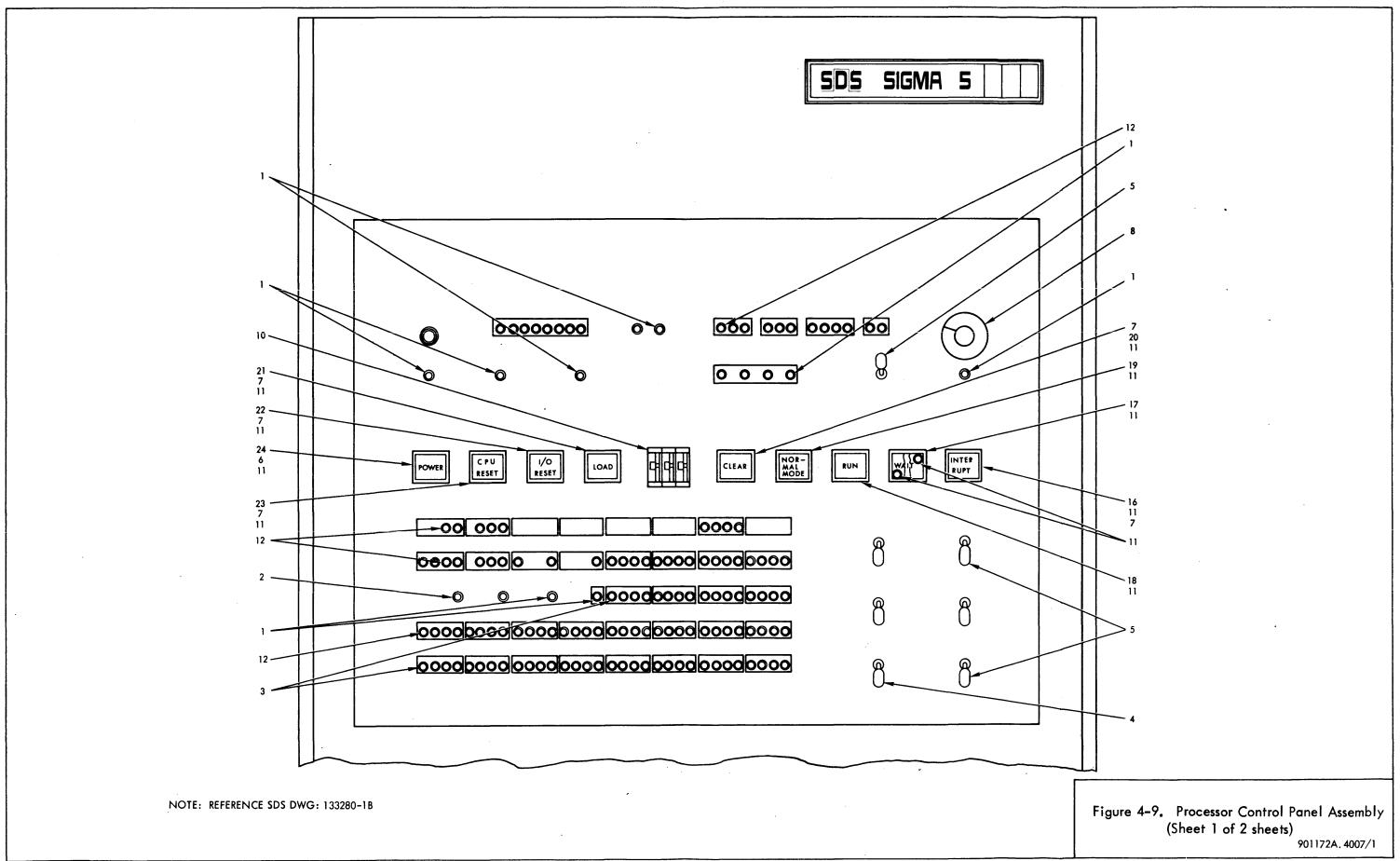

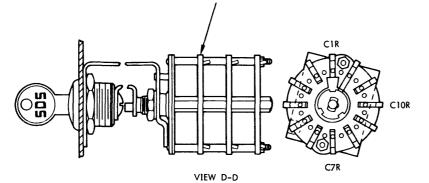

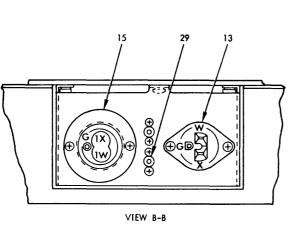

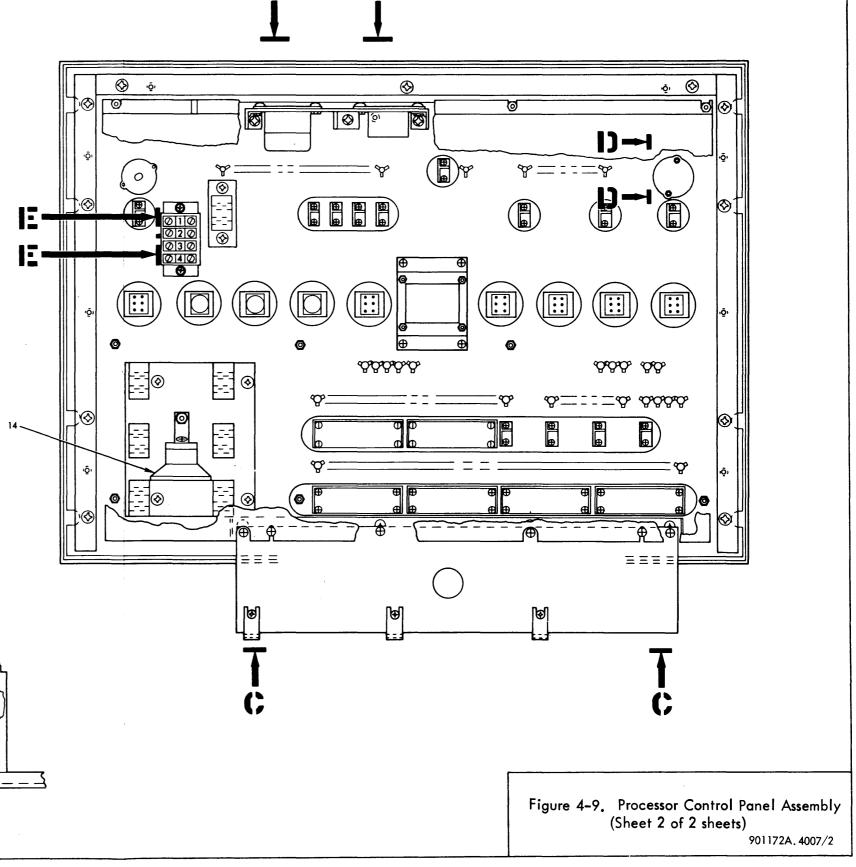

| 4-9    | Processor Control Panel Assembly                                                       | 4-29           |

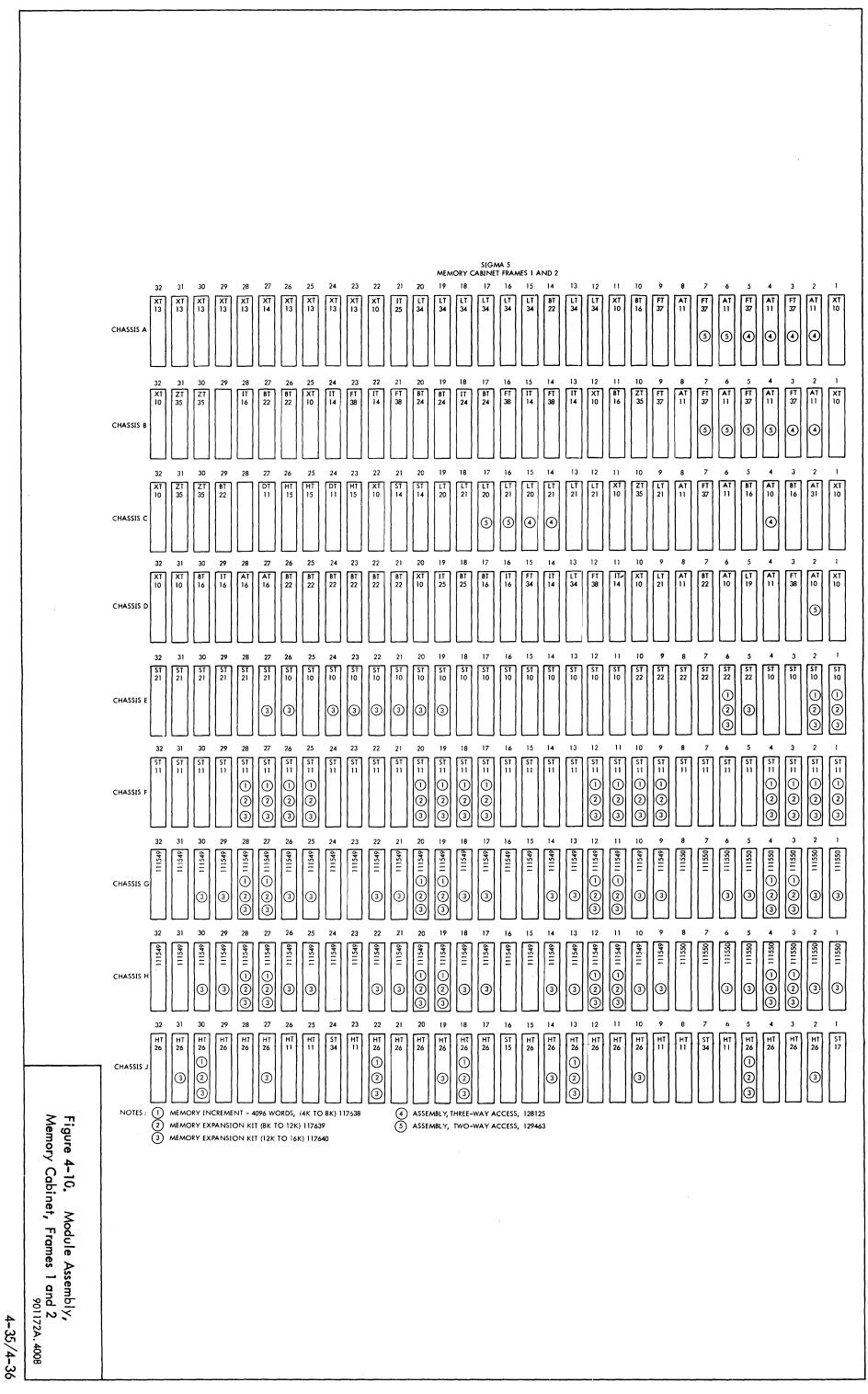

| 4-10   | Module Assembly, Memory Cabinet, Frames 1 and 2                                        | 4-35           |

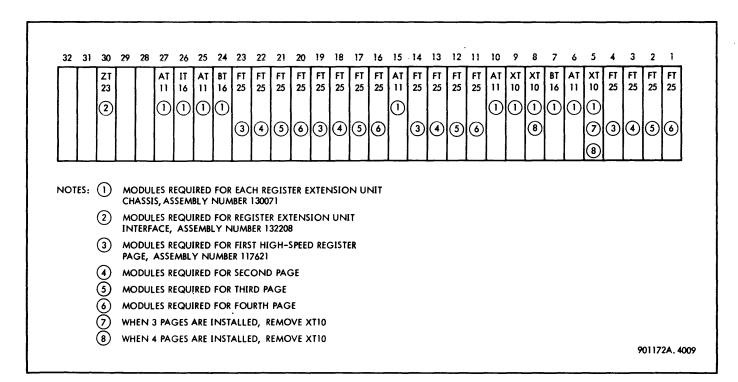

| 4-11   | Module Assembly, Register Extension Unit, Register Interface, High-Speed Register Page | 4-39<br>4-42   |

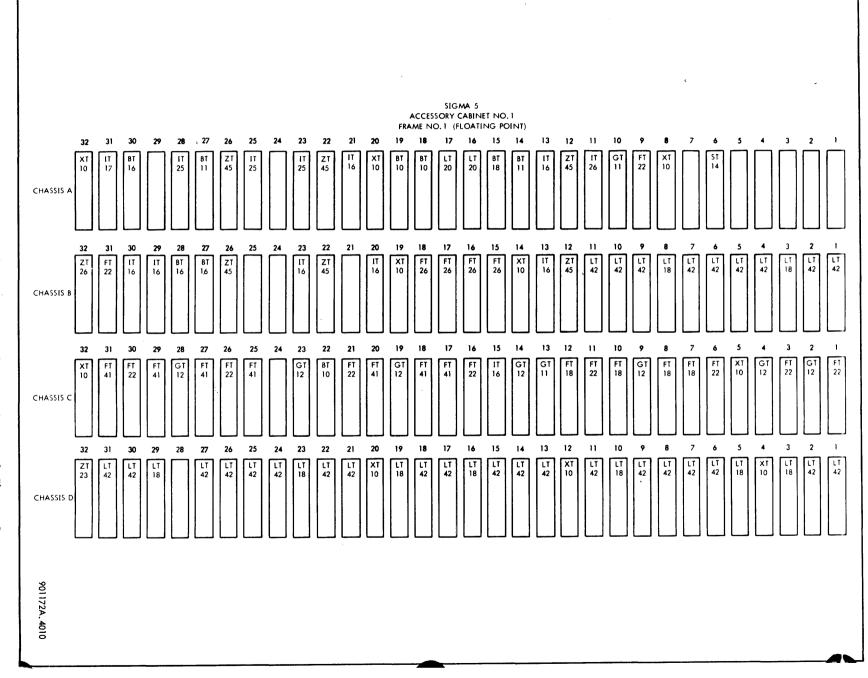

| 4-12   | Module Assemblies, Accessory Cabinet No. 1, Frame 1, Floating Point                    | 4-42<br>4-43   |

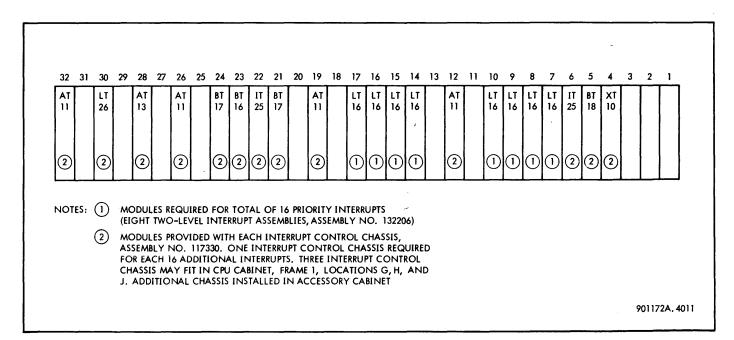

| 4-13   | Module Assembly, Interrupt Control Chassis.                                            | 4-43<br>4-51   |

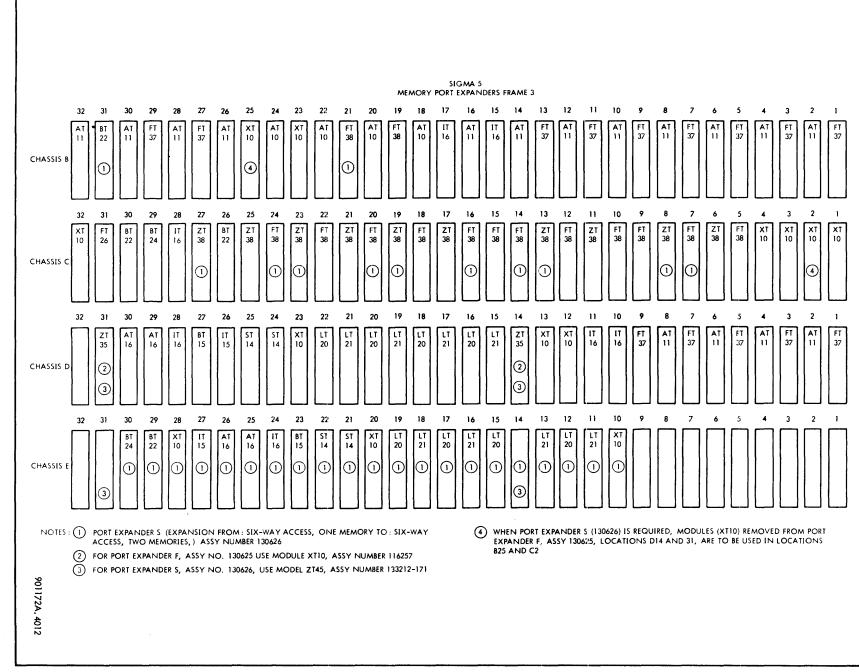

| 4-14   | Assemblies, Memory Port Expanders, Frame 3                                             | 4-31           |

•

#### LIST OF TABLES

| Table        | Title                                                                                  | Page                            |

|--------------|----------------------------------------------------------------------------------------|---------------------------------|

| 1-1          | Main Units                                                                             | 1-7                             |

| 1-2          | Optional Features                                                                      | 1-7                             |

| 1-3          | Maximum Computer System IOP Combinations                                               | 1-9                             |

| 1-4          | General Specifications                                                                 | 1-11                            |

| 1-5          | Power Supply Input Power Specifications                                                | 1-11                            |

| 1-6          | Computer Power Requirements                                                            | 1-11                            |

| 2-1          | Controls and Indicators, PCP Programmer's Section                                      | 2-3                             |

| 2-2          | Controls and Indicators, PCP Maintenance Section                                       | 2-7                             |

| 2-3          | Basic Instructions                                                                     | 2-17                            |

| 3-1          | Adder Operations                                                                       | 3-34                            |

| 3-2          | A Plus D Truth Table                                                                   | 3-35                            |

| 3-3          | A Minus D Truth Table                                                                  | 3-35                            |

| 3-4          | D Minus A Truth Table                                                                  | 3-36                            |

| 3-5          | A Minus 1 Truth Table                                                                  | 3-36                            |

| 3-6          | D Minus 1 Truth Table                                                                  | 3-37                            |

| 3-7          | REU Interface Signals                                                                  | 3–50                            |

| 3–8          | Memory Protection Functions                                                            | 3-65                            |

| 3-9          | Trap Sequence                                                                          | 3-71                            |

| 3-10         | Trap Codes and Address Digits                                                          | 3-73                            |

| 3-11         | Interrupt Sequence                                                                     | 3-80                            |

| 3-12         | Significant States of Interrupt Circuit                                                | 3-86                            |

| 3-13         | Function of Codes for WD Interrupt Control Mode                                        | 3-93                            |

| 3-14         | Signals Enabled by Codes for WD Interrupt Control Mode, and Resulting Changes of State | 3-94                            |

| 3-15         | Sigma 5 Memory Models and Options                                                      | 3-95                            |

| 3-16         | Interleaving Address Bit Exchange                                                      | 3-101                           |

| 3-17         | Core Characteristics                                                                   | 3-127                           |

| 3-18         | Phase 10 (ENDE) Sequence                                                               | 3-174                           |

| 3-19         | Preparation Phases Sequence                                                            | 3-178                           |

| 3-20         | Load Immediate Sequence                                                                | 3-204                           |

| 3-21         | Load Byte Sequence                                                                     | 3-206                           |

| 3-22         | Load Word and Load Halfword Sequence                                                   | 3-208                           |

| 3-23         | Load Doubleword Sequence                                                               | 3-210                           |

| 3-24         | Load Complement Halfword Sequence                                                      | 3-213                           |

| 3-25         | Load Complement Word Sequence                                                          | 3-215                           |

| 3-26         | Load Complement Doubleword Sequence                                                    | 3-217                           |

| 3-27         | Load Conditions and Floating Control Sequence                                          | 3-220                           |

| 3-28         | Load Conditions and Floating Control Immediate Sequence                                | 3-221                           |

| 3-29         | Load Register Pointer Sequence                                                         | 3-223                           |

| 330          | Load Absolute Halfword Sequence                                                        | 3-225                           |

| 3-31         | Load Absolute Word Sequence                                                            | 3-227                           |

| 3-32         | Load Absolute Doubleword Sequence                                                      | 3-230                           |

| 3-33         | Store Byte Sequence                                                                    | 3-235                           |

| 3-34         | Store Halfword Sequence                                                                | 3-237                           |

| 3-35         | Store Word Sequence                                                                    | 3-239                           |

| 336          | Store Doubleword Sequence                                                              | 3-241                           |

| 3-37         | Store Conditions and Floating Control                                                  | 3-243<br>3-244                  |

| 3-38         | Add Word to Memory Sequence                                                            |                                 |

| 3-39         | Exchange Word Sequence                                                                 | 3-247                           |

| 3-40         | Load Selective Sequence                                                                | 3-250                           |

| 3-41         | Store Selective Sequence                                                               | 3-254                           |

| 3-42<br>3-43 | Compare Selective Sequence                                                             | 3-258                           |

| 3-43<br>3-44 | Analyze Sequence                                                                       | 3 <b>-264</b><br>3 <b>-</b> 271 |

| 3-44<br>3-45 | Interpret Sequence                                                                     | 3-271                           |

| 3-45<br>3-46 | Add Immediate Sequence                                                                 | 3-274                           |

| 3-40         | AH and SH Sequence                                                                     | 3-2/0                           |

#### LIST OF TABLES (Cont.)

| Table         | Title                                                     | Page           |

|---------------|-----------------------------------------------------------|----------------|

| 3-47          | AW and SW Sequence                                        | 3 <b>-2</b> 78 |

| 3-48          | Add Doubleword and Subtract Doubleword Sequence           | 3-281          |

| 3-49          | Bit Weights and Operations for Bit–Pair Multiplication    | 3-288          |

| 3 <b>-</b> 50 | Multiply Immediate and Multiply Word Sequence             | 3-290          |

| 3-51          | Multiply Halfword Sequence                                | 3-296          |

| 3 <b>-</b> 52 | Divide Halfword and Divide Word With Odd R Field Sequence | 3-305          |

| 3-53          | Divide Word Sequence (Even R Field)                       | 3-311          |

| 3-54          | Modify and Test Byte Sequence                             | 3-318          |

| 3 <b>-</b> 55 | Modify and Test Halfword Sequence                         | 3-322          |

| 3-56          | Modify and Test Word Sequence                             | 3-327          |

| 3 <b>-</b> 57 | Compare Sequence (CI, CB, CH, CW)                         | 3-332          |

| 3-58          | Compare Doubleword Sequence                               | 3-337          |

| 3-59          | Compare With Limits in Register Sequence                  | 3-341          |

| 3-60          | Compare With Limits in Memory Sequence                    | 3-345          |

| 3-61          | OR, EOR, AND Sequence                                     | 3-350          |

| 3-62          | Shift Sequence                                            | 3-357          |

| 3-63          | Shift Floating Sequence                                   | 3-368          |

| 3-64          | Floating Point Condition Code Setting                     | 3-381          |

| 3-65          | FAS, FSS, FAL, FSL Sequence                               | 3-383          |

| 3-66          | FMS, FML Sequence                                         | 3-402          |

| 3-67          | FDS, FDL Sequence                                         | 3-421          |

| 3-68          | Push Word Sequence                                        | 3-442          |

| 3-69          | Pull Word Sequence                                        | 3-454          |

| 3-70          | Push Multiple Sequence                                    | 3-467          |

| 3-71          | Pull Multiple Sequence                                    | 3-480          |

| 3-72          | Modify Stack Pointer Sequence                             | 3-494          |

| 3-73          | Load Multiple Sequence                                    | 3-502          |

| 3-74          | Store Multiple Sequence                                   | 3-505          |

| 3-75          | Branch on Conditions Set Sequence                         | 3-509          |

| 3-76          | Branch on Conditions Reset Sequence                       | 3-511          |

| 3-77          | Branch and Link Sequence                                  | 3-514          |

| 3-78          | Branch on Decrementing Register Sequence                  | 3-516          |

| 3-79          | Branch on Incrementing Register Sequence                  | 3-518          |

| 3-80          | Execute Sequence                                          | 3-521          |

| 3-81          | CAL1 Through CAL4 Sequence                                | 3-522          |

| 3-82          | Program Status Doubleword Storage                         | 3-524          |

| 3-83          | Load Program Status Doubleword Sequence                   | 3-526          |

| 3-84          | Exchange Program Status Doubleword Sequence               | 3-532          |

| 3-85          | Move to Memory Control Sequence                           | 3-544          |

| 3-86          | Wait Sequence                                             | 3-551          |

| 3-87          | Read Direct Sequence                                      | 3-554          |

| 3-88          | Write Direct Sequence                                     | 3-559          |

| 3-89          | SIO, TIO, TDV, HIO Sequence for MIOP                      | 3-568          |

| 3-90          | SIO, TIO, TDV, HIO Sequence for Integral IOP.             | 3-577          |

| 3-91          | AIO Sequence, MIOP                                        | 3-589          |

| 3-92          | AIO Sequence for Integral IOP                             | 3-593          |

| 3-93          | Glossary of CPU and Integral IOP Signals                  | 3-600          |

| 3-94          | Glossary of Floating Point Signals                        | 3-612          |

| 3-95          | Glossary of Memory Signals                                | 3-616          |

| 3-96          | Switch Positions for Floating Point Information Display   | 3-645          |

| 3-97          | PCP Control Switches.                                     | 3-649          |

| 3-98          | PCP Indicators                                            | 3-653          |

| 3-99          | Control Mode Lock Switch Status                           | 3-655          |

| 3-100         | Reset Sequence Chart                                      | 3-658          |

| 3-101         | Insert PSW1/Insert PSW2 Sequence                          | 3-663          |

|               |                                                           |                |

## LIST OF TABLES (Cont.)

| Table        | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page           |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3-102        | DATA ENTER/CLEAR Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-667          |

| 3-103        | Store INSTR ADDR/STORE SELECT ADDR Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-669          |

| 3-104        | DISPLAY INSTR ADDR/DISPLAY SELECT ADDR Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3 <b>-6</b> 70 |

| 3-105        | INSTR ADDR INCREMENT Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-671          |

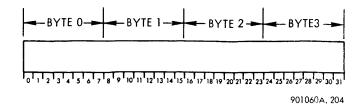

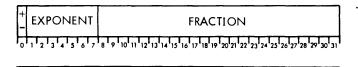

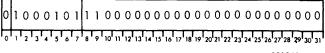

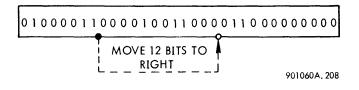

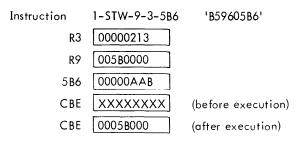

| 3-106        | Clear Memory Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>3-6</b> 73  |