# QM-1 HARDWARE LEVEL USER'S MANUAL

| Q | Q Q          | M  |     | M  | 1     |

|---|--------------|----|-----|----|-------|

| ð | Q            | MM | 4   | MM | 11    |

| Q | Q            | M  | M M | M  | 1 1   |

| Q | Q            | M  | M   | M  | 1     |

| ð | Q            | M  |     | M  | <br>1 |

| Q | Q            | M  |     | M  | 1     |

| a | 0 0          | M  |     | M  | 1     |

| ລ | Ĵ            | M  |     | M  | 1     |

| Q | <b>0</b> 2 0 | M  |     | M  | 11111 |

HARDWARE LEVEL

USER'S MANUAL

Second Edition

Revision 2

August 31, 1974

NANDDATA CORPORATION

2457 Wehrle Drive

Williamsville, New York 14221

716-631-5880

Copyright c 1972 NANDDATA CORPORATION

# TABLE OF CONTENTS

| 1        | SCOPE               | AND PURPOSE                                                        | 9              |

|----------|---------------------|--------------------------------------------------------------------|----------------|

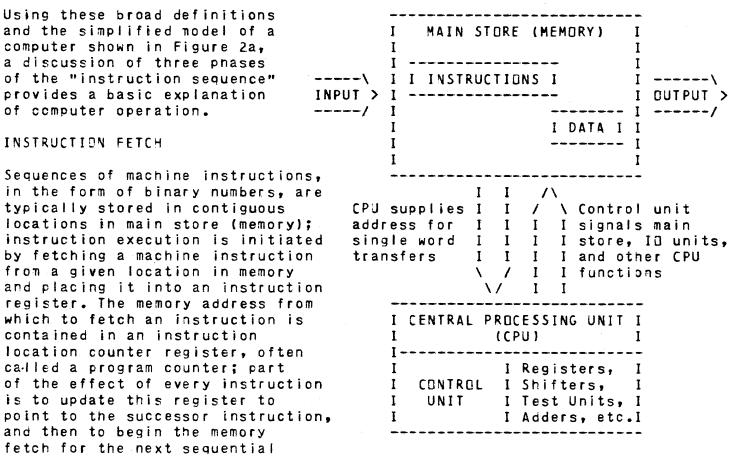

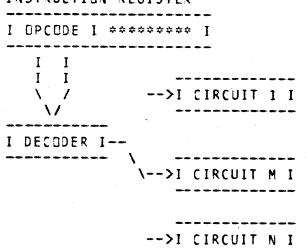

| 2        | INTRO<br>2.1<br>2.2 | DUCTION TO MICROPROGRAMMING AND THE QM-1BASIC INSTRUCTION SEQUENCE | 10<br>11<br>12 |

|          | 2.3                 | HEEC DE MICOODDOCCAMMINE                                           | 14             |

|          | 2.4                 | HODITONIAL AND VERTICAL CONTROL                                    | 16             |

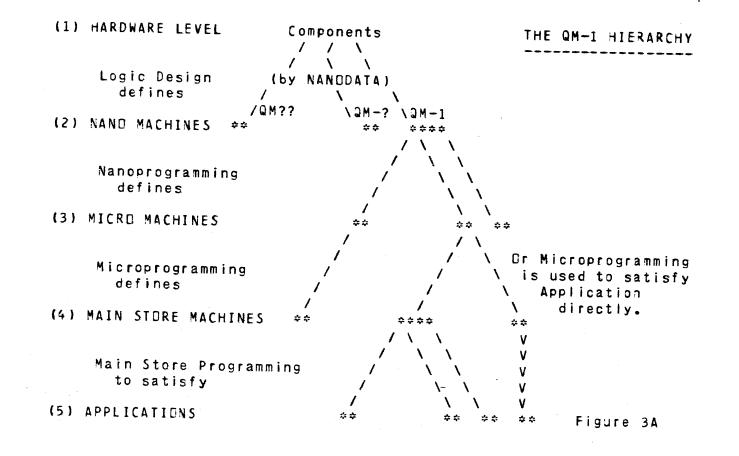

|          | 2.5                 | THE QM-1 CONTROL HIERARCHY                                         | 18             |

| 3        | JSER                | AND MACHINE HIERARCHIES                                            | 20             |

| <u> </u> | 2M-1                | FUNCTIONAL SPECIFICATIONS, PART I                                  | 23             |

|          | 4.1                 |                                                                    | 23             |

|          | 4.2                 | MAIDD DESCRIPCES AND DREAMTATION                                   | 24             |

|          |                     | A 2 1 MAIDD RESTAC STRECTURE AND LOCAL STORE                       | 24             |

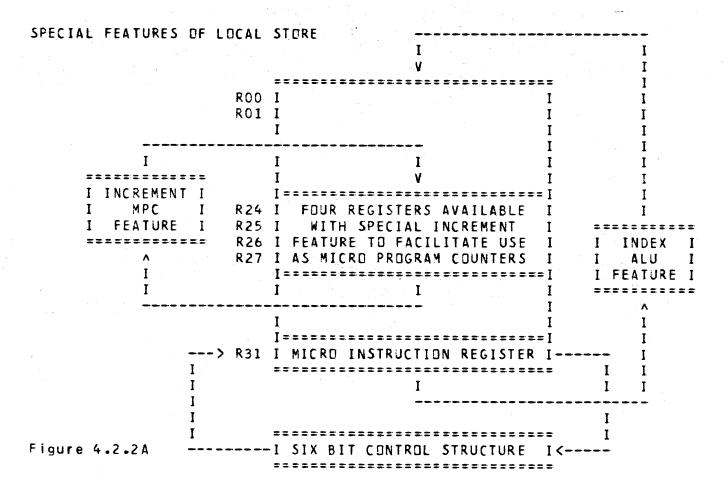

|          |                     | / 2 2 1961 CTODE CDECTAL EFATHDEC                                  | 27             |

|          |                     | 4 2 2 1 MICRO INSTRUCTION REGISTER                                 | 21             |

|          |                     | 4.2.2.2 MICRO PROGRAM COUNTERS                                     | 28<br>28       |

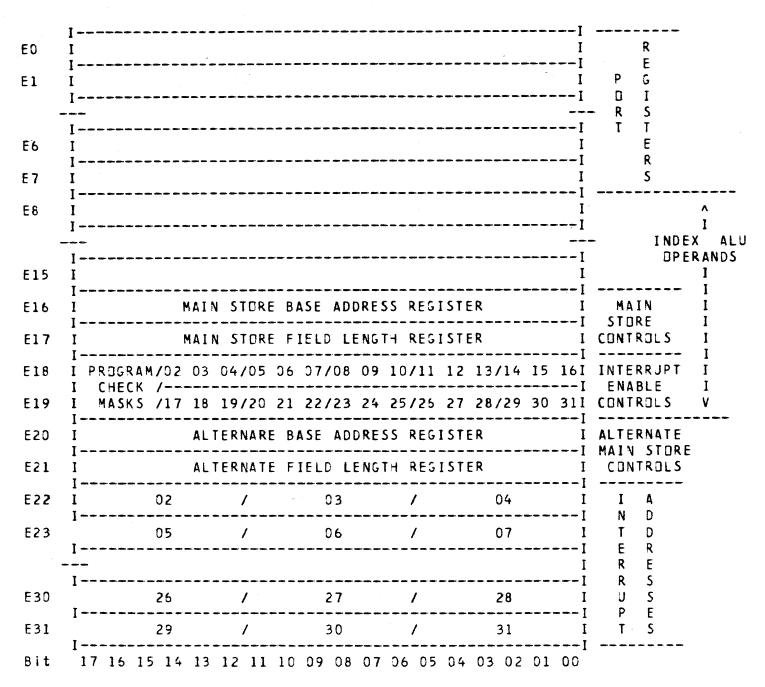

|          |                     | 4.2.2.3 INDEX ALU FEATURE                                          | 29             |

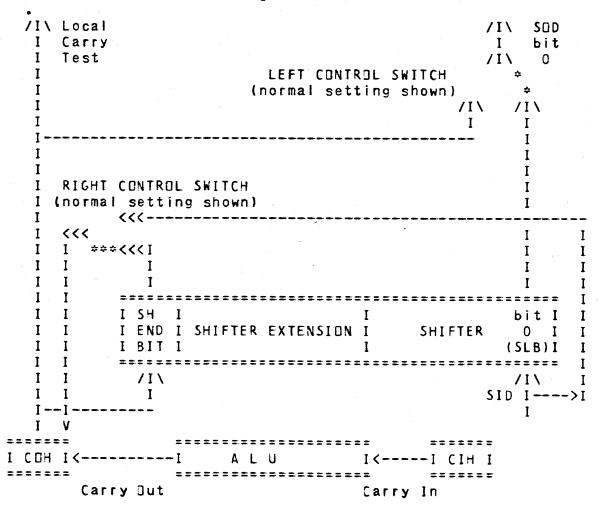

|          |                     | 4.2.3 ALU AND SHIFTER                                              | 29             |

|          |                     |                                                                    | 30             |

|          |                     |                                                                    | 31             |

|          |                     |                                                                    | 3              |

|          |                     |                                                                    | 34             |

|          |                     |                                                                    | 3              |

|          |                     | 4.2.3.6 SIXTEEN-BIT MODE                                           | 36             |

|          |                     | 4.2.5 EXTERNAL STORE                                               | 3              |

|          |                     | 4.2.6 MAIN STORE                                                   | 3              |

|          |                     | 4.2.6.1 GENERAL                                                    | 3              |

|          |                     | 4.2.6.2 MS DPERATIONS                                              | 41             |

|          |                     | 4.2.6.3 MS ADDRESSING AND PROTECTION (QM-1 option)                 | 4              |

|          |                     | / 2 4 / DMI HMIT /OM-1 option)                                     | 4              |

|          | 4 3                 | CIV DIT CONTROL CIRUCTURE                                          | . 4            |

|          | 7 • 3               | / 2 1 /ENEDAL                                                      | 4,1            |

|          |                     | / 2 2 [ [ [ [ ] ] ] ] ]                                            | 4              |

|          |                     | / 2 2 1 CENEDAL                                                    | - 4            |

|          |                     | 4 2 2 2 RUS CONTROL FIS                                            | 4              |

|          |                     | 4.3.2.3 SPECIAL F'S                                                | . 4            |

|       | 4.3.2.4 6'5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|       | 4.3.3 AJX FIELDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

|       | 4.3.4 ALUF (QM-1 OPTION)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| 4.4   | TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| 4.5   | NANDPROGRAM CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|       | 4.5.1 CONTROL MATRIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|       | 4.5.2 NANDSTORE ADDRESSING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - |

|       | 4.5.2.1 PRIORITY SELECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

|       | 4.5.2.2 PROGRAM CHECK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|       | 4.5.2.3 NANOBRANCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|       | 4.5.2.4 EXTERNAL INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _ |

|       | 4.5.3 NANDPROGRAM COUNTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

|       | 4.5.3.1 GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|       | 4.5.3.2 MICROINSTRUCTION EXECUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _ |

|       | 4.5.4 NANDPROGRAM FLOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _ |

|       | 4.5.4.1 NANDPROGRAM CONNECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _ |

|       | 4.5.4.2 INTERRUPTIBILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - |

|       | 4.5.4.3 HOLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

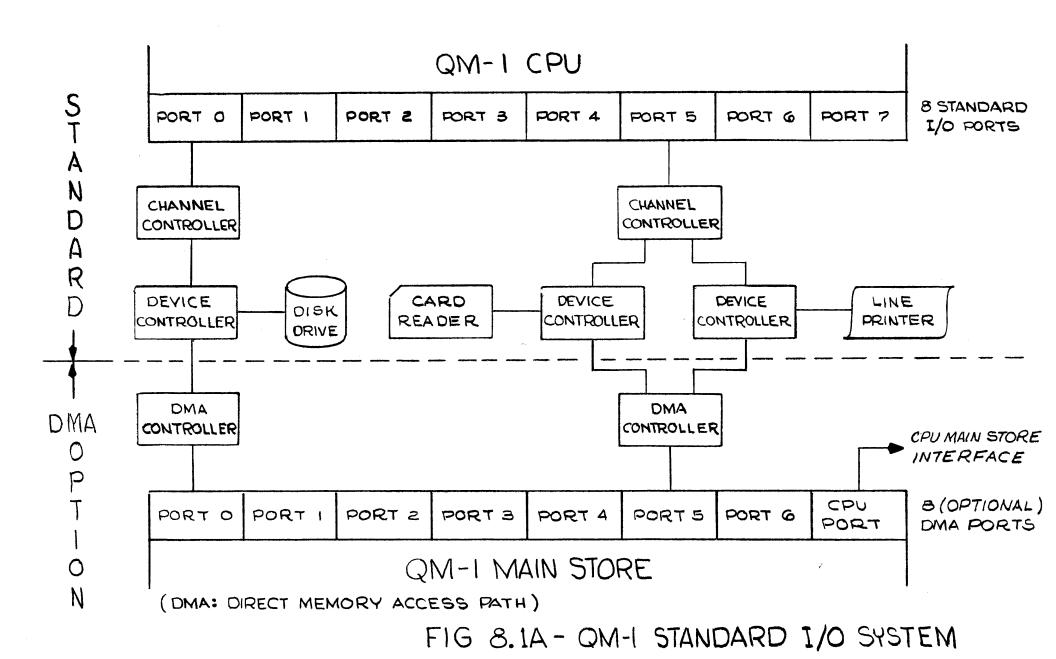

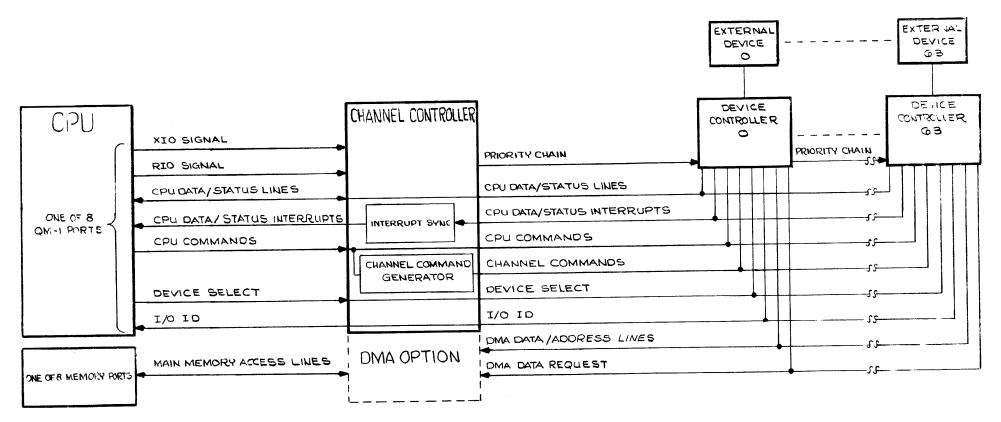

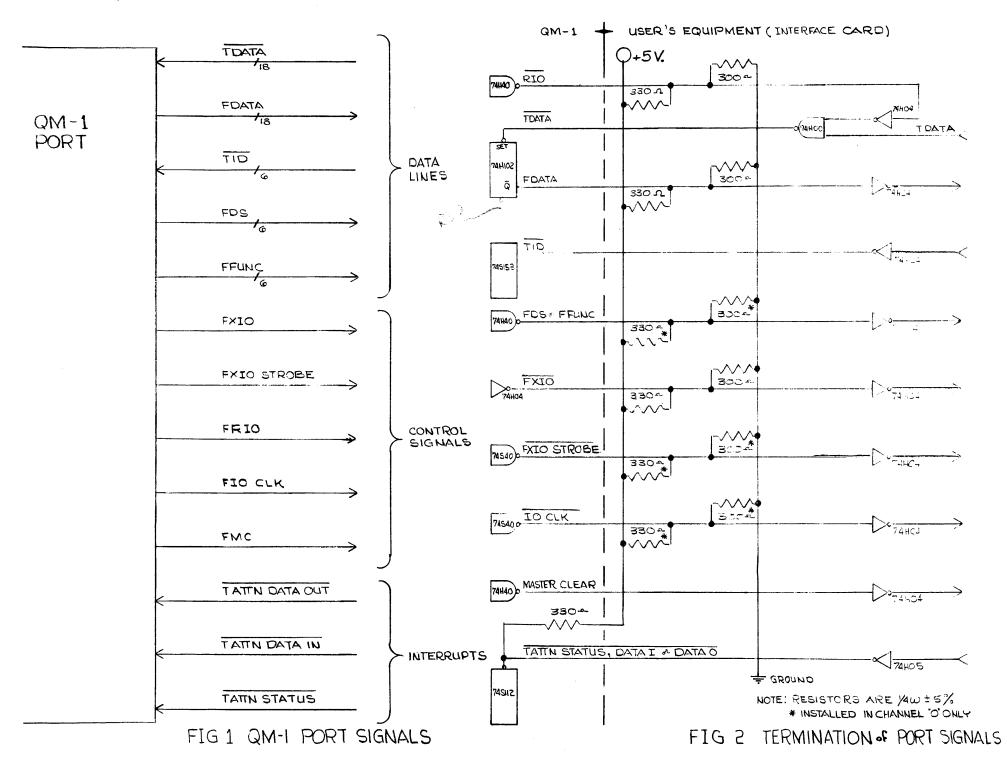

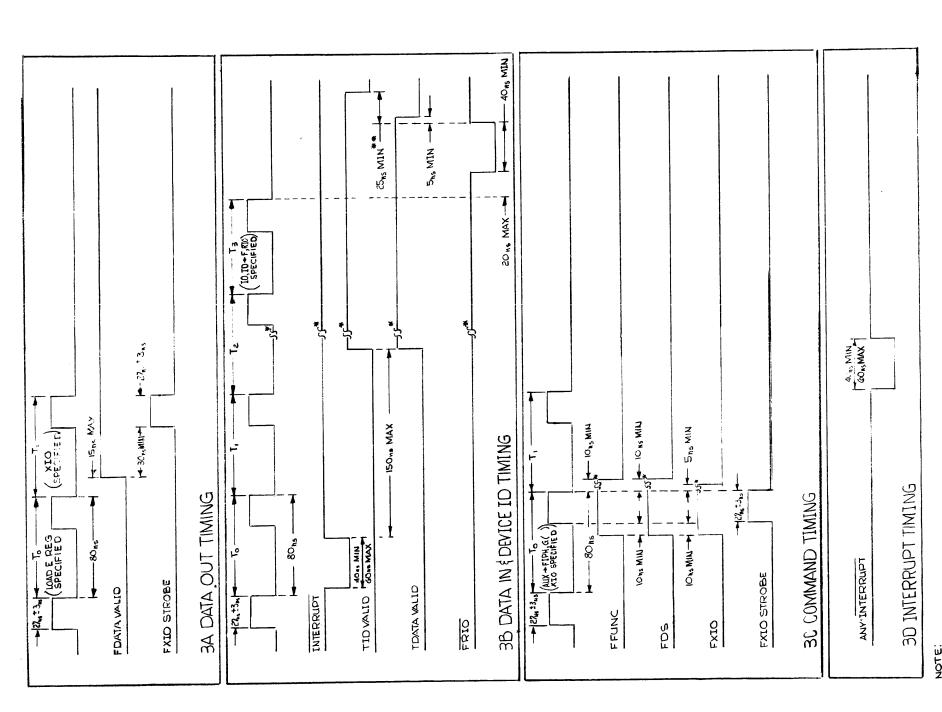

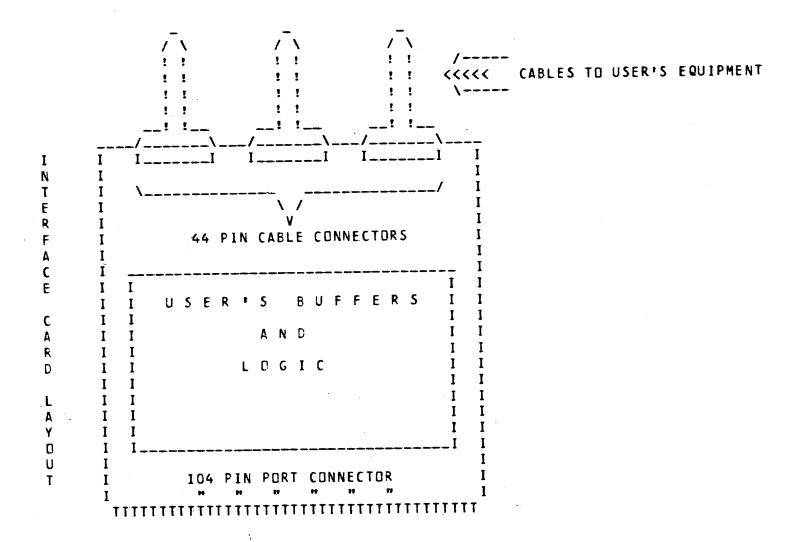

| 4.5   | EXTERNAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _ |

| 4.7   | WRITING NANDSTORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _ |

| 4 • 8 | READ-ONLY MEMORIES AND MACHINE START                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _ |

| QM-1  | FUNCTIONAL SPECIFICATIONS, PART II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _ |

| 5.1   | GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _ |

| 5.2   | SUMMARY OF NANDPRIMITIVE CONTROLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

|       | 5.2.1 K-VECTOR CONTROL FIELDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|       | 5.2.2 T-VECTOR CONTROL FIELDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _ |

| 5.3   | FUNDAMENTAL TIMING CONSIDERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _ |

|       | 5.3.1 GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _ |

|       | 5.3.2 LEADING EDGE FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _ |

|       | 5.3.3 TRAILING EDGE EVENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _ |

|       | 5.3.3.1 T-CLOCK EVENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

|       | 5.3.3.2 F-CLOCK EVENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

|       | 5.3.3.3 R-CLOCK EVENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _ |

|       | 5.3.4 R31 OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - |

| 5.4   | MEMORY REFERENCE FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _ |