## The NABU 1100 System: A Technical Guide

#### NOTICE

Copyright © 1981, Nabu Manufacturing Corporation, Ottawa, Canada.

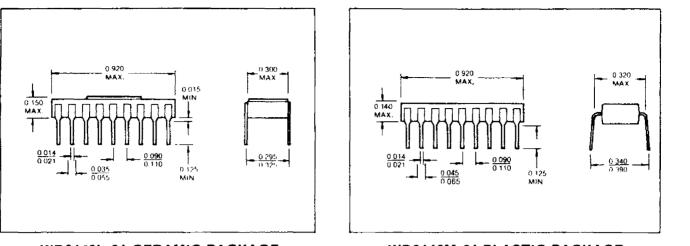

Sections of this manual have been reproduced with the permission of the manufacturers involved; Intel Corporation, NEC Information Systems Inc., NEC Microcomputers, Volker-Craig Ltd., Western Digital, and Zilog Inc.

Because of our policy of constantly searching for ways to improve our products, all specifications are subject to change without notice.

#### DIRECTORY

**1. INTRODUCTION**

2. SYSTEM MAINTENANCE

3. THE COMPUTER - Manufactured by Nabu Corporation

4. THE KEYBOARD/TERMINAL - Manufactured by Volker-Craig Limited

5. THE PRINTER - Manufactured by NEC Information Systems Inc.

#### INTRODUCTION

The following technical manual for the Nabu 1100 System is designed to familiarize you with the components, internal hardware, and capabilities of your new system.

Basically, the manual contains documentation from the manufacturers of the system's components; such as Nabu, Volker-Craig, NEC, etc. It has been written for the knowledgeable user, with additional information included for those at an engineering level.

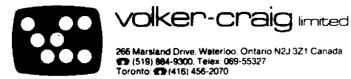

The computer itself, the keyboard/terminal, and the optional printer are the components of your system. The computer is manufactured by Nabu, and comes housed in a specially designed moveable cabinet, with two drawers. The lower drawer can be used for storage of diskettes etc., while the upper drawer contains the hardware associated with the computer. The system features 64K user memory capacity, and uses the Z-80A microprocessing unit developed by Zilog. Total storage capacity of the system is 2 Megabytes, with the use of floppy diskettes. As well, the system provides interfaces for printer and controls.

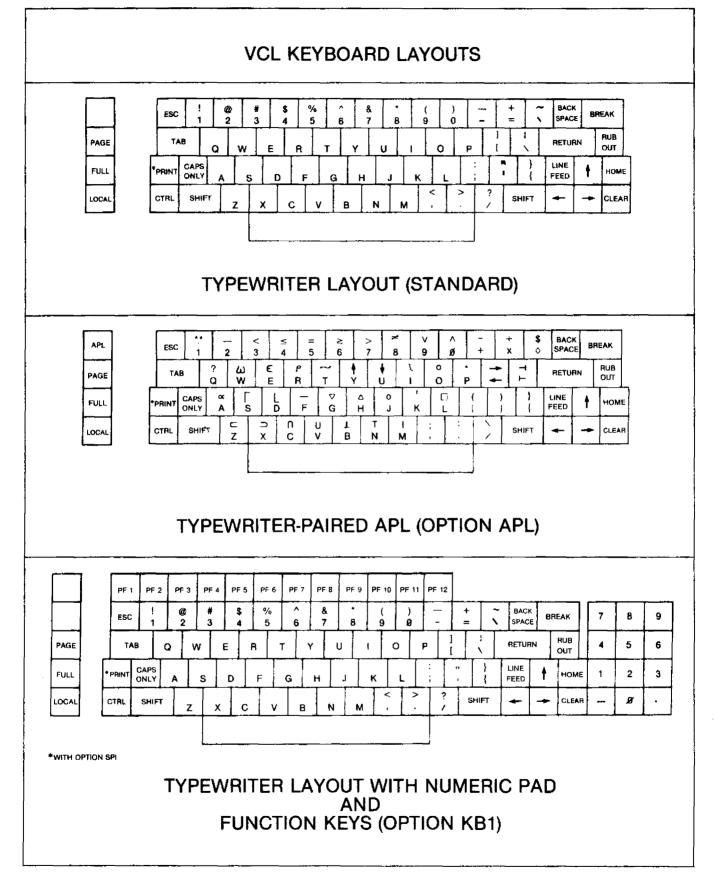

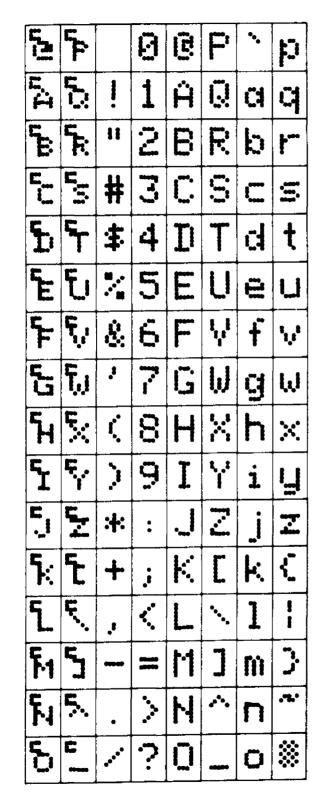

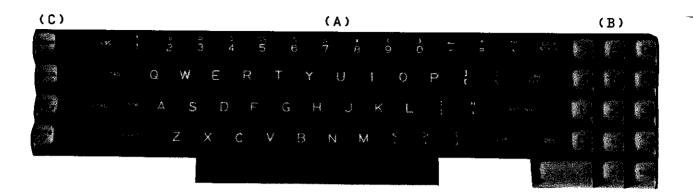

The keyboard/terminal is manufactured by Volker-Craig, and is microprocessor based; providing a full set of standard functions as well as a variety of options. The non-glare screen can display up to 24 lines x 80 characters (a total of 1920 character positions). The keyboard is detachable and features a full set of punctuation and special symbols, a variety of control keys, and a numeric keypad.

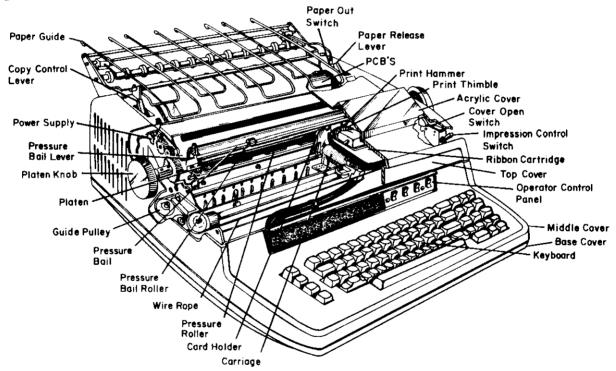

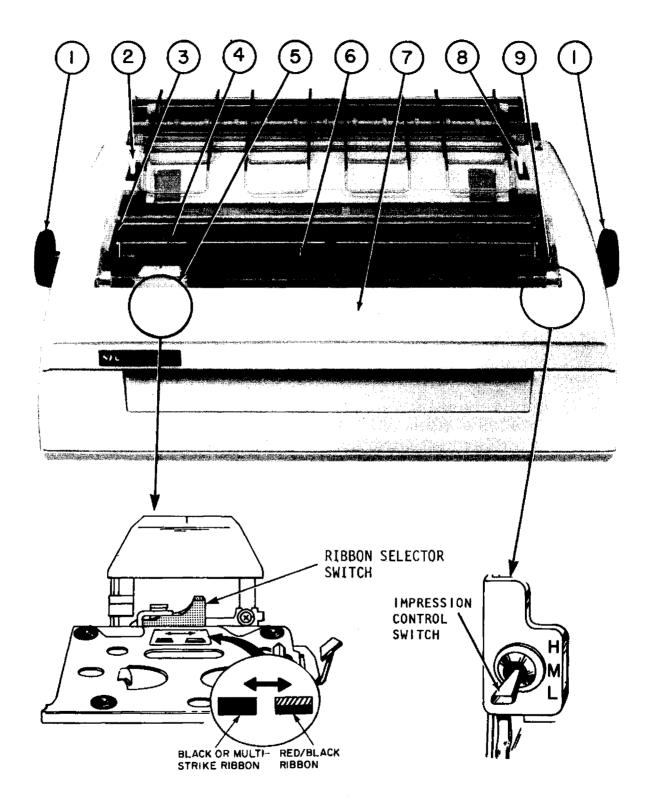

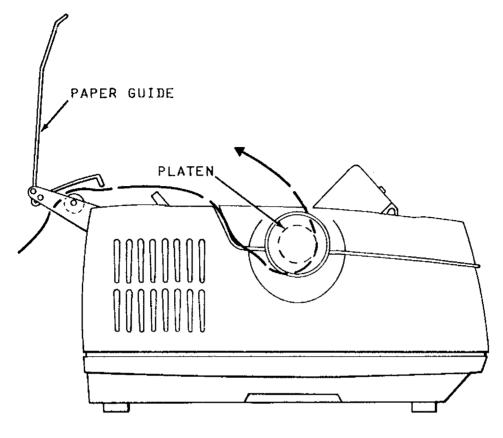

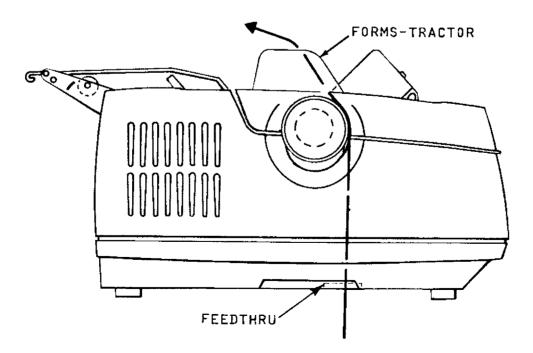

Printer options for the Nabu 1100 System include a NEC Spinwriter 5510/20, a NEC 3510/20, or a Centronics printer. Although these three options are available, the most common option is the NEC Spinwriter 5510/20, which is a letter-quality printer with a printing speed of up to 660 words a minute. The Spinwriter features an interchangeable, rotating thimble which contains up to 128 fully formatted characters, and has a color printing option.

Now that the system has been introduced and briefly described; the manufacturer's documentation on the system components will follow. This information should help you to understand, operate and maintain your system, in order to obtain the best possible performance from it!

#### SYSTEM MAINTENANCE

Maintenance of your new computer system should be one of your most important consideration, since proper maintenance can help avoid computer downtime and costly repairs.

General maintenance of the system involves periodic checks of the hardware. This preventive maintenance inspection should be done every six months by a qualified service Technician.

Regular cleaning should be done by the operator at least once a month as follows:

- vacuum under the system cabinet

- vacuum paper dust out of printer

- clean cabinet, printer, and screen with any spray cleaner and a soft cloth. \*

\* NOTE: Spray the cleaner only on the cloth, NOT ON THE EQUIPMENT.

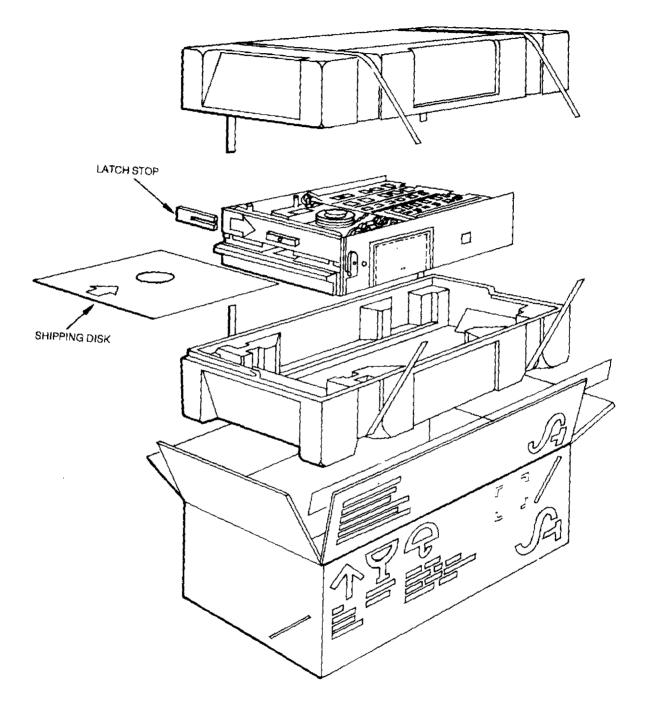

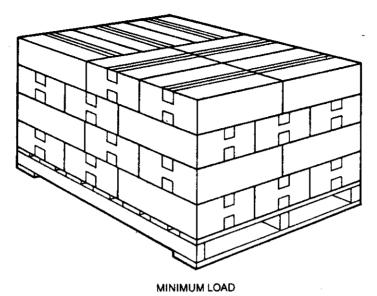

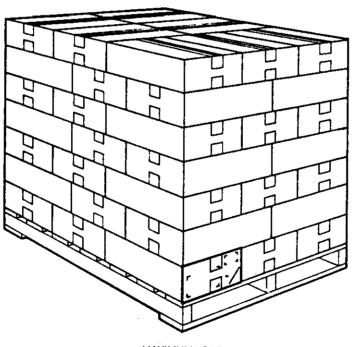

The system cabinet has been installed with rollers, for maneuverability when cleaning etc. However, if the system is to be moved a long distance (to another office building for example), we recommend you repack it in its original cartons, to avoid damage.

## The Computer

Manufactured by Nabu Corporation

.

#### DIRECTORY

#### INTRODUCTION

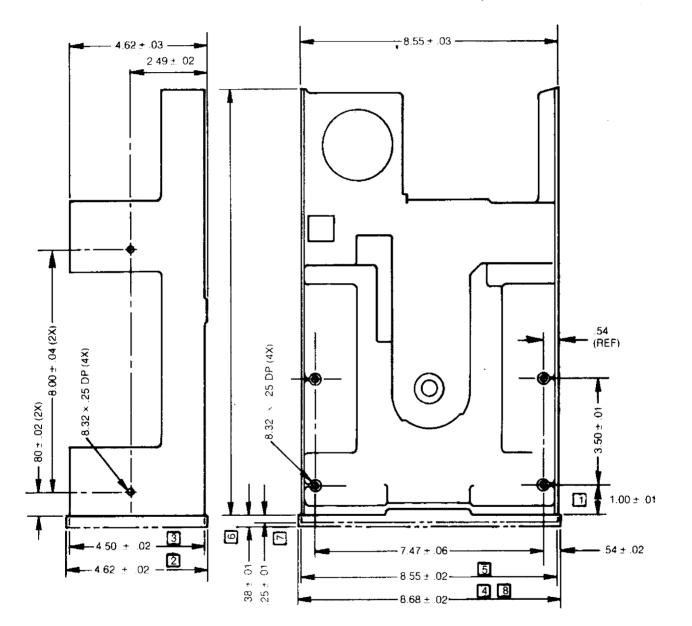

TABLE 1: IEEE S-100 Bus UtilizationTABLE 2: Board Positions In Card CagePower SupplyFIGURE 1: System Power Supply Schematic

#### 1.0: CPU BOARD

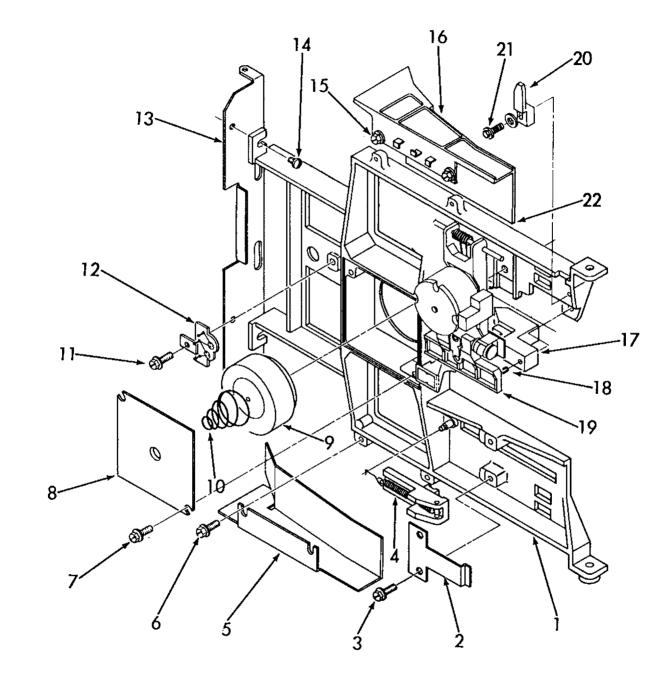

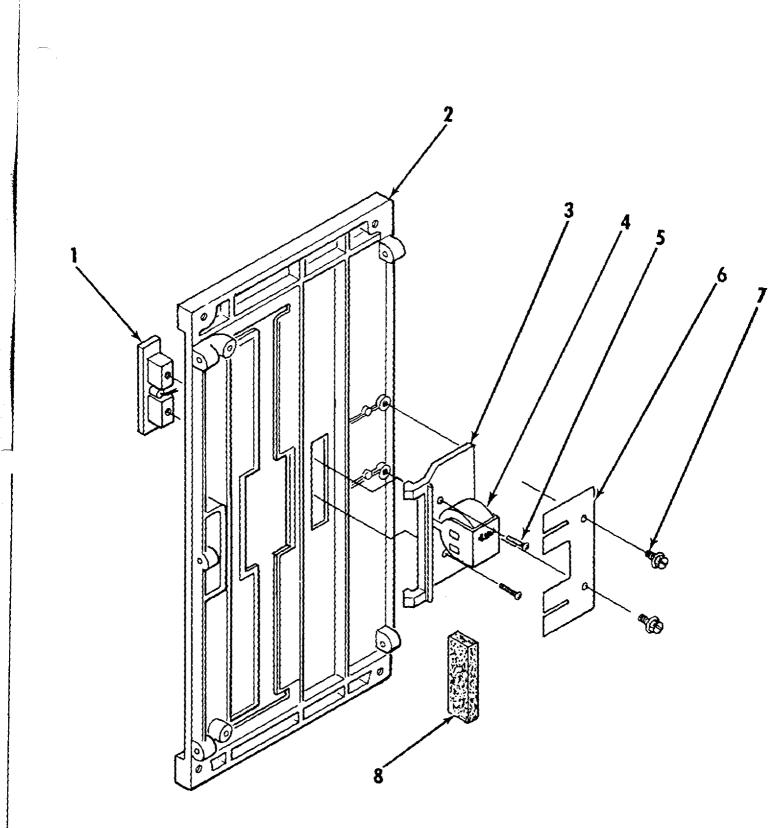

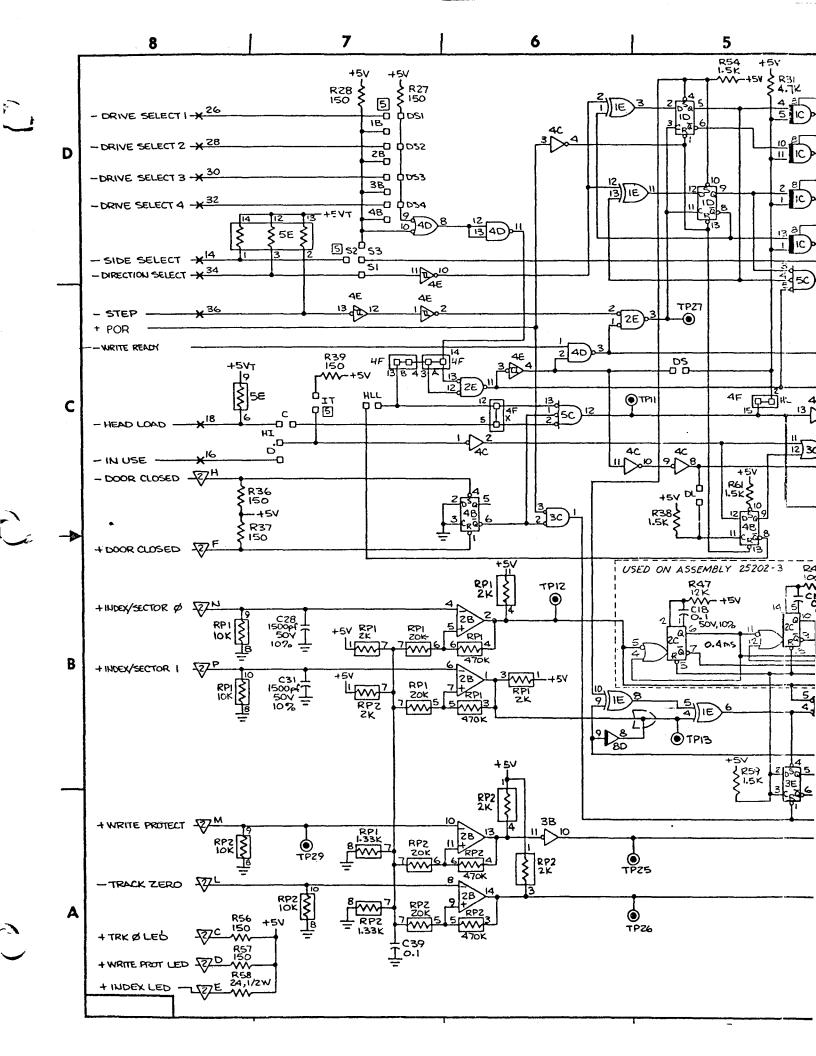

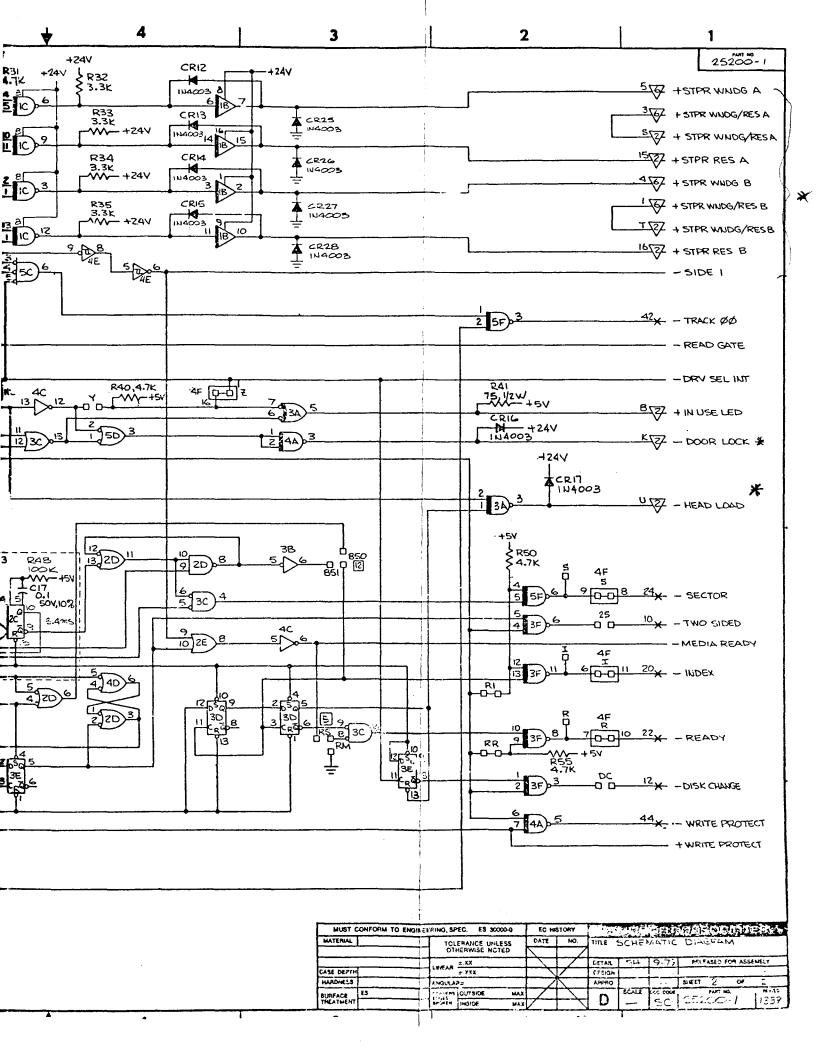

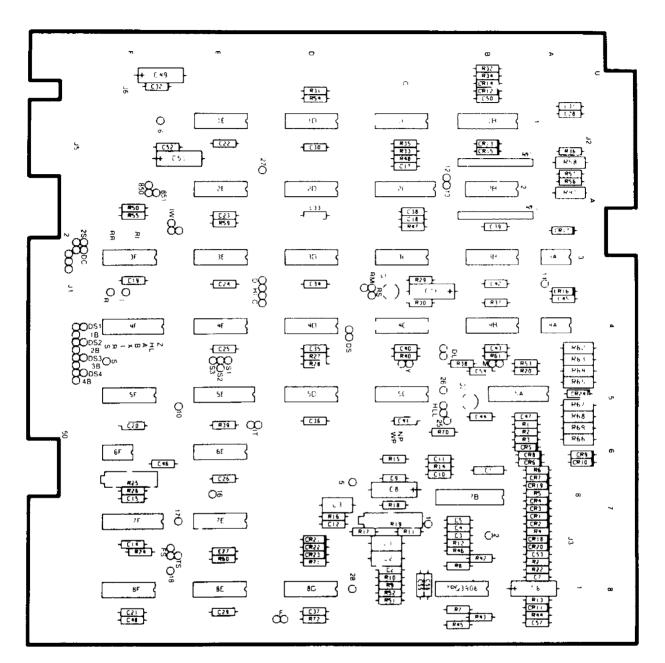

General Information Specific Features CPU Board Parts List FIGURE 2: Schematic Diagram of CPU Board FIGURE 3: CPU Board Layout

#### 2.0: 64K DYNAMIC MEMORY BOARD

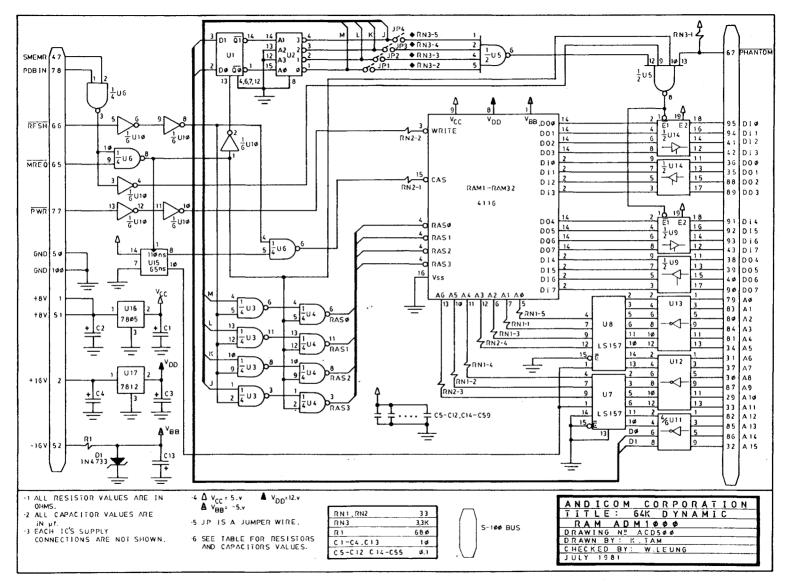

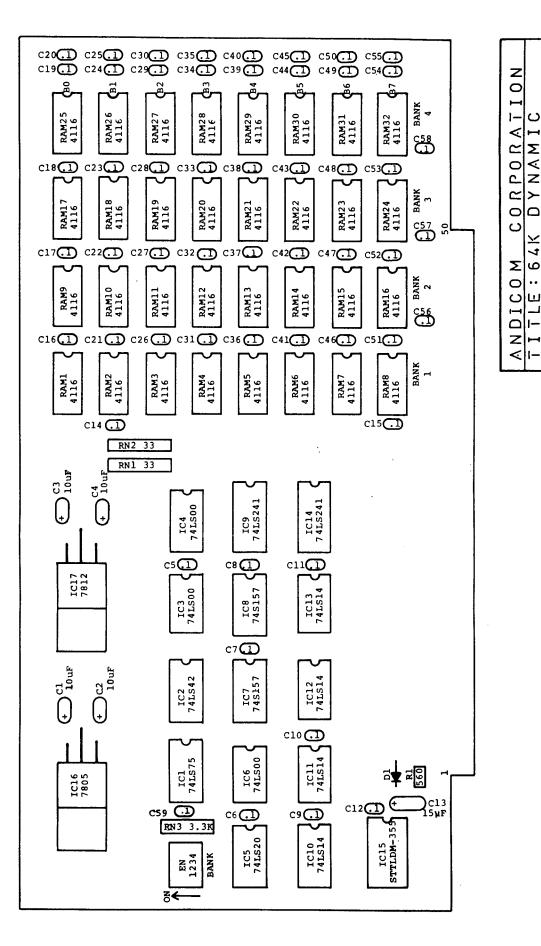

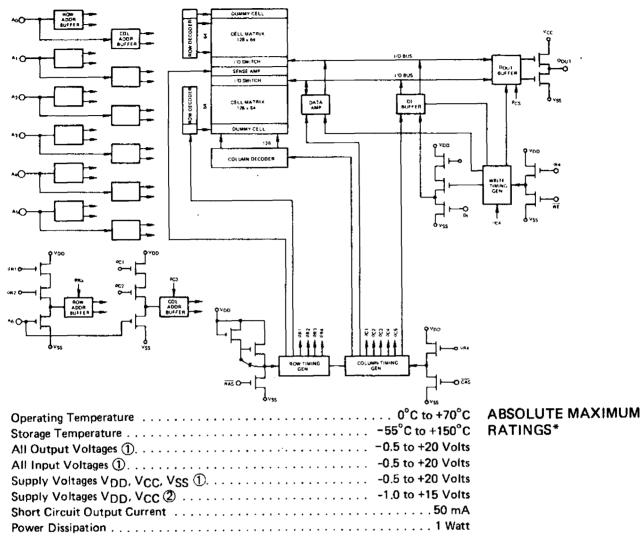

General Information Specific Features Memory Board Parts List FIGURE 4: Schematic Diagram of Dynamic Memory Board FIGURE 5: Dynamic Memory Board Layout

#### 3.0 INPUT/OUTPUT BOARD

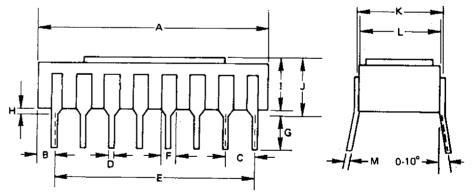

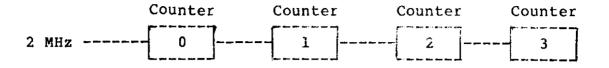

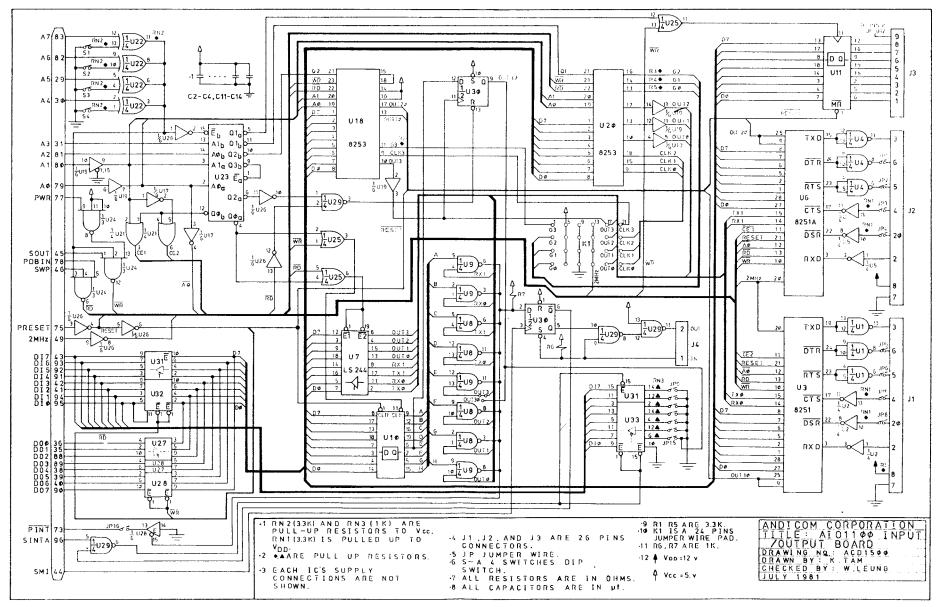

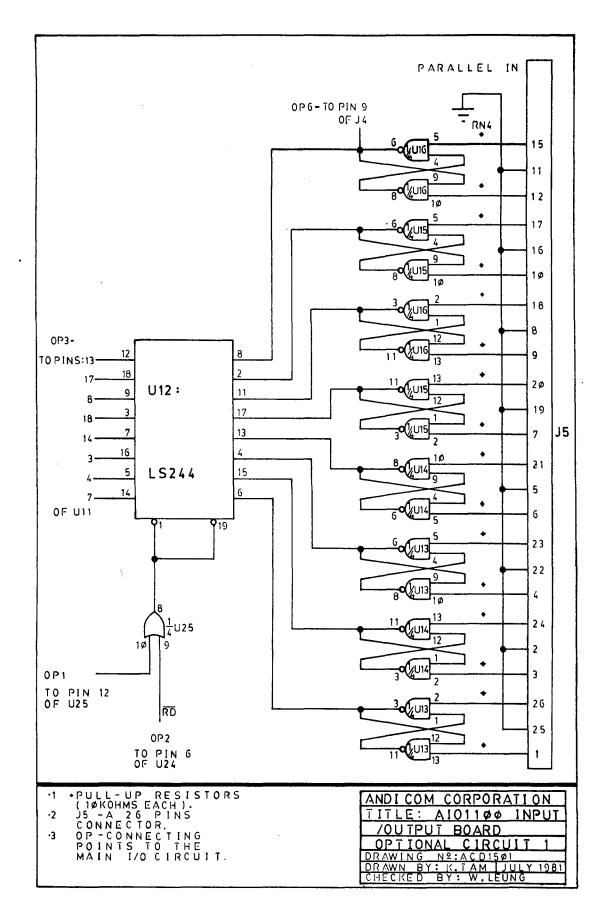

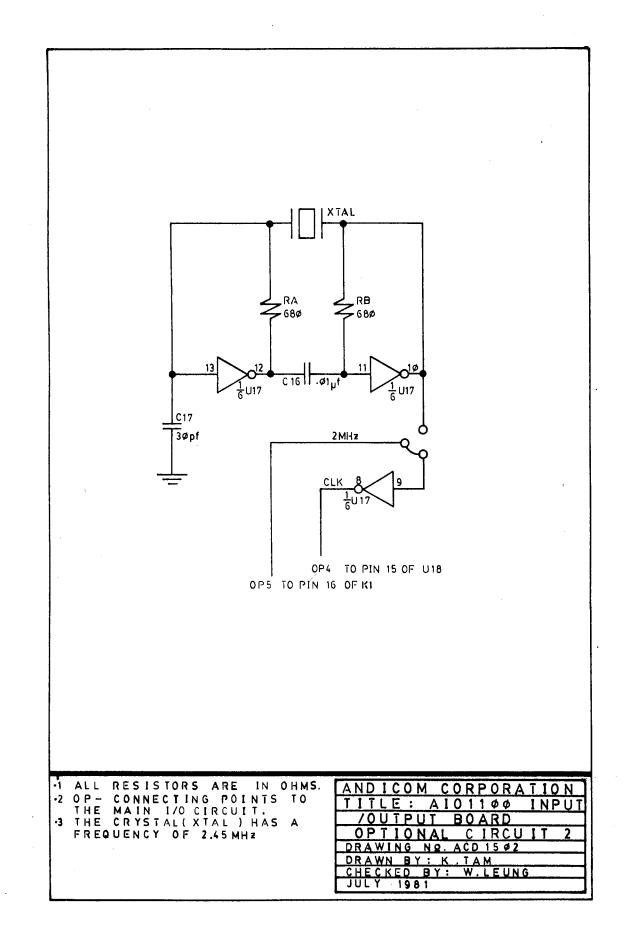

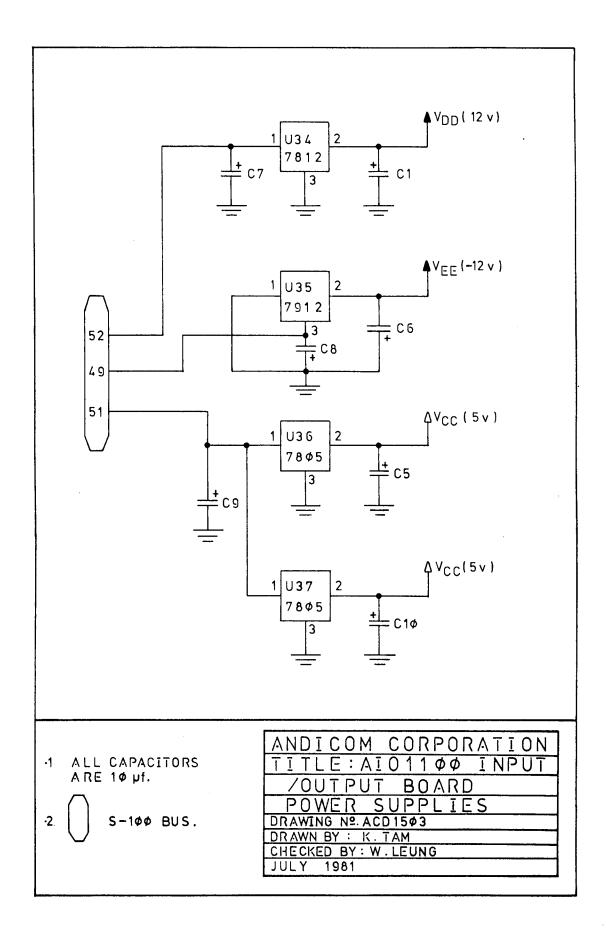

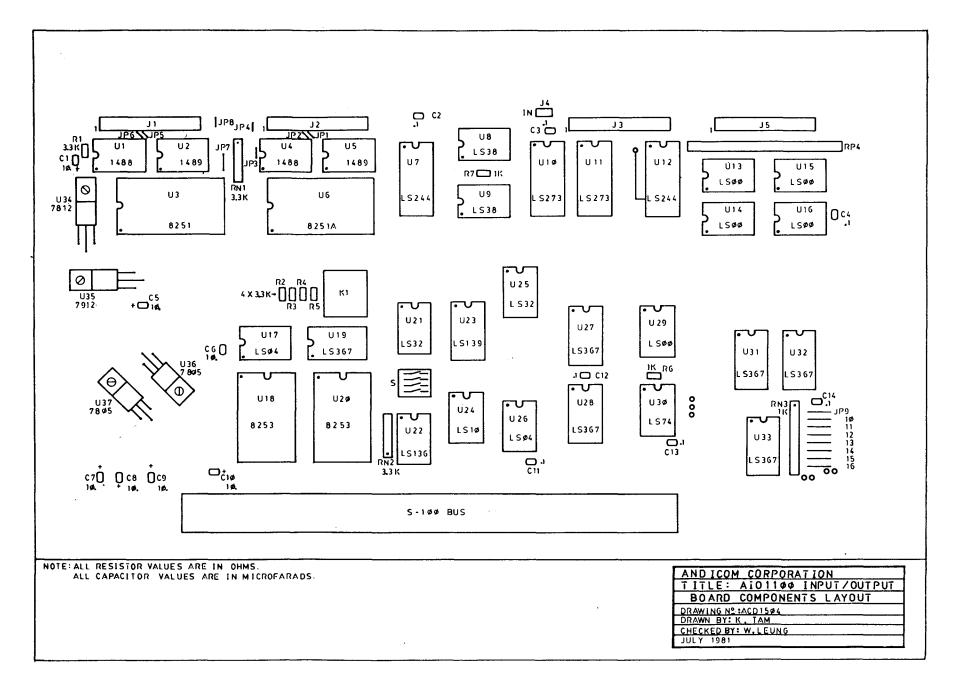

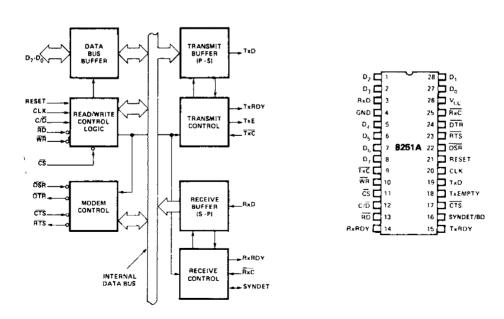

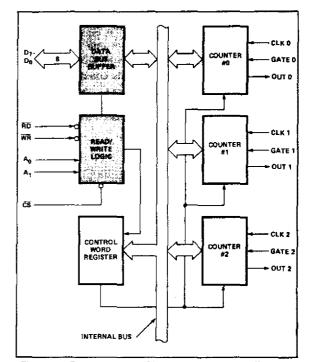

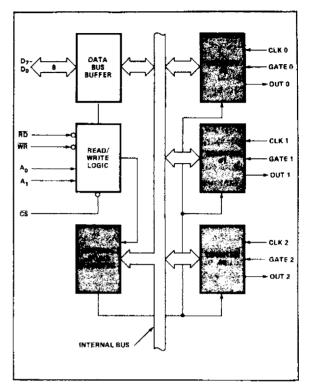

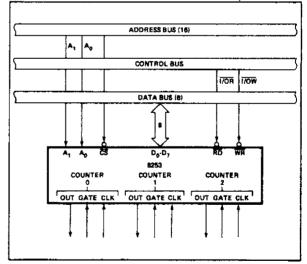

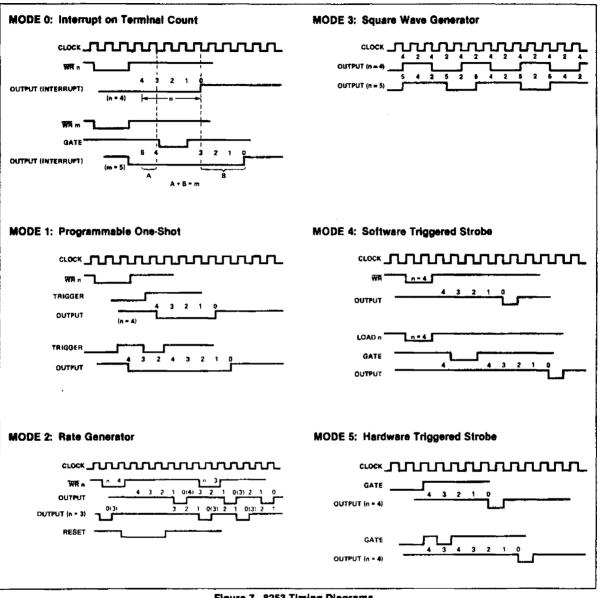

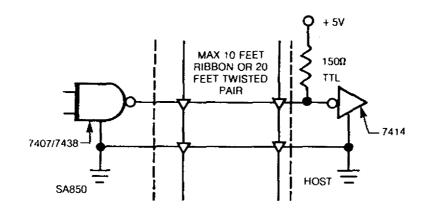

General Information Specific Features Input/Output Board Parts List FIGURE 6: Schematic Diagram of Input/Output Board FIGURE 7: Input/Output Board Optional Circuit #1 FIGURE 8: Input/Output Board Optional Circuit #2 FIGURE 9: Input/Output Board Power Supply FIGURE 10: Input/Output Board Layout

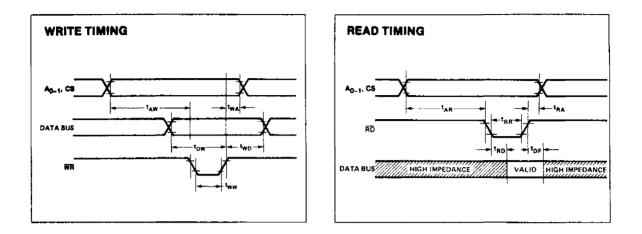

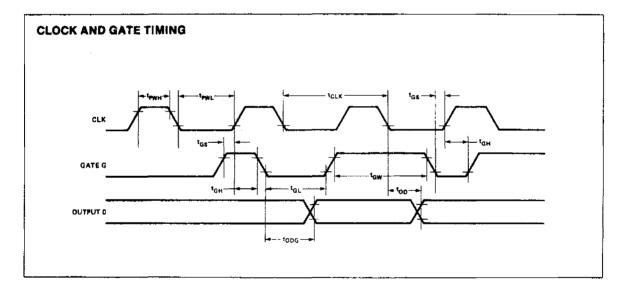

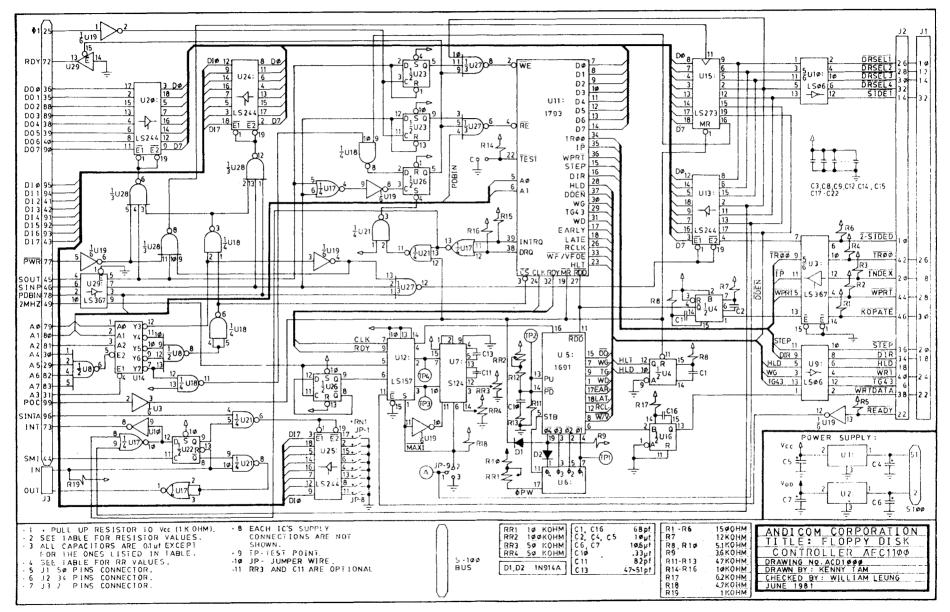

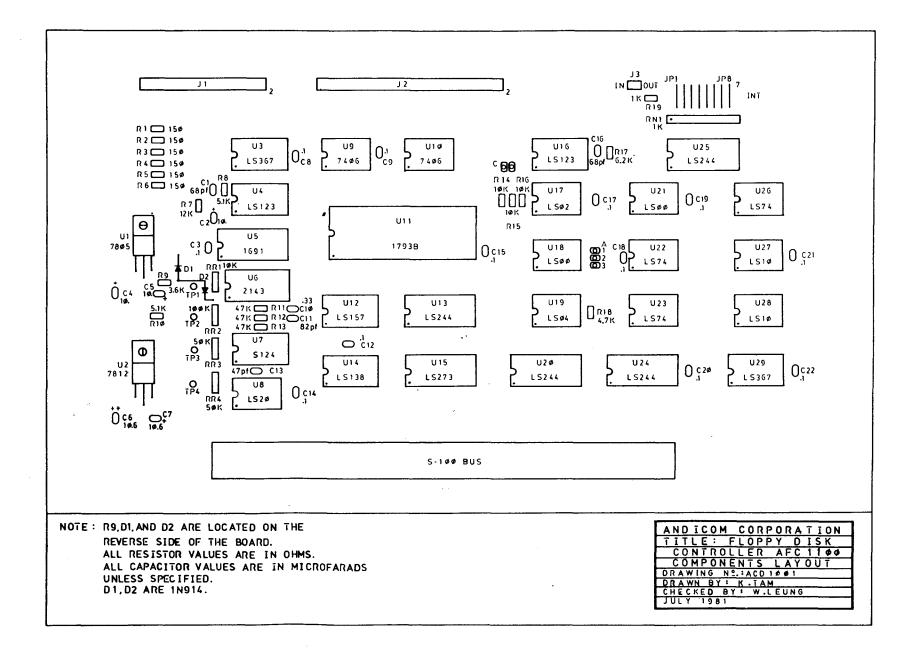

#### 4.0 FLOPPY DISK DRIVE CONTROLLER BOARD

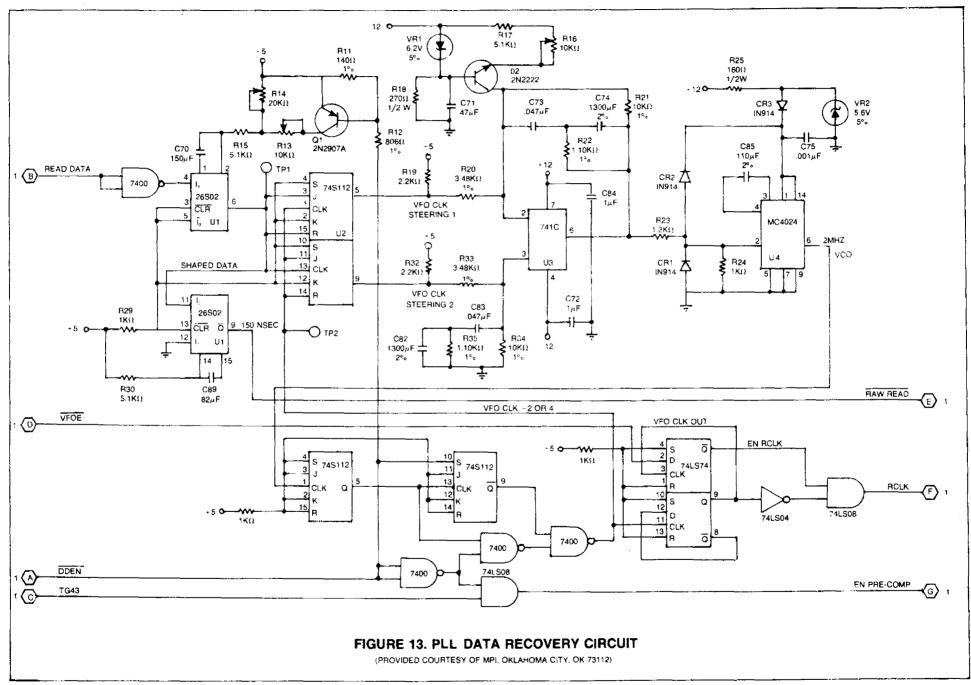

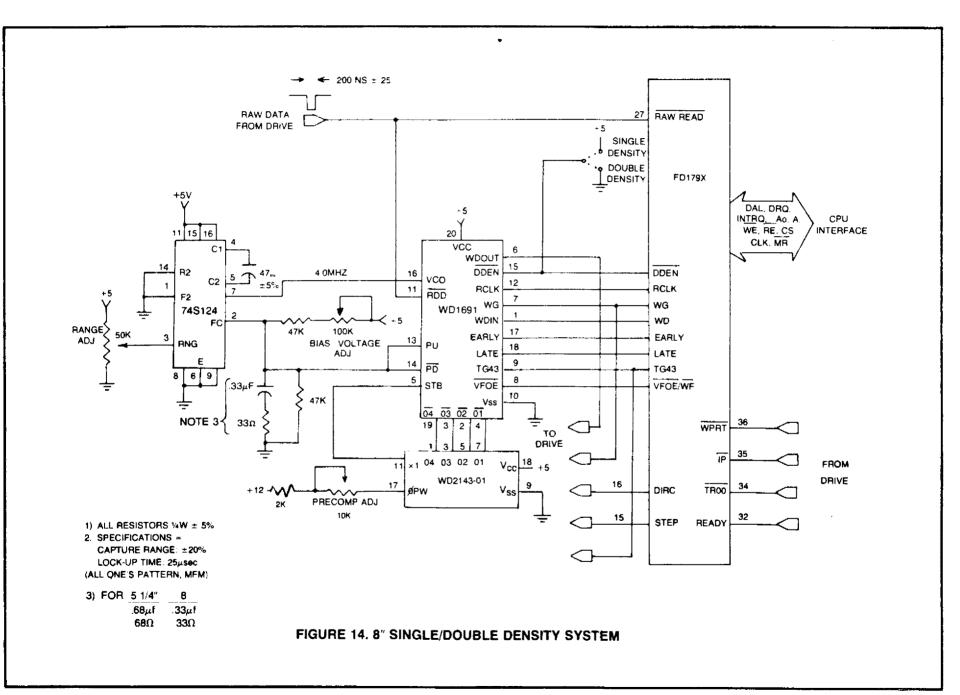

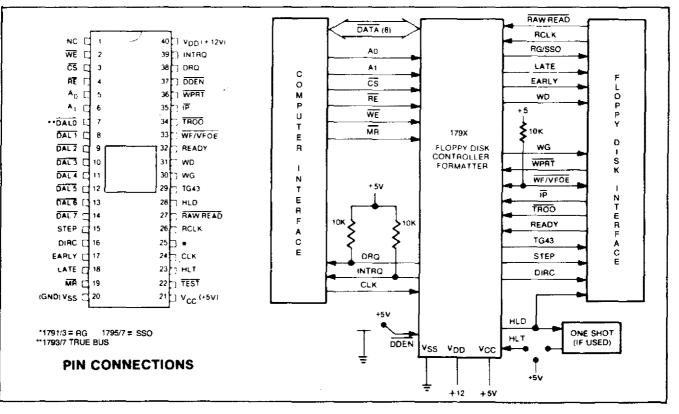

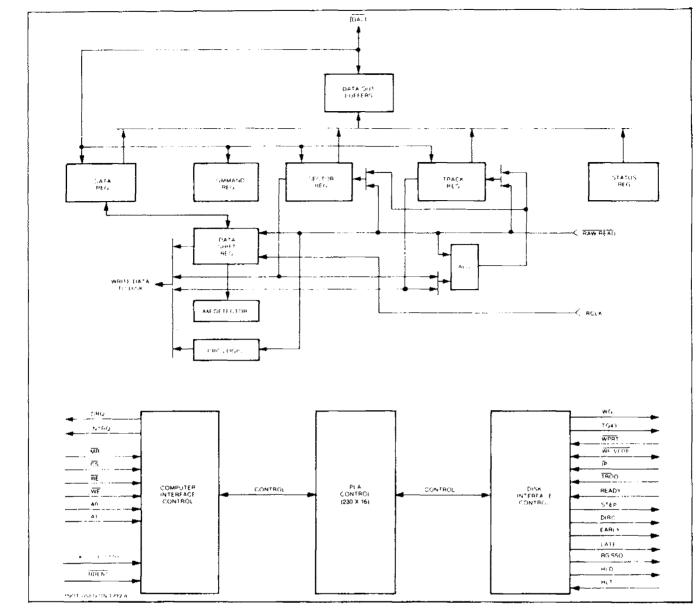

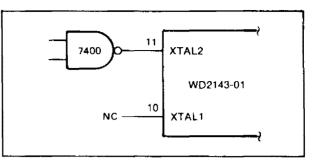

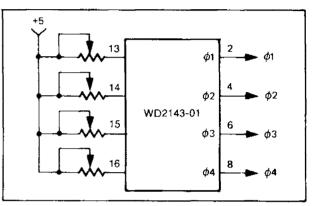

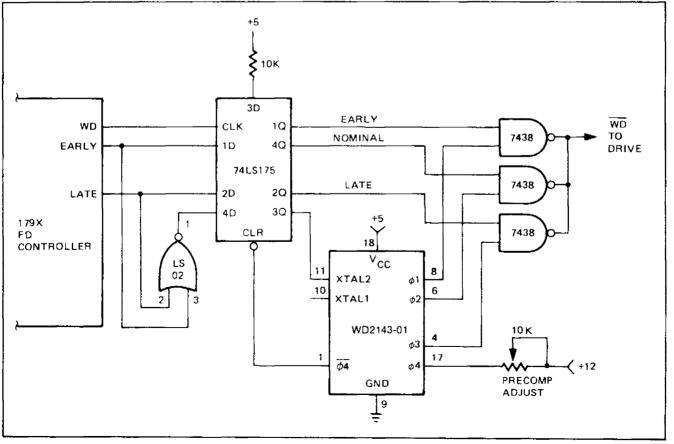

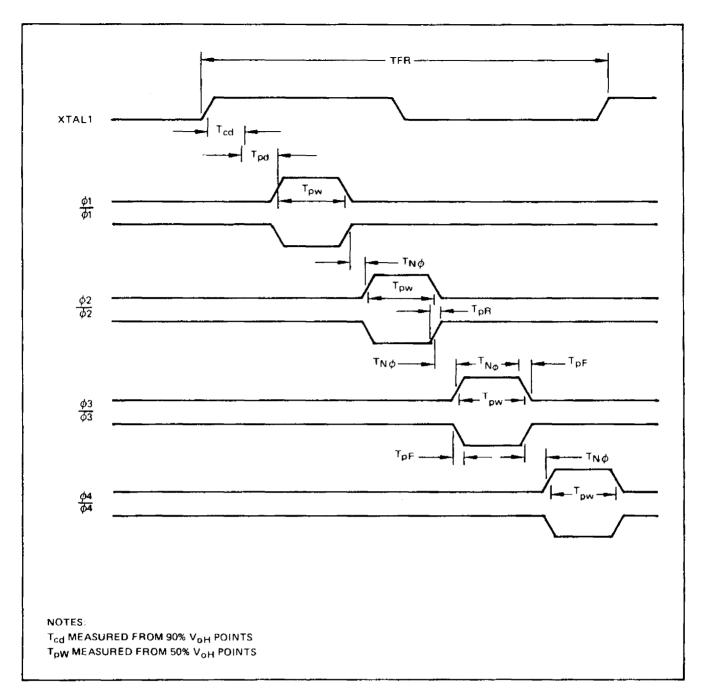

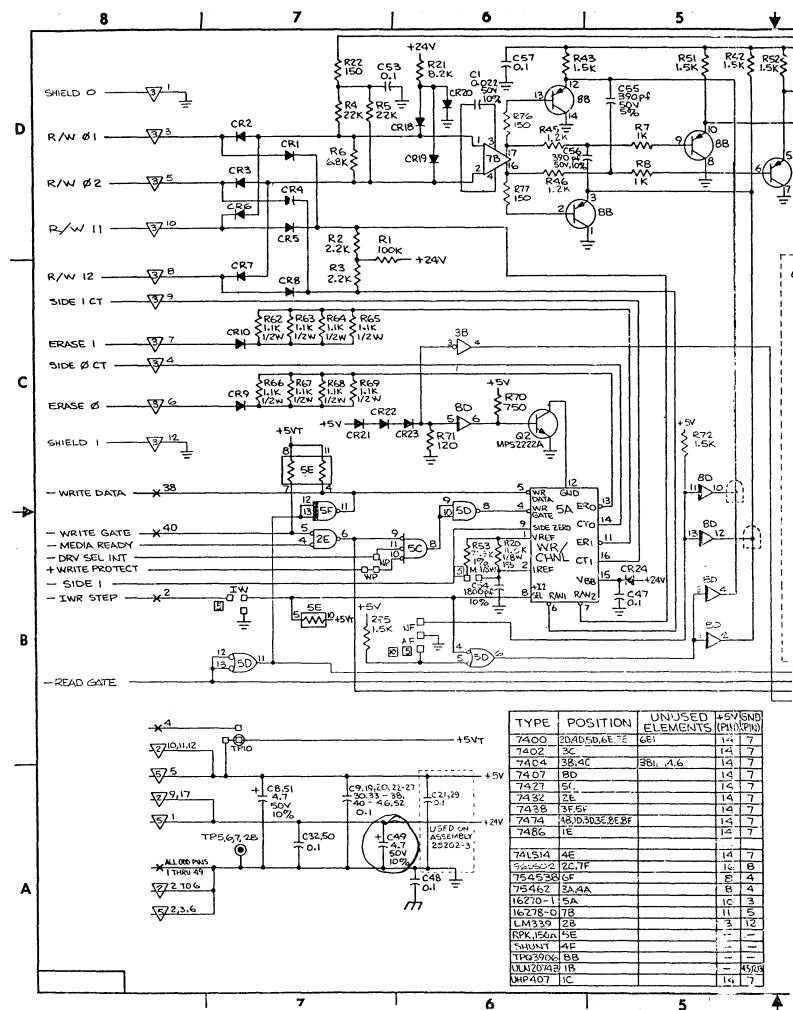

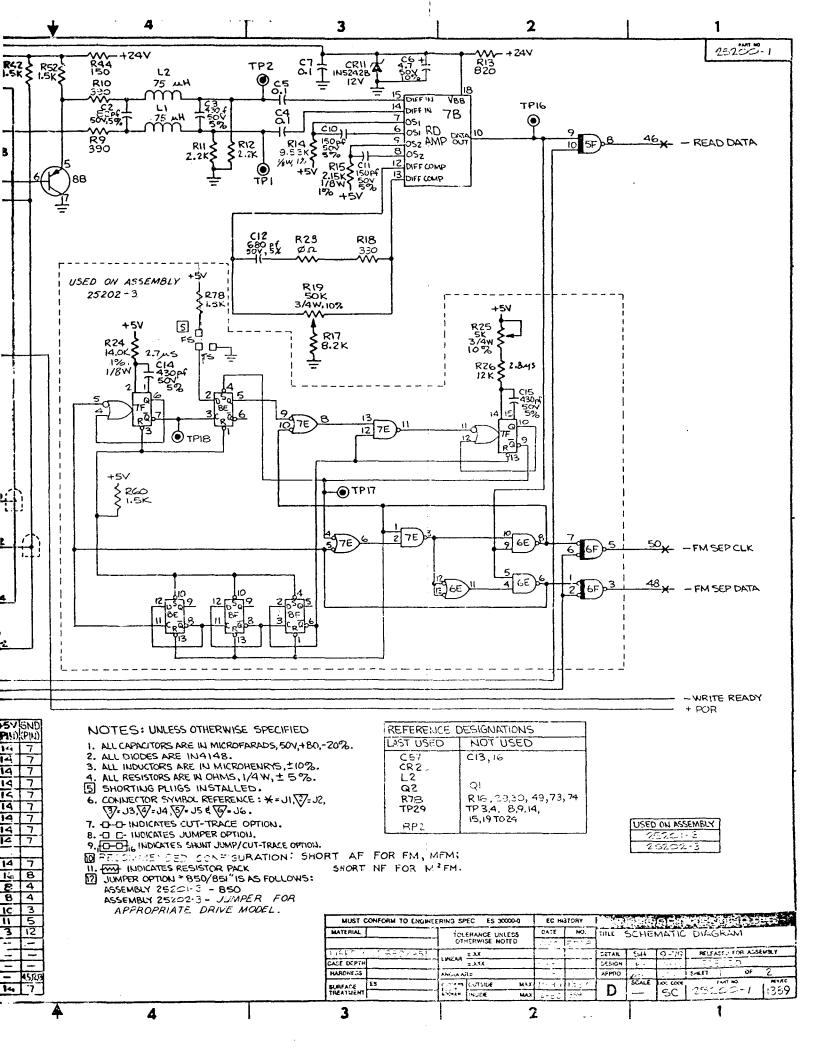

General Information Specific Features Floppy Disk Drive Controller Parts List FIGURE 11: Schematic Diagram of Floppy Controller Board FIGURE 12: Floppy Disk Controller Board Layout

#### INTRODUCTION

Congratulations on the purchase of your new Nabu 1100 Computer; you have invested in a sophisticated and reliable microprocessing unit. This system uses the powerful Zilog Z-80A microprocessor chip, and is equipped with 2 double-sided, double-density floppy Disk Drives. It features 64K user memory capacity; 62K of which is designated as R/W memory, and 2K as R/O memory. Total storage capacity for the system, using floppy diskettes, is 2 Megabytes (1 Megabyte per Drive).

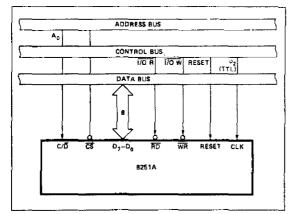

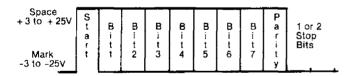

The system is equipped with two RS-232C Serial 1/0 ports with programmable Baud Rate. These 1/0 ports facilitate the use of both a console and a printer; or any two peripherals you may require. As well, a parallel output port is provided for the use of the optional Centronics dot matrix printer. Another feature of the system is the programmable timer, which can be used to implement a real time clock for the system.

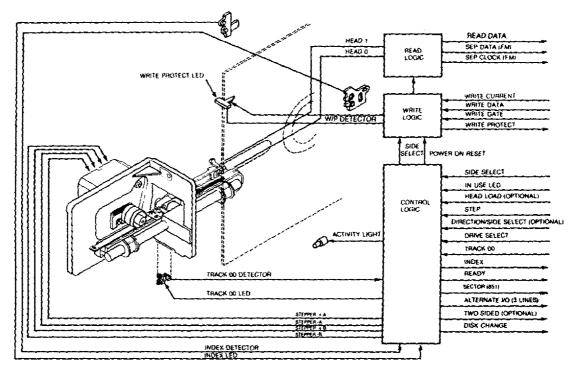

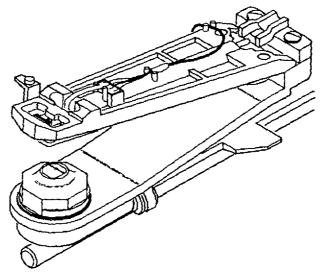

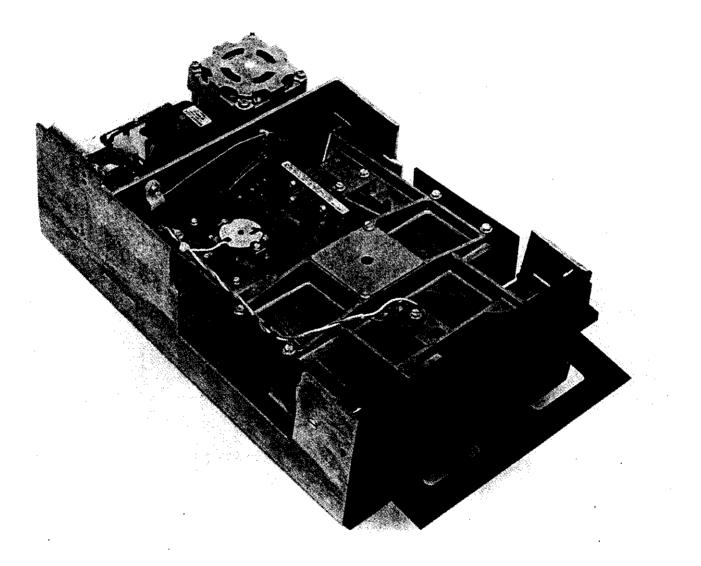

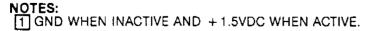

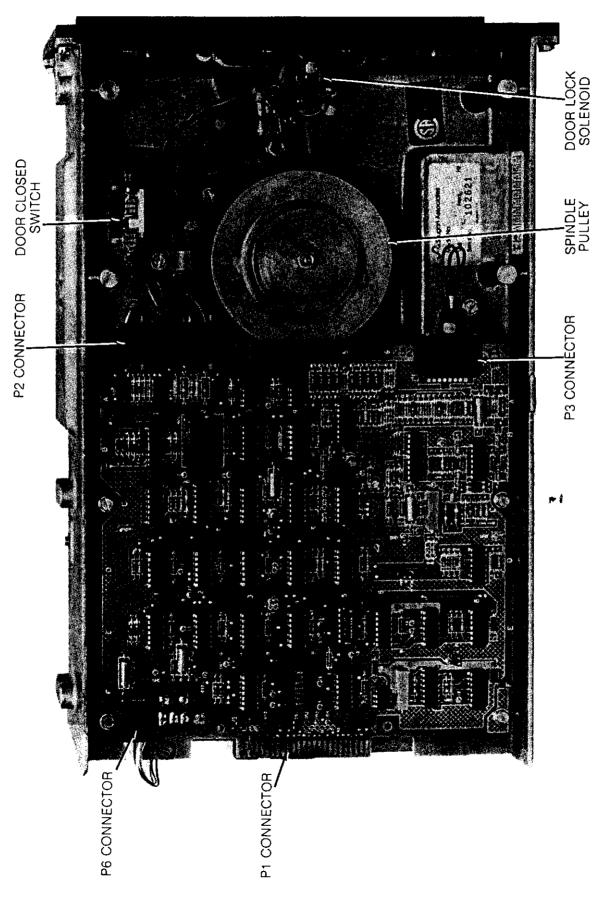

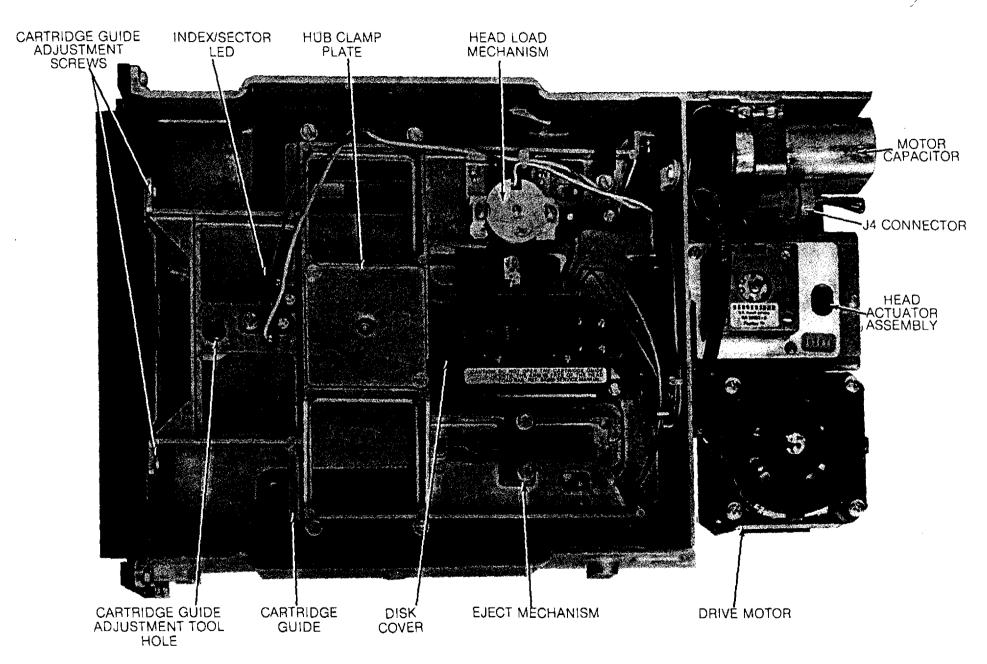

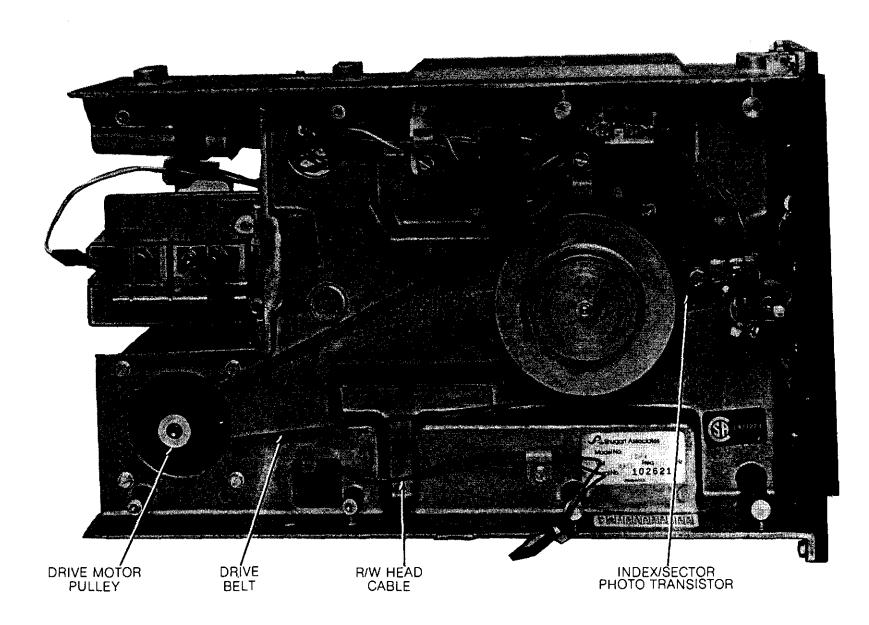

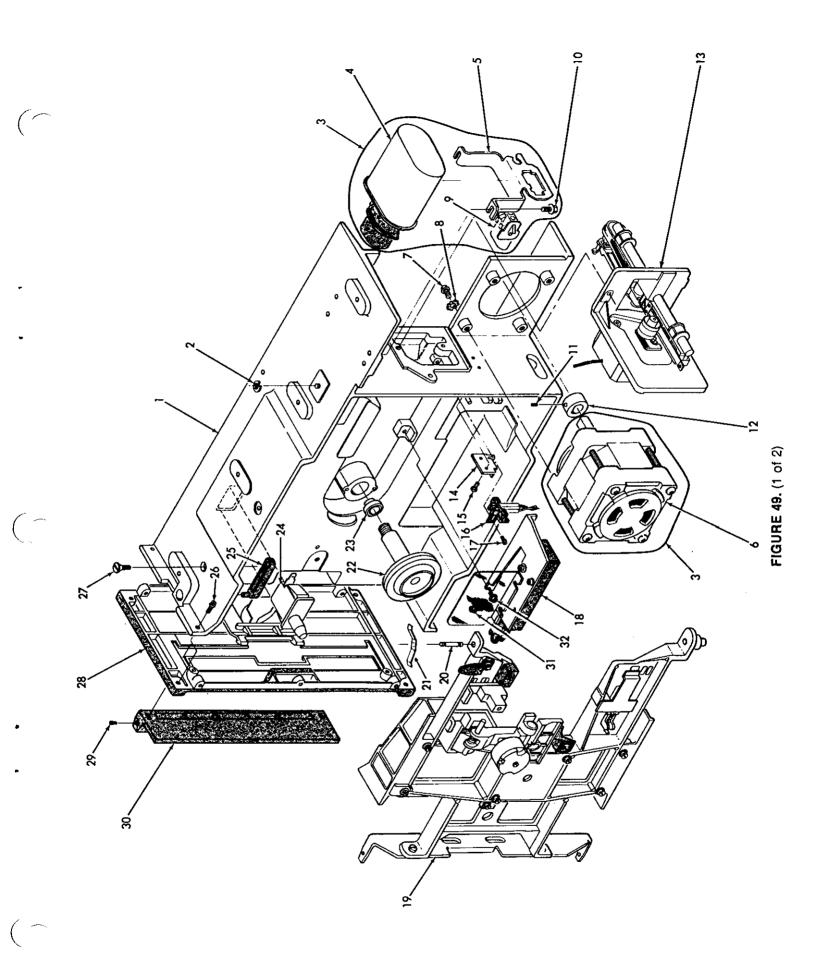

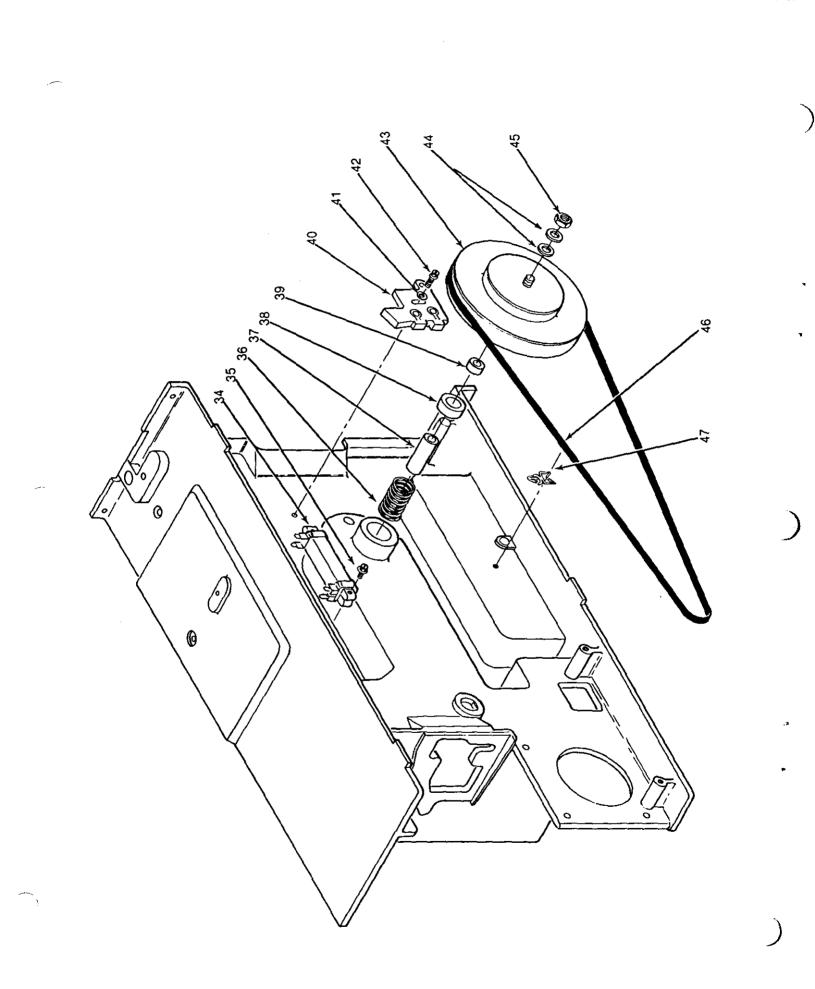

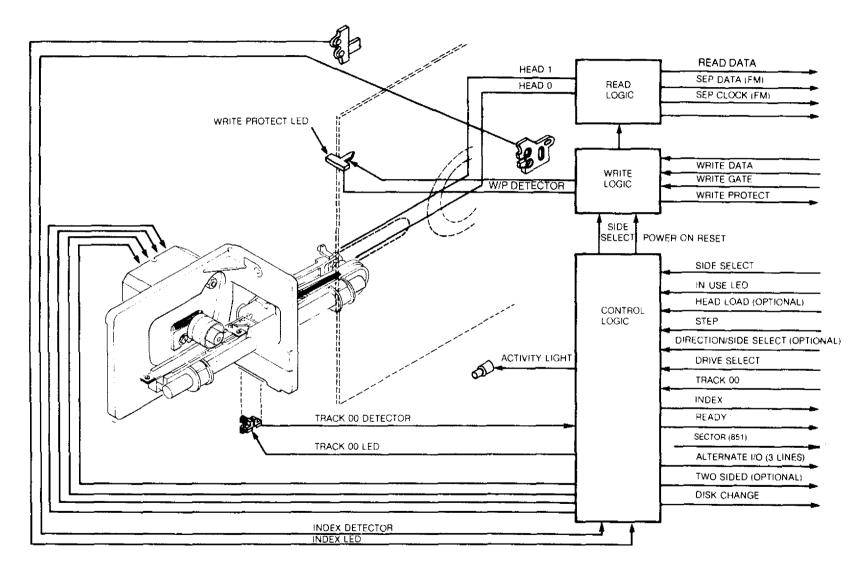

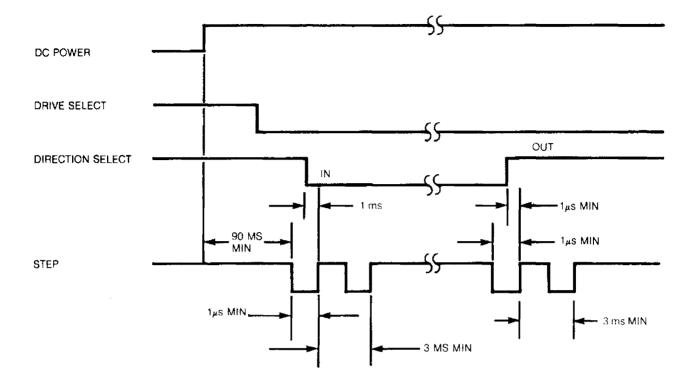

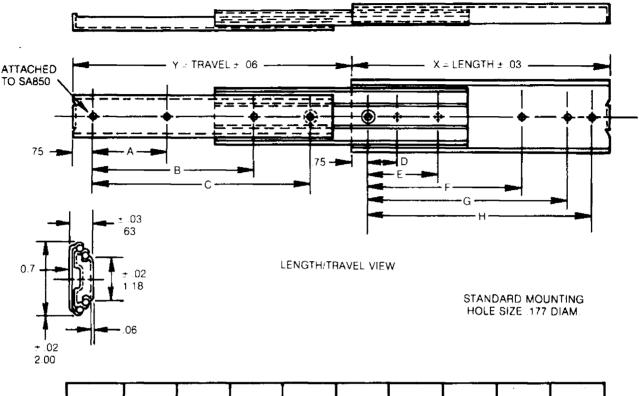

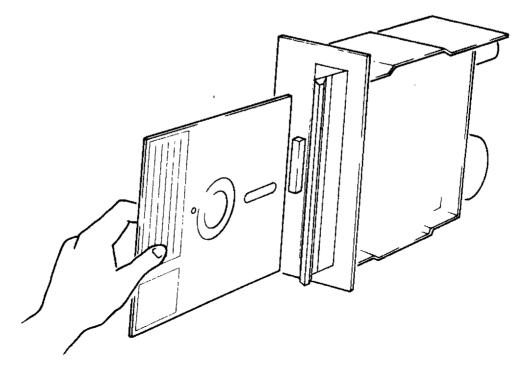

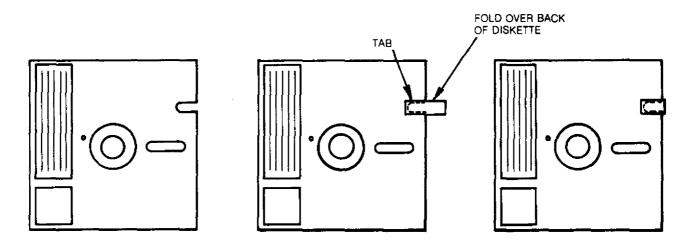

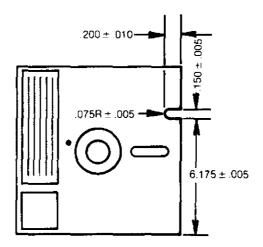

The computer hardware is located in the upper drawer of the specially designed cabinet. Directly against the right side of the drawer as you open it are the Disk Drives, manufactured by Shugart. They feature low heat dissipation, improved access time, capacity for single or double density recording on standard diskettes, and write protection and programmable door lock for improved data security. The Shugart Disk Drive manual has been included for further information.

To the left of the Disk Drives is the card cage containing the printed circuit boards, which plug into a standard S-100 Bus. There have been some modifications to certain pin functions, and these are indicated in the S-100 Bus table included in the manual. Attached to the boards are the interconnecting cables used to interface between the various components of the system. The four printed circuit boards (CPU, Memory, Input/Output, and Floppy Controller) are described in detail in the manual, and complete circuit diagrams for each board have been included.

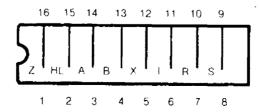

#### TABLE 1: IEEE S-100 BUS UTILIZATION

PIN # SIGNAL NAME IMPLEMENTATION

. .....

|                   | +8 Volts    | Power supply                                      |

|-------------------|-------------|---------------------------------------------------|

| 1<br>2            | +16 Volts   | Power supply                                      |

| 3                 | XRDY (S)    | Not implemented                                   |

| 4                 | VIO*(S)     | Not implemented                                   |

| 5                 |             | Not implemented                                   |

| 5                 | VI1*(S)     | -                                                 |

| 6                 | VI2*(S)     | Not implemented                                   |

| 7                 | VI3*(S)     | Not implemented                                   |

| 8                 | VI4*(S)     | Not implemented                                   |

| 9                 | VI5*(S)     | Not implemented                                   |

| 10                | VI6*(S)     | Not implemented                                   |

| 11                | VI7*(S)     | Not implemented                                   |

| 12                | NMI*(S)     | Implemented but not used                          |

| 13                | PWRFAIL*(B) | Not implemented                                   |

| 14                | DMA3*(M)    | Not implemented                                   |

| 15                | A18 (M)     | Not implemented                                   |

| 16                | A16 (M)     | Not implemented                                   |

| 17                | A17 (M)     | Not implemented                                   |

| 18                | SDSB*(M)    | Disables the 8 status signals                     |

| 19                | CDSB*(M)    | Disables the 5 control output signals             |

| 20                | GDN (B)     | Ground (not implemented)                          |

| 21                | NDEF        | Not to be defined                                 |

| 22                | ADSB*(M)    | Disables the 16 address signals                   |

| 23                | DODSB*(M)   | Disables the 8 data output signals                |

| 24                | Ø (B)       | Master timing signal                              |

| 25                | pSTVAL*(M)  | Status valid strobe                               |

|                   |             |                                                   |

| $\frac{26}{1127}$ | pHLDA (M)   | Hold control signal                               |

|                   | PWAIT       | Indicates processor is in wait state              |

| 28                | RFU         | Reserved for future use                           |

| 29                | A5 (M)      | Address bit 5                                     |

| 30                | A4 (M)      | Address bit 4                                     |

| 31                | A3 (M)      | Address bit 3                                     |

| 32                | A15 (M)     | Address bit 15                                    |

| 33                | A12 (M)     | Address bit 12                                    |

| 34                | A9 (M)      | Address bit 9                                     |

| 35                | DOl (M)     | Data out bit 1                                    |

| 36                | DOO (M)     | Data out bit 0                                    |

| 37                | Al0 (M)     | Address bit 10                                    |

| 38                | DO4 (M)     | Data out bit 4                                    |

| 39                | D05 (M)     | Data out bit 5                                    |

| 40                | DO6 (M)     | Data out bit 6                                    |

| 41                | DI2 (S)     | Data in bit 2                                     |

| 42                | DI3 (S)     | Data in bit 3                                     |

| 43                | DI7 (S)     | Data in bit 7                                     |

| 44                | sMl (M)     | Op-code fetch status signal                       |

| 45                | SOUT (M)    | Transfer status signal                            |

| 46                | SINP (M)    | Transfer status signal                            |

| 47                | SMEMR (M)   | Memory read status signal                         |

| 48                | SHLTA (M)   |                                                   |

| 49                | CLOCK (B)   | HLT acknowledge $2$ MHz (0.5%) $40-60$ dutu guale |

| 50                | GND (B)     | 2 MHz (0.5%) 40-60% duty cycle<br>Ground          |

| 50                | (ע) עת      | Ground                                            |

|                   |             |                                                   |

| 51234567890123456789012345677777778901234<br>t+ | +8 Volts (B)<br>-16 Volts (B)<br>GND (B)<br>SLAVE CLR*(B)<br>DMA0*(M)<br>DMA1*(M)<br>DMA1*(M)<br>DMA2*(M)<br>SXTRQ*(M)<br>A19 (M)<br>SIXTN*(S)<br>A20 (M)<br>A21 (M)<br>A22 (M)<br>A22 (M)<br>A23 (M)<br>MREQ<br>MRFSH<br>PHANTOM*(M/S)<br>MWRT (B)<br>RFU<br>GND (B)<br>RFU<br>GND (B)<br>RFU<br>RDY (S)<br>INT*(S)<br>HOLD*(M)<br>RESET*(B)<br>pSYNC (M)<br>pWR*(M)<br>PDBIN (M)<br>A1 (M)<br>A2 (M)<br>A6 (M)<br>A7 (M)<br>A8 (M) | Power supply<br>Power supply<br>Ground (not implemented)<br>Reset bus slaves<br>Not implemented<br>Not implemented<br>Not implemented<br>Not implemented<br>Not implemented<br>Not implemented<br>Not implemented<br>Not implemented<br>Not implemented<br>Not implemented<br>Memory request<br>Memory refresh<br>Enables phantom slaves<br>Memory write<br>Reserved for future use<br>Ground (not implemented)<br>Reserved for future use<br>Ready input<br>Primary interrupt request<br>HOLD control signal<br>Resets bus master devices<br>Control signal identifying BS1<br>Data bus control signal<br>Data in control signal<br>Address bit 0<br>Address bit 1<br>Address bit 2<br>Address bit 7<br>Address bit 8 |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82                                              | A6 (M)                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 85                                              | A13 (M)                                                                                                                                                                                                                                                                                                                                                                                                                              | Address bit 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 86<br>87                                        | Al4 (M)<br>All (M)                                                                                                                                                                                                                                                                                                                                                                                                                   | Address bit 14<br>Address bit 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 88                                              | DO2 (M)                                                                                                                                                                                                                                                                                                                                                                                                                              | Data out bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 89                                              | DO3 (M)                                                                                                                                                                                                                                                                                                                                                                                                                              | Data out bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 90                                              | DO7 (M)                                                                                                                                                                                                                                                                                                                                                                                                                              | Data out bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 91                                              | DI4 (S)                                                                                                                                                                                                                                                                                                                                                                                                                              | Data in bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 92                                              | DI5 (S)                                                                                                                                                                                                                                                                                                                                                                                                                              | Data in bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 93                                              | DI6 (S)                                                                                                                                                                                                                                                                                                                                                                                                                              | Data in bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 94                                              | DI1 (S)                                                                                                                                                                                                                                                                                                                                                                                                                              | Data in bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 95                                              | DIO (S)                                                                                                                                                                                                                                                                                                                                                                                                                              | Data in bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 96<br>97                                        | SINTA (M)<br>SWO*(M)                                                                                                                                                                                                                                                                                                                                                                                                                 | Interrupt status signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $^{9}_{98}$                                     | FREQ                                                                                                                                                                                                                                                                                                                                                                                                                                 | Data out status signal<br>Status signal for 4 MHz clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 99                                              | POC*(B)                                                                                                                                                                                                                                                                                                                                                                                                                              | Power-on clear signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 100                                             | GND (B)                                                                                                                                                                                                                                                                                                                                                                                                                              | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                 | \-/                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

These signals are not defined in the standard but are used in the system for the Z-80A microprocessor memory control signal.

**††** These signals are non-standard

. . . .

..\_..

#### TABLE 2: BOARD POSITIONS IN CARD CAGE

- 1. Empty

- 2. FLOPPY DISK CONTROLLER BOARD

- 3. INPUT/OUTPUT BOARD

- 4. Empty

- 5. CPU BOARD

- 6. Empty

- 7. MEMORY BOARD

- 8. Empty

- NOTE: Positions indicated are numbered from left to right as viewed from the front of the cabinet.

#### POWER SUPPLY

The S3 power supply (from Sunny International) is an openframe module located behind the two drives in the top drawer of the Nabu system. It provides unregulated +8, +16, and -16 volts for the S-100 bus and regulated +5, -5 and +24 volts for the disk drives. It consists of four major components: transformer, rectifiers, filter capacitors, and regulators.

The transformer primary has two 110V windings. They are connected in parallel for use with a 110V supply, and in series for use with a 220V supply.

#### SPECIFICATIONS:

------

INPUT: 110 Volts AC, 60 Hz, single phase

OUTPUT: Unregulated: +8 Volts @ 14A, +16 Volts @ 3A, -16 Volts @ 3A

Regulated: +5 Volts @ 4A, -5 Volts @ 1A, +24 Volts @ 4A

1.0 CPU BOARD

#### GENERAL INFORMATION

The Nabu ACP-1101 CPU Board is designed to bring the full power of the Zilog 2-80A microprocessor to the S-100 bus. The CPU board has provision for up to three 2716 type EPROM's (for a total of 6K bytes), and two 2114 type static RAM's (for a total of 1K bytes). The base address of this memory block can be set using on-board jumpers. The board also performs an automatic jump to a user selected memory address on system start-up or reset. The clock frequency of the main processor is also selectable between 2 and 4 MHz. When the 4 MHz clock frequency is used, the board automatically inserts one wait state when the on-board EPROM or RAM is accessed.

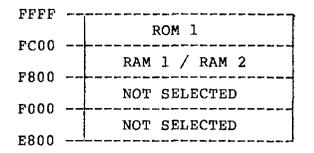

When used in the Nabu 1100 computer system, the board operates at a 4 MHz clock rate, with one 2716 EPROM and two 2114 RAM's addressed from F800H to FFFFH.

#### SPECIFIC FEATURES

#### Clock Frequency Selection

The Nabu ACP-1101 may be clocked either at 4 MHz or 2 MHz. The operating frequency is selectable with Jumper 8 (JP-8). (Please refer to the board layout for the location of all jumpers). Connecting this jumper sets the operating clock frequency to 2 MHz. The standard CPU card is shipped with the jumper disconnected and runs reliably at 4 MHz.

Pin 98, labelled as FREQ, on the S-100 bus, is used by the Nabu system as an indicator line for the operating frequency. For 4 MHz operation the line will be high; for 2 MHz it is low.

#### Automatic Power-On Jump

When system power is turned on, or a reset signal is received, the CPU jumps to one of two hundred and fifty-six possible memory locations. The jump address is selected by the eight address jumpers JP-9 to JP-16. Only the eight most significant address bits (A15 - A8) are used to decode the jump address. The eight least significant address bits (A7 - A0) are taken as logic 0 as shown on the next page.

Power-On Jump Address: X 0 0 A7 - A0, always at logic 0 A15 - A8, selected by user

The standard Nabu CPU board has the power-on jump address set at FC00H (jumpers JP-15 and JP-16 installed).

#### <u>On-Board Memory Selection</u>

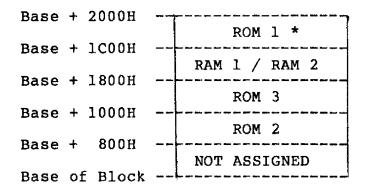

The Nabu CPU board offers a maximum of six kilo-bytes of onboard memory, which consists of three  $2K \times 8$  (2716 type) EPROM's and two  $1K \times 4$  (2114 type) static RAM's. IC sockets are provided on the board for the memory chips. The memory address for the on-board EPROM's and RAM's are grouped as a block. Within the block, the individual memory chips are allocated as follows:

\*Only the upper 1K of ROM 1 is used.

The RAM is configured as 1024 x 4 bits (2114 type). RAM 1 stores data bits D0, D7, D6, and D5; and RAM 2 stores data bits D4, D3, D2, and D1.

The base address of the block is set by jumpers JP-1 through JP-3. The three most-significant address bits are used to set the address of the block. Table 1 (on the following page), lists the possible base addresses of the block corresponding to each jumper connection.

| JUME | PERS | (JP) | STARTT | NG ADDRESS ( | TN HEX) OF. | ······································ |

|------|------|------|--------|--------------|-------------|----------------------------------------|

|      |      |      |        |              |             |                                        |

| 1    | 2    | 3    | ROM 2  | ROM 3        | RAM 1/RAM 2 | ROM 1                                  |

| 0    | 0    | 0    | 0800   | 1000         | 1800        | 1C00                                   |

|      | v    | Ū    |        |              | 1000        | 1000                                   |

| 0    | 0    | 1    | 2800   | 3000         | 3800        | 3C00                                   |

| 0    | 1    | 0    | 4800   | 5000         | 5800        | 5C00                                   |

| 0    | 1    | 1    | 6800   | 7000         | 7800        | 7C00                                   |

| 1    | 0    | 0    | 8800   | 9000         | 9800        | 9C00                                   |

| 1    | 0    | 1    | A800   | B000         | B800        | BC00                                   |

| 1    | 1    | 0    | C800   | D000         | D800        | DC00                                   |

| 1    | 1    | 1    | E800   | F000         | F800        | FC00                                   |

| L    |      |      |        |              |             |                                        |

'l' represents 'Jumper is connected'

'0' represents 'Jumper is disconnected'

TABLE 1: Jumper Connection And Starting Address of Memory

The enabling of these memory chips is done by connecting jumpers JP-5, JP-6, and JP-7 in the selection area S-1. JP-5 enables ROM 2, JP-6 enables ROM 3, and JP-7 enables ROM 1 and RAM 1/ RAM 2, as seen in the figure below. (Note that ROM 1 and RAM 1/ RAM 2 are enabled together, and so both must be used together).

Selection 000000 Area S-1 0000000 Jumpers (JP) 567 Connected to enable ROM 1/ RAM's Connected to enable ROM 3 Connected to enable ROM 2

In addition, enabling on-board RAM's and EPROM's renders any external devices or memory at the selected address-block inaccessible to a read instruction. However, a write operation will write into all devices located there.

The standard Nabu ACP-1101 is shipped with the following memory setting:

Selection

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

o

The memory map corresponding to the standard setting would be:

When both the 4 MHz operating frequency, and the on-board EPROM's and RAM's are chosen, (as in the standard Nabu ACP-1101 setting), one wait-cycle is automatically inserted by the CPU logic circuitry.

#### Refresh Enable

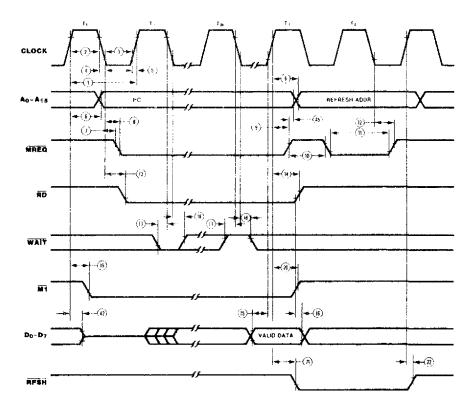

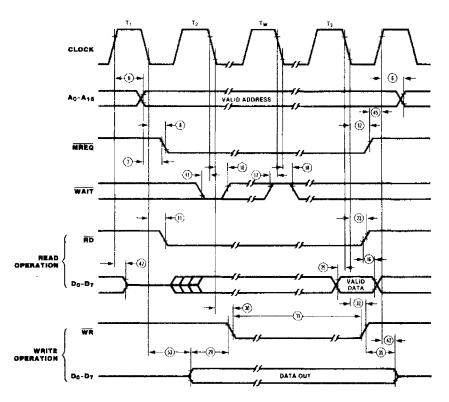

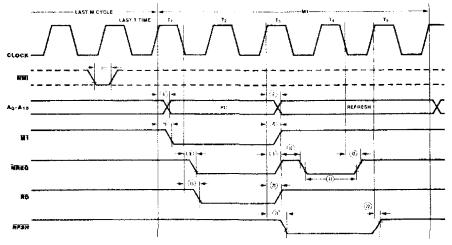

Dynamic RAM's periodically require a refresh to maintain the data stored within the memory cell. The Nabu CPU board brings the memory-refresh signal from the Zilog Z-80A microprocessor to the S-100 bus. Pin 66 on the S-100 bus is designated by Nabu as the memory-refresh signal, RFSH. The memory request signal from the Z-80A processor is also brought out to the S-100 bus. Pin 65 (named as MREQ), is used to indicate a valid memory address on the address bus.

#### NABU ACP-1101 CPU BOARD PARTS LIST

#### Integrated Circuits

| U1-U4<br>U5                      | 2114<br>74LS136      | 1024 x 4-bit NMOS static RAM<br>Quadruple 2-input NOR with open-                        |

|----------------------------------|----------------------|-----------------------------------------------------------------------------------------|

| U6                               | 74LS42               | collector outputs<br>4-line-to-10-line decoder                                          |

| U7<br>U8, U9, U28,               | 74LS20               | Dual 4-input NAND                                                                       |

| U30-U34                          | 74LS241              | Octal buffer/line-driver with 3-state outputs                                           |

| U10<br>U11                       | 74LS175<br>74LS123   | Quadruple D-type flip-flop<br>Dual retriggerable monostable<br>multivibrator with clear |

| U12, U17, U20,                   |                      | multivibrator with clear                                                                |

| U23, U24                         | 74LS74               | Dual D-type rising-edge-triggered flip-<br>flop with preset and clear                   |

| U13                              | 74LS132              | Quadruple 2-input NAND with Schmitt-<br>triggered inputs                                |

| U14, U21                         | 74LS04               | Hex inverter                                                                            |

| U15                              | 74LS08               | Quadruple 2-input AND                                                                   |

| U16                              | 74LS32               | Quadruple 2-input OR                                                                    |

| U18<br>U19                       | Z-80A-CPU<br>74LS157 | Central processing unit (4 MHz)<br>Quadruple 2-line-to-l-line multiplexer               |

| U22, U25, U35                    | 74LS02               | Quadruple 2-input NOR                                                                   |

| U26                              | 74LS367              | Hex non-inverting bus-driver                                                            |

| U27                              | 74LS14               | Hex inverter with Schmitt-triggered                                                     |

|                                  |                      | inputs                                                                                  |

| U <b>29,</b> U36                 | 74LS368              | Hex inverting bus-driver                                                                |

| U37, U38                         | 7805                 | 5 V positive voltage regulator                                                          |

| ROM1-ROM3                        | 2716                 | 2716 EPROM with bootstrap program                                                       |

| Transistors:                     |                      |                                                                                         |

| Ql                               | 2N4124               | NPN silicon transistor                                                                  |

| Q2                               | 2N4126               | PNP silicon transistor                                                                  |

| Diodes:                          |                      |                                                                                         |

| D1, D2                           | 1N914A               | Silicon switching diode                                                                 |

| <u>Capacitors:</u>               |                      |                                                                                         |

| C1-C10, C13-C19<br>C19-C24, C25, | 5,                   |                                                                                         |

| C26, C30, C31                    |                      | 0.1 µF                                                                                  |

| C11, C18                         |                      | 33 pF disc                                                                              |

| C12                              |                      | 22 µF, 16 V tantalum electrolytic                                                       |

| C16, C27-C29                     |                      | 10 µF, 16 V tantalum electrolytic                                                       |

| C17                              |                      | 10 nF                                                                                   |

<u>Resistors:</u>

| R1, R2         | 10 k 🔨                                                                |

|----------------|-----------------------------------------------------------------------|

| R3, R5-R7, R11 | lkA                                                                   |

| R4             | 100 <u>N</u>                                                          |

| R8             | 220 A                                                                 |

| R9             | 22 A                                                                  |

| R10            | 100 k A                                                               |

| RN1-RN3        | 9-resistor pack of $1 \text{ k} \Lambda$ resistors with common pin #1 |

#### Crystal:

XTAL

8.000 MHz parallel-resonant

Ouantity Description

| 16 | 14 pin socket              |

|----|----------------------------|

| 7  | 16 pin socket              |

| 4  | 18 pin socket              |

| 8  | 20 pin socket              |

| 3  | 24 pin socket              |

| 1  | 40 pin socket              |

| 1  | Delta 680-0.5-220 Heatsink |

| 6  | #6-32 x 3/8" machine screw |

| 6  | #6-32 nuts                 |

| 1  | p.c. board                 |

NOTE: The following 11 pages have been reproduced by permission of Zilog, Inc. © 1979, 80, 81. This material shall not be reproduced without the written consent of Zilog, Inc.

Z-80A is a trademark of Zilog, Inc., with whom the publisher is not associated.

\_\_\_\_\_ \_\_\_ \_\_\_\_

\_\_\_\_\_

### Z8400 Z80° CPU Central Processing Unit

### Product Specification

#### March 1981

- The instruction set contains 158 instructions. The 78 instructions of the 8080A are included as a subset; 8080A software compatibility is maintained.

- Six MHz, 4 MHz and 2.5 MHz clocks for the Z80B, Z80A, and Z80 CPU result in rapid instruction execution with consequent high data throughput.

- The extensive instruction set includes string, bit, byte, and word operations. Block searches and block transfers together with indexed and relative addressing result in the most powerful data handling capabilities in the microcomputer industry.

- The Z80 microprocessors and associated family of peripheral controllers are linked by a vectored interrupt system. This system

MREO

iono

RĎ

WR

AFSH

HALT

WAIT

INT

NI

RESET

BUSREO

BUSACK

CLK

+ 5 V

GND

Z80 CPU

**Figure 1.** Pin Functions

SYSTEM CONTROL

CPU CONTROL

CPU BUS CONTROL A

A,

A3

A,

A<sub>5</sub>

A

A

A

A.

A<sub>1</sub>

A<sub>13</sub>

A11

D,

D<sub>1</sub>

$\mathfrak{p}_2$

$\mathbf{D}_2$

De

D,

D

n-

ADDRESS RUS

DATA

808

may be daisy-chained to allow implementation of a priority interrupt scheme. Little, if any, additional logic is required for daisy-chaining.

- Duplicate sets of both general-purpose and flag registers are provided, easing the design and operation of system software through single-context switching, background-foreground programming, and single-level interrupt processing. In addition, two 16-bit index registers facilitate program processing of tables and arrays.

- There are three modes of high speed interrupt processing: 8080 compatible, non-Z80 peripheral device, and Z80 Family peripheral with or without daisy chain.

- On-chip dynamic memory refresh counter.

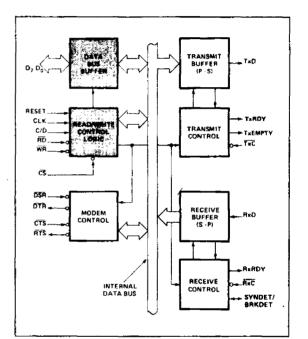

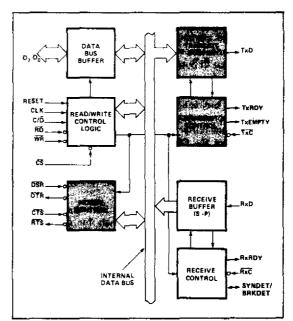

Figure 2. Pin Assignments

Features

#### General Description

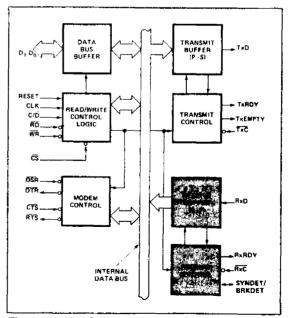

The Z80 Z80A, and Z80B CPUs are thirdgeneration single-chip microprocessors with exceptional computational power. They offer higher system throughput and more efficient memory utilization than comparable secondand third-generation microprocessors. The internal registers contain 208 bits of read/write memory that are accessible to the programmer These registers include two sets of six generalpurpose registers which may be used individually as either 8-bit registers or as 16-bit register pairs. In addition, there are two sets of accumulator and flag registers 👘 group of "Exchange' instructions makes either set of main or alternate registers accessible to the programmer. The alternate set allows operation in foreground-background mode or it may

be reserved for very fast interrupt response.

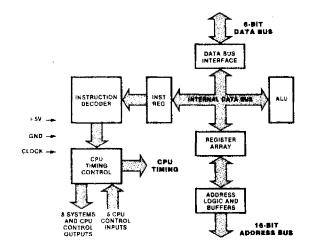

The Z80 also contains a Stack Pointer, Program Counter, two index registers, a Refresh register (counter), and an Interrupt register. The CPU is easy to incorporate into a system since it requires only a single +5 V power source, all output signals are fully decoded and timed to control standard memory or peripheral circuits, and is supported by an extensive family of peripheral controllers. The internal block diagram (Figure 3) shows the primary functions of the Z80 processors. Subsequent text provides more detail on the Z80 I/O controller family, registers, instruction set, interrupts and daisy chaining, and CPU timing.

Figure 3. 280 CPU Block Diagram

| Z80 Micro-<br>processor<br>Family | The Zilog Z80 microprocessor is the central<br>element of a comprehensive microprocessor<br>product family. This family works together in                                                                                                                   | each of which has an 8-bit prescaler. Each of the four channels may be configured to operate in either counter or timer mode.                                                                                                  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | most applications with minimum requirements<br>for additional logic, facilitating the design of<br>efficient and cost-effective microcomputer-<br>based systems.                                                                                            | <ul> <li>The DMA (Direct Memory Access) con-<br/>troller provides dual port data transfer<br/>operations and the ability to terminate data<br/>transfer as a result of a pattern match.</li> </ul>                             |

|                                   | Zilog has designed five components to pro-<br>vide extensive support for the Z80 micro-<br>processor. These are:<br>The PIO (Parallel Input/Output) operates in<br>both data-byte I/O transfer mode (with<br>handshaking) and in bit mode (without          | The SIO (Serial Input/Output) controller<br>offers two channels. It is capable of<br>operating in a variety of programmable<br>modes for both synchronous and asyn-<br>chronous communication, including<br>Bi-Synch and SDLC. |

|                                   | <ul> <li>handshaking). The PIO may be configured to interface with standard parallel peripheral devices such as printers, tape punches, and keyboards.</li> <li>The CTC (Counter/Timer Circuit) features four programmable 8-bit counter/timers,</li> </ul> | ■ The DART (Dual Asynchronous Receiver/<br>Transmitter) device provides low cost<br>asynchronous serial communication. It has<br>two channels and a full modem control<br>interface.                                           |

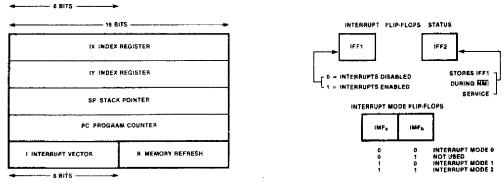

Figure 4 shows three groups of registers within the Z80 CPU. The first group consists of duplicate sets of 8-bit registers: a principal set and an alternate set (designated by '[prime], e.g., A'). Both sets consist of the Accumulator Register, the Flag Register, and six general-purpose registers. Transfer of data between these duplicate sets of registers is accomplished by use of "Exchange" instructions. The result is faster response to interrupts and easy, efficient implementation of such versatile programming techniques as backgroundforeground data processing. The second set of registers consists of six registers with assigned functions. These are the I (Interrupt Register), the R (Refresh Register), the IX and IY (Index Registers), the SP (Stack Pointer), and the PC (Program Counter). The third group consists of two interrupt status flip-flops, plus an additional pair of flip-flops which assists in identifying the interrupt mode at any particular time. Table 1 provides further information on these registers.

MAIN REGISTER SET

ALTERNATE REGISTER SET

| A ACCUMULATOR     | F FLAG REGISTER   | A' ACCUMULATOR     | F' FLAG REGISTER   |

|-------------------|-------------------|--------------------|--------------------|

| B GENERAL PURPOSE | C GENERAL PURPOSE | B' GENERAL PURPOSE | C' GENERAL PURPOSE |

| D GENERAL PURPOSE | E GENERAL PURPOSE | D' GENERAL PURPOSE | E' GENERAL PURPOSE |

| H GENERAL PURPOSE | L GENERAL PURPOSE | H' GENERAL PURPOSE | L' GENERAL PURPOSE |

Figure 4. CPU Registers

Z80 CPU

Registers

| 80 CPU     | Re                | gister             | Size (Bits) | Remarks                                                                                                                                                         |

|------------|-------------------|--------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | A, A'             | Accumulator        | 8           | Stores an operand or the results of an operation.                                                                                                               |

| Continued) | F, F'             | Flags              | 8           | See Instruction Set.                                                                                                                                            |

|            | B, B'             | General Purpose    | 8           | Can be used separately or as a 16-bit register with C.                                                                                                          |

|            | C, C'             | General Purpose    | 8           | See B, above.                                                                                                                                                   |

|            | DD'               | General Purpose    | 8           | Can be used separately or as a 16-bit register with E.                                                                                                          |

|            | Ε, Ε΄             | General Purpose    | 8           | See D, above.                                                                                                                                                   |

|            | Н, Н'             | General Purpose    | 8           | Can be used separately or as a 16-bit register with L.                                                                                                          |

|            | L, L'             | General Purpose    | 8           | See H_above.                                                                                                                                                    |

|            |                   |                    |             | Note: The (B,C), (D,E), and (H,L) sets are combined as follows:<br>B - High byte - C - Low byte<br>D - High byte - E - Low byte<br>H - High byte - L - Low byte |

|            | I                 | Interrupt Register | 8           | Stores upper eight bits of memory address for vectored interrupt processing.                                                                                    |

|            | R                 | Refresh Register   | 8           | Provides user-transparent dynamic memory refresh. Automatically<br>incremented and placed on the address bus during each<br>instruction fetch cycle.            |

|            | IX                | Index Register     | 16          | Used for indexed addressing.                                                                                                                                    |

|            | Ι¥                | Index Register     | 16          | Same as IX, above.                                                                                                                                              |

|            | SP                | Stack Pointer      | 16          | Stores addresses or data temporarily. See Push or Pop in instruc-<br>tion set.                                                                                  |

|            | PC                | Program Counter    | 16          | Holds address of next instruction.                                                                                                                              |

|            | $IFF_1$ - $IFF_2$ | Interrupt Enable   | Flip Flops  | Set or reset to indicate interrupt status (see Figure 4).                                                                                                       |

|            | IMFa-IMFb         | Interrupt Mode     | Flip-Flops  | Reflect Interrupt mode (see Figure 4).                                                                                                                          |

Table 1. 280 CPU Registers

Interrupts: General Operation The CPU accepts two interrupt input signals: NMI and INT. The NMI is a non-maskable interrupt and has the highest priority. INT is a lower priority interrupt since it requires that interrupts be enabled in software in order to operate. Either NMI or INT can be connected to multiple peripheral devices in a wired-OR configuration.

The Z80 has a single response mode for interrupt service for the non-maskable interrupt. The maskable interrupt, INT, has three programmable response modes available. These are:

Mode 0 -- compatible with the 8080 microprocessor.  Mode 1 — Peripheral Interrupt service, for use with non-8080/Z80 systems.

Mode 2 — a vectored interrupt scheme, usually daisy-chained, for use with Z80 Family and compatible peripheral devices.

The CPU services interrupts by sampling the NMI and INT signals at the rising edge of the last clock of an instruction. Further interrupt service processing depends upon the type of interrupt that was detected. Details on interrupt responses are shown in the CPU Timing Section.

Interrupts: General Operation (Continued) Non-Maskable Interrupt (NMI). The nonmaskable interrupt cannot be disabled by program control and therefore will be accepted at at all times by the CPU. NMI is usually reserved for servicing only the highest priority type interrupts, such as that for orderly shutdown after power failure has been detected. After recognition of the NMI signal (providing BUSREQ is not active), the CPU jumps to restart location 0066H. Normally, software starting at this address contains the interrupt service routine.

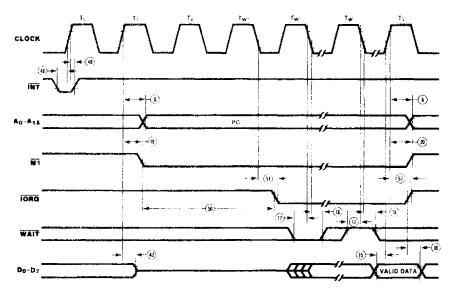

**Maskable Interrupt (INT).** Regardless of the interrupt mode set by the user, the Z80 response to a maskable interrupt input follows a common timing cycle. After the interrupt has been detected by the CPU (provided that interrupts are enabled and BUSREQ is not active) a special interrupt processing cycle begins. This is a special fetch (MI) cycle in which IORQ becomes active rather than MREQ, as in a normal MI cycle. In addition, this special MI cycle is automatically extended by two WAIT states, to allow for the time required to acknowledge the interrupt request and to place the interrupt vector on the bus.

**Mode 0 Interrupt Operation.** This mode is compatible with the 8080 microprocessor interrupt service procedures. The interrupting device places an instruction on the data bus, which is then acted on six times by the CPU. This is normally a Restart Instruction, which will initiate an unconditional jump to the selected one of eight restart locations in page zero of memory.

**Mode 1 Interrupt Operation.** Mode 1 operation is very similar to that for the NMI. The principal difference is that the Mode 1 interrupt has a vector address of 0038H only.

**Mode 2 Interrupt Operation.** This interrupt mode has been designed to utilize most effectively the capabilities of the Z80 microprocessor and its associated peripheral family. The interrupting peripheral device selects the starting address of the interrupt service routine. It does this by placing an 8-bit address vector on the data bus during the interrupt acknowledge cycle. The high-order byte of the interrupt service routine address is supplied by the I (Interrupt) register. This flexibility in selecting the interrupt service routine address allows the peripheral device to use several different types of service routines. These routines may be located at any available location in memory. Since the interrupting device supplies the low-order byte of the 2-byte vector, bit 0 (A<sub>0</sub>) must be a zero.

#### Interrupt Priority (Daisy Chaining and

**Nested Interrupts).** The interrupt priority of each peripheral device is determined by its physical location within a daisy-chain configuration. Each device in the chain has an interrupt enable input line (IEI) and an interrupt enable output line (IEO), which is fed to the next lower priority device. The first device in the daisy chain has its IEI input hardwared to a High level. The first device has highest priority, while each succeeding device has a corresponding lower priority. This arrangement permits the CPU to select the highest priority interrupt from several simultaneously interrupting peripherals.

The interrupting device disables its IEO line to the next lower priority peripheral until it has been serviced. After servicing, its IEO line is raised, allowing lower priority peripherals to demand interrupt servicing.

The Z80 CPU will nest (queue) any pending interrupts or interrupts received while a selected peripheral is being serviced.

**Interrupt Enable/Disable Operation.** Two flip-flops,  $IFF_1$  and  $IFF_2$ , referred to in the register description are used to signal the CPU interrupt status. Operation of the two flip-flops is described in Table 2. For more details, refer to the *Z80 CPU Technical Manual* and *Z80* Assembly Language Manual.

| Action                          | IFFI             | IFF <sub>3</sub> | Comments                                                                              |

|---------------------------------|------------------|------------------|---------------------------------------------------------------------------------------|

| CPU Reset                       | 0                | 0                | Maskable interrupt<br>INT disabled                                                    |

| DI instruction<br>execution     | 0                | 0                | Maskable interrupt<br>INT disabled                                                    |

| EI instruction<br>execution     | 1                | 1                | Maskable interrupt<br>INT enabled                                                     |

| LD A,I instruction<br>execution | •                | •                | $IFF_2 - Parity flag$                                                                 |

| LD A,R instruction<br>execution | •                | ٠                | $IFF_2 \rightarrow Parity flag$                                                       |

| Accept NMI                      | 0                | IFF <sub>1</sub> | IFF <sub>1</sub> — IFF <sub>2</sub><br>(Maskable inter-<br>rupt INT disabled)         |

| RETN instruction<br>execution   | IFF <sub>2</sub> | •                | IFF <sub>2</sub> → IFF <sub>1</sub> at<br>completion of an<br>NMI service<br>routine. |

Table 2. State of Flip-Flope

#### Instruction The Z80 microprocessor has one of the most Set powerful and versatile instruction sets available in any 8-bit microprocessor. It includes such unique operations as a block move for fast, efficient data transfers within

memory or between memory and I/O. It also allows operations on any bit in any location in memory.

The following is a summary of the Z80 instruction set and shows the assembly language mnemonic, the operation, the flag status, and gives comments on each instruction. The Z80 CPU Technical Manual (03-0029-01) and Assembly Longuage Programming Manual (03-0002-01) contain significantly more details for programming use.

The instructions are divided into the following categories:

- 🛛 8-bit loads

- 🗆 16-bit loads

- □ Exchanges, block transfers, and searches

- □ 8-bit arithmetic and logic operations

- 🛛 General-purpose arithmetic and CPU control

- □ 16-bit arithmetic operations

- Rotates and shifts

- □ Bit set, reset, and test operations

- [] Jumps

- □ Calls, returns, and restarts

- □ Input and output operations

A variety of addressing modes are implemented to permit efficient and fast data transfer between various registers, memory locations, and input/output devices. These addressing modes include:

- 🗇 Immediate

- □ Immediate extended

- L Modified page zero

- 🗇 Relative

- $\square$  Extended

- □ Indexed

- 🗆 Register

- II Register indirect

- 🗆 Implied

- 🗆 Bit

| 3-Bit<br>Load | Mnemonic                     | Symbolic<br>Operation      | s | z |        | F)<br>H | aga    | P/V | N | с | Opcode<br>78 543 210 Hex                         |        | No.of M<br>Cycles |         | Comments                            |

|---------------|------------------------------|----------------------------|---|---|--------|---------|--------|-----|---|---|--------------------------------------------------|--------|-------------------|---------|-------------------------------------|

| Froup         | LD r, r'<br>LD r, n          | r - r'<br>$r \leftarrow n$ | • |   | X<br>X |         | X<br>X | :   | • | : | 01 e r'<br>00 r 110<br>- n                       | 1<br>2 | 1<br>2            | 4<br>7  | <u>r, r' Reg.</u><br>000 B<br>001 C |

|               | LD r. (HL)<br>LD r. (IX+d)   | r = (HL)<br>r = (IX + d)   | : | : | X<br>X | :       | X<br>X | •   | : | : | 01 r 110<br>11 011 101 DD<br>01 r 101            | 3      | 2<br>5            | 7<br>19 | 010 D<br>011 E<br>100 H             |

|               | $LD r_{c} (IY + d)$          | $r \rightarrow (iY + d)$   | ٠ | • | X      | •       | x      | •   | • | ٠ | d<br>11 111 101 FD<br>01 r 110<br>d              | 3      | 5                 | 19      | 101 L<br>111 A                      |

|               | LD (HL), r<br>LD (IX + d), r | (HL) ← r<br>(IX + d) — r   | • | : | X<br>X | •       | X<br>X | :   | : | : | 01 110 r<br>11 011 101 DD<br>01 110 r            | 1<br>3 | <b>2</b><br>5     | 7<br>19 |                                     |

|               | LD (IY + d), r               | (I <b>Y</b> + d) - r       | • | • | Х      | •       | X      | •   | • | • | ←d→<br>11 111 101 FD<br>01 110 r<br>−d→          | 3      | 5                 | 19      |                                     |

|               | LD (HL), n                   | (HL) ⊷ n                   | • | ٠ | Х      | ٠       | X      | ٠   | ٠ | • | 00 110 110 36                                    | 2      | 3                 | 10      |                                     |

|               | I.D (I <b>X + d</b> ), n     | $a \rightarrow (b + XI)$   | ٠ | ٠ | х      | •       | X      | •   | • | • | - n →<br>11 311 101 DD<br>00 110 110 36<br>- d → | 4      | 5                 | 19      |                                     |

|               | LD (lY+d), n                 | (IY + d) — n               | • | • | X      | ٠       | X      | •   | • | ٠ | 11 111 101 FD<br>00 110 110 36<br>+ d →          | 4      | 5                 | 19      |                                     |

|               | LD A, (BC)                   | A (BC)                     |   |   | х      |         | х      |     |   | • | - p -<br>00 001 010 0A                           | 1      | 2                 | 7       |                                     |

|               | LD A. (DE)                   | $A \leftarrow (DE)$        | • | ٠ | х      | ٠       | Х      | ٠   | • | • | 00 GH 010 1A                                     | 1      | 2                 | 7       |                                     |

|               | LD A, (nn)                   | (מח) – A                   | • | • | x      | •       | X      | •   | • | • | 00 111 010 3A<br>- n -<br>- n -                  | 3      | 4                 | 13      |                                     |

|               | LD (BC) A                    | (BC) ~ A                   | • | • | Х      | ٠       | Х      | 9   | ٠ |   | 00 000 010 02                                    | 1      | 2                 | 7       |                                     |

|               | LD (DE), A                   | (DE) ~ A                   |   | ٠ | х      | ٠       | Х      | •   | ٠ | • | 00 010 010 12                                    | 1      | 2                 | 7       |                                     |

|               | LD (nn), A                   | (nn) ← Å                   | • | • | X      | •       | Х      | •   | • | • | 00 110 010 32                                    | 3      | 4                 | 13      |                                     |

|               | LD A, I                      | A ← 1                      | ı | ţ | X      | 0       | X      | IFF | 0 | • | 11 101 101 ED<br>01 010 111 57                   | 2      | 2                 | 9       |                                     |

|               | LD A. R                      | A ⊷ R                      | 1 | 1 | X      | Ç       | X      | IFF | 0 | • | 11 101 101 ED<br>01 011 111 5F                   | 2      | 2                 | 9       |                                     |

|               | LD I, A                      | 1 - A                      | • | • | Х      | ٠       | x      | ٠   | ٠ | ٠ | 11 101 101 ED<br>01 000 111 47                   | 2      | 2                 | 9       |                                     |

|               | LD R. A                      | R - A                      | • | • | x      | ٠       | X      | ٠   | • | • | 11 103 101 ED<br>01 001 111 4F                   | 2      | 2                 | 9       |                                     |

NOTES: if, if means any of the registers A. B. C. D. E. H. L. IFF the content of the interrupt enable flip dop. (IFF) is copied into the PV II.g. For an explanation of thig notation and symbols for memoria tables, see Symbolic Notation section following tables.

| 6-Bit Load<br>Group | Masmonic               | Symbolic<br>Operation                                                                          | 5         | 2     |        | H<br>H | ags    | P/V     | N     | с       |        | Opcode<br>78 543 210 1              |            | No.at<br>Bytes | No.at M<br>Cycles | No.ct T<br>States | Comments                                |

|---------------------|------------------------|------------------------------------------------------------------------------------------------|-----------|-------|--------|--------|--------|---------|-------|---------|--------|-------------------------------------|------------|----------------|-------------------|-------------------|-----------------------------------------|

|                     | LD dd, nn              | dd ← nn                                                                                        | •         | •     | х      | •      | X      | •       | •     | •       | (      | 00 dd0 001<br>← n →                 |            | 3              | 3                 | 10                | dd Pair<br>00 BC                        |

|                     | 10.19                  | 11                                                                                             |           |       | v      | _      | v      |         |       |         |        | ⊷ n →                               | ~~         |                |                   |                   | 01 DE                                   |

|                     | LD IX, nn              | IX — nn                                                                                        | •         | •     | x      | •      | Х      | *       | •     | •       |        | 1) 011 101 1<br>90 100 001          |            | 4              | 4                 | 14                | 10 HL<br>11 SP                          |

|                     | 1017                   | W                                                                                              | _         |       | v      | _      | v      |         |       | _       |        | - n -<br>- n                        |            |                |                   |                   |                                         |

|                     | LD IY, nn              | IY nn                                                                                          | •         | •     | x      | •      | X      | •       | •     | •       |        | 11 111 101 :<br>XG 100 001          |            | 4              | 4                 | 14                |                                         |