# Microdata

## Microdata MICRO-ONE USER'S MANUAL

# MICRO-ONE

## **USER'S MANUAL**

## UM 20001506 OCTOBER, 1975

#### **PROPRIETARY INFORMATION**

The information contained herein is proprietary to and considered a trade secret of Microdata Corporation and shall not be reproduced in whole or part without the written authorization of Microdata Corporation.

98820 75 1011A © 1975 Microdata Corporation TM Trademark of Microdata Corporation Printed in U.S.A.

## **Microdata**

Microdata Corporation 17481 Red Hill Avenue Irvine, California 92714 (714) 540-6730 TWX: 910-595-1764

## MICRO ONE USER'S MANUAL

### TABLE OF CONTENTS

|           |                                                     | Page |

|-----------|-----------------------------------------------------|------|

| SECTION 1 | ARCHITECTURE                                        |      |

| 1.0       | SYSTEM ORGANIZATION                                 | 1-1  |

| 1.1       | General Characteristics                             | 1-1  |

| 1.2       | Registers and File                                  | 1-6  |

|           |                                                     | 1-6  |

| 1.2.1     | T Register                                          |      |

| 1.2.2     | M Register                                          | 1-7  |

| 1.2.3     | N Register                                          | 1-7  |

| 1.2.4     | L Register                                          | 1-7  |

| 1.2.5     | U Register                                          | 1-7  |

| 1.2.6     | R Register                                          | 1-7  |

| 1.2.7     | LINK Register                                       | 1-7  |

| 1.2.8     | I/O Control Register                                | 1-7  |

| 1.2.9     | File Registers                                      | 1-8  |

| 1.3       | •                                                   | 1-8  |

|           | Memory Descriptions                                 |      |

| 1.3.1     | Core Memory                                         | 1-8  |

| 1.3.2     | MOS Memory                                          | 1-9  |

| 1.3.3     | Control Memory                                      | 1-9  |

| 1.3.4     | Memory Busy Delays                                  | 1-9  |

| 1.3.5     | Memory Data Delays                                  | 1-9  |

| 1.3.6     | Read-Only Memory Delays                             | 1-9  |

| 1.4       | Status and Condition Flags                          | 1-10 |

| 1.4.1     | Internal Status                                     | 1-10 |

| 1.4.2     | Condition Flags                                     | 1-10 |

| 1.5       | Byte I/O Interface                                  | 1-11 |

| 1.5.1     | Byte I/O Bus                                        | 1-11 |

| 1.6       | -                                                   | 1-11 |

|           | External Priority Interrupts                        |      |

| 1.7       | Real-Time Clock                                     | 1-13 |

| 1.8       | Power-Fail/Automatic Restart                        | 1-13 |

| 1.9       | Arithmetic Functions                                | 1-14 |

|           |                                                     |      |

|           |                                                     |      |

| SECTION 2 | MICROCOMMAND REPERTOIRE                             |      |

| 2.0       | GENERAL                                             | 2-1  |

| 2.1       | Command Formats                                     | 2-1  |

| 2.1.1     | Literal Commands                                    | 2-1  |

| 2.1.2     | Operate Commands                                    | 2-1  |

| 2.1.3     | Execute Command                                     | 2-2  |

| 2.1.4     | Formats for Execute Commands                        | 2-2  |

|           |                                                     |      |

| 2.1.5     | Literal Commands                                    | 2-3  |

| 2.1.6     | Operate Commands                                    | 2-3  |

| 2.1.7     | Terms and Symbols Used in the Command Descriptions  | 2-4  |

| 2.2       | Microcommands - Formats, Descriptions, and Examples | 2-4  |

| 2.2.1     | LT Load T                                           | 2-4  |

| 2.2.2     | LM Load M                                           | 2-5  |

| 2.2.3     | LN Load N                                           | 2-5  |

| 2.2.4     | LU Load U                                           | 2-6  |

| 2.2.5     | LZ Load Zero Control                                | 2-6  |

|           |                                                     |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LS Load Seven Control<br>JP Jump<br>L Register Organization<br>LF Load File<br>AF Add to File<br>TZ Test If Zero<br>TN Test If Not Zero<br>CP Compare<br>K Control<br>Standard Output Functions<br>Standard Input Functions<br>A Add<br>S Subtract<br>R Read Memory W Write Memory<br>C Copy<br>O Or                                                                                                                                        | 2-7<br>2-8<br>2-10<br>2-10<br>2-11<br>2-13<br>2-14<br>2-15<br>2-17<br>2-17<br>2-23<br>2-26<br>2-28<br>2-33<br>2-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| X Exclusive Or                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-37<br>2-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-39<br>2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| E Execute                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MICRO-ONE I/O AND MEMORY INTERFACE<br>General Discussion<br>I/O Organization<br>Serial I/O Interface<br>Byte I/O Interface<br>Breasant Controlled I/O                                                                                                                                                                                                                                                                                       | 3-1<br>3-1<br>3-1<br>3-1<br>3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Direct Memory Access Port                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BYTE I/O INTERFACE<br>Introduction<br>Byte I/O Bus<br>Input Data Lines<br>Output Data Lines<br>Output Control Lines<br>Output Control Lines<br>Control Lines IO1X/ through IO3X/<br>Lines CPH1 and CPH2/.<br>Control Line MRST/<br>Control Line PROT/, PRIN/<br>Spare Lines<br>Control Line SELO/, SELI/.<br>Byte I/O Fundamentals<br>Device Addresses<br>Device Orders<br>Status Bytes<br>Function Bytes<br>Byte I/O Operations and Timing | $\begin{array}{c} 4-1 \\ 4-1 \\ 4-1 \\ 4-1 \\ 4-3 \\ 4-3 \\ 4-4 \\ 4-5 \\ 4-5 \\ 4-5 \\ 4-5 \\ 4-6 \\ 4-7 \\ 4-9 \\ 4-9 \\ 4-9 \\ 4-9 \\ 4-10 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                             | JP Jump<br>L Register Organization<br>LF Load File<br>AF Add to File<br>TZ Test If Zero<br>TN Test If Not Zero<br>CP Compare<br>K Control<br>Standard Output Functions<br>Standard Input Functions<br>Standard Input Functions<br>Standard Input Functions<br>A Add<br>S Subtract<br>R Read Memory W Write Memory<br>C Copy<br>0 Or<br>X Exclusive Or<br>N And<br>H Shift<br>E Execute<br>MICRO-ONE I/O AND MEMORY INTERFACE<br>General Discussion<br>I/O Organization<br>Serial I/O Interface<br>Byte I/O Interface<br>Program-Controlled I/O<br>Concurrent I/O<br>External Priority Interrupts<br>Direct Memory Access Port<br>BYTE I/O INTERFACE<br>Introduction<br>Byte I/O Bus<br>Input Data Lines<br>Output Data Lines<br>Output Data Lines<br>Output Control Lines<br>Control Line SELO/, SELI/.<br>Byte I/O Fundamentals<br>Device Addresses<br>Device Orders<br>Status Bytes |

.

ii

|                    |                                               | Page       |

|--------------------|-----------------------------------------------|------------|

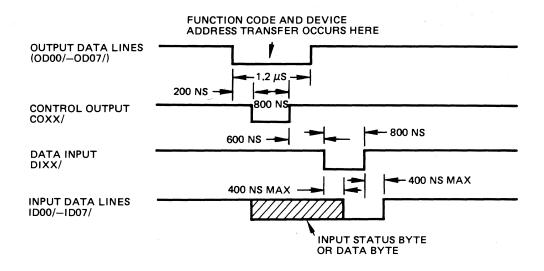

| 4.4.1              | Program Controlled I/O Operations             | 4-10       |

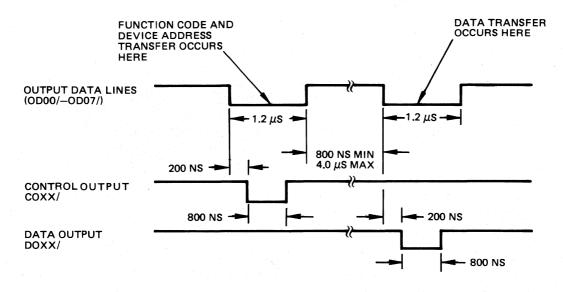

| 4.4.1.1            | Address/Order Phase                           | 4-11       |

| 4.4.1.2            | Transfer Phase                                | 4-12       |

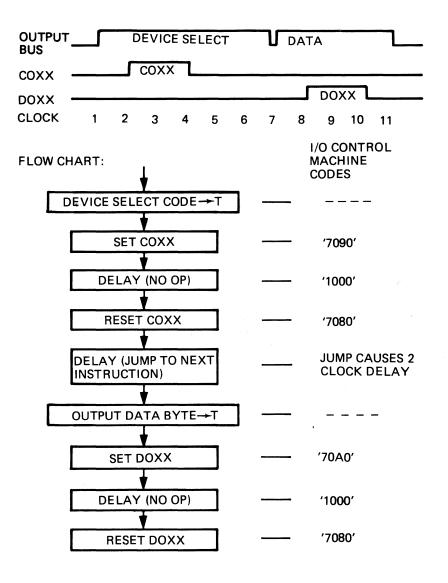

| 4.4.1.3            | Data Output Operations                        | 4-12       |

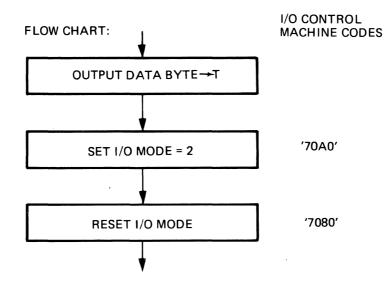

| 4.4.1.4            | Function Output Operations                    | 4-12       |

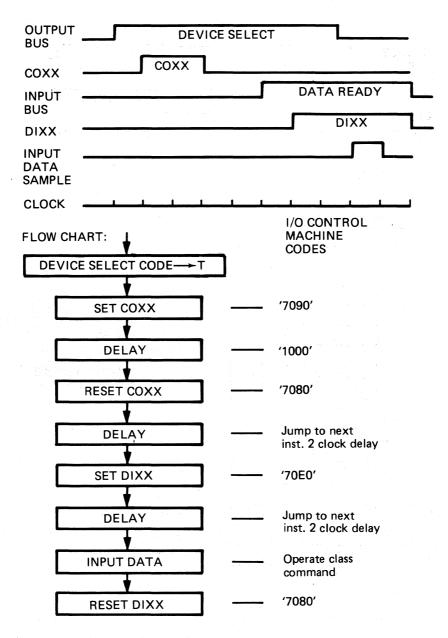

| 4.4.1.5            | Data Input Operations                         | 4-13       |

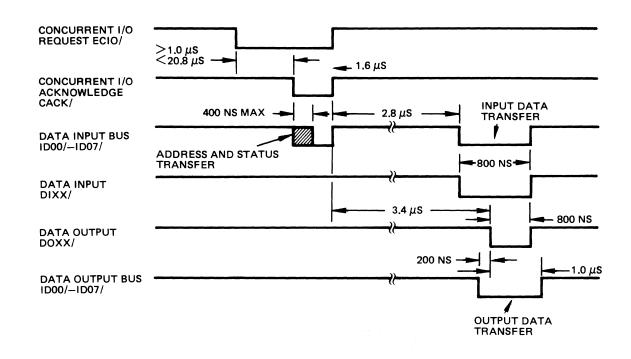

| 4.5                | Concurrent I/O Operation                      | 4-14       |

| 4.5.1              | Concurrent I/O Timing                         | 4-14       |

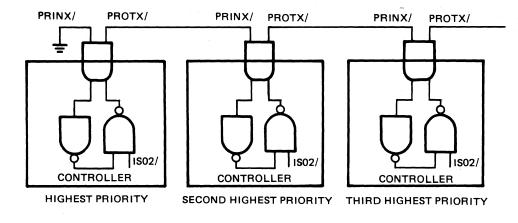

| 4.6                | External Interrupt Operation                  | 4-16       |

| 4.6.1              | Priority Determination                        | 4-17       |

| 4.6.2              | External Interrupt Requests                   | 4-18       |

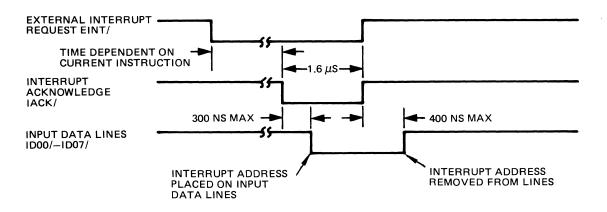

| 4.6.3              | Interrupt Sequence and Timing                 | 4-18       |

|                    | Interrope bequence and immig                  |            |

| SECTION 5          | MICRO-ONE CPU READ/WRITE MEMORY INTERFACE     |            |

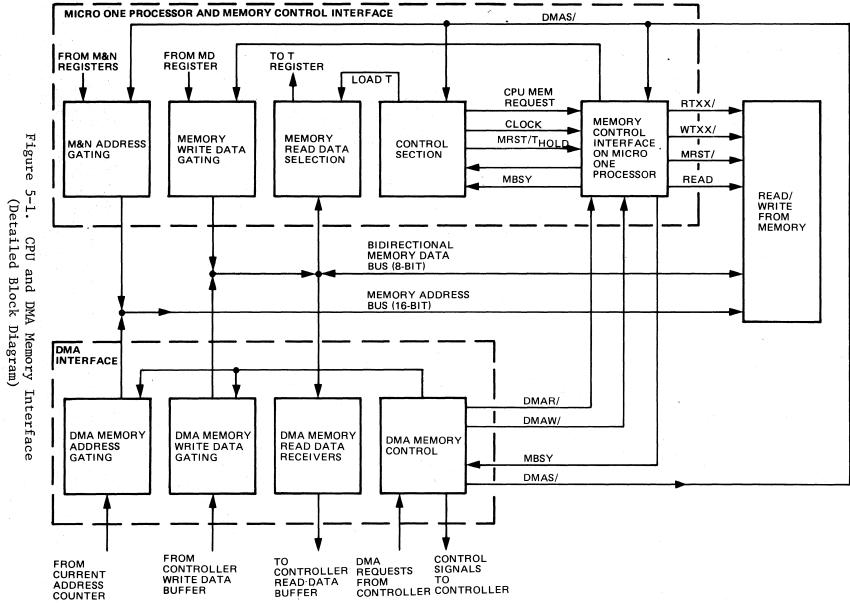

| 5.1                | Processor and Memory Interface                | 5-1        |

| 5.1.1              | Control Section                               | 5-1        |

| 5.1.2              | Memory Read Data Selection Logic              | 5-3        |

| 5.1.3              | Memory Write Data Gating Logic                | 5-3        |

| 5.1.4              | M and N Register Address Gating Logic         | 5-3        |

| 5.2                | Memory Control Interface                      | 5-3        |

| CECHTON (          | DIDECH MENORY ACCECC DODM                     |            |

| SECTION 6          | DIRECT MEMORY ACCESS PORT                     | 6-1        |

| 6.1                | Introduction                                  | 6-1<br>6-1 |

| 6.2                | Functional Description                        | 6-3        |

| 6.2.1              | DMA Interface                                 | 6-3<br>6-3 |

| 6.2.2<br>6.2.3     | DMA Memory Control Logic                      | 6-4        |

|                    | DMA Memory Read Data Receivers                | 6-4<br>6-4 |

| 6.2.4<br>6.2.5     | DMA Memory Write Gating Logic                 |            |

|                    | DMA Memory Address Gating Logic               | 6-4<br>6-4 |

| 6.3<br>6.3.1       | DMA Port/Memory Control Interface Timing      | 6-5        |

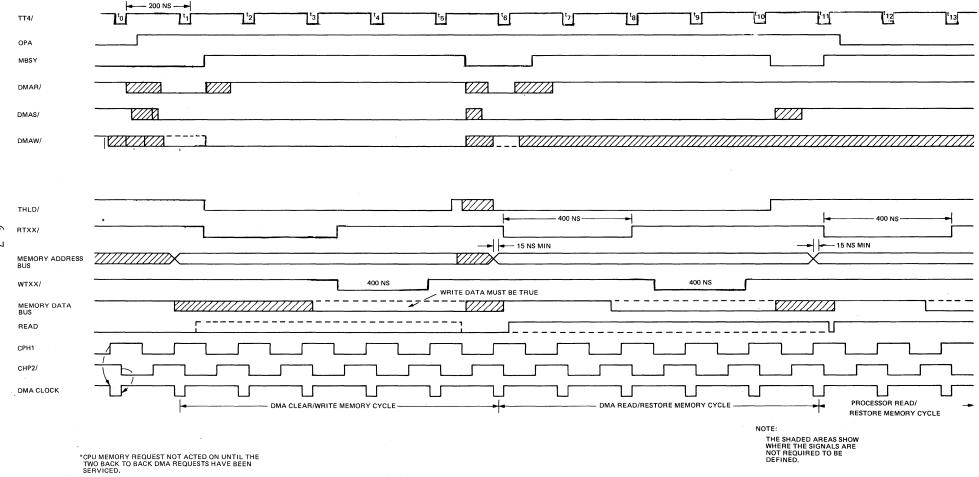

| 6.3.2              | Clock Signals                                 | 6-5<br>6-5 |

| 6.3.2.1            | DMA Port Signals                              | 6-5        |

|                    | DMA Request (DMAR/)                           | 6-5<br>6-5 |

| 6.3.2.2            | DMA Write (DMAW/)                             | 6-6        |

| 6.3.2.3<br>6.3.2.4 | Memory Busy (MBSY)<br>Memory Addresses        | 0-0<br>6-6 |

| 6.3.2.5            | Write Data                                    | 6-6        |

| 6.3.2.6            | Read Data                                     | 6-8        |

| 0.J.2.0            | Reau Data                                     | 0-0        |

| SECTION 7          | SERIAL I/O INTERFACE                          |            |

| 7.1                | Introduction                                  | 7-1        |

| 7.2                | Use as Teletype Controller                    | 7-1        |

| 7.2.1              | General Operation                             | 7-1        |

| 7.2.2              | Character Assembly and Disassembly            | 7-1        |

| 7.2.3              | Serial I/O Instructions                       | 7-4        |

| 7.2.4              | Teletype Interface Connection                 | 7-4        |

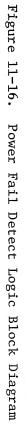

| SECTION 8          | MICRO-ONE BACKPLANE CONNECTOR SIGNAL LIST     |            |

| 8.1                | I/O Controllers and DMA Interface Signal List | 8-1        |

| 8.2                | Serial TTY (J2)                               | 8-1        |

| 8.3                | Front Panel (Cable) Connector (J3)            | 8-1        |

|                    |                                               |            |

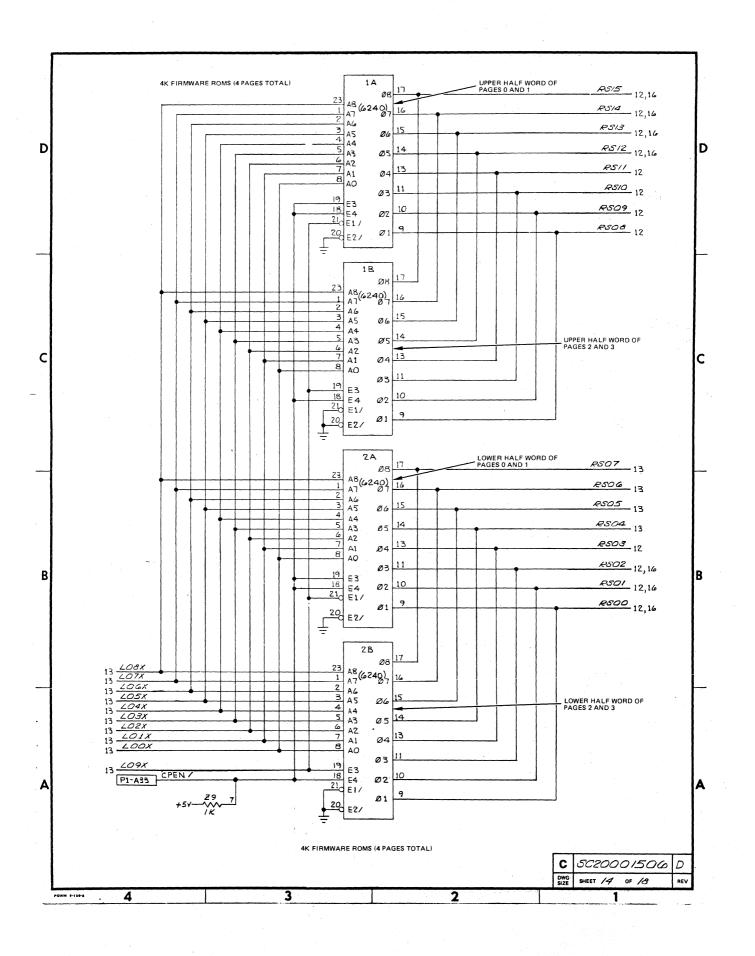

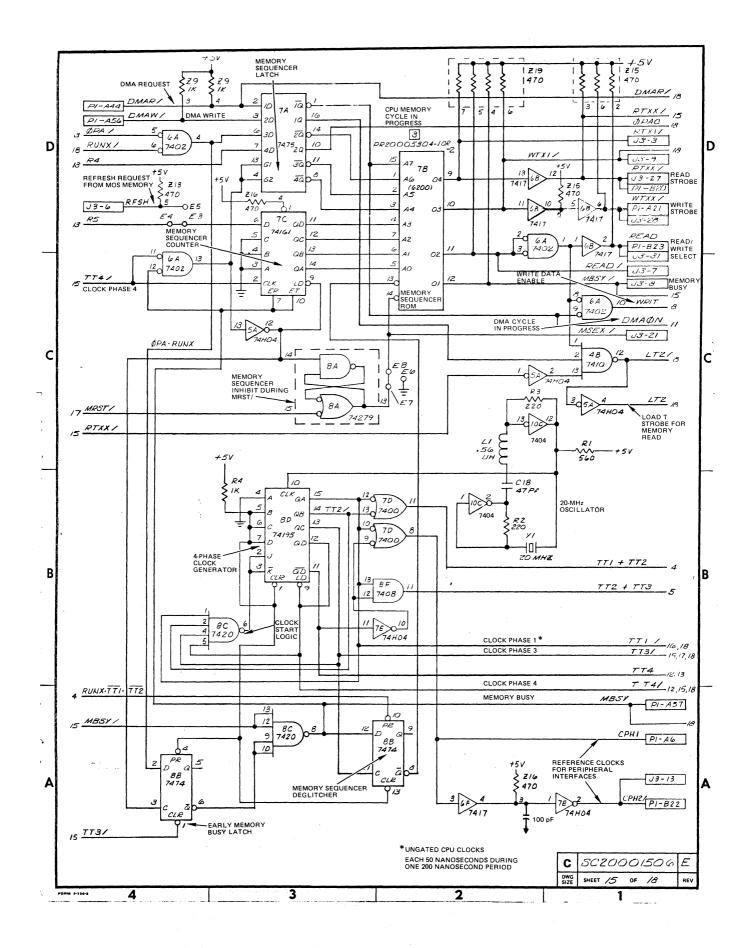

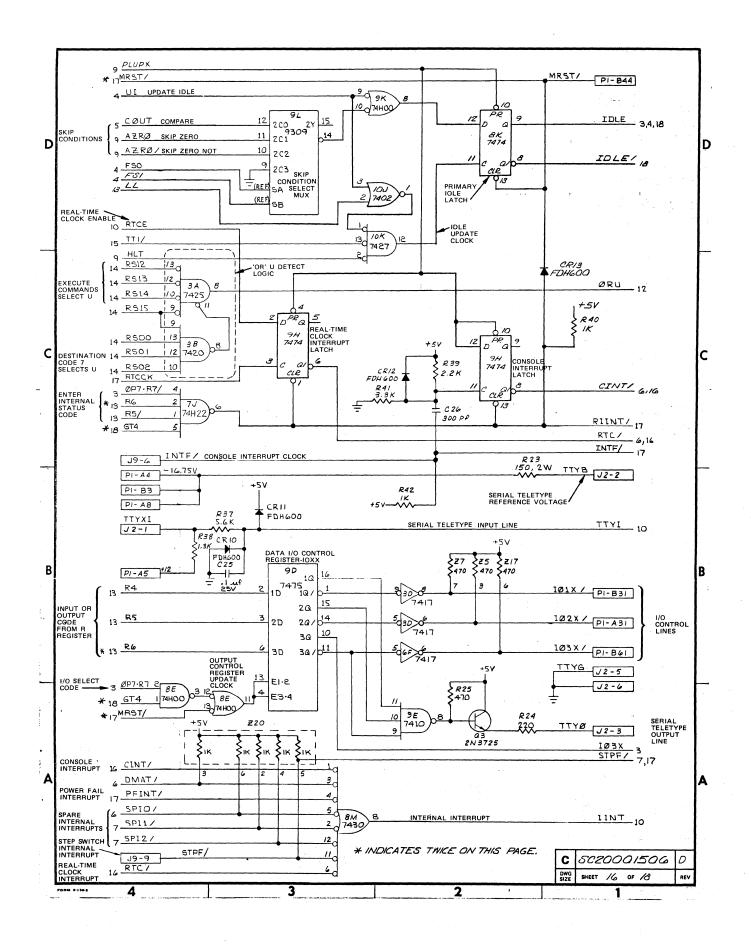

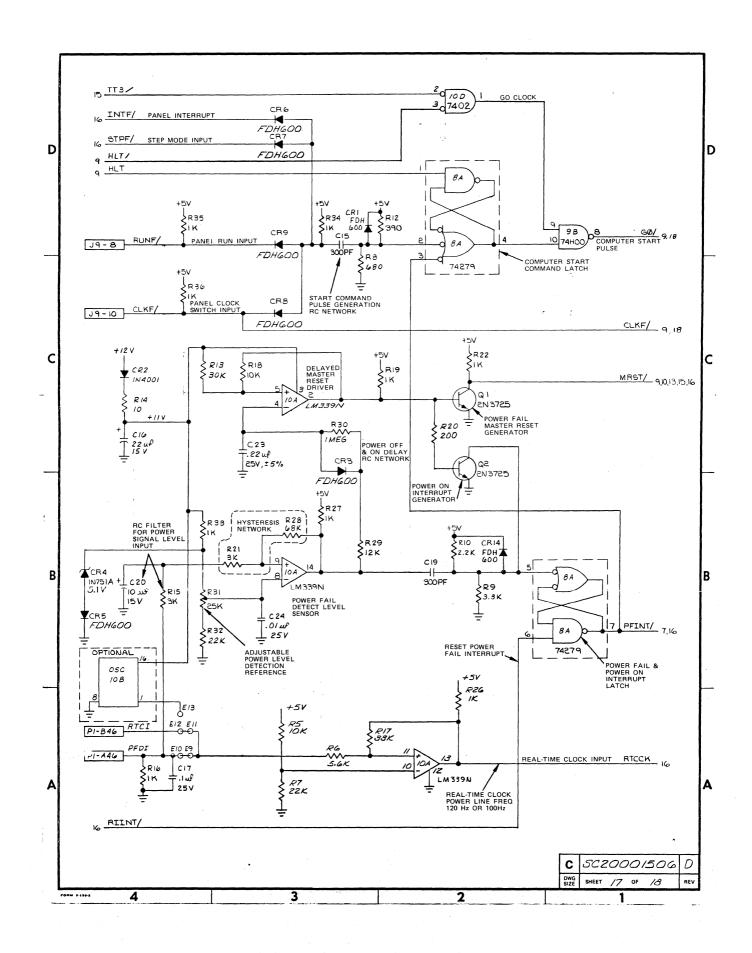

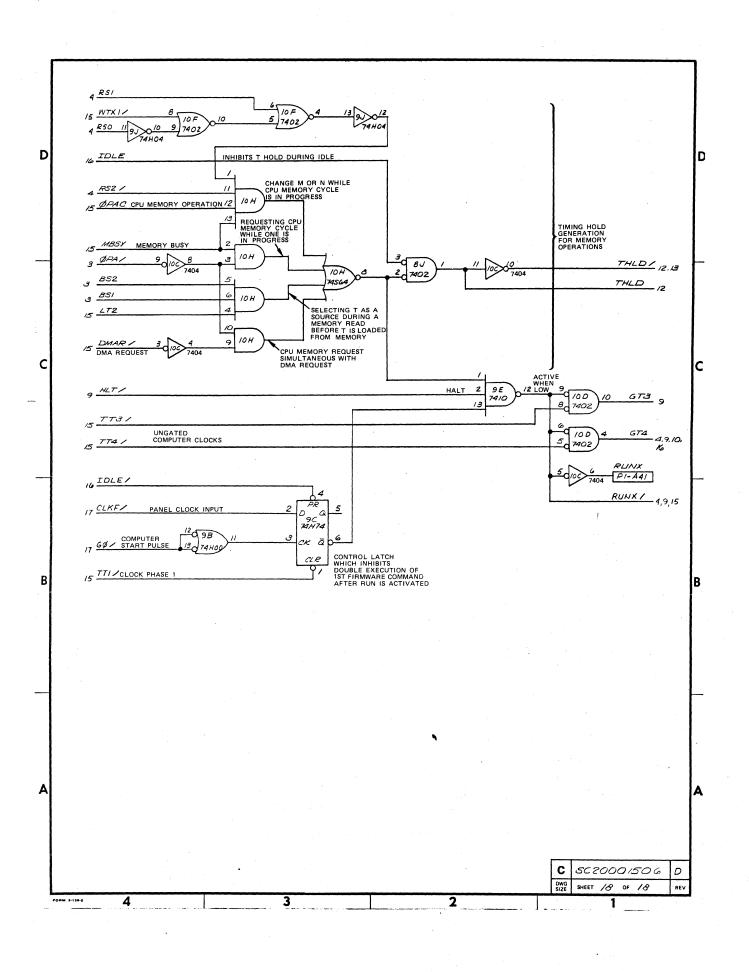

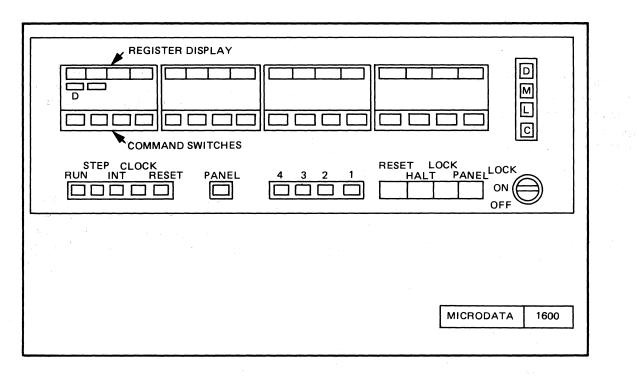

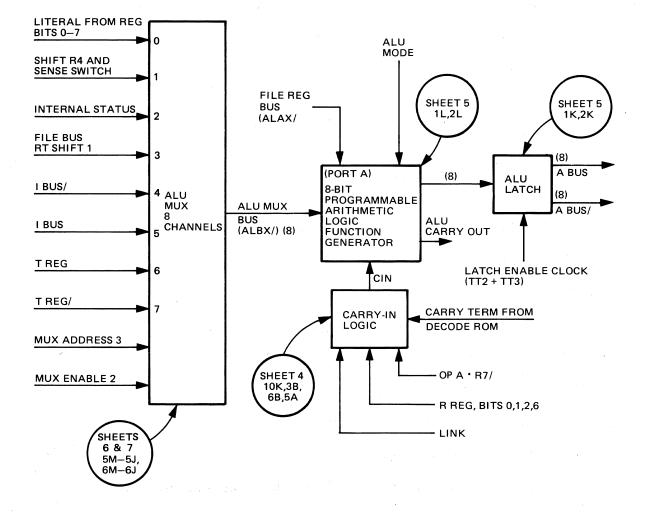

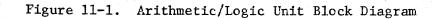

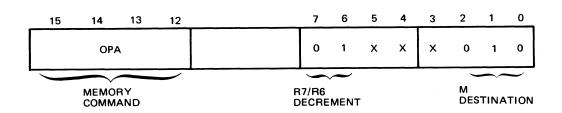

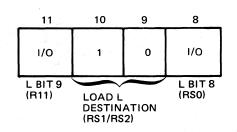

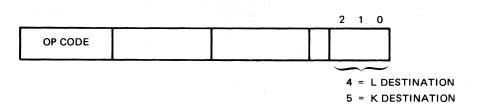

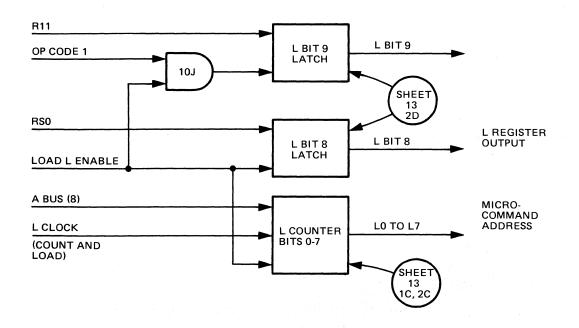

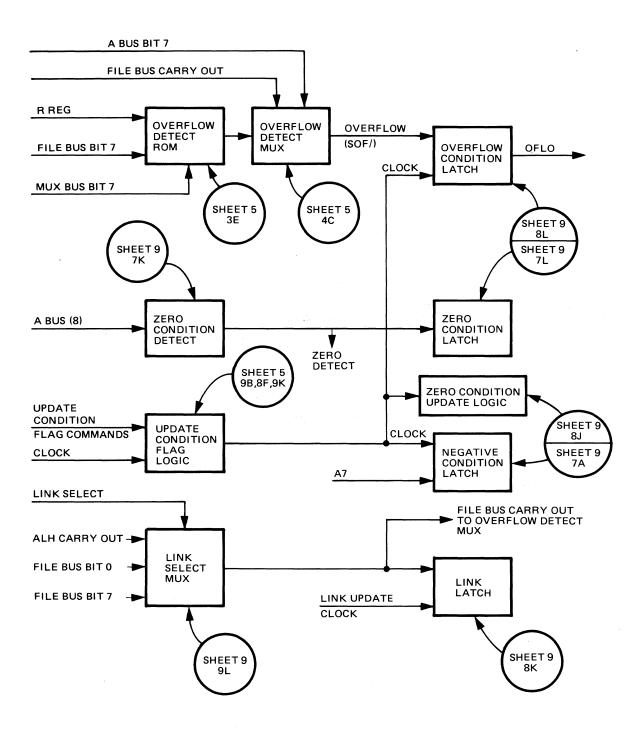

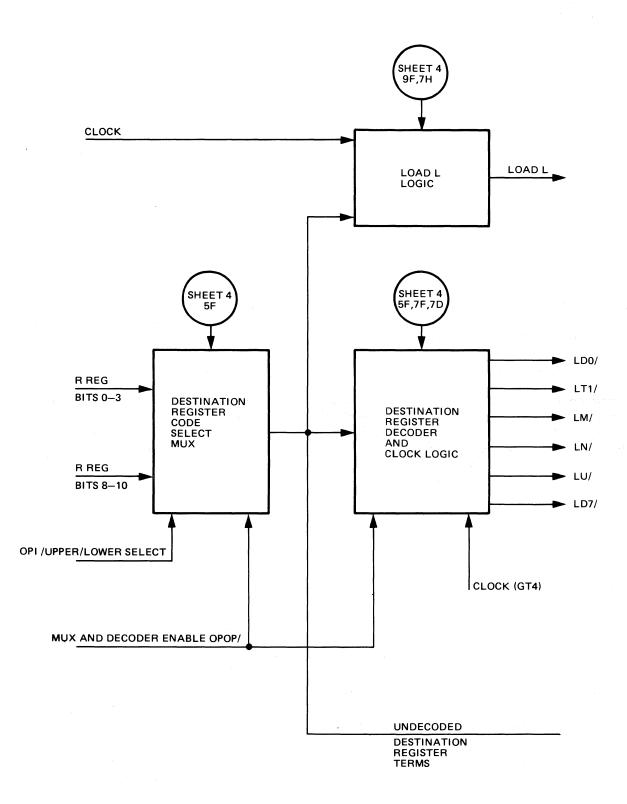

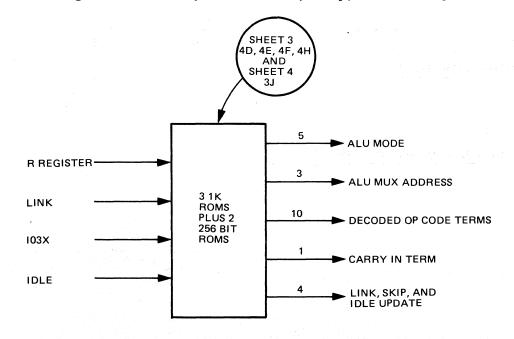

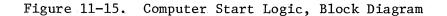

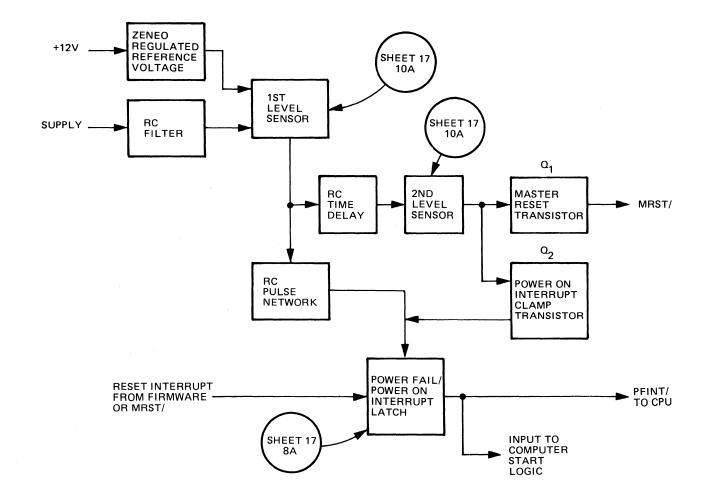

SECTION 9 I/O INTERFACE SIGNAL GLOSSARY OPERATOR CONTROLS SECTION 10 10 - 110.1 Consoles System Console (Standard 1600 System Console) 10 - 110.1.1 10 - 110.1.2 Basic Console Displays on System Console 10 - 110.2 10 - 310.2.1 Data Display 10.2.2 10 - 3Run 10 - 310.2.3 Halt 10.2.4 10 - 3Lock 10 - 310.2.5 Scan 10.2.6 Pane1 10 - 310 - 310.2.7 Address Stop 10.3 Switches and System Console 10 - 310.3.1 Display Selector 10 - 310 - 410.4 Command Switches 10.4.1 10 - 4Panel Switch 10.4.2 Sense Switches 10 - 410.4.3 10 - 4Run 10.4.4 10 - 4Step 10 - 410.4.5 Interrupt 10 - 410.4.6 Clock 10.4.7 10 - 5Reset 10.4.8 On'Off-Lock 10 - 510.5 10 - 5Address Sync 10.6 Register Display and Entry 10-510.6.1 Display 10 - 510.6.2 Enter 10 - 510.7 Operating Procedures -- System Console 10 - 6SECTION 11 MICRO ONE CPU OPERATIONAL DESCRIPTION 11.1 General 11-1 11.1.1 Arithmetic Logic Unit and Multiplexer 11-1 11.1.2 Carry In 11 - 3T. Register 11.2 11 - 711.3 File Registers 11-9 R and U Registers 11.4 11-9 11.5 L Register 11-9 11.5.1 L or K Destination in an Operate Command 11-12 11.6 Condition and Link Logic 11 - 1411.7 Memory Address Registers (M and N) 11 - 1411.8 Destination Register Clock Logic 11 - 1411.9 Command Decode ROMs 11 - 1811.10 Programmed Input/Output 11 - 1911.11 11-19 Interrupts 11.12 Memory Sequencer (Core Memory Version) 11-22 11.13 Computer Clock and Run Control 11 - 2611.14 Run/Halt Control 11 - 2611-29 11.15 Computer Start Logic 11-29 Automatic Power Fail and Power on Detection Function 11.16

SECTION 12

SCHEMATICS

#### LIST OF ILLUSTRATIONS

## Figure No.

## <u>Title</u>

Page

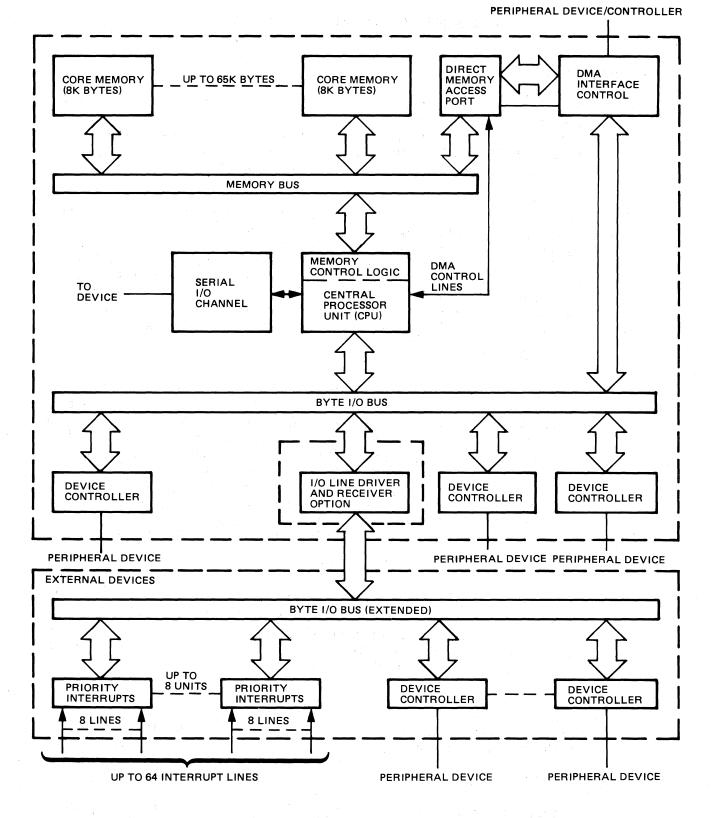

| 1-1   | Micro-One Block Diagram                        | 1-2   |

|-------|------------------------------------------------|-------|

| 1-2   | Backplane Interconnections                     | 1-12  |

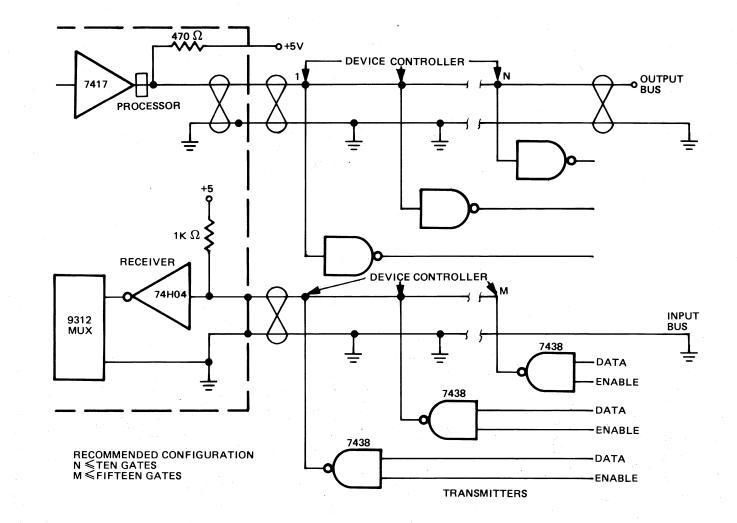

| 3-1   | Typical Micro-One Series I/O Configuration     | 3-2   |

| 4-1   | Micro-One I/O Bus Lines                        | 4-2   |

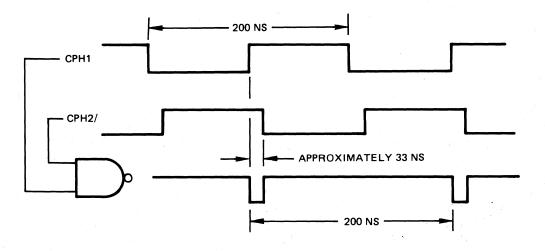

| 4-2   | Relationship of Control Signals CPH1 and CPH2/ | 4-4   |

| 4-3   | Data or Function Output Timing                 | 4-12  |

| 4-4   | Data or Status Input Timing                    | 4-14  |

| 4-5   | Concurrent I/O Timing                          | 4-15  |

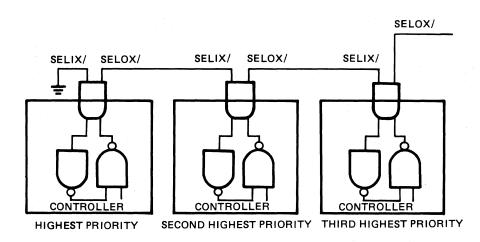

| 4-6   | Typical Priority Scheme                        | 4-17  |

| 4-7   | Typical Selection Acknowledgment Scheme        | 4-18  |

| 4-8   | External Interrupt Timing                      | 4-19  |

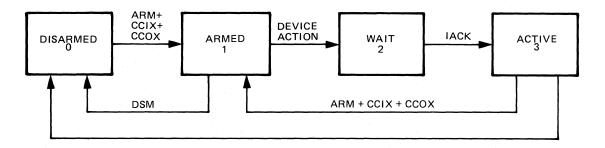

| 4-9   | Interrupt Sequencer States                     | 4-20  |

| 5-1   | CPU and DMA Memory Interface                   | 5-2   |

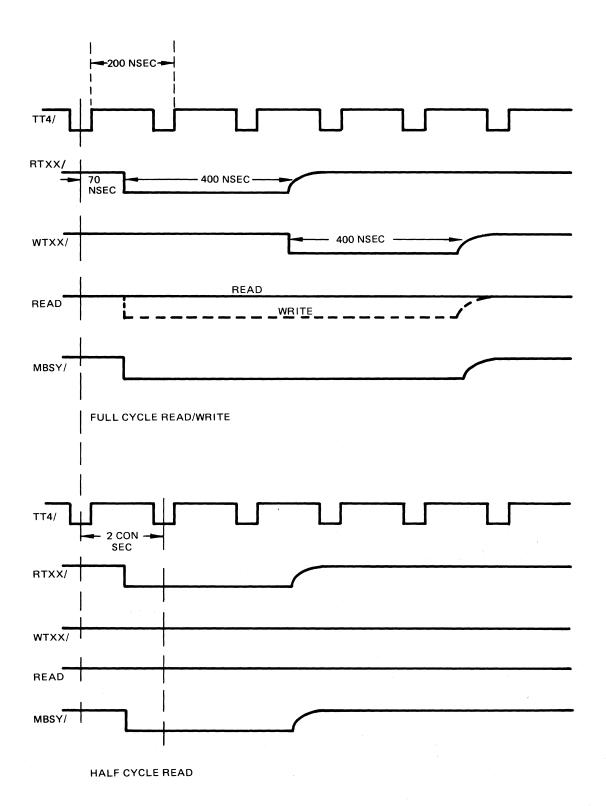

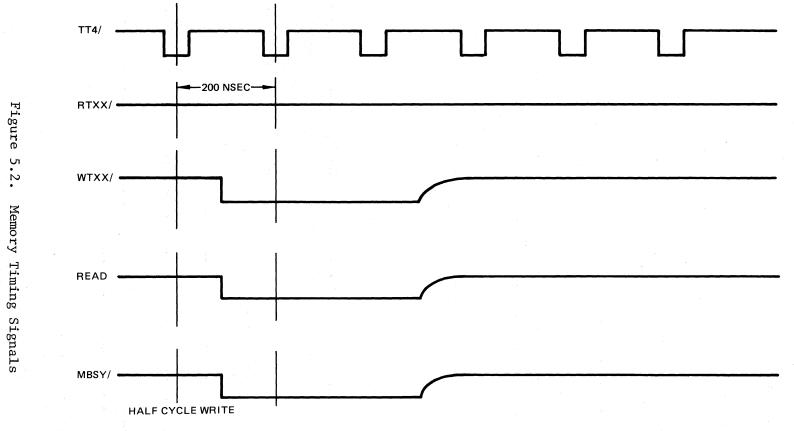

| 5-2   | Half Cycle Read                                | 5-5   |

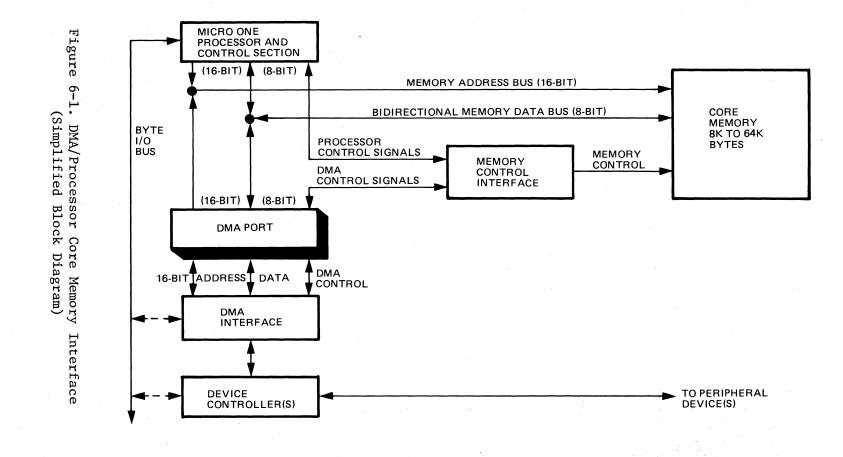

| 6-1   | DMA/Processor Core Memory Interface            | 6-2   |

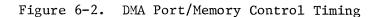

| 6-2   | DMA Port/Memory Control Timing                 | 6-7   |

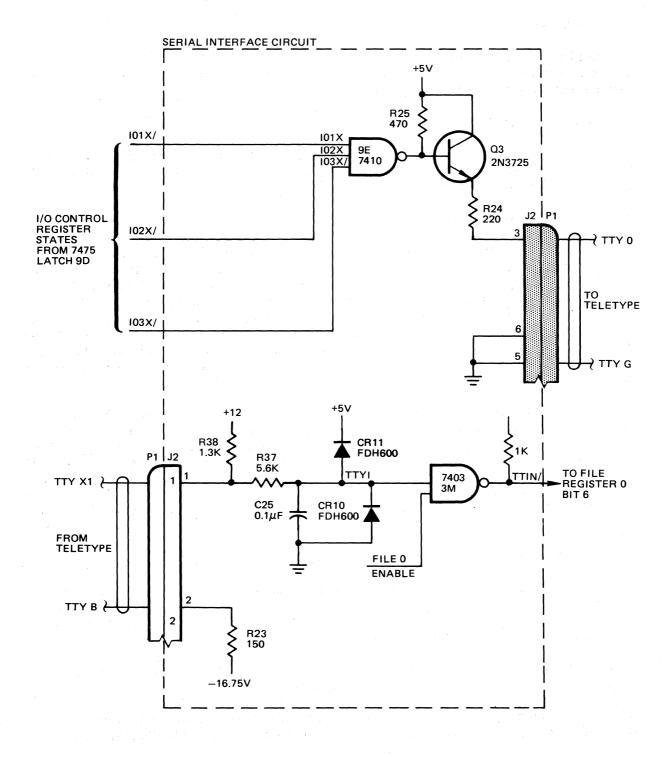

| 7-1   | Serial I/O Interface Circuit                   | 7-2   |

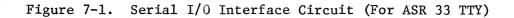

| 7-2   | Serial I/O Timing                              | 7-3   |

| 10-1  | MICRO 1600 System Control                      | 10-2  |

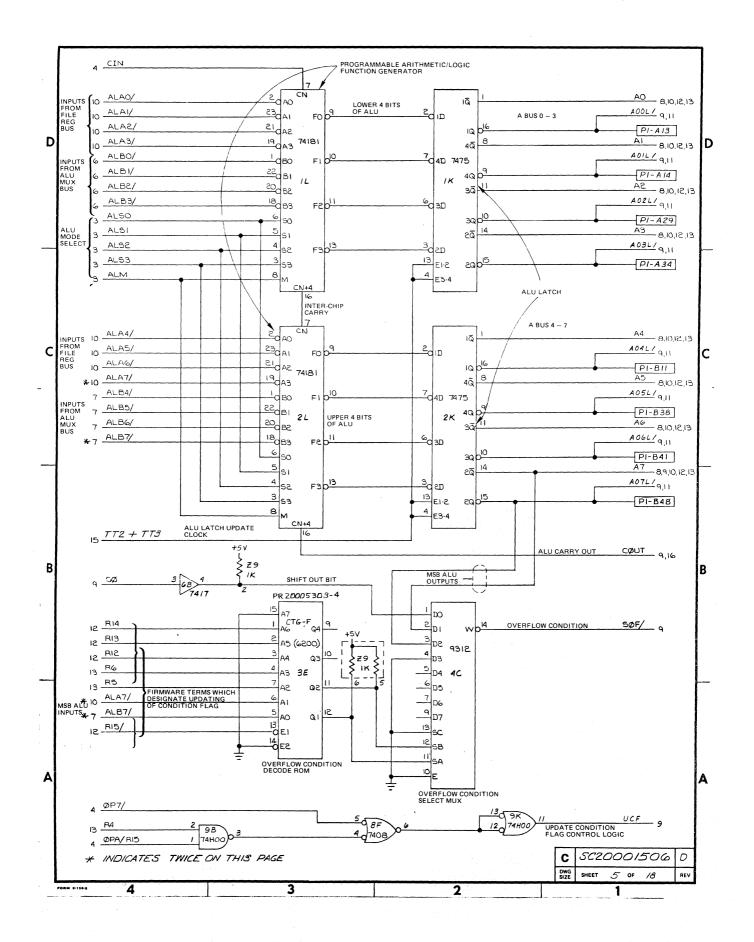

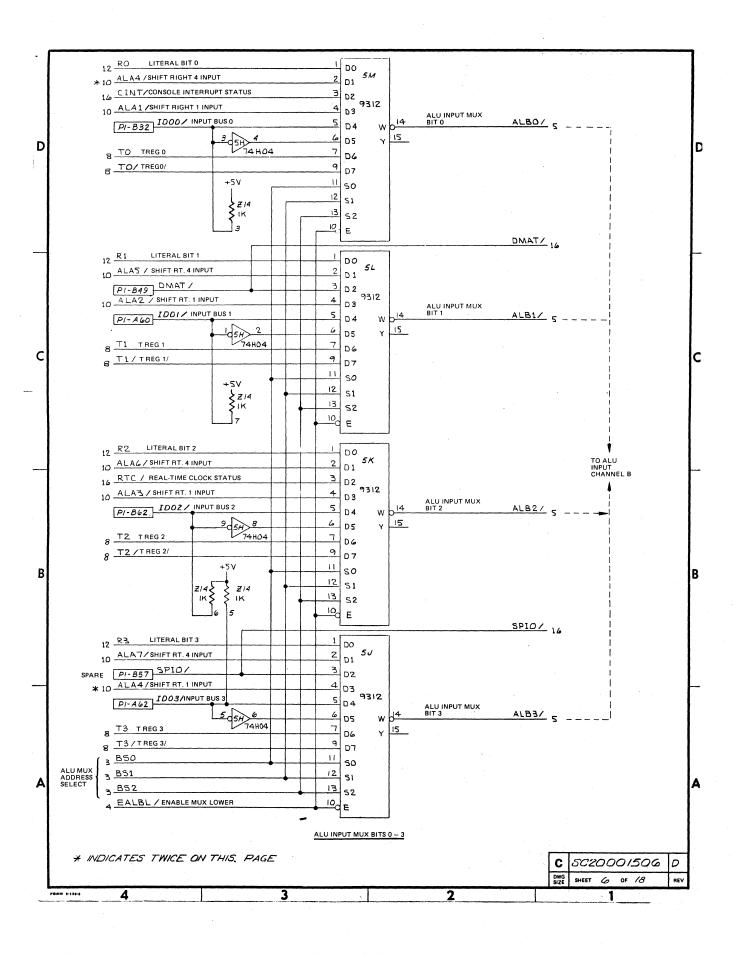

| 11-1  | Arithmetic/Logic Unit Block Diagram            | 11-2  |

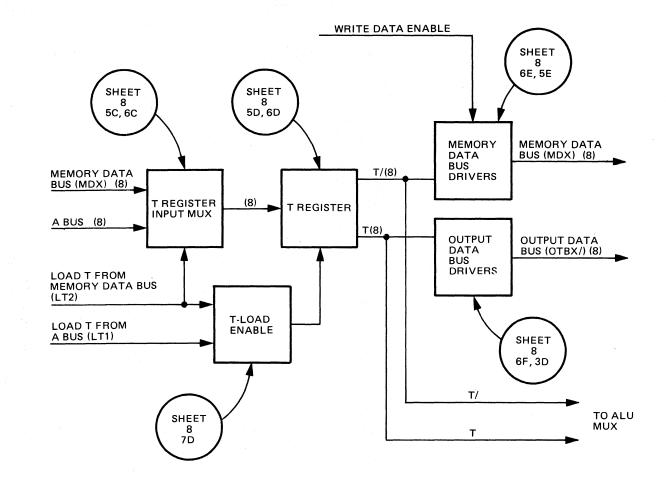

| 11-2  | 2-Register Block Diagram                       | 11-8  |

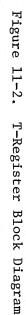

| 11-3  | Fill Registers Block Diagram                   | 11-10 |

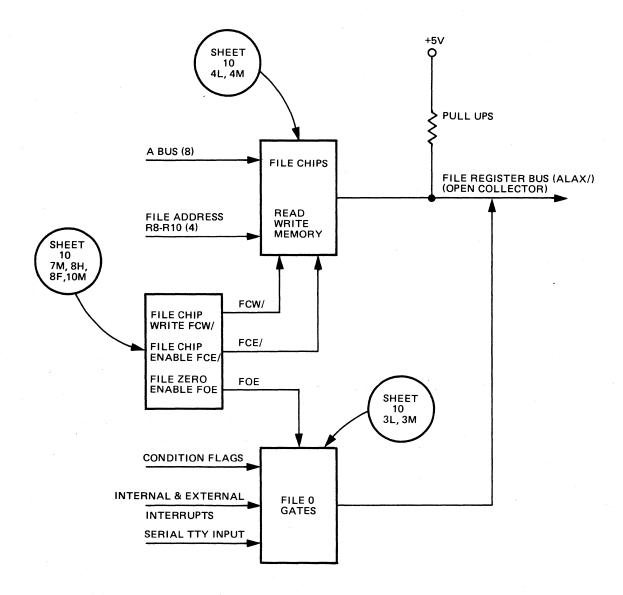

| 11-4  | R and U Register Block Diagram                 | 11-11 |

| 11-5  | L Register Block Diagram                       | 11-13 |

| 11-6  | Condition & Link Register                      | 11-15 |

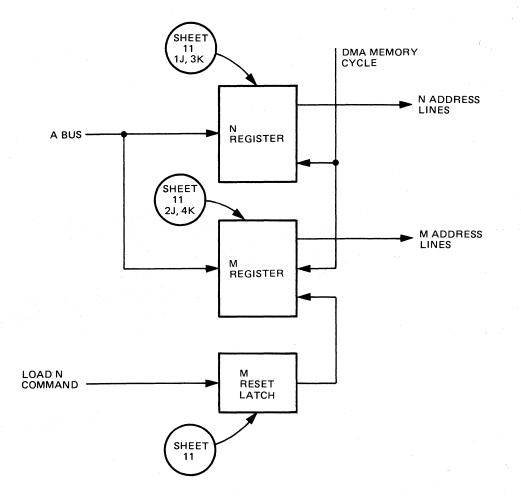

| 11-7  | M and N Address Registers                      | 11-16 |

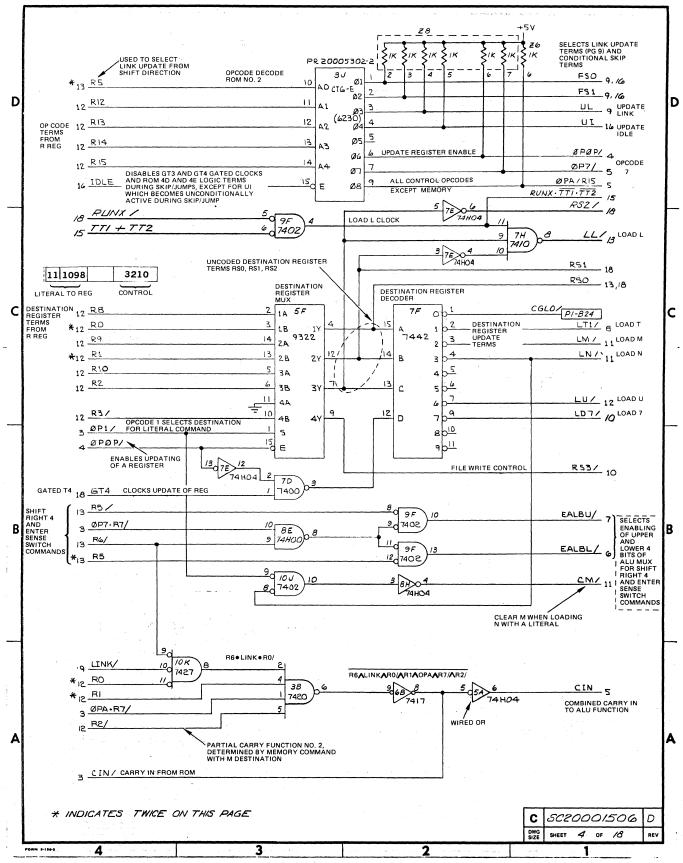

| 11-8  | Destination Register Clock Logic               | 11-17 |

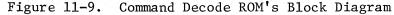

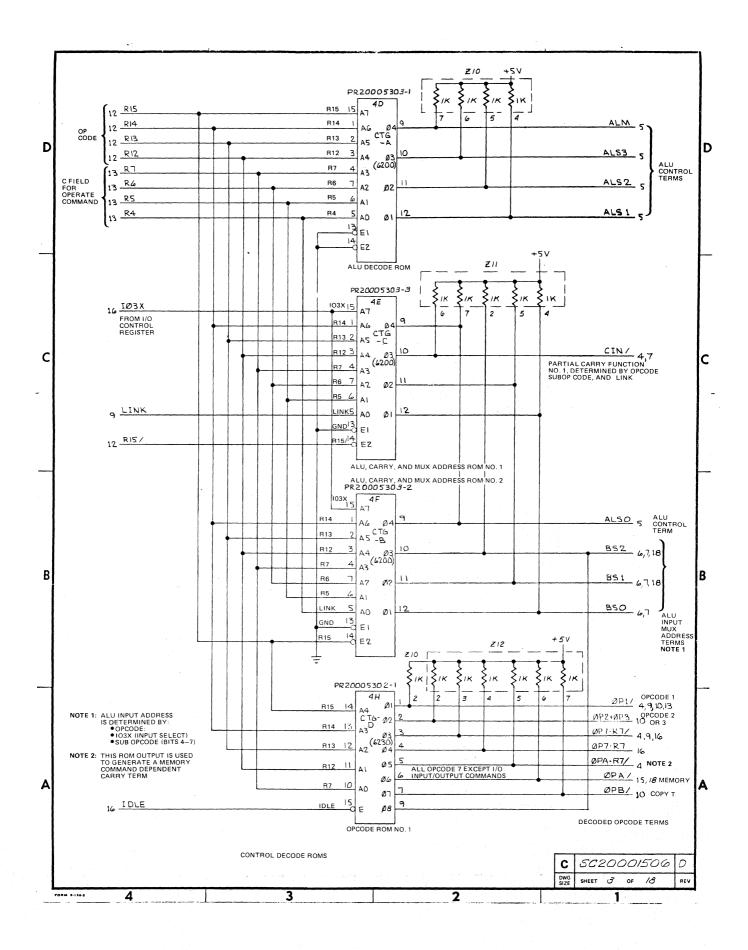

| 11-9  | Command Decode ROM's Block Diagram             | 11-18 |

| 11-10 | Programmed I/O Block Diagram                   | 11-20 |

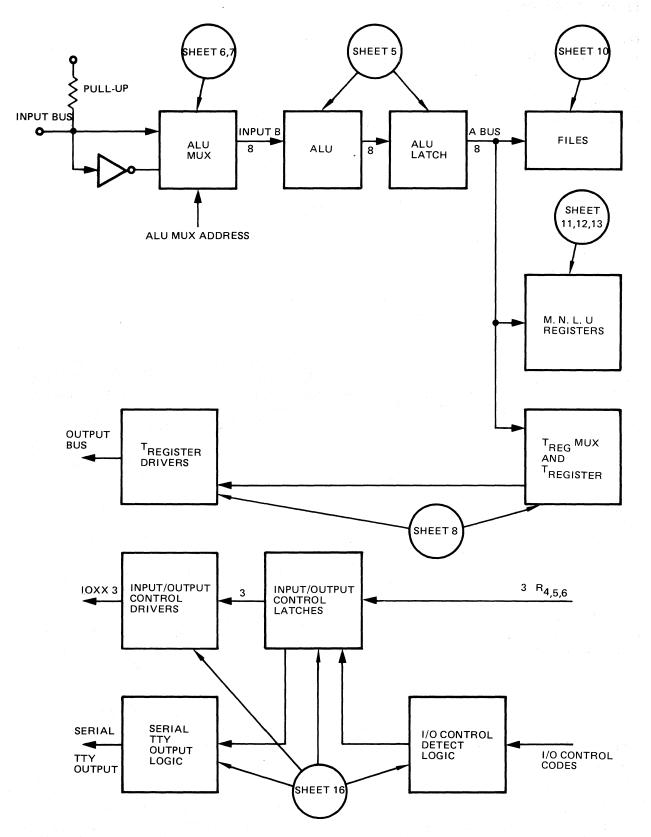

| 11-11 | Interrupts                                     | 11-21 |

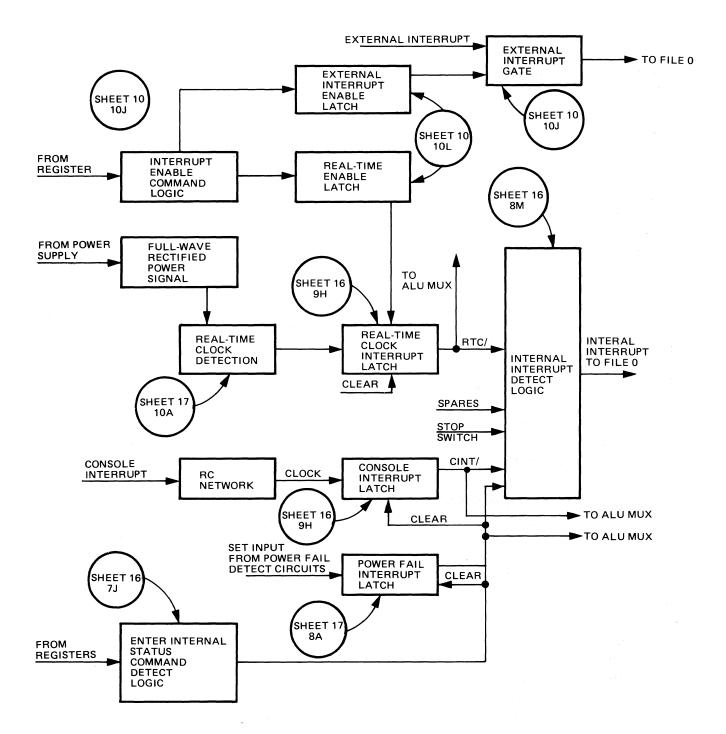

| 11-12 | Memory Controller Block Diagram                | 11-23 |

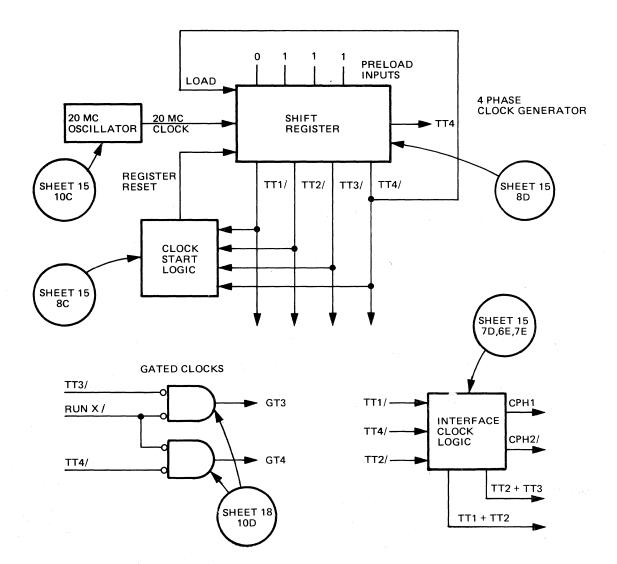

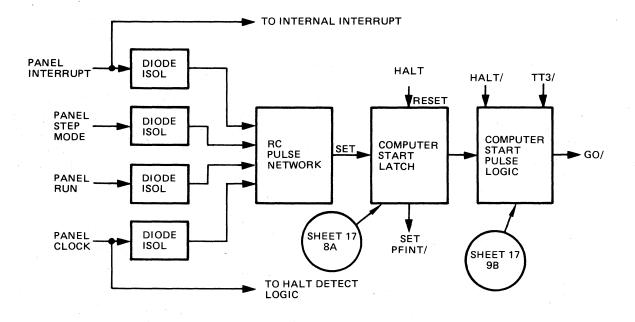

| 11-13 | Clock Generation Logic, Block Diagram          | 11-27 |

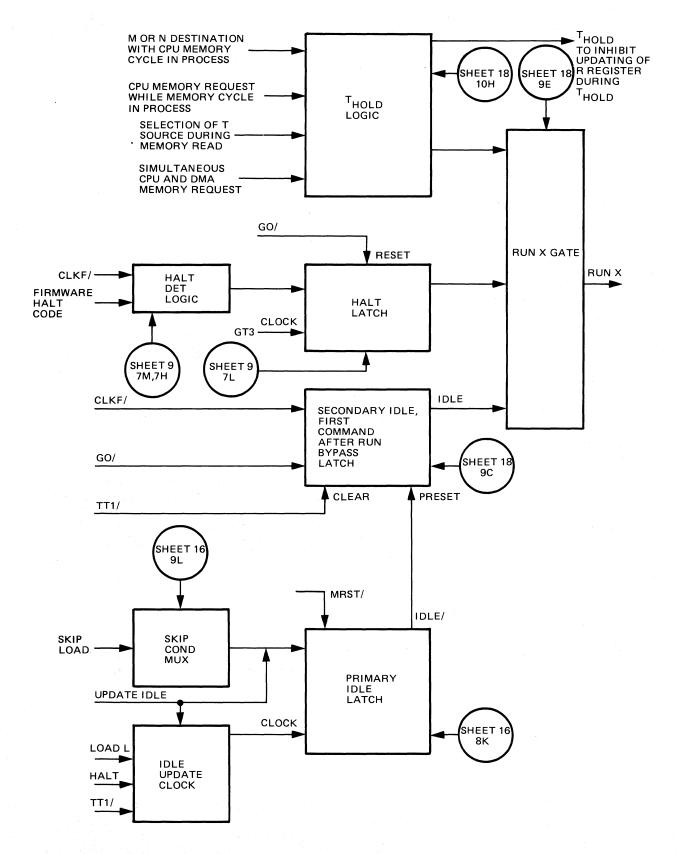

| 11-14 | Run/Halt Control Block Diagram                 | 11-28 |

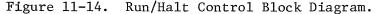

| 11-15 | Computer Start Logic, Block Diagram            | 11-30 |

| 11-16 | Power Fail Detect Block Diagram                | 11-31 |

|       |                                                |       |

## LIST OF TABLES

| Table No. | Title                                                                                                                                                                            | Page |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1-1       | Microcommand Set                                                                                                                                                                 | 1-3  |

| 1-2       | File Register O Flags                                                                                                                                                            | 1-8  |

| 1-3       | Internal Status Bits                                                                                                                                                             | 1-10 |

| 2-1       | Register Designation for Operate Commands                                                                                                                                        | 2-2  |

| 2-2       | Standard I/O Control Codes                                                                                                                                                       | 2-20 |

| 2-3       |                                                                                                                                                                                  | 2-24 |

| 2-4       |                                                                                                                                                                                  | 2-25 |

| 2-5       |                                                                                                                                                                                  | 226  |

| 2-6       | 전 1997년 1월 1997년 1월 1997년 1997년 1997년 1997년 1997년 1997년 1997년<br>1997년 - 1997년 1 | 2-26 |

| 4-1       | I/O Control States                                                                                                                                                               | 4-4  |

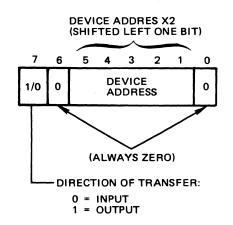

| 4-2       | Standard I/O Device Addresses                                                                                                                                                    | 4-7  |

| 4-3       | Standard Device Order                                                                                                                                                            | 4-8  |

| 4-4       | Typical Status Byte Definition                                                                                                                                                   | 4-10 |

| 4-5       | Interrupt Sequence States                                                                                                                                                        | 4-20 |

| 8-1       | Micro-One Backplane Connector Signal List                                                                                                                                        | 8-2  |

| 8-2       | MOS Memory Interface Connector List                                                                                                                                              | 8-4  |

| 9-1       | I/O Interface Signal Glossary                                                                                                                                                    | 9-1  |

| 11-1      | ALU MUX Addresses, ALU Modes, and Carry In                                                                                                                                       | 11-4 |

## SECTION 1 ARCHITECTURE

#### SECTION 1

#### ARCHITECTURE

#### 1.0 SYSTEM ORGANIZATION

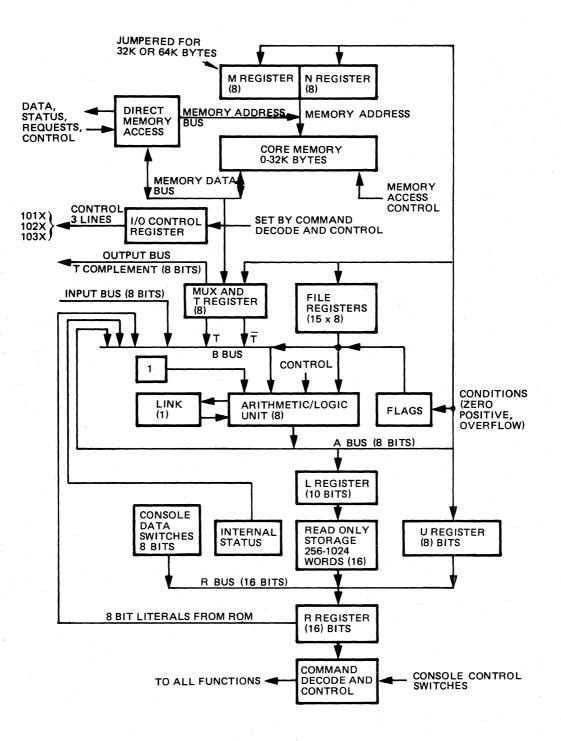

The Micro-One Computer is a bus-organized system, constructed around a file of 15 programmable registers, which feature microprogrammed control. The basic elements of the system are shown in the block diagram of Figure 1-1. The system executes 15 basic microcommands with many variations, plus a code-variable execute command shown in Table 1-1. All microcommands are 16-bits long and are in one of three standard formats. Micro-One microprograms are established in a Read-Only-Memory (ROM) and thereafter become an integral part of the system's hardware. The microprogram can be changed by replacing the ROM devices. Commands read out of the ROM control all aspects of Micro-One's operation and are executed in a single 200 nanosecond machine clock cycle.

Micro-One's 8-bit Arithmetic/Logic Unit (ALU) performs all data manipulation, including: addition, subtraction, logical AND, logical OR, logical Exclusive OR, and 1-bit left and right shifts. The output of the logic network is the A-bus which is the input to the files and other system registers; all data byte movement occurs on this bus. The A-bus extends to the backplane and can be used for special I/O functions. The output of the register file is one of the inputs to the ALU, the other input is the B-bus. B-bus inputs are determined by the type of command, its options, and the I/O mode. B-bus inputs are the true and the complement outputs of the T register, the input bus, and the 8-bit literal contained in certain commands, and four external sense lines.

The memory data and address buses communicate between the core memory modules, the processor, and the Direct Memory Access (DMA) port. Either the processor or the DMA port may operate with the memory, with DMA having operational priority.

#### 1.1 GENERAL CHARACTERISTICS

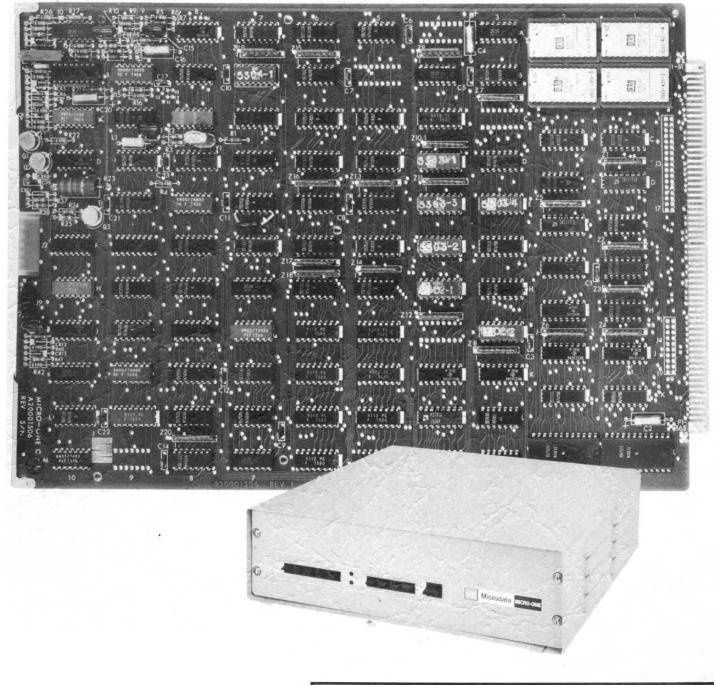

The heart of the Micro-One system is mounted on a single  $8-1/2 \ge 12$ -inch printed circuit board which contains the basic CPU and the 1K ROM. There is a connection and interface control for a piggyback MOS memory of up to 8K bytes in 1K increments. Additional characteristics include:

- Core memory addressing to 64K bytes, or strap selectable to 32K bytes for operation with Micro-One/21 firmware.

- 1.0 Microsecond memory speed (full cycle)

- 8-Bit memory bytes

- Up to 1024 words of read only storage

- Two versions of control consoles

Figure 1-1. Micro-One Block Diagram

| <b></b> |                           | •                                     |                                                                      |                                                    | · · · · · · · · · · · · · · · · · · ·                                                           |                                                                                                                                                                                                                                      |

|---------|---------------------------|---------------------------------------|----------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.     | Name                      | Class In-<br>struction                | Code                                                                 | Mnemonic                                           | Literal to Register<br>Subfunctions                                                             | Operations                                                                                                                                                                                                                           |

| 0       | Execute                   | Execute                               | 0XXX                                                                 | Е                                                  | NA                                                                                              | OX is ORed with U Register                                                                                                                                                                                                           |

| 1       | Literal<br>to<br>Register | Literal<br>Class<br>Commands          | 10XX<br>11XX<br>12XX<br>13XX<br>14XX<br>15XX<br>16XX<br>16XX<br>17XX | LZ<br>LT<br>LM<br>JP<br>JP<br>JP<br>JP<br>LU<br>LU | Load Zero<br>Load T<br>Load M<br>Load N<br>Jump<br>Jump<br>Jump<br>Jump<br>Load U<br>Load Seven | No operation<br>XX replace contents of T<br>XX replace contents of M<br>XX replace N & M is cleared.<br>to page 0.<br>to page 1.<br>to page 2.<br>to page 3.<br>XX replaces contents of U.<br>Internal Controls                      |

| 2       | Load File                 |                                       | 2fXX                                                                 | LF                                                 | N/A                                                                                             | f = file number                                                                                                                                                                                                                      |

| 3       | Add to File               |                                       | 3fXX                                                                 | AF                                                 | N/A                                                                                             | f = file number                                                                                                                                                                                                                      |

| 4       | Test If Zero              |                                       | 4fXX                                                                 | TZ                                                 | N/A                                                                                             | Skip on no bits match, if file<br>f of the ones in the XX.                                                                                                                                                                           |

| 5       | Test Not Zero             |                                       | 5fXX                                                                 | TN                                                 | N/A                                                                                             | Skip on any bits match in file f of the ones in X.                                                                                                                                                                                   |

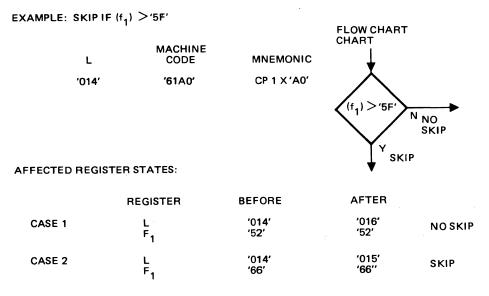

| 6       | Compare                   |                                       | 6fXX                                                                 | СР                                                 | N/A                                                                                             | Skip on f + XX>2 <sup>8</sup> -1<br>c Field (Binary)                                                                                                                                                                                 |

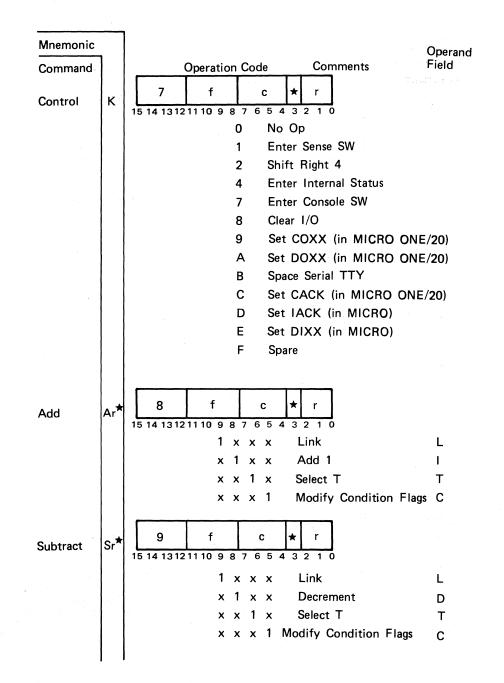

| 7       | Control                   | Operate<br>Class<br>Commands<br>C fie |                                                                      | K<br>destination<br>F,M,N,L,U                      | register<br>N/A                                                                                 | 0000 No operation<br>0001 Enter Sense Switches<br>0010 Shift Right Four Bits<br>0100 Enter Internal Status<br>0111 Enter Console Switches<br>1000 Clear I/O Mode<br>1001 Control Output<br>1010 Data Output<br>1011 Space Serial TTY |

|         |                           |                                       |                                                                      |                                                    |                                                                                                 |                                                                                                                                                                                                                                      |

Table 1-1. Microcommand Set

1-3

| No. | Name                 | Class In-<br>struction       | Code  | Mnemonic | Literal to Register<br>Subfunctions | C field (binary)                                                                                               |

|-----|----------------------|------------------------------|-------|----------|-------------------------------------|----------------------------------------------------------------------------------------------------------------|

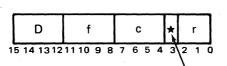

| 7   | Control              | Operate<br>Class<br>Commands | 7fc*r |          | N/A                                 | 1100 Concurrent Acknowledge<br>1101 Interrupt Acknowledge<br>1110 Data Input<br>1111 Spare                     |

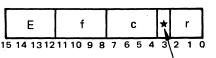

| 8   | Add                  |                              | 8fc*r | А        | N/A                                 | 0001 Modify Flags<br>0010 File + T<br>0100 Sum + 1<br>1000 Sum + Link Bit                                      |

| 9   | Subtract             |                              | 9fc*r | S        | N/A                                 | 0001 Modify Flags<br>0010 File + T Complement<br>0100 Inhibit Increment<br>1000 Difference + Line              |

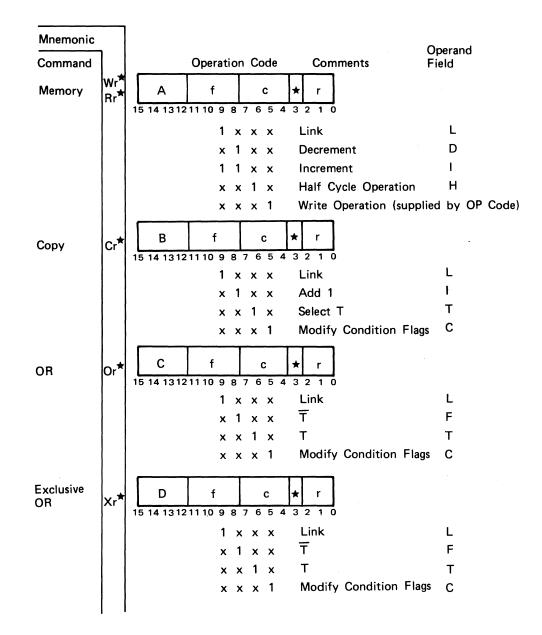

| 10  | Read/Write<br>Memory |                              | Afc*r | R/S      | N/A                                 | 00XX Transfer<br>01XX Decrement<br>10XX Add Link<br>11XX Increment<br>XX1X Half Cycle<br>XXX1 Write (Not Read) |

| 11  | Сору                 |                              | Bfc*r | С        | N/A                                 | XXX1 Modify Flags<br>XX1X Select T<br>X1XX Select + 1<br>1XXX Select Link                                      |

| 12  | OR                   |                              | Cfc*r | 0        | N/A                                 | XXX1 Modify Flags<br>XX1X Select T<br>X1XX Select T Complement<br>1XXX Linked Zero Test                        |

### Table 1-1. Microcommand Set (Continued)

| No. | Name         | Code  | Mnemonic | Literal to Register<br>Subfunctions | C field (binary)                                                             |

|-----|--------------|-------|----------|-------------------------------------|------------------------------------------------------------------------------|

| 13  | Exclusive OR | Dfc*r | Х        |                                     | Same as OR                                                                   |

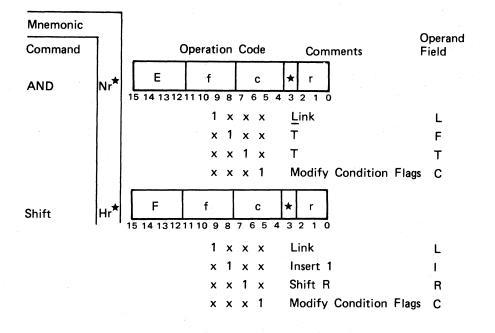

| 14  | AND          | Efc*r | N        |                                     | Same as OR                                                                   |

| 15  | Shift        | Ffc*r | H        |                                     | XXX1 Modify Flags<br>XX1X Shift Right<br>X1XX Insert ONE<br>1XXX Insert Link |

Table 1-1. Microcommand Set (Continued)

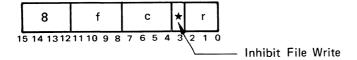

NOTE: If\* = 0, result of operation is placed in file (f).

- (1) f = file address

- 2 c = sub op code field

- (3) \* = inhibit file write

- (4) r = destination field

1-5

- TTL integrated circuitry

- Operating temperature 0 to 50°C; relative humidity 90%

- Compatibility with Micro 1600 interface controllers

- Power: +5V, 3A with 1K ROM

- Power fail detect and auto restart standard (requires full wave rectified 8V peak signal supplied from power supply)

- 120 Hz real-time-clock standard

- Serial TTY interface standard

- Single channel external interrupt

- Concurrent I/O using the programmed I/O bus

- Bidirectional memory data bus

- Separate 8-bit output and input data buses

- ROM memory sequencer which can be programmed for CORE OR MOS memory timing

#### 1.2 REGISTERS AND FILE

There are eight CPU registers and 15 file registers. Each of the eight CPU registers has a specific use in the processor, while the files are used for general storage and flags.

#### 1.2.1 T Register

The 8-bit T register serves as the operand register for most of the operate class commands, and as a buffer register for output and memory operations. Both the true and complement output of the T register can be gated to the B-bus as an operand. When both the contents of T and its complement are selected as operands, the effective operand is all 1-bits; if neither is selected the operand is all 0-bits.

The T register can be loaded directly from ROM using a Load T instruction, from core memory on a Read instruction, or it may be loaded from a file register from the input bus, or from itself (such as when incrementing T) by designating T as the destination register of an operate class command. All programmed outputs, including control and data bytes, go out via the T register.

#### 1.2.2 M Register

The eight-bit M register contains the eight high-order bits of the processor memory address. This register is gated onto the Memory Address bus at all times except during a DMA operation. The M register can be loaded directly from ROM using a Load M command, or can be loaded by designating M as the destination register of an operate class command. The M register is cleared on a Load N command.

#### 1.2.3 N Register

The eight-bit N register contain the eight low-order bits of the processor memory address. This register is gated onto the Memory Address bus at all times except during a DMA memory operation. The N register can be loaded directly from ROM using a Load N command, or by being designated as the destination register of an operate class command.

#### 1.2.4 L Register

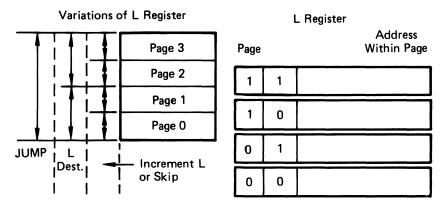

The 10-bit L register is the program counter and contains the read-only storage address of the next command to be executed, unless it is altered by a Jump command. The eight low-order bits of the L register serve as a counter which is incremented by one at each clock time when the processor is running unless a command execution delay is imposed. L is loaded by a Load L command, or as a destination register of an operate class command.

#### 1.2.5 U Register

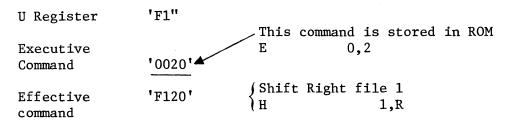

The eight-bit U register is used to modify the output of the read-only storage. For commands with Op Code O or nonliteral instructions with destination of 7, the contents of the U register are Inclusive-ORed with the eight high order bits of the ROM output as it is gated into the R register. This allows for dynamic modification and changing of operation codes and file register designators. U is loaded by a Load U command or as a destination register of an operate class command.

#### 1.2.6 R Register

The 16-bit R register holds the present microcommand being executed. Its output is decoded and controls the operation of the processor at each clock time.

#### 1.2.7 LINK Register

The one-bit LINK register holds the ALU'S high order carry from Add, Subtract, and Compare commands and the shifted off end bit from the Shift command.

#### 1.2.8 I/O Control Register

This three-bit register generates the control signals for the I/O bus, Seven separate control signals can be developed by decoding the register outputs. It is loaded and cleared by a control command, placing the timing of I/O control signals under command control. There are three output modes and four input modes. The high-order bit of the register is the input flag. When this bit is a 1-bit, the input bus is substituted for the T register when it is selected, and is the source of data when executing an external I/O control command.

#### 1.2.9 File Registers

Files consist of 15 eight-bit operational registers plus one File Zero register. All commands, except Load Register with Literal (Op-1), specify the file which will provide one input to the ALU. All file registers are functionally identical except for file register 0 which contains eight flags, and cannot be used for general storage. The flags of file register 0 are given in Table 1-2.

| Bit | Flag                        |

|-----|-----------------------------|

| 0   | Overflow Result Condition   |

| 1   | Negative Result Condition   |

| 2   | Zero Result Conditon        |

| 3   | Concurrent I/O Request Line |

| 4   | Internal Interrupt          |

| 5   | I/O Reply Line              |

| 6   | Serial Teletype             |

| 7   | External Interrupt Line     |

|  | Table | 1-2. | File | Register | 0 | Flags |

|--|-------|------|------|----------|---|-------|

|--|-------|------|------|----------|---|-------|

#### **1.3 MEMORY DESCRIPTIONS**

A brief functional description of the Micro-One's memories, memory busy, and memory data delays is provided in paragraphs 1.3.1 through 1.3.6.

#### 1.3.1 Core Memory

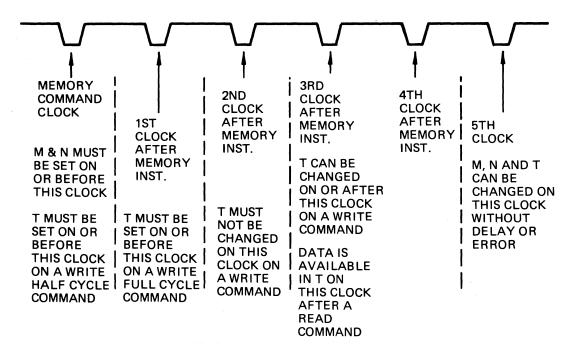

The magnetic core memory of the Micro-One is organized into pluggable modules of 8K or 16K bytes. Addressed at the byte level, the memory is operated in read or write, and full or half-cycle operations. The full-cycle memory timing is five 200 ns clock cycles (1.0 microsecond); the half-cycle timing in the system is three clock cycles (600 ns). For a read operation, the accessed data is placed in the T register two clock cycles after the start of the memory operation. Full cycle regeneration of the data in the memory does not require the use of the T register and T may be modified by the microprogram before completion of the restore part of the cycle.

#### 1.3.2 MOS Memory

The MOS memory of the Micro-One is organized into modules of 1K bytes with up to 8K bytes available. The memory is mounted piggyback on the Micro-One circuit board so that additional connectors are not required.

#### 1.3.3 Control Memory

The read-only memory provides storage for commands and constants of the microprogram. Its output is gated into the R register where it controls system operation at the next clock time.

The ROM is always accessed for the next command while the current command is being executed. This look-ahead ability achieves faster command execution time. When the sequence of command execution is altered by a jump or skip, and additional cycle must be taken to perform an access before the next command is executed. When the unit is halted, the L register contains the address of the first command to be executed when operation is resumed.

Each command is executed in a single clock cycle time although execution may be delayed because of core memory or read-only memory operations. The system clock rate is 20 MHz, and the clock cycle is 200 nanoseconds.

#### 1.3.4 Memory Busy Delays

When the memory is busy due to processor or DMA operations and a read/write command or a command to modify M or N registers awaits execution, a delay will occur until the memory operation is completed. These commands are executed on the last clock of the memory half or full cycle. If a DMA request is pending at the time a read or write memory command is to be executed, execution is delayed to give the DMA memory priority.

#### 1.3.5 Memory Data Delays

Operate class commands which select the contents of either the T register or its complement during the first two cycles of a processor memory read operation are executed during the third cycle of the read operation. This allows time for the accessed byte to be placed in the T register.

#### 1.3.6 Read-Only Memory Delays

An extra cycle is required for command execution for the following conditions because of the look-ahead nature of the read-only memory:

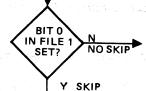

- a. Jump command.

- b. Test if Zero command when a skip occurs.

- c. Test if not Zero command when a skip occurs.

- d. Compare command when a skip occurs.

- e. Operate class commands which have the L register designated as a destination.

#### 1.4 STATUS AND CONDITION FLAGS

Status and Condition flags are described in the following paragraphs,

#### 1.4.1 Internal Status

Eight internal status bits are provided in Micro-One to designate a particular internal interrupt condition. When any of the internal status bits is a 1-bit, the internal interrupt flag (bit-4) in file register 0 is also a 1-bit. This flag is tested by the microprogram to detect the presence of the internal interrupt condition. The internal status bits are entered via the B-bus into the selected file register by a control command, at which time the status bits are cleared. The assignments for the eight internal status bits are given in Table 1-3.

| Bit | Interrupt Status             |

|-----|------------------------------|

| 0   | Console Interrupt            |

| 1   | DMA termination              |

| 2   | Real-Time Clock Interrupt    |

| 3   | (Spare 0)                    |

| 4   | (Spare 1)                    |

| 5   | (Spare 2)                    |

| 6   | Console Step Switch          |

| 7   | Power Fail/Restart Interrupt |

#### Table 1-3. Internal Status Bits

#### 1.4.2 Condition Flags

The Overflow, Negative and Zero conditions resulting from an operation involving the ALU can be stored in File Register 0. (See Table 1-2.) condition flags are updated for command 7 and for commands 8, 9, B-F if bit 4 is a 1-bit. These condition flags can be tested by the microprogram for implementing various conditional operations. Definitions of the condition flags follows:

a. Overflow - The Overflow Condition Flag stores the arithmetic overflow condition during an add, subtract or copy command. It stores the shifted off end bit during a shift command. Arithmetic overflow occurs when the result exceeds the range of the computer's 8-bit registers.

- b. Negative The Negative Condition Flag stores the high-order bit of the result on the A-bus since the 2's complement number system uses the most significant bit as the sign bit.

- c. Zero The Zero Condition flag stores the zero condition of the result. The zero test can be linked over multiple byte operations under control of the LINK modifier (bit 7) of operate instructions, When this bit is 1, the Zero Condition flag may not be set to indicate the zero condition of the current byte, but may only be reset to indicate a non-zero result. For this flag to indicate zero over multiple bytes it must be set by a zero result on the first operation which will have the LINK modifier zero, and not be reset by non-zero conditions on succeeding bytes which will have the LINK modifier a one.

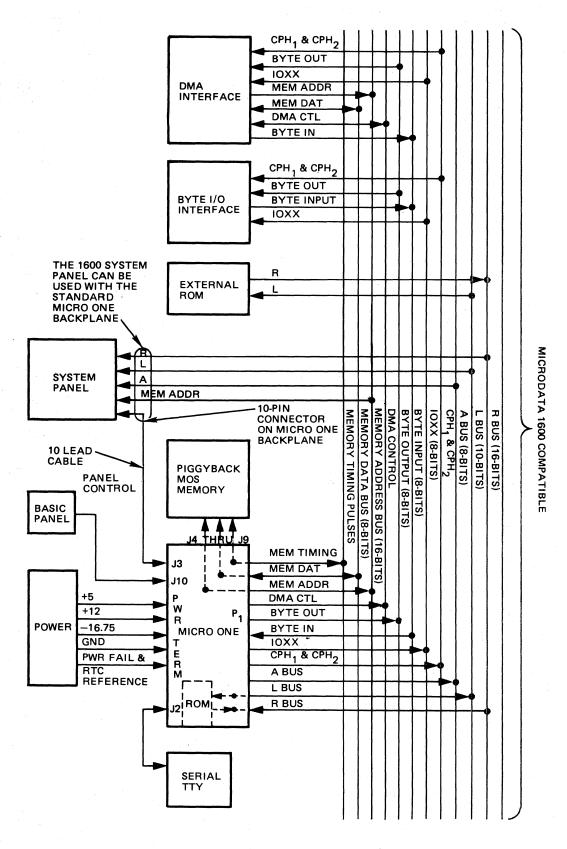

#### 1.5 BYTE I/O INTERFACE

The Micro-One provides an extremely fast elementary I/O capability. (The basic interconnections are shown in Figure 1-2.) The data paths and control functions are simple elements, sequenced from the control memory with flexible disciplines. With the fast (200 ns/step) control memory, firmware microprograms in control memory can react with a high degree of versatility in timing, data paths and I/O capabilities. This includes priority interrupts, fully-buffered data channels, macroprogrammable transfers, and special purpose communication multiplexer channels.

The byte I/O interface provides the facility for transferring bytes over a party line I/O bus under microprogram control. Standard Micro-One firmwave provides both programmed I/O and concurrent I/O transfer capability, along with a priority interrupt system. The basic I/O element is the Byte I/O bus.

#### 1.5.1 Byte I/O Bus

Data transfers through the byte I/O interface are basically two-phase operations. During the first phase, a control byte is placed on the Byte I/O bus before the actual transfer of data. The control byte contains a device address specifying the address of one of the I/O controllers on the bus, and a device order code signifying the type of operation to be performed during the transfer (data, status, or function transfer, etc),

All controllers on the bus examine the device number, but only the addressed controller accepts the control byte and logically connects itself to the bus for the subsequent data byte transfer. During the second phase of the byte I/O operation, a single byte is transferred to or from the controller, After each byte transfer the controller disconnects itself from the bus,

Figure 1-2. Backplane Interconnections

#### 1.6 EXTERNAL PRIORITY INTERRUPTS

The Micro-One external interrupt system operates through the byte I/O interface in the computer mainframe. Interrupts can originate from device controllers or from an optional Priority Interrupt interface board connected to the Byte I/O bus. This interface board controls eight external interrupt signals.

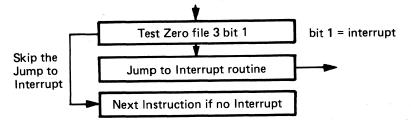

The byte I/O interface contains a single external interrupt request line common to all controllers on the Byte I/O bus, and a priority line that progresses sequentially through all controllers on the bus. Each I/O controller receives priority from the preceding controller in the priority chain and, if it is not ready to request an interrupt, passes it along to the next controller in the line. When a controller has priority and is ready to request an interrupt the priority signal is halted and the Interrupt Request signal is activated. After the I/O request is acknowledged, the controller places an address byte on the I/O bus. The processor uses this byte to transfer program control to the proper interrupt servicing routine.

#### 1.7 REAL-TIME CLOCK

The standard real-time clock function provides an internal interrupt at a 120 Hz rate. This can be used at the macroprogramming level as a realtime clock. The timing is derived from the power line where it is full-wave rectified. An optional input and jumper select is provided to make it possible to use an externally supplied real-time clock signal at rates other than 120 Hz.

When the timing signal occurs, it provides an internal interrupt by setting condition flag bit 4 and bit 2 of the internal status byte. The timing signal internal interrupt may be disabled and enabled by commands 1710 and 1720 respectively. The microprogram must detect the internal interrupt and take appropriate action. (Special real-time clock interrupt handling firmware is available with the Micro-One.)

#### 1.8 POWER-FAIL/AUTOMATIC RESTART

The power-fail and automatic restart function provides the following;

- a. An internal interrupt by setting condition flag bit 5 and bit 7 of the internal status byte upon detection of primary power loss,

- b. A processor reset when the computer is halted after loss of primary power.

- c. A processor rest for over 100 milliseconds after power is applied.

- d. Automatic switch to run mode after the power-on reset period,

- e. Power-restart interrupt immediately after automatic switch to run mode.

A power-fail interrupt detected while the processor is in the Run mode can be used to store processor registers and to halt the processor. The automatic processor reset that follows the halt and the one following power-on prevents any spurious operations in the core memory. At power-on, the processor reset clears the L register causing the processor to start at ROM location 0. The power-fail interrupt which occurs at this time can be detected and treated as a restart interrupt to cause a restoring of the processor registers. Standard power-fail/automatic restart interrupt firmware is available. The +12V power to the Micro-One must remain above +5V during a power-fail as the two voltages collapse.

#### **1.9 ARITHMETIC FUNCTIONS**

The Micro One uses a 2's complement binary number system. The registers and memory cells are 8 bits in length. For programming convenience, entering data, printing out, and preparing punched paper tape, the 8 bits are organized into two hexadecimal digits. The hexadecimal digits, with their decimal and binary equivalents, are as follows:

| Decimal | Hexadecimal | Binary |

|---------|-------------|--------|

| 0       | 0           | 0000   |

| 1       | 1           | 0001   |

| 2       | 2           | 0010   |

| 3       | 3           | 0011   |

| 4       | 4           | 0100   |

| 5       | 5           | 0101   |

| 6       | 6           | 0110   |

| 7       | 7           | 0111   |

| 8       | 8           | 1000   |

| 9       | 9           | 1001   |

| 10      | Α           | 1010   |

| 11      | В           | 1011   |

| 12      | C           | 1100   |

| 13      | D           | 1101   |

| 14      | Ε           | 1110   |

| 15      | F           | 1111   |

Throughout this document hexadecimal numbers are identified with single quotes;

133 N AA N

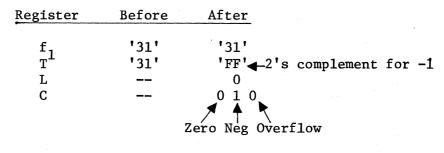

For addition functions, the two numbers are added directly with the carry out of the most significant bit going to Link, and overflow setting the overflow bit, if designated in the command.

For subtraction, one number is converted to a 2's complement and added to the other.

For single byte operations, with a 2's complement number system, the range of numbers is as follows:

| Binary   | Hexadecimal | Decimal |          |

|----------|-------------|---------|----------|

| 01111111 | '7F'        | +127    | POSITIVE |

|          |             |         |          |

| 0000001  | '01'        | + 1     |          |

| 0000000  | 1001        | 0       |          |

| 1111111  | 'FF'        | 1       |          |

| 11111111 |             | - 1     | NEGATIVE |

| 11111110 | 'FE'        | - 2     |          |

|          |             |         |          |

| 10000000 | <b>'80'</b> | -128    |          |

In general, arithmetic overflow occurs whenever the number range (+127 to -128) of the Micro One is exceeded on an arithmetic operation. As can be seen in the examples, the link bit may be set even though an overflow did not occur. This is the result of using a 2's complement number system.

## SECTION 2

#### MICROCOMMAND REPERTOIRE

#### SECTION 2

#### MICROCOMMAND REPERTOIRE

#### 2.0 GENERAL

This section contains description of all Micro-One commands. With each description is a diagram showing the format of the command and its operation code, given in hexadecimal. Above each diagram is the command's mnemonic code and the name of the command. Under each diagram is a description of the command, followed by a list of the registers and indicators that can be affected by the command. The timing of each command is one clock cycle (200 nsecs) unless the L register is designated as the destination of the result, in which case the command execution time is two cycles.

#### 2.1 COMMAND FORMATS

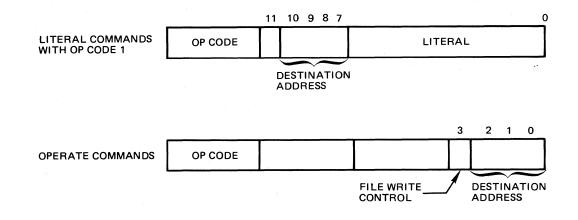

There are three basic command formats. Each command is 16 bits long and is contained in a single read-only memory location.

The formats are literal commands, operate commands and execute commands.

#### 2.1.1 Literal Commands

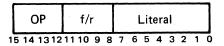

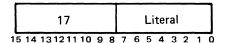

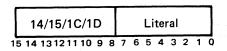

The literal class commands have the following format;

In this format the operation code occupies the four high-order bits. Bits 11-8 contain either a file register designator (f) or a register or control group designator (r). Bits 7-0 comtain an 8-bit literal which is transferred as an operand to the B bus.

#### 2.1.2 Operate Commands

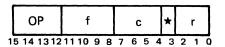

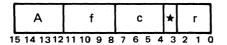

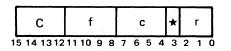

The operate class commands have the following format:

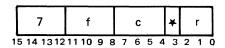

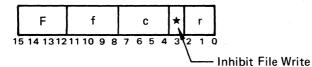

In this format the operation code occupies the four high-order bits. Bits 11-9 contain a file register designator (f) which specifies 1 of the 16 file registers to be used in command execution. Bits 7-4 contain control option bits (c) which are unique to the specific command. When bit 3 is a 1, the result of an operate class command is inhibited from being placed in the designated file register. Symbolically, this is specified to the program assembler by appending an \* to the command mnemonic. The register designator (r) in bits 2-0 specifies a processor register destination to receive the result of the operation. Since there is only one file register selected at a time, the only file register that can receive the result of a particular operate command is the same file register selected for the operand. The register's identifier is added as a second character of the command mnemonic. Table 2-1 contains the register codes.

| Designator | Mnemonic | Register                                                     |  |  |  |  |  |  |  |

|------------|----------|--------------------------------------------------------------|--|--|--|--|--|--|--|

| 0          |          | none                                                         |  |  |  |  |  |  |  |

| 1          | Т        | T Register                                                   |  |  |  |  |  |  |  |

| 2          | М        | M Register                                                   |  |  |  |  |  |  |  |

| 3          | N        | N Register                                                   |  |  |  |  |  |  |  |

| 4          | L        | L Register-addresses: 000-OFF and 200-2FF                    |  |  |  |  |  |  |  |

| 5          | K        | L Register-addresses; 100-1FF and 300-3FF                    |  |  |  |  |  |  |  |

| 6          | U U      | U Register                                                   |  |  |  |  |  |  |  |

| 7          | S        | U Register ORed into command (except for<br>Control command) |  |  |  |  |  |  |  |

Table 2-1. Register Designators for Operate Commands

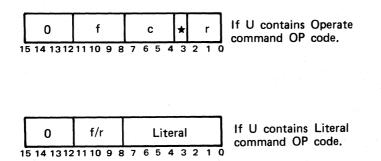

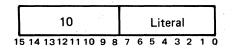

#### 2.1.3 Execute Command

The execute command causes the contents of the U register to be ORed with the 8 high-order bits of the command to form an effective command. This operation is also performed when r=7 for the operate class commands. The execute command has zero bits in the four high order bits. The remainder of the command has the format required for the effective command to be executed.

#### 2.1.4 Formats for Execute Commands

#### 2.1.5 Literal Commands

The literal commands, listed by Op Code are as follows:

| Op Code | Command       |

|---------|---------------|

| 1       | Load Register |

| 2       | Load File     |

| 3       | Add to File   |

| 4       | Test Zero     |

| 5       | Test Not Zero |

| 6       | Compare       |

The literal commands are used to load constants into various Micro-One registers, to test for bit configurations and data values in file registers, and to load or add constants to file registers. Eight of the 16 bits are used as command, and the other 8 are available as data.

#### 2.1.6 Operate Commands

The operate commands, listed by Op Code are as follows:

| <u>Op</u> | Code | Command      |

|-----------|------|--------------|

|           | 7    | Control      |

|           | 8    | Add          |

|           | 9    | Subtract     |

|           | Α    | Memory       |

|           | В    | Copy         |

|           | C    | OR           |

|           | D    | EXCLUSIVE OR |

|           | Ε    | AND          |

|           | F    | SHIFT        |

The operate commands are used to control the flow of data in or out and through the Micro-One computer, and to perform the arithmetic and logic functions in the computer.

With this powerful command set, it is possible to implement all of the data handling and control functions of a larger computer.

2.1.7 Terms and Symbols Used in the Command Descriptions

| (f <sub>1</sub> )   | Contents of file 1                                  |

|---------------------|-----------------------------------------------------|

| (f <sub>1</sub> )►T | Contents of file 1 to T register                    |

| • • • •             | Indeterminate value or function                     |

| 'AA'                | Hexadecimal number in flow chart                    |

| X'AA'               | Hexadecimal constant in assembly language statement |

Affected Register States

For each command, certain registers are modified. These are described in examples as affected registers.

∧ LOGICAL AND ∨ LOGICAL OR ∀LOGICAL EXCLUSIVE OR

$\mathbf{L}$ '024'

Effective address of L register as used in examples. Because of the lookahead feature of the Micro-One, the actual L address is one higher than indicated in the examples.

#### 2.2 MICROCOMMANDS - FORMATS, DESCRIPTIONS, AND EXAMPLES

The formats of the examples for each command have been selected to facilitate explanation of that particular command. Because of the difference in characteristics and utilization of the various commands, and associated data patterns, the example formats are different for each command category.

2.2.1 LT Load T

|   | 11/19 |    |    |    |    |   | Li | ter | al | 1. |   |   |   |   |   |  |

|---|-------|----|----|----|----|---|----|-----|----|----|---|---|---|---|---|--|

| 1 | 5 14  | 13 | 12 | 11 | 10 | 9 | 8  | 7   | 6  | 5  | 4 | 3 | 2 | 1 | 0 |  |

The contents of the 8-bit literal field are placed in the T register. The condition flags and Link register are not effected.

This command is used to provide constant data values, bit patterns for comparison tests, masks, and I/O control codes, which are most conveniently used in the T register.

Example: Load T with hexadecimal value 'AA'

| L     | Machine<br>Code | Assembly<br>Language | Flow Chart<br>Notation |

|-------|-----------------|----------------------|------------------------|

| '024' | '11AA'          | LT X'AA'             | 'AA'► T                |

#### Effected register states:

| Register | Before | After |  |  |  |  |

|----------|--------|-------|--|--|--|--|

| L        | '024'  | '025  |  |  |  |  |

| T        |        | 'AA'  |  |  |  |  |

Command execution time - 200 nsecs

2.2.2 LM Load M

| 12                    | Literal |   |   |   |   |   | ] |   |

|-----------------------|---------|---|---|---|---|---|---|---|

| 15 14 13 12 11 10 9 8 | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

The contents of the 8-bit literal field are placed in the M register. The condition flags and Link register are not effected.

This command is used to set the M register for accessing dedicated core locations. The M register is also modified by designation as destination register in operate commands.

Example: Load M with page address hexadecimal value '55'

| <u>L</u>              | Machine | Assembly | Flow Chart |

|-----------------------|---------|----------|------------|

|                       | Code    | Language | Notation   |

| <b>'</b> 134 <b>'</b> | '1255'  | LM X'55' | '55'▶ M    |

Effected register states

| Register | Before  | After |

|----------|---------|-------|

| L        | '134'   | '135' |

| Μ        | • • • • | '55'  |

Command execution time - 200 nsecs

2.2.3 LN Load N

| 13                |   |   |   | Literal |   |   |   |   |   |   |

|-------------------|---|---|---|---------|---|---|---|---|---|---|

| 15 14 13 12 11 10 | 9 | 8 | 7 | 6       | 5 | 4 | 3 | 2 | 1 | 0 |

The contents of the 8-bit literal field are placed in the N register and the M register is cleared. The condition flags and Link register are not effected.

The command is used to set the N register for accessing dedicated core locating locations. If the location is in page 0 of core ('0000'-'00FF'), only this command is required to set both the M and N registers, since M is automatically cleared. If M is not to be page 0, then N must first be set, followed by M.

Example: Load N with address hexadecimal value "F" and set M = '00'

| L     | Machine | Assembly | Flow Chart                |

|-------|---------|----------|---------------------------|

|       | Code    | Language | Notation                  |

| '235' | '13FF'  | LN X'FF' | 'FF' <b>≻</b> N<br>'00'►M |

Effected register states

| Register | Before | Afte | er       |

|----------|--------|------|----------|

| L        | '235'  | '236 | 5'       |

| Μ        |        | 'FF  | r        |

| N        |        | '00' | t to set |

Command execution time - 200 nsecs

2.2.4 LU Load U

| Г  |    |    |   |    |   |    |   |         |   |   |   |   |   |   |   |   |  |

|----|----|----|---|----|---|----|---|---------|---|---|---|---|---|---|---|---|--|

|    | 16 |    |   |    |   |    |   | Literal |   |   |   |   |   |   |   |   |  |

| 15 | 14 | 13 | 1 | 21 | 1 | 10 | 9 | 8       | 7 | 6 | 5 | 4 | 3 | 2 | 1 | ō |  |

This command is used to place specific command codes into the U register, which is used in conjunction with general function EXECUTE class commands. The U register can also be modified by being designated as the destination register in an operate command. The differences in utilization of these two approaches for modifying the U register are described in a later paragraph which discusses U register applications.

When modifying the U register, it is necessary to place at least one command between the modifying command and a command which uses the U register as an input. Otherwise an undefined value of U may be used.

2.2.5 LZ Load Zero Control

When this command or an operate command with destination 0 is executed, a pulse called CGLO of approximately 50 nsecs width is generated. CGLO is

available on the I/O and option board connectors of the Micro-One. During the CGLO of a literal command, the literal value is on the A bus, which is available on the back plane. An 8-bit control latch can be set by this command and used for any purpose, such as enabling counters, interrupts, or control lines. Since the CGLO also occurs on dest. O, logic must be provided to detect the literal command (OP1) and enable the CGLO only when an OP1 has occurred.

2.2.6 LS Load Seven Control

The 8 bits of the literal perform control functions as described below:

- 1700 No operation

- 1701 Enable serial teletype. The serial teletype input is gated into bit 6 of file register 0. The serial teletype value is available at all times.

- 1704 Disable external interrupts: recognition of external interrupts is inhibited.

- 1708 Enable external interrupts: recognition of external interrupts is enabled.

- 1710 Disable real-time clock: the real-time clock and interrupt are disabled.

- 1720 Enable real-time clock: the real-time clock and interrupt are enabled.

- 1740 Spare

- 1780 Halt: the processor is halted.

Command execution time - 200 nsecs.

Non-conflicting commands can be executed simultaneously. For example, enable external interrupts can be combined with enable real-time clock. The bits of the literal parts of the commands are ORed to produce the hexadecimal code.

| Example:               | Machine<br>Code |      | Literal<br>Bits |  |  |  |

|------------------------|-----------------|------|-----------------|--|--|--|

| Enable Interrupts      | 1708            | 0000 | 1000            |  |  |  |

| Enable Real-Time Clock | 1720            | 0010 | 0000            |  |  |  |

| Composite Command      | 1728            | 0010 | 1000            |  |  |  |

2.2.7 JP Jump

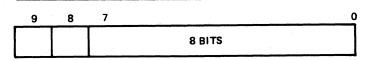

The contents of the 8-bit literal are placed in the 8 low-order bits of the L register; the content of bit 8 is placed in Lg and the content of bit 11 is placed in Lg. The location of the next command to be executed is at the address specified by the new contents of the L register. The execution time of the command is two cycles. The jump operation codes for the four 256-word pages in read-only memory are as follows: