7300022

# RGB - GRAPH Color Graphics Controller

MANUAL NO. 167M0-05A-1

## **RGB - GRAPH**

# Color Graphics Controller

MANUAL NO. 167MO-05A-1

## FEATURES

- 512 x 512 x 4 or 1024 x 512 x 2 SOFTWARE SELECTABLE RESOLUTION

- MULTIBUS® PLUG-IN

- 4 BIT PLANES

- PAN and SCROLL

- VECTOR PLOT

- EXPANDABLE

- SCREEN PRESET

- BIT PLANE WRITE ENABLE

- INDEPENDENT X and Y ZOOM

- DMA TRANSFERS

- HARDWARE CLIPPING

- VIDEO BUS

- LIGHT PEN INTERFACE

- VIDEO OUTPUT ENABLE

- PROGRAMMABLE DISPLAY FORMAT

MULTIBUS<sup>®</sup> is a registered trade mark of INTEL CORP.

## **RGB - GRAPH**

## Color Graphics Controller

MANUAL NO. 176M0-05A-0

## TABLE OF CONTENTS

| Section                                                                                                                                                                      | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | Page                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0                                                                                                                                                                          | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | 1                                                                                                                                                 |

| 2.0<br>2.1<br>2.2<br>2.3                                                                                                                                                     | Functional Description<br>Display Memory Access<br>Display Manipulation<br>Video                                                                                                                                                                                                                                                                                                                                                                                                         | ·<br>• • | 3<br>3<br>5<br>5                                                                                                                                  |

| 3.0                                                                                                                                                                          | Start-Up Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 5                                                                                                                                                 |

| 4.0<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>4.3.9<br>4.3.10<br>4.3.11<br>4.3.12<br>4.3.13<br>4.3.15<br>4.3.16<br>4.4 | Programming<br>Format Programming Tables<br>Format Parameter Calculations<br>Registers<br>X-Register Low<br>X-Register High<br>Y-Register High<br>Data Register Low<br>Data Register High<br>Status Register High<br>Status Register<br>Control Register No. 1<br>Control Register No. 2<br>Auxiliary Light Pen Register<br>Control Register No. 3<br>Control Register No. 4<br>CRTC Status Register<br>CRTC Address Register<br>CRTC Data Sheet<br>Vector Register<br>The Zoom Function |          | 8<br>10<br>11<br>12<br>12<br>12<br>12<br>13<br>13<br>13<br>13<br>13<br>13<br>14<br>14<br>15<br>16<br>17<br>17<br>18<br>18<br>18<br>19<br>19<br>20 |

| 5.0<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13                                                                           | Straps<br>I/O Base Address Straps<br>Data Straps<br>DMA Base Address Straps<br>Straps for Control Registers 3 and 4<br>Frame Grab Straps<br>TTL Video Straps<br>Sync and Blanking Straps<br>Register Read Disable Straps<br>V Reset Stap<br>Character Clock Strap<br>Master Slave Straps<br>Bit Plane Control Strap<br>Light Pen Straps                                                                                                                                                  |          | 22<br>22<br>23<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>26<br>26<br>26<br>26                                                      |

## TABLE OF CONTENTS (Cont'd)

| Sec | ti | on |

|-----|----|----|

|     |    |    |

<u>Title</u>

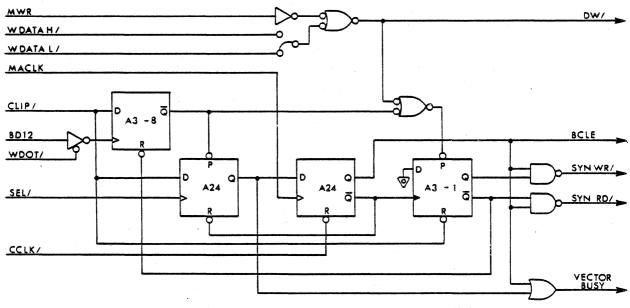

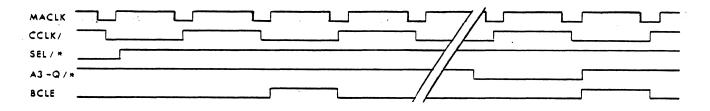

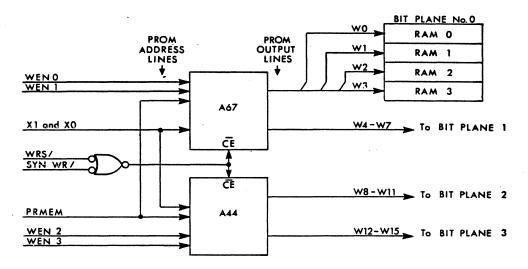

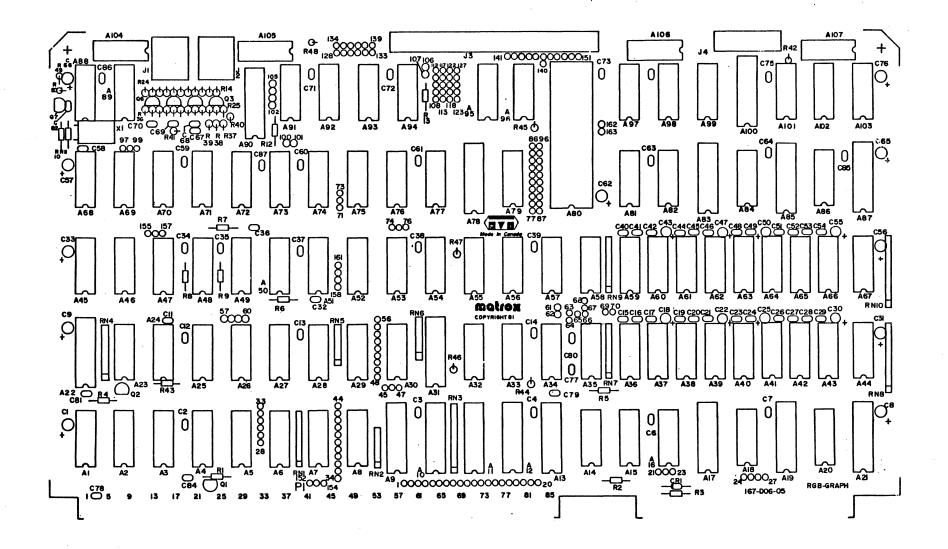

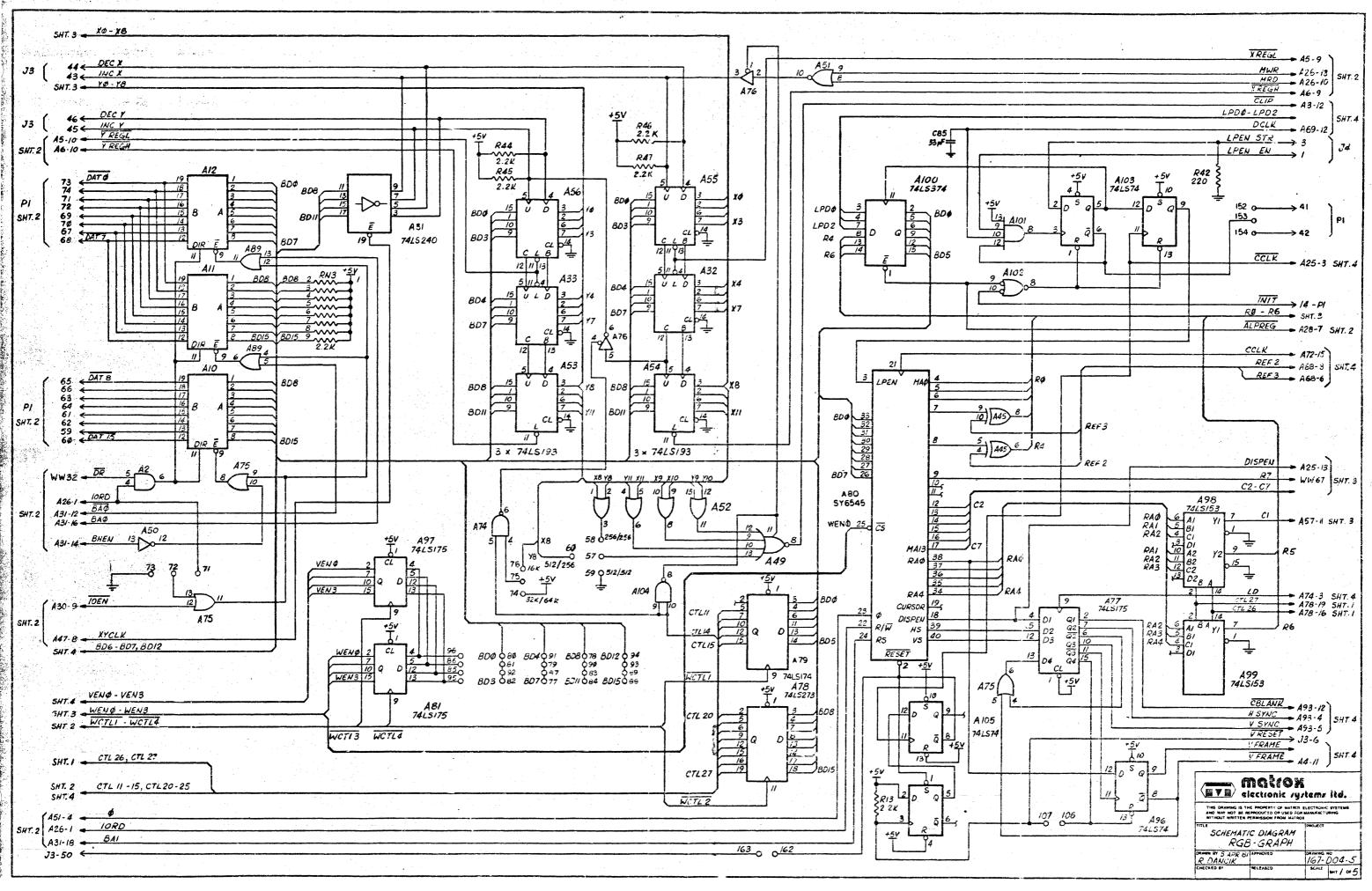

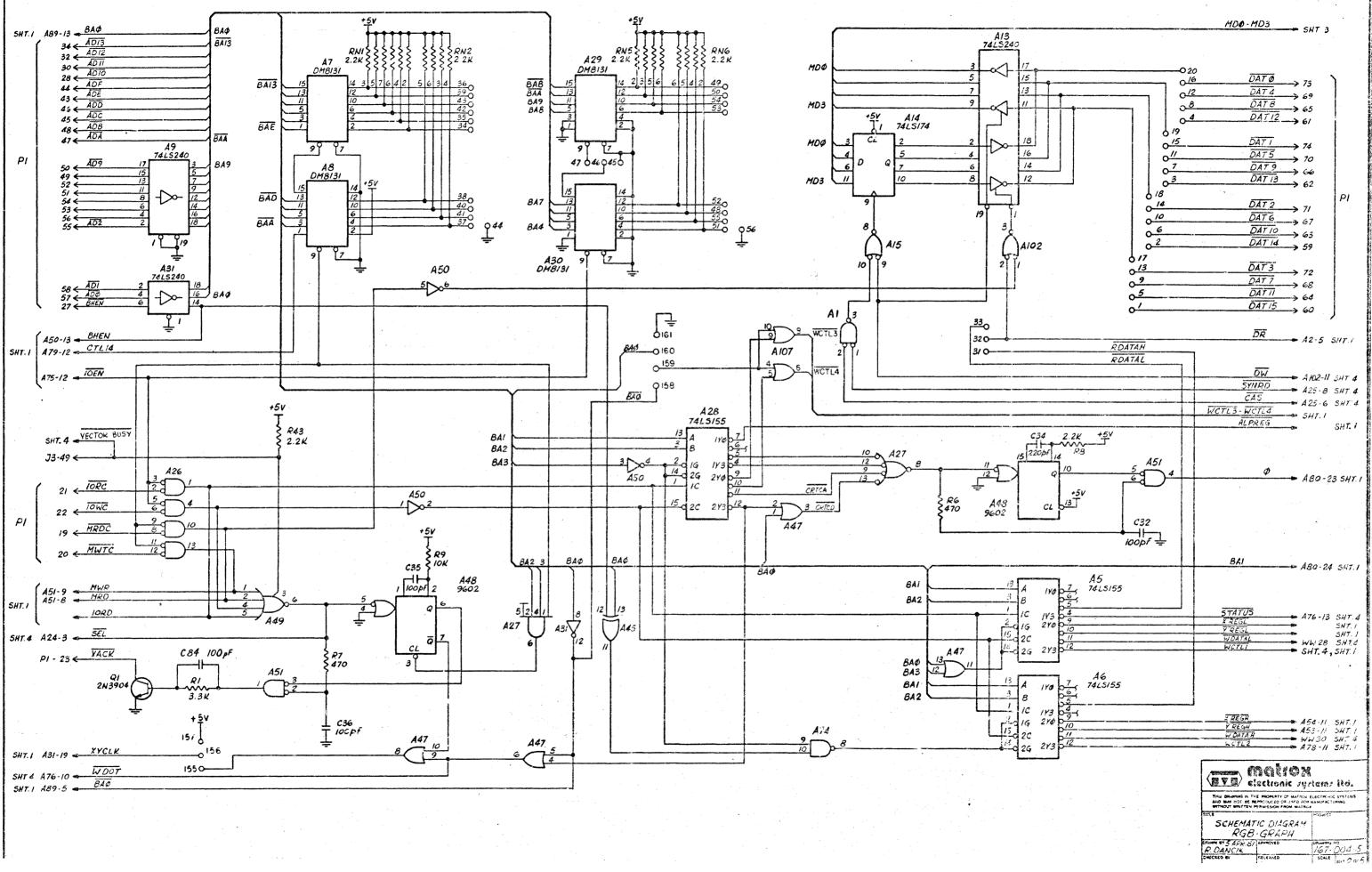

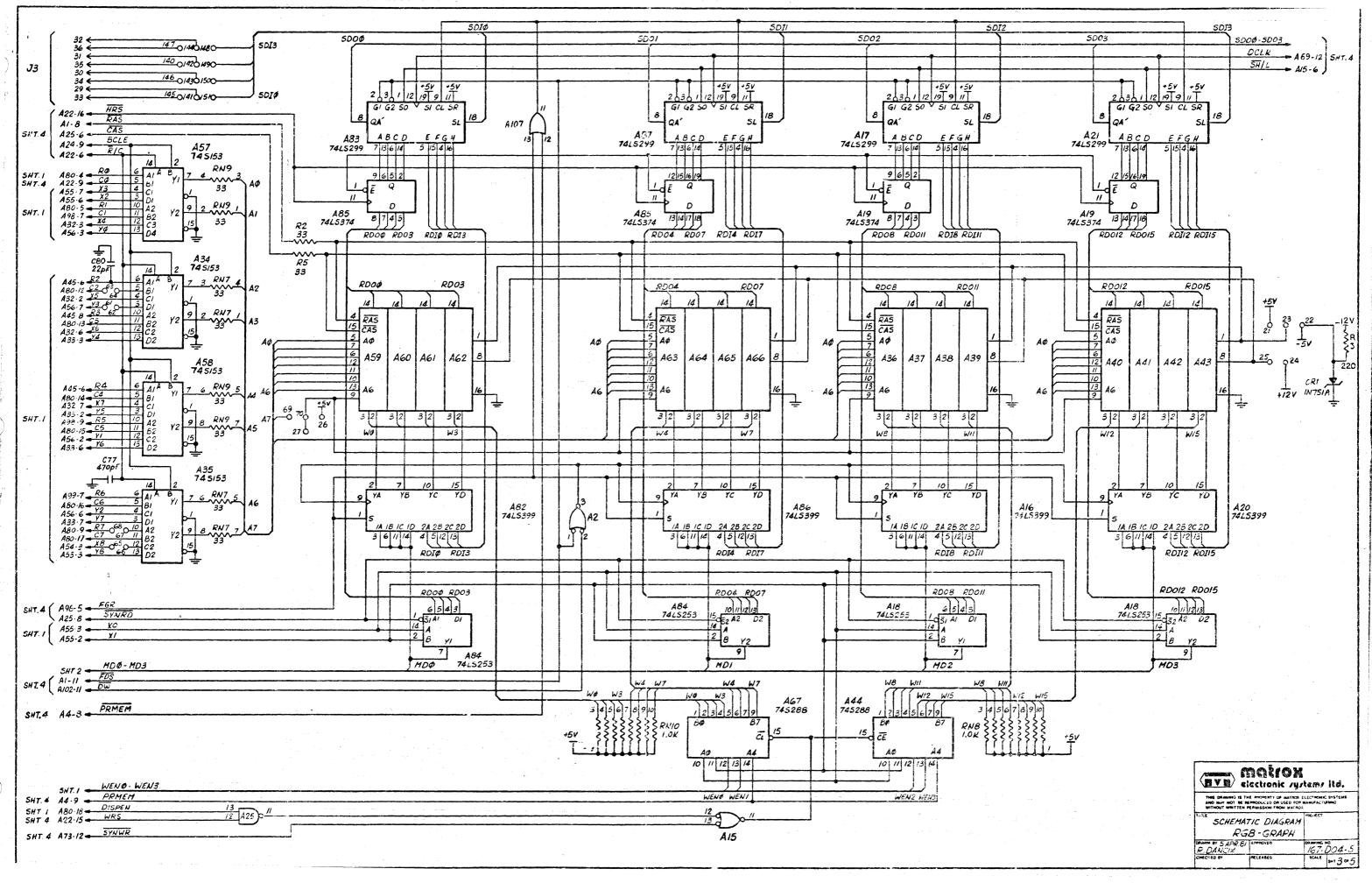

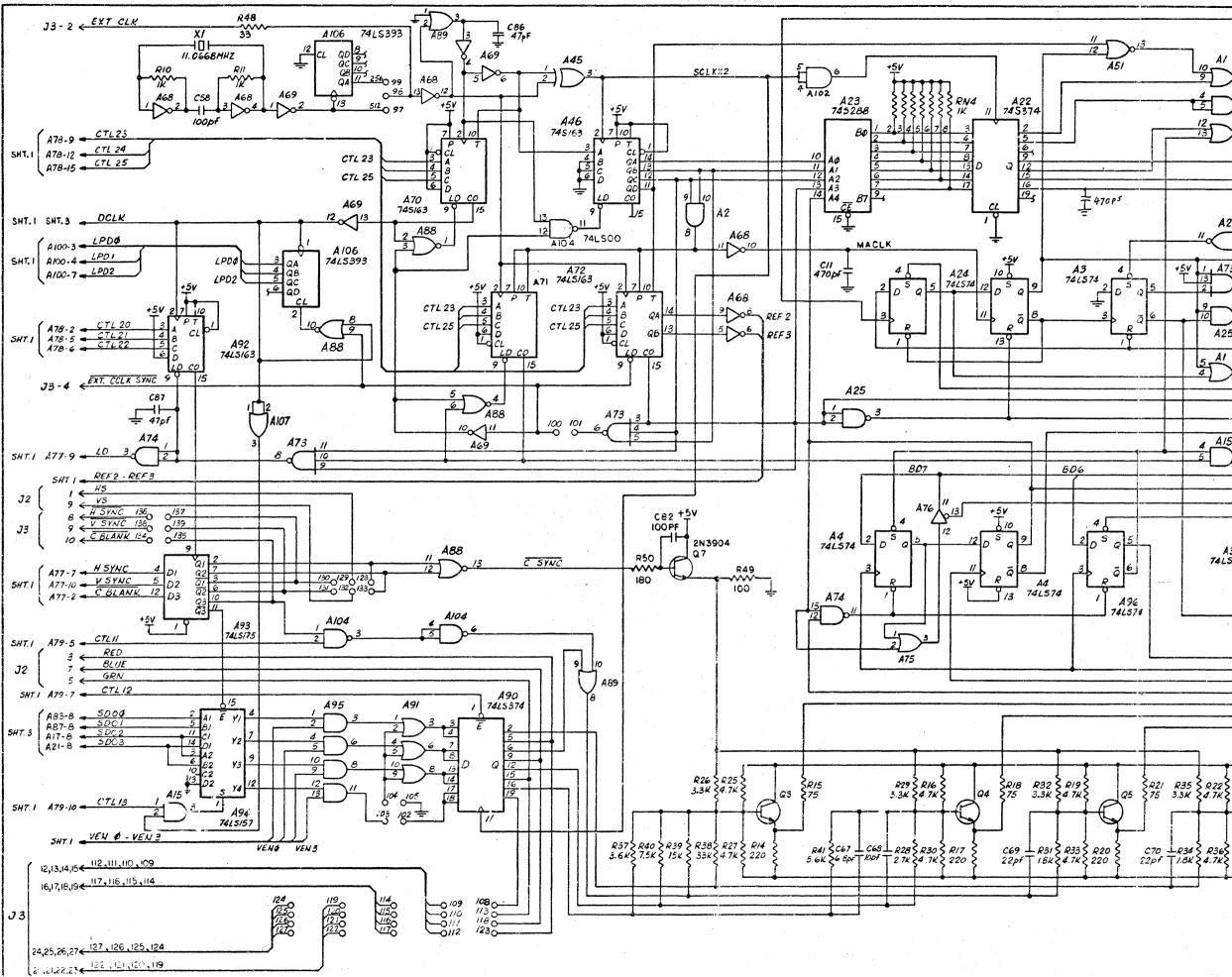

| 6.0<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7 | Circuit Description<br>Bit Plane<br>Central Timing<br>Frame Grab and Preset Control<br>Memory Access Control<br>Display Memory Write Access<br>Refresh Addressing<br>Video Output | 27<br>28<br>29<br>30<br>31<br>32<br>33<br>34 |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

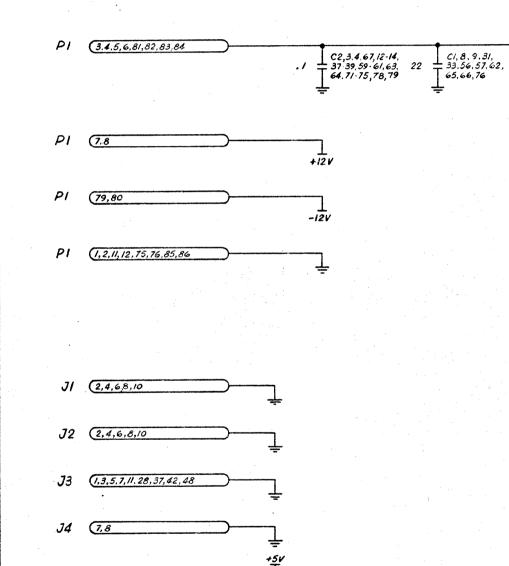

| 7.0<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5               | Connectors<br>PI (Bus Connector)<br>JI (Composite Video)<br>J2 (Direct Drive Outputs)<br>J3 (Video Bus)<br>J4 (Light Pen)                                                         | 35<br>35<br>36<br>36<br>36<br>37             |

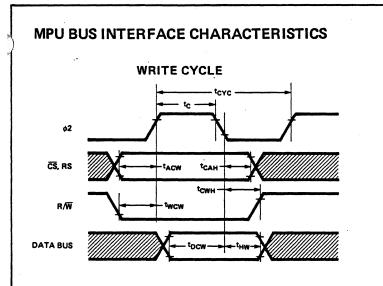

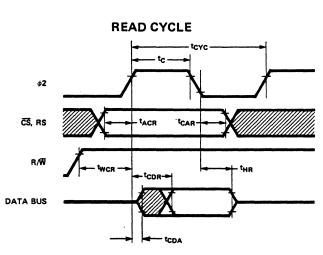

| 8.0<br>8.1<br>8.2                                    | Read/Write Timing<br>DMA Access Timing<br>I/O Access Timing                                                                                                                       | 38<br>38<br>39                               |

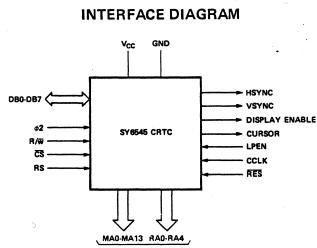

| 9.0                                                  | Applications                                                                                                                                                                      | 40                                           |

| 10.0                                                 | Maintenance and Warranty                                                                                                                                                          | 42                                           |

| 11.0                                                 | Ordering Information                                                                                                                                                              | 42                                           |

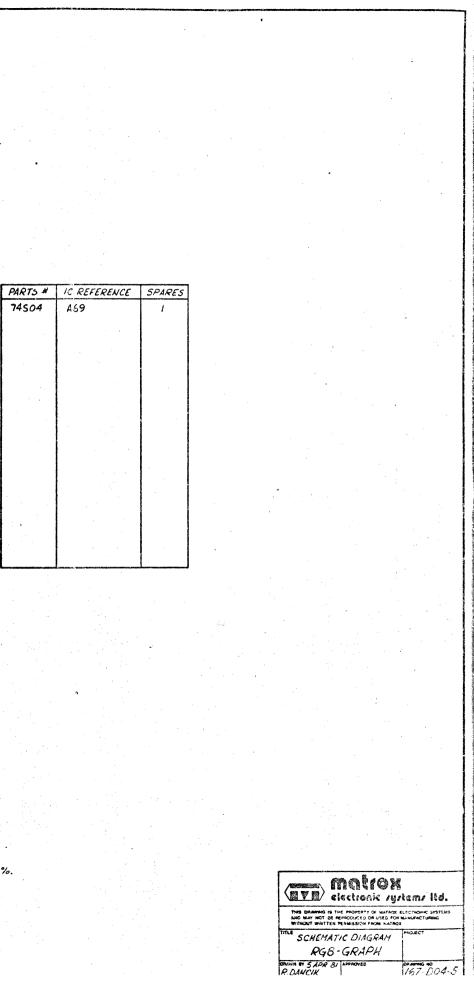

| 12.0                                                 | Data Sheets                                                                                                                                                                       | 43                                           |

| 13.0                                                 | Schematics                                                                                                                                                                        |                                              |

#### **1.0** SPECIFICATIONS:

Bus:

- Multibus plug-in. - 8 or 16 bit CPU.

- Resolution:

- RGB-Graph/16-1. 256 pixels x 256 pixels x 1 bit

- RGB-Graph/16-4. 256 pixels x 256 pixels x 4 bits

- RGB-Graph/32-1. 512 pixels x 256 pixels x 1 bit

- RGB-Graph/32-4. 512 pixels x 256 pixels x 4 bits

- RGB-Graph/64-1. 512 pixels x 512 pixels x 1 bit\*

- RGB-Graph/64-4. 512 pixels x 512 pixels x 4 bits\*

- The horizontal resolution of the -4 models can be doubled by sacrificing two bit planes.

\*On 480 pixels of the 512 pixel vertical resolution are displayed at any given time.

#### Display Memory Access:

- Normal: programmed I/O via X and Y address registers and data port.

- DMA: occupies 1K of system memory space.

- Access Time from CMD to XACK/:

- 500 ns to Address Register, Data Register, Status Register, and Vector Register.

- 50 ns to all other locations (DMA included) if no internal cycle resulting from a previous access is in process; if a subsequent access is made while an internal cycle is still in process, XACK/ will not be generated until that cycle is ended. See Table 1.1 for access cycle times.

| T           | X-Y  | CYCLE TIME (10.000MHz XTAL) |         |            |  |  |  |

|-------------|------|-----------------------------|---------|------------|--|--|--|

| RG8-GRAPH   | ZOOM | BEST TIME                   | AVERAGE | WORST TIME |  |  |  |

|             | X1   | 800n s                      | 1460ns  | 2.4us      |  |  |  |

| /16         | X2   | 800n s                      | 1230ns  | 2.4us      |  |  |  |

| F           | X4   | 800ns                       | 1020ns  | 2.4us      |  |  |  |

|             | Xl   | 400m s                      | 730ns   | 1.2us      |  |  |  |

| 132 AND 164 | X2   | 400n s                      | 615ns   | 1.2us      |  |  |  |

|             | X4   | 400ns                       | 510ns   | 1.2us      |  |  |  |

Table 1.1 - CYCLE TIMES

#### Special Functions:

- Independent X and Y Zoom:

- X-Zoom by 1,2,3,4,5,6,7, or 8

- Y-Zoom by 1,2, or 4

- Scroll and Pan:

- . horizontal pan with single pixel precision

- . vertical scroll with 8 pixel precision

- Fast preset of display to value in data port.

- DMA access to the Display Memory.

- Light Pen Register.

- Vector Plot.

- Access to each bit plane can be independently software disabled.

#### 1.0 <u>SPECIFICATIONS</u> (Cont'd):

- The video output from each bit plane can be independently software disabled.

- The TTL video outputs can be put in high impedence mode by software.

- Allows several RGB-Graphs to occupy the same position on the video bus.

- . Allows more than one RGB-Graph to use the same monitor.

- The fourth bit plane can be superimposed on the others.

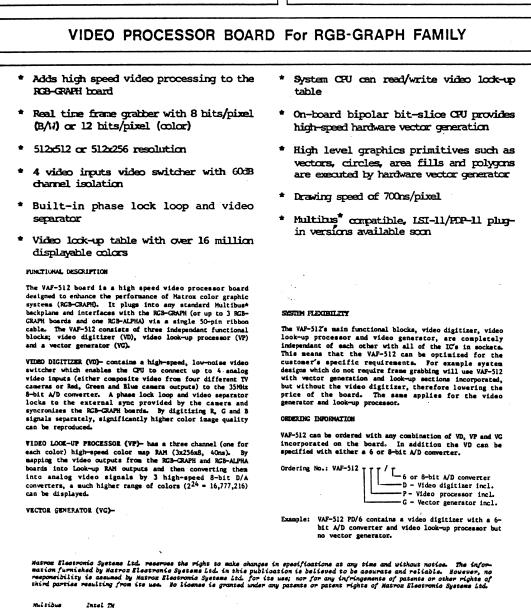

- Single or continuous frame grab with external frame grabber.

- Clipping of X and Y Registers.

- Grey scale DAC (functional only on boards with 4 bit planes).

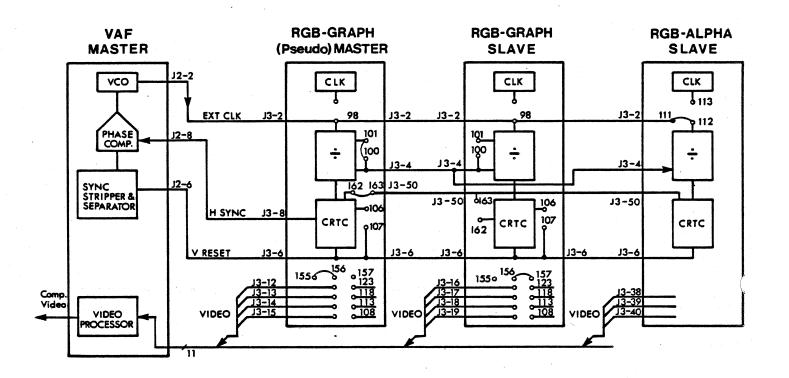

#### Video Bus:

- 16 bits of graphics video

- 8 bits of frame grab data

- Sync and control signals

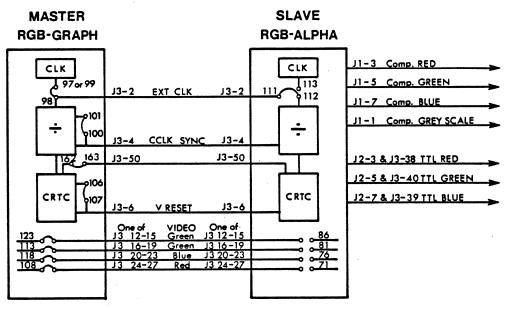

- Allows use of the RGB-Graph in groups of up to 4 (16 bits/pixel).

- Allows use of the RGB-Graph with the RGB-Alpha alphanumeric controller.

- Allows use of the RGB-Graph with the VAF board.

I/0:

- Occupies 16 I/O locations

- 3 or 12 bit I/O addresses

- Board I/O space can be strap-positioned on any 16 address boundary.

- T.V. Standard:

- European (50 Hz) or American (60 Hz) operation.

- Fully functional with 10 MHz RGB monitor.

- Grey scale functions with 10 MHz black and white monitor.

- Functional with standard and direct drive monitors.

#### Connectors:

- Pl, standard Multibus 86 pin edge connector: bus signals.

- J1, 10 pin right angle header AMP # 87578-2: composite video.

- J2, 10 pin right angle header AMP # 87578-2: outputs for direct drive monitors.

- J3, 50 pin right angle header MOLEX # 10-55-3505 (# 6874): video bus.

- J4, 10 pin right angle header MOLEX # 10-55-3103 (# 4700): light pen signals.

#### 1.0 SPECIFICATIONS (Cont'd):

| Power Requirements: | - RGB-Graph/16-1:                    |

|---------------------|--------------------------------------|

|                     | • +5V 5% @ 1.5A<br>• +12V 5% @ 35mA  |

|                     | • −12V 5% @ 30mA                     |

|                     | - RGB-Graph/16-4:                    |

|                     | • +5V 5% @ 1.8A                      |

|                     | • +12V 5% @ 128mA                    |

|                     | • −12V 5% @ 30mA                     |

|                     | - RGB-Graph/32-1: +5V 5% @ 2.0A      |

|                     | - RGB-Graph/32-4: +5V 5% @ 2.25A     |

|                     | - RGB-Graph/64-1: +5V 5% @ 2.5A      |

|                     | - RGB-Graph/64-4: +5V 5% @ 0.3A      |

| Dimensions:         | - Standard Multibus card size: 12 in |

|                     | inches (17.15 cm) high by 0.5 inche  |

nches (30.48 cm) wide by 6.75 ches (1.25 cm) thick.

Environmental:

- Operating temperature: 0 to 55 C - Relative humidity 0% to 90% non condensing.

#### 2.0 FUNCTIONAL DESCRIPTION:

The RGB-Graph is a Multibus compatible color graphics video controller board for use with RGB monitors. It is available in several models with maximum resolutions ranging from 256 pixels by 256 pixels by one bit plane to 512 pixels by 512 pixels by four bit planes. The 4 bit plane models can merge bit planes to double the horizontal resolution. The display format is set by the user during the programmed I/Oinitialization of the board.

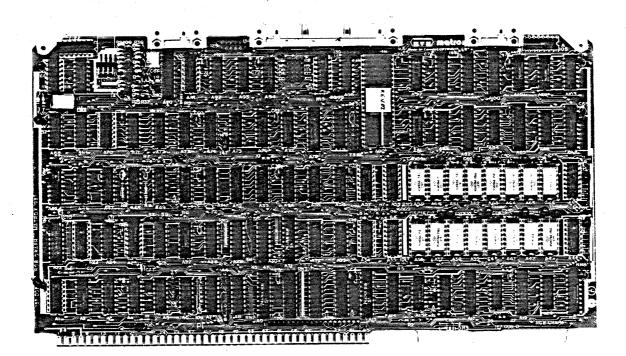

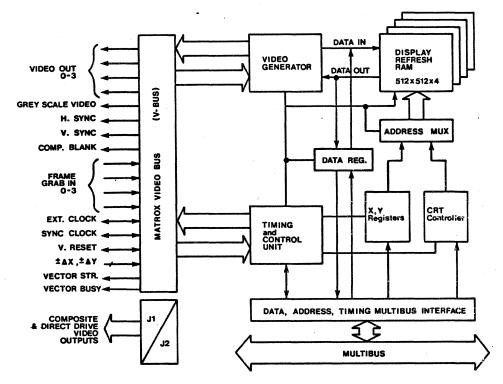

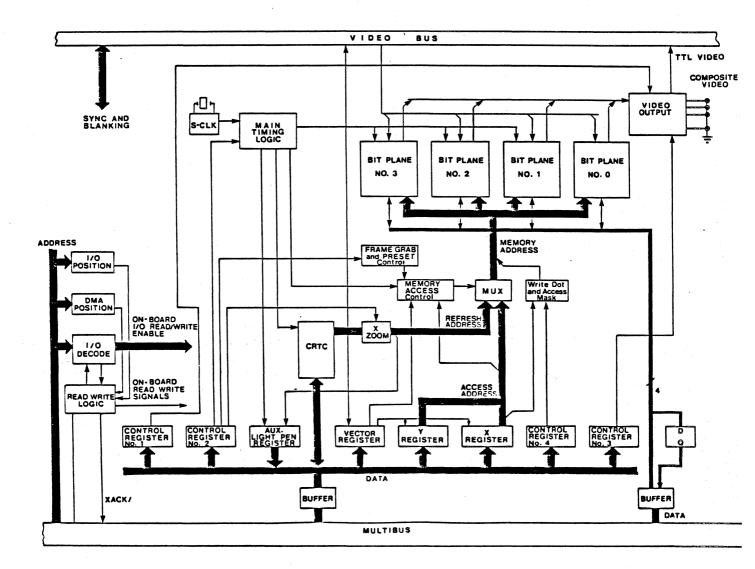

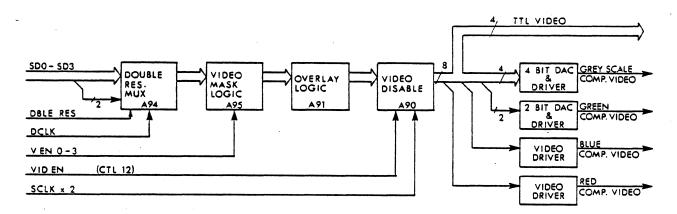

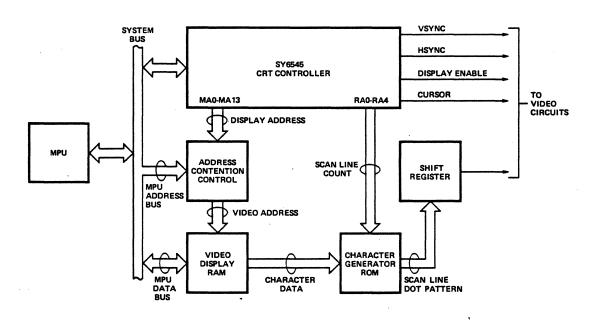

#### Figure 2.1 - RGB-GRAPH BLOCK DIAGRAM

#### 2.1 DISPLAY MEMORY ACCESS:

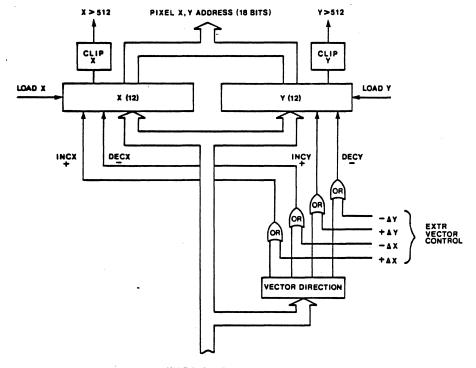

The RGB-Graph's display memory is normally accessed by programmed I/O: Display Memory locations corresponding to pixels are pointed to by the X and Y registers, and are accessed through the Data Register. The X and Y Registers, which contain the pixel's horizontal and vertical coordinates respectively, can be accessed by direct I/O or their contents can be modified via the Vector Register. Depending on the command loaded into it, the Vector Register increments or decrements, independently, the X and Y registers, and it can be commanded to automatically write the contents of the Data Register into the Display Memory. The Vector Register is used to rapidly draw horizontal, vertical or angular lines.

MULTIBUS DATA BUS Figure 2.2 - X AND Y REGISTERS

The Display Memory can also be accessed by an external DMA controller. When the RGB-Graph is used in DMA mode, it occupies 1K of system address space, that is positioned via straps. The DMA controller does each block transfer into this same 1K address block which is mapped into different areas of the Display Memory by the X and Y Registers. As the transfer proceeds, the X and Y Registers are automatically incremented.

The RGB-Graph also has a fast preset function which uses one command to fill the entire Display Memory with the data contained in the Data Register. Similarly, provision has been made for the Display Memory to be loaded from an external frame grabbing A to D converter. Both operations are completed in one frame period.

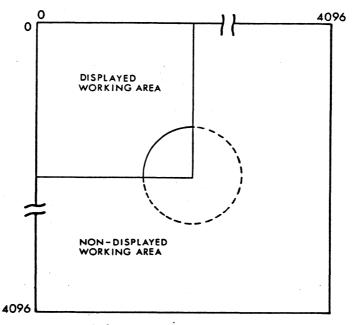

When the RGB-Graph is not in DMA Mode, the X and Y Registers are clipped so that any data written to pixels outside the display format will not wrap around on the Display. This provides a total working area, displayed and non-displayed, of 4096 pixels by 4096 pixels for all formats (see figure 2.3).

#### 2.1 DISPLAY MEMORY ACCESS (Cont'd):

Figure 2.3 - NON-DISPLAYED WORKING AREA

If the user wants the image to wrap around he can put the board in DMA mode, and use the usual I/O access to the Display Memory.

Normally all bit planes are written to simultaneously; however, the RGB-Graph has a mask register which allows write access to be interdicted to any or all of the bit planes.

#### 2.2 DISPLAY MANIPULATION:

The RGB-Graph allows the user to zoom into the display. That is to say, a portion of the display can be selected and expanded to replace the original image from which it was taken. Horizontal expansion (x-zoom) and vertical expansion (y-zoom) are independently controlled allowing the user to make distorting as well as non-distorting zooms. Horizontal zooms can be made by factors of 1, 2, 3, 4, 5, 6, 7 and 8; vertical zooms can be made by factors of 1, 2, and 4.

The display can be panned horizontally with single pixel precision in both directions, and it can be vertically scrolled with 8 pixel precision in both directions.

A series of light pen registers are provided which allow the CPU to determine the position of a light pen to within one pixel.

#### 2.3 VIDEO:

The RGB-Graph has three composite video outputs for color (red, green and blue). One of these outputs (nominally green) can be intensity controlled by a 2 bit D/A converter connected to bit planes 2 and 3. A 4 bit D/A converter supplies another composite video output for grey scale applications. Each bit plane also has two separate TTL video outputs: one for direct drive monitors and one for the video bus connector. The video bus is a connection system that allows the RGB-Graph to be used with other video control products from Matrox (see section 9).

The video outputs can be controlled via a video mask register and by a video enable bit in Control Register No. 1. The video mask register allows the user to individually disable output from any of the bit planes: the disabled outputs, TTL and composite video, go to black. The video enable bit disables all of the outputs together: the composite outputs go to black and the TTL outputs go to high impedence mode (tristate). The high impedence mode allows more than one RGB-Graph to share the same direct drive monitor and it allows several boards to occupy the same position on the video bus.

If required, the video from bit plane 4 can be disconnected from the 2 bit color output and used to overlay the video from bit planes 1, 2, and 3: this can be an AND, NAND, OR, or XOR operation. The overlay allows the fourth bit plane to be used for alphanumeric or similar data.

### 3.0 <u>START-UP PROCEDURE</u>:

The following familiarization procedure will not be valid if the as-shipped strap configuration is changed or if a direct drive monitor is used.

- 1. Visually inspect the board for any shipping damage.

- 2. Plug the board into a Multibus system and connect an R.G.B. monitor. The video connections will depend on the monitor used; however, section 7 shows where to find any of the video or sync signals that might be required. If one of the RGB-Graph-1 models is being used it will only have one bit plane which should be connected to a monochrome monitor via the red composite video output.

- 3. Use the procedure in table 3.1 to initialize the display. It will establish the maximum single density format for the particular RGB-Graph model being used.

|                                                                                                                                                     |       |       | DA    | T.A.  | ۰.    |       |                                                                                                                                                                                                                                                     |                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| STEP                                                                                                                                                | /1    | 6     | • /:  | 32    | 1     | 54    | 1/0<br>LOCATION                                                                                                                                                                                                                                     | COMMENTS                                                                                                   |

|                                                                                                                                                     | 60 HZ | 50 HZ | 60 HZ | 50 HZ | 60 HZ | 50 HZ | ан (т. 1997)<br>1997 - С. 1997 - С. 1<br>1997 - С. 1997 - С. 19 |                                                                                                            |

| 1                                                                                                                                                   | 2 OH  | A6H.                                                                                                                                                                                                                                                | Control Register No. 1 is initialized;<br>video enabled, single density, no DMA, no                        |

| 2                                                                                                                                                   | 2 OH  | A6H                                                                                                                                                                                                                                                 | frame grab, no preset. Note that two<br>identical outputs are required to in-<br>initialize this register. |

| 3                                                                                                                                                   | 3FH   | 3FH   | 3FH   | 3FH   | 3FH   | Зғн   | A7H                                                                                                                                                                                                                                                 | Control Register No. 2 is initialized;<br>X-Pan=0, X-Zoom=1, Y-Zoom=1.                                     |

| 4                                                                                                                                                   | OFH   | OFH   | OFH   | OFH   | OFH   | OFH   | A8H                                                                                                                                                                                                                                                 | Control Register No. 3 is initialized; all video outputs are enabled.                                      |

| 5                                                                                                                                                   | 00н   | 00н   | 00н   | 00H   | 00H   | 00H   | AAH                                                                                                                                                                                                                                                 | Control Register No. 4 is initialized;<br>access to all bit planes is enabled.                             |

| 6                                                                                                                                                   | 00H   | OOH   | 00H   | 00H   | 00H   | OOH   | ACH                                                                                                                                                                                                                                                 | The horizontal total minus one is                                                                          |

| 7                                                                                                                                                   | 27H   | 27H   | 4FH   | 4FH   | 4FH   | 4EH   | AEH                                                                                                                                                                                                                                                 | written to CRTC-RO.                                                                                        |

| 8                                                                                                                                                   | 01H   | 01H   | 01H   | 01H   | 01H   | 01H   | ACH                                                                                                                                                                                                                                                 | The format width, in cells, is written                                                                     |

| 9                                                                                                                                                   | 20H   | 20H   | 40H   | 40H   | 40H   | 40H   | AEH                                                                                                                                                                                                                                                 | to CRTC-R1.                                                                                                |

| 10                                                                                                                                                  | 02H   | 02H   | 02H   | 02H   | 02H   | 02H   | ACH                                                                                                                                                                                                                                                 | The horizontal sync position is written                                                                    |

| 11                                                                                                                                                  | 21H   | 21H   | 45H   | 45H   | 45H   | 45H-  | AEH                                                                                                                                                                                                                                                 | to CRTC-R2.                                                                                                |

| 12                                                                                                                                                  | 03H   | 03H   | 03H   | 03H   | 03H   | 03H   | ACH                                                                                                                                                                                                                                                 | The horizontal and vertical sync widths                                                                    |

| 13                                                                                                                                                  | 33H   | 33H   | 36H   | 36H   | 36H   | 36H   | AEH                                                                                                                                                                                                                                                 | are written to CRTC-R3.                                                                                    |

| 14                                                                                                                                                  | 04H   | 04H   | 04H   | 04H   | 04H   | 04H   | ACH                                                                                                                                                                                                                                                 | The vertical total minus one is written                                                                    |

| 15                                                                                                                                                  | 1FH   | 26H   | 1FH   | 26H   | 3FH   | 4DH   | AEH                                                                                                                                                                                                                                                 | to CRTC-R4.                                                                                                |

| 16                                                                                                                                                  | 05H   | 05H   | 05H   | 05H   | 05H   | 05H   | ACH                                                                                                                                                                                                                                                 | The vertical adjust parameter is written                                                                   |

| 17                                                                                                                                                  | 04H   | 00H   | 04H   | OOH   | 04H   | 00H   | AEH                                                                                                                                                                                                                                                 | to CRIC-R5.                                                                                                |

| 18                                                                                                                                                  | 06H   | 06H   | 06H   | 06H   | 06H   | 06H   | ACH                                                                                                                                                                                                                                                 | The format height, in cells, is written                                                                    |

| 19                                                                                                                                                  | 1EH   | 20H   | 1EH   | 20H   | 3CH   | 40H   | AEH                                                                                                                                                                                                                                                 | to CRTC-R6.                                                                                                |

| 20                                                                                                                                                  | 07H   | 07H   | 07H   | 07H   | 07H   | 07₩   | ACH                                                                                                                                                                                                                                                 | The vertical sync position is written to                                                                   |

| 21                                                                                                                                                  | lfh   | 24H   | 1FH   | 24H   | 3 DH  | 4BH   | AEH                                                                                                                                                                                                                                                 | CRTC-R7.                                                                                                   |

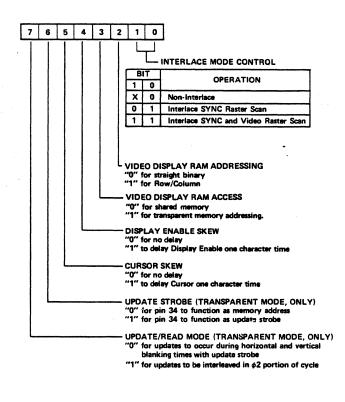

| 22                                                                                                                                                  | 08H   | 08H   | 08H   | 08H   | 08H   | 08H   | ACH                                                                                                                                                                                                                                                 | CRTC-R8 is programmed for row and column                                                                   |

| 23                                                                                                                                                  | 04H   | 04H   | 04H   | 04H   | 07H   | 07H   | AEH                                                                                                                                                                                                                                                 | addressing & to appropriate interlace mode                                                                 |

| 24                                                                                                                                                  | 09H   | 09H   | 09H   | 09H   | 09H   | 09H   | ACH                                                                                                                                                                                                                                                 | The No. of scan lines/field per cell row                                                                   |

| 25                                                                                                                                                  | 07H   | 07H   | 07H   | 07H   | 07H   | 07H   | AEH                                                                                                                                                                                                                                                 | minus one is written to CRTC-R9.                                                                           |

| 26                                                                                                                                                  | OCH   | 0CH   | OCH   | OCH   | 0CH   | OCH   | ACH                                                                                                                                                                                                                                                 | The starting address is set to row zero                                                                    |

| 27                                                                                                                                                  | 00H   | 00H   | 00H   | 00H   | 00H   | OOH   | AEH                                                                                                                                                                                                                                                 | column zero.                                                                                               |

| 28                                                                                                                                                  | ODH   | ODH   | ODH   | ODH   | ODH   | ODH   | ACH                                                                                                                                                                                                                                                 | · · · ·                                                                                                    |

| 29                                                                                                                                                  | 00H   | OOH   | 00H   | OOH   | 00H   | OOH   | AEH                                                                                                                                                                                                                                                 |                                                                                                            |

| Following the above steps in order, output the 50 or 60Hz data that corresponds to the board's model No. $(/16-/64)$ to the I/O location indicated. |       |       |       |       |       |       |                                                                                                                                                                                                                                                     |                                                                                                            |

Table 3.1 - DISPLAY INITIALIZATION

- 4. The display should now be showing random data. Clear the display by outputting OOH to the Data Register at A4H then outputting AOH to Control Register no. 1 at A6H.

- 5. Enter and run the following program, which will fill an RGB display with vertical color bars. On a monochrome monitor, it will be seen as a series of vertical bars at different positions across the screen.

#### 3.0 START-UP PROCEDURE (Cont'd)

| ADDRESS | OP-CODE | MNEMONIC    | ADDRESS | OP-CODE | MNEMONIC    |

|---------|---------|-------------|---------|---------|-------------|

| 100     | 3E      | LD, A, OF   | 11A     | A3      |             |

| 101     | OF      |             | 11B     | , 7B    | LD A, E     |

| 102     | - D3    | OUT A8, A   | 11C     | D3      | OUT A4, A   |

| 103     | A8      |             | 11D     | A4      |             |

| 104     | 01      | LD BC,01 FF | 11E     | 79      | LD A, C     |

| 105     | FF      |             | 11F     | A7      | AND A       |

| 106     | 01      |             | 120     | C2      | JP NZ,0114  |

| 107     | 21      | LD HL, 0000 | 121     | 14      |             |

| 108     | 00      |             | 122     | 01      |             |

| 109     | 00      |             | 123     | 05      | DEC B       |

| 10A     | 1E      | LD E, 3F    | 124     | F2      | JP P, 0114  |

| 10B     | 3F      |             | 125     | 14      |             |

| 10C     | 16      | LD D, 08    | 126     | 01      |             |

| 10D     | 08      |             | 127     | 23      | INC HL      |

| 10E     | 7D      | LD A, L     | 128     | 01      | LD BC, 01FF |

| 10F     | D3      | OUT AO, A   | 129     | FF      |             |

| 110     | A0      |             | 12A     | 01      |             |

| 111     | 7 C     | LD A, H     | 12B     | 15      | DEC D       |

| 112     | D3      | OUT A1, A   | 12C     | C2      | JP NZ, 010E |

| 113     | Al      |             | 12D     | OE      |             |

| 114     | OD      | DEC C       | 12E     | 01      |             |

| 115     | 79      | LDA, C      | 12F     | 1D      | DEC E       |

| 116     | D3      | OUT A2, A   | 130     | F2      | JP P, 010C  |

| 117     | A2      |             | . 131   | 0C      |             |

| 118     | 78      | LD A, B     | 132     | 01      |             |

| 119     | D3      | OUT A3, A   | 133     | 76      | HALT        |

#### COLOR BARS

#### 4.0 PROGRAMMING:

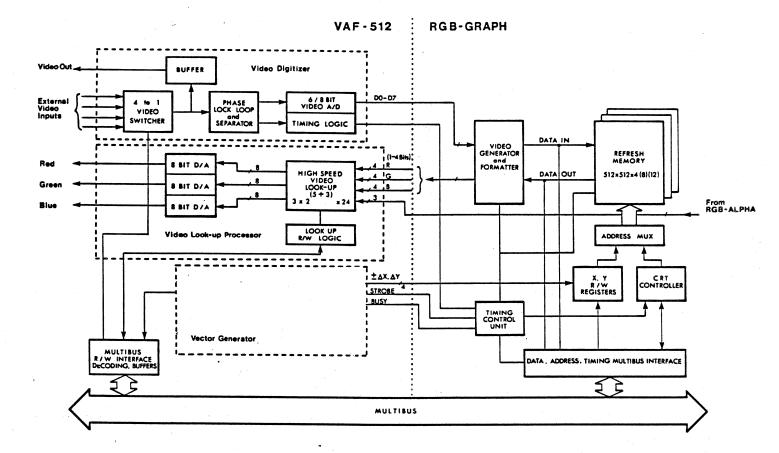

The RGB-GRAPH is initialized and controlled by programmed I/O to a series of registers. There are 15 directly accessed registers plus 14 CRTC registers that are indirectly accessed through an address register and data port. Section 4.3 contains detailed descriptions of the directly accessed registers and the CRTC data sheets in Section 12 contain descriptions of the CRTC registers. Table 4.1 gives a brief overview of the directly accessed registers.

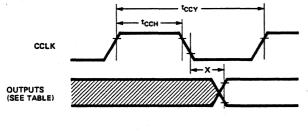

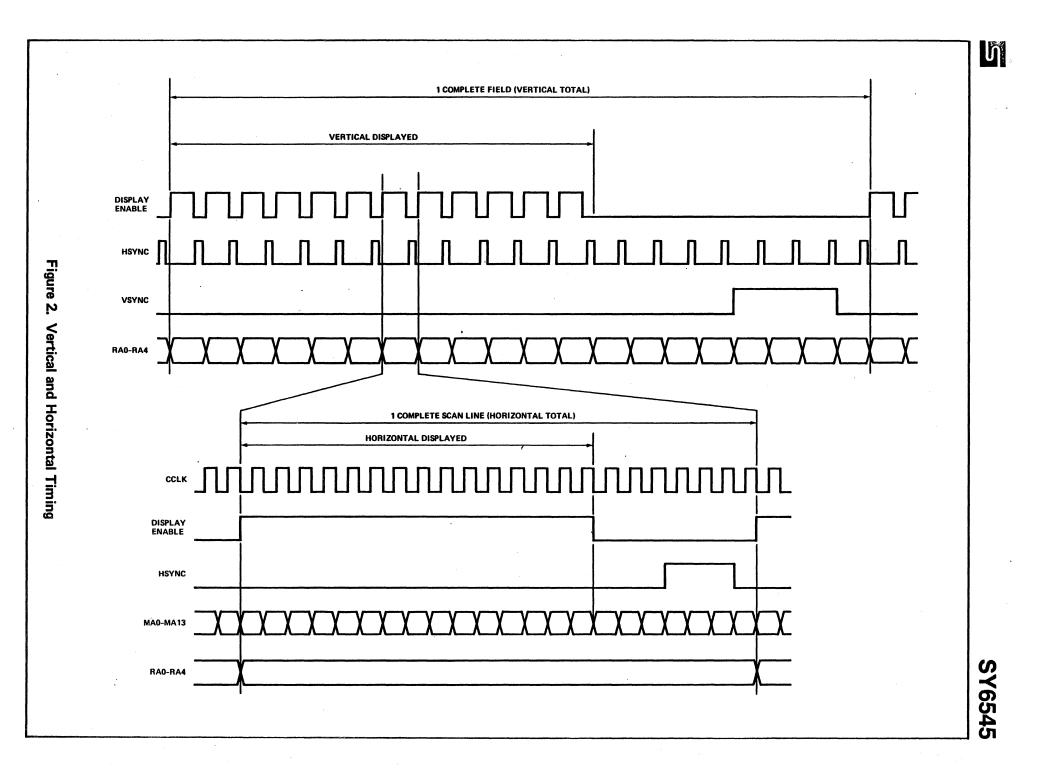

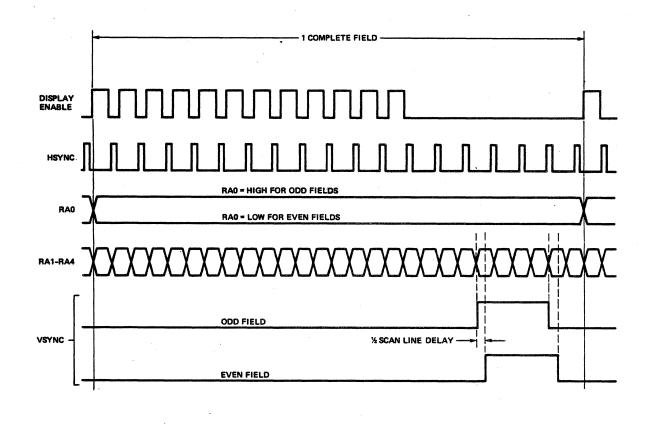

Because the CRTC was intended for use with alphanumeric displays, the data sheets refer to characters and the character clock; however, as far as the RGB-GRAPH is concerned, the user should read "8 x 8 pixel graphics cell" instead of "character", and "cell clock" instead of "character clock".

The display format is established during the initialization routine by writing the format parameters to Control Register No. 2 and certain CRTC registers. Table 4.1 shows which parameter must be written to which register to establish the standard maximum density format for the particular model of RGB-GRAPH that is being used. The user may, however, wish to establish a non-standard format to facilitate some graphics applications. If this is the case, the format parameters can be calculated using the formula given in Section 4.2.

Note that section 4.4 has been dedicated to the zoom function.

### 4.0 PROGRAMMING (Cont'd):

| RELATIVE                                                                                                                                                                            | DIRECTION     | NAME                              | FUNCTION                                                                                       |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------|------------------------------------------------------------------------------------------------|--|--|--|

| 00 <sub>H</sub>                                                                                                                                                                     | WRITE<br>ONLY | X-Register LOW                    | Pixel X-coordinate (XO-X7)                                                                     |  |  |  |

| 01 <sub>H</sub>                                                                                                                                                                     | WRITE<br>ONLY | X-Register HIGH                   | Pixel X-coordinate (X8-X11)                                                                    |  |  |  |

| 02 <sub>H</sub>                                                                                                                                                                     | WRITE<br>ONLY | Y-Register LOW                    | Pixel Y-coordinate (Y0-Y7)                                                                     |  |  |  |

| 03 <sub>H</sub>                                                                                                                                                                     | WRITE<br>ONLY | Y-Register HIGH                   | Pixel Y-coordinate (Y8-Y11)                                                                    |  |  |  |

| 04 <sub>H</sub>                                                                                                                                                                     | WRITE<br>READ | Data Reg. LOW                     | Data registers contain pixel data<br>(color). From 4 bits/pixel (1 x RGB-                      |  |  |  |

| 05 <sub>H</sub>                                                                                                                                                                     | WRITE<br>READ | Data Reg. HIGH                    | GRAPH) to 16 bits/pixel (4 x RGB-<br>GRAPH) user strappable.                                   |  |  |  |

| 06 <sub>H</sub>                                                                                                                                                                     | READ<br>ONLY  | Status Register                   | CLEAR/, PRESET/, Frame Grab Flag                                                               |  |  |  |

| 06 <sub>H</sub>                                                                                                                                                                     | WRITE<br>ONLY | Control Register<br>Number 1      | Video Enable, Double Resolution,<br>DMA Mode, Continous Frame Grab,<br>Display Preset Control. |  |  |  |

| 07 <sub>H</sub>                                                                                                                                                                     | WRITE<br>ONLY | Control Register<br>Number 2      | X-Pan, X-Zoom, Y-Zoom                                                                          |  |  |  |

| 08 <sub>H</sub>                                                                                                                                                                     | READ<br>ONLY  | Aux. Light Pen<br>Register        | Light Pen Pixel Position                                                                       |  |  |  |

| 08 <sub>H</sub>                                                                                                                                                                     | WRITE<br>ONLY | Control Register<br>Number 3 LOW  | Video enable register (Video Mask)<br>From 4 bits/pixel (1 x RGB-GRAPH) to                     |  |  |  |

| 09 <sub>H</sub>                                                                                                                                                                     | WRITE<br>ONLY | Control Register<br>Number 3 HIGH | 16 bits/pixel (4 x RGB-GRAPH) user<br>strappable within two bytes.                             |  |  |  |

| 0A <sub>H</sub>                                                                                                                                                                     | WRITE<br>ONLY | Control Register<br>Number 4 LOW  | (Preset Mask)                                                                                  |  |  |  |

| ОВ <sub>Н</sub>                                                                                                                                                                     | WRITE<br>ONLY | Control Register<br>Number 4 HIGH | From 4 bits to 16 bits, user<br>strappable within two bytes                                    |  |  |  |

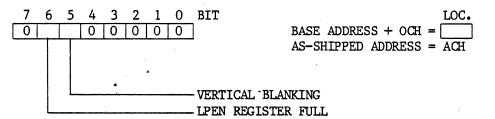

| OC <sub>H</sub>                                                                                                                                                                     | READ<br>ONLY  | CRTC Status<br>Register           | Vertical Blanking Flag<br>Light Pen Register Full Flag                                         |  |  |  |

| OC H                                                                                                                                                                                | WRITE<br>ONLY | CRTC Address<br>Register*         | Address for CRTC's Internal Reg.                                                               |  |  |  |

| OEH                                                                                                                                                                                 | WRITE<br>READ | CRTC Data<br>Register*            | Data Port for CRTC's Internal Reg.                                                             |  |  |  |

| OFH                                                                                                                                                                                 | WRITE<br>ONLY | Vector Register                   | Increment/decrement control for<br>X,Y registers for vector plots                              |  |  |  |

| * These two registers indirectly access 14 more registers within the<br>CRTC, specifying such video parameters as horizontal and vertical<br>Sync, Blanking, Frequency Format, etc. |               |                                   |                                                                                                |  |  |  |

Table 4.1 - DIRECTLY ACCESSED REGISTER-OVERVIEW

#### 4.1 FORMAT PROGRAMMING TABLES

The following table shows which format parameters must be written to which registers to establish the standard maximum density formats. Note that there is a column of American parameters (60Hz) and a column of European (50Hz) parameters for each model of the RGB-Graph. Note that for American Standard displays, only 480 pixels of the 512 vertical resolution are visable at any time. The non-displayed portion can be scrolled onto the screen.

| RGB-GRAPH            | /16       |      | /32   |           | /64  |           |      |

|----------------------|-----------|------|-------|-----------|------|-----------|------|

| SINGLE DENSITY FORMA | 256 x 256 |      | 512 > | 512 x 256 |      | 512 x 512 |      |

| AMERICAN / EUROPEAN  |           | 60HZ | 50HZ  | 60HZ      | 50HZ | 60HZ      | 50HZ |

| Control Register No. | 2         | 3FH  | 3FH   | 3FH       | 3FH  | 3FH       | 3 FH |

| H. Total             | RO        | 27H  | 27H   | 4FH       | 4FH  | 4FH       | 4 FH |

| H. Displayed,        | R1        | 2 OH | 2 OH  | 40H       | 4 OH | 40H       | 4 OH |

| H. Sync. Position,   | R2        | 21H  | 21H   | 45H       | 45H  | 45H       | 45H  |

| V. & H. Sync Width   | R3        | 33H  | 33H   | 36H       | 36H  | 36H       | 36H  |

| V. Total,            | R4        | lfh  | 26H   | 1FH       | 26H  | 3FH       | 4 DH |

| V. Adjust,           | R5        | 04H  | OOH   | 04H       | 00H  | 04H       | OOH  |

| V. Displayed,        | R6        | 1EH  | 2 OH  | 1EH       | 2 OH | 3 CH      | 4 OH |

| V. Sync. Position,   | R7        | lFH  | 24H   | 1FH       | 24H  | 3 DH      | 4BH  |

| Mode Control,        | R8        | 04H  | 04H   | 04H       | 04H  | 07H       | 07H  |

| Scan Line            | R9        | 07H  | 07H   | 07H       | 07H  | 07H       | 07H  |

| Display Start High   | R12       | OOH  | OOH   | OOH       | OOH  | OOH       | 00H  |

| Display Start Low    | R13       | OOH  | 00н   | ООН       | ООН  | ООН       | OOH  |

Table 4.2 - STANDARD FORMATS

#### 4.2 FORMAT PARAMETER CALCULATIONS:

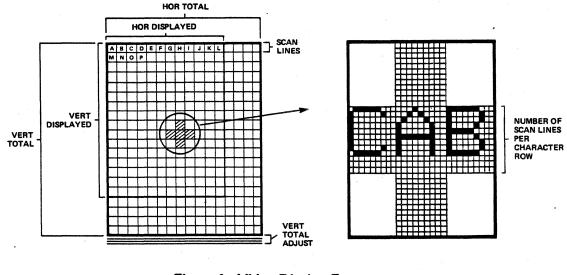

The RGB-GRAPH's format is set by the X and Y zoom factors in Control Register No. 2 and by format parameters written to registers in the board's CRTC. Because the CRTC, an LSI video controller chip, was designed primarily to refresh alphanumerics displays, it sees the display as a field of graphics cells equivalent to characters and it refreshes the display at that level. Each of these graphics cells is 8 pixels by 8 pixels in size; display refresh at the pixel level within the cells is taken care of by circuitry external to the CRTC. Because the format is programmed in the CRTC, which operates at the cell level, the number of pixels in the X or Y axis of any format must be a multiple of 8. If the user conforms to this restriction, he can use the formulas in this section to calculate the parameters for a large number of different formats. The only other restriction, of course, is that the number of pixels in the format times the number of bit planes used must not exceed the capacity of the Display Memory.

In some cases, the user may find that the display does not cover as much of the CRT as might be wished. If such is the case he still has the option of changing the crystal to a lower frequency.

The following is a list of formulas that can be used to calculate the format parameters for irregular formats or the parameter changes required for zoom operations:

4.2

- FORMAT PARAMETER CALCULATIONS:

- 1. Dot Clock = Crystal Freq. X-Zoom Factor

- 2. Cell Clock =  $\frac{\text{Dot Clock}}{8}$

The Cell Clock is the same as the character clock referred to in the CRTC data sheets.

3. HORIZONTAL TOTAL = Monitor Spec. Horiz. Scan Period Cell Clock Period

Choose the nearest integer minus one. This value is written in HEX format to RO.

4. HORIZONTAL DISPLAYED = <u>Total X-Axis Pixels</u>

This is the number of graphics cells in the X-AXIS of the format and is written in HEX to Rl.

5. HORIZONTAL SYNC. POSITION H. Displayed + (<u>H. Total - H. Displayed</u>) 2

This value may require adjustment. It is written in HEX to R2

- 6. ACTUAL HORIZONTAL SCAN PERIOD = <u>Horizontal Total</u> Cell Clock

- 7. CELL ROW PERIOD = Y-Zoom Factor x 8 x Actual Horizontal Scan Period

- 8. VERTICAL TOTAL = <u>Vertical Scan Period</u> Cell Row Period

This value minus one is written in HEX to R4. The vertical scan period is 16.667ms on American systems and 20.000ms for European systems.

- 9. VERTICAL TOTAL ADJUST = (<u>Vertical Scan Period</u> -(<u>V. Total x Cell Row Period</u>)) Actual Horizontal Scan Period Choose the nearest integer. This value is written in HEX to R5.

- 10. VERTICAL DISPLAYED = <u>Total Y-Axis Pixels</u> 8 This value is written in HEX to R6.

- 11. VERTICAL SYNC. POSITION V. Displayed + (V. Total -V. Displayed) Adjust the value as required. It is written in HEX to R7.

- 12. SCAN LINE = 8 x Y ZOOM FACTOR This value minus one is written in HEX to R9.

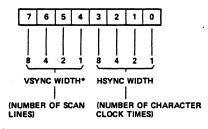

- 13. HORIZONTAL SYNC. WIDTH = <u>Monitor Spec. H. Sync. Width</u> Cell Clock Period Choose the nearest integer. This value goes to bits 0-3 of R3.

- 14. VERTICAL SYNC WIDTH = <u>Monitor Spec. V. Sync. Width</u> Actual Horizontal Scan Period Choose the nearest integer. This value goes to bits 4-7 of R3.

#### 4.3 REGISTERS:

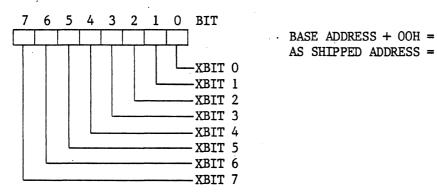

#### 4.3.1 X-REGISTER LOW:

WRITE ONLY

This register holds the lower 8 bits of the X coordinate of the display memory location that is to be accessed.

LOC.

AOH

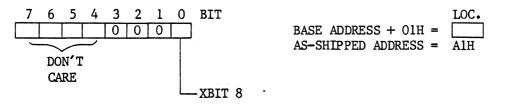

#### 4.3.2 X-REGISTER HIGH:

WRITE ONLY

This register holds the 9th bit of the X coordinate for the RGB-GRAPH/32 and the RGB-GRAPH/64. If a One is written to any of bits 1-3 the clipping circuit will interdict memory access. This also applies to Bit 0 on the RGB-GRAPH/16.

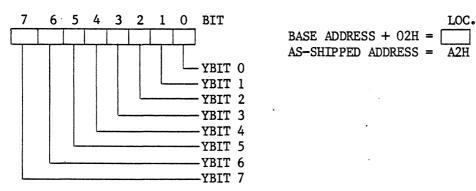

#### 4.3.3 Y-REGISTER LOW:

#### WRITE ONLY

This register holds the lower 8 bits of the Y coordinate of the display memory location that is to be accessed.

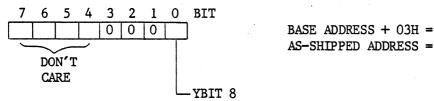

4.3.4 Y-REGISTER HIGH:

WRITE ONLY

This register holds the 9th bit of the Y coordinate for the RGB-GRAPH/64. If a One is written to any of Bits 1-3 the clipping circuit will interdict memory access. This also applies to Bit 0 on the RGB-GRAPH/16 and RGB-GRAPH/32.

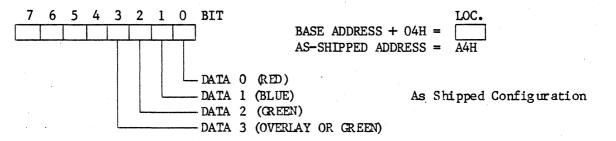

#### 4.3.5 DATA REGISTER LOW:

#### READ/WRITE

Any four bits of this register can be used as a data port to the Display Memory if the appropriate straps are installed (see Section 5.2). When the board is shipped, straps are installed which allow the display memory to be accessed through the four least significant bits of this register, as shown above. Bits not selected for use are don't care for write and zero for read.

#### 4.3.6 DATA REGISTER HIGH:

READ/WRITE

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | BIT |

|---|---|---|---|---|---|---|---|-----|

|   |   |   |   |   |   |   |   |     |

LOC. BASE ADDRESS + 05H = AS-SHIPPED ADDRESS = A5H

As in the case of the Data Register Low, any four bits of this register can be used as a data port to the Display Memory if the appropriate straps are installed (see Section 5-3). Any bits not selected are "don't care" for write and zero for read.

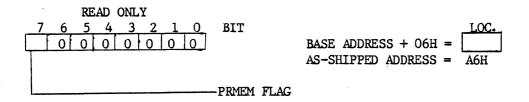

#### 4.3.7 STATUS REGISTER:

- Bit 7: PRMEM FLAG. When this bit is one, the memory is being preset or a frame grab is in process. When this bit is zero, the memory is neither being preset nor is a frame grab in process.

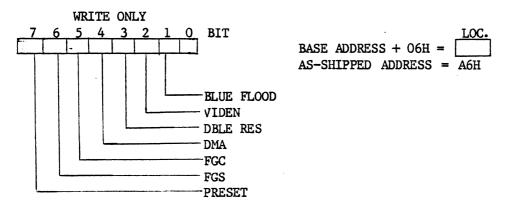

- 4.3.8 CONTROL REGISTER NO. 1

- BIT 1: BLUE FLOOD. When this bit is zero, operation is normal. When this bit is one, the Blue output is driven on during active video. BLUE FLOOD is used to provide a visible raster to trigger the light pen. When activated, it is only generated on the composite video output; the TTL output are not affected.

- Bit 2: VIDEN. When this bit is zero, TTL video is enabled. When this bit is one, TTL video is in high impedence (tri-state) mode.

- Bit 3: DBLE RES. When this bit is one, bit planes 0 and 2 are multiplexed together and bit planes 1 and 3 are multiplexed together to provide twice the X-AXIS resolution. Note however, that the bits per pixel are halved. When this bit is zero, resolution is normal and there are four independent bit planes.

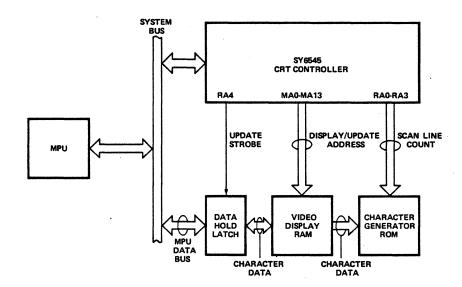

- Bit 4: DMA. When this bit is one, the Display Memory can be accessed by DMA. All DMA transfers are made at the same 1K block of system address space, the base address of which, is set by straps (see Section 5.4). This system address space is mapped into different areas of the Display Memory, before the block transfer, by loading the X and Y Registers with the transfer's Display Memory starting address minus one. As the transfer proceeds, the X and Y Registers are automatically incremented before each byte transfer. When several 1K blocks are sequentially transferred to or from contiguous Display Memory, the X-Y starting address need only be loaded before the first block transfer.

When bit 4 is zero the RGB-GRAPH's Display Memory is accessed normally and the X and Y registers must be loaded with a new set of coordinates before each byte or word transfer.

#### 4.3.8 CONTROL REGISTER NO. 1 (Cont'd):

- Bit 5: FGC. When this bit is 0, the RGB-GRAPH operates in continuous frame grab mode. If a frame grabber is connected, the board will continually grab and display sequential frames: in effect, it will display what the camera sees. When the bit is 1, the RGB-GRAPH will freeze the frame that was in the display memory at the time the bit changed state. The user can watch the action, then freeze it.

- Bit 6: FGS. This bit is also provided for frame-grabbing operations. If a one is written to FGS, the RGB-GRAPH will grab and hold a single frame of video information. It will continue to display the information until one is again written to FGS, at which time a new frame will be grabbed. If a zero is written to this bit, it will have no effect.

- Bit 7: PRESET. When a one is written to this bit, the Display Memory will be preset to the value in the Data Register. If a zero is written to this bit, it will have no effect.

- NOTE: During initialization, the output operation to this register must be repeated twice. After initialization, one output is enough to load the register.

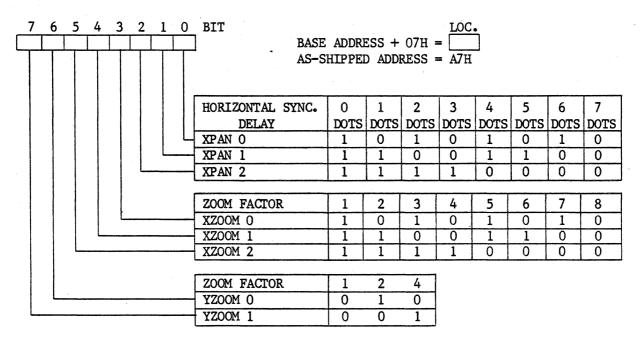

#### 4.3.9 CONTROL REGISTER NO. 2:

WRITE ONLY

NOTE: X zooms of greater than 4 are not possible when using the 256 x 256 format.

#### 4.3.9 CONTROL REGISTER NO. 2 (Cont'd):

- Bit O-2: XPANO-XPAN2. These three bits are used in conjunction with the CRTC starting address registers (R12 and R14) to horizontally pan the display. XPANO-XPAN2 can be set to delay the horizontal sync. pulse by 1 through 7 dots (see Table above). A pan is accomplished by sequentially incrementing this delay until it reaches 7 dots then resetting XPANO-XPAN2 and incrementing the CRTC starting address registers during vertical blanking. This operation is repeated at a rate that will give the required pan speed.

- Bit 3-5: XZ00MO-XZ00M2. These three bits are used in conjunction with several CRTC registers (R0, R1, R2, R3, R12, R13) to expand the display along the horizontal axis (see Section 4.4).

- Bit 6 & 7: YZOOMO and YZOOM1. These two bits are used in conjunction with several CRTC registers (R3, R4, R5, R6, R7, R9, R12, R13) to expand the display along the vertical axis (see Section 4.4).

NOTE: For a normal display, X and Y zoom factors of one must be loaded.

#### 4.3.10 AUXILIARY LIGHT PEN REGISTER:

READ ONLY

|                        | LOC. |

|------------------------|------|

| BASE ADDRESS + $08H =$ |      |

| AS-SHIPPED ADDRESS =   | A8H  |

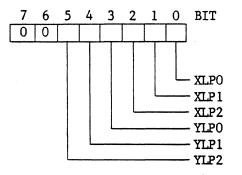

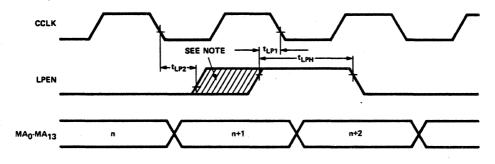

- Bits O-2: XLPO-XLP2. These bits are the three least significant bits of the light pen X coordinate. The most significant bits are provided by CRTC R17: bits O-4 represent XLP3-XLP7 for 256 x 256 formats and bits O-5 represent XLP3-XLP8 for 512 x 512 formats. Note that the data from CRTC R17 must be shifted to the left three bits before they can be combined with XLPO-XLP2 from this register. Unused bits in CRTC R17 are zero.

- Bits 3-5: YLPO-YLP2. These bits are the three least significant bits of the light pen Y coordinate. The most significant digits are provided by CRTC R16: bits 0-4 represent YLP3-YLP7 for 256 x 256 formats and bits 0-5 represent YLP3-YLP8 for 512 x 512 formats. Note that the data from CRTC R16 must be shifted three spaces to the left before it can be combined with YLP0-YLP2 from this register. Unused bits in CRTC R16 are zero.

#### 4.3.11 CONTROL REGISTER NO. 3:

#### WRITE ONLY

WRITE ONLY

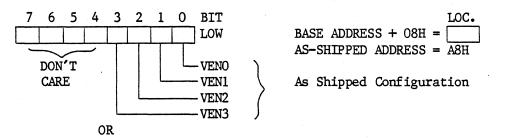

The four video enable bits can be strapped to any four bits in the two I/O locations shown above (see Section 5.4), and must be strapped to the same four bits that are used by the data port (see Section 4.3.5). The as-shipped configuration is shown here.

- Bit 0: VENO. When this bit is one, video from bit plane 0 is enabled. When this bit is zero, video from bit plane 0 is disabled.

- Bit 1: VEN1. When this bit is one, video from bit plane 1 is enabled. When this bit is zero, video from bit plane 1 is disabled.

- Bit 2: VEN2. When this bit is one, video from bit plane 2 is enabled. When this bit is zero, video from bit plane 2 is disabled.

- Bit 3: VEN3. When this bit is one, video from bit plane 3 is enabled. When this bit is zero, video from bit plane 3 is disabled.

#### 4.3.12 CONTROL REGISTER NO. 4:

WRITE ONLY

#### 4.3.12 CONTROL REGISTER NO. 4 (Cont'd):

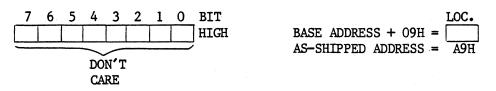

The four bits of Control Register No. 3 can be strapped to any four bits in the two I/O locations shown above (see Section 5.4) and must be strapped to the same four bits that are used as the data port. The as-shipped configuration is shown here.

- Bit 0: WENO/CRTC SEL/. When this bit is zero, bit plane 0 and the CRTC can be written to. When this bit is one, bit plane 0 and the CRTC cannot be written to. The CRTC SEL/ function is required for master slave configurations where the CRTCs of two or more boards at the same address are programmed differently.

- Bit 1: WEN1/. When this bit is zero, bit plane 1 can be written to. When this bit is one, bit plane 1 cannot be written to.

- Bit 2: WEN2/ When this bit is zero, bit plane 2 can be written to. When this bit is one, bit plane 2 cannot be written to.

- Bit 3: WEN3% When this bit is zero, bit plane 3 can be written to. When this bit is one, bit plane 3 cannot be written to.

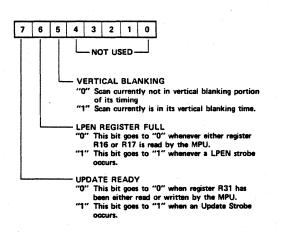

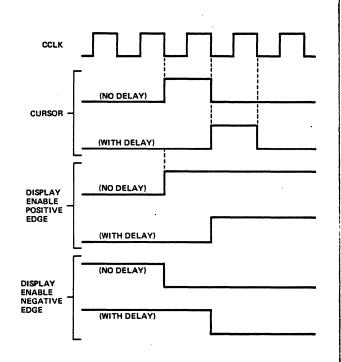

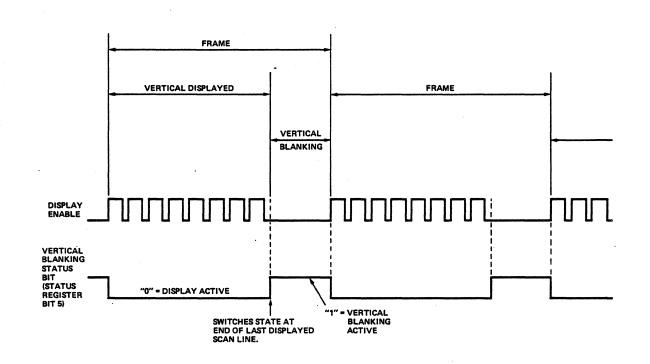

#### 4.3.13 CRTC STATUS REGISTER:

READ ONLY

- Bit 5: VERTICAL BLANKING. When this bit is one, the scan is in vertical blanking. When this bit is zero, the scan is not in vertical blanking.

- Bit 6: LPEN REGISTER FULL. This bit goes to one whenever a light pen strobe occurs. This bit goes to zero whenever either CRTC R16 or R17 are read.

#### 4.3.14 CRTC ADDRESS REGISTER:

WRITE ONLY

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | BIT | LOC.                                  |

|---|---|---|---|---|---|---|---|-----|---------------------------------------|

|   | Τ |   |   |   |   |   |   | ]   | BASE ADDRESS + OCH =                  |

|   |   |   |   |   |   |   |   | •   | AS-SHIPPED ADDRESS = $\overline{ACH}$ |

When one of the CRTC registers is to be accessed, its address is placed in this register, then data is input or output through the CRTC Data Register. Addresses and descriptions for the CRTC registers are found in the CRTC data sheets.

#### 4.3.15 CRTC DATA REGISTER:

#### READ/WRITE

BASE ADDRESS + OEH = AS-SHIPPED ADDRESS = AEH

This location is the data port to and from the CRTC.

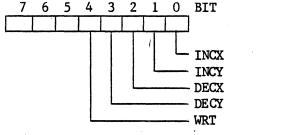

#### 4.3.16 VECTOR REGISTER:

#### WRITE ONLY

|                    |   | LOC. |

|--------------------|---|------|

| BASE ADDRESS + OFH | = |      |

| AS-SHIPPED ADDRESS | = | AFH  |

- BIT 0: INCX. When a one is written to this bit, the X-Register is incremented. Writing a zero to this bit has no effect on the X-Y coordinates.

- Bit 1: INCY. When a one is written to this bit, the Y-Register is incremented. Writing a zero to this bit has no effect on the X-Y coordinates.

- Bit 2: DECX. When a one is written to this bit, the X-Register is decremented. Writing a zero to this bit has no effect on the X-Y coordinates.

- Bit 3: DECY. When a one is written to this bit, the Y-Register is decremented. Writing a zero to this bit has no effect on the X-Y coordinates.

- Bit 4: WRT. When this bit is zero, the contents of the Data Register are automatically written to the Display Memory when the Vector Registor is loaded. When this bit is one, data is not automatically written to the Display Memory when the Vector Register is loaded.

NOTE: The Vector Register will not function properly if the RGB-GRAPH is in DMA mode.

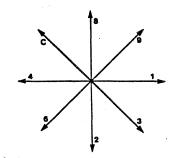

Figure 5-1 shows the direction that the graphics trace will take when different values are written to the Vector Register.

Figure 4.1 - VECTOR DIRECTION (BIT 0-3)

#### 4.4 THE ZOOM FUNCTION::

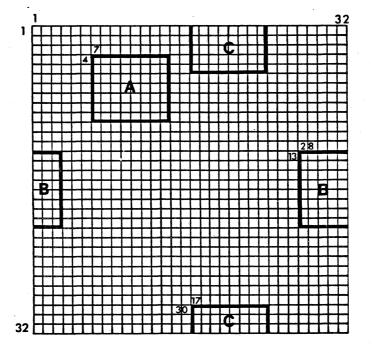

The zoom function allows the user to select a portion of the display and enlarge it to replace the original image from which it was taken. Resolution in the enlarged section is not affected, since it contains the same number of pixels before and after the zoom. Horizontal expansion (X zoom) and vertical expansion (Y zoom) are independently controlled by the user. It can be expanded vertically by factors of 2, 3, 4, 5, 6, 7, and 8 in the 512 x 512 and 512 x 256 formats, and by 2, 3, and 4 in the 256 x 256 format. Since identical horizontal and vertical zoom factors are required to maintain correct image proportions, the horizontal zoom factors of 2 and 4 are the most useful. The remaining horizontal zoom factors should not, however, be ignored since they can be used for controlled distortion of an image.

When considering the zoom function, the display should be considered as a field of graphics cells, each of which is composed of  $8 \times 8$  pixels in a normal resolution display or 16 x 8 pixels in a double resolution display.

The number of these cells in the display depends on the type of RGB-GRAPH used: 32 columns by 32 rows for the RGB-GRAPH/16, 64 columns and 32 rows for the RGB-GRAPH/32, and 64 columns and 64 rows for the RGB-GRAPH/64. The zoom window (the area to be enlarged) is defined in terms of these cells. Integer values must be used.

The size of the zoom window should be selected so that the actual display is the same size before and after the zoom. The post zoom display can, if necessary, be smaller; however, if it is larger, it will most likely overshoot the CRT and there may be problems programming the CRTC. The best way to determine the size of the zoom window is to divide the times one format X and Y axes, in cells, by the zoom factors to be used. If the result is not an interger value, choose the next lower integer. For example, if a times two X and Y zoom was made into the display of a RGB-GRAPH/64 (64 x 64 cells), the area to be enlarged would be 32 cells x 32 cells. If a distorting zoom of 4 times on the Y axis and 3 on the X axis was made into the same display, the area to be enlarged would be 21 cells (X axis) by 16 cells (Y axis). Table 4.2 gives the sizes, in cells, of zoom windows to be enlarged for X-Y zooms of 2 and 4.

| [ | RGB-GRAPH | 1        | 6        | /3       | 32       | /64      |          |  |  |

|---|-----------|----------|----------|----------|----------|----------|----------|--|--|

|   | AXIS      | ×        | Y        | X        | Y        | X        | Y        |  |  |

| [ | TIMES 2   | 16 Cells | 16 Cells | 32 Cells | 16 Cells | 32 Cells | 32 Cells |  |  |

|   | TIMES 4   | 8 Cells  | 8 Cells  | 16 Cells | 8 Cells  | 16 Cells | 16 Cells |  |  |

Figure 4.2 - THE MOST USED ZOOM WINDOW SIZES

When doing a zoom, the user first decides the X and Y zoom factors to be used, and then, knowing the times 1 format, he determines the size of the zoom window. He then places an imaginary frame the size of the zoom window around the part of the image to be enlarged. The row and column numbers of the cell in the upper left hand corner of that frame are then written to CRTC register Rl2 and Rl3 respectively. Finally, the zoom factors are written to Control Register No. 2 (see Section 4.3.9) and the format parameters in the CRTC Registers are adjusted to accommodate them. This adjustment is necessary because the Dot Clock is set by the X zoom factor and the number of scan lines per pixel is set by the Y-zoom factor.

#### 4.4 THE ZOOM FUNCTION (Cont'd):

Table 4.3 shows the CRTC register values for non-distorting times 2 and times 4 zooms. When other zoom factors are used, the adjusted CRTC register values can be calculated using the formulas found in section 4.2.

| RG8-GRAPH              |       | 11   | 6     |      |       | / 3  | 2     |      |       | 1    | 64    |      |

|------------------------|-------|------|-------|------|-------|------|-------|------|-------|------|-------|------|

| ZOOM FACTORS           | 2 X 2 |      | 4 X 4 |      | 2 X 2 |      | 4 X 4 |      | 2 X 2 |      | 4 X 4 |      |

| AMERICAN / EUROPEAN    | 60HZ  | 50HZ |

| CONTROL REGISTER NO. 2 | 77H   | 77H  | A7H   | A7H  | 77H   | 77H  | A7H   | A7H  | 77H   | 77H  | A7H   | A7H  |

| HORIZONTAL TOTAL       | 13H   | 13H  | 09H   | 09H  | 27H   | 27H  | 13H   | 13H  | 27H   | 27H  | 13H   | 13H  |

| HORIZONTAL DISPLAYED   | 10H   | 10H  | 08H   | 08H  | 20H   | 20H  | 10H   | 10H  | 2 OH  | 20H  | 10H   | 10H  |

| H. SYNC POSITION       | 10H   | 10H  | 08H   | 08H  | 23H   | 23H  | 11H   | 11H  | 23H   | 23H  | 11H   | 11H  |

| V. AND H. SYNC WIDTH   | 32H   | 32H  | 31H   | 31H  | 33H   | 33H  | 32H   | 32H  | 3 3 H | 33H  | 32H   | 32H  |

| VERTICAL TOTAL         | OFH   | 12H  | 07H   | 08H  | OFH   | 12H  | 07H   | 08H  | 1FH   | 26H  | OFH   | 12H  |

| VERTICAL ADJUST        | 04H   | 08H  | 04H   | 18H  | 04H   | 08H  | 04H   | 18H  | 04H   | 00H  | 04H   | 08H  |

| VERTICAL DISPLAYED     | OEH   | 10H  | 07H   | 05H  | OEH   | 10H  | 07H   | 05H  | 1EH   | 20H  | 0EH   | 10H  |

| V. SYNC POSITION       | OFH   | 11H  | 07н   | 07H  | OFH   | 11H  | 07H   | 07H  | 1EH   | 24H  | OFH   | 11H  |

| MODE CONTROL           | 04H   | 04H  | 04H   | 04H  | 04H   | 04H  | 04H   | 04H  | 07H   | 07H  | 07H   | 07H  |

| SCAN LINE              | OFH   | OFH  | 1FH   | 1FH  | OFH - | OFH  | 1FH   | 1FH  | OFH   | OFH  | 1FH   | 1FH  |

Table 4.3 - FORMAT PARAMETERS FOR NON-DISTORTING ZOOMS

Figure 4.2 represents a 256 x 256 display and shows three areas (A, B and C) that might be zoomed into using X and Y zoom factors of 4. Note that where the zoom window overshoots the display it wraps around.

Figure 4.2 - TYPICAL ZOOM AREAS IN A 256 X 256 FORMAT

#### 5.0 STRAPS:

Strap options on the RGB-Graph are implemented by interconnecting numbered wire wrap pins. In this manual, straps between any two wire wrap pins are referred to in the following ways:

14-15 IN indicates that wire wrap pin 14 is connected to wire wrap pin 15. 14-15 OUT indicates that wire wrap pin 14 is not connected to wire wrap pin 15.  $14 \leftrightarrow 15$  indicates that wire wrap pin 14 is connected to wire wrap pin 15.

#### 5.1 I/O BASE ADDRESS STRAPS:

| ADDRESS BIT                       | ADRB    | ADRA            | ADR9              | ADR8                | ADR7             | ADR6              | ADR5              | ADR4  |

|-----------------------------------|---------|-----------------|-------------------|---------------------|------------------|-------------------|-------------------|-------|

| CORRESPONDING STRAP               | *49-56  | *50-56          | *54 <b>-</b> 56   | *53-56              | 52 <b>-</b> 56   | 48-56             | 55-56             | 51-56 |

| BIT = ZERO                        | OUT     | OUT             | IN                | IN                  | IN               | IN                | IN                | IN    |

| BIT = ONE                         | IN      | IN              | OUT               | OUT                 | OUT              | OUT               | OUT               | OUT   |

| *Not used with 8-b<br>I/O address | Also St | trap 45-<br>45- | -46 IN<br>-46 OUT | 46–47 01<br>46–47 1 | UT For<br>IN For | 8-Bit A<br>16-Bit | ddress<br>Address |       |

#### Table 5.1 - I/O BASE ADDRESS STRAPS

#### 5.2 DATA STRAPS:

Table 5.2 shows how the RGB-Graph's 4 bit data port can be strapped to ay 4 bit nibble in the Multibus's 16 bit data bus.

| INTERNAL | PIN | AS-SHIPPED | PIN   | BUS      |

|----------|-----|------------|-------|----------|

| DATA BUS |     | STRAPS     | F 114 | DATA BUS |

|          |     |            | 16    | DAT O    |

| MD0      | 20  |            | 12    | DAT 4    |

|          |     |            | 8     | DAT 8    |

| RED      |     |            | 4     | DAT 12   |

|          |     | -          | 15    | DAT 1    |

| MD1      | 19  | -          | 11    | DAT 5    |

|          |     |            | 7     | DAT 9    |

| BLUE     |     |            | 3     | DAT 13   |

|          |     | -          | 14    | DAT 2    |

| MD2      | 18  |            | 10    | DAT 6    |

|          | 10  |            | 6     | DAT 10   |

| GREEN    |     |            | 2     | DAT 14   |

|          |     |            | 13    | DAT 3    |

|          |     |            | 9     | DAT 7    |

| MD3      | 17  |            | 5     | DAT 11   |

| OVERLAY  |     |            | 1     | DAT 15   |

#### Table 5.2 - DATA STRAPS

### 5.2 DATA STRAPS (Cont'd):

The nibble selected must be completely within either the high byte or the low byte, and depending on which byte it occupies one of the two following two strap configurations must be implemented.

DATA PORT IN LOW BYTE (AS-SHIPPED) = 32-33 IN 28-29 IN DATA PORT IN HIGH BYTE = 31-32 IN 29-30 IN

#### 5.3 DMA BASE ADDRESS:

Table 5.3 shows the straps used to set the base address of the 1K block of system address space used for DMA transfers.

| ADDRESS BIT         | ADI3  | ADI2  | ADII  | ADIO    | ADRF  | ADRE  | ADRD  | ADRC  | ADRB  | ADRA  |

|---------------------|-------|-------|-------|---------|-------|-------|-------|-------|-------|-------|

| CORRESPONDING STRAP | 36-44 | 39-44 | 43-44 | 42 - 44 | 35-44 | 34-44 | 38-44 | 40-44 | 41-44 | 37-44 |

| BIT = ZERO          | OUT   | OUT   | OUT   | OUT     | OUT   | OUT   | OUT   | OUT   | OUT   | OUT   |

| BIT = ONE           | IN    | IN    | IN    | IN      | IN    | IN    | IN    | IN    | IN    | IN    |

#### Table 5.3 - DMA BASE ADDRESS STRAPS

#### 5.4 STRAPS FOR CONTROL REGISTERS 3 AND 4:

Bits 0-3 of Control Register 3 and 4 must be strapped to the same Multibus data lines used by bits 0-3 of the data port (see table 5.4).

| REGISTER       | PIN                                                                                                                                                                                                  | AS-SHIPPED<br>STRAPS | PIN | BUS<br>DATA BIT |  |  |  |  |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|-----------------|--|--|--|--|--|--|--|

|                |                                                                                                                                                                                                      | -                    | 80  | DAT O           |  |  |  |  |  |  |  |

| VEN O          |                                                                                                                                                                                                      |                      | 91  | DAT 4           |  |  |  |  |  |  |  |

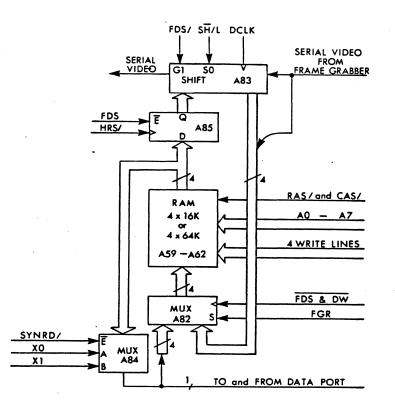

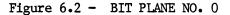

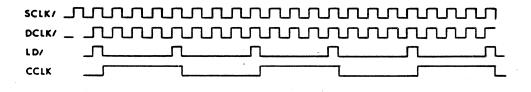

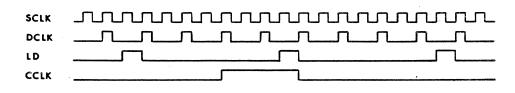

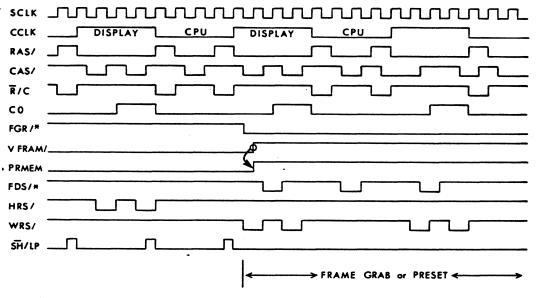

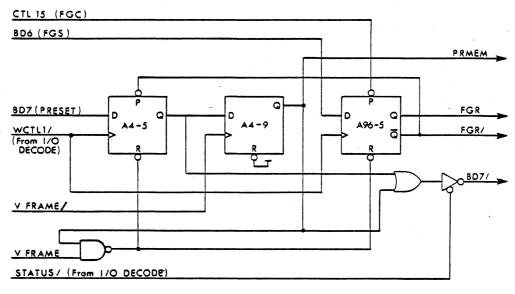

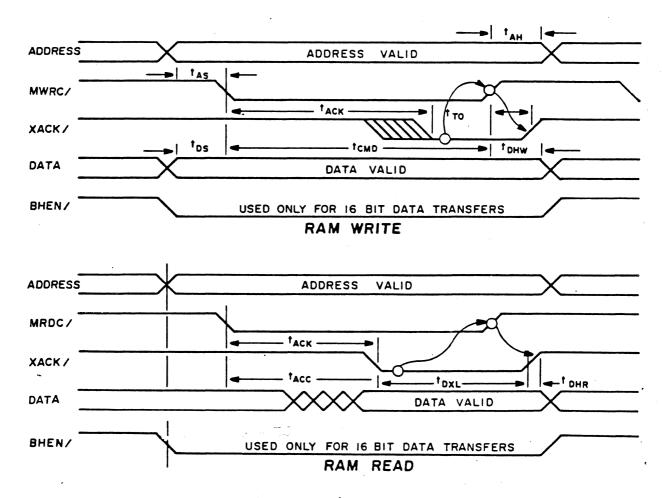

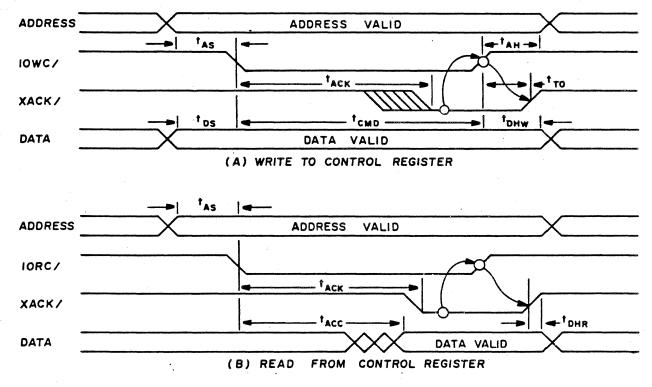

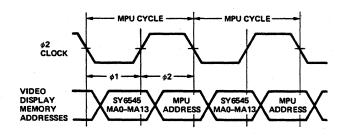

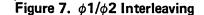

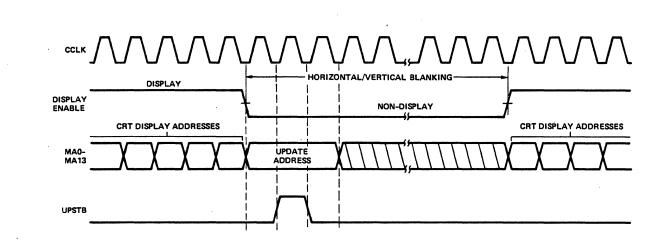

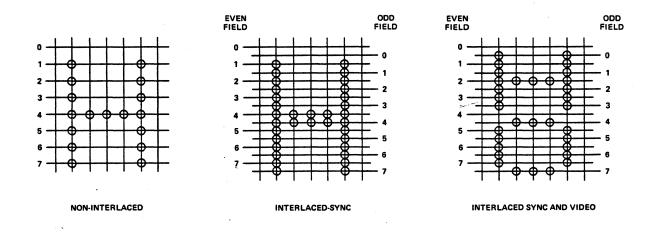

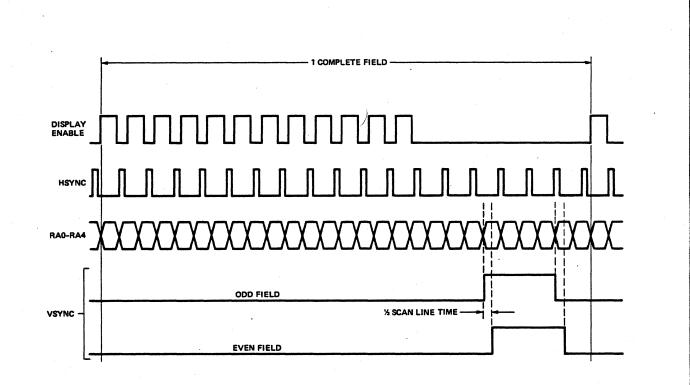

| and            | 96                                                                                                                                                                                                   |                      | 78  | DAT 8           |  |  |  |  |  |  |  |