# Series 3000 Technical Reference Manual

**MAD Intelligent Systems**

2950 Zanker Road San Jose, CA 95134

#### **Notice to Users**

Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

The user is warned that the shielded cables provided with this equipment MUST be used. A failure to use shielded cables may result in excessive radio-frequency emissions in violation of FCC Rules, for which the user would be responsible. If any extension cables are used they must also be shielded and the shields connected by means of metal-shell connectors so that there is a full 360 degrees of connection; pigtail connections are not good enough for radio frequencies.

#### Copyright

Copyright 1987 by MAD Intelligent Systems, Inc. All rights reserved. No part of this publication may be transmitted, transcribed, reproduced, stored in any retrieval system or translated into any language or computer language in any form or by any means, mechanical, electronic, magnetic, optical, chemical, manual or otherwise, without the prior written permission of MAD Intelligent Systems, Inc., 2950 Zanker Road, San Jose, CA 95134.

#### **Disclaimer**

MAD Intelligent Systems, Inc. does not make representations or warranties to the contents of this publication and disclaims any warranties of merchantability or fitness for a particular purpose. Additionally, MAD Intelligent Systems, Inc. reserves the right to revise and make changes to the content of this publication without obligation to inform any person of such revision.

MS-DOS is a registered trademark of Microsoft, Inc.

UNIX is a registered trademark of AT & T

Part Number 500026

Revision B of September 1988

Joyce De Mattei, Writer

## **About This Manual**

This manual, which is written for technical maintenance personnel, system designers, and applications programmers, contains design and maintenance information for the Series 3000 Intelligent Workstation. Information about the workstation includes:

- A system overview

- · The motherboard

- The Basic Input/Output System (BIOS) firmware

- The keyboard controller

- The memory board

- The Advanced Graphics Controller and optional PC Video Emulator

- The power supply

- Product specifications

## Organization

This section summarizes each of the chapters in this manual.

Chapter 1. "Overview" is a description of the Series 3000 Intelligent Workstation.

Chapter 2. "Motherboard" defines the overall operation and performance of the major components on the motherboard, including the 80386 microprocessor. The optional 80287/80387 numerics coprocessor modes and functions are discussed, with a brief reference to the 82C301 bus controller and the 82C302 memory controller. The chapter also contains programming and interface information needed to develop software.

Chapter 3. "BIOS" provides the BIOS programming information on input/output control used by systems and applications programmers when developing software.

Chapter 4. "Keyboard" describes the operation of the keyboard controller, which is on the motherboard. Programming and interface information is included.

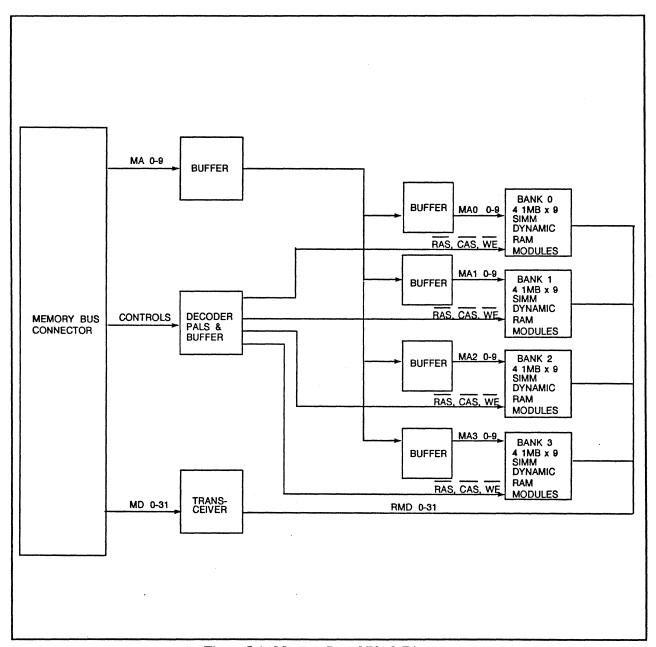

Chapter 5. "Memory" contains the specifications and instructions for the 32-bit memory board.

Chapter 6. "Advanced Graphics Controller" describes the video controller that supports video monitors. This chapter also describes the optional PC Video Emulator board which piggybacks onto the Advanced Graphics Controller for MS-DOS operation.

Chapter 7. "Power Supply" describes the power supply requirements.

Appendix A. "Product Specifications" lists the specifications for the Series 3000 Intelligent Workstation.

### **Related Documents**

For further technical information about the Series 3000 Intelligent Workstation, refer to the following manuals:

- Series 3000 Customer Engineer's Manual (MAD Part Number 500027)

- RD<sup>2</sup>S 3000 User's Guide (MAD Part Number 500025)

- Monochrome Monitor Manual (MAD Part Number 500053)

- M4 Optical Mouse Technical Reference Manual, Mouse Systems Corporation (MAD Part Number 500434)

In addition, the following manuals contain technical information you might need:

- YD-380B-PC, C. Itoh Electronics, Inc. (Order Number FDL-525041 Rev. A)

- M255XA 51/4" Mini Flexible Disk Drives Product Specifications, Fujitsu (Order Number RS-007-062785)

- WD-1003-WA2 Winchester Disk/Floppy Disketter Controller Preliminary OEM Manual, Western Digital Corporation

- Wangtec PC-36 Controller OEM Manual, Wangtec, Inc. (Order Number 20593-001)

- Miniscribe VI Product Manual, Models 6032, 6053, 6074, 6085, Part Number 1011, Rev. P4, Miniscribe Corporation (Order Number 170046)

- iAPX 386 Programmer's Reference Manual, Intel Corporation (Order Number 230985)

- *iAPX 386 Hardware Reference Manual*, Intel Corporation (Order Number 231732)

- *iAPX 386 System Software Writer's Guide*, Intel Corporation (Order Number 231499)

- *Microsystem Component Handbook*, Intel Corporation (Order Number 230843-004)

- iAPX 80387 Hardware Reference Manual, Intel Corporation (Order Number 231732-001)

- *iAPX 80386 Data Sheet*, Intel Corporation (Order Number 231630)

- CS 8230 AT/386 CHIPSet Hardware Reference Manual, Chips and Technologies

- 82C206 Hardware Reference Manual, Chips and Technologies

- PC-36 Internal Tape Backup System User's Manual, Wangtek, Inc. (Part Number 63009-001)

- 82786 Graphics Coprocessor User's Manual, Intel Corporation (Order Number 231933-002)

- 82786 CHMOS Graphics Coprocessor, Intel Corporation (Order Number 231676-002)

- 82786 Hardware Configuration Applications Note AP-270, Intel Corporation (Order Number 292007-002)

- 82786 CHMOS Graphics Coprocessor Architectural Overview Applications Note AP-259, Intel Corporation (Order Number 122711-002)

- Bt451 RAMDAC Data Sheet, Brooktree Corporation (Order Number DS011a-9/85)

## Contents

| Chapter 1. Overview                      | 1-1  |

|------------------------------------------|------|

| Introduction                             | 1-2  |

| Workstation Features                     | 1-3  |

| MAD/ix                                   |      |

| Microprocessor                           |      |

| Main Memory                              |      |

| Monitor                                  |      |

| Advanced Graphics Controller             |      |

| Keylock Feature                          | 1-4  |

| Keyboard                                 | 1-4  |

| Mouse                                    |      |

| Floppy Disk Drive                        |      |

| Disk Controller                          |      |

| Hard Disk Drive                          |      |

| Cartridge Tape Drive                     |      |

| Power Supply                             |      |

| Expansion Options                        |      |

| Chapter 2. Motherboard                   | 2-1  |

| Introduction                             | 2-2  |

| Microprocessor                           | 2-5  |

| Numerics Coprocessor                     |      |

| Memory                                   |      |

| Read Only Memory                         |      |

| Random Access Memory                     |      |

| CMOS RAM Configuration                   | 2-13 |

| Diagnostic Status Byte (0Eh)             |      |

| Shutdown Status Byte (0Fh)               |      |

| Floppy Disk Drive Type Byte (10h)        |      |

| Address 11h                              |      |

| Hard Disk Type 1 Through 14 (12h)        |      |

| Reserved and Equipment Byte (13h, 14h)   |      |

| Low and High Base Memory Bytes (15h,16h) | 2-17 |

| Low and High Base Memory Bytes (17h, 18h)      | 2-17 |

|------------------------------------------------|------|

| Hard Disk Type (19h)                           | 2-17 |

| CMOS Checksum (2Eh, 2Fh)                       | 2-18 |

| Low and High Expansion Memory Bytes (30h, 31h) |      |

| Date Century Byte (32h)                        |      |

| Information Flags (33h)                        | 2-18 |

| DMA Controller                                 | 2-19 |

| DMA Channels                                   |      |

| Programming the 8-Bit DMA Channels             |      |

| Programming the 16-Bit DMA Channels            | 2-21 |

| Timers/Counters                                | 2-23 |

| Interrupts                                     | 2-25 |

| VLSI Controllers                               | 2-27 |

| 82C301 Bus Controller                          | 2-27 |

| Clock Generation and Reset Control             | 2-28 |

| Processor Clock Selection                      | 2-30 |

| AT Bus Clock Selection                         | 2-31 |

| Reset Control                                  |      |

| Configuration Registers                        |      |

| 82C302 Memory Controller                       |      |

| I/O Mapping                                    |      |

| DRAM Array Configuration and Timing            | 2-35 |

| I/O Functions                                  | 2-37 |

| Signal Definitions                             | 2-38 |

| I/O Address Map                                | 2-42 |

| Speaker                                        | 2-62 |

| Variable Capacitors                            | 2-63 |

| Real-Time Clock                                | 2-64 |

| Status Register A (0Ah)                        |      |

| Status Register B (0Bh)                        | 2-64 |

| Status Register C (0Ch)                        | 2-65 |

| Status Register D (0Dh)                        |      |

| Parallel Port Controller                       | 2-67 |

| Serial Port Controller                         | 2-69 |

| Motherboard Settings                           | 2-76 |

| Jumpers                                        |      |

| Switches                                       |      |

| Test Points and Indicators                     | 2-80 |

| Chapter 3. BIOS       3-1         Introduction       3-2         Using the BIOS       3-3         Passing Parameters       3-3         Selected Interrupt Vectors and Parameter Pointers       3-4         Other Read/Write Memory Use       3-8         Keyboard Use and Encoding       3-13         Encoding       3-13         Character Codes       3-13         Extended Functions       3-13         Shift States       3-14         Other characteristics       3-17         Reset Handling       3-18         Chapter 4. Keyboard       4-1         Introduction       4-2         Keyboard Communication       4-2         Keyboard Communication       4-4         Receiving Data From the Keyboard       4-4         Scan Code Translation       4-4         Sending Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Output Buffer       4-12         Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches       5 |                | O Connectorswer       |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|------|

| Using the BIOS       3-3         Passing Parameters       3-3         Selected Interrupt Vectors and Parameter Pointers       3-4         Other Read/Write Memory Use       3-8         Keyboard Use and Encoding       3-13         Encoding       3-13         Character Codes       3-13         Extended Functions       3-13         Shift States       3-14         Other characteristics       3-17         Reset Handling       3-18         Chapter 4. Keyboard       4-1         Introduction       4-2         Keyboard Communication       4-4         Receiving Data From the Keyboard       4-4         Scan Code Translation       4-4         Sending Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Output Buffer       4-12         Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                            | •              |                       |      |

| Passing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Introduction   | on                    | 3-2  |

| Passing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Using the      | BIOS                  | 3-3  |

| Selected Interrupt Vectors and Parameter Pointers       3-4         Other Read/Write Memory Use       3-8         Keyboard Use and Encoding       3-13         Encoding       3-13         Character Codes       3-13         Shift States       3-13         Shift States       3-14         Other characteristics       3-17         Reset Handling       3-18         Chapter 4. Keyboard       4-1         Introduction       4-2         Keyboard Communication       4-4         Receiving Data From the Keyboard       4-4         Scan Code Translation       4-4         Scanding Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Output Buffer       4-12         Input Buffer       4-12         Input Joutput Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                      | _              |                       |      |

| Other Read/Write Memory Use       3-8         Keyboard Use and Encoding       3-13         Encoding       3-13         Character Codes       3-13         Extended Functions       3-13         Shift States       3-14         Other characteristics       3-17         Reset Handling       3-18         Chapter 4. Keyboard       4-1         Introduction       4-2         Keyboard Communication       4-4         Receiving Data From the Keyboard       4-4         Scan Code Translation       4-4         Sending Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Status Register       4-10         Output Buffer       4-12         Input Buffer       4-12         Input Buffer       4-12         Input Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                   |                |                       |      |

| Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                       |      |

| Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Keyboard       | Use and Encoding      | 3-13 |

| Character Codes         3-13           Extended Functions         3-13           Shift States         3-14           Other characteristics         3-17           Reset Handling         3-18           Chapter 4. Keyboard         4-1           Introduction         4-2           Keyboard Communication         4-4           Receiving Data From the Keyboard         4-4           Scan Code Translation         4-4           Sending Data to the Keyboard         4-8           Keyboard Interface Inhibit         4-9           CPU Interface         4-10           Status Register         4-10           Output Buffer         4-12           Input/Output Ports         4-16           Keyboard Connector         4-18           Chapter 5. Memory         5-1           Introduction         5-2           Switches, Connectors, LEDs and Test Points         5-6           Switches         5-6                                                                                                                                                                                        |                |                       |      |

| Extended Functions   3-13   Shift States   3-14   Other characteristics   3-17   Reset Handling   3-18      Chapter 4. Keyboard   4-1     Introduction   4-2     Keyboard Communication   4-4     Receiving Data From the Keyboard   4-4     Scan Code Translation   4-4     Sending Data to the Keyboard   4-8     Keyboard Interface Inhibit   4-9     CPU Interface   4-10     Output Buffer   4-12     Input Buffer   4-12     Input Buffer   4-16     Keyboard Connector   4-18      Chapter 5. Memory   5-1     Introduction   5-2     Switches, Connectors, LEDs and Test Points   5-6     Switches   5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                       |      |

| Other characteristics       3-17         Reset Handling       3-18         Chapter 4. Keyboard       4-1         Introduction       4-2         Keyboard Communication       4-4         Receiving Data From the Keyboard       4-4         Scan Code Translation       4-4         Sending Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Status Register       4-10         Output Buffer       4-12         Input Buffer       4-12         Input Juput/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                             |                |                       |      |

| Reset Handling       3-18         Chapter 4. Keyboard       4-1         Introduction       4-2         Keyboard Communication       4-4         Receiving Data From the Keyboard       4-4         Scan Code Translation       4-4         Sending Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Status Register       4-10         Output Buffer       4-12         Input Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                            | S              | hift States           | 3-14 |

| Chapter 4. Keyboard       4-1         Introduction       4-2         Keyboard Communication       4-4         Receiving Data From the Keyboard       4-4         Scan Code Translation       4-4         Sending Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Status Register       4-10         Output Buffer       4-12         Input Pouts       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C              | Other characteristics | 3-17 |

| Introduction       4-2         Keyboard Communication       4-4         Receiving Data From the Keyboard       4-4         Scan Code Translation       4-4         Sending Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Status Register       4-10         Output Buffer       4-12         Input Buffer       4-12         Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reset Han      | dling                 | 3-18 |

| Keyboard Communication       4-4         Receiving Data From the Keyboard       4-4         Scan Code Translation       4-4         Sending Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Status Register       4-10         Output Buffer       4-12         Input Buffer       4-12         Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter 4. Key | yboard                | 4-1  |

| Receiving Data From the Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Introduction   | on                    | 4-2  |

| Receiving Data From the Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Keyboard       | Communication         | 4-4  |

| Scan Code Translation       4-4         Sending Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Status Register       4-10         Output Buffer       4-12         Input Buffer       4-12         Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                       |      |

| Sending Data to the Keyboard       4-8         Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Status Register       4-10         Output Buffer       4-12         Input Buffer       4-12         Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                       |      |

| Keyboard Interface Inhibit       4-9         CPU Interface       4-10         Status Register       4-10         Output Buffer       4-12         Input Buffer       4-12         Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                       |      |

| Status Register       4-10         Output Buffer       4-12         Input Buffer       4-12         Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                       |      |

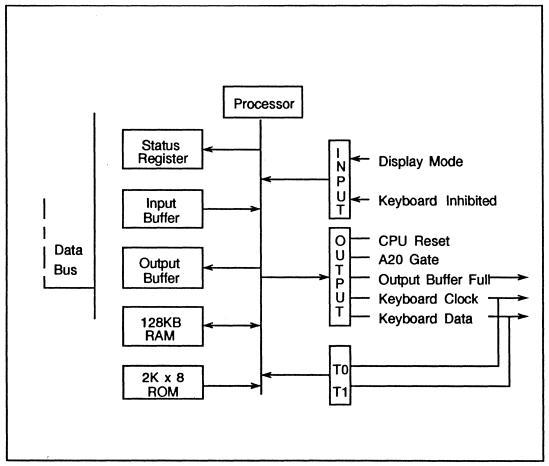

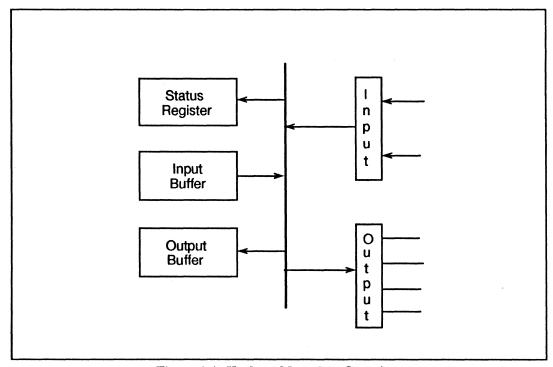

| Status Register       4-10         Output Buffer       4-12         Input Buffer       4-12         Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CPU Inter      | face                  | 4-10 |

| Output Buffer       4-12         Input Buffer       4-12         Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                       |      |

| Input Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                       |      |

| Input/Output Ports       4-16         Keyboard Connector       4-18         Chapter 5. Memory       5-1         Introduction       5-2         Switches, Connectors, LEDs and Test Points       5-6         Switches       5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                       |      |

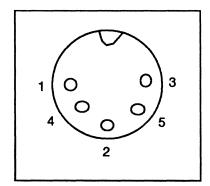

| Keyboard Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                       |      |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                       |      |

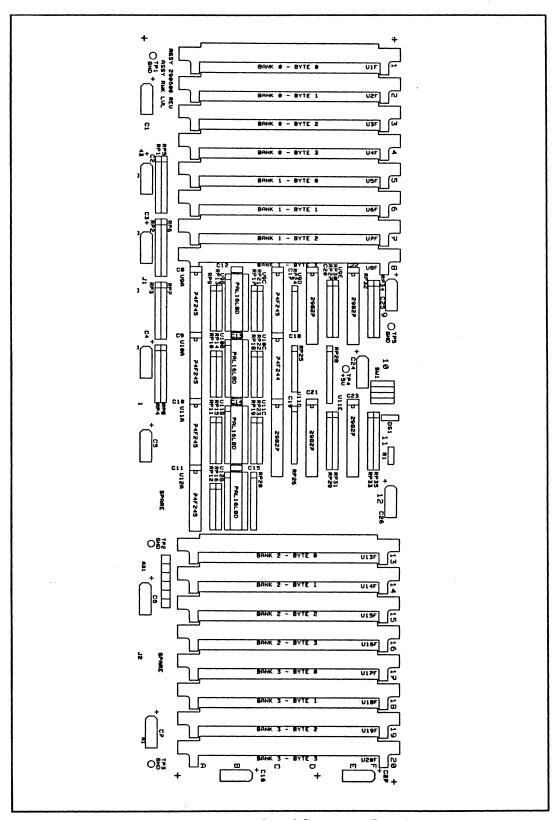

| Switches, Connectors, LEDs and Test Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Chapter 5. Me  | mory                  | 5-1  |

| Switches, Connectors, LEDs and Test Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Introduction   | on                    | 5-2  |

| Switches5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                       |      |

|    | LEDs                                   | 5-11 |

|----|----------------------------------------|------|

|    | Test Points                            | 5-11 |

|    | Installation                           | 5-12 |

| Ch | napter 6. Advanced Graphics Controller | 6-1  |

|    | Introduction                           | 6-2  |

|    | Overview                               | 6-3  |

|    | Summary of Functions                   | 6-4  |

|    | Controller Major Components            | 6-6  |

|    | Display Buffer                         | 6-9  |

|    | 82786 Graphics Coprocessor             |      |

|    | RAMDACTM                               |      |

|    | EPROM                                  | 6-12 |

|    | Clock Circuits                         | 6-13 |

|    | Window Manager Logic                   | 6-13 |

|    | Dot Manager Logic                      |      |

|    | Bus Interface Logic                    | 6-14 |

|    | AGC Jumpers, Switches, and Connectors  | 6-15 |

|    | Optional PVE Board Major Components    | 6-19 |

|    | CGA Emulation Logic                    | 6-22 |

|    | MDA Emulation Logic                    | 6-22 |

|    | ASCII Character Generator              | 6-23 |

|    | Mode and Color Select Logic            | 6-24 |

|    | State Machine Logic                    |      |

|    | Bus Interface Logic                    | 6-25 |

|    | PVE Board Switches and Connectors      | 6-26 |

|    | Attaching the PVE to the Controller    | 6-28 |

|    | Programming the AGC                    | 6-30 |

|    | Programming the PVE Board              | 6-38 |

|    | Display Buffer                         |      |

|    | Alphanumeric Character Generation      |      |

|    | Graphics                               | 6-43 |

|    | Registers                              | 6-45 |

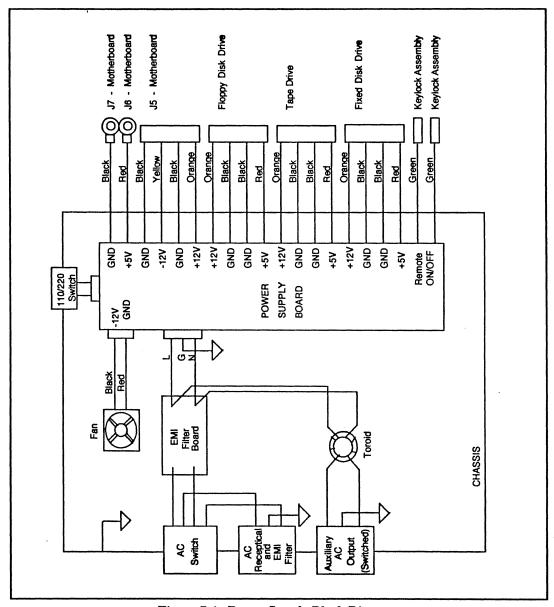

| Chapter 7. Power Supply            | 7-1         |

|------------------------------------|-------------|

| Introduction                       | 7-2         |

| Changing the Voltage               |             |

|                                    |             |

| Input                              |             |

| Output                             | 7-5         |

| Appendix A. Product Specifications | A-1         |

| System Unit                        | A-2         |

| Motherboard                        |             |

| Memory                             | A-3         |

| Hard Disk Drive                    |             |

| Disk Controller Board              | A-3         |

| Floppy Disk Drives                 |             |

| Streaming Tape Backup Subsystem    | A-4         |

| Advanced Graphics Controller       |             |

| Input/Output                       |             |

| Power Supply                       |             |

| Supported Operating Systems        |             |

| MAD Software                       |             |

| Back Panel Connectors              |             |

| Physical Dimensions                |             |

| Operating Environment              |             |

| System Weight                      | A-5         |

| Options                            | <b>A</b> -6 |

| Numeric Coprocessor                |             |

| AGC PVE Board                      |             |

| 1 Serial/1 Parallel I/O Controller | A-6         |

# **Figures**

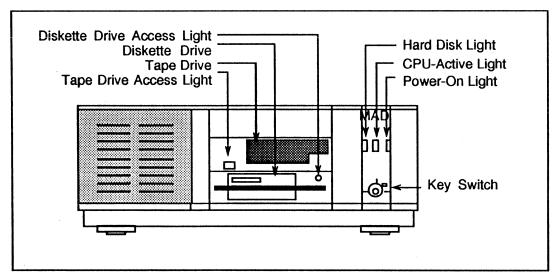

| Figure 1-1.  | Typical System Unit                                  | . 1-2 |

|--------------|------------------------------------------------------|-------|

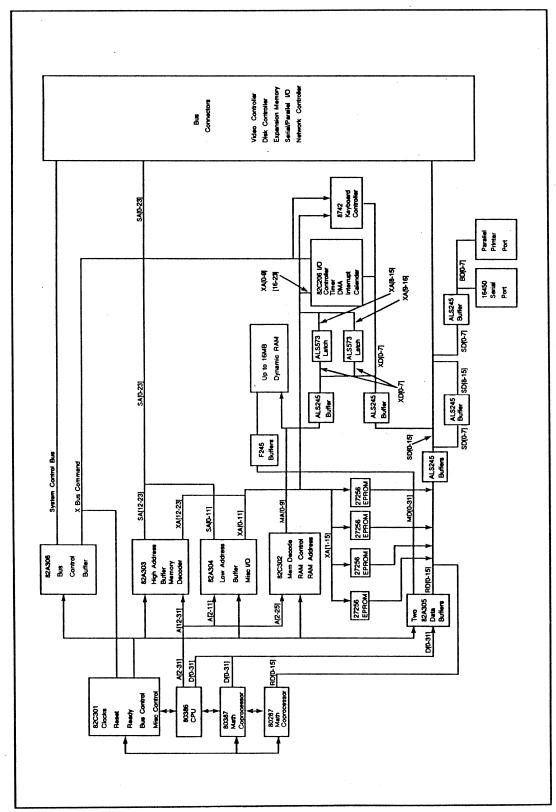

| Figure 2-1.  | Motherboard Block Diagram                            | . 2-3 |

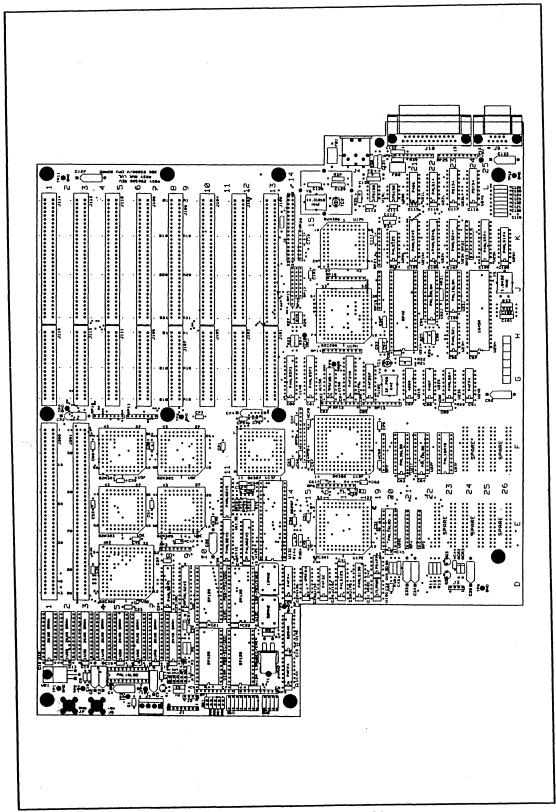

| Figure 2-2.  | Motherboard Assembly                                 | . 2-4 |

| Figure 2-3.  | Table of 80386 Cycle Times                           | . 2-5 |

| Figure 2-4.  | Table of Data Types                                  | . 2-7 |

| Figure 2-5.  | 80287/80387 Numerics Coprocessor Port Addresses      | . 2-8 |

|              | RAM Address Spacing Enable                           |       |

| Figure 2-7.  | System Memory Map (1MB Systems)                      | 2-11  |

| Figure 2-8.  | System Memory Map (16MB Systems)                     | 2-12  |

| Figure 2-9.  | BIOS Hard Disk Parameters (Part 1)                   | 2-15  |

| Figure 2-9.  | BIOS Hard Disk Parameters (Part 2)                   | 2-16  |

| Figure 2-10. | DMA Channel Allocations                              | 2-19  |

|              | DMA Page Register Port Addresses                     |       |

| Figure 2-12. | Address Generation for DMA Channel 3 through 0       | 2-20  |

|              | Address Generation for DMA Channel 7 through 5       |       |

| Figure 2-14  | DMA Controller 1 Port Addresses                      | 2-21  |

| Figure 2-15. | DMA Controller 2 Port Addresses                      | 2-22  |

| Figure 2-16  | Programmable Interval Timer Channels                 | 2-23  |

| Figure 2-17. | PIT Port Addresses                                   | 2-24  |

| Figure 2-18  | Interrupt Level Assignments                          | 2-25  |

|              | Master Interrupt Controller                          |       |

|              | . Slave Interrupt Controller                         |       |

|              | . Configuration Register Access Ports                |       |

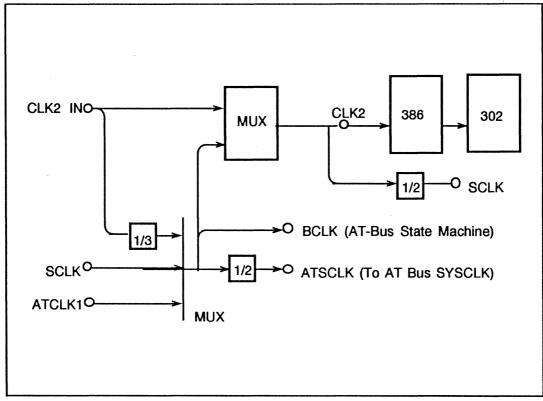

| _            | . 82C301 Bus Controller Functional Block Diagram     |       |

|              | . CLK2 and ATSCLK Clock Selection                    |       |

| Figure 2-24  | Examples of BCLK and SYSCLK                          | 2-31  |

|              | . 82C301 Bus Controller Configuration Registers      |       |

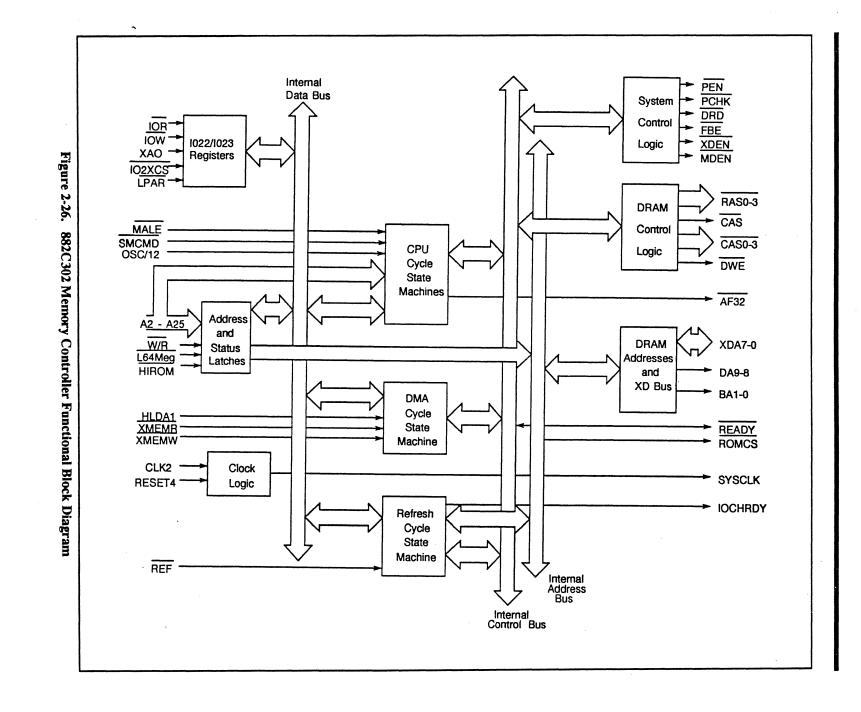

|              | . 882C302 Memory Controller Functional Block Diagram |       |

| Figure 2-27  | . Control and Address Space Map Registers            | 2-35  |

|              | . DRAM Configuration/Timing Register Summary         |       |

| Figure 2-29  | . System I/O Address Map (Summary)                   | 2-43  |

| Figure 2-30  | . 82C206 (Byte DMA 1)                                | 2-44  |

| Figure 2-31  | .' 82C206 (Master Interrupt Controller 1)            | 2-44  |

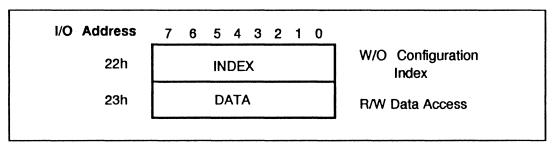

| Figure 2-32  | . CS 8230 Configuration Ports                        | 2-44  |

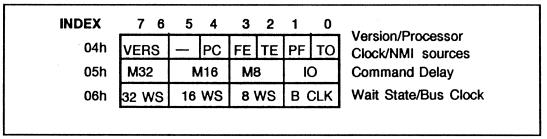

|              | . Index 04h (Version, Processor Clock, NMI Sources)  |       |

| •            |                                                      | 2-45  |

| Figure 2-35. | Index 06h (Wait State and Bus Clock Select)     | 2-46 |

|--------------|-------------------------------------------------|------|

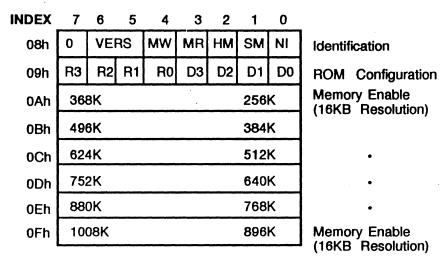

|              | Index 08h (Identification)                      |      |

| Figure 2-37. | Index 09h (RAM/ROM Configuration in Boot Area)  | 2-48 |

| Figure 2-38. | Index OAh (Address Map for 040000h - 05FFFFh)   | 2-49 |

| Figure 2-39. | Index 0Bh (Address Map for 060000h - 07FFFFh)   | 2-49 |

| Figure 2-40. | Index OCh (Address Map for 080000h - 09FFFFh)   | 2-50 |

| Figure 2-41. | Index ODh (Address Map for 0A0000h - 0BFFFFh)   | 2-50 |

| Figure 2-42. | Index 0Eh (Address Map for 0C0000h - 0DFFFFh)   | 2-51 |

| Figure 2-43. | Index OFh (Address Map for 0E0000h - 0FFFFFh)   | 2-51 |

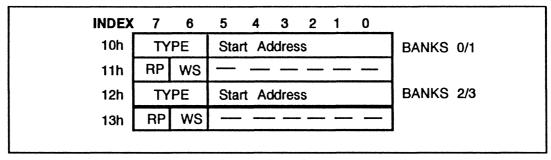

| Figure 2-44. | Index 10h (Bank 0 and 1 Type and Start Address) | 2-52 |

| Figure 2-45. | Index 11h (Bank 0 and 1 Timing)                 | 2-52 |

| Figure 2-46. | Index 12h (Bank 2 and 3 Type and Start Address) | 2-52 |

| _            | Index 13h (Bank 2 and 3 Timing)                 |      |

| Figure 2-48. | Index 28h (Parity)                              | 2-53 |

| Figure 2-49. | Index 29h (Parity)                              | 2-53 |

| Figure 2-50. | 82C206 Programmable Interval Timer              | 2-54 |

| Figure 2-51. | 8742 8-Bit Microcomputer                        | 2-54 |

|              | 8742 I/O Bits                                   |      |

| Figure 2-53. | 82C301 TTL I/O Status and Control               | 2-55 |

|              | NMI Enable and Calendar Address                 |      |

| Figure 2-55. | 82C206 Calendar Data Port                       | 2-56 |

| Figure 2-56. | Calendar RAM Locations                          | 2-57 |

| Figure 2-57. | 82C206 DMA Page Register                        | 2-58 |

| Figure 2-58. | 82C206 Slave Interrupt Controller 2             | 2-58 |

|              | 82C206 Word DMA 2                               |      |

| Figure 2-60. | 80387/80287 Math Coprocessor Ports              | 2-59 |

| Figure 2-61. | LPT2 Parallel Port                              | 2-60 |

| Figure 2-62. | COM2 Serial Port                                | 2-60 |

| Figure 2-63. | LPT1 Parallel Port                              | 2-61 |

| Figure 2-64. | COM1 Serial Port                                | 2-61 |

| Figure 2-65. | Speaker Connector J2                            | 2-62 |

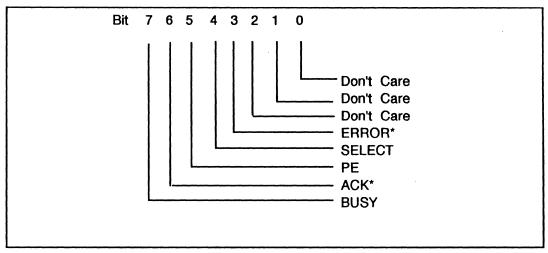

| Figure 2-66. | Parallel Port Status Register                   | 2-67 |

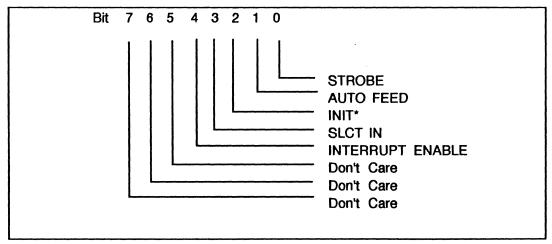

| Figure 2-67. | Parallel Port Control Register                  | 2-67 |

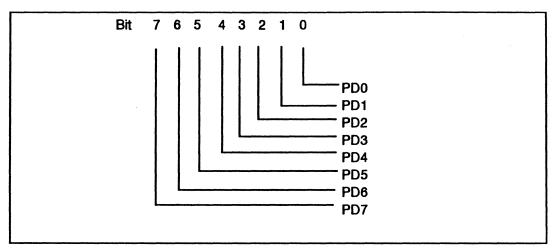

| Figure 2-68. | Parallel Port Data Register                     | 2-68 |

| Figure 2-69. | Serial Port Control and Status Registers        | 2-70 |

| Figure 2-70. | Baud Rate Selection                             | 2-71 |

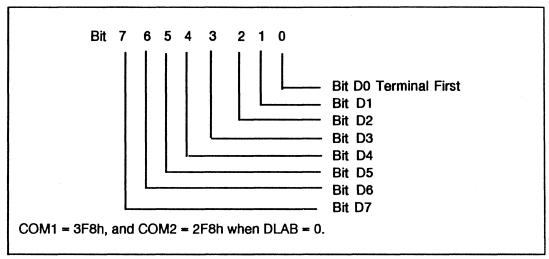

| Figure 2-71. | Transmit/Receive Buffer Register                | 2-72 |

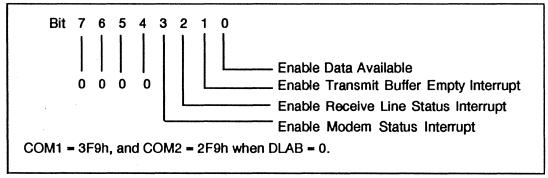

| Figure 2-72. | Interrupt Enable Register                       | 2-72 |

|              | Interrupt Identification Register               |      |

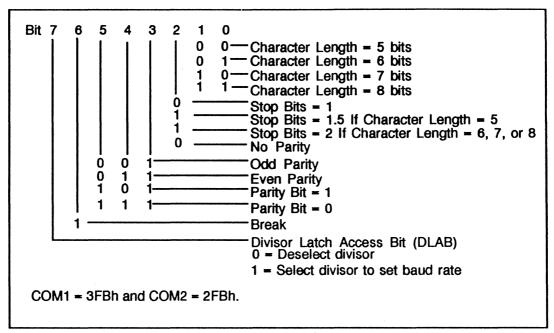

| Figure 2-74. | Line Control Register                           | 2-74 |

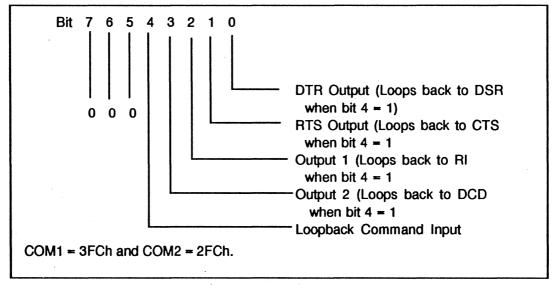

| . Modem Control Register                             | 2-74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

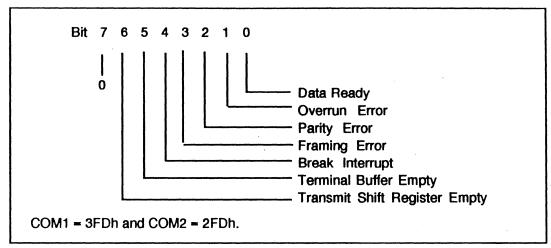

| Line Status Register                                 | 2-75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

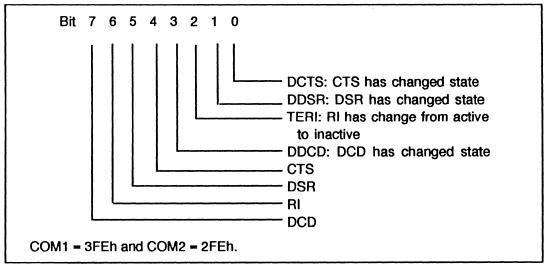

| . Modem Status Register                              | 2-75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

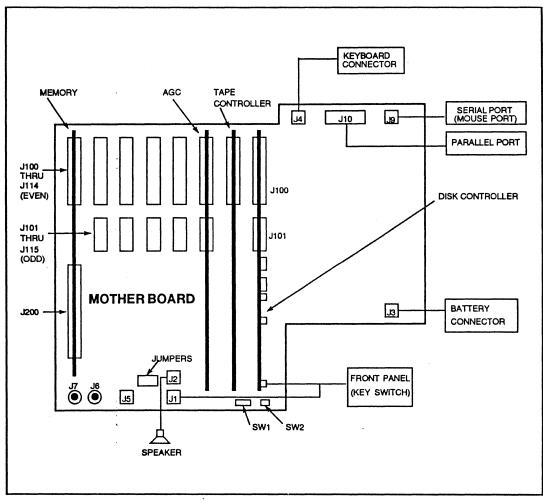

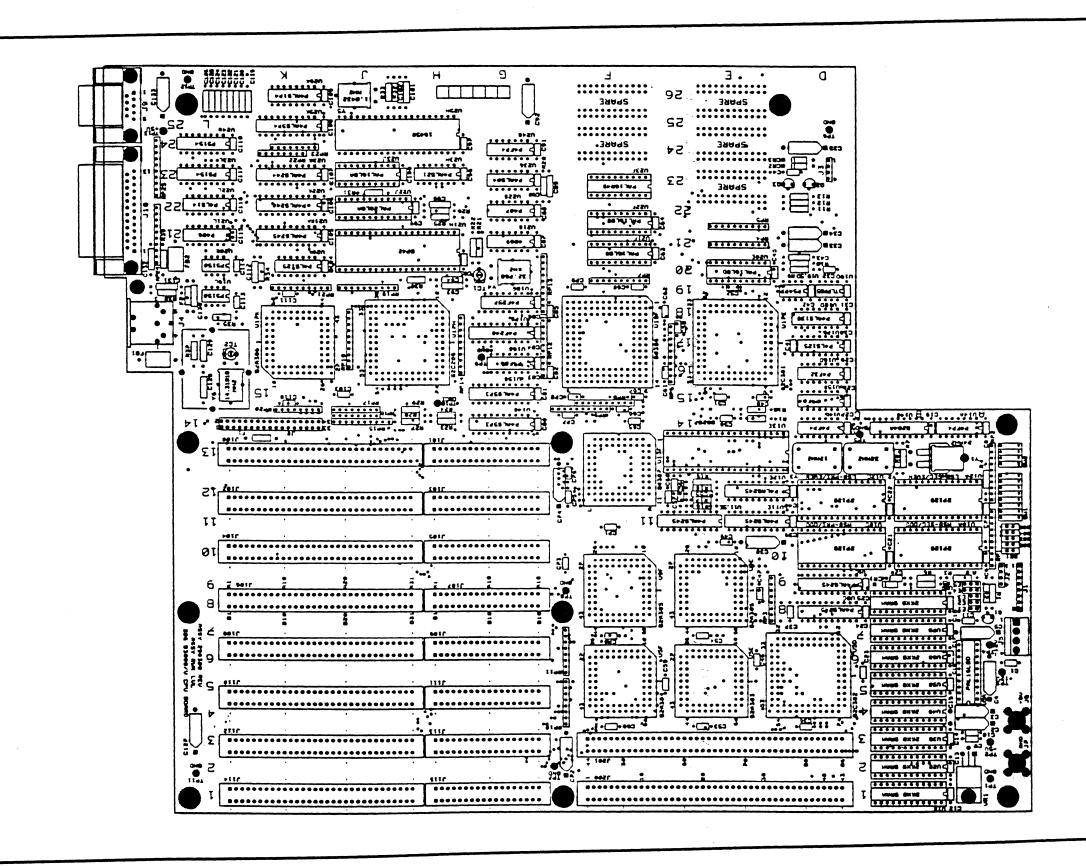

| . Motherboard Component Locations                    | 2-76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <u>-</u>                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| . Switch SW2                                         | 2-79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| . Test Points                                        | 2-80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| . LED Indicators                                     | 2-80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| . LED Connector J1                                   | 2-81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| . I/O Expansion Bus J100 Through J114 (Even), Part 2 | 2-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |