NuMachine Technical Summary

SDU Operating System SDU General Description

Mouse Manual LMI Printer Software Manual

> VR-Series Monitor Z29 Monitor

Ethernet Multibus

#### LMI DOCUMENTATION SYSTEM MAP

\*\* indicates location of tab divider

\*\*LMI Lambda Technical Summary

\*\*LMI Lambda Field Service Manual

\*\*NuMachine Installation and User Manual

\*\*Introduction to the Lambda

\*\*Programming on the Lambda

RELEASE NOTES:

\*\*System 94 Notes

\*\*System 98 Notes \*\*Common LISP Notes

LISP 1: The LISP Machine Manual, Part 1

\*\*Introduction Primitive Object Types Evaluation

Flow of Control Manipulating List Structure

\*\*Symbols Numbers Arravs Strings

\*\*Functions Closures Stack Groups Locatives Subprimitives Areas

\*\*The Compiler

Macros The LOOP Iteration Macro

\*\*Defstruct

LISP 2: The LISP Machine Manual, Part 2

\*\*Objects, Message Passing, and Flavors \*\*The I/O System Naming of Files

The Chaosnet

\*\*Packages Maintaining Large Systems Processes

Errors and Debugging

\*\*How to Read Assembly Language Querying the User Initializations Dates and Times

Miscellaneous Useful Functions \*\*Indices

LISP 3:

\*\*Introduction to the Window System

\*\*The Window System Manual

\*\*ZMAIL

\*\*Prolog

\*\*InterLISP

EDITORS:

\*\*ZMACS Introductory Manual

\*\*ZMACS Reference Manual

\*\*Mince

\*\*Scribble

UNIX 1:

\*\*NuMachine Release and Update Information

\*\*NuMachine Operating System

\*\*UNIX Programmer's Manual, V. 1: Section 1: Section 1

Sections 2-8

\*\*Fortran Installation Memo

UNIX 2:UNIX Programmer's Manual, Vol. 2

\*\*The UNIX Time-sharing System

An Introduction to the UNIX Shell An Introduction to the UNIX Shell

Typing Documents on the UNIX System

A Guide to Preparing Documents with -ms

Tbl--A Program to Format Tables

NROFF/TROFF User's Manual

A TROFF Tutorial

\*\*The C Programming Language Reference Manual

\*\*The C Programming Language Reference

Recent Changes to C

Lint, A C Program Checker

Make--A Program for Maintaining

Computer Programs

\*\*UNIX Programming--Second Edition

A Tutorial Introduction to ADB

Yacc: Yet Another Compiler-Compiler

Lex--A Lexical Analyzer Cenerator

\*\*A Portable Fortran 77 Compiler

RATFOR--A Preprocessor for a

Rational Fortran

The M4 Macro Processor

SED--A Non-Interactive Text Editor

Awk--A Pattern Scanning and

Processing Language (2d. ed.)

Processing Language (2d. ed.) DC--An Interactive Desk Calculator BC--An Arbitrary Precision Desk-Calculator Language

An Introduction to Display Editing

\*\*The UNIX I/O System

On the Security of UNIX

Password Security: A Case History

HARDWARE 1:

\*\*NuMachine Technical Summary \*\*SDU Operating System

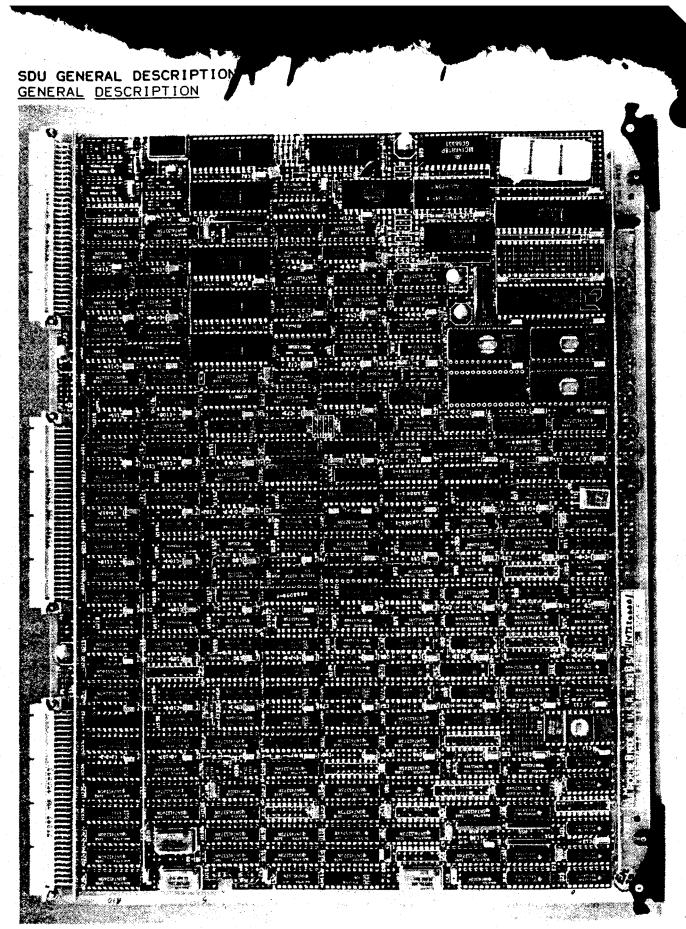

SDU General Description

\*\*Mouse Manual

LMI Printer Software Manual

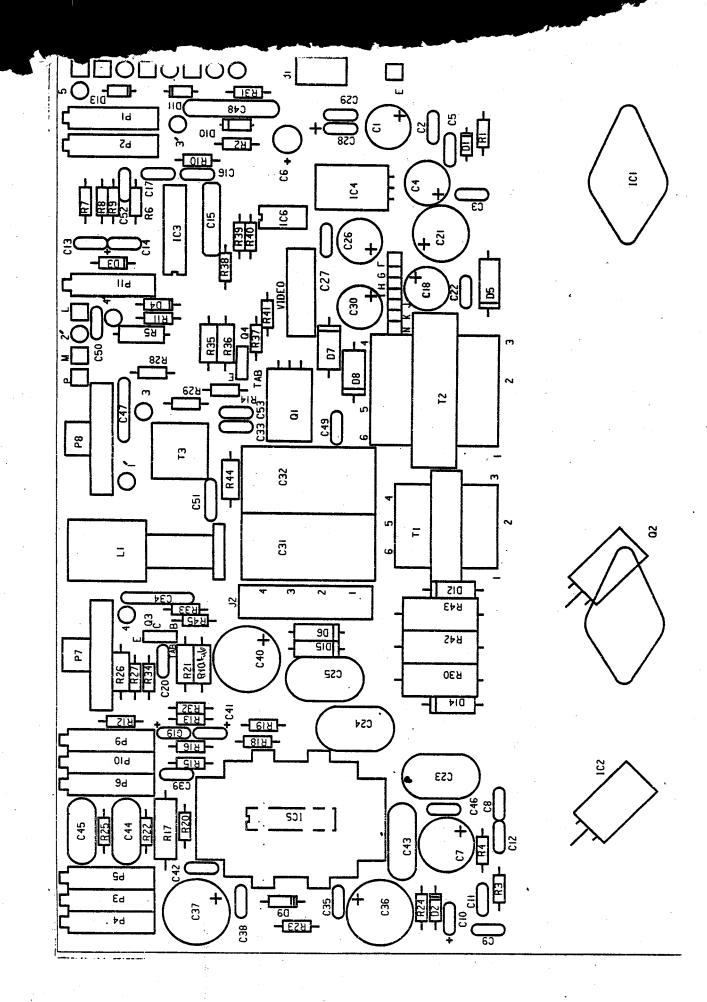

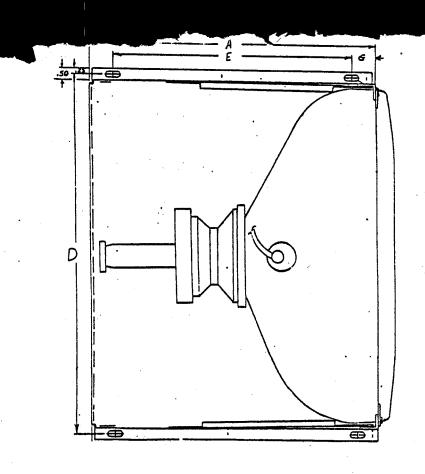

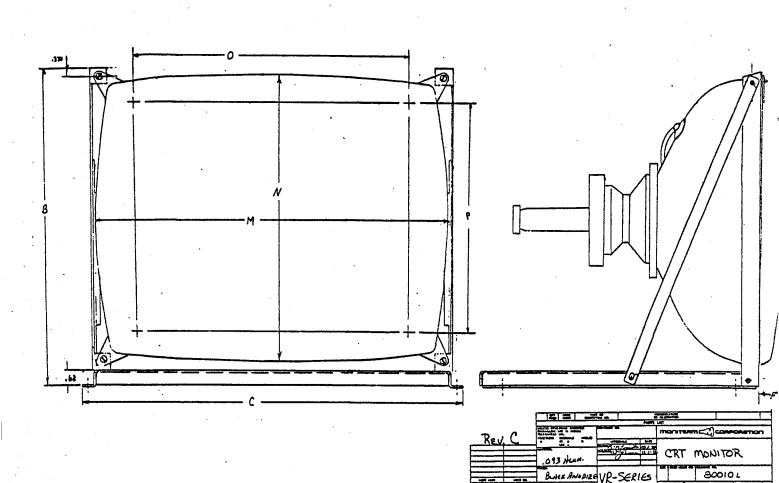

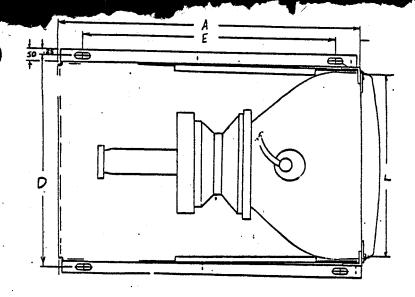

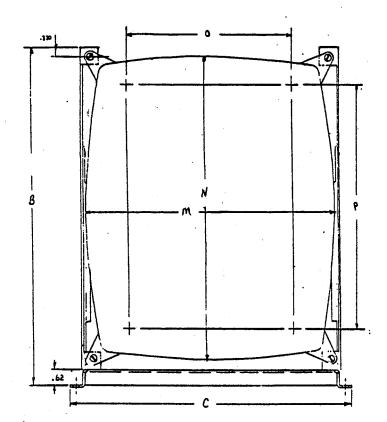

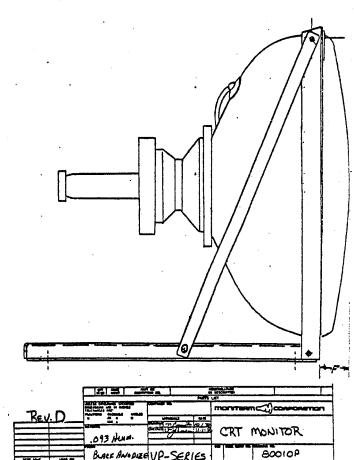

\*\*VR-Series Monitor

Z29 Monitor

\*\*Ethernet Multibus

HARDWARE 2:

\*\*SMD 2181 Controller Board

\*\*Fujitsu Disk Drive (Micro or Mini)

\*\*Cipher Tape Drive 1/4"

HARDWARE 3:

\*\*Cipher Tape Drive 1/2"

\*\*Tapemaster Product Spec

\*\*Tapemaster Application Note

OPTIONS:

\*\* (varies according to options purchased)

Nu Machine Technical Summary TI-2242820-0001

Information furnished in this document is believed to be accurate and reliable. However, no responsibility is assumed by Texas Instruments for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Texas Instruments. Texas Instruments reserves the right to change product specifications at any time.

UNIX<sup>tm</sup> is a trademark of American Telephone & Telegraph.

Multibus<sup>tm</sup> is a trademark of Intel Corp.

Ethernet<sup>tm</sup> is a trademark of Xerox Corp.

Copyright © 1982 Texas Instruments All rights reserved.

## **NU MACHINE TECHNICAL SUMMARY**

## Contents

| 1 | INTRODUCTION 1.1 System Origin 1.2 The System 1.3 Applications                                                                                                                                                                                | 1<br>1<br>1<br>4           |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2 | THE NUBUS 2.1 Overview 2.2 NuBus Signals 2.3 Data Transfer Operations 2.4 Multiprocessor Support 2.4.1 Arbitration 2.4.2 Interrupts                                                                                                           | . 7<br>7<br>7<br>8<br>10   |

| 3 | 68010 PROCESSOR BOARD 3.1 Virtual Address Space 3.2 Main Functions of the CPU Board 3.2.1 68010 Microprocessor 3.2.2 Cache Operation 3.2.3 Cache Control 3.2.4 Cache ID 3.2.5 Address Translation 3.2.6 Interrupt Mechanism 3.2.7 CPU Control | 11<br>11<br>12             |

| 4 | SYSTEM DIAGNOSTIC UNIT                                                                                                                                                                                                                        | 21                         |

| 5 | MULTIBUS INTERFACE 5.1 Conversion 5.1.1 NuBus-to-Multibus Conversion 5.1.2 Multibus-to-NuBus Conversion 5.2 Interrupt Mapping                                                                                                                 | 25<br>25<br>28             |

|   | 5.3 Lockup Prevention                                                                                                                                                                                                                         | 28                         |

| 6 | VIDEO DISPLAY SUBSYSTEM 6.1 Main Functions of the Video Display Subsystem 6.2 Serial Ports                                                                                                                                                    | 29<br>29<br>31             |

| 7 | MAIN MEMORY 7.1 Main Functions of the Memory Board                                                                                                                                                                                            | 33<br>33                   |

| 8 | SOFTWARE 8.1 SDU Monitor and Diagnostics 8.1.1 SDU Monitor                                                                                                                                                                                    | 35<br>35                   |

|   | 8.1.2 Diagnostics 8.2 Nu Machine Operating System 8.2.1 Overview 8.2.2 Nu Machine Operating System Kernel 8.2.3 Utilities                                                                                                                     | 37                         |

|   | 8.3 Future Plans                                                                                                                                                                                                                              | 41                         |

| 9 | NU MACHINE PACKAGING 9.1 Monitor, Keyboard and Mouse 9.2 Office Module 9.3 I/O Interconnection 9.4 Rack Module                                                                                                                                | 43<br>43<br>43<br>44<br>44 |

|   | 9.5 Summary                                                                                                                                                                                                                                   | 45                         |

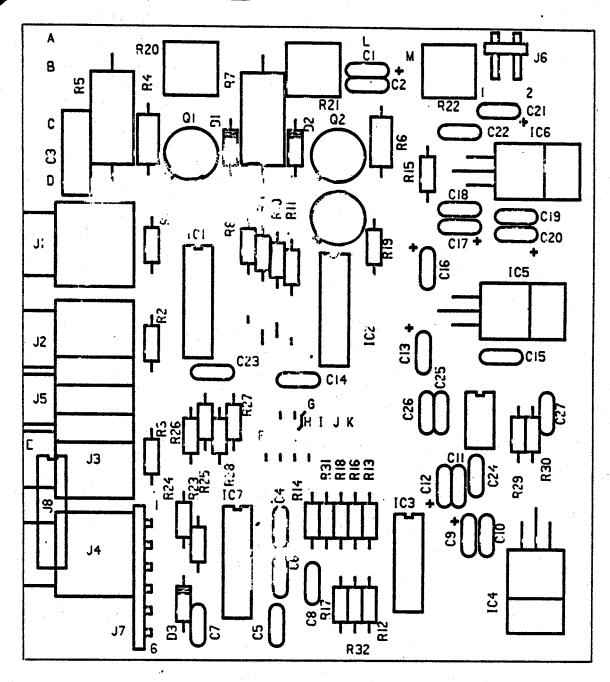

## List of Figures

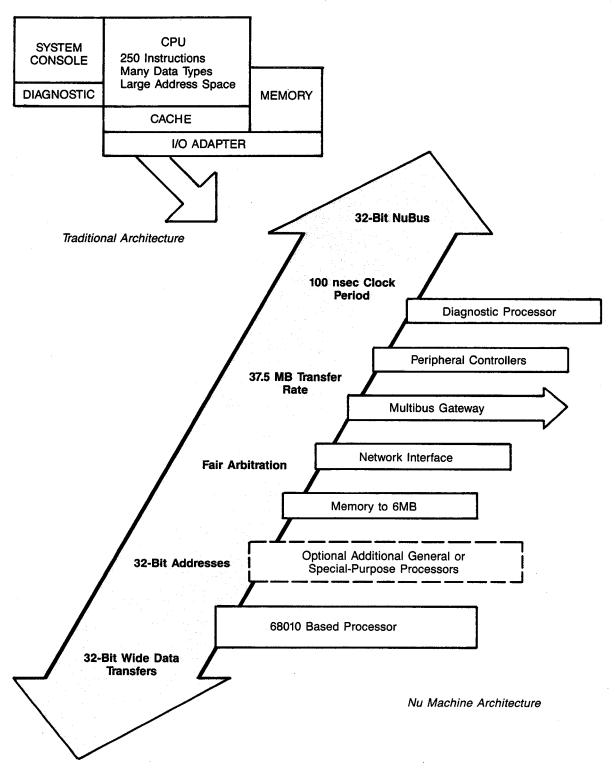

| Figure 1-1. | Comparison of Traditional and Nu Machine Architectures | 2  |

|-------------|--------------------------------------------------------|----|

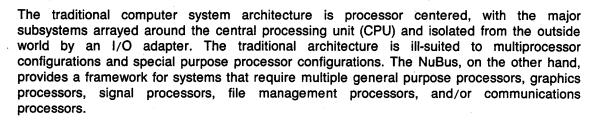

| Figure 2-1. | Layout of Words, Halfwords, and Bytes                  | 9  |

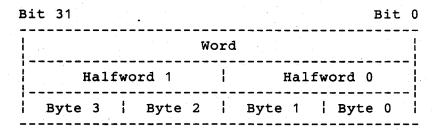

| Figure 3-1. | Virtual Address Space Concept                          | 12 |

| Figure 3-2. | Block Diagram of CPU Board                             | 13 |

| Figure 3-3. | Data Cache Entry (Parity, Tag Field, and Data)         | 14 |

| Figure 3-4. | Cache Control                                          | 15 |

| Figure 3-5. | Cache Status                                           | 15 |

| Figure 3-6. | Virtual-to-Physical Address Translation                | 17 |

| Figure 3-7. | Representation of Physical Address                     | 18 |

| Figure 3-8. | PTE Description                                        | 18 |

| Figure 3-9. | Definitions of Access Bits                             | 19 |

| Figure 4-1. | System Diagnostic Unit Block Diagram                   | 22 |

| Figure 5-1. | NuBus-to-Multibus Memory Space Conversion              | 25 |

| Figure 5-2. | NuBus-to-Multibus I/O Space Conversion                 | 26 |

| Figure 5-3. | Multibus-to-NuBus Conversion                           | 27 |

| Figure 5-4. | Multibus-to-NuBus Address Conversion                   | 28 |

| Figure 6-1. | Block Diagram — B/W Video Display Subsystem            | 30 |

| Figure 7-1. | Memory Board Block Diagram                             | 33 |

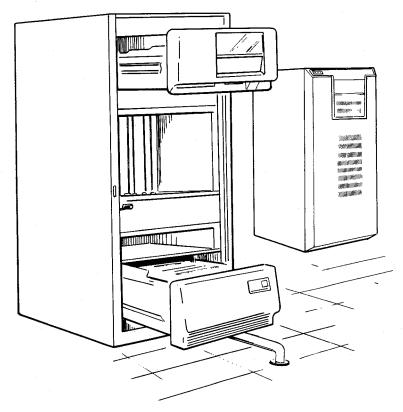

| Figure 9-1. | Office Module Cabinet and Contents                     | 43 |

| Figure 9-2. | Rack Module and Component Layout                       | 45 |

## 1.1 System Origins

The Nu Machine is based on the advanced NuBus technology developed at the Laboratory for Computer Science at the Massachusetts Institute of Technology.

The NuBus and Nu Machine architectures were developed to solve computing needs which were not served by commercially available equipment. The goal was to create a workstation-oriented computer with the following features:

- Processor independent

- State-of-the-art backplane bus

- Network and Graphics oriented

In April 1981, after the initial breadboard Nu Machines were constructed at M.I.T. and the UNIX<sup>TM</sup> operating system was ported to it, the design was licensed to Western Digital Corporation to be re-engineered and marketed as a commercial product. By late 1982, Western Digital had completed the redesign but decided not to enter the workstation business. Texas Instruments acquired the Nu Machine/NuBus technology including the original development group located in Irvine, California.

## 1.2 The System

Although always conceived of as a workstation, the Nu Machine is designed to be a general purpose, flexible, high-performance computer. The Nu Machine is a communications centered architecture in which the NuBus is a wide and efficiently controlled data freeway, providing exchange of information among processors, memory, mass storage, and remote computers (via networks). This approach is a departure from other computers. Figure 1 – 1 contrasts the NuBus architecture with a traditional supermini.

Figure 1-1. Comparison of Traditional and Nu Machine Architectures.

The Nu Machine incorporates these technologies:

#### NuBus

The NuBus provides a maximum transfer rate of 37.5 Mbytes per second, a bandwidth required for high-end applications involving multiple processors and future high-performance peripherals. OEMs may attach processors and controllers of their own design directly to the NuBus. The system implementor can have each processor running a different operating system, or have multiple processors running one operating system.

The NuBus itself provides many of the key Nu Machine features. Reliability is enhanced by the use of DIN connectors rather than card edge connectors. The bus supports autoconfiguration and eliminates the need for "DIP" switches and jumpers. The features that support multiprocessing are high bandwidth, dynamically redirectable interrupts and "fair" bus arbitration. TI is working with standards organizations, proposing that NuBus technology be adopted as an industry standard.

#### 68010-based CPU with Cache Memory

The central processor of the Nu Machine has a 4K byte 45 nanosecond cache memory and a sophisticated memory management system implemented in hardware. These features allow the 68010 to form the heart of a very high performance card. Because the NuBus supports 32 bits of data and address, it is well suited to take advantage of the forthcoming 68020 processor. The processor independence of the bus allows future processors to be built around other standard microprocessor families or special purpose instruction sets as justified by market needs.

### System Diagnostic Unit (SDU)

This multifunction board provides many features previously available only on much larger computers. The SDU is independent from the rest of the computer in that it contains an 8088 processor, RAM, ROM, and serial ports. It can be used under local or remote access to execute bus, board, and system diagnostics.

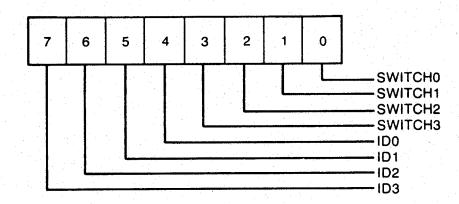

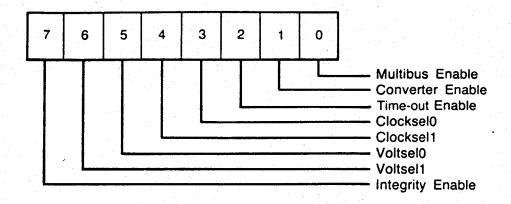

By reading ID ROMS on individual cards, the SDU performs an autoconfiguration, allowing the system to use a new/replacement card immediately, and then bootstraps the system software. Under program control the SDU can margin both the system clock and +5 volt power supply to test system robustness and aid in fault isolation.

An independent function of the SDU board is the conversion between the NuBus and the Multibus<sup>TM</sup>. This conversion allows masters on either bus to address slaves on the other bus, and is hardware implemented.

#### Multibus Subsystem

A large selection of third party I/O controllers are accessible through use of the NuBus-to-Multibus converter. The Multibus Subsystem operates independently of the NuBus, except during cycles which use them both.

#### High Resolution Raster Graphics

The  $800 \times 1024$  60Hz *non*interlaced display produces the precise drawings and mixed, multifort text and graphics needed by engineering workstation users.

#### Networking Capabilities

The Nu Machine Ethernet<sup>™</sup> networking capabilities provide dedicated computing resources under the direct control of the user, while also facilitating inter-user communication and sharing of resources.

#### Nu Machine Operating System

The operating system ported from Bell Laboratories UNIX, is very well suited to the technical work station software needs. Adaptations and enhancements have been made to support the high resolution graphics and other Nu Machine hardware features.

#### Attractive, Functional Packaging.

There are two primary configurations of Nu Machine. The smaller "office" unit is designed to fit under a work surface and be acoustically quiet, and the 19" rack model, which supports larger peripherals, is more suited to computer room operations.

The office unit has a 12 slot card cage and supports a  $\frac{1}{4}$ " cartridge tape drive and an 8" 84 megabyte disk. The rack unit has a 21 slot card cage and supports a  $\frac{1}{2}$ " streaming tape unit and a 474 megabyte disk. In both models, all cables attach to the rear of the card cage rather than to printed circuit cards, thus simplifying maintenance. Careful design of the motherboard and cabling reduces RF radiation at the source. In the office system, peripherals and power supplies are mounted on easy-to-remove plates to simplify maintenance and to easily accommodate the mounting requirements of many different makes of peripherals.

The optional 15" high resolution graphics portrait display used with both Nu Machine configurations is designed to have a very small footprint on the user's work surface. The monitor provides connections for the low profile keyboard and mouse. The monitor/keyboard/mouse assembly can be up to 200 feet from the Nu Machine itself.

## 1.3 Applications

The long life expectancy of the NuBus and the high degree of modularity and processor independence make the Nu Machine boards and chassis a fundamental system for the OEM or systems integrator. These features make the Nu Machine particularly attractive to OEMs who plan to create special purpose processors, especially if high bandwidth and

multiprocessing are required. For example, a current Nu Machine customer is delivering Nu Machines with a proprietary Lisp processor for Artificial Intelligence applications. The resulting combination of the Lisp and 68010 processor allows their users to do development in Lisp and still have access to the growing base of UNIX software.

Other possible applications for the Nu Machine include VLSI circuit design, printed circuit board design, mechanical design, mapping and cartography, civil engineering, architecture, and Computer-Aided Engineering (CAE).

An advantage of the Nu Machine is its ability to support teams. Many of the above applications involve large databases which must be shared by team members. The volume of data may be cumbersome when moved across a local network. With a NuBus, several processors can directly access the same disk and memory, creating what in essence is a 300M bit-per-second very "local" network. For example, several users each with a dedicated processor and operating system could have rapid access to the complete project database within the limits of their access privileges.

The common denominator of all these applications is the requirement for networking in combination with high-performance processing and graphics. The NuBus makes the Nu Machine a uniquely flexible and powerful tool in the hands of a skilled system architect.

## 2.1 Overview

The NuBus interface is the flexible bus structure which allows the various system components, including the 68010 CPU board, memory board, video interfaces, network interfaces, and peripheral controllers, to interact with each other. It supports direct addressability of more than four gigabytes of memory through 32-bit byte addressing, and data transactions of 8-, 16-, and 32-bits. Block transfers of multiple words are supported to achieve maximum bandwidth.

The bus structure is built on a master-slave concept. For each transaction, a device takes control of the NuBus interface, thus becoming a "master," and addresses another unit to be a "slave" for that transaction. The slave device, on decoding its address, acts on the command provided by the master. A simple handshake protocol between the master and slave allows modules of different speeds to use the NuBus interface.

The flexibility of the NuBus plus its high bandwidth allow multiple master modules to be connected for multiprocessing configurations. Fair arbitration among the bus masters gives each processor an essentially equal share of the bus bandwidth.

Any module on the NuBus can interrupt a processor module by writing into an area of address space that is monitored by that processor. This "event" mechanism is an important aspect of multiprocessor support. Interrupt lines are eliminated and interrupts may be dynamically reassigned to different processors.

In summary, important NuBus features are:

- All bus signals, power and grounds are contained within a single 96-pin DIN connector;

- 32-bits of data multiplexed with 32-bits of address;

- Distributed bus arbitration that implements fair bus bandwidth sharing. Arbitration may take place simultaneously with data transfer operations;

- Simple handshake protocol synchronized to clock cycles;

- "Memory-mapped" interrupt scheme that supports multiprocessors;

- Increased bus bandwidth through block transfers;

- · Board addressing by slot position rather than jumpers or switches; and

- Address and data transfer integrity may be protected by parity logic.

The NuBus supports the unified bus interconnection of up to 16 system modules. The motherboard presents each board location with a unique identification number. Any system module can occupy any board location; thus, jumpers, or switches on individual cards and special backplane wiring are not needed to define address space.

## 2.2 NuBus Signals

The NuBus signals are grouped into five classes based on the function performed. The five classes are:

#### Card Slot Identification

4 signals; assigns the physical location to each module.

#### Control

6 signals; performs all control functions. These functions are as follows:

- RESET/ (where "/" indicates a negative true signal);

- CLK/ (Clock);

- START/ signals the beginning of data transfer;

- ACK/ (Transfer Acknowledge) indicates the end of data transfer;

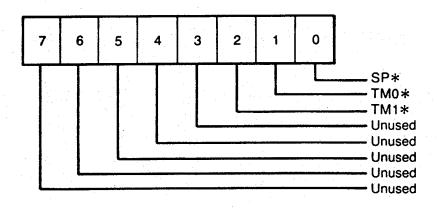

- TM0/and TM1/ (Transfer Mode 0 and 1) are encoded by the current bus master to indicate type of transfer.

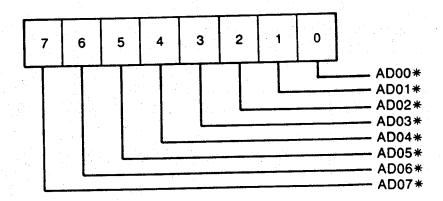

#### Address/Data

32 signals; carries 32-bit address at beginning of cycle and 32 bits of data within remainder of cycle.

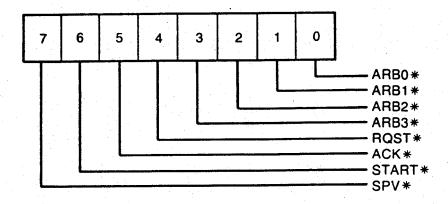

#### Bus

5 signals; regulates bus arbitration.

#### Parity

#### 2 signals

- SP/ (System Parity) transmits parity information between cards implementing NuBus parity checking.

- SPV/ (System Parity Valid) indicates whether system parity is valid or not for that transaction.

The NuBus also includes conductors that carry power and ground signals. Voltages available are +5, -5, +12, and -12. Critical signals are isolated and surrounded by power and ground lines to minimize crosstalk.

## 2.3 Data Transfer Operations

Data transfer on the NuBus is accomplished using a synchronous master/slave protocol. Bus transactions are synchronous to the system clock and their durations are multiples of the clock period. The protocol uses two handshake signals to coordinate the transfer: START/ (generated by the current bus master) and either TMO/ or ACK/ (generated by the slave).

Information is placed on the bus synchronous with the rising (assertion) edge and is sampled on the falling (sample) edge of the clock cycle. This technique provides protection from race conditions caused by bus transmission skews.

#### Read Transactions

Read operations with data widths of 8, 16, and 32 bits are selected by the transfer mode lines (TMx) and the two low-order address lines. The current bus master is responsible for selecting the appropriate byte or halfword for internal use if all 32 bits are not relevant.

#### Write Transactions

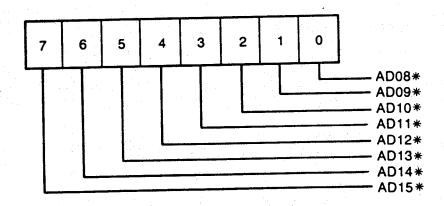

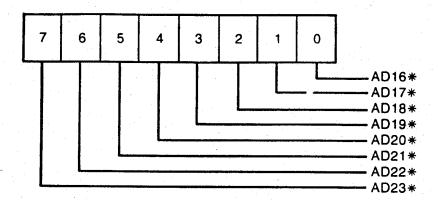

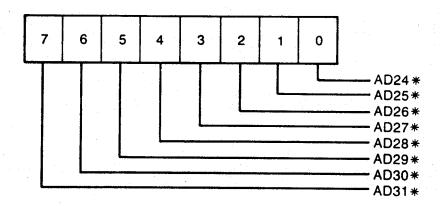

Write operations with data widths of 8, 16, and 32 bits are selected by the transfer mode lines (TMx) and the two low-order address lines. Bytes, halfwords, and words are organized as shown in Figure 2-1.

Figure 2-1. Layout of Words, Halfwords, and Bytes.

The current bus master has the responsibility of aligning the data to be written onto the appropriate ADx/ lines for halfword and byte writes. For example, a write byte 3 requires that the data be placed on AD24/ through AD31/; all other ADx/ lines are not defined and can be driven to any state.

#### Block Read

Block reads on the NuBus consist of a single command/address transfer initiated by the current bus master, followed by "N" 32-bit data outputs from sequential ascending locations of the addressed slave. "N" is equal to 2-, 4-, 8-, or 16-word blocks and is determined by AD2/, AD3/, AD4/, and AD5/ on the START/ cycle.

#### **Block Write**

Block writes on the NuBus are similar to block reads except the TM1/ (read/write) is driven to the write state during the START/ cycle, and the current bus master drives the data bus while the slave accepts data.

#### Error Acknowledgement

The two TMx lines are encoded at ACK time to indicate whether or not the bus transfer was successful. Four states are possible:

#### **ACK**

Successful completion of transfer.

#### NAK

Unsuccessful completion of transfer because of an error condition.

#### **Timeout**

Unsuccessful completion of transfer because "N" bus cycles elapsed while the bus was "busy" (between START and ACK).

#### Try Again Later

Unsuccessful completion of transfer but no error condition exists; the master should rearbitrate for the bus and try again.

## 2.4 Multiprocessor Support

Advanced arbitration and interrupt techniques provide the primary hardware support for multiprocessing.

#### 2.4.1 Arbitration

Arbitration for the NuBus takes place each time control is transferred between bus masters. The winner of the arbitration contest takes control of the bus and retains control until an arbitration contest is won by another bus master. (Actual transfer of control does not occur until after the current bus master completes the data transfer in progress.)

The NuBus provides fair bandwidth sharing between processors in a multiprocessor system. The sharing is accomplished by a rule which is:

If several devices request the bus at a certain time, they are given the bus in priority order — highest to lowest. Fairness is provided by the rule that no new bus requests can originate from any device, including those in this group, until all devices in that group have acquired the bus.

This rule guarantees that processors of higher physical priority do not starve a processor of lower priority.

Once a bus master has acquired the NuBus, it is, by definition the highest priority bus master of the group of modules still requesting the bus. An undivided set of data transfers, such as in the "test-and-set" operation, can be accomplished by the bus master continually arbitrating for, and winning, the bus.

An arbitration contest takes place only when control of the bus must be transferred between bus masters. Therefore, if no other processor has requested the bus, the current bus master may initiate data transfers without first rearbitrating for use of the bus. This capability relieves the current bus master from the overhead of arbitrating for use of an idle bus and is termed "parking" or "glomming."

#### 2.4.2 Interrupts

A processor module can be interrupted by any module on the NuBus performing a write transaction operation into memory space monitored by the processor. No unique lines or protocols are required. The address used to post the interrupt can be at any location in the address space. This allows interrupts to be posted to individual processors in a multiprocessor system and allows the priority of the interrupt to be software specified by memory-mapping the priority level.

## 3 68010 PROCESSOR BOARD

The CPU board design incorporates a single Motorola 68010 microprocessor, a high-speed cache memory, and a virtual memory translation unit. The main computational resource of the Nu Machine, the 68010 generates 24-bit virtual addresses, which allow access to 16M bytes per virtual address space. These addresses are termed "virtual" because each address is not the actual NuBus address in physical memory. Instead, a state machine on the board translates the virtual addresses to physical addresses.

Main features of the CPU board are:

#### 68010

- 32-Bit Arithmetic

- 17 Registers

- 24-Bit Virtual Addresses for Each Process

- 10 MHz Operation

- Byte Addressability

#### • 4 KB Data Cache

— No Wait States on Cache "Hits"

#### • "Demand Paging" Virtual Memory Implementation

- Translation Engine to Translate Virtual Addresses to Physical Addresses

- 512-Entry Translation "Look-Aside" Buffer

- Sufficient context stacking to permit recovery from page faults.

## 3.1 Virtual Address Space

In a typical multiprogramming environment, several "tasks" are active at the same time. The Nu Machine CPU provides separate virtual address spaces for each of these tasks.

Because even a single virtual address space may be too large to be contained in the available main memory, the active part of the virtual address space must be mapped to the available physical address space. To affect mapping, the physical and virtual memory are divided into 1K byte units called pages. A page of virtual memory is mapped either to a page in physical memory or to a page in mass storage.

Figure 3-1 is a simple representation of the virtual address space concept. It shows two virtual address spaces with most pages associated with unique physical memory pages. The second page in space "A" and the third page in space "B" are, in fact, the same page of physical memory.

A virtual memory scheme is needed to provide a large address space and yet allow programs to run on hardware with smaller memory size. The virtual memory hardware and software assign virtual addresses to specific physical memory locations in real-time while the process is executing, in some cases, having to bring the required location into memory from the disk. Usually the physical memory assigned to different processes will be non-overlapping. The paging mechanism, however, allows one physical location to be mapped into the virtual address spaces of two or more processes to implement data or code sharing.

Figure 3-1. Virtual Address Space Concept.

Virtual-to-physical address mapping is only one part of a virtual memory scheme. The other parts provided by the Nu Machine hardware and software are a "fault recoverable" CPU and a page replacement algorithm.

## 3.2 Main Functions of the CPU Board

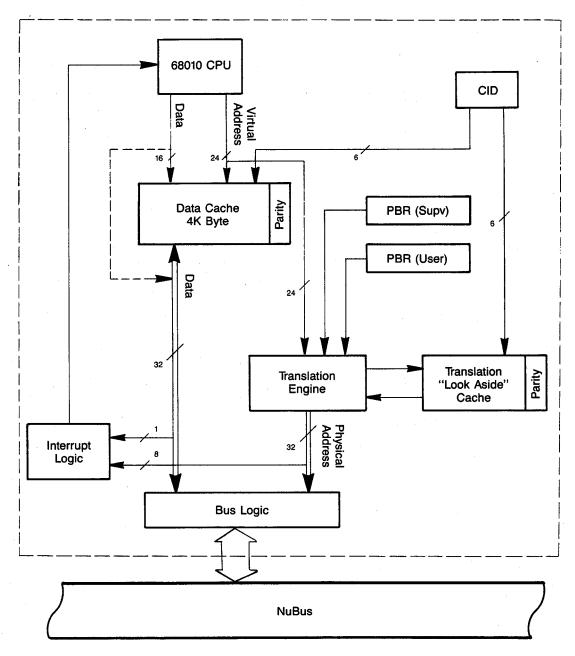

Figure 3-2 is a simplified block diagram of the CPU board showing the main functions.

Figure 3-2. Block Diagram of CPU Board.

#### 3.2.1 68010 Microprocessor

The 68010 microprocessor is a version of the 68000 which can correctly recover from a virtual memory page fault. The occurrence of a page fault (the page referenced does not reside in physical main memory) causes the 68010 to stack its internal machine state. At this point, the 68010 executes the software that causes the page to be brought into memory. The 68010 then retrieves its previous internal machine state and picks up execution at the point of the original page fault.

#### 3.2.2 Cache Operation

The 4K byte, write-through data cache provides the CPU with high-speed access to frequently used words of main memory. Both instructions and data are stored in this unit and are treated equivalently. This set-associative cache contains 1024 one-word entries and carries byte parity. If desired, the cache can be disabled for diagnostics or to allow reduced performance providing graceful degradation in the event of cache failure.

The cache operates in a manner similar to many super minicomputers. A search of the cache determines if the desired data item is present. The search is performed for all 68010 memory reference operations as long as the cache is enabled. Each word of virtual memory has a place in the cache where it will be stored, if it is in the cache. The cache must examine only the location in which the word would be found if it were present.

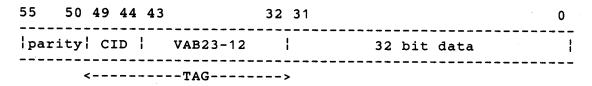

The entry in the cache where a word is stored, if it is stored at all, is determined by the lower 10 bits of the address. That is, data from location 2003(Hex) would be stored in the third location of the cache as would data from location 5003(Hex). Only one of these pieces of data may be cached at any instant in time. The lower 10 bits of the address emitted by the 68010 are used to address the 1024 entry cache in implementing that operation of the CPU. The address tag, or upper 12 bits of the virtual address space of stored information, is compared with the upper 12 bits of the emitted address. Figure 3-3 represents a cache entry.

Figure 3-3. Data Cache Entry (Parity, Tag Field, and Data).

A "hit" occurs when the 12-bit address tag field stored at that entry matches the emitted address being sought by that particular 68010 cycle. The "hit" rate for this particular cache is approximately 85%.

A "miss" occurs when the upper 12 bits of the emitted address of the 68010 do not match the 12-bit address tag field of the stored data. The virtual address must then be translated into the physical address so that the bus logic will read the complete 32-bit word over the bus. The desired data item is placed in the cache entry at which the miss occurred, overwriting whatever data and address tag were there.

The write-through feature insures cache integrity because this cache is always a copy of memory. Therefore, on write operations when a hit or miss is made, address translation and bus logic are always invoked causing the written data to go into main memory. Thus, main memory is always a true copy of the state of the virtual address base, and the cache is a copy of that data. The cache is checked for a hit even on a write because if a hit occurs, that cache cell must be updated to the new value.

#### 3.2.3 Cache Control

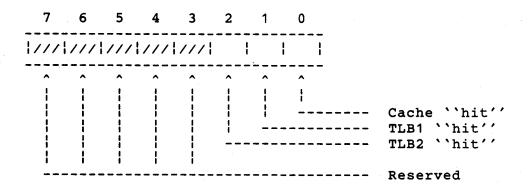

The cache data integrity is protected by byte parity across the data and tag fields. Any entry showing a parity error does not cause a hit and is treated as a normal miss except that the parity error flag in the error status register is set. Figure 3-4 shows the cache control register, and Figure 3-5 shows the cache "hit" status register.

For diagnostic purposes, the cache may be partially enabled or disabled via bits in the cache control. Partial enabling allows a diagnostic to test the cache without instructing itself to be cached.

Figure 3-4. Cache Control.

Figure 3-5. Cache Status.

An aspect of cache control that is not directly implemented by the cache logic itself is the ability *not* to cache selected pages of virtual memory. This capability allows support of writable, shared data areas; for instance, semaphores which must be accessed by multiple processes. The selective caching of pages is *not* directly implemented by logic in the caching section. Rather, the determination of which pages are not to be cached is a feature of the translation system.

Another application of selected caching is I/O registers. The selective caching of pages is not directly implemented by logic in the caching section. Rather, the determination of which pages are not to be cached is a feature of the translation system. When an I/O register is read multiple times, the desired data is not multiple copies of the first value but, instead, the current state of the I/O register.

#### 3.2.4 Cache ID

Since the data cache on the Nu Machine is directly connected to the 68010 CPU, it caches data related to virtual address.

The advantages of this approach are obvious. Having the high speed cache (45 nanoseconds RAM) as close in the architecture as possible to the CPU eliminates wait states for the 10MHz 68010. In the future, faster microprocessors could be accommodated by increasing the speed of the cache memory path.

In other systems, this approach would have the disadvantage of taking extra time for cache flushes on every context switch. However, in the Nu Machine, a six-bit register and six extra bits of tag increase the speed at which the cache may be "flushed." The six extra bits of tag are called the cache identification (CID) field. Each active virtual address space has a unique six-bit CID code. When contexts are switched, the six-bit CID register associated with the 68010 CPU is changed. Therefore, cached data from previous virtual address spaces are immediately invalidated (flushed). An actual flush must be performed *only* between every sixty-four context switches.

#### 3.2.5 Address Translation

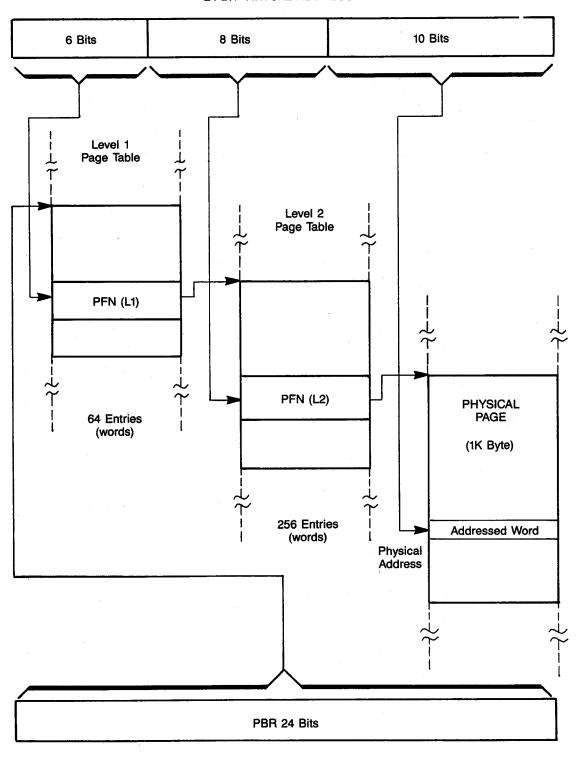

The CPU card provides hardware to translate 24-bit virtual addresses to 32-bit physical addresses in 1024 byte page increments. Each page can be marked as resident/nonresident by the "valid entry" bit; has read and write access protection for both supervisor and user modes; has a bit to disable data caching on the page; and has both a page-accessed and a page-modified bit.

Address translation of the virtual address is accomplished by the translation engine and is based on two levels of page maps. The level-one page map defines the physical addresses of the level-two map. The level-two map defines the physical addresses of the virtual address space. The level-one map is 64 words long and the level-two map is 256 words long. The first page level table *must* be resident in main memory. Second level page tables may be resident or "paged" out to the disk.

Figure 3 – 6 illustrates the following explanation of the virtual-to physical address operation.

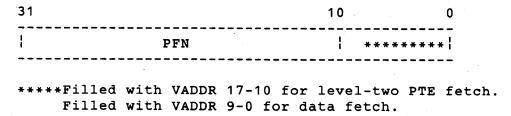

### 24-BIT VIRTUAL ADDRESS

Figure 3-6. Virtual-to-Physical Address Translation.

Abbreviations used in this description are:

- CID is a cache ID number.

- PADDR is the physical address.

- PBR is the process base register.

- PFN is a page frame number.

- PTE is a page table entry a 32-bit word that represents the physical mapping for one virtual page.

- PTE1 and PTE2 are level-one and level-two PTEs, respectively.

- VADDR is the virtual address from the CPU.

First, one of two 24-bit PBRs on the CPU card points to the start of the first level page table. (The hardware contains two PBRs — one for supervisor mode and one for user mode.) Then the first six bits of the VADDR (bits 23 through 18) are appended to the PBR to form a physical address for a PTE in the level one page map. This PTE is read from memory.

Next, the PFN of the PTE from the level-one page-table are appended to bits 17 through 10 of the VADDR. This forms the physical address of a PTE in the level-two map. This PTE is read from memory.

Finally, the PFN of this level-two PTE is appended to bits 9 through 0 of the VADDR. This represents the final physical address. Figure 3-7 represents the PFN from the level-one page table plus the virtual address bits and the data bits.

Figure 3-7. Representation of Physical Address.

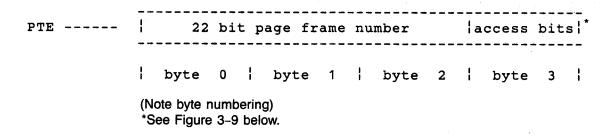

PTEs, as shown in Figure 3-8 have a field, the PFN, that contains the high-order 22 bits of the physical address of a page. Pages always begin on multiples of 1024 bytes; therefore, the PFN with 10 bits of 0s concatenated is the address of the page.

Figure 3-8. PTE Description.

Each memory reference is checked for read and write access privileges and for the validity of the PTE. Figure 3 – 9 shows the definitions of the access bits.

```

Access bits: BIT 31 - RESERVED

BIT 30 - RESERVED

BIT 29 - PRIVILEGE BIT 1 (PV1) \ ACCESS

BIT 28 - PRIVILEGE BIT 0 (PV0) / PRIVILEGE

BIT 27 - UPDATE CACHE

BIT 26 - VALID ENTRY (page resident/nonresident)

BIT 25 - ACCESSED

BIT 24 - MODIFIED

```

Figure 3-9. Definitions of Access Bits.

The access privileges are further illustrated in Table 3-1.

TABLE 3-1. Privilege Bits

| PV1 | PV0        |   | ACCESS PI  | RIVIL | EGE        |        |

|-----|------------|---|------------|-------|------------|--------|

|     |            |   |            |       |            |        |

| 0   | 0          | > | Supervisor | R on  | 1 <b>y</b> |        |

| 0   | 1          | > | Supervisor |       | -          |        |

| 1   | 0          | > | Supervisor | R/W,  | User       | R only |

| 1   | <b>, 1</b> | > | Supervisor | R/W,  | User       | R/W    |

If a bit is "modified," a memory write sets it in the level-two PTE, which, if not already set, in turn, sets the "modified" bit in the level-one PTE.

Translation 'Look Aside' Buffer If the CPU hardware implemented address translation only as just described, each processor reference would cause two memory accesses to do translation. To speed up these translations, another caching mechanism, the Translation 'Look Aside' Buffer (TLAB), holds an additional 512 second-level PTEs and 64 first-level PTEs. All caches are updated as necessary by the translation engine.

Therefore, if a "hit" occurs on a second-level PTE, no memory references are necessary for translation. If a hit occurs on a first-level PTE, one memory reference is required, and in the rare case where a hit does not occur, two memory references are required to translate the address.

#### 3.2.6 Interrupt Mechanism

The 68010 microprocessor supports seven levels of interrupt priorities, labeled one through seven, with seven having the highest priorities. The Nu Machine CPU unit provides 32 unique vectored interrupts for each of these levels, totaling 224 possible cases. As described in Section 2.1 on the NuBus, the bus does not require traditional interrupt signals.

The shortcoming of traditional interrupt approaches is that they do not support multiprocessing. In a multiprocessor environment, interrupts or "events" must be dynamically assignable to any of many processing elements.

Interrupts, like memory and I/O, are memory-mapped in the single NuBus address space. Therefore, computing units can readily interrupt each other or can even interrupt themselves from high-level language programs.

On the NuBus, events are posted by *ordinary* bus write cycles to *special* areas of the address space to which the CPU units respond. Logic on the CPU board translates all writes to that region into 68010 interrupts. These interrupts are latched and presented to the 68010 in priority order.

The priority level of an event is determined by its address within the 224-word area. For example, the top 32 words of the area correspond to level-seven interrupts; the next 32 words correspond to level-six interrupts, and so forth. When the 68010 requests the interrupt vector, it is given the unique address of the highest priority interrupt. This action immediately clears the particular interrupt.

#### 3.2.7 CPU Control

The CPU control logic is primarily a debugging tool. The "Stop CPU" control bit may be used to halt the 68010 microprocessor upon completion of its current cycle. The halt request may then be removed allowing the 68010 to continue or begin instruction execution. Writing the "Single-Step CPU" bit enables the single step function. That is, when the 68010 begins its bus cycle, the stop CPU bit is turned on and, upon completion of that bus cycle, the microprocessor halts. The halt status of the 68010 may be obtained by reading the "Halt Status" bit.

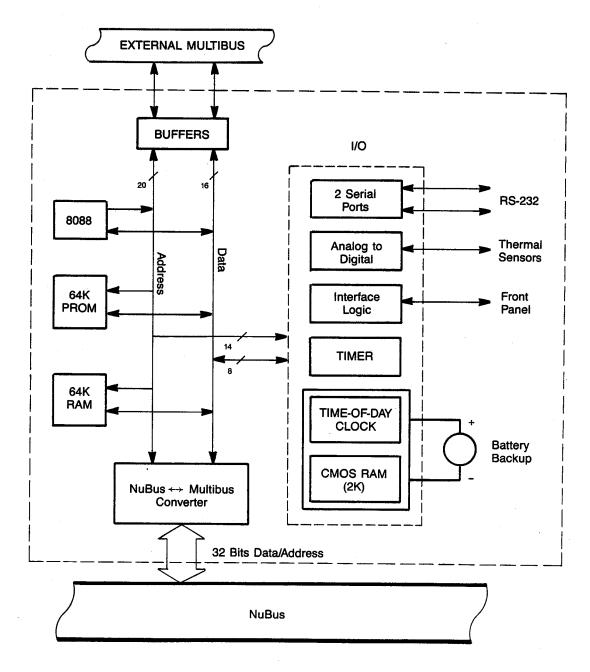

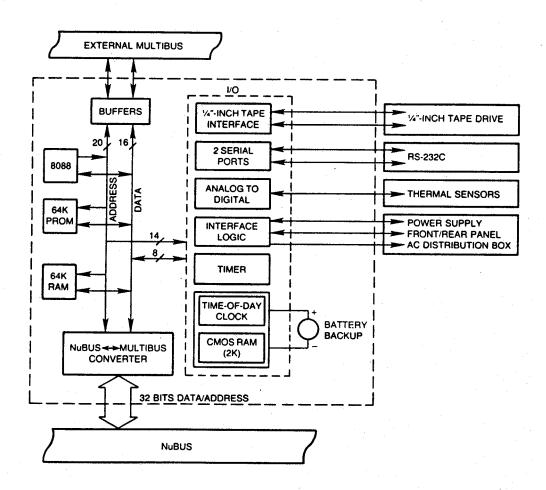

## 4 SYSTEM DIAGNOSTIC UNIT

The System Diagnostic Unit (SDU) is present in all NuBus systems to provide many important one-per-system functions and "smart" front-end and diagnostic capabilities. By concentrating these functions on the SDU, rather than on separate CPU cards, the system is able to support multiple processors without conflict.

On power-up, the SDU verifies the integrity of the bus through a series of bus transfer tests. The SDU then identifies all boards within its system environment; initiates and monitors diagnostic and self-test routines to ensure that the boards are functioning properly; signals the operator, using an on-board serial I/O facility, if any boards have malfunctioned; and then initiates the system bootstrap program.

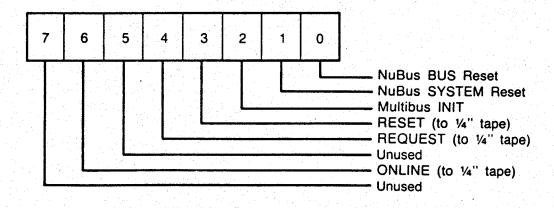

The SDU also serves as the NuBus-to-Multibus converter. Facilities are provided for mapping Multibus cycles into NuBus cycles and vice versa; for mapping Multibus interrupts into NuBus events; and for generating Multibus interrupts from the NuBus.

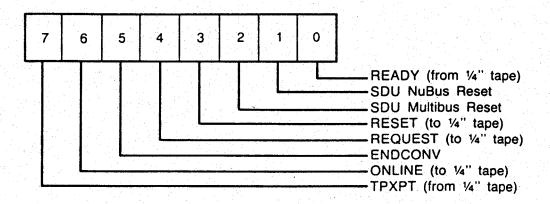

The SDU consists of an Intel 8088 microprocessor with on-board memory, two serial I/O ports for communication with the operator and peripherals, and many other system maintenance and diagnostic features. A functional block diagram is show in Figure 4 – 1.

The main features of the SDU are:

System Clock

The SDU is the source of the 75% duty cycle, 10 MHz System Clock (CLK/), to which all bus operations are synchronized. The system clock rate can be programmatically margined up or down for diagnostic purposes.

#### Timeout Recovery

The SDU provides NuBus timeout recovery by monitoring the time between the START/ and ACK/ control signals. If more than 256 clock cycles occur, the SDU asserts the ACK/ signal with the appropriate TM0 and TM1 code for a timeout.

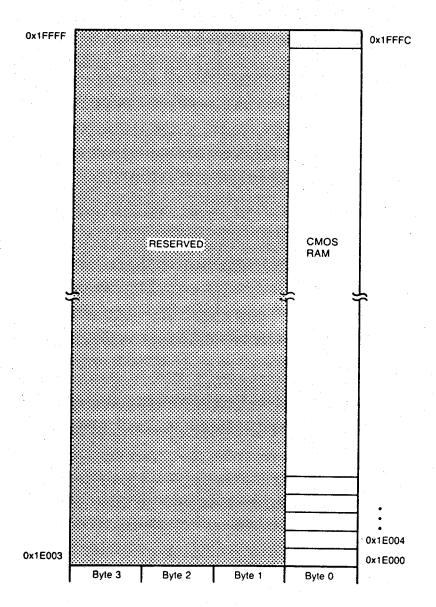

#### Nonvolatile Features

The SDU contains 2K bytes of battery backed-up CMOS RAM. This memory is used to store the system configuration information in a nonvolatile manner. The SDU also provides a battery backed-up time-of-day clock.

#### 1/4" Tape Interface

The SDU contains a ¼" streaming tape drive interface. This feature provides low cost transportable media for the Nu Machine. Since this interface is on the SDU, diagnostic routines can be loaded from this tape and yet the diagnostic unit remains self contained.

Figure 4-1. System Diagnostic Unit Block Diagram.

#### Interval Timer

The SDU contains a programmable timer for generating periodic events to specific CPUs. The timer may be used for many important system functions, such as process scheduling.

#### Debug/Diagnostic Facilities

The SDU provides the operator of the NuBus system several diagnostic tools. A monitor in the SDU's PROMs allows either serial port to be used to read and write bus locations, to initiate SDU self tests, and to execute diagnostics. The NuBus diagnostic hardware verifies the integrity of the bus.

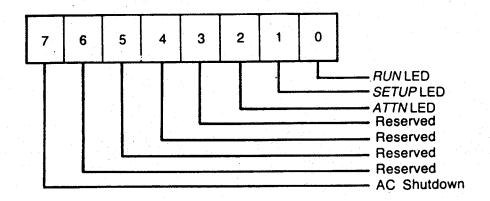

#### System Status Display

On power-up, the SDU first runs a self test, next a bus test, and then individual board tests. The SDU uses the front panel LEDs to summarize the results of the tests, and the detailed results may be read using the system console. A LED on each board is automatically turned on at power-up, and turned off by the SDU if that board passes power-up diagnostics. A board with its LED on is therefore presumed bad.

#### Serial Port

The SDU contains two serial communications ports, either of which may be used as the smart front panel/remote diagnostics port, depending on the position of the diagnostic rotary switch. Otherwise, they are both available as general-purpose serial ports.

#### Power Supply Interface

The interface to the power supply includes several lines in addition to the actual current carrying cables. These lines are ACPF, DCOT, MARGHI, MARGLO, and ACOFF. The SDU provides the system interface to these lines. ACPF (AC power fail) is generated by the power supply. The SDU then posts "events" to the installed CPU's so that they can take appropriate action. DCOT (DC out of tolerance) indicates that the +5 volt supply is within tolerance (+/-5%). When this signal is active the SDU generates a system reset. MARGHI and MARGLO are signals from the SDU by which the +5 volt supply can be margined +/-7%. ACOFF is a signal from the SDU to the AC distribution box by which the SDU can shut off the AC power under user control or due to temperature excesses.

#### System Boot

The NuBus system boots automatically on power-up by action taken by the SDU. However, if for any reason program control is lost or undefined, the system may be reinitialized from the SDU manually. A system halt, reset, and reboot may be initiated from the console serial port.

NuBus/Multibus Translation

The NuBus/Multibus interface is explained in Section 5.

## 5 MULTIBUS INTERFACE

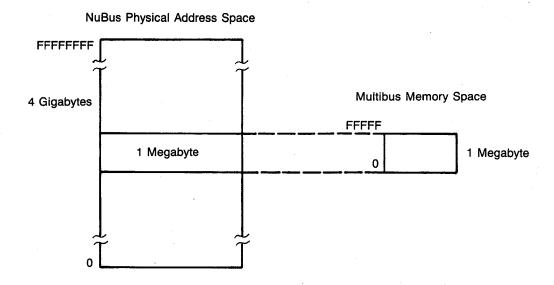

Although the Nu Machine is designed around the high bandwidth NuBus, the Multibus (IEEE-796) is also part of the system. The two buses operate independently from one another except during a conversion. This combination provides NuBus advantages such as flexibility, speed, expandability, and multiprocessing with Multibus peripheral controller options. Further, Nu Machine users might use any of a large number (approximately 900-1000) of Multibus-compatible, board-level products from over 100 manufacturers.

## 5.1 Conversion

The NuBus/Multibus converter resides on the System Diagnostic Unit (SDU). Bus conversion in both directions is done by hardware mapping logic and requires no intervention by the 8088 microprocessor.

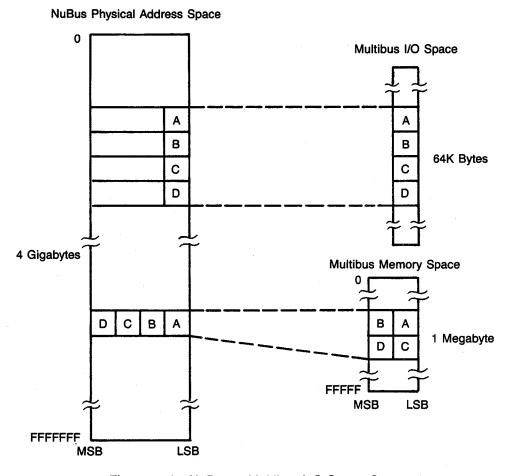

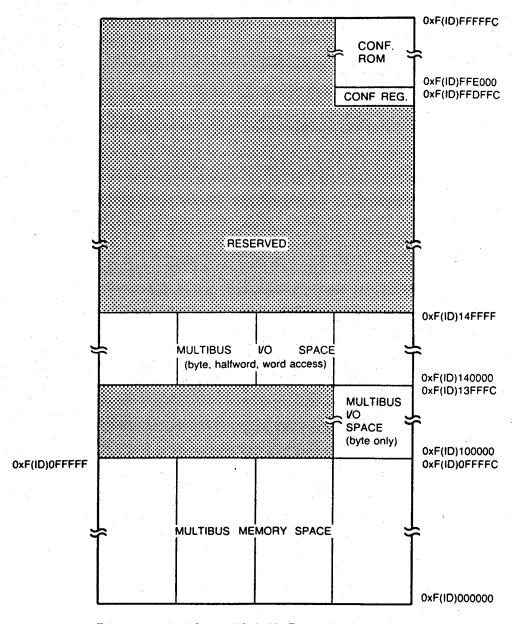

The Multibus interface is termed transparent because it translates NuBus transactions and Multibus transactions into each other. Further, the NuBus processor can access data or even execute programs out of the Multibus memory while conversion is taking place. Figure 5-1 illustrates how the transparent conversion acts like a "bus window." The entire Multibus memory space appears in the NuBus slot space of the SDU. When an address emitted by a NuBus master falls into this "window," the converter acquires Multibus mastership.

Figure 5-1. NuBus-to-Multibus Memory Space Conversion.

#### 5.1.1 NuBus-to-Multibus Conversion

Memory Space NuBus 8- and 16-bit transactions are converted directly into 8- and 16-bit Multibus transactions. That is, the converter translates a transfer acknowledge on the Multibus to a transfer acknowledge on the NuBus. Bus conversions occur at bus speeds. NuBus 32-bit transactions are turned into two separate Multibus transactions to successive addresses.

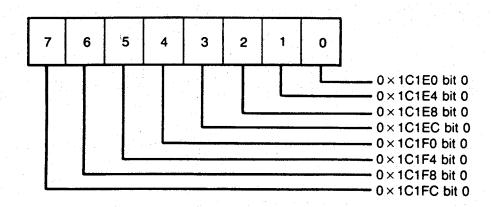

I/O Space The 64K byte Multibus I/O space is mapped by the converter to a 64K-word region in the NuBus SDU slot space. Each byte of the Multibus I/O space is mapped to a separate word of the NuBus space. Thus, NuBus masters that are only capable of performing 16- or 32-bit operations are able to access individual byte locations in the Multibus I/O space. Figure 5-2 illustrates the Multibus I/O space mapping.

Figure 5-2. NuBus-to-Multibus I/O Space Conversion.

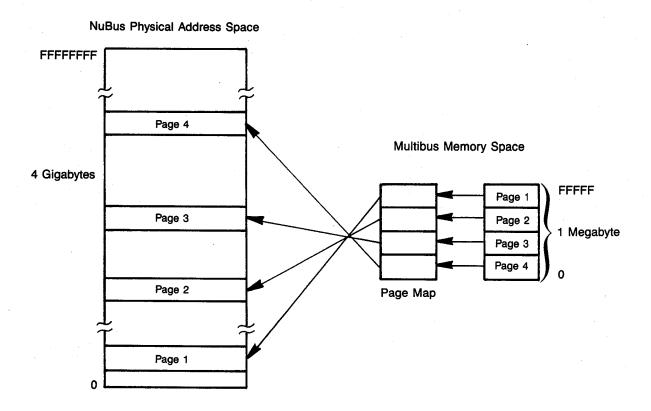

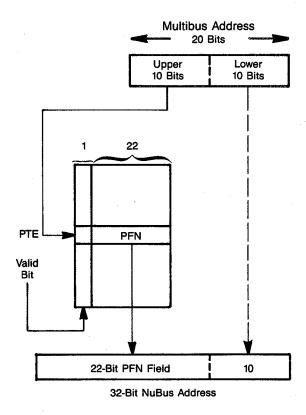

#### 5.1.2 Multibus-to-NuBus Conversion

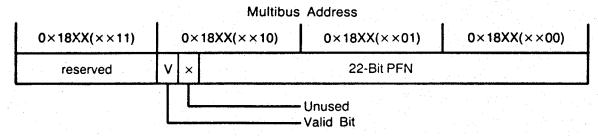

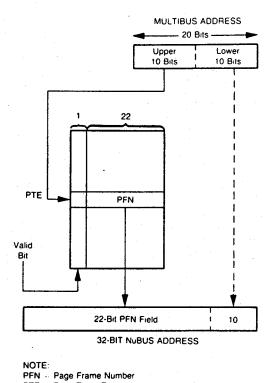

On every Multibus cycle, the converter (which is a slave device on the Multibus) checks to see if it is being addressed. This test to determine if the Multibus address page may be converted to a NuBus page is accomplished by using the upper 10 bits of the Multibus address to reference the Multi-to-Nu page map. A bit in each entry in this page map, called

the Valid Entry bit, determines if a conversion is to take place. If a conversion is required, the 22-bit PFN (page frame number) field of the PTE (page table entry) determines the page of NuBus memory referenced. The completed translation of the NuBus address is the concatenation of the 22-bit PFN field with the lower 10 bits of the Multibus address. Figures 5-3 and 5-4 show this process from two points of view.

Figure 5-3. Multibus-to-NuBus Conversion.

Figure 5-4. Multibus-to-NuBus Address Conversion.

## 5.2 Interrupt Mapping

Multi-to-Nu

The mapping of Multibus interrupts is handled by the 8088 processor on the SDU board. When a Multibus interrupt is received by the 8088, the 8088 uses a table that associates Multibus interrupts with NuBus interrupt address locations to write into the NuBus address space. This causes the appropriate interrupt.

Nu-to-Multi

Event cycles on the NuBus are mapped into Multibus interrupts by an addressable latch on the SDU. The NuBus writes to this area of the address space to create Multibus interrupts.

## 5.3 Lockup Prevention

In bus conversion, the potential exists that when both buses request the other a "deadly embrace" could occur. The Nu Machine protocol, however, provides an elegant solution to this problem.

If a NuBus master requests use of the Multibus converter at the same time that a Multibus master has requested the NuBus, the SDU returns a "Try Again Later" response. This informs the NuBus master that it is unable to respond at that moment. The NuBus master then releases control of the NuBus and must rearbitrate for the NuBus again at a later time. This scheme frees the conversion path allowing the Multi-to-Nu transfer to finish.

## 6 VIDEO DISPLAY SUBSYSTEM

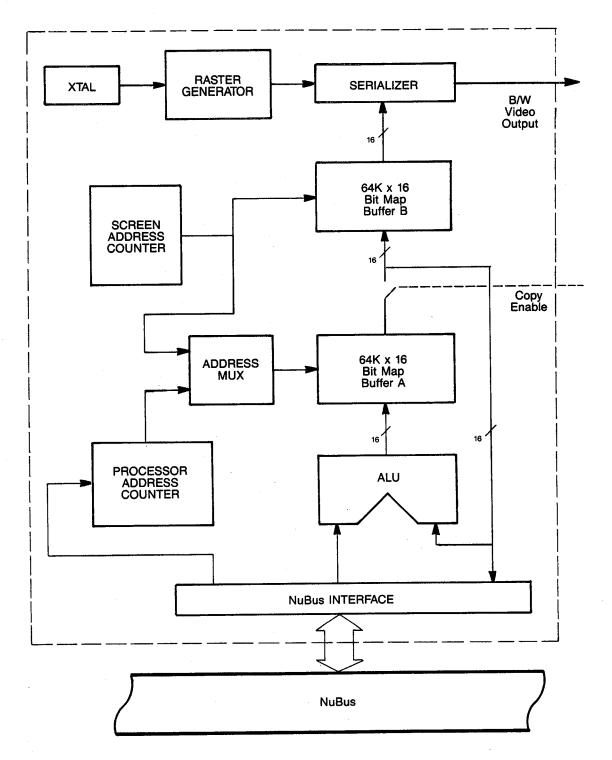

The video display subsystem is a single-board text and graphics display system. It utilizes a bit-map memory plane and video control circuitry to drive a high resolution noninterlaced monitor. Two video buffers on the board provide high bandwidth from the NuBus and high bandwidth to the display monitor. This board can be a master on the NuBus in order to generate interrupts.

Features of the video display subsystem are:

- One megabit of dedicated display memory (dual buffered);

- 1/60th of a second per screen update;

- 64K RAMs;

- Programmable number of words per line and lines per frame;

- Arithmetic Logic Unit (ALU) supports on-board logical functions such as XOR;

- Normal/reverse video;

- Horizontal, vertical, and composite synchronous outputs;

- TTL and ECL video outputs available;

- Programmable interrupt generations using vertical blank;

- Maximum pixel display rate of 70 MHz; and

- Two RS-232 serial ports for keyboard/mouse interface.

## 6.1 Main Functions of the Video Display Subsystem

The video display subsystem uses two dual-ported memory arrays. This unique approach enables the display to be refreshed from the video memory while, at the same time, the display may be changed by writing into the bit-map memory. Figure 6-1 is a functional block diagram of the board.

Figure 6-1. Block Diagram — B/W Video Display Subsystem.

The dual-ported arrays, called "A" and "B", are each a  $16 \times 64 \text{K}$  memory. The lower (or B) memory is constantly addressed by the refresh address counters and may continually repaint the screen by providing a 70-Mbyte bit stream. This design leaves the "A" bit map free to accept new data from the processor controlling the graphics.

As seen in the block diagram, not only may data be written from the bus directly into memory "A", but also a read-modify-write cycle using a single ALU on the video board may be performed. This architecture allows information written to the board to be ORed, ANDed, or EXCLUSIVE ORed with values already in the bit map. This read-modify-write and on-board ALU allows many common operations to be performed within the video card itself.

In order for updated information to appear on the screen, bits are copied from the "A" memory to the "B" memory. In fact, when the "A" memory is not being accessed by the NuBus, it is copied into the "B" memory providing a continual update. However, the NuBus has priority over the copy/update operation, which provides the maximum bandwidth for delivering new information to the display.

The screen has the capability to show the old image until the new image is ready to be displayed. For this feature, the copy operation is inhibited by turning off the "COPY" bit in the command register. In this state, new information is written into the "A" memory is *not* displayed on the screen. Instead, the screen keeps refreshing the old information from the "B" memory. When the update is complete, the "COPY" bit is turned on, causing the new information to appear on the screen in one frame time (1/60th of a second). This makes the Nu Machine suitable for animation and other applications where it would be undesirable to watch the screen being gradually updated.

Another advanced feature is the scan line table, a RAM that contains the starting addresses of each scan line in the "B" memory. This mechanism is used for scrolling and making rapid changes in small portions of the screen. It also could enable display screens with different aspect ratios, to be used, thereby enhancing the subsystem's flexibility.

## 6.2 Serial Ports

Two RS-232 serial ports on the video display board complete the man-machine interface. Although unrelated to the production of video signals, they support the keyboard and mouse which may be associated with each display.

Software requirements for servicing the RS-232 ports are simplified by a small amount of hardware buffering. There are 4 bytes of FIFO on the input side of each port and 2 bytes of FIFO on the output side of each port.

Nu Machine Technical Summary Texas Instruments

The Nu Machine memory board is a self-contained memory controller and ½ Mbyte memory array that includes logic to support error correction, block transfers, and error logging. The memory board interfaces to the NuBus as a "slave" device, responding to requests from a bus master. Up to 14 memory boards can be installed in the Nu Machine, yielding a maximum of 7M bytes of available physical memory.

# 7.1 Main Functions of the Memory Board

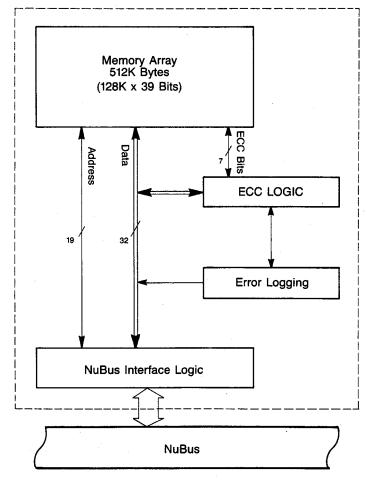

The main functions of the memory board reads, writes, and error detection are discussed below. A functional block diagram of the memory board is shown in Figure 7-1.

The memory board uses a 32/39 modified hamming code for error correction and detection; seven ECC (Error Correction Code) bits are appended to each 32-bit data word. This code enables correction of all single-bit errors and allows detection of all double-bit errors within the 39-bit word (32 data bits plus seven ECC bits). Additionally, some multiple-bit errors are detected. A multiple-bit error is one in which three or more bits in a particular word are in error.

Figure 7-1. Memory Board Block Diagram.

# Nu Machine Technical Summary Texas Instruments

**Read Operations** — A read cycle always results in a 32-bit array access. However, a full 32-bit read of the array generates the correct data on the bus for all size objects because of the way byte and half-word reads are specified.

The memory board checks the data for errors on all read cycles and then performs one of three operations:

- If no errors are detected, data are placed on the bus, and a bus transfer complete (ACK) response is given.

- If a single-bit error is detected, it is corrected, and the corrected data are placed on the bus with a bus transfer complete (ACK) response. This correction is transparent to the bus master. The corrected data are *not* written back to memory.

- If a double-bit error is detected, an error condition (NAK) response is given, and the data transferred are undefined.

Write Operations — Write cycles may result in 8-, 16-, or 32-bit data transfers. All write operations are carried out "off-line." That is, the data are latched, the bus transfer completed (ACK) signal is given, and the bus is released while the write operation is completed.

A 32-bit transfer is the simplest write operation. The latched data are presented to memory, a corresponding seven-bit ECC pattern is generated, and both are written to the addressed location. On 8- and 16-bit write transfers, a read of the addressed location is performed first. One of three things then occurs.

- If no errors are detected, the new data are substituted for the old data; a new ECC pattern is generated; and the new word and ECC are written in the addressed location.

- If a single-bit error is detected, it is corrected before the new data are substituted. This new word and its ECC pattern are then written in memory.

- If a double-bit error occurs, the write portion of the partial write is not performed. Thus, the data with the error are left in memory so that a subsequent read will detect an error. No indication of the error is immediately returned.

**Block Read Operation** — Block read cycles result in 2-, 4-, 8-, or 16-word (32-bits/word) block transfers. Each word of data is read and the data are checked for errors. Then one of three operations is performed.

- If no errors are detected, the data are placed on the bus. If that transfer is the last one, a bus transfer complete (ACK) response is given. If that transfer is not the last one, and intermediate "ACK" is given and the transfer continues.

- If a single-bit error is detected, it is corrected, and the corrected data are placed on the bus. If that transfer is the last one, a bus transfer complete (ACK) response is given. If that transfer is not the last one, an "intermediate" ACK is given and the transfer continues.

- If a double-bit error is detected, undefined data are transferred, an error condition (NAK) response is given, and the block transfer terminates.

Block Write Operation — Block write cycles result in 2-, 4-, 8-, or 16-word block transfers. Each word of data are latched and acknowledged. (An "intermediate" ACK response is given for all words except the last word transferred.) When the last word is transferred, a Bus Transfer Complete (ACK) response is given, and the bus transfer is complete. Each word of data is latched and presented to memory; a corresponding seven-bit ECC pattern is generated; and both are written to the addressed location. Then the address is incremented to the next word. This process occurs for each word of data to be written until all words have been transferred. Because complete words are written, no errors can occur on a block write operation.

Two categories of software are available with the Nu Machine. The first category consists of the SDU Monitor and the diagnostics that run under that monitor.

The second category of software is the Nu Machine Operating System. This is a port of Bell Lab's UNIX Operating System. The Nu Machine Operating System is derived from UNIX, Seventh Edition and contains, in addition to the normal UNIX commands and kernel, enhancements from the Berkeley version of UNIX and a proprietary window system for the Nu Machine video display subsystem. Of course, the Nu Machine Operating System will not run on Nu Machines that do not contain a 68010 processor board.

# 8.1 SDU Monitor and Diagnostics

#### 8.1.1 SDU Monitor

The SDU Monitor's primary function is to provide device independence for the diagnostics, bootstraps and other commands that run on the SDU. In addition, certain primitive commands built into the Monitor allow the user or service representative to probe the hardware even if the mass storage devices are broken.

A mode switch on the back of the machine selects a console device to access the SDU Monitor. One hardwired position selects a serial port on the SDU and sets it to operate at 300 baud. The functions of the other switch positions are defined by data in a non-volatile RAM.

Primitive Commands Primitive commands available on the SDU Monitor are:

- Reading and writing NuBus and Multibus locations;

- · Selectively resetting and enabling the buses;

- Clock and voltage margining to aid in diagnosis;

- · Copying data between devices; and

- Downloading commands from the serial ports.

Device Support The Monitor has a uniform device access mechanism similar to that provided by UNIX. In fact, some UNIX commands can be recompiled and run directly under the Monitor. Several device drivers are built into the Monitor. In addition, the Monitor has a facility for installing new device drivers while it is in operation. Device support is provided for:

- · Serial ports on the SDU;

- The high resolution display and keyboard;

- The Multibus SMD controller;

- The Multibus 1/2-inch tape controller;

- The ¼-inch tape controller;

- The non-volatile RAM; and

- The time-of-day clock.

For many of the devices, both raw and structured access is provided. For example, the disk may be accessed as a simple sequential byte stream and may also be accessed via a UNIX file system driver. The file system driver is not built into the Monitor but rather is "booted" from the disk when

## Nu Machine Technical Summary Texas Instruments

it is first accessed. This means that it can be replaced by different format file systems. Similarly, the tapes can be accessed both as a byte stream and as a structured file system in the UNIX "tar" format.

Loadable Commands To expand the command repertoire, the Monitor loads commands from several of the devices into RAM on the SDU, passes on arguments to these commands, and runs the commands. Commands are normally loaded from the disk but can also be loaded from the tapes or via host machine serial ports. Loadable commands perform I/O via standard input and output streams, unaware of which device they are talking to.

More important loadable commands are:

- The "setup" program used to manipulate non-volatile RAM;

- The main system and board diagnostics;

- The Nu Machine Operating System bootstrap program;

- The UNIX file system checker; and

- The UNIX dump program.

## 8.1.2 Diagnostics

Nu Machine diagnostics conveniently verify the correct functions of the system and aid in the debugging of a downed machine. Two kinds of diagnostics are available: startup diagnostics and loadable diagnostics. Both forms of diagnostics run under the Monitor; however, the startup diagnostics are simpler and return only an error code rather than the more extensive output of the main system diagnostics.

Startup Diagnostics Startup diagnostics are loaded from ROMs on each board as part of the power up sequence. They provide a relatively quick verification of the correct functioning of a board but do not provide much information as to the nature of any errors. Being resident on the boards, these diagnostics do not require any peripherals to be functioning and are always appropriate for the board on which they reside.

SDU Loadable Diagnostics Loadable diagnostics on the mass storage devices verify the correct functioning of system components. These diagnostics take longer to run but provide more information about each test performed and conditions on the device. Loadable diagnostics run on the SDU make only minimal assumptions about how much of the system is functioning. If the SDU and bus are functioning, boards can be independently tested.

All loadable diagnostics are written in a high level language, C, and use a common procedure that specifies the flow control and user interface. Therefore, loadable diagnostics are relatively simple to use and provide highly structured input and output for machine interpretation. Once an operator learns to use one diagnostic he has essentially learned all of them. They have a command-oriented interface, similar to UNIX commands, instead of menus. This interface is more effective for remote diagnostics and lends itself to machine automated diagnostic procedures.

Diagnostic Development Kit The development tools used to create the Nu Machine diagnostics are available as a software option for those who wish to write their own SDU programs and diagnostics for experimental boards.

Included in this kit are:

- a C compiler, assembler and linker for the 8088;

- a standard set of C runtime routines; and

- a library of standard Nu Machine diagnostic routines.

The tools run under the Nu Machine Operating System implementation but since they are written in C, they could also be ported to other machines.

# 8.2 Nu Machine Operating System

#### 8.2.1 Overview

The Nu Machine Operating System is a port of UNIX Version 7 with extensions that run on the 68010 processor board and make use of the Nu Machine I/O devices. It consists of the kernel, and includes language processors, text processing tools, and system maintenance utilities. To port the kernel, the machine dependent modules of UNIX such as the memory management and the device drivers have been re-written to be appropriate to the Nu Machine. Most of the machine independent modules, as well as the commands were simply recompiled without change.

UNIX was selected as a basis for the Nu Machine Operating System because its applications are broad and its advantages are both practical and technical. UNIX is perhaps the most popular programming environment available. It is capable of supporting the most demanding applications as well as providing an effective base for every-day applications. Many people have been exposed to UNIX at universities, providing a large base of users and programmers familiar with the system. Since UNIX has been readily ported to many machines, there is a wide selection of application software available and a large market ready for further applications.

On the technical side, UNIX offers a variety of advantages:

It is a timesharing system.

Additional terminals and users can be conveniently added to the system at minimal cost. Even in a single user environment the user may have additional activities, such as print spoolers and network demons, operating on his behalf.

Terminals, files and other processes have identical I/O.

This dramatically extends the power of UNIX applications. Since input can come from files as easily as from terminals, output can be saved in a file for later processing or evaluation. Furthermore, input can come directly from other programs and be passed directly to other programs for further processing in any particular run of an application. Programs can be connected together as building blocks combining their effectiveness in a multiplicative way.

A tree-structured file system with access protection.

The hierarchy of directories provides a simple, convenient method for organizing files. Access protection promotes cooperation in a multiuser environment by permitting the user to decide to what extent he should trust others.

## **Nu Machine Technical Summary Texas Instruments**

UNIX is simple.

The kernel is small and easily understood. The commands are easy to learn and operate. Overall, UNIX is remarkably free of annoying restrictions and arbitrary details. Although simple, UNIX has great sophistication able to provide adequate performance while retaining generality.

### 8.2.2 Nu Machine Operating System Kernel

The Nu Machine Operating System kernel is the control program which implements the system calls that all application programs use and the device drivers that access the hardware devices. The kernel is a recompilation of UNIX, Version 7, with portions changed to adapt UNIX to the Nu Machine. These changes primarily affect the memory management routines and the device drivers.

The Nu Machine 68010 processor uses page-oriented memory management. Within memory, page tables describe the virtual-to-physical address mapping for a particular process. The memory management scheme supports the full 24 bit address space of the 68010 processor. It also takes advantage of the rapid context switch mechanism provided by the cache ID bits in cache entries and the process base register. In the current release, processes are swapped as is done in the standard UNIX implementation. Therefore, the process size is limited to the amount of physical memory installed on a particular machine. Future releases will operate in a demand page mode which will take full advantage of the Nu Machine's hardware capabilities.

Additional and modified drivers are provided for all the standard Nu Machine peripherals. These include:

SMD disk

The disk driver takes advantage of the bad track mapping provided by the controller. It performs an elevator algorithm sort on the disk queue to minimize head movement.

1/2 " tape

The ½ inch tape streamer operates the tape in start/stop mode for an effective tape speed of 25 inches per second. It performs extensive error checking and automatic retries on error conditions.

1/4 " tape

The ¼ inch tape operates in streaming mode at a peak tape speed of 90 inches per second. Controller limitations force all tape blocks to be multiples of 512 bytes.

SDU USARTs

Two serial ports are provided on the SDU. These ports are operated in asynchronous mode with full baud rate control and limited modem control. Two teletype line disciplines are provided—the standard UNIX, Version 7, discipline and the more advanced Berkeley line discipline. Depending on the contents of the "/etc/ttys" file, these ports may be configured to support either a terminal with a normal login process or a special demon such as a line printer spooler.

**VCMEM**

This driver, referred to as the Raster Scan Display driver or RSD, implements a powerful window system. Drivers support the window system, including the virtual terminal interface with ANSI X3.64 command sequences, the Nu Machine keyboard, and the mouse.

#### 8.2.3 Utilities

The Nu Machine command environment is the standard set of tools delivered with the operating system. The tools may be divided into three groups: text processing and miscellaneous tools, programming tools, and the window system and graphics.

Text Processing and Miscellaneous Tools Most of the commands provided by UNIX, Version 7, are available on the Nu Machine operating system. These include the Bourne shell, the file system utility commands such as *Is, cp, mkdir,* and various miscellaneous commands such as the desk calculator *bc,* the online manual *man,* and the electronic mail program *mail.* In addition to the Version 7 commands, commands from other sources, especially the Berkeley C shell, have been included.

Text processing tools available on the Nu Machine operating system include the line editor ed, the regular expression search program grep, and the text formatter nroff. Additional Berkeley tools include the screen editor vi and the file perusal program page, both of which use the terminal support package termcaps.

Programming Tools Two compilers, a C compiler and a Fortran compiler are currently supplied with the Nu Machine operating system. They are both different variations of the same compiler, the UNIX Portable C Compiler, with different front ends. The C version embodies all the features of the Kernighan and Ritchie book, The C Programming Language, and generates 32 bit ints. The Fortran version implements Fortran 77 and includes a Ratfor front end. Both versions generate assembly code that, as part of the compile, is fed to an assembler for the 68010. This assembler is available for special purpose routines.

Nu Machine compilers support separate compilation and linking which dramatically speeds the building of large programs. Extensive libraries of support routines are provided that exploit the linking mechanism. Those on the Nu Machine include the *standard I/O library*, a library of floating point routines, required since the 68010 does not have a hardware floating point, a mathematics library and the Berkeley terminal independent I/O libraries, *curses* and *termlib*.

The Source Code Control System is a collection of programs that implement version control. They keep track of different versions, pull together the various pieces of the code and keep them up to date, and check code for portability to other environments. They can be used to control any sort of text file, not just programs. The program *make* uses the modification date of files to determine which subportions of a program need to be rebuilt to make the program up-to-date and allows the programmer to specify what tools to invoke to create the program. There is a program for C called *lint* that checks for portability across machines and performs a variety of other useful checks to identify errors that the compiler would not catch.

To aid in debugging programs, a powerful UNIX debugging tool, adb, is available on the Nu Machine. Similarly, to aid in understanding program behavior a trace package is available that allows the programmer to count how many times each subroutine is called and to compute what percentage of total execution time is spent in each routine.

## Nu Machine Technical Summary Texas Instruments

The Window System and Graphics The window system is an extension of the kernel and user commands that provides multiple virtual terminals on the Nu Machine high resolution display. This feature of the Nu Machine Operating System is not a standard part of UNIX, and was derived at M.I.T. The window system implements the following features:

Multiple windows

A window is a raster of pixels, that is, a rectangular array of dots either on or off. Each window is treated as an independent entity by the window system and may be used to implement a virtual terminal. Logical windows are mapped to physical portions of the high resolution screen. They may be partially or totally occluded, that is, covered up by other windows. The user may change the mapping of windows to the screen, moving windows and causing, for example, an occluded window to be exposed. When a process tries to write to an occluded window, it will block until the window is fully exposed.

Terminal emulation

One window function is to implement a virtual terminal so that when a user process writes to a window, characters appear on the screen. One window is designated as the keyboard window and can be identified by a blinking cursor. Characters typed on the keyboard appear in this window. The keyboard may be detached from one window and attached to another, effectively switching it between processes. As part of the terminal emulation, ANSI X3.64 control sequences move the cursor, and erase portions of the screen. This emulation is known as *termcaps*.

Multiple fonts

Another aspect to terminal emulation is that the user can specify the font, ie. the size and shape of characters displayed in the window. Each window can support multiple fonts and the user can switch between them with control commands.

Screen mapping

The user may map a window directly into the address space of a process. The window simply appears as an array of bits in the address space. In this way, the program can directly control each bit of the window and implement its own graphics routines and character painting for maximum efficiency without any intervening code.

Mouse support

The window system includes a mouse driver that permits an application program to read the current position and button state of the mouse and optionally gives the program an interrupt when the position or button state changes. The mouse is associated with the current keyboard window and changes between windows as the keyboard moves.

In addition to the code inside the kernel, several commands permit the user to manipulate the screen. A graphics library is available to aid in developing programs that use features of the high resolution screen. User commands are available to create new windows, change the properties of a window, change fonts and to display UNIX plot format data in a window. This last command, *trsd*, can be used in conjunction with standard UNIX commands to create graphs on the screen and draw other kinds of pictures. *Trsd* makes use of the graphics library *libg*, a set of routines to draw vectors, manipulate rasters and paint characters onto the screen.

## 8.3 Future Plans

The following items describe planned enhancements that will be available in future releases of the Nu Machine Operating System.

Demand paging