# DUAL PORT COMMUNICATIONS ADAPTER

## HARDWARE REFERENCE MANUAL

Document: 49-522 R00 Assembly: 480040

23 September, 1985

Copyright (C) 1985, by C3, Inc.

1

The information contained in this manual is proprietary in nature and is considered the property of C3, Inc. Reproduction of this manual, in part or in whole, is prohibited without prior authorization from C3, Inc.

## Table of Contents

## 1 Introduction

2

| 1.1<br>1.2 | Product Overview<br>Product Specifications |    |

|------------|--------------------------------------------|----|

| Progra     | amming Specification                       |    |

| 2.1        | Overview                                   | 2  |

| 2.2        | Command Byte                               |    |

| 2.3        | Status Byte                                |    |

| 2.4        | Data Transfers                             |    |

| 2.5        | Interrupts                                 | 8  |

| 2.6        | Typical Code Sequences                     | 10 |

## 3 Theory of Operation

| 3.1   | Overview 1                    | 12 |

|-------|-------------------------------|----|

| 3.2   | Bus Transceiver Logic 1       | 12 |

| 3.3   | Address Logic 1               | 13 |

| 3.4   | Bus Control Logic 1           | 14 |

| 3.5   | Status Logic 1                | 15 |

| 3.6   | Command Logic 1               | 16 |

| 3.7   | 2661C/Control Logic 1         | 16 |

| 3.8   | Interrupt Logic 1             | ٤9 |

| 3.8.1 | Interrupt State Logic 2       | 2Ø |

| 3.8.2 | Interrupt Setting Logic 2     | 20 |

| 3.8.3 | Interrupt Arbitration Logic 2 | 21 |

| 3.9   | Line Drivers and Receivers 2  | 22 |

| 3.10  | Baud Rate Clock 2             | 23 |

|       |                               |    |

## 4 Configuration Specification

| 4.1 | Overview                         | 24 |

|-----|----------------------------------|----|

| 4.2 | Address Selection                | 24 |

| 4.3 | Control Line Switches            | 26 |

| 4.4 | Clock Selection Jumpers          | 27 |

| 4.5 | Communication Standard Selection | 28 |

## 5 External Interfaces

| 5.1 | Overview           | ЗØ |

|-----|--------------------|----|

| 5.2 | Connector Ø        | 30 |

| 5.3 | Connectors 1 and 2 | 31 |

## 6 Installation

| 6.1 | Overview                 | 32 |

|-----|--------------------------|----|

| 6.2 | Unpacking                | 32 |

| 6.3 | Location                 | 32 |

| 6.4 | Backplane Considerations | 32 |

## Appendix A: 2661C EPCI Data Sheet

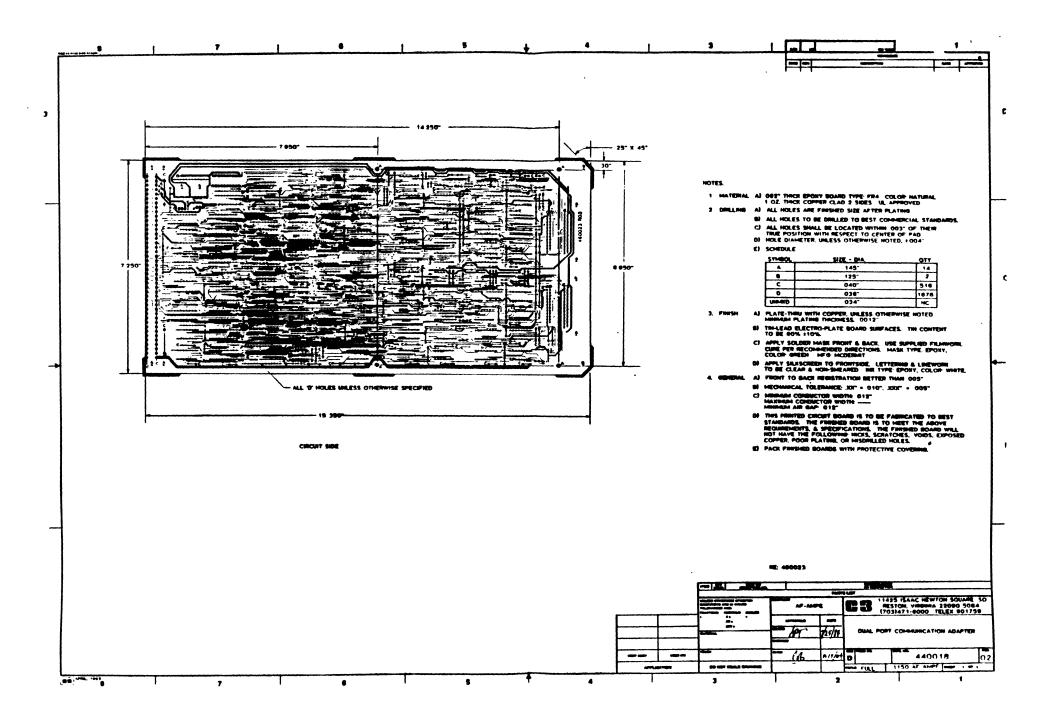

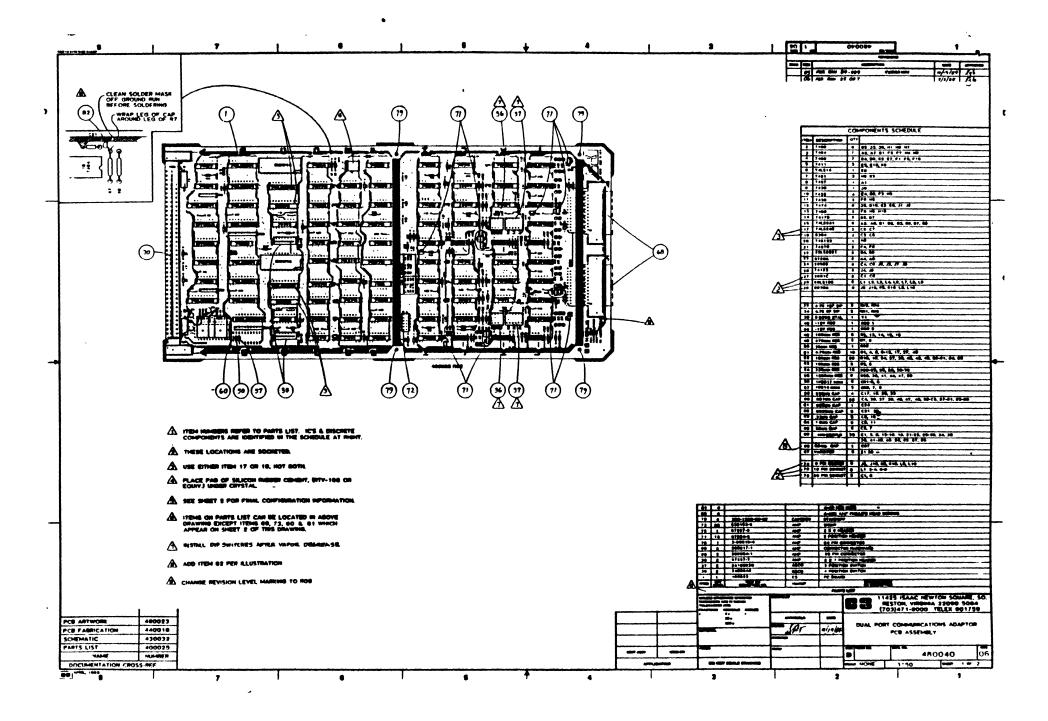

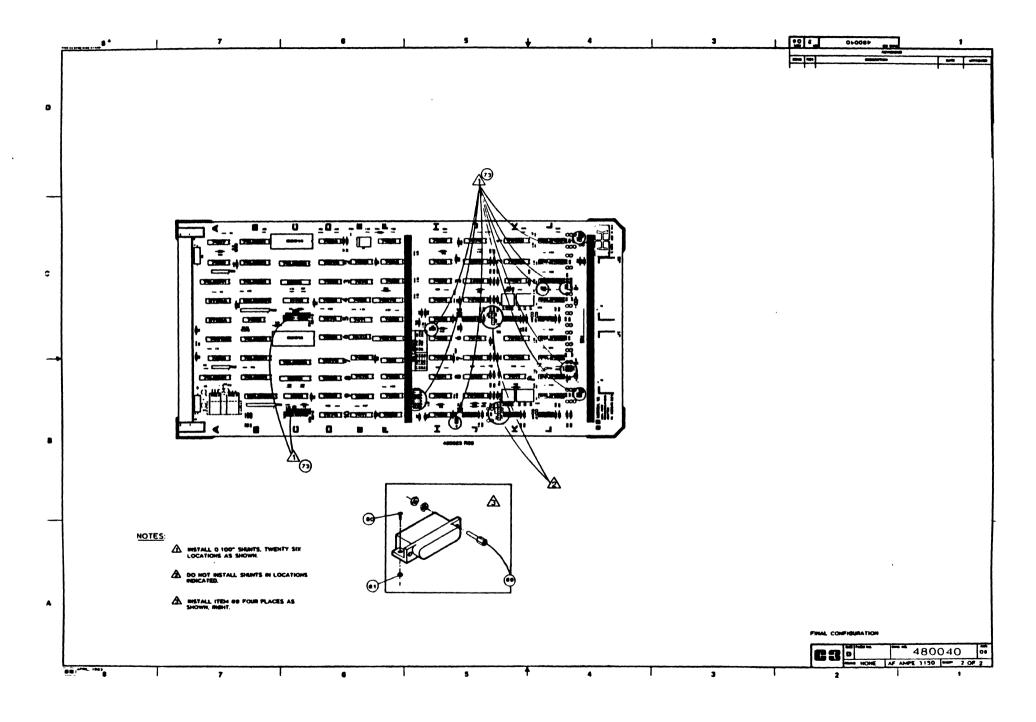

Appendix B: Engineering Drawings

## List of Figures

| 3-1 | 2661C Chip Enable Timing            | 18 |

|-----|-------------------------------------|----|

| 3-2 | Transmit/Receive Clock Logic        | 19 |

| 4-1 | DPCA Configuration Option Locations | 25 |

## List of Tables

| 2-1 | Interrupt State Command Bits 3       |

|-----|--------------------------------------|

| 2-2 | Register Select Command Bits 4       |

| 2-3 | DPCA Interrupt Sources               |

| 4-1 | High Order Address Selection 24      |

| 4-2 | Control Line Switch Settings         |

| 4-3 | Clock Selection Jumpers 27           |

| 4-4 | Clock Selection Configurations 27    |

| 4-5 | Communication Standards Selection 29 |

| 5-1 | Connector Ø Pinout 30                |

| 5-2 | Connector 1 and 2 Pinout 31          |

.

## Revision History

-

| Rev | Date     | Description     |

|-----|----------|-----------------|

| RØØ | Ø9/23/85 | Initial Release |

## 1 Introduction

#### 1.1 Product Overview

The C3, Inc. Dual Port Communications Adapter (DPCA) interfaces the Perkin-Elmer Multiplexor (MUX) bus with two serial communications interfaces. These interfaces may be used for communication with a variety of terminals, serial printers, modems, and other equipment.

Each of the two ports has the following features:

- Complies with EIA standards RS-232 and RS-423, FED-STD-1030A, and MIL-STD-188-114 (unbalanced) - Inverted or non-inverted data

- Operates in synchronous, asynchronous, or isochronous modes

- o Uses internal or external baud rate clocking

- o Operates in full or half duplex modes

- o 16 software programmable baud rates ranging from 50 to

19200 baud

- o Data character lengths of 5 to 8 bits with an additional parity bit (odd or even) if desired

- Synchronous operation with 8- or 16-bit synchronization, transparent or non-transparent, automatic sync insertion and stripping

- Asynchronous operation with 1, 1.5, or 2 stop bits; parity, overrun, and framing error detection; line break detection and generation; and false start bit detection

- Dynamic reconfiguration of operating mode, character length, and baud rate

- Full modem control capability including reverse channel (secondary transmit and receive data) and ring detect

#### 1.2 Product Specifications

| Board size<br>Power requirements | 7 inch Perkin-Elmer format<br>+5 VDC: 2.0 amp            |

|----------------------------------|----------------------------------------------------------|

| •                                | +15 -0.4/+1.0 VDC: 0.1 amp<br>-15 -1.0/+0.4 VDC: 0.1 amp |

| Data transmission format         | 5-8 data bits, 50-19200<br>baud async or sync            |

| Comm output levels               | +5.5 volts                                               |

#### 2 **Programming Specification**

#### 2.1 Overview

The DPCA contains two identical serial ports. Each serial port may independently operate in half or full duplex mode. Two consecutive addresses are used for each port, the first even, the second, odd. The even address is used for receive transfers while the odd is used for transmit transfers. In half duplex operation, receive and transmit both use the even address.

The heart of each serial port (or channel) is a Signetics 2661C Enhanced Programmable Communications Interface (EPCI) integrated circuit. This is a bus-oriented version of a Universal Synchronous/Asynchronous Receiver/Transmitter (USART) which is designed to operate on a microprocessor data bus. The DPCA adapts this device to the Perkin-Elmer MUX bus.

The 2661C's contain several registers used for setting up operating modes, determining device status, and for transmitting and receiving data. Perkin-Elmer Output Commands to the DPCA select these internal registers, control interrupts, and select general DPCA modes. Data written to a DPCA channel (via a Write Data instruction) goes into the register of the EPCI specified in the last Output Command to that channel. Data read from the DPCA also comes from the register last specified.

Appendix A of this document is the data sheet from Signetics which describes in detail the capabilities, operation, and techniques for use of the EPCI.

The following sections of this chapter detail the various Perkin-Elmer I/O operations available on the DPCA.

#### 2.2 Command Byte

The DPCA command byte controls interrupts, sets operating mode (half/full duplex, read/write), controls communication interface signals, and selects which register in the 2661C EPCI may be accessed by Read or Write Data instructions. It may be issued to the even or odd device address with the same results EXCEPT for the setting of transmit/receive mode. See the discussion of command bit 15, below for details. The command byte has the following format.

| Ø8        | 09 | 10     | 11    | 12  | 13      | 14 | 15   |

|-----------|----|--------|-------|-----|---------|----|------|

| Interrupt |    | Half   | Reset | RCT | Registe |    |      |

| Control   |    | Duplex | EPCI  |     | AØ      | Al | Mode |

|           |    |        |       |     |         |    |      |

Bit Ø8 and Ø9 - Interrupt Control

These bits are used together following Perkin-Elmer interrupt control convention with bit 15 selecting either the transmit or receive side of the port being addressed. Their function is defined in Table 2-1, below.

| I   | Bit |    |                                     |

|-----|-----|----|-------------------------------------|

| Ø 8 | Ø9  | 15 | Function                            |

| Ø   | Ø   | Ø  | No change to receive interrupts     |

| Ø   | 1   | Ø  | Enable receive interrupts           |

| 1   | Ø   | Ø  | Disable (queue) receive interrupts  |

| 1   | 1   | Ø  | Disarm receive interrupt            |

| Ø   | Ø   | 1  | No change to transmit interrupts    |

| Ø   | 1   | 1  | Enable transmit interrupts          |

| 1   | Ø   | 1  | Disable (queue) transmit interrupts |

| 1   | 1   | 1  | Disarm transmit interrupts          |

Table 2-1. Interrupt State Command Bits

#### Bit 10 - Half Duplex

When 1, this bit selects the half duplex mode of operation. When Ø, it selects full duplex operation. This bit affects how the transmit or receive sense status register is selected (see section 2.3), whether transmit interrupts occur on the even or odd address (see section 2.5), how "clear to send" transmit interrupts are generated (see section 2.5), and how the "request to send" output is enabled (see discussion of bit 15, below).

Bit 11 - Reset EPCI

This bit activates the RESET pin on the 2661C when 1. This causes a master reset of the 2661C EPCI for the channel being accessed, on both the transmit and receive sections of the device. It terminates any EPCI activity and clears its internal mode, command, and status registers. The EPCI is in its idle mode until reinitialized.

- Bit 12 Reverse Channel Transmit (RCT) This bit controls the state of the Reverse Channel Transmit output pin, pin 14, on the communication connector for the port being addressed. When this bit is 1, pin 14 assumes an active (high) state. When this bit is 0, pin 14 assumes an inactive (low) state.

- Bit 13 and 14 Register Select These bits select which of the internal registers of the 2661C EPCI will be accessed by subsequent read and write data commands. Table 2-2, below, describes the registers selected by these bits.

| AØ | Al | Read Data        | Write Data        |

|----|----|------------------|-------------------|

| Ø  | Ø  | Recv Holding Reg | Trans Holding Reg |

| Ø  | 1  | Mode Reg l & 2   | Mode Reg l & 2    |

| 1  | Ø  | EPCI Status Reg  | Synl/Syn2/DLE Reg |

| 1  | 1  | EPCI Command Reg | EPCI Command Reg  |

Table 2-2. Register Select Command Bits

Bit 15 - Transmit Mode

This bit controls whether this command applies to the transmit or receive side of the addressed DPCA channel. When 1 this bit indicates an affect on the transmit side, when  $\emptyset$  to the receive side. It is used in conjunction with the interrupt control bits,  $\emptyset 8$  and  $\emptyset 9$ , to determine if transmit or receive interrupts are to be affected. When in half duplex mode, it puts the channel in either transmit or receive mode (affecting transmit or receive status register selection and the generation of "clear to send" interrupts on the transmit side).

In either full or half duplex mode, this bit affects generation of the "request to send" (RTS) output, pin 4. RTS is generated by the DPCA if the corresponding bit is set in the 2661C EPCI Command Register (refer to Appendix A, page 7) and the channel is in transmit mode.

SPECIAL NOTE: In full duplex operation (bit 10 off), transmit or receive mode may only be selected from the odd (transmit) device address. In full duplex mode, bit 15 of the even (receive) address may be used for selecting transmit or receive interrupt control but it has no affect on enabling of the "RTS" output.

At system power-up (or system clear), the board is in a state that can be emulated by output commands of Clh then DØh, that is, interrupts (both transmit and receive) are disarmed, the 2661C EPCI is reset, the board is in full duplex and receive modes, RCT is off, and AØ,Al is ØØ (selecting the 2661C holding registers).

#### 2.3 Status Byte

The DPCA has two separate status bytes, one for transmit status, one for receive status. In full duplex mode, receive status is returned when a sense status is issued to the even device address while transmit status is returned from the odd address.

In half duplex mode, receive status is returned when the last command issued had a Ø in bit 15 (the Transmit Mode bit). Transmit status is returned if bit 15 was 1. In half duplex mode the same status is returned from either the even or odd device address.

Several of the status bits are extracted from the 2661C internal status register by the DPCA logic. The 2661C status register is read once by each sense status (or interrupt acknowledge cycle) from the Perkin-Elmer processor.

The receive status byte has the following format.

| 1 | Ø8   | 09     | 10     | 11   | 12   | 13  | 14   | 15   |

|---|------|--------|--------|------|------|-----|------|------|

|   | Over | Parity | FE/    | Ring | Recv | RCR | -DCD | -DSR |

|   | Run  |        | Sync D | -    | Busy |     |      |      |

|   |      |        |        |      |      |     |      |      |

Bit Ø8 - Overrun

- This bit, when 1, indicates that the previous character received into the receive holding register of the 2661C was not read by the processor at the time a new character was received into it. This bit is cleared when the Reset command bit is issued via an output command, when the 2661C receiver is disabled, or when a reset error command is written to the 2661C command register. This bit is extracted from the 2661C internal status register.

- Bit Ø9 Parity Error This bit, when set, indicates a received parity

error. It is cleared when the next character is loaded into the receive holding register of the 2661C, when the Reset command bit is issued via an output command, when the 2661C receiver is disabled, or when a reset error command is written to the 2661C command register. This bit is extracted from the 2661C status register. Consult Appendix A for further details.

Bit 10 - Framing Error/Sync Detect In asynchronous modes of operation, this bit indicates that the received character was not framed by a stop bit. (Only the first stop bit is checked if more than one was received.) If the received character was Ø and this bit is 1, it is likely that a break condition may be present. This bit is cleared in asynchronous mode when the reset error command is written to the 2661C command register.

> In synchronous transparent mode it indicates the receipt of the specified 8 or 16 bit sync sequence or, after initial synchronization, the receipt of a DLE-Sync pair. In synchronous mode, this bit is cleared by a sense status or by reading the 2661C status register. CAUTION: It has been observed that the 2661C occasionally clears this bit before it can be read if the DPCA is in a tight sense status loop.

> This bit is also cleared when the Reset command bit is issued via an output command or when the 2661C receiver is disabled in either sync or async mode. This bit is extracted from the 2661C status register. Consult Appendix A for further details.

Bit 11 - Ring This bit is 1 when the Ring signal line from the communication line, pin 22, is on (high).

#### Bit 12 - Receive Busy

This bit, when 1, indicates that no data byte is ready to be read from the 2661C receive holding register. It is generated directly by the -RxRDY output pin from the 2661C. This bit is set when the processor reads the receive holding register or when the receiver is disabled.

Bit 13 - RCR (Reverse Channel Receive)

This bit is 1 when the RCR signal line from the

communication line, pin 16, is on (high).

- Bit 14 -DCD (Not Data Carrier Detect) This bit is 1 when the DCD signal line from the communication line, pin 8, is off (low). This bit is extracted from the 2661C status register.

- Bit 15 -DSR (Not Data Set Ready) This bit is 1 when the DSR signal line from the communication line, pin 6, is off (low). This bit is extracted from the 2661C status register.

The transmit status byte has the following format.

| 1 | Ø8 | 09 | 10 | 11   | 12    | 13  | 14   | 15   |

|---|----|----|----|------|-------|-----|------|------|

|   | Ø  | Ø  | Ø  | Ring | Trans | RCR | -CTS | -DSR |

|   |    |    |    |      | Busy  |     |      |      |

|   |    |    |    |      |       |     |      |      |

Bit 11 - Ring

(See Transmit Status register bit 11, above.)

Bit 12 - Transmit Busy

This bit, when 1, indicates that the transmit holding register of the 2661C has been loaded by the processor and the data has not been transferred to the transmit shift register. This bit is initially Ø when the transmitter is enabled. It is generated directly by the -TxRDY output pin from the 2661C. Consult Appendix A for further information.

- Bit 13 RCR (Reverse Channel Receive) (See Transmit Status register bit 13, above.)

- Bit 14 -CTS (Not Clear to Send) This bit is 1 when the CTS signal line from the communication line, pin 5, is off (low). This bit reflects the -CTS input bit to the 2661C. It must be Ø for the transmitter to operate. If it goes high during transmission, the character in the transmit shift register is completed before transmission stops. Consult Appendix A for further explanation.

- Bit 15 -DSR (Not Data Set Ready) (See Transmit Status register bit 15, above.)

#### 2.4 Data Transfers

Data transfers, read data and write data, on the DPCA transfer data into or out of the 2661C register specified in the last output command instruction. Refer to Table 2-2, above, for the register select codes. Data transfers may be done to either the even or odd address with exactly the same effect.

Transfers to the transmit holding register in the 2661C  $(A\emptyset=A1=\emptyset)$  should be done only when the transmit sense status register Transmit Busy bit, 12, is  $\emptyset$ . Likewise, reading of data from the 2661C internal receive holding register  $(A\emptyset=A1=\emptyset)$  should only occur when the receive sense status register Receive Busy bit is  $\emptyset$ . Transfers to the other internal registers are not governed by the busy bits.

Refer to Appendix A for 2661C EPCI usage. This document defines the 2661C's internal registers and the recommended initialization sequence for the device. If the device has been initialized for transmitting, the Transmit Busy status bit should be Ø, indicating that the 2661C is ready to accept a data byte. If initialized for receiving data, Receive Busy status should be 1, indicating no data available. If Receive Busy is Ø, a byte may be read from the receive holding register to force Receive Busy to 1.

#### 2.5 Interrupts

Each channel of the DPCA has two different types of interrupts, one for transmit and one for receive. These interrupts are separately controllable by command to the DPCA, see section 2.2 for details. These interrupt circuits may be in one of three states. (These states are standard for Perkin-Elmer controllers.) They are:

- Enabled Interrupts generated by the channel are passed through to the processor.

- 2) Disabled Interrupts generated by the channel are not passed to the processor but are queued. When the interrupt logic is later enabled, a queued interrupt will be passed to the processor.

- Disarmed Interrupts generated by the channel are neither passed on to the processor nor queued. Any queued interrupts are ignored.

At power up, all interrupt circuits on the DPCA are disarmed.

The conditions which cause transmit and receive interrupts are shown in Table 2-3, below. NOTE: The transmit interrupt caused by the 1 to 0 transition of the -CTS signal only occurs when the channel is in half duplex, transmit mode. This interrupt is also generated if -CTS is 0 when half duplex, transmit mode is entered.

| Signal | Transition Interrupt     |  |

|--------|--------------------------|--|

| Ring   | Ø to 1 Receive           |  |

| -DCD   | Ø to 1, 1 to Ø Receive   |  |

| RCR    | Ø to 1, 1 to Ø Receive   |  |

| -DSR   | Ø to 1 Receive           |  |

| RxBusy | l to Ø Receive           |  |

| TxBusy | l to Ø Transmit          |  |

| -CTS   | Ø to 1, 1 to Ø* Transmit |  |

|        | *see note in text        |  |

\*see note in text

Table 2-3. DPCA Interrupt Sources

In full duplex operation, receive interrupts come from the even device address and transmit interrupts from the odd device address. In half duplex mode, both receive and transmit interrupts use the even device address.

Within the DPCA board, the following interrupt priority is followed:

- 1) Channel A Receive Interrupt (highest)

- 2) Channel A Transmit Interrupt

- 3) Channel B Receive Interrupt

- 4) Channel B Transmit Interrupt (lowest)

NOTE: During the interrupt acknowledge cycle, the Perkin-Elmer processor issues a sense status to the interrupting device. This sense status resets the "Sync Detect" status bit, if set. See section 2.3, above, for more information.

#### 2.6 Typical Code Sequence

This section presents the flow for a few typical code sequences for controlling a DPCA.

Note in these examples that the last Output Command to the channel contains 00 in the register select field and that processor interrupts are disallowed while the register select bits are nonzero. This keeps transmit and receive logic from interfering with each other during full duplex operation.

```

/*

Reset the DPCA hardware. This sequence

*/

/* emulates conditions found at Power-up or

*/

/* Init for the channel being accessed

*/

ResetChannel:

OutputCommand Clh /* disarm Tx ints */

OutputCommand DØh /* disarm Rx ints, init 2661 */

Initialize the 2661C internal registers

/*

*/

InitChannel:

LockoutInterrupts

OutputCommand Ø2h /* select mode regs */

Call InitEpciModeRegs /* see appendix A */

OutputCommand Ø4h /* select sync regs */

Call InitEpciSyncRegs /* see appendix A */

OutputCommand Ø0h /* select hold regs */

AllowInterrupts

AllowInterrupts

*/

/* Start-up transmitter

StartTransmitter:

LockoutInterrupts

OutputCommand Ø6h /* select cmd reg */

WriteData (TxInitCmd) /* init cmd reg */

OutputCommand 41h /* select holding regs

& enable Tx ints */

AllowInterrupts

/* Stop transmitter

*/

StopTransmitter:

LockoutInterrupts

OutputCommand Ø6h /* select cmd reg */

WriteData (TxStopCmd) /* modify cmd reg */

OutputCommand Clh /* select holding regs

& disarm Tx ints */

AllowInterrupts

```

| /*   | Start-up receiver     |      | */                           |

|------|-----------------------|------|------------------------------|

| Star | tReceiver:            |      |                              |

|      | LockoutInterrupts     |      |                              |

|      | OutputCommand Ø6h     | /*   | <pre>select cmd reg */</pre> |

|      | WriteData (RxInitCmd) |      | init cmd reg */              |

|      | OutputCommand 40h     | /*   | select holding regs          |

|      |                       | •    | & enable Rx ints */          |

|      | AllowInterrupts       |      | ,                            |

| /*   | Stop receiver         |      | */                           |

| Stop | Receiver:             |      |                              |

|      | LockoutInterrupts     |      | •                            |

|      | OutputCommand Ø6h     | /*   | <pre>select cmd reg */</pre> |

|      | WriteData (RxStopCmd) | /*   | modify cmd reg */            |

|      | OutputCommand COh     | ` /* | select holding regs          |

|      | <b>1</b> ]]           |      | & disarm Rx ints */          |

|      | AllowInterrupts       |      |                              |

•

## 3 Theory of Operation

#### 3.1 Overview

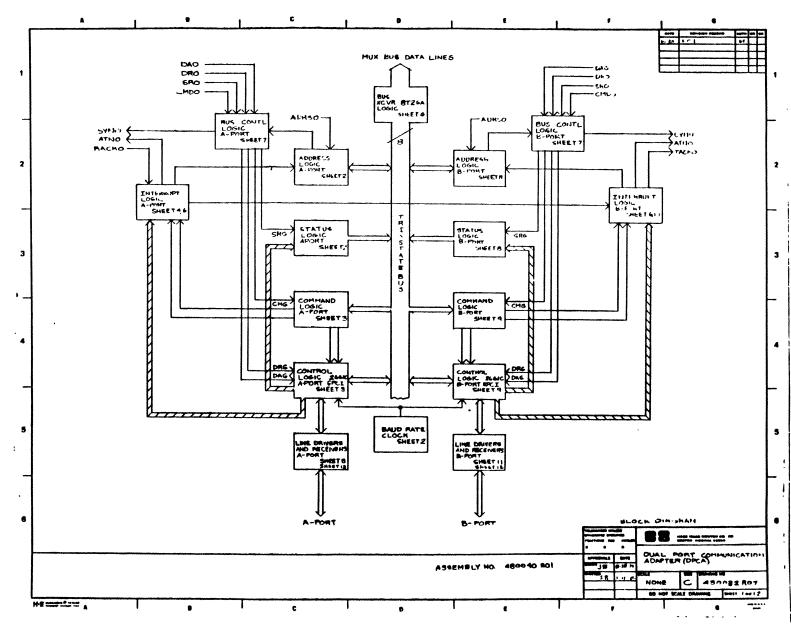

The C3 Dual Port Communication Adapter (DPCA) contains two independent serial communication ports on a single halfboard. The two ports (or channels) are identical in function.

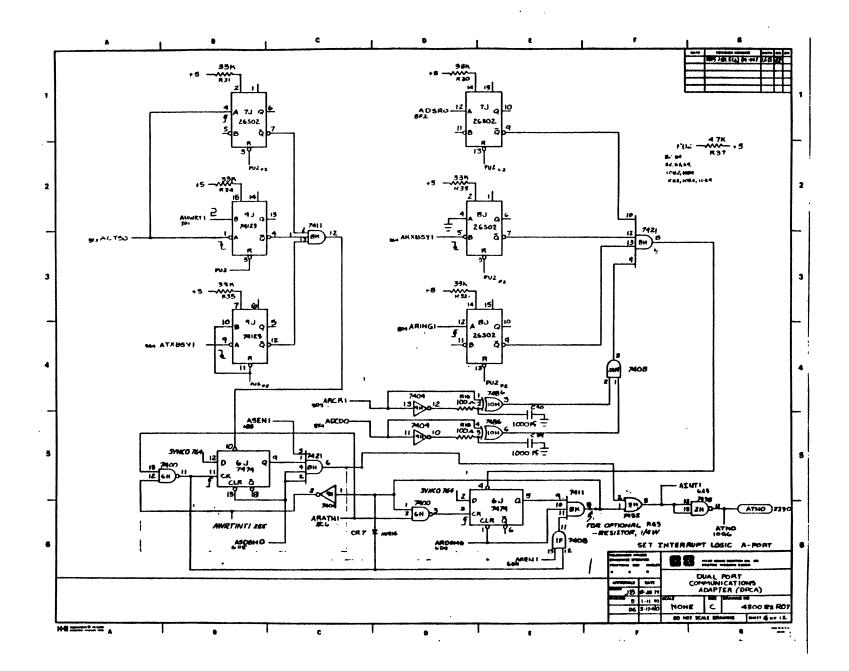

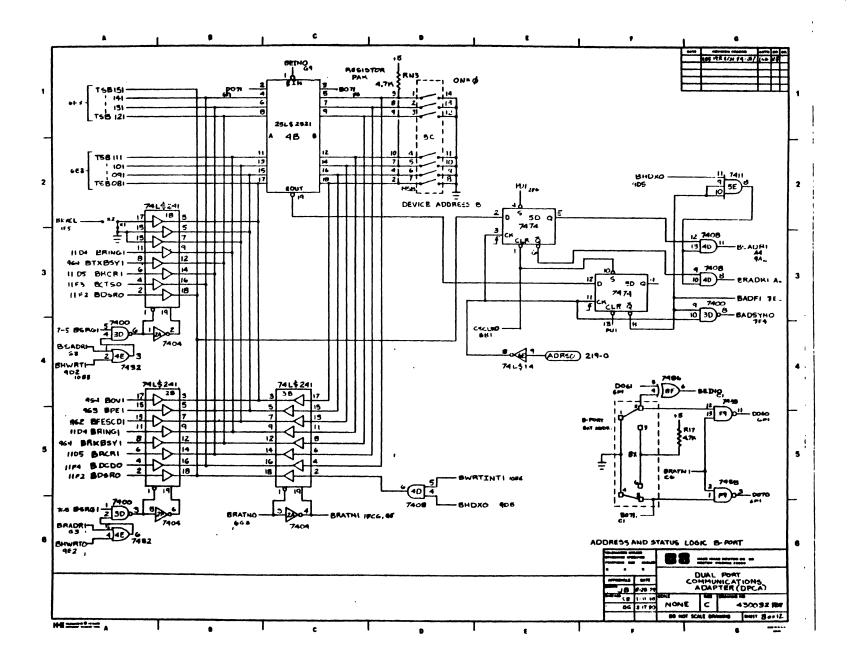

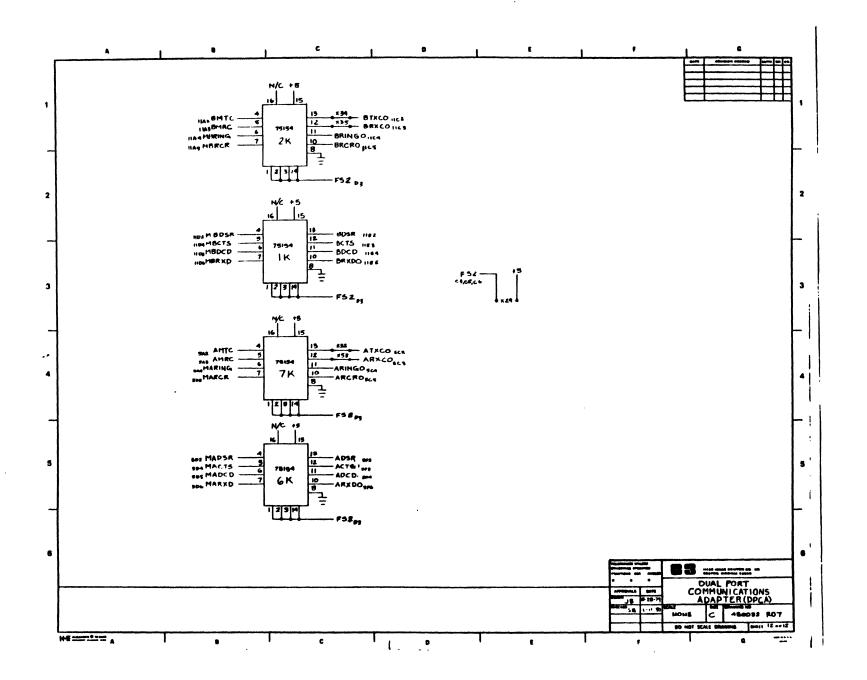

The functional block diagram for the DPCA is shown on sheet 1 of the schematic drawings in Appendix B. This chapter presents the theory of operation for each functional block. Where the two ports have separate but identical blocks, only the A port is discussed.

References are made throughout this chapter to the schematic drawing for the DPCA contained in Appendix B. These references are of the form [pPzZz] where "P" is the page (sheet) number of the schematic and "ZZ" is the zone on that sheet in alphabetic column and numeric row. Signal names ending with "Ø" are active low, those ending with "l" are active high.

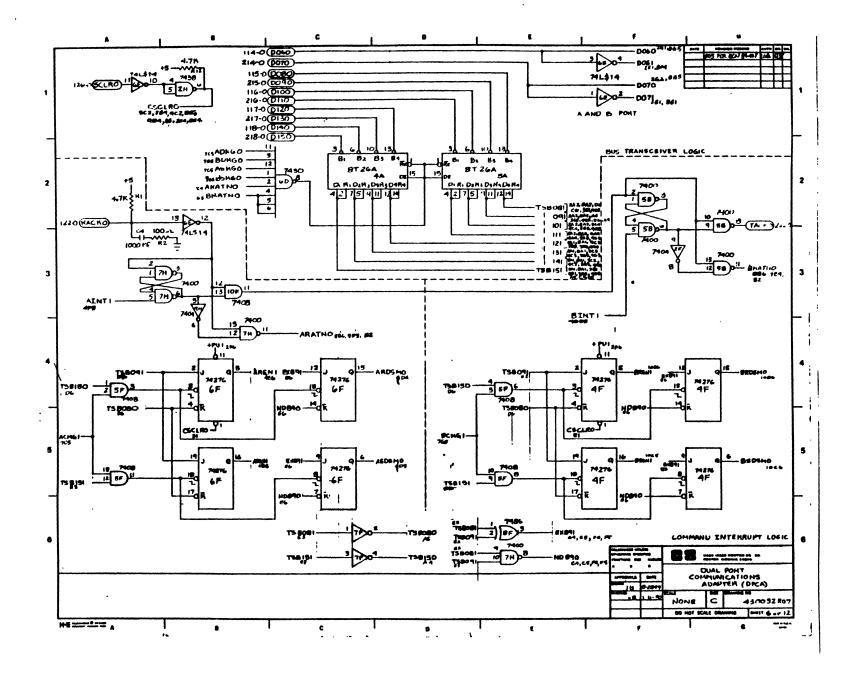

#### 3.2 Bus Transceiver Logic

The DPCA is a byte oriented device and therefore uses only the low-order eight bits of the MUX bus for data transfers. These signals are buffered using a pair of 8T26A tri-state transceivers [p6zD2]. This buffered tri-state bus, TSB081 through TSB151, is used throughout the DPCA by both the A and the B port logics. This bus normally is driven from the MUX bus. During transfers from the DPCA to the processor, the transceivers are turned around to drive the MUX bus from the tri-state bus.

This turn around occurs during data requests (ADRGØ or BDRGØ), status requests (ASRGØ or BSRGØ), or interrupt acknowledgment cycles (ARATNØ or BRATNØ), controlled by a 7430 8-input NAND gate [p6zC2].

The transceiver logic also provides Schmidt input receivers for the system clear signal (SCLRØ) and the data signals (DØ6Ø and DØ7Ø) from the MUX bus. These extra data bits are used for address recognition purposes only. The buffered system clear signal, CSCLRØ, is used throughout the board for initializing latches and the 2661C EPCI's at system power-up and system reset.

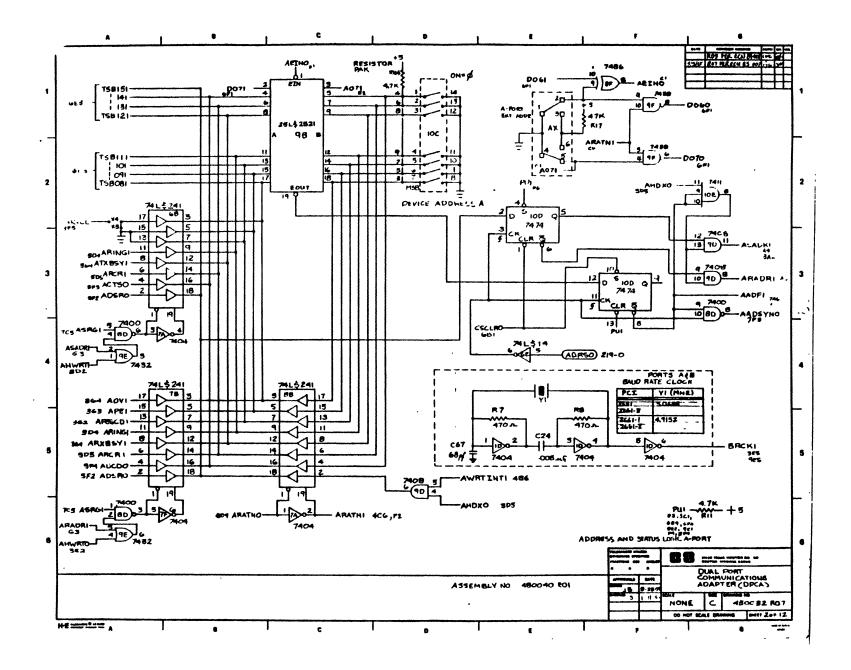

#### 3.3 Address Logic

The DPCA has separate address logic for the A and the B ports. Each port responds to two addresses, determined by the high-order nine bits of the ten bit device address. The even port (low-order address bit is  $\emptyset$ ) is used for receive side transfers in full duplex mode and for all transfers in half duplex mode. The odd port is used for transmit transfers in full duplex mode.

This logic has the function of recognizing the port address, determining if the even or odd address is being used, acknowledging the address transfer from the processor, and generating the interrupt vector for interrupt acknowledgment cycles.

The Perkin-Elmer MUX bus uses a 10-bit device address. The low order ten data bits of the MUX bus are used for this address. To select a device, the processor places the board's address on the MUX bus and then asserts ADRSØ on the bus. This address is held on the bus until the addressed board responds with SYNCØ to acknowledge this transfer.

The port address is configured by a 7-position device address jumper strip [p2zD2] and by a 6-position extra address jumper [p2zE2]. The selected address is constantly being compared with the contents of bits Ø6 through 14 of the local tri-state bus by an XOR gate [p2zF1], which produces a low when DØ61 matches the high order selection, and a 25LS2521 8-bit comparator [p2zC1].

The leading edge of ADRSØ from the processor latches the output of this comparison into the address flag latch [p2zF3] to produce the signal AADF1, which indicates that this port is addressed. Simultaneously, the low order address bit is latched from TSB151 by a 7474 [p2zE3] to determine if the even (receive) or odd (transmit) device address has been selected.

If the port is addressed and in full duplex mode, the A Send Address signal, ASADR1 [p2zG3], or the A Receive Address signal, ARADR1 [p2zG3], is activated if this odd address latch is 1 or 0, respectively.

The signal AADSYNØ [p2zG3] is used to generate the SYNCØ output to the processor. This signal acknowledges that the board has been addressed. It is active only while ADRSØ is on and the address flag latch is active. During the interrupt acknowledge cycle, the address logic places the device address onto the tri-state bus for transfer to the processor. This is done by a 74LS241 non-inverting octal buffer [p2zC5] on receipt of the A Receive Attention (ARATNØ) signal [p2zC6]. The low order bit of this returned address is 1, indicating the odd (transmit) device, only when a transmit interrupt is present (AWRTINT1) and the port is in full duplex mode. The two high order address bits are driven directly onto the MUX bus by the 7438 gates located at [p2zF1] and [p2zF2].

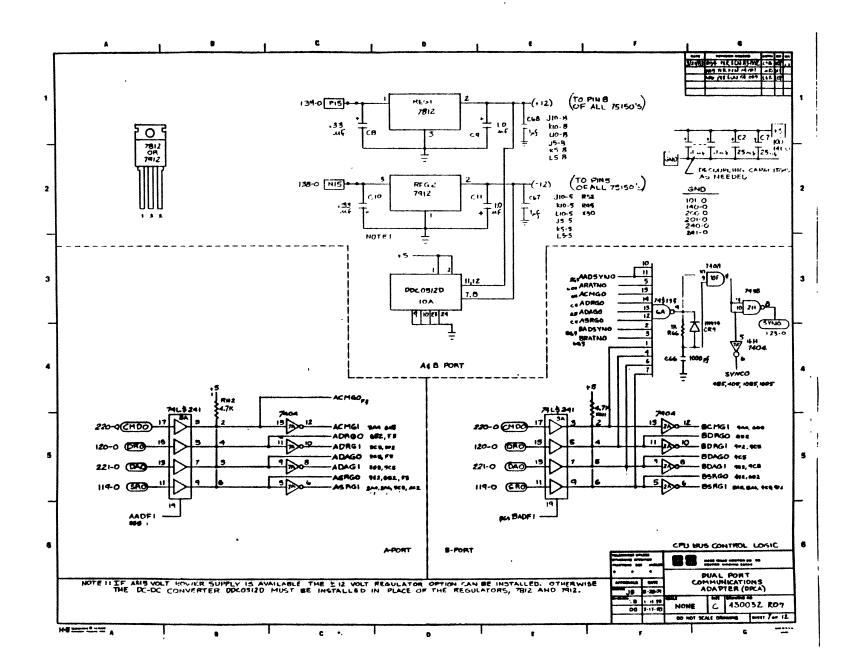

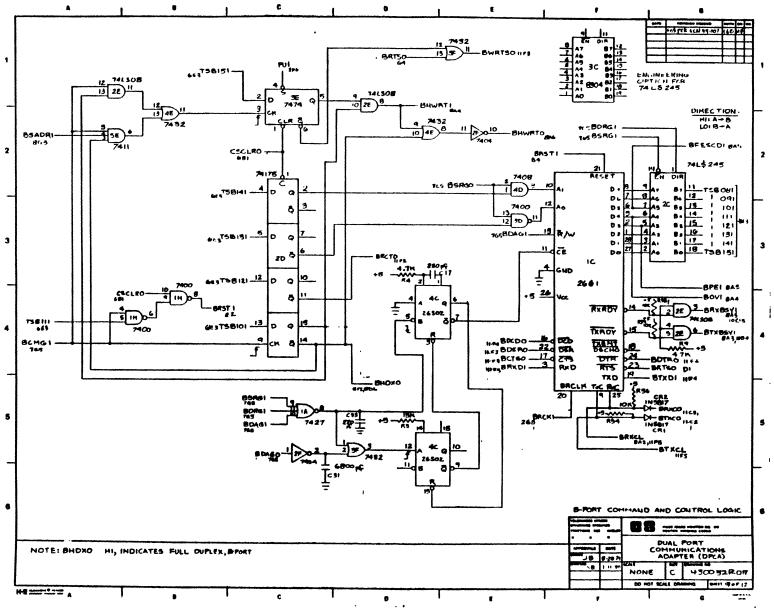

#### 3.4 Bus Control Logic

This logic receives the MUX bus data transfer control signals and gates them with the address flag signals from the A and B port address logic to generate the gated control signals used throughout the DPCA logic modules. In addition, the data transfer acknowledge signal, SYNCØ, is generated by this logic.

Four MUX bus control signals, command (CMDØ), status request (SRØ), data request (DRØ), and data available (DAØ), are received by a 74LS241 non-inverting tri-state buffer [p7zB5]. This buffer is enabled by the A Address Flag signal, AADF1. When not enabled, the outputs of the '241 are in high impedance mode, allowing the 4.7 Kohm pull-up resistors to force the signals inactive (high) when the port is not addressed by the processor.

The MUX bus data transfer acknowledge signal, SYNCØ (or SYNØ) [p7zG3] must be generated by the addressed port in response to all transfers to or from that port on the MUX bus. The six types of transfers are:

- 1) Address transfer (ADRSØ)

- 2) Command (CMDØ)

- 3) Status Request (SRØ)

- 4) Data Available (DAØ)

- 5) Data Request (DRØ)

- 6) Interrupt acknowledge (RACKØ)

These signals, after appropriate gating through both ports, are logically ORed by the 74S133 13-input NAND gate [p7zF3]. When any of these signals is asserted, C66 [p7zF4] begins

charging through R66. After approximately 350 ns., the output of the 7408 [p7zG3] goes high, generating SYN0. When the control signal is deasserted, SYN0 is immediately released and C66 is quickly discharged through CR9. The 350 ns. delay allows data to stabilize on the MUX bus when the DPCA is transmitting to the host. Although generated for data coming from the processor as well, the delay is not required in this case.

#### 3.5 Status Logic

Each port of the DPCA has two status registers, one for receive status and one for transmit. The A port receive status register is generated by a 74LS241 8-bit non-inverting buffer [p2zB5]. This buffer, when enabled, places a variety of signals onto the DPCA's tri-state bus. The buffer is enabled when the gated status request signal, ASRG1 [p2zA6], is active and either the port is in full duplex mode and the even device is being addressed (ARADR1) or the port is in half duplex receive mode (AHWRT0 false).

Similarly, the transmit status register is a 74LS241 [p2zB3] which is enabled when gated status request is active and either the port is in full duplex mode and the odd device is being addressed (ASADR1) or the port is in half duplex transmit mode (AHWRT1).

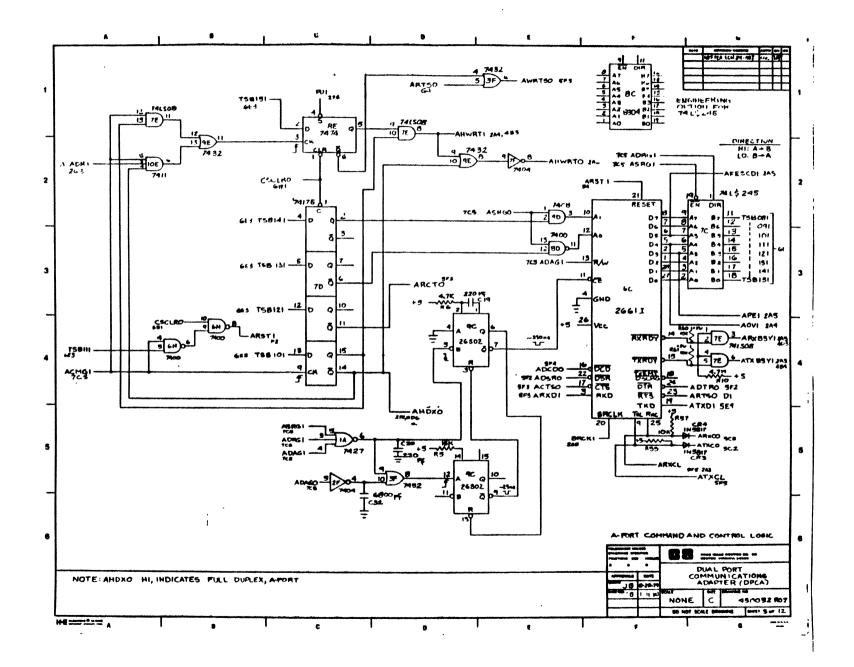

#### 3.6 Command Logic

Each port of the DPCA has its own command logic, and these logics are identical in function. The DPCA command logic captures command data transmitted by the processor.

The command data processed by the command logic set the operating modes for the port, select which internal register(s) of the 2661C EPCI are to be accessed, reset the 2661C, and determine the state of the Reverse Channel Transmit output on the communication port. The high-order two command data bits are used for interrupt control and are discussed in section 3.8.1, below.

When the port is addressed (either even or odd address) and CMDØ is asserted on the MUX bus, the gated command signal, ACMG1 [p3zA4] is generated by the DPCA control logic. On the leading edge of this signal, bits 10, 12, 13, and 14 are latched into a 74175 guad D-type latch [p3zC3&C4]. These bits are "Half Duplex", "RCT", "A0", and "A1", respectively. Data bit 15, "Transmit Mode", is latched into the transmit/receive mode latch [p3zCl] at this time only if the port is in (or entering) half duplex mode (command bit 10 = 1) or if the port is in full duplex mode and the odd (transmit) address is being accessed. Therefore, if the channel is in full duplex mode and a command is issued to the even (receive) address, transmit/receive mode is not modified.

If the "Reset EPCI" bit of the command, bit 11, is on, the signal ARST1 [p3zB4] is generated for the duration of the CMDØ pulse from the processor. This signal causes the 2661C EPCI reset pin to be activated. Note that ARST1 is also generated by system clear (CSCLRØ), which comes from the MUX bus SCLRØ signal.

Two additional signals are generated by this logic, AHWRT1 [p3zD2] and AHWRT0 [p3zE2]. The first signal is generated when the board is in half duplex and transmit (write) mode. The second is generated when the board is in half duplex and receive mode.

#### 3.7 2661C/Control Logic

This logic contains the 2661C Enhanced Programmable Communications Interface (EPCI) and the logic which directly controls it. Refer to Appendix A for a detailed discussion of the 2661C and its pin functions.

Three MUX bus operations transfer data into or out of the 2661C: data request (DRØ), data available (DAØ), and status request (SRØ). During status requests, the 2661C is disconnected from the tri-state bus, its internal status register is selected, and three of the status bits are routed to the receive status register.

The 7400 and 7408 gating on the A0 and A1 inputs to the 2661C [p3zE2&E3] allows the A0 and A1 bits from the command latches through to the 2661C unless a status request is in process for this port. In that case, A0 and A1 are forced to 1 and 0, respectively, to select the internal status register.

A 74LS245 8-bit tri-state transceiver [p3zG3] is used for controlling the 2661C's access to the tri-state bus. During a status request, the transceiver is disabled, allowing the 2661C data pins to freely drive the appropriate receive status register bits. At all other times, the transceiver is enabled. It normally transfers data on the tri-state bus to the 2661C data pins. When a data request is issued to the port, however, the direction of the transceiver is altered to allow the 2661C to drive its data onto the tri-state bus and from there onto the MUX bus.

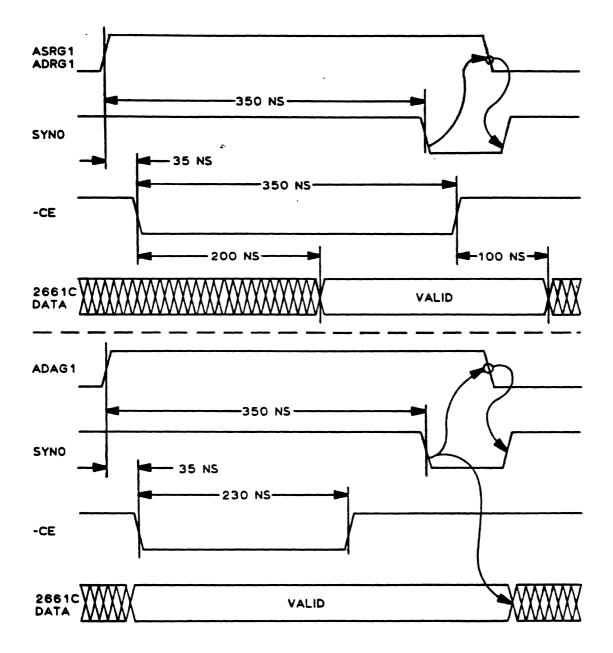

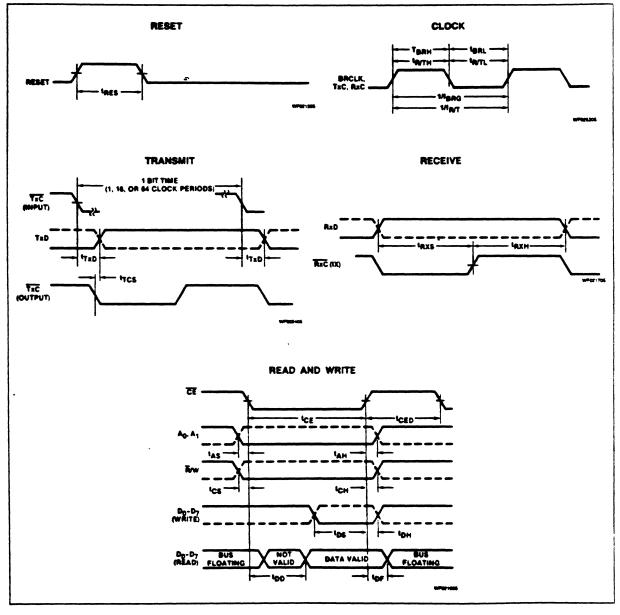

The 2661C has several requirements on its chip enable (-CE) input. The chip enable signal must be active for a minimum of 250 ns. On reads from the 2661C, data is not valid until 200 ns. after chip enable is asserted and it is valid for at least 100 ns. after chip enable is deasserted. On writes to the 2661C, data is accepted on the trailing edge of the chip enable signal. (This differs from Perkin-Elmer convention, where data is normally accepted from the processor on the leading edge of the control signal - ADRSØ, CMDØ, or DAØ.)

To handle these requirements, two one-shots and some special timing circuitry have been provided. Refer to the timing diagram in Figure 3-1, below, for an illustration of the chip enable timing for status requests, data requests, and data available. For both status requests and data requests, the 26S02 chip enable one-shot [p3zD4] is triggered for a maximum of approximately 350 ns. This triggering is delayed slightly (approximately 35 ns.) by C20 [p3zD5] from the leading edge of ASRG1 and ADRG1.

For writes to the 2661C, data available (ADAG1) triggers the chip enable one-shot, delayed about 35 ns. by C20. Simultaneously, C32 [p3zC6] starts charging up. After approximately 230 ns., the voltage on C32 gets to a sufficient level to trigger the chip enable reset one-shot. This resets the chip enable one-shot, ending the chip enable (-CE) for the 2661C. At this point, the data presented to the 2661C data pins is loaded into the specified register.

The transmit and receive ready pins on the 2661C, -TxRDY and -RxRDY, are open drain outputs. These signals are pulled up by 10 Kohm resistors and buffered by 74LS08 gates [p3zG4] to form the receive and transmit busy signals, ARXBSY1 and ATXBSY1.

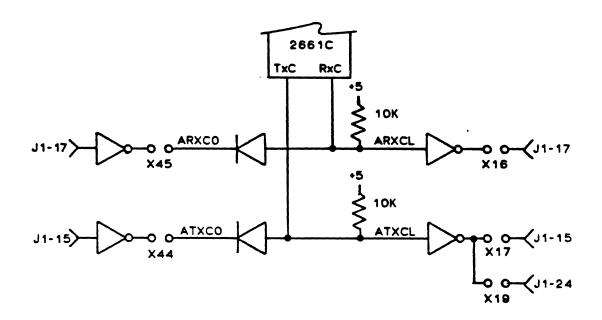

The transmit and receive clock pins on the 2661C, TxC and RxC, are bidirectional - they may be either inputs or outputs. Direction for these pins is determined by the 2661C internal mode register setting. Figure 3-2, below, is a representation of the transmit and receive clock circuitry on the board. When using an externally supplied transmit clock on port A, jumper X17 must be opened to keep the DPCA driver from controlling pin 15 of the communication connector. X44 is installed to allow the external transmit clock

Figure 3-1. 2661C Chip Enable Timing

to enter the 2661C. When the receiver output is high, the 10 Kohm pull-up resistor at the 2661C keeps its input high. When the receiver output goes low, the 2661C pin is pulled low through the diode.

Figure 3-2. Transmit/Receive Clock Logic

When using an internally supplied receive clock on port A, X45 should be removed and X16 installed. With X15 open, the output of the receiver, ARXCØ, goes high. For externally supplied clocks, X45 should be installed and X16 removed.

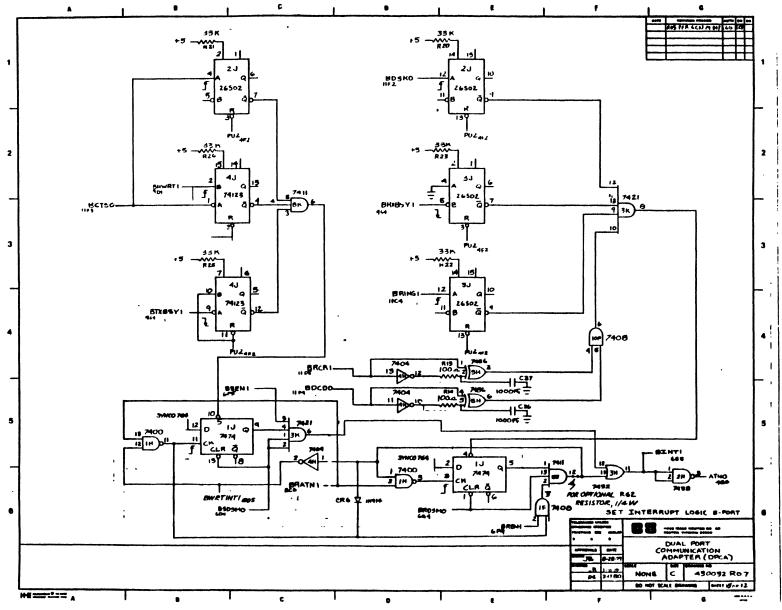

#### 3.8 Interrupt Logic

The DPCA has four sources of interrupts: transmit interrupts and receive interrupts from both the A and B ports. The logic for these interrupts is more closely shared by the two ports than that for most other functions on the board. The DPCA interrupt logic consists of three parts: the interrupt state logic, the interrupt setting logic, and the interrupt arbitration logic.

## 3.8.1 Interrupt State Logic

As discussed in section 2.5, the interrupt logic for the DPCA may be in three states: enabled, disabled, and disarmed. For each of the four sources of interrupts, two latches are used to maintain that source's state. One latch is active if the interrupt is enabled, the other if it is armed.

The port A receive state latches are typical of the four. These latches are 74276 J-K latches with negative clocking. The enable latch [p6zB4] has as its clock the gated command signal, ACMG1, ANDed with TSB150. Therefore the latch changes state on the trailing edge of an A port command having a Ø in bit 15. Its J input is TSBØ91 and its -K input is TSBØ81. Therefore, there is no change when bits 8 and 9 are Ø, it goes high when bit 8 is 1 and bit 9 is Ø, it goes low when bit 8 is Ø and bit 9 is 1. When both bits 8 and 9 are high, this latch changes state. Therefore, when a disarm command is issued, the output of the enable latch is unknown. (In this case, it doesn't matter.)

The interrupt armed latch [p6zC4] has the same clocking as the enable latch. Its J input is 1 if bits 8 and 9 differ. Its -K input is 0 only if bits 8 and 9 are 1. Therefore, there is no change when bits 8 and 9 are 0, it goes high when bits 8 and 9 differ, and it goes low when bits 8 and 9 are 1. This latch cannot enter the toggling state.

Both latches are cleared at system clear.

#### 3.8.2 Interrupt Setting Logic

The interrupt setting logic for the A port is identical to that for the B port. The A port logic is discussed here. There are separate interrupt latches for transmit and receive interrupts. The transmit interrupt latch [p4zB5] is held cleared when the transmit state is disarmed.

When interrupts are armed (enabled or disabled), the transmit interrupt latch may be set by firing any of three oneshots. The rising edge of ACTSØ (CTS comm signal going inactive) fires a 26SØ2 [p4zB1]. A 74123 [p4zB2] is triggered when ACTSØ is low and AHWRT1 is high (the port is in half duplex transmit mode). Therefore this triggering occurs if in half duplex transmit mode when CTS is activated or if CTS is active when the port is placed into half duplex transmit mode. A third one-shot, a 74123 [p4zB4], is triggered when transmit busy (ATXBSY1) falls. Once the transmit interrupt latch is set, it is gated with the enable and armed (ASEN1 and ASDSMØ) signals to generate the MUX bus attention signal, ATNØ [p4zG6]. This latch stays set until the transmit interrupt is acknowledged.

To acknowledge the transmit interrupt, the interrupt arbitration logic generates the A port received attention (ARATN1) signal [p4zC6].

The receive interrupt request is inverted and fed to the transmit interrupt logic as AWRTINT1 [p4zB6]. If no receive interrupt request is present, the output of the 7400 NAND gate [p4zB5] goes low when ARATN1 goes active and the transmit latch is clocked when ARATN1 ends. While a transmit interrupt request is being acknowledged, receive interrupts are redundantly inhibited by the 7408 gate [p4zE6] and by CR7 [p4zD6].

Receive interrupts have priority over transmit interrupts. If the receive interrupt latch [p4zE6] is active and enabled, the 7400 transmit interrupt acknowledge gate [p4zB5] is disabled because AWRTINT1 is off. The receipt of ARATN1 therefore clears the receive interrupt latch [p4zE6].

The receive interrupt latch is set when:

- o The data set ready (DSR) comm signal drops, forcing ADSRØ to go high and trigger a 26SØ2 one-shot [p4zE1],

- o The receive busy signal (ARXBSY1) signal drops, triggering a 26SØ2 one-shot [p4zE3],

- The ring comm signal becomes active, forcing ARING high and thereby triggering a 26SØ2 one-shot [p4zE4],

- o The reverse channel receive (RCR) comm signal changes, forcing ARCR1 to change. This causes a momentary low from a 7486 XOR gate [p4zE4], or

- The data carrier detect (DCD) comm signal changes, changing ADCD1 and thereby pulsing the output of an XOR gate [p4zE5] low.

#### 3.8.3 Interrupt Arbitration Logic

The RACKØ signal is sent by the processor in response to an attention request (ATNØ) by one or more boards on the MUX bus. The RACKØ signal is daisy-chained from board to board. The board with the highest interrupt priority gets RACKØ first. If it does not have an interrupt pending it passes it to the next board in the interrupt chain by activating

49-522 RØØ

TACKØ, which is connected to the RACKØ signal of the next board.

The interrupt arbitration logic is used to route the received interrupt acknowledge signal, RACKØ [p6zA2], to either the A port, the B port, or to the next board in the interrupt acknowledge chain.

If the A port is requesting an interrupt (AINT1 is high), the acknowledge is passed to the A port via ARATNØ [p6zC4]. If the A port is not requesting an interrupt but the B port is (BINT1 is high), the acknowledge is passed to the B port via BRATNØ [p6zG3]. Otherwise, the transmit acknowledge signal, TACKØ [p6zG2], is activated and sent to the next board in the acknowledge chain.

Cross-coupled NAND gates are used to inhibit changes to the acknowledge routing while an acknowledge is in progress. For instance, if a B port interrupt is being acknowledged and AINT1 comes active while BRATNØ is active, BRATNØ continues to be active for the duration of the RACKØ signal, even though the A port has a higher interrupt priority than the B port. ARATNØ does not go active until the next RACKØ signal comes to the board.

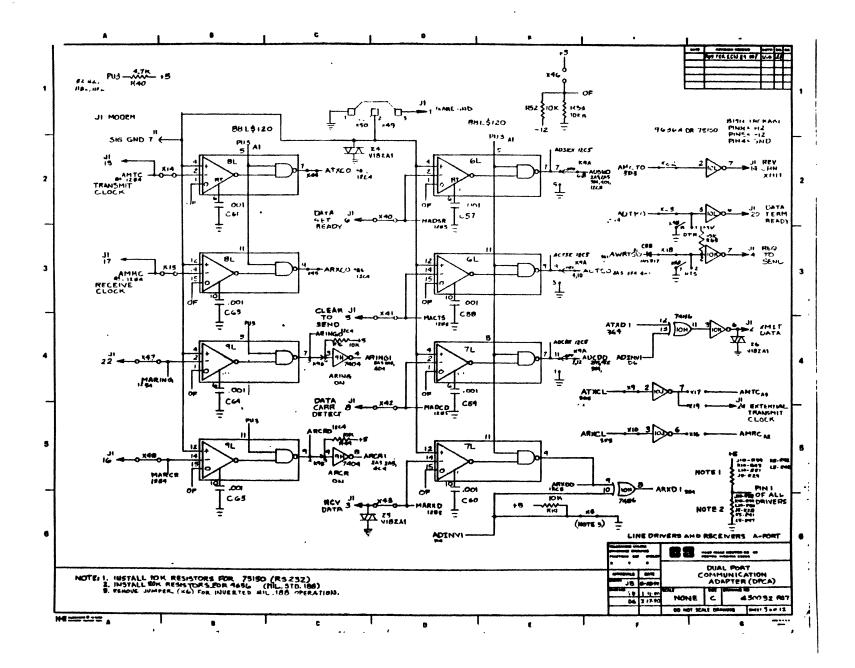

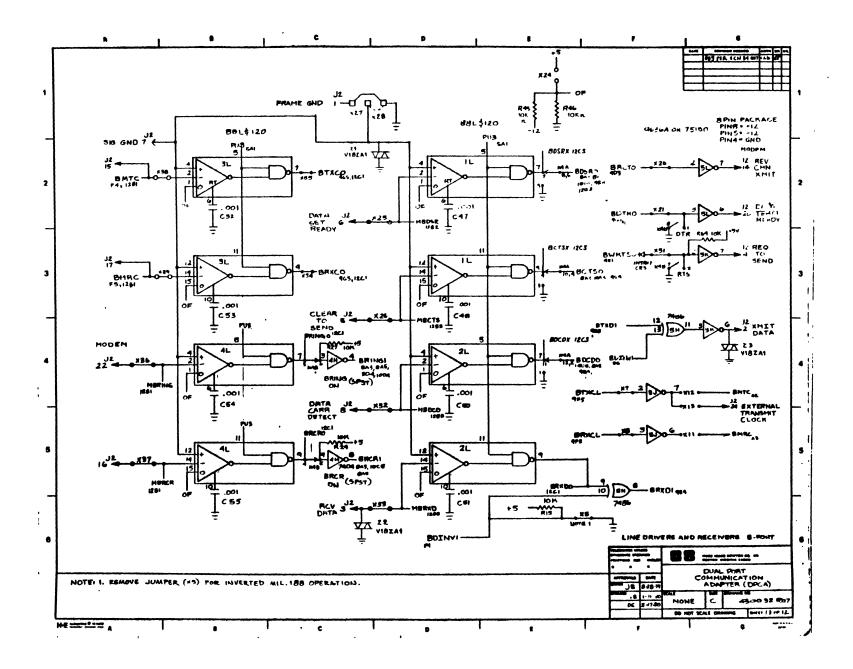

#### 3.9 Line Drivers and Receivers

The DPCA is designed to comply with EIA standards RS-232 and RS-423 (FED-STD-1030A). It also complies with MIL-STD-188-114 for unbalanced signals. The receivers are 88LS120 balanced receivers configured as inverters. All receivers have a common ground reference line which connects to pin 7 of the comm connector. This ground is also connected to logic ground on the DPCA via jumper X50 [p5zC1] for the A port (jumper X28 [p11zC1] for the B port). For RS-423 and MIL-STD-188-114 usage, this jumper should be removed so that pin 7 becomes receive common and is isolated from logic ground. For RS-232, this jumper should be installed.

Each receiver has a .001 mfd response control capacitor, for example, C61 [p5zB2]. This is used for suppression of high frequency noise on the input line. An offset voltage of approximately -6 volts is generated by the R52/R53 divider network. This offset voltage forces the inverting input to be above approximately 0.6 volts before the gate switches. This is to ensure that the receiver output is high if its inverting output is disconnected. The drivers used on the DPCA are 9636As. These drivers are inverting and generate output signal levels of 5.5 volts or -5.5 volts. These levels allow compatibility with all the comm standards met by this board.

Pin 1 of the 9636As is used for a waveshaping resistor. A value of 120 Kohm is used, causing a rise and fall time in the output of approximately 15 microseconds. This allows compliance with MIL-STD-188-114 for baud rates up to 19.2 Kbaud. The signal rise and fall transitions are shaped as linear ramps. These slower rise and fall times cut down on cross talk generated within comm cabling connected to the DPCA.

In certain MIL-STD-188-114 applications, it is necessary to invert the sense of the transmit and receive data signals. This inversion is accomplished using 7486 XOR gates [p5zG4&F5]. When jumper X6 [p5zE6] (X5 [p11zE6] for the B port) is installed, ADINV1 is low and the XORs do not invert the data signals. X6 is usually installed.

Four V18ZAl variators are used on each port to protect the most commonly used signal lines: frame ground (pin 1), transmit data (pin 2), receive data (pin 3), and signal ground (pin 7), from high energy transients on the comm line.

Note: Sheet 12 of the DPCA schematics depicts RS-232 line receivers which are no longer used on the DPCA. These receivers are not compliant with RS-423 and MIL-STD-188-114. Also, the schematics indicate that 75150s may be substituted for the 9636As in RS-232 applications. To maintain compatibility with RS-423, 75150s are no longer used on DPCAs.

#### 3.19 Baud Rate Clock

A standard crystal oscillator circuit is used on the DPCA. This circuit [p2zE5&F5] uses a 5.0688 MHz crystal only, since only the 2661C (formerly 2661-3) version of the EPCI is used on the board.

#### 4 Configuration Specification

#### 4.1 Overview

As stated in chapter 1, the DPCA is a flexible communication interface board. Much of its flexibility is due to the power of the 2661C Enhanced Programmable Communication Interface (EPCI) chip. The rest of its flexibility is due to the configuration options available on the board.

Hardware configuration of the DPCA is performed using DIP switches and jumper shunts.

#### 4.2 Address Selection

The DPCA contains two independently addressable ports, designated A and B. Each port recognizes two 10-bit addresses. The nine high-order address bits are selectable and the low-order bit is either 0 or 1 to select the receive logic or the transmit logic when the port is operating in full duplex mode.

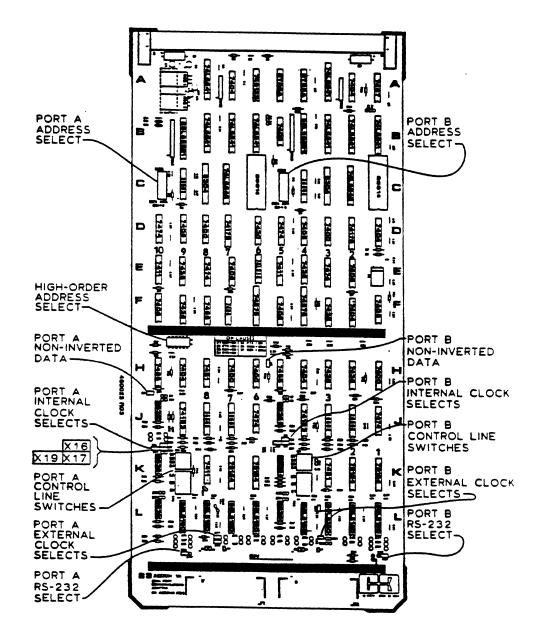

The two high-order address bits for both ports are selected by the jumper strip at coordinate 9G on the circuit board. Refer to Figure 4-1. This jumper strip has a column labeled "A" and one labeled "B". To select the proper address range for the ports, set the jumpers in the appropriate column as indicated in Table 4-1, below.

| Address Range | Bit 6 | Bit 7 |  |

|---------------|-------|-------|--|

| Øxxh          | 1-2   | 4-5   |  |

| lxxh          | 1-2   | 5-6   |  |

| 2xxh          | 2-3   | 4-5   |  |

| <u> </u>      | 2-3   | 5-6   |  |

Table 4-1. High Order Address Selection

The low order address selection for the A and B ports is accomplished using the jumper strips at board location 10C and 5C, respectively. (On some board versions, there are DIP switches at these locations.) There are only seven

Figure 4-1. DPCA Configuration Option Locations

positions to be selected here since the least significant address bit is software selected.

The most significant bit (MSB) of these seven is indicated on the board. (Refer to Figure 4-1.) When a jumper is installed across a position (or a DIP switch position is "on" or "closed"), the corresponding address bit is Ø.

For example, to select address xC4h (where x is set by the high-order address select jumpers):

(MSB) Address Bit: 08 09 10 11 12 13 14 (15) Selection: - X X X - X -Binary: 1 1 0 0 0 1 0 (0) = C4hwhere: - = off (open)X = on (closed)

#### 4.3 Control Line Switches

Certain of the communication line control signals may be forced active or inactive. Such forcing may be required in certain applications where control signals are not provided by the comm line cable.

Two packages of DIP switches are used for controlling these functions. These switches are at board location 9K for the A port and 4K for the B port. (Refer to Figure 4-1.) The switch positions are labeled "S1" through "S7". The func-tion of these switches is shown in Table 4-2, below. In the table, "Enable" means the signal transitions normally, "On" means the signal is forced active, "Off" means the signal is forced inactive.

| Pos      | Signal | Pin        | Dir | Off    | On     |

|----------|--------|------------|-----|--------|--------|

| Sl       | DCD    | 8          | In  | Enable | On     |

| S 2      | CTS    | 5          | In  | Enable | On     |

| S 3      | DSR    | <b>6</b> . | In  | Enable | On     |

| S 4      | DTR    | 20         | Out | Enable | On     |

| S 5      | RTS    | 4          | Out | Enable | On     |

| S6       | Ring   | 22         | In  | Off    | Enable |

| <u> </u> | RCR    | 16         | In  | Off    | Enable |

Table 4-2. Control Line Switch Settings

Note that the DCD signal must be active (or forced active) for the DPCA to receive data from the comm line. Similarly, the CTS signal must be active (or forced active) to transmit data to the comm line. These signals must be supplied for the hardware (the 2661C) to allow transfers in the appropriate direction. If not supplied by the comm line connector, the appropriate switch must be turned on for these transfers to occur.

#### 4.4 Clock Selection Jumpers

The DPCA allows for selection of internal or external clocking of data. Clock signals are used during synchronous and isochronous data transfers for timing the transitions of the transmit and receive data lines. Clocks are unused in asynchronous operations.

The jumper positions used for clock selection and their functions are shown in Table 4-3, below. Table 4-4 illustrates standard configurations for these jumpers.

| A Port      | B Port | Function                     |

|-------------|--------|------------------------------|

| X16         | X11    | Connect RxC Driver to pin 17 |

| X17         | X12    | Connect TxC Driver to pin 15 |

| <b>X</b> 19 | X13    | Connect TxC Driver to pin 24 |

| X44         | X55    | Connect TxC Receiver Output  |

| X45         | X54    | Connect RxC Receiver Output  |

Table 4-3. Clock Selection Jumpers

|                      |   | P | 1:  | X16   | X17   | X19   | X44 | X45 |

|----------------------|---|---|-----|-------|-------|-------|-----|-----|

| Clock Selection      |   | E | 3:  | X11   | X12   | X13   | X55 | X54 |

| Internal RxC         |   |   |     | X     |       |       |     | -   |

| External RxC         |   |   |     | -     |       |       |     | Х   |

| Internal TxC         |   |   |     |       | Х     |       | -   |     |

| External TxC         |   |   |     |       | -     |       | Х   |     |

| TxC to pin 24        |   |   |     |       |       | Х     |     |     |

| No pin 24 connection |   |   |     |       |       | -     |     |     |

| where:               | - | = | j١  | umpei | r ren | noved | 3   |     |

|                      | X | = | ງ່າ | umper | r ins | stal  | led |     |

|                      |   |   | 5   | -     |       |       |     |     |

Table 4-4. Clock Selection Configurations

When using asynchronous communications, the port may be configured for external or internal clocks, even though internal clocking is used. Care should be used, however, if external clocking is configured. The corresponding clock pins on the comm connector must be either disconnected, grounded, or at a negative voltage. They must not be at a high signalling level, which may in time result in damage to the 2661C EPCI. In asynchronous cabling, pins 15 and 17 usually are disconnected.

#### 4.5 Communication Standard Selection

The DPCA is compliant with several communications standards, RS-232, RS-423 (FED-STD-1030A), and the unbalanced signalling requirements of MIL-STD-188-114. The operational differences between these standards are few on the DPCA.

For RS-232 communications, a common signalling ground is used for signals being transmitted and received by a device. For RS-423 and MIL-STD-188-114, a separate ground must be provided for signals being transmitted and those being received. These grounds are called "send common" and "receive common".

When using RS-423 and MIL-STD-188-114 signalling, jumper X50 for port A or jumper X28 for port B must be removed. (Refer to Figure 4-1 for these jumper locations.) These jumpers connect the send and receive commons. These jumpers should be installed for RS-232 operation.

There are no standard pin locations defined in RS-423 or MIL-STD-188-114 for the send and receive commons. On the DPCA, pin 1 is send common and pin 7 is receive common. When interconnecting two devices, send common on one device should be connected to receive common on the other.

In certain MIL-STD-188-114 communications systems transmit and receive data (pins 2 and 3) are inverted in sense from those used for RS-232 and RS-423. Jumper X6 for port A and X5 for port B allow for inversion of these two signals. When one of these jumpers is installed, data has customary sense for the corresponding channel. When removed, data is inverted.

| Α:                             | X6 | X5Ø |

|--------------------------------|----|-----|

| Function B:                    | X5 | X28 |

| RS-423 operation               | X  | -   |

| MIL-STD-188-114, inverted data |    | -   |

| MIL-STD-188-114, normal data   | Х  | -   |

| RS-232 operation               | X  | X   |

| where: - = jumper removed      |    |     |

| X = jumper installed           |    |     |

The communication standard selection options are summarized in Table 4-5, below.

Table 4-5. Communication Standards Selection

•

.

#### 5 **External Interfaces**

## 5.1 Overview

The Dual Port Communication Adapter (DPCA) has three external connections, one to the Perkin-Elmer MUX Bus (Connector  $\emptyset$ ), and two 25-pin D-type communication line connectors.

This chapter presents the pinouts for these connectors.

#### 5.2 Connector Ø

Connector Ø is an 84-pin connector which mates with the Perkin-Elmer Multiplexor (MUX) bus. It contains all of the data, handshake, and power connections required for operation on the channel Ø side of this bus. The connector used is AMP type 3-86018-4, or equivalent.

| Pin | Dir | Signal  | Pin | Dir | Signal |

|-----|-----|---------|-----|-----|--------|

| 100 |     | +5 VDC  | 200 |     | GND    |

| 101 |     | GND     | 201 |     | GND    |

| 114 | I/0 | DØ6Ø    | 214 | I/0 | DØ7Ø   |

| 115 | I/0 | DØ8Ø    | 215 | I/0 | DØ9Ø   |

| 116 | I/0 | D100    | 216 | I/0 | D110   |

| 117 | I/0 | D120    | 217 | I/0 | D130   |

| 118 | I/0 | D140    | 218 | I/0 | D150   |

| 119 | I   | SRØ     | 219 | I   | ADRSØ  |

| 120 | I   | DRØ     | 220 | I   | CMDØ   |

| 121 |     |         | 221 | I   | DAØ ·  |

| 122 | I   | RACKØ   | 222 | 0   | TACKØ  |

| 123 | 0   | SYNØ    | 223 | 0   | ATNØ   |

| 126 | I   | SCLRØ   | 226 |     |        |

| 138 |     | -15 VDC | 238 |     |        |

| 139 |     | +15 VDC | 239 |     |        |

| 140 |     | GND     | 240 |     | GND    |

| 141 |     | +5 VDC  | 241 |     | GND    |

|     |     |         |     |     |        |

The following pins are used on Connector Ø:

Table 5-1. Connector Ø Pinout

#### 5.3 Connectors 1 and 2

Connectors 1 and 2 are 25-pin D-type male connectors used, respectively, for the port A and B communication channels. The connector pinouts are defined in accordance with EIA standard RS-232. The connectors used are AMP type 206604-1, or equivalent.

The following pins are used on both Connectors 1 (port A) and 2 (port B):

| Pir | n Dir | Signal |                          |

|-----|-------|--------|--------------------------|

| 1   | -     | RC     | Recv Common, Sig Gnd     |

| 2   | 0     | TXD    | Transmit Data            |

| 3   | I     | RXD    | Receive Data             |

| 4   | 0     | RTS    | Request to Send          |

| 5   | I     | CTS    | Clear to Send            |

| 6   | I     | DSR    | Data Set Ready           |

| 7   | -     | GND    | Send Common, Sig Gnd     |

| 8   | I     | DCD    | Data Carrier Detect      |

| 14  | 0     | RCT    | Reverse Channel Transmit |

| 15  | I/0   | TxC    | Transmit Clock           |

| 16  | I     | RCR    | Reverse Channel Receive  |

| 17  | I/0   | RxC    | Receive Clock            |

| 20  | Ö     | DTR    | Data Terminal Ready      |

| 22  | I     | RI     | Ring Indicator           |

| 24  | 0     | TT     | Transmit Timing (TxC)    |

Table 5-2. Connector 1 and 2 Pinout

#### Installation 6

### 6.1 Overview

This chapter provides the necessary information for the installation of one or two Dual Port Communications Adapters (DPCAs). The DPCA is contained on a 7 inch Perkin-Elmer format half-board. This half-board must be combined with another half-board device or a half-board blank to be properly installed in the 15 inch Perkin-Elmer I/O chassis. These must be joined using a Perkin-Elmer 16-398 Half Board Adapter Kit. Depending on configuration, the DPCA may be either the left or right half-board - or both.

### 6.2 Unpacking

The DPCA is normally installed at the factory and no special unpacking instructions are required. It is only necessary to ensure that the module is properly seated on the backplane connector.

If the DPCA is shipped separately, unpack it carefully and check for damage and loose integrated circuits before installation. Verify that the various jumper options are properly installed. (Refer to Chapter 4 for details.)

If the DPCA is replacing an existing board, ensure that the configuration strapping and switch settings match the unit being replaced.

### 6.3 Location

The DPCA may be installed in an I/O slot in a CPU chassis or I/O expansion chassis. This slot must be under direct control of the processor MUX bus or under a DIOS, subchannel controller, or C3 Manual Bus Switch.

### 6.4 Backplane Considerations

The RACKØ/TACKØ jumper must be removed from any slot containing a DPCA. (This jumper runs between pins 122 and 222 on the backplane connector for the board.)

The DPCA requires +15 volt power. This power is available on 7/32 chassis on pins 138 (-15 volts) and 139 (+15 volts). If this power is not present on the chassis, an external power supply must be provided to furnish these voltages. The supply must be properly sized to meet the requirements of all the DPCAs which it is to power. (Refer to Chapter 1 for these power requirements.)

24

### APPENDIX A

### 2661C EPCI Data Sheet

•

The following data sheet is reprinted by permission of Signetics Corporation, a subsidiary of U.S. Philips Corporation.

# **Signetics**

#### **Microprocessor Products**

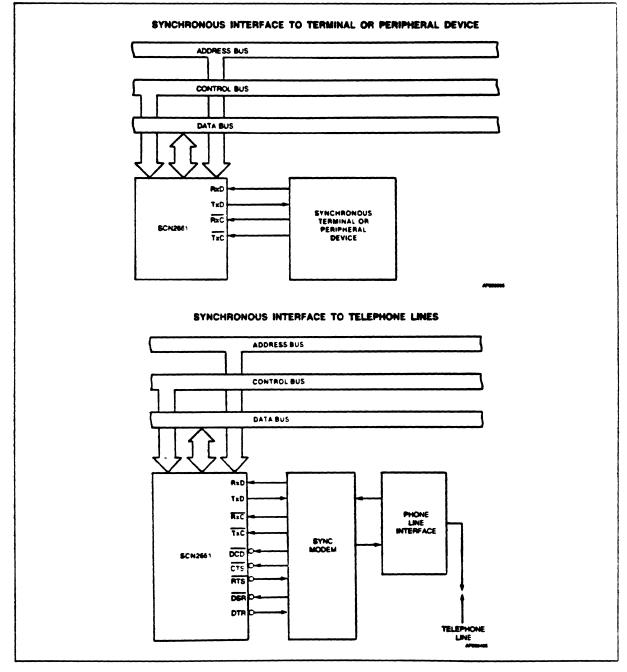

#### DESCRIPTION

The Signetics SCN2661 EPCI is a universal synchronous/asynchronous data communications controller chip that is an enhanced version of the SCN2651. It Interfaces easily to all 8-bit and 16-bit microprocessors and may be used in a polled or interrupt driven system environment. The SCN2661 accepts programmed instructions from the microprocessor while supporting many serial data communications disciplines – synchronous and asynchronous – in the full or half-duplex mode. Special support for BISYNC is provided.

The EPCI serializes parallel data characters received from the microprocessor for transmission. Simultaneously, it can receive serial data and convert it into parallel data characters for input to the microcomputer.

The SCN2661 contains a baud rate generator which can be programmed to either accept an external clock or to generate internal transmit or receive clocks. Sixteen different baud rates can be selected under program control when operating in the internal clock mode. Each version of the EPCI (A, B, C) has a different set of baud rates.

#### FEATURES

- Synchronous operation

5- to 8-bit characters plus

- parity - Single or double SYN operation

- Internal or external character synchronization

- Transparent or non-transparent mode

- Transparent mode DLE stuffing (Tx) and detection (Rx)

- Automatic SYN or DLE-SYN insertion SYN, DLE and DLE-SYN stripping

- Odd, even, or no parity

- Local or remote maintenance loopback mode

- Baud rate: dc to 1M bps (1X clock)

# SCN2661/SCN68661 Enhanced Programmable Communications Interface (EPCI)

### Product Specification

- Asynchronous operation

- 5- to 8-bit characters plus parity

- 1, 1½ or 2 stop bits transmitted

- Odd, even, or no parity - Parity, overrun and traming

- error detection Line break detection and

- generation - False start bit detection

- Automatic serial echo mode

- (echopiex)

- Local or remote maintenance loopback mode

- Baud rate: dc to 1M bps (1X clock) dc to 62.5K bps (16X clock) dc to 15.625K bps (64X clock)

#### **OTHER FEATURES**

- Internal or external baud rate clock

- 3 baud rate sets

- 16 internal rates for each set

Double buffered transmitter and receiver

- Dynamic character length

switching

- Full or half-duplex operation

- TTL compatible inputs and outputs

- RxC and TxC pins are short circuit protected

- Single 5V power supply

- No system clock required

#### APPLICATIONS

- Intelligent terminals

- Network processors

- Front-end processors

- Remote data concentrators

- Computer-to-computer links

- Serial peripherals

- BISYNC adaptors

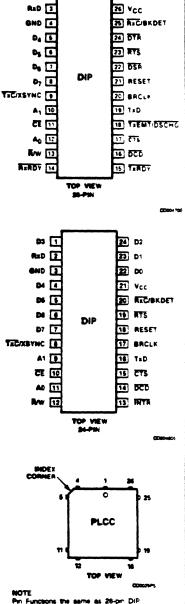

**PIN CONFIGURATION**

February 20, 1985

853-0086-77351

### SCN2661/SCN68661

### ORDERING CODE

|             | V <sub>CC</sub> = 5V ± 5% |                 |                 |  |  |  |  |

|-------------|---------------------------|-----------------|-----------------|--|--|--|--|

|             | Commercia!                | Automotive      | Military '      |  |  |  |  |

| PACKAGES    | 0°C to +70°C              | -40°C to +85°C  | -55°C to +125°C |  |  |  |  |

| Ceramic DIP | SCN2661AC1128             | SCN2661AA1128   | SCN2661AM1128   |  |  |  |  |

| 28-Pin      | SCN2661BC1128             | SCN2661BA1128   | SCN2661BM1128   |  |  |  |  |

| 0.6" Wide   | SCN2661CC1128             | SCN2661CA1128   | SCN2661CM1128   |  |  |  |  |

| Plastic DIP | SCN2661AC1N28             |                 |                 |  |  |  |  |

| 28-Pin      | SCN2661BC1N28             | Contact Factory | Not Available   |  |  |  |  |

| 0.6" Wide   | SCN2661CC1N28             |                 |                 |  |  |  |  |

| Plastic DIP | SCN2661AC1N24             |                 |                 |  |  |  |  |

| 24-Pin      | SCN2661BC1N24             | Contact Factory | Not Available   |  |  |  |  |

| 0.4" Wide   | SCN2661CC1N24             |                 |                 |  |  |  |  |

| Plastic LCC | SCN2661AC1A28             |                 |                 |  |  |  |  |

|             | SCN2661BC1A28             | Contact Factory | Not Available   |  |  |  |  |

|             | SCN2661CC1A28             |                 |                 |  |  |  |  |

NOTES:

1. See table 1 for baud rates. Specify SCN2661A, B, or C depending on baud rate selected

2. The SCN68661 is identical to the SCN2661 Order using part numbers above

The EPCI is available in two packages a 28pin (0.6" wide) DIP and a 24-pin (0.4" wide) DIP. The following are the differences between the 24-pin and the 28-pin versions

- The 24-pin version provides a single interrupt output (INTR) instead of the three interrupt outputs (RxRDY, TxRDY, TxEMT/DSCHG) supplied on the 28-pin version. INTR will be asserted (low) when one or more of the status bits SR0, SR1 or SR2 is a logic one.

- 2. Two modern interface pins, the DTR output and the DSR input, are eliminated in the 24-pin version. Because of this, status bit SR7 should be ignored and the setting of status bit SR2 due to a data set change (DSCHG) can be caused only by a change of the DCD input. Since the DTR output is eliminated, command register bit CR1 does not perform any function, although it remains writable and readable.

Other than the above, the functional operation, DC electrical characteristics, and AC electrical characteristics of the 24-pin version are identical to the 28-pin version.

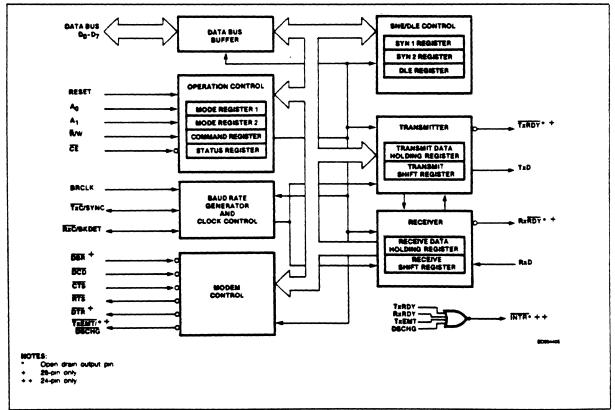

### **BLOCK DIAGRAM**

February 20, 1985

### 2

### SCN2661/SCN68661

#### BLOCK DIAGRAM

The EPCI consists of six major sections. These are the transmitter, receiver, timing, operation control, modem control and SYN/ DLE control These sections communicate with each other via an internal data bus and an internal control bus. The internal data bus interfaces to the microprocessor data bus via a data bus buffer.

#### **Operation Control**

This functional block stores configuration and operation commands from the CPU and generates appropriate signals to vanous internal sections to control the overall device operation. It contains read and write circuits to permit communications with the microprocesaor via the data bus and contains mode registers 1 and 2, the command register, and the status register. Details of register addressing and protocol are presented in the EPCI programming section of this data sheet

#### Timing

The EPCI contains a baud rate generator (BRG) which is programmable to accept external transmit or receive clocks or to divide an external clock to perform data communications. The unit can generate 16 commonly used baud rates, any one of which can be selected for full-duplex operation. See table 1.

#### Receiver

The receiver accepts senal data on the RxD pin, converts this senal input to parallel format, checks for bits or characters that are unque to the communication technique and sends an "assembled character to the CPU

#### Transmitter

The transmitter accepts parallel data from the CPU, converts it to a serial bit stream, inserts the appropriate characters or bits (based on the communication technique) and outputs a composite serial stream of data on the TxD output pin.

#### Modem Control

The modem control section provides interfacing for three input signals and three output signals used for "handshaking" and status indication between the CPU and a modem

#### **SYN/DLE** Control

This section contains control circuitry and three 8-bit registers storing the SYN1, SYN2, and DLE characters provided by the CPU These registers are used in the synchronous mode of operation to provide the characters required for synchronization, idle fill and data transparency

# Table 1. BAUD RATE GENERATOR CHARACTERISTICS SCN2661A (BRCLK = 4.9152MHz)

| NR23 - 20    | BAUD RATE | ACTUAL<br>FREQUENCY<br>16X CLOCK | PERCENT<br>ERROR | DIVISOR |  |

|--------------|-----------|----------------------------------|------------------|---------|--|

| 0000         | 50        | 0.8kHz                           | -                | 6144    |  |

| 0001         | 75        | 1.2                              |                  | 4096    |  |

| <b>0</b> 010 | 110       | 1.7598                           | -0.01            | 2793    |  |

| 0011         | 134.5     | 2.152                            |                  | 2284    |  |

| 0100         | 150       | 2.4                              |                  | 2048    |  |

| 0101         | 200       | 3.2                              |                  | 1536    |  |

| 0110         | 300       | 4.8                              |                  | 1024    |  |

| 0111         | 600       | 9.6                              |                  | 512     |  |

| 1000         | 1050      | 16.8329                          | 0.196            | 292     |  |

| <b>10</b> 01 | 1200      | 19.2                             |                  | 256     |  |

| 1010         | 1800      | 28.7438                          | -0.19            | 171     |  |

| 1011         | 2000      | 31.9168                          | -0.26            | 154     |  |

| 1100         | 2400      | 38.4                             | -                | 128     |  |

| 1101         | 4800      | 76.8                             |                  | 64      |  |

| 1110         | 9600      | 153.6                            |                  | 32      |  |

| 1111         | 19200     | 307.2                            |                  | 16      |  |

#### SCN2661B (BRCLK = 4.9152MHz)

| <b>N</b> R23 - 20 | BAUD RATE | ACTUAL<br>FREQUENCY<br>16X CLOCK | PERCENT<br>ERROR | DIVISOR |

|-------------------|-----------|----------------------------------|------------------|---------|

| 0000              | 45.5      | 0.7279kHz                        | 0.005            | 6752    |

| 0001              | 50        | 0.8                              | -                | 6144    |

| 0010              | 75        | 1.2                              |                  | 4096    |

| 0011              | 110       | 1.7598                           | -0.01            | 2793    |

| 0100              | 134 5     | 2.152                            |                  | 2284    |

| 0101              | 150       | 2.4                              |                  | 2048    |

| 0110              | 300       | 4.8                              |                  | 1024    |

| 0111              | 600       | 9.6                              |                  | 512     |

| 1000              | 1200      | 19.2                             |                  | 256     |

| 1001              | 1800      | 28.7438                          | -0 19            | 171     |

| 1010              | 2000      | 31.9168                          | -0.26            | 154     |

| 1011              | 2400      | 38.4                             |                  | . 128   |

| 1100              | 4800      | 76.8                             |                  | 64      |

| 1101              | 9600      | 153.6                            | -                | 32      |

| 1110              | 19200     | 307.2                            |                  | 16      |

| 1111              | 38400     | 614.4                            |                  | 8       |

#### SCN2661C (BRCLK = 5.0688MHz)

| MR23 - 20 | BAUD RATE | ACTUAL<br>FREQUENCY<br>16X CLOCK | PERCENT<br>ERROR | DIVISOR      |

|-----------|-----------|----------------------------------|------------------|--------------|

| 0000      | 50        | 0.8kHz                           | -                | 6336         |

| 0001      | 75        | 1.2                              |                  | 4224         |

| 0010      | 110       | 1.76                             |                  | <b>288</b> 0 |

| 0011      | 134.5     | 2.1523                           | 0.016            | 2355         |

| 0100      | 150       | 2.4                              |                  | 2112         |

| 0101      | 300       | 4.8                              | -                | 1056         |

| 0110      | 600       | 9.6                              |                  | 528          |

| 0111      | 1200      | 19.2                             |                  | 264          |

| 1000      | 1800      | 28.8                             |                  | 176          |

| 1001      | 2000      | 32.061                           | 0.253            | 158          |

| 1010      | 2400      | 38.4                             |                  | 132          |

| 1011      | 3600      | 57.6                             |                  | 88           |

| 1100      | 4800      | 76.8                             | -                | 66           |

| 1101      | 7200      | 115.2                            |                  | 44           |

| 1110      | 9600      | 153.6                            | -                | 33           |

| 1111      | 19200     | 316.8                            | 3.125            | 16           |

NOTE:

16X clock is used in asynchronous mode in synchronous mode, clock multiplier is 1X and BRG can be used only for  $\mathsf{TxC}$

# SCN2661/SCN68661

#### **OPERATION**

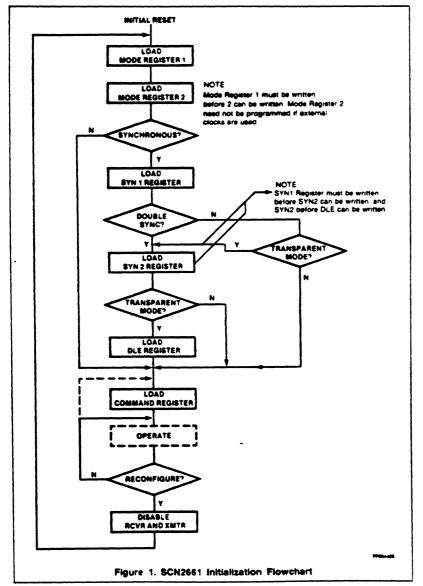

The functional operation of the SCN2661 is programmed by a set of control words supplied by the CPU. These control words specity items such as synchronous or asynchronous mode, baud rate, number of bits per character, etc. The programming procedure is described in the EPCI programming section of the data sheet.

After programming, the EPCI is ready to perform the desired communications functions. The receiver performs senal to parallel conversion of data received from a modern or equivalent device. The transmitter converts perallel data received from the CPU to a senal bit stream. These actions are accomplished within the framework specified by the control words

#### Receiver

The SCN2661 is conditioned to receive data when the DCD input is low and the RxEN bit in the command register is true. In the asynchronous mode, the receiver looks for a highto-low (mark to space) transition of the start bit on the RxD input line. If a transition is detected, the state of the RxD line is sampled again after a delay of one-half of a bit time. If RxD is now high, the search for a valid start bit is begun again. If RxD is still low, a valid start bit is assumed and the receiver continues to sample the input line at one bit time intervals until the proper number of data bits, the parity bit, and one stop bit have been assembled The data are then transferred to the receive data holding register, the RxRDY bit in the status register is set, and the RxRDY output is asserted. If the character length is less than 8 bits, the high order unused bits in the holding register are set to zero. The parity error, framing error, and overrun error status bits are strobed into the status register on the positive going edge of RxC corresponding to the received character boundary. If the stop bit is present, the receiver will immediately begin its search for the next start bit. If the stop bit is absent (framing error), the receiver will interpret a space as a start bit if it persists into the next bit time interval. If a break condition is detected (RxD is low for the entire character as well as the stop bit), only one character consisting of all zeros (with the FE status bit SR5 set) will be transferred to the holding register. The RxD input must return to a high condition before a search for the next start bit begins

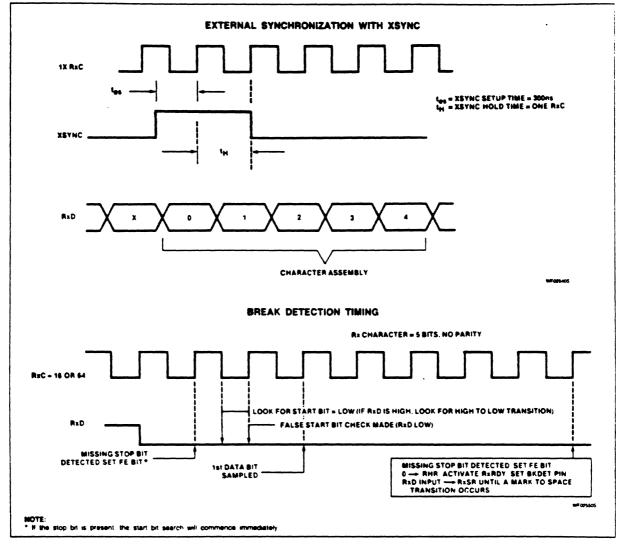

Pin 25 can be programmed to be a break detect output by appropriate setting of MR27-MR24 If so, a detected break will cause that pin to go high. When RxD returns to mark for one RxC time, pin 25 will go low. Refer to the break detection timing diagram

| February | 20, | 1985 |

|----------|-----|------|

|----------|-----|------|

| Table | 2. | CPU-RELATED | SIGNAL |

|-------|----|-------------|--------|

|       |    |             |        |

| PIN NAME                        | 24-<br>PIN | 28-<br>PIN | INPUT/<br>OUTPUT | FUNCTION .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------|------------|------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                           | ×          | ×          | 1                | A high on this input performs a master reset of<br>the 2661. This signal asynchronously termi-<br>nates any device activity and clears the mode<br>command and status registers. The device<br>assumes the idle state and remains there unt<br>initialized with the appropriate control words                                                                                                                                                                                                                                                                        |