# 82420/82430 PCIset ISA and EISA Bridges

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

MDS is an ordering code only and is not used as a product name or trademark. MDS is a registered trademark of Mohawk Data Sciences Corporation.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

© INTEL CORPORATION 1993

## 82420/82430 PCIset Cache/Memory Subsystem

| CONTENTS                                | PAGE |

|-----------------------------------------|------|

| 82420 PCIset                            | 1    |

| 82430 PCIset FOR THE PENTIUM™ PROCESSOR |      |

| 82374EB EISA SYSTEM COMPONENT (ESC)     |      |

| 82375EB PCI-EISA BRIDGE (PCEB)          |      |

| 82378IB SYSTEM I/O (SIO)                |      |

# intel

## INTEL 82420 PCIset

Intel's 82420 PCIset enables workstation level of performance for Intel486™ CPU desktop systems. The Peripheral Component Interconnect Bus (PCI) is driving a new architecture for PC's—eliminating the I/O bottleneck of standard expansion busses. PCI provides a glueless interface for high performance peripherals such as LAN, SCSI, graphics and video to be placed onto a fast local bus. By utilizing this technology and incorporating read/write bursts along with write buffers into the 82420 PCIset, a new level of PC graphics is now possible for today's Intel486 CPU desktop systems.

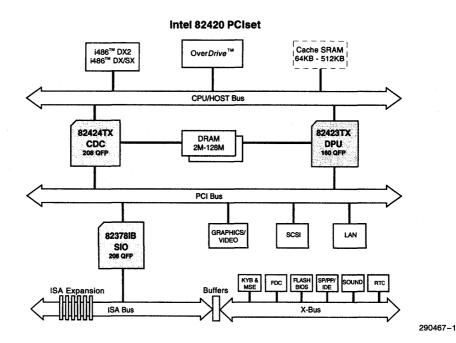

The Intel 82420 PCIset is comprised of three components: the 82424TX Cache DRAM Controller (CDC), the 82423TX Data Path Unit (DPU), and the 82378IB System I/O (SIO). The CDC and DPU provide the core system architecture while the SIO is a PCI master/slave agent which bridges the core architecture to the ISA standard expansion bus. Intel also offers two components, the 82374EB (ESC) and 82375EB (PCEB), that work in conjunction to bridge the PCI bus to the EISA expansion bus. Refer to the ESC and PCEB data sheets for information regarding the EISA bridge components.

The chip set supports the Intel486 family as well as the write-back caching capability of Intel's future OverDrive<sup>TM</sup> processor for the Intel486 DX2. The high performance memory subsystem supports 4-1-2-1 DRAM accesses at 33 MHz and concurrent operation between PCI bus masters while the CPU accesses memory. An integrated second level cache can be programmed for write-through or write-back operation.

Intel486 SX, Intel486 DX, Intel486 DX2, and OverDrive are trademarks of Intel Corporation.

## **Product Highlights**

82424TX—Cache DRAM Controller (CDC)

- Concurrent Linefill during Copyback Cycles

- Supports Intel486 CPU Family and OverDrive Processors

- Supports Future OverDrive Upgrade Processor in Write-Back Cache Mode

- 64K-512K Level 2 Cache Support

- Level 2 Cache Configurable as Write-Back or Write-Through

- 208-Pin QFP Package

#### 82423TX—Data Path Unit (DPU)

- Highly Integrated

- Four Dword Write Buffers

- Zero Wait States for CPU Write Cycles

- PCI Burst Write Capability

- 160-Pin QFP Package

#### **Product Description**

The 82424TX Cache DRAM Controller (CDC) is a single-chip bridge from the CPU to the PCI bus. It provides the integrated functionality of a second level cache controller, a DRAM controller, and a PCI bus controller. It also features an optimized memory subsystem. The CDC is a dual ported device with one port as the host port and the other as the PCI port.

The 82423TX Data Path Unit (DPU) integrates the host data, memory data, and PCI data interface, DPU control/parity and four deep posted write 82378IB—System I/O Component (SIO)

- Supports Fast DMA Type A, B, or F Cycles

- Supports DMA Scatter/Gather

- Arbitration Logic for Four PCI Masters

- Reusable across Multiple Platforms

- Directly Drives Six External ISA Slots

- Integrates Many of Today's Common I/O Functions

- 208-Pin QFP Package

buffers. With glue and buffers integrated directly into the DPU, the Intel 82420 PCIset reduces board space requirements. The DPU's posted write buffers allow CPU write cycles to be executed as 0 wait states.

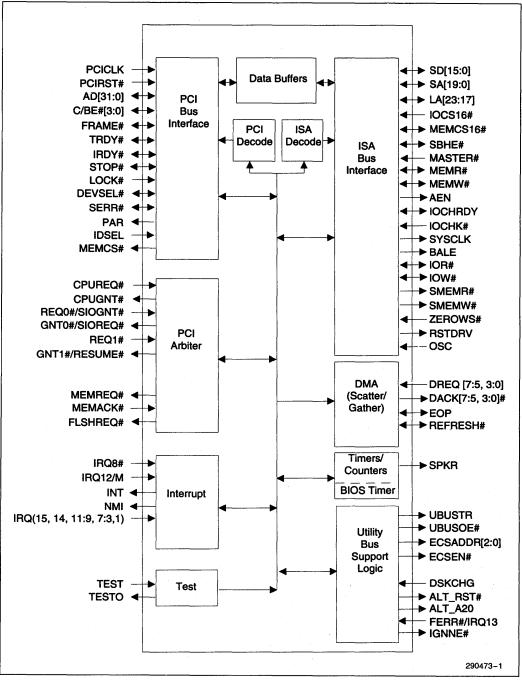

The 82378IB System I/O (SIO) is a dual ported device which acts as a bridge between the PCI and standard ISA I/O bus. This component can be used with future Intel PCIsets. The SIO integrates the functionality of an ISA controller, PCI controller, fast 32-bit DMA controller, and standard system I/O functions.

## 82430 PCIset FOR THE PENTIUM™ PROCESSOR

- Supports the Pentium<sup>TM</sup> Processor at 60 MHz or 66.667 MHz

- Interfaces the Host and Standard Buses to the Peripheral Component Interconnect (PCI) Local Bus Operating at 30 MHz or 33.33 MHz

- Up to 132 Mbytes/sec Transfer Rate

- Full Concurrency between CPU Host Bus and PCI Bus Transactions

- Integrated Cache Controller Provided for Optional Second Level Cache

- 256 Kbyte or 512 Kbyte Cache

- Write-Back or Write-Through Policy

- Standard or Burst SRAM

- Integrated Tag RAM for Cost Savings on Second Level Cache

- Provides a 64-Bit Interface to DRAM Memory

- From 2 Mbytes to 192 Mbytes of Main Memory

- 70 ns and 60 ns DRAMs Supported

- Supports the Pipelined Address Mode of the Pentium Processor for Higher Performance

- Optional ISA or EISA Standard Bus Interface

- Single Component ISA Controller

- Two Component EISA Bus Interface

- Minimal External Logic Required

- Supports Burst Read and Writes of Memory from the Host and PCI Buses

- Five Integrated Write Posting and Read Prefetch Buffers Increase CPU and PCI Master Performance

- Host CPU Writes to PCI in Zero Wait State PCI Bursts with Optional TRDY# Connection

- Integrated Low Skew Host Bus Clock Driver for Cost and Board Space Savings

- PCIset Operates Synchronous to the 66.667 MHz CPU and 33.33 MHz PCI Clocks

- Byte Parity Support for the Host/PCI and Main Memory Buses

— Optional Parity on the Second Level Cache

The 82430 PCIset provides the Host/PCI bridge, cache/main memory controller, and an I/O subsystem core (either PCI/EISA or PCI/ISA bridge) for the next generation of high-performance personal computers based on the Pentium microprocessor. System designers can take advantage of the power of the PCI (Peripheral Component Interconnect) bus for the local I/O while maintaining access to the large base of EISA and ISA expansion cards, and corresponding software applications. Extensive buffering and buffer management within the bridges ensures maximum efficiency in all three bus environments (Host CPU, PCI, and EISA/ISA Buses).

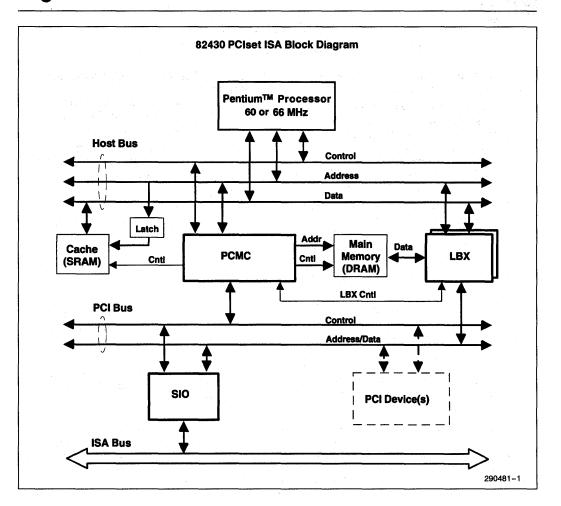

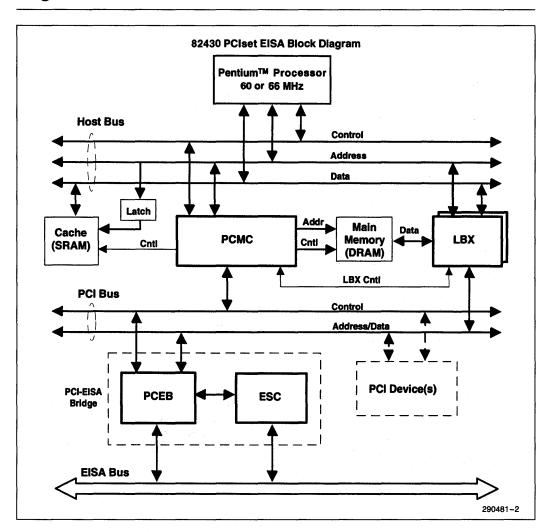

The 82430 PCIset consists of the 82434LX PCI/Cache/Memory Controller (PCMC) and the 82433LX Local Bus Accelerator (LBX) components, plus, either a PCI/ISA bridge or a PCI/EISA bridge. The PCMC and LBX provide the core cache and main memory architecture and serve as the Host/PCI bridge. For an ISA-based system, the 82430 PCIset includes the 82378IB System I/O (SIO) component as the PCI/ISA bridge. For an ISA-based system, the 82430 PCIset includes the 82375EB PCI/EISA Bridge (PCEB) and the 82374EB EISA System Component (ESC). The PCEB and ESC work in tandem to form the complete PCI/EISA bridge. Both the ISA and EISA-based systems are shown on the following pages.

Pentium is a trademark of Intel Corporation.

int<sub>e</sub>l.

82430 PCIset

int<sub>e</sub>l.

# intel

## 82434LX PCI/CACHE/MEMORY CONTROLLER (PCMC)

- Supports the 64-Bit Pentium™ Processor at 60 MHz and 66.667 MHz

- Supports Pipelined Addressing Capability of the Pentium Microprocessor

- High Performance CPU/PCI/Memory Interfaces via Posted-Write/Read-Prefetch Buffers

- Fully Synchronous 33.33 MHz PCI Bus Interface with Full Bus Master Capability

- Supports the Pentium Processor Cache (First Level Cache) in either Write-Through or Write-Back Mode

- Programmable Attribute Map of DOS and BIOS Regions for System Flexibility

- Integrated Low Skew Clock Driver for Distributing 66.667 MHz Clock

- Integrated Second Level Cache Controller

- Integrated Cache Tag RAM

- Write-Through and Write-Back Cache Modes

- Direct-Mapped Organization

- Supports Standard and Burst SRAMs

- 256 KByte and 512 KByte Sizes

- Cache Hit Cycle of 3-1-1-1 on Reads and Writes Using Burst SRAMs

- Cache Hit Cycle of 3-2-2-2 on Reads and 4-2-2-2 on Writes Using Standard SRAMs

- Integrated DRAM Controller

- Supports 2 MBytes to 192 MBytes of Cacheable Main Memory

- Supports DRAM Access Times of 70 ns and 60 ns

- CPU Writes Posted to DRAM at 4-1-1-1

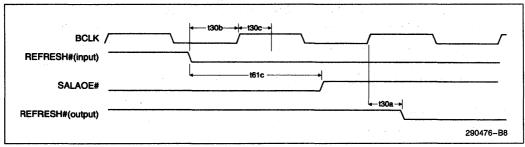

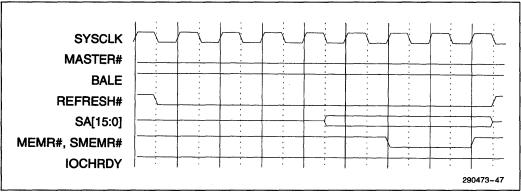

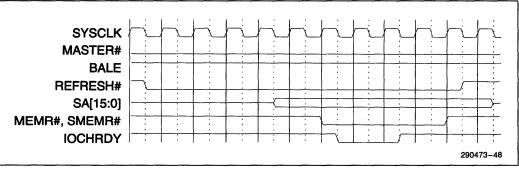

- Refresh Cycles Decoupled from ISA Refresh to Reduce the DRAM Access Latency

- Refresh by RAS#-Only, or CAS#before-RAS#, in Single or Burst of Four

- Host/PCI Bridge

- Translates CPU Cycles into PCI Bus Cycles

- Translates Back-to-Back Sequential CPU Writes into PCI Burst Cycles

- Burst Mode Writes to PCI in Zero PCI Wait States (i.e., Data Transfer Every Cycle)

- Full Concurrency between CPU-to-Main Memory and PCI-to-PCI Transactions

- Full Concurrency between CPU-to-Second Level Cache and PCI-to-Main Memory Transactions

- Same Core Cache and Memory System Logic Design for ISA or EISA Systems

- Cache Snoop Filter Ensures Data Consistency for PCI-to-Main Memory Transactions

- PCMC (208-Pin QFP) Uses 5V CMOS Technology

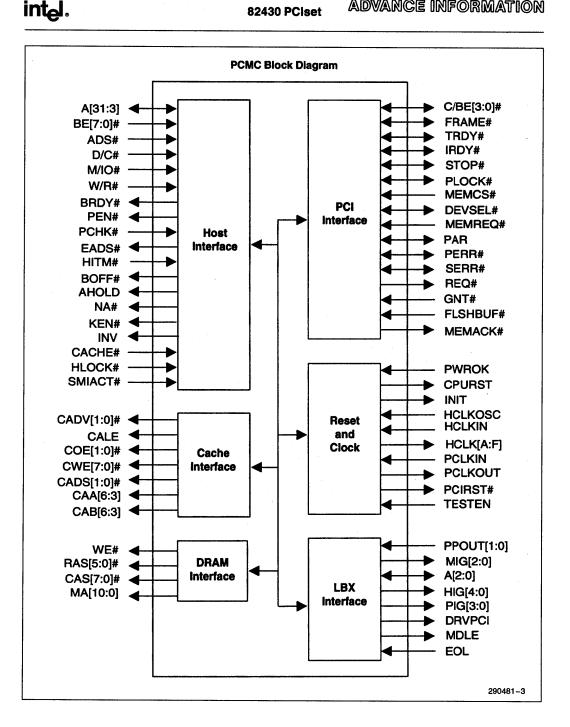

The 82434LX PCI, Cache, Memory Controller (PCMC) integrates the cache and main memory DRAM control functions and provides the bus control for transfers between the CPU, cache, main memory, and the Peripheral Component Interconnect (PCI) Local Bus. The cache controller supports both write-through and write-back cache policies and cache sizes of 256 KBytes and 512 KBytes. The cache memory can be implemented with either standard or burst SRAMs. The PCMC cache controller integrates a high-performance Tag RAM to reduce system cost. Up to twelve single-sided SIMMs or six double-sided SIMMs provide a maximum of 192 MBytes of main memory. The PCMC is intended to be used with the 82433LX Local Bus Accelerator (LBX). The LBX provides the Host-to-PCI address path and data paths between the CPU/cache, main memory, and PCI. The LBX also contains posted write buffers and read-prefetch buffers. Together, these two components provide a full function data path to main memory and form a PCI bridge to the Host subsystem (CPU/cache).

# intel

## 82433LX LOCAL BUS ACCELERATOR (LBX)

- Supports the Full 64-Bit Pentium™ Processor Data Bus at 66.667 MHz

- Provides a 64-Bit Interface to DRAM Memory and a 32-Bit Interface to PCI

- Five Integrated Write Posting and Read Prefetch Buffers Increase CPU and PCI Master Performance

- --- CPU-to-Memory Posted Write Buffer 4 Quadwords Deep

- PCI-to-Memory Posted Write Buffer Two Buffers, 4 Dwords Each

- --- PCI-to-Memory Read Prefetch Buffer 4 Quadwords Deep

- CPU-to-PCI Posted Write Buffer 4 Dwords Deep

- CPU-to-PCI Read Prefetch Buffer 4 Dwords Deep

- Host-to-Memory and Host-to-PCI Write Posting Buffers Permit Near Zero Wait State Write Performance

- Dual-Port Architecture Allows Concurrent Operations on the Host and PCI Buses

- Operates Synchronous to the 66.667 MHz CPU and 33.33 MHz PCI Clocks

- Supports Burst Read and Writes of Memory from the Host and PCI Buses

- Host CPU Writes to PCI in Zero Wait State PCI Bursts with Optional TRDY# Connection

- Byte Parity Support for the Host and Memory Buses

- Optional Parity Generation for Host to Memory Transfers

- Optional Parity Checking for the Secondary Cache Residing on the Host Data Bus

- Parity Checking for Host and PCI Memory Reads

- Parity Generation for PCI to Memory Writes

- 160-Pin QFP Package

- 5V CMOS Technology

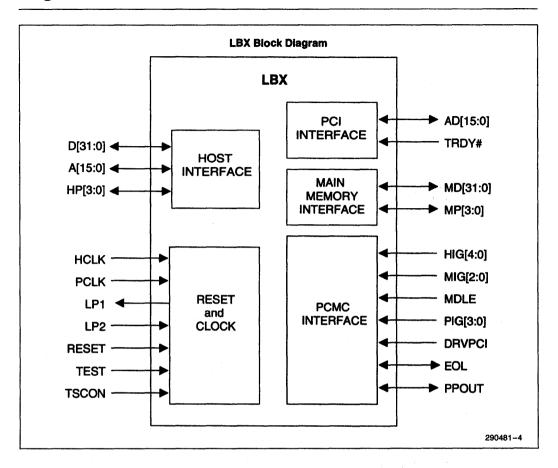

Two 82433LX Local Bus Accelerator (LBX) components provide a 64-bit data path between the Host CPU/ cache and main memory, a 32-bit data path between the Host CPU and Peripheral Component Interconnect (PCI) Local Bus, and a 32-bit data path between the PCI bus and main memory. The dual-port architecture allows concurrent operations on the Host and PCI Buses. The LBXs incorporate three write posting buffers and two read prefetch buffers to increase Pentium processor and PCI Master performance. The LBX supports byte parity for the Host and main memory buses. The LBX is intended to be used with the 82434LX PCI/ Cache/Memory Controller (PCMC). During bus operations between the Host, main memory, and PCI, the PCMC commands the LBXs to perform functions such as latching address and data, merging data, and enabling output buffers. Together, these three components form a "host bridge" which provides a full function dual-port data path interface, linking the Host CPU and PCI bus to main memory. int<sub>e</sub>l.

## 82375EB PCI/EISA BRIDGE (PCEB)

- Provides the Bridge between the PCI Bus and EISA Bus

- 100% PCI and EISA Compatible — PCI and EISA Master/Slave Interface

- Directly Drives 10 PCI Loads and 8 EISA Slots

- Supports PCI at 25 MHz to 33.33 MHz

- Data Buffers Improve Performance

- Four 32-Bit PCI-to-EISA Posted Write Buffers

- Four 16-Byte EISA-to-PCI Read/Write Line Buffers

- EISA-to-PCI Read Prefetch

- --- EISA-to-PCI and PCI-to-EISA Write Posting

- Data Buffer Management Ensures Data Coherency

- Flush Posted Write Buffers

- Flush or Invalidate Line Buffers

- Instruct All PCI Devices to Flush Buffers Pointing to PCI Bus before Granting EISA Access to PCI

- Burst Transfers on both the PCI and EISA Buses

- 32-Bit Data Paths

- Integrated EISA Data Swap Buffers

- Arbitration for PCI Devices

Supports Six PCI Masters

- Fixed, Rotating, or a Combination of the Two

- PCI and EISA Address Decoding and Mapping

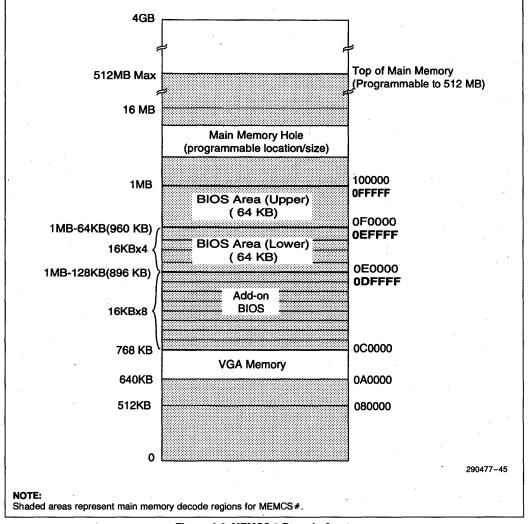

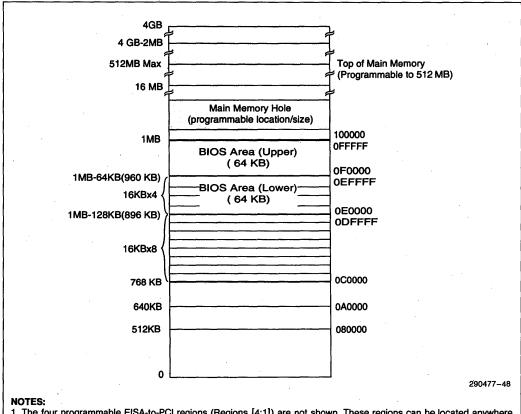

- Positive Decode of Main Memory Areas (MEMCS# Generation)

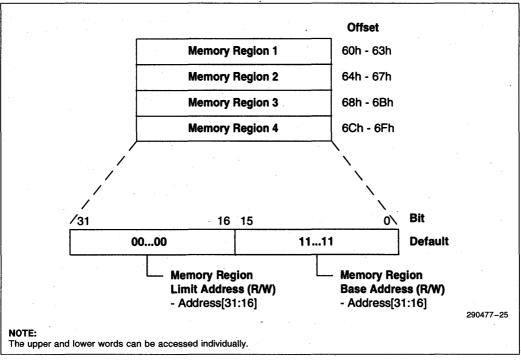

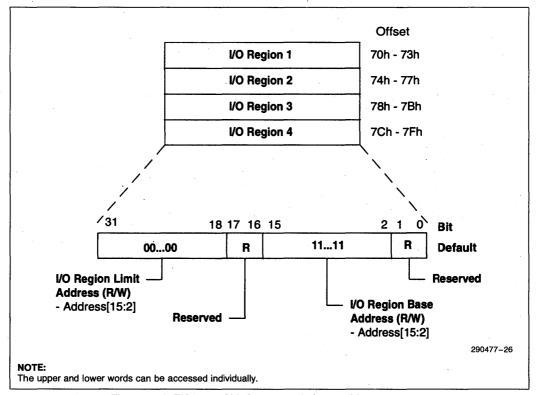

- Four Programmable PCI Memory Space Regions

- Four Programmable PCI I/O Space Regions

- Programmable Main Memory Address Decoding

- Main Memory Sizes up to 512 MBytes

- Access Attributes for 15 Memory Segments in First 1 MByte of Main Memory

- Programmable Main Memory Hole

- Integrated 16-Bit BIOS Timer

- 208-Pin QFP Package

- 5V CMOS Technology

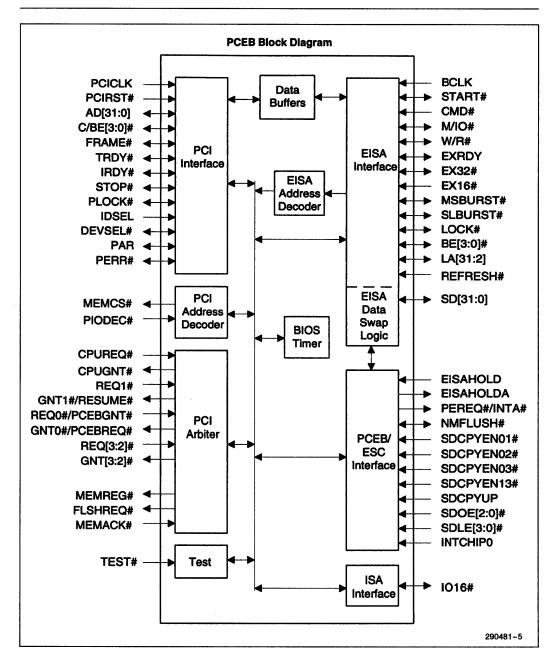

The 82375EB PCI-EISA Bridge (PCEB) provides the master/slave functions on both the Peripheral Component Interconnect (PCI) Local Bus and the EISA Bus. Functioning as a bridge between the PCI and EISA buses, the PCEB provides the address and data paths, bus controls, and bus protocol translation for PCI-to-EISA and EISA-to-PCI transfers. Extensive data buffering in both directions increases system performance by maximizing PCI and EISA Bus efficiency and allowing concurrency on the two buses. The PCEB's buffer management mechanism ensures data coherency. The PCEB integrates central bus control functions including a programmable bus arbiter for the PCI Bus and EISA data swap logic for the EISA Bus. Integrated system functions include PCI parity generation, system error reporting, and programmable PCI and EISA memory and I/O address space mapping and decoding. The PCEB also contains a BIOS Timer that can be used to implement timing loops. The PCEB is intended to be used with the EISA System Component (ESC) to provide an EISA I/O subsystem interface. intel.

## 82374EB EISA SYSTEM CONTROLLER (ESC)

- Integrates EISA Compatible Bus Controller

- Translates Cycles between EISA and ISA Bus

- Supports EISA Burst and Standard Cycles

- Supports ISA No Wait State Cycles

- Supports Byte Assembly/ Disassembly for 8-Bit, 16-Bit and 32-Bit Transfers

- Supports Bus Frequency up to 8.33 MHz

- Supports Eight EISA Slots

- Directly Drives Address, Data and Control Signals for Eight Slots

- Decodes Address for Eight Slot Specific AENs

- Provides Enhanced DMA Controller — Provides Scatter-Gather Function

- Supports Type A, Type B, Type C (Burst), and Compatible DMA Transfers

- Provides Seven Independently Programmable Channels

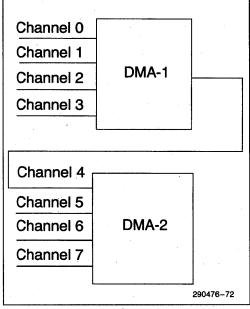

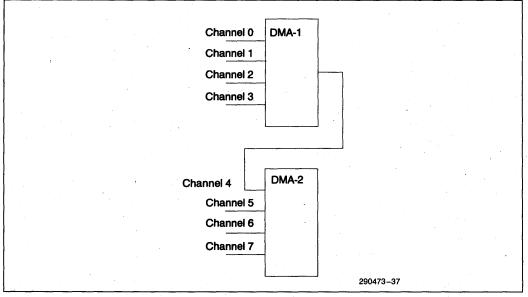

- Integrates Two 82C37A Compatible DMA Controllers

- Provides High Performance Arbitration

Supports Eight EISA Masters and PCEB

- Supports ISA Masters, DMA Channels, and Refresh

- Provides Programmable Arbitration Scheme for Fixed, Rotating, or Combination Priority

- Integrates Support Logic for X-Bus Peripherals and More

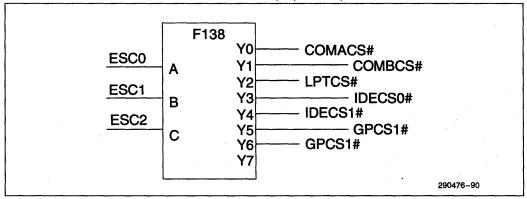

- Generates Chip Selects/Encoded Chip Selects for Floppy and Keyboard Controller, IDE, Parallel/Serial Ports, and General Purpose Peripherals

- Provides Interface for Real Time Clock

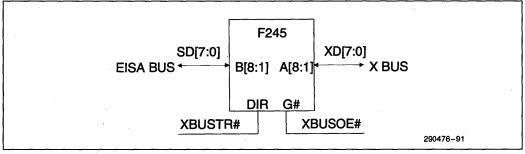

- Generates Control Signals for X-Bus Data Transceiver

- Integrates Port 92, Mouse Interrupt, and Coprocessor Error Reporting

- Integrates the Functionality of Two 82C59 Interrupt Controllers and Two 82C54 Timers

- Provides 14 Programmable Channels for Edge or Level Interrupts

- Provides 4 PCI Interrupts Routable to Any of 11 Interrupt Channels

- Supports Timer Function for Refresh Request, System Timer, Speaker Tone, Fail Safe Timer, and Periodic CPU Speed Control

- Generates Non-Maskable Interrupts (NMI)

- PCI System Errors

- PCI Parity Errors

- EISA Bus Parity Errors

- Fail Safe Timer

- Bus Timeout

- --- Via Software Control

- Provides BIOS Interface

- Supports 512 KBytes of Flash or EPROM BIOS on the X Bus

- Allows BIOS on PCI

- Supports Integrated VGA BIOS

- 208-Pin QFP Package

- 5V CMOS Technology

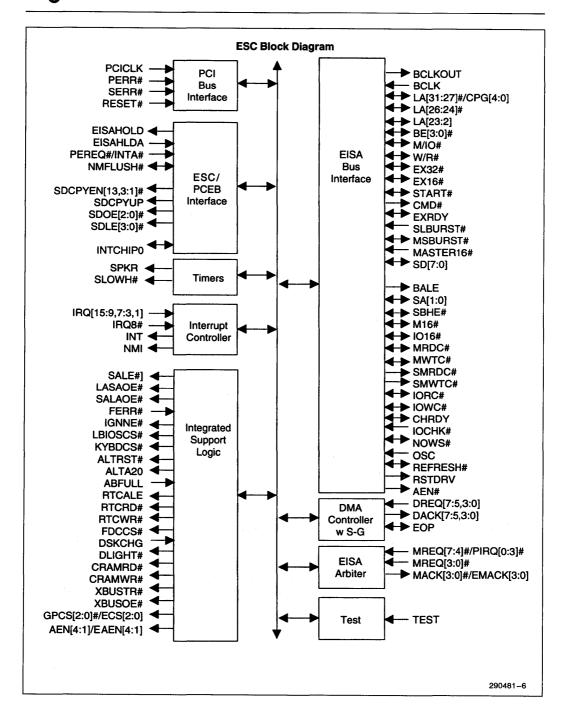

The 82374EB EISA System Component (ESC) provides all the EISA system compatible functions. The ESC, with the PCEB, provides all the functions to implement an EISA to PCI bridge and EISA I/O subsystem. The ESC integrates the common I/O functions found in today's EISA based PC systems. The ESC incorporates the logic for an EISA (master and slave) interface, EISA Bus Controller, enhanced seven channel DMA controller with Scatter-Gather support, EISA arbitration, 14 channel interrupt controller, five programmable timer/counters, and non-maskable interrupt (NMI) control logic. The ESC also integrates support logic to decode peripheral devices such as the Flash BIOS, Real Time Clock, Keyboard/Mouse Controller, Floppy Controller, two Serial Ports, one Parallel Port, and IDE Hard Disk Drive.

int\_l.

# intel

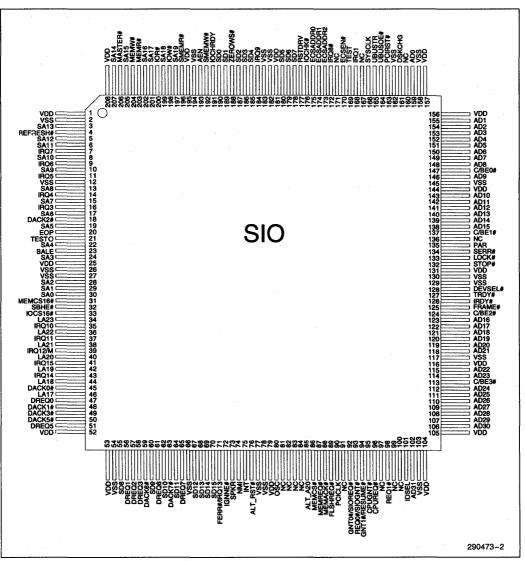

## 82378IB SYSTEM I/O (SIO)

- Provides the Bridge between the PCI Bus and ISA Bus

- 100% PCI and ISA Compatible

- PCI and ISA Master/Slave Interface - Directly Drives 10 PCI Loads and 6

- ISA Slots — Supports PCI at 25 MHz and

- 33.33 MHz — Supports ISA from 6 MHz to 8.33 MHz

- Enhanced DMA Functions

- Scatter/Gather

- Fast DMA Type A, B, and F

- Compatible DMA Transfers

- 32-Bit Addressability

- Seven Independently Programmable Channels

- Functionality of Two 82C37A DMA Controllers

- Integrated Data Buffers to Improve Performance

- 32-Bit Posted Memory Write Buffer to ISA

- Integrated 16-Bit BIOS Timer

- Arbitration for PCI Devices

- Four PCI Masters Are Supported

- Fixed, Rotating, or a Combination of the Two

- Arbitration for ISA Devices

ISA Masters

- DMA and Refresh

- Utility Bus (X-Bus) Peripheral Support

- Provides Chip Select Decode

- Controls Lower X-Bus Data Byte Transceiver

- Integrates Port 92, Mouse Interrupt, Coprocessor Error Reporting

- Integrates the Functionality of One 82C54 Timer

- System Timer

- Refresh Request

- Speaker Tone Output

- Integrates the Functionality of Two 82C59 Interrupt Controllers

— 14 Interrupts Supported

- Non-Maskable Interrupts (NMI)

PCI System Errors

ISA Parity Errors

- 208-Pin QFP Package

- 5V CMOS Technology

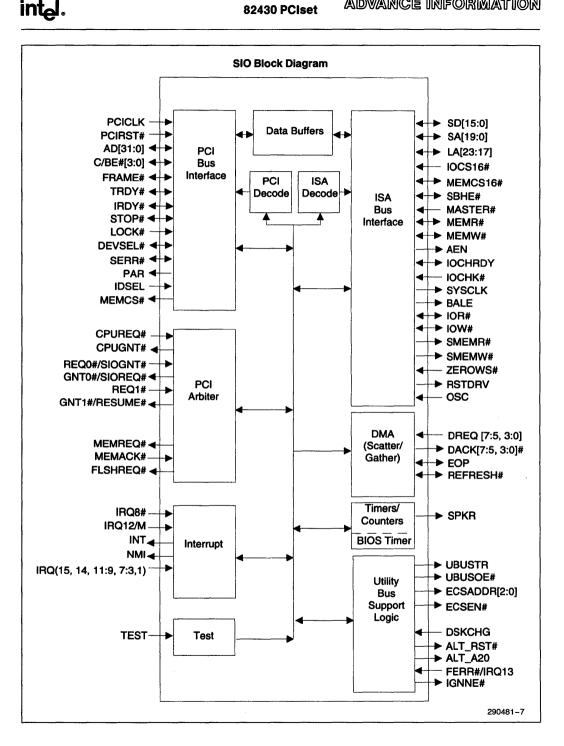

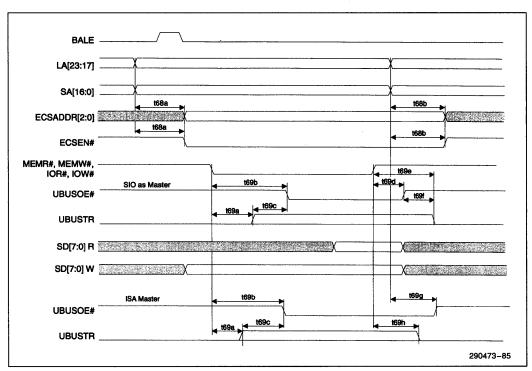

The 82378IB System I/O (SIO) component provides the bridge between the PCI local bus and the ISA expansion bus. The SIO also integrates many of the common I/O functions found in today's ISA based PC systems. The SIO incorporates the logic for a PCI interface (master and slave), ISA interface (master and slave), enhanced seven channel DMA controller that supports fast DMA transfers and Scatter/Gather, data buffers to isolate the PCI bus from the ISA bus and to enhance performance, PCI and ISA arbitration, 14 level interrupt controller, a 16-bit BIOS timer, three programmable timer/counters, and non-maskable-interrupt (NMI) control logic. The SIO also provides decode for peripheral devices such as the Flash BIOS, Real Time Clock, Keyboard/Mouse Controller, Floppy Controller, two Serial Ports, one Parallel Port, and IDE Hard Disk Drive.

ADVANCE INFORMATION

82430 PCIset

## 82374EB EISA SYSTEM COMPONENT (ESC)

- Integrates EISA Compatible Bus Controller

- Translates Cycles between EISA and ISA Bus

- Supports EISA Burst and Standard Cycles

- Supports ISA No Wait State Cycles

- Supports Byte Assembly/ Disassembly for 8-, 16- and 32-Bit Transfers

- Supports Bus Frequency up to 8.33 MHz

- Supports Eight EISA slots

- Directly Drives Address, Data and Control Signals for Eight Slots

- Decodes Address for Eight Slot Specific AENs

- Provides Enhanced DMA Controller

- Provides Scatter-Gather Function

- Supports Type A, Type B, Type C (Burst), and Compatible DMA Transfers

- --- Provides Seven Independently Programmable Channels

- Integrates Two 82C37A Compatible DMA Controllers

- Provides High Performance Arbitration

- --- Supports Eight EISA Masters and PCEB

- Supports ISA Masters, DMA Channels, and Refresh

- Provides Programmable Arbitration Scheme for Fixed, Rotating, or Combination Priority

- Integrates Support Logic for X-Bus Peripheral and More

- Generates Chip Selects/Encoded Chip Selects for Floppy and Keyboard Controller, IDE, Parallel/ Serial Ports, and General Purpose Peripherals

- Provides Interface for Real Time Clock

- Generates Control Signals for X-Bus Data Transceiver

- Integrates Port 92, Mouse Interrupt, and Coprocessor Error Reporting

- Integrates the Functionality of two 82C59 Interrupt Controllers and two 82C54 Timers

- Provides 14 Programmable Channels for Edge or Level Interrupts

- Provides 4 PCI Interrupts Routible to Any of 11 Interrupt Channels

- Supports Timer Function for Refresh Request, System Timer, Speaker Tone, Fail Safe Timer, and Periodic CPU Speed Control

- Generates Non-Maskable Interrupts (NMI)

- PCI System Errors

- PCI Parity Errors

- EISA Bus Parity Errors

- Fail Safe Timer

- Bus Timeout

- Via Software Control

- Provides BIOS Interface

- Supports 512 Kbytes of Flash or EPROM BIOS on the X-Bus

- Allows BIOS on PCI

- Supports Integrated VGA BIOS

- 208-Pin QFP Package

The 82374EB EISA System Component (ESC) provides all the EISA system compatible functions. The ESC with the PCEB provide all the functions to implement an EISA to PCI bridge and EISA I/O subsystem. The ESC integrates the common I/O functions found in today's EISA based PC systems. The ESC incorporates the logic for a EISA (master and slave) interface, EISA Bus Controller, enhanced seven channel DMA controller with Scatter-Gather support, EISA arbitration, 14 channel interrupt controller, five programmable timer/counters, and non-maskable-interrupt (NMI) control logic. The ESC also integrates support logic to decode peripheral devices such as the Flash BIOS, Real Time Clock, Keyboard/Mouse Controller, Floppy Controller, two Serial Ports, one Parallel Port, and IDE Hard Disk Drive.

Manufactured and tested for Intel Corporation by LSI Logic in accordance with LSI's internal standards. Windows® is a registered trademark of Microsoft Corporation. Win-NT™ is trademarked by Microsoft Corporation.

# 82374EB EISA System Component

## CONTENTS

| 1.0 ARCHITECTURAL OVERVIEW 23                          | 3 |

|--------------------------------------------------------|---|

| 1.1 PCEB Overview                                      | 5 |

| 1.2 ESC Overview                                       | 7 |

| 2.0 SIGNAL DESCRIPTION 27                              | 7 |

| 2.1 PCI Local Bus Interface Signals 28                 | 8 |

| 2.2 EISA Bus Interface Signals 29                      |   |

| 2.3 ISA Bus Signals                                    |   |

| 2.4 DMA Signal Description                             |   |

| 2.5 EISA Arbitration Signals                           |   |

| 2.6 Timer Unit Signal 36                               |   |

| 2.7 Interrupt Controller Signals 36                    |   |

| 2.8 ESC/PCEB Interface Signals 37                      | 7 |

| 2.8.1 Arbitration and Interrupt<br>Acknowledge Control | 7 |

| 2.8.2 PCEB Buffer Coherency                            | - |

| Control                                                |   |

| 2.9 Integrated Logic Signals                           |   |

| 2.9.1 EISA Address Buffer                              |   |

| Control                                                | 9 |

| 2.9.2 Coprocessor Interface 39                         |   |

| 2.9.3 BIOS Interface                                   | 9 |

| 2.9.4 Keyboard Controller<br>Interface 40              | 0 |

| 2.9.5 Real Time Clock Interface 40                     | 0 |

| 2.9.6 Floppy Disk Controller<br>Interface 4            | 1 |

| 2.9.7 Configuration RAM                                |   |

| Interface 4<br>2.9.8 X-Bus Control and General         | ٦ |

| Purpose Decode                                         | 2 |

| 2.10 Testing4                                          |   |

| 3.0 ESC REGISTER DESCRIPTION 44                        | 3 |

| 3.1 ESC Configuration Registers 4                      | 3 |

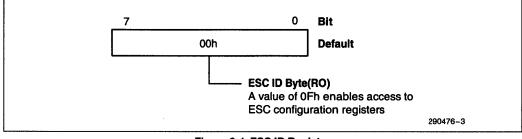

| 3.1.1 ESCID—ESC ID Register 4                          | 3 |

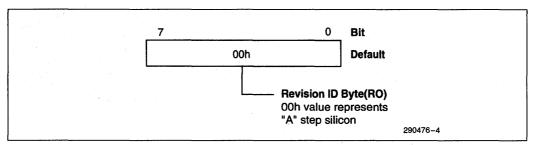

| 3.1.2 RID—Revision ID Register 4                       |   |

| 3.1.3 MS—MODE Select<br>Register                       | 5 |

| 3.1.4 BIOSCSA—BIOS Chip Select                         |   |

| Register 4                                             | 6 |

| PAGE     | CONTENTS PAGE                                                               |

|----------|-----------------------------------------------------------------------------|

| 23       | 3.1.5 BIOSCSB—BIOS Chip Select<br>Register                                  |

| 25<br>27 | 3.1.6 CLKDIV—EISA Clock Divisor<br>Register                                 |

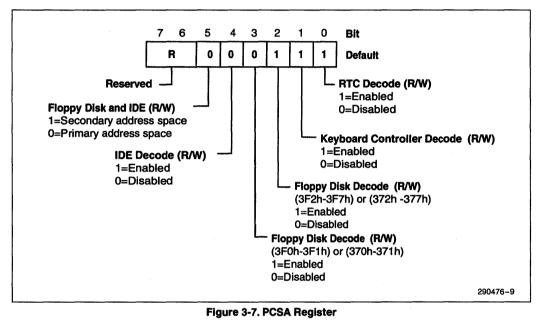

| 27       | 3.1.7 PCSA—Peripheral Chip Select                                           |

| 28       | A Register                                                                  |

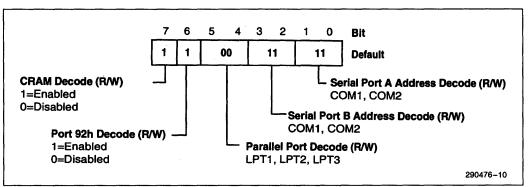

| 29       | 3.1.8 PCSB—Peripheral Chip Select<br>B Register 50                          |

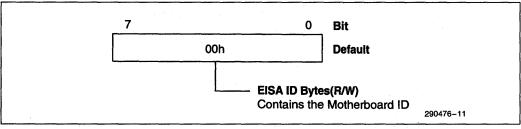

| 31       | 3.1.9 EISAID[4:1]—EISA ID<br>Registers                                      |

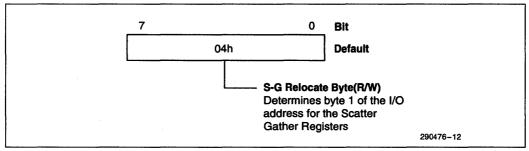

| 34       | 3.1.10 SGRBA—Scatter-Gather                                                 |

| 35<br>36 | Relocate Base Address<br>Register53                                         |

| 36       | 3.1.11 PIRQ[0:3] #—PIRQ Route                                               |

| 37       | Control Registers 54                                                        |

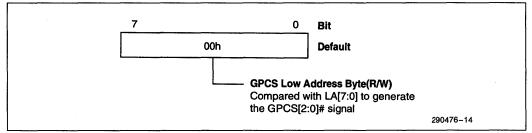

| 37       | 3.1.12 GPCSLA[2:0]—General<br>Purpose Chip Select Low<br>Address Register   |

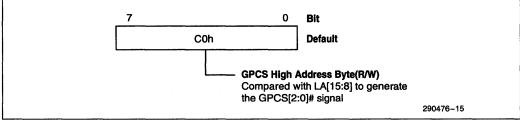

| 37       | 3.1.13 GPCSHA[2:0]—General<br>Purpose Chip Select High<br>Address Register  |

| 38       | Address Register                                                            |

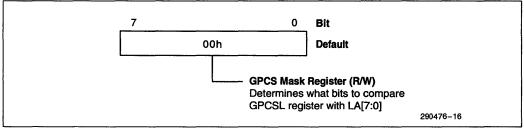

| 39       | 3.1.14 GPCSM[2:0]—General<br>Purpose Chip Select Mask<br>Register           |

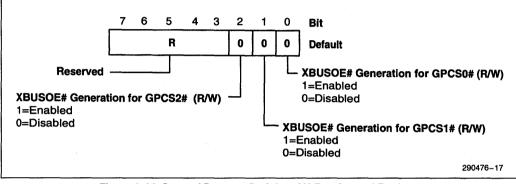

| 39       | 3.1.15 GPXBC—General Purpose                                                |

| 39<br>39 | Peripheral X-Bus Control<br>Register                                        |

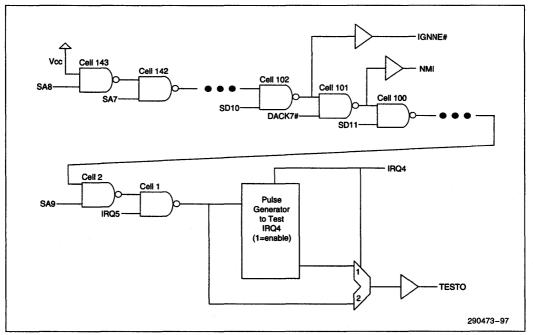

|          | 3.1.16 Test Control Register                                                |

| 40       | 3.2 DMA Register Description 59                                             |

| 40       | 3.2.1 DCOM—Command<br>Register                                              |

| 41       | 3.2.2 DCM—DMA Channel Mode<br>Register                                      |

| 41       | 3.2.3 DCEM—DMA Channel<br>Extended Mode Register                            |

| 42       | 3.2.4 DR—DMA Request                                                        |

| 42       | <b>Register</b> 65                                                          |

| 43       | 3.2.5 Mask Register—Write Single<br>Mask Bit                                |

| 43       | 3.2.6 Mask Register—Write All                                               |

| 43       | Mask Register Bits 67                                                       |

| 44       | 3.2.7 DS—DMA Status Register 68                                             |

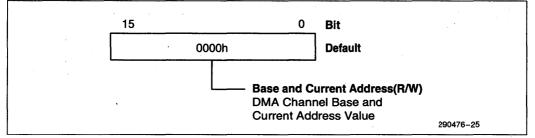

| 45<br>ct | 3.2.8 DMA Base and Current<br>Address Register (8237<br>Compatible Segment) |

|          |                                                                             |

## CONTENTS

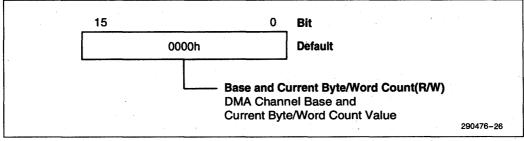

| 3.2.9 DMA Base and Current Byte/<br>Word Count Register (8237<br>Compatible Segment)                        |

|-------------------------------------------------------------------------------------------------------------|

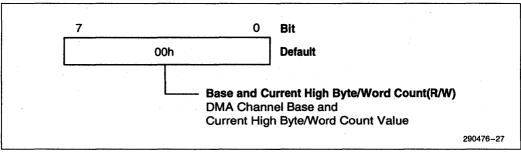

| 3.2.10 DMA Base and Current High<br>Byte/Word Count Register DMA<br>Base High Byte/Word Count<br>Register71 |

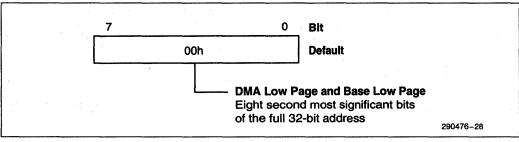

| 3.2.11 DMA Memory Low Page<br>Register DMA Memory Base Low<br>Page Register72                               |

| 3.2.12 DMA Page Register                                                                                    |

| 3.2.13 DMA Low Page Refresh<br>Register74                                                                   |

| 3.2.14 DMA Memory High Page<br>Register DMA Memory Base High<br>Page Register                               |

| 3.2.15 DMA High Page Register<br>Refresh                                                                    |

| 3.2.16 Stop Registers                                                                                       |

| 3.2.17 Chaining Mode Register 78                                                                            |

| 3.2.18 Chaining Mode Status<br>Register                                                                     |

| 3.2.19 Channel Interrupt Status<br>Register                                                                 |

| 3.2.20 Chain Buffer Expiration<br>Control Register                                                          |

| 3.2.21 Scatter-Gather Command<br>Register                                                                   |

| 3.2.22 Scatter-Gather Status<br>Register                                                                    |

| 3.2.23 Scatter-Gather Descriptor<br>Table Pointer Register                                                  |

| 3.2.24 Clear Byte Pointer Flip-Flop<br>Register                                                             |

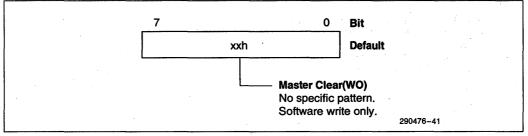

| 3.2.25 DMC—DMA Master Clear<br>Register                                                                     |

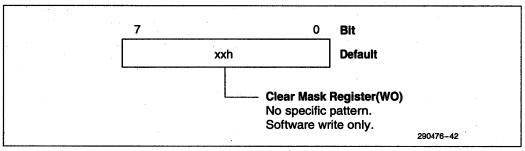

| 3.2.26 DCM—DMA Clear Mask<br>Register                                                                       |

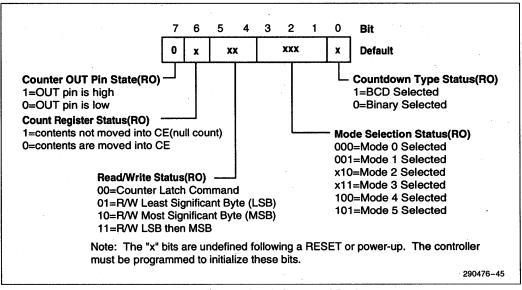

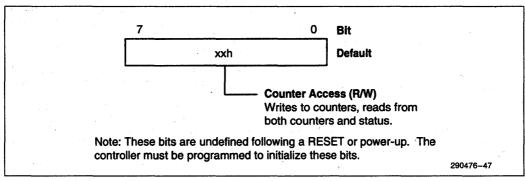

| 3.3 Timer Unit Registers                                                                                    |

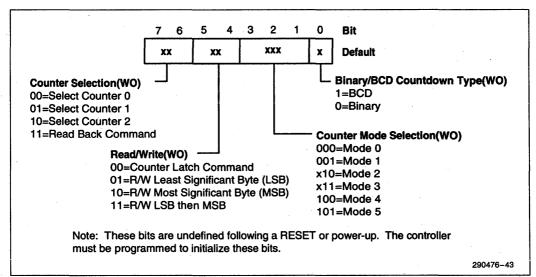

| 3.3.1 TCW—Timer Control Word<br>Register                                                                    |

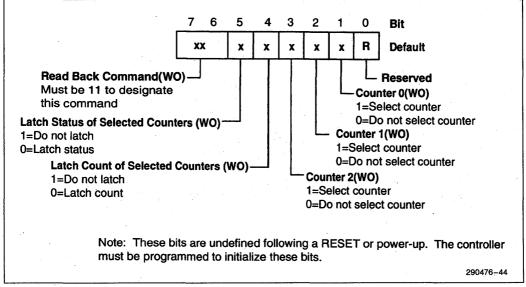

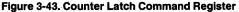

| 3.3.2 Timer Read Back Command<br>Register                                                                   |

| 3.3.3 Counter Latch Command<br>Register                                                                     |

## CONTENTS

PAGE

| 0.0.4 Timer Otatus Dute Formet                          |      |

|---------------------------------------------------------|------|

| 3.3.4 Timer Status Byte Format<br>Register              | . 95 |

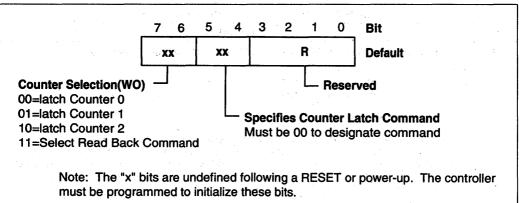

| 3.3.5 Counter Access Ports                              | . 97 |

| 3.4 Interrupt Controller Registers                      | . 98 |

| 3.4.1 ICW1—Initialization Command<br>Word 1             | . 98 |

| 3.4.2 ICW2—Initialization Command<br>Word 2             |      |

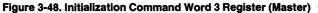

| 3.4.3 ICW3—Initialization Command<br>Word 3 (Master)    | 100  |

| 3.4.4 ICW3—Initialization Command<br>Word 3 (Slave)     | 102  |

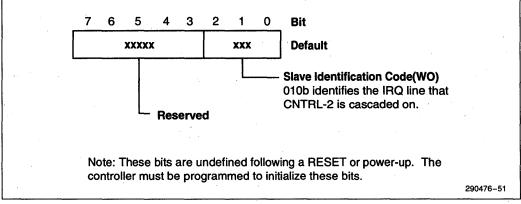

| 3.4.5 ICW4—Initialization Command<br>Word 4             | 103  |

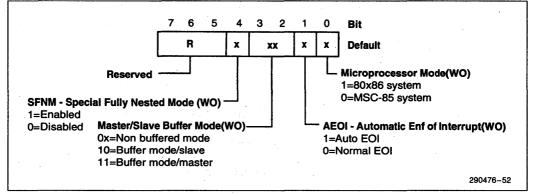

| 3.4.6 OCW1—Operation Control<br>Word 1                  | 104  |

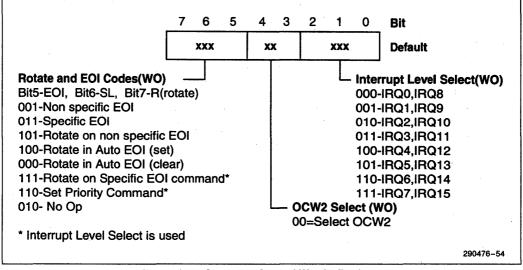

| 3.4.7 OCW2—Operation Control<br>Word 2                  | 105  |

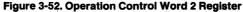

| 3.4.8 OCW3—Operation Control<br>Word 3                  | 106  |

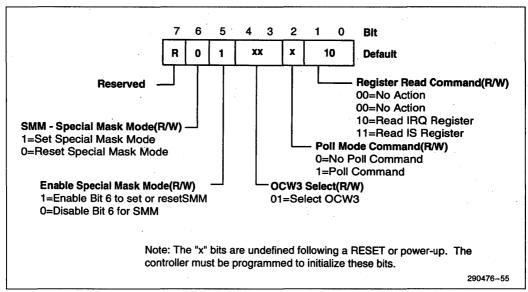

| 3.4.9 Edge/Level Control<br>Register                    | 108  |

| 3.4.10 NMI Status and Control<br>Register               | 109  |

| 3.4.11 NMI Control and Real-Time<br>Clock Address       | 111  |

| 3.4.12 NMI Extended Status and<br>Control Register      |      |

| 3.4.13 Software NMI Generation                          | 114  |

| 3.5 EISA Configuration, Floppy<br>Support, and Port 92h | 115  |

| 3.5.1 Configuration RAM Page<br>Register                | 115  |

| 3.5.2 Digital Output Register                           |      |

| 3.5.3 Port 92 Register                                  |      |

| 3.5.4 Last EISA Bus Master<br>Granted Register          |      |

| 4.0 ADDRESS DECODING                                    |      |

| 4.1 BIOS Memory Space                                   |      |

| 4.2 I/O Addresses Contained within                      |      |

| the ESC                                                 |      |

| 4.3 Configuration Addresses                             |      |

| 4.4 X-Bus Peripherals                                   | 129  |

PAGE

## **CONTENTS**

PAGE

| 5.0 EISA CONTROLLER FUNCTIONAL<br>DESCRIPTION     | 31 |

|---------------------------------------------------|----|

| 5.1 Overview                                      |    |

| 5.2 Clock Generation1                             | 31 |

| 5.2.1 Clock Stretching1                           | 31 |

| 5.3 EISA Master Cycles 1                          | 32 |

| 5.3.1 EISA Master to 32 EISA<br>Slave 1           | 32 |

| 5.3.2 EISA Master to 16-Bit ISA<br>Slave 1        | 34 |

| 5.3.3 EISA Master to 8-Bit EISA/<br>ISA Slaves 1: | 34 |

| 5.3.4 EISA Master Back-Off 1                      | 35 |

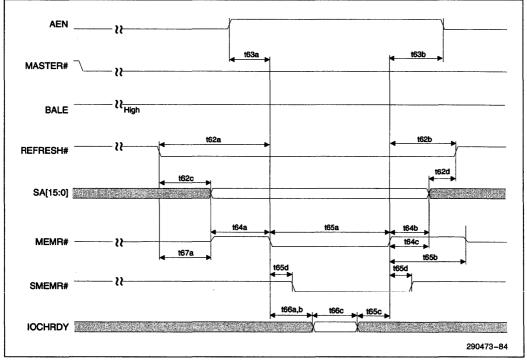

| 5.4 ISA Master Cycles 13                          | 36 |

| 5.4.1 ISA Master to 32-Bit/16-Bit<br>EISA Slave1  | 36 |

| 5.4.2 ISA Master to 16-Bit ISA<br>Slave 1         | 36 |

| 5.4.3 ISA Master to 8-Bit EISA/ISA<br>Slave 1     | 37 |

| 5.4.4 ISA Wait State Generation 1                 | 37 |

| 5.5 Mis-Match Cycles 13                           | 38 |

| 5.6 Data Swap Buffer Control Logic 1              | 39 |

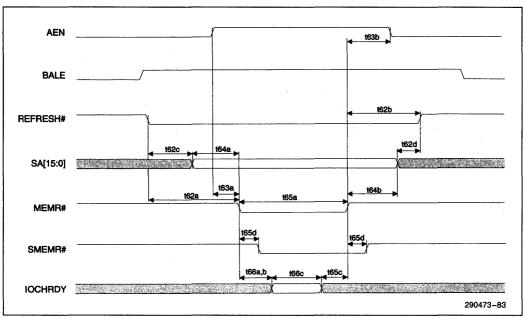

| 5.7 Servicing DMA Cycles 1                        | 39 |

| 5.8 Refresh Cycles 18                             | 39 |

| 5.9 EISA Slot Support 14                          | 40 |

| 5.9.1 AEN Generation14                            | 40 |

| 5.9.2 MACKx# Generation1                          | 41 |

| 6.0 DMA CONTROLLER                                | 42 |

| 6.1 DMA Controller Overview14                     | 42 |

| 6.2 DMA Transfer Modes 14                         | 42 |

| 6.2.1 Single Transfer Mode1                       | 43 |

| 6.2.2 Block Transfer Mode1                        | 43 |

| 6.2.3 Demand Transfer Mode 1                      | 43 |

| 6.2.4 Cascade Mode 1                              | 43 |

| 6.3 DMA Transfer Types1                           | 43 |

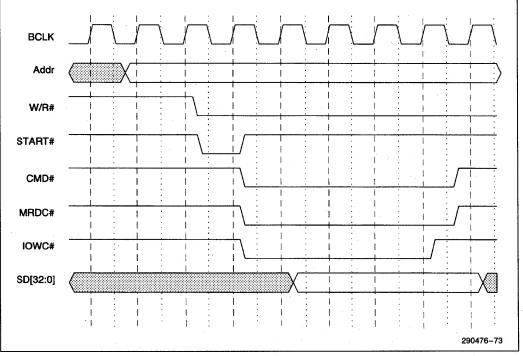

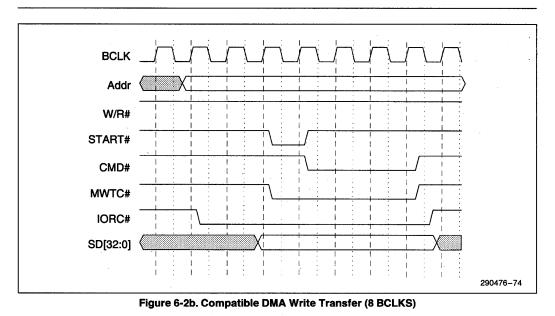

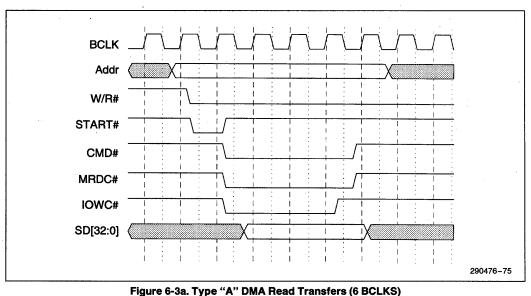

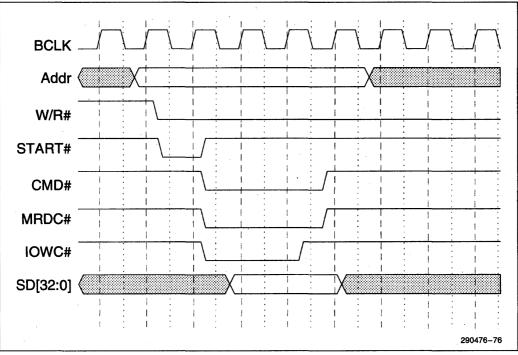

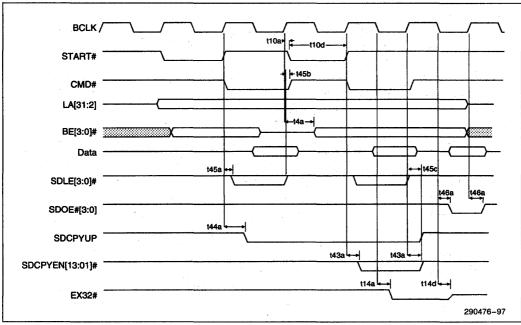

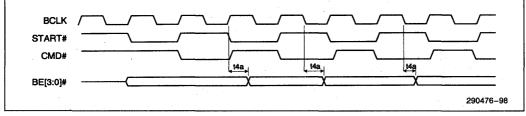

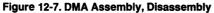

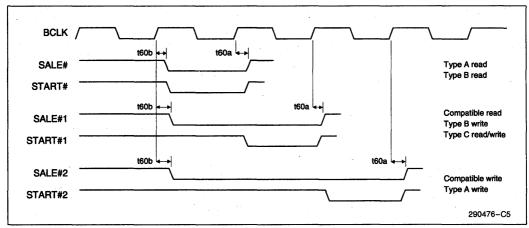

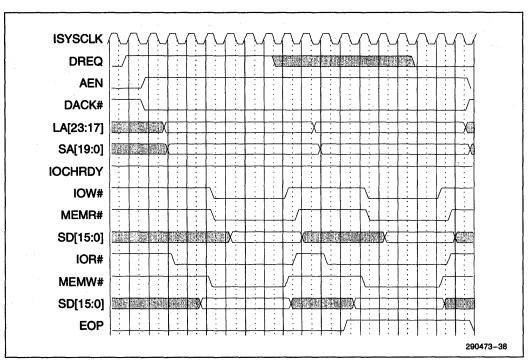

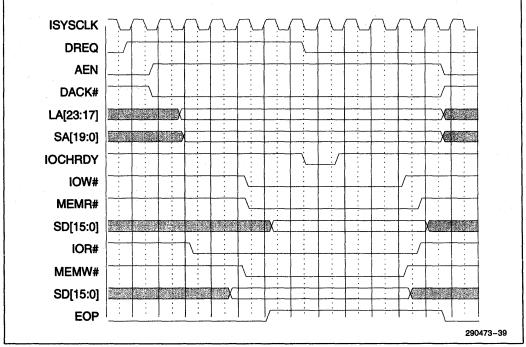

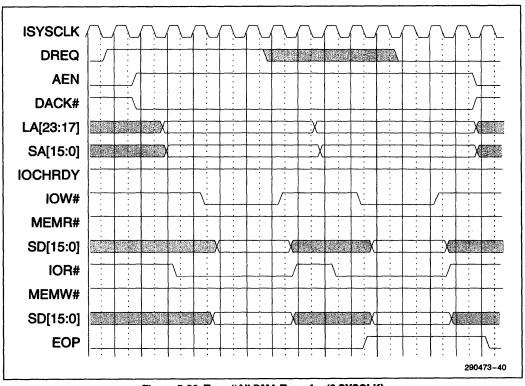

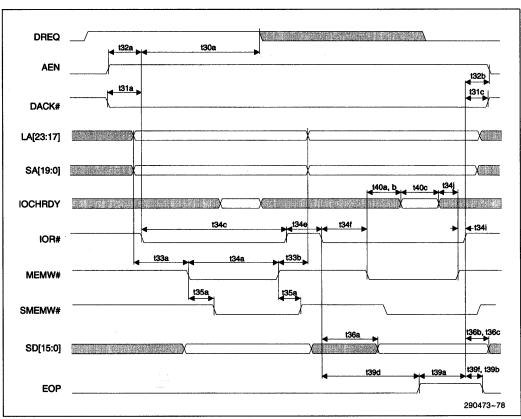

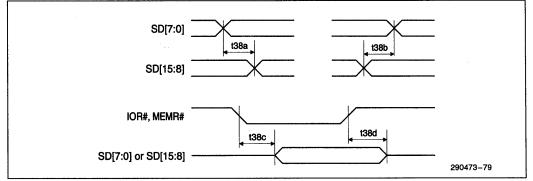

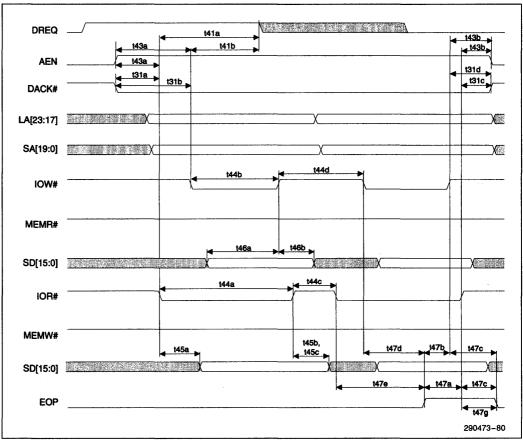

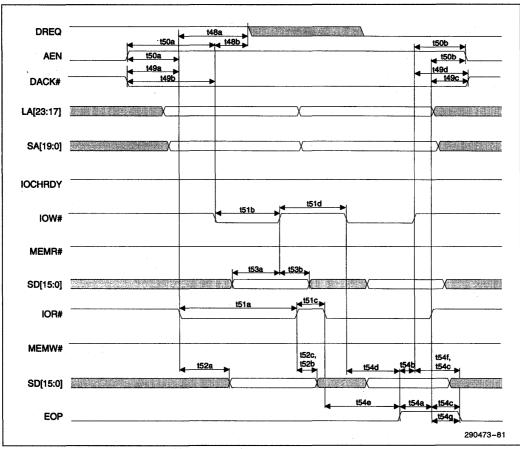

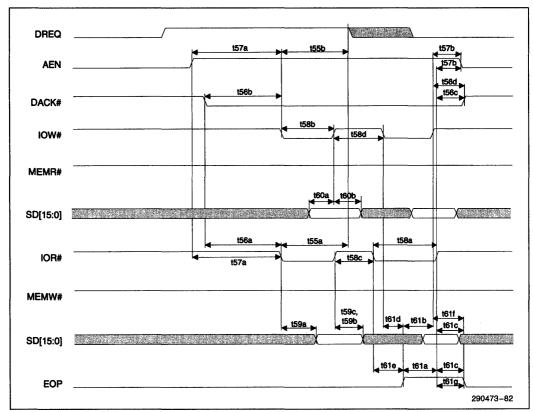

| 6.4 DMA Timing 1                                  | 44 |

| 6.4.1 Compatible Timings 1                        |    |

| 6.4.2 Type "A" Timing 1                           | 45 |

| 6.4.3 Type "B" Timing 1                           | 46 |

| 6.4.4 Type "C" (Burst) Timing 1                   | 47 |

| 6.5 Channel Priority1                             | 48 |

## CONTENTS

| CONTENTS PAG                                                                | λĒ |

|-----------------------------------------------------------------------------|----|

| 6.6 Scatter-Gather Functional                                               |    |

| Description 1<br>6.7 Register Functionality 1                               | 48 |

|                                                                             |    |

| 6.7.1 Address Compatibility<br>Mode1                                        | 50 |

| 6.7.2 Summary of the DMA Transfer<br>Sizes 1                                | 50 |

| 6.7.3 Address Shifting When<br>Programmed for 16-Bit I/O Count<br>by Words1 | 51 |

| 6.7.4 Stop Registers (Ring Buffer<br>Data Structure)1                       | 51 |

| 6.7.5 Buffer Chaining Mode and<br>Status Registers                          | 52 |

| 6.7.6 Autoinitialize 1                                                      |    |

| 6.8 Software Commands 1                                                     | 52 |

| 6.8.1 Clear Byte Pointer Flip-Flop 1                                        | 52 |

| 6.8.2 DMA Master Clear 1                                                    | 53 |

| 6.8.3 Clear Mask Register 1                                                 | 53 |

| 6.9 Terminal Count/EOP Summary 1                                            | 53 |

| 6.10 Buffer Chaining 1                                                      | 53 |

| 6.11 Refresh Unit 1                                                         | 54 |

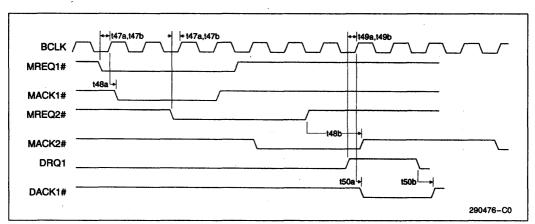

| 7.0 EISA BUS ARBITRATION 1                                                  | 54 |

| 7.1 Arbitration Priority 1                                                  |    |

| 7.2 Preemption1                                                             | 55 |

| 7.2.1 PCEB EISA Bus Acquisition<br>and PCEB Preemption                      | 55 |

| 7.2.2 EISA Master Preemption 1                                              | 56 |

| 7.2.3 DMA Preemption 1                                                      | 56 |

| 7.3 Slave Timeouts 1                                                        | 56 |

| 7.4 Arbitration During Non-Maskable<br>Interrupts1                          | 57 |

| 8.0 INTERVAL TIMERS 1                                                       | 57 |

| 8.1 Interval Timer Address Map 1                                            |    |

| 8.2 Programming the Interval Timer 1                                        |    |

| 9.0 INTERRUPT CONTROLLER 1                                                  | 61 |

| 9.1 Interrupt Controller Internal<br>Registers1                             | 63 |

| 9.2 Interrupt Sequence 1                                                    |    |

| 9.3 80x86 Mode 1                                                            |    |

| 9.4 ESC Interrupt Acknowledge Cycle1                                        | 64 |

## CONTENTS

| 9.5 Programming the Interrupt<br>Controller               |

|-----------------------------------------------------------|

| 9.6 End-of-Interrupt Operation 166                        |

| 9.6.1 End of Interrupt (EOI) 166                          |

| 9.6.2 Automatic End of Interrupt<br>(AEOI) Mode           |

| 9.7 Modes of Operation 167                                |

| 9.7.1 Fully Nested Mode 167                               |

| 9.7.2 The Special Fully Nested<br>Mode167                 |

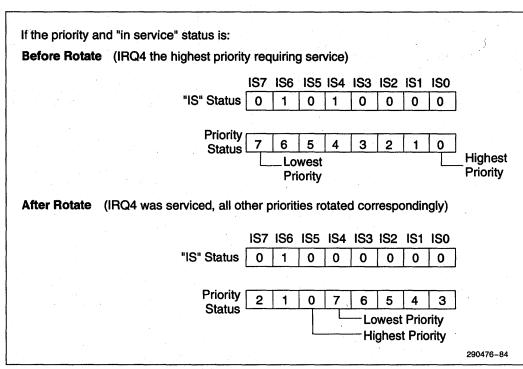

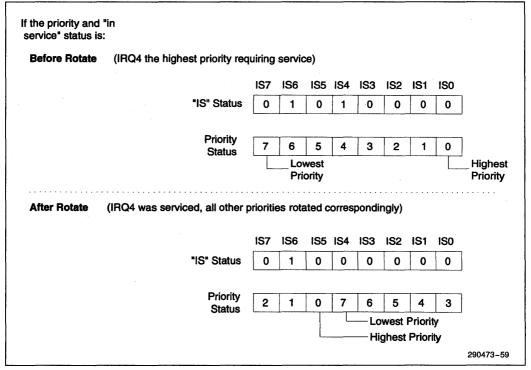

| 9.7.3 Automatic Rotation (Equal<br>Priority Devices)      |

| 9.7.4 Specific Rotation (Specific<br>Priority)            |

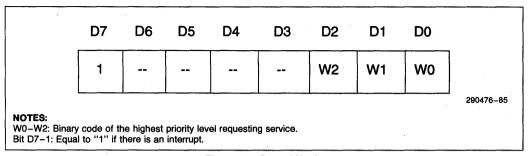

| 9.7.5 Poll Command 168                                    |

| 9.7.6 Cascade Mode 169                                    |

| 9.7.7 Edge and Level Triggered<br>Modes 169               |

| 9.8 Register Functionality                                |

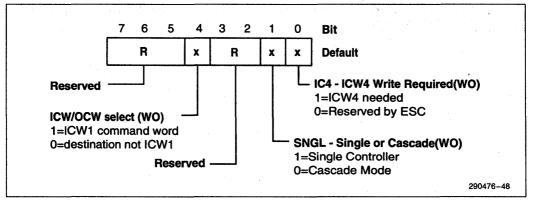

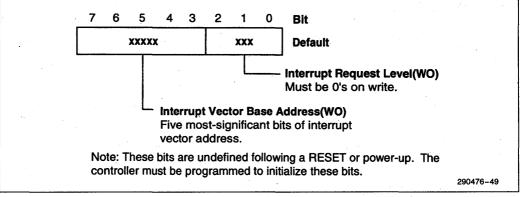

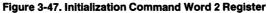

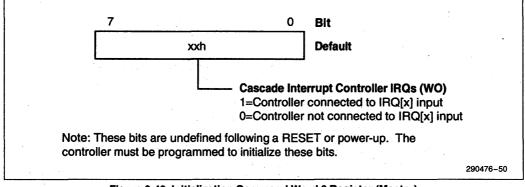

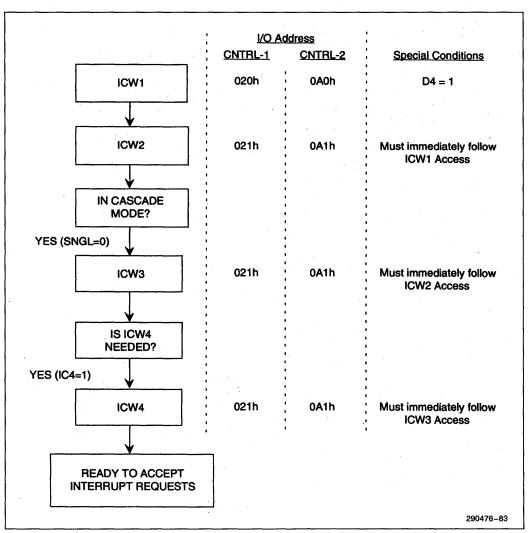

| 9.8.1 Initialization Command<br>Words 170                 |

| 9.8.2 Operation Control Words<br>(OCWS)                   |

| 9.9 Interrupt Masks 170                                   |

| 9.9.1 Masking on an Individual<br>Interrupt Request Basis |

| 9.9.2 Special Mask Mode 170                               |

| 9.10 Reading the Interrupt Controller<br>Status           |

| 9.11 Non-Maskable Interrupt (NMI) 171                     |

| <b>10.0 PCEB/ESC INTERFACE</b>                            |

| 10.1 Arbitration Control Signals 173                      |

| 10.2 EISA Data Swap Buffer Control                        |

| Signals                                                   |

## CONTENTS

PAGE

| 10.3 Interrupt Acknowledge Control 17       |

|---------------------------------------------|

| 11.0 INTEGRATED SUPPORT LOGIC 17            |

| 11.1 EISA Address Buffer Control 17         |

| 11.2 Coprocessor Interface                  |

| 11.3 BIOS Interface 170                     |

| 11.4 Keyboard Controller Interface 17       |

| 11.5 Real Time Clock 17                     |

| 11.6 Floppy Disk Control Interface 17       |

| 11.7 Configuration RAM Interface 17         |

| 11.8 General Purpose Peripherals,           |

| IDE, Parallel Port, and Serial Port         |

| 11.9 X-Bus Control and General              |

| Purpose Decode 179                          |

| 12.0 ELECTRICAL                             |

| CHARACTERISTICS 180                         |

| 12.1 Maximum Ratings 18                     |

| 12.2 D.C. Characteristics                   |

| 12.2.1 Junction Temperature                 |

| Specifications                              |

| Specifications                              |

| 12.2.3 PCI Local Bus D.C.                   |

| Specifications                              |

| 12.3 A.C. Characteristics                   |

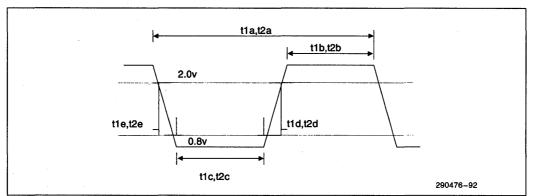

| 12.3.1 Clock Signals A.C.<br>Specifications |

| 12.3.2 A.C. Specifications                  |

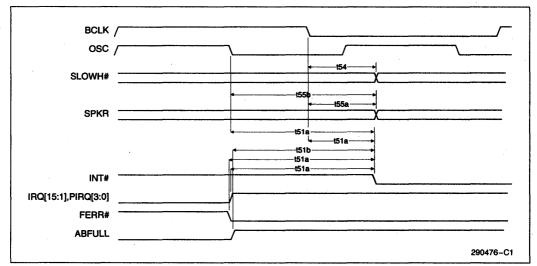

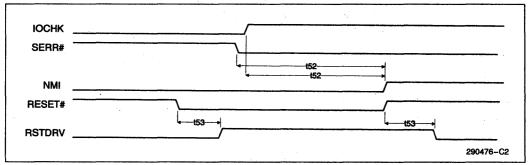

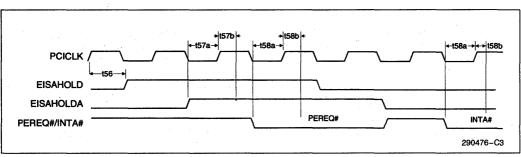

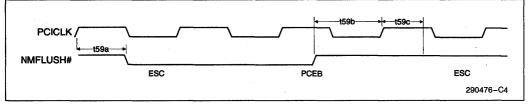

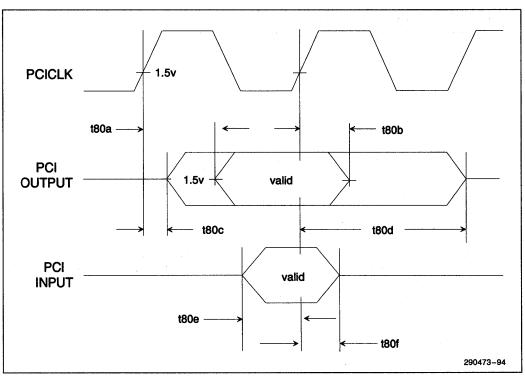

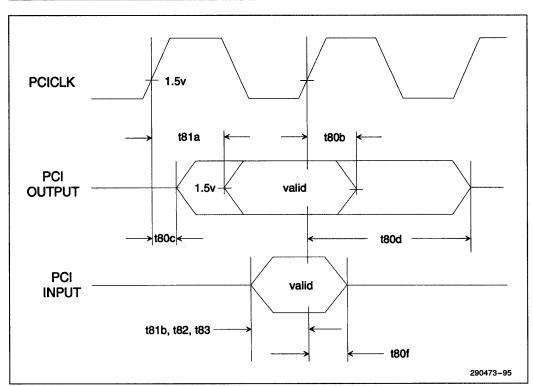

| 12.3.3 A.C. Timing Waveforms 19/            |

| · ·                                         |

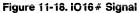

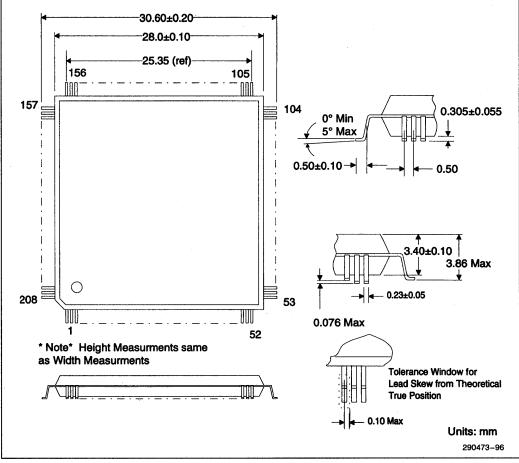

| 13.0 PINOUT AND PACKAGE<br>INFORMATION      |

|                                             |

PAGE

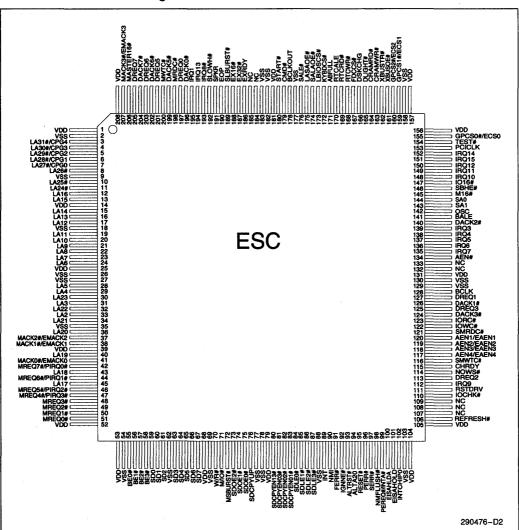

| 13.1 Pinout and Pin Assignment | <br>204 |

|--------------------------------|---------|

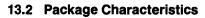

| 13.2 Package Characteristics   | <br>209 |

intel.

### **1.0 ARCHITECTURAL OVERVIEW**

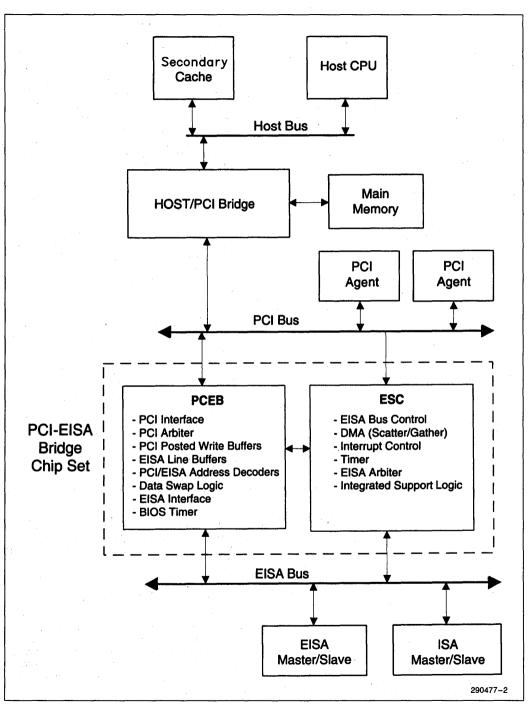

The PCI-EISA bridge chip set provides an I/O subsystem core for the next generation of high-performance personal computers (e.g., those based on the Intel486™ or Pentium™ CPU). System designers can take advantage of the power of the PCI (Peripheral Component Interconnect) for the local I/O bus while maintaining access to the large base of EISA and ISA expansion cards, and corresponding software applications. Extensive buffering and buffer management within the PCI-EISA bridge ensures maximum efficiency in both bus environments.

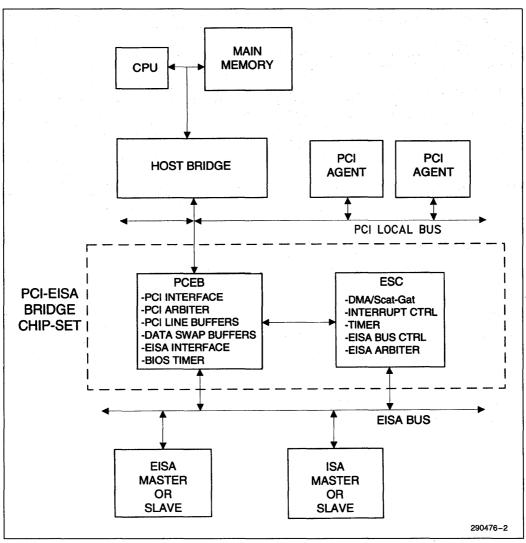

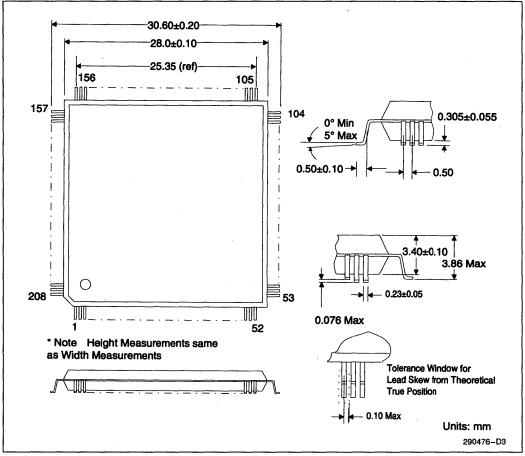

The chip set consists of two components—the 82375EB, PCI-EISA Bridge (PCEB) and the 82374EB, EISA System Component (ESC). These components work in tandem to provide an EISA I/O subsystem interface for personal computer platforms based on the PCI standard. This section provides an overview of the PCI and EISA Bus hierarchy followed by an overview of the PCEB and ESC components.

#### **Bus Hierarchy—Concurrent Operations**

Figure 1-0 shows a block diagram of a typical system using the PCI-EISA Bridge chip set. The system contains three levels of buses structured in the following hierarchy:

- Host Bus as the execution bus

- PCI Local Bus as a primary I/O bus

- EISA Bus as a secondary I/O bus

This bus hierarchy allows concurrency for simultaneous operations on all three bus environments. Data buffering permits concurrency for operations that crossover into another bus environment. For example, a PCI device could post data into the PCEB, permitting the PCI Local Bus transaction to complete in a minimum time and freeing up the PCI Local Bus for further transactions. The PCI device does not have to wait for the transfer to complete to its final destination. Meanwhile, any ongoing EISA Bus transactions are permitted to complete. The posted data is then transferred to its EISA Bus destination when the EISA Bus is available. The PCI-EISA Bridge chip set implements extensive buffering for PCI-to-EISA and EISA-to-PCI bus transactions. In addition to concurrency for the operations that cross bus environments, data buffering allows the fastest operations within a particular bus environment (via PCI burst transfers and EISA burst transfers).

The PCI local bus with 132 MByte/sec and EISA with 33 MByte/sec peak data transfer rate represent bus environments with significantly different bandwidths. Without buffering, transfers that cross the single bus environment are performed at the speed of the slower bus. Data buffers provide a mechanism for data rate adoption so that the operation of the fast bus environment (PCI), i.e., usable bandwidth, is not significantly impacted by the slower bus environment (EISA).

int\_.

Figure 1-1. PCI-EISA Chip Set System Block Diagram

#### **PCI Local Bus**

The PCI Local Bus has been defined to address the growing industry needs for a standardized *local bus* that is not directly dependent on the speed and the size of the processor bus. New generations of personal computer system software such as Windows<sup>®</sup> and Win-NT<sup>TM</sup> with sophisticated graphical interfaces, multi-tasking and multi-threading bring new requirements that traditional PC I/O architectures can not satisfy. In addition to the higher bandwidth, reli-

ability and robustness of the I/O subsystem is becoming increasingly important. The PCI environment addresses these needs and provides an upgrade path for the future. PCI features include:

- Processor independent

- · Multiplexed, burst mode operation

- Synchronous at frequencies from 20 MHz-33 MHz

- 120 MByte/sec usable throughput (132 MByte/sec peak) for 32-bit data path

- 240 MByte/sec usable throughput (264 MByte/sec peak) for 64-bit data path

- Optional 64-bit data path with operations that are transparent with the 32-bit data path

- Low latency random access (60 ns write access latency to slave registers from a master parked on the bus)

- Capable of full concurrency with processor/memory subsystem

- Full multi-master capability allowing any PCI master peer-to-peer access to any PCI slave

- · Hidden (overlapped) central arbitration

- Low pin count for cost effective component packaging (address/data multiplexed)

- Address and data parity

- Three physical address spaces: memory, I/O, and configuration

- Comprehensive support for autoconfiguration through a defined set of standard configuration functions

System partitioning shown in Figure 1-0 illustrates how the PCI can be used as a common interface between different portions of a system platform that are typically supplied by the chip set vendor. These portions are the Host/PCI Bridge (including a main memory DRAM controller and an optional L2 cache controller) and the PCI-EISA Bridge. Thus, the PCI allows a system I/O core design to be decoupled from the processor/memory treadmill, enabling the I/O core to provide maximum benefit over multiple generations of processor/memory technology. For this reason, the PCI-EISA Bridge can be used with different processors (i.e., derivatives of the i486 or the new generation processors such as Pentium). Regardless of the new requirements imposed on the processor side of the Host/PCI Bridge (e.g., 64-bit data path, 3.3V interface, etc.) the PCI side remains unchanged which allows reusability not only of the rest of the platform chip set (i.e., PCI-EISA Bridge) but also of all other I/O functions interfaced at the PCI level. These functions typically include graphics, SCSI, and LAN.

#### **EISA Bus**

The EISA bus in the system shown in the Figure 1-0 represents a second level I/O bus. It allows personal computer platforms built around the PCI as a primary I/O bus to leverage the large EISA/ISA product base. Combinations of PCI and EISA buses, both of which can be used to provide expansion functions, will satisfy even the most demanding applications.

Along with compatibility with 16-bit and 8-bit ISA hardware and software, the EISA bus provides the following key features:

- 32-bit addressing and 32-bit data path

- 33 MByte/sec bus bandwidth

82374EB

- Multiple bus master support through efficient arbitration

- Support for autoconfiguration

#### **Integrated Bus Central Control Functions**

The PCI-EISA Bridge chip set integrates central bus functions on both the PCI and EISA Buses. For the PCI Local Bus, the functions include PCI Local Bus arbitration and default bus driver. For the EISA Bus, central functions include the EISA Bus controller and EISA arbiter are integrated in the ESC component and EISA Data Swap Logic is integrated in the PCEB.

#### Integrated System Functions

The PCI-EISA Bridge chip set integrates system functions including PCI parity and system errors reporting, buffer coherency management protocol, PCI and EISA memory and I/O address space mapping and decoding. For maximum flexibility all of these functions are programmable allowing for variety of optional features.

#### 1.1 PCEB Overview

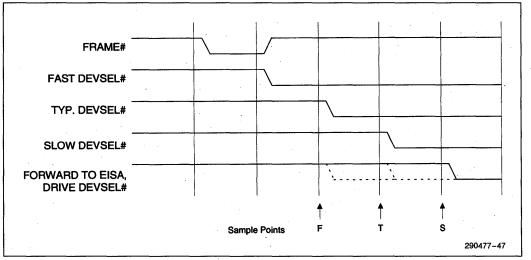

The PCEB provides the interface (bridge) between PCI and EISA buses by translating bus protocols in both directions. It uses extensive buffering on both the PCI and EISA interfaces to allow concurrent bus operations. The PCEB also implements the PCI central support functions (e.g., PCI arbitration, error signal support, and subtractive decoding). The major functions provided by the PCEB are described in this section.

#### **PCI Local Bus Interface**

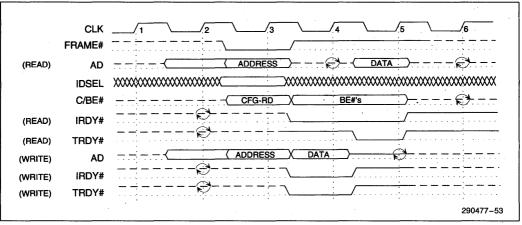

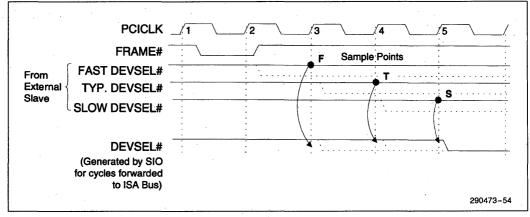

The PCEB can be either a master or slave on the PCI Local Bus and supports bus frequencies from 25 MHz to 33 MHz. For PCI-initiated transfers, the PCEB can only be a slave. The PCEB becomes a slave when it positively decodes the cycle. The PCEB also becomes a slave for unclaimed cycles on the PCI Local Bus. These unclaimed cycles are either negatively or subtractively decoded by the PCEB and forwarded to the EISA Bus.

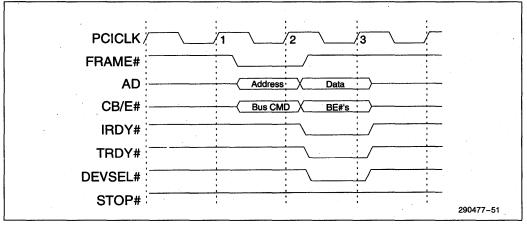

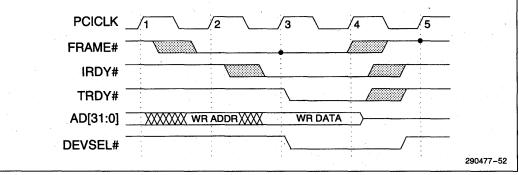

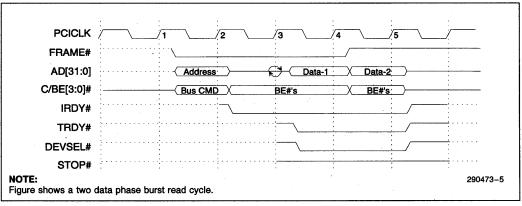

As a slave, the PCEB supports single cycle transfers for memory, I/O, and configuration operations and burst cycles for memory operations. Note that, burst transfers cannot be performed to the PCEB's internal registers. Burst memory write cycles to the EISA Bus can transfer up to four Dwords, depending on available space in the PCEB's Posted Write Buffers. When space is no longer available in the buffers, the PCEB terminates the transaction. This supports the Incremental Latency Mechanism as defined in the Peripheral Component Interconnect (PCI) Specification. Note that, if the Posted Write Buffers are disabled, PCI burst operations are not performed and all transfers are single cycle.

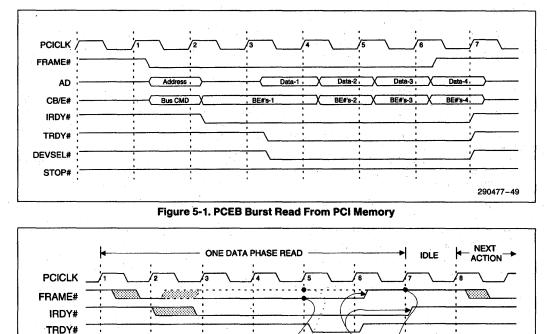

For EISA-initiated transfers to the PCI Local Bus, the PCEB is a PCI master. The PCEB permits EISA devices to access either PCI memory or I/O. While all PCI I/O transfers are single cycle, PCI memory cycles can be either single cycle or burst, depending on the status of the PCEB's Line Buffers. During EISA reads of PCI memory, the PCEB uses a burst read cycle of four Dwords to prefetch data into a Line Buffer. During EISA-to-PCI memory writes, the PCEB uses PCI burst cycles to flush the Line Buffers. The PCEB contains a programmable Master Latency Timer that provides the PCEB with a guaranteed time slice on the PCI Local Bus, after which it surrenders the bus.

As a master on the PCI Local Bus, the PCEB generates address and command signal (C/BE#) parity for read and write cycles, and data parity for write cycles. As a slave, the PCEB generates data parity for read cycles. Parity checking is not supported.

The PCEB, as a resource, can be locked by any PCI master. In the context of locked cycles, the entire PCEB subsystem (including the EISA Bus) is considered a single resource.

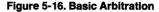

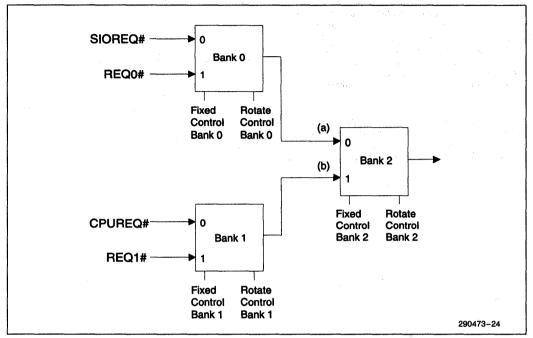

#### **PCI Local Bus Arbitration**

The PCI arbiter supports six PCI masters—The Host/PCI bridge, PCEB, and four other PCI masters. The arbiter can be programmed for twelve fixed priority schemes, a rotating scheme, or a combination of the fixed and rotating schemes. The arbiter can be programmed for bus parking that permits the Host/PCI Bridge default access to the PCI Local Bus when no other device is requesting service. The arbiter also contains an efficient PCI retry mechanism to minimize PCI Local Bus thrashing when the PCEB generates a retry. The arbiter can be disabled, if an external arbiter is used.

#### **EISA Bus Interface**

The PCEB contains a fully EISA-compatible master and slave interface. The PCEB directly drives eight EISA slots without external data or address buffering. The PCEB is only a master or slave on the EISA Bus for transfers between the EISA Bus and PCI Local Bus. For transfers contained to the EISA Bus, the PCEB is never a master or slave. However, the data swap logic contained in the PCEB is involved in these transfers, if data size translation is needed. The PCEB also provide support for I/O recovery.

EISA/ISA masters and DMA can access PCI memory or I/O. The PCEB only forwards EISA cycles to the PCI Local Bus if the address of the transfer matches one of the address ranges programmed into the PCEB for EISA-to-PCI positive decode. This includes the main memory segments used for generating MEMCS# from the EISA Bus, one of the four programmable memory regions, or one of the four programmable I/O regions. For EISA-initiated accesses to the PCI Local Bus, the PCEB is a slave on the EISA Bus. I/O accesses are always non-buffered and memory accesses can be either non-buffered or buffered via the Line Buffers. For buffered accesses, burst cycles are supported.

During PCI-initiated cycles to the EISA Bus, the PCEB is an EISA master. For memory write operations through the Posted Write Buffers, the PCEB uses EISA burst transfers, if supported by the slave, to flush the buffers. Otherwise, single cycle transfers are used. Single cycle transfers are used for all I/O cycles and memory reads.

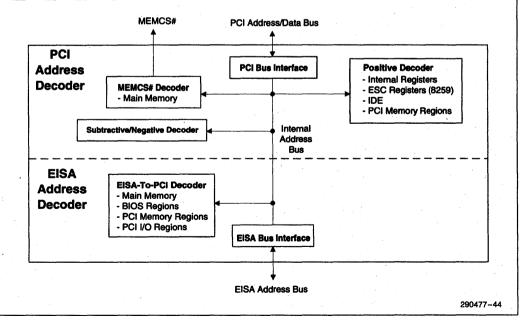

#### PCI/EISA Address Decoding

The PCEB contains two address decoders—one to decode PCI-initiated cycles and the other to decode EISA-initiated cycles. The two decoders permit the PCI and EISA Buses to operate concurrently.

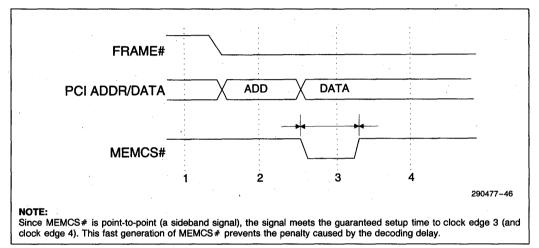

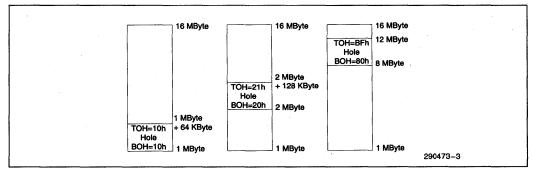

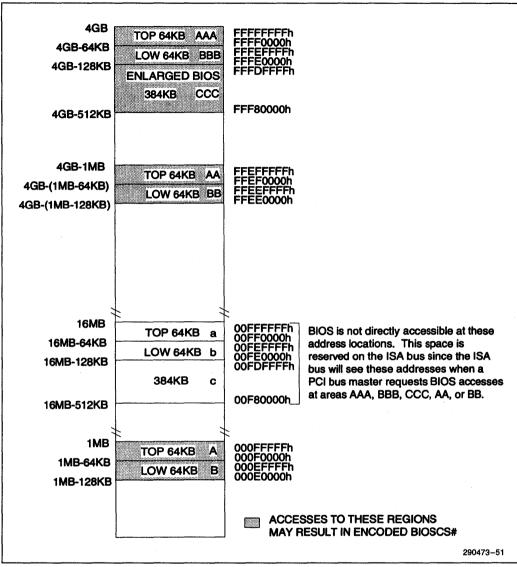

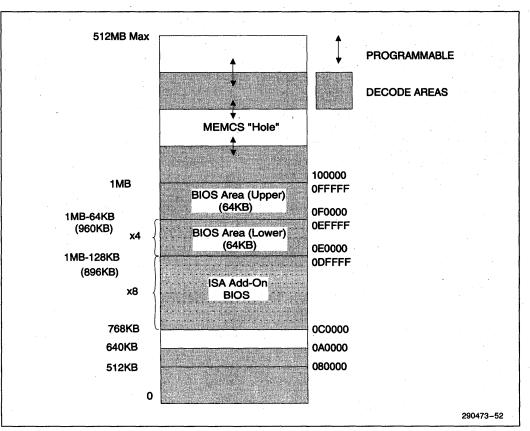

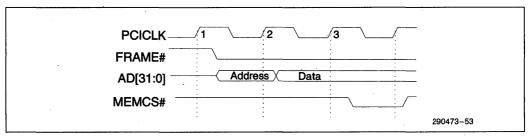

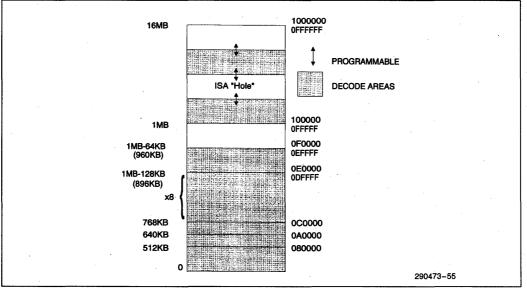

The PCEB can also be programmed to provide main memory address decoding on behalf of the Host/ PCI bridge. When programmed, the PCEB monitors the PCI and EISA bus cycle addresses, and generates a memory chip select signal (MEMCS#) indicating that the current cycle is targeted to main memory residing behind the Host/PCI bridge. Programmable features include, read/write attributes for specific memory segments and the enabling/disabling of a memory hole. If MEMCS# is not used, this feature can be disabled.

In addition to the main memory address decoding, there are four programmable memory regions and four programmable I/O regions for EISA-initiated cycles. EISA/ISA master or DMA accesses to one of these regions are forwarded to the PCI Local Bus.

#### **Data Buffering**

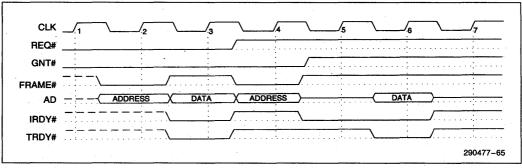

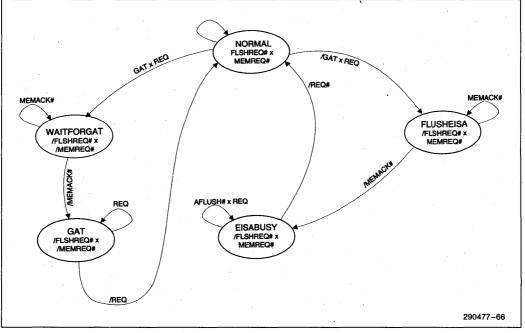

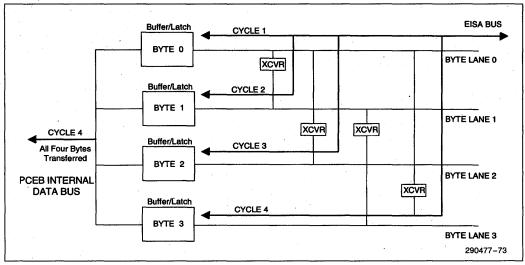

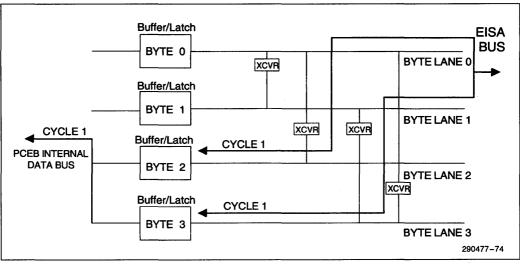

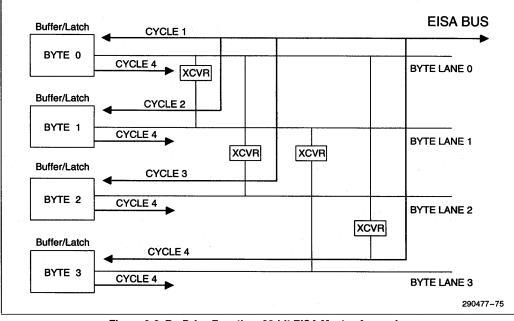

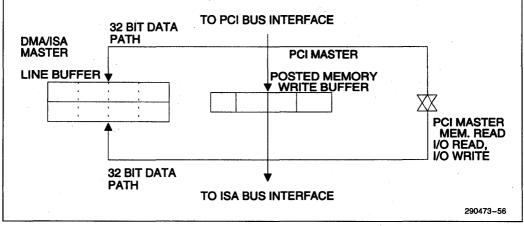

To isolate the slower EISA Bus from the PCI Local Bus, the PCEB provides two types of data buffers. Buffer management control guarantees data coherency. Four Dword wide Posted Write Buffers permit posting of PCI-initiated memory write cycles to the EISA Bus. For EISA-initiated cycles to the PCI Bus, there are four 16-byte wide Line Buffers. These buffers permit prefetching of PCI memory read data and posting of PCI memory write data.

By using burst transactions to fill or flush these buffers, if appropriate, the PCEB maximizes bus efficiency. For example, an EISA device could fill a Line Buffer with byte, word, or Dword transfers and the PCEB would use a PCI burst cycle to flush the filled line to PCI memory.

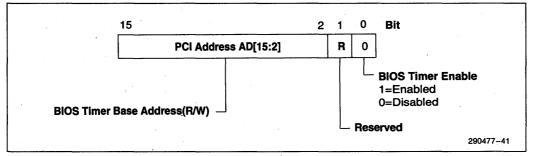

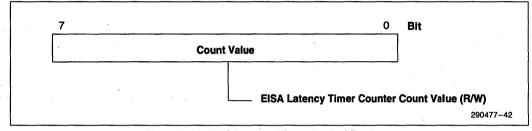

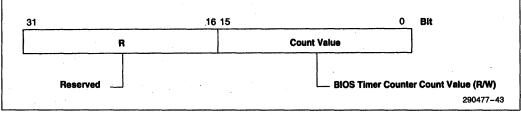

#### **BIOS Timer**

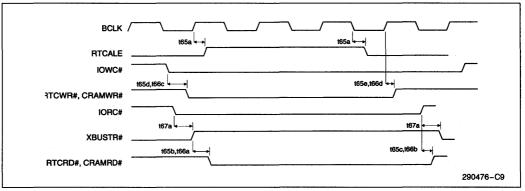

The PCEB has a 16-bit BIOS Timer. The timer can be used by BIOS software to implement timing loops. The timer count rate is derived from the EISA clock (BCLK) and has an accuracy of  $\pm 1 \ \mu$ s.

### 1.2 ESC Overview

The ESC implements system functions (e.g., timer/ counter, DMA, and interrupt controller) and EISA subsystem control functions (e.g., EISA bus controller and EISA bus arbiter). The major functions provided by the ESC are described in this section.

#### **EISA Controller**

The ESC incorporates a 32-bit master and an 8-bit slave. The ESC directly drives eight EISA slots without external data or address buffering. EISA system clock (BCLK) generation is integrated by dividing the PCI clock (divide by 3 or divide by 4) and wait state generation is provided. The AENx and MACKx signals provide a direct interface to four EISA slots and supports eight EISA slots with encoded AENx and MACKx signals.

The ESC contains an 8-bit data bus (lower 8 bits of the EISA data bus) that is used to program the ESC's internal registers. Note that for transfers between the PCI and EISA Buses, the PCEB provides the data path. Thus, the ESC does not require a full 32-bit data bus. A full 32-bit address bus is provided and is used during refresh cycles and for DMA operations.

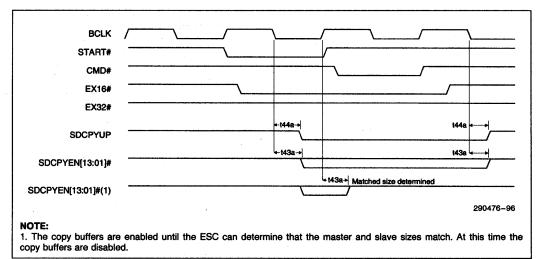

The ESC performs cycle translation between the EISA Bus and ISA Bus. For mis-matched master/ slave combinations, the ESC controls the data swap logic that is located in the PCEB. This control is provided through the PCEB/ESC interface.

#### DMA Controller

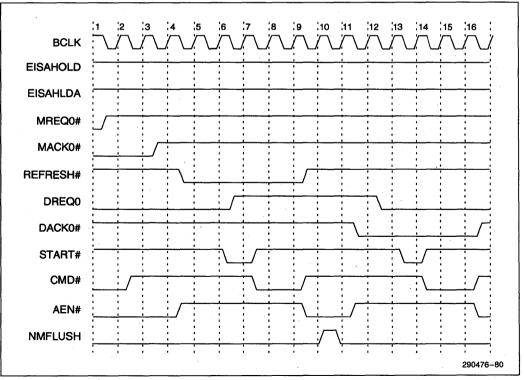

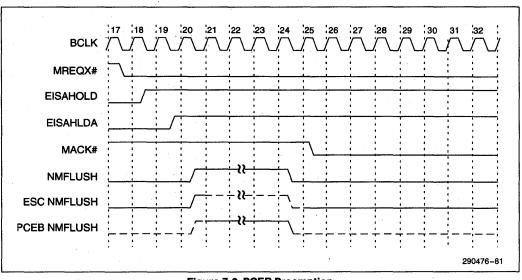

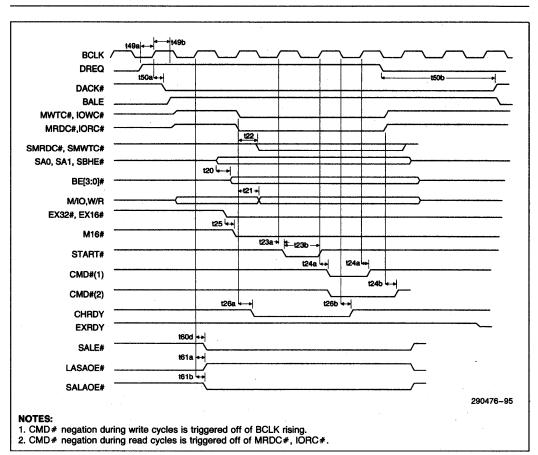

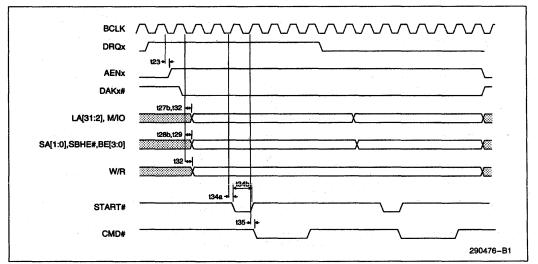

The ESC incorporates the functionality of two 82C37 DMA controllers with seven independently programmable channels. Each channel can be programmed for 8-bit or 16-bit DMA device size, and ISA-compatible, type "A", type "B", or type "C" timings. Full 32-bit addressing is provided. The DMA controller is also responsible for generating refresh cycles.

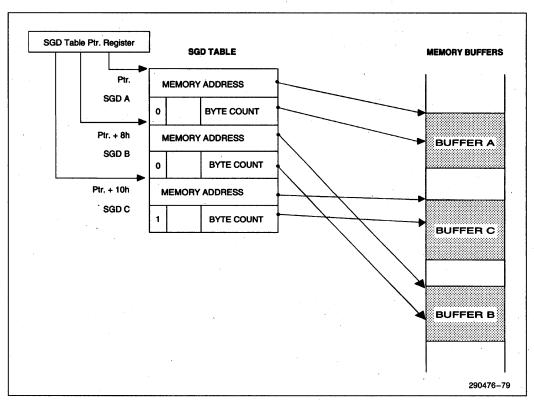

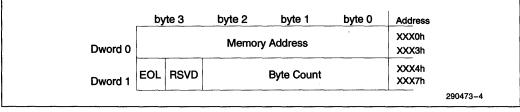

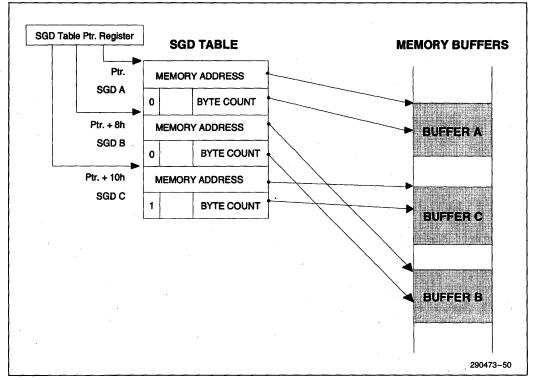

The DMA controller supports an enhanced feature called scatter/gather. This feature provides the capability of transferring multiple buffers between memory and I/O without CPU intervention. In scatter/gather mode, the DMA can read the memory address and word count from an array of buffer descriptors, located in main memory, called the scatter/gather descriptor (SGD) table. This allows the DMA controller to sustain DMA transfers until all of the buffers in the SGD table are handled.

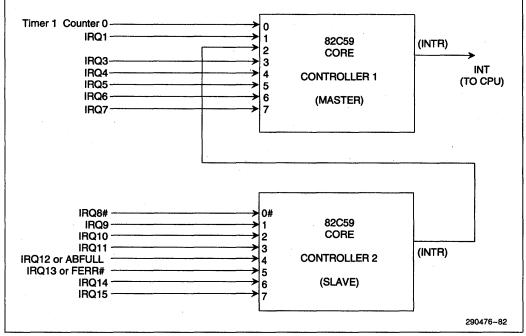

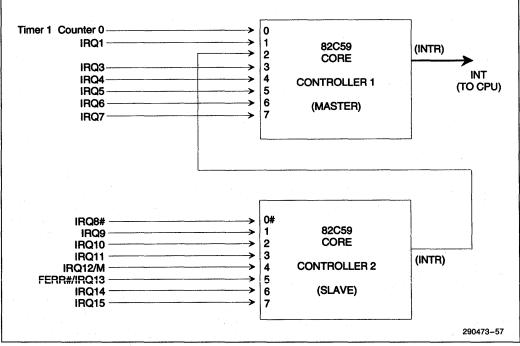

#### Interrupt Controller

The ESC contains an EISA compatible interrupt controller that incorporates the functionality of two 82C59 Interrupt Controllers. The two interrupt controllers are cascaded providing 14 external and two internal interrupts.

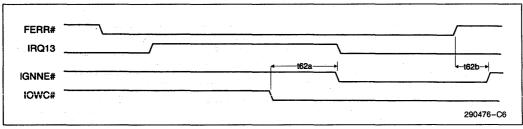

#### Timer/Counter

The ESC provides two 82C54 compatible timers (Timer 1 and Timer 2). The counters in Timer 1 support the system timer interrupt (IRQ0#), refresh request, and a speaker tone output (SPKR). The counters in Timer 2 support fail-safe timeout functions and the CPU speed control.

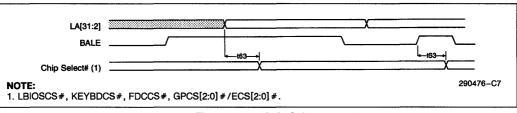

#### **Integrated Support Logic**

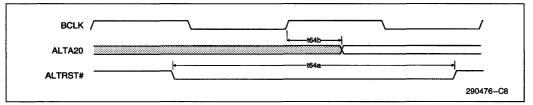

To minimize the chip count for board designs, the ESC incorporates a number extended features. The ESC provides support for ALTA20 (Fast A20GATE) and ALTRST with I/O Port 92h. The ESC generates the control signals for SA address buffers and X-Bus buffer. The ESC also provides chip selects for BIOS, the keyboard controller, the floppy disk controller, and three general purpose devices. Support for generating chip selects with an external decoder is provided for IDE, a parallel port, and a serial port. The ESC provides support for a PC/AT compatible coprocessor interface and IRQ13 generation.

### 2.0 SIGNAL DESCRIPTION

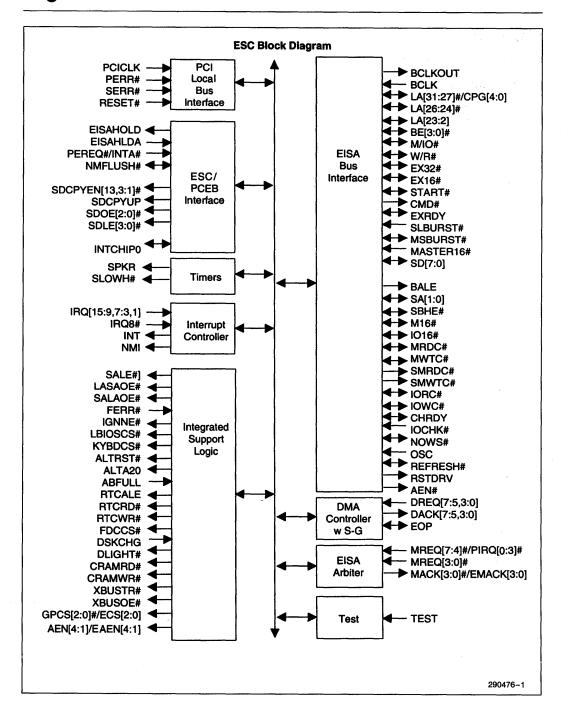

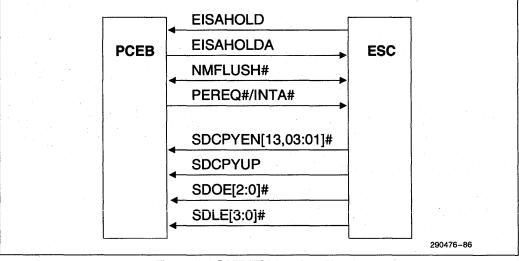

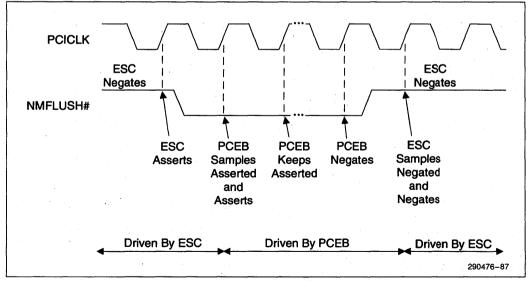

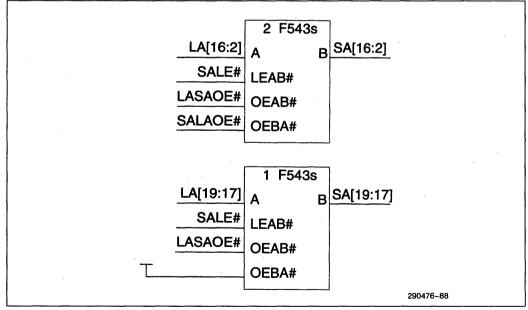

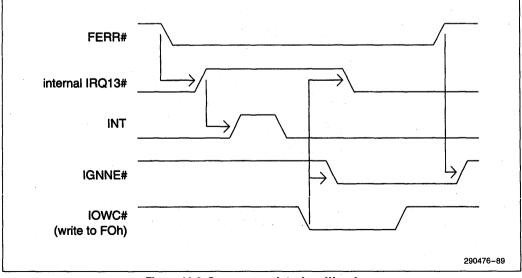

This section provides a detail description of each signal. The signals (Figure 2-1) are arranged in functional group according to their associated interface.

The "#" symbol at the end of a signal indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not presented after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term **assert**, or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive. The following notations are used to describe the signal type.

- in Input is a standard input-only signal.

- out Totem Pole Output is a standard active driver.

- o/d Open Drain Input/Output.

- t/s Tri-State is a bi-directional, tri-state input/output pin.

- s/t/s Sustained Tri-State is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives a s/t/s pin low must drive it high for at least one clock before letting it float. A new agent can not start driving a s/t/s signal any sooner than one clock after the previous owner tristates it. A pull-up sustains the inactive state until another agent drives it and is provided by the central resource.

| Pin<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                                                        |

|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

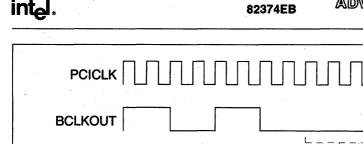

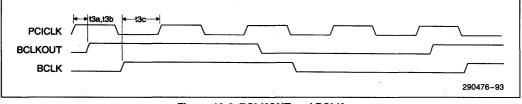

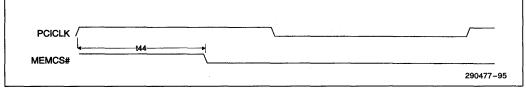

| PCICLK      | in   | PCI CLOCK: PCICLK provides timing for all transactions on the PCI Local Bus. The ESC uses the PCI Clock (PCICLK) to generate EISA Bus Clock (BCLK). The PCICLK is divided by 3 or 4 to generate the BCLK. The EISA Bridge supports PCI Clock frequencies of 25 MHz through 33 MHz.                                                                 |

| PERR#       | in   | <b>PARITY ERROR:</b> PERR# indicates a data parity error. PERR# may be pulsed active by any agent that detects an error condition. Upon sampling PERR# active, the ESC generates an NMI interrupt to the CPU.                                                                                                                                      |

| SERR#       | in   | SYSTEM ERROR: SERR # may be pulsed active by any agent that detects an error condition. Upon sampling SERR # active, the ESC generates an NMI interrupt to the CPU.                                                                                                                                                                                |

| RESET#      | in   | SYSTEM RESET: RESET # forces the entire ESC Chip into a known state. All internal ESC state machines are reset and all registers are set to their default values. RESET # may be asynchronous to PCICLK when asserted or negated. Although asynchronous, negation must be a clean, bounce-free edge. The ESC uses RESET to generate RSTDRV signal. |

### 2.1 PCI Local Bus Interface Signals

## 2.2 EISA Bus Interface Signals

| Pin<br>Name                    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLKOUT                        | out  | <b>EISA BUS CLOCK OUTPUT:</b> BCLKOUT is typically buffered to create EISA Bus Clock (BCLK). The BCLK is the system clock used to synchronize events on the EISA/ISA bus. The BCLKOUT is generated by dividing the PCICLK. The ESC uses a divide by 3 or divide by 4 to generate the BCLKOUT.                                                                                                                              |

| BCLK                           | in   | <b>EISA BUS CLOCK:</b> BCLK is an input to the ESC device. This ESC uses the BCLK to synchronize events on the EISA bus. The ESC generates or samples all the EISA/ISA bus signals on either the rising or the falling edge of BCLK.                                                                                                                                                                                       |

| LA[31:27] # /<br>CPG[4:0]      | t/s  | EISA ADDRESS BUS/CONFIGURATION RAM PAGE ADDRESS: These are<br>multiplexed signals. These signals behave as the EISA address bus under all<br>conditions except during access cycle to the Configuration RAM.                                                                                                                                                                                                               |

|                                |      | <b>EISA ADDRESS BUS:</b> LA[31:27] # are directly connected to the EISA address bus. The ESC uses the address bus in conjunction with the BE[3:0] # signals as inputs to decode accesses to its internal resources except in DMA and Refresh modes. During DMA and Refresh modes, these are outputs, and the ESC uses these signals in conjunction with BE[3:0] # to drive Memory address.                                 |

|                                |      | <b>CONFIGURATION RAM PAGE ADDRESS:</b> CPG[4:0] are connected to<br>Configuration SRAM address lines. During I/O access to $0800h-08FFh$ , the ESC<br>drives these signals with the configuration page address (the value contained in<br>register 0C00h). The Configuration RAM Page Address function can be disabled<br>by setting Mode Select register bit $5 = 0$ .                                                    |

| LA[26:24] #<br>and<br>LA[23:2] | t/s  | <b>EISA ADDRESS BUS:</b> These signals are directly connected to the EISA address bus. The ESC uses the address bus in conjunction with the BE[3:0] # signals as inputs to decode accesses to its internal resources except in DMA and Refresh modes. During DMA and Refresh modes, these are outputs, and the ESC uses these signals in conjunction with BE[3:0] # to drive Memory address.                               |

| BE[3:0] <i>#</i>               | t/s  | <b>BYTE ENABLES:</b> BE[3:0] # signals are directly connected to the EISA address<br>bus. These signals indicate which byte on the 32-bit EISA data bus are involved<br>in the current cycle. BE[3:0] # are inputs during EISA master cycles which do not<br>require assembly/disassembly operation. For EISA master assembly/<br>disassembly cycles, ISA master cycles, DMA, and Refresh cycles BE[3:0] # are<br>outputs. |

|                                |      | BE0 #: Corresponds to byte lane 0-SD[7:0]                                                                                                                                                                                                                                                                                                                                                                                  |

|                                |      | BE1 #: Corresponds to byte lane 0-SD[15:8]                                                                                                                                                                                                                                                                                                                                                                                 |

|                                |      | BE2#: Corresponds to byte lane 0-SD[23:16]<br>BE3#: Corresponds to byte lane 0-SD[31:24]                                                                                                                                                                                                                                                                                                                                   |

| M/IO#                          | t/s  | <b>MEMORY OR I/O CYCLE:</b> M/IO # signal is used to differentiate between<br>memory cycles and I/O cycles on the EISA bus. A High value on this signal<br>indicates a memory cycle, and a Low value indicates an I/O cycle. M/IO # is an<br>input to the ESC during EISA master cycles, and M/IO # is an output during ISA,<br>DMA, and ESC initiated Refresh cycles. M/IO # is floated during ISA master                 |

| W/R#                           | t/s  | initiated Refresh cycles.<br>WRITE OR READ CYCLE: W/R# signal is used to differentiate between write<br>and read cycles on the EISA bus. A High value on this signal indicates a Write<br>cycle, and a Low value indicates a Read cycle. W/R# is an input to the ESC<br>during EISA master cycles, and W/R# is an output during ISA, DMA, and<br>Refresh cycles.                                                           |

82374EB

## 2.2 EISA Bus Interface Signals (Continued)

| Pin<br>Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

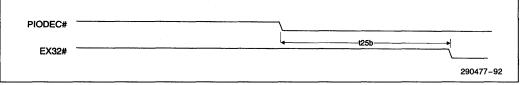

| EX32 <i>#</i> | o/d  | <b>EISA 32-BIT DEVICE DECODE:</b> EX32 # signal is asserted by a 32-bit EISA slave device. EX32 # assertion indicates that an EISA device has been selected as a slave, and the device has a 32-bit data bus size. The ESC uses this signal as an input as part of its slave decode to determine if data size translation and/or cycle translation is required. EX32 # is an output of the ESC during the last portion of the mis-matched cycle. This is an indication to the backed-off EISA master that the data translation has been completed. The backed-off EISA master uses this signal to start driving the EISA bus again.                                                                                                                                                                                                                                                     |

| EX16#         | o/d  | <b>EISA 16-BIT DEVICE DECODE:</b> EX16 # signal is asserted by a 16-bit EISA slave device. EX16 # assertion indicates that an EISA device has been selected as a slave, and the device has a 16-bit data bus size. The ESC uses this signal as an input as part of its slave decode to determine if data size translation and/or cycle translation is required. EX16 # is an output of the ESC during the last portion of the mis-matched cycle. This is an indication to the backed-off EISA master that the data translation has been completed. The backed-off EISA master uses this signal to start driving the EISA bus again.                                                                                                                                                                                                                                                     |

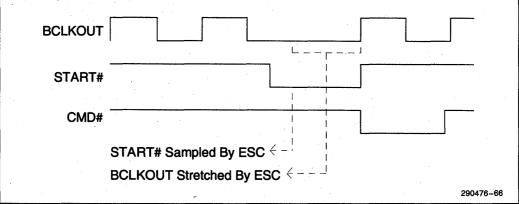

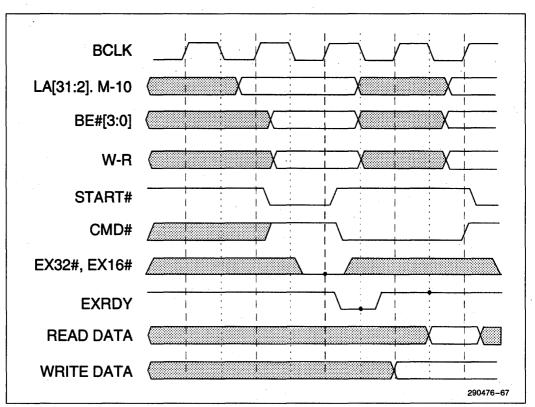

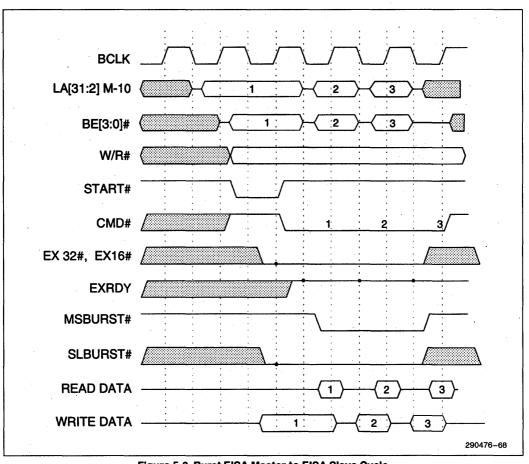

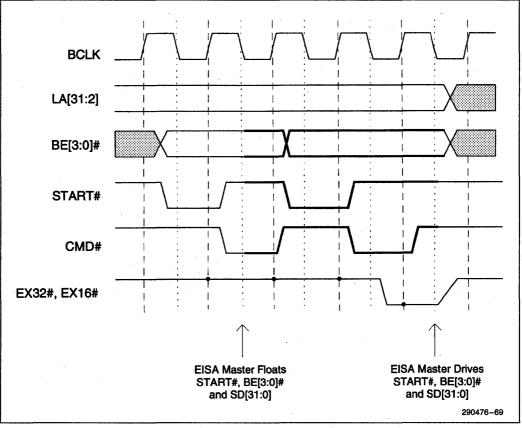

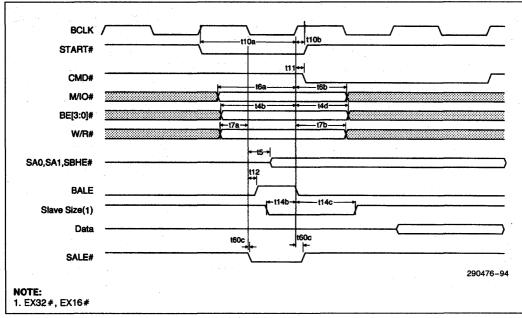

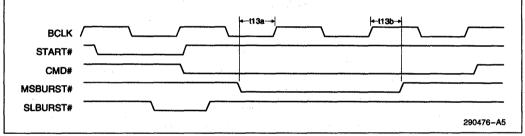

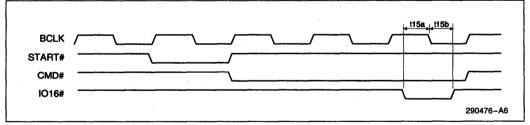

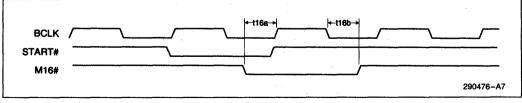

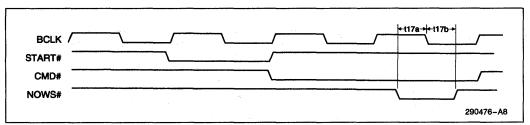

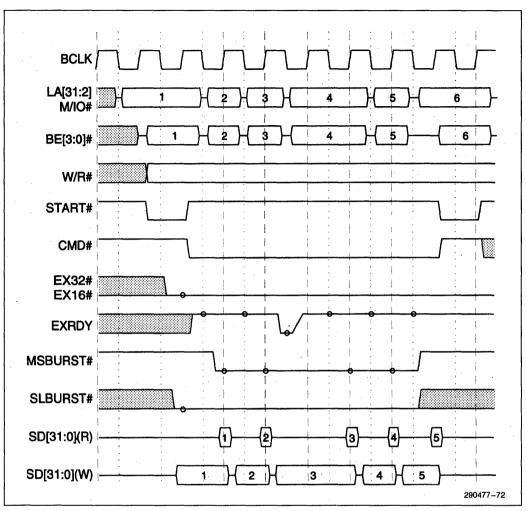

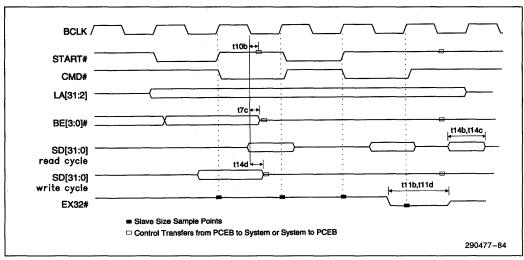

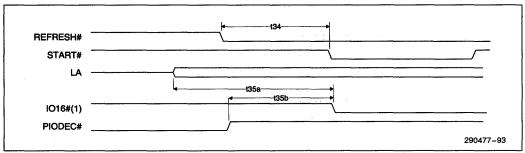

| START#        | t/s  | <b>START CYCLE:</b> START # signal provides timing control at the start of an EISA cycle. START # is asserted for one BCLK. START # is an input to the ESC during EISA master cycles except portions of the EISA master to mis-matched slave cycles where it becomes an output. During ISA, DMA, and Refresh cycles START # is an output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

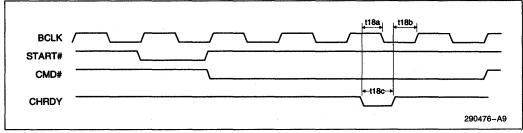

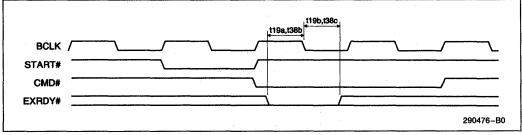

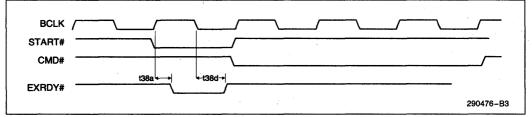

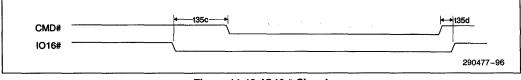

| CMD#          | out  | <b>COMMAND:</b> CMD# signal provides timing control within an EISA cycle. The ESC is a central resource of the CMD# signal, and the ESC generates CMD# during all EISA cycles. CMD# is asserted from the rising edge of BCLK simultaneously with the negation of START#, and remains asserted until the end of the cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

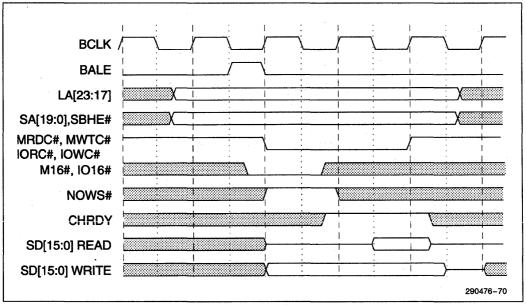

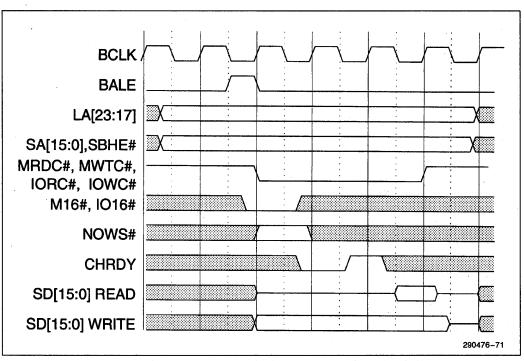

| EXRDY         | o/d  | <b>EISA READY:</b> EXRDY signal is deasserted by EISA slave devices to add wait states to a cycle. EXRDY is an input to the ESC for EISA master cycles, ISA master cycles, and DMA cycles where an EISA slave has responded with EX32# or EX16# asserted. The ESC samples EXRDY on the falling edge of BCLK after CMD# is asserted (except during DMA compatible cycles). During DMA compatible cycles, EXRDY is sampled on the second falling edge of BCLK after CMD# is driven active. For all types of cycles if EXRDY is sampled inactive, the ESC keeps sampling it on every falling edge of BCLK #. EXRDY is an output for EISA master cycles decoded as accesses to the ESC internal registers. ESC forces EXRDY low for one BCLK at the start of a potential DMA burst write cycle to insure that the initial write data is held long enough to be sampled by the memory slave. |

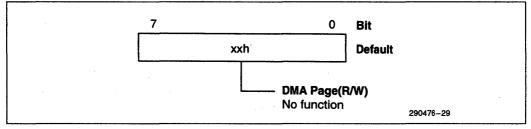

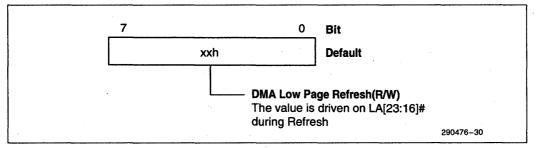

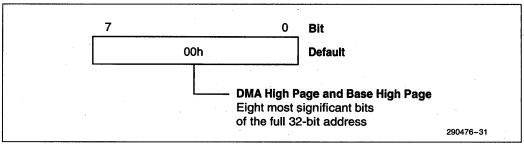

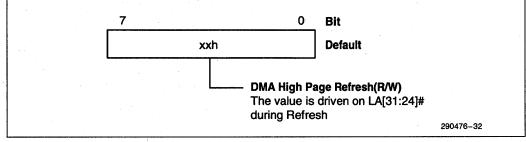

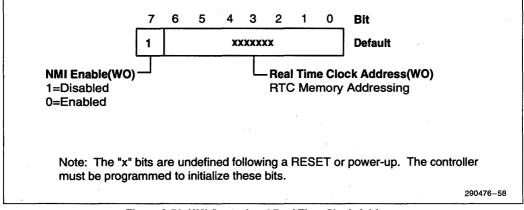

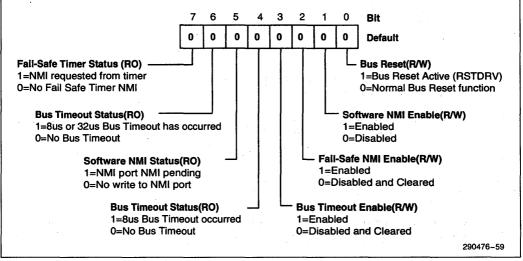

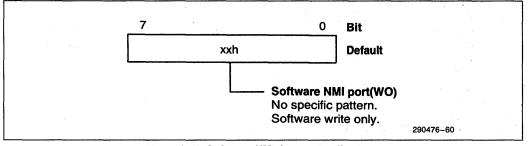

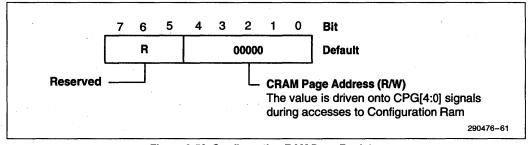

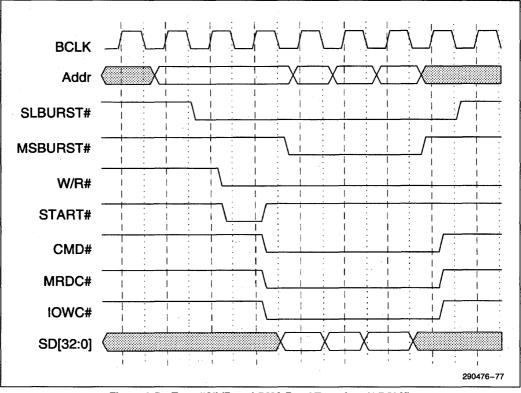

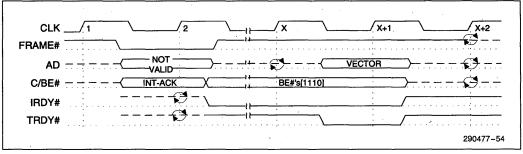

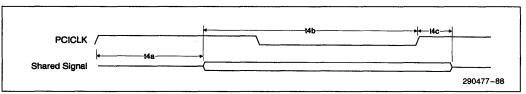

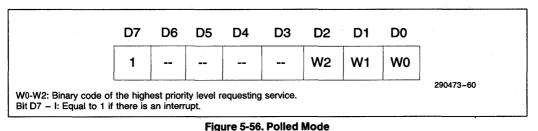

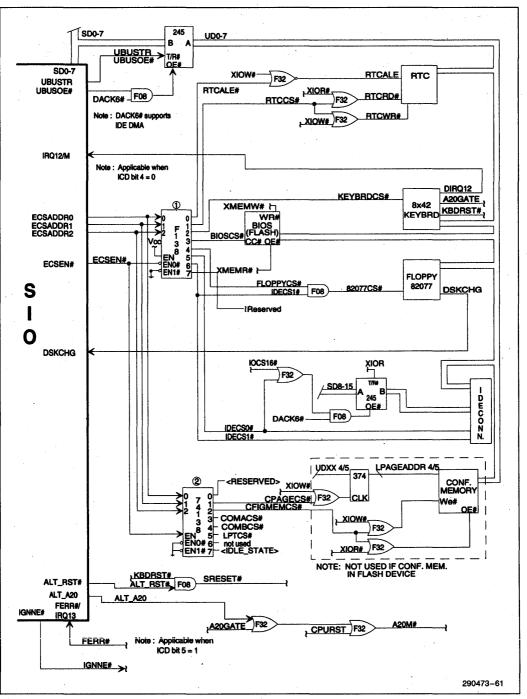

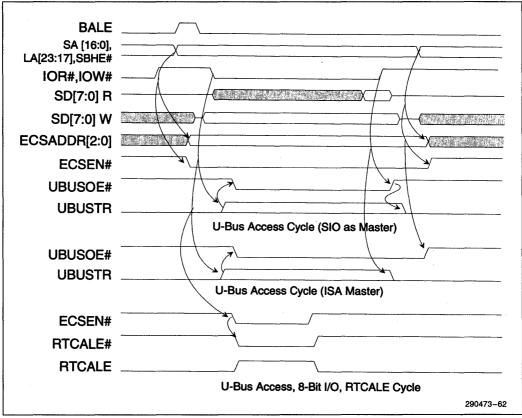

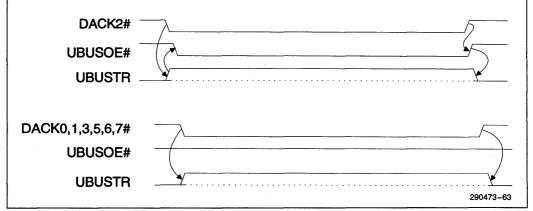

| SLBURST#      | in   | <b>SLAVE BURST:</b> SLBURST# signal is asserted by an EISA slave to indicate that the device is capable of accepting EISA burst cycles. The ESC samples SLBURST# on the rising edge of BCLK at the end of START# for all EISA cycles. During DMA cycles, the ESC samples SLBURST# twice; once on the rising edge of BCLK at the beginning of START# and again on the rising edge of BCLK at the end of START#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |