# Customer Engineering Instruction-Reference

IBM

Instruction-Reference IBM 7909 Data Channel

# Preface

This Instruction-Reference manual covers internal operations and maintenance of the IBM 7909 Data Channel as attached to IBM 7090/7094 Data Processing Systems.

Operations are not followed into the various adapters because the 1-0 interface is thoroughly explained in an initial section. Therefore, all explanations are with respect to the channel side of the interface. Specific information on the various devices may be obtained from the following publications:

- IBM 7631 File Control CE-IR Manual, Form R23-2541-2

- IBM 1301 Disk Storage CE Manual of Instruction, Form 227-5582

IBM 1301 Model 1 and Model 2 Disk Storage and

IBM 1302 Model 1 and Model 2 Disk Storage with

IBM 7090, 7094, and 7094-2 Data Processing Systems, Form A22-6785

IBM 7320 Drum Storage, Form A22-6747

IBM 7340 Hypertape Drive Model I, Form A22-6746

- IBM 7340 Hypertape Drive Reference Manual, Form A22-6616

- *IBM 1414-Model 3, 4, 5, 6, 8 CE-IR Manual, Form* R23-2590

- IBM 1414-6 I-O Synchronizer CE-IR Manual, Form R23-9914

- IBM 1414-6 Input-Output Synchronizer (7090/7094 Systems Bulletin), Form G22-6625

- IBM 7750 Program Transmission Control 1410, 7000 CE Manual of Instruction, Form 223-2540

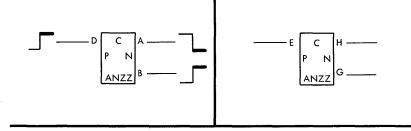

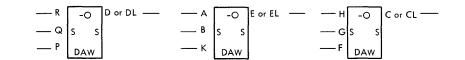

To satisfy the varied preferences of customer engineers using this manual, three types of figures are used: condensed logic, sequence charts, and flow charts. The condensed logic charts are as near to actual systems as possible with lines converted to positive-type logic. In maintaining this positive logic, in-phase outputs are used to indicate an active (conditions met) state from the condensed logic blocks. This is contrary to the S level NOR circuitry because NOR always produces a change in level between input and output. However, the condensed logic does not deal with plus (+) or minus (-) levels (only pure logic). Clearly labeled out-of-phase outputs are also used in some cases to simplify the figures by eliminating the cluttering effect of inverter blocks.

The material in this manual has been written to engineering change level 252610. Future engineering changes, however, may change the logic and machine operation from that presented in this manual.

For simplicity, the prefix 50 has been omitted from Systems numbers in flow charts, logic diagrams, and sequence charts.

Material contained in the Customer Engineering Instruction-Reference Manual Supplement *IBM* 7909 *Data Channel*, Form R23-2571 is included in this manual.

In this manual simplex I-O interface is the same as standard interface and simplex BCD translation is the same as standard BCD translation.

Copies of this and other IBM publications can be obtained through IBM Branch Offices Address comments concerning the contents of this publication to: IBM Corporation, CE Manuals, Dept. B96, PO Box 390, Poughkeepsie, N.Y.

# Contents

| <b>7909 Data Channel</b> 7909 Attachments         Maximum System Considerations         7909 Data Channel Timings.         Physical Description         Interpanel Connections         Input-Output Connector Rows.         7909-7607 Compatibility.         Channel Priority         Priority System—Multi-Channel.         Internal Channel Priority Logic—B Time.         Demand Delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5<br>5<br>7<br>7<br>12<br>12<br>13<br>13<br>13<br>15                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Simplex I-O Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17                                                                         |

| Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                         |

| Interlocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                                         |

| Initiation of Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                                         |

| Information Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18                                                                         |

| Termination of Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19                                                                         |

| Asynchronous Signaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20                                                                         |

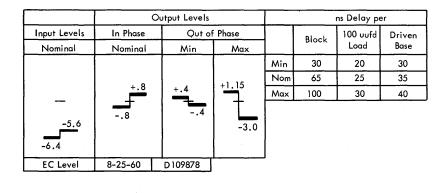

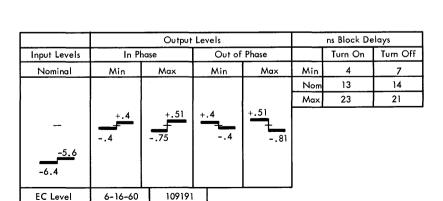

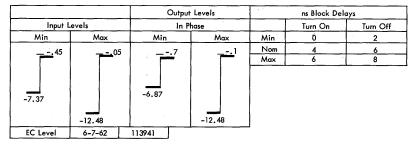

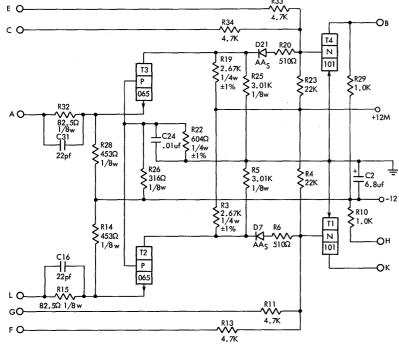

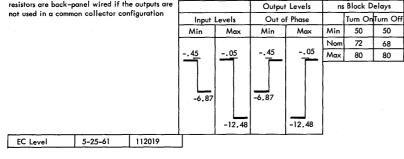

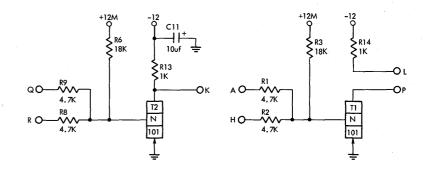

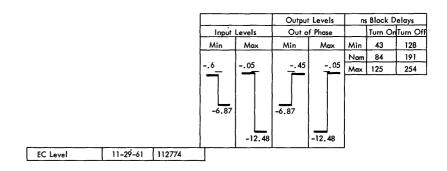

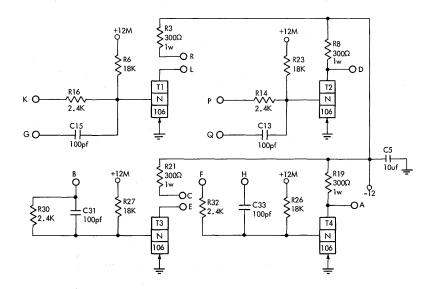

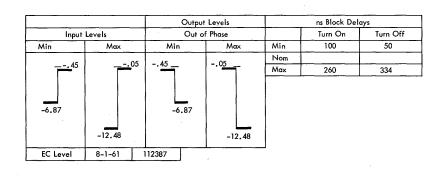

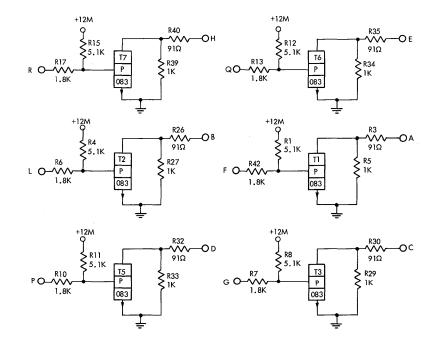

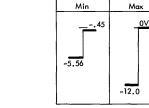

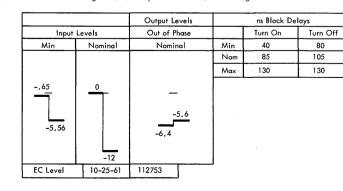

| Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                                         |

| Channel Organization and Functional Units<br>Decoders<br>Registers<br>Data Register<br>Assembly Register<br>Character Register<br>Check Condition Register<br>SCD Status Register<br>Storage Register<br>Counters<br>Counters<br>Command Counter<br>Word Counter<br>Word Counter<br>Word Counter<br>Word Counter<br>Word Counter<br>Address Counter.<br>Address Counter.<br>Adders<br>Adder Look-Ahead<br>Switches<br>Storage Bus In<br>Storage Bus Out<br>MAR Switch In<br>MAR Switch In<br>MAR Switch In<br>Character In Switch<br>Character Cut Switch<br>Rings<br>Character Ring<br>Assembly Ring. | 22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22 |

| BCD-Binary Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41                                                                         |

| Translators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41                                                                         |

| Parity Bit Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46                                                                         |

| Computer Instructions         Reset and Start Channel—RSCA.         Start Channel—STCA.         Store Channel—SCHA         Store Channel Diagnostic—SCDA.         Enable—ENB         Restore Channel Traps—RCT.         Reset Channel—RICA.         7909 Channel Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48<br>48<br>51<br>52<br>53<br>53<br>54<br>56                               |

| Command Cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56                                                                         |

| Control—CTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57                                                                         |

| Control and Write—CTLW<br>Control and Read—CTLR                      | 57<br>61     |

|----------------------------------------------------------------------|--------------|

| Sense—SNS<br>Copy and Proceed—CPYP                                   | 61<br>63     |

| Copy and Disconnect—CPYD                                             | 63           |

| Transfer in Channel—TCH                                              | 64           |

| Wait and Transfer—WTR<br>Trap and Wait—TWT                           | 64<br>65     |

| Load and Assembly Register—LAR                                       | 66           |

| Store Assembly Register—SAR                                          | 68<br>68     |

| Load Control Counter—LCC                                             | 72           |

| Insert Control Counter-ICC                                           | 72           |

| Transfer and Decrement Counter—TDC<br>Transfer On Conditions Met—TCM | 73<br>74     |

| Transmit—XMT                                                         | 75           |

| Data Flow                                                            | 81           |

| Writing<br>Core Storage to Channel                                   | 81<br>81     |

| Channel to I-O                                                       | 86           |

| Reading                                                              | 86           |

| I-O to Channel                                                       | 86<br>87     |

| Stop Condition                                                       | 87           |

| End Condition                                                        | 91<br>97     |

| Channel Trap<br>Channel Interrupt                                    | 97<br>97     |

| Channel Assignments and Connections                                  | 98           |

| Interrupt Operation                                                  | 98<br>101    |

| Unusual End                                                          | 104          |

|                                                                      | 104          |

|                                                                      | 106<br>107   |

| Check Conditions                                                     | 107          |

|                                                                      | 108          |

|                                                                      | 108<br>108   |

| Interface (Adapter) Check                                            | 109          |

| Check Reset                                                          | 110          |

|                                                                      | 112          |

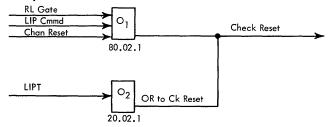

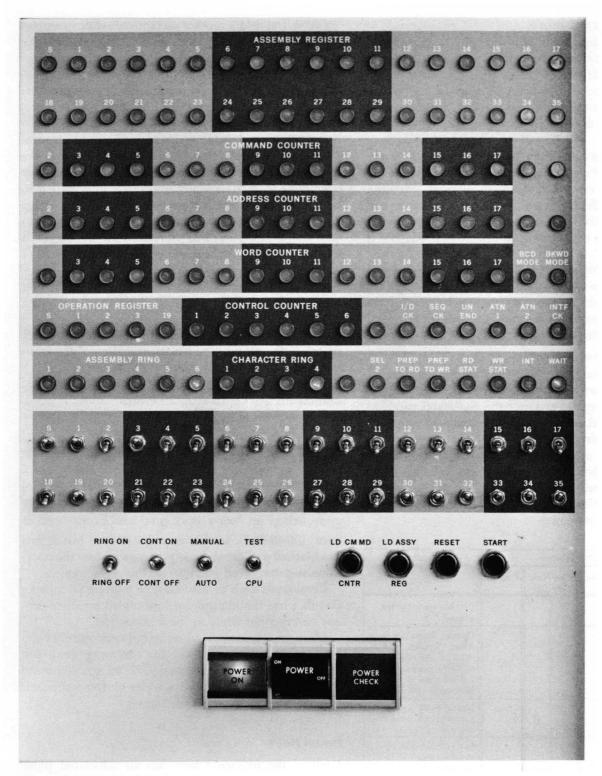

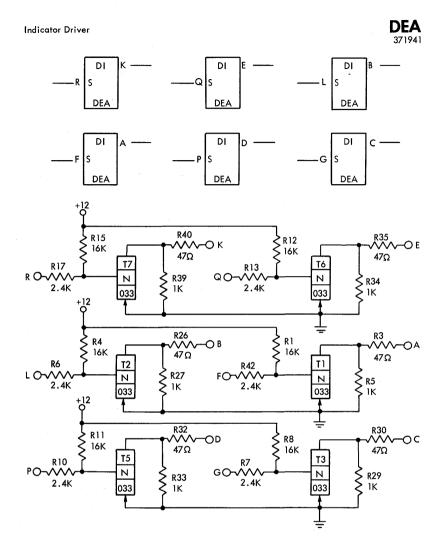

| Panel Lights<br>Panel Switches                                       | 112<br>112   |

| Panel Keys                                                           | 114          |

| Operator's Lights and Switches                                       | 116          |

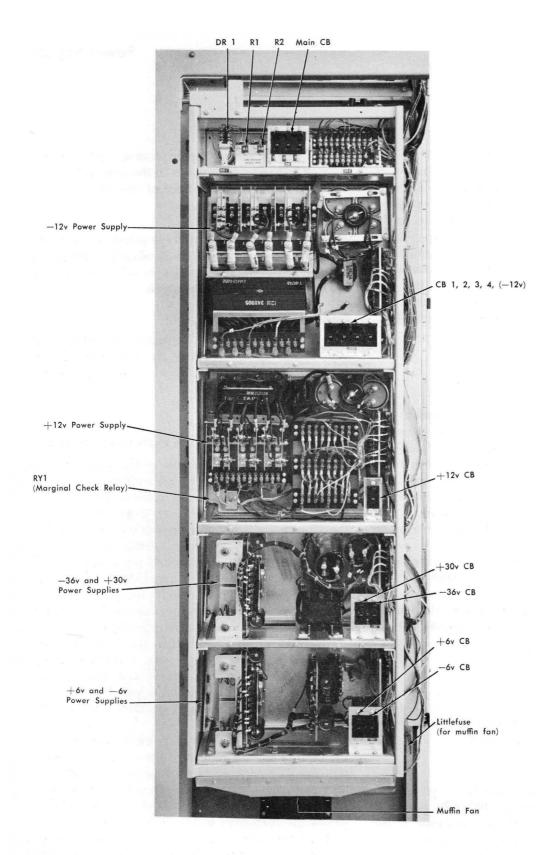

| Power Supply                                                         | 117          |

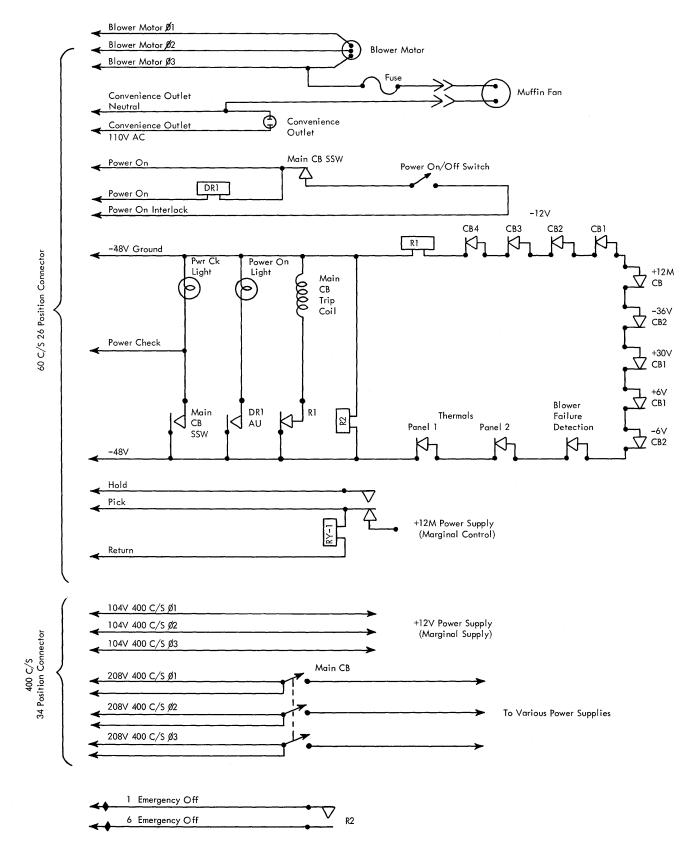

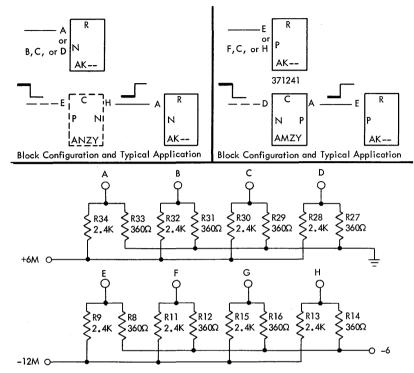

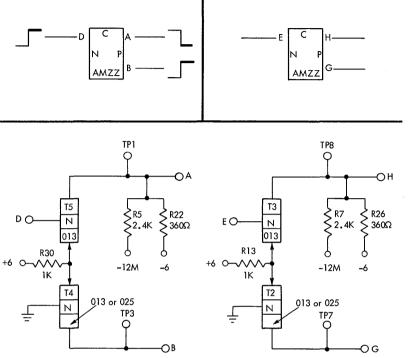

| Lights and Switches<br>Power Supply Control and Protection Circuits  | $117 \\ 117$ |

| Power Supply Color Coding                                            | 120          |

| Marginal Voltage Requirements                                        | 120          |

| Appendix A—Test Panel Operation for<br>Checking 7909 Registers       | 121          |

| Appendix B—Triggers and Locations                                    | 122          |

| Appendix C—Circuit Card Reference                                    |              |

| Information                                                          | 124          |

| Appendix D—Hypertape Reference Information                           | 140          |

| Appendix E—7631 File Control Reference<br>Information                | 141          |

| Appendix F—1414-6 Reference Information                              | 142          |

|                                                                      | ~            |

# Illustrations

| Figuri          | e Title                                                                                               | Page       |

|-----------------|-------------------------------------------------------------------------------------------------------|------------|

| 7909 I          | Data Channel                                                                                          |            |

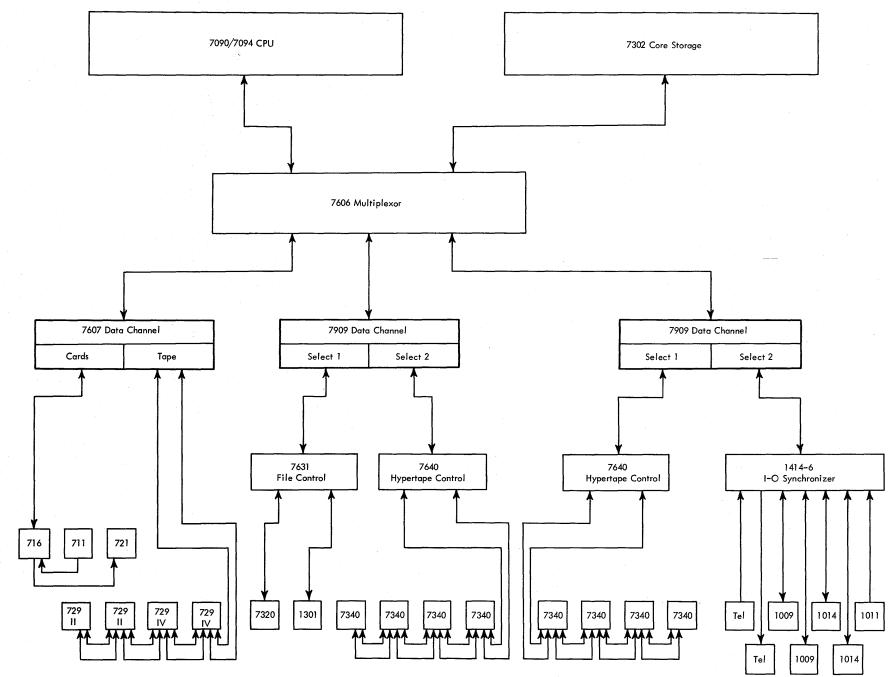

| 1               | 7090/7094 Channel Configuration                                                                       | 6          |

| 2               | System Weight Table                                                                                   | 7          |

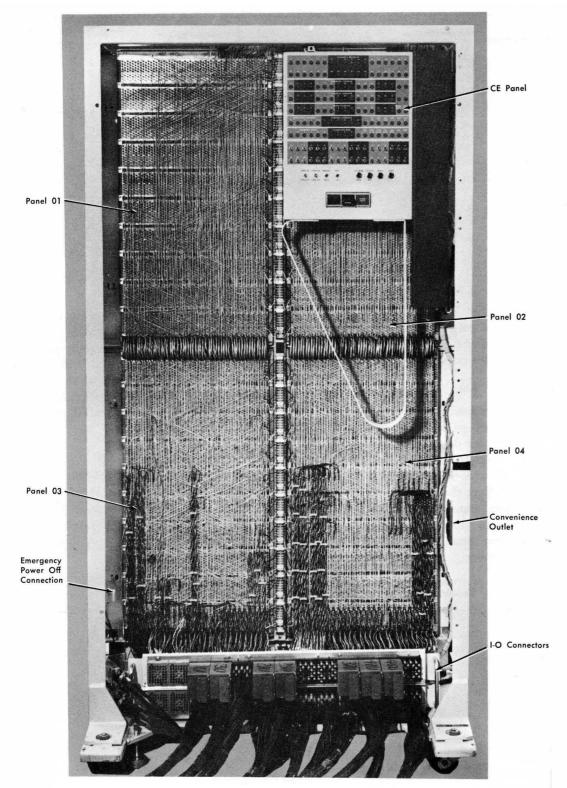

| 3               | Physical Layout—Front View                                                                            | 8          |

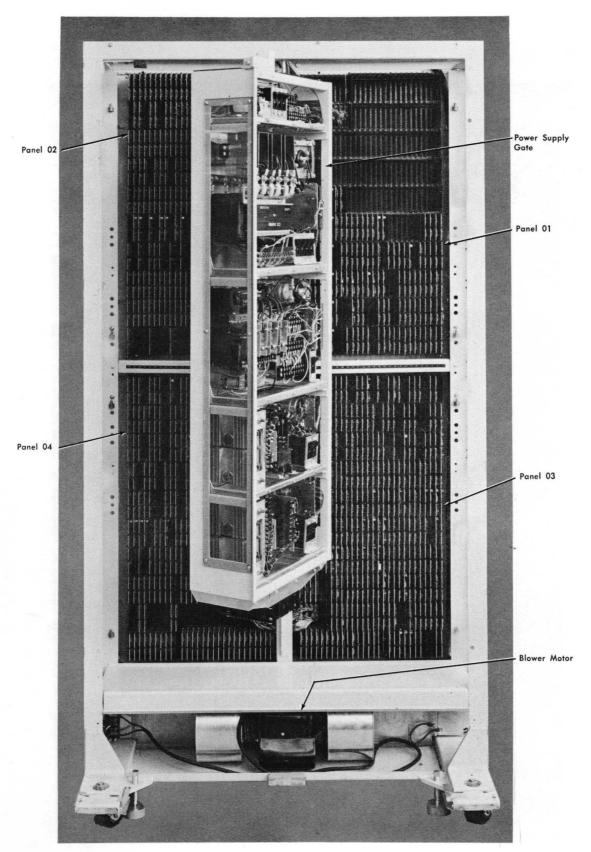

| 4               | Physical Layout—Rear View                                                                             | 9          |

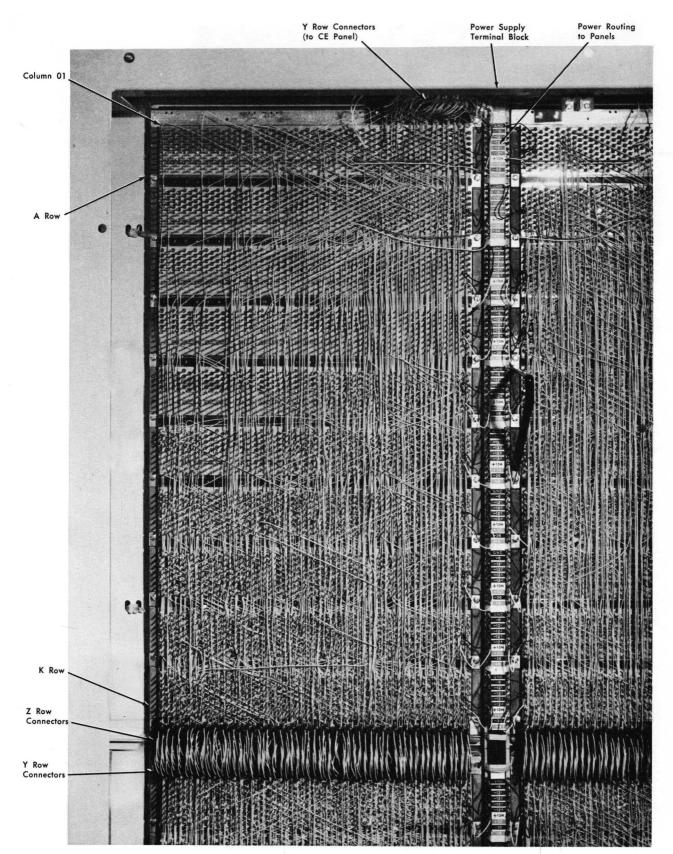

| 5               | SMS Panel 01                                                                                          | 10         |

| 6               | I-O Connectors                                                                                        |            |

| 7               | 7607-7909 Instruction Compatability                                                                   | 12         |

| 8               | Channel Command Comparisons                                                                           | 12         |

| 9               | Inter-Channel Priority Connections                                                                    | 13         |

| 10              | Channel Priority Logic                                                                                | 14         |

| 11              | Channel Priority Sequence Chart                                                                       | 14         |

| 12              | Demand Delay Sequence Chart                                                                           | 15         |

| a. 1            |                                                                                                       |            |

|                 | ex I-O Interface                                                                                      |            |

| 13              | Interface Functional Grouping                                                                         | 17         |

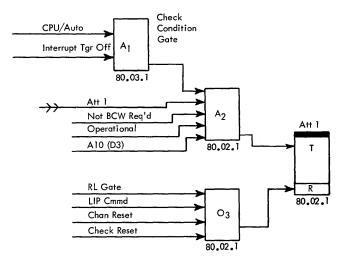

| 14              | Attention 1 Condensed Logic                                                                           | 20         |

| 15              | Cable Connector Assignments                                                                           | 21         |

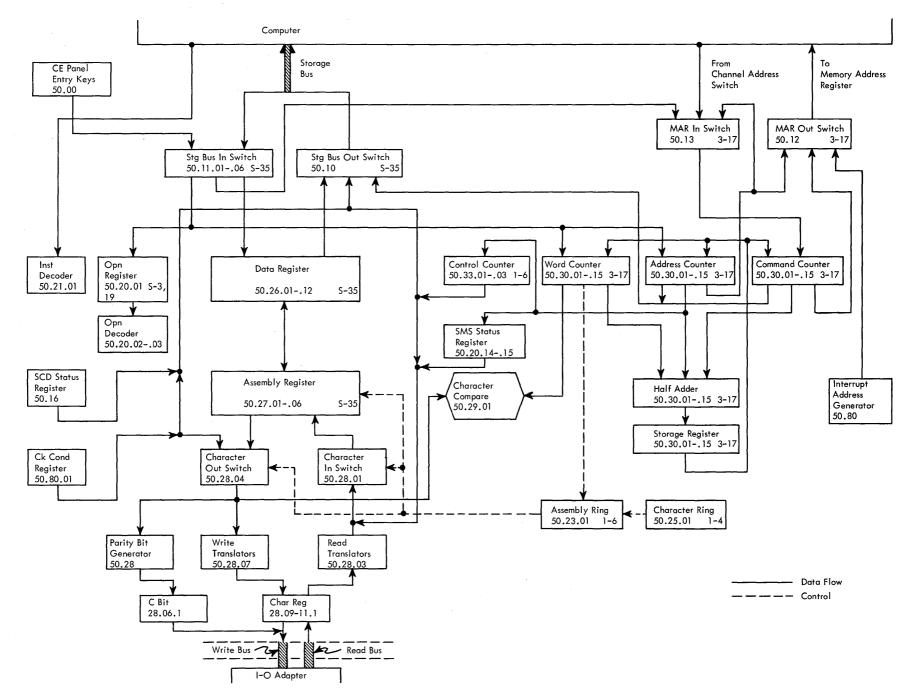

| 16              | 7909 Functional Units and Data Flow                                                                   | 23         |

| Chann           | el Organization and Functional Units                                                                  |            |

|                 |                                                                                                       | 25         |

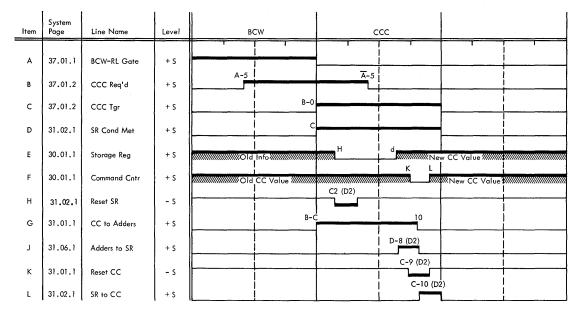

| 17<br>18        | Command Counter Position 17<br>Command Counter Cycle Sequence Chart                                   | 25         |

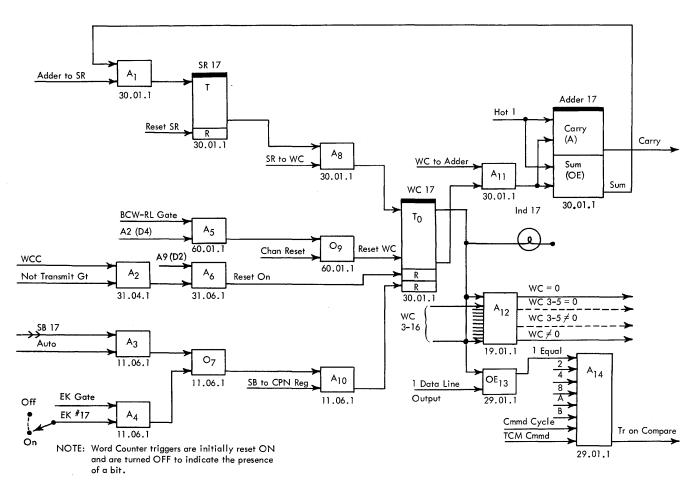

| $10 \\ 19$      |                                                                                                       | 20<br>26   |

| 19<br>20        | WC Complement Addition                                                                                | 20<br>27   |

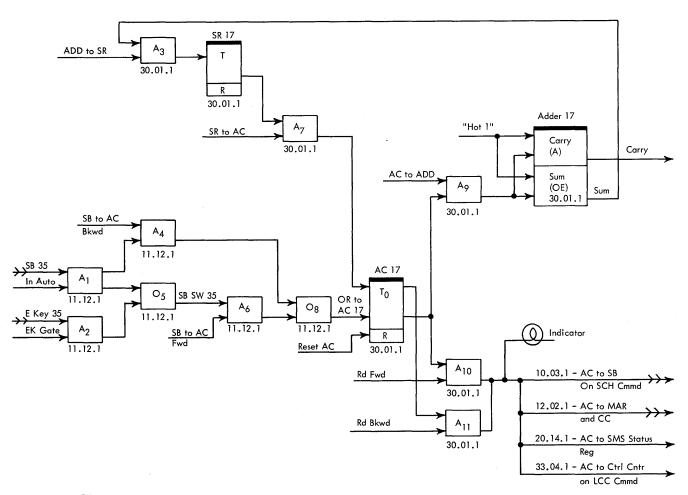

| 20<br>21        |                                                                                                       | 28         |

| 21<br>22        | WCC and ACC Sequence Chart                                                                            |            |

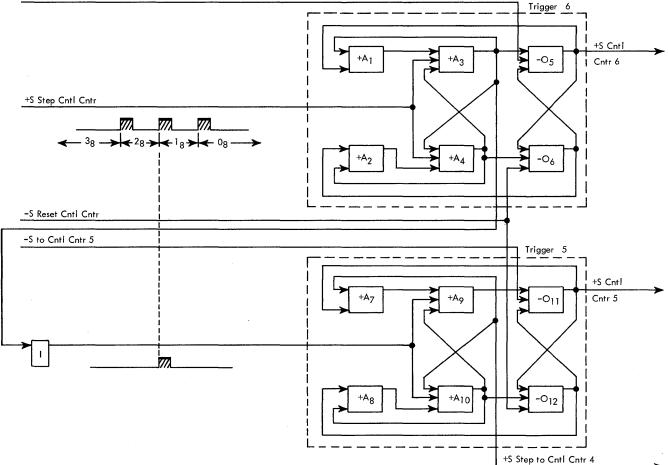

| $\frac{22}{23}$ | Control Counter                                                                                       | 31         |

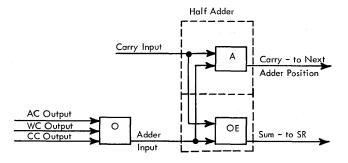

| $\frac{23}{24}$ | Half Adder Position                                                                                   | 31         |

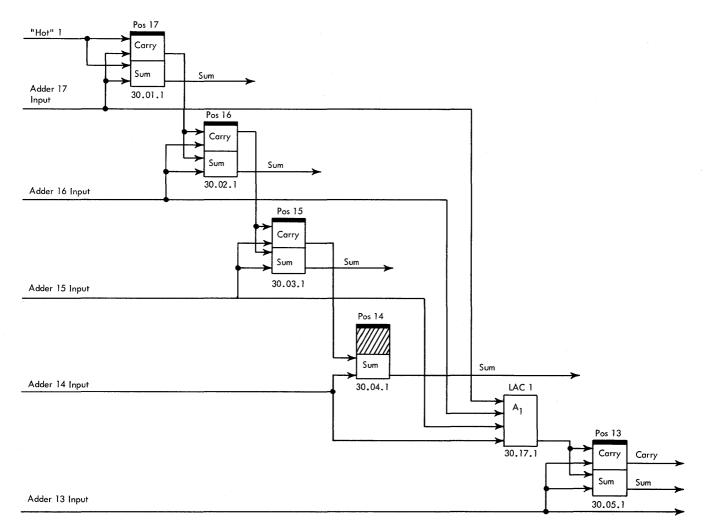

| $\frac{24}{25}$ | Adder Look-Ahead                                                                                      | 32         |

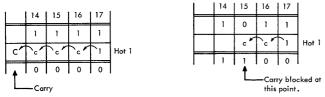

| $\frac{20}{26}$ | Adder Look-Ahead Grouping                                                                             | 33         |

| $\frac{20}{27}$ | Character Ring Condensed Logic                                                                        | 34         |

| 28              | Character Ring Sequence Chart                                                                         | 35         |

| $\frac{20}{29}$ | Character Ring Functions                                                                              | 35         |

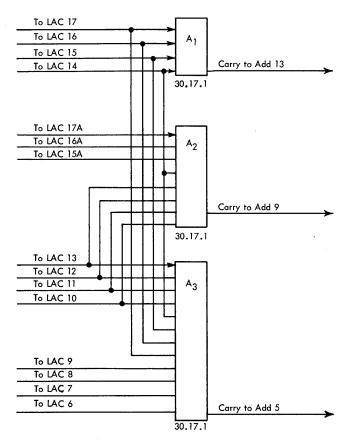

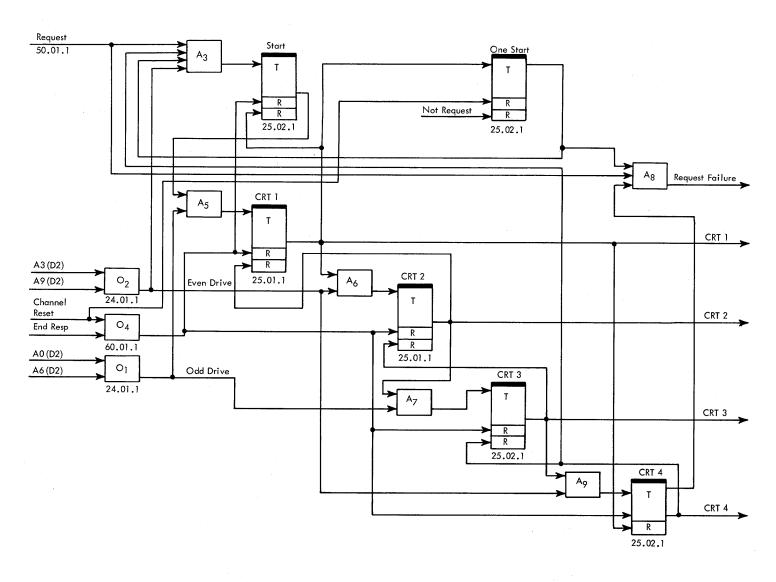

| 29<br>30        | Request Failure Sequence Chart                                                                        | 36         |

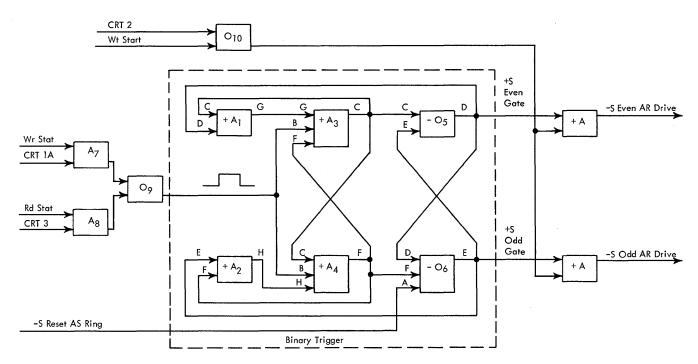

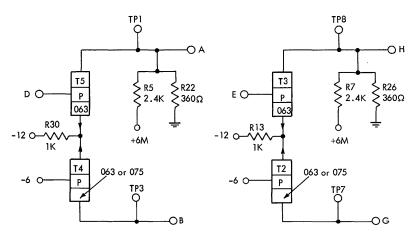

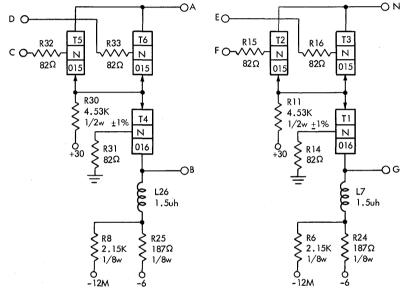

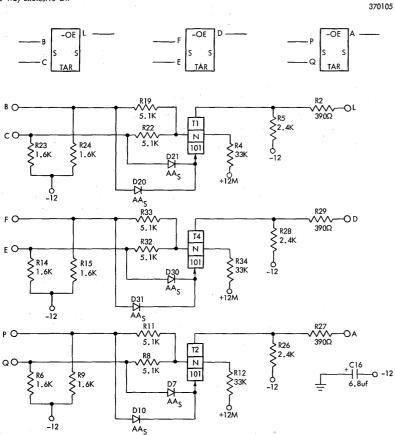

| 31              | Assembly Ring Drive Circuit (Binary Trigger)                                                          | 36         |

| 32              | Assembly Ring Drive Cricuit (Bhary Trigger)<br>Assembly Ring Drive Trigger Sequence Chart<br>for Read | 37         |

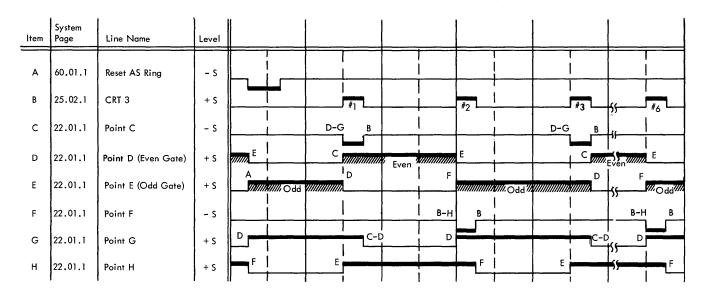

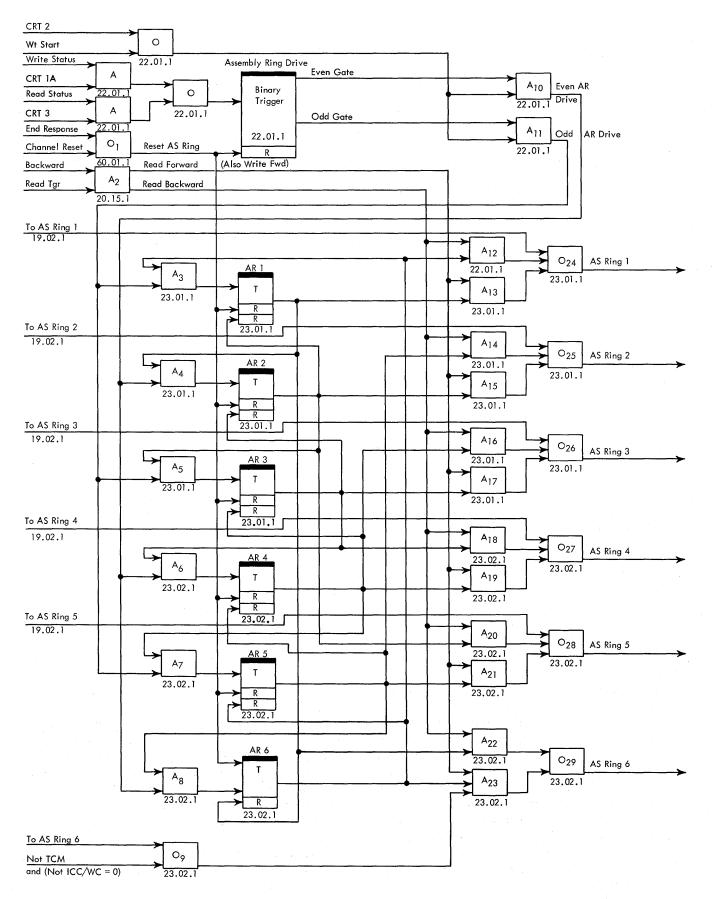

| 33              | Assembly Ring Condensed Logic                                                                         | 38         |

| 34              | Assembly Ring Sequence Chart For Read                                                                 | 39         |

| 35              | Assembly Ring Sequence Chart For Write                                                                | 40         |

| 00              | resembly rung bequence chart for write                                                                | -10        |

| BCD I           | Binary Translation                                                                                    |            |

| 36              | Simplex BCD Translation                                                                               | 41         |

| 37              | Character Coding and Translations                                                                     | 42         |

| 38              | Write BCD Translation                                                                                 | 43         |

| 39              | Write BCD Translator                                                                                  | 44         |

| 40              | Read Simplex BCD Translation                                                                          | 45         |

| 41              | Read BCD Translator                                                                                   | 47         |

| 42              | Parity Bit Generator                                                                                  | 47         |

| Comp            | iter Instructions                                                                                     |            |

| 43              |                                                                                                       | 40         |

| 43              | RSC/STC Flow Chart<br>RSC Sequence Chart                                                              | 49<br>50   |

| 44              | STC Sequence Chart                                                                                    | $50 \\ 51$ |

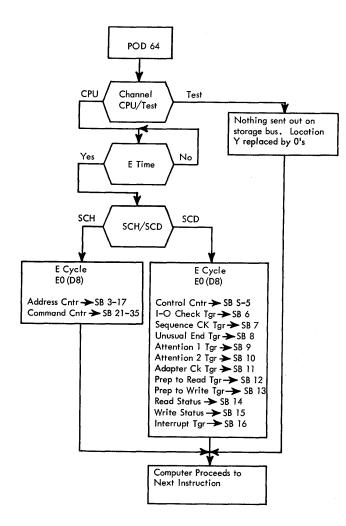

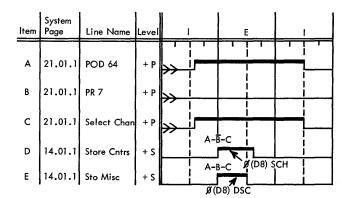

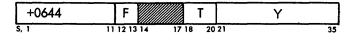

| 43<br>46        | SCH/SCD Flow Chart                                                                                    | 51         |

| 40              | SCH/SCD Sequence Chart.                                                                               | 52         |

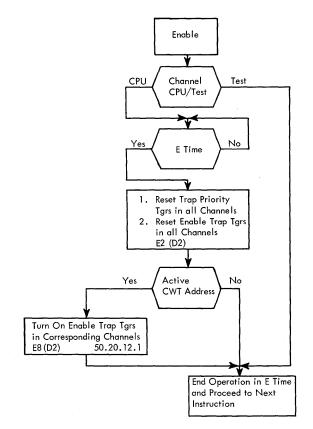

| 48              | Enable Flow Chart                                                                                     | 53         |

| 49              | Enable Flow Chart                                                                                     | 53         |

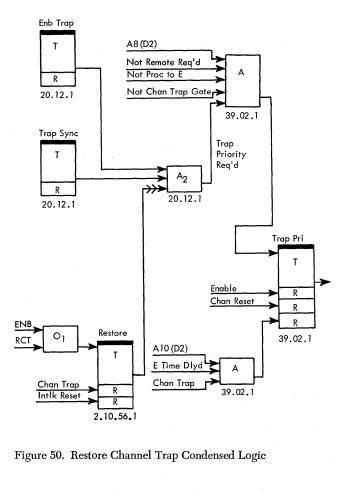

| 50              | Restore Channel Trap Condensed Logic                                                                  | 53<br>54   |

| 51              | Restore Channel Trap Condensed Logic                                                                  | 54         |

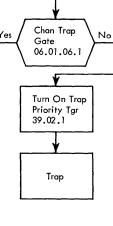

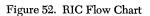

| 52              | RIC Flow Chart                                                                                        | 55         |

| 53              | RIC Sequence Chart                                                                                    |            |

|                 |                                                                                                       |            |

| FIGUR      | e Title                                                                   | Page       |

|------------|---------------------------------------------------------------------------|------------|

| 7909       | Channel Commands                                                          |            |

| 54         | 7909 Commands                                                             | . 56       |

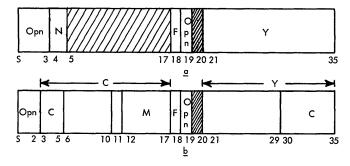

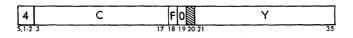

| 55         | Command Formats                                                           | . 56       |

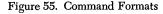

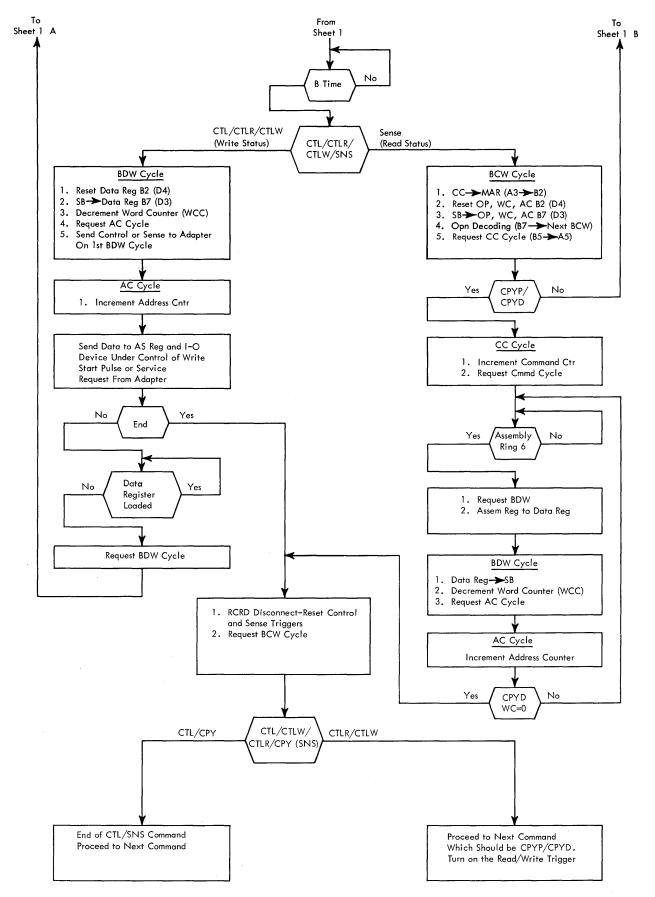

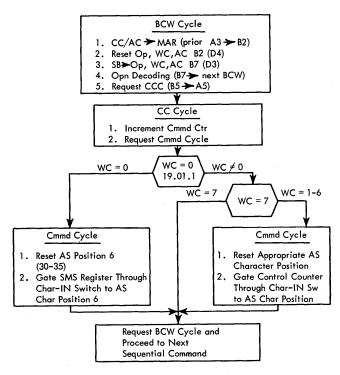

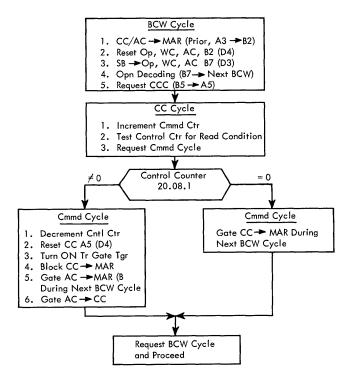

| 56         | CTL/CTLW/CTLR/SNS Flow Chart (Sheet 1).                                   | . 58       |

|            | CTL/CTLW/CTLR/SNS Flow Chart (Sheet 2).                                   | . 59       |

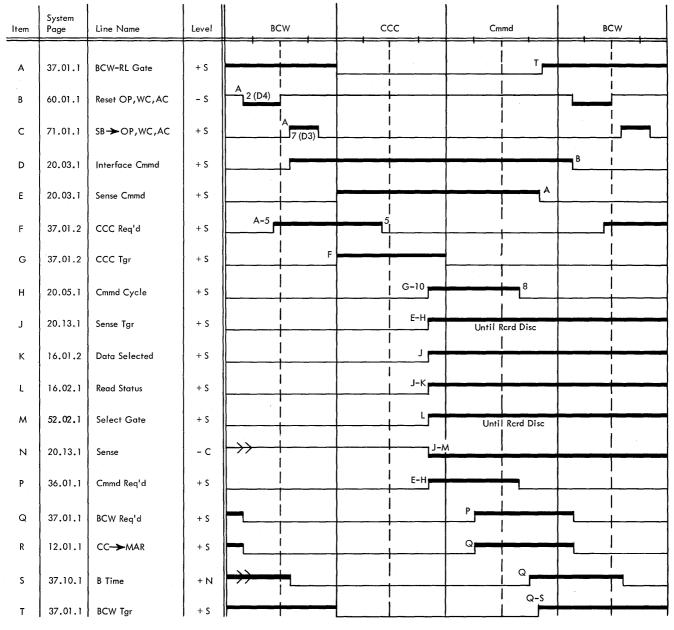

| 57         | CTL/CTLW/CTLR Sequence Chart                                              |            |

| 58         | SNS Sequence Chart                                                        |            |

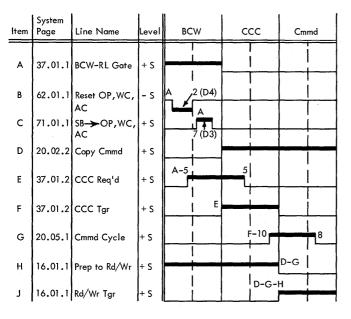

| 59         | CPYP-CPYD Sequence Chart                                                  |            |

| 60         | TCH Sequence Chart                                                        |            |

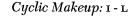

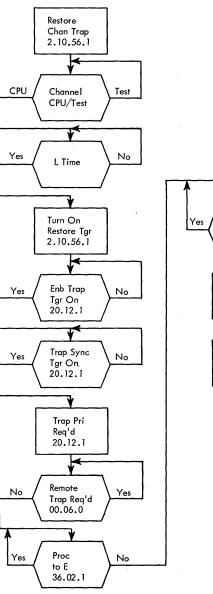

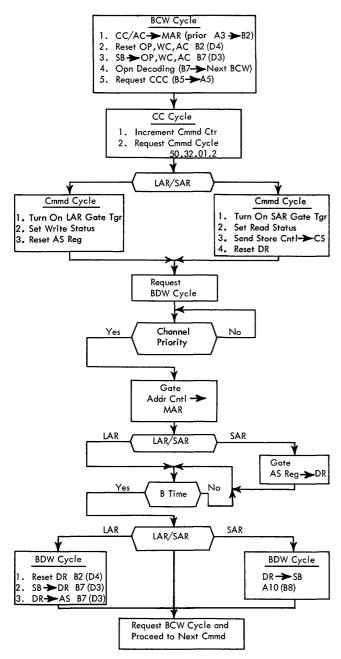

| 61         | WTR/TWT Flow Chart                                                        |            |

| 62         | WTR Sequence Chart                                                        |            |

| 63         | TWT Sequence Chart                                                        |            |

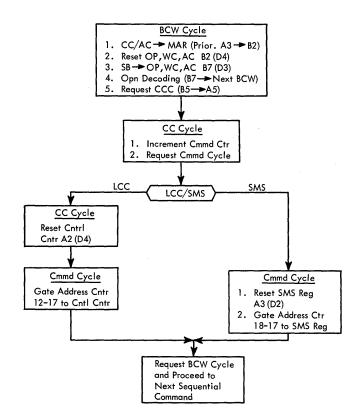

| 64         | LAR/SAR Flow Chart                                                        | ~ ~        |

| 65         | LAR Sequence Chart                                                        |            |

| 66         | SAR Sequence Chart                                                        |            |

| 67<br>68   | SMS Sequence Chart                                                        | . 71       |

| 68<br>69   | LCC Sequence Chart                                                        |            |

| 69<br>70   | ICC Flow Chart                                                            |            |

| 70         | ICC Flow Chart                                                            |            |

| $71 \\ 72$ | TDC Flow Chart                                                            |            |

| 73         | TDC Sequence Chart                                                        |            |

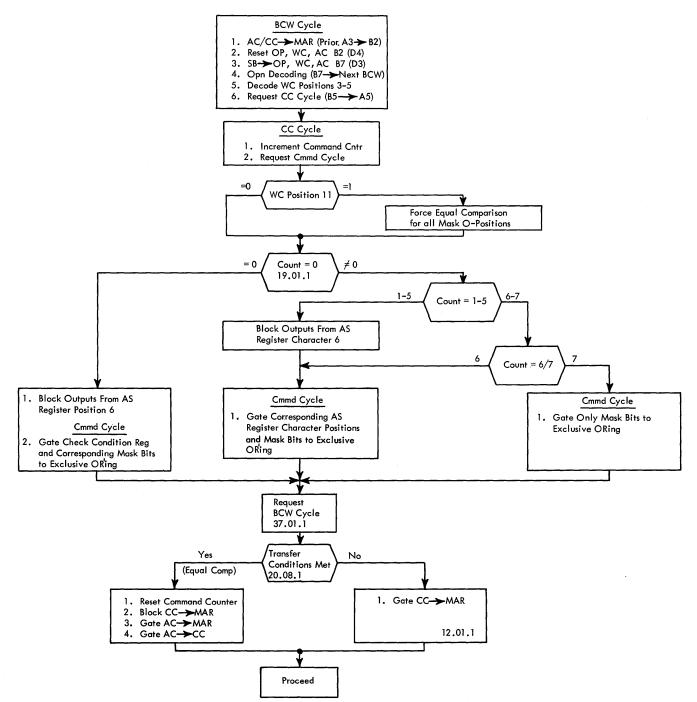

| 73<br>74   | TCM Flow Chart                                                            |            |

| 75         | TCM Flow Chart                                                            |            |

| 76         | Transmit Flow Chart                                                       |            |

| 77         | Transmit Sequence Chart                                                   |            |

|            |                                                                           |            |

| Data I     | Flow                                                                      |            |

| 78         | Core Storage to Channel                                                   | . 82       |

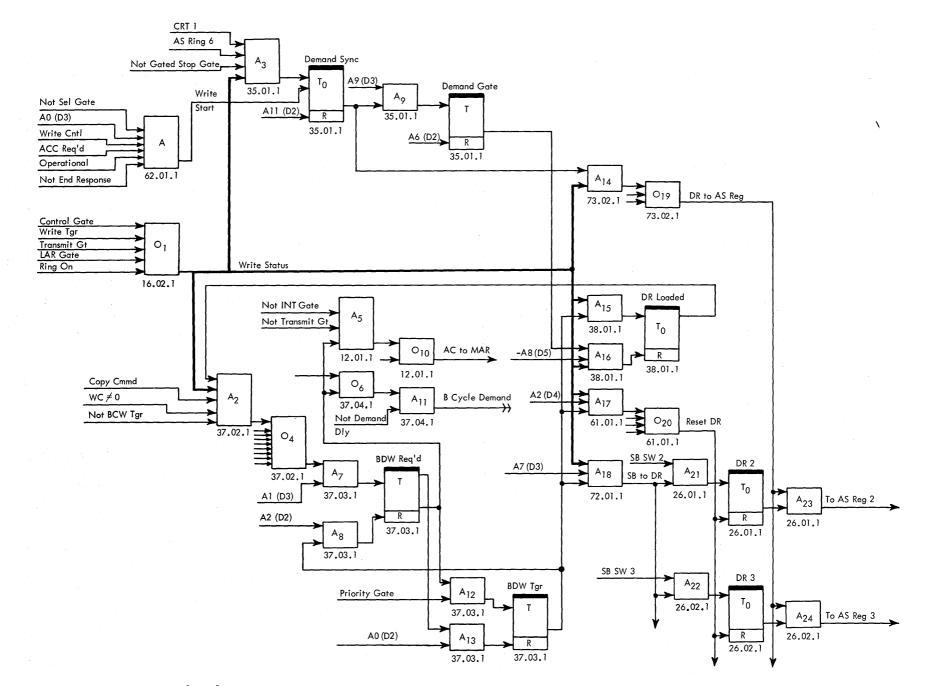

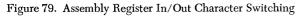

| 79         | Assembly Register In/Out Character Switching                              | . 83       |

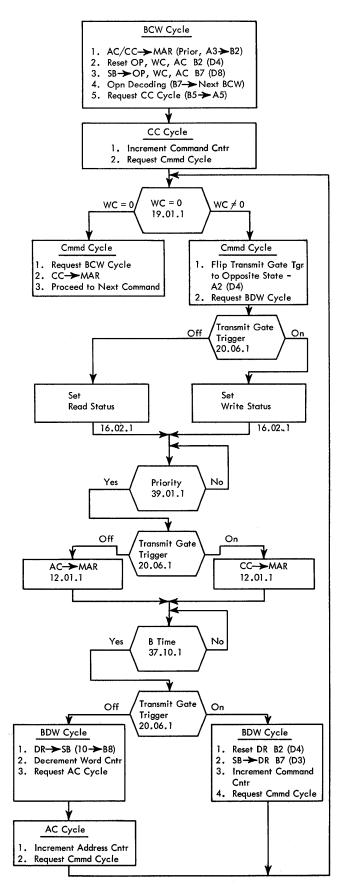

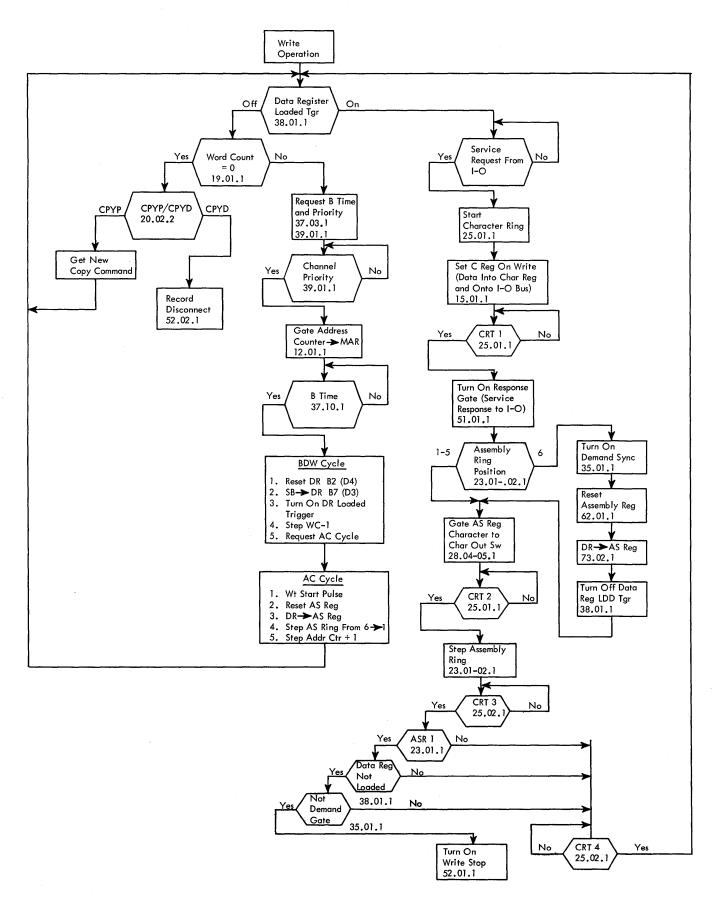

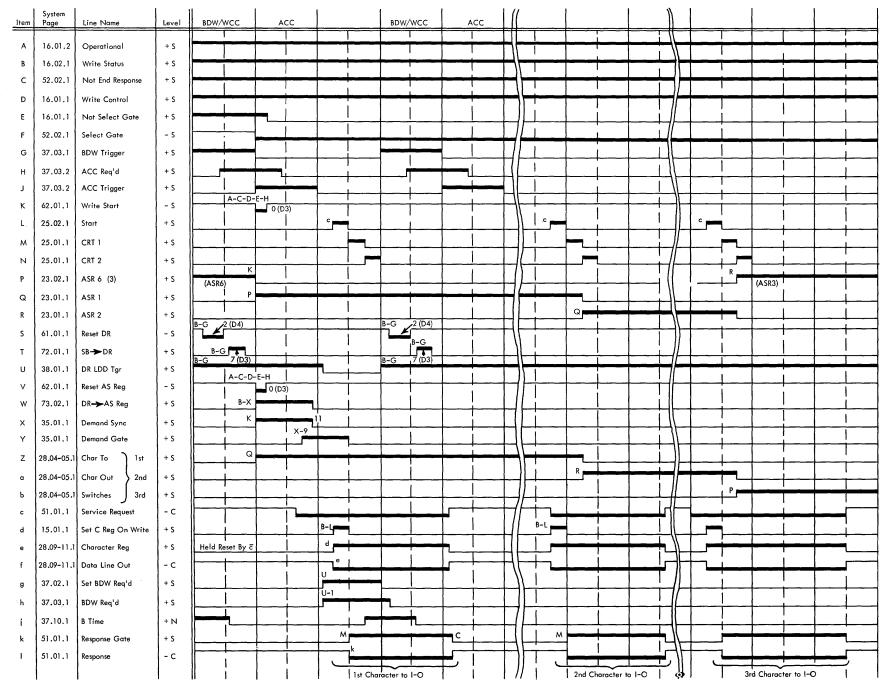

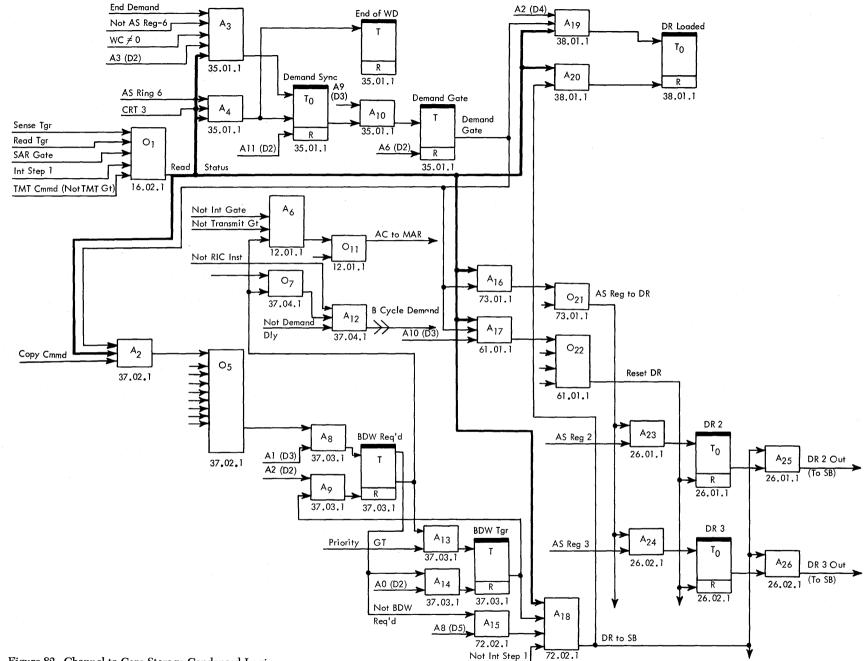

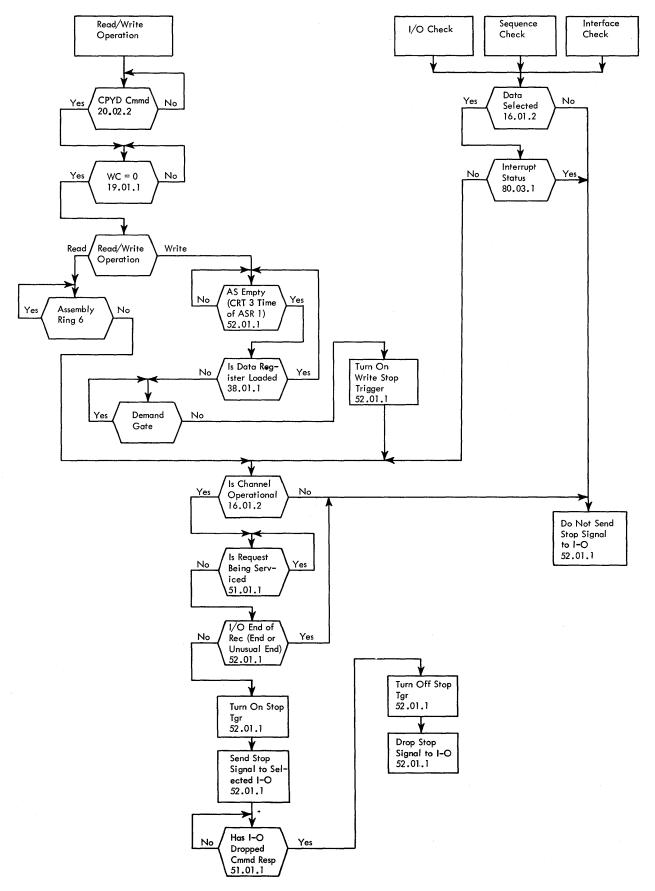

| 80         | Channel Write Operation Flow Chart                                        | . 84       |

| 81         | Channel Write Operation Sequence Chart                                    |            |

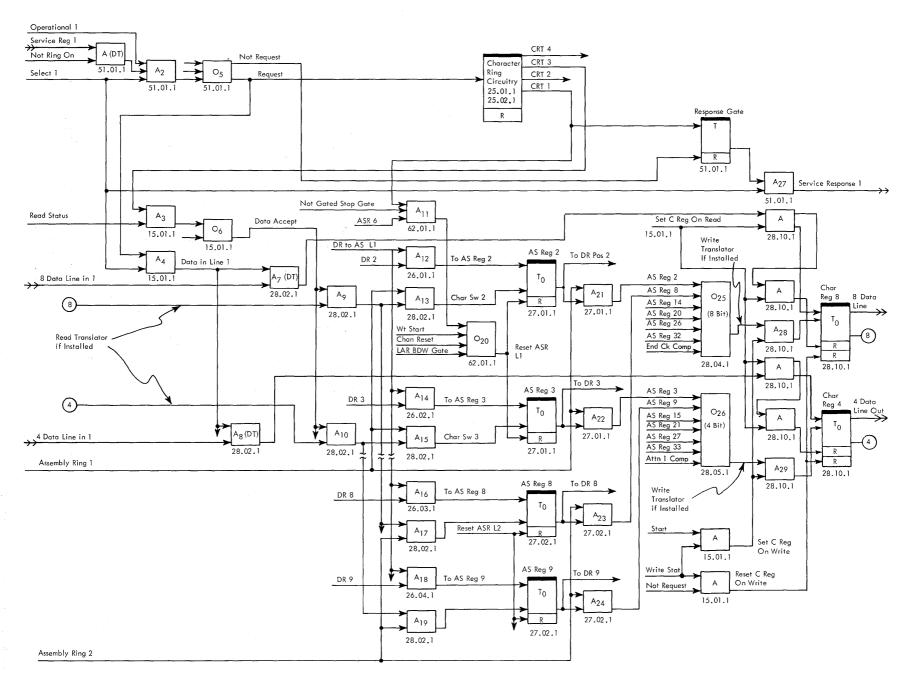

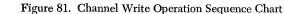

| 82         | Channel to Core Storage Condensed Logic                                   |            |

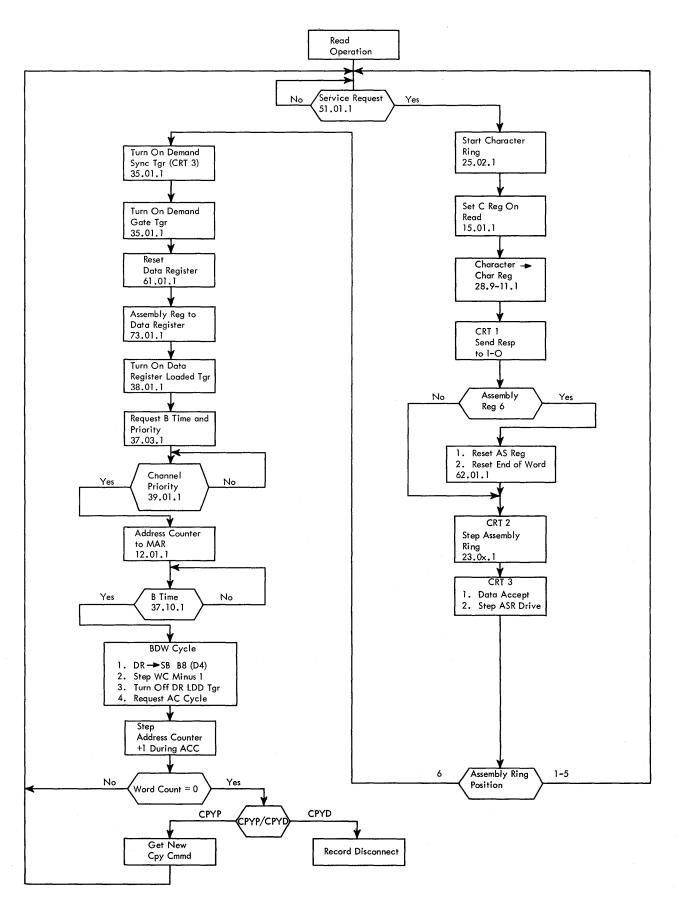

| 83         | Channel Read Operation Flow Chart                                         |            |

| 84         | Channel Read Sequence Chart                                               |            |

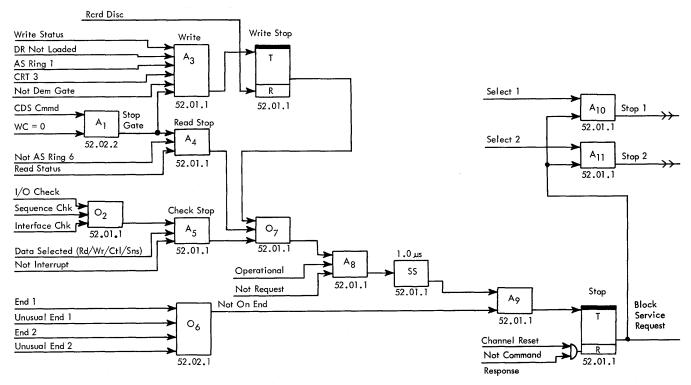

| 85         | Stop Condition Condensed Logic                                            |            |

| 86         | Stop Condition Flow Chart                                                 |            |

| 87         | Stop Condition Sequence Chart                                             |            |

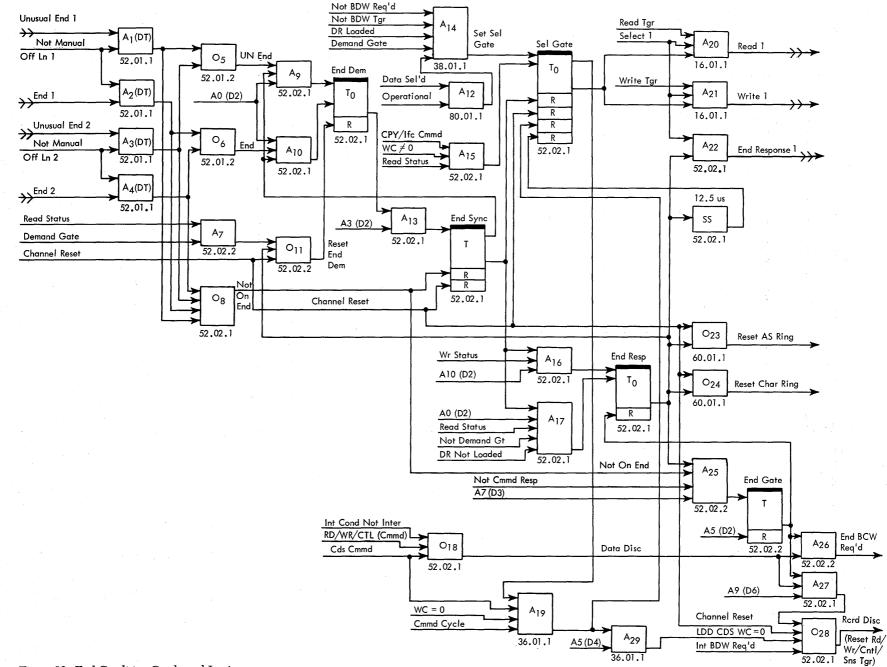

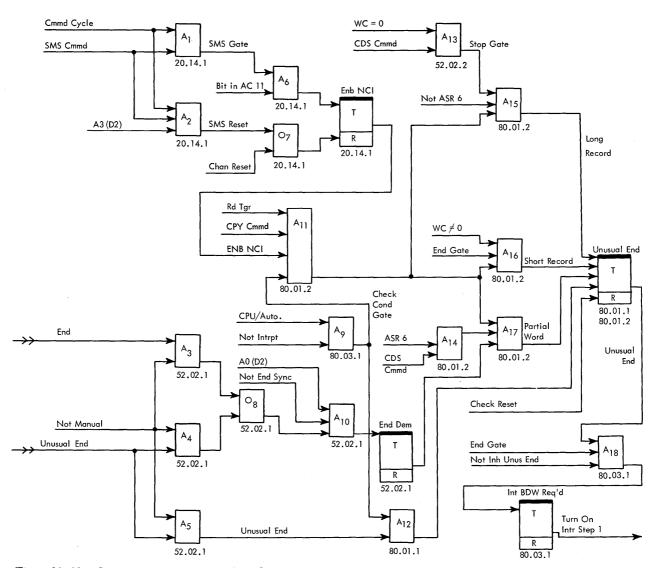

| 88         | End Condition Condensed Logic                                             |            |

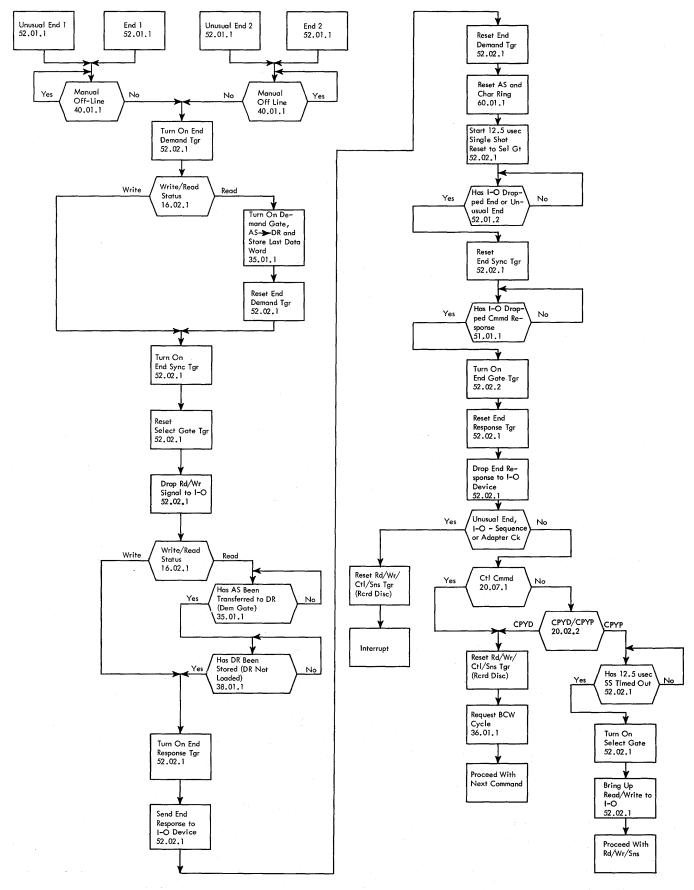

| 89         | End Condition Flow Chart                                                  |            |

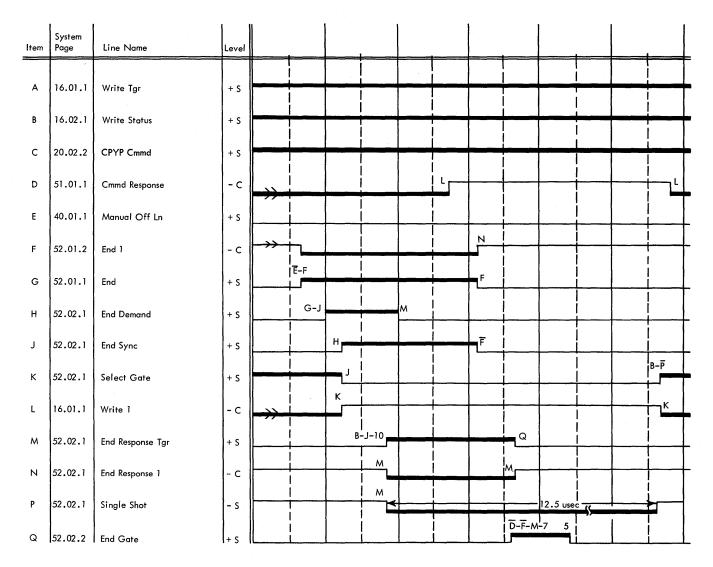

| 90         | End Condition Sequence Chart.                                             |            |

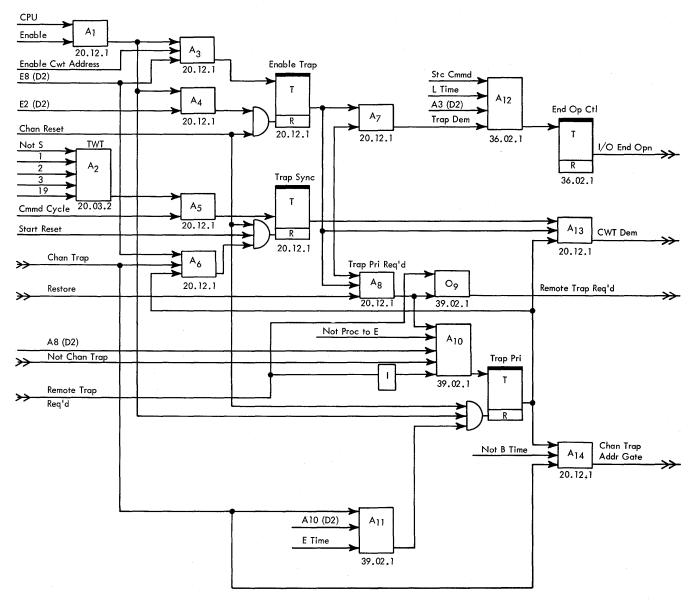

| 91         | Channel Trap Condensed Logic                                              |            |

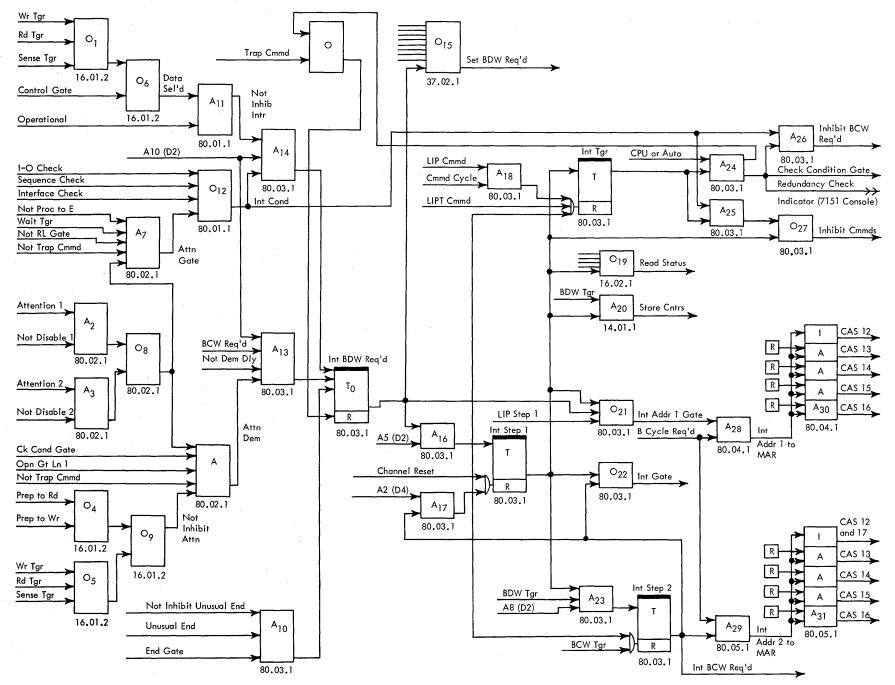

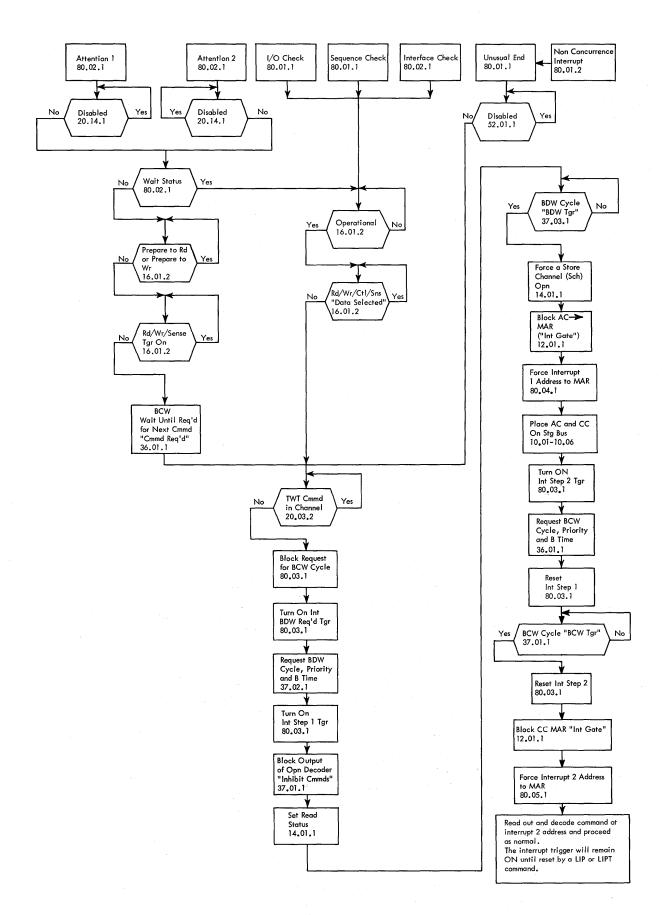

| 92<br>93   | Channel Interrupt Condensed Logic                                         |            |

| 93<br>94   | Non-Concurrence Interrupt Condensed Logic<br>Channel Interrupt Logic Flow |            |

| 95         | Channel Interrupt Logic Flow                                              |            |

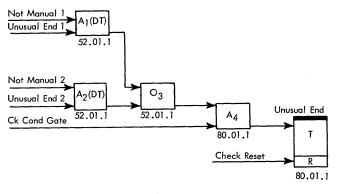

| 96         | Unusual End Condensed Logic                                               |            |

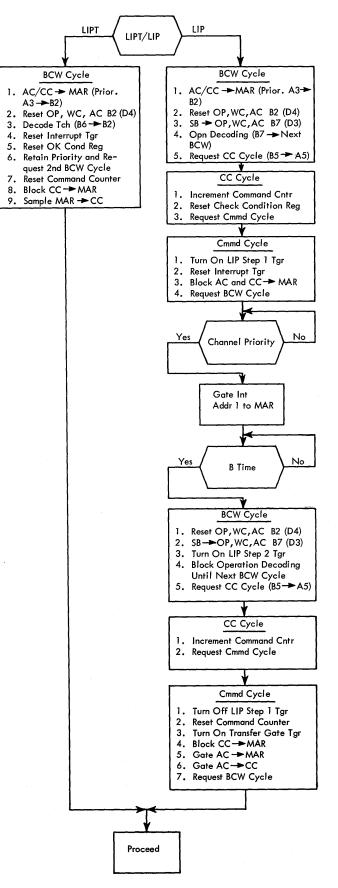

| 97         | LIP/LIPT Flow Chart.                                                      | 104        |

| .98        | LIP Sequence Chart.                                                       |            |

| 99         | LIPT Sequence Chart                                                       |            |

| 100        | Indirect Addressing Sequence Chart                                        |            |

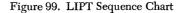

| 101        | I-O Check Condensed Logic                                                 |            |

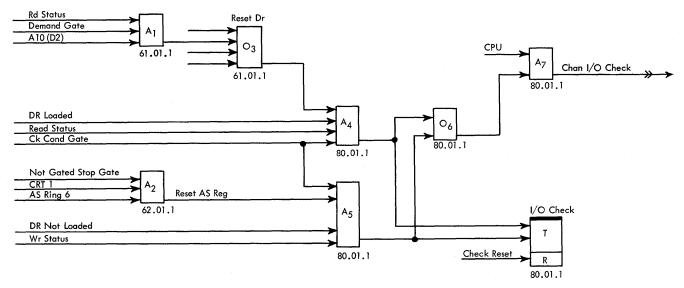

| 102        | Sequence Check Condensed Logic                                            |            |

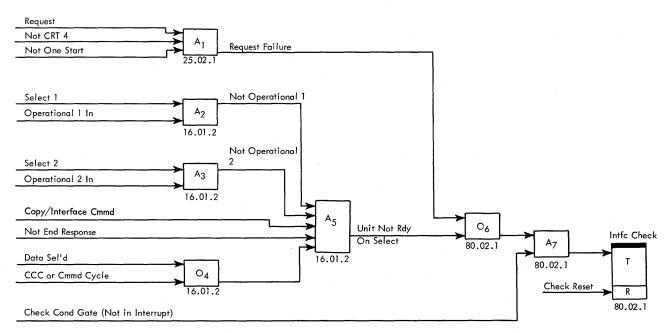

| 103        | Interface Check Condensed Logic                                           |            |

| 104        | Check Reset Condensed Logic                                               |            |

|            | 0                                                                         |            |

| CE Te      | st Panel                                                                  |            |

| 105        | CE Test Panel                                                             |            |

| 106        | CE Panel Operations                                                       |            |

| 107        | Manual (Single-Step Mode) Operation                                       | 115        |

| Power      | Supply                                                                    |            |

|            |                                                                           | 110        |

| 108        | Power Supply Locations                                                    | 118<br>119 |

| 109        | Power Supply Controls                                                     | . 119      |

The IBM 7909 Data Channel is a stored program device designed to increase the capabilities of the IBM 7090/ 7094 Data Processing Systems. It attaches to the IBM 7606 Multiplexor in the same manner as the IBM 7607 Data Channel, and controls data flow between core storage and a variety of input-output devices. Communication and data flow between the channel and 1-0 adapter are through a simplex 1-0 interface.

The many commands at its disposal give the 7909 Data Channel powerful capabilities for performing logic and testing operations in addition to the normal control of data transmission.

An automatic interrupt feature extends the computer trap concept to the channel and, therefore, gives the channel an ability to monitor continually and independently specific conditions either from within itself or from the 1-0 adapter.

The IBM 7302 Core Storage acts as a common storage medium for both the computer instructions and channel commands. Access to core storage to obtain these commands or transmit data is on a shared-time basis with the computer program.

To eliminate confusion and establish terminology, note the following:

*Instructions* are executed by the computer.

*Commands* are executed by the channel.

Orders are executed by the 1-0 adapter.

The computer is required to initiate a channel operation. Once started, however, the channel makes the necessary requests for storage cycles and executes its own program of testing, transferring, or transmitting data completely independent of the main computer. If previously enabled for control word traps, the channel has the ability to interrupt the computer program; thus, communications are available between the channel and computer at all times.

Optional features add flexibility to the channel's operation. The IBM 7909 Data Channel Switch Optional Feature permits attachment of one or two inputoutput control units to one 7909 Data Channel. The IBM 7909 Data Channel BCD Translation Optional Feature provides automatic BCD translation of information transmitted between an I-O adapter and the 7909 Data Channel. The IBM 7909 Data Channel Read Backward Optional Feature facilitates processing data received from a recorded tape being read in a backward direction. Characters are assembled in reverse order and stored in descending core storage locations.

# 7909 Attachments

A variety of input-output devices and appropriate adapters can be attached to a 7909 oriented system.

The IBM 7631 File Control with the IBM 1301 Disk Storage provides a capacity of more than 55 million characters of storage for each disk storage unit.

The IBM 7320 Drum Storage and IBM 7631 File Control with drum attachment feature bridge the gap between a high-speed, limited capacity core storage and slower, large capacity random-access disks and magnetic tape. The capacity of the 7320 is 1.12 million six-bit characters and the character rate is 202.8 KC.

The IBM 7640 Hypertape Control with the IBM 7340 Hypertape Drive introduces a new concept in magnetic tape devices. Character rates can be as high as 170,000 alphameric characters (28,330 words) per second.

The IBM 1414-6 Input-Output Synchronizer permits the attachment of communication-oriented and paper tape devices such as:

ивм 1009 Data Transmission Unit

вм 1011 Paper Tape Reader

**IBM 1014** Remote Inquiry Units

**Telegraphic Input-Output Units**

Figure 1 shows a 7090/7094 system with attached devices.

#### **Maximum System Considerations**

A maximum combination of eight 7607 and 7909 Data Channels may be attached to a 7090 or 7094 system. Individual channel character rates and physical limitation (cable lengths), however, may reduce this to less than eight.

A weight table has been prepared (Figure 2) as a guide to the system planner in determining the maximum possible 7090 or 7094 system configuration. The following are assumed:

1. 7909 Data Channel timings are assigned in accordance with the table under "7909 Data Channel timings."

2. No one channel will require more than three consecutive storage cycles.

3. Channel priority is assigned with the greatest weights on the highest priority channels.

The maximum operable system is then defined as that system where the sum of the weights of attached

7909 Data Channel 5

Figure 1. 7090/7094 Channel Configuration

$\mathcal{J}_{1}^{I}$

6

| Data        | <u></u>                              | Nominal        | Weight/ | Weight/Channel |  |

|-------------|--------------------------------------|----------------|---------|----------------|--|

| Channel     | Attached Device                      | Character Rate | 7090    | 7094           |  |

| 7607        | 729 11/V at 200 BP1                  | 15 KC          | 2.1     | 1.9            |  |

| Mod 1,2,3,4 | 729 IV∕VI at 200 BPI                 | 22.5 KC        | 3.2     | 2.8            |  |

|             | 729 11/V at 556 BP1                  | 41.7 KC        | 6.2     | 5.2            |  |

|             | 729 V at 800 BPI                     | 60 KC          | 9.4     | 7.6            |  |

|             | 729 IV/VI at 556 BPI                 | 62.5 KC        | 9.9     | 7.9            |  |

|             | 729 VI at 800 BPI                    | 90 KC          | 15.6    | 11.7           |  |

| 7909        | 7750 Programmed Transmission Control | 71.5 KC        | 9.4     | 7.6            |  |

| 1           | 1301 Disk Storage                    | 90 KC          | 12.4    | 9.6            |  |

|             | 1414 VI I-O Synchronizer             | 91 KC          | 12.0    | 9.7            |  |

|             | 7340 Hypertape Drive                 | 170 KC         | 37.2    | 23.0           |  |

|             | 7320 Drum Storage                    | 202.8          | 42.9    | 24.4           |  |

Note: If a channel has devices attached with two different weights, the highest weight of the two will be assigned for the channel.

Figure 2. System Weight Table

devices is less than or equal to 100. If assumption 3 cannot be satisfied, the sum of the weight must be less than or equal to 70. Operation cannot be guaranteed on a system that does not meet this criteria.

### 7909 Data Channel Timings

7909 Data Channel timings are determined by installation of an appropriate SMS card assembly in card location 05A3D21. These timings are dependent upon total systems weight as explained in the preceding section and must be assigned in accordance with the following table. These timings affect the execution of all 7909 operations except data transmission under COPY control. The time required to transmit one word under a transmit command (two storage cycles) is given as information for each timing.

| Total Syste | MS WEIGHT   |        | Average Time to   |

|-------------|-------------|--------|-------------------|

| FROM        | то          | CAPCUT | Transmit One Word |

| 0           | 15          | 9      | 13.1 µs           |

| 16          | 45          | 10     | 74.2 μs           |

| 46          | 75          | 11     | 96.0 µs           |

| 76          | 81          | 12     | $122.2 \ \mu s$   |

| 82          | 89          | 13     | 152.7 μs          |

| 90          | 100         | 14     | 183.3 µs          |

| 7909 Timing | Assignments |        |                   |

# **Physical Description**

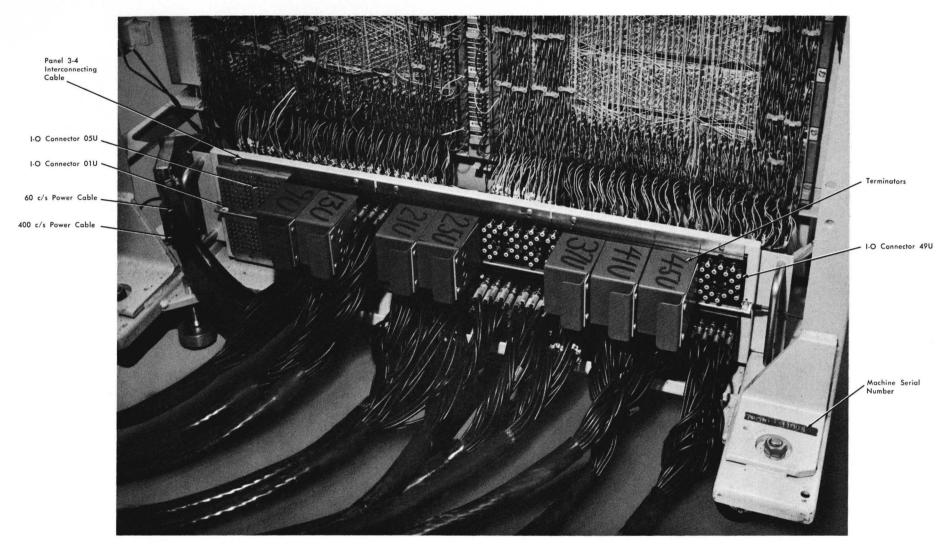

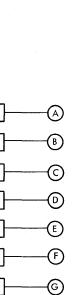

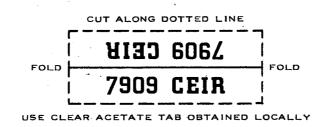

The 7909 Data Channel (Figures 3, 4, 5, and 6) is a rack and panel module containing four SMS panels. Each panel contains ten rows of 28 sms card sockets. From the wiring side, the panels are designated 1-4, left to right, top to bottom. 1-0 connector rows are located below the two lower panels and designated row U (upper) and row L (lower).

A CE test panel is hinged to the upper right front section of the module and can be easily swung out of the way when scoping points on panel 2.

Hinged to the center post in the back of the module is a self-contained power supply capable of producing the various voltages required within the logic panels. Power to the 7909 is supplied by the IBM 7618 Power Control through two cable connections at the lower left front section of the module. The upper cable supplies 60 cps power while the lower cable supplies 400 cps.

#### Logic Panel

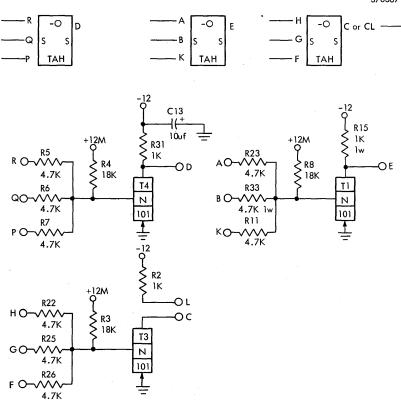

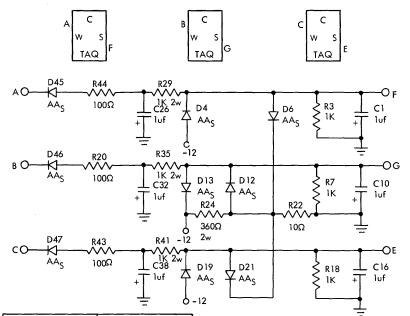

The 10 x 28 panel (Figure 5) contains 280 sms sockets forming a matrix 28 columns wide by 10 rows long. The columns are designated 01 through 28 (left to right), and the rows are designated A through K (top to bottom). Each sms socket has 16 pins, A through R (excluding I and O), as follows:

| А |    |     |   |  |

|---|----|-----|---|--|

| ~ | ı. | ł   | В |  |

| С | 1  | I   | D |  |

| Е | I  | I   | F |  |

| G |    | 1   | н |  |

| J | I. |     |   |  |

|   | ì  |     | к |  |

| L |    | 1   | м |  |

| Ν |    | 1   | Р |  |

| Q | I  | •   |   |  |

|   |    | - 1 | R |  |

# Interpanel Connections

Several methods of interpanel connections are used on the 7909. Eight-pin Y and Z row connector blocks are mounted above and below each of the four panels. Connections between panels 1-3 and 2-4 are made by short push-on, solderless jumper wires which run from the Z row of the upper panel to the Y row of the panel below (Figure 5).

Figure 3. Physical Layout—Front View

Figure 4. Physical Layout-Rear View

Figure 5. SMS Panel 01

Figure 6. I-O Connectors

Connections between panels 3 and 4 are made by a short, laced jumper cable which runs between the Z connector blocks at the bottom of the module (Figure 6). Additional connections are made by means of paddle-terminated cables from positions J24-J28 of panel 3 to J01-J05 of panel 4.

Connections between panels 1 and 2 are made by paddle-terminated cables that are not visible from the wiring side of the machine. Positions B19-B28 of panel 1 connect to B01-B10 of panel 2. In addition, positions A27-A28 of panel 1 connect to positions A4-A5 of panel 2.

A partial set of Y connectors at the top of panels 1 and 2 provide connections to the hinged CE panel in the front of the machine.

Y and Z connector pins are labeled as follows:

#### **Input-Output Connector Rows**

1-0 connector rows (Figure 6) for the module are located below the logic panels; the rows are designated row U (upper) and row L (lower), top to bottom. The 7909 uses 20- and 40-position biscuit connectors: 13 connectors per row numbered  $01, 05, 09, 13 \dots 45, 49$ from left to right as viewed from the wiring side of the machine. 7909 1-0 connector Systems page designations are:

| Frame     | Module | Row                          | Column | Pin   |

|-----------|--------|------------------------------|--------|-------|

| 05        | Α      | U or L                       | 01-49  | 01-40 |

| Examples: |        | —Service Rec<br>—Service Res |        |       |

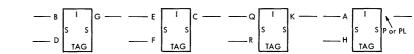

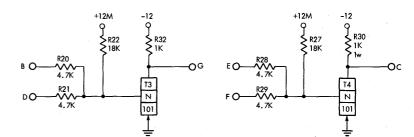

Column position 01 upper and 01 lower (40-position connectors) connects interface 1; the upper connector receives signals from the adapter (read cable) while the lower connector sends signals to the adapter (write cable). Position 05 has a corresponding use for interface 2 when the data channel switch optional feature is installed.

The remaining eleven connectors (20-position connectors), positions 09-49, receive the necessary assignment cables from the 7606 multiplexor. These cables connect to the lower receptacles and are terminated, where necessary, by terminator boxes in the corresponding upper positions. If there are other channels on this bank, however, the eleven upper connectors act as a jumper point for the signal cables to the next channel in line.

The twisted-pair wire connections receiving signals from the 1-0 cables are connected directly to the pins of panels 3 and 4.

# 7909-7607 Compatibility

The 7607 and 7909 Data Channels are not program compatible. A 7607 program presented to a 7909 will hang up the computer at the first select instruction (RDS, WRS, REW, BSR, and so on).

A 7909 program presented to a 7607 will cause an 1-0 check as soon as a channel operation is attempted. This results because a RCH (+0540) was not preceded by a select instruction.

A 7607 instruction, such as BTT, ETT, TRC, and TEF, which tests indicators in their execution, operates as though the indicator were always OFF. Select instructions receive no end operation signal from the 7909 and therefore cause the computer to hang up. Other instructions operate in an exact manner, have minor variations, or no effect whatsoever. Figure 7 shows computer instruction compatibility and Figure 8 shows a comparison of channel commands.

| 7607               |               | 7909            |                                       |

|--------------------|---------------|-----------------|---------------------------------------|

| IOT                |               |                 |                                       |

| ENB                |               | IOT<br>ENB *    |                                       |

|                    | -37           |                 |                                       |

| RCT                |               | RCT *           |                                       |

| SCH (x)<br>RCH (x) | <b>~</b>      | SCH (x) **      |                                       |

|                    | <b>~</b>      | RSC (x)         |                                       |

| LCH (x)            | <del></del> > | STC (x)         |                                       |

| <u>TCO (x)</u>     | <u> </u>      | TCO (x)         |                                       |

| TCN (x)            | <b>&gt;</b>   | TCN (x)         |                                       |

| BTT (x)            |               | Always Skips    |                                       |

| ETT (x)            | >             | (Indicator Off) |                                       |

| TRC (x)            | >             | Always Proceed  |                                       |

| TEF (x)            |               | (Indicator Off) |                                       |

| RDC (x)            |               | No Effect       |                                       |

| RDS                |               |                 |                                       |

| WRS                |               |                 |                                       |

| BSR                |               | Hangup          |                                       |

| BSF                | <b>&gt;</b>   | Computer        |                                       |

| WEF                |               | (No End Op      |                                       |

| REW                | >             | Control)        |                                       |

| RUN                |               |                 |                                       |

| SDN                |               |                 |                                       |

| No Effect          |               | RIC (x)         |                                       |

| SCH (x)            | 4             | SCD (x)         | · · · · · · · · · · · · · · · · · · · |

\* Control word trap only available \*\* 7607 stores Location Cntr in decrement and Addr Cntr in address of location Y and saves op code and bit in 19. 7909 stores Cmmd Cntr in address and Addr Cntr in decrement of location Y (the 7909 does not store the operation register)

Figure 7. 7607-7909 Instruction Compatability

|           | 7909 0                        | ommand                   |  |

|-----------|-------------------------------|--------------------------|--|

| 7607 Cmmd | WC $\geq$ 40,000 <sub>8</sub> | WC < 40,000 <sub>8</sub> |  |

| IOCD      | w                             | TR                       |  |

| IOCP      | C                             | Р                        |  |

| IORP      | CTLW                          | CTL                      |  |

| IOCT      | CI                            | γD                       |  |

| IORT      | TWT                           | LAR                      |  |

| IOSP      | TDC                           | x                        |  |

|           | x                             | SMS                      |  |

| IOCDN     | XMT                           |                          |  |

| IOCPN     | X                             | X                        |  |

| IORPN     | SNS                           | CTLR                     |  |

| IOCTN     | т                             | CM                       |  |

| IORTN     | X                             | SAR                      |  |

| IOSPN     | LCC                           | LIP                      |  |

| IOSTN     | ICC                           |                          |  |

| тсн       | TCH (IF 19 = 0)               | LIPT (IF 19 = 1)         |  |

X = 7909 Hangup

No 7909 Commands will cause a hangup if loaded into a 7607

Figure 8. Channel Command Comparisons

# **Channel Priority**

No two devices can use core storage during the same period of time. Therefore, with as many as eight individual channels and a computer sharing a common core storage, some method must be used to control these cycles without inter-conflict.

A priority system is used to provide this systematic dispensing of core storage cycles. Any channel having obtained priority has all of its immediate demands fulfilled before relinquishing priority to another channel. The immediate demands of all channels are satisfied before the computer can regain control and use core storage for its own purposes.

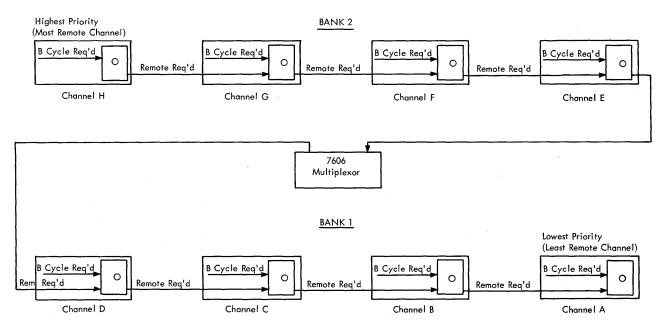

# Priority System—Multi-Channel

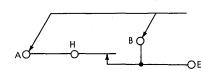

Priority (Figure 9) is unnecessary with only one channel connected to the system; the computer allows B times as requested. The need for B cycles is determined by the commands and conditions within each individual channel and could occur simultaneously on two or all channels attached to the system. The order in which each channel is serviced is from "most remote" to "least remote."

Physical connections to the computer are made at the multiplexor as bank 1 and bank 2. The last channel on bank 2 is normally the most remote and the farthest channel on bank 1, the least remote. Actually, banks 1 and 2 play no logical part in the operation; the eight channels can be considered as one continuous series connection.

Note that a "B cycle required" generated by a channel causes a remote required signal to be propagated to the lower priority units. The effect of this line is to block lower priority servicing until the higher priority channels have their immediate needs completely satisfied. Channel H (Figure 9) has no remote required input signal and will be serviced first; channel A has no remote required output signal and will be serviced last. (Channel designations are independent of priority; those in Figure 9 are used as examples only.)

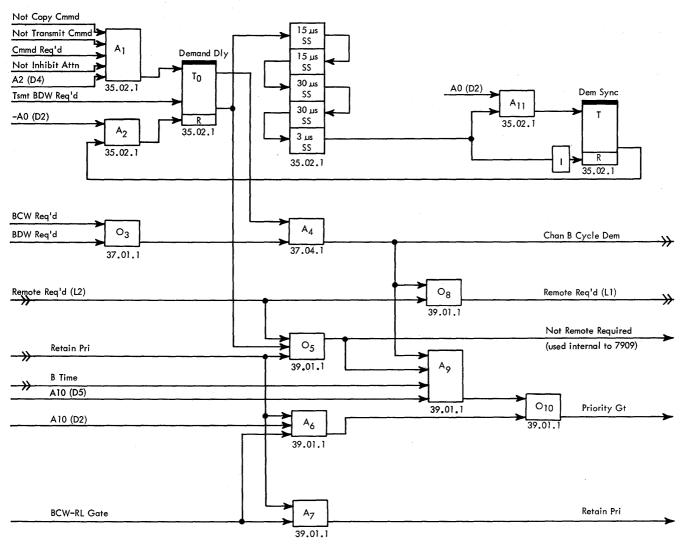

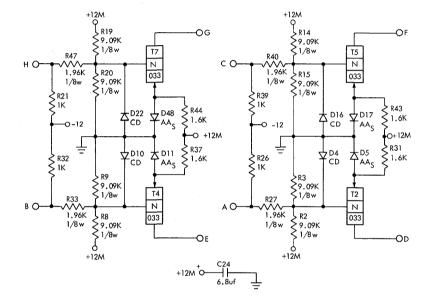

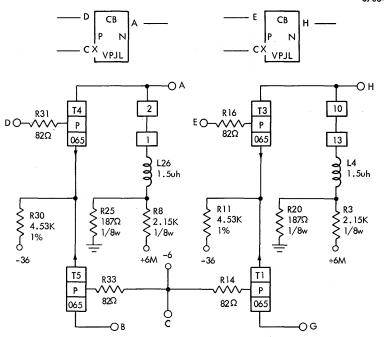

#### Internal Channel Priority Logic—B Time

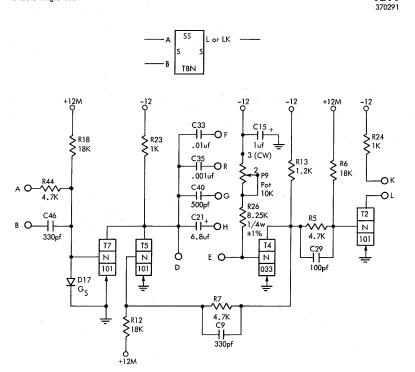

Requests for B time (Figures 10 and 11) by the channel may be made immediately or, in other cases, delayed for a period of time. For simplicity, assume that the "demand delay" circuitry at the top of Figure 10 does not exist.

Figure 9. Inter-Channel Priority Connections

Figure 10. Channel Priority Logic

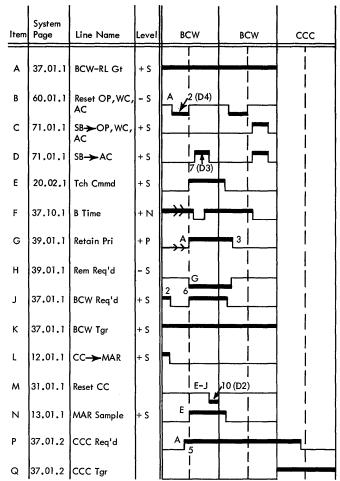

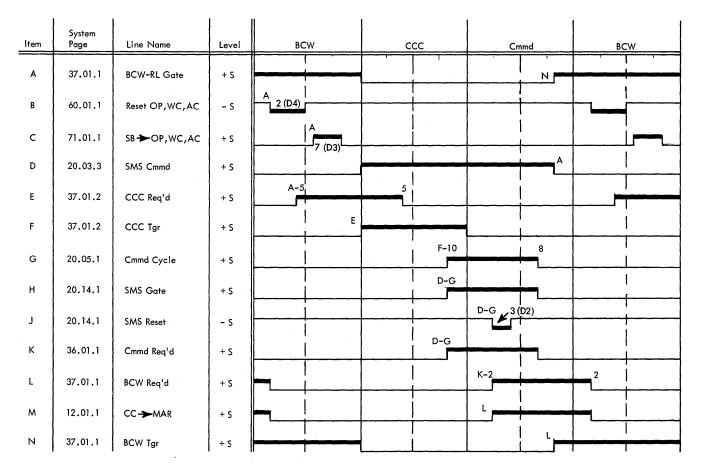

| ltem | System<br>Page | Line Name             | Level |                                       | Higher Priority<br>BCW Cycle | This Channels<br>BCW Cycle |  |

|------|----------------|-----------------------|-------|---------------------------------------|------------------------------|----------------------------|--|

| A    | 37.01.1        | BCW Req'd             | + S   | 3                                     | 1                            | G-2                        |  |

| В    | 37.04.1        | B Cycle Dem           | + P   | →  <br>≫_ 「                           |                              |                            |  |

| с    | 39.01.1        | Remote Req'd (Line 2) | + P   | 3  <br>                               | 2  <br>                      | <br>                       |  |

| D    | 39.01.1        | Remote Req'd (Line 1) | + P   | <b>→</b>                              |                              |                            |  |

| E    | 37.10.1        | B Time                | + N   | →→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→ | 7 B-9                        |                            |  |

| F    | 39.01.1        | Priority Gt           | + S   |                                       | А- <u>С</u> -е               | l<br>T                     |  |

| G    | 37.01.1        | BCW Tgr               | + S   |                                       |                              |                            |  |

Figure 11. Channel Priority Sequence Chart

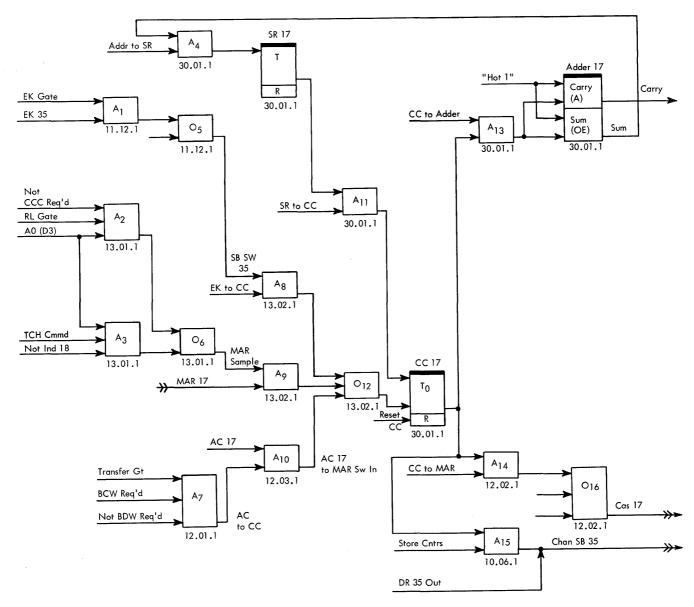

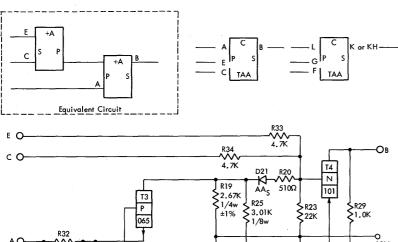

Either a BCW required or BDW required signal from the channel circuits will, via  $O_3$  and  $A_4$ , demand a B-cycle from the computer. This demand line is common for all channels and may be activated by any one of them. At the same time that a request is made for B time (3 time of the cycle), a remote required line is initiated by  $O_8$  and propagated to the lower priority channels as described in the previous section. With no other higher unit requesting, the next B time issued from the computer will be acceptable to this channel at  $A_9$ . "B time" becomes active at 9 time of the first available cycle as determined by the computer's program. "Priority gate" at  $O_{10}$  becomes active at 10 time, causing the appropriate BCW or BDW trigger to be set so that the next cycle will be either a BCW or BDW.

If a higher priority channel had requested B time simultaneously, "remote required" would have conditioned  $O_5$  with the result of blocking  $A_9$ . At this point the decision is made as to whether the common B time line from the computer is for use in this channel or one of higher priority. When all higher demands are satisfied, the input remote required line falls and allows  $A_9$  to become active. Note that as long as any channel is demanding, B times continue until all channel requirements are fulfilled.

Circuits  $A_6$  and  $A_7$  pertain to TCH or indirectly addressed commands as recognized by the multiplexor and is discussed under "Indirect Addressing." The purpose, however, is to retain priority within the channel so that an additional BCW cycle is made available.

# **Demand Delay**

Data transmission commands such as reading, writing, control, and sense require B time almost immediately upon request because their operation is governed by the speed of the attached I-O device. The 7909, however, is really a small computer by itself with many logical and functional commands at its disposal. Each of these commands requires and requests either BDW or BCW cycles to perform its functions. If several of these commands were to be executed in quick succession, one channel could easily monopolize B time and prevent data in other channels from being properly stored.

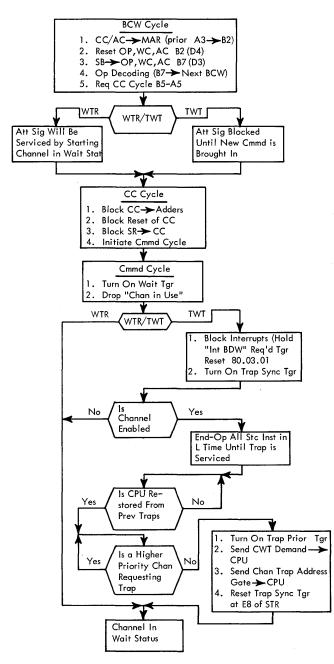

To eliminate this problem, any non-essential requests for B time are delayed by an amount dependent on the number of operating channels attached to the system. The demand delay trigger (Figures 10 and 12) is turned on by the channel's request for a new command (BCW) cycle as indicated by the input, "CMMD required," at  $A_1$ . An exception to this is between CPYP commands for data transmission where the system is time-limited by the 1-0 device. "Inhibit attn" blocks  $A_1$ in this particular case.

The demand delay trigger, coming on, blocks  $A_4$  and prevents sending B cycle demands to the computer. At the same time, a chain of single-shots is started to produce an appropriate time delay before allowing the trigger to be reset by  $A_2$ . Five single-shots are available in the machine and may be inserted or eliminated to produce a delay of 0-90  $\mu$ s. The last 3- $\mu$ s single-shot must always be used, for it provides the

| ltem | System<br>Page | Line Name    | Level |        |       |                          |     |        | BCW |

|------|----------------|--------------|-------|--------|-------|--------------------------|-----|--------|-----|

| А    | 36.01.1        | Cmmd Req'd   | + S   | 10     | 8     |                          |     |        |     |

| В    | 35.02.1        | Demand Delay | - s   | ^^     |       |                          |     | F-2    |     |

| с    | 35.02.1        | Single-Shots | + \$  | B      | 15-90 | usec                     |     |        |     |

| D    | 37.01.1        | BCW Req'd    | + S   | <br>   | A-3   |                          |     |        | 2   |

| Ē    | 35.02.1        | 3 usec SS    | + S   |        | <br>  |                          | C   | usec   |     |

| F    | 35.02.1        | Demand Sync  | + S   |        |       |                          | E-0 |        |     |

| G    | 37.04.1        | B Cycle Dem  | + P   | <br> ≫ |       |                          |     |        | 2   |

| н    | 37.10.1        | B Time       | + N   | »      |       | <u></u>                  |     | G-9    |     |

| J    | 39.01.1        | Priority Gt  | + S   |        | Fo    | ssible B Time<br>r Other |     | D-H-10 |     |

| к    | 37.01.1        | BCW Tgr      | + S   |        |       | anne!                    |     | D-J    |     |

|      |                |              |       | 1      |       | 1                        |     |        |     |

Figure 12. Demand Delay Sequence Chart

necessary synchronization. The first 0 time after the  $3-\mu s$  single-shot starts timing out turns on the demand sync trigger through  $A_{11}$ . The trigger output gates  $A_2$ , and the demand sync trigger is reset at the next 2-time.  $A_4$  becomes active and allows a "channel B cycle demand" to be sent to the computer.

The transmit command could consume many BDW cycles if large blocks of data were being shifted within storage. Because of this, "TSMT BDW required" also activates the demand delay circuitry so as not to fully monopolize core storage.

# DEMAND DELAY SINGLE-SHOT TIMING

The total demand delay to be used is governed by the system configuration. Refer to Figure 2 and the table under "7909 Data Channel Timings" and also to the section on "Maximum System Configuration" to calculate the system weight and appropriate channel cap-cut. The  $Y3 \cdot \cdot$  jumper card is located at 05A3D21. Systems 50.00.32.0 shows the cap-cut numbers and corresponding timings.

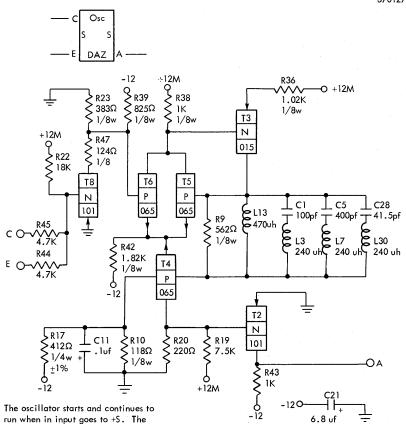

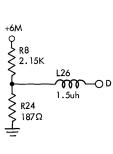

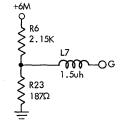

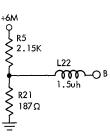

Each of the single-shots listed below is adjustable and must meet the specified timing durations within  $\pm 10$  percent.

| Name         | Systems    | LOCATION | CARD | TIMING |

|--------------|------------|----------|------|--------|

| Demand Delay | 50.35.02.1 | 05A3C24  | TBN  | 15 µs  |

| Demand Delay | 50.35.02.1 | 05A3D24  | TBN  | 15 µs  |

| Demand Delay | 50.35.02.1 | 05A3E23  | TBN  | 30 µs  |

| Demand Delay | 50.35.02.1 | 05A3D22  | TBN  | 30 µs  |

| Demand Delay | 50.35.02.1 | 05A3E22  | TBN  | 3 μs   |

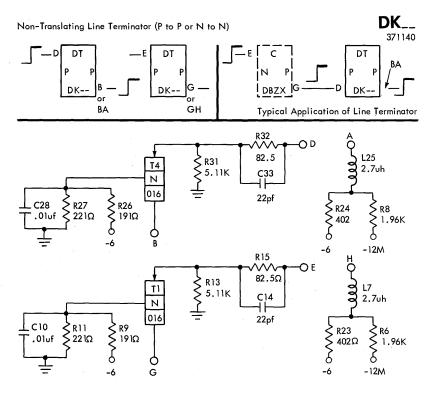

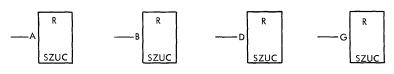

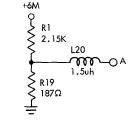

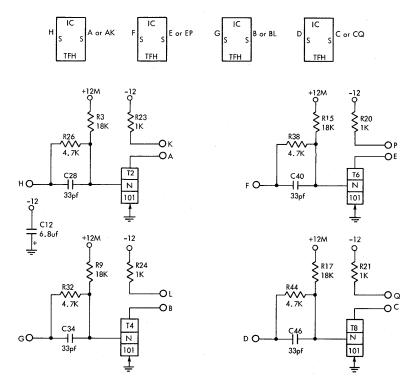

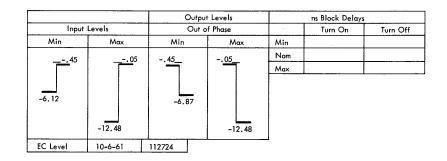

The simplex I-O interface consists of two signal cables which connect an individual input-output adapter to a computer or channel. This is the extent of hardware; the most important part is the specific definitions associated with the signals within the cables. These signals are defined explicitly in regard to: function, timing, electrical characteristics, and connector pin assignments.

With the interface, it is possible to achieve a uniform means of communicating control information and data between computers and 1-0 equipment. The result is the design of a wide variety of processors and 1-0 devices for interconnections; adoption by 1-0 programming to standard 1-0 control program packages; elimination of redundancy in development and design effort; and reduction in manufacturing and service costs. In this manual the most important advantage is that, knowing the logic and demands of the simplex 1-0 interface, we need not concern our discussions with any particular 1-0 device.

Whether the channel is operating with a 7631 Disk Control, 7640 Hypertape, 1414-6 Synchronizer, 7750 Programmed Transmission Control, or any other present or future device need not directly concern the reader; all will operate on an identical request-response basis.

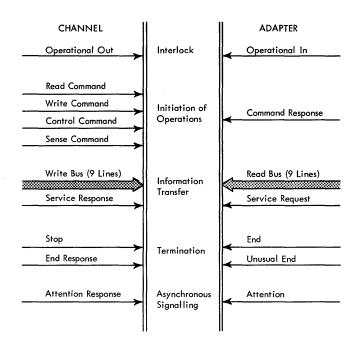

# **Functional Description**

The interface is divided functionally into five groups of lines (Figure 13). Generally, any signal must be maintained until its corresponding response is provided by the receiving unit.

# Interlocks

Two lines are used to interlock completely the channel and I-O device. Each line reflects the operational status of the unit at its driver end.

Operational Out: Lines from the channel are significant only when "operational out" is up. The downstate of the operational out signal is used to reset the 1-0. Unless the 1-0 is in an off-line mode, any down-state of sufficient duration to cause a response from the particular circuit family provides the reset. The meaning of the reset is defined by the 1-0. To insure a proper reset, the operational out line must remain down for at least  $6 \mu s$ .

Figure 13. Interface Functional Grouping

Operational In: During simplex operation, lines from the I-O are significant only when "operational in" is up. When "Operational in" is down, the I-O normally will not respond to any signals from the computer.

# **Initiation of Operations**

An I-O operation is initiated by one of the four commands (READ, WRITE, CONTROL, and SENSE) and their common response (COMMAND RESPONSE). Both READ and SENSE establish transfer of information from the inputoutput to the channel. READ is associated with the transfer of data while SENSE is associated with the transfer of status information of the input-output. Both WRITE and CONTROL establish transfer of information from the channel to the I-O. WRITE is associated with transfer of data while CONTROL is associated with the transfer of orders to the I-O. Commands are executed over the interface sequentially. An operation associated with any of the four commands must be properly terminated prior to issuance of the next command.

*Read Command:* The read command line is used to signal the 1-0 to cause the next block to be read into the computer. The read command signal, as well as all other command signals, is loop-checked by the command response line.

The read command signal must not be initiated unless "command response" is down, and unless "stop" and "end response" are either down or are dropped at the time "read command" is raised. The read command signal must remain up until the rise of "command response." It must fall before the rise of "end response."

Write Command: The write command line is used to signal the 1-0 to proceed with writing a block of data. Loop checking and signal timing specifications are the same as for "read command."

*Control Command:* The control command line is used to signal the 1-0 that it must accept orders from the computer over the write bus and must perform the operation encoded in the order. Examples are: rewind, backspace, and so on. Loop checking and signal timing specifications are the same as for "read command."

Sense Command: The sense command line is used to signal the I-O to send status information to the computer over the read bus. The information sent depends on the definition of the sense operation for the particular I-O concerned. Examples are: error indicators, rewind, or seek status. Loop checking and signal timing specifications are the same as for "read command."

Command Response: The command response line is used to signal the channel in recognition of a signal on any of the four command lines. It indicates the ability of the I-O to initiate the command.

The command response signal must rise within 6  $\mu$ s of the rise of any of the four commands. If, because of skew, "stop" or "end response" from the preceding operation overlaps the command, "command response" cannot rise until "stop" and "end response" are down. "Command response" must not fall during the execution of the command; it must fall within 6  $\mu$ s of the rise of "end of response."

#### **Information Transfer**

Information is transmitted over the "read bus" and the "write bus" on the demand and response basis. Demand is indicated by "service request" and response by "service response." Information is transferred parallel by byte. The byte may be up to eight bits in size. The 7909 Data Channel, however, uses only six of the eight available data lines. The remaining two positions are inoperative.

Organization of Information: The "read bus" and the "write bus" of the interface are insensitive to any codes. Information on the read and the write bus is arranged so that bit position 0 of a bus always carries the highest order bit, with bits in descending order being assigned to bit positions of the bus string in computer or 1-0 storage (the bit from bit position 0 of a byte always adjoins the bit from bit position 7 of the preceding byte). As a result, a message consisting of several bytes always appears as follows: bus bit positions 0, 1, 2, 3, 4, 5, 6, 7, 0, 1, 2, and so on.

When a byte transmitted over the interface consists of less than eight bits, the bits must be placed in the highest-numbered contiguous bit positions of the bus. Thus, when a channel or an 1-0 device transmits over the interface only the six bits of the BCD code, bit B is placed in bit position 2 of the bus, bit A in bit position 3, etc., and bit 1 is placed in position 7. When a channel or an 1-0 device places information on or receives information from only four lines of a bus, it must use bit positions 4, 5, 6, and 7 (sense data use bit positions 3, 5, 6, and 7). Any unused lines of the read or write bus must include the low-numbered bit positions of the bus, i.e., bit position 0 and adjacent bit positions. The parity bit of any byte must always appear in the parity bit position. Unused lines must always present logical zeros to the receiving end.

Write Bus: The write bus is used for sending both data and control information to the 1-0. It consists of nine lines: eight data lines plus one line for odd parity. Not all of these lines need be used. Data must be valid on the write bus from the rise of "service response" until the fall of "service request." The assignment of bit positions on the nine lines on the write bus is:

| Line Name          | 7909 Assignment |

|--------------------|-----------------|

| Parity Bit         | Bit C           |

| Bus Éit Position 0 | Unused          |

| Bus Bit Position 1 | Unused          |

| Bus Bit Position 2 | Bit B           |

| Bus Bit Position 3 | Bit A           |

| Bus Bit Position 4 | Bit 8           |

| Bus Bit Position 5 | Bit 4           |

| But Bit Position 6 | Bit 2           |

| Bus Bit Position 7 | Bit 1           |

Read Bus: The read bus is used for sending both data and sense information to the channel. It consists of nine lines: eight data lines plus one line for odd parity. Not all of these lines need be used. Data must be valid on the read bus from the rise of "service request" until the rise of "service response" unless the permitted modification to the definition of service request is used. In the latter case, the availability of data on the read bus may lag the rise of "service request" by an adjustable time. This time may not be longer than the shortest interval in which the particular channel can accept data after the rise of "service request." The assignment of bit positions on the nine lines of the read bus is the same as for the write bus.

Service Request: The "service request" line is used to signal the channel when the 1-0 wants to transmit or receive a byte of information. During read and sense operations, "service request" rises when information is available on the read bus and "service response" is down. The rise of "service request" must be delayed sufficiently to guarantee that it does not precede data when measured at the cable connectors at the channel under the worst case skew conditions. Skew that is caused within channel circuitry must be accommodated by the channel. Within the above skew limitations, data must be valid until the rise of "service response." During write and control operations, "service request" rises when, or before, information is required on the write bus and "service response" is down.

The service request signal must fall after the rise of "service response." During read and sense operations, "service request" must fall within 6  $\mu$ s of the rise of "service response."

When the next cycle time is reached (in the case of cyclic devices), and "service response" has not occurred, the 1-0 must drop "service request" and must recognize an over-run condition. For these cyclic 1-0, the minimum interval between the rise of "service response" and the fall of "service request" must be part of the 1-0 specifications.

To improve the system's performance, the rise of "service request" can be advanced relative to the time the data are valid on the read bus from the timing as just described. The rise of "service request" can precede the data by an amount of time that is the shortest interval in which the particular channel can accept data after receiving "service request." If this modification to the basic definition is used, the amount of this advance must be adjustable at the time of installation.

Service Response: The service response line is used to signal the I-O in recognition of a signal on the service request line. "Service response" indicates to the I-O that the channel is transmitting or has received information on the data busses.

During write and control operations, the rise of "service response" indicates that data are available on the write bus. The rise of "service response" must be delayed sufficiently to guarantee that it does not precede data when measured at the cable connectors at the channel under the worst case skew conditions. Skew that is caused within cables and I-O circuitry must be accommodated by the I-O. Within the above skew limitations, data must be valid from the rise of "service response" until the fall of "service request." During read and sense operations, "service response" must rise when the channel has accepted the information on the read bus.

The service response signal must rise before the fall of "service request." In the case of cyclic devices, "service response" must rise before the fall of "service request" by a time specified by the I-O. If "service response" rises too late, the I-O must recognize the over-run condition. The service response signal must remain up until the fall of "service request." It must fall after the fall of "service request."

# **Termination of Operations**

An operation may be terminated by either the channel or the 1-0. The channel accomplishes this by the stop signal. The 1-0 indicates successful completion with "end" and abnormal completion by "unusual end." In either case the channel responds with "end response." The cause of "unusual end" may be determined by analysis of the status information obtained by a subsequent "sense command."

Stop: The stop line is used to signal the 1-0 that the channel has recognized the end of a record or operation. If the 1-0 recognizes the end of operation first and generates an "end" or "unusual end," no stop signal occurs.

Upon receipt of the stop signal, the I-O proceeds to its normal ending point. No further "service request" is sent and no further "service response" is expected. To complete the ending procedure, the I-O device sends an end or unusual end signal at the proper time and receives in return an "end response" from the channel.

The stop signal may rise any time when "command response" is up except when both "service request" and "service response" are also up. If "stop" is issued when "service request" is up, it replaces "service response." In this case, on read and sense operations data on the read bus are not accepted.

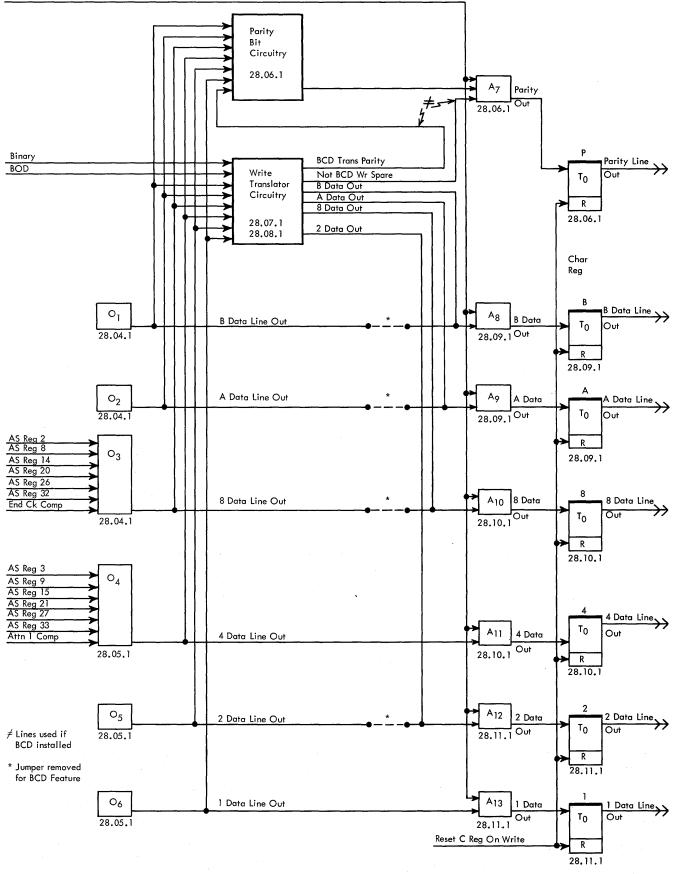

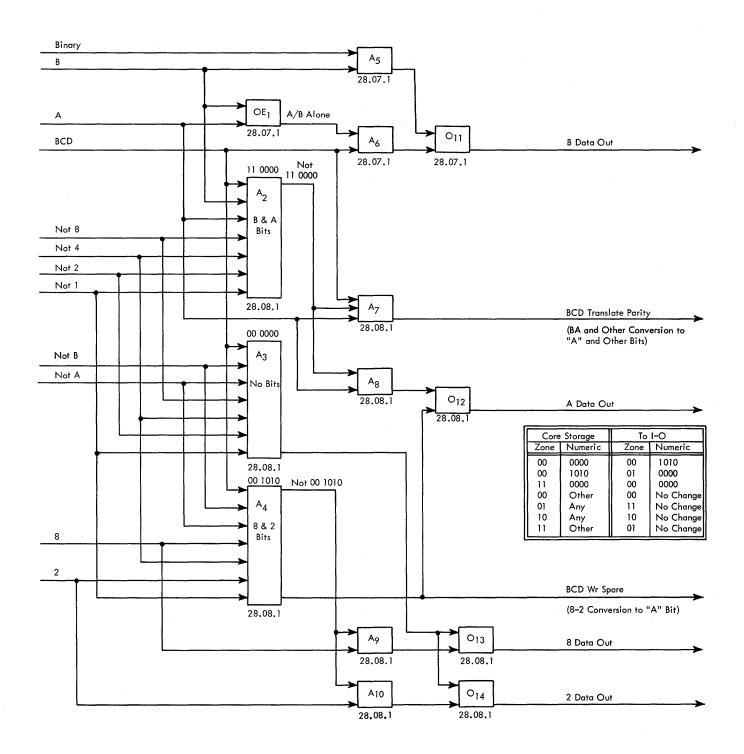

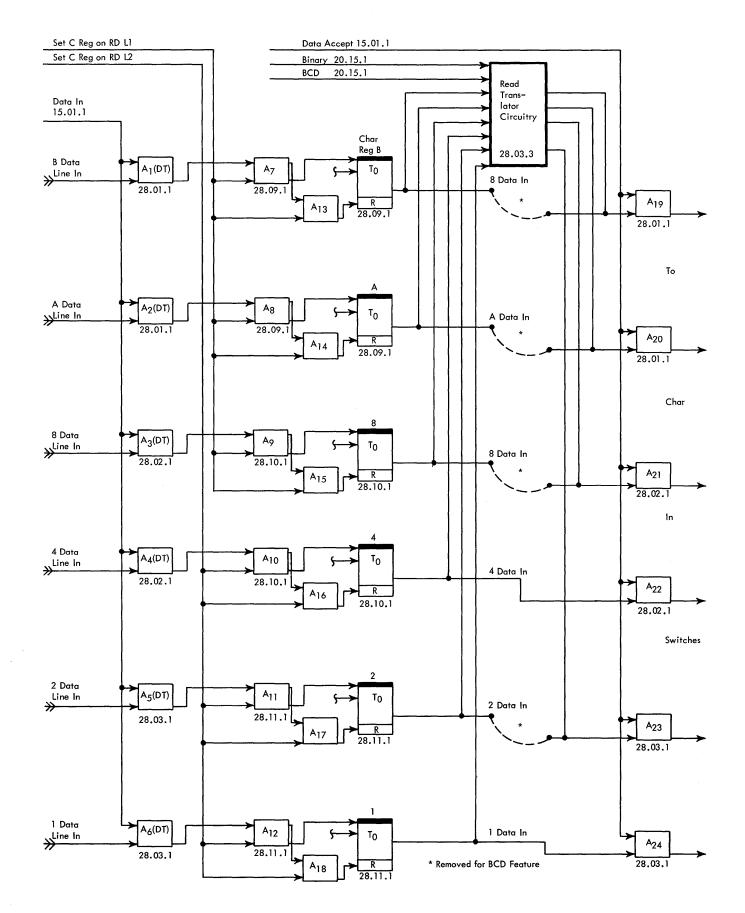

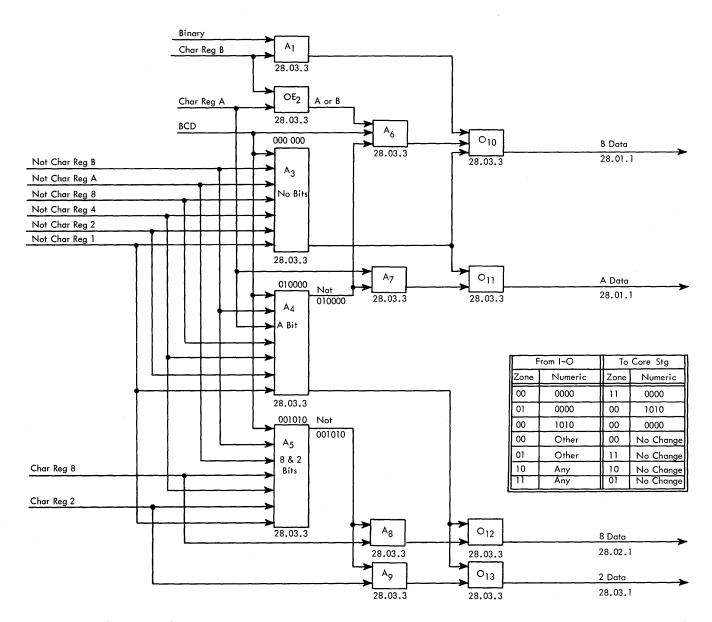

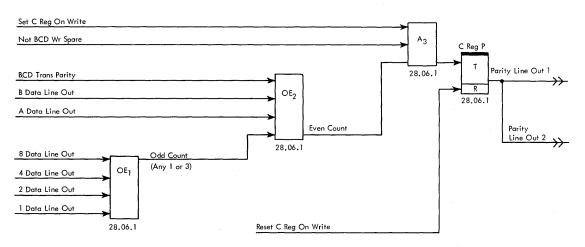

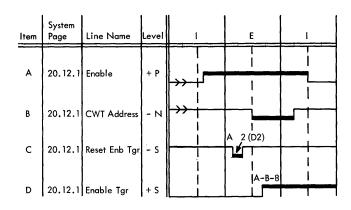

The stop signal must remain up until the fall of "command response" and must fall when or before a new command signal is sent to the I-O.