## 360 INTRODUCTORY PROGRAMMING

# <u>360PGM</u>

STUDENT WORKBOOK

CAI #48

REVISION 1 8/25/70

## INDEX

| PAGE          |            |

|---------------|------------|

| 1-1           |            |

| 1 <b>-</b> 8  | н н<br>Нас |

| 1-16          |            |

| 1-26          |            |

| 3-1           |            |

| 3-9           |            |

| 3-13          |            |

|               |            |

| 3-18          |            |

| 3-23          |            |

| 3–25          |            |

| 3-28          |            |

| 3-31          |            |

| 3-34          |            |

| 3-41          |            |

|               | · .        |

| 3-45          | ÷          |

| 3-48          |            |

| 4-1           |            |

| 4-6           |            |

| 4-11          |            |

| 4-21          |            |

| 4 <b>-</b> 23 |            |

| 4-27          |            |

| 4-32          |            |

| 4-34          |            |

|               |            |

TITLE FIXED-POINT INST. LOGICAL INST. BRANCHING INST. STATUS SWITCHING LOAD STORE ADD SUBTRACT BRANCH ON CONDITION COMPARE MULTIPLY DIVIDE SHIFT FIXED-POINT DATA FORMATS (PACK AND UNPACK) CONVERT TO BINARY CONVERT TO DECIMAL MOVE AND OR TEST UNDER MASK COMPARE LOGICAL SHIFT LOGICAL LOAD ADDRESS TRANSLATE

| PAGE            | TTTLE                      |

|-----------------|----------------------------|

|                 |                            |

| 4-37            | TRANSLATE AND TEST         |

| 4-41            | EXECUTE                    |

| 14 <u></u> 1314 | INSERT CHARACTER           |

| 4-46            | STORE CHARACTER            |

| 5-1             | BRANCH ON COUNT            |

| 5-4             | BRANCH ON INDEX            |

| 5-8             | BRANCH AND LINK            |

| 5-11            | SUPERVISOR CALL            |

| 5-13            | SET PROGRAM MASK           |

| 5-15            | SET SYSTEM MASK            |

| 5-17            | LOAD PSW                   |

| 5-19            | STORAGE KEYS (SSK AND ISK) |

| 5–23            | TEST AND SET               |

| 9-1             | DECIMAL INST.              |

| 9–8             | ADD DECIMAL                |

| 9-11            | ZERO AND ADD               |

| 9-14            | SUBTRACT DECIMAL           |

| 9–17            | MULTIPLY DECIMAL           |

| 9–19            | DIVIDE DECIMAL             |

| 9-22            | COMPARE DECIMAL            |

| 9–24            | EDIT                       |

| 9-24            |                            |

| 11-1         |             |   | I/O INST.              |

|--------------|-------------|---|------------------------|

| 11-16        |             |   | START I/O              |

| 11-19        | • • • • • • |   | TEST I/O               |

| 11-21        |             | 4 | HALT I/O               |

| 12 <b>-1</b> |             | • | I/O PROGRAMMING PROJEC |

|              |             |   |                        |

#### FIXED-POINT INSTRUCTIONS

#### FIXED-POINT

The fixed-point instruction set performs binary arithmetic on operands serving as addresses, index quantities, and counts, as well as fixed-point data. In general, both operands are signed and 32 bits long. Negative quantities are held in two's-complement form. One operand is always in one of the 16 general registers; the other operand may be in main storage or in a general register.

The instruction set provides for loading, adding, subtracting, comparing, multiplying, dividing, and storing, as well as for the sign control, radix (base) conversion, and shifting of fixedpoint operands. The entire instruction set is included in the standard instruction set.

The condition code is set as a result of all sign control, add, subtract, compare, and shift operations.

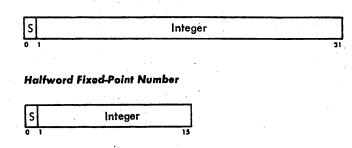

#### DATA FORMAT

Fixed-point numbers occupy a fixed-length format consisting of a one-bit sign followed by the integer field. When held in one of the general registers, a fixed-point quantity has a 31-bit integer field and occupies all 32 bits of the register. Some multiply, divide, and shift operations use an operand consisting of 64 bits with a 63-bit integer field. These operands are located in a pair of adjacent general registers and are addressed by an even address referring to the leftmost register of the pair. The sign-bit position of the rightmost register contains

of the integer. In register-to-register operations the same register may be specified for both operand locations.

Full Word Fixed-Point Number

Fixed-point data in main storage occupy a 32-bit word or a 16-bit halfword, with a binary integer field of 31 or 15 bits, respectively. The conversion instructions use a 64bit decimal field. These data must be located on integral storage boundaries for these units of information, that is, double word, fullword, or halfword operands must be addressed with three, two, or one low-order address bit(s) set to zero.

A halfword operand in main storage is extended to a fullword as the operand is fetched from storage. Subsequently, the operand participates as a fullword operand.

In all discussions of fixed-point numbers in this publication, the expression "32-bit signed integer" denotes a 31-bit integer with a sign bit, and the expression "64-bit signed integer" denotes a 63-bit integer with a sign bit.

## NUMBER REPRESENTATION

All fixed-point operands are treated as signed integers. Positive numbers are represented in true binary notation

with the sign bit set to zero. Negative numbers are represented in two's-complement notation with a one in the sign bit.

Two's-complement notation does not include a negative zero. It has a number range in which the set of negative numbers is one larger than the set of positive numbers. The maximum positive number consists of an all-one integer field with a sign bit of zero, whereas the maximum negative number (the negative number with the greatest absolute value) consists of an all-zero integer field with a one-bit for sign.

The CPU cannot represent the complement of the maximum negative number. When an operation, such as subtraction from zero, produces the complement of the maximum negative number, the number remains unchanged, and a fixed-point overflow exception is recognized. An overflow does not result, however, when the number is complemented and the final result is within the representable range. An example of this case is a subtraction from minus one. The product of two maximum negative numbers is representable as a double-length positive number.

The sign bit is leftmost in a number. In an arithmetic operation, a carry out of the integer field changes the sign. However, in algebraic left-shifting the sign bit does not change even if significant high-order bits are shifted out of the integer field.

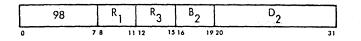

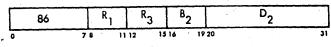

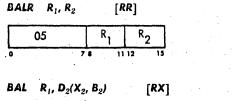

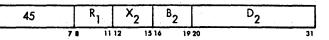

### INSTRUCTION FORMAT

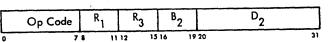

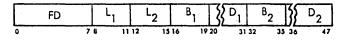

Fixed-point instructions use the following three formats:

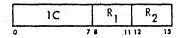

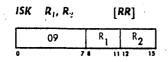

Op Code

R1

R2

0

7

11

12

15

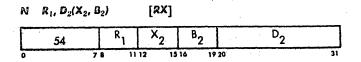

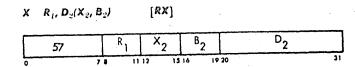

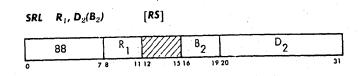

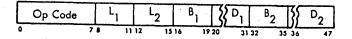

**RX Format** Op Code  $R_1$   $X_2$   $B_2$   $D_2$

**RS Format**

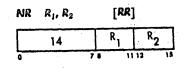

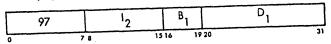

In these formats, R1 specifies the general register containing the first operand. The second operand location, if any, is defined differently for each format.

In the RR format, the R2 field specifies the general register containing the second operand. The same register may be specified for the first and second operand.

In the RX format, the contents of the general registers specified by the X2 and B2 fields are added to the content of the D2 field to form an address designating the storage location of the second operand.

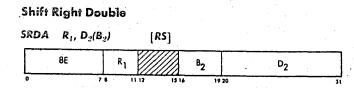

In the RS format, the content of the general register specified by the B2 field is added to the content of the D2 field. This sum designates the storage location of the second operand in LOAD MULTIPLE and STORE MULTIPLE. In the shift operations, the sum specifies the number of bits of the shift. The R3 field specifies the address of a general register in LOAD MULTIPLE and STORE MULTIPLE and is ignored in the shift operations.

A zero in an X2 or B2 field indicates the absence of the corresponding address component.

An instruction can specify the same general register both for address modification and for operand location. Address modification is always completed before operation execution.

Results replace the first operand, except for STORE and CONVERT TO DECIMAL, where the result replaces the second operand.

The contents of all general registers and storage locations participating in the addressing or execution part of an operation remain unchanged, except for the storing of the final result.

NOTE: In the detailed descriptions of the individual instructions, the mnemonic and the symbolic operand designation for the IBM System/360 assembley language are shown with each instruction. For LOAD AND TEST, for example, LTR is the mnemonic and R1, R2 the operand designation.

## FIXED-POINT PROGRAM INTERRUPTIONS

Exceptional operand designations, data, or results cause a program interruption. When a program interruption occurs, the current PSW is stored as an old PSW, and a new PSW is obtained. The interruption code in the old PSW identifies the cause of the interruption. The following exceptions cause a program interruption in fixed-point arithmetic.

Protection: The key of an operand in storage does not match the protection key in the PSW. The operation is suppressed for a store violation. Therefore, the condition code and data in registers and storage remain unchanged. The only exception is STORE MULTIPLE, which is terminated; the amount of data stored is unpredictable and should not be used for further computation. The operation is terminated on any fetch violation.

Addressing: An address designates an operand location outside the available storage for a particular installation. In most cases, the operation is terminated. Therefore, the result data are unpredictable and should not be used for further computation. The exceptions are STORE, STORE HALFWORD, and CONVERT TO DECIMAL, which are suppressed. Operand addresses are tested only when used to address storage. Addresses used as a shift amount are not tested. The address restrictions do not apply to the components from which an address is generated - the content of the D2 field and the contents of the registers specified by X2 and B2.

Specification: A double-word operand is not located on a 64-bit boundary, a fullword operand is not located on a 32-bit boundary, a halfword operand is not located on a 16-bit boundary, or an instruction specifies an odd register address for a pair of general registers containing a 64-bit operand. The operation is suppressed. Therefore, the condition code and data in registers and storage remain unchanged.

Data: A sign or a digit code of the decimal operand in CONVERT TO BINARY is incorrect. The operation is suppressed. Therefore, the condition code and data in registers and storage remain unchanged.

Fixed-Point Overflow: The result of a sign-control add, subtract, or shift operation overflows. The interruption occurs only when the fixed-point overflow mask bit is one. The operation is completed by placing the truncated low-order result in the register and setting the condition code to 3. The overflow bits are lost. In add-type operations the sign stored in the register is the opposite of the sign of the sum or difference. In shift operations the sign of the shifted number remains unchanged. The state of the mask bit does not affect the result.

Fixed-Point Divide: The quotient of a division exceeds the register size, including division by zero, or the result in CONVERT TO BINARY exceeds 31 bits. Division is suppressed. Therefore, data in the registers remain unchanged. The conversion is completed by recording the truncated low-order result in the register.

## LOGICAL INSTRUCTIONS

A set of instructions is provided for the logical manipulation of data. Generally, the operands are treated as eightbit bytes. In a few cases the left or right four bits of a byte are treated separately or operands are shifted a bit at a time. The operands are either in storage or in general registers. Some operands are introduced from the instruction stream.

Processing of data in storage proceeds left to right through fields which may start at any byte position. In the general registers, the processing, as a rule, involves the entire register contents.

The set of logical operations includes moving, comparing, bit testing, translating, and shift operations. All logical operations are part of the standard instruction set.

The condition code is set as a result of all logical comparing, connecting, testing, and editing operations.

## DATA FORMAT

Data reside in general registers or in storage or are introduced from the instruction stream. The data size may be a single or doubleword, a single character, or variable length. When two operands participate they have equal length.

Fixed-Longth Logical Information

Logical Data

Data in general registers normally occupy all 32 bits. Bits are treated uniformly, and no distinction is made between sign and numeric bits. In a few operations, only the loworder eight bits of a register participate, leaving the remaining 24 bits unchanged. In some shift operations, 64 bits of an even/odd pair of registers participate.

The LOAD ADDRESS introduces a 24-bit address into a general register. The high-order eight bits of the register are made zero.

In storage-to-register operations, the storage data occupy either a word of 32 bits or a byte of eight bits. The word must be located on word boundaries, that is, its address must have the two low-order bits zero.

Variable-Length Logical Information

| Character | Character |    | <br>Character |

|-----------|-----------|----|---------------|

| )         | 6         | 16 |               |

In storage-to-storage operations, data have a variable fieldlength format, starting at any byte address and continuing for up to a total of 256 bytes. Processing is left to right.

Operations introducing data from the instruction stream into into storage, as immediate data, are restricted to an eightbit byte. Only one byte is introduced from the instruction stream, and only one byte in storage participates. Use of general register 1 is implied in TRANSLATE AND TEST. A 24-bit address may be placed in this register during operation. The TRANSLATE AND TEST also implies general register 2. The low-order eight bits of register 2 may be replaced by a function byte during a translate-and-test operation.

The translating operations use a list of arbitrary values. A list provides a relation between an argument (the quantity used to reference the list) and the function (the content of the location related to the argument). The purpose of the translation may be to convert data from one code to another code or to perform a control function.

A list is specified by an initial address - the address designating the leftmost byte location of the list. The byte from the operand to be translated is the argument. The actual address used to address the list is obtained by adding the argument to the low-order positions of the initial address. As a consequence, the list contains 256 eight-bit function bytes. In cases where it is known that not all eight-bit argument values will occur, it may be possible to reduce the size of the list.

In a storage-to-storage operation, the operand fields may be defined in such a way that they overlap. The effect of this overlap depends upon the operation. When the operands remain unchanged, as in the COMPARE or TRANSLATE AND TEST, overlapping does not affect the execution of the operation.

In the case of MOVE, and TRANSLATE, one operand is replaced by new data, and the execution of the operation may be affected by the amount of overlap and the manner in which data are fetched or stored. For purposes of evaluating the effect of overlapped operands, consider that data are handled one eightbit byte at a time. All overlapping fields are considered valid.

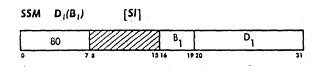

#### INSTRUCTION FORMAT

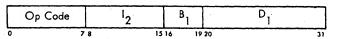

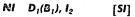

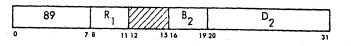

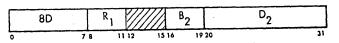

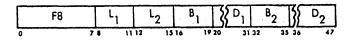

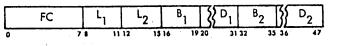

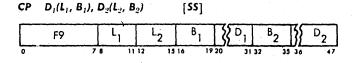

Logical instructions use the following five formats:

| R | R Format |    |   |      |   |

|---|----------|----|---|------|---|

|   | Op Code  |    | R | R    | 2 |

| 0 |          | 78 | 1 | 1 12 | 1 |

**RX** Format

|         |                |       | · · · · · · · · · · · · · · · · · · · | and the second |  |

|---------|----------------|-------|---------------------------------------|------------------------------------------------------------------------------------------------------------------|--|

| Op Code | R <sub>1</sub> | ×2    | <sup>B</sup> 2                        | D <sub>2</sub>                                                                                                   |  |

| 0 7     | 8 11           | 12 15 | 16 19                                 | 20 31                                                                                                            |  |

**RS** Format

| Op Code | T  | R  | R <sub>3</sub> | <sup>B</sup> 2 | D <sub>2</sub> |    |

|---------|----|----|----------------|----------------|----------------|----|

| )       | 78 | 11 | 12 15          | 16 .19         | 20             | 31 |

SI Format

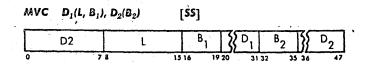

SS Format

In the RR, RX, and RS formats, the content of the register specified by Rl is called the first operand.

In the SI and SS formats, the contents of the general register specified by Bl is added to the content of the Dl field to form an address. This address designates the leftmost byte of the first operand field. The number of bytes to the right of this first byte is specified by the L field in the SS format. In the SI format the operand size is one byte.

In the RR format, the R2 field specifies the register containing the second operand. The same register may be specified for the first and second operand.

In the RX format, the contents of the general registers specified by the X2 and B2 fields are added to the content of the D2 field to form the address of the second operand.

In the RS format, used for shift operations, the contents of the general register specified by the B2 field is added to the content of the D2 field. This sum is not used as an address but specifies the number of bits of the shift. The R3 field is ignored in the shift operations.

In the SI format, the second operand is the eight-bit immediate data field, I2, of the instruction.

In the SS format, the content of the general register specified by B2 is added to the content of the D2 field to form the address of the second operand. The second operand field has the same length as the first operand field.

A zero in any of the X2, B1, or B2 fields indicates the absence of the corresponding address or shift-amount component. An instruction can specify the same general register both for

address modification and for operand location. Address modification is always completed prior to operation execution.

Results replace the first operand, except in STORE CHARACTER, where the result replaces the second operand. A variablelength result is never stored outside the field specified by the address and length.

The contents of all general registers and storage locations participating in the addressing or execution of an operation generally remain unchanged. Exceptions are the result locations, general register 1 in EDIT AND MARK, and general registers 1 and 2 in TRANSLATE AND TEST.

NOTE: In the detailed descriptions of the individual instructions, the mnemonic and the symbolic operand designation for the new IBM System/360 assembly language are shown with each instruction: For MOVE NUMERICS, for example, MVN is the mnemonic and D1 (L,B1), D2 (B2) the operand designation.

## LOGICAL OPERATION EXCEPTIONS

Exceptional operation codes, operand designations, data, or results cause a program interruption. When the interruption occurs, the current PSW is stored in an old PSW and a new PSW is obtained. The interruption code in the old PSW identifies the cause of the interruption. The following exceptions cause a program interruption in logical operations.

Protection: The key of an operand in storage does not match the protection key in the PSW. The operation is suppressed on a store violation. Therefore, the condition code and data in registers and storage remain unchanged. The only exceptions are the variable length, storage-to-storage operations (those containing a length specification), which are terminated. The operation is terminated on any fetch violation. For terminated operations, the result data and condition code, if affected, are unpredicatable and should not be used for further computation.

Addressing: An address designates an operand location outside the available storage for the installation: In most cases, the operation is terminated. The result data and the condition code, if affected, are unpredictable and should not be used for further computation. The exceptions are the immediate operations; AND (NI), EXCLUSIVE OR (XI), OR (OI) and MOVE (MVI) plus the STORE CHARACTER (STC), which are suppressed.

Specification: A fullword operand in a storage-to-register operation is not located on a 32-bit boundary or an odd register address is specified for a pair of general registers containing a 64-bit operand. The operation is suppressed. Therefore, the condition code and data in registers and storage remain unchanged.

Data: A digit code of the second operand in EDIT or EDIT AND MARK is invalid. The operation is terminated. The result data and the condition code are unpredictable and should not be used

for further computation.

Operand addresses are tested only when used to address storage. Addresses used as a shift amount are not tested. Similarly, the address generated by the use of LOAD ADDRESS is not tested. The address restrictions do not apply to the components from which an address is generated - the contents of the Dl and D2 fields, and the contents of the registers specified by X2, Bl, and B2.

#### BRANCHING INSTRUCTIONS

Instructions are performed by the central processing unit primarily in the sequential order of their locations. A departure from this normal sequential operation may occur when branching is performed. The branching instructions provide a means for making a two-way choice, to reference a subroutine, or to repeat a segment of coding, such as a loop.

Branching is performed by introducing a branch address as a new instruction address.

The branch address may be obtained from one of the general registers or it may be the address specified by the instruction. The branch address is independent of the updated instruction address.

The detailed operation of branching is determined by the condition code which is part of the program status word (PSW) or by the results in the general registers which are specified in the loop-closing operations.

During a branching operation, the rightmost half of the PSW, including the updated instruction address, may be stored before the instruction address is replaced by the branch address. The stored information may be used to link the new instruction sequence with the preceding sequence.

The instruction EXECUTE is grouped with the branching instructions. The branch address of EXECUTE designates a single ininstruction to be inserted in the instruction sequence. The updated instruction address normally is not changed in this operation, and only the instruction located at the branch address is executed.

All branching operations are provided in the standard instruction set.

#### NORMAL SEQUENTIAL OPERATION

Normally, operation of the CPU is controlled by instructions taken in sequence. An instruction is fetched from a location specified by the instruction-address field of the PSW. The instruction address is increased by the number of bytes of the instruction to address the next instruction in sequence. This new instruction, replaces the previous contents of the instruction-address field in the PSW. The current instruction is executed, and the same steps are repeated, using the updated instruction address to fetch the next instruction.

Conceptually, an instruction is fetched from storage after the preceding operation is completed and before execution of the current operation.

A change in the sequential operation may be caused by branching, status switching, interruption, or manual intervention. Sequential operation is initiated and terminated from the system control panel.

Programming Note

It is possible to modify an instruction in storage by means of the immediately preceding instruction.

#### SEQUENTIAL OPERATION EXCEPTIONS

Exceptional instruction addresses or operation codes cause a program interruption. When the interruption occurs, the current PSW is stored as an old PSW, and a new PSW is obtained. The interruption code in the old PSW identifies the cause of the interruption. (In this manual, part of the description of each class of instructions is a list of the program interruptions that may occur for these instructions.) The new PSW is not checked for exceptions when it becomes current. These checks occur when the next instruction is executed. The following program interruptions may occur in normal instruction sequencing, independently of the instruction performed.

Operation: An operation exception occurs when the CPU attempts to decode an operation code that is not assigned. The operation exception can be accompanied by an addressing or specification exception if the instruction class associated with the undefined operation has uniform requirements or operand designation. An instruction class is a group of instructions whose four leftmost bits are identical.

Protection: A protection exception occurs when an attempt is made to fetch an instruction halfword from a fetch-protected location. This error can occur when normal instruction sequencing goes from an unprotected region into a protected

region, or following a branching or load-PSW operation or an interruption.

Addressing: An addressing exception occurs when an instruction halfword is located outside the available storage for the particular installation.

Specification: A specification exception occurs when the instruction address in the PSW is odd. This odd address error can occur only after a branching or load PSW operation or after an interruption.

A specification exception will occur when the protection key is nonzero and the protection feature is not installed. This error can occur after a PSW is loaded or after an interruption.

In each case, the instruction is suppressed; therefore, the condition code and data in storage and register remain unchanged. The instruction address stored as part of the old PSW has been updated by the number of halfwords indicated by the instruction length code in the old PSW.

## Programming Notes

When a program interruption occurs, the current PSW is stored in the old PSW location. The instruction address stored as part of this old PSW is thus the updated instruction address, having been updated by the number of halfwords indicated in the instruction-length code of the same PSW. The interruption

code in this old PSW identifies the cause of the interruption and aids in the programmed interpretation of the old PSW.

If the new PSW for a program interruption has an unacceptable instruction address, another program interruption occurs. Since this second program interruption introduces the same unacceptable instruction address, a string of program interruptions is established which may be broken only by an external or I/O interruption. If these interruptions also have an unacceptable new PSW, new supervisor information must be introduced by initial program loading or by manual intervention.

## DECISION-MAKING

Branching may be conditional or unconditional. Unconditional branches replace the updated instruction address with the branch address. Conditional branches may use the branch address or may leave the updated instruction address unchanged. When branching takes place, the instruction is called successful; otherwise, it is called unsuccessful.

Whether a conditional branch is successful depends on the result of operations concurrent with the branch or preceding the branch. The former case is represented by BRANCH ON COUNT and the branch-on-index instructions. The latter case is represented by BRANCH ON CONDITION, which inspects the condition code that reflects the result of a previous arithmetic, logical, or I/O operation.

The condition code provides a means for data-depended decision-making. The code is inspected to qualify the execution of the condition-branch instructions. The code is set by some operations to reflect the result of the operation, independently of the previous setting of the code. The code remains unchanged for all other operations.

The condition code occupies bit positions 34 and 35 of the PSW. When the PSW is stored during status switching, the condition code is preserved as part of the PSW. Similarly, the condition code is stored as part of the rightmost half of the PSW in a branch-and-link operation. A new condition code is obtained by a LOAD PSW OR SET PROGRAM MASK or by the new PSW loaded as a result of an interruption.

The condition code indicates the outcome of some of the arithmetic, logical, or I/O operations. It is not changed for any branching operation, except for EXECUTE. In the case of EXECUTE, the condition code is set or left unchanged by the subject instruction, as would have been the case had the subject instruction been in the normal instruction stream.

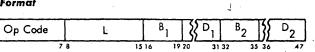

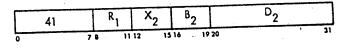

#### INSTRUCTION FORMATS

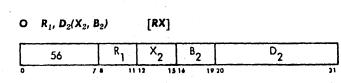

Branching instructions use the following three formats:

| 13                            |                               |                                              |

|-------------------------------|-------------------------------|----------------------------------------------|

| <Β                            |                               |                                              |

| ( <u></u> B                   |                               |                                              |

| 4 1 . 4 1                     | D <sub>2</sub>                |                                              |

| 1516 19:                      | 20                            |                                              |

|                               |                               |                                              |

| R <sub>3</sub> B <sub>2</sub> | D <sub>2</sub>                | ·                                            |

|                               | R <sub>3</sub> B <sub>2</sub> | R <sub>3</sub> B <sub>2</sub> D <sub>2</sub> |

In these formats Rl specifies the address of a general register. In BRANCH ON CONDITION a mask field (Ml) identifies the bit values of the condition code. The branch address is defined differently for the three formats.

In the RR format, the R2 field specifies the address of a general register containing the branch address, except when R2 is zero, which indicates no branching. The same register may be specified by R1 and R2.

In the RX format, the contents of the general registers specified by the X2 and B2 fields are added to the content of the D2 field to form the branch address.

In the RS format, the content of the general register specified by the B2 field is added to the content of the D2 field to form the branch address. The R3 field in this format specifies the location of the second operand and

implies the location of the third operand. The first operand is specified by the Rl field. The third operation location is always odd. If the R3 field specifies and even register, the third operand is obtained from the next higher addressed register. If the R3 field specifies an odd register, the third operand location coincides with the second operand location.

A zero in a B2 or X2 field indicates the absence of the corresponding address component.

An instruction can specify the same general register for both address modification and operand location. The order in which the contents of the general register are used for the different parts of an operation is:

- 1. Address computation.

- 2. Arithmetic or link information storage.

- 3. Replacement of the instruction address by the branch address obtained under step 1.

Results are placed in the general register specified by Rl. Except for the storing of the final results, the contents of all general registers and storage locations participating in the addressing or execution part of an operation remain unchanged.

NOTE: In the detailed descriptions of the individual instructions, the mnemonic and the symbolic operand designation for the IBM System/360 assembly language are shown with each instruction. For BRANCH ON INDEX HIGH, for example, BXH is the mnemonic and Rl, R3, D2(B2) the operand designation.

Programming Note

In several instructions the branch address may be specified in two ways: in the RX format, the branch address is the address specified by X2, B2, and D2; in the RR format, the branch address is in the low-order 24 bits of the register specified by R2. Note that the relation of the two formats in branch-address specification is not the same as in operandaddress specification. For operands, the address specified by X2, B2, and D2 is the operand address, but the register specified by R2 contains the operand itself.

## EXECUTE EXCEPTIONS

Exceptional operand designations and a subject-instruction operation code specifying EXECUTE cause a program interruption. When the interruption occurs, the current PSW is stored as an old PSW, and a new PSW is obtained. The interruption code in the old PSW identifies the cause. Exceptions that cause a program interruption in the use of EXECUTE are:

Execute: An EXECUTE instruction has as its subject instruction another execute.

Protection: An EXECUTE specifies a subject instruction halfword in a fetch-protected area.

Addressing: The branch address of EXECUTE designates an instruction-halfword location outside the available storage for the particular installation.

Specification: The branch address of EXECUTE is odd.

These four execptions occur only for EXECUTE. The instruction is suppressed. Therefore, the condition code and data in registers and storage remain unchanged.

Exceptions arising for the subject instruction of EXECUTE are the same as would have arisen had the subject instruction been in the normal instruction stream. However, the instruction address stored in the old PSW is the address of the instruction following EXECUTE. Similarly, the instruction-length code in the old PSW is the instruction length code (2) of EXECUTE.

The address restrictions do not apply to the components from which an address is generated - the content of the Dl field and the content of the register specified by Bl.

Programming Note

An unavailable or odd branch address of a successful branch is detected during the execution of the next instruction and not as part of the branch.

## STATUS SWITCHING INSTRUCTIONS

A set of operations is provided to switch the status of the CPU, of storage, and of communications between systems.

The overall CPU status is determined by several program-state alternatives, each of which can be changed independently to its opposite and most of which are indicated by a bit in the program status word (PSW). The CPU status is further defined by the instruction address, the condition code, the instruction-length code, the storage-protection key, and the interruption code. These all occupy fields in the PSW.

Protection of main storage is achieved by matching a key in storage with a protection key in the PSW or in a channel. The protection status of storage may be changed by introducing new storage keys, using SET STORAGE KEY. The storage keys may be inspected by using INSERT STORAGE KEY.

## PROGRAM STATES

The four types of program-state alternatives, which determine the overall CPU status, are named Problem/Supervisor, Wait/ Running, Masked/Interruptible, and Stopped/Operating. These states differ in the way they affect the CPU functions and in the way their status is indicated and switched. The masked states have several alternatives; all other states have only one alternative.

All program states are independent of each other in their function, indication, and status switching. Status switching

does not affect the contents of the arithmetic registers or the execution of I/O operations but may affect the timer operation.

## PROBLEM STATE

The choice between supervisor and problem state determines whether the full set of instructions is valid. The names of these states reflect their normal use.

In the problem state all I/O, protection, and direct-control instructions are invalid, as well as LOAD PSW, SET SYSTEM MASK, and DIAGNOSE. These are called priviledged instructions. A priviledged instruction encountered in the problem state constitutes a priviledge-operation exception and causes a program interruption. In the supervisor state all instructions are valid.

When bit 15 of the PSW is zero, the CPU is in the supervisor state. When bit 15 is one, the CPU is in the problem state. The supervisor state is not indicated on the operator sections of the system control panel.

The CPU is switched between problem and supervisor state by changing bit 15 of the PSW. This bit can be changed only by introducing a new PSW. Thus status switching may be performed by LOAD PSW, using a new PSW with the desired value of bit 15. Since LOAD PSW is a priviledged instruction, the CPU must be in the supervisor state prior to the switch. A new PSW is also introduced when the CPU is interrupted. The SUPERVISOR CALL

causes an interruption and thus may change the CPU state. Similarly, initial program loading introduces a new PSW and with it a new CPU state. The new PSW may introduce the problem or supervisor state regardless of the preceding state. No explicit operator control is provided for changing the supervisor state.

## WAIT STATE

In the wait state no instructions are processed, and storage is not addressed repeatedly, whereas in the running state, instruction fetching and execution proceed in the normal manner.

When bit 14 of the PSW is one, the CPU is waiting. When bit 14 is zero, the CPU is in the running state. The wait state is indicated on the operator control section of the system control panel by the wait light.

The CPU is switched between wait and running state by changing bit 14 of the PSW. This bit can be changed only be introducing an entire new PSW, as is the case with the problemstate bit. Thus, switching from the running state may be achieved by the priviledged instruction LOAD PSW, by an interruption such as for SUPERVISOR CALL, or by initial program loading. Switching from the wait state may be achieved by an I/O or external interruption, or again, by initial program loading. The new PSW may introduce the wait or running state regardless of the preceding state. No explicit operator control is provided for changing the wait state.

To leave the wait state without manual intervention, the CPU should be interruptible for some active I/O or external interruption source.

## MASKED STATES

The CPU may be masked or interruptible for all I/O, external, and machine-check interruptions and for some program interruptions. When the CPU is interruptible for a class of interruptions, these interruptions are accepted. When the CPU is masked, the system interruptions remain pending, while the program and machine-check interruptions are ignored.

The system mask bits (PSW bits 0-7), the program mask bits (PSW bits 36-39), and the machine-check mask bit (PSW bit 13) indicate as a group the masked state of the CPU. When a mask bit is one, the CPU is interruptible for the corresponding interruptions. When the mask bit is zero, these interruptions are masked off. The system mask bits indicate the masked state of the CPU for multiplexor and selector channels and the external signals. The program mask bits indicate the masked state for four of the 15 types of program exceptions. The machine-check mask bit pertains to all machine checks. Program interruptions not maskable, as well as the supervisor-call interruption, are always taken. The masked states are not indicated on the operator sections of the system control panel.

Most mask bits do not affect the execution of CPU operations. The only exception is the significance mask bit, which determines the manner in which a floating-point operation is completed when a significance exception occurs.

The interruptible state of the CPU is switched by changing the mask bits in the PSW. The program mask may be changed separately by SET PROGRAM MASK, and the system mask may be changed separately by the privileged instruction SET SYSTEM MASK. The machine-check bit can be changed only by introducing an entire new PSW, as in the case with the problemstate and wait-state bits. Thus, change in the entire masked status may be achieved by the privileged instruction LOAD PSW, by an interruption such as for SUPERVISOR CALL, or by initial program loading. The new PSW may introduce a new masked state regardless of the preceding state. No explicit operator control is provided for changing the masked state.

To prevent an interruption-handling routine from being interrupted before necessary housekeeping steps are performed, the new PSW for that interruption should mask the CPU for further interruptions of the kind that caused the interruption.

## PROTECTION

Protection is provided to protect the contents of certain areas of main storage from destruction (or misuse) caused by erroneous storing (or storing and fetching) of information during the execution of a program. Locations may be protected against store violations or against store and fetch violations but never against fetch violations alone. This protection is achieved by identifying blocks of storage with a key and comparing this key with a protection key

supplied with the data to be stored. The detection of a mismatch causes the access to be suppressed, and a protection exception is recognized.

The key in storage is not part of addressable storage. The key is changed by SET STORAGE KEY and is inspected by INSERT STORAGE KEY. The protection key of the CPU occupies bits 8-11 of the PSW.

The protection system is always active. It is independent of the problem, supervisor, or masked state of the CPU and of the type of instruction or I/O command being executed.

When an instruction causes a protection mismatch, the protected main-storage location remains unchanged.

## PROGRAM STATUS WORD

The PSW contains all information not contained in storage or registers but required for proper program execution. By storing the PSW, the program can preserve the detailed status of the CPU for subsequent inspection. By loading a new PSW or part of a PSW, the state of the CPU may be changed.

In certain circumstances all of the PSW is stored or loaded; in others, only part of it. The entire PSW is stored, and a new PSW is introduced when the CPU is interrupted. The rightmost 32 bits are stored in BRANCH AND LINK. The LOAD PSW introduces a new PSW; SET PROGRAM-

MASK introduces a new condition code and program-mask field in the PSW; SET SYSTEM MASK introduces a new systemmask field.

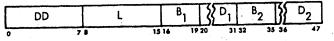

The PSW has the following format:

Program Status Word

| Sy    | stem  | Mask            | Key  | AMWP        | Interruption C | Code |

|-------|-------|-----------------|------|-------------|----------------|------|

| 0     |       | 7               | 8 11 | 12 15       | 16             | 31   |

| ILC   | cc    | Program<br>Mask |      | Instruction | n Address      |      |

| 32 33 | 34 35 | 36 39           | 40   |             |                | 63   |

#### INSTRUCTION FORMAT

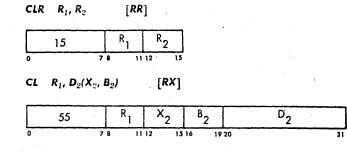

Status-switching instructions use the following two formats: RR Format

| Op Code | э | R    | R <sub>2</sub> |  |

|---------|---|------|----------------|--|

| 0       | 7 | 8 11 | 12 15          |  |

SI Format

| Op Code | ۱ <sub>2</sub> | B     | D     |  |

|---------|----------------|-------|-------|--|

| 0 7     | 8 15           | 16 19 | 20 31 |  |

In the RR format, the Rl field specifies a general register, except for SUPERVISOR CALL. The R2 field specifies a general register in SET STORAGE KEY and INSERT STORAGE KEY. The Rl and R2 fields in SUPERVISOR CALL contain an identification code. In SET PROGRAM MASK the R2 field is ignored.

In the SI format the eight-bit immediate field (I2) of the instruction contains an identification code. The I2 field is ignored in LOAD PSW, SET SYSTEM MASK, and TEST AND SET. The content of the general register specified by Bl is added to the content of the Dl field to form an address designating the location of an operand in storage. Only one operand location is required in status-switching operations. A zero in the Bl field indicates the absence of the corresponding address component.

NOTE: In the detailed descriptions of the individual instructions, the mnemonic and the symbolic operand designation for the IBM System/360 assembly language are shown with each instruction. For LOAD PSW, for example, LPSW is the mnemonic and Dl(Bl) the operand designation.

### STATUS-SWITCHING EXCEPTIONS

Exceptional instructions, operand designations, or data cause a program interruption. When the interruption occurs, the current PSW is stored as an old PSW, and a new PSW identifies the cause of the interruption. The following exception conditions cause a program interruption in status-switching operations.

Operation: The protection feature is not installed and the instruction is SET STORAGE KEY OR INSERT STORAGE KEY.

Privileged Operation: A LOAD PSW, SET SYSTEM MASK, SET STORAGE KEY, INSERT STORAGE KEY, or DIAGNOSE is encountered while the CPU is in the problem state.

Protection: The key of an operand in storage does not match the protection key in the PSW. The instruction is suppressed on a store violation, except for TEST AND SET, which is terminated. The operation is terminated on a fetch violation.

Addressing: An address designates a location outside the available storage for the installation. The operation is terminated, except for DIAGNOSE, which is suppressed.

Specification: The operand address of a LOAD PSW does not have all three low-order bits zero; the operand address of DIAGNOSE does not have as many low-order zero bits as required for the particular CPU; the block address specified by SET STORAGE KEY OR INSERT STORAGE KEY does not have the four low-order bits all zero; or the protection feature is not installed and a PSW with a nonzero protection key is introduced.

When an instruction is suppressed, storage and external signals remain unchanged, and the PSW is not changed by information from storage.

When an interruption is taken, the instruction address stored as part of the old PSW has been updated by the number of halfwords indicated by the instruction-length code in the old PSW.

Operand addresses are tested only when used to address storage. The address restrictions do not apply to the components from which an address is generated: the content of the Dl field and the content of the register specified by Bl.

LOAD

The primary purpose of the LOAD instruction is to transfer the contents of any location to that of another location. The location of the data to be transferred is specified by the second address field. The first address field specifies the location to which the data will be transferred. The second operand remains unchanged.

The term "Operand" refers to the data that is operated on by the instruction. The location of the Operand is specified by the "address field." The "first address field" has a subscript 1 attached as; R1 or D1 (B1). The "second address field" is also described by its subscripts as; R2 or D2(X2,B2).

The following LOAD instructions exhibit additional characteristics:

- LH Expands a halfword operand to a fullword operand by propagating the sign bit to the left through the 16 high-order bit positions.

- LTR Sets the Condition Code as a result of the data contained in the second operand.

- LCR The second operand is changed to the two's complement form when transferred.

- LPR The second operand is changed to a positive number (IF NEGATIVE)

- LNR The second operand is changed to a negative number (IF POSITIVE)

LM Allows more than one register to be loaded at a time.

Load

LR R1, R2 [RR] R<sub>2</sub> R<sub>1</sub> 18 11 12  $L R_1, D_2(X_2, B_2)$  [RX] R<sub>1</sub> D2 X<sub>2</sub> <sup>B</sup>2 58 15 16 19 20 11 12 78

- The fullword specified by the second address field [R2 or D2(X2,B2)] is placed in the register specified by the first address field (R1).

- 2. The second operand remains unchanged.

## EXAMPLES

| 1. | LR<br>Load the | (Load R<br>contents |     |                      | 5 into register 3. |            |  |  |

|----|----------------|---------------------|-----|----------------------|--------------------|------------|--|--|

|    | SYMBOLIC       | LR 3,5              |     |                      | MACHINE            | 18 35      |  |  |

| •  |                |                     |     | Before               | After              |            |  |  |

|    | GPR<br>GPR     | 3<br>5              |     | 96 0A CD<br>00 19 86 |                    |            |  |  |

| 2. | L<br>Lord the  | (Load)              | o f | storage ad           | drogg 100          | ר (הואדים) |  |  |

Load the contents of storage address 1000 (FIELD1) into register 7. (GPR F = 00 00 10 00)

SYMBOLIC L 7,FIELDI MACHINE 58 70 F0 00

|         | · · · · |    | Bet | Eore | 2   |    | Aft | ter |    |  |

|---------|---------|----|-----|------|-----|----|-----|-----|----|--|

| GPR     | 7       | 00 | 00  | 00   | 0.0 | 00 | 00  | FC  | DE |  |

| Storage | 1000    | 00 | 00  | FC   | DE  | 00 | 00  | FC  | DE |  |

## CONDITION CODE

1. Remains unchanged

# PROGRAM INTERRUPTIONS

- 1. Protection (fetch L only)

- 2. Addressing (L only)

- 3. Specification (L only)

Load Halfword

| LH | R <sub>1</sub> , D <sub>2</sub> (X <sub>2</sub> , | 8 <sub>2</sub> ) | [RX]  |                | ·  |    |

|----|---------------------------------------------------|------------------|-------|----------------|----|----|

|    | 48                                                | R <sub>1</sub>   | ×2    | <sup>B</sup> 2 | D2 |    |

| 0  | 7                                                 | 8 11             | 12 15 | 16 19          | 20 | 31 |

- The halfword second operand [D2(X2,B2)] is placed 1. in the register specified by the first address field (R1).

- The halfword operand is expanded to a fullword by 2. propagating the sign bit through the 16 high-order bit positions.

- The second operand remains unchanged. 3.

### EXAMPLES

1. LΗ Load the halfword contents of storage location 1002 (FIELD1+2) into register C.  $(GPR F = 00 \ 00 \ 10 \ 00)$

SYMBOLIC LH 12, FIELD1+2 MACHINE 48 CO FO 02

|         |      |    | Before |    |    |    | After |    |    |

|---------|------|----|--------|----|----|----|-------|----|----|

| GPR     |      | 00 | 00     | 00 | 00 | FF | FF    | 9F | 10 |

| Storage | 1000 | F0 | 80     | 9F | 10 | FO | 80    | 9F | 10 |

CONDITION CODE

Remains unchanged 1.

PROGRAM INTERRUPTIONS

المراجع فتقتص المراجع

- Protection (fetch only) 1.

- 2. Addressing

- Specification 3.

Load and Test

[*RR*] LTR  $R_1, R_2$

| 12  | R    | <sup>R</sup> 2 |

|-----|------|----------------|

| 0 7 | 8 11 | 12 15          |

- The contents of the register specified by the second 1. operand (R2) are placed in the location specified by the first operand (R1).

- The sign and value of the second operand determines 2. the setting of the Condition Code.

- 3. The second operand remains unchanged.

### EXAMPLES

LTR (Load and Test Register) Load the contents of register 1 into register A and set the Condition Code.

SYMBOLIC

LTR 10,1

MACHINE 12 A1

Before

After

GPR 1

0C 10 00 00

0C 10 00 00

GPR A

AB 19 24 35

0C 10 00 00

Condition Code

2. LTR

Test the contents of register 2 without loading into another location. SYMBOLIC LTR 2,2 MACHINE 12 22

|     | алан<br>Алан<br>Алан |   | Before     | , • | Aft | er |    |

|-----|----------------------|---|------------|-----|-----|----|----|

| GPR | 2                    | 9 | 1 23 45 6A | 91  | 23  | 45 | 6A |

Condition Code 1

#### CONDITION CODE

- 0 Operand is zero

- 1 Operand is negative 2 Operand is positive

- .

3

#### PROGRAM INTERRUPTIONS

\_\_\_\_

1. None

Load Complement

LCR  $R_1, R_2$  [RR]

13 R2

The contents of the register specified by the second address field (R2) are placed in the register designated by the first address field (R1).

2. The second operand is complemented prior to placing in the first operand location.

- 3. A second operand containing a value of zero would remain unchanged.

- 4. A second operand containing the maximum negative number will not be complemented and will cause a fixed point overflow. The Condition Code is set to 3.

- 5. Both positive and negative values are complemented.

### EXAMPLES

1. LCR (Load Complement Register) Complement and load the contents of register 5 into register 8.

SYMBOLIC LCR 8,6 MACHINE 13 86

| GPR |   |    | Before |    |    |    | After |    |    |  |  |

|-----|---|----|--------|----|----|----|-------|----|----|--|--|

|     | 6 | FF | FF     | FF | FF | FF | FF    | FF | FF |  |  |

| GPR | 8 | 00 | 00     | 00 | 00 | 00 | 00    | 00 | 01 |  |  |

Condition Code 2

LCR 2.

Complement the contents of register D.

SYMBOLIC LCR 13,13 MACHINE 13 DD

|          |         |    | Bet | fore | <u>ع</u> , , |          | Afi | ter |    |  |

|----------|---------|----|-----|------|--------------|----------|-----|-----|----|--|

| GPR      | D       | 00 | 00  | 00   | AC           | FF       | FF  | FF  | 54 |  |

| Conditio | on Code | 1  |     |      |              | <u>.</u> |     |     |    |  |

## CONDITION CODE

- Result is zero 0

- Result is negative 1

- Result is positive 2

3 Overflow

### PROGRAM INTERRUPTIONS

### 1. Fixed Point Overflow

Load Positive

| LPR | R <sub>1</sub> , R <sub>2</sub> | [ <i>RR</i> ] |

|-----|---------------------------------|---------------|

|     |                                 |               |

| 10  | R    | <sup>R</sup> 2 |  |

|-----|------|----------------|--|

| 0 7 | 8 11 | 12 15          |  |

- The absolute value contained in the register speci-1. fied by the second address field (R2) is placed in the register specified by the first address field (R1).

- Negative numbers are complemented while positive 2. numbers remain unchanged.

- 3. A second operand containing the value of zero remains unchanged.

- A second operand containing the maximum negative num-4. ber will not be complemented and will cause a fixed point overflow. The Condition Code is set to 3.

EXAMPLES

1.

LPR

(Load Positive Registers)

Load the absolute value of register E into register 0.

SYMBOLIC LPR 0,14

MACHINE 10 OE

|        |          |     | Bet | Eor |            |                      | Aft | <u>er</u> |           |  |

|--------|----------|-----|-----|-----|------------|----------------------|-----|-----------|-----------|--|

| GPR    | 0        | 79  | 0A  | 05  | 63         | 3A                   | FC  | 19        | <b>A8</b> |  |

| GPR    | Έ        | 3A  | FC  | 19  | <b>A</b> 8 | 3A                   | FC  | 19        | 8A        |  |

| Condit | ion Code | e 2 |     |     |            | н. — н. <sup>2</sup> |     |           |           |  |

2. LPR

> Change the contents of register 9 to its absolute value.

| SYMBOLIC | LPR 9,9                               |        | MACHINE 10 | 99          |

|----------|---------------------------------------|--------|------------|-------------|

|          |                                       |        |            | - 44 - 14 A |

| · · · ·  | · · · · · · · · · · · · · · · · · · · | Before | 7 ft or    |             |

|  | 1. A. | Belore | AILEI                                                                                                          |  |

|--|-------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------|--|

|  |                                           |        | the second s |  |

GPR 9 80 00 00 01 7F FF FF FF

Condition Code 2

CONDITION CODE

- 0 Result is zero

- 1 ----

- 2 Result is positive 3

- Overflow

PROGRAM INTERRUPTIONS

1. Fixed Point overflow

Load Negative

LNR  $R_1, R_2$  [RR]

11

- The two's complement of the absolute value contained 1. in the register specified by the second address field (R2) is placed in the register specified by the first address field (R1).

- Positive numbers are complemented while negative num-2. bers remain unchanged.

- З. A second operand containing the value of zero remains unchanged.

## EXAMPLES

1. LNR

Complement the absolute value contained in register 3 and place in register 7.

SYMBOLIC LNR 7,3

## MACHINE 11 73

|     |   |    |    | Before |    |    |    | After |    |  |

|-----|---|----|----|--------|----|----|----|-------|----|--|

| GPR | 3 | 70 | 00 | 00     | 10 | 70 | 00 | 00    | 10 |  |

| GPR | 7 | 00 | 00 | 00     | 00 | 8F | FF | FF    | FO |  |

Condition Code 1

2. LNR

Complement the absolute value contained in register 8.

SYMBOLIC

LNR 8,8

MACHINE 11 88

Before

After

GPR

8

90 00 00 00

90 00 00 00

Condition Code

1

CONDITION CODE

0 Result is zero 1 Result is negative 2 --3 --

PROGRAM INTERRUPTIONS

1. None

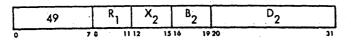

Load Multiple

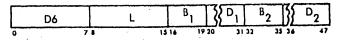

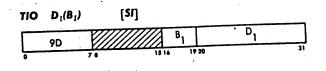

$LM R_1, R_3, D_2(B_2)$  [RS]

- The general registers starting with the register specified by the first address field (R1) and ending with the register specified by the third address field (R3) are loaded from the locations designated by the second address field (B2,D2).

- 2. The registers are loaded from storage beginning at the address specified by the second address field and continuing in increments of four bytes until all specified registers are loaded.

- 3. The registers are loaded in ascending order beginning with the register specified by R1 and continuing up to and including the register specified by R3.

- 4. All combinations of register addresses specified by Rl and R3 are valid.

- 5. When the address specified by R3 is less than R1, the register addresses wrap around from F to 0.

- 6. The second operand remains unchanged.

### EXAMPLES

1. LM

Load registers 9 through B from storage locations 1000 (DATA) through 100B. (GPR  $F = 00 \ 00 \ 10 \ 00$ )

SYMBOLIC LM 9,11, DATA MACHINE 98 9B F0 00

| •        |         |      | 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - |     |       |    |       |      |

|----------|---------|------|-----------------------------------------------------------------------------------------------------------------|-----|-------|----|-------|------|

|          |         |      |                                                                                                                 | Bef | ore   |    | After | -    |

|          | GPR     | 9    | 00                                                                                                              | 00  | 00 00 | 00 | 00 02 | 2 00 |

|          | GPR     | Α    | 00                                                                                                              | 00  | 00 00 | 00 | 00 00 | 04   |

|          | GPR     | В    | 00                                                                                                              | 00  | 00 00 | 00 | 00 F( | C DE |

|          | Storage | 1000 | 00                                                                                                              | 00  | 02 00 | 00 | 00 02 | 2 00 |

|          | •       | 1004 | 00                                                                                                              | 00  | 00 04 | 00 | 00.00 | 04.  |

| - 1.<br> |         | 1008 | 00                                                                                                              | 00  | FC DE | 00 | 00 F( | DE   |

|          |         |      |                                                                                                                 |     |       |    |       |      |

2.

LM

Load register E through 1 from storage locations 1000 (DATA) through 100F. (GRP F = 00 00 10 00)

SYMBOLIC LM 14,1,DATA

# MACHINE 98 E1 F0 00

|         |      | Before      | After       |

|---------|------|-------------|-------------|

| GPR     | E    | 00 00 00 05 | 12 34 56 AC |

| GPR     | F    | 00 00 10 00 | 00 00 10 00 |

| GPR     | 0    | 23 1C 1A 23 | AB CD EF 01 |

| GPR     | 1    | 5A 7C 00 00 | 13 72 A2 19 |

| Storage | 1000 | 12 34 56 AC | 12 34 56 AC |

|         | 1004 | 00 00 10 00 | 00 00 10 00 |

|         | 1008 | AB CD EF 01 | AB CD EF 01 |

|         | 100C | 13 72 A2 19 | 13 72 A2 19 |

## CONDITION CODE

Remains unchanged 1.

## PROGRAMMING INTERRUPTIONS

- Protection (fetch only) Addressing 1.

- 2.

- 3. Specification

### STORE

The STORE instruction is used to transfer the contents of the General Purpose Registers to main storage. The location of the data to be transferred is specified by the first and third (when applicable) address fields. The second address field designates the beginning address in main storage where the data will be placed.

The following STORE instructions exhibit additional characteristics:

STH Stores the low-order 16 bits of a register.

STM Stores more than one register at a time.

Store

ST  $R_1, D_2(X_2, B_2)$  [RX]

| - |     |      |                |       | · · · · · · · · · · · · · · · · · · · |

|---|-----|------|----------------|-------|---------------------------------------|

| Г | 50  | R,   | X <sub>2</sub> | Bo    | Do                                    |

| L |     | . 1  | 2              | 2     | 2                                     |

| 0 | . 7 | 8 11 | 12 15          | 16 19 | 20 31                                 |

1. The contents of the register specified by the first address field (R1) are stored at the location designated by the address field [D2(X2,B2)].

### EXAMPLES

1. ST (Store)

Store the contents of register D into storage location 1004 (DATA+4). (GPR F = 00 00 10 00)

SYMBOLIC

ST 13,DATA+4

MACHINE

50 D0 F0 04

Before

After

GPR

D

0A C1 85 69

0A C1 85 69

Storage 1004 OF F0 16 72 OA C1 85 69

# CONDITION CODE

1. Remains unchanged

PROGRAMMING INTERRUPTIONS

- 1. Protection (store only)

- 2. Addressing

- 3. Specification

Store Malfword

STH  $R_1$ ,  $D_2(X_2, B_2)$  [RX]

1. The low-order 16 bits of the register specified by the first address field (R1) are stored at location designated by the address field [D2(X2,B2)].

## EXAMPLE

1. STH (Store Halfword)

Store the low order two bytes of register 0 into

storage location 1000 (DATA). (GPR F = 00 00 10 00)

SYMBOLIC STH 0, DATA MACHINE 40 00 F0 00

|   |         |      | Before |    |    |    | After |    |    |    |

|---|---------|------|--------|----|----|----|-------|----|----|----|

| , | GPR     | 0    | 00     | FC | 04 | 50 | 00    | FC | 04 | 50 |

|   | Storage | 1000 | FE     | D9 | 16 | 25 | Ó4    | 50 | 16 | 25 |

### CONDITION CODE

1. Remains unchanged.

### PROGRAM INTERRUTPIONS

- 1. Protection (store only)

- 2. Addressing

- 3. Specification

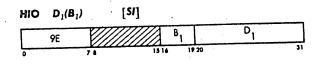

**Store Multiple**

STM R1, R3, D2(B2) [RS] D\_2 <sup>R</sup>3 90 19 20 11 12 15 16 78

- The general register starting with the register specified by the first address field (R1) and ending with the register specified by the third address field (R3) are stored in the location designated by the second address field (D2,B2).

- 2. The registers are stored in ascending order beginning with the register specified by the first address field and continuing until all specified registers are stored.

- 3. The beginning storage address is incremented by 4 bytes after each register is stored. This continues until all specified registers have been stored.

- 4. All combinations of register address specified by Rl and R3 are valid.

- 5. When the address specified by R3 is less than R1, the register addresses wrap around from F to 0.

EXAMPLES

1.

STM (Store Multiple) Store the contents of register 4 and 5 into storage location 1000 (DATA) through 1007. (GPR F = 00 00 10 00)

| SYMBOL | IC STM 4 | ,5,DATA | · ·                  | MACHINE 90           | 45 F0 00 |

|--------|----------|---------|----------------------|----------------------|----------|

|        |          |         | Before               | After                |          |

|        |          |         | 00 00 Al<br>01 1A 23 | 46 00 00<br>00 01 1A |          |

| S      | torage   |         | AE FC D4<br>00 00 02 | 46 00 00<br>00 01 1A |          |

2. STM

Store the content of registers F and 0 into storage location 1008 (DATA+8) through 100F. (GPR F = 0000 1000)

| SYM | BOLIC STM  | 15,0,DA7     | 'A+8           | arta<br>Alta arta arta | MACHI                                                                                                                            | NE 90          | FO FO | 08 |

|-----|------------|--------------|----------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------|-------|----|

| -   |            |              | Be             | fore                   | ан Алтан.<br>Адартан Алтан.<br>Алтан Алтан А | After          | -     |    |

|     | GPR<br>GPR | 0<br>F       | 00 00<br>00 00 | ) 00 04<br>) 10 00     | 1 C C C C C C C C C C C C C C C C C C C                                                                                          | 00 00<br>00 10 |       | •  |

|     | Storage    | 1008<br>100C |                | 00 08                  |                                                                                                                                  | 00 10          |       | ·  |

# CONDITION CODE

1. Remains unchanged.

# PROGRAM INTERRUPTIONS

- Protection (store only)

Addressing

Specification

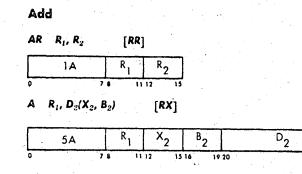

ADD

The ADD instruction is used to perform the addition of two operands. The second operand is added to the first operand and the result replaces the contents of the first operand.

The following ADD instructions exhibit additional characteristics:

- AH Prior to the addition, it expands a halfword operand to a fullword by propagating the sign bit through the the 16 high-order bits positions.

- AL Following the add, it records the occurrence of a carry out of the sign position in the Condition Code.

The contents of the location specified by the second address field (R2 or D2(X2,B2)) are added to the contents of the register specified by the first address field (R1).

- 2. The sum replaces the first operand (R1).

- 3. Addition is performed by adding all 32 bits of both operands.

- If the carry out of the sign-bit position and the high-order numeric bit position agree, the sum is satisfactory. If they disagree, an overflow occurs.

A positive overflow results in a negative sum.

- 6. A negative overflow results in a positive sum.

7. A register may be added to itself.

## EXAMPLES

1.

AR (Add Registers) Add the contents of register 4 to the contents of register 7 and have the result placed in register 7.

SYMBOLIC AR 7,4 MACHINE 1A 74

|     | 14 |   | Before |    |    | <br>After |  |    |    |    |    |

|-----|----|---|--------|----|----|-----------|--|----|----|----|----|

| GPR | :  | 4 | 70     | 00 | 12 | 3C        |  | 70 | 00 | 12 | 3C |

| GPR |    | 7 | 00     | 00 | 0A | 81        |  | 70 | 00 | 1C | BD |

Condition Code 2

2. A (Add)

Add the fullword contents of storage location 1000 (OPER1) to register 3. (GPR  $F = 00 \ 00 \ 10 \ 00$ )

SYMBOLIC A 3, OPER1

MACHINE 5A 30 F0 00

|         |      | Before      | After       |  |  |

|---------|------|-------------|-------------|--|--|

| GPR     | 3    | 00 00 00 04 | 00 00 00 03 |  |  |

| Storage | 1000 | FF FF FF FF | FF FF FF FF |  |  |

|         |      |             |             |  |  |

Condition Code 2

CONDITION CODE

- 0 Sum is zero

- 1 Sum is negative

- 2 Sum is positive

- 3 Overflow

PROGRAM INTERRUPTIONS

- 1. Protection (fetch A only)

- 2. Addressing (A only)

- 3. Specification (A only)

- 4. Fixed-point overflow

Add Halfword

| $AH_{1}, R_{1}, D_{2}(X_{2}, B_{2})$ | [RX] |

|--------------------------------------|------|

|--------------------------------------|------|

| 4A | R <sub>1</sub> | X <sub>2</sub> | <sup>B</sup> 2 | D <sub>2</sub> |    |

|----|----------------|----------------|----------------|----------------|----|

| 0  | 7 6 11         | 12 15          | 16 19          | 20             | 31 |

- The halfword designated by the second address field (D2 (X2,B2)) is added to the register specified by the first address field (R1).

- 2. The halfword second operand is expanded to a fullword, prior to addition, by propagating the sign-bit value through the 16 high-order bit positions.

- 3. The sum replaces the contents of the register specified by the first address field (R1).

- 4. Addition is performed by adding all 32 bits of both operands.

- 5. If the carry out of the sign-bit position and the highorder numeric bit position agree, the sum is satisfactory. If they disagree, an overflow occurs.

6. A positive overflow results in a positive sum.

## EXAMPLES

1. AH (Add Halfword)

Add the halfword contents of storage location 1002

(OPER1+2) to register 5.

|   | SYMBOLIC  | AH 5, OPER1+2 |     |     |      |    | MACHINE 4A 50 F0 |     |    |    | FO | 02 |  |

|---|-----------|---------------|-----|-----|------|----|------------------|-----|----|----|----|----|--|

|   |           |               |     | Bei | fore |    | •                | Aft | er |    |    |    |  |

|   | GPR       | 5             | 8.0 | 00  | 00.0 | 01 | 80               | 00  | 00 | 00 |    |    |  |

|   | Storage   | 1000          | 00  | 00  | FF H | FF | 00               | 00  | FF | FF |    |    |  |

| • | Condition | Code          | 1   |     |      |    |                  |     |    |    |    |    |  |

### CONDITION CODE

- 0 Sum is zero

- 1 Sum is negative

- 2 Sum is positive

- 3 Overflow

## PROGRAM INTERRUPTIONS

- 1. Protection (fetch only)

- 2. Addressing

- 3. Specification

- 4. Fixed-point overflow

Add Logical

ALR  $R_1, R_2$  [RR]

۱E 78 11 12

AL

$$R_1$$

,  $D_2(X_2, B_2)$  [RX]

- The contents of the second address field [R2 or D2 (X2,B2)] are added to the register specified by the first address field (R1).

- 2. The sum replaces the first operand (R1).

- 3. Logical addition is performed by adding all 32 bits of both operands without further change to the resulting sign bit.

- 4. An overflow condition is not indicated.

- 5. A carry out of the sign position is recorded in the the Condition Code.

## EXAMPLES

1. ALR (Add Logical Register) Logically add the contents of register 9 to register 7 and place the sum in register 7.

| SYMBOLIC | ALR 7,9 | MACHINE            | 1E 79       |

|----------|---------|--------------------|-------------|

|          |         | Before             | After       |

| GPR      | 7       | 00 00 00 30        | 00 00 01 30 |

| GPR      | 9       | 00 00 01 00        | 00 00 01 00 |

| Conditi  | on Codo | <b>1 1 1 1 1 1</b> |             |

Condition Code 1

AL (Add Logical) Logically add the contents of register 9 to 2. AL storage location 1004 (OPER1+4). (GPR F = 00 00 10 00)

SYMBOLIC AL 9, OPER1+4 MACHINE 5E 90 FO 04

## Before

# After

80 00 00 GPR 9 00 00 00 00 01 Storage 1004 80 00 00 01 80 00 00 01

Condition Code 3

# CONDITION CODE

- 0 Sum is zero (no carry)

- 1 Sum is not zero (no carry)

- 2 Sum is zero (carry)

- 3 Sum is not zero (carry)

# PROGRAM INTERRUPTIONS

- 1. Protection (fetch AL only)

- Addressing (AL only)

Specification (AL only)

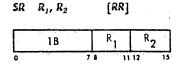

## SUBTRACT

The primary purpose of the SUBTRACT instruction is to find the difference between two operands. The location specified by the second address field contains the subtrahend. The minuend is contained in the register specified by the first address field. The first operand is replaced by the difference.

The following SUBTRACT instructions exhibit additional characteristics:

SH Prior to subtraction the halfword operand is expanded to a full word by propagating the sign bit through the high-order 16 bit positions.

SL Following the subtraction it records the occurrence of a carry out of the sign position in the Condition Code.

Subtract

$S R_1, D_2(X_2, B_2)$  [RX]

| 5B  | R <sub>1</sub> | ×2    | <sup>8</sup> 2 | D <sub>2</sub> |    |

|-----|----------------|-------|----------------|----------------|----|

| 0 7 | 8 11           | 12 15 | 16 19 20       | 0              | 31 |

- The contents of the location specified by the second address field [R2 or D2(X2,B2)] are subtracted from the contents of the register specified by the first address field (R1).

- 2. The difference replaces the first (R1).

- 3. Subtraction is performed by complement addition.

- 4. If the carry out of the sign-bit position and the high-order numeric bit position agree, the difference is satisfactory. If they disagree, an overflow occurs.

- 5. A register may be cleared by subtracting it from itself.

EXAMPLES

1. SR (Subtract Register) Subtract the contents of register 7 from the contents of register 5.

SYMBOLIC SR 5,7 MACHINE 1B 57

|       |     |    |    | After |      |    |    |    |

|-------|-----|----|----|-------|------|----|----|----|

| GPR 5 | 00  | 00 | 2F | ED    | 00   | 00 | 2E | lF |

| GPR 7 | .00 | 00 | 01 | CE    | · 00 | 00 | 01 | CE |

Condition Code 2

2. SR

Clear register 7 by subtraction.

SYMBOLIC

SR 7,7

MACHINE 1B 77

Before

After

| GPR | 7 |   | 00 | 0,0 | 01 | CE | 0.0 | 00 | 00 | 00 |

|-----|---|---|----|-----|----|----|-----|----|----|----|

|     | • | · |    |     |    |    |     |    |    |    |

|     |   |   |    |     |    |    |     |    |    |    |

Condition Code 0

3. S (Subtract)

Subtract the fullword contents at storage location 200C (HOURS+12) from register C. (GPR F = 00 00 20 00)

SYMBOLIC S 12,HOURS+12

MACHINE 5B C0 F0 0C

GPR

C

80 00 00 00

00 00 00

Storage

200C

80 00 00 00

80 00 00 00

Condition Code

0

0

0

## CONDITION CODE

Difference is zero

Difference is negative

Difference is positive

Overflow

#### PROGRAM INTERRUPTIONS

- Protection (fetch S only)

Addressing (S only)

- 3. Specification (S only)

- 4. Fixed-point overflow

#### Subtract Halfword

SH  $R_1, D_2(X_2, B_2)$  [RX]

| 4B | R <sub>1</sub> | ×2    | <sup>8</sup> 2 | D <sub>2</sub> | ] |

|----|----------------|-------|----------------|----------------|---|

| 0  | 78 11          | 12 15 | 16 19          | 20 31          | Ē |

- The halfword designated by the second address field (D2(X2,B2)) is subtracted from the contents of the register specified by the first address field (R1).

- 2. The halfword operand is expanded to a fullword, prior to subtraction, by propagating the sign-bit value through the 16 high-order bit positions.

- 3. The difference replaces the first operand.

- 4. Subtraction is performed by complement addition of all 32 bits of both operands.

- 5. If the carry out of the sign-bit position and the high-order numeric bit position agree, the difference is satisfactory. If they disagree, an overflow occurs.

EXAMPLES

1. SH (Subtract Halfword)

Subtract the halfword operand at storage location

2000 (HOURS) from the contents of register E.

(GPR F = 00 00 20 00)

| SYMBOLIC  | SH 14, HOURS |    | MACHINE |     |    | 4B  | ΕO  | FO | 00 |