IBM Customer Engineering Manual of Instruction

IBM 1410-1401 Compatibility

Customer Engineering Manual of Instruction 1410 - 1401 Compatibility

© 1961, 1963 by International Business Machines Corporation

#### MINOR REVISION (January 1963)

This edition, Form 223-2597, is a revision of the section entitled "1401 Compatibility" (pages 333 through 411) of Customer Engineering Manual of Instruction, 1410 Data Processing System, Form 225-6549-1. Principal changes in this edition are:

| PAGE | SUBJECT              |

|------|----------------------|

| 13   | Indexing             |

| 55   | I-O Error Conditions |

Address comments regarding the content of this publication to: IBM Corporation, Dept 296, PO Box 390, Poughkeepsie, N. Y.

# Contents

| 1410-1401 Compatibility                              |     | 5   |

|------------------------------------------------------|-----|-----|

| Zone and Auxiliary Binary Adders                     |     | 5   |

| Instruction Read-Out                                 |     | 5   |

| Indexing                                             |     | 13  |

| indexnig                                             |     |     |

| Data Handling                                        |     | 17  |

| Move Numeric D                                       |     | 17  |

| Move Zone                                            |     | 17  |

| Move Characters to Record or Group Mark/Word Mark    |     | 18  |

| Move Characters to A or B Word Mark M (A) (B), M (A  |     |     |

|                                                      |     | 20  |

| Load Characters to A-Word Mark L (A) (B), L (A).     |     | 20  |

| Move Characters and Suppress Zeros Z (A) (B) $\dots$ |     |     |

| Compare C (A) (B) $\dots$                            |     |     |

| Move Characters and Edit E (A) (B)                   | • • | 20  |

|                                                      |     | ~ 1 |

| Arithmetic                                           | ••• | 21  |

| Add and Subtract                                     |     |     |

| Zero and Add, Zero and Subtract                      | • • | 21  |

| Multiply and Divide                                  | ••  | 21  |

|                                                      |     |     |

| Logic Operations                                     |     | 22  |

|                                                      | •   |     |

| Branch (B) B (I) b                                   | •   | 44  |

| Branch, if indicator on B (I) d                      | •   | 42  |

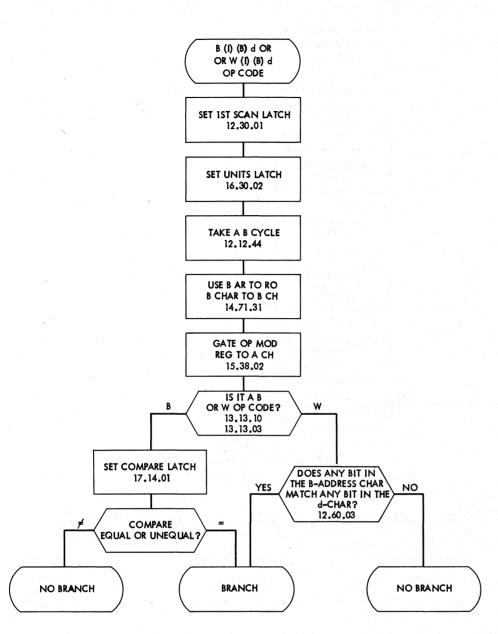

| Branch, if Character is Equal B (I) (B) d            | •   | 23  |

| Branch, if Bit Equal W (I) (B) d                     | •   | 23  |

| Branch if WM and/or Zone V (1) (B) d                 | • , | 24  |

| Miscellaneous                                   | 27 |

|-------------------------------------------------|----|

| Store A-Address Register                        | 27 |

| Store B-Address Register                        | 27 |

| Modify Address                                  | 27 |

| No Operation (N)                                | 35 |

| Halt (.)                                        | 35 |

| Halt and Branch Op . (I)                        | 35 |

| Set Word Mark, (A) (B)                          | 35 |

| Clear Word Mark (A) (B)                         | 36 |

| Clear Storage/ (A)                              | 36 |

| Clear Storage and Branch/ (I) (B)               | 36 |

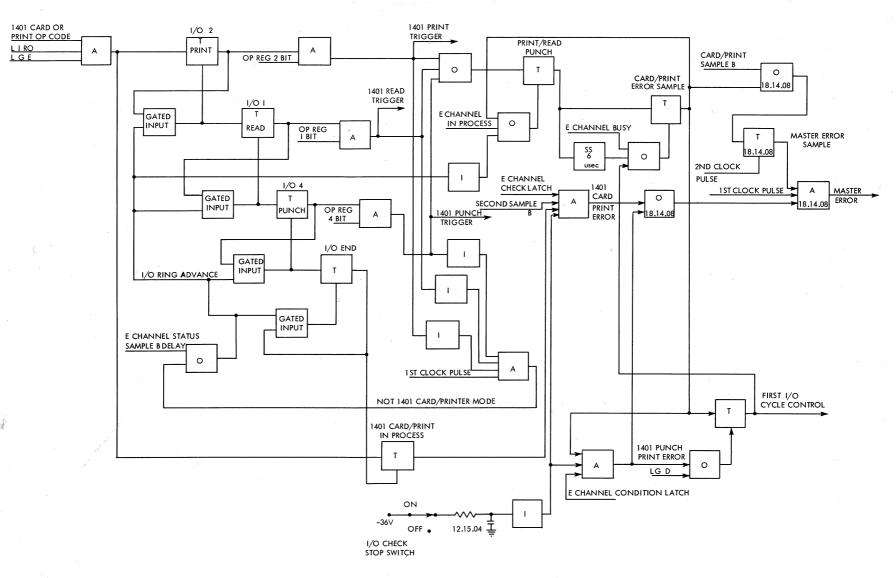

| Input-Output Instructions                       | 38 |

| Read a Card                                     | 38 |

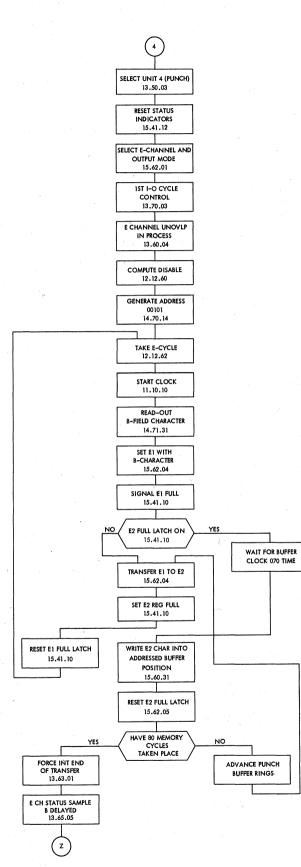

| Punch a Card                                    | 43 |

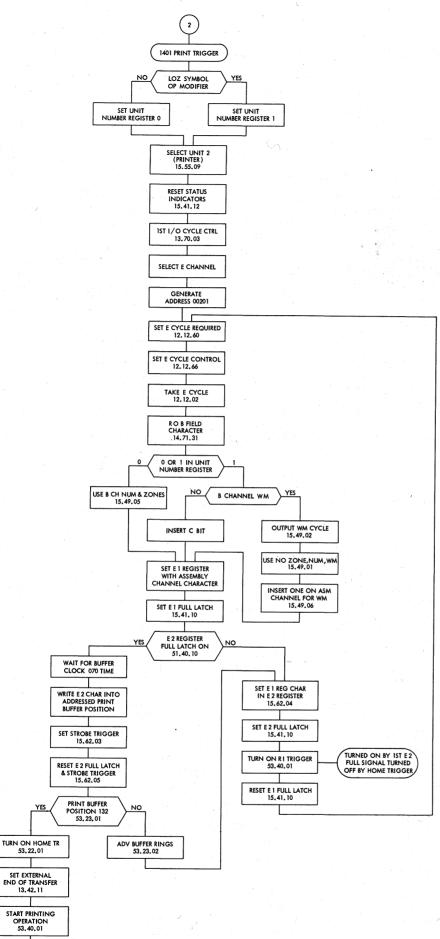

| Print a Line                                    | 46 |

| Write Word Marks                                | 49 |

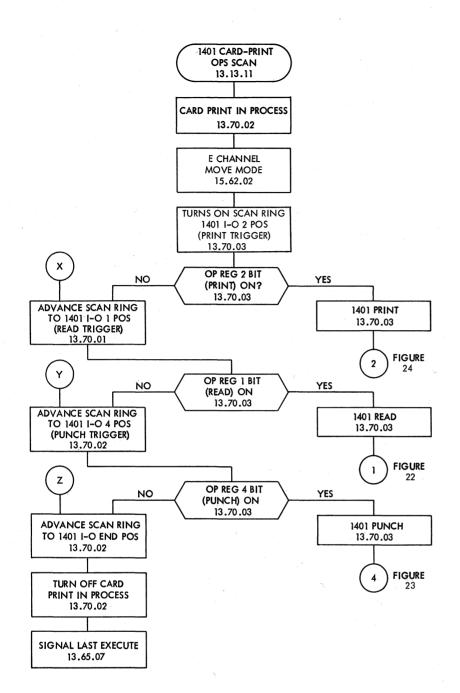

| Combination Card-Print Instructions             | 50 |

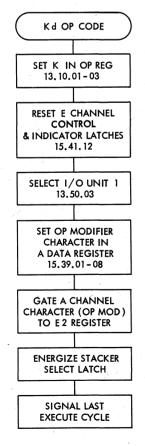

| Select Stacker                                  | 50 |

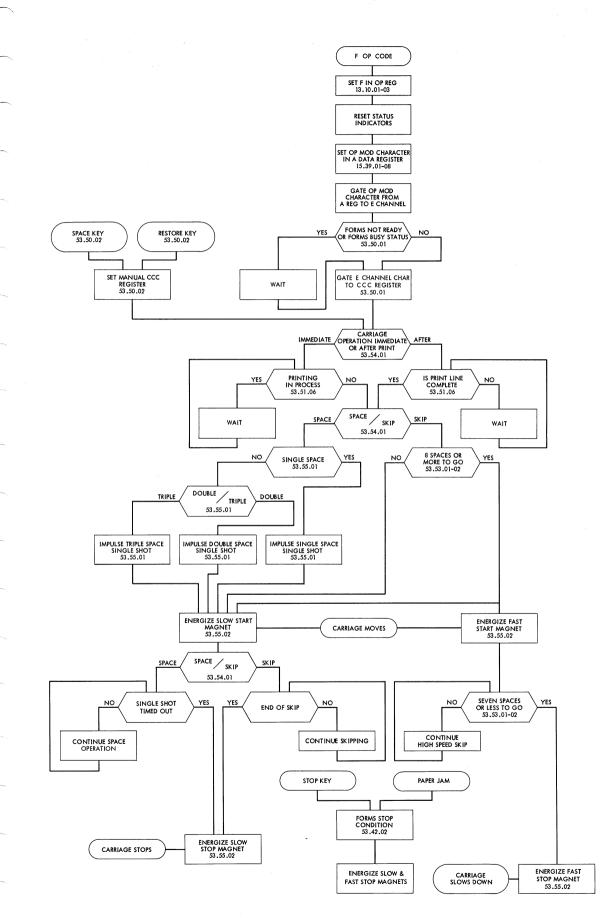

| Carriage Control                                | 51 |

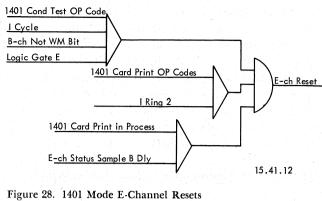

| Card-Print-Branch Instructions                  | 52 |

| Stacker Select or Control Carriage and Branch   | 54 |

| Start Read Feed and Start Punch Feed            | 55 |

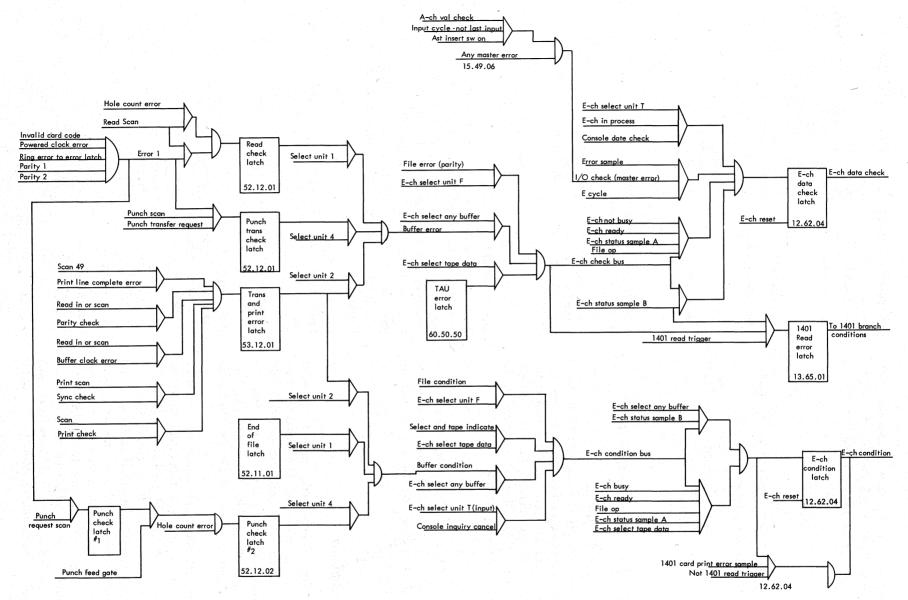

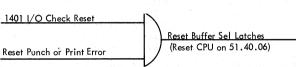

| I-O Error Conditions                            | 55 |

| 1401 Read Error (1401 I-O Check Stop Switch On) | 55 |

| Reader End of File                              | 55 |

| 1401 Punch Errors                               | 55 |

| 1401 Print Errors                               | 58 |

|                                                 |    |

ala an

The basic design of the IBM 1410 Data Processing System permits the running of many programs as originally written for IBM 1401 Data Processing System. The compatibility switch on the CE panel of the IBM 1415 Console enables a 1410 system to utilize programs written for all models of the 1401 (A, B, C, D, E, and F). This manual assumes a knowledge of the basic 1410 Data Processing System.

One major difference occurs when the IBM 1410 system operates in the 1401 mode. This is the use of the three-position addresses. The digit portion of the address locates storage positions 000 through 999. The zones over the units and hundreds positions are assigned binary values to increase the number of addresses to 15,999. The A-zone over the hundreds position has a digit value of 1 or 1,000. An address T33 (T is A, 2, 1 bits) locates storage position 01333. The digit values of the other zones are:

| $B \equiv 2$ | · · · · · · · · · · · · · · · · · · · | B = 8 |

|--------------|---------------------------------------|-------|

| $A \equiv 1$ |                                       | A = 4 |

| Hund         | Tens                                  | Units |

The address to locate position 15,999 is I 9 I (I is A, B, 8, 1 bits).

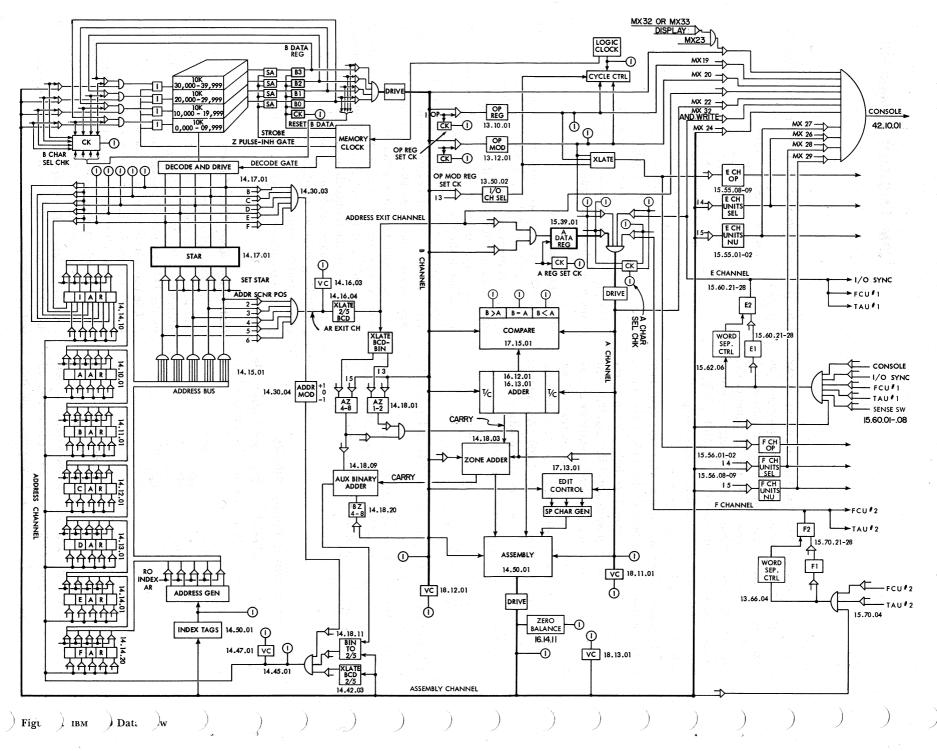

Some 1401 operations require the addition of two addresses. To handle these operations on a 1410 system requires the addition of the zone adder and the auxiliary binary adder.

## Zone and Auxiliary Binary Adders

The zone adder combines the binary 1 and 2 bits while the auxiliary binary adder combines the 4 and 8 bits. For example:

| AUX BIN ADDR | ZONE ADDER             |

|--------------|------------------------|

|              | 8421                   |

| Add A —      | 0111 = 7               |

| B —          | 0110 = 6               |

|              | 0001                   |

| Carry        | 11                     |

|              | $\overline{1101 = 13}$ |

Notice that each position must be able to carry into the next position. On the data flow diagram (Figure 1) the line from the zone adder to the auxiliary binary adder is the zone adder carry. In adding two addresses together, there can be a carry from the hundreds position digits that are added in the adder. For example:

| BINARY          | 8421 | DECIMAL         |

|-----------------|------|-----------------|

|                 |      | l B             |

|                 |      | AA              |

| A-field         | 0111 | $821 \pm 07821$ |

|                 |      | AA              |

| <b>B</b> -field | 0101 | $380 \pm 05380$ |

|                 | 0010 | 101             |

| Carry           | 1 11 | 1               |

|                 | 1    | В               |

|                 |      | AA              |

|                 | 1101 | $201 \pm 13201$ |

On the data flow diagram, the line from the adder to the zone adder is the adder carry.

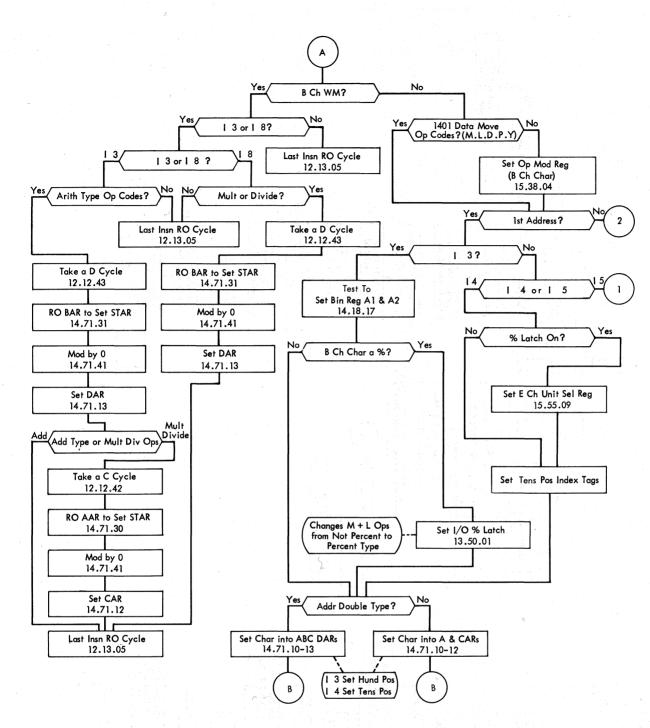

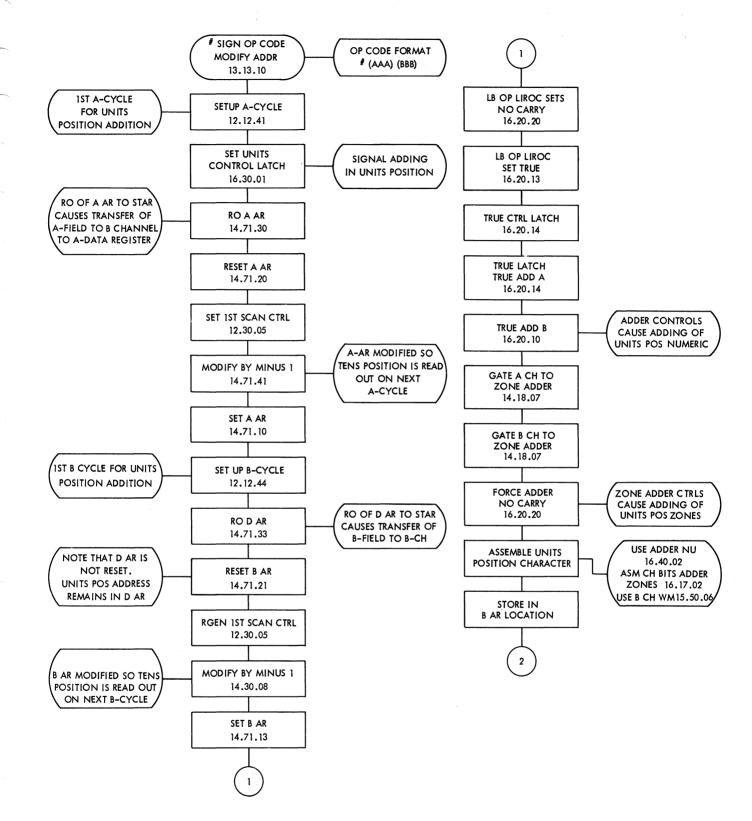

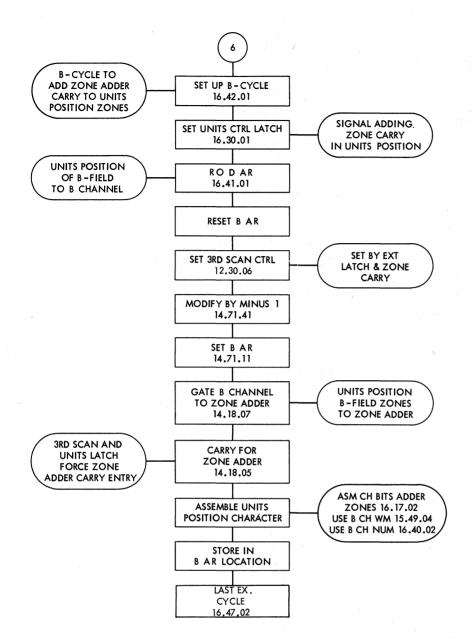

#### **Operation (Figure 2)**

When the zones are available to the zone adder, the A zones combine and the B zones combine. A carry from the A zones feeds to the B zones. A carry into the zone adder combines with the A and B zones to control the output of the zone adder. The output of the zone added is the two zones, plus a zone check bit that maintains odd parity. Two B zones or a carry into a B zone causes a zone adder carry that feeds to the auxiliary binary adder. The auxiliary binary adder combines the units-positions zones and the zone-adder carry. The output of the zone adder feeds to the assembly unit, and the output of the auxiliary binary adder feeds to the compatibility translator BCD to twoof-five. Zone adder and aux binary adder outputs are available as soon as the inputs are conditioned. No zone assembly controls are used. (See adder zone inputs to assembly on Systems 15. 50. 05, 06, 07.)

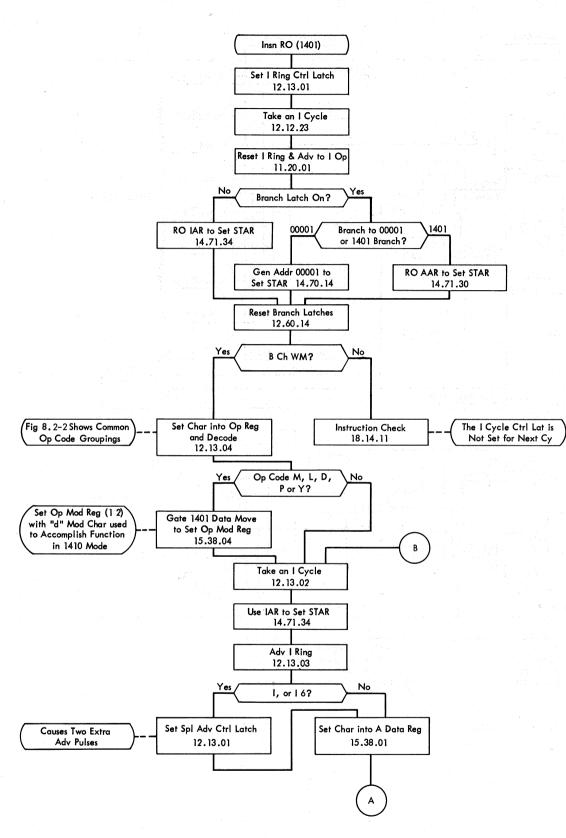

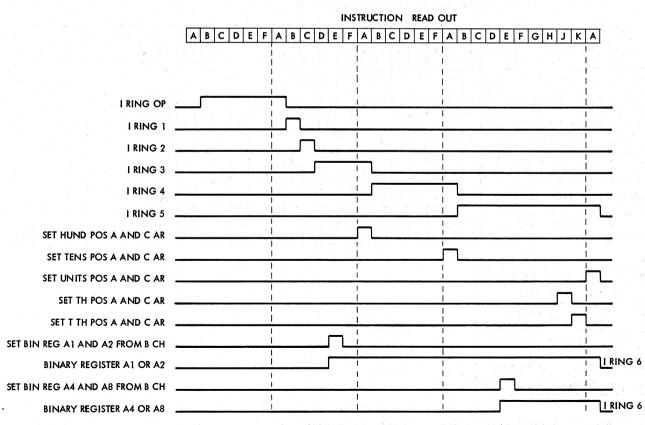

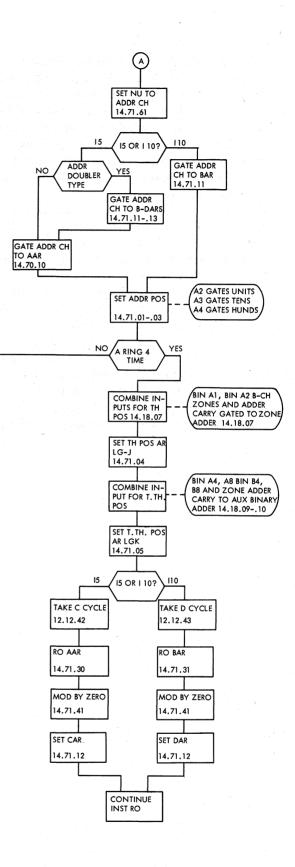

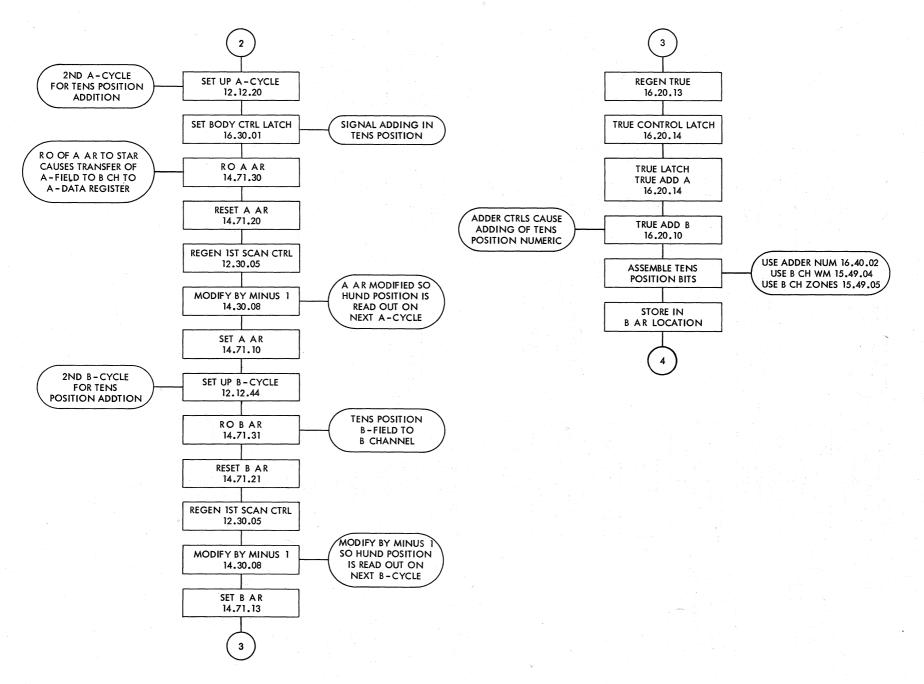

#### Instruction Read-Out (Figure 3)

Instruction read-out of a 1401 instruction uses the zone and auxiliary binary to convert the three-position addresses to the five-position addresses that are used by the 1410 to address storage by the 1410.

The instruction word is reverse scanned (+1) with the op code as the first character read out of storage. The op code must contain a word mark (WM) to be set into the op register. As in the 1410 mode, a failure to have a WM prevents the next I-cycle and causes an instruction check. The character in the op register is decoded to control the remainder of instruction readout (Figure 4).

To Assembly

Zone Adder Carry

To Compat

Bin to 2/5

Trans

4 Bit

8 Bit

Figure 3A. Instruction Read-Out (IBM 1401 Mode)

Figure 3B. Instruction Read-Out (IBM 1401 Mode)

$\cap$

Figure 3C. Instruction Read-Out (IBM 1401 Mode)

|                                |      |         |         |          | 1.2                | <u> </u>                       |                   |            | r .        |                |            | ŕ.               | r  |                  |                |        |   |                          |     |     | -        |   |      |     | <u> </u> | -              |                                       |                                         | <u> </u>         |   |    |

|--------------------------------|------|---------|---------|----------|--------------------|--------------------------------|-------------------|------------|------------|----------------|------------|------------------|----|------------------|----------------|--------|---|--------------------------|-----|-----|----------|---|------|-----|----------|----------------|---------------------------------------|-----------------------------------------|------------------|---|----|

| COMMON OP CODE GROUPING        | ?    | !       | A       | S        | 0                  | %                              | E                 | Z          | C          | W              | V,         | 1                | •  | ,                | П              | U      | # | D                        | Р   | Y   | B        | Н | Q    | 1-7 | 8        | 9              | M                                     | L                                       | К                | F | N  |

| PERCENT TYPE OP CODES          |      |         |         |          |                    |                                |                   |            |            |                |            |                  |    |                  | 1              | х      |   |                          |     |     |          |   |      |     |          |                | %                                     | %                                       |                  |   |    |

| NOT PERCENT TYPE OP CODES      | x    | x       | x       | x        | x                  | x                              | x                 | x          | х          | x              | x          | x                | x  | х                | x              |        |   | х                        | x   | X   | BS<br>BL |   |      |     |          |                | ~                                     | %                                       |                  |   | ¢. |

| ADDR DOUBLE OP CODES           | X    | x       | x       | x        |                    |                                |                   | ÷          |            |                |            | x                |    | X                | x              |        |   |                          |     |     | BS       |   | 18.2 |     |          |                | 1. · ·                                | -                                       |                  |   |    |

| NOT ADDR DOUBLE OP CODES       | 44.5 |         |         |          | x                  | X                              | x                 | x          | X          | X              | х          |                  | x  | 04,<br>1         |                | X      |   | X                        | x   | х   | BL       | X | X    |     |          |                | %/                                    | %/                                      | x                | x |    |

| 1 ADDR PLUS MOD OP CODES       |      |         | 2.3     |          | 5.2                |                                |                   | an an<br>T |            |                |            |                  |    |                  |                | X      |   |                          | с.  |     | BS       |   |      |     |          |                |                                       |                                         |                  |   | -  |

| 2 ADDR NO MOD OP CODES         | x    | x       | ×       | x        | x                  | x                              | x                 | ×          | x          |                |            | x                |    | x                | х              |        |   |                          |     |     |          |   |      |     |          |                |                                       |                                         |                  |   | -  |

| 2 ADDR PLUS MOD OP CODES       |      |         |         |          |                    |                                |                   |            |            | х              | x          | ан<br>1913 - Эли |    |                  |                |        |   | x                        | x   | х   | BL       |   |      |     |          |                | %                                     | %/~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |                  |   |    |

| TWO ADDRESS OP CODES           | х    | x       | x       | x        | x                  | x                              | x                 | x          | x          | х              | x          | x                |    | x                | x              | une.   |   | x                        | x   | x   | BL       |   |      |     | 1.       |                | %                                     | %                                       |                  |   |    |

| ADDR TYPE OP CODES             | x    | x       | x       | X        | X                  | x                              | x                 | x          | x          | x              | X          | x                | x  | x                | x              | X      |   | x                        | x   | x   | BS       |   |      |     |          |                |                                       | %                                       |                  |   |    |

| 2 CHAR ONLY OP CODES           |      |         |         |          | 144.5              |                                |                   |            |            | Alter          |            |                  |    |                  |                |        |   |                          |     |     |          |   |      |     |          |                | r ~                                   |                                         | x                | X | -  |

| C CYCLE OP CODES               |      |         |         |          | x                  | x                              |                   |            |            |                |            | 14.1             |    | 12               | in di<br>Maria |        |   |                          |     | 1.4 |          |   |      |     |          |                |                                       |                                         |                  |   |    |

| NO C OR D CYCLE OP CODES       |      |         |         | - S - I  |                    |                                | х                 | x          | x          | X              | х          | x                | x  | x                | x              | 10     |   | x                        | x   | x   | BS       |   |      |     |          |                | 76                                    | 76                                      |                  |   |    |

| NO D CYCLE AT I RING 6 OPS     | х    | x       | x       | x        |                    |                                | x                 | x          | x          | x              | Χ.         | x                | x  | x                | x              |        |   | x                        | x   | x   | BL       |   |      |     | 1        |                | 76                                    | 76                                      |                  |   |    |

| NO INDEX ON 1ST ADDR OPS       |      |         |         |          |                    |                                |                   | 1          |            |                |            |                  |    |                  |                | х      |   | 1.2                      | 1   |     |          |   |      |     |          |                | %                                     | %                                       |                  |   |    |

| RESET TYPE OP CODES            | X    | х       |         |          |                    |                                |                   |            |            |                |            |                  |    |                  |                |        |   |                          |     |     |          |   |      |     |          | 5 - 5 - 5<br>- |                                       |                                         |                  |   |    |

| ADD OR SUBT OP CODES           |      |         | ×       | x        |                    |                                |                   |            |            | 1, e.e.        |            |                  |    |                  |                |        |   |                          |     |     | 1        |   |      |     | 1 N      |                |                                       |                                         |                  |   |    |

| MPY OR DIV OP CODES            |      |         |         |          | X                  | x                              |                   |            |            |                |            |                  |    |                  |                |        |   |                          |     |     |          |   |      |     |          |                |                                       | -                                       |                  |   |    |

| ADD TYPE OP CODES              | x    | x       | x       | x        |                    |                                |                   |            | 1.1        |                |            |                  |    |                  | Ng ti          |        |   |                          |     | 11  |          |   |      |     |          |                |                                       |                                         |                  |   |    |

| ARITH TYPE OP CODES            | X    | x       | x       | x        | x                  | x                              |                   | 1          |            |                |            |                  |    |                  |                |        |   |                          |     |     |          |   |      |     |          |                |                                       |                                         |                  |   |    |

| E OR Z OP CODES                |      |         |         | -        |                    |                                | ×                 | ×          |            |                |            | 12               | 1. |                  |                | s. Pri |   |                          | 1.0 | 2   |          |   |      |     |          |                |                                       |                                         |                  |   |    |

| COMPARE TYPE OP CODES          |      | 1.<br>N |         |          | 122                | 1.94                           |                   |            | x          | 1.<br>1. an t- |            |                  |    | -                |                |        | 1 |                          | 1   |     | BL       |   |      |     |          |                |                                       |                                         |                  |   |    |

| BRANCH TYPE OP CODES           |      |         | 1.11    | 1        |                    |                                |                   |            | 17         | x              | х          | x                | x  | 1.12             |                | in i   |   |                          | 1   |     | BS       |   |      |     | 1.1      |                |                                       | 1.1                                     |                  |   |    |

| NO BRANCH OP CODES             | х    | x       | x       | x        | x                  | x                              | x                 | ×          | x          | , 40 c.        |            |                  |    | x                | х              | X      |   | х                        | x   | х   |          |   |      |     |          |                | %                                     | %                                       | x                | x |    |

| WORD MARK OP CODES             | -    | 2       |         |          |                    |                                |                   | -          |            |                |            |                  | 1  | x                | x              |        |   |                          |     |     |          |   |      |     |          |                | r ~~                                  | ~~~                                     |                  |   |    |

| M OR L OP CODES                | 19   |         |         |          |                    |                                |                   |            |            |                |            | -                |    | e <sup>nte</sup> |                |        |   |                          |     |     |          |   |      |     |          |                | ₹                                     | 7%                                      |                  |   |    |

| 1401 STORAGE AR OP CODES       |      |         |         |          |                    |                                |                   |            |            |                |            |                  |    |                  |                |        |   |                          |     |     |          | X | x    |     |          |                |                                       |                                         |                  |   |    |

| 1401 NO OP LIROC               |      |         |         |          |                    |                                | 1                 | 1          |            |                |            |                  |    |                  |                |        |   |                          |     |     |          |   |      |     | х        | x              |                                       |                                         |                  |   | х  |

| 1401 CARD OR PRINT             |      |         |         |          | 1.0                | 12                             |                   |            |            |                |            |                  |    |                  |                |        |   |                          |     |     |          |   |      | x   |          |                |                                       |                                         | · 1              |   |    |

| IST SCAN FIRST OP CODES        | х    | x       | ×       | x        | x                  | x                              | x                 | ×          | x          | x              | x          | x                |    | x                | x              |        | × |                          |     |     | BL       | x | x    |     |          |                | 1.                                    |                                         |                  |   |    |

| A CYCLE FIRST OP CODES         | x    | x       | X       | x        | x                  | x                              | x                 | x          | x          |                |            |                  |    | x                | x              |        | x | х                        | x   | х   |          |   |      |     |          |                | ₩                                     | %                                       |                  |   |    |

| STD A CYCLE OP CODES           | х    | ×       | x       | x        | x                  | x                              | ×                 | x          | <b>x</b> . |                |            |                  |    |                  |                |        | x | X                        | x   | х   |          |   |      |     |          |                | ₩.                                    | ₹                                       |                  |   |    |

| B CYCLE FIRST OP CODES         |      |         |         |          |                    |                                |                   |            |            | X              | x          | x                |    |                  |                | а      |   |                          |     |     | BL       |   |      |     |          |                |                                       |                                         |                  |   |    |

| A REG TO A CH ON B CYCLE OPS   | х    | x       | x       | x        | x                  | x                              | x                 | x          | x          |                | 200 A.     | X                | x  | x                | x              |        | x | х                        | x   | X   |          | X | X    |     |          |                | 7%                                    | ₩                                       | 1                |   |    |

| OP MOD TO A CH ON B CYCLE OPS  | _    |         |         | <i>.</i> |                    |                                |                   |            |            | x              | x          |                  |    |                  | 40.0           | х      |   | і<br>1 <sub>800</sub> Б. |     | Q   | BS<br>BL |   |      |     | 1        |                |                                       |                                         | x                | x |    |

| LOAD MEM ON B CYCLE OP CODES   | x    | x       | x       | x        | x                  | x                              | x                 | x          |            |                |            |                  |    |                  |                |        | X | x                        | x   | х   |          |   |      |     |          |                | ₩                                     | 7%                                      | $ \neg \uparrow$ |   |    |

| REGEN MEM ON B CYCLE OP CODES  |      |         | -       |          | 1                  |                                |                   |            | x          | x              | x          |                  | x  |                  |                |        |   |                          |     |     | BS       |   |      |     |          |                |                                       |                                         | x                | x |    |

| STOP AT F ON B CYCLE OP CODES  |      | 17. AND |         |          | 11 11 1<br>1 1 1 1 |                                | 0 2 4 4<br>14 9 1 |            |            | x              | <b>X</b> . | x                | x  |                  |                |        |   |                          |     |     | BS       |   |      |     |          |                |                                       |                                         |                  |   |    |

| STOP AT J ON B CYCLE OP CODES  | х    | x       | a gir i |          | x                  | x                              | x                 | x          |            |                |            |                  |    | 1                |                | <br>   | x | x                        | x   | х   | -        |   |      |     |          |                | 76                                    | 7%                                      |                  |   |    |

| READ OUT B AR ON SCAN B CY OPS |      |         |         |          |                    | 2 - 5 - 1 - 1<br>2 - 5 - 1 - 1 | x                 | x          | x          | х              | x          | x                | X  | X                | x              |        |   | X                        | x   | x   | BS<br>BL |   |      |     |          |                | ₹                                     | <b>%</b>                                | ·                | - |    |

| READ OUT A AR ON A CYCLE OPS   | x    | x       | x       | x        |                    |                                | x                 | x          | x          |                |            |                  |    | x                | X              |        | x | x                        | x   | X   |          | x | X    |     | 1.<br>   |                | 76                                    | 7%                                      |                  |   |    |

|                                |      |         | 1       | I        | 1                  | L                              | <b>.</b>          |            |            |                |            |                  | 1  | ·                | L              |        | · |                          | I   |     | L        | L |      |     | L        | L              | لــــــــــــــــــــــــــــــــــــ |                                         | ł                |   | ]  |

1401 OP CODES

$\frown$

$\left( \gamma \right)$

| NOIL   |               |                |

|--------|---------------|----------------|

| SYMBOL | MEANING       | TYPICAL FORMAT |

| BS     | B SHORT       | B (I) d        |

| BL     | B LONG        | B (I) (B)d     |

| Μ%     | M PERCENT     | M (%UX) (B)d   |

| Μ%     | M NOT PERCENT | M (A) (B)      |

| L%     | L PERCENT     | L (%UX) (B)d   |

| LW     | L NOT PERCENT | L (A) (B)      |

Figure 4. IBM 1410 Common Op-Code Grouping, IBM 1401 Compatibility

The I-ring advances to II during the second I-cycle that sets the "spl adv ctrl" latch to advance the I-ring to I3. Every character read out during instruction read-out sets into the A-data register.

Op codes M, L, D, P, and Y are 1401 data move op codes. When one of these is decoded in the op decode, it causes the op modifier register to set with the d-modifier character that is used by the corresponding 1410 data move op code.

For example, a 1401 D-op code moves the numeric portion of a single A-field character to the B-field. At I-ring-2-time (LCC of the second I-cycle) this op code sets the op modifier register with a 1 bit only. All M- or L-op codes are assumed to be 1401 data move op codes at I2, and they set the op modifier register accordingly. At 13, if these op codes are 1-0 op codes, the percent latch sets and the op mod register resets with R or W modifier at 111. For all op codes except 1401 data move operations, the op modifier register sets with every character except the one at the last instruction Ro cycle.

The zones of the character that reads out at 13 time are stored in the auxiliary binary registers A1 and A2. The digit is gated to the address channel where it is set into the A and C address registers or the A, B, C, and D address registers (address-double type). The I-ring advances to I4, and the next character reads out. Any zones over this character set into the tens position index tag latches. The digits are stored in the address registers.

The ring is now advanced to 15 where the zones (over the units position of the address) are set into the binary register A4 and A8 latches. The zones from binary registers A and A2 are gated to the zone adder where they combine with no-zones on the B side of the adder. At the same time, the zones from binary registers A4 and A8 combine in the auxiliary binary adder.

The output from the zone adder is gated through the assembly to the 1401 compatibility translator where (along with the output of the auxiliary binary adder) it is translated into the thousands and tenthousands positions of the address at LCJ and LCK, respectively (Figure 5).

The I-ring advances to I6 where the "spl adv ctrl" latch again sets to advance the ring to I8. The second address reads out from I8 to I10.

Instruction read-out ends when the B-channel wm over the next op code is sensed. The set-wm op code and 1401 condition test op code end the instructions read-out at II1 and I8, respectively, without a word mark to the right of the instruction word.

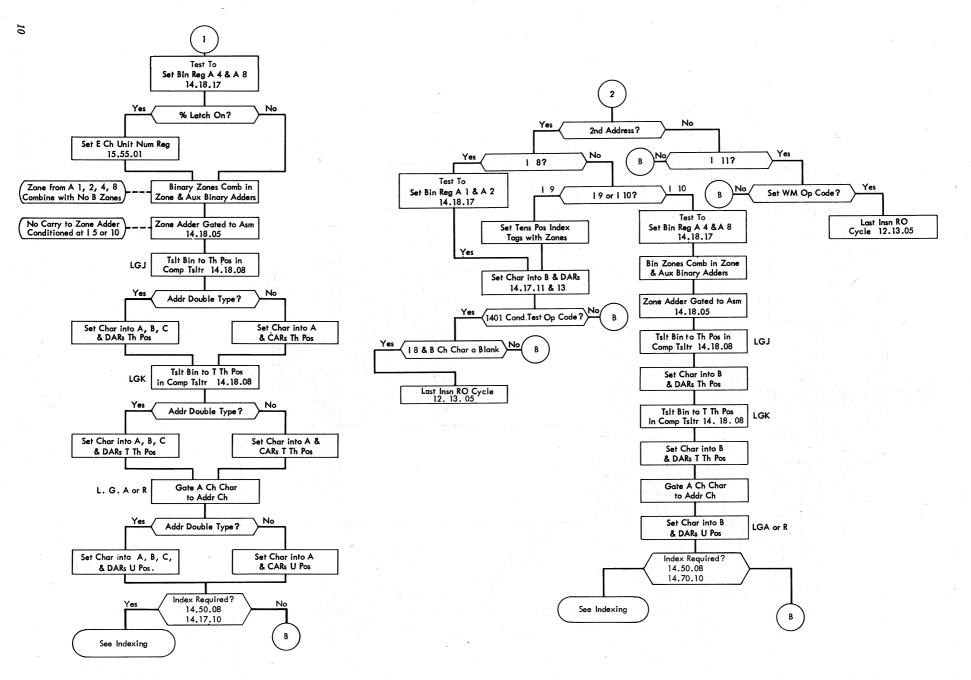

Figure 5. Zone Adder Timing, Instruction Read-Out

## Indexing

Indexing in the 1401 mode is the same as in the 1410. However, selection of index registers is limited in the 1401 mode because of the use of zone bits over the units and hundreds positions of the three-character 1401 address that represent the thousands and tenthousands position of the 1410 address. Thus, only the A and B bits over the tens position of the 1401 address character can be used to select the index register. The A and B bits provide only four combinations. These four combinations select index registers as indicated:

| INDEX TAG                                  | REGISTER                                                                                                        | ADDRESS                   |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------|

| None                                       | ter and the second s | in an <u>ea</u> n a tao a |

| $\mathbf{A}$ , $\mathbf{A}$ , $\mathbf{A}$ | 13                                                                                                              | 00087-89                  |

| В                                          | 14                                                                                                              | 00092-94                  |

| A and B                                    | 15                                                                                                              | 00097-99                  |

The following example represents typical 1401 instruction-word format with index bits:

|    | A  | Α |    | Α  | A |    |  |

|----|----|---|----|----|---|----|--|

|    | В  | В |    | В  |   | В  |  |

| Op | (1 | 1 | 1) | (3 | 3 | 3) |  |

d

d

This becomes:

| (0 3 1 1 1) | (1 1 3 3 3) |

|-------------|-------------|

| Indexed by  | Indexed by  |

| contents of | contents of |

| 00097-99    | 00087-89    |

Instruction read-out begins in the usual manner with the read-out of the op code from memory. The operation continues as previously explained until I-ring-4 time when the read-out of the tens position detects the index tags. The ten-position index-tag latches set at I-ring-4, LG-A time. This in turn sets the X-cycle control, and starts the A-ring at I-ring-5, LG-F time.

When the 1410 operates in the 1401 mode, both Aand B-index tags are forced in the hundreds position. This, in combination with the ten-position index tags, selects index registers 13, 14 or 15.

At the end of I-ring-5 time, the A-address has read from memory and converted into a five-digit-numeric address in the AAR and CAR. Instruction read-out now temporarily halts to permit indexing of the A-address. The I-ring-5 line remains up until the end of the indexing operation. I6 then turns on to continue the instruction read-out.

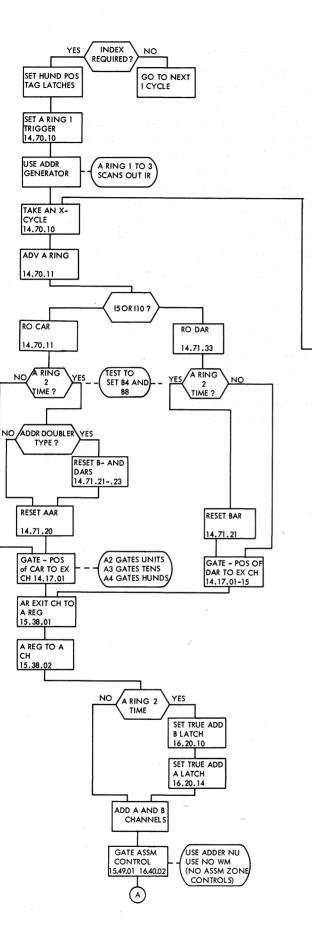

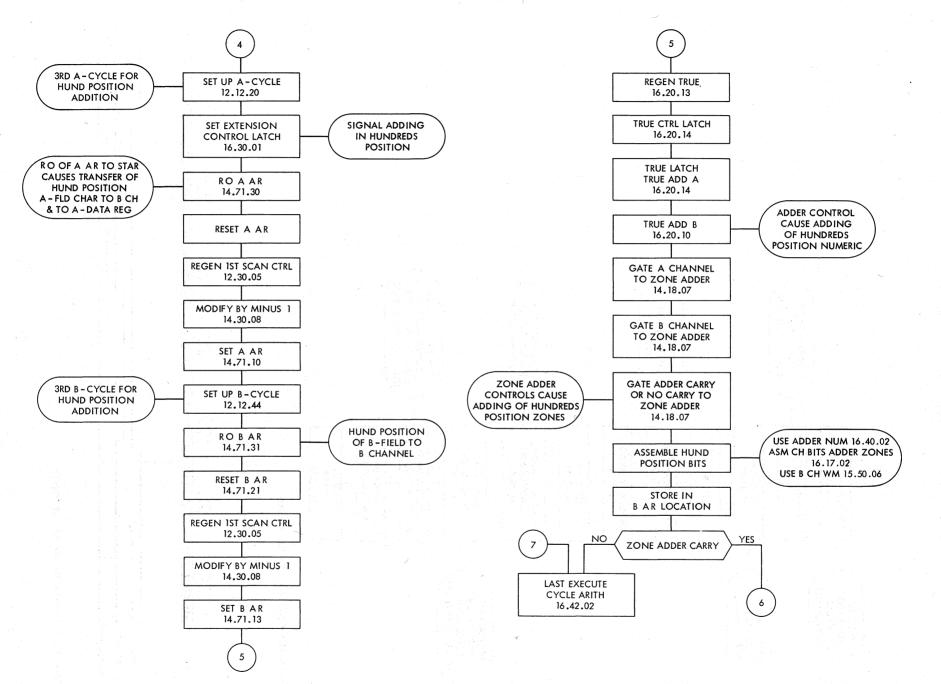

The index tags determine which index register the address generator selects. The address generator sets the STAR. Each position of the index field reads out in sequence to the B-channel starting with the units. This operates the same as 1410 indexing. The following sequence of events, shown in Figures 6 and 7, takes place:

1. Read out units position of index register. At A-ring-1, LG-A time, the address generator sets the STAR to read out the units position of the index register. The zone-bit index tags in the tens position of the A address determine the address to be generated. The read-out of memory is placed on the B channel for entry into the adder. Typical contents of an index register in 1401 mode are:

The zone bits over the units and hundreds position provide the two high-order positions of the index register contents.

2. Set binary register B4 and B8. The zone bits over the units position also read out to the B channel and set in the B4 and B8 binary register at A-ring-2, LG-E time. These zone bits are added later in the auxiliary binary adder to the zone bits over the units position of the address of the instruction that is being indexed. These zone bits (A4, A8) are still in the A-binary register because the register is not reset until I-ring-6 time of instruction read-out.

3. Reset AAR. The AAR is reset at A-ring-2, LG-F time because the indexed instruction reads into the AAR. The CAR is not reset, but retains the numeric values of the unindexed instruction.

4. Read out units position instruction character to A channel. The units character of the CAR (contains the A address) reads out, translates from two-of-five to BCD, and sets in the A-data register at LG-D time of the first X cycle.

5. Add units position of the index word to the units position of the instruction word. The adder is now used to add the numerical portion of the units character of the instruction address from the A-data register to the numerical portion of the units character of the index word (from memory but now on the B channel). The sum is placed in the AAR units position at A-ring-2, LG-H time.

6. Add tens-position characters. At A-ring-3 time the tens-position character from the CAR adds to the tens-position character from the index register. The result sets in the AAR at A-ring-3, LG-H time.

7. A-ring cycling. Only three A-ring times, in addition to A1, are required to index the three-character 1401 program address. The index register and instruction zone bits must add in the zone adder and auxiliary binary adder so that the thousands and tenthousands characters can set in the AAR. To provide time for this, the A-ring-4 is extended to include-LG-J and K.

| -  |                                               | ,       |       | G 4 TIME          | I RING 5 TIME I RING 3 TIME ARING 3 TIME ARING 4 TIME C CYCLE      |

|----|-----------------------------------------------|---------|-------|-------------------|--------------------------------------------------------------------|

| -  | SIGNAL NAME                                   | 100     | ATION | LOGIC             |                                                                    |

| -  | +S SET T POS INDEX TAGS                       | 11C1    | A 17C | 14.70.12          | SET BY I RING 4, 4, LG+A, B CH NOT WM                              |

| 2  | T POS (A, B, C) INDEX TAGS                    |         |       | 14.50.02          |                                                                    |

| 3  | +S INDEX REQUIRED                             | 1182    | D 17E | 14.50.08          |                                                                    |

| 4  | +S I CYCLE                                    | 1101    | H22H  | 12.12.04          | 4 I RING 5 7, A RING 2, 3                                          |

| 5  | +S SET X CYCLE CTRL                           | 11C1    | F05D  | 12.12.45          |                                                                    |

| 6  | +S X CYCLE CTRL                               | 1101    | G23D  | 12.12.23          | 3,5 1 3,5 1 3,5 1 3,5 1 3,5 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1  |

| 7  | +S X CYCLÉ                                    | nci     | G22A  | 12.12.05          |                                                                    |

| 8  | SET H POS INDEX LAT (A, B)                    | <u></u> |       | 14.70.13          |                                                                    |

| 9  | -S SET A RING I TRIGGER                       | nci     | A04D  | 14.70.10          |                                                                    |

| 10 | +S RO INDEX AR                                | ncı     | D03A  | 14.70.13          | <u>с 6 U 6 Т 6 H 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1</u>           |

| 11 | +S INDEX CTRL NUMBER ONE                      | 1182    | D26C  | 14.50.03          |                                                                    |

| 12 | -S ADDRESS GEN UP 1 8 BIT                     | 1182    | A2IE  | 14.50.04<br>03    |                                                                    |

| 13 | AR BUS UP I AND 8 BIT                         |         |       | 14.15.01          |                                                                    |

| 14 | -S ADDR GEN T POS 0 8 BIT                     | 1182    | 825D  | 14.50.06<br>06    |                                                                    |

| 15 | AR BUS TP (0, 8) BITS<br>2 AND 8 BITS = 0     |         |       | 14.15.04          |                                                                    |

| 16 | AR BUS H, TH, AND T TY                        |         |       | 14.15.13          |                                                                    |

| 17 | +S SET MEM AR GATED                           | 1182    | G26A  | 14.17.16          |                                                                    |

| 18 | +S INDEX A AR                                 | 1101    | A08R  | 14.70.10          |                                                                    |

| 19 | +S ROCAR                                      | nci     | CIIE  | 14.71.32          | 18 B TO LAST LG 18 LG-B TO LAST LG 1 B TO LAST LG 1 B TO LAST LG 1 |

| 20 | +S A RING ADV                                 | HCI     | A05D  | 14.70.11          | LG-B LG-B LG-B LG-B LG-B LG-B LG-B LG-B                            |

| 21 | +S ADDR SCNR 2 POS                            | ncı     | D 13L | 14.70.02          |                                                                    |

| 22 | +S SW AR EXIT CH TO A REG                     | 11C3    | E 18R | 15.38.01          |                                                                    |

| 23 | +S GATE A DATA REG TO A CH                    | 11C3    | C 178 | 15,38.02          |                                                                    |

| 24 | +S TRUE ADD A                                 | 11C2    | F09A  | 16.20.14          |                                                                    |

| 25 | -S START 1401 INDEX                           | 11C2    | E15C  | 16.20.12          | <b>7</b>                                                           |

| 26 | +S TRUE ADD B                                 | 11C2    | E12C  | 16.20.10          | 25                                                                 |

| 27 | +S USE ADDER NU                               | 11C2    | Сізк  | 16.40.02          |                                                                    |

| 28 | +S SET NU TO ADDR CH                          | າດ      | A058  | 14.71.61          | 7 LGH 7 LG-H 7 LG-H                                                |

| 29 | ADDR CH NU TSLTR LINES                        |         |       | TO 05<br>14.42.03 | 28 LG-H [T] 28 LG-H [T] 28 LG-H [T]                                |

| 30 | -S RESET A AR                                 | 1101    | B20H  | 14.71.20          |                                                                    |

| 31 | +S INDEX GATE                                 | 1C2     | B 16D | 11.10.07          | 7 і ġ-н 7 і ġ-н 7 і ġ-н 7 і ġ-ң, ў, к н ј ј к                      |

| 32 | +S SET A AR                                   | nci     | C26G  | 14.71.10          | 18, 31 18, 31 18, 31 18, 31                                        |

| 33 | +S SET AR U POS                               | 11C1    | 808A  | 14.71.01          |                                                                    |

| 34 | BIN REG B4 (OR B8)                            |         |       | 14.18.20          | 7 A RING 2 LG-E ADDR SCNR 4 POS 14, 70-04                          |

| 35 | +S ADDR SCNR 3 POS                            | 1101    | D 138 | 14.70.03          | A RING 3 TIME   A RING 4 TIME                                      |

| 36 | +S SET AR T POS                               | 1101    | 808C  | 14.71.02          |                                                                    |

| 37 | +S GATE B CH TO ZONE ADDER<br>+S SET AR H POS | 11C3    | A21C  | 14.18.07          | i7                                                                 |

| 38 |                                               | 11C1    | BO8H  |                   |                                                                    |

|    | +S GT BIN REG AI & 2 TO ZN ADDER              | 11C3    | A21E  | 14.18.07          |                                                                    |

| 40 | AUX BIN ADDER                                 |         |       | 14.18.10          |                                                                    |

|    | +S TSLT BIN TO TH POS                         | 11C3    | A 18C | 14,18.08          |                                                                    |

|    | +S TSLT BIN TO T TH POS                       | 11C3    | 8 18D | 14.18.08          |                                                                    |

|    | +S SET AR TH POS                              | 11C1    | C 15A | 14.71.04          |                                                                    |

| 44 | +S SET AR T TH POS                            | 1101    | C 15H | 14.71.05          |                                                                    |

|    | +S SET C CYCLE CTRL                           | (IC)    | GIIG  | 12.12.42          | 1401 MODE A RING 4, I RING 5                                       |

|    | +S C CYCLE CONTROL                            | 11C1    | G2ID  | 12.12.20          | 45, i LAST LOGIC'GATE'                                             |

| 47 | -S RESET C AR                                 | nci     | C25H  | 14.71.22          | 46 LG-B EARLY                                                      |

| 48 | +S ROAAR                                      | 1101    | CIIG  | 14.71.30          | ig \$P Å, 46, i RiNg's                                             |

| 49 | +S SET C AR                                   | 1101    | C 26E | 14.71.12          | 46 LG-8, Ċ, D, EF I UTTHITHT                                       |

| 50 | +S SET I CYCLE CONTROL                        | 1101    | J08D  | 12.13.02          |                                                                    |

|    | +S I CYCLE CONTROL                            | nci     | H12G  | 12.12.23          |                                                                    |

Figure 6. 1401 Mode Indexing Sequence

Figure 7. 1401 Mode Indexing

8. Add hundreds-position numeric characters. At A-ring-4 time, the hundreds-position character reads from the index register to the B channel. Also during A-ring-4 time, the hundreds-position character from the CAR reads into the A-data register, and then to the A channel. The result of the hundreds-position addition passes through the assembly area through the BCD-to-two-of-five translator, and sets in the AAR at A-ring-4, LG-H time.

9. Enter zone bits in the zone and auxiliary binary adders. The zone bits from the instruction address are still in the A1, A2, A4, and A8 binary-register latches where they were set during instruction readout. The zone bits from the index-register units-position character were previously set in the B4 and B8 binary-register latches. The zone bits from the indexregister hundreds position (B1 and B2), via the B channel, are set directly into the zone adder.

10. Add zone bits. The instruction-word zone-bits A1 and A2 add to the index-word zone-bits B1 and B2 in the zone adder. Any carry from the hundreds-position CPU adder operation also enters in the zone adder. The result of the addition transfers to assembly.

Any carry from the zone adder addition adds in the auxiliary binary adder to the instruction-word zonebits A4 and A8, and to the index-register zone-bits, B4 and B8.

11. Translate zone-addition output to two-of-five code and set AAR. The result of the zone-adder operation is brought via the assembly area to the compatibility translator. The result of the auxiliary binary-adder operation is also brought to the compatibility translator. The binary results of the zone-bit addition are translated to the two-of-five code. The result represents the value of the indexed thousands and ten-thousands characters of the instruction word. The thousands position sets in the AAR at A-ring-4, LG-J time. The ten-thousands position sets in the AAR at K time. As previously noted, the hundreds position sets at LG-H time.

12. Transfer the indexed AAR to the CAR. Indexing is now complete. A C cycle is taken to read out the indexed A address of the instruction from the AAR. This is modified by zero and set in the CAR. I-cycle control is turned on and the B portion of the instruction begins with I-ring-6 time. The 1401 D, P, Y, M  $(\overline{\%})$  and L  $(\overline{\%})$  op codes perform nearly the same function as the 1410 D-op code. There is this significant variation: the 1410 uses different op modifiers to perform different types of move operations; the 1401 instruction requires a different op code to obtain variations of the basic move operation.

By comparing the 1410 D-op code and modifications with the 1401 D, P, Y, M and L operations, it can be seen that in order to duplicate the operation in 1401 mode, it is necessary to generate an appropriate op modifier. This occurs at I2 time.

The op modifier is generated for the various move and load operations in accordance with the following table:

| 1401 INSTRUCTION                                                    | d-character<br>to be generat |   | BITS                                                                                    |

|---------------------------------------------------------------------|------------------------------|---|-----------------------------------------------------------------------------------------|

| Move numeric                                                        | D (A) (B)                    | 1 | $1, \overline{2}, \overline{4}, \overline{8}, \overline{A}, \overline{B}, \overline{C}$ |

| Move zones                                                          | Y (A) (B)                    | 2 | 1, 2, 4, 8, A, B, C                                                                     |

| Move character to<br>record, or group-<br>mark with a word-<br>mark | P (A) (B)                    |   | 1, 2, <del>4</del> , 8, A, B, <del>C</del>                                              |

| Move characters to<br>A or B wm                                     | M (A) (B)                    | С | 1, 2, 4, 8, A, B, C                                                                     |

| Load characters to<br>A-field WM                                    | L(A) (B), L (A)              | x | 1, 2, 4, 8, A, B, C                                                                     |

The A and B bits, along with the 8 bit, determine when the data transfer should end.

| OP MODIFIER BITS | STOP AT                   |

|------------------|---------------------------|

| 8, A, B          | lst wm—A-field            |

| 8, A, B          | lst wm—A or B-field       |

| 8, A, B          | lst RM or GM, WM, A-field |

| 8, Ā, <b>B</b>   | After one position        |

The 8 bit determines the direction of the scan:

1. 8 bit: Reverse scan.

2. Not 8 bit: Forward scan.

The 1, 2, and 4 bits of the op modifier determine which portion of the A-field characters transfers:

| OP MODIFIER BITS | USE           |

|------------------|---------------|

| 1                | A-field-num   |

| Not 1            | B-field-num   |

| 2                | A-field-zones |

| Not 2            | B-field-zones |

| 4                | A-field wm    |

| Not 4            | B-field wм    |

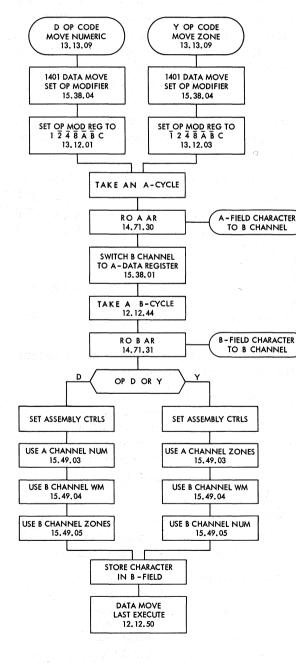

## Move Numeric (D)

The 1401 D-op code moves the numeric portion (8-4-2-1) of the single character in the A address to the B address. The zone portions (AB) and word marks are not disturbed at either address.

#### **Op-Modifier Function**

The 1401 D-op does not have a modifier. The proper 1410 modifier must be set in the op modifier register to get the desired transfer. The following 1410 functions must be performed:

- 1. Transfer A-field numeric (op modifier bit 1).

- 2. Retain B-field WM (op modifier bit  $\overline{4}$ ).

- 3. Retain B-field zone (op modifier bit  $\overline{2}$ ).

- 4. End data transfer after one positon (op modifier bit  $\overline{8}$   $\overline{A}$   $\overline{B}$ ).

#### **Operation (Figure 8)**

The op modifier register sets to  $1\ \overline{2}\ \overline{4}\ \overline{8}\ \overline{A}\ \overline{B}\ \overline{C}$  to cause the 1410 to function as indicated in the preceding section. Cycling of the 1410 occurs as with a normal 1410 D-op. The same op-code-grouping lines come up. During the A cycle the A-field character reads out of storage and sets into the A-data register. During the following B cycle the B-field character reads out to the B channel. The 1-bit op-modifier character brings up assembly controls to gate the Afield numeric from the A-channel, and to gate the B-field zone and WM from the B channel to the core storage B-field address. The  $\overline{8}\ \overline{A}\ \overline{B}$  op-modifier character ends the operation after one A cycle and one B cycle.

## Move Zone

The 1401 Y-op code moves the zone positions (AB) from the A address to the B address. The numeric portion of each character is not disturbed at either address.

#### **Op-Modifier Function**

The Y-op code does not exist in the 1410. Therefore, a D-move op with the proper modifier accomplishes the

1401 op Y function in the 1410. The following 1410 functions must be performed. The indicated op-modifier bits must be set.

| 1410 FUNCTIONS                       | <b>OP MODIFIER BITS</b> |

|--------------------------------------|-------------------------|

| Transfer A-field zones               | Set Bit 2               |

| Retain B-field WM                    | Set Bit Not 4           |

| Retain B-field numeric               | Set Bit Not 1           |

| End data transfer after one position | Set Bits 8 A B          |

|                                      |                         |

#### **Operation (Figure 8)**

The op modifier register sets to  $1\ \overline{2}\ \overline{4}\ \overline{8}\ \overline{A}\ \overline{B}\ \overline{C}$  to cause the 1410 to function as indicated in the preceding paragraph. The operation continues the same as the move numeric 1401 op code. The only difference is the setting of the op modifier register and the assembly unit controls.

#### Circuits

Set op-modifier register to  $\overline{1}$   $\overline{2}$   $\overline{4}$   $\overline{8}$   $\overline{A}$   $\overline{B}$   $\overline{C}$ . This operates the same as the move numeric op code. See the section "Move Numeric (D)." The only difference is that the 2-op-modifier register bit is set instead of the 1 bit.

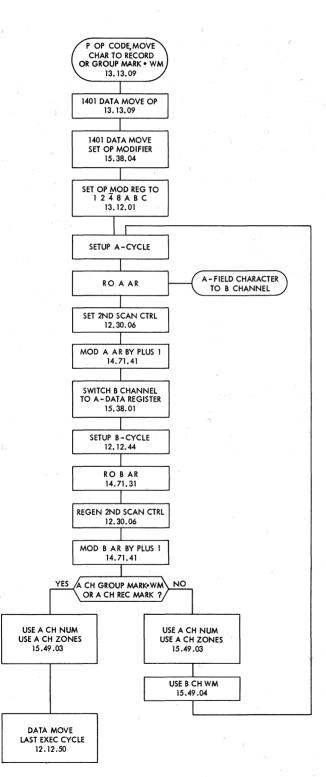

## Move Characters to Record or Group Mark/Word Mark

The 1401 P-op code moves an entire record from one core storage area to another. The A and B addresses specify the high-order position of each area of storage. Transmission starts at the high-order address of the A field and continues until a record mark (A82 bits) or a group mark with a word mark (BA 8 4 2 1 WM) is sensed in the A field. The record mark or group mark with a word mark transfers to the B field. Word marks in the B field remain unchanged. A-field word marks do not transmit.

The P-op code does not exist with the 1410. Therefore, a D-move op with the proper modifier accomplishes the 1401 op P-function with the 1410.

#### **Op-Modifier Function**

The 1401 P-op does not have an op modifier. Therefore, the proper 1410 D-op code modifier must be set in the op modifier register to get the desired transfer of data. The following 1410 functions must be performed:

| 1410 FUNCTIONS             |

|----------------------------|

| Transfer A-field numeric   |

| Transfer A-field zones     |

| Retain B-field wм          |

| Transfer high to low-order |

| Stop operation with 1st    |

| RM OT GM · WM A field      |

OP-MODIFIER BITS Bit 1 Bit 2 Bit not 4 Bit 8 8 A B

Figure 8. 1401 Mode, Move Numeric and Move Zone

Figure 9. 1401 Mode, Move Character to RM or GM WM

#### **Operation (Figure 9)**

The op modifier register sets to  $1\ 2\ \overline{4}\ 8\ A\ B\ \overline{C}$  to cause the 1410 to function as indicated in the preceding paragraph. After this is done, alternate A and B cycles perform the operation. Details of this op code are covered in *IBM Customer Engineering Instruction-Reference, 1410 Data Processing System* (Form 223-2599).

The 1- and 2-bit lines from the op modifier register bring up the assembly controls that gate to storage in the B-field location the desired portions of the A- and B-channel characters with the proper parity. The next character of the A field reads out on the following A cycle, and the operation continues by alternate A and B cycles, until a WM reads out and combines with the  $\overline{8}$  A B bits from the op modifier register to end the operation.

## Move Characters to A or B Word Mark M (A) (B), M (A)

The M-op code moves data in storage from the A-field address to the B-field address. The first word mark encountered in either field stops the operation. In the case of a single address instruction, the B address is taken from the BAR and does not have to be written or interpreted as part of the instruction. The first wM encountered stops the operation as in the "2 address instruction."

#### **Op-Modifier Function**

The 1401 M-op does not have a modifier. The appropriate 1410 modifier must be set in the op-modifier register to get the desired transfer. The following 1410 functions must be performed:

| 1410 FUNCTIONS            | <b>OP-MODIFIER BITS</b> |

|---------------------------|-------------------------|

| Transfer A-field numeric  | Bit 1                   |

| Transfer A-field zones    | Bit 2                   |

| Retain B-field wM         | Bit $\overline{4}$      |

| Set first scan            | Bit 8                   |

| End operation at first WM | Bit 8 A B               |

| A or B field              |                         |

#### Operation

During the 12 cycle the op modifier register sets to  $1 \ 2 \ \overline{4} \ \overline{8}$  A B C to cause the proper 1410 functions as indicated in "Op-Modifier Function." Also, the controls set up for an A cycle. The first character of the A field reads out during the A cycle, and sets into the A-data register. The next cycle is a B cycle, during which the first character of the B field reads out and is placed on the B channel.

## Load Characters to A-Word Mark L (A) (B), L (A)

The L-op code moves the data and the word mark in storage from the A-field address to the B-field address. The A-field word mark stops the operation. B-field word marks clear unless the B field is larger than the A field.

#### **Op-Modifier Function**

The 1401 L-op does not have a modifier. The appropriate 1410 modifier must be set in the op-modifier register to effect the desired transfer. The following 1410 functions must be performed:

| 1410 FUNCTIONS             | <b>OP-MODIFIER BITS</b> |

|----------------------------|-------------------------|

| Transfer A-field numeric   | Bit 1                   |

| Transfer A-field zones     | Bit 2                   |

| Transfer A-field word mark | Bit 4                   |

Set the first scan-and-end-operation at first A-field WM: Op mod  $\overline{8}$  A  $\overline{B}$  bit.

#### Operation

During the I2 cycle the op modifier register sets to  $1 \ 2 \ 4 \ \overline{8} \ \overline{A} \ \overline{B} \ C$  to cause the proper 1410 functions as indicated in "op modifier function." Also, the controls set for an A cycle, and the first character of the A field reads out and sets in the A-data register. The next cycle is a B cycle, during which the first character of the B field reads out and is placed on the B channel. The 1-, 2-, and 4-bit lines from the op-modifier register bring up the assembly controls that gate to storage, in the B-field location, the numerical, zone and wm of the A-channel characters that have the proper parity. B-field wm, if any, clears from storage. The next character of the A field reads out on the following A cycle, and the operation continues by alternate A and B cycles until an A-channel wm combines with the  $\overline{8}$  A  $\overline{B}$  bits from the op modifier register to end the operation.

## Move Characters and Suppress Zeros Z (A) (B)

The function, operation and circuits of the execute phase of Z (A) (B) in 1401 mode are the same as the standard 1410 operation. NOTE: on Systems 13.13.03, Z-op decode is common to both operations. Details of this op code, and the following two op codes are covered in *IBM Customer Engineering Instruction Reference*, 1410 Data Processing System (Form 223-2599).

## Compare C (A) (B)

The function, operation, and circuits of the execute phase of C (A) (B) in 1401 mode are the same as the standard 1410 operation except for set of high-lowequal that does not occur in the 1401 mode for singlecharacter C-ops. C-op decode (13. 13. 03) is common to both operations.

#### Move Characters and Edit E (A) (B)

The edit operation in 1401 mode is acomplished exactly as in 1410 program execution. E-op decode (13. 13. 02) is common.

## Arithmetic

## Add and Subtract

These op codes operate the same as in 1410 mode except for the sign, zones and overflow controls.

## Sign

If the signs of the fields and type of op code require a true-add, the zones from the units position of the B field are used as the sign of the result.

If a complement-add is required, the sign of the B field is used as the sign of the result but it is inserted in the standard form (B bit only, minus; AB bits, plus). If a recomplement cycle is required, the sign of the B field is inverted to a standard sign.

#### Zones

All zones in the B field are removed, except the units position sign or high-order position on true-add.

#### Overflow

An adder carry during the B cycle, in which a B-channel word mark is sensed, indicates an overflow condition. This sets the arithmetic overflow latch, which is testable, by a branch instruction.

The adder carry is also gated to the zone adder, where is it combined with any A- or B-channel zones. The zone adder output is gated through the assembly and is stored in the high-order position of the B field. For example:

| A-field          | 8 0             | 2 |

|------------------|-----------------|---|

| <b>B</b> -field  | <b>v</b><br>2 9 | 1 |

|                  | Ă               |   |

| Arith Overflow - | -09             | 3 |

If the B field high-order position contains A and B bits prior to an overflow, the arithmetic overflow latch will be set, but there will be no zone bits over the result in the B field.

### Zero and Add, Zero and Subtract

The adder is not used for these op codes. The numeric portion of the A channel is gated through assembly. The sign of the A field is used on zero and add, and is inverted on zero and subtract. No other zones are used. Zeros are inserted on the assembly channel for all extra, high-order positions of the B field.

#### **Multiply and Divide**

These op codes operate the same as in 1410 mode. The arithmetic overflow latch sets instead of the divide overflow latch.

## Logic Operations

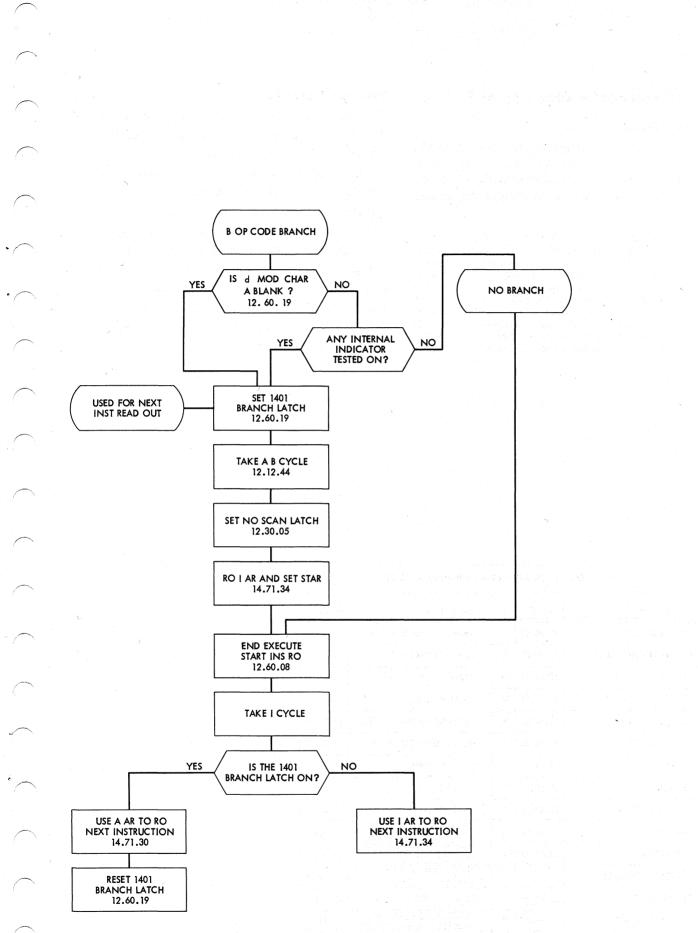

## Branch (B) B (I) b

The B-op code with an I address and a blank d-modifier or no modifier is an unconditional branch. This means that the normal program sequence is interrupted and continued at any desired point, as specified by the I address, without testing for specific conditions.

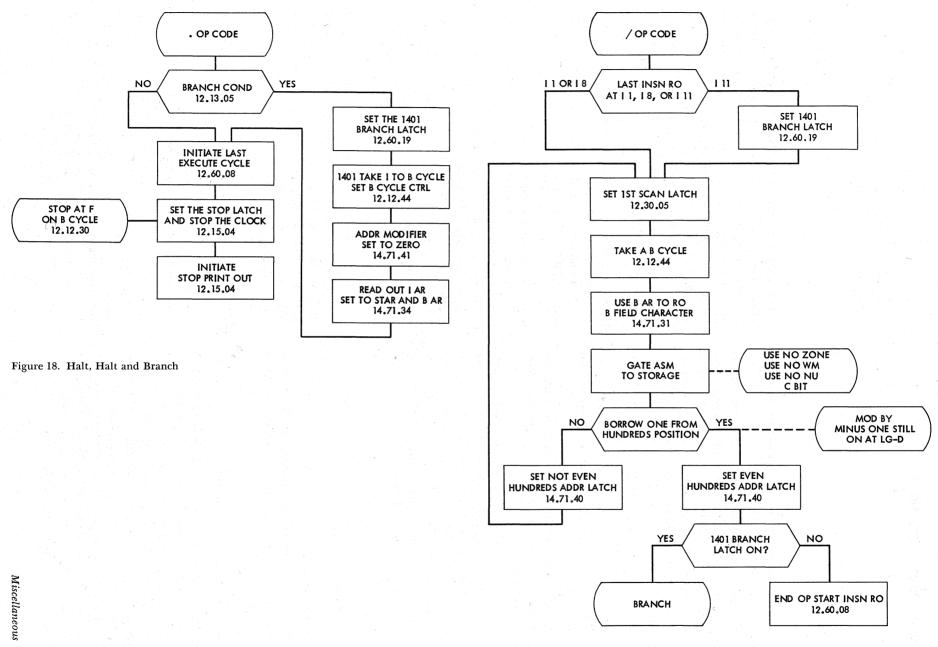

#### **Operation (Figure 10)**

When a branch is required, the CPU takes a B cycle. During the B cycle, the IAR reads out to the STAR through the modifier to the BAR. A modify-by-zero condition exists in the modifier because the no-scan latch is set.

The 1401 branch latch sets to cause the AAR to read out to STAR for the I-op cycle of the instruction readout.

This is the start of normal instruction read-out for the first branch routine instruction.

## Branch, if Indicator On B (I) d

#### **Op-Code Function**

The d-character modifier specifies the condition to be tested. If the indicator tested is off, the next instruction in sequence is taken. If the indicator tested is on, the program branches to the I address.

Figure 11 illustrates the d-modifiers and the indicators they test.

#### **Operation (Figure 10)**

At I-ring-8 time, during instruction read-out, the opmodifier register sets with the op-modifier character and is decoded.

The op-modifier decode compares with the indicators and at I-ring-9 time (last instruction Ro cycle) either the branch or no-branch condition is brought up. "No-branch" causes the last execute cycle that initiates the instruction read-out of the NSI. The 1401 branch latch causes the extra B cycle, as covered in the section "Branch (B)."

## Branch, if Character Is Equal B (I) (B) d

## **Op-Code Function**

This instruction code causes the single character at the B address to compare to the d-character. If the bit configuration is the same, the program branches to the I-address. If it is not the same, the program continues in sequence. The d-character can be any combination of the six BCD code bits (A B 8421).

#### **Operation (Figure 12)**

At I-ring-11 time, during instruction read-out, the opmodifier register sets with the op-modifier character. At I-ring-12 time, the first scan-control latch sets and a B cycle starts. The character at the B-field address reads to the B channel. The op-modifier register is gated to the A channel and a comparison is made between A and B channels in the compare unit. If the equal latch sets, the program branches to the I address in the AAR. In all other cases the program continues to the NSI.

#### Branch, if Bit Equal W (I) (B) d

#### **Op-Code Function**

This instruction compares the character at the B address, bit by bit, with the d-character. If any bit in the character at the B address matches any bit in the configuration of the d-character, the program branches to the I address. The d-character can contain any character or any combination of bits that can exist in a single position of core storage. wm and C bits are not compared.

#### **Operation (Figure 12)**

At I-ring-11 time, during instruction read-out, the opmodifier register sets with the op-modifier character. At I-ring-12 time, the first scan-control latch sets and a B cycle starts. The character at the B-field address reads to the B channel. The op modifier register is gated to the A-channel and the bits compare. Any bit on both channels starts a branch.

Figure 10. Branch Unconditional and Branch if Indicator On

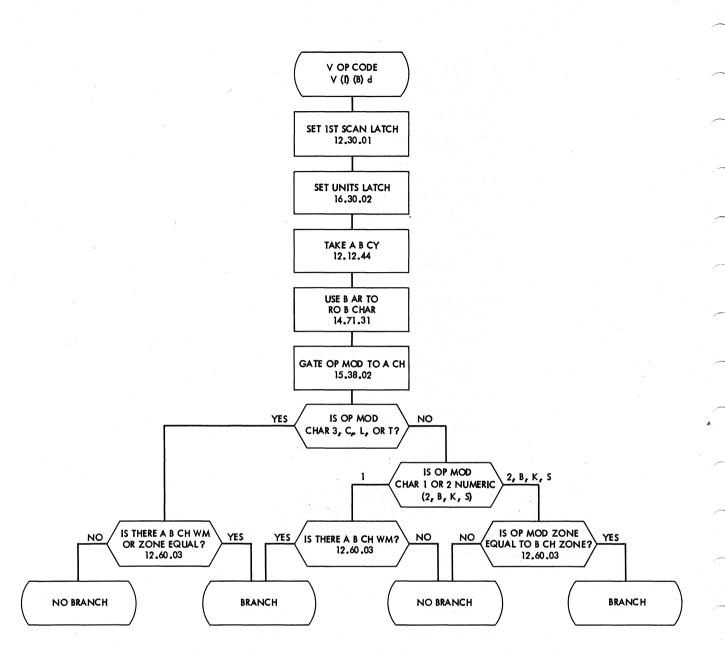

## Branch, if WM and/or Zone V (I) (B) d

## **Op-Code Function**

This op code tests the character that is located in the B address for the condition specified by the d-character, and branches to the I address, if the condition is met. The d-modifiers and the conditions they specify are as follows:

| d-charact | ER BITS    | CONTROL                  | LOGIC    |

|-----------|------------|--------------------------|----------|

| 1         | 1          | Word mark                | 13.12.17 |

| 2         | 2          | No zone (no A, no B bit) | 13.12.17 |

| В         | <b>BA2</b> | 12-zone (A · B bits)     | 13.12.11 |

| K         | В 2        | 11-zone (B, A bit)       | 13.12.16 |

| S         | A 2        | Zero-zone (A, no B bit)  | 13.12.10 |

| 3         | 21         | Either a wm or no-zone   | 13.12.17 |

| С         | BA21       | Either a wm or 12-zone   | 13.12.15 |

| L         | B 2 1      | Either a wm or 11-zone   | 13.12.16 |

| Т         | A 2 1      | Either a WM or zero-zone | 13.12.10 |

## **Operation (Figure 13)**

This operation duplicates the B-op code until the character designated by the BAR reads to the B channel. At this point, the bits on the B channel are tested for the configuration specified by the d-modifier. The d-modifier was gated to the A channel.

If the conditions imposed by the d-modifier (see the table in the preceding paragraph) are met, a branch starts. Otherwise, the program proceeds with the NSI.

The test of the B-address character is made by switching the result of zone bit compare ( $\equiv$  or  $\neq$ ) with the op modifier 1 and/or 2 bits. The choice of d-characters makes it possible to test for several combinations of WM and zone bits.

|   | CHARACTER           | AT d FOR B (( | ) d BR/ | ANCH IF INDICATOR ON                            |          |

|---|---------------------|---------------|---------|-------------------------------------------------|----------|

| d | BRANCH ON           | LOGIC         | d       | BRANCH ON                                       | LOGIC    |

| Ы | UNCONDITIONAL       | 12.60.01      | S       | EQUAL COMPARE B = A                             | 12.60.01 |

| 9 | CARRIAGE CHANNEL #9 | 12.60.01      | T       | LOW COMPARE B <a< td=""><td>12.60.01</td></a<>  | 12.60.01 |

| A | "LAST CARD" SWITCH  | 12.60.18      | υ       | HIGH COMPARE B>A                                | 12.60.01 |

| B | SENSE SWITCH B      | 12.60.18      | V       |                                                 | 12.60.17 |

| С | SENSE SWITCH C      | 12.60.18      | w       | FILE WRONG LENGTH REC                           | 12.60.17 |

| D | SENSE SWITCH D      | 12.60.18      | x       | FILE ADDRESS COMPARE                            | 12.60.17 |

| E | SENSE SWITCH E      | 12.60.18      | Y       | ANY FILE CHECK                                  | 12.60.17 |

| F | SENSE SWITCH F      | 12.60.18      | z       | OVERFLOW                                        | 12.60.02 |

| G | SENSE SWITCH G      | 12.60.18      | *       | INQUIRY CLEAR                                   | 12.60.17 |

| κ | END OF REEL         | 12.60.05      | ?       | READER ERROR IF I/O CHK<br>STOP SWITCH OFF      | 12.60.18 |

| L | TAPE ERROR          | 12.60.17      | !       | PUNCH ERROR IF I/O CHK<br>STOP SWITCH OFF       | 12.60.17 |

| N | ACCESS INOPERABLE   |               | +       | PRINTER ERROR IF I/O CHK<br>STOP SWITCH OFF     | 12.60.17 |

| P | PRINTER BUSY        | 12.60.17      | @       | CARRIAGE CHANNEL #12                            | 12.60.01 |

| Q | INQUIRY REQUEST     | 12.60.02      | %       | PROCESSING CHECK WITH<br>PROCESS CHK SWITCH OFF | 12.60.18 |

| R | CARRIAGE BUSY       | 12.60.15      | 1       | UNEQUAL COMPARE B ≠ A                           | 12.60.01 |

Figure 11. Character At d for Branch If Indicator On

Figure 12. Branch if Character is Equal; Branch if Bit is Equal

•

•

## Miscellaneous

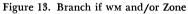

#### Store A—Address Register

#### **Op-Code Function**

The 1401 Q-op code stores the contents of the Aaddress register from the previous operation in the three-position field that has its units position defined by the A address of the store-A-address-register instruction. Word marks in the A-field are retained. The instruction format is: Q (AAA).

#### **Operation (Figure 14)**

The A address of the Q-op code reads into the AAR on the instruction read-out cycle. The AAR, however, contains the address that must be stored. Therefore, the A address left from the previous operation must move to the BAR before the new A address reads in. This is done during a B cycle that occurs just after the Q-op is detected at I-op time. After the B cycle, the I ring advances, and the (AAA) address reads into the AAR.

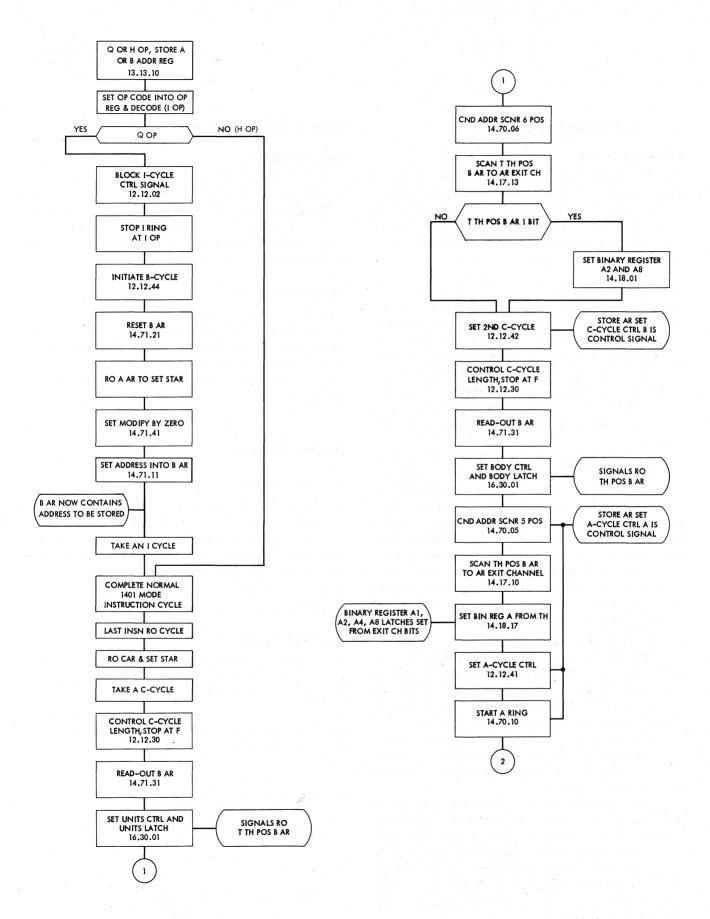

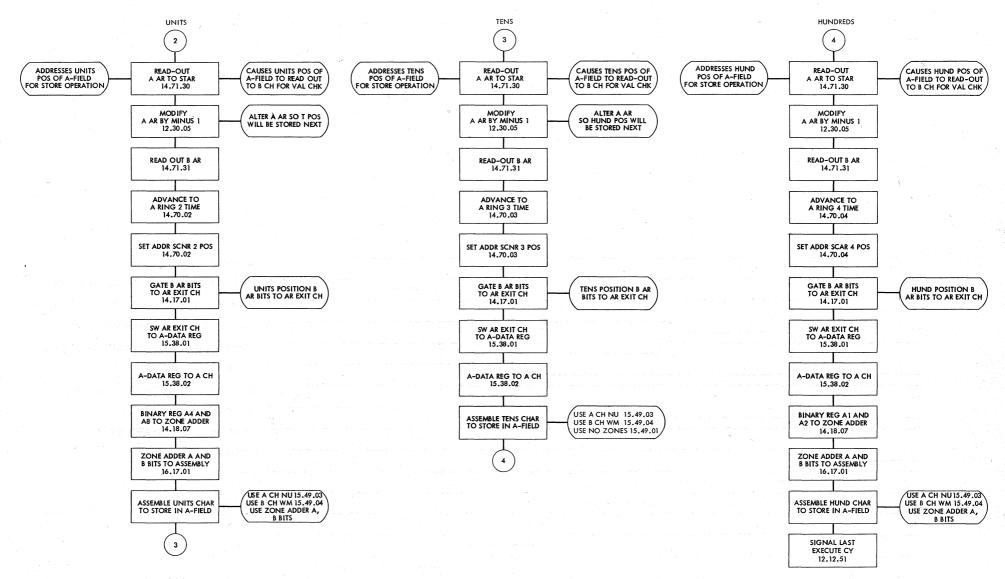

The BAR contains a five-digit numeric 1410 address. In 1401 mode, a three-digit address with appropriate zones over the units and hundreds positions must be stored. The units, tens and hundreds positions of the BAR are stored on A cycles during following steps of the A ring. The zones over the units and hundreds that represent thousands and ten-thousands position values must be stored at the same time as the numeric portion of the character. To do this, the thousands and ten-thousands positions of the BAR read out to the binary register during two C cycles before the storage operation (Figure 15).

During the storage operation, at A-ring-2 time, the units position of the BAR reads out via the address exit channel to the A-data register, to the A channel, and to assembly. At the same time, the A4 and A8 binary registers are gated out to the zone adder. The zone adder output is gated to the assembly area to combine with the numeric bits from the A channel. The resulting character reads into storage in the location addressed by the AAR.

At A-ring-3 time, the tens position numeric bit reads out of the BAR, via the A channel, to storage. No zones are involved. At A-ring-4 time, the hundreds position numeric bit reads out of the BAR to assembly the same as the units position. The binaryregister A1 and A2 outputs are gated through the zone adder to assembly to form the zone portion of the character to be stored.

## Store B—Address Register

#### **Op-Code Function**

The 1401 H-op code stores the contents of the Baddress register from the previous operation in the three-position field that has its units position defined by the A address of the store-B-address-register instruction. Word marks in the A field are retained. The instruction format is: H (AAA).

#### **Operation (Figure 14)**

The (AAA) address reads into the AAR in the usual manner. Because the address to be stored is already in the BAR, no transfer from the AAR to the BAR is needed. Thus, the B cycle after I-op time is not necessary. The operation proceeds in the same manner as the Q-op code.

### Modify Address

#### **Op-Code Function**

The # (AAA) (BBB) instruction adds the three-character field specified by the A address to the B-address field. The three numeric positions and zones over the units and hundreds positions of each field added, and the three-position result (including appropriate zones), are stored in the B field. Word marks are ignored and remain unchanged in both fields.

#### **Operation (Figure 16)**

Three sets of A and B cycles add the address from the B field to the modifier in the A field. The modified address is then stored back in the B field. The zone bits over the B-field units and hundreds positions must be added to the zone bits over the modifier. The problem is illustrated in the following example:

| Contents of B address t | o be modified            | A = 1<br>B = 2 B = 8<br>9 6 5                                                          |

|-------------------------|--------------------------|----------------------------------------------------------------------------------------|

| Contents of A address   | modifier                 | $\begin{array}{c} B \equiv 2\\ 0 & 0 & 0\\ \hline A \equiv 1 & A \equiv 4 \end{array}$ |

|                         | Sum                      | $\begin{array}{c} B = 8 \\ 9 6 5 \end{array}$                                          |

| In 1410 numerical form  | 11965<br>+ 2000<br>13965 |                                                                                        |

Miscellaneous 27

Figure 14A. IBM 1401 Mode Store AAR or BAR

Figure 14B. IBM 1401 Mode Store AAR or BAR

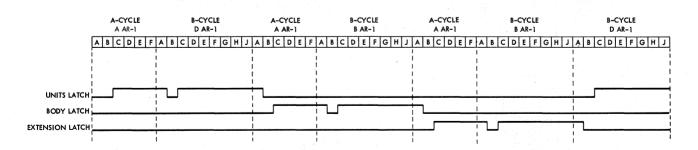

## C-CYCLE C-CYCLE A-CYCLE A-CYCLE A-CYCLE A B C D E F A B C D E F A B C D E F A B C D E F G H J A B C D E F G H J A B C D E F G H J A B C D E F G H J 1<sub>6</sub>|17|18 UNITS LATCH BODY LATCH A RING 1 A RING 2 A RING 3 A RING 4 SET A2, A8 FROM BCD TO BIN XLATE BINARY REGISTER A2, A8 SET A1, A2, A4, A8 FROM BCD TO BIN XLATE BINARY REGISTER A1, A2, A4, A8 GATE B AR UNITS POS TO ADDR EXIT CHANNEL GATE B AR TENS POS TO ADDR EXIT CHANNEL GATE B AR HUND POS TO ADDR EXIT CHANNEL GATE B AR T TH POS TO ADDR EXIT CHANNEL GATE B AR TH POS TO ADDR EXIT CHANNEL

ADDRESS STORE

Figure 15. 1401 Mode Address Store Sequence

Figure 16A. 1401 Mode Modify Address

Figure 16B. 1401 Mode Modify Address

32

Figure 16C. 1401 Mode Modify Address

Miscellaneous 33

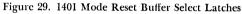

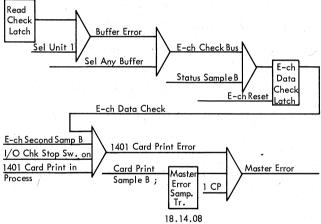

Figure 16D. 1401 Mode Modify Address