# Customer Engineering Instruction-Reference

1411 Input-Output Operations

Instruction-Reference

1411 Input-Output Operations

#### **Preface**

This manual provides instructional and reference material for input-output (1-0) operations of the IBM 1411 Processing Unit. The manual contains five logical segments.

- 1. "I-O Principles of Operation" presents basic concepts of data flow, data control, and channel status indicators.

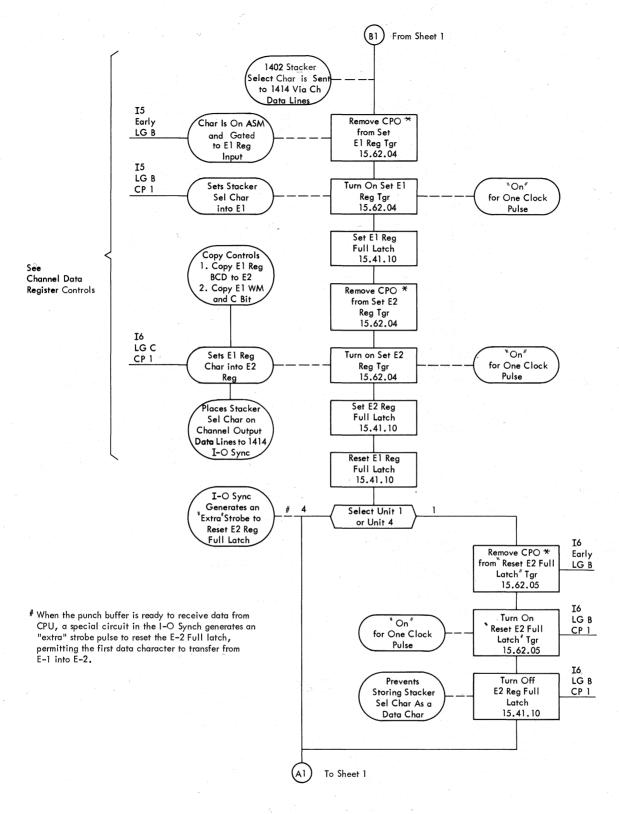

- 2. "Channel Data Register Controls" presents register operation as a functional unit because operation is the same for all 1-0 devices.

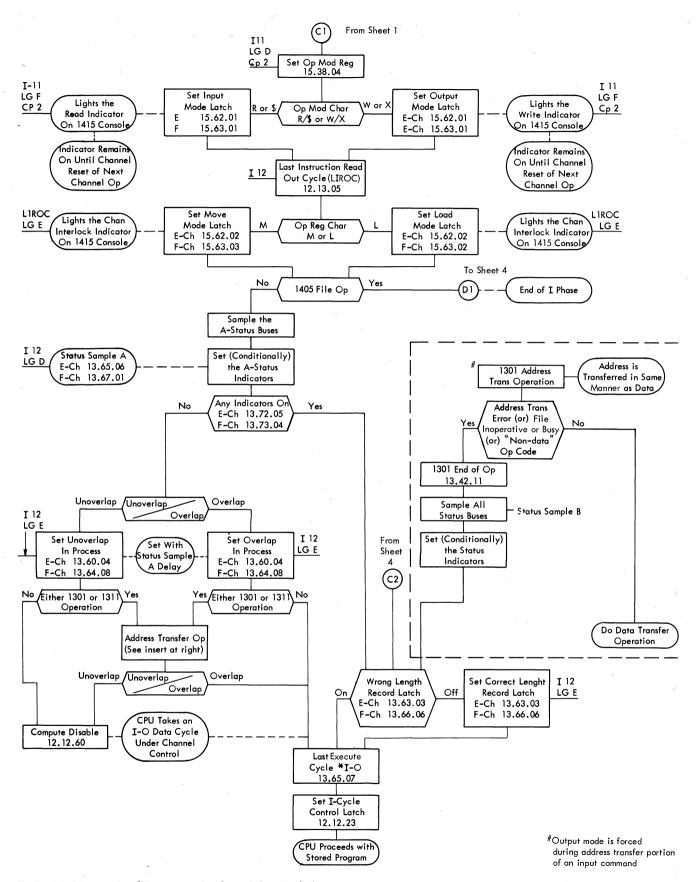

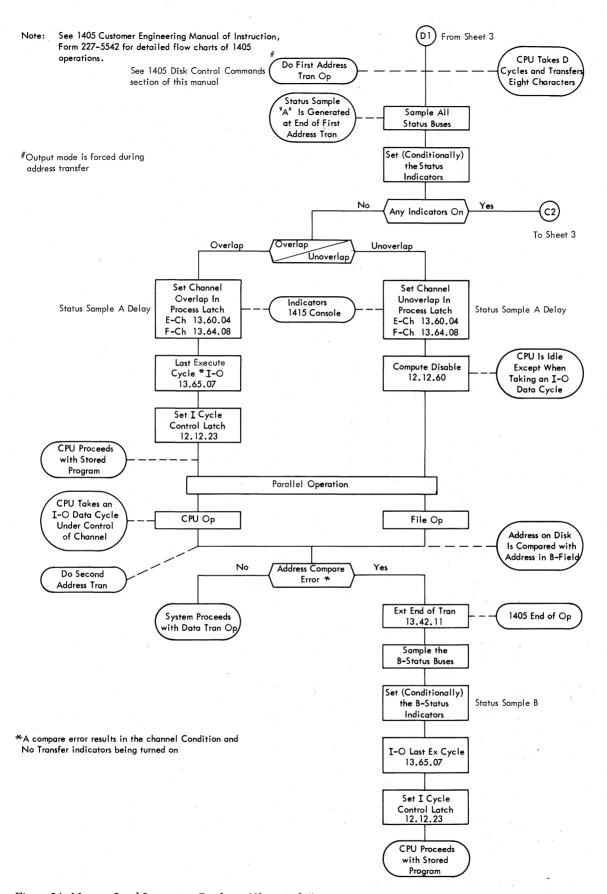

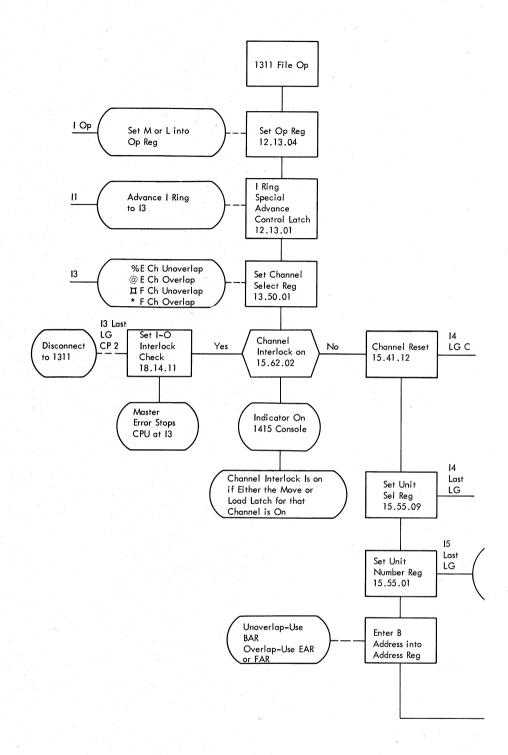

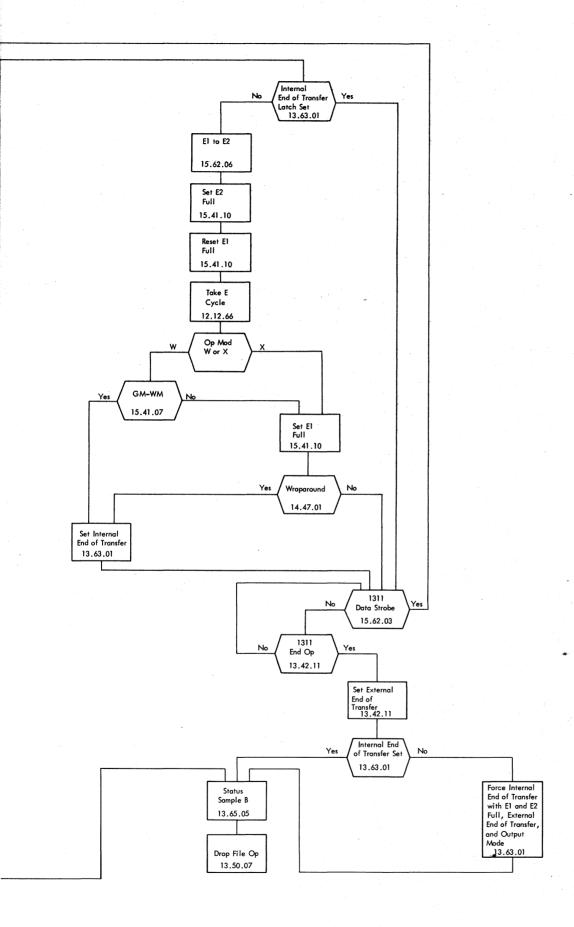

- 3. "r-o Sequence" presents the machine logic highlights of a move or load command.

- 4. Specific IBM 1411 I-0 operations this manual describes 1411 functions, and tie-in for the following IBM I-0 devices (Page 85).

- a. 1402 Card Read Punch

- b. 1403 Printer

- c. 1011 Paper Tape Reader

- d. 1405 Disk Storage Unit

- e. 1311 Disk Storage Unit

- 5. The "Reference Section" in the back of the manual contains status indicator charts and condensed logic.

This manual does not cover operation of the 1-0 devices; refer to the appropriate manual for the 1-0 devices.

1411 functions for devices not listed above are presented in the manual for that device. A list of IBM 1410 system manuals is in the *IBM 1410 Customer Engineering Handbook*, Form 223-2588, and in IBM 1410 CEM Service Aid 72.

Users of this manual should be familiar with the information presented in *IBM 1410 Systems Fundamentals*, Form 223-2589.

# Contents

| Input-Output Principles of Operation               | 5        | 1411-1403 Printer Operation                                  | . 81         |

|----------------------------------------------------|----------|--------------------------------------------------------------|--------------|

| Input-Output Units                                 | 5        | Printer Load Command                                         | . 81         |

| INPUT-OUTPUT SYNCHRONIZERS                         | 5        | Printer Move Command                                         | . 81         |

| INPUT-OUTPUT CHANNELS                              | 7        | I-Phase Sequence                                             |              |

| Data Flow                                          | 7        | I-Phase Channel Status Indicators E-Phase Sequence           | . 91<br>. 92 |

| Data Transmission                                  | 8        | E-Phase Channel Status Indicators                            | 93           |

| Channel Data Registers Channel Status Indicators   | 9<br>14  | FORMS CONTROL COMMAND                                        | . 93         |

| Instruction Format – Move or Load                  | 17       | I-Phase Sequence                                             | 93           |

| Op Code Character                                  | 17       | I-Phase Channel Status Indicators                            |              |

| X-Control Field                                    | 17       | Branch If Printer Carriage Busy Command                      | 97           |

| B-Address                                          | 18       | 1411-1011 Paper-Tape Reader Operation                        | . 98         |

| d-Character                                        | 18       | Paper-Tape Reader Move or Load Command                       |              |

| Processing Overlap                                 | 18       | I-Phase Sequence                                             | 98           |

|                                                    |          | E-Phase Sequence                                             |              |

| Channel Data Register Controls                     | 21       | Buffer Operation                                             |              |

| REGISTER COMPONENTS AND CONTROLS.                  | 21       | Circuits                                                     | 105          |

| Move Mode Operation                                | 21       | 1411-1405 Disk Storage Operation                             | 110          |

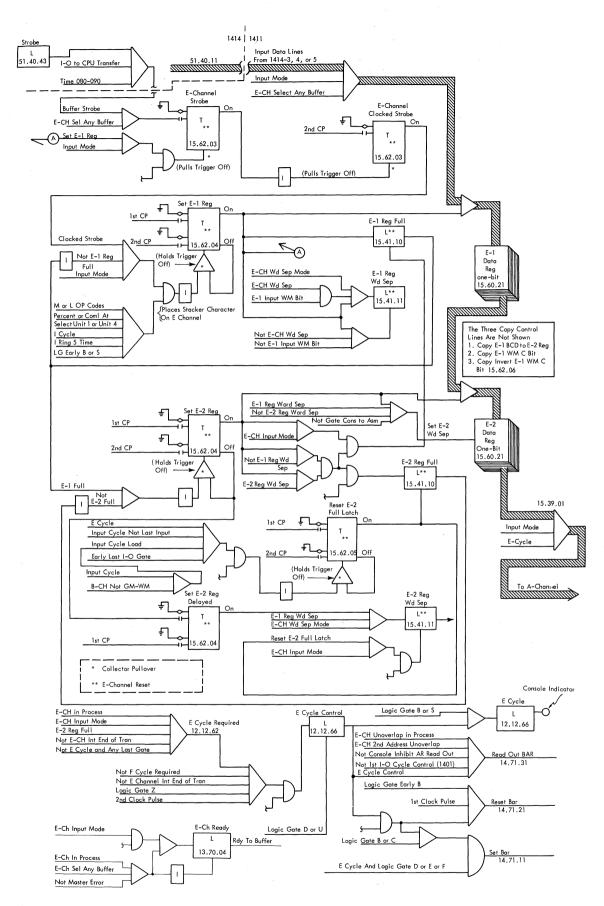

| Input Mode                                         | 22       | SEEK DISK RECORD                                             | 110          |

| Output Mode                                        | 24       | Function                                                     |              |

| Load Mode Operation                                | 29       | Operation                                                    |              |

|                                                    |          | DISK-ADDRESS TRANSFER First Address Transfer                 |              |

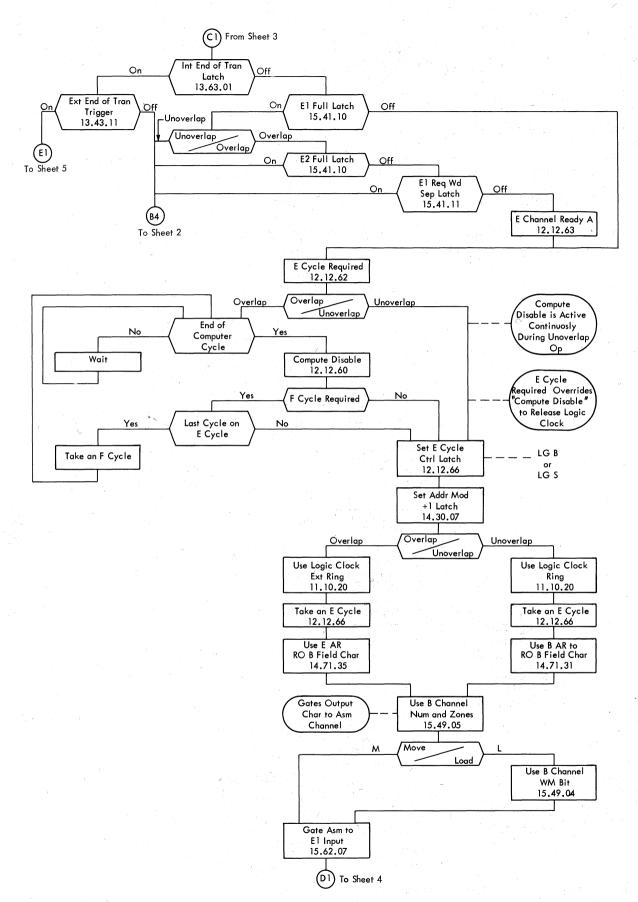

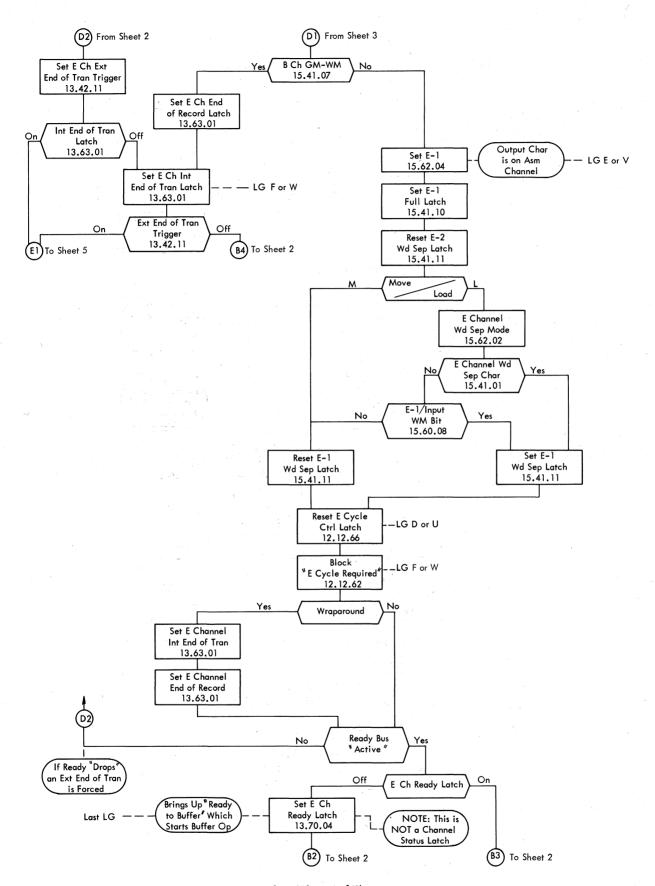

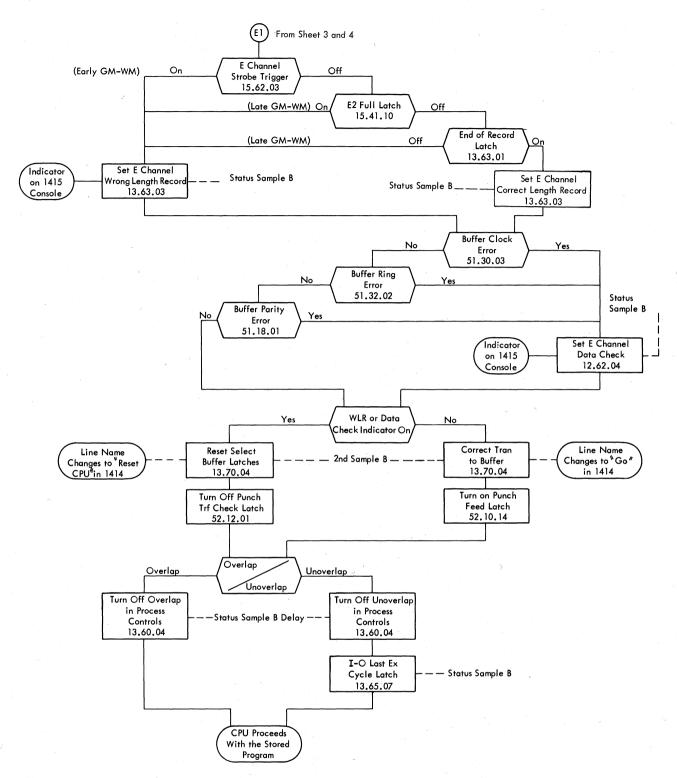

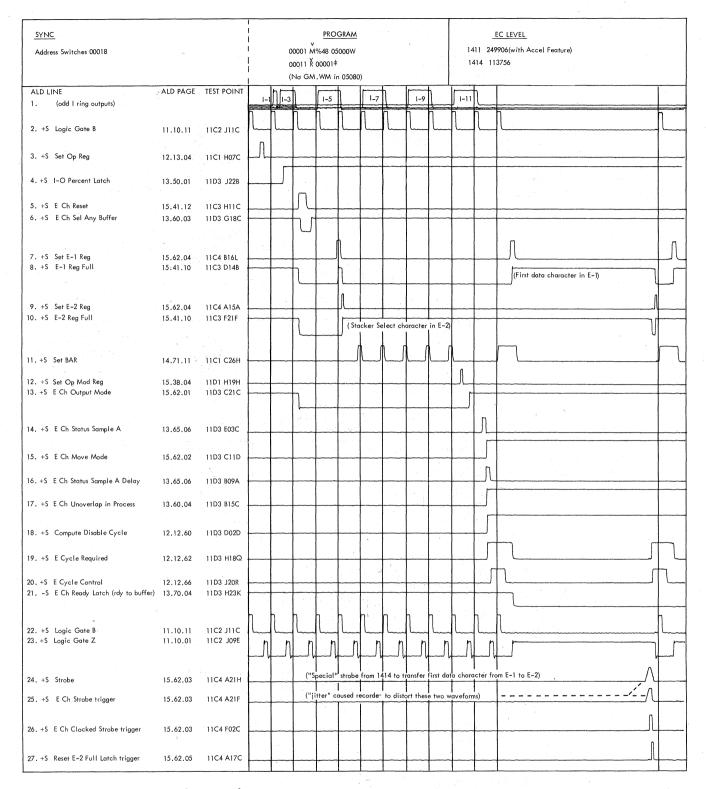

| I-O Sequence                                       | 20       | Second Address Transfer                                      |              |

|                                                    | 32       | DISK WRITE                                                   | 121          |

| I-Phase Functions<br>Selection                     | 32<br>32 | Write a Single Record                                        | 121          |

| I-Phase Status Indicators                          |          | Disk Read                                                    |              |

|                                                    | 32       | Function                                                     |              |

| I-Phase Logic Flow                                 | 34       | Operation DISK WRITE ADDRESS                                 |              |

| E-Phase Functions Initiation                       | 35<br>35 | Function                                                     |              |

| E-Phase Status Indicators                          | 42       | Operation                                                    |              |

| Processing Overlap Logic                           | 42       | 1410 Data Brassasian System One water                        |              |

|                                                    |          | 1410 Data Processing System Operation with 1311 Disk Storage | 100          |

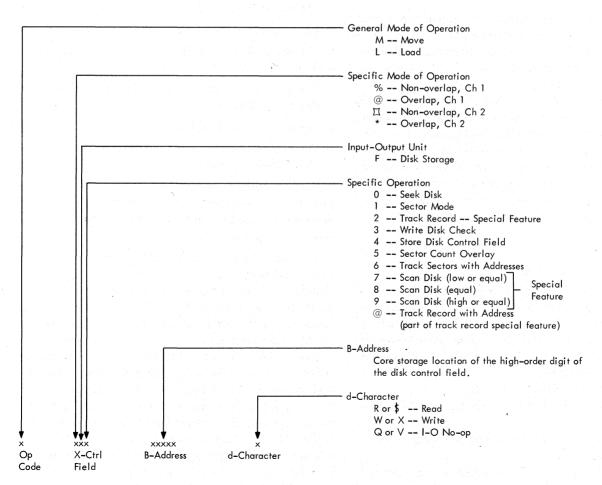

| Service Note                                       | 46       | Instruction Format                                           |              |

| I-O No-Op Command                                  | 46<br>47 | Operation Code                                               |              |

| Summary: Ose of the 1-0 No-op Command              | 41       | X-Control Field                                              | 129          |

|                                                    |          | B-Address                                                    |              |

| 1411-1402 Reader Operation                         | 48       | d-Character                                                  |              |

| READER MOVE OR LOAD COMMAND                        | 48       | 1410/1311 Instructions                                       |              |

| I-Phase Sequence                                   | 58       | Seek Disk<br>Sector Mode                                     |              |

| I-Phase Channel Status Indicators E-Phase Sequence | 59<br>59 | Write Disk Check                                             | 133          |

| E-Phase Channel Status Indicators                  | 60       | Store Disk Control Field                                     | 133          |

| READER SELECT STACKER AND FEED COMMAND             | 63       | Track Sectors with Addresses                                 | 133          |

| I-Phase Sequence                                   | 63       | Track Record with Address Track Record                       | 134          |

| I-Phase Channel Status Indicators                  | 66       | Sector Count Overlay                                         | 134          |

|                                                    |          | Scan Disk                                                    | 135          |

| 1411-1402 Punch Operation                          | 67       | I-O No Operation                                             | 135          |

|                                                    |          | 1410 Operation                                               | 136          |

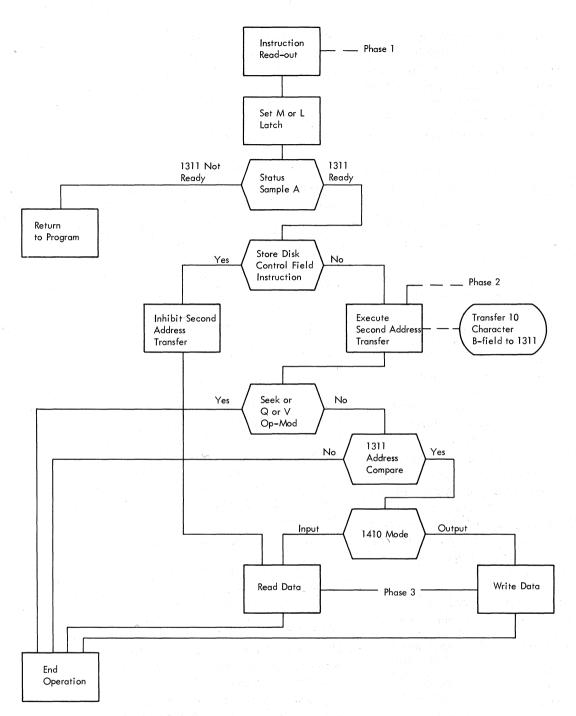

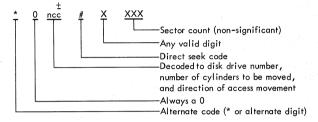

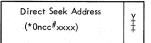

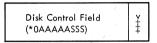

| Punch Move or Load Command I-Phase Sequence        | 67<br>76 | Instruction Read-Out<br>Second Address Transfer              | 136          |

| I-Phase Channel Status Indicators                  | 77       | Data Transfers                                               |              |

| E-Phase Sequence                                   | 78       |                                                              |              |

| E-Phase Channel Status Indicators                  | 79       | Reference Section                                            | 143          |

# Figures

| FIGURE   | TITLE                                                                                   | PAGE | FIGURE     | TITLE                                                                          | PAGE |

|----------|-----------------------------------------------------------------------------------------|------|------------|--------------------------------------------------------------------------------|------|

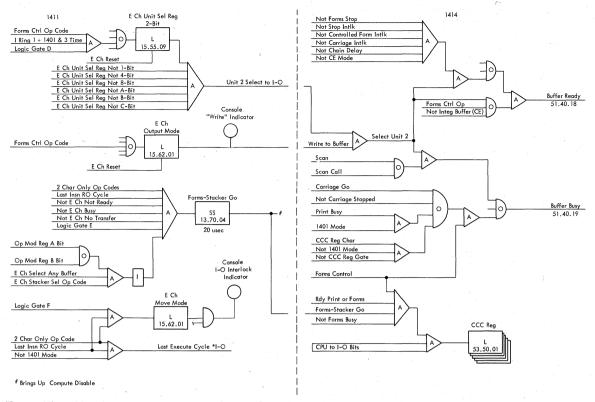

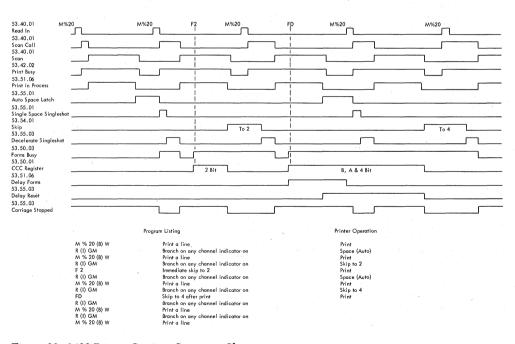

| Input-C  | output Principles of Operation                                                          |      | 61         | 1403 Print Command Timing Chart                                                | 88   |

| 1        | I-O Units and Synchronizers                                                             | . 5  | 62         | Channel Register Operation — Printer                                           |      |

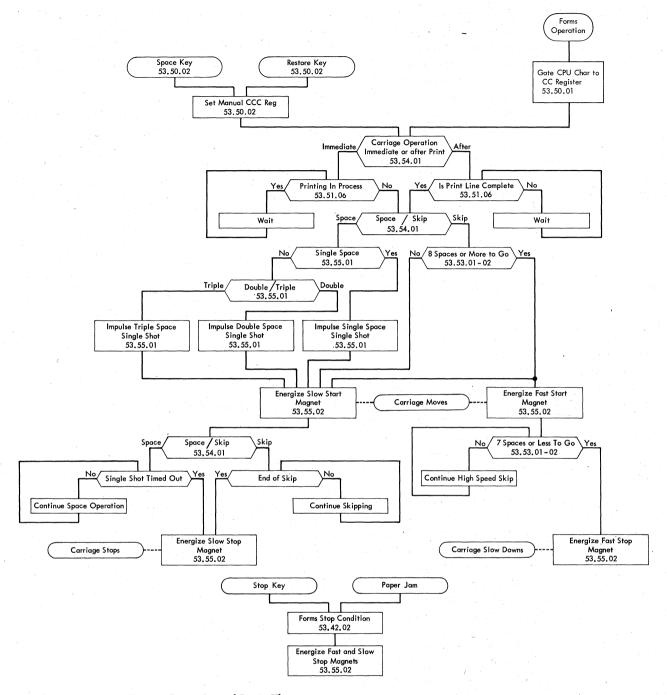

| 2        | 1410 Configurator                                                                       | . 6  | 63         | 1411-1403 Printer Forms Control Logic Flow                                     | 94   |

| 3        | Buffered Reader Operation                                                               |      | 64         | 1403 Forms Control Timing Chart                                                | 95   |

| 4        | I-O Data Flow                                                                           |      | 65         | 1411-1403 Printer Forms Control – Condensed Logic                              | 96   |

| 5        | Word Separator Processing                                                               |      | 66         | 1403 Printer Carriage Sequence Chart                                           |      |

| 6        | Data Transmission — Input Data Transmission — Output                                    |      |            | 011 Paper-Tape Reader Operation                                                |      |

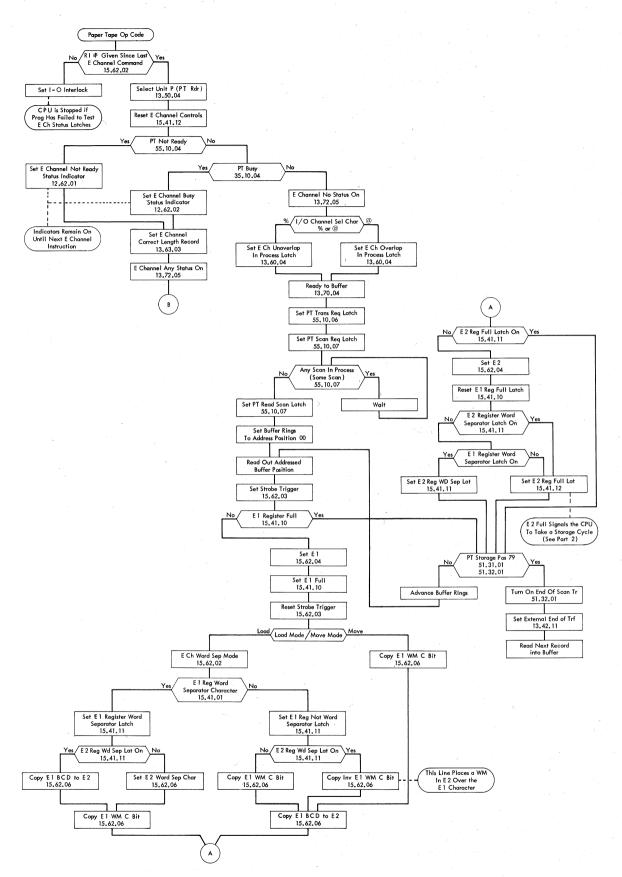

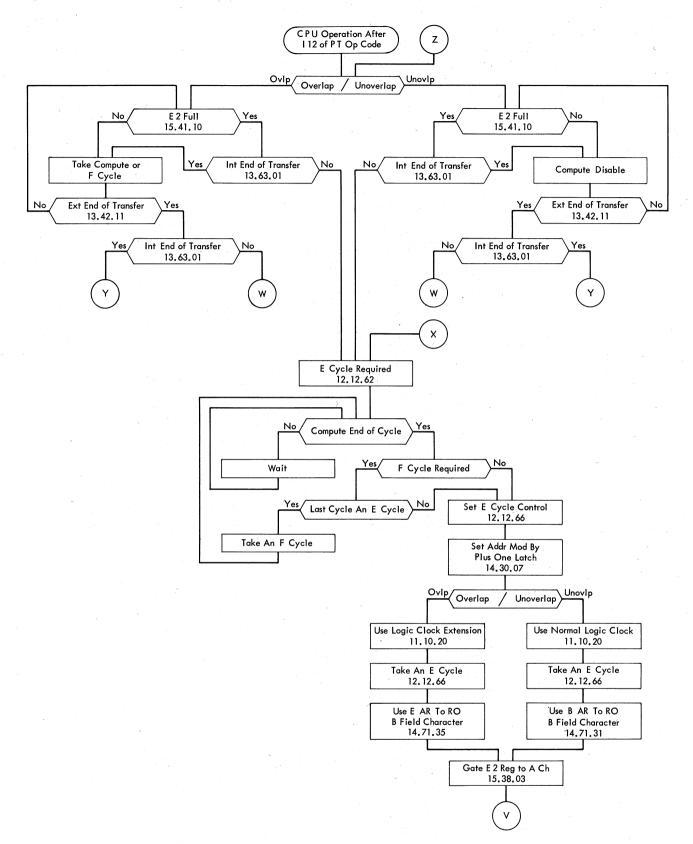

| 8        | Channel Data Registers                                                                  |      | 67         | Paper-Tape Move or Load                                                        | 99   |

| 9        | Console Indicators                                                                      | . 13 | 68         | IBM 1414 Integrated Synchronizer Data Flow                                     |      |

| 10       | Channel Status Indicators                                                               |      | 69         | Paper-Tape Read-In                                                             |      |

| 11       | Move or Load Instruction Format                                                         |      | 70         | Paper-Tape Character Storage                                                   | 105  |

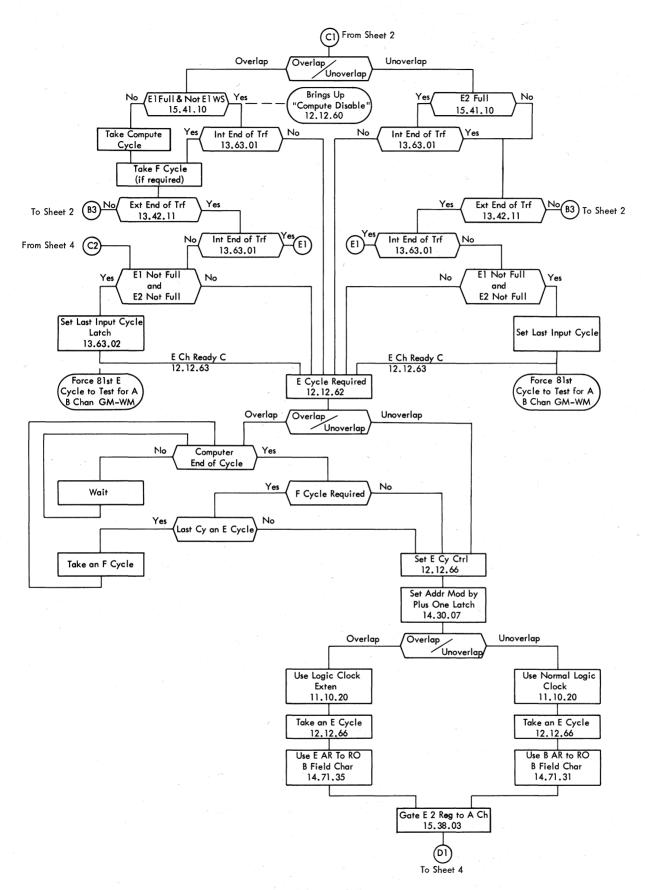

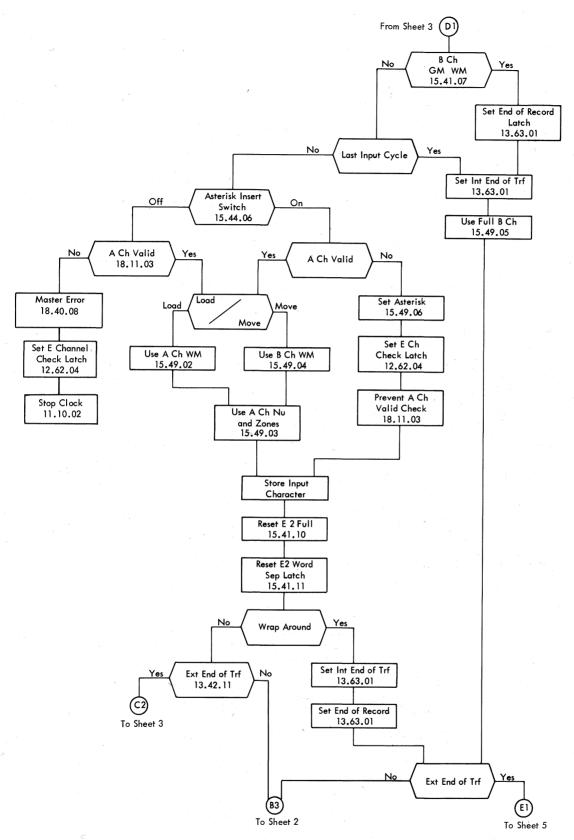

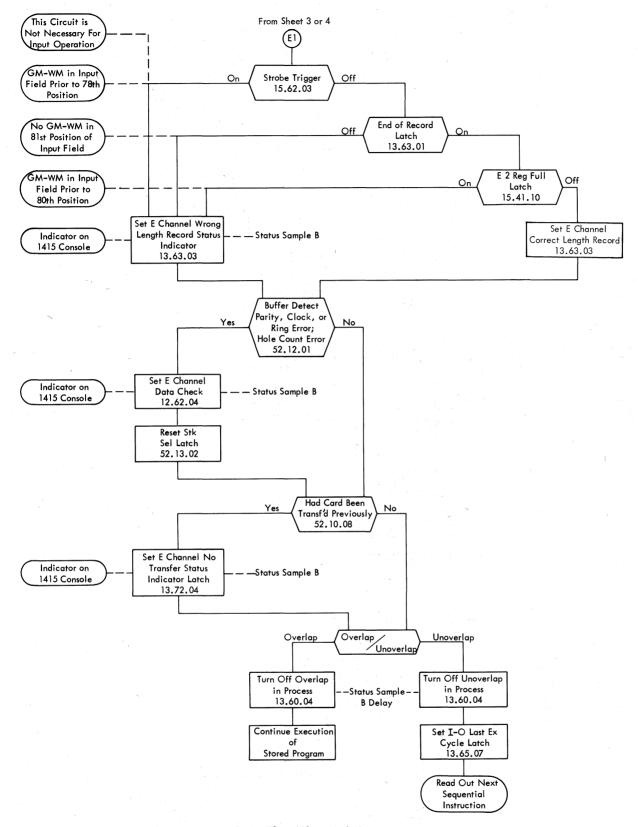

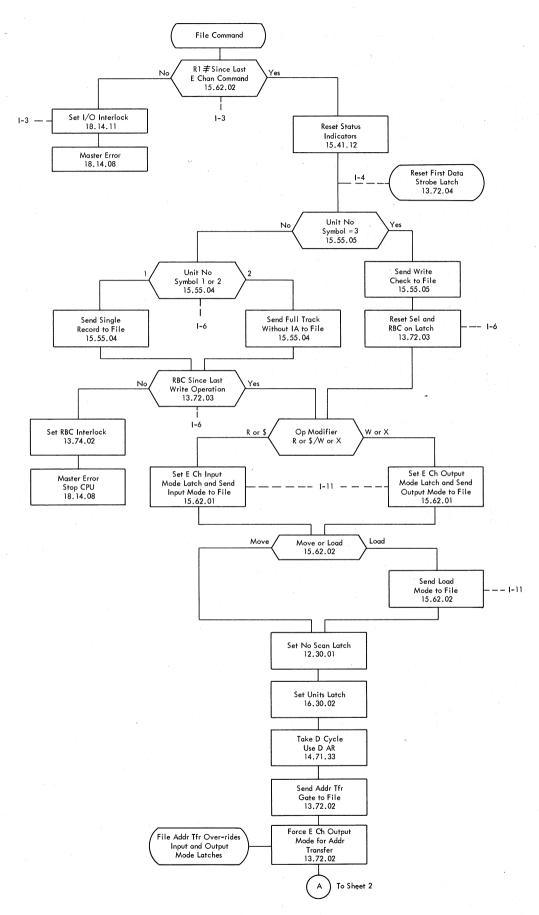

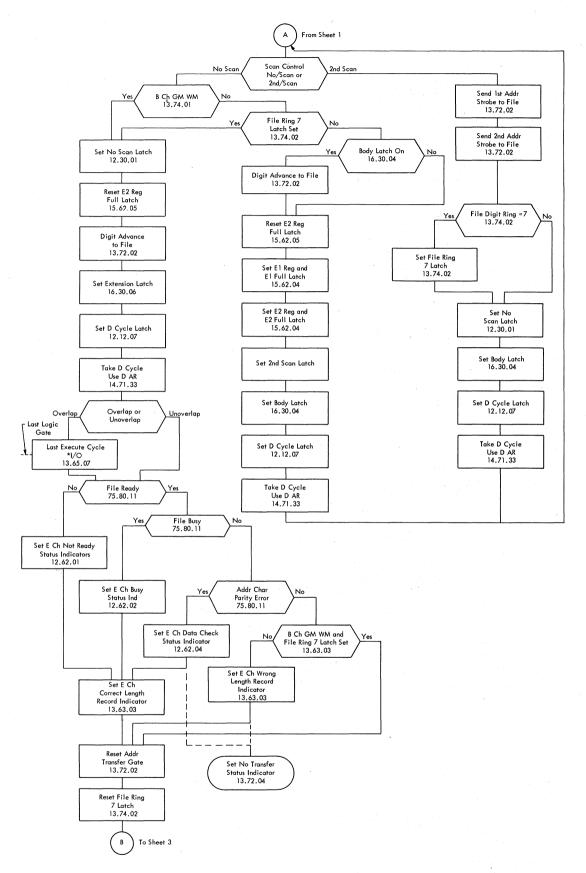

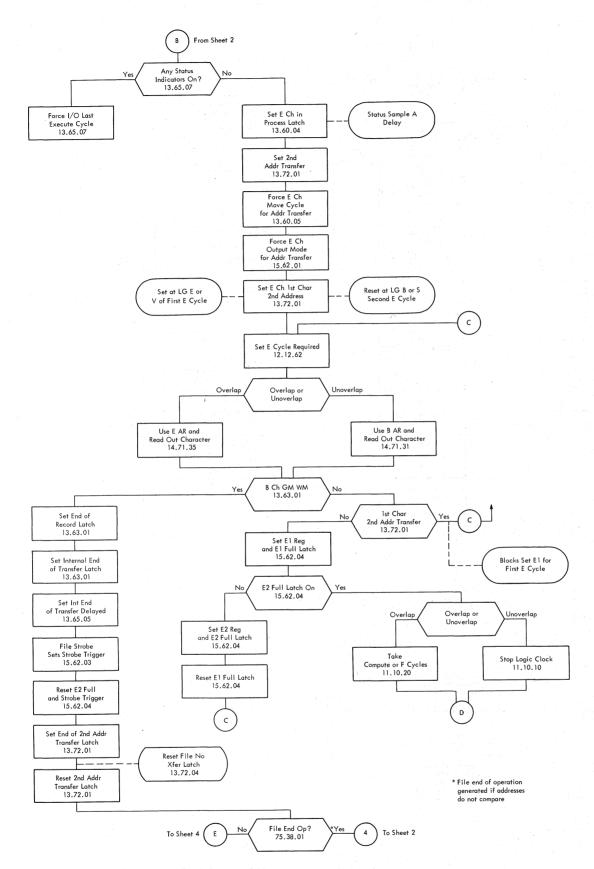

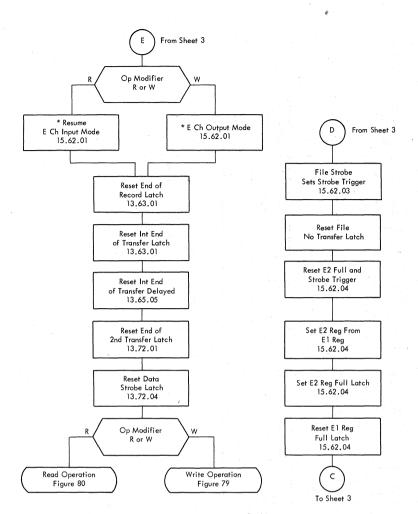

| 12       | Move or Load Command Logic Flow                                                         | . 19 | 1411-14    | 405 Disk Storage Operation                                                     |      |

| 13       | Processing Overlap                                                                      | . 20 | 71         | 1405 Disk Storage Instruction Read-Out                                         |      |

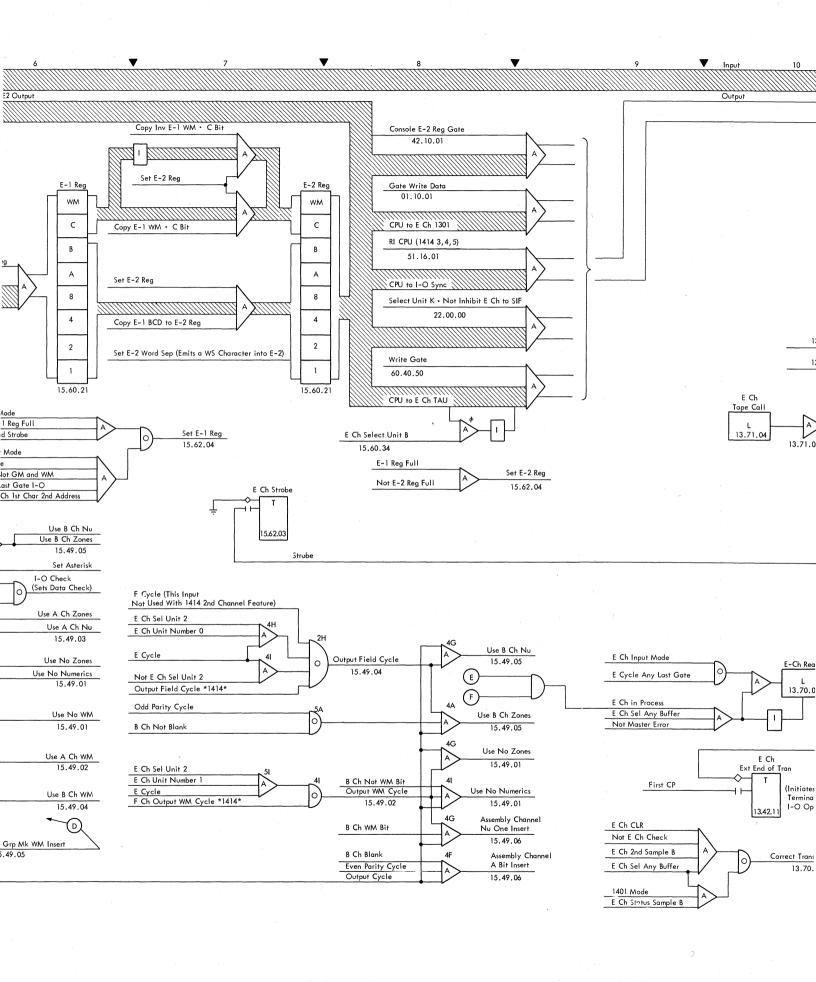

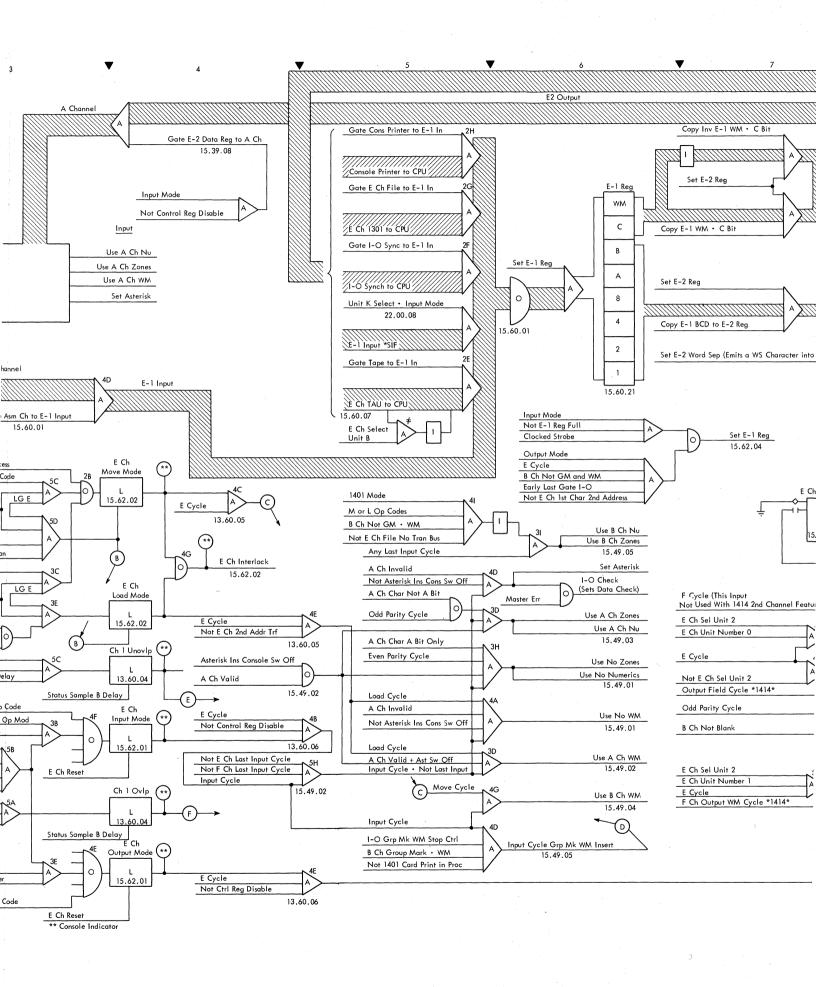

| Channe   | l Data Register Controls                                                                |      |            | Timing Chart                                                                   |      |

| 14       | E-1 and E-2 Register Latches                                                            |      | 72         | Disk Unit Address                                                              |      |

| 15       | Set E-1 Register Trigger – ALD                                                          |      | 73         | Disk Seek Operation Chart                                                      |      |

| 16       | Set E-1 Register Trigger — Condensed Logic                                              |      | 74<br>75   | 1405 Seek Disk Record Timing Chart                                             |      |

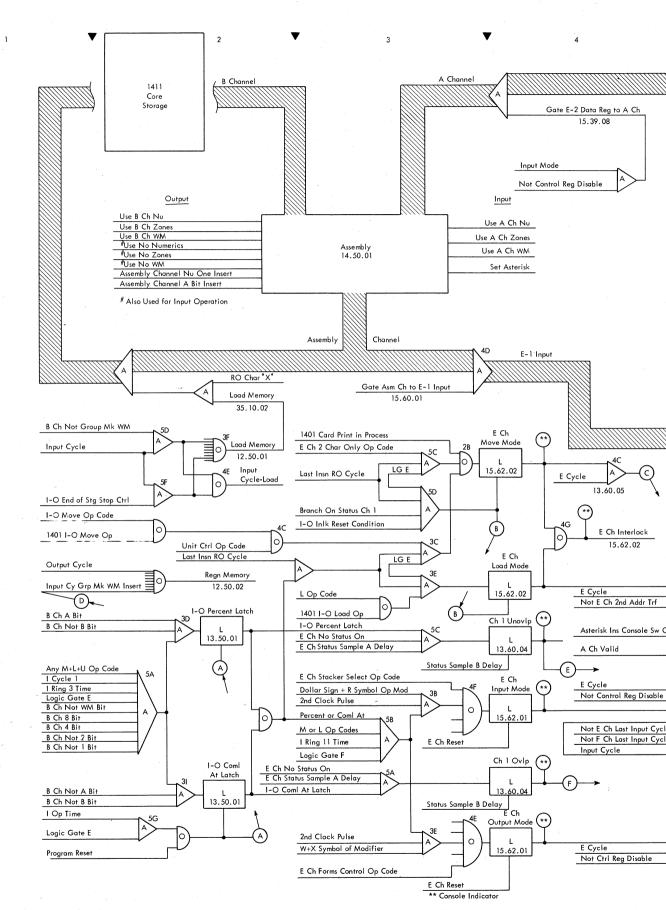

| 17<br>18 | E-Channel Data Flow Controls                                                            |      | 76         | Disk Address Transfer                                                          |      |

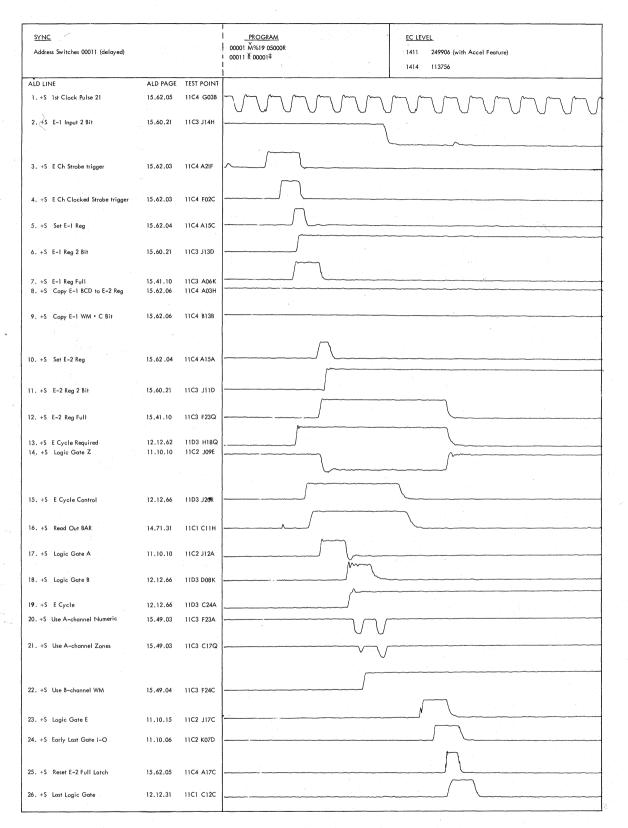

| 19       | E-1 and E-2 Input Timing Chart                                                          |      | 77         | 1405 Disk Storage First Address Transfer                                       |      |

| 20       | Channel Register Operation – Input Move Mode                                            |      |            | Timing Chart                                                                   | 120  |

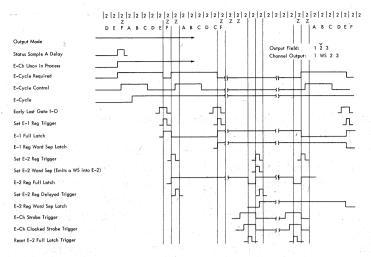

| 21       | Channel Register Operation — Output Move Mode                                           |      | 78         | 1405 Disk Storage Second Address Transfer                                      |      |

| 22       | E-1 and E-2 Output Timing Chart                                                         |      |            | Timing Chart                                                                   | 122  |

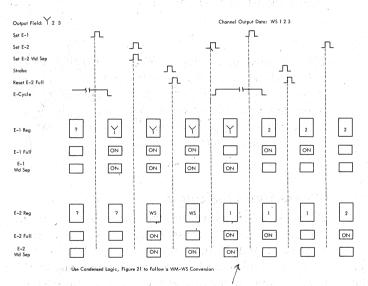

| 23       | Channel Register Operation – Load Mode                                                  | . 30 | 79         | Write Operation                                                                | 123  |

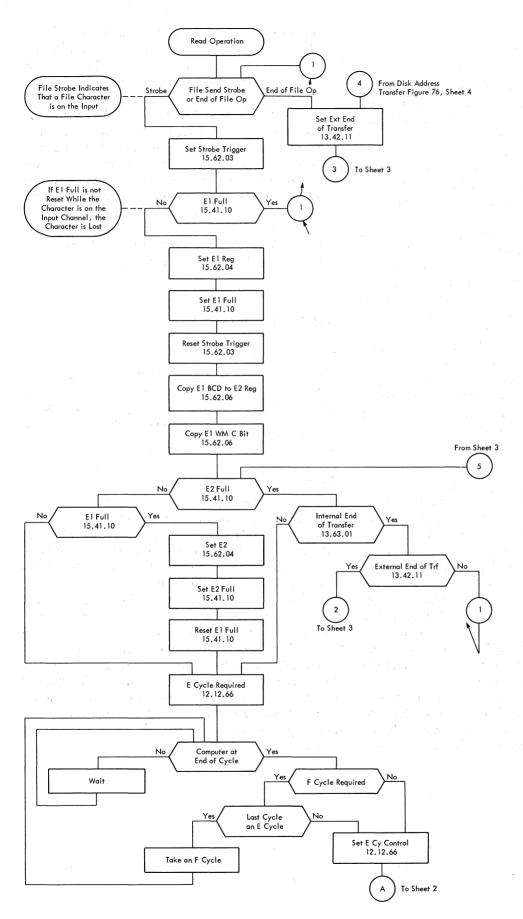

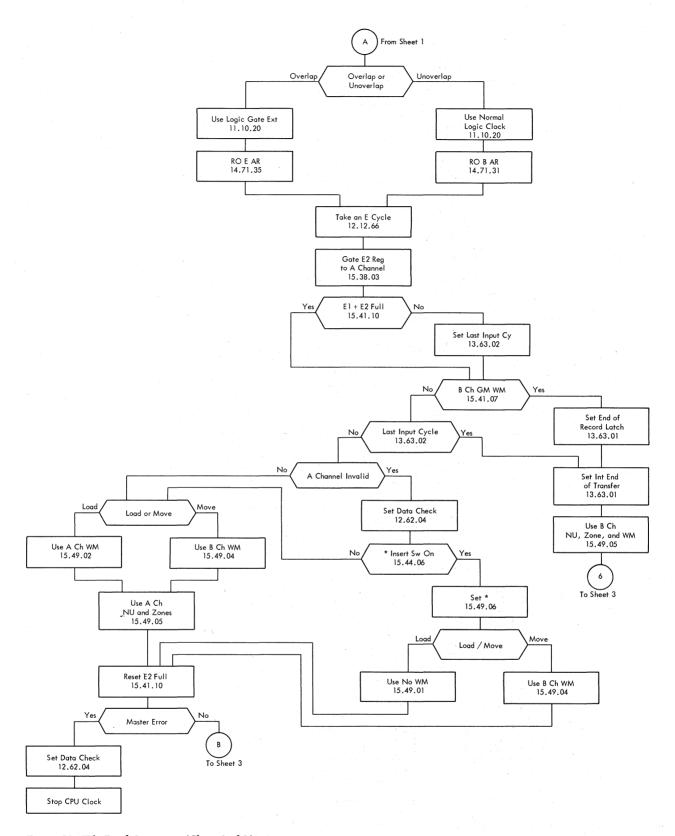

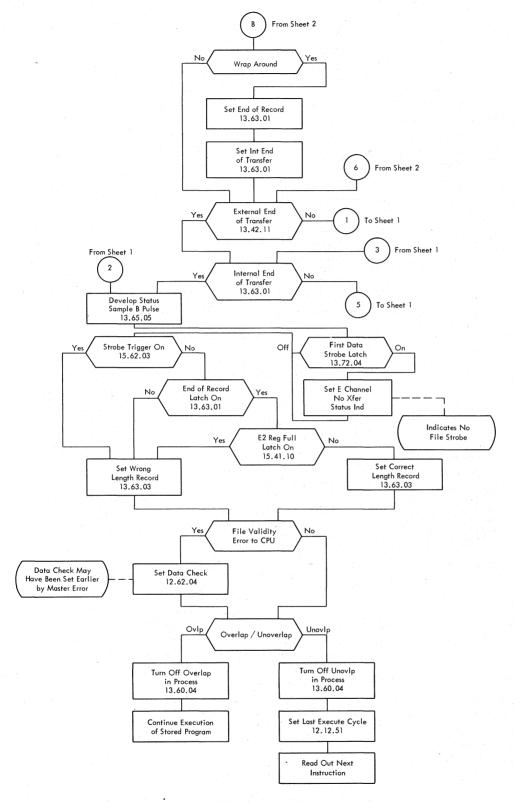

| 24       | E-1 and E-2 Sequence Chart — Output Load Mod                                            |      | 80         | File Read Operation                                                            | 126  |

| 25       | Word Separator Processing - Output                                                      |      |            | ystem Operation with 1311                                                      |      |

| 26       | Word Separator Processing - Input                                                       | . 31 | 81         | 1410 Op Codes for 1311                                                         | 129  |

| I-O Seq  | uence                                                                                   |      | 82         | 1410-1311 Simplified Operation                                                 |      |

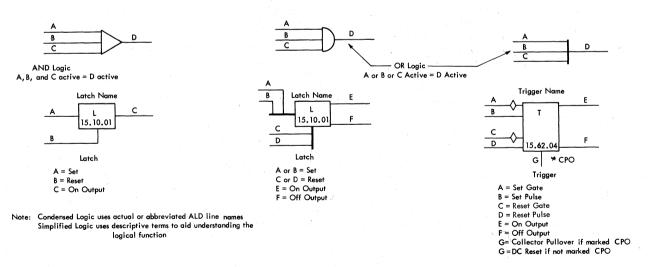

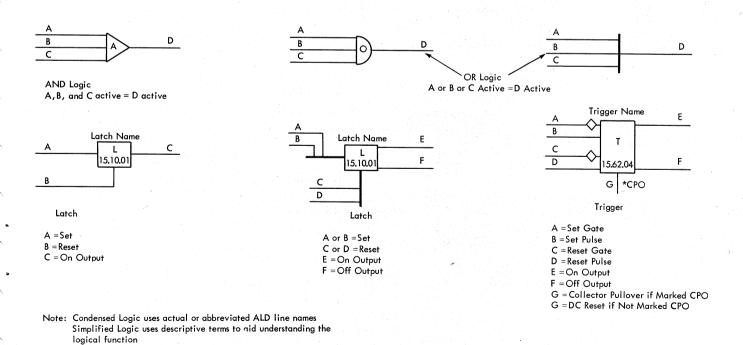

| 27       | Condensed Logic Symbols                                                                 |      | 83         | Instruction Read-Out                                                           | 137  |

| 28       | Channel Status Checking - Basic Logic Flow                                              |      | 84<br>85   | Input and Output Mode Operation                                                |      |

| 29       | Channel Status Checking — Basic Timing                                                  |      |            |                                                                                | 141  |

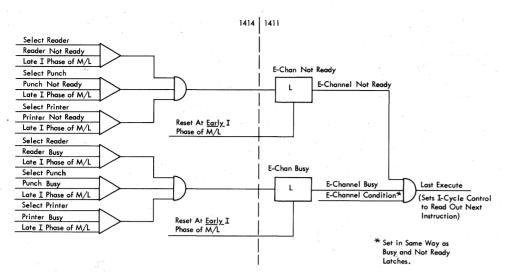

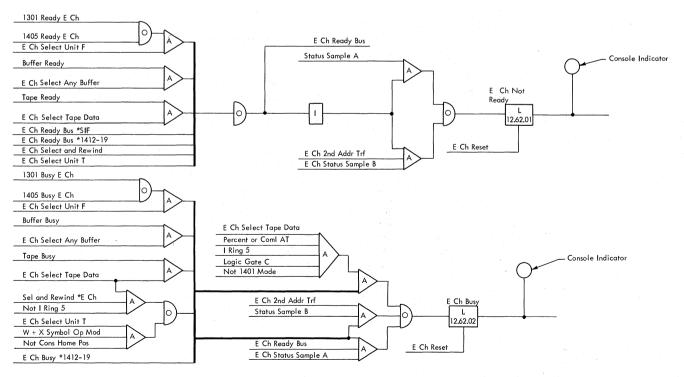

| 30       | Channel Not Ready and Busy – Simplified Logic                                           |      |            | nce Section                                                                    | 1.40 |

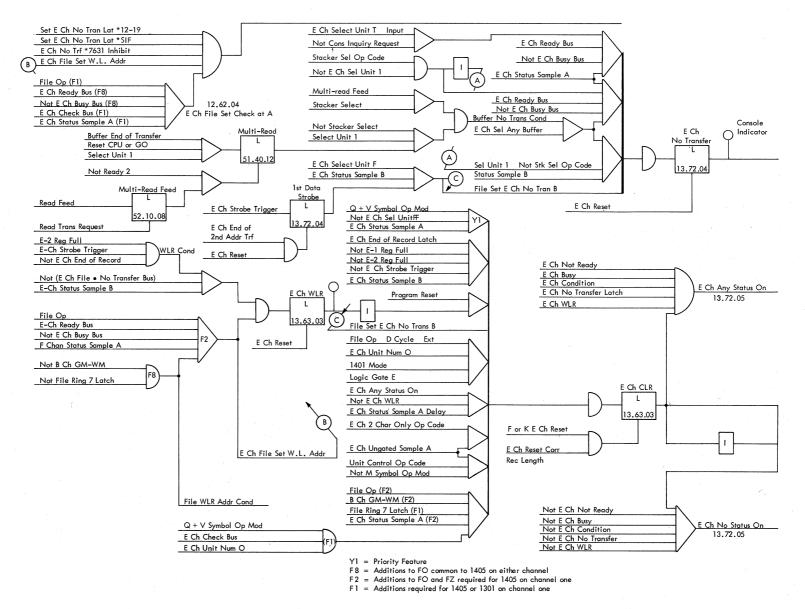

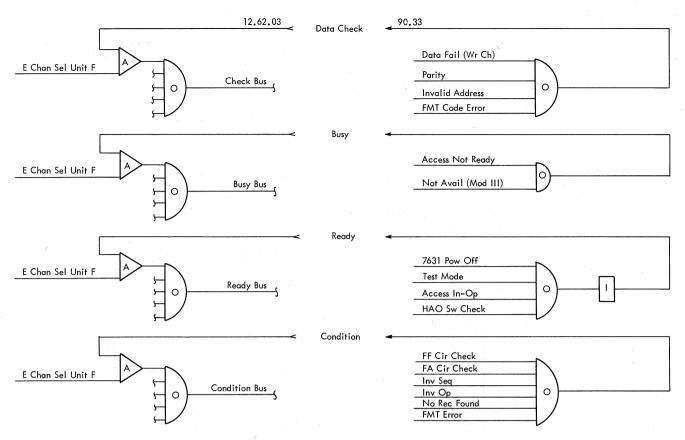

| 31<br>32 | Channel Not Ready and Busy — Condensed Logic<br>Channel Condition                       |      | 86         | Status Indicator Chart — 1402 Card Read Punch 1442-3 Card Reader               |      |

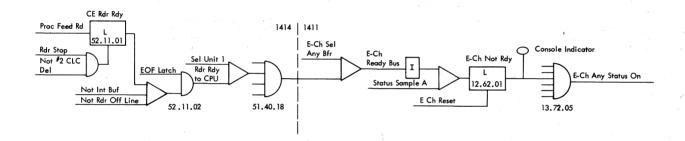

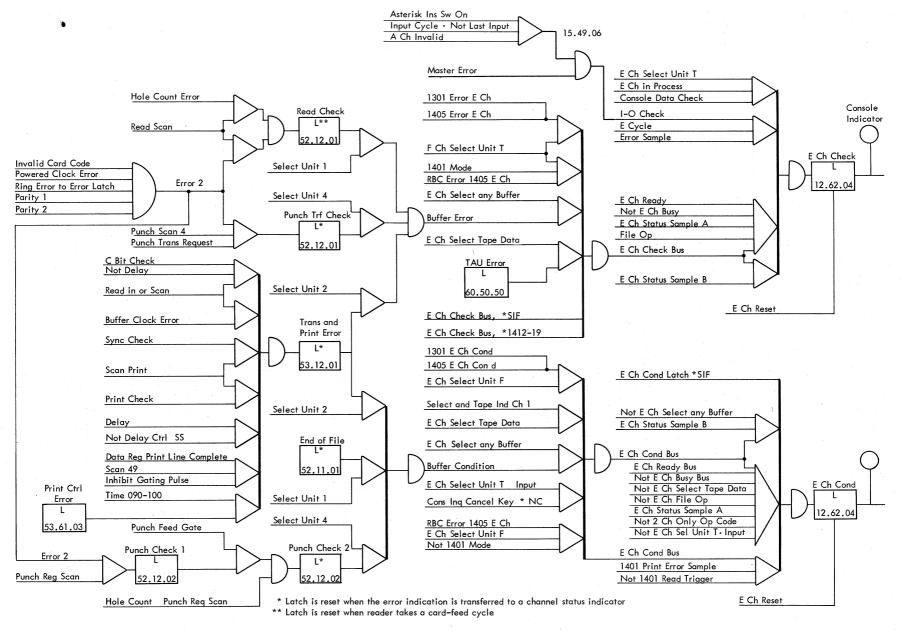

| 33       | Any Status On                                                                           |      | 87<br>88   | Status Indicator Chart — 1403 Printer                                          |      |

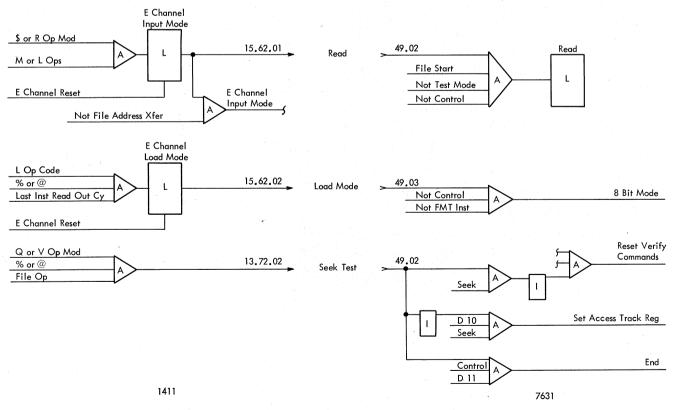

| 34       | Move or Load Instruction Read-Out                                                       |      | 89         | Status Indicator Chart — 1415 Console                                          |      |

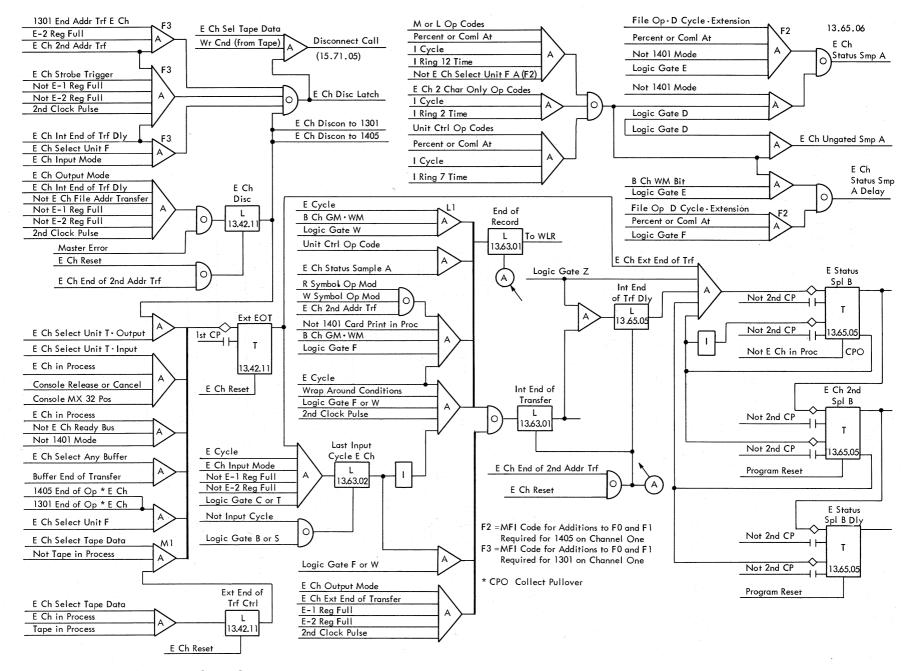

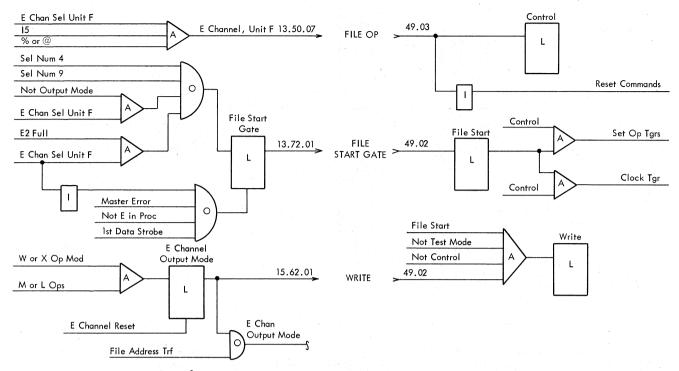

| 35       | Channel Control Latches - Simplified Logic                                              |      | 90         | Status Indicator Chart — 729-7330 Tape                                         |      |

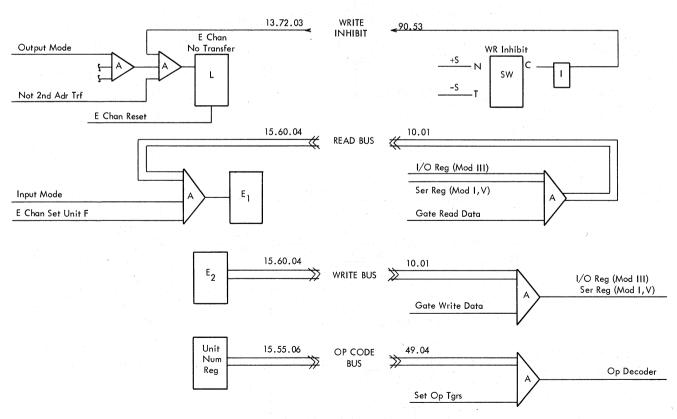

| 36       | Input End of Transfer Timing Chart                                                      |      | 91         | Status Indicator Chart — 7750 PTC                                              | 146  |

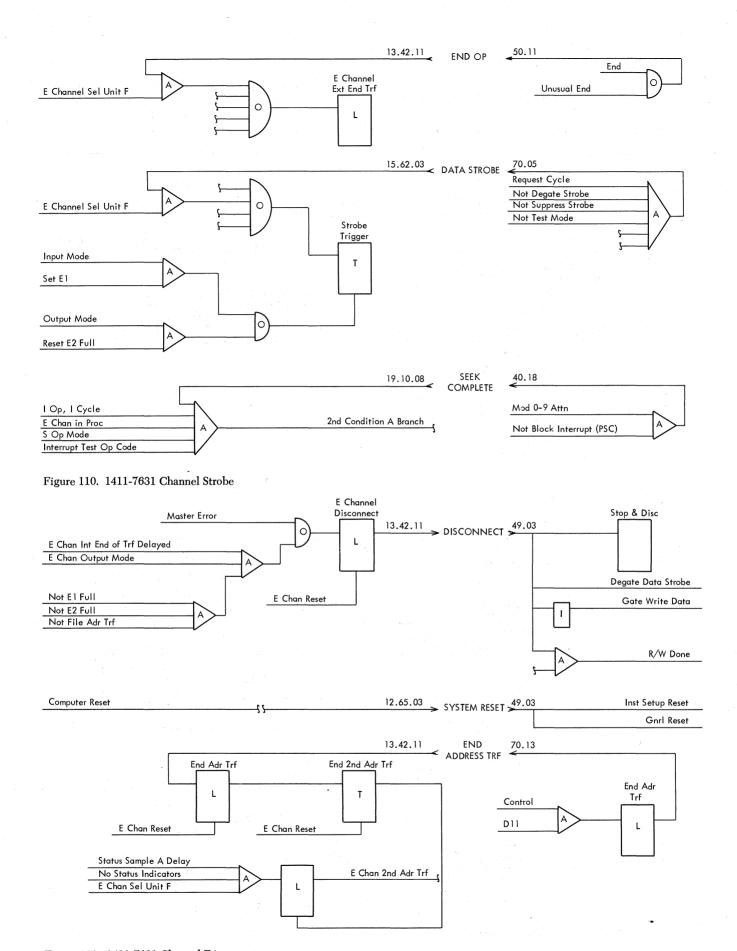

| 37       | Channel Data Check – Condensed Logic                                                    |      | 92         | Status Indicator Chart — 1014 Inquiry Station,                                 |      |

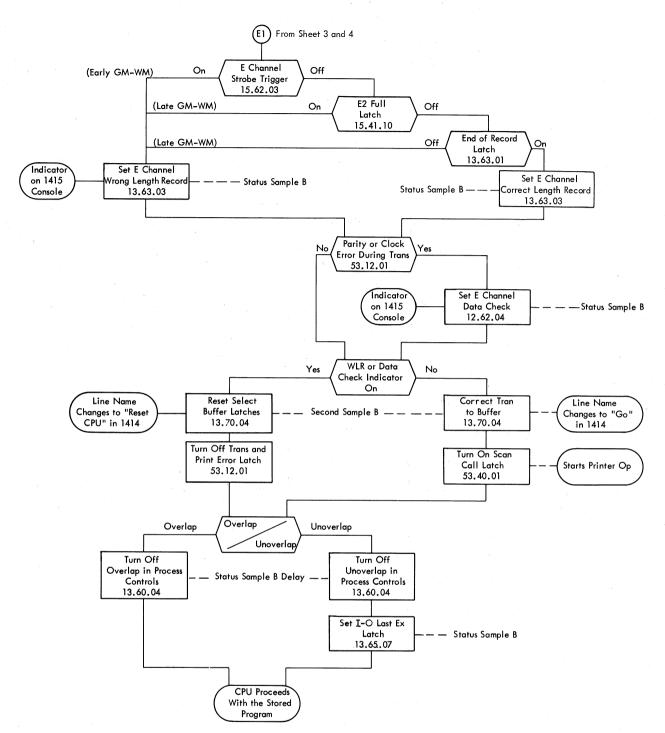

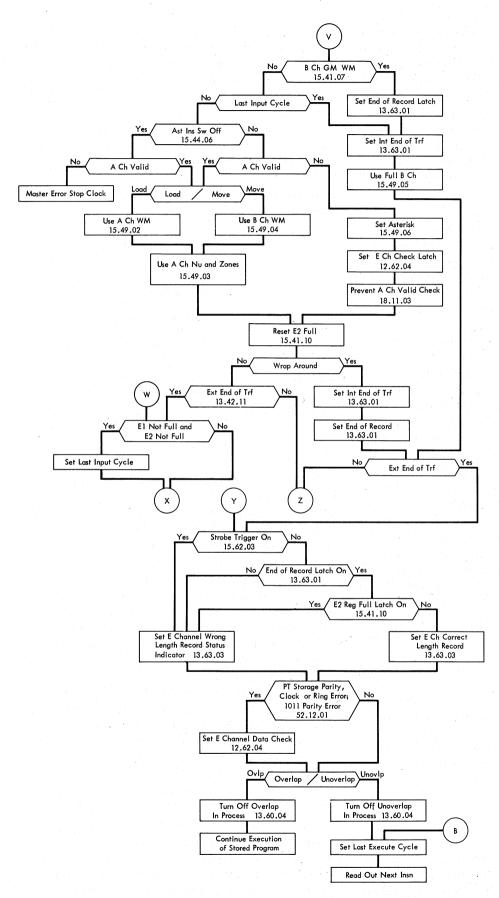

| 38       | Channel Wrong Length Record                                                             | . 45 | 4.5        | 1011 Paper Tape                                                                | 146  |

| 1411-14  | 102 Reader Operation                                                                    |      | 93         | Status Indicator Chart — Telegraph and 1009 DTU                                |      |

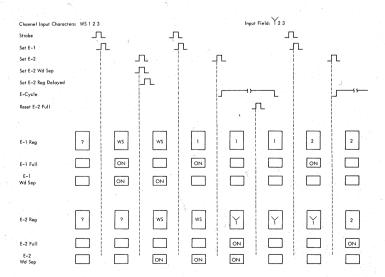

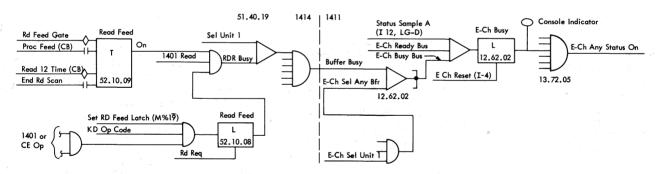

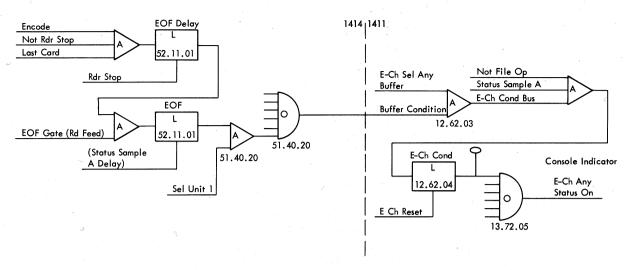

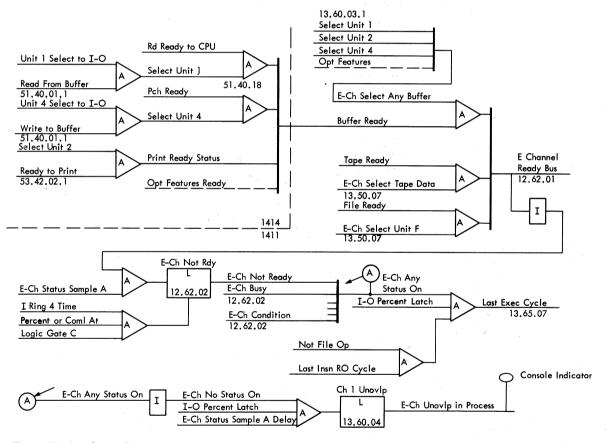

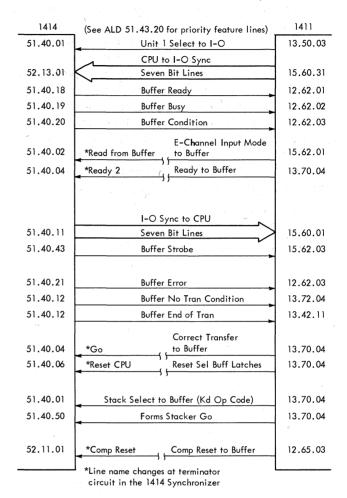

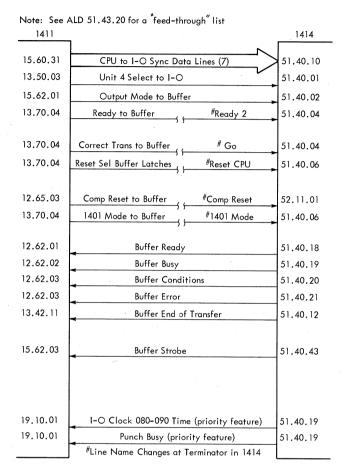

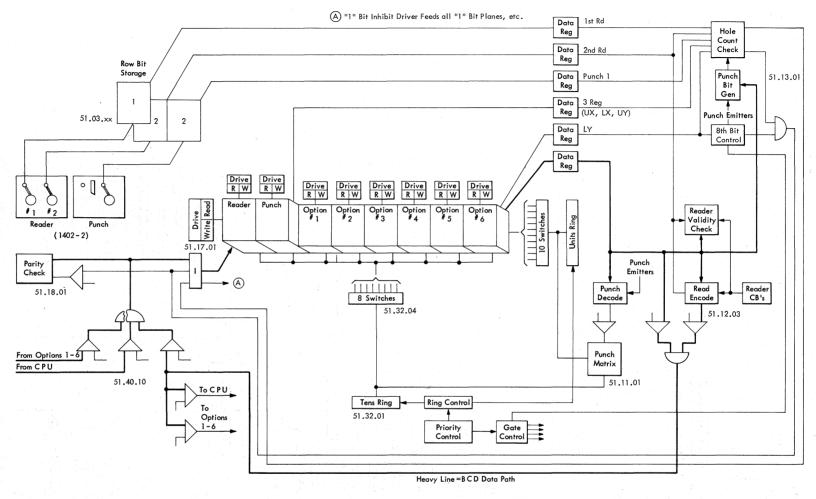

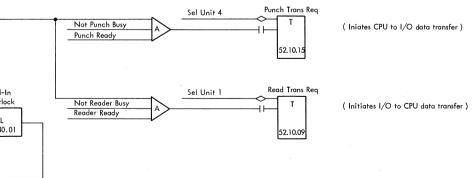

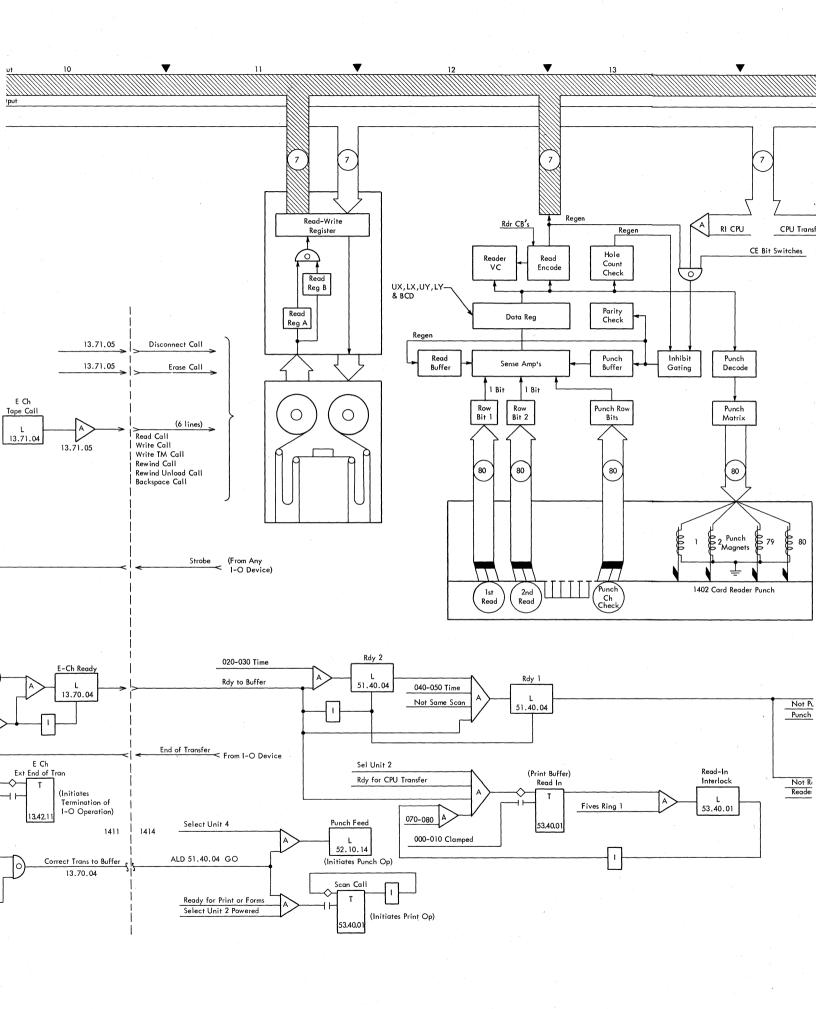

| 39       | Channel Lines – Reader                                                                  | . 48 | 94         | Status Indicator Chart — 1301 Disk Storage                                     |      |

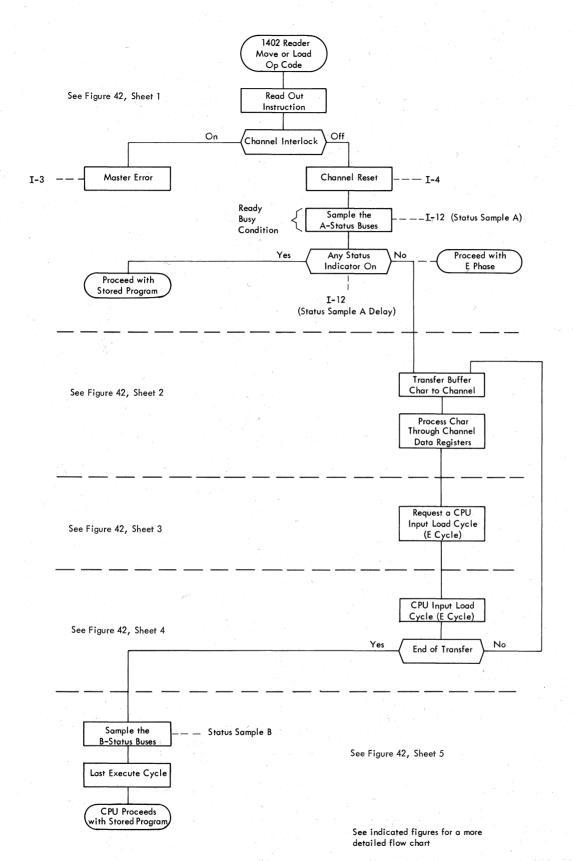

| 40       | 1411-1402 Reader Operation — Basic Logic                                                |      | 95<br>96   | Status Indicator Chart — 1412 MCR<br>Status Indicator Chart — 1419 MCR         |      |

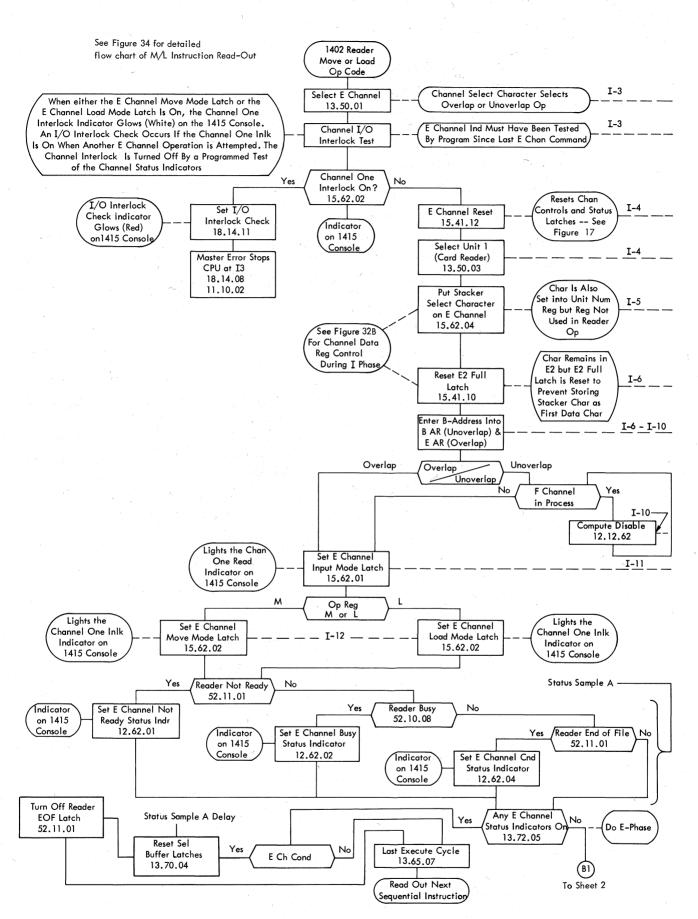

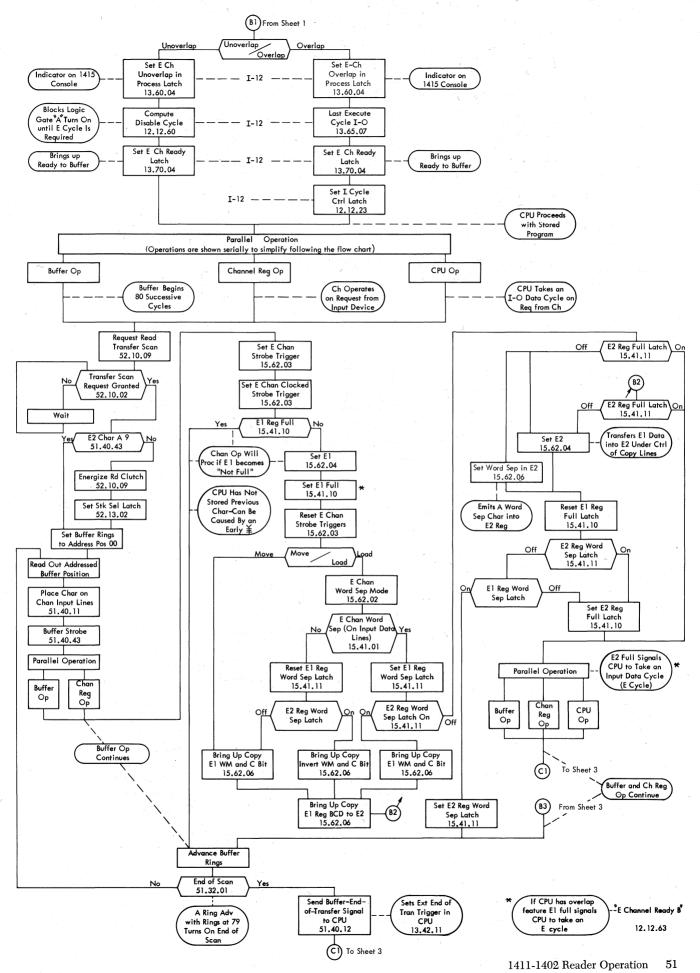

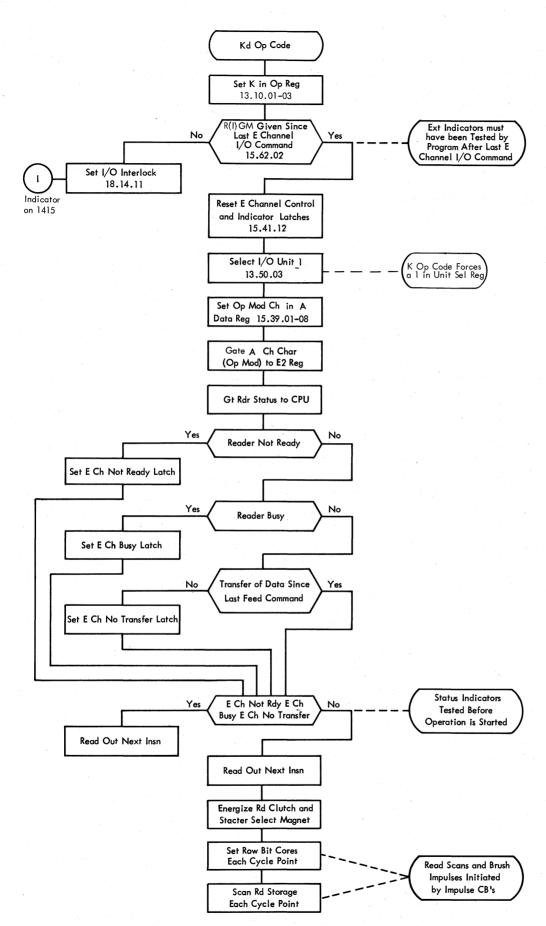

| 41       | 1411-1402 Reader Operation – Logic Flow                                                 |      | 97         | Status Indicator Chart — 1419 MCR.  Status Indicator Chart — 1405 Disk Storage |      |

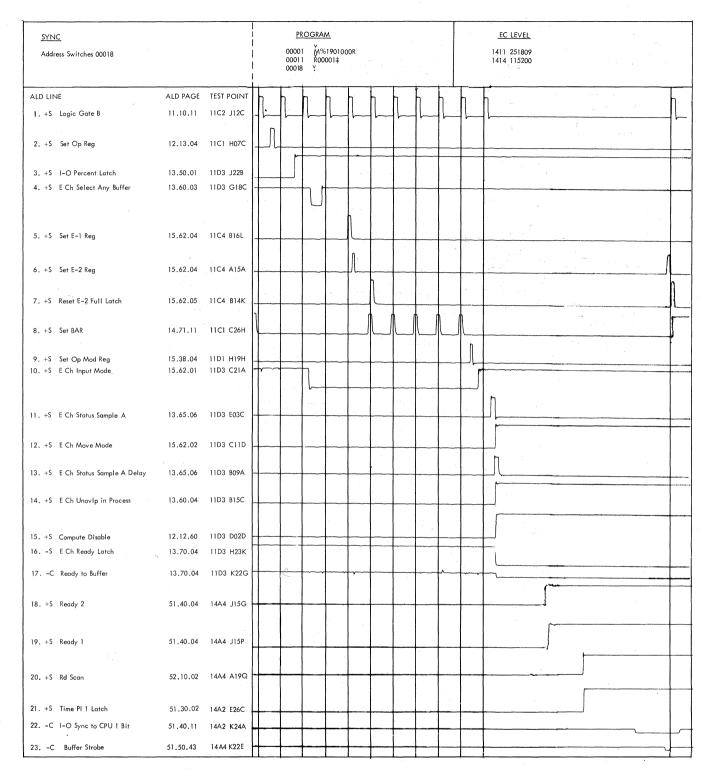

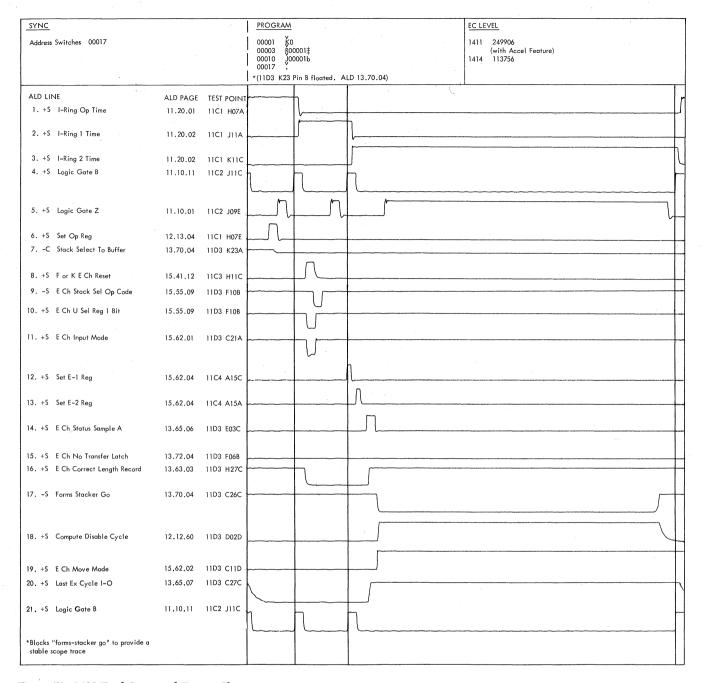

| 42       | 1402 Read Command Timing Chart                                                          |      | 98         | Condensed Logic Symbols                                                        |      |

| 43<br>44 | Channel Register Operation – Reader                                                     |      | 99         | I-O Data Flow Controls                                                         |      |

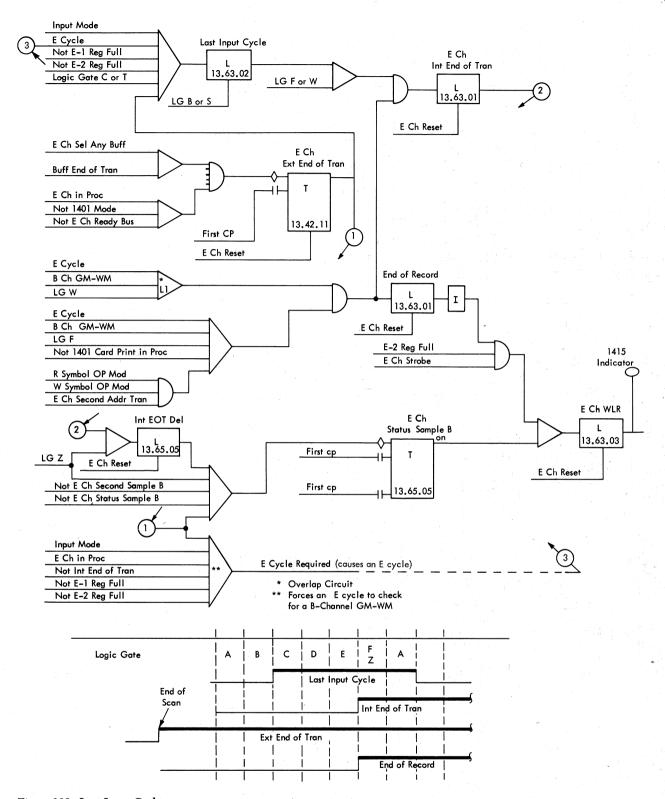

| 45       | Reader No Transfer – Simplified Logic                                                   |      | 100        | Last Input Cycle                                                               |      |

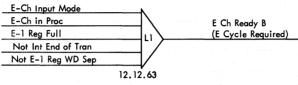

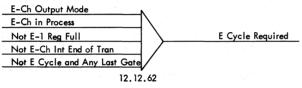

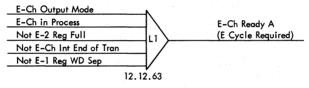

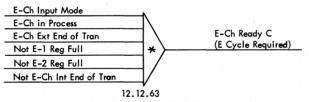

| 46       | Reader No Transfer – Condensed Logic                                                    |      | 101        | E-Channel Status Sample A & B                                                  |      |

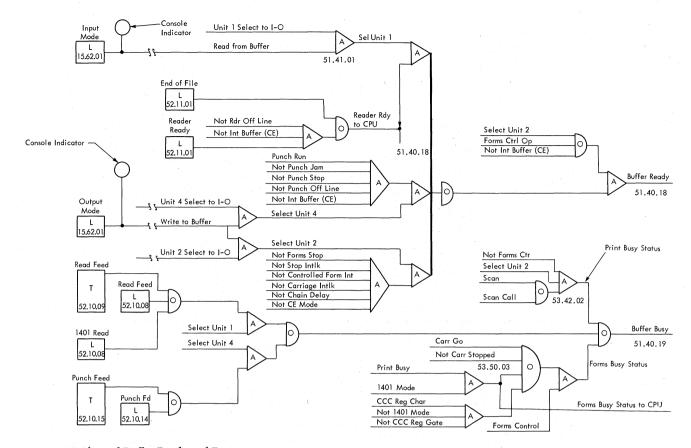

| 47       | Reader Programming — Channel No Transfer                                                |      | 102        | E-Channel Buffer Ready and Busy                                                |      |

|          | Indicator                                                                               | . 62 | 103        | E-Channel Not Ready and Busy                                                   |      |

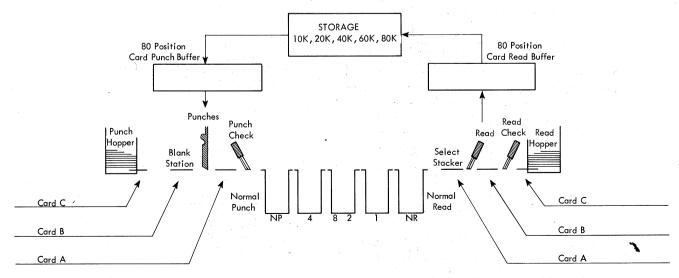

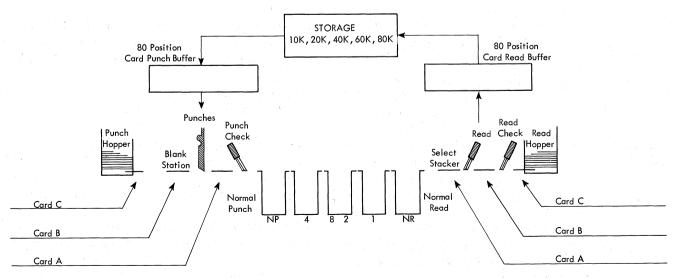

| 48       | 1402 Card Transport                                                                     |      | 104        | E-Channel Check and Condition                                                  |      |

| 49       | 1411-1402 Reader Feed Command Logic Flow                                                |      | 105<br>106 | E-Channel WLR and No Transfer 1411-7631 Channel Status Lines                   |      |

| 50       | 1402 Feed Command Timing Chart                                                          | . 65 | 107        | 1411-7631 Read Control                                                         |      |

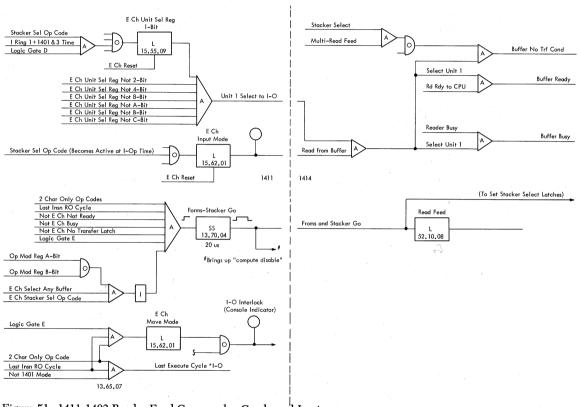

| 51       | 1411-1402 Reader Feed Command – Condensed Logic                                         | . 66 | 108        | 1411-7631 Write Control                                                        |      |

| 1411 1   | _                                                                                       | . 00 | 109        | 1411-7631 Read and Write Busses                                                |      |

|          | 102 Punch Operation                                                                     |      | 110        | 1411-7631 Channel Strobe                                                       |      |

| 52       | Channel Lines – Punch                                                                   |      | 111        | 1411-7631 Channel Disconnect                                                   |      |

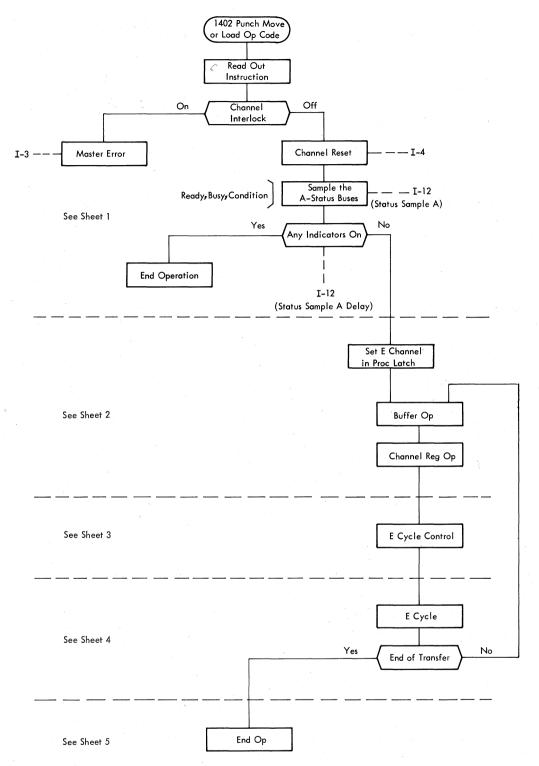

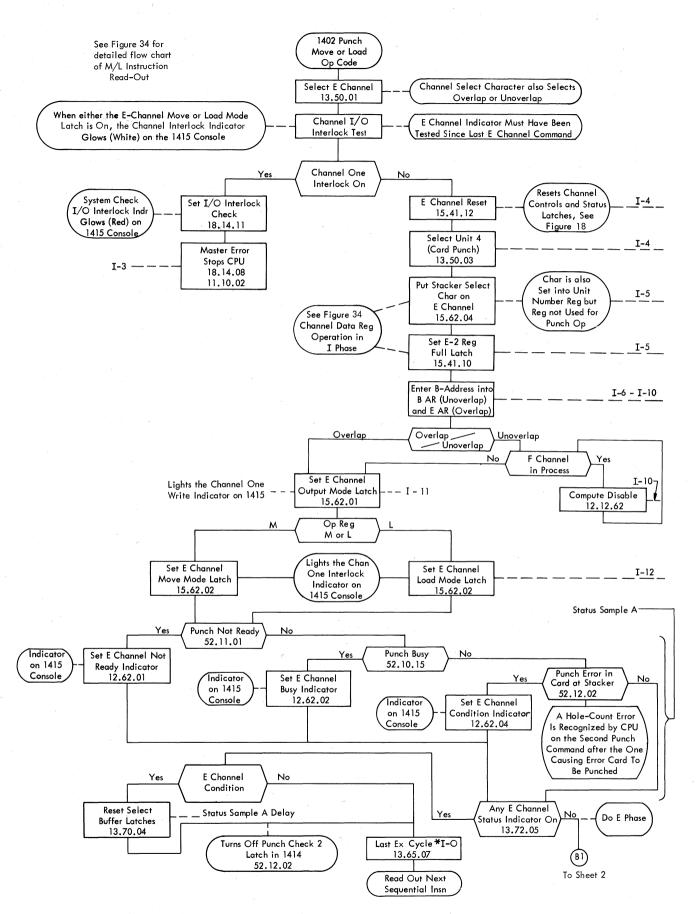

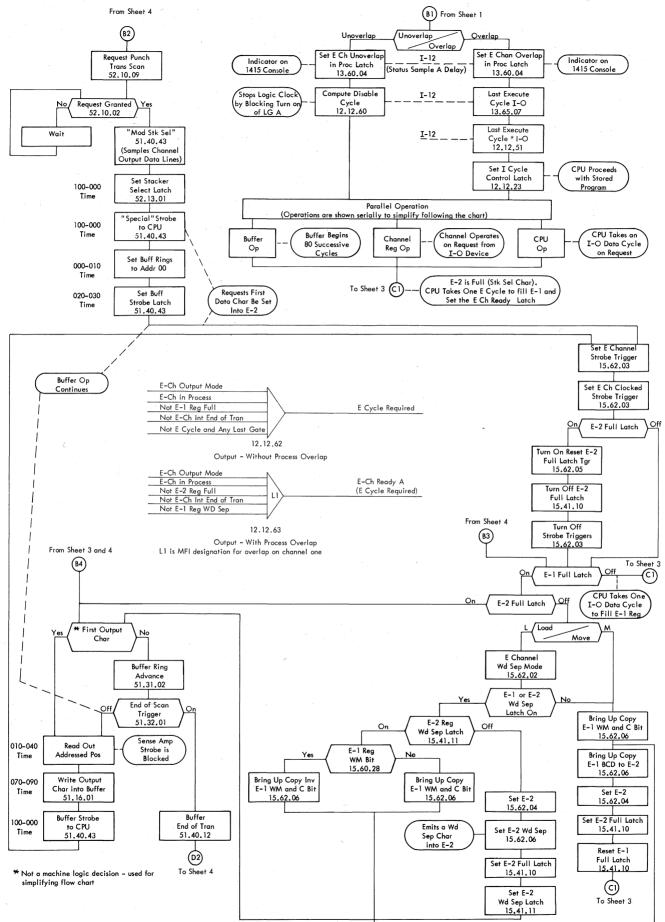

| 53<br>54 | 1411-1402 Punch Operation — Basic Logic Flow.<br>1411-1402 Punch Operation — Logic Flow |      | 112        | 1411-1414 Error Resets                                                         |      |

| 55       | 1402 Punch Command Timing Chart                                                         |      | 113        | E-Channel Strobe                                                               |      |

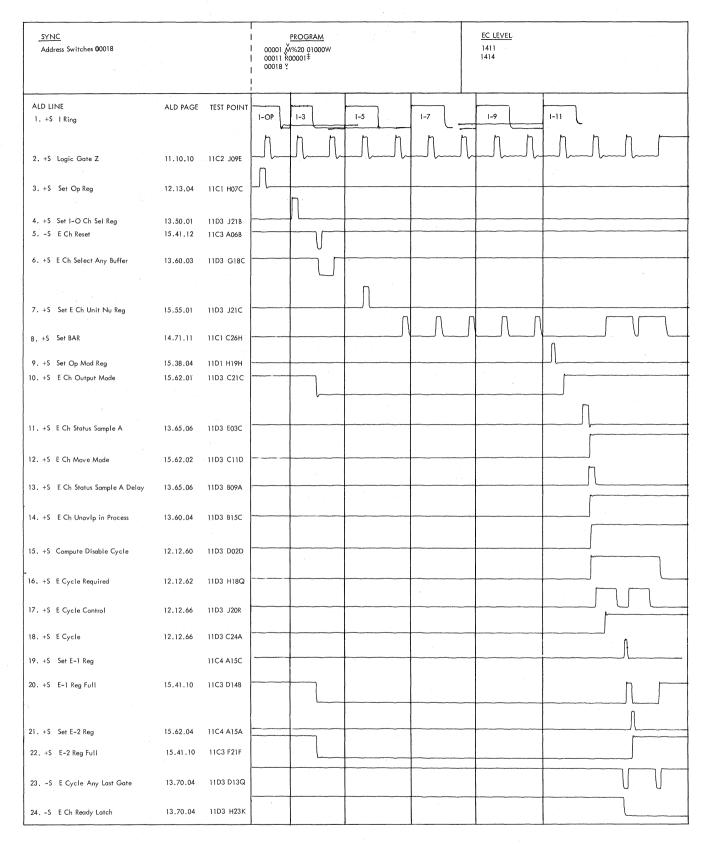

| 56       | Channel Register Operation – Punch                                                      |      | 114        | Channel Register Operation E-Cycle Required                                    | 160  |

| 57       | 1402 Card Transport                                                                     |      | 115<br>116 | E- and F-Cycle Control                                                         |      |

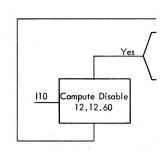

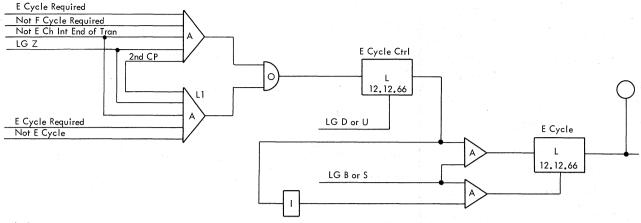

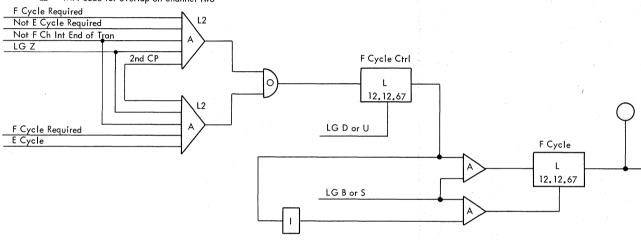

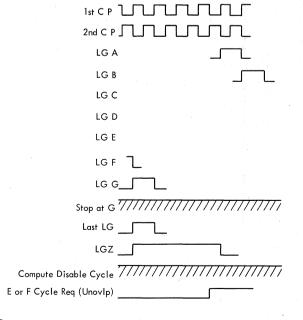

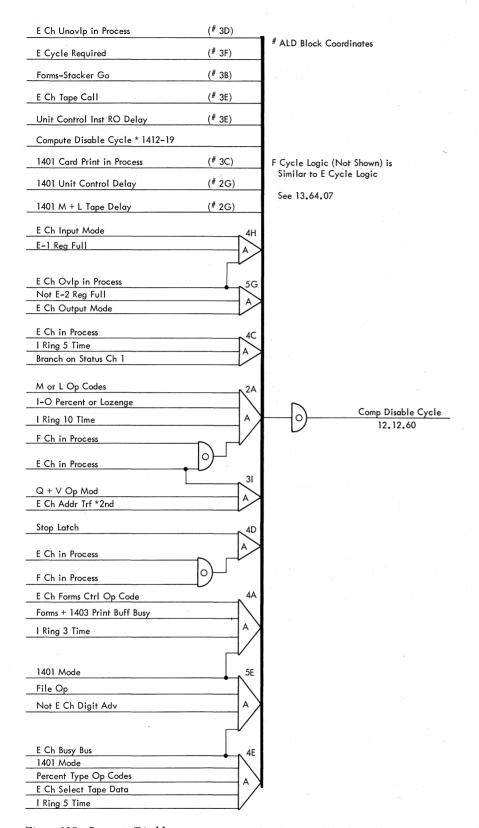

| 1411-14  | 103 Printer Operation                                                                   |      | 117        | Compute Disable Cycle                                                          |      |

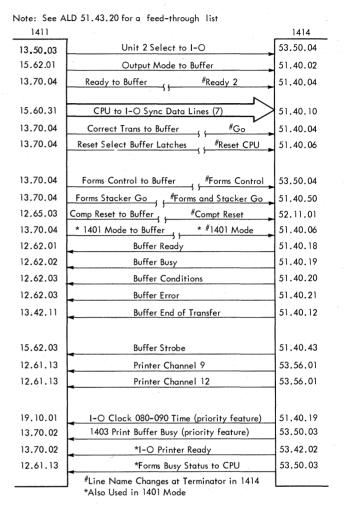

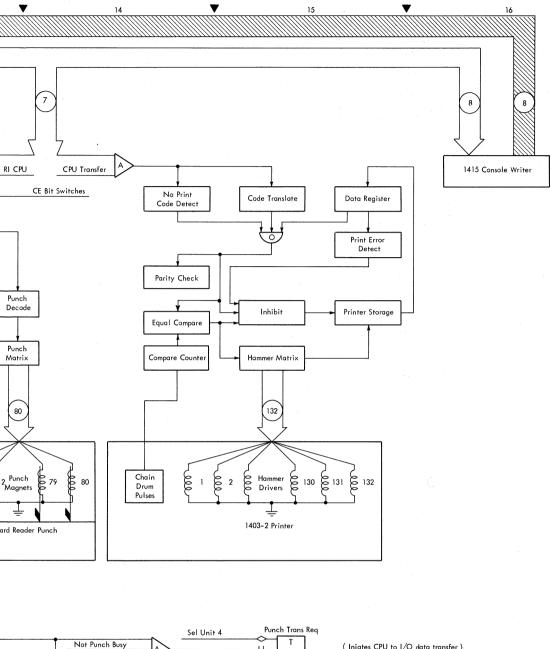

| 58       | Channel Lines – Printer                                                                 | . 81 | 118        | Compute Disable                                                                |      |

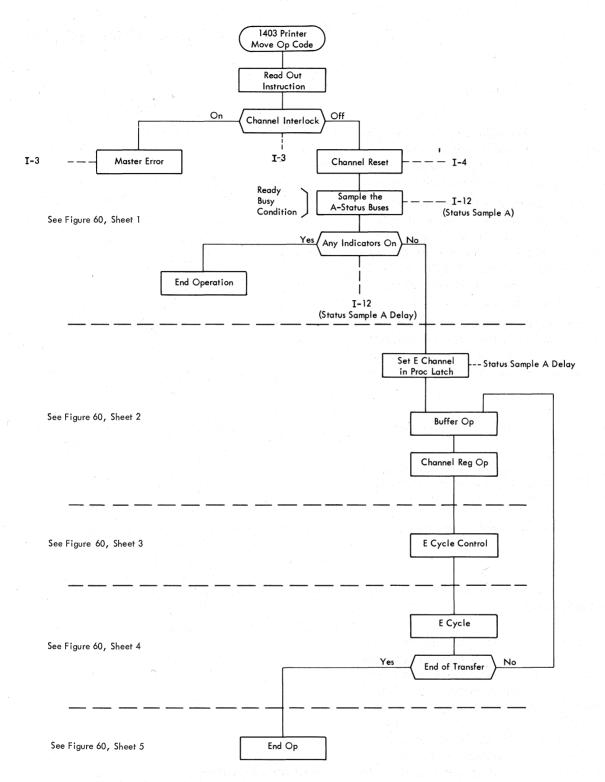

| 59       | 1411-1403 Printer Operation — Basic Logic Flow                                          |      | 119        | Logic Ring Control                                                             |      |

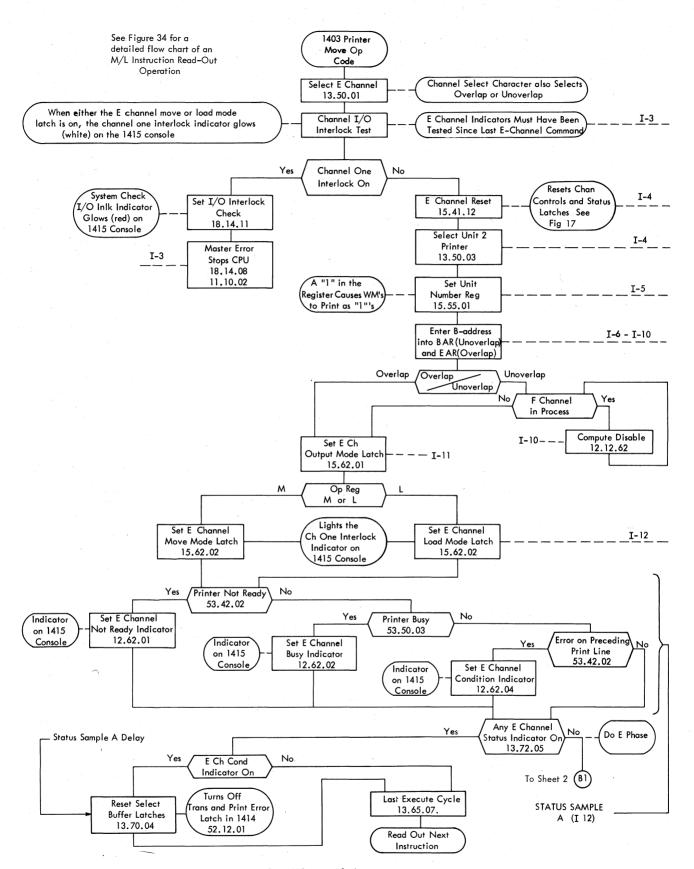

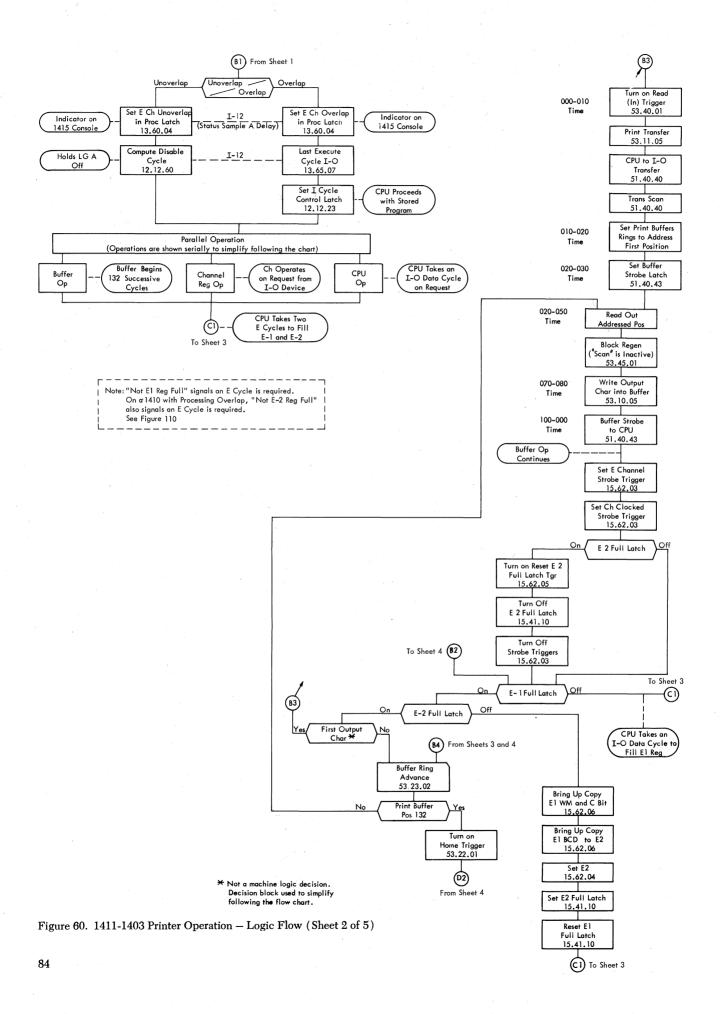

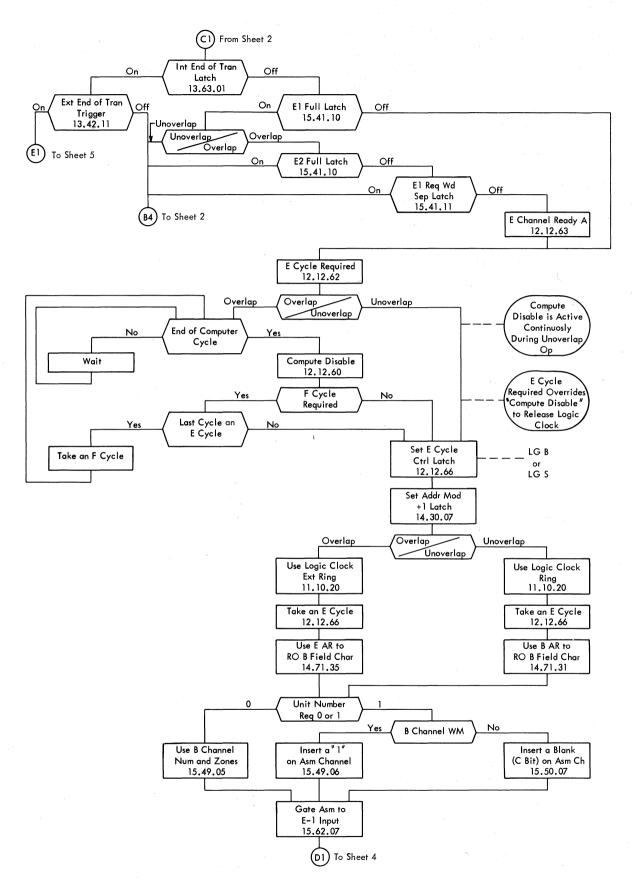

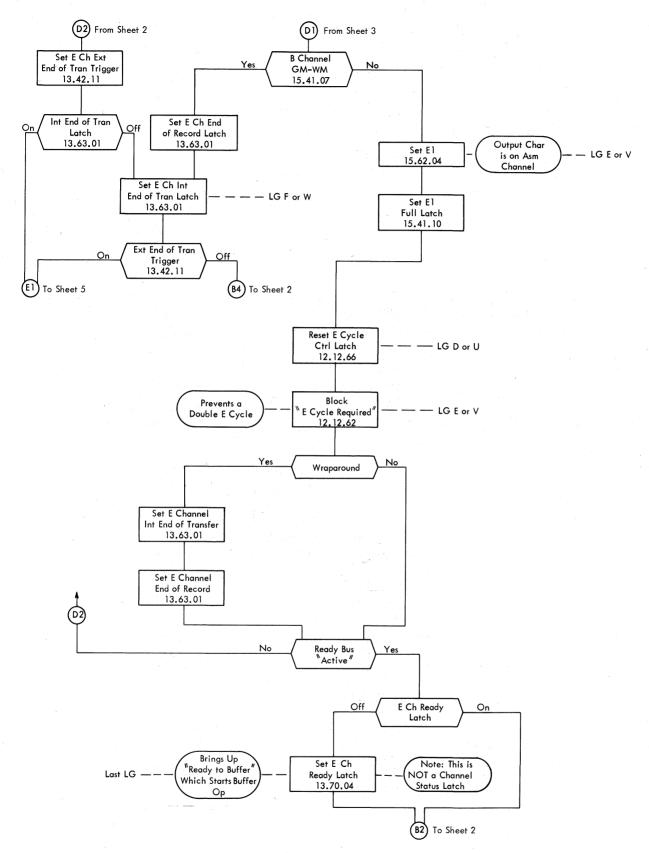

| 60       | 1411-1403 Printer Operation — Logic Flow                                                |      | 120        | I-O Last Execute                                                               |      |

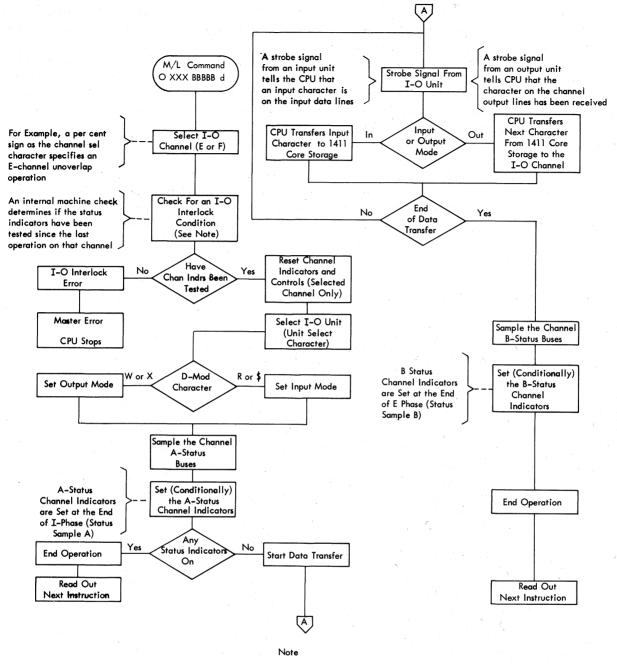

Input-output principles apply to all input-output (1-0) devices of the IBM 1410 Data Processing System. The basic 1-0 move or load command (M/L XXX BBBBB d) is used with all 1-0 devices. Disk storage devices (IBM 1301, IBM 1311, and IBM 1405) operate similarly to other 1-0 devices except that an address transfer operation precedes the transfer of data to the disk unit.

I-O commands control data transfer between an I-O device and the IBM 1411 Processing Unit (CPU). Data transfer from an I-O device to the CPU is called input operation. Data transfer from the CPU to an I-O device is called output operation. Some special I-O commands do not transfer data; instead they control I-O unit functions such as paper feeding (printer) and stacker pocket selection (reader). These document control commands for card I-O units, and unit control commands for tape units, are described in the section for the I-O device using that command.

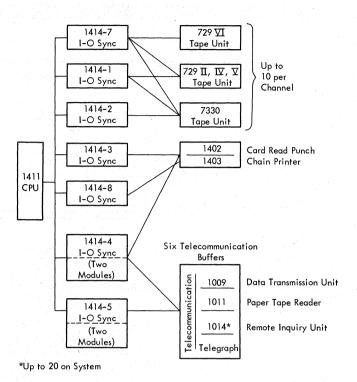

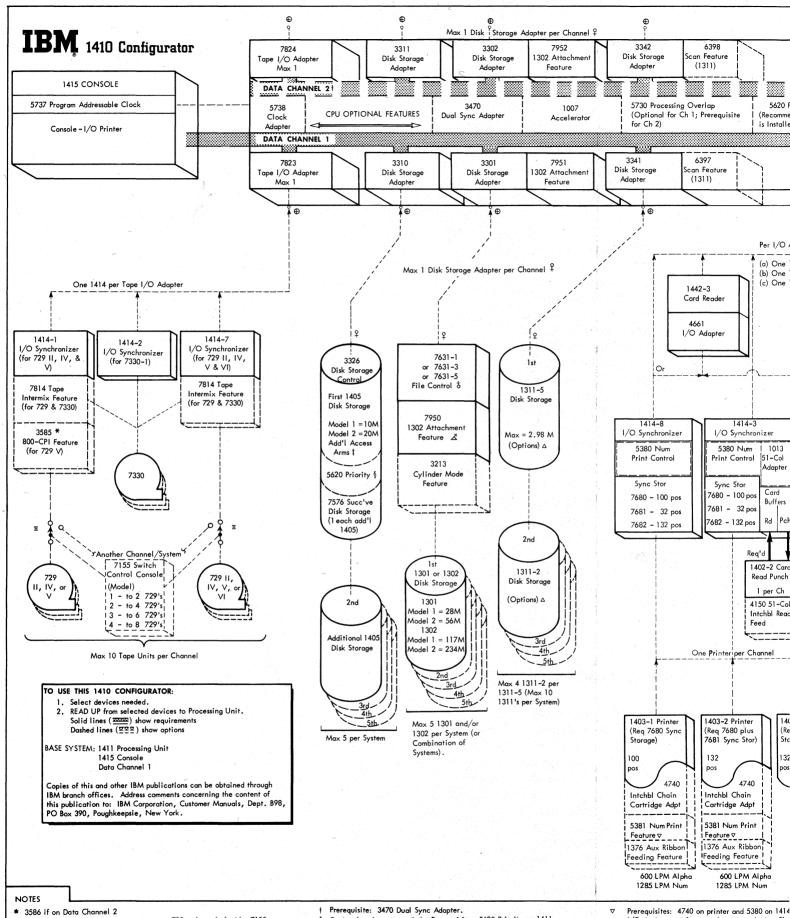

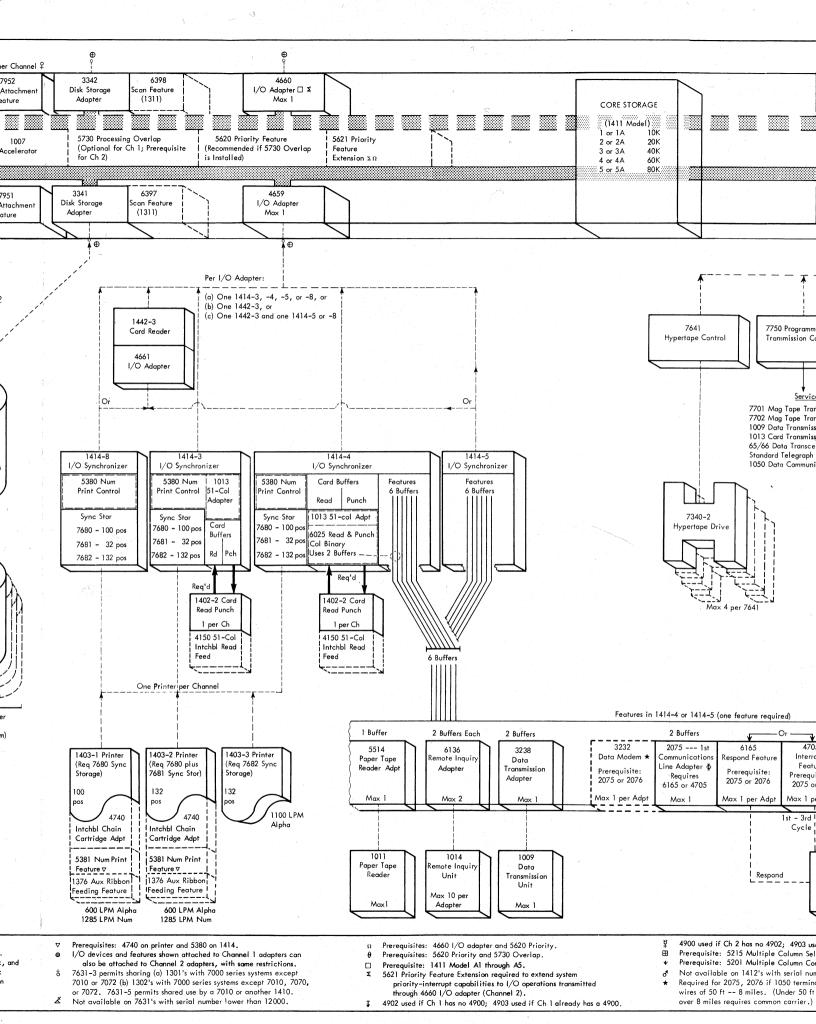

## Input-Output Units

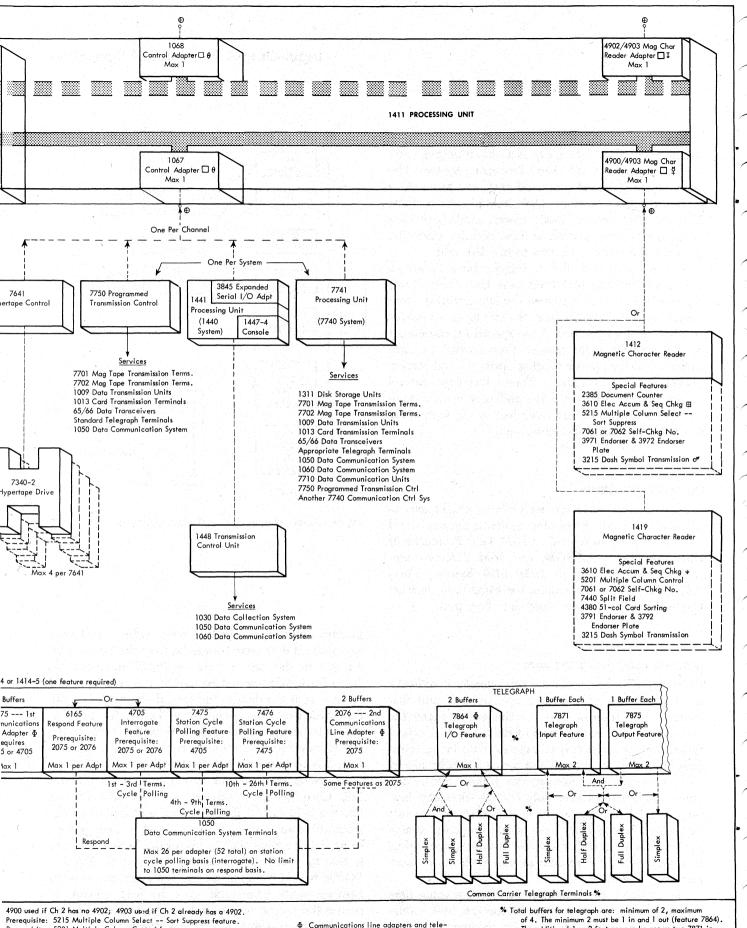

A number of 1-0 units are available as attachments to the 1BM 1410 Data Processing System (Figures 1 and 2). 1-0 units are described in IBM 1410 Principles of Operation, Form A22-0526, and IBM Telecommunications Equipment with IBM 1410 System, Form A22-0525. The 1-0 units share the same basic instruction word and the same basic data flow path.

#### **Input-Output Synchronizers**

Because the I-O units and the CPU operate at different speeds, most I-O units have a synchronizer unit that controls data transfer between the I-O unit and the CPU, and supervises operation of the I-O unit. Synchronizers provide temporary storage for data being transferred between the I-O unit and the CPU. Synchronizers, then, provide buffer storage for input-output data. Some synchronizers have only a single-character buffer, while others, such as the synchronizer for the IBM 1402 Card Read Punch, have 80-position core storage buffers. The term *buffer* as used in this manual refers to a synchronizer core storage unit with 80 or more positions of storage.

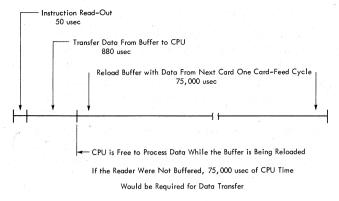

The buffering of 1-0 units reduces CPU waiting time during transfer of data between the CPU and a relatively slow 1-0 unit; for example, compare the data

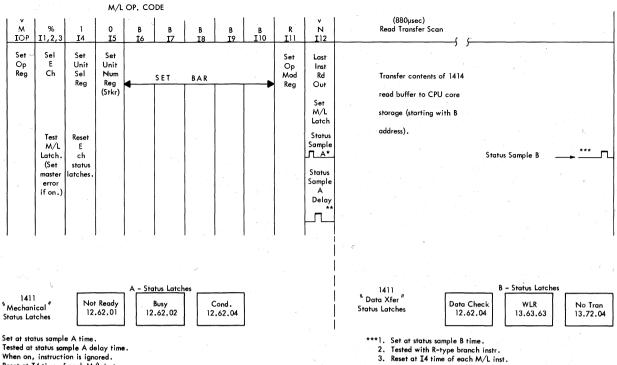

Figure 1. Input-Output Units and Synchronizers

transfer times of unbuffered versus buffered IBM 1402 operation. If data were transferred from the 1402 reader directly to the CPU, a total of 75,000 microseconds (card feed cycle) would be required to read one card and transmit the data to the CPU. If the card data are first loaded into the synchronizer buffer, the time required to transmit 80 characters from the buffer to the CPU is only 880 microseconds because data are transferred at an 11-microsecond rate (Figure 3). The IBM 1410 system employs buffered operation for the IBM 1402 Card Reader Punch and the івм 1403 Printer. For the 1410 to benefit from input unit buffering, the interval between read commands must be long enough to permit the input unit to reload the buffer. The CPU is free to process data during the interval. For the 1410 to benefit from output unit buffering, the interval between write commands must be long enough to permit the output unit to unload the buffer. The CPU is free to process data during the interval.

₹ 7830 Tape Switching Feature read on any 729 to be switched by 7155.

1 1008 for Model 1, 1009 for Model 2. Max of 2 additional access arms per 1405 and 12 access arms per system.

Can mix 1301 and 1302 on same channel. Can mix 1301 and 1302 with 1311 if 1311 on different channel. Cannot mix 1405 with 1301, 1302, or 1311 on system.

Optional and recommended. Prerequisite: 5620 Priority on 1411.

Optional features on 1311-5: 6400 Seek Overlap, 6396 Scan Disk, and 8011 Track Record; on 1311-2: 6400 Seek Overlap only. Seek Overlap on 1311-5 necessitates Seek Overlap on all companion 1311-2's. 6396 Scan Disk on 1311 necessitates 6397 or 6398 Scan Feature on CPU.

I/O devices and features shown attached to Cha also be attached to Channel 2 adapters, with

7631–3 permits sharing (a) 1301's with 7000 se 7010 or 7072 (b) 1302's with 7000 series system or 7072. 7631-5 permits shared use by a 7010

Not available on 7631's with serial number lov

Prerequisite: 5215 Multiple Column Select -- Sort Suppress feature Prerequisite: 5201 Multiple Column Control feature.

Not available on 1412's with serial number lower than 10058. Required for 2075, 2076 if 1050 terminals use customer-provided wires of 50 ft -- 8 miles. (Under 50 ft permits direct interface; over 8 miles requires common carrier.)

Φ Communications line adapters and telegraph features cannot be installed on same 1414 (use the same space). % Total buffers for telegraph are: minimum of 2, maximum of 4. The minimum 2 must be 1 in and 1 out (feature 7864). The additional 1 or 2 features can be one or two 7871 in, one or two 7875 out, or one 7871 in and one 7875 out. Simplex = one way only Half Duplex = two ways, one at a time Full Duplex = two ways simultaneously.

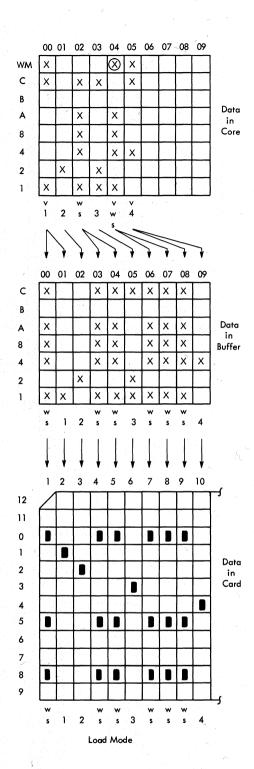

Figure 3. Buffered Reader Operation

#### **Input-Output Channels**

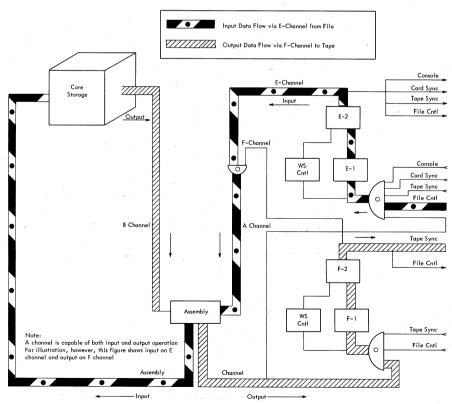

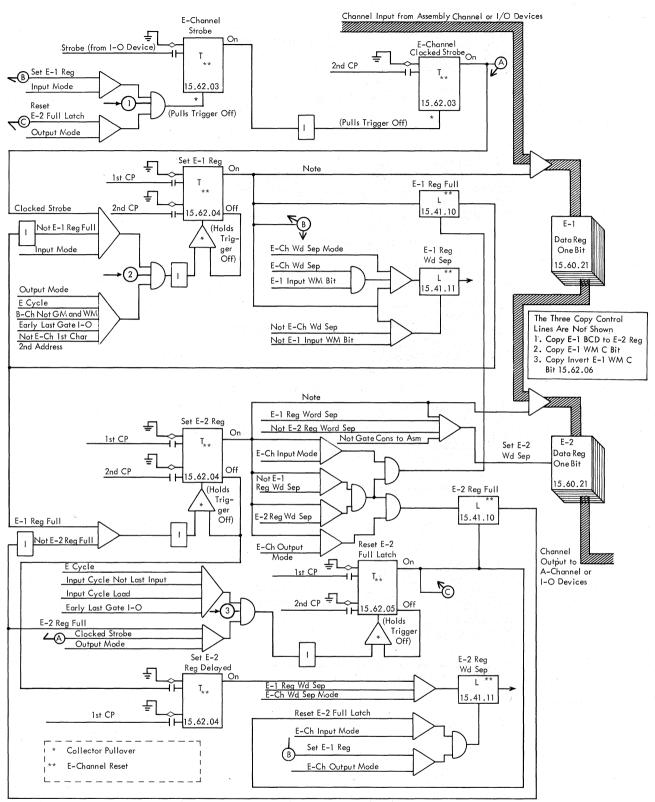

An I-O channel consists of input and output data lines, channel data registers 1 and 2, and control lines between the CPU and the I-O devices. Channel 1 (E-channel) is a standard feature on the IBM 1410. Channel 2 (F-channel) is an optional feature. Each channel has two eight-bit, single character channel data registers that provide buffering for overlap operation, and wmws conversion for data transfer operations with I-O devices that cannot handle word marks. Because the

two channels operate the same, only E-channel operation is described.

#### **Data Flow**

Channels 1 and 2 are capable of input and output operation, but not at the same time. Figure 4 shows input data flow on E-channel and output data flow on F-channel. Note that data transfer on input or output is always from data register 1 into data register 2 thus permitting the same register transfer controls to be used for both input and output operation. The processing overlap feature, described later, permits both channels to operate while the CPU is processing data.

Input: During E-channel input operation, the input data lines carry information from the 1-0 unit to E-channel data register 1 (E-1). Data in E-1 are transferred to E-channel data register 2 (E-2), gated to A-channel, assembly channel, and into the core storage of the IBM 1411. Input data are checked for odd parity on A-channel and the assembly channel; F-channel input operation is similar.

Output: During an F-channel output operation, information is read out of the core storage of the IBM 1411; gated to the B-channel, assembly channel, and into F-1; information appears on the output data lines after an F-1 to F-2 data transfer. Output data are checked for odd parity on B-channel and the assembly channel; E-channel output operation is similar.

Figure 4. I-O Data Flow

#### **Data Transmission**

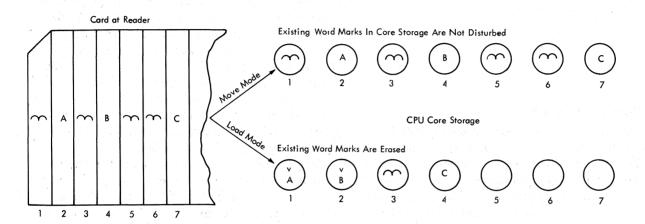

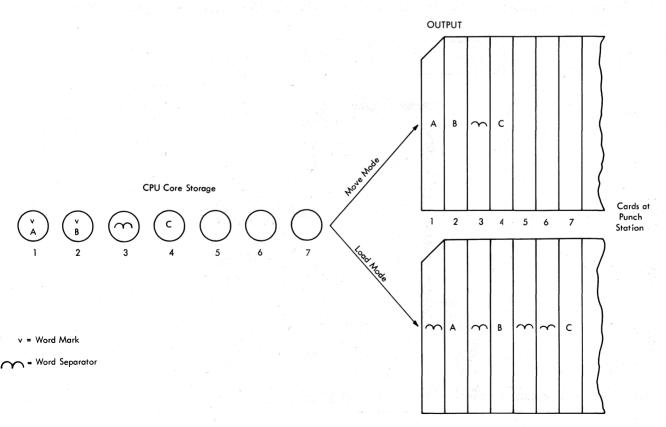

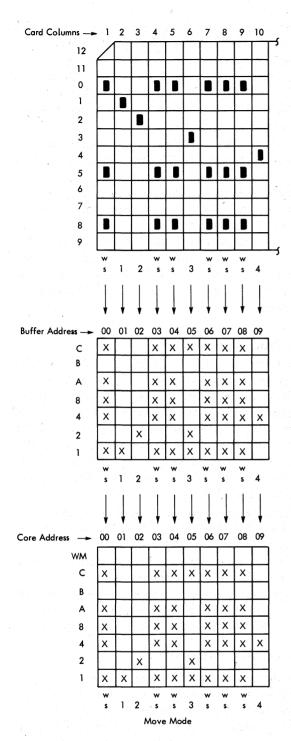

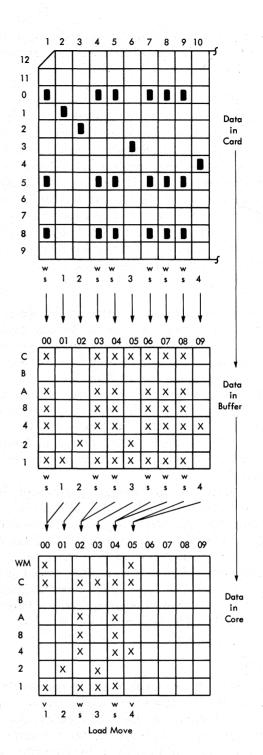

An I-O instruction controlling data transfer must specify one of two modes of transmission: load mode or move mode. Load mode operation processes word marks and word separator characters. Move mode operation ignores word marks; word separator characters are transferred the same as any binary coded decimal (BCD) character (Figure 5).

EIGHT-BIT DEVICES

The core storage of the IBM 1411 is an eight-bit device because it can write a word mark (wm), along with a BCD character, into a single core storage location. A BCD character with a wm is called a wm character. The data registers and data buses of the 1411 also can handle eight-bit characters. The wm bit is included in the character bit count, and odd parity is maintained.

The IBM 1415 Console and the disk storage units (IBM 1301, IBM 1311, and IBM 1405) are eight-bit de-

INPUT

Figure 5. Word Separator Processing

vices and hence can handle word mark characters. All other 1-0 units are seven-bit devices and can handle only seven-bit characters.

#### SEVEN-BIT DEVICES

All I-0 units except the disk storage units are seven-bit devices. They cannot handle word mark characters; for example, the 1402 reader is a seven-bit device because a wm-A (A) that requires only a single core storage location in the 1411 requires two locations (card columns) when represented in the IBM card code. One column contains the card code representation of the word mark called a word separator character (0, 5, 8), and the following column contains the card code representation of the A (12, 1).

#### MOVE MODE

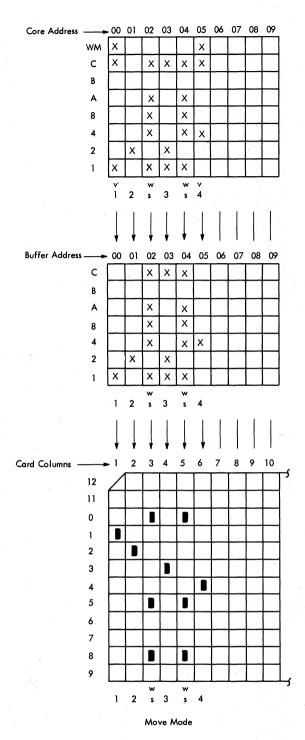

Word marks are ignored in move mode operation. Characters are transferred on a one-for-one basis; a single input character results in a single 1411 core storage character, and a single 1411 core storage character results in a single output character.

Input: During move mode data transmission (Figure 6), punched card information from the 1402 reader is encoded into BCD as it is being read into the 1414 buffer, and the information is transferred, unchanged, to core storage. Existing word marks in core storage are retained.

Output: Only zone and numeric portions of characters are transferred to the buffer of the IBM 1414 Input/Output Synchronizer (Figure 7). The assembly controls invert the C-bit and ignore the word mark of B-channel wm characters, removing the word mark, and maintaining odd parity of characters placed on the assembly channel. Characters on the assembly channel are gated into the channel registers. The BCD information in the 1414 buffer is decoded into IBM card code as it is being punched.

#### LOAD MODE

Word marks are transmitted along with the associated BCD characters. Characters are transferred on a one-for-one basis between the CPU and eight-bit devices. Characters transferred between the CPU and seven-bit devices require special handling if they are wm characters or ws characters. During input operation with a seven-bit device, ws characters are converted to word marks; during output operation, word marks are converted to ws characters. Conversion occurs within the channel data registers. Characters other than ws characters or wm characters are transferred on a one-for-one basis. A description of load mode channel operation for seven-bit 1-0 devices follows.

Input: Word separator characters are converted into word marks, combined with the following character,

and the resultant wm character is transferred to the 1411 core storage (Figure 6). Exception: two consecutive word separator characters result in a single word separator character with no word mark (C, A, 8, 4, 1) being transferred to 1411 core storage. A wm-ws character (WM, A, 8, 4, 1) cannot be read into the CPU from a seven-bit 1-0 device.

Output: wm characters are transmitted to the 1-0 device as two characters. The first character is a ws character representing the word mark; the second character is the BCD portion of the wm character. Exception: one ws character in 1411 core storage results in two ws characters being transferred to the 1-0 device. A word mark over a ws character (Figure 7 — note circled wm) has no effect on the output character. A ws character, with or without a word mark, results in two word separator characters being transferred to the 1-0 device.

#### **Channel Data Registers**

The 1411 has two eight-bit, single-character channel data registers for each channel; E-1 and E-2 registers for E-channel and F-1 and F-2 registers for F-channel. The registers provide two-character buffering (necessary for overlap operation), wm-ws conversion for seven-bit 1-0 units, and parity correction during wm-ws conversion. Parity inversion for even parity tape operation is made on the data lines entering and leaving the channel data registers.

Because operation on both channels is the same, only E-1 and E-2 functions are described here. During input operation the CPU tries to keep E-1 and E-2 empty, and during output to keep E-1 and E-2 full. The channel data registers are never reset; a set pulse enters a character into the register, replacing the existing character. Actual circuit operation is described in the Channel Data Register Controls section.

#### MOVE MODE CHARACTER PROCESSING

All E-channel data, input or output, is first set into E-1, is transferred to E-2, and appears on the channel data lines. The data are then available to A-channel (input) or to the 1-0 devices (output). Load mode operation with eight-bit 1-0 devices and any move mode operation employ a simple E-1 to E-2 data transfer operation (Figure 8) controlled by two lines:

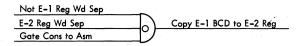

Copy E-1 BCD to E-2

Copy E-1 wм and C-bit

The copy lines determine what information is transferred when the set pulse occurs. Set pulses are generated from the CPU clock, which runs continuously unless the CPU is in stop status. The CPU logic ring, however, runs only when a CPU I-O data cycle is required (unoverlapped operation).

Figure 6. Data Transmission - Input

#### LOAD MODE CHARACTER PROCESSING

Load mode operation with a seven-bit 1-0 device causes the channel data registers to operate in word separator mode.

Two additional control lines are used in word separator mode:

Set E-2 word separator (sets a ws character into E-2) Copy invert E-1 wm and C-bit

*Input:* One of three cases exists during input load mode:

- 1. E-1 character is not a ws character.

- 2. E-1 character is a ws character followed by a different character.

- 3. E-1 character is a ws character followed by another ws character.

Figure 7. Data Transmission - Output

#### Case 1-

Characters are copied the same as in move mode. Case 2 —

- a. A ws in E-1 sets a ws into E-2 (the ws in E-2 serves no purpose during input operation).

- b. The BCD portion of the following character is copied from E-1 into E-2.

c. The E-1 wm and C-bit lines (no wm is present) are inverted and copied into E-2, producing an odd parity wm character in E-2 that is transferred to 1411 core storage. Note that steps b and c replace the ws character in E-2 before the contents of E-2 are transferred to 1411 core storage.

Figure 8. Channel Data Registers

Figure 10. Channel Status Indicators

#### Case 3 –

- a. A ws in E-1 sets a ws into E-2 (the ws in E-2 serves no purpose during input operation).

- b. The BCD portion of the following character is copied from E-1 into E-2.

- c. The E-1 wm and C bit (no wm present) are copied into E-2, producing an odd parity character that is transferred to 1411 core storage. Note that steps b and c replaced the first ws character in E-2 with the second ws character before the contents of E-2 were transferred to 1411 core storage. (two ws characters were combined into one).

Output: One of four cases exists during output:

- 1. E-1 character is not a ws or wm character.

- 2. E-1 character is a wm character.

- 3. E-1 character is a ws character.

- 4. E-1 character is a wm-ws character.

#### Case 1-

Characters are copied as in move mode.

#### Case 2-

- a. A wm in E-1 sets a ws into E-2. No further register operation occurs until the ws is received by the output unit.

- b. The BCD portion of the WM character is copied from E-1 to E-2.

- c. The wm and C-bit lines are inverted and copied from E-1 into E-2, removing the wm and maintaining odd parity.

#### Case 3-

- a. A ws in E-1 sets a ws into E-2. No further register operation occurs until the ws is received by the output unit.

- b. The BCD portion of the ws character is copied from E-1 into E-2.

- c. The wm and C-bit (no wm present) are copied from E-1 into E-2, producing another ws character in E-2 from the single ws character in E-1.

#### Case 4-

A wm-ws character in E-1 is processed the same way as a ws character except the wm and C-bit lines are inverted when copied from E-1 into E-2, removing the wm and maintaining odd parity.

#### **Channel Status Indicators**

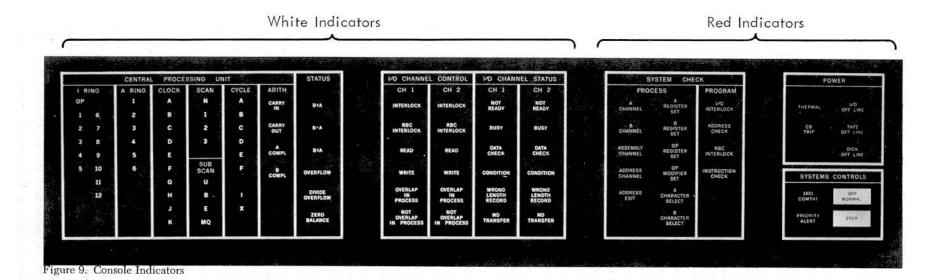

Each I-O channel has six status indicators (latches), with console indicating lamps, that reveal information about the previous operation on that channel (Figures 9 and 10). The six indicators can be interrogated at any time by the program. All I-O units on a channel are served by the same six channel status indicators, although some units, such as the IBM 1403 Printer, do not use all six indicators. Because operation is the

same for both channels, only E-channel status indicator operation is described.

The basic 1-0 command provides three distinct functions:

#### 1. Selecting

- a. Selects 1-0 channel

- b. Selects 1-0 unit

- c. Selects mode of transmission (move or load)

- d. Selects input or output

- e. Selects overlap or unoverlap

#### 2. Sensing

- a. Senses status of 1-0 devices

- b. Senses status (or validity) of data transfers

#### 3. Executing

An I-O unit is selected and sensed (its status is sampled; if the I-O unit indicates proper status, CPU executes the I-O command.

When an I-O unit is sensed, channel status indicators are set to "remember" the status of the selected unit.

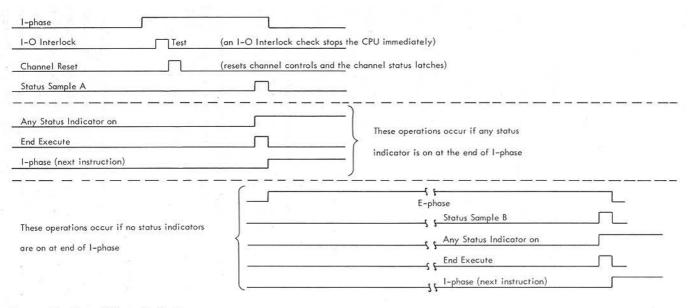

Early in the I-phase of an I-O operation, the six status latches are reset. Twice during an I-O operation, the latches are set by sampling selected conditions; they retain this information until another I-O operation occurs on that channel. The conditions selected for sampling are determined by the type of I-O unit selected and by the direction of data flow (input or output). Because of this selective method of setting the status latches, only a general description of status latch operation can be given here. For specific information on conditions that set the status latches, refer to the status indicator charts and the condensed logic in the reference section of this manual.

The status latches must be interrogated by the program between 1-0 operations because their information is lost when the latches reset during the next 1-0 operation. A failure of the program to interrogate the status latches is detected by an automatic test within the CPU, resulting in a system check that causes a master error to stop the CPU with the 1-0 interlock indicator glowing in the system check section of the IBM 1415 Console (Figure 9). Examples of 1-0 programming sequences are given in a following section which describes the 1-0 interlock check.

Status latches are set at only two times during an I-O operation, either at the end of I-phase or at the end of E-phase. A-status indicators are set at the end of I-phase (status sample A); B-status indicators are set at the end of E-phase (status sample B). These indicators are set conditionally; that is, only when the selected conditions are present at status sample time. Figure 10 shows the six channel status indicators grouped in their most common arrangement. Note that the condition indicator and the no transfer indicator may be either A-status or B-status indicators, depend-

ing on the 1-0 operation. The selected conditions represented by the condition and the no transfer indicators vary according to the type of 1-0 unit selected and according to the direction of data flow, input or output. In the following description, the condition and no transfer indicator functions are briefly described for the 1402 reader operation. The four remaining status latches: not ready, busy, data check, and wrong length record, represent much the same conditions for all 1-0 operations.

#### A-STATUS INDICATORS (I-PHASE INDICATORS)

A-status latches are set at status sample A time (end of I-phase), and they indicate the status of the selected unit, in contrast to the B-status latches which indicate the status of the data transfer operation. If any status latch is on at the end of I-phase, the operation is ended (no E-phase) and the program proceeds to the next sequential instruction (Figure 10).

Not Ready: The ready line from the selected 1-0 device is gated to the channel ready bus. If the ready line is active, the ready bus becomes active, blocking the set of the channel not ready status latched.

Busy: The busy line from the selected 1-0 device is gated to the channel busy bus. With both the busy bus and the ready bus active, status sample A turns on the channel busy status latch.

Condition: The condition status latch is an A-status indicator for all channel operations that transfer data between the CPU and the IBM 1414, Models 3, 4, 5, and 8. In 1402 reader operation, for example, reader end-of-file status is gated to the channel condition bus. With the condition bus and the ready bus both active, the condition status latch is turned on at status sample A time.

#### **B-STATUS INDICATORS (E-PHASE INDICATORS)**

B-status latches are set at status sample B time (end of E-phase), and they indicate the status of the data transfer operation. In contrast to the A-status indicators, they have no effect on subsequent CPU operation except through a programmed branch as a result of interrogating the status indicators.

Data Check: A data error, and in some cases a control circuit error, from an I-O device is gated to the channel check bus, gating the set of the channel check status latch at status sample B time. During input operation, a parity error character on the A-channel sets the check status latch immediately because the error condition is gone when the check bus is sampled at status sample B time.

An asterisk insert switch on the 1415 ce panel is available to the operator or Customer Engineer for use in handling parity error input characters during input

operation. With the asterisk insert switch off, a parity error input character detected on the A-channel causes a master error which stops the CPU. With the asterisk insert switch on, a parity error input character detected on the A-channel causes an asterisk to be stored in place of the error character. Master error is blocked and the operation continues. The channel check status latch is *always* turned on by a parity error input character on the A-channel, regardless of the setting of the asterisk insert switch.

Parity error characters can be read into core storage by switching asterisk insert switch to off, switching the print out control switch to INHIBIT, and turning the check control switch to RESTART.

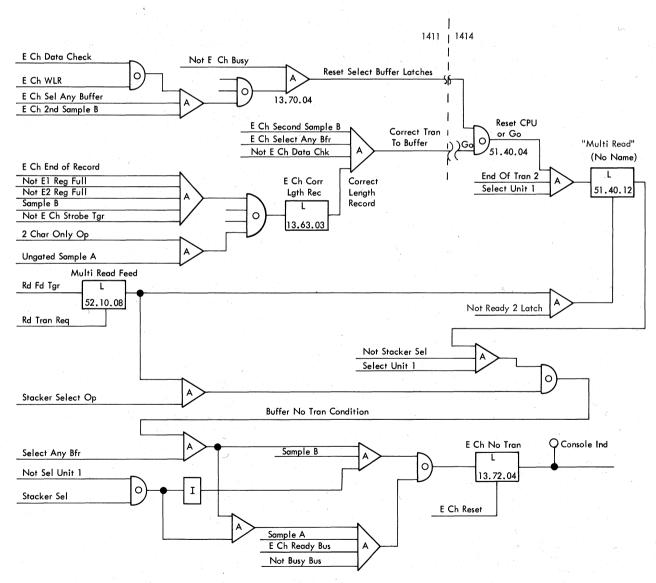

Wrong Length Record: Input and output field lengths in 1411 core storage are controlled by a GM-WM character in the 1411 core storage location following the last position of the field. The GM-WM is placed in the input or output field by programming or by the console operator. When the GM-WM is sensed during input or output operation, an internal end of transfer condition occurs which terminates transfer of data between 1411 core storage and the channel data registers. If no GM-WM is placed in an input or output field, a wrong length record indication occurs during 1-0 operations using those fields.

The wrong length record (WLR) status latch operates as follows:

- 1. Input operation: The number of input characters must correspond to the number of positions in the input field or the WLR status latch will be turned on at status sample B time. No more characters are transferred from the channel data registers to 1411 core storage after the internal end of transfer condition occurs.

- 2. Output operation with fixed-length record 1-0 devices: The number of characters in the output field must correspond to the record length specified for the selected 1-0 device, or the wlr status latch is turned on at status sample B time. When a wlr indicator is turned on during output operation with a buffered 1-0 unit, the output unit will not write the record; for example, if a 79 character record is transferred to the punch buffer in the 1414 1-0 Synchronizer, no punch or card feeding operation occurs in the 1402 punch.

- 3. Output operation with variable-length record 1-0 devices: The GM-WM in the output field terminates data transfer. The WLR status latch is not set (not used).

When load mode operation is performed with a seven-bit I-o device, wm-ws character conversion must be considered in computing record length; for example, 80 word separator characters placed on the channel input data lines result in only 40 input characters (ws characters) being stored in the input field

in the 1411 core storage. Conversely, the 40 characters in the 1411 core storage result in 80 output characters (ws characters) on the channel output data lines during output operation.

Record length is also controlled by the d-character of the 1-0 instruction, which may have any one of four d-characters:

R (read): Accepts input characters until an input field GM-WM is sensed, the end of storage is sensed, or the input unit signals end of transfer.

*\$ (read):* Accepts input characters until the end of storage is reached.

W (write): Transfers characters to the channel until an output field cM-WM is sensed, the end of storage is sensed, or the output unit signals an end of transfer.

X (write): Transfers characters to output unit until end of storage is sensed or the output unit signals an end of transfer.

The X and \$ d-characters are used primarily for memory dump routines in tape operations.

I-O record lengths are checked by a correct length record latch as well as the wrong length record latch, providing a double check; for example, to branch on a branch on wrong length record instruction requires the WLR latch to be on and the CLR latch off.

I-O commands are terminated at the end of I-phase if any status latches are on, including the correct length record latch. Special I-O commands for the tape unit control (U op codes) involving no data transfer (no E-phase) force on the correct length record latch to terminate the operation.

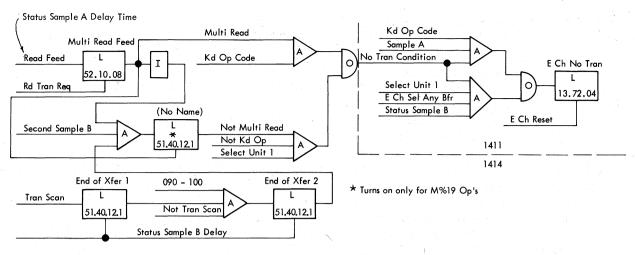

No Transfer: The selected condition represented by the no transfer status latch varies with the 1-0 operation. The following example briefly describes the function of the no transfer indicator as used with the 1402 reader; three instructions are available:

| Read a card     | M%10 | Transfers contents of buffer to |

|-----------------|------|---------------------------------|

|                 |      | CPU and causes next card        |

|                 |      | to be read into the buffer.     |

| Read the buffer | M%19 | Transfers contents of buffer to |

|                 |      | CPU. No card feed cycle.        |

| Feed a card     | Kd   | Causes a card to be read into   |

|                 |      | the buffer. No buffer to        |

|                 |      | CPU data transfer.              |

Multiple buffer transfer operations or multiple feed a card instructions result in a no transfer indication. The usual programming sequence is: feed a card, read the buffer, feed a card, read the buffer, and so on. (Refer to the appropriate section of the manual for operation of the no transfer latch during a particular op code.)

#### CHANNEL I-O INTERLOCK

The stored program must interrogate the channel status indicators between successive operations on the same channel or a system program check (1-0 interlock)

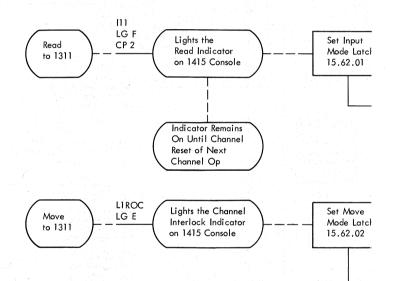

occurs and the system stops. At the end of I-phase of a channel 1 I-O operation, the op code (M or L) conditions the turn-on of either the E-channel move latch or the E-channel load latch. Either latch being on will light the channel 1 interlock indicator in the I-O channel control section of the IBM 1415 console indicator panel (Figure 9). If the channel 1 interlock indicator is still on when channel 1 is again selected for an I-O operation, the system stops with the systems check I-O interlock indicator on. Special I-O commands (op codes F, K, and U) also turn on the channel interlock and require a programmed test of the channel status indicators the same as M and L op codes.

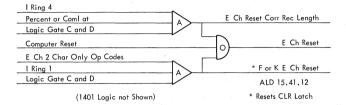

The interlock (move or load latch) for channel 1 is turned off as follows:

1. The stored program encounters a branch on any channel 1 status indicator instruction (R IIIIId). The interlock is turned off regardless of whether or not a branch occurs.

Note: The branch on channel 1 status indicator instruction is also referred to as a branch on external indicator instruction.

Mnemonic BEX 1 (Channel 1) BEX 2 (Channel 2)

- 2. The stored program encounters a branch on selected channel 1 indicator instruction and a branch occurs.

- 3. E-channel reset line active (an E-channel reset occurs during I-phase of a channel 1 I-0 instruction if the I-0 interlock test is satisfied).

- 4. Computer reset line active (a computer reset forces an E-channel reset).

Channel 1 status indicators are tested with an R-type op code. The d-character in the instruction format selects the indicator to be tested. The format for the branch if channel status indicator on is:

| OP CODE       | I-ADDRESS      | $_{ m d\text{-ch}}$ | ARACTER     |

|---------------|----------------|---------------------|-------------|

| R (channel 1) | XXXXX          | (see follo          | wing table) |

| X (channel 2) | XXXXX          | (see follo          | wing table) |

|               |                |                     | 5 - 18      |

|               |                |                     |             |

| d-character   | SELECTED INDIC | ATOR                | MNEMONIC    |

| 1-bit         | Not Ready      |                     | BNR         |

| 2-bit         | Busy           |                     | BCB         |

| 4-bit         | Data Check     |                     | BER         |

| 8-bit         | Condition      |                     | BEF         |

| A-bit         | No Transfer    |                     | BNT         |

| B-bit         | Wrong Length   | Record              | BWL         |

More than one status indicator may be tested with a single instruction by using a d-character with a combination of bits; for example:

R (I) 3 Tests both Not Ready and Busy

$R (I) \equiv Tests all six indicators$

Mnemonic: BEX1 Address, 3

BEX1 Address, ≢

A branch to the I-address occurs if any one of the selected indicators are on.

If the system is equipped with the processing Overlap feature, the program should test the overlap in process indicator before testing the channel status indicators. If the channel status indicators are interrogated by the program before the overlapped operation is completed, the CPU is interlocked (computing is suspended) until the channel operation is completed. This is done because a valid interrogation of the status indicators cannot be made until the end of the operation and all status indicators have been set.

The following example shows simple 1-0 program-

| mmg.  |                         |                                                   |

|-------|-------------------------|---------------------------------------------------|

| 00001 | M%11BBBBBR              | Read a card                                       |

| 00011 | R000012                 | If busy, try again                                |

| 00015 | Ř01000≢                 | Branch if any status indicator on                 |

| 00025 | AAAAAABBBBB             | Process data                                      |

| 00036 | M%44BBBBBW              | Punch a card                                      |

| 00046 | Ř000362                 | If busy, try again                                |

| 00053 | Ř04000≢                 | Branch if any status indicator on                 |

| 00060 | <b>ў</b> 00001 <b>%</b> | Branch to repeat program                          |

| 00067 | <b>Y.V</b>              |                                                   |

| 01000 | RXXXXX1                 | Conditional branch to not ready type routine      |

| 01007 | RXXXXX8                 | Conditional branch to end of file routine         |

| 01014 | RXXXXX4                 | Conditional branch to data check type out routine |

| 01021 | RXXXXXb (A-bit)         | Conditional branch to no transfer routine         |

| 01028 | RXXXXX— (B-bit)         | Conditional branch to wrong length record routine |

If the reader is busy when the read instruction is attempted, the E-channel busy indicator is turned on and the operation is ended immediately (no E-phase). The branch on busy instruction causes the CPU to attempt the read operation repeatedly until the reader is no longer busy. When the reader is no longer busy, the E-channel busy indicator is not turned on, and Ephase (data transfer) of the read instruction occurs. At the end of E-phase, the B-status channel indicators are set (conditionally), and the program proceeds to the next sequential instruction. The next sequential instruction is the branch on busy instruction. Because the busy indicator was not set during the I-phase of the read instruction, no branch occurs. The reader itself is busy at this time, but it was not busy at the time the busy bus was sampled at status sample A time of the read instruction. Note that the branch on busy instruction tests the channel status indicator, not the current status of the 1-0 unit.

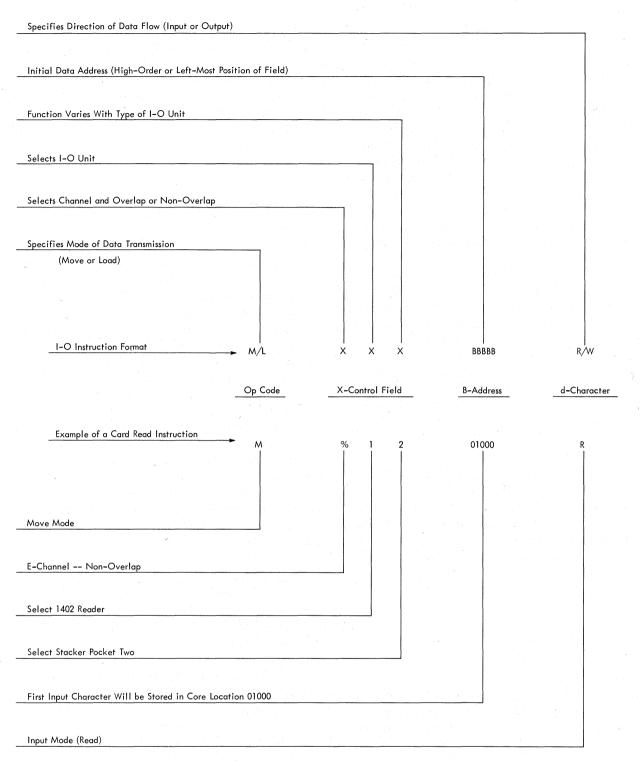

#### Instruction Format — Move or Load

One basic instruction word is common to all 1-0 devices. See Figure 11. Special instructions (op codes F,

#### Basic I-O Command

| Instruction format:              | 0  | XXX           | RRRF | R A |                        |  |

|----------------------------------|----|---------------|------|-----|------------------------|--|

|                                  |    | O XXX BBBBB d |      |     |                        |  |

| Example: (card read)             | W, | M %12 03000 R |      |     |                        |  |

| Specifies data transmission mode |    | 0             | M    |     | Move mode              |  |

| Selects channel and overlap or   |    | X             | %    |     | E channel, unoverlap   |  |

| unoverlap operation              |    |               |      |     |                        |  |

| Selects I-O unit                 |    | X             | 1    |     | Select reader          |  |

| (function varies with I-O unit)  |    | Χ             | 2    |     | Select stacker 2       |  |

| Initial data address             |    | В             | 0    |     | Store first input char |  |

| (five digits)                    |    |               |      |     | in address 03000       |  |

|                                  |    | В             | 3    |     |                        |  |

|                                  |    | В             | 0    |     |                        |  |

|                                  |    | В             | 0    |     |                        |  |

|                                  |    | В             | 0    |     | F - 1                  |  |

| Specifies direction of data flow |    | d             | R    |     | Read (input mode)      |  |

| (input or output)                |    |               |      |     |                        |  |

#### d-characters

- Accept input characters until a GM-WM is sensed in the input field

- \$ Accept input characters until the end of storage is sensed

- W Transfer output characters until a GM-WM is sensed in the output field

X Transfer output characters until the end of storage is sensed

Figure 11. Move or Load Instruction Format

K, and U) are described with the device employing that op code. Instruction formats are shown on the IBM 1410 Data Processing System Reference Card, Form X24-6502.

#### **Op Code Character**

The op code character is set into the op register and brings up the op code grouping lines to control subsequent events. The op code also determines the mode of data transmission: move mode or load mode. An M op code specifies move mode; an L specifies load mode.

A 1410 system with the process overlap feature is able to initiate an 1-0 operation and then proceed with the stored program while the 1-0 operation is in process. Consequently, the CPU must "remember" the op code. If does so by setting either the channel move mode latch or the channel load mode latch during late I-phase of any move or load op code. The E-channel move or load latch will light the channel 1 interlock indicator in the 1-0 channel control section of the IBM 1415 Console (Figure 9).

#### X-Control Field

Characters in the X-control field provide channel and unit selection. These characters may be gated onto the address channel as first address characters in the same manner as any other two address instruction, but the characters are not read into any address register. During I-phase first address time of an I-O instruction, the address check circuits permit 8-4 (8-bit, 4-bit) combination characters on the assembly channel, to avoid an address check from the channel select character

$(\%, \square, @ \text{ or } *)$ . The character 4 (in two of five code) is emitted onto the address channel in place of the 8-bit, 4-bit channel select character.

Channel Selection: The hundreds position of the X-control field contains the special character that determines which one of the four channel select latches is set.

Percent sign % E-channel unoverlap in process

Commercial at @ E-channel overlap in process

Asterisk \* F-channel unoverlap in process

Lozenge □ F-channel overlap in process

Each latch has an indicator in the 1-0 channel control section on the IBM 1415 Console. Note that the character selects overlap or unoverlap operation as well as selecting the channel.

Unit Selection: The tens position of the X-control field contains the unit select character which is set into the unit select register. The character 1, for example, selects the 1402 reader, conditioning the circuits between the reader synchronizer (IBM 1414) and the CPU.

Unit Number Selection: The units position of the X-control field contains the unit number character which is set into the unit number register. The function of the unit number character varies with the 1-0 device selected. During reader operation, for example, a 1 selects the reader stacker pocket number 1. During IBM 1402 Card Read Punch move or load op codes, the unit number is sent to the synchronizer over the channel output data lines and, although the unit number character is set into the unit number register, the register is not used.

#### **B-address**

The B-address is the initial data address. During input operation, the first input character is stored in this address. The next character is stored in the next higher storage location. During output operation, the first output character is taken from this initial address and the next character is taken from the next higher storage location. During I-phase of unoverlapped operation, the working address register is the B-address register (BAR). For overlapped operation, the E-address register (EAR) is the working address register.

#### d-character

The d-character is set into the op modifier register and specifies input or output mode. An R specifies input mode (read) and a W specifies output mode (write). The output of the op modifier register is used to gate the setting of either the channel input mode latch or the output mode latch late in I-phase of the I-o instruction, leaving the op modifier register free to accept another character in case of overlap operation.

The on output of the E-channel input mode latch lights the E-channel read indicator in the channel control section of the IBM 1415 Console. The on output of the E-channel output mode latch lights the E-channel write indicator on the 1415 (Figure 9). F-channel latches have the same name as the console indicators. Figure 12 shows a simplified logic flow for move or load command.

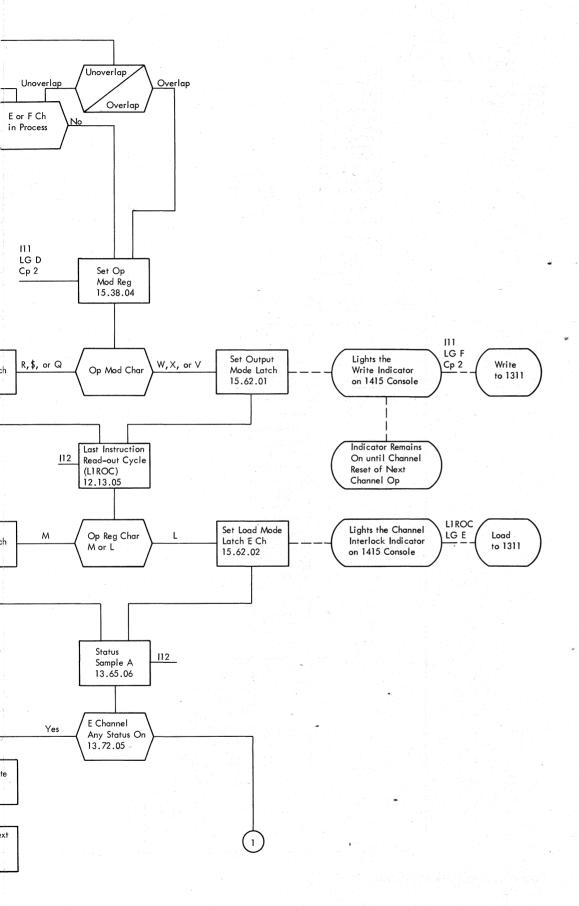

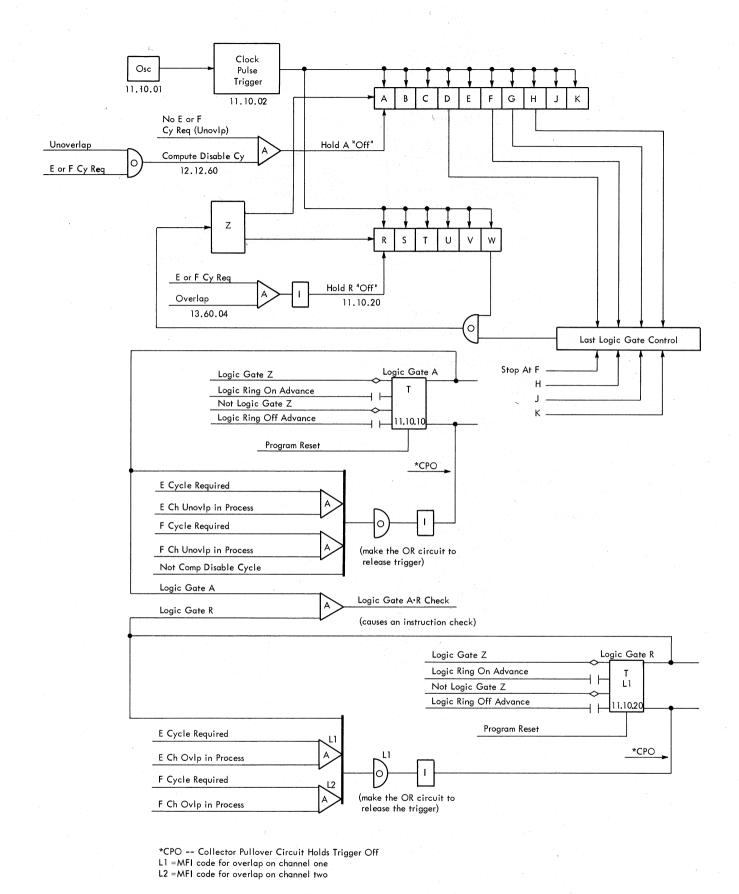

#### **Processing Overlap**

The process overlap feature permits a 1410 system to process data (compute) while an input-output (1-0) operation is being performed. Process overlap is an optional feature, not on a basic 1410 system. A basic 1410 system is interlocked (unable to compute) during an 1-0 operation, remaining idle except when an 1-0 data cycle is required to transfer a character between core storage and the 1-0 channel.

With process overlap, the 1410 system may use this idle time to take compute cycles. The computing is interrupted (disabled) when an 1-0 data cycle is required. Computing is resumed when the 1-0 data cycle is completed.

Compute cycles use the normal logic gate ring; overlapped 1-0 operations use a logic gate extension ring. Computing is interrupted by disabling the logic gate ring. The 1-0 data cycle starts the logic gate extension ring which times the operations for that cycle.

The process overlap feature is optional on a single-channel system; required on a two-channel system. The priority feature is recommended on systems equipped with process overlap. (See SRL IBM Priority Feature, Form A22-0530).

The process overlap feature requires additional circuits and components such as:

Logic clock extension ring

E-address register (EAR) for E-channel

F-address register (FAR) for F-channel (if a two-channel system)

E-channel overlap in process indicator

F-channel overlap in process indicator

Compute disable circuitry

E-cycle and F-cycle control circuitry

The overlap in process indicators can be interrogated by the stored program. Programming considerations for systems with the process overlap feature are described in *IBM 1410 Principles of Operation*, Form A22-0526.

Some general rules concerning processing overlap are:

1. Only one 1-0 unit can be operated per channel at any given time, whether or not overlap mode is being used.

The program must test the channel status indicators between successive I–O operations on the same channel.

The I-O Interlock test is satisfied by:

- 1. A branch-any-indicator instruction R (I) GM.

- 2. A successful branch on a selected channel indicator.

Figure 12. Move or Load Command Logic Flow

- 2. If one channel is operating in overlap mode, the other channel may not operate in unoverlap. However, both channels may operate simultaneously in overlap mode.

- 3. Status indicators should be tested for the last I-O instruction just prior to executing another I-O instruction. If the program attempts to check the indicators before the channel operation is complete, compute disable interrupts the program until the channel operation is finished.

- 4. The E-channel has priority unless the last cycle was an E-cycle.

- 5. A \$ d-character (read to end of storage) is effective only with an unoverlapped read command. An

- overlapped read command with a \$ d-character is treated the same as an overlapped read command with an R d-character.

- 6. An X d-character (write to end of storage) is effective only with an unoverlapped write command. An overlapped write command with an X d-character is treated the same as an overlapped write command with a W d-character.

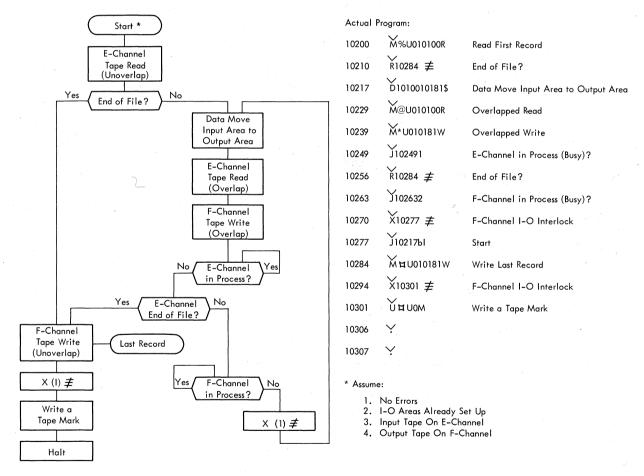

Figure 13 illustrates a typical application of processing overlap. A reel of tape on the E-channel is being copied onto a reel of tape on the F-channel. The reading and writing is done in overlap mode so the time between the E- and F-cycles can be used to move the data from an input area of memory to an output area.

Figure 13. Processing Overlap

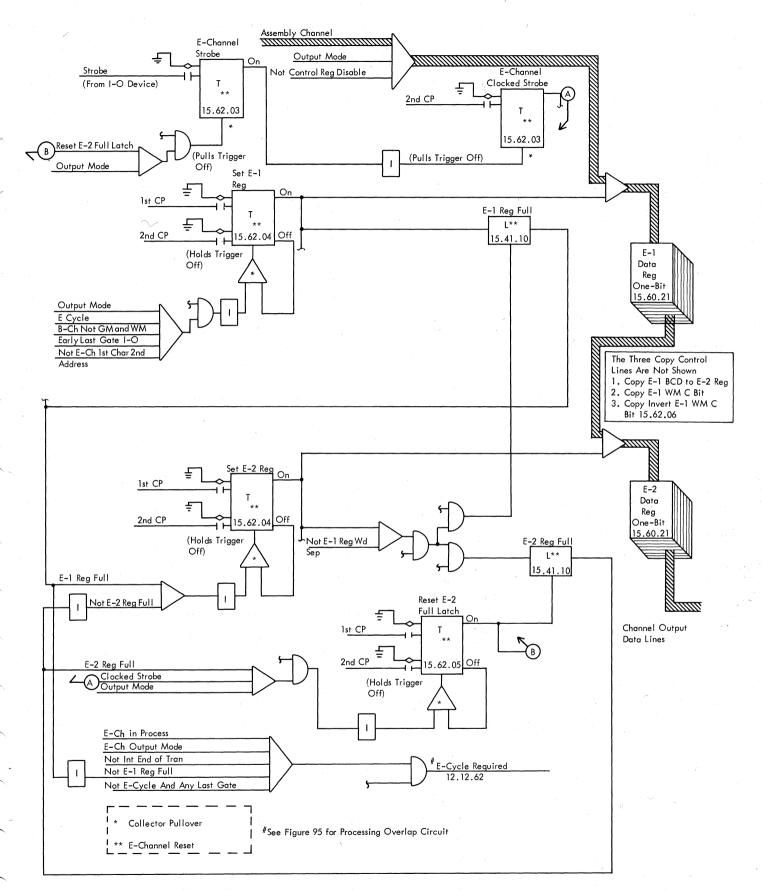

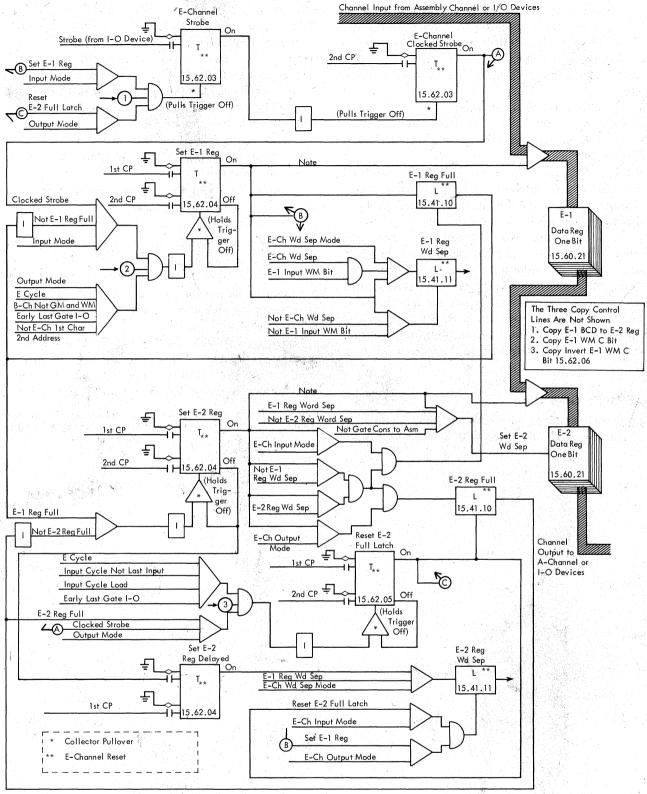

Each channel has two eight-bit data registers and associated control circuits. Operation is basically the same for all types of 1-0 operations. The registers are used for transfer of data during E-phase, and also, in the case of the IBM 1402 Card Read Punch, for transfer of the stacker select character during I-phase.

For ease in learning channel register operation, the presentation is divided into four sections:

- 1. Register components and controls

- 2. Input operation move mode

- 3. Output operation move mode

- Input-output operation load mode (word separator mode)

## **Register Components and Controls**

Because both E- and F-channels are similar, only E-channel operation is described. In some cases, line names in the ALD's may vary slightly between E-channel and F-channel, but the operation is identical.

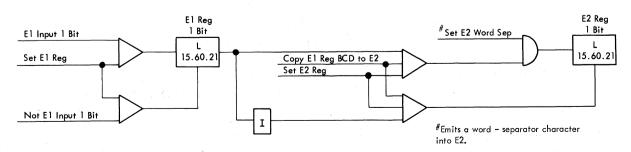

Data Registers: The registers have no reset, retaining one character until a new character is set into the register. A register is made up of eight latches (Figure 14). Each channel has two registers:

Data Register one (E-1 or F-1) Data Register two (E-2 or F-2)

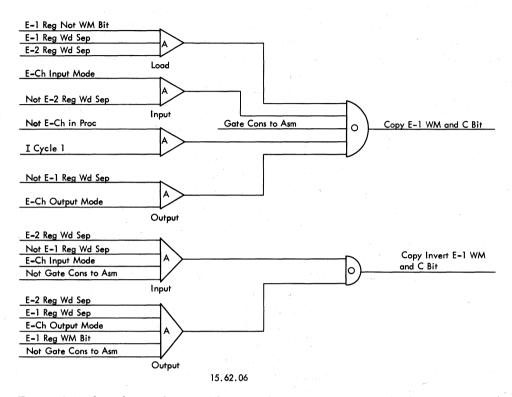

Data Flow Controls (Copy Controls): Data flow from E-1 to E-2 is controlled by the four lines:

Copy E-1 BCD to E-2 Reg

Copy E-1 WM and C-Bit

\*Set E-2 Word Separator (emits a WS into E-2)

\*Copy Invert E-1 WM and C-Bit

\*Used only in word separator mode.

Transfer Controls: The transfer (set) lines determine when the data is transferred from E-1 to E-2, in con-

trast to the copy controls which determine what data is transferred.

| Set E-1 Register     | (sets E-1 to the character at E-1 input, Figures 15 and 16) |

|----------------------|-------------------------------------------------------------|

| Set E-2 Register     | (sets E-2 to the character in                               |

|                      | E-1)                                                        |

| E-1 Reg Full         | (indicates a new character has                              |

|                      | been set into E-1)                                          |

| E-2 Reg Full         | (indicates a new character has                              |

|                      | been set into E-2)                                          |

| Reset E-2 Full Latch | (calls for a new character in                               |

|                      | E-2)                                                        |

Word Separator Controls: Additional controls are required to enable the registers to process word separator characters and wm characters.

E-1 Reg Word Separator E-2 Reg Word Separator Set E-2 Reg Delayed

Five "rules" to remember are:

- 1. Direction of data flow is always from E-1 to E-2.

- 2. A register transfer (E-1 to E-2) always occurs when E-1 is full and E-2 is not full.

- 3. During input operation, the CPU tries to keep E-2 empty (not full).

- 4. During output operation, the CPU tries to keep E-1 full.

- 5. Channel data registers have no reset. The old character remains in the register until the register is set to the bit and no-bit configuration of a new character.

# **Move Mode Operation**

Channel register operation is first presented in move mode. Load mode operation requires additional circuits and is described later.

Figure 14. E-1 and E-2 Register Latches

† Collector Pullover

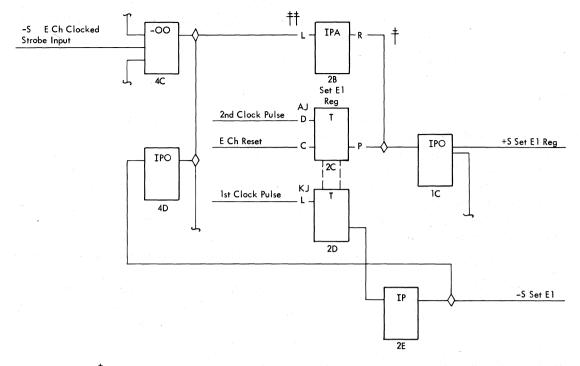

†† A +Sat pin L of "IPA" at co-ord 2B will remove the collector pullover, permitting the next 1st clock pulse to turn trigger on. The "IPO" at co-ord 4D prevents the trigger from being turned off by collector pullover, insuring that trigger remains on for a full clock pulse.

Figure 15. Set E-1 Register Trigger - ALD

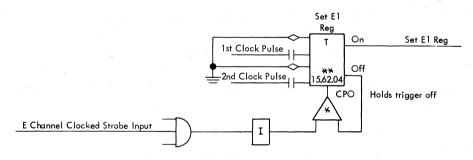

\* Collector Pullover

To permit easy identification of the collector pullover circuit, it is shown as a reset input into the bottom of the logic block

\*\* E-Channel Reset

Figure 16. Set E-1 Register Trigger - Condensed Logic

Note: Close timing relationships occur in the channel circuits. Excessive delay(s) in logic circuits may cause machine failures.

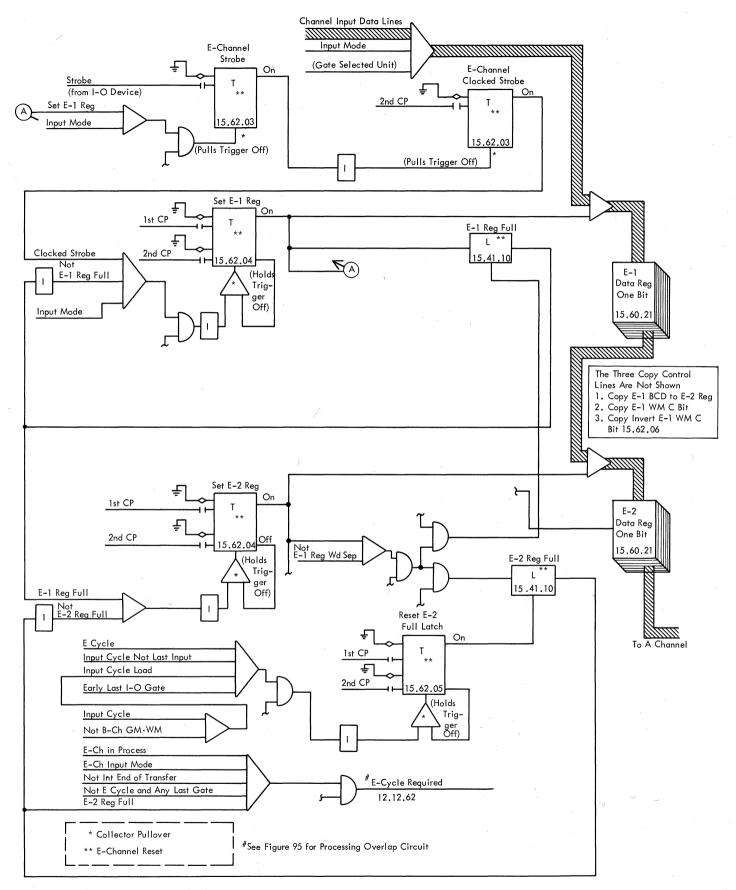

#### **Input Mode**

During input mode 1-0 operation, an input character on the channel input lines is transferred through the channel data registers, the A-channel, assembly channel, and into 1411 core storage.

Assume an input data transfer operation on Echannel is starting and the following copy control lines are active:

An E-channel Reset (Figure 18) occurs at the beginning of an 1-0 operation, resetting the channel controls. The two channel data registers are considered empty (not full) because the E-channel reset turns off the E-1 reg full latch and the E-2 reg full latch. (See Figure 19.)

*Strobe:* The input device generates strobe, signalling the channel controls that a character is on the channel input data lines (Figure 20).

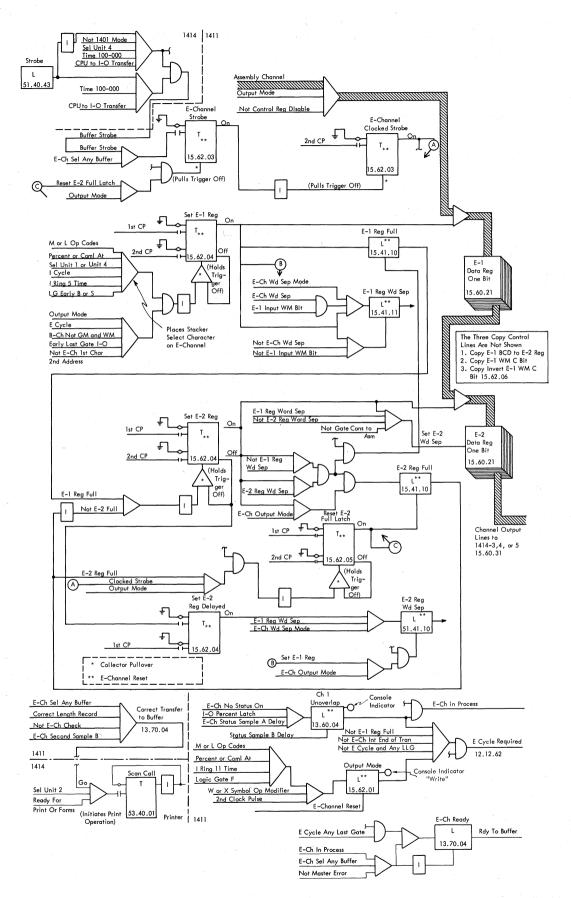

Figure 17. E-Channel Data Flow Controls

*E-channel Strobe Trigger*: The rise of the strobe signal from the input device turns on the E-channel strobe trigger which removes the collector pullover from the E-channel clocked strobe trigger. The rise of the next 2nd clock pulse turns on the trigger.

E-channel Clocked Strobe Trigger: "Clocked strobe" AND's with "input mode" and "not E-1 reg full" to remove the collector pullover from the "set E-1 reg trigger," permitting the trigger to turn on at the rise of the next 1st clock pulse (Figures 15 and 16).

Set E-1 Reg Trigger: The on output of this trigger:

- 1. Sets the E-1 register to the bit configuration of the input lines.

- 2. Sets the E-1 register full latch.

- 3. Pulls over (off) the E-channel strobe trigger which in turn pulls over (off) the E-channel clocked strobe trigger.

The following clock pulse (2nd clock pulse) turns off the set E-1 reg trigger. Note that the collector pull-over circuit is and ed with the off output of the trigger. This prevents the trigger from being pulled off but permits the trigger to be held off once it is turned off

by a 2nd clock pulse. The AND circuit insures that the trigger remains on for a full clock pulse.

E-1 Full Latch: This latch is turned on when E-1 is set, indicating that E-1 contains a new character. With the E-1 full latch on and the E-2 full latch off, the collector pullover is removed from the set E-2 reg trigger and the rise of the next 1st clock pulse turns the trigger on.

Set E-2 Reg Trigger: The on output of this trigger:

- 1. Sets the E-2 register to the data gated from E-1 to E-2 by the copy control lines.

- 2. AND's with "not E-1 reg wd sep" to set the E-2 reg full latch, and reset the E-1 reg full latch.

The next 2nd clock pulse turns off the set E-2 reg trigger and it is held off by the collector pullover circuit.

E-2 Reg Full Latch: The on output of this latch AND's with "E-channel in process" and other conditions to bring up "E-cycle required." The CPU takes an I-O data cycle (E-cycle) and the data from E-2 is gated to the A-channel, assembly channel, and into core storage. Near the end of the E-cycle, "early last gate I-O" AND's with other conditions to remove the collector

|                                         | E Channel Re | set 15.41.12                     |             |

|-----------------------------------------|--------------|----------------------------------|-------------|

| E Ch Not Ready latch                    | 12.62.01     | E-1 Reg Word Sep latch           | 15.41.11    |

| E Ch Busy latch                         | 12.62.02     | E-2 Reg Word Sep latch           | 15.41.11    |

| E Ch Condition latch                    | 12.62.04     | E Ch Unit Sel Reg                | 15.55.08-09 |

| E Ch Check latch                        | 12.62.04     | E Ch Unit Num Reg                | 15.55.01-02 |

| E Ch No Transfer latch                  | 13.72.04     | E Ch Int End of Tran Delay latch | 13.65.05    |

| E Ch WLR latch                          | 13.63.03     | E Ch Int End of Tran             | 13.63.01    |

| E Ch CLR latch (special reset)          | 13.63.03     | E Ch End of Record latch         | 13.63.01    |

| * * * * * * * * * * * * * * * * * * * * |              | E Ch Ext End of Tran Ctrl latch  | 13.42.11    |

| Input Mode latch                        | 15.62.01     | E Ch Ext End of Tran Trigger     | 13.42.11    |

| Output Mode latch                       | 15.62.01     | E Ch Disc latch                  | 13.42.11    |

| E Ch Move Mode latch                    | 15.62.02     |                                  |             |

| E Ch Load Mode latch                    | 15,62,02     | File Start latch                 | 13.72.01    |

|                                         |              | 2nd Addr Tran latch              | 13.72.01    |

| E Ch Strobe trigger                     | 15,62.03     | 1st Char 2nd Addr Ctrl latch     | 13.72.01    |

| E Ch clocked Strobe trigger             | 15,62,03     | 1st Char 2nd Addr latch          | 13.72.01    |

| Set E-1 Reg trigger                     | 15.62.04     | E Ch End Addr Tran latch         | 13.72.01    |

| Set E-2 Reg trigger                     | 15,62,04     | File Strobe latch                | 13.72.02    |

| Reset E-2 Full Latch trigger            | 15.62.05     | File Addr Tran Gate latch        | 13.72.02    |

| E-1 Reg Full latch                      | 15.41.10     | 1st Data Strobe latch            | 13.72.04    |

| E=2 Reg Full latch                      | 15.41.10     |                                  |             |

Figure 18. E-Channel Reset

pullover from the reset E-2 reg full latch trigger, permitting the next 1st clock pulse to turn the trigger on.

Reset E-2 Full Latch Trigger: The on output of this trigger resets the E-2 reg full latch and the following clock pulse (2nd clock pulse) turns off the reset E-2 full latch trigger.

The sequence is complete; both data registers are empty (not full) and ready to receive another input character. Note that both registers do not have to be empty for the channel to receive another input character. Only E-1 must be empty in order to accept another character from the channel input data lines.

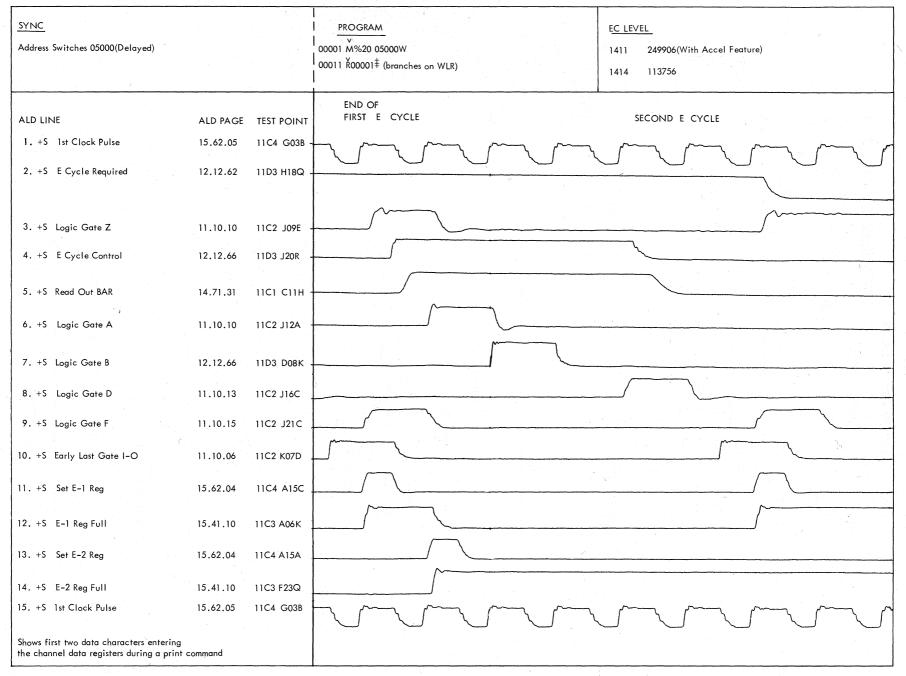

#### **Output Mode**

During output mode operation (Figure 21), an output character in core storage is transferred to the channel data registers via the B-channel and assembly channel. The character in E-2 appears on the channel output data lines which are sampled by the output device (Figure 22).

Assume the following:

E-channel Reset has occurred (Figure 17) Copy E-1 BCD to E-2 Reg line is active (Figure 18) Copy E-1 WM and C-Bit line is active (Figure 18) E-1 and E-2 are not full E-cycle Required: This line becomes active at the end of I-phase when "E-channel in process" and's with "not E-1 reg full" and other conditions to request the CPU to take an I-O data cycle (E-cycle) to transfer an output character to E-1. Near the end of the E-cycle, when the output character is on the assembly channel and available to E-1, "early last gate I-O" AND's with "output mode" and other conditions to remove the collector pullover from the set E-1 reg trigger, permitting the trigger to turn on at the rise of the next 1st clock pulse (Figure 100).

Set E-1 Reg Trigger: The on output of this trigger:

- 1. Sets the E-1 register to the bit configuration of the input lines.

- 2. Sets the E-1 reg full latch.

The following clock pulse (2nd clock pulse) turns off the set E-1 reg trigger.

E-1 Reg Full Latch: This latch is turned on when E-1 is set, indicating that E-1 contains a new character. With the E-1 full latch on and the E-2 full latch off, the collector pullover is removed from the set E-2 reg trigger and the rise of the next 1st clock pulse turns the trigger on.

Set E-2 Reg Trigger: The on output of this trigger:

- 1. Sets the E-2 register to the data gated from E-1 to E-2 by the copy control lines.

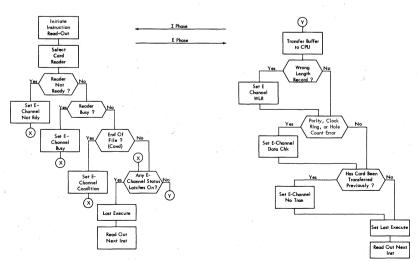

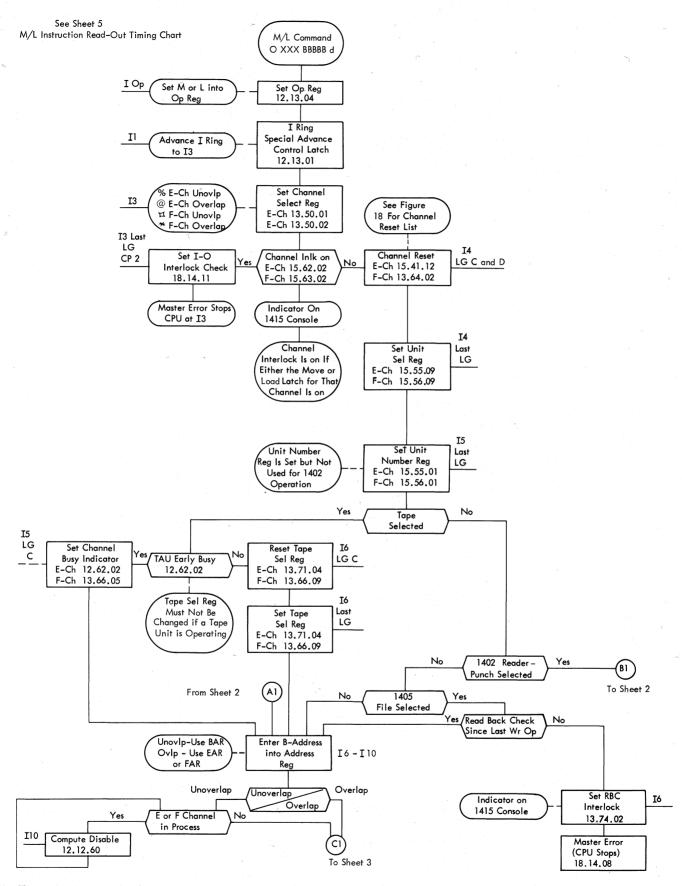

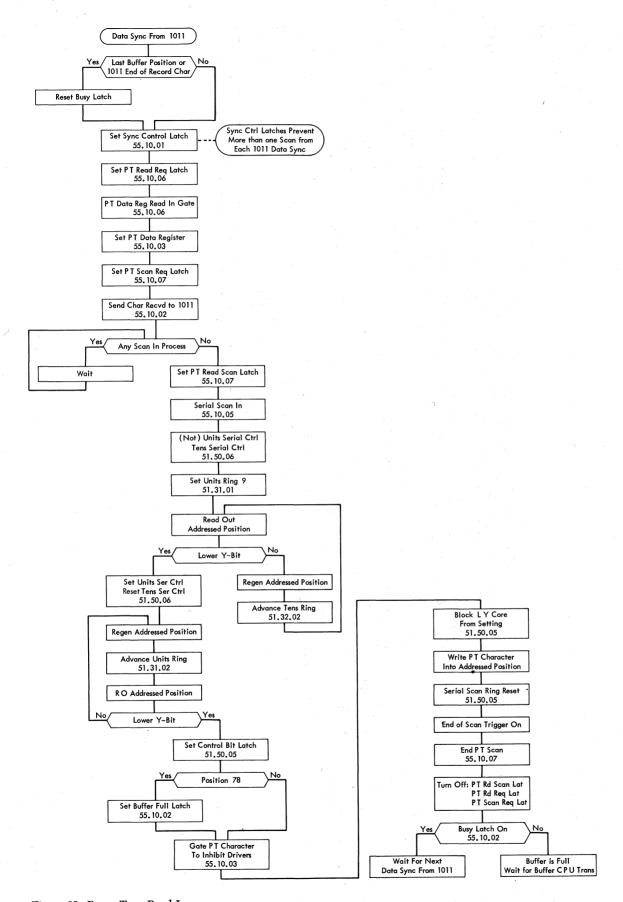

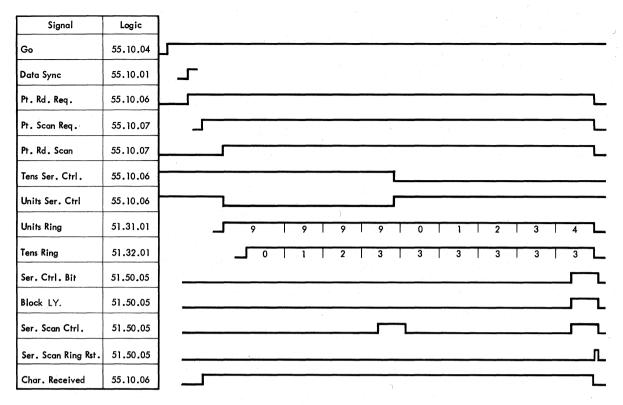

- 2. AND'S with "not E-1 reg wd sep" to set the E-2 reg full latch and reset the E-1 reg full latch. The next 2nd clock pulse turns off the set E-2 reg trigger and it is held off by the collector pullover circuit.