HP64000 Logic Development System

# Model 64151A Emulation Memory Controller

HEWLETT PACKARD

# CERTIFICATION

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

# WARRANTY

This Hewlett-Packard system product is warranted against defects in materials and workmanship for a period of 90 days from date of installation. During the warranty period, HP will, at its options, either repair or replace products which prove to be defective.

Warranty service of this product will be performed at Buyer's facility at no charge within HP service travel areas. Outside HP service travel areas, warranty service will be performed at Buyer's facility only upon HP's prior agreement and Buyer shall pay HP's round trip travel expenses. In all other cases, products must be returned to a service facility designated by HP.

For products returned to HP for warranty service. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

# ASSISTANCE

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

CW&A 2/81

**PRINTED: MAY 1982**

# SAFETY SUMMARY

The following general safety precautions must be observed during all phases of operation, service, and repair of this instrument. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the instrument. Hewlett-Packard Company assumes no liability for the customer's failure to comply with these requirements.

#### **GROUND THE INSTRUMENT.**

To minimize shock hazard, the instrument chassis and cabinet must be connected to an electrical ground. The instrument is equipped with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

#### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE.

Do not operate the instrument in the presence of flammable gases or fumes. Operation of any electrical instrument in such an environment constitutes a definite safety hazard.

#### **KEEP AWAY FROM LIVE CIRCUITS.**

Operating personnel must not remove instrument covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### DO NOT SERVICE OR ADJUST ALONE.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### DO NOT SUBSTITUTE PARTS OR MODIFY INSTRUMENT.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the instrument. Return the instrument to a Hewlett-Packard Sales and Service Office for service and repair to ensure that safety features are maintained.

#### DANGEROUS PROCEDURE WARNINGS.

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

Dangerous voltages, capable of causing death, are present in this instrument. Use extreme caution when handling, testing, and adjusting.

SS-1-1/76

# **TABLE OF CONTENTS**

| Sect | tion                 | Page                                                               |

|------|----------------------|--------------------------------------------------------------------|

| Ι    | GENE                 | ERAL INFORMATION1-1                                                |

|      | 1-1.<br>1-3.<br>1-5. | Introduction1-1<br>Safety Considerations1-1<br>Instruments Covered |

|      |                      | by this Manual1-1                                                  |

|      | 1-10.                | Description1-1                                                     |

|      | 1 - 12.              | Accessories Supplied1-1                                            |

|      | 1-14.                | Additional Equipment Required1-1                                   |

| II   | INST                 | ALLATION2-1                                                        |

|      | 2-1.                 | Introduction2-1                                                    |

|      | 2-3.                 | Initial Inspection2-1                                              |

|      | 2-5.                 | Installation2-1                                                    |

|      | 2-7.                 | Removal                                                            |

|      | 2-9.                 | Operating Environment                                              |

|      | 2-11.                | Storage and Shipment2-4                                            |

|      | 2-12.                | Environment2-4                                                     |

|      | 2-14.                | Original Packaging2-4                                              |

|      | 2-16.                | Other Packaging2-4                                                 |

| III  | OPER                 | ATION                                                              |

| IV   | PERF                 | ORMANCE TESTS4-1                                                   |

|      | 4-1.                 | Introduction4-1                                                    |

|      | 4-4.                 | Troubleshooting Flowchart                                          |

|      | 4-6.                 | Performance Verification4-1                                        |

|      | 4-9.                 | Processor Control Test4-1                                          |

|      | 4-14.                | Emulation Bus Test4-2                                              |

|      | 4-16.                | Data                                                               |

|      | 4-21.                | Address 4-3                                                        |

|      | 4-26.                | Foreground Test4-4                                                 |

|      | 4-28.                | Release                                                            |

|      | 4-33.                | Run                                                                |

|      | 4-38.                | Processor Break                                                    |

| Secti | on             |                                 | Page |  |

|-------|----------------|---------------------------------|------|--|

|       | 4-43.          | Illegal Memory Reference        | 4-5  |  |

|       | 4-48.          | Write to ROM                    |      |  |

|       | 4-53.          | Illegal Opcode                  |      |  |

| v     | ADJUS          | STMENTS                         | 5-1  |  |

| VI    | REPLA          | ACEABLE PARTS                   | 6-1  |  |

|       | 6-1.           | Introduction                    | 6-1  |  |

|       | 6-3.           | Exchange Assemblies             |      |  |

|       | 6-5.           | Abbreviations                   |      |  |

|       | 6-7.           | Replaceable Parts List          |      |  |

|       | 6-9.           | Ordering Information            | 6-1  |  |

|       | 6-12.          | Direct Mail Order System        | 6-2  |  |

| VII   | MANUAL CHANGES |                                 |      |  |

|       | 7-1.           | Introduction                    | 7-1  |  |

|       | 7-3.           | Manual Changes                  | 7-1  |  |

|       | 7-6.           | Other Changes                   | 7-2  |  |

| VIII  | SERVI          | CE                              | 8-1  |  |

|       | 8-1.           | Introduction                    |      |  |

|       | 8-3.           | Safety                          |      |  |

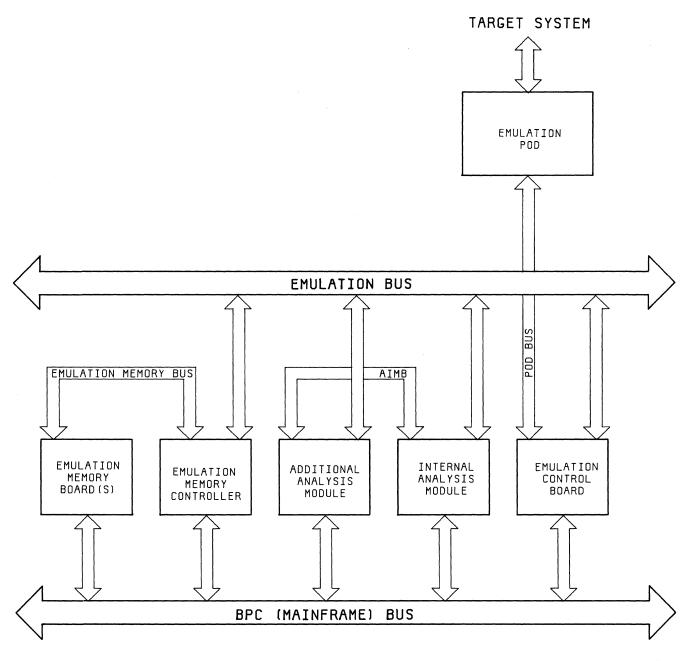

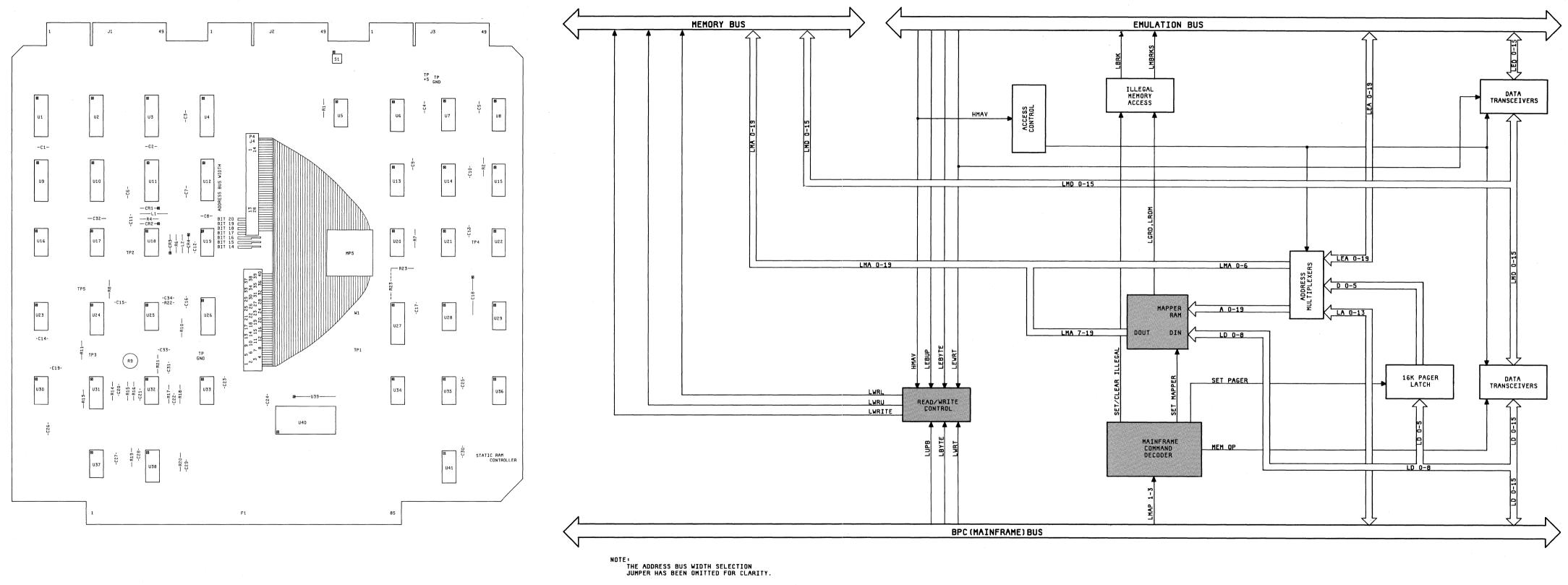

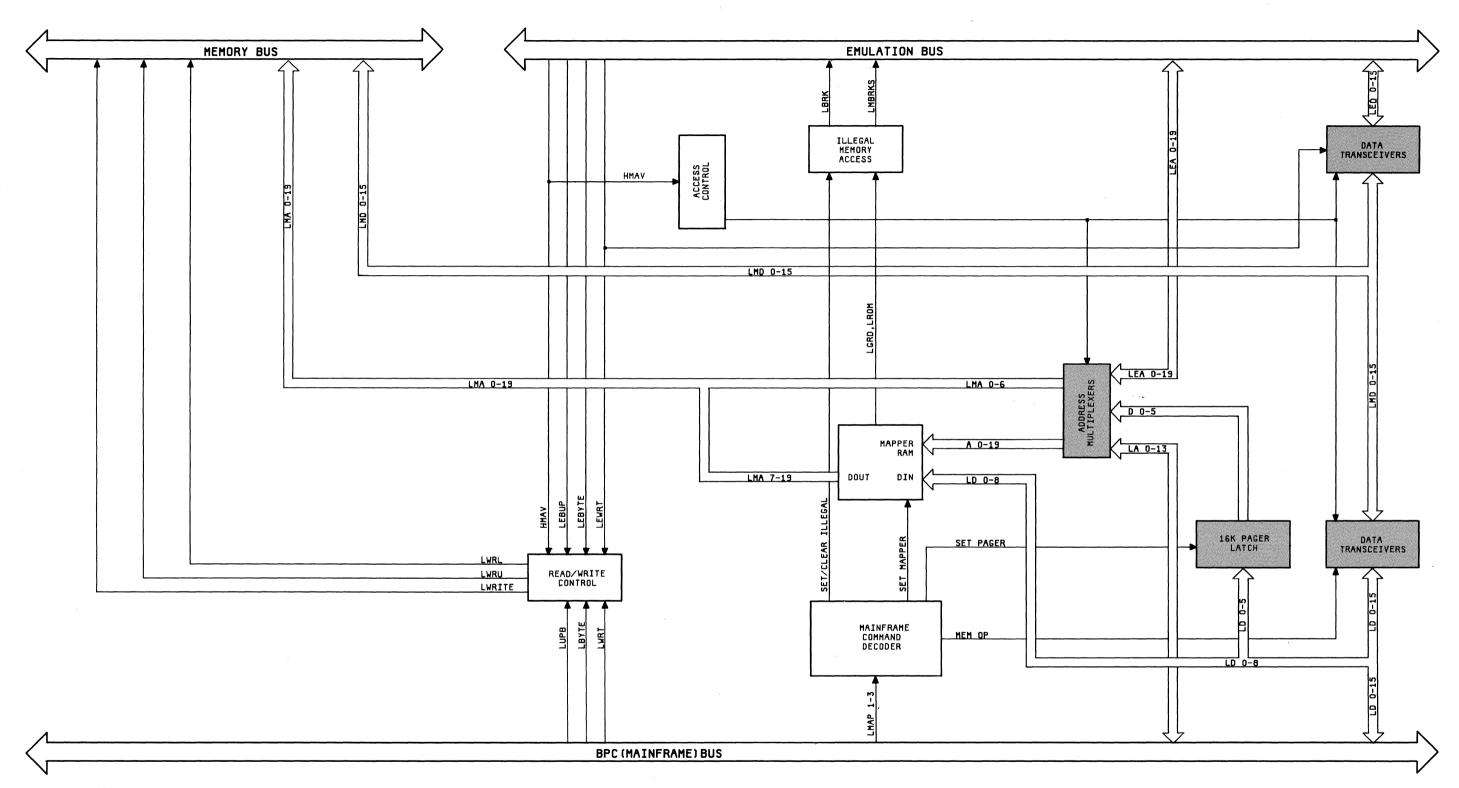

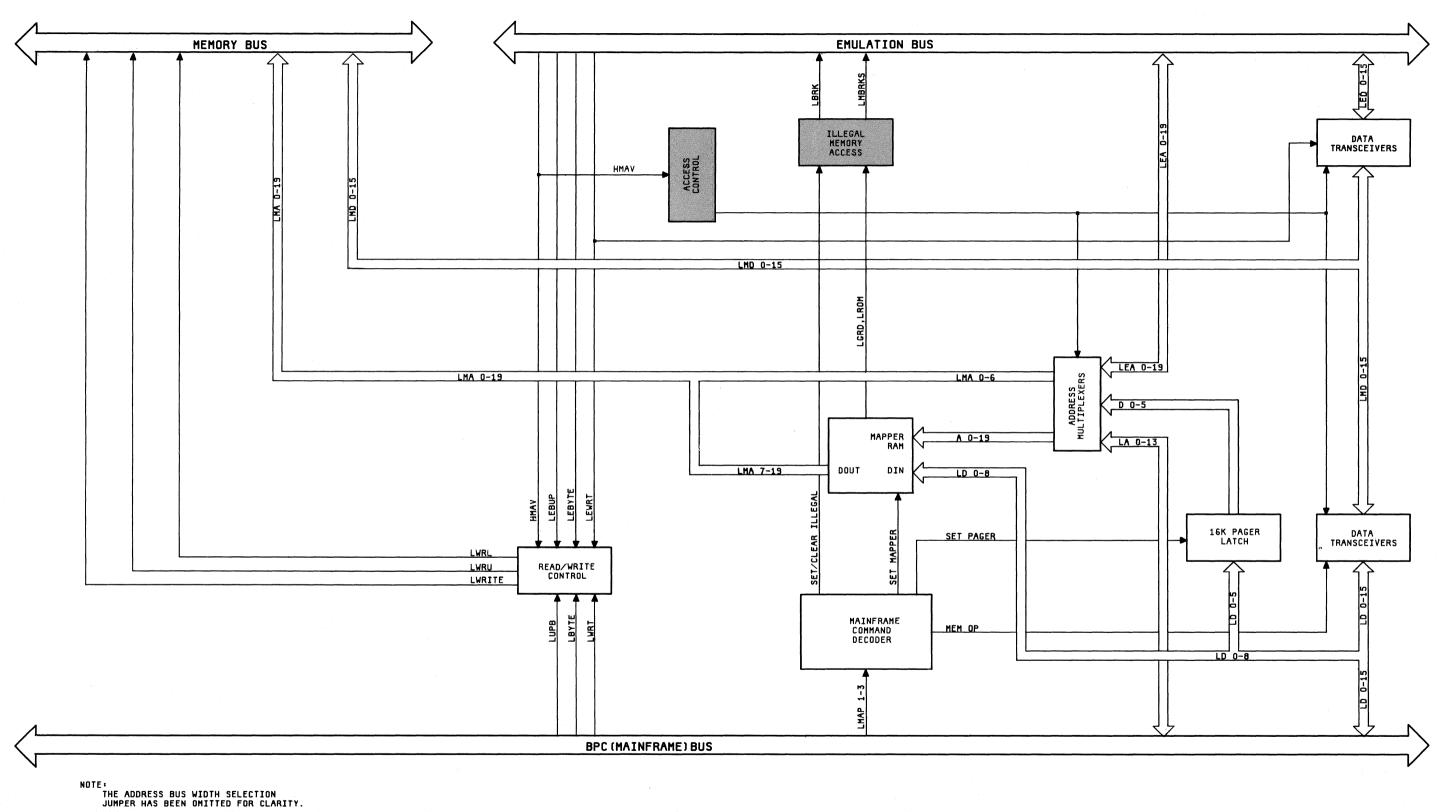

|       | 8-5.           | Emulation Subsystem Block Diagr |      |  |

|       | 8-7.           | Description                     |      |  |

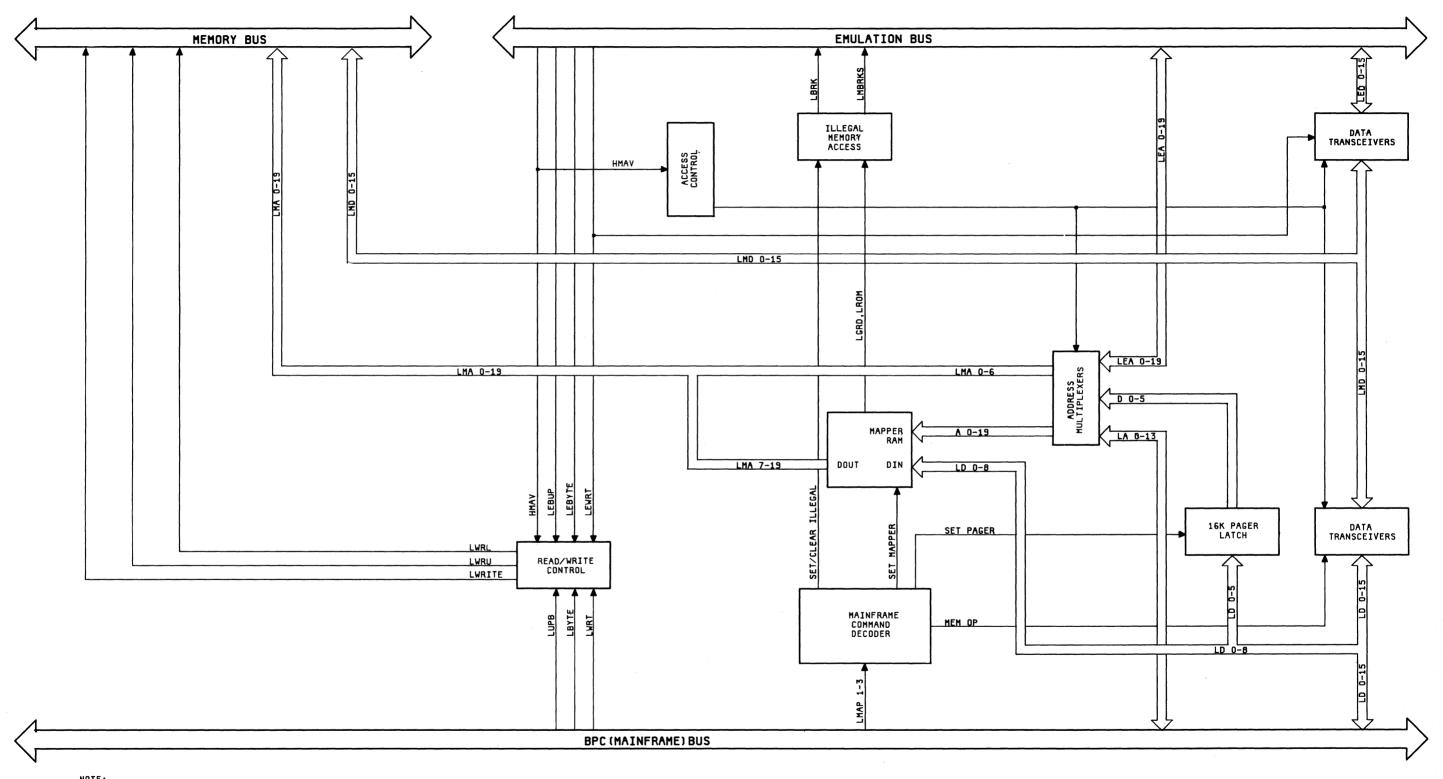

|       | 8-13.          | Emulation Memory Controller     |      |  |

|       |                | Block Diagram                   | 8-3  |  |

|       | 8-15.          | Description                     | 8-3  |  |

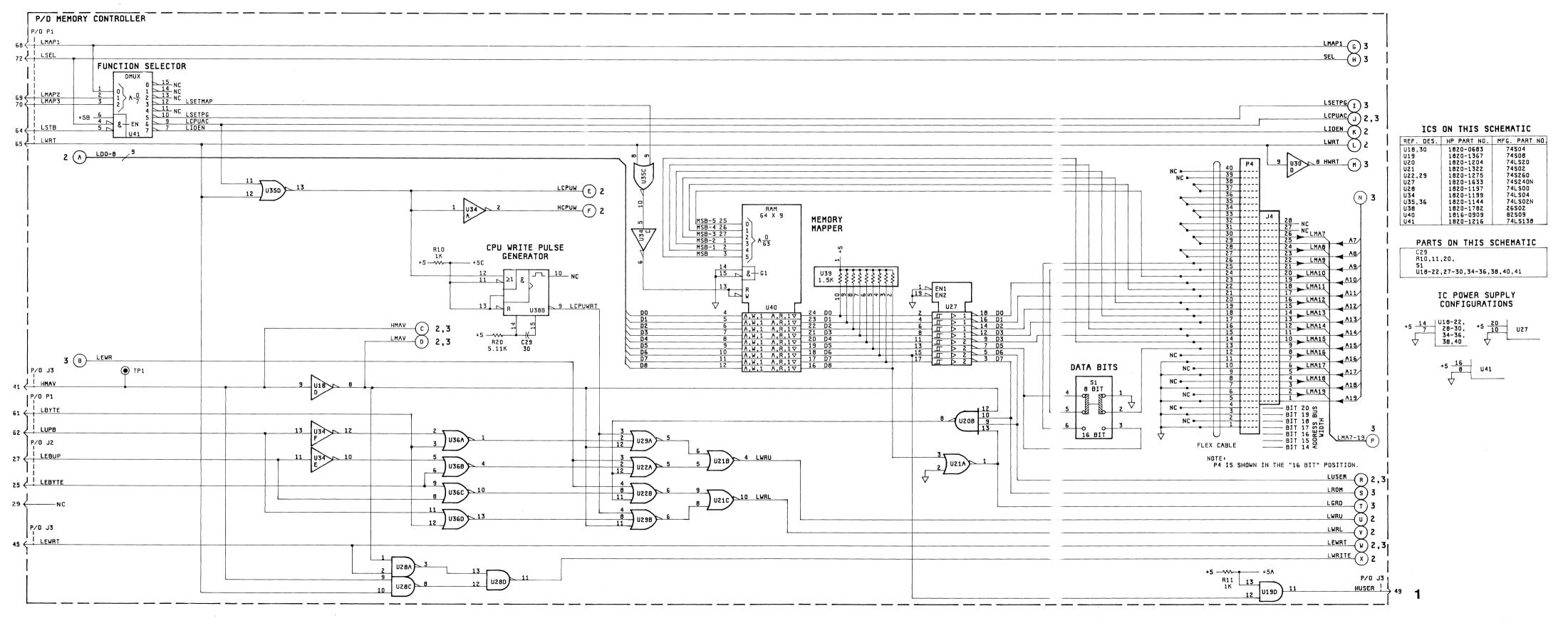

|       | 8-24.          | Theory of Operation             | 8-3  |  |

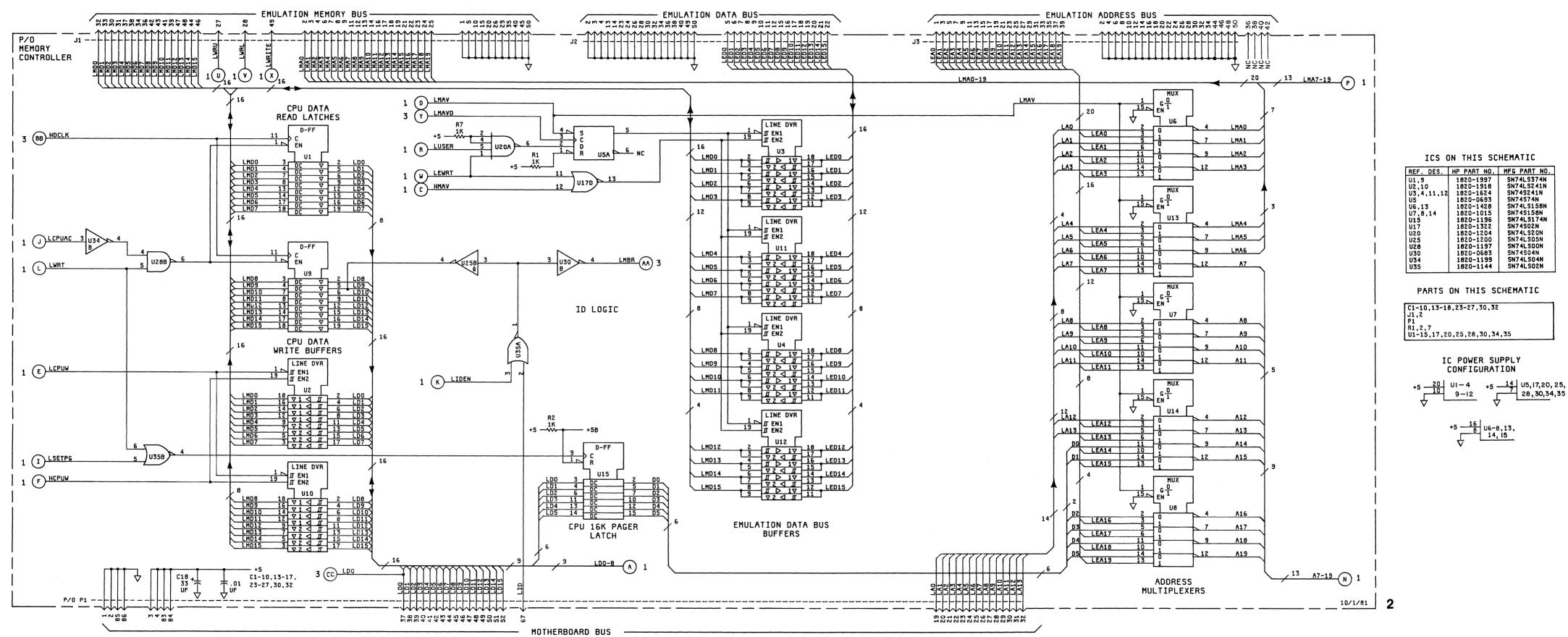

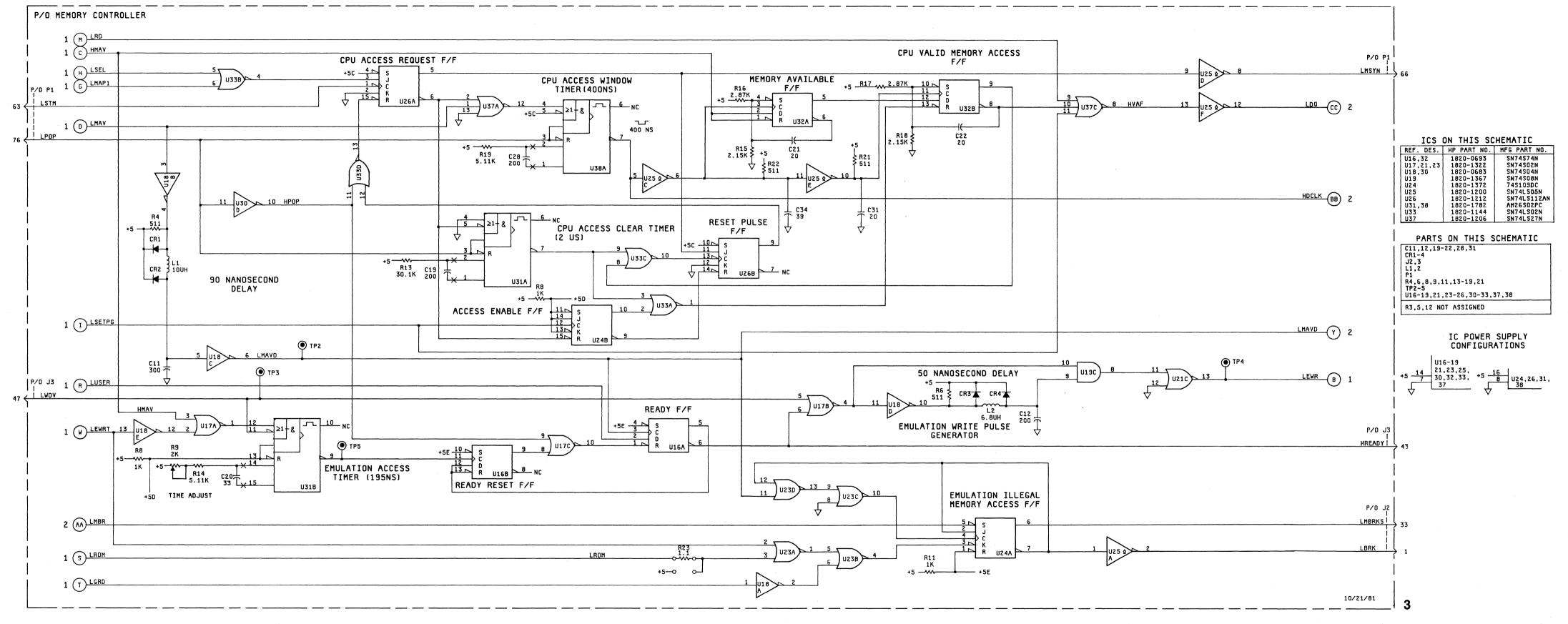

|       | 8-26.          | Schematic 1                     |      |  |

|       | 8-31.          | Schematic 2                     |      |  |

|       | 8-38.          | Schematic 3                     |      |  |

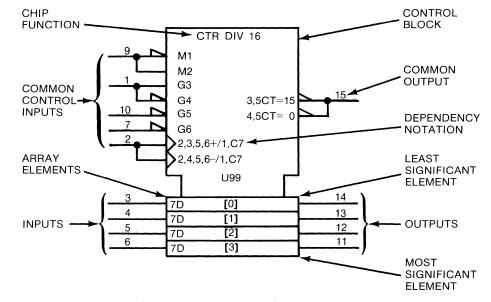

|       | 8-49.          | Logic Convention                |      |  |

|       | 8-53.          | Mnemonics                       | 8-6  |  |

# LIST OF ILLUSTRATIONS

| Figure               | Title                                                                                             | Page                       |

|----------------------|---------------------------------------------------------------------------------------------------|----------------------------|

| 1-1.                 | Model 64151A Memory Controller                                                                    | 1-0                        |

| 2-1.<br>2-2.<br>2-3. | Address Bus Width Selection<br>Recommended Card Cage Configuratio<br>Write to ROM Jumper Position | n2-3                       |

| 4-1.<br>4-2.         | Model 64151A Troubleshooting<br>Flowchart<br>Awaiting Command Status                              |                            |

| 4-3.                 | Option Test Card Slot<br>Listing                                                                  |                            |

| 4-4.<br>4-5.<br>4-6. | Memory Performance Verification<br>Processor Control Test<br>Emulation Bus Test                   | $\dots 4-8$<br>$\dots 4-8$ |

| Figure                       | Title Page                                                                                                                                                                |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-7.                         | Foreground Test 4-8                                                                                                                                                       |

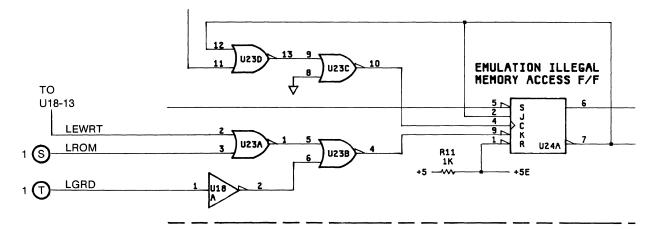

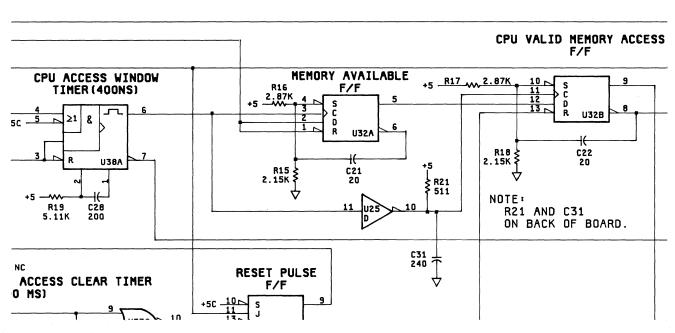

| 7-1.<br>7-2.                 | Illegal Memory Access Circuitry7-3CPU Access Circuitry7-3                                                                                                                 |

| 8-1.<br>8-2.<br>8-3.<br>8-4. | Emulation Subsystem Block Diagram8-2<br>Model 64151A Block Diagram8-5<br>Model 64151A Component Locator8-14<br>Service Sheet 1, Memory Mapper and<br>Write Strobe Control |

| 8-6.                         | and Address Multiplexers                                                                                                                                                  |

| 0-0.                         | Circuitry                                                                                                                                                                 |

# LIST OF TABLES

| Table        | Title                                                           | Page | Table                | Title                                                  | Page |

|--------------|-----------------------------------------------------------------|------|----------------------|--------------------------------------------------------|------|

| 6-1.<br>6-2. | Reference Designators and<br>Abbreviations<br>Replaceable Parts |      | 7-1.<br>8-1.<br>8-2. | Manual Changes<br>Mnemonics<br>Schematic Diagram Notes | 8-7  |

| 0-2.<br>6-3. | Manufacturers' Codes                                            |      | 8-2.<br>8-3.         | Logic Symbols                                          |      |

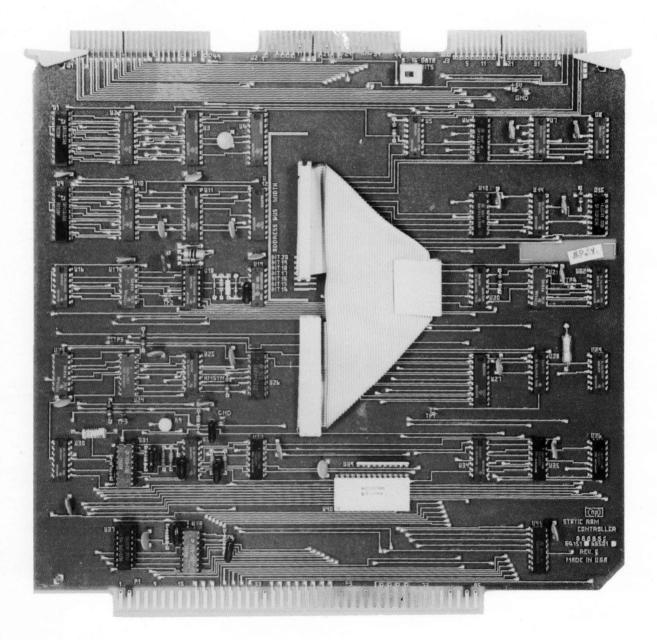

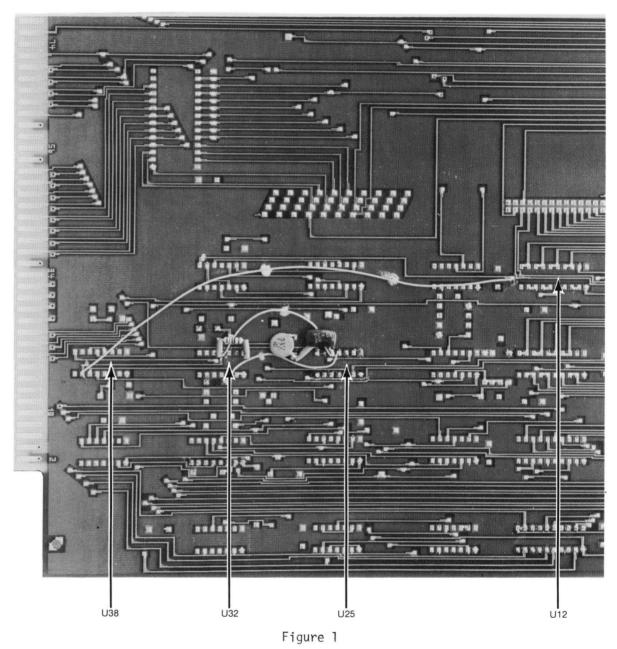

Figure 1-1. Model 64151A Memory Controller

# SECTION I

# GENERAL INFORMATION

# 1-1. INTRODUCTION.

1-2. This service manual contains technical information concerning the application, troubleshooting, and theory of operation for the Model 64151A Emulation Memory Controller as used in the HP 64000 Logic Development System. Figure 1-1 is an illustration of the Model 64151A Memory Controller.

# **1-3. SAFETY CONSIDERATIONS.**

1-4. There are no electrical shock hazards associated with this PC board since there are no high voltages present. There are, however, high voltages associated with the 64000 Mainframe and appropriate warnings are given where a hazard may exist.

# 1-5. INSTRUMENTS COVERED BY THIS MANUAL.

1-6. Attached to the instrument or printed on the printed circuit board is the repair number. The repair number is in the form: 0000A00000. It is in two parts; the first four digits and the letter are the repair prefix, and the last five are the suffix. The prefix is the same for all identical instruments. The suffix, however, is assigned sequentially and is different for each instrument. The contents of this manual apply to instruments with the repair number prefix(es) listed on the title page.

1-7. An instrument manufactured after the printing of this manual may have a repair number prefix that is not listed on the title page. This unlisted repair number prefix indicates that the instrument is different from those described in this manual. The manual for this newer instrument is accompanied by a Manual Changes supplement. This supplement contains "change information" that explains how to adapt the manual for the newer instrument.

1-8. In addition to change information, the supplement contains information for correcting errors in the manual. To keep this manual as current as possible, Hewlett-Packard recommends that you periodically request the latest Manual Changes supplement. The supplement for this manual is identified with the manual print date and part number, both of which appear on the manual title page. Complimentary copies of the supplement are available from Hewlett-Packard Sales/Service Office.

1-9. For information concerning a repair number prefix that is not listed on the title page or in the Manual Changes supplement, contact your nearest Hewlett-Packard Sales/Service Office.

# 1-10. DESCRIPTION.

1-11. The Model 64151A Emulation Memory Control Board drives the Emulation Memory Boards for the purpose of storing and retrieving emulation data from both the host processor and the target system. Up to 64k words can be mapped in any location in memory as ROM, RAM or illegal memory as defined by the user. Mapping control is provided by the Memory Control Board.

# 1-12. ACCESSORIES SUPPLIED.

1-13. The 64151A Emulation Memory Controller is supplied with one (1) 8120-3351 bus cable; and two (2) 8120-3352 bus cables, which are used to connect the Memory Controller to the Emulation Control Board, Analysis Module, and Static RAM Boards. Installation of these cables is covered in Section II.

# 1-14. ADDITIONAL EQUIPMENT REQUIRED.

1-15. The Model 64151A Emulation Memory Controller must be installed in a Model 64000 Mainframe with a minimum of one Static RAM Board (Models 64152B, 64153B, or 64154B) to have a functional emulation memory subsystem.

# SECTION II

### INSTALLATION

# 2-1. INTRODUCTION.

2-2. This section provides installation instructions for the Model 64151A Emulation Memory Controller. Also included is information concerning initial inspection, damage claims, environmental considerations, and storage and shipment.

# 2-3. INITIAL INSPECTION.

2-4. Inspect the shipping container for damage. If the shipping container or cushioning material is damaged, it should be kept until the contents have been checked for completeness and the Model 64151A has been checked mechanically and electrically. If the contents are incomplete, if there is mechanical damage or defect, or if the Model 64151A does not pass performance verification, notify the nearest Hewlett-Packard Sales/Service Office. If the shipping container or cushioning material is damaged notify the carrier as well as the Hewlett-Packard Sales/Service Office. Keep the shipping materials for carrier's inspection. The HP office will arrange for repair or replacement at HP option without waiting for claim settlement.

# 2-5. INSTALLATION.

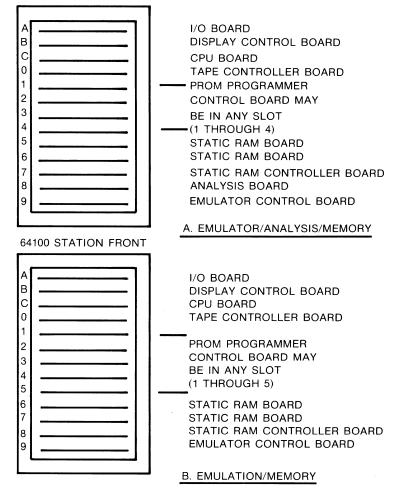

2-6. The Model 64151A Emulation Memory Controller is installed using the following procedure. Figure 2-2 shows the recommended location of the emulation option boards for two typical configurations: Emulation Memory only and Emulation Memory with Analysis.

#### NOTE

There must be one Memory Controller for every four Emulation Memory Boards, regardless of the amount of memory per board.

- a. Turn off power to the 64000 station.

- b. Loosen the two hold-down screws and remove the card cage access cover.

- c. Set the "Data Bits" switch (S1) on the Emulation Memory Controller to the proper data bus width of the emulation processor: 8 bits wide or 16 bits wide.

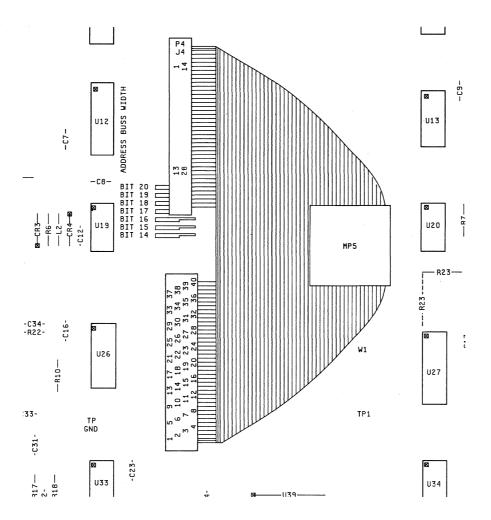

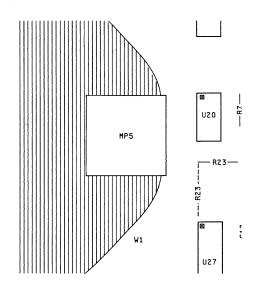

- d. Set the "Address Bus Width" jumper cable on the Emulation Memory Controller to "16" by moving the jumper cable connector vertically on the male connector block (J4) until the dash next to "16" just appears underneath the cable connector. Refer to figure 2-1.

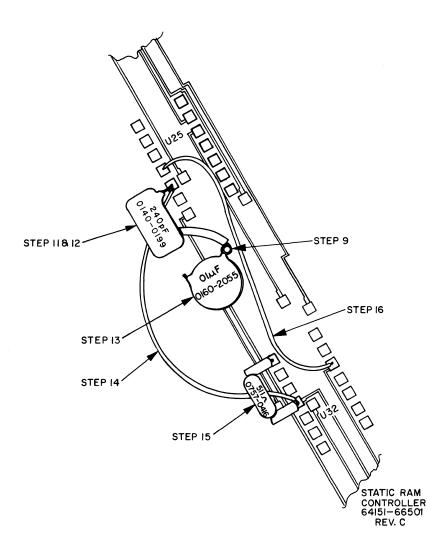

- e. Determine whether it is desired to have the Model 64151A cause an emulation break on a Write to ROM. If so, move R23 so that U27 pin 3 and U23 pin 3 will be connected via R23 (R23 horizontal on board, refer to figure 2-3). If the break on Write to ROM feature is to be disabled, then move R23 so that U23 pin 3 will be connected to +5 volts via R23 (R23 vertical on board, refer to figure 2-3). Refer to Section IV for information on the implications concerning this modification as related to Emulation Memory Controller Performance Verification. Note that this modification is only applicable to certain repair prefix numbers; refer to Section VII.

- f. Making sure that the component side of the Emulation Memory Controller Board faces the front of the 64000 station, align the board with the card guide rails of the selected installation slot (figure 2-2) and press down the board until the P1 connector (large edge connector on board) seats in the motherboard connector of the mainframe.

- g. Install the selected Emulation Memory Boards (8k,16k, or 32k) by repeating step "f" the appropriate number of times. Note that the maximum number of 32k memory boards for an 8-bit user system is two, which gives an emulation memory capacity of 64 kilobytes. The maximum number of 32k memory boards for a 16-bit user system is four, which gives an emulation memory capacity of 128 kilobytes.

Figure 2-1. Address Bus Width Selection

- h. Connect the Emulation Memory Bus ribbon cable across the left-hand set of edge connectors (as you face the front of the development station). The bus cable is keyed so that it will fit on the edge connectors in only one position.

- i. Connect the Emulation Bus cables across the two right-hand sets of edge connectors (as you face the front of the development station). The bus cables are keyed so that they will fit on the edge connectors in only one position.

- j. Reinstall the card cage access cover and tighten the 2 screws.

64100 STATION FRONT

Figure 2-2. Recommended Card Cage Configuration

Figure 2-3. Write to ROM Jumper Position

#### 2-7. REMOVAL.

2-8. Removal of the Model 64151A Emulation Memory Controller is covered in the following procedure.

- a. Turn off power to the 64000 station.

- b. Loosen the two hold-down screws and remove the card cage access cover.

- c. Remove the two Emulation Bus ribbon cables.

- d. Remove the Memory Bus ribbon cable.

- e. Pull up on the two extractor levers until the Memory Controller clears the card cage.

# 2-9. OPERATING ENVIRONMENT.

2-10. The Model 64151A may be operated in environments within the following limits:

| Temperature | $\dots \dots 0^{\circ}C \text{ to } +40^{\circ}C$ |

|-------------|---------------------------------------------------|

| Humidity    | 5% to 80% relative humidity at +40°C              |

| Altitude    |                                                   |

It should be protected from temperature extremes which cause condensation within the instrument.

#### 2-11. STORAGE AND SHIPMENT.

#### 2-12. ENVIRONMENT.

2-13. The Model 64151A may be stored or shipped in environments within the following limits:

| Temperature    | 40°C to +75°C   |

|----------------|-----------------|

| Humidity       | ative humidity  |

| Altitude 15 00 | 0 m (50 000 ft) |

#### 2-14. ORIGINAL PACKAGING.

2-15. Containers and packing materials identical to those used in factory packaging are available through Hewlett-Packard Sales/Service Offices.

#### 2-16. OTHER PACKAGING.

- 2-17. The following general instructions should be used for re-packing with commercially available materials:

- a. Wrap the Model 64151A in heavy paper or plastic.

- b. Use a strong shipping container. A double-wall carton made of 350-pound test material is adequate.

- c. Use a layer of shock-absorbing material 70 to 100 mm (3 to 4 inch) thick around all sides of the Model 64151A to provide firm cushioning and prevent movement inside the container.

- d. Seal shipping container securely.

- e. Mark shipping container FRAGILE to insure careful handling.

- f. In any correspondence, refer to instrument by model number and full serial number.

# **SECTION III**

# **OPERATION**

The operation of the Emulation Memory Controller Board is transparent and thus requires no interaction with the operator. Refer to the Emulator/Analyzer Operator's Manual for a complete explanation of emulation operation and partitioning memory space.

.

#### **SECTION IV**

### PERFORMANCE TESTS

#### 4-1. INTRODUCTION.

4-2. This section describes the Performance Verification (PV) for the Model 64151A Emulation Memory Controller. The PV procedures are in support of the Hewlett-Packard Blue Stripe exchange program; therefore, troubleshooting procedures are given to the board level only.

4-3. For convenience, the figures for the PV are grouped together at the end of this section.

# 4-4. TROUBLESHOOTING FLOWCHART.

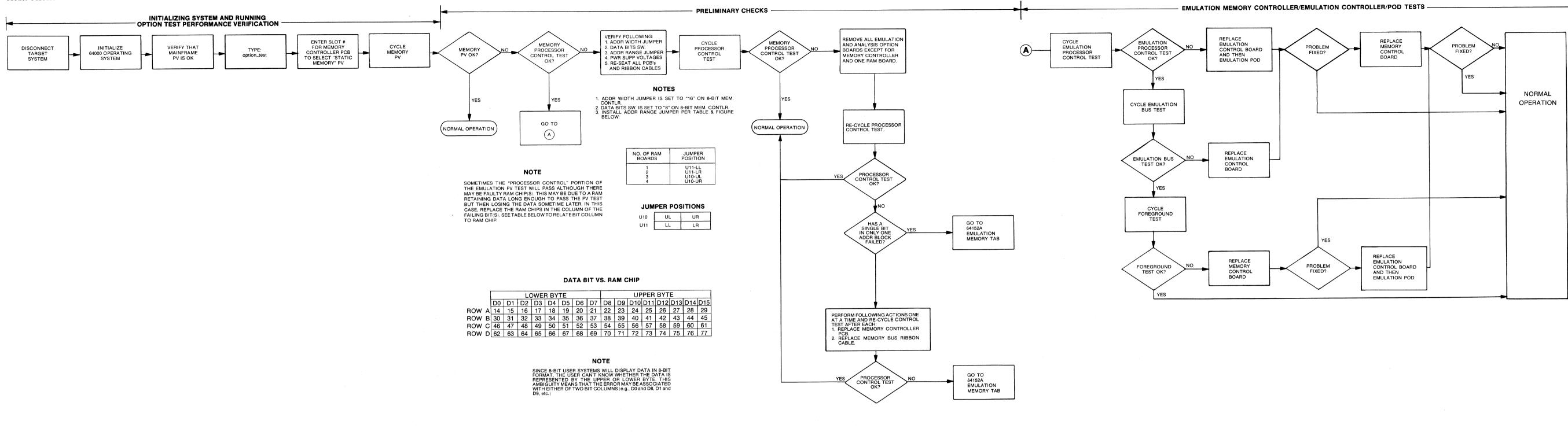

4-5. Figure 4-1 is a flowchart which should be used when troubleshooting an Emulation Memory System which seems to be defective.

#### 4-6. PERFORMANCE VERIFICATION.

4-7. The PV for the Model 64151A Emulation Memory Controller is a subset of the 64000 system option\_test PV. The option\_test PV tests all possible option modules that can be configured within the expansion slots of the 64000 Mainframe.

4-8. To test the Model 64151A Emulation Memory Controller, proceed as follows:

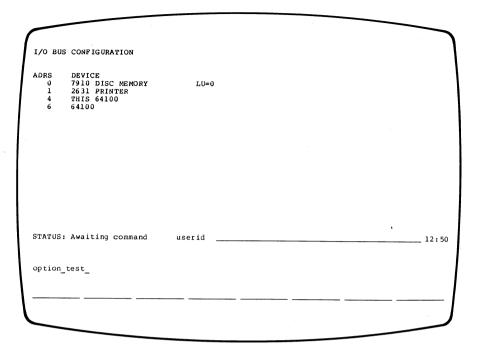

a. With the operating system initialized and awaiting a command, manually type or use the softkey:

option\_test RETURN

Refer to figure 4-2.

b. The PV software will now display a directory of the installed option boards and their card slot number (refer to figure 4-3). Locate the "Static Memory" and enter the card slot number. For example, in figure 4-3 the Static Memory is in card-slot number 7. Therefore, enter:

7 RETURN

- c. A menu will now be displayed listing the three major tests available to exercise the Model 64151A (refer to figure 4-4). The test that is highlighted is the one that will be run if the **start** softkey is pressed. If a test other than the one that is highlighted is desired, press the **next test** softkey. The **next test** softkey is used to step through the tests displayed on the menu. To cause the option\_test software to automatically execute each test in sequence, press the **cycle** softkey. The **next test** softkey can be used to exit the cycle mode.

- d. Cycle through the Model 64151A PV tests. If no failures are observed, the Model 64151A operates correctly, and the testing may be terminated as described in the next paragraph. If a failure is observed, use the test descriptions given in the following sections along with the troubleshooting flowchart to isolate the failure.

- e. To terminate execution of the Static RAM PV, press the **end** softkey. This returns the display to the Option Test PV card slot directory. If end is pressed at this level, the Option Test PV is completely exited and the system is returned to the awaiting command status.

# 4-9. PROCESSOR CONTROL TEST. (Figure 4-5.)

4-10. Purpose — verifies that the mainframe CPU interface circuitry on the Model 64151A and also verifies that the static RAM boards work correctly.

4-11. What — The mainframe CPU programs the memory mapper on the Model 64151A, then writes data to blocks of emulation memory. The CPU then reads the data back and compares it with the data written.

4-12. Results — A hexadecimal status word is formed for each block of memory, indicating which bits of data failed by placing a "one" in the appropriate bit position of the status word. The status is decoded as follows:

| Error | HEX<br>0000 =                                                                                                                                                                                                     | BINARY<br>0000<br>PONM | 0 0 0 0<br>L KJ I | 0 0 0 0<br>HGFE | 0 0 0 0<br>DCBA |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|-----------------|-----------------|

| Where | $\begin{array}{l} A &= D0 \\ B &= D1 \\ C &= D2 \\ D &= D3 \\ E &= D4 \\ F &= D5 \\ G &= D6 \\ H &= D7 \\ I &= D8 \\ J &= D9 \\ K &= D10 \\ L &= D11 \\ M &= D12 \\ N &= D13 \\ O &= D14 \\ P &= D15 \end{array}$ |                        |                   |                 |                 |

For example, if the status message reads "Error = 1248", then D3, D6, D9 and D12 are bad.

4-13. Troubleshooting — A failure in this test is most likely to occur on the Model 64151A or a Static RAM Board. Use the Troubleshooting Flowchart (figure 4-1).

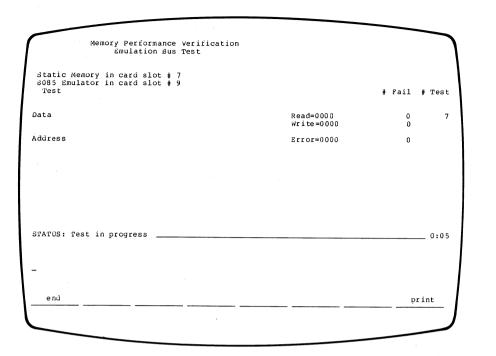

#### 4-14. EMULATION BUS TEST. (Figure 4-6.)

4-15. The Emulation Bus Test consists of two subtests: Data and Address. Each is described in the following paragraphs.

#### 4-16. DATA.

4-17. Purpose — to verify that data bus communication is possible between the emulation control board and the Model 64151A Emulation Memory Controller.

4-18. What — The mainframe CPU starts this test by mapping two 1k blocks of emulation memory at opposite ends of a 64k address range. The CPU then writes data in a walking one/zero pattern to these two blocks of memory through the Memory Controller. The emulation control board is then directed to read this data and the mainframe CPU verifies that correct data was transferred. Next, the CPU commands the emulation control board to write an inverse data pattern to the two memory blocks. Finally, the CPU reads emulation memory through the Memory Control Board to verify that the data was written correctly.

4-19. Results — There are two hexadecimal status messages, Read and Write. The Read message indicates problems with the emulation controller's ability to read emulation memory. The Write message indicates problems with the emulation controller's ability to write data into emulation memory. Errors are represented by placing a "one" in the status word at the position of each failing data bit. The messages are therefore decoded as follows (Read and Write status are decoded in the same way):

| Read<br>(Write) | HEX<br>0000 =                                                                                                                                                                                                     | BINARY<br>0000<br>PONM | 0 0 0 0<br>L K J I | 0 0 0 0<br>HGFE | 0 0 0 0<br>DCBA |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------|-----------------|-----------------|

| Where           | $\begin{array}{l} A &= D0 \\ B &= D1 \\ C &= D2 \\ D &= D3 \\ E &= D4 \\ F &= D5 \\ G &= D6 \\ H &= D7 \\ I &= D8 \\ J &= D9 \\ K &= D10 \\ L &= D11 \\ M &= D12 \\ N &= D13 \\ O &= D14 \\ P &= D15 \end{array}$ |                        |                    |                 |                 |

For example, if the status message reads "Write = 1248", then D3, D6, D9 and D12 are failing.

4-20. Troubleshooting — A failure in this test could be caused by the emulator pod, emulation control board, or the Model 64151A Memory Controller. Refer to the Troubleshooting Flowchart (figure 4-1).

#### 4-21. ADDRESS.

4-22. Purpose — to verify that the emulation controller can generate proper addresses on the emulation bus and that they are transmitted to emulation memory.

4-23. What — This test is similar to the Data Test except that a walking one/zero pattern is used to test the address bus. Any data bus failures in this test are assumed to represent address failures and are indicated as such on the status line; therefore, Data Test must pass before Address Test results can be considered valid.

4-24. Results — A hexadecimal status message is used to indicate address bus failures. A "one" is placed in the status word at the position of each failing bit. The message is therefore decoded as follows:

| Error | HEX<br>0000 =                                                                                                                                                                                                     | BINARY<br>0 0 0 0<br>P O MN | 0 0 0 0<br>L K J I | 0 0 0 0<br>HGFE | 0 0 0 0<br>DCBA |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|-----------------|-----------------|

| Where | $\begin{array}{l} A &= A0 \\ B &= A1 \\ C &= A2 \\ D &= A3 \\ E &= A4 \\ F &= A5 \\ G &= A6 \\ H &= A7 \\ I &= A8 \\ J &= A9 \\ K &= A10 \\ L &= A11 \\ M &= A12 \\ N &= A13 \\ O &= A14 \\ P &= A15 \end{array}$ |                             |                    |                 |                 |

For example, if the status message reads "Error = 1248", then A3, A6, A9, and A12 are failing.

4-25. Troubleshooting — A failure in this test could be caused by the Emulator Pod, Emulation Control Board, or the Model 64151A Memory Controller. Refer to the Troubleshooting Flowchart (figure 4-1).

# 4-26. FOREGROUND TEST. (Figure 4-7.)

4-27. The Foreground Test consists of six subtests. They are: Release, Run, Processor Break, Illegal Memory Reference, Write to ROM, and Illegal Opcode. Each is described in the following sections.

#### 4-28. RELEASE.

4-29. Purpose — verifies that the emulator can execute a program from background memory (on the emulation controller) and modify a background memory location.

4-30. What — The mainframe CPU loads a program into background memory and commands the emulator to run the program. The CPU waits a defined amount of time, then checks to make sure that a background memory location was changed. The emulator's status is also checked.

4-31. Results – No status information is displayed.

4-32. Troubleshooting — Failures in this test normally indicate problems with the Emulation Control Board or the Emulator Pod. Refer to the Troubleshooting Flowchart (figure 4-1).

#### 4-33. RUN.

4-34. Purpose — verifies that the emulator can execute a program residing in emulation memory.

4-35. What — The mainframe CPU maps emulation memory into two blocks: 0-1k as emulation RAM; and 2-3k as emulation ROM. A program is then loaded into emulation ROM and the emulator is directed to execute the program. The program causes the emulator to read a location then write to a location in RAM. The mainframe CPU checks to verify that the data was written correctly.

4-36. Results — a hexadecimal status word is formed to indicate the status of the emulator. A "one" is placed in the bit position of each status line that fails. This message is decoded as follows:

|        | HEX    | BINARY |                 |                 | ,               |

|--------|--------|--------|-----------------|-----------------|-----------------|

| Status | 0000 = | 0000   | $0 \ 0 \ 0 \ 0$ | $0 \ 0 \ 0 \ 0$ | $0 \ 0 \ 0 \ 0$ |

|        |        | XXXA   | BCDE            | XXXX            | XXXX            |

Where

- A = Memory cycle clock not present

- B = Background mode operation

- C = Illegal opcode

- D = Memory caused break (may be any one of the following)

- undefined memory

- write to ROM

- illegal memory access

- E = Break has occurred on this board

- X = Don't care status bits

For example, if the status line reads "Status = 1200", then the memory cycle clock and memory break are failing.

4-37. Troubleshooting — Failures may occur on either the Emulator Pod, Emulation Control Board, or the Memory Controller. Refer to the Troubleshooting Flowchart (figure 4-1).

#### 4-38. PROCESSOR BREAK.

4-39. Purpose — verifies that the emulator responds properly to a mainframe CPU break command.

4-40. What — The mainframe CPU loads a program into emulation memory and commands the emulator to run. The CPU then asserts the emulator break and verifies emulator status and last opcode address.

4-41. Results — A hexadecimal status word is formed to indicate the status of the emulator. A "one" is placed in the bit position of each status line that fails. This message is decoded as follows:

|        | HEX    | BINARY |      |                 |                 |

|--------|--------|--------|------|-----------------|-----------------|

| Status | 0000 = | 0000   | 0000 | $0 \ 0 \ 0 \ 0$ | $0 \ 0 \ 0 \ 0$ |

|        |        | XXXA   | BCDE | XXXX            | ХХХХ            |

Where

A = Memory cycle clock not present

B = Background mode operation

C = Illegal opcode

D = Memory caused break (may be any one of the following)

- undefined memory

- write to ROM

- illegal memory access

- E = Break has occurred on this board

- X = Don't care status bits

For example, if the status line reads "Status = 1200", then the memory cycle clock and memory break are failing.

4-42. Troubleshooting — Failures may occur on either the Emulator Pod, Emulation Control Board, or Memory Controller. Refer to the Troubleshooting Flowchart (figure 4-1).

#### 4-43. ILLEGAL MEMORY REFERENCE.

4-44. Purpose — to verify that the Model 64151A Memory Controller can properly cause an emulator break when an illegal memory access is attempted by the emulator.

4-45. What — The mainframe CPU loads a program into emulation memory and commands the emulator to run. The program contains instructions which cause the emulator to attempt an access of emulation memory that has been mapped as guarded. The CPU then verifies that the Memory Controller causes an emulator break. The emulator status and last opcode address is then verified.

4-46. Results — No status information is displayed.

4-47. Troubleshooting — A failure in this test could occur on the Emulator Pod, Emulation Control Board, or the Memory Controller. Refer to the Troubleshooting Flowchart (figure 4-1).

#### 4-48. WRITE TO ROM.

4-49. Purpose — to verify that the Model 64151A Memory Controller can properly cause an emulator break when the emulator attempts to access memory mapped as ROM.

#### NOTE

On Model 64151A Emulation Memory Controllers with a repair number prefix of 2153A and above, the break on Write to ROM feature can be defeated by moving a jumper. When this feature is defeated, the Memory Controller will fail the Write to ROM portion of Foreground Test.

4-50. What — The mainframe CPU loads a program into emulation memory and commands the emulator to execute the program. The program contains instructions which cause the emulator to attempt a write to emulation memory that has been mapped as ROM. The CPU verifies that the Memory Controller asserts an emulator break, and also verifies proper emulator status and last opcode address.

4-51. Results — No status information is displayed.

4-52. Troubleshooting — A failure in this test could occur on the Emulator Pod, Emulation Control Board, or Memory Controller. Refer to the Troubleshooting Flowchart (figure 4-1).

#### 4-53. ILLEGAL OPCODE.

4-54. Purpose — to verify that an emulator break is generated upon detection of an illegal opcode.

5

4-55. What — The mainframe CPU loads a program into emulation memory and commands the emulator to execute the program. The program contains several illegal opcodes. The CPU verifies that the illegal opcode circuit on the Emulation Control Board properly detects these opcodes and generates an emulator break.

4-56. Results - No status information is displayed.

4-57. Troubleshooting — A failure in this test could occur on the Emulator Pod, Emulation Control Board, or Memory Controller. Refer to the Troubleshooting Flowchart (figure 4-1).

|       |    |    | LC | OWE | R BY | TE |    |     |    |    | UP  | P |

|-------|----|----|----|-----|------|----|----|-----|----|----|-----|---|

|       | D0 | D1 | D2 | D3  | D4   | D5 | D6 | D7  | D8 | D9 | D10 | D |

| ROW A | 14 | 15 | 16 | 17  | 18   | 19 | 20 | -21 | 22 | 23 | 24  | 2 |

| ROW B | 30 | 31 | 32 | 33  | 34   | 35 | 36 | 37  | 38 | 39 | 40  | 4 |

| ROW C | 46 | 47 | 48 | 49  | 50   | 51 | 52 | 53  | 54 | 55 | 56  | 5 |

| ROW D | 62 | 63 | 64 | 65  | 66   | 67 | 68 | 69  | 70 | 71 | 72  | 7 |

|       |    |    |    |     |      |    |    |     |    |    |     |   |

NOTE

REPEAT THE ABOVE TEST FOR EACH RAM BOARD.

Figure 4-2. Awaiting Command Status

| $\frown$    |                                                                        | HP 64000 Option B                          | Performance | Verification |          |

|-------------|------------------------------------------------------------------------|--------------------------------------------|-------------|--------------|----------|

| Card #      | ID #                                                                   | Module                                     |             |              |          |

| 7<br>8<br>9 | 0200H<br>0100H<br>0003H                                                | Static Memory<br>Analysis<br>8085 Emulator |             |              |          |

|             |                                                                        |                                            |             |              |          |

|             |                                                                        |                                            |             |              |          |

|             |                                                                        |                                            |             |              |          |

|             |                                                                        |                                            |             |              |          |

| STATUS: A   | waiting te                                                             | st selection                               |             | *            | <br>0:03 |

| 7           |                                                                        |                                            |             |              |          |

| e nd        | <slot #<="" td=""><td>&gt;</td><td></td><td></td><td>print</td></slot> | >                                          |             |              | print    |

|             | ,                                                                      |                                            |             |              | J        |

Figure 4-3. Option Test Card Slot Listing

| Memory Performance Verification                                  |          |      |

|------------------------------------------------------------------|----------|------|

| Static Memory in card slot # 7<br>8085 Emulator in card slot # 9 |          |      |

| Test                                                             | # Fail # | Test |

| Processor Control                                                | 0        | 0    |

| Emulation dus                                                    | 0        | 0    |

| Foreground                                                       | 0        | 0    |

|                                                                  |          |      |

| STAFUS: Awaiting test selection                                  |          | 0:04 |

| _ ·                                                              |          |      |

|                                                                  | prin     | t    |

|                                                                  |          |      |

|                                                                  |          |      |

Figure 4-4. Memory Performance Verification

|                           |                            | ormance Verifica<br>sor Control Test |                        |         |        |     |

|---------------------------|----------------------------|--------------------------------------|------------------------|---------|--------|-----|

| Static Memo<br>8085 Emula | ory in card<br>for in card | slot # 7<br>slot # 9                 | # *                    | rests = | 0      |     |

| вјоск #                   | Error                      | # Fail                               | Block #                | Error   | # Fail |     |

| 0 — 4К<br>4 — 8К          | 0000                       | 0                                    | 32 - 36K<br>36 - 40K   | 0000    | 0      |     |

| 8 - 12К<br>12 - 16К       | 0 0 0 0<br>0 0 0 0         | U<br>O                               | 40 - 44K<br>44 - 48K   | 0000    | 0      |     |

| 16 - 20K                  | 0000                       | 0                                    | 44 - 48 K<br>48 - 52 K | 0000    | 0      |     |

| 20 - 24K                  | 0000                       | 0                                    | 52 - 56K               | 0 0 0 0 | 0      |     |

| 24 – 28K<br>28 – 32K      | 0000                       | 0<br>0                               | 56 - 60K<br>60 - 64K   | 0000    | 0      |     |

|                           |                            |                                      |                        |         |        |     |

| TATUS: Test               | in progress                |                                      |                        |         |        | . 0 |

|                           |                            |                                      |                        |         |        |     |

|                           |                            |                                      |                        |         |        |     |

| end                       | avalo po                   | white the state                      |                        |         |        |     |

| enu                       | cycle ne                   | xt_test star                         | t                      |         | pr     | int |

Figure 4-5. Processor Control Test

Figure 4-6. Emulation Bus Test

### Memory Performance Verification Foreground Test Static Memory in card slot # 7 8085 Emulator in card slot # 9 Test # Fail # Test Release 0 Run Status=0000 0 Processor Break Status=0000 0 Illegai Memory Reference 0 write to Rom 0 Illegal Opcode 0 STATUS: Test in progress 0:06 end print

Figure 4-7. Foreground Test

# FIGURES 4-2 thru 4-7 LOCATED UNDER FOLD

4-8

¥\*

# **SECTION V**

# **ADJUSTMENTS**

The Model 64151A Emulation Memory Controller has one adjustment. This adjustment (R9) is set by factory personnel using software which is not available to customers or field personnel. It is recommended that the calibration not be disturbed. If repair to the timing section of the Model 64151A is made, contact your local HP Sales/Service Office concerning procedures for returning the board to the factory for readjustment.

# SECTION VI

# **REPLACEABLE PARTS**

# 6-1. INTRODUCTION.

6-2. This section contains information for ordering parts. Table 6-1 lists abbreviations used in the parts list and throughout the manual. Table 6-2 lists all replaceable parts in reference designator order. Table 6-3 contains the names and addresses that correspond to the manufacturer's five digit code numbers.

# 6-3. EXCHANGE ASSEMBLIES.

6-4. The Model 64151A is available through the Hewlett-Packard Corporate Parts Center by Blue Stripe Exchange. Exchange, factory repaired and tested assemblies are available only on a trade-in basis; therefore, assemblies required for spare parts stock must be ordered by the new assembly part number (found in table 6-2, Replaceable Parts). To order Blue Stripe Exchange assemblies, use the following part number:

A1: 64151-69503

# 6-5. ABBREVIATIONS.

6-6. Table 6-1 lists abbreviations used in the parts list, schematics and throughout the manual. In some cases, two forms of the abbreviations are used: one all in capital letters, and one partial or no capitals. This occurs because the abbreviations in the parts list are always capitals. However, in the schematics and other parts of the manual, other abbreviation forms are used with both lowercase and uppercase letters.

# 6-7. REPLACEABLE PARTS LIST.

6-8. Table 6-2 is the list of replaceable parts and is organized as follows:

- a. Chassis-mounted parts in alphanumeric order by reference designation.

- b. Electrical assemblies and their components in alphanumerical order by reference designation.

- c. Miscellaneous.

The information given for each part consists of the following:

- a. The Hewlett-Packard part number and the check digit.

- b. The total quantity (Qty) in the instrument.

- c. The description of the part.

- d. A five-digit code that indicates the manufacturer.

- e. The manufacturer's part number.

The total quantity for each part is given only once - at the first appearance of the part number in the list.

# 6-9. ORDERING INFORMATION.

6-10. To order a part listed in the replaceable parts table, quote the Hewlett-Packard part number and check digit, indicate the quantity required, and address the order to the nearest Hewlett-Packard Sales/Service Office.

6-11. To order a part that is not listed in the replaceable parts table, include the instrument model number, instrument repair number, the description and function of the part, and the number of parts required. Address the order to the nearest Hewlett-Packard Sales/Service Office.

# 6-12. DIRECT MAIL ORDER SYSTEM.

6-13. Within the USA, Hewlett-Packard can supply parts through a direct mail order system. Advantages of using the system are as follows:

- a. Direct ordering and shipment from the HP Parts Center in Mountain View, California.

- b. No maximum and minimum on any mail order (there is a minimum order amount for parts ordered through a local HP Sales/Service Office when the orders require billing and invoicing).

- c. Prepaid transportation (there is a small handling charge for each order).

- d. No invoices to provide these advantages, a check or money order must accompany each order.

6-14. Mail-order forms and specific ordering information are available through your local HP Sales/Service Office. Addresses and phone numbers are located at the back of this manual.

|      |                                  |         | REFERENCE DE            | SIGNATORS |                          |            |                       |

|------|----------------------------------|---------|-------------------------|-----------|--------------------------|------------|-----------------------|

| Å    | = assembly                       | F       | = fuse                  | МР        | = mechanical part        | U          | = integrated circuit  |

| 3    | = motor                          | FL      | = filter                | Р         | = plug                   | v          | = vacuum, tube, neon  |

| т    | = battery                        | IC      | = integrated circuit    | Q         | = transistor             |            | bulb, photocell, etc  |

| ;    | = capacitor                      | J       | = jack                  | R         | = resistor               | VR         | = voltage regulator   |

| P    | = coupler                        | к       | = relay                 | RT        | = thermistor             | w          | = cable               |

| R    | = diode                          | L       | = inductor              | S         | = switch                 | х          | = socket              |

| L    | = delay line                     | LS      | = loud speaker          | т         | = transformer            | Y          | = crystal             |

| S    | = device signaling (lamp)        | м       | = meter                 | тв        | = terminal board         | Z          | = tuned cavity networ |

|      | = misc electronic part           | МК      | = microphone            | ТР        | = test point             |            |                       |

|      |                                  |         | ABBREVI                 | ATIONS    |                          |            |                       |

|      | = amperes                        | н       | = henries               | N/O       | = normally open          | RMO        | = rack mount only     |

| FC   | = automatic frequency<br>control | HDW     | = hardware              | NOM       | = nominal                | RMS        | = root-mean square    |

| MPL  | = amplifier                      | HEX     | = hexagonal             | NPO       | = negative positive zero | RWV        | = reverse working     |

|      |                                  | HG      | = mercury               |           | (zero temperature        |            | voltage               |

| FO   | = beat frequency oscillator      | HR      | = hour(s)               |           | coefficient)             |            |                       |

| E CU | = beryllium copper               | HZ      | = hertz                 | NPN       | = negative-positive-     | S-B        | = slow-blow           |

| н    | = binder head                    |         |                         |           | negative                 | SCR        | = screw               |

| Р    | = bandpass                       |         |                         | NRFR      | = not recommended for    | SE         | = selenium            |

| RS   | = brass                          | IF      | = intermediate freq     |           | field replacement        | SECT       | = section(s)          |

| wo   | = backward wave oscillator       |         | = impregnated           | NSR       | = not separately         | SEMICON    | = semiconductor       |

|      |                                  | INCD    | = incandescent          |           | replaceable              | SI         | = silicon             |

| CW   | = counter-clockwise              | INCL    | = include(s)            |           |                          | SIL        | = silver              |

| ER   | = ceramic                        | INS     | = insulation(ed)        | OBD       | = order by description   | SL         | = slide               |

| мо   | = cabinet mount only             | INT     | = internal              | он        | = oval head              | SPG        | = spring              |

| OEF  | = coeficient                     |         |                         | ox        | = oxide                  | SPL        | = special             |

| ом   | = common                         | к       | = kilo=1000             |           |                          | SST        | = stainless steel     |

| OMP  | = composition                    |         |                         |           |                          | SR         | = split ring          |

| OMPL | = complete                       | LH      | = left hand             | Р         | = peak                   | STL        | = steel               |

| ONN  | = connector                      | LIN     | = linear taper          | PC        | = printed circuit        |            |                       |

| Р    | = cadmium plate                  | LK WASH | = lock washer           | PF        | = picofarads= 10-12      | ТА         | = tantalum            |

| RT   | = cathode-ray tube               | LOG     | = logarithmic taper     |           | farads                   | TD         | = time delay          |

| w    | = clockwise                      | LPF     | = low pass filter       | PH BRZ    | = phosphor bronze        | TGL        | = toggle              |

|      |                                  |         |                         | PHL       | = phillips               | THD        | = thread              |

| EPC  | = deposited carbon               | M       | = milli=10-3            | PIV       | = peak inverse voltage   | TI         | = titanium            |

| R    | = drive                          | MEG     | = meg=10 <sup>6</sup>   | PNP       | = positive-negative-     | TOL        | = tolerance           |

|      |                                  | MET FLM | = metal film            |           | positive                 | TRIM       | = trimmer             |

| LECT | = electrolytic                   | MET OX  | = metallic oxide        | P/O       | = part of                | тwт        | = traveling wave tube |

| NCAP | = encapsulated                   | MFR     | = manufacturer          | POLY      | = polystyrene            |            |                       |

| хт   | = external                       | MHZ     | = mega hertz            | PORC      | = porcelain              | U          | = micro=10-6          |

|      |                                  | MINAT   | = miniature             | POS       | = position(s)            |            |                       |

|      | = farads                         | мом     | = momentary             | POT       | = potentiometer          | VAR        | = variable            |

| н    | = flat head                      | MOS     | = metal oxide substrate | PP        | = peak-to-peak           | VDCW       | = dc working volts    |

| IL H | = fillister head                 | MTG     | = mounting              | PT        | = point                  |            |                       |

| XD   | = fixed                          | MY      | = "mylar"               | PWV       | = peak working voltage   | <b>W</b> / | = with                |

|      |                                  |         |                         |           |                          | w          | = watts               |

| i    | = giga (109)                     | N       | = nano (10-9)           | RECT      | = rectifier              | wiv        | = working inverse     |

| E    | = germanium                      | N/C     | = normally closed       | RF        | = radio frequency        |            | voltage               |

| iL   | = glass                          | NE      | = neon                  | RH        | = round head or          | ww         | = wirewound           |

| RD   | = ground(ed)                     | NI PL   | = nickel plate          |           | right hand               | W/O        | = without             |

#### Table 6-1. Reference Designators and Abbreviations

# Table 6-2. Replaceable Parts

| Reference<br>Designation                           | HP Part<br>Number                                                          | C<br>D                     | Qty              | Description                                                                                                                                                                                                    | Mfr<br>Code                                        | Mfr Part Number                                                                                  |

|----------------------------------------------------|----------------------------------------------------------------------------|----------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------|

| A1                                                 | 64151-66503                                                                | 8                          | 1                | EMULATION MEMORY CONTROLLER                                                                                                                                                                                    | 28480                                              | 64151-66503                                                                                      |

| A1C1<br>A1C2<br>A1C3<br>A1C4<br>A1C5               | 0160-2055<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055 | 9<br>9<br>9<br>9<br>9<br>9 | 23               | CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER | 28480<br>28480<br>28480<br>28480<br>28480<br>28480 | 0160-2055<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055                       |

| A1C6<br>A1C7<br>A1C8<br>A1C9<br>A1C10              | 0160-2055<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055 | 9<br>9<br>9<br>9<br>9      |                  | CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER | 28480<br>28480<br>28480<br>28480<br>28480<br>28480 | 0160-2055<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055                       |

| A1C11<br>A1C12<br>A1C13<br>A1C13<br>A1C14<br>A1C15 | 0160-2207<br>0140-0198<br>0160-2055<br>0160-2055<br>0160-2055              | 35999                      | 1<br>2           | CAPACITOR-FXD 300PF +-5X 300VDC MICA<br>CAPACITOR-FXD 200PF +-5X 300VDC MICA<br>CAPACITOR-FXD .01UF +80-20X 100VDC CER<br>CAPACITOR-FXD .01UF +80-20X 100VDC CER<br>CAPACITOR-FXD .01UF +80-20X 100VDC CER     | 28480<br>72136<br>28480<br>28480<br>28480          | 0160-2207<br>DM15F201J0300WV1CR<br>0160-2055<br>0160-2055<br>0160-2055                           |

| A1C16<br>A1C17<br>A1C18<br>A1C19<br>A1C20          | 0160-2055<br>0160-2055<br>0180-0229<br>0160-0161<br>0160-2200              | 9<br>9<br>7<br>4<br>6      | 1<br>1<br>1      | CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD 33UF+-10% 10VDC TA<br>CAPACITOR-FXD .01UF +-10% 200VDC POLYE<br>CAPACITOR-FXD 43PF +-5% 300VDC MICA          | 28480<br>28480<br>56289<br>28480<br>28480          | 0160-2055<br>0160-2055<br>150D336X9010B2<br>0160-0161<br>0160-2200                               |

| A1021<br>A1022<br>A1023<br>A1023<br>A1024<br>A1025 | 0160-2198<br>0160-2198<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055 | 1<br>1<br>9<br>9<br>9      | 3                | CAPACITOR-FXD 20PF +-5% 300VDC MICA<br>CAPACITOR-FXD 20PF +-5% 300VDC MICA<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER       | 28480<br>28480<br>28480<br>28480<br>28480<br>28480 | 0160-2198<br>0160-2198<br>0160-2055<br>0160-2055<br>0160-2055                                    |

| A1C26<br>A1C27<br>A1C28<br>A1C29<br>A1C30          | 0160-2055<br>0160-2055<br>0140-0198<br>0140-0203<br>0160-2055              | 99539                      | 1                | CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD 200PF +-5% 300VDC MICA<br>CAPACITOR-FXD 30PF +-5% 500VDC MICA<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER      | 28480<br>28480<br>72136<br>72136<br>28480          | 0160-2055<br>0160-2055<br>DM15F20170300WV1CR<br>DM15F20170300WV1CR<br>0160-2055                  |

| A1C31<br>A1C32<br>A1C33<br>A1C34                   | 0160-2198<br>0160-2055<br>0160-2055<br>0140-0190                           | 1<br>9<br>9<br>7           | 1                | CAPACITOR-FXD 20PF +-5% 300VDC MICA<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD .01UF +80-20% 100VDC CER<br>CAPACITOR-FXD 39PF +-5% 300VDC MICA                                                 | 28480<br>28480<br>28480<br>72136                   | 0160-2198<br>0160-2055<br>0160-2055<br>DM15E390J0300WV1CR                                        |

| A1CR1<br>A1CR2<br>A1CR3<br>A1CR4                   | 1901-0040<br>1901-0040<br>1901-0040<br>1901-0040<br>1901-0040              | 1<br>1<br>1                | 4                | DIODE-SWITCHING 30V 50MA 2NS DO-35<br>DIODE-SWITCHING 30V 50MA 2NS DO-35<br>DIODE-SWITCHING 30V 50MA 2NS DO-35<br>DIODE-SWITCHING 30V 50MA 2NS DO-35                                                           | 28480<br>28480<br>28480<br>28480<br>28480          | 1901-0040<br>1901-0040<br>1901-0040<br>1901-0040<br>1901-0040                                    |

| A1J4                                               | 1251-5823                                                                  | 9                          | 1                | CONNECTOR 28-PIN M POST TYPE                                                                                                                                                                                   | 28480                                              | 1251-5823                                                                                        |

| A1L1<br>A1L2                                       | 9140-0114<br>9100-2264                                                     | 4                          | 1<br>1           | INDUCTOR RF-CH-MLD 10UH 10% .166DX.385LG<br>INDUCTOR RF-CH-MLD 6.8UH 10% .105DX.26LG                                                                                                                           | 28480<br>28480                                     | 9140-0114<br>9100-2264                                                                           |

| A1MP1<br>A1MP2<br>A1MP3<br>A1MP4<br>A1MP5          | 1480-0116<br>64151-85001<br>64151-85002<br>7124-0271<br>1400-0611          | 8<br>1<br>2<br>8<br>0      | 2<br>1<br>1<br>1 | PIN-GRV .062-IN-DIA .25-IN-LG STL<br>EXTRACTOR-P.C. BOARD<br>EXTRACTOR-P.C. BOARD<br>LABEL-ORANGE DOT<br>CLAMP-CABLE                                                                                           | 28480<br>28480<br>28480<br>85480<br>06915          | 1480-0116<br>64151-85001<br>64151-85002<br>GD25 TAPE B-810-OR<br>CFCC-8                          |

| A1R1<br>A1R2<br>A1R3                               | 0684-1021<br>0684-1021                                                     | 7<br>7                     | 6                | RESISTOR 1K 10% .25W FC TC=-400/+600<br>RESISTOR 1K 10% .25W FC TC=-400/+600<br>NOT ASSIGNED                                                                                                                   | 01121<br>01121                                     | CB1021<br>CB1021                                                                                 |

| A1R4<br>A1R5                                       | 0757-0416                                                                  | 7                          | 4                | RESISTOR 511 1% .125W F TC=0+-100<br>NOT ASSIGNED                                                                                                                                                              | 24526                                              | C4-1/8-T0-511R-F                                                                                 |

| A1R6<br>A1R7<br>A1R8<br>A1R9<br>A1R10              | 0757-0416<br>0684-1021<br>0684-1021<br>2100-2497<br>0684-1021              | 7<br>7<br>7<br>9<br>7      | 1                | RESISTOR 511 12 .125W F TC=0+-100<br>RESISTOR 1K 10% .25W FC TC=-400/+600<br>RESISTOR 1K 10% .25W FC TC=-400/+600<br>RESISTOR-TRMR 2K 10% C TOP-ADJ 1-TRN<br>RESISTOR-1KM 10% .25W FC TC=-400/+600             | 24526<br>01121<br>01121<br>73138<br>01121          | C4-1/8-T0-511R-F<br>CB1021<br>CB1021<br>82PR2K<br>CB1021                                         |

| A1R11<br>A1R12                                     | 0684-1021                                                                  | 7                          |                  | RESISTOR 1K 10% .25W FC TC=-400/+600<br>Not Assigned                                                                                                                                                           | 01121                                              | CB1021                                                                                           |

| A1R13<br>A1R14<br>A1R15                            | 0757-0453<br>0757-0438<br>0698-0084                                        | 239                        | 1<br>3<br>2      | RESISTOR 30.1K 1% .125W F TC=0+-100<br>RESISTOR 5.11K 1% .125W F TC=0+-100<br>RESISTOR 2.15K 1% .125W F TC=0+-100                                                                                              | 24546<br>24546<br>24546                            | C4-1/8-T0-3012-F<br>C4-1/8-T0-5111-F<br>C4-1/8-T0-2151-F                                         |

| A1R16<br>A1R17<br>A1R18<br>A1R19<br>A1R20          | 0698-3151<br>0698-3151<br>0698-0084<br>0757-0438<br>0757-0438              | 77933                      | 2                | RESISTOR 2.87K 1% .125W F TC=0+-100<br>RESISTOR 2.87K 1% .125W F TC=0+-100<br>RESISTOR 2.15K 1% .125W F TC=0+-100<br>RESISTOR 5.11K 1% .125W F TC=0+-100<br>RESISTOR 5.11K 1% .125W F TC=0+-100                | 24546<br>24546<br>24546<br>24546<br>24546<br>24546 | C4-1/8-T0-2871-F<br>C4-1/8-T0-2871-F<br>C4-1/8-T0-2151-F<br>C4-1/8-T0-5111-F<br>C4-1/8-T0-5111-F |

| A1R21<br>A1R22<br>A1R23                            | 0757-0416<br>0757-0416<br>06 <b>9</b> 8-8271                               | 772                        | 1                | RESISTOR 511 1% .125W F TC=0+-100<br>RESISTOR 511 1% .125W F TC=0+-100<br>RESISTOR 1.1 5% .25W F TC=0+-100                                                                                                     | 24526<br>24526<br>11502                            | C4-1/8-T0-511R-F<br>C4-1/8-T0-511R-F<br>TF07-1/4-T0-1R1-J                                        |

| A151                                               | 3101-0458                                                                  | 1                          | 1                | SWITCH-SL DPDT SUBMIN .02A 20VDC PC                                                                                                                                                                            | 28480                                              | 3101-0458                                                                                        |

|                                                    |                                                                            |                            |                  |                                                                                                                                                                                                                |                                                    |                                                                                                  |

See introduction to this section for ordering information.

# Table 6-2. Replaceable Parts (Cont'd)

| Reference<br>Designation                                                                            | HP Part<br>Number                                                                                                                               | C<br>D                | Qty          | Description                                                                                                                                                                                                                                                                                                                                                                                                          | Mfr<br>Code                                                                                              | Mfr Part Number                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1TP1<br>A1TP2<br>A1TP3<br>A1TP4<br>A1TP5                                                           | 0360-0535<br>0360-0535<br>0360-0535<br>0360-0535<br>0360-0535<br>0360-0535                                                                      | 0<br>0<br>0<br>0      | 8            | TERMINAL TEST POINT PCB<br>TERMINAL TEST POINT PCB<br>TERMINAL TEST POINT PCB<br>TERMINAL TEST POINT PCB<br>TERMINAL TEST POINT PCB                                                                                                                                                                                                                                                                                  | 00000<br>00000<br>00000<br>00000<br>00000<br>00000                                                       | ORDER BY DESCRIPTION<br>ORDER BY DESCRIPTION<br>ORDER BY DESCRIPTION<br>ORDER BY DESCRIPTION<br>ORDER BY DESCRIPTION                                         |

| A1TP6<br>A1TP7<br>A1TP8                                                                             | 0360-0535<br>0360-0535<br>0360-0535                                                                                                             | 0<br>0<br>0           |              | TERMINAL TEST POINT PCB<br>TERMINAL TEST POINT PCB<br>TERMINAL TEST POINT PCB                                                                                                                                                                                                                                                                                                                                        | 00000<br>00000<br>00000                                                                                  | ORDER BY DESCRIPTION<br>ORDER BY DESCRIPTION<br>ORDER BY DESCRIPTION                                                                                         |

| A1U1<br>A1U2<br>A1U3<br>A1U4                                                                        | 1820-1997<br>1820-1918<br>1820-1624<br>1820-1624                                                                                                | 7277                  | 2 2 <b>4</b> | IC FF TTL LS D-TYPE POS-EDGE-TRIG PRL-IN<br>IC BFR TTL LS LINE DRVR OCTL<br>IC BFR TTL S OCTL 1-INP<br>IC BFR TTL S OCTL 1-INP                                                                                                                                                                                                                                                                                       | 01295<br>01295<br>01295<br>01295<br>01295                                                                | SN74LS374N<br>SN74LS241N<br>SN74S241N<br>SN74S241N<br>SN74S241N                                                                                              |

| A1U5<br>A1U6<br>A1U7<br>A1U8<br>A1U9<br>A1U10<br>A1U11<br>A1U11<br>A1U12<br>A1U13<br>A1U14<br>A1U15 | $1820-0693\\1820-1429\\1820-1015\\1820-1015\\1820-1997\\1820-1997\\1820-1624\\1820-1624\\1820-1624\\1820-1428\\1820-1428\\1820-1015\\1820-1196$ | 89007277908           | 3<br>2<br>3  | IC FF TTL S D-TYPE POS-EDGE-TRIG<br>IC MUXR/DATA-SEL TTL LS 2-TO-1-LINE GUAD<br>IC MUXR/DATA-SEL TTL S 2-TO-1-LINE GUAD<br>IC MUXR/DATA-SEL TTL S 2-TO-1-LINE GUAD<br>IC FF TTL LS D-TYPE POS-EDGE-TRIG PRL-IN<br>IC BFR TTL LS LINE DRVR OCTL<br>IC BFR TTL S OCTL 1-INP<br>IC BFR TTL S OCTL 1-INP<br>IC BFR TTL S OCTL 1-INP<br>IC MUXR/DATA-SEL TTL LS 2-TO-1-LINE GUAD<br>IC FF TTL LS D-TYPE POS-EDGE-TRIG COM | 01295<br>01295<br>01295<br>01295<br>01295<br>01295<br>01295<br>01295<br>01295<br>01295<br>01295<br>01295 | SN74S74N<br>SN74LS158N<br>SN74S158N<br>SN74S158N<br>SN74LS374N<br>SN74LS241N<br>SN74S241N<br>SN74S241N<br>SN74S241N<br>SN74S158N<br>SN74LS158N<br>SN74LS158N |

| A1U16<br>A1U17<br>A1U18<br>A1U19<br>A1U20                                                           | 1820-0693<br>1820-1322<br>1820-0683<br>1820-1367<br>1820-1204                                                                                   | 82659                 | 3211         | IC FF TTL S D-TYPE POS-EDGE-TRIG<br>IC GATE TTL S NOR QUAD 2-INP<br>IC INV TTL S HEX 1-INP<br>IC GATE TTL S AND QUAD 2-INP<br>IC GATE TTL LS NAND DUAL 4-INP                                                                                                                                                                                                                                                         | 01295<br>01295<br>01295<br>01295<br>01295<br>01295                                                       | SN74574N<br>SN74502N<br>SN74504N<br>SN74508N<br>SN74LS20N                                                                                                    |