# PDP-11/94-E System User and Maintenance Guide

Order Number EK-PDP94-MG-001

#### September 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Copyright © Digital Equipment Corporation 1990

All Rights Reserved. Printed in U.S.A.

**DECwriter**

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

The following are trademarks of Digital Equipment Corporation:

DIBOL UNIBUS DEC/CMS EduSystem VAX **DEC/MMS** IAS **VAXcluster DECnet MASSBUS VMS** DECsystem-10 PDP VT DECSYSTEM-20 PDT **DECUS** RSTS

RSX

digillal

Mate-N-Lok is a trademark of AMP, Inc.

This document was prepared and published by Educational Services Development and Publishing, Digital Equipment Corporation.

# Contents

| About This Guide |         |                                             |      |

|------------------|---------|---------------------------------------------|------|

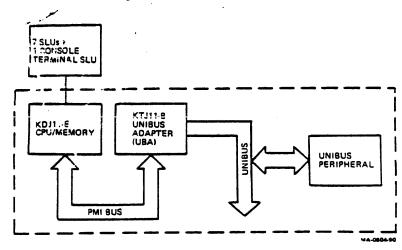

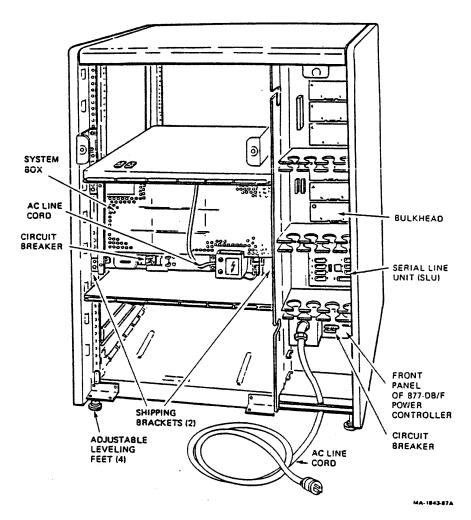

| 1                | Syst    | tem Overview                                |      |

|                  | 1.1     | Introduction                                | 1-1  |

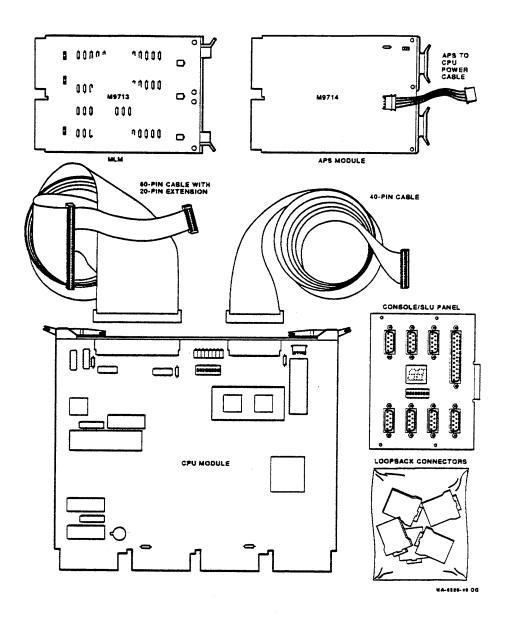

|                  | 1.2     | System Components                           | 1-1  |

|                  | 1.2.1   | •                                           | 1–3  |

|                  | 1.2.2   | KTJ11-B UNIBUS Adapter Module (M8191)       | 1–3  |

|                  | 1.2.3   | UNIBUS Terminator Module (M9302)            | 1–3  |

|                  | 1.2.4   | Minimum Load Module (M9713)                 | 1–3  |

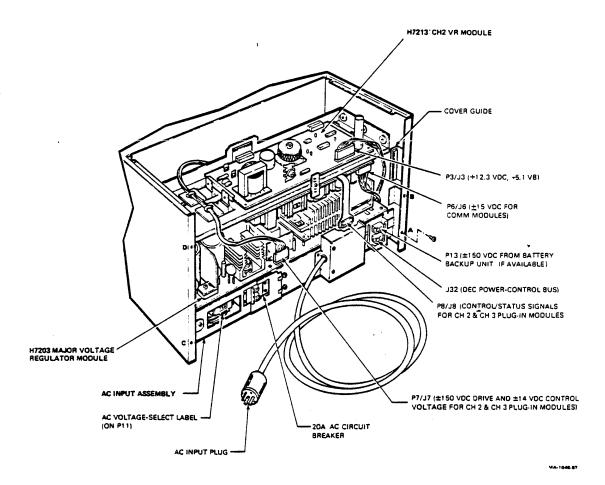

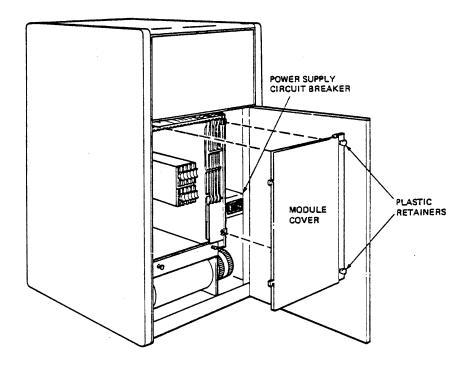

|                  | 1.2.5   | Power Supply                                | 1–4  |

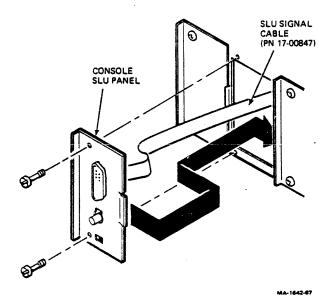

|                  | 1.2.6   | Console/Serial Line Unit (SLU) Panel        | 1-4  |

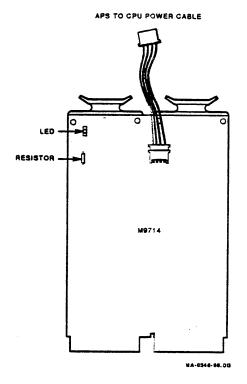

|                  | 1.2.7   | Alternate Power Source (APS) Module (M9714) | 1-4  |

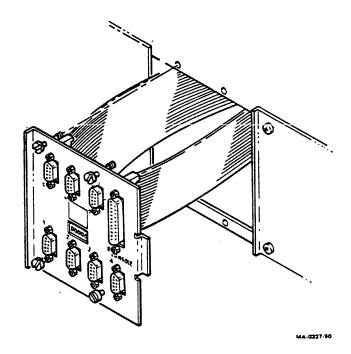

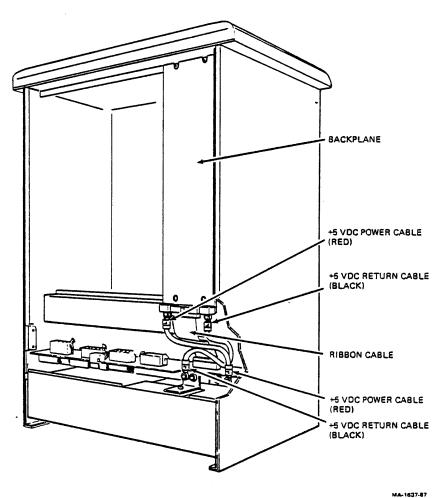

|                  | 1.2.8   | CPU Backplane Assembly                      | 1-5  |

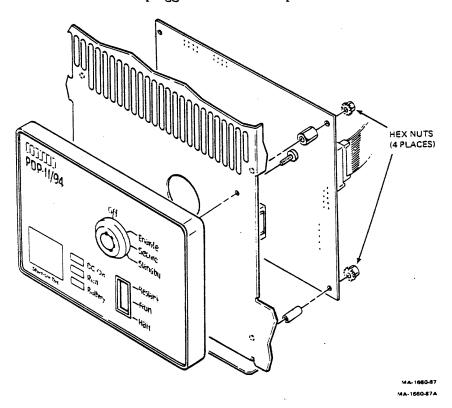

|                  | 1.2.9   | Front Panel Assembly                        | 1–5  |

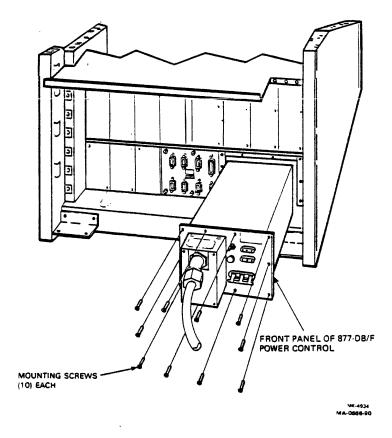

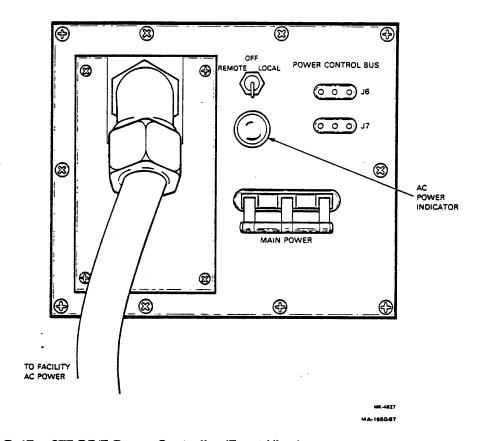

|                  | 1.2.10  | Cabinet Power Controller                    | 1–6  |

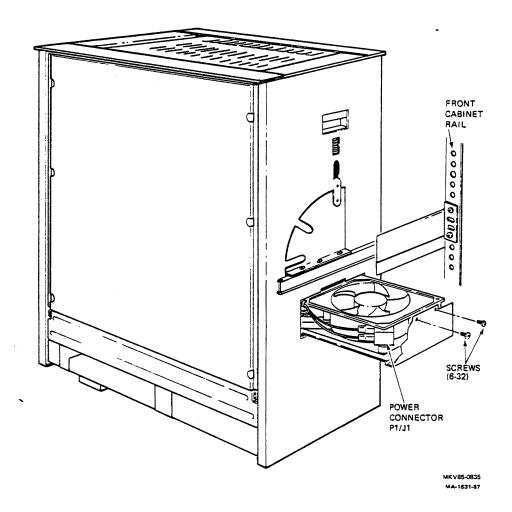

|                  | 1.2.11  | Cooling                                     | 1–6  |

|                  | 1.2.12  | 2 Additional Expansion Options              | 1–6  |

|                  | 1.2.13  | System Configuration                        | 1–6  |

|                  | 1.3     | System Specifications                       | 1–9  |

|                  | 1.4     | Related Documents                           | 1-12 |

|                  | 1.4.1   | Digital Personnel Ordering Information      | 1-12 |

|                  | 1.5     | Customer Ordering Information               | 1-12 |

|                  |         |                                             |      |

| 2                | Unp     | acking and Installing                       |      |

|                  | 2.1     | General                                     | 2-1  |

|                  | 2.2     | Site Considerations                         | 2-1  |

|                  | 2.2.1   | Physical Requirements                       | 2-1  |

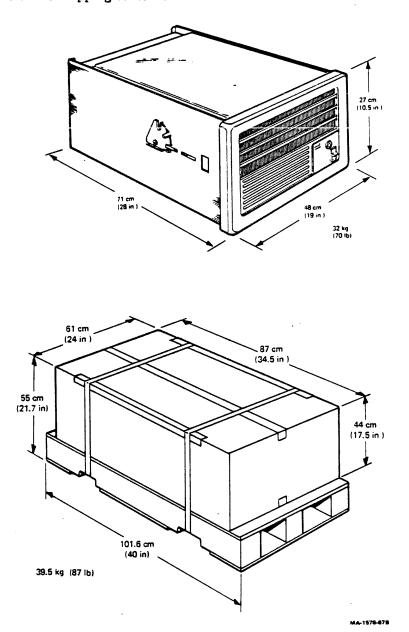

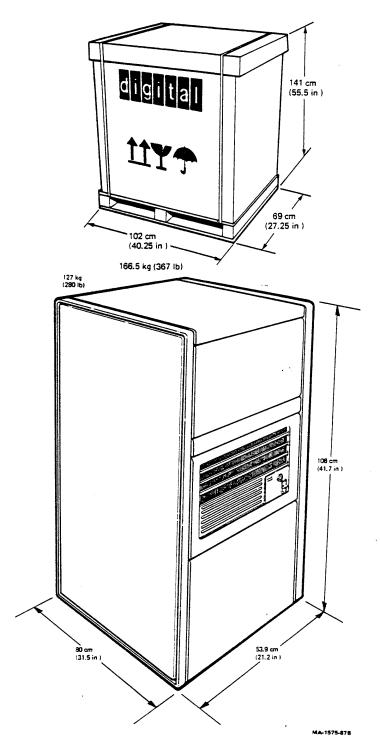

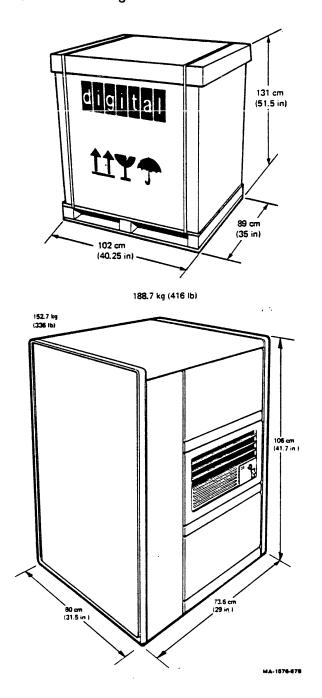

|                  | 2.2.2   | System Dimensions                           | 2–2  |

|                  | 2.2.3   | Temperature and Humidity                    | 2–5  |

|                  | 2.2.4   | Acoustical Dampening                        | 2–5  |

|                  | . 2.2.5 | Lighting                                    | 2–5  |

|                  | 2.2.6   | Static Electricity                          | 2–6  |

|                  | 2.2.7   | Electrical Interference                     | 2–6  |

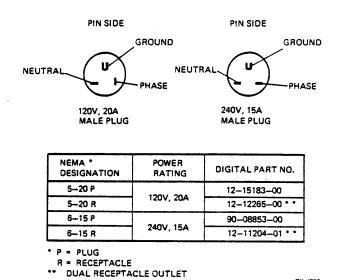

|   | 2.2.8 A   | C Input Power Requirements                                | 2–6  |

|---|-----------|-----------------------------------------------------------|------|

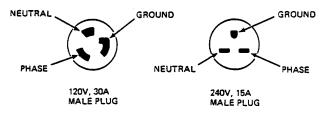

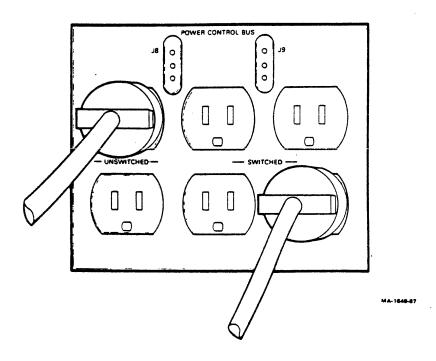

|   | 2.2.9 P   | ower Connections (AC)                                     | 2–6  |

|   | 2.2.10 S  | ystem Grounding                                           | 2–8  |

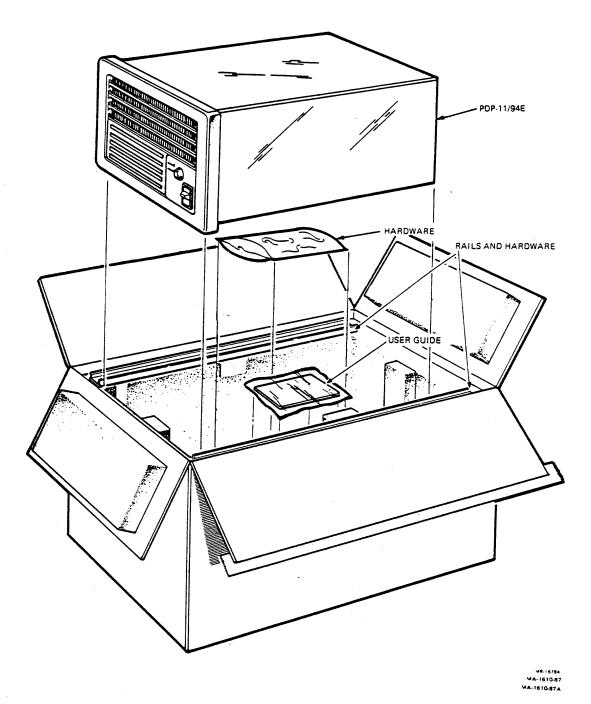

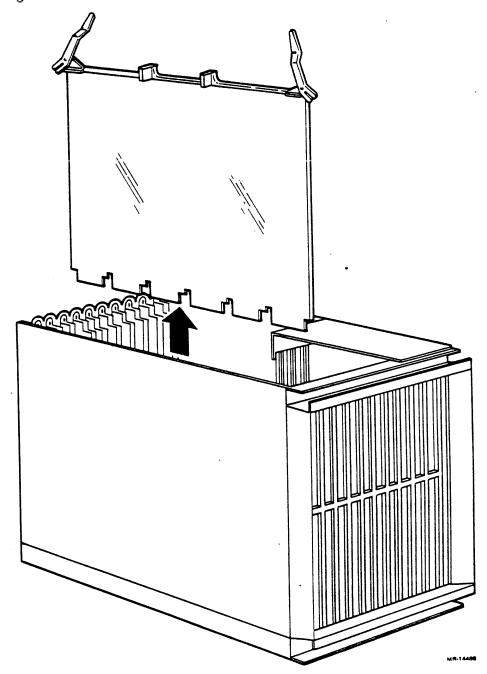

|   | 2.3 Unp   | packing                                                   | 2–8  |

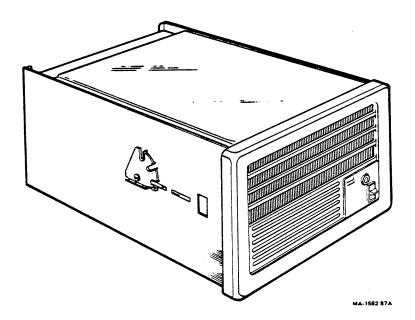

|   | 2.3.1 P   | DP-11/94-E Unpacking Instructions                         | 2-8  |

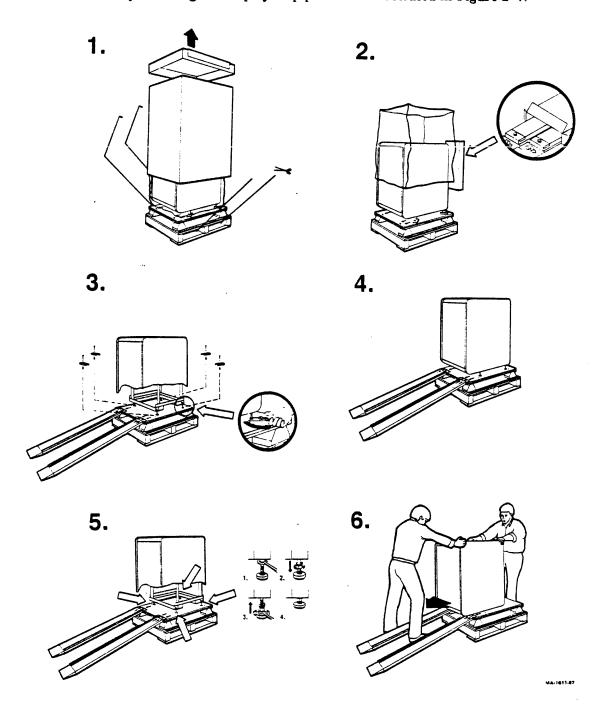

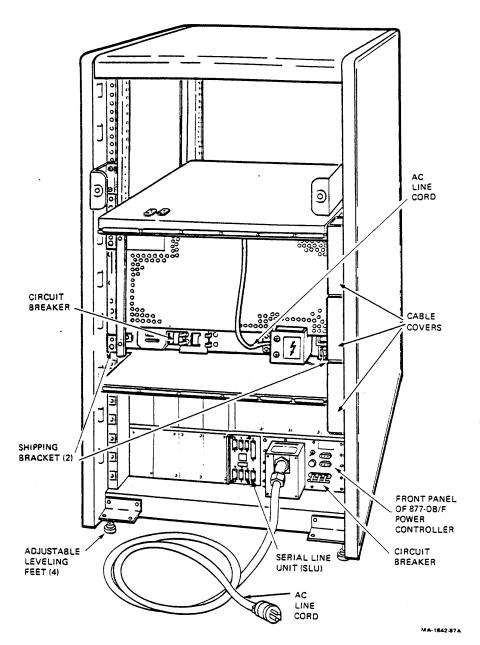

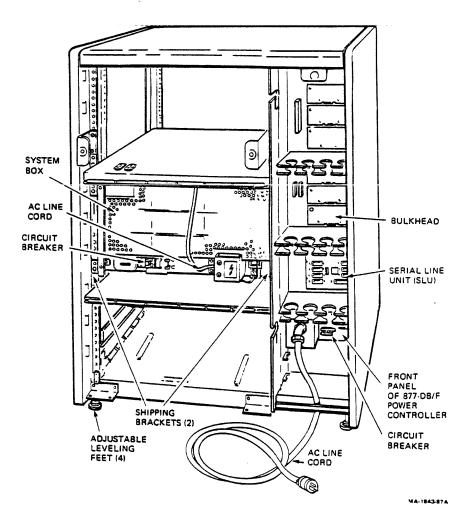

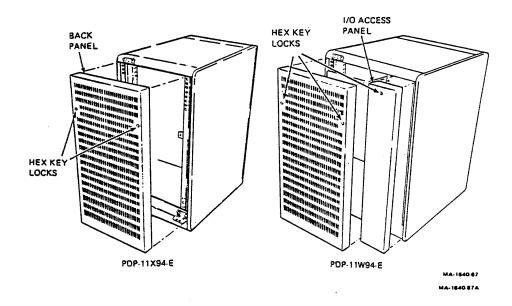

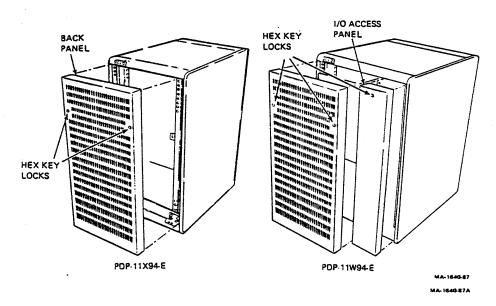

|   | 2.3.2 P   | DP-11X94-E and PDP-11W94-E Unpacking                      | 2-9  |

|   | 2.4 Inst  | allation                                                  | 2-11 |

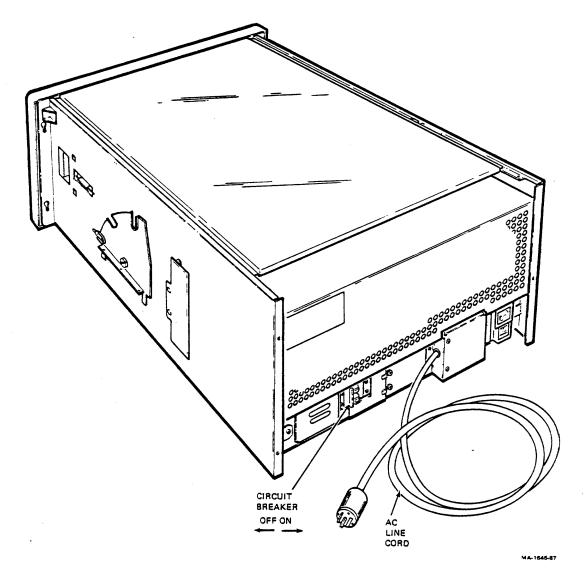

|   | 2.4.1 P   | DP-11/94-E Installation                                   | 2-11 |

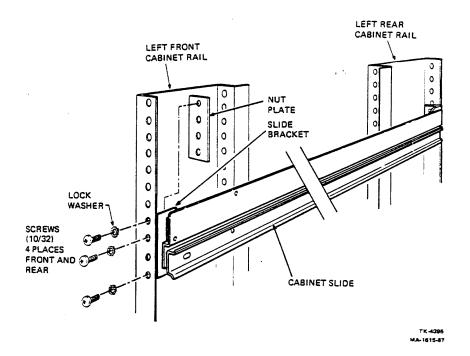

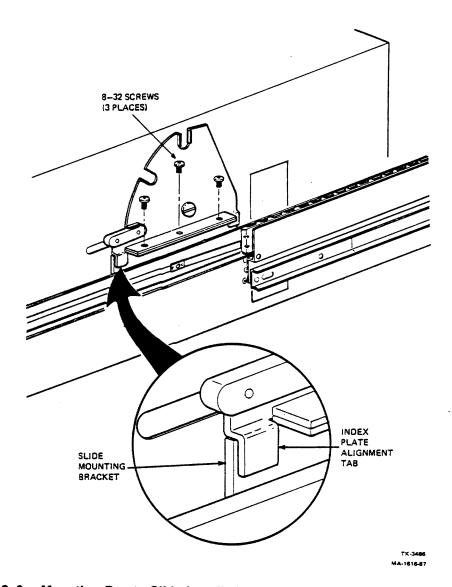

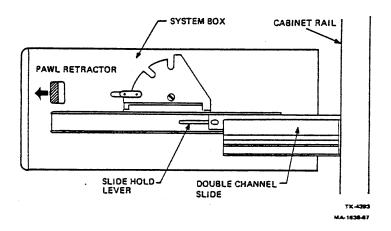

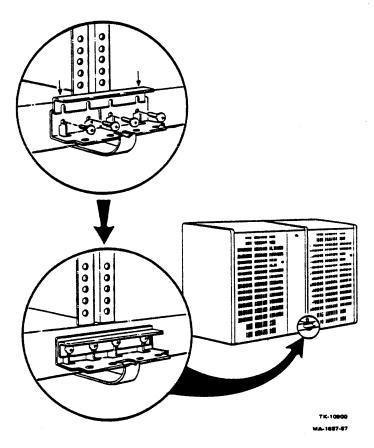

|   | 2.4.1.1   | Slide Assembly Mounting                                   |      |

|   | 2.4.1.2   | Mounting the System Box to the Slide Assembly             |      |

|   | 2.4.1.3   | Mounting the Console/Serial Line Unit Panel               |      |

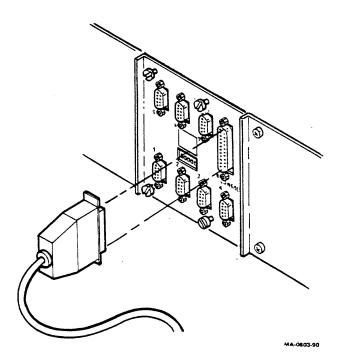

|   | 2.4.1.4   | Console/SLU Terminal Connection                           |      |

|   | 2.4.1.5   | AC Power Cord Connection                                  |      |

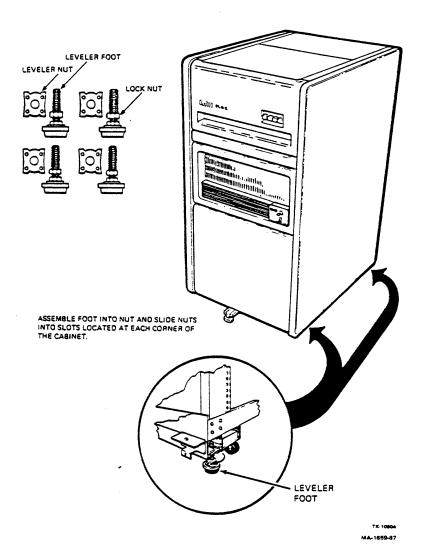

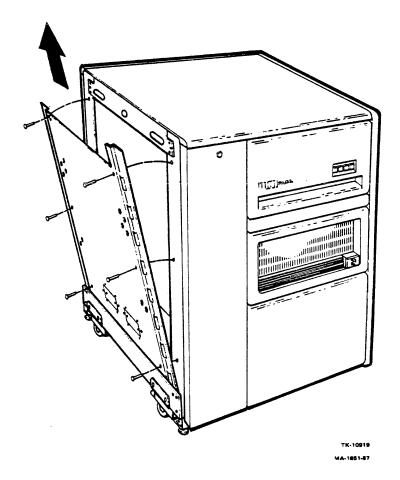

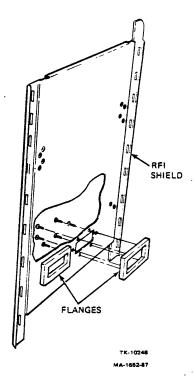

|   | 2.4.2 P   | DP-11X94-E and PDP-11W94-E Cabinet System Installation    |      |

|   |           | able Management                                           |      |

|   |           | peration Check                                            |      |

|   |           | •                                                         |      |

| 3 | Operation | on                                                        |      |

| 3 | •         |                                                           |      |

|   |           | eral                                                      | 3–1  |

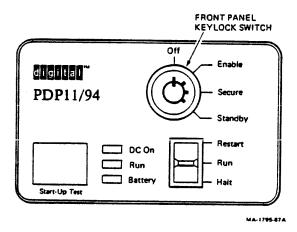

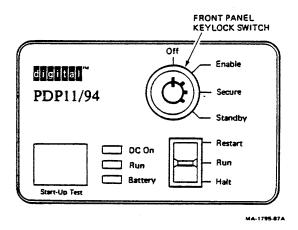

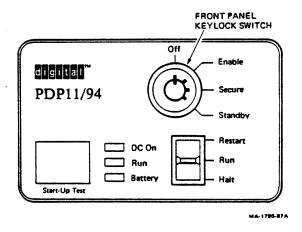

|   | 3.2 From  | nt Panel                                                  | 3–1  |

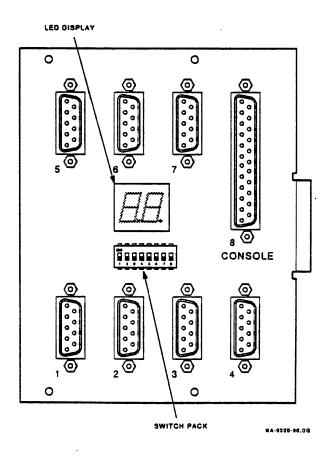

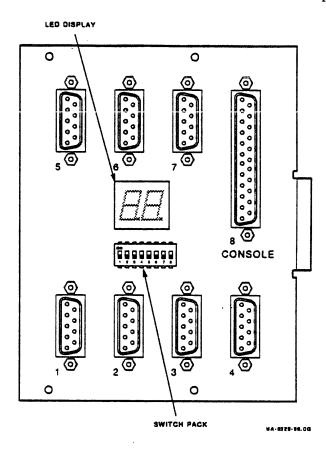

|   | 3.3 Con   | sole/Serial Line Unit Panel Switches                      | 3-4  |

|   | 3.4 Ope   | ration Overview                                           | 3–6  |

|   | 3.5 Har   | d Copy Terminal Support                                   | 3–7  |

|   | 3.5.1 B   | oot Command                                               | 3–8  |

|   | 3.5.1.1   | Transferring Control to Non-Digital Boot Modules          | 3–9  |

|   | 3.5.1.2   | Error Detection During the Boot Command                   | 3-10 |

|   | 3.5.2 D   | riagnostic Command                                        | 3-11 |

|   | 3.5.3 H   | [elp Command                                              | 3-13 |

|   | 3.5.4 L   | ist Command                                               | 3-13 |

|   | 3.5.5 · M | Iap Command                                               | 3-15 |

|   |           | etup Command                                              | 3–15 |

|   | 3.5.6.1   | Setup Mode Command 1 - Exit                               | 3-17 |

|   | 3.5.6.2   | Setup Mode Command 2 - Select Configuration Parameters    | 3-17 |

|   | 3.5.6.3   | Setup Mode Command 3 - Select Diagnostic Configuration    | 3-26 |

|   | 3.5.6.4   | Setup Mode Command 4 - Select Serial Line Parameters      | 3-27 |

|   | 3.5.6.5   | Setup Mode Command 5 - Select Boot Parameters             | 3-29 |

|   | 3.5.6.6   | Setup Mode Command 6 - List Available Boot Programs       | 3–31 |

|   | 3.5.6.7   | Setup Mode Command 7 - Factory Setting                    | 3-32 |

|   | 3.5.6.8   | Setup Mode Command 8 - Save The Setup Table In The EEPROM | 3–33 |

|   | 3.5.6.9   | Setup Mode Command 9 - Load EEPROM Data Into The Setup    | o—00 |

|   |           | Table                                                     | 3–33 |

|   | 3.5.6.10  | Setup Mode Command 10 - Load EEPROM Boot Program Into     |      |

|   |           | Memory                                                    | 3–34 |

|   | 3.5.6.11 Setup Mode Command 11 - Edit or Create EEPROM Boot Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3–34       |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   | 3.5.6.12 Setup Mode Command 12 - Save a Boot Program In The EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-36       |

|   | 3.5.6.13 Setup Mode Command 13 - Delete a Saved EEPROM Boot.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|   | Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3–37       |

|   | The state of the s | 3–37       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|   | 3.6 Video Terminal Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3–39       |

|   | 3.6.1 Moving Through the Menus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3–39       |

|   | 3.6.2 Types of Function Fields - Video Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3–39       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-40       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-45       |

|   | Total Descripting Tests Executed Opon Fower-Op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-45       |

|   | pototomis and precedents an individual lest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-46       |

|   | a croad of least 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-46       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3–46       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|   | 3.7 DCJ-11 Micro ODT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-48       |

|   | 3.7.0.1 ODT Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3–49       |

| 4 | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|   | 4.1 General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4–1        |

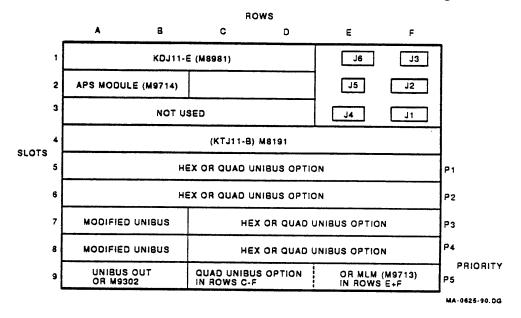

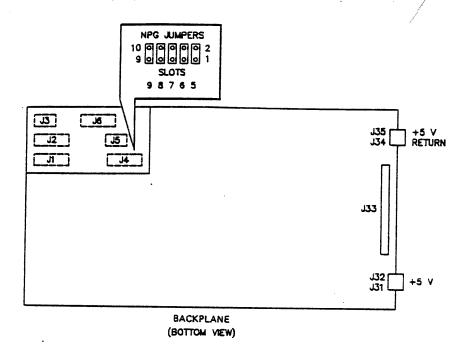

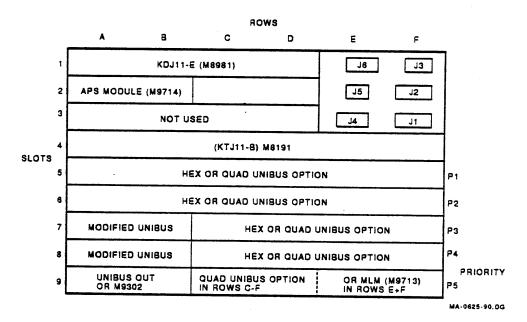

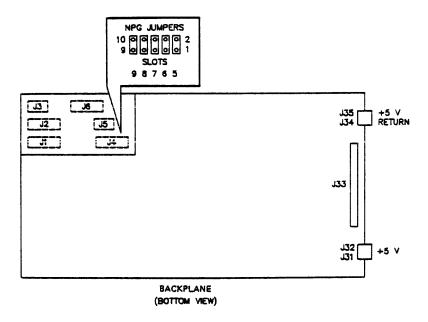

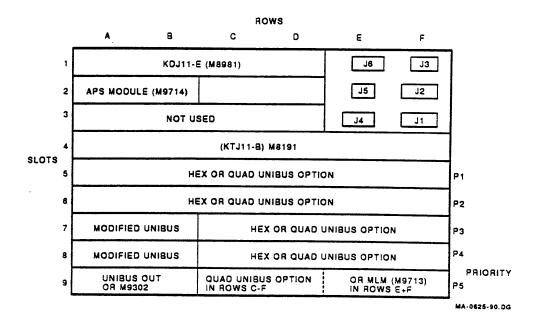

|   | 4.2 Backplane Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-1        |

|   | 4.2.1 Backplane Configuration Rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-2        |

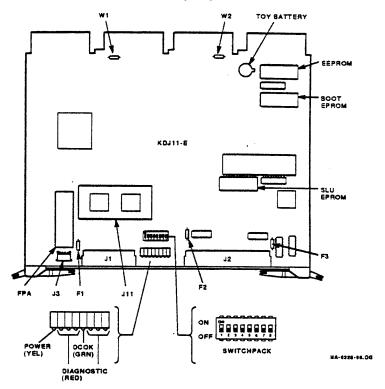

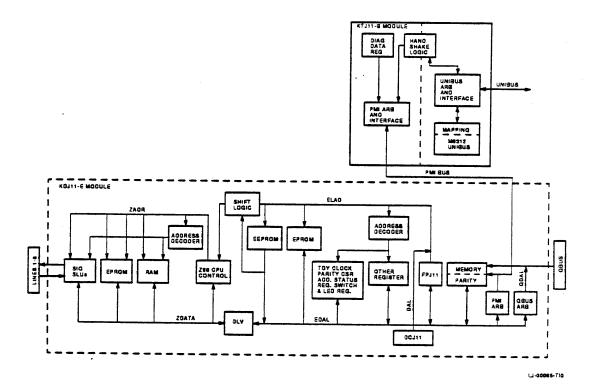

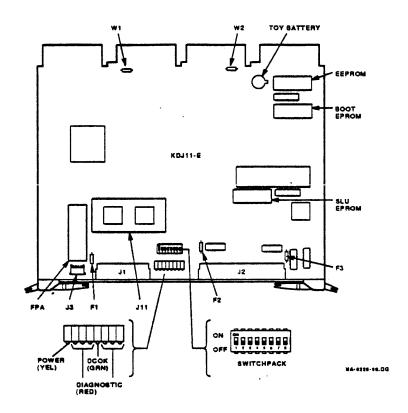

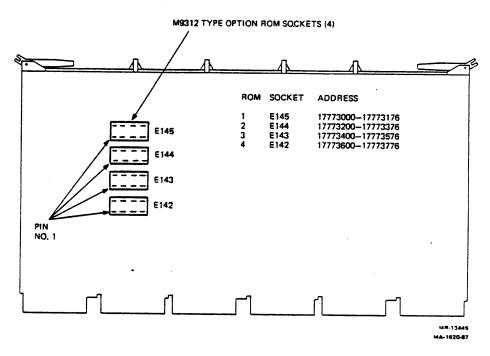

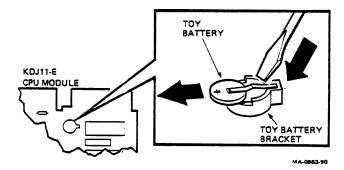

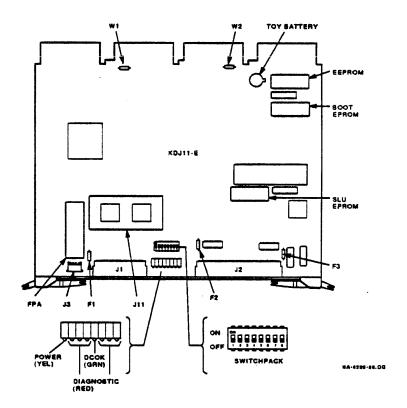

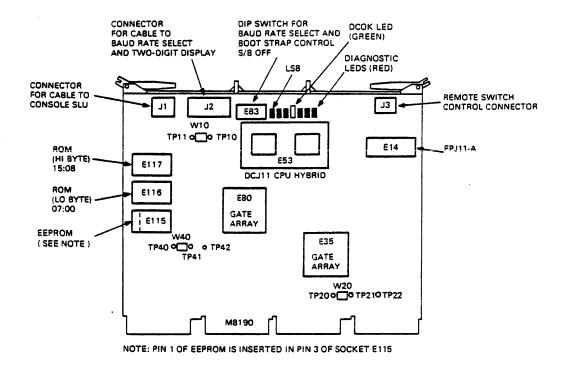

|   | 4.3 KDJ11-E CPU Module Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   | 4.3.1 KDJ11-E Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3<br>4-4 |

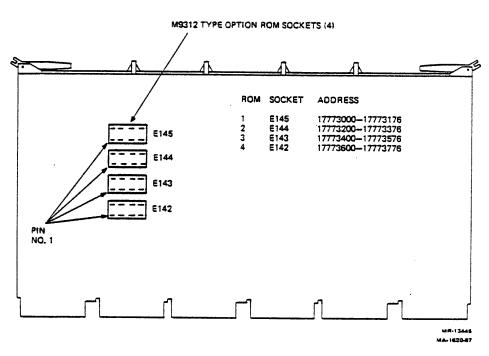

|   | 4.4 KTJ11-B UNIBUS Adapter Module Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-4        |

|   | 4.4.1 KTJ11-B UNIBUS Adapter Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-6        |

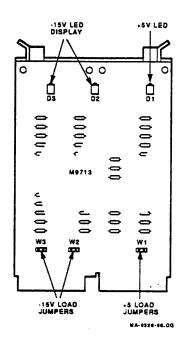

|   | 4.5 Minimum Load Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4–6        |

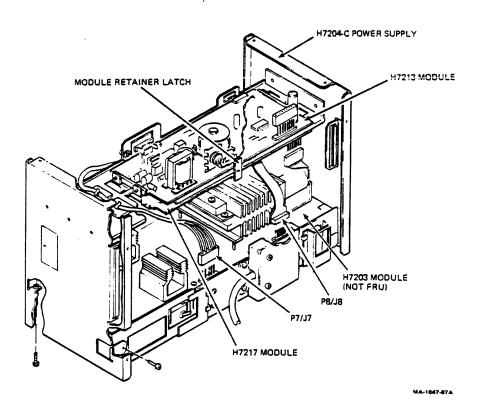

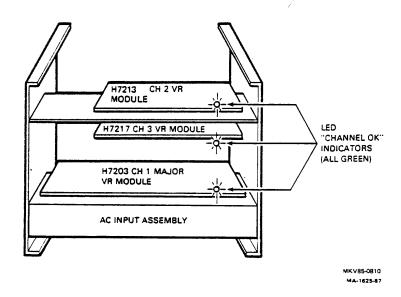

|   | 4.6 Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4–8        |

| 5 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|   | 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-1        |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5–2        |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5–6        |