# PDP-11/44 System Technical Manual

# PDP-11/44 System Technical Manual

## Copyright © 1980 by Digital Equipment Corporation

#### All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10     | MASSBUS |

|---------|------------------|---------|

| DEC     | DECSYSTEM-20     | OMNIBUS |

| PDP     | DIBOL            | OS/8    |

| DECUS   | <b>EDUSYSTEM</b> | RSTS    |

| UNIBUS  | VAX              | RSX     |

|         | VMS              | IAS     |

## **CONTENTS**

|           |                                       | Page  |

|-----------|---------------------------------------|-------|

| PREFACE   |                                       |       |

| CHAPTER 1 | INTRODUCTION                          |       |

| 1.1       | GENERAL                               | 1_1   |

| 1.2       | EQUIPMENT DESCRIPTION                 | 1_3   |

| 1.2.1     | PDP-11/44 CA, -CB Processor System    | 1-3   |

| 1.2.2     | PDP-11X44 Processor System            | 1-3   |

| 1.2.3     | Standard Hardware Components          |       |

| 1.2.4     | Hardware Options                      | 1-5   |

| 1.3       | EQUIPMENT SPECIFICATIONS              | 1-5   |

| 1.3.1     | PDP-11/44 System Specifications       | 1-6   |

| 1.3.2     | PDP-11X44 System Specifications       | 1-7   |

| 1.3.3     | H7140 AA, -AB Power Supply Electrical | 1-7   |

|           | Specifications                        | 1_9   |

| 1.4       | SYSTEM DESCRIPTION                    | 1-10  |

| 1.4.1     | KD11-Z Central Processor              | 1-10  |

| 1.4.1.1   | Data Path Module (M7094)              | 1-12  |

| 1.4.1.2   | Control Module (M7095)                | 1-12  |

| 1.4.1.3   | Multifunction Module (M7096)          | 1-12  |

| 1.4.1.4   | UNIBUS Interface Module (M7098)       | 1-12  |

| 1.4.1.5   | Console Interface Module (M7090)      | 1-13  |

| 1.4.2     | MOS Memory                            | 1-13  |

| 1.4.3     | KK11-B Cache Memory                   | 1-13  |

| 1.4.4     | UNIBUS Terminator (M9302)             | 1-13  |

| 1.4.5     | Optional Modules and Devices          | 1-13  |

| 1.4.5.1   | FP11-F Floating-Point Processor       | 1-13  |

| 1.4.5.2   | KE44-A Commercial Instruction Set     | 1-15  |

|           | Processor                             | 1-13  |

| 1.4.5.3   | TU58 DECtape II                       |       |

| 1.4.5.4   | Standard PDP-11 Peripheral Devices    | 1-13  |

| 1.5       | RELATED DOCUMENTS                     | 1-14  |

| 1.5.1     | DIGITAL Personnel Ordering            | 1-1-7 |

| 1.5.2     | Customer Ordering Information         | 1-15  |

|           |                                       | 1 13  |

| CHAPTER 2 | OPERATION                             |       |

| 2.1       | FRONT CONTROL PANEL                   | 2-1   |

| 2.2       | CONSOLE COMMANDS                      | 2-1   |

| 2.2.1     | Special Functions                     | 2-3   |

| 2.2.1.1   | Console Command Qualifiers            | 2-3   |

| 2.2.1.2   | Special Address Field Characters      | 2-4   |

| 2.2.1.3   | Control Characters                    | 2-4   |

| 2.2.2     | ADDER Command                         | 2-7   |

| 2.2.3     | BOOT Command                          | 2-8   |

| 2.2.4     | CONTINUE Command                      |       |

| 2.2.5     | DEPOSIT Command                       | 2-11  |

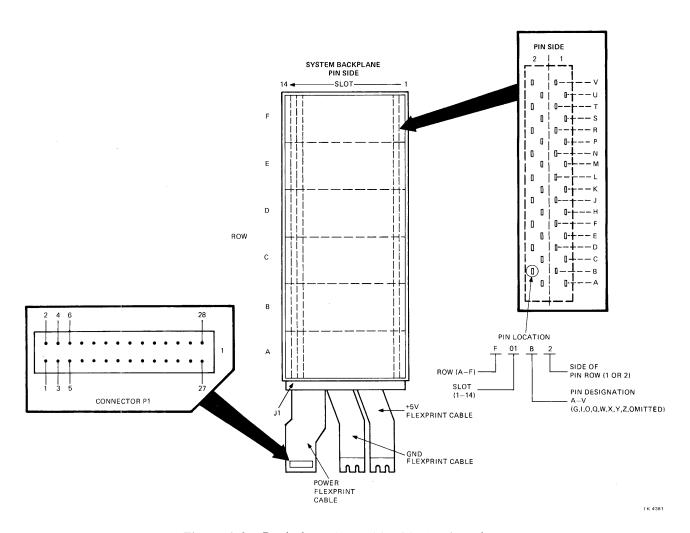

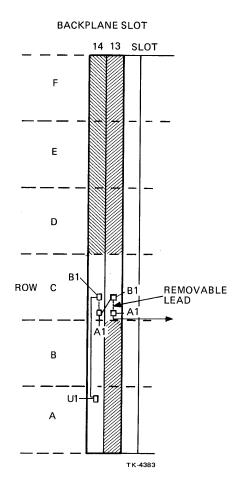

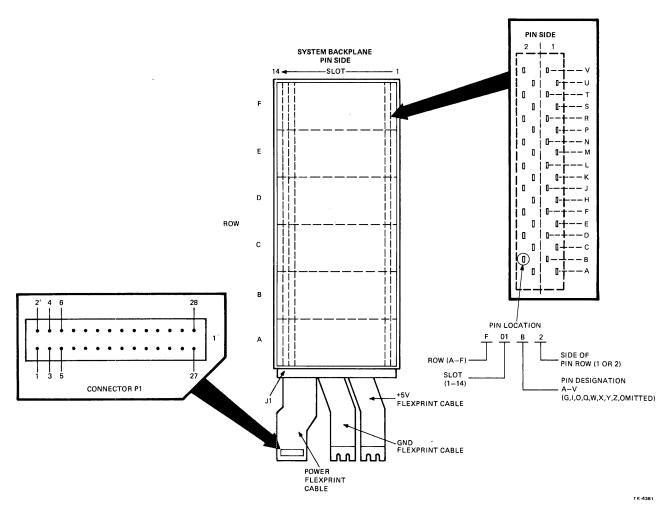

| 3.1.1     | Backplane Assembly Pin Designations         | 3-3<br>3-6  |

|-----------|---------------------------------------------|-------------|

| 3.1       | PROCESSOR BACKPLANE ASSIGNMENTS             |             |

| CHAPTER 3 | CPU CONFIGURATION                           |             |

| 2.3.4.6   | Page Descriptor Register                    | 2-44        |

| 2.3.4.5   | Page Address Registers                      |             |

| 2.3.4.4   | Status Register SR3                         |             |

| 2.3.4.3   | Status Register SR2                         |             |

| 2.3.4.2   | Status Register SR1                         |             |

| 2.3.4.1   | Status Register 0 (SR0)                     |             |

| 2.3.4     | Memory Management Registers                 |             |

|           | Cache Error Register                        |             |

| 2.3.3.4   | Cache Control/Status Register               |             |

| 2.3.3.4   |                                             |             |

| 2.3.3.3   | Cache Maintenance Register                  |             |

| 2.3.3.2   | Cache Hit Register                          |             |

| 2.3.3.1   | Cache Memory Data Register                  |             |

| 2.3.3     | Cache Memory I/O Page Registers             | 2-34        |

| 2.3.2.10  | Line Time Clock Control/Status Register     | 2-33        |

| 2.3.2.9   | Signal Register                             | 2-32        |

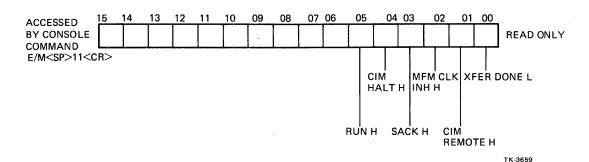

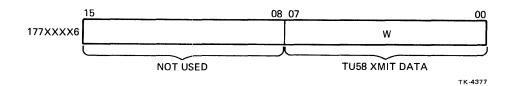

| 2.3.2.8   | TU58 Transmitter Data Buffer Register       | 2-32        |

| 2.3.2.7   | TU58 Transmitter Control/Status Register    | 2-30        |

| 2.3.2.6   | TU58 Receiver Buffer Register               |             |

| 2.3.2.5   | TU58 Receiver Control/Status Register       |             |

|           | Register                                    | 2-28        |

| 2.3.2.4   | Console Terminal Transmitter Buffer         |             |

|           | Register                                    | 2-27        |

| 2.3.2.3   | Console Terminal Transmitter Control/Status |             |

| 2 2 2 2   | Register                                    | 2-26        |

| 2.3.2.2   | Console Terminal Receiver Data Buffer       | 2 2 -       |

| 2222      | Register                                    | 2-25        |

| 2.3.2.1   | Console Terminal Receiver Control/Status    | 2 25        |

| 2.3.2.1   |                                             | <b>2-23</b> |

| 2.3.1.4   | Multifunction Module Register               |             |

| 2.3.1.4   | General Registers                           | 2-22        |

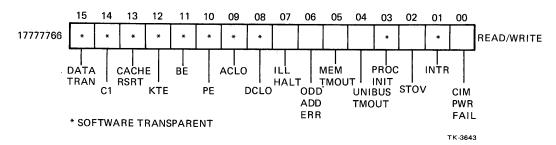

| 2.3.1.2   | Error Register                              | 2-22        |

| 2.3.1.1   | Program Interrupt Request Register          | 2-20        |

| 2.3.1.1   | Processor Status Word                       | 2-20        |

| 2.3.1     | CPU Registers                               |             |

| 2.3       | PDP-11/44 REGISTERS.                        | 2-18        |

| 2.2.17    | Summary of Commands                         |             |

| 2.2.16    | Summary of Errors                           | 2-17        |

| 2.2.15    | REPEAT Command                              | 2-17        |

| 2.2.14    | BINARY LOAD/UNLOAD Command                  |             |

| 2.2.13    | SELF-TEST Command                           |             |

| 2.2.12    | START Command                               |             |

| 2.2.11    | SINGLE-INSTRUCTION-STEP Command             |             |

| 2.2.10    | MICROSTEP Command                           |             |

| 2.2.9     | INITIALIZE Command                          |             |

| 2.2.8     | HALT Command                                |             |

| 2.2.7     | FILL Command                                |             |

| 2.2.6     | EXAMINE Command                             |             |

|           |                                             |             |

| 3.1.3                   | SPC Module Installation                                                                                                                                       |                                              |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 3.2                     | MODULE CURRENT REQUIREMENTS                                                                                                                                   |                                              |

| 3.2.1                   | DC Power Requirements                                                                                                                                         | 3-7                                          |

| 3.2.2                   | H7140-AA, -ÂB DC Power Outputs                                                                                                                                | 3-9                                          |

| 3.3                     | MODULE SWITCHES, JUMPERS AND INDICATORS                                                                                                                       |                                              |

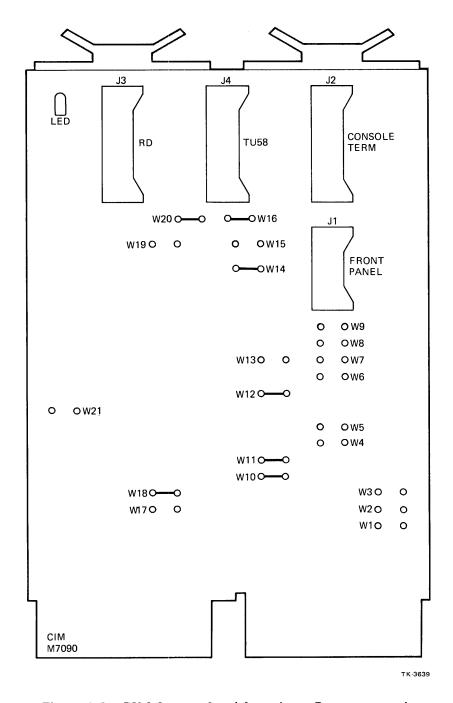

| 3.3.1                   | Console Interface Module (M7090)                                                                                                                              |                                              |

| 3.3.1.1                 | Console Terminal Configurations                                                                                                                               |                                              |

| 3.3.1.2                 | TU58 DECtape II Configuration                                                                                                                                 | 3-11                                         |

| 3.3.1.3                 | Remote Diagnosis Configuration                                                                                                                                | 3-14                                         |

| 3.3.1.4                 | Voltage Monitoring                                                                                                                                            | 3-14                                         |

| 3.3.1.5                 | LED Indicator                                                                                                                                                 | 3-14                                         |

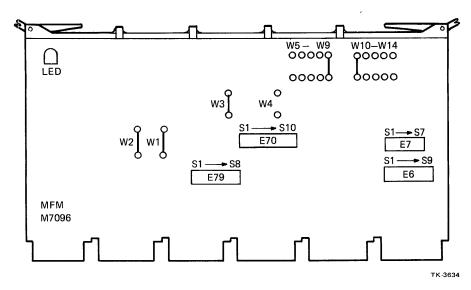

| 3.3.2                   | Multifunction Module (M7096)                                                                                                                                  |                                              |

| 3.3.2.1                 | Console Terminal Jumper Leads Selections                                                                                                                      |                                              |

| 3.3.2.2                 | MFM Console Terminal Baud Rate Selection                                                                                                                      |                                              |

| 3.3.2.3                 | MFM TU58 DECtape II Jumper Leads                                                                                                                              |                                              |

| 3.3.2.4                 | MFM TU58 Baud Rate Selection                                                                                                                                  |                                              |

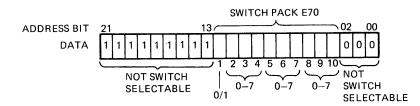

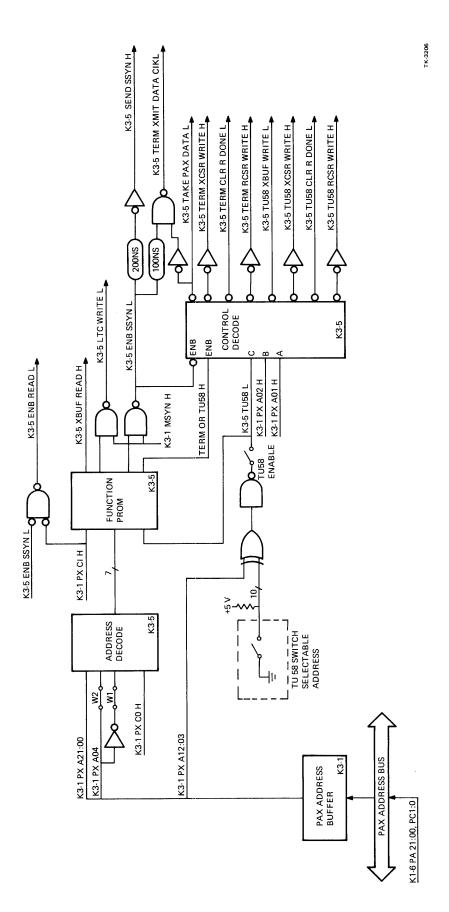

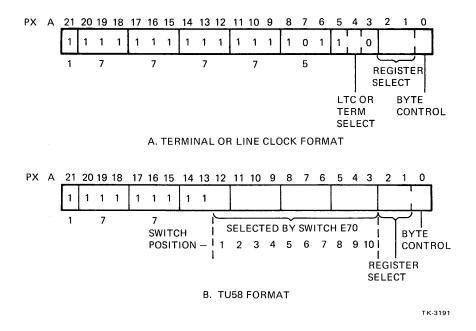

| 3.3.2.5                 | MFM TU58 Device Address Selection                                                                                                                             |                                              |

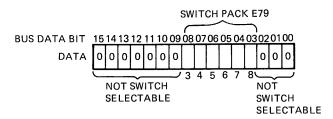

| 3.3.2.6                 | TU58 Vector Address Selection                                                                                                                                 |                                              |

| 3.3.2.7                 | Line Time Clock Enable/Disable                                                                                                                                | 3-18                                         |

| 3.3.3                   | UNIBUS Interface Module (M7098)                                                                                                                               | 3-18                                         |

| 3.3.3.1                 | UBI Jumper Leads and Memory Page                                                                                                                              |                                              |

|                         | Selection                                                                                                                                                     | 3-18                                         |

| 3.3.3.2                 | Diagnostic and Bootstrap Loader ROMs                                                                                                                          | 3-21                                         |

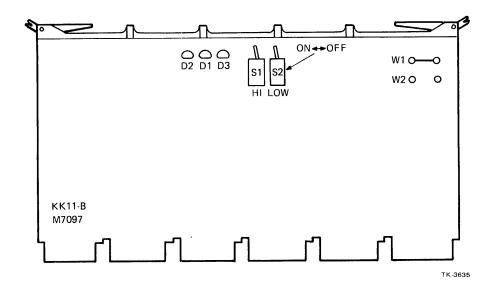

| 3.3.4                   | Cache Memory Module (M7097)                                                                                                                                   | 3-23                                         |

| 3.3.4.1                 | LED Indicator Functions                                                                                                                                       | 3-24                                         |

| 3.3.4.2                 | Multiport Memory Selection                                                                                                                                    | 3-24                                         |

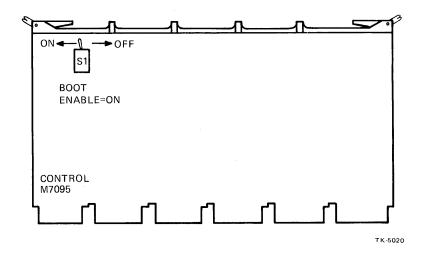

| 3.3.5                   | Control Module (M7095)                                                                                                                                        | 3-24                                         |

|                         |                                                                                                                                                               |                                              |

| CYLL DEED 4             | TRICITAL I A TOTANI                                                                                                                                           |                                              |

| CHAPTER 4               | INSTALLATION                                                                                                                                                  |                                              |

| 4.1                     | SITE CONSIDERATIONS                                                                                                                                           | 4-1                                          |

| 4.1.1                   | Temperature and Humidity                                                                                                                                      |                                              |

| 4.1.2                   | Acoustical Dampening                                                                                                                                          |                                              |

| 4.1.3                   | Lighting                                                                                                                                                      |                                              |

| 4.1.4                   | Static Electricity                                                                                                                                            | 4-2                                          |

| 4.1.5                   | Shock and Vibration                                                                                                                                           |                                              |

| 4.1.6                   | Electrical Interference                                                                                                                                       |                                              |

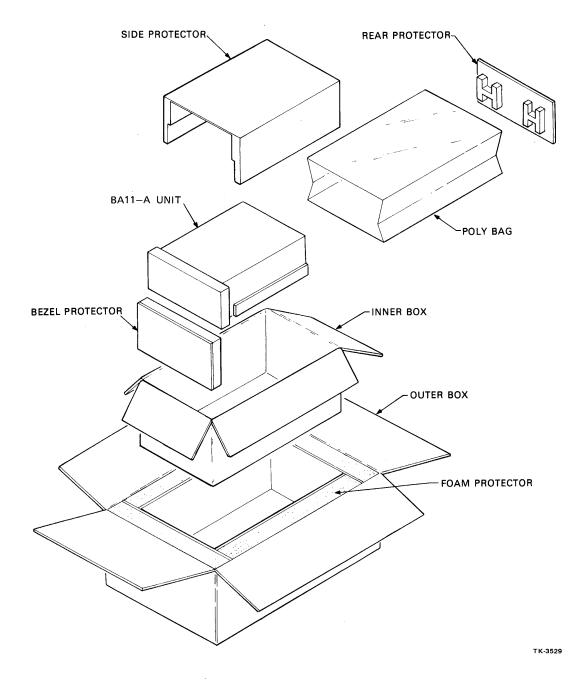

| 4.2                     | UNPACKING                                                                                                                                                     | 4-2                                          |

| 4.2.1                   | PDP-11/44-CA, -CB Unit Removal                                                                                                                                | 4-2                                          |

| 4.2.2                   | PDP-11X44-CA, -CB Cabinet Removal                                                                                                                             |                                              |

| 4.2.2.1                 | Shipping Restraint Removal                                                                                                                                    |                                              |

| 4.3                     | FOUIPMENT DIMENSIONS                                                                                                                                          | 4-8                                          |

| 4.4                     | AC INPUT POWER REOUIREMENTS                                                                                                                                   | 4-8                                          |

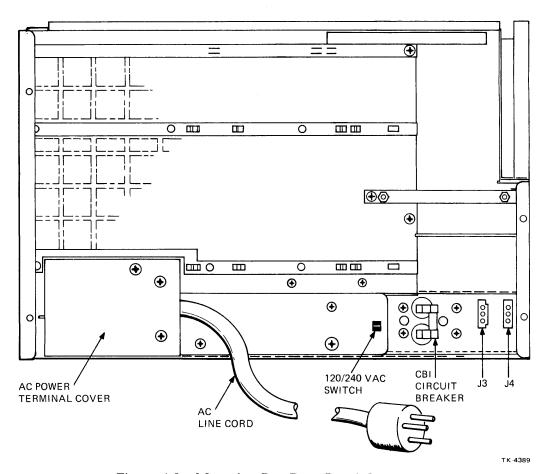

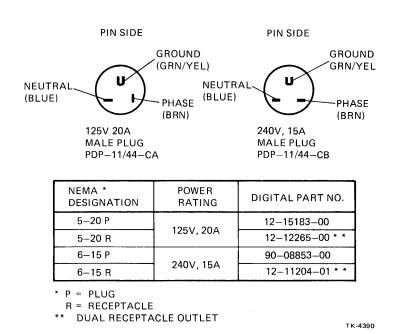

| 4.4.1                   | Power Connections (AC)                                                                                                                                        | 4-10                                         |

| 4.4.2                   |                                                                                                                                                               | 4-10                                         |

|                         | System Grounding                                                                                                                                              |                                              |

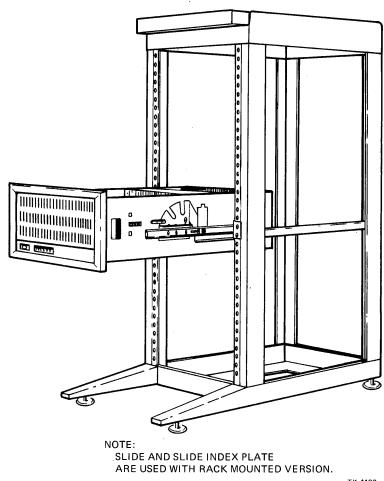

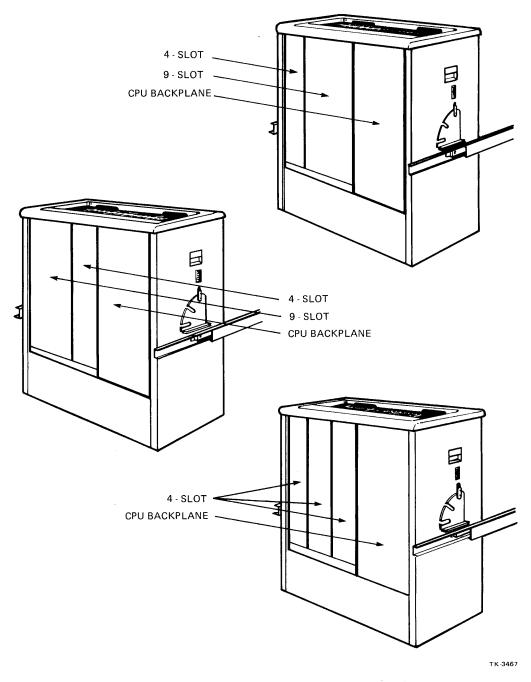

| 4.5                     | System GroundingPDP-11/44 MOUNTING BOX INSTALLATION                                                                                                           | 4-12                                         |

| 4.5<br>4.5.1            | PDP-11/44 MOUNTING BOX INSTALLATION                                                                                                                           | 4-12<br>4-13                                 |

| 4.5.1                   | PDP-11/44 MOUNTING BOX INSTALLATION                                                                                                                           | 4-12<br>4-13<br>4-14                         |

| 4.5.1<br>4.5.2          | PDP-11/44 MOUNTING BOX INSTALLATION  Index Plate Mounting  Slide Assembly Mounting  Mounting Box to Slide Installation                                        | 4-12<br>4-13<br>4-14<br>4-17                 |

| 4.5.1                   | PDP-11/44 MOUNTING BOX INSTALLATION  Index Plate Mounting  Slide Assembly Mounting  Mounting Box to Slide Installation  PDP-11X44 SYSTEM CABINET INSTALLATION | 4-12<br>4-13<br>4-14<br>4-17<br>4-19         |

| 4.5.1<br>4.5.2<br>4.5.3 | PDP-11/44 MOUNTING BOX INSTALLATION  Index Plate Mounting  Slide Assembly Mounting  Mounting Box to Slide Installation                                        | 4-12<br>4-13<br>4-14<br>4-17<br>4-19<br>4-19 |

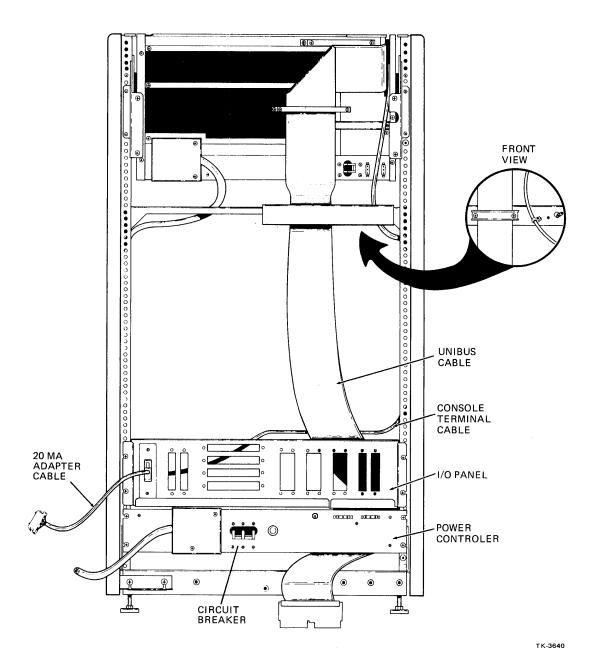

| 4.7       | CABLE ROUTING                                     | 4-21           |

|-----------|---------------------------------------------------|----------------|

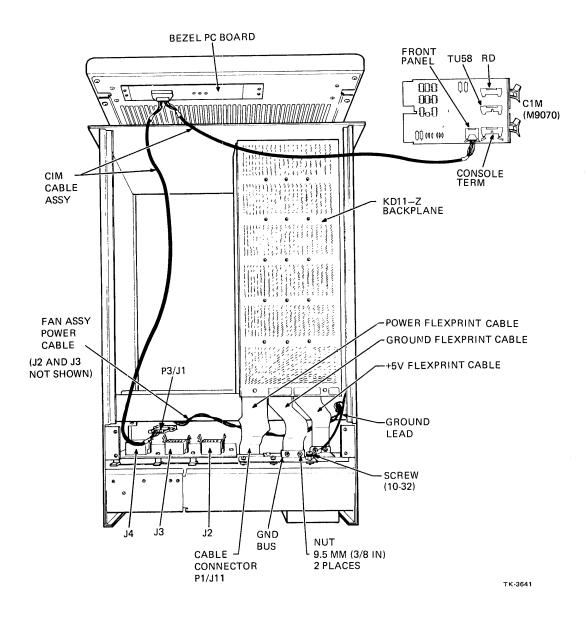

| 4.7.1     | Mounting Box Cable Routing                        | 4-21           |

| 4.7.2     | PDP-11X44 Cabinet Cable Routing                   |                |

| 4.8       | POWER CHECKS                                      |                |

| 4.8.1     | AC Power Distribution                             | 4-22           |

| 4.8.1.1   | Initial AC Power Checks                           |                |

| 4.8.2     | DC Power Distribution                             | 4-23           |

| 4.8.2.1   | DC Power Checks                                   | 4-23           |

| 4.9       | PERFORMANCE EVALUATION                            |                |

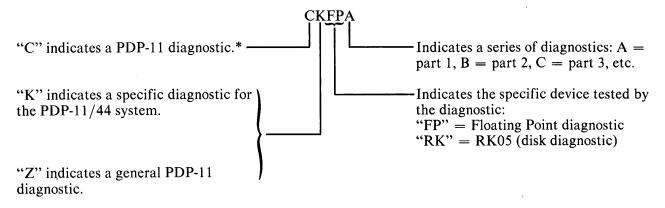

| 4.9.1     | MAINDEC Diagnostic Programs                       | 4-25           |

| 4.9.1.1   | Diagnostic Designations                           |                |

| 4.9.2     | Internal Diagnostic Programs                      | 4-26           |

| CHAPTER 5 | REMOVAL/REPLACEMENT PROCEDURES                    |                |

| 5.1       | BA11-AA, -AB MOUNTING BOX IN SYSTEM CABINET       | 5-1            |

| 5.1.1     | Mounting Box Removal                              | 5-2            |

| 5.1.2     | Interface Bracket Removal/Installation            | 5-8            |

| 5.1.3     | Mounting Box Replacement                          | 5-8            |

| 5.2       | BA11-AA, -AB SLIDE MOUNTED REMOVAL/REPLACEMENT    | 5-10           |

| 5.3       | FAN ASSEMBLY                                      | 5-10           |

| 5.3.1     | Fan Assembly Removal/Replacement                  | 5-10           |

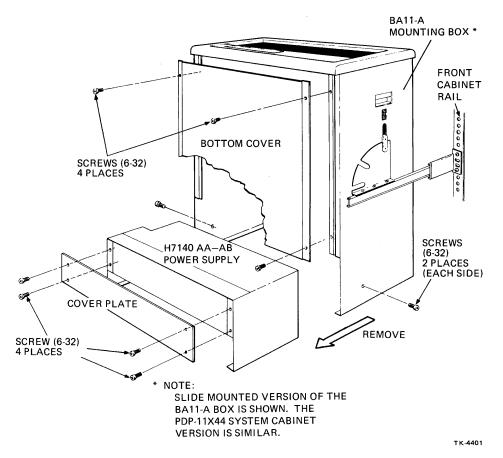

| 5.4       | H7140-AA, -AB POWER SÚPPLY<br>REMOVAL/REPLACEMENT |                |

| 5.4.1     | Power Supply Removal                              | 5-12           |

| 5.4.2     | Power Supply Replacement                          |                |

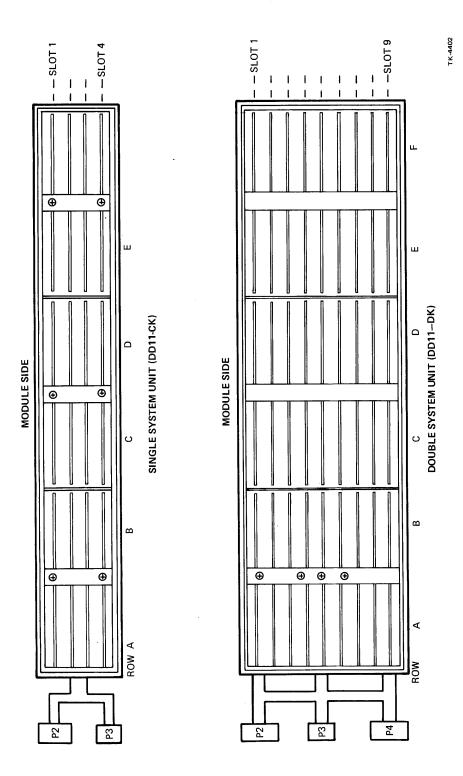

| 5.5       | OPTIONAL BACKPLANE ASSEMBLIES                     | 5-16           |

| 5.5.1     | Optional Backplane Configurations                 |                |

| 5.5.2     | Backplane Assembly Installation                   |                |

| 5.5.3     | Backplane Connector Assignments                   | 5-21           |

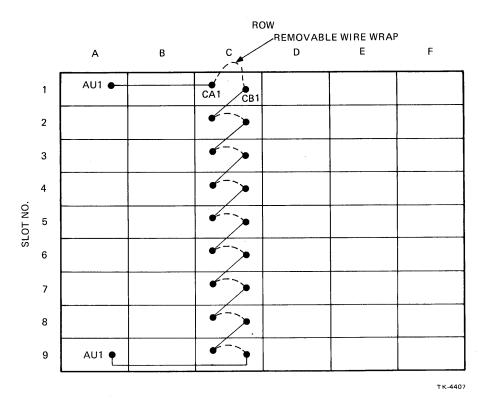

| 5.5.4     | NPG and BG Jumper Lead Routing                    |                |

| 5.5.5     | Standard and Modified Backplane Locations         | 5-23           |

| 5.5.6     | SPC Backplane Locations                           | 5-23           |

| 5.5.7     | Backplane Power Connections                       | 5-23           |

|           | •                                                 | J- <b>2</b> ,5 |

| CHAPTER 6 | DETAILED FUNCTIONAL DESCRIPTION                   |                |

| 6.1       | INTRODUCTION                                      |                |

| 6.2       | CONTROL STORE                                     | 6-1            |

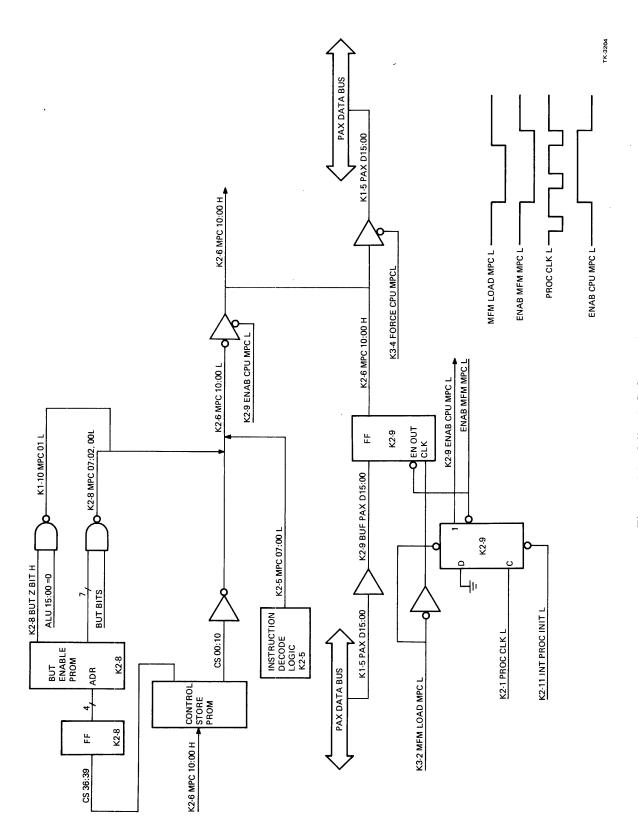

| 6.2.1     | MicroPC Generation                                | 6-1            |

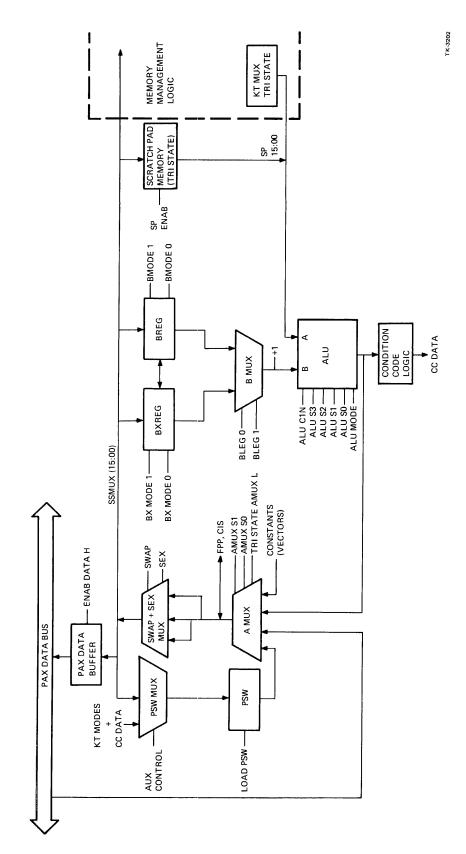

| 6.3       | DATA PATH                                         | 6-5            |

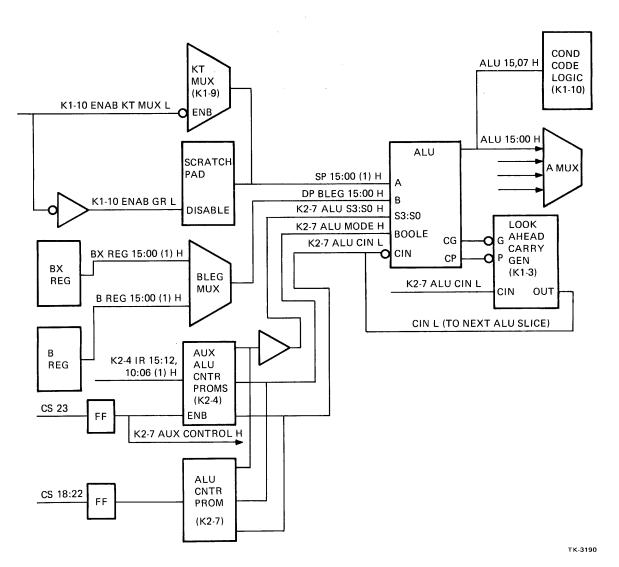

| 6.3.1     | Arithmetic Logic Unit (ALU)                       | 6-5            |

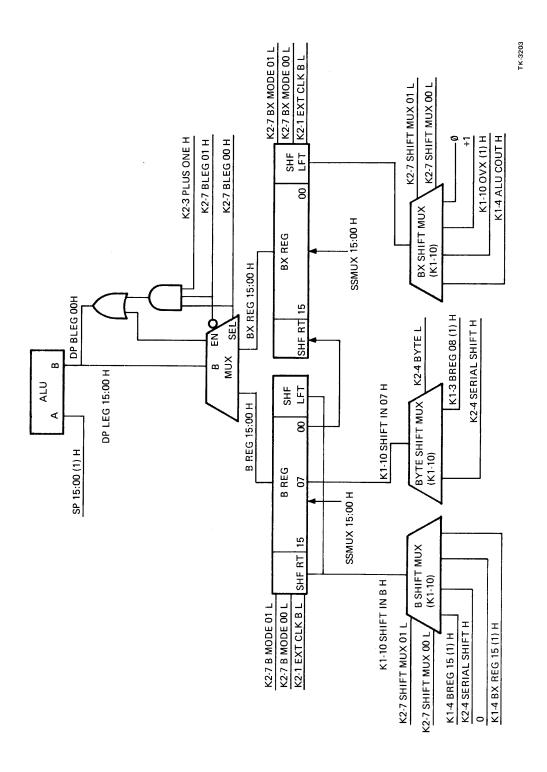

| 6.3.2     | ALU B-Leg Logic                                   | 6-5            |

| 6.3.3     | ALU Multiplexer (AMUX)                            |                |

| 6.3.4     | Swap Sign Extend Multiplexer (SSMUX)              | 6-12           |

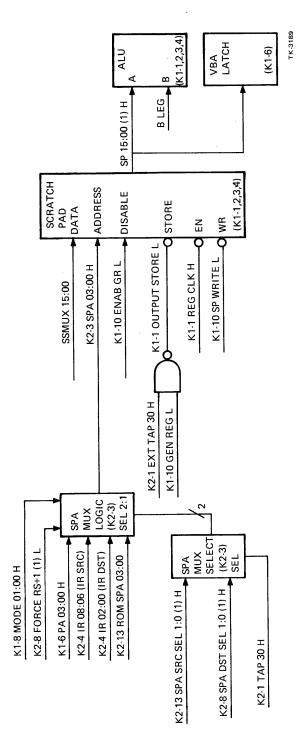

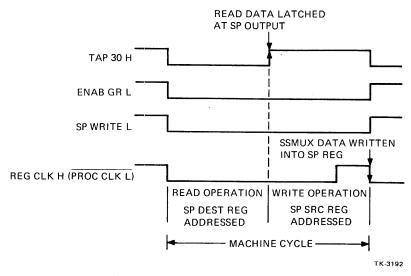

| 6.3.5     | Scratchpad Memory                                 | 6-12           |

| 6.3.5.1   | Scratchpad Operation                              | 6-14           |

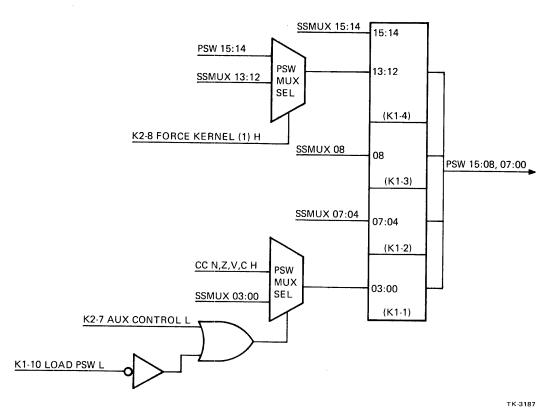

| 6.3.6     | Processor Status Word (PSW)                       |                |

| 6.4       | INSTRUCTION DECODE                                |                |

| 6.4.1     | Instruction Classes                               | 6-17           |

| 6.4.1.1   | Double Operand and Branch Instructions            | . 6-17         |

| 6.4.1.2   | Single Operand Instructions                       | 6-18           |

| 6.4.1.3  | Miscellaneous Instructions                           | 6-18                 |

|----------|------------------------------------------------------|----------------------|

| 6.4.2    | Miscellaneous Decoding for Reset Instruction         |                      |

|          | and T Bit                                            | 6-19                 |

| 6.4.3    | ALU Auxilliary Control                               | 6-19                 |

| 6.5      | DATA TRANSFEŘ LOGIC                                  | 6-21                 |

| 6.5.1    | UNIBUS Transfer Logic                                | 6-21                 |

| 6.5.1.1  | Processor Clock Inhibit                              |                      |

| 6.5.1.2  | UNIBUS Synchronization                               | 6-21<br>6-21         |

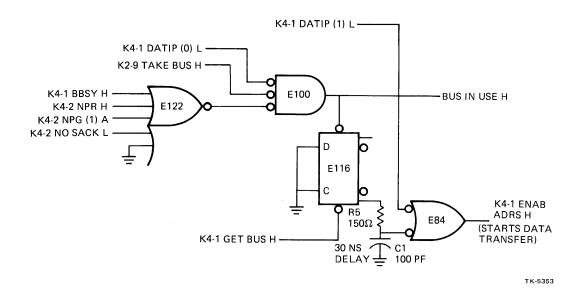

| 6.5.1.3  | Bus Control                                          |                      |

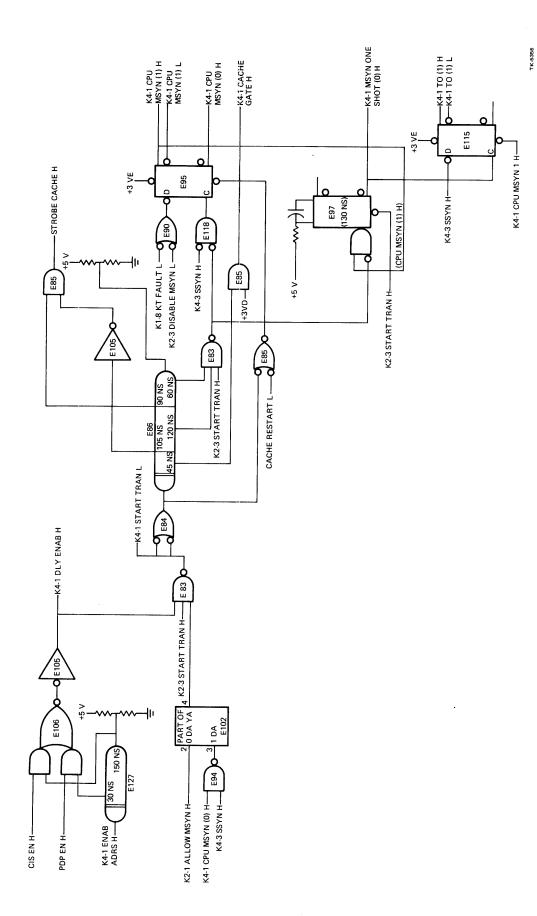

| 6.5.1.4  | Generation of MSYN and MSYN/SSYN Timeout             | 0-22<br>6 22         |

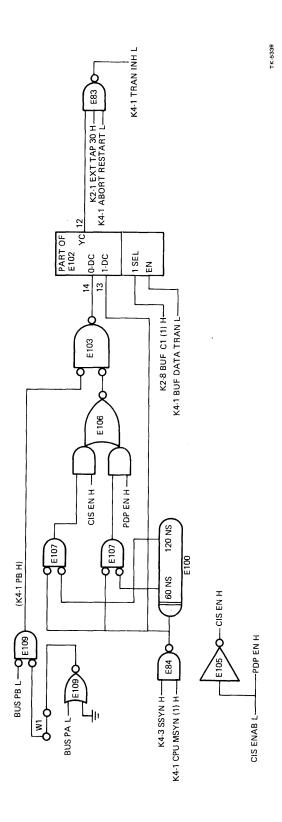

| 6.5.1.5  | Restarting Processor Clock                           | 0-23<br>6 25         |

| 6.5.2    |                                                      |                      |

| 6.5.2.1  | Bus Arbitration                                      |                      |

|          | Bus Requests                                         | 6-25                 |

| 6.5.2.2  | Request Synchronization                              |                      |

| 6.5.2.3  | SACK Timeout                                         |                      |

| 6.5.2.4  | Programmed Interrupt Request (PIRQ)                  |                      |

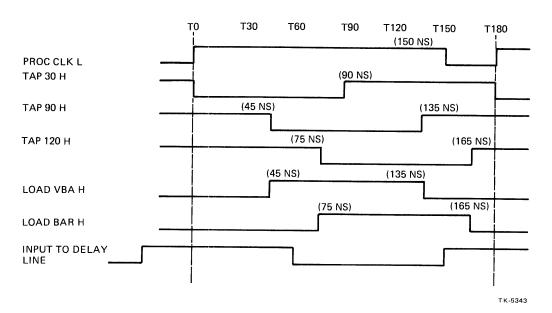

| 6.5.3    | Error Logic                                          |                      |

| 6.5.4    | Cache Interface                                      |                      |

| 6.6      | SYSTEM CLOCK                                         | 6-30                 |

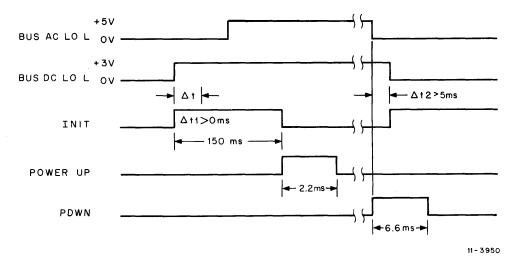

| 6.7      | POWER FAIL/AUTO RESTART                              | 6-33                 |

| 6.8      | MEMORY MÁNAGEMENT                                    | 6-36                 |

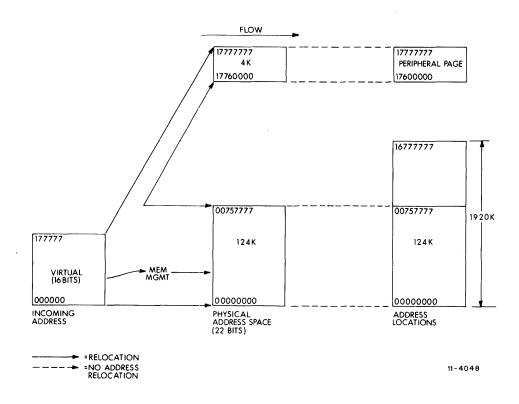

| 6.8.1    | Relocation                                           |                      |

| 6.8.1.1  | Address Mapping                                      |                      |

| 6.8.1.2  | Address Translation                                  |                      |

| 6.8.2    | Protection                                           |                      |

| 6.8.3    | Page Address Registers (PAR)                         |                      |

| 6.8.4    | Page Descriptor Registers (PDR)                      |                      |

| 6.8.5    | Memory Management Fault Logic                        | 6-50                 |

| 6.8.6    | I and D Space                                        | 0-30<br>6 <b>5</b> 1 |

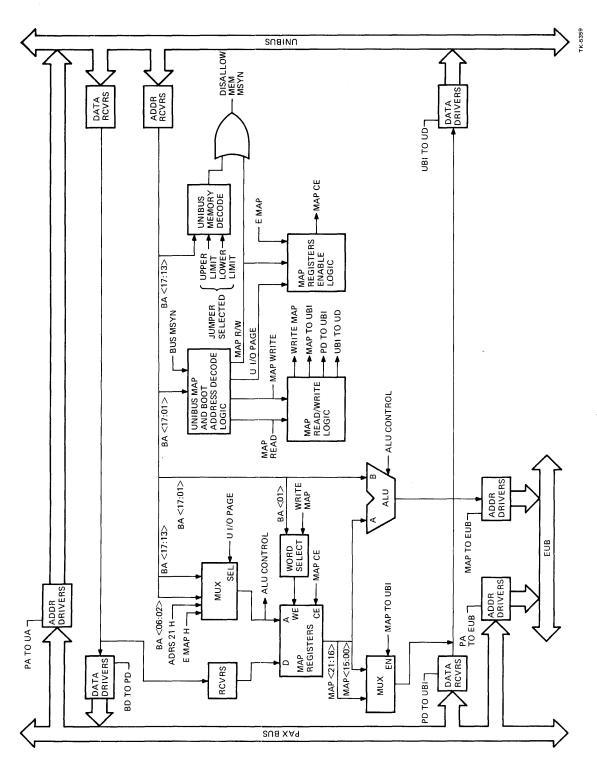

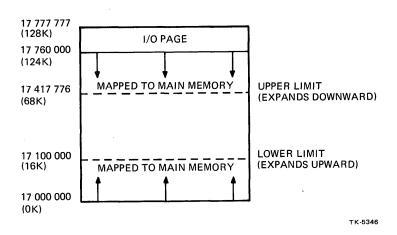

| 6.9      | UNIBUS MAP                                           | 0-31<br>6 52         |

| 6.9.1    |                                                      |                      |

| 6.9.2    | Map Control                                          |                      |

| 6.9.3    | Map Addressing and Relocation                        |                      |

|          | Addressing Limits                                    | 6-55                 |

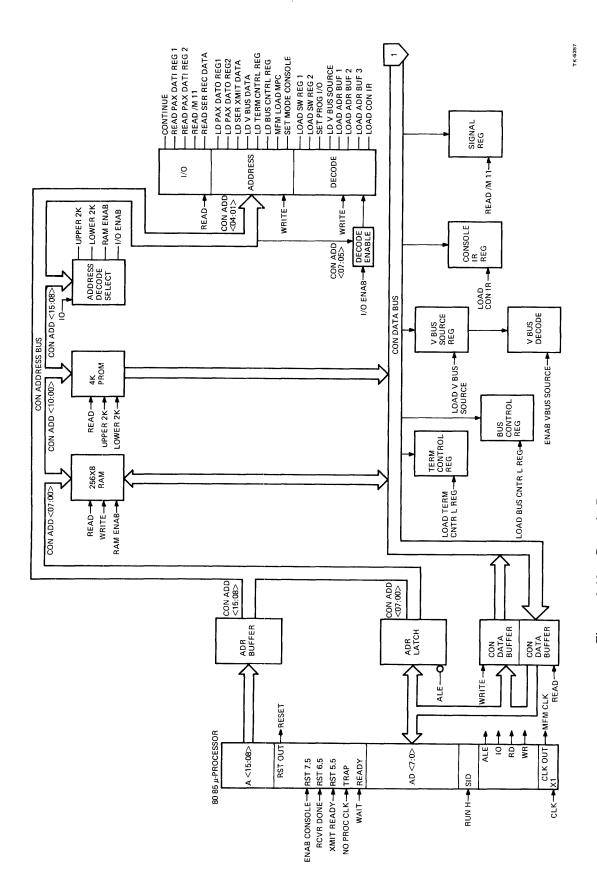

| 6.10     | CONSOLE PROCESSOR                                    |                      |

| 6.10.1   | 8085 Addressing                                      |                      |

| 6.10.2   | Console Data Flow                                    |                      |

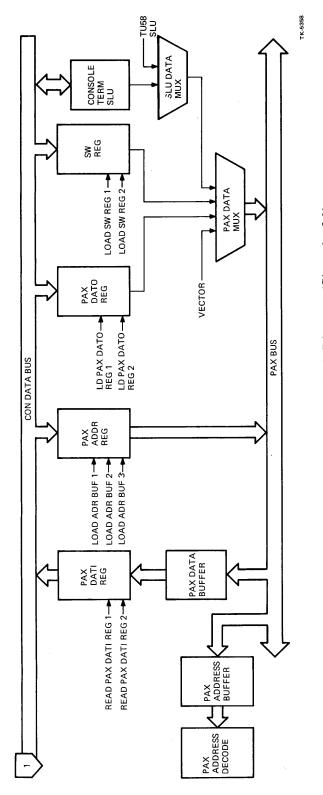

| 6.10.3   | Console-to-PAX Interface                             |                      |

| 6.10.4   | Operation During Command Execution                   |                      |

| 6.11     | SERIAL LINE UNITS                                    |                      |

| 6.11.1   | Console Terminal SLU                                 | 6-63                 |

| 6.11.1.1 | Transmitter Operation (Terminal UART)                | 6-65                 |

| 6.11.1.2 | Receiver Operation (Terminal UART)                   | 6-65                 |

| 6.11.1.3 | Console Terminal Baud Rate Logic                     | 6-66                 |

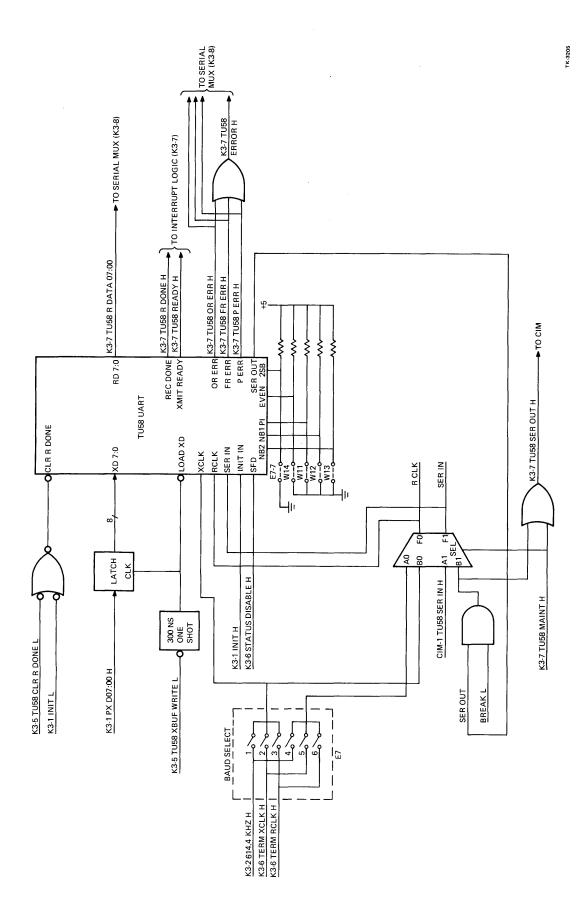

| 6.11.2   | TU58 SLU                                             | 6-66                 |

| 6.11.2.1 | Transmitter Operation (TU58 UART)                    | 6-66                 |

| 6.11.2.2 | Receiver Operation (TU58 UART)                       | 6-68                 |

| 6.11.2.3 | Baud Rate Logic                                      |                      |

| 6.11.3   | Address Selection                                    |                      |

| 6.11.4   | Console Terminal and TU58 Register Descriptions 6-73 |                      |

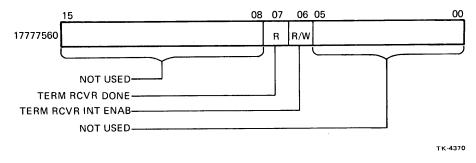

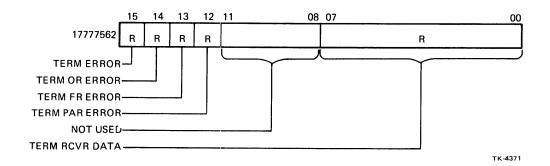

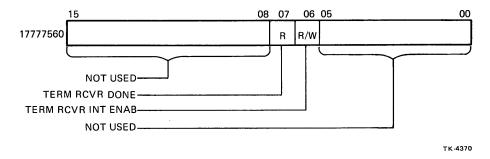

| 6.11.4.1 | Terminal Receiver Status Register                    | 6-73                 |

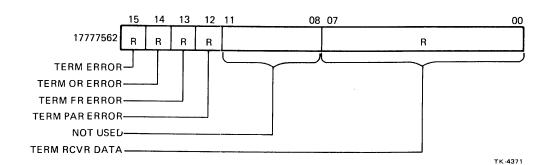

| 6.11.4.2 | Terminal Receiver Buffer Register                    | 6-7 <i>3</i>         |

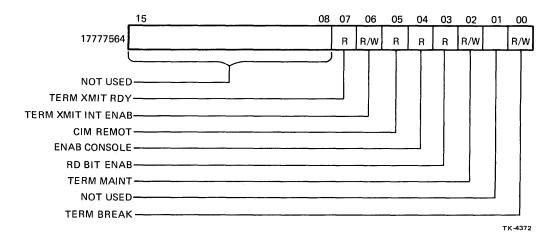

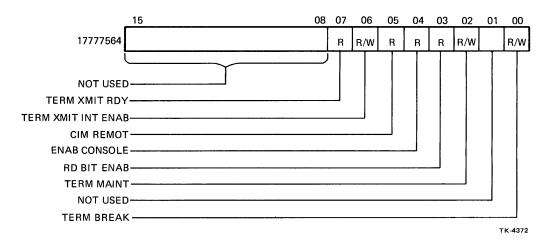

| 6.11.4.3 | Terminal Transmitter Status Register                 |                      |

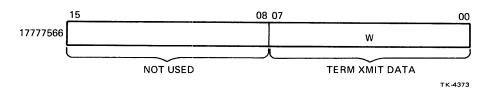

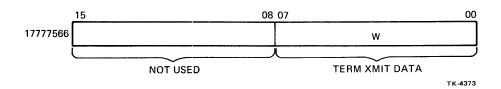

| 6.11.4.4 | Terminal Transmitter Status Register                 |                      |

| U.11.T.T | reminar ranshitter bullet Negistel                   | 0-/0                 |

| 6.11.4.5   | Line Clock Status Register                    |      |

|------------|-----------------------------------------------|------|

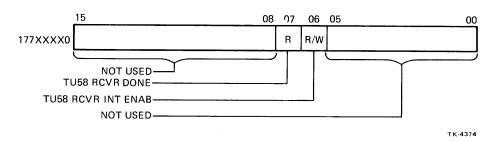

| 6.11.4.6   | TU58 Receiver Status Register                 | 6-77 |

| 6.11.4.7   | TU58 Receiver Buffer Register                 | 6-78 |

| 6.11.4.8   | TU58 Transmitter Status Register              | 6-79 |

| 6.11.4.9   | TU58 Transmitter Buffer Register              | 6-80 |

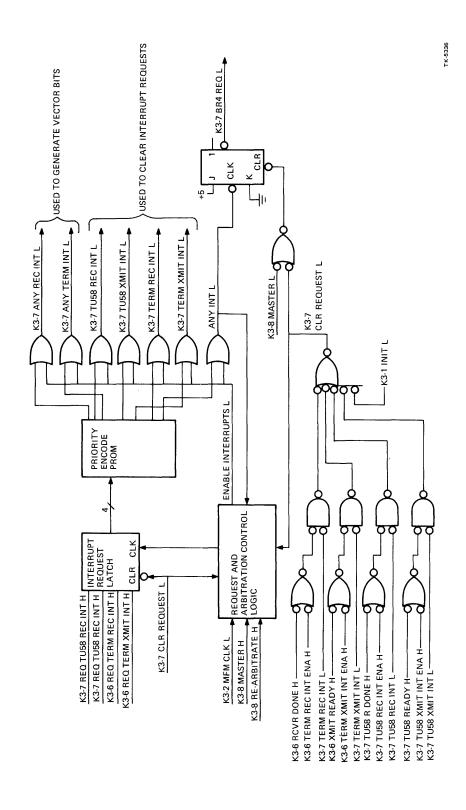

| 6.11.5     | Interrupt Request Logic                       | 6-80 |

| 6.11.5.1   | Arbitration Between Terminal and TU58         |      |

|            | Interrupts                                    |      |

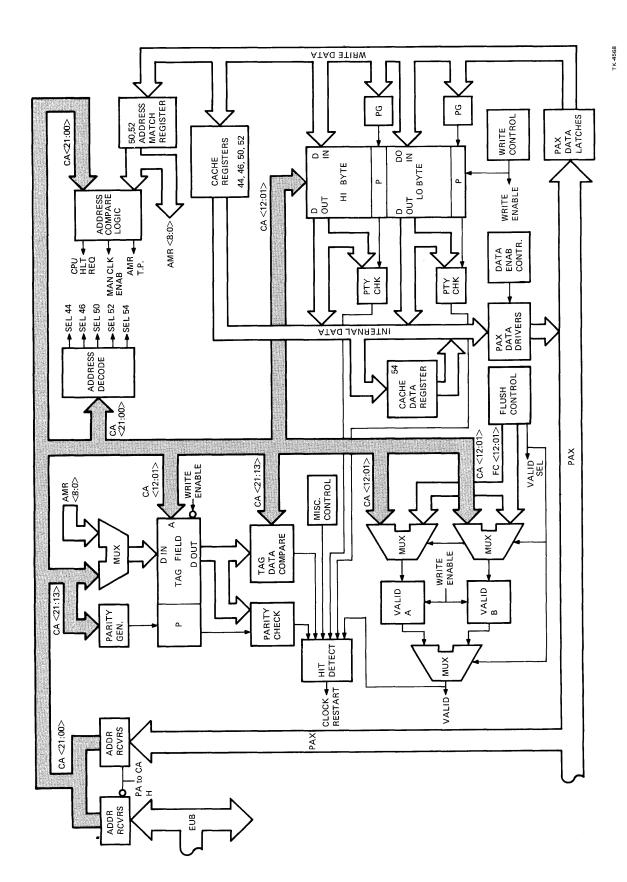

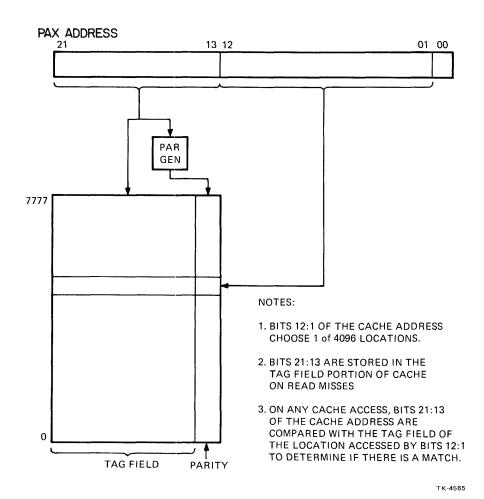

| 6.12       | KK11-B CACHE                                  |      |

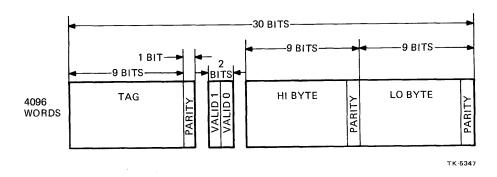

| 6.12.1     | Memory Organization                           |      |

| 6.12.2     | Interface Logic                               |      |

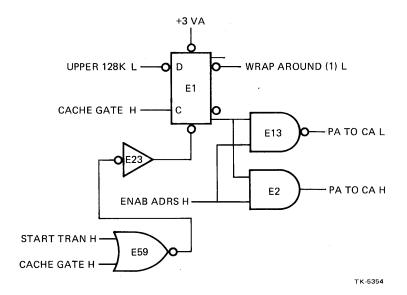

| 6.12.3     | Address Logic                                 |      |

| 6.12.4     | Data Control                                  |      |

| 6.12.4.1   | Write Data Latching                           |      |

| 6.12.4.2   | Read Data Enable                              |      |

| 6.12.5     | Cache Array                                   |      |

| 6.12.5.1   | Data Section                                  |      |

| 6.12.5.2   | Tag Section                                   |      |

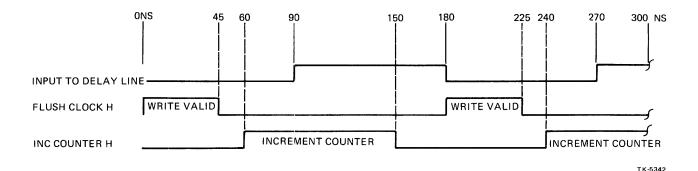

| 6.12.6     | Cache Flush Control                           |      |

| 6.12.7     | Valid Control Logic                           |      |

| 6.12.8     | Write Control Logic                           |      |

| 6.12.9     | Hit Detect Logic                              |      |

| 6.12.10    | Cache Register Control                        |      |

| 6.12.11    | Address Match Logic                           |      |

| 6.12.12    | Cache Registers                               | 6-97 |

|            | FIGURES                                       |      |

|            |                                               |      |

| Figure No. | Title                                         | Page |

| 1-1        | PDP-11/44 System Configurations               | 1-2  |

| 1-1        | PDP-11/44-CA, -CB in Mounting Box             | 1-4  |

| 1-3        | Typical PDP-11/44 System and Selected Options |      |

2-1

2-2 2-3

2-4 2-5

2-6

2-7

2-8

2-9 2-10

2-11

2-12

2-13 2-14

2-15

2-16

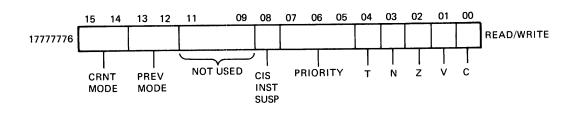

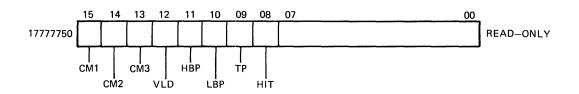

PSW Register Format 2-20

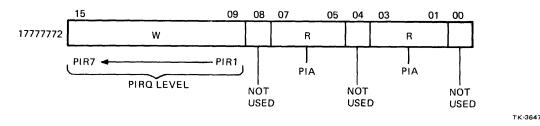

PIR Register Format ...... 2-22

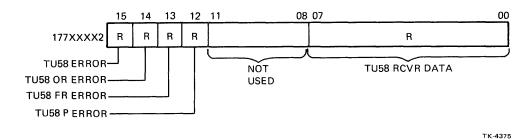

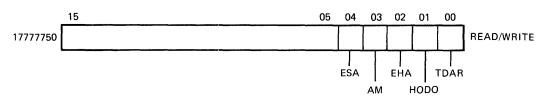

TU58 RCSR Format.......2-29

TU58 RBUF Format 2-30

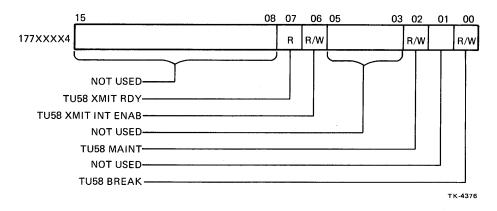

TU58 XCSR Format 2-31

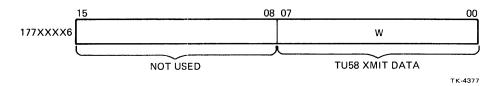

Signal Register Format 2-32

Cache CDR Format 2-34

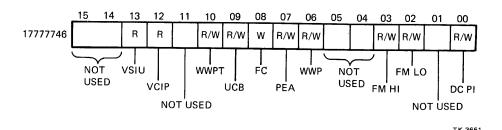

| 2-17                     | Cache CMR Format                                         | 2-36 |

|--------------------------|----------------------------------------------------------|------|

| 2-18                     | Cache CCSR Format                                        | 2-37 |

| 2-19                     | Cache CME Format                                         | 2-39 |

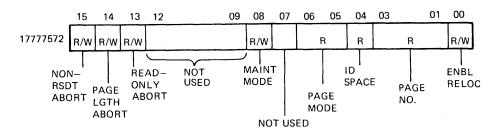

| 2-20                     | Memory Management SR0 Format                             | 2-40 |

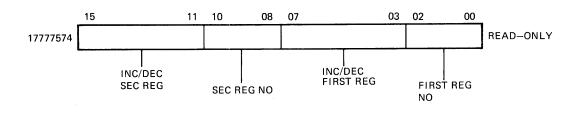

| 2-21                     | Memory Management SR1 Format                             | 2-42 |

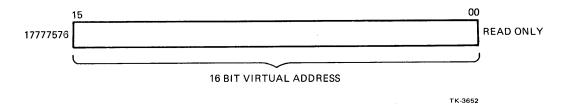

| 2-22                     | Memory Management SR2 Format                             | 2-43 |

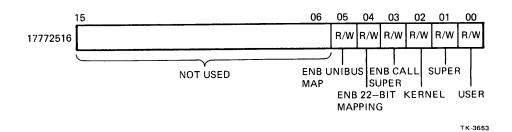

| 2-23                     | Memory Management SR3 Format                             | 2-43 |

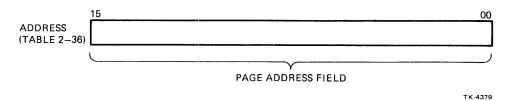

| 2-24                     | Memory Management PAR Format                             | 2-44 |

| 2-25                     | Memory Management PDR Format                             | 2-45 |

| 3-1                      | Backplane Module Locations                               | 3-1  |

| 3-2                      | Backplane Assembly, Pin Designations                     | 3-3  |

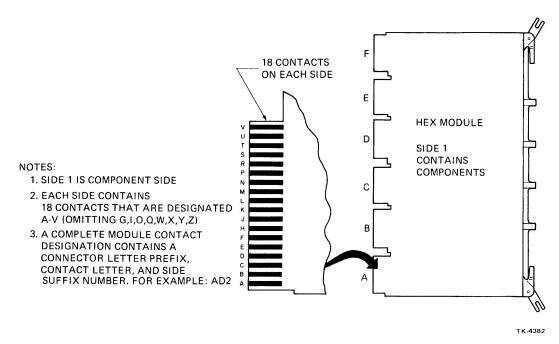

| 3-3                      | Module Contact Designations                              | 3-6  |

| 3-4                      | SPC Slots, NPG Jumper Lead Locations                     | 3-7  |

| 3-5                      | CIM Jumper Lead Locations, Connectors and                |      |

|                          | LED Indicator                                            | 3-12 |

| 3-6                      | MFM Jumper Lead Locations, Switches and                  |      |

| -                        | LED Indicator                                            | 3-15 |

| 3-7                      | TU58 Device Address Selection                            | 3-17 |

| 3-8                      | TU58 Vector Address Selection                            | 3-17 |

| 3-9                      | UBI Module. Switch and Jumper Lead Locations             | 3-18 |

| 3-10                     | Cache Memory Module, Switches, LED Indicators and Jumper |      |

| _ 10                     | Lead Locations                                           | 3-24 |

| 3-11                     | Control Module, Bootstrap Control Switch                 | 3-25 |

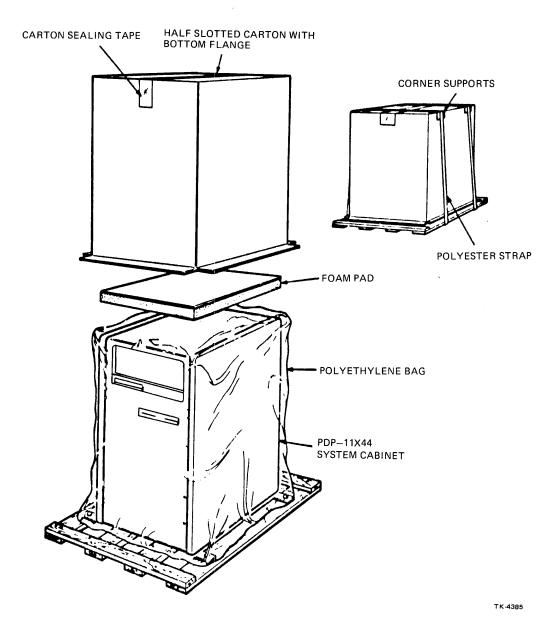

| 4-1                      | PDP-11/44 Unit Unpacking                                 | 4-3  |

| 4-2                      | PDP-11X44 Cabinet Unpacking                              | 4-4  |

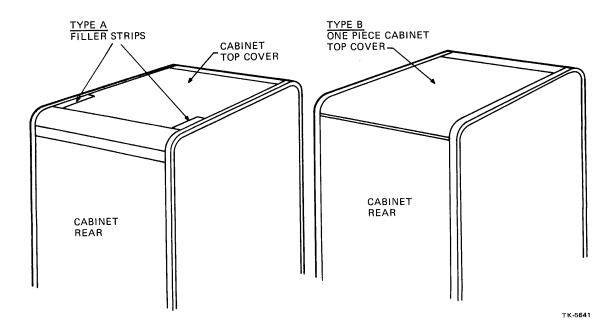

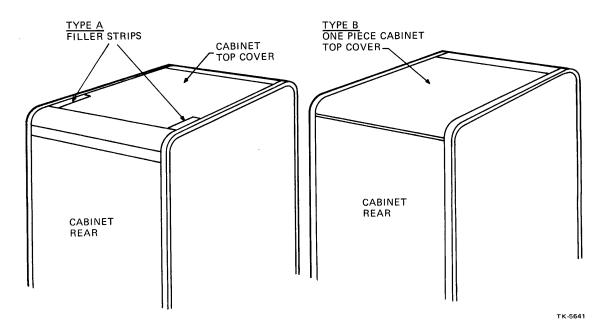

| 4-3                      | PDP-11X44 Cabinet Type Identification                    | 4-5  |

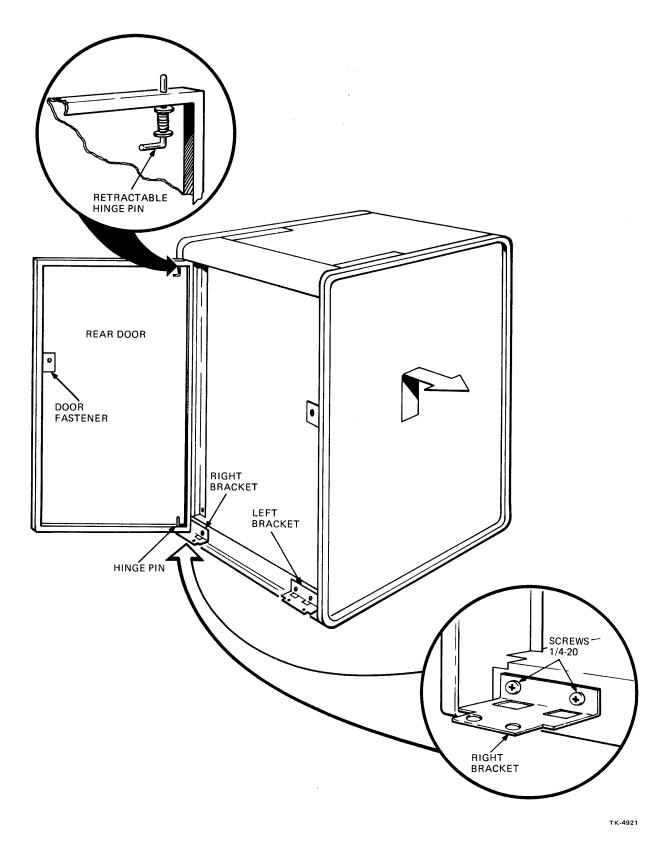

| 4-4                      | Left and Right Side Panel Removal                        | 4-6  |

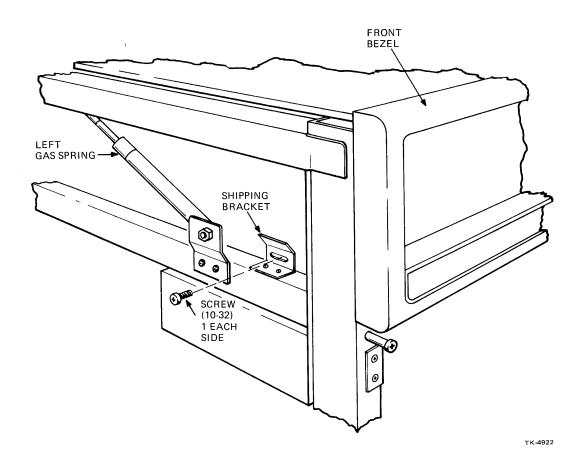

| 4-5                      | Shipping Bracket Location                                | 4-7  |

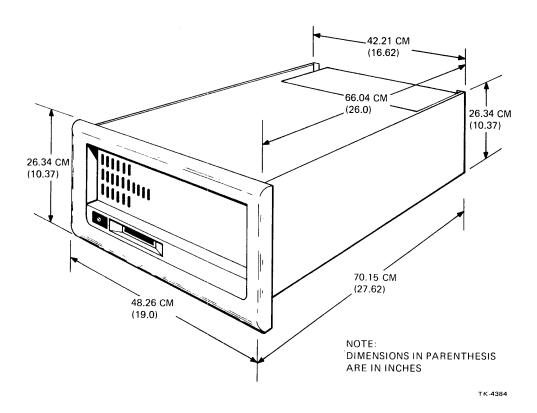

| 4-6                      | PDP-11/44 Unit Dimensions                                | 4-8  |

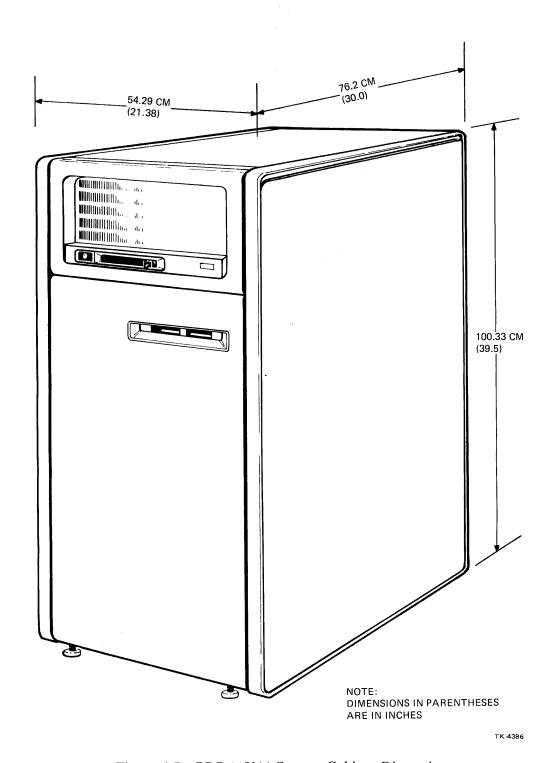

| 4-7                      | PDP-11X44 System Cabinet Dimensions                      | 4-9  |

| 4-8                      | Mounting Box Rear Panel Components                       | 4-11 |

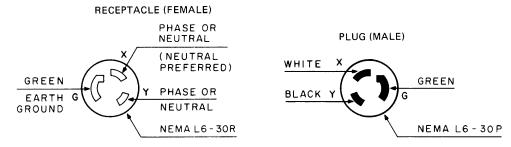

| 4-9                      | PDP-11/44-CA, -CB AC Power Connector Specifications      | 4-11 |

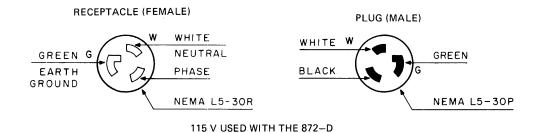

| 4-10                     | 972 D. F. Power Controller Input Power                   |      |

| 7 10                     | Specifications                                           | 4-12 |

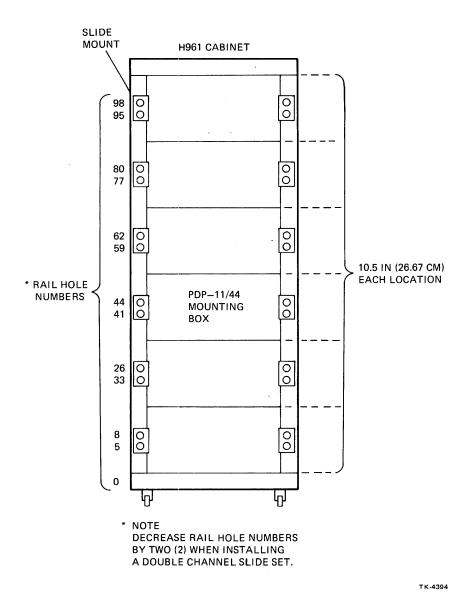

| 4-11                     | Mounting Box in H961 Cabinet                             | 4-13 |

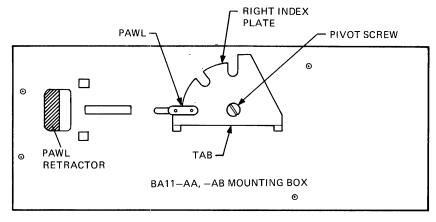

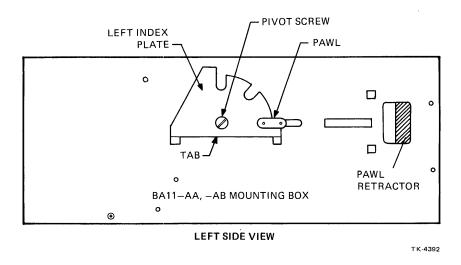

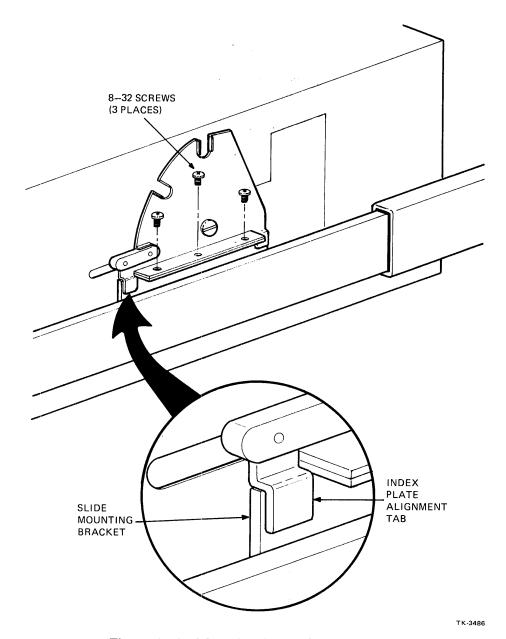

| 4-12                     | BA11-AAAB Mounting Box Index Plate Installation          | 4-14 |

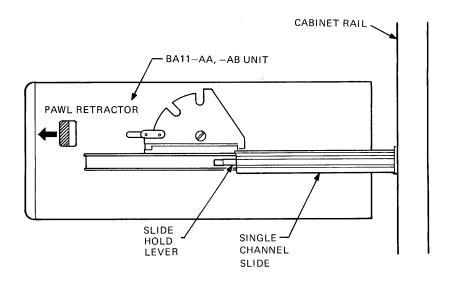

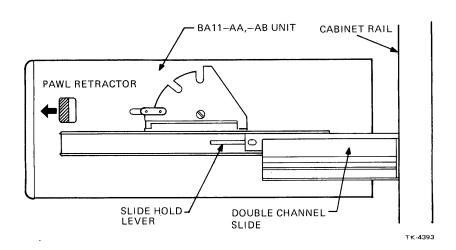

| 4-13                     | Single- and Double-Channel Slide Assemblies              | 4-15 |

| 4-14                     | H961 Cabinet Slide Mounting Locations                    | 4-16 |

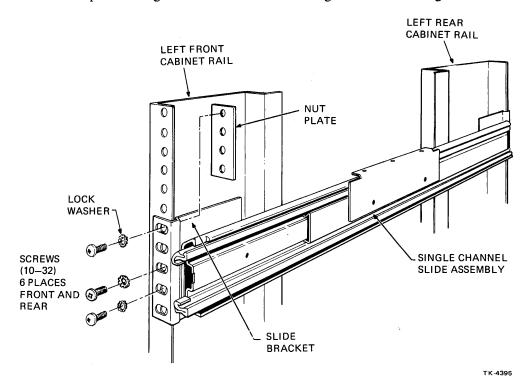

| 4-15                     | Cabinet Slide Installation                               | 4-1/ |

| 4-16                     | Mounting Box to Slide Installation                       | 4-18 |

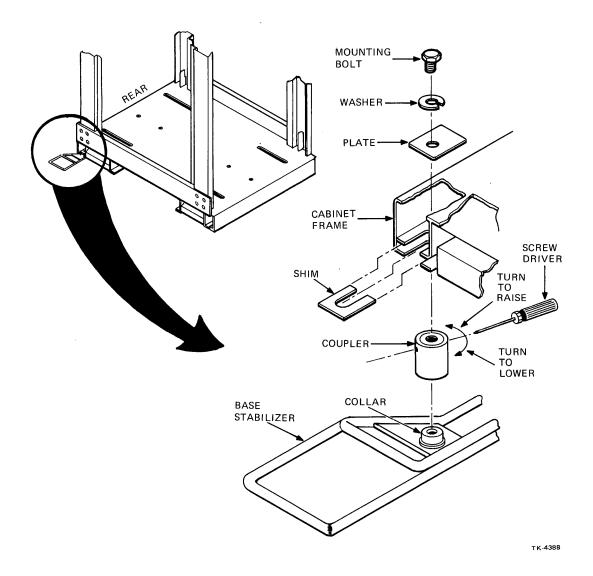

| <del>4</del> -10<br>4-17 | Cabinet Stabilizer Mounting                              | 4-19 |

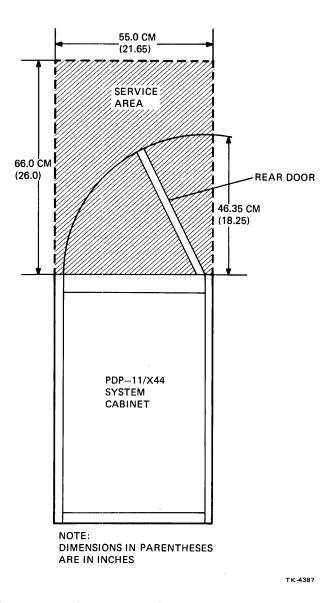

| 4-18                     | PDP-11X44 System Cabinet Service Area                    | 4-20 |

| 4-19                     | BA11-A Cable Routing Locations                           | 4-21 |

| 4-20                     | PDP-11X44 Cabinet Cable Routing                          | 4-22 |

| 4-20<br>4-21             | Backplane Assembly, Pin Designations                     | 4-24 |

| 5-1                      | PDP-11X44 Cabinet Type Identification                    | 5-1  |

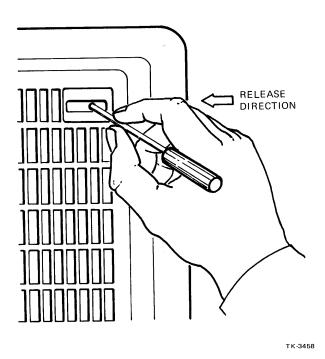

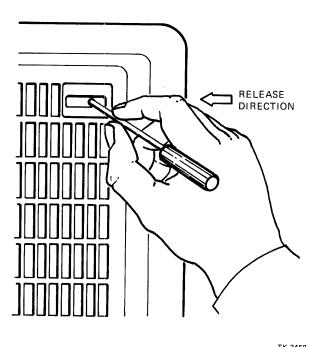

| 5-1<br>5-2               | PDP-11X44 Systems Cabinet Mounting Box Release Lever     | 5-3  |

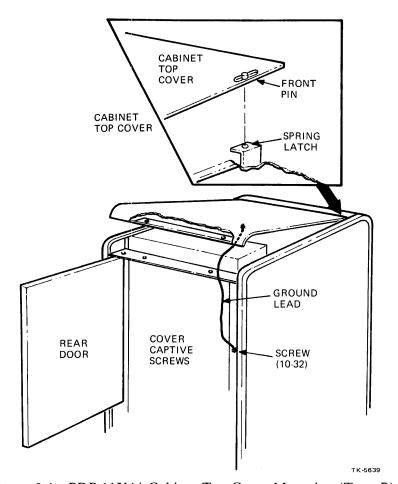

| 5-2<br>5-3               | PDP-11X44 Top Cover Mounting (Type A)                    | 5-4  |

| 5-3<br>5-4               | PDP-11X44 Cabinet Top Cover Mounting (Type B)            | 5-4  |

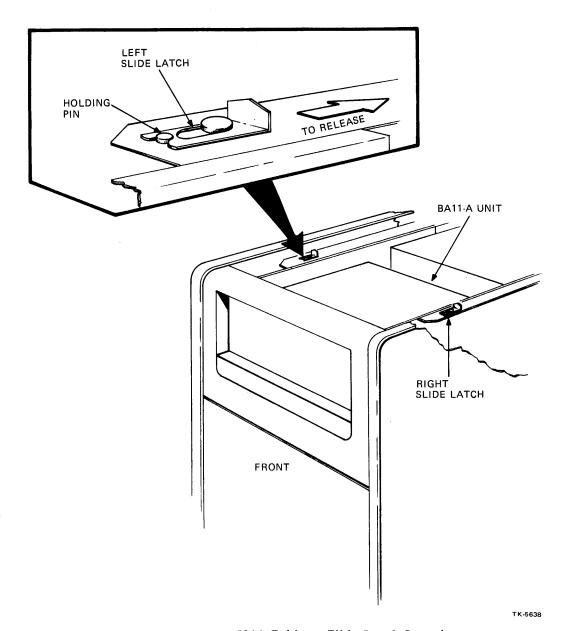

| 5- <del>4</del><br>5-5   | PDP-11X44, Slide Latch Locations                         | 5-5  |

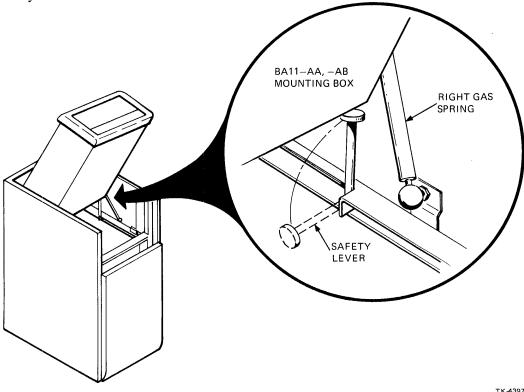

| 5-6                      | PDP-11X44 Cabinet Safety Lever                           |      |

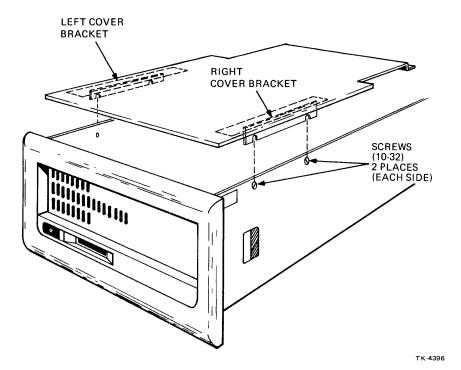

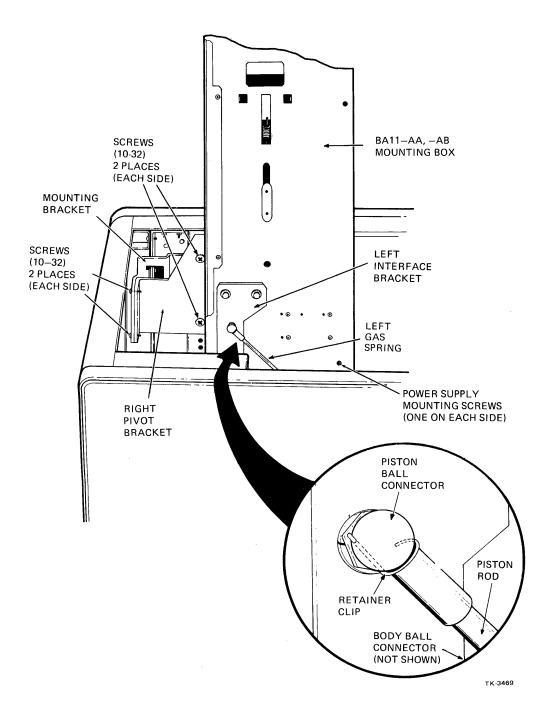

| 5-6<br>5-7               | PDP-11X44 Cabinet Mounting Box Hardware                  |      |

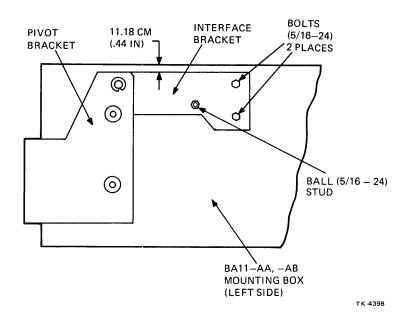

| 5-7<br>5-8               | Interface Bracket Mounting                               | 5-8  |

|                          |                                                          |      |

| 5-9          | Mounting Box Release Lever                        | 5-10                     |

|--------------|---------------------------------------------------|--------------------------|

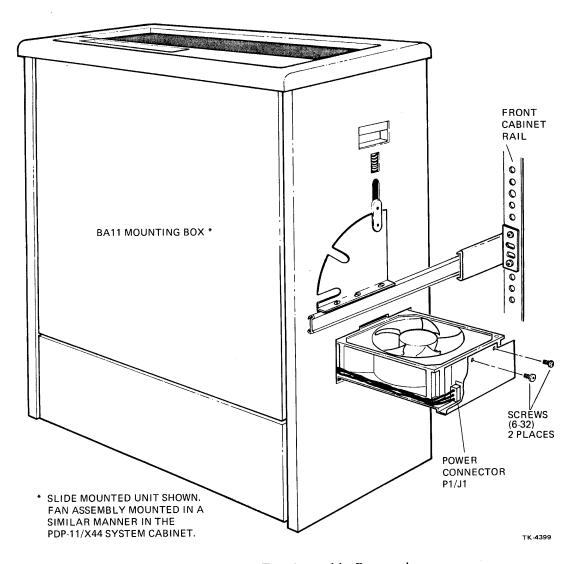

| 5-10         | Fan Assembly Removal                              | 5-11                     |

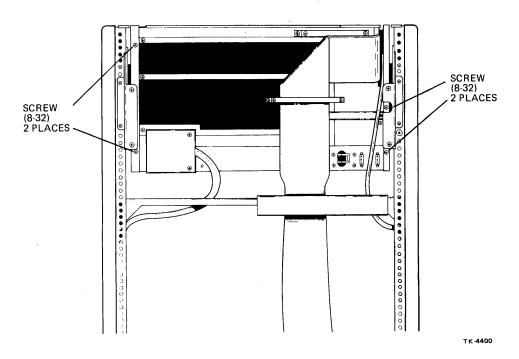

| 5-11         | Power Supply Assembly, Rear Mounting Screws       | 5-13                     |

| 5-12         | Power Supply Assembly Removal                     | 5-13                     |

| 5-13         | Power Lead Connections                            | 5-14                     |

| 5-14         | Power Distribution Panel and Connectors           | 5-15                     |

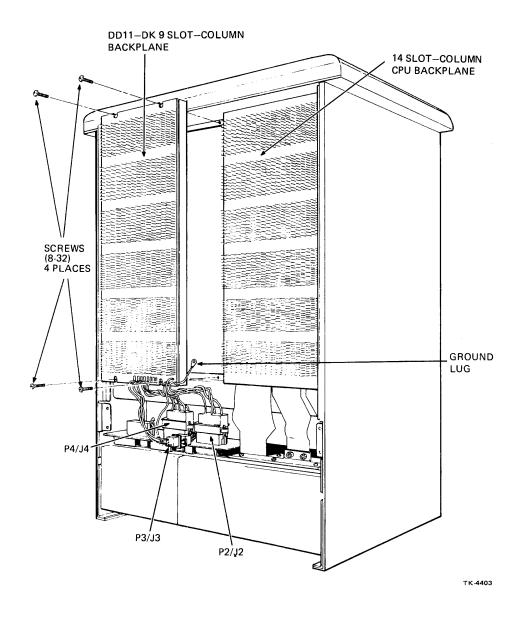

| 5-15         | Optional Backplane Assemblies                     | 5-17                     |

| 5-16         | Optional Backplane Configurations                 | 5-19                     |

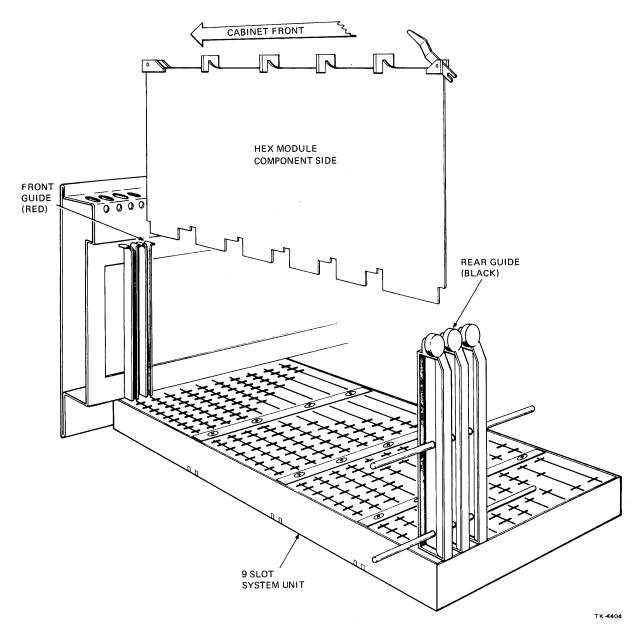

| 5-17         | Backplane Assembly Mounting                       | 5-20                     |

| 5-18         | Backplane Assembly Alignment                      | 5-21                     |

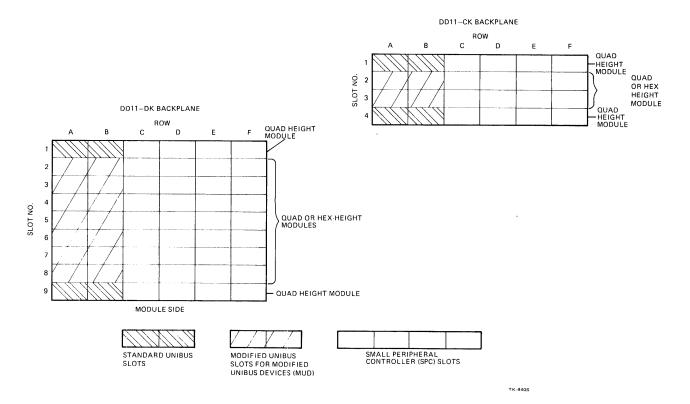

| 5-19         | Optional Backplane Slot Assignments               | 5-22                     |

| 5-20         | NPG Jumper Leads Routing                          | 5-23                     |

| 5-21         | Standard and Modified Backplane Pin Assignments   | 5-24                     |

| 5-22         | SPC Backplane Pin Assignments                     | 5-25                     |

| 5-23         | Backplane Power Connector Pin Designations        | 5-26                     |

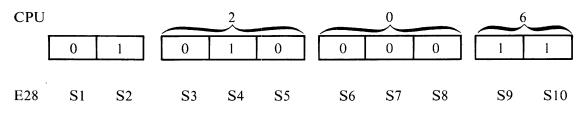

| 6-1          | KD11-Z Microinstruction Format                    | 6-2                      |

| 6-2          | MicroPC Generation                                |                          |

| 6-3          | Data Path Block Diagram                           |                          |

| 6-4          | Arithmetic Logic Unit                             |                          |

| 6-5          | ALU B-Leg Logic                                   |                          |

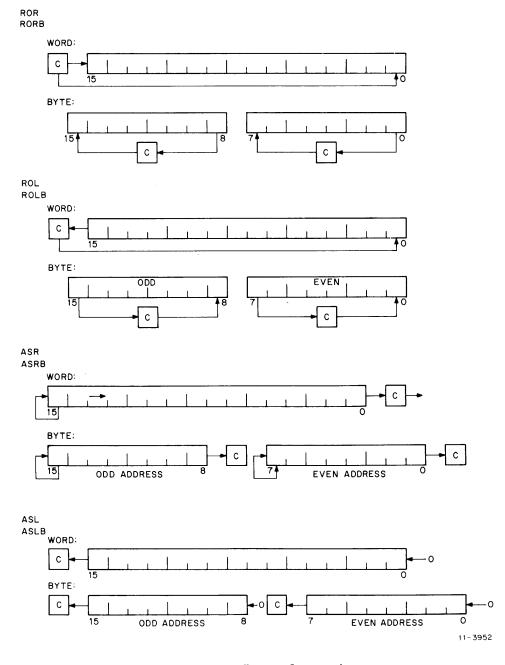

| 6-6          | Rotate Instructions                               |                          |

| 6-7          | Scratchpad Logic                                  |                          |

| 6-8          | Scratchpad Timing                                 |                          |

| 6-9          | PSW Logic                                         | 6-1 <del>4</del><br>6-16 |

| 6-10         | UNIBUS Synchronizer                               | 6 22                     |

| 6-11         | Generation of MSYN and MSYN/SSYN Timeout          | 0-22<br>6 24             |

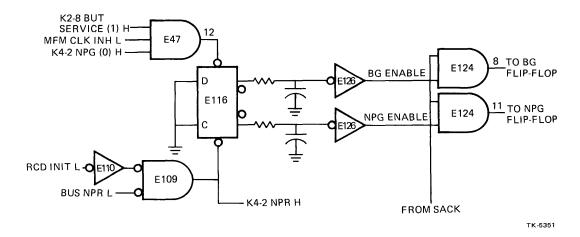

| 6-12         | Deskew Logic                                      | 6 26                     |

| 6-13         | Request Synchronization                           | 0-20<br>6 27             |

| 6-14         | SACK Timeout                                      |                          |

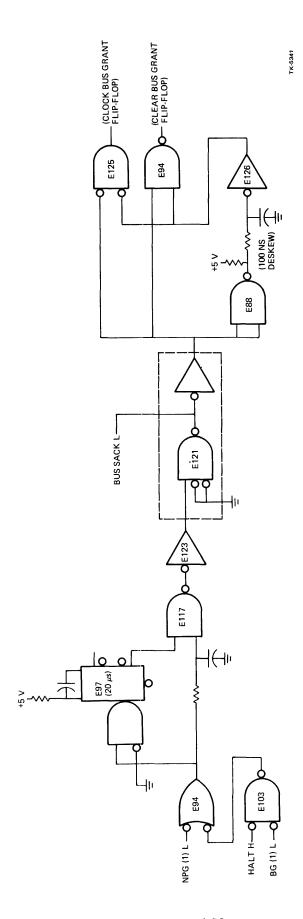

| 6-15         | Transfer Error Logic                              | 6-28                     |

| 6-16         | Generation of ABORT RESTART L and ABORT H         | 0-29                     |

| 6-17         |                                                   |                          |

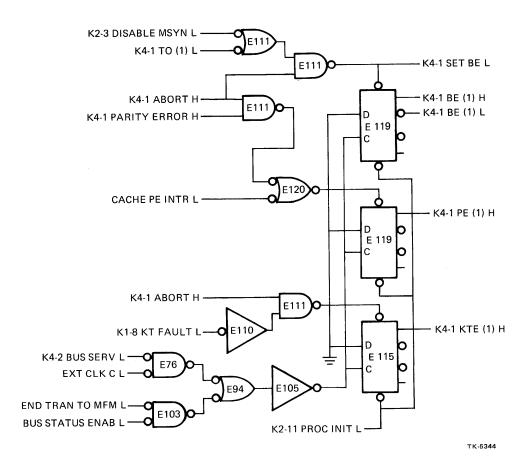

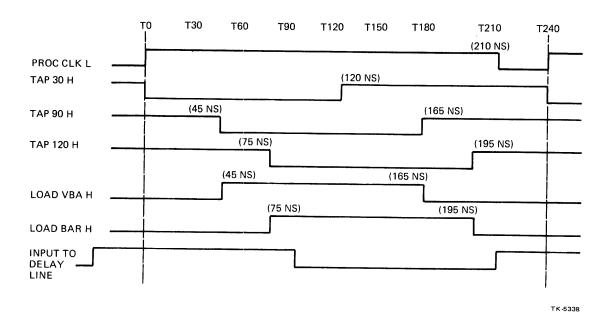

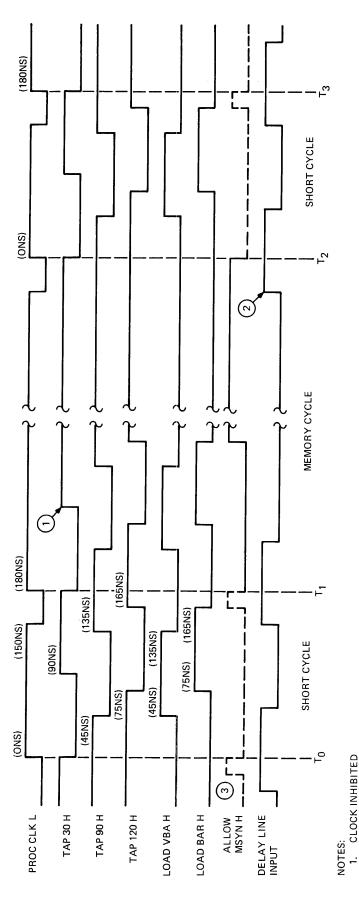

| 6-18         | PDP-11/44 System Clock Short Cycle Timing Diagram | 6-32                     |

| 6-19         | PDP-11/44 System Clock Long Cycle Timing Diagram  | 6-32                     |

| 0-19         | PDP-11/44 System Clock Timing Diagram with Memory |                          |

| 6-20         | Cycle                                             | 6-34                     |

| 6-20<br>6-21 | BUS AC LO and DC LO Timing Diagram                | 6-35                     |

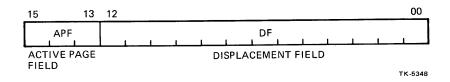

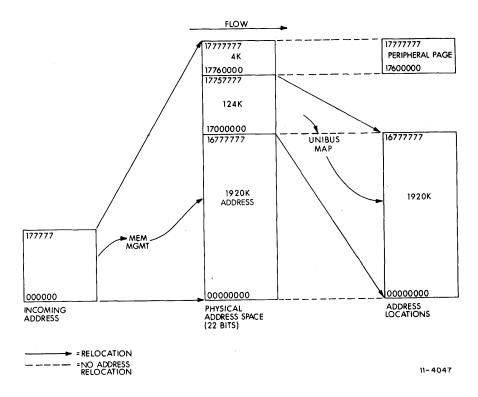

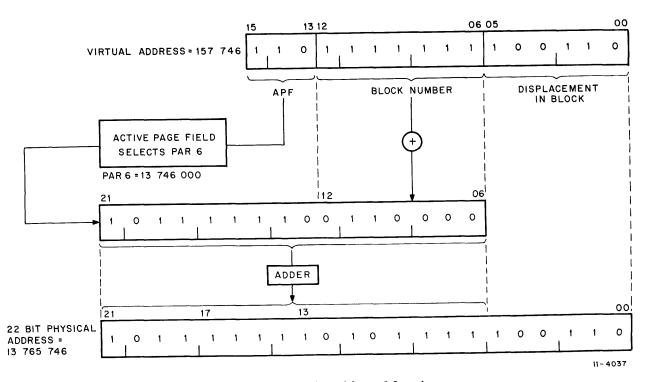

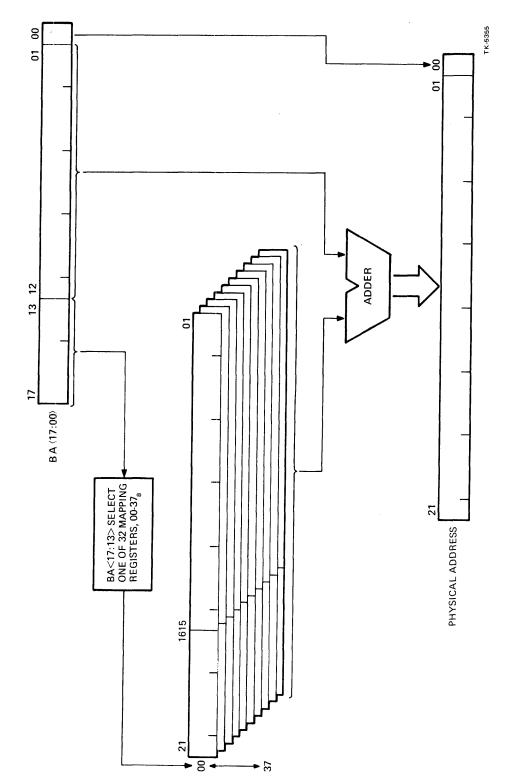

| 6-21<br>6-22 | Interpretation of VBA                             | 6-37                     |

| 6-22<br>6-23 | Displacement Field                                | 6-38                     |

| 6-23<br>6-24 | Construction of PA                                | 6-38                     |

| 6-24<br>6-25 | Memory Management Block Diagram                   | 6-40                     |

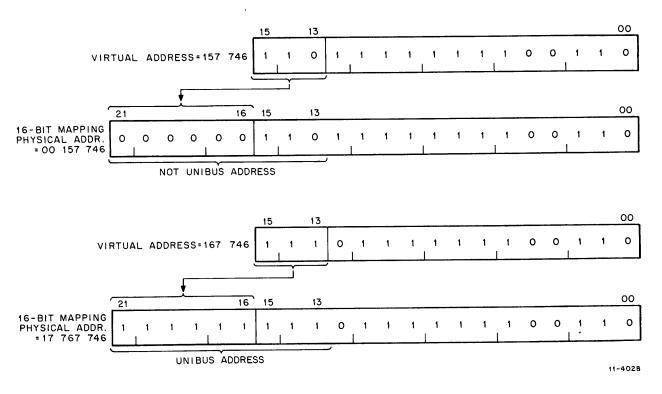

|              | 16-Bit Mapping                                    | 6-41                     |

| 6-26         | 16-Bit Mapping: Generation of PA                  | 6-41                     |

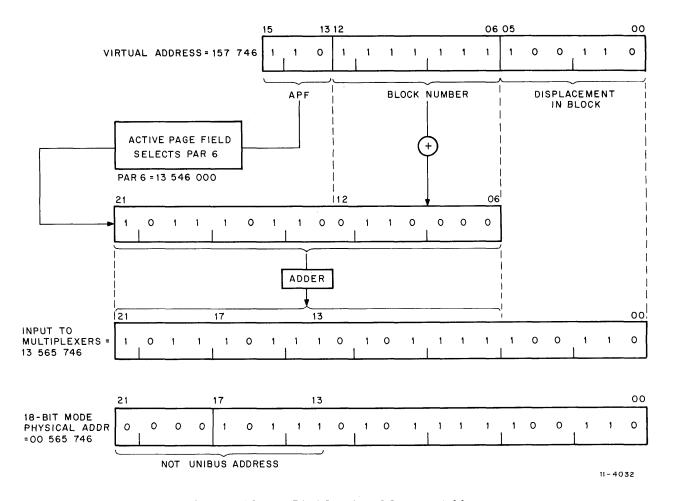

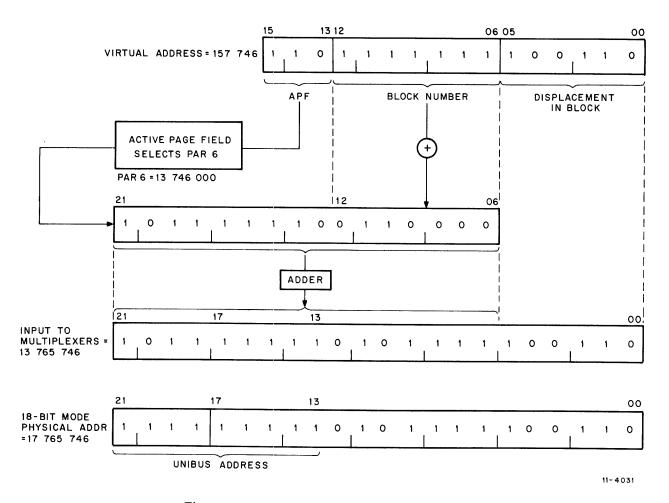

| 6-27         | 18-Bit Mapping                                    | 6-42                     |

| 6-28         | 18-Bit Mapping: Memory Address                    | 6-43                     |

| 6-29         | 18-Bit Mapping: UNIBUS Address                    | 6-44                     |

| 6-30         | 22-Bit Mapping                                    | 6-45                     |

| 6-31         | 22-Bit Address Mapping                            | 6-45                     |

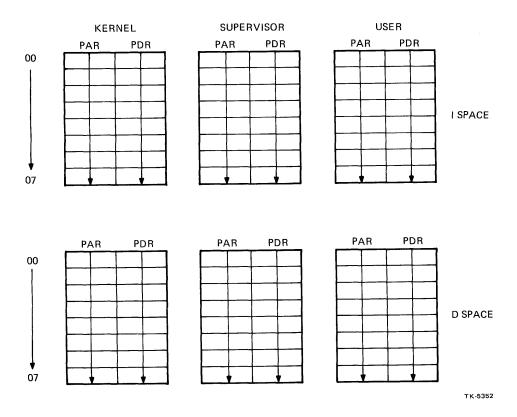

| 6-32         | Memory Management Relocation Registers            | 6-47                     |

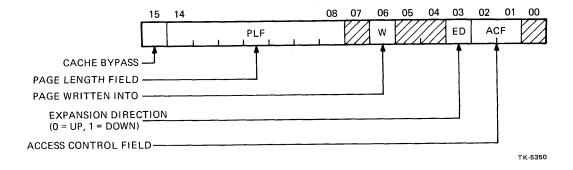

| 6-33         | Page Descriptor Register                          | 6-47                     |

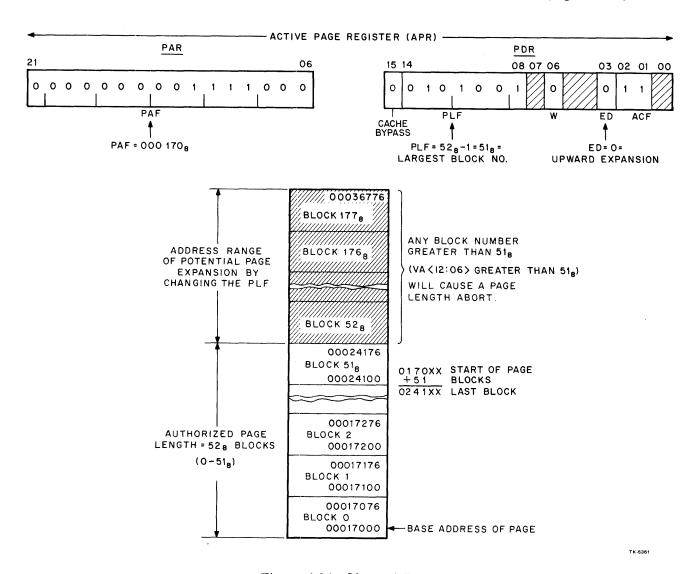

| 6-34         | Upward Expansion                                  | 6-48                     |

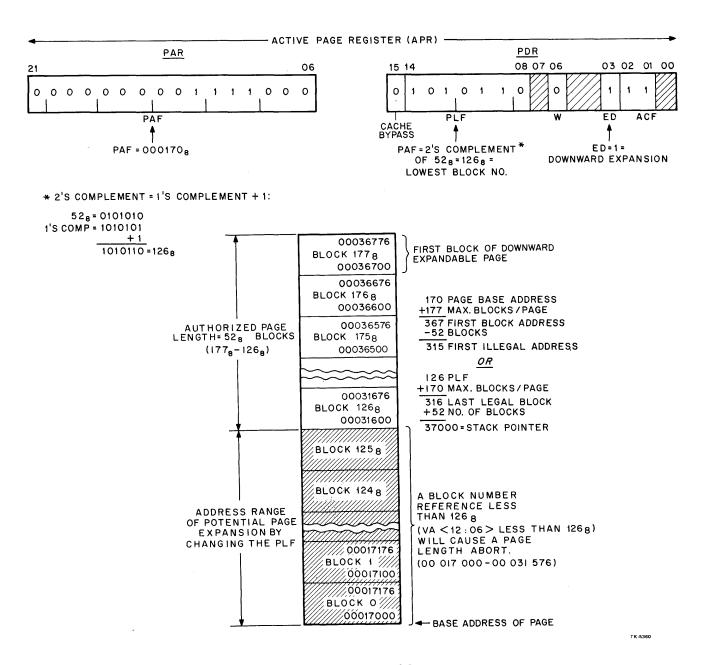

| 6-35         | Downward Expansion                                | 6-49                     |

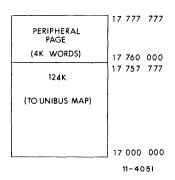

| 6-36         | UNIBUS Address Space                              |                          |

| 6-37         | UNIBUS Man Block Diagram                          | 6.54                     |

| 6-38 | Construction of the PA                            | . 6-56 |

|------|---------------------------------------------------|--------|

| 6-39 | UNIBUS Map Addressing Limits                      | . 6-57 |

| 6-40 | Console Processor Block Diagram                   | . 6-58 |

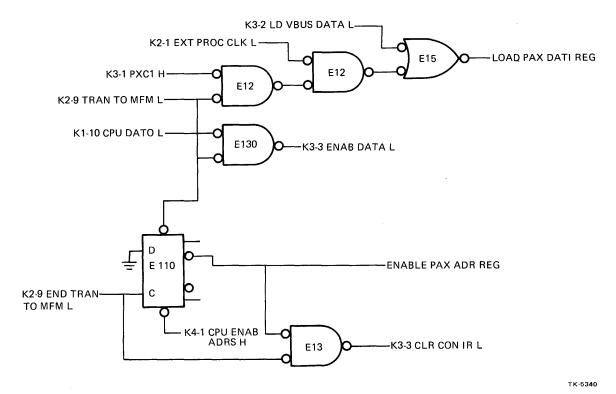

| 6-41 | Console Processor to PAX, Interface Control Logic | 6-63   |

| 6-42 | Console Terminal SLU                              | . 6-64 |

| 6-43 | TU58 SLU                                          | . 6-67 |

| 6-44 | Address Selection Logic                           | . 6-70 |

| 6-45 | SLU Address Format                                | . 6-71 |

| 6-46 | Terminal Receiver Status Register                 | . 6-73 |

| 6-47 | Terminal Receiver Buffer Register                 | . 6-74 |

| 6-48 | Terminal Transmitter Status Register              | 6-75   |

| 6-49 | Terminal Transmitter Buffer Register              | . 6-76 |

| 6-50 | Line Clock Status Register                        | . 6-77 |

| 6-51 | TU58 Receiver Status Register                     | . 6-77 |

| 6-52 | TU58 Receiver Buffer Register                     | . 6-78 |

| 6-53 | TU58 Transmitter Status Register                  | 6-79   |

| 6-54 | TU58 Transmitter Buffer Register                  | . 6-80 |

| 6-55 | Terminal and TU58 Interrupt Arbitration Logic     | 6-82   |

| 6-56 | KK11-B Cache Memory Block Diagram                 | 6-83   |

| 6-57 | Cache Memory Addressing                           | 6-84   |

| 6-58 | Cache Memory Organization                         | 6-85   |

| 6-59 | Cache Address Multiplexer Control Logic           | 6-89   |

| 6-60 | Cache Flush Timing Diagram                        | 6-92   |

|      |                                                   |        |

|      |                                                   |        |

|      | TABLES                                            |        |

| Table No. | Title                                           | Page |

|-----------|-------------------------------------------------|------|

| 1-1       | Processor System Designations                   | 1-3  |

| 1-2       | PDP-11/44 Standard Hardware Components          | 1-5  |

| 1-3       | Hardware Options                                | 1-6  |

| 1-4       | PDP-11/44-CA, -CB Equipment Specifications      | 1-6  |

| 1-5       | PDP-11X44-CACB Equipment Specifications         | 1-8  |

| 1-6       | H7140-AA, -AB Power Supply Specifications       | 1-9  |

| 1-7       | Related Publications                            | 1-14 |

| 2-1       | Front Panel Switches and Indicators             | 2-2  |

| 2-2       | Console Mode Commands                           | 2-4  |

| 2-3       | Console Command Terms and Characters            | 2-4  |

| 2-4       | Console Command Qualifiers                      | 2-5  |

| 2-5       | Special Address Field Characters                | 2-6  |

| 2-6       | Control Characters                              | 2-6  |

| 2-7       | Device Bootstrap Identifiers                    | 2-9  |

| 2-8       | Bootstrap ROM Identifiers                       | 2-10 |

| 2-9       | DEPOSIT Command Qualifiers                      | 2-12 |

| 2-10      | EXAMINE Command Qualifiers                      | 2-12 |

| 2-11      | Summary of Errors                               | 2-18 |

| 2-11      | Console Command Summary                         | 2-19 |

| 2-12      | PDP-11/44 CPU and I/O Device Register Address   | 2-20 |

| 2-13      | Processor Status Word Register Bit Descriptions | 2-21 |

| 2-15 | Processor Interrupt Request Register Bit         |              |

|------|--------------------------------------------------|--------------|

|      | Descriptions                                     | 2-23         |

| 2-16 | Error Register Bit Descriptions                  | 2-23         |

| 2-17 | General Register Addresses                       | 2-25         |

| 2-18 | Console Terminal RCSR Bit Descriptions.          | 2-26         |

| 2-19 | Console Terminal RBUF Bit Descriptions           | 2-26         |

| 2-20 | Console Terminal XCSR Bit Descriptions.          | 2-25<br>2-25 |

| 2-21 | Console Terminal XBUF Bit Descriptions.          | )_2(         |

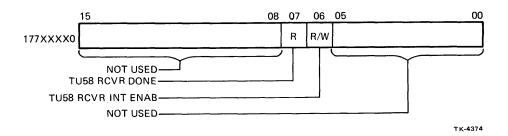

| 2-22 | TU58 RCSR Bit Descriptions.                      | ) 20         |

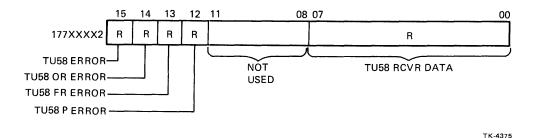

| 2-23 | TU58 RBUF Bit Descriptions                       | )-23         |

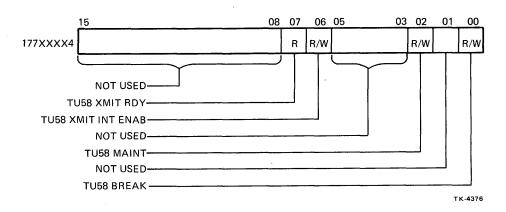

| 2-24 | TU58 XCSR Bit Descriptions                       | 1-30<br>1-31 |

| 2-25 | TU58 XBUF Bit Descriptions.                      | 1-31         |

| 2-26 | Signal Register Bit Descriptions                 | :-3∠<br>1-31 |

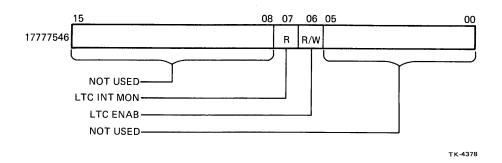

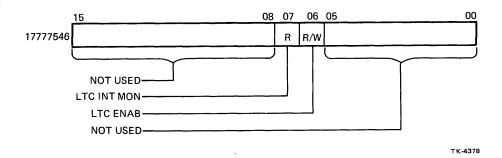

| 2-27 | Line Time Clock (LKS) Bit Descriptions           | 33           |

| 2-28 | Line Time Clock (LKS) Bit Descriptions           | 34           |

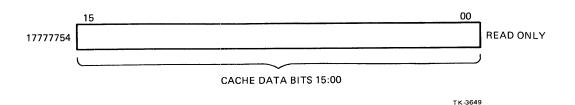

| 2-29 | Cache CDR Bit Descriptions                       | :-34         |

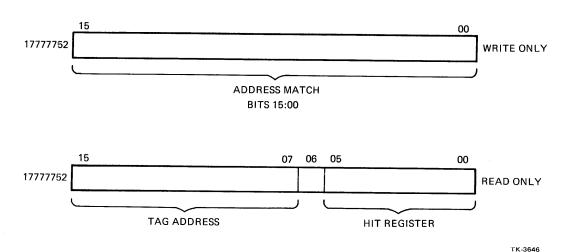

| 2-29 | Cache CHR Bit Descriptions                       | 2-35         |

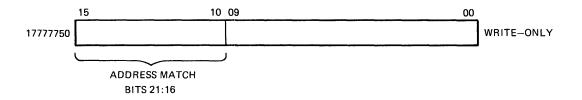

| 2-30 | Cache CMR Bit Descriptions                       | 36           |

| 2-31 | Cache CCSR Bit Descriptions                      | 2-38         |

| 2-32 | Cache CME Bit Descriptions                       | 2-40         |

| 2-33 | SR0 Bit Descriptions                             | 41           |

|      | SR1 Bit Descriptions                             | :-42         |

| 2-35 | SR2 Bit Description                              | :-43         |

| 2-36 | SR3 Bit Descriptions                             | :-43         |

| 2-37 | PAR Bit Description                              | 44           |

| 2-38 | PAR/PDR UNIBUS Addresses                         | 45           |

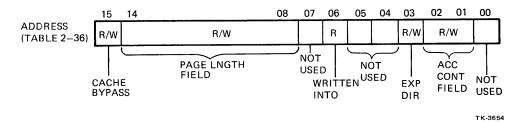

| 2-39 | PDR Bit Descriptions                             | -46          |

| 3-1  | Standard CPU Backplane Modules                   | 3-2          |

| 3-2  | Optional CPU Backplane Modules                   | 3-2          |

| 3-3  | CPU Backplane Connector P1, Signals and Voltages | 3-4          |

| 3-4  | CPU Backplane Voltage Distribution               | 3-4          |

| 3-5  | CPU Backplane Ground Distribution                | 3-5          |

| 3-6  | SPC Location, Signal Identification              | 3-8          |

| 3-7  | CPU Module Current Requirements                  | -10          |

| 3-8  | H7140-AA, -AB Power Supply Maximum               |              |

| • •  | Output Current                                   | -10          |

| 3-9  | -15 V, +15 Vdc Option Power Requirements         | -11          |

| 3-10 | Console Terminal Configuration, 20 mA Interface  | -13          |

| 3-11 | Console Terminal Configuration, EIA Interface    | -13          |

| 3-12 | TU58 DECtape II, EIA Configuration               | -13          |

| 3-13 | MFM Console Terminal Jumper Lead Configuration   | -14          |

| 3-14 | MFM Console Terminal Baud Rate Selection         | -15          |

| 3-15 | MFM TU58 Jumper Lead Configurations              | -16          |

| 3-16 | MFM TU58 Baud Rate Selection (Switch Pack E7)    | -17          |

| 3-17 | Line Time Clock Operation                        | -18          |

| 3-18 | UBI Module Jumper Lead Functions                 | -19          |

| 3-19 | UNIBUS Map Jumper Leads, Lower Limit             | -19          |

| 3-20 | UNIBUS Map Jumper Leads, Upper Limit             | -20          |

| 3-21 | CPU Diagnostic and Bootstrap Loader              |              |

|      | ROM Addresses                                    | -22          |

| 3-22 | Bootstrap ROM Locations                          | -23          |

| 3-23 | Device ROM Part Numbers                          | -23          |

| 3-24 | Cache Module, LED Indicator Functions            | -24          |

| 4-1  |                                                  | 10           |

| 4-2 | CPU Backplane Connector P1, Signals and Voltages | 4-24 |

|-----|--------------------------------------------------|------|

| 4-3 | PDP-11/44 MAINDEC Diagnostic Programs            |      |

| 4-4 | UBI Diagnostic ROM Error Indicators              |      |

| 5-1 | Optional Backplane Assemblies                    | 5-16 |

| 5-2 | Backplane Assembly Types                         | 5-18 |

| 5-3 | Power Connector Signal Assignments for DD11-CK   | 5-26 |

| 5-4 | Power Connector Signal Assignments for DD11-DK   |      |

| 6-1 | Error Logic Outputs                              | 6-31 |

| 6-2 | Address Mapping Modes                            | 6-39 |

| 6-3 | Memory Management Fault PROM Inputs              |      |

| 6-4 | Memory Management Fault PROM Outputs             |      |

| 6-5 | Access to UNIBUS Map Registers                   |      |

| 6-6 | TU58 Baud Rate Selection                         |      |

| 6-7 | Cache Read/Write Response                        |      |

|     |                                                  |      |

#### **PREFACE**

The PDP-11/44 is a midrange computer system which is available in a standard configuration and is expandable by the user to conform to specific user requirements.

This manual defines the standard system and provides the information required to unpack and install the system in a cabinet, and to wire the system for operation. This manual also gives a detailed functional description of the KD11-Z Central Processor used in the PDP-11/44.

Chapter 1, Introduction – Includes a general description of the PDP-11/44 system and the modules supplied with the unit. The chapter also describes the features and capability of the system, the available options, and the equipment specifications, including the power supply.

Chapter 2, Operation – Describes the front panel controls and indicators, the console commands available, and register bit assignments.

Chapter 3, Configuration – Provides the module current requirements and information on placement in the processor backplane, and the switch and jumper lead information required to configure the modules for specific requirements.

Chapter 4, Installation – Provides the information necessary to prepare the installation area, to connect the unit to ac power and to mount the unit into a PDP-11/44 system cabinet or standard 48.26 cm (19 in) cabinet.

Chapter 5, Removal/Replacement Procedures – Describes the procedures required to remove and replace the main units and assemblies and to install additional backplanes for expansion of the system functions.

Chapter 6, Detailed Functional Description – Describes each of the major logic elements of the KD11-Z Central Processor.

## CHAPTER 1 INTRODUCTION

The PDP-11/44 processor consists of CPU modules, memory modules, and interface modules enclosed in the BA11-AA or BA11-AB mounting box. The box includes a front control panel and power supply. The mounting box can be installed in a standard 48.26 cm (19 in) rack or cabinet or in a DIGITAL system cabinet.

The PDP-11X44 system consists of the PDP-11/44 processor mounted into the 100 cm (40 in) low-profile, top-loading H9642 cabinet. This cabinet conforms in style to other DIGITAL PDP-11 peripheral unit cabinets.

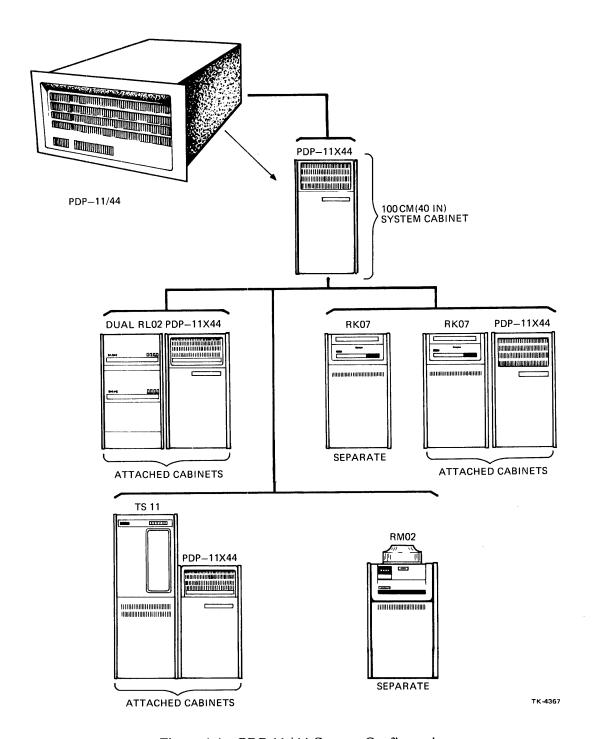

Figure 1-1 shows several typical PDP-11X44 system configurations that include disk drive units and magnetic tape units. The PDP-11X44 cabinet attaches to the RL02 and RK07 Disk Drive Units and to the TS11 Magnetic Tape Unit.

#### 1.1 GENERAL

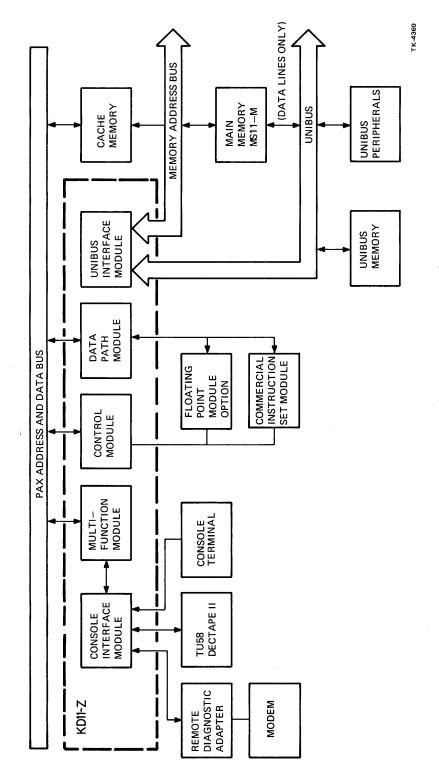

The PDP-11/44 and the PDP-11X44 are medium range, general purpose computer systems which operate with 16-bit data words and provide 22 bits for memory addressing. A total of one megabyte of main memory can be included with the system in increments of 256K bytes. The system includes the complete instruction set of the PDP-11/70 processor except for the FD MAINT INST instruction. Two additional instructions, Move From Processor Type (MFPT) and Call to Supervisor Mode (CSM), are included.

The systems also include an 8K byte cache memory and the extended instruction set (EIS). A microprocessor interprets the ASCII codes from the console terminal and allows the functions previously performed at the console switches to be initiated at the console terminal.

A floating-point processor and a commercial instruction set processor are available as options with the system.

The PDP-11X44 system includes a dual TU58 DECtape II cartridge tape unit used to load diagnostic programs and to update software. The following operating software systems are compatible with the PDP-11/44 and PDP-11X44 systems.

| Software | Version | Software | Version |

|----------|---------|----------|---------|

| RT-11    | V4.0    | CTS-500  | V5.0    |

| RSX-11M  | V3.2    | DSM-11   | V2.0    |

| RSX-11S  | V3.2    | TRAX     | V2.0    |

| RSX-11M+ | V1.0    | COBOL-11 | V4B     |

| RSTS/E   | V7.0    | MACRO-11 | V4.0    |

Figure 1-1 PDP-11/44 System Configurations

#### 1.2 EQUIPMENT DESCRIPTION

The PDP-11/44 and PDP-11X44 processor systems are available to operate with either 120 Vac or 240 Vac input power. Table 1-1 lists and describes the components included with each system.

**Table 1-1 Processor System Designations**

| Designation  | Description                                                                                                                                                                                                                                                                      |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDP-11/44-CA | Contains a CPU, 256K bytes of ECC MOS memory, two EIA serial line units, one for the console terminal and one for the TU58 tape transport (not included), BA11-AA mounting box with cabinet, mounting slides and a filter distribution panel. Operates with 120 Vac input power. |

| PDP-11/44-CB | Same as PDP-11/44-CA except the mounting box is a BA11-AB wired for 240 Vac input power.                                                                                                                                                                                         |

| PDP-11X44-CA | Same as PDP-11/44-CA except the BA11-AA mounting box is installed in an H9642 system cabinet which includes a dual TU58 tape unit and power control unit for 120 Vac input power.                                                                                                |

| PDP-11X44-CB | Same as PDP-11X44-CA except it is wired for 240 Vac input power.                                                                                                                                                                                                                 |

#### 1.2.1 PDP-11/44-CA, -CB Processor System

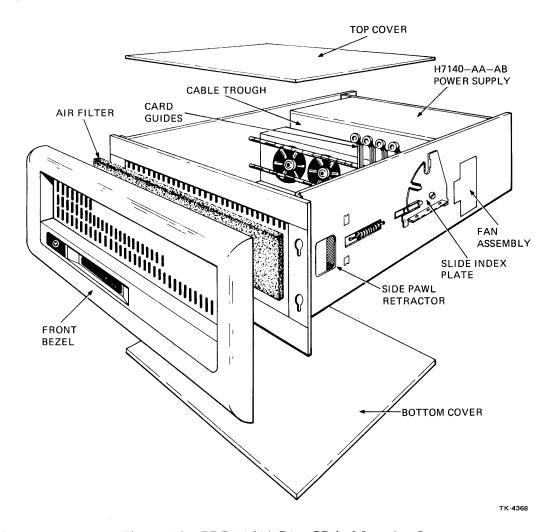

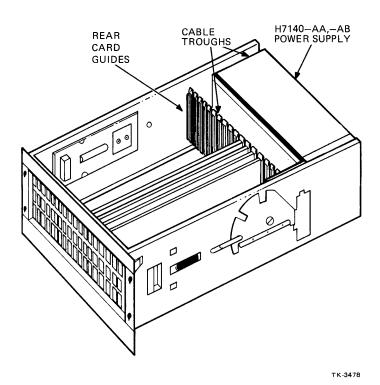

The PDP-11/44-CA, -CB processors are supplied in the BA11-AA, -AB mounting box shown in Figure 1-2. The mounting box contains a 14-slot (column) backplane assembly with the system modules installed, a fan assembly, and an H7140-AA, -AB power supply assembly. The fan assembly contains three fans and provides cooling for the modules and power supply. The fans are mounted on a slide, for ease of removal, and are powered by the power supply. A bezel is attached to the front of the mounting box and contains a control panel and ventilating slots for air circulation. An open-cell foam filter is located directly behind the front bezel and may be easily removed for cleaning.

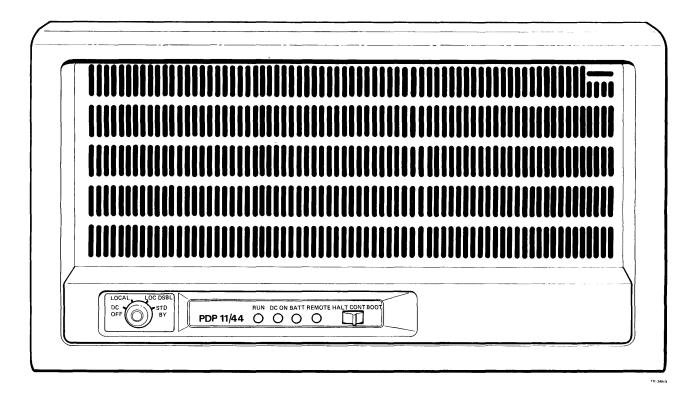

A control panel, located on the lower section of the front bezel, contains a keyswitch, panel switch, and indicators to select and indicate operating conditions. A removable top and bottom cover is also supplied with the mounting box.

Attached to each side of the mounting box is a slide index plate which allows the unit to be rotated to a vertical position, when the unit is mounted in a cabinet, onto the slides that are provided with the unit. The slide index plates are released by the side pawl retractors also located on each side of the unit, toward the front.

The BA11-AA, -AB box provides a 14-slot CPU backplane and 29 card guides at the front and rear of the unit to allow additional modules to be installed. One DD11-DK 9-slot, double-system unit and one DD11-K single-system unit or three DD11-CK single-system units may be installed and connected directly to the power supply by the cables and connectors attached to the system units. These system units provide additional mounting space for I/O device options.

Figure 1-2 PDP-11/44-CA, -CB in Mounting Box

#### 1.2.2 PDP-11X44 Processor System

The PDP-11X44-CA, -CB consists of the components described for the PDP-11/44-CA, -CB which are mounted in a system cabinet as shown on the frontispiece. Mounted below the front bezel is a dual TU58 tape unit which enables the loading of diagnostic programs from cassettes and provides data storage for up to 256K bytes of information.

The BA11-AA, -AB mounting box is attached to the top of the cabinet and can be released and tilted vertically for servicing. When tilted, the mounting box is supported by two gas springs. A hinged panel is provided at the front and the rear of the cabinet to allow access to the power controller unit provided with the cabinet, to the battery backup unit which is supplied as an option, and to the I/O connector panel.

## 1.2.3 Standard Hardware Components

Table 1-2 lists the standard hardware supplied with each PDP-11/44 system.

Table 1-2 PDP-11/44 Standard Hardware Components

| Quantity | Description                                                                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | KD11-Z Central Processor consisting of:                                                                                                                   |

|          | (M7090) Console Interface Module<br>(M7094) Data Path Module<br>(M7095) Control Module<br>(M7096) Multifunction Module<br>(M7098) UNIBUS Interface Module |

| 1        | MS11-MB ECC MOS Memory (256K bytes)                                                                                                                       |

| 1        | 8K byte cache memory on hex-height module (M7097).                                                                                                        |

| 1        | BA11-AA (120 Vac) or BA11-AB (240 Vac) mounting box with power supply and DD11-DK backplane (70-16502)                                                    |

| 1        | M9302 UNIBUS Terminator Module                                                                                                                            |

| 1        | M9642 Cabinet (PDP-11/X44-CA, -CB only)                                                                                                                   |

| 1        | TU58 Dual Tape Drive (PDP-11/X44-CA, -CB only)                                                                                                            |

| 1        | 872-D Power Controller Unit (PDP-11/X44-CA, -CB only)                                                                                                     |

| 1        | I/O Connector Panel                                                                                                                                       |

#### 1.2.4 Hardware Options

The standard PDP-11/44 system capabilities can be expanded with the installation of several available hardware options which are listed in Table 1-3.

## 1.3 EQUIPMENT SPECIFICATIONS

The following paragraphs contain the mechanical/environmental specifications for the PDP-11/44 and PDP-11X44 equipment. Detailed specifications for the peripheral devices supplied with these units are contained in the user's guide associated with the device.

**Table 1-3 Hardware Options**

| Designation  | Description                                                                                        |

|--------------|----------------------------------------------------------------------------------------------------|

| MS11-MB      | 256K bytes ECC memory on hex-height module                                                         |

| MS11-MC      | Same as MS11-MB except 512K bytes on two hex-height modules                                        |

| MS11-MD      | Same as MS11-MB except 758K bytes                                                                  |

| FP11-F       | Floating-point processor on hex-height module (M7093)                                              |

| KE44-A       | Commercial instruction set processor on a quad-height module (M7091) and hex-height module (M7092) |

| H7750-BA     | Battery backup unit 120 Vac/60 Hz, 240 Vac/50 Hz                                                   |

| H7750-BD     | Same as H7750-BA except for 240 Vac/50 Hz                                                          |

| TU58-CA      | Dual cassette tape transport                                                                       |

| BA11-AE, -AF | Expander box for PDP-11/44 system expansion; includes power supply                                 |

1.3.1 PDP-11/44 System Specifications

Table 1-4 lists the equipment specifications for the basic PDP-11/44 unit. When the system is operated with a TU58 DECtape II option, the specifications will be similar to those listed in Table 1-5 for the PDP-11X44 system.

Table 1-4 PDP-11/44-CA, -CB Equipment Specifications

| Characteristic                        | Description                                                                                                            |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Mechanical                            |                                                                                                                        |

| Overall dimensions (with front bezel) | 70.15 cm long $\times$ 48.26 cm wide $\times$ 26.34 cm high (27.62 in long $\times$ 19 in wide $\times$ 10.37 in high) |

| Weight                                |                                                                                                                        |

| Unpacked                              | 32.66 kg (72 lb)                                                                                                       |

| Packed                                | 36.2 kg (80 lb)                                                                                                        |

|                                       |                                                                                                                        |

Table 1-4 PDP-11/44-CA, -CB Equipment Specifications (Cont)

| Characteristics                              | Description                                                                                                                                                                               |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Environmental*                               |                                                                                                                                                                                           |

| Temperature                                  |                                                                                                                                                                                           |

| Operating                                    | 5° C to 50° C (41° F to 122° F)                                                                                                                                                           |

| Nonoperating                                 | -40° C to 66° C (-40° F to 151° F)                                                                                                                                                        |

| Humidity                                     |                                                                                                                                                                                           |

| Operating                                    | 10% to 95% relative (RH) with a maximum wet bulb of 32° C (90° F) and a minimum dew point of 2° C (36° F)                                                                                 |

| Nonoperating                                 | 50% relative (RH) or less to 95% (RH) or less with a maximum wet bulb of 46° C (115° F)                                                                                                   |

| Vibration                                    |                                                                                                                                                                                           |

| Operating                                    | 5 to 22 Hz: 0.01 in DA; 22 to 500 Hz: 0.25 Gpk. Sweep rate of 1.0 octave/min. All three axes.                                                                                             |

| Nonoperating (PDP-11/44 packed for shipment) | Vertical Axis Random Vibration: 1.4 Grms overall from 10 to 300 Hz; duration: 1 h. Longitudinal & Lateral Axis Random Vibration: 0.68 Grms overall from 10 to 200 Hz; duration: 1 h. each |

| Altitude                                     |                                                                                                                                                                                           |

| Operating                                    | 0 to 2.4 km (8000 ft)                                                                                                                                                                     |

| Nonoperating                                 | 9.1 km (30000 ft)                                                                                                                                                                         |

| Shock                                        |                                                                                                                                                                                           |

| Operating                                    | 10 Gpk for 10 ms $(+3 \text{ ms})$ , $1/2 \text{ sine wave, vertical axis only}$                                                                                                          |

| Nonoperating                                 | Flat drop for a 6 in height, 3 drops total (vertical direction only)                                                                                                                      |

<sup>\*</sup>The operating temperature and humidity for PDP-11/44 systems, which include magnetic tape units, disk units, or card readers, is the same as defined in Table 1-5 for the PDP-11X44 system.

1.3.2 PDP-11X44 System Specifications

Table 1-5 lists the equipment specifications for the PDP-11X44 system including the TU58.

Table 1-5 PDP-11X44-CA, -CB Equipment Specifications

| Characteristic                               | Description                                                                                                                                                                              |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mechanical                                   |                                                                                                                                                                                          |

| Cabinet dimensions                           | 76.2 cm long $\times$ 54.29 cm wide $\times$ 100.33 cm high (30 in long $\times$ 21.38 in wide $\times$ 39.5 in high) (not including leveling feet)                                      |

| Weight                                       |                                                                                                                                                                                          |

| Unpacked                                     | 140.6 kg (310 lb)                                                                                                                                                                        |

| Packed                                       | 181 kg (400 lb)                                                                                                                                                                          |

| Environmental                                |                                                                                                                                                                                          |

| Temperature                                  |                                                                                                                                                                                          |

| Operating                                    | 10° C to 40° C (50° F to 104° F)                                                                                                                                                         |

| Nonoperating                                 | –40° C to 66° C (–40° C to 151° F)                                                                                                                                                       |

| Humidity                                     |                                                                                                                                                                                          |

| Operating                                    | 10% to 90% relative (RH) with a maximum wet bulb of 28° C (82° F) and a minimum dew point of 2° C (36° F)                                                                                |

| Nonoperating                                 | 50% relative (RH) or less to 95% (RH) or less with a maximum wet bulb of 46° C (115° F)                                                                                                  |

| Vibration                                    |                                                                                                                                                                                          |

| Operating                                    | 5 to 22 Hz: 0.01 in DA; 22 to 500 Hz: 0.25 Gpk. Sweep rate of 1.0 octave/min. All three axes.                                                                                            |

| Nonoperating (PDP-11X44 packed for shipment) | Vertical Axis Random Vibration: 1.4 Grms overall from 10 to 300 Hz; duration: 1 h. Longitudinal & Lateral Axis Random Vibration: 0.68 Grms overall from 10 to 200 Hz; duration: 1 h each |

| Altitude                                     |                                                                                                                                                                                          |

| Operating                                    | 0 to 2.4 km (8000 ft)                                                                                                                                                                    |

| Nonoperating                                 | 9.1 km (30000 ft)                                                                                                                                                                        |

| Shock                                        |                                                                                                                                                                                          |

| Operating                                    | 10 Gpk for 10 ms $(+3 \text{ ms})$ , $1/2 \text{ sine wave, vertical axis only}$                                                                                                         |

| Nonoperating                                 | Flat drop from a 6 in height, 3 drops total (vertical direction only)                                                                                                                    |

1.3.3 H7140-AA, -AB Power Supply Electrical Specifications

Table 1-6 lists the electrical specifications of the H7140-AA, -AB power supplies.

Table 1-6 H7140-AA, -AB Power Supply Specifications

| Characteristics        | Description                                                                                                                               |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

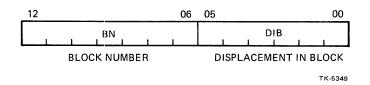

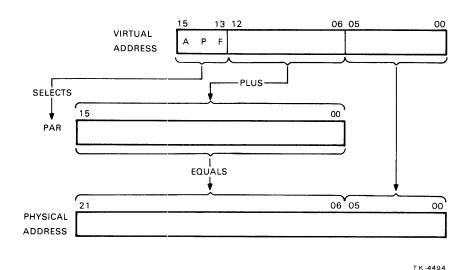

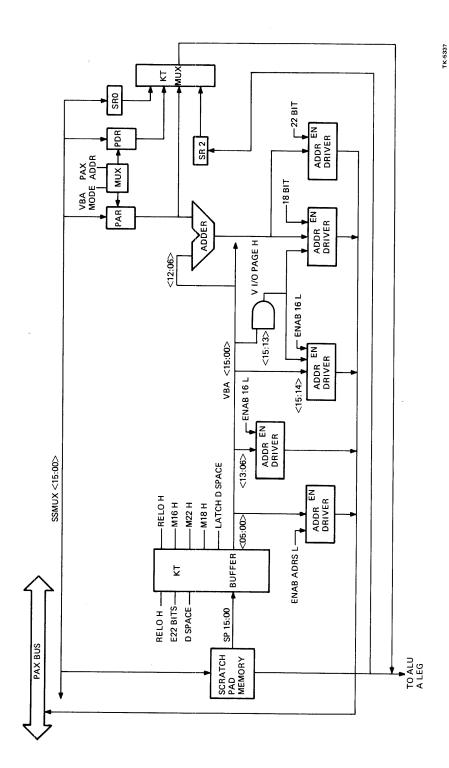

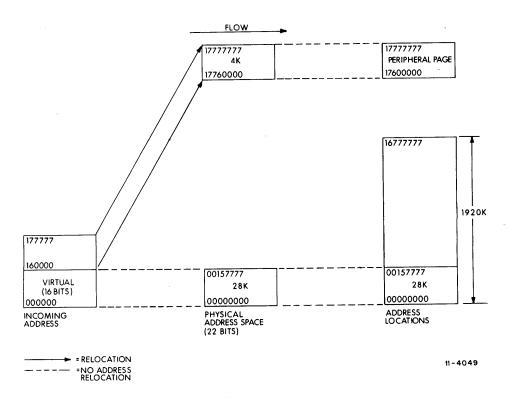

| H7140-AA               |                                                                                                                                           |