77715975 **H**

# CONTROL DATA® WREN<sup>™</sup>I DISK DRIVE MODEL 9415

GENERAL DESCRIPTION OPERATION INSTALLATION AND CHECKOUT THEORY DIAGRAMS MAINTENANCE PARTS DATA

**MAINTENANCE MANUAL**

A15-ES8

#### WREN I MAINTENANCE MANUAL

|        | -                        | r                              |   |   |   |            |   |   |   |   |    |                                                 |  |

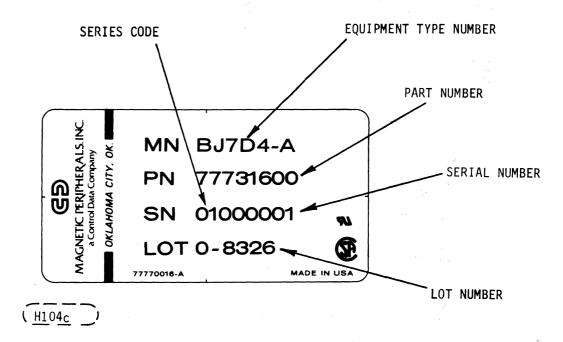

|--------|--------------------------|--------------------------------|---|---|---|------------|---|---|---|---|----|-------------------------------------------------|--|

| R<br>E | DATE                     | MANUAL/SECTION REVISION STATUS |   |   |   |            |   |   |   |   |    | CHANGE                                          |  |

| v      | e de Ér                  | 1                              | 2 | 3 | 4 | <u>,</u> 5 | 6 | 7 | 8 | 9 | 10 | AUTHORITY                                       |  |

| A      | ISSUE                    | A                              | A | A | A | A          | Α | Α |   |   |    | Walanans R. Mett                                |  |

| в      | IL 84 FEB7               | A                              | Α | Α | Α | В          | Α | Α |   |   |    | PL 59207                                        |  |

| С      | UL 84 FEBIT              | Α                              | A | Α | A | C          | A | Α |   |   |    | PL 59211                                        |  |

| D      | IL 84 APR9               | A                              | Α | В | A | С          | A | Α |   |   |    | PL 59233                                        |  |

| E      | 84 کر<br>ii thru viAus 3 | В                              | В | С | В | D          | в | в |   |   |    | PL 59282                                        |  |

| F      | ii and ivocra            | В                              | в | С | В | D          | в | в |   |   |    | PL 59302                                        |  |

| G      | ii JAN24                 |                                | В | D | в | D          | В | В |   |   |    | PL 59337                                        |  |

| H      | ii                       | в                              | в | D | в | Е          | В | в |   |   |    | PL 59387                                        |  |

|        |                          |                                |   |   |   |            |   |   | , |   |    |                                                 |  |

|        |                          |                                |   |   |   |            |   |   | · |   |    |                                                 |  |

|        |                          |                                |   |   |   |            |   |   |   |   |    |                                                 |  |

|        | 2                        |                                |   |   |   |            |   |   |   |   |    |                                                 |  |

|        |                          |                                |   |   |   |            |   |   |   |   |    |                                                 |  |

| E.     |                          |                                |   |   |   |            |   |   |   |   | •  |                                                 |  |

| 1      |                          |                                | , |   |   |            |   |   |   |   | 1  |                                                 |  |

|        |                          |                                |   |   |   |            |   |   |   |   |    |                                                 |  |

|        |                          |                                |   |   |   |            |   |   |   |   |    |                                                 |  |

|        |                          |                                |   |   |   |            |   |   |   |   |    | ha Anna Anna ann an ann an ann an ann an ann an |  |

|        |                          |                                |   |   |   |            |   |   |   |   |    |                                                 |  |

|        |                          |                                |   |   |   |            |   |   | · |   |    |                                                 |  |

REVISION I, O, Q, S, X and Z are not used.

C 1984, 1985

MAGNETIC PERIPHERALS INC. Printed in the United States of America All Rights Reserved ii Address all comments concerning this publication to the distributor or use the enclosed user comment sheet located in the back of this publication. PREFACE

This manual provides the information needed to install, operate, maintain, troubleshoot, and refurbish the WREN I DISK DRIVES Model 9415-3 (BJ7D4-A) and Model 9415-5 (BJ7D5-A)

The total content of the Manual is comprised of seven (7) sections, each having a unique publication number and is contained in one volume. The manual's publication number (77715975) should be used when making reference to the WREN I Maintenance Manual.

The following table identifies the contents of this manual:

#### SECTION NUMBER/TITLE

#### DRAWING NUMBER

| 1 | GENERAL DESCRIPTION       | 77715976 |

|---|---------------------------|----------|

| 2 | OPERATION                 | 77715977 |

| 3 | INSTALLATION AND CHECKOUT | 77715978 |

| 4 | THEORY                    | 77715979 |

| 5 | DIAGRAMS                  | 77715980 |

| 6 | MAINTENANCE               | 77715981 |

| 7 | PARTS DATA                | 77715982 |

#### EMI NOTICE

WARNING: This equipment generates, uses and can radiate radio frequency energy, and if not installed and used in accordance with instructions manual, cause interference to radio the may communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of the FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

#### SAFETY INSTRUCTIONS

- 1. The WREN is to be installed in a customer supplied cabinet where the surrounding air does not exceed 46° C.

- 2. Four (4) 6-32 UNC-2A screws are required for installation.

- 3. The power requirements are:

- +5 VDC <u>+</u>3% 1.5 A

+12 VDC <u>+</u>5% 2.5 A (4 A for 30 seconds)

- 4. The power supply must satisfy safety requirements for SELV (Safety Extra Low Voltage) circuits.

- Service is to be provided only by trained service personnel.

The incorporation of the WREN into a customer-supplied

- 6. The incorporation of the WREN into a customer-supplied cabinet must meet the appropriate safety requirements of the country in which it is to be used (eg. UL, IEC 380).

77715975-E

#### SICHERHEITSANLEITUNG

4.

- Das Gerat ist ein Einbaugerat, vorgesehen fur eine maximale Umgebungstemperatur von 46<sup>o</sup> C.

- Zur Befestigung des Wren-Drives werden 4 Schrauben 6-32 UNC-2A benotigt.

- 3. Als Versorgungsspannungen werden benotigt:

- +5 VDC <u>+</u>3% 1.5 A

- +12 VDC <u>+</u>5% 2.5 A (4.0 A fur ca. 30 Sek.)

- Die Versorgungsspannung muss SELV entsprechen.

- 5. Alle Arbeiten durfen nur von ausgebildetem Servicepersonal durchgefuhrt werden.

- 6. Der Einbau des Drives muss den Anforderungen gemass DIN IEC 380/VDE 0806/8.81 entsprechen.

# WARNING

This product is an electromechanical device which could present hazards if improperly handled. The device should be maintained only by qualified personnel in accordance with instructions contained in this manual and sound safety practices. Careless disassembly or maintenance procedures may result in damage to the device or injury to personnel. Observe all <u>CAUTIONS</u> or <u>WARNINGS</u> attached to the device or contained in this manual.

These <u>WARNINGS</u> and or <u>CAUTIONS</u> are not exhaustive. The possible manufacturer cannot know in advance all maintenance procedures, or tools, which may be devised by persons who choose not to follow the instructions in this manual. Any deviation from the prescribed procedures may risks which have been evaluated entail not by the manufacturer.

Any persons who use a non-approved procedure or tool must satisfy themselves that no injury to personnel, no damage to the device, and no deterioration of device performance will result.

77715975-F

## TABLE OF CONTENTS

| EMI NOT                                                     | E<br>TICE                                                                                                                                                                                                                                                                                          | 111<br>iii<br>iii                                                         |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| GENERAI                                                     | L DESCRIPTION                                                                                                                                                                                                                                                                                      |                                                                           |

| 1.1<br>1.2                                                  | INTRODUCTION.<br>GENERAL DESCRIPTION.<br>1.2.1 Standard Features.<br>1.2.2 Optional Features.<br>1.2.3 Accessories.<br>1.2.4 Major Components.                                                                                                                                                     | 1-1<br>1-1<br>1-1<br>1-1<br>1-2<br>1-2                                    |

| OPERAT                                                      | ION                                                                                                                                                                                                                                                                                                |                                                                           |

| 2.1<br>2.2                                                  | INTRODUCTION<br>OPERATING AND PRELIMINARY DIAGNOSIS PROCEDURE<br>2.2.1 Operating Instructions<br>2.2.2 Front Panel Indicator (Available only with<br>Front Panel Kit)                                                                                                                              | 2-1<br>2-1<br>2-1<br>2-1                                                  |

| INSTAL                                                      | LATION AND CHECKOUT                                                                                                                                                                                                                                                                                |                                                                           |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | INTRODUCTION.<br>UNPACKING.<br>OPERATING ENVIRONMENT.<br>SPACE ALLOCATION AND MOUNTING REQUIREMENTS.<br>MOUNTING ORIENTATIONS.<br>3.5.1 Vertical Orientation Mounting.<br>3.5.2 Horizontal Orientation Mounting.<br>DRIVE CABLING.<br>DRIVE SELECTION.<br>AUTO VELOCITY ADJUST.<br>SELF SEEK TEST. | 3-1<br>3-1<br>3-3<br>3-3<br>3-3<br>3-6<br>3-6<br>3-6<br>3-8<br>3-9<br>3-9 |

| 3.9<br>3.10<br>3.11                                         | DIFFERENTIAL TERMINATION JUMPER<br>INITIAL CHECKOUT AND STARTUP PROCEDURE                                                                                                                                                                                                                          | 3-9<br>3-9<br>3-9                                                         |

| THEORY                                                      | OF OPERATION                                                                                                                                                                                                                                                                                       |                                                                           |

| 4.0<br>4.1                                                  | THEORY OF OPERATION, WREN I DISK DRIVES                                                                                                                                                                                                                                                            | 4-1<br>4-1                                                                |

| ASSEMBLIES (CDC AND SEAGATE INTERFACES)      | 4-1 |

|----------------------------------------------|-----|

| 4.2.1 Mechanical Assemblies (CDC and Seagate |     |

| Interfaces)                                  | 4-1 |

77715975-E

4.2

v

# TABLE OF CONTENTS CONTD.

| 4.3    | FUNCTIONAL DESCRIPTION (CDC AND SEAGATE INTERFACES)                                                                      | 4-5        |

|--------|--------------------------------------------------------------------------------------------------------------------------|------------|

|        | <ul><li>4.3.1 General (CDC and Seagate Interfaces)</li><li>4.3.2 Overall Drive Control System (CDC and Seagate</li></ul> | 4-5        |

|        | Interfaces)                                                                                                              | 4-8        |

|        | 4.3.3 Head Positioning System (CDC and Seagate                                                                           |            |

|        | Interfaces)                                                                                                              | 4-26       |

|        | 4.3.4 Read/Write System (CDC Interface)                                                                                  | 4-44       |

|        | 4.3.5 Read/Write System (Seagate Interface)                                                                              | 4-51       |

|        | 4.3.6 Auxiliary Systems (CDC and Seagate                                                                                 |            |

|        | Interfaces                                                                                                               | 4-61       |

| DIAGRA | AMS                                                                                                                      |            |

| 5.1    | INTRODUCTION                                                                                                             | 5-1        |

| 5.2    | SCHEMATIC/PWA ORDERING                                                                                                   | 5-1        |

| J. 2   |                                                                                                                          | 7-1        |

| MAINTE | ENANCE                                                                                                                   |            |

| 6.1    | INTRODUCTION                                                                                                             | 6-1        |

| 6.2    | SAFETY AND SPECIAL MAINTENANCE PRECAUTIONS                                                                               | 6-1        |

| 6.3    | MAINTENANCE TOOLS                                                                                                        | 6-2        |

| 6.4    | MAINTENANCE PROCEDURES                                                                                                   | 6-2        |

| 6.5    | REMOVAL AND REPLACEMENT PROCEDURES OUTSIDE                                                                               |            |

|        | SEALED AREA                                                                                                              | 6-2<br>6-3 |

|        | 6.5.1 LED/Mount Removal and Replacement<br>6.5.2 R/W Preamp PWA Removal and Replacement                                  | 6-3        |

|        | 6.5.3 Servo PWA Removal and Replacement                                                                                  | 6-4        |

|        | 6.5.4 Data PWA Removal and Replacement                                                                                   | 6-4        |

|        | 6.5.5 Ground Spring Removal and Replacement                                                                              | 6-4        |

|        | 6.5.6 Brake Mechanism Removal and Replacement                                                                            | 6-5        |

| PARTS  | DATA                                                                                                                     |            |

| 7.1    | INTRODUCTION                                                                                                             | 7-1        |

|        |                                                                                                                          |            |

77715975-E

#### 1.1 INTRODUCTION

The CDC Model 9415 WREN I Disk Drive is a small, low-cost, medium performance, random-access rotating-disk, mass-memory device designed to record and recover data on up to three rigid 5-1/4 inch nonremoveable fixed disk media. The WREN uses low-mass flying read/write heads attached to a precisely controlled rotary positioner.

#### 1.2 GENERAL DESCRIPTION

## 1.2.1 STANDARD FEATURES

The following standard features of the Model 9415 WREN I Disk Drive are:

- Either Seagate Interface (Model 9415-5) or CDC Interface (Model 9415-3).

- Full data recovery circuitry for drives with CDC interface.

- Sealed disk, head, and actuator chamber.

- No preventive maintenance required.

- LSI circuitry for high reliability.

- Low audible noise for office environments.

- Vertical (side) or horizontal (bottom) mounting.

- Low power consumption.

- Rotary voice-coil actuator.

- Terminators.

- Shock mounts.

#### 1.2.2 OPTIONAL FEATURES

The following optional features (factory-installed only) are available for the WREN I.

- 21 or 35 megabytes rigid fixed-disk data storage capacity for units with CDC interface (Model 9415-3).

- 21.7 or 36.2 megabytes rigid fixed-disk data storage capacity for units with Seagate interface (Model 9415-5).

#### 77715976- B

## 1.2.3 ACCESSORIES

The following accessories are available for the WREN and must be ordered and shipped separately:

• Front panel kit, 77712595.

Power supply - includes five-foot power cable.

9410-3 to 9415-3 Interface Adapter Kit, TBD, for Model 9415-3.

• Lark Device Interface Adapter, 77732426, for Model 9415-3.

• Top Mount PWA Adapter, 77715495.

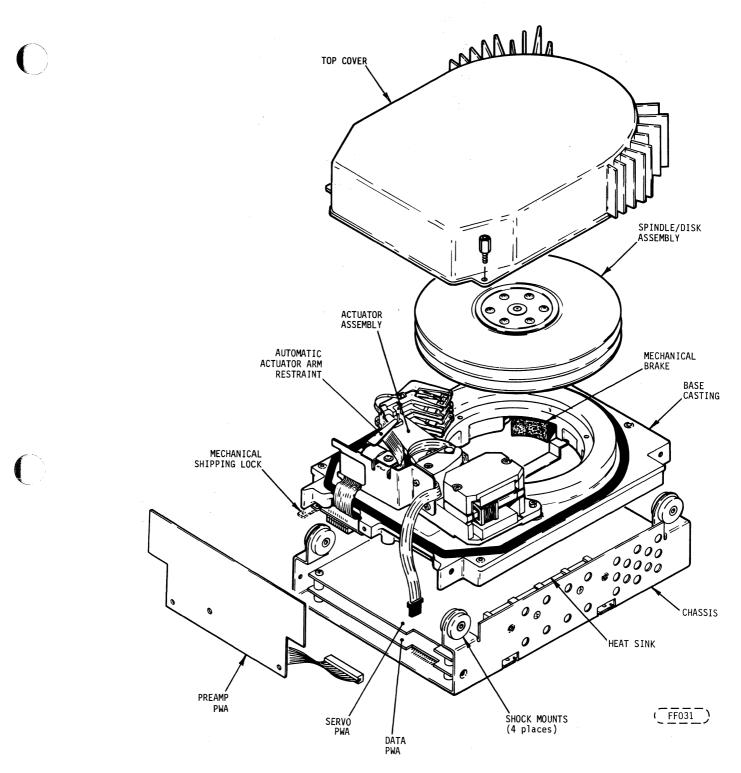

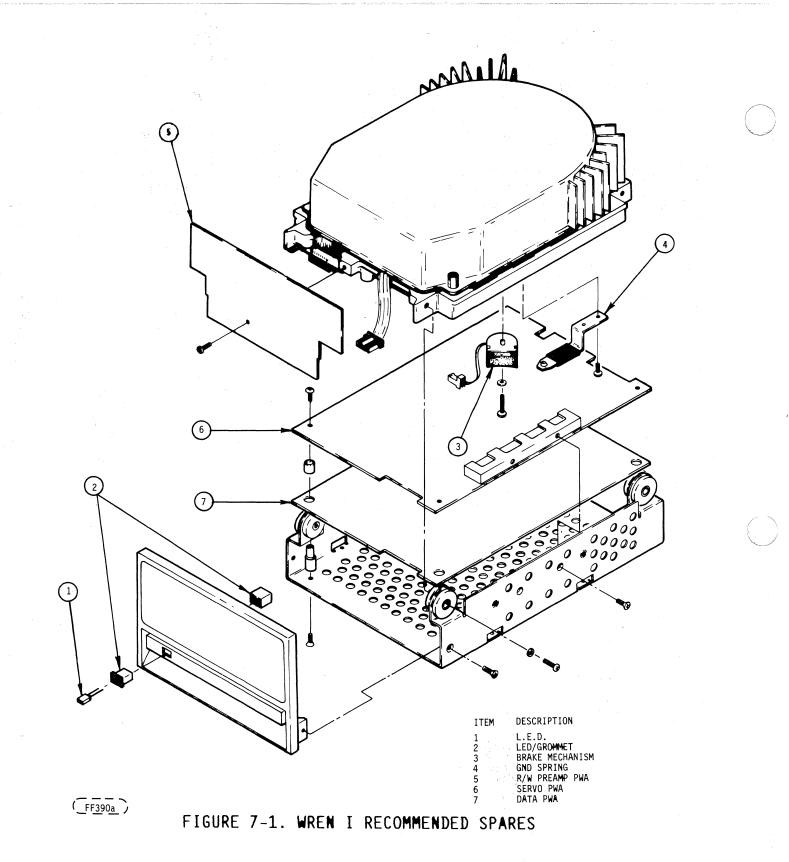

1.2.4 MAJOR COMPONENTS

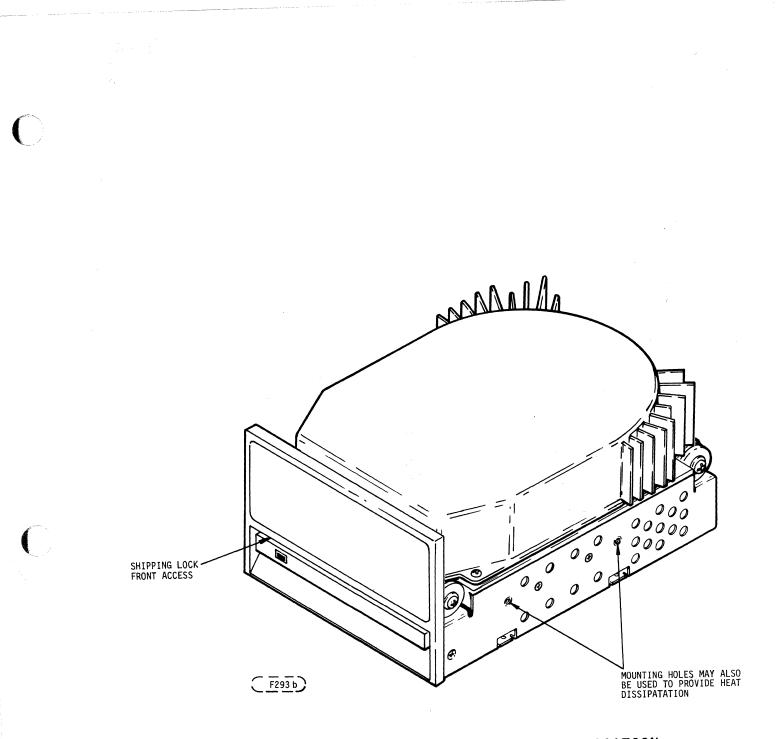

The major components of the WREN are shown in Figure 1-1.

#### CAUTION

<u>NEVER</u> remove the top cover of the WREN. This exploded view is for information only. Servicing items in the upper sealed environmental enclosure (heads, media, actuator, etc.) requires special facilities. Only the printed circuit boards and solenoid brake external to the sealed area can be replaced without special facilities.

FIGURE 1-1. MODEL 9415 WREN I

1-3/1-4

## OPERATION

#### 2.1 INTRODUCTION

There is only one mechanical function required of the operator: to ensure that power is applied. During routine computer operations, the operator should, of course, note any malfunctions or problems and report them.

#### 2.2 OPERATING AND PRELIMINARY DIAGNOSIS PROCEDURE

Due to the sophisticated design and special equipment required to repair the WREN, most repairs may only be effected at a properly equipped and staffed depot service and repair facility. These repair facilities will be capable of performing all warranty and routine repair activities.

Because the front panel indicator provides limited failure conditions (see paragraph 2.2.2) and no operator/drive interaction is required, operating systems must contain sufficient error reporting information to allow the operator to make preliminary diagnosis of problems. In other words, software must adequately inform the operator if any technical difficulties arise. In multi-unit installations, logical and physical identification are necessary for the operator to identify a defective unit.

#### 2.2.1 OPERATING INSTRUCTIONS

- 1. The following conditions must be met to initiate operation of the disk drive.

- a. The DC power cable from the power supply must be connected.

- b. Mechanical shipping lock must be in operating position.

- 2. The operating temperature of the drive is  $50^{\circ}$  to  $115^{\circ}$ F (10° to 46° C) with a maximum temperature change of 18° F (10° C) per hour.

- 3. In case of a malfunction, the unit is to be serviced only by trained personnel.

- 2.2.2 FRONT PANEL INDICATOR (AVAILABLE ONLY WITH FRONT PANEL KIT.)

The front panel indicator under normal operation will serve as a Drive Selected indicator. It will also flash to indicate a drive failure when one of the following conditions exist.

- 1. Rotor is locked.

- 2. Spindle speed exceeds +5% tolerance for more than 30 seconds.

- 3. The WREN cannot load heads after 6 attempts (i.e. mechanical shipping lock left on, PLO does not lock, automatic arm restraint fails to release, etc.).

77715977-B

2-1/2-2

2

#### 3.1 INTRODUCTION

This section provides the information and procedures necessary to install and checkout the CDC Model 9415 WREN I Disk Drive. The WREN is designed, manufactured, and tested with a "Plug-in and Play" installation philosophy. Basically, this philosophy minimizes the requirements for a highly trained person to integrate a WREN into their system.

#### 3.2 UNPACKING

Visually inspect the shipping container for any obvious damage. During unpacking, exercise care so that any tools being used do not cause damage to the unit. As the drive is unpacked, inspect it for possible shipping damage. All claims of this type should be filed promptly with the transporter involved. If a claim is filed for damages, save the original packing materials.

#### CAUTION

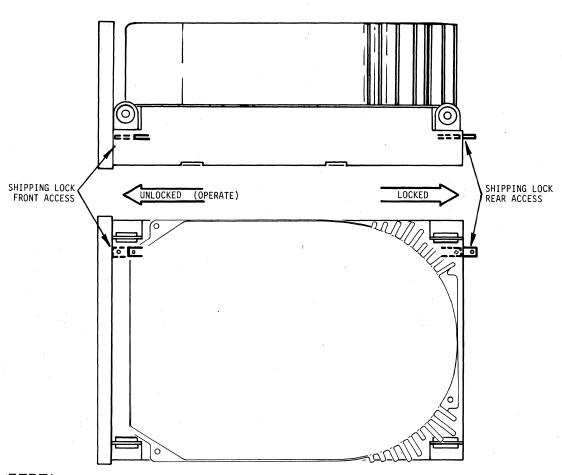

Figure 3-1 shows the mechanical shipping lock which is accessible from both the front and the rear of the WREN. To prevent damage to the read/write heads or the disk itself, move the mechanical shipping lock to the operating position only after installation has been completed.

After the drive is unpacked, inspect the drive for any visual damage. Compare all parts listed on the shipping bill with the received equipment. Discrepancies or damage should be reported to the Sales Representative. Save the packing materials; they can be used for reshipment.

## 3.3 OPERATING ENVIRONMENT

The environmental conditions required for optimum performance of the disk drive are, in general, the same as those in an office environment with minimum or no environmental control. These conditions are:

Temperature $50^{\circ}$  to  $115^{\circ}$  F ( $10^{\circ}$  to  $46^{\circ}$  C)Humidity20% to 80%Altitude-983 to +6,562 feet (-300 to +2,000 meters)

77715978-C

The room temperature should not change more than  $18^{\circ}$  F ( $10^{\circ}$  C) per hour. Relative humidity should be kept between 20% and 80%. Avoid high relative humidity as much as possible since it can cause condensation in the drive. Very low relative humidity should also be avoided because it can lead to particle attraction and accumulation by static electricity.

(FF164a)

REAR ACCESS

THE SHIPPING LOCK WILL PROTRUDE OUT THE REAR IN THE LOCKED POSITION. A HOLE IN THE ARM OF THE LOCK IS PROVIDED FOR ACTIVATING THE LOCK.

FRONT ACCESS

A HOLE IN THE FRONT PANEL ALLOWS FRONT ACCESSIBILITY TO THE SHIPPING LOCK.

## FIGURE 3-1. MECHANICAL SHIPPING LOCK POSITION

77715978-C

3.4 SPACE ALLOCATION AND MOUNTING REQUIREMENTS

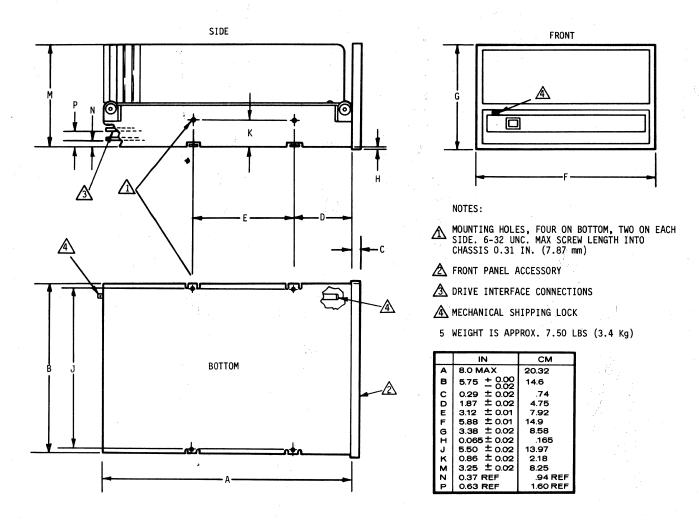

Figure 3-2 shows overall dimensions of the drive for determining space allocation and mounting requirements.

The WREN is designed for multiple unit installation in a standard 19-inch rack. Since the WREN is a fixed drive, slides are not provided, but tapped holes are placed at various locations, on the chassis for mounting in the enclosure.

The WREN uses air from the rotating disks for cooling the PWA's and mechanical components. The WREN design also uses the outer case to dissipate heat. Direct contact to the internal WREN heat sink can be made through the two mounting holes on the right side of the WREN (see Figure 3-3). Good metal to metal thermal contact of this surface with the customer cabinet mounting hardware is highly recommended for optimized heat transfer. Consideration should also be given to minimizing restriction of airflow through cooling holes in the drive.

A sometimes overlooked consideration when mounting several drives in the same enclosure is heat dissipation. Because power supplies, for example, are typically heavy and produce large amounts of heat, they are usually mounted in the bottom of an enclosure. This heat rises to the top of the cabinet or enclosure and the temperature can increase drastically. Cabinet ventilation, either by natural convection or forced cooling, must be provided to keep the internal air temperature around the disk drive within the limits specified in paragraph 3.3.

3.5 MOUNTING ORIENTATIONS

#### CAUTION

The drive should never be shipped without the mechanical shipping lock in the locked position to prevent damage to the disk and/or heads.

There are only two mounting orientations: disk in a horizontal plane and disks in a vertical plane. In either the horizontal or vertical mounting, the uppermost casting surface should be in a level position or drive performance may be affected.

## 3.5.1 VERTICAL ORIENTATION MOUNTING

In the vertical orientation, the drive must be mounted so that the mechanical shipping lock is in the up position as shown in Figure 3-1. This is to ensure that the read/write heads will return to the dedicated landing zone when power is removed.

77715978-C

(\_FF036\_)

## FIGURE 3-2. MOUNTING DIMENSIONS

77715978-C

FIGURE 3-3. HEAT SINK MOUNTING HOLE LOCATION

Two tapped holes are provided on each side of the drive for securing the drive to the enclosure (cabinet). The drive may be bolted to an overhead member in a suspended mount and/or bolted from below in a supportive mount. Screws with 6-32 threads and sufficient length to allow several threads of engagement in the casting after passing through the cabinet mounting member should be used. Maximum screw penetration into WREN chassis should not exceed 0.31 inch.

#### 3.5.2 HORIZONTAL ORIENTATION MOUNTING

As shown in Figure 3-2, four 6-32 tapped holes are provided in the base of the chassis to facilitate mounting in the horizontal position.

The WREN may be mounted directly to the rack using size 6-32 screws. Place the drive in the rack or cabinet and secure it with screws with sufficient length to ensure adequate thread engagement and such that screw penetration into the WREN chassis does not exceed 0.31 inch.

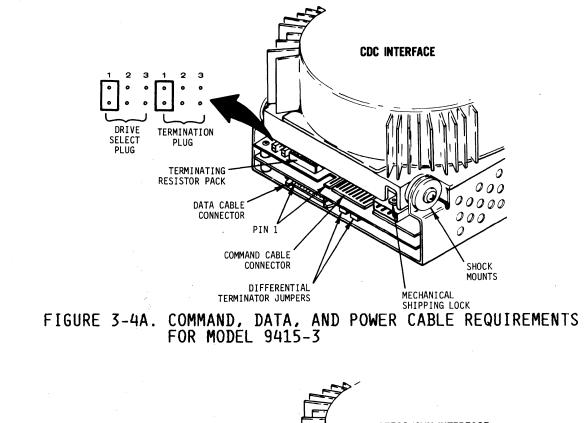

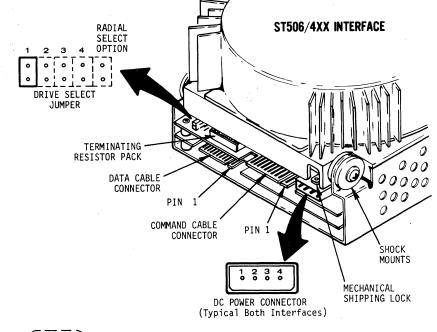

## 3.6 DRIVE CABLING

The required connections to the drive are power and signal cables. All input/output cables exit at the rear of the disk drive. The signal cables consist of a command interface cable and a data interface cable. Figure 3-4 shows the orientation of the command, DC power and data connectors.

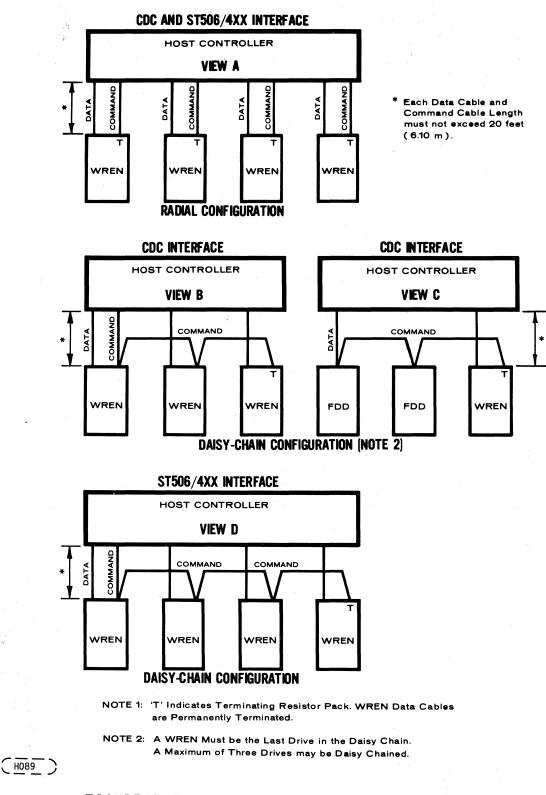

Figure 3-5 shows the intercabling and terminator placement for the various drive connection arrangements. Shown are radial and daisychained system configurations. A single drive would be connected as shown for the radial configuration.

Terminator resistor packs are included in each drive. The terminator consist of a DIP resistor module which is plugged into a DIP socket in each drive. (See Figure 3-4 and 3-6 for location.) An equivalent terminator must be provided in the controller on each input signal line from the WREN to the controller.

#### RADIAL CONFIGURATION

View A of Figure 3-5 shows each drive interfaced to its own Command cable, which, in turn, allows interfacing of more than four drives and a variety of system operational techniques. Each drive has its Data cable and Command cable radially connected to the host controller. The length of each individual cable must not exceed 20 feet (6.1 meters). Terminator resistors must be installed in the host controller for each Data cable and for each Command cable.

77715978-C

FIGURE 3-4B. COMMAND, DATA, AND POWER CABLE REQUIREMENTS FOR MODEL 9415-5

77715978-C

Each Command cable is terminated in the drive by installing the terminating resistor pack. Each Data cable is terminated in the drive by resistors mounted on the Servo PWA.

#### DAISYCHAINED CONFIGURATION

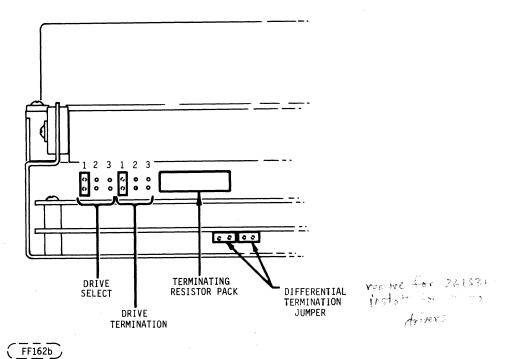

In a daisychain configuration, the Data cables are connected in a radial configuration and the drives are connected in daisychain on the Command cable. The total length of all Command cables used shall be less than or equal to 20 feet (6.1 m). The logical address of each drive in the daisychain is determined by the "DRIVE SELECT" plug on the Servo PWA (Figure 3-6A and 3-6B). Each Data and Command cable must be terminated in the Host Controller.

Units with the CDC Interface (Model 9415-3) can have up to three drives daisychained (Figure 3-5A and 3-5B). Of the three drives, one or two can be Flexible Disk Drives, however the last drive in the daisychain must be a WREN to insure that WREN unique lines are terminated. This last drive in the daisychain requires a Terminating Resistor pack. These resistor packs must be removed from the other drives (if WRENS) in the daisychain.

Units with the ST506/4XX Interface can also be connected in a daisychain configuration of the Command cable. (Figure 3-5A and 3-5B.) Up to four WRENS can be daisychained, however, Flexible Disk Drives cannot be a part of the daisychain. Again, the last WREN in the daisychain will have the Command cable terminated by use of the termination resistor pack. The pack will be removed from all other WRENS in the daisychain.

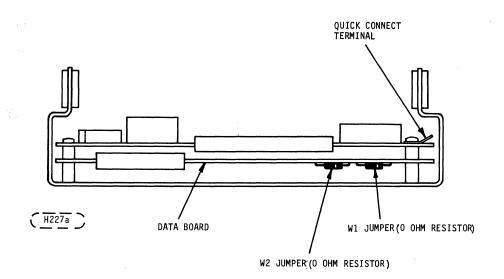

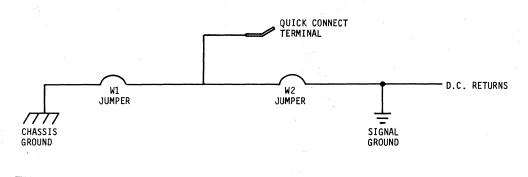

#### SIGNAL/CHASSIS GROUNDS

The WREN I Disk Drives are manufactured with the signal and chassis grounds common. Zero ohm resistors (designated W1 and W2) on the Data board allows modificaton of this relationship at the customer's option. The results of connecting/disconnecting the zero ohm resistors are listed in Table 3-1. The customer can select any of these grounding options by removing W1 and/or W2.

77715978-D

W1 W2 RESULT

- X X Grounds common, quick connect terminal tied to common ground (as manufacatured)

- X O Grounds separate, quick connect terminal tied to chassis ground

- 0 X Grounds separate, quick connect terminal tied to signal ground

- 0 0 Grounds separate, quick connect terminal floating

X = Connected

0 = Not Connected

See Figure 3-4C for physical locations of Wl and W2 and Figure 3-4D for schematic.

Zero ohm resistors are on the data boards of drives which are series code four and above. The series code of the drive is indicated by the first two digits of the serial number, ie, 04000001.

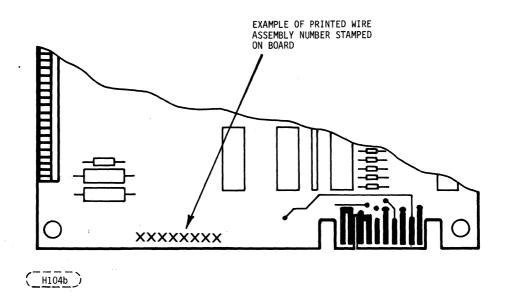

FIGURE 3-4C. PHYSICAL LOCATION OF W1 AND W2.

#### (<u>H227b</u>)

### FIGURE 3-4D. SCHEMATIC DIAGRAM OF W1 AND W2.

## 3.7 DRIVE SELECTION

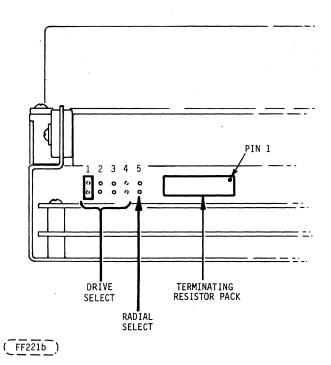

The logical address of the WREN Disk Drives is selected by installing a jumper into the appropriate location on the DRIVE SELECT header which is available from the back of the drive and located on the SERVO PWA. (See Figure 3-6A and 3-6B.) This selection is done at the time of installation.

The drives with the CDC Interface (Model 9415-3) have three locations in the header for drive selection and three for termination of the drive select lines. The drive select jumper and the termination jumper are to occupy the same location, i.e. 1 and 1, 2 and 2, or 3 and 3. For radial configurations, it is recommended that these jumpers be in location 1.

For daisychain configurations, the jumpers should be in position 1, 2, or 3 depending on the location of the drive in the daisychain. If the daisychain contains Flexible Disk Drives, the drive select termination will not be used as the FDDS do not have this feature.

77715978-D

The drives with the ST506 Interface (Model 9415-5) have five locations in the header for drive selection. If the drive is to be operated in a radial configuration, the jumper should be in location five. For a daisychain configuration, the jumper should be in position 1, 2, 3, or 4, depending on the location of the drive in the daisychain.

#### 3.8 AUTO VELOCITY ADJUST

After power has been applied and spindle speed is in tolerance, the WREN actuator will perform several seeks (approximately 15) to fine tune the actuator for optimum performance. After all seeks are complete, the heads will be loaded over cylinder 00.

#### 3.9 SELF SEEK TEST

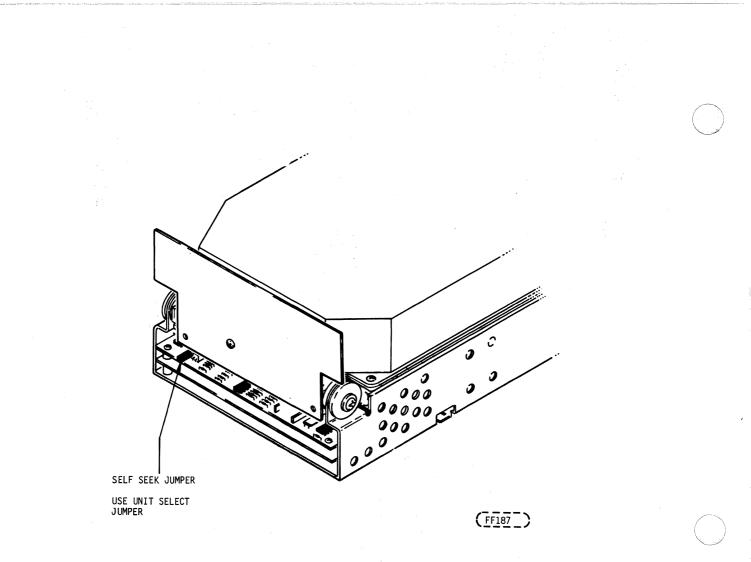

The WREN I has the capability to perform full stroke seeks by installing a jumper as shown in Figure 3-7. Use a UNIT SELECT jumper for this test. Removal of the front panel is required. The jumper must be installed prior to power-up. The full stroke seeks are performed immediately after the auto velocity adjust is performed. Full strokes will continue until the WREN is powered down or jumper is removed.

## 3.10 DIFFERENTIAL TERMINATION JUMPER

The differential receivers used in the WREN with the CDC Interface are compatible with both 26LS31 differential drivers or 75110 differential drivers. However, a different termination network is required for each configuration. Two jumpers are provided on the WREN as shown in Figure 3-6A. When both jumpers are installed, the WREN is configured for 75110 operation. When both jumpers are removed the WREN is configured for 26LS31 operation.

#### 3.11 INITIAL CHECKOUT AND STARTUP PROCEDURE

- 1. Mount the Drives either horizontally or vertically in the enclosure using standard hardware.

- 2. Connect the cables for either radial or daisychained configuration. Terminate as required.

- 3. Connect the Command cable, a 34-conductor ribbon cable, between the Controller and the Drive.

- 4. Connect the Data cable, a 20-conductor ribbon cable, between the Controller and the Drive.

- 5. Attach DC power cable from power supply to connector on the rear of the WREN.

- 6. Move the mechanical shipping lock to the operating position.

- 7. Apply power to the drive. Front Panel Indicator will flash if the shipping lock is not released.

- 8. Run system diagnostics to ensure the operability of the disk subsystem.

77715978-D

FIGURE 3-5. INTERFACE CABLING OPTIONS

77715978-D

FIGURE 3-6A. DRIVE SELECT AND TERMINATING JUMPER LOCATIONS MODEL 9415-3

FIGURE 3-6B. DRIVE SELECT AND TERMINATING JUMPER LOCATIONS MODEL 9415-5

77715978-D

77715978-D

#### THEORY OF OPERATION

## 4.0 THEORY OF OPERATION, WREN I DISK DRIVES

#### 4.1 INTRODUCTION

The Theory of Operation Section will cover both WREN I Disk Drives (i.e., the drive with the CDC Interface, Model 9415-3, and the drive with the Seagate Interface, Model 9415-5). The paragraphs of Section 4.0 will be identified as to whether it applies to the drives with the CDC Interface, the drives with the Seagate Interface or both.

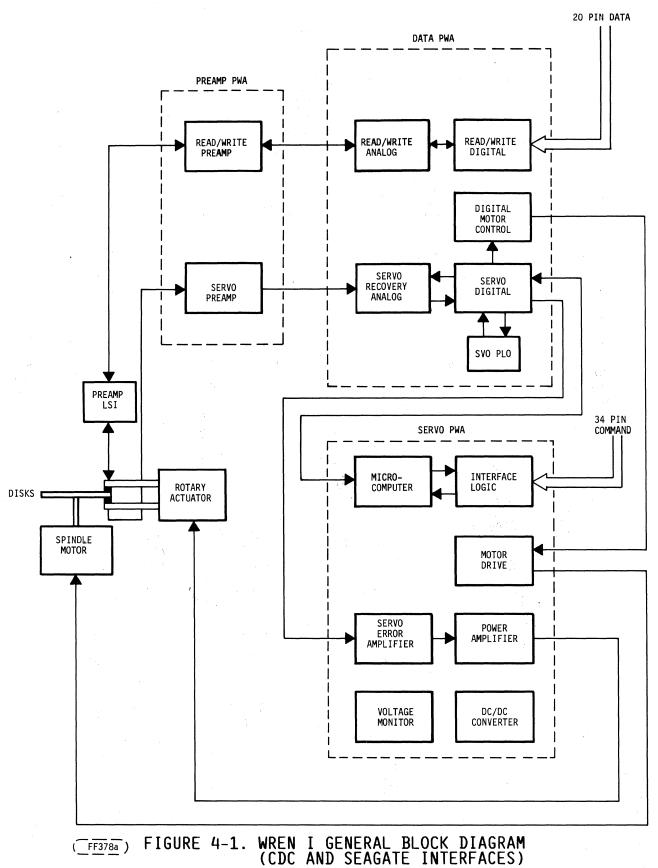

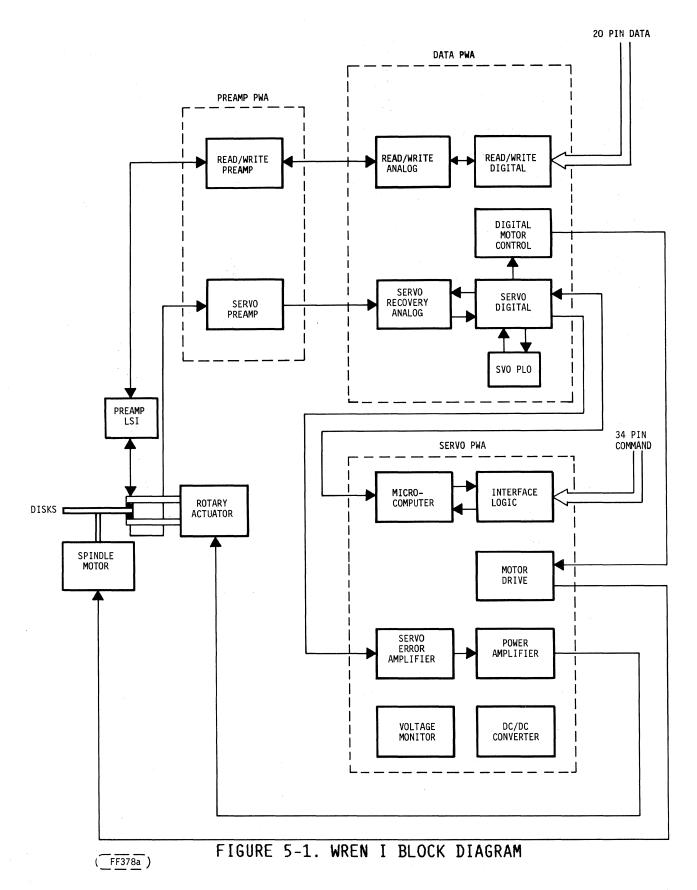

The general block diagram of the WREN I is shown in Figure 4-1. Other block diagrams will be used to aid in the description of the drives.

Logic signal names may be followed by the symbol "+L" or "-L". Active high (+4 volts for TTL or -0.8 volts for ECL) have "+L" while active low (+0.8 volts for TTL or -1.7 volts for ECL) have "-L". ECL signals may also indicate active high with "-P" and active low with "-N" suffix.

Integrated circuit pins will be identified by IC location and pin number. For example, "U25-12" is pin 12 of IC at location U25.

4.2 ASSEMBLIES (CDC AND SEAGATE INTERFACES)

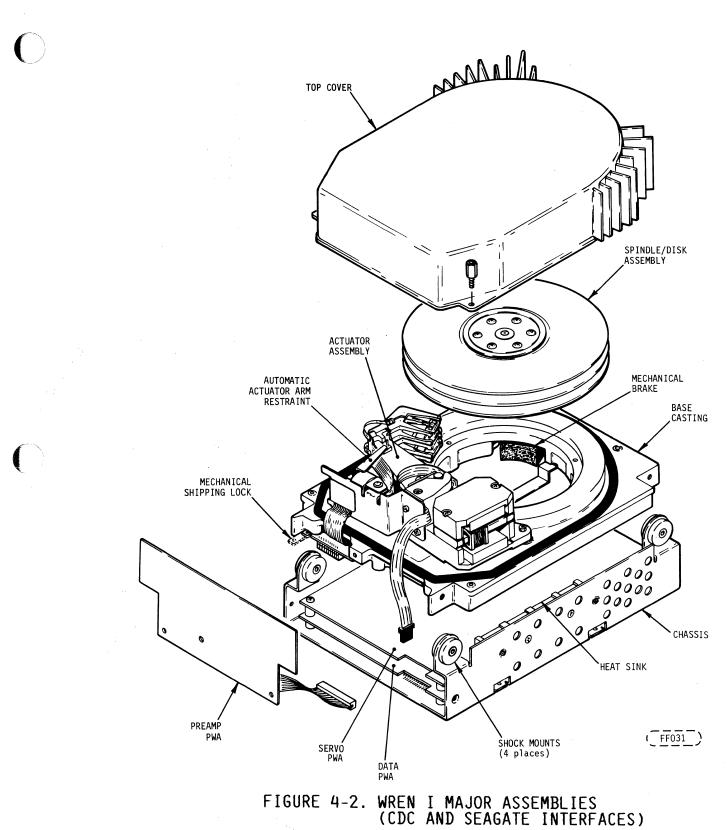

Figure 4-2 illustrates the physical placement of the major assemblies of the WREN I Disk Drive. The following paragraphs describe the operation of these assemblies.

4.2.1 MECHANICAL ASSEMBLIES (CDC AND SEAGATE INTERFACES)

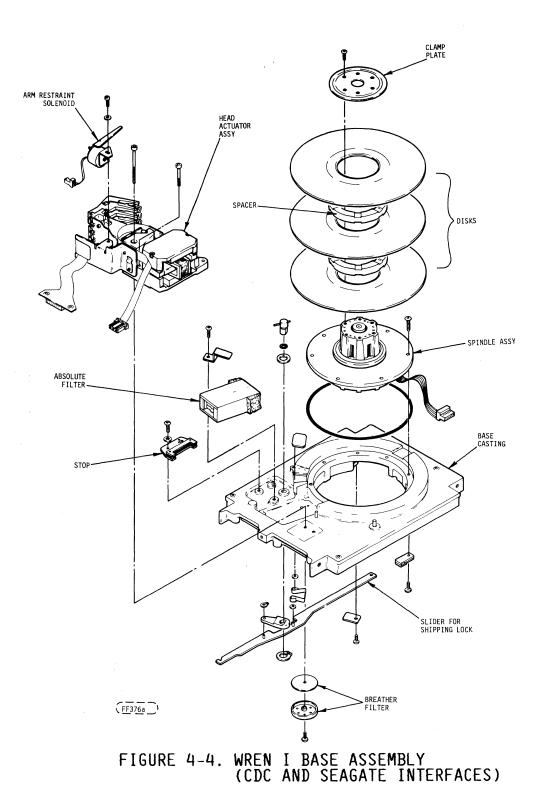

There are just two major subassemblies which make up a WREN I Disk Drive (Figure 4-2). The base assembly contains the media, filtration system and spindle motor. The base is built and tested as a unit and then mated with the actuator assembly. The actuator assembly contains the bobbin, coil, magnets, rotary arm and heads. After the actuator is mated to the base the information needed to position the heads is written on the bottom surface of the bottom disk. This operation is called servo track writing (STW). After STW the stop is installed and adjusted. The stop keeps the servo head over the servo data and will be adjusted only in connection with STW. The cover assembly is then installed with three screws. These operations are performed in special clean rooms to keep the media contamination free. For this reason the top cover of a WREN should not be removed. The assemblies and components described in the following paragraphs are in an environmentally sealed area and shall be serviced at factory level depot ONLY. See Maintenance Section 6 for the items of General Maintenance.

77715979-B

77715979-B

77715979-B

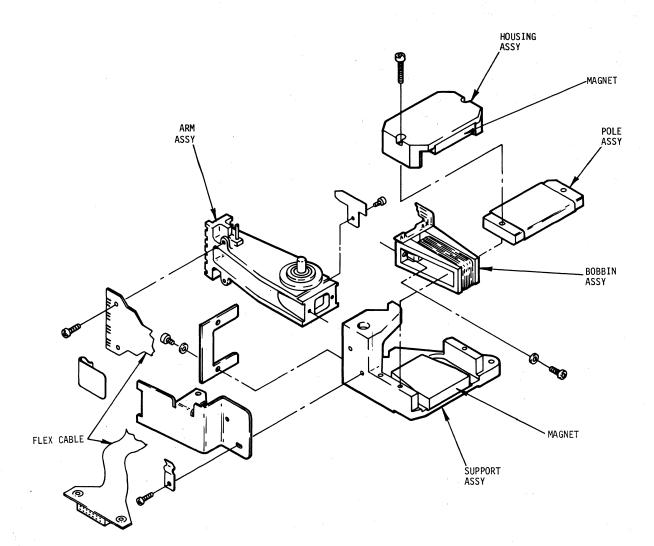

## 4.2.1.1 ACTUATOR ASSEMBLY (CDC AND SEAGATE INTERFACES)

The WREN I actuator is a rotary voice coil positioner. The voice coil can be thought of as a motor that moves through only a small angle. The motor stator consists of two permanent magnets, one upper and one lower, and a core bar (Figure 4-3). The motor rotor is a coil on a bobbin which fits around the stator core. By controlling the magnitude and direction of the rotor current, the rotor can be positioned any where in its range. The bobbin is attached to the rotary arm which provides the head mounting.

There are two bearings mounted in a bore thru the area. A shaft runs thru these bearings. This shaft is held in two V shape grooves on the housing which holds the magnets. The housing is later mounted to the base deck. Connection is made to the bobbin thru a three conductor flex cable.

The heads are mounted by screwing them into six slots at the end of the actuator arm. Each head has a short flex cable on it which must be soldered to a flex cable on the actuator arm.

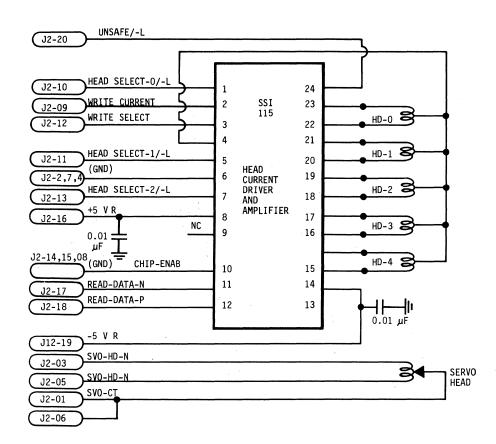

The flex cable on the actuator arm has an SSI115 integrated circuit on it. The signals to and from the five data heads pass thru this circuit. The signal from the servo head passes directly to the connector which passes all signals to the Preamp PWA.

Removal and replacement of the actuator is a depot level maintenance procedure ONLY.

#### 4.2.1.2 BASE ASSEMBLY (CDC AND SEAGATE INTERFACES)

The base assembly consists of the base casting, spindle assembly, head actuator assembly and two filtration systems as shown in Figure 4-4.

The base casting is the frame of the drive and all assemblies mount to it. The base casting also divides the drive into sealed and unsealed compartments. The area above the base casting and under the cover is sealed and provides a clean environment. The heads in the WREN fly at only 15 to 18 microinches, therefore the air in the sealed compartment must be kept very clean.

The spindle to which the disks are attached is an integral part of the spindle motor. The disks are the recording media for the drive. The recording surface of each disk is coated with a layer of magnetic iron oxide and related binders. The WREN Disks also have a lubricant over the oxide, this reduces the friction when the heads are landing. The drive can have up to three disks, each separated by a spacer. The whole assembly is held together by a clamp plate which bolts to the top of the spindle hub. The assembly then is bolted to the base casting with the spindle shaft protruding through the base.

77715979-B

The spindle motor is a two phase brushless DC motor. The motor rotor mounted on the opposite end from the spindle which serves as a braking surface and has fan blades which provides some air flow to cool the electronics. A grounding spring rests on the center of the rotor and bolts to the base casting, this provides a path for any static electricity generated by the head-disk interface to flow to the ground.

The arm restraint solenoid holds the arm and heads over the landing zone next to the spindle when power is not applied. The shipping lock reinforces the holding action to assure heads will not move during any shocks that may occur during shipping.

A brake on the bottom of the drive presses against the rotor of the spindle motor anytime power is not applied to the drive. This brake stops the spindle quickly to protect the surface of the disk in the landing zone.

The first of the filtration is a breather filter. It is bolted over a hole in the base casting and provides clean air to equalize the pressure between the sealed compartment and the outside world. The second system is a recirculating absolute filter. It removes any foreign material that may be present in the sealed compartment. Air is pulled out of the filter by the low pressure created near the spindle. Air then can circulate thru open areas in the spindle and flow out across all the disks. Some of the air will flow through this filter whenever the disk is spun. Over the life of the drive all the air in the sealed compartment will be cleaned many times.

Any servicing of the spindle assembly, spindle motor and filters is a depot level procedure ONLY.

4.3 FUNCTIONAL DESCRIPTION (CDC AND SEAGATE INTERFACES)

4.3.1 GENERAL (CDC AND SEAGATE INTERFACES)

This description is organized into the following major headings:

- Overall Drive Control System

- Head Positioning System

- Read/Write System

- Auxiliary Systems

77715979-B

(\_FF377a)

## FIGURE 4-3. WREN I ACTUATOR ASSEMBLY (CDC AND SEAGATE INTERFACES)

# 4.3.2 OVERALL DRIVE CONTROL SYSTEM (CDC AND SEAGATE INTERFACES)

The WREN is under the control (excluding any control exerted by the controller via the interface lines) of the Microcomputer on the Servo PWA. The Microcomputer system is described in the following paragraphs. Any further details of the Microcomputer Theory must be taken from vendor publications for the various chips in the Microcomputer System.

#### 4.3.2.1 MICROCOMPUTER OVERVIEW (CDC INTERFACE)

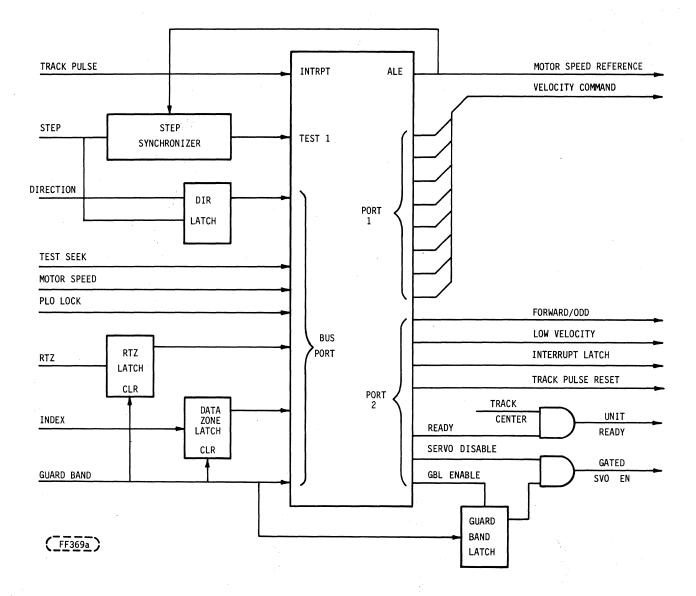

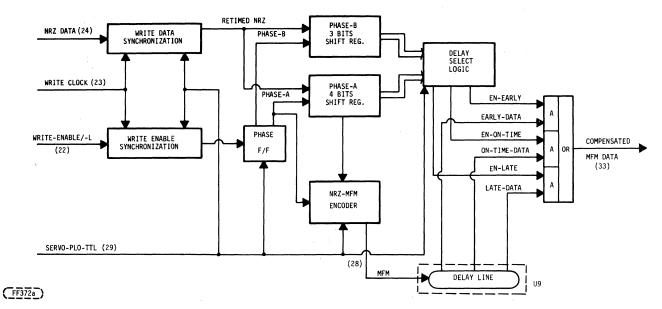

Figure 4-5 shows a simplified block diagram of the microcomputer. The microcomputer is an 8749 with two kilobytes of internal program memory. The microcomputer has no control of the read/write section with the exception of the write current magnitude.

When a step is received from the command cable interface, it is synchronized with the microcomputer clock and applied to the Test 1 input of the 8749. This causes a firmware counter to be incremented with each step pulse. The interface direction line is latched with the step pulse and applied to one of the Bus Port inputs. These two lines have all the information needed to cause a seek operation.

When a seek is in progress, track-crossing pulses are generated in the servo LSI logic; these are applied to the 8749's Interrupt input. This input remains active until the Interrupt is serviced and a track-pulse reset is sent to the servo LSI on a Port 2 line. In this manner, the microcomputer keeps track of all incoming step pulses and track crossings that occur. The address latch enable (ALE) signal is also sent to the spindle motor control as a reference signal for motor speed. During a seek, a seven-bit velocity command is output on Port 1 and goes to a D/A converter in the servo amplifier. The eighth bit on Port 1 is active for a high velocity command, and inactive for a low velocity command. A line from Port 2, titled "VCLO" (Velocity Command Low) is active for a low velocity command, and inactive for a high velocity command. During coarse mode either, but not both, line must be active. If both lines are inactive this indicates fine mode. These lines are used in conjunction with the forward/odd lines. Forward refers to a seek from a lower to a higher numbered cylinder. In the coarse mode, this line is active during a forward seek and inactive during a reverse seek. When the drive switches to the fine mode this line is active when the target track is even and inactive when the target track is odd.

77715979-B

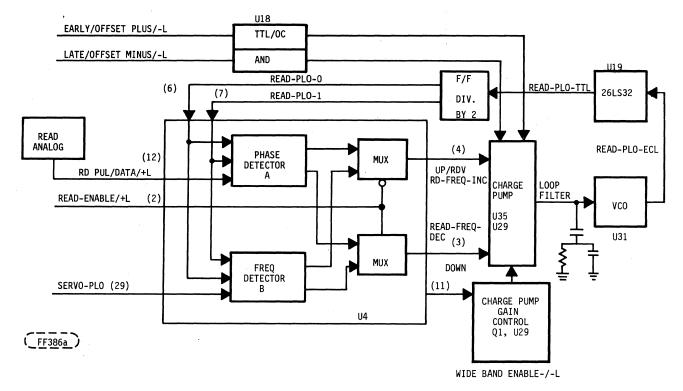

Two lines from Port 2 generate Power-On Reset. If the track pulse reset and Disable Servo lines are both active, Power-On Reset is active. If either line is inactive, Power-On Reset is inactive. During start-up, Power-On Reset is active for approximately 6 seconds. This enables the current regulator in the spindle motor control. When it is inactive, it enables the speed regulator. It is also used to provide appropriate resets to sequential logic contained in the drive electronics. During start-up, motor speed is monitored on the Bus Port from the Motor Speed line. The phase lock oscillator (PLO) lock line is continuously monitored. Also during start-up, the servo is disabled via the Servo Disable line.

When the servo PLO is locked and the spindle motor is up to speed, head loading can commence. This is accomplished by the microcomputer issuing a velocity command, detecting guard band, performing an RTZ, and switching back to fine mode on cylinder zero. The data zone latch is set by Index. Index code is written and guard band only in the data zones. This enables the microcomputer to distinguish between these zones and the start zone.

There is a guard band latch external to the microcomputer that will disable the servo if guard band is encountered after the initial head load. During the head load and return to zero (RTZ) operations, this latch is disabled because guard band is then used to locate cylinder zero. This disable is activated by the guard band latch clear line from Port 2.

There is one other input to the Bus Port, called Test Seek. This input can be grounded with a jumper shunt and causes the drive to go into a continuous test seek following head load and the calibrate operation.

With the completion of head load, the microcomputer puts the drive through an automatic calibration procedure. During the calibrate sequence, a test seek is performed and timed by the microcomputer. When the microcomputer detects that the test seek is too slow, a short pulse is output on the Servo Disable line. This pulse is too short to actually permit the servo to disable but cause the automatic gain control (AGC) amplifier gain to decrease one step. This sequence is then repeated until the test seek is performed in the required time. The drive then returns to cylinder zero and sets the ready line. The ready line serves to indicate that the drive is on cylinder and ready to read or write. It will be false whenever the heads are outside the data zone, performing a seek operation, or off track center with the write gate enabled.

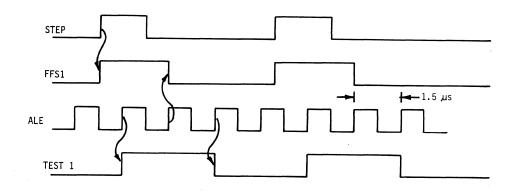

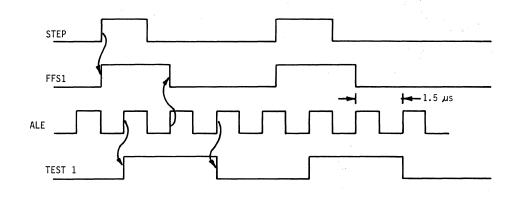

The servo will be disabled and the ready line made false at any time that loss of servo PLO lock is detected. A timing diagram for the step-pulse synchronizer is shown in Figure 4-7.

77715979-B

## 4.3.2.2 MICROCOMPUTER OVERVIEW (SEAGATE INTERFACE)

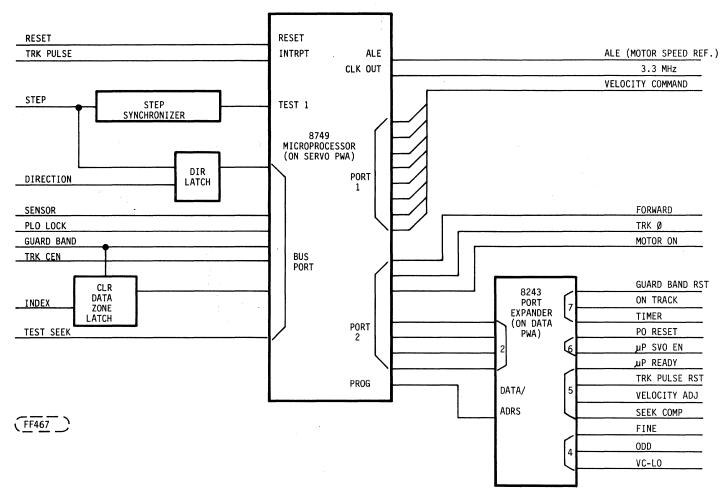

Figure 4-6 shows a simplified block diagram of the microcomputer. The microcomputer is an 8749 with two kilobytes of internal program memory. It also uses an 8243 port expander to increase the number of output signals. The microcomputer has no control of the read/write section with the exception of the write current magnitude.

When a step is received from the command cable interface, it is synchronized with the microcomputer clock and applied to the Test 1 input of the 8749. This causes a counter to be incremented with each step pulse. The interface direction line is latched with the step pulse and applied to one of the Bus Port inputs. These two lines have all the information needed to cause a seek operation.

When a seek is in progress, track-crossing pulses are generated in the servo LSI logic; these are applied to the 8749's Interrupt input. This input remains active until the Interrupt is serviced and a track-pulse reset is sent to the servo LSI on a Port 2 line. In this manner, the microcomputer keeps track of all incoming step pulses and track crossings that occur. The address latch enable (ALE) signal is sent to the spindle motor control as a clock for the speed regulator. During a seek, a seven-bit velocity command is output on Port 1 and goes to a D/A converter in the servo amplifier. The eighth bit on Port 1 is active for a high velocity command, and inactive for a low velocity command. A line from the port expander, titled "VCLO" (Velocity Command Low) is active for a low velocity command, and inactive for a high velocity command. The FINE signal puts the servo system into either the fine or coarse mode of operation. This signal is used in conjunction with the forward/odd lines. Forward refers to a seek from a lower to a higher numbered cylinder. In the coarse mode, this line is active during a forward seek and inactive during a reverse seek. When the drive switches to the fine mode this line is active when the target track is even and inactive when the target track is odd.

The Power On Reset signal originates from the port expander. During start-up, Power-On Reset is active for approximately 6 seconds. This enables the current regulator in the spindle motor control. When it is inactive, it enables the speed regulator. It is also used to provide appropriate resets to sequential logic contained in the drive electronics. During start-up, motor speed is monitored on the Bus Port from the Motor Speed line. The phase lock oscillator (PLO) lock line is continuously monitored. Also during start-up, the servo is disabled via the Servo Disable line.

77715979-B

When the servo PLO is locked and the spindle motor is up to speed, head loading can commence. This is accomplished bv the microcomputer issuing a velocity command, detecting guard band, performing an RTZ, and switching back to fine mode on cylinder zero. The data zone latch is set by Index. Index code is written only data in the zone. This enables the microcomputer to distinguish between the data zone and the start zone.

There is a guard band latch external to the microcomputer that will disable the servo if guard band is encountered after the initial head load. During the head loading, this latch is disabled while setting on Track "O" or while performing a seek to Track "O". This is true because Track "O" is in the guard band. This disable is activated by the guard band latch clear line from the port expander.

There is one other input to the Bus Port, called Test Seek. This input can be grounded with a jumper shunt and causes the drive to go into a continuous test seek following head load and the calibrate operation.

With the completion of head load, the microcomputer puts the drive through an automatic calibration procedure. During the calibrate sequence, a test seek is performed and timed by the microcomputer. When the microcomputer detects that the test seek is too slow, a short pulse is output on the Velocity adjust line. This pulse causes the automatic gain control (AGC) amplifier gain to decrease one step. This sequence is then repeated until the test seek is performed in the required time. The drive then returns to cylinder zero and sets the ready line. The ready line serves to indicate that the drive is on cylinder and ready to read or write. It will be false whenever the heads are outside the data zone. The SEEK COMP line issues a pulse at the end of a seek to set the seek complete latch.

A servo will be disabled and the ready line made false at any time that loss of servo PLO lock is detected. A timing diagram for the step-pulse synchronizer is shown in Figure 4-9.

4.3.3.3 MICROCOMPUTER FIRMWARE ROUTINES (CDC INTERFACE)

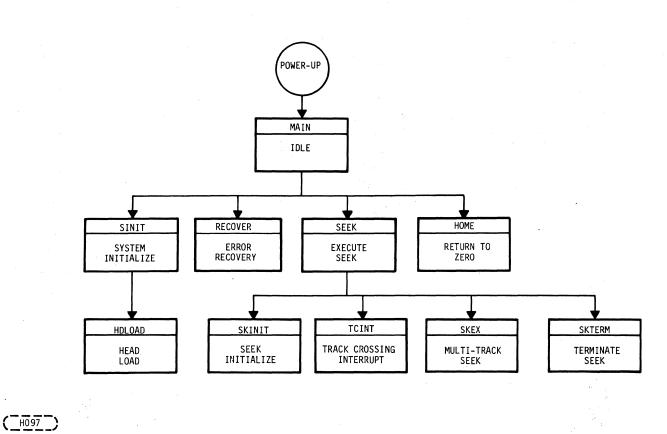

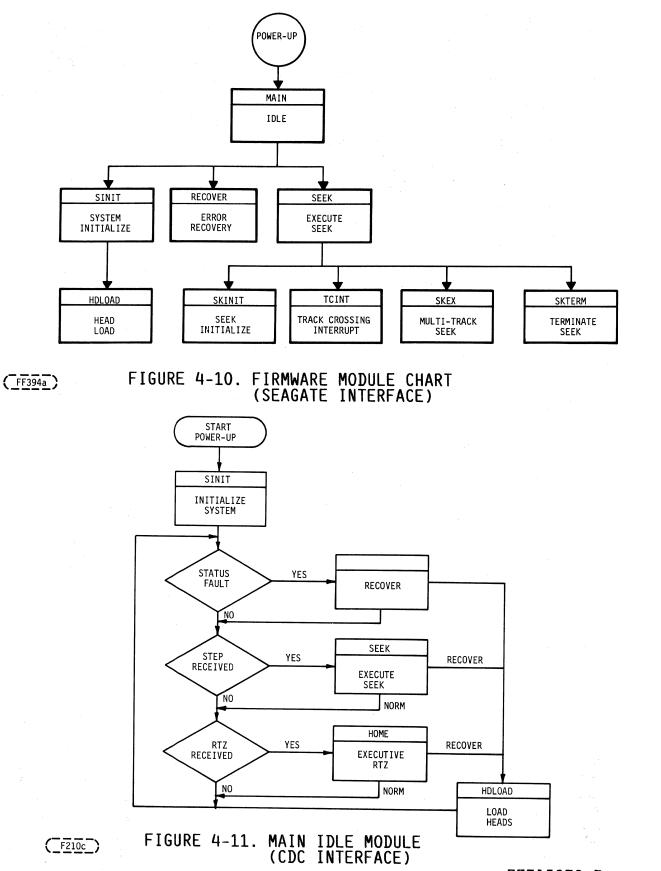

The flow charts that follow illustrate the manner in which the microcomputer controls servo operation in the WREN. Figure 4-8 shows a chart of the primary modules that make up the WREN firmware. On power-up, the program enters and always returns to the Main Idle module. During start-up, the program exits the Main Idle module and goes to the System Initialize module. Following System Initialize, it then goes to the Head Load module. Upon completion of Head Load, the program branches back to the Main Idle Loop.

## 4.3.3.4 MICROCOMPUTER FIRMWARE ROUTINES (SEAGATE INTERFACE)

The flow charts that follow illustrate the manner in which the microcomputer controls servo operation in the WREN. Figure 4-10 shows a chart of the primary modules that make up the WREN firmware. On power-up, the program starts and always returns to the Main Idle module. During start-up, the program exits the Main Idle module and goes to the System Initialize module. Following System Initialize, it then goes to the Head Load module. Upon completion of Head Load, the program branches back to the Main Idle Loop.

FIGURE 4.5. WREN I MICROCOMPUTER BLOCK DIAGRAM (CDC INTERFACE)

77715979-B

FIGURE 4-7. WREN I MICROCOMPUTER STEP PULSE SYNCHRONIZER (CDC INTERFACE)

77715979-B

FIGURE 4-8. FIRMWARE MODULE CHART (CDC INTERFACE)

(\_\_\_\_\_F210a\_\_\_)

FIGURE 4-9. WREN I MICROCOMPUTER STEP PULSE SYNCHRONIZER (SEAGATE INTERFACE)

77715979-B

#### (A) MAIN IDLE LOOP MODULE (CDC INTERFACE)

Assuming a normal power-up sequence has been completed, the program goes to the Main Idle Loop (Figure 4-11). Upon receipt of a Step pulse, the program will branch to the Seek module. From the Seek module, it proceeds to the Seek Initialize module. From the Seek Initialize module, it branches to a seek execution module. At the conclusion of a seek, it will go to the Terminate module. Upon completion of the Seek Terminate, it will return to the Main Idle Loop.

An RTZ command will cause a branching to the Home Module. When the operation is completed, it will return to the Main Idle Loop. In the Main Idle Loop the processor checks for three possible status fault conditions (1) incorrect motor speed, (2) loss of servo PLO lock and (3) servo systems disabled (an internal flag). If a Status Fault condition is present, the program will go into one of several recovery routines. Normally it is during this time that the servo is disabled and the heads would be reloaded. In the event of a servo disable, the microcomputer will automatically attempt to reload heads to cylinder zero. If there are six a trap unsuccessful attempts, state is entered. Operator intervention is the only way out of a trap state. Cycling power will restart the program and a new System Initialize sequence will be attempted.

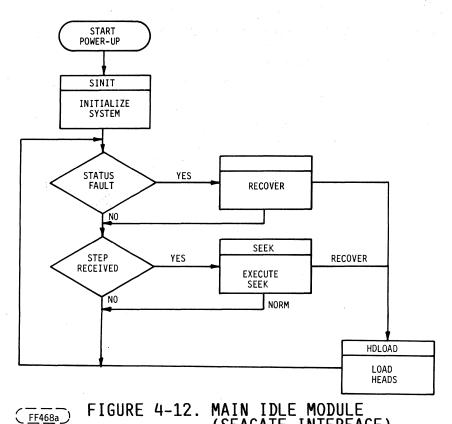

(B) MAIN IDLE LOOP MODULE (SEAGATE INTERFACE)

Assuming a normal power-up sequence has been completed, the program goes to the Main Idle Loop (Figure 4-12). Upon receipt of a Step pulse, the program will branch to the Seek module. From the Seek module, it proceeds to the Seek Initialize module. From the Seek Initialize module, it branches to a seek execution module. At the conclusion of a seek, it will go to the Terminate module. Upon completion of the Seek Terminate, it will return to the Main Idle Loop.

In the Main Idle Loop the processor checks for three possible status fault conditions (1) incorrect motor speed, (2) loss of servo PLO lock and (3) servo system disabled (an internal flag). If a Status Fault condition is present, the program will go into one of several recovery routines. Normally it is during this time that the servo is disabled and the heads would be reloaded. In the event of a servo disable, the microcomputer will automatically attempt to reload heads to cylinder zero. If there are six unsuccessful attempts, a trap state entered. is Operator intervention is the only way out of a trap state. Cycling power will restart the program and a new System Initialize sequence will be attempted.

77715979-B

4-16

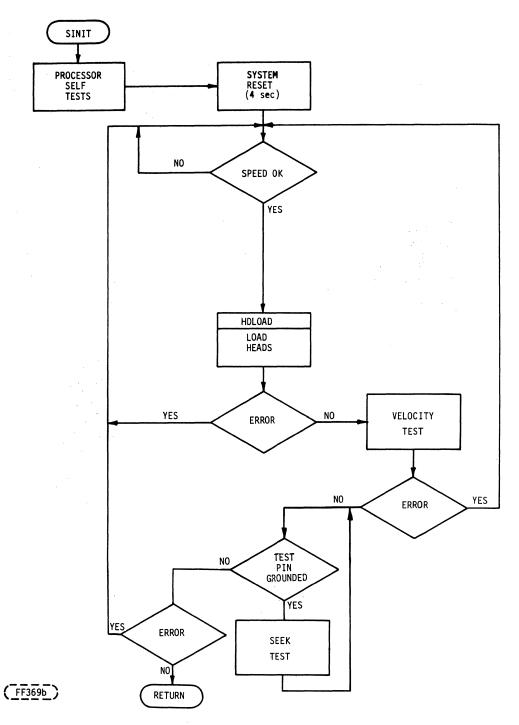

#### (C) SYSTEM INITIALIZE MODULE (CDC AND SEAGATE INTERFACES)

The System Initialize module (Figure 4-13) starts with processor self-tests, then issues a System Reset for 4 seconds to bring the motor up to speed. A speed check is made, then the program branches to the Head Load routine. Following the Head Load, a velocity test is performed. This test will be attempted repeatedly, incrementing the velocity each time the test fails, until the test passes. There is then a check to see if the seek test pin has been grounded, and if so, the seek test continues. If not, errors are checked and the module returns to the Main Idle Loop.

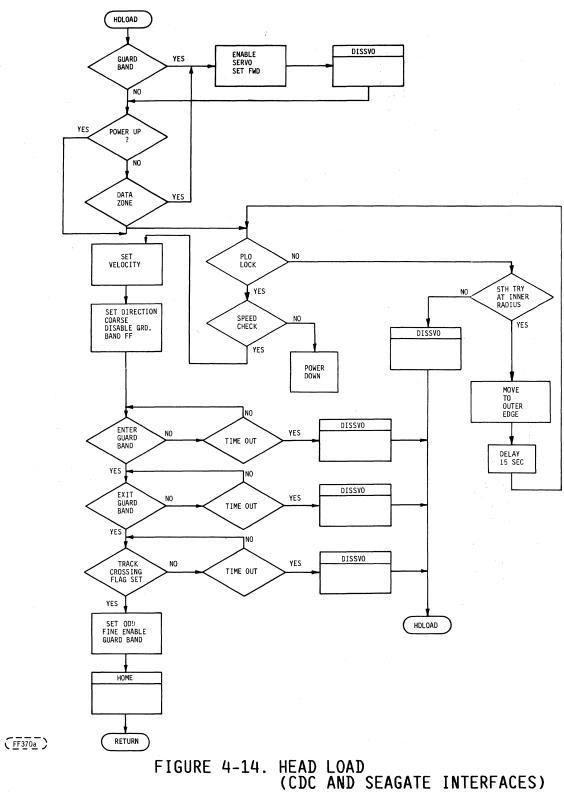

(D) HEAD LOAD MODULE (CDC AND SEAGATE INTERFACES)

In the Head Load routine (Figure 4-14) the presence of a guard band dibit signal pattern is checked. In the start zone, there should be no guard band. Next the data zone is checked. If the head load is occurring during a power-up, the data zone flip-flop may be in an ambiguous state. In this case the data zone check is skipped.

The next step is to move the arm out of the start zone across the disk and to position it on Track O.

The head load velocity command is issued, the reverse and coarse load are enabled, the guard band detector is disabled and the positioner movement begins. After guard band is detected, the sequence continues looking for the exit of guard band. After exiting guard band, the first track-crossing pulse detected sets the Odd and Fine mode. The guard band latch is now enabled.

If during the start of a head load the guard band is detected in the start zone, the servo will be enabled and set in Forward. This is an attempt to drive the arm back into the start zone. It should be noted that during a head load sequence at this point, if data zone is detected, the same form of recovery results.

After the arm is commanded to move a timer will be started in anticipation of detecting guard band. If this timer times out, the servo is disabled. Once in guard band, a similar time-out test occurs which if failed also results in disabling the servo. Following exit of guard band, if a track crossing is not detected within an appropriate time-out, the servo will also be disabled.

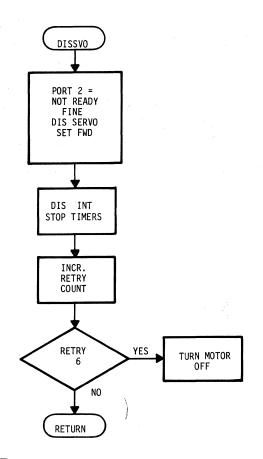

The Disable Servo Routine (DISSVO) is described in Figure 4-22.

77715979-B

## (SEAGATE INTERFACE)

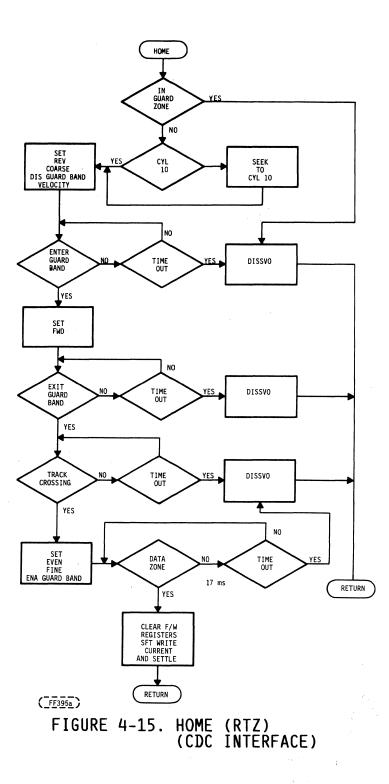

## (E) RETURN TO ZERO MODULE (CDC INTERFACE)

When the Home (RTZ) module is called, the actuator should not be in the guard band (see Figure 4-15). If it is, the Disable Servo routine is called. Anytime the Disable Servo is applied, a return is made immediately afterward to the caller of the Return to Zero module.

If no guard band is detected, a seek to cylinder 10 is done if the actuator is on a large cylinder number. Then the home velocity is set, reverse coarse mode is set, and guard band disabled.

The servo is expected to enter the guard band next. If it doesn't, the Disable Servo routine is applied. When guard band is detected, the direction is set to forward, and the guard band is expected to disappear. If it doesn't, the Disable Servo routine is applied. When guard band becomes false, a track crossing interrupt is expected. If none is detected, the Disable Servo routine is applied. When the interrupt is received, even and fine modes are set, and guard band is enabled.

The servo should be entering the data zone. If it doesn't, the Disable Servo routine is called. When the data zone is detected, firmware registers are cleared, write current set, and some settling time allowed for the actuator before return.

77715979-B

FIGURE 4-13. SYSTEM INITIALIZE (CDC AND SEAGATE INTERFACES)

77715979-B

77715979-B

$\bigcirc$

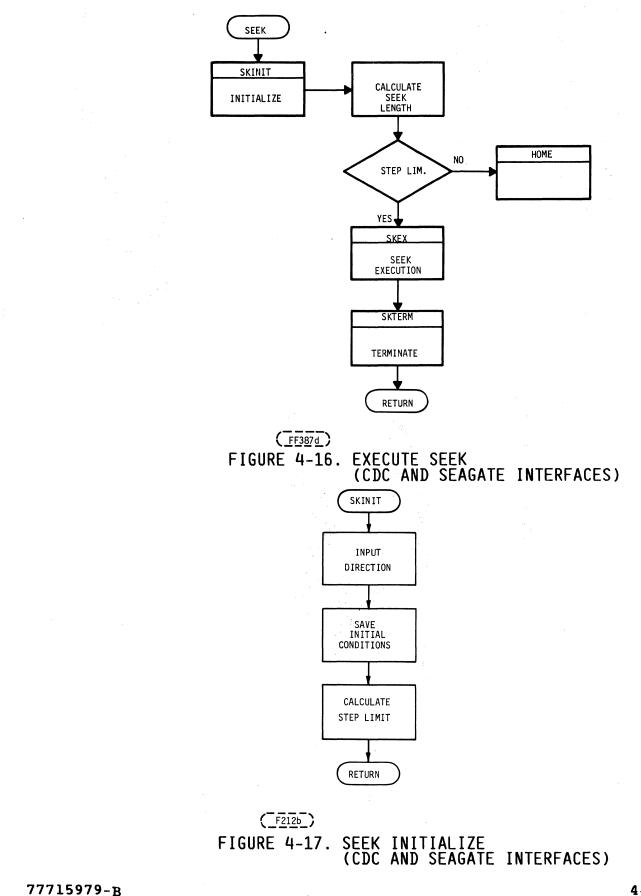

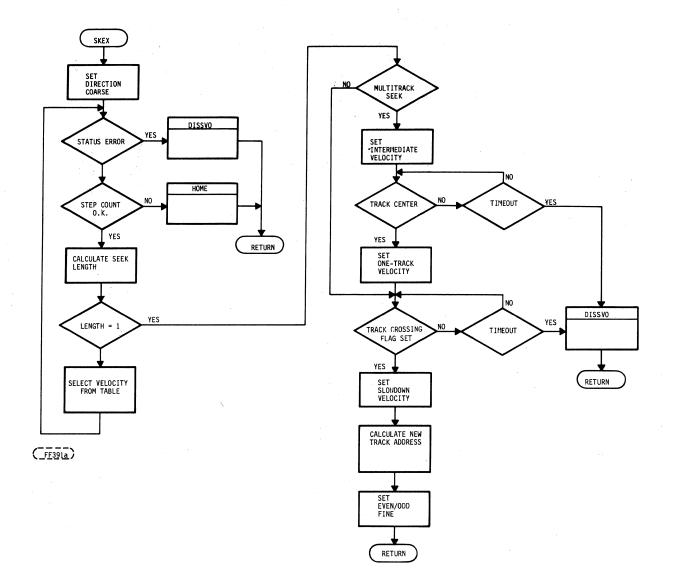

#### (F) EXECUTE SEEK (CDC AND SEAGATE INTERFACES)

When a Step pulse is received from the command interface, a branch is made from the Main Idle Loop into the Seek module (Figure 4-16). First a Seek Initialize routine is carried out. This will be covered in a later paragraph. Next the seek length is calculated based on a number of Step pulses that have been received to this point. A test is performed to determine if the seek length has exceeded the limit of the data zone. If this occurs, an automatic RTZ is performed by branching to the Home or RTZ module. If the step limit has not been exceeded, a branch is made to Seek Execution module. On return from the seek module, the program will continue into the Seek Terminate module, and finally a return to the idle mode.

(G) SEEK INITIALIZE MODULE (CDC AND SEAGATE INTERFACES)

In the Seek Initialize module (Figure 4-17), the direction input is read and stored. Next all initial conditions are saved and the step limit, or a number of steps acceptable without exiting the data zone, is calculated. There is then a return to the seek module.

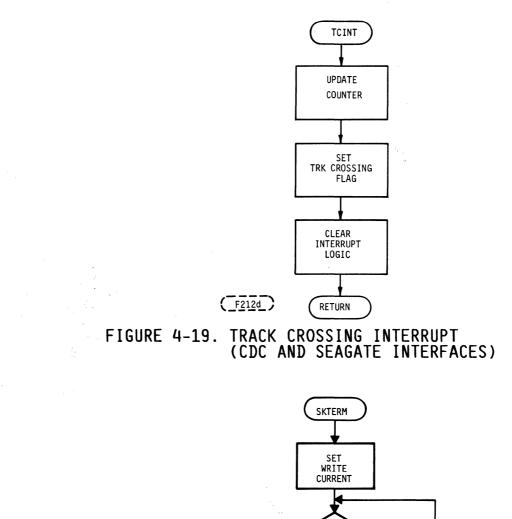

Once a seek has started, when a cylinder is crossed, a track crossing interrupt will be received (Figure 4-19). When servicing the interrupt, the current address counter is updated. Next the track-crossing flag will be set, the interrupt logic will be cleared and there is a return to the sending module.

(H) MULTI TRACK SEEK MODULE (CDC AND SEAGATE INTERFACES)

The Seek Execution module (Figure 4-16) first sets the direction and coarse mode, then a large loop is entered. While the seek is taking place, the status is monitored. If an error occurs, the servo is disabled. The step count is also monitored. A step limit has already been established at this point, and if it is exceeded, a return is made to the main seek module. Each time the step count is determined, the number of steps left can be calculated. This value will determine the velocity to send. This loop is exited when only one step is left in the seek, at which time it must be determined if this was a one-track seek to begin with or not. If it was, nothing is done to the velocity at this point, but if this was a multi-track seek, an intermediate velocity is sent out. Then when track center is observed, the one-track seek velocity is In either case, the last track-crossing interrupt sent. is expected. If it does not come soon enough (or if track center does not come for a multi-track seek) the Disable-Servo routine is called and a return made to the main seek module. If the last track-crossing interrupt is detected, the new track address is calculated, fine mode is set, and return is made to the main seek module.

77715979-B

FIGURE 4-18. MULTI-TRACK SEEK (CDC AND SEAGATE INTERFACES)

FIGURE 4-20. SEEK TERMINATE (CDC AND SEAGATE INTERFACES)

( FF387a )

77715979-B

(I) TRACK CROSSING INTERRUPT MODULE (CDC AND SEAGATE INTERFACES)

The Track Crossing Interrupt updates the counter that records which track the head is on. It also sets a track crossing flag so that the multiseek module knows when a track is crossed.

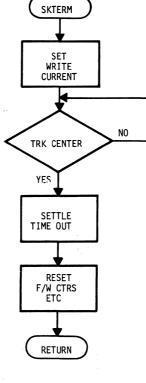

(J) SEEK TERMINATE MODULE (CDC AND SEAGATE INTERFACES)

The Seek Terminate module is used to complete a seek. The system is in Fine mode upon entering this module. First an eight-bit word is output on Port 1. This word sets the write current level used if a write command is received for this cylinder address. Then a track-center signal is detected which starts a settling timeout. This lasts approximately three microseconds. Lastly, firmware counters are reset.

(K) ERROR RECOVERY MODULE (CDC AND SEAGATE INTERFACES)

The Recover module (Figure 4-21) first checks the PLO lock, if the PLO is unlocked, filter runout is checked. If not, a check for servo error is made. Filter runout is checked on error. Next guard band is checked, if guard band is found, the guard band filter runout is checked. If guard band is not found, control is turned back to the calling module. This completes the fast recover module. If filter runout is not all right, Disable servo is called first.

(L) DISABLE SERVO MODULE (CDC AND SEAGATE INTERFACES)

In the Disable Servo Routine (Figure 4-22) the following lines are set inactive:

- Guard band latch

- Ready

The track-crossing interrupt and step counter are also disabled. Then a re-entry counter is incremented and tested to see if this is the sixth pass. If it is, the processor stops and will do nothing until the drive is powered down and up again. If not, control is returned to the calling module.

4.3.3 HEAD POSITIONING SYSTEM (CDC AND SEAGATE INTERFACES)

4.3.3.1 GENERAL (CDC AND SEAGATE INTERFACES)

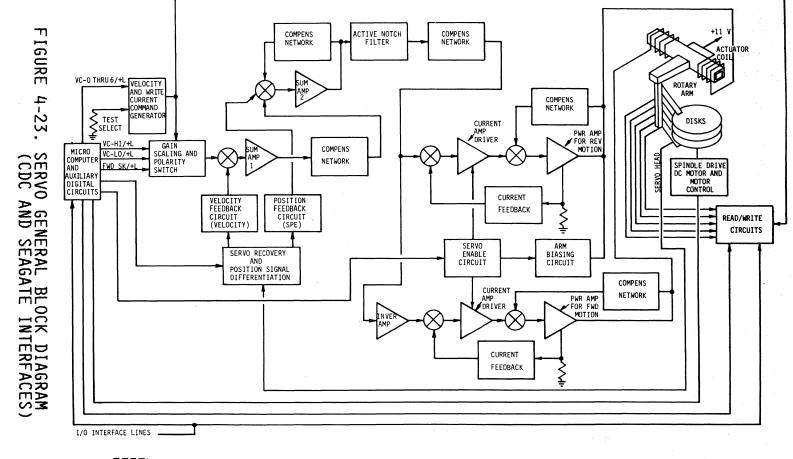

The data heads are positioned on the disk by a closed loop servo system (Figure 4-23). Mounted on the same actuator as the data head is a servo head which reads the specially formatted information on the servo surface (lower surface of the bottom disk). This information is decoded and amplified for the error signal needed to keep the actuator on track. The microcomputer provides a command signal to move from track to track.

77715979-B

The servo system contains a position loop, a velocity loop and a current loop. Figure 4-23 is a simplified block diagram of the servo system. The current loop is analog while the velocity and position loops are a combination of digital and analog circuitry. The compensation loops are not shown for simplicity. The positioning servo system utilizes velocity information that is obtained by differentiation of position signals.

The positioning operation begins when the system controller sends a step and direction command. The microcomputer then initiates and controls the seek. There are times when the microcomputer initiates a seek without a system controller command. Initial head-load and recovery from faults are two of these times.

FIGURE 4-21. RECOVER (CDC AND SEAGATE INTERFACES)

## (<u>FISTE</u>) FIGURE 4-22. DISABLE SERVO (CDC AND SEAGATE INTERFACES)

The microcomputer counts the number of tracks to be traversed and searches a velocity profile table for the correct velocity command code. The microcomputer outputs a digital number representing the the velocity profile table. initial velocity taken from Α digital to analog converter generates an analog voltage which is and the actuator voice coil. The amplified applied to microcomputer also switches the servo circuit into the velocity mode. This begins the move to the destination track and causes information on the servo surface to be decoded into a velocity feedback signal. Each time the center of a track is crossed, the servo circuitry detects it and informs the microcomputer. The target track distance is then recalculated. As the heads approach the target track the microcomputer reduces the velocity. When the heads are within less than one-half track of their destination the microcomputer switches the servo to the fine mode.

77715979-B

In the fine mode the information on the servo surface is decoded into positional feedback. The microcomputer also decides if the target track is odd or even and sets a line to tell the servo circuit which track to center on.

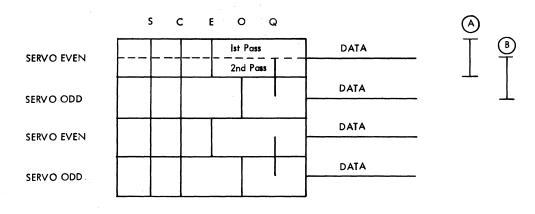

## 4.3.3.2 SERVO SURFACE FORMAT (CDC AND SEAGATE INTERFACES)

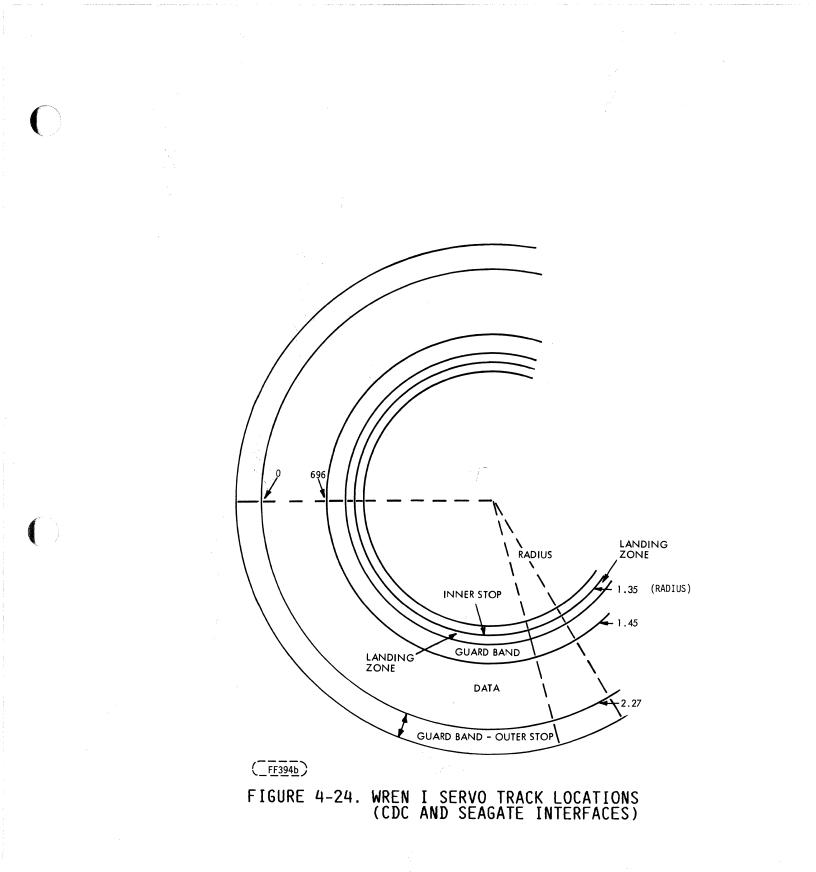

The Servo surface is divided into four zones as shown in Figure 4-24. The data zone defines the read/write area on the other surfaces (Track 00 to 696). The guard bands have coded information to tell the drive when the heads are outside the data zone. The WREN uses a landing zone because the heads are over media at all times. Flying and landing the heads in this zone prevents damage to customer data when cycling power. The landing zone also has data to enable the servo timing circuits to synchronize during start-up. Special data on Track -79 is used during manufacturing to set the mechanical stop.

The servo format used in the WREN is composed of a five-dibit pattern. There are 2688 servo fields per track. The individual dibits within the servo field are called:

- SyncCode

- Even

- b Ddd

- Quadrature

The sync bits are used to lock the PLO which then provides the basic timing to decode the rest of the dibits. The code bit is used to mark the index and to differentiate the data zone from the guard band. The even, odd and quadrature bits are used to drive the position and velocity feedback signals. 4-30

(FF296a)

77715979-B

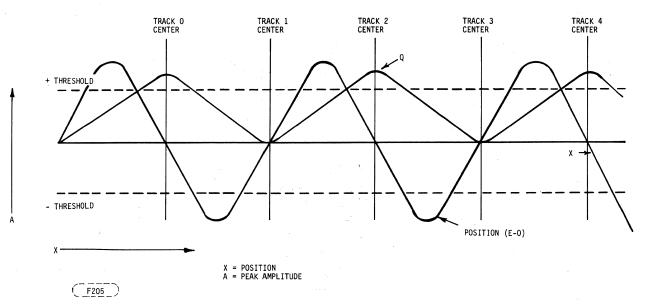

Servo tracks come in two varieties, even and odd. All tracks have sync bits. The code bit is present in the guard band, but only in every other field. The code bit is also present for four fields at the beginning of each data track to mark the index. Only even tracks have even bits and only odd tracks have odd bits. The quadrature bit is written half on the outside of the even track and half on the inside of the odd track as shown in Figure 4-25.

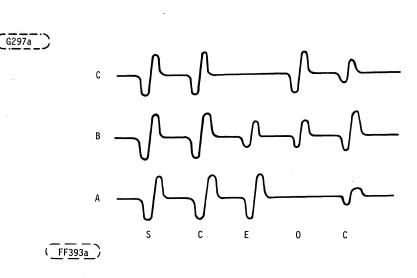

Data tracks on the other surfaces are offset one-half track from servo tracks, this means that when the servo head is halfway between an odd and even track the data head is on track center. Dibit pattern B in Figure 4-25 shows what the servo information will look like when the data head is on track center. NOTE: That the odd and even bits are of equal amplitude and the quadrature bit is a maximum amplitude. The servo circuits find the center of data tracks by subtracting the peak values of the odd dibits from the peak values of even dibits (see Figure 4-26). When this value is zero the data heads are centered. If the peak values of the quadrature dibit are also zero the track is odd. On the other hand if the quadrature dibit are at their maximum value the track is even.

When the servo is in the velocity mode the absolute value of the slope of the position signal is used as the velocity feedback. However, this slope has a discontinuity between tracks due to a change in sign. Therefore, when the position signal is over a set threshold the absolute value of the quadrature slope is used as the velocity feedback.

## 4.3.3.3 DETAILED POSITIONING SYSTEM DESCRIPTION (CDC INTERFACE)

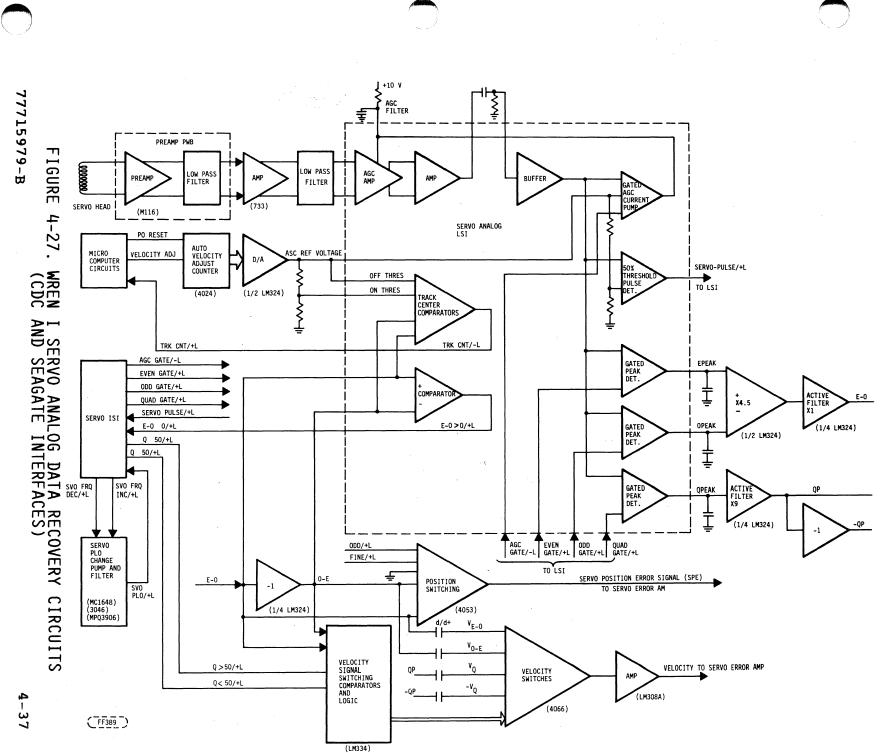

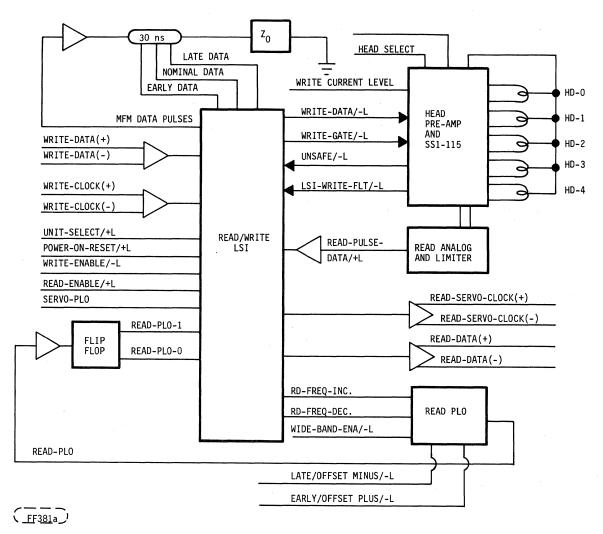

A block diagram of the WREN Servo System is shown in Figure 4-19. Two signals derived by the Servo Analog Data Recovery circuits are position and velocity signals. A block diagram of the analog circuits used to provide these signals is shown in Figure 4-27. These signals are used by the closed loop servo system to control the seeking and positioning of the heads. The analog circuits are controlled by the digital LSI circuit, which provides the proper gating signals, and by the microcomputer.

A detailed description of the functions of the circuits shown in Figure 4-27 is as follows:

77715979-B

4-33

© |

# FIGURE 4-26. DERIVED POSITION AND QUADRATURE SIGNALS (CDC AND SEAGATE INTERFACES)

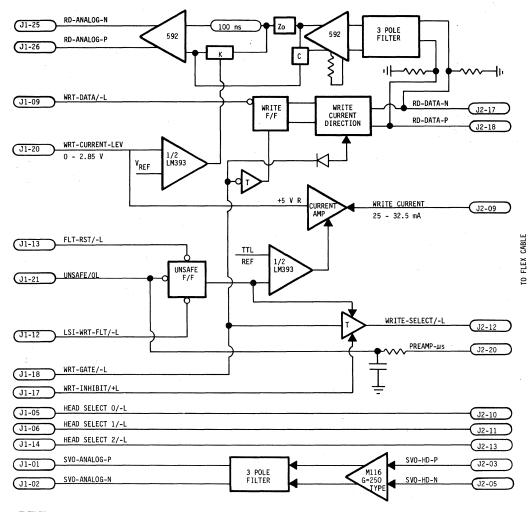

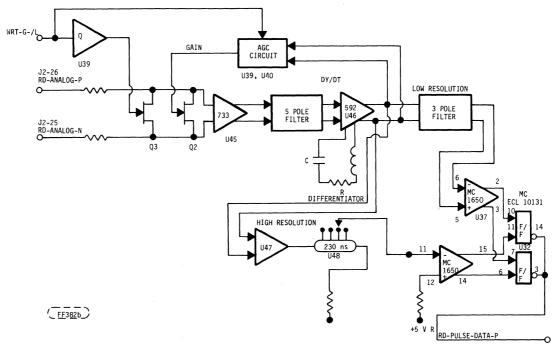

The signal from the servo disk is amplified by a low noise preamp (M116) and filtered. This preamp is located on the Preamp PWA. The output is sent to the Data PWA where it is again amplified (733) and filtered and applied to the Servo Analog LSI chip. The Analog LSI chip contains an automatic gain control (AGC) amp which is the controlling element in an AGC loop contained within the chip. Also in the chip is a high speed comparator with a threshold set at 50% of the peak dibit level which outputs a pulse when any dibits amplitude exceed 50% of the peak AGC level. The input signal from the 733 amp is applied to the AGC amp in the analog LSI. It is then amplified again and coupled to a buffer amp. The buffer amp drives a gated AGC current pump detector. The detector is gated such that only the sync dibit is used for AGC. The combined action of the AGC system is to produce a constant amplitude sync dibit at the output of the buffer amp. The AGC reference voltage controls the peak amplitude of the output of the buffer. This voltage is supplied externally to the LSI chip by a D/A converter circuit. The reference voltage is set up during a calibration cycle when power is applied to the drive.

77715979-B

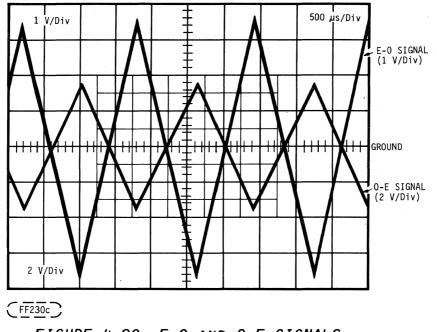

The internal buffer output is also applied to three gated peak detectors which peak detect the three position dibits, even, odd and quad. The even and odd peak detectors are applied to difference amps with a gain of 4.5. The output of the difference amp is filtered by a two-pole active filter. This signal is E-O (even-odd) and is inverted to produce O-E (odd-even). These signals are shown in Figure 4-28. During seeks no position feedback is used and the position switching circuit grounds the SPE signal (servo position error). During track following mode (FINE) the position switching circuit selects either the E-O or O-E signal depending upon what polarity track (even or odd) is to be followed.

The velocity signal is developed from the position signal by taking the derivative of the E-O and O-E signals. These two velocity signals, (i.e.Ve-o and Vo-e) are applied to the velocity switches. These signals are of opposite polarity and the proper one is selected depending upon the position of the head over an even or odd track. The position of the head is determined by the servo digital LSI which detects the presence or absence of a Q dibit pulse. This signal is outputted by the LSI as Q 50 and Q 50. These two signals control what velocity feedback signal is used. As the head moves between tracks, the E-O and O-E signals become non-linear and their velocity signals are not accurate. To overcome this a quadrature dibit is written on the servo surface which is offset by 1/2 track from the even and odd dibits. This dibit is peak detected by the Q peak detector and amplified and filtered to generate the Qp signal.

This is inverted and becomes -Qp, Qp and -Qp are also differentiated to produce two other velocity signals  $V_Q$  and  $-V_Q$ . One of these signals is selected by comparing the amplitudes of the E-O and O-E signals. If either of these go too positive and enter their nonlinear region the velocity feedback signal is switched to the  $V_Q$  or  $-V_Q$  signal. The output from the velocity switches is buffered by an amplifier (LM308A) and this output is applied to the servo error amp as the velocity feedback.

gain of the position and velocity feedback signals The is controlled by the amplitude of dibits that are peak detected. The amplitude of the dibits is set by the AGC system which is referenced to an external voltage (AGC REF VOLTAGE). By changing the reference voltage the amount of feedback to the servo loop may be changed. This fact is used to adjust the velocity feedback signal to the exact amount required independent of component tolerances, etc. This is done upon power up sequence under control of the microcomputer circuits. The microcomputer does test seeks during which it measures the velocity of the arm. If the velocity is incorrect it will increment the auto velocity adjust counter which changes the AGC REF VOLTAGE. Another test seek is performed and the process repeats until the correct velocity is achieved. This adjusts for errors associated with normal component tolerances.

Also located in the Servo Analog LSI are several comparator circuits. One of these is the Track Center Comparators which tells the microcomputer circuit that the head has reached the center of the track. This is used in the settle routine and also will indicate if the head has gone off track for some reason. Another comparator simply senses if the E-O signal is positive (E-O>0). This signal is used by the servo digital LSI in the track crossing generator circuit.

In addition to the position and velocity signals, the analog circuits of the servo system provides the following functional groups. (See Figure 4-27.)

- Velocity and write current command generator

- Actuator drive circuits:

- 1. Gain scaling and polarity switch

- 2. Summing amplifiers

- 3. Power amplifier

- Servo system velocity feedback circuit

- Servo system position feedback and offset generating circuit

- Active notch filter and compensation networks

- Servo enable and rotary arm biasing circuit.

FIGURE 4-28. E-O AND O-E SIGNALS (CDC AND SEAGATE INTERFACES)

The velocity and write current command generator is located on the Servo PWA. The microcomputer outputs a seven bit digital command by proper activation of the VC-0/+L through VC-6/+L lines to the digital to analog converter (DAC) U26. The DAC output is connected to current to voltage converter U22-1. Scaling of the DAC output is accomplished at the factory by selecting the value of the test select resistor R70. The two velocity ranges are chosen by the microcomputer by activating the VC-LO/+L or VC-HI/+L lines. The gain scaling of the amplifier U-34 is provided thru analog switches U30-14 and U30-4. The ODD/-L line controls the direction determining the inverting or of the seek by noninverting configuration of the polarity switching amplifier U22-7. When "HIGH" the actuator drive circuits provide ODD/-L line is set "REVERSE" motion of the rotary arm (from lower numbered tracks towards higher numbered tracks). When seek is complete and both and R149 lines VC-HI/+L, VC-LO/+L are set "LOW", R148 are disconnected from U22-7 and U34 output is grounded. This allows write current levels to be set at U22-1 without affecting the servo system. Summing amplifier U21 in the seek mode subtracts the velocity feedback signal from the velocity command signal to generate the velocity error signal.

77715979-B

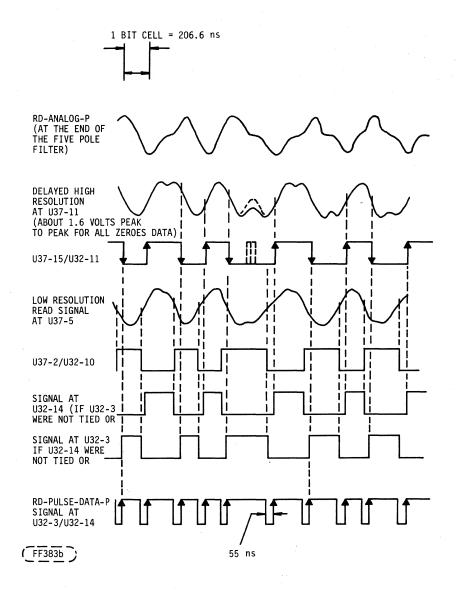

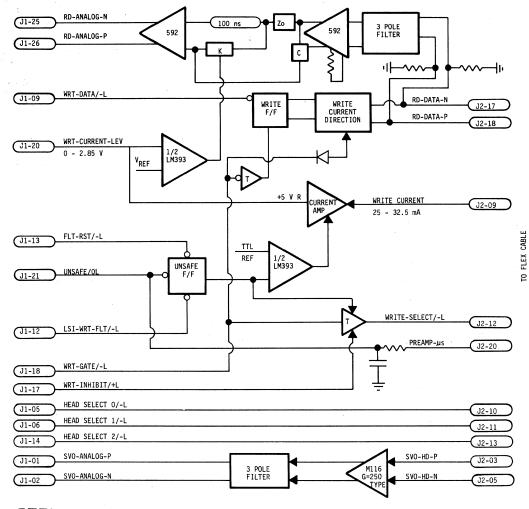

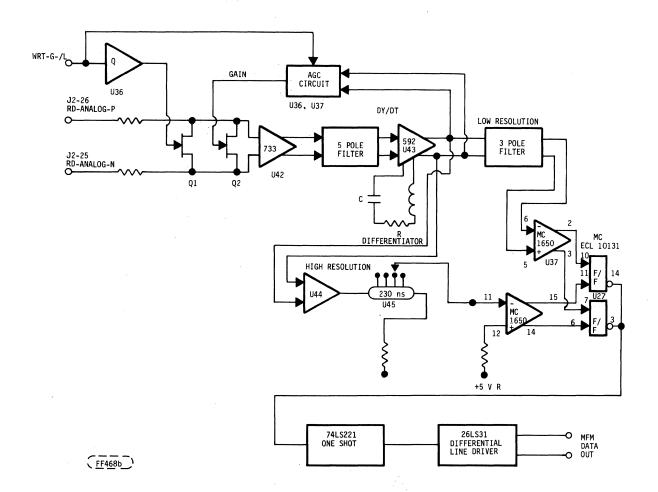

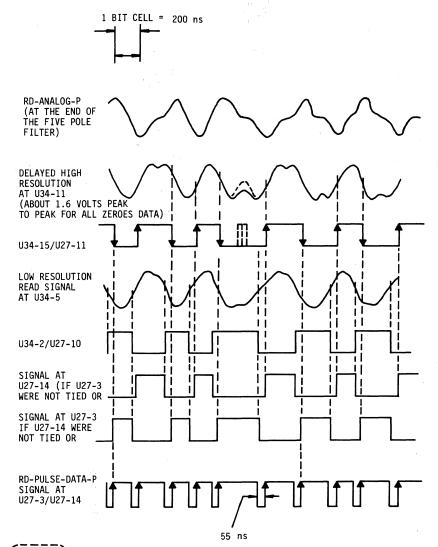

The velocity error signal drives the power amplifier through amplifier Ul4 and active notch filter Ul0-7. During the seek mode the line FINE/+L is "LOW" and position feedback signal is removed. When the rotary arm is positioned on track (FINE/+L is "HIGH") the position signal will be active.