Sabre Disc Drive

Aug-93

ST8741J ST8741N ST8741ND ST8741ND ST8851J ST8851K ST8851N ST8851ND ST8123J ST81123J ST81123J ST81236K ST81236N ST81236ND

Theory Manual (All Interfaces)

Overview of the Drive Power and Control Functions Interface Functions Servo Surface Decoding Seek Functions Read/Write Functions Detecting and Analyzing Errors

Publication Number: 83325690-F

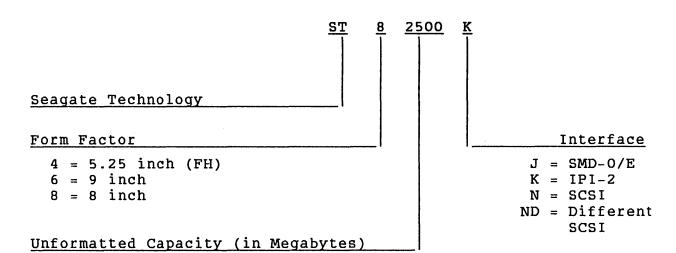

#### Seagate Disc Drive Product Numbers

#### Copyright Notice

Seagate, Seagate Technology, and the Seagate logo are registered trademarks of Seagate Technology, Inc. This publication is copyrighted with all rights reserved and may not be copied, in whole or in part, without written permission of Seagate Technology, Inc.

Seagate reserves the right to change product offerings or specifications without notice.

Publication Number: 83325690 Revision: F Date: April, 1991

© 1991 By Seagate Technology, Inc. Technical Publications Department 12701 Whitewater Drive Minnetonka, MN 55343

We value your comments. A comment sheet is provided at the back of this manual.

Printed in the United States of America

## CONTENTS

| Preface                                      | f-13 |

|----------------------------------------------|------|

| Important Safety Information and Precautions | f-19 |

| Abbreviations                                | f-23 |

|                                              |      |

| 1. OVERVIEW OF THE DRIVE                     |      |

| Introduction                                 | 1-1  |

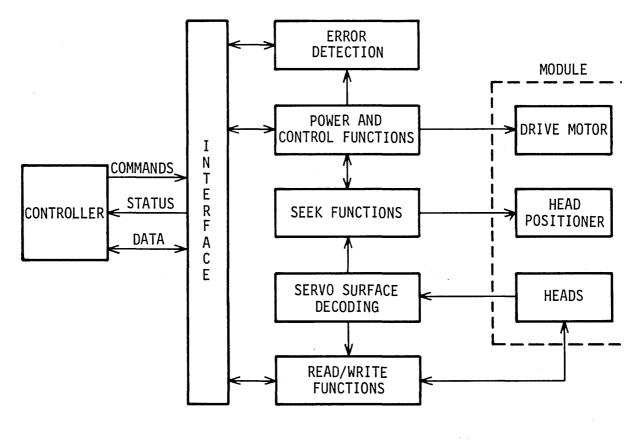

| Drive Functional Description                 | 1-1  |

| Summary of Drive Operations                  | 1-4  |

| Ongoing Operations                           | 1-4  |

| Commanded Operations                         | 1-5  |

| How to Use This Manual                       | 1-7  |

|                                              |      |

| 2. POWER AND CONTROL FUNCTIONS               |      |

| Introduction                                 | 2-1  |

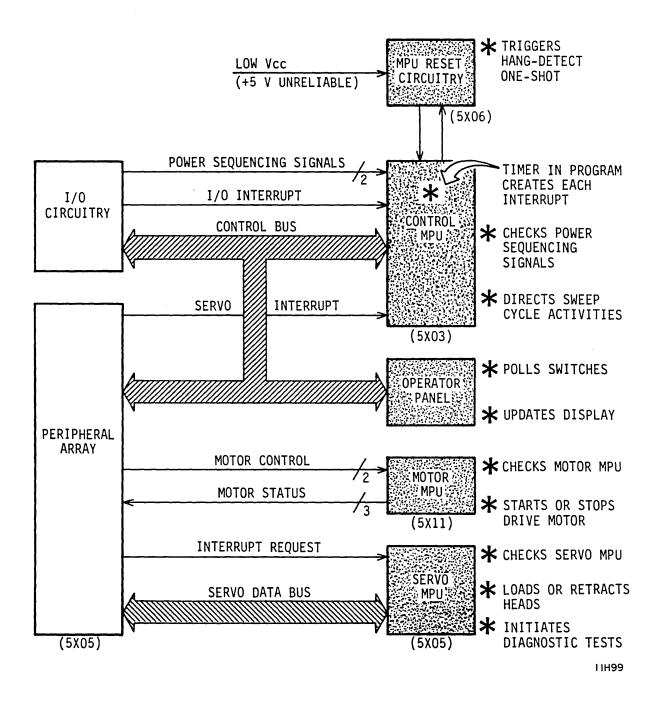

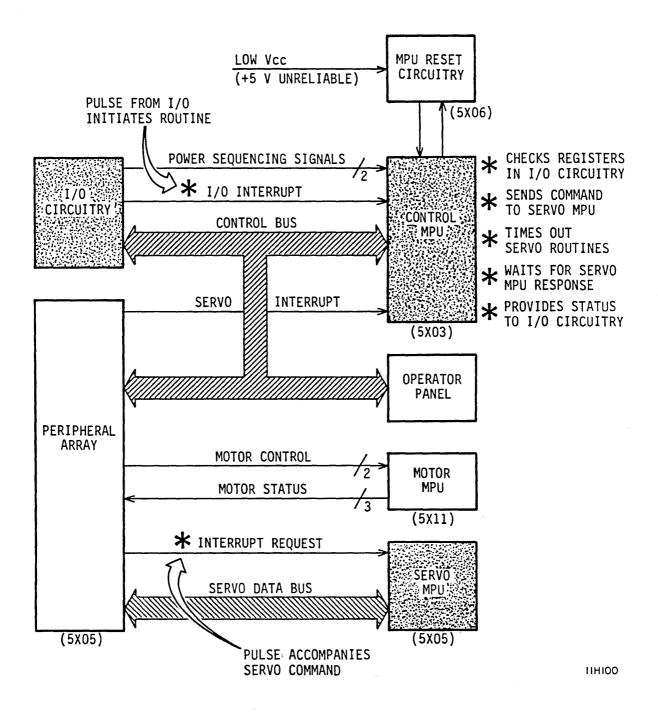

| Microprocessor Control System Functions      | 2-1  |

| Timer Interrupt                              | 2-2  |

| I/O Interrupt                                | 2-4  |

| Servo Interrupt                              | 2-4  |

| Power Functions                              | 2-7  |

| Power Distribution                           | 2-7  |

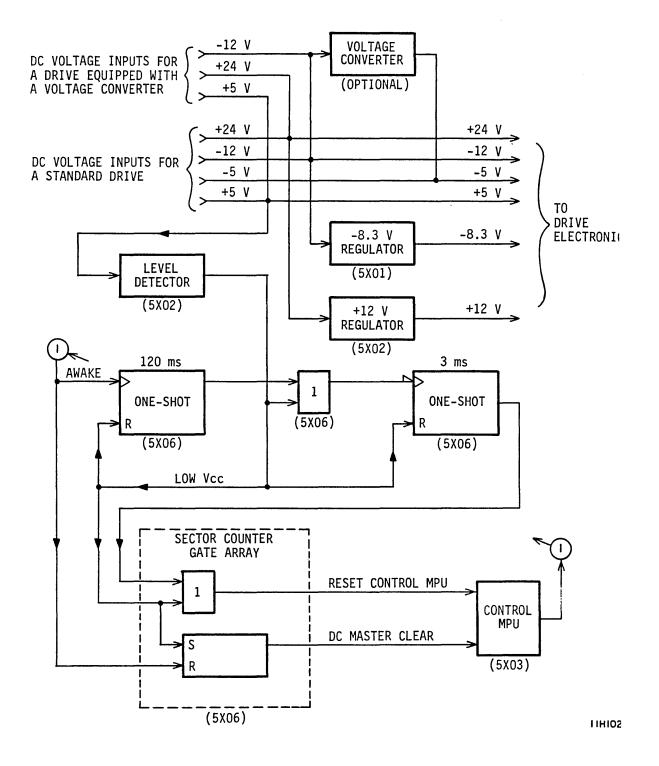

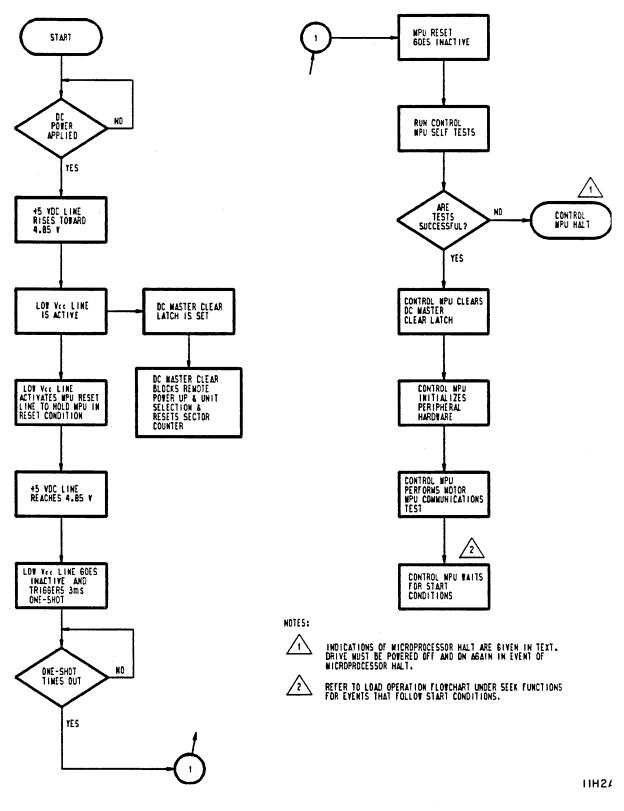

| Power On Sequence                            | 2-9  |

| Power On Initialization                      | 2-9  |

| Control Board Initialization                 | 2-9  |

| SCSI I/O Board Initialization                | 2-11 |

| IPI I/O Board Initialization                 | 2-13 |

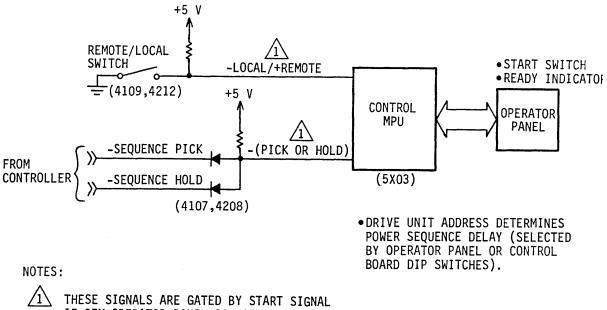

| Power Sequencing                             | 2-13 |

| Power Sequencing on SMD Interface Drives     | 2-14 |

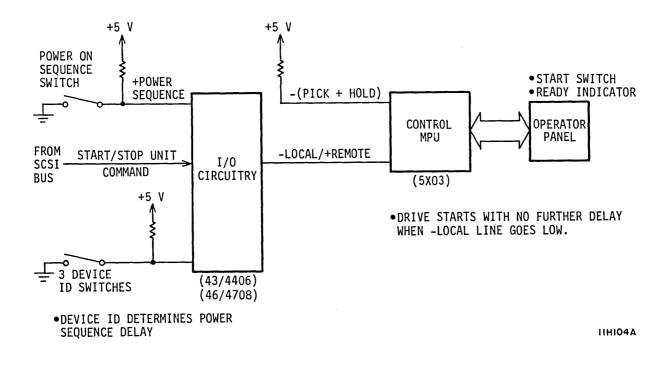

| Power Sequencing on SCSI Interface Drives    | 2-15 |

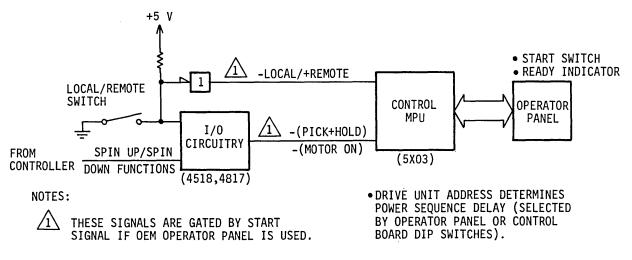

| Power Sequencing on IPI Interface Drives     | 2-16 |

| Load Operation                               | 2-17 |

| Power Off Sequence                     | 2-17          |

|----------------------------------------|---------------|

| Loss of Start Conditions               | 2-17          |

| Loss of DC Power                       | 2-18          |

| Disc Rotation and Head Loading         | 2-19          |

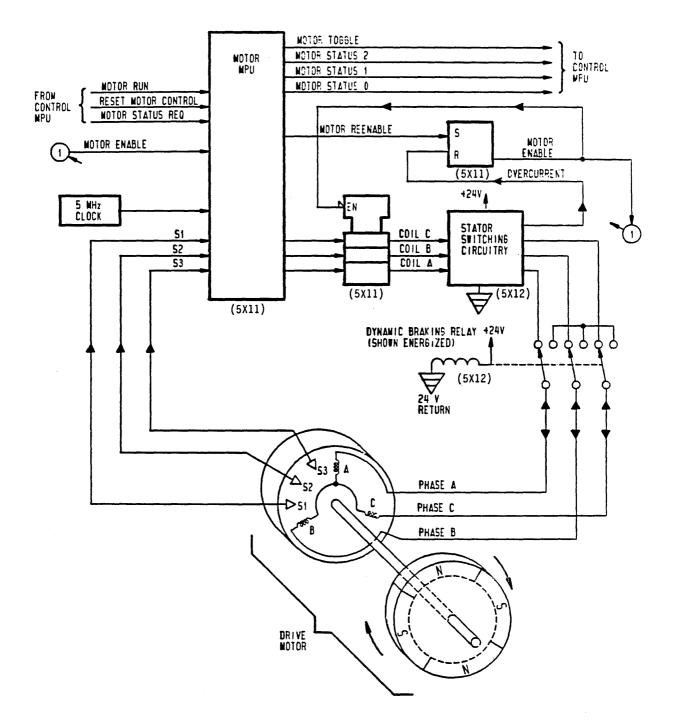

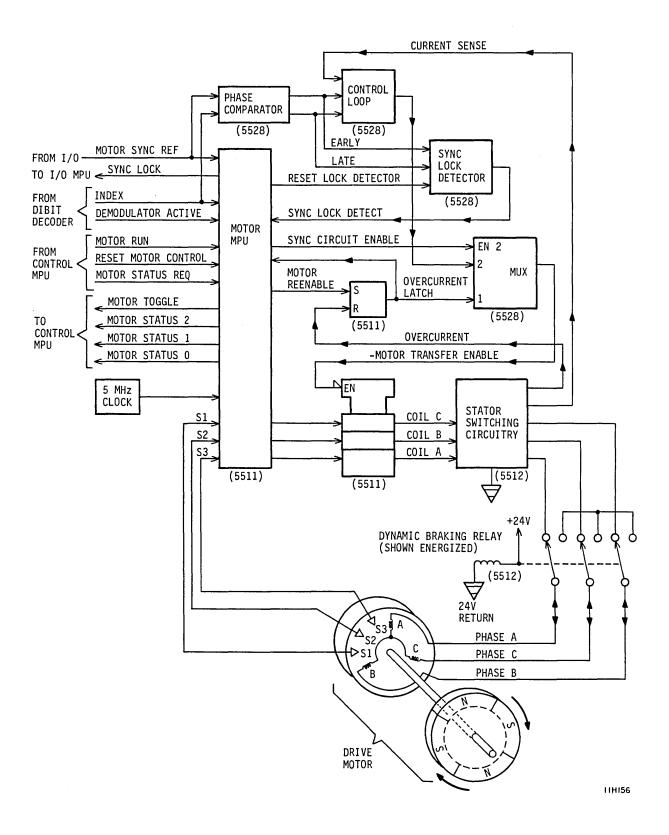

| Controlling the Disc Rotation          | 2-19          |

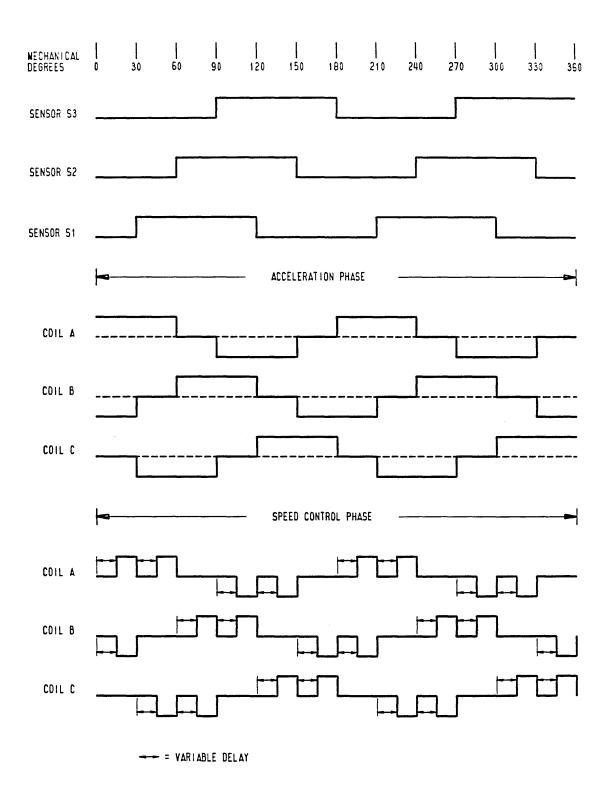

| Standard Motor Speed Control           | 2-19          |

| Synchronized Motor Speed Control       | 2-23          |

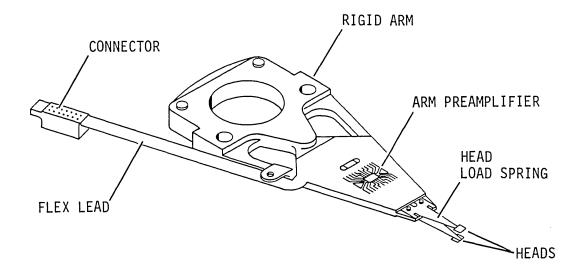

| Loading and Retracting the Heads       | 2-26          |

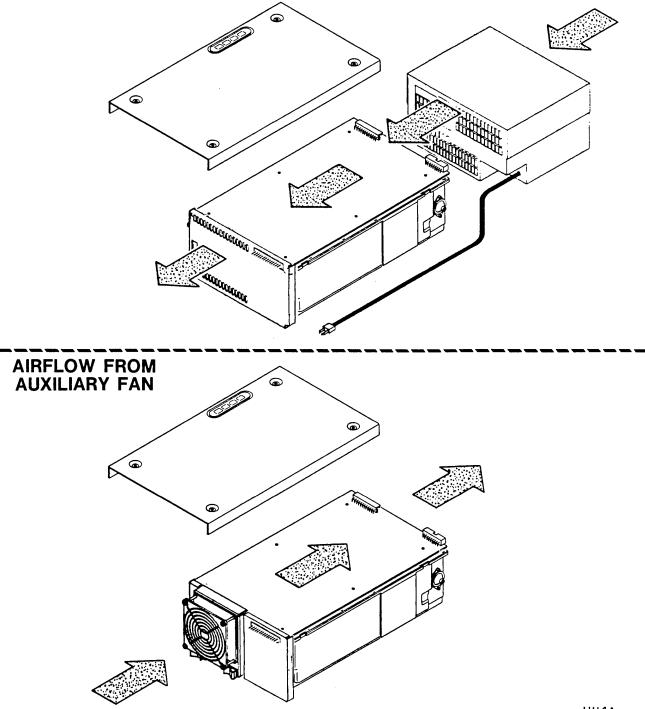

| Ventilation System                     | 2-27          |

| 3. INTERFACE FUNCTIONS                 |               |

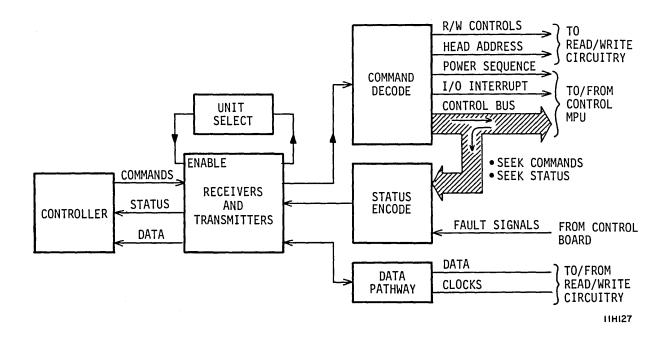

| Introduction                           | 3-1           |

| 3A. SMD INTERFACE FUNCTIONS            |               |

| Introduction                           | 3 <b>A</b> -1 |

| Interface Operation                    | 3A-1          |

| I/O Cables                             | 3A-1          |

| I/O Signal Processing                  | 3A-7          |

| Unit Selection                         | 3A-21         |

| Single-Channel Unit Selection          | 3A-22         |

| Dual-Channel Unit Selection            | 3A-24         |

| General                                | 3A-24         |

| Select and Reserve Function            | 3A-27         |

| Release Function                       | 3A-31         |

| Priority Select Function               | 3A-31         |

| Disable Function                       | 3A-32         |

| 3B. SCSI INTERFACE FUNCTIONS           |               |

| Introduction                           | 3B-1          |

| SCSI Bus Configuration                 | 3B-1          |

| SCSI Controller                        | 3B-5          |

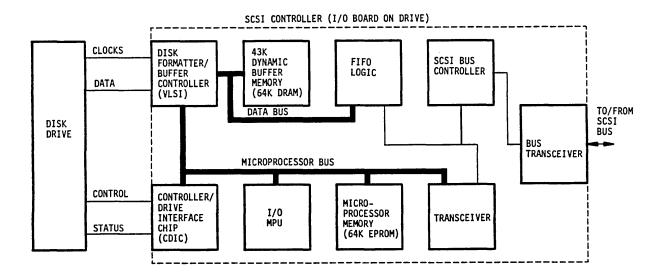

| Standard SCSI Controller               | 3B-5          |

| Disc Formatter and Buffer Controller   | 3B-6          |

| I/O MPU                                | 3B-6          |

| Controller/Drive Interface Chip (CDIC) | 3B-6          |

| SCSI Bus Controller (SBC)              | 3B-6  |

|----------------------------------------|-------|

| Transceivers                           | 3B-7  |

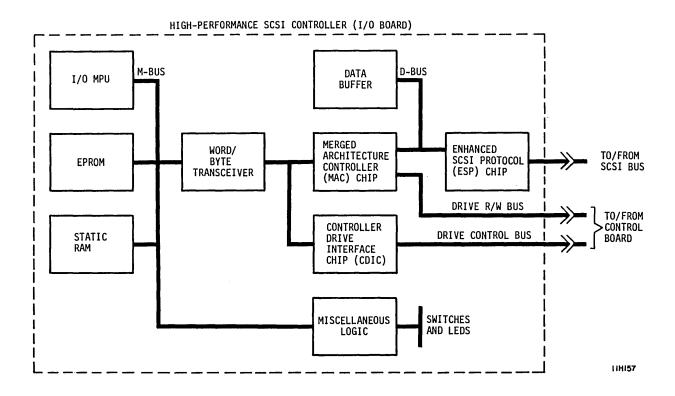

| High-Performance SCSI Controller       | 3B-7  |

| MAC Disc Formatter                     | 3B-8  |

| MAC Buffer Controller                  | 3B-8  |

| I/O MPU                                | 3B-9  |

| Controller/Drive Interface Chip (CDIC) | 3B-9  |

| Enhanced SCSI Protocol (ESP) Chip      | 3B-9  |

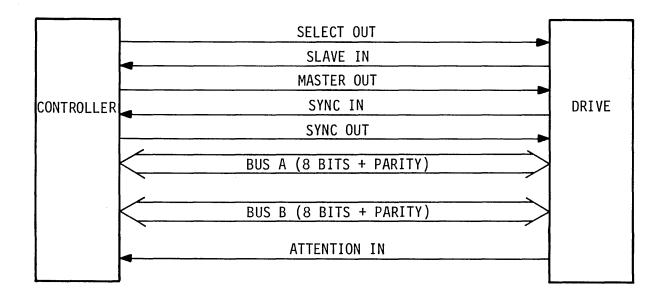

| I/O Signal Processing                  | 3B-9  |

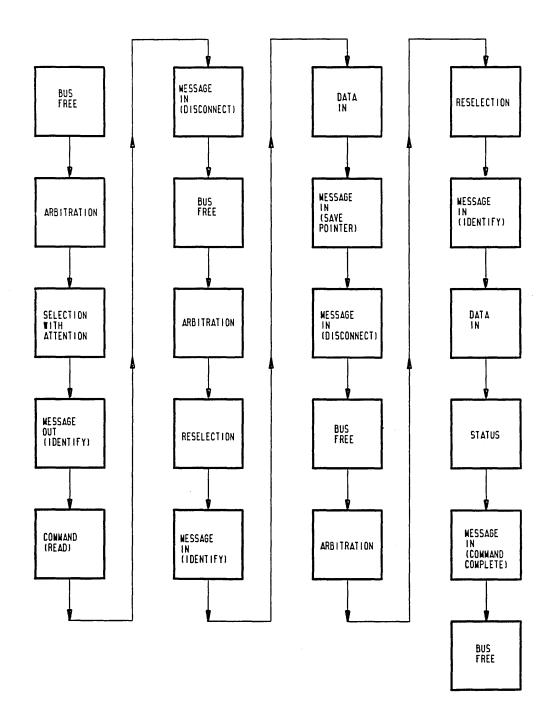

| SCSI Bus Phases                        | 3B-9  |

| SCSI Command Execution                 | 3B-10 |

| 3C. IPI INTERFACE FUNCTIONS            |       |

| Introduction                           | 3C-1  |

| Interface Operation                    | 3C-1  |

| I/O Cables                             | 3C-2  |

| I/O Circuit Description                | 3C-4  |

| I/O Board with Standard Read/Write     | 3C-4  |

| I/O Board with Parallel Read/Write     | 3C-6  |

| Interface Signal Processing            | 3C-8  |

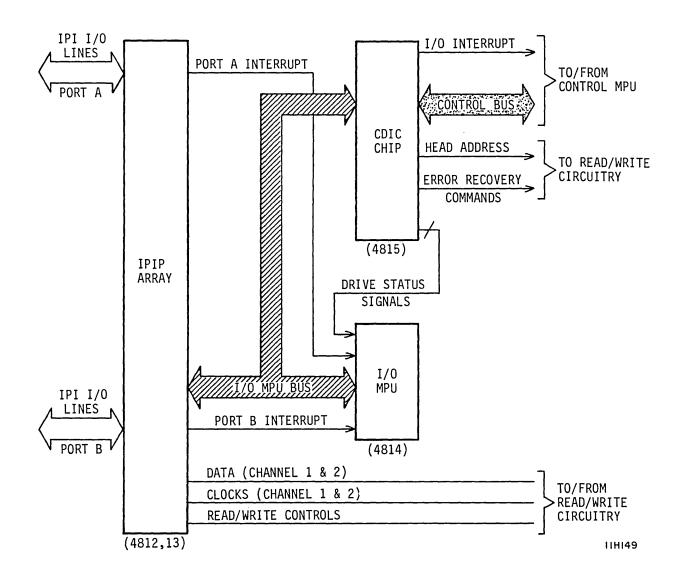

| States                                 | 3C-8  |

| Sequences                              | 3C-13 |

| Bus Controls                           | 3C-16 |

| Command Controls                       | 3C-16 |

| Response Controls                      | 3C-17 |

| Data Controls                          | 3C-18 |

| Status                                 | 3C-21 |

| Status Response                        | 3C-21 |

| Extended Status Response               | 3C-21 |

| Unit Selection                         | 3C-26 |

| General                                | 3C-26 |

| Drive Accessibility                    | 3C-27 |

| Select                                 | 3C-27 |

| Priority Select                        | 3C-28 |

| Reserve                                | 3C-28 |

| Priority Reserve    | 3C-28 |

|---------------------|-------|

| Release             | 3C-28 |

| Port Enable/Disable | 3C-29 |

| Attention           | 3C-29 |

| 4. SERVO SURFACE DECODING       |       |

|---------------------------------|-------|

| Introduction                    | 4-1   |

| Dibit Recording Scheme          | 4-1   |

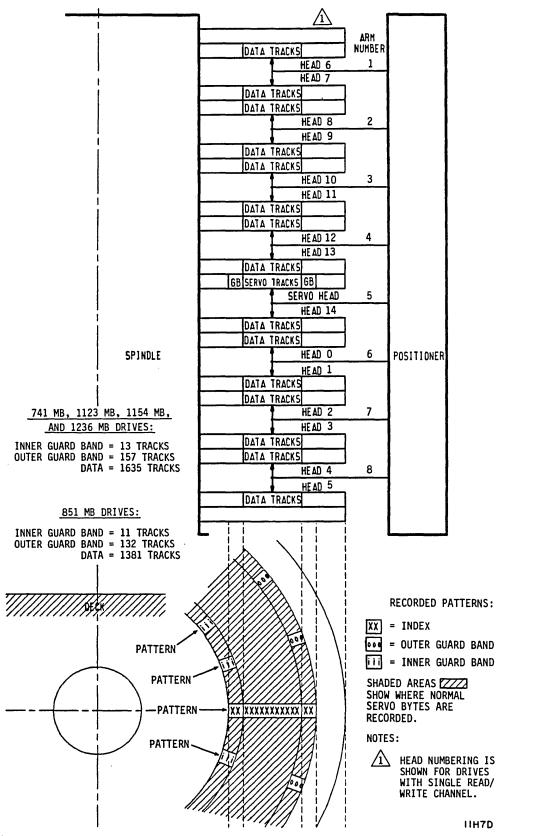

| Servo Surface Format            | 4 - 4 |

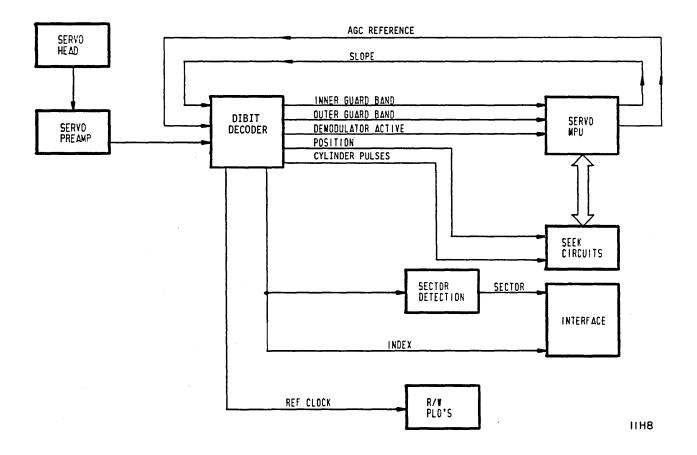

| Dibit Decoder Circuit Operation | 4-6   |

| System Overview                 | 4-6   |

| Dibit Input Circuitry           | 4-8   |

| Servo PLO and Timing Logic      | 4-10  |

| Position Circuits               | 4-12  |

| Index and Guard Band Decoding   | 4-14  |

| Sector Detection                | 4-15  |

| 5. SEEK FUNCTIONS           |       |

|-----------------------------|-------|

| Introduction                | 5-1   |

| System Overview             | 5-1   |

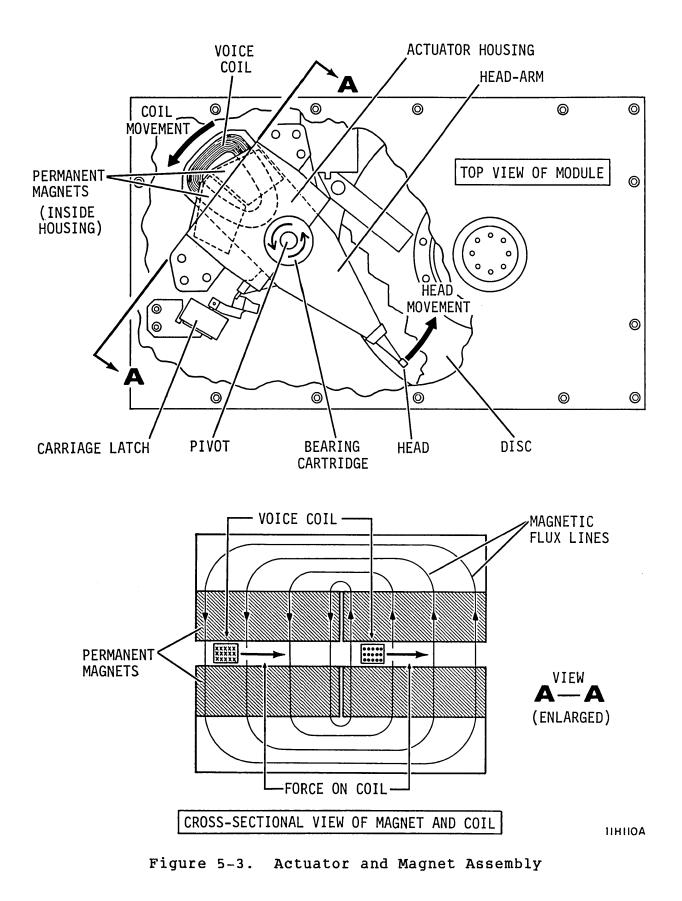

| Actuator and Magnet         | 5-4   |

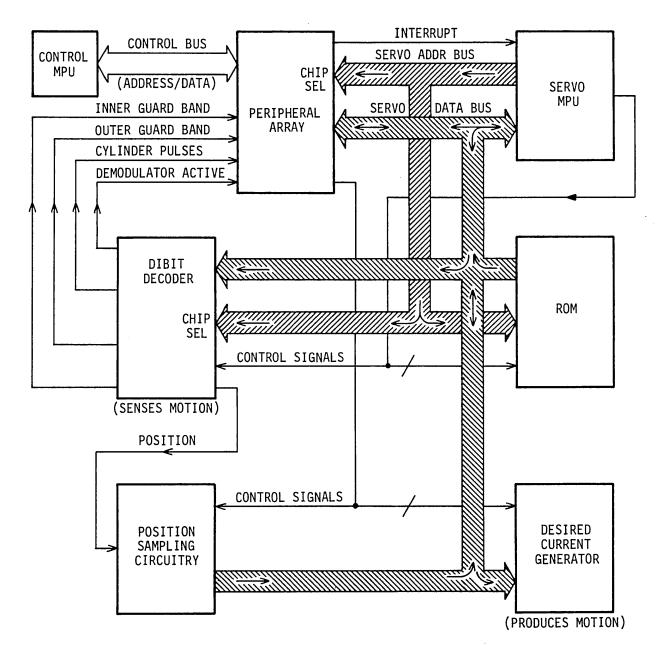

| Servo Circuit Functions     | 5-6   |

| Servo MPU                   | 5-6   |

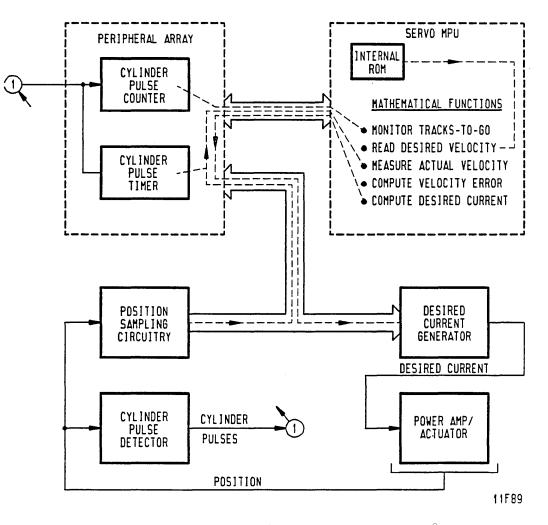

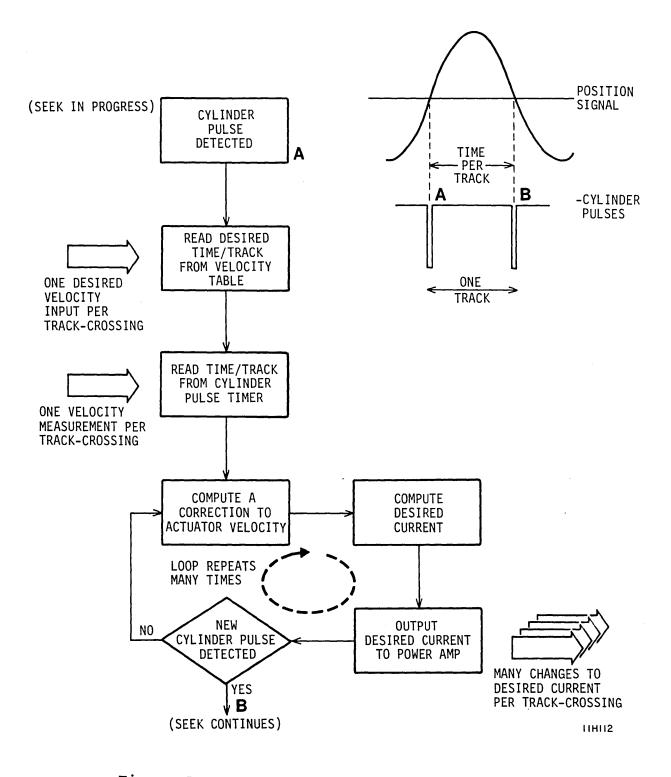

| Coarse Loop Operation       | 5 – 9 |

| High-Speed Control          | 5-10  |

| Low-Speed Control           | 5-12  |

| Fine Loop Operation         | 5-14  |

| Servo Offsets               | 5-16  |

| Desired Current Generator   | 5-17  |

| Position Sampling Circuitry | 5-18  |

| Power Amplifier             | 5-19  |

| Types of Seeks              | 5-21  |

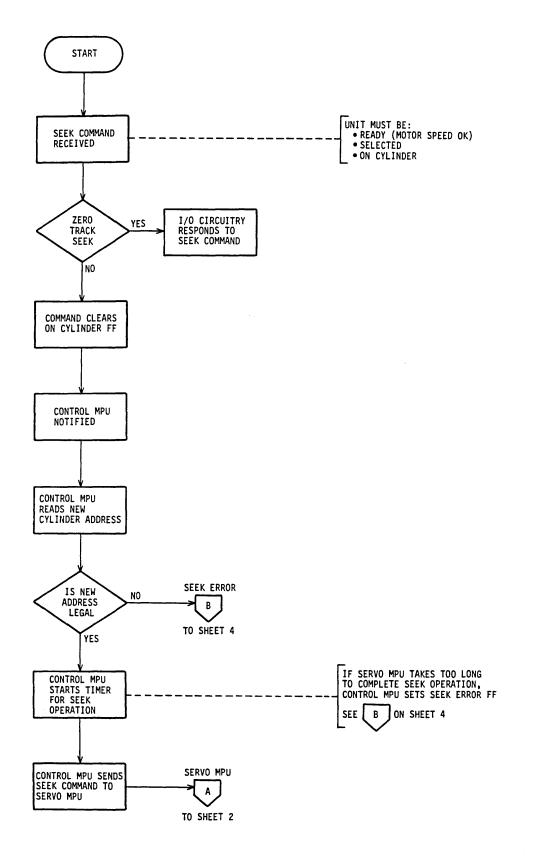

| Load Operation              | 5-21  |

| Normal Seek                 | 5-29  |

| Return to Zero Seek         | 5-36  |

| Track Following                   | 5-42  |

|-----------------------------------|-------|

| Unload Operation                  | 5-42  |

| Sweep Cycle                       | 5-43  |

| 6. READ/WRITE FUNCTIONS           |       |

| Introduction                      | 6-1   |

| Read/Write Overview               | 6-2   |

| Basic Read/Write Principles       | 6-5   |

| How the Heads Read and Write      | 6-5   |

| Principles of 2-7 Recording       | 6-7   |

| 6A. STANDARD READ/WRITE FUNCTIONS |       |

| Introduction                      | 6A-1  |

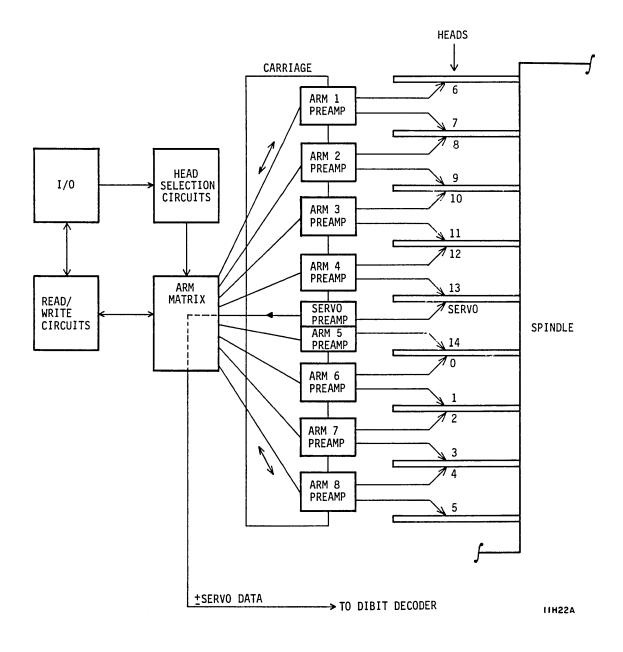

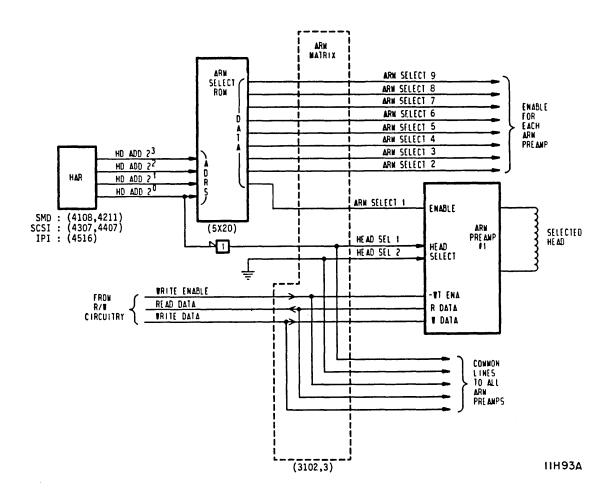

| Head Selection                    | 6A-2  |

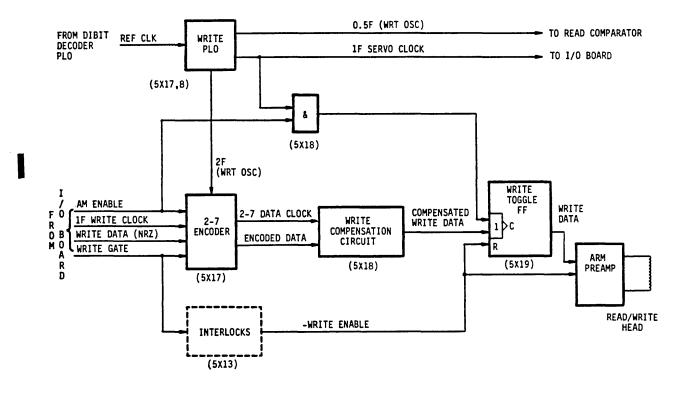

| Write Circuits                    | 6A-6  |

| General                           | 6A-6  |

| Write PLO                         | 6A-7  |

| 2-7 Encoder                       | 6A-9  |

| Write Compensation Circuit        | 6A-10 |

| Write Toggle FF                   | 6A-12 |

| Arm Preamplifier                  | 6A-13 |

| Read Circuits                     | 6A-14 |

| General                           | 6A-14 |

| Arm Preamplifier                  | 6A-15 |

| Data Latch Circuit                | 6A-16 |

| Read Comparator and PLO           | 6A-18 |

| 2-7 Decoder                       | 6A-20 |

| Address Mark Detection            | 6A-22 |

| 6B. PARALLEL READ/WRITE FUNCTIONS |       |

| Introduction                      | 6B-1  |

| Head Selection                    | 6B-2  |

| Write Circuits                    | 6B-5  |

| Read Circuits                     | 6B-6  |

| 7. DETECTING AND ANALYZING ERRORS                 |       |

|---------------------------------------------------|-------|

| Introduction                                      | 7-1   |

| Error Conditions                                  | 7-1   |

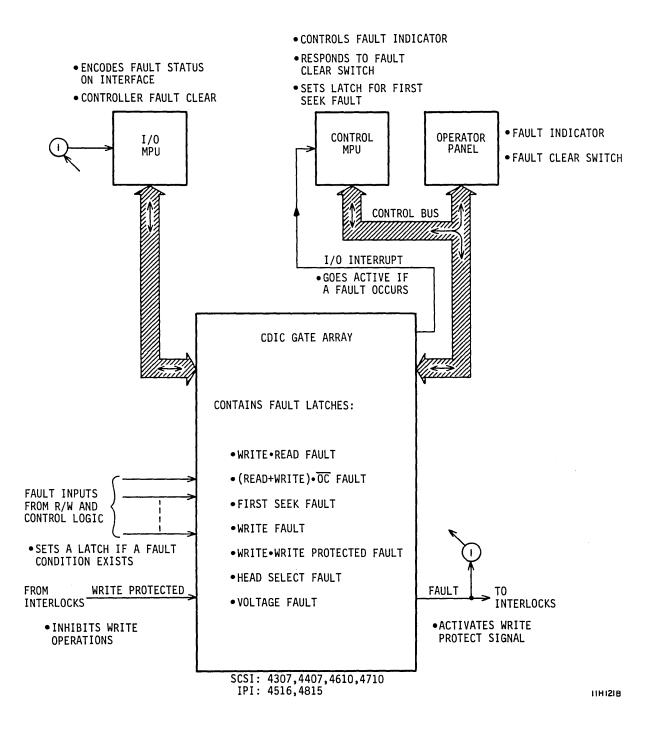

| How Errors are Recorded and Cleared               | 7-1   |

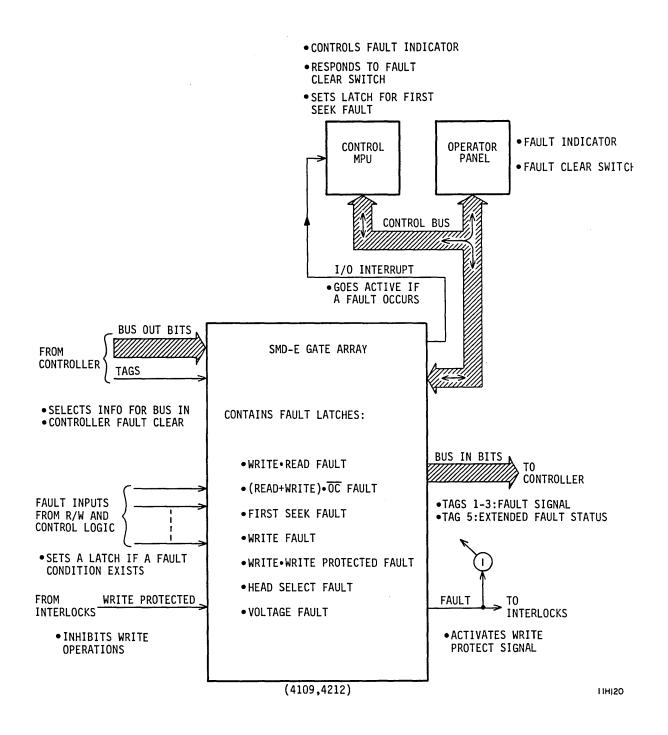

| Error Latch Circuitry                             | 7-1   |

| Communicating Errors                              | 7-4   |

| Errors on the SMD Interface                       | 7-4   |

| Errors on the SCSI Interface                      | 7-5   |

| Errors on the IPI Interface                       | 7-5   |

| How Errors are Detected                           | 7-6   |

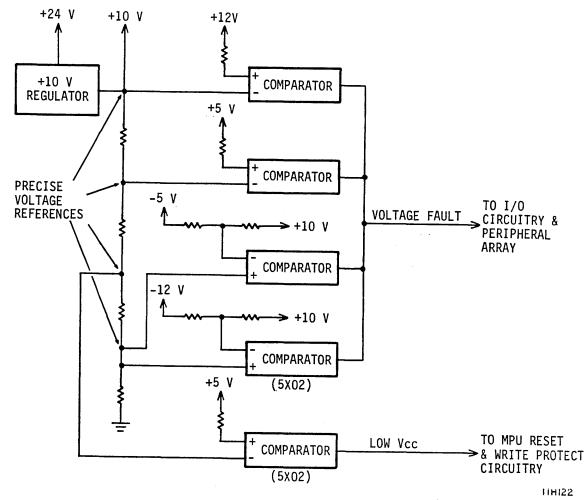

| Voltage Fault                                     | 7-6   |

| Read or Write and Off Cylinder Fault              | 7-7   |

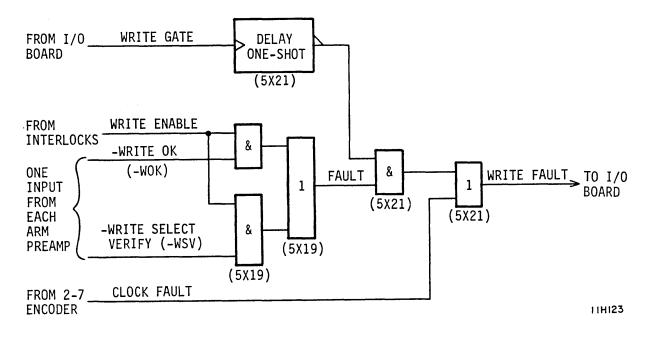

| Write Fault                                       | 7-7   |

| Head Select Fault                                 | 7 - 8 |

| Read and Write Fault                              | 7-8   |

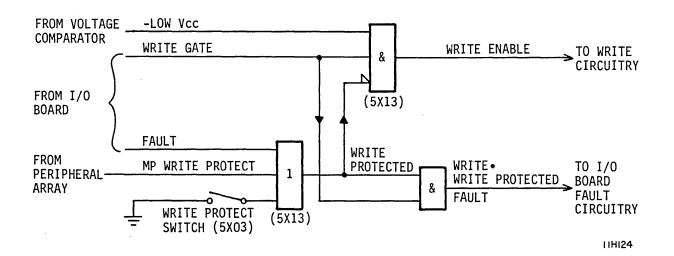

| Write and Write Protected Fault                   | 7-9   |

| First Seek Fault                                  | 7 – 9 |

| Seek Error                                        | 7-10  |

| Operator Panel and Status/Control Panel Functions | 7-11  |

| Diagnostic Functions                              | 7-15  |

| Testing SMD-E Interface Drives                    | 7-15  |

| Testing SCSI Interface Drives                     | 7-16  |

| Testing IPI Interface Drives                      | 7-17  |

## FIGURES

| 1-1 | Drive Functional Block Diagram      | 1-2  |

|-----|-------------------------------------|------|

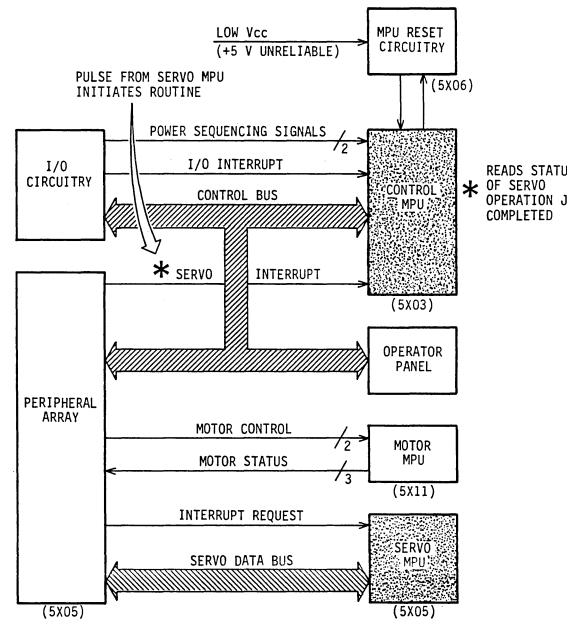

| 2-1 | Control MPU and its Timer Interrupt | 2-3  |

| 2-2 | Control MPU and its I/O Interrupt   | 2-5  |

| 2-3 | Control MPU and its Servo Interrupt | 2-6  |

| 2-4 | Power Distribution and MPU Reset    | 2-8  |

| 2-5 | Power On Sequence Flowchart         | 2-10 |

| 2-6 | SMD Power Sequencing Circuitry      | 2-14 |

| SCSI Power Sequencing Circuitry                | 2-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPI Power Sequencing Circuitry                 | 2-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Standard Motor Speed Control Logic             | 2-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Speed Control Waveforms and Timing             | 2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Synchronized Motor Speed Control Logic         | 2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Head-Arm Assembly                              | 2-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Drive Ventilation                              | 2-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Interface Functions Block Diagram              | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interface Lines                                | 3A-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

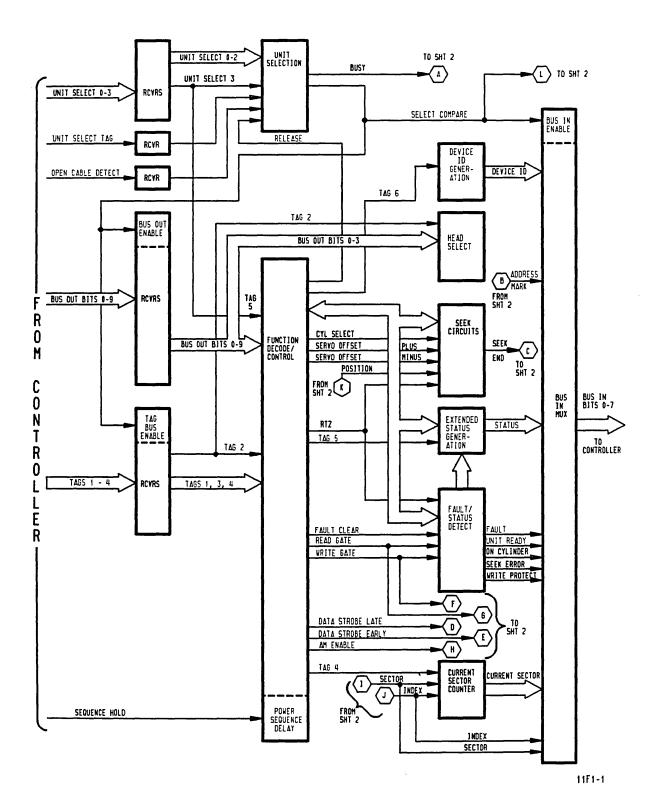

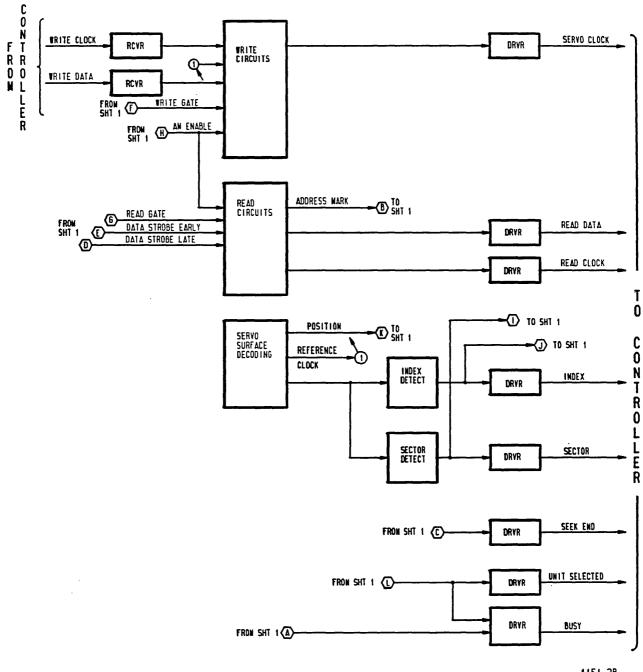

| Drive I/O Signal Processing                    | 3A-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

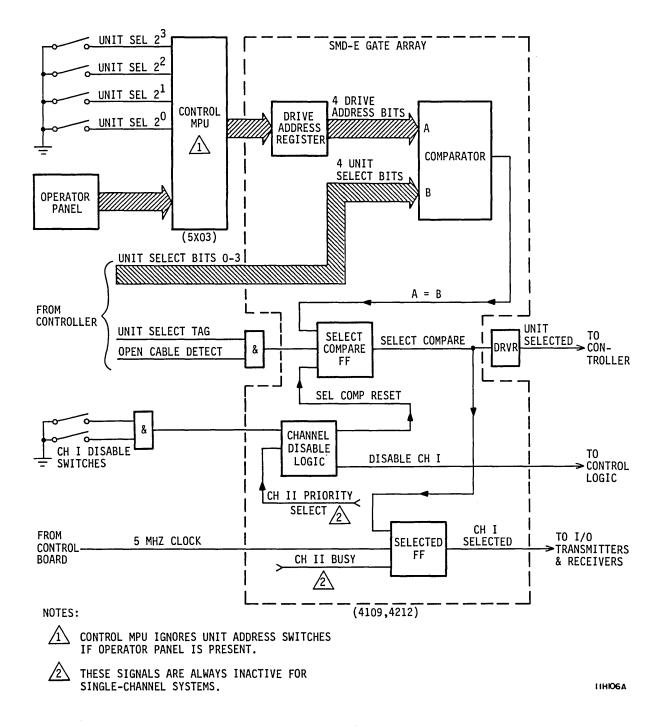

| Unit Select Logic (Single-Channel)             | 3A-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

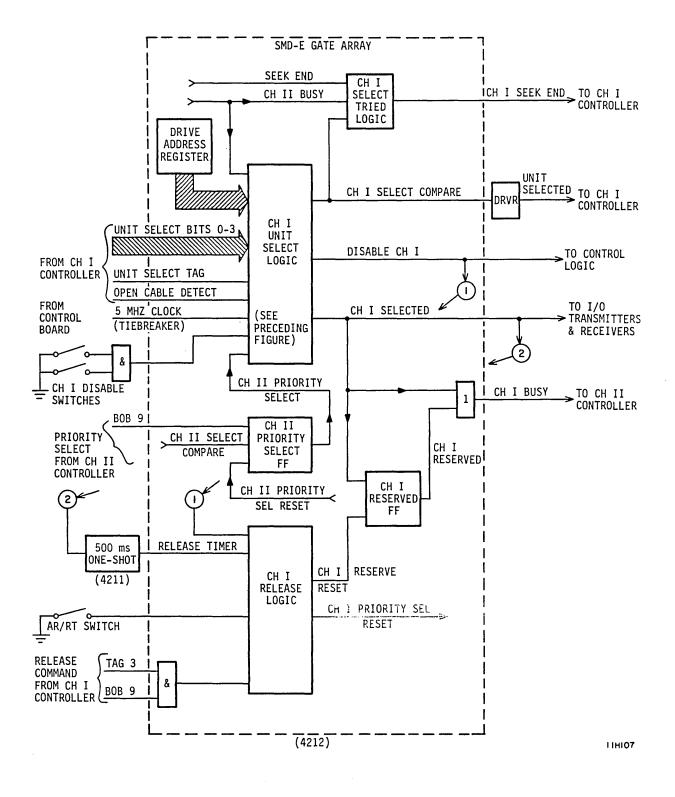

| Channel I Dual-Channel Logic                   | 3A-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

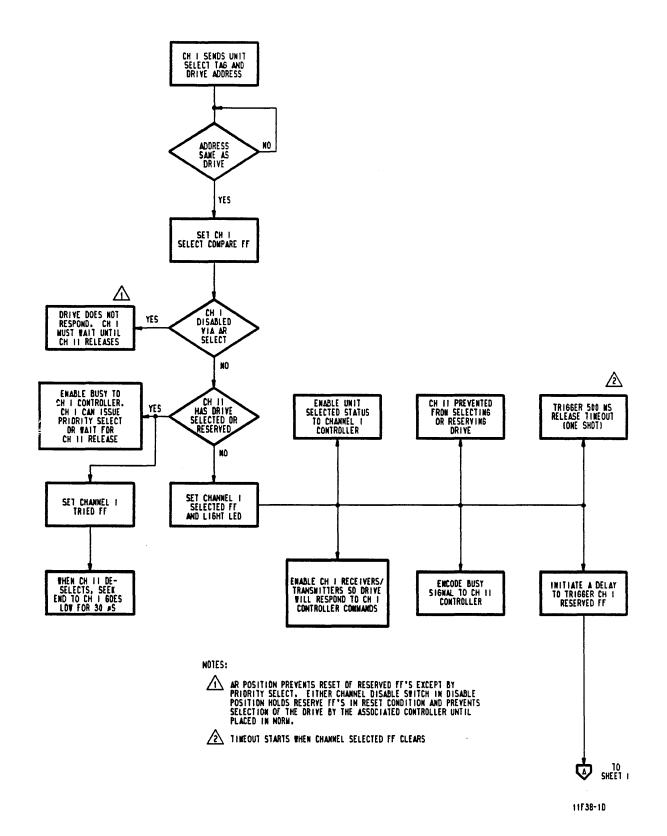

| Dual-Channel Selection Flowchart               | 3A-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

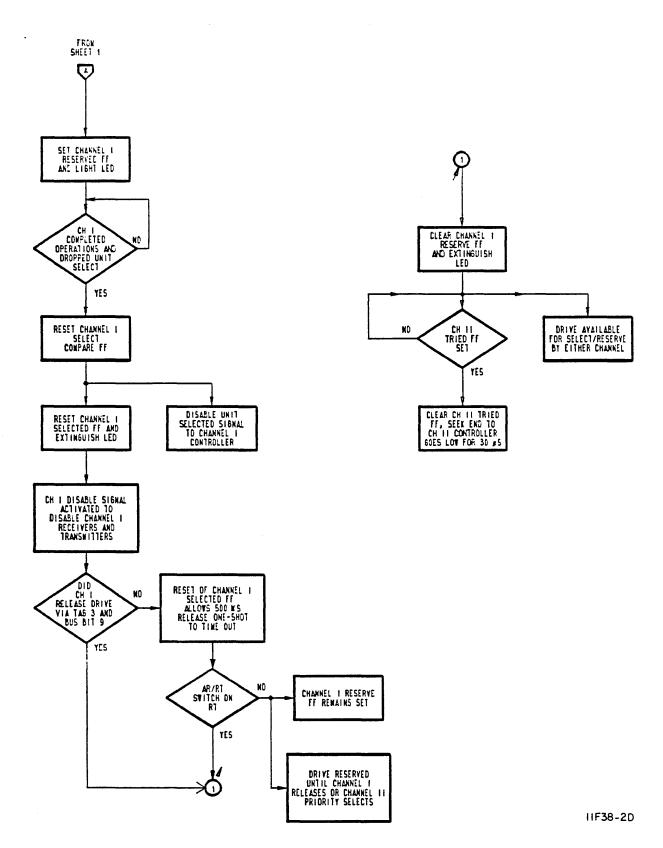

| SCSI Bus Configuration                         | 3B-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

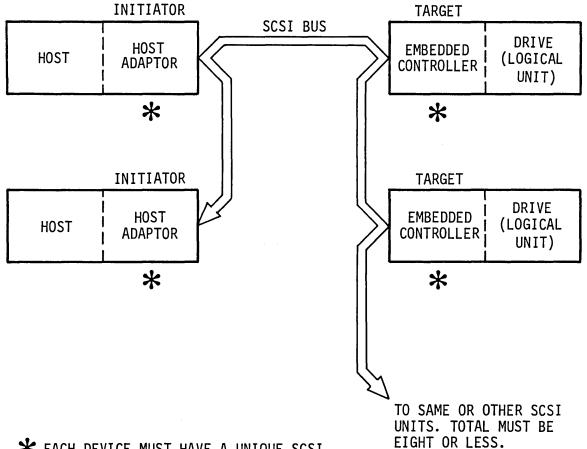

| SCSI Bus Signal Lines                          | 3B-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Standard SCSI Controller Block Diagram         | 3B-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| High-Performance SCSI Controller Block Diagram | 3B-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Sequence of Typical Commands                   | 3B-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Status Codes                                   | 3B-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

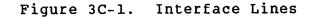

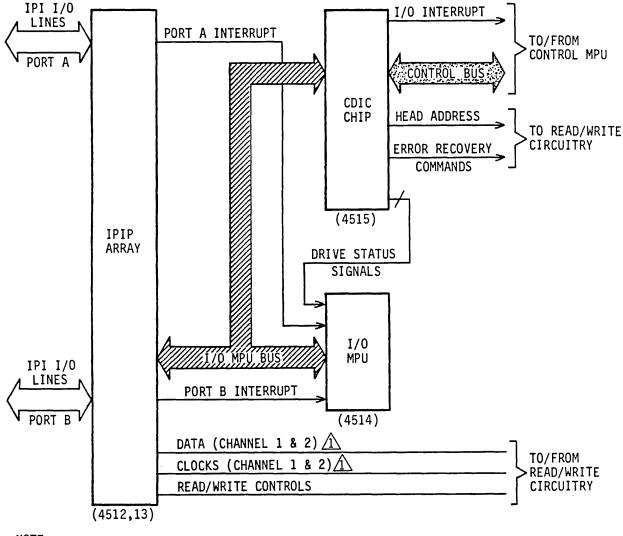

| Interface Lines                                | 3C-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IPI I/O Block Diagram (Standard Read/Write)    | 3C-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IPI I/O Block Diagram (Parallel Read/Write)    | 3C-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bus State Diagram                              | 3C-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Status Response                                | 3C-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Extended Status Response                       | 3C-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

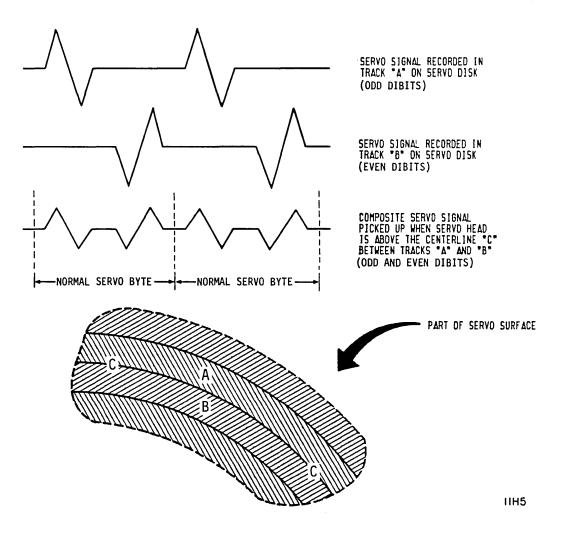

| Dibit Pattern                                  | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

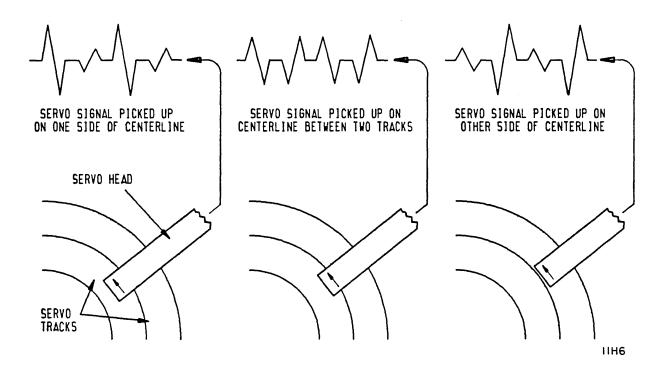

| Dibit Signal Variations                        | 4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Servo Disc Format                              | 4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

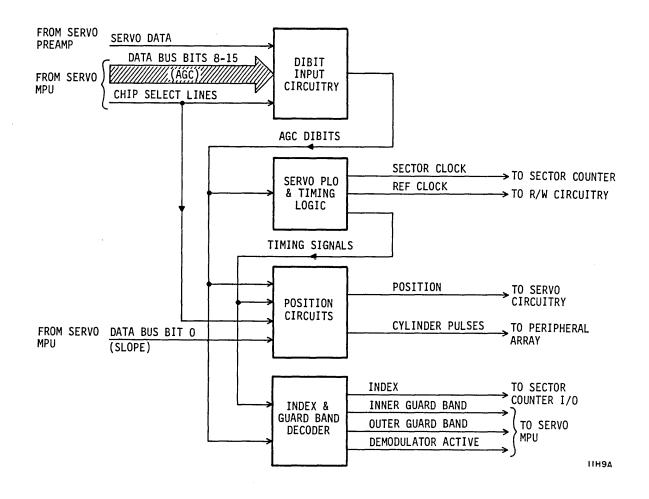

| Dibit Decoder System Diagram                   | 4-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

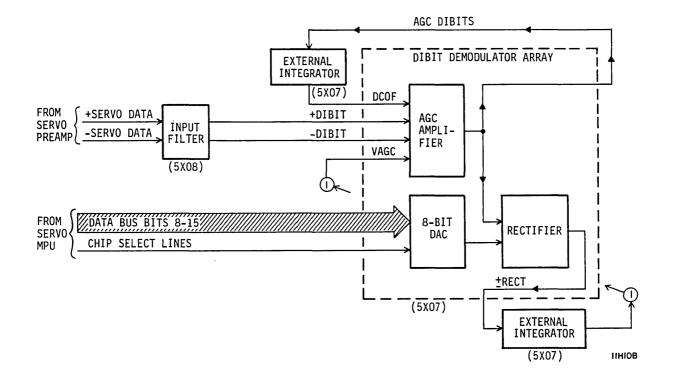

| Dibit Decoder Block Diagram                    | 4-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Dibit Input Circuitry                          | 4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

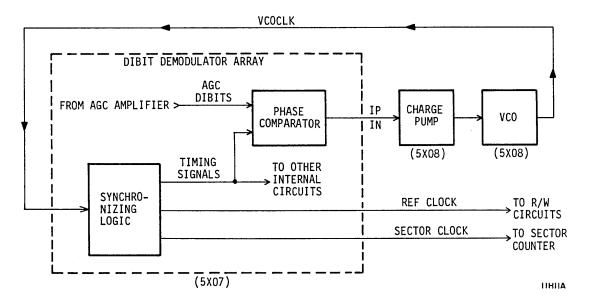

| Servo PLO and Timing Circuitry                 | 4-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

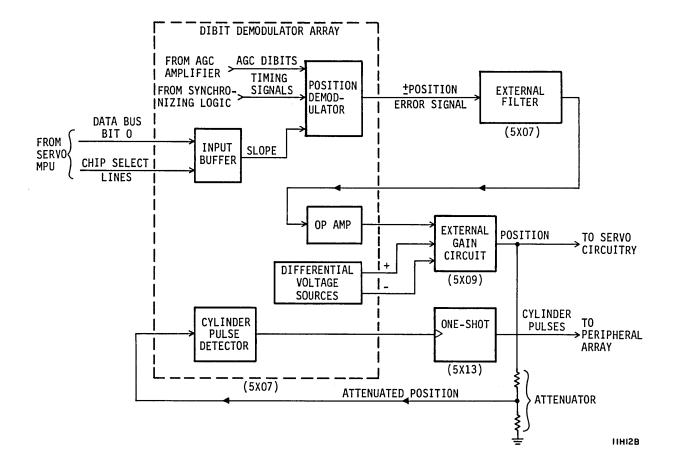

| Position Circuits                              | 4-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

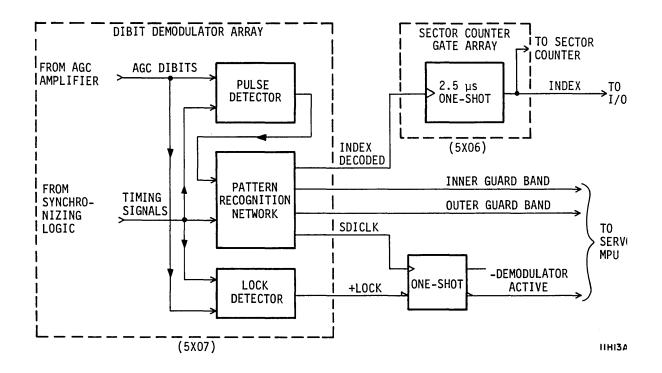

| Index and Guard Band Decoder                   | 4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

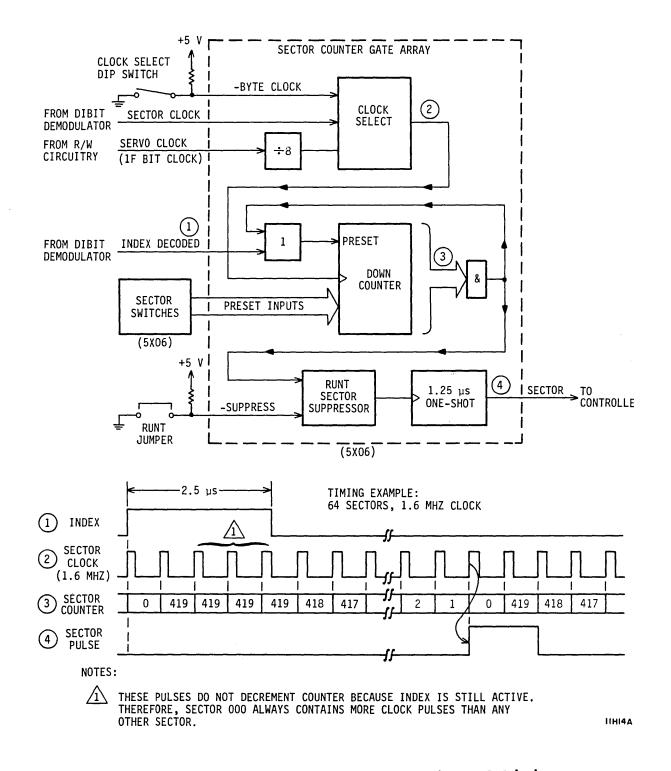

| Sector Detection Logic and Timing              | 4-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                | IPI Power Sequencing Circuitry<br>Standard Motor Speed Control Logic<br>Speed Control Waveforms and Timing<br>Synchronized Motor Speed Control Logic<br>Head-Arm Assembly<br>Drive Ventilation<br>Interface Functions Block Diagram<br>Interface Lines<br>Drive I/O Signal Processing<br>Unit Select Logic (Single-Channel)<br>Channel I Dual-Channel Logic<br>Dual-Channel Selection Flowchart<br>SCSI Bus Configuration<br>SCSI Bus Signal Lines<br>Standard SCSI Controller Block Diagram<br>High-Performance SCSI Controller Block Diagram<br>Sequence of Typical Commands<br>Status Codes<br>Interface Lines<br>IPI I/O Block Diagram (Standard Read/Write)<br>IPI I/O Block Diagram (Parallel Read/Write)<br>Bus State Diagram<br>Status Response<br>Extended Status Response<br>Dibit Pattern<br>Dibit Signal Variations<br>Servo Disc Format<br>Dibit Decoder System Diagram<br>Dibit Decoder Block Diagram<br>Dibit Input Circuitry<br>Servo PLO and Timing Circuitry<br>Position Circuits<br>Index and Guard Band Decoder |

...

\$

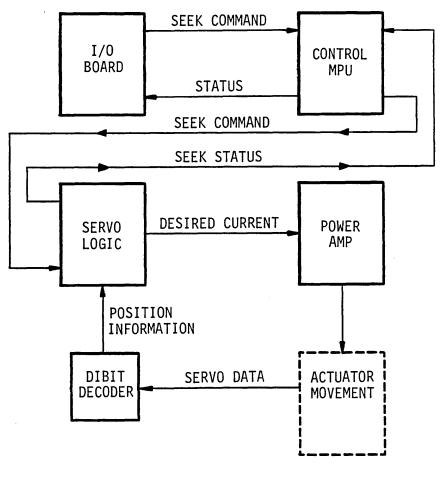

| 5-1   | Seek Functions Block Diagram           | 5-2   |

|-------|----------------------------------------|-------|

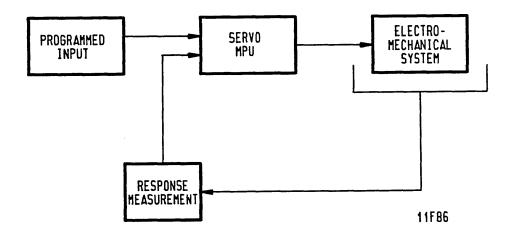

| 5-2   | Generalized Servo Loop                 | 5 - 3 |

| 5-3   | Actuator and Magnet Assembly           | 5-5   |

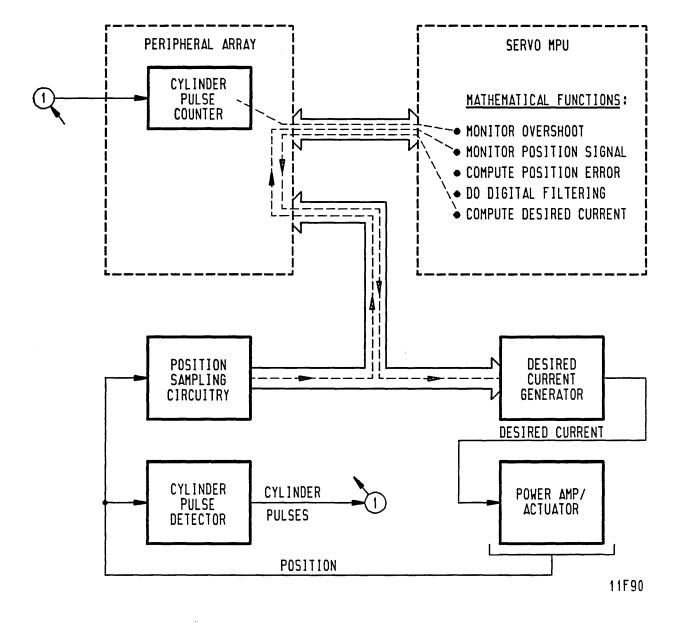

| 5-4   | Servo MPU and Associated Circuitry     | 5-7   |

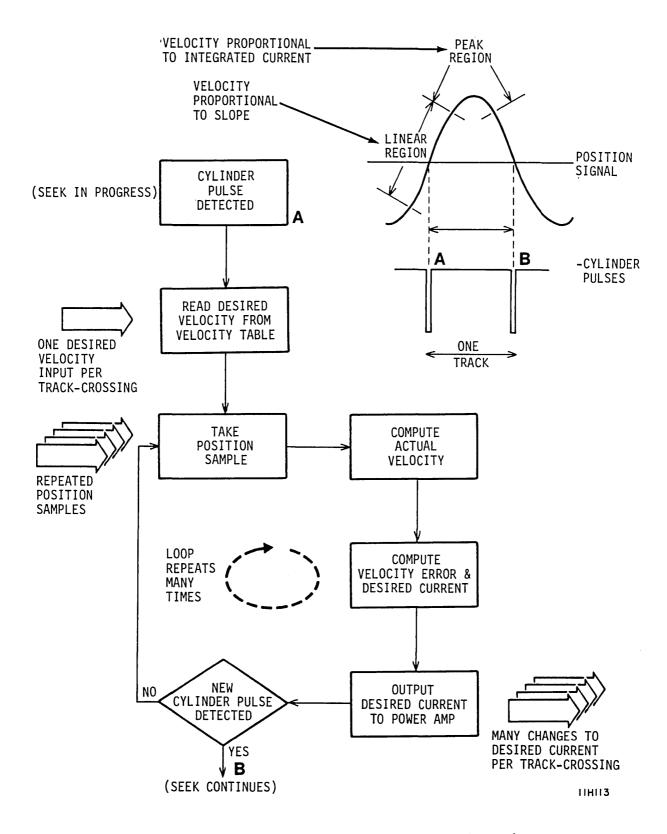

| 5-5   | Simplified Coarse Servo Loop           | 5–9   |

| 5-6   | One Track of a High-Speed Seek         | 5-11  |

| 5-7   | One Track of a Low-Speed Seek          | 5-13  |

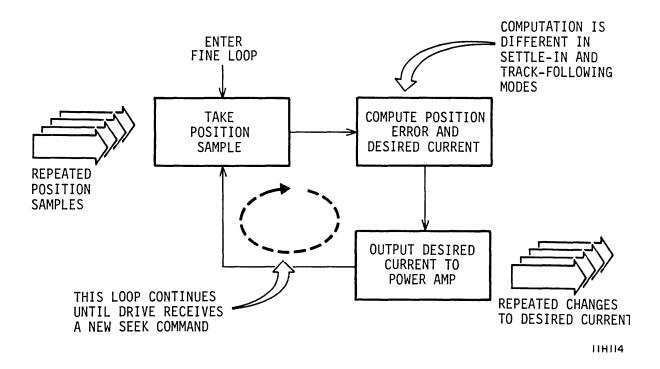

| 5-8   | Simplified Fine Servo Loop             | 5-15  |

| 5-9   | Staying on Track with Position Control | 5-16  |

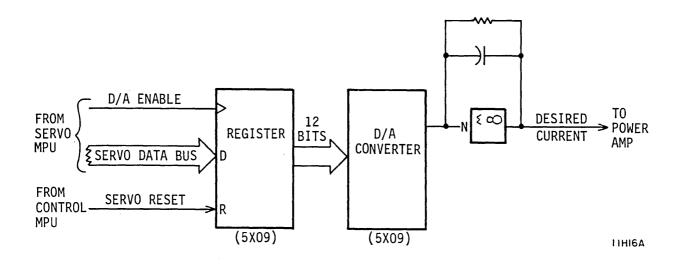

| 5-10  | Desired Current Generator              | 5-17  |

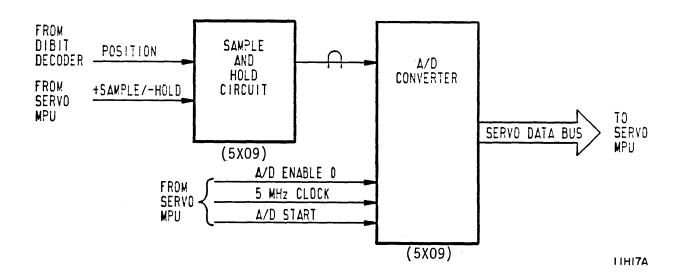

| 5-11  | Position Sampling Circuitry            | 5-18  |

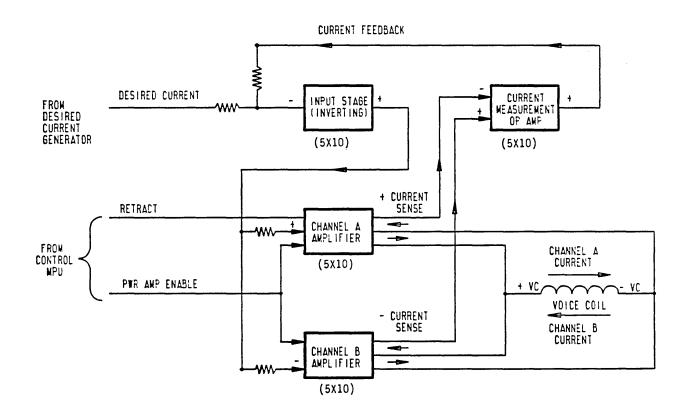

| 5-12  | Power Amplifier Circuitry              | 5-19  |

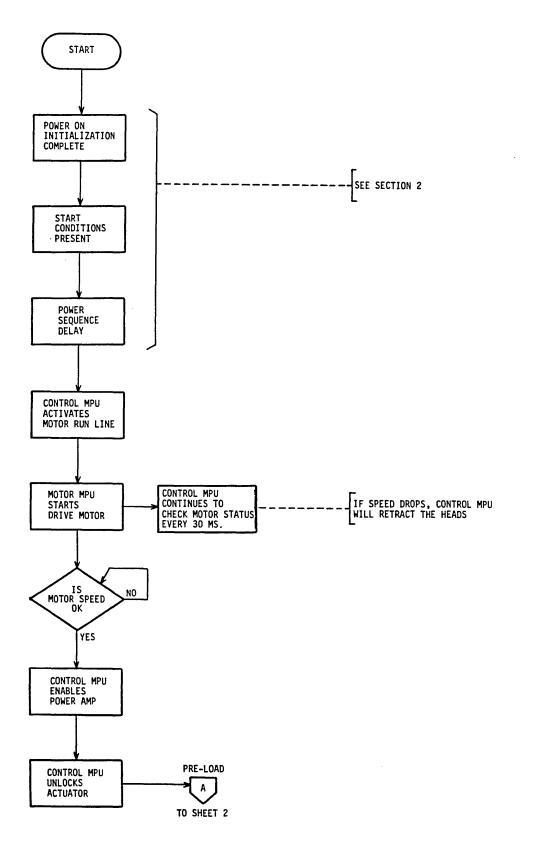

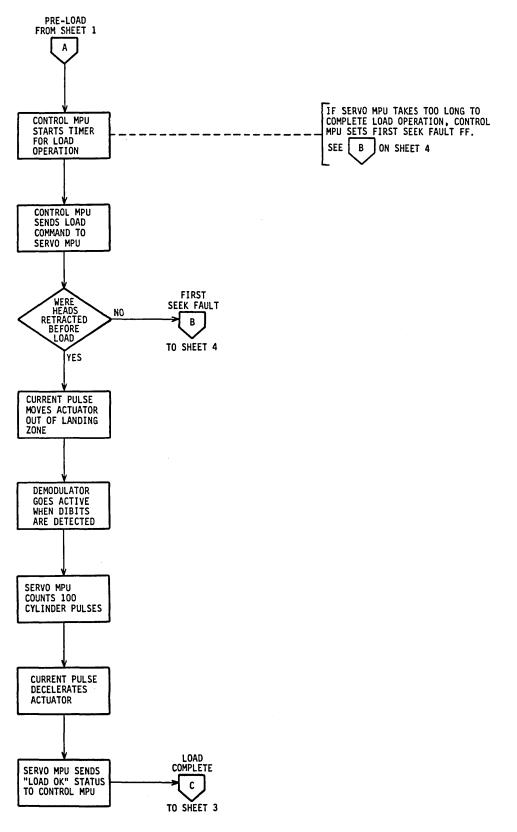

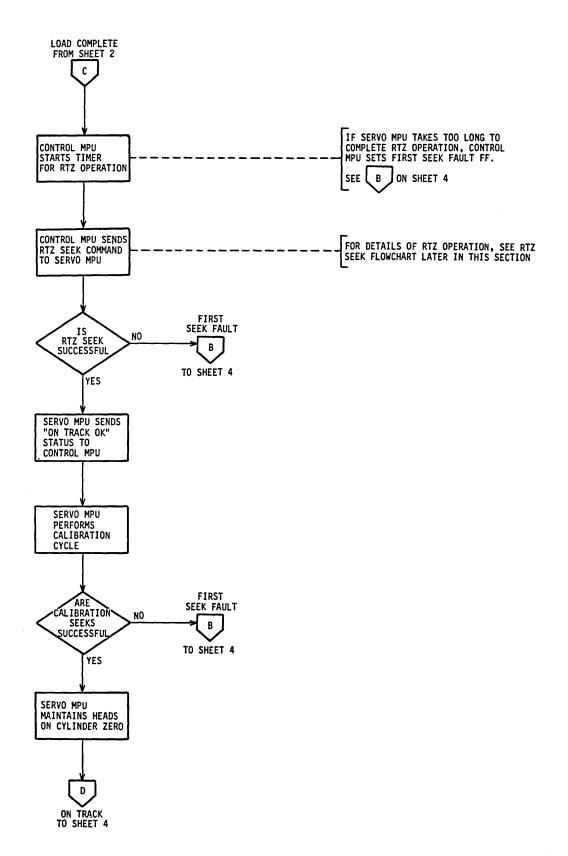

| 5-13  | Load Operation Flowchart               | 5-22  |

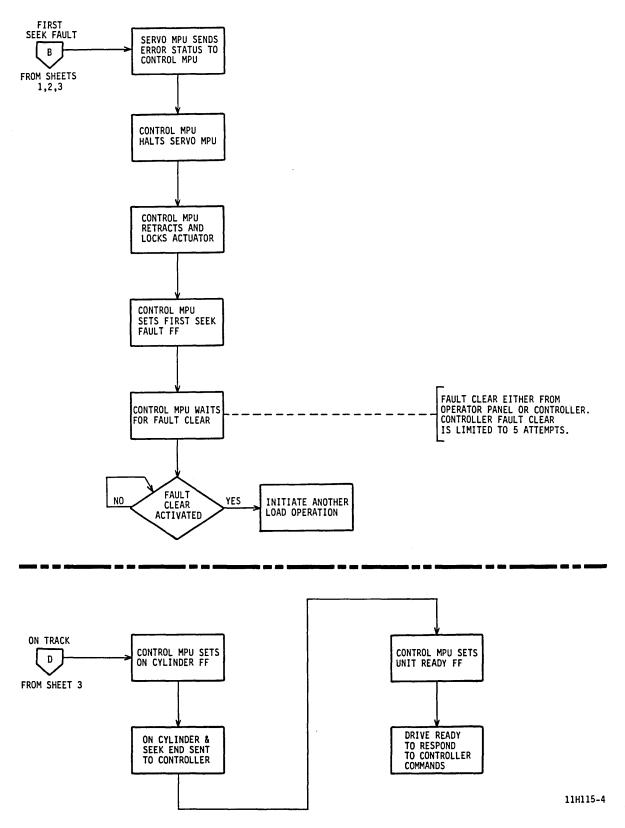

| 5-14  | Load Seek Trajectory                   | 5-27  |

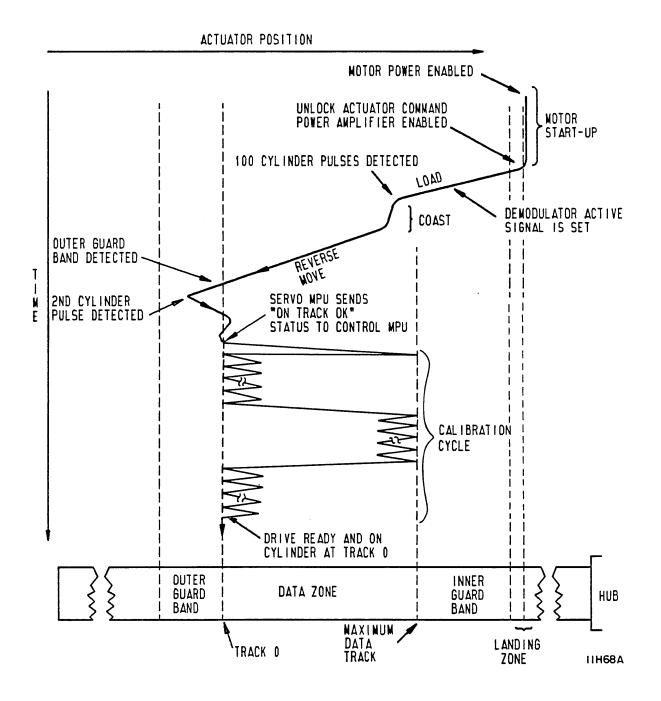

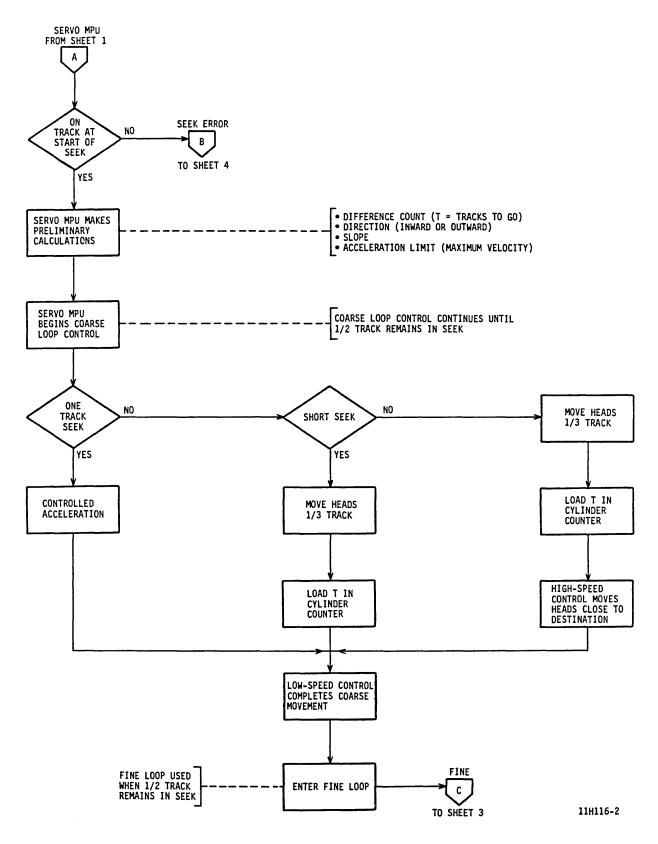

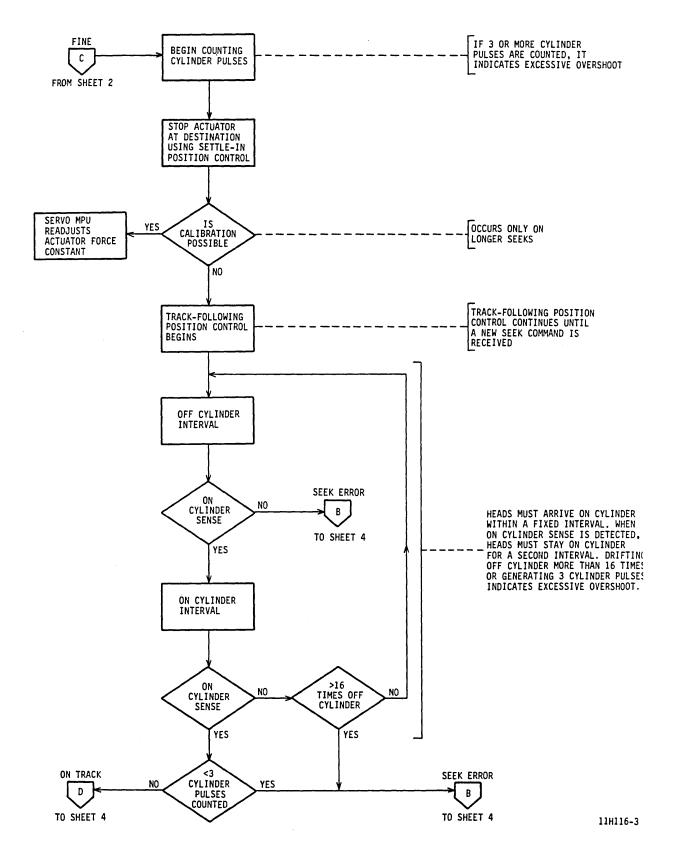

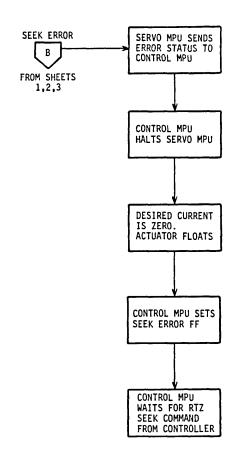

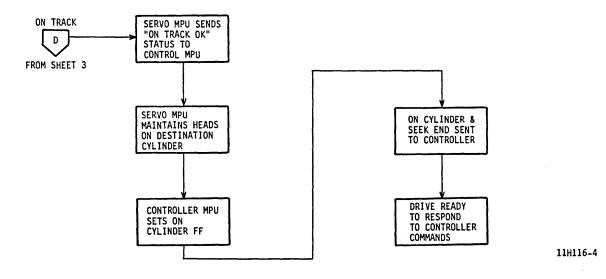

| 5-15  | Normal Seek Flowchart                  | 5-30  |

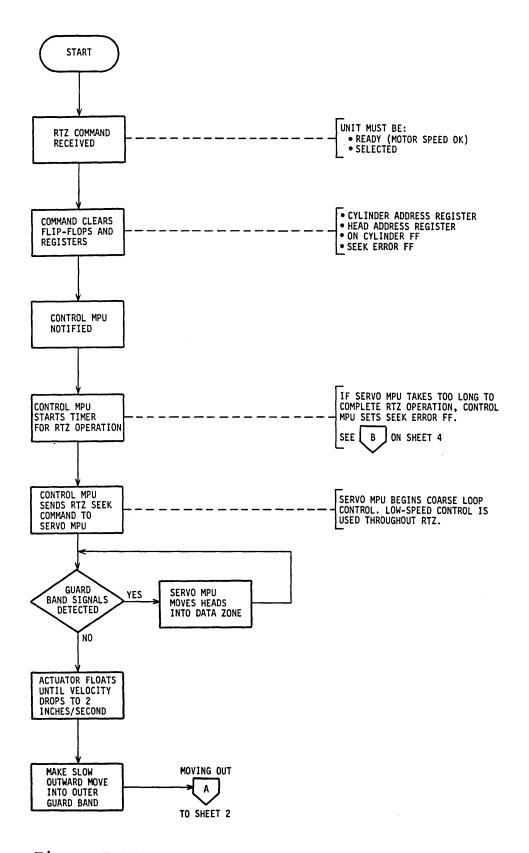

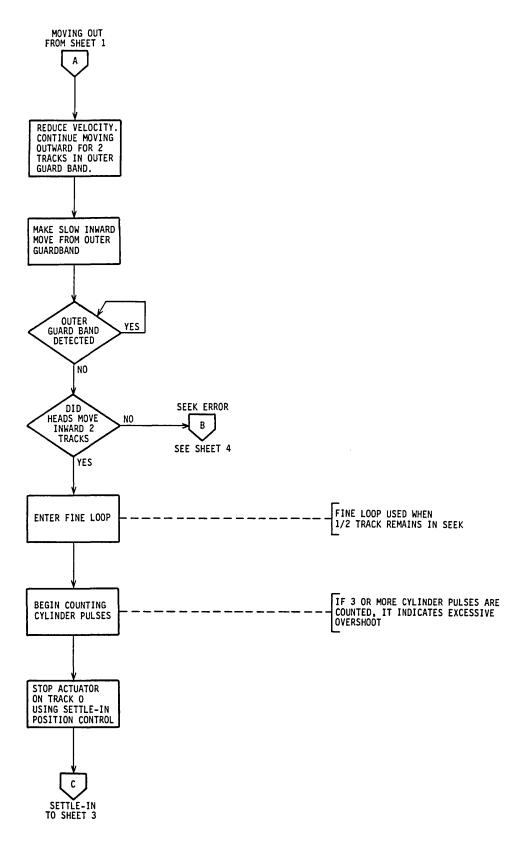

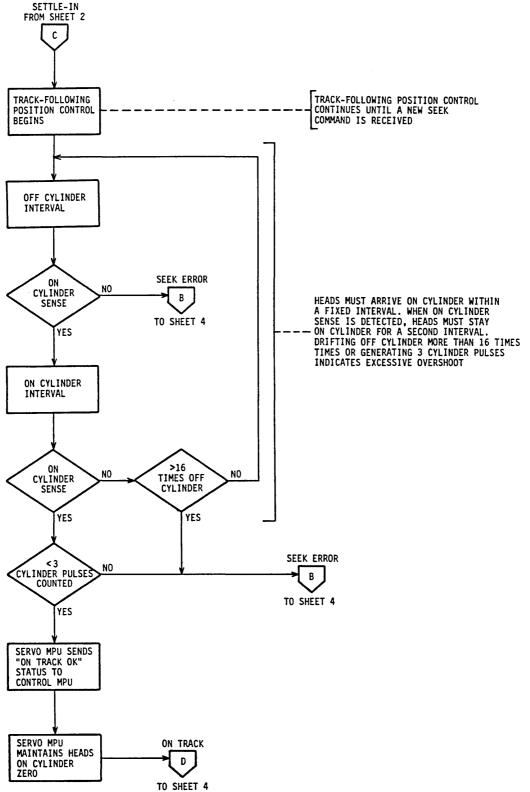

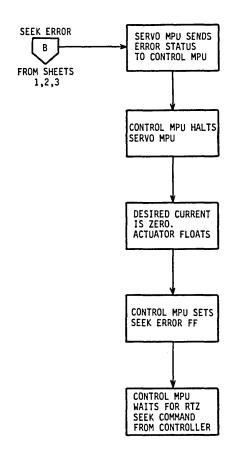

| 5-16  | Return to Zero (RTZ) Seek              | 5-38  |

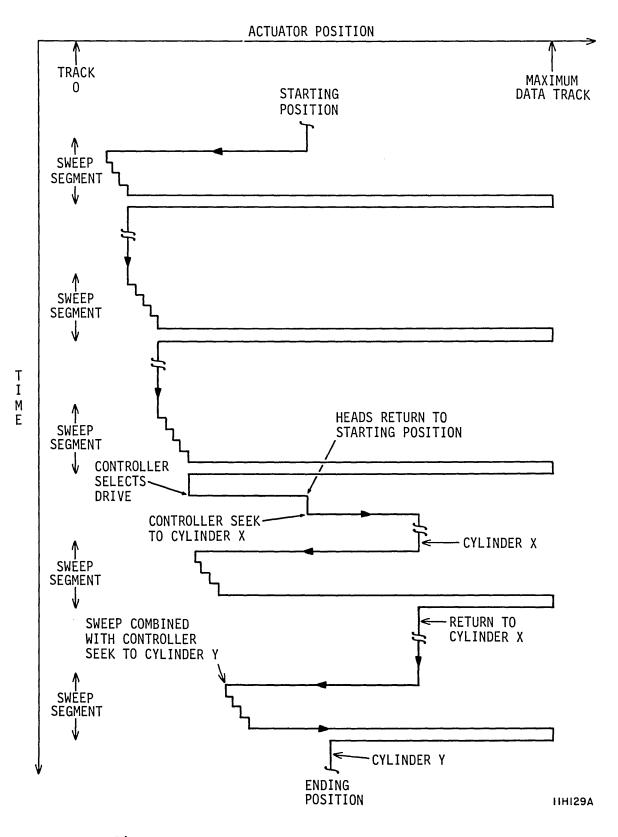

| 5-17  | Typical Sweep Cycle Activity           | 5-45  |

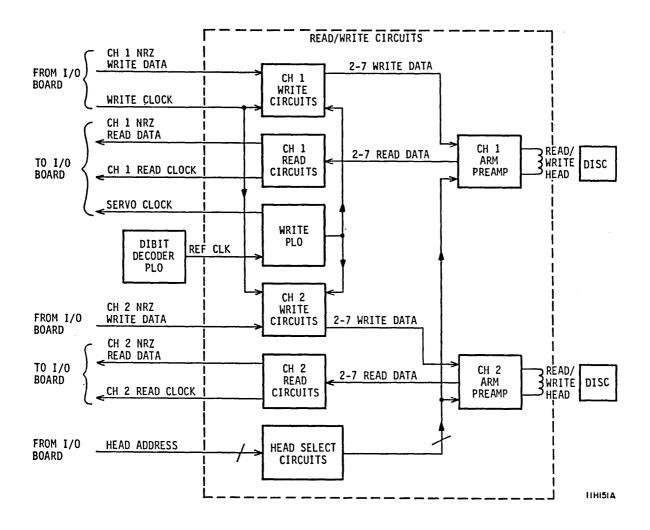

| 6-1   | Standard Read/Write Circuits           | 6-2   |

| 6-2   | Parallel Read/Write Circuits           | 6-3   |

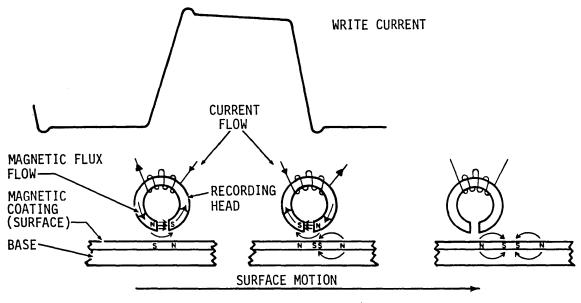

| 6-3   | Writing Data                           | 6-5   |

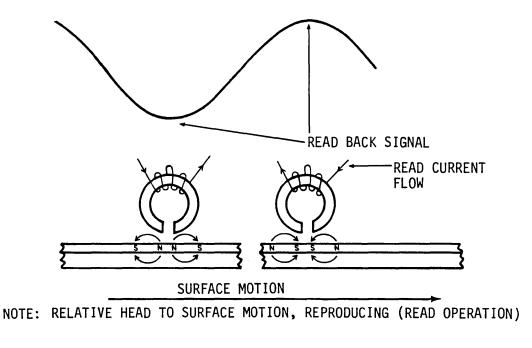

| 6-4   | Reading Data                           | 6-6   |

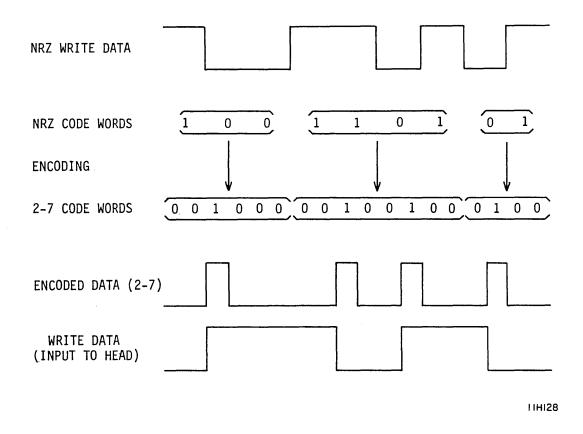

| 6-5   | Converting from NRZ to 2-7 Data        | 6-8   |

| 6A-1  | Read/Write Heads                       | 6A-3  |

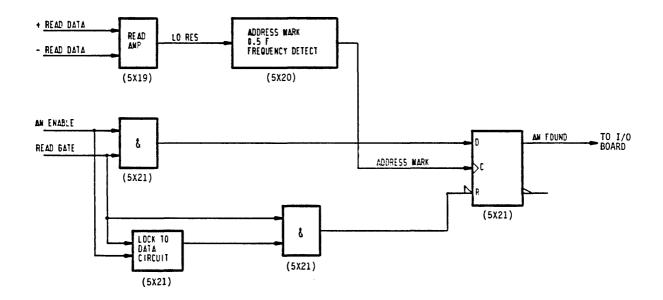

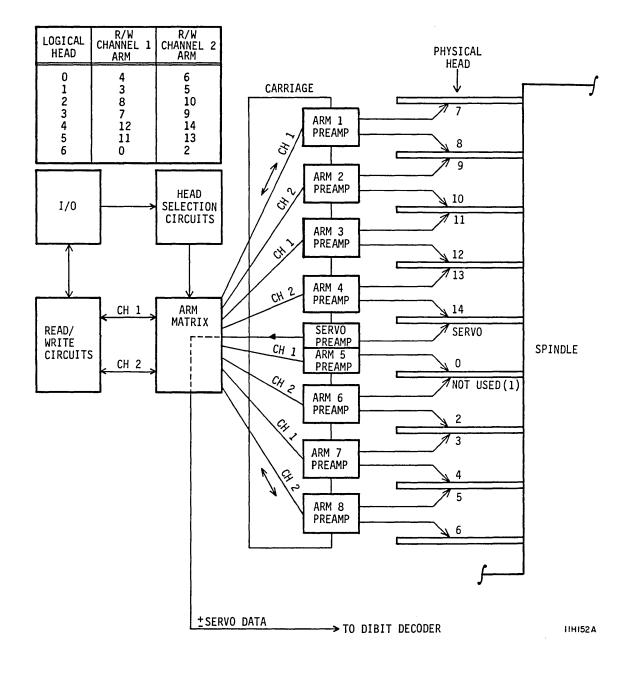

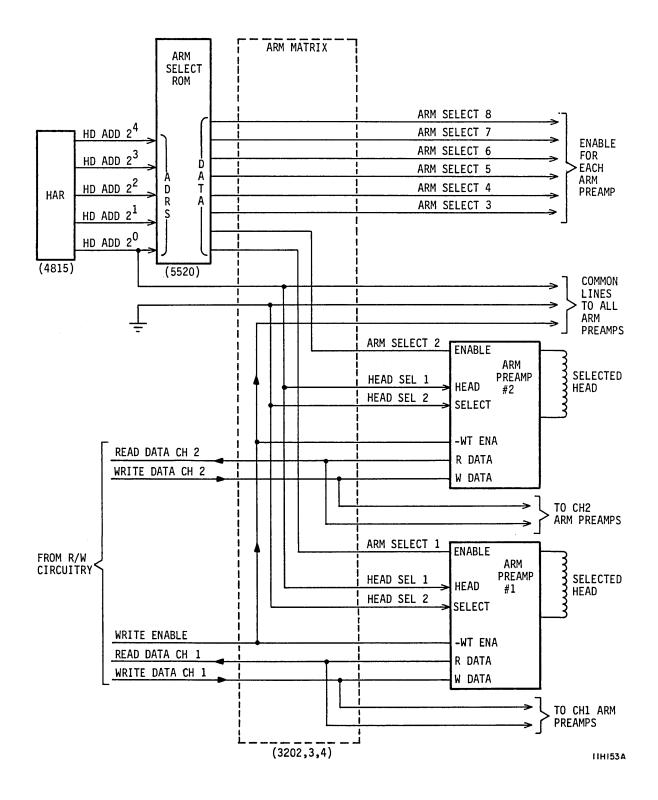

| 6A-2  | Head Selection Circuits                | 6A-4  |

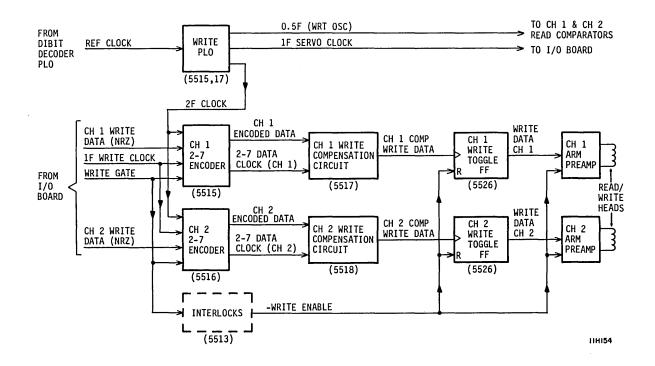

| 6A-3  | Write Circuits Block Diagram           | 6A-6  |

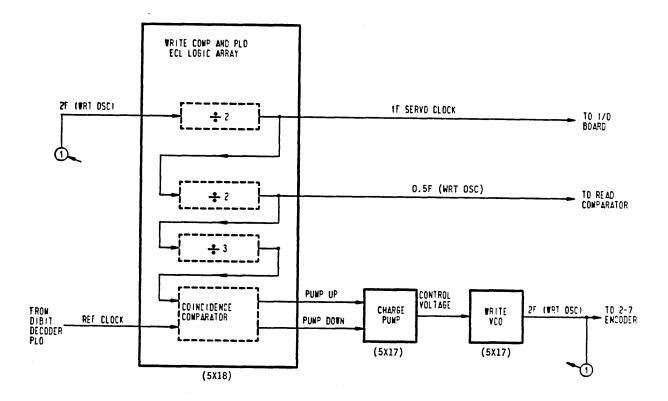

| 6A-4  | Write PLO Block Diagram                | 6A-8  |

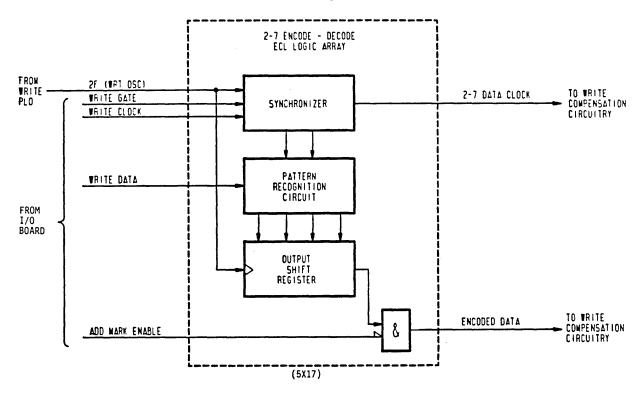

| 6A-5  | 2-7 Encoder Block Diagram              | 6A-9  |

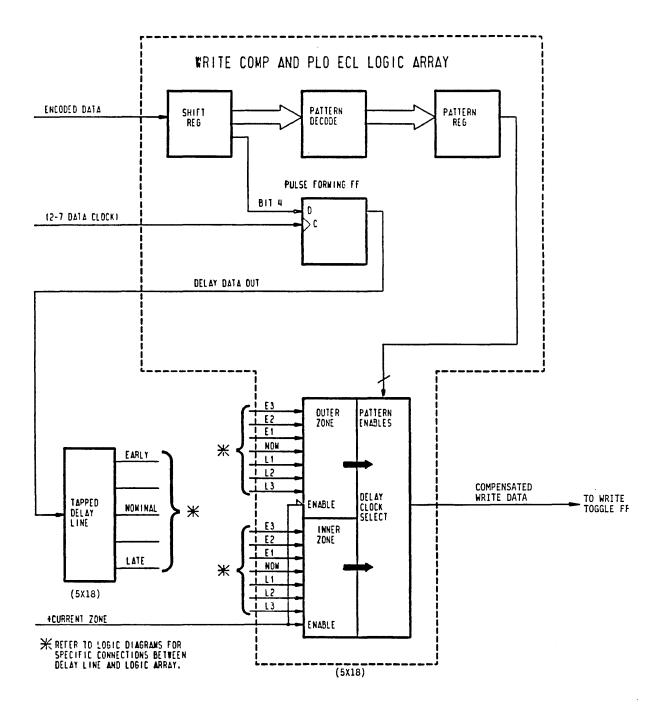

| 6A-6  | Write Compensation Block Diagram       | 6A-11 |

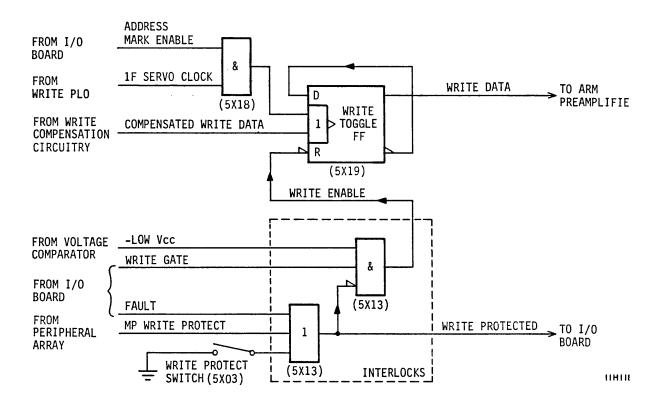

| 6A-7  | Write Toggle FF and Interlocks         | 6A-12 |

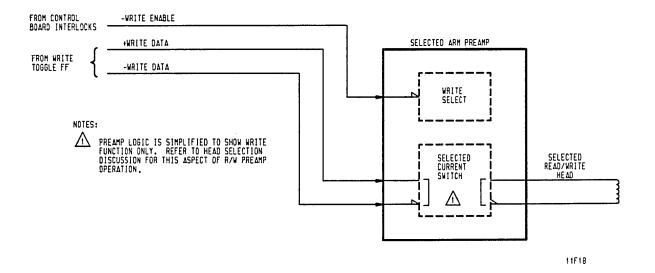

| 6A-8  | Arm Preamplifier in Write Operations   | 6A-13 |

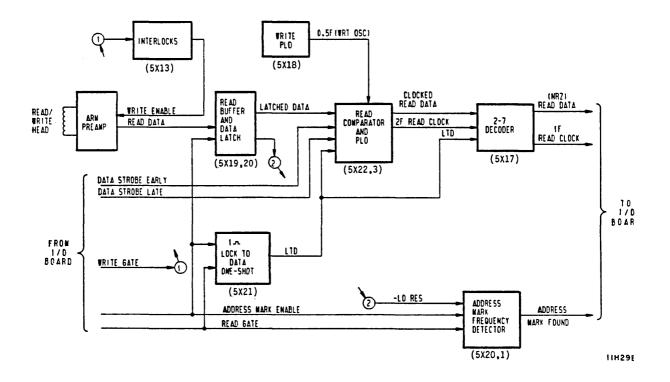

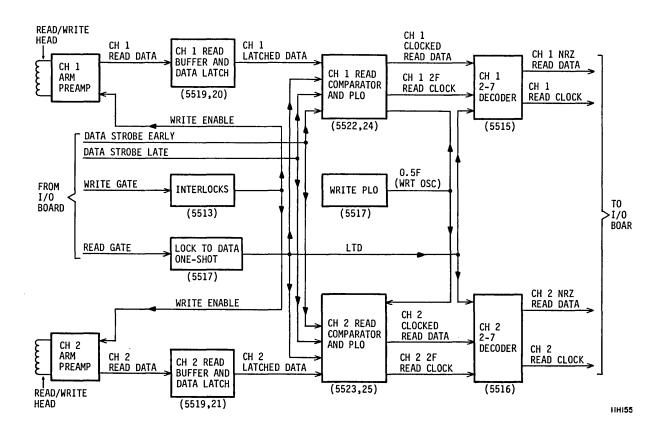

| 6A-9  | Read Circuits Block Diagram            | 6A-14 |

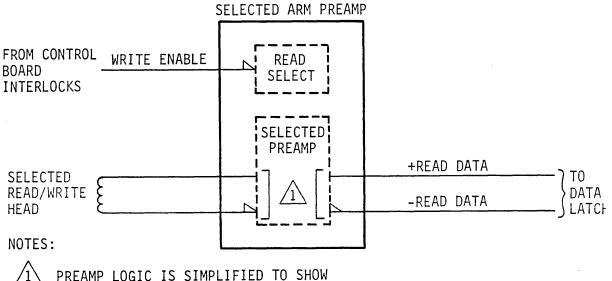

| 6A-10 | Arm Preamplifier in Read Operations    | 6A-16 |

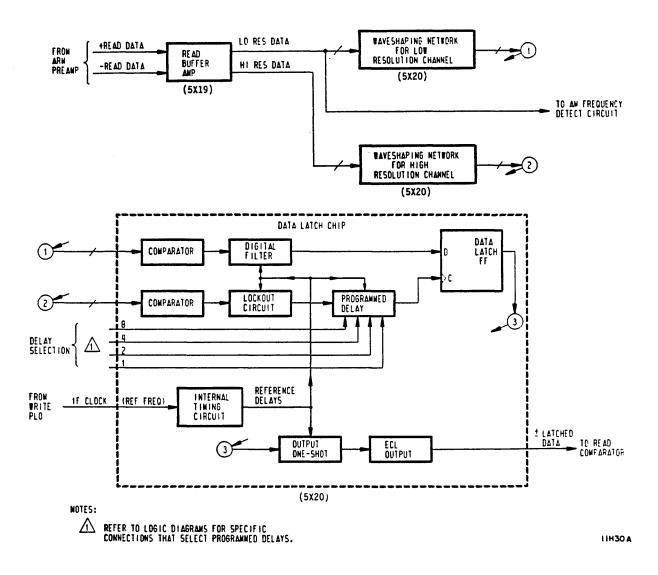

| 6A-11 | Data Latch Block Diagram               | 6A-17 |

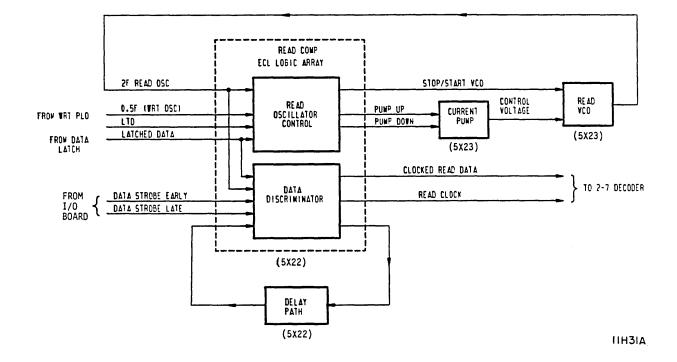

| 6A-12 | Read Comparator and PLO Block Diagram  | 6A-19 |

| 6A-13 | 2-7 Decoder Block Diagram              | 6A-21 |

|       |                                        |       |

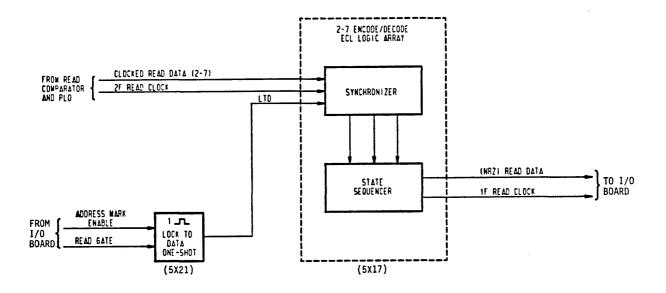

| 6A-14 | Address Mark Detector Block Diagram        | 6A-22 |

|-------|--------------------------------------------|-------|

| 6B-1  | Read/Write Heads (Parallel)                | 6B-3  |

| 6B-2  | Head Selection Circuits (Parallel)         | 6B-4  |

| 6B-3  | Write Circuits Block Diagram (Parallel)    | 6B-5  |

| 6B-4  | Read Circuits Block Diagram (Parallel)     | 6B-6  |

| 7-1   | SMD Error Circuitry                        | 7-2   |

| 7-2   | SCSI and IPI Error Circuitry               | 7-3   |

| 7-3   | Detecting Voltage Faults                   | 7-6   |

| 7-4   | Detecting Write Faults                     | 7-8   |

| 7-5   | Detecting Write and Write Protected Faults | 7-9   |

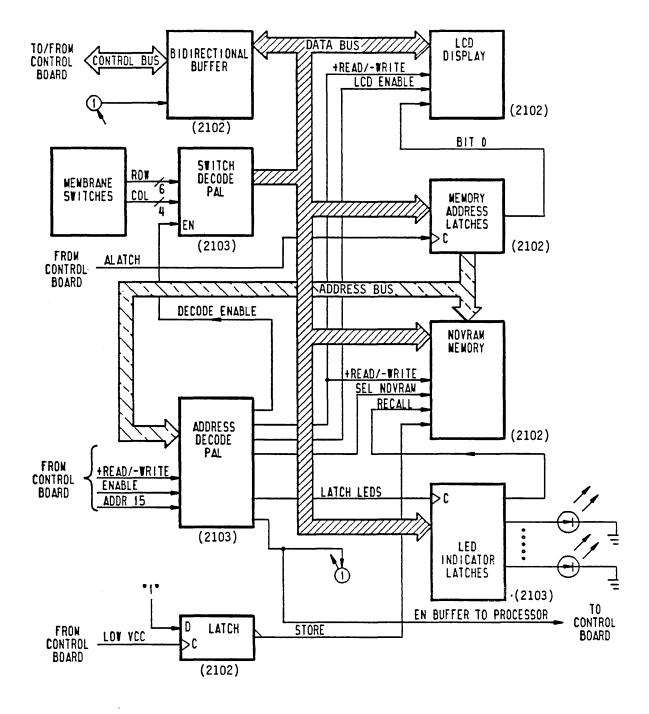

| 7-6   | Status/Control Panel Block Diagram         | 7-12  |

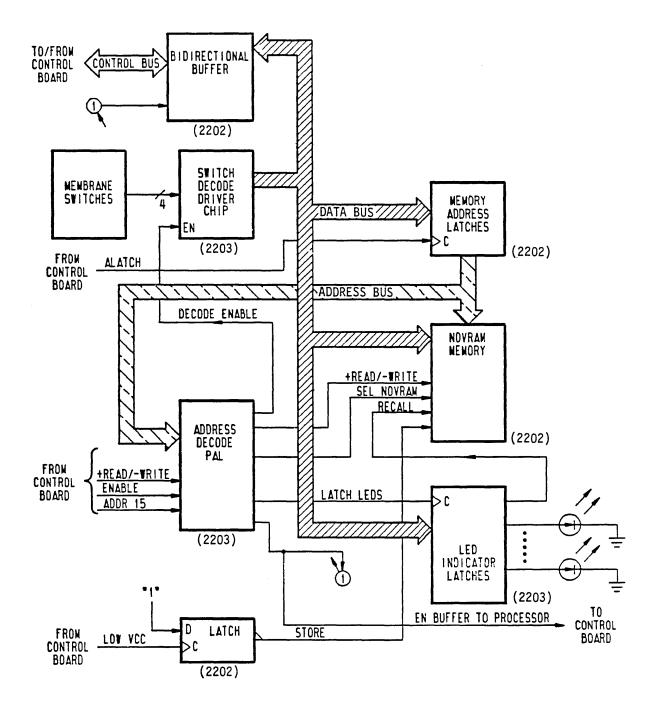

| 7-7   | Operator Panel Block Diagram               | 7-13  |

## TABLES

| 3 <b>A</b> -1 | Controller to Drive Interface Lines        | 3A-3  |

|---------------|--------------------------------------------|-------|

| 3A-2          | Drive to Controller Interface Lines        | 3A-5  |

| 3A-3          | Summary of Tag/Bus Decoding                | 3A-10 |

| 3A-4          | Tag/Bus Command Decode Functions           | 3A-12 |

| 3A-5          | Dual-Channel Unit Select Circuit Functions | 3A-26 |

| 3B-1          | SCSI Bus Signal Lines                      | 3B-4  |

| 3B-2          | SCSI Bus Phase Descriptions                | 3B-10 |

| 3B-3          | Command Set                                | 3B-12 |

| 3B-4          | Information Transfer Phases                | 3B-15 |

| 3B-5          | Message Code Descriptions                  | 3B-16 |

| 3C-1          | Interface Lines                            | 3C-3  |

| 3C-2          | Interface State Functions                  | 3C-10 |

| 3C-3          | Sequences                                  | 3C-14 |

| 3C-4          | Command Summary                            | 3C-16 |

| 3C-5          | Response Summary                           | 3C-18 |

| 3C-6          | Data Control Summary                       | 3C-19 |

| 4-1           | Clock Frequencies for the Servo PLO        | 4-11  |

| 4-2           | Sector Counter Data                        | 4-17  |

| 6-1  | Symbols for Read/Write Frequencies    | 6-4   |

|------|---------------------------------------|-------|

| 6-2  | Translation Between NRZ and 2-7 Codes | 6-8   |

| 6A-1 | Head Select Addressing                | 6A-5  |

| 6A-2 | Write Circuit Functions               | 6A-7  |

| 6A-3 | Read Circuit Functions                | 6A-15 |

### PREFACE

This manual describes the theory of operation of the Seagate Sabre disc drives listed later in this preface. It is prepared for customer engineers and other technical personnel directly involved with maintaining the drive.

The information in this manual is presented as follows:

| Section 1 | – Overview of the Drive          |  |

|-----------|----------------------------------|--|

| Section 2 | - Power and Control Functions    |  |

| Section 3 | - Interface Functions            |  |

| Section 4 | - Servo Surface Decoding         |  |

| Section 5 | - Seek Functions                 |  |

| Section 6 | - Read/Write Functions           |  |

| Section 7 | - Detecting and Analyzing Errors |  |

Section 1 provides a guide to the overall organization of the manual with brief descriptions of each section.

New features, technical changes, additions, and deletions in this manual are indicated as follows:

- A vertical bar in the outer margin of a page marks the changed area.

- A dot by the page number indicates the entire page contains new or changed information.

- A vertical bar by the page number indicates the information was moved from another page, but there were no technical or editorial changes.

The following manuals apply to the SABRE and are available from:

Seagate Technology, Inc. Customer Services 12701 Whitewater Drive Minnetonka, MN 55343 Phone: (612) 931-8612 pisconnected Fax: (612) 931-8817 Publication No. <u>Title</u>

- 83325660 Pocket Reference (summarizes status codes and diagnostic operation for drives with the SMD and IPI interfaces)

- 83325690 Theory Manual

- 83325700 Parts Data Manual (contains listings of field replaceable parts, manufacturer's recommended spare parts, and accessories)

- 83325710 SMD Interface User's Manual (contains general description, operation, installation and checkout information)

- 83325720 Maintenance Manual

- 83325730 Diagrams Manual

- 83325810 Pocket Reference (summarizes status codes and diagnostic operation for drives with the SCSI interface)

- 83325860 SCSI Interface User's Manual (contains general description, operation, installation and checkout information)

- 83326010 IPI Interface User's Manual (contains general description, operation, installation and checkout information)

- 83327150 Special Supplement (applies to PA8K2D)

- 83327160 Special Supplement (applies to half-rack mounting kit)

For more information about the interfaces described in this manual, you can request copies of interface specifications from your Seagate sales representative. The following specifications are available:

| Specification No. | <u>Title</u>                                                              |

|-------------------|---------------------------------------------------------------------------|

| 64712402          | SMD-E Interface Specification                                             |

| 64721701          | Interface Specification for the Small<br>Computer System Interface (SCSI) |

| 64731600          | Interface Specification for IPI-2<br>Intelligent Peripheral Interface     |

### The following is a list of drives that this manual applies to:

| Equipment<br>Number | Model<br>Number | Interface               | Data Capa-<br>city (MB) | Sector Length |

|---------------------|-----------------|-------------------------|-------------------------|---------------|

| PA8G1A              | ST8741J         | Single Channel SMD      | 741                     | Unspecified   |

| PA8G2A              | ST8741J         | Dual Channel SMD        | 741                     | Unspecified   |

| PA8G2C              | ST8741J         | Dual Channel SMD        | 741                     | Unspecified   |

| PA8G2D              | ST8741J         | Dual Channel SMD        | 741                     | Unspecified   |

| PA8G2E              | ST8741J         | Dual Channel SMD        | 741                     | Unspecified   |

| PA8H1A              | ST8741ND        | STD SCSI (Differential) | 741                     | 512 Bytes     |

| PA8H1B              | ST8741N         | STD SCSI (Single-ended) | 741                     | 512 Bytes     |

| PA8H1C              | ST8741ND        | STD SCSI (Differential) | 741                     | 256 Bytes     |

| PA8H1D              | ST8741N         | STD SCSI (Single-ended) | 741                     | 256 Bytes     |

| PA8H1E              | ST8741ND        | STD SCSI (Differential) | 741                     | 512 Bytes     |

| PA8K1A              | ST8851J         | Single Channel SMD      | 851                     | Unspecified   |

| PA8K2A              | ST8851J         | Dual Channel SMD        | 851                     | Unspecified   |

| PA8K2D              | ST8851J         | Dual Channel SMD        | 851                     | Unspecified   |

| PA8K2E              | ST8851J         | Dual Channel SMD        | 851                     | Unspecified   |

| PA8K2F              | ST8851J         | Dual Channel SMD        | 851                     | Unspecified   |

| PA8K2G              | ST8851J         | Dual Channel SMD        | 851                     | Unspecified   |

| РА8К2Н              | ST8851J         | Dual Channel SMD        | 851                     | Unspecified   |

| PA8K2J              | ST8851J         | Dual Channel SMD        | 851                     | Unspecified   |

| PA8K2K              | ST8851J         | Dual Channel SMD        | 851                     | Unspecified   |

| PA8L1A              | ST8851ND        | STD SCSI (Differential) | 851                     | 512 Bytes     |

| PA8L1B              | ST8851N         | STD SCSI (Single-ended) | 851                     | 512 Bytes     |

| PA8L1C              | ST8851ND        | STD SCSI (Differential) | 851                     | 256 Bytes     |

| PA8L1D              | ST8851N         | STD SCSI (Single-ended) | 851                     | 256 Bytes     |

| PA8L1E              | ST8851ND        | STD SCSI (Differential) | 851                     | 512 Bytes     |

| PA8L1K              | ST8851N         | STD SCSI (Single-ended) | 851                     | 512 Bytes     |

| PA8M2A              | ST8851K         | IPI                     | 851                     | Std Format    |

| PA8M2B              | ST8851K         | IPI                     | 851                     | 512 Bytes     |

| PA8M2C              | ST8851K         | IPI                     | 851                     | 1024 Bytes    |

| PA8M2D              | ST8851K         | IPI                     | 851                     | Std Format    |

| PA8N1A              | ST81236J        | Single Channel SMD      | 1236                    | Unspecified   |

|                     |                 | Continued               |                         |               |

| Equipment<br>Number | Model<br>Number | Interface              | Data Capa-<br>city (MB) | Sector Length |

|---------------------|-----------------|------------------------|-------------------------|---------------|

| PA8N2A              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2B              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2C              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2D              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2E              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2F              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2G              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2H              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2J              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2K              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2L              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8N2M              | ST81236J        | Dual Channel SMD       | 1236                    | Unspecified   |

| PA8P1A              | ST81236ND       | HP SCSI (Differential) | 1236                    | 512 Bytes     |

| PA8P1B              | ST81236N        | HP SCSI (Single-ended) | 1236                    | 512 Bytes     |

| PA8P1C              | ST81236ND       | HP SCSI (Differential) | 1236                    | 256 Bytes     |

| PA8P1D              | ST81236N        | HP SCSI (Single-ended) | 1236                    | 256 Bytes     |

| PA8P1E              | ST81236ND       | HP SCSI (Differential) | 1236                    | 512 Bytes     |

| PA8P1F              | ST81236ND       | HP SCSI (Differential) | 1236                    | 512 Bytes     |

| PA8P1G              | ST81236ND       | HP SCSI (Differential) | 1236                    | 256 Bytes     |

| PA8P1H              | ST81236N        | HP SCSI (Single-ended) | 1236                    | 512 Bytes     |

| PA8P3A              | ST81236ND       | HP SCSI (Differential) | 1236                    | 256 Bytes     |

| PA8P3B              | ST81236ND       | HP SCSI (Differential) | 1236                    | 512 Bytes     |

| PA8P3C              | ST81236ND       | HP SCSI (Differential) | 1236                    | 256 Bytes     |

| PA8P3D              | ST81236ND       | HP SCSI (Differential) | 1236                    | 512 Bytes     |

| PA8P3E              | ST81236ND       | HP SCSI (Differential) | 1236                    | 256 Bytes     |

| PA8P3F              | ST81236ND       | HP SCSI (Differential) | 1236                    | 512 Bytes     |

| PA8R2A              | ST81236K        | IPI                    | 1236                    | Std Format    |

| PA8R2B              | ST81236K        | IPI                    | 1236                    | 512 Bytes     |

| PA8R2C              | ST81236K        | IPI                    | 1236                    | 1024 Bytes    |

| PA8R2D              | ST81236K        | IPI                    | 1236                    | 288 Bytes     |

|                     |                 |                        |                         |               |

| Equipment<br>Number | Model<br>Number | Interface             | Data Capa-<br>city (MB) | Sector Length |

|---------------------|-----------------|-----------------------|-------------------------|---------------|

| PA8R2E              | ST81236K        | IPI                   | 1236                    | 2308 Bytes    |

| PA8R2H              | ST81236K        | IPI                   | 1236                    | Std Format    |

| PA8R2J              | ST81236K        | IPI                   | 1236                    | Std Format    |

| PA8W2A              | ST81123J        | Dual Channel SMD      | 1123                    | Unspecified   |

| PA8W2B              | ST81123J        | Dual Channel SMD      | 1123                    | Unspecified   |

| PA8W2C              | ST81123J        | Dual Channel SMD      | 1123                    | Unspecified   |

| PA8W2D              | ST81123J        | Dual Channel SMD      | 1123                    | Unspecified   |

| PA8Y2A              | ST81154K        | IPI (2-Head Parallel) | 1154                    | Unspecified   |

| PA8Y2D              | ST81154K        | IPI (2-Head Parallel) | 1154                    | Unspecified   |

| PA8Y2E              | ST81154K        | IPI (2-Head Parallel) | 1154                    | Unspecified   |

| PA8Y2F              | ST81154K        | IPI (2-Head Parallel) | 1154                    | Unspecified   |

|                     |                 |                       |                         |               |

.

### **IMPORTANT SAFETY INFORMATION AND PRECAUTIONS**

Use of proper safety and repair techniques is important for safe, reliable operation of this unit. Service should be done only by qualified persons. We recommend the procedures in this manual as effective ways of servicing the unit. Some procedures require the use of special tools. For proper maintenance and safety, you must use these tools as recommended.

The procedures in this manual and labels on the unit contain warnings and cautions that must be carefully read and followed to minimize or eliminate the risk of personal injury. The warnings point out conditions or practices that may endanger you or others. The cautions point out conditions or practices that may damage the unit, possibly making it unsafe for use.

You must also understand that these warnings and cautions are not exhaustive. We cannot possibly know, evaluate, and advise you of all the ways in which maintenance might be performed or the possible risk of each technique. Consequently, we have not completed any such broad evaluation. If you use a non-approved procedure or tool, first ensure that the method you choose will not risk either your safety or unit performance.

For the safety of yourself and others, observe the following warnings and precautions.

- Perform all maintenance by following the procedures in this manual.

- Follow all cautions and warnings in the procedures and on unit labels.

- Use the special tools called out in the procedures.

- Use sound safety practices when operating or repairing the unit.

- Use caution when troubleshooting a unit that has voltages present. Remove power from unit before servicing or replacing parts.

- Wear safety glasses when servicing units.

- Wear safety shoes when removing or replacing heavy parts.

- Use only designated Seagate replacement parts.

Non-Seagate replacement parts can adversely affect safety in addition to degrading reliability, increasing maintenance downtime, and voiding warranty coverage.

- Use care while working with the power supply because line voltages are always present when the ac power cord is connected to a power source. Setting the power supply switch to position "O" disables dc power to the drive but has no effect on ac power within the supply. For complete safety, remove the ac power plug from the site power outlet.

- The site power outlet shall be installed near the equipment and shall be easily accessible.

- In case of fire or other emergency, isolate the drive from main power by removing the drive power plug from the ac outlet. In situations where pulling the plug is not possible or practical, use the system main power disconnect to isolate the drives from main power.

- In an IT power system, a disconnect device shall be provided which simultaneously interrupts all phase and neutral conductors.

- WARNING: In IT power systems, the unearthed neutral is considered as a phase conductor. For such IT power systems, double pole/neutral fusing is required.

- When the drive is mounted in an equipment rack or cabinet, ensure that the internal temperature of the rack or cabinet will not exceed the limits defined for the drive. Where units are stacked vertically, pay special attention to the top where temperatures are usually highest.

- This drive is designed to be installed and operated in accordance with UL1950, IEC380, IEC950, EN 60950, CSA C22.2 154, CSA C22.2 220, and VDE0806.

- Follow the precautions listed under Protecting the Drive From Electrostatic Discharge.

- If the power supply is placed on a bench for testing, position the supply so all ventilation holes are open, to allow proper air flow to internal components.

- Do not attempt to disassemble the module. It is not field repairable. Replace the entire module assembly if it is defective.

- Always deenergize drive before removing or installing circuit boards, cables, or any other electrical components.

- Do not operate the drive over an extended period of time without the top cover installed.

- The power supply is designed to be connected to an IT network.

- Do not attempt to disassemble the power supply. It is not field repairable. Replace the entire supply if it is defective.

- If you do not use a recommended Seagate power supply, ensure the supply meets the specifications in this manual and is designed to be used in accordance with UL1950, IEC380, IEC950, EN 60950, CSA C22.2 154, CSA C22.2 220, and VDE0806.

## **ABBREVIATIONS**

| Α       | Ampere                             | CLR   | Clear                          |

|---------|------------------------------------|-------|--------------------------------|

| ABV     | Above                              | cm    | Centimetre                     |

| ac      | Alternating Current                | CNTR  | Counter                        |

| ADD     | Address                            | COMP  | Comparator                     |

| ADDR    | Address                            | CONT  | Control                        |

| ADJ     | Adjust                             | CONTD | Continued                      |

| ADRS    | Address                            | СТ    | Center Tap                     |

| AGC     | Automatic Gain Control             | CYL   | Cylinder                       |

| ALT     | Alternate                          | D/A   | Digital to Analog              |

| AM      | Address Mark                       | DAC   | Digital-to-Analog<br>Converter |

| AME     | Address Mark Enable                | dc    | Direct Current                 |

| AMP     | Amplifier, Ampere                  |       |                                |

| ASSY    | Assembly                           | DET   | Detect                         |

| BLW     | Below                              | DIFF  | Differential                   |

| С       | Celsius                            | DIV   | Division                       |

| CB      | Circuit Breaker                    | DLY   | Delay                          |

| CDA     | Complete Drive                     | DMA   | Direct Memory Access           |

| 0.511   | Assembly                           | DRVR  | Driver                         |

| CDIC    | Controller/Drive<br>Interface Chip | ECC   | Error Correction Code          |

| <b></b> | -                                  | ECL   | Emitter Coupled Logic          |

| CH      | Channel                            | ECO   | Engineering Change             |

| СНК     | Check                              |       | Order                          |

| CLK     | Clock                              |       |                                |

## ABBREVIATIONS (Contd)

| EMD  | Eight-Inch Module      | ID         | Identification                    |

|------|------------------------|------------|-----------------------------------|

|      | Drive                  | IDENT      | Identification                    |

| EN   | Enable                 | in         | Inch                              |

| ENBL | Enable                 |            |                                   |

| ESP  | Enhanced SCSI Protocol | IND        | Index                             |

| EXT  | External               | INTRPT     | Interrupt                         |

| F    | Fahrenheit, Fuse       | 1/0        | Input/Output                      |

| FCO  | Field Change Order     | IPB        | Illustrated Parts<br>Breakdown    |

| FDBK | Feedback               | IPC        | Interface Protocol<br>Circuit     |

| FIG  | Figure                 | IPI        | Intelligent                       |

| FLT  | Fault                  |            | Peripheral Interface              |

| FRU  | Field Replaceable Unit | IPIP       | IPI Parallel                      |

| ft   | Foot                   | kg         | Kilogram                          |

| FWD  | Forward                | kW         | Kilowatt                          |

| GND  | Ground                 | 1 <b>b</b> | Pound                             |

| HD   | Head                   | LCD        | Liquid Crystal Display            |

| HEX  | Hexagon, Hexadecimal   | LED        | Light Emitting Diode              |

| Hg   | Mercury                | LSB        | Least Significant Bit             |

| HP   | High Performance       | LSI        | Large Scale                       |

| HR   | High Resolution        |            | Integration                       |

| HYST | Hysteresis             | LTD        | Lock to Data                      |

| Hz   | Hertz                  | m          | Metre                             |

| IC   | Integrated Circuit     | MAC        | Merged Architecture<br>Controller |

| . –  |                        |            |                                   |

## ABBREVIATIONS (Contd)

| МАХ       | Maximum              | PG    | Page                      |

|-----------|----------------------|-------|---------------------------|

| MB        | Megabyte             | PLO   | Phase Lock Oscillator     |

| MEM       | Memory               | PROC  | Procedure                 |

| MHz       | Megahertz            | PROG  | Programmable              |

| mm        | Millimetre           | PS    | Power Supply              |

| MPU       | Microprocessor Unit  | PWR   | Power                     |

| MRK       | Mark                 | RCVR  | Receiver                  |

| ms        | Millisecond          | RD    | Read                      |

| MSB       | Most Significant Bit | RDY   | Ready                     |

| MTR       | Motor                | RECT  | Rectified                 |

| mV        | Millivolt            | REF   | Reference                 |

| NC        | No Connection        | REQ   | Request                   |

| NORM      | Normal               | RES   | Resolution                |

| NRZ       | Non Return to Zero   | REV   | Reverse, Revision         |

| ns        | Nanosecond           | RGTR  | Register                  |

| OC        | On Cylinder          | r/min | Revolutions Per Minute    |