# **GD**CONTROL DATA

## DISK STORAGE SUBSYSTEM CDC 33800 CDC 895 HIS MSU 8200 BZ640 BZ8G1 BZ8H1 FV716 FV7A5

TROUBLESHOOTING INTRODUCTION ROUTINE DESCRIPTIONS OPERATING PROCEDURES

HARDWARE DIAGNOSTIC REFERENCE MANUAL

### **REVISION RECORD**

| REVISION                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                          |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A<br>(10-10-83)             | Manual released.                                                                                                                                                                                                                                                                                                                     |

| B<br>(02-08-84)             | Incorporate Engineering/Field Change Order<br>DJ18013 (Revision J of MF126H disk). Revised<br>sense information and routine descriptions.<br>Added Fault Symptom Codes and the following<br>routines: C87 Test 2, C91, and C95. Miscel-<br>laneous technical and editorial changes. This<br>edition obsoletes all previous editions. |

| C<br>(10-12-84)             | Incorporate Engineering Change Order DJ18014<br>(Revision K of MF126H disk) and DJ18017 (Revi-<br>sion M of MF126H disk). This edition obsoletes<br>all previous editions.                                                                                                                                                           |

| D<br>(06-11-85)             | Miscellaneous technical and editorial changes.<br>Incorporate the following Engineering Change<br>Orders (no Field Change Orders) against the<br>following MF packages (numbers/letters in<br>parentheses are disk tabs/revisions):<br>MF126H                                                                                        |

|                             | 18021 (13/P)-Add test D to routines CAO and CA1<br>18027 (14/R)-Add routine C9F                                                                                                                                                                                                                                                      |

|                             | MF131H<br>18023 (01/B), 18025 (02/C)-Miscellaneous tech-<br>nical changes                                                                                                                                                                                                                                                            |

|                             | <u>MF132H</u><br>18022 (01/B), 18024 (02/C)-Miscellaneous tech-<br>nical changes                                                                                                                                                                                                                                                     |

|                             | <br>                                                                                                                                                                                                                                                                                                                                 |

| VISION LETTI<br>D X ARE NOT |                                                                                                                                                                                                                                                                                                                                      |

© 1983, 1984, 1985 By Control Data Corporation Printed in the United States of America

No the State of the second second

Address comments concerning this<br/>manual to:<br/>Control Data Corporation<br/>Technical Publications Dept.<br/>7801 Computer Avenue<br/>Minneapolis, Mn 55435<br/>or use Comment Sheet in the back<br/>of America

### LIST OF EFFECTIVE PAGES

#### Sheet 1 of 5

. .

.

• • • New features, as well as changes, deletions, and additions to information in this manual are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE    | <u>REV</u> | PAGE          | REV            | 3                |

|---------|------------|---------------|----------------|------------------|

| Cover   |            | xxxi          | С              | ţ                |

| Blank   | · _        | xxxii         | C              | 5                |

| Title P | -          | xxxiii        | С              | -110-110-i       |

| ii      | D          | xxxiv         | С              |                  |

| iii     | D          | XXXV          | С              | •                |

| iv      | D          | Blank         | -              |                  |

| v       | D          | S-l Div       | -              |                  |

| vi      | D          | Blank         | -              |                  |

| vi-a    | D          | 1-1           | С.             | · · · ·          |

| Blank   | -          | 1-2           | С              | f .              |

| vii     | c          | 1-3           | С              |                  |

| viii    | С          | 1-4           | C<br>C         | :                |

| ix      | D          | 1-5           | С              | >                |

| x       | D          | 1-6           | С              | 1                |

| xi      | D          | 1-7           | D              |                  |

| xii     | D          | 1-8           | с с с с с<br>с |                  |

| xiii    | D          | 1-9           | С              |                  |

| xiv     | D          | 1-10          | С              |                  |

| xv      | D          | 1-11          | С              |                  |

| xvi     | D          | 1-12          |                |                  |

| xvii    | D          | 1-13          | С              |                  |

| xviii   | D          | 1-14          | С              |                  |

| xix     | D          | 1-15          | С              |                  |

| xx      | D          | Blank         | -              |                  |

| xxi     | D          | S-lA Div      | -              |                  |

| xxii    | D          | Blank         | -              |                  |

| xxiii   | D          | 1A-1          | С              | • • <del>1</del> |

| xxiv    | D          | 1A-2          | C<br>C<br>C    | nn<br>N          |

| xxv     | D          | 1A-3          | C              | •                |

| xxvi    | D          | 1A-4          |                |                  |

| xxvii   | D          | 1A-5          | C              | 6.0              |

| xxviii  | D          | 1A-6          | С              |                  |

| xxix    | С          | 1 <b>A</b> -7 | C              |                  |

| XXX     | С          | 1A-8          | С              |                  |

83337530 D

iii

n sheri ak sa 19 at s

. . .

-

. . . . .

t.<u>1</u>.5

### Sheet 2 of 5

.

| PAGE     | REV    | PAGE  | REV           |

|----------|--------|-------|---------------|

| 1A-9     | С      | 1C-6  | С             |

| 1A-10    | С      | 1C-7  | D             |

| 1A-11    | D      | 1C-8  | С             |

| 1A-12    | D      | 1C-9  | D             |

| S-1B Div | -      | 1C-10 | С             |

| Blank    |        | 1C-11 | с<br>с<br>с   |

| 1B-1     | С      | 1C-12 |               |

| 1B-2     | D      | Blank |               |

| 1B-3     | D      | 1C-14 | D             |

| 1B-4     | D      | 1C-15 | D             |

| 1B-5     | D      | 1C-16 | D             |

| 1B-6     | D      | 1C-17 | D             |

| 1B-7     | D      | 1C-18 | C ·           |

| 1B-8     | D      | 1C-19 | С             |

| 1B-9     | D      | 1C-20 | C             |

| 1B-10    | D      | 1C-21 | D             |

| 1B-11    | D      | 1C-22 | С             |

| 1B-12    | D      | 1C-23 | D             |

| 1B-13    | D      | 1C-24 | C             |

| 1B-14    | D      | 1C-25 | C             |

| 1B-15    | D      | 1C-26 | С             |

| 1B-16    | D      | 1C-27 | D             |

| 1B-17    | D      | 1C-28 | С             |

| 1B-18    | D      | 1C-29 | С             |

| 1B-19    | D      | 1C-30 | С             |

| 1B-20    | D      | 1C-31 | С             |

| 1B-21    | D      | 1C-32 | С             |

| 1B-22    | D      | 1C-33 | С             |

| 1B-23    | D      | 1C-34 | С             |

| 1B-24    | D      | 1C-35 | С             |

| 1B-25    | D      | 1C-36 | 0000000000000 |

| 1B-26    | D      | 1C-37 | С             |

| 1B-27    | D      | 1C-38 | С             |

| Blank    | -      | 1C-39 | С             |

| S-1C Div | -      | 1C-40 | · C           |

| Blank    | -      | 1C-41 | D             |

| 1C-1     | С      | 1C-42 | D             |

| 1C-2     | С      | 1C-43 | D             |

| 1C-3     | С      | 1C-44 | C             |

| 1C-4     | C<br>C | 1C-45 | С             |

| 1C-5     | D      | 1C-46 | C             |

|          |        |       |               |

ω.

Sheet 3 of 5

| PAGE                                                                                                                                                                                                                                                                                                                    | REV                                     | PAGE                                                                                                                                                                                                                                                                                           | REV |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1C-47<br>1C-48<br>1C-49<br>1C-50<br>1C-51<br>1C-52<br>1C-53<br>1C-54<br>1C-55<br>1C-56<br>1C-57<br>1C-58<br>1C-59<br>1C-60<br>1C-61<br>1C-62<br>1C-63<br>1C-63<br>1C-64<br>1C-65<br>1C-65<br>1C-67<br>1C-68<br>1C-69<br>1C-70<br>1C-71<br>1C-72<br>1C-72<br>1C-73<br>1C-74<br>1C-75<br>1C-76<br>1C-77<br>1C-78<br>1C-79 | 000000000000000000000000000000000000000 | Blank<br>1D-1<br>1D-2<br>1D-3<br>1D-4<br>1D-5<br>1D-6<br>1D-7<br>1D-8<br>1D-9<br>1D-10<br>1D-11<br>1D-12<br>1D-13<br>1D-14<br>1D-15<br>1D-16<br>1D-17<br>1D-18<br>1D-19<br>1D-20<br>1D-21<br>1D-22<br>1D-23<br>1D-24<br>1D-25<br>1D-26<br>1D-27<br>1D-28<br>1D-29<br>1D-30<br>S-2 Div<br>Blank |     |

| 1C-79                                                                                                                                                                                                                                                                                                                   | D                                       | Blank                                                                                                                                                                                                                                                                                          | -   |

| 1C-80                                                                                                                                                                                                                                                                                                                   | D                                       | 2-1                                                                                                                                                                                                                                                                                            | D   |

| 1C-81                                                                                                                                                                                                                                                                                                                   | D                                       | 2-2                                                                                                                                                                                                                                                                                            | C   |

| 1C-82                                                                                                                                                                                                                                                                                                                   | D                                       | 2-3                                                                                                                                                                                                                                                                                            | C   |

| 1C-83                                                                                                                                                                                                                                                                                                                   | D                                       | 2-4                                                                                                                                                                                                                                                                                            | C   |

| 1C-84                                                                                                                                                                                                                                                                                                                   | D                                       | 2-5                                                                                                                                                                                                                                                                                            | D   |

| 1C-85                                                                                                                                                                                                                                                                                                                   | D                                       | 2-6                                                                                                                                                                                                                                                                                            | D   |

| 1C-86                                                                                                                                                                                                                                                                                                                   | D                                       | 2-7                                                                                                                                                                                                                                                                                            | D   |

| S-1D Div                                                                                                                                                                                                                                                                                                                | -                                       | 2-8                                                                                                                                                                                                                                                                                            | D   |

#### 83337530 D

v

Sheet 4 of 5

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PAGE  | REV      | PAGE      | <u>rev</u> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|-----------|------------|

| Blank- $2A^{-}41$ D $2A-1$ C $2A-42$ D $2A-2$ C $2A-42$ D $2A-3$ C $2A-43$ D $2A-4$ C $2A-44$ D $2A-5$ D $2A-46$ D $2A-6$ D $2A-47$ D $2A-7$ D $2A-48$ D $2A-7$ D $2A-49$ D $2A-7$ D $2A-47$ D $2A-7$ D $2A-50$ D $2A-11$ D $2A-51$ D $2A-12$ D $2A-55$ D $2A-14$ D $2A-56$ D $2A-17$ D $2A-60$ D $2A-18$ D $2A-59$ D $2A-20$ D $S-3$ Div $2A-21$ DBlank- $2A-24$ D $3-3$ C $2A-25$ D $3-1$ C $2A-26$ D $3-5$ C $2A-30$ D $3-9$ C $2A-31$ D $3-10$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D <td>d d</td> <td></td> <td>• • • • •</td> <td></td> | d d   |          | • • • • • |            |

| 2A-1C $2A-42$ D $2A-2$ C $2A-43$ D $2A-3$ C $2A-43$ D $2A-4$ C $2A-44$ D $2A-4$ C $2A-45$ D $2A-4$ D $2A-46$ D $2A-6$ D $2A-47$ D $2A-7$ D $2A-48$ D $2A-7$ D $2A-48$ D $2A-7$ D $2A-48$ D $2A-7$ D $2A-50$ D $2A-7$ D $2A-50$ D $2A-10$ D $2A-51$ D $2A-11$ D $2A-52$ D $2A-12$ D $2A-53$ D $2A-14$ D $2A-55$ D $2A-15$ D $2A-56$ D $2A-16$ D $2A-57$ D $2A-17$ D $2A-58$ D $2A-18$ D $2A-59$ D $2A-19$ D $2A-60$ D $2A-20$ D $S-3$ Div- $2A-21$ DBlank- $2A-22$ D $3-1$ C $2A-24$ D $3-3$ C $2A-25$ D $3-4$ C $2A-26$ D $3-7$ D $2A-27$ D $3-6$ C $2A-30$ D $3-9$ C $2A-31$ D $3-10$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D $2A-36$ D $3-15$ D $2A-37$ DBlank- <td></td> <td><b>-</b></td> <td></td> <td></td>         |       | <b>-</b> |           |            |

| 2A-3C $2A-44$ D $2A-4$ C $2A-45$ D $2A-5$ D $2A-46$ D $2A-6$ D $2A-47$ D $2A-6$ D $2A-47$ D $2A-7$ D $2A-48$ D $2A-8$ D $2A-49$ D $2A-9$ D $2A-50$ D $2A-10$ D $2A-51$ D $2A-11$ D $2A-52$ D $2A-12$ D $2A-53$ D $2A-14$ D $2A-54$ D $2A-14$ D $2A-55$ D $2A-14$ D $2A-56$ D $2A-16$ D $2A-57$ D $2A-17$ D $2A-59$ D $2A-18$ D $2A-59$ D $2A-19$ D $2A-60$ D $2A-20$ D $S-3$ Div $2A-21$ DBlank- $2A-23$ D $3-1$ C $2A-24$ D $3-3$ C $2A-25$ D $3-4$ C $2A-26$ D $3-5$ C $2A-27$ D $3-6$ C $2A-30$ D $3-9$ C $2A-31$ D $3-10$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D $2A-36$ D $3-15$ D $2A-37$ DBlank- $2A-38$ D $S-3A$ Div                                                                                             |       | -        |           |            |

| 2A-3C $2A-44$ D $2A-4$ C $2A-45$ D $2A-5$ D $2A-46$ D $2A-6$ D $2A-47$ D $2A-6$ D $2A-47$ D $2A-7$ D $2A-48$ D $2A-8$ D $2A-49$ D $2A-9$ D $2A-50$ D $2A-10$ D $2A-51$ D $2A-11$ D $2A-52$ D $2A-12$ D $2A-53$ D $2A-14$ D $2A-54$ D $2A-14$ D $2A-55$ D $2A-14$ D $2A-56$ D $2A-16$ D $2A-57$ D $2A-17$ D $2A-59$ D $2A-18$ D $2A-59$ D $2A-19$ D $2A-60$ D $2A-20$ D $S-3$ Div $2A-21$ DBlank- $2A-23$ D $3-1$ C $2A-24$ D $3-3$ C $2A-25$ D $3-4$ C $2A-26$ D $3-5$ C $2A-27$ D $3-6$ C $2A-30$ D $3-9$ C $2A-31$ D $3-10$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D $2A-36$ D $3-15$ D $2A-37$ DBlank- $2A-38$ D $S-3A$ Div                                                                                             |       |          |           |            |

| 2A-4C $2A-45$ D $2A-5$ D $2A-46$ D $2A-6$ D $2A-47$ D $2A-7$ D $2A-47$ D $2A-7$ D $2A-48$ D $2A-8$ D $2A-49$ D $2A-9$ D $2A-50$ D $2A-10$ D $2A-51$ D $2A-11$ D $2A-52$ D $2A-14$ D $2A-53$ D $2A-15$ D $2A-54$ D $2A-16$ D $2A-56$ D $2A-16$ D $2A-57$ D $2A-16$ D $2A-57$ D $2A-17$ D $2A-58$ D $2A-18$ D $2A-59$ D $2A-19$ D $2A-60$ D $2A-20$ DS-3Div $2A-21$ DBlank- $2A-23$ D $3-1$ C $2A-24$ D $3-3$ C $2A-25$ D $3-4$ C $2A-26$ D $3-5$ C $2A-27$ D $3-6$ C $2A-30$ D $3-9$ C $2A-31$ D $3-10$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D $2A-36$ D $3-15$ D $2A-37$ DBlank- $2A-38$ D $S-3A$ Div                                                                                                                    |       |          |           |            |

| 2A-5D $2A-46$ D $2A-6$ D $2A-47$ D $2A-7$ D $2A-48$ D $2A-8$ D $2A-49$ D $2A-9$ D $2A-50$ D $2A-10$ D $2A-51$ D $2A-11$ D $2A-52$ D $2A-12$ D $2A-53$ D $2A-13$ D $2A-54$ D $2A-14$ D $2A-56$ D $2A-15$ D $2A-56$ D $2A-16$ D $2A-57$ D $2A-18$ D $2A-59$ D $2A-19$ D $2A-60$ D $2A-20$ D $S-3$ Div $2A-24$ D $3-1$ C $2A-25$ D $3-4$ C $2A-24$ D $3-3$ C $2A-24$ D $3-5$ C $2A-27$ D $3-6$ C $2A-28$ D $3-7$ D $2A-29$ D $3-8$ C $2A-30$ D $3-9$ C $2A-31$ D $3-10$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D $2A-36$ D $3-15$ D $2A-37$ DBlank- $2A-38$ D $S-3A$ Div                                                                                                                                                      |       |          |           |            |

| 2A-6D $2A-47$ D $2A-7$ D $2A-48$ D $2A-8$ D $2A-49$ D $2A-9$ D $2A-50$ D $2A-10$ D $2A-51$ D $2A-11$ D $2A-52$ D $2A-12$ D $2A-53$ D $2A-13$ D $2A-54$ D $2A-14$ D $2A-55$ D $2A-15$ D $2A-56$ D $2A-16$ D $2A-57$ D $2A-17$ D $2A-58$ D $2A-18$ D $2A-59$ D $2A-20$ DS-3Div $2A-21$ DBlank- $2A-23$ D $3-2$ C $2A-24$ D $3-3$ C $2A-25$ D $3-4$ C $2A-26$ D $3-5$ C $2A-27$ D $3-6$ C $2A-28$ D $3-7$ D $2A-29$ D $3-8$ C $2A-31$ D $3-10$ C $2A-32$ D $3-11$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D $2A-36$ D $3-15$ D $2A-38$ D $S-3A$ Div                                                                                                                                                                            |       |          |           |            |

| 2A-7D $2A-48$ D $2A-8$ D $2A-49$ D $2A-9$ D $2A-50$ D $2A-10$ D $2A-51$ D $2A-11$ D $2A-52$ D $2A-12$ D $2A-53$ D $2A-13$ D $2A-54$ D $2A-14$ D $2A-56$ D $2A-15$ D $2A-56$ D $2A-16$ D $2A-57$ D $2A-17$ D $2A-58$ D $2A-18$ D $2A-59$ D $2A-19$ D $2A-60$ D $2A-20$ DS-3Div $2A-21$ DBlank- $2A-23$ D $3-2$ C $2A-24$ D $3-3$ C $2A-25$ D $3-4$ C $2A-26$ D $3-5$ C $2A-27$ D $3-6$ C $2A-28$ D $3-7$ D $2A-29$ D $3-8$ C $2A-31$ D $3-10$ C $2A-32$ D $3-11$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D $2A-36$ D $3-15$ D $2A-38$ D $S-3A$ Div                                                                                                                                                                           |       |          |           |            |

| 2A-8D $2A-49$ D $2A-9$ D $2A-50$ D $2A-10$ D $2A-51$ D $2A-11$ D $2A-52$ D $2A-12$ D $2A-52$ D $2A-13$ D $2A-52$ D $2A-14$ D $2A-53$ D $2A-15$ D $2A-54$ D $2A-14$ D $2A-56$ D $2A-15$ D $2A-56$ D $2A-16$ D $2A-57$ D $2A-17$ D $2A-58$ D $2A-18$ D $2A-59$ D $2A-19$ D $2A-60$ D $2A-20$ D $S-3$ Div $2A-21$ DBlank- $2A-22$ D $3-1$ C $2A-23$ D $3-2$ C $2A-24$ D $3-3$ C $2A-25$ D $3-4$ C $2A-26$ D $3-5$ C $2A-27$ D $3-6$ C $2A-29$ D $3-8$ C $2A-30$ D $3-9$ C $2A-31$ D $3-10$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D $2A-36$ D $3-15$ D $2A-37$ DBlank- $2A-38$ D $S-3A$ Div                                                                                                                                   |       |          |           | -          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |          |           |            |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           |            |

| 2A-11D $2A-52$ D $2A-12$ D $2A-53$ D $2A-13$ D $2A-53$ D $2A-13$ D $2A-54$ D $2A-14$ D $2A-55$ D $2A-15$ D $2A-56$ D $2A-16$ D $2A-57$ D $2A-16$ D $2A-57$ D $2A-17$ D $2A-58$ D $2A-18$ D $2A-59$ D $2A-19$ D $2A-60$ D $2A-20$ D $S-3$ Div- $2A-21$ DBlank- $2A-22$ D $3-1$ C $2A-23$ D $3-2$ C $2A-24$ D $3-3$ C $2A-25$ D $3-4$ C $2A-26$ D $3-5$ C $2A-27$ D $3-6$ C $2A-28$ D $3-7$ D $2A-29$ D $3-8$ C $2A-31$ D $3-10$ C $2A-32$ D $3-11$ C $2A-33$ D $3-12$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D $2A-36$ D $3-15$ D $2A-38$ D $S-3A$ Div                                                                                                                                                                      |       |          |           |            |

| 2A-12D $2A-53$ D $2A-13$ D $2A-54$ D $2A-14$ D $2A-55$ D $2A-15$ D $2A-56$ D $2A-16$ D $2A-57$ D $2A-16$ D $2A-59$ D $2A-17$ D $2A-59$ D $2A-18$ D $2A-60$ D $2A-20$ D $S-3$ Div- $2A-21$ DBlank- $2A-23$ D $3-1$ C $2A-24$ D $3-3$ C $2A-25$ D $3-4$ C $2A-26$ D $3-5$ C $2A-27$ D $3-6$ C $2A-28$ D $3-7$ D $2A-29$ D $3-8$ C $2A-31$ D $3-10$ C $2A-33$ D $3-12$ C $2A-34$ D $3-13$ C $2A-35$ D $3-14$ D $2A-36$ D $3-15$ D $2A-38$ D $S-3A$ Div-                                                                                                                                                                                                                                                                      |       |          |           |            |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |          |           | _          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |          |           |            |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | D        |           | D          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | D        |           | D          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           | D          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           | _          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           |            |

| 2A-20DS-3 Div-2A-21DBlank-2A-22D3-1C2A-23D3-2C2A-24D3-3C2A-25D3-4C2A-26D3-5C2A-27D3-6C2A-28D3-7D2A-29D3-8C2A-30D3-9C2A-31D3-10C2A-32D3-11C2A-34D3-13C2A-35D3-14D2A-36D3-15D2A-37DBlank-2A-38DS-3A Div-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |          |           | -          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           | D          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           | -          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           |            |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           | С          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           | С          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           | C          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |          |           | С          |

| 2A-28D3-7D2A-29D3-8C2A-30D3-9C2A-31D3-10C2A-32D3-11C2A-33D3-12C2A-34D3-13C2A-35D3-14D2A-36D3-15D2A-37DBlank-2A-38DS-3A Div-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |          |           |            |

| 2A-29D3-8C2A-30D3-9C2A-31D3-10C2A-32D3-11C2A-33D3-12C2A-34D3-13C2A-35D3-14D2A-36D3-15D2A-37DBlank-2A-38DS-3A Div-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |          |           |            |

| 2A-30D3-9C2A-31D3-10C2A-32D3-11C2A-33D3-12C2A-34D3-13C2A-35D3-14D2A-36D3-15D2A-37DBlank-2A-38DS-3A Div-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |          |           | D          |

| 2A-31D3-10C2A-32D3-11C2A-33D3-12C2A-34D3-13C2A-35D3-14D2A-36D3-15D2A-37DBlank-2A-38DS-3A Div-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |          |           | С          |

| 2A-33D3-12C2A-34D3-13C2A-35D3-14D2A-36D3-15D2A-37DBlank-2A-38DS-3A Div-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |          |           | С          |

| 2A-33D3-12C2A-34D3-13C2A-35D3-14D2A-36D3-15D2A-37DBlank-2A-38DS-3A Div-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |          |           | С          |

| 2A-34D3-13C2A-35D3-14D2A-36D3-15D2A-37DBlank-2A-38DS-3A Div-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |          |           | C          |

| 2A-35D3-14D2A-36D3-15D2A-37DBlank-2A-38DS-3A Div-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |          |           |            |

| 2A-36         D         3-15         D           2A-37         D         Blank         -           2A-38         D         S-3A Div         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |          |           |            |

| 2A-37         D         Blank         -           2A-38         D         S-3A Div         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |          |           |            |

| 2A-38 D S-3A Div -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |          |           | D          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | D        |           | -          |

| 2A-39 D Blank -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |          |           | -          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2A-39 | . D      | Blank     | -          |

Sheet 5 of 5

| <b>`</b> |

|----------|

| ,        |

| )        |

| )        |

| )        |

| -        |

| -        |

| 2        |

| 2        |

| 2        |

| -        |

| -        |

|          |

| 2        |

| 2        |

| -        |

| -        |

| -        |

| -        |

|          |

|          |

|          |

.

.

vi-a

· · · -•

### PREFACE

#### INTRODUCTION

This manual contains troubleshooting information for customer engineers and other technical personnel who will be maintaining the CONTROL DATA® FV716/FV7A5 Head of String Controller (HSC) and BZ640/BZ8G1/BZ8H1 Disk Storage Unit (DSU).

The CDC 33800, CDC 895, and MSU 8200 disk storage subsystems are physically identical; however, the 33800 is used on IBM systems, the 895 is used on CDC systems, and the 8200 is used on HIS systems. Therefore, any internal reference in this manual pertaining to SOLEX, EREP, and OLTEP apply only to 33800 subsystems used with IBM systems.

Abbreviations are listed on page xxix.

Terminology used in this manual is as follows:

- The term "controller" refers to the next higher-level unit to which the DSU is connected.

- The terms "DSU" and "drive" are interchangeable.

- The term "device" refers to one of four possible devices (spindles) that comprise a DSU. The terms drive and device, therefore, are not interchangeable.

#### MANUAL ORGANIZATION

Information in this manual is divided into four sections:

- Section 1 -- Troubleshooting Introduction: provides general background information explaining the troubleshooting philosophy, troubleshooting technique, and general reference information helpful in analyzing a problem. Also contains sense information and power troubleshooting procedures.

- Section 2 -- Inline Diagnostics/Utilities: contains descriptions of inline diagnostic routines and tests, along with utility routines.

vii

- Section 3 -- Operating Procedures: contains procedures for running diagnostic and utility routines from the maintenance panel.

- Section 4 -- Terminal Operating Procedures: contains a procedure for running diagnostics and utility routines from the terminal.

#### OTHER MANUALS

For error code information, refer to the Troubleshooting Guide, Publication Number 83337540.

Refer to the Disk Memory Subsystem Installation Manual (Publication Number 83321400) for the following information:

- A list of all manuals needed to maintain and troubleshoot the HSC and DSU. (This information is contained in the Preface of that manual.)

- A list of all available microprogram disks. (This information is contained in section 1 of that manual.)

- A list of all applicable equipment numbers.

#### CONVENTIONS

Conventions used in this manual are:

- Logical zero and logical one are abbreviated as 0 and 1, respectively.

- Bytes and bits are numbered from left to right, beginning with 0.

- The leftmost byte/bit is most significant; the rightmost bit is least significant.

- "X" in a bit position indicates unknown or don't care.

- All address references are hexadecimal.

### CONTENTS

٠

| Abbreviations                              | xxix        |

|--------------------------------------------|-------------|

| ADDLeviations                              | XXIX        |

| 1. TROUBLESHOOTING INTRODUCTION            |             |

| Introduction                               | 1-1         |

| Safety Precautions                         | 1-1         |

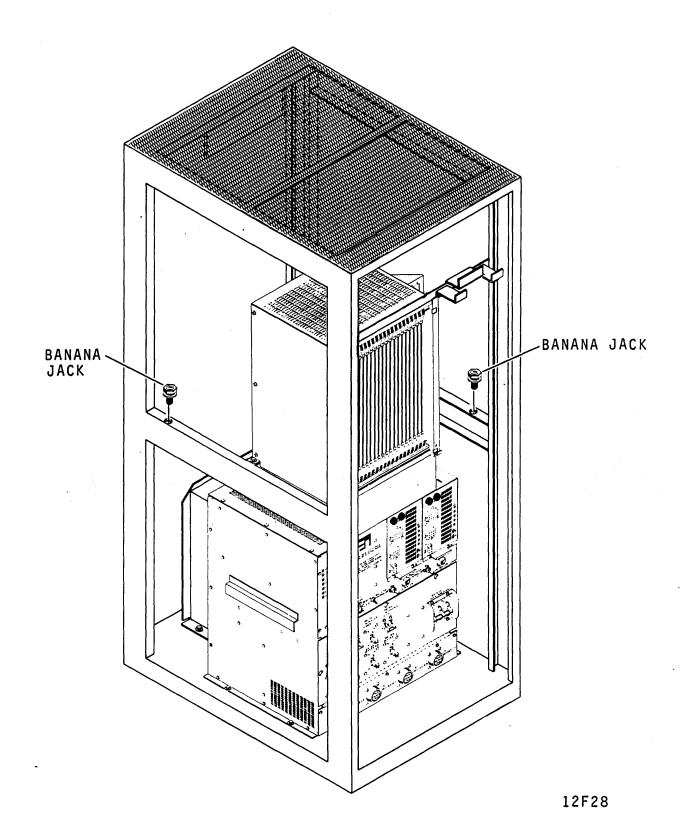

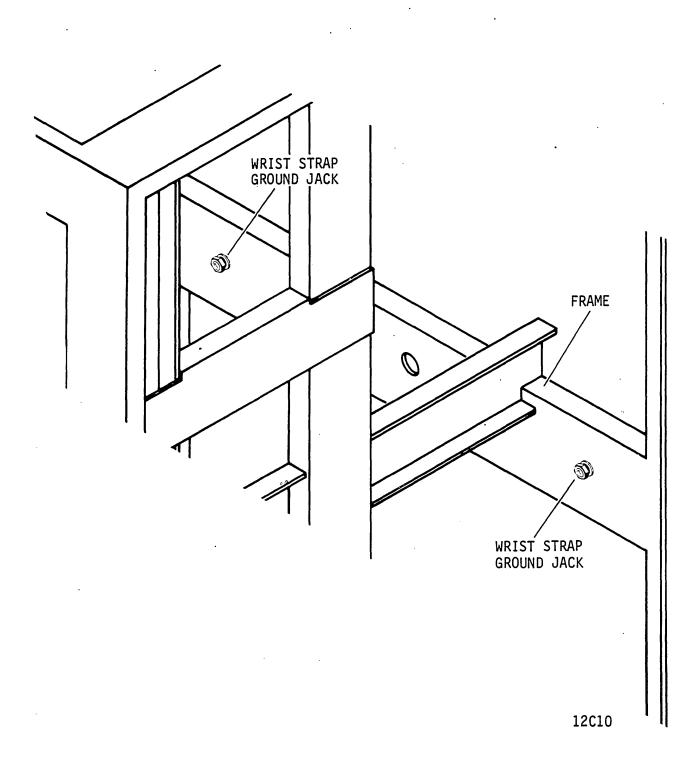

| Electrostatically Sensitive Precautions    | 1-2         |

| Test Equipment Precautions                 | l-6         |

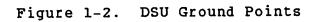

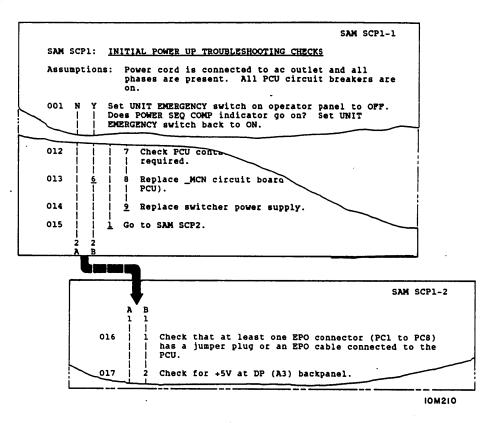

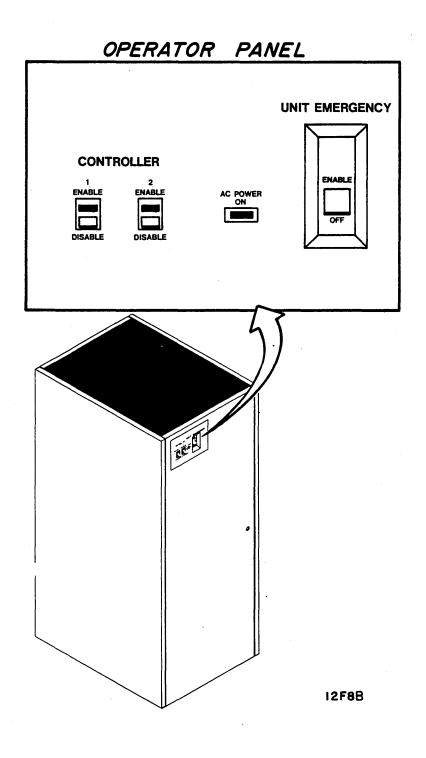

| Using the SAM (Structured Analysis Method) | <b>1</b> -6 |

| Troubleshooting Technique                  | 1-10        |

| Collect Available Data                     | 1-10        |

| Defining Deviation                         | 1-11        |

| Propose Theory of Cause                    | 1-11        |

| Test Theory                                | 1-11        |

| Intermittent Problems                      | 1-12        |

| Problem Not Found                          | 1-13        |

| On-Line Error Analysis Methods             | 1-14        |

| SOLEX                                      | 1-14        |

| EREP Program                               | 1-15        |

| 1A. POWER                                  |             |

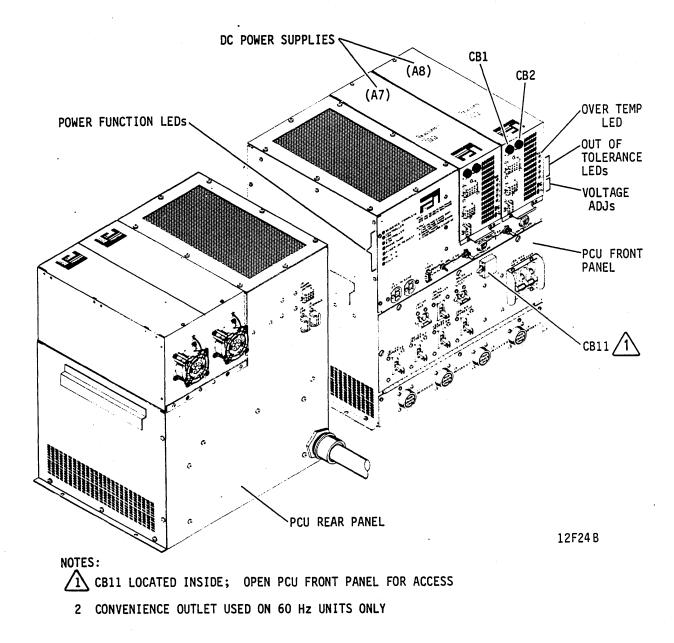

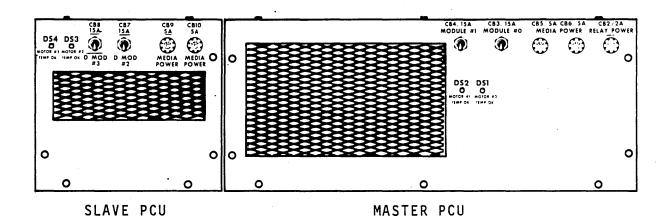

| Introduction                               | 1A- 1       |

| Power On/Off Procedures                    | 1A- 1       |

| Powering Off/On a Single Controller        | 1A-1        |

| Powering Off/On a Single Device            | 1A-2        |

| Powering Off a Drive String                | 1A-3        |

| Powering On a Drive String                 | 1A- 3       |

| SAMs                                       | 1A-4        |

| HSC Voltage Checks                         | 1A-11       |

| Device Voltage Checks                      | 1A-11       |

ix

| 1B. FAULT SYMPTOM CODE INDEX                 |       |

|----------------------------------------------|-------|

| Introduction                                 | 1B-1  |

| Multiple Error Symptoms                      | 1B-1  |

| Diagnostic Procedure                         | 1B-2  |

| Fault Symptom Code Index (FSCI)              | 1B-2  |

| 1C. SENSE INFORMATION                        |       |

| Introduction ·                               | 1C-1  |

| Format 0 Program or System Checks            | 1C-1  |

| Format 1 Device Equipment Checks             | 1C-2  |

| Format 4 Uncorrectable Data Checks           | 1C-2  |

| Format 5 Correctable Data Checks             | 1C-3  |

| Format 6 Usage/Overrun Error Statistics      | 1C-3  |

| Format 7 Controller Check-1                  | 1C-3  |

| Format 8 Controller Equipment Checks         | 1C-4  |

| Sense Bytes 0 through 7                      | 1C-4  |

| Sense Byte 0 Unit Check Description          | 1C-18 |

| Byte O, Bit O Command Reject                 | 1C-18 |

| Byte O, Bit 1 Intervention Required          | 1C-18 |

| Byte 0, Bit 2 Channel Bus Out Parity Check   | 1C-18 |

| Byte O, Bit 3 Equipment Check                | 1C-18 |

| Byte O, Bit 4 Data Check                     | 1C-18 |

| Byte O, Bit 5 Channel Overrun                | 1C-19 |

| Byte O, Bits 6 and 7 Not Used                | 1C-19 |

| Sense Byte 1 Unit Check Description          | 1C-19 |

| Byte 1, Bit O Permanent Error                | 1C-19 |

| Byte 1, Bit 1 Invalid Track Format (w/o SMB) | 1C-19 |

| Byte 1, Bit 1 Invalid Track Format (w/SMB)   | 1C-19 |

| Byte 1, Bit 2 End of Cylinder                | 1C-19 |

| Byte 1, Bit 3 Message to Operator            | 1C-20 |

| Byte 1, Bit 4 No Record Found (w/o SMB)      | 1C-20 |

| Byte 1, Bit 4 No Record Found (w/SMB)        | 1C-20 |

| Byte 1, Bit 5 File Protected                 | 1C-20 |

| Byte 1, Bits 6 and 7 Not Used                | 1C-20 |

83337530 D

| Sense Byte 2 Unit Check Description                                      | 1C-21          |

|--------------------------------------------------------------------------|----------------|

| Byte 2, Bit 0 Not Used                                                   | 1C-21          |

| Byte 2, Bit 1 Correctable Error                                          | 1C-21          |

| Byte 2, Bit 2 First Logged Error                                         | 1C-21          |

| Byte 2, Bit 3 Environmental Data Present                                 | 1C-21          |

| Byte 2, Bits 4 and 5 Not Used (w/o SMB)                                  | 1C-21          |

| Byte 2, Bit 4 Intent Violation (w/SMB)                                   | 1C-21          |

| Byte 2, Bit 5 Imprecise Ending (w/SMB)                                   | 1C-21          |

| Byte 2, Bits 6 and 7 Not Used                                            | 1C-22          |

| Sense Byte 3 Restart Command/Controller Physical<br>Identifier (w/o SMB) | 1C- 22         |

| Sense Byte 3 Residual Record Count (w/SMB)                               | 1C-23          |

| Sense Byte 4 Device Physical Identifier                                  | 1C-23          |

| Byte 4, Bit 0 DPSE Function                                              | 1C-23          |

| Byte 4, Bit 1 Not Used                                                   | 1C-23          |

| Byte 4, Bit 2 Permanent Path Error                                       | 1C-23          |

| Byte 4, Bit 2 Reserved                                                   | 1C-24          |

| Byte 4, Bits 4-7 Device Address                                          | 1C-24          |

| Sense Bytes 5 and 6 Seek Address                                         | 1C-24          |

| -                                                                        | 1C-24          |

| Sense Byte 7 Format/Message                                              | 1C-24<br>1C-24 |

| Byte 7, Bits 0 through 3 Sense Byte Format                               |                |

| Byte 7, Bits 4 through 7 Message Code                                    | 1C-25          |

| Format 1 Messages, Byte 7                                                | 1C-25          |

| Format 1, Byte 7, Message 0 No Message                                   | 1C-25          |

| Format 1, Byte 7, Message 1 Device Status 1 Not<br>As Expected           | 1C-25          |

| Format 1, Byte 7, Message 2 Reserved                                     | 1C-26          |

| Format 1, Byte 7, Message 3 Index Missing                                | 1C-26          |

| Format 1, Byte 7, Message 4 Interrupt Not                                |                |

| Resettable                                                               | 1C-26          |

| Format 1, Byte 7, Message 5 Device Does Not<br>Respond to Selection      | 1C-26          |

| Format 1, Byte 7, Message 6 Device Check-2 or                            |                |

| Set Sector Incomplete                                                    | 1C-26          |

| Format 1, Byte 7, Message 7 Head Address<br>Miscompare                   | 1C-26          |

.

.

.

.

| Format 1, Byte 7, Message 8 Device Status 1<br>Invalid                          | 1C-27 |

|---------------------------------------------------------------------------------|-------|

| Format 1, Byte 7, Message 9 Device Not Ready<br>For Customer Work               | 1C-27 |

| Format 1, Byte 7, Message A Track Physical<br>Address Miscompare While Oriented | lC-27 |

| Format 1, Byte 7, Message B Not Used                                            | 1C-27 |

| Format 1, Byte 7, Message C Drive Motor Switch<br>Sensed                        | 1C-27 |

| Format 1, Byte 7, Message D Seek Incomplete                                     | 1C-27 |

| Format 1, Byte 7, Message E Cylinder Address<br>Miscompare                      | 1C-27 |

| Format 1, Byte 7, Message F Offset Active Not<br>Resettable                     | 1C-28 |

| Format 4 Messages, Byte 7                                                       | 1C-28 |

| Format 4, Byte 7, Message 0 Home Address, ECC<br>Uncorrectable                  | 1C-28 |

| Format 4, Byte 7, Message 1 Count Area, ECC<br>Úncorrectable                    | 1C-28 |

| Format 4, Byte 7, Message 2 Key Area, ECC<br>Uncorrectable                      | 1C-28 |

| Format 4, Byte 7, Message 3 Data Area, ECC<br>Uncorrectable                     | 1C-28 |

| Format 4, Byte 7, Message 4 Home Address Area,<br>No Sync Byte Found            | 1C-28 |

| Format 4, Byte 7, Message 5 Count Area, No Sync<br>Byte Found                   | 1C-29 |

| Format 4, Byte 7, Message 6 Key Area, No Sync<br>Byte Found                     | 1C-29 |

| Format 4, Byte 7, Message 7 Data Area, No Sync<br>Byte Found                    | 1C-29 |

| Format 4, Byte 7, Message 8 HA Area, ECC<br>Uncorrectable with Offset Active    | 1C-29 |

| Format 4, Byte 7, Message 9 Count Area, ECC<br>Uncorrectable with Offset Active | 1C-29 |

| Format 4, Byte 7, Message A Key Area, ECC<br>Uncorrectable with Offset Active   | 1C-29 |

| Format 4, Byte 7, Message B Data Area, ECC<br>Uncorrectable with Offset Active  | 1C-29 |

| Format 4, Byte 7, Message C HA Area, No Sync<br>Byte Found with Offset Active   | 1C-30 |

.

83337530 D

.

.

.

•

| Format 4, Byte 7, Message D Count Area, No Sync<br>Byte Found with Offset Active | 1C-30  |

|----------------------------------------------------------------------------------|--------|

| Format 4, Byte 7, Message E Key Area, No Sync<br>Byte Found with Offset Active   | 1C-30  |

| Format 4, Byte 7, Message F Data Area, No Sync<br>Byte Found with Offset Active  | 1C-30  |

| Format 5 Messages, Byte 7                                                        | 1C-30  |

| Format 5, Byte 7, Message 0 Home Address Area                                    | 1C-30  |

| Format 5, Byte 7, Message 1 Count Area                                           | 1C-31  |

| Format 5, Byte 7, Message 2 Key Area                                             | 1C-31  |

| Format 5, Byte 7, Message 3 Data Area                                            | 1C-31  |

| Format 5, Byte 7, Messages 4-7 Not Used                                          | 1C-31  |

| Format 5, Byte 7, Message 8 Home Address Area,<br>Offset Active                  | 1C-31  |

| Format 5, Byte 7, Message 9 Count Area, Offset<br>Active                         | 1C-31  |

| Format 5, Byte 7, Message A Key Area, Offset<br>Active                           | 1C-31  |

| Format 5, Byte 7, Message B Data Area, Offset<br>Active                          | 1C-31  |

| Format 5, Byte 7, Messages C-F Not Used                                          | 1C-31  |

| Format 7 Messages, Byte 7                                                        | 1C-32  |

| Format 7, Byte 7, Message 0 RCC Initiated by a<br>Connection Check Alert         | 1C-32  |

| Format 7, Byte 7, Message 1 RCCl Sequence Not<br>Successful                      | 1C- 32 |

| Format 7, Byte 7, Message 2 RCC1 and RCC2<br>Sequence Not Successful             | 1C-32  |

| Format 7, Byte 7, Message 3 Invalid Tag In<br>During Selection Sequence          | 1C- 32 |

| Format 7, Byte 7, Message 4 Extra RCC Required                                   | 1C-33  |

| Format 7, Byte 7, Message 5 Invalid DDC<br>Selection Response                    | 1C-33  |

| Format 7, Byte 7, Message 6 Missing End<br>Operation, Transfer Was Complete      | 1C-33  |

| Format 7, Byte 7, Message 7 Missing End<br>Operation, Transfer Was Incomplete    | 1C-33  |

| Format 7, Byte 7, Message 8 Invalid Tag In for<br>an Immediate Command Sequence  | 1C-34  |

.

xiii

Format 7, Byte 7, Message 9 -- Invalid Tag In for an Extended Command Sequence 1C - 34Format 7, Byte 7, Message A -- Storage Director Microcode Timed Out on Deselection 1C - 34Format 7, Byte 7, Message B -- No Selection Response After Poll Interrupt 1C - 34Format 7, Byte 7, Message C -- Controller Not Available 1C-35 Format 7, Byte 7, Messages D through F -- Not Used 1C-35 Format 8 Messages, Byte 7 1C-35 Format 8, Byte 7, Message 0 -- No Message 1C-35 Format 8, Byte 7, Message 1 -- ECC Hardware Check 1C-35 Format 8, Byte 7, Message 2 -- Reserved 1C - 35Format 8, Byte 7, Message 3 -- Unexpected End Operation Response Code Received 1C - 35Format 8, Byte 7, Message 4 -- End Operation Received with Transfer Count Not Equal to Zero 1C-36 Format 8, Byte 7, Message 5 -- End Operation Received with Transfer Count Equal to Zero 1C-36 Format 8, Byte 7, Message 6 -- DPSE Cleanup Checks on Channel or System Reset 1C-36 Format 8, Byte 7, Messages 7-F -- Not Used 1C-36 Format 1, Sense Bytes 8 through 23 -- Device Equipment Checks 1C-36 Format 1, Sense Byte 8 -- DDC Bus Out 0 1C-36 Format 1, Sense Byte 9 -- DDC Bus In 1 1C-37 Format 1, Byte 9, Bit 0 -- Index Found 1C-37 Format 1, Byte 9, Bit 1 -- No Sync Byte Found and No Data Found 1C-37 Format 1, Byte 9, Bits 2-7 -- End Operation Codes 1C-38 Format 1, Sense Byte 10 -- Device Power Status 1C - 40Format 1, Byte 10, Bit 0 -- Voltage Margins Active 1C-40 Format 1, Byte 10, Bit 1 -- Motor Thermal 1C - 40Format 1, Byte 10, Bit 2 -- No Air Flow 1C-40 Format 1, Byte 10, Bit 3 -- Device Sequence Complete 1C - 40Format 1, Byte 10, Bit 4 -- Motor Run Latch On 1C - 40Format 1, Byte 10, Bit 5 -- Motor Contactor Active 1C-40 Format 1, Byte 10, Bit 6 -- Motor Brake Latch On 1C - 41

Format 1, Byte 10, Bit 7 -- Brake Applied 1C - 41Format 1, Sense Byte 11 -- Device Check Register 1C - 41Format 1, Byte 11, Bit 0 -- Error Flag (Checkpoint 1C - 41Check) Format 1, Byte 11, Bit 1 -- Servo Control Check 1C - 41Format 1, Byte 11, Bit 2 -- RPS Check 1C - 41Format 1, Byte 11, Bit 3 -- Checkpoint Log Parity Error 1C - 42Format 1, Byte 11, Bit 4 -- Not Used 1C-42 Format 1, Byte 11, Bit 5 -- Power Card Check 1C-42 Format 1, Byte 11, Bit 6 -- Read/Write Check 1C - 42Format 1, Byte 11, Bit 7 -- Not Used 1C-42 Format 1, Sense Byte 12 -- Read/Write Status 1 1C - 42Format 1, Byte 12, Bits 0 and 1 -- Read/Write Check 1C-42 Format 1, Byte 12, Bits 2-4 -- Matrix Sense 1C - 42Format 1, Byte 12, Bits 5-7 -- Not Used 1C - 43Format 1, Sense Byte 13 -- Read/Write Status 2 1C - 43Format 1, Byte 13, Bit 0 -- Read/Write Check 1C - 43Format 1, Byte 13, Bit 1 -- Pad Check 1C - 43Format 1, Byte 13, Bit 2 -- Write Sequence Check 1C - 44Format 1, Byte 13, Bit 3 -- Read Sequence Check 1C - 44Format 1, Byte 13, Bit 4 -- Read/Write Control Check 1C - 44Format 1, Byte 13, Bit 5 -- Write Overrun Check 1C-44 Format 1, Byte 13, Bit 6 -- Read/Write Servo Check 1C-44 Format 1, Byte 13, Bit 7 -- HAR Parity Check 1C-44 Format 1, Sense Byte 14 -- Not Used 1C - 44Format 1, Sense Byte 15 -- Checkpoint Log 1C - 44Format 1, Byte 15, Bits 0-3 -- Routine 1C - 45Format 1, Byte 15, Bits 4-7 -- Checkpoints 1C - 45Format 1, Sense Bytes 16 and 17 -- Physical Track Address Read or Expected Status 1C - 51Format 1, Sense Byte 18 -- Not Used 1C-51 Format 1, Sense Byte 19 -- Device Status 1 1C-51 Format 1, Byte 19, Bit 0 -- Pad in Progress 1C - 52Format 1, Byte 19, Bit 1 -- Servo Inhibited 1C-52

Format 1, Byte 19, Bit 2 -- Seek Incomplete 1C - 52Format 1, Byte 19, Bit 3 -- Device Check-2 or Set Sector Incomplete 1C-52 Format 1, Byte 19, Bit 4 -- On Line 1C-52 Format 1, Byte 19, Bit 5 -- HDA Attention 1C - 52Format 1, Byte 19, Bit 6 -- Device Busy 1C - 53Format 1, Byte 19, Bit 7 -- Seek or Set Sector 1C-53 Interrupt or Sector Search Format 1, Sense Byte 20 -- Device Status 2 1C-54 Format 1, Byte 20, Bit 0 -- Device Logic Disabled 1C-54 Format 1, Byte 20, Bit 1 -- Surge Complete 1C - 54Format 1, Byte 20, Bit 2 -- Offset Active 1C-55 Format 1, Byte 20, Bit 3 -- Spindle Off 1C-55 Format 1, Byte 20, Bits 4 and 5 -- Not Used 1C-55 Format 1, Byte 20, Bit 6 -- Right Access Mechanism 1C-55 Selected Format 1, Byte 20, Bit 7 -- Left Access Mechanism Selected 1C--55 Format 1, Sense Byte 21 -- Storage Director Physical Identifier 1C-55 Format 1, Sense Bytes 22 and 23 -- Fault Symptom Code 1C-55 Format 4, Sense Bytes 8 through 23 -- Uncorrectable Data Checks 1C-56 Format 4, Sense Bytes 8-12 -- Record Identification 1C-56 Format 4, Sense Byte 13 -- Sector Number 1C-56 Format 4, Sense Byte 14 -- Controller Physical Identifier 1C-57 Format 4, Sense Byte 15 -- Head Offset Increment/Direction 1C-57 Format 4, Sense Bytes 16-20 -- Not Used 1C-57 Format 4, Sense Byte 21 -- Storage Director Physical Identifier 1C-57 Format 4, Sense Bytes 22 and 23 -- Fault Symptom Code 1C-57 Format 5, Sense Bytes 8 through 23 -- Correctable Data Checks 1C-57 Format 5, Sense Bytes 8-12 -- Record Identification 1C-58 Format 5, Sense Byte 13 -- Sector Number 1C-58 Format 5, Sense Byte 14 -- Controller Physical Identifier 1C - 58

Format 5, Sense Bytes 15, 16, and 17 -- With Sense Byte 2, Bit 3 On 1C-58 Format 5, Sense Bytes 15, 16, and 17 -- With Sense Byte 2, Bit 3 Off 1C-59 Format 5, Sense Bytes 18 and 19 -- Error Displacement 1C-59 Format 5, Sense Bytes 20-23 -- Error Pattern 1C-59 Format 6, Sense Bytes 8 through 23 -- Usage/Overrun Error Statistics 1C-59 Format 6, Sense Bytes 8-11 -- Bytes Read/Searched 1C-60 Format 6, Sense Bytes 12-15 -- Not Used 1C - 60Format 6, Sense Bytes 16 and 17 -- Number of Motion Seeks 1C - 60Format 6, Sense Bytes 18-20 -- Not Used 1C-60 Format 6, Sense Byte 21 -- Storage Director Physical Identifier 1C - 60Format 6, Sense Bytes 22 and 23 -- Not Used 1C-60 Format 7, Sense Bytes 8 through 23 -- Controller Check-1 1C-60 Format 7, Sense Byte 8 -- DDC Bus Out - Command Code 1C-61 Format 7, Sense Byte 9 -- DDC Bus In 1C-62 Format 7, Sense Byte 10 -- DTI and XES Register Contents 1C-62 Format 7, Byte 10, Bit 0 -- Connection Check Alert 1C-62 Format 7, Byte 10, Bit 1 -- Tag In Check 1C-62 Format 7, Byte 10, Bit 2 -- Sync In Check 1C-62 Format 7, Byte 10, Bit 3 -- DDC Bus In Parity Check 1C-62 Format 7, Byte 10, Bit 4 -- Null Disconnect 1C-62 Format 7, Byte 10, Bit 5 -- Valid/Sync In 1C-62 Format 7, Byte 10, Bit 6 -- Selected Null 1C-63 Format 7, Byte 10, Bit 7 -- End Operation 1C-63 Format 7, Sense Byte 11 -- Controller Check Alert 1C - 63Format 7, Byte 11, Bit 0 -- Controller 0 CCA 1C - 63Format 7, Byte 11, Bit 1 -- Controller 1 CCA 1C-63 Format 7, Byte 11, Bit 2 -- Controller 0 DPSE Force Release 1C-63 Format 7, Byte 11, Bit 3 -- Controller 1 DPSE Force Release 1C - 63Format 7, Byte 11, Bit 4 -- Controller 0 Power On 1C-64

Format 7, Byte 11, Bit 5 -- Controller 1 Power On 1C - 64Format 7, Byte 11, Bits 6 and 7 -- Not Used 1C - 64Format 7, Sense Byte 12 - Controller 0 Check-1 (CCA) 1C - 64Format 7, Byte 12, Bits 0-2 -- Check-1 Isolation 1C - 64Bits Format 7, Byte 12, Bit 3 -- DDC Bus Out Parity Check 1C - 65Format 7, Byte 12, Bit 4 -- Controller Clock Check 1C-65 Format 7, Byte 12, Bit 5 -- Controller Sequencer Check-1 1C-65 Format 7, Byte 12, Bit 6 -- DDC Bus In Parity Check-1 1C-65 Format 7, Byte 12, Bit 7 -- Not Used 1C - 65Format 7, Sense Byte 13 -- Controller 0 Check-1 (CCA) 1C-65 Format 7, Byte 13, Bit 0 -- DDC Tag Out Sequence 1C - 66Check Format 7, Byte 13, Bit 1 -- Oriented Tag Sequence 1C-66 Check-1 Format 7, Byte 13, Bit 2 -- Sequencer Detected Check-1 1C-66 Format 7, Byte 13, Bit 3 -- DDC Float Check 1C-66 Format 7, Byte 13, Bit 4 -- RCC Clock Check 1C-66 Format 7, Byte 13, Bits 5-7 -- Not Used 1C-66 Format 7, Sense Byte 14 -- Controller 1 Check-1 (CCA) 1C-67 Format 7, Byte 14, Bits 0-2 -- Check-1 Isolation Bits 1C-67 Format 7, Byte 14, Bit 3 -- DDC Bus Out Parity Check 1C - 67Format 7, Byte 14, Bit 4 -- Controller Clock Check 1C-67 Format 7, Byte 14, Bit 5 -- Controller Sequencer Check-1 1C-68 Format 7, Byte 14, Bit 6 -- DDC Bus In Parity 1C-68 Check Format 7, Byte 14, Bit 7 -- Not Used 1C-68 Format 7, Sense Byte 15 -- Controller 1 Check-1 (CCA) 1C-68 Format 7, Byte 15, Bit 0 -- DDC Tag Out Sequence 1C-68 Check Format 7, Byte 15, Bit 1 -- Oriented Tag Sequence 1C-68 Check-1

Format 7, Byte 15, Bit 2 -- Sequencer Detected Check-1 1C-69 Format 7, Byte 15, Bit 3 -- DDC Float Check 1C - 69Format 7, Byte 15, Bit 4 -- RCC Clock Check 1C-69 Format 7, Byte 15, Bits 5-7 -- Not Used 1C - 69Format 7, Sense Bytes 16 and 17 -- Controller 0 Sequencer Address and Status 1C - 69Format 7, Byte 17, Bit 4 -- Power On Complete 1C-69 Format 7, Byte 17, Bit 5 -- Check-2 Active 1C-69 Format 7, Byte 17, Bit 6 -- Successful Data Transfer 1C - 70Format 7, Byte 17, Bit 7 -- Upper Memory Enabled 1C - 70Format 7, Sense Bytes 18 and 19 -- Controller 1 Sequence Address and Status 1C-70 Format 7, Byte 19, Bit 4 -- Power On Complete 1C - 70Format 7, Byte 19, Bit 5 -- Check-2 Active 1C - 70Format 7, Byte 19, Bit 6 -- Successful Data Transfer 1C-70 Format 7, Byte 19, Bit 7 -- Upper Memory Enabled 1C-70 Format 7, Sense Byte 20 -- Byte 7 Data - For Message С 1C - 71Format 7. Sense Byte 21 -- Storage Director Physical Identifier 1C-71 Format 7, Sense Bytes 22 and 23 -- Fault Symptom Code 1C-71 Format 8, Sense Bytes 8 through 23 -- Controller Equipment Checks 1C-71 Format 8, Sense Byte 8 -- DDC Bus Out 1C-72 Format 8, Sense Byte 9 -- DDC Bus In (End Operation Code) 1C-72 Format 8, Sense Byte 10 -- DTI and XES Register Contents 1C - 74Format 8, Byte 10, Bit 0 -- Connection Check Alert 1C-74 Format 8, Byte 10, Bit 1 -- Tag In Check 1C - 74Format 8, Byte 10, Bit 2 -- Sync In Check 1C - 74Format 8, Byte 10, Bit 3 -- DDC Bus In Parity Check 1C - 74Format 8, Byte 10, Bit 4 -- Null/Disconnect 1C - 75Format 8, Byte 10, Bit 5 -- Valid/Sync In 1C-75 Format 8, Byte 10, Bit 6 -- Selected Null 1C-75

Format 8, Byte 10, Bit 7 -- End Operation 1C-75 Format 8, Sense Byte 11 -- Fault Log Byte A 1C-75 Format 8, Byte 11, Bit 0 -- SERDES Error 1C - 75Format 8, Byte 11, Bit 1 -- CODEC Wrap Error 1C - 75Format 8, Byte 11, Bit 2 -- Software-Check-2 1C-75 Format 8, Byte 11, Bit 3 -- Missing Servo Check 1C-76 Format 8, Byte 11, Bit 4 -- CDP Input Bus Parity Check 1C-76 Format 8, Byte 11, Bit 5 -- Power Interrupt 1C - 76Format 8, Byte 11, Bit 6 -- Internal CDP Tag or Data Out Register Parity 1C-76 Format 8, Byte 11, Bit 7 -- Power Supply Tolerance 1C-76 Check Format 8, Sense Byte 12 -- Fault Log Byte B 1C - 76Format 8, Byte 12, Bit 0 -- Write Control Check 1C-76 Format 8, Byte 12, Bit 1 -- Not Used 1C-76 Format 8, Byte 12, Bit 2 -- DDC Write OP Parity 1C-77 Check Format 8, Byte 12, Bit 3 -- DDC Bus In Parity ·Check 1C-77 Format 8, Byte 12, Bits 4 and 5 -- Port Select Bits 0 and 1 1C-77 Format 8, Byte 12, Bit 6 -- Not Used 1C-77 Format 8, Byte 12, Bit 7 -- CDP Port Check-1 1C-77 Format 8, Sense Byte 13 -- Fault Log Byte C 1C-77 Format 8, Byte 13, Bit 0 -- ECC Bus Parity Check 1C-77 Format 8, Byte 13, Bit 1 -- CDP Bidir Data Parity 1C-77 Check Format 8, Byte 13, Bit 2 -- Sync In/Sync Out Error 1C-78 Format 8, Byte 13, Bit 3 -- CDP 12 Data Output Parity Error 1C-78 Format 8, Byte 13, Bits 4 and 5 -- String 1C-78 Configuration Format 8, Byte 13, Bit 6 -- CDP 12 Path Busy Parity Error 1C - 78Format 8, Byte 13, Bit 7 -- CDP Data Lock Parity Check 1C - 78Format 8, Sense Byte 14 -- Fault Log Byte D 1C - 78Format 8, Byte 14, Bits 0-3 -- Device Check-1 1C-79

Format 8, Byte 14, Bit 4 -- Device Clock Check 1C - 79Format 8, Byte 14, Bit 5 -- Isolation Bit 1C - 79Format 8, Byte 14, Bits 6 and 7 -- Port Select Bits 2 and 3 1C - 79Format 8, Sense Byte 15 -- Fault Log Byte E 1C-79 Format 8, Byte 15, Bit 0 -- DPSE Memory Parity 1C-79 Error Format 8, Byte 15, Bit 1 -- DPSE Data Bus Parity Error 1C-79 Format 8, Byte 15, Bit 2 -- DPSE Memory Compare Error 1C - 80Format 8, Byte 15, Bit 3 -- DPSE Alternate Controller Parity Error 1C-80 Format 8, Byte 15, Bit 4 -- DPSE Address Parity Error 1C-80 Format 8, Byte 15, Bit 5 -- Not Used 1C - 80Format 8, Byte 15, Bit 6 -- DPSE Lock Bus Parity Error 1C-80 Format 8, Byte 15, Bit 7 -- Not Used 1C-80 Format 8, Sense Bytes 16 and 17 -- Selected Controller Sequencer Address and Status 1C-80 Format 8, Byte 17, Bit 4 -- Power On Complete 1C-81 Format 8, Byte 17, Bit 5 -- Check-2 Active 1C-81 Format 8, Byte 17, Bit 6 -- Successful Data Transfer 1C-81 Format 8, Byte 17, Bit 7 -- Upper Memory Enabled 1C-81 Format 8, Sense Byte 18 -- Fault Log Byte F 1C-81 Format 8, Byte 18, Bit 0 -- R/W Bus Out Parity Check 1C-81 Format 8, Byte 18, Bit 1 -- ALU Output Parity Error 1C-81 Format 8, Byte 18, Bit 2 -- Reference Data Parity Error 1C-81 Format 8, Byte 18, Bit 3 -- Read Parity Check 1C-82 Format 8, Byte 18, Bit 4 -- Delta Frequency Check 1C-82 Format 8, Byte 18, Bits 5-7 -- Not Used 1C-82 Format 8, Sense Byte 19 -- Device Status 1 1C - 82Format 8, Byte 19, Bit 0 -- Pad In Progress 1C-82 Format 8, Byte 19, Bit 1 -- Servo Inhibited 1C-82