Customer Engineering Instruction Manual

• • •

•

D

•

THEORY of OPERATION

Customer Engineering Instruction Manual

# CONTROL DATA® 1604-A COMPUTER

THEORY of OPERATION

| RECORD of REVISIONS |                                                        |  |  |  |

|---------------------|--------------------------------------------------------|--|--|--|

| REVISION            | REVISION NOTES                                         |  |  |  |

| А                   | Publication Change Order 14546, no Product Designation |  |  |  |

| <b>(</b> 8-29-66)   | change. Pages 2-3, 4-25, 6-1, 6-2, 6-4 and 6-5 revised |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

|                     |                                                        |  |  |  |

Pub. No. 60118700 September, 1966 © 1966, Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 4201 North Lexington Avenue St. Paul, Minnesota 55112 I

I

or use Comment Sheet located in back of this manual.

# CONTENTS

| Chapter 1.           | Introduction |       |

|----------------------|--------------|-------|

| Description          |              | 1 - 1 |

| Input/Output Section |              | 1-4   |

| Arithmetic Section   |              | 1-4   |

| Storage Section      |              | 1-4   |

| Control Section      |              | 1-4   |

•

•

# Chapter 2. Control Section

| Introduction                                 | 2-1  |

|----------------------------------------------|------|

| Instruction Format                           | 2-2  |

| Operation Code                               | 2-2  |

| Translation of Operation Code                | 2-3  |

| Designator                                   | 2-4  |

| Translation of the Designator                | 2-6  |

| Base Execution Address                       | 2-6  |

| Program Control Register                     | 2-7  |

| The U <sub>2</sub> Accumulator               | 2-7  |

| Index Registers                              | 2-9  |

| Address Buffer Register                      | 2-9  |

| Functions of the R Register                  | 2-10 |

| Counting and Complementing<br>In R           | 2-10 |

| Program Address Register                     | 2-13 |

| Counting in P                                | 2-13 |

| Parallel Transmission Inverter<br>Ranks      | 2-14 |

| Control Sequences                            | 2-15 |

| Relation of Control and Storage<br>Sequences | 2-18 |

| Read Next Instruction Sequence               | 2-20 |

| Acquisition of New<br>Instruction Word       | 2-20 |

| Start and Stop                                                  | 2-20 |

|-----------------------------------------------------------------|------|

| Initial Start                                                   | 2-20 |

| Step                                                            | 2-23 |

| Stop Instruction                                                | 2-23 |

| Breakpoint Stop                                                 | 2-23 |

| Fault Stop                                                      | 2-23 |

| Start from Stop                                                 | 2-23 |

| Preliminary Steps in<br>Address Modification                    | 2-24 |

| Preliminary Control and<br>Arithmetic Steps                     | 2-24 |

| Interrupt Termination                                           | 2-24 |

| Indirect Addressing                                             | 2-26 |

| Normal Jump Sequence                                            | 2-27 |

| Zero Address Sequence                                           | 2-29 |

| Read Operand Sequence                                           | 2-29 |

| Write Operand Sequence                                          | 2-30 |

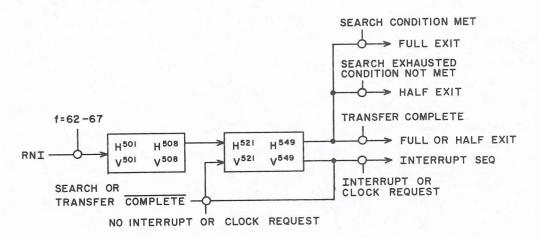

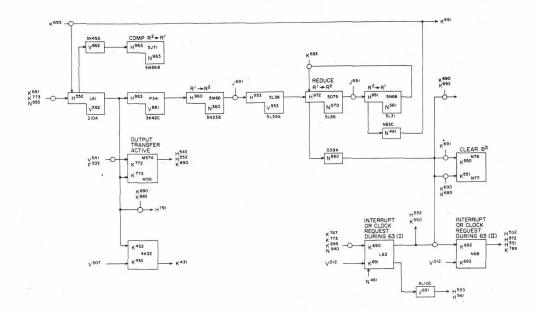

| Search and Transfer Sequence                                    | 2-31 |

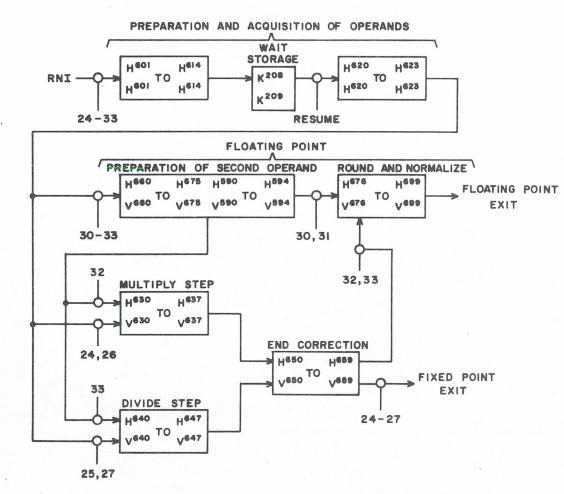

| Iterative Sequence                                              | 2-32 |

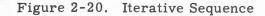

| External Function Sequence                                      | 2-33 |

| Interrupt Sequence                                              | 2-34 |

| Interrupt                                                       | 2-34 |

| Advance Clock                                                   | 2-34 |

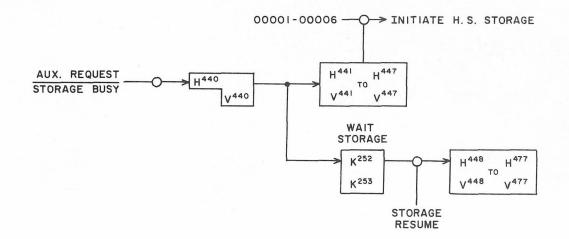

| Buffer Control Section                                          | 2-35 |

| Auxiliary Sequence                                              | 2-35 |

| High Speed Storage Sequence                                     | 2-36 |

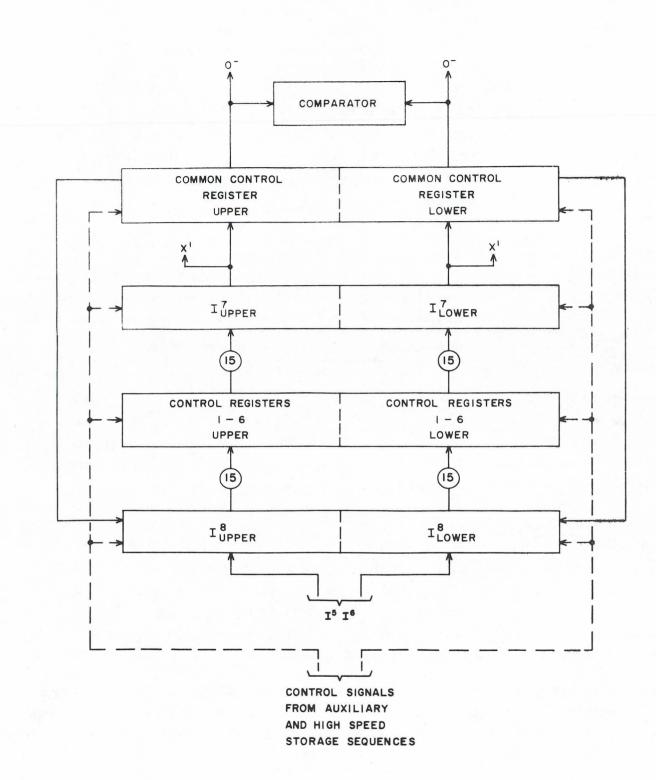

| Control Registers, Common<br>Control Register and<br>Comparator | 2-36 |

| Inverter Ranks $I^7$ and $I^8$                                  | 2-36 |

| Auxiliary Scanner                                               | 2-36 |

| Static Control                                                  | 2-38 |

|                                                                 | 2 00 |

| Breakpoint Address                 | 2-38 |

|------------------------------------|------|

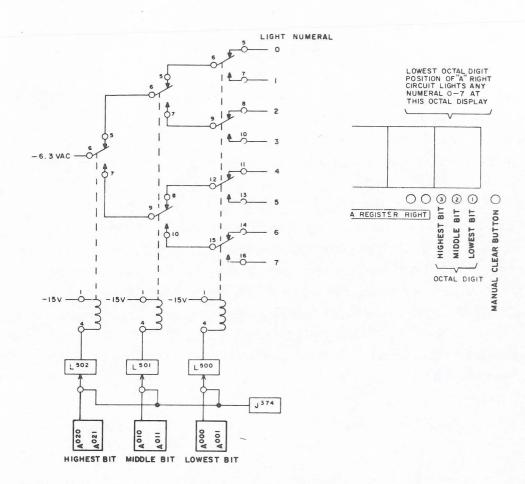

| Console Display                    | 2-38 |

| Resynchronizing                    | 2-40 |

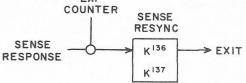

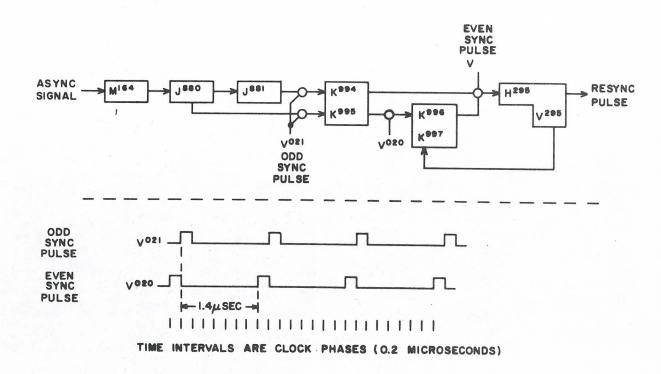

| Resynchronizing Circuit            | 2-40 |

| Runt Pulses                        | 2-41 |

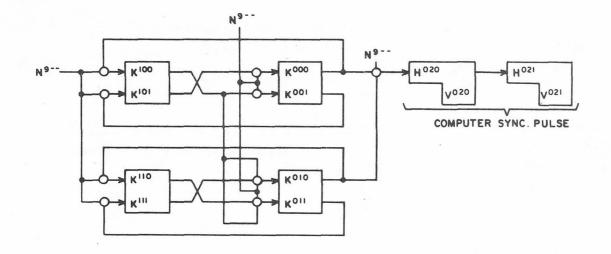

| Resynchronizing Counter and Pulses | 2-41 |

| Jump Instructions                  | 2-42 |

| Normal Jump                        | 2-42 |

| Return Jump                        | 2-43 |

| Program Example                    | 2-44 |

| Skip Instructions                  | 2-44 |

| Computer Operating Controls        | 2-45 |

| Start-Step Switch                  | 2-45 |

| Clear Switch                       | 2-46 |

| Computer Master Clear              | 2-46 |

| External Master Clear              | 2-48 |

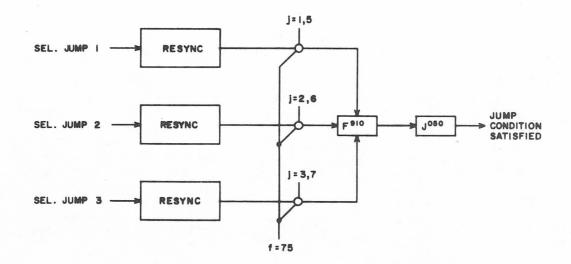

| Selective Jump Switches            | 2-48 |

| Selective Stop Switches            | 2-49 |

| Storage Test Switches              | 2-49 |

| Master Clock                       | 2-50 |

# Chapter 3. Arithmetic Section

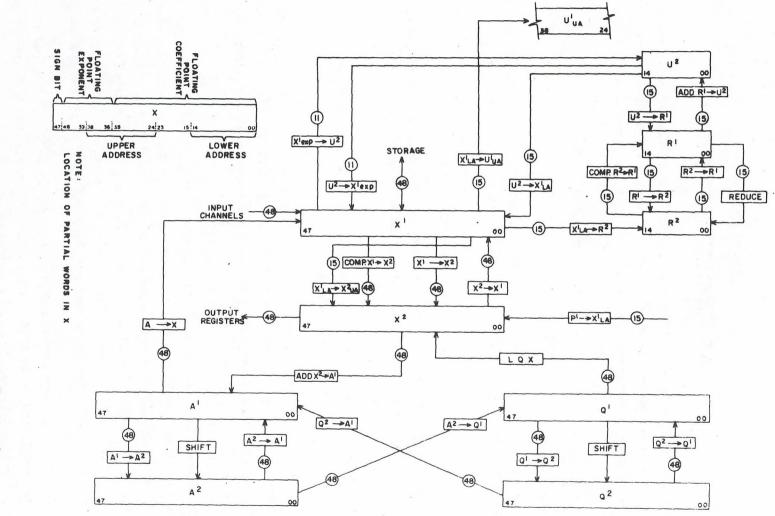

| Arithmetic Registers         | 3-1 |

|------------------------------|-----|

| Accumulator                  | 3-1 |

| Q Register                   | 3-4 |

| X Register                   | 3-4 |

| Registers Used in Arithmetic |     |

| Operations                   | 3-4 |

| Basic Operations             | 3-5 |

| Binary Arithmetic            | 3-5 |

| Addition                     | 3-7 |

| Sensing for First Condition  | 3-7 |

| Sensing for Second Condition | 3-7 |

| Combining Two Conditions     | 3-8 |

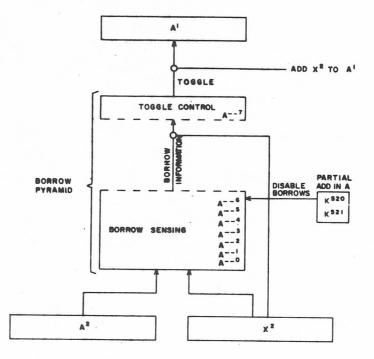

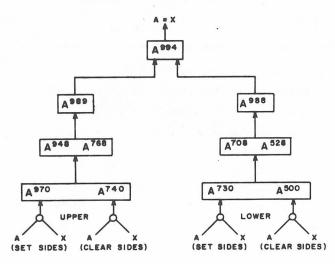

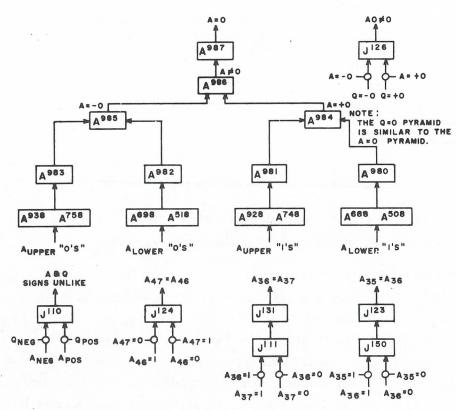

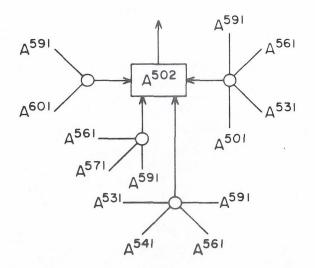

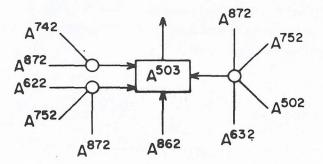

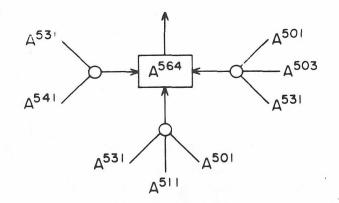

| Borrow Pyramid               | 3-9 |

| Subtraction                                | 3-9  |

|--------------------------------------------|------|

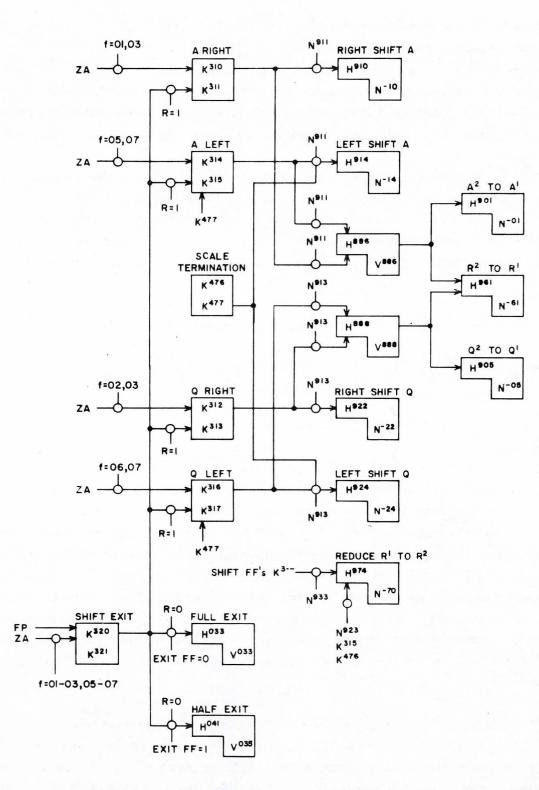

| Shifting                                   | 3-10 |

| Shift Instructions                         | 3-11 |

| Shifting in Multiplication and Division    | 3-13 |

| Shifting in Floating Point<br>Instructions | 3-13 |

| Shifting in Scale Instructions             | 3-13 |

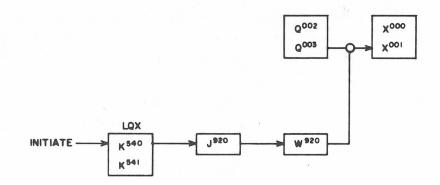

| Iterative Sequence                         | 3-13 |

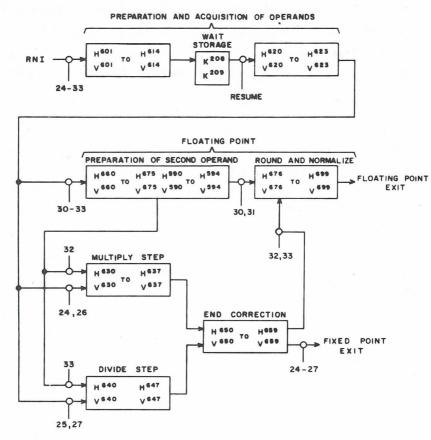

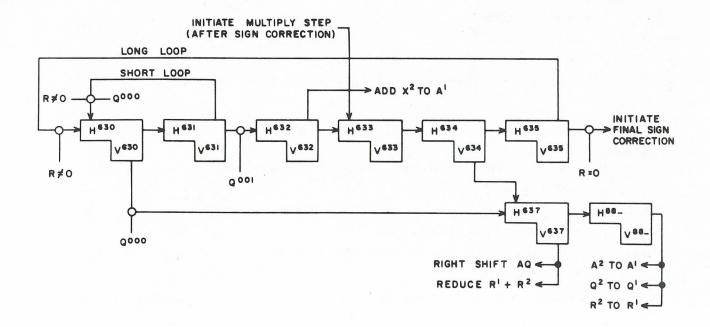

| Multiplication                             | 3-13 |

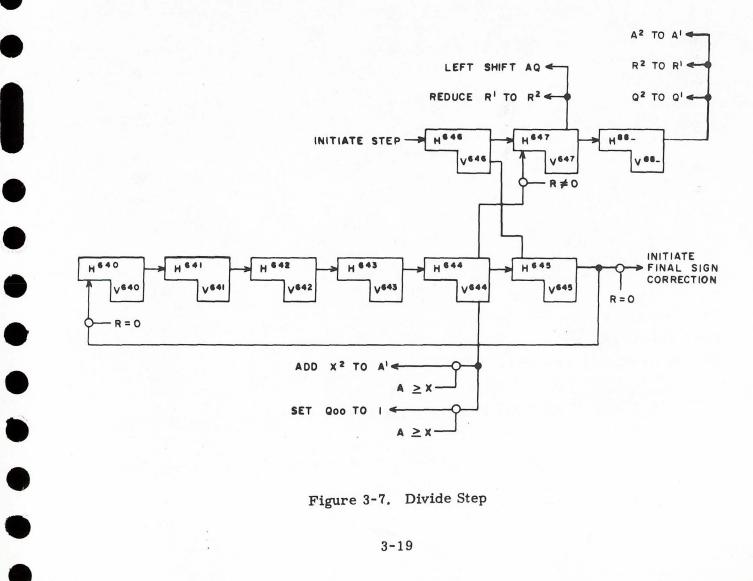

| Division                                   | 3-18 |

| Initial Sign Correction                    | 3-18 |

| Division Phase                             | 3-19 |

| Final Sign Correction                      | 3-20 |

| Floating Point                             | 3-21 |

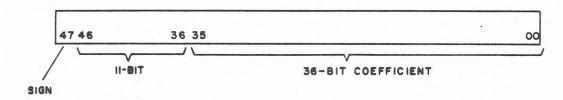

| Coefficient                                | 3-21 |

| Exponent                                   | 3-21 |

| Floating Point Operation                   | 3-23 |

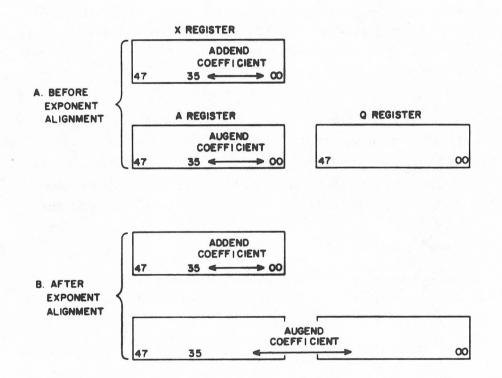

| Addition                                   | 3-24 |

| Subtraction                                | 3-25 |

| Multiplication                             | 3-26 |

| Division                                   | 3-27 |

| Logical Product                            | 3-27 |

| Register Sensing Circuits                  | 3-29 |

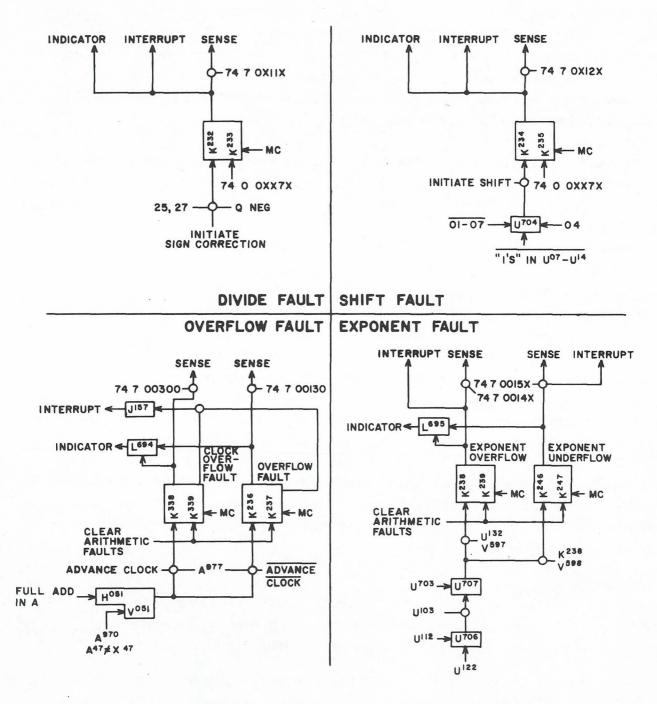

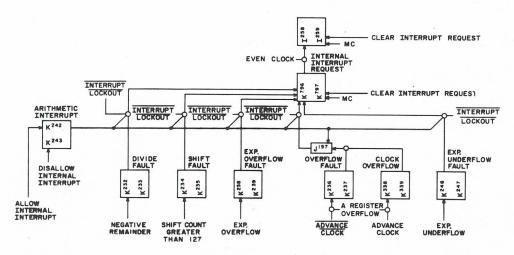

| Arithmetic Faults                          | 3-31 |

| Divide Faults                              | 3-31 |

| Shift Faults                               | 3-31 |

| Overflow Faults                            | 3-33 |

| Exponent Faults                            | 3-33 |

| Fault Control                              | 3-33 |

|                                            |      |

| Chapter 4. Storage Section                 |      |

| Introduction                               | 4-1  |

| Principles of Magnetic Core<br>Storage     | 4-3  |

| Magnetic Cores                             | 4-5  |

| Memory Planes                              | 4-7  |

| Memory Plane Assembly                    | 4-8               |

|------------------------------------------|-------------------|

| Address Selection                        | 4-10              |

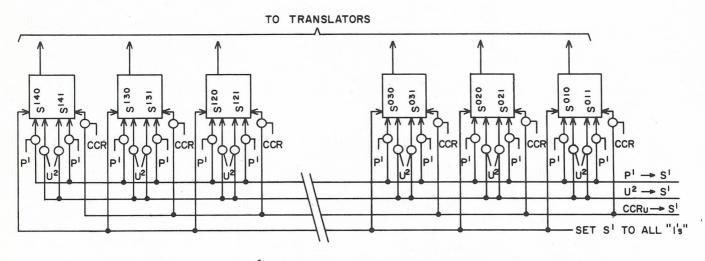

| S Register                               | 4-12              |

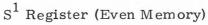

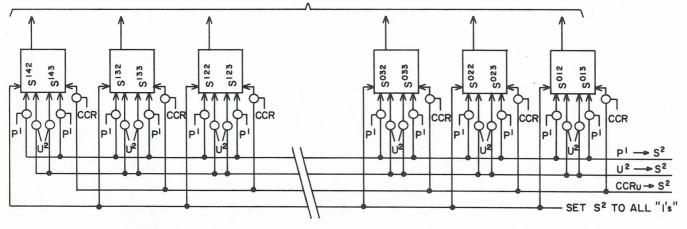

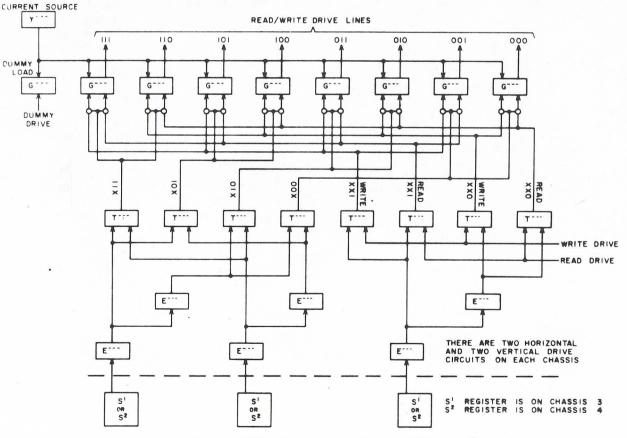

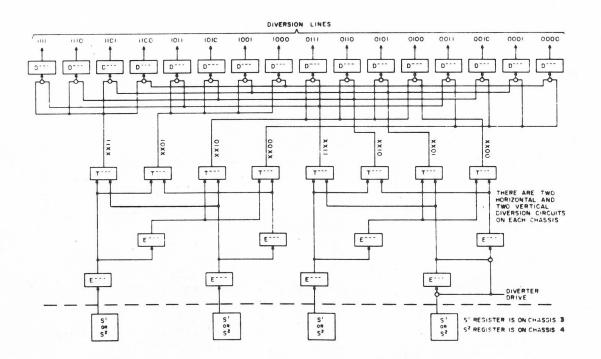

| Horizontal and Vertical Drivers          | 4-12              |

| Horizontal and Vertical Diverters        | 4-16              |

| Memory Place Circuits                    | 4-17              |

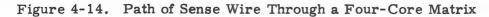

| Sensing Circuit                          | 4-17              |

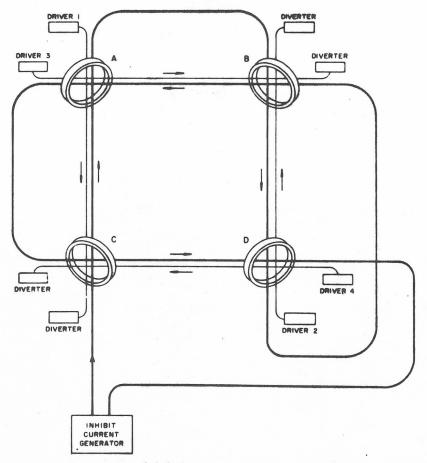

| Inhibit Circuits                         | 4-20              |

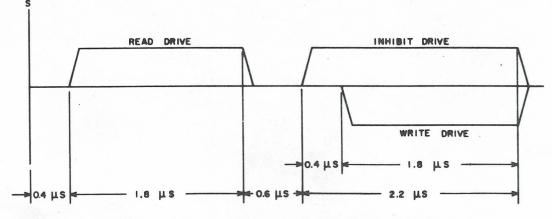

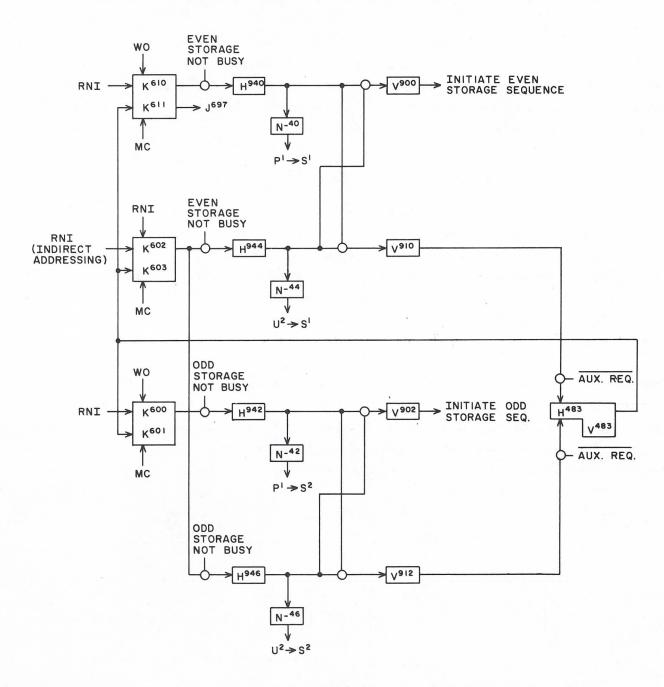

| Storage Sequence Control                 | 4-21              |

| Initiate Storage Reference<br>Circuit    | 4-23              |

| Sequence Controls                        | 4-23              |

| Timing Pulse Generator                   | 4-23              |

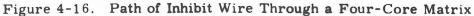

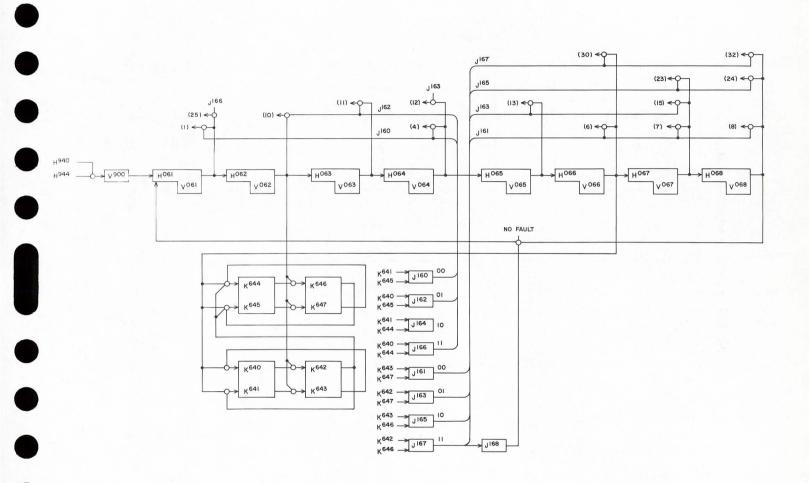

| Drive Generators and Pulse<br>Generators | 4-27              |

| Fault Detector                           | 4-31              |

| Electronic Theory of Storage<br>Circuits | 4-31 Ch           |

| Drive Generator (Type 51)                | 4-32 1            |

| Diverter (Type 52)                       | 4-33              |

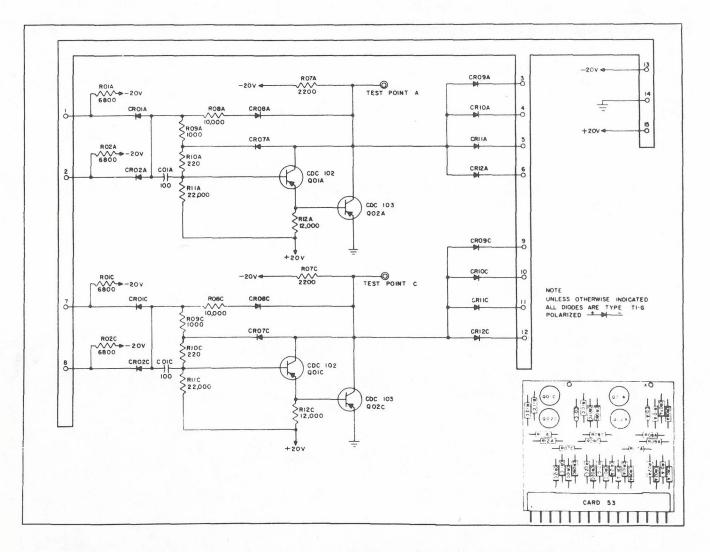

| Selector (Type 53)                       | 4-34              |

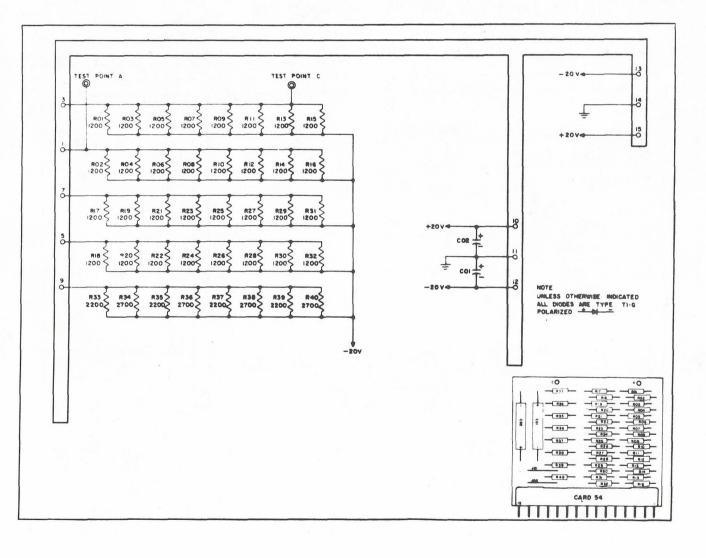

| Current Source (Type 54)                 | 4-35              |

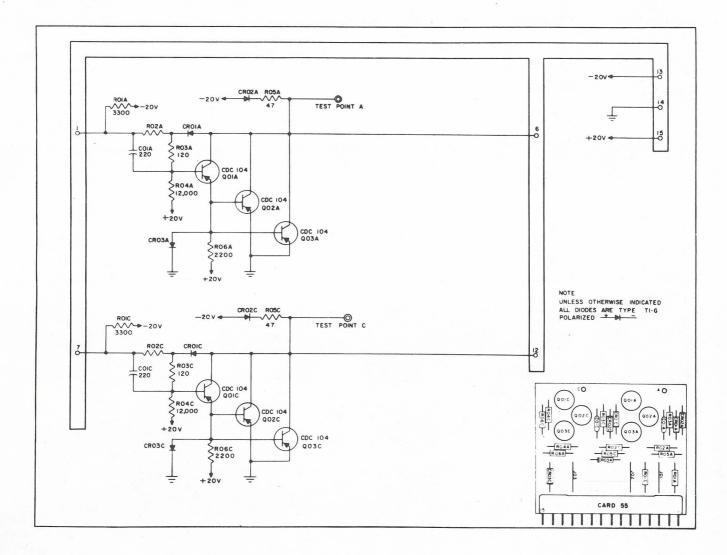

| Inhibit Generator (Type 55)              | 4-36              |

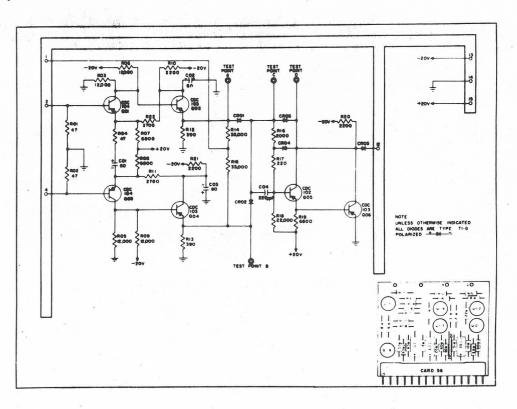

| Sense Amplifier (Type 56)                | 4-37              |

| Chapter 5. Input/Output Section          |                   |

| Data Transmission                        | 5-1               |

| Buffering                                | 5-1               |

| Communication Paths                      | 5-1               |

| Data and Control Information<br>Lines    | 5-2               |

| Buffer Control                           | 5-5               |

| Buffer Operations                        | 5-6               |

| Store Terminal Address                   | 5-8               |

| Sensing for Channel Inactive             | 5-8               |

| Selecting Equipment and Mode             | 5-12 <sup>H</sup> |

| Sensing Condition of Equipment           | 5-12 Ch           |

| Activating the Channel                   | 5-13 <sub>T</sub> |

•

۲

6

| High Speed Storage                      | F 10 |

|-----------------------------------------|------|

| Sequence                                | 5-13 |

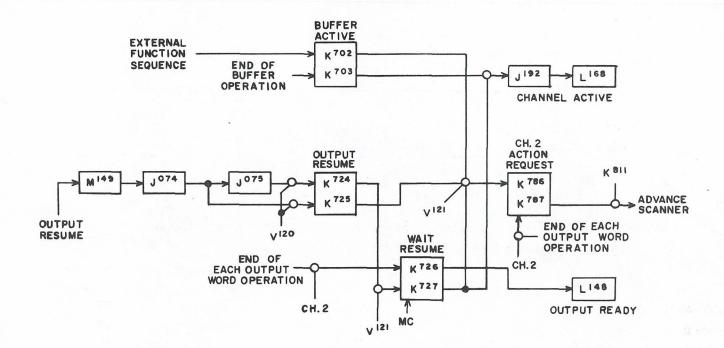

| Ready/Resume Logic<br>(Output)          | 5-14 |

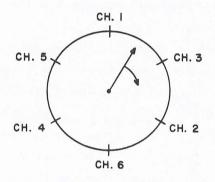

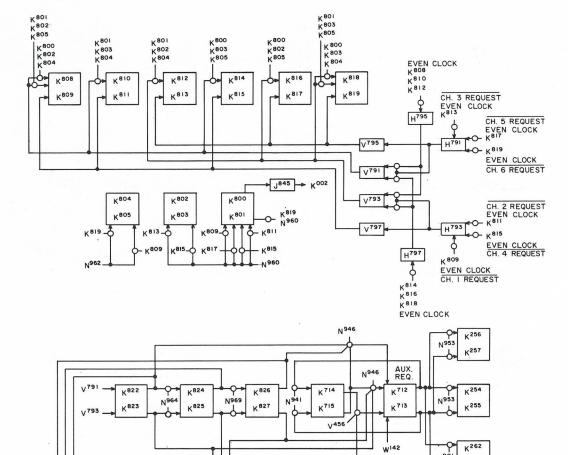

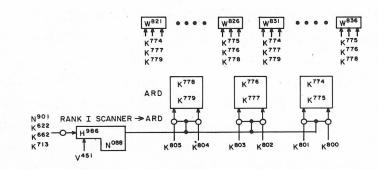

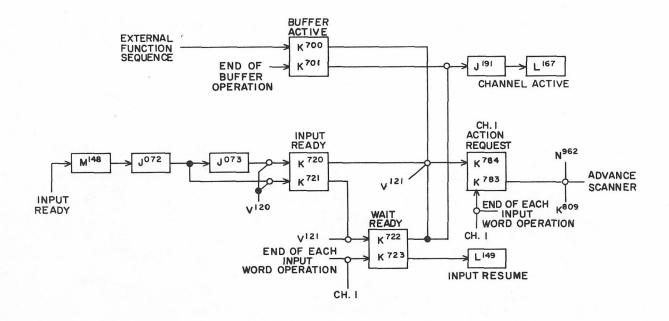

| Auxiliary Scanner                       | 5-14 |

| Auxiliary Sequence                      | 5-17 |

| Ready/Resume Logic (Input)              | 5-18 |

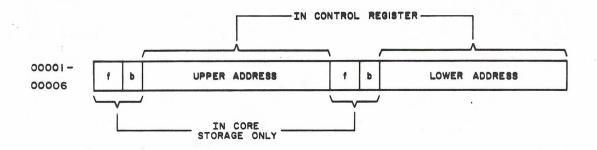

| Buffering to or From 00001 - 00006      | 5-19 |

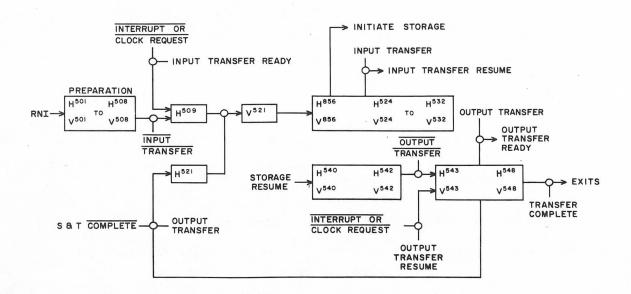

| Transfer                                | 5-20 |

| Preparation                             | 5-21 |

| Input Transfer - 62                     | 5-21 |

| Interrupt or Clock Request<br>During 62 | 5-22 |

| Output Transfer - 63                    | 5-22 |

| Interrupt on Clock Request<br>During 63 | 5-24 |

| apter 6. Interrupt and Real Time Cl     | ock  |

| Interrupt                               | 6-1  |

| Types of Interrupts                     | 6-1  |

| Internal Interrupts                     | 6-2  |

| External Interrupts                     | 6-3  |

| Interrupt Scanner                       | 6-4  |

| Interrupt Sequence Entrance             | 6-7  |

| Interrupt Entrance from Exit            | 6-7  |

| Internal Interrupt During RNI           | 6-7  |

| Interrupt During Output<br>Transfer     | 6-7  |

| Interrupt During Input<br>Transfer      | 6-7  |

| Interrupt During Storage<br>Search      | 6-7  |

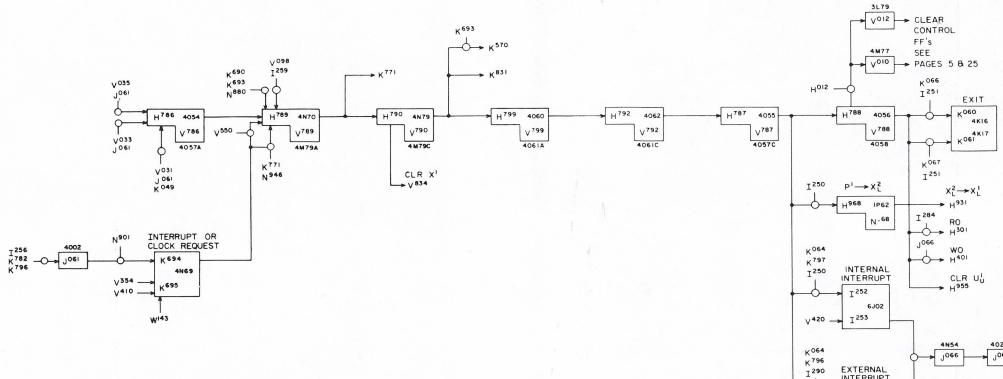

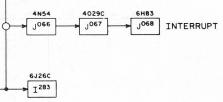

| Interrupt Sequence                      | 6-11 |

| Interrupt Subroutine                    | 6-12 |

| Return to Main Program                  | 6-13 |

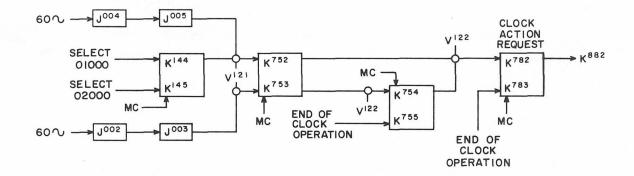

| Real Time Clock                         | 6-14 |

| apter 7. Console Input/Output Equip     | ment |

Modes for Handling Data 7-1

| Exte       | ernal Functions                                              | 7-2          | Typewr | riter                                                        | 7-15  |   |

|------------|--------------------------------------------------------------|--------------|--------|--------------------------------------------------------------|-------|---|

| Se         | lect Codes                                                   | 7-2          | Type   | ewriter Codes                                                | 7-15  |   |

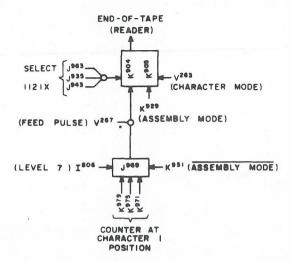

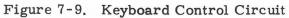

| Se         | ense Codes                                                   | 7-4          | Keyl   | poard Operation                                              | 7-17  |   |

| Input      | Distributor                                                  | 7-5          | Type   | ewriter Output Operation                                     | 7-20  |   |

| Outpu      | at Distributor                                               | 7-7          | Chapt  | er 8. Power and Cooling                                      |       |   |

| Pape       | r Tape Reader                                                | 7-9          |        |                                                              |       |   |

| M          | anual Controls                                               | 7-9          |        | Requirements                                                 | 8-1   |   |

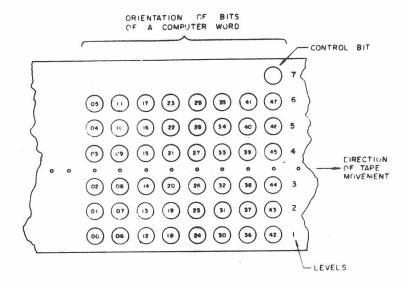

| Pa         | aper Tape                                                    | 7-9          |        | ower Distribution                                            | 8-1   |   |

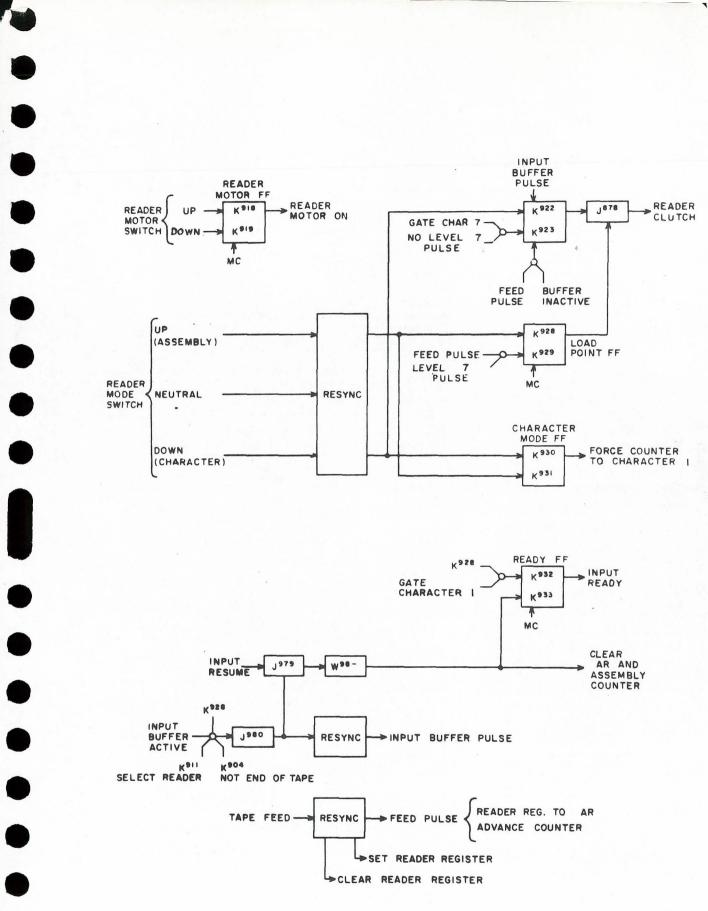

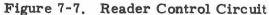

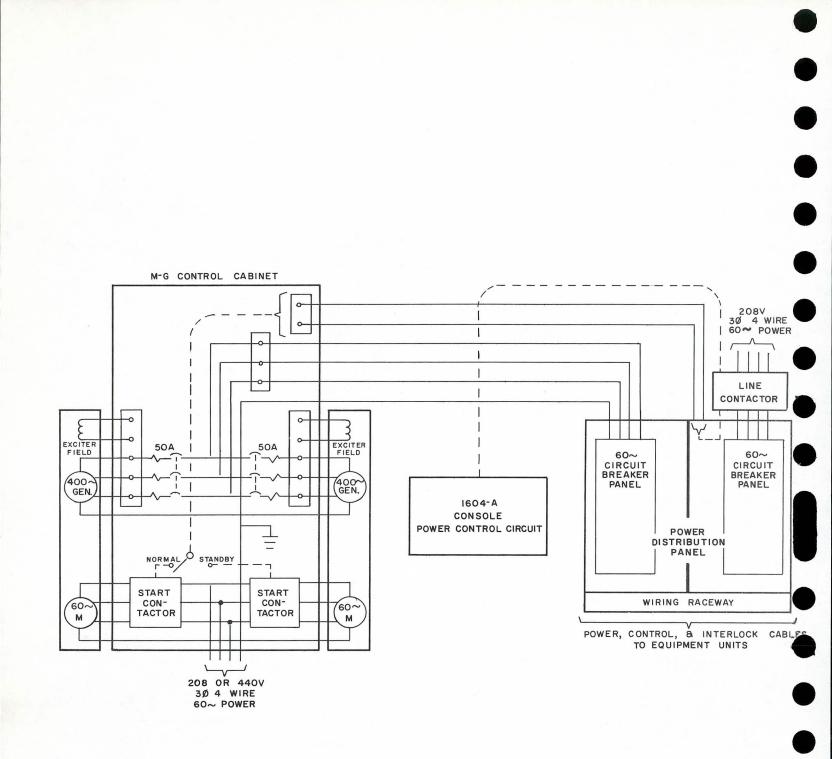

| Re         | eader Operation                                              | 7-10         |        | System                                                       | 8-3   |   |

| Au         | ito Load Control                                             | 7-13         | Prot   | ective Interlock System                                      | 8-3   |   |

| Pape:      | r Tape Punch                                                 | 7-14         |        | Appendixes                                                   |       |   |

| Pu         | anch Controls                                                | 7-14         | A B    | orrow Pyramid                                                | A - 1 |   |

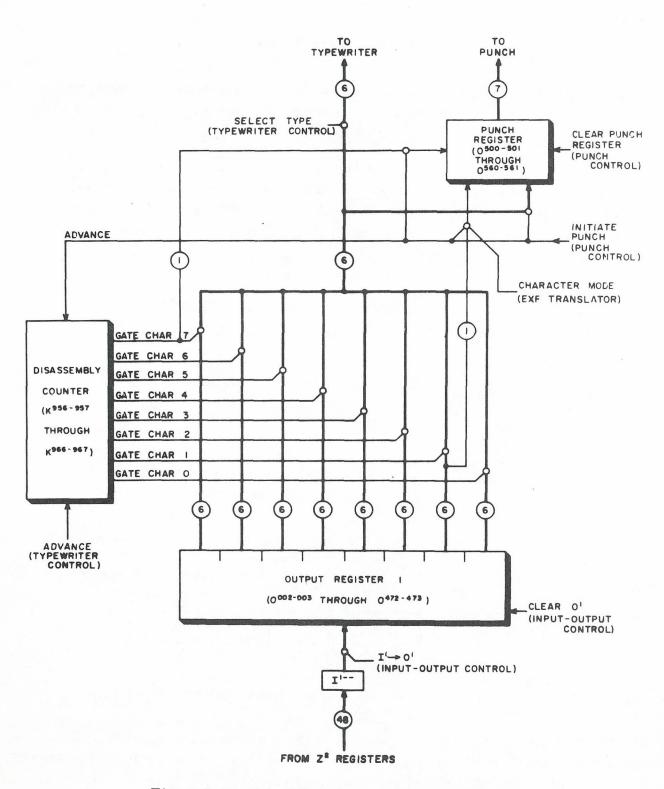

| Ρι         | unch Operation                                               | 7-14         | ВG     | lossary of Terms                                             | B-1   |   |

|            |                                                              |              | C L    | ist of Instructions                                          | C-1   | , |

|            |                                                              | FIGUR        | ES     |                                                              |       |   |

|            |                                                              | 1 10 010     | 20     |                                                              |       |   |

| 1-1<br>1-2 | Typical 1604-A System<br>Simplified Diagram of the           | 1-2          | 2-14   | Indirect Addressing Part<br>of RNI                           | 2-28  |   |

| 1-2        | Computer                                                     | 1-3          | 2-15   | Normal Jump Sequence                                         | 2-28  |   |

| 1-3        | Composition of 48-bit<br>Instruction Word                    | 1-5          | 2-16   | Basic Chain of Control<br>Delays in Zero Address<br>Sequence | 2-29  |   |

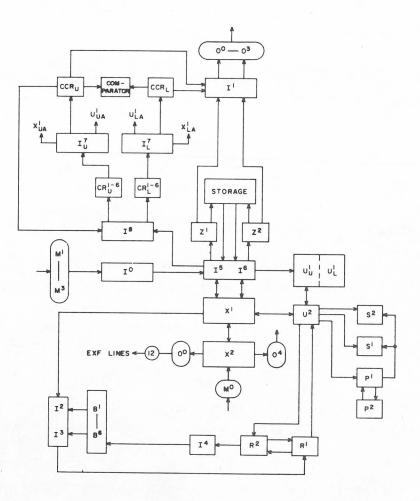

| 2-1        | Block Diagram of Computer<br>Control                         | 2-1          | 2-17   | Basic Chain of Control<br>Delays in RO Sequence              | 2-20  |   |

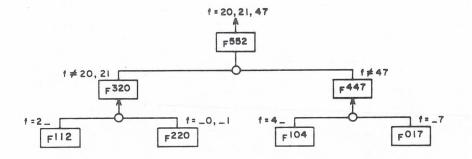

| 2-2        | Structure of Operation Code<br>Translator                    | 2-3          | 2-20   | Iterative Sequence                                           | 2-32  |   |

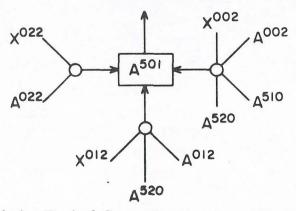

| 2-3        | Translator, Second Level                                     | 2-4          | 2-21   | Block Diagram of EXF                                         |       |   |

| 2-4        | U Register                                                   | 2-7          |        | Sequence                                                     | 2-33  |   |

| 2-5        | Adding in U2 Accumulator                                     | 2-8          | 2-22   | Block Diagram of Interrupt<br>Sequence                       | 2-34  |   |

| 2-6<br>2-7 | R Register Counting Structure<br>Parallel Transmission Paths | 2-11<br>2-14 | 2-23   | Block Diagram of Auxiliary<br>Sequence                       | 2-35  |   |

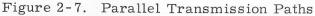

| 2-8        | Example of a Sequence                                        | 2-17         | 2-24   | Pictorial Representation                                     |       |   |

| 2-9        | Over-all Sequence Control                                    | 2-18         |        | of Scanner                                                   | 2-37  |   |

| 2-10       | Relation of Control and<br>Storage Sequences                 | 2-19         | 2-25   | Digit Display, Lowest<br>Octal Digit of A                    | 2-39  |   |

| 2-11       | Form of RNI for Acquiring                                    |              | 2-26   | Console Display                                              | 2-39  |   |

|            | Instructions                                                 | 2-21         | 2-27   | Resynchronizing Circuit                                      | 2-40  |   |

| 2-12       | RNI For Start and Stop                                       | 2-22         | 2-28   | Resynchronizing Counter                                      | 2-42  |   |

| 2-13       | RNI For Interrupt Termination                                | 2-25         | 2-29   | Connection of Start-Step<br>Switch to RNI                    | 2-47  |   |

|            |                                                              |              | 2-30   | Sampling Selective Jump                                      |       |   |

2-30 Sampling Selective Jump Conditions 2-48 1

Ô

7

| 2-31 | Master Clock Oscillator<br>Waveforms                                               | 2-51 |

|------|------------------------------------------------------------------------------------|------|

| 3-1  | Over-All Block Diagram of<br>Arithmetic Section                                    | 3-2  |

| 3-2  | Typical State of A Register                                                        | 3-3  |

| 3-3  | Relation of Borrow Pyramid<br>to A and X Registers                                 | 3-10 |

| 3-4  | Shift Control                                                                      | 3-12 |

| 3-5  | Iterative Sequence                                                                 | 3-14 |

| 3-6  | Multiply Step                                                                      | 3-17 |

| 3-7  | Divide Step                                                                        | 3-19 |

| 3-8  | Relation of Coefficients in<br>Addition                                            | 3-25 |

| 3-9  | Register Sensing Networks                                                          | 3-30 |

| 3-10 | Arithmetic Faults                                                                  | 3-32 |

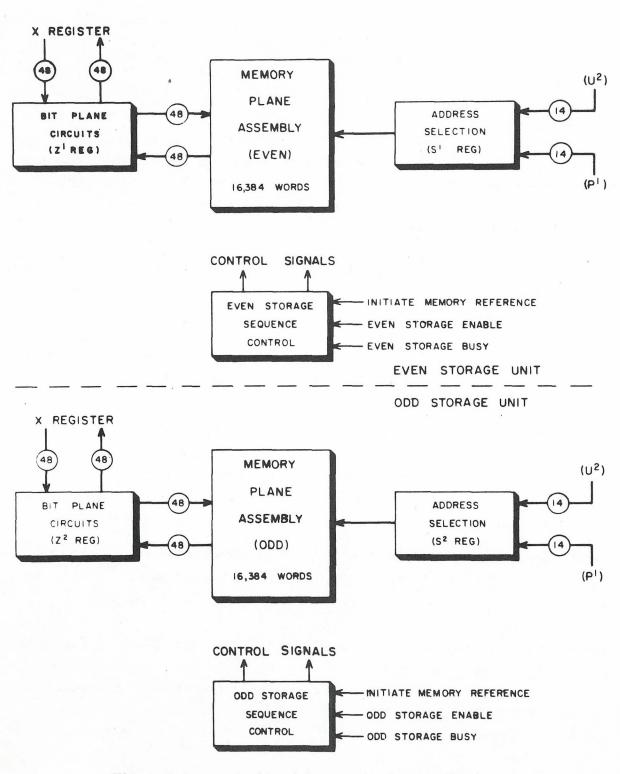

| 4-1  | Logical Divisions of the<br>Storage Section                                        | 4-2  |

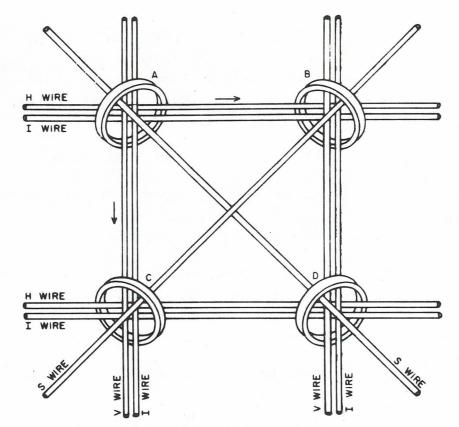

| 4-2  | Magnetic Core Matrix                                                               | 4-4  |

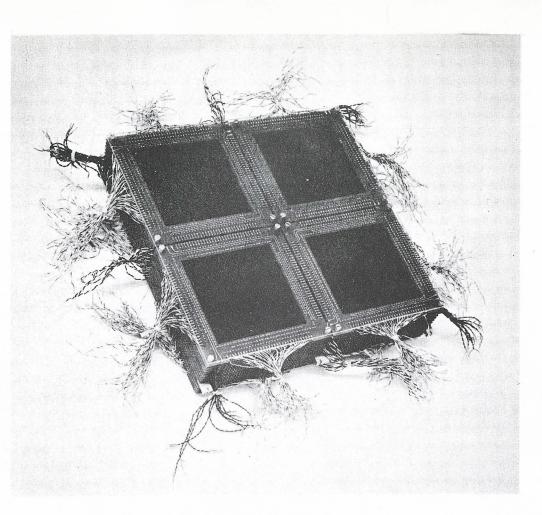

| 4-3  | Memory Plane Stack                                                                 | 4-5  |

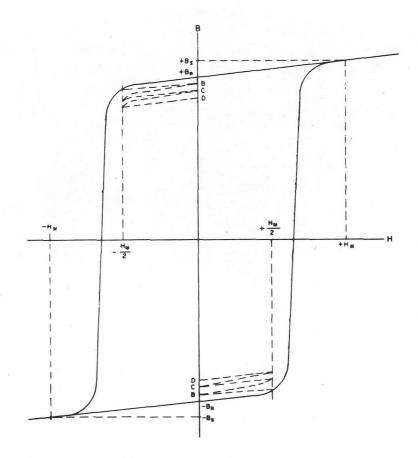

| 4-4  | Hysteresis Diagram                                                                 | 4-6  |

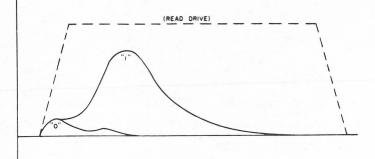

| 4-5  | Voltage on Sense Winding as<br>a Result of Read Drive                              | 4-7  |

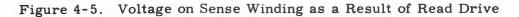

| 4-6  | Memory Board                                                                       | 4-7  |

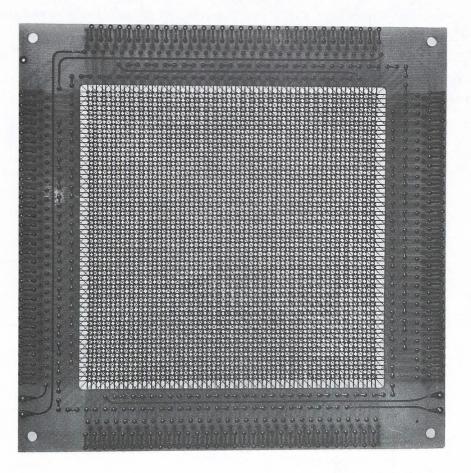

| 4-7  | Distribution of Memory Plane<br>Assemblies                                         | 4-8  |

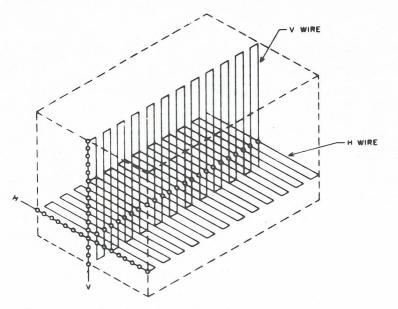

| 4-8  | Intersection of H and V<br>Wires                                                   | 4-9  |

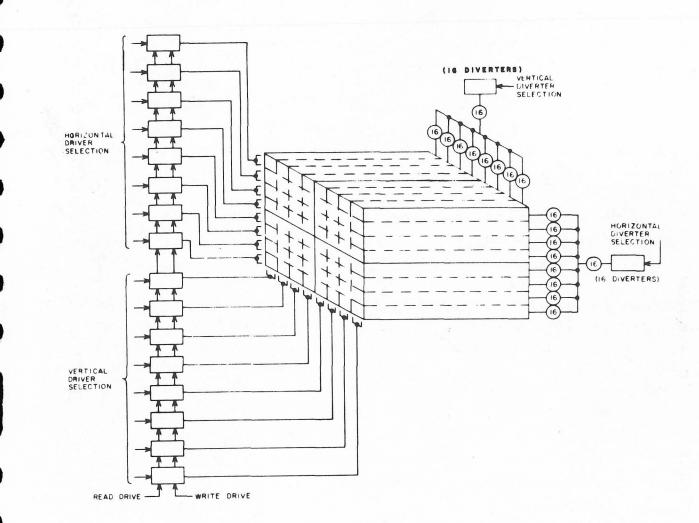

| 4-9  | Connection of Drive Lines<br>and Diversion Lines                                   | 4-11 |

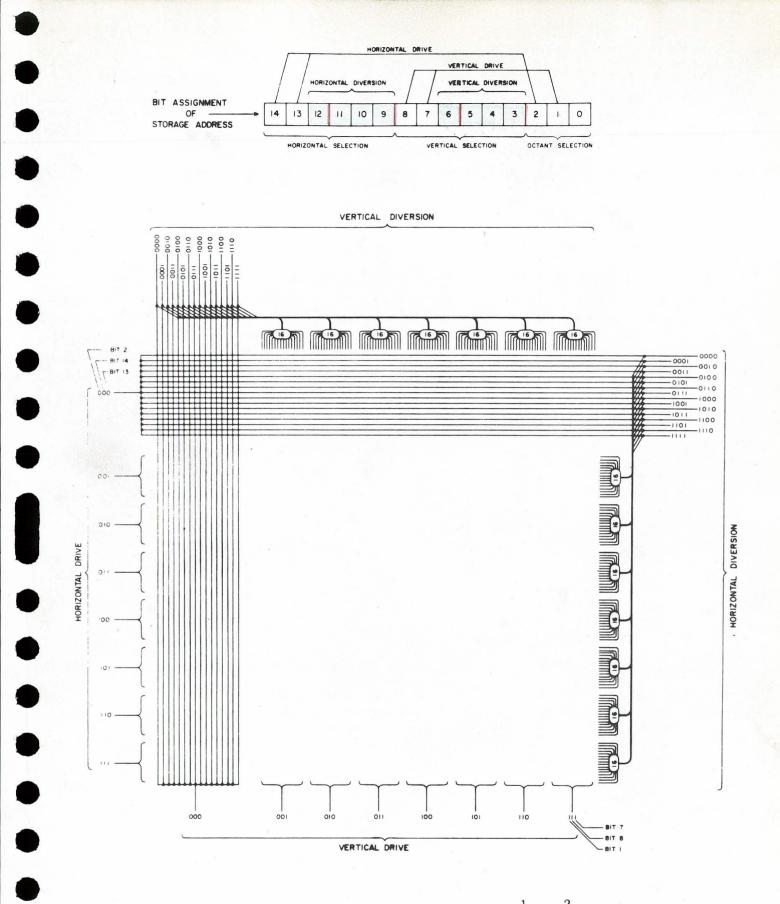

| 4-10 | Drivers and Diverters<br>Selected by S <sup>1</sup> or S <sup>2</sup><br>Registers | 4-13 |

| 4-11 | $S^1$ and $S^2$ Registers                                                          | 4-14 |

| 4-12 | Typical Horizontal or Vertical                                                     | TIT  |

| 1 12 | Drive Circuit                                                                      | 4-15 |

| 4-13 | Horizontal or Vertical Diver-<br>sion Circuit                                      | 4-16 |

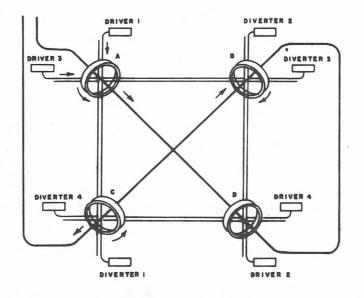

| 4-14 | Path of Sense Wire Through<br>a Four-Core Matrix                                   | 4-18 |

| 4-15 | Typical Stage of the Memory<br>Plane Control                                       | 4-19 |

| 4-16 | Path of Inhibit Wire Through<br>a Four-Core Matrix               | 4-20 |

|------|------------------------------------------------------------------|------|

| 4-17 | Basic Pulse Sequence for<br>Storage Reference                    | 4-21 |

| 4-18 | Storage Reference Circuit                                        | 4-22 |

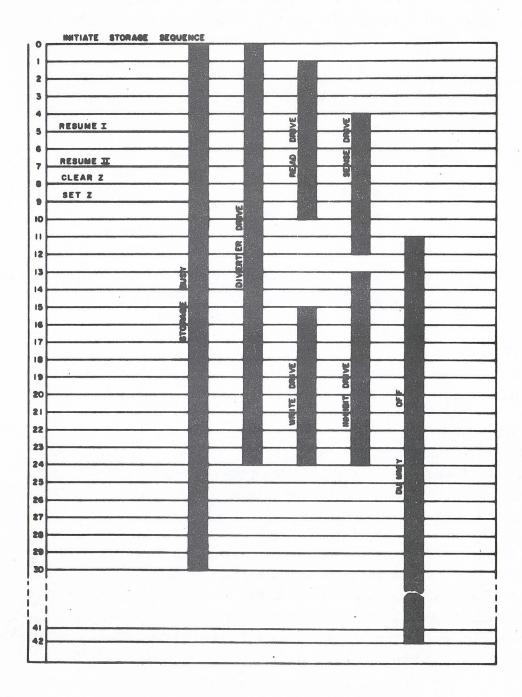

| 4-19 | Sequence of Pulses Generated<br>by Control Sequence              | 4-24 |

| 4-20 | Timing Pulse Generator of<br>Even Storage Sequence<br>Control    | 4-25 |

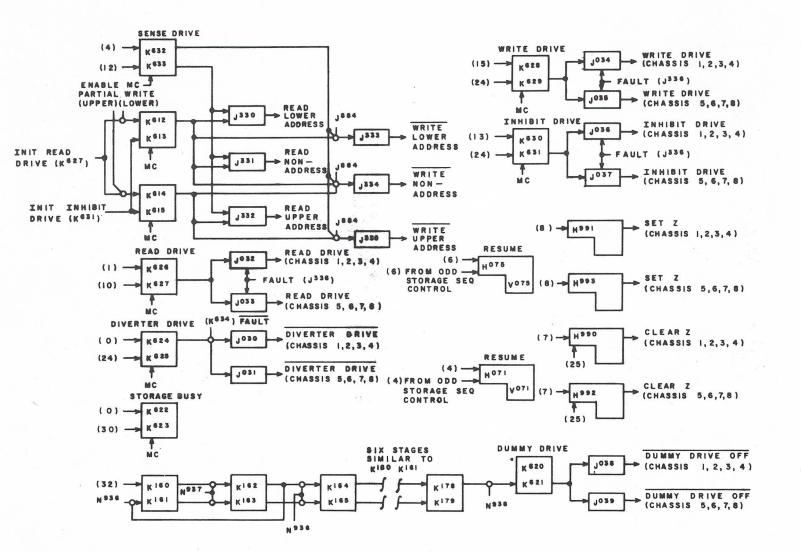

| 4-21 | Drive and Pulse Generator<br>of Even Storage Sequence<br>Control | 4-30 |

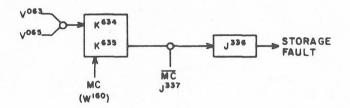

| 4-22 | Fault Detector of Even<br>Storage Unit                           | 4-31 |

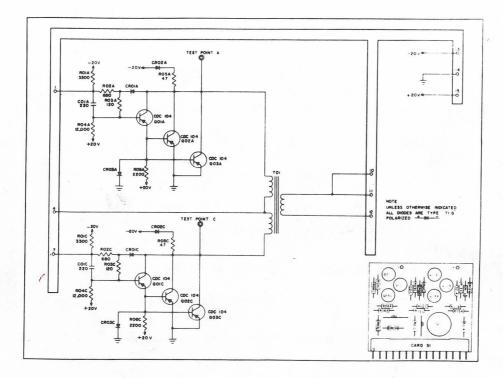

| 4-23 | Drive Generator (Card<br>Type 51)                                | 4-32 |

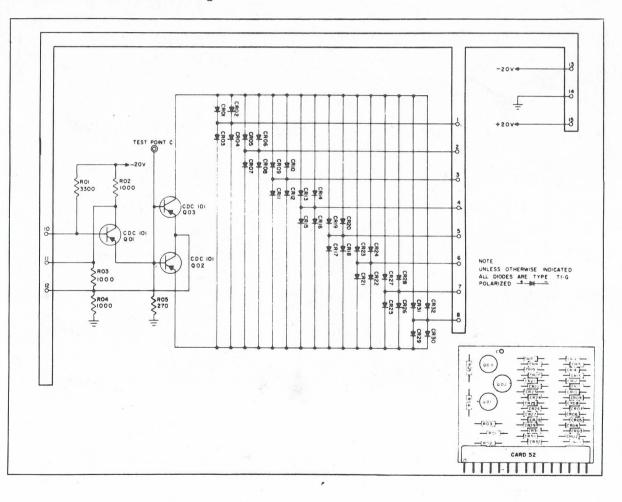

| 4-24 | Diverter (Card Type 52)                                          | 4-33 |

| 4-25 | Selector (Card Type 53)                                          | 4-34 |

| 4-26 | Current Source (Card<br>Type 54)                                 | 4-35 |

| 4-27 | Inhibit Generator (Card<br>Type 55)                              | 4-36 |

| 4-28 | Sense Amplifier (Card<br>Type 56)                                | 4-37 |

| 5-1  | Block Diagram of Buffer<br>Control                               | 5-7  |

| 5-2  | Structure of Control Words                                       | 5-8  |

| 5-3  | External Function Select/<br>Sense Code                          | 5-9  |

| 5-4  | External Function Sequence                                       | 5-11 |

| 5-5  | External Function Inverters                                      | 5-13 |

| 5-6  | Ready/Resume Logic -<br>Channel 2                                | 5-15 |

| 5-7  | Auxiliary Scanner                                                | 5-16 |

| 5-8  | Ready/Resume Logic -<br>Channel 1                                | 5-18 |

| 5-9  | Block Diagram of Search<br>and Transfer Sequence                 | 5-20 |

| 5-10 | Temporary Termination of<br>S & T Sequence During 63             | 5-24 |

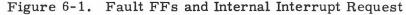

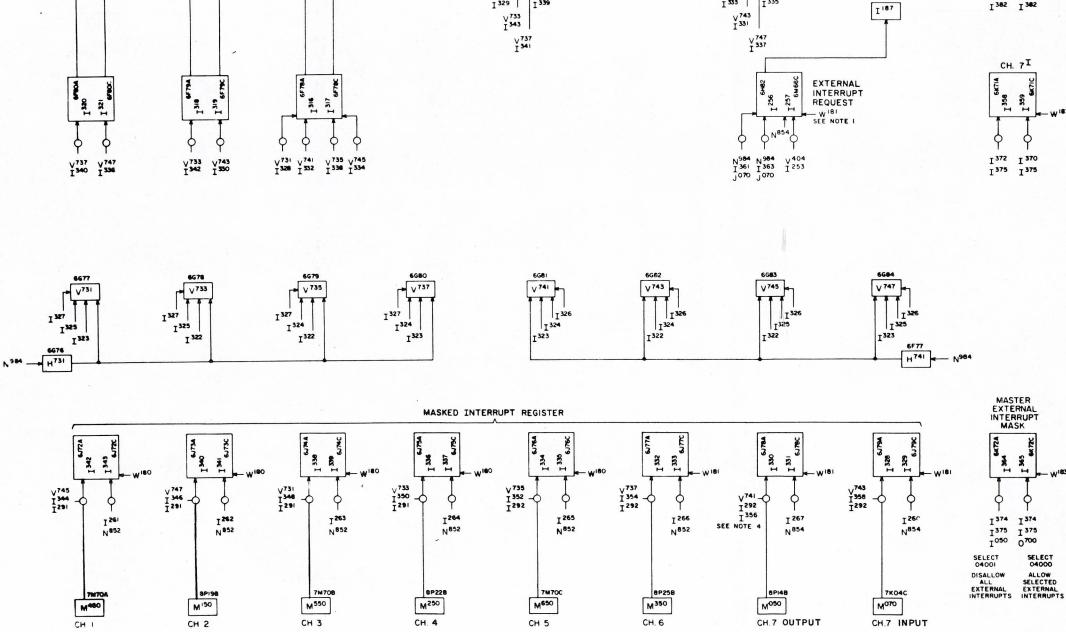

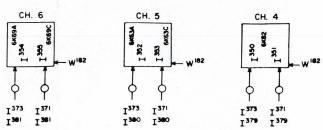

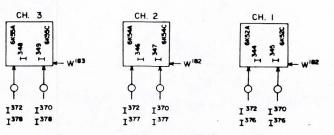

| 6-1  | Fault FFs and Internal<br>Interrupt Request                      | 6-2  |

| 6-2 | Masked Interrupt Register and<br>Interrupt Scanner        | 6-5  |  |

|-----|-----------------------------------------------------------|------|--|

| 6-3 | Interrupt Sequence                                        | 6-7  |  |

| 6-4 | Real Time Clock                                           | 6-14 |  |

| 6-5 | Setting Advance Clock FF                                  | 6-15 |  |

| 7-1 | External Function Translator                              | 7-3  |  |

| 7-2 | Sense Circuit Console<br>Equipment                        | 7-5  |  |

| 7-3 | Input Distributor, Simplified<br>Diagram                  | 7-6  |  |

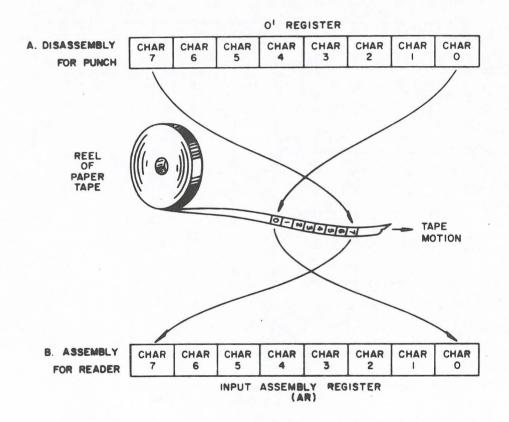

| 7-4 | Character Orientation in Reg-<br>isters and on Paper Tape | 7-7  |  |

| 7-5  | Output Distributor Simpli-<br>fied Diagram | 7-8  |

|------|--------------------------------------------|------|

| 7-6  | Seven Level Punched<br>Paper Tape          | 7-10 |

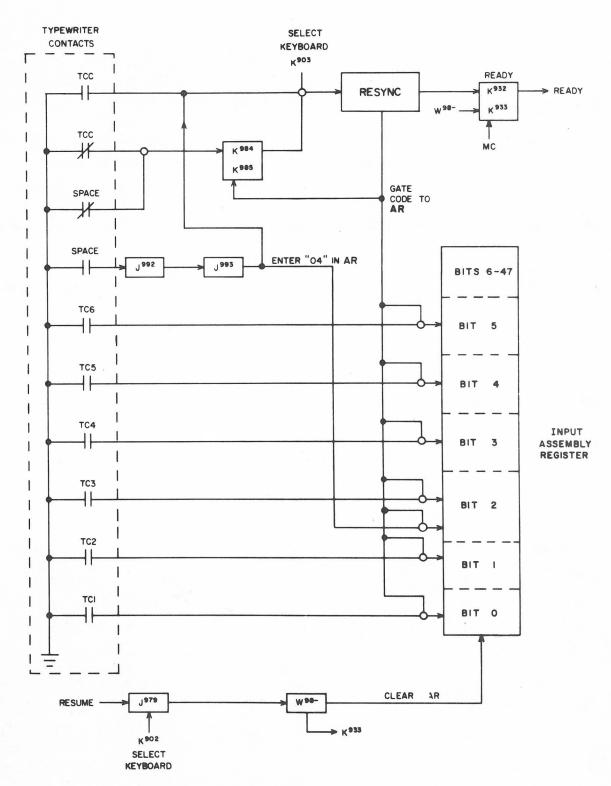

| 7-7  | Reader Control Circuit                     | 7-11 |

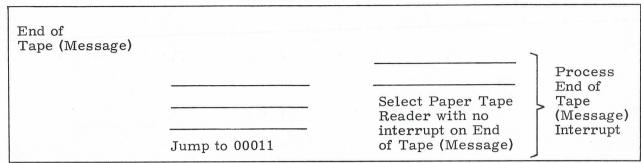

| 7-8  | End-of-Tape Circuit                        | 7-13 |

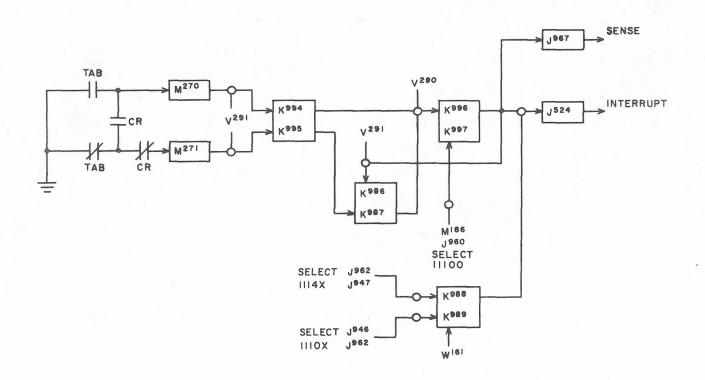

| 7-9  | Keyboard Control Circuit                   | 7-18 |

| 7-10 | Carriage Return, Interrupt<br>Circuit      | 7-19 |

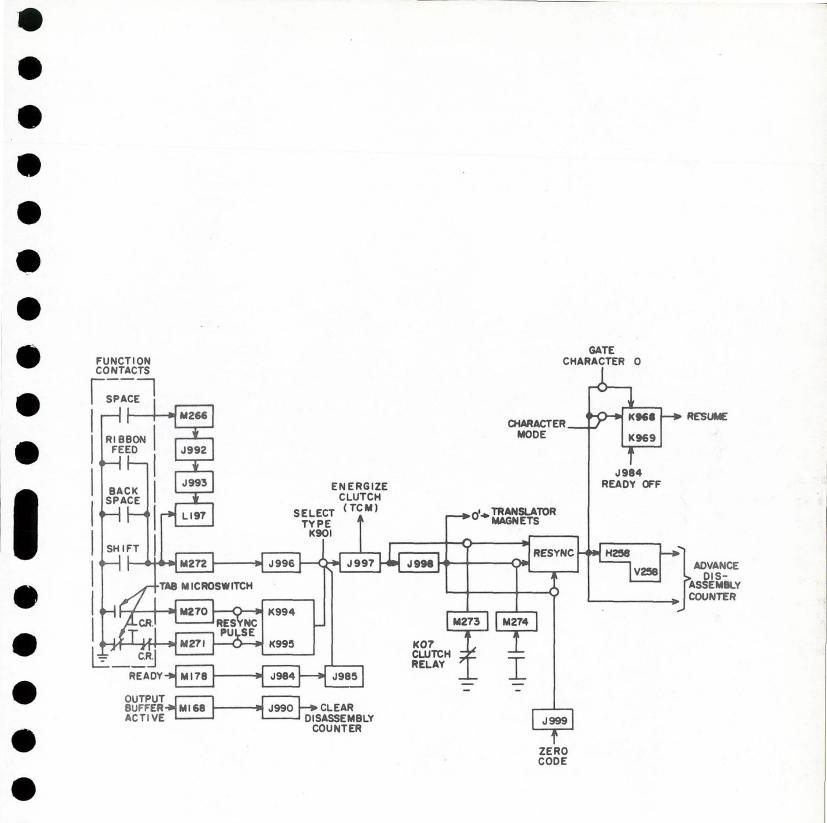

| 7-11 | Typewriter Control Circuit<br>(Output)     | 7-21 |

|      |                                            |      |

# TABLES

| 2-1 | Designation of Base Execution<br>Address                                                 | 2-6  |  |

|-----|------------------------------------------------------------------------------------------|------|--|

| 2-2 | Control Sequences                                                                        | 2-15 |  |

| 3-1 | Decimal and Binary<br>Equivalents                                                        | 3-5  |  |

| 3-2 | Binary Subtraction                                                                       | 3-8  |  |

| 4-1 | Timing Pulse Generator of<br>Even Storage Sequence<br>Control: Complete Counter<br>Cycle | 4-26 |  |

| 4-2 | Timing Pulse Generator,<br>Source of Timing Pulses                                       | 4-29 |  |

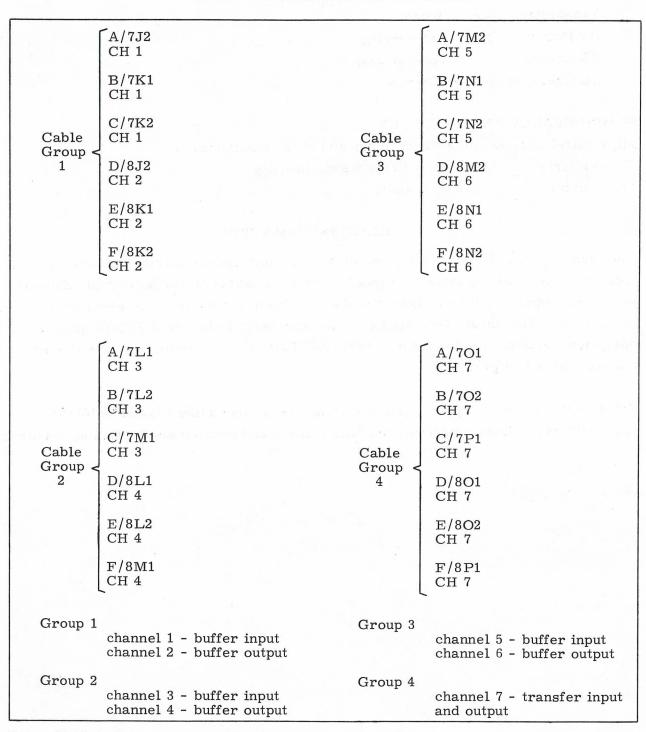

| 5-1 | Line Assignment of a Given<br>Cable Group - Data Lines                                   | 5-3  |  |

|     |                                                                                          |      |  |

| 5-2    | Line Assignment of a Given<br>Cable Group - Control | 5 4  |

|--------|-----------------------------------------------------|------|

|        | Lines                                               | 5-4  |

| 5-3    | Sense Codes                                         | 5-9  |

| 6-1    | Interrupt Locations                                 | 6-1  |

| 6-2    | Internal Fault Codes                                | 6-3  |

| 6-3    | External Interrupt Codes                            | 6-3  |

| 6-4    | Typical Interrupt Subroutine                        | 6-10 |

| 7-1    | Select Codes for Console<br>Equipment               | 7-4  |

| 7-2    | Sense Codes for Console                             |      |

|        | Equipment                                           | 7-4  |

| 7-3    | Reader Operation                                    | 7-12 |

| 7-4    | Typewriter Codes                                    | 7-16 |

| e yn i |                                                     |      |

# CHAPTER 1 INTRODUCTION DESCRIPTION

This manual describes the operation of the central computer and console. Chapter 1 is an introduction to the computer. Chapters 2 - 5 analyze in detail the major sections of the computer: control, arithmetic, storage, and input/output. Chapter 6 describes the interrupt and real time clock operations. Chapters 7 - 8 describe the console-mounted external equipment and the power system.

Supplementary material:

1604-A Customer Engineering Diagrams Manual CDC 60024300

1604-A Input/Output Specifications CDC 60024400

1604-A Reference Manual CDC 60024500

1604-A Customer Engineering Instruction Manual, Part 2 Maintenance CDC 60118800

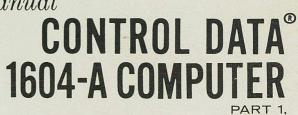

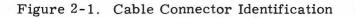

The 1604-A computer consists of the main computer cabinet and the console. A 1604-A system (figure 1-1) may include several external equipments which are connected to the computer by means of the adaptors. The adaptors provide data buffers and control circuits for card reader and punch, line printer and tape units.

The main cabinet contains the computer and the control circuits for the external equipment at the console. The operator's panel on the console provides indicators and operating controls. The monitor typewriter, paper tape punch and paper tape reader are on the console.

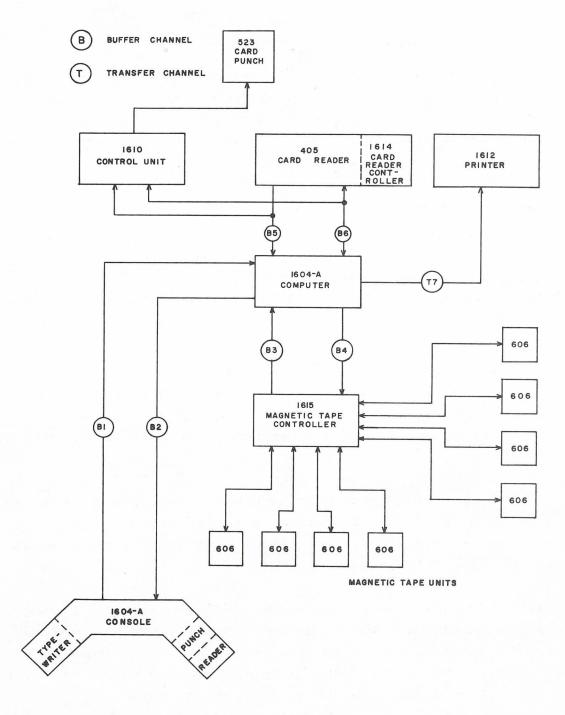

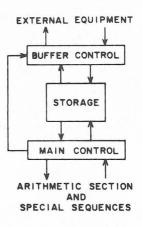

There are four major sections in the computer (figure 1-2): (1) Input/output provides communication between the computer and external equipments; (2) Arithmetic performs the arithmetic and logical operations to execute instructions; (3) Storage provides internal storage for data and instructions; and (4) Control coordinates and sequences all the operations which carry out the execution of an instruction.

Figure 1-1. Typical 1604-A System

1-2

Figure 1-2. Simplified Diagram of the Computer

# INPUT/OUTPUT SECTION

The Input/Output section of the computer provides the methods for data exchange and for proper control of information transmission between the computer and the various external equipments.

# ARITHMETIC SECTION

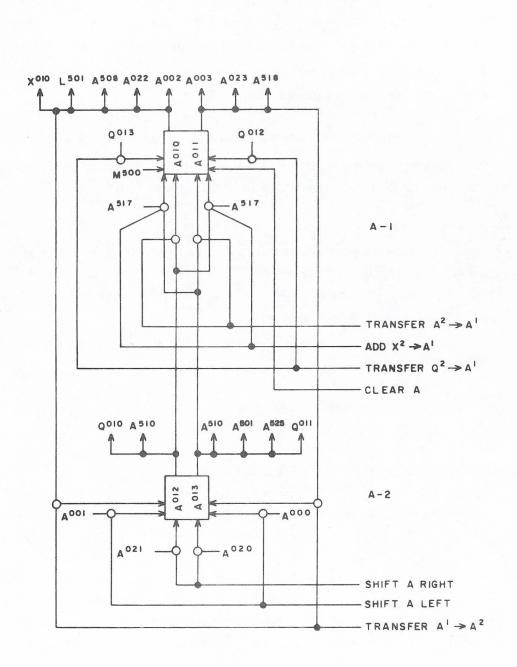

The A register (Accumulator) is the principal arithmetic register. This register provides for the parallel addition of the X register to its content; it can be shifted either separately or in conjunction with the Q register.

The Q register is an auxiliary arithmetic register used in more complicated arithmetic operations. In combination with the X register it forms logical products and can be shifted either separately or in conjunction with A.

# STORAGE SECTION

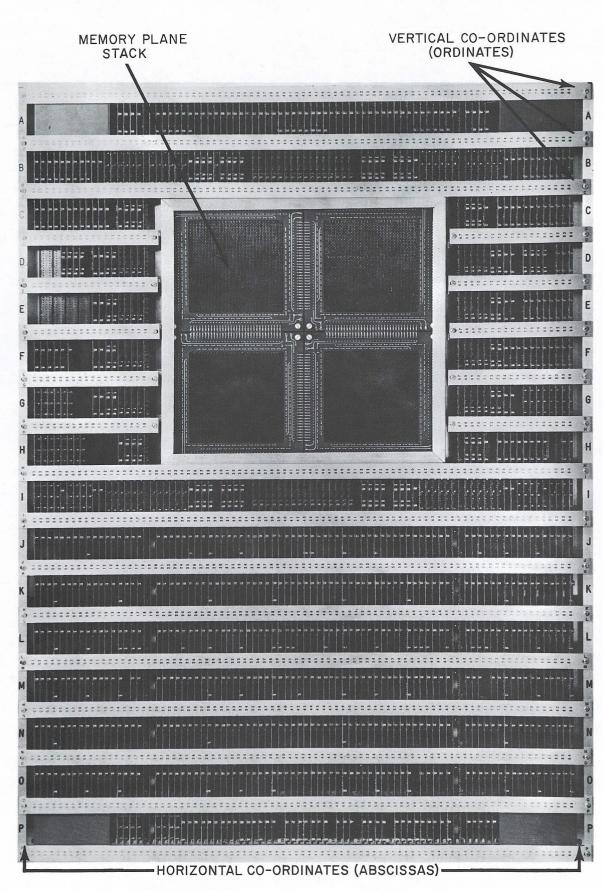

Each of the two magnetic core storage units contain 16, 384 locations or addresses for 48-bit words; the total storage capacity is 32, 768 words. All odd storage addresses reference one storage unit; all even addresses, the other.

Words to be read out of storage are transferred via inverter rank  $I^5$  (even storage) or  $I^6$  (odd storage) to the appropriate register. Words to be written into a storage unit are transmitted via  $I^5$  or  $I^6$  to the Z register, which is then sampled to determine what is to be entered into storage.

# CONTROL SECTION

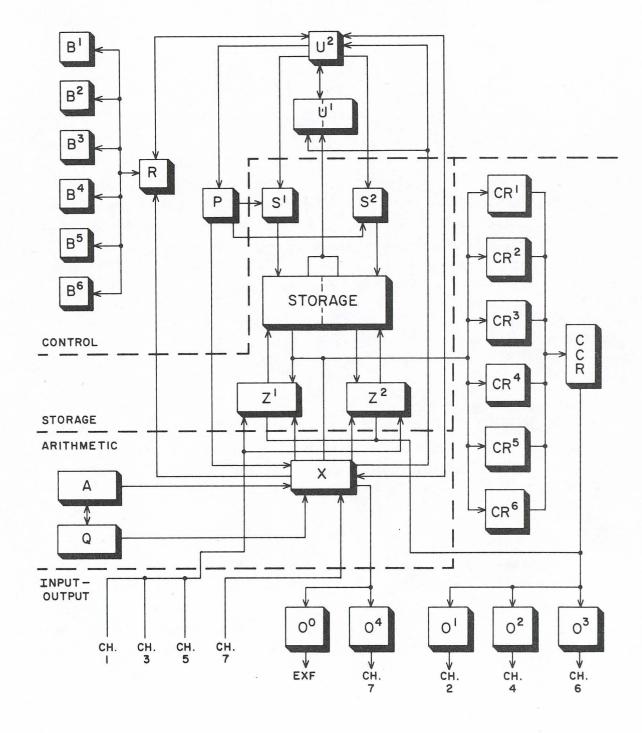

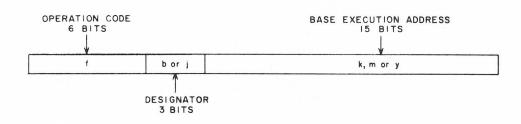

The control section acquires an instruction from storage, interprets it, and sends the required commands to other sections. A 24-bit instruction is composed of three parts or codes, designated by the letters f, b and m (figure 1-3). A program word is a pair of 24-bit instructions, which together occupy one storage location. The higher-order 24 bits of such a word are called the upper instruction and the remaining 24 bits, the lower instruction.

1 - 4

The six index registers ( $B^1$  through  $B^6$ ) provide for modification of the execution addresses of instruction.

•

The P register, program address register, provides continuity by generating in sequence the storage addresses in which the individual steps of the program are contained.

The program control register,  $U^1$ , holds a program word while the two instructions contained in it are executed. The 48-bit instruction word is taken from the storage location specified by P and entered into  $U^1$ . The upper instruction is always executed first. Execution of the lower instruction follows, except when the upper instruction is a jump or conditional skip.

The auxiliary program control register,  $U^2$ , is an accumulator used primarily in the modification of the base execution address.

The address buffer register, R, is used in transmissions to and from the B registers and is also used as a counter during the execution of several instructions.

The following is an example of how this typically operates:

Address 00500 contains the following pair of instructions: upper instruction 14 (Add) and lower instruction 50 (Enter Index). The P register holds the address 00500 (even storage). The upper 14 bits of P are sent to  $S^1$ . The storage reference is initiated and the 48-bit word (instruction pair) is read from address 00500. The word is entered into  $U^1$ .

From this point on the operations of the computer are conditioned directly or indirectly by the 24-bit instruction in the upper half of  $U^1$ , Add. The purpose of this

instruction is to add the quantity in the storage location specified by the execution address to the contents of A.

The index code, b, and operation code, f, are now translated and  $(B^b)$ \* is transmitted to  $R^1$ . At the same time the 15-bit base execution address is transmitted from  $U^1$  to  $U^2$ . The contents of  $R^1$  are added to  $U^2$  to yield the execution address, M, which specifies the location of the operand.

Depending on whether the lowest bit of  $U^2$  is a "0" or a "1", the remaining 14 bits are transmitted to  $S^1$  or  $S^2$  in preparation for reading the operand to be added to A. The storage reference is initiated, the operand is entered into X, and X is added to A.

The computer is ready to execute the next instruction contained in the lower 24 bits of  $U^1$ . The upper half of  $U^1$  is cleared and the lower half transmitted to the upper half, so that  $U^1$  upper holds instruction 50 (Enter Index). The purpose of this instruction is to place the 15-bit base execution address in index register b. Following translation of f and b, the base execution address is transmitted from  $U^1$  to  $U^2$ . Now  $U^2$  is transmitted to R, and R in turn is transmitted to the B register specified by b and the execution of the instruction is complete.

$*(B^{b})$  = the contents of the B register specified by the b portion of the instruction.

# CHAPTER 2 CONTROL SECTION INTRODUCTION

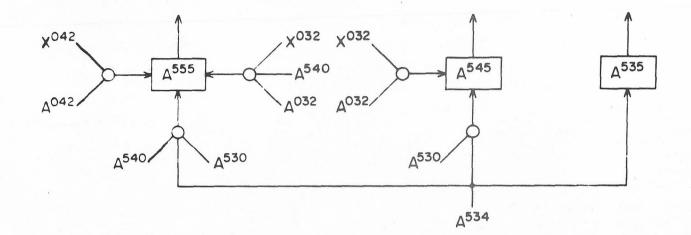

The control section of the computer is composed of two parts, main control and buffer control.

Main control directs the interpretation and execution of instructions and establishes the timing to perform the instructions in the proper sequence. When an exchange of data with external equipment is called for, main control initiates the exchange and then gives control of the exchange to buffer control. Main control is then free to continue executing other instructions while data exchange is taking place.

Buffer control accepts control of data exchange operations, supervises the exchange, and signals main control when the operation is completed. Buffer control is described lated in this chapter and in chapter 5.

Figure 2-1. Block Diagram of Computer Control

#### INSTRUCTION FORMAT

The commands which execute instructions and exchange data between the computer and external equipment are issued by a sequence. The issuing of commands is controlled directly or indirectly by the instruction in the Program Control register,  $U^1$ . The 24-bit instruction format is shown below.

•

Each of the 62 instructions has a unique 6-bit operation code, f, which designates the instruction. The translation of f establishes the condition required within the control section for the execution of the instruction.

The next three bits are the designator, b or j. When the designator refers to an Index register, B, it is denoted by b. The contents of the designated Index register,  $(B^b)$ , are usually added to the base execution address, the right 15 bits of the instruction. The base execution address usually refers to a memory location, m.  $(B^b)$  is added to m to give the actual address, M, of the operand. When b = 0, m is the operand address. When b = 7, indirect addressing is used. Indirect addressing is explained on page 2-26.

In Jump and Stop instructions the designator is called j and indicates the condition necessary for the jump or stop.

# OPERATION CODE

This 6-bit code specifies an instruction and controls the operation of the computer during the execution of the instruction. There are  $64_{10}$  Octal codes; 62 Specify instructions, and codes 00 and 77 represent fault conditions that halt the computer.

2 - 2

#### Translation of Operation Code

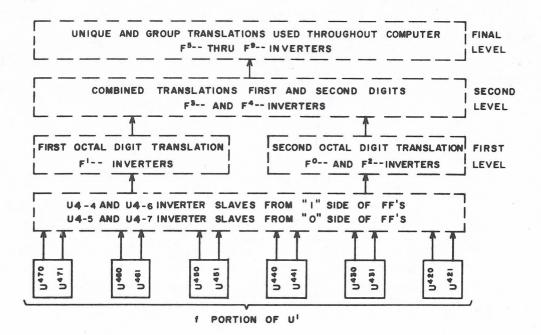

Prior to the execution of the instruction designated by the value of f, the operation code is translated by a network of single inverters which samples the upper six bits of  $U^1$ . The results of the translation go to the various sections of the machine to gate commands which carry out the required operations.

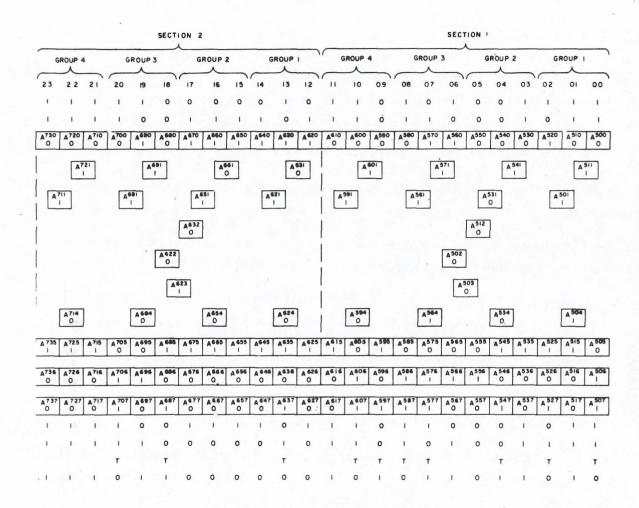

The translator (figure 2-2) uses several levels of logic in forming the outputs which gate commands. Outputs from the upper six FFs of  $U^1$  are connected to single inverter slaves. The set side of each FF has a U4-4 and U4-6 inverter slave; the clear side of each FF has a U4-5 and a U4-7 inverter slaves.

Figure 2-2. Structure of Operation Code Translator

The first level translation is divided into two parts; i.e., one concerned with the second octal digit of f (U42-, U43-, U44-), and the other with the first octal digit (U45-, U46-, U47-). All F0-- and F2-- inverters translate the second octal digit. All F1-- inverters translate the first octal digit.

Unique (single-value) translations of the second octal digit are provided by F000 through F007. When the output of one of these inverters is "1", the second octal digit has the value given in the third superscript digit of the inverter designation; e.g., a "1" from F007 indicates that the second digit is 7. The F2-- inverters provide partial, or incomplete, translations of the second octal digit. These translations are duplicated by several slave inverters.

The F1-- inverters, which uniquely translate the first octal digit, use the last digit of the inverter designation to indicate the value translated. Thus, F105 indicates that the first octal digit is 5.

In the second level of the translator the outputs of first level inverters that translate individually the first and the second octal digits are combined to specify either a unique value of the Operation code or a group of values. The F3-- and F4-- inverters combine the translations of the first and second digits in figure 2-3. Outputs of the F3-- and F4-- inverters go to F5-- or F6-- which supply the translations throughout the computer.

Figure 2-3. Translator, Second Level

# **DESIGNATOR**

When the 3-bit designator in an instruction specifies the Index register, B, it is denoted by the letter b. When b = 0, no modification of the execution address occurs; with b = 7, indirect addressing is used. Instruction 50 with b = 0 performs no operation but "passes" to the next instruction. In instructions 62-67, b = 0 specifies that exactly one word is to be transferred or searched.

When used as a condition designator, as in instructions 22, 23, and 74-76, the 3-bit quantity is denoted by the letter j which is interpreted as follows:

22 A Jump: 23 Q Jump: 0 - Jump if register content is zero

1 - Jump if register content is not zero

- 2 Jump if register content is positive

- 3 Jump if register content is negative

- 4 Return jump if register content is zero

- 5 Return jump if register content is not zero

- 6 Return jump if register content is positive

- 7 Return jump if register content is negative

75 Selective Jump:

- 0 Jump unconditionally

- 1 Jump if jump key one is set

- 2 Jump if jump key two is set

- 3 Jump if jump key three is set

- 4 Return jump unconditionally

- 5 Return jump if jump key one is set

- 6 Return jump if jump key two is set

- 7 Return jump if jump key three is set

76 Selective Stop:

- 0 Stop uncondtionally (normal jump)

- 1 Stop if stop key one is set (normal jump)

- 2 Stop if stop key two is set (normal jump)

- 3 Stop if stop key three is set (normal jump)

- 4 Stop unconditionally (return jump)

- 5 Stop if stop key one is set (return jump)

- 6 Stop if stop key two is set (return jump)

- 7 Stop if stop key three is set (return jump)

Only the stop may be conditioned; the jump occurs unconditionally when the computer is restarted or when the stop condition is not met.

74 External Function:

- 0 Select external equipment

- 1 Activate communication channel one

- 2 Activate communication channel two

74 External Function:

- 3 Activate communication channel three

- 4 Activate communication channel four

- 5 Activate communication channel five

- 6 Activate communication channel six

- 7 Sense external condition

# Translation of the Designator

Inverters F700 through F707 translate the eight possible values of the designator. A "0" output from one of these inverters indicates the value given by the third superscript digit in the symbol; a "0" output from F705 indicates that the value is 5. Since the outputs of these inverters feed inverter slaves, the designator translation is in normal form ("1") when it is used for gating.

# BASE EXECUTION ADDRESS

The base execution address (lower 15 bits of an instruction) has three functions, depending upon the instruction used (see table 2-1).

| Instructions                              | Use                                         | Denoted |   |                                                     |

|-------------------------------------------|---------------------------------------------|---------|---|-----------------------------------------------------|

| 12-33, 36-47,<br>52, 53, 55-73,<br>75, 76 | Specifies storage<br>location of<br>operand | m       | M |                                                     |

| 14, 10, 11, 50<br>51, 54, 74              | As operand                                  | У       | Y | After modification by addition of (B <sup>b</sup> ) |

| 01-03, 05-07,<br>34, 35                   | As shift count                              | k       | К |                                                     |

#### TABLE 2-1. DESIGNATION OF BASE EXECUTION ADDRESS

The base execution address is transmitted from the upper instruction in  $U^1$  to  $U^2$  in the execution of all instructions. If it is to be modified,  $B^b$  is transmitted to  $R^1$  (the Address Buffer register) and then  $R^1$  is added to  $U^2$ . When the operand is procured from or sent to storage,  $U^2$  is transmitted to  $S^1$  or  $S^2$ . When  $U^2$  is to be used as the operand or shift count, it is transmitted to  $X^1$  or  $R^1$ .

## PROGRAM CONTROL REGISTER

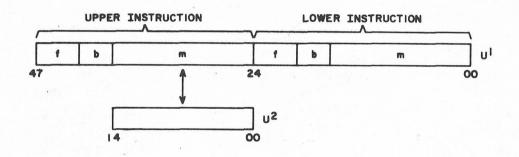

The Program Control register, U, holds the 48-bit instruction word during execution of the two 24-bit instructions (figure 2-4). All operations necessary to execute an instruction are governed by the contents of this register.

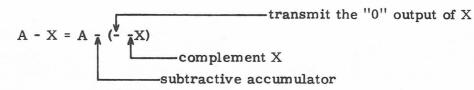

The U register consists of two ranks of FFs. Rank  $U^1$ , 48-bits in length, stores the instruction word during execution of the two instructions. Rank  $U^2$ , 15-bits in length, is a subtractive accumulator with a borrow pyramid. Transmission paths connect  $U^2$  with the m portion of the upper half of  $U^1$ .

The instruction word is read from storage and entered into  $U^1$ . Execution of the upper instruction occurs first; the lower instruction is then transmitted to the upper half of  $U^1$  and executed. Thus the current instruction is always in the upper half of  $U^1$ .

Figure 2-4. U Register

The primary function of  $U^2$  is to modify the execution address, m, of the instruction in the upper half of  $U^1$  by adding the contents of  $B^b$  to it.

After transmitting m from  $U^1$  to  $U^2$  and transmitting (B<sup>b</sup>) to R, R is added to  $U^2$  and the sum is formed in  $U^2$ . The modified execution address in  $U^2$  for most instructions specifies the location of the operand in storage.

# THE U<sup>2</sup> ACCUMULATOR

•

•

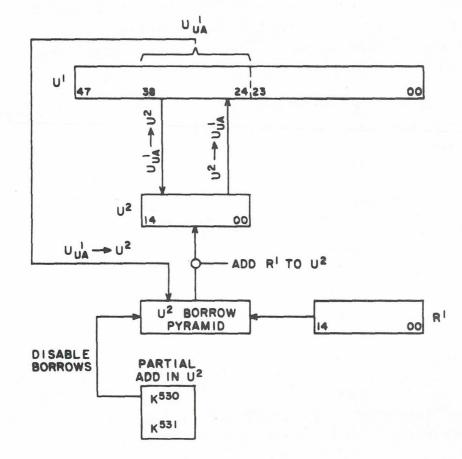

$U^2$  is a 15-bit subtractive accumulator that provides for the addition of  $R^1$  to its content. This accumulator is simular in structure to the A register (the 48-bit accumulator). Two ranks of FFs are necessary for the addition operation. Stages  $U^{24}$  through  $U^{38}$  of  $U^1$  (upper address) form the rank that is sampled by the pyramid (figure 2-5). The  $U^2$  FFs constitute the other rank, which receives the sum.

Figure 2-5. Adding in U<sup>2</sup> Accumulator

Prior to the addition of  $R^1$  to  $U^2$ , the  $U^1_{UA} \rightarrow U^2$  or  $U^2 \rightarrow U^1_{UA}$  command insures that both ranks hold the same quantity. Following this, the borrow pyramid samples  $U^1_{UA}$  and  $R^1$  to determine the stages of  $U^2$  that must be toggled in order for  $U^1_{UA} + R^1$  to be formed in  $U^2$ . This occurs when the command Add  $R^1$  to  $U^2$  is given. The  $U^2$  accumulator has provisions for disabling the borrow pyramid so that each bit of  $U^2$  is toggled if the corresponding bit of  $R^1$  is "1". The pyramid is disabled when the Partial Add in  $U^2$  FF (K530/531) is set. Thus the Add  $R^1$  to  $U^2$  command accomplishes a selective toggling function when K530/531 is set. However, when this FF is cleared, a full addition results from the Add  $R^1$  to  $U^2$  command. The partial addition of  $R^1$  to  $U^2$  is often used in transmitting B to another register such as X. B goes to R and  $R^1$  is partially added to  $U^2$ , with  $U^2$  sent to X.

In addition, if either  $B^{b}$  or  $U^{2}$  has a "1" in the highest bit, it is treated as a negative number expressed in one's complement form. Thus if the quantities m = 00005 and  $B^{b}$  = 77776 are added, the sum is 00004. The same result is obtained when the values of  $B^{b}$  and  $U^{2}$  are interchanged.

## INDEX REGISTERS

There are six Index registers,  $B^1$  through  $B^6$ . In most instructions the B registers hold quantities to be added to the base execution address. For Search instructions (64-67),  $(B^b)$  indicates the number of items to be searched. The B registers have no provision for arithmetic operations. When such an operation is required on an index quantity,  $(B^b)$  is entered in R or  $U^2$  and the operation is performed there; the result is returned to  $B^b$ .

Transmissions into a B register come from  $R^2$  via the  $I^4$  single-inverter rank (figure 2-7). Each B register provides outputs to either  $I^2$  or  $I^3$ , which are in turn gated to  $R^1$ . For this transmission the "0" output of the register FFs is used due to the single inversion of  $I^2$  or  $I^3$ .

Equation symbol assignments for the B registers are different from other registers. The first digit of the superscript identifies the register; second and third digits indicate the stage. The "0" side is not identified by the odd character of the third digit; instead, the "0" side is indicated if the second and third digits are 50 or greater. The stage with which such a symbol is associated is found by subtracting 50 from the last two digits. For example, B563 is the "0" side of stage 13 of  $B^5$ .

## ADDRESS BUFFER REGISTER

The 15-bit Address Buffer register R provides for counting and complementing as well as for storage. As a counter it operates subtractively.

The R register consists of two ranks of FFs,  $R^1$  and  $R^2$ . Inverter rank  $I^2$  receives inputs from control which set it to predetermined values;  $I^2$  is then transmitted to  $R^1$  (figure 2-6).

# FUNCTIONS OF THE R REGISTER

- 1) All transmissions to and from the B registers go through R.

- 2) The base execution address of the current instruction is modified by addition of the quantity in R (obtained from  $B^b$ ) to  $U^2$ .

••••

- 3) R acts as the shift counter in Shift instructions.

- 4) In the integer and fractional Multiply and Divide instructions, R records the number of partial multiplications and divisions which remain to be performed.

- 5) In floating point instructions, R performs arithmetic operations on one of the two exponents.

## COUNTING AND COMPLEMENTING IN R

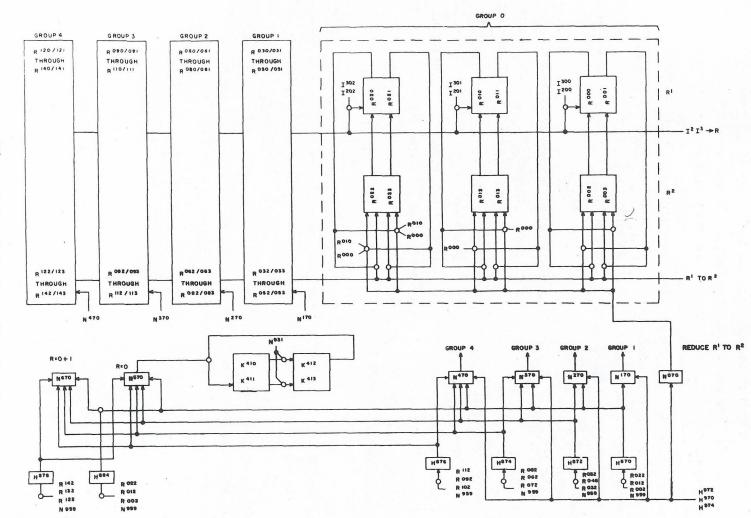

The R register is a two's complement, open-ended subtractive counter with a modulus of  $2^{15}$ . In counting, the bits of R are toggled to form the quantity (R<sup>1</sup>) -1 in R<sup>2</sup>. The command Reduce R<sup>1</sup> to R<sup>2</sup> subtracts "1" from the first stage, R<sup>00</sup> (figure 2-6). When R<sup>00</sup> is "0", a borrow from R<sup>01</sup> is required. Similarly, a borrow is required from R<sup>02</sup> if both R<sup>00</sup> and R<sup>01</sup> are "0". Thus, in general, a borrow is required from stage n if all stages lower than n are "0". Borrows are accomplished by toggling a stage of R<sup>2</sup> with the corresponding stage of R<sup>1</sup> when the command occurs.

For sensing the borrows,  $R^1$  and  $R^2$  are organized as five 3-bit groups, each of which is a small counter. Just as "1" is borrowed from  $R^{01}$  only if  $R^{00}$  is "0", "1" is borrowed from the second group only if the stages of the first group are each "0". A borrow is made from a group only when all stages of the next lower group are "0".

In each group, H87- senses when the three stages of the group are "0". This condition is indicated by a "0" output from H87-. Outputs of H87- of lower-order groups are used by higher-order groups to determine whether a borrow is required. A borrow is required from the fifth group only when the outputs of H870, H872, H874, and H876 are "0".

Figure 2-6. R Register Counting Structure

2~11

Within a group from which a borrow is required, the first stage is toggled by the Reduce  $R^1$  to  $R^2$  command. The second stage is toggled if the first stage is "0". The third stage is toggled only if both the first and second stages are "0".

Complementing is performed in R by transmitting the complement of the bits in  $R^2$  to  $R^1$ . For many uses of R it is necessary to sense when the quantity in R is "0"; the H87- terms sense this condition. The outputs of all five H87- terms are combined by both N570 and N670. When the five inputs to each are "0", all 15 stages of R contain "0". This condition is indicated by a "1" from N570 or N670.

•

There is an important difference, however, between the indications of the R = 0 condition given by N570 and N670. To account for this difference it is necessary to consider the interval between the time when the Reduce  $R^1$  to  $R^2$  command is given and the time when the state of R resulting from this reduction is reflected at the output of N570. The interval is two clock periods, one for toggling  $R^2$  and one for the R = 0 control delay. In certain cases, such as Shift instructions, sensing the R = 0 condition must not lag the Reduce command by such an interval. Furthermore, since in these cases it is known that R is reduced to "0", it is possible to anticipate the time at which this occurs by sensing when R = 1. The output of N670 is a "1" not only when R = 0 but also when R = 1.

By using FFs K410/411 and K412/413, it is possible to obtain a pulse two clock times after R is reduced to "0" and to obtain just one such pulse despite the fact that when R is reduced to "0" the output of N570 may be a "1" for some time. This is done by setting K410/411 to "1", which in turn sets K412/413 to "1". After R = 0 the latter FF causes the former to be cleared. This results in K412/413 being cleared one clock time later. In order to uniquely specify the first time the output of N570 is a "1", it is only necessary to combine a "1" output from K412/413 in an AND with N570.

When R is employed as an additive rather than a subtractive counter, the sequence of commands is:

Complement  $R^2$  to  $R^1$   $R^1 \rightarrow R^2$ Reduce  $R^1$  to  $R^2$ Complement  $R^2$  to  $R^1$  $R^1 \rightarrow R^2$

Following this sequence  $R^2$  holds the initial quantity plus one.

2 - 12

## PROGRAM ADDRESS REGISTER

The Program Address register, P register, holds the address of each instruction word. After the upper and lower instructions of a word are executed, the quantity in P is advanced by one to the address of the next instruction. Thus the P register is a counter.

The initial address of a program is entered into P manually at the control console.

When the computer executes a Return Jump instruction, (P) + 1 is stored to provide for return to the next instruction in the program. The address specified in the Jump instruction is then entered into P from the U register.

The contents of  $P^1$  are transmitted to  $P^2$  every odd clock phase so that  $P^2$  always equals  $P^1$ .

# COUNTING IN P

The P register is a two's complement additive counter with a modulus of  $2^{15}$ . The bits of P are toggled to form the quantity  $P^2 + 1$  in  $P^1$ . The command to advance P occurs each time the Read Next Instruction (RNI) sequence is entered from a full exit. This command always adds one to the first stage,  $P^{00}$ . If  $P^{00}$  is a one when the command occurs, a carry to  $P^{01}$  is required. Similarly, a carry to  $P^{02}$  is required if both  $P^{00}$  and  $P^{01}$  are one. A carry to any stage, n, is required if all stages lower than n are "1's". Carries are accomplished by toggling a stage of  $P^1$  with the corresponding stage of  $P^2$ .

$P^1$  and  $P^2$  are organized as five three-bit groups, each of which is a small counter. Group 1 is increased for each Advance P command. Group 2 is increased only if all the bits of group one are ones when the Advance P command is received. Group 3 is increased only if both groups 1 and 2 are all ones, etc. Except for the fact that P is an additive counter, its counting structure is similar to that of the R register (figure 2-6).

Special gates provide for setting P to addresses 00007-00017 when an interrupt condition occurs. Storage locations 0007-000017 are used to enter into an exit from interrupt routines.

The P register and the setting of the Breakpoint switch are sampled and compared during every RNI sequence. The logic for this comparison is discussed under breakpoint.

# PARALLEL TRANSMISSION INVERTER RANKS

Many of the parallel transmission paths between registers involve a rank of inverters. Figure 2-7 shows the major transmission paths and the nine inverter ranks. The purpose of inverter ranks is to increase the input or output capacity of a register. For example, rank  $I^4$  as a slave for R increases the number of outputs from R to the Index registers. Each inverter of  $I^4$  requires only one output from R, and the inverter provides six outputs to the Index registers.

•

In addition to increasing the number of transmission paths available, some inverter ranks perform other operations.  $I^2$  has special logic connected to its input that is used to set R to the proper shift count for Iterative instructions.

2 - 14

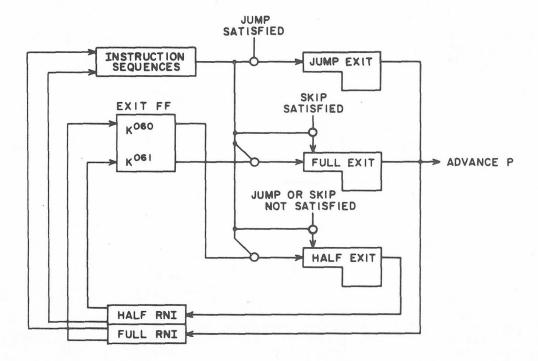

# CONTROL SEQUENCES

The timing of commands within the computer is done by control sequences. The main sequences and the computer instructions which they control are listed in table 2-2. Command timing charts, contained in Part 2 of the Customer Engineering Instruction Manual, show the complete list of sequence commands for each instruction or operation.

•••••

| SEQUENCE              |       | SYMBOL | INSTRUCTION                                              |

|-----------------------|-------|--------|----------------------------------------------------------|

| Read Next Instruction | RNI   | Н09-   | All instructions                                         |

| Normal Jump           | NJ    | H10-   | (22, 23, 75, 76) (j = 0-3)                               |

| Zero Address          | ZA    | H2     | 01-11, 34, 35, 50, 51, 54, 55                            |

| Read Operand          | RO    | Н3     | 12-17, 36-46, 52, 53, 70-73,<br>Advance Clock            |

| Write Operand         | WO    | H4     | 20, 21, 47, 56-61, (22, 23, 75, 76) (j = 4-7), Interrupt |

| Search and Transfer   | S & T | H5     | 62-67                                                    |

| Iterative             | I     | H6     | 24-33                                                    |

| External Function     | EXF   | H7     | 74                                                       |

| Auxiliary             | Aux   | H71-   | Buffer                                                   |

|                       |       | Н76-   |                                                          |

| High Speed Storage    | HSS   | H17-   | 74.1-6, Buffer (addresses<br>00001-6)                    |

|                       |       | H18-   |                                                          |

| Interrupt             | INTER | H78-   | Interrupt and Advance Clock                              |

| TABLE 2-2. CONTROL SE | QUENCES |  |

|-----------------------|---------|--|

|-----------------------|---------|--|

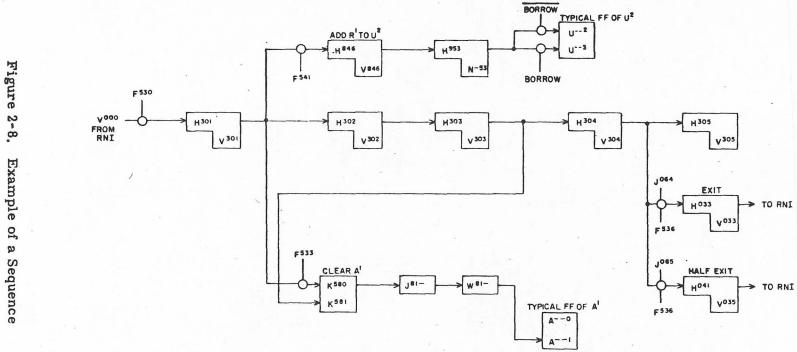

Instructions are executed by the Read Next Instruction (RNI) sequence and one other. For example, instruction 14 (Add), is executed by the RNI sequence followed by the Read Operand (RO) sequence. RNI enters the 24-bit instruction word in the upper half of  $U^1$  and RO obtains the operand from storage and performs the addition. Each sequence consists of a series of control delays. In the hypothetical sequence of figure 2-8 the basic series of control delays have H3-- and V3-- symbols.

The sequence is initiated when a single pulse from RNI is gated into H301 by F530. This pulse moves down the chain of control delays at the rate of one control delay per clock period (0.2 microsecond). H301 receives this pulse at time 0. The time scale shows relative time positions for later control delays. There are two methods for generating commands. The first is illustrated by the command Add R<sup>1</sup> to U<sup>2</sup>. This means of generating commands is fully clocked. A control delay with clocked output applies the Command signal at a definite time to the FFs of the register in use. After the sequence is initiated, the H846-V846 control delay is set at time one if the condition given by F541 is met. At time two, H953-N-53 is entered by the output of V846. At time three, the command reaches the FFs of U<sup>2</sup>. By time four, the command is complete and the quantity available at the outputs of the U<sup>2</sup> register FFs.

It is pertinent at this point to explain why the Add  $R^1$  to  $U^2$  command is, in this case, generated by the use of H846-V846. The command could be generated and occur at time three by providing an input to H953 from V302, instead of taking an output from V301 and going through H846-V846 to H953. In fact, this is done in some of the several instances for which the Add  $R^1$  to  $U^2$  command is generated. However, the total number of instances in which this command is generated is greater than the maximum number of inputs possible for H953. Additional capacity of H953 is provided by H846. All control delays with H8-- symbols increase the input capacity of the H9-- control delays are called initiates, indicating they do not actually supply the command to the register.

The second method of generating commands is illustrated by the Clear  $A^1$  command (figure 2-8). A Clear  $A^1$  FF is set; the "1" output goes from single inverters J81- through W81- to the "0" side of  $A^1$ . When K580/581 is set to "1", W81- provides a "1" input to the "0" side of the  $A^1$  FFs which clears  $A^1$ . The Clear  $A^1$  FF is set at time one and cleared at time three. The transmissions from the output of the Clear  $A^1$ FF through J81- and W81- to the  $A^1$  FFs are not clocked.  $A^1$  is cleared between time two (minimum) and time three (maximum).

Whether a full or half exit is taken in figure 2-8 is determined by J064 and J065, slaves of the Exit FF. If the current instruction is a lower instruction, a full exit is taken and

2-17

TIME SCALE

10

12

1 3

1 4

1 5

RNI reads up another instruction word from storage. In some cases the exit is taken before the present instruction is completed. This allows RNI to prepare for the next instruction at the same time the present instruction is being finalized. The over-all relationship of exits, RNI, and the sequences is shown in figure 2-9. •

Figure 2-9. Over-all Sequence Control

# RELATION OF CONTROL AND STORAGE SEQUENCES

For Control sequences which initiate a storage reference it is necessary to maintain proper timing between the Control sequence and the Storage sequence. Successive references to different storage units (even and odd) can overlap, but successive references to the same unit cannot overlap. Wait Storage FFs in the Control sequence allow for variability in the time when a storage reference may begin and maintain synchronization with the Storage sequence (figure 2-10). Usually this FF is set when the Initiate Storage FF is set. The Control sequence continues with those commands that need not be timed with the Storage sequence. The Storage Resume signal indicates the Storage sequence has read the word from the specified address and can be sampled from  $I^5$  or  $I^6$ . The Resume signal and the set output of the Wait Storage FF are combined in an AND to restart the Control sequence.

A. SYNCHRONIZING CONTROL SEQUENCE WITH READ TIME OF STORAGE SEQUENCE.

B. SYNCHRONIZING CONTROL SEQUENCE WITH BEGINNING OF STORAGE SEQUENCE.

Figure 2-10. Relation of Control and Storage Sequences

## READ NEXT INSTRUCTION SEQUENCE

The Read Next Instruction (RNI) sequence performs the following functions:

- 1) Acquisition of a new instruction word.

- 2) Start and stop

- 3) Preliminary steps in address modification

- 4) Preliminary control and arithmetic steps

- 5) Indirect addressing

# Acquisition Of New Instruction Word

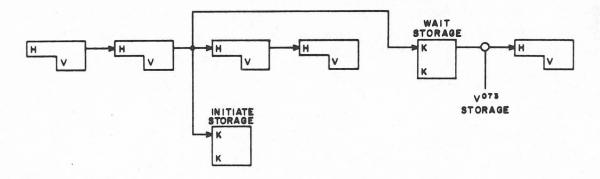

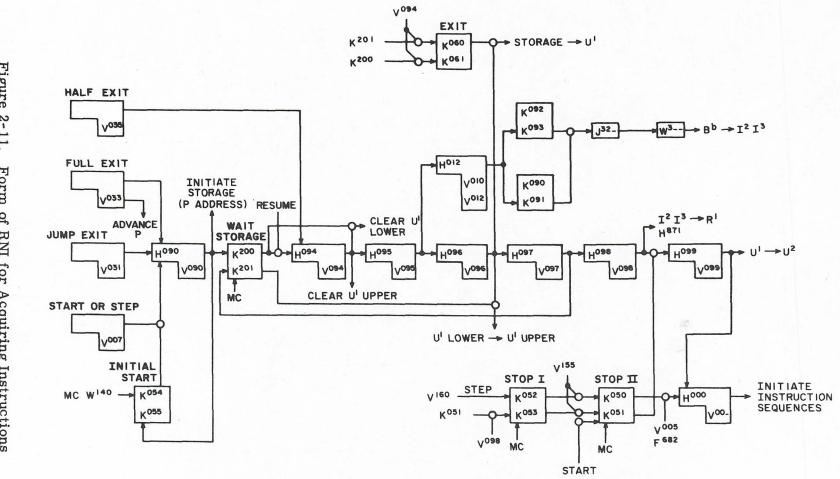

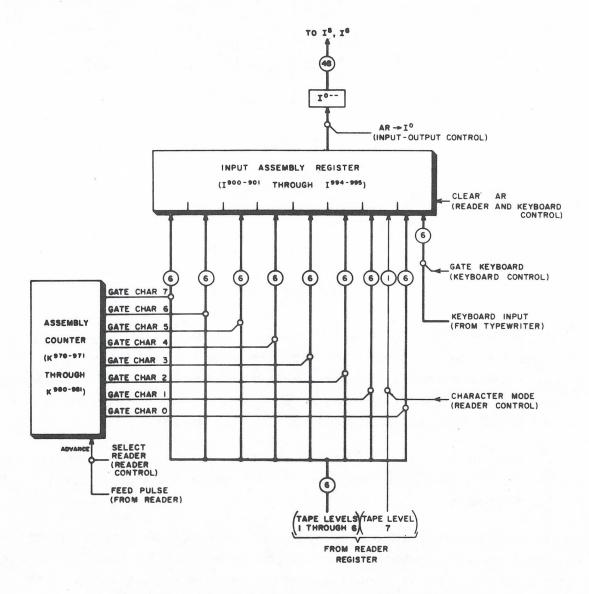

Two 24-bit instruction words may be stored in a 48-bit storage location. The RNI sequence (figure 2-11) can transfer the 48-bit quantity to the U<sup>1</sup> register, making the 24-bit quantity in U<sup>1</sup> upper (U<sup>1</sup><sub>U</sub>) available as the next instruction or transfer the 24-bit quantity from U<sup>1</sup> lower (U<sup>1</sup><sub>L</sub>) to U<sup>1</sup><sub>U</sub>.

The sequence steps from initial start, full exit, or jump exit are:

Initiate storage (P Address) Wait storage Storage resume Set Exit FF Clear U<sup>1</sup> upper and lower Transmit storage to U<sup>1</sup>

The corresponding steps from half exit are:

Clear Exit FF Clear U<sup>1</sup> upper only Transmit U<sup>1</sup> lower to U<sup>1</sup> upper.

# Start And Stop

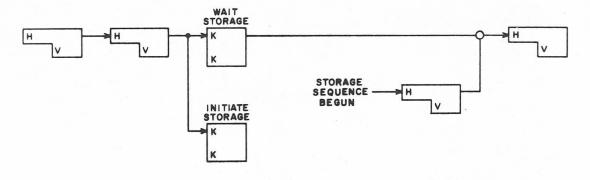

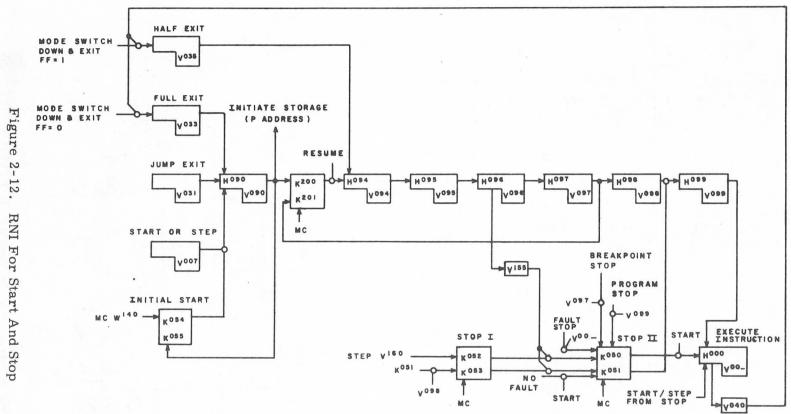

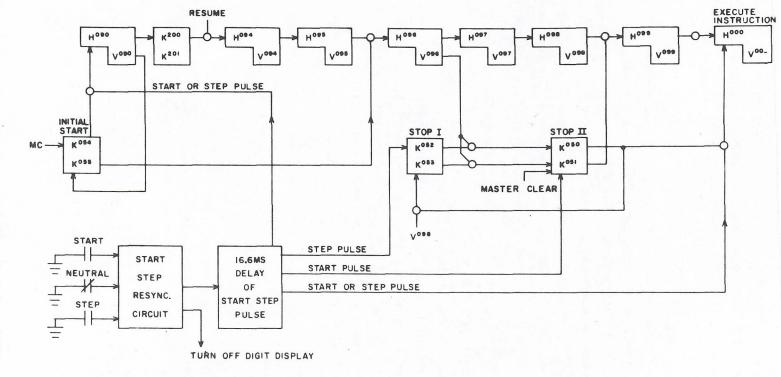

The RNI sequence, along with manual control logic, provides for initial starting, stopping, starting from stop, and stepping the 1604-A. A simplified diagram of RNI for these operations is shown in figure 2-12.

<u>Initial Start</u>: To start the computer initially, a Master Clear signal is required to set the Initial Start FF (K054/055). When the Start switch is operated, K055 gates the Start pulse into H090 to initiate RNI.

Figure 2-11. Form of, **RNI for Acquiring Instructions**

2 - 21

<u>Step</u> Stepping is used to execute one instruction at a time and stop after each one. If the Start/Step key is pressed to Step when the Initial Start FF is set, RNI is initiated at H090. However, stepping sets the Stop I FF, V155 transfers Stop I to Stop II, and the last control delay of RNI is disabled. Stepping again (step from stop condition) initiates RNI at H000 and one instruction is executed. Thereafter, one instruction is executed each time the Start/Step switch is pressed to Step. If the Start/Step switch is pressed to Step while the computer is operating, Stop I is set; the next RNI transfers Stop I to Stop II, and the computer stops. The computer can then be stepped or started from the stop condition in the normal manner.

Stop Instruction When the condition specified in a Selective Stop instruction (76) is satisfied, the Stop II FF is set. In this case Stop II is not set in time to disable H099 but it is set in time to stop the normal jump sequence which is the only sequence a 76 instruction can initiate. When the computer is restarted, f still equals 76 and the normal jump sequence is executed.

Breakpoint Stop The breakpoint translator compares the address of each new instruction word (content of P register) with the setting of the Breakpoint switches (see page 2-38). When the address and the breakpoint setting become equal, Stop II is set, and H099 is disabled before execution of the upper instruction of the breakpoint address.

<u>Fault Stop</u> The 1604-A has no function codes 00 or 77 and these two codes are considered faults. If the f portion of the instruction read by RNI equals 00 or 77, Stop II is set and the last control delay of RNI (H099) is disabled.

Start From Stop When the computer is restarted from stop, Stop II is cleared, RNI is entered at H000, and the computer proceeds directly to an instruction sequence except in the case where the computer is stopped by a fault condition. Fault conditions must be cleared (e.g., set f manually to some number other than 00 to 77) before Stop II can be cleared and the computer started from stop. When the computer is started from a breakpoint stop, the upper instruction at the breakpoing address is executed and the computer stops again in RNI (because P still holds the breakpoint address). Starting a second time causes the computer to execute the lower breakpoint instruction and then proceed to the next instruction without stopping.

## Sweep Mode

When the Mode switch on the 1604-A console is in the Down (Sweep) position, RNI does not initiate an instruction sequence but takes a full or half exit according to the setting of

the Exit FF. Thus in Sweep mode, the content of all storage locations can be read by RNI and displayed without executing any of the instructions.

## Preliminary Steps in Address Modification

When the b designator is 1-6, the base execution address may be modified by the addition of  $(B^b)$ . RNI takes the following preliminary steps in address modification (figure 2-11).

• • •

$$Bb to I2 or I3I2 or I3 to R1U1 to U2$$

Preliminary Control and Arithmetic Steps

Clear  $X^1$ Set Partial Add in A FF  $Q^1$  to  $Q^2$  $R^1$  to  $R^2$

## Interrupt Termination

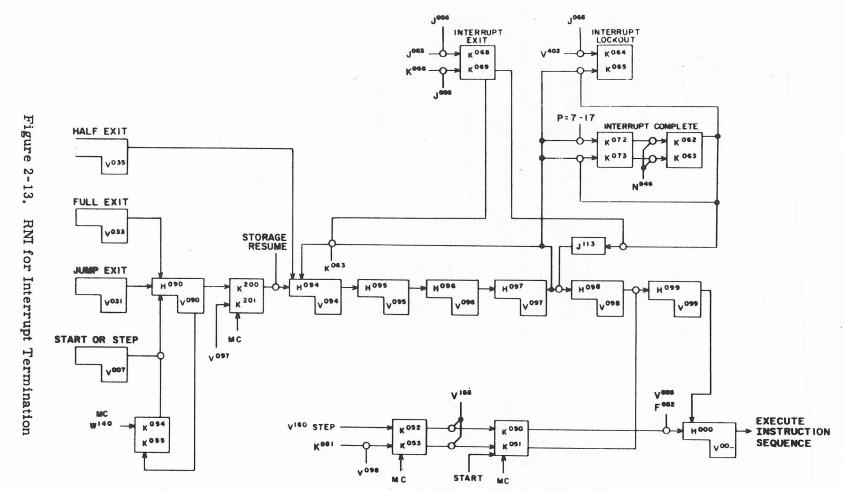

An Interrupt signal causes the computer to temporarily interrupt the main program to perform a special routine of instructions (figure 2-13).

When the interrupt routine is finished, the main program is returned to by:

- 1) Jump to address 00007 00017:

- a) sets P to 00007 00017

- b) initiates full RNI from jump exit

- 2) Full RNI from step 1b:

- a) reads content 00007 00017 into  $U^1$

- b) sets Interrupt Complete FF (K072/073)

- 3) Execution of upper instruction at 00007 00017:

- a) jumps to next instruction of main program

- b) initiates full RNI from jump exit

- 4) Full RNI from step 3b:

- a) clears Interrupt Lockout FF

- b) clears K072/073 (Interrupt Complete FF)

- c) continues from V097 to H098 if Interrupt Exit FF is set

- d) goes to H094 from V097 if Interrupt Exit FF is "0" (half RNI)

- e) after step 4d, K062/063 is cleared to enable AND from V097 to H098

#### Indirect Addressing

Indirect addressing is often chosen for programs involving a great deal of address modification because it simplifies programming and reduces the running time. In direct addressing the execution address indicates the location of the operand; in indirect addressing the execution address indicates the location of the operand address. An additional memory reference is required to obtain the operand.

All instructions except 22, 23, 74, 75 and 76 may be used with either direct or indirect addressing. Indirect addressing occurs when b = 7.

Examples: Below are two examples of indirect addressing.

| Address | Uppe | r Ins | truction | Lower Instructio |   |       |

|---------|------|-------|----------|------------------|---|-------|

|         | f    | b     | m        | f                | b | m     |

| 05012   | 36   | 3     | 71331    | 14               | 7 | 00367 |

| 00367   |      |       |          | 42               | 2 | 11135 |

Because b is 3 in the upper instruction, direct addressing is used.  $B^3$  is added to 71331 to produce the address of the operand. In the lower instruction, because b is 7, indirect addressing is used; therefore m is the location of the new operand.

•

Now the lower 18 bits are read out of address 00367 (remaining upper bits are ignored). These 18 bits are substituted in the Program Control register for the original 18-bit quantity made up of b and m. As a consequence, the current instruction becomes 14 2 11135. The designator is examined again; since it is not 7, the address of the operand is  $11135 + (B^2)$ . If the new value of b had been 7, a second indirect addressing operation would have resulted.

| Address | Uppe | er Inst | ruction | Low | er Inst | ruction |

|---------|------|---------|---------|-----|---------|---------|

|         | f    | b       | m       | f   | b       | m       |

| 05013   | 01   | 7       | 04006   | 12  | 6       | 71331   |

| 04006   |      |         |         |     | 7       | 11466   |

| 11466   |      |         |         |     | 0       | 00012   |

|         |      |         |         |     | •       | 0001    |

Since b is 7 in this instruction, the lower 18 bits at address 04006 are substituted in the Program Control register which then holds 01 7 11466. Since b is again 7, the lower 18 bits in address 11466 are entered into the Program Control register. Because b is zero, 00012 is used as the execution address.

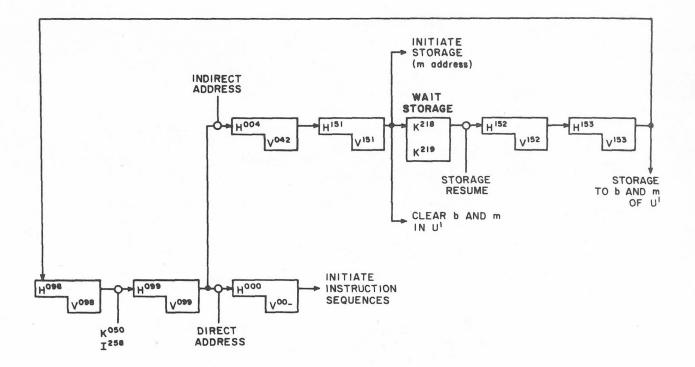

Indirect addressing is accomplished by RNI (figure 2-14). By the time RNI has progressed to V099, f and b have been translated; direct or indirect addressing is selected. Conditions for the choice are:

> Indirect Addressing - f  $\neq$  22, 23, 74-76 and b = 7 Direct Addressing - f = 22, 23, 74-76 or b  $\neq$  7

The steps for indirect addressing are:

Initiate storage (on address m) Clear b and m parts of U<sup>1</sup> Wait storage Transmit storage to b and m part of U<sup>1</sup>

At the end of this sequence a new 18-bit quantity occupies the b and m portions of  $U^{1}_{U}$ . A pulse from V153 (figure 2-14) then re-enters the RNI sequence at H098 and the new instruction is executed.

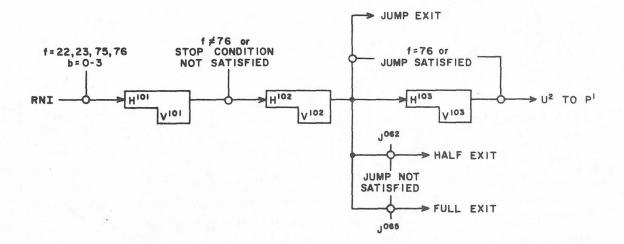

NORMAL JUMP SEQUENCE

The Normal Jump (NJ) sequence is used by instructions 22, 23, 75 and 76, when j = 0-3.

When the jump condition is met, this sequence transmits  $U^2$  to  $P^1$  (figure 2-15) entering the address of the first instruction of a new program in P. The jump exit is then taken to initiate the full RNI and read the pair of instructions at address P. If the jump condition is not met, the full exit or half exit is taken to initiate the full or half RNI.

Figure 2-14. Indirect Addressing Part of RNI

Instruction 76, Selective Stop, provides for a jump whether or not the conditions for stopping are met. When the stop condition is met, the AND to H102 is disabled and operation stops. When operation is resumed by either start or step, the NJ sequence is initiated, the AND to H102 is enabled and the jump is completed.

#### ZERO ADDRESS SEQUENCE

The Zero Address (ZA) sequence performs the basic operation for instructions 01-11, 34, 35, 50, 51, 54, and 55. This sequence makes no storage reference; the execution address is the operand for these instructions.

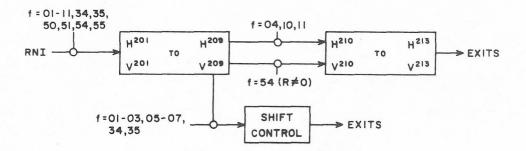

The chain of control delays forming the basis of the ZA sequence consists of two parts (figure 2-16). All ZA instructions use the first part; only instructions 04, 10, 11, and 54 (with  $R \neq 0$ ) use the last part. Most of the commands for ZA instructions are generated from this chain of control delays. However, the commands for shifting and reducing R in instructions 01-03, 05-07, 34, and 35 are generated independently of the main chain by the shift control. The chain establishes the conditions which permit these commands to occur until the terminating conditions are reached.

Figure 2-16. Basic Chain of Control Delays in Zero Address Sequence

#### READ OPERAND SEQUENCE

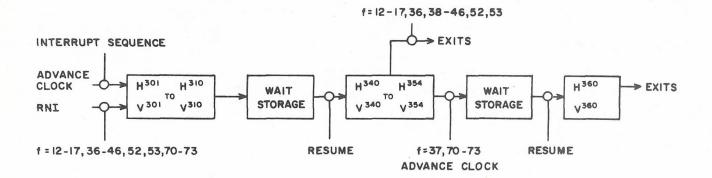

Instructions 12-17, 36-46, 52, 53, 70-73, and Advance Clock use the RO (Read Operand) sequence (figure 2-17). These instructions all read from storage; Advance Clock and instructions 37 and 70-73 also store an operand at the conclusion of the sequence.

Figure 2-17. Basic Chain of Control Delays in RO Sequence

## WRITE OPERAND SEQUENCE

Interrupt and instructions 20, 21, 47, 56-61 for all values of the designator and Return Jump instructions (22, 23, 75 and 76 with designator values of 4-7) use the WO (Write Operand) sequence. It is initiated at H401 and all WO instructions except 56 and 57 which initiate the sequence at H406 after initiating a storage sequence.

#### SEARCH AND TRANSFER SEQUENCE

The Search and Transfer sequence (S & T) performs search instructions 64-67 and transfer instructions 62 and 63. The search instructions inspect a specified list of operands for one which meets the condition "operand equal to A" or "operand greater than A." The transfer instructions exchange a block of data with Input-Output equipment.

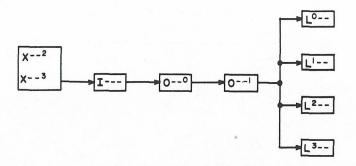

Figure 2-19. Basic Block Diagram of Search and Transfer

The S & T sequence (figure 2-19) consists of two main parts; preparation and loop. Preparation sets up the addresses and other initial conditions. The loop produces a series of search or transfer commands which is repeated for each word searched or transferred. The number of repetitions required is indicated by the quantity in  $B^b$ which is reduced by one during each repetition. The block of storage locations involved in Search and Transfer instructions is specified by  $B^b$  and m, the execution address. The first word searched or transferred is at the address  $(B^b) + m-1$ . The last word is at address m. When b = 0, only the word at address m is searched or transferred.

A Search instruction provides for a conditional skip and is used in the upper position of a program step. Ordinarily it involves repeating the loop for each word until:

- A word is found that meets the search condition; search terminates and a full exit is made to the next instruction step.

- 2) The entire list of words has been searched without finding one that meets the search condition, in which case a half exit is made to the lower instruction of the current step.

A Transfer operation consists of one repetition of the loop for each word. When all have been transferred, a full or half exit is taken depending upon whether the instruction is in the lower or upper position.

## ITERATIVE SEQUENCE

The commands which execute the Multiply, Divide, and Floating-Point instructions (24-27, 30-33) derive from the Iterative sequence (I). This sequence (figure 2-20) executes instructions by iterative or repetitive action. For example, the repetitive additions of the multiplicand form the product in multiplication.

A detailed discussion of the Iterative sequence appears in chapter 3 where the complex arithmetic operations using this sequence are described.

•

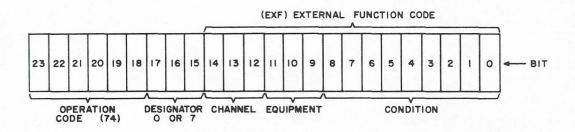

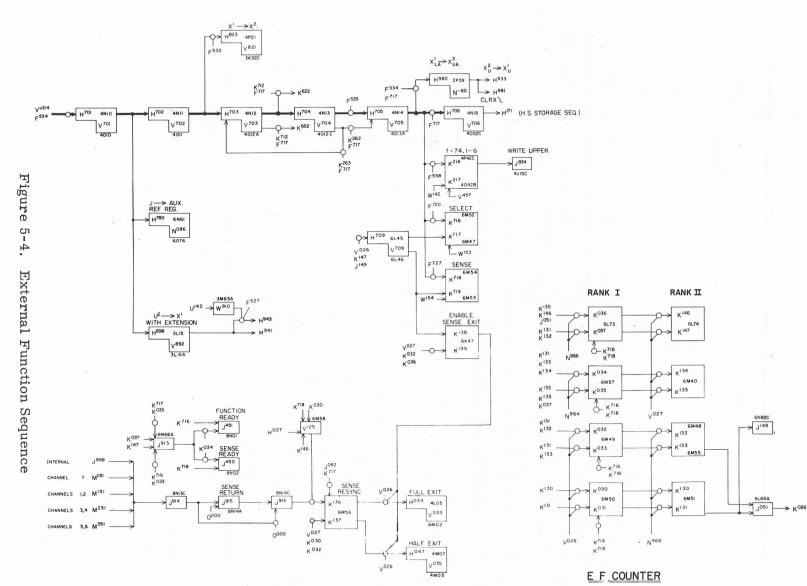

#### EXTERNAL FUNCTION SEQUENCE

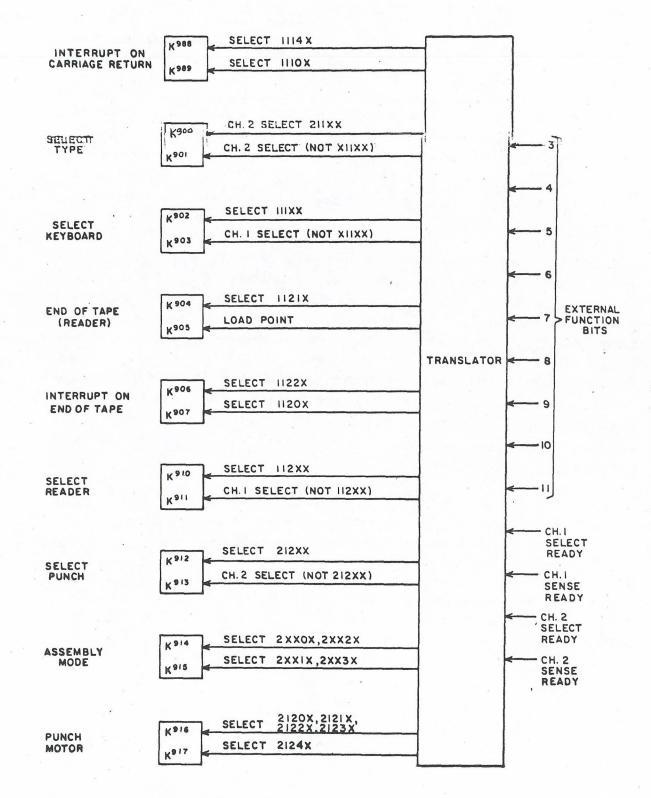

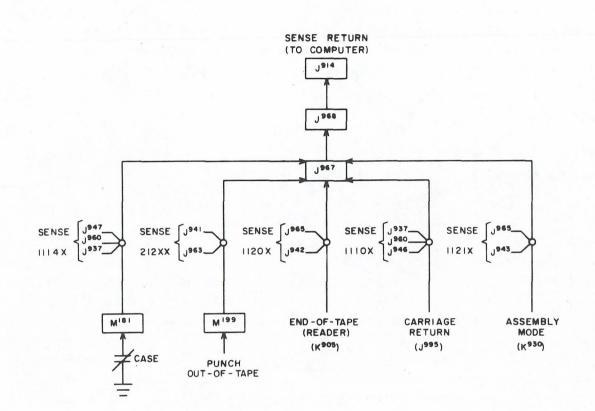

The External Function (EXF) sequence (figure 2-21) executes the 74 instruction to select operating conditions for external and console equipment, sense the condition of external and console equipment, sense internal faults, and activate buffer communcation channels 1-6. The value of the designator, j, is used to determine which of its duties the EXF sequence is to do. High speed storage sequence is used in conjunction with EXF sequence to execute the Activate command (j = 1-6). A 74.0 instruction selects the operating condition for external or console equipment. A 74.7 instruction is used to sense equipment conditions and faults within the computer. When the 74 instruction is used with j = 1-6, a buffer channel is activated.

Figure 2-21. Block Diagram of EXF Sequence

## INTERRUPT SEQUENCE

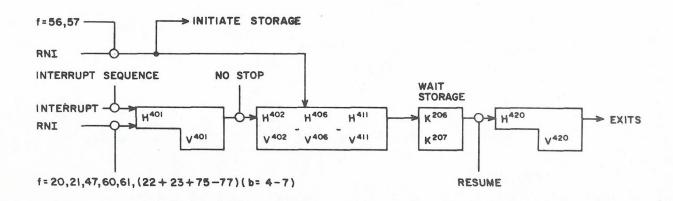

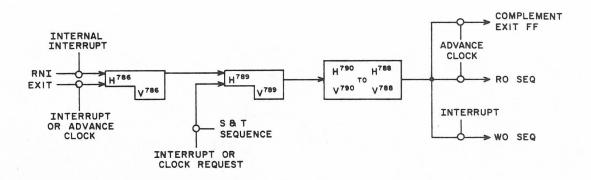

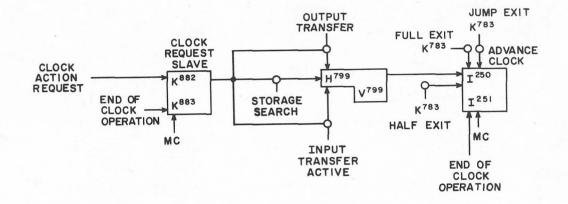

When an interrupt or clock request occurs, the Interrupt sequence is initiated. This sequence (figure 2-22) can be entered between any two program steps or during a Search or Transfer instruction.

## Interrupt

To process an interrupt request, the WO sequence follows the Interrupt sequence. The content of P is stored to provide for return to the main program and a jump is made to an interrupt subroutine. The interrupt subroutine senses and corrects the condition causing interrupt and then returns to the main program. Interrupt is discussed in detail in chapter 6.

#### Advance Clock