# **AEGIS** Internals and Data Structures

. 9

Order No. N/A Revision 00 Software Release 9.0

Apollo Computer Inc. 330 Billerica Road Chelmsford, MA 01824 Copyright © 1986 Apollo Computer Inc.

All rights reserved.

Printed in U.S.A.

First Printing:

January 1, 1986

This document was produced using the SCRIBE document preparation system. (SCRIBE is a registered trademark of Unilogic, Ltd.)

APOLLO and DOMAIN are registered trademarks of Apollo Computer Inc.

AEGIS, DGR, DOMAIN/Bridge, DOMAIN/Dialogue, DOMAIN/IX, DOMAIN/Laser-26, DOMAIN/PCI, DOMAIN/SNA, DOMAIN/VACCESS, D3M, DPSS, DSEE, GMR, and GPR are trademarks of Apollo Computer Inc.

Apollo Computer Inc. reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should in all cases consult Apollo Computer Inc. to determine whether any such changes have been made.

THE TERMS AND CONDITIONS GOVERNING THE SALE OF APOLLO COMPUTER INC. HARDWARE PRODUCTS AND THE LICENSING OF APOLLO COMPUTER INC. SOFTWARE CONSIST SOLELY OF THOSE SET FORTH IN THE WRITTEN CONTRACTS BETWEEN APOLLO COMPUTER INC. AND ITS CUSTOMERS. NO REPRESENTATION OR OTHER AFFIRMATION OF FACT CONTAINED IN THIS PUBLICATION, INCLUDING BUT NOT LIMITED TO STATEMENTS REGARDING CAPACITY, RESPONSE-TIME PERFORMANCE, SUITABILITY FOR USE OR PERFORMANCE OF PRODUCTS DESCRIBED HEREIN SHALL BE DEEMED TO BE A WARRANTY BY APOLLO COMPUTER INC. FOR ANY PURPOSE, OR GIVE RISE TO ANY LIABILITY BY APOLLO COMPUTER INC. WHATSOEVER.

IN NO EVENT SHALL APOLLO COMPUTER INC. BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATING TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT, EVEN IF APOLLO COMPUTER INC. HAS BEEN ADVISED, KNEW OR SHOULD HAVE KNOWN OF THE POSSIBILITY OF SUCH DAMAGES.

THE SOFTWARE PROGRAMS DESCRIBED IN THIS DOCUMENT ARE CONFIDENTIAL INFORMATION AND PROPRIETARY PRODUCTS OF APOLLO COMPUTER INC. OR ITS LICENSORS.

# Preface

The AEGIS Internals and Data Structures manual describes the algorithms and data structures that comprise the AEGIS operating system kernel, Software Release 9.0. It includes detailed descriptions of the following kernel services:

- Memory management

- Local and remote file systems

- Process management

- Network management

- Naming interface

- System initialization

This manual intends to describe only the services provided by the AEGIS kernel; subsequent internals documents will describe the user-mode AEGIS functions.

# Audience

STREE STREET

AUTOMATINA A USE

This manual is intended for new and existing employees of Apollo's Research and Development group who need a detailed explanation of AEGIS operating system architecture. The manual is also intended for selected OEM customers with source code licenses who sign or have signed a non-disclosure agreement with Apollo Computer.

### Organization of this Manual

This manual contains 29 chapters that are organized into six sections.

- Section I (Chapters 1 and 2) contains two introductory chapters that describe the philosophy behind AEGIS system design and provide an overview of AEGIS system components, both kernel and user-mode.

- Section II (Chapters 3 through 8) describes the components of the object storage system, the naming interface, and the object locating service.

- Section III (Chapters 9 through 13) describes the virtual memory management system.

- Section IV (Chapters 14 through 19) describes the process environment. It contains chapters that describe level 1 and level 2 processes, eventcounts, fault handling, and SVC dispatching.

- Section V (Chapters 20 through 24) describes the hardware and software components of the network interface.

- Section VI (Chapters 25 through 29) describe the system initialization procedure.

The manual also contains two appendixes.

# **Documentation Conventions**

Unless otherwise noted in the text, this manual uses the following conventions:

- UPPERCASE Uppercase words or characters in formats and command descriptions represent commands or keywords that you must use literally.

- lowercase Lowercase words or characters in formats and command descriptions represent values that you must supply.

- [] Square brackets enclose optional items in formats and command descriptions. In sample Pascal statements, square beackets assume their Pascal meanings.

- { } Braces enclose a list from which you must choose an item in format and command descriptions. In simple Pascal statements, braces assume their Pascal meanings.

- A vertical bar separates items in a list of choices.

- <> Angle brackets enclose the name of a key on the keyboard.

- CTRL/Z The notation CTRL/ followed by the name of a key indicates a control character sequence. You should hold down the <CTRL> key while typing the character.

- Horizontal ellipsis points indicate that the preceding item can be repeated one or more times.

Vertical ellipsis points mean that irrelevant parts of a figure or example have been omitted.

## Suggested Reading Paths

Although this manual discusses some aspects of DOMAIN system hardware as they relate to DOMAIN system software, it does not provide a complete description of processor, network, or display hardware implementations. For such information, refer to the Apollo publications listed below:

- The DOMAIN System MULTIBUS Reference document, which describes Apollo Computer's implementation of the Intel MULTIBUS.

- The Engineering Handbook, (for internal use only), which gives brief descriptions of processor, memory, I/O and display hardware implementations and provides diagrams of control and status registers.

- The Programming with DOMAIN Advanced System Calls manual, which documents a set of unreleased system services, such as the file utility (FU) and the command line handler (CL).

- The Extending Your DOMAIN Streams manual, which describes the extensible streams interface (IOS).

ł

The Writing Device Drivers with GPIO Calls manual, which describes how to use the general-purpose I/O system services to write device drivers for customer-supplied devices.

• The DOMAIN Assembler Reference manual, which describes the DOMAIN assembler and gives information about object module format.

For information on processor hardware, refer to the following Motorola publications:

- The Motorola MC68020 32-Bit Microprocessor User's Manual. Prentice-Hall, Inc. 1984.

- The Motorola 16-Bit Microprocessor User's Manual, Third Edition. Prentice-Hall, Inc. 1982.

# Contents

| Chapter 1 AEGIS System Design                                              |       | 1-1         |

|----------------------------------------------------------------------------|-------|-------------|

| 1.1. The Distributed System Design                                         |       | 1-1         |

| 1.2. The Integrated System Design                                          |       | 1-1         |

| 1.3. Local Area Networking Design                                          |       | 1-3         |

| 1.4. Typed File Design                                                     |       | 1-3         |

| 1.5. AEGIS as a Personal Workstation System                                |       | 1-4         |

|                                                                            |       | • •         |

| •                                                                          |       |             |

| Chapter 2 AEGIS System Overview                                            |       | 2-1         |

| 2.1. Interaction of AEGIS Kernel and User Components                       |       | 2-1         |

| 2.2. AEGIS Kernel Services                                                 |       | 2-2         |

| 2.2.1. File Management                                                     |       | 2-2         |

| 2.2.1.1. Object Management                                                 |       | 2-2         |

| 2.2.1.2. Object Naming                                                     |       | 2-3         |

| 2.2.2. Process Management                                                  |       | 2-3         |

| 2.2.2.1. Level 1 Processes                                                 | · · · | 2-3         |

| 2.2.2.2. Level 2 Processes                                                 |       | 2-3<br>2-4  |

| 2.2.2.3. Process Synchronization                                           |       | 2-4<br>2-5  |

| 2.2.2.4. Process Scheduling                                                |       | 2-5<br>2-6  |

| 2.2.2.5. Trap, Interrupt, and Fault Handling                               |       | 2-0<br>2-6  |

| 2.2.3. Layout of Virtual Address Space                                     |       | 2-0<br>2-6  |

| 2.2.3. Dayout of Virtual Address Space<br>2.2.4. Virtual Memory Management |       | 2-0<br>2-8  |

| 2.2.4.1. Mapping                                                           |       |             |

| 2.2.4.2. Demand Paging                                                     |       | 2-8         |

| 2.2.4.2. Demand Faging<br>2.2.5. Network Management                        |       | <b>2-</b> 8 |

|                                                                            |       | 2-9         |

| 2.2.6. I/O Management                                                      |       | 2-10        |

| 2.2.7. Time Management<br>2.3. Access Control Mechanisms                   |       | 2-10        |

|                                                                            |       | 2-11        |

| 2.3.1. Processor Access Modes                                              |       | 2-11        |

| 2.3.2. Access Control Lists                                                |       | 2-11        |

| 2.3.3. Object Locking                                                      |       | 2-11        |

| 2.3.4. Resource Control                                                    |       | 2-11        |

| 2.4. The User Program Environment                                          |       | 2-12        |

| 2.4.1. The Process Manager                                                 |       | 2-12        |

| 2.4.2. Libraries                                                           |       | 2-13        |

| 2.5. The User Environment                                                  |       | 2-13        |

| 2.6. The Display Manager                                                   |       | 2-13        |

| 2.7. System Initialization                                                 |       | 2-14        |

|                                                                            |       |             |

|                                                                            |       |             |

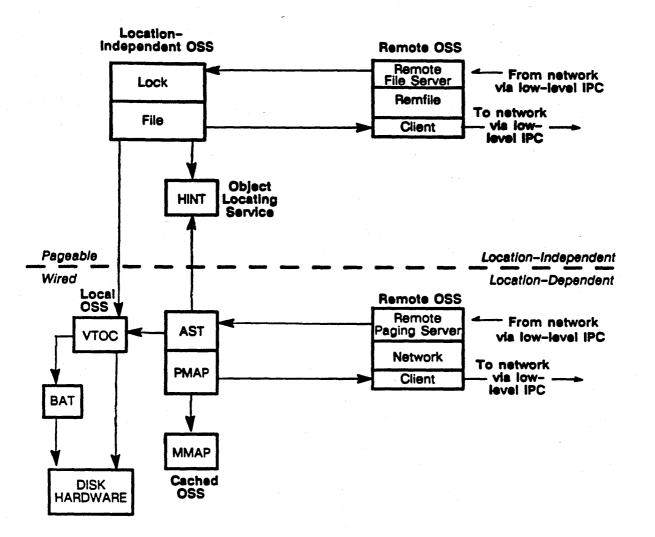

| Chapter 3 Object Storage System Overview                                   |       | 8-1         |

| 3.1. Object Page and Segment                                               |       | 3-1         |

| 3.2. Object Attributes                                                     |       | 3-2         |

| 3.2.1. System Type                                                         |       | 3-3         |

| 3.2.2. Concurrency Control                                                 |       | 3-3         |

|                                                                            |       |             |

)

Contents

vii

| 3.2.3. Permanent and Temporary Attributes                                                | 3-3                    |

|------------------------------------------------------------------------------------------|------------------------|

| 3.2.4. Immutable Attribute                                                               | 3-4                    |

| 3.2.5. Salvaged Flag                                                                     | 3-4                    |

| 3.2.6. ACL UID                                                                           | 3-4                    |

|                                                                                          | 3-4                    |

| 3.2.7. Object Type UID                                                                   | 3-4                    |

| 3.2.8. Miscellaneous Object Attributes                                                   | 3-4<br>3-4             |

| 3.2.9. Reference Count                                                                   |                        |

| 3.2.10. Lock Key Attribute                                                               | 3-5                    |

| 3.3. Unique Identifiers                                                                  | 3-5                    |

| 3.3.1. UIDs as Object Locators                                                           | 3-6                    |

| 3.3.2. Generating UIDs                                                                   | 3-6                    |

| 3.3.3. Guaranteeing UID Uniqueness                                                       | 3-6                    |

| 3.3.4. Canned UIDs                                                                       | 3-7                    |

| 3.4. Local Object Storage Components                                                     | 3-7                    |

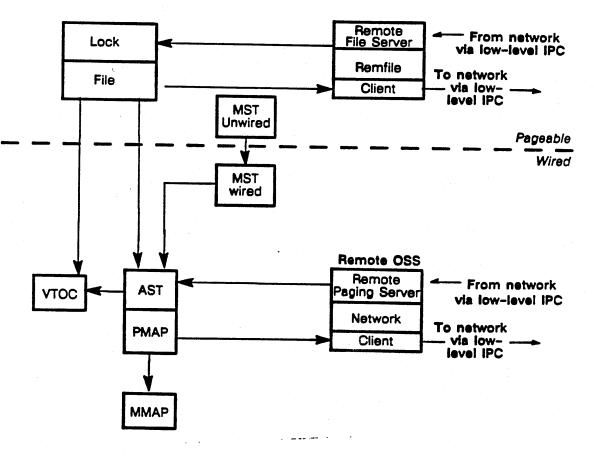

| 3.5. Remote Object Storage Components                                                    | 3-7                    |

| 3.5.1. The NETWORK Manager                                                               | 3-8                    |

| 3.5.2. The Remote File Manager                                                           | <b>3-</b> 8            |

| 3.6. Cached OSS Components                                                               | 3-8                    |

| 3.7. The Object Locating Service                                                         | 3-9                    |

| 3.8. The Object Management Service                                                       | 3-10                   |

| 3.9. Lock Management                                                                     | 3-10                   |

|                                                                                          |                        |

|                                                                                          |                        |

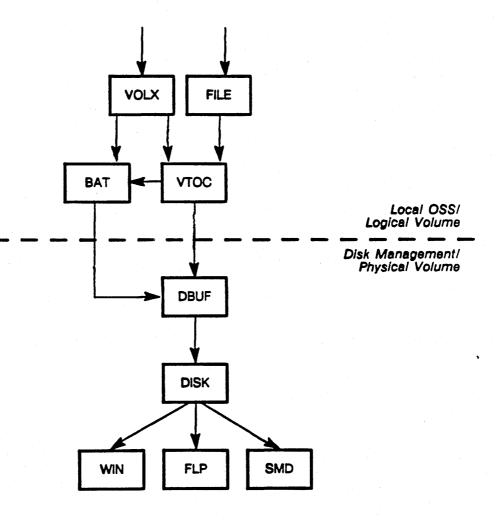

| Chapter 4 Local Object Storage System                                                    | 4-1                    |

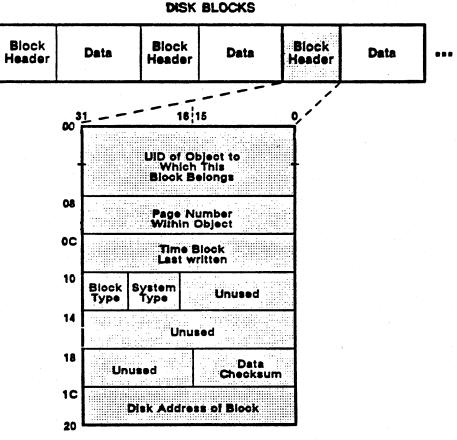

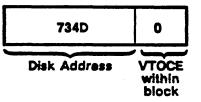

| 4.1. Disk Block Format                                                                   | 4-2                    |

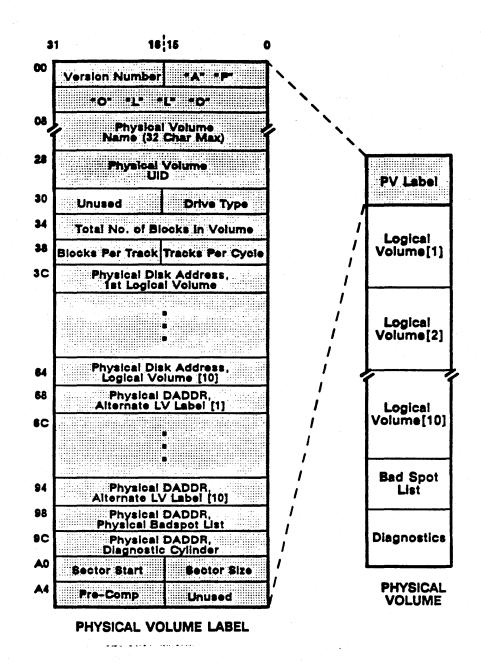

| 4.2. Physical Volume Structure                                                           | 4-4                    |

| 4.2.1 Physical Volume Label                                                              | 4-4                    |

| 4.2.2. Badspot Cylinder                                                                  | 4-4                    |

| 4.2.3. Diagnostics Cylinder                                                              | 4-6                    |

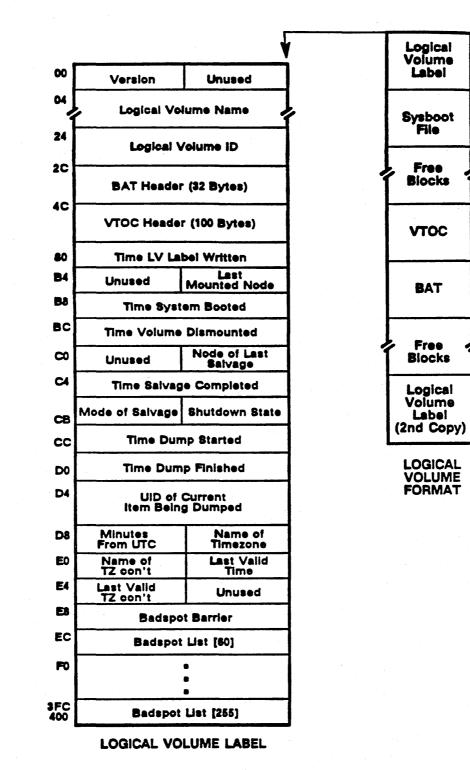

| 4.3. Logical Volume Structure                                                            | 4-6                    |

|                                                                                          | 4-8                    |

| 4.3.1. Logical Volume Labe?<br>4.3.2. Block Allocation to SYSBOOT                        | <del>1-</del> 0<br>4-8 |

|                                                                                          | 4-0<br>4-8             |

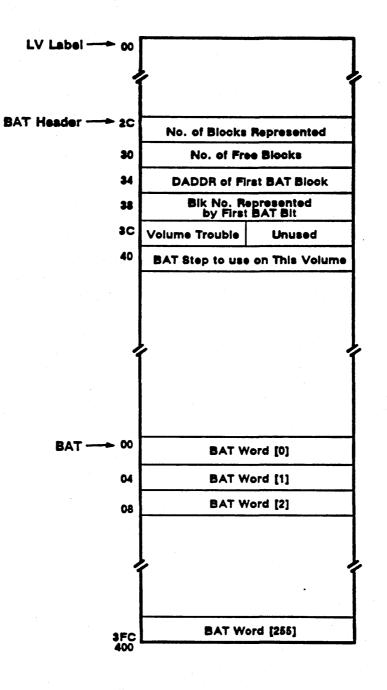

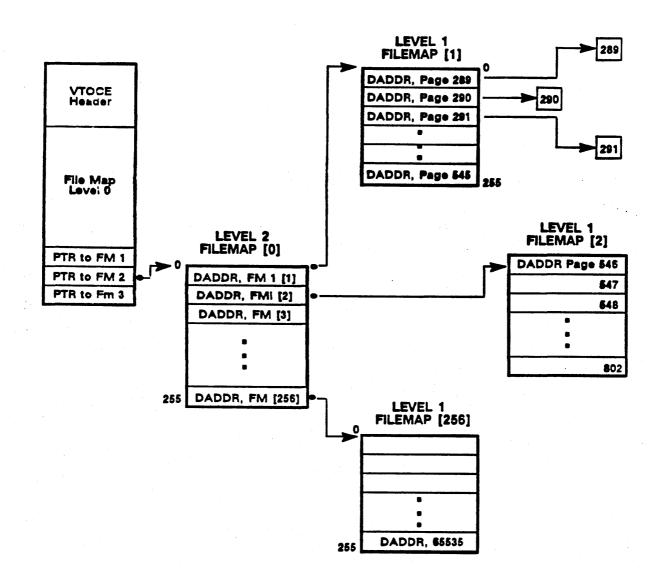

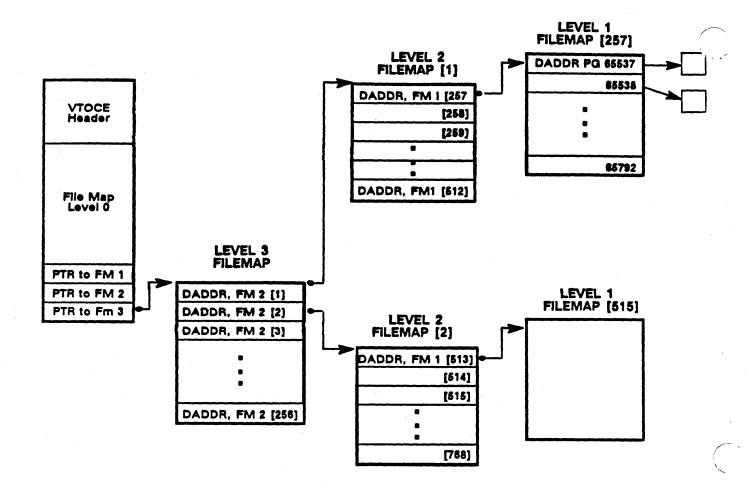

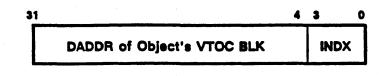

| 4.3.3. Block Availability Table (BAT)<br>4.3.4. Volume Table of Contents Data Structures |                        |

|                                                                                          | 4-10                   |

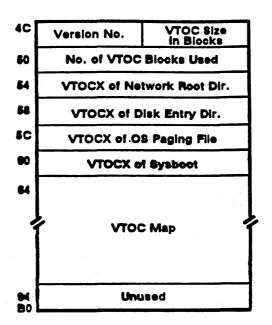

| 4.3.4.1. VTOC Header                                                                     | 4-10                   |

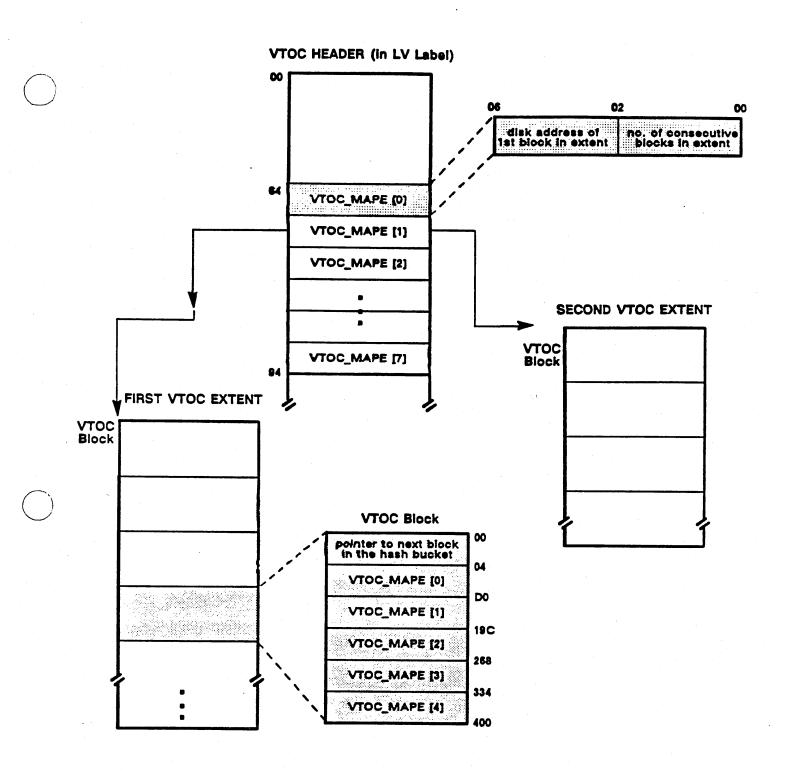

| 4.3.4.2. The VTOC Map                                                                    | 4-12                   |

| 4.3.4.3. The VTOC Block                                                                  | 4-12                   |

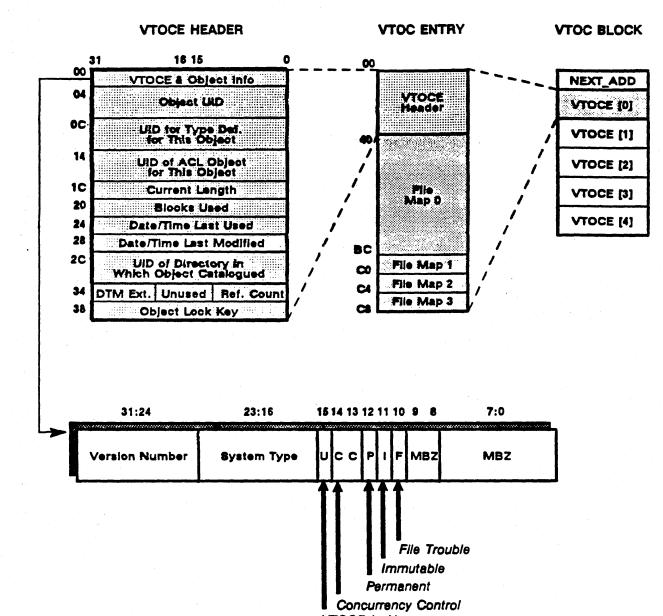

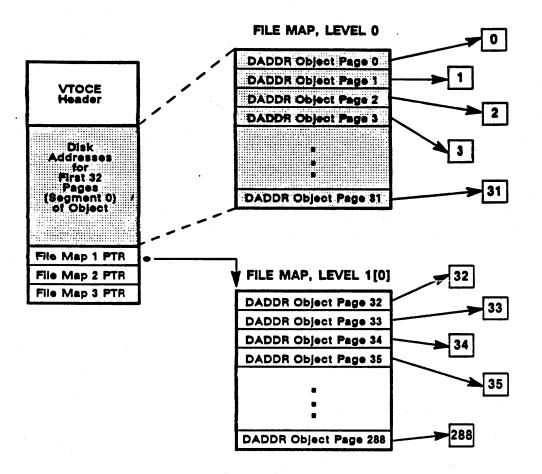

| 4.3.4.4. VTOC Entries                                                                    | 4-14                   |

| 4.4. VTOC and BAT Managers                                                               | 4-19                   |

| 4.4.1. Locating an Object in the VTOC                                                    | 4-19                   |

| 4.4.2. Creating an Object                                                                | <b>4-20</b>            |

| 4.4.3. Allocating Blocks on Disk                                                         | 4-21                   |

|                                                                                          |                        |

|                                                                                          |                        |

| Chapter 5 Object Management                                                              | 5-1                    |

| 5.1. MST Manager Object Management                                                       | 5-2                    |

| 5.2. FILE Manager Object Management                                                      | 5-2                    |

| 5.2.1 Object Creation                                                                    | 5-3                    |

| •                                                                                        | 5-3                    |

| 5.2.2. Object Deletion                                                                   | J-J                    |

· ....

viii

| 5.3. Reading and Writing Object Attributes<br>5.4. Locating Objects |   | 5-3<br>5-4  |

|---------------------------------------------------------------------|---|-------------|

| 5.5. Force-Writes and Force-Purification                            |   | 5-4         |

|                                                                     |   |             |

| Chapter 8 Object Lock Management                                    |   | 6-1         |

| 6.1. Controlling Concurrent Access                                  |   | 6-1         |

| 6.1.1. Concurrency Mode                                             |   | 6-1         |

| 6.1.1.1. No Concurrency Control                                     |   | 6-1         |

| 8.1.1.2. Protected Concurrency Control                              |   | 6-2         |

| 6.1.1.3. Shared Concurrency Control                                 |   | 6-2         |

| 6.1.2. Access Mode                                                  |   | 6-2         |

| 6.1.3. Lock Compatibility                                           |   | 6-3         |

| 6.1.4. The Lock Table                                               | * | 6-4         |

| 6.1.5. Lock Key                                                     |   | 6-5         |

| 6.1.6. Obtaining a Lock                                             |   | 6-6         |

| 6.1.7. Changing a Lock's Access Mode                                |   | <b>6-</b> 6 |

| 6.2. Maintaining Consistent Data                                    |   | <b>6-</b> 6 |

| 6.2.1. Lock Verification                                            |   | 6-7         |

|                                                                     |   |             |

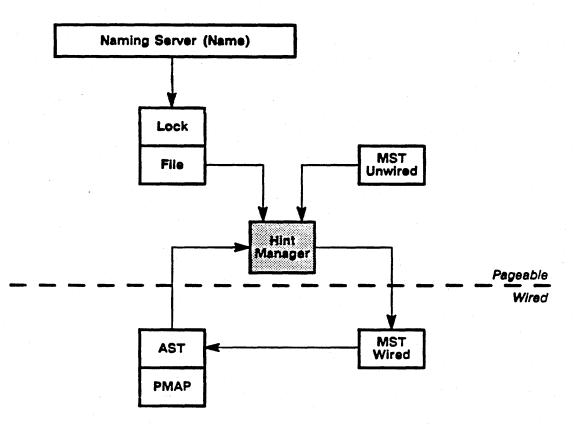

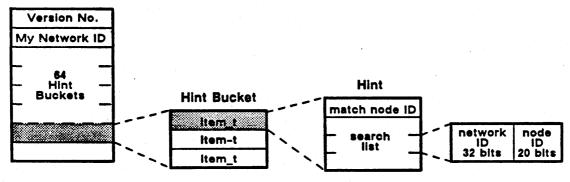

| Chapter 7 Object Leasting on the Hint Manager                       |   | <b>7-</b> 1 |

| Chapter 7 Object Location, or the Hint Manager                      |   | 7-1         |

| 7.1. Hint File Structure                                            |   | 7-2         |

| 7.2. Hint File Initialization and Shutdown                          |   | 7-2         |

| 7.3. Adding Hints to a Hint File                                    |   | 7-3         |

| 7.3.1. How the Hint Manager Updates a Hint File                     |   | 7-3         |

| 7.3.2. Hints from ASKNODE                                           |   | 7-4         |

| 7.3.3. Hints from the Naming Server                                 |   | 7-4         |

| 7.3.4. Hints from the File Manager                                  |   | 7-5         |

| 7.4. Reading a Hint File                                            |   | 7-5         |

| 7.4.1. How the Hint Manager Finds Hints                             |   | 7-5         |

| 7.4.2. Hint File Reading by the Naming Server                       |   | 7-6         |

| 7.4.3. Hint File Reading by the AST and FILE Managers               |   | <b>7-</b> 6 |

|                                                                     |   |             |

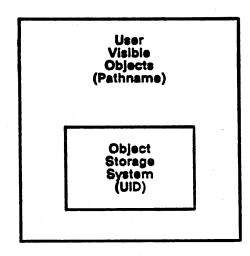

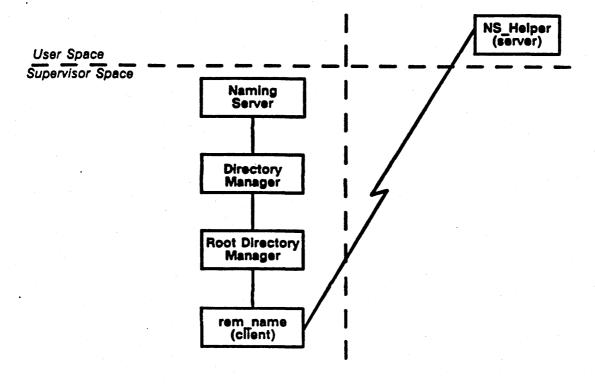

| Chapter 8 The Naming Interface                                      |   | 8-1         |

|                                                                     |   |             |

| 8.1. Pathnames, Directories, and UIDs                               |   | 8-1         |

| 8.2. Managers of the Naming Interface                               |   | 8-2         |

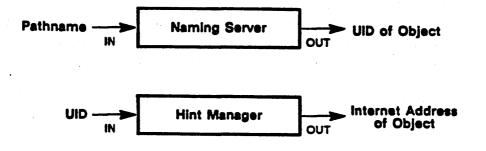

| 8.2.1. Naming Server                                                |   | 8-2         |

| 8.2.2. The Directory Manager                                        |   | 8-3         |

| 8.2.3. The Naming Server Helper and Client Software                 |   | 8-3         |

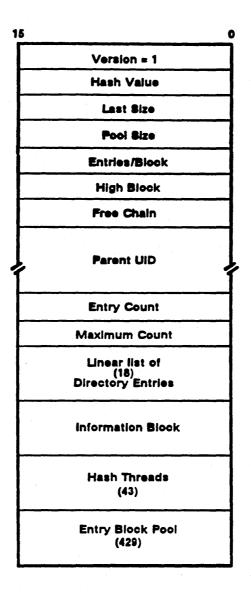

| 8.3. Format of a Directory                                          |   | 8-4         |

| 8.3.1. Directory Header                                             |   | 8-5         |

| 8.3.2. Linear List                                                  |   | 8-6         |

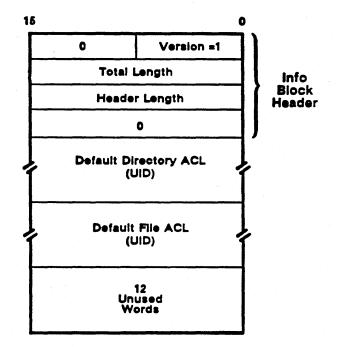

| 8.3.3. Information Block                                            |   | 8-7         |

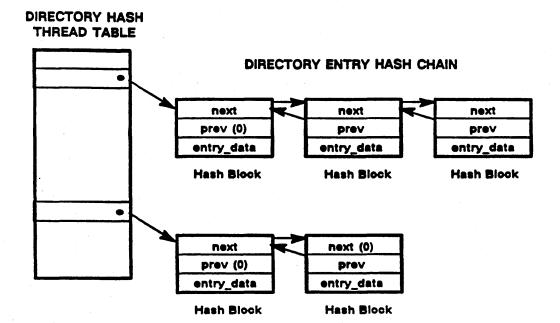

| 8.3.4. Hash Thread Table                                            |   | 8-7         |

| 8.3.5. Directory Entry Blocks                                       |   | 8-8         |

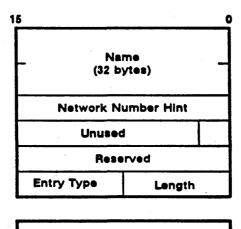

| 8.3.6. Entry Block Data Format                                      |   | 8-9         |

|                                                                     |   |             |

| 8.4. Directory Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-11                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 8.4.1. Opening Directories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8-11                                                                                                                                          |

| 8.4.2. Closing Directories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8-12                                                                                                                                          |

| 8.4.3. Adding Entries to Directories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-12                                                                                                                                          |

| 8.4.4. Searching Directories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8-13                                                                                                                                          |

| 8.4.5. Managing The Network Root Directory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8-13                                                                                                                                          |

| 8.5. Pathname Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-13                                                                                                                                          |

| 8.5.1. Interaction of Naming Server and Hint Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-14                                                                                                                                          |

| 8.5.2. Resolution Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8-15                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                               |

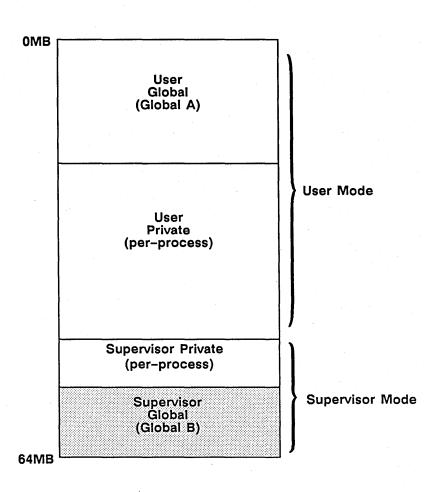

| Chapter 9 Virtual Address Space Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9-1                                                                                                                                           |

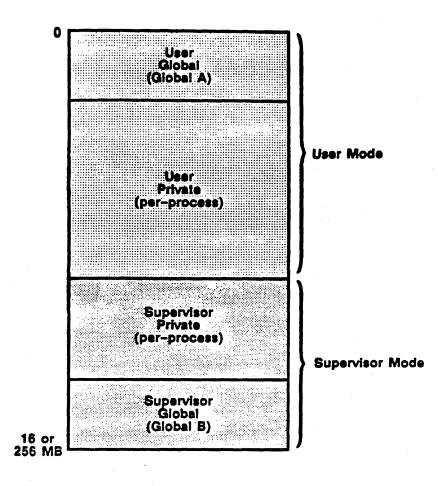

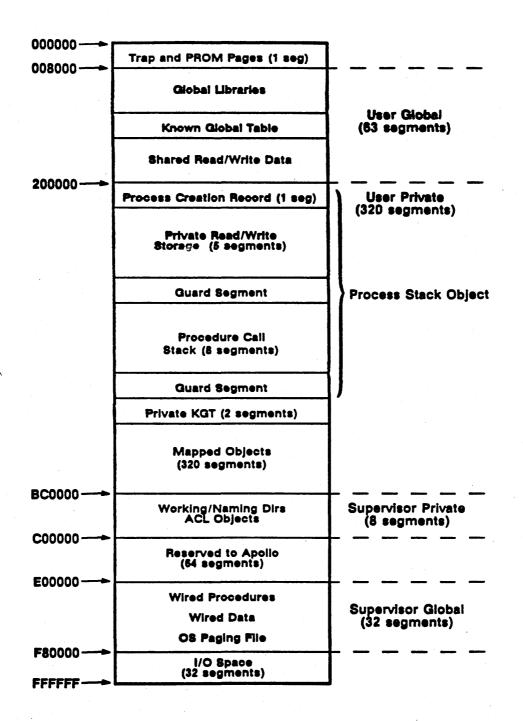

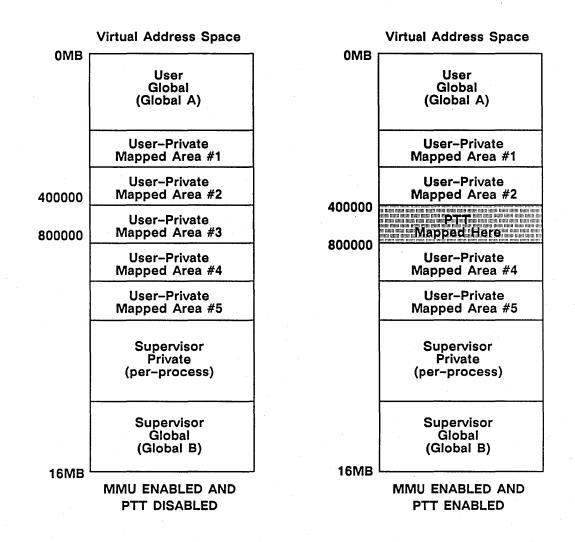

| 9.1. Virtual Address Space on 16-Megabyte Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <del>9-</del> 1                                                                                                                               |

| 9.1.1. Trap and PROM Pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-1<br>9-1                                                                                                                                    |

| 9.1.2. User Global Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9-3                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9-3<br>9-3                                                                                                                                    |

| 9.1.3. User Private Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                               |

| 9.1.4. Supervisor Private Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9-3<br>0 8                                                                                                                                    |

| 9.1.5. Supervisor Global Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9-3                                                                                                                                           |

| 9.1.5.1. The OS Paging File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9-4                                                                                                                                           |

| 9.1.5.2. Whole Cloth Pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-4                                                                                                                                           |

| 9.1.5.3. Wired RFC Pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9-4                                                                                                                                           |

| 9.1.6. I/O Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9-4                                                                                                                                           |

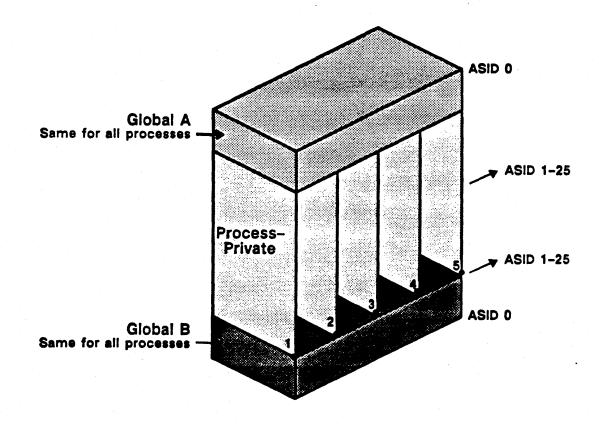

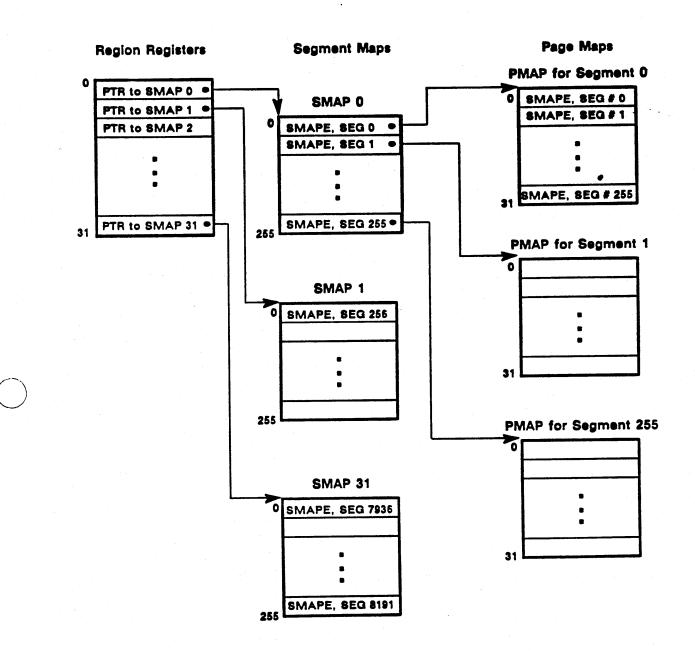

| 9.2. Virtual Address Space on 256-Megabyte Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9-5                                                                                                                                           |

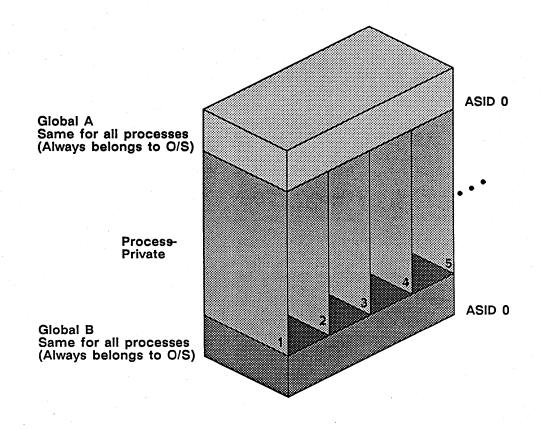

| 9.3. Virtual Address Space Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-7                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                               |

| Chapter 10 Virtual Memory Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-1                                                                                                                                          |

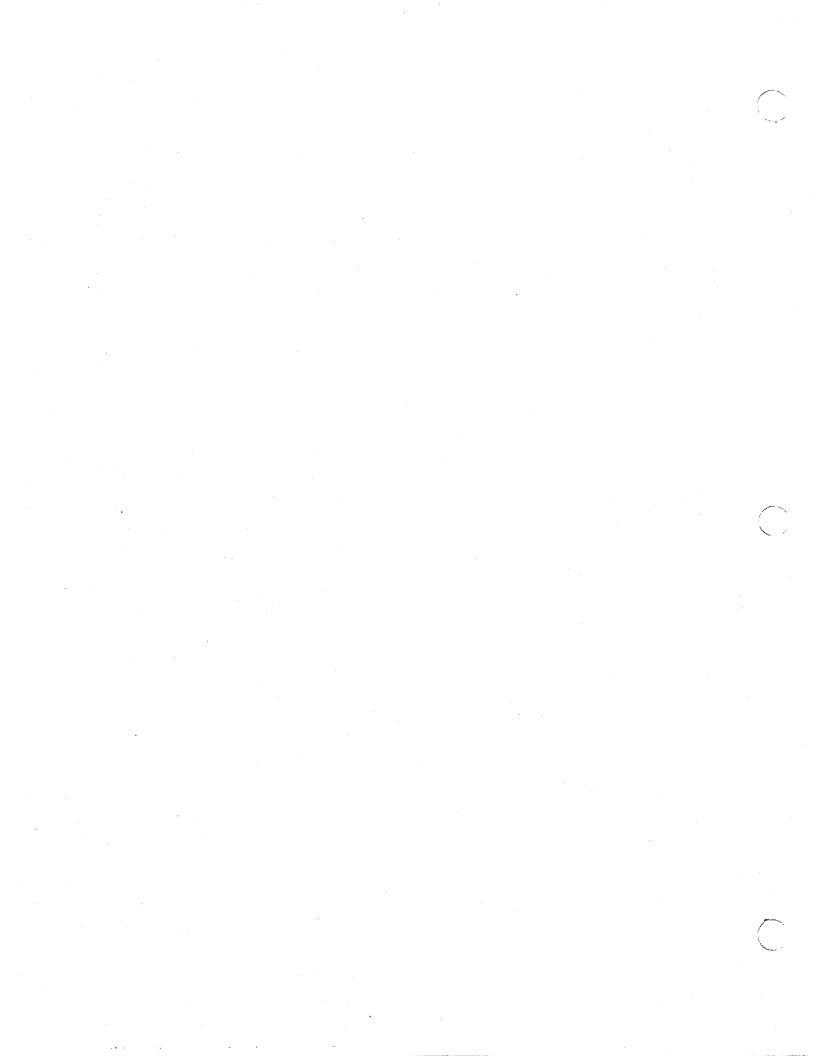

| 10.1. Object Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10-1                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                               |

| 10.0 Mintual Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10.9                                                                                                                                          |

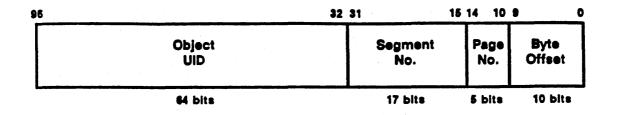

| 10.2. Virtual Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10-2                                                                                                                                          |

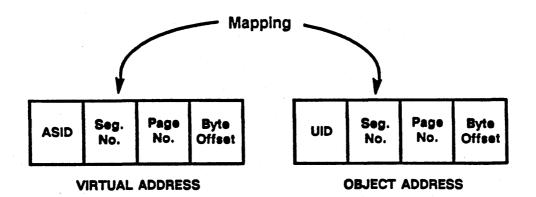

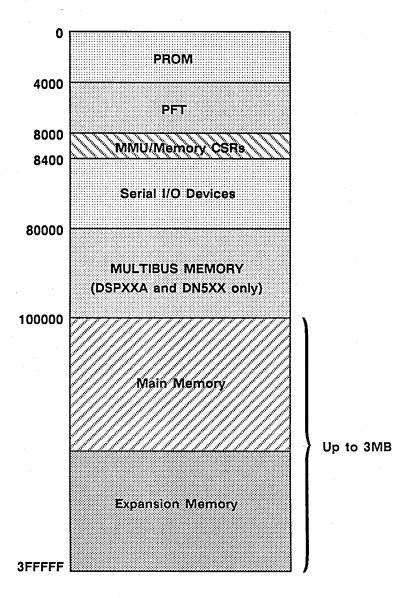

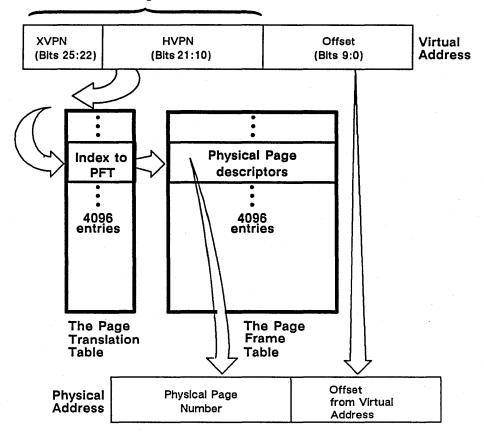

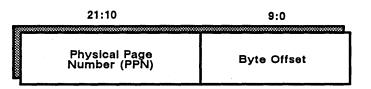

| 10.3. Physical Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10-3                                                                                                                                          |

| 10.3. Physical Addresses<br>10.4. Mapping Objects to Process Private Virtual Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10-3<br>10-4                                                                                                                                  |

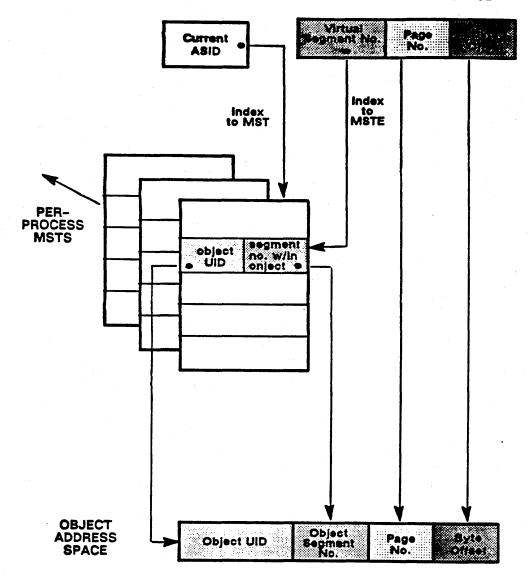

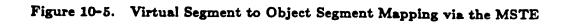

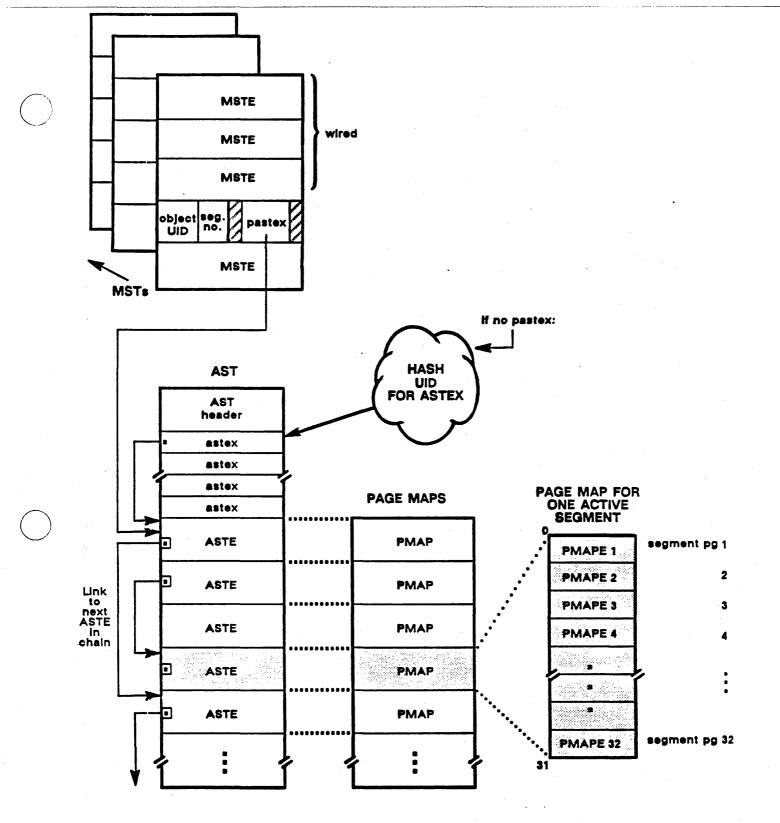

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10-3<br>10-4<br>10-4                                                                                                                          |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10-3<br>10-4<br>10-4<br>10-4                                                                                                                  |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-3<br>10-4<br>10-4<br>10-4<br>10-6                                                                                                          |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                | 10-3<br>10-4<br>10-4<br>10-4<br>10-6<br>10-6                                                                                                  |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> </ul>                                                                                                                                                                                                                                                                                                                                                                    | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6                                                                                                  |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> <li>10.6.1.1. The Active Segment Table</li> </ul>                                                                                                                                                                                                                                                                                                                        | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6<br>10-8                                                                                          |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> <li>10.6.1.1. The Active Segment Table</li> <li>10.6.1.2. The Segment Page Map</li> </ul>                                                                                                                                                                                                                                                                                | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6<br>10-8<br>10-8                                                                                  |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> <li>10.6.1.1. The Active Segment Table</li> <li>10.6.1.2. The Segment Page Map</li> <li>10.6.1.3. The AST Manager</li> </ul>                                                                                                                                                                                                                                             | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6<br>10-8<br>10-8<br>10-8<br>10-10                                                                 |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> <li>10.6.1.1. The Active Segment Table</li> <li>10.6.1.2. The Segment Page Map</li> <li>10.6.1.3. The AST Manager</li> <li>10.6.1.4. Relationship Between Mapped and Active Segments</li> </ul>                                                                                                                                                                          | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6<br>10-8<br>10-8<br>10-8<br>10-10<br>10-10                                                        |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6.1 Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> <li>10.6.1.1. The Active Segment Table</li> <li>10.6.1.2. The Segment Page Map</li> <li>10.6.1.3. The AST Manager</li> <li>10.6.1.4. Relationship Between Mapped and Active Segments</li> <li>10.6.2. Associating Object Pages with Physical Pages</li> </ul>                                                                                                           | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6<br>10-8<br>10-8<br>10-8<br>10-10<br>10-10<br>10-11                                               |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> <li>10.6.1.1. The Active Segment Table</li> <li>10.6.1.2. The Segment Page Map</li> <li>10.6.1.3. The AST Manager</li> <li>10.6.1.4. Relationship Between Mapped and Active Segments</li> <li>10.6.2. Associating Object Pages with Physical Pages</li> </ul>                                                                                                            | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6<br>10-8<br>10-8<br>10-8<br>10-10<br>10-10<br>10-11<br>10-11                                      |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> <li>10.6.1.1. The Active Segment Table</li> <li>10.6.1.2. The Segment Page Map</li> <li>10.6.1.3. The AST Manager</li> <li>10.6.1.4. Relationship Between Mapped and Active Segments</li> <li>10.6.2. Associating Object Pages with Physical Pages</li> <li>10.6.2.1. Allocating Physical Pages</li> </ul>                                                               | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6<br>10-8<br>10-8<br>10-8<br>10-10<br>10-10<br>10-10<br>10-11<br>10-11<br>10-11                    |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> <li>10.6.1.1. The Active Segment Table</li> <li>10.6.1.2. The Segment Page Map</li> <li>10.6.1.3. The AST Manager</li> <li>10.6.1.4. Relationship Between Mapped and Active Segments</li> <li>10.6.2. Associating Object Pages with Physical Pages</li> <li>10.6.2.2. Fetching Object Pages</li> <li>10.7. Translating From Virtual to Physical Address Space</li> </ul> | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6<br>10-8<br>10-8<br>10-8<br>10-10<br>10-10<br>10-10<br>10-11<br>10-11<br>10-11<br>10-12<br>10-12  |

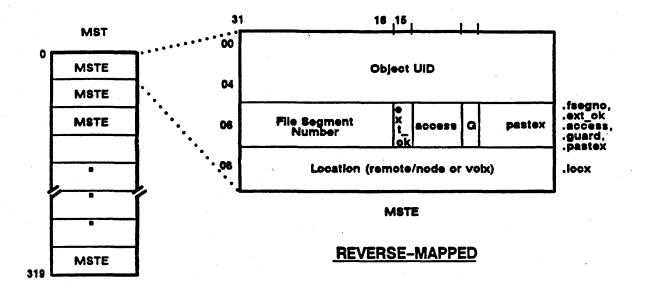

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> <li>10.6.1.1. The Active Segment Table</li> <li>10.6.1.2. The Segment Page Map</li> <li>10.6.1.3. The AST Manager</li> <li>10.6.1.4. Relationship Between Mapped and Active Segments</li> <li>10.6.2.1. Allocating Physical Pages</li> <li>10.6.2.2. Fetching Object Pages</li> <li>10.7.1. Reverse-Mapped Data Structures</li> </ul>                                    | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6<br>10-8<br>10-8<br>10-10<br>10-10<br>10-10<br>10-11<br>10-11<br>10-11<br>10-12<br>10-12<br>10-13 |

| <ul> <li>10.3. Physical Addresses</li> <li>10.4. Mapping Objects to Process Private Virtual Address Space</li> <li>10.4.1. The Mapped Segment Table</li> <li>10.4.2. The MST Manager</li> <li>10.5. Mapping Objects to Global Address Space</li> <li>10.6. Binding Objects to Physical Address Space</li> <li>10.6.1. Activating Object Segments</li> <li>10.6.1.1. The Active Segment Table</li> <li>10.6.1.2. The Segment Page Map</li> <li>10.6.1.3. The AST Manager</li> <li>10.6.1.4. Relationship Between Mapped and Active Segments</li> <li>10.6.2. Associating Object Pages with Physical Pages</li> <li>10.6.2.2. Fetching Object Pages</li> <li>10.7. Translating From Virtual to Physical Address Space</li> </ul> | 10-3<br>10-4<br>10-4<br>10-6<br>10-6<br>10-6<br>10-8<br>10-8<br>10-8<br>10-10<br>10-10<br>10-10<br>10-11<br>10-11<br>10-11<br>10-12<br>10-12  |

. . . .

. .

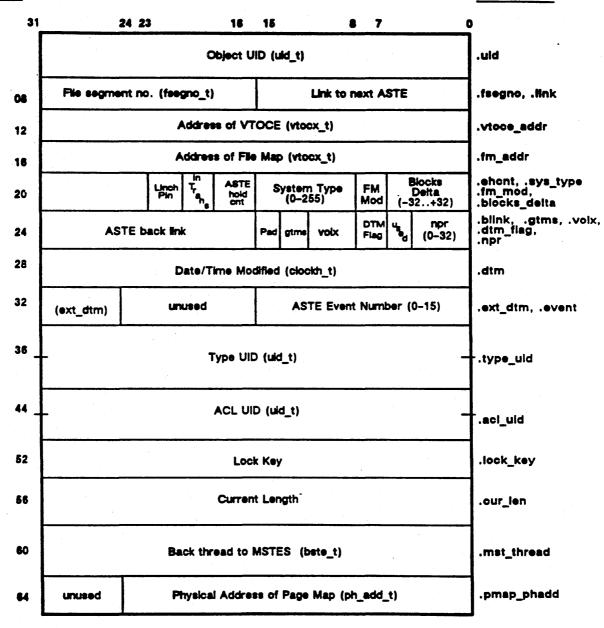

| Chapter 11 Memory Management Data Structures              | 11-1  |

|-----------------------------------------------------------|-------|

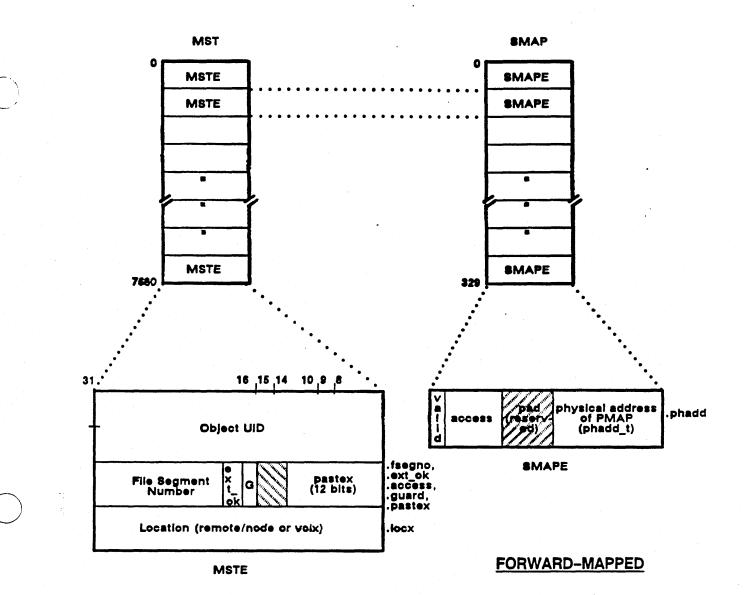

| 11.1. Mapped Segment Data Structures                      | 11-1  |

| 11.1.1. Object to Virtual Segment Association             | 11-1  |

| 11.1.2. Pointers to Other Structures                      | 11-2  |

| 11.1.3. Location Information                              | 11-2  |

| 11.1.4. Access Modes                                      | 11-3  |

| 11.1.5. File Extension                                    | 11-4  |

| 11.1.6. Guard Bit                                         | 11-4  |

| 11.1.7. Touch-Ahead Count                                 | 11-5  |

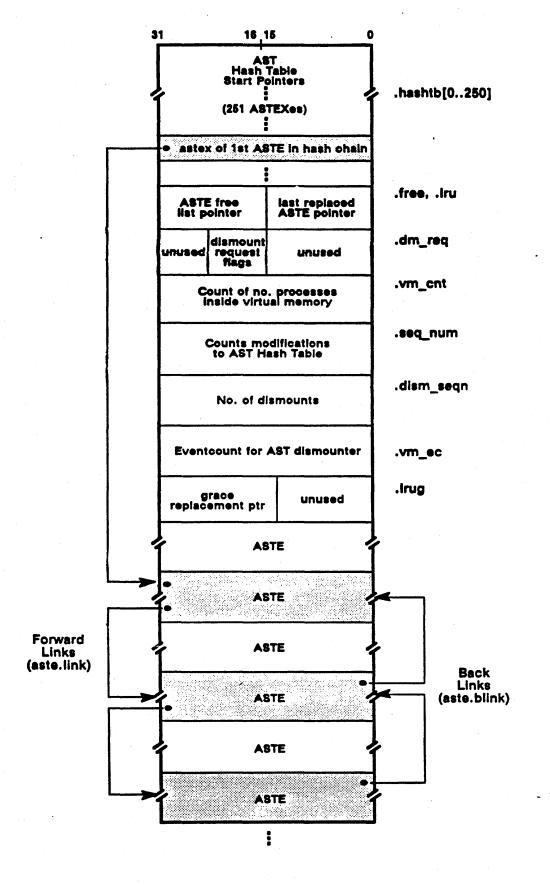

| 11.2. Active Segment Data Structures                      | 11-5  |

| 11.2.1. Active Segment Table Header                       | 11-5  |

| 11.2.1.1. Linked List Pointers                            | 11-5  |

| 11.2.1.2. AST State Information                           | 11-5  |

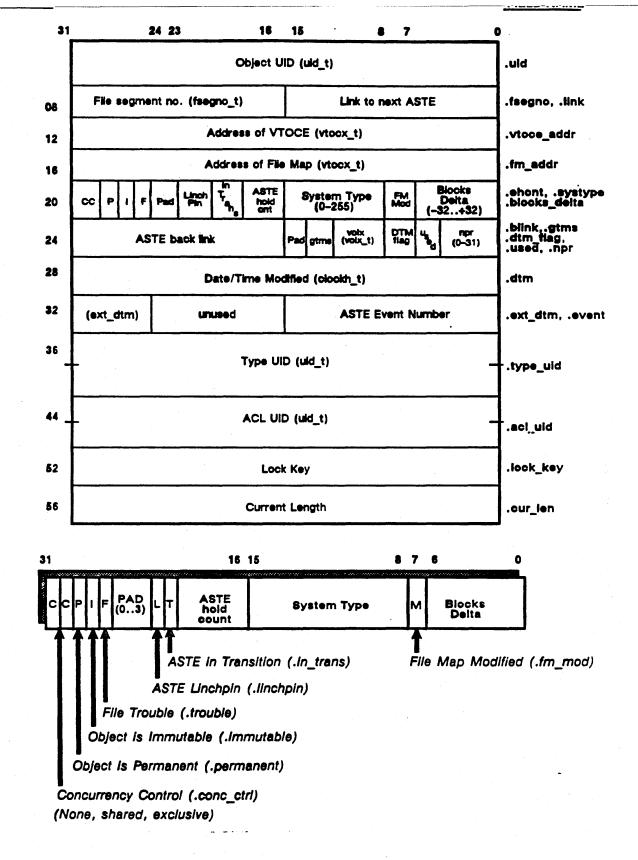

| 11.2.2. Active Segment Table Entries                      | 11-7  |

| 11.2.2.1. VTOCE Information                               | 11-8  |

| 11.2.2.2. ASTE Replacement Information                    |       |

| 11.2.2.3. Linchpin and Back Thread Links                  | 11-11 |

| 11.2.2.4. Object Modification Information                 | 11-11 |

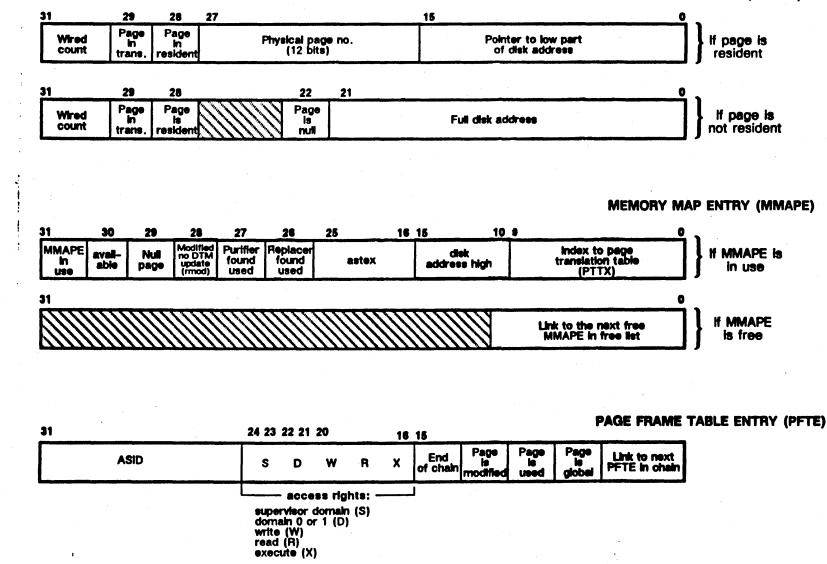

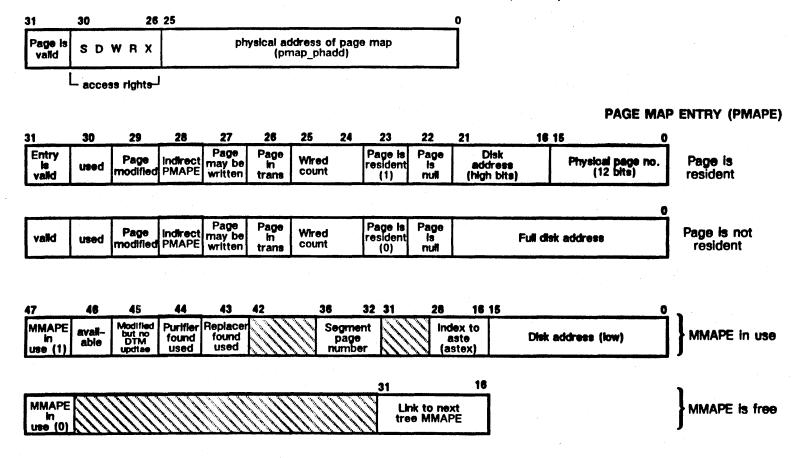

| 11.3. Physical Page Data Structures                       | 11-12 |

| 11.3.1. Modified Status                                   | 11-13 |

| 11.3.2. Valid Status                                      | 11-13 |

|                                                           | 11-16 |

| 11.3.3. Usage Status                                      | 11-16 |

| 11.3.4. Physical Memory Status                            | 11-16 |

| 11.3.5. Access Rights                                     | 11-17 |

| 11.3.6. Location in Memory and on Disk                    | 11-17 |

| 11.3.7. Page Replacement Status                           | 11-17 |

| 11.3.8. Pointers to Other Structures                      | 11-19 |

| Chapter 12 Mapping, Activation, and Purification          | 12-1  |

| 12.1. Summary of MST Operations                           |       |

| 12.1.1. MST Routines Called From User Space               | 12-1  |

| 12.1.2. MST Routines Called from the Kernel               | 12-1  |

|                                                           | 12-2  |

| 12.1.2.1. Kernel-Level Mapping Modules                    | 12-2  |

| 12.1.2.2. Touch and Wire Operations                       | 12-2  |

| 12.1.2.3. Modules used by the PROC2 Manager               | 12-3  |

| 12.1.2.4. MST Modules Called During System Initialization | 12-3  |

| 12.1.2.5. Modules Used in Cross-Process Debugging         | 12-4  |

| 12.1.3. Modules Called Within the MST manager             | 12-4  |

| 12.1.4. Mapping Object Segments                           | 12-5  |

| 12.1.5. Determining the Address Space                     | 12-5  |

| 12.1.6. Checking Access Rights                            | 12-5  |

| 12.1.7. Getting the Information about the Object          | 12-6  |

| 12.1.8. Loading the Mapped Segment Data Structures        | 12-6  |

| 12.2. Active Segment Operations                           | 12-6  |

| 12.2.1. ASTE Activation                                   | 12-7  |

| 12.2.1.1. Finding a Free ASTE                             | 12-7  |

| 12.2.1.2. Loading the ASTE                                | 12-7  |

| 12.2.1.3. Adding the ASTE to the Linked List              | 12-7  |

$\bigcirc$

$\bigcirc$

| 12.2 2. ASTE Deactivation                        | 12-8              |

|--------------------------------------------------|-------------------|

| 12.2.3. ASTE Replacement                         | 12-8              |

| 12.2.4. Updating the VTOC                        | 12-9              |

| 12.3. Page Purification                          | 12-9              |

| 12.3.1. Demand-Based Purification                | 12-10             |

| 12.3.2. Time-based Purification                  | 12-10             |

| 12.3.3. Local Page Purification                  | 12-11             |

| 12.3.4. Remote Page Purification                 | 12-11             |

| 12.3.4.1. Building the Page-Out Request          | 12-11             |

| 12.3.4.2. Handling the Page-Out Request          | 12-11             |

| 12.3.4.3. Page-Out Post-Processing               | 12-12             |

| 12.3.5. Page Allocation for Remote Operations    | 12-12             |

|                                                  |                   |

|                                                  |                   |

| Chapter 13 Page Fault Resolution                 | 13-1              |

|                                                  |                   |

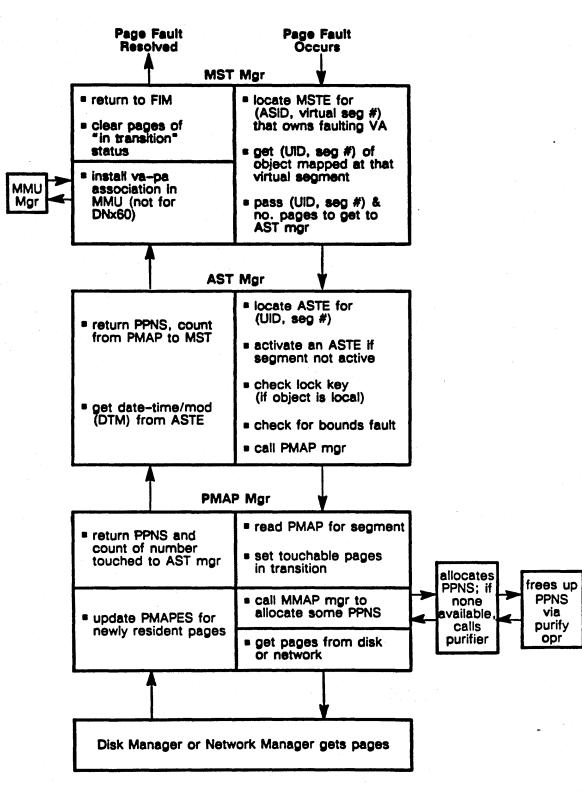

| 13.1. Handling a Typical Page Fault              | 13-1              |

| 13.1.1. MST Page Fault Handling                  | 13-3              |

| 13.1.2. AST Page Fault Handling                  | 13-3              |

| 13.1.2.1. AST Locking During Page Fault Handling | 13-3              |

| 13.1.2.2. Locating and Activating the Segment    | 13-3              |

| 13.1.3. PMAP Page Fault Handling                 | 13-4              |

| 13.1.3.1. Page Locking                           | 13-5              |

| 13.1.3.2. Determining the Type of Page Fault     | 13-5              |

| 13.1.3.3. Fetching Pages from Disk               | 13-6              |

| 13.2. Completing the Typical Page Fault          | 13-6              |

| 13.3. Handling Growth Faults                     | 13-7              |

| 13.4. Handling Null Pages                        | 13-8              |

| 13.5. Handling Resident Page Faults              | 13-8              |

| 13.6. Handling Sharing Faults                    | 13-9              |

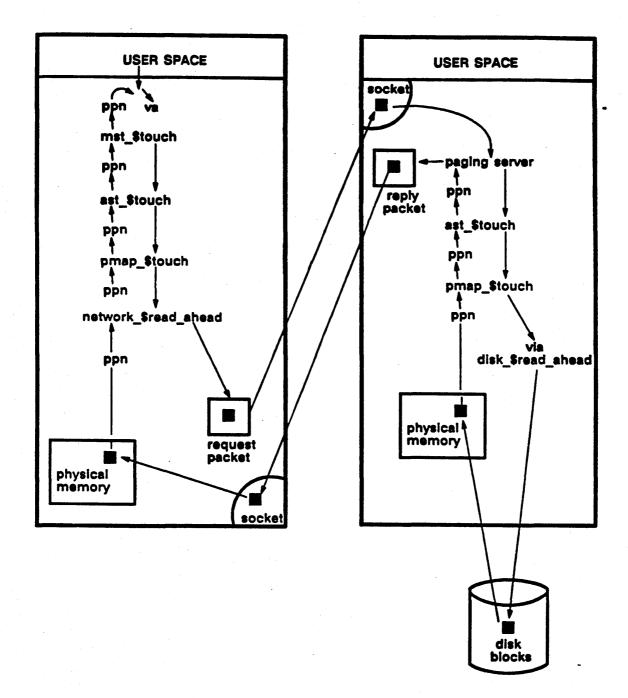

| 13.7. Remote Page Fault Handling                 | 13-9              |

| 13.7.1. Allocating Network Buffer Pages          | 13-11             |

| 13.7.2. NETWORK Client Side Paging Operations    | 13-11             |

| 13.7.3. NETWORK Server Side Paging Operations    | 13-11             |

| 13.7.3.1. Processing the Page-In Request         | 13-11             |

| 13.7.3.2. Concurrency Control Checking           | 13-11             |

| 13.7.3.3. Fetching Pages for a Remote Request    | 13-12             |

| 13.7.4. Remote Page Fault Completion             | 13-12             |

| 13.7.5. Network Errors During Remote Page Faults | 13-13             |

| 13.7.6. Creating Additional Paging Servers       | 13-13             |

|                                                  |                   |

|                                                  |                   |

| Chapter 14 Process Management Overview           | 14-1              |

| And the set a reason with Barren A for the       | 47 <sup>-</sup> 4 |

|                                                  |                   |

| Chapter 15 Level 1 Process Management            | 15-1              |

| ATCHART TA TRACE I T LARCES MET CHART            | TA-T              |

| 15.1. Processor State                            | 15-1              |

| 15.1.1. Process Stack Pointers                   | 15-1              |

| 15.1.2. Address Space ID                         | 15-1              |

| 15.1.3. Process Virtual Time Clock               | 15-2              |

|                                                  |                   |

Contents

xii

| 15.2. Scheduling State                                      | 15-2     |

|-------------------------------------------------------------|----------|

| 15.2.1. Process Priority                                    | 15-2     |

| 15.2.2. Resource Locks                                      | 15-3     |

| 15.2.3. Process State                                       | 15-4     |

| 15.2.4. Time Slice                                          | 15-5     |

| 15.3. Special Level 1 Processes                             | 15-5     |

| 15.4. Level 1 Process Data Structures                       | 15-6     |

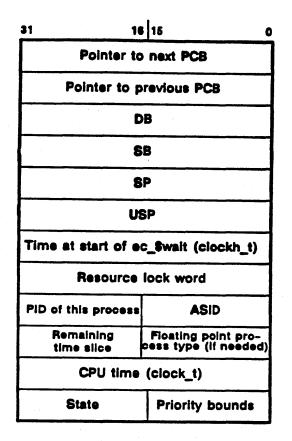

| 15.4.1. Process Control Block                               | 15-6     |

| 15.4.2. Ready List                                          | 15-6     |

| 15.4.3. Process Type ID                                     | 15-7     |

| 15.5. PROC1 Manager Operations                              | 15-8     |

| 15.5.1. Process Creation and Deletion                       | 15-8     |

| 15.5.1.1. Binding and Unbinding                             | 15-8     |

| 15.5.1.2. Stack Allocation                                  | -        |

| 15.5.1.3. Creating Special Level 1 Processes                | 15-8     |

| 15.5.2. Resource Lock Handling                              | 15-9     |

| 15.5.3. Process Suspension                                  | 15-9     |

| 15.6. Implementation of PROC1 Operations                    | 15-9     |

| 15.6.1. Dispatching                                         | 15-10    |

|                                                             | 15-10    |

| 15.6.1.1. The Dispatching Algorithm                         | 15-11    |

| 15.6.1.2. Dispatching and the Null Process                  | 15-11    |

| 15.6.2. Interrupt Handling                                  | 15-12    |

| 15.6.2.1. Interrupt Eventcount Advance                      | 15-13    |

| 15.6.2.2. Interrupt Exit                                    | 15-13    |

| 15.6.3. Process Scheduling                                  | 15-13    |

| 15.6.3.1. Priority and Time Slice End                       | 15-14    |

| 15.6.3.2. Priority and Eventcount Waits                     | 15-14    |

| 15.6.3.3. Priority and Resource Locks                       | 15-14    |

| 15.6.3.4. Maintaining the Ready List                        | 15-15    |

|                                                             |          |

|                                                             |          |

| Chapter 16 Level 2 Process Management                       | 16-1     |

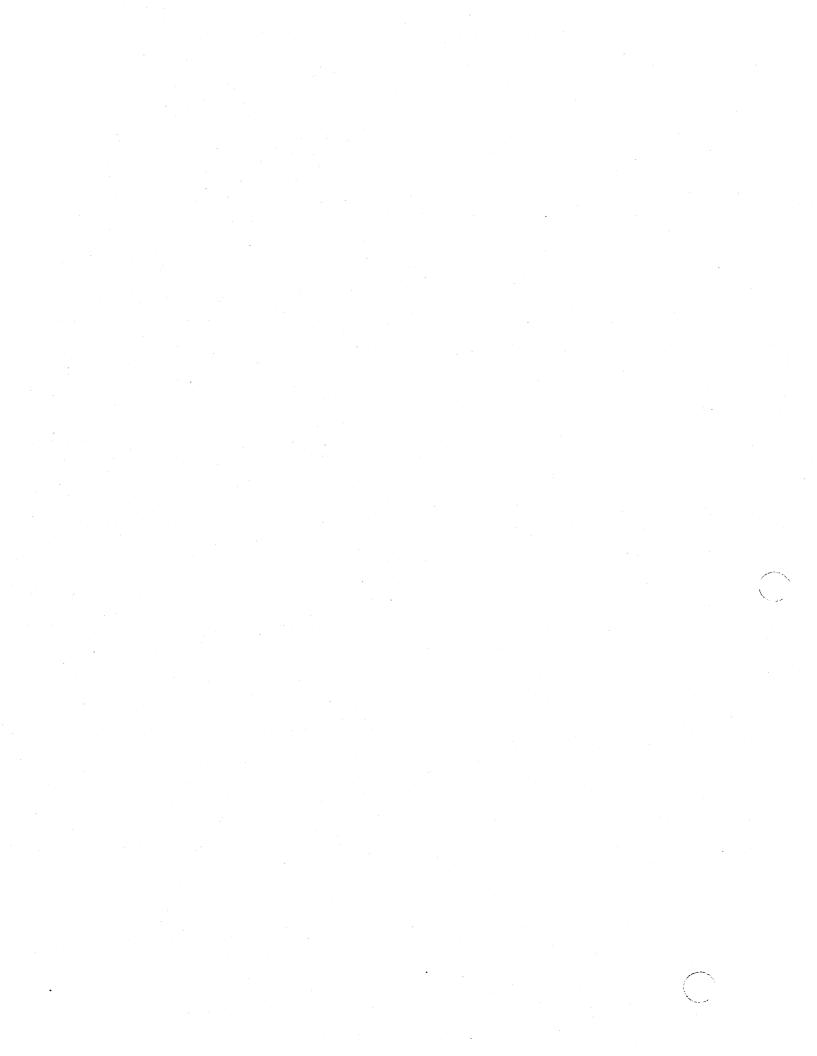

| 16.1. Level 2 Process Context                               |          |

| 16.1.1. The Stack Object                                    | 16-1     |

| 16.1.1.1. The Process Creation Record                       | 16-3     |

| 16.1.1.2. Read/Write Storage                                | 16-3     |

| 16.1.1.3. The Procedure Call Stack                          | 16-3     |

| 16.1.2. Orphan Status                                       | 16-3     |

| 16.1.3. Server Status                                       | 16-3     |

| 16.1.4. Process ID Information                              | 16-4     |

|                                                             | 16-4     |

| 16.1.5. Process Group Information<br>16.2. PROC2 Operations | 16-4     |

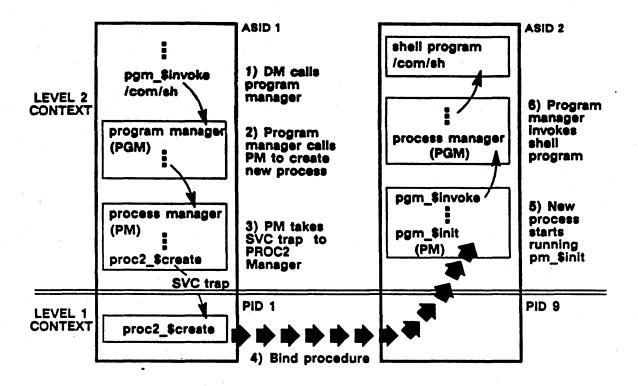

| 16.2.1. Process Creation                                    | 16-5     |

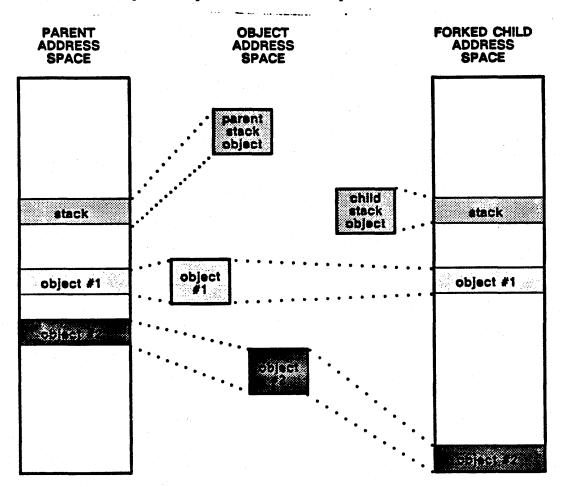

| 16.2.2. Process Forking                                     | 16-5     |

| 16.2.2. Process Forking<br>16.2.3. Process Deletion         | 16-5     |

|                                                             | 16-7     |

| 16.2.3.1. Releasing Per-Process Resources                   | 16-7     |

| 16.2.3.2. Notifying the Parent Process                      | 16-7     |

| 16.2.3.3. Freeing the Stack Object                          | 16-8     |

| 16.2.4. Stack Object Allocation                             | 16-8     |

| 16.2.5. Maintaining Level 2 Context                         | 16-9     |

| 16.2.6. Maintaining Process Names                           | <br>16-9 |

Contents

xiii

| 16.2.7. Suspend/Resume Operations                  |        | 16-9  |

|----------------------------------------------------|--------|-------|

|                                                    |        |       |

| Chapter 17 Eventcounts and Mutual Exclusion        |        | 17-1  |

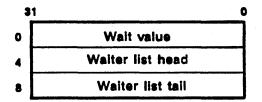

| 17.1. Level 1 Eventcounts                          |        | 17-1  |

| 17.1.1. Waiting on a Level 1 Eventcount            |        | 17-2  |

| 17.1.2. Advancing a Level 1 Eventcount             |        | 17-3  |

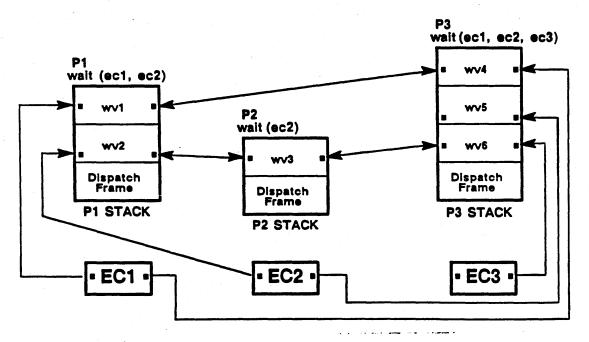

| 17.2. Level 2 Eventcounts                          |        | 17-3  |

| 17.2.1. Creating a Level 2 Eventcount              |        | 17-3  |

| 17.2.2. Waiting on Eventcounts                     |        | 17-5  |

| 17.2.3. Advancing an Eventcount                    | - 15 A | 17-5  |

| 17.3. Mutual Exclusion on Resource Locks           |        | 17-7  |

| Chapter 18 Fault Handling in the AEGIS Kernel      |        | 18-1  |

| Chapter 16 Faut Handling in the ADGIS Kernel       |        | 10-1  |

| 18.1. Processor Fault Handling                     |        | 18-1  |

| 18.2. AEGIS Fault Handling                         | •      | 18-1  |

| 18.2.1. Determining Where the Fault Occurred       |        | 18-2  |

| 18.2.1.1. Handling Supervisor-Mode Faults          |        | 18-2  |

| 18.2.1.2. Handling User-Mode Faults                |        | 18-2  |

| 18.2.2. Handling Privileged Instruction Violations |        | 18-3  |

| 18.2.3. Handling MMU-Related Errors                |        | 18-3  |

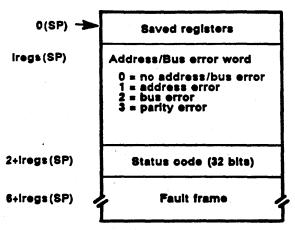

| 18.2.4. Common Fault Handling                      |        | 18-3  |

| 18.2.4.1. Checking for GPIO Faults                 |        | 18-4  |

| 18.2.4.2. Checking for Fault on Fault              |        | 18-5  |

| 18.2.4.3. Locating the User Fault Handler          |        | 18-5  |

| 18.2.4.4. Validating the User Stack Pointer        |        | 18-5  |

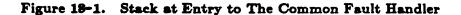

| 18.2.4.5. Building the Diagnostic Fault Frame      |        | 18-5  |

| 18.2.4.6. Reflecting the Fault to User Mode        |        | 18-7  |

| 18.3. Handling SVC Faults                          | -<br>- | 18-8  |

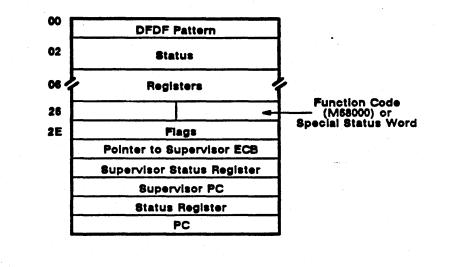

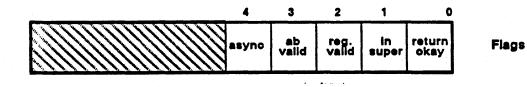

| 18.4. Asynchronous Fault Handling                  |        | 18-8  |