# amdahl®

AMDAHL 580 Large Scale Integrated Circuit Manual

Publication Number: X1023.0-02A

August 1981

COPY NUMBER

#### **REVISION NOTICE**

This manual replaces the ALTA LSI Circuit Manual. Additional information has been added for clarification.

21.1

#### ABSTRACT

Mr To

This publication provides the 580 Large Scale Integration (LSI) circuit chip wiring rules, logic design restrictions, and delay equations. The information is presented for the 580 logic designers so they may become cognizant of the configuration networks, become familiar with the wiring rules, and understand the LSI macros..

#### **READER COMMENT FORM**

. . . . .

A reader comment form is provided at the end of this manual. If this form is not available, comments and suggestions may be sent to Amdahl Corporation, Technical Publications Department, Mail Stop 323, P.O. Box 470, Sunnyvale, CA 94086. All comments and suggestions become the property of Amdahl Corporation.

فأوالوا والمراجع والمؤتفي and and and an sec are registered trademarks of Amdahl Corporation.

99 ... © 1981 Amdahl Corporation, All rights reserved. Printed in U.S.A.

All specifications are subject to change without notice.

#### AMDAHL COMPANY PRIVATE

## CONTENTS

| CH | AP?      | $\Gamma ER 1 - INTRODUCTION \dots 1 - 1$                                                                                                                                                                      | L            |

|----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|    | 1.1      | Impedance Matching                                                                                                                                                                                            | L            |

|    | 1.2      | Testability                                                                                                                                                                                                   | Ĺ            |

|    |          |                                                                                                                                                                                                               |              |

| CH | AP?      | <b>TER 2 — OFF-CHIP WIRING RULES</b> 2-1                                                                                                                                                                      | L            |

|    | 2.1      | Definitions                                                                                                                                                                                                   | L            |

|    | 2.2      | General Wiring Rules 2-3                                                                                                                                                                                      | 3            |

|    |          | 2.2.1 Wiring Principle                                                                                                                                                                                        | 3            |

|    |          | 2.2.2 Termination                                                                                                                                                                                             | 3            |

|    |          | 2.2.3 Loop                                                                                                                                                                                                    | 3            |

|    |          | 2.2.4 Wiring Resistance                                                                                                                                                                                       | 3            |

|    |          | 2.2.5 Wiring Materials 2-4                                                                                                                                                                                    | Ł            |

|    |          | 2.2.6 Unused Inputs                                                                                                                                                                                           | 5            |

|    | 2.3      | Wiring Rules for Single 90 ohm Terminated Nets 2-5                                                                                                                                                            |              |

|    |          | 2.3.1 High Performance Terminated (Short/Lightly Loaded) Nets 2-5                                                                                                                                             |              |

|    |          | 2.3.2 General Terminated Net Wiring Rules                                                                                                                                                                     |              |

|    |          | 2.3.3 Critical Net Fanout                                                                                                                                                                                     |              |

|    |          | 2.3.4 Termination Resistor $\ldots \ldots \ldots$                                             |              |

|    |          | 2.3.5 Multiple Base Inputs 2-7                                                                                                                                                                                |              |

|    |          | 2.3.6 Input Biasing                                                                                                                                                                                           |              |

|    |          | 2.3.7 Driver Choice                                                                                                                                                                                           |              |

|    |          | 2.3.8 Driver Location $2-7$                                                                                                                                                                                   |              |

|    |          | 2.3.9 Driving Off Stack 2-8                                                                                                                                                                                   | 2            |

|    |          | 2.3.10 Basic Logic Cards with LSI                                                                                                                                                                             | ₹∵           |

|    | 2.4      | 2.3.10 Basic Logic Cards with LSI<br>Dotted Emitter Follower Wiring Rules<br>2.4.1 Current Changing Rate                                                                                                      | <b>}</b> ≘.' |

|    |          | 2.4.1 Current Changing Rate                                                                                                                                                                                   | ;<br>;       |

|    |          | 2.4.2 Maximum Distance Between Dots                                                                                                                                                                           | ý            |

|    |          | 2.4.3 Maximum Distant Between Dots for Different Chin Outputs                                                                                                                                                 | ie s         |

|    | 2.5      | 2.4.3 Maximum Distant Between Dots for Different Chip Outputs 27-11<br>Non-Critical Interconnection 2-12                                                                                                      | ,            |

|    |          | 2.5.1 Non-Critical Net Types                                                                                                                                                                                  | )            |

|    |          | 2.5.2 Short Stub (Type 1) Non-Critical Net Delay Calculation                                                                                                                                                  | į            |

|    |          | 2.5.3 Long Stub (Type 2) Non-Critical Net Delay Calculation (1)                                                                                                                                               |              |

|    |          | 2.5.4 Calculation Example of $T_{pd max}$                                                                                                                                                                     |              |

|    | 2.6      | Parallel Wire Pules                                                                                                                                                                                           | 125.<br>1    |

|    | 2.0      | Parallel Wire Rules   2-17     2.6.1 Geometric Factors   2-17                                                                                                                                                 | r.           |

|    |          | 2.6.2 Intra-MCC Net                                                                                                                                                                                           | <u>،</u> د   |

|    |          | 2.6.2 Intra-MCC Net (Sidepanel) $2-16$                                                                                                                                                                        | )<br>)       |

|    |          | 2.6.1       Geometric Factors       2-17         2.6.2       Intra-MCC Net       2-18         2.6.3       Inter-MCC Net (Sidepanel)       2-19         2.6.4       MCC I/O Pin Physical Assignment       2-20 | /<br>∿∹:     |

|    |          | 2.6.4 MCC I/O Fin Physical Assignment                                                                                                                                                                         | /<br>        |

|    | 2.7      | 2.6.4 MCC I/O Pin Physical Assignment                                                                                                                                                                         | • .<br>• · · |

|    | 4.1      | <b>2.7.1</b> Wiring Principle $2 - 22$                                                                                                                                                                        | )<br>)       |

|    |          |                                                                                                                                                                                                               |              |

|    |          | 2.7.2 Discrete Wire Stub                                                                                                                                                                                      |              |

|    |          | 2.7.3 General Discrete Wire Selection Rule                                                                                                                                                                    |              |

|    |          |                                                                                                                                                                                                               |              |

|    | <u>.</u> | 2.7.5 Twin Lead Wire Split                                                                                                                                                                                    |              |

|    | 2.8      | Clock Distribution                                                                                                                                                                                            | <b>)</b> [ ] |

ī

| CHAPT      | <b>ER 3 — COMMON BUS</b>                               |        |

|------------|--------------------------------------------------------|--------|

| 3.1        | General                                                |        |

| 3.2        | Common Bus System Design                               |        |

|            | 3.2.1 Modified Bus Impedance and Propagation Delay     |        |

|            | 3.2.2 Bus Analysis                                     |        |

|            | 3.2.3 Review of Bus Analysis                           | 3-0    |

| CHAPT      | ER 4 — RANDOM ACCESS MEMORY WIRING RULES               | 4-1    |

|            | General Rules                                          |        |

|            | Wiring in Array Section                                |        |

| 4.3        | Parallel Wiring in Array Section                       |        |

| - h        | 4.3.1 Separation Between Array Wiring and Other Wiring |        |

|            | 4.3.2 Read/Write Control Signal (Write Enable)         |        |

| 4.4        | Pull Down                                              |        |

| 4.5        | Tie Down (Unused Input)                                |        |

| 4.6        | Data-Out Dot-ORing                                     |        |

| 4.7        | RAM Driver Fan-Out                                     |        |

| 4.8<br>4.9 | LSI and RAM Module Mix Restrictions                    |        |

| 4.9        |                                                        | 4-0    |

| CHAPT      | ER 5 - DELAY EQUATIONS                                 | 5 - 1  |

| 5.1        | On-Chip Delay Equation                                 |        |

| 5.2        | On-Chip Loading Parameters                             |        |

| 0.4        |                                                        |        |

|            | 5.2.1 T <sub>in</sub> Definitions                      |        |

|            | 5.2.2 T <sub>circuit</sub> Definitions                 |        |

|            | 5.2.3 T <sub>out</sub> Definitions                     |        |

| 5.3        | On-Chip Delay Terms                                    |        |

|            | 5.3.1 T <sub>in</sub> Definitions                      |        |

|            | 5.3.2 T <sub>fanin</sub> Definitions                   |        |

|            | 5.3.3 T <sub>circuit</sub> Definitions                 | 5 – 5  |

|            | 5.3.4 Macro Identifications                            | 5 - 5  |

|            | 5.3.5 T <sub>out</sub> Definitions                     | 5 - 33 |

|            | 5.3.6 T <sub>BD</sub> Definitions                      | 5 - 34 |

|            | 5.3.7 TEDOT Definitions                                | 5 – 35 |

|            |                                                        | 5 – 35 |

| 5.4        | Off-Chip Delay Equation                                | 5 - 37 |

|            |                                                        | 5 - 37 |

|            |                                                        | 5 - 38 |

|            |                                                        | 5 - 40 |

| 5.6        |                                                        | 5 - 40 |

| 0.0        |                                                        | 5 - 40 |

|            |                                                        | 5 - 40 |

|            |                                                        | 5 - 40 |

|            | 5.6.3 T <sub>line</sub> Definitions                    | 0 - 40 |

| 5.7        |                                                                                                                                                                      | ξ)  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | 5.7.1 Definitions of Delay Equation $5-41$                                                                                                                           |     |

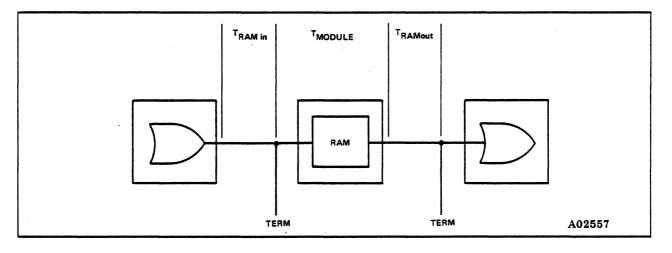

|            | 5.7.2 Input Net Delay ( $T_{RAMIN}$ )                                                                                                                                |     |

|            | 5.7.3 Intra-Module Delay $(T_{MODULE})$                                                                                                                              |     |

|            | 5.7.4 Output Net Delay ( $T_{RAMOUT}$ )                                                                                                                              |     |

|            | 5.7.5 Examples of Entry Net Calculations                                                                                                                             |     |

| 5.8        | Capacitive Loading                                                                                                                                                   |     |

|            | 3 Capacitive Loading       5 – 53         5.8.1 On-Chip Metalization Capacitance       5 – 53                                                                        | . ) |

|            | 5.8.2 Off-Chip Metalization Capacitance                                                                                                                              |     |

|            | 5.8.3 Delay Prediction for Accuracy and Tolerance 54.4.4.4.4.4.4.4.4.5.4.5.4.5.4.5.4.                                                                                |     |

| CHAP       | ر المحمد المحمد التي يتحدد التي المحمد التي المحمد التي المحمد التي المحمد التي المحمد التي المحمد التي المحمد<br>TER 6 — CHIP DESIGN                                |     |

| 6.1        |                                                                                                                                                                      |     |

| 6.2        |                                                                                                                                                                      |     |

|            | 6.2.1 Cell Numbering                                                                                                                                                 |     |

|            | 6.2.2 Cell I/O                                                                                                                                                       |     |

|            | 6.2.3 Average Interconnect Length                                                                                                                                    |     |

|            | 6.2.4 Emitter Followers 6-5                                                                                                                                          |     |

|            | 6.2.5 Bonding Pads                                                                                                                                                   |     |

| 6.3        |                                                                                                                                                                      |     |

|            | 6.3.1 Macro Outputs                                                                                                                                                  | 15  |

|            | 6.3.2 Fan Out                                                                                                                                                        |     |

|            | 6.3.3 Emitter Dotting                                                                                                                                                |     |

|            | 6.3.4 Multiple Emitter Output (Macro 02, 21, 22) $\ldots \ldots 6-7$                                  |     |

|            | 6.3.5 Special Outputs 6-7                                                                                                                                            |     |

|            | 6.3.6 Gate Inputs (Bases) $\ldots$ $6-7$                                                                                                                             |     |

| 6.4        | Limitations of Internal Net Wire                                                                                                                                     |     |

| <b>.</b> - | 6.4.1 Limitation of Wiring Length for External Emitter Followers $466$ , $23$ , $1$ , $20$ , $6$ – 11                                                                |     |

| 6.5        |                                                                                                                                                                      |     |

|            | 6.5.1 Power Consumption of MB12K LSI Chip $\dots \dots \dots$        |     |

|            | 6.5.2 Internal EF (Pint. ef)                                                                                                                                         |     |

|            | 6.5.3 External EF (Pext. ef) $\dots \dots \dots$                     |     |

|            | 6.5.5 Power Consumption Computation of MB12K LSI $\dots \dots \dots$ |     |

|            | 6.5.5 Power Consumption Computation of MB12K LSI                                                                                                                     |     |

| 6.6        |                                                                                                                                                                      |     |

| 6.6<br>6.7 | •                                                                                                                                                                    |     |

| 6.8        |                                                                                                                                                                      |     |

| 0.0        | 6.8.1 Simultaneous Emitter Follower Switching                                                                                                                        |     |

|            | 6.8.2 Skewing EF Switching $\ldots \ldots \ldots$    |     |

|            | 6.8.3 Exceptions to Simultaneous EF Switching Rules $6-16$                                                                                                           |     |

|            | 6.8.4 Additional Delay                                                                                                                                               |     |

|            | C.C.4 Additional Delay                                                                                                                                               |     |

|            |                                                                                                                                                                      |     |

v

|     | CHAPTER 7 — LATCH RESTRICTIONS                     |       |   |      | <br>. 7-1  |

|-----|----------------------------------------------------|-------|---|------|------------|

| 7.1 | General                                            | • • • |   |      | <br>. 7-1  |

| 7.2 | Skewed Clock Driver                                |       |   | •••• | <br>. 7-6  |

| 7.3 | In-Phase Latch Restrictions                        |       |   |      | <br>. 7-7  |

|     | 7.3.1 Glitches                                     | • • • |   |      | <br>. 7-7  |

| 7.4 | Out-of-Phase Latch Restrictions                    |       |   |      | <br>7 - 10 |

| 7.5 | Master-Slave Latches                               |       |   |      | <br>7 - 12 |

| -   | 7.5.1 Out-of-Phase Master/Slave Latch Restrictions | s     |   |      | <br>7 - 13 |

|     | 7.5.2 In-Phase Master/Slave Latch Restrictions     |       | • |      | <br>7 - 14 |

394.000

(

## FIGURES

۰,

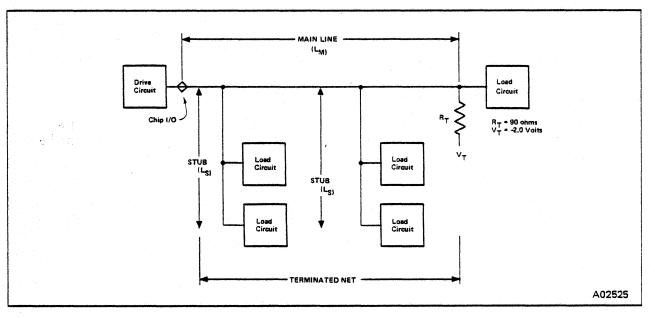

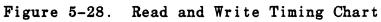

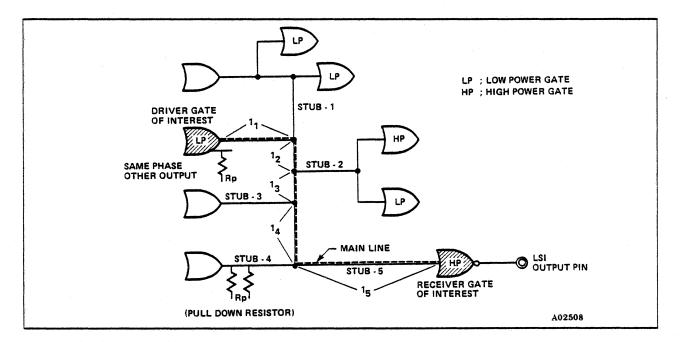

| 2-1.            | A Typical Off-Chip Wiring Net                                                                                                                          | 2 - 2  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

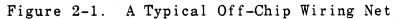

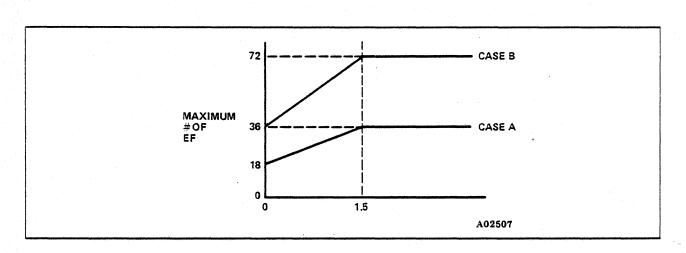

| 2-2.            | Maximum Fanout                                                                                                                                         |        |

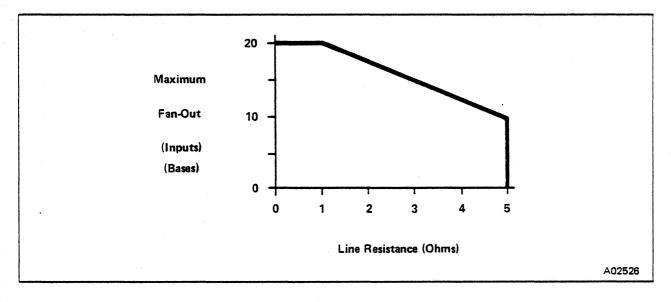

| 2-3.            | Definitions of tBA and tBC                                                                                                                             | 2-9    |

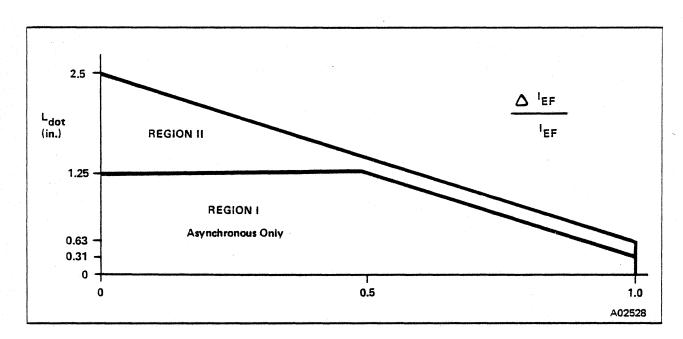

| -2-4.           | Maximum Distance Between Dots for Same Chip Outputs                                                                                                    | 2 - 10 |

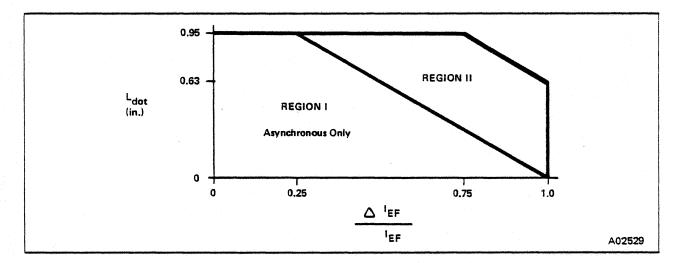

| 2-5.            | Maximum Distance Between Dots for Different Chip Outputs                                                                                               | 2 - 10 |

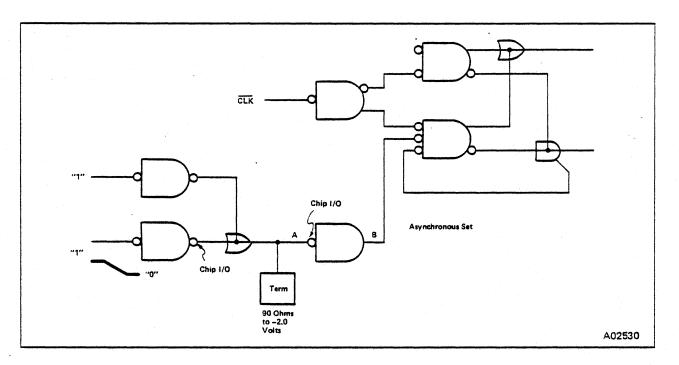

| 2-6.            | Typical Dot-OR Circuit for Calculation                                                                                                                 | 2 - 12 |

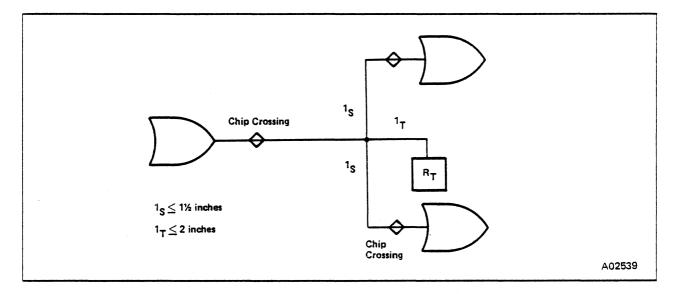

| 2-7.            | Type 1 Delay Equation                                                                                                                                  | 2 - 13 |

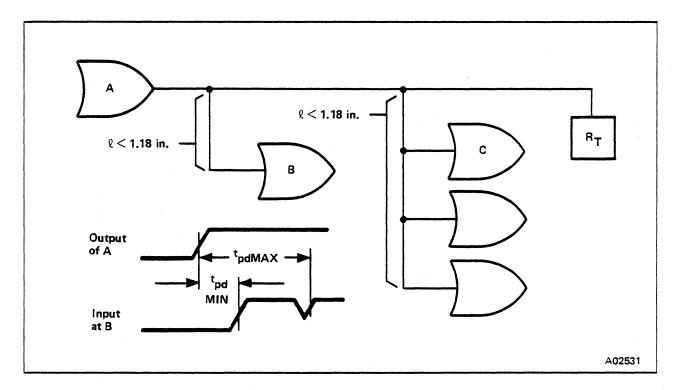

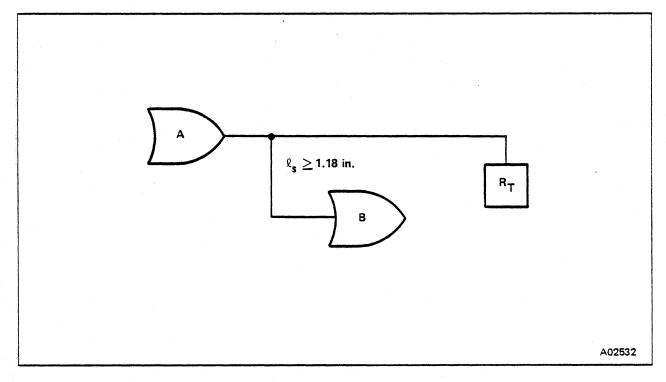

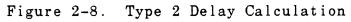

| 2-8.            | Type 2 Delay Calculation                                                                                                                               | 2 - 14 |

| 2-9.            | Example of Type 2 Non-Critical Net                                                                                                                     | 2 - 15 |

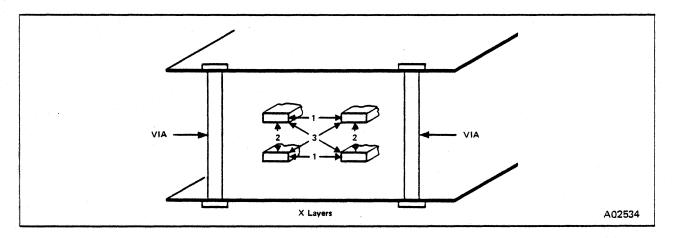

| 2 - 10.         | Three Types of Parallelism                                                                                                                             | 2 - 18 |

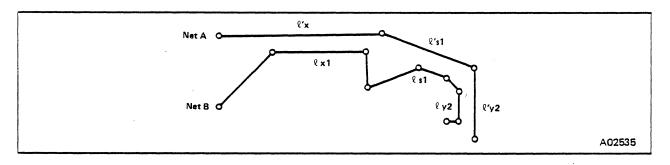

| 2-11.           | Parallel Nets on MCCs                                                                                                                                  | 2 - 19 |

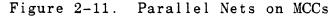

| 2-12.           | Calculation for Maximum Parallel Lengths on MCC                                                                                                        | 2 - 19 |

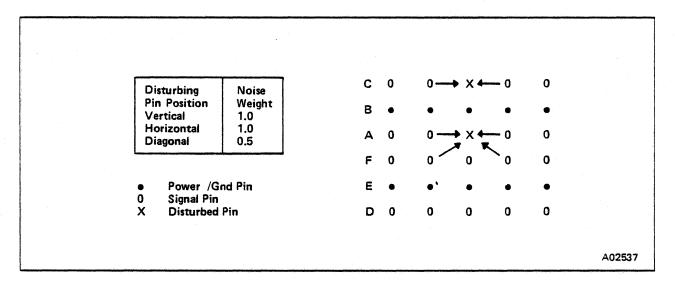

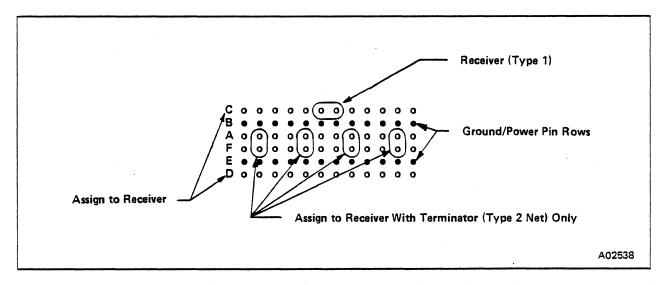

| 2-13.           | Noise Coupling Weight                                                                                                                                  | 2 - 20 |

| 2 - 14.         | Simplified I/O Assignment                                                                                                                              | 2 - 21 |

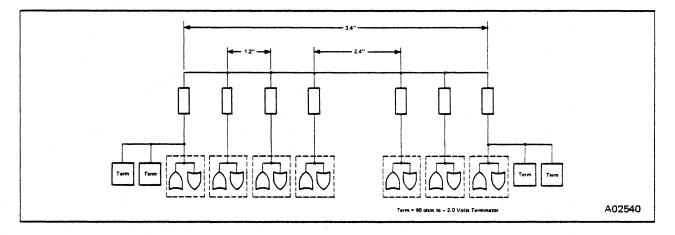

| 2-15.           | MCC Clock Distribution                                                                                                                                 | 2 - 23 |

| 3-1.            | Typical 580 Bus Line                                                                                                                                   | 3 - 2  |

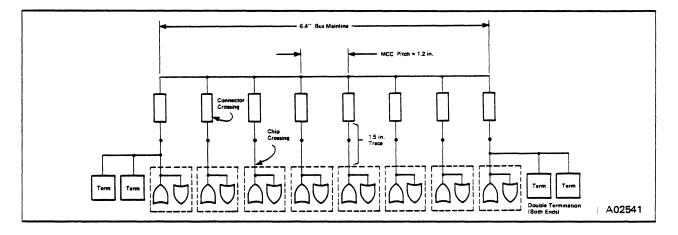

| 3-2.            | MCCs Connected by a Single Bus Line                                                                                                                    | 3 - 5  |

| 4-1.            | Preferred Distribution Design                                                                                                                          | 4 - 2  |

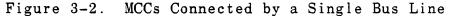

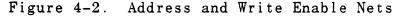

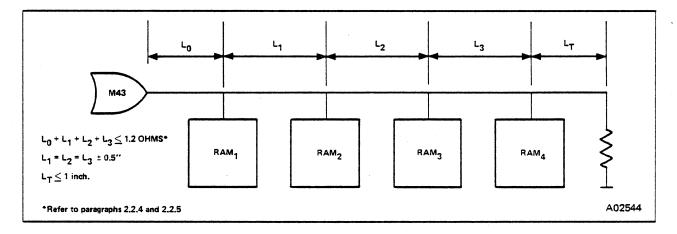

| 4 2.            | Address and Write Enable Nets                                                                                                                          | 4 - 3  |

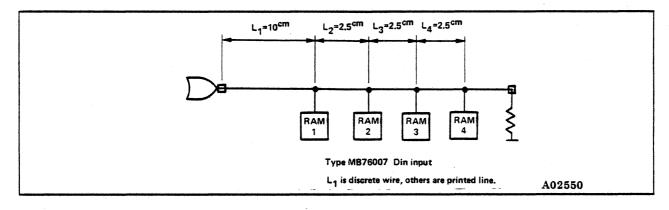

| - <b>4</b> - 3. | Block Select and Data-In Nets                                                                                                                          |        |

| 4-4.            | Spacing Restrictions                                                                                                                                   | 4 - 4  |

| 4 - 5.          | RAM Module I/O Assignments                                                                                                                             |        |

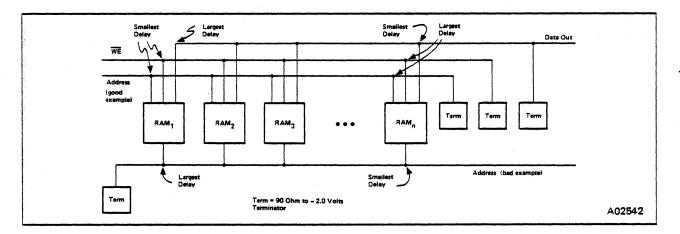

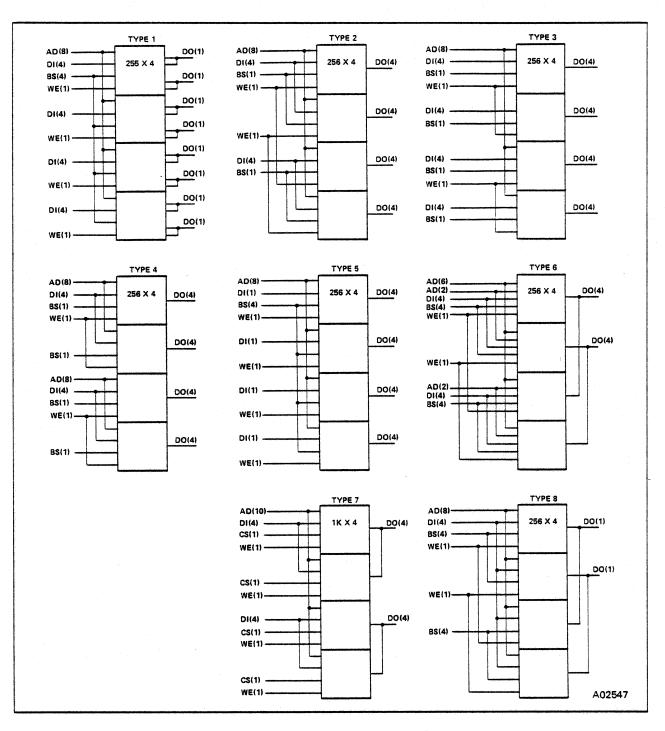

| 4-6.            | RAM Module Block Diagram                                                                                                                               | 4 - 6  |

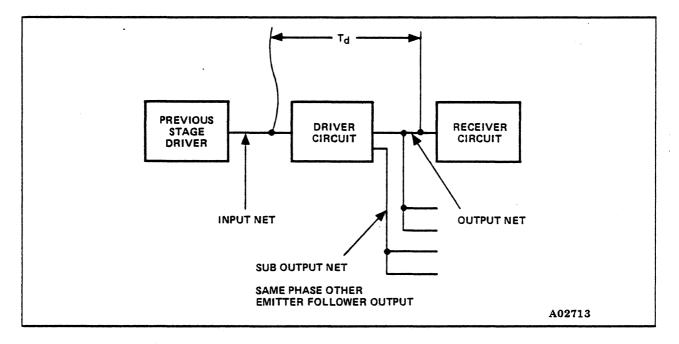

| 5 – 1.          | Delay Definition                                                                                                                                       | 5 - 1  |

| 5 – 2.          | Definition of Switching Types                                                                                                                          | 5 - 2  |

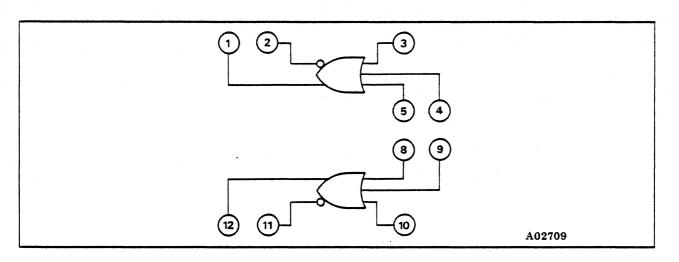

| 5 – 3.          | Dual, 3-Input OR/NOR Macro 01 (Half-Macro)                                                                                                             | 5-8    |

| 5-4.            | Single, 5-Input, 2 OR/2 NOR Macro 02 (Half-Macro)                                                                                                      | 5-8    |

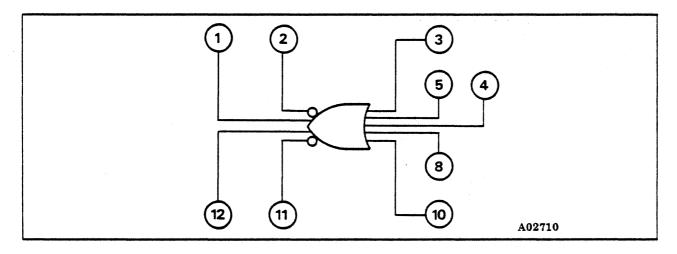

| 5 - 5.          | Dual, 3-Input, 2 NOR Macro 03 (Half-Macro)                                                                                                             | 5 - 10 |

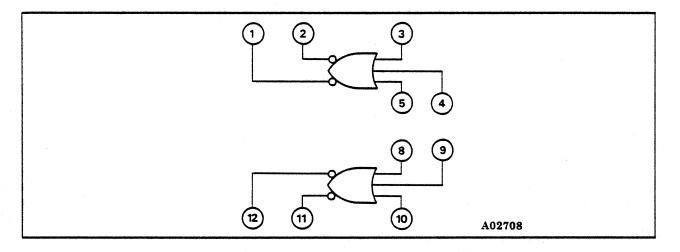

| 5 - 6.          | Dual, 3-Input, 2 OR Macro 04 (Half-Macro)                                                                                                              | 5 - 11 |

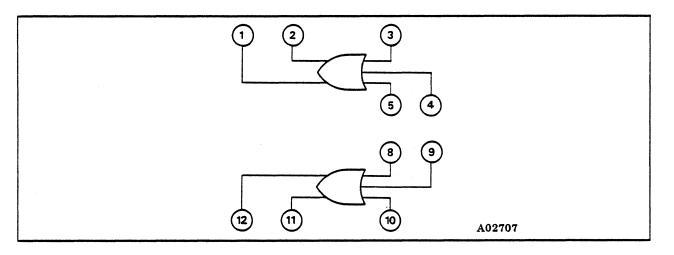

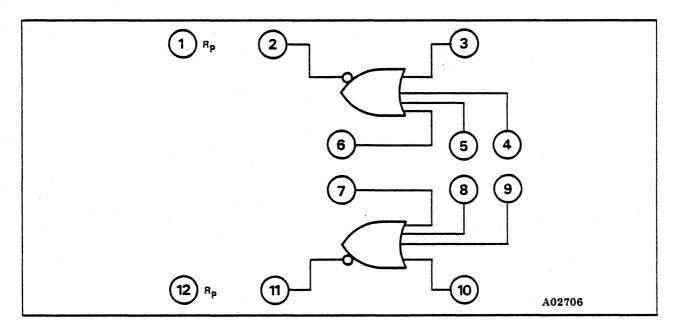

| 5-7.            | Dual, 4-Input NOR Macro 05 (Half-Macro)                                                                                                                | 5 - 12 |

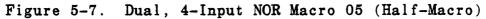

| 5 – 8.          | Single, 8-Input, 3 NOR Macro 08 (Half-Macro)                                                                                                           | 5 - 13 |

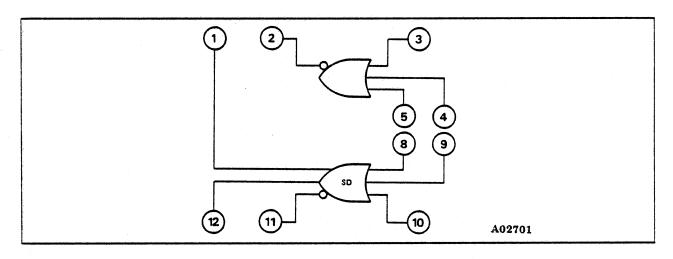

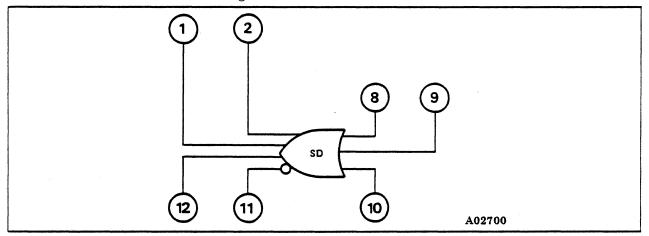

| 5 - 9.          | Two Wide, 3-Input OR-AND/Dual, 3-Input NOR Macro 11                                                                                                    | 5 - 14 |

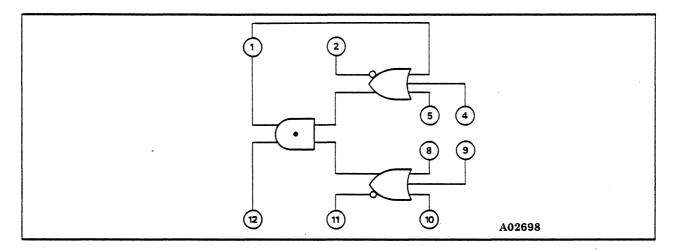

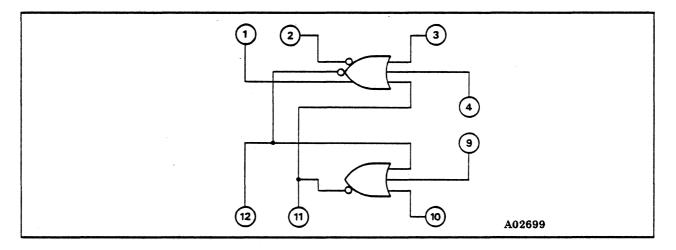

| 5 - 10.         | Two Wide, 3-Input NOR-AND/2 Wide, 3-Input OR-AND Macro 12                                                                                              | 5 - 16 |

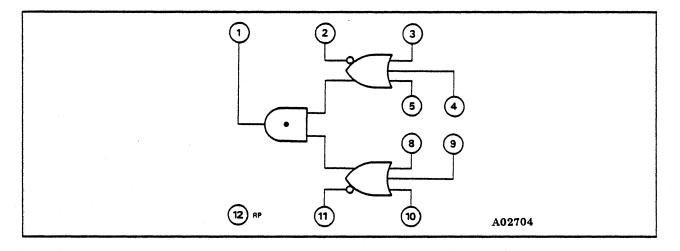

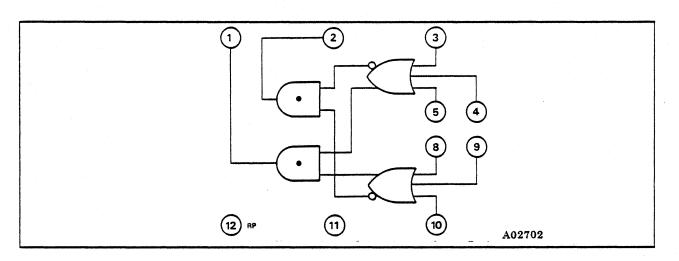

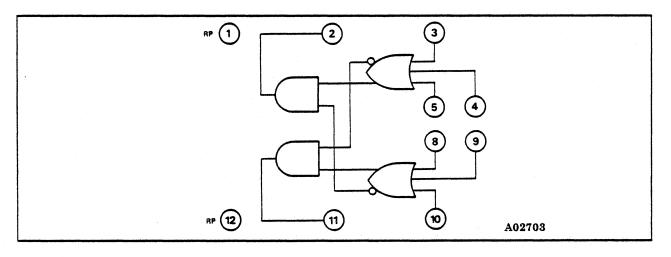

| 5 - 11.         | Macro 13                                                                                                                                               | 5 - 16 |

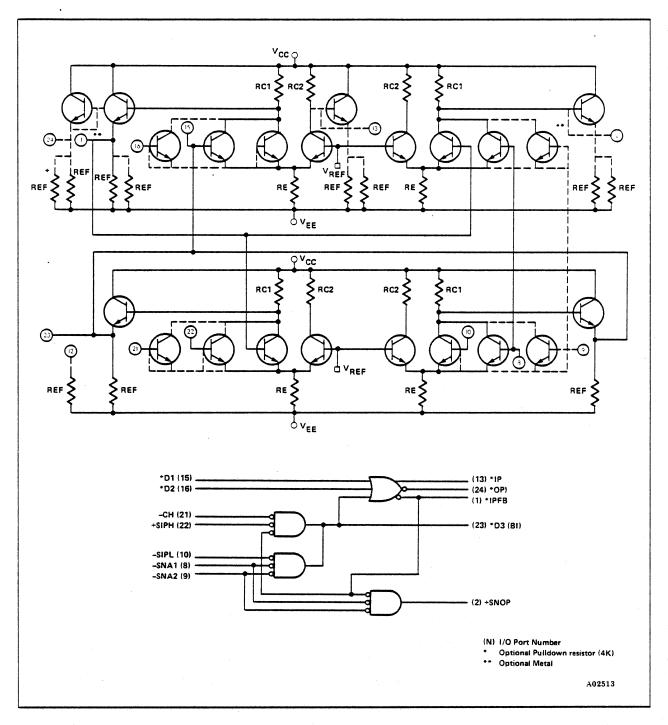

| 5 - 12.         | 3-Input NOR/3-Input 2 Sample Skewed Driver Macro 21                                                                                                    | 5 - 18 |

| (4 V)           | "你们,我们就是你们,你们就是你们的你们,你们就是你们的你?""你们,你们就是你们的你们,你们就是你们的你们,你们就是你们的你?"<br>我们的你们就是你们就是你们就你们的你?""你们,你们们你们们,你们就是你们的你?""你们,你们们你们们,你们们不是你们的你?""你们,你们们不是你们的吗?""你们 |        |

vi

| 5 – 13.                                                                                                                                                 | 3-Input, 3 Sample Skewed Driver Macro 22 (Half-Macro)                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5 – 19                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

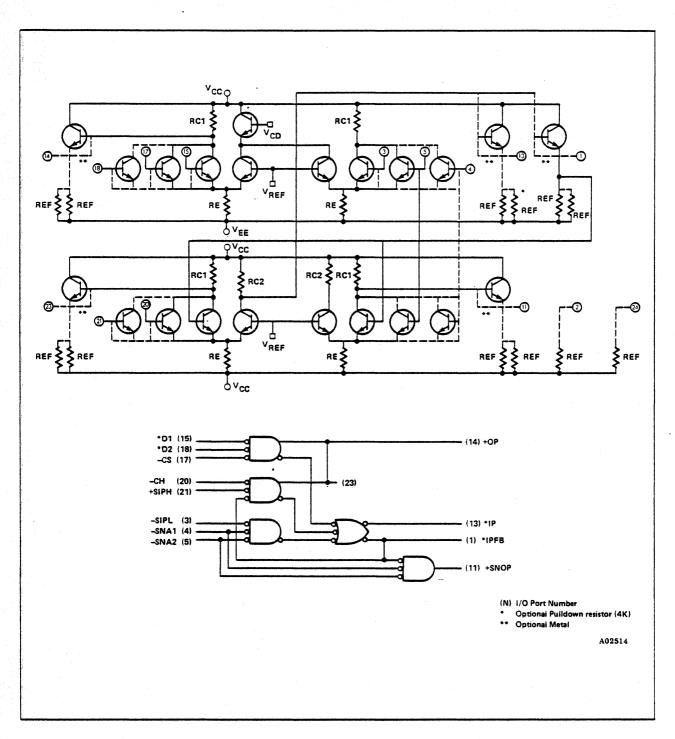

| 5 - 14.                                                                                                                                                 | In-Phase Latch without Scan-In/Scan-Out Macro 31                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5 - 21                                                                                                                                                                                                                                                                              |

| 5 - 15.                                                                                                                                                 | Out-of-Phase Latch without Scan-In/Scan-Out Macro 32                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5 – 21                                                                                                                                                                                                                                                                              |

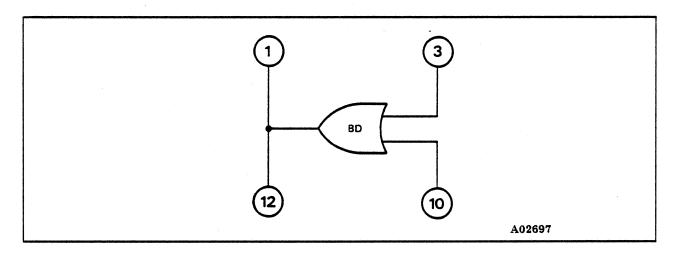

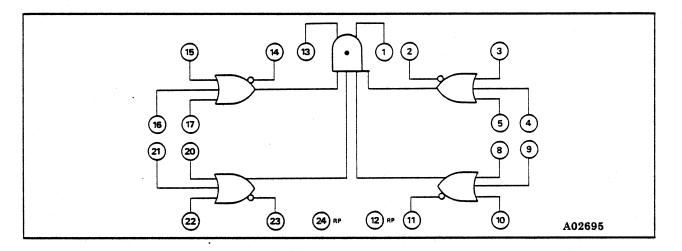

| 5 – 16.                                                                                                                                                 | OR Bus Driver Macro 42 (Half-Macro)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 - 23                                                                                                                                                                                                                                                                              |

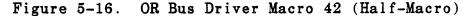

| 5 – 17.                                                                                                                                                 | OR/NOR Memory Driver Macro 43 (Half-Macro)                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 - 24                                                                                                                                                                                                                                                                              |

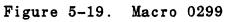

| 5 – 18.                                                                                                                                                 | Macro 0199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 - 25                                                                                                                                                                                                                                                                              |

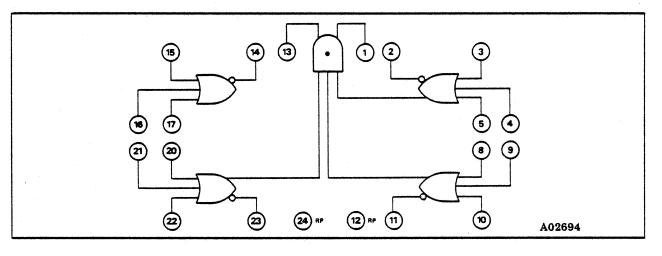

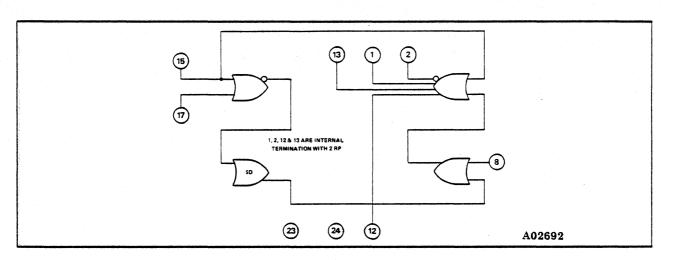

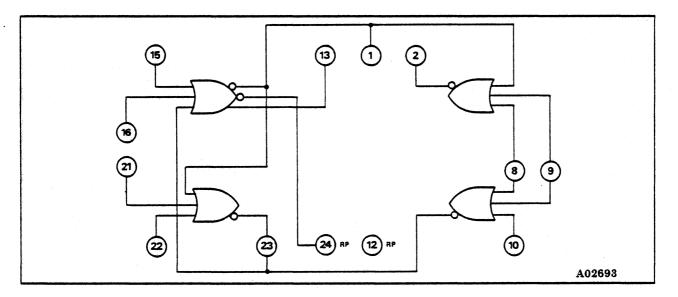

| 5 – 19.                                                                                                                                                 | Macro 0299                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 - 26                                                                                                                                                                                                                                                                              |

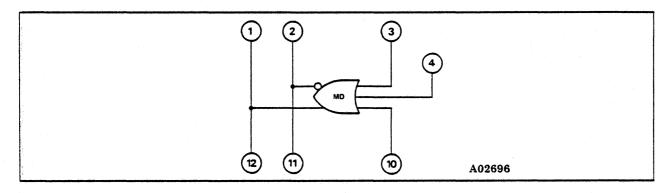

| 5 – 20.                                                                                                                                                 | Clock Chopper Macro 2399 (Full Macro)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5 – 28                                                                                                                                                                                                                                                                              |

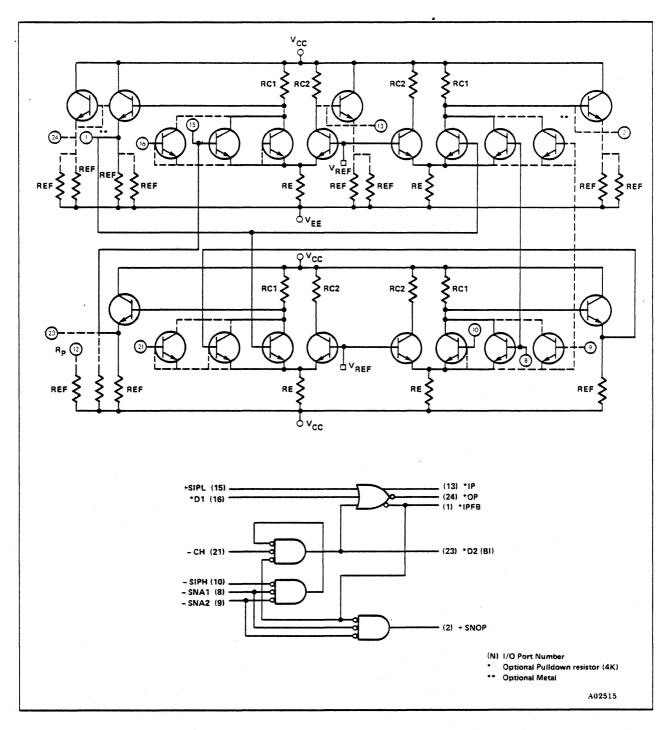

| 5 - 21.                                                                                                                                                 | Out-of-Phase Latch with Scan-In/Scan-Out Macro 3199                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 <b>-</b> 28                                                                                                                                                                                                                                                                       |

| 5 - 22.                                                                                                                                                 | In-Phase Latch with Scan-In/Scan-Out Macro 3299                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 - 31                                                                                                                                                                                                                                                                              |

| 5 - 23.                                                                                                                                                 | Out-of-Phase Latch with Scan-In/Scan-Out Macro 3399                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 - 31                                                                                                                                                                                                                                                                              |

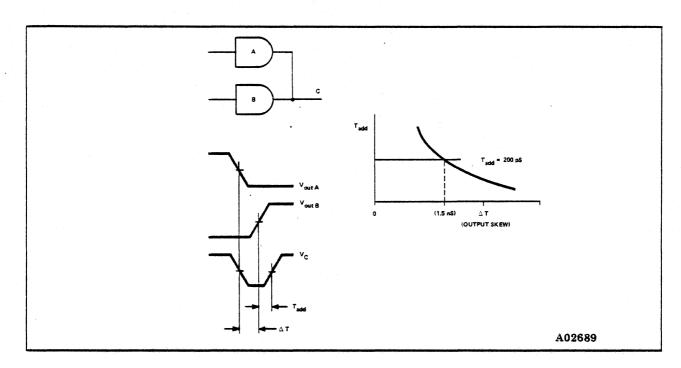

| 5 - 24.                                                                                                                                                 | Definition of T <sub>add</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5 – 36                                                                                                                                                                                                                                                                              |

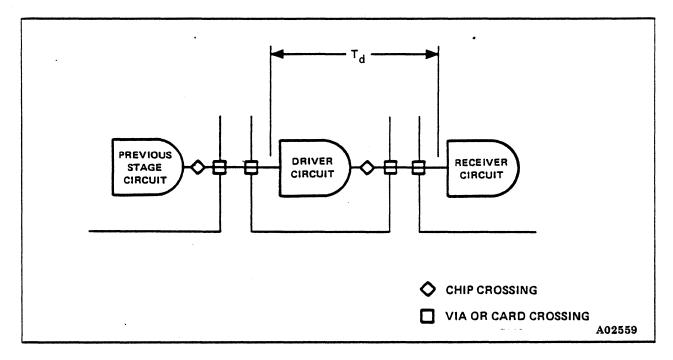

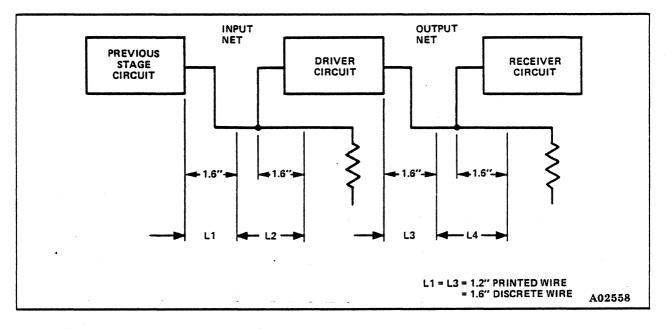

| 5 – 25.                                                                                                                                                 | Off-Chip Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5 – 37                                                                                                                                                                                                                                                                              |

| 5 – 26.                                                                                                                                                 | Off-Chip Loading Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5 – 39                                                                                                                                                                                                                                                                              |

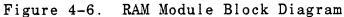

| 5 – 27.                                                                                                                                                 | Basic RAM Module Delay Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5 - 41                                                                                                                                                                                                                                                                              |

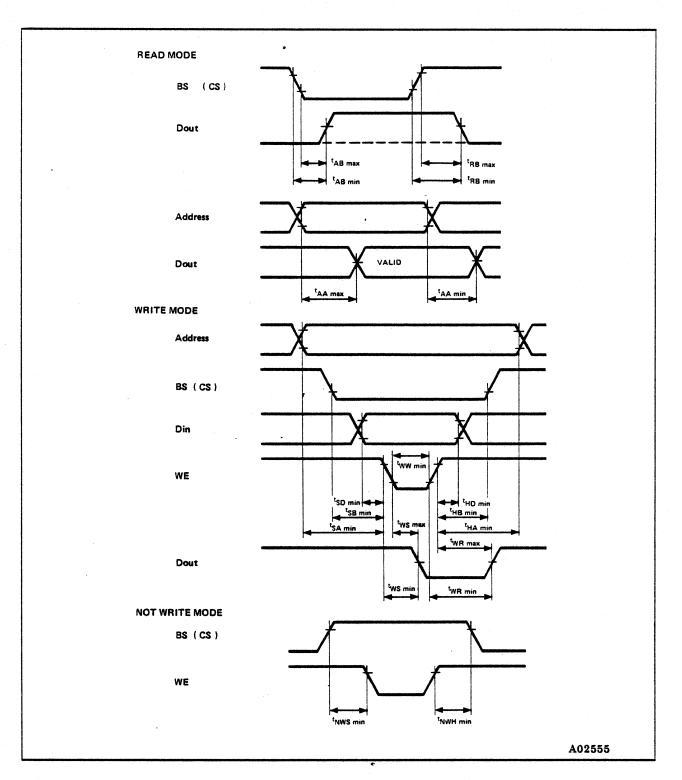

| 5 - 28.                                                                                                                                                 | Read and Write Timing Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5 - 44                                                                                                                                                                                                                                                                              |

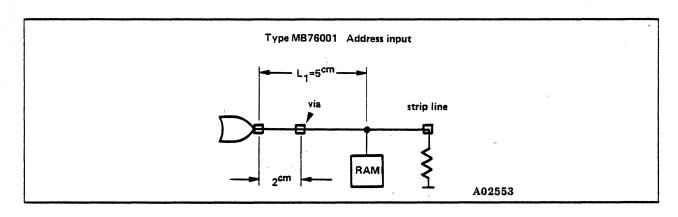

| 5 – 29.                                                                                                                                                 | Driver Fan-out is One Input Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 - 48                                                                                                                                                                                                                                                                              |

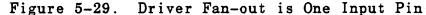

| 5 – 30.                                                                                                                                                 | Driver Fan-out with Two Input Pins (Up-Min)                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5 - 49                                                                                                                                                                                                                                                                              |

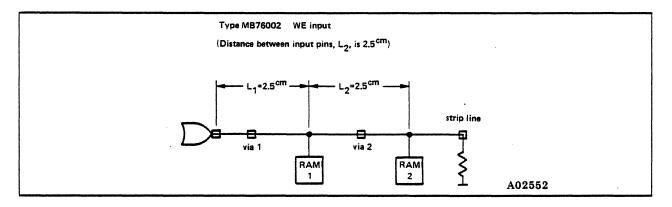

| 5 - 31.                                                                                                                                                 | Driver Fan-out with Two Input Pins (Up-Max)                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5 - 50                                                                                                                                                                                                                                                                              |

| 5 - 32.                                                                                                                                                 | Driver Fan-out with Four Input Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 – 52                                                                                                                                                                                                                                                                              |

|                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                     |

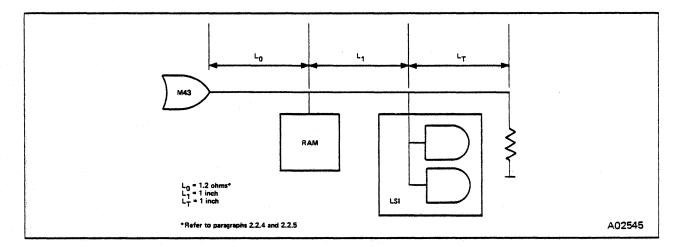

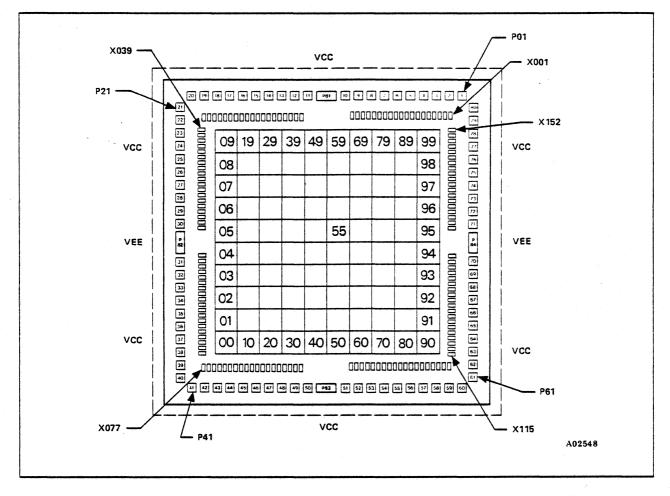

| 6 – 1.                                                                                                                                                  | LSI Cell Numbering (Chip Top View, Cooling STUD Down)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                     |

| 6 - 1.<br>6 - 2.                                                                                                                                        | LSI Cell Numbering (Chip Top View, Cooling STUD Down)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                     |

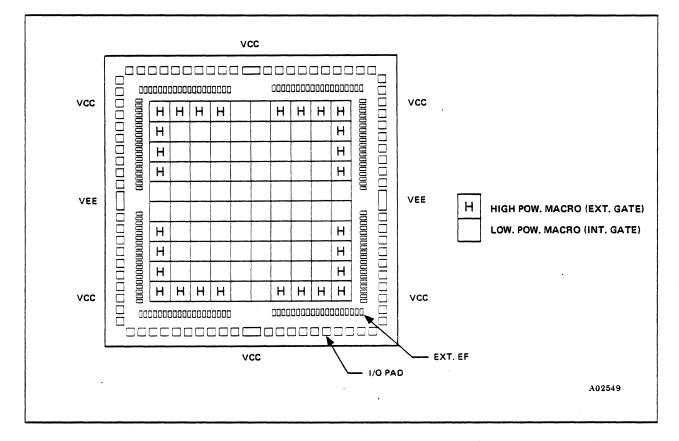

|                                                                                                                                                         | High/Low Power Cell Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $6-3 \\ 6-4$                                                                                                                                                                                                                                                                        |

| 6 – 2.                                                                                                                                                  | High/Low Power Cell Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-3<br>6-4<br>6-10                                                                                                                                                                                                                                                                  |

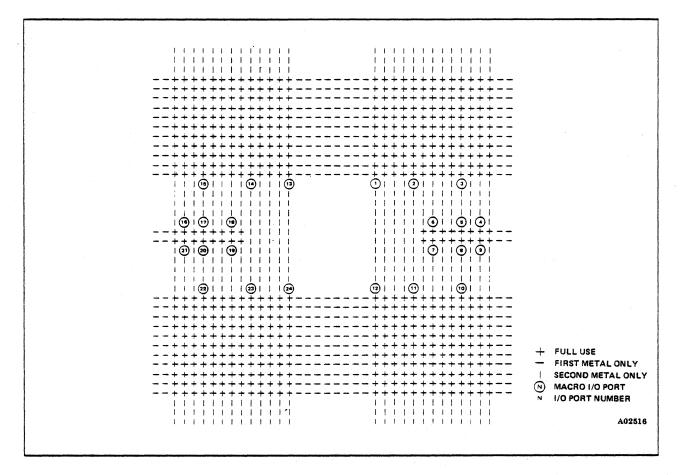

| 6 – 2.<br>6 – 3.                                                                                                                                        | High/Low Power Cell Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-3<br>6-4<br>6-10<br>6-18                                                                                                                                                                                                                                                          |

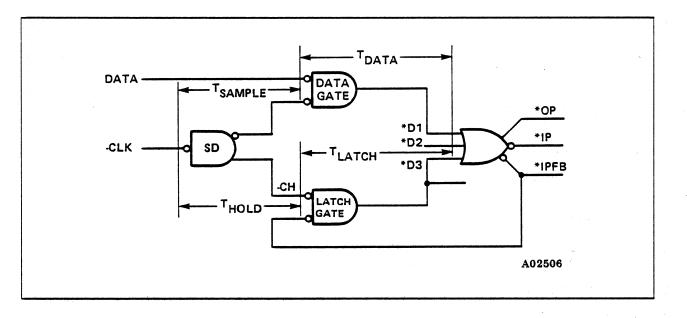

| 6 - 2.<br>6 - 3.<br>6 - 4.<br>6 - 5.<br>7 - 1.                                                                                                          | High/Low Power Cell Placement       Interconnect Grid and I/O Hit Ports (Full Macro)         Interconnect Grid and I/O Hit Ports (Full Macro)       Interconnect Grid and I/O Hit Ports (Full Macro)         Limitations of Internal Net       Interconnect Grid and I/O Hit Ports (Full Macro)         Switching Skew       Interconnect Grid And I/O Hit Ports (Full Macro)         Macro 31 In-Phase Latch       Interconnect Grid And I/O Hit Ports (Full Macro)                                    | 6-3<br>6-4<br>6-10<br>6-18<br>7-1                                                                                                                                                                                                                                                   |

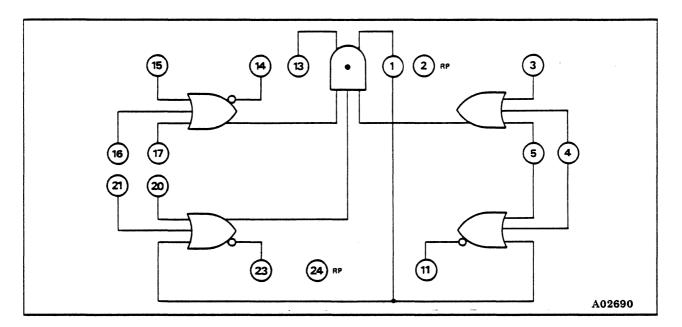

| 6-2.<br>6-3.<br>6-4.<br>6-5.<br>7-1.<br>7-2.                                                                                                            | High/Low Power Cell Placement       Interconnect Grid and I/O Hit Ports (Full Macro)         Interconnect Grid and I/O Hit Ports (Full Macro)       Interconnect Grid and I/O Hit Ports (Full Macro)         Limitations of Internal Net       Interconnect Grid and I/O Hit Ports (Full Macro)         Switching Skew       Interconnect Grid And I/O Hit Ports (Full Macro)         Macro 31 In-Phase Latch       Interconnect Grid And I/O Hit Ports (Full Macro)                                    | 6-3<br>6-4<br>6-10<br>6-18<br>7-1                                                                                                                                                                                                                                                   |

| 6 - 2.<br>6 - 3.<br>6 - 4.<br>6 - 5.<br>7 - 1.                                                                                                          | High/Low Power Cell Placement         Interconnect Grid and I/O Hit Ports (Full Macro)         Limitations of Internal Net         Switching Skew         Macro 31 In-Phase Latch         Macro 32 Out-of-Phase Latch         Macro 3199 Out-of-Phase Latch                                                                                                                                                                                                                                             | $ \begin{array}{r} 6-3 \\ 6-4 \\ 6-10 \\ 6-18 \\ 7-1 \\ 7-2 \\ 7-3 \\ \end{array} $                                                                                                                                                                                                 |

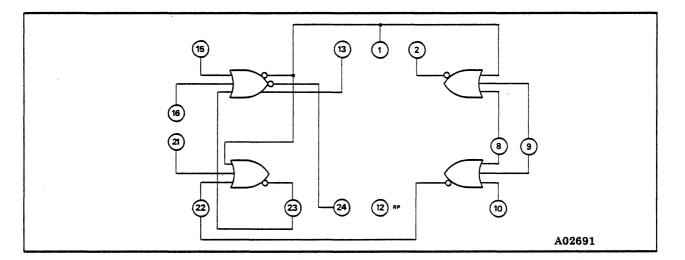

| 6-2.<br>6-3.<br>6-4.<br>6-5.<br>7-1.<br>7-2.                                                                                                            | High/Low Power Cell Placement         Interconnect Grid and I/O Hit Ports (Full Macro)         Limitations of Internal Net         Switching Skew         Macro 31 In-Phase Latch         Macro 32 Out-of-Phase Latch         Macro 3199 Out-of-Phase Latch         Macro 3299 In-Phase Latch                                                                                                                                                                                                           | $ \begin{array}{r} 6-3\\ 6-4\\ 6-10\\ 6-18\\ 7-1\\ 7-2\\ 7-3\\ 7-4 \end{array} $                                                                                                                                                                                                    |

| $\begin{array}{c} 6-2. \\ 6-3. \\ 6-4. \\ 6-5. \\ 7-1. \\ 7-2. \\ 7-3. \\ 7-4. \\ 7-5. \end{array}$                                                     | High/Low Power Cell PlacementInterconnect Grid and I/O Hit Ports (Full Macro)Limitations of Internal NetSwitching SkewMacro 31 In-Phase LatchMacro 32 Out-of-Phase LatchMacro 3199 Out-of-Phase LatchMacro 3299 In-Phase LatchMacro 3399 Out-of-Phase Latch                                                                                                                                                                                                                                             | $ \begin{array}{r} 6-3\\6-4\\6-10\\6-18\\7-1\\7-2\\7-3\\7-4\\7-5\end{array} $                                                                                                                                                                                                       |

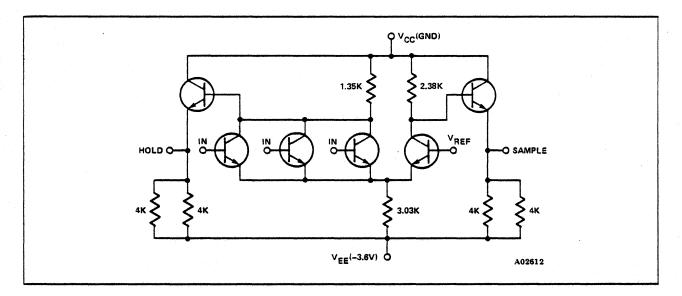

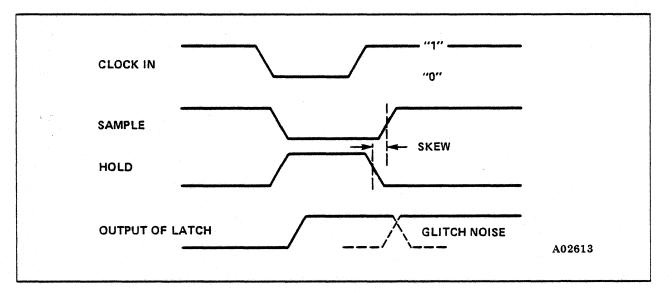

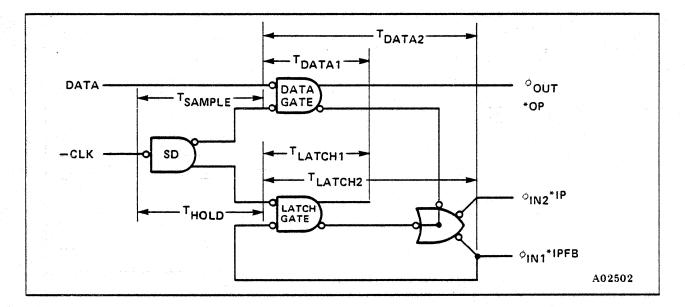

| $\begin{array}{c} 6-2. \\ 6-3. \\ 6-4. \\ 6-5. \\ 7-1. \\ 7-2. \\ 7-3. \\ 7-4. \\ 7-5. \\ 7-6. \end{array}$                                             | High/Low Power Cell PlacementInterconnect Grid and I/O Hit Ports (Full Macro)Limitations of Internal NetSwitching SkewMacro 31 In-Phase LatchMacro 32 Out-of-Phase LatchMacro 3199 Out-of-Phase LatchMacro 3299 In-Phase LatchMacro 3399 Out-of-Phase LatchSkewed Clock Driver Schematic                                                                                                                                                                                                                | $ \begin{array}{r} 6-3\\6-4\\6-10\\6-18\\7-1\\7-2\\7-3\\7-4\\7-5\\7-6\end{array} $                                                                                                                                                                                                  |

| $\begin{array}{c} 6-2. \\ 6-3. \\ 6-4. \\ 6-5. \\ 7-1. \\ 7-2. \\ 7-3. \\ 7-4. \\ 7-5. \\ 7-6. \\ 7-7. \end{array}$                                     | High/Low Power Cell PlacementInterconnect Grid and I/O Hit Ports (Full Macro)Limitations of Internal NetSwitching SkewMacro 31 In-Phase LatchMacro 32 Out-of-Phase LatchMacro 3199 Out-of-Phase LatchMacro 3299 In-Phase LatchMacro 3399 Out-of-Phase LatchSkewed Clock Driver SchematicSkewed Driver (SD) Signal Waveform                                                                                                                                                                              | $ \begin{array}{r} 6 - 3 \\ 6 - 4 \\ 6 - 10 \\ 6 - 18 \\ 7 - 1 \\ 7 - 2 \\ 7 - 3 \\ 7 - 4 \\ 7 - 5 \\ 7 - 6 \\ 7 - 6 \\ 7 - 6 \\ \end{array} $                                                                                                                                      |

| $\begin{array}{c} 6-2. \\ 6-3. \\ 6-4. \\ 6-5. \\ 7-1. \\ 7-2. \\ 7-3. \\ 7-4. \\ 7-5. \\ 7-6. \\ 7-7. \\ 7-8. \end{array}$                             | High/Low Power Cell PlacementInterconnect Grid and I/O Hit Ports (Full Macro)Limitations of Internal NetSwitching SkewMacro 31 In-Phase LatchMacro 32 Out-of-Phase LatchMacro 3199 Out-of-Phase LatchMacro 3299 In-Phase LatchMacro 3399 Out-of-Phase LatchSkewed Clock Driver SchematicSkewed Driver (SD) Signal Waveform                                                                                                                                                                              | $ \begin{array}{r} 6 - 3 \\ 6 - 4 \\ 6 - 10 \\ 6 - 18 \\ 7 - 1 \\ 7 - 2 \\ 7 - 3 \\ 7 - 4 \\ 7 - 5 \\ 7 - 6 \\ 7 - 6 \\ 7 - 6 \\ \end{array} $                                                                                                                                      |

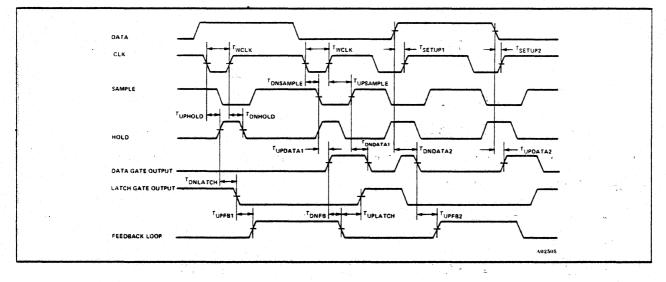

| $\begin{array}{c} 6-2.\\ 6-3.\\ 6-4.\\ 6-5.\\ 7-1.\\ 7-2.\\ 7-3.\\ 7-4.\\ 7-5.\\ 7-6.\\ 7-7.\\ 7-8.\\ 7-9. \end{array}$                                 | High/Low Power Cell PlacementInterconnect Grid and I/O Hit Ports (Full Macro)Limitations of Internal NetSwitching SkewMacro 31 In-Phase LatchMacro 32 Out-of-Phase LatchMacro 3199 Out-of-Phase LatchMacro 3299 In-Phase LatchMacro 3399 Out-of-Phase LatchSkewed Clock Driver SchematicSkewed Driver (SD) Signal Waveform                                                                                                                                                                              | $ \begin{array}{r} 6 - 3 \\ 6 - 4 \\ 6 - 10 \\ 6 - 18 \\ 7 - 1 \\ 7 - 2 \\ 7 - 3 \\ 7 - 4 \\ 7 - 5 \\ 7 - 6 \\ 7 - 6 \\ 7 - 6 \\ \end{array} $                                                                                                                                      |

| $\begin{array}{c} 6-2.\\ 6-3.\\ 6-4.\\ 6-5.\\ 7-1.\\ 7-2.\\ 7-3.\\ 7-4.\\ 7-5.\\ 7-6.\\ 7-7.\\ 7-8.\\ 7-9.\\ 7-10. \end{array}$                         | High/Low Power Cell PlacementInterconnect Grid and I/O Hit Ports (Full Macro)Limitations of Internal NetSwitching SkewMacro 31 In-Phase LatchMacro 32 Out-of-Phase LatchMacro 3199 Out-of-Phase LatchMacro 3299 In-Phase LatchMacro 3399 Out-of-Phase LatchSkewed Clock Driver SchematicSkewed Driver (SD) Signal WaveformIn-Phase Latch Timing DiagramsOut-of-Phase Latch Path Definitions                                                                                                             | $\begin{array}{c} 6 & -3 \\ 6 & -4 \\ 6 & -10 \\ 6 & -18 \\ 7 & -1 \\ 7 & -2 \\ 7 & -3 \\ 7 & -4 \\ 7 & -5 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -8 \\ 7 & -9 \\ 7 & -11 \end{array}$                                                                                                |

| $\begin{array}{c} 6-2.\\ 6-3.\\ 6-4.\\ 6-5.\\ 7-1.\\ 7-2.\\ 7-3.\\ 7-4.\\ 7-5.\\ 7-6.\\ 7-7.\\ 7-8.\\ 7-9.\\ 7-9.\\ 7-10.\\ 7-11. \end{array}$          | High/Low Power Cell PlacementInterconnect Grid and I/O Hit Ports (Full Macro)Limitations of Internal NetSwitching SkewMacro 31 In-Phase LatchMacro 32 Out-of-Phase LatchMacro 3199 Out-of-Phase LatchMacro 3299 In-Phase LatchMacro 3399 Out-of-Phase LatchSkewed Clock Driver SchematicSkewed Driver (SD) Signal WaveformIn-Phase Latch Timing DiagramsOut-of-Phase Latch Path DefinitionsOut-of-Phase Latch Timing Diagram                                                                            | $\begin{array}{c} 6 & -3 \\ 6 & -4 \\ 6 & -10 \\ 6 & -18 \\ 7 & -1 \\ 7 & -2 \\ 7 & -3 \\ 7 & -4 \\ 7 & -5 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -8 \\ 7 & -9 \\ 7 & -11 \\ 7 & -12 \end{array}$                                                                                     |

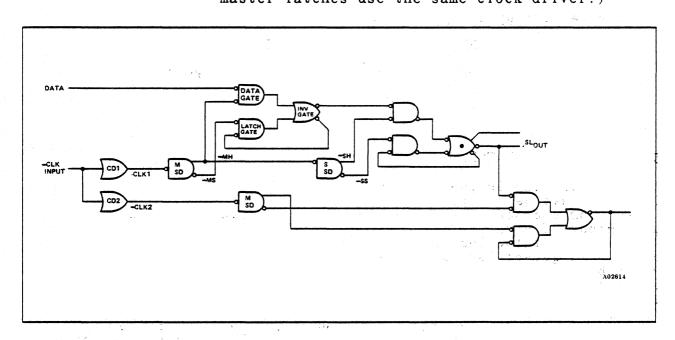

| $\begin{array}{c} 6-2.\\ 6-3.\\ 6-4.\\ 6-5.\\ 7-1.\\ 7-2.\\ 7-3.\\ 7-4.\\ 7-5.\\ 7-6.\\ 7-7.\\ 7-8.\\ 7-9.\\ 7-10.\\ 7-11.\\ 7-12. \end{array}$         | High/Low Power Cell PlacementInterconnect Grid and I/O Hit Ports (Full Macro)Limitations of Internal NetSwitching SkewMacro 31 In-Phase LatchMacro 32 Out-of-Phase LatchMacro 3199 Out-of-Phase LatchMacro 3299 In-Phase LatchMacro 3399 Out-of-Phase LatchSkewed Clock Driver SchematicSkewed Driver (SD) Signal WaveformIn-Phase Latch Timing DiagramsOut-of-Phase Latch Timing DiagramOut-of-Phase Latch Timing DiagramOut-of-Phase Latch Timing DiagramOut-of-Phase Latch Timing Diagram            | $\begin{array}{c} 6 & -3 \\ 6 & -4 \\ 6 & -10 \\ 6 & -18 \\ 7 & -1 \\ 7 & -2 \\ 7 & -3 \\ 7 & -4 \\ 7 & -5 \\ 7 & -6 \\ 7 & -6 \\ 7 & -8 \\ 7 & -11 \\ 7 & -12 \\ 7 & -12 \\ 7 & -13 \end{array}$                                                                                   |

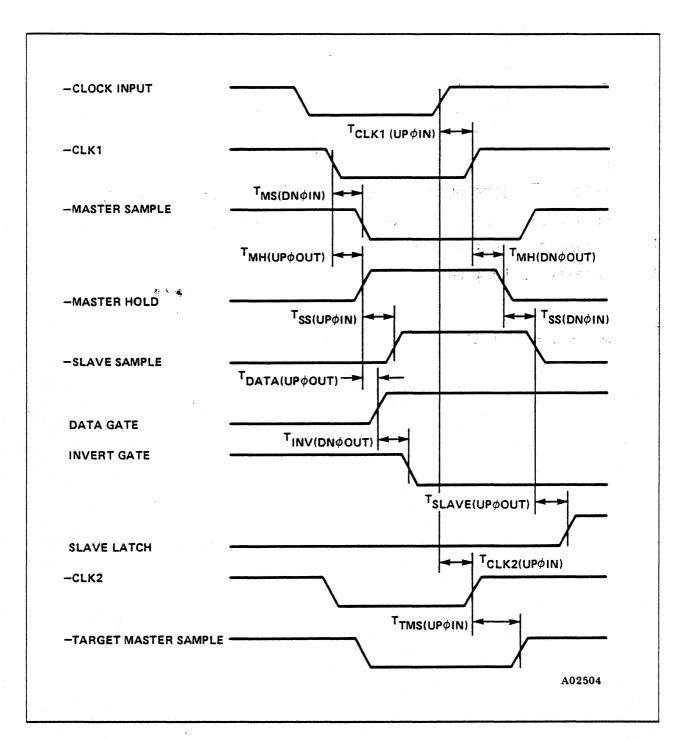

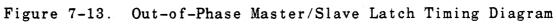

| $\begin{array}{c} 6-2.\\ 6-3.\\ 6-4.\\ 6-5.\\ 7-1.\\ 7-2.\\ 7-3.\\ 7-4.\\ 7-5.\\ 7-6.\\ 7-7.\\ 7-8.\\ 7-9.\\ 7-10.\\ 7-11.\\ 7-12.\\ 7-13. \end{array}$ | High/Low Power Cell PlacementInterconnect Grid and I/O Hit Ports (Full Macro)Limitations of Internal NetSwitching SkewMacro 31 In-Phase LatchMacro 32 Out-of-Phase LatchMacro 3199 Out-of-Phase LatchMacro 3299 In-Phase LatchMacro 3399 Out-of-Phase LatchSkewed Clock Driver SchematicSkewed Driver (SD) Signal WaveformIn-Phase Latch Timing DiagramsOut-of-Phase Latch Timing DiagramOut-of-Phase Latch Timing DiagramOut-of-Phase Master/Slave LatchOut-of-Phase Master/Slave Latch Timing Diagram | $\begin{array}{c} 6 & -3 \\ 6 & -4 \\ 6 & -10 \\ 6 & -18 \\ 7 & -1 \\ 7 & -2 \\ 7 & -3 \\ 7 & -4 \\ 7 & -5 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -12 \\ 7 & -12 \\ 7 & -12 \\ 7 & -15 \end{array}$                                 |

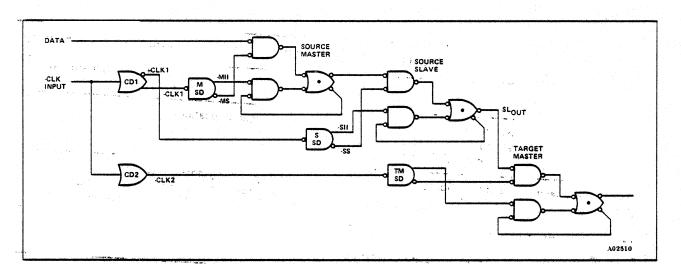

| $\begin{array}{c} 6-2.\\ 6-3.\\ 6-4.\\ 6-5.\\ 7-1.\\ 7-2.\\ 7-3.\\ 7-4.\\ 7-5.\\ 7-6.\\ 7-7.\\ 7-8.\\ 7-9.\\ 7-10.\\ 7-11.\\ 7-12. \end{array}$         | High/Low Power Cell PlacementInterconnect Grid and I/O Hit Ports (Full Macro)Limitations of Internal NetSwitching SkewMacro 31 In-Phase LatchMacro 32 Out-of-Phase LatchMacro 3199 Out-of-Phase LatchMacro 3299 In-Phase LatchMacro 3399 Out-of-Phase LatchSkewed Clock Driver SchematicSkewed Driver (SD) Signal WaveformIn-Phase Latch Timing DiagramsOut-of-Phase Latch Timing DiagramOut-of-Phase Latch Timing DiagramOut-of-Phase Latch Timing DiagramOut-of-Phase Latch Timing Diagram            | $\begin{array}{c} 6 & -3 \\ 6 & -4 \\ 6 & -10 \\ 6 & -18 \\ 7 & -1 \\ 7 & -2 \\ 7 & -3 \\ 7 & -4 \\ 7 & -5 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -6 \\ 7 & -12 \\ 7 & -11 \\ 7 & -12 \\ 7 & -13 \\ 7 & -15 \\ 7 & -16 \end{array}$ |

vii

## TABLES

| 2 – 1.       | Off-Chip Wiring Definitions                           | 2 - 1  |

|--------------|-------------------------------------------------------|--------|

| 2 – 2.       | Wiring Resistance Limitations                         | 2-4    |

| 2 – 3.       | Wiring Materials Resistance Cross Reference           | 2 – 5  |

| 2 - 4.       | EF Dotting Restrictions                               |        |

| 2 - 5.       | Delay Calculation of Example in Figure 2-9            | 2 - 16 |

| <b>2</b> -6. | Maximum Parallel Net Length in Inches and Grid Units  |        |

| 2 - 7.       | MCC I/O Noise Limits                                  | 2 - 21 |

| 4 – 1.       | 580 RAM Module Pin Assignment                         | 4-8    |

| 5 - 1.       | T <sub>in</sub> Definitions and Cross References      | 5 - 4  |

| 5 – 2.       | T <sub>fanin</sub> Definitions and Cross References   | 5 - 5  |

| 5 - 3.       | Macro Identification and Description Locational Chart |        |

| 5 - 4.       | Macro 01 Characteristics                              |        |

| 5 - 5.       | Macro 02 Characteristics                              | 5-9    |

| 5-6.         | Macro 03 Characteristics                              | 5 - 10 |

| 5 – 7.       | Macro 04 Characteristics                              | 5 - 11 |

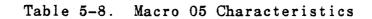

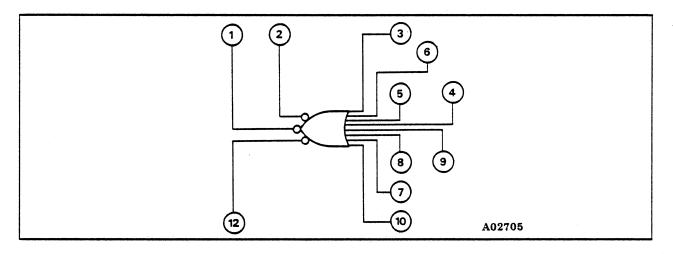

| 5 – 8.       | Macro 05 Characteristics                              | 5 - 12 |

| 5 – 9.       | Macro 08 Characteristics                              | 5 - 13 |

| 5 – 10.      | Macro 11 Characteristics                              | 5 - 14 |

| 5 - 11.      | Macro 12 Characteristics                              | 5 - 15 |

| 5 - 12.      | Macro 13 Characteristics                              | 5 - 17 |

| 5 - 13.      | Macro 21 Characteristics                              | 5 - 18 |

| 5 - 14.      | Macro 22 Characteristics                              | 5 - 19 |

| 5 - 15.      | Macro 31 Characteristics                              | 5 - 20 |

| 5 - 16.      | Macro 32 Characteristics                              | 5 - 22 |

| 5-17.        | Macro 42 Characteristics                              | 5 - 23 |

| 5 - 18.      | Macro 43 Characteristics                              | 5 - 24 |

| 5 - 19.      | Macro 0199 Characteristics                            | 5 - 25 |

| 5 - 20.      | Macro 0299 Characteristics                            | 5 - 26 |

| 5-21.        | Macro 2399 Characteristics                            | 5 - 27 |

| 5 - 22.      | Macro 3199 Characteristics                            | 5 - 29 |

| 5 - 23.      | Macro 3299 Characteristics                            | 5 - 30 |

| 5 - 24.      | Macro 3399 Characteristics                            | 5 - 32 |

| 5 - 25.      | Main Coefficients                                     | 5 - 33 |

| 5 - 26.      | Feedback Coefficients                                 | 5 - 34 |

| 5 - 27.      | T <sub>BD</sub> Coefficients                          | 5 - 35 |

| 5 - 28.      |                                                       |        |

| 5 - 29.      | T <sub>in</sub> Coefficients                          | 5 - 40 |

| 5 - 30.      | T <sub>out</sub> Coefficients                         | 5 - 40 |

| 5 - 31.      | T <sub>RAMIN</sub> Equation Formats                   | 5 - 42 |

| 5 - 32.      | T <sub>RAMIN</sub> Equation Coefficients              | 5 - 43 |

| 5 - 33.      | Intra-Module Delay and RAM Timing Requirements        | 5 - 45 |

| 5 - 34.      | Output Net Delay Times                                | 5 - 46 |

| 5 - 35.      | Macro Multiple Base Input (Excluding Bases)           | 5 - 53 |

| 5 - 36.      | Macro Re-entry Pin (Excluding Bases)                  | 5 - 54 |

| 5 - 37.      | Intra Macro Net without Pin (Excluding Bases)         |        |

|              |                                                       |        |

| E 90    | Wining Someonte (MNIN, MNION)                                                                                                                    | ł. |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5 - 50. | Wiring Segments (MNIN, MNON) $\dots \dots \dots$ | È  |

| 5 – 39. | Wire Loading Units                                                                                                                               | 5  |

| 5 - 40. | RAM Input/Output Loading 5-57                                                                                                                    | 7  |

| 6 – 1.  | EF Dotting Restrictions                                                                                                                          | 7  |

| 6 – 2.  | Macros with Multiple Emitter Followers                                                                                                           | 3  |

| 6 – 3.  | $L_N$ (Limited Length)                                                                                                                           | )  |

| 6 - 4.  | Nominal Power Dissipation (Milliwatts)                                                                                                           | 2  |

| 6 – 5.  | Power Consumption of MB12K LSI                                                                                                                   | 3  |

|         | Nominal Power Dissipation with One Pull Down Resistor                                                                                            |    |

| 6 – 7.  | Simultaneous EF Switching Limitations 6-17                                                                                                       | 7  |

| 6 – 8.  | Simultaneous EF Switching Case Determination                                                                                                     | 3  |

|         | •                                                                                                                                                |    |

#### AMDAHL COMPANY PRIVATE

### CHAPTER 1 – INTRODUCTION

Amdahl 580 LSI represents the state of the art in high speed, bipolar LSI logic. The propagation delay may be as small as 350 ps per gate. Design rules are required to fully utilize the very high performance of 580 LSI circuit chips and at the same time achieve reliable operation.

#### 1.1 IMPEDANCE MATCHING

As a result of fast rise and fall times (less than 1 ns), the Current Switch Emitter Follower (CSEF) circuit family is designed to drive a 90 ohm matched impedance system whenever communication is done off-chip. The terminating resistor is a hybrid integrated R-pack of 90 ohms, returned to -2.0 volts.

#### 1.2 TESTABILITY

Another important consideration for an LSI system is testability. Some logic design standardizations and restrictions are necessary to enhance testability.

LSI Circuit Manual

AMDAHL COMPANY PRIVATE

## CHAPTER 2 - OFF-CHIP WIRING RULES

## 2.1 **DEFINITIONS**

Table 2-1 lists the definitions and rules that apply to off-chip terminated nets. Figure 2-1 is a typical off-chip wiring net illustration.

| TERMS                    | DEFINITIONS                                                                                                                                                                                                                                                                                            |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Network<br>(Net)         | Refers to the wire which connects a group of<br>driving circuits and load circuits that are<br>electrically connected together to perform some<br>logic function.                                                                                                                                      |

| Main Line (LM)           | The longest distance in the net measured from a driver circuit output to a terminator.                                                                                                                                                                                                                 |