**MARCH 1985**

## A PennWell Publication GONPUTER DESIGN

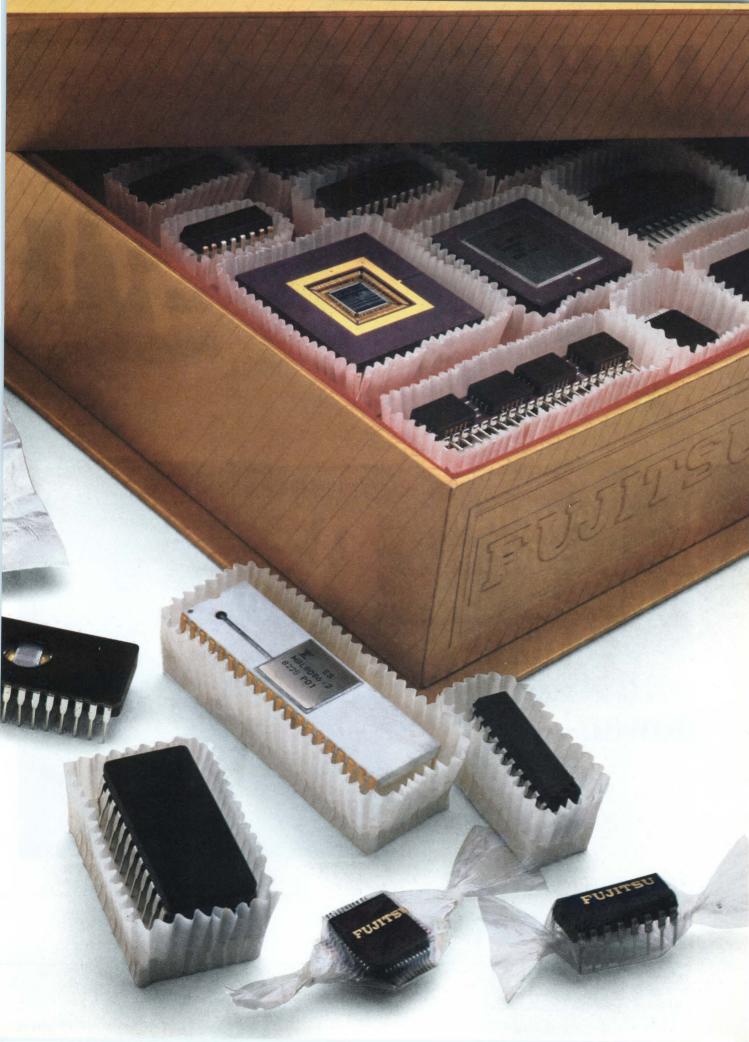

### **CUSTOM/SEMICUSTOM ICs**

ARTIFICIAL INTELLIGENCE TECHNIQUES EASE VLSI DESIGN

EXPLORATORY DEVELOPMENT SYSTEMS MANAGE UNCERTAINTY

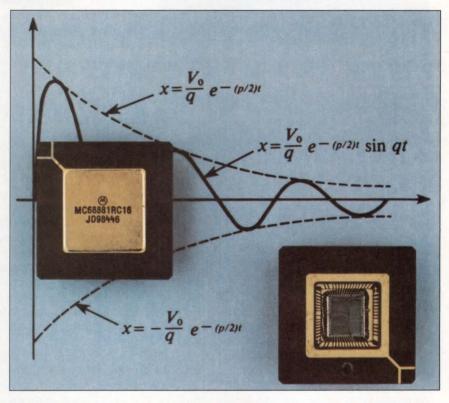

> DISK CONTROL ICs FIGHT DATA ERRORS

## ROCKWELL SEMICONDUCTOR TECHNOLOGY CREATES THE NEXT GENERATION OF INTEGRAL MODEMS.

### Our third-generation VLSI capabilities give you support at any level.

Building modems into your product line used to be a complicated and costly process. But Rockwell International's latest generation of VLSI integral modems is changing all that.

Today, our VLSI capabilities mean that we can support your design requirements at any level: you can order VLSI chip sets; standard cards with all data rates interchangeable; or custom cards designed to fit your specific shape, connector and software integration requirements.

In fact, we can offer a simple, economical solution to virtually any application requirement from 1200 to 9600 bps. Since our modems include both a microprocessor bus and an RS232C interface, they can be easily designed into computers, from micros to mainframes; plus G2-G3 facsimile machines, multiplexers, terminals and, of course, box modems.

What's more, Rockwell is the only supplier of fullduplex, dial 2400 bps VLSI integral modems. And all of our modems are as reliable as they are versatile. Based on our customers' experience with over a half million Rockwell integral modems in use around the world, we've been able to document an MTBF of 200,000 hours nearly 23 years between service calls. Performance-wise, transmission is virtually error-free

> over unconditioned or dial-up phone lines because our integral modems offer auto-adaptive equalization.

We are the world's largest supplier of high-speed modem subsystems and devices. Ask your sales representative or distributor for a quote today, and you'll see that we have a distinct advantage in price and delivery lead times, too.

Rockwell integral modems. A generation ahead of all the rest.

#### Rockwell Semiconductor Products Division

Rockwell International, P.O. Box C, MS 501-300, Newport Beach, CA 92660. Call toll free (800) 854-8099. In California: (800) 422-4230.

...where science gets down to business

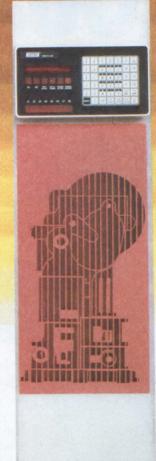

Model 6470 Cartridge Tape System

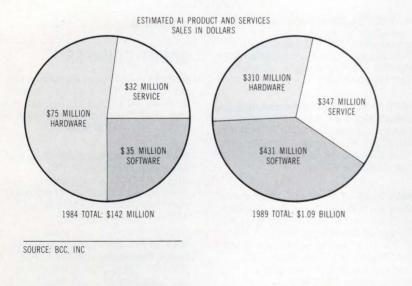

## Thinking Big — really big!

And why not? Kennedy's Model 6470  $\frac{1}{4}$ " cartridge tape drive has every reason to think that it's big — it behaves as if it were a  $\frac{1}{2}$ " tape drive.

#### Examples:

- Model 6470 uses standard 1/2" tape interface.

- It has the same functions as a larger 1/2" tape drive.

- The cost is 1/3 less than 1/2" tape drives.

- It's 1/10 the size of 1/2" drives.

- It packs more data per reel than P.E. drives (54 MBYTES).

- Finally, Model 6470 operates on the same tape handlers as ½" drives.

Model 6470 is a start/stop device with the capability of streaming data at 37.5 IPS, providing much greater flexibility than in comparable drives.

Other features include low power consumption, consuming total power of under 50 watts: diagnostic and fault isolation, with On-Line Self Test and Off-Line Self Test Routines.

Model 6470 — it's not guilty of delusions of grandeur. It really can perform as a  $\frac{1}{2}$ " tape drive. Give us a call. We'll prove it.

#### KENNEDY

An Allegheny International Company 1600 Shamrock Ave. Monrovia, CA 91016 (818) 357-8831 RCA TELEX 247019 KNDY-UR

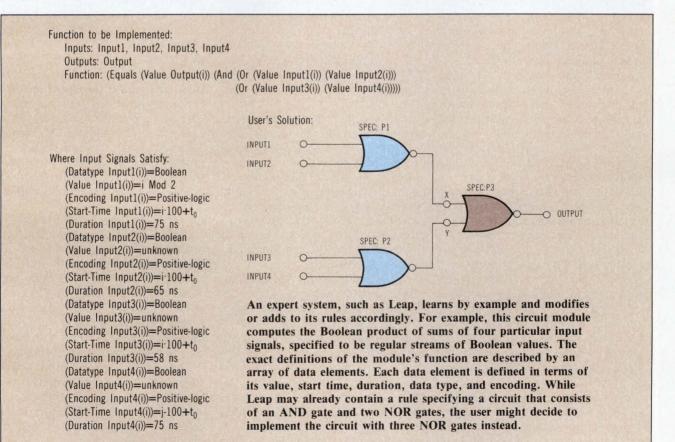

### **KENNEDY · QUALITY · COUNT ON IT**

**CIRCLE 2**

## **COMPUTER DESIGN**<sup>®</sup>

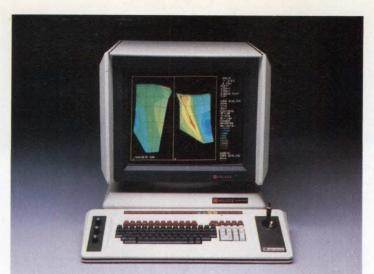

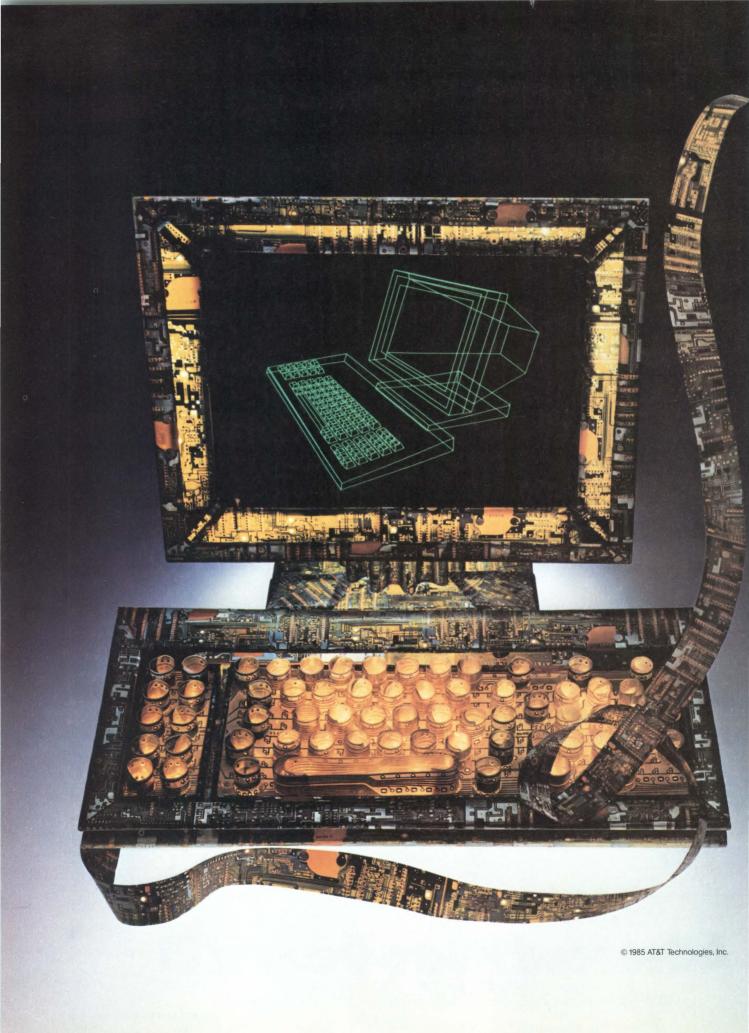

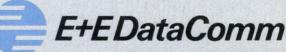

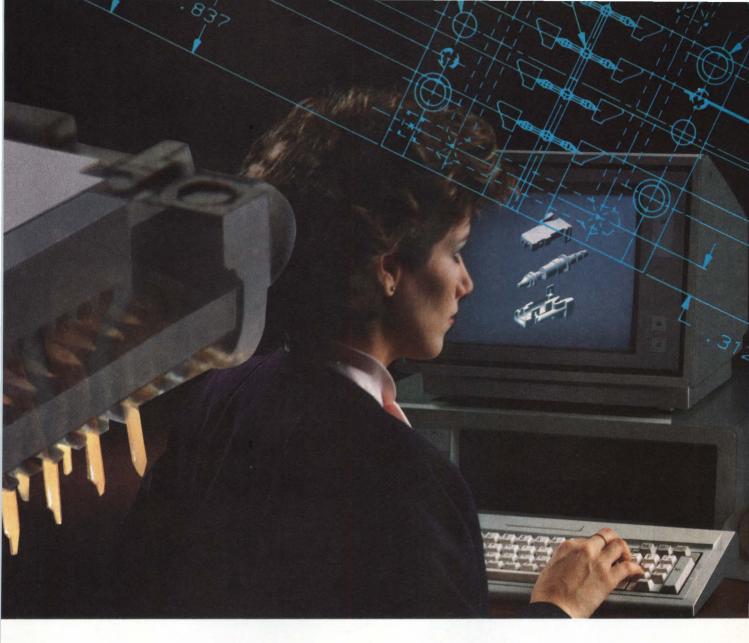

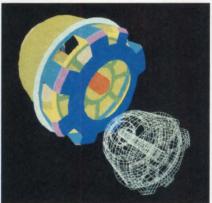

This month's cover is a computer-generated 3-D solid model designed at Coddbarrett Associates, Inc. The data base was constructed and illustrated by Mary Codd.

#### SPECIAL REPORT ON CUSTOM/SEMICUSTOM ICs

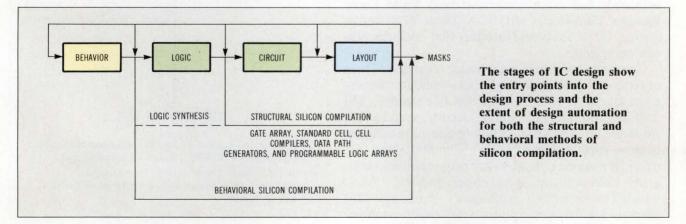

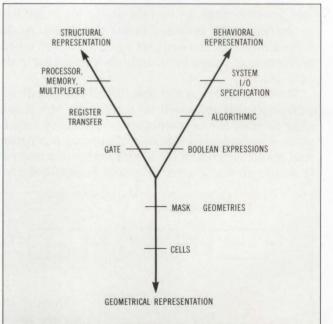

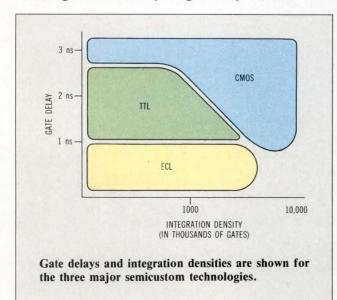

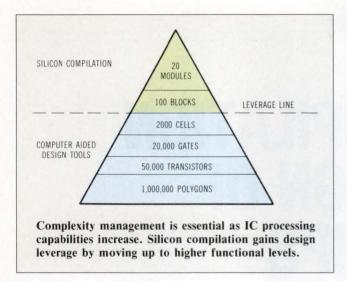

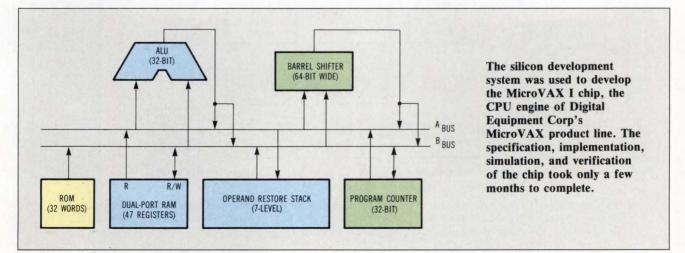

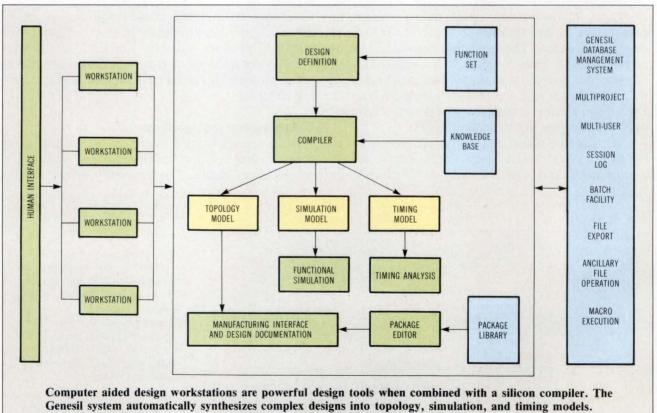

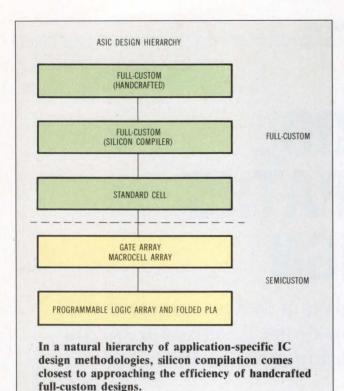

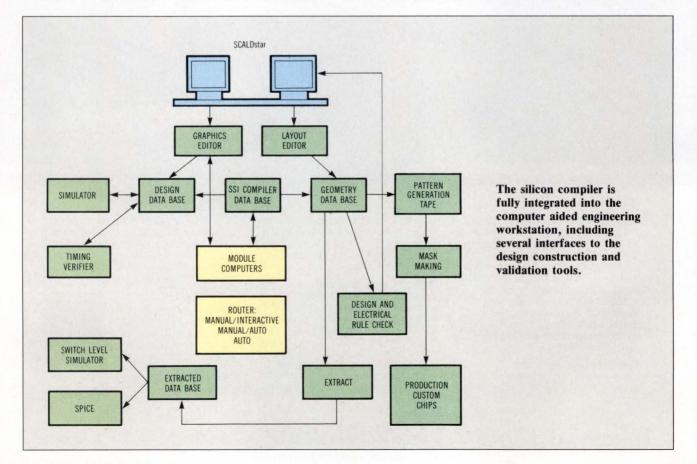

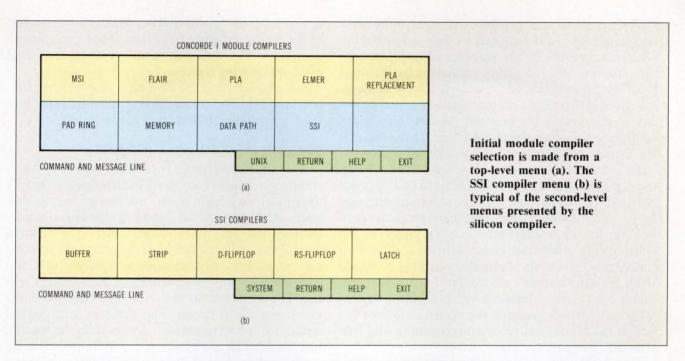

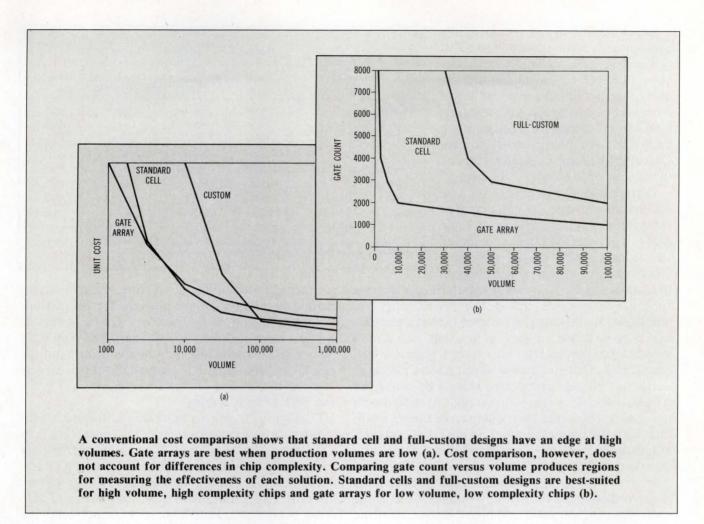

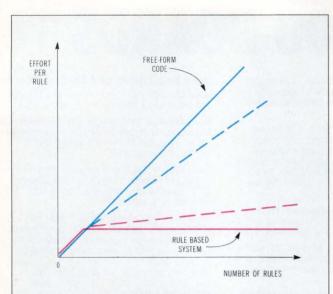

- **89** Application-specific ICs will account for the majority of chips going into production during the next few years. Their rapid acceptance has come about because computer aided engineering and design tools have become more capable, lower in price, and more widely available. But new approaches, such as silicon compilation, will accelerate the growth of ASICs even more by allowing system designers—without the chip-level knowledge of silicon gurus—to turn their ideas into silicon.

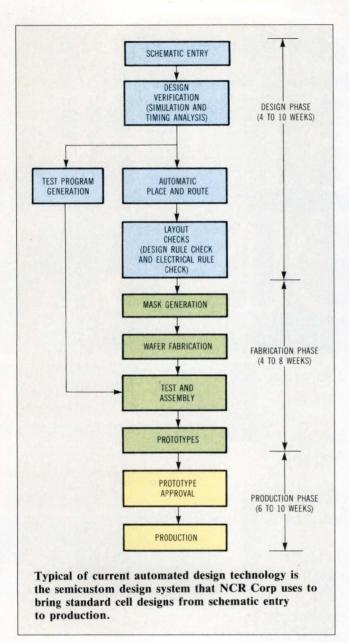

- **91** Design tools pace custom/semicustom IC development The penetration of application-specific ICs into systems depends on the availability of design tools that eliminate a designer's need to know the intricacies of silicon technology.

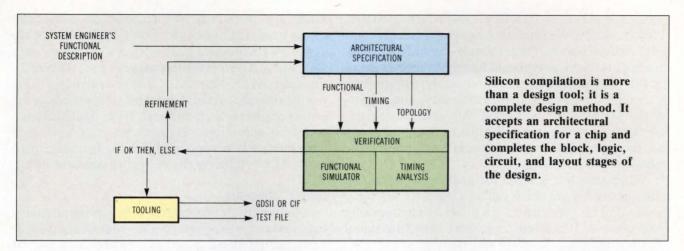

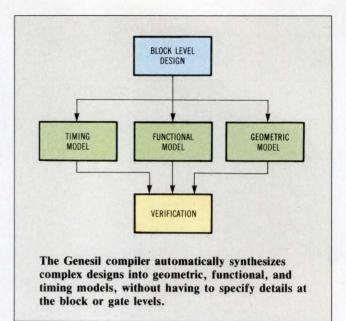

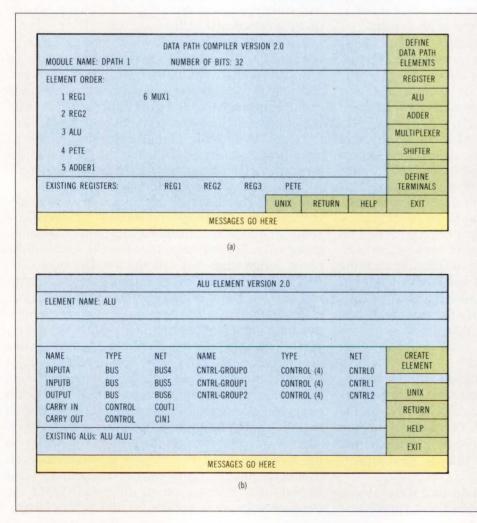

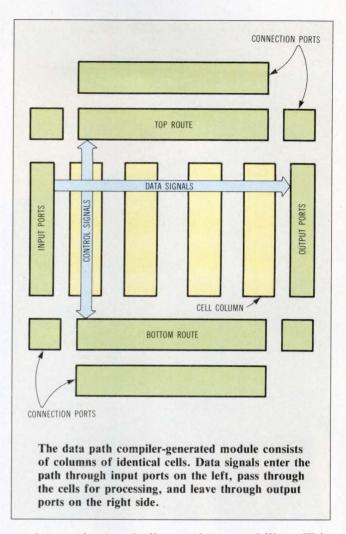

- **105** Silicon compilation speeds design of complex chips Silicon compilation creates a full-custom circuit with the silicon efficiency of a handcrafted design, but with fewer resources and a shorter development cycle.

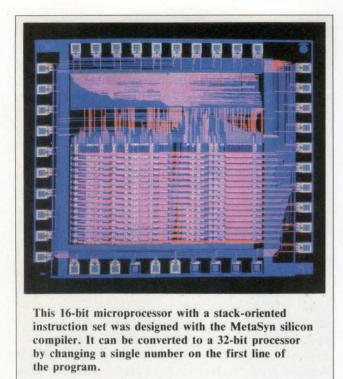

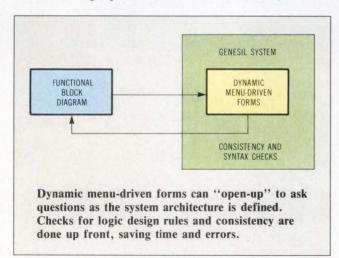

- **115 Top-down tool opens new paths to chip design** Silicon compilation software gives a system engineer with no chip design experience a top-down design tool for the development of CMOS application-specific ICs.

- **125** Converting gate array designs to standard cells With the freedom to easily and inexpensively transform a gate array into a standard cell, designers can delay decision-making and improve production efficiency.

| 23 | Memory systems:<br>Optical disks promise massive storage                        |

|----|---------------------------------------------------------------------------------|

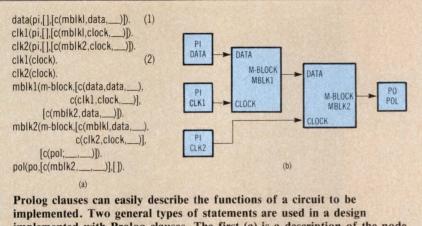

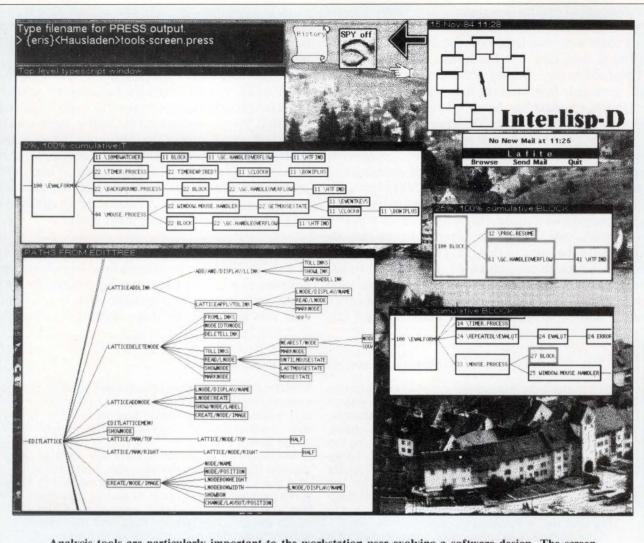

| 33 | Integrated circuits:<br>AI techniques aim to ease VLSI design                   |

| 39 | Software:<br>Unix interface standard on the way                                 |

| 59 | Control & automation: Page 80                                                   |

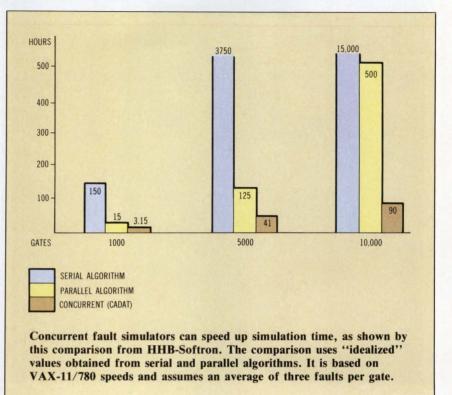

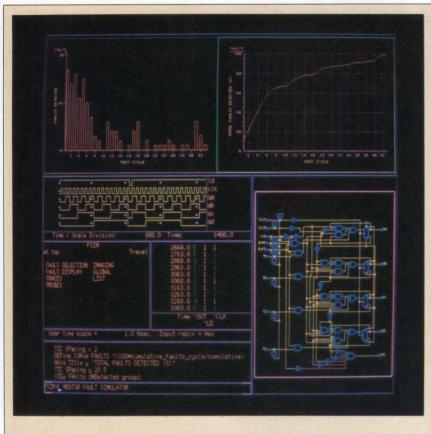

| 71 | Test & development:<br>Fault simulation becomes design verification tool        |

| 80 | Software:<br>Applications dominate Computer Graphics '85                        |

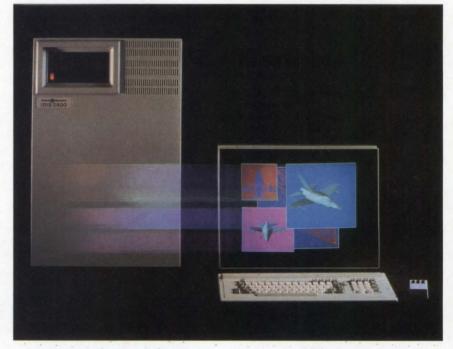

| 84 | Computers: Page 71<br>Electro celebrates anniversary with a glimpse at tomorrow |

|    |                                                                                 |

|    |                                                                                 |

Vol 24, No. 3

March 1985

#### SYSTEM DESIGN

- **133** Software: **Programming the uncertain with exploratory systems** Artificial intelligence development systems are ideally suited to the coding of complex programs because they can cope with the uncertainty that is often present.

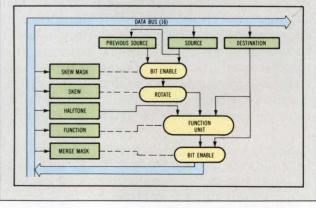

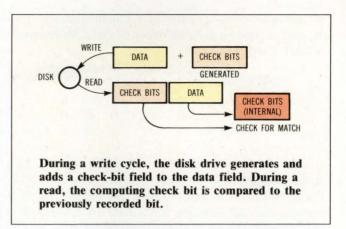

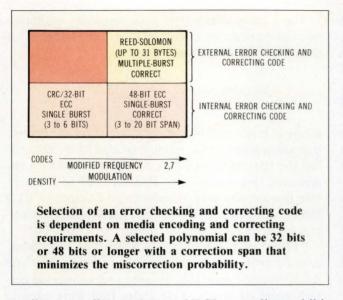

- 147 Integrated circuits: Disk system ICs combat data errors Disk drive controller ICs that implement advanced and flexible error correction techniques require little development work by the designer, yet provide powerful methods of coping with hard errors in disk drives.

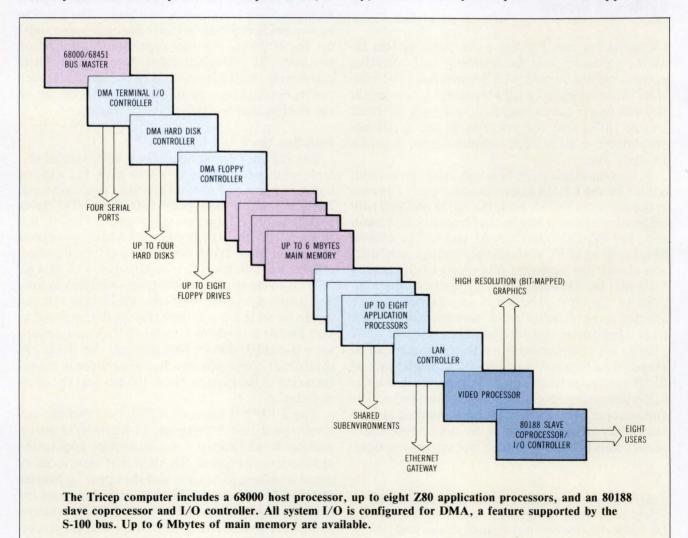

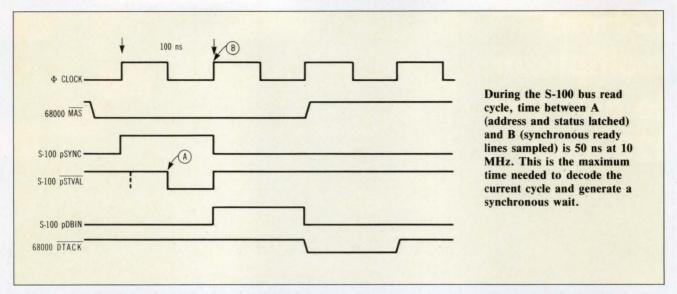

- **161** Computers: S-100 bus adapted to 68000-based Unix computer Although the S-100 bus poses some challenges to system designers, it provides adequate memory support for a multi-user Unix computer and permits multiple DMA devices.

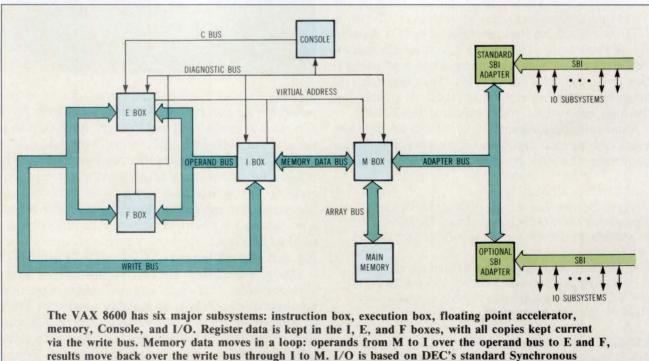

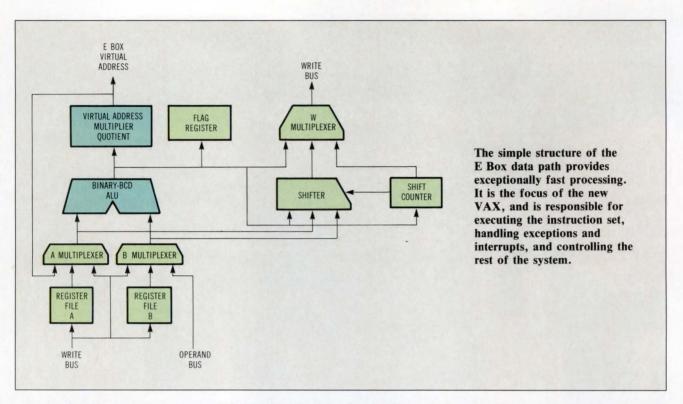

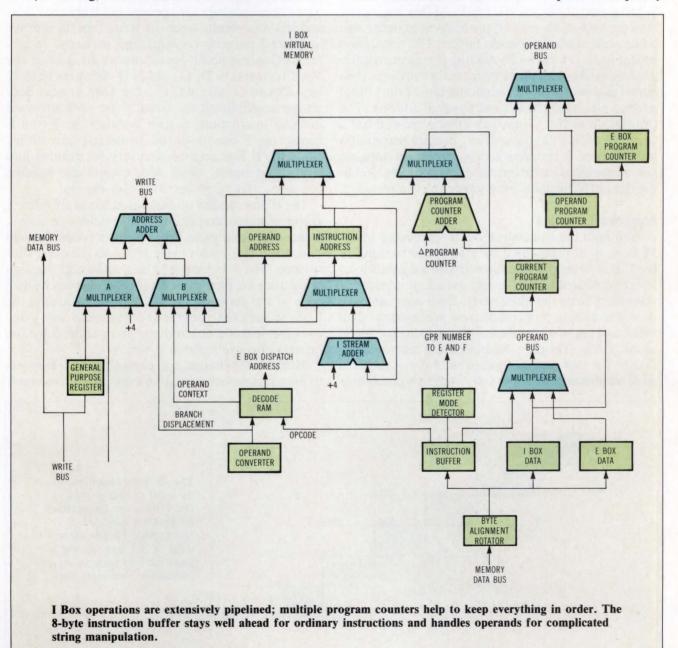

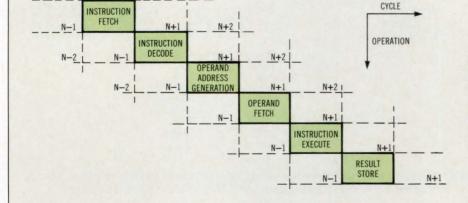

- **173** Computers: New VAX squeezes mainframe power into mini package While retaining features common to the 32-bit VAX family, the 8600 uses large-scale processing concepts that include a dedicated memory bus and pipelined operations in both instruction processing and memory references.

- **183** Test & development: **Debugger alleviates realtime programming complications** Realtime systems using microprocessors present special problems in debugging. A debugger specifically tailored to deal with concurrency can provide more reliable code for systems that must deal with the real world.

| DEPARTMENTS                                                                         | SYSTEM COMPONENTS                                                                          |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 7 Up front<br>13 Editorial                                                          | <b>193 Integrated circuits:</b><br>Floating point unit executes to<br>80 bits of precision |

| <ol> <li>17 Literature</li> <li>19 Market forecasts</li> <li>20 Calendar</li> </ol> | 194 Computers:<br>Enhanced array processor peaks<br>at 38 MFLOPS Page 196                  |

| 21 Designer's bookcase                                                              | 194 Memory systems:<br>MiniWinchester supplies top-level performance                       |

| 22 System showcase<br>24 Advertisers' index                                         | <b>196 Test &amp; development:</b><br>Geometry engine powers design workstation            |

| <ul><li>26 Recruitment</li><li>29 Reader inquiry card</li></ul>                     | <b>198 Test &amp; development:</b><br>Graphics controllers tout large display-list memory  |

| 29 Change of address card                                                           | <b>198 Computers:</b><br>Supermini employs ECL and pipelining for 32-bit computations      |

|                                                                                     | <b>199 Integrated circuits:</b><br>CMOS chip breathes new life into byte-wide processing   |

## MICROVAX I LETS YOU START SMALL IN A VERY BIG WAY.

All supermicros let you start out small. Most run into problems, however, when your applications start getting big.

That's why Digital's Micro-VAX I™ supermicro is such an intelligent solution. It limits your risk – not your capabilities.

For starters, MicroVAX I is a member of the VAX<sup>™</sup> systems family; it provides a full set of VAX resources. That's saying a lot, because VAX systems are the industry standard for 32-bit computing.

MicroVMS<sup>™</sup> our VMS<sup>™</sup> operating system for MicroVAX, lets you develop applications for any VAX using the comprehensive set of proven development tools provided by the VAX computing environment.

You get all the VMS editors, debuggers, database managers, screen managers, utilities and communications options. You can use advanced VMS languages – including Pascal, FORTRAN, C, Bliss, COBOL and Ada.<sup>®</sup> And through the VMS common calling standard, you can combine routines written in different languages within the same program.

This software sophistication lets you cost-effectively dedicate the MicroVAX I system to highly complex tasks. In areas like proc-

© Digital Equipment Corporation 1985 Digital: the Digital logo, MicroVAX, VAX, MicroVMS, VMS, VAXcluster, PDP-11, VAXELN, MicroPDP-11, Q-bus, DECnet and ULTHX-32m are trademarks of Digital Equipment Corporation. Ada® is a trademark of Logital Equipment Corporation. Ada® is a trademark of AT&T Bell Laboratories.

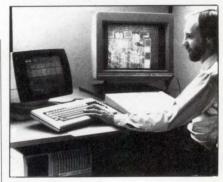

ess control, signal and image processing, CAD/CAM, mathematical simulation, seismic analysis and automatic test. There's no end to the uses for MicroVAX.

#### THE BIGGEST GROWTH PATH IN THE INDUSTRY STARTS HERE.

The sky's the limit for applications you develop on MicroVAX. They can run on every VAX in the family – including our top-of-theline VAX 8600 and VAXcluster<sup>™</sup> systems. Through upward expansion and shared resource networking, the computing power at your disposal is virtually inexhaustible. You can go from a supermicro to a mainframe-level system without changing your software. And that's an advantage no other supermicro supplier can match.

Conversely, you can download VAX applications to MicroVAX I systems. All non-privileged commands and the full VAX instruction set are supported, so your applications will run with little or no modification.

There's even VAXELN™ software, a complete Pascal-based development toolkit, that runs on VMS and MicroVMS. With VAXELN, it's easy to create dedicated realtime applications for MicroVAX and VAX systems. By leaving out the overhead, VAXELN gives you a highly efficient runtime environment.

Starting with MicroVAX I, you can grow all the way to the VAX 8600 system .....

MICRO

VAX

#### PART OF A GROWING FAMILY OF SUPERMICROS.

Our 32-bit MicroVAX I systems have a lot in common with our 16-bit Micro-PDP-11<sup>™</sup> supermicros. They all use the same Q-bus<sup>™</sup> data transfer architecture. So they all support the same peripherals.

That's a substantial benefit, because Q-bus is an industrystandard bus, with many options available from Digital and independent vendors. Hundreds of peripheral products are available to make your MicroVAX configurations complete.

Commonality between MicroVAX I and MicroPDP-11 systems is also maintained in file structure, communications options, languages and even many applications. All of which expands your options and provides unlimited opportunities for growth.

#### DECNET, YOUR UNIVERSAL NETWORKING STRATEGY.

When you're ready to distribute your applications via MicroVAX I systems, DECnet™ software makes it easy. MicroVAX supports DECnet to give you a complete set of local and wide area networking facilities. Your options include local communications via

V/AX

our implementation of the most advanced level of the Ethernet local area network available today. And wide area com-

munications via dial up or leased lines, or public packet-switched X.25 networks. Further, you can establish these local and remote systems links transparently to the user and the program.

Digital's networking facilities also let you take advantage of the computing resources of non-Digital systems. The extensive selection of standard protocols

#### ULTRIX, YOUR TRANSPORTABLE OPERATING SYSTEM.

If you need UNIX<sup>®</sup> software capabilities, our MicroVAX I system can readily provide them. It supports ULTRIX-32m<sup>™</sup> software, our enhanced, fully supported UNIX software for MicroVAX.

ULTRIX-32m includes all Berkeley 4.2 features, in addition to Digital's enhancements that simplify error reporting and recovery.

available to you with the Micro-

3780, 3271, X.25 and SNA, All

mented not just at the hardware

So if you want to start small,

VAX I system includes 2780/

these facilities are fully imple-

level, but through software

as well.

ULTRIX-32m applications can run throughout the VAX family. Our PDP-11™ and MicroPDP-11 systems families also support a version of ULTRIX software. And that lets you extend a single application across a vast range of systems. You can go from lowcost MicroPDP-11/23 and MicroVAX I systems all the way to our high performance VAX 8600 systems with one, multi-purpose solution. Think how that will extend your reach in your market. start big with the MicroVAX I system. You'll get the 4-gigabyte address range, the powerful instruction sets, the incomparable development tools and vast software selection that has made our VAX systems the most popular 32-bit computers in the world. And you'll get it all with the economy and convenience of a supermicro package.

#### BEST ENGINEERED MEANS ENGINEERED TO A PLAN.

Our MicroVAX I supermicro, like all Digital hardware and software products, is engineered to conform to an overall computing strategy. This means our systems are engineered to work together easily and expand economically. Only Digital provides you with a single, integrated computing strategy, from chips to 32-bit VAX systems and direct from desktop to data center.

If you believe that your company could benefit from our very growth-oriented MicroVAX I system, contact your nearest Digital sales office or a Digital Authorized Industrial Distributor. Or call: 1-800-DIGITAL, ext. 230.

#### THE BEST ENGINEERED COMPUTERS IN THE WORLD.

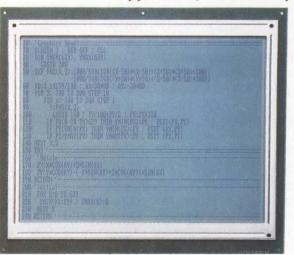

or very LL 4q0write(ca\$conn,0('-'),1,0status); LL 8SB(0,0khaffer,size(khuffer)); ctual = dq\$read(c1\$conn,0khuffer,size(khuffer),0status); adax = 0; WHILE khuffer(kindux) = ' '; kindex = kindex + 1; 0; ndex = 0; ese\$incomplete = true; 4HILE pares\$incomplete; har = khuffer(cinduxtkindux); if Class := x') MH0 (char < 'z') THEN char = char - 200; bf FINDD(@valc,char,size(valc)) (> 8fffh THEN b; b = b; b

command(cindex+1) = char cindex = cindex + 1;

SE parse\$incomplete = false; f cindex = size(command) THEM parse\$incomplete = false;

cindex = 8 THEN GOTO mext\$input; ccommand(1) = 'E') AND (ccommand(2) = 'X') AND (ccommand(3) = 'I') AND (ccomm n Block Bulata Evenue 5tat = find Cent == more==

> TCS has erroneously used the Intel trademark\*BMX\*to describe or nume some of a products. All RTCS products that use that trademark now use "RTX" instead IS DOS is a trademark of Microsoft, Inc. COSM and BMPC are trademarks of BMM Inc.

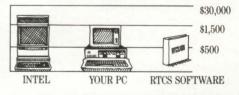

Extend the capabilities of your PC/MS-DOS™ based system and duplicate the Intel<sup>™</sup> Series III, IV, and 86/310 with RTCS software development tools.

Don't buy expensive hardware to get the exact same professional development capabilities. For around \$500, the RTCS/UDI Universal Development Interface software lets you use Intel Series III Microcomputer Development System software, available from RTCS, on your IBM PC<sup>™</sup> or any other MS-DOS-based computer. And Intel software runs up to 20% faster on your PC using the RTCS/UDI.

### DID YOU KNOW YOU'RE ALREADY SITTING ON A \$30,000 INTEL SYSTEM?

PC RTR

Fortune 500 companies like IBM, General Electric, Honeywell, and over 1,500 others have found the RTCS/UDI easier to use with higher performance than most Intel systems. Besides the obvious expenditure comparison, they see Intel Systems as

special purpose computers with limited software. But with RTCS, a PC/MS-DOS-based computer becomes a reliable performer with a wide repertoire of software possibilities.

Also available from RTCS is PC/RTX, Real-Time, Multi-user Multi-tasking Operating System for IBM PC and others; Intel languages such as Pascal, Fortran, PL/M,<sup>™</sup> and C Compilers; Utilities such as high level software debuggers, as well as a wide range of software support supplied with the RTCS/UDI at no additional cost.

Before you go out and buy expensive hardware for capabilities you're already sitting on, call RTCS today. **(805) 987-9781**

Getting the most from what you have.

1390 Flynn Road, Camarillo, CA 93010 Telex: 467897 RTCS CI CIRCLE 4

## **UP FRONT**

#### IBM unveils Sierra...

IBM has announced its "Sierra" 3090 series of advanced mainframe computers amid criticism of the machines' performance and delivery dates. The first model of the 3090 series will not be available until November. That version, the model 200, nearly doubles the capabilities of the 308XX series, IBM's current top-of-the-line mainframe. The model 400, offering twice the performance of the 200, will not be available until the second quarter of 1987. Competitors were cheered by the long lead time of IBM's announcement. "We're confident that our price and performance are still very competitive," said an Amdahl representative. He pointed out that Amdahl's 580 series currently outperforms the best IBM has to offer, but its performance will be about 20 percent below that of the 200. Amdahl's 5880 performs about 24 million instructions per second, while the 308XX series tops out about 16 MIPS. Industry estimates place the IBM models 200 and 400 about 28 and 50 MIPS, respectively. IBM's new models are priced consistently with its previous mainframes, costing about \$200,000 per MIPS. Anticipating shipment of the new model. IBM lowered the price on its 380XX series about five percent. Soon after, Amdahl countered with a similar reduction in the price of its 580 series. -W.E.S.

#### ... and switches to Unix System V

IBM surprised many when it switched its support from Unix System III to System V for both its mainframes and personal computers. The recent announcement marked the first time IBM had endorsed a competitor's operating system for its mainframe computers, and indicated a change in strategy for its desktop machines. PC/IX, the XT version of Unix, was modeled after Unix System III, but is being adapted to System V. Microsoft's Xenix, another XT/AT version of Unix, is likewise being modified for System V compatibility.—W.E.S.

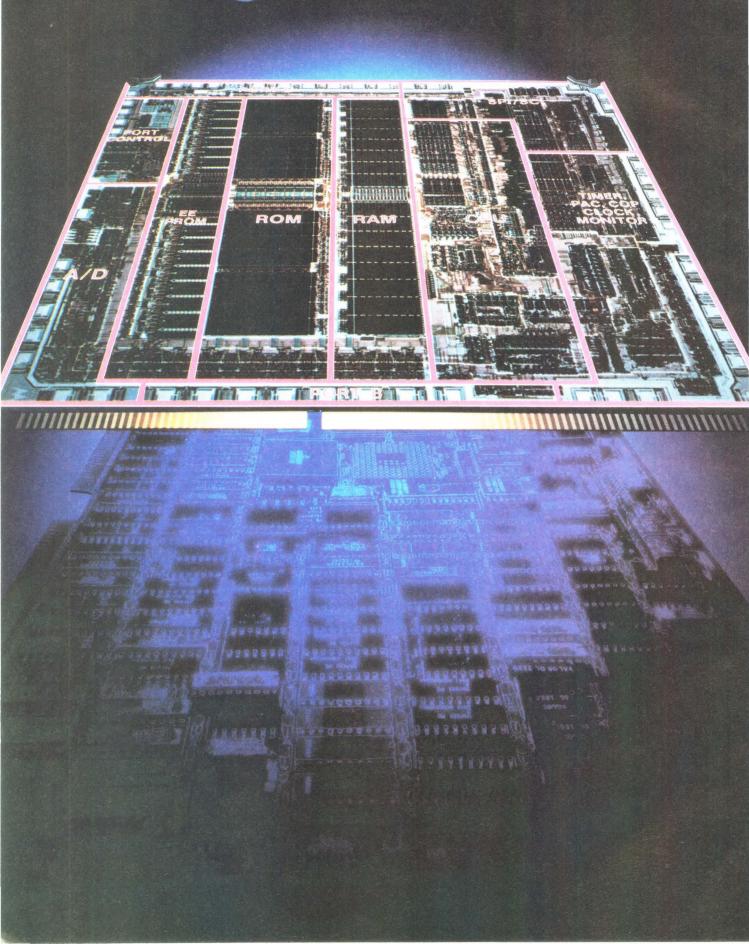

#### Bit-slice processors will join standard cell libraries

CMOS bit-slice processors will become standard entries in at least two semicustom IC libraries within the next six months. Both General Electric's Semiconductor Div of Research Triangle Park. NC and RCA Solid State of Somerville, NJ plan to offer 2900 family bit slices in 2-micron CMOS technology as core cells on semicustom chips. These can be enhanced with peripheral circuits to form custom single-chip microcomputers. The CMOS versions of the 2900 series should run at speeds comparable to their bipolar counterparts, but with a mere 10 percent of the bipolars' power requirements. "We chose bit slices instead of 8086-type processors to allow the user maximum area for expansion around the core processor," explains Chuck Gregory, research and development engineering manager of GE's custom IC department. GE's 2901 and 2910 will be silicon in June. RCA's semicustom bit-slice core processor will be based on its GPU 6502 bit-slice family. Scheduled for release this fall, RCA's semicustom chip will comprise up to four subchips, each individually configured for the desired peripheral circuits.—N.M.

(continued on page 8)

#### **UP FRONT**

(continued from page 7)

#### **Program models IC dopant behavior**

Researchers now have a way to predict the effects of introducing boron, arsenic, and phosphorus into a two-lavered silicon structure. Aptly named Predict, this VAX-based software from the Microelectronics Center of North Carolina (Research Triangle Park, NC) solves coupled equations describing dopant behavior and oxide growth without the need to fine-tune default parameters for each process. The designer need not specify the silicon layer's thickness or the grid spacing. Predict selects the minimum grid spacing that will work with its algorithm. The program produces data on the thickness of the oxide layer resulting from each processing step, plus the sheet resistances of the n and p regions. Included in the printout are the chemical and electrical concentration versus depth for the various impurities. With a grid spacing of 0.01 to 0.03 microns and the maximum number of grid points preset to 200, the useful depth of the silicon layer is between 2 and 6 microns. "The process designer is assured the accuracy of the process results without performing hundreds of simulations or running experimental wafers," says Richard Fair, MCNC's vice president of research program management. MCNC plans to license the program to universities for the cost of the tape, and will soon market it to industry. -N.M.

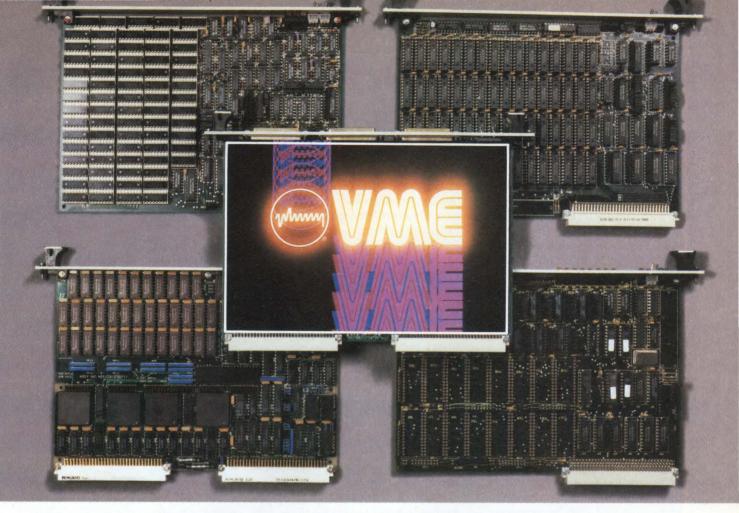

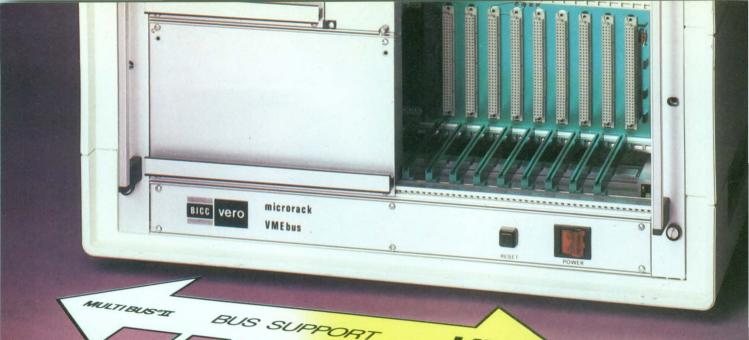

#### Vendors cautious about Multibus II

Multibus vendors took a wait-and-see stance after Intel's long-awaited introduction of the first Multibus II boards at Mini/Micro West. Already two years behind the introduction of the VMEbus products, 32-bit Multibus II has some catching up to do. The question is whether or not there is still a need for Multibus II. Multibus I suppliers, such as Scientific Micro Systems (Mountain View, Calif) Central Data Corporation (Champlaign, Ill) and Xylogics (Burlington, Mass), are watching the market before plunging in. "Multibus II will be very successful, but it's running late," says Michael Kalashian, marketing director for Scientific Micro Systems. "VME is a bit more real right now." Nevertheless, John Beaston, marketing manager for Intel's Multibus II division in Hillsboro, Ore, remains optimistic. "I think you'll see them move away from their wait-and-see attitude in a couple of months," he predicts. -R.G.

#### AI expert calls for national effort to develop superchips

Artificial intelligence applications will require hundreds of billion-gate superchips by the turn of the century, according to Professor Raj Reddy of Carnegie Mellon University, Pittsburgh, Pa. "Designers must have per-use access to a national facility holding a proprietary data base of hardware and software designs," says Reddy, this year's keynote speaker at New York's International Solid State Circuits Conference. Reddy claims this facility will reduce design duplication so superchips can be designed faster. Furthermore, says Reddy, companies and universities should pool their resources to meet the large computational requirements of AI.—N.M.

(continued on page 10)

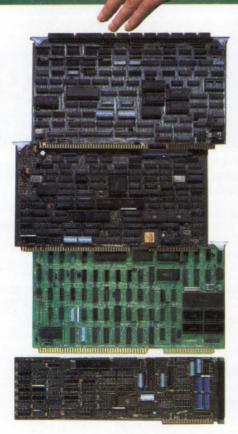

For nearly two decades, Dataram has been leading the way in memory technology, supplying more memory than any other company to leading minicomputer manufacturers, end users, systems houses, OEMs and others throughout the world.

Experience that translates into superior design and reliable performance for you today. That means more for you — more capacity, more capability, more reliability, and more performance with more savings...so you can get more from your minicomputer.

Want to learn more? Contact Dataram at (609) 799-0071 today.

## for DEC users

- VAX 11/780 Series Compatible

- 4.0 MB with ECC

- Socketed DRAMs

- Spare DRAM on Board

- Low Cost

- System Expansion to 64 MB in a Single Cabinet

- Q-Bus Compatible

- 2.0 MB

- 85 nsec Access Time

- Block Mode DMA

- Dual Board

- On-Board CSR

- Full-Function Parity

Dataram satisfies all your VAX, Q-Bus, and UNIBUS memory requirements.

## DATARAM

Dataram Corporation D Princeton Road Cranbury, New Jersey 08512 (609) 799-0071 TWX: 510-685-2542

#### **UP FRONT**

(continued from page 8)

#### Macro LSI cells integrate simple standard cells

Harris Semiconductor is shifting its semicustom approach to combine its standard cells into macro LSI cells, offering these larger chips as part of the standard cell library. Harris's Melbourne, Fla design center will offer the designer a line of 80C86-family peripheral parts as building blocks for integrating several functions on a single chip. "The current required to drive external capacitance loads drops significantly in a semicustom design because most of the I/O interfacing is done internally," says J.W. Scherer, marketing director for the semicustom product line. A typical discrete configuration of an interval timer, parallel I/O, FIFO, UART, control logic, priority interrupt controller, and oscillator requires 202 pins. The semicustom equivalent requires 84. Three of the currently available blocks exceed 2000 gates. Typical circuit densities reach the equivalent of 7000 two-input NAND gates. Harris is using the same scaled SAJI IV CMOS process it uses for its standard RAM, 80C86, 80C88, and peripheral chips to produce the semicustom LSI cells. This gives the chips a minimum feature size of 2 microns. The designer can easily mix and match the macro LSI parts with simpler cells to create full custom systems. -N.M.

#### Honeywell challenges lead in factory automation

Manufacturing automation will be a major factor in Honeywell's future, according to chairman and CEO Edson Spencer. Spencer claims the company expects to be a leading supplier of integrated information and control systems for manufacturing automation by the end of the decade. Honeywell will target segments of a market that will reach \$50 billion by 1990 and near \$100 billion by 1995. The company's current products include a plant management system and a supervisory work center. A system for distributed manufacturing control should be ready late in the year. Eventually, Honeywell plans to introduce a universal controller that will interface programmable controllers and process controllers. The plant network will be Ethernet-based initially, but will support the General Motors Manufacturing Automation Protocol when standards are better defined.—*S.F.S.*

#### Semiconductor market growth to continue

Contrary to many economists' predictions of a recession in the semiconductor industry, at least one major market research firm believes 1984's upward trend will continue into 1985. Integrated Circuit Engineering of Scottsdale, Ariz anticipates 11 percent worldwide growth in semiconductor trade. That would be an increase from \$32 billion in 1984 to \$35.63 billion in 1985. ICE's long-term forecast includes a recessionary period from 1986 to 1987, but that would not keep the industry from reaching \$90 billion by 1990, ICE believes.—N.M.

COMPUTER DESIGN© 1985 (ISSN-0010-4566) is published monthly by PennWell Publishing Company, Advanced Technology Group, 119 Russell St., Littleton, MA 01460. Second-class postage paid at Littleton, MA 01460 and additional mailing offices. COMPUTER DESIGN is distributed without charge to U.S. and W. Europe-based engineers and engineering managers responsible for computer-based equipment and systems design. Subscription rate for others is \$600 in U.S.A. and \$85 elsewhere. Single-copy price is \$6.00 in U.S.A. and \$8.50 elsewhere. Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Rd., Ann Arbor, MI 48106. Officers of PennWell Publishing Company, 1421 S. Sheridan, Tulsa, OK 74101; P. C. Lauinger, Chairman; Philip C. Lauinger, Jr., President; Joseph A. Wolking, Executive Vice President; H. Mason Fackert, Carl J. Lawrence, Group Vice Presidents; L. John Ford, Vice President; V. John Maney, Vice President/Finance.

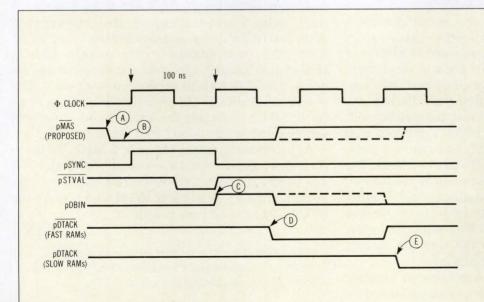

COMPUTER DESIGN is a registered trademark. All rights reserved. No materials may be reprinted without permission. Phone (617) 486-9501.

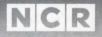

## HIGHER INTELLIGENCE

Could your Discover the develop-

design projects use help from a higher source? newest generation of intelligent microprocessor ment equipment from ZAX Corporation.

ZAX intro-development duces the first, true 32-bit universal microprocessor system featuring ZAX ICD-series in-circuit emula-tors and DIGITAL'S MicroVAX I<sup>™</sup> super-microcomputer. The ZAX/VAX connec-tion delivers the highest level of power and flexibility by offering professional development systems and software integration products which support both multi-processor and multi-user capabilities, while maintaining full compatibility with larger VAX/VMS computer systems.

To find out more about how to THRUST your design projects to new heights, call the leader in microprocessor development systems -

ZAX Corporation • 800/421-0982 • 714/474-1170

Zax Corporation 2572 White Road, Irvine, California 92714 (714) 474-1170 • 800-421-0982 • TLX 183829

Gould...Innovation and Quality in Real-time Systems

## **THE FIREBREATHERS.** Leaders since the beginning of Real-time.

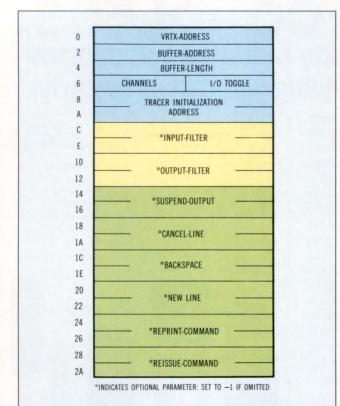

Legends have a way of being based on fact. Gould Firebreathers are legendary in the land of Real-time and our leadership and superiority are no myth.

Gould ignited the Real-time fire two decades ago. Since then, scientific and industrial computer users have been hot on Gould. In the simulation, energy, oil and gas, laboratory and computational markets, Gould Firebreathers are the choice of virtually all the leading companies that implement Real-time systems.

Gould had the first Real-time minicomputer in 1965. We again brought sophisticated Real-time users out of the Dark Ages with the first 32-bit Real-time mini in 1969 and the first supermini in 1975. And we're still the leader in superminicomputer performance. When it works and it's proven, history does repeat itself. Be a part of history in the making. Bring Gould into your Real-time realm. Firebreathing power from the beginning, for today...and tomorrow.

#### Gould Inc., Computer Systems Division, 6901 West Sunrise Boulevard, Fort Lauderdale, FL 33313 1-800-327-9716.

## **TWO NEAL AWARDS FOR OUR EDITORS**

According to a popular but scientifically invalid cliche, lightning never strikes twice in the same place. Similarly, people in the business trade press have long held the view that winning two Jesse H. Neal Awards for editorial achievement in the same year is virtually impossible. These prestigious awards, presented by the American Business Press association, are often characterized as the "Pulitzer Prize of the business press." I am pleased to be able to announce, therefore, that the editors of *Computer Design* have just defied the odds and captured two Neal Awards

for articles published last year.

To put this achievement into perspective, I should point out that this year marks the first time Computer Design has won a Neal Award. Also, as far as we can determine, none of the magazines against which we compete has ever won two first place Neal Awards in a single vear-although some of them have won pairs of Certificates of Merit, or runnerup awards. Our awards were for best series of analysis articles (from our September 1984 issue on "Future Computers: System Design Beyond 1984") and best staff-written editorial (for "The Computer Illiteracy Threat," published in February 1984). The editors honored for the analysis articles were Nicolas Mokhoff (Issue Editor), Harvey Hindin (Special Features Editor), John Bond (Senior Editor), Michael Elphick (Editor in Chief), Sydney Shapiro (Managing Editor), and Leslie Ann Wheeler (Assis-

tant Managing Editor). In addition, Elphick and Wheeler received awards for the signed editorial. The editors received their awards at a luncheon in New York City on February 28.

Of course, while winning two Neal Awards in the same year is a long-shot bet, it is by no means the random event implied by the formidable odds. It has more to do with skill than luck. Or, as professional golfer Lee Trevino once said, "Sure, it's a game of luck, but I find the more I practice the luckier I get."

Certainly, the editors of *Computer Design* have worked hard at their game for the past few years. Based on solid research of both the technology they cover and of your specific information needs, they have steadily improved the magazine's content and presentation. The improvements have been measured not only in readership studies but also in less prestigious but nonetheless important technical writing competitions. For example, the competition organized by the Boston Chapter of the Society for Technical Communication has allowed us to measure our progress each year in terms of the number of awards received, whereas if we had merely looked at our failure to win Neal Awards in earlier years, we might have become discouraged. In the local STC competition, we steadily won more and more awards each year—this year we had nine awardwinning entries, including three awards of Excellence (first

prize) and three awards of Distinction (second prize).

Credit for our achievements has to go to many more people beyond the awardwinning editors. The management of PennWell Publishing, both at our parent company in Tulsa, Oklahoma, and at our Advanced Technology Group in Littleton, Massachusetts, has demonstrated a continuing commitment to editorial excellence and has never asked us to sacrifice quality for short-term profit. Other editors who did not win Neal Awards nevertheless made equal contributions. Immediately after the awardwinning September issue last year, we published two issues in October. So some editors, such as Peg Killmon in Littleton, and Tom Williams in Sunnyvale, California, were asked to concentrate their efforts on subsequent issues. And, of course, a supporting cast of associate editors, field editors, copy editors,

artists, and production people rounded out our efforts on each issue.

Finally, we owe a lot to you, our readers. Without you, this magazine could not exist. More importantly, however, your escalating needs for vital information have pushed us to increasingly higher levels of performance. One major criterion by which Neal Award entries are judged is the service to the reader and to the field covered by the magazine. The judges thought we served you well. We hope you agree.

mild left

Michael S. Elphick Editor in Chief

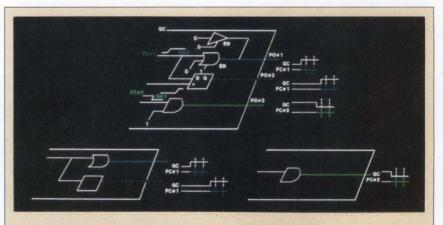

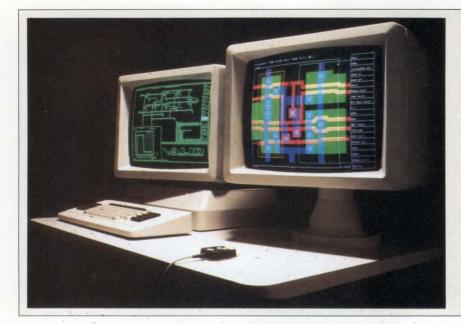

## In semicustom CAE, only Mentor Graphics knows how to get around the block.

If you're responsible for logic design, chances are that silicon implementation is not near and dear to your heart.

But *somebody*'s got to do it, right? Wrong.

If you're working with standard cells or gate arrays, there is now a CAE system that can do it for you.

The IDEA Series<sup>™</sup> from Mentor Graphics.

The impact on your productivity? Just short of staggering. Months of layout work compressed into hours. 98 to 100

per cent of the layout task completed without human intervention.

At the heart of this landmark achievement are automatic placement and automatic routing algorithms unique to Mentor Graphics.

No one does it better. Or faster.

Imagine. A 2400-gate design placed and routed in just 3 hours, 15 minutes. Completely and automatically. With 95% gate utilization.

Even after the routing and placement puzzle is solved, Mentor Graphics superior intelligence stays with you. Every move you make during cleanup work is monitored by the system to ensure you stick to the layout rules. You're even presented with legal alternatives to head off mistakes before you make them.

And to top it off, the wire delay values produced during the layout can be back-annotated into the original logic design for super-accurate simulations.

Consider the big picture, too. With the IDEA Series, you have a complete set of integrated engineering tools that come into play long before layout. A fully integrated path all the way from schematic entry to simulation to layout to prototype verification.

You design faster, better and less expensively.

It's all part of a vision unique to Mentor Graphics, the technological leader in Computer-Aided Engineering. Let us show you where this vision can take you.

Call us toll-free for an overview brochure and the number of your nearest sales office.

Phone **800-547-7390** (In Oregon call 284-7357).

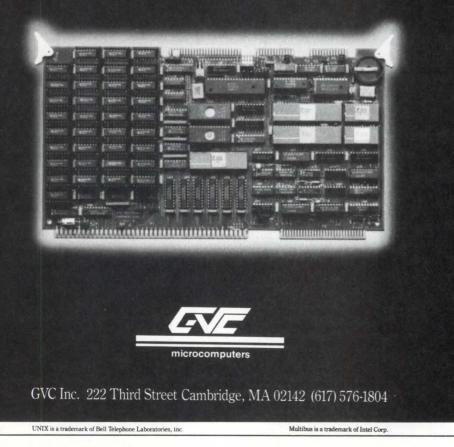

### GVC-16 COMPLETE UNIX SUPPORT ON A SINGLE MULTIBUS BOARD

With the GVC-16 all the resources needed for a complete multi-user virtual memory UNIX system are contained on a single Multibus board. Perfect as the heart of a workstation product, the GVC-16 includes:

- National Semiconductor 32016 CPU with full 32-bit internal operation.

- 512kb-2 Megabyte on board no- wait state Dual Port RAM.

- Available Floating Point Unit— 32 bit floating point multiply in less than 5 µsec.

- Winchester Disk Interface.

- Four serial (RS-232) Ports.

- Berkeley 4.1 UNIX available.

Priced at \$1975. (OEM qty.), the GVC-16 is available from stock.

Also available:

GVC-16 system—a complete 4 user UNIX box with 1 Megabyte of memory, 40 Megabyte disk storage, 4 slot Multibus back plane and UNIX software. \$9,990 (qty. 1).

### **COMPUTER DESIGN**

*Editorial/Executive Offices:* The PennWell Building, Littleton, MA 01460, Tel: (617) 486-9501

Editor in Chief, Michael S. Elphick

Executive Editor, John Miklosz Managing Editor, Sydney F. Shapiro Assistant Managing Editor, Leslie Ann Wheeler Art Director, Emilie Whitcomb Senior Editor, John Bond Senior Editor, Peg Killmon Senior Editor, William E. Suvdam, Jr. Senior Associate Editor. Malinda E. Banash Associate Editor, Jack Vaughan Copy Editors. Helen McElwee, Nancy E. Purcell, Leah A. Rappaport, Ann Marie Tisevich Editorial Assistants, Vickie Frechette, Susan M. Wheatley Special Features Editor, James W. Hughes Consulting Editor, Saul B. Dinman New York Field Office: 120 Mineola Blvd, Suite 510, Mineola, NY 11501, Tel: (516) 741-4780 Senior Editor, Nicolas Mokhoff Special Features Editor, Harvey J. Hindin Western Field Office: 540 Weddell Dr, Suite 8 Sunnyvale, CA 94089, Tel: (408) 745-0715 West Coast Managing Editor, Tom Williams Senior Editor, Bill W. Furlow Field Editor, Richard Goering Editorial Assistant, Robin L. Weatherwax Production Director, Linda M. Wright Production Manager, Philip Korn Production Assistant, Elizabeth Mogren Staff Artist, Jay Gordon Technical Art, Designline Ad Traffic Coordinator, Debra L. Stone Printing Services, Padraic Wagoner National Sales Manager, Frederick A. Stanley Circulation Director, Robert P. Dromgoole Business Development Manager, Leslie Ringe Promotion Director, Steve Fedor Marketing Services Coordinator, Linda J. Battle Publisher, Frederic H. Landmann ennWell

Advanced Technology Group 119 Russell St, Littleton, MA 01460 Tel: (617) 486-9501

H. Mason Fackert, Group Vice President Daniel R. Campbell, Vice Pres. Admin. Kirk S. Campbell, Finance Director John M. Abernathy, MIS/DP Director Patricia M. Armstrong, Admin. Services Mgr.

### Microprocessor programming made simple.

"Keep it simple" was the principle of the 14th Century English philosopher William of Occam and it has even more validity today. Faced with the problems of sophisticated computer systems, designers have found that ever more complex programming languages are further complicating their tasks. Until now.

### Occam. Created for system design and implementation.

When we started designing our new VLSI family of 10-MIP transputers, we built on William's simple philosophy. To take advantage of the possibilities opened up by the transputer, we needed to create a language capable of properly addressing parallelism and multiprocessor systems.

With the ability to describe concurrency (whether timeshared or real) and to handle messagepassing at the lowest level of the language, all aspects of a system can be described, designed and implemented in occam. From interrupt handling through signal processing to screen editors to artificial intelligence. And on.

But occam is not limited to our

transputer family. It provides an efficient, responsive implementation language for systems built on today's microprocessors. It also opens up future possibilities with its performance-enhancing multiprocessor capabilities. And INMOS now offers a product to let you exploit occam's total capability in your system.

### Simplify your job with the Occam Programming System.

The Occam Programming System (OPS) gives you the tools for complete VAX / VMS software development. This package includes an integrated editor / checker, an optimizing VAX compiler and full documentation. This gives you a supportive environment for the development of occam programs

What's more, the occam programs developed and proven on the OPS will give you a head start for work with the INMOS transputer. Extensions to the OPS will be available which will allow occam programs to run on the transputer.

And if you have a requirement to program the transputer in other popular high-level languages, other extensions will include compilers for C, Fortran, and Pascal.

#### Get started today.

Contact us for our information pack on occam, the Occam Programming System and the transputer. You'll be surprised how simple your life can be.

For quick response, call us at (303) 630-4000 or write: Occam, P.O. Box 16000, Colorado Springs, CO 80935.

inmos. and occam are trademarks of the Inmos Group of Companies

## EMULEX HAS THE CORNERSTONE FOR SYSTEM BUILDING FLEXIBILITY.

## AND, WE'VE GOT ALL THE OTHER BUILDING BLOCKS, TOO.

With Emulex's SCSI products as the cornerstone for your mini/micro computer systems, you can continue to build on your investment. Our SCSI-based products offer you convenient building blocks with which to assemble, update, mix or interchange different types of peripheral storage devices to your computer system. Couple that with the industry's widest range of advanced products and you have the single best source for your system building needs. Products with performance, quality and reliability that's unsurpassed.

#### PUT MORE INTO YOUR SYSTEMS WITH EMULEX/SCSI MICRO SUBSYSTEMS.

Compact, versatile Emulex/SCSI micro subsystems provide you a variety of cost-effective storage and backup devices. Choose the enclosure you desire—desktop, rack or tower—disk size—36, 67 or 110 MB formatted capacity—and the type of backup most meaningful to your application. Top that off with the ability to interface virtually any CPU type and you have a powerful and complete storage solution.

SABRE, combines on-line storage and file backup capability in a compact unit housing a 5¼" Winchester disk drive and an 8" removable cartridge disk.

Javelin, an extremely versatile storage system designed to satisfy

a wide range of OEM and end user applications. Space accommodations for two SCSI peripherals, either one 5¼" disk drive and one 60 MB ¼" cartridge tape streamer, or two disks.

Decathlon, available in a rack mount or an attractive tower/pedestal model, contains up to three  $5\frac{1}{4}$ " peripherals, with a choice of Winchester disks and a 60 MB  $\frac{1}{4}$ " streaming tape drive.

#### EMULEX'S HOST ADAPTERS CAN FIT SCSI INTO YOUR PLANS.

Emulex/SCSI host adapters are available for QBus and Unibus systems, IEEE 796 Multibus systems, the IBM PC/XT and PC/AT and compatibles. We've designed these host adapters to take full advantage of the versatility and high performance of the SCSI.

#### THE SCSI POTENTIAL. THERE'S PLENTY OF IT.

SCSI allows you system building ease and maximum flexibility through the use of a common I/O bus and standard peripheral interface. All Emulex/SCSI-based products feature these enhancement benefits.

| FEATURE                      | BENEFIT                                                                                                              |

|------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Arbitration                  | Permits concurrent I/O oper-<br>ations between different devices<br>by prioritizing bus usage.                       |

| Disconnect/<br>Reselect      | Maximizes bus utilization by<br>providing devices an orderly<br>scheme to release and regain<br>bus control.         |

| Сору                         | Permits data transfer between devices without host intervention.                                                     |

| Search<br>Data               | Used to search one or more<br>logical blocks for less than,<br>greater than or equal to<br>a specified data pattern. |

| Reserve/<br>Release          | Device can be reserved for exclusive use by a single host in multiple host configuration.                            |

| High Level<br>Command<br>Set | Provides host with device independence for a given type of device.                                                   |

|                              |                                                                                                                      |

### GET MORE INTO YOUR SYSTEMS WITH EMULEX/SCSI CONTROLLERS.

Our Medalist and Champion SCSI controllers can interface any ST506 or ESDI  $5\frac{1}{4}$ " Winchester disk drive. And our Titleist can interface most  $\frac{1}{4}$ " streaming tape drives.

#### EMULEX CAN FIT SCSI INTO YOUR PLANS.

If you're looking for a solid cornerstone and the widest range of building blocks to put together powerful and efficient mini/micro subsystems, then talk to Emulex.

For detailed information on Emulex/SCSI products, call toll free (800) 854-7112. In California (714) 662-5600. Or write: Emulex Corporation, 3545 Harbor Blvd., P.O. Box 6725, Costa Mesa, CA 92626.

|                | nmediate  60-120 days  Info. only  call  Quantity per year: |

|----------------|-------------------------------------------------------------|

| Specify Comput | er/Peripherals in use or planned:                           |

|                | 🗆 Multibus                                                  |

|                | Other                                                       |

|                |                                                             |

| Name           |                                                             |

|                | Phone                                                       |

|                | Phone                                                       |

| Title          | Phone                                                       |

IBM PC, XT, AT are registered trademarks of International Business Machines Corporation. QBus and Unibus are registered trademarks of Digital Equipment Corporation.

## **The Microterminal**

14 Rugged, Ready-Made Data and Control Terminals Help Systems and

Machines Work Harder, Faster, Smarter

....

A B REPORT OF A CONTRACT

## **Work Force**

- Up to 40-character alpha and numeric displays, 80-character I/O buffers

- Baud rates to 19,200

- Large, easy-to-use keypads

- Dust- and water-resistant front panels

- Mount on any flat surface

- RS-232C, RS-422, and 20mA current loop interface options

- Drop up to 63 Microterminals on one serial interface

- Up to 16 programmable function keys

- Bar code and magnetic stripe readers

- Polled and nonpolled operation

Put your machines and systems to work with Microterminals Call or write us today for complete specifications on all 14 models.

Data Acquisition and Control Systems Division P.O. Box 11400 Tucson, AZ 85734 (602) 746-1111

BURR-BROWN

Putting Technology To Work For You

**CIRCLE 11**

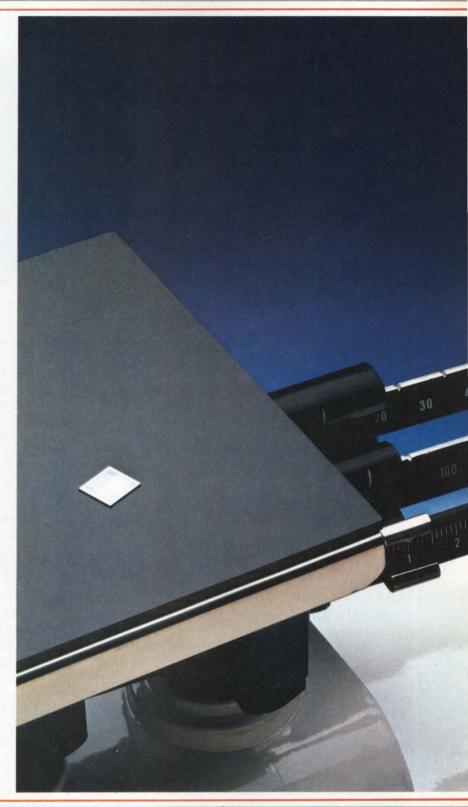

# A CRASH COURSE IN DISK AND DRIVE TESTING:

#### **Disk Testing**

ADE RVA instruments will show you how to test excessive acceleration, flatness, radial waviness, datum positioning, axial run-out and thickness.

#### Head/Assembly Testing

ADE RVA instruments give you advanced instruction on head positioning accuracy, head motion studies, dynamic flight characteristics, pitching and rolling.

ADE RVA instruments maintain quality control from design through production. Only ADE systems can measure dynamic displacements from tenths of microinches to thousandths of an inch from 0 to 50 KHz frequency response. Sign up for the ADE course (every major manufacturer of disks and drives already has).

#### Spindle Testing

Learn the nuances of testing axial and radial runouts, bearing quality, axial/radial acceleration, non-repetitive runout, radial resonance, wobble, and high frequency vibration.

#### **ADE** Corporation

77 Rowe Street Newton, MA 02166 Telephone: (617) 969-0600 Telex: 922415

#### **Optical disks promise massive storage**

Compact optical disk drives are eliminating offline data and program storage constraints. By packing gigabytes of data on easily removable media, optical drives have a significant impact as data storage peripherals.

Although optical disks supply far greater capacity than possible with current magnetic disk drives, they are slower. Nevertheless, optical disk drives are still faster than secondary storage units based on tape technology. The relative speed and capacity of optical drives, along with the technology's current write-once limitations, place these storage units in a new position as a tertiary online storage device.

Two of the several varieties of optical disk technologies stand out as online storage devices. Optical ROM (OROM) or compact disk (CD) ROM drives have read-only capability. Data or programs must be prerecorded during the media manufacturing process. Write-once, read-mostly

optical disk drives extend their utility by providing the facility to record data while online to the computer.

Digital optical data disks measuring about 5 in. in diameter derive from digital audio disks. Today, they are breaking open new applications as a means for software and database distribution that exercise the vast capacities of optical technology. Optical devices using 12- and 8-in. diameter disks show their stuff in archival settings, as well as in data processing applications. In data processing, per-

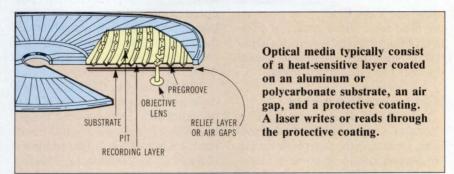

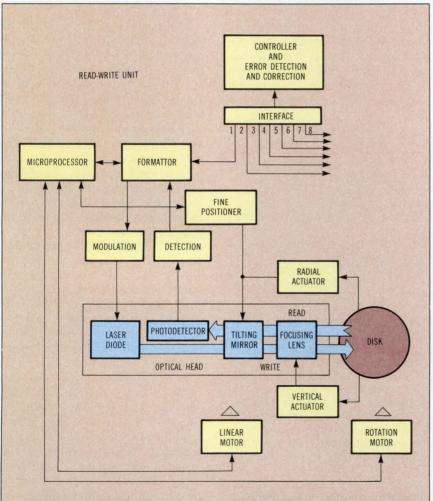

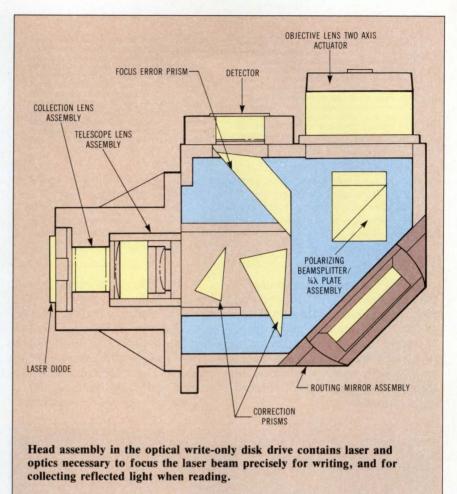

#### Inside an optical drive

Optical disk drives share many functionally similar parts with magnetic disk drives. The primary differences lie in the optical head and the recording medium. An optical head consists, basically, of semiconductor laser diode, beam collection lens, polarizing beam splitter, quarterwave plate, routing mirror, two-axis head, and detector with associated beam forming optics.

The laser emits a coherent beam of light that diverges as it leaves the laser. This light is gathered by the collection lens and made into a collimated (parallel) beam of light. This beam enters the beam splitter and goes through the quarter-wave plate where its polarization is rotated 90 degrees. It then passes to the objective lens in the two-axis actuator system.

The actuator system moves this lens vertically under control of the focus servo to direct the beam on the recording layer inside the optical disk. Under tracking servo control, radial movement centers the beam on the pregrooved track where it makes a mark or reads a bit of data.

Light that is reflected from the disk's surface when the beam hits it is collected and collimated by the objective lens. It then travels through the quarter-wave plate and is again rotated 90 degrees. Since it is now 180 degrees out of phase, it reflects from the beam splitter instead of passing through. This routes the beam onto a quad photodetector. The signal produced by the photodetector is amplified to produce both a read channel data signal and feedback for focus and tracking servos.

Since a written mark on the surface of the disk will reflect less light than an unwritten spot, the difference in reflectivity can be detected as an amplitude modulation in the signal that is passed to the read channel. When the read channel data signal is processed, it provides the data and clock at the drive interface. ceived disadvantages—inability to erase the disk and slow access—are countered by their capacity for massive amounts of information and the ability to remove the media from the drive.

#### **OROMs** make their mark

Immediate applications of OROM drives center on their extensive storage capacity, according to Gerald Finn, vice president and general manager of Sony's Component Products Div in Paramus, NJ. "The CD ROM system gives software houses the capability to put dozens of complex programs with their instruction manuals on a single disk. This allows users to learn programs interactively without referring to a book."

He adds that CD ROMs provide a cost-effective alternative to the recurring communications charges incurred in accessing large central data bases. This is possible because CD ROMs permit entire data bases to be sent to the field. Moreover, the disk takes up less space per megabyte of capacity than any conventional memory device and can be adopted to all computer systems, says John Messerschmitt, vice president of North American Philips Corp in New York.

Although use of CD ROMs as a low cost mass data distribution system promises to be a high growth area, Finn says CD ROMs are not intended to supplant other types of storage. Messerschmitt reinforces this: "CD ROMs offer no recording capability and are not a replacement for existing memory forms. They simply fulfill different requirements."

Optical disks in general offer multiple advantages over conventional magnetic media, according to Dr David H. Davies, project manager of 3M's Optical Recording Project in Mountain View, Calif. "The potential for head wear, head crash, or magnetic field problems is virtually eliminated. And, the high capacity means the cost per bit is much lower."

#### Mass produced mechanisms

Sony's CD ROM, the CDU-1, "parallels the design of audio CD systems, permitting the same basic devices for players and the same disk manufacturing techniques to be used," says Finn. These systems use mechanisms and media similar to those developed for consumer digital audio disk units. With the adoption of stringent error correction techniques, they supply the low bit error rates demanded by computer OEMs. Large quantities of lasers, tracking mechanisms, and servo mechanisms have been produced to meet the acceptance of the laser audio disks. The availability of these proven low cost components has enabled OROM systems to be produced for less than \$500.

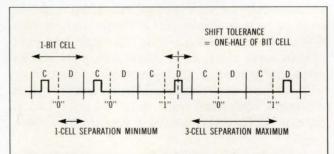

The disk used in CD ROMs has a capacity for storing up to 600 Mbytes of digital data. Data is stored serially in 2-Kbyte blocks on a spiral track. Each 2-Kbyte block can be addressed individually in 100 ms to 1 s. This format, proposed as a standard by Sony and NA Philips, has been adopted for these mass-produced read-only disks. Using this format, drives provide a serial data rate of 1.41 Mbits/s, the same as the real disk data rate. Data buffering and error

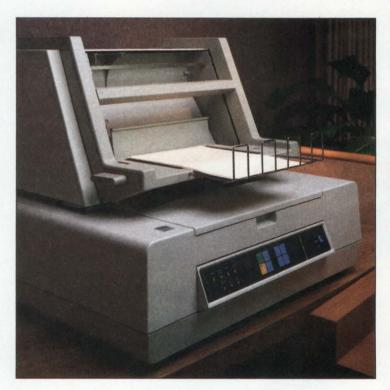

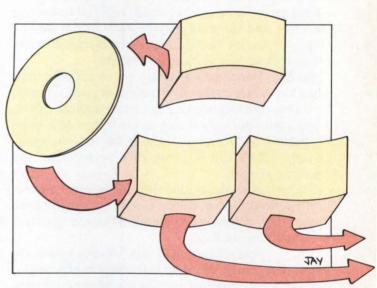

Read/write system of the write-only optical disk drive contains an optical head as well as electronics and mechanisms necessary to position the head in the proper location on a disk's surface.

correction are performed in the host computer controller.

CD ROMs using the format are structured with a lead-in area, a program area, and a lead-out area. Program areas can contain up to 99 information tracks, each divided into as many as 99 blocks. Data fields within each data block consist of a 12-byte sync field, 4-byte header, 2048 bytes of data, and 288 bytes of auxiliary data. The ability to access data randomly derives from information embedded in the header field that is present at the beginning of each track. The header contains 3-byte sector address and mode byte.

Depending on the mode value, the auxiliary field may contain either additional error detection and correction data, or may be available to the user. Use of extended error correction and detection codes can bring the error rate of the disk to  $10^{-17}$ . The disk itself has a bit error rate of  $10^{-5}$ , and use of Cross Interleaved Reed-Solomon Code on data read from the disk brings this to  $10^{-11}$ .

#### A little bit closer

The writable, nonerasable drives now coming into full production suit another set of applications-many yet to be developed. These "writeonce" drives, appearing with 12-in. (30-cm) or the 8-in. diameter disk favored by Japanese manufacturers. use a semiconductor laser diode that can be modulated. This allows them to read and write. This diode laser allows an optical drive to be packaged in a box that fits in a standard 19-in. rack, just slightly smaller than that required for a 14-in. Winchester drive. Its 12-in. diameter disk can store about 1 Gbyte of data on a single surface. Prices for Japanese, European, and U.S. units, complete with controller, all fall in the \$15,000 range.

Available from Optimem, Alcatel Thomson Gigadisc, and Optical Storage International as well as from Hitachi, Panasonic, Toshiba, and NEC, write-once, read-mostly drives are distinguished from read only or compact disk units by the ability to write data directly on the disk within the drive. This eliminates the mastering process and allows data to be handled in a manner that more closely resembles traditional magnetic methods. Attention must be paid to the problem of how best to handle a storage unit that does not provide the ability to modify data once written.

#### Appearances may be deceiving

Although write-once drives using 12-in. diameter disks store about the same amount of data on each surface, almost everything else about them is different. The manner in which data is recorded and the type of media on which it is recorded distinguish the drives in the 12-in. format. The drives also differ in access time and data rates, as well as in the construction of the cartridge in which the optical media are housed.

Similarities in format and media between the OP 1000 from Optimem (Sunnyvale, Calif) and the Alcatel Thomson (Redondo Beach, Calif) Gigadisc 1001 derive from the longterm relationship between their parent companies, Xerox and Thomson-CSF. Even though these two units employ the same media (supplied by Alcatel), the same recording format, and interface to the host over the SCSI interface, their optical and mechanical designs differ.

Yet, Leo LaBonte, East Coast sales manager for Alcatel, maintains that disks written on Optimem drives can be read on Alcatel drives, and vice versa. According to Optimem's director of marketing, Larry Fujitani, this degree of compatibility, along with the fact that both drives and media have two sources (unique situation in the current optical disk industry), increases their chances for survival. Fujitani adds that these factors give them a better chance of developing standards around their formats.

Alcatel claims that adding a few more commands to its SCSI set allows it to provide a direct copy feature. This feature, according to LaBonte, permits two drives to be synchronized. Thus, data can be transferred directly from one drive to another during the copying process. He adds that this is essential to organizations concerned with maintaining security, and that it significantly reduces the time required to make copies.

Other drives, those developed by Hitachi and Optical Storage Interna-

tional (Santa Clara, Calif), for example, do not share this degree of compatibility. Hitachi's model 301 differs from these drives in recording format, type of media, and transfer rate. OSI's LaserDrive 1000 has adopted the SCSI interface. But, like the Hitachi unit, the LaserDrive uses ablative (pit forming) technology media, rather than implementing bubble forming technology used by Optimem and Alcatel.

Choice of media, according to Taroon Kamdar, director of marketing at OSI, is an important aspect for archival storage. He points out that the ablative technology that OSI uses actually burns a hole into the sensitive layer of the disk where data is recorded. While using a similar optical system, Optimem and Alcatel have chosen media technology that forms a bubble on the surface of the sensitive layer where data is recorded.

Ablative technology, Kamdar claims, "has proven superior in terms of shelf life of the data once it is recorded on the media." These claims of superior data retention, he says, are based on extensive research into various methods for recording data onto optical media. The studies were performed by NV Philips, Control Data's partner in OSI. However, Alcatel and Optimem specify the same 5-year shelf life before recording and greater than 10-year lifetime after recording for their media.

Another distinct difference between the drives lies in the method used to verify whether data have actually been recorded on the disk's sensitive layer and whether that data can be read back accurately. OSI claims to have improved upon the direct read after write (DRAW) method that is used by Fujitsu, Hitachi, Optimem, Alcaltel and others, with what is known as direct read during write (DRDW) techniques.

In DRDW, when the drive receives a command to write, it not only

#### SYSTEM TECHNOLOGY MEMORY SYSTEMS

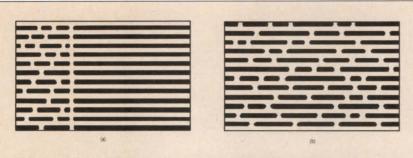

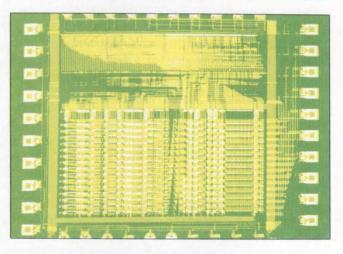

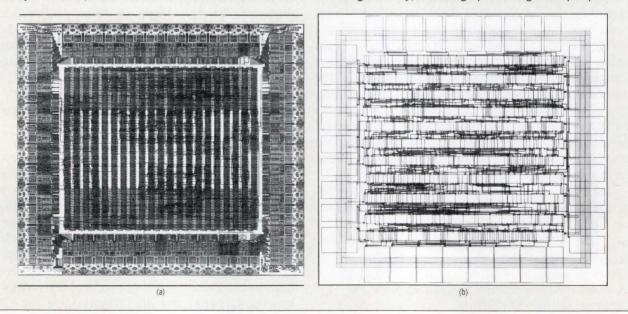

Magnified many times, these sections of read-only and write-once optical media show distinct differences. Write-once media (a) have pregrooves that also contain sector information (left) to aid in locating data. Actual user data is recorded along grooves (right) within the user portion of the tracks. Read-only media (b) contain data as well as address information. No distinction is apparent between the two types of information.

writes but verifies simultaneously that the write actually occurred. The technique uses essentially the same optics as those used for read and write. It is merely "a technically clever way to use the same laser beam that is used to write to tell whether or not a good write was achieved," according to Kamdar.

When other drives receive a write command, they put out a write pulse to record data on the media. They must then wait one revolution of the disk before they can read the data to verify whether the write was done properly. This means that even when writing sector to sector, 60, 70, or 100 ms may elapse before a good

write can be verified. In terms of performance, Kamdar says, "this makes the OSI drive far more efficient than other drives."

Another distinction between drives lies in the realm of user friendliness. This difference is in respect to the cartridge that houses the media and protects it from damage when the disk is outside of the drive.

For the Optimem drive to read a particular disk, the cartridge with the media is first inserted into a slot on the drive. The cartridge sleeve is then pulled out, leaving the disk itself within the drive. The sleeve must then be inserted into a separate slot for storage. This requires three motions for insertion, and consequently, it requires another three for removal. OSI's drive, on the other hand, spins the media within the cartridge after the cartridge containing the media has been inserted. This not only affords continuous protection for the media, but provides more convenience for the user as well.

#### **Planning for the future**

Smaller drives now under development, and probably available in the spring, will store about half a gigabyte per side. Using a 4.7-in. (12-cm) platter (the same size as accepted CD ROMs) or moving into the 5<sup>1</sup>/<sub>4</sub>-in. diameter of conventional floppy disks, the drives will implement similar write-once techniques and media. Targeting vendors that develop 5<sup>1</sup>/<sub>4</sub>-in. form factor drives, both Hitachi/Maxell and 3M have released specifications for disks that will provide capacity for 250 to 500 Mbytes/side.

Drives expected to appear around mid-year will rely on such media. One of these, from Information Storage, Inc, in Colorado Springs, Colo is reported to store a conservative 100 Mbytes. This capacity is attained by recording at about 11,500 bits/in. and 14,000 tracks/in. This conservative design should help to meet the unit's full production price target of \$500 in quantity—a price that is necessary to fit the projected desktop computer market.

Although formal announcements have not been made, it is clear that other companies will be joining ISI

## HOW TO DOUBLE YOUR CONTROL WITHOUT DOUBLING YOUR CONTROLLER.

If your plans for controlling disk and tape drives call for two boards and two CPU slots, you can now cut your plans in half.

And use the SPECTRA 25 LSI-11 emulating multifunction controller instead. You'll get all the control of separate disk and tape boards in just half the space. Half the slots. Half the spares. While using less power.

SPECTRA 25 is the smarter way to handle SMD/Winchester and ½-inch tape drives, and

it's the first and only multifunction controller designed for DEC Q-BUS® computers.

Its block-mode data transfer capability can increase your throughput by up to 50%. And it performs Error Correction Code (ECC) independently of the operating system. All 32 bits worth.

SPECTRA 25 fully emulates DEC's RM02/5 and RM80 disk subsystems, and TS11 tape subsystem. It can run two SMD disk drives and four tape drives, in any combination. Plus an  $E^2$ PROM lets you easily reconfigure while the controller is in your system.

But SPECTRA 25 puts something else in your system, too: proven reliability. Because you're working with half as many parts and pre-tested ICs.

You're also working with excellent documentation that's regularly updated. And the most comprehensive one year warranty in the industry. All backed by responsive nationwide service.

**SPECTRA 25** is the multifunction controller that doubles your control. And your advantage on the competition. Before you look at Emulex or Dilog, consider the SPECTRA 25 from Spectra Logic. It could be all the controller you'll ever need. For further information on our expanding family of controllers for DEC Q-BUS and UNIBUS® computers, call or write us today.

|                             | SPECTRA 15*/<br>SPECTRA 25           | SPECTRA 111*/<br>SPECTRA 121         | SPECTRA 12*/<br>SPECTRA 21  |

|-----------------------------|--------------------------------------|--------------------------------------|-----------------------------|

| BUS                         | Q-BUS<br>(Block-mode)                | UNIBUS                               | UNIBUS                      |

| Disk<br>Emulation           | RM02/05,<br>RM80, RP06<br>(2 drives) | RM02/05,<br>RM80, RP06<br>(4 drives) | RK06/07<br>(4 drives)       |

| Tape<br>Emulation           | TS11<br>(4 drives)                   | TS11<br>(4 drives)                   | TS11, TM11<br>(4, 8 drives) |

| Disk Transfer<br>Rate (SMD) | 2.0MB/sec                            | 2.0MB/sec                            | 2.0MB/sec                   |

| Configurable<br>On-Line     | Yes                                  | Yes                                  | No                          |

| *Single function            | disk controller                      |                                      |                             |

Spectra Logic Corporation, 297 North Bernardo Avenue, Mountain View, CA 94043, (415) 964-2211, TWX 910-339-9566, TELEX 172524 SPL MNTV. International Sales Office: The Netherlands (31) 23 273744, TELEX 71080 SPECL.

A Cipher Data Products Company.

#### Manufacturing the media for optical systems

The process of producing an optical disk—whether intended for use in an optical ROM or write-once, read-mostly drive—begins with a digital format recording on tape. The mastering process uses a system made up of a processor, encoder, and laser cutter to create glass masters. Digital information is recorded on the master by exposing a photoresist layer (or coating) on the glass plate (or substrate) to a laser beam. This beam cuts pits or raises bubbles in the photoresist layer. The resulting marks correspond to digital 1s and 0s.

After the glass master is developed, it is coated with a thin conductive layer. An electroplating process lays down a thick metal layer on top of the conductive material. This yields a metal master that can be separated and used to produce stampers. When placed in an injection molding machine, the stampers then transfer the recorded pattern of marks onto a transparent disk formed by injecting a high grade polycarbonate resin.

After molding, this transparent disk is placed in a vacuum chamber where a very thin layer of aluminum coats its surface. This layer reflects the drive's laser beam, allowing information to be read from the disk. The pits or bubbles reproduced in this aluminum layer are protected by an ultraviolet curing layer that is applied over the aluminum.

The process used to manufacture media for use with write-once optical systems differs in one respect from that used to form compact disk ROMs. In the latter instance, a different modulation code is used to turn the laser beam on or off. While the compact disk ROM process writes tracking information, address information, and data, the process used for write-once media writes only the pregroove. No matter whether intended for use with ablative or bubble raising media, this pregroove provides the drive with the radial servo tracking feedback, data synchronization, and preformatting to supply head positioning feedback. This puts the precision needs to achieve high areal densities on the disk rather than in the drive.

in the 5<sup>1</sup>/<sub>4</sub>-in. market. OSI is developing a unit that exhibits a standard 5<sup>1</sup>/<sub>4</sub>-in. footprint. Optimem also has a unit underway, and Alcatel projects a 1986 timeframe for introduction of a unit using 5<sup>1</sup>/<sub>4</sub>-in. diameter media. Although IBM is said to be working on a drive of this type, and is known to have optical development projects underway, exact product plans remain unclear.

In addition to the arrival of downsized write-once drives, optical aficionados can soon expect to be doubling storage capacity on 12-in. diameter media. Widespread availability of two-sided media will make recording and reading both sides of the media common in these drives.

Fueling interest in optical storage devices is the possibility that long-term efforts aimed at developing reversible media have finally produced an optical drive with a magnetic drive's read/write capability. Recent developments in this area include an erasable read/write drive based on the magneto-optic technology demonstrated in prototype by Canon in Japan. Matsushita's Panasonic Div has also demonstrated reversible media based on phase-change technology.

#### A step at a time

Meanwhile, a solution to the problem encountered in getting acceptable life times for reversible media appears within reach. Sony claims it has come up with an amorphous film that shows only minimal degradation of signal and noise after more than a million write/erase cycles. Hitachi has developed an optical disk alloy that changes color when heated and rapidly cooled. This color is reversed by reheating and slowly cooling the material.

Such developments will eventually produce reversible media that are stable enough to retain data for the 10 year period required in archival applications. Further, they will endure sufficient read/erase cycles to prove cost-effective in ordinary data recording applications. Commercially available drives using this media will follow closely, because, in this case, the necessary optical systems are not out of reach.

Reversibility, although a longsought goal, is only one step forward in optical storage technology. Another area stimulating research and development is the attempt to match access times and data rates of optical drives to those of magnetic disk drives. Access times will fall when a smaller optical head assembly can be devised.

These developments can be expected within the next few years. To increase the data rate, it will be necessary to increase the rotational speed of the disk. Since this requires that the laser provide a higher power output, this achievement awaits the creation of more powerful laser diodes.

A long-life laser diode with acceptable noise characteristics that can produce the 100-mW peak power output necessary may appear within the next two or three years, according to Alan Bell of IBM's San Jose Research Div. An alternative under review by RCA and Bell Labs is use of arrays of laser diodes that can record or read data in parallel from adjacent tracks. This would yield higher data rates without an increase in the rotational speed or output power level of lasers in the array.

Success in these and related efforts will provide optical disk drives with the opportunity to dethrone magnetic recording media. In the interim, growing demands for online data storage will draw from each technology those features that best suit specific needs. Optical drives now hold under 1 percent of the storage peripheral market. Raymond Freeman of Freeman Assoc (Santa Barbara, Calif), one authority in the optical market area, however, predicts that from the 6000 units bought in 1984 the optical share will grow to some 2.4 million units in 1990.

> -Peg Killmon, Senior Editor

SYSTEM TECHNOLOGY (continued on page 33)

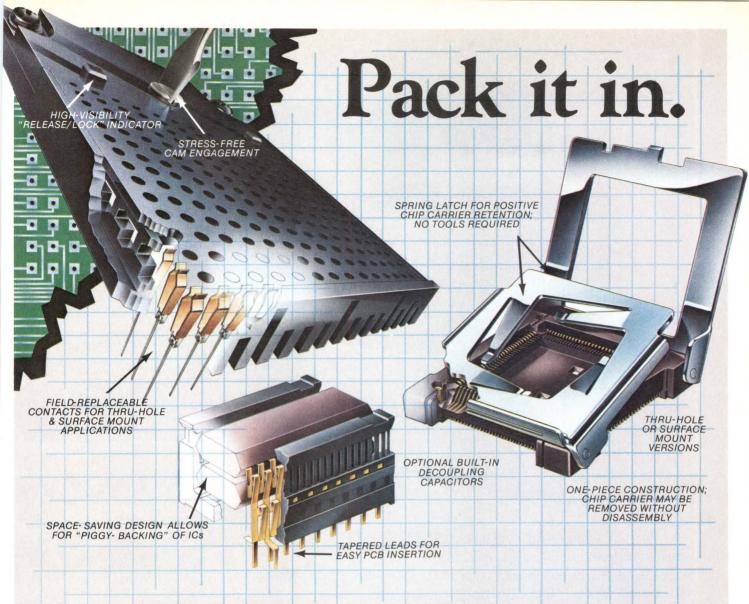

#### Now...socket complex VLSI packages with Ansley<sup>®</sup> IC interconnect devices.

The Electronics Group of Thomas & Betts responds to the increasing complexity of integrated circuits.

**Ansley<sup>®</sup> Pin Grid Array Connectors** feature zero-insertion-force design for dense terminal counts as high as 625 I/O. They interface popular pin grid array packages while offering advantages over conventional systems: selective plating, high-performance glass-filled thermoplastic materials, and stress-free cam engagement to open each dual redundant contact.

Ansley<sup>®</sup> Leadless Chip Carrier Connectors interconnect microprocessor and gate arrays, as well as high-density custom logic semiconductor devices. In standard terminal counts of 68, 84, 132 and 164, they're designed to accept JEDEC leadless Type A packages with .050" and .025" centerlines, and allow for access-probing of contact leads after board installation.

#### Ansley<sup>®</sup> Stacked DIP Sockets

double IĆ packaging densities by enabling designers to vertically stack two standard plastic or ceramic DIP packages. Available in 16 through 28 positions, the Stacked DIP Socket accommodates both memory and logic/support devices.

For more data on these products, and our screw-machine line of DIP and PGA sockets, contact Technical Service, Thomas & Betts Corporation, Electronics Group, 920 Route 202, Raritan, NJ 08869; (201) 469-4000.

SEE OUR SHORT FORM CATALOG IN THE '84/'85 EDITION OF EEM

Where Interconnection Meets Imagination.

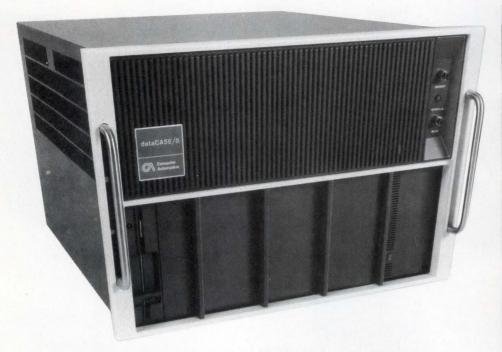

# CARTOS dataCASE/5.

It's true. Because our CARTOS dataCASE/5<sup>™</sup> real-time computer system behaves like 64 virtual machines.

So. Its real-time capability is all yours. Even when you're sharing the system with 63 other demanding environments.

Believe it. With up to 4 MB of main memory, CARTOS dataCASE/5 is real-time that's right for the rigors of the industrial world. Tough. Strong. Reliable. CARTOS is already hard at work in oil fields and nuclear power plants as well as robotized assembly lines and sophisticated transportation systems.

CARTOS dataCASE/5 is flexible, too. Use whatever media you want. Put it wherever you want. In a rack. On the floor. Or atop a desk.

Just imagine. You can tell everyone you're buying 64 real-time systems. And then call us. Computer Automation. (714) 833-8830, Ext. 353. TWX: 910-595-1767. 18651 Von Karman, Irvine, CA 92713. © 1985 Computer Automation, Inc.

CIRCLE 16

# BUY ONE, GET 63 FREE.

# CAD without CACHE<sup>™</sup> is like life without water.

Now CACHE brings the CAD design process to life with the information you need. No more long dry spells while you wait for your CAD Library to be created. CACHE offers the design engineer a comprehensive component library of

| Tell me more a | bout how | CACHE ca | an add | life to n | ny |

|----------------|----------|----------|--------|-----------|----|

| CAD system.    |          |          |        |           |    |

| Name            |                           |          | _ |

|-----------------|---------------------------|----------|---|

| Title           |                           |          | _ |

| Company         | Contraction of the second |          |   |

| Address         |                           |          | 1 |

| City            | State                     | Zip      |   |

| Sond to: INACON | International 43          | 80 South |   |