# EPLD Application Guide with XC7000 Data Sheets

# April 1995

Xilinx, the Xilinx logo, and XACT are registered trademarks of Xilinx, Inc. All XC-prefix product designations, Dual-block, XEPLD, UIM, Logic Cell, and LCA are trademarks of Xilinx, Inc. The Programmable Logic Company is a Service Mark of Xilinx Inc. PAL and PALASM are registered trademarks of Advanced Micro Devices, Inc. ABEL is a trademark of DATA I/O Corporation. CUPL is a trademark of Logical Devices, Inc. All other trademarks are property of their respective owners.

Xilinx does not assume any liability arising out of the application or use of any product described herein; nor does it convey any license under its patents, copyrights or maskwork rights or any rights of others. Xilinx reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, will not assume responsibility for the use of any circuitry described other than circuitry entry entry entry described other than circuitry entry entry

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

©1995 Xilinx, Inc. All rights reserved.

# **SECTION TITLES**

1 Applications

2 XC7300 EPLD Family

3 XC7200A EPLD Family

4 Packages

5 Software and Programming

6 Quality, Testing and Reliability

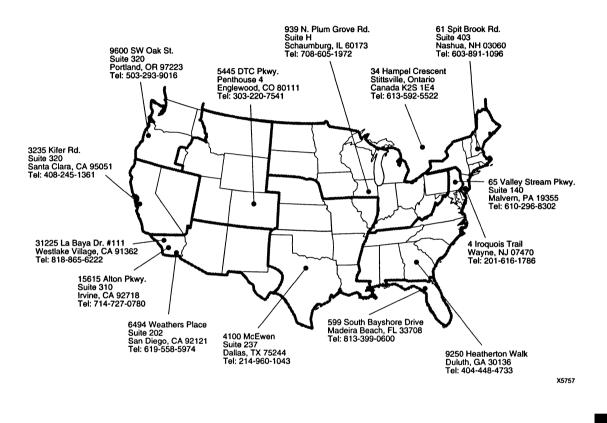

7 Sales Offices

# XILINX<sup>®</sup>

# **SECTION 1**

# **1** Applications

- 2 XC7300 EPLD Family

- 3 XC7200A EPLD Family

- 4 Packages

- 5 Software and Programming

- 6 Quality, Testing and Reliability

- 7 Sales Offices

# XILINX<sup>°</sup>

# Applications

| Direrct PAL Conversion Using Xilinx EPLDs                                       | 1-1  |

|---------------------------------------------------------------------------------|------|

| A Zero Wait State Synchronous DRAM Controller<br>For the Pentium Microprocessor | 1-9  |

| Designing Flexible PCI Interfaces With Xilinx EPLDs                             | 1-29 |

| Designing With the XC7336 and XC7318                                            | 1-49 |

| Using Xilinx EPLDs in Mixed Voltage Systems                                     | 1-61 |

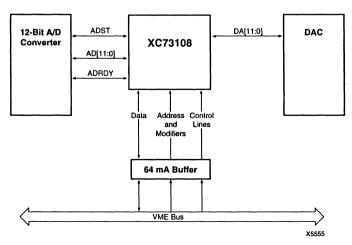

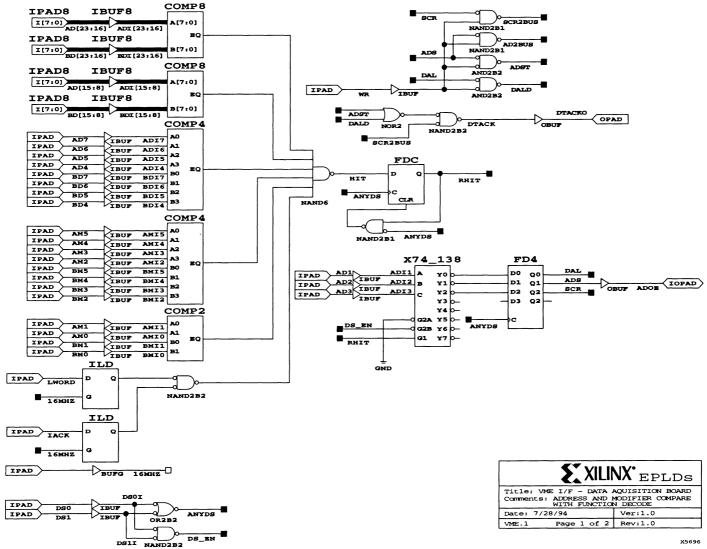

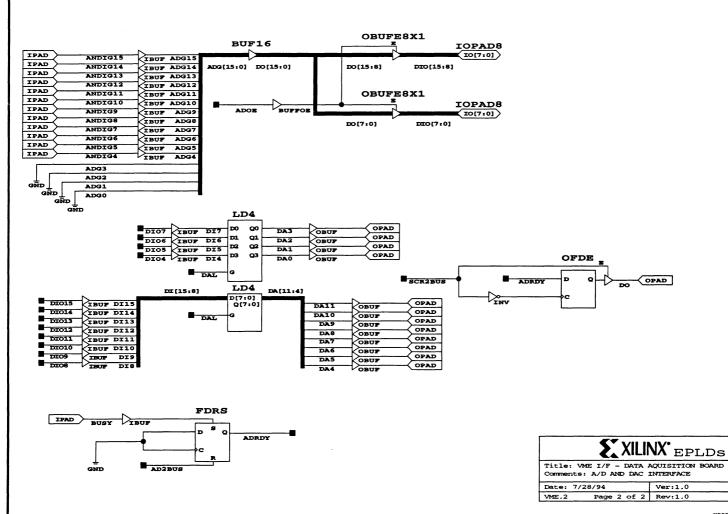

| VME Data Acquisition Interface and Control<br>in a Xilinx XC7000                | 1-65 |

R.

# XILINX<sup>®</sup>

# Direct PAL Conversion Using Xilinx EPLDs

Application Note

# January 1995

# Introduction

In order to remain competitive in the marketplace, companies are being driven to reduce product manufacturing costs while adding more features and improving reliability. Users of low density discrete PALs are turning to higher density erasable programmable logic devices (EPLDs) to meet these goals.

PALs are easy devices to use. Device timing is fixed, routing issues are nonexistent and the device architectures are simple and understandable. Many EPLDs however, exhibit timing unpredictability, routing limitations, and limited functionality that can trap the unwary first-time EPLD user. Couple that with the task of learning how to use new design-entry software, and what appeared to be a simple task can turn into a nightmare.

This application note shows how Xilinx EPLDs can be used to simplify the task of reducing the number of discrete low density PALs on a board. This direct PAL conversion is made possible by a unique combination of :

- Architectural features

- Software methodology

- Broad product family

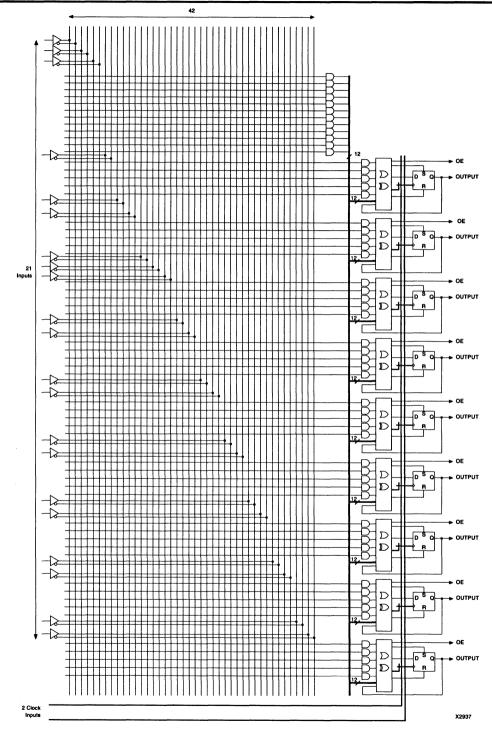

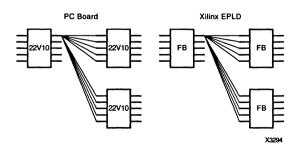

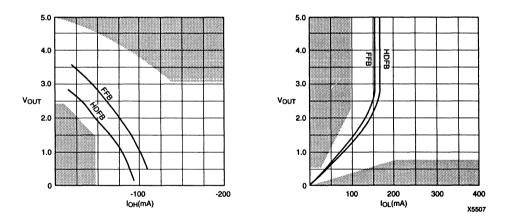

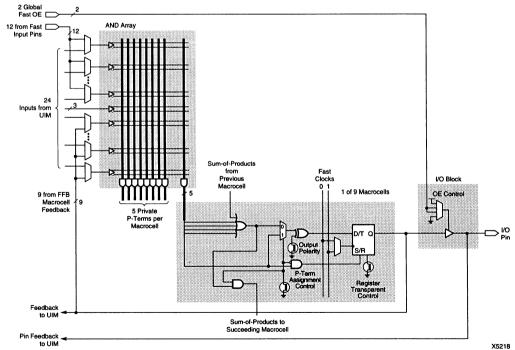

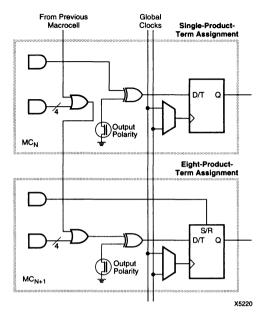

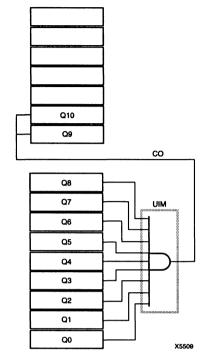

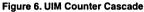

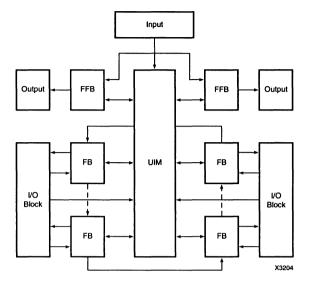

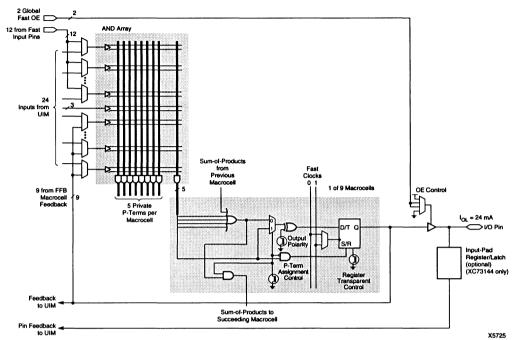

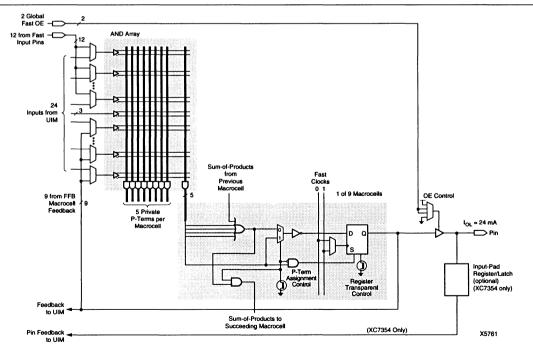

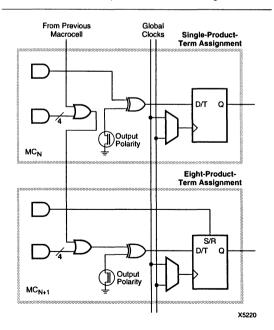

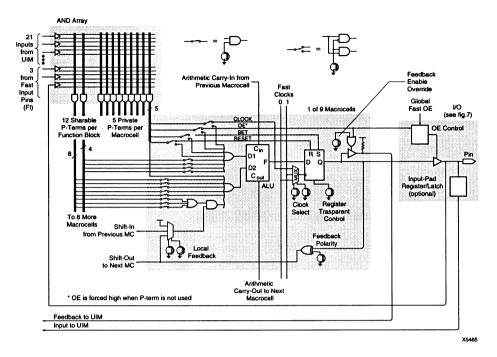

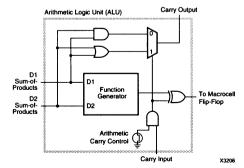

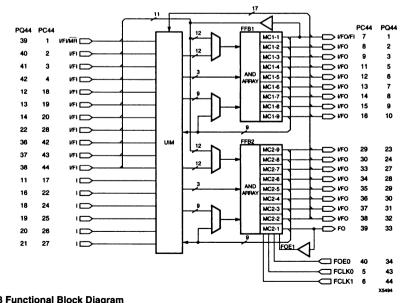

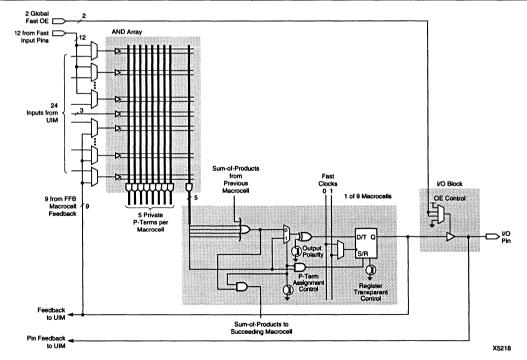

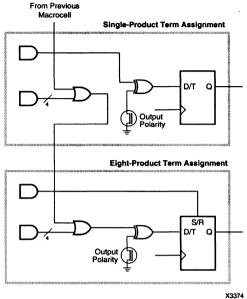

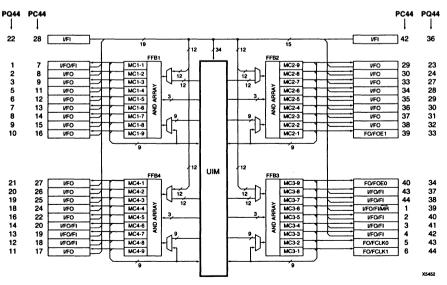

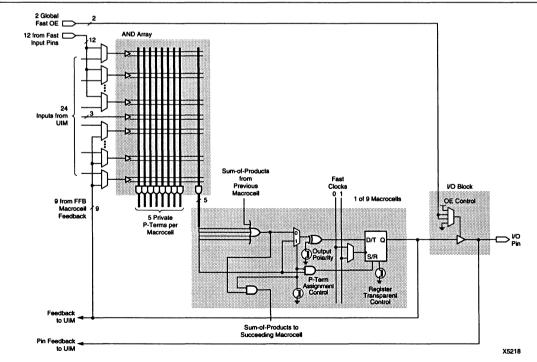

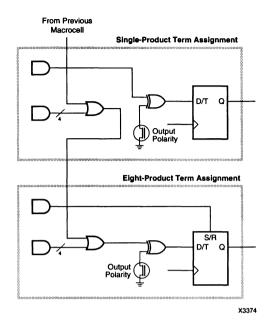

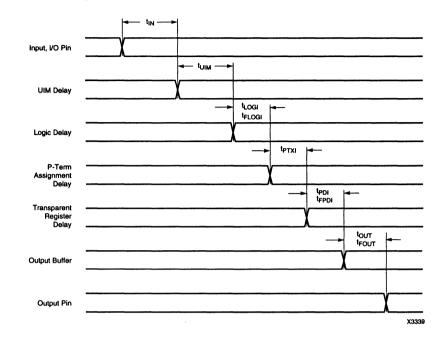

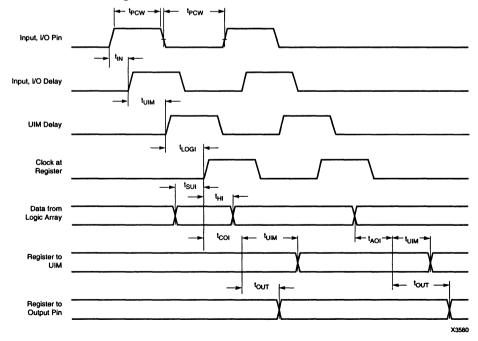

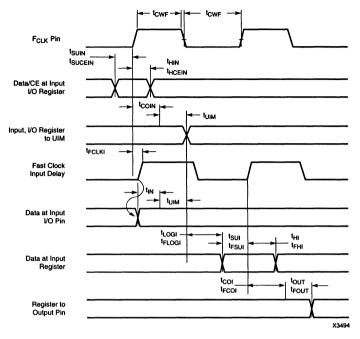

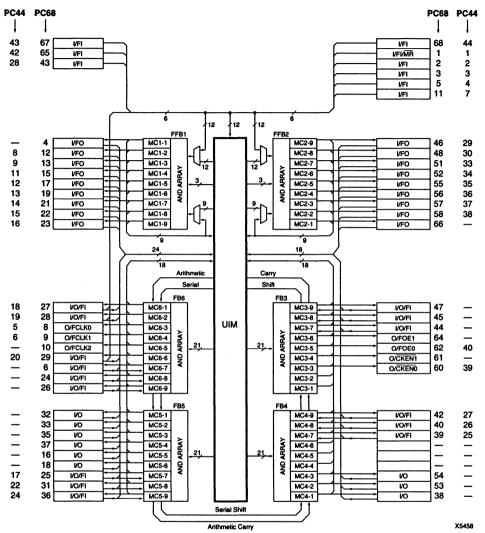

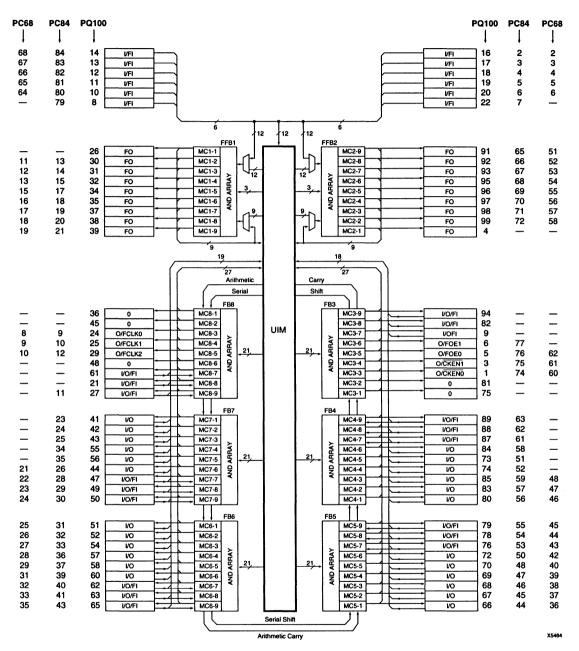

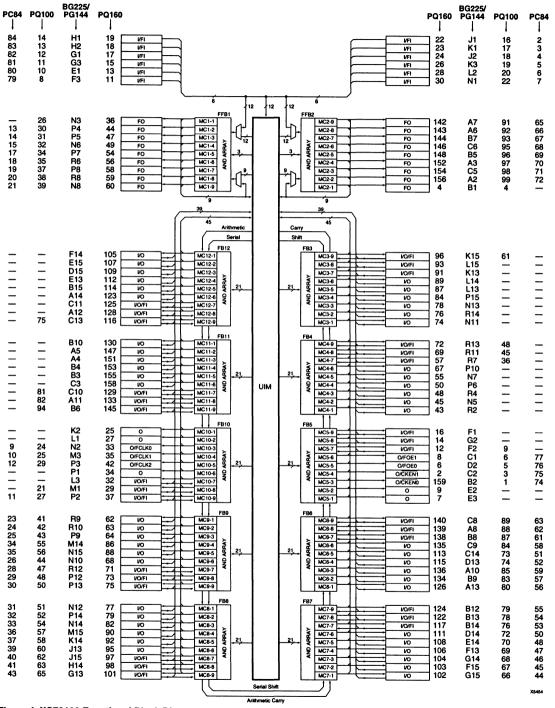

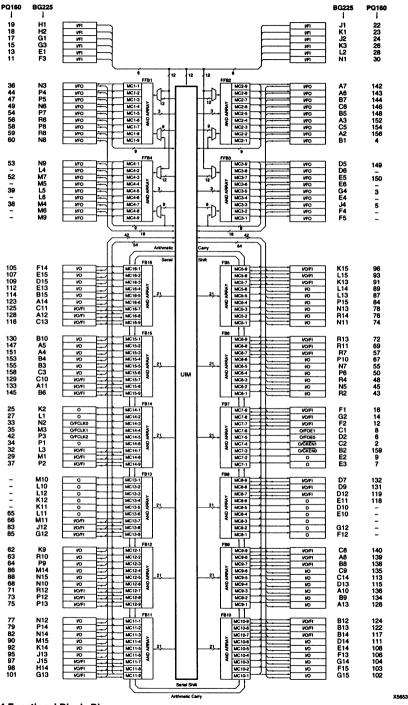

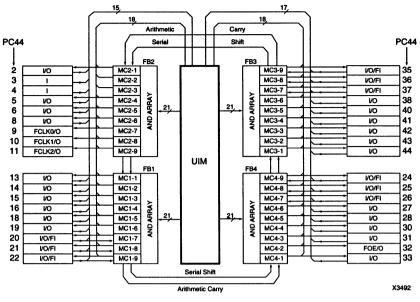

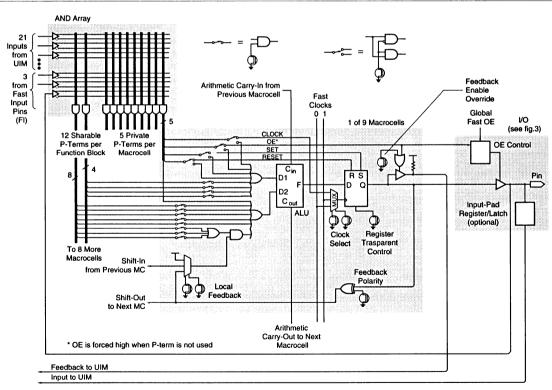

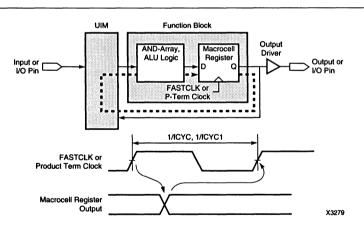

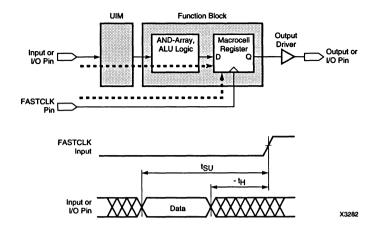

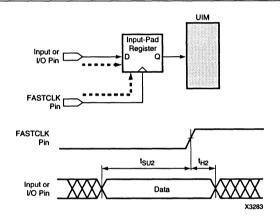

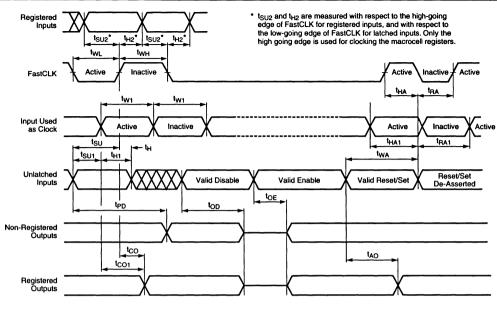

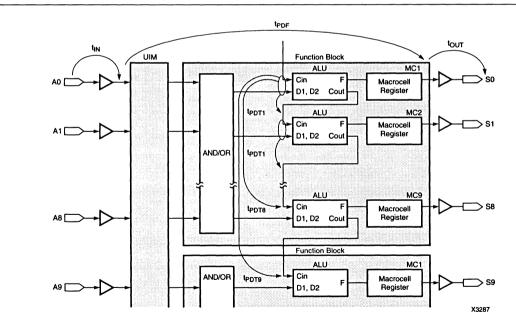

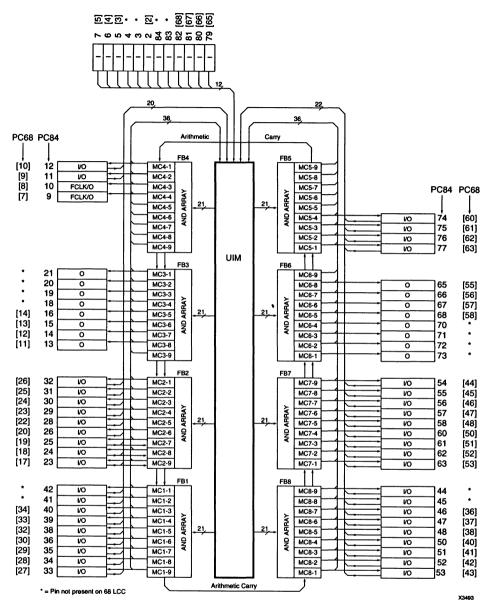

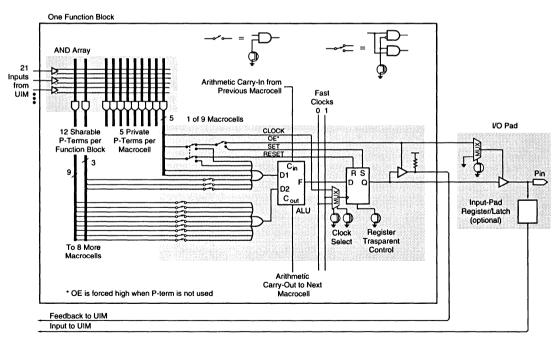

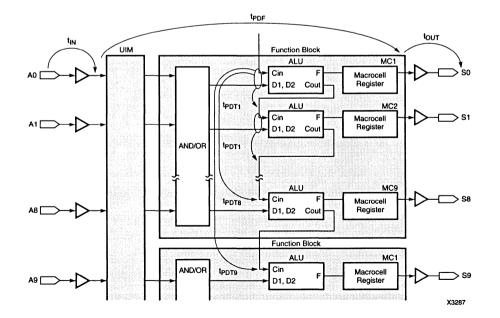

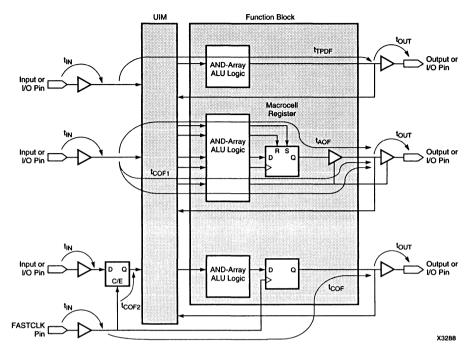

# Xilinx EPLD Architecture

In order to support direct PAL conversion, Xilinx XC7000 EPLDs have a PAL-like architecture. Each device consists of several PAL-like logic blocks, called Function Blocks (FBs), on a single IC, all interconnected by a fully populated switch matrix. Each FB can be thought of as a 21V9 PAL, with 21 complementary inputs and an AND-OR array with 57 product terms feeding 9 outputs. The Xilinx EPLD Function Block is highly flexible superset of the low density PAL. The product term intensive FB has five individual product terms per output. In addition, there are 12 product terms that are shared between all 9 outputs. Each output can be configured as either registered or combinatorial. Each register has individual set, reset and output enable control and can be clocked either individually or by global clocks. In addition, each output has an available XOR gate that can be used for XOR functions or toggle flip flop emulation.

Although product-term-intensive, the timing is fixed. No matter whether the output is performing a single product-term function or a 17 product-term function with the XOR gate, the timing doesn't change.

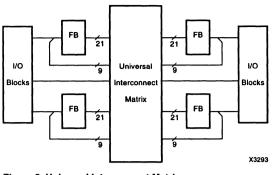

All of the Function Blocks on a Xilinx EPLD are interconnected by a fully populated Universal Interconnect Matrix (UIM<sup>™</sup>).

Unlike other vendor's sparsely populated matrices that create routing problems and have fanout-dependent timing, the UIM is a fully populated, non-blocking switch matrix that features a constant delay, independent of fanout. Every Function Block output and every signal from every input and I/O pin all feed into the UIM. The UIM in turn drives every input of every FB. This means that each Function Block input can be driven by any input pin, any I/O pin and any Function Block output – just like connecting PALs on a board, but better.

In addition to serving as an interconnect, the UIM may also function as very wide input AND array. This allows the EPLD to generate product terms in the UIM similar to a low density PAL AND array. The propagation delay is fixed regardless of the number of signals used to generate the product term, or the source and destination of those signals.

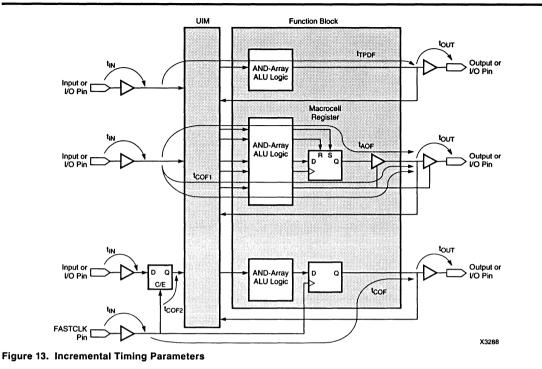

Figure 1. Xilinx EPLD PAL-Like Function Block

Figure 2. Universal Interconnect Matrix

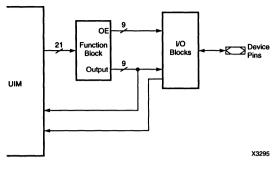

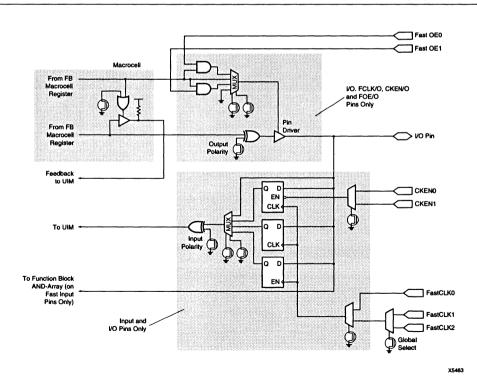

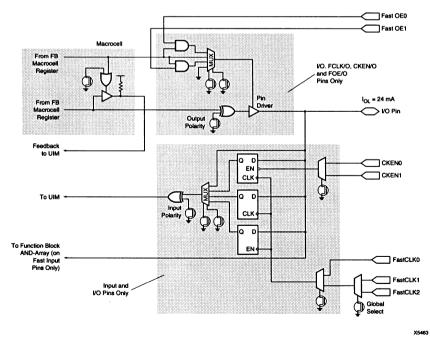

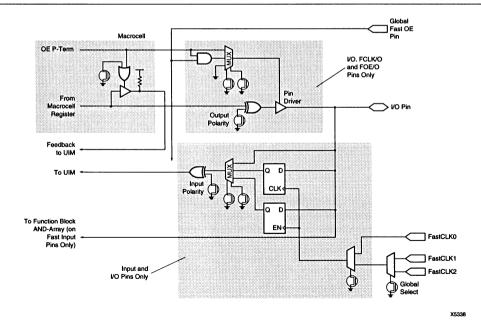

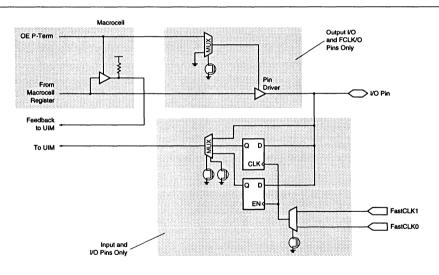

Figure 4. I/O Block

The EPLD has programmable I/O blocks for driving the device pins. The I/O blocks can be used to decouple the Function Block's outputs from the device pins so the Function Block outputs may be buried while still retaining the use of the pin as a device input. The I/O blocks also provide output inversion control and the ability to latch and register input signals.

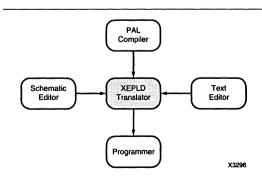

# Xilinx EPLD Software

When it comes to programmable logic, silicon is only part of the solution. Software is required to translate ideas into reality. The Xilinx EPLD Translator (XEPLD<sup>™</sup>) works with industry standard PAL logic compilers and languages such as ABEL, CUPL and PALASM. One can directly import JEDEC files from old, proven designs using 22V10s and 20V8s.

The XEPLD system allows design entry with familiar front end tools. Once the design is entered, XEPLD simply acts as a fitter, taking the design description and mapping it into the chosen Xilinx EPLD.

In addition to being easy to use, XEPLD is very powerful. One of the most important functions of a fitter for high density programmable logic is Automatic Partitioning. The design can be entered without having to first partition it into Function Block-size pieces. This lets the designer concentrate on the functionality of the design, not its physical implementation.

# The PAL Conversion Process

The PAL conversion process is begun by identifying which group of PALs are to be converted to a single EPLD. Then choose the appropriate Xilinx EPLD, based on the I/O and logic requirements. Xilinx makes this process easier by offering each device in a variety of footprint-compatible packages. This flexibility allows the designer to upgrade to a higher density device without having to change the board layout, should the logic requirements change.

Since the timing of the Xilinx EPLD is absolutely predictable, it is an easy matter to verify that the design will meet all critical timing requirements. By eliminating delays getting on and off chip, even 5 ns PALs can be converted to a single Xilinx EPLD.

The choice of whether to do equation-based design entry or schematic-based design entry is based primarily on the user's preference. Equation-based entry allows the user to concatenate PALASM equations from multiple PAL files without any restrictions on the PAL type.

On the other hand, schematic-based design entry may be easier to conceptualize, and it allows the user to directly

Figure 3. The 100% Interconnect

Figure 5. Development System Overview

X5613

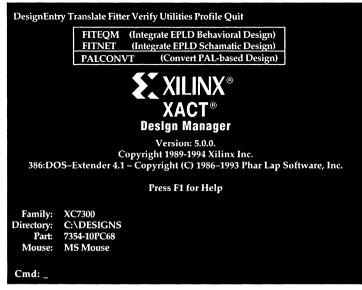

Figure 6. Automatic PALCONVT Ulility Runs Under the Xilinx Design Manager

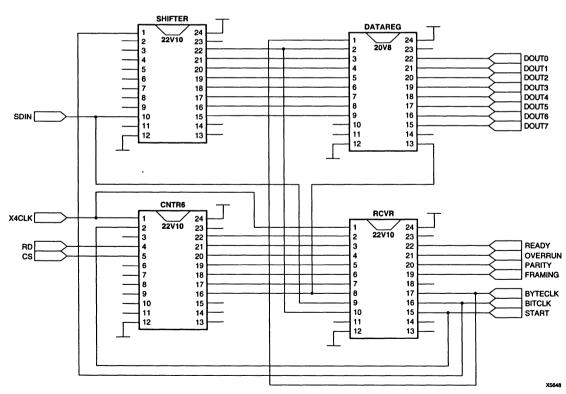

Figure 7. Original UART Design

#### PATTERN uartdemo.pld - file made by PALCNVT command

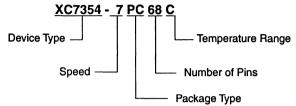

; Behavioral design example for XC7354-xxPC68 ; Demo usage: fitegn -e uartdemo -p 7354

CHIP uartdemo XEPLD

INCLUDE\_EQN 'shifter.pld' INCLUDE\_EQN 'rcvr.pld' INCLUDE\_EQN 'datareg.pld' INCLUDE\_EQN 'cntr6.pld'

#### INPUTPIN SDIN X4CLK RD CS OUTPUTPIN DOUT7 DOUT6 DOUT5 DOUT4 DOUT3 DOUT2 DOUT1 DOUT0

NODE D7 D6 D5 D4 D3 D2 D1 D0 C0 C1 C2 C3 C4 C5 PAR READ

; declarations added after palconvt:

outputpin start byteclk bitclk framing parity overun ready

EQUATIONS ; equations added after palconvt:

| START.PRLD   | = GND; |

|--------------|--------|

| BITCLK.PRLD  | = GND; |

| READY.PRLD   | = GND; |

| BYTECLK.PRLD | = GND; |

| OVERUN.PRLD  | = GND; |

| PAR.PRLD     | = GND; |

| PARITY.PRLD  | = GND; |

| FRAMING.PRLD | = GND; |

|              |        |

Figure 8. Design File UARTDEMO.PLD

import JEDEC files for 22V10 and 20V8 PALs (PALASM equations may be used for other PAL types).

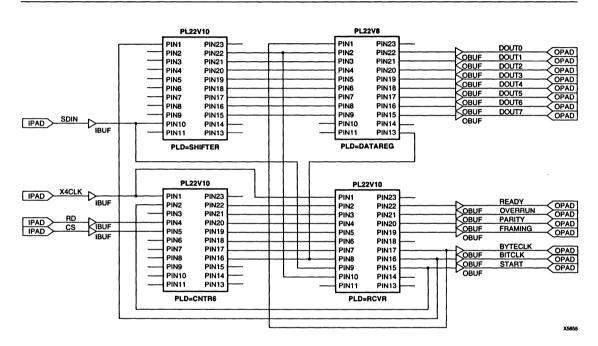

The following examples show how to use XEPLD to directly convert a multiple-PAL design to a single Xilinx EPLD. The examples show the use of both equation and schematicbased design entry methods. The design, shown in Figure 7, implements a UART originally implemented with three 22V10s and a single 20V8.

### **Equation-Based Design Entry**

Direct PAL conversion is easily accomplished with a modular design approach. Each PAL in the design can be treated as an individual module. A Top-Level design file, created by the XEPLD PALCONVT utility simply links all of the modules together.

The design file UARTDEMO.PLD, shown in Figure 8, was created with PALCONVT. This file is written in PLUSASM, the XEPLD native syntax, and should look very familiar to those familiar with PALASM. The CHIP statement contains the filename of the Top-Level file and targets a Xilinx EPLD. INCLUDE\_EQN keywords instruct XEPLD to concatenate the PALASM equations contained in each of the included files that were generated by the PAL compiler. INPUTPIN, OUTPUTPIN and NODE keywords then follow to define the device inputs, outputs and nodes.

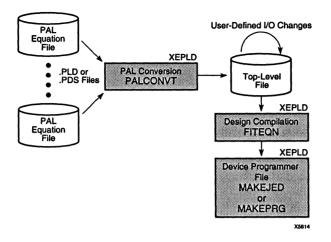

The EQUATIONS keyword indicates where the equations section of the design file begins. After reading this keyword, XEPLD reads all of the equations in the included files, automatically partitions the equations and converts the multiple-PAL design into a single chip solution. This design flow is illustrated in Figure 9.

For each PAL in the design, generate a PALASM2 Boolean equation file from the original PAL source code. This is easily done with the XEPLD utility PLA2EQNX (for ABEL) or the CUPL -c compiler option. At this time, verify that the signal names in each PAL pinlist establishes the proper signal connectivity for the design.

After generating the Boolean equation files, invoke XEPLD and do the following:

· Select the target device

Open up the FAMILY menu and select the XC7300 device family. Then open up the PART menu and select the target Xilinx EPLD.

• Create the Top-Level file

Use the FITTER -> PALCONVT command to create the Top-Level File, selecting the PAL equation files (.PLD or .PDS) that you want to link together with the Create new

Figure 9. PAL File Conversion Diagram

Figure 10. Schematic-Based Design Flow

PLD and PAL Interconnect option. Edit the pin declaration statements in the file to suit the design's I/O requirements.

· Fit the design

Run FITTER -> FITEQN to implement the design in the target device.

· Generate the programming file

Run VERIFY -> MAKEPRG to generate the Hex format programming file.

The device can now be programmed and the correct operation verified.

# **Schematic - Based Design Entry**

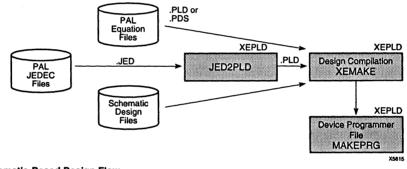

The schematic design entry flow is also simple and straightforward. The XC7000 component library contains 22V10 and 20V8 PALs to simplify the PAL conversion process. It is a simple matter to connect the PALs exactly as in the original design and import JEDEC files that

describe their functionality. For other PAL types, PLUS-ASM compatible PALASM2 Boolean equation files can be targeted at generic 20 and 24-pin PAL symbols in the XC7000 library. Instructions showing how to use ABEL, CUPL and PALASM to generate the required equation files appear in the Xilinx EPLD Handbook. XEPLD then processes the netlist and PAL files to convert the design to a single-chip solution. The design flow is illustrated in Figure 10.

After generating the proper files with a PAL compiler, use a schematic editor to capture the design. Assign the PLD=<file\_name> attribute to each PAL in the schematic, linking it to an intermediate file describing its function. Save the design and process it as shown:

Import 22V10/20V8 JEDEC Files

Run TRANLATE -> JED2PLD for each JEDEC file in

the design selecting the JEDEC file to import and the

PAL type (22V10 or 20V8).

# Compile the Design

Run TRANSLATE -> XEMAKE -> DONE. Select the name of the schematic with the Make Intelhex Bitmap option and assign an identifying signature, design.a.

XEPLD automatically processes the entire design, optimizing, partitioning, and mapping the logic into the target device, then generating a programming file with a unique identifying signature. The device can now be programmed, installed on the board and correct system operation verified.

#### Conclusion

This application note demonstrates how easy it is to directly convert PAL based designs to a single Xilinx XC7000 EPLD without any redesign. This direct PAL conversion process is only possible when the target device logic blocks have a PAL-like architecture, the interconnect matrix is fully populated, and chip timing is deterministic. All of these features are incorporated in the XC7000 EPLDs. The EPLD Translator software simplifies this task by interfacing directly to the most popular third party design tools.

Figure 11. PAL\_UART Schematic

I.

# XILINX<sup>®</sup>

# March 1995

# Introduction

This application note presents a main memory subsystem solution for any speed grade Pentium microprocessor with a 66 MHz bus clock and is capable of supporting zero wait-state transfers. This is achieved without relying on a second level cache to improve system performance. Instead, this memory subsystem takes advantage of the Pentium's pipelined access mode and memory interleaving to achieve zero wait-state accesses.

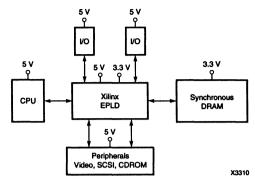

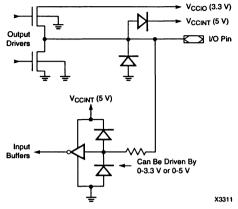

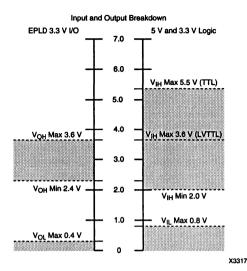

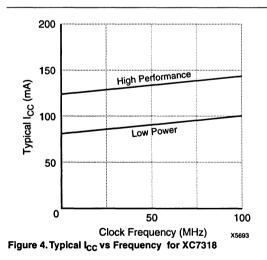

The control logic required to implement the DRAM controller needs to be fast enough to run at the processor bus clock frequency and wide enough to decode signals from the both CPU and the two memory controller state machines (one for each bank of memory). The control logic must also have 3.3 V I/O capability to interface directly to the DRAM without additional buffers. In addition, to minimize the microprocessor's output signal loading, especially on the /ADS strobe, chip count needs to be minimized.

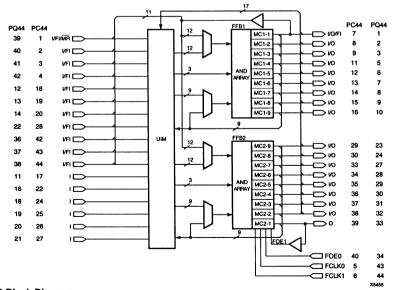

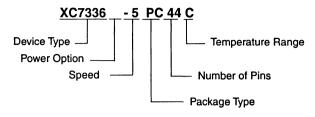

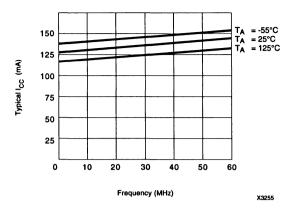

A 44-pin Xilinx XC7354-10 EPLD integrates the DRAM control functions into a single chip. This device has an internal cycle time of 77 MHz and features register delays compatible with both the Pentium microprocessor and synchronous DRAM. It's 3.3 V I/O can drive the synchronous DRAM directly, avoiding the delays introduced by external level-shifting buffers.

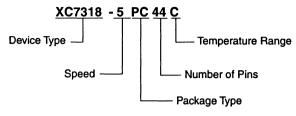

The DRAM address multiplexing and pipelining is handled by a 44-pin XC7318-7 EPLD. It's 3.3 V I/O and 24 mA drive make it well suited for driving the DRAM array address bus.

Before proceeding with the memory system description, a quick review of the Pentium and synchronous DRAM operation may be helpful to those readers not familiar with these devices.

### **Pentium Bus Operation**

The Pentium processor is connected to the system through a synchronous bus that operates at up to 66 MHz. A bus cycle begins with the Pentium driving an address and asserting bus cycle definition pins with a valid address strobe and ends when the last burst ready signal is returned to indicate that the bus cycle is complete. A single read or write transfer takes two clock cycles to complete without any wait states. When performing cache fill or write back cycles the processor uses a burst transfer mechanism instead. The opening access of the burst transfer still

# A Zero Wait State Synchronous DRAM Controller for the Pentium Microprocessor

# **Application Note**

takes two clock cycles, but the second, third and forth data transfer only take one clock each.

When accessing memory, the processor requires the memory controller to determine if the access will result in a burst transfer. If a burst transfer is performed, the memory controller is required to generate the burst addresses since the processor only provides the address for the opening access of the burst.

The Pentium also has the capability of pipelining accesses to improve memory system performance. Pipelining allows the memory subsystem to begin a new memory access while the previous memory access is still in progress. This feature reduces the latency required to perform the opening accesses of burst transfers.

In this design, the Pentium is connected to the EPLD through the address bus and cycle definition signals. The Pentium cycle definition signals used in this design are address strobe (/ADS), write/read (WRITE) and cacheability (/CACHE). The address bus and byte enables (BE[0:7]), are decoded to generate the correct DRAM access signals. The EPLD generates burst ready (/BRDY) to terminate the access and next address (/NA) to indicate that it is ready to begin a pipelined memory access.

# Synchronous DRAM Operation

Synchronous DRAMs are designed for use in high-bandwidth main memory subsystems. They derive their high performance through the use of internal address pipelining, and are able to provide valid data on every rising clock edge after the clock latency period has elapsed. Unlike a standard DRAM however, an internal mode register must be initialized to control how the device operates before any memory accesses take place. In addition, these 3.3 V memories can't be directly driven by programmable logic with standard TTL and CMOS output levels. Their low voltage TTL inputs must be driven by logic that has LVTTL compatible I/O such as the Xilinx XC7000 devices.

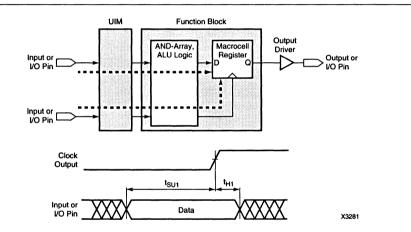

These devices have a synchronous interface to the system with level sensitive strobes and address inputs that are sampled on rising clock edges. Data is also clocked into and out of the DRAM on rising clock edges. The address bus is multiplexed as on a standard DRAM but the addresses are clocked into the chip when the address strobes are sampled active. This means that the designer does not need to be concerned about maintaining precise control of the timing relationships between the address strobes and address inputs or the write strobe and data. The designer need only ensure that the inputs meet the synchronous DRAM input setup and hold requirement.

The EPLD issues commands to the DRAM through four control inputs; row address strobe (/RAS), column address strobe (/CAS), write (/WE) and chip select (/CS). Although these signals have the same names as a conventional DRAM, they need only be sampled active for one clock cycle when commands are issued. The data mask inputs (DQM) control the output buffers during read cycles and data masks during write cycles. The clock enable (CKE) is not used in this design.

# Memory Subsystem Performance

Simulation studies by Intel show that Pentium performance during cache fills is more sensitive to wait states incurred during burst read transfers than to wait states incurred during the opening transfer of the burst. This is because every wait state incurred while bursting affects three transfers and has a larger impact on bus utilization than the wait states that occur once during the opening transfer.

Compared to read cycles, the Pentium's in-system performance was observed to be much less sensitive to wait states during write cycles. However, if a DMA controller is present in the system, wait states during each transfer of a block write operation could have a significant impact on system performance.

Therefore, this memory subsystem was designed to perform zero wait accesses for both read and write burst transfers. The latencies incurred during the opening access of each burst cycle could be partially, and in some cases completely, hidden by taking advantage of the processor's pipelined access capability. Thus, pipelined burst reads by the CPU and pipelined DMA burst reads and writes can be completed in as little as five clock cycles as shown in Table 1.

| Table | 1. Memory | System | Performance |

|-------|-----------|--------|-------------|

|-------|-----------|--------|-------------|

| Сусіе Туре                               | Clocks  |

|------------------------------------------|---------|

| Burst Read Cycle                         | 9-1-1-1 |

| Pipelined Burst Read (Alternate Bank)    | 2-1-1-1 |

| Burst Write                              | 4-1-1-1 |

| Pipelined Burst Write (Alternating Bank) | 2-1-1-1 |

# Memory Subsystem Overview

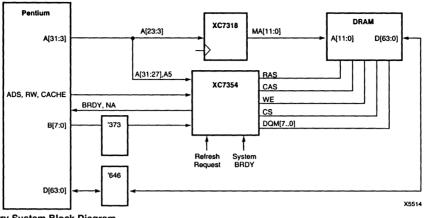

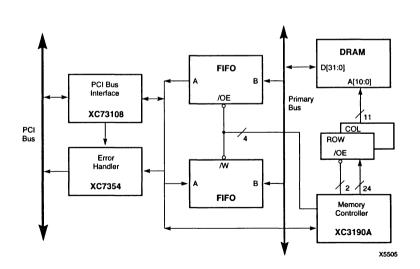

A block diagram of the memory subsystem is shown in Figure 1. The 16 MByte DRAM memory array consists of

eight byte wide synchronous DRAM. These 16MBit devices are organized internally as two 1Mx8 banks. Since each bank can be accessed independently through common address and data pins, external address latches and data path multiplexors are not required when implementing a two-bank interleaved system.

The registered DRAM address multiplexor logic multiplexes and pipelines the DRAM row and column addresses during normal accesses as well as generating the proper DRAM addresses during the DRAM mode register write cycle. This is a good example of the I/O intensive high performance applications that the 44-pin XC7318 was designed for.

The DRAM controller was implemented in a single 44-pin XC7354. The DRAM controller logic contains two independent DRAM control state machines; one state machine for each memory bank. These state machines share common CPU inputs and control the DRAM through shared output control signals, however they allow each bank of DRAM to be accessed independently of the other. One of the state machines also is responsible for performing the DRAM mode register write cycle after system reset. In addition to controlling the DRAM, this logic also generates the CPU Next Address signal to support address pipelining and consolidates the system's /BRDY inputs for the CPU.

Registered '646 type transceivers were used to pipeline data between the DRAM array and the CPU. Although this introduces one additional period of clock latency, this permits the data path logic to complete each data transfer in one clock while bursting.

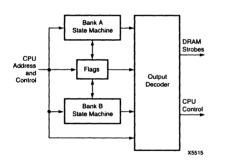

# **DRAM Controller Overview**

The DRAM controller consists of two independent state machines, a set of internal flags and a registered output decoder, and as shown in Figure 2. The two state machines share control of a single set of registered outputs that decode each machine's state bits, cycle termination signals and data masks. The nine flags control inter-state-machine communication and latch memory access requests, refresh cycle requests, and CPU cycle definition signals as shown in Table 2.

The ABEL-HDL code in Appendix A contains comments that completely describe the internal operation of the DRAM controller. The design files, compressed into XAPP049A.ZIP are also available on the Xilinx BBS.

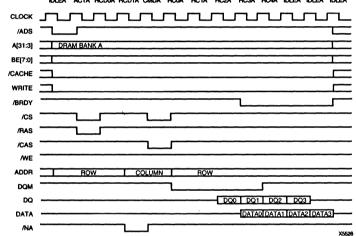

# **Memory Access Descriptions**

Several types of memory accesses are illustrated to show how the Pentium, DRAM controller and synchronous memory work together in this memory subsystem. Timing diagrams are used to show waveforms as well as the internal states of the memory controller state machines.

Figure 1. Memory System Block Diagram

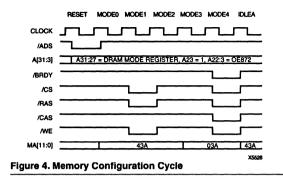

## **Memory Configuration Cycle**

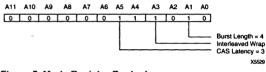

Unlike conventional DRAM, an internal mode register must be loaded to configure the DRAM for the desired operating characteristics. The DRAM was configured for a CAS latency of three clock cycles, and an interleaved address wrap and a four transfer burst to conform to the Pentium address wrap sequence and burst length. The mode register contents to be loaded are shown in Figure 3.

Figure 2. DRAM Controller Block Diagram

#### Table 2. DRAM Controller Flags

#### Figure 3. Mode Register Contents

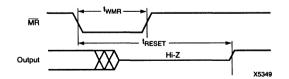

When the DRAM mode register address space is accessed by the CPU, the DRAM controller precharges both memory banks, then asserts the appropriate control signals to load the mode register as shown in Figure 4. During the memory precharge command, DRAM address bit A10 must be a 1 to precharge both banks of memory, however a 0 must be loaded into A10 of the mode register. The DRAM controller uses the address multiplexor to manipulate this address bit during the memory configuration cycle.

Once the memory configuration cycle is complete, the controller asserts /BRDY to terminate the CPU bus access. The memory controller is now ready to respond to memory access and refresh requests.

| Flag                                                 | Definition                                                  |

|------------------------------------------------------|-------------------------------------------------------------|

| Rfrq                                                 | Refresh Request                                             |

| BankA_Pending<br>BankB_Pending                       | Latched CPU Access Request                                  |

| BankA_Write, BankA_Cache<br>BankB_Write, BankB_Cache | Identifies Read/Write and Burst Read/Write Access Start     |

| WaitA<br>WaitB                                       | State Machine Wait State Outputs Used to Defer Access Start |

#### **Read Cycles**

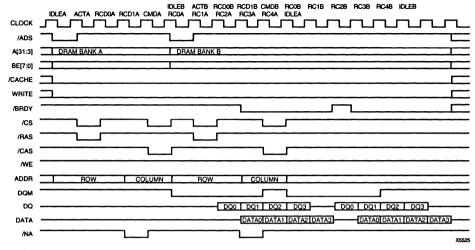

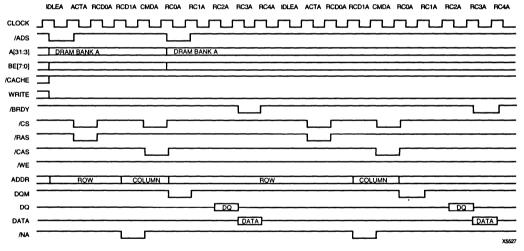

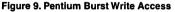

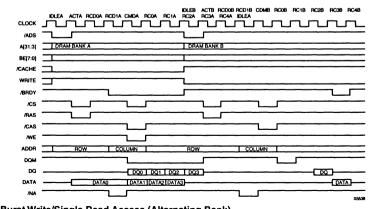

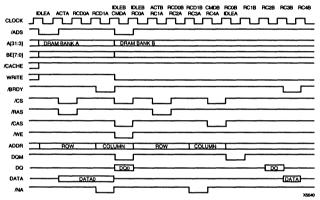

The Pentium performs a four transfer burst access when filling its on-chip cache as shown in Figure 5. If the memory bank is already precharged the access takes twelve clock cycles. However, the controller is ready to start a pipelined memory access after only five clock cycles have elapsed. By interleaving accesses between memory banks, a pipelined cache fill can be completed without any wait-states as shown in Figure 6.

I

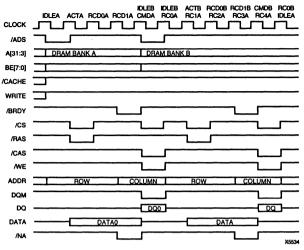

IDLEA ACTA RCDOA RCD1A CMDA RCOA RC1A RC2A RC3A RC4A IDLEA IDLEA IDLEA

Figure 5. Pentium Burst Read Access

Figure 6. Pentium Pipelined Cache Fill

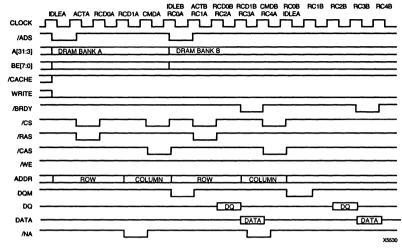

#### Figure 7. Pentium Single Read/Single Read Access (Same Bank)

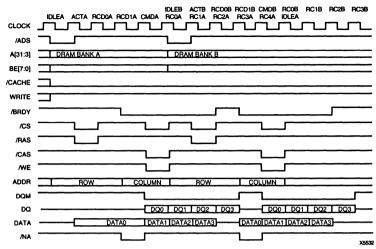

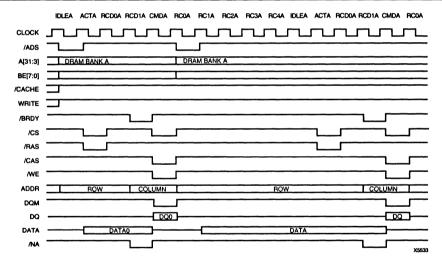

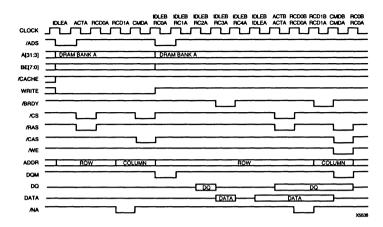

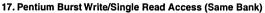

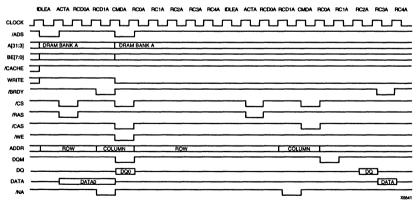

With the memory banks divided on 32 byte boundaries to maximize burst transfer performance, pipelined single data reads may have a higher likelihood of hitting the same bank as shown in Figure 7. However, if the alternate bank is hit the access takes only five clock cycles as shown in Figure 8.

Figure 8. Pentium Single Read/Single Read Access (Alternate Bank)

#### Write Cycles

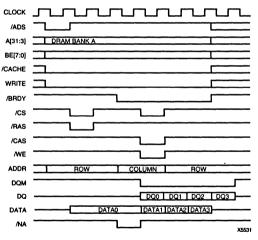

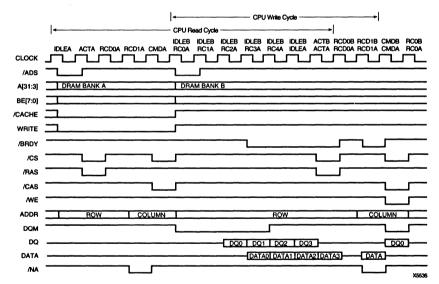

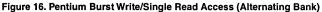

The Pentium also performs four transfer burst write cycles when writing back the contents of its on-chip cache to the main memory. If the memory bank is already precharged this takes seven clock cycles as shown in Figure 9. The Pentium processor will not pipeline write cycles into write cycles. However, if the system DMA controller performs pipelined burst write accesses, each access can be completed in as few as five clock cycles as shown in Figure 10.

Figure 11. Pentium Single Write/Single Write Access (Same Bank)

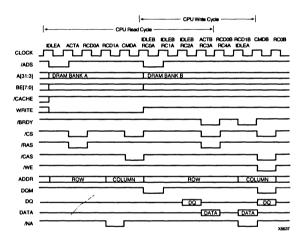

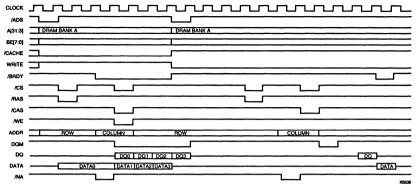

With the memory banks divided on 32 byte boundaries to maximize burst transfer performance, pipelined single data writes may have a higher likelihood of hitting the same bank as shown in Figure 11. However, if the alternate bank is hit the access takes only five clock cycles as shown in Figure 12.

## Read/Write and Write/Read Cycles

Examples of write cycles that follow read cycles are shown in Figures 13, 14 and 15. Examples of read cycles

that follow write cycles are shown in Figures 16, 17, 18 and 19.

Figure 14. Pentium Single Read/Single Write Access (Pipelined, Same Bank)

Figure 19. Pentium Single Write/Single Read Access (Same Bank)

### Refresh Cycle

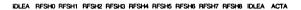

The DRAM controller accepts refresh requests from an off-chip refresh timer. The controller latches the external refresh request and synchronizes it before it is sampled by the Bank B state machine. The state machine arbitrates between the refresh and access request, servicing the access request after the refresh cycle has been performed as shown in Figure 20.

### Figure 20. Refresh Cycle

#### **Design Considerations**

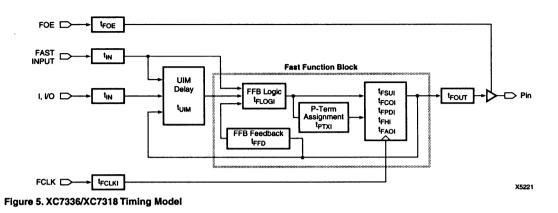

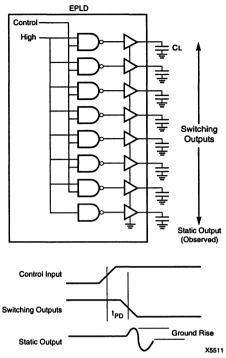

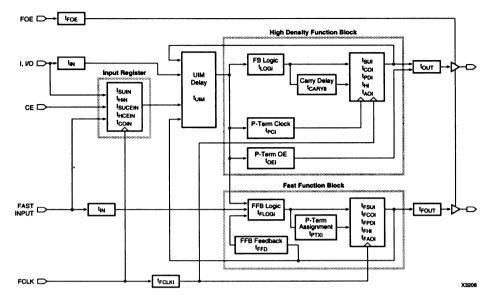

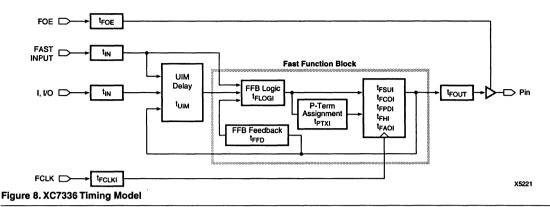

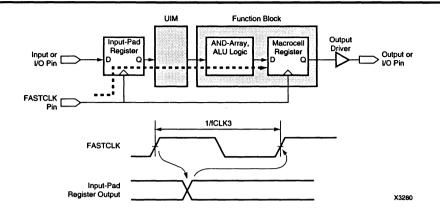

Xilinx EPLDs are optimized for designs that require very high speed logic paths and complex state machines. To meet the different speed/density requirements of the these functions, the Xilinx XC7354 features two different types of logic blocks on a single IC. This Dual-Block<sup>TM</sup> architecture combines High Density Function Blocks optimized for density, and simpler Fast Function Blocks (driven directly from Fast Input pins) optimized for speed, on the same device. By featuring multiple types of logic blocks on a single device with a 100% populated switch matrix that guarantees 100% routing with 100% utilization, the Xilinx EPLD avoids the classical trade-offs of speed vs. density vs. routing resources.

This section discusses the design's timing requirements and design considerations. It shows how best to take advantage of the Xilinx XC7000 Dual-Block architecture to meet those requirements. Timing information is based on the worst case AC specifications for the XC7354-10 published in the 1994 Xilinx Programmable Logic Data Book. Timing information for the Pentium is taken from the 1993 Pentium Processor User's Manual.

| Device     | t <sub>SU</sub> | t <sub>co</sub> |

|------------|-----------------|-----------------|

| Pentium-66 | 5.0             | 8.0             |

| XC7354-10  | 5.0             | 8.0             |

| XC7318-7   | 4.0             | 5.5             |

#### **Critical Timing Parameters**

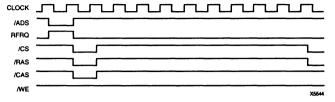

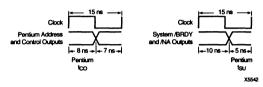

To interface with the Pentium, the register delays of the programmable logic must be Pentium compatible. Since the Pentium address and control signals used in this design become valid 8 ns after the rising edge of clock, the system has only 7 ns to recognize these signals on the next clock edge. The Pentium requires that its /BRDY and /NA inputs be valid 5 ns and 4.5 ns, respectively, before the rising edge of clock leaving the system 10 ns (including board trace delays) to generate these control signals.

Figure 21. Pentium Requirements for Control Path Timing

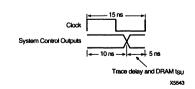

Synchronous DRAM features fast setup times for both control and data inputs. The XC7354-10 supplied control signals are available no later than 10 ns after the rising edge of clock. This allows 5 ns for trace delay and DRAM  $t_{SU}$  which means the XC7354-10 is compatible with synchronous DRAM timing requirements.

#### Handling of Critical Signals

In many designs, there are only a limited number of critical input and/or output signals. Critical signals are easily flagged by using property statements in the ABEL-HDL code. The software then automatically assigns critical input signals to the Fast Input pins, and partitions the critical logic functions into the Fast Function Blocks.

The critical DRAM controller input signals in this design are the Pentium address lines, /ADS strobe and WRITE. The DRAM controller needs to decode the Pentium address lines and the /ADS strobe within one clock cycle to detect an access to the DRAM address space. The bank state machines also need to sample the WRITE signal during the first clock cycle to determine if the requested access can potentially conflict with another access that may be in progress.

Figure 22. Synchronous DRAM Timing Requirements

To minimize setup to clock for these signals, they are assigned to the Fast Input pins and the state bits and DRAM strobes that sample these signals in the first clock cycle are assigned to the Fast Function Blocks. Fast Input setup to clock on the XC7354-10 is 5 ns, however one additional ns is required in this design because some of the logic functions assigned to the Fast Function Blocks require product terms from adjacent Macrocell. This allows 1ns for chip-to-chip delay.

The critical DRAM controller output signals are the Pentium /BRDY and /NA inputs and the registered multiplexor row/column select line. These functions are assigned to Fast Function Blocks to take advantage of their 8 ns clock to output delay. This allows 2 ns for chip-to-chip delay between the DRAM controller and the Pentium, and 4 ns between the DRAM controller and the multiplexor.

Not all of the state machine bits are critical in this design. States were assigned in a way that only two state bits from each state machine make transitions based on Fast Inputs. This gives the software the freedom to map the other state bits into the more product-term intensive High Density Function Blocks. This state assignment technique takes full advantage of the Dual Block architecture for product term intensive state machines that require fast register setup times.

Likewise, only the DRAM /RAS and /CS strobes need to make transitions based on Fast Inputs. The remaining DRAM control signals can be mapped into the High Den-

sity Function Blocks. Their 10 ns clock to output still allows 2.5 ns for chip to chip delays between the DRAM controller and the DRAM.

### Conclusion

High performance memory subsystems for the Pentium do not require expensive, power hungry second level caches. Systems based on synchronous DRAM using 3.3 V I/O compatible Xilinx 7000 EPLDs for the control function enable the designer to implement a cost effective, high performance system with a minimum of components.

Ŋ

The Xilinx Dual Block architecture features logic blocks optimized for the critical paths of a Pentium memory subsystem, and logic blocks dense enough to implement two memory controllers, one for each bank of memory, in a single 44-pin device. This control logic supports the high performance access modes of both the Pentium and synchronous DRAM.

#### References

Intel Corporation, *Pentium<sup>TM</sup> Processor User's Manual*, 1993

Ghaznavi, Raheel, *An Example Memory Subsystem for the Pentium<sup>TM</sup> Microprocessor*, Application Note AP-478,1993, Intel Corporation, Santa Clara, CA.

Xilinx, Inc., The Programmable Logic Data Book, 1994

## Appendix A

Module Pentium

title 'Synchronous DRAM Controller for Pentium';

pentium device;

plusasm property 'partition ffb ras cs banka\_pending bankb\_pending banka0'; plusasm property 'partition ffb banka1 bankb0 bankb4 brdy na'; plusasm property 'inputpin (fi) ads a31 a30 a29 a28 a27 a5 write';

" Inputs

clock

pin; " 66MH

ads

pin; " Pentiti

a31,a30,a29,a28,a27,a5

pin; " Pentiti

be0,be1,be2,be3,be4,be5,be6,be7

pin; " Pentiti

write

pin; " Pentiti

'brdrst

pin; " Pentiti

'brdrst

pin; " Pentiti

'brdrst

pin; " Pentiti

'brdrst

pin; " Syste

brdy\_in

pin; " Syste

pin; " 66MHz system clock pin; " Pentium address strobe pin; " Pentium address signals pin; " Pentium byte enables pin; " Pentium write signal pin; " Pentium cache signal pin; Board reset pin; " Refresh timer refresh request pin; " System burst ready input to controller

| " Outputs                          |                                                              |

|------------------------------------|--------------------------------------------------------------|

| ras,cas,we,cs                      | pin istype 'reg'; * DRAM control signals                     |

| dgm0,dgm1,dgm2,dgm3                | pin istype 'reg'; " DRAM data mask signals                   |

| dqm4,dqm5,dqm6,dqm7                | pin istype 'reg';                                            |

| mux                                | pin istype 'reg'; " address mux control                      |

| brdy                               | pin istype 'reg'; " Pentium ready signal                     |

| •                                  |                                                              |

| na                                 | pin istype 'reg'; " Pentium next address                     |

| " Nodes                            |                                                              |

| banka_pending                      | node istype 'reg'; " DRAM bank A access request pending flag |

| bankb_pending                      | node istype 'reg'; " DRAM bank B access request pending flag |

| banka_write                        | node istype 'reg'; " Identify DRAM bank A write cycle        |

| bankb_write                        | node istype 'reg'; " Identify DRAM bank B write cycle        |

| banka cache                        | node istype 'reg'; " Identify DRAM bank A burst cycle        |

| bankb_cache                        | node istype 'reg'; " Identify DRAM bank B burst cycle        |

| waita                              | node istype 'reg'; " Wait for bank A                         |

| waitb                              | node istype 'reg'; " Wait for bank B                         |

| Wall                               | node istype reg, wat in bank b                               |

| banka0,banka1,banka2,banka3        | node istype 'reg'; " Bank A state bits                       |

| bankb0,bankb1,bankb2               | node istype 'reg'; " Bank B state bits                       |

| bankb3,bankb4                      | node istype 'reg';                                           |

| brdya_extend                       | node istype 'reg'; * Extend brdy for one                     |

|                                    | " clock during burst                                         |

|                                    | " read cycles                                                |

| brdyb_extend                       | node istype 'reg'; " Extend brdy for one                     |

| . –                                | " clock during burst                                         |

|                                    | " read cycles                                                |

| brdya                              | node istype 'reg'; " bank A brdy                             |

|                                    |                                                              |

| brdyb                              | node istype 'reg'; * bank B brdy                             |

| dqma,dqmb                          | node istype 'reg'; " data mask enables                       |

| sync_refresh                       | node istype 'reg'; " Syncs refresh input                     |

| rfrq                               | node istype 'reg'; " Refresh flag                            |

|                                    |                                                              |

| " Variables                        |                                                              |

| * State bit fields, bank addresses | and DRAM mode register address                               |

|                                    |                                                              |

| banka_state | = [banka3,banka2,banka1,banka0];        |

|-------------|-----------------------------------------|

| bankb_state | = [bankb4,bankb3,bankb2,bankb1,bankb0]; |

| banka       | = a31 & a30 & a29 & !a28 & !a27 & !a5;  |

| bankb       | = a31 & a30 & a29 & !a28 & !a27 & a5;   |

| mode        | = a31 & a30 & a29 & !a28 & a27 & a5;    |

**BANK A State Bit Definition**

BANK B State Bit Definition

| idleb | = [1,1,1,1,1]; |

|-------|----------------|

| actb  | = [1,1,1,1,0]; |

| rcd0b |                |

|       | = [1,1,1,0,0]; |

| rcd1b | = [1,1,1,0,1]; |

| cmdb  | = [1,1,0,0,1]; |

| rc0b  | = [1,1,0,1,1]; |

| rc1b  | = [1,1,0,0,0]; |

| rc2b  | = [1,0,0,0,0]; |

| rc3b  | = [1,0,0,0,1]; |

| rc4b  | = [1,0,0,1,1]; |

| rfsh0 | = [0,1,1,1,0]; |

| rfsh1 | = [0,1,1,0,0]; |

| rfsh2 | = [0,1,1,0,1]; |

| rfsh3 | = [0,1,0,0,1]; |

| rfsh4 | = [0,1,0,1,1]; |

| rfsh5 | = [0,1,0,0,0]; |

| rfsh6 | = [0,0,0,0,0]; |

| rfsh7 | = [0,0,0,0,1]; |

| rfsh8 | = [0,0,0,1,1]; |

" Refresh request clear flag

cir rfrg = (bankb state == rfsh8);

" Clear refresh flag when " refresh cycle is completed n.

@dcset

state\_diagram banka\_state;

"This state machine controls the DRAM mode load and bank A access cycles.

"The board reset signal puts the state machine in the RESET state. It then

" waits until the Pentium performs an access to the DRAM's mode control

" register. When an access to the register is detected, the state machine

" will precharge both memory banks before asserting the mode load command to

\* the DRAM, then cycle through to the IDLE state for normal operation. Once

" the mode load sequence has been run, access requests and refresh requests " will be honored.

\* Accesses start if Pentium requests an access or there is a request pending.

" The access will be deferred if there is a refresh request pending or if

\* the regested access is a write cycle and the other bank is performing one of

" three cycles. If the other bank is performing a burst read, then the access

" will not start until the other bank has entered the IDLE state. If the other

\* bank is performing a single read, then the access will not start until the

" other bank has entered state RC2. If the other bank is performing a single

" write, then the access will not start until the other bank has entered state

\* RC0. Once the access starts, the state machine will run through

\* the access sequence without stopping, then return to the IDLE state.

state reseta: if !ads & mode then mode0; else reseta;

state mode0: goto mode1; state mode1: goto mode2; state mode2: goto mode3; state mode3: goto mode4; state mode4: goto idlea;

state idlea:

if (!ads & banka # !banka\_pending) & !rfrg & !(!waitb & write) then acta: else idlea;

state acta: goto rcd0a; state rcd0a: goto rcd1a; state rcd1a: goto crd1a; state crda: goto rc0a; state cr0a: goto rc1a; state rc1a: goto rc2a; state rc2a: goto rc3a; state rc3a: goto rc4a; state rc4a: goto idlea;

#### state\_diagram bankb\_state;

" This state machine controls the DRAM refresh and bank B access cycles.

The board reset signal puts the state machine in the RESET state.

" It then waits until the bank A state machine has completed it's mode load

\* sequence and entered the IDLEA state. Once the bank A state machine has

\* entered IDLEA, this state machine can honor any pending refresh requests.

\* Accesses start if Pentium requests an access or there is a request pending.

"The access will be deferred if there is a refresh request pending or if

" the reqested access is a write cycle and the other bank is performing one of

" three cycles. If the other bank is performing a burst read, then the access

" will not start until the other bank has entered the IDLE state. If the other

bank is performing a single read, then the access will not start until the

other bank has entered state RC2. If the other bank is performing a single

" write, then the access will not start until the other bank has entered state

" RC0. Once the access starts, the state machine will run through

" the access sequence without stopping, then return to the IDLE state.

state idleb:

if rfrq & (banka\_state == idlea) then rfsh0;

```

else if (lads & bankb # !bankb_pending) & !rfrq & !(!waita & write) then actb;

```

else idleb;

state actb: goto rcd0b; state rcd0b: goto rcd1b; state rcd1b: goto rcd1b; state crdb: goto rc0b; state crdb: goto rc0b; state rc1b: goto rc2b; state rc2b: goto rc3b; state rc3b: goto rc4b; state rc4b: goto idleb;

state rfsh0: goto rfsh1; state rfsh1: goto rfsh2; state rfsh2: goto rfsh2; state rfsh3: goto rfsh4; state rfsh3: goto rfsh4; state rfsh4: goto rfsh6; state rfsh6: goto rfsh6; state rfsh6: goto rfsh7; state rfsh6: goto rfsh8; state rfsh8: goto idleb;

equations

Define Flags and Status Bits

" The refresh request flag is set by external refresh requests. The external

\* signal is synchronized with an input pad register by the optimization

" software. The flag is cleared when the refresh cycle is completed.

sync\_refresh := refresh; sync\_refresh.ck = clock;

rfrq := sync\_refresh # rfrq & !clr\_rfrq; rfrq.ck = clock;

" The bank pending bits capture Pentium access request signals. If the

" bank state machine is in the IDLE state, the access will start without

" waiting another clock for the pending bit to go true. But if the state

" machine is in another state, the pending bit will start another access

```

* cycle once the state machine returns to the IDLE state.

```

```

"The pending bits will be cleared when the access begins.

```

There are two status bits required for each bank to identify the type of

access cycle being run. The access bits are driven by the WRITE and CACHE

" inputs and are used to identify read/write and burst read/write accesses.

" for the cycle in progress.

The write status bits remain valid through state RC4. They are driven high

when the IDLE state is entered and remain high until they are updated

by the bank state machine. When the write status bits are high, the other

" bank is free to start its access.

The cache status bits remain updated until the next access is started because they are used to extend brdy during burst read cycles.

```

Since the status bits are not updated until the bank state machines are

in the ACT state, input setup time to clock is not an issue even if these

```

" bits are not mapped into FFBs.

```

banka_write := (banka_state == rc4a)

# (banka_state == idlea)

# write & (banka_state == acta)

# banka_write & ((banka_state == acta)

# (banka_state == rcd1a)

#(banka_state == rc0a)

#(banka_state == rc0a)

#(banka_state == rc2a)

#(banka_state == rc2a)

#(banka_state == rc3a));

```

```

banka_write.ck = clock;

```

```

banka_cache := cache & (banka_state == acta)

# banka_cache & ((banka_state == rcd0a)

#(banka_state == rcd1a)

#(banka_state == crd1a)

#(banka_state == rc0a)

#(banka_state == rc2a)

#(banka_state == rc2a)

#(banka_state == rc3a)

#(banka_state == rc4a)

#(banka_state == idlea));

```

```

banka_cache.ck = clock;

```

" Update flag " and keep it valid " until access is " completed

" Cycle done

\* Keep it high

" Update flag

- " and keep it valid

- " until next access

- \* starts

\* Cycle done

" Keep it high

```

Update flag

```

- and keep it valid until access is

- " completed

bankb cache := cache & (bankb state == actb) Update flag and keep it valid # bankb\_cache & ((bankb\_state == rcd0b) #(bankb\_state == rcd1b) until next access #(bankb\_state == cmdb) \* starts #(bankb\_state == rc0b) #(bankb\_state == rc1b) #(bankb\_state == rc2b) #(bankb\_state == rc3b) #(bankb\_state == rc4b #(bankb\_state == idleb));  $bankb_cache.ck = clock;$ \* Define Bank State Machine Wait Signals " WAITA and WAITB are used by each state machine to control when the other \* state machine is permitted to start its access cycle. If a write access is " requested, the access will not start until the other bank has reached a \* certain point when performing any one of 3 types of cycles. " If the other bank is performing a burst read, then the access " will not start until the other bank has entered the IDLE state. If the other " bank is performing a single read, then the access will not start until the other bank has entered state RC2. If the other bank is performing a single write, then the access will not start until the other bank has entered state \* RC0. waita := !banka\_write & !banka\_cache & ((banka\_state == cmda) " wait for #(banka\_state == rc0a) \* burst read #(banka\_state == rc1a) #(banka\_state == rc2a) #(banka\_state == rc3a)) # !banka\_write & banka\_cache & ((banka\_state == cmda) " wait for single read #(banka\_state == rc0a)) # banka write & banka cache & (banka state == rcd1a); " wait for \* single write waita.ck = clock: waitb := !bankb\_write & !bankb\_cache & ((bankb\_state == cmdb) " wait for " burst read #(bankb\_state == rc0b) #(bankb\_state == rc1b) #(bankb\_state == rc2b)

#(bankb\_state == rc3b)) \* wait for # !bankb\_write & bankb\_cache & ((bankb\_state == cmdb) #(bankb\_state == rc0b)) " single read # bankb\_write & bankb\_cache & (bankb\_state == rcd1b); " wait for \* single write waitb.ck = clock: \* Define DRAM Control Signals " RAS is pulsed low for bank active, refresh and mode load commands !ras := (banka\_state == idlea) & (!ads & banka # !banka\_pending) \* A access & Irfrq & (Iwaitb & write) # (bankb\_state == idleb) & (lads & bankb # lbankb\_pending) \* B access & !frq & (lanka\_state == idlea) & (lankb\_state == idlea) # rfrq & (banka\_state == idlea) & (bankb\_state == idlea) \* Refresh \* Precharge # (banka\_state == mode0) # (banka\_state == mode3); and Mode " Load ras.ck = clock; " CS is pulsed low for all DRAM commands !cs := (banka\_state == idlea) & (!ads & banka # !banka\_pending) " A access & Irfrq & I(Iwaitb & write) \* B access # (bankb\_state == idleb) & (!ads & bankb # !bankb\_pending) & Irfrq & I(Iwaita & write) \* Precharge & # (banka\_state == modé0) \* Mode Load # (banka\_state == mode3) # rfrq & (banka\_state == idlea) & (bankb\_state == idleb) \* Refresh # (banka\_state == rcd1a) Command A Command B # (bankb\_state == rcd1b);

#### A Zero Wait State Synchronous DRAM Controller for the Pentium Microprocessor

1

cs.ck = clock: \* CAS is pulsed low for read/write, refresh and mode load commands lcas := (banka state == rcd1a) Command A \* Command B # (bankb state == rcd1b) # rfrg & (banka\_state == idlea) & (bankb\_state == idleb) \* Refresh Mode Load # (banka state == mode3); cas.ck = clock; \*WE is pulsed low for write and mode load commands !we := (banka\_state == rcd1a) & write Write A " Write B # (bankb\_state == rcd1b) & write \* Precharge & # (banka state == mode0) # (banka\_state == mode3); Mode Load we.ck = clock; \* The DRAM data mask DQM signals are driven low to enable reads and " writes to each bank. Each bank state machine has individual control of " the data mask enable signal (dqma and dqmb). These enables go low one clock before DQM is required off chip. During read cycles, the enables are driven by decoded state bits. During write cycles, they always lag each bank's brdy (brdya or brdyb) signal by one clock. !doma := (banka state == rcd1a) & !banka write " Read # ((banka\_state == cmda) # (banka\_state == rc0a) # (banka\_state == rc1a)) & !banka\_write & !banka\_cache Burst Read # !brdya & banka\_write; " Write dqma.ck = clock; !dqmb := (bankb\_state == rcd1b) & !bankb\_write " Read # ((bankb\_state == cmdb) # (bankb\_state == rc0b) # (bankb\_state == rc1b)) & !bankb\_write & !bankb\_cache Burst Read " Write # !brdva & bankb write: damb.ck = clock;\* All data masks, dqm[0:7], go low during read cycles when enabled by \* the banka and bankb state machines. During write cycles however, only the \* selected data mask signals, as selected by the latched Pentium byte " enables, go low. ![dgm0..dgm7] := !dgma & ![be0..be7] & banka\_write # Idqma & Ibanka\_write # Idomb & I[be0..be7] & bankb write # !dqmb & !bankb\_write; [dqm0..dqm7].ck = clock; "Define Pentium Burst Ready and Next Address signals \* Each bank state machine controls its own brdy signal. This signal goes low one clock cycle before it is required off chip. During " read cycles it is driven by decoded state bits and latched cache \* and write bits. It is extended one clock during burst reads because " the state machine has returned to the idle state before the Pentium has " finished its burst read access. " During write cycles, the write cycle status bits (banka\_write and " bankb\_write) are not updated unti RCD0, Therefore, the write signal " is sampled when the state machine is in state ACT, not the status bit. " Since the write signal is sampled in ACTA, the setup time is not " critical for the status bits and brdy signals. " During mode load, the bank A state machine will drive brdya low \* to terminate the Pentium bus cycle. !brdya := (banka\_state == rc1a) & !banka\_write " Read Burst Read # ((banka\_state == rc2a) # (banka\_state == rc3a) # brdya\_extend) & !banka\_cache & !banka\_write " Write # (banka\_state == acta) & write # ((banka\_state == rcd0a) # (banka\_state == rcd1a) # (banka\_state == cmda)) & banka\_cache & banka\_write Burst Write # (banka state == mode3); Mode load brdya.ck = clock;

| brdya_extend := (banka_state == rc4a);<br>brdya_extend.ck = clock;                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|

| <pre>!brdyb := (bankb_state == rc1b) &amp; lbankb_write     # ((bankb_state == rc2b) # (bankb_state == rc3b)     # brdyb_extend) &amp; lbankb_cache &amp; lbankb_write     # (bankb_state == actb) &amp; write     # ((bankb_state == rcd0) # (bankb_state == rcd1     # (bankb_state == crd0b)) &amp; lbankb_cache &amp; bank     # brdy_in; brdyb.ck = clock;</pre>                                                         |                                                                                                                    |  |

| <pre>brdyb_extend := (bankb_state == rc4b);<br/>brdyb_extend.ck = clock;</pre>                                                                                                                                                                                                                                                                                                                                                |                                                                                                                    |  |

| !brdy := !brdya # !brdyb;<br>brdy.ck = clock;                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                    |  |

| "Assert Next Address when either bank is exiting state                                                                                                                                                                                                                                                                                                                                                                        | RCD0                                                                                                               |  |

| !na := (banka_state == rcd0a)<br># (bankb_state == rcd0b);<br>na.ck = clock;                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                    |  |

| Select column address when MUX is low                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |  |

| <pre>!mux := (banka_state == acta)     # (banka_state == ccd0a)     # (bankb_state == actb)     # (banka_state == rcd0b)     # (banka_state == mode1)     # (banka_state == mode2); mux.ck = clock;</pre>                                                                                                                                                                                                                     | <ul> <li>bank A access</li> <li>bank B access</li> <li>Precharge &amp;</li> <li>Mode Load</li> </ul>               |  |

| banka_state.ck = clock;<br>bankb_state.ck = clock;                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                    |  |

| end;                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                    |  |

| Module Selector<br>•<br>title 'Row/Column Address Multiplexor for Synchronous<br>Jeffrey Goldberg<br>Xilinx';<br>selector device;                                                                                                                                                                                                                                                                                             | s DRAM                                                                                                             |  |

| " Inputs                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                    |  |

| clock<br>mux<br>r0,r1,r2,r3,r4,r5,r6,r7,r8,r9,r10,r11<br>c0,c1,c2,c3,c4,c5,c6,c7,c8                                                                                                                                                                                                                                                                                                                                           | pin; " 66MHz system clock<br>pin; " Row/Column Select<br>pin; " Row address inputs<br>pin; " Column address inputs |  |

| <ul> <li>MUX, R11 and R[8:0] must be sampled during the first clock</li> <li>period of a CPU access, therefore they are declared as fast inputs.</li> <li>R9 and R10 drive combinatorial outputs, and can take the UIM path.</li> <li>C[8:0] are sampled later in the access, so they are not critical.</li> </ul>                                                                                                            |                                                                                                                    |  |

| plusasm property 'inputpin (fi) r0,r1,r2,r3,r4,r5,r6,r7,r8                                                                                                                                                                                                                                                                                                                                                                    | ,r11,mux';                                                                                                         |  |

| * Outputs<br>ma0,ma1,ma2,ma3,ma4,ma5,ma6,ma7,ma8,ma11<br>ma9,ma10                                                                                                                                                                                                                                                                                                                                                             | pin istype 'reg'; "DRAM address lines<br>pin istype 'com';                                                         |  |

| <ul> <li>The synchronous DRAM used in this design are organized internally as two</li> <li>1MEGx8 banks. The row address is determined by ma[0:10] and the column</li> <li>address by ma[0:8]. MA9 and MA10 are don't cares when the column address is</li> <li>being driven during memory accesses but must be driven low when the DRAM</li> <li>mode register is being loaded MA11 is the DRAM bank select input</li> </ul> |                                                                                                                    |  |

ţ

#### The CPU address bus should be connected to the multiplexor as shown below. CPU ADDRESS LINE MULTIPLEXOR INPUT

| • | CPU ADDRESS LINE | MULTIPLEXOR IN  |

|---|------------------|-----------------|

| • | a3               | c0              |

| • | a4               | c1              |

| • | a5               | r11<br>c2<br>c3 |

|   | a6               | c2              |

|   | a7               | c3              |

|   | a8               | c4              |

|   | a9               | c5              |

| • | a10              | c6              |

|   | a11              | с7              |

|   | a12              | c8              |

|   | a13              | r0              |

|   | a14              | r1              |

|   | a15              | r2              |

|   | a16              | r3              |

|   | a17              | r4              |

|   | a18              | r5              |

|   | a19              | r6              |

|   | a20              | r7              |

|   | a21              | r8              |

|   | a22              | r9              |

|   | a23              | r10             |

|   |                  |                 |

\* Row address is selected when mux is high, column address when mux is low.

| equations<br>[ma8ma0] := [r8r0] & mux<br># [c8c0] & Imux; | <ul> <li>These bits are registered because the</li> <li>column address must held valid one additional</li> <li>clock cycle during a Pentium single write</li> <li>access</li> </ul>                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ma9 = r9;                                                 | * MA9 is a don't care during column access * so a multiplexor is not needed                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ma10 = r10 & mux;                                         | <ul> <li>MA10 is only used as a row address input</li> <li>during memory access cycles. MA10 must be</li> <li>high when the precharge command is issued</li> <li>by the DRAM controller prior to performing</li> <li>a mode load, but must be low when the mode</li> <li>load command is issued. Therefore, when the</li> <li>preload command is issued, MA10 will follow</li> <li>r10, but when the mode load command is issued</li> <li>ma10 will be driven low because the DRAM</li> <li>controller drives mux low.</li> </ul> |

| ma11 := r11;                                              | <ul> <li>The bank select bit must be the same for the</li> <li>row access and column access commands, so a</li> <li>multiplexor is not needed. This bit is</li> <li>registered for the same reasons as ma[8:0].</li> </ul>                                                                                                                                                                                                                                                                                                        |

| [ma8ma0].ck = clock;                                      | registered for the same reasons as majo.oj.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

[ma8..ma0].ck = clock; ma11.ck = clock; end;

# Designing Flexible PCI Interfaces With Xilinx EPLDs

# January 1995

# Abstract

Peripheral Component Interconnect (PCI) is becoming a fundamental building block of today's high-performance PC and workstation peripherals, and developing products that meet the stringent PCI Local Bus Specification (PCI LBS) is the next challenge for system designers.

Xilinx provides a wide range of programmable logic devices that help designers develop PCI-compliant highperformance solutions. The XC7300 Erasable Programmable Logic Devices (EPLDs) offer designers a wide range of programmable logic options that are fully compliant with the PCI LBS.

This application note describes the building blocks of a flexible PCI target interface implemented with XC7300 EPLDs and serves as a guide for designing PCI bus interfaces. To get assistance in evaluating Xilinx EPLDs and FPGAs for your PCI designs, e-mail your design requirements to **pci@xilinx.com** or call the Xilinx Applications hotline at 1-800-255-7778.

# **PCI Local Bus Overview**

PCI specifies a 32-bit or 64-bit bus with multiplexed address and data lines. It is used as an interconnect between highly integrated peripheral controller compoApplication Note - Version 2.0

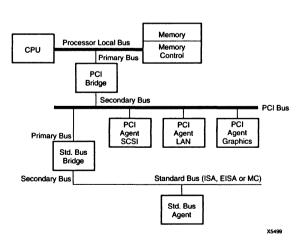

nents, peripheral add-in boards, and processor/memory systems. Figure 1 shows a typical PCI-based system. The basic system architecture consists of a processor and memory subsystem connected by the processor's local bus. The host bridge connects the local bus and the PCI bus, allowing them to communicate.

High performance peripherals (such as SCSI, LAN, graphics) directly connect to the PCI bus, giving them a high-bandwidth, low latency path to memory. Also shown is a standard bus bridge, that allows low-cost system expansion using a standard bus.

Each agent connected to the PCI bus functions as either a PCI target (slave) or combined PCI initiator/target (master/slave). The initiator function enables an agent to take control of the bus and drive the address, data, and control signals. Target functions cannot initiate bus transfers and rely on initiators to transfer data to them.

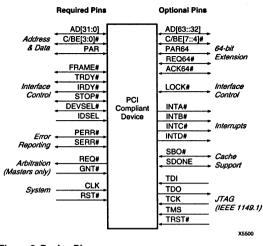

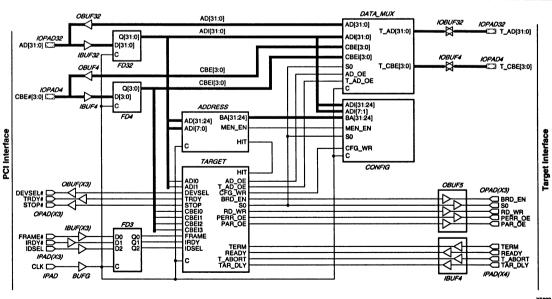

#### **PCI Interface Signals**

The PCI interface requires a minimum of 47 pins for a target-only device and 49 pins for an initiator to handle data, address, interface control, arbitration, and system functions. Figure 2 on the next page shows the pins in a initiator/target device, with required pins listed on the left side and optional pins listed on the right side.

Figure 1. Typical System Architecture

Table 1 lists a summary of the PCI signal pins. A "#" following the signal name indicates the signal is active-low. In this document, PCI signal names appear as **bold**. The signal types are defined as follows:

- in A standard input-only signal.

- out A standard active drive totem pole output.

- t/s A bi-directional, 3-state I/O pin.

- s/t/s A sustained, active-low, 3-state signal; must be high 1 cycle before going low.

- o/d An open drain signal; allows multiple devices to share signals as a wired-OR.

#### 3.3 V and 5 V Signaling Environment Support

The PCI specification defines both 3.3 volt and 5 volt signaling environments and recommends building universal boards with I/O buffers powered by connector-dependent voltage rails as shown in Figure 3. PCI cards and connectors are keyed to manage both 5 V and 3.3 V environments. In one orientation, the connector is keyed to accept boards using the 5 V system signaling environment. When turned 180°, the key is positioned to accept boards using 3.3 V signaling. Universal boards accept either 3.3 V or 5 V signaling.

The Xilinx XC7300 EPLDs have dual voltage I/O buffers designed to meet these specifications and are ideal for dual voltage operation of the universal board.

I

#### **Table 1. PCI Signal Summary**

| Signal     | Туре  | Description                                                                     |

|------------|-------|---------------------------------------------------------------------------------|

| AD[31:0]   | t/s   | Address and Data Bus.                                                           |

| C/BE[3:0]# | t/s   | Bus Command and Byte Enable.                                                    |

| CLK        | in    | PCI System Clock.                                                               |

| DEVSEL#    | s/t/s | Device Select. Signals that the target has decoded its address.                 |

| FRAME#     | s/t/s | Cycle Frame. Identifies start and length of bus transaction.                    |

| GNT#       | t/s   | Grant. Signals that the master has been granted bus access.                     |

| IDSEL      | in    | Initialization Device Select. Identifies the device selected for configuration. |

| IRDY#      | s/t/s | Initiator Ready. Signals when the master is ready to complete a data transfer.  |

| PAR        | t/s   | Parity for AD[31:0] and C/BE[3:0].                                              |

| PERR#      | s/t/s | Parity Error.                                                                   |

| REQ#       | out   | Request. Signals a master's request to use the bus.                             |

| RST#       | in    | PCI System Reset.                                                               |

| STOP#      | s/t/s | Stop. Signals that the target request to stop the current transaction.          |

| TRDY#      | s/t/s | Target Ready. Signals that the target is ready to complete the data transfer.   |

Figure 3. PCI Card Connector Arrangement

#### **PCI Bus Commands**

All PCI devices must respond to configuration read/write commands. PCI targets that contain relocatable functions/registers can provide host agents (initiators) the option of mapping those functions into memory space, allowing a device to work where I/O space is not available.

The PCI bus commands, encoded on the **CBE[3:0]#** pins, are summarized in Table 2.

#### Table 2. PCI Command Summary

| C/BE[3:0]# | Command                     |

|------------|-----------------------------|

| 0000       | Interrupt Acknowledge       |

| 0001       | Special Cycle               |

| 0010       | I/O Read                    |

| 0011       | I/O Write                   |

| 0100       | Reserved                    |

| 0101       | Reserved                    |

| 0110       | Memory Read                 |

| 0111       | Memory Write                |

| 1000       | Reserved                    |

| 1001       | Reserved                    |

| 1010       | Configuration Read          |

| 1011       | Configuration Write         |

| 1100       | Memory Read Multiple        |

| 1101       | Dual Address Cycle          |

| 1110       | Memory Read Line            |

| 1111       | Memory Write and Invalidate |

#### PCI Address Space

PCI defines three address spaces: memory, I/O, and configuration. Memory and I/O spaces are the same as those for Intel microprocessors; configuration space is unique to PCI.

PCI configuration space is divided into a predefined header region (64 bytes) and a device dependent region (192) bytes. A PCI-compliant device is not required to implement all (256 byte) registers. However, all unimplemented registers must return a value of zero when read. The format for the predefined header portion is shown in Table 3; the grey regions indicate the minimum required registers.

The PCI definition also provides for a fully software driven initialization and configuration via a separate configuration address space. One method of implementing this is to pass configuration requests to dedicated memory in the host interface. The designs in Appendices A and B contain configuration cycle decode logic and control signals to support these "pass through" configuration requests to host memory.

The Base Address Register is used by the operating system to determine the Memory or I/O space requirements of a device. In this design, the interface assumes a 16 MB address space (24-bits). The upper 8 bits of the Base Address Register have been implemented with read-write capability and the lower 24 bits always return a read value of zero. To expand or contract the address space allocated, the user simply adjusts the size of the Base Address Register and its associated address comparator.

#### Table 3. Configuration Space Header

| 31      | 16                     | 15               | 0                  |     |  |  |

|---------|------------------------|------------------|--------------------|-----|--|--|

| Dev     | ice ID                 | Vend             | 00h                |     |  |  |

| St      | atus                   | Com              | mand               | 04h |  |  |

|         | Class Co               | ode              | Revision ID        | 08h |  |  |

| BIST    | Header<br>Type         | Latency<br>Timer | Cache Line<br>Size | 0Ch |  |  |

|         | Base Address Registers |                  |                    |     |  |  |

|         |                        | Reserved         |                    | 28h |  |  |

|         |                        | Reserved         |                    | 2Ch |  |  |

|         | Expansion              | ROM Base Ad      | dress              | 30h |  |  |

|         | Reserved               |                  |                    |     |  |  |

|         |                        | Reserved         |                    | 38h |  |  |

| Max_Lat | Min_Gnt                | Interrupt Pin    | Interrupt<br>Line  | 3Ch |  |  |

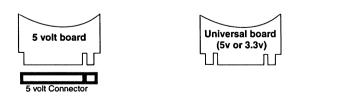

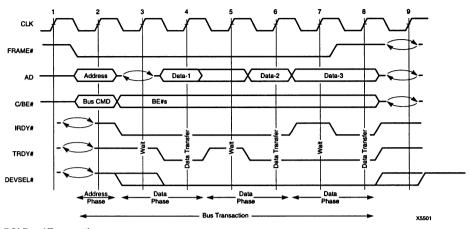

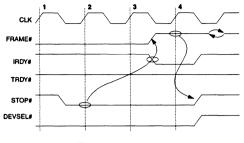

Figure 4. PCI Read Transaction

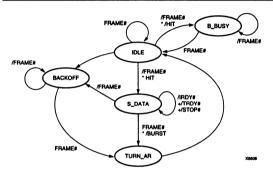

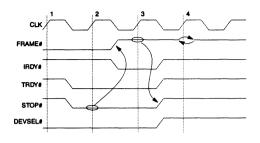

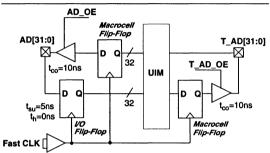

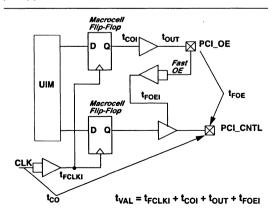

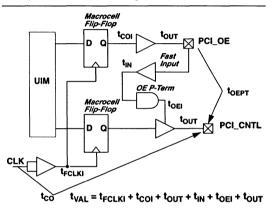

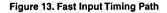

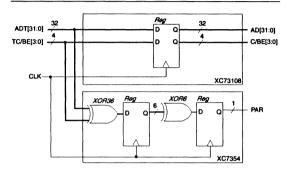

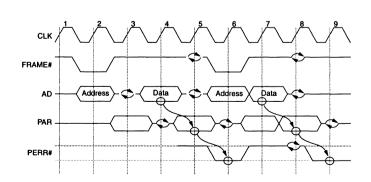

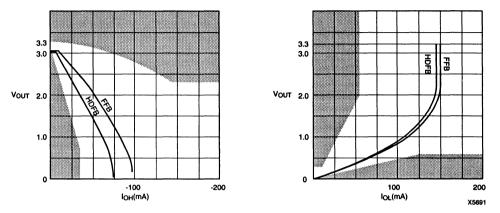

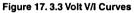

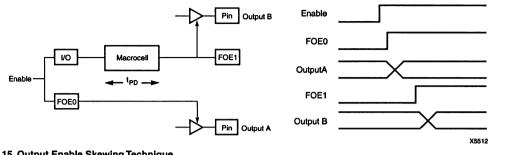

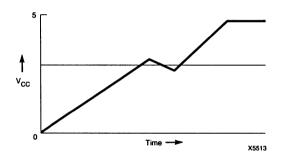

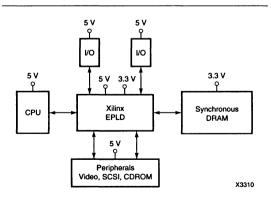

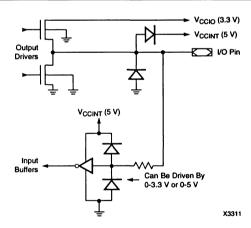

#### Data Transfer Timing