# XC9500 CPLD Application Guide with Data Sheets

February 1996

# XC9500 CPLD Application Guide with Data Sheets

2100 Logic Drive San Jose, California 95124 Telephone: (408) 559-7778 Fax: (408) 559-7114

February 1996

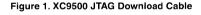

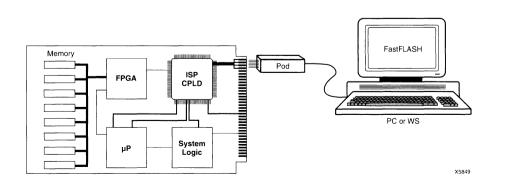

Xilinx, the Xilinx logo, and XACT are registered trademarks of Xilinx, Inc. All XC-prefix product designations, Dual-block, XEPLD, UIM, Logic Cell, and LCA are trademarks of Xilinx, Inc. The Programmable Gate Array Company is a Service Mark of Xilinx Inc. PAL and PALASM are registered trademarks of Advanced Micro Devices, Inc. ABEL is a trademark of DATA I/O Corporation. CUPL is a trademark of Logical Devices, Inc. All other trademarks are property of their respective owners.

Xilinx does not assume any liability arising out of the application or use of any product described herein; nor does it convey any license under its patents, copyrights or maskwork rights or any rights of others. Xilinx reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, will not assume responsibility for the use of any circuitry described other than circuitry entirely embodied in its products. Manufactured under one or more of the following U. S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,783,607; 4,820,937; 4,821,233; 4,835,418; 4,847,612; 4,853,626; 4,855,619; 4,855,669; 4,870,302; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858. Xilinx cannot assume responsibility for any circuits shown or represent that they are free from patent infringement or of any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

©1996 Xilinx, Inc. All rights reserved.

# **SECTION TITLES**

**1** Product Overview

2 Applications

- 3 XC9500 Product Description and Specifications

- 4 Packages

- 5 JTAG Software

- 6 Quality, Testing and Reliability

- 7 Sales Offices

# TABLE OF CONTENTS

| 1 | Product Overview                                                  |      |

|---|-------------------------------------------------------------------|------|

|   | Introduction to XC9500 CPLDs                                      | 1-1  |

|   | FastFLASH Technology: A New Electrically Erasable CPLD Technology | 1-3  |

| 2 | Applications                                                      |      |

|   | Designing With XC9500 CPLDs                                       | 2-1  |

|   | Pin Preassigning With XC9500 CPLDs                                | 2-9  |

|   | XC9500 CPLD Embedded Diagnostics                                  | 2-13 |

|   | XC95108 CPLD High Performance System Controller                   | 2-17 |

|   | XC95108 CPLD Serial Stream Interface                              | 2-19 |

| 3 | XC9500 Product Description and Specifications                     |      |

|   | XC9500 In-System Programmable CPLD Family                         | 3-1  |

|   | XC9536 In-System Programmable CPLD                                | 3-15 |

|   | XC9572 In-System Programmable CPLD                                | 3-21 |

|   | XC95108 In-System Programmable CPLD                               | 3-25 |

|   | XC95144 In-System Programmable CPLD                               | 3-33 |

|   | XC95180 In-System Programmable CPLD                               | 3-39 |

|   | XC95216 In-System Programmable CPLD                               | 3-45 |

|   | XC95288 In-System Programmable CPLD                               | 3-53 |

| 4 | Packages                                                          |      |

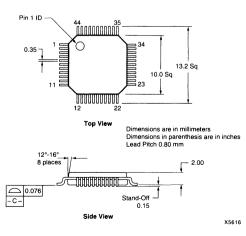

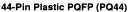

|   | 44-Pin Plastic PLCC                                               | 4-1  |

|   | 44-Pin Plastic PQFP                                               | 4-1  |

|   | 44-Pin Plastic VQFP                                               | 4-1  |

|   | 84-Pin Plastic PLCC                                               | 4-2  |

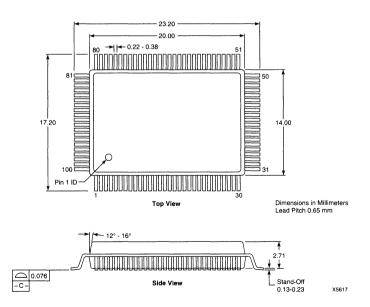

|   | 100-Pin Plastic PQFP                                              | 4-2  |

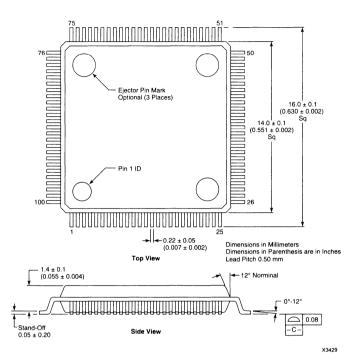

|   | 100-Pin Plastic TQFP                                              | 4-3  |

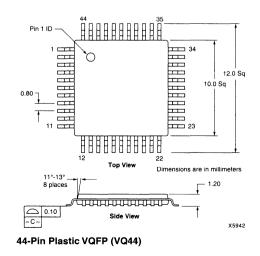

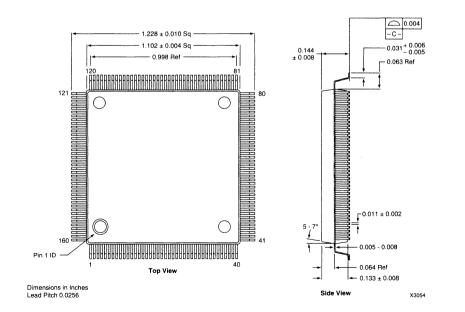

|   | 160-Pin Plastic PQFP                                              | 4-3  |

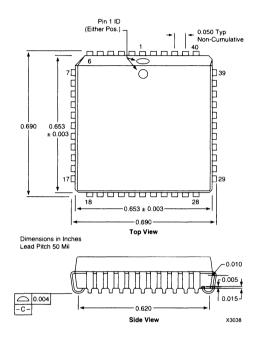

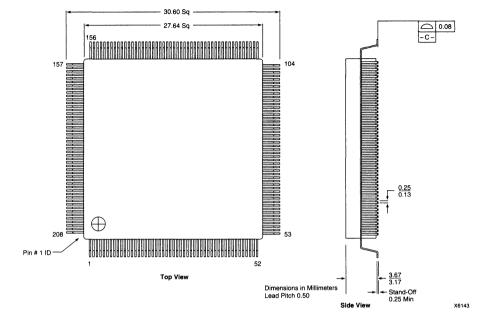

|   | 208-Pin Power QFP                                                 | 4-4  |

| 5 | JTAG Software                                                     |      |

|   | Using the XC9500 JTAG Boundary-Scan Interface                     | 5-1  |

| 6 | Quality, Testing and Reliability                                  |      |

|   | Xilinx Quality Assurance                                          | 6-1  |

| 7 | Sales Offices                                                     |      |

|   | Sales Offices                                                     | 7-1  |

|   |                                                                   |      |

, .

# **SECTION 1**

# **1 Product Overview**

- 2 Applications

- 3 XC9500 Product Description and Specifications

- 4 Packages

- 5 JTAG Software

- 6 Quality, Testing and Reliability

- 7 Sales Offices

# Introduction to FastFLASH<sup>™</sup> XC9500 CPLDs

## February 1996

Introduced in October 1995, the new XC9500 family of 5 V in-system programmable devices represents the next generation of CPLD solutions from Xilinx. Based on the innovative FastFLASH process technology, the XC9500 family incorporates a unique combination of product features specifically developed to meet all the needs for in-system programmability throughout what is typically known as the "customer's product life cycle".

This product life cycle starts with board level prototyping and system debug, programming and board level testing during manufacturing, and finally, field upgrades. The XC9500 addresses all these needs with industry-leading features such as 5 V ISP, predictable pin-to-pin delays as fast as 5 ns, density to 6,400 gates, 10,000 program/ erase cycles, superior pin-locking and extended IEEE 1149.1 JTAG support. Add to this the industry's first 5 V FastFLASH process technology specifically optimized for high-performance in-system programmable CPLDs and Xilinx now has a product which offers customers the industry's best in-system programmable CPLD for their complete product life cycle. This applications guide assists the CPLD user throughout every phase of their end product. Topics critical to in-system programmability such as pin pre-assignment and field upgrades where adding new features to a current product can be done by changing the software, with no hardware impact are included. In addition, there are detailed technical product specifications.

Xilinx products have always been designed to create a dramatically faster and more efficient product development process. By using these new XC9500 in-system programmable logic devices, customers can now add to those benefits the flexibility, performance, reliability and testability necessary for supporting the ever-shorter product life cycles.

## February 1996

## Summary

The Xilinx FastFLASH technology is a new 0.6 micron, double-polysilicon, 2-layer metal CMOS flash technology for CPLDs. The technology is capable of 5 V in system programming, high cell density needed for pinlocking, and a high endurance level of 10,000 in-system program/erase cycles. Compared to typical CPLD-EEPROM technology, FastFLASH technology affords advantages in reliability, density, and performance. The technology compatibility with industry-leading flash processes ensures the scalability of the basic process and the availability of foundry capacity.

#### Background

CPLDs are programmable by the user to implement the desired logic function. As non-volatile devices, CPLDs retain the programmed information even after power has been removed. This ability is provided by the underlying non-volatile process technology.

The process technology for CPLDs traditionally follows non-volatile memory (NVM) technologies. EPROM memory technology offers excellent memory cell density and low process cost, although it is not electrically erasable. EEPROM technology offers electrical erasability and reasonable process cost. However, it requires a relatively large memory cell size and offers limited endurance. Flash technology, which may be viewed as an electrically erasable extension of EPROM technology, offers the best long term technology solution by providing the cell density of EPROM, the electrical erasability of EEPROM, excellent endurance characteristics, and long term process cost benefits.

Compared to EEPROM technology, the proprietary Fast-FLASH technology supports the needs of CPLDs by providing:

- high-performance logic capability

- high memory cell density

- electrical erasability

- 5 V program and erase

- high reliability and endurance

- process scalability

This document describes the FastFLASH process technology and compares it with EEPROM technology.

# FastFLASH Technology: A New Electrically Erasable CPLD Technology

#### **EEPROM** Technology

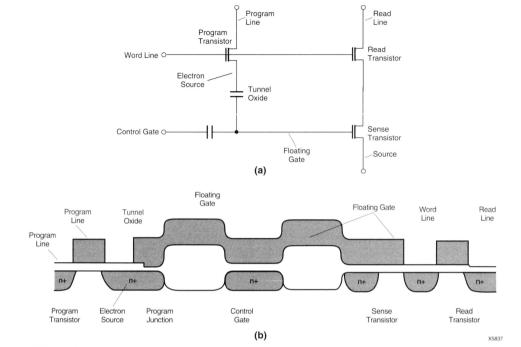

EEPROM technology was the first electrically erasable technology used for CPLDs. The programmable element is a special thin oxide capacitor that conducts a small current when a sufficient voltage is applied across the oxide. The tunnel oxide, approximately 80 Angstroms thick, is used to inject or extract charge from a floating gate via Fowler-Nordheim tunneling. The floating gate is connected to the gate of a sense transistor in order to sense the programming state. In addition to the tunnel oxide capacitor and sense transistor, two more transistors and an additional control capacitor is required to create a single EEPROM cell that can be programmed, erased, and used in a CPLD application.

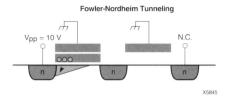

Figure 1 shows the schematic and cross-section of an EEPROM cell used in CPLDs. The tunnel oxide capacitor transports charge to and from the floating gate, which controls the the sense transistor. Two additional transistors are used for program and read operations. A control gate capacitor is needed to transfer voltage to the floating node for program and erase operations. Compared to standard CMOS logic processes, three additional device structures must be created for the EEPROM cell: the tunnel oxide capacitor, the control gate capacitor and the high-voltage transistor. The resulting process complexity makes the process and EEPROM cell more difficult to scale on future generations of technology.

The EEPROM cell density is poor since each cell is a circuit consisting of five separate device structures. The EEPROM cell area in a typical 0.6 micron technology is 75 to 100 square microns. The poor cell density directly affects the pin-locking ability of the architecture since more routing switches greatly increases the overall die size. The large cell size also introduces parasitic capacitances which limit the overall performance.

#### FastFLASH Technology

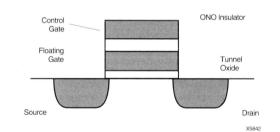

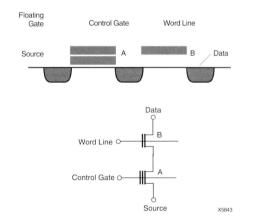

FastFLASH technology is compatible with industry-leading flash processes. The basic programmable element is the flash transistor which incorporates the floating gate into the device structure for improved cell area (see Figure 2). The flash transistor is incorporated into the FastFLASH cell by the addition of an NMOS transistor in series (shown in Figure 3).

#### FastFLASH Technology

#### Figure 1. EEPROM Cell (a) Schematic and (b) Cross-section

Figure 2. Flash Transistor Cross-section in FastFLASH Technology

Figure 3. FastFLASH Cell Schematic and Cross Section

Erased FastFLASH Cell

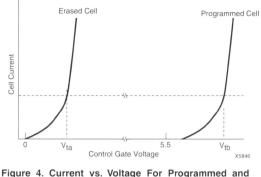

The behavior of an individual flash transistor can be changed by either programming or erasing operations. When a flash transistor is in the erased state, the threshold voltage ( $V_{ta}$ ) is approximately 1 V. When the transistor is programmed, its threshold voltage ( $V_{tb}$ ) is increased sufficiently above 5.5 V so that the transistor cannot be turned on during user logic operation. (See Figure 4.)

The physical structure of the flash transistor includes a floating gate polysilicon layer that is isolated from the silicon substrate by a thin oxide approximately 100 Angstroms thick. Above the floating gate is the control gate polysilicon layer, with an insulating oxide-nitride-oxide layer between them. The control gate is driven by internal logic circuits, while the floating gate is left unconnected. When the flash transistor is in the erased state, there is no net charge on the floating gate. By modifying the net electrical charge on the floating gate, the threshold voltage may be increased to 6 V or more.

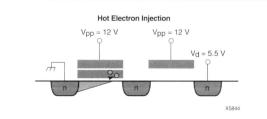

The flash transistor is programmed by applying approximately 12 volts to the control gate, 5.5 volts to the drain, and 0 volts to the source (see Figure 5). The voltages can be supplied by internal voltage pumps or externally by a device programmer. During the programming operation, channel hot electrons (CHE) are created near the pinch-off region. Some CHEs have sufficient thermal

Figure 5. FastFLASH Cell Programming Operation

Figure 6. FastFLASH Cell Erase Operation

energy to pass through the thin oxide and remain on the floating gate. The collected electrons create a net negative voltage on the floating gate that opposes the electric field emanating from the control gate. The result is a net increase in the threshold voltage.

The flash transistor can then be erased by applying 0 volts to the control gate and approximately 10 volts to the source with the drain left floating. See Figure 6. In this case, the electric field between the floating gate and the source node is increased to the point when Fowler-Nordheim tunneling can take place. Excess electrons are transported from the floating gate to the source. The transistor is designed to make the erase process self-limiting. As electrons are removed from the floating gate, the electric field decreases. FN tunneling effectively stops when the floating gate is electrically neutral.

## **Reliability and Endurance**

The reliability of the programmable cell relates to data retention and endurance. Data retention is how long the cell can keep its programmed and erased states. Endurance is the number of times a cell can be programmed and erased before failure.

When a cell is programmed and electrons are injected into the floating cell, the net charge should remain indefinitely. In practice, charge leaks off -- typically tens of years under normal storage and operating conditions. The charge transport can occur due to direct tunneling and thermal leakage. Direct tunneling is exponentially dependent on electric field. Generally, the direct tunneling leakage current is very small and largely negligible. Thermal leakage is the dominant leakage component. The leakage characteristics have been thoroughly characterized and modelled.

Endurance is determined by the magnitude of the applied E field and the quality of the thin oxide used for program and erase. When program and erase operations are performed in both FastFLASH and EEPROM cells, electrons are transported across the oxide in the direction of the applied electric field in both CHE injection and FN tunneling operations.

Endurance failures occur in the alteration of the tunnel oxide characteristics with repeated charge transport across the oxide. In FastFLASH technology, the maximum electric field is approximately 10 MV/cm. Consequently, the major cause of endurance failure is electron trapping in the tunnel oxide. After a large number of reprogramming cycles (typically over 100,000 and up to 1 million cycles), traps can be created within the oxide. When a sufficient number of electric field is distorted. The result is reduced program and erase efficiency, and erased states. The FastFLASH technology endurance failure is a gradual degradation rather than an abrupt failure.

In EEPROM cells, the program and erase fields are 15 to 20 MV/cm. The substantially higher field makes the EEPROM cell susceptible to destructive tunnel oxide breakdown and electron trapping in the oxide. Since the oxide is physically ruptured, the cell is permanently damaged. The EEPROM endurance failure mechanism is a hard failure and difficult to screen.

In both flash and EEPROM technologies, oxide quality control becomes important. In typical CPLD EEPROM technologies, the tunnel oxide is approximately 80 Angstroms, among the thinnest tunneling oxides in use today. In contrast, FastFLASH technology uses industrystandard process steps to achieve a high-quality tunnel oxide of approximately 100 Angstroms. There is a difference between the endurance of a single cell, and the overall endurance of the CPLD product which may use 100,000 cells or more. For the CPLD, failure statistics of a large number of cells suggest that the product endurance is typically 1.5 orders of magnitude lower than the endurance of an individual cell.

By using a significantly thicker tunnel oxide and lower electric fields than EEPROM technologies, the Fast-FLASH technology offers an endurance level of 10,000 cycles. This is compared with only 100 to 1000 cycles for current EEPROM CPLDs.

### **Cell Density**

The FastFLASH cell, with its flash transistor and series read transistor, is considerably smaller than the comparable EEPROM cell with five device structures. Figure 7 shows the relative layouts of the FastFLASH cell and an EEPROM cell. The FastFLASH cell is approximately 25 square microns in 0.6 micron technology. In contrast, the EEPROM cell is approximately 75 to 100 square microns, or 3 to 4 times larger. Therefore, FastFLASH offers three or more times cell density than EEPROM technology.

Cell density is important in CPLD technology, since each routing switch is controlled by a programmable cell. EEPROM-based CPLD architectures use fewer programmable cells for routing, directly impacting the routability and pin-locking capability.

Figure 7. Layout Comparison of FastFLASH Cell (a) and EEPROM Cell (b)

### **Process Scalability**

Process scalability is the ease of shrinking the process and chips to future generations of technology with smaller chip sizes, lower chip costs, and faster chips. It is important to ensure that a migration path to cost and speed improvements, as well as continued availability of the process to meet production requirements.

Factors that contribute to process scalability include:

- Number of different device structures

- Scalability of the programmable cell

- · Compatibility with main-stream memory processes

The leading flash memory technologies are double-polysilicon, stacked gate technologies with CHE injection for programming and FN tunneling for erase. These technologies offer superior process scaling and continued improvements in technology developments for cost and speed. Since the FastFLASH technology is compatible with these process technologies, it will continue to enjoy continued process migration to tighter geometries.

In contrast, EEPROM technology used in CPLDs are not used in high-volume memory technologies. Combined with a complex cell structure, EEPROM technologies are substantially more difficult to migrate to tighter geometries.

#### Conclusion

FastFLASH technology offers significant advantages in reliability, density, and performance over comparable EEPROM technologies. By utilizing a flash transistor structure that is compatible with the leading non-volatile memory technology, process scalability and future foundry availability is ensured.

#### References

- C.Hu, "Nonvolatile Semiconductor Memories : Technology, Design, and applications" IEEE press, New York, 1991.

- (2) C.Hu, "Thin oxide reliability", IEDM Tech. Digest pp 368-371, 1985.

- (3) S.K.Lai, V.K.Dham and D.Guterman, "Comparison and trends in today's dominant E<sup>2</sup> technologies", IEDM Tec. Dig., pp 580-583, 1986.

- (4) B.Dipert and L.Hebert, "Flash memory goes mainstream", IEEE spectrum, pp 48-52, October 1993.

# **SECTION 2**

**1** Product Overview

# 2 Applications

- 3 XC9500 Product Description and Specifications

- 4 Packages

- 5 JTAG Software

- 6 Quality, Testing and Reliability

- 7 Sales Offices

г.

# Designing With XC9500 CPLDs

### February 1996

#### Introduction

Xilinx XC9500 CPLDs solve a wide range of logic and state machine problems for today's high performance digital systems. This application note gives a series of useful design examples and practical details for successful designs. Since the architecture is uniform across the XC9500 family, these design techniques apply to all devices.

#### **XC9500 Architecture**

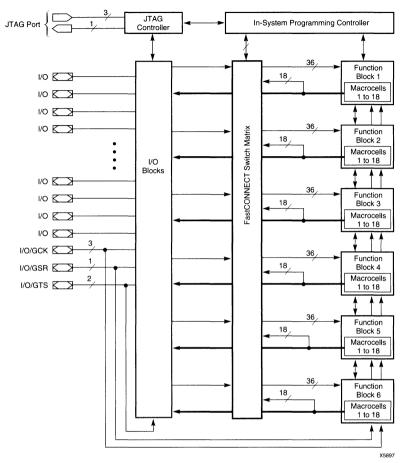

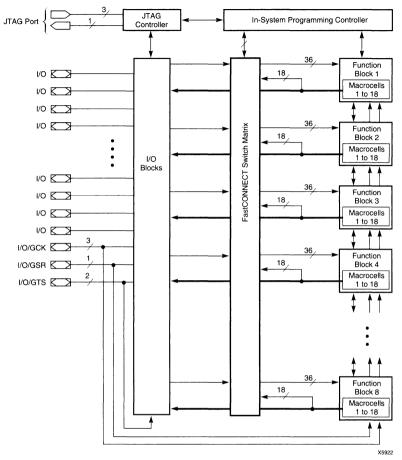

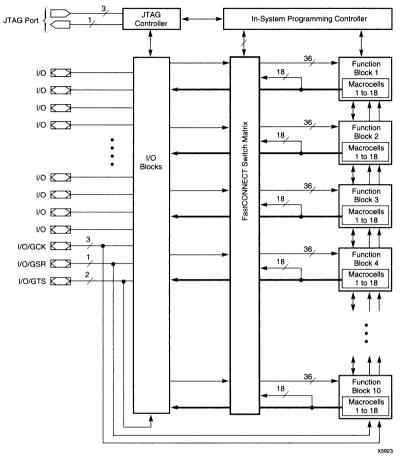

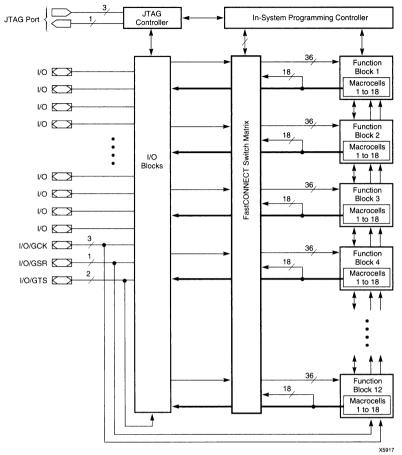

The XC9500 architecture is comprised of multiple identical function blocks internally connected with a fully populated FastCONNECT switch matrix. The XC9500 function block has 18 macrocells per block and supports pin-to- pin speeds as fast as 5 ns with clock rates up to 125 MHz. I/O signals can interface with 5 V, 3.3 V or both levels. Current software support includes XACT*step*, ABEL, VHDL, Verilog and operates with additional 3rd party schematic and simulation environments. Figure 1 shows the global XC9500 architecture. Note the regular structure of high speed function blocks centrally connected by FastCONNECT and surrounded by pins. Signals enter and exit on the pins, form logic operations within the function blocks and form connections and logic operations within FastCONNECT. Each section will be briefly discussed, to show key functionality.

#### Interconnect within Function Blocks

Function blocks have 36 input sites. The blocks receive signals from FastCONNECT and block input pins. The logic blocks generate 18 signals per function block from the 18 macrocells in each block. Each macrocell signal can drive its own dedicated I/O pin or feedback by entering FastCONNECT. Additional local paths exist within the function block to connect signals at high speed.

#### FastCONNECT

FastCONNECT attaches high speed pin-signals to the function blocks. It also connects every macrocell output to the function blocks through a fully populated crosspoint

#### Figure 1. XC9500 Architecture

## Application Note

switch. This connectibility supports design changes when an XC9500 is attached to the printed circuit board.

#### **Function Blocks**

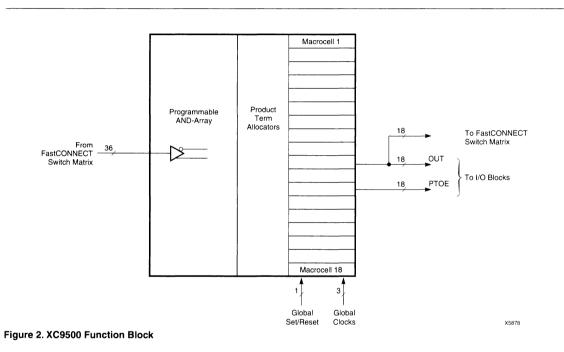

The function blocks (Figure 2) are groups of 18 macrocells. Each Function Block has 90 p-terms which can be assigned to any of the 18 macrocells via a proprietary allocation mechanism. This provides optimum logic flexibility within the function block and helps ensure pinlocked designs. Highest possible performance is attained by the software assigning a uniform five product terms per macrocell. The macrocell outputs can then drive output pins and/or feedback to both FastCONNECT and the function block in which it resides.

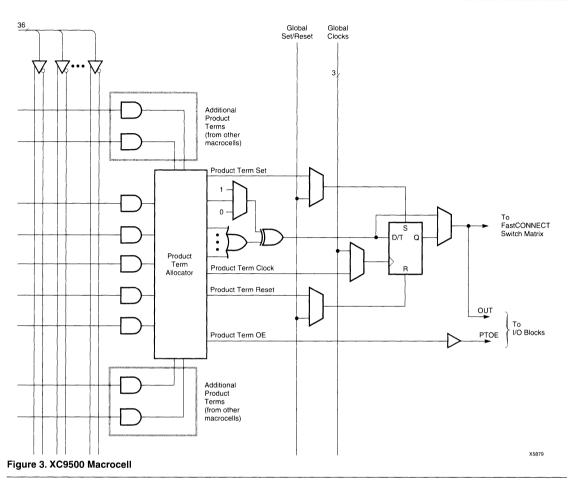

#### The Macrocell

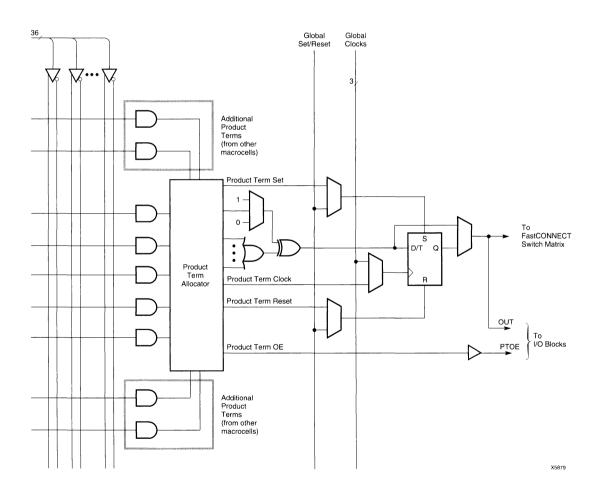

In the default mode, there are 5 product terms that OR together driving the D input to the macrocell flip flop (see Figure 3). The most common arrangement includes an EX-OR gate capable of performing parity, full addition or logical inversion.

Another configuration exports product terms to a neighboring macrocell, increasing that macrocell's available product terms. Product term exporting is shown in Figure 3. Assigning all product terms as needed across the function block is possible.

As shown, XC9500 flip-flops can be configured as a D or T flip-flop. This permits efficient counters to be built using but a few gates to drive the state transitions. Table 1 summarizes the number of p-terms needed to build up common logic functions. Most datapath functions require one or fewer macrocells per bit.

#### Table 1: Macrocell/Product Term Allocation

| Data Operation    | P-Term Used |  |  |

|-------------------|-------------|--|--|

| Shift Register    | 2           |  |  |

| Counters          | 2-4         |  |  |

| n:1 Mux           | n           |  |  |

| Adder             | 6           |  |  |

| EX-OR             | 2           |  |  |

| Storage registers | 1           |  |  |

Figure 2. XC9500 Function Blocks

Table 2 shows the pin compatibility of the XC9500 family. Specifically, designs can be migrated among the parts. In many cases, greater density with equivalent speed can be gained by using larger parts. Should a design initially target a small part, the exact same design can be moved into larger parts, if additional capability is required. This capability helps designs maintain their pin assignments if additional logic capacity is needed in a socket that is already committed to a printed circuit board.

#### **Automatic Software**

The design examples presented are shown using ABELwhich is simple and easy to understand. Typically,

|              | XC9536 | XC9572                                    | XC95108 | XC95144 | XC95180 | XC95216 | XC95288 |

|--------------|--------|-------------------------------------------|---------|---------|---------|---------|---------|

| 44-Pin PLCC  | 34     |                                           |         |         |         |         |         |

| 44-Pin VQFP  | 34     | - <u> </u>                                |         |         |         |         |         |

| 84-Pin PLCC  |        | 69                                        | 69      |         |         |         |         |

| 100-Pin PQFP |        | 72                                        | 81      | 81      |         |         |         |

| 100-Pin TQFP |        | 72                                        | 81      |         |         |         |         |

| 160-Pin PQFP |        |                                           | 108     | 133     | 133     | 133     |         |

| 208-Pin PQFP |        | · · · <u> · · · · · · · · · · · · · ·</u> |         |         | 168     | 168     | 168     |

Table 2: XC9500 Available Packages and Device I/O Pins

Note: Does not include the dedicated JTAG pins.

designers won't designate specific function mapping into XC9500 designs, but occasionally, designers like to control how a solution is implemented, so these methods may be of interest.

Boolean operators used by ABEL are simply !,# and & for INVERT, OR and AND, respectively. Combinational logic expressions are formed with a simple equal (=) sign with operands and operators located on the right hand side of the expression.

Flip-flop expressions are formed by writing expressions for the specific control pins of the flip flop. The D-input is a special case, where the equal sign is replaced by the compound symbol :=. Clock inputs are determined by the syntax FFname.clk, and reset inputs are designated by FFname.rst.

A design file contains a header section including optional documentation sections and mandatory declaration of inputs, outputs, global signals and any user preferred arrangement of functions.

#### Logic AND

FastCONNECT is capable of combining signals with a wire AND function. As single lines enter FastCON-NECT, they are assigned to function block inputs, making connections. However, multiple lines driving a FastCONNECT connection form a wired AND function, that is useful for making additional logic. This feature increases both the logic capacity and available entry points to the Function Blocks.

#### Gates

The following expressions show the basic logic operations.

ABAR = !A;

AORB = A#B;

AANDB = A&B;

ANORB = !(A#B);

ANANDB = !(A&B);

AEXORB = A\$B;

AEXNORB = A!\$B;

#### **Muxes and Decoders**

Using the above methods, compound expressions are formed to build up logic functions. Using A0 to A3, B0 to B3 and SEL (select) as inputs, a multiplexer follows:

DAT0 = SEL&A0 # !SEL&B0;

DAT1 = SEL&A1 # !SEL&B1;

DAT2 = SEL&A2 # !SEL&B2;

DAT3 = SEL&A3 # !SEL&B3;

The approach extends to larger multiplexers. The above uses one macrocell per data bit and leaves behind two unused product terms in each macrocell. To take advantage of four product terms per macrocell, the idea expands as follows:

DAT0 = S1&S0&D0 # S1&!S0&C0 # !S1&S0&B0 #!S1&!S0&A0 DAT1 = S1&S0&D1 # S1&!S0&C1 # !S1&S0&B1 #!S1&!S0&A1 DAT2 = S1&S0&D2 # S1&!S0&C2 # !S1&S0&B2 #!S1&!S0&A2 DAT3 = S1&S0&D3 # S1&!S0&C3 # !S1&S0&B3 #!S1&!S0&A3

Very high speed decoders can be built in the macrocells to form SRAM select signals, but do not use all of the macrocell product terms or the flip flop in most cases. Decoders are formed as follow:

DEC0 = !A3&!A2&!A1&!A0 DEC1 = !A3&!A2&!A1&A0; DEC2 = !A3&!A2&A1&!A0;

#### Registers

Simple registers are formed as follows:

A:= DATAINPUT; A.CLK = CLOCK; A.RST = RESET;

This describes a D flip flop with its input tied to something named DATAINPUT, its clock tied to a signal called CLOCK and its reset input tied to a signal called RESET.

#### Shift Registers

Cascading registers results in a shift register as follows:

A:=DATAINPUT; B:=A; C:=B; D:=C; A.CLK = CLOCK; B.CLK = CLOCK; C.CLK = CLOCK; D.CLK = CLOCK; A.RST = RESET; B.RST = RESET; C.RST = RESET; D.RST = RESET; This shifter uses four macrocells. If the signals designated A,B,C,D are declared as outputs, they will appear somewhere at the pins of an XC9500 part. If A,B,C and D are declared as nodes (internal points), the software buries them.

#### Counters

Counters can be built in a number of different ways. The most efficient is to have the macrocell flip flops configured as T flip-flops. The following equations form T flip-flops, add logic to load, hold, increment and clear the flip-flops. Note the compact vector notation:

module Tcount

title '4 bit counter with load and clear'

```

D0..D3

pin:

Q3..Q0

pin istype 'reg_T';

CLK. I0. I1

pin:

Data = [D3..D0];

Count = [Q3..Q0];

Mode = [11, 10];

Clear = [0.0]:

Hold

= [0, 1];

Load = [1,0];

Inc

= [1,1];

equations

Count.T = ((Count.q+1) & (Mode == Inc)

```

```

# (Count.q) & (Mode == Hold)

# (Data) & (Mode == Load)

# ( 0 ) & (Mode == Clear))

$ Count.q

Count.C = CLK:

```

end

#### Comparators

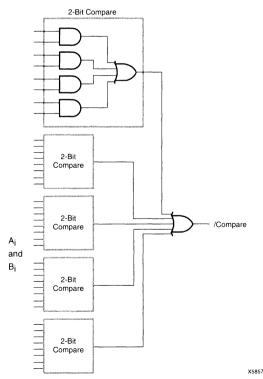

Comparators are easily handled by the XC9500 macrocell. Single bit comparators do not use all available macrocell product terms. A more efficient use is to handle four bits at a time to generate multiple compares per macrocell:

COMP = !B1&!B0&!A1&!A0 + B1&!B0&A1&!A0 !B1&B0&!A1&A0 + B1&B0&A1&A0

Next, several COMP signals can be gated together to detect equality across larger groups of bits. Each group of four bits uses 4 function block inputs and several four bit compares can occur per function block. Another macrocell then forms the composite function of all the bit compares, as needed. Figure 4 shows this technique expanded to a 10-bit comparator, which is commonly used on the most significant address lines of a 32-bit microprocessor's address lines.

#### Parity

Similar to compares, parity can be calculated with multiple data bits per macrocell. The first three bits are calculated using four p-terms ORed. This result is then delivered to the macrocell EX-OR where a fourth data variable is introduced.

#### Latches

Occasionally, designers need a transparent latch within an XC9500 device. The latch is formed by feeding the macrocell combinatorial logic back upon itself per the following equation:

Q = ENA&DATA + !ENA&Q + Q&DATA

The signal Q&DATA is included to eliminate a hazard, making the Q output glitch free.

#### Practical Considerations for XC9500 Designs

XC9500 CPLDs offer additional system features. By following a few simple rules, the XC9500 device interfaces with systems using 3.3 V and 5 V devices. Also, very high speed CPLDs behave much better if standard high performance printed circuit board techniques are adhered to, so a small checklist is appropriate for those rules. Best CPLD behavior is obtained by following a

Figure 4. 10-Bit Comparator

few guidelines with respect to the power-on Master Reset capability.

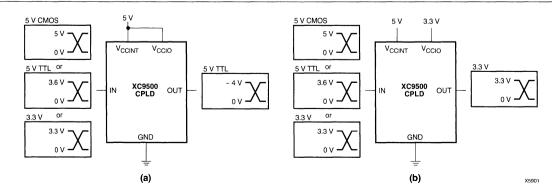

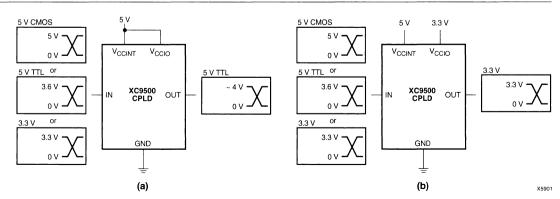

#### **Mixed Voltage Operation**

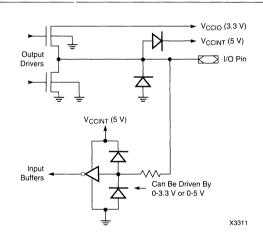

XC9500 CPLDs support mixed voltage systems combining both 3.3 and 5 Volt components. (See Figure 5). The XC9500 family contains both logic and level shifting functions in a single programmable device. This eliminates the need for discrete level translation buffers. These CPLDs feature split power supply rails. The internal core logic always runs at 5 volts for the fastest possible performance. The output buffers can be powered by either 5 volts or 3.3 volts by connecting the I/O V<sub>CC</sub> to a 3.3 volt or 5 volt supply. True TTL compatibility allows XC9500 CPLDs to drive and be driven by any combination of 3.3 and 5 volt logic without any performance penalty, even when the I/O V<sub>CC</sub> pins are powered by 3.3 volts.

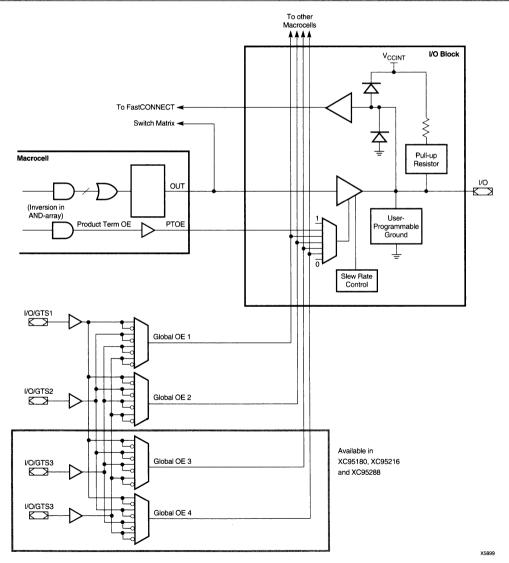

The XC9500 I/O structure is shown in Figure 6. Input protection diodes are connected to the internal 5 volt power supply rail and not the output buffer supply rail. This allows the input to withstand a maximum voltage of >5 volts, even when the I/O power pins connect to 3.3 volts. Since both output transistors are N-channel devices, there is no parasitic diode to be forward biased if the output is 3-stated and a 5 volt device is driving the XC9500 I/O pin. The CPLD then operates on a bus including both 3.3 V and 5 V devices.

Since the input protection circuitry is powered by the 5 volt core logic supply, the 5 volt supply must always be powered up before the 3.3 volt I/O supply. This prevents external 3.3 V devices from forward biasing the protection diodes. Similarly, the 3.3 volt I/O supply must be powered down before the 5 volt core logic supply. This is not an issue with 5 volt only systems.

XC9500 devices are TTL-compatible with 3.3 and 5 volt logic as shown in Figure 7. The 5 volt TTL logic input thresholds are VIH = 2.0 V and VIL = 0.8 V. XC9500 CPLDs drive HIGH greater than 2.4 V and LOW below 0.4 V at rated output drive currents, with at least 400 mV noise margin.

#### **High Speed Design Considerations**

XC9500 CPLDs are offered with pin-to-pin delays as fast as 7.5 and 5 ns. The actual parts may in fact be somewhat faster. Additional care should be taken when using these parts, because of this speed, so that adjoining chips will operate properly.

Many high speed designs also require high current drive outputs for handling capacitive loads. XC9500 CPLDs provide 24 mA drivers to eliminate the need for additional buffering that might impact system speed. This results in a need to manage the total current being switched, so a strategy to do that is provided.

Figure 6. XC9500 I/O Structure

Figure 5. Typical Mixed Voltage System

Figure 7. XC9500 CPLD Driving 3.3 V and 5 V Components

As with other high speed logic devices, XC9500 CPLDs should use low inductance capacitors located as close as possible to the  $V_{CC}$  and GND pins when mounted on a PC board. Care should be taken to mount the devices so that the PC interconnect traces are as close as possible to the target signal destinations.

# Layout Checklist:

Complying with the following checklist assures a successful design with XC9500 CPLDs:

- 1. Tie unused inputs to ground.

- 2. Locate XC9500 CPLDs near chips they drive or are driven from to minimize transmission line effects.

- 3. Use wide spacing between fast signal lines (particularly clocks) to minimize crosstalk.

- 4. Power pins (V<sub>CC</sub> and GND) are recommended to be placed on separate printed circuit board planes. Fast signals should reside on another plane, as well.

- Decouple the chip V<sub>CC</sub> with a 0.1 microfarad capacitor directly connecting each physical chip V<sub>CC</sub> to the nearest ground plane. Low inductance, surface mounted capacitors are recommended.

- 6. Decouple the printed circuit board power inputs with 0.1  $\mu$ F ceramic (high frequency) and 100  $\mu$ F electrolytic (low frequency) filter capacitors.

- 7. All device ground pins must be connected together.

Avoid using sockets to attach XC9500 CPLDs to the PCB. Direct soldered connection minimizes inductance and reduces ground rise. XC9500 CPLDs are specifically designed for direct PCB attachment without need for sockets.

# Managing Ground Rise

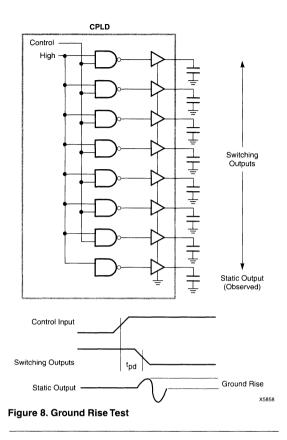

Today's high performance designers must also be aware of additional factors that can affect the performance of fast, high-current drive systems. As mentioned earlier, possible voltage rise on device ground pins can affect the driven output levels and be sensed by the switching CPLD.

Figure 8 shows how ground rise is typically observed with today's high-performance CPLDs. In this setup, multiple outputs are switched with a control variable, while one output is constantly being driven low and observed. As the multiple outputs switch, their in rushing current converges at the ground pin(s) of the CPLD. Lead impedance causes the reference ground to develop a voltage higher than before the switching occurred. The result is that the static output being observed also develops an observable voltage swing.

All digital ICs have this property. No harm is caused to the system unless the voltage swing on the static output is capable of switching another circuit down the line. Problems can occur if the voltage swing is excessive. This effect is particularly significant if the static (quiet) signal is attached to another circuit's clock input.

Two factors contribute to this ground rise. First, the amount of capacitive load being driven is important because charge on this capacitance is the source of the in rushing current. Second, the number of simultaneous switching outputs is a factor since each switching output adds to the total capacitance being discharged.

The XC9500 family includes User Programmable Ground for internal chip signal management. XC9500 devices are in symmetric packages with multiple ground pins. However, some designs need more ground pins for current.

User Programmable Ground allows the device I/O pins to be configured as additional ground pins. Tying programmable ground pins to the external ground connection reduces system noise. XACT*step* software automatically connects unused macrocell outputs to ground.

The following checklist will reduce unnecessary ground noise:

1. Pinout only essential outputs. Intermediate shifter bits, and counter bits that need not drive outputs should remain buried.

- 2. Minimize the number of outputs switching simultaneously.

- 3. Two global clock inputs can be managed similar to the two GTS signals, by delaying one to gain signal skew.

- 4. Additional grounding can lower ground rise effects, and may be dealt with simply. Unused outputs can be tied directly to the PCB ground. This splits the current driven into heavily loaded ground pins and lowers the voltage rise.

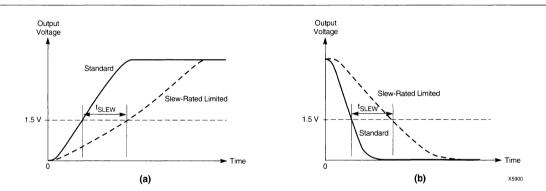

- 5. Signal skewing can also reduce ground rise. This can be achieved by mixing ordinary and fast slew outputs. Only assign fast slew to signals that require it.

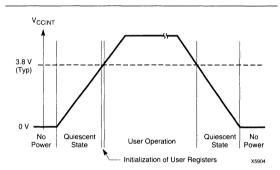

#### Power On Master Reset

XC9500 devices undergo a short internal initialization sequence upon device powerup. During this time the outputs remain 3-stated while the device is configured from its internal registers. While the internal initialization sequence occurs the device outputs remain 3-stated until the sequence is complete. Although the outputs are 3-stated, they are gently pulled up through 10K ohm impedance pullups. Alternate Master Reset can be accomplished by using the ISPEX JTAG instruction.

# Conclusions

By using the techniques discribed in this application note, designers achieve a solution to their high-performance logic requirements with the XC9500 family. The XC9500 family datasheet contains additional descriptions of the important system features.

# Pin Preassigning With XC9500 CPLDs

### February 1996

Application Note

# Summary

This application note details the planning required for successful pin preassigning with XC9500 CPLDs.

Xilinx Family

XC9500 CPLDs

# Demonstrates

A step by step procedure to assure best results for designing when the pinouts are preassigned.

Guidelines to follow for best results.

# Introduction

Reducing time to market is critical in today's high performance digital marketplace. Designers need to prototype their products as swiftly as possible. Many designers estimate their CPLD design needs and predict the pinouts required in advance to remove the printed circuit board bottleneck from the prototype schedule. The XC9500 CPLD architecture permits preassigning pins with a high degree of success by following a few simple guidelines. The architecture also allows future edits to the design while maintaining the existing pinout. However, some planning of the design at the outset is necessary. This application note details guidelines for successful pin preassignment.

Many designs can be partitioned into datapath and control logic portions. Datapath operations are regular, bit operation oriented and maintain relative positions among the bits. Datapath operations also maintain their functionality once they are designed.

Control operations change as timing is adjusted through the design cycle and specifications are altered. These operations evolve as a design progresses. Control operations are much less structured than data operations. The design strategy is different.

Obtaining a reasonable estimate of the design's logic requirements for both control and datapath operations is the key to preassigned pinouts. Once an estimate is obtained, pins are assigned with a high degree of confidence that the function block driving the pins will have the available resources to connect the logic needs of the corresponding macrocells. It is importatant to remember that since the design needs for datapath and control operations are different, estimating their initial requirements differ. Actual completion of the design with the software making the appropriate pin assignments assures sucess.

# XC9500 Routing Resources

XC9500 CPLDs combine a locally efficient logic block with a globally flexible interconnect structure to provide ideal connectibility for a very large spectrum of designs. Here are a few of the key qualities of the logic block:

- a. 36 input signals presented to the logic block

- b. Automatic allocation of product terms as needed within the function block. The average is 5 product terms per macrocell, but up to 15 is easily obtained and more can be had when needed.

- c. Formation of efficient counters, multiplexers, shifters and parity circuits with an efficiency of one macrocell or less per bit. The remaining logic is available for use by functions needing more logic.

Here are some properties of the interconnect structure:

- a. Any input pin connects to any function block with constant high speed across the entire device.

- b. Any macrocell output can connect to its own or any other function block with complete freedom.

- c. Macrocells can be internally bused with bit level independent 3-state control forming internal databuses with global access to all logic blocks. No other CPLD architecture offers this capability, which saves macrocell logic by using the routing resources to form multiplexers.

These features are essential for editing integrated circuits already attached to boards. The flexibility of the XC9500 routing resources compensates for virtually all design changes.

## **Datapath Guidelines**

Datapath operations include storage, shifting, multiplexing, arithmetic, comparison and boolean operations. In

the majority of cases, estimating the logic needs for a single bit is sufficient to quickly estimate the entire datapath. Table 1 gives the macrocell needs of various data operations.

| Table | 1: | Macrocell/Product Term | Allocation |

|-------|----|------------------------|------------|

|-------|----|------------------------|------------|

| Data Operation    | P-Term Used |

|-------------------|-------------|

| Shift Register    | 2           |

| Counters          | 2-4         |

| n:1 Mux           | n           |

| Adder             | 6           |

| EX-OR             | 2           |

| Storage registers | 1           |

The primary guideline is to interleave output functions that need many product terms with functions that need few.

The design software easily finds the product terms for functions with excessive requirements from neighboring macrocells requiring few. As shown in Table 1, there are few functions requiring more than 4 product terms per macrocell. This suggests that all functions will easily fit into incremental macrocell units. The adder, which requires more than one macrocell (i.e. one for the full adder sum bit and additional carry logic distributed among the adder bits) and the n:1 Mux which may need more product terms than a single macrocell can supply are exceptions.

#### **Control Path Guidelines**

Control logic is less straightforward than datapath logic since the control circuitry's logic needs vary and the tim-

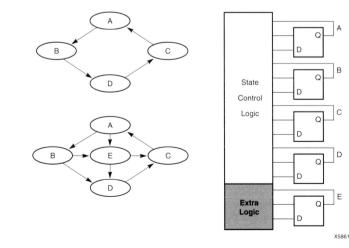

ing is tight. Simple combinatorial control signals are easy to estimate, however state machines are not. However, one-hot encoded state machines, which are flipflop rich and input logic lean, may be used for estimation purposes. One-hot encoding works because:

- a. There is no required sophisticated state encoding

- b. The input signals can be managed in a straightforward way

- c. Performance degradation can be quantified at the initial estimation time.

- d. One-hot state machines are easily edited to add or delete states without upsetting the state encoding.

- e. Encoded state machines usually produce more compact logic with no speed degradation in a CPLD, but one hot solutions give a worst-case estimation.

Editing one-hot machines without significantly altering the overall structure of the machine is easy. States may be inserted or deleted without major impact on the next state and output logic encoding. One-hot designs can also be implemented in either the Mealy or Moore versions as required. Figure 1 shows the basic one hot encoding structure. The shaded region of the figure shows additional logic added to alter the four state machine (A,B,C,D) to a five-state machine (A,B,C,D,E) without complete reencoding of the machine.

#### Recommendations

The general guidelines to preassign pins are very simple:

1. Do an estimated design first and let the design software assign the pins.

Figure 1. One-Hot Encoded State Machine Editing

- 2. Alternately minimize risk by estimating the design needs yourself:

- a. partition data and control portions

- b. estimate the needs of each portion

- c. consider one hot control unit designs to permit future editing and stable pin assignments

- 3. The following cell arrangement techniques should be adhered to:

- a. Spread the outputs among all function blocks

- b. Within Function Blocks, spread macrocells evenly, with unused macrocells interleaved.

- c. Assign outputs using common inputs to the same function blocks

- d. Don't use global pins (clocks, resets, tri-state enables) for logic inputs or outputs unless the global pins are not needed.

4. XC9500 CPLDs have common footprint packages for various density parts. By designing for the smallest capacity in a specific package footprint, there is always the option of a pin compatible density upgrade that matches the existing pinout. Table 2 below shows the available packages and device I/O pins in the XC9500 family.

### Conclusion

Pin preassigning is successfully achieved with XC9500 CPLDs by following simple guidelines. It is always recommended to do an estimated design and let the design software assign pins before committing to a printed circuit board. The benefits of preassignment include faster time to prototype and ultimately faster time to market. Xilinx XC9500 CPLDs provide the speed and flexibility to make this goal a reality.

|              | XC9536 | XC9572 | XC95108 | XC95144 | XC95180 | XC95216 | XC95288 |

|--------------|--------|--------|---------|---------|---------|---------|---------|

| 44-Pin PLCC  | 34     |        |         |         |         |         |         |

| 44-Pin VQFP  | 34     |        |         |         |         |         |         |

| 84-Pin PLCC  |        | 69     | 69      |         |         |         |         |

| 100-Pin PQFP |        | 72     | 81      | 81      |         |         |         |

| 100-Pin TQFP |        | 72     | 81      |         |         |         |         |

| 160-Pin PQFP |        |        | 108     | 133     | 133     | 133     |         |

| 208-Pin PQFP |        |        |         |         | 168     | 168     | 168     |

### Table 2: XC9500 Available Packages and I/O Device Pins

Note: Does not include the dedicated JTAG pins.

# XC9500 CPLD Embedded Diagnostics

### February 1996

### **Application Note**

### Summary

This application note describes how to build signature analysis circuitry into a remote system to isolate problems.

# Xilinx Family

XC9500 CPLDs

#### Demonstrates

Using Linear Feedback Shift Registers to calculate signatures.

Planning for designs that will be altered in the future.

Overlaying diagnostic circuitry after a system has been installed in the field.

## Introduction

Today's high performance systems are at a level of complexity where it may be difficult to determine functionality in a remote environment. Data communication systems and remote data acquisition are examples of this model. Designers need embedded diagnostics to isolate and identify potential problems before assigning on-site field personnel. Using available chip resources for test circuitry is an effective way to design embedded diagnostics. The function is accomplished by allocating extra circuitry or reprogramming existing circuitry in the system. XC9500 CPLDs may be used for either approach. However some planning in the original system design is necessary. This application note outlines the signature analysis approach to design remote embedded diagnostics.

## Signature Analysis Fundamentals

Various nodes (outputs or signal points) in a system will exhibit repeatable behavior patterns under identical input signal sequences. Incorrect behavior will generate different sequences. Comparing the sequences in the failing system to the previously recorded node sequences will identify the problem.

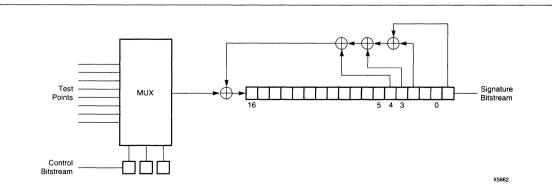

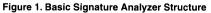

This approach requires a large number of storage cells and circuitry to perform the comparisons. Signature analysis identifies a set of critical "test points" in a system. It also captures an encoded binary pattern using a polynomi encoding scheme similar to that of cyclic Linear Feedback Shift Registers (LFSRs). The circuitry consists of a moderate-sized shift register with Exclusive-Or functions embedded at key positions. These functions generate distinctive patterns called signatures. Figure 1 shows a typical setup of a signature analyzer in symbolic form.

### XC9500 CPLD Signature Support

High performance CPLDs are frequently used in memory and system controllers. Memory controllers are centrally located and multiprocessing systems may have several CPLDs on different cards. This makes CPLDs a natural place to embed diagnostic circuitry. Here is a natural strategy to follow:

- Verify microprocessor operation at initialization by capturing signatures transitioning out of reset.

- Verify more signatures as the processor steps through its bootstrap ROM.

- Capture signatures as the processor tests the memory and subsequent I/O operations.

Figure 2 shows how such a configuration might be built.

XC9500 CPLDs easily implement any or all of the Figure 2 system. However, it is possible to build the signature analyzer for free. During the previously mentioned strategy, the DRAM may not be involved in the system diagnostic while the processor is booting from ROM. In this case, the signature analyzer is constructed from the logic later used as the DRAM controller. While the DRAM is tested, unused data communication's or I/O circuitry acts as the signature analyzer. Therefore different system pieces could be reused or adapted to suit the diagnostic needs.

#### **Test Strategy Overview**

The signature analyzer is a multiplexed shift register with Ex-Or gates. The shift register must be initialized. However, some patterns are inappropriate. For example, all zero initialization causes a signature analyzer to fail. The ability to initialize the register to a known pattern is necessary.

The test points, shown in Figure 1, are selected with a three bit serial register and a mux. The signatures must be unique. Each test point has an identical starting point.

Before signature testing occurs, capture known good signatures and store them for future comparison. Use exactly the same procedure outlined below:

- · Aim the mux at a chosen test point

- · Initialize the Linear Feedback Shift Register (LFSR)

- · Enable the LFSR

- · Enable the device under test (DUT)

- · Count operation cycles of DUT until complete

- Disable the LFSR and DUT

- Read back signature

- · Compare this signature to the known good signature

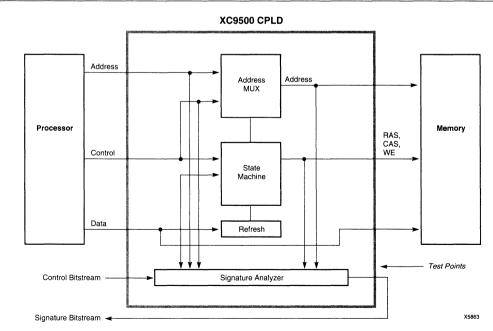

Figure 2. Embedded Signature Analyzer

Managing the sequence of captured patterns is important. Once a board has passed all signature tests, the scope of the diagnostic can be increased. For example, analizing data communication circuits with selected loopback tests. Additional tests may also be performed using the signature method. (See Figure 3).

#### **Practical Considerations**

Here are some guidelines to use when designing signature analysis experiments:

- Synchronous behavior is the most repeatable and the most desirable to use for signature analysis.

- Selection of test points should be done so their global influence is a factor for selection. Any processor status/ control lines which enable data transfers, generate interrupts or make bus requests are candidates.

- Most signatures are unique. However, there is a remote possibility of obtaining aliases. Check for aliases during the initial capture of healthy behavior.

- Table 1 supplies a set of feedback equations for building LFSRs which are the basic components for signature analyzers. Data entry can be Ex-Or'ed with the feedback input variable (n in this case).

- · Avoid initializing the signature register with all 0s.

- Supplement signature analysis with other diagnostics, such as memory tests and disk CRC diagnostics.

Figure 3. Adding in Data Communication Loopback

Table 1. LSFR Feedback Equations

| n  | Feedback Equation                         |  |  |  |  |

|----|-------------------------------------------|--|--|--|--|

| 2  | X2 = X1 ⊕ X0                              |  |  |  |  |

| 3  | X3 = X1 ⊕ X0                              |  |  |  |  |

| 4  | X4 = X1 ⊕ X0                              |  |  |  |  |

| 5  | X5 = X2 ⊕ X0                              |  |  |  |  |

| 6  | X6 = X1 ⊕ X0                              |  |  |  |  |

| 7  | X7 = X3 ⊕ X0                              |  |  |  |  |

| 8  | $X8 = X4 \oplus X3 \oplus X2 \oplus X0$   |  |  |  |  |

| 12 | $X12 = X6 \oplus X4 \oplus X1 \oplus X0$  |  |  |  |  |

| 16 | $X16 = X5 \oplus X4 \oplus X3 \oplus X0$  |  |  |  |  |

| 20 | X20 = X3 ⊕ X0                             |  |  |  |  |

| 24 | $X24 = X7 \oplus X2 \oplus X1 \oplus X0$  |  |  |  |  |

| 28 | X28 = X3 ⊕ X0                             |  |  |  |  |

| 32 | $X30 = X22 \oplus X2 \oplus X1 \oplus X0$ |  |  |  |  |

### Conclusion

XC9500 CPLDs provide the technology to build effective but inexpensive embedded test circuitry in a wide range of microprocessor systems. However, this capability is not limited to microprocessor diagnostics, and may be easily expanded to include a wider range of digital systems.

# References

- Logic Design Principles (with emphasis on Testable Semicustom Circuits), E.J. McCluskey, Prentice-Hall, 1986

- 2. Design of Testable Logic Circuits, R.G. Bennets, Addison-Wesley, 1984

- 3. Digital Design (Principles and Practices), J. Wakerly, Prentice-Hall, 1994

# XC95108 CPLD High Performance System Controller

#### February 1996

Application Note

### Summary

The XC95108 is shown as a single chip high performance system controller. It handles all the address decode, state machines, and logic needs of a high performance microprocessor.

## Xilinx Family

XC9500 CPLDs

## Demonstrates

XC95108 device for high performance system applications.

### Introduction

Today's modern computer systems have many different components. In addition to high-speed processors and system buses, the high performance system requires sophisticated interface logic and state machines. The need for this circuitry to support advanced system components is a main functional block of complete high performance systems. The XC95108 is an ideal solution for high performance system controllers. This application note outlines the use of state machines, address decoders and data path routing in support of high-performance systems.

A high performance system controller could implement any of the following features:

- · Power-on logic

- · System memory map decode

- DRAM state machine

- · Flash memory state machine

- SDRAM state achine

- · System peripheral interfaces

- Data path routing

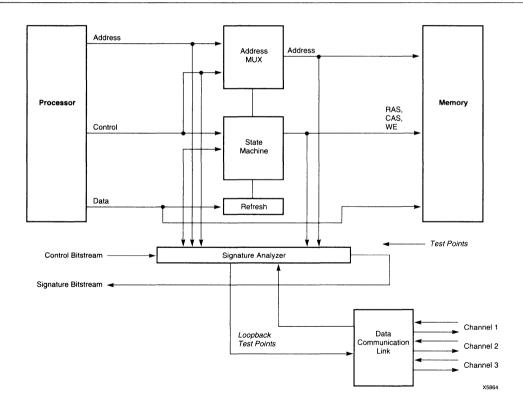

The XC95108 can implement all of these functions. An outline of the functional requirements for each of the different interfaces follows. A typical system controller block diagram is shown in Figure 1.

## **Power-On Logic**

A high performance system requires the proper start-up sequence for each different system circuit. The logic and power-up sequence of different components are an important element of the complete system design. Different components require reset and configuration, based on a predetermined power-up sequence. A power-up sequence might include some of the following functions:

- Reset signals

- Tristate data paths

- · System clocks

- · Control signals

- · Self-test

Most of these functions are built with relatively few macrocells (2-10). The 5 volt in-system programmable capability of the XC95108 permits any future modification of the power-up sequence.

#### System Memory Map Decode

High performance systems require a memory map of all component accessible by the processor. System components are mapped into the address space based on their size and specific requirements. Most decode needs require wide fan-in, high speed (7 ns or less) and high current drive. The XC95108 delivers each of these requirements.

Figure 1. Typical High-Performance System Controller

The memory map function of the processor may require as many as ten macrocells. The memory map function also uses a large number of signal I/O pins. Memory decode may require as many as 40 signals pins. The ISP functionality of the XC95108 permits easy modification of the memory map.

#### **DRAM State Machine**

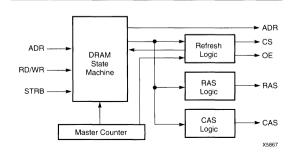

High performance systems include many different technologies. DRAM is the main memory type for todayís high performance systems. However, there are many different kinds of DRAM and each requires a different state machine.

The memory state machine usually performs the wait state generation and the refresh requirements of the interface. The DRAM controller also handles CAS and RAS generation.

The DRAM state machine may also require as many as ten macrocells. Another ten macrocells may be required for the remaining logic in the DRAM controller. A simple DRAM controller block diagram is shown in Figure 2.

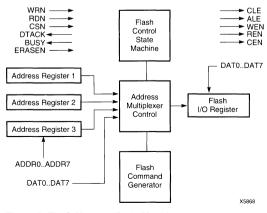

#### Flash Memory Controller

An increasing number of high performance systems are being created with Flash memory devices. (See Figure 3). These non-volatile memory devices permit in-system modification. When configured as a Flash memory controller, the XC95108 responds to read, erase, and program commands and generates the corresponding control strobes. The controller also handles the address segmentation and data multiplexing.

#### **SDRAM State Machine**

High performance systems require a new type of DRAM called Synchronous DRAM (SDRAM). The SDRAM interface has a complex state machine that may require future modifications as SDRAM technologies evolve. SDRAM devices from different vendors use different commands and protocols.

Figure 2. DRAM State Machine

The XC95108 permits modification of the SDRAM interface as a field upgrade. The interface requires about 15 macrocells and 20 signals. The SDRAM interface controls the address map segmentation and strobes for the high performance system.

#### **System Peripheral Interfaces**

System peripheral devices handle many functions of in high-performance systems. A fast system bus acts as the interface to the rest of the system. Peripheral Component Interconnect (PCI) is a high-speed bus supported by many vendors.

The XC95108 device is PCI compliant. The device could serve as either of a PCI bus target or a PCI bus initiator depending on the application requirements. The state machine for the bus functions requires between ten and twenty macrocells. The XC95108 may also form the data path and parity generation PCI functions.

#### Data Path Routing

Data path routing requirements of a high-performance system can be very significant. Many components of the system require different address and data signals. The assignment of the separate data and address bus signals to the components is a primary data path routing function.

The XC95108 is offered in multiple package and I/O combinations to deliver the necessary macrocells and signal pins. The JTAG ISP function allows in-system modification of data path routing.

#### Conclusions

The XC95108 can be used as a high-performance system controller. The requirements for these controllers are described in this application note. Details of specific counter, multiplexer, and data path building blocks are discussed in *Designing with XC9500 CPLDs*.

Figure 3. Flash Memory State Machine

#

# XC95108 CPLD Serial Stream Interface

February 1996

Application Note

# Summary

The XC95108 is shown as a Serial Data Stream (SDS) application for datacom/telecom systems. Additionally, performance monitoring capabilities are outlined.

### Xilinx Family

XC9500 CPLDs

### Demonstrates

XC95108 device for datacom/telecom applications

XC95108 performance monitoring and remote field upgrade.

### Introduction

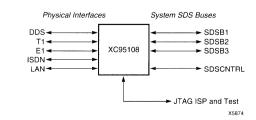

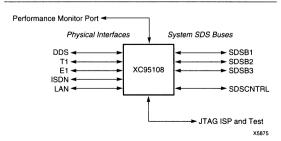

Today's modern communications systems have many different SDS physical interfaces and components. The XC95108 is ideal for multiplexing and control of these different interfaces. This application note demonstrates the use of counters, shifters, and multiplexers in support of the SDS interface requirements.

# **Communications System Block Diagram**

In all datacom/telecom systems, there are many different physical interface requirements and multiple system buses. The combination of the different interfaces and protocols is a main function of the system. Implementing a given interface, requires a physical electrical interface and a data framer for the protocol and transport layer processing of the SDS.

The connection of the physical interface circuit and framer to the rest of the system is done using a system data bus. The interface of different data streams into system data buses is an excellent application for the XC95108. A simple block diagram of some typical SDS XC95108 interfaces is shown in Figure 1.

# XC95108 SDS Application Example

A typical system requires a variety of different physical interfaces to be supported. Each physical interface circuit needs similar information related to the following:

- Channel boundary information

- Channel signaling Information

- · Efficient CRC generation and checking

- Channel error conditions and status

SDS interfaces have some common characteristics. Each different interface processes the physical circuit and a framer. The framer removes encoding and embedded clock information. The I/O signals of the framer are divided into three categories:

- Channel data

- Channel control

- Signaling information

These signals are common to the different physical interface signals. The XC95108 interprets them to control SDS.

#### **Different SDS Physical Interfaces**

Direct Digital Service (DDS) is a simple 56/64 Kilobit/s digital interface for the simple digital terminal. This connection is typical for credit card verification, bank machines, and any other low bandwidth digital service requirement.

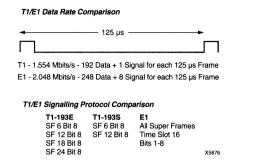

T1/E1 are the two main broad band interface bandwidths of the current digital telecom WAN hierarchy. The T1 interface is a 1.554 Megabit/s digital interface comprised of 24 x 64 Kilobit/s channels into a 125 uSecond frame. The E1 interface characteristics are 32 x 64 Kilobit/s channels into a 125 uSecond frame resulting in a bit rate of 2.56 Megabits/s.

Integrated Services Digital Network (ISDN) basic rate service is equivalent to 2 DDS service channels, each of 64 Kilobits/s, and a 16 Kilobits/s signaling channel. This service is frequently referred to as 2B+D or ISDN BRI.

Integrated Services Digital Network (ISDN) primary rate is the combination of 32 64 Kilobits/s channels similar to the E1 standard. This medium bandwidth wide area network interface allows integrated voice and data switching systems.

Ethernet is by far the most popular digital LAN physical interface standard. Current Ethernet is a 10 Megabits/s implementation over either coaxal or twisted copper pair cables. The 100 Megabits/s version of Ethernet is also available but not yet widely used.

Fiber Digital Data Interface (FDDI) is a 100 Megabits/s interface that has been increasing in popularity over the last few years. FDDI is best suited for LAN servers and high bandwidth data applications.

A Token Ring system of either 4 or 16 Megabits/s offers some new LAN system advantages over traditional Ethernet only backbone networks. An increase in the Token Ring switched network, connected to a high bandwidth backbone, is becoming more popular and will increase in the next few years.

#### **Different Data Packet Standards**

Each physical interface has the option of switching between different transport layer standards. The actual content and context of the data packets sent over a physical network link depends on the current standard being used. The need to support many different data packet formats will only increase with the expansion of new and diverse bearer services.

The physical interface is a small part of the complete functioning system. The data from the physical interface must be routed and processed by the correct protocol standard. The need to support future physical interface circuits and new standards requires flexible SDS interfaces.

#### T1/E1 System Upgrade Example

Current standard datacom/telecom SDS systems are increasing in complexity and capacity. Interface and framer circuits for different SDS formats are single channel device solutions. Dual and quad density SDS interface circuits will increase the complexity of the interface requiring more logic capacity.

The XC95108 is ideal for the previous system upgrade example. Consider the T1/E1 type interface circuit. The current single SDS interface of 1.554 and 2.048 MHz implements a set of logic functions for the system. The XC95108 requires a small amount logic capacity for counters, multiplexers, shifters, and state machines. When the interface is expanded to handle more streams, extra logic in the XC95108 is available. The appropriate data parameters are shown in Figure 2.

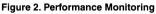

# **XC95108 Performance Monitoring**

The XC95108, as an SDS interface, allows for performance monitoring of the data content. Typical performance monitoring includes loop back testing, clear channel signaling and bit-error rate testing. These circuits require state machines, counters and pattern recognizers. The reconfigurability of the XC95108 "in-system", allows modification of the device to build these circuits. The required logic overhead is substantial. Device reconfiguration also eliminates the need for maintaining monitoring logic at all times. Figure 3 shows an additional performance monitoring port added to the SDS interface.

In addition to performance monitoring, the XC95108 may be remotely configured as any of the circuits. The choice of monitoring circuits can be made adaptively to suit the needs of the system administrator. The XC95108 JTAG circuitry permits in-system modification of the design by downloading changes as required.

#### Conclusions

The XC95108 meets all SDS interface requirements for datacom/telecom applications. With the XC95108 JTAGbased in-system programmable capability, users may easily build adaptive protocol data frame handlers. The XC95108 also handles built-in performance monitoring, thus eliminating the need for redundant circuitry in the design. Many of the building blocks described in this application note are discussed in more detail in *Designing with XC9500 CPLDs*.

#

# **SECTION 3**

- **1** Product Overview

- 2 Applications

# **3 XC9500 Product Description and Specifications**

- 4 Packages

- 5 JTAG Software

- 6 Quality, Testing and Reliability

- 7 Sales Offices

# February 1996

### Features

- High-performance

- 5 ns pin-to-pin logic delays on all pins

- f<sub>CNT</sub> to 125 MHz

- Large density range

- 36 to 288 macrocells with 800 to 6,400 usable gates

- 5 V in-system programmable

- Endurance of 10,000 program/erase cycles

- Program/erase over full voltage and temperature range

- · Enhanced pin-locking architecture

- Flexible 36V18 Function Block

- 90 product terms drive any or all of 18 macrocells within Function Block

- Global and product term clocks, output enables, set and reset signals

- Extensive IEEE Std 1149.1 boundary-scan (JTAG) support

- Programmable power reduction mode in each macrocell

- · Slew rate control on individual outputs

- · User programmable ground pin capability

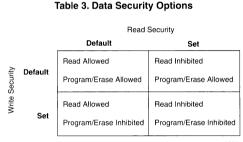

- Extended pattern security features for design protection

- High-drive 24 mA outputs with 3.3 V or 5 V I/O capability

- PCI compliant (-5, -7, -10 speed grades)

- Advanced 0.6μm CMOS 5V FastFLASH technology

# XC9500 In-System Programmable CPLD Family

#### **Preliminary Product Information**

# Description

The XC9500 CPLD family provides advanced in-system programming and test capabilities for high performance, general purpose logic integration. All devices are in-system programmable for a minimum of 10,000 program/ erase cycles. Extensive IEEE 1149.1 (JTAG) boundaryscan support is also included on all family members.

As shown in Table 1, the seven devices of the XC9500 family range in logic density from 800 to over 6,400 usable gates with 36 to 288 registers respectively. Multiple package options and associated I/O capacity are shown in Table 2. The XC9500 family is fully pin-compatible allowing easy design migration across multiple density options in a given package footprint.

The XC9500 architectural features address the requirements of in-system programmability. Enhanced pinlocking capability avoids costly board rework. An expanded JTAG instruction set allows version control of programming patterns and in-system debugging. In-system programming throughout the full device operating range and a minimum of 10,000 program/erase cycles provide worry-free reconfigurations and system field upgrades.

Advanced system features include output slew rate control and user-programmable ground pins to help reduce system noise. I/Os may be configured for 3.3 V or 5 V operation. All outputs provide 24 mA drive.

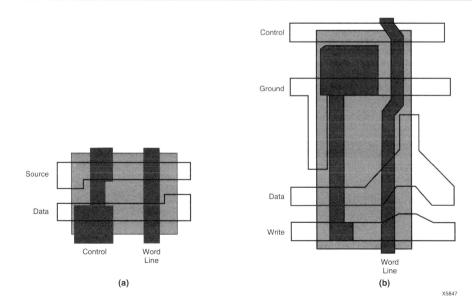

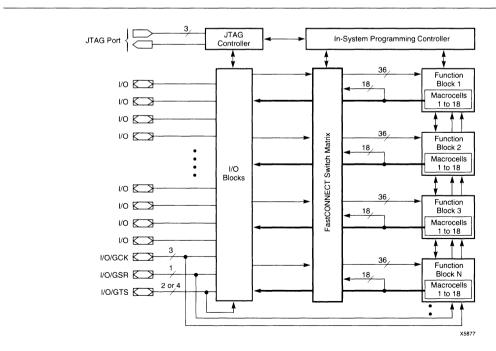

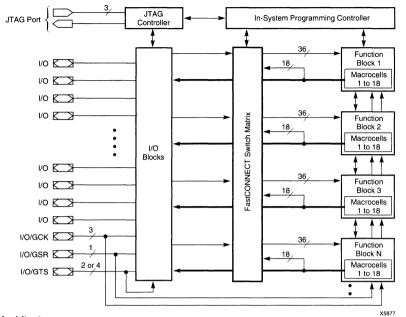

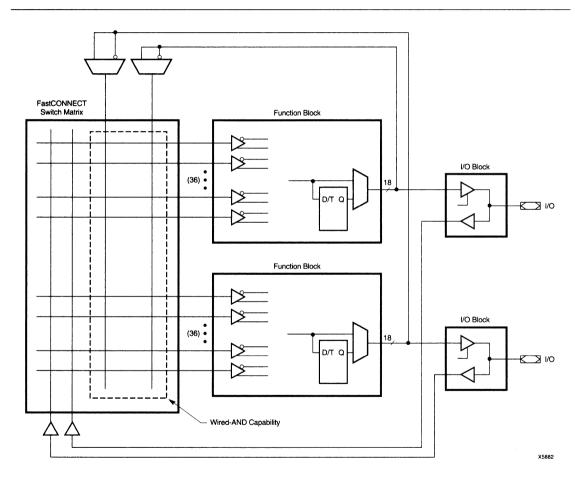

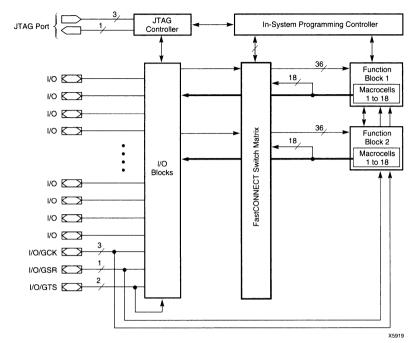

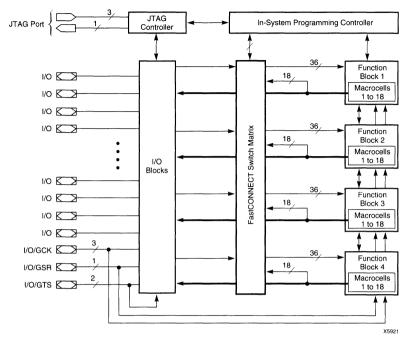

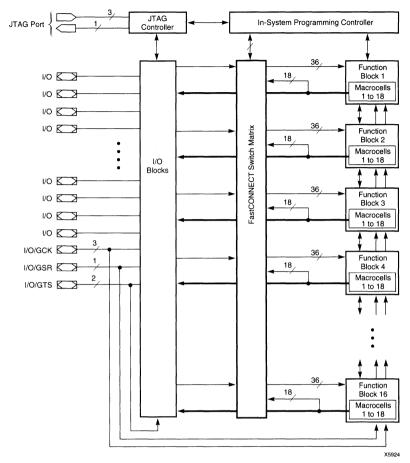

#### **Architecture Description**

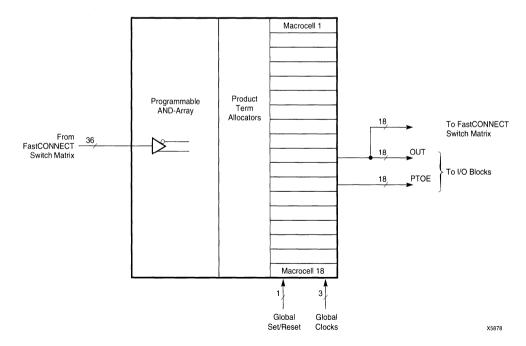

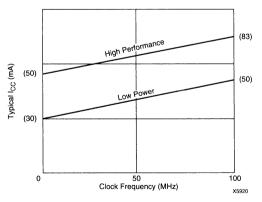

Each XC9500 device is a subsystem consisting of multiple Function Blocks (FBs) and I/O Blocks (IOBs) fully interconnected by the FastCONNECT switch matrix. The IOB provides buffering for device inputs and outputs. Each FB provides programmable logic capability with 36 inputs and 18 outputs. The FastCONNECT switch matrix connects all FB outputs and input signals to the FB inputs. For each FB, 12 to 18 outputs (depending on package pin-count) and associated output enable signals drive directly to the IOBs. See Figure 1.

#### Figure 1. XC9500 Architecture

Note: Function Block outputs indicated by bold line drive directly to I/O Blocks

|                           | XC9536 | XC9572 | XC95108 | XC95144 | XC95180 | XC95216 | XC95288 |

|---------------------------|--------|--------|---------|---------|---------|---------|---------|

| Macrocells                | 36     | 72     | 108     | 144     | 180     | 216     | 288     |

| Usable Gates              | 800    | 1,600  | 2,400   | 3,200   | 4,000   | 4,800   | 6,400   |

| Registers                 | 36     | 72     | 108     | 144     | 180     | 216     | 288     |

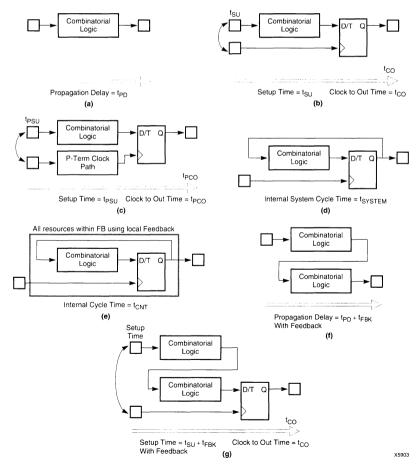

| t <sub>PD</sub> (ns)      | 5      | 7.5    | 7.5     | 7.5     | 10      | 10      | 10      |

| t <sub>SU</sub> (ns)      | 4.5    | 5.5    | 5.5     | 5.5     | 6.5     | 6.5     | 6.5     |

| t <sub>CO</sub> (ns)      | 4.5    | 5.5    | 5.5     | 5.5     | 6.5     | 6.5     | 6.5     |

| f <sub>CNT</sub> (MHz)    | 125    | 125    | 125     | 125     | 111     | 111     | 111     |

| f <sub>SYSTEM</sub> (MHz) | 100    | 83     | 83      | 83      | 67      | 67      | 67      |

#### Table 1. XC9500 Device Family

Note:  $f_{CNT}$  = Operating frequency for 16-bit counters

f<sub>SYSTEM</sub> = Internal operating frequency for general purpose system designs spanning multiple FBs.

#### Table 2. Available Packages and Device I/O Pins

|              | XC9536 | XC9572 | XC95108 | XC95144 | XC95180 | XC95216 | XC95288 |

|--------------|--------|--------|---------|---------|---------|---------|---------|

| 44-Pin PLCC  | 34     |        |         |         |         |         |         |

| 44-Pin VQFP  | 34     |        |         |         |         |         |         |

| 84-Pin PLCC  |        | 69     | 69      |         |         |         |         |

| 100-Pin PQFP |        | 72     | 81      | 81      |         |         |         |

| 100-Pin TQFP |        | 72     | 81      |         |         |         |         |

| 160-Pin PQFP |        |        | 108     | 133     | 133     | 133     |         |

| 208-Pin HQFP |        |        | 1       |         | 168     | 168     | 168     |

Note: Does not include the dedicated JTAG pins.

# **Function Block**

Each Function Block as shown in Figure 2, is comprised of 18 independent macrocells, each capable of implementing a combinatorial or registered function. The FB also receives global clock, output enable, and set/reset signals. The FB generates 18 outputs that drive the FastCONNECT switch matrix. These 18 outputs and their corresponding output enable signals also drive the IOB. Logic within the FB is implemented using a sum-of-products representation. Thirty-six inputs provide 72 true and complement signals into the programmable ANDarray to form 90 product terms. Any number of these product terms, up to the 90 available, can be allocated to each macrocell by the product term allocator.

Each FB supports local feedback paths that allow any number of FB outputs to drive into its own programmable AND-array without going outside the FB.

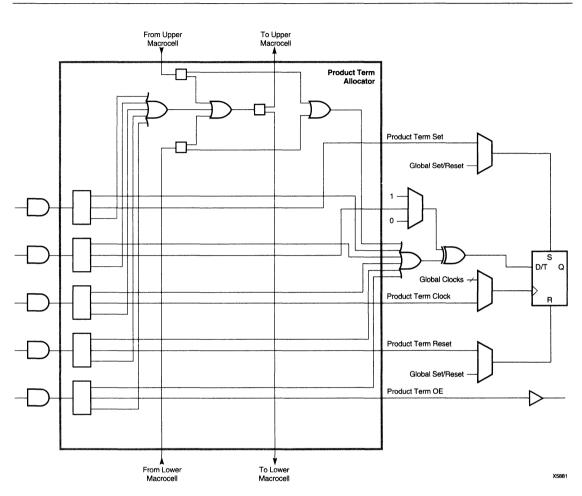

#### Macrocell

Each XC9500 macrocell may be individually configured for a combinatorial or registered function. The macrocell and associated FB logic is shown in Figure 3.

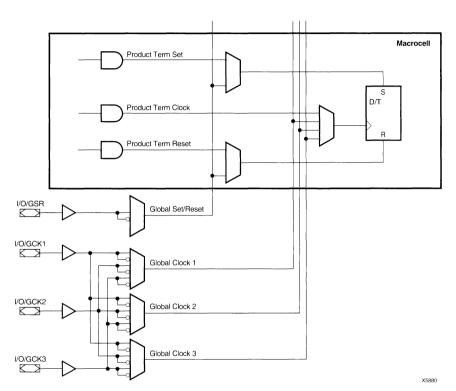

Five direct product terms from the AND-array are available for use as primary data inputs (to the OR and XOR gates) to implement combinatorial functions, or as control inputs including clock, set/reset, and output enable. The product term allocator associated with each macrocell selects how the five direct terms are used. The macrocell register can be configured as a D-type or T-type flip-flop, or it may be bypassed for combinatorial operation. Each register supports both asynchronous set and reset operations. During power-up, all user registers are initialized to the user-defined preload state (default to 0).

Figure 3. XC9500 Macrocell Within Function Block

All global control signals are available to each individual macrocell, including clock, set/reset, and output enable signals. As shown in Figure 4, the macrocell register clock originates from either of three global clocks or a product term clock. Both true and complement polarities of a GCK pin can be used within the device. A GSR input is also provided to allow user registers to be set to a user-defined state.

Figure 4. Macrocell Clock and Set/Reset Capability

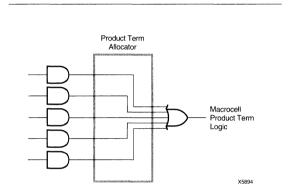

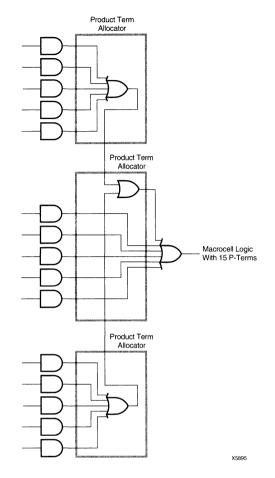

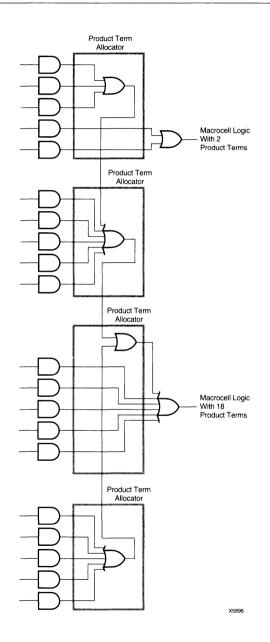

# **Product Term Allocator**

The product term allocator controls how the five direct product terms are assigned to each macrocell. For example, all five direct terms can drive the OR function as shown in Figure 5.