## **Table of Contents**

Custom/Logic.

MEMORIES

Memories. 2

MICRO

Military. 4

Systems.

Quality Assurance.

Synertek Inc. A Subsidiary of Honeywell

3001 Stender Way Santa Clara, CA 95054 Telephone (408) 988-5600 TWX: 910-338-0135

General Information. /

### Contents

| Pe                                                     | age   |

|--------------------------------------------------------|-------|

| Chapter 1. Custom Logic                                | 1-1   |

| SY7110/SY7111. 300 PBS FSK Modem                       | . 1-9 |

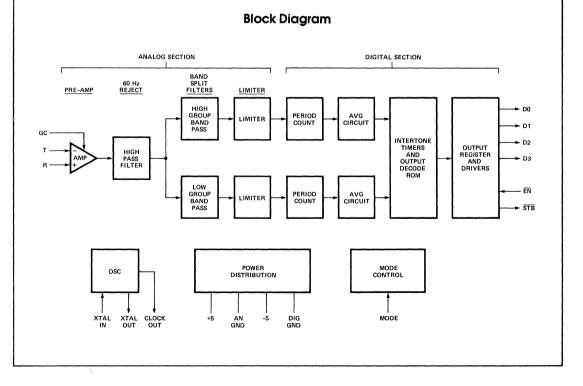

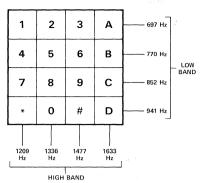

| SY7100, DTMF Receiver                                  | 1-17  |

|                                                        |       |

| Chapter 2. Memories                                    | 2-1   |

| RAM Selector Guide                                     |       |

| ROM Selector Guide                                     |       |

| EEPROM Selector Guide                                  |       |

| RAM Cross Reference Guide                              |       |

| ROM Cross Reference Guide                              |       |

|                                                        |       |

| Random Access Memory (RAM)                             |       |

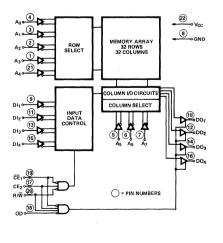

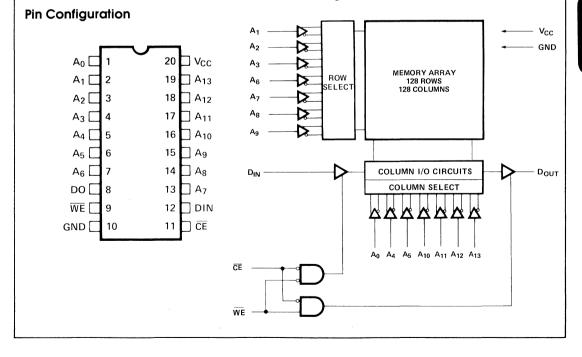

| SY2101, 256 x 4-Bit Static RAM                         |       |

| SY2111, 256 x 4-Bit Static RAM                         |       |

| SY2112, 256 x 4-Bit Static RAM                         |       |

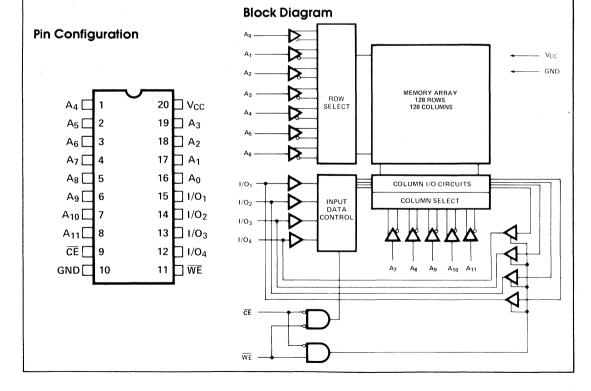

| SY2114A, 1024 x 4-Bit Static RAM                       |       |

| SY2128, 2048 x 8-Bit Static RAM                        | 2-29  |

| SY2129, 2048 x 8-Bit Static RAM                        |       |

| SY2147H, 4096 x 1-Bit Static RAM                       |       |

| SY2148H, 1024 x 4-Bit Static RAM                       | 2-41  |

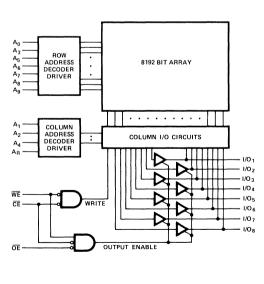

| SY2149H, 1024 x 4-Bit Static RAM                       | 2-45  |

| SY2158, 1024 x 8-Bit Static RAM                        |       |

| SY2159, 1024 x 8-Bit Static RAM                        | 2-53  |

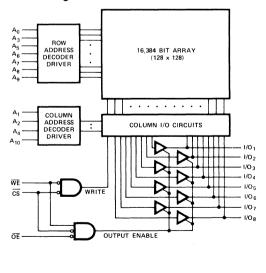

| SY2167, 16,384 x 1-Bit Static RAM                      |       |

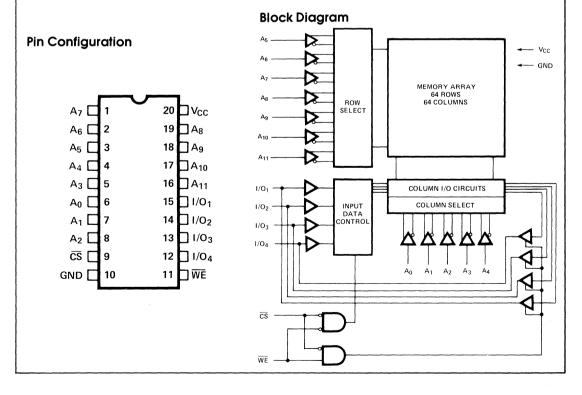

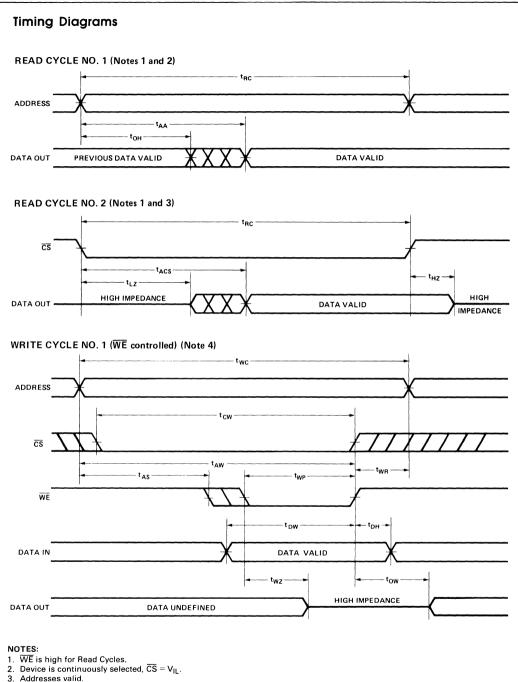

| SY2168, 4096 x 4-Bit Static RAM                        | 2-61  |

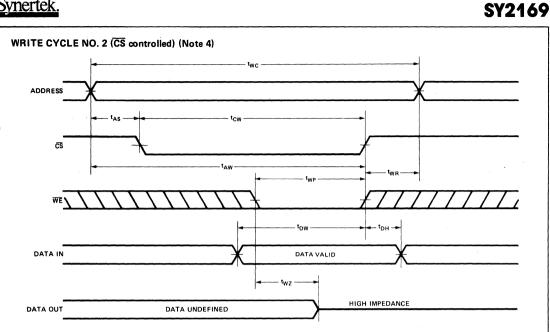

| SY2169, 4096 x 4-Bit Static RAM                        |       |

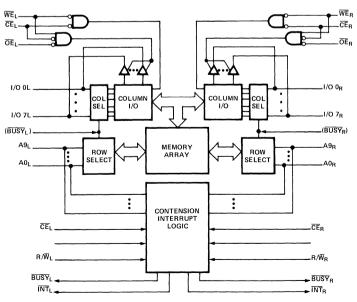

| SY21D1, 1024 x 8-Bit Dual Port RAM                     | 2-69  |

| Read Only Memory (ROM)                                 | 2-71  |

| SY2316B, 2048 x 8-Bit ROM                              | 2-73  |

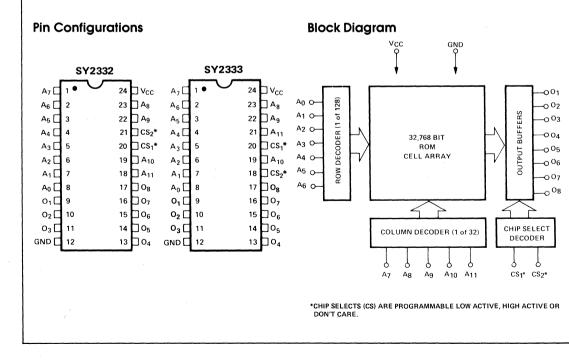

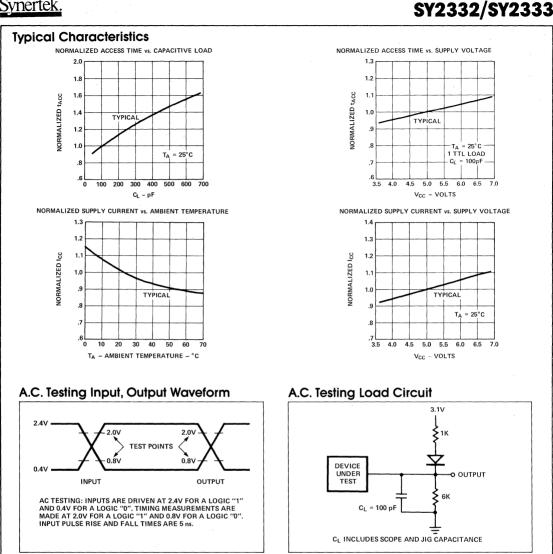

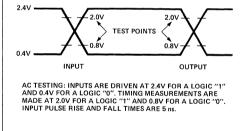

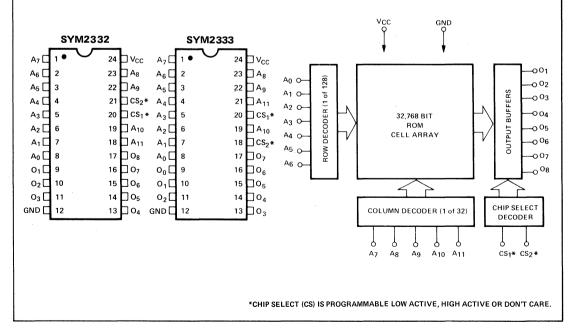

| SY2332/3, 4096 x 8-Bit ROM                             | 2-76  |

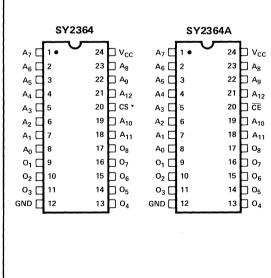

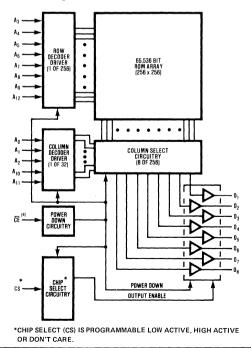

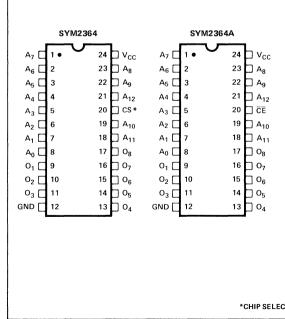

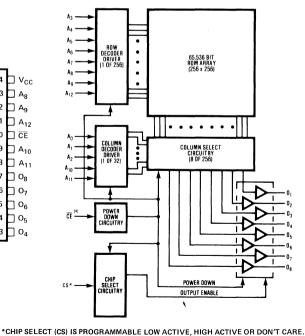

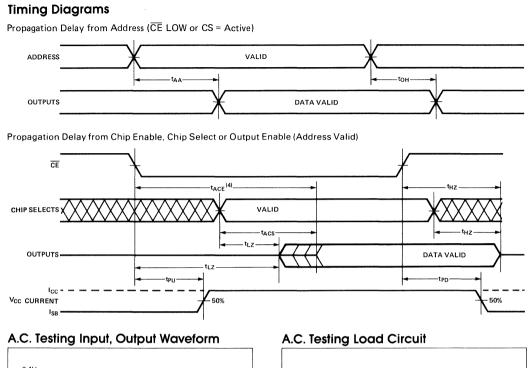

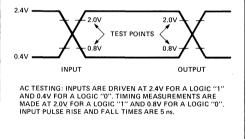

| SY2364/A, 8192 x 8-Bit ROM                             | 2-79  |

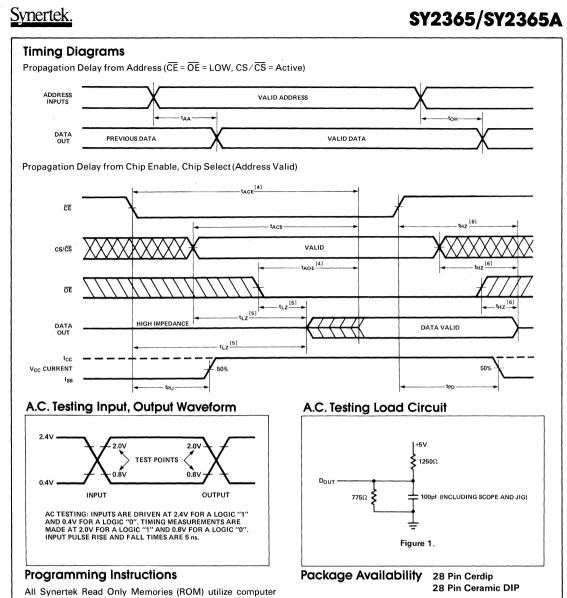

| SY2365/A, 8192 x 8-Bit ROM                             | 2-82  |

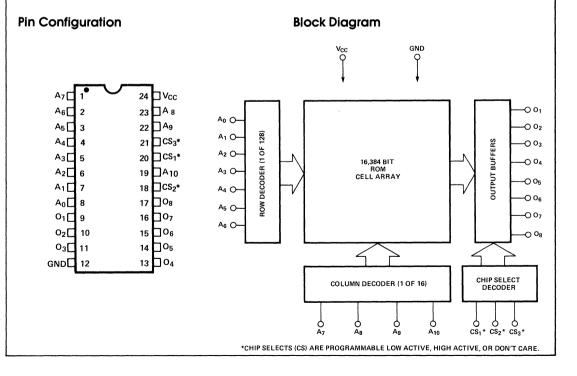

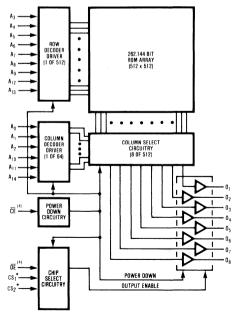

| SY23128/A, 16,384 x 8-Bit ROM                          | 2-85  |

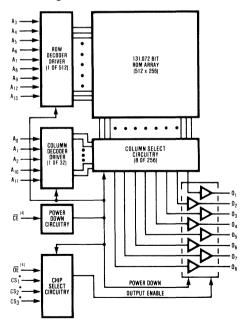

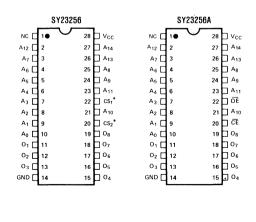

| SY23256/A, 32,768 x 8-Bit ROM                          | 2-88  |

| SY3308, 1024 x 8-Bit ROM                               | 2-91  |

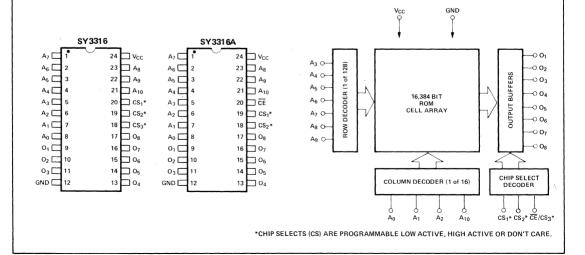

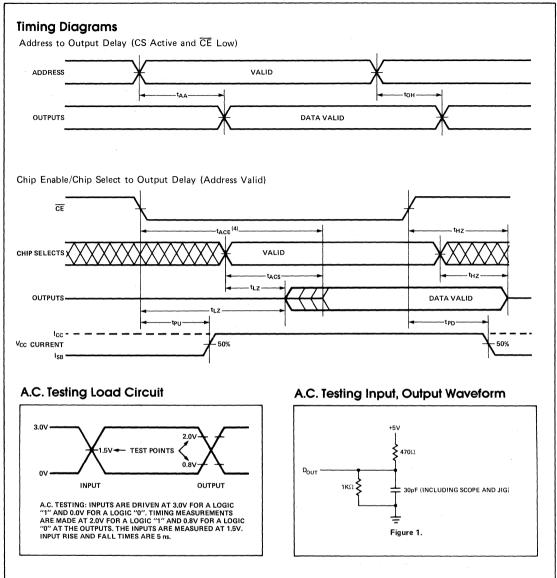

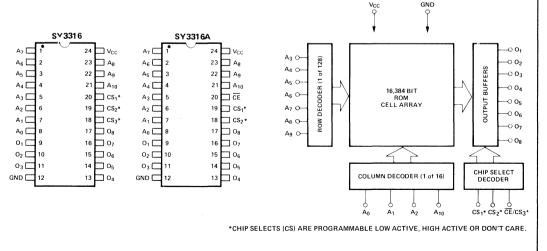

| SY3316/A, 2048 x 8-Bit ROM                             | 2-96  |

| SY3308R, 1024 x 8-Bit ROM                              | 2-97  |

| SY3316R, 2048 x 8-Bit ROM                              | 2-101 |

| SY6364, 8192 x 8-Bit ROM                               | 2-105 |

| SY6365, 8192 x 8-Bit ROM                               | 2-105 |

| Programming Instructions                               | 2-106 |

| Electrically Erasable PROM (EEPROM)                    | 2-109 |

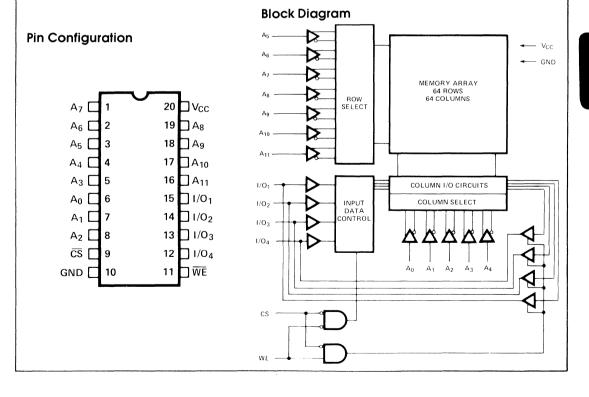

| SY2801A, 64 x 4-Bit EEPROM                             | 2-111 |

| SY2802E, 256 x 8-Bit EEPROM                            | 2-115 |

|                                                        | 2-110 |

| Chapter 3. Microprocessors                             | 3-1   |

| Microprocessors and Peripherals                        | 0-1   |

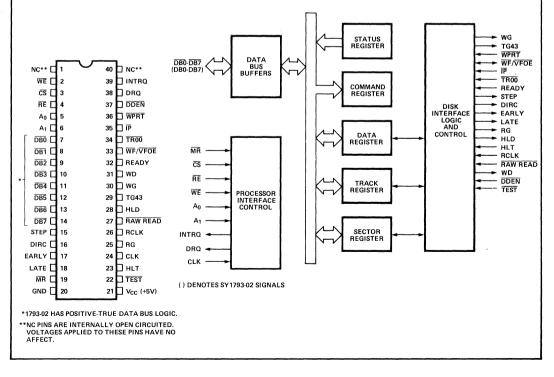

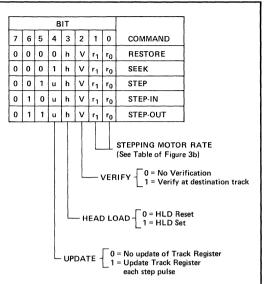

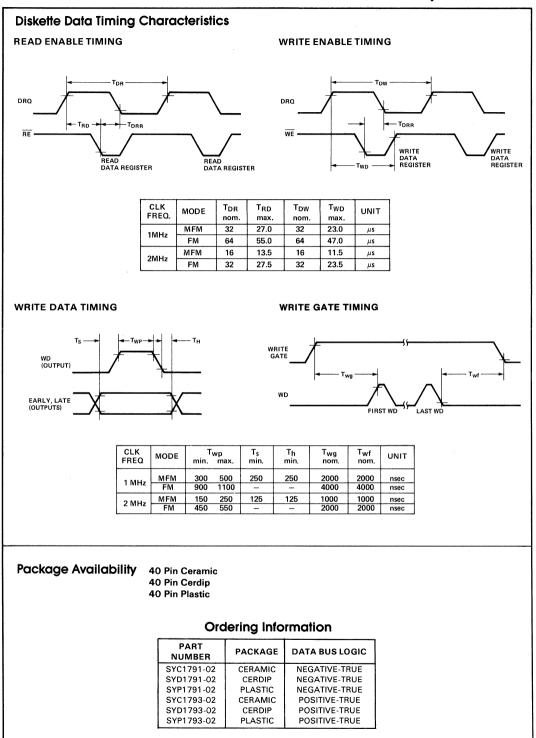

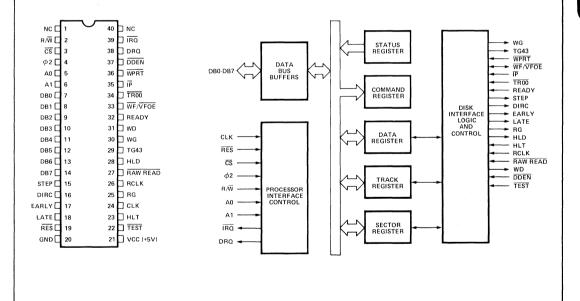

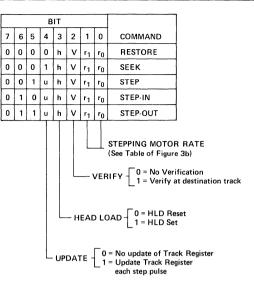

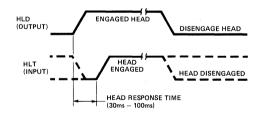

| SY1791-02/SY1793-02, Floppy Disk Controller            | 3-5   |

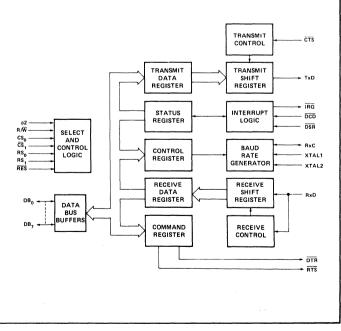

| SY2661, Enhanced Programmable Communications Interface | 3-21  |

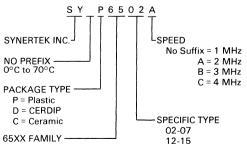

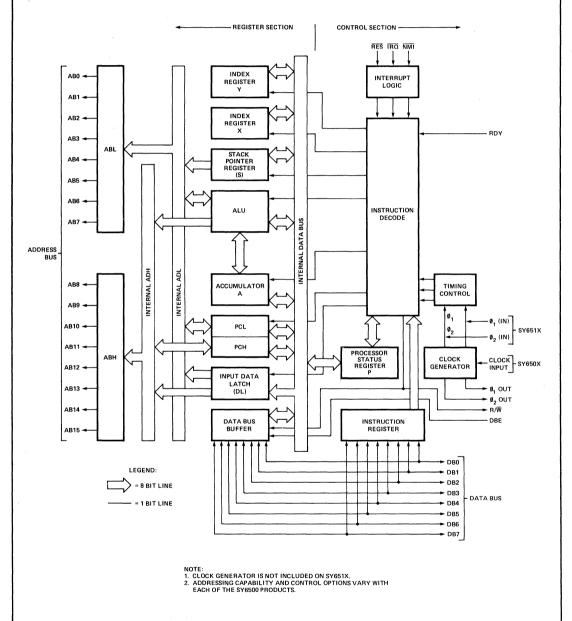

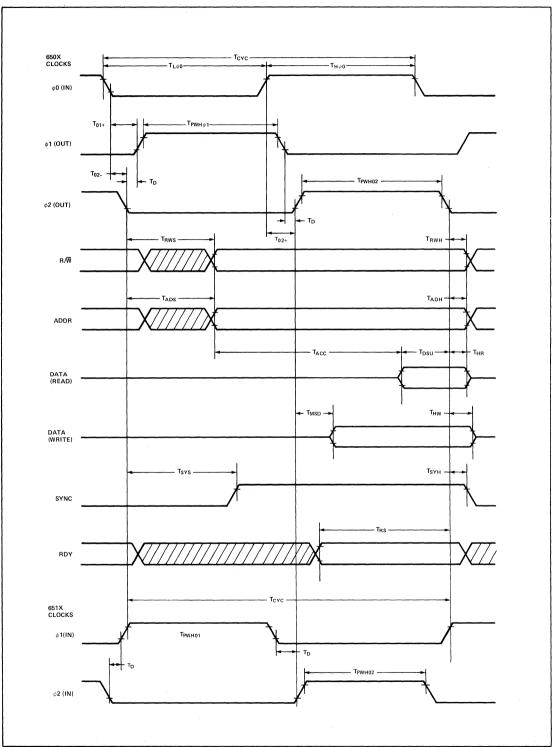

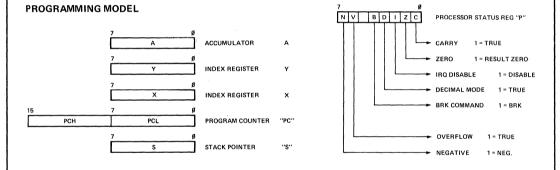

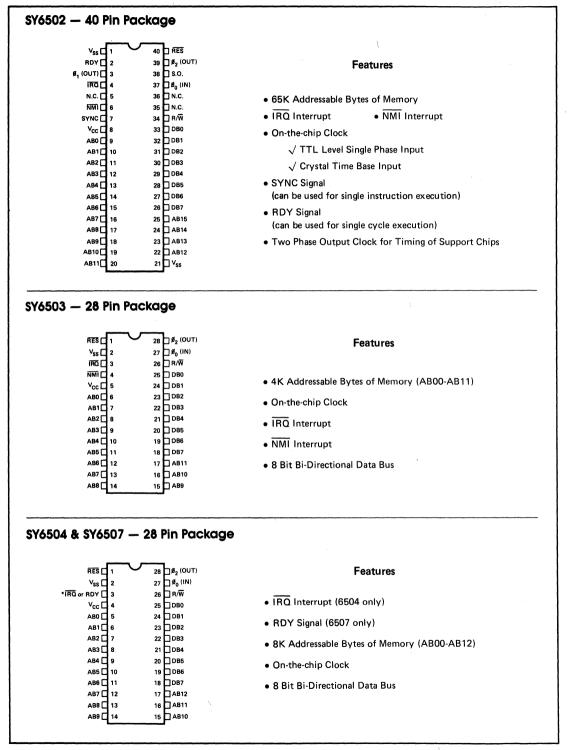

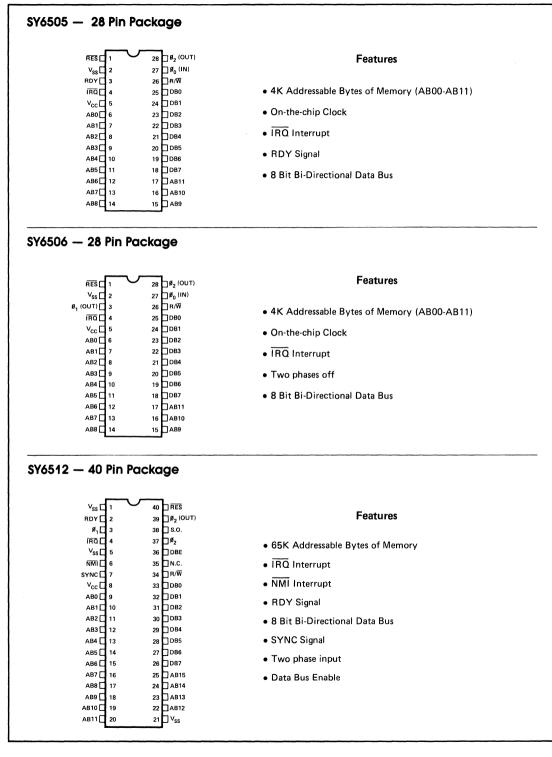

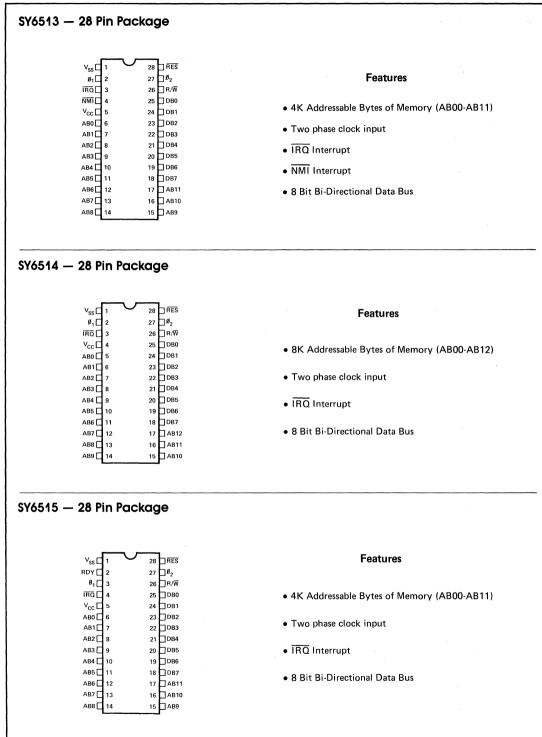

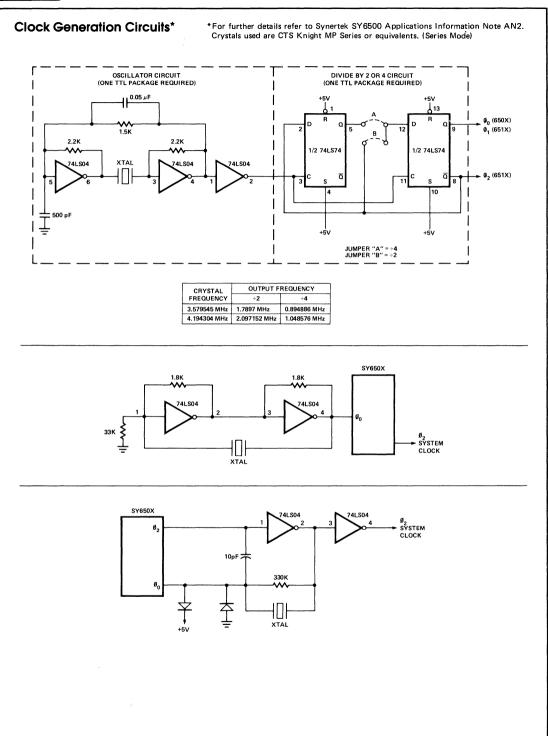

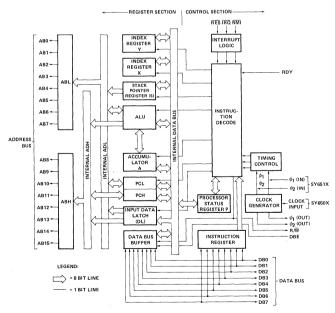

| SY6500, 8-Bit Microprocessor Family                    | 3-35  |

| SYE6500/A 8-Bit Microprocessor Family                  | 3-48  |

### Contents(Contd.)

#### Page

4-19

4-23

4-36

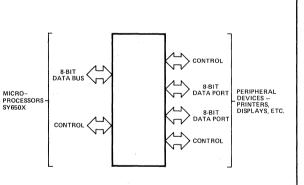

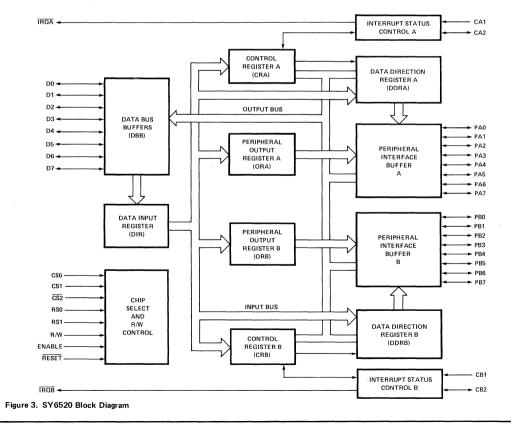

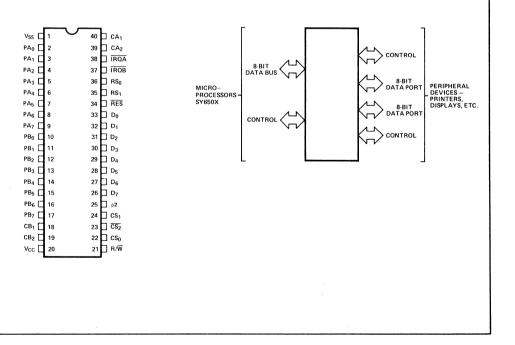

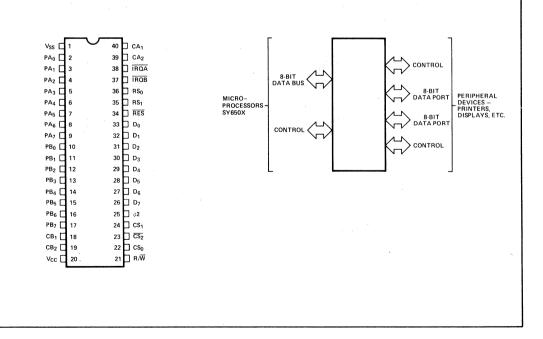

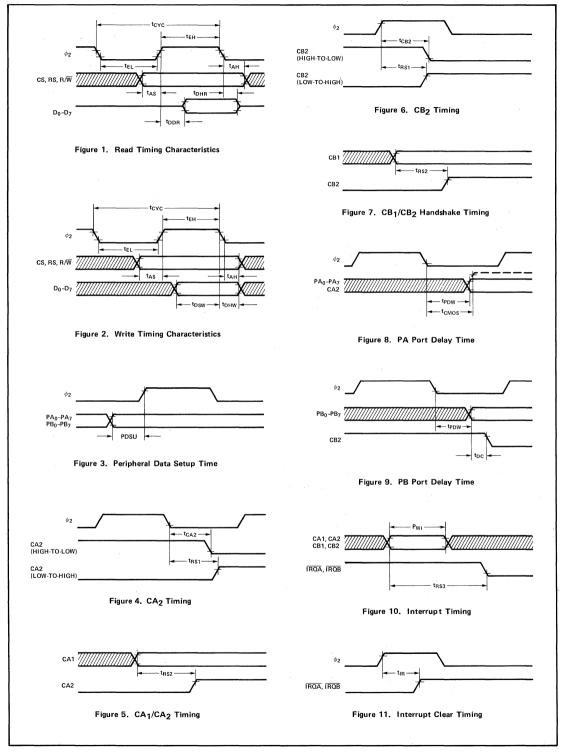

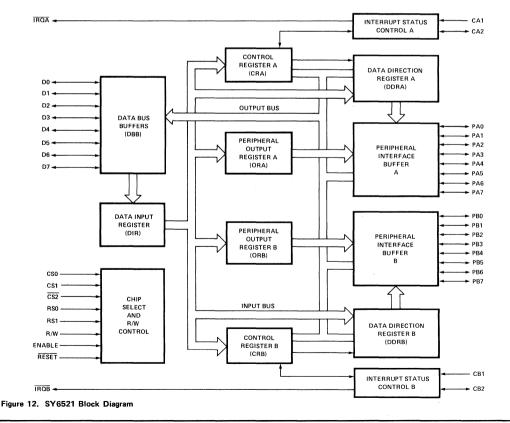

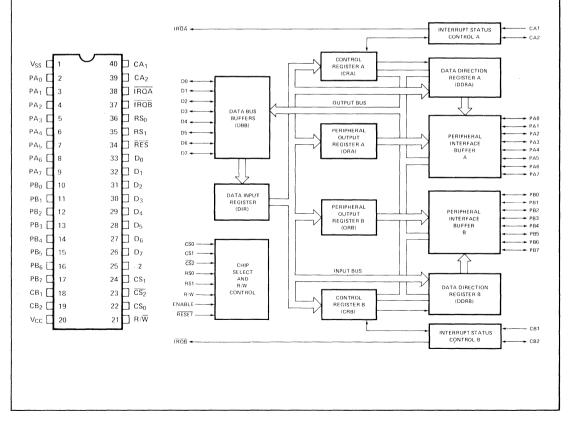

|     | SY6520/A; SY6820/SY68B20, Peripheral Interface Adapter    | 3-50  |

|-----|-----------------------------------------------------------|-------|

|     | SYE6520/A; SYE6820/SYE68B20, Peripheral Interface Adapter | 3-62  |

|     | SY6521/A; SY6821/SY68B21, Peripheral Interface Adapter    | 3-64  |

|     | SYE6521/A; SYE6821/SY68B21, Peripheral Interface Adapter  |       |

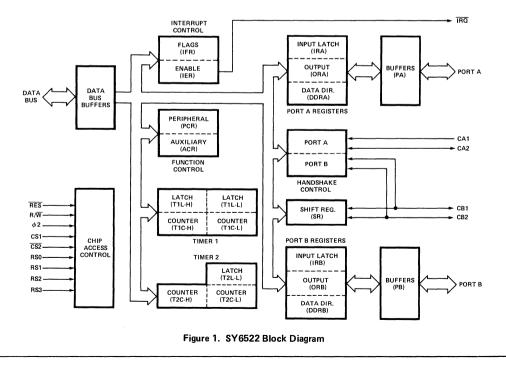

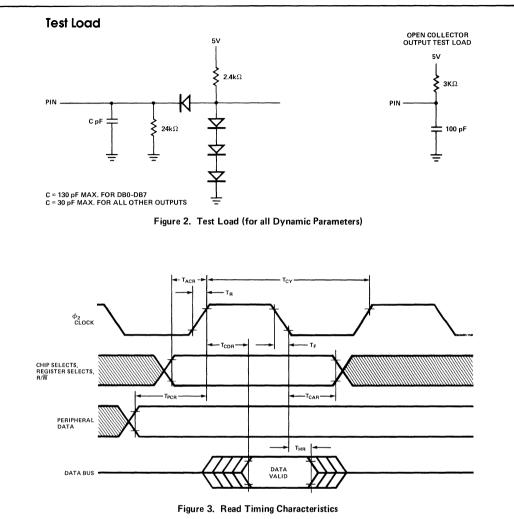

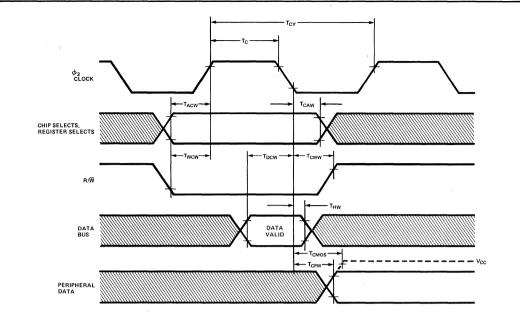

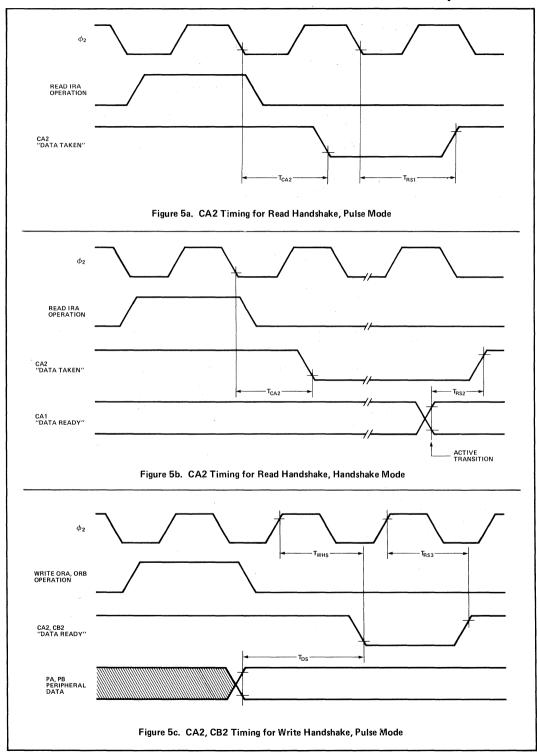

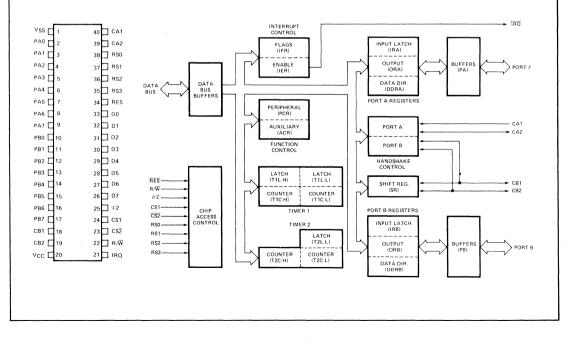

|     | SY6522/A, Versatile Interface Adapter                     | 3-79  |

|     | SYE6522/A, Versatile Interface Adapter                    | 3-99  |

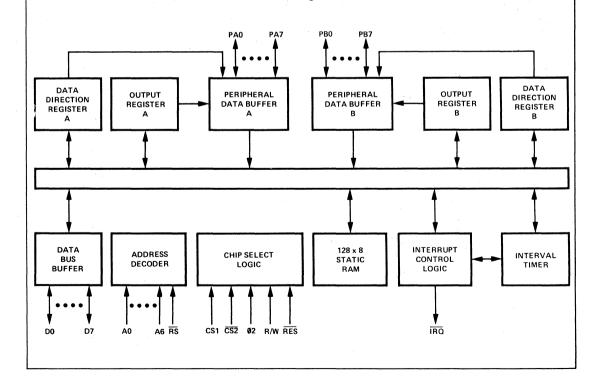

|     | SY6530, Memory, I/O, Timer Array                          | 3-101 |

|     | SY6532, RAM, I/O, Timer Array                             | 3-112 |

|     | SYE6532/A, RAM, I/O, Timer Array                          | 3-120 |

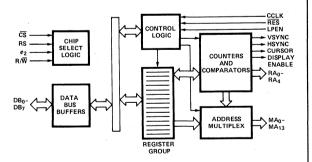

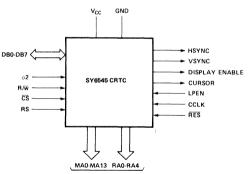

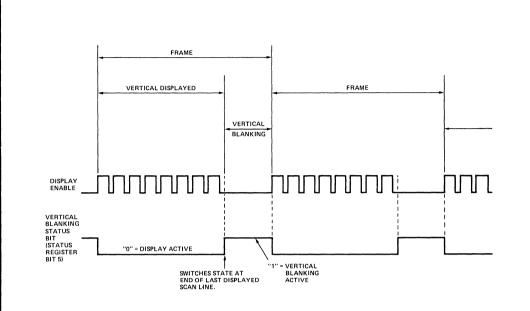

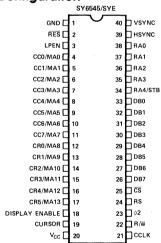

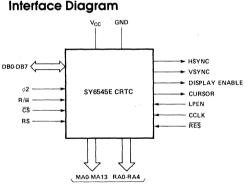

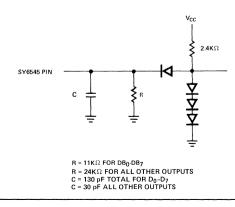

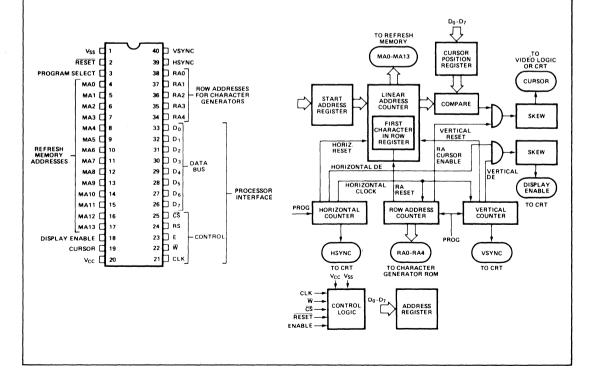

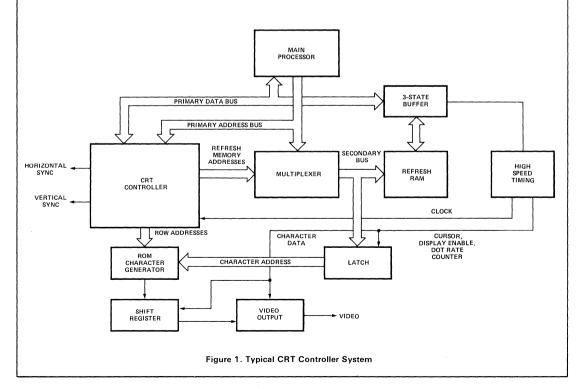

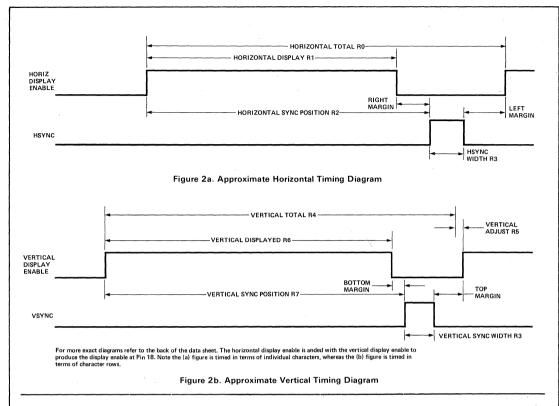

|     | SY6545-1, CRT Controller                                  | 3-122 |

|     |                                                           | 3-136 |

|     | SY6545R, CRT Controller                                   | 3-148 |

|     |                                                           | 3-160 |

|     |                                                           | 3-176 |

|     |                                                           | 3-177 |

|     |                                                           | 3-185 |

|     |                                                           | 3-187 |

|     |                                                           | 3-201 |

|     |                                                           | 3-216 |

|     | · · ·                                                     | 3-219 |

|     | SY65C22, CMOS Versatile Interface Adapter                 |       |

|     | SY65C32, CMOS RAM, I/O, Timer Array                       |       |

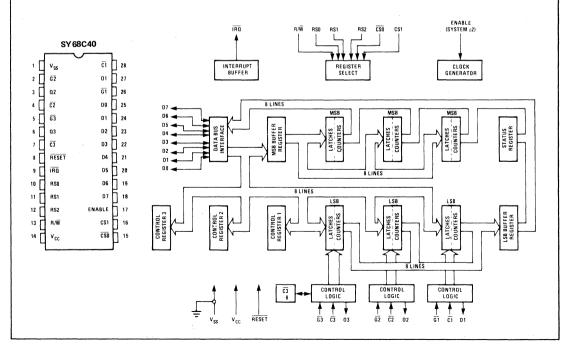

|     | SY68C40, CMOS Programmable Timer                          |       |

|     | -                                                         | 3-223 |

|     |                                                           | 00    |

|     | Microcomputers                                            |       |

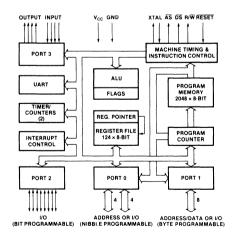

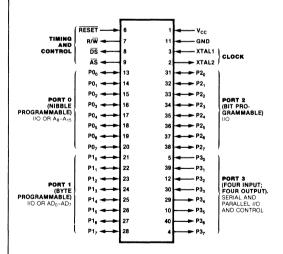

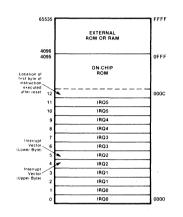

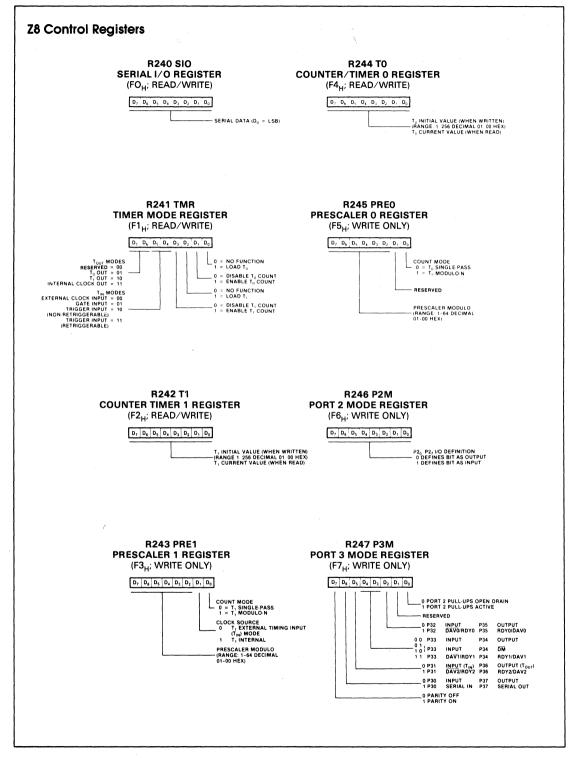

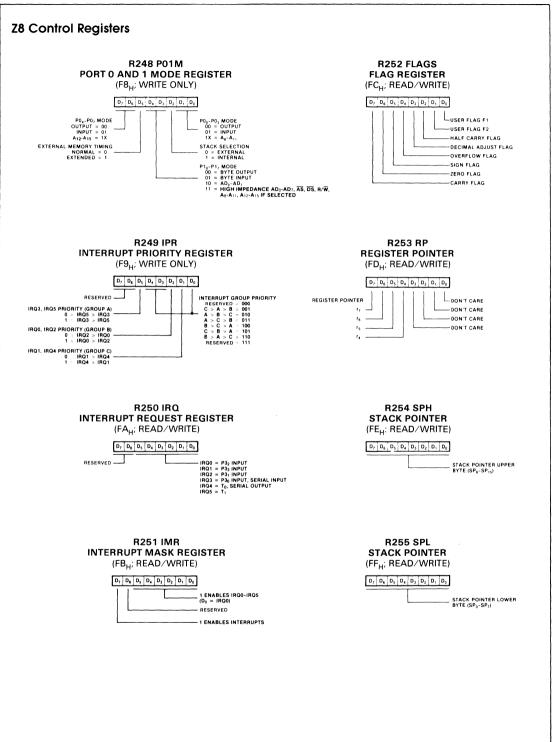

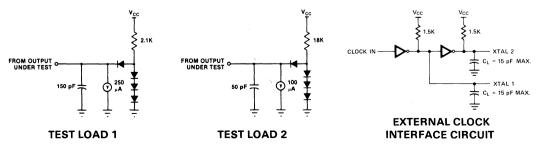

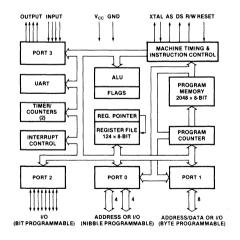

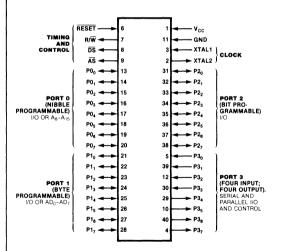

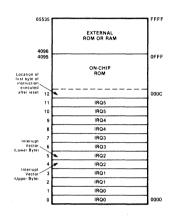

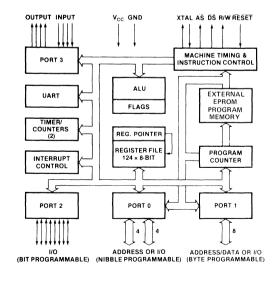

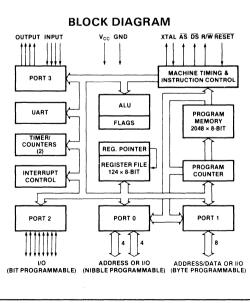

|     | Z8601/Z8602, Z8 Family of Single-Chip Microcomputers      |       |

|     | Z8603, Microcomputer Protopak/-Emulator                   |       |

|     | Z8611/Z8612, Z8 Family of Single-Chip Microcomputers      |       |

|     | Z8613, Microcomputer Protopak/-Emulator                   | 3-259 |

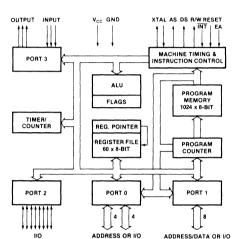

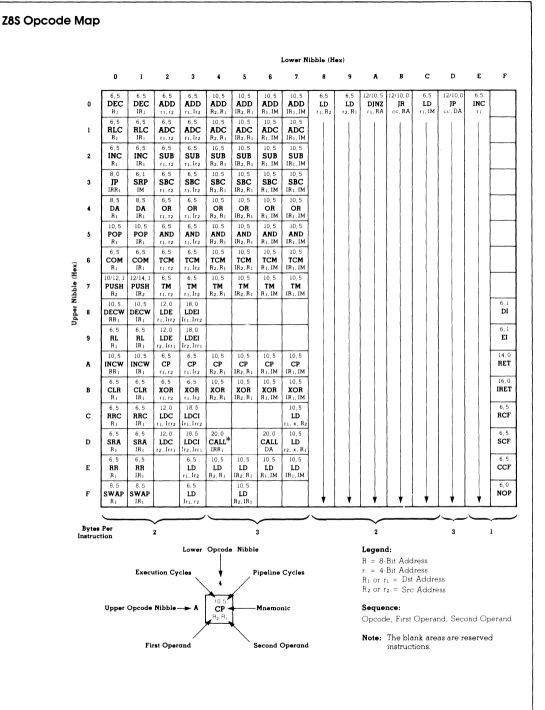

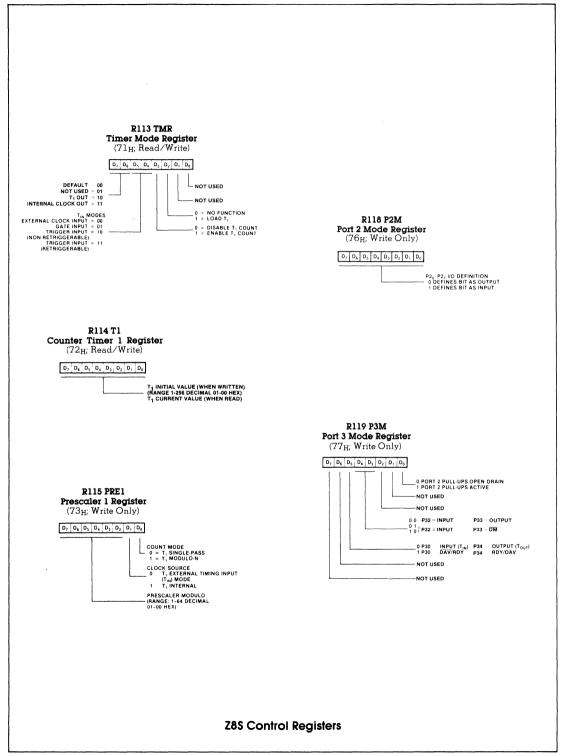

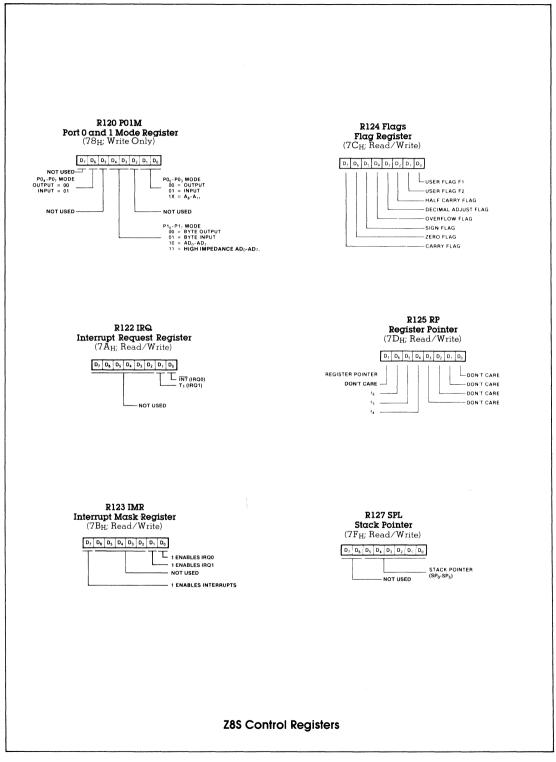

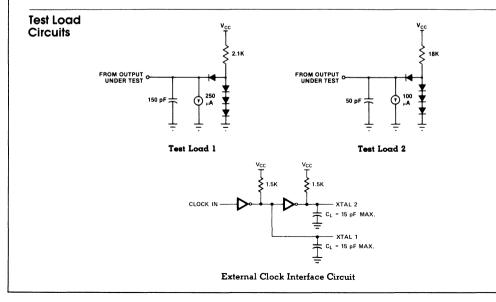

|     | Z8S MCU, Microcomputer                                    | 3-261 |

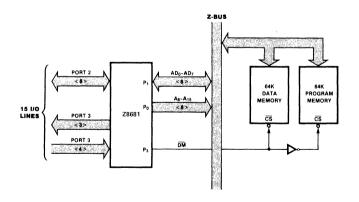

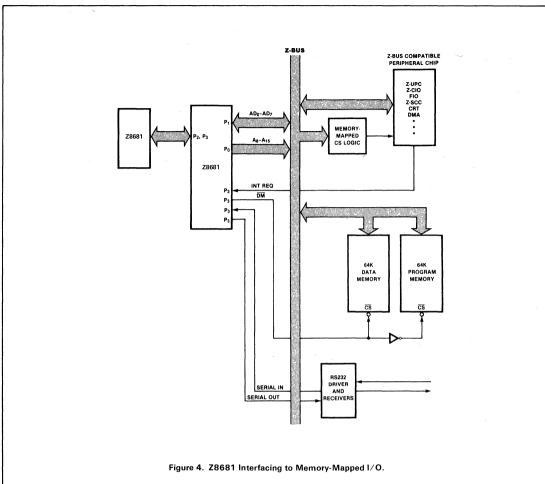

|     | Z8681, Z8 Family Z8681 Microcomputer                      | 3-276 |

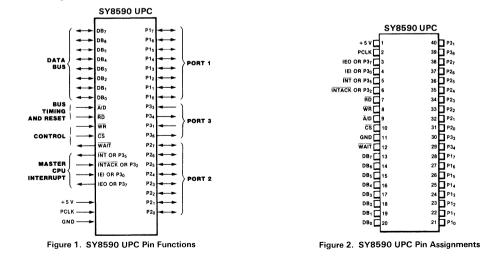

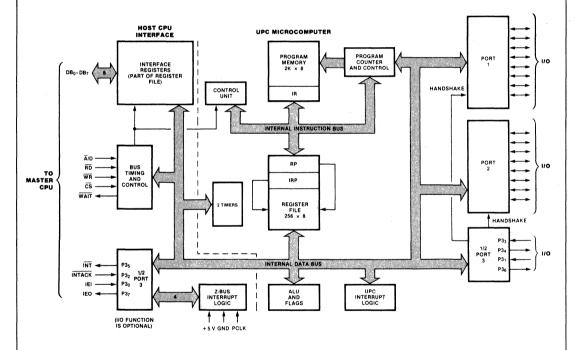

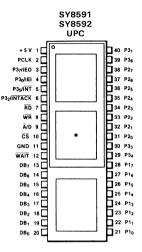

|     | Z8590, UPC Universal Peripheral Controller                | 3-279 |

|     | Z86C01, Single-Chip CMOS Microcomputer with 2K ROM        | 3-299 |

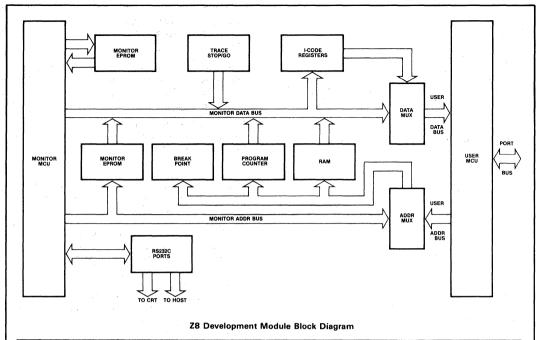

|     | Z8™, Z8 Development Module                                | 3-303 |

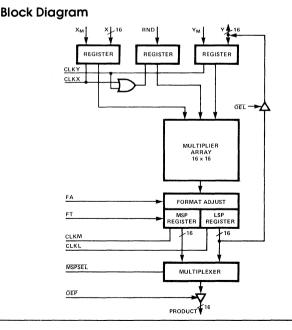

|     | SY66016, High-Speed 16 x 16 Parallel Multiplier           | 3-307 |

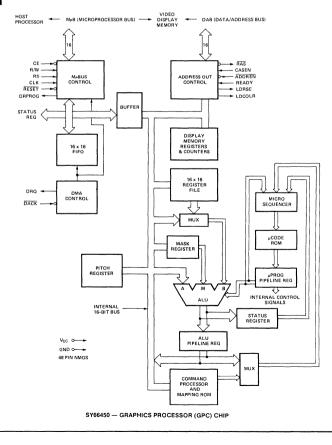

|     | SY66450, Graphic Processor                                | 3-309 |

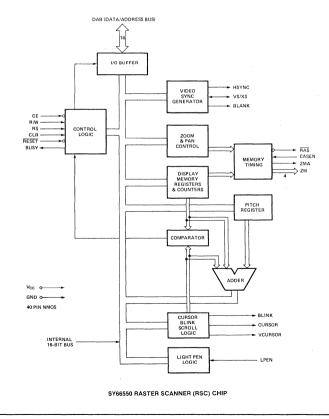

|     | SY66550, Raster Scanner                                   | 3-310 |

|     |                                                           |       |

| Cha | pter 4. Military                                          |       |

|     |                                                           |       |

|     | SYM2114A, 1024 x 4-Bit Static RAM                         |       |

|     | SYM2128, 2048 x 8-Bit Static RAM                          |       |

|     | SYM2129, 2048 x 8-Bit Static RAM                          |       |

|     | SYM2147H. 4096 x 1-Bit Static RAM                         | 4-15  |

SYM2148H, 1024 x 4-Bit Static RAM .....

SYM2149H, 1024 x 4-Bit Static RAM .....

SYM2167, 16,384 x 1-Bit Static RAM ..... 4-27 SYM2168, 4096 x 4-Bit Static RAM ...... 4-28 SYM2169, 4096 x 4-Bit Static RAM ...... 4-29 SYM2364/A, 8192 x 8 ROM ...... 4-33 SYM2365/A, 8192 x 8 ROM .....

## Contents(Contd.)

|                                                                           | Page  |

|---------------------------------------------------------------------------|-------|

| SYM3316/A, 2048 x 8 High Speed ROM                                        | 4-39  |

| SYM23128/A, 16,384 x 8 ROM                                                | 4-41  |

| SYM23256 / A, 32,768 x 8 ROM                                              | 4-43  |

| Chapter 5. Systems                                                        | . 5-1 |

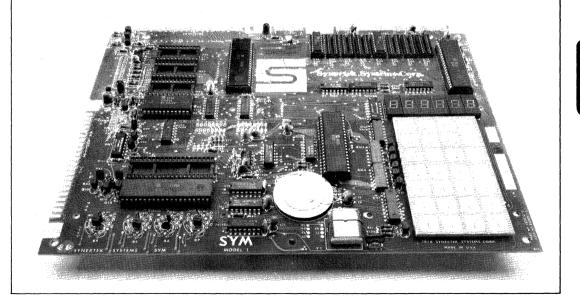

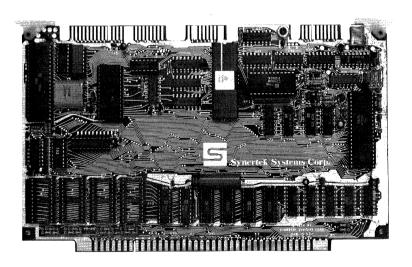

| SYM-1, Single Board Computer                                              |       |

| SYM-1/68, SYM-1/69, Single Board Computers                                | 5-4   |

| MOD-68, MOD-69, Adapter Board                                             | 5-4   |

| SYM-2, Single Board Computer                                              | 5-5   |

| SM100, OEM Version of SYM-1                                               | 5-6   |

| SRM-1, SRM-3, Static RAM Memory Kit                                       | 5-6   |

| BAS-1, Full Function BASIC                                                |       |

| RAE-1, Resident Assembler/Editor/Loader                                   |       |

| <b>№</b> OR-1, Forth                                                      | 5-8   |

| EPS-1, SYM-1 Diagnostic Program                                           | 5-8   |

| PEX-1, Port Expansion and Connector Kit                                   | 5-9   |

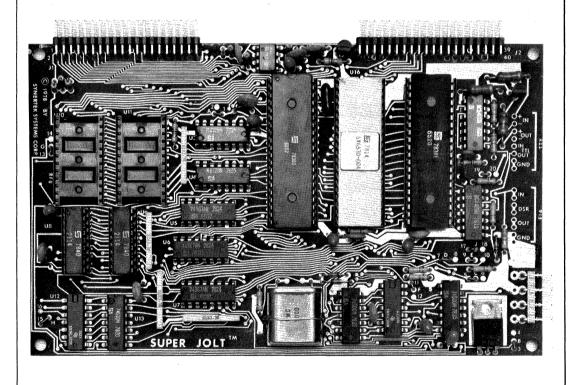

| CP110, Super Jolt CPU Board                                               |       |

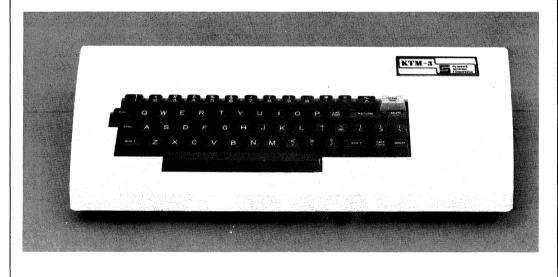

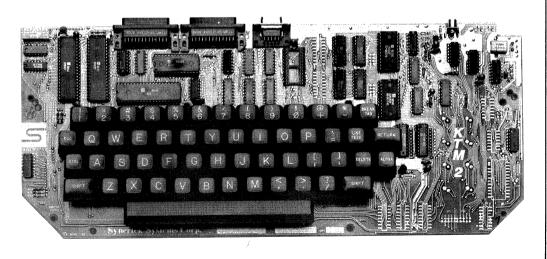

| KTM-2, Keyboard Terminal Module                                           |       |

| KTM-3, The Tubeless Terminal                                              |       |

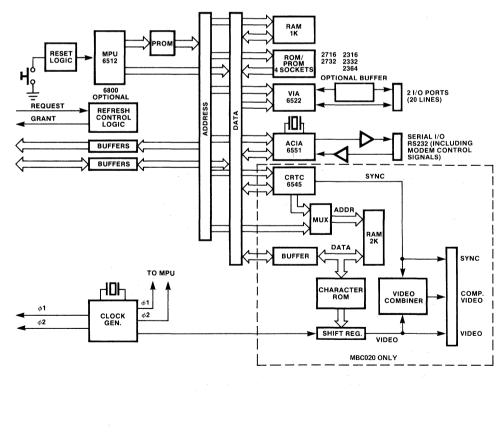

| MBC010/MBC020, CPU/Video Board                                            |       |

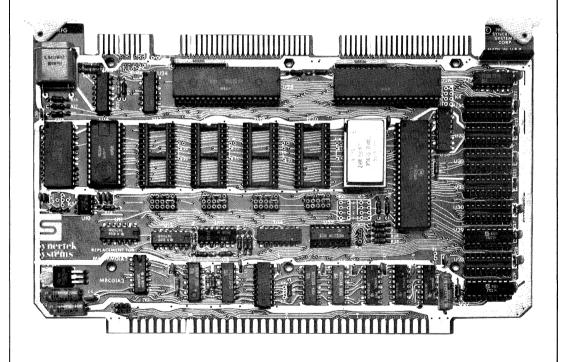

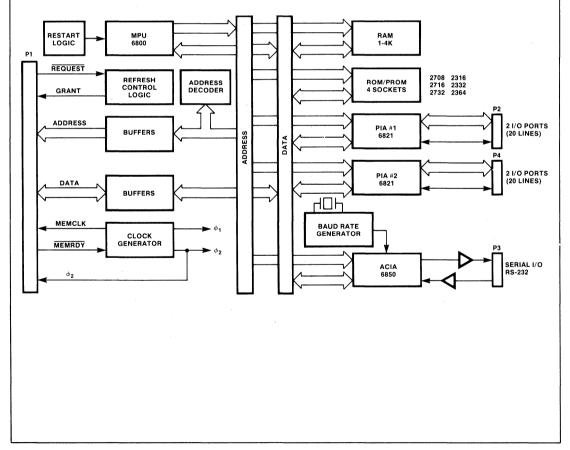

| MBC01A2/MBC01A2-1, Single Board Computer Motorola Micromodule Replacement |       |

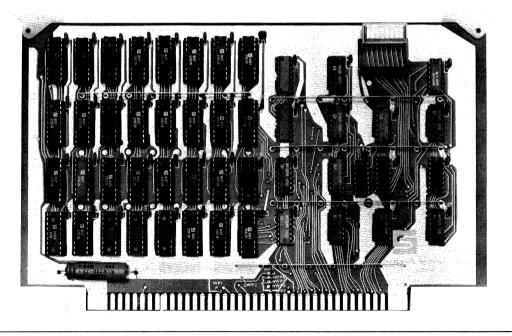

| MBC008/016, Static RAM Modules                                            |       |

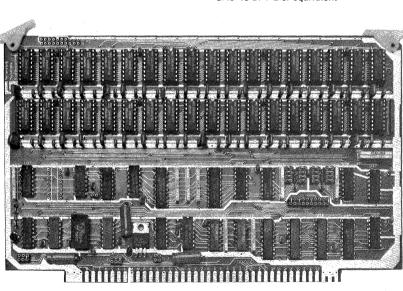

| MBC016D, MBC032D, MBC048D, MBC064D, Dynamic RAM Boards                    | 5-18  |

| MBC081/MBC091/MBC092/MBC093, EPROM Programmer/Prototyping                 |       |

| Board/Extenders                                                           |       |

| MBC210, Floppy Disk Controller                                            |       |

| MBC510, Combo I/O Board                                                   |       |

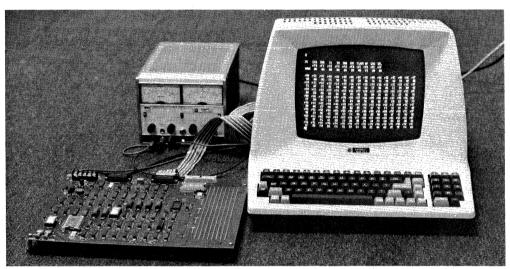

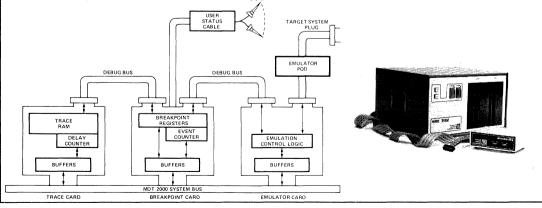

| MDT 2000, Micro Development System for Z8 and SY6500 Processors           | 5-21  |

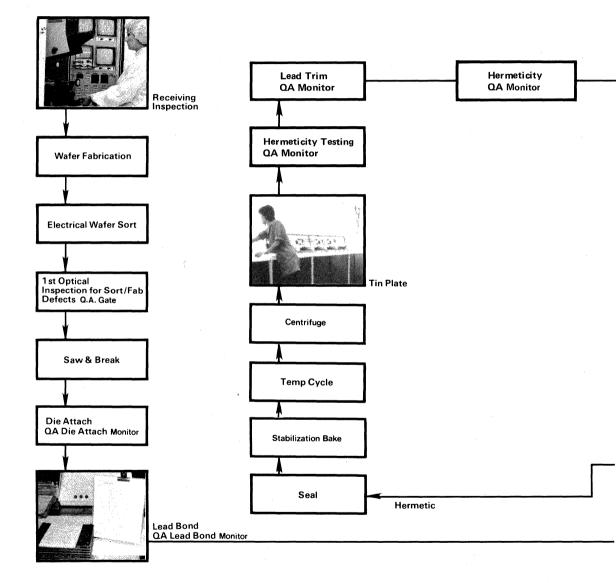

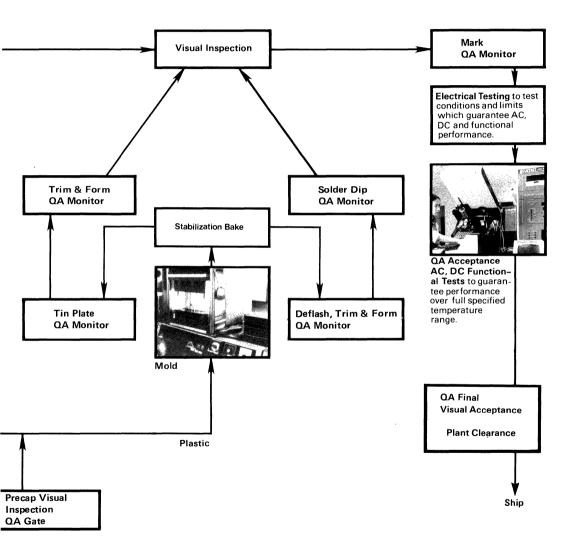

| Chapter 6. Quality Assurance                                              | 6-1   |

| Chapter 7. General Information                                            | 7.4   |

|                                                                           |       |

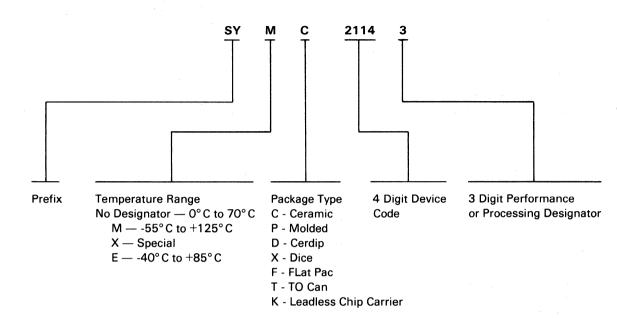

| Ordering Information                                                      |       |

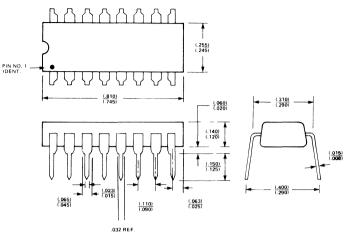

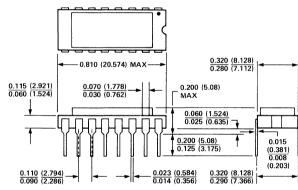

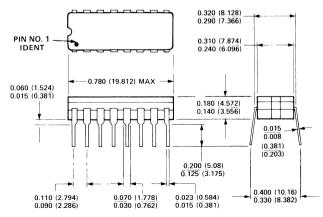

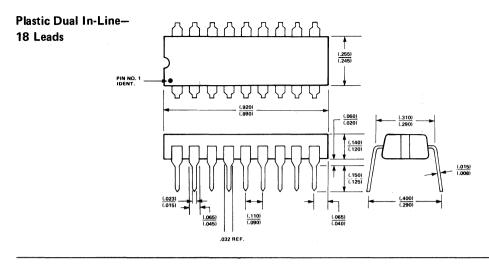

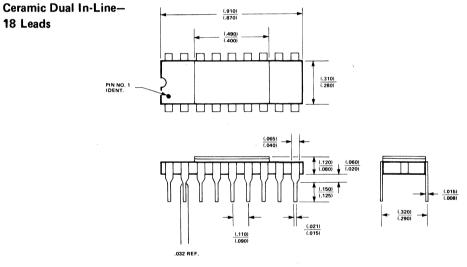

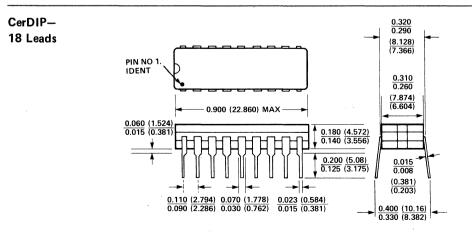

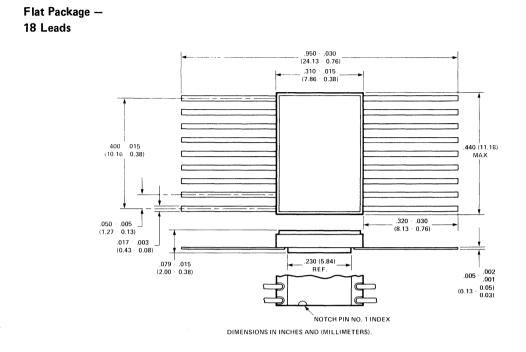

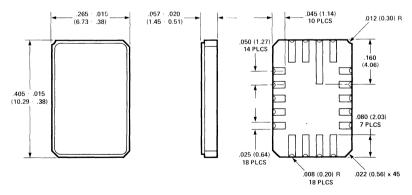

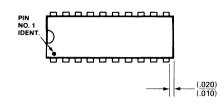

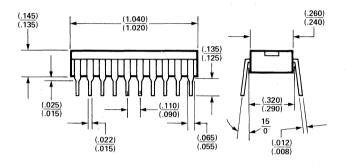

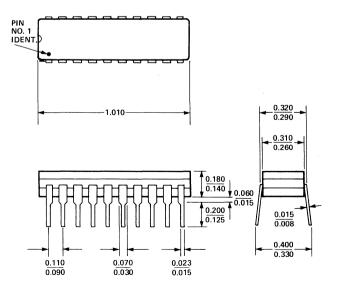

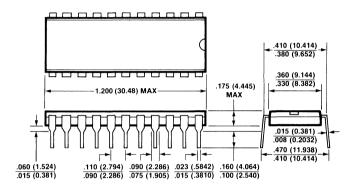

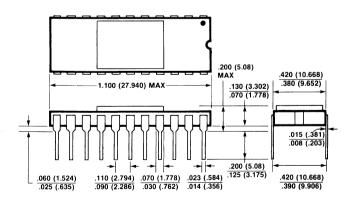

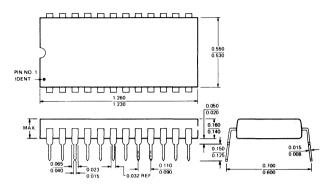

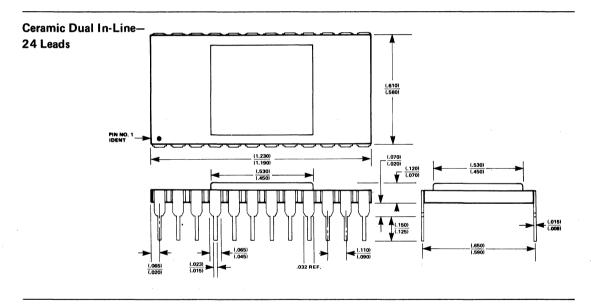

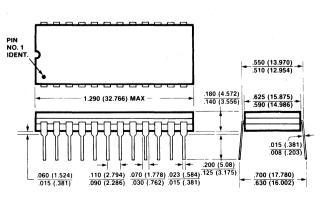

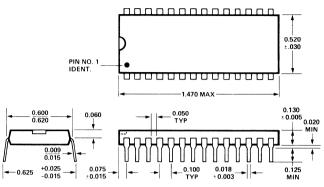

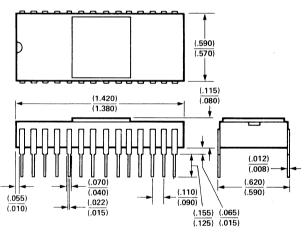

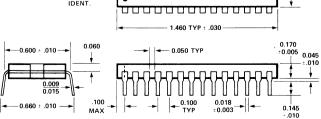

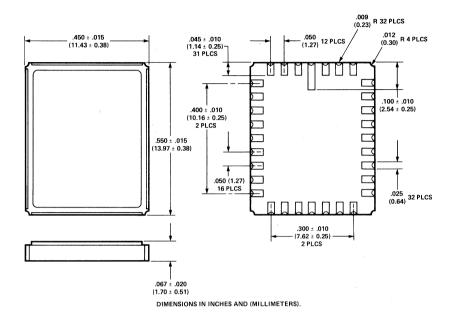

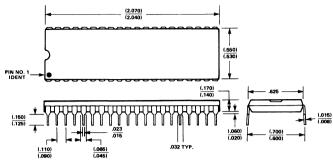

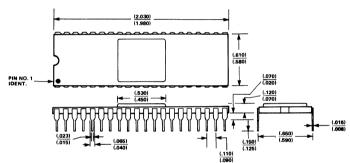

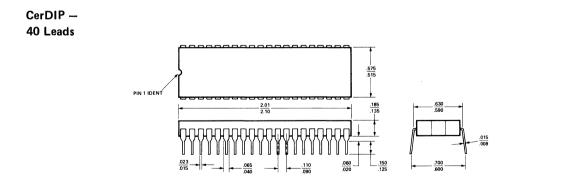

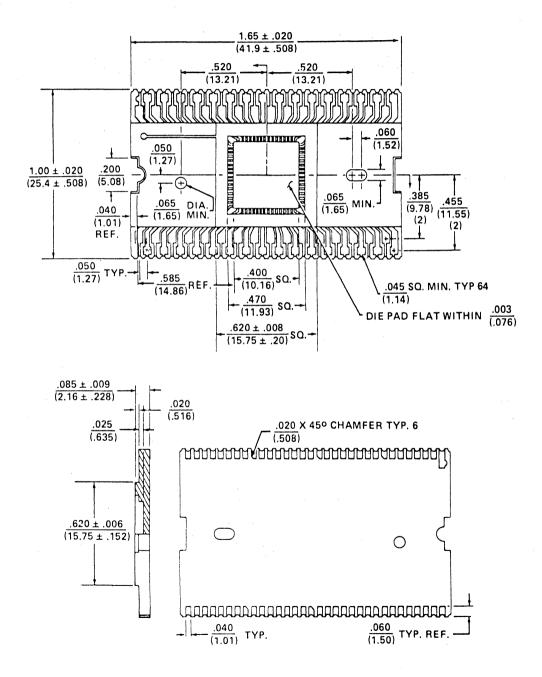

| Packaging Diagrams                                                        |       |

| Application Notes                                                         |       |

| Conversion Tables                                                         |       |

| Representative/Distributor Listing                                        | 7-17  |

### **Numerical Index**

|                     | Page |            | Page  |

|---------------------|------|------------|-------|

| Z8 <sup>™</sup>     |      | SY2149HL   |       |

| SY1791-02/SY1793-02 |      | SY2149HL-3 |       |

| SY2101-1            | 2-9  | SY2158A-2  | 2-49  |

| SY2101A             | 2-9  | SY2158A-3  | 2-49  |

| SY2101A-2           | 2-9  | SY2158A-4  | 2-49  |

| SY2101A-4           | 2-9  | SY2158B-2  | 2-49  |

| SY2111-1            | 2-14 | SY2158B-3  | 2-49  |

| SY2111A             | 2-14 | SY2158B-4  | 2-49  |

| SY2111A-2           | 2-14 | SY2159A-2  | 2-53  |

| SY2111A-4           | 2-14 | SY2159A-3  | 2-53  |

| SY2112-1            | 2-19 | SY2159A-4  | 2-53  |

| SY2112A             |      | SY2159B-2  | 2-53  |

| SY2112A-2           |      | SY2159B-3  |       |

| SY2112A-4           |      | SY2159B-4  |       |

| SY2114AL-1          |      | SY2167     |       |

| SY2114AL-2          |      | SY2167-3   |       |

| SY2114AL-3          |      | SY2168     |       |

| SY2114AL-5          |      | SY2168-3   |       |

| SY2114AL-5          |      | SY2169     |       |

| SY2128-1            |      | SY2169-3   |       |

|                     |      |            |       |

| SY2128-2            |      | SY21D1     |       |

| SY2128-3            |      | SY2316B    |       |

| SY2128-4            |      | SY2316B-2  |       |

| SY2128L-1           |      | SY2316B-3  |       |

| SY2128L-2           |      | SY2332     |       |

| SY2128L-3           |      | SY2332-2   |       |

| SY2128L-4           |      | SY2332-3   |       |

| SY2129-1            |      | SY2333     |       |

| SY2129-2            |      | SY2333-2   |       |

| SY2129-3            |      | SY2333-3   |       |

| SY2129-4            |      | SY2364     |       |

| SY2129L-1           |      | SY2364-2   | - · · |

| SY2129L-2           |      | SY2364-3   |       |

| SY2129L-3           |      | SY2364A    |       |

| SY2129L-4           |      | SY2364A-2  | 2-79  |

| SY2147H             | 2-37 | SY2364A-3  | 2-79  |

| SY2147H-1           | 2-37 | SY2365     | 2-82  |

| SY2147H-2           | 2-37 | SY2365-2   | 2-82  |

| SY2147H-3           | 2-37 | SY2365-3   | 2-82  |

| SY2147HL            | 2-37 | SY2365A    | 2-82  |

| SY2147HL-3          | 2-37 | SY2365A-2  | 2-82  |

| SY2148H             | 2-41 | SY2365A-3  | 2-82  |

| SY2148H-2           | 2-41 | SY2661     | 3-21  |

| SY2148H-3           | 2-41 | SY2801A    | 2-111 |

| SY2148HL            | 2-41 | SY2802E    | 2-115 |

| SY2148HL-3          | 2-41 | SY3308     | 2-91  |

| SY2149H             | 2-45 | SY3308R    | 2-97  |

| SY2149H-2           | 2-45 | SY3316     | 2-94  |

| SY2149H-3           |      | SY3316A    |       |

|                     |      |            |       |

## Numerical Index (Contd.)

|               | age  |

|---------------|------|

| SY3316R2-     |      |

| SY63642-      | -105 |

| SY63652-      | 105  |

| SY6500        | 3-35 |

| SYE6500/6500A | 3-48 |

| SY6520/6520A  |      |

| SY6820/68B20  | 3-50 |

| SYE6520/6820  |      |

|               | 3-62 |

| SY6521/6821   |      |

|               | 3-64 |

| SYE6521/6821  |      |

|               | 3-76 |

|               | 3-79 |

|               | 3-99 |

| SY6530        |      |

| SY6532        |      |

| SYE6532/6532A |      |

| SY6545-1      |      |

| SY6545R       |      |

| SY6545E       |      |

| SY6551        |      |

| SYE6551/6551A |      |

| SY6591/6591A  |      |

| SY65C00       |      |

| SY65C20       |      |

| SY65C22       |      |

| SY65C32       |      |

| SY65C51       |      |

| SY6845R       |      |

|               | 2-85 |

|               | 2-85 |

|               | 2-85 |

|               | 2-85 |

|               | 2-85 |

|               | 2-85 |

|               | 2-88 |

|               | 2-88 |

|               | 2-88 |

|               | 2-88 |

|               | 2-88 |

|               | 2-88 |

| SY66016       |      |

| SY66450       |      |

| SY66550       |      |

| SY68045       |      |

| SY68C40       | -222 |

| Ζ8™                                                                | Page<br>3-303 |

|--------------------------------------------------------------------|---------------|

| Z85 MCU                                                            |               |

|                                                                    | 3-261         |

| Z8590<br>Z8601                                                     | 3-279         |

|                                                                    | 3-224         |

|                                                                    | 3-224         |

| Z8603                                                              | 3-240         |

| Z8611                                                              | 3-242         |

| Z8612<br>Z8613                                                     | 3-242         |

|                                                                    | 3-242         |

| Z8681                                                              | 3-276         |

| Z86C01                                                             | 3-299         |

| Military Grade Products: $T_A = -55^{\circ} C$ to $+125^{\circ} C$ | ł             |

|                                                                    |               |

|                                                                    |               |

| SYM2114A-4                                                         |               |

| SYM2114A-5                                                         | ••••          |

| SYM2114AL-3                                                        |               |

| SYM2114AL-4                                                        |               |

| SYM2114AL-5                                                        |               |

| SYM2128-3<br>SYM2128-4                                             |               |

|                                                                    |               |

|                                                                    | 4-11          |

|                                                                    | 4-11          |

|                                                                    | 4-15          |

|                                                                    | 4-15          |

|                                                                    | 4-15          |

| SYM2148H-3<br>SYM2148H                                             | 4-19<br>4-19  |

| SYM2148H-6                                                         | 4-19          |

| SYM2149H-3                                                         | 4-23          |

| SYM2149H                                                           | 4-23          |

| SYM2149H-6                                                         | 4-23          |

| SYM2167                                                            | 4-27          |

| SYM2168                                                            | 4-28          |

| SYM2169                                                            | 4-29          |

| SYM2332                                                            | 4-30          |

| SYM2333                                                            | 4-30          |

| SYM2364                                                            | 4-33          |

| SYM2364-3                                                          | 4-33          |

| SYM2364A                                                           | 4-33          |

| SYM2364A-3                                                         | 4-33          |

| SYM2365                                                            | 4-36          |

| SYM2365-3                                                          | 4-36          |

| SYM2365A                                                           | 4-36          |

| SYM2365A-3                                                         | 4-36          |

| SYM23128                                                           | 4-42          |

| SYM23128-3                                                         | 4-42          |

## Numerical Index (Contd.)

| `           | 1 | Page |

|-------------|---|------|

| SYM3316     |   | 4-39 |

| SYM3316A    |   | 4-39 |

| SYM23128A   |   | 4-42 |

| SYM23128A-3 |   | 4-42 |

| SYM23256    |   | 4-44 |

| SYM23256-3  |   | 4-44 |

| SYM23256A   |   | 4-44 |

| SYM23256A-3 |   | 4-44 |

#### Systems

| BAS-1 5-7    | 7 |

|--------------|---|

| CP110 5-10   | כ |

| EPS-1 5-8    | 3 |

| FOR-1 5-8    |   |

| КТМ-2 5-1    | I |

| КТМ-3 5-12   | 2 |

| MBC008 5-17  | 7 |

| MBC010 5-13  | 3 |

| MBC020 5-13  | 3 |

| MBC01A2 5-15 | j |

|                  | Page |

|------------------|------|

| MBC01A2-1        | 5-15 |

| MBC016           | 5-17 |

| MBC016D          | 5-18 |

| MBC032D          | 5-18 |

| MBC048D          | 5-18 |

| MBC064D          | 5-18 |

| MBC081           | 5-19 |

| MBC091           | 5-19 |

| MBC092           | 5-19 |

| MBC093           | 5-19 |

| MBC210           | 5-20 |

| MBC510           | 5-20 |

| MDT 2000         | 5-21 |

| MOD-68; MOD-69   | 5-5  |

| RAE-1            | 5-7  |

| SRM-1; SRM-3     | 5-6  |

| SYM-1            | 5-3  |

| SYM-1/68; SYM-69 | 5-4  |

| SYM100           | 5-6  |

| SYM-2            | 5-5  |

|                  |      |

# Custom/Logic.

### Page Number

| Veri n          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                | التي والديني والمتعاد المساد الم                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Service Standards                                                                                                | 1.5 (1.4 (1.5 (1.5 (1.5 (1.5 (1.5 (1.5 (1.5 (1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | and the second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| A               | the first course and the second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11/11 game 1                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |

| -               | and the second s       |                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-3                                                                                                            |

|                 | hy Go                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | م المانية المحتومية                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 S S S S S S S S S S S S S S S S S S S                                                                          | e in consideration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - E = Y -                                                                                                      |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INCTON                                                                                                         | <b>A</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100 A.                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |

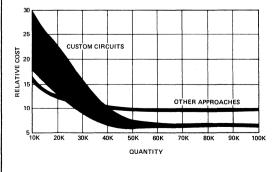

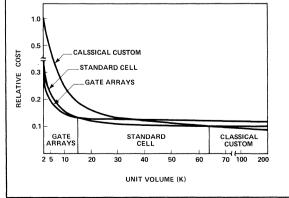

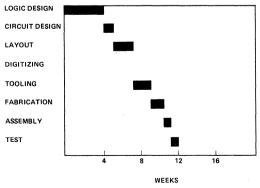

| · W             | HY UU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Custon                                                                                                         | LR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |