YOUR LOCAL DISTRIBUTOR IS Emitter Electronic Distributors SANTA ANA (714) 557-7131 LOS ANGELES (213) 299-7760 SUNNYVALE (408) 734-5470

### Introduction

Synertek, founded in 1973, has developed a broad line of MOS/LSI circuits. Today, these devices include Shift Registers, "N"MOS Static RAMs, "C"MOS Static RAMs, ROMs, EPROMs, a full complement of Systems, an expanding family of Microprocessors, timekeeping circuits, and finally a unique capability for custom MOS circuits. Synertek's fabrication capability includes advanced "N" channel, "P" channel, CMOS depletion load and HMOS Silicon Gate processes.

Synertek, a recognized leader in ROM capability, can handle many different types of customer inputs with turn-around times for prototypes of less than 2 to 3 weeks. Assembly capacity is located both here in the U.S. as well as in offshore facilities.

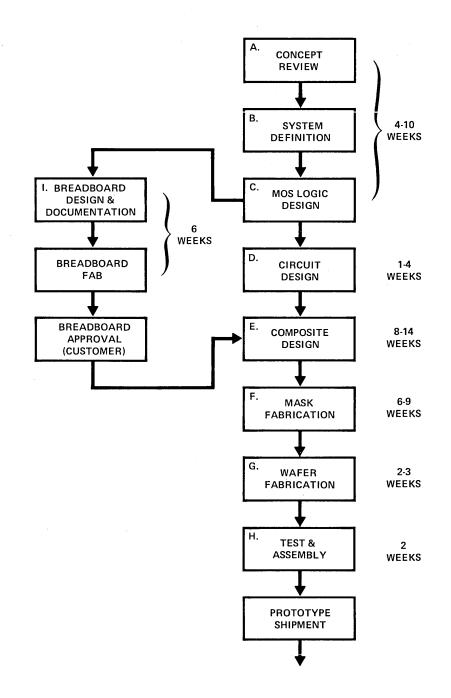

Custom MOS circuit design and production are an integral part of Synertek's present and future business plans. Whether the circuit design project starts at the feasibility stage or at the point where our customers provide tooling (reticles, tapes, etc.), Synertek is organized to quickly and efficiently handle the most difficult custom design.

This catalog provides complete technical information on our expanding line of Synertek Memories, Microprocessors, Timekeeping Circuits, Systems, and Custom capability. Additional information may be obtained by contacting your local Synertek Representative or Distributor, or by contacting Product Marketing in Santa Clara, California at (408) 988-5600.

©1979 Synertek, Inc.

Numerical Index, Functional Index and Product Replacement Guide 1

Shift Registers 2

**Random Access Memories 3**

**Read Only Memories and EPROMs 4**

**Microprocessors 5**

**Timekeeping Products 6**

**Custom Capabilities 7**

Systems 8

# Synertek<sup>®</sup>, Inc.

P.O. Box 552, Santa Clara, Ca 95052 Tel: (408) 988-5600, TWX: 910-338-0135

**General Information 9**

Synertek<sup>®</sup>, Inc. 1979 Data Catalog

GENERAL

SVSTEMS

TIMEKEEPING PRODUCTS

MICRO-PROCESSORS

ROMs EPROMs

RAMs

SHIFT REGISTERS

INDEX

# Numerical Index, Functional Index and Product Replacement Guide

Conduct the coments

1

## Numerical Index

INDEX

| SY1402A         Quad 256 Bit Dynamic MOS Shift Register         2-2           SY1404A         Single 1024 Bit Dynamic MOS         2-1           SY1404A         Single 1024 Bit Dynamic MOS         2-2           SY1101A         256x4 Bit Static MOS RAM (350 nsec)         3-3           SY2101A-2         256x4 Bit Static MOS RAM (450 nsec)         3-3           SY2101A-2         256x4 Bit Static MOS RAM (450 nsec)         3-3           SY2101A-2         256x4 Bit Static MOS RAM (450 nsec)         3-11           SY2102-1         1024x1 Bit Static MOS RAM (500 nsec)         3-11           SY2102A-1         1024x1 Bit Static MOS RAM (500 nsec)         3-11           SY2102A-1         1024x1 Bit Static MOS RAM (500 nsec)         3-11           SY2102A-1         1024x1 Bit Static MOS RAM (500 nsec)         3-11           SY2102A-1         1024x1 Bit Static MOS RAM (200 nsec)         3-15           SY21102-1         1024x1 Bit Static MOS RAM (200 nsec)         3-17           SY2102A         1024x1 Bit Static MOS RAM (200 nsec)         3-17           SY2102B         1024x1 Bit Static MOS RAM (300 nsec)         3-17           SY21102         1024x1 Bit Static MOS RAM (300 nsec)         3-17           SY21102B         1024x1 Bit Static MOS RAM (300 nsec)         3-17                                                               |                   |                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------|

| SY1404A         Single 1024 Bit Dynamic MOS         2-2           SY2101-1         256x4 Bit Static MOS RAM (350 nsec)         3-3           SY2101A-2         256x4 Bit Static MOS RAM (250 nsec)         3-3           SY2101A-4         256x4 Bit Static MOS RAM (250 nsec)         3-3           SY2101A-2         256x4 Bit Static MOS RAM (250 nsec)         3-3           SY2101-1         226x4 Bit Static MOS RAM (250 nsec)         3-11           SY2102-1         1024x1 Bit Static MOS RAM (500 nsec)         3-11           SY2102-1         1024x1 Bit Static MOS RAM (500 nsec)         3-11           SY2102-1         1024x1 Bit Static MOS RAM (500 nsec)         3-11           SY2102-1         1024x1 Bit Static MOS RAM (500 nsec)         3-11           SY2102-1         1024x1 Bit Static MOS RAM (200 nsec)         3-15           SY21102         1024x1 Bit Static MOS RAM (200 nsec)         3-17           SY21102-1         1024x1 Bit Static MOS RAM (200 nsec)         3-17           SY21102-1         1024x1 Bit Static MOS RAM (200 nsec)         3-17           SY21102-1         1024x1 Bit Static MOS RAM (200 nsec)         3-17           SY21102-1         1024x1 Bit Static MOS RAM (200 nsec)         3-17           SY21102-1         1024x1 Bit Static MOS RAM (200 nsec)         3-21                                                    |                   |                                           |

| Shift Register         2-2           SY2101-1         256x4 Bit Static MOS RAM (500 nsec)         3-3           SY2101A-2         256x4 Bit Static MOS RAM (250 nsec)         3-3           SY2101A-2         256x4 Bit Static MOS RAM (250 nsec)         3-3           SY2101A-2         256x4 Bit Static MOS RAM (250 nsec)         3-3           SY2101A-2         256x4 Bit Static MOS RAM (200 nsec)         3-7           SY2102-1         1024x1 Bit Static MOS RAM (200 nsec)         3-11           SY2102-2         1024x1 Bit Static MOS RAM (500 nsec)         3-11           SY2102-1         1024x1 Bit Static MOS RAM (500 nsec)         3-11           SY2102-1         1024x1 Bit Static MOS RAM (200 nsec)         3-15           SY21102         1024x1 Bit Static MOS RAM (200 nsec)         3-17           SY21102-1         1024x1 Bit Static MOS RAM         200 nsec)         3-17           SY21102-1         1024x1 Bit Static MOS RAM         200 nsec)         3-17           SY21102-1         1024x1 Bit Static MOS RAM         200 nsec)         3-17           SY21102-1         1024x1 Bit Static MOS RAM         200 nsec)         3-17           SY21102-1         1024x1 Bit Static MOS RAM (500 nsec)         3-17           SY21102         1024x1 Bit Static MOS RAM (50 nsec)                                                                    |                   |                                           |

| SY2101-1         256x4 Bit Static MOS RAM (500 nsec)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SY1404A           |                                           |

| SY2101A       256x4 Bit Static MOS RAM (350 nsec)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SV2101-1          |                                           |

| SY2101A-2       256x4 Bit Static MOS RAM (250 nsec)       .3-3         SY21H01       256x4 Bit Static MOS RAM (175 nsec)       .3-7         SY21H01-2       256x4 Bit Static MOS RAM (200 nsec)       .3-7         SY21H01-2       1024x1 Bit Static MOS RAM (200 nsec)       .3-11         SY2102-1       1024x1 Bit Static MOS RAM (250 nsec)       .3-11         SY2102-1       1024x1 Bit Static MOS RAM (650 nsec)       .3-11         SY2102-1       1024x1 Bit Static MOS RAM (650 nsec)       .3-11         SY2102-1       1024x1 Bit Static MOS RAM (650 nsec)       .3-11         SY2102-1       1024x1 Bit Static MOS RAM (200 nsec)       .3-15         SY21102       1024x1 Bit Static MOS RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |                                           |

| SY2101A-4       256x4 Bit Static MOS RAM (450 nsec)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                                           |

| SY21H01       256x4 Bit Static MOS RAM (175 nsec)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |                                           |

| SY21H01-2       256x4 Bit Static MOS RAM (200 nsec)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                                           |

| SY2102-1       1024x1 Bit Static MOS RAM (500 nsec)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                                           |

| SY2102A-2       1024x1 Bit Static MOS RAM (250 nsec)       3-11         SY2102A-4       1024x1 Bit Static MOS RAM (650 nsec)       3-11         SY2102-6       1024x1 Bit Static MOS RAM (650 nsec)       3-11         SY2102-6       1024x1 Bit Static MOS RAM (200 nsec)       3-15         SY21102       1024x1 Bit Static MOS RAM (200 nsec)       3-15         SY21102       1024x1 Bit Static MOS RAM       3-17         SY21102       1024x1 Bit Static MOS RAM       3-17         SY211021       1024x1 Bit Static MOS RAM       3-17         SY211024       1024x1 Bit Static MOS RAM       3-17         SY211028       1024x1 Bit Static MOS RAM       3-17         SY211028       1024x1 Bit Static MOS RAM       3-17         SY21112       256x4 Bit Static MOS RAM (500 nsec)       3-21         SY21114       256x4 Bit Static MOS RAM (500 nsec)       3-21         SY2111A-2       256x4 Bit Static MOS RAM (200 nsec)       3-225         SY2111A-2       256x4 Bit Static MOS RAM (200 nsec)       3-225         SY2112A       256x4 Bit Static MOS RAM (200 nsec)       3-23         SY2112A-2       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY2112A       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY2112A-2                                                                                                                           | SY2102-1          |                                           |

| SY2102A-4       1024x1 Bit Static MOS RAM (450 nsec)       3-11         SY2102-1L       1024x1 Bit Static MOS RAM (650 nsec)       3-11         SY2102-1L       1024x1 Bit Static MOS RAM (650 nsec)       3-15         SY21H02       1024x1 Bit Static MOS RAM (200 nsec)       3-15         SY21L02       1024x1 Bit Static MOS RAM       3-17         SY21L02B       1024x1 Bit Static MOS RAM       3-17         SY2111A       256x4 Bit Static MOS RAM (350 nsec)       3-17         SY2111A       256x4 Bit Static MOS RAM (350 nsec)       3-21         SY2111A       256x4 Bit Static MOS RAM (350 nsec)       3-21         SY2111A       256x4 Bit Static MOS RAM (250 nsec)       3-25         SY2111A       256x4 Bit Static MOS RAM (250 nsec)       3-25         SY2112A       256x4 Bit Static MOS RAM (250 nsec)       3-29         SY2112A       256x4 Bit Static MOS RAM (250 nsec)       3-29         SY2112A       256x4 Bit Static MOS RAM (250 nsec)       3-39         SY2112A       256x4 Bit Static MOS RAM (250 nsec)       3-39         SY2112A       <                                                                                                                       |                   |                                           |

| SY2102-6       1024x1 Bit Static MOS RAM (650 nsec)       3-11         SY21H02       1024x1 Bit Static MOS RAM (175 nsec)       3-15         SY21L02       1024x1 Bit Static MOS RAM       200 nsec)       3-15         SY21L02       1024x1 Bit Static MOS RAM       3-17         SY21L02-1       1024x1 Bit Static MOS RAM       3-17         SY21L02-1       1024x1 Bit Static MOS RAM       3-17         SY21L02-1       1024x1 Bit Static MOS RAM       3-17         SY21L02B       1024x1 Bit Static MOS RAM       3-17         SY21L02B       1024x1 Bit Static MOS RAM       3-17         SY21L02B       1024x1 Bit Static MOS RAM       3-17         SY2111-1       256x4 Bit Static MOS RAM (350 nsec)       3-21         SY2111A       256x4 Bit Static MOS RAM (350 nsec)       3-21         SY2111A       256x4 Bit Static MOS RAM (175 nsec)       3-25         SY2112-1       256x4 Bit Static MOS RAM (200 nsec)       3-29         SY2112-2       256x4 Bit Static MOS RAM (200 nsec)       3-29         SY2112-2       256x4 Bit Static MOS RAM (450 nsec)       3-35         SY2112-2       256x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114-2       256x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2                                                                                                                                     | SY2102A-4         |                                           |

| SY21H02       1024x1 Bit Static MOS RAM (175 nsec)       3-15         SY21L02       1024x1 Bit Static MOS RAM (200 nsec)       3-15         SY21L02       1024x1 Bit Static MOS RAM (200 nsec)       3-17         SY21L02-1       1024x1 Bit Static MOS RAM (200 nsec)       3-17         SY21L02A       1024x1 Bit Static MOS RAM (200 nsec)       3-17         SY21L02B       1024x1 Bit Static MOS RAM (200 nsec)       3-17         SY21L02B       1024x1 Bit Static MOS RAM (350 nsec)       3-17         SY21L02B       1024x1 Bit Static MOS RAM (350 nsec)       3-21         SY2111A       256x4 Bit Static MOS RAM (250 nsec)       3-21         SY2111A-2       256x4 Bit Static MOS RAM (450 nsec)       3-25         SY2111A-2       256x4 Bit Static MOS RAM (200 nsec)       3-25         SY2112-1       256x4 Bit Static MOS RAM (200 nsec)       3-29         SY2112-2       256x4 Bit Static MOS RAM (200 nsec)       3-29         SY2112-2       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY2112-2       256x4 Bit Static MOS RAM (200 nsec)       3-39         SY2112-2       256x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       256x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       266x4 Bit Static MOS RAM (200 nsec)                                                                                          | SY2102-1L         | 1024x1 Bit Static MOS RAM (500 nsec) 3-11 |

| SY21H02-2       1024x1 Bit Static MOS RAM (200 nsec)       3-15         SY21L02       1024x1 Bit Static MOS RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SY2102-6          | 1024x1 Bit Static MOS RAM (650 nsec) 3-11 |

| SY21L02         1024x1 Bit Static MOS RAM<br>Low Power (1 µs)         3-17           SY21L02-1         1024x1 Bit Static MOS RAM<br>Low Power (500 nsec)         3-17           SY21L02A         1024x1 Bit Static MOS RAM<br>Low Power (350 nsec)         3-17           SY21L02B         1024x1 Bit Static MOS RAM<br>Low Power (400 nsec)         3-17           SY21L02B         1024x1 Bit Static MOS RAM (500 nsec)         3-17           SY2111A         256x4 Bit Static MOS RAM (350 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (450 nsec)         3-21           SY2111A         256x4 Bit Static MOS RAM (450 nsec)         3-25           SY2111-2         256x4 Bit Static MOS RAM (200 nsec)         3-25           SY2112-1         256x4 Bit Static MOS RAM (500 nsec)         3-29           SY2112A         256x4 Bit Static MOS RAM (500 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY2112A-2         256x4 Bit Static MOS RAM (450 nsec)         3-39           SY21142         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142         1024x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142         1024x4 Bit Static MOS RAM         3-39           SY21142         1024x4 Bit Static MOS RAM         3-39 </td <td></td> <td></td> |                   |                                           |

| Low Power (1 μs)         3-17           SY21L02-1         1024x1 Bit Static MOS RAM         3-17           SY21L02A         1024x1 Bit Static MOS RAM         3-17           SY21L02B         1024x1 Bit Static MOS RAM (350 nsec)         3-21           SY2111A         256x4 Bit Static MOS RAM (250 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (175 nsec)         3-25           SY2111A-2         256x4 Bit Static MOS RAM (350 nsec)         3-29           SY2112A-1         256x4 Bit Static MOS RAM (350 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (450 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (450 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (450 nsec)         3-39           SY2114D-2         256x4 Bit Static MOS RAM (450 nsec)         3-39           SY21142-2         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY211412         1024x4 Bit Static MOS RAM (300 nsec)         3-39           SY211412         1024x4 Bit Static MOS RAM <t< td=""><td></td><td></td></t<>                                             |                   |                                           |

| SY21L02-1         1024x1 Bit Static MOS RAM<br>Low Power (500 nsec)         3-17           SY21L02A         1024x1 Bit Static MOS RAM<br>Low Power (350 nsec)         3-17           SY21L02B         1024x1 Bit Static MOS RAM<br>Low Power (400 nsec)         3-17           SY21L02A         256x4 Bit Static MOS RAM (500 nsec)         3-21           SY2111-1         256x4 Bit Static MOS RAM (500 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (250 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (175 nsec)         3-25           SY2112-1         256x4 Bit Static MOS RAM (200 nsec)         3-29           SY2112A         256x4 Bit Static MOS RAM (500 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (250 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (250 nsec)         3-39           SY21142         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142         1024x4 Bit Static MOS RAM         200 nsec)         3-39           SY21142         1024x4 Bit Static MOS RAM         200 nsec)         3-39           SY21142         1024x4 Bit S                                    | SY21L02           |                                           |

| Low Power (500 nsec)         3-17           SY21L02A         1024x1 Bit Static MOS RAM           Low Power (350 nsec)         3-17           SY21L02B         1024x1 Bit Static MOS RAM           Low Power (400 nsec)         3-17           SY21L02B         1024x1 Bit Static MOS RAM (500 nsec)         3-21           SY2111A         256x4 Bit Static MOS RAM (350 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (450 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (250 nsec)         3-25           SY2111A-2         256x4 Bit Static MOS RAM (500 nsec)         3-25           SY2112A-1         256x4 Bit Static MOS RAM (500 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (250 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142-2         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142-1         1024x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142-1         1024x4 Bit Static MOS RAM         3-39           SY21142-1         1024x4 Bit Static MOS RAM         3-39           SY21142-1         1024x4 Bit Static MOS RAM         3-39           SY21142-2         1024x4 Bit Static MOS RAM <t< td=""><td>01011 00 1</td><td></td></t<>                                          | 01011 00 1        |                                           |

| SY21L02A         1024x1 Bit Static MOS RAM<br>Low Power (350 nsec)         3-17           SY21L02B         1024x1 Bit Static MOS RAM<br>Low Power (400 nsec)         3-17           SY2110-1         256x4 Bit Static MOS RAM (500 nsec)         3-21           SY2111A         256x4 Bit Static MOS RAM (250 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (175 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (175 nsec)         3-25           SY2111-2         256x4 Bit Static MOS RAM (200 nsec)         3-29           SY2112A         256x4 Bit Static MOS RAM (250 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (250 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (250 nsec)         3-39           SY2114         256x4 Bit Static MOS RAM (200 nsec)         3-35           SY2114         1024x4 Bit Static MOS RAM (200 nsec)         3-39           SY2114-1         1024x4 Bit Static MOS RAM (300 nsec)         3-39           SY2114-2         1024x4 Bit Static MOS RAM (300 nsec)         3-39           SY2114-1         1024x4 Bit Static MOS RAM         300 nsec)         3-39           SY2114-2         1024x4 Bit Static MOS RAM         300 nsec)         3-39           SY2114L         1024x4 Bit Static MOS                                       | 5121102-1         |                                           |

| Low Power (350 nsec)         3-17           SY21L02B         1024x1 Bit Static MOS RAM           Low Power (400 nsec)         3-17           SY2111-1         256x4 Bit Static MOS RAM (500 nsec)         3-21           SY2111A         256x4 Bit Static MOS RAM (250 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (450 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (450 nsec)         3-21           SY21112-1         256x4 Bit Static MOS RAM (175 nsec)         3-25           SY2112-1         256x4 Bit Static MOS RAM (200 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (200 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (200 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142-2         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142-2         256x4 Bit Static MOS RAM (200 nsec)         3-39           SY21142-1         1024x4 Bit Static MOS RAM (300 nsec)         3-39           SY21142         1024x4 Bit Static MOS RAM         200 nsec)         3-39           SY2114L-2         1024x4 Bit Static MOS RAM         200 nsec)         3-39           SY2114L-2         1024x4 Bit Static MOS RAM (                                                              | SY211 02A         |                                           |

| SY21L02B         1024x1 Bit Static MOS RAM<br>Low Power (400 nsec)         3-17           SY2111-1         256x4 Bit Static MOS RAM (500 nsec)         3-21           SY2111A         256x4 Bit Static MOS RAM (350 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (450 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (450 nsec)         3-21           SY2111A-2         256x4 Bit Static MOS RAM (450 nsec)         3-25           SY2112A         256x4 Bit Static MOS RAM (500 nsec)         3-25           SY2112A         256x4 Bit Static MOS RAM (350 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (450 nsec)         3-29           SY2112A-2         256x4 Bit Static MOS RAM (200 nsec)         3-35           SY2114         1024x4 Bit Static MOS RAM (200 nsec)         3-39           SY2114-2         1024x4 Bit Static MOS RAM (200 nsec)         3-39           SY2114-1         1024x4 Bit Static MOS RAM         3-39           SY2114-2         1024x4 Bit Static MOS RAM         3-39           SY2114L-2                                                                      | OTETEOEX          |                                           |

| SY2111-1       256x4 Bit Static MOS RAM (500 nsec)       3-21         SY2111A       256x4 Bit Static MOS RAM (350 nsec)       3-21         SY2111A-2       256x4 Bit Static MOS RAM (250 nsec)       3-21         SY2111A-2       256x4 Bit Static MOS RAM (250 nsec)       3-21         SY21H11       256x4 Bit Static MOS RAM (200 nsec)       3-25         SY2112-1       256x4 Bit Static MOS RAM (500 nsec)       3-29         SY2112A       256x4 Bit Static MOS RAM (500 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (250 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114A       256x4 Bit Static MOS RAM (175 nsec)       3-35         SY21142       256x4 Bit Static MOS RAM (200 nsec)       3-39         SY21142       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY21142       1024x4 Bit Static MOS RAM       3-39         SY21142       1024x4 Bit Static MOS RAM       3-39         SY2114L       1024x4 Bit Static MOS RAM       3-39         SY2114L-2       1024x4 Bit Static MOS RAM       3-39         SY2114L       1024x4 Bit Static MOS RAM       3-39         SY2114L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2                                                                                                                        | SY21L02B          |                                           |

| SY2111A       256x4 Bit Static MOS RAM (350 nsec)       3-21         SY2111A-2       256x4 Bit Static MOS RAM (250 nsec)       3-21         SY2111A-4       256x4 Bit Static MOS RAM (450 nsec)       3-21         SY2111       256x4 Bit Static MOS RAM (175 nsec)       3-25         SY2112-1       256x4 Bit Static MOS RAM (200 nsec)       3-25         SY2112A       256x4 Bit Static MOS RAM (350 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (250 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY2112A-2       256x4 Bit Static MOS RAM (200 nsec)       3-33         SY2114-2       256x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-31         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec) <td></td> <td>Low Power (400 nsec) 3-17</td>                                      |                   | Low Power (400 nsec) 3-17                 |

| SY2111A-2       256x4 Bit Static MOS RAM (250 nsec)       3-21         SY2111A-4       256x4 Bit Static MOS RAM (450 nsec)       3-21         SY21H1       256x4 Bit Static MOS RAM (175 nsec)       3-25         SY21H11-2       256x4 Bit Static MOS RAM (200 nsec)       3-25         SY2112A1       256x4 Bit Static MOS RAM (300 nsec)       3-29         SY2112A2       256x4 Bit Static MOS RAM (250 nsec)       3-29         SY2112A42       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY2112A42       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY21142       256x4 Bit Static MOS RAM (200 nsec)       3-39         SY21142       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY21142       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY21142       1024x4 Bit Static MOS RAM       3-39         SY21142       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY21142       1024x4 Bit Static MOS RAM (200 nsec)       3-31         SY21424                                                                                                                           |                   |                                           |

| SY2111A-4       256x4 Bit Static MOS RAM (450 nsec)       3-21         SY21H11       256x4 Bit Static MOS RAM (200 nsec)       3-25         SY21H11-2       256x4 Bit Static MOS RAM (200 nsec)       3-25         SY2112-1       256x4 Bit Static MOS RAM (300 nsec)       3-29         SY2112A       256x4 Bit Static MOS RAM (450 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114-2       256x4 Bit Static MOS RAM (450 nsec)       3-35         SY2114       1024x4 Bit Static MOS RAM (450 nsec)       3-33         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-3       1024x4 Bit Static MOS RAM       300 nsec)       3-39         SY2114-1       1024x4 Bit Static MOS RAM       3-39       39         SY2114-2       1024x4 Bit Static MOS RAM       3-39       39         SY2114L-3       1024x4 Bit Static MOS RAM       3-39       3-39         SY2114L-3       1024x4 Bit Static MOS RAM       3-39       39         SY2114L-4       1024x4 Bit Static MOS RAM       3-39       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-47         SY2142LV-3<                                                                                                                            |                   |                                           |

| SY21H11       256x4 Bit Static MOS RAM (175 nsec)       3-25         SY21H11-2       256x4 Bit Static MOS RAM (200 nsec)       3-25         SY2112-1       256x4 Bit Static MOS RAM (500 nsec)       3-29         SY2112A       256x4 Bit Static MOS RAM (350 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (450 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (450 nsec)       3-39         SY2112A-2       256x4 Bit Static MOS RAM (175 nsec)       3-35         SY21142-2       256x4 Bit Static MOS RAM (200 nsec)       3-39         SY21142       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-3       1024x4 Bit Static MOS RAM (300 nsec)       3-39         SY2114L       1024x4 Bit Static MOS RAM       3-39         SY2114L-2       1024x4 Bit Static MOS RAM       3-39         SY2114L-3       1024x4 Bit Static MOS RAM       3-39         SY2114L-4       1024x4 Bit Static MOS RAM       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-4       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-47                                                                                                                |                   |                                           |

| SY21H11-2       256x4 Bit Static MOS RAM (200 nsec)       3-25         SY2112-1       256x4 Bit Static MOS RAM (300 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (350 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (200 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (450 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (450 nsec)       3-35         SY2114-2       256x4 Bit Static MOS RAM (200 nsec)       3-33         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-1       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114L-4       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-31         SY2114L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142L-1       1024x4 Bit Static MOS RAM (200                                                                                |                   |                                           |

| SY2112-1       256x4 Bit Static MOS RAM (500 nsec)       3-29         SY2112A       256x4 Bit Static MOS RAM (350 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (250 nsec)       3-29         SY2112A-4       256x4 Bit Static MOS RAM (450 nsec)       3-35         SY2112A-2       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY21H12-2       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY2114       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-1       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-1       1024x4 Bit Static MOS RAM       100 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM       100 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM       100 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (450 nsec)       3-37         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-37         SY2114L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-47         SY2114LV-3       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142                                                                                                          |                   |                                           |

| SY2112A       256x4 Bit Static MOS RAM (350 nsec)       3-29         SY2112A-2       256x4 Bit Static MOS RAM (250 nsec)       3-29         SY2112A-4       256x4 Bit Static MOS RAM (450 nsec)       3-35         SY21H12       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY21H12-2       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY21H2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY21H4-1       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY21H4-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-1       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114LV-3       1024x4 Bit Static MOS RAM (200 nsec)       3-347         SY2114LV-3       1024x4 Bit Static MOS RAM (200 nsec)       3-47         SY2142       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142       1024x4 Bit Static MOS RAM (200 nsec)                                                                                      |                   |                                           |

| SY2112A-2       256x4 Bit Static MOS RAM (250 nsec)       3-29         SY2112A-4       256x4 Bit Static MOS RAM (450 nsec)       3-35         SY21H12       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY21H12       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY21H2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-1       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114LV       1024x4 Bit Static MOS RAM (450 nsec)       3-37         SY2114LV-1       1024x4 Bit Static MOS RAM (200 nsec)       3-47         SY2114LV-2       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-3       1024x4 Bit Static MOS RAM (300 nsec)       3-51         SY2142-3       1024x4 Bit Static MOS RAM (300 nsec)       3-51         SY2142-4       1024x4 Bit Static MOS RAM (450 nsec)       3-51         SY2142L-2       1024x4 Bit Static MOS RAM (200 nsec                                                                               |                   | · · · · · · · · · · · · · · · · · · ·     |

| SY2112A-4       256x4 Bit Static MOS RAM (450 nsec)       3-29         SY21H12       256x4 Bit Static MOS RAM (175 nsec)       3-35         SY21H12-2       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY2114       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-1       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-4       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114LV       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114LV-2       1024x4 Bit Static MOS RAM (200 nsec)       3-31         SY2142L       1024x4 Bit Static MOS RAM (200 nsec)       3-47         SY2142L       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142L-3       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142L-3       1024x4 Bit Static MOS RAM (200 ns                                                                               |                   |                                           |

| SY21H12       256x4 Bit Static MOS RAM (175 nsec)       3-35         SY21H12-2       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY2114       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-1       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114L       1024x4 Bit Static MOS RAM Low Power (450 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM Low Power (200 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM Low Power (200 nsec)       3-39         SY2114L-4       1024x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114L-7       1024x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114LV       1024x4 Bit Static MOS RAM (200 nsec)       3-47         SY2114LV-3       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-1       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-2       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-3       1024x4 Bit Static MOS RAM (450 nsec)       3-51         SY2142-4       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142L-3       1024                                                                               |                   |                                           |

| SY21H12-2       256x4 Bit Static MOS RAM (200 nsec)       3-35         SY2114       1024x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-3       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-1       1024x4 Bit Static MOS RAM (200 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM Low Power (450 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM Low Power (200 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM Low Power (300 nsec)       3-39         SY2114L-4       1024x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114LV-3       1024x4 Bit Static MOS RAM (200 nsec)       3-47         SY2114LV-3       1024x4 Bit Static MOS RAM (200 nsec)       3-47         SY2142       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-2       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-2       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-3       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-4       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142L-3       1                                                                               |                   |                                           |

| SY2114       1024x4 Bit Static MOS RAM (450 nsec)       3-39         SY2114-2       1024x4 Static MOS RAM (200 nsec)       3-39         SY2114-3       1024x4 Bit Static MOS RAM (300 nsec)       3-39         SY2114-1       1024x4 Bit Static MOS RAM (300 nsec)       3-39         SY2114-2       1024x4 Bit Static MOS RAM Low Power (450 nsec)       3-39         SY2114L-2       1024x4 Bit Static MOS RAM Low Power (200 nsec)       3-39         SY2114L-3       1024x4 Bit Static MOS RAM Low Power (300 nsec)       3-39         SY2114L-4       1024x4 Bit Static MOS RAM Low Power (300 nsec)       3-39         SY2114L-5       1024x4 Bit Static MOS RAM (450 nsec)       3-47         SY2114L-4       1024x4 Bit Static MOS RAM (200 nsec)       3-47         SY2142       1024x4 Bit Static MOS RAM (300 nsec)       3-51         SY2142-1       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-2       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-3       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-4       1024x4 Bit Static MOS RAM (200 nsec)       3-51         SY2142-5       1024x4 Bit Static MOS RAM (200 nsec)       3-55         SY2142L-2       1024x4 Bit Static MOS RAM (200 nsec)       3-55         SY2142L-2       <                                                                           |                   |                                           |

| SY2114-2       1024x4 Static MOS RAM (200 nsec)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |                                           |

| SY2114-3         1024x4 Bit Static MOS RAM (300 nsec) 3-39           SY2114L         1024x4 Bit Static MOS RAM           Low Power (450 nsec)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SY2114-2          |                                           |

| Low Power (450 nsec)         3-39           SY2114L-2         1024x4 Bit Static MOS RAM<br>Low Power (200 nsec)         3-39           SY2114L-3         1024x4 Bit Static MOS RAM<br>Low Power (300 nsec)         3-39           SY2114L-3         1024x4 Bit Static MOS RAM<br>Low Power (300 nsec)         3-39           SY2114LV         1024x4 Bit Static MOS RAM<br>Low Power (300 nsec)         3-39           SY2114LV-2         1024x4 Bit Static MOS RAM (450 nsec)         3-47           SY2114LV-3         1024x4 Bit Static MOS RAM (200 nsec)         3-47           SY2142         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142-1         1024x4 Bit Static MOS RAM (450 nsec)         3-51           SY2142-2         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-3         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142L-3         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142LV-3         1024x4 Bit Static MOS RAM (200 nsec)         3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (50 nsec)         3-55           SY2147-4         4096x1 Bit Static MOS RAM (50 nsec)         <           | SY2114-3          |                                           |

| SY2114L-2         1024x4 Bit Static MOS RAM<br>Low Power (200 nsec)         3-39           SY2114L-3         1024x4 Bit Static MOS RAM<br>Low Power (300 nsec)         3-39           SY2114L-3         1024x4 Bit Static MOS RAM<br>Low Power (300 nsec)         3-39           SY2114LV         1024x4 Bit Static MOS RAM (450 nsec)         3-47           SY2114LV-3         1024x4 Bit Static MOS RAM (200 nsec)         3-47           SY2114LV-3         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-3         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142L         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142L-2         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142L-2         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142LV         1024x4 Bit Static MOS RAM (200 nsec)         3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (200 nsec)         3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2147         4096x1 Bit Static MOS RAM (50 nsec)         3-59           SY2147         4096x1 Bit Static MOS RA                  | SY2114L           | 1024x4 Bit Static MOS RAM                 |

| Low Power (200 nsec)         3-39           SY2114L-3         1024x4 Bit Static MOS RAM           Low Power (300 nsec)         3-39           SY2114LV         1024x4 Bit Static MOS RAM (200 nsec)         3-37           SY2114LV-2         1024x4 Bit Static MOS RAM (200 nsec)         3-47           SY2114LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-47           SY2114LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-47           SY2142         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142-1         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142-2         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142-3         1024x4 Bit Static MOS RAM (450 nsec)         3-51           SY2142-4         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-2         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142L-2         1024x4 Bit Static MOS RAM (200 nsec)         3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (200 nsec)         3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (200 nsec)         3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-59           SY2147-4         4096x1 Bit Static MOS RAM (50 nsec)                                                      |                   |                                           |

| SY2114L-3         1024x4 Bit Static MOS RAM<br>Low Power (300 nsec)         3-39           SY2114LV         1024x4 Bit Static MOS RAM (450 nsec)         3-47           SY2114LV-2         1024x4 Bit Static MOS RAM (200 nsec)         3-47           SY2114LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-47           SY2114LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-2         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142-3         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-1         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-2         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142L-3         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142L-4         1024x4 Bit Static MOS RAM (200 nsec)         3-55           SY2142LV-1         1024x4 Bit Static MOS RAM (200 nsec)         3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (70 nsec)         3-59           SY2147         4096x1 Bit Static MOS RAM (55 nsec)         3-59           SY2147         4096x1 Bit Static MOS RAM (50 nsec)                                 | SY2114L-2         |                                           |

| Low Power (300 nsec)         3-39           SY2114LV         1024x4 Bit Static MOS RAM (450 nsec)         3-47           SY2114LV-2         1024x4 Bit Static MOS RAM (200 nsec)         3-47           SY2114LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-47           SY2142         1024x4 Bit Static MOS RAM (300 nsec)         3-47           SY2142         1024x4 Bit Static MOS RAM (450 nsec)         3-51           SY2142         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-1         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142-1         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-2         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-3         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-1         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2147         4096x1 Bit Static MOS RAM (50 nsec)         3-59           SY2147         4096x1 Bit Static MOS RAM (50 nsec)         3-59           SYM2114         Military 1024x4 Static MOS RAM (50 nsec)         3-59           SYM2114                                                     | 0.000000          |                                           |

| SY2114LV       1024x4 Bit Static MOS RAM (450 nsec) 3-47         SY2114LV-2       1024x4 Bit Static MOS RAM (200 nsec) 3-47         SY2114LV-3       1024x4 Bit Static MOS RAM (300 nsec) 3-47         SY2142       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142-1       1024x4 Bit Static MOS RAM (450 nsec) 3-51         SY2142-1       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142-1       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142L       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142L-2       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142L-2       1024x4 Bit Static MOS RAM (200 nsec) 3-51         SY2142L-2       1024x4 Bit Static MOS RAM (200 nsec) 3-51         SY2142LV       1024x4 Bit Static MOS RAM (200 nsec) 3-51         SY2142LV-2       1024x4 Bit Static MOS RAM (200 nsec) 3-55         SY2142LV-2       1024x4 Bit Static MOS RAM (200 nsec) 3-55         SY2147L       4096x1 Bit Static MOS RAM (50 nsec) 3-59         SY2147       4096x1 Bit Static MOS RAM (50 nsec) 3-59         SYM2114       Military 1024x4 Static MOS RAM         (-55° C to +125° C) (450 nsec) 3-59         SYM2114       Military 1024x4 Static MOS RAM         (-55° C to +125° C) (300 nsec) 3-43         SY2                                                                                                 | SY2114L-3         |                                           |

| SY2114LV-2       1024x4 Bit Static MOS RAM (200 nsec) 3-47         SY2114LV-3       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142       1024x4 Bit Static MOS RAM (200 nsec) 3-51         SY2142-2       1024x4 Bit Static MOS RAM (200 nsec) 3-51         SY2142-3       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142-3       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142-1       1024x4 Bit Static MOS RAM (450 nsec) 3-51         SY2142L       1024x4 Bit Static MOS RAM (450 nsec) 3-51         SY2142L-3       1024x4 Bit Static MOS RAM (200 nsec) 3-51         SY2142L-3       1024x4 Bit Static MOS RAM (200 nsec) 3-51         SY2142L-4       1024x4 Bit Static MOS RAM (200 nsec) 3-55         SY2142LV-1       1024x4 Bit Static MOS RAM (200 nsec) 3-55         SY2142LV-2       1024x4 Bit Static MOS RAM (300 nsec) 3-55         SY2147       4096x1 Bit Static MOS RAM (70 nsec) 3-59         SY2147       4096x1 Bit Static MOS RAM (70 nsec) 3-59         SYM2114       Military 1024x4 Static MOS RAM         (-55° C to +125° C) (450 nsec) 3-43         SYM2114-3       Military 1024x4 Static MOS RAM         (-55° C to +125° C) (300 nsec) 3-43         SY2316A       2048x8 Static MOS ROM (550 nsec) 4-3         SY231                                                                                                    | SV2114LV          |                                           |

| SY2114LV-3       1024x4 Bit Static MOS RAM (300 nsec) 3-47         SY2142       1024x4 Bit Static MOS RAM (450 nsec) 3-51         SY2142-2       1024x4 Bit Static MOS RAM (200 nsec) 3-51         SY2142-3       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142-1       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142-2       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142L-3       1024x4 Bit Static MOS RAM (200 nsec) 3-51         SY2142L-3       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142L-3       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142LV-1       1024x4 Bit Static MOS RAM (300 nsec) 3-51         SY2142LV-2       1024x4 Bit Static MOS RAM (300 nsec) 3-55         SY2142LV-3       1024x4 Bit Static MOS RAM (300 nsec) 3-55         SY2147       4096x1 Bit Static MOS RAM (300 nsec) 3-59         SY2147       4096x1 Bit Static MOS RAM (70 nsec) 3-59         SYM2144       Military 1024x4 Static MOS RAM (70 nsec) 3-59         SYM2114       Military 1024x4 Static MOS RAM (70 nsec) 3-59         SYM214-3       Military 1024x4 Static MOS RAM (70 nsec) 3-59         SYM2144       Military 1024x4 Static MOS RAM (70 nsec) 3-59         SYM2144       Military 1024x4 Static MOS RAM (70 nsec) 3-59                                                                                           |                   |                                           |

| SY2142         1024x4 Bit Static MOS RAM (450 nsec)         3-51           SY2142-2         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-3         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142-1         1024x4 Bit Static MOS RAM (450 nsec)         3-51           SY2142-2         1024x4 Bit Static MOS RAM (450 nsec)         3-51           SY2142-1         1024x4 Bit Static MOS RAM (450 nsec)         3-51           SY2142L-3         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142LV-1         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2147         4096x1 Bit Static MOS RAM (70 nsec)         3-59           SY2147         4096x1 Bit Static MOS RAM (70 nsec)         3-59           SY2147         4096x1 Bit Static MOS RAM (70 nsec)         3-59           SY2147         M096x1 Bit Static MOS RAM (70 nsec)         3-59           SY2147         M096x1 Bit Static MOS RAM (50 nsec)         3-43           SYM2114         Military 1024x4 Static MOS RAM (70 nsec)         3-43           SY2316A         2048x8 Static MOS ROM (550 nsec)         3-43                                                   |                   |                                           |

| SY2142-2         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142-3         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142L         1024x4 Bit Static MOS RAM (450 nsec)         3-51           SY2142L-2         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142L-2         1024x4 Bit Static MOS RAM (200 nsec)         3-51           SY2142L-2         1024x4 Bit Static MOS RAM (300 nsec)         3-51           SY2142LV         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (200 nsec)         3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2147L         4096x1 Bit Static MOS RAM (70 nsec)         3-59           SY2147-3         4096x1 Bit Static MOS RAM (55 nsec)         3-59           SYM2114         Military 1024x4 Static MOS RAM         3-59           SYM2114         Military 1024x4 Static MOS RAM         3-43           SY2316A         2048x8 Static MOS ROM (550 nsec)         3-43           SY2316B         2048x8 Static MOS ROM (450 nsec)         4-3                                                                                                                                        |                   |                                           |

| SY2142-3         1024x4 Bit Static MOS RAM (300 nsec) 3-51           SY2142L         1024x4 Bit Static MOS RAM (450 nsec) 3-51           SY2142L-2         1024x4 Bit Static MOS RAM (200 nsec) 3-51           SY2142L-3         1024x4 Bit Static MOS RAM (200 nsec) 3-51           SY2142L-4         1024x4 Bit Static MOS RAM (300 nsec) 3-51           SY2142L-7         1024x4 Bit Static MOS RAM (300 nsec) 3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (200 nsec) 3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec) 3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec) 3-59           SY2147         4096x1 Bit Static MOS RAM (55 nsec) 3-59           SY2147         4096x1 Bit Static MOS RAM (50 nsec) 3-59           SYM2114         Military 1024x4 Static MOS RAM (50 nsec) 3-59           SYM2114         Military 1024x4 Static MOS RAM (50 nsec) 3-43           SY2316A         2048x8 Static MOS ROM (550 nsec) 3-43           SY2316B         2048x8 Static MOS ROM (450 nsec) 4-3                                                                                                                                                                                                                                                                                                                           | SY2142-2          |                                           |

| SY2142L-2         1024x4 Bit Static MOS RAM (200 nsec) 3-51           SY2142L-3         1024x4 Bit Static MOS RAM (300 nsec) 3-51           SY2142LV         1024x4 Bit Static MOS RAM (300 nsec) 3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (450 nsec) 3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec) 3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec) 3-55           SY2147         4096x1 Bit Static MOS RAM (300 nsec) 3-59           SY2147         4096x1 Bit Static MOS RAM (55 nsec) 3-59           SY2147         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SY2147         M096x1 Bit Static MOS RAM (70 nsec) 3-59           SYM2114         Military 1024x4 Static MOS RAM (70 nsec) 3-59           SYM2114         Military 1024x4 Static MOS RAM (-55° C to +125°C) (450 nsec) 3-43           SYM2114-3         Military 1024x4 Static MOS RAM (-55° C to +125°C) (300 nsec) 3-43           SY2316A         2048x8 Static MOS ROM (550 nsec) 4-3           SY2316B         2048x8 Static MOS ROM (450 nsec) 4-3                                                                                                                                                                                                                                                                                     | SY2142-3          | 1024x4 Bit Static MOS RAM (300 nsec) 3-51 |

| SY2142L-3         1024x4 Bit Static MOS RAM (300 nsec) 3-51           SY2142LV         1024x4 Bit Static MOS RAM (450 nsec) 3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (200 nsec) 3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec) 3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec) 3-55           SY2147         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SY2147.1         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SY2147         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SY2147         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SYM2114         Military 1024x4 Static MOS RAM (70 nsec) 3-59           SYM2114         Military 1024x4 Static MOS RAM (70 nsec) 3-43           SYM2114-3         Military 1024x4 Static MOS RAM (70 nsec) 3-43           SYM2114-3         Military 1024x4 Static MOS RAM (-55° C to +125° C) (450 nsec) 3-43           SY2316A         2048x8 Static MOS ROM (550 nsec) 4-3           SY2316B         2048x8 Static MOS ROM (450 nsec) 4-3                                                                                                                                                                                                                                                                                                   |                   |                                           |

| SY2142LV         1024x4 Bit Static MOS RAM (450 nsec)         3-55           SY2142LV-2         1024x4 Bit Static MOS RAM (200 nsec)         3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec)         3-55           SY2147         4096x1 Bit Static MOS RAM (70 nsec)         3-59           SY2147-3         4096x1 Bit Static MOS RAM (55 nsec)         3-59           SY2147L         4096x1 Bit Static MOS RAM (50 nsec)         3-59           SYM2114         Military 1024x4 Static MOS RAM         (-55° C to +125° C) (450 nsec)         3-43           SYM2114-3         Military 1024x4 Static MOS RAM         (-55° C to +125° C) (300 nsec)         3-43           SY2316A         2048x8 Static MOS ROM (550 nsec)         4-3         3           SY2316B         2048x8 Static MOS ROM (450 nsec)         4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |                                           |

| SY2142LV-2         1024x4 Bit Static MOS RAM (200 nsec) 3-55           SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec) 3-55           SY2147         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SY2147-3         4096x1 Bit Static MOS RAM (55 nsec) 3-59           SY2147-1         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SYM2114         Military 1024x4 Static MOS RAM (50 nsec) 3-59           SYM2114         Military 1024x4 Static MOS RAM (-55° C to +125°C) (450 nsec) 3-43           SYM2114-3         Military 1024x4 Static MOS RAM (-55° C to +125°C) (300 nsec) 3-43           SY2316A         2048x8 Static MOS ROM (550 nsec) 4-3           SY2316B         2048x8 Static MOS ROM (450 nsec) 4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   | · · ·                                     |

| SY2142LV-3         1024x4 Bit Static MOS RAM (300 nsec) 3-55           SY2147         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SY2147-3         4096x1 Bit Static MOS RAM (55 nsec) 3-59           SY2147-4         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SY2147         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SY2147L         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SYM2114         Military 1024x4 Static MOS RAM (-55°C to +125°C) (450 nsec) 3-43           SYM2114-3         Military 1024x4 Static MOS RAM (-55°C to +125°C) (300 nsec) 3-43           SY2316A         2048x8 Static MOS ROM (550 nsec) 4-3           SY2316B         2048x8 Static MOS ROM (450 nsec) 4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |                                           |

| SY2147         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SY2147-3         4096x1 Bit Static MOS RAM (55 nsec) 3-59           SY2147L         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SYM2114         4096x1 Bit Static MOS RAM (70 nsec) 3-59           SYM2114         Military 1024x4 Static MOS RAM (70 nsec) 3-53           SYM2114-3         Military 1024x4 Static MOS RAM (-55° C to +125° C) (450 nsec) 3-43           SYM2114-3         Military 1024x4 Static MOS RAM (-55° C to +125° C) (300 nsec) 3-43           SY2316A         2048x8 Static MOS ROM (550 nsec) 4-3           SY2316B         2048x8 Static MOS ROM (450 nsec) 4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |                                           |