#### **1.85C471 OVERVIEW**

#### **1.1 Introduction**

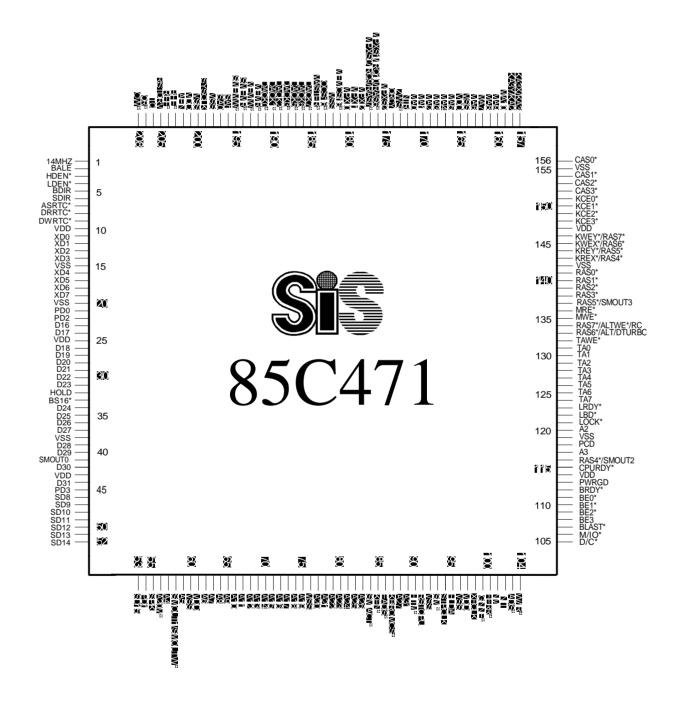

The SiS85C471 single chip controller supports Intel's 80486DX2/DX/SX/SL Enhanced, P24D/P24T/P24C CPU, Cyrix's Cx486S2 (M6/M7) CPU and AMD's Am486DXL/DXL2 CPU.

The SiS85C471 is a high performance, 100% PC/AT compatible single chip controller, designed for cached/non-cached P24D/P24T/P24C, M6/M7 or 486 PC systems. The high integration of the powerful cache controller, the DRAM controller, the CPU interfaces, the bus controller, the data buffers and the peripheral controllers provides an easy and economical solution for compact board manufacturing.

In addition to supporting burst reads for the cache line fills of the CPU, the SiS85C471 is capable of accepting burst write data of the CPU's internal cache dirty line(s) during CPU write-back cycles. The support of the CPU burst write cycle is optional through the control of the Configuration Registers. The SiS85C471 supports the cache size up to 1 MB and the DRAM size up to 128 MB.

The SiS85C471 has a built-in cache controller which supports direct mapped writethrough/write-back cache. The programmable AT-bus clock supports are compatible with AT-bus timing requirements for different PC systems.

In addition, the local bus interfaces, the integration of the DMA Controllers, Interrupt Controllers and Timers/Counters are designed to be a higher performance, more compact, and more cost-effective product for a P24D/P24T/P24C, 486SX/DX/DX2/SL-Enhanced, Am486DXL/DXL2, or a Cx486S2 (M6/M7) PC/AT system.

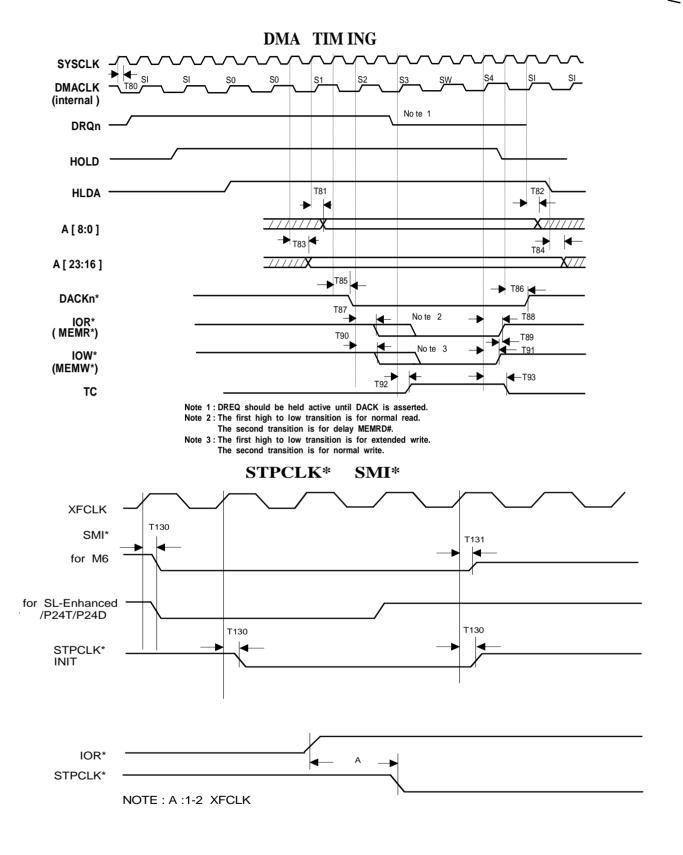

The SiS85C471 provides power saving features to allow a system, through the control of BIOS, to reduce the CPU clock frequency from 50MHz down to 0 MHz(STOP CLOCK) when the system is idle.

To support the SL-Enchanced 486, M6/M7, P24D/P24T/P24C's Am486DXL/DXL2 STPCLK/SMI features, the SiS85C471 also implements the corresponding logics to support STPCLK /SMI for power saving.

The SiS85C471 supports the VL-Bus applications including (1) CPU accesses VL-Bus targets, (2) VL-Bus master mode, and (3) DMA or ISA master accesses VL-Bus targets.

The SiS85C471 provides flexible ways in configuring the system depending on whether cache or VESA local bus masters are supported. The different configurations require different numbers of external components.

#### **1.2 Features**

- Fully IBM PC/AT Compatible. 80486DX2/DX/SX/SL Enhanced, P24D/P24T/P24C, M6/M7 and Am486DXL/Am486DXL2 Single Chip Controller

- Supports L1 Cache Write back CPU (P24T/P24D/M6/M7) systems

- Direct Mapped Cache Controller

- Write-Back or Write-Through Schemes

- Bank Interleave or Non-Interleave Cache

- 0/1 Wait State Cache Write Hit

- Flexible Cache Size : 32/64/128/256/512KB or 1MB

- 7 bits or 8 bits TAG addresses

- Flexible 2-1-1-1, 3-1-1-1, 2-2-2-2 and 3-2-2-2 Burst Read/Write Timing

- Fast Page Burst Mode DRAM Controller

- 4 Banks up to 128MB of DRAMs

- 256K/512K/1M/2M/4M/16MxN DRAM Type

- Programmable DRAM Speed

- Double-sided SIMMs

- Two Programmable Non-Cacheable Regions (64KB-4MB area)

- CAS before RAS Transparent DRAM Refresh

- BIOS/Video ROM Cacheable

- Shadow RAM in Increments of 32KB - Option to Disable Cache in Shadow RAM Area

- 256K Memory Relocation

- 8042 Emulation of Fast A20GATE and CPU Reset

- Supports Port 92h

- Hardware/Software De-Turbo Switch

- Supports Two VL-Bus Master

- Supports Flash Memory

- Supports Double/Single frequency input

- CPU Operating frequency 0-100 MHz

- Supports Power Management Mode

- Supports the SMM and the SMI

- CPU Stop Clock Function

- Four Power Saving States

- Long and Short System Timers

- Supports the APM control

- Supports Break Switch control

- Power Saving also on non-SMI CPU

- More System Event Monitoring and the Power Saving Control

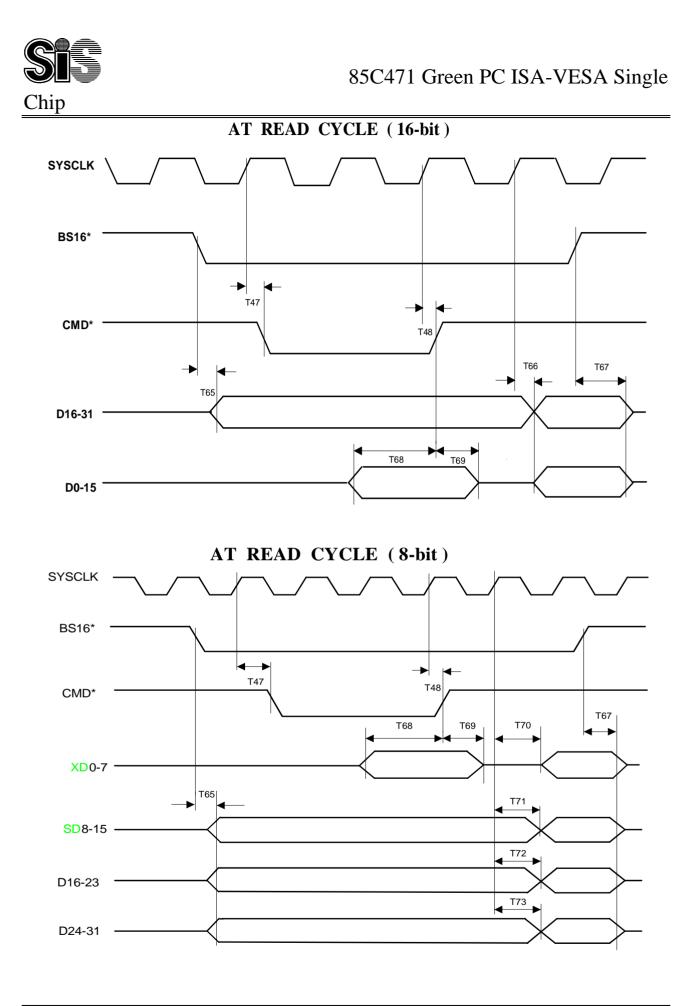

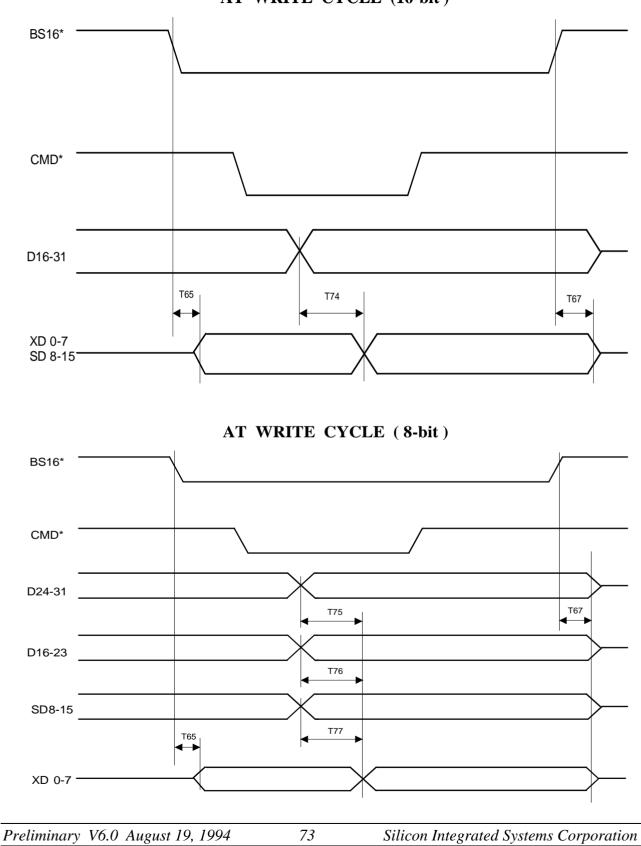

- AT Bus State Machine and Controller

- Synchronous/Asynchronous AT Bus Clock

- Programmable AT Bus Speed

- 1/2,1/3,1/4,1/5,1/6,1/8,1/10 of Input Clock or 7.159MHz

- Programmable Wait State Generation

- 1 or 2 Wait States for 16-Bit Transfers

- 4 or 5 Wait States for 8-Bit Transfers

- Programmable I/O Recovery Time

- Programmable driving current for the DRAM and the ISA bus signals

- 32-Bit Data Buffer Between CPU and AT System

- Data Conversion and Swapping Logic for 32-/16-/8-Bit Transfers During CPU and DMA Cycles

- Data Latches for AT Read Cycles

- Parity Generation and Detection Logic

- Port B Register and NMI Logic

- Integrated Peripheral Controllers

- 8259A x2 / 8237x2 / 8254 / 74LS612

- 387/487SX and Weitek 3167/4167 Coprocessors Interface

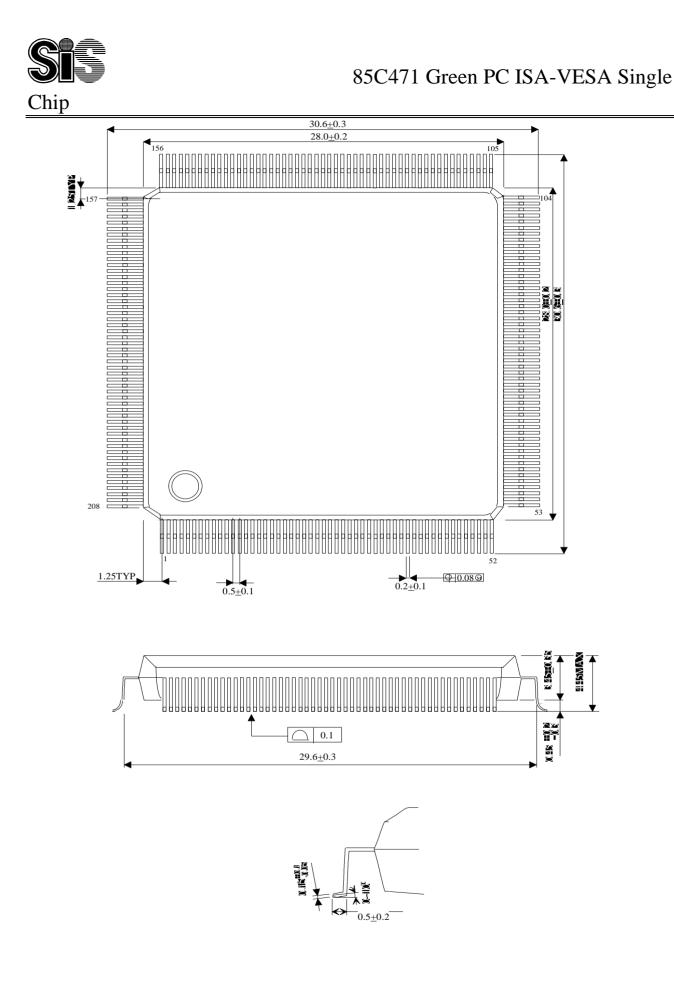

- 208-Pin PQFP

- 0.8µm Low Power CMOS Technology

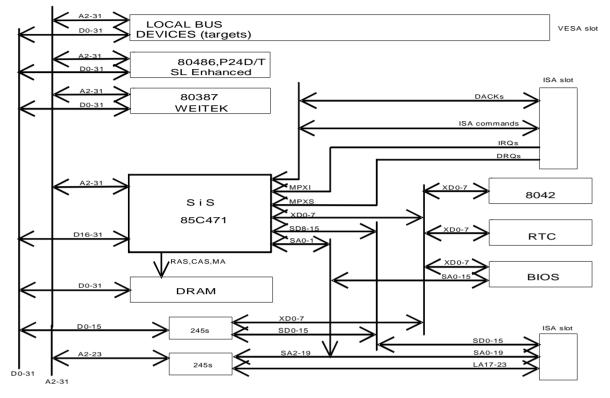

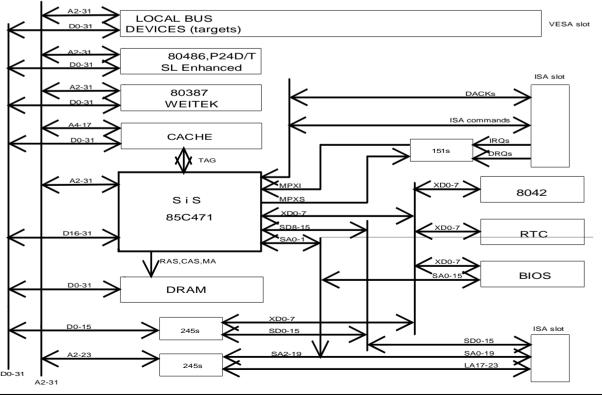

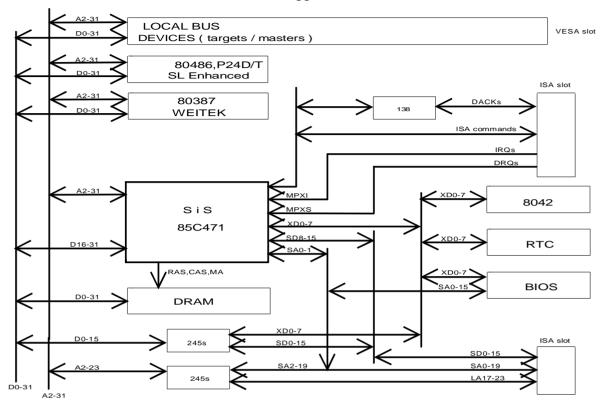

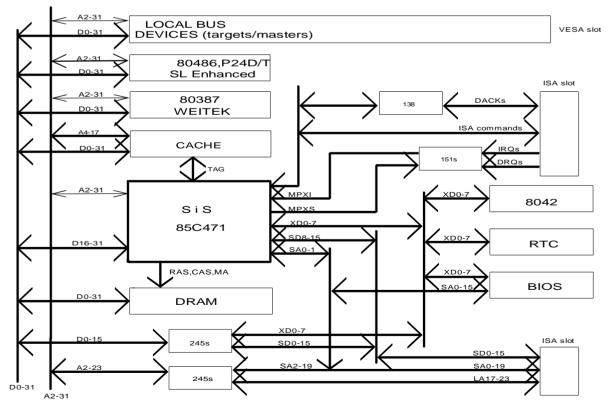

#### 1.3 Block Diagram

#### VESA TARGETs without CACHE application

#### VESA TARGETs with CACHE application

Preliminary V6.0 August 19, 1994 4 Silicon Integrated Systems Corporation

#### Two VESA MASTERs without CACHE application

#### Two VESA MASTERs With CACHE application

5

Preliminary V6.0 August 19, 1994

Silicon Integrated Systems Corporation

#### **2 FUNCTIONAL DESCRIPTION**

#### 2.1 Cache Controller

#### 2.1.1 Direct Mapped Cache

In a write-through cache system, data are written to the main memory while or immediately after they are written into the cache. So the main memory always contains valid data.

Cache is a good way in de-coupling the fast processor from the slow main memory and gets the best performance for the processor. Direct-mapped cache is the most straight-forward, flexible, easy-to-implement and cost-effective cache structure. A 2/4-way set-associative cache has better performance than the direct-mapped cache, but the performance difference is negligible when the cache size is large enough (e.g. 64KB). The SiS85C471 supports both write through and write back, for both the first level and the second level caches. To maintain the caches coherency, the SiS85C471 allows the CPU or the VL-Master to write back the entire dirty line to either the second level caches or the main memory via a completed burst write transfer. The SiS85C471 also provides a fast 8-bit/7-bit tag comparator and all the control logics for the second level cache of the 80486 processor. To implement a secondary cache, users only need to add SRAMs for the tag and the data memory onto the system. The maximum configurable cache size through the register is 1 MB.

#### 2.1.2 Write-Back vs. Write-Through

When the contents of the cache data are modified by the processor, the main memory has to be updated. Failing to do so will raise an inconsistency problem when the stale data in the main memory are accessed. There are two approaches to update the main memory. The first is the write-through method and the second is the write-back (also called "copy-back") method. In a write-back cache system, there is a dirty bit for each cache data line. When a write hit occurs in a cache line, the corresponding "alter" bit will be set. The data are written to the main memory when the line is replaced by a cache line fill. When a cache line fill occurs, the cache controller checks the corresponding "alter" bit. If the "alter" bit is set, the cache data will then be written to the main memory before the cache line fill starts.

A write-back cache offers higher performance than a write-through cache if writes to the main memory are much slower than to the cache. A write-back cache is also favored when data are written to a memory location several times in the cache before they are written into the main memory. The performance advantage of the write-back cache over write-through cache is software dependent.

The SiS85C471 can be configured to support a write-back or write-through cache. The TAG address field of the SiS85C471 for the caches can either be programmed in 7-bit or 8-bit wide. Besides tag and data RAMs, a write-back cache may need a SRAM for the dirty bits if the TAG RAM and the ALTER RAM can not be shared in one SRAM. So, a write-back cache may have better performance, but costs more than a write-through cache. The cost/effectiveness is justified by application requirements.

| Preliminary V6.0 August 19, | 1994 6 | Silicon Integrated Systems Corporation |

|-----------------------------|--------|----------------------------------------|

|                             |        |                                        |

#### 2.1.3 80486 Burst Cache Line Fill

The internal cache of the 80486 has a 16-byte line size. When a read miss occurs in the internal cache, the 80486 initiates off-chip memory read cycles to update the current cache line. The 80486 reads the 16-byte block (4 doublewords). To increase the bus throughput, the 80486 provides a burst mode transfer. Four doublewords can be read sequentially in 5 processor clocks (2-1-1).

The second level cache provided by the SiS85C471 also has a 16-byte line size. It supports the 80486 burst read cycles to do the fastest cache line fill. When the 80486 internal and external caches encounter a read miss, they are both updated with the data line read from the DRAMs simultaneously.

In addition to supporting burst reads for the cache line fills of the CPU, the SiS85C471 is capable of accepting burst write data of the CPU's internal cache dirty line(s) during CPU write back cycles. The CPU burst write support is optional by programming the Configuration Registers. The SiS85C471 supports the cache size up to 1MB and the DRAM size up to 128MB.

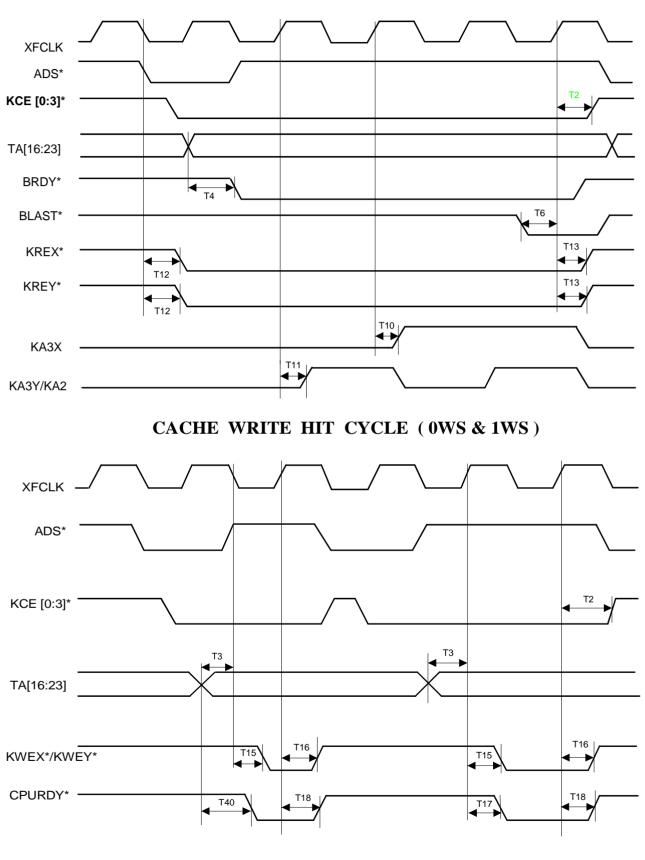

#### 2.1.4 Cache Update Policy

For CPU cycles, the contents of the cache memory are updated when either the cache read miss or write hit occurs. Tag and data RAMs are both updated in the cache read miss cycles. In the cache write hit cycles, the SiS85C471 updates only the data RAM. In the cache write miss cycles, the CPU writes data into the main memory (DRAMs), while the cache memory remains unchanged. The "alter" bit of the data line in a write-back cache is reset in a cache update (read miss) cycle and set in a write hit cycle.

When the cache is disabled, all the CPU reads from the memory are treated as cache read misses, so both tag and data RAMs are updated. This feature is used to initialize the cache memory before it is enabled.

In DMA/ISA master cycles, the cache data RAMs are written when a write hit occurs to assure the cache coherency. Cache memory is not accessed in DMA/ISA master write miss or read cycles for the write-through cache. For the write-back cache, DMA/ISA master read hit cycles are conducted to the cache, not to the DRAMs.

#### 2.1.5 Cache Size Options

| Cache Size | Tag RAM | Alter RAM | Data RAM  | Cacheable<br>Size |

|------------|---------|-----------|-----------|-------------------|

| 32KB       | 2Kx8    | 2Kx1      | 8Kx8 x4   | 8MB               |

| 64KB       | 4Kx8    | 4Kx1      | 8Kx8 x8   | 16MB              |

| 128KB      | 8Kx8    | 8Kx1      | 32Kx8 x4  | 32MB              |

| 256KB      | 16Kx8   | 16Kx1     | 32Kx8 x8  | 64MB              |

| 512KB      | 32Kx8   | 32Kx1     | 128Kx8 x4 | 128MB             |

| 1M         | 64Kx8   | 64Kx1     | 128Kx8x8  | 128MB             |

7

#### (A) 8-bit wide TAG address field

#### (B) 7-bit wide TAG address field

| Cache Size | Tag RAM +<br>Alter RAM | Data RAM  | Cacheable<br>Size |

|------------|------------------------|-----------|-------------------|

| 32KB       | 2Kx8                   | 8Kx8 x4   | 4MB               |

| 64KB       | 4Kx8                   | 8Kx8 x8   | 8MB               |

| 128KB      | 8Kx8                   | 32Kx8 x4  | 16MB              |

| 256KB      | 16Kx8                  | 32Kx8 x8  | 32MB              |

| 512KB      | 32Kx8                  | 128Kx8 x4 | 64MB              |

| 1M         | 64Kx8                  | 128Kx8x8  | 128MB             |

The cacheable DRAM size is determined by cache size because the tag address field is always 8-bit wide. The on-board memory beyond the cacheable size is not cacheable. It is still cacheable for the 80486 internal cache.

#### **2.1.6 Cache Speed Options**

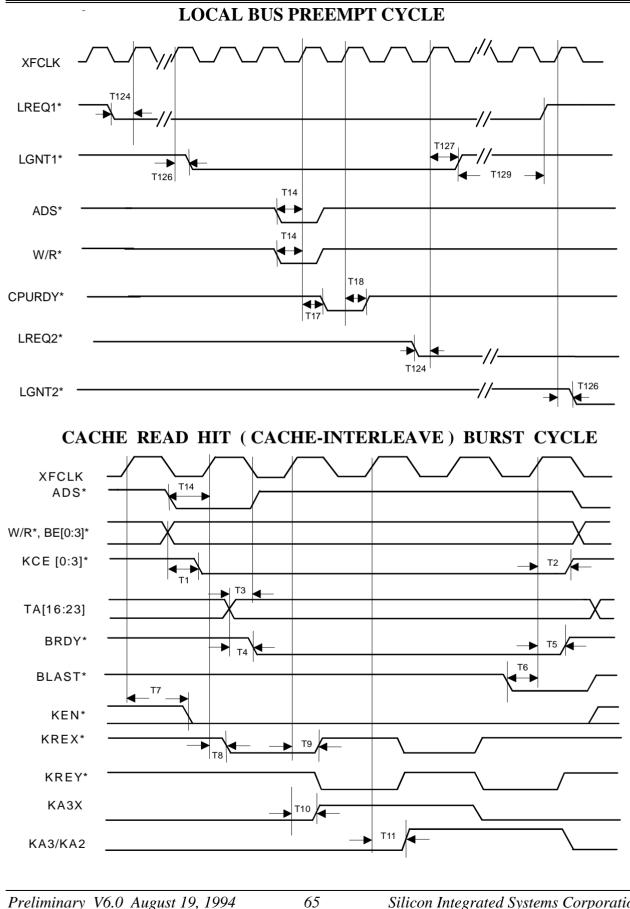

The external cache can be configured as non-interleaved or two-bank interleaved. Two-bank interleaved cache can use slower cache data RAMs but needs more data RAM chips.

The SiS85C471 provides four cache read speed options : 2-1-1-1, 3-1-1-1, 2-2-2-2 and 3-2-2-2, and two options for cache write cycles : 2T or 3T. The cache read speed x-y-y-y is selected via bit 7 of configuration register 50 (x) and bit 0 of configuration register 51 (y). The 2T cache write is applicable only when the first cycle of a burst cache read is also set to 2T (2-1-1-1 or 2-2-2-2).

The following is the table of cache configurations and the suggested speeds of the SRAMs in implementing the cache data RAMs for various CPU speeds.

| Cache Configuration   | 25MHz<br>CPU | 33MHz<br>CPU | 40MHz<br>CPU | 50MHz<br>CPU |

|-----------------------|--------------|--------------|--------------|--------------|

| 2-1-2 Interleave (*1) | -35 (*2)     | -20          | -12          |              |

| 2-1-2 Non-interleave  | -25          | -15          |              |              |

| 2-1-3 Interleave      | -40          | -25          | -20          |              |

| 2-1-3 Non-interleave  | -25          | -15          |              |              |

| 3-1-3 Interleave      | -45          | -25          | -20          | -12          |

| 3-1-3 Non-interleave  | -25          | -15          |              |              |

| 2-2-2 Non-interleave  | -35          | -20          | -12          |              |

| 2-2-3 Non-interleave  | -40          | -25          | -20          |              |

| 3-2-3 Non-interleave  | -65          | -45          | -35          | -25          |

| 3-2-3 Interleave      | -80          | -55          | -45          | -30          |

#### Note: \*1. x-y-z means x-y-y-y burst read and zT write cycle. \*2. -m means the access speed of SRAMs in ns.

Preliminary V6.0 August 19, 1994

The following is the table of cache configu-rations and suggested speeds of the SRAMs in implementing the cache tag and alter RAMs for various CPU speeds.

| Cache Configuration | 25MHz<br>CPU | 33MHz<br>CPU | 40MHz<br>CPU | 50MHz<br>CPU |

|---------------------|--------------|--------------|--------------|--------------|

| 2-X-2               | -25          | -20          | -12          |              |

| 2-X-3               | -35          | -25          | -15          |              |

| 3-X-3               | -45          | -35          | -25          | -20          |

#### Note: X represents either 1T or 2T cycles.

#### 2.1.7 Non-Cacheable Regions

In some applications, users prefer a block of memory not to be cached. The SiS85C471 provides two programmable non-cacheable regions to serve this function.

Only the on-board DRAMs directly controlled by SiS85C471 are cacheable. The memory residing on the AT bus is non-cacheable. When a memory space is mapped by both the on-board DRAMs and AT add-in memory, the CPU accesses will be conducted to the on-board DRAMs.

If the AT add-in memory is to be accessed instead of the on-board DRAMs in the overlapped memory space, the two non-cacheable regions can be used to disable the on-board DRAMs in the programmed space.

The sizes and starting addresses of the two non-cacheable regions are programmable in the configuration registers 54, 55, 56 and 57. The validity of the starting address bits depends on the size of the related non-cacheable region as shown in the table below.

| Size | A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 64K  | V   | V   | V   | V   | V   | V   | V   | V   |

| 128K | V   | V   | V   | V   | V   | V   | V   | Х   |

| 256K | V   | V   | V   | V   | V   | V   | Х   | Х   |

| 512K | V   | V   | V   | V   | V   | Х   | Х   | Х   |

| 1M   | V   | V   | V   | V   | Х   | Х   | Х   | Х   |

| 2M   | V   | V   | V   | Х   | Х   | Х   | Х   | Х   |

| 4M   | V   | V   | Х   | Х   | Х   | Х   | Х   | Х   |

V = Valid

X = Don't Care

#### 2.1.8 Cache Initialization

The second level cache supported by SiS85C471 does NOT provide the valid bits for the data lines. All the cache data are assumed valid once the cache is enabled. All the cache lines must be filled with valid data before the cache enable bit is turned on. The cache initialization can be done through sequential reads to a block of on-board DRAMs which is equal to or larger than the cache in size.

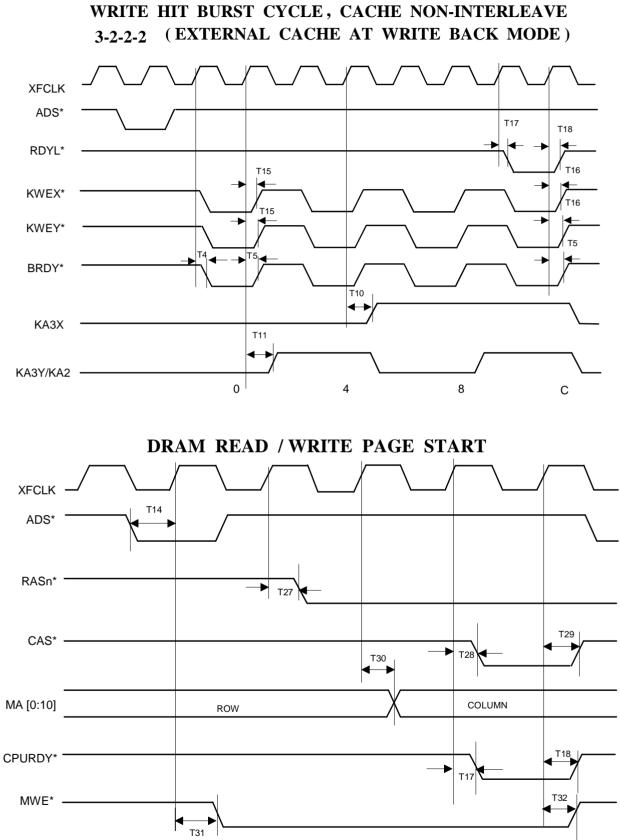

#### 2.2 DRAM Controller

#### 2.2.1 DRAM Speed Options

The SiS85C471 provides 4 read and 2 write speed options in the configuration register. A table of page hit cycle times of all the possible speed configurations is listed as follows:

|         | Read | 486 Burst Read | <u>Write</u> |

|---------|------|----------------|--------------|

| Fastest | 3    | 3-2-2-2        | 2            |

| Faster  | 4    | 4-3-3-3        | 2/3          |

| Slower  | 5    | 5-4-4-4        | 2/3          |

| Slowest | 6    | 6-5-5-5        | 4            |

#### Note: The unit of the above table is in T cycles.

There will be plenty of timing margin if "Fastest" is used for 25MHz 80486, "Faster" for 33MHz 80486, "Slower" for 40MHz 80486, and "Slowest" for 50MHz 80486. The table below shows the DRAM access timing for different speed configurations.

#### 2.2.2 DRAM Size Configuration

The SiS85C471 supports 53 DRAM configurations in 4 banks. Besides the traditional 256K/1M/4M xN DRAMs, the new 512K /2M/8M/16M xN DRAMs are also supported.

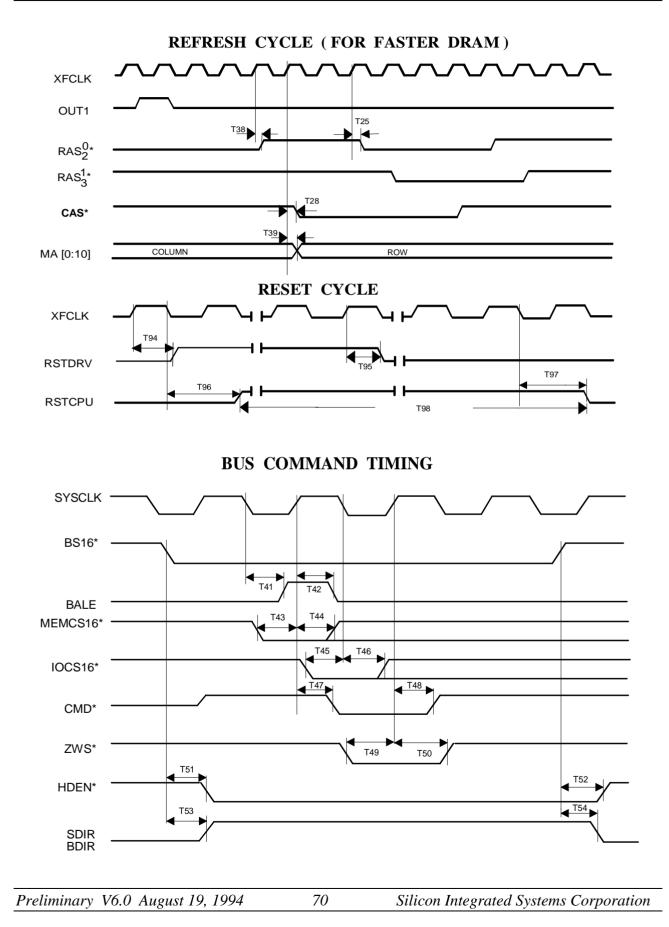

#### Refresh

In the original PC/AT design, the CPU is held off (i.e. HLDA asserted) during the DRAM refresh cycles. It happens once every 15us and takes at least 0.5us for each occurrance.

In SiS85C471, refresh can be selected to hold the CPU or not by setting bit 5 of the configuration register 58.

The DRAM speeds are becoming faster and the time needed for each refresh cycle is getting shorter. For example, the refresh cycle time for 100ns DRAMs is 180ns minimum. In a system with cache, most of the CPU accesses are referred to the cache, so the DRAM usage (percent of time the DRAMs are accessed by the CPU) is significantly reduced.

#### **DRAM Access Timing**

|      | Fastest | Faster | Slower | Slowest |                      |

|------|---------|--------|--------|---------|----------------------|

| Trcd | 1.5T    | 2T     | 2T     | 3T      | RAS-to-CAS delay     |

| Tcas | 1.5T    | 2T     | 3T     | 3T      | Read CAS pulse width |

| Trp  | 3T      | 3T     | 4T     | 5T      | RAS precharge        |

| Тср  | 0.5T    | 1T     | 1T     | 2T      | CAS precharge        |

In the SiS85C471, the main memory refresh is independent of the AT-bus refresh so the cycle time is shorter (not necessary to follow the standard AT-bus timing). When doing the main memory refresh, the CPU is NOT held off so it may execute the program in the cache. If the CPU accesses the main memory while the refresh cycle is going, the access will be pending until the refresh cycle is finished.

The following table lists the refresh-related RAS timings of the on-board DRAMs :

|            | Fastest | <u>Faster</u> | <u>Slower</u> | <u>Slowest</u> |

|------------|---------|---------------|---------------|----------------|

| RAS        | 3T      | 3T            | 4T            | 5T             |

| pre-charge | ;       |               |               |                |

| RAS active | e 3T    | 4T            | 4T            | 5T             |

If hidden refresh is selected on the AT bus, the AT bus refresh cycles are issued every 15us when there is no access from the CPU, the local bus masters, the DMA controllers, or the bus master on the AT bus. The CPU will not feel the existence of the AT bus refresh cycles unless it issues an AT bus cycle or cache miss cycle while the refresh cycle is going on. The controller arbitrates among the CPU AT cycle, the DMA/master request, and the AT bus refresh cycle so that they can be executed one after another when more than one intend to use the AT bus at the same time.

The SiS85C471 has a slow refresh feature to cut the refresh frequency down to 1/4. It should be selected only when the system is equipped with slow-refresh DRAMs.

The refresh scheme of the CPU local DRAMs is CAS-before-RAS refresh. The CASes go active at least one T before the RASes in local memory refresh cycles.

To reduce the power noise caused by the refresh cycles, the RASes of the odd banks go active one T after the RASes of the even banks. It is called the "staggered refresh".

#### 2.2.3 Shadow RAM

The Memory space 0A0000-0FFFFFh is reserved for the video RAM, the I/O and system BIOS ROMs. Accesses to this area should not be conducted to the main memory in standard PC/AT systems. Since the speed of the DRAMs is significantly faster than that of the ROMs, the overall system performance can be improved if contents of the BIOS ROMs are copied to the unused DRAM area (0A0000- 0FFFFFh), and the CPU accesses to this area are conducted to the DRAMs instead of to the BIOS ROMs. This is called the "Shadow RAM".

The SiS85C471 provides shadows to 0C0000-0EFFFh in 32KB granularity and shadow to 0F0000-0FFFFh. The shadow RAMs are non-cacheable by default. The shadow RAMs in C0000-C7FFFh and F0000-FFFFFh can be programmed to being cacheable.

| Preliminary V6.0 August 19, 1994 11 Silica | on Integrated Systems Corporation |

|--------------------------------------------|-----------------------------------|

|--------------------------------------------|-----------------------------------|

#### 2.2.4 256KB Relocation

The SiS85C471 provides the 256KB DRAM relocation from 0A0000-0BFFFFh and 0D0000-0EFFFFh to the top of the configured DRAM.

This function works for the DRAM sizes of 1MB, 2MB, 4MB, 6MB and 8MB when the shadowing of D and E segments is disabled.

#### 2.2.5 72-pin SIMM Module Support

The SiS85C471 supports 72-pin double-sided SIMM modules. Please refer to Register 59 bit 5-0 on page 27 for details.

#### 2.3 ROM/Flash ROM Support

The SiS85C471 provides a chip select signal for the system BIOS ROM. The memory space assigned to the ROM/Flash ROM is the highest 64/128KB of the real (1MB) and the protected (4GB) address modes of the 80486/P24D/P24T/P24C CPUs.

The system BIOS ROM can be shadowed to the DRAMs to improve performance. When the RAM shadowing feature is turned on, the accesses to the system BIOS with addresses below 100000h will be channeled to the DRAMs.

#### 2.4 Fast A20GATE And CPU Reset/Port 92h

In the original PC/AT design, the A20GATE and CPU Reset (RC) are controlled by the 8042 keyboard controller to switch the CPU between the real and protected address modes and to warm boot the system. The operation of 8042 is slow. If address mode switching happens frequently, execution speed will be affected.

The SiS85C471 provides an 8042 emulation to generate the A20GATE and CPU reset signals in hardware. This feature is software transparent.

The SiS85C471 also provides a control port, I/O port hex 0092, to generate the A20GATE and the CPU reset. The following shows the definitions of bit 1 and bit 0 of the port 092h that are used for the generation of those two signals.

- Bit 1: This bit is internally OR'ed with the FAST\_A20\_GATE. Writing an "1" to this bit will force A20M to go high active. Upon reset, this bit goes low.

- Bit 0: This bit can be set to "0" by a CPU reset or a IO write operation. A transition of this bit from "0" to "1" will have the INIT signal go active. The minimum delay from the transition of this to the INIT active is 2 to 6 μs.

#### **2.5 Local Bus Support**

The SiS85C471 uses LBD\* (Local Bus Device) and LRDY\* (Local Bus Device Ready) pins to implement Local Bus Device Architecture such as Weitek 3167/4167 and VESA VL-Bus devices.

| Preliminary V6.0 August 19, 1994 12 Silicon Integrated Systems Corpo | 12 Silicon Integrated Systems Corporation |

|----------------------------------------------------------------------|-------------------------------------------|

|----------------------------------------------------------------------|-------------------------------------------|

When there are more than one local bus devices, their LBD\* signals should be "ANDed" together before connecting to the SiS85C471.

The SiS85C471 samples the LBD\* input at the end of T2 when DRAM speed is set to "FASTEST" or "FASTER", and at the end of T3 when DRAM speed is "SLOWER" or "SLOWEST". The LBD\* pin should be asserted before the sampling point if the current cycle is a local bus cycle. Bit 1 of Register 58 can be programmed to overwrite the sampling point described above.

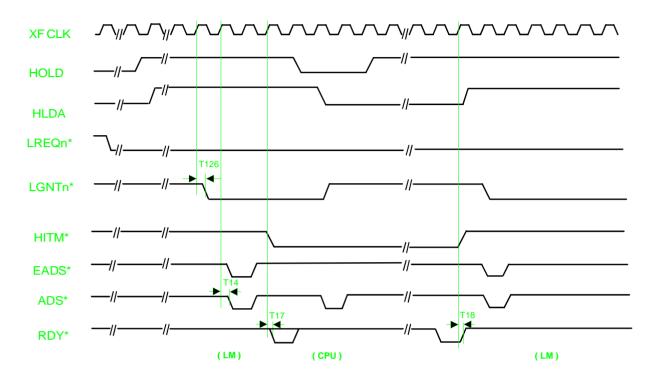

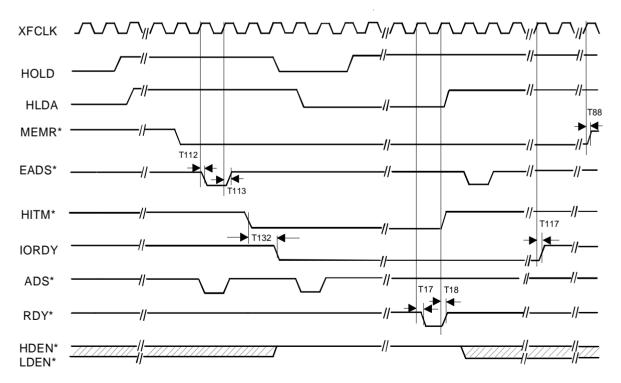

#### 2.5.1 VESA VL-Bus Interface

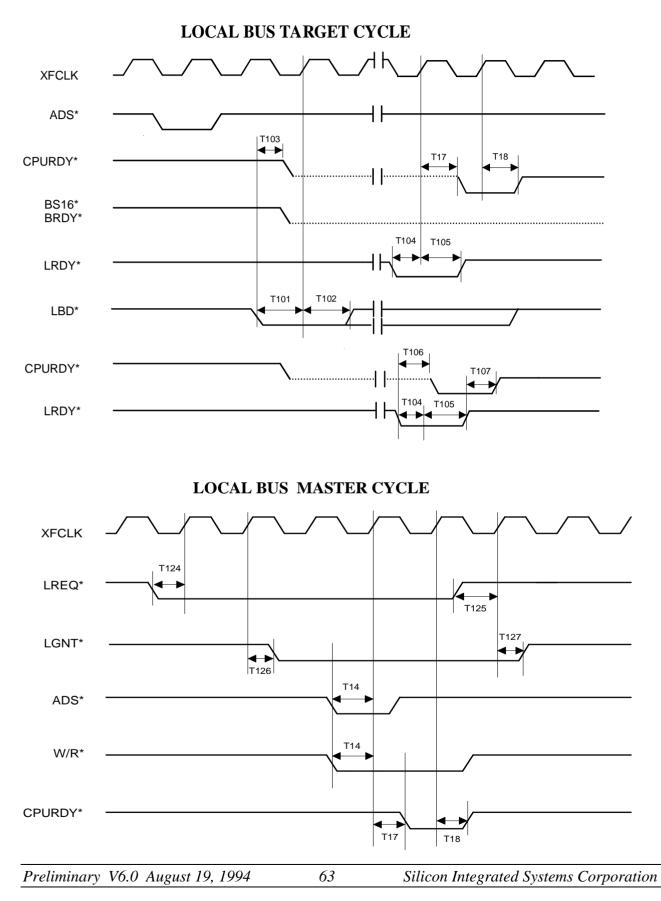

The SiS85C471 provides VESA local bus supports as follows :

#### A. Local bus device is accessed by CPU :

- •When a local bus device decodes the bus definition/address and determines this is its cycle at the start of a CPU bus cycle, it should assert LBD\* to inform the SiS85C471 this is a local bus device cycle.

- •The local bus cycle can be terminated in two ways :

- 1. The local bus device asserts LRDY\* to the SiS85C471. The SiS85C471 will generate the CPURDY\* by either synchronizing the LRDY\* with the CPU clock (synchronous mode) or passing LRDY\* directly to the output buffer (transparent mode) determined by Bit 0 of Register 58 being 0 (default) or 1.

- 2. The local bus device can assert BRDY\* to indicate the burst mode transfer support. The SiS85C471 also monitors BRDY\* when LBD\* is detected asserted. When the SiS85C471 detects that both BLAST\* from the CPU and BRDY\* from the local bus device are asserted, the SiS85C471 will end the burst transfer cycle.

- •BS16\* support: If the local bus device is capable of doing 16-bit transfers only, it should assert BS16\* to the CPU to indicate that another cycle may be necessary.

#### **B.** Local bus master cycles

- •The SiS85C471 supports two local bus masters. When a local bus master needs to take over the bus, it issues bus request signal to the SiS85C471. The SiS85C471 waits until there is no other local bus cycle pending before issuing the bus grant signal to indicate that the local bus master can start to access the system targets. The local bus masters can access all the system resources including on-board memory, the ISA-bus devices, and the local bus targets.

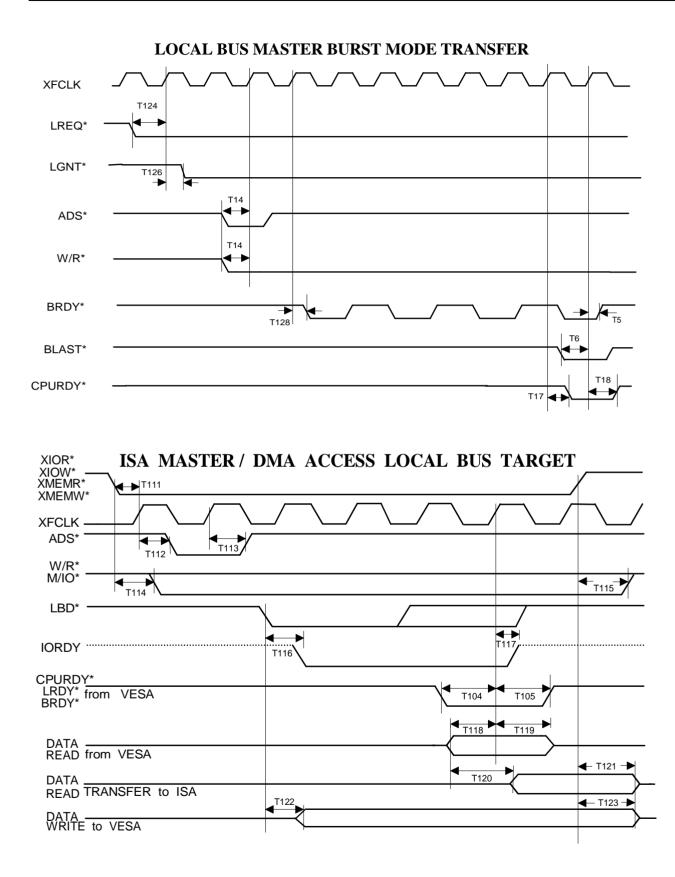

- •The local bus master can perform burst mode transfers while accessing on-board memory or a local bus target that supports burst transfers. After detecting three BRDY\*s, the local bus master issues BLAST\* to indicate the last burst cycle. The local bus masters which do not wish to burst, must drive BLAST\* low when they own the bus.

#### C. DMA/ISA master accesses local bus target

| - Freuminary v0.0 August 19. 1994 $-$ 15 $-$ Suicon miggraied Systems Cordoral | Preliminarv | V6.0 August 19, 1994 | 13 | Silicon Integrated Systems Corporation |

|--------------------------------------------------------------------------------|-------------|----------------------|----|----------------------------------------|

|--------------------------------------------------------------------------------|-------------|----------------------|----|----------------------------------------|

- •When the address coming from ISA bus in a DMA or an ISA bus master cycle selects a local bus target.

- •The ADS\*, M/IO\*, and W/R\* are driven by the SiS85C471 in this cycle and the timing is designed to meet the spec. of VESA local bus.

- •The local bus target asserts LBD\* to indicate that the local bus target is selected.

- •The SiS85C471 deasserts IORDY low to keep the cycle active until the LRDY\* is asserted low by the local bus target. then the SiS85C471 asserts IORDY high to terminate the cycle.

- •ISA command will be negated at least 1 AT clock after IORDY being asserted. In a local bus read cycle, the data will be invalid after CPURDY\* (RDYRTN\*) is asserted. The SiS85C471 latches data and keeps the data valid until the ISA bus command is negated.

#### 2.6 Turbo Switch

The 486 systems are fast, so it is possible for them to run into problems with some applications. The SiS85C471 offers a De-Turbo function that can be controlled through a hardware switch or software programming. When the De-Turbo function is ON, the system speed can be reduced by 1/3 or 2/3 selected by bit 4 of the configuration register 58.

#### 2.7 Advanced Clock

To increase the setup time margins of the chip output buffers in a high speed system, the SiS85C471's clock input XFCLK, the "Advanced clock", leads the CPU clock by 3~5 ns. The cache read control signals, the local bus control signals, and others can be issued early to increase the margin of cache data RAM access time and the setup time.

#### **2.8 Clock Generation**

The CPU clock speed is too fast for slow AT bus. To overcome this problem, the SiS85C471 provides a flexible software- controlled selections of the clock used for the AT bus state machine. The SiS85C471 operates the AT bus state machine at the AT bus clock which is determined by the configuration register and can be selected as 1/2, 1/3, 1/4, 1/5, 1/6, 1/8 or 1/10 of the input clock, or 7.159 MHz.

Whenever the configuration is changed, the clock frequency switches accordingly with glitch-free transition.

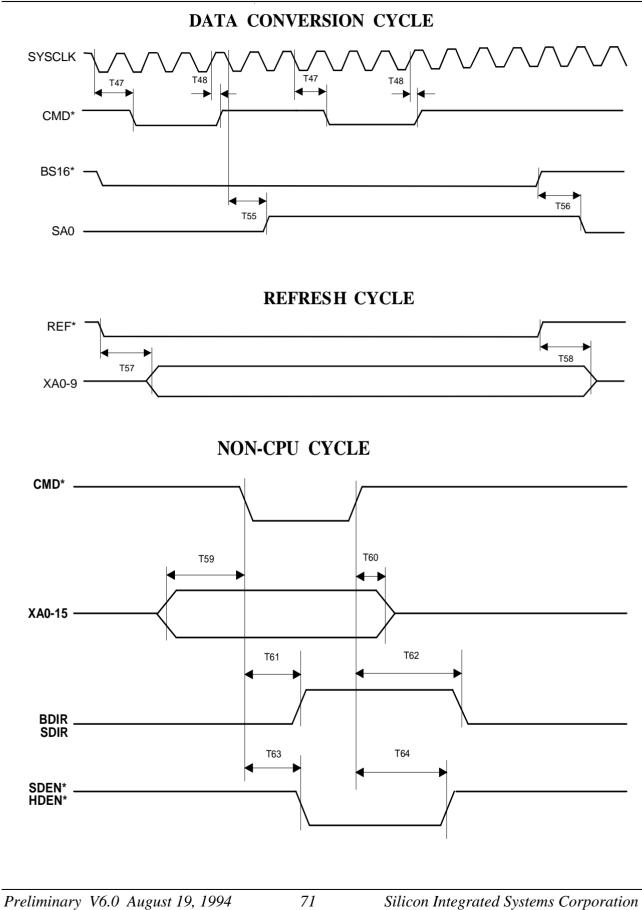

#### 2.9 AT Bus State Machine

The SiS85C471 starts an AT bus cycle when the current cycle is not a local bus or a local memory cycle. The SiS85C471 asserts BS16\* to the CPU or the local bus master and starts driving BALE signal in the AT-TS state.

It then enters into the command cycle AT-TC and provides the timing signals for the AT bus cycle and terminates the cycle by asserting CPURDY\* signal.

To determine the bus size, MEMCS16\* signal is sampled at the falling edge of BALE during memory cycle or IOCS16\* is sampled at the falling edge of BALE after the command is active

Preliminary V6.0 August 19, 199414Silicon Integrated Systems Corporation

in an I/O cycle. The command cycle is terminated only when IORDY is active and all programmed wait states have been executed.

The period of command cycle is selected by the configuration register. For 16-bit transfers, the default is 1 wait state and can be selected as 2 wait states. For 8-bit transfer, the default is 4 wait states and can be selected as 5 wait states. No command delay is inserted for 16-bit memory cycles and 1/2 SYSCLK command delay is inserted for other cycles.

IORDY is sampled at the start of every AT-TC state. The command cycle will not complete until all programmed wait states have be executed and IORDY is sampled high. If ZWS\* is detected LOW at the middle of the AT-TC state, the current AT cycle will be terminated immediately.

During a read cycle, the data read from a device may be lost after the command completes. The SiS85C471 latches the data immediately after the read command is inactive and holds the data until the AT cycle ends. The "Read Latch" function is active for all AT bus read cycles, except during DMA, ISA bus Master, or local RAM read cycles.

The shortest command recovery time is two AT clock cycles in this chip. It can be too short for some I/O devices. A configuration register is provided to selected the I/O command recovery time for 16-bit transfers and for 8-bit transfers. Please refer to the configuration register 61 description for detail.

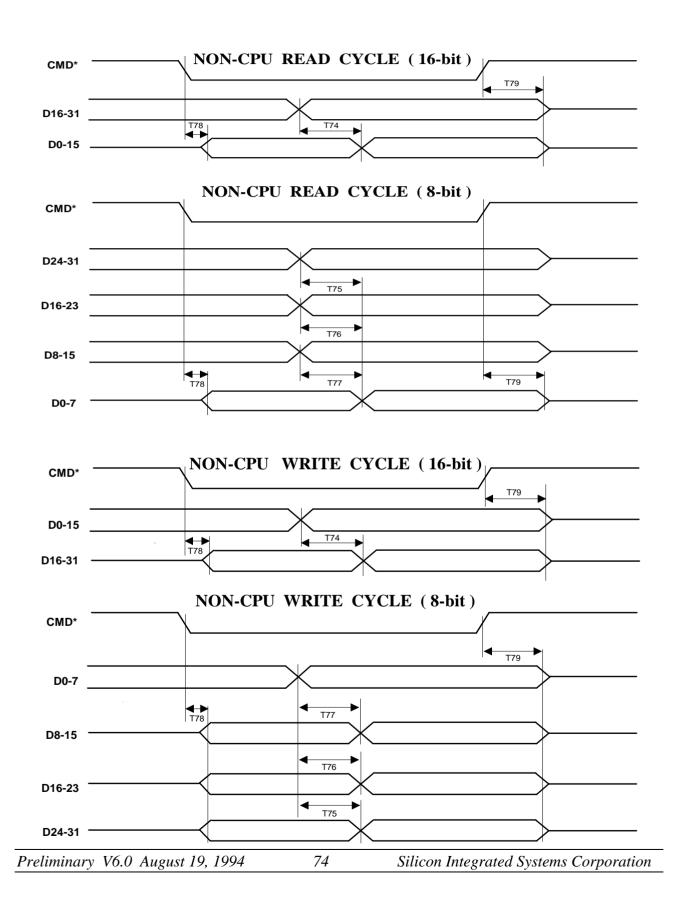

#### 2.10 Data Conversion Logic

If both MEMCS16\* and IOCS16\* are sampled negated, the current cycle is an 8-bit cycle. The AT state machine performs data conversion if the CPU executes a 16-bit read or write during an 8-bit transfer. Besides data conversion, the data are also swapped if necessary. In DMA or ISA Master cycles, data swapping is also processed if necessary. The system checks the command, address, and related control signals and then arranges required swapping.

BE0\*-BE3\* can not be used to select the devices on AT bus directly. BE0\*-BE3\* are inputs in AT cycles to generate SA1, SA0, and BHE\* signals. In a DMA cycle, BE0\*-BE3\* are generated from SA1 and SA0 to access the local memory. The SiS85C471 checks these four byte enable signals in an AT cycle and determines if it is a 16-bit cycle and whether data conversion should be performed.

The SiS85C471 separates a 16-bit read or write operation into two 8-bit transfers and drives SA0 high in the second cycle. In the meanwhile, the SiS85C471 executes the data swapping process among the 32-bit, 16-bit and 8-bit data buses.

#### 2.11 Port B Register/NMI Logic

The SiS85C471 provides accesses to Port B defined by IBM PC/AT. The bit definitions of Port B register are as follows :

| <u>Bit</u> | <u>Contents</u>             |   |      |   |  |

|------------|-----------------------------|---|------|---|--|

| 0          | GATE2 - Timer 2 Gate        |   |      |   |  |

| 1          | SPKEN - Speaker Data        |   |      |   |  |

| 2          | PCKEN - Parity Check Enable |   |      |   |  |

|            |                             | ~ | <br> | ~ |  |

- 3 IOCHCKEN I/O Channel Check Enable

- 4 REFRESH Refresh Detect

- 5 OUT2 Timer 2 Out

- 6 IOCHCK I/O Channel Check

- 7 PCK Parity Check

The NMI logic in the SiS85C471 enables and latches the I/O or parity error to generate a nonmaskable interrupt to the CPU if NMI is enabled. NMI is enabled when bit 7 of port 70h is clear to 0. NMI is disabled if it is set to 1.

#### 2.12 Bus Buffer Control Logic

During an AT-bus read cycle, the data from the responding device are latched immediately after the read command is inactive and are held stable till the end of the AT cycle.

The SiS85C471 provides 16-bit to 8-bit or 8-bit to 16-bit data bus conversion in AT cycles. In DMA cycles, 32-bit, 16-bit and 8-bit data bus conversions are provided.

#### 2.13 Parity Generation/Detection

During memory write cycles, the SiS85C471 generates even parity for each of the four bytes. The parity bits PD0- PD3 are written to the parity memory in the system DRAMs. During memory read cycles, the SiS85C471 checks for even parity for each byte read. If odd parity is detected, the SiS85C471 flags a parity error. The SiS85C471 detects the error and generates NMI when enabled. The parity error can be cleared by programming parity check disable, which is defined by Bit 2 of port B register.

#### **2.14 Peripheral Controllers**

The SiS85C471 contains Peripheral Controllers which include two 8237 DMA Controllers, a 74LS612 Mapper, two 8259 Interrupt Controllers, and an 8254 Counter/Timer.

#### **2.15 DMA Controllers**

Two DMA controllers are connected in such a manner as to provide the user with four DMA channels (DMA1) for 8-bit transfers and three DMA channels (DMA2) for 16-bit transfers (the first 16-bit DMA channel is used for cascading to DMA1). The DMA address mapper, the 74LS612, is used to drive the upper address lines during DMA cycles.

#### **2.16 Interrupt Controllers**

Two interrupt controllers, namely INTC1 and INTC2, are provided in the SiS85C471. Each controller supports 8 channels of interrupts, so in total, the SiS85C471 supports 16 levels of interrupts. Of the 16 channels, two channels are connected internally to support internal devices, allowing 14 user-definable interrupt channels. The two internally connected channels are :

Channel 0 -Counter/Timer Counter 0 Interrupt Channel 2 -Cascade to Slave Interrupt Controller (INTC2)

#### 2.17 Counter/Timer

The Counter/Timer (CTC) subsystem contains three independent counters. The clock input of each counter is connected to a clock of 1.19MHz which is derived from dividing the

Preliminary V6.0 August 19, 1994 16 Silicon Integrated Systems Corporation

14.318MHz input by 12. Counter 0 is connected to Interrupt 0 of INTC1. It is used as a multilevel interrupt to the system for such task as time keeping or task-switching. Counter 1 can be programmed to generate pulses or square waves for used by external devices and Counter 2 is a full function Counter/Timer which has a gate input for controlling the internal counter. This counter can be used as an internal counter, a timer, or as a gated rate or pulse generator.

#### 2.18 Clock and Wait State Control

The Clock and Wait State Control subsystem performs four functions : control of the DMA command width; control of the CPU read cycle length; control of the CPU write cycle length and selection of the DMA clock rate. All the functions are user selectable by writing to the Configuration Register located at address 023h.

Writing or reading this register is accom-plished by first writing a 01h to location 022h to select the Configuration Register. After the Configuration Register 01h is selected, a write or read cycle can be issued to access the data register located at 023h.

#### 2.19 Peripheral Controllers Address Map

#### **DMA Controller Address Map**

| DMA1 | DMA2 | XIOR* | XIOW* | Flip<br>Flop | Register Function                                     |

|------|------|-------|-------|--------------|-------------------------------------------------------|

| 000h | 0C0h | 0     | 1     | 0            | Read channel 0 current address low byte               |

|      |      | 0     | 1     | 1            | Read channel 0 current address high byte              |

|      |      | 1     | 0     | 0            | Write channel 0 base and current address low byte     |

|      |      | 1     | 0     | 1            | Write channel 0 base and current address high byte    |

| 001h | 0C2h | 0     | 1     | 0            | Read channel 0 current word count low byte            |

|      |      | 0     | 1     | 1            | Read channel 0 current word count high byte           |

|      |      | 1     | 0     | 0            | Write channel 0 base and current word count low byte  |

|      |      | 1     | 0     | 1            | Write channel 0 base and current word count high byte |

| 002h | 0C4h | 0     | 1     | 0            | Read channel 1 current address low byte               |

|      |      | 0     | 1     | 1            | Read channel 1 current address high byte              |

|      |      | 1     | 0     | 0            | Write channel 1 base and current address low byte     |

|      |      | 1     | 0     | 1            | Write channel 1 base and current address high byte    |

| 003h | 0C6h | 0     | 1     | 0            | Read channel 1 current word count low byte            |

|      |      | 0     | 1     | 1            | Read channel 1 current word count high byte           |

|      |      | 1     | 0     | 0            | Write channel 1 base and current word count low byte  |

|      |      | 1     | 0     | 1            | Write channel 1 base and current word count high byte |

| 004h | 0C8h | 0     | 1     | 0            | Read channel 2 current address low byte               |

|      |      | 0     | 1     | 1            | Read channel 2 current address high byte              |

|      |      | 1     | 0     | 0            | Write channel 2 base and current address low byte     |

|      |      | 1     | 0     | 1            | Write channel 2 base and current address high byte    |

| 005h | 0CAh | 0     | 1     | 0            | Read channel 2 current word count low byte            |

|      |      | 0     | 1     | 1            | Read channel 2 current word count high byte           |

|      |      | 1     | 0     | 0            | Write channel 2 base and current word count low byte  |

|      |      | 1     | 0     | 1            | Write channel 2 base and current word count high byte |

| 006h | 0CCh | 0     | 1     | 0            | Read channel 3 current address low byte               |

|      |      | 0     | 1     | 1            | Read channel 3 current address high byte              |

|      |      | 1     | 0     | 0            | Write channel 3 base and current address low byte     |

|      |      | 1     | 0     | 1            | Write channel 3 base and current address high byte    |

Preliminary V6.0 August 19, 1994

| 007h | 0CEh | 0 | 1 | 0 | Read channel 3 current word count low byte            |  |

|------|------|---|---|---|-------------------------------------------------------|--|

|      |      | 0 | 1 | 1 | Read channel 3 current word count high byte           |  |

|      |      | 1 | 0 | 0 | Write channel 3 base and current word count low byte  |  |

|      |      | 1 | 0 | 1 | Write channel 3 base and current word count high byte |  |

An internal flip-flop is used to supplement the addressing of the Count and Address registers. This flip-flop selects between high and low bytes of these registers and toggles each time a read or write occurs to any of these registers.

| DMA1 | DMA2 | XIOR* | XIOW* | Flip<br>Flop | Register Function                        |

|------|------|-------|-------|--------------|------------------------------------------|

| 008h | 0D0h | 0     | 1     | Х            | Read status register                     |

|      |      | 1     | 0     | Х            | Write command register                   |

| 009h | 0D2h | 0     | 1     | Х            | Read DMA request register                |

|      |      | 1     | 0     | Х            | Write DMA request register               |

| 00Ah | 0D4h | 0     | 1     | Х            | Read mode register                       |

|      |      | 1     | 0     | Х            | Write single bit DMA request mask        |

|      |      |       |       |              | register                                 |

| 00Bh | 0D6h | 0     | 1     | Х            | Read mode register                       |

|      |      | 1     | 0     | Х            | Write mode register                      |

| 00Ch | 0D8h | 0     | 1     | Х            | Set byte pointer flip-flop               |

|      |      | 1     | 0     | Х            | Clear byte pointer flip-flop             |

| 00Dh | 0DAh | 0     | 1     | Х            | Read temporary register                  |

|      |      |       |       |              | Master clear                             |

| 00Eh | 0DCh | 0     | 1     | Х            | Clear mode register counter              |

|      |      | 1     | 0     | Х            | Clear all DMA request mask register bits |

| 00Fh | 0DEh | 0     | 1     | Х            | Read all DMA request mask register bits  |

|      |      | 1     | 0     | Х            | Write all DMA request mask register bits |

**DMA Controllers Address Map** (continued)

#### **DMA Address Extension Register Map**

| Address | Register Function            |

|---------|------------------------------|

| 080h    | Unused                       |

| 081h    | 8-bit DMA Channel 2 (DACK2)  |

| 082h    | 8-bit DMA Channel 3 (DACK3)  |

| 083h    | 8-bit DMA Channel 1 (DACK1)  |

| 084h    | Unused                       |

| 085h    | Unused                       |

| 086h    | Unused                       |

| 087h    | 8-bit DMA Channel 0 (DACK0)  |

| 088h    | Unused                       |

| 089h    | 16-bit DMA Channel 2 (DACK6) |

| 08Ah    | 16-bit DMA Channel 3 (DACK7) |

| 08Bh    | 16-bit DMA Channel 1 (DACK5) |

| 08Ch    | Unused                       |

| 08Dh    | Unused                       |

| 08Eh    | Unused                       |

| 08Fh    | Refresh cycle                |

#### **Interrupt Controller Address Map**

| Register | Туре  | I/O Port  | b7  | b6   | b5  | b4  | b3  | b2  | b1   | b0  |

|----------|-------|-----------|-----|------|-----|-----|-----|-----|------|-----|

| ICW1     | WRO   | 20h (A0h) | Х   | х    | Х   | SI  | LTM | Х   | SM   | Х   |

| ICW2     | WRO   | 21h (A1h) | V7  | V6   | V5  | V4  | V3  | Х   | Х    | Х   |

| ICW3     | WRO   | 21h       | S7  | S6   | S5  | S5  | S3  | S2  | S1   | S0  |

| ICW3     | WRO   | A1h       | 0   | 0    | 0   | 0   | 0   | ID2 | ID1  | ID0 |

| ICW4     | WRO   | 21h (A1h) | Х   | Х    | Х   | EMI | Х   | Х   | AEOI | Х   |

| OCW1     | RD/WR | 21h (A1h) | M7  | M6   | M5  | M4  | M3  | M2  | M1   | MO  |

| OCW2     | WRO   | 20h (A0h) | R   | SL   | EOI | SI  | 2/3 | L2  | L1   | L0  |

| OCW3     | WRO   | 20h (A0h) | 0   | ESSM | SMM | SI  | 2/3 | ΡM  | RR   | RIS |

| IR       | RDO   | 20h (A0h) | IR7 | IR6  | IR5 | IR4 | IR3 | IR2 | IR1  | IR0 |

| IS       | RDO   | 20h (A0h) | IS7 | IS6  | IS5 | IS4 | IS3 | IS2 | IS1  | IS0 |

#### Note :

| WRO = | Write only register |

|-------|---------------------|

|-------|---------------------|

RDO = Read only register

- RD/WR = Read/Write register

- X = Don't care

#### **Counter/Timer Address Map**

| <u>Address</u> | <b>Function</b>             |

|----------------|-----------------------------|

| 040h           | Counter 0 read/write        |

| 041h           | Counter 1 read/write        |

| 042h           | Counter 2 read/write        |

| 043h           | Control register write only |

Preliminary V6.0 August 19, 1994

#### 2.20 Green PC Function

In order to support Intel, Cyrix SMI functions, the SiS85C471 provides SMI\* (pin 93), STPCLK\* (pin 94) and SMIACT\*/ SMADS\* (pin 84) for power saving. To support AMD Am486DXL SMI function, the SiS85C471 also provides SMI\*(pin93) and SMIADS\*(pin 84) for power saving.

The basic concept of green function depends on system timer reloading. If no system event happened and the timer reaches count, the SiS85C471 enters SMM or slows down CPU speed. If the processor of the system does not support SMI\*, STPCLK\* pin can still be used to reduce the CPU speed, but additional application circuit is necessary to reduce the CPU speed by 10% descending.

The SiS85C471 provides two timers, the system event timer and the I/O event timer, to support the GREEN PC functions. Each timer can be used to monitor different events. All the devices therefore can be programmed to enter standby mode at different time zones. Each device could be independent to other devices in entering or waking up from the standby mode. Once a device is entering the standby mode, the I/O timer will be reloaded for the next device to enter the standby mode.

The selected device will enter the standby mode or the off mode when a time out of the corresponding timer happens. The SMI handler will enable the corresponding bit of the Register 68 if the device enters the standby mode. The corresponding bit of the Register 69 will be set when wake-up condition for the device in standby mode is detected. The device then will return back to normal mode by the SMI handler.

The SiS85C471 also supports the clock throttling mode. If the throttling mode is enabled, the STPCLK\* signal will go inactive while an IRQ0 request is served. Hence the operating system timer will not stop while the CPU operation is stopped in the suspend mode.

Bit 7 of register 5B is used to enable/disable SMM. Registers 5C-5E define un-monitored interrupt vectors. Register 63 defines the SM-RAM address and stop clock condition. Registers 64-65 are used to define Software\_SMI address. Registers 66 and 67 are used to select IRQn to break the stop clock. Register 6A defines system management output port SMOUT 7-0. System timer is defined in registers 6D-6F.

### **3. CONFIGURATION REGISTERS**

There are several configuration registers in the SiS85C471. An indexing scheme is used to access the registers. Port 22h is the index register and port 23h is the data register.

The configuration registers are accessed by first writing the index to port 22h and immediately followed by a read from or a write to port 23h. The index is reset after each data access. Every data access to port 23h must be preceded by an index write to port 22h, even if the same register is being accessed. All the reserved bits should be set to the value indicated in the register table for future compatibility purpose.

The contents of the configuration registers are listed in the following sections.

#### System Hardware Configuration

Six pins in the SiS85C471 are used for trapping purpose to identify the hardware configurations at the power-up stage (PWRGD is low).

The pin is defined to be 1 if a pull up resistor is used; and it is 0 if a pull down resistor is used. A pull up or pull down resistor of 2.2k is adequate for the trapping purpose. The definitions of the pins are listed below :

#### **3.1 Hardware Trap Definition**

#### DACK1\* DACK0\* CPU Type Select

| - | - |                               |

|---|---|-------------------------------|

| 0 | 0 | Reserved                      |

| • |   |                               |

| 0 | 1 | M7/Am486DXL/Am486DXL2         |

| 1 | 0 | 486DX2/DX/SX/SL Enhanced/P24C |

| I | U |                               |

| 1 | 1 | P24D/P24T                     |

|   | 1 | 1 240/1 241                   |

#### DACK2\*

- 1 Cache system

- 0 Non-cache system

#### DACK3\*

471 internal operating frequency = XFCLK

471 internal operating frequency = 1/2 XFCLK

#### (For more details, please refer to the application circuit.)

#### SPK

- 1 Signal DACKn defined as master request and grand signal of VESA bus

- 0 Retrieve DACKn definition

#### SMOUT0 (In Cache System)

- 0 Pin 176 = RAS6\* and Pin 177 = RAS7\* (only for the systems with the 85C407)

- 1 Pin 176 = MPXS1 and Pin 177 = MPXS0

#### **3.2 Configuration Registers**

**Register 50** (index50) Hardware Default = 00

#### bit 7, 6 DRAM Speed (See DRAM Speed Options on page 10)

- 00 : Slowest

- 01 : Slower

- 10 : Faster

- 11 : Fastest

Bit 7 also defines the first transfer of burst cache read and burst cache write cycle time: 0/1 : 3T/2T

#### bit 5 DRAM Write CAS Pulse Width

0:2T 1:1T

bit 4 Support CPU internal cache write back control

- 0 : Disabled

- 1 : Enabled

When using P24T/D or M6/M7, this bit may be programmed. Otherwise, this bit should be set to 0.

#### bit 3 External cache write back enable

- 0 : Disabled (Write Through)

- 1 : Enabled (Write Back)

#### bit 2 Pin 138 multiplex output control

- 0 : RAS3\*

- 1 : MA11

When 16M SIMM DRAM configuration is set, pin 138 functions as MA11 and bank 3 supports no DRAM.

- bit 1 Burst write enable

- 0 : Disabled

- 1 : Enabled

When register 50 bit 4 is set, this bit may be programmed. Otherwise, this bit should be set to 0.

#### bit 0 INIT active enable 0 : Disabled 1 : Enabled When using P24T/D/C, M6/M7, SL Enhanced 486, this bit should be set to 1.

**Register 51** (index 51) Hardware Default = 00

|   | bit 7           | Cache Enable<br>0 : Disabled<br>1 : Enabled                                                                                                                                       |

|---|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | bit 6,5,4       | <b>Cache size</b><br>000 : 32KB<br>001 : 64KB<br>010 : 128KB<br>011 : 256KB<br>100 : 512KB<br>101 : 1MB                                                                           |

|   | bit 3           | Cache Interleave Enable<br>0 : Disabled<br>1 : Enabled<br>If there are two banks cache, this bit should be set to 1.                                                              |

|   | bit 2           | Cache On/Off<br>0 : Off<br>1 : On<br>When this bit is disabled, all memory access will be fetched from DRAM<br>directly instead of from cache.                                    |

|   | bit 1           | Single / Burst Cache Write Cycle<br>For single cache write cycle<br>0 : 3T<br>1 : 2T<br>For burst cache write cycle, it denotes the last three transfer cycle<br>0 : 2T<br>1 : 1T |

|   | bit 0           | Cache Burst Read Cycle<br>0 : 1T<br>1 : 2T                                                                                                                                        |

| R | Register 52 (ii | ndex 52) Hardware Default = 00                                                                                                                                                    |

|   | bit 7           | Shadow RAM Read Enable                                                                                                                                                            |

|   | bit 6           | Shadow RAM Write Protection Enable                                                                                                                                                |

|   | bit 5           | E8000h - EFFFFh Shadow RAM Enable                                                                                                                                                 |

|   | bit 4           | E0000h - E7FFFh Shadow RAM Enable                                                                                                                                                 |

Preliminary V6.0 August 19, 199423Silicon Integrated Systems Corporation

| bit 3           | D8000h - DFFFFh Shadow RAM Enable                                                           |

|-----------------|---------------------------------------------------------------------------------------------|

| bit 2           | D0000h - D7FFFh Shadow RAM Enable                                                           |

| bit 1           | C8000h - CFFFFh Shadow RAM Enable                                                           |

| bit 0           | C0000h - C7FFFh Shadow RAM Enable                                                           |

| bit 0-7         | 0 : Disabled<br>1 : Enabled                                                                 |

| Register 53 (in | ndex 53) Hardware Default = 00                                                              |

| bit 7           | <b>System BIOS ROM Size</b><br>0 : 64K<br>1 : 128K                                          |

| bit 6           | Combine System BIOS with C0000h - C7FFFh region for ROM area<br>0 : Disabled<br>1 : Enabled |

| bit 5           | F0000h ~ FFFFFh Shadow RAM Cacheable<br>0 : Non-Cacheable<br>1 : Cacheable                  |

| bit 4           | <b>C0000h ~ C7FFFh Shadow RAM Cacheable</b><br>0 : Non-Cacheable<br>1 : Cacheable           |

| bit 3, 2, 1     | DMA Cycle Up to 128MB Program A26, A25 and A24                                              |

| bit 0           | <b>Data Parity check enable</b><br>0 : Disabled<br>1 : Enabled                              |

| Register 54 (i  | ndex 54) Hardware Default = 00                                                              |

| bit 7           | Allocation of Non-cacheable Area #1<br>0 : Local DRAM<br>1 : AT Bus, local DRAM disabled    |

| bit 6~4        | Size of Non-Cacheable Area #1 (within 16MB)<br>000 : 0KB (disabled)<br>001 : 64KB<br>010 : 128KB<br>011 : 256KB<br>100 : 512KB<br>101 : 1MB<br>110 : 2MB<br>111 : 4MB  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3          | Allocation of Non-Cacheable Area #2<br>0 : Local DRAM<br>1 : AT Bus, local DRAM disabled                                                                               |

| bit 2~0        | Size of Non-Cacheable Area #2 (within 128MB)<br>000 : 0KB (disabled)<br>001 : 64KB<br>010 : 128KB<br>011 : 256KB<br>100 : 512KB<br>101 : 1MB<br>110 : 2MB<br>111 : 4MB |

| Register 55 (i | ndex 55) Hardware Default = 00                                                                                                                                         |

| bit 7~0        | A23~A16 of Non-Cacheable Area #1 (within 16MB)                                                                                                                         |

| Register 56 (i | ndex 56) Hardware Default = 00                                                                                                                                         |

| bit 7~0        | A23~A16 of Non-Cacheable Area #2 (within 128MB)                                                                                                                        |

| Register 57 (i | ndex 57) Hardware Default = 00                                                                                                                                         |

| bit 7, 6, 5    | A26, A25 and A24 of Non-Cacheable Area #2                                                                                                                              |

| bit 4          | Fast Reset Emulation Enable<br>0 : Disabled<br>1 : Enabled                                                                                                             |

| bit 3          | Fast Reset Latency Control 0 : 2us                                                                                                                                     |

1 : 6us

| bit 2           | Slow Refresh Enable (1:4)<br>0 : Normal Refresh<br>1 : Slow Refresh                                |

|-----------------|----------------------------------------------------------------------------------------------------|

| bit 1           | Gate A20 Emulation Enable<br>0 : Disabled<br>1 : Enabled                                           |

| bit 0           | Cache Sizing Enable<br>0 : Normal Operation<br>1 : Always Cache hit                                |

| Register 58 (ir | ndex 58) Hardware Default = 00                                                                     |

| bit 7           | Slow CPU (below 25MHz) Enable<br>0 : Disabled<br>1 : Enabled                                       |

| bit 6           | DRAM Write Cycle<br>0 : 1 wait state<br>1 : 0 wait state                                           |

| bit 5           | Refresh Cycle Hold CPU<br>0 : Enabled<br>1 : Disabled (set Hidden Refresh)                         |

| bit 4           | <b>De-turbo Hold Time</b> (Every 12us)<br>0 : Hold 4us<br>1 : Hold 8us                             |

| bit 3           | Reserved and should be written with 0.                                                             |

| bit 2           | <b>Combine System BIOS with C8000h - CFFFFh region for ROM area</b><br>0 : Disabled<br>1 : Enabled |

| bit 1           | Latch Local Bus Device (LDEV*) in T2/T3<br>0 : T3<br>1 : T2                                        |

| bit 0           | Select Local Bus Ready (LRDY*)<br>0 : Synchronize in next clock<br>1 : Transparent                 |

Register 59 (index 59) Hardware Default =00

- bit 7 De-Turbo On / Off

- 0 : Turbo

- 1 : De-Turbo

bit 6

#### De-Turbo Switch Enable

0 : De-Turbo switch enabled

1 : Always turbo, ignore the status of turbo switch

#### bit 5 - 0 DRAM Size Configuration (note: S = Single side, D = Double side )

|                  | Bank-0          | Bank-1    | Bank-2     | Bank-3          | Total          |

|------------------|-----------------|-----------|------------|-----------------|----------------|

| 000000           | 256K*36-S       |           |            |                 | 1MB            |

| 000001           | 256K*36-S       | 256K*36-S |            |                 | 2MB            |

| 000010           | 256K*36-S       | 256K*36-S | 512K*36-D  |                 | 4MB            |

| 000011           | 256K*36-S       | 256K*36-S | 1M*36-S    |                 | 6MB            |

| 000100           | 256K*36-S       | 256K*36-S | 512K*36-D  | 1M*36-S         | 8MB            |

| 000101           | 256K*36-S       | 256K*36-S | 1M*36-S    | 1M*36-S         | 10MB           |

| 000110           | 256K*36-S       | 256K*36-S | 4M*36-S    |                 | 18MB           |

| 000111           | 512K*36-D       |           |            |                 | 2MB            |

| 001000           | 512K*36-D       | 512K*36-D |            |                 | 4MB            |

| 001001           | 512K*36-D       | 1M*36-S   |            |                 | 6MB            |

| 001010           | 512K*36-D       | 512K*36-D | 1M*36-S    |                 | 8MB            |

| 001011           | 512K*36-D       | 512K*36-D | 1M*36-S    | 1M*36-S         | 12MB           |

| 001100           | 512K*36-D       | 4M*36-S   |            |                 | 18MB           |

| 001101           | 512K*36-D       | 512K*36-D | 4M*36-S    |                 | 20MB           |

| 001110           | 512K*36-D       | 512K*36-D | 1M*36-S    | 4M*36-S         | 24MB           |

| 001111           | 512K*36-D       | 512K*36-D | 4M*36-S    | 4M*36-S         | 36MB           |

| 010000           | 1M*36-S         |           |            |                 | 4MB            |

| 010001           | 1M*36-S         | 1M*36-S   |            |                 | 8MB            |

| 010010           | 1M*36-S         | 1M*36-S   | 1M*36-S    |                 | 12MB           |

| 010011           | 1M*36-S         | 1M*36-S   | 1M*36-S    | 1M*36-S         | 16MB           |

| 010100           | 1M*36-S         | 4M*36-S   |            |                 | 20MB           |

| 010101           | 1M*36-S         | 1M*36-S   | 4M*36-S    |                 | 24MB           |

| 010110           | 1M*36-S         | 4M*36-S   | 4M*36-S    |                 | 36MB           |

| 010111           | 1M*36-S         | 1M*36-S   | 4M*36-S    | 4M*36-S         | 40MB           |

| 011000           | 2M*36-D         |           |            |                 | 8MB            |

| 011001           | 2M*36-D         | 2M*36-D   |            |                 | 16MB           |

| 011010           | 2M*36-D         | 2M*36-D   | 2M*36-D    |                 | 24MB           |

| 011011           |                 | 2M*36-D   | 2M*36-D    | 2M*36-D         | 32MB           |

| 011100           | 4M*36-S         |           |            |                 | 16MB           |

| 011101           |                 | 4M*36-S   |            |                 | 32MB           |

| 011110           | 4M*36-S         | 4M*36-S   | 4M*36-S    |                 | 48MB           |

| 011111           |                 | 4M*36-S   | 4M*36-S    | 4M*36-S         | 64MB           |

| 100000           |                 | 1M*36-S   |            |                 | 5MB            |

| 100001           |                 | 4M*36-S   |            |                 | 17MB           |

| 100010           | 256K*36-S       | 16M*36-S  |            |                 | 65MB           |

| 100011           |                 | 2M*36-D   |            |                 | 12MB           |

| 100100           | 1M*36-S         | 16M*36-S  |            |                 | 68MB           |

| 100101           | 1M*36-S         | 1M*36-S   | 16M*36-S   |                 | 72MB           |

| Preliminary V6.0 | August 19, 1994 | 27        | Silicon In | tegrated System | is Corporation |

| 100110 | 4M*36-S  | 16M*36-S |          |         | 80MB  |

|--------|----------|----------|----------|---------|-------|

| 100111 | 4M*36-S  | 4M*36-S  | 16M*36-S |         | 96MB  |

| 101000 | 16M*36-S |          |          |         | 64MB  |

| 101001 | 16M*36-S | 16M*36-S |          |         | 128MB |

| 101010 | 1M*36-S  | 8M*36-D  |          |         | 36MB  |

| 101011 | 1M*36-S  | 8M*36-D  | 8M*36-D  |         | 68MB  |

| 101100 | 1M*36-S  | 1M*36-S  | 8M*36-D  |         | 40MB  |

| 101101 | 1M*36-S  | 1M*36-S  | 8M*36-D  | 8M*36-D | 72MB  |

| 101110 | 4M*36-S  | 8M*36-D  |          |         | 48MB  |

| 101111 | 4M*36-S  | 8M*36-D  | 8M*36-D  |         | 80MB  |

| 110000 | 4M*36-S  | 4M*36-S  | 8M*36-D  |         | 64MB  |

| 110001 | 4M*36-S  | 4M*36-S  | 8M*36-D  | 8M*36-D | 96MB  |

| 110010 | 8M*36-D  |          |          |         | 32MB  |

| 110011 | 8M*36-D  | 8M*36-D  |          |         | 64MB  |

| 110100 | 8M*36-D  | 8M*36-D  | 8M*36-D  |         | 96MB  |

| 110101 | 8M*36-D  | 8M*36-D  | 8M*36-D  | 8M*36-D | 128MB |

| 110110 | 1M*36-S  | 2M*36-D  | 2M*36-D  |         | 20MB  |

| 110111 | 1M*36-S  | 2M*36-D  | 2M*36-D  | 2M*36-D | 28MB  |

| 111000 | 1M*36-S  | 1M*36-S  | 2M*36-D  |         | 16MB  |

| 111001 | 1M*36-S  | 1M*36-S  | 2M*36-D  | 2M*36-D | 24MB  |

| 111010 | 2M*36-D  | 4M*36-S  |          |         | 24MB  |

| 111011 | 2M*36-D  | 2M*36-D  | 2M*36-D  | 4M*36-S | 40MB  |

| 111100 | 2M*36-D  | 2M*36-D  | 4M*36-S  |         | 32MB  |

| 111101 | 2M*36-D  | 2M*36-D  | 4M*36-S  | 4M*36-S | 48MB  |

| 111110 | 2M*36-D  | 2M*36-D  | 8M*36-D  |         | 48MB  |

| 111111 | 2M*36-D  | 2M*36-D  | 8M*36-D  | 8M*36-D | 80MB  |

|        |          |          |          |         |       |

**Register 5A** Hardware Default = 00

bit 7 Reserved and Should be Written with 0

# bit 6 Overwrite the Cache Read Cycle Time 0 : Keep the access time that defined in the Register 50 bit 7. 1 : Force all the first cycle time of cache access to be 2T, it overwrites the bit 7 of register 50.

- bit 5 Reserved and Should be Written with 0

- bit 4 Reading the De-Turbo Status (Read Only) 0 : Turbo 1 : De-Turbo

- bit 3-2 Reserved and Should be Written with 0

#### bit 1 M7 CPU's L1 Cache Burst Write Timing Control

- 0 : Always support 3-2-2-2, regardless register 51 bit 1 and register 50 bit 7.

- 1 : Be able to support 2-1-1-1 This bit is vaild only when M7 CPU is used.

. . . .

| bit 0       | Local Master Acess DRAM Cycle CASh Delay 1T active<br>0 : Disable<br>1 : Enable |

|-------------|---------------------------------------------------------------------------------|

| Register 5B | Hardware Default = 00                                                           |

| bit 7       | SMM Enable                                                                      |

\_ \_ . . . \_ \_

0: Disabled

- - -

1 : Enabled

This bit is used to enable/disable the generation of SMI\* or IRQ12/15 interrupt.

#### **Stop Clock enable** bit 6

0: Disabled

1: Enabled

This bit is used to enable/disable the generation of STPCLK\* signal. When enabled, a sequence of reading I/O port 043h followed by reading I/O port 070h forces SiS85C471 to assert STPCLK\*.

#### **STPCLK\*** Auto Generation Select bit 5

0: Disabled

1: Enabled

When enabled, the SiS85C471 asserts STPCLK\* when the system timer expires, the break switch is pressed or the software SMI port is accessed.

#### bit 4 System Management Mode Request Selection

0: By IRQ

1: By SMI

The SiS85C471 provides an alternative way to enter system management mode by using IRQn for those CPUs that do not have SMI\* input pin. Note that , when bit 5 of Register 5B is set to 1, this bit should be set to 1. (For more details, please refer to Register 68,69)

#### bit 3 **IRQn Channel Selection** 0: SELECT IRQ12 1: SELECT IRQ15 This bit is valid only when Register 5B bit 4 is set to 0.

#### bit 2

#### SYSCLK Frequency Auto-Switch

0 : Disable

1 : Enable

During CPU clock scaling, SYSCLK will be changed to 7.159 MHz. Once CPU clock is resumed to the normal state, the SYSCLK will return to the frequency defined by register 60 bit 7-5 after 30ms. CPU clock scaling can be triggered by an active SMOUTn or STPCLK\*.

#### bit 1 Relocate enable

1 : Disabled

0 : Enabled

If this bit is enabled and segments D and E are non-shadowed, and DRAM size is 1MB ,2MB, 4MB, 5MB, 6MB or 8MB, then 256KB DRAM relocation is enabled. Note that, when SMM RAM is used, this bit should be set to 1.

#### bit 0 Reserved

#### Register 5C Interrupt vector address trap mask 1

- bit 7 ~ 0

bit [7:0] correspond to interrupt vector address of A[9:2]. If an interrupt event such as IRQn, INTn, or NMI occurs, CPU always accesses the corresponding interrupt vector from memory 0h to 03ffh. This register is used to mask out an interrupt vector while the SiS85C471 is monitoring interrupt events. (default should be set to INT8 )

- **Register 5D** Interrupt vector address trap mask 2

- bit 7 ~ 0 Correspond to address bit of A[9:2]

- Register 5E Interrupt vector address trap mask 3

- bit 7 ~ 0 Correspond to address bit of A[9:2]

#### **Register 5F**

| bit 7 | Pin 41 Mutiplex Output Control  |  |

|-------|---------------------------------|--|

|       | 0: Pin 41 functions as SMOUT0   |  |

|       | 1: Pin 41 functions as FLASHWE* |  |

|       |                                 |  |

- bit 6 FLASHWE\* Activity Control 0: FLASHWE\* is driven low 1: FLASHWE\* is driven high

- bit 5FLASHWE\* Program Control0: FLASHWE\* is always high1: FLASHWE\* can be programmed by setting register 5F bit 6This bit also controls the function of register 75 bit 0, please refer toregister 75 bit 0.

Preliminary V6.0 August 19, 199430Silicon Integrated Systems Corporation

| bit 4          | <b>Reload Events of System Event Timer Include Those Events</b><br><b>Monitored by I/O Device Standby Timer</b><br>0 : Disable<br>1 : Enable                                                                                                                   |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3,2        | System Eevent Timer and I/O Device Standby Timer Time Base<br>Select<br>00 : 9.374 second<br>01 : 1.171 second<br>10 : 35.759 micro second<br>11 : 0.139 micro second                                                                                          |

| bit 1          | Reserved and should be written to 0.                                                                                                                                                                                                                           |

| bit 0          | Any Activity of Break Event Generate a SMI<br>0: Disable<br>1: Enable<br>The break events are defined in register 63 bit 3-0. If this bit is enabled,<br>any active break event will generate a SMI and set register 69 bit 3.                                 |

| Register 60 (i | index 60) Hardware Default = 00                                                                                                                                                                                                                                |

| bit 7 ~ 5      | Bus Clock Frequency Selection<br>000 : BUSCLK = 7.159 MHz<br>001 : BUSCLK = 1/10 XFCLK<br>010 : BUSCLK = 1/8 XFCLK<br>011 : BUSCLK = 1/6 XFCLK<br>100 : BUSCLK = 1/6 XFCLK<br>101 : BUSCLK = 1/4 XFCLK<br>110 : BUSCLK = 1/3 XFCLK<br>111 : BUSCLK = 1/2 XFCLK |

| bit 4          | <b>Zero Wait for 16-bit Memory or I/O Command</b><br>0: Disable<br>1: Enable                                                                                                                                                                                   |

| bit 3          | <b>16-bit I/O Read Cycle Command without Command Delay</b><br>0: Disable<br>1: Enable                                                                                                                                                                          |

| bit 2          | Decrease 16-bit I/O Read Cycle One AT Bus Clock                                                                                                                                                                                                                |

- 0: Disable

- 1: Enable

- bit 1~0 Reserved

Register 61 (index 61) Hardware Default = 09

| bit 7, 6                  | <b>16-Bit I/O Cycle Command Recovery Time Selection</b><br>00 : 8 BUSCLK<br>01 : 5 BUSCLK<br>10 : 3 BUSCLK<br>11 : 2 BUSCLK |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| bit 5, 4                  | 8-Bit I/O Cycle Command Recovery Time Selection<br>00 : 16 BUSCLK<br>01 : 11 BUSCLK<br>10 : 7 BUSCLK<br>11 : 4 BUSCLK       |

| bit 3                     | Reserved and should be written with 1                                                                                       |

| bit 2                     | <b>16-bit Memory, I/O Wait State Selection</b><br>0 : 2 wait states<br>1 : 1 wait states                                    |

| bit 1                     | <b>8-bit Memory, I/O Wait State Selection</b><br>0 : 5 wait states<br>1 : 4 wait states                                     |

| bit 0                     | Reserved and should be written with 1                                                                                       |

|                           |                                                                                                                             |

| Register 62               | Reserved                                                                                                                    |

| Register 62<br>bit 7      | Reserved<br>Reserved                                                                                                        |

| •                         |                                                                                                                             |

| bit 7                     | Reserved                                                                                                                    |

| bit 7<br>bit 6            | Reserved<br>Reserved and should be written with 1                                                                           |

| bit 7<br>bit 6<br>bit 5-0 | Reserved<br>Reserved and should be written with 1                                                                           |

Preliminary V6.0 August 19, 1994 32 Silicon Integrated Systems Corporation

| SI<br>Chip       | 85C471 Green PC ISA-VESA Single                                                                                                                                                                                                                                                                                                  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3            | Stop Clock /Clock Scaling/Clock Throttling Break by IRQn<br>0 : Disabled<br>1 : Enabled<br>This bit is used to allow IRQn to break system from idle mode when set.                                                                                                                                                               |

| bit 2            | Stop Clock /Clock Scaling/Clock Throttling Break by NMI<br>0 : Disabled<br>1 : Enabled<br>This bit is used to allow NMI to break system from idle mode when set.                                                                                                                                                                 |

| bit 1            | Stop Clock /Clock Scaling/Clock Throttling Break by DMA Request<br>0 : Disabled<br>1 : Enabled<br>This bit is used to allow any DMA request to break system from idle<br>mode.                                                                                                                                                   |

| bit 0            | Stop Clock /Clock Scaling/Clock Throttling Break by Local Master<br>request<br>0 : Disabled<br>1 : Enabled<br>This bit is used to allow any local master request to break system from<br>idle mode.                                                                                                                              |

| Register 64      | Define Software_SMI low byte address A7 - A0                                                                                                                                                                                                                                                                                     |

| bit 7 ~ 0        | This register defines the lower 8 bits of SW_SMI address trap address. bit[7:0] correspond to address A[7:0]. If SW_SMI is enabled (defined in register 68, bit 1), an I/O write to the address defined in Registers 64 and 65 will force the SiS85C471 to generate software SMI*. The software SMI* can be used to support APM. |