## DESIGNING WITH FIELD-EFFECT TRANSISTORS

## DESIGNING WITH FIELD-EFFECT TRANSISTORS

### SILICONIX INC.

Editor in Chief

Arthur D. Evans

#### McGRAW-HILL BOOK COMPANY

New York St. Louis San Francisco Auckland Bogotá Hamburg Johannesburg London Madrid Mexico Montreal New Delhi Panama Paris São Paulo Singapore Sydney Tokyo Toronto Library of Congress Cataloging in Publication Data

Siliconix Incorporated. Designing with field-effect transistors.

Includes index. 1. Field-effect transistors. 2. Transistor circuits. 3. Electronic circuit design. I. Evans, Arthur D. II. Title. TK7871.95.S54 1981 621.3815'284 80–15690 ISBN 0-07-057449-9

Copyright © 1981 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

567890 KPKP 89876543

The editors for this book were Tyler G. Hicks and Geraldine Fahey, the designer was Elliot Epstein, and the production supervisor was Sally Fliess. It was set in Baskerville by The Kingsport Press.

Printed and bound by The Kingsport Press.

### **CONTENTS**

Preface ix **FIELD-EFFECT TRANSISTOR THEORY** 1 **PARAMETERS AND SPECIFICATIONS** 25 **LOW-FREQUENCY CIRCUITS** 61 **4**

HIGH-FREQUENCY CIRCUITS 137

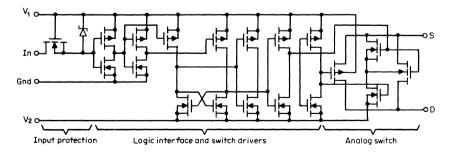

> 5 ANALOG SWITCHES 193

#### 6

#### VOLTAGE-CONTROLLED RESISTORS AND FET CURRENT SOURCES 233

#### 7 POWER FETs 255

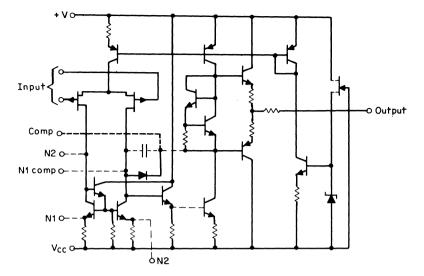

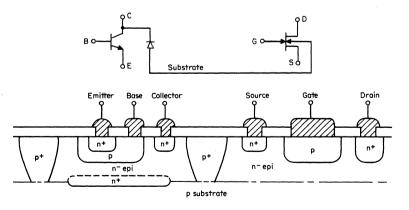

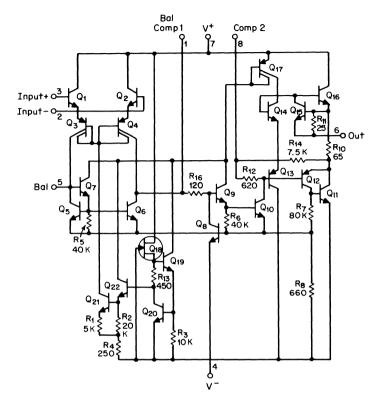

#### 8 FETs IN INTEGRATED CIRCUITS 281

**INDEX** 289

## **CONTRIBUTORS**

Written by the Applications Engineering Staff of Siliconix Incorporated

Editor in Chief

**ARTHUR D. EVANS**

**Contributors**

Arthur D. Evans Walt Heinzer Ed Oxner Lee Shaeffer (Chapters 1, 2, and 5) (Chapters 3 and 6) (Chapter 4) (Chapters 7 and 8)

The purpose of this book is to aid the electronics circuit designer in the utilization of the field-effect transistor (FET). Since its emergence from the development laboratory in about 1962, the FET has become an important and widely used component in the electronic industry.

With its importance increasing annually, both as a discrete component and in integrated circuits, it is essential that the serious circuit designer have an insight into how the FET behaves under different circuit and environmental conditions. It is also helpful to understand how its physical and electrical characteristics are interrelated. This book goes just deep enough into FET theory to provide that insight.

After the introductory chapter describing how the device works, the interrelationship of the various FET characteristics and how they relate to typical data sheet specifications is discussed.

Subsequent chapters deal with various categories of circuit applications of the FET. The order of these application chapters is rather arbitrary; each chapter stands on its own. Detailed circuit design examples are given to illustrate applications.

As this book was being readied for publication, the availability of FETs designed for power applications was expanding rapidly. The chapter on Power FETs spotlights this relatively new field.

Art Evans

# 1

## FIELD-EFFECT TRANSISTOR THEORY

- 1-1 Introduction

- 1-2 The Junction FET

- 1-3 The MOSFET (Insulated-Gate FET)

- 1-4 FET Symbols

- 1-5 Physical Characteristics of FETs

- 1-6 Summary

#### **1-1 INTRODUCTION**

This handbook is designed principally for the FET user. The primary emphasis has been placed on allowing the reader to learn necessary information quickly, without becoming bogged down in complicated analyses. The first two chapters provide sufficient background information to answer many questions asked by FET circuit design engineers. The aim of these chapters is to give design engineers an intuitive sense of how to manipulate the circuits presented in the remaining chapters, which contain both theory and "cookbook" applications. Some knowledge by the reader of semiconductor theory is assumed. A prior understanding of the concept of conduction by electrons and holes, of the "forward" and "reverse" characteristics of a p-n junction, and of the "depletion" region at a p-n junction will be helpful in understanding FET theory.

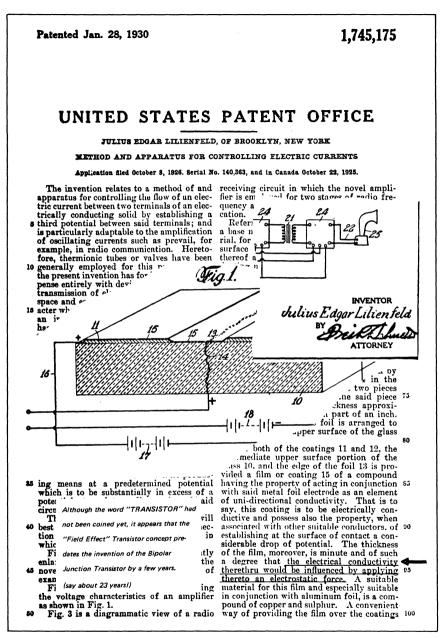

There are two general types of transistors: bipolar and unipolar. The unipolar, more commonly called the "field-effect transistor" (FET), is the subject of this book. The concept of controlling the electronic conduction in a solid by an electric field predates the invention of the bipolar transistor. J. E. Lilienfeld filed for a patent on such a device in 1925, as shown in Fig. 1-1. W. Shockley presented a comprehensive theory

FIGURE 1-1 "FET" patent.

of the field-effect transistor in 1952.<sup>2</sup> However, the commercial availability of the FET in the early 1960s followed the bipolar transistor by 8 or 10 years. The superior performance of the FET in many circuit applications previously utilizing bipolar transistors or vacuum tubes resulted in a rapid growth in its acceptance as an important electronic component.

Several types of semiconductor materials have been used for making FETs: silicon, germanium, gallium arsenide, and others. By far the most widely used is silicon, and unless otherwise specified all device types discussed in this book are silicon types.

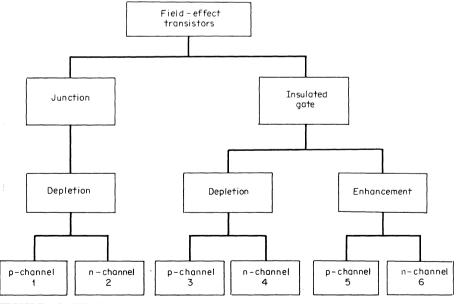

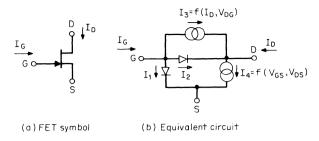

The field-effect transistor (FET) is a class of electronic semiconductor device in which the conduction of a "channel" between source (S) and drain (D) terminals is controlled by an electric field impressed upon the channel via a gate (G) terminal. The conducting channel may utilize *n*-type carriers (electrons) or *p*-type carriers (holes). The electric field which controls the channel conduction may be introduced via a *p*-*n* junction (for a "junction" FET), a metal plate separated from the semiconductor channel by an oxide dielectric (for a metal-oxide-semiconductor FET), or a combination of the two methods. The polarity of the controlling electric field is a function of the type of carriers in the channel. A FET "family tree" is shown in Fig. 1-2.

FIGURE 1-2 FET family tree.

#### **1-2 THE JUNCTION FET**

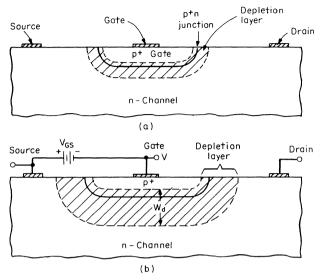

A section view of a junction field-effect transistor (JFET) is shown in Fig. 1-3. This structure contains, between the source and the drain contacts, an *n*-type "channel" embedded in a *p*-type silicon substrate. If it is assumed that the *p*-*n* junction forms a barrier to current flow, then it can be seen that channel conduction is a function of the channel width, length, and thickness and of the density and mobility of the carriers. In this structure current can flow equally well in either direction through the channel; i.e., the drain may be positive or negative with respect to the source.

FIGURE 1-3 Junction-type field-effect transistor.

#### 1-2-1 Channel Conductance (g<sub>ds</sub>)

We will examine how the channel conduction is controlled by a gateto-channel voltage. As indicated in Fig. 1-4*a*, at the *p*-*n* (gate-to-channel) junction there is a depletion layer. If there is an abrupt change from a high concentration of holes in the gate region (*p*-type) to a much lower concentration of electrons in the channel region (*n*-type), then most of the depletion width will occur in the channel. The depletion width is proportional to the square root of the junction potential.<sup>2</sup>

$$W_d = \left(\frac{V_{bi} \pm V_{GS}}{K_1 N_c}\right)^{1/2}$$

where  $W_d$  = junction depletion width

$V_{bi}$  = built-in junction potential

$V_{GS}$  = reverse or forward bias applied to gate-channel junction

$K_1 = \text{constant}$

$N_{\rm c}$  = channel carrier concentration

The channel conduction is decreased as the junction depletion width is increased and thus can be controlled by the gate-source voltage  $V_{GS}$ .

FIGURE 1-4 Depletion layer at  $p^+n$  junction.

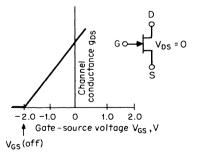

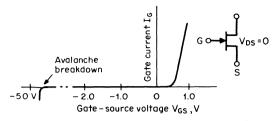

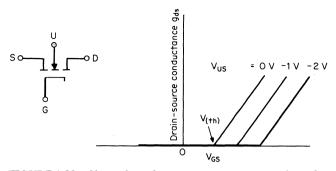

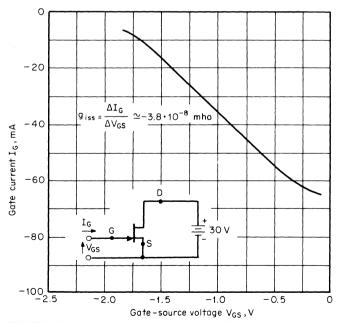

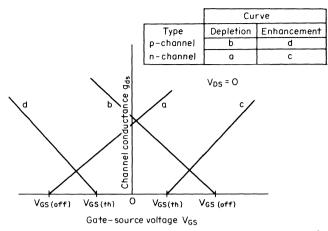

The channel conduction  $g_{ds}$  of a typical JFET as a function of the junction voltage is shown in Fig. 1-5. The characteristic is shown with zero volts between the "source" and the "drain"; thus the depletion thickness is uniform along the channel length. The voltage at which the channel conduction approaches zero is the "gate cutoff voltage," and is given the symbol  $V_{GS(off)}$ . The polarity of  $V_{GS(off)}$  is such that the *p*-*n* gate-channel junction is *reverse*-biased. A forward bias at the gate junction will increase channel conduction because of the resulting decrease in depletion layers; however, as indicated in Fig. 1-6, a *forward* gate-channel bias results in a large increase in gate current. In the FET

FIGURE 1-5 Channel conductance vs. gate-channel voltage.

FIGURE 1-6 Gate current vs. gate-source voltage.

symbol shown in Fig. 1-5, note that the direction of the arrow at the gate-channel junction shows the direction of easy gate-current flow. (This is similar to the p-n diode symbol.) In its reverse-bias mode, the gate "leakage" current may be only a few picoamperes; thus the low-frequency input impedance of the FET is very high. In most JFET applications the forward gate-bias mode is not used because of the resulting low

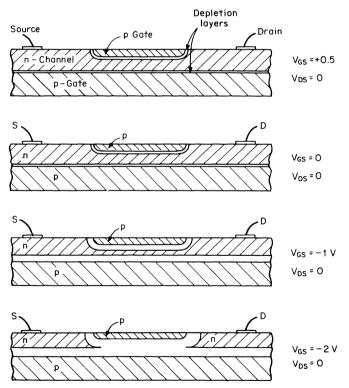

FIGURE 1-7 Concept of depletion in channel as function of gateto-channel voltage ( $V_{DS} = 0$ ).

FIGURE 1-8 Channel depletion vs. drain-source voltage.

input impedance. At some relatively high reverse gate-channel voltage, avalanche breakdown will occur at the p-n junction. This places an upper limit on the device operating voltage.

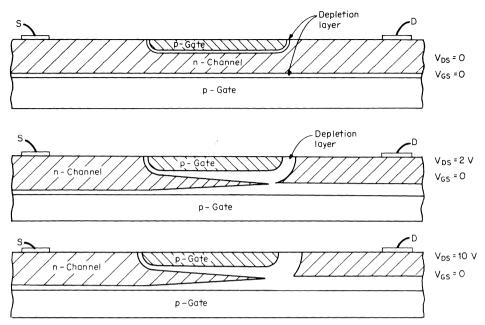

Figure 1-7 presents a concept of the depletion in the channel at various gate-channel voltages. These sketches assume zero drain current so that there is no voltage drop along the channel length. If a positive voltage is applied to the drain, with the gate-source voltage at zero, a nonuniform depletion width occurs along the channel as shown in Fig. 1-8. As  $V_{DS}$  is made more positive, the depletion layer at the drain end of the channel increases, and thus the incremental channel conduction decreases; if the channel is long (compared to its thickness), then the channel will "pinch off" at the drain end and channel current will saturate at a draingate voltage approximately equal to  $-V_{GStoff}$ . Further increases in drain voltage will have little effect upon drain current; hence the current "saturates."

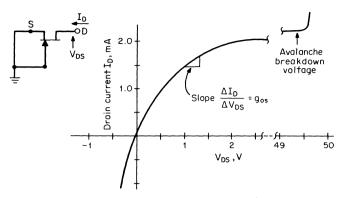

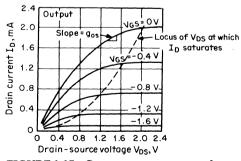

Figure 1-9 shows the drain current  $I_D$  vs. drain-source voltage  $V_{DS}$  with gate-source voltage  $V_{GS}$  at zero. As  $V_{DS}$  is made more positive, the depletion layer at the drain end of the channel increases, and thus the incremental channel conduction decreases. The slope  $\Delta I_D / \Delta V_{DS}$  continues to decrease as  $V_{DS}$  is increased, until at some high voltage breakdown occurs. In the negative quadrant a rapid increase in drain current occurs because the drain-gate junction becomes forward-biased. The

FIGURE 1-9 Drain current vs. drain-source voltage.

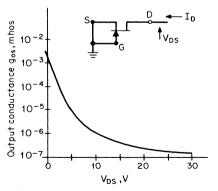

JFET is not normally operated in this quadrant more than a few tenths of a volt. Figure 1-10 shows the magnitude of  $\Delta I_D / \Delta V_{DS}$  as a function of  $V_{DS}$  for a typical FET. This is the output conductance  $g_{os}$  of the FET operating in a common-source configuration.

With reference to Fig. 1-8, it may appear that when  $V_{DS}$  exceeds "pinchoff," no current can flow. However, there does exist an electric field across this "depletion" region and a supply of carriers (electrons) at the source end of the channel; thus carriers will drift across the depletion region just as they drift across the collector-base depletion region in a bipolar transistor. As  $V_{DS}$ , approaches the pinchoff value, the drain current  $I_D$  tends to limit at a saturation level.

#### 1-2-2 Effect of Channel Length

The degree of saturation is a function of the device geometry. A long channel will become more saturated (have a lower  $\Delta I_D / \Delta V_{DS}$ ) than a

FIGURE 1-10 Output conductance vs. drain-source voltage.

short channel; however, the long channel will also have a lower initial channel conductance than will the short channel. For the short-channel device (where length-to-thickness ratio is less than about 4), drain-voltage "pinchoff" may be higher than  $-V_{GS(off)}$ . This is because the minimum channel width does not occur directly under the gate junction but is shifted toward the drain terminal. A concept of the shape of a short channel vs. drain voltage is shown in Fig. 1-11. It has been calculated<sup>1</sup> that for a channel length-to-thickness ratio of unity, drain voltage at which saturation occurs will be approximately 1.6 times  $-V_{GS(off)}$ .

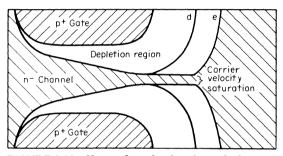

For the short-channel FET an effect known as carrier "velocity saturation" may cause drain current to saturate before minimum channel width is reached. This effect occurs because at high electric fields, carrier mobil-

FIGURE 1-11 Shape of conductive channel when carrier velocity saturation occurs. (Reprinted with permission from *Solid State Electronics*, vol. 10, J. R. Hauser, "Characteristics of JFET Devices with Small Channel Length-to-Width Ratios," © 1967, Pergamon Press, Ltd.)

ity is no longer constant but becomes inversely proportional to the electric field. For fields greater than this critical value, drift velocity no longer increases with increasing field; hence the drain current saturates. Figure 1-11 shows channel shape, calculated by Hauser,<sup>1</sup> when carrier velocity saturation occurs. Most devices designed for high-frequency and highpower application have short channels. For these devices drain-current saturation may be due to carrier velocity saturation instead of channel "pinchoff."

#### 1-2-3 Transconductance (g<sub>fs</sub>)

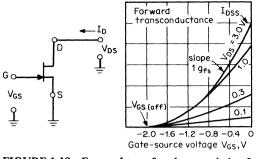

A useful circuit design characteristic is the effect of gate-source voltage upon drain current. A family of these  $I_D$  versus  $V_{GS}$  "transconductance" characteristics for a long-channel FET is shown in Fig. 1-12. The data

FIGURE 1-12 Forward transfer characteristic of *n*-channel JFET (slope  $\Delta I_D / \Delta V_{GS} = g_{fs}$ ).

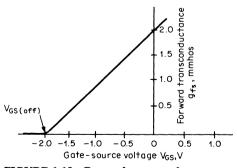

for these curves were obtained using a 2N4868 which had a  $V_{GS(off)}$  of approximately 2 V. If  $V_{DS}$  is greater than  $-V_{GS(off)}$ , then the shape of the transconductance curve is fairly independent of  $V_{DS}$ . The slope  $(\Delta I_{DS}/\Delta V_{GS})$  is the forward transconductance  $g_{fs}$ . Figure 1-13 shows  $g_{fs}$  vs.  $V_{GS}$ for  $V_{DS} \ge -V_{GS(off)}$ . The similarity of the curve of Fig. 1-13 to Fig. 1-5 is normal;  $g_{fs}$  and  $g_{os}$  are approximately linear functions of  $(V_{GS} - V_{GS(off)})$ .

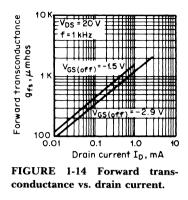

Another characteristic of interest to circuit designers is the relationship  $g_{fs}$  vs.  $I_D$ . Such a curve is shown in Fig. 1-14. This curve indicates that  $g_{fs}$  is an approximate function of  $(I_D)^{1/2}$ . This square-root relationship is common for long-channel JFETs and means that in an *RC*-coupled amplifier, voltage gain may be increased by operating at lower drain currents, if  $I_D R_L$  is kept constant.

A family of common-source output characteristics is given in Fig. 1-15. Note that as the gate is made more negative, the saturated value of  $I_D$  is decreased and the value of  $V_{DS}$  at which saturation occurs is decreased by the approximate magnitude of  $V_{GS}$ . Drain-current saturation

FIGURE 1-13 Forward transconductance vs. gate-source voltage.

occurs at a fixed drain-to-gate voltage; thus, if the gate is biased negative with reference to the source, saturation occurs at a lower drain-source voltage.

#### 1-2-4 Capacitance

The capacitance per unit area of the p-n junction between the gate and the source and drain is a function of the junction depletion-layer thickness. The depletion layer acts as a dielectric between the p and n conducting regions. A reverse bias on the p-n junction causes the depletion layer to increase and thus the capacitance to decrease. Concepts of the junction depletion as a function of gate-to-channel voltage and of drainto-source voltage are shown in Figs. 1-7 and 1-8. Theory indicates that the capacitance of an abrupt junction is an inverse function of the square root of the junction voltage. In most amplifier applications the draingate voltage is greater than the source-gate voltage; thus the drain-gate capacitance will be lower than the source-gate capacitance.

FIGURE 1-15 Common-source output characteristics (2N4868).

#### 1-2-5 Temperature Effects

The effect of device temperature upon device characteristics can be related to three factors:

- 1. Carrier *mobility* is an inverse function of temperature. This causes the channel conductivity to have a negative temperature coefficient.

- 2. Ionization of carriers is a function of temperature. For an *n*-channel JFET the donor impurities in the channel region are fully ionized at about -200°C; thus in the -55 to +125°C range, the effect of temperature upon channel carrier density is small. However, thermal generation of hole-electron pairs within the depletion region of the gatechannel junction results in a significant reverse gate-current vs. temperature coefficient. This effect results in an approximate doubling of reverse gate "leakage" current for each 10 to 12°C increase in temperature.

- 3. Temperature increases also cause a decrease in the *thickness* of the depletion layer at the channel-gate junction. This results in an increase in channel thickness and an increase in the magnitude of  $V_{GS(off)}$ .

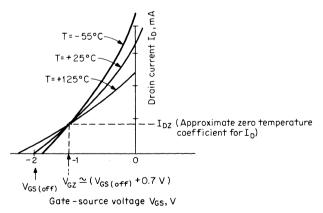

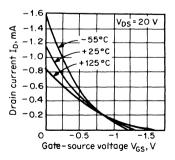

Characteristics 1 and 3 have opposing effects upon channel conduction. This is illustrated in Fig. 1-16, which shows transfer characteristics at three temperatures. For this device,  $I_D$  at  $V_{GS} = 0$  has a negative temperature coefficient. This is due to the negative temperature coeffi-

FIGURE 1-16 FET transconductance characteristics vs. temperature.

cient of carrier mobility. At a value of  $V_{GS}$  about 0.7 V above  $V_{GS(off)}$ ,  $I_D$  has a near-zero temperature coefficient because these two characteristics compensate each other.

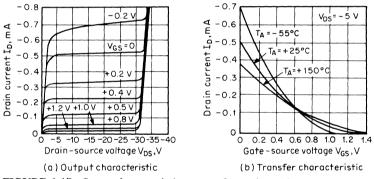

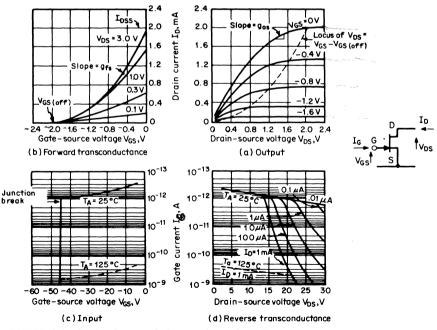

#### 1-2-6 p-Channel JFET

The foregoing discussion of the JFET has assumed that the channel was *n*-type. A *p*-channel FET has similar characteristics, with the major difference being a change in the polarities. Characteristic curves of a *p*-channel device are given in Fig. 1-17. *P*-type carriers (holes) have lower mobility than *n*-type carriers (electrons); thus for devices of similar dimensions and channel carrier density, the *n*-type FET will have a higher channel conductance than the *p*-type device. For a given channel conductance and pinchoff voltage, the *p*-channel FET will typically have higher interelectrode capacitance and higher junction leakage than the *n*-channel device.

FIGURE 1-17 Some characteristic curves for *p*-channel JFETs (2N2608).

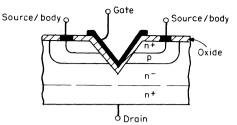

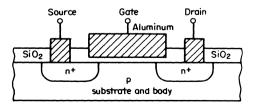

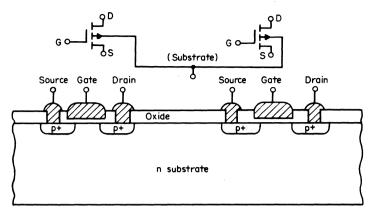

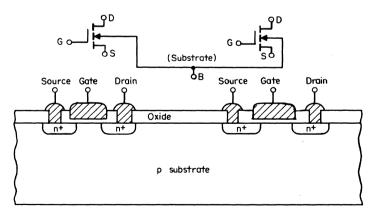

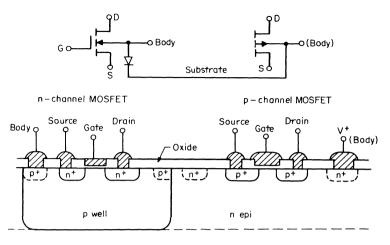

#### **1-3 THE MOSFET (INSULATED-GATE FET)**

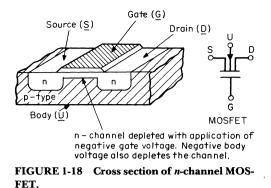

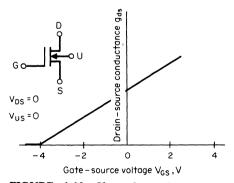

A cross section of an *n*-channel MOSFET is shown, in Fig. 1-18. With this structure the *n*-channel conduction may be controlled by a voltage applied between gate and source, by one applied between body and source, or by a combination. A very important characteristic of this structure is that the gate is separated from the channel by a very low-leakage dielectric (typically silicon oxide). This permits the gate-channel voltage to be positive or negative. For the *n*-channel structure of Fig. 1-18, a positive gate-source voltage will increase channel conduction, while a negative voltage will decrease channel conduction, as shown in Fig. 1-19. Since no conducting path exists between the control gate and the rest of the structure, the gate-to-channel resistance of a typical device

(2N3631) exceeds  $10^{16} \Omega$ . This is true with positive or negative voltage applied to the gate. An upper limit on gate voltage is imposed by the dielectric breakdown of the thin oxide under the gate metal. Unlike in a *p*-*n* junction, the breakdown of the oxide dielectric results in permanent damage to the oxide; thus this condition must be avoided.

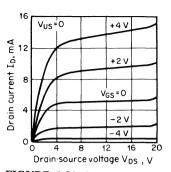

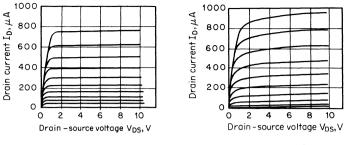

A family of output characteristics of an *n*-channel MOSFET is given in Fig. 1-20. Note the similarity of these characteristics to those of the *n*-channel JFET shown in Fig. 1-15. The MOSFET characteristics, however, include curves with both positive and negative gate voltage. For the *n*-channel JFET a positive gate voltage would forward-bias the gatesource *p*-*n* junction. This does not occur with the MOS structure shown. (Some MOSFET devices, however, have a zener diode connection between the gate and the body to limit the voltage that may be impressed across the gate oxide, as a protection for the oxide.) For the *n*-channel MOSFET a positive gate voltage is said to "enhance" the channel; a

FIGURE 1-19 Channel conduction vs. gate voltage for *n*-channel MOSFET.

FIGURE 1-20 Common-source output characteristics of *n*-channel MOSFET (normally on device.).

negative voltage "depletes" the channel. This is a "normally on" device—that is, when  $V_{GS} = 0$ , a conducting channel exists between drain and source.

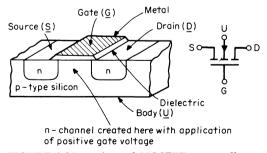

A normally OFF MOSFET is shown in Fig. 1-21. In this structure no channel exists between drain and source unless a gate voltage is applied. A positive voltage applied to the gate, with respect to source and drain, creates a conducting channel by pulling carriers (electrons for the *n*-channel type, holes for the *p*-channel type) from the source and drain regions and from the body into the upper layers of the substrate under the gate. The thickness and conduction of the channel thus created are a function of the gate-source, gate-drain, and gate-body voltages. The gate-source voltage  $V_{GS}$  at which channel conduction just begins to occur is called the "threshold voltage"  $V_{GS(th)}$ .  $V_{GS(th)}$  is a function of the thickness of the oxide under the gate, *p*-type carrier density in the body under the gate, and body-source voltage  $V_{US}$ . The body could

FIGURE 1-21 *n*-channel MOSFET—normally off enhancement type.

FIGURE 1-22 Channel conductance vs. gate-source voltage for MOSFET showing the effect of "body" bias.

be designed to function as a junction-type control gate but is usually designed to have minimum effect upon the channel conduction and threshold voltage. In many device types the body is internally connected (shorted) to the source terminal, in which case the source-drain voltage is limited to one polarity to avoid forward-biasing the drain-body diode. Figure 1-22 shows channel conduction  $g_{ds}$  versus  $V_{GS}$  with  $V_{US}$  as a parameter. With this particular device,  $V_{US}$  has a great effect upon  $V_{GS}$  (th) and  $g_{ds}$ . In many device designs the body effect is less than that shown.

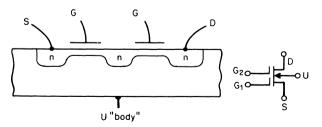

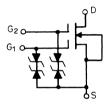

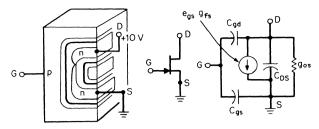

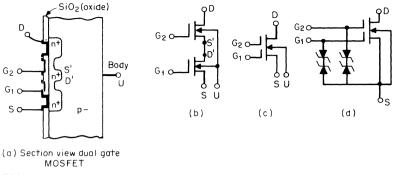

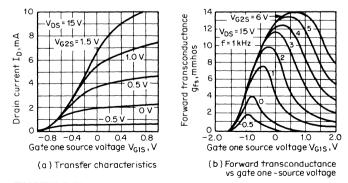

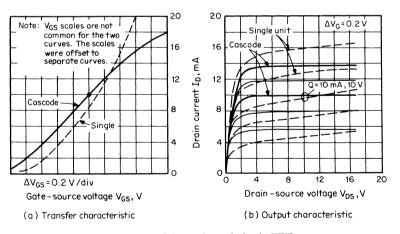

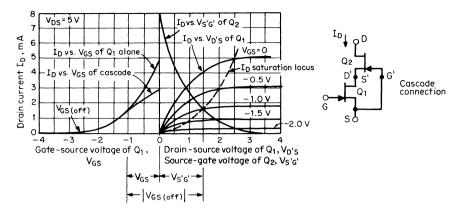

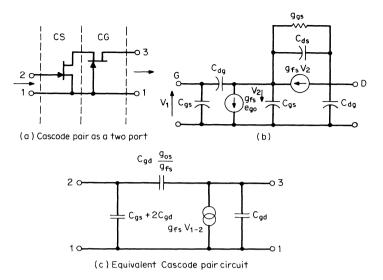

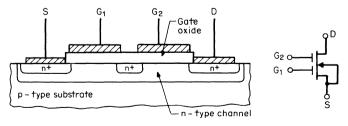

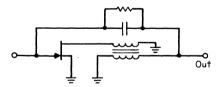

#### 1-3-1 Dual-Gate MOSFET

A useful structure for high-frequency applications is the dual-gate MOS-FET. This device, as shown in Fig. 1-23, has two control gates between the drain and the source. Typically in a high-frequency amplifier,  $G_1$  is utilized as the signal input terminal and  $G_2$  is at signal ground. This results in very low drain-to- $G_1$  feedback capacitance. This operating mode is similar to the "Cascode" operation of vacuum tubes.  $G_2$  is also commonly utilized as an automatic gain control element.

FIGURE 1-23 Dual-gate MOSFET.

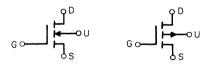

#### **1-4 FET SYMBOLS**

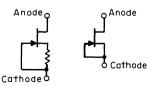

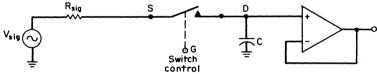

The FET "family tree" shown in Fig. 1-2 indicates six different types. A different schematic symbol is utilized for each of these types. Figure 1-24 relates the symbols to the device types. Note that the direction of the arrow between the gate or body terminal and the channel will indicate the channel type. The "channel" of the enhancement types of MOS is broken, indicating that a channel must be "enhanced" to make the device operative.

These symbols will be utilized in the chapters that follow. Understanding these symbols will aid in understanding symbols for new device types that may be developed. Many device types are symmetrical with respect to source and drain; that is, source and drain functions may be interchanged. However, there are also devices which are not symmetrical. The symbol locates the gate electrode adjacent to the end of the device which is characterized by the manufacturer as the "source"

(a) JFET depletion type

(b) MOSFET depletion type

(c) MOSFET enhancement type

(d) MOSFET enhancement type with internal zener diode to protect gate oxide

(e) n - channel dual-gate depletion type MOSFET with gate protection diodes and body internally connected to source

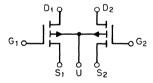

(f) Dual p-channel enhancement-type MOSFET with common body

(g) n-channel JFETs designed to function as a "constant current" diode terminal. (An attempt has been made to utilize symbols that correspond to IEEE/ANSI/IEC and industry standards.)

As a word of caution, it should be pointed out that many schematics in technical literature neglect to show the "body" terminal of MOSFETs. In *most* cases it may be assumed that the body is internally connected to the source terminal; however, there are many cases in which the body is connected to some other potential, especially when the device is used as an analog switch. In integrated circuits, the body is often common to many MOSFETs within the same circuit.

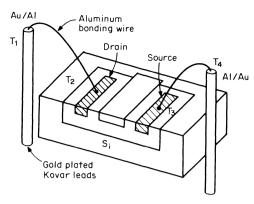

#### **1-5 PHYSICAL CHARACTERISTICS OF FETS**

FET design and manufacturing details are beyond the scope of this book; however, a brief survey of some of the physical characteristics may be worthwhile. Manufacturing methods are similar to those utilized in other semiconductor devices such as integrated circuits, transistors, and diodes. Dimensions of the active areas, such as channel thickness, width, and length, may be controlled by a combination of epitaxial thickness, diffusion, ion implanting, etching, and photolithographic techniques.

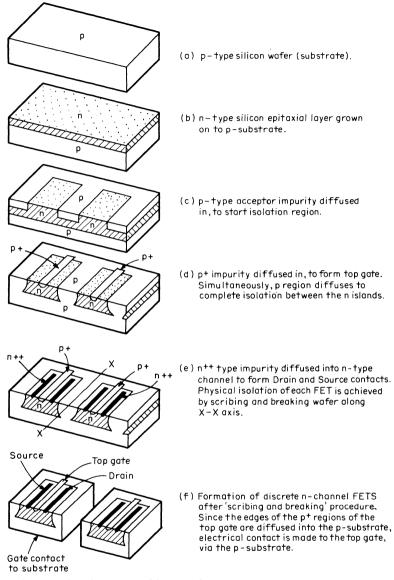

#### 1-5-1 Typical JFET Structures

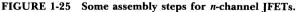

Figure 1-25 shows some of the steps involved in the manufacture of one type of *n*-channel JFET. The starting material in this case is a wafer of high-purity monocrystalline silicon which has been doped with an acceptor impurity (p-type). Onto this wafer a layer of silicon is epitaxially grown to a precisely controlled thickness and with a closely controlled donor (*n*-type) impurity concentration. A layer of silicon dioxide (glass) is formed on the wafer surface. By photolithographic techniques certain regions of this oxide are removed. The remaining oxide functions as a mask or barrier to p-type atoms, which are diffused into the unmasked regions. The masked region shown in Fig. 1-25c will become the source, drain, and channel region of the finished FET. A second oxidation, masking, and diffusion operation is used to create a top p-type gate which separates the source and drain. The depth of the top-gate diffusion and the initial thickness of the epitaxial layers determine the channel thickness. The width of the top gate stripe determines the channel length (source-to-drain dimension). Small variations in photographic dimensions, diffusion depths, epitaxial-layer thickness, and donor and acceptor impurity density will have an effect upon channel conduction, pinchoff voltage, gate-to-channel capacitance, and junction breakdown voltage. Lack of precise control of the physical parameters results in a production

spread of the electrical characteristics of a given device type. In many instances a family of device types may be produced from a given set of photographic masks by varying the thickness of the epitaxial layer and the depth of the top-gate diffusion.

For a given channel thickness, width, and carrier concentrations, conduction will be an inverse function of channel length. For the structure described in Fig. 1-25 this length is controlled by the photographic process of etching the oxide window for top-gate diffusion, and by the sideways diffusion of the top gate. As the window size is decreased to make shorter, higher-conduction channels, control of the photographic process becomes more difficult. Because short channels are important for high-conduction and high-frequency devices, several methods for creating short-channel structures not so dependent upon very small photographic dimensions have been developed.

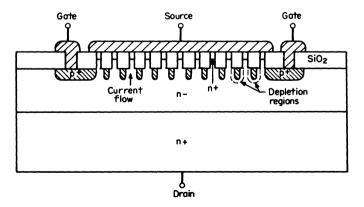

#### 1-5-2 Short-Channel MOSFETs (VMOS and DMOS)

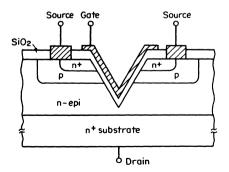

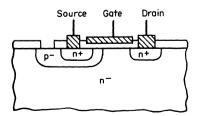

Two significant techniques are being utilized to produce short-channel MOSFETs. Both utilize the difference in depth of two diffusions instead of photolithographic techniques to control channel length. The differences in the two techniques relate to the geometry employed. In one type the channel is oriented parallel to the chip surface (as with the previously described MOSFET). It is commonly called the DMOS (for diffused-channel MOS). The second type has its channel oriented approximately vertical to the chip surface. While its channel is also controlled by diffusion, it is commonly called the VMOS (for vertical-channel MOS). Section views of the two types are shown in Fig. 1-26, both of which are *n*-channel types. The *p*-type "body" diffusions and the  $n^+$ type source diffusions in the DMOS may be made through the same window opening in the oxide. The p type is allowed to diffuse slightly deeper than the n type; the difference becomes the channel length. The  $n^+$  drain contact for the DMOS is diffused through a window in the oxide a short distance from the drain end of the channel region. The  $n^+$  drain contact for the VMOS is the substrate of the chip; thus the entire back side forms the drain. In the DMOS the gate metal is deposited on the surface of the oxide above the  $p^-$  region where the channel is formed. For the VMOS, a V groove is first etched down through the  $n^+$  source and the  $p^-$  body regions. The vertical dimension of this V groove is determined by the width of the oxide window and the crystallographic structure of the silicon wafer. This is achieved by using a chemical that preferentially etches along certain crystal planes. As with the other MOS types described, the process is completed by growing oxide over the channel region and applying metalization to the gate, source, and body regions (for this device the drain is the back of the chip).

(a) VMOS (vertical channel MOS)

<sup>(</sup>b) DMOS (double - diffused MOS)

FIGURE 1-26 Short-channel MOS structures.

The  $n^-$  region between the drain contact and the "body" forms a depletion region which results in a low drain-to-body and drain-to-gate capacitance—an important feature for high-frequency applications and high-speed switching. The  $n^-$  region also provides a means of achieving a high drain-voltage rating while still maintaining a short, high-conductance channel. The VMOS structure gives better utilization of the silicon surface because the substrate is utilized for the drain. Also, both sides of the V groove are utilized for channels; thus two current paths are available for a single gate finger.

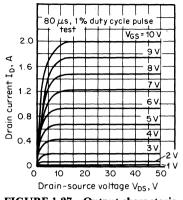

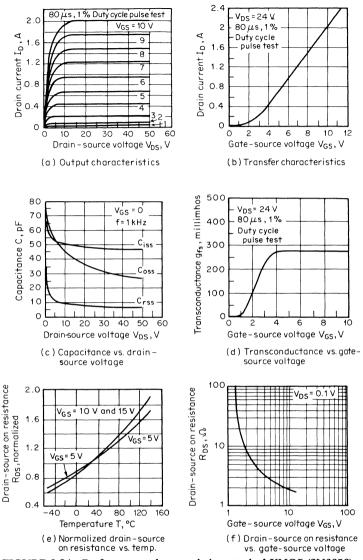

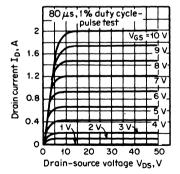

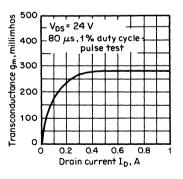

The short-channel VMOS structure has permitted the introduction of MOSFETs into high-power, high-frequency applications. No minoritycarrier storage times (as encountered with bipolar types) are involved in switching the unit oFF; switching 1 A of drain current in less than 4 ns is typical. Figure 1-27 shows some of the characteristics of Siliconix VMOS type 2N6661. This unit has a 2-A, 90-V rating. The drain current has a negative temperature coefficient; this means that in power applications devices can be paralleled without encountering "current hogging" problems of the type encountered when bipolar transistors are paralleled.

#### 1-5-3 Short-Channel JFET

The short-channel JFET has a high conductance advantage, similar to the short-channel MOSFET. Vertical channel structures have been described by Teszner and Gicquel,<sup>3</sup> by R. Zuleeg,<sup>4</sup> and by others. Because

FIGURE 1-27 Output characteristics of VMOS (Siliconix type 2N6661).

of their relatively high input capacitance, their use has been primarily limited to linear hi-fi equipment.

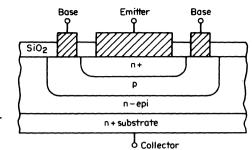

A section view of a vertical short-channel JFET as described by Zuleeg<sup>4</sup> is shown in Fig. 1-28. Here the p-type gate structure is buried within the *n*-channel region separating the source and the drain.

FIGURE 1-28 Gate structure and depletion region shape near channel pinchoff in a verticalchannel JFET. (Reprinted with permission from *Solid State Electronics*, vol. 10, R. Zuleeg, "Multi-channel Field-Effect Transistor, Theory and Experiment," © 1967, Pergamon Press, Ltd.)

#### 1-5-4 Gallium Arsenide FETs (GaAs FET)

The majority of the FETs currently available utilize silicon as the semiconductor material. Additional materials are being used in the development of new FETs, primarily aimed at achieving higher-gain bandwidths and lower high-frequency noise. The ideal high-frequency FET needs a base material that can simultaneously offer high carrier mobility, high drift velocity, and high avalanche breakdown. The semiconductor crystal gallium arsenide (GaAs) offers mobility seven times that of silicon and drift velocity 70 percent over silicon. However, the avalanche breakdown field for GaAs is only one-fourth that of silicon; thus high-power performance requires much higher currents. Because the techniques are less advanced, manufacturing costs are greater for GaAs than for silicon. These devices are making a significant contribution to amplifier design in the gigahertz range.

#### 1-6 SUMMARY

This chapter has given a qualitative description of several types of fieldeffect transistors. As the presentation is aimed at the FET user, device design details have been avoided.

Chapter 2 presents a more detailed electrical description of the FET, including mathematical interrelationships of the various characteristics such as pinchoff voltage, drain saturation current, transconductance, channel on resistance, temperature coefficients, and inner-electrode capacitance.

Other chapters will be devoted to applications of FETs in such circuit functions as analog switches, amplifiers, mixers, oscillators, voltage converters, voltage-controlled resistors, and constant current sources.

Although the commercial availability of FETs followed the bipolar transistor by 8 to 10 years, this device has become a very valuable component in electronic circuits. Integrated circuits in such devices as computers, memories, and electronic TV games make extensive use of MOSFETs. TV and FM tuners and hi-fi amplifiers utilize FETs as input stages because of their superior low-noise performance. Ionization-chamber-type smoke detectors utilize a MOSFET input-stage amplifier because of the very low leakage of the MOSFET gate. Analog multiplexer systems incorporate FETs and analog switches because of the absence of junction offsets in the oN state and the bidirectional blocking capability in the oFF state. Recent developments in the manufacture of short-channel FETs, such as VMOS, have increased power capabilities and have resulted in increasing high-power, high-frequency applications, a few of which are presented in the chapters that follow.

#### REFERENCES

- 1. Hauser, J. R., "Characteristics of JFET Devices with Small Channel Length-to-Width Ratios," Solid State Electronics, 10:577-587, 1967.

- 2. Shockley, W., "A Unipolar Field-Effect Transistor," *Proceedings, IRE,* 40:1365-1376, 1952.

- 3. Teszner, S., and R. Gicquel, "Gridistor—A New Field-Effect Device," *Proceedings, IEEE*, 52:1502–1513, 1964.

- 4. Zuleeg, R., "Multi-channel Field-Effect Transistor, Theory and Experiment," *Solid-State Electronics*, **10**:559–576, 1967.

#### **BIBLIOGRAPHY**

Das, M. B., and J. M. Moore: "Measurements and Interpretation of Low-Frequency Noise in FETs," *IEEE Transactions on Electron Devices*, ED-21 (4):247–257, April 1974.

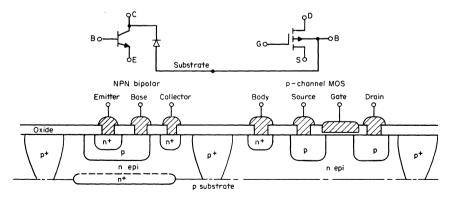

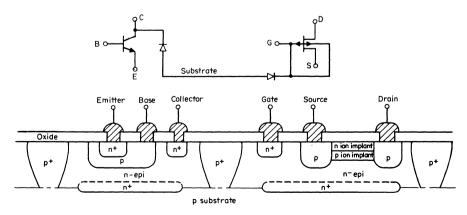

Hartmann, K.: "Noise Characterization of Linear Circuits," *IEEE Transactions on Circuits and Systems*, 10:581-589, October 1976. "Japanese Take Two Steps Forward in MOS-Bipolar Compatibility," *Electronics*, p. 207, October 13, 1969.

Sam, C. T.: "Theory of Low-Frequency Generation Noise in JFETs," Proceedings, IEEE, 52:795-814, 1964.

Sze, S. M.: Physics of Semiconductor Devices, John Wiley and Sons, Inc., New York, 1969.

Vander Kooi, M., and L. Ragle: "MOS Moves into Higher-Power Applications," *Electronics*, 98–103, June 24, 1976.

van der Ziel, A.: "Gate Noise in FETs at Moderately High Frequencies," Proceedings, IEEE, 51:461-467, 1963.

-----: "Thermal Noise in FETs," Proceedings, IRE, 50:1808-1812, 1962.

## 2

## PARAMETERS AND SPECIFICATIONS

- 2-1 Introduction

- 2-2 Static Characteristics, JFET

- 2-3 Gate-Current Characteristics

- 2-4 Small-Signal Coefficients

- 2-5 JFET Capacitances

- 2-6 Noise Characteristics

- 2-7 Characteristic Interrelationships

- 2-8 MOSFET Characteristics

- 2-9 Analog Switch Parameters

- 2-10 Temperature Effects

- 2-11 Derating Factors

- 2-12 Glossary of Terms and Abbreviations

#### 2-1 INTRODUCTION

Chapter 1 was intended primarily to impart an understanding of the underlying phenomena of the field-effect transistor rather than to serve as an exact analysis of its behavior. To derive the relationship between  $I_D$ ,  $V_{DS}$ , and  $V_{GS}$  from purely theoretical considerations would be difficult and is hardly justifiable from a user's standpoint. From a practical standpoint, it is often preferable to represent the device characteristics by experimentally determined curves rather than by exact mathematical expressions, because the effects of donor and acceptor impurity concentrations, initial channel and depletion-layer thickness, photographic mask configurations, and alignments, and variations of these within a device type are thus taken into account. The equations presented in this chapter should not be considered exact, but do give close approximations of the performance of most devices. They follow, for the most part, FET

theory presented by Shockley<sup>5</sup> and others<sup>1,2</sup>; however, certain physical characteristics assumed in theory are sometimes difficult to achieve in practice. For example, the original Shockley theory assumed abrupt junctions, uniform channel conductivity, and a carrier mobility independent of electric field intensity. Real devices, made by diffusion techniques, have some gradation of junctions and channel conductivity. In short-channel FETs the field at the drain end of the channel is typically high enough to cause some reduction in carrier mobility.

For the initial discussions about static characteristics and the interrelationship of various parameters, we will use as an example a device which has a relatively long channel. Later the effect of shortening the channel length will be discussed.

#### 2-2 STATIC CHARACTERISTICS, JFET

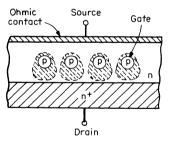

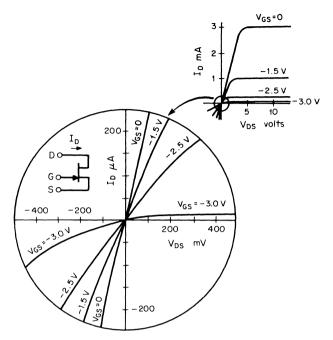

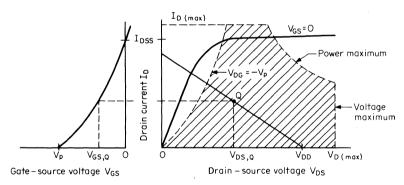

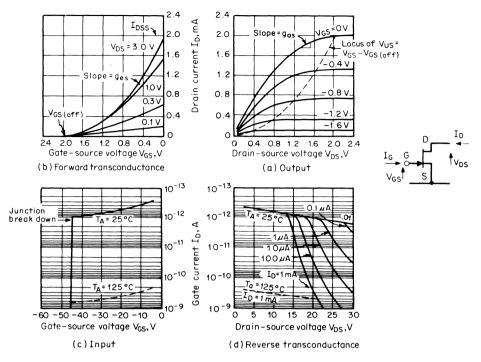

In general, in a three-terminal device, the drain current  $I_D$  is a function of two variables,  $V_{DS}$  and  $V_{GS}$ . This function is best represented by families of characteristic curves, as shown in Fig. 2-1. These curves are for the "common-source" configuration, with the drain as the output and the

FIGURE 2-1 Static characteristics—n-channel JFET.

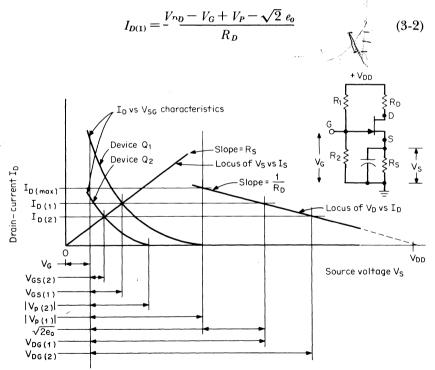

gate as the input. They reveal that for this device, if  $V_{DS}$  is greater than about 2 V (but less than the drain breakdown),  $I_D$  is primarily determined by the gate voltage  $V_{GS}$ . Under these conditions it is valid for small signals to characterize the FET by a single transfer characteristic curve, commonly called the "forward transconductance curve," such as the upper curve shown in Fig. 2-1b. Some of the relationships between the forward transfer curve and the output characteristic curves of Fig. 2-1*a* will be examined. The value of  $V_{CS}$  which reduces  $I_D$  to approximately zero is the gate-source cutoff voltage,  $V_{GS(off)}$ . With reference to the output curve, Fig. 2-1*a*, note that the drain current at  $V_{GS} = 0$  tends to become saturated at a drain voltage approximately equal in magnitude to  $-V_{GS(off)}$ . This drain voltage is often referred to as the pinchoff voltage  $V_p$ ; however, in this text pinchoff voltage is used interchangeably with gate-source cutoff voltage.  $V_P$  will have the same meaning as  $V_{GS(off)}$ . The symbol  $I_{DSS}$  is commonly used to indicate the value of saturated drain current at  $V_{GS} = 0$ .

The forward transconductance characteristic of Fig. 2-1b can be approximated by a power law relation expressed as

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_{GS(\text{off}}} \right)^n \tag{2-1}$$

if  $V_{DS} \ge -V_{GS(off)}$ . By differentiation the small-signal transconductance  $g_{fs}$  is given by

$$g_{fs} = \frac{dI_D}{dV_{GS}} = -n \frac{I_{DSS}}{V_{GS(\text{off})}} \left(1 - \frac{V_{GS}}{V_{GS(\text{off})}}\right)^{n-1}$$

(2-2)

Some texts indicate a value of 3/2 for *n*; however, experimental measurements on a number of *n*-channel JFET geometries indicate that the exponent *n* is close to 2, which is the value derived in an approximate treatment by R. D. Middlebrook.<sup>2</sup>

A useful relationship between  $g_{fso}$ ,  $I_{DSS}$ , and  $V_{GS(off)}$  is derived from the ratio of Eqs. (2-2) and (2-1).

$$\frac{g_{fs}}{I_D} = n(V_{GS} - V_{GS(\text{off})})^{-1}$$

(2-3)

At  $V_{GS} = 0$ ,  $I_D = I_{DSS}$  and  $g_{fs} = g_{fso}$ . Using 2 as the value of the constant *n* leads to

$$g_{fso} = -2 \frac{I_{DSS}}{V_{GS(off)}} \tag{2-4}$$

For *n*-channel FETs  $I_{DSS}$  is positive and  $V_{GS(off)}$  is negative; for *p*-channel FETs  $I_{DSS}$  is negative and  $V_{GS(off)}$  is positive; thus  $g_{fs}$  is a positive quantity for both *p*- and *n*-channel FETs.

Equation (2-1) indicates that for  $V_{GS} = V_{GS \text{ (off)}}$ ,  $I_D = 0$ . In a real device

FIGURE 2-2 Drain current vs. gate-source voltage—*n*-channel JFET (2N4868A).

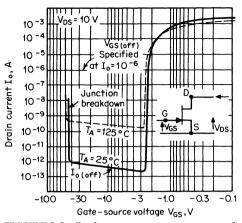

this does not happen. Starting from zero, as the gate voltage is made more negative, the drain current decreases until it reaches a very low value equal to the drain-gate leakage current. At this value the source current will consist of source-gate leakage. Any further increase in the magnitude of the negative gate voltage will result in an increase in  $I_D$ leakage. For the small-signal device illustrated, this minimum  $I_D$  is on the order of  $2 \times 10^{-13}$  A.

A more detailed  $I_D$ -vs.- $V_{GS}$  characteristic is shown in Fig. 2-2, in which the data are plotted on logarithmic paper to show the current magnitude near "cutoff." Because  $I_D$  does not go to zero, the error of Eq. (2-1) increases as  $V_{GS}$  approaches  $V_{GS(off)}$ . From a practical measurement standpoint,  $V_{GS(off)}$  is usually specified at an  $I_D$  value greater than the minimum expected value. The symbol  $I_{D(off)}$  is used for the approximate minimum value of  $I_D$ . Device types characterized for switching applications will usually specify both  $V_{GS(off)}$  and  $I_{D(off)}$ , as shown in the example for the 2N3970 specification:

| Characteristic                           | Min | Max | Unit | Text conditions                                   |

|------------------------------------------|-----|-----|------|---------------------------------------------------|

| $I_{D(off)}$ drain cutoff current        |     | 250 | pA   | $V_{DS} = 20 \text{ V}, \ V_{GS} = -12 \text{ V}$ |

| $V_{GS(off)}$ gate-source cutoff voltage | -4  | -10 | v    | $V_{DS} = 20 \text{ V}, I_D = 1 \text{ nA}$       |

For this device  $V_{GS(off)}$  is specified as that value of  $V_{GS}$  required to reduce  $I_D$  to 1 nA, with a  $V_{DS}$  of 20 V.

As is shown by the data plotted in Fig. 2-2, when the FET is to be used as a switch, the value of  $V_{GS}$  for the switch OFF condition should be a little greater than the data sheet-specified maximum  $V_{GS(off)}$ .

Figure 2-2 shows that at a very high negative value of  $V_{GS}$ , there occurs a rapid increase in  $I_D$ . This is the voltage at which avalanche "breakdown" occurs at the drain-gate *n-p* junction; it sets an absolute maximum rating on the drain-gate voltage for the device. In practice, the device data sheet will usually specify a minimum value for gate-to-drain and gate-to-source breakdown, as shown in the 2N3970 specification:

| Characteristic                           | Min | Max | Unit | Test conditions                        |

|------------------------------------------|-----|-----|------|----------------------------------------|

| BV <sub>GSS</sub> gate reverse breakdown |     |     |      |                                        |

| voltage                                  | -40 |     | V    | $I_G = 1 \ \mu \text{A}, \ V_{DS} = 0$ |

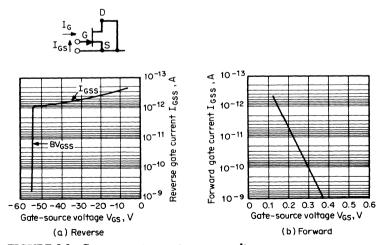

Since the test conditions set  $V_{DS} = 0$ , this specification ensures that both drain-to-gate and source-to-gate breakdown will be equal to or greater than 40 V. The value of  $I_G$  for the test condition is greater than the normal gate leakage current of the device.  $I_G$ -vs.- $V_{GS}$  curves are shown in Fig. 2-3 with test points for  $BV_{GSS}$  and  $I_{GSS}$  indicated.  $I_{GSS}$ is the gate leakage current at a specified value of  $V_{GS}$  with  $V_{DS} = 0$ . Forward gate characteristics are not usually specified because few applications require operation in this mode. The curve of Fig. 2-3*b* is typical

FIGURE 2-3 Gate current vs. gate-source voltage.

**DESIGNING WITH FIELD EFFECT TRANSISTORS**

for a small-signal JFET with the gate *forward*-biased. Operation with a few tenths of a volt forward gate signal is satisfactory if a few hundred picoamperes of gate current permits proper circuit performance.

The output characteristic curve for  $V_{GS} = 0$  of Fig. 2-1*a* approximately follows the equation

$$I_D = g_{dso} V_{DS} \left( 1 + \frac{V_{DS}}{2V_{GS(\text{off}})} \right)$$

(2-5)

where  $g_{dso} = \text{slope } dI_D/dV_{DS}$  at  $V_{GS}$  and  $V_{DS} = 0$ . It has been shown that  $g_{dso} = g_{fso}$ ; therefore, by utilizing Eq. (2-4), Eq. (2-5) can be given as

$$I_D = \frac{2I_{DSS}}{-V_{GS(\text{off})}} V_{DS} \left(1 + \frac{V_{DS}}{2V_{GS(\text{off})}}\right)$$

(2-6)

If we rearrange terms and for convenience let  $V_p = V_{GS(off)}$ , we get

$$I_D = I_{DSS} \left[ 2 \frac{V_{DS}}{-V_p} - \left(\frac{V_{DS}}{V_p}\right)^2 \right]$$

(2-7)

This equation is not valid when  $V_{DS}$  exceeds  $-V_p$ . It indicates that as  $V_{DS}$  approaches  $-V_p$ , the rate of change of  $I_D$  with changing  $V_{DS}$  decreases and reaches zero at  $V_{DS} = V_p$ . In a real device  $dI_D/dV_{DS}$  does not reach zero.

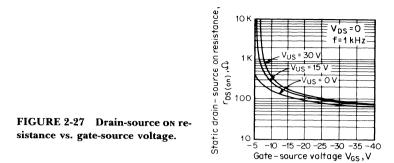

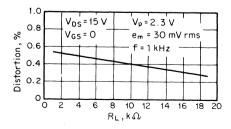

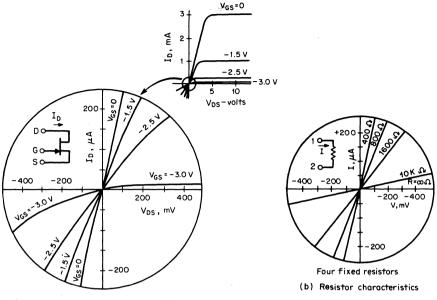

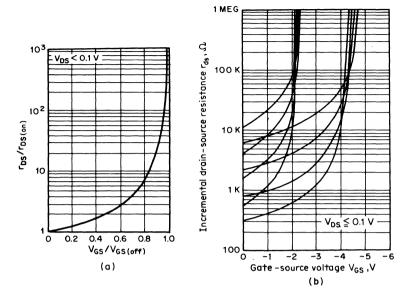

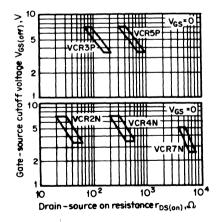

For some types of applications of the FET, it is helpful to understand the characteristics at very low values of  $V_{DS}$ , such as those shown in Fig. 2-4. A "very low value" is one which is small compared to the magnitude of  $V_{GS} - V_{GS(off)}$ . In this region  $V_{DS}$  is small enough to have little effect upon channel thickness, so that the  $I_D/V_{DS}$  slope is nearly linear. Since the slope is a function of  $V_{GS}$ , the FET can be utilized as a voltage-controlled resistor. The conductance slope ( $\Delta I_D/V_{DS}$ ) at  $V_{DS} = 0$  is approximately a linear function of  $V_{GS} - V_{GS(off)}$ .

If  $g_{ds}$  at  $V_{GS} = 0$  is given the term  $g_{dso}$ , then

$$g_{ds} = g_{dso} \left( 1 - \frac{V_{GS}}{V_{GS(\text{off})}} \right) \tag{2-8}$$

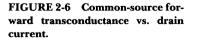

with  $V_{DS} = 0$ . A plot of this characteristic is shown in Fig. 2-5, along with  $g_{fs}$  and  $I_D$  characteristics.

The relationship between  $g_{dso}$ ,  $V_{GS(off)}$ , and  $I_{DSS}$  is given by the equation

$$g_{dso} = -2 \frac{I_{DSS}}{V_{GS(off)}}$$

(2-9)

where  $I_{DSS}$  and  $V_{GS(off)}$  are as indicated in Fig. 2-1. It is important to note that Eqs. (2-8) and (2-9) and the  $g_{ds}$  curve of Fig. 2-5 are valid

FIGURE 2-4 *n*-channel JFET output characteristic enlarged around  $V_{DS} = 0$ .

only for the case where  $V_{DS}$  is very small compared to  $V_p$ . Drain-source conductance at higher values of  $V_{DS}$  will be discussed later. FETs designed to be used as voltage-controlled resistors typically have a high  $V_{GS(off)}$  because the  $V_{DS}/(V_{GS} - V_{GS(off)})$  ratio should be low to keep distortion low.

**FIGURE 2-5**  $I_D$ ,  $g_{fs}$ , and  $g_{ds}$  versus gate-source voltage.

In analog switching applications,  $V_{GS}$  is usually set at zero for the ON condition and at a voltage greater than  $V_{GS(off)}$  for the OFF condition. A maximum value of ON resistance is usually specified at a small value of  $I_D$  or  $V_{DS}$ , or by a small-signal ac measurement at  $V_{DS} = 0$ .

|                                                                 | 2N2 | 3970 |      | Test conditions                  |  |

|-----------------------------------------------------------------|-----|------|------|----------------------------------|--|

| Characteristic                                                  | Min | Max  | Unit |                                  |  |

| <i>r<sub>DS (on)</sub> static drain-source</i><br>ON resistance |     | 30   | Ω    | $V_{GS} = 0, I_D = 1 \text{ mA}$ |  |

| <i>r<sub>ds (on)</sub> drain-source on</i><br>resistance        |     | 30   | Ω    | $V_{GS} = 0, f = 1 \text{ kHz}$  |  |

For the ac method, the signal frequency should be low enough that reactance effects can be neglected.

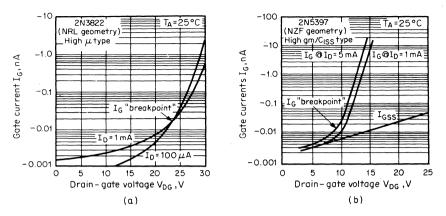

# 2-3 GATE-CURRENT CHARACTERISTICS

The gate current  $I_G$  of a JFET not only is a function of  $V_{GS}$  and  $V_{GD}$ but also may be a function of  $I_D$ . Figure 2-1d shows gate-current characteristics of type 2N4868A. This device has a  $BV_{GSS}$  in excess of 40 V; however, when the device is biased such that drain-to-source current is permitted to flow (a normal amplifier condition), then the gate-current "breakpoint" occurs at a lower drain-to-gate voltage. This breakpoint is a function of basic device design and is usually in the 10- to 30-V range. Beyond this breakpoint,  $I_G$  is approximately a *linear* function of  $I_D$  and an exponential function of  $V_{DS}$ . At  $V_{DS} = 0$ , the gate current is due to the collection by the gate of thermally generated minority carriers within the space-charge region at the gate-channel junction. When source-to-drain current is permitted to flow through the space-charge region at the drain end of the channel, additional minority carriers are generated due to electrons colliding with silicon atoms. The number of minority carriers created is a linear function of the channel current flowing and an exponential function of the electric field resulting from VDG.

This  $I_G$  breakpoint dependency upon  $I_D$  occurs at higher voltages in *p*-channel JFETs because of the lower mobility and lower ionization rates of holes in the drain space-charge region.

For both *n*-channel and *p*-channel JFETs the value of  $I_{GSS}$  and  $I_G$  below the breakpoint is approximately proportional to  $\sqrt{V_{GS}}$  and  $\sqrt{V_{GD}}$ . A further discussion of  $I_G$  is given in Sec. 3-8-2.

#### 2-4 SMALL-SIGNAL COEFFICIENTS

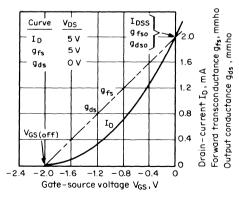

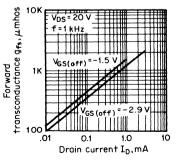

Because FETs are employed largely in circuits having varying currents and voltages, their dynamic characteristics are of interest. Referring to Fig. 2-1b, the slope of the curve or rate of change of  $I_D$  with respect to  $V_{GS}$  is important. This slope is the forward (gate-to-drain) transconductance of the FET, and is given the symbol  $g_{fs}$ . As is apparent in Fig. 2-1b,  $g_{fs}$  is a function of  $I_D$ , decreasing as  $I_D$  is decreased. Figure 2-6 shows the relationship between  $g_{fs}$  and  $I_D$  for a typical FET type. Curves for two devices of the same geometry but having different  $V_{GS(off)}$  values are included to show that  $g_{fs}$  is also a function of  $V_{GS(off)}$ . The relationships of these three parameters, shown graphically in Fig. 2-6, are mathematically expressed by Eqs. (2-10), (2-11), and (2-12).

$$g_{fso} = -2 \frac{I_{DSS}}{V_{GS(off)}} \tag{2-10}$$

and

$$g_{fs} = g_{fso} \left( 1 - \frac{V_{GS}}{V_{GS(off)}} \right)$$

(2-11)

also

$$g_{fs} = g_{fso} \left(\frac{I_D}{I_{DSS}}\right)^{1/2}$$

(2-12)

The exponent  $\frac{1}{2}$  in Eq. (2-12) is indicated by the slope of the curves of Fig. 2-6. A plot of  $g_{fs}$  versus  $V_{GS}$  is shown in Fig. 2-5. Note the similarity of the curves and equations for  $g_{fs}$  and  $g_{ds}$ . It should be pointed out that the constant in Eq. (2-10) and the exponent in Eq. (2-12) may not be exact, but for most device designs these numbers will be close.

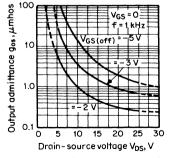

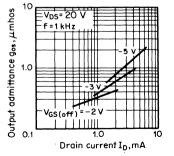

Referring to Fig. 2-1*a*, the small-signal output conductance is the slope  $\Delta I_D / \Delta V_{DS}$  at a constant value of  $V_{GS}$ . The term  $g_{os}$  is used to symbolize this parameter. It is apparent that  $g_{os}$  is a function of  $V_{DS}$  and  $I_D$ .

At  $V_{DS} = 0$ ,  $g_{os}$  is equal to the  $g_{dso}$  discussed in association with Eq. (2-8). As  $V_{DS}$  is increased,  $g_{os}$  decreases. For voltage-amplifier applications, a low  $g_{os}$  is of importance because the maximum voltage gain is limited by the ratio  $g_{fs}/g_{os}$ . If  $I_D$  really saturated at  $-V_{GS(off)}$ , then  $g_{os}$  would drop to zero at  $V_{DG}$  equal to or greater than  $-V_{GS(off)}$ . Most device types designed for small-signal low-frequency amplifiers will have  $g_{fs}/g_{os}$  ratios in excess of 100 (for  $V_{DS} > -V_{GS(off)}$ ). Figure 2-7 shows  $g_{os}$  versus  $V_{DS}$  for typical *n*-channel JFETs. Figure 2-8 shows  $g_{os}$  versus  $I_D$  for a constant value of  $V_{DS}$ . The curves of Figs. 2-6, 2-7, and 2-8 reveal two important points about devices of a given basic design: When operated at a given value of  $I_D$ , the device with the lower  $V_{GS(off)}$  will have a higher  $g_{fs}$  and a lower  $g_{os}$ . For a given power-supply voltage, available voltage gain is inversely proportional to  $V_{GS(off)}$ . Also, lower values of  $V_{GS(off)}$  permit use of lower-voltage supplies.

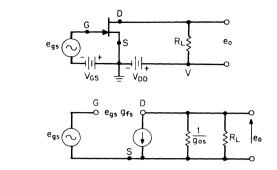

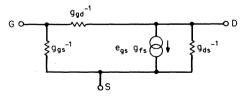

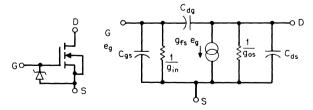

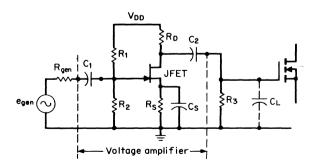

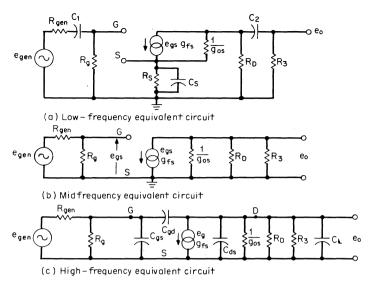

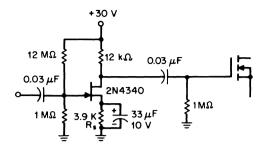

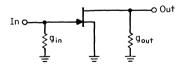

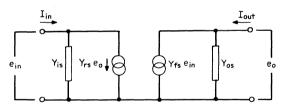

A simplified common-source FET voltage-amplifier circuit and its lowfrequency equivalent circuit are shown in Fig. 2-9. This equivalent circuit neglects reactive components and dc leakages. It is given here to show the equivalent circuit location of the  $g_{fs}$  and  $g_{os}$  parameters discussed above. The voltage amplification with this circuit is

$$A_v = \frac{e_o}{e_g} = -g_{fs} \left( \frac{R_L}{1 + g_{os} R_L} \right) \tag{2-13}$$

If  $g_{os}$  is small compared to  $1/R_L$ , then Eq. (2-8) reduces to

$$A_v = -g_{fs} R_L \tag{2-14}$$

The negative sign indicates that the phase of the signal is inverted.

The low-frequency input conductance  $g_{iss}$  contains two principal components: the gate-source conductance  $(g_{gs} = \Delta I_G / \Delta V_{GS})$  and the gate-drain conductance  $(g_{gd} = \Delta I_G / \Delta V_{GD})$ :

$$g_{iss} = g_{gs} + g_{gd} \tag{2-15}$$

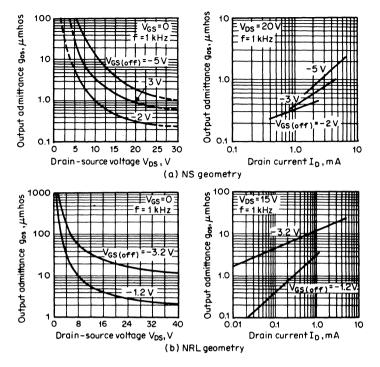

FIGURE 2-7 Output admittance vs. drain-source voltage.

FIGURE 2-8 Output admittance vs. drain current.

FIGURE 2-9 FET voltage amplifier and equivalent circuit (low-frequency simplified).

As indicated in the curves of Fig. 2-1*c* and *d*,  $g_{iss}$  for a small-signal device is on the order of  $10^{-14}$  if  $V_{GS}$  is below junction breakdown and  $V_{DS}$  is below the  $I_G$  breakpoint. In an amplifier configuration the effect of  $g_{gd}$  will be increased by the voltage gain of the amplifier. For a circuit such as that shown in Fig. 2-9, the low-frequency input conductance would be

$$g_{is} = g_{gs} + g_{gd}(1 + g_{fs}R_L) \tag{2-16}$$

(assuming that  $1/g_{os} >> R_L$ ).

Even with a voltage gain of 10, gis of the FET amplifier will be less

FIGURE 2-10 Gate input characteristic when  $V_{DS}$  exceeds the  $I_G$  breakpoint.

DESIGNING WITH FIELD EFFECT TRANSISTORS

than  $10^{-12}$  mho at room temperature. Consequently, a FET has a low-frequency input resistance in excess of  $10^{12} \Omega$ , since resistance is the reciprocal of conductance.

At values of  $V_{DS}$  greater than the  $I_G$  breakpoint (see Fig. 2-1*d*), the dc value of  $I_G$  increases sharply. Above this corner the quantity  $g_{gd}$ becomes negative, resulting in  $g_{iss}$  going through zero and becoming negative. This occurs because  $I_G$  in this region is approximately a linear function of  $I_D$ . Since  $\Delta I_D = g_{fs} \Delta V_{GS}$ , a positive change in  $V_{GS}$  results in an increase in  $I_D$ , which in turn causes an increase in the magnitude of  $I_G$ . Since  $I_G$  is negative,  $\Delta I_G$  is negative; therefore  $g_{gd}$  will be negative. Figure 2-10 is a plot of experimental data obtained from a typical JFET operating with  $V_{DS}$  greater than the  $I_G$  breakpoint. These data show that the input conductance  $g_{iss}$  is negative for this bias condition. A transition from positive  $g_{iss}$  to negative  $g_{iss}$  will occur near the knee of the  $I_G$ -vs.- $V_{DS}$  curves shown in Fig. 2-1*d*. The FET low-frequency equivalent circuit with the gate conductance components added is shown in Fig. 2-11. The  $g_{iss}$  characteristic is not normally specified in FET data sheets; however, its magnitude can be estimated from the  $I_G$  specification.

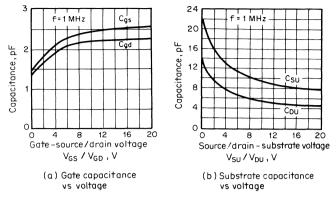

# 2-5 JFET CAPACITANCES

As the operating frequency is increased, device capacitances become important parameters. For the JFET the principal capacitance is that of the gate-channel junction. The value and geometrical distribution of this capacitance are functions of the voltages  $V_{GS}$  and  $V_{GD}$  because these voltages have a direct effect upon the junction depletion-layer thickness. For abrupt junctions the capacitance per unit area is

$$C = \left(\frac{K}{V_{bi} + V_G}\right)^{1/2} \tag{2-17}$$

Abrupt junctions are not achieved in the typical FET structure. The channel may consist of an epitaxial n-type layer on a p-type substrate and with a diffused p-type top gate. The diffusion process will cause

FIGURE 2-11 JFET low-frequency equivalent.

FIGURE 2-12 JFET capacitances, intermediate-frequency model.

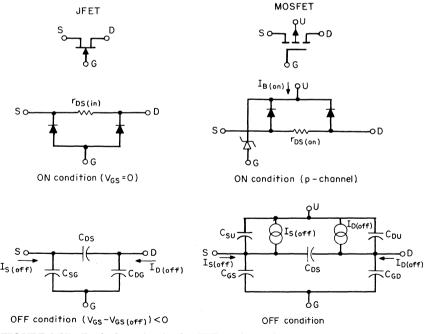

some gradation of the junctions. For a graded junction the exponent of Eq. (2-17) would be  $\frac{1}{3}$  instead of  $\frac{1}{3}$ . In a functioning circuit the analysis of gate-to-channel capacitance is complicated by the nonuniform depletion width along the channel. The gate-drain depletion width will be greater than the gate-source depletion width, thus Cgd usually will be lower than  $C_{as}$ . Figure 2-12 shows the equivalent-circuit location of these capacitances, plus the drain-source capacitance, and gives a concept of the relative depletion-layer thickness of the drain-gate and source-gate junctions. This sketch is intended to explain why the value of  $C_{gd}$  is typically less than that of  $C_{qs}$ . In some applications where  $V_{GD}$  and  $V_{GS}$ are approximately equal (such as in an analog switch or voltage-controlled resistor circuit),  $C_{ad}$  and  $C_{as}$  may be approximately equal. The  $C_{ds}$  component is largely the device header (package) capacitance and is typically small compared to the other two components; however, at very high frequencies it must be considered. Devices designed specifically for high frequencies often utilize a special low-capacity package configuration.

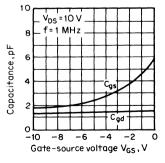

Figure 2-13 shows the effect of gate voltage upon  $C_{gs}$  and  $C_{gd}$  for a typical JFET designed for high-frequency (450-MHz) applications (Siliconix type U310). The  $C_{gd}$  curve is lower than the  $C_{gs}$  because of the 10-V  $V_{DS}$  bias (at  $V_{GS} = 0$ ,  $V_{GD} = -10$  V). These capacitances increase

FIGURE 2-13 Junction capacitances vs. gate voltage.

the input and feedback admittance and limit the wideband amplifier performance.

Because FET capacitances are sensitive to applied voltages, the circuit designer must examine the test conditions used in the device data-sheet specifications. For example, the device types listed below can be made from the same basic geometry, but capacitances are specified under different test conditions for each type.

| FET<br>type      | Characteristic                                                           | Max<br>pF    | Test<br>conditions                                                                |                        |

|------------------|--------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------|------------------------|

| 2N4092           | <i>C</i> <sub>iss</sub> common-source input capacitance                  | 16           | $V_{DS} = 20, V_{GS} = -5$                                                        | f = 1  MHz             |

| 2N4092           | <i>C</i> <sub>rss</sub> common-source<br>reverse transfer<br>capacitance | 5            | $V_{DS} = 0, V_{GS} = -20 \text{ V}$                                              |                        |

| 2N4392<br>2N4392 | C <sub>iss</sub><br>C <sub>rss</sub>                                     | 14<br>3.5    | $V_{Dg} = 20, V_{GS} = 0$<br>$V_{DS} = 0, V_{GS} = -7 \text{ V}$                  | f = 1 MHz              |

| 2N4857<br>2N4857 | C <sub>iss</sub><br>C <sub>rss</sub>                                     | 18<br>8      | $V_{DS} = 0, V_{GS} = -10 \text{ V}$<br>$V_{DS} = 0, V_{GS} = -10 \text{ V}$      | f = 1 MHz              |

| 2N5564<br>2N5564 | C <sub>iss</sub><br>C <sub>rss</sub>                                     | 12<br>3      | $V_{DG} = 12, I_D = 2 \text{ mA}$<br>$V_{DG} = 12, I_D = 2 \text{ mA}$            | f = 1 MHz<br>f = 1 MHz |

| 2N5638<br>2N5638 | C <sub>iss</sub><br>C <sub>rss</sub>                                     | 10<br>4      | $V_{DS} = 0, V_{GS} = -12 \text{ V}$                                              | f = 1 MHz              |

| J111             | $C_{dg(off)}$<br>$C_{sg(off)}$<br>$C_{dg(on)} + C_{sg(on)}$              | 5<br>5<br>28 | $V_{DS} = 0, V_{GS} = -10$<br>$V_{DS} = 0, V_{GS} = -10$<br>$V_{DS} = V_{GS} = 0$ |                        |

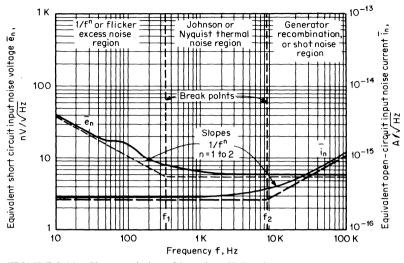

# 2-6 NOISE CHARACTERISTICS

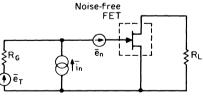

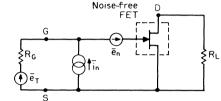

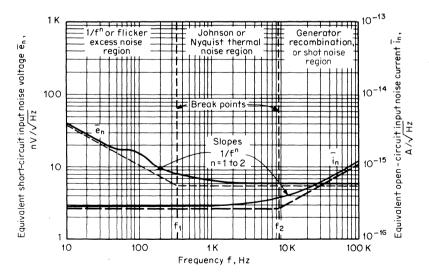

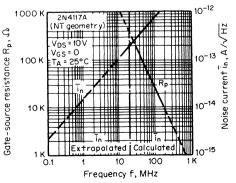

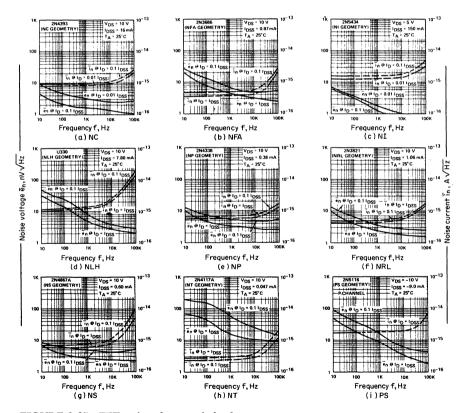

Electrical noise generated within a FET is usually represented by equivalent noise sources,  $\bar{e}_n$  and  $\bar{i}_n$ . Both noise voltage  $\bar{e}_n$  and noise current  $\bar{i}_n$  are frequency-dependent and have the characteristics shown in Fig. 2-14.

An equivalent noise circuit is shown in Fig. 2-15. Above the frequency  $f_1$ ,  $\bar{e}_n$  is approximately given by:

$$\bar{e}_n \simeq \left(4KTB \frac{0.67}{g_{fs}}\right)^{1/2} \tag{2-18}$$

where  $K = 1.374 \times 10^{-23}$  J/K

T = absolute temperature in kelvins (273 K = 0°C)

FIGURE 2-14 Characteristics of junction FET noise.

B = frequency range in hertz

$g_{fs}$  = transconductance of FET

With the input short-circuited, the noise voltage across the load  $R_L$  resulting from the FET is

Output noise voltage =  $\bar{e}_n A_V$

Below the frequency  $f_1$ ,  $\bar{e}_n$  increases proportional to  $1/f^n$  and is expressed as

$$\bar{e}_n = \left[4KTB\left(\frac{0.67}{g_{fs}}\right)\left(1 + \frac{f_1}{f^n}\right)\right]^{1/2}$$

(2-19)

FIGURE 2-15 Equivalent FET noise circuit.

The low-frequency corner  $f_1$  for JFETs is typically in the 100-Hz to 1-kHz range, and the exponent *n* is usually between 1 and 2. As indicated by the equations,  $\bar{e}_n$  is inversely proportional to the square root of  $g_{fs}$ .

The equivalent input noise current  $i_n$  is caused by the current in the gate-to-channel junction. Its approximate value below  $f_2$  is

$$\bar{i}_n = (2qI_GB)^{1/2} \tag{2-20}$$

where  $q = 1602 \times 10^{-19}$

B = frequency range in hertz

$I_G = dc$  gate current

This expression is fairly accurate when  $I_G$  is the result of the active device conductance. Typically  $i_n$  will be lower than the calculated value because part of  $I_G$  is due to conductance across the device package.

At higher frequencies (above  $f_2$ ),

$$\bar{\tilde{h}}_n = \left(\frac{4KTB}{R_P}\right)^{1/2} \tag{2-21}$$

where  $R_P$  = real part of gate input impedance. The high-frequency corner  $f_2$  is typically in the range of 5 to 50 kHz.

Another form of noise is known as "popcorn" or burst noise, the causes of which have not been completely identified. It shows up as a random short-duration step-function change in drain current, equivalent to an input gate-source voltage change of a few tenths of a microvolt. A more detailed discussion of FET noise is presented in Chapter 3.

# 2-7 CHARACTERISTIC INTERRELATIONSHIPS

When the time comes to select a FET for a particular circuit application, it is helpful to have an understanding of the interrelationship of the various electrical parameters. If the quantity requirements are to be large, it may be economically desirable to generate a specification tailored to the specific application. If one designs a circuit utilizing a standard catalog device type, for example, and finds that the design can tolerate a wider range of  $V_{GS(off)}$  (maximum to minimum), the part supplier may be able to offer a lower-price unit. However, if the range of a related parameter such as the drain saturation current  $I_{DSS}$  is not also widened, then the wider  $V_{GS(off)}$  spread may be of no help. For a given "geometry" (determined by a set of photographic masks), both  $V_{GS(off)}$ and  $I_{DSS}$  are affected by conductivity and thickness of the channel. These are determined by one or more non-mask-related process steps, such as epitaxial growth, channel diffusion, gate diffusion, or ion implantation. These parameters are also affected by variations in the masking operations involved in the etching of oxide windows for top gate diffusions, especially on very short channel structures. The approximate equations for the JFET structure indicate the relationship between the electrical parameters and the geometric parameters.

#### **PARAMETERS AND SPECIFICATIONS**

$$g_{fso} = K_1 \frac{W}{L} T \tag{2-22}$$

$$V_{GS(off)} = K_2 T^2$$

(2-23)

$$V_{DSS} = K_3 \frac{W}{L} T^3 \tag{2-24}$$

where W = width

L = length

T = thickness of the channel

If one varies only the thickness, then  $V_{GS(off)}$ ,  $g_{fso}$ , and  $I_{D(sat)}$  will change in an interrelated manner.

$$I_{DSS} = K_4 \ (V_{GS(\text{off})})^{3/2} \tag{2-25}$$

$$g_{fso} = K_5 \ (V_{GS(off)})^{1/2} \tag{2-26}$$

$$g_{fso} = \frac{2I_{DSS}}{V_{GS(off)}} \tag{2-27}$$

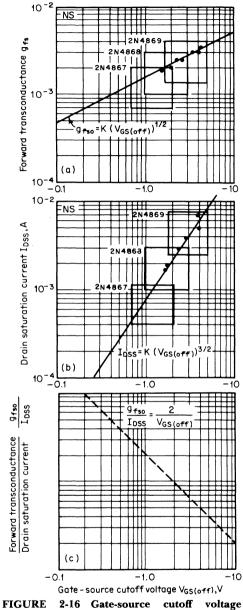

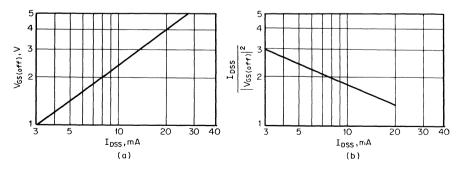

Figure 2-16 shows the interrelationship of these three parameters for a particular JFET geometry. Each dot on these plots represents a particular device. The data were obtained from devices where the only intentional change was in the "top" gate diffusion time to create a change in the channel thickness. The fact that the dots do not all fall on a single line indicates that there were other variations such as donor and acceptor concentrations. This type of variation from the "ideal" control is typical of semiconductor manufacturing processes. From this one geometry or "generic type," several device types may be characterized. For example, the specification limits for three types are indicated on the plot. The complete JEDEC registered characteristics for these device types are given in Table 2-1.

The major differences are due to a difference in channel thickness. The units with a high value of  $V_{GS(off)}$  have a thick channel, while those with a low  $V_{GS(off)}$  have a thin channel. The data of Fig. 2-16 show that for a given value of  $V_{GS(off)}$ , the ranges of  $I_{DSS}$  and  $g_{fso}$  are limited. It should be emphasized that the data are for a particular device geometry and manufacturing process. It is possible to produce devices which meet the specified electrical characteristics using different geometries and processes; therefore, a plot of device types from a different manufacturer will not necessarily coincide with that shown in Fig. 2-16.

The data shown in Fig. 2-16*a* and *b* were used to calculate a  $g_{fso}/I_{DSS}$  ratio. This characteristic, which is an inverse function of  $V_{GS(off)}$ , is plotted in Fig. 2-16*c*. These data indicate that for a given geometry, a higher  $g_{fso}/I_{DSS}$  ratio is achieved with the units having lower  $V_{GS(off)}$ .

41

|                                 |        |                      |                                                    |      | 4867<br>1867A  |      | 4868<br>1868A  |      | 4869<br>1869A  |                        |                                                                          |                                                        |                  |

|---------------------------------|--------|----------------------|----------------------------------------------------|------|----------------|------|----------------|------|----------------|------------------------|--------------------------------------------------------------------------|--------------------------------------------------------|------------------|

|                                 |        |                      | Characteristic                                     | Min  | Max            | Min  | Max            | Min  | Max            | Unit                   |                                                                          | Test conditions                                        |                  |

| $\frac{1}{2}$                   | s      | I <sub>GSS</sub>     | gate reverse current                               |      | -0.25<br>-0.25 |      | -0.25<br>-0.25 |      | -0.25<br>-0.25 | nA<br>µA               | $V_{GS} = -30 \text{ V}$                                                 | , $V_{DS} = 0$                                         | 150°C            |

| 2                               | t<br>a | BV <sub>GSS</sub>    | gate-source breakdown<br>voltage                   | -40  |                | -40  |                | -40  |                | V                      | $I_G = -1 \ \mu A,$                                                      | $V_{DS} = 0$                                           | 100 0            |

| 4                               | t<br>i | V <sub>GS(off)</sub> | gate-source cutoff voltage                         | -0.7 | -2             | -1   | -3             | -1.8 | -5             | 1                      | $V_{\rm DS}=20~{\rm V},~{\rm J}$                                         | $I_D = 1 \ \mu A$                                      |                  |

| 5                               | c      | I <sub>DSS</sub>     | saturation drain current<br>(note 2)               | 0.4  | 1.2            | 1    | 3              | 2.5  | 7.5            | mA                     | $V_{DS} = 20 \text{ V},$                                                 | $V_{GS} = 0$                                           |                  |

| 6                               |        | g <sub>fs</sub>      | common-source forward<br>transconductance (note 2) | 700  | 2000           | 1000 | 3000           | 1300 | 4000           | μmho                   |                                                                          |                                                        | f = 1  kHz       |

| 7                               |        | gos                  | common-source output<br>conductance                |      | 1.5            |      | 4              |      | 10             |                        | $V_{DS} = 20 \text{ V},$                                                 | $V_{\rm ex} = 0$                                       | J I KILL         |

| 8                               | D      | Crss                 | common-source reverse<br>transfer capacitance      |      | 5              |      | 5              |      | 5              | рF                     | $v_{DS} - 20$ V, $v_{GS} = 0$                                            |                                                        | f = 1  MHz       |

| 9                               | y<br>n | Ciss                 | common-source input<br>capacitance                 |      | 25             |      | 25             |      | 25             | pr                     |                                                                          |                                                        | j = 1 MHZ        |

| 10                              | a      |                      |                                                    |      | 20             |      | 20             |      | 20             |                        |                                                                          | 2N4867 Series                                          | f = 10 Hz        |

| 11                              | m<br>i | ēn                   | short-circuit equivalent                           |      | 10             |      | 10             |      | 10             | $\frac{nV}{\sqrt{Hz}}$ | $V_{\rm DS}=10~{\rm V},$                                                 | 2N4867A Series                                         | <i>J</i> = 10 Hz |

| $\frac{10}{11}$ $\frac{12}{13}$ | с      |                      | input noise voltage                                |      | 10             |      | 10             |      | 10             | VIIZ                   | $V_{GS}=0$                                                               | 2N4867 Series                                          | f = 1  kHz       |

| 13                              |        |                      |                                                    |      | 5              |      | 5              |      | 5              |                        |                                                                          | 2N4867A Series                                         |                  |

| 14                              |        | NF                   | spot noise figure                                  |      | 1              |      | 1.             |      | 1              | dB                     | $V_{DS} = 10 \text{ V}, I$ $R_{gen} = \frac{20 \text{ K}}{5 \text{ K}},$ | V <sub>GS</sub> = 0<br>2N4867 Series<br>2N4867A Series | f = 1  kHz       |

## TABLE 2-1 ELECTRICAL CHARACTERISTICS (25°C UNLESS OTHERWISE NOTED)\*

\* JEDEC registered data.

NOTES:

<sup>1</sup> Due to symmetrical geometry, these units may be operated with source and drain leads interchanged.

<sup>2</sup> Pulse test duration = 2 ms.

42

NS

FIGURE 2-16 Gate-source cutoff voltage  $V_{GS(off)}$ , in volts, relationship of  $I_{DSS}$ ,  $g_{fso}$ , and ratio  $g_{fs}/I_{DSS}$ .

FIGURE 2-17 JFET geometry selection guide.

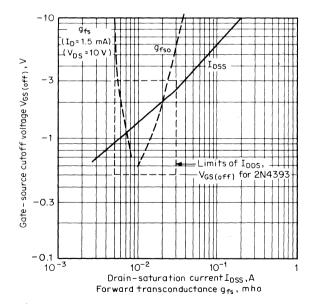

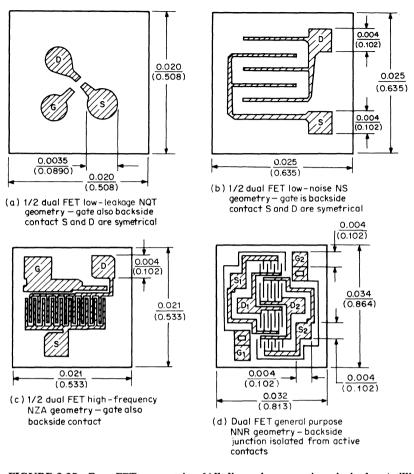

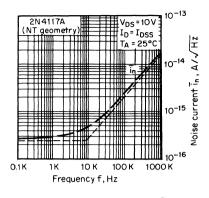

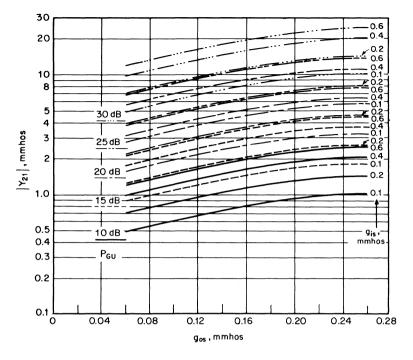

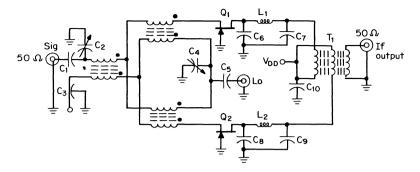

Characteristics of a variety of *n*-channel JFET geometries are given in Fig. 2-17. The interrelationship of characteristics related to channel thickness is shown in curves *a*, *b*, *c*, and *d*. Other geometry-related characteristics are shown in graphs *e*, *f*, *g*, and *h*. The geometries are identified by two- or three-letter codes, such as NT, NZA, or NC. These manufacturing codes are used by Siliconix Incorporated to designate their particular FET chip designs and are not necessarily those used by other manufacturers. These letter codes are related to device part numbers in the Geometry section of Siliconix Incorporated's "Field Effect Transistor Data Book." For example, from that book, one can find that the NC geometry is used to make device types 2N3970–72, 2N4091–93, 2N4391– 93, 2N4856–61, 2N4856A-6–61A, 2N5564–66, 2N5653–54, and Siliconix type J111–13. As indicated by this list, the NC geometry has wide use. Its relatively short channel gives it a reasonably good  $g_{fs}/C_{iss}$  ratio, which makes it useful in UHF/VHF oscillator and amplifier applications up to about 400 MHz.

The NQT geometry is a dual narrow-channel device. It has a low  $g_{fs}$ , but because of its small size it has very low gate-leakage current; some matched duals characterized from the NQT geometry have an operating  $I_G$  specification of 0.1 pA max.

# 2-8 MOSFET CHARACTERISTICS

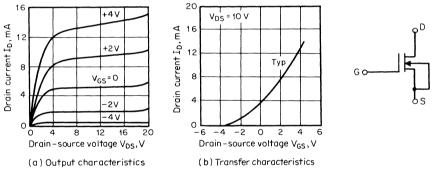

Common-source output and forward transconductance characteristics for two types of MOSFETs are given in Figs. 2-18 and 2-19. Figure 2-18 is for an *n*-channel depletion-mode device type 2N3631. The output and transfer characteristics indicate that gate-source voltage may be positive or negative.

FIGURE 2-18 Characteristics of n-channel depletion-type MOSFET (2N3631).

FIGURE 2-19 Characteristics of n-channel enhancement-type MOSFET (M116).

An important characteristic of this device, compared with a JFET, is the very low gate current. Input leakage resistance is typically greater than  $10^{15} \Omega$ .

This low input leakage characteristic makes this device useful in ultrahigh input-impedance amplifiers for circuits such as ionization-chamber input-type smoke detectors, pH measurement instruments, and proximity sensors. Caution must be exercised in handling this unit because it contains no protective circuit for the gate oxide. A gate-to-channel voltage in excess of  $\pm 60$  V may cause permanent damage to the oxide. In this particular geometry the body is internally connected to the source.

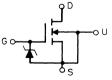

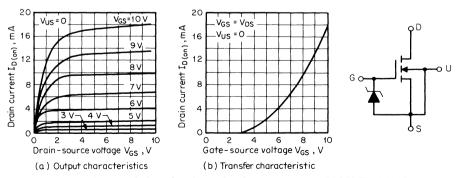

Figure 2-19 shows characteristics for an *n*-channel enhancement-mode device which has incorporated a gate-protecting diode connected between the gate terminal and the body of the MOSFET. This diode is designed to have a breakdown voltage of less than the voltage which would damage the gate oxide but greater than the normal gate operating voltage range. The diode limits the magnitude of the negative-going gate-body voltage to about 0.6 V, and the positive gate-body voltage to about 50 V.

The transconductance and output characteristics of the MOSFET are similar to those of the JFET. The transconductance curve is shifted along the  $V_{GS}$  axis for the "normally OFF" enhancement-type device, so that a positive gate-source voltage is required to turn this unit on. The  $V_{GS}$  at which channel conductance just starts is called the "gatesource threshold voltage" and is given the symbol  $V_{GS(th)}$ . This corresponds to the  $V_{GS(off)}$  of the depletion-type devices. The transconductance equations of the two types are similar, i.e.,

$$I_D = \frac{K}{2} \left( V_{GS} - V_{GS(\text{off})} \right)^2$$

(2-28*a*)

where  $V_{GS} > V_{GS(off)}$  (depletion type)

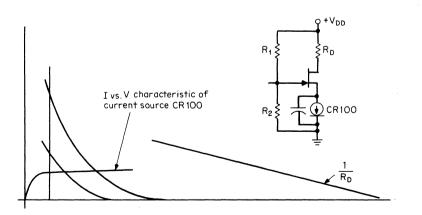

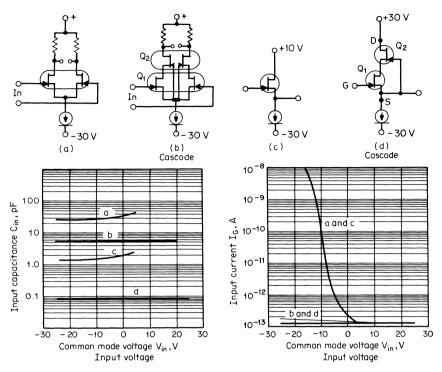

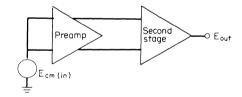

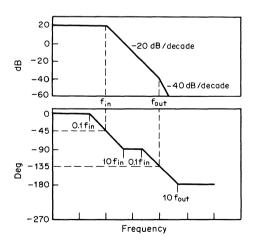

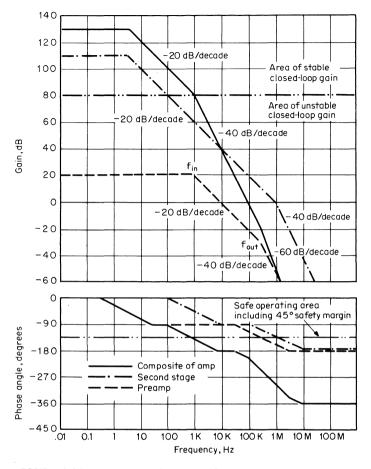

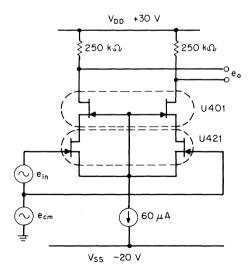

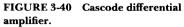

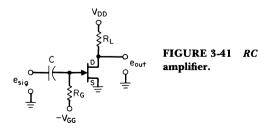

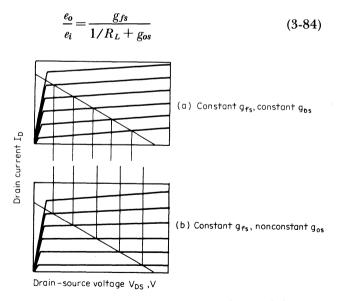

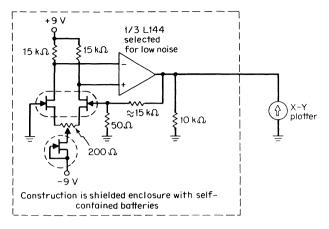

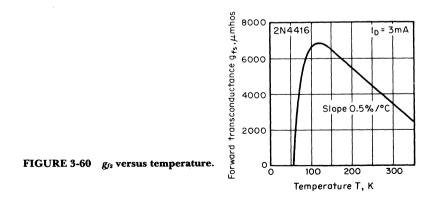

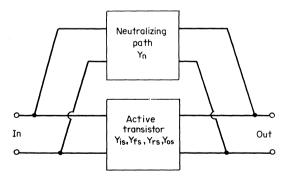

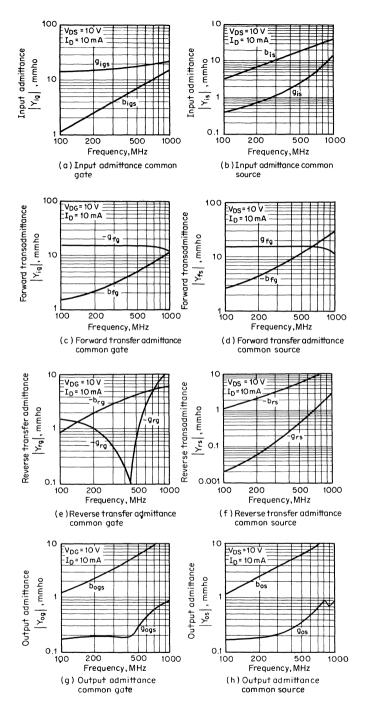

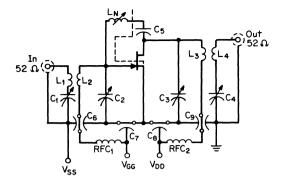

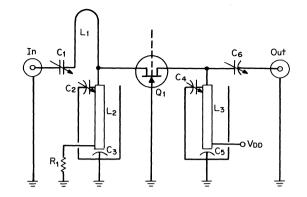

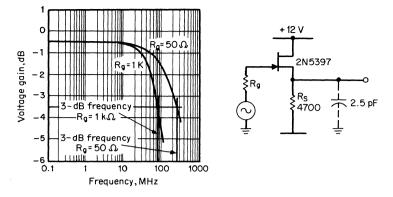

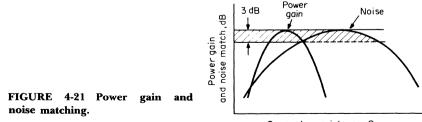

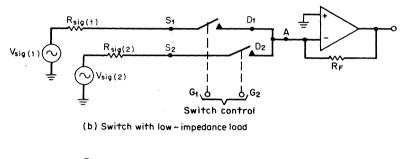

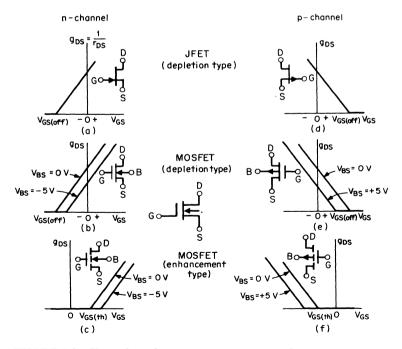

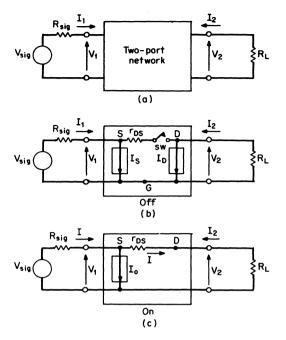

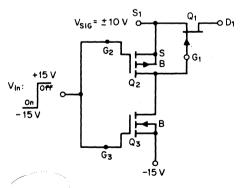

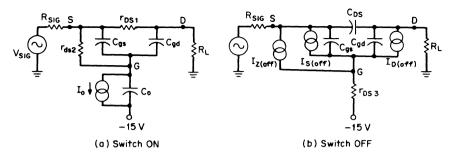

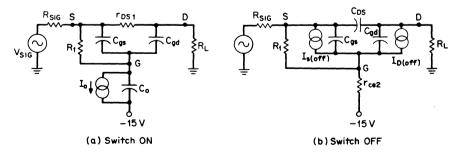

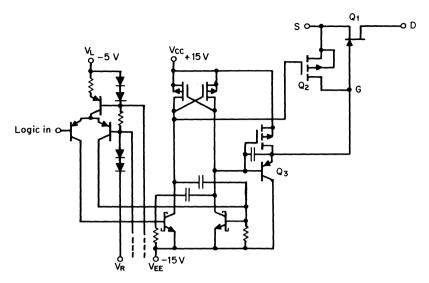

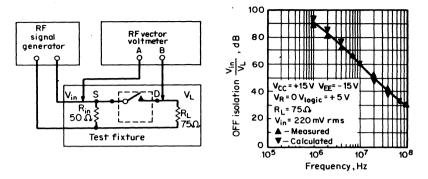

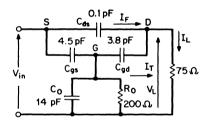

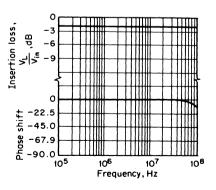

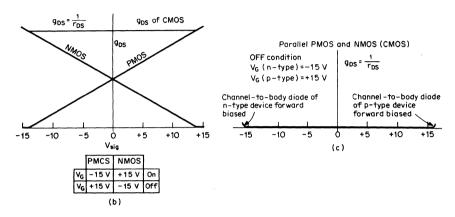

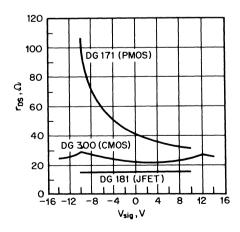

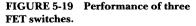

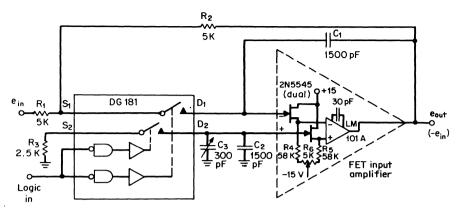

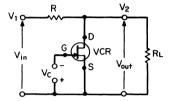

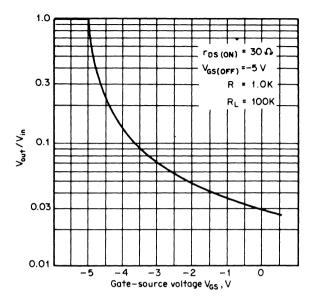

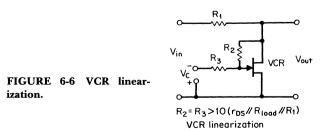

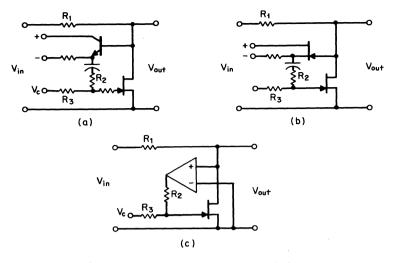

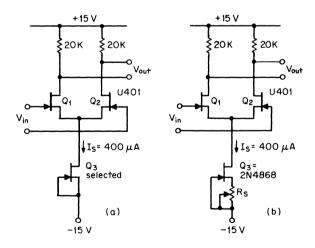

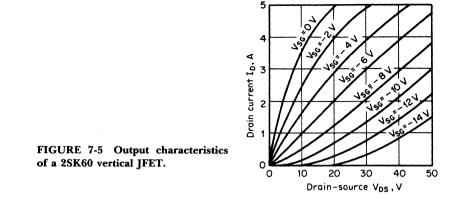

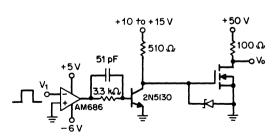

$$I_D = \frac{K}{2} \left( V_{GS} - V_{GS(\text{th})} \right)^2 \tag{2-28b}$$