PLESSEY

SEMICONDUCTOR

SPRODUCTS

# DIGITAL integrated circuit databook

# PLESSEY SEMICONDUCTOR PRODUCTS

# DIGITAL integrated circuit databook

august 1975

## product index

### **DIGITAL INTEGRATED CIRCUITS**

Page

|                    |                                                           | 1 aye    |

|--------------------|-----------------------------------------------------------|----------|

| Process Control    | l Circuits                                                |          |

| SP520              | Gray code counter                                         | 3        |

| SP521              | Binary rate multiplier                                    | 7        |

| SP522              | Phase lock, divider and comparator                        | 11       |

|                    | · · ·                                                     |          |

| Interface Circui   | its                                                       |          |

| SP705              | Crystal oscillator circuit                                | 17       |

| SP721              | Balanced line driver                                      | 17<br>20 |

| SP722              | Balanced line receiver                                    | 20       |

| SP723              | Balanced line receiver with complementary O/Ps            | 20       |

| SP724              | Dual balanced line receiver                               | 20       |

| SP761B             | 5 relay drivers, 150mA                                    | 24       |

| SP762B             | 5 relay drivers, 200mA                                    | 24       |

| SP763B             | 10 relay drivers, 50mA                                    | 28       |

| SP764B             | 10 relay drivers, 150mA                                   | 28       |

| SP765B             | 10 relay drivers, 200mA                                   | 28       |

| PECL II            |                                                           |          |

|                    |                                                           |          |

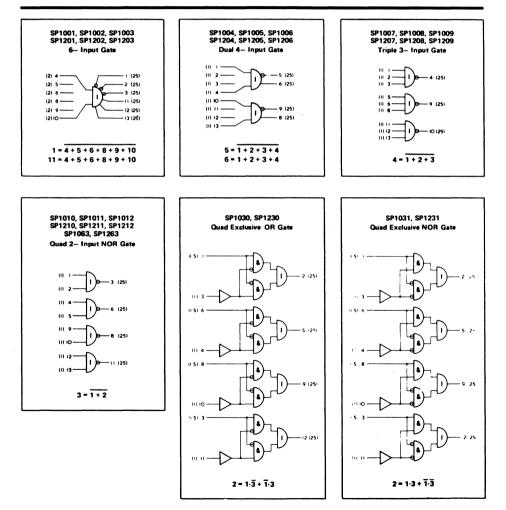

| SP1001B            | Single 6-I/P gate                                         | 35       |

| SP1004B            | Dual 4-1/P gate                                           | 35       |

| SP1007B            | Triple 3-I/P gate                                         | 35       |

| SP1010B            | Quad 2-1/P gate                                           | 35       |

| SP1013B<br>SP1014B | AC coupled J-K Flip Flop (85MHz)                          | 35       |

| SP1020B            | Dual R-S Flip Flop (positive clock)<br>Quad line receiver | 35       |

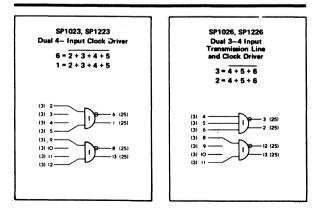

| SP1023B            | Dual 4-I/P OR/NOR clock driver                            | 35       |

| SP1026B            | Dual 3/4 - I/P transmission line and clock driver         | 35<br>35 |

| SP1027B            | AC coupled J-K Flip Flop (120MHz)                         | 35       |

| SP1030B            | Quad exclusive OR gate                                    | 35       |

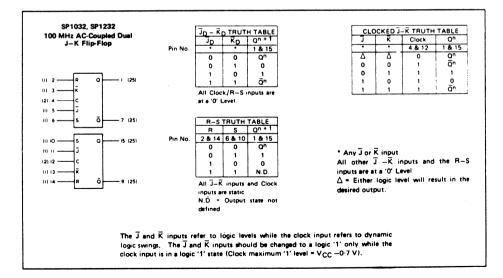

| SP1032B            | AC coupled dual J-K Flip Flop 100MHz clock                | 36       |

| SP1033B            | Dual R-S Flip Flop (single rail, positive clock           | 36       |

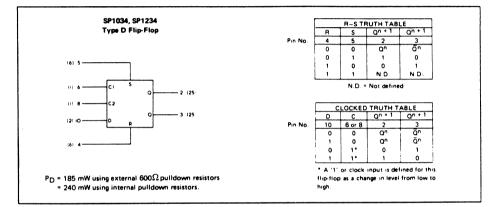

| SP1034B            | Type D Flip Flop                                          | 36       |

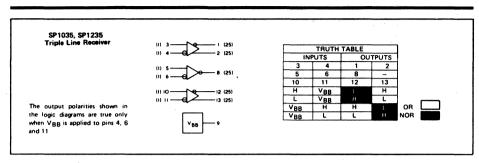

| SP1035B            | Triple line receiver                                      | 36       |

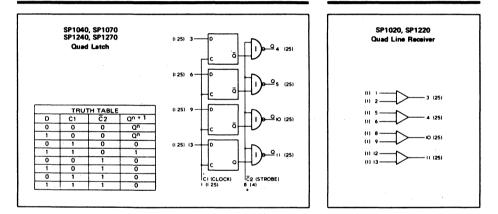

| SP1039B            | Quad level translator (PECL to saturated logic)           | 36       |

| SP1048B            | Quad 2-I/P NAND gates                                     | 36       |

|                    |                                                           |          |

| PECL III           |                                                           |          |

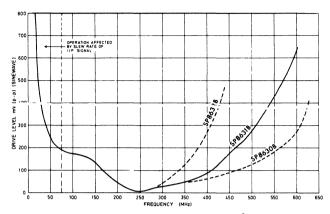

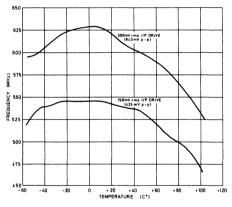

| SP1648B            | Voltage controlled oscillator                             | 45       |

| SP1650B            | Dual A/D comparator                                       | 53       |

| SP1651B            | Dual A/D comparator                                       | 53       |

| SP1658B            | Voltage controlled mulivibrator                           | 65       |

| SP1660B            | Dual 4-I/P OR/NOR gate Hi-Z                               | 69       |

| SP1661B            | Dual 4-I/P OR/NOR gate Lo-Z                               | 44       |

| SP1662B<br>SP1663B | Quad 2-I/P NOR gate HI-Z<br>Quad 2-I/P NOR gate Lo-Z      | 73       |

| SP1664B            | Quad 2-1/P OR gate Hi-Z                                   | 44       |

| SP1665B            | Quad 2-I/P OR gate Lo-Z                                   | 77       |

| SP1666B            | Dual clocked R-S Flip Flop Hi-Z                           | 44       |

| SP1667B            | Dual clocked R-S Flip Flop Lo-Z                           | 81<br>44 |

| SP1668B            | Dual clock latch Hi-Z                                     | 44<br>85 |

| SP1669B            | Dual clock latch Lo-Z                                     | 65<br>44 |

| SP1670B            | Master slave D Flip Flop Hi-Z                             | 89       |

| SP1671B            | Master slave D Flip Flop Lo-Z                             | 44       |

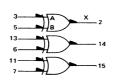

| SP1672B            | Triple 2-I/P exclusive OR gate Hi-Z                       | 97       |

| SP1673B            | Triple 2-1/P exclusive OR gate Lo-Z                       | 44       |

| SP1674B            | Triple 2-I/P exclusive NOR gate Hi-Z                      | 101      |

| SP1675B            | Triple 2-I/P exclusive NOR gate Lo-Z                      | 44       |

| SP1690B<br>SP1692B | UHF prescaler type D Flip Flop<br>Quad line receiver      | 105      |

| OF 1092D           |                                                           | 111      |

|                    |                                                           |          |

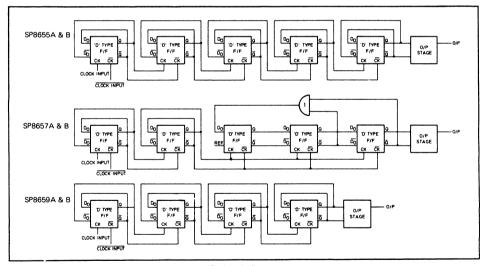

| SP8000 SERII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ES HIGH SPEED DIVIDERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| SP8600<br>SP8601<br>SP8602<br>SP8603<br>SP8604<br>SP8613<br>SP8614<br>SP8615<br>SP8616D<br>SP8616D<br>SP8621<br>SP8622<br>SP8630<br>SP8631<br>SP8632<br>SP8634<br>SP8632<br>SP8634<br>SP8635<br>SP8636<br>SP8641<br>SP8642<br>SP8643<br>SP8650<br>SP8651<br>SP8652<br>SP8655<br>SP8655<br>SP8655<br>SP8665<br>SP8665<br>SP8666<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667<br>SP8667 | 250MHz $\div$ 4<br>150MHz $\div$ 4<br>500MHz $\div$ 2<br>400MHz $\div$ 2<br>300MHz $\div$ 2<br>300MHz $\div$ 4<br>800MHz $\div$ 4<br>900MHz $\div$ 4<br>900MHz $\div$ 4<br>900MHz $\div$ 4<br>300MHz $\div$ 5<br>200MHz $\div$ 5<br>200MHz $\div$ 10<br>500MHz $\div$ 10<br>700MHz $\div$ 10<br>600MHz $\div$ 10<br>800MHz $\div$ 10<br>900MHz $\div$ 10<br>10 (BDC)<br>500MHz $\div$ 10 (BDC)<br>500MHz $\div$ 10 (BDC)<br>500MHz $\div$ 10 (BDC)<br>200MHz $\div$ 10 (BDC)<br>200MHz $\div$ 10 (BDC)<br>200MHz $\div$ 10(11<br>350MHz $\div$ 10/11<br>350MHz $\div$ 10/11<br>600MHz $\div$ 16<br>500MHz $\div$ 16<br>16<br>16<br>16<br>16<br>17<br>16<br>17<br>17<br>16<br>17<br>10<br>1.2 GHz $\div$ 10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10 | 115<br>119<br>123<br>123<br>127<br>127<br>127<br>127<br>127<br>127<br>131<br>131<br>133<br>133<br>133<br>133<br>133<br>133<br>137<br>137 |

| SP8690B<br>MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 200MHz ÷ 10/11 Low power, AC input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 155<br>157                                                                                                                               |

| MP1013A<br>MP3409B<br>MP3417B<br>MP9100<br>MP9200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Universal asynchronous receiver/transmitter<br>Quad 80-BIT dynamic shift register<br>Quad 64-BIT dynamic shift register<br>Push button telephone dialer<br>Repertory telephone store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 165<br>173<br>173<br>177<br>181                                                                                                          |

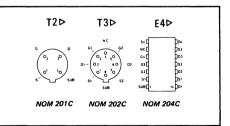

| MNOS (NON-Y<br>NOM201<br>NOM202<br>NOM204<br>NOM401C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VOLATILE MEMORY ELEMENTS)<br>Single MNOS transistor<br>Dual MNOS transistor<br>Quad MNOS transistor<br>8 x 8 MNOS array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 187<br>187<br>187<br>193                                                                                                                 |

Process control circuits Interface circuits

SP520 SERIES PROCESS CONTROL CIRCUITS

## **SP520B**

#### **GRAY CODE COUNTER**

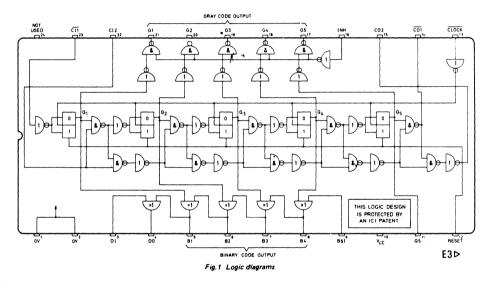

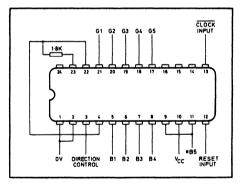

The SP520 digital integrated circuit is an RTL 5-bit up/down counter in positive logic with both Gray code and natural binary code TTL-compatible outputs. Other inputs and outputs use modified RTL to give improved noise immunity.

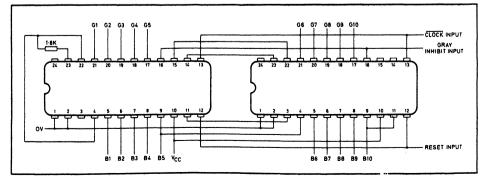

SP520 counters can be cascaded by suitable external connections to give a counter with any multiple of 5 bits. The counter is of a non-overflow design and will operate with an input frequency in excess of 1MHz. It can be reset to the 00000 state and the Gray O/Ps can be inhibited for "wired OR" applications.

| Pin No. | Function                                               | Pin No. | Function                                             |

|---------|--------------------------------------------------------|---------|------------------------------------------------------|

| 1       | Common rail (0V)                                       | 14      | Inhibit carry O/P to 1st flip-flop of next           |

| 2       | Common rail (0V)                                       |         | counter (C01)                                        |

| 3       | Counter external direction control (Logic '0'<br>= up) | 15      | Enable carry O/P to gate chain of next counter (CO2) |

| 4       | Binary code O/P direction (D <sub>o</sub> )            | 16      | Inhibit I/P for all Gray O/Ps except auxiliary       |

| 5       | Binary code O/P Bit 1 (B1)                             |         | Gray code O/P Bit 5 (INH)                            |

| 6       | Binary code O/P Bit 2 (B2)                             | 17      | Gray code O/P Bit 5 (G5)                             |

| 7       | Binary code O/P Bit 3 (B3)                             | 18      | Gray code O/P Bit 4 (G4)                             |

| 8       | Binary code O/P Bit 4 (B4)                             | 19      | Gray code O/P Bit 3 (G3)                             |

| 9       | Binary code I/P Bit 5 (B5I)                            | 20      | Gray code O/P Bit 2 (G2)                             |

| 10      | Positive supply rail (VCC)                             | 21      | Gray code O/P Bit 1 (G1)                             |

| 11      | Auxiliary Gray code O/P Bit 5 (Q5)                     | 22      | Enable gate chain I/P (CI2)                          |

| 12      | Reset I/P for all flip-flop stages (forces             | 23      | Inhibit I/P to 1st flip-flop (CI1)                   |

| 13      | 00000 state)<br>Clock I/P                              | 24      | No connection                                        |

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated)

$T_{amb} = 0^{\circ}C \text{ to } +70^{\circ}C$  $V_{CC} = 5.0V \pm 0.25V$

|                                                                                                                      | 1   | Value |     |          |                                                  |

|----------------------------------------------------------------------------------------------------------------------|-----|-------|-----|----------|--------------------------------------------------|

| Characteristic                                                                                                       | Min | Тур   | Max | Units    | Conditions                                       |

|                                                                                                                      |     |       |     |          |                                                  |

| Counter external direction control (pin 3),<br>Binary code I/P bit 5 (pin 9), and Enable<br>gate chain I/P (pin 22): |     |       |     |          |                                                  |

| Input voltage 'High'                                                                                                 | 3.0 |       |     | v        |                                                  |

| Input voltage 'Low'                                                                                                  |     |       | 1.0 | V        | · · · · · · · · · · · · · · · · · · ·            |

| Input current                                                                                                        |     |       | 25  | μA       | V <sub>in</sub> = 3.0V                           |

| Inhibit I/P for Gray O/Ps (pin 16)<br>Input voltage 'High'                                                           | 3.0 |       |     | v        |                                                  |

| Input voltage 'Low'                                                                                                  | 0.0 |       | 1.0 | v        |                                                  |

| Input current 'High'                                                                                                 |     |       | 250 | μA       | V <sub>in</sub> = 3.0V                           |

| Input current 'Low'                                                                                                  |     |       | 50  | μA       | V <sub>in</sub> = 1.0V                           |

| Reset I/P for all flip-flops (pin 12)                                                                                |     |       |     |          |                                                  |

| Input voltage 'High'                                                                                                 | 2.3 |       |     | v        |                                                  |

| Input voltage 'Low'                                                                                                  |     |       | 0.8 | v        | with voltage drive                               |

| Input current<br>Input current 'High'                                                                                | 1.0 |       | 3.5 | mA<br>mA | V<br>With current drive                          |

| Clock I/P (pin 13)                                                                                                   |     |       |     |          |                                                  |

| Input voltage 'High'                                                                                                 | 3.0 |       |     | v        | See note 1                                       |

| Input voltage 'Low'                                                                                                  |     |       | 1.0 | v        |                                                  |

| Input current                                                                                                        |     |       | 200 | μA       | V <sub>in</sub> = 3.0V                           |

| Input clock frequency                                                                                                |     |       | 1   | MHz      | 1:1 mark = space ratio                           |

| Input slew rate                                                                                                      | 20  |       |     | V/µs     | See note 2                                       |

| Inhibit I/P to 1st flip-flop (pin 23)                                                                                |     |       |     |          |                                                  |

| Input voltage 'High'                                                                                                 | 2.3 |       |     | v        | See note 3                                       |

| Input voltage 'Low'                                                                                                  |     |       | 0.8 | v        |                                                  |

| Input current                                                                                                        |     |       | 2.0 | mA       | T <sub>amb</sub> = +70°C, V <sub>in</sub> = 2.3V |

| Input slew rate                                                                                                      | 20  |       |     | V/µs     | See note 2                                       |

| OUTPUT CHARACTERISTICS                                                                                               |     |       |     |          |                                                  |

| Binary code O/P bits 1-4 (pins 5-8)                                                                                  |     |       |     |          |                                                  |

| Output voltage 'Low'                                                                                                 |     |       | 0.4 | v        | Sink current = 6.4mA                             |

| Output voltage 'High'                                                                                                |     | Vcc   |     | V        | l <sub>out</sub> = 0mA                           |

| Output impedance in 'High' state                                                                                     |     | 6.0   | 8.0 | kΩ       |                                                  |

| Binary code O/P direction (pin 4)                                                                                    |     |       |     |          |                                                  |

| Output voltage 'Low'                                                                                                 |     |       | 0.4 | V        | Sink current = 6.4mA                             |

| Output voltage 'High'<br>Output impedance in 'High' state                                                            |     | Vcc   | 2.6 | V<br>kΩ  | l <sub>out</sub> = 0mA                           |

|                                                                                                                      |     |       | 2.0 | K36      |                                                  |

| Aux. Gray code O/P bit 5 (pin 11)<br>Output voltage 'Low'                                                            |     |       |     |          | Sigh guarant = 2.20/                             |

| Output voltage 'Low'<br>Output voltage 'High'                                                                        |     | Vaa   | 0.4 | v<br>v   | Sink current = 3.2V                              |

| Output impedance in 'High' state                                                                                     |     | Vcc   | 8.0 | kΩ       | l <sub>out</sub> = 0mA                           |

| Gray code O/Ps bits 1-5 (pins 17-21)                                                                                 |     |       |     |          |                                                  |

| Output voltage 'Low'                                                                                                 |     |       | 0.4 | v        | Sink current = 8.0mA                             |

| Output voltage 'High'                                                                                                |     | 4.2   |     | v        | lout = 0mA                                       |

| Output impedance in 'High' state                                                                                     |     |       | 3.4 | kΩ       |                                                  |

| Output leakage to earth in inhibited state                                                                           |     |       | 20  | μA       | T <sub>chip</sub> = 100°C                        |

|                                                     | Value |      |     |       | <b>O</b> a lititati                     |  |

|-----------------------------------------------------|-------|------|-----|-------|-----------------------------------------|--|

| Characteristic                                      |       | Тур  | Max | Units | Conditions                              |  |

| Inhibit carry O/P to 1st flip-flop of next counter. |       |      |     |       |                                         |  |

| Output voltage 'Low' (pin 14)                       |       |      | 0.4 | V     | $R_{pd} = 4k\Omega$ (see notes 4 and 5) |  |

| Output voltage 'High'                               | 2.4   | 2.75 | 3.2 | V     | <b>F</b>                                |  |

| Enable carry O/P to gate chain of next counter      |       |      |     |       |                                         |  |

| Output voltage 'Low' (pin 15)                       |       |      | 0.4 | V     | Sink current = 3.2mA                    |  |

| Output voltage 'High'                               |       | Vcc  | 1   | V     | l <sub>out</sub> = 0mA                  |  |

| Output impedance in 'High' state                    |       |      | 4.8 | kΩ    |                                         |  |

| Power supply drain current (pin 10)                 |       | 70   | 96  | mA    | V <sub>CC</sub> = 5.0V, clock I/P = 0V  |  |

NOTES

- 2. The flip-flops need fast edges for reliable toggling.

- In the high state the input current is directly proportional to the input voltage and increases at approximately 1mA/V. It might therefore be desirable to limit the maximum input voltage.

- 4. An emitter follower output will not sink current and is not therefore suitable for interfacing directly with TTL or DTL.

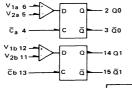

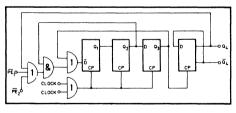

Fig.2 SP520 connected as a 5-bit counter

#### ABSOLUTE MAXIMUM RATINGS

Continuous +ve supply voltage Continuous +ve input voltage

+7V

not greater than the supply voltage in use

Max. operating junction temp Storage Temperature

+175°C -50°C to +175°C

Fig.3 Two SP520s connected as a 10-bit counter

<sup>1.</sup> In the high state the input level affects the overall power consumption. The chip power consumption increases by approximately 12.5mW and it might therefore be desirable to limit the clock input voltage with, say, a zener diode.

## SP520 SERIES PROCESS CONTROL CIRCUITS

## SP521B

#### **BINARY RATE MULTIPLIER**

A binary rate multiplier (BRM) is a form of programmable divider in which the number of pulses appearing at the output for each full period of the counter is equal to the value of the binary number present on the binary inputs. Thus, if the binary word input to a BRM is, say, 10101 (=21) then, for every 32 clock pulses counted only 21 will be gated onto the output.

The SP521 is a binary rate multiplier with two sets of binary control inputs, each associated with its own clock

phase. The phase 1 controls operate in conjunction with the counter chain clock ( $\phi$ 1). The phase 2 controls operate in conjunction with a separate clock ( $\phi$ 2) which can be antiphase with  $\phi$ 1 clock and interlaced with it. Phase 1 and phase 2 outputs can be combined by wiring them together.

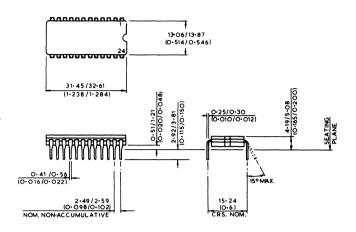

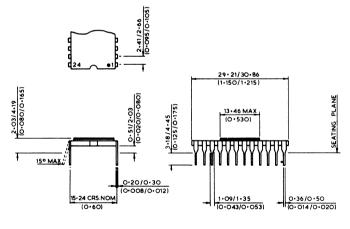

The operating temperature range of the SP521 is  $0^{\circ}$ C to +70°C and the nominal supply voltages are 0V and +5V. The device, is available in 24-lead D.I.L 0.6 inch spacing ceramic packages.

#### **OPERATING NOTES**

The phase 1 controls operate in conjunction with the master clock pulses of the BRM counter chain ( $\phi$ 1 clock). The inputs operate with true positive logic and have CCSL-compatible input requirements. The phase 2 controls have standard RTL type inputs and operate with inverse positive logic in conjunction with the  $\phi$ 2 clock.

Phase 1 and phase 2 outputs are emitter followers with non-standard logic levels -- the logic levels being set by

the logic levels of the phase 1 inputs and the  $\psi$ 2 clock input respectively. In a multiple-package BRM (i.e. > 5 bits) the phase 1 outputs are wired together to give the required output. If the  $\psi$ 2 clock input is interlaced with the  $\psi$ 1 clock, the phase 2 outputs can be wire-ORed with the phase 1 outputs to give a continuous pulse train. The maximum  $\psi$ 1 and  $\phi$ 2 clock input frequency is in excess of 1MHz

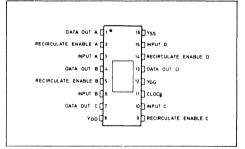

#### **PIN CONNECTIONS**

| Pin No. | Function                                     | Pin No. | Function                                       |

|---------|----------------------------------------------|---------|------------------------------------------------|

| 1       | No connection                                | 14      | Inhibit I/P to 1st flip-flop (CI1)             |

| 2       | Clock I/P Ø1 (BRM drive)                     | 15      | Enable gate chain I/P (Cl <sub>2</sub> )       |

| 3       | Positive supply rail (VCC)                   | 16      | Phase 1 O/P (¢1 OUT)                           |

| 4       | Clock I/P Ø2                                 | 17      | Phase 1 Binary Control Input (true) Bit 5      |

| 5       | Phase 2 Binary control input (inverse) Bit 1 |         | (S5ø1)                                         |

|         | (\$1\$\$\phi2)                               | 18      | Phase 1 Binary Control Input (true) Bit 4      |

| 6       | Phase 2 Binary control input (inverse) Bit 2 |         | (S4ø1)                                         |

|         | ( <u>52</u> ¢2)                              | 19      | Phase 1 Binary Control Input (true) Bit 3      |

| 7       | Phase 2 Binary control input (inverse) Bit 3 |         | (S3 <i>\varphi</i> 1)                          |

|         | ( <del>S3</del> ¢2)                          | 20      | Phase 1 Binary Control Input (true) Bit 2      |

| 8       | Phase 2 Binary control input (inverse) Bit 4 |         | (S2¢1)                                         |

|         | ( <del>S4</del> ψ́2)                         | 21      | Phase 1 Binary Control Input (true) Bit 1      |

| 9       | Phase 2 Binary control input (inverse) Bit 5 |         | (S1ø1)                                         |

|         | (S5¢2)                                       | 22      | Enable carry O/P to gate chain of next BRM     |

| 10      | Phase 2 O/P (¢2 OUT)                         | {       | (CO <sub>2</sub> )                             |

| 11      | Common Rail, 0 volts                         | 23      | Inhibit carry O/P to 1st flip-flop of next BRM |

| 12      | No connection                                |         | (CO <sub>1</sub> )                             |

| 13      | No connection                                | 24      | No connection                                  |

#### ELECTRICAL CHARACTERISTICS

Test conditions (unless otherwise stated)

Tamb =  $0^{\circ}$ C to +70°C

V<sub>CC</sub> = 5.0V ±0.25V

|                                                                                                                                                                              |                   | Value |                         |                           |                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------------------------|---------------------------|----------------------------------------------------------------|

| Characteristic                                                                                                                                                               | Min.              | Тур.  | Max.                    | Units                     | Conditions                                                     |

| INPUT CONDITIONS                                                                                                                                                             |                   |       |                         |                           |                                                                |

| Clock ψ1 I/P pin 2<br>Input voltage 'high'<br>Input voltage 'low'<br>Input current<br>Input slew rate<br>Clock ψ2 I/P (pin 4)<br>Input voltage 'high'<br>Input voltage 'low' | 3.0<br>20<br>3.1  |       | 1.0<br>200<br>T.0       | ν<br>ν<br>μΑ<br>ν/μS<br>ν | See note 1<br>VIN = 3.0V<br>See note 2                         |

| Input voltage low<br>Input current<br>Binary phase 1 control inputs, bits 1 to 5 (pins 17 to 21)<br>Input voltage 'high'<br>Input voltage 'low'<br>Input current             | 3.1               |       | 1.0<br>150<br>1.0<br>20 | μΑ<br>V<br>V<br>μΑ        | V <sub>IN</sub> = 3.1V<br>See note 3<br>V <sub>IN</sub> = 3.1V |

| Phase 2 Binary control inputs, bits 1 to 5 (pins 5 to 9)<br>Input voltage 'high'<br>Input voltage 'low'<br>Input current<br>Input base resistor<br>Input current 'high'      | 1.0<br>1.0<br>200 |       | 0.5<br>0.5              | V<br>V<br>mA<br>kΩ<br>μA  | Voltage<br>VIN = 1V<br>Current drive                           |

| Inhibit I/P to 1st flip-flop (pin 14)<br>Input voltage 'high'<br>Input voltage 'low'<br>Input current<br>Input slew rate                                                     | 2.0<br>20         |       | 1.0<br>2.0              | V<br>V<br>mA<br>V/µS      | See note 1<br>V <sub>IN</sub> = 2.0V<br>See note 2             |

|                                                            |      | Value |      | [     |                                |

|------------------------------------------------------------|------|-------|------|-------|--------------------------------|

| Characteristic                                             | Min. | Тур.  | Max. | Units | Conditions                     |

| Enable gate chain I/P (pin 15)                             |      |       |      |       |                                |

| Input voltage 'high'                                       | 3.1  |       |      | v     |                                |

| Input voltage 'low'                                        |      |       | 1.0  | V     |                                |

| Input current                                              |      |       | 20   | μA    | V <sub>IN</sub> = 3.1V         |

| OUTPUT CHARACTERISTICS                                     |      |       |      |       |                                |

| Phase 1 and phase 2 O/P's (pins 10 & 16) (Emitter follower |      |       |      |       |                                |

| outputs. See notes 3 and 4.)                               |      |       | 1    |       |                                |

| Output high level                                          | 3.0  |       |      | v     | Phase 1 I/Ps & Clock           |

|                                                            |      |       |      |       | 02 I/P connected to            |

|                                                            |      |       |      | 1     | $V_{CC}(+5V)$ via 8 k $\Omega$ |

|                                                            |      |       | 1    |       | resistor. $R_{pd} = 4k\Omega$  |

| Output low level                                           |      |       | 0.4  | v     |                                |

| Enable carry O/P to gate chain of next BRM (pin 22)        |      |       |      |       |                                |

| Output low level                                           |      |       | 0.4  | v     | Sink current = 1.6mA           |

| Output high level                                          |      | Vcc   |      | v     | IOUT = 0mA                     |

| Output impedance                                           |      |       | 4.4  | kΩ    |                                |

| Inhibit carry O/P to 1st flip-flop of next BRM (pin 23)    |      |       |      |       |                                |

| Output voltage 'high'                                      | 2.1  |       | 3.1  | v     | R <sub>pd</sub> = 4kΩ          |

| Output voltage 'low'                                       |      |       | 0.8  | v     | See note 4                     |

| Power supply drain current (pin 3)                         |      | 35    | 60   | mA    | Vcc = +5V,                     |

| ·                                                          |      |       |      |       | Clock 01 I/P = 0V              |

|                                                            |      |       |      |       | Inhibit I/P = OV               |

2. The flip-flops need fast input edges for reliable toggling.

3. The voltage levels of the high states of the phase 1 and phase 2 outputs depend on the input voltages of the phase 1 binary inputs and the clock \$\phi\_2\$ input respectively. In each case the output voltage level will be approximately 2VBE more positive than the appropriate input. voltage. These outputs have no internal pulldown resistors.

4. An emitter follower output will not sink current and is not therefore suitable for interfacing directly with TTL or DTL.

#### **ABSOLUTE MAXIMUM RATINGS**

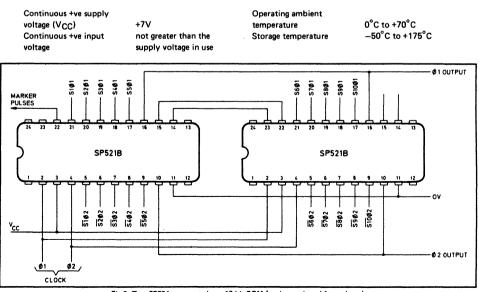

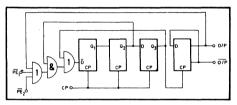

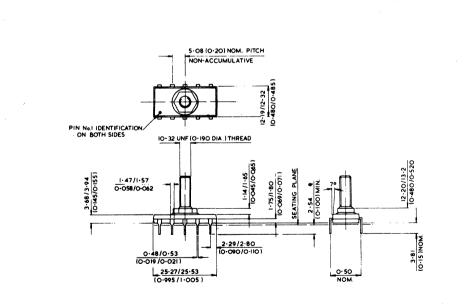

Fig.2 Two SP521s connected as a 10-bit BRM (packages viewed from above)

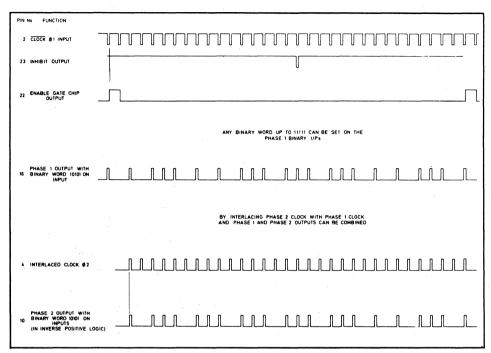

Fig.3 SP521 logic states (5-bit BRM). Enable gate chain input held at logic '1', Inhibit 1st flip-flop held at logic '0'.

## SP520 SERIES PROCESS CONTROL CIRCUITS

## **SP**522B

#### PHASE LOCK, DIVIDER & COMPARATOR

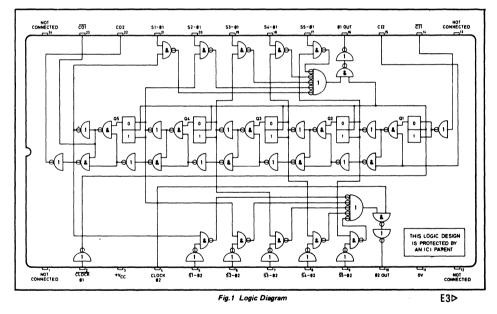

The SP522B is the most specialised of the SP52U series of RTL argital integrated circuits. It contains a frequency divide-by-eight and interlacing circuit, a frequency comparator and digital filter, and an input phase-locking circuit.

#### **Frequency divider**

The clock input frequency of the dividing circuit is referred to as 8f. An output is provided at a quarter of the clock frequency (2f), and 2 interlaced outputs are provided at one eighth of the clock frequency,  $1f\phi 1$  and  $1f\phi 2$ . The maximum clock frequency of the divider chain is in excess of 2MHz.

#### Frequency comparator and filter

The frequency comparator is a five-state up/down counter which can be reset to the central symmetrical state. The reset input to the comparator is NORed with the  $1f\phi 1$  signal. There is one count up input to the counter and two alternative count down inputs, one of which is compatible with CCSL logic. Two direction outputs are provided and one difference frequency output.

When the counter has been set into the central state

by the reset there must be a difference of three pulses between the count up and count down inputs before there is a pulse in the difference frequency output. This means that a small amount of jitter in one input relative to the other will not appear at the output.

#### Phase lock circuit

The phase lock circuit accepts a random phase input (e.g. from a flowmeter transducer) and locks it to the phase of the master clock (8f input). The maximum frequency at which the phase lock circuit will work satisfactorily is 3.2f. A race condition can occur on switching on, but if the master clock and the input signal are phase independent it clears itself very quickly. The phase-locked output at pin 3 is intended to be used as the count up input to the frequency comparator, and is then connected externally to pin 10.

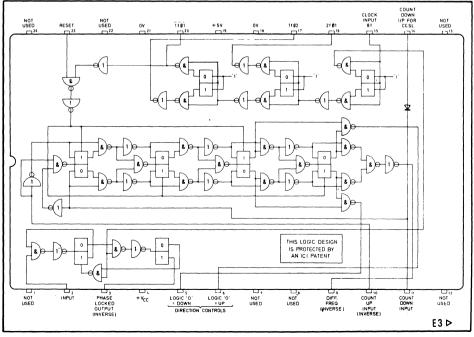

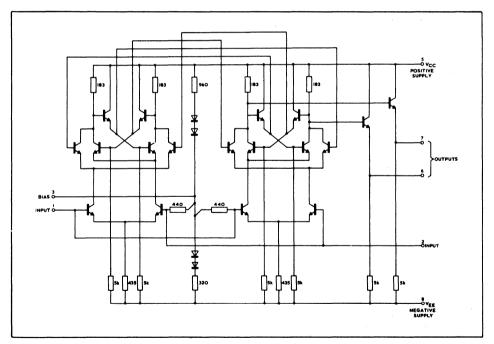

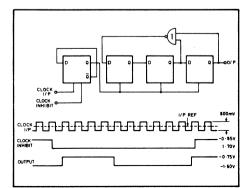

Fig. 1 SP522B Logic diagram

#### PIN CONNECTIONS

| Pin No. | No. Function Pin No.                     |    | Function                                 |

|---------|------------------------------------------|----|------------------------------------------|

| 1       | No connection                            | 13 | No connection                            |

| 2       | Input frequency signal (inverse phase)   | 14 | Additional comparator count down I/P for |

| 3       | Phase lock O/P (inverse phase)           |    | CCSL logic                               |

| 4       | Positive supply rail +V <sub>CC</sub>    | 15 | Master clock I/P (8f)                    |

| 5       | Direction control O/P (logic '0' = down) | 16 | 2f ø1 O/P                                |

| 6       | Direction control O/P (logic '0' = up)   | 17 | 1f \$\phi 2 O/P                          |

| 7       | No connection                            | 18 | Common rail 0V                           |

| 8       | No connection                            | 19 | Positive supply rail +VCC                |

| 9       | Difference frequency – comparator O/P    | 20 | 1f φ1 O/P                                |

|         | (inverse phase)                          | 21 | Common rail 0V                           |

| 10      | Comparator count up I/P (inverse phase)  | 22 | No connection                            |

| 11      | Comparator count down I/P                | 23 | Reset comparator I/P (true)              |

| 12      | No connection                            | 24 | No connection                            |

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):  $T_{amb} = 0^{\circ}C$  to +70°C  $V_{CC} = 5.0V \pm 0.25V$

|                                    |      | Value |      |       |                                      |

|------------------------------------|------|-------|------|-------|--------------------------------------|

| Characteristic                     | Min. | Тур.  | Max. | Units | Conditions                           |

| INPUT CONDITIONS                   |      |       |      |       |                                      |

| Input frequency signal (pin 2)     |      |       |      |       | See note 1                           |

| Input voltage 'high'               | 2.7  |       |      | ·ν    |                                      |

| Input voltage 'low'                |      |       | 1.0  | v     |                                      |

| Input current                      |      |       | 20   | μA    | V <sub>IN</sub> = 2.7V               |

| Input slew rate                    | 1    |       |      | V/µS  | See note 2                           |

| Comparator count-up input (pin 10) | -    |       |      |       | Ň                                    |

| Input voltage 'high'               | 0.95 |       |      | l v   | Voltage                              |

| Input voltage 'low'                |      |       | 0.5  | v     | drive                                |

| Input current                      |      | 0.75  | 1.0  | mA    | V <sub>IN</sub> = 0,95V <sup>)</sup> |

| Input base resistor                | 420  |       |      | Ω     |                                      |

| I/P current 'high'                 | 150  |       |      | μA    | Current drive                        |

| Comparator count-down I/P (pin 11) |      |       | 1    |       |                                      |

| Input voltage 'high'               | 1.0  |       |      | V I   | Voltage                              |

| Input voltage 'low'                |      |       | 0.5  | V V   | drive                                |

| Input current                      |      | 1.0   | 2.0  | mA    | V <sub>IN</sub> = 1.0V               |

|                                    |      |       |      |       | T <sub>amb</sub> = 70°C              |

| Input base resistor                | 350  |       |      | Ω     |                                      |

| Input current 'high'               | 900  |       |      | μA    | Current drive                        |

| ****                                                  | [    | Value |      |       | · · · · · · · · · · · · · · · · · · · |

|-------------------------------------------------------|------|-------|------|-------|---------------------------------------|

| Characteristic                                        | Min. | Тур.  | Max. | Units | Conditions                            |

| Additional count down I/P (pin 14)                    |      |       |      |       |                                       |

| Input voltage 'high'                                  | 2.2  |       |      | v     |                                       |

| Input voltage 'low'                                   |      |       | 1.0  | V     |                                       |

| Input current                                         |      |       | 30   | μA    | V <sub>IN</sub> = 2.2V                |

| Master clock I/P (pin 15)                             |      |       |      |       |                                       |

| input voltage night                                   | 2.7  | ł     | 1    | · ·   |                                       |

| Input voltage 'low'                                   |      |       | 1.0  | v     |                                       |

| Input current                                         |      |       | 20   | μA    | VIN = 2.7V                            |

| Input slew rate                                       | 1    | 1     |      | V/µS  | See note 2                            |

| Reset comparator I/P (pin 23)                         |      |       |      |       |                                       |

| Input voltage 'high'                                  | 2.7  |       |      | v     |                                       |

| Input voltage 'low'                                   |      |       | 1.0  | v     |                                       |

| Input current                                         |      |       | 20   | μA    | V <sub>IN</sub> = 2.7V                |

| OUTPUT CHARACTERISTICS                                |      |       |      |       |                                       |

| Phase Lock O/P (pin 3)                                |      |       |      |       | See note 4                            |

| Output 'low'                                          |      |       | 0.4  | v     | Sink current = 1.6mA                  |

| Output 'high'                                         | 1.1  |       |      | v     | IOUT = 0mA                            |

| Output impedance in high state                        |      |       | 7.2  | kΩ    | .001 0                                |

| Direction control O/PS (Pins 5 & 6)                   |      |       |      |       |                                       |

| Output 'low'                                          | [    |       | 0.4  | v     | Sink current = 1.6mA                  |

| Output 'high'                                         |      | Vcc   | 0.1  | v     | IOUT = 0mA                            |

| Output impedance in high state                        |      |       | 6.5  | kΩ    | .001                                  |

| Difference fremency-comparator O/P (pin 9)            |      |       |      |       |                                       |

| Output voltage 'high'                                 | 3.1  | 3.5   | 3.8  | v     |                                       |

| Output voltage 'low'                                  |      | 0.0   | 0.4  | v     | See note 5                            |

|                                                       |      |       |      |       |                                       |

| 2f ¢1 O/P (pin 16)<br>Output voltage 'low'            |      |       | 0.4  | v     | Sink current = 1.6mA                  |

| Output voltage 'high'                                 |      | Vcc   | 0.4  | v     |                                       |

| Output voltage high<br>Output impedance in high state |      | Vec   | 5.2  | kΩ    | IOUT = 0mA                            |

|                                                       |      |       | 0.2  | N32   |                                       |

| 1f φ2 O/P (pin 17)                                    |      |       |      |       |                                       |

| Output voltage 'high'                                 | 3.5  |       |      | V     |                                       |

| Output voltage 'low'                                  |      |       | 1.0  | V     | See note 5                            |

| 1f φ1 O/P (pin 20)                                    |      |       |      |       |                                       |

| Output voltage 'high'                                 | 3.1  |       | 3.8  | v     |                                       |

| Output voltage 'low'                                  |      | 0.0   | 0.4  | v     | See note 5                            |

| Power supply drain current                            |      | 70    | 82   | mA    | V <sub>CC</sub> ≕ 5V                  |

NOTES

1 There is a 25% probability of a race condition occurring in the phase lock circuit when power is first applied. To ensure that the circuit is brought into its correct operating condition an input clock transition ('1' → '0') must occur while the 4f¢1 clock is in the logic '1' state. In most systems, where the input clock and the master clock are not synchronous, this happens very quickly.

2 The input flip-flops need fast edges for reliable toggling.

3 For the count-down input there is an option of an RTL input (pin 11) or a CCSL compatible input (pin 14). When the RTL input is used the CCSL input should be connected to the 0V rail. When the CCSL input is used, the RTL input should be left open circuit.

4 The logic '1' level of this output is very low and is only suitable for driving an RTL input directly. If required, however, special interface techniques (such as grounded base, emitter input cascode type circuit) can be used to extract the O/P from this pin without further loading the logic '1' level.

5 Pins 9, 17 and 20 are emitter follower outputs and will not sink current. These outputs are not therefore suitable for interfacing directly with TTL or DTL.

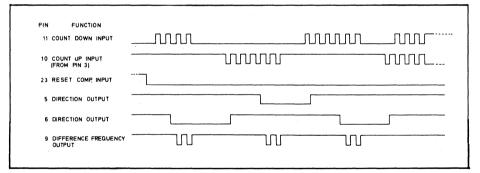

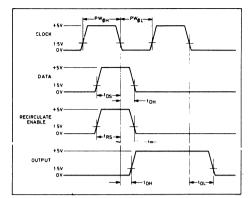

| PIN FUNCTION                  |   |

|-------------------------------|---|

| 15 MASTER CLOCK<br>INPUT (81) |   |

| 16 2f@1                       |   |

| 17 1182                       | ſ |

| 20 1181                       |   |

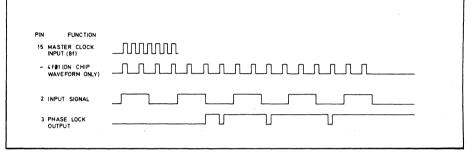

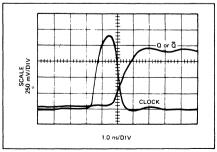

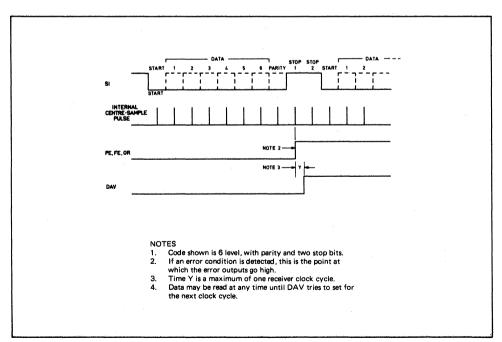

Fig. 2 Frequency divider logic timing

Fig. 3 Phase lock timing, illustrating recovery from race condition

Fig. 4 Frequency comparator and filter timing

#### ABSOLUTE MAXIMUM RATINGS

Continuous +ve supply voltage+7VContinuous +ve input voltagenot greater than the supply voltage in use'Operating ambient temperature0° C to +70° CStorage temperature-50° C to +175° C

#### APPLICATION NOTES

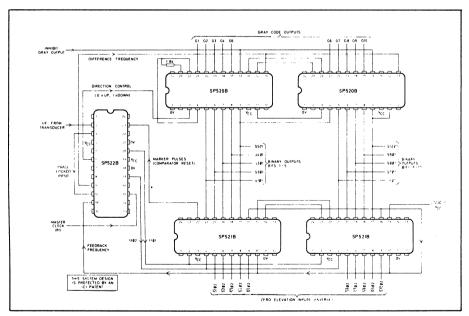

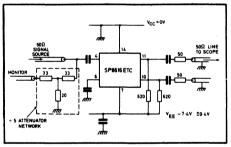

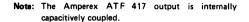

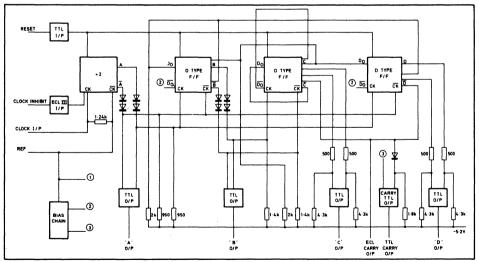

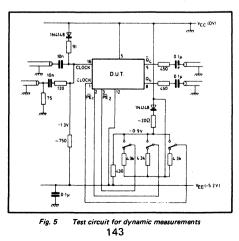

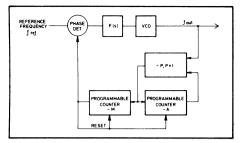

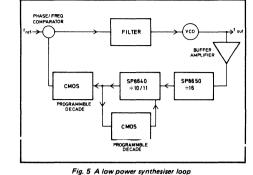

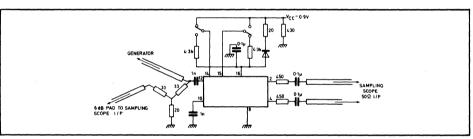

Fig. 5 shows a 10-bit frequency-to-digital encoder using the SP522B together with other elements of the SP520 series. The encoder provides continuous parallel digital output in non-ambiguous Gray code, and is capable of giving an immediate correct response to an interrogation signal at any time. This application note should be read in conjunction with the SP520B and SP521B data sheets.

The encoder employs the continuous feedback principle. The input frequency is first phased-locked to the master clock input to the SP522B then applied, together with the feedback frequency from the binary rate multiplier (SP521B), to the frequency comparator in the SP522B. Any difference frequency that results is applied to the clock inputs of the SP520B Gray code counter. A direction control signal is also applied to one SP520B (least significant 5 bits) to determine the up/down mode of the counter. Binary-coded outputs from the SP520B's form the numerical multipliers that determine the number of output pulses in each cycle (i.e. the feedback frequency) of the binary rate multipliers.

The feedback frequency is taken from pin 16 of each SP521B to pin 14 of the SP522B and is in phase with the  $1f\phi1$  clock signal. The phase 2 outputs of the SP521B's (pin 10) are in phase with 1fd2 clock and are interlaced with the main feedback frequency signal when pins 10 and pins 16 are wired-ORed. Negative binary inputs (pins 5 to 9 on each SP521B) determine the number of pulses in this stream and can therefore be used to provide a zero elevation facility.

The Gray code outputs of each SP520B are interrogated by taking the 'inhibit Gray output' (pin 14) to logic '0'; the outputs can, however, be continuously displayed using the binary-coded outputs (pins 5 to 9) to drive numerical indicators via a suitable interface.

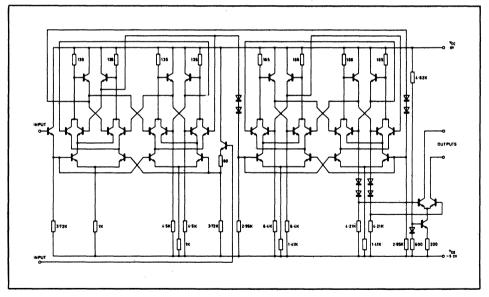

Fig. 5 Frequency-to-digital encoder

SP700 SERIES INTERFACE CIRCUITS

PROVISIONAL DATA

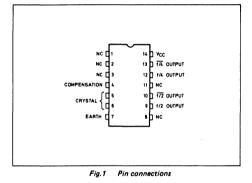

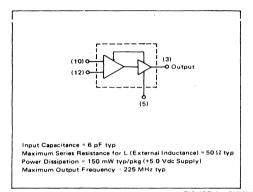

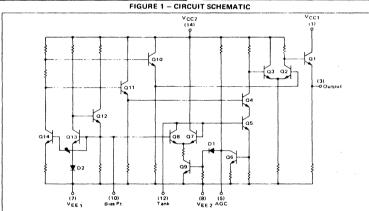

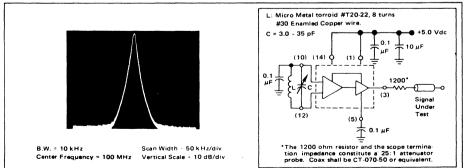

## SP705B CRYSTAL CONTROLLED INTEGRATED CIRCUIT OSCILLATOR

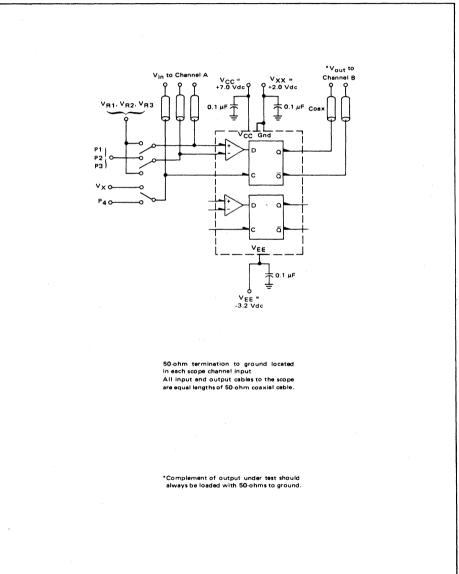

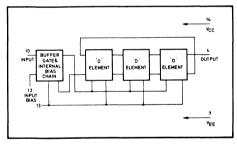

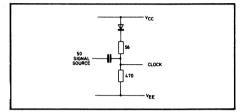

The SP705B is a square wave oscillator circuit designed to operate in conjunction with an AT cut quartz crystal of effective series resistance less than 300 ohms. Four TTL outputs are provided, related in frequency to the crystal frequency f as follows: f/2, f/4,  $\overline{f/2}$  and  $\overline{f/4}$ . The SP705B is therefore ideally suited to either single or multi-phase TTL clock applications

- Operating Frequency up to 10 MHz

- f/2 and f/4 outputs

- 4 TTL Level outputs

- Operates from +5V TTL Supply

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

$V_{CC} = +5V$

| Characteristic                | Symbol          | Va   | lue  | Units | Conditions                                          |

|-------------------------------|-----------------|------|------|-------|-----------------------------------------------------|

|                               |                 | Min. | Max. |       |                                                     |

| High state output voltage     | V <sub>он</sub> | 2.6  |      | v     | V <sub>CC</sub> = 4.75V<br>I <sub>OH</sub> = 0.2 mA |

| Low state output voltage      | VOL             |      | 0.4  | v     | V <sub>CC</sub> = 5.25V<br>I <sub>OL</sub> = 8 mA   |

| Supply current                | Icc             |      | 35   | mA    | V <sub>CC</sub> = 5V                                |

| Output rise time (10% to 90%) | tR              |      | 20   | ns    | V <sub>CC</sub> = 5V                                |

| Output fall time (90% to 10%) | t⊨              |      | 20   | ' ns  | V <sub>CC</sub> = 5V                                |

| Operating frequency (f)       | ·               |      | 10   | MHz   |                                                     |

| Operating temp range          |                 | 0    | 70   | °c    |                                                     |

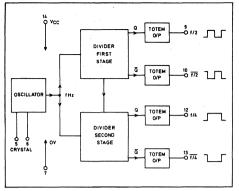

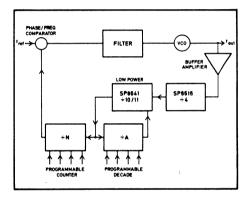

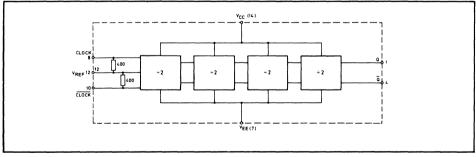

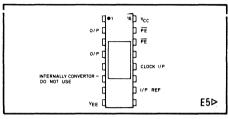

Fig. 2 SP705B block diagram

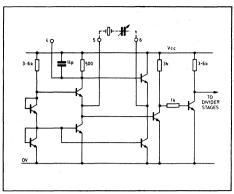

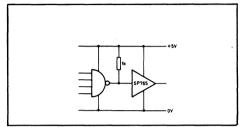

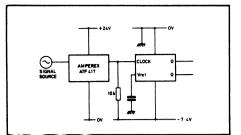

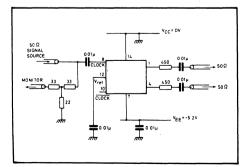

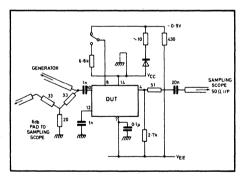

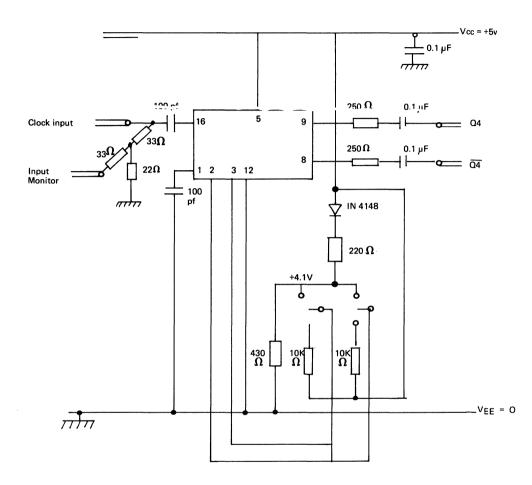

Fig. 3 Circuit diagram of SP705B oscillator

#### CIRCUIT DESCRIPTION

The crystal maintaining circuit consists of an emitter-coupled oscillator, with the emitter resistors replaced by constant-current generators. The crystal is connected, usually in series with a 20pF capacitor, between pins 5 and 6. The 20pF capacitor can be replaced with a mechanical trimmer to allow small changes in frequency to be made, as shown in Fig. 3.

The circuit is designed to provide low crystal drive levels – typically, less than 0.15mW at 5MHz. This is well within crystal manufacturers' limit of 0.5mW.

The compensation point, pin 4 is made available so that the compensation capacitance can be increased if necessary. However the 14pF capacitor included on the chip is usually sufficient to prevent spurious oscillation at high frequencies.

####

Fig. 4 Deviation from nominal crystal frequency

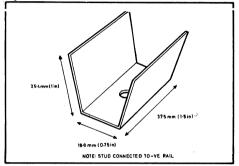

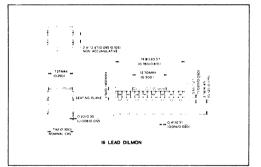

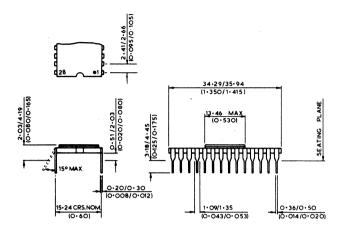

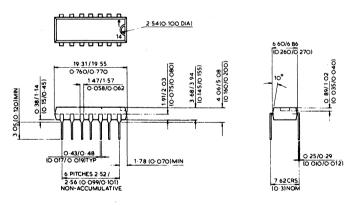

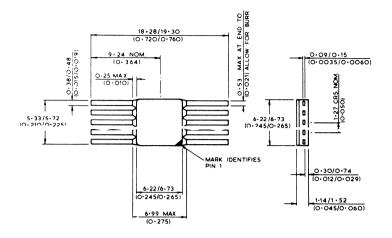

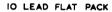

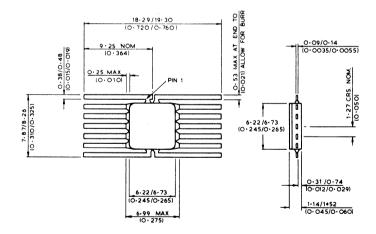

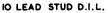

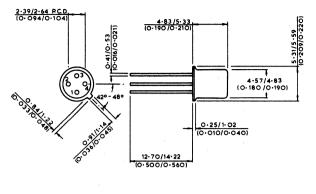

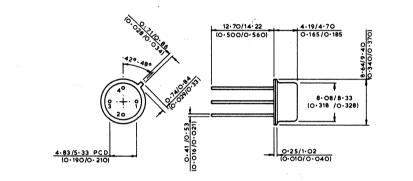

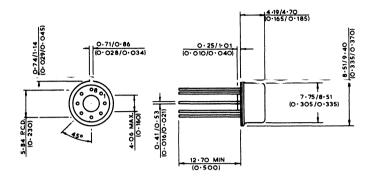

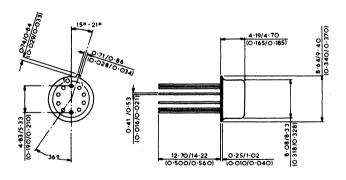

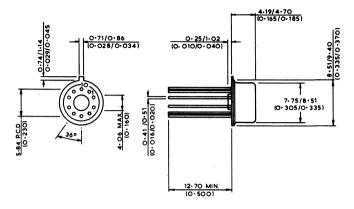

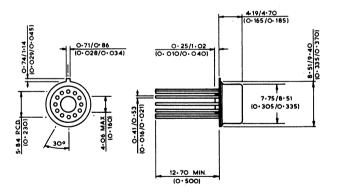

#### PACKAGE DETAILS

Dimensions are shown thus: mm (in)

This publication is issued to provide outline information only and fundes specifically agreed to the contrary by the contract or be regarded as a representation relating to the products or services concerned. We reserve the right to alte without notice the specification, design, price or condition of supply of any product or service.

18

# PLESSEY SEMICONDUCTORS

## SP720 SERIES INTERFACE CIRCUITS

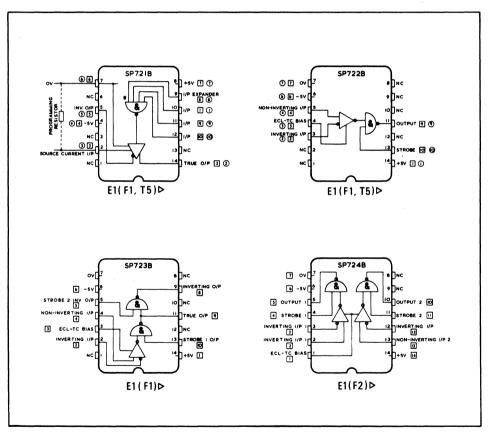

#### SP721B BALANCED LINE DRIVER SP722B BALANCED LINE RECEIVER

SP723B BALANCED LINE RECEIVER WITH COMPLEMENTARY OUTPUTS

#### SP724B DUAL BALANCED LINE RECEIVER

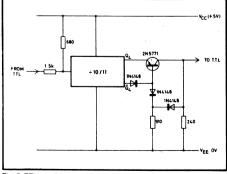

The SP721B, SP722B, SP723B and SP724B circuits are designed for interfacing between TTL/DTL logic and balanced transmission lines. The SP721B line driver produces an output which is essentially a current sink into one of the two lines. The magnitude of the current is nominally twice that of an externally programmed source current. The receiver circuits will accept antiphase signals from a line with a d.c. level several volts remote from earth potential.

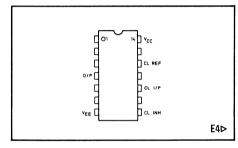

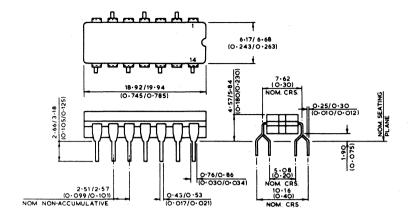

Fig. 1 Logic and dual-in-line peckage connection diagrams. Connections for peckage options shown thus: 🗆 = Flatpeck, O = TO-5.

#### Absolute Maximum Ratings (all devices unless otherwise stated)

| Storage temperature range<br>Operating temperature range<br>Dissipation (at T <sub>amb</sub> = 70°C) | –55°C to +175°C<br>0°C to +70°C | Line input excursion (receivers) | ±5V, or power<br>supply rail values,<br>whichever are the |

|------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------|-----------------------------------------------------------|

|                                                                                                      |                                 |                                  |                                                           |

| (SP721B)                                                                                             | 300 mW                          |                                  | lower                                                     |

| Positive supply                                                                                      | +6·5V                           | Line output excursion (SP721B)   | +5V to neg. supply                                        |

| Negative supply                                                                                      | _–6·5V                          | Line input differential voltage  |                                                           |

| Logic input excursion                                                                                | +5V to -0.5V                    | (receivers)                      | 6V                                                        |

|                                                                                                      | •                               | Source current input (SP721B)    | 20mA                                                      |

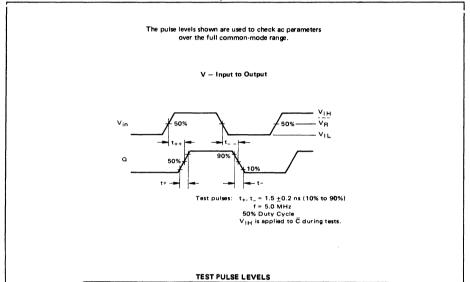

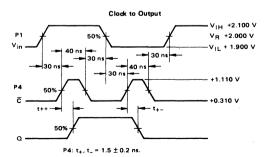

Electrical Characteristics (SP7210) @ Vic = 151/ 15%, Vic - 154 15%, T = 0 to 70°0

| Characteristic                                                   |      | Value |      | Units                   | Test conditions        |  |

|------------------------------------------------------------------|------|-------|------|-------------------------|------------------------|--|

| Characteristic                                                   | Min. | Typ.  | Max. | Units                   |                        |  |

| 'Input voltage for logic 'O' O/P                                 | 0    |       | 800  | mV                      | -                      |  |

| Input current for logic 'O' O/P                                  |      |       | 1.6  | mA (neg.)               | V <sub>IN</sub> = 0.4V |  |

| Input voltage for logic '1' O/P                                  | 2.0  |       |      | v                       | -                      |  |

| Input current for logic '1' O/P                                  |      |       | 40   | μΑ                      | V <sub>IN</sub> = 2·4V |  |

| Output current at pin 5 for logic '0' O/P                        |      |       | 1.0  | μΑ                      |                        |  |

| Output current at pin 14 for logic '0' O/P                       | 1.4  | 2.0   | 2.6  | /unit source<br>current | Note 1                 |  |

| Output current at pin 14 for logic '1' O/P                       |      |       | 1.0  | μΑ                      | Note 1                 |  |

| Output current at pin 5 for logic '1' O/P                        | 1.4  | 2.0   | 2∙6  | /unit source<br>current | Note 1                 |  |

| Output current difference<br>between logic 'O' and logic '1'     |      |       | 100  | μА                      | Note 1                 |  |

| Permissible output voltage excursion                             | -3   |       | +3   | v                       | Notes 1 and 2          |  |

| Mean propagation delay<br>(t <sub>pu</sub> + t <sub>pd</sub> )/2 |      | 15    |      | nS                      | Note 3                 |  |

| Propagation delay skew                                           |      |       | 5    | nS                      | Note 4                 |  |

| Dissipation                                                      |      | 150   | 260  | mW                      | Note 5                 |  |

| Supply current (+5V)                                             |      | 5.5   | 7.0  | mA                      | h                      |  |

| Supply current (-5V)                                             |      | 33    | 45   | mA                      | SOURCE = 10mA          |  |

#### SP721B Test Notes (D.I.L. package pins quoted)

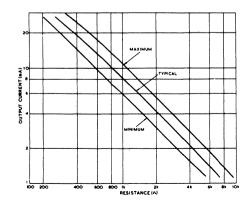

- This result holds for the source current in the range 1 to 10mA (pin 2) and this current is normally determined by a resistor from pin 2 to ground (see fig. 2).

- The voltage indicated is an absolute voltage and to determine the common mode value, the signal voltage must be subtracted from the absolute voltage. The maximum signal voltage=2-6 x source current x effective load resistor.

- The time period measured, is from the time when the input passes through the threshold of the circuit, until the output currents at pins 14 and 5, are equal.

- 4. The propagation delay skew is the time for which the sum of the current at pins 14 and 5 differs from the d.c. value by more than 50% on switching the output state.

- A duty cycle of 50% is assumed, but if the output is permanently in the logic '1' state the dissipation will be 10mW higher. The source current is set at 10mA.

Fig. 2 Output current v. resistance between pin 2 and OV, assuming 5% tolerance on resistance

#### Electrical Characteristics (SP722/3/4B) @ $V_{CC}$ = +5V ±5%, Vee = -5V ±5%, T = 0 to 70°C.

| Characteristic                      | Circuit                 | Value |                |                   | Units          | Test conditions             |  |

|-------------------------------------|-------------------------|-------|----------------|-------------------|----------------|-----------------------------|--|

| Characteristic                      | Circuit                 | Min.  | Тур.           | Max.              | Units          | l est conditions            |  |

| Input voltage<br>(common mode)      | All                     | -3    | 0              | +3                | v              | -                           |  |

| Input offset                        | SP722<br>SP723/724      | 5     | 4·5<br>10      | 15<br>15          | mV<br>mV       | VOUT = 1.5V                 |  |

| Input threshold                     | All                     |       | 4.5            |                   | m∨             | Note 1                      |  |

| Input current                       | All                     |       |                | 100               | μΑ             | -                           |  |

| Input capacitance                   | All                     |       | 1              | 2                 | pF             | Note 2                      |  |

| Input current for logic 'O' I/P     | All                     |       |                | 1.6               | mA (neg.)      | V <sub>IN</sub> = 0.4V      |  |

| Input current for<br>logic '1' I/P  | All                     |       |                | 120               | μΑ             | V <sub>IN</sub> = 2·4V      |  |

| Output voltage for<br>logic '0' O/P | All                     |       |                | 400               | mV             | l <sub>o</sub> = 0 to 16mA  |  |

| Output voltage for<br>logic '1' O/P | All                     | 2.4   |                |                   | v              | l <sub>o</sub> = 0 to 400μΑ |  |

| Mean propagation<br>delay           | All                     |       | 20             |                   | nS             | · _                         |  |

| Dissipation                         | SP722<br>SP723<br>SP724 |       | 170            | 145<br>155<br>230 | mW<br>mW<br>mW | -<br>-<br>-                 |  |

| Short circuit output<br>current     | All                     | 18    |                | 55                | mA             | Note 3                      |  |

| Supply current<br>(+5V)             | SP722<br>SP723<br>SP724 |       | 12<br>13<br>19 | 16<br>18<br>27    | mA<br>mA<br>mA |                             |  |

| Supply current<br>(-5V)             | All                     |       | 9              | 12.5              | mA             | -                           |  |

#### SP722B, SP723B and SP724B Test Notes

- 1. Measured from offset to give full logic 'O' or logic '1' at output.

- As input passes through threshold, capacitance temporarily rises to 10pF.

- Not more than one output should be shorted at any one time. This parameter is measured at the maximum recommended supply voltage.

#### **Operating Notes**

The SP721B Balanced line driver, accepts TTL logic inputs, and its output to line is in the form of a differential current sink. The current flows from the line into one of the two output terminals, setting up a differential voltage on the line. The magnitude of this current sink is determined by the value of external programming resistor between pins 7 and 2 (Fig. 1), and is nominally twice the current flowing into pin 2. The size of the differential voltage produced on the line, is dependent on the current chosen and the differential impedance of the line.

A recommended standard is 8mA (minimum) into a 100  $\Omega$  line giving an 800mV differential signal.

The line receivers will accept up to a 3V common mode input without being affected, responding only to differential signals producing TTL compatible outputs.

#### Point to Point Working

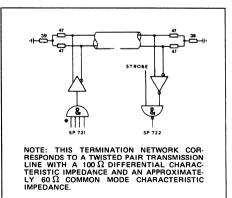

Fig. 3 shows a typical configuration with balanced matched lines terminated at both ends. It is possible to match only the differential impedance, but problems may arise from reflected common mode signals which may then exceed the 3V limit. To overcome this problem, the network shown gives a common mode termination of about 60  $\Omega_{\rm c}$  corresponding to a typical screened sheath pair cable. Using low loss cable in this way, signals can be transmitted a distance of at least 150 metres, at clock rates up to 5 MHz.

The common mode line figure of 3V can be improved by attenuating the cable signals to the receiver, at the expense of differential sensitivity. Typically an attenuation up to 5 times (14 dB) may be used before the differential error becomes excessive.

When more than one receiver or transmitter are used it is important that all transmitters and receivers connected to a line are always connected to common power supplies.

continued . . .

#### **Distribution of Multiple Receivers**

Each receiver has only a small disturbing influence, so several receivers may be connected on to one line at different points. However it is possible that common mode problems may be accentuated, so it is often advisable to carry out attenuation as suggested in the paragraph on point to point working.

#### **Multiple Transmitters for Highway Working**

By strobing the programming current supplied to pin 2 of the SP21B, the output from that transmitter can be switched on or off. This however produces a large common mode shock which takes time to decay, the decay time depending on the line length and line characteristics. Thus the SP721B can be used for block data transfer, provided sufficient time is allowed between blocks, for the common mode shocks to decay.

## SP700 SERIES INTERFACE CIRCUITS

## NEW PRODUCT DATA

## SP761B 12V POWER INTERFACE CIRCUIT

## SP762B 5V POWER INTERFACE CIRCUIT

The SP761B and SP762B are bipolar integrated circuits, each incorporating five current amplifiers for interfacing between MOS/TTL devices and loads requiring high drive currents. The SP761B is designed to operate from a +12V supply rail and the SP762B from +5V.

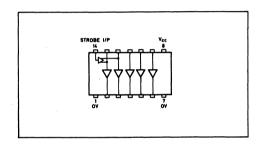

Both types are provided with a strobe input which drives two of the amplifiers so that their outputs may be connected in parallel for higher output current capability.

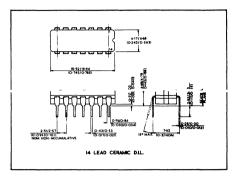

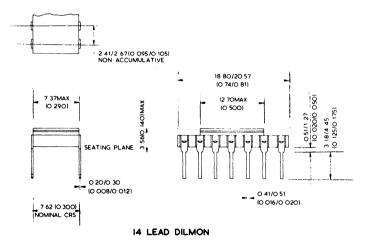

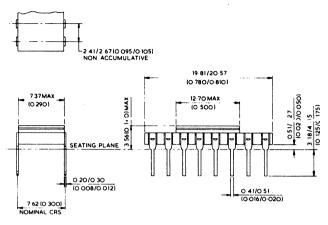

The circuits operate over a temperature range of  $0^{\circ}$ C to +70°C and are mounted in 14-lead ceramic DIL package.

Although primarily designed to drive printing solenoids in calculators, these circuits can be used in a variety of applications requiring high drive currents.

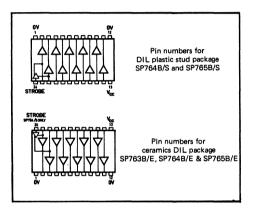

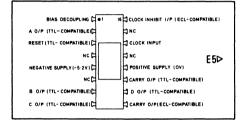

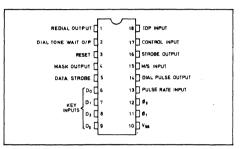

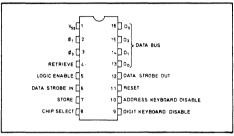

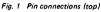

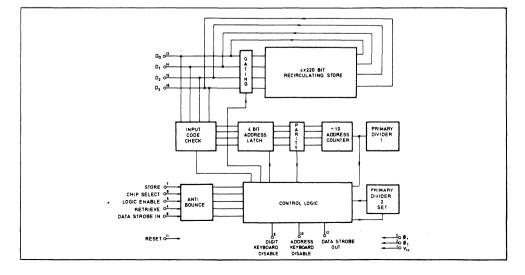

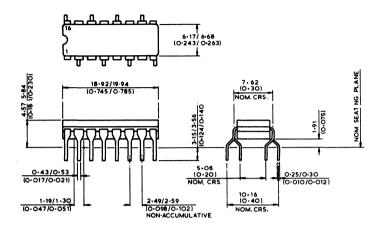

Fig. 1 Pin connections (top)

#### FEATURES

- Input MOS/TTL Capability

- Output 200 mA Capability

- Five Channels per Package

- Open Collector Output

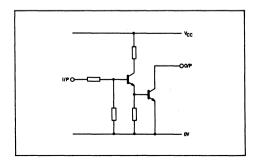

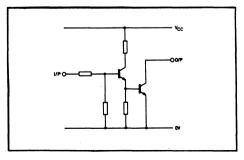

Fig. 2 Functional diagram (one driver)

#### APPLICATIONS

- Driving Solenoids

- Driving Relays

- Driving LEDs

- Driving Filament Lamps

- Driving Cores

- TTL-to-MOS Translator

#### ABSOLUTE MAXIMUM RATINGS

Output collector voltage

26V

Supply voltage, SP761B

+15V

Supply voltage, SP762B

+7V

Storage temp.

-55°C to +125°C

Chip operating temp.

+125°C

Ambient operating temp.

0°C to +70°C

#### **ELECTRICAL CHARACTERISTICS**

| Ob an advaitable                        | <b>T</b> | Va   | Value (note 1) |      |       | Conditions               |  |

|-----------------------------------------|----------|------|----------------|------|-------|--------------------------|--|

| Characteristic                          | Туре     | Min. | Тур.           | Max. | Units | Conditions               |  |

| Supply voltage V <sub>CC</sub>          | SP761B   | 11   | 12             | 13   | v     | See note 2               |  |

|                                         | SP762B   | 4.5  | 5              | 5.5  | v     | See note 2               |  |

| Quiescent supply current                | SP761B   |      | 8              |      | mA    | All inputs low           |  |

|                                         | SP762B   |      | 10             |      | mA    | All inputs low           |  |

| On state supply current,<br>per element | Both     |      | 12             |      | mA    | I <sub>IH</sub> = 1mA    |  |

| input Current ing                       | SPICIB   | 1    |                | 4    | mA    | iout = 150mA             |  |

| Input voltage VIH                       | SP761B   |      | 4              |      | v     | l <sub>IH</sub> = 1mA    |  |

| Input current IIL                       | SP761B   |      |                | 50   | μA    |                          |  |

| Input voltage VIH                       | SP762B   | 2.7  |                | 5.5  | v     | l <sub>out</sub> = 200mA |  |

| Input current IIH                       | SP762B   |      | 1              |      | mA    | V <sub>IH</sub> = 2.7V   |  |

| Input voltage VIL                       | SP762B   |      |                | 1    | v     |                          |  |

| Output current lout                     | SP761B   |      |                | 150  | mA    | I <sub>IH</sub> = 1mA    |  |

|                                         | SP762B   |      |                | 200  | mA    | V <sub>IH</sub> = 2.7V   |  |

| Output voltage V <sub>OL</sub>          | SP761B   |      | 1.0            | 1.2  | v     | l <sub>out</sub> = 150mA |  |

|                                         | SP762B   |      | 1.3            | 1.6  | V     | l <sub>out</sub> = 200mA |  |

| Output voltage V <sub>OH</sub>          | Both     |      |                | 26   | V V   |                          |  |

| Output breakdown voltage                | Both     | 26   |                |      | l v   | See note 3               |  |

| Duty cycle                              | SP761B   | 1    |                | 40   | %     |                          |  |

|                                         | SP762B   |      |                | 33   | %     | All outputs at           |  |

| On time                                 |          |      |                | 2    | s     | l <sub>out</sub> max.    |  |

NOTES

1. Both OV supply pins 1 and 7 must be connected at all times.

2. Min. and max. limits apply to the temperature range 0°C to +70°C. All typical values are quoted for V<sub>CC</sub> = Typical and T<sub>amb</sub> = +25°C.

3. External clamping diodes must be used when driving inductive loads.

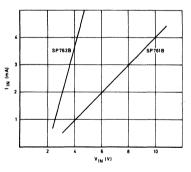

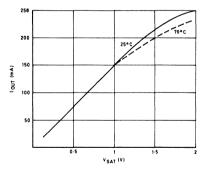

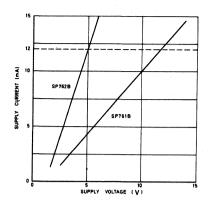

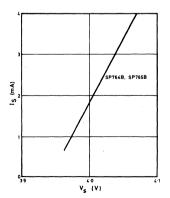

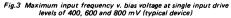

Fig. 3 Input characteristic (including strobe)  $T_{amb} = +25^{\circ}C$

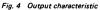

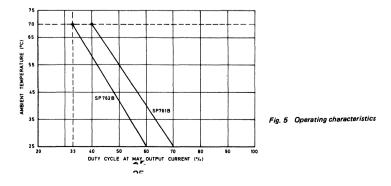

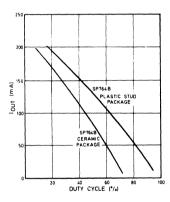

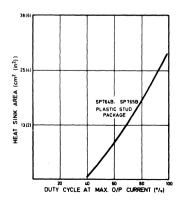

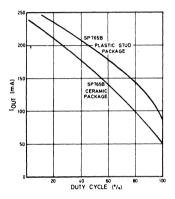

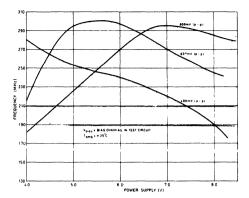

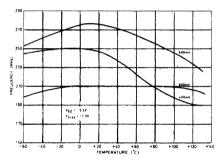

Fig. 6 Operating characteristics at +70°C

#### **OPERATING NOTES**

#### Interfacing

The SP761B is designed to interface directly with MOS devices, accepting free drain input currents in the range 1 mA to 4 mA. Current limiting input resistors are incorporated on-chip to reduce power dissipation in the MOS circuit. The resistor is approximately 2 k $\Omega$ , giving an input voltage of 4V at 1 mA.

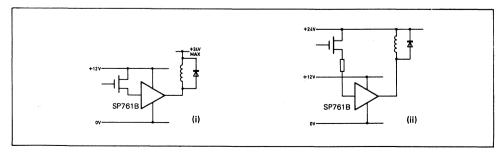

Fig. 8 shows (i) a direct interface to MOS and (ii) an interface using an external resistor to further limit input current when driven from a high voltage source.

The SP762B will interface directly with standard TTL over the temperature range 0°C to +70°C, a TTL logic '1' making current available at the SP762B output. Although TTL is not specified to source more than 400  $\mu$ A at logic '1' level, the majority of gates will in fact supply approximately 5 mA and still maintain a logic '1' level in excess of 2.7V. Since the input resistors of the SP762B are approximately 600 $\Omega$ , then one TTL output is capable of driving up to 5 SP762B inputs. When driving only one input of an SP762B, the input current will limit at approximately 2 mA at 3.4V. Open-collector TTL gates can also be used to drive the SP762B, provided that each TTL output has an external load resistor, the value of which will depend on the fanout required.

The characteristics of the strobe input are the same as for the individual inputs and therefore the above comments also apply to this input.

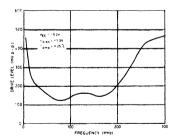

Fig. 7 On state supply current drain per element

#### **Unused Inputs**

When using the strobe input, inputs 1 and 2 must be left floating. However, inputs 1 and 2 can be used completely independently in the same way as the other inputs. Any other unused inputs can either be left floating or tied to the negative supply rail.

#### **Output Capability**

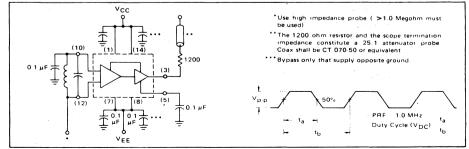

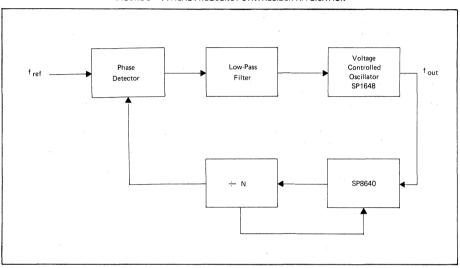

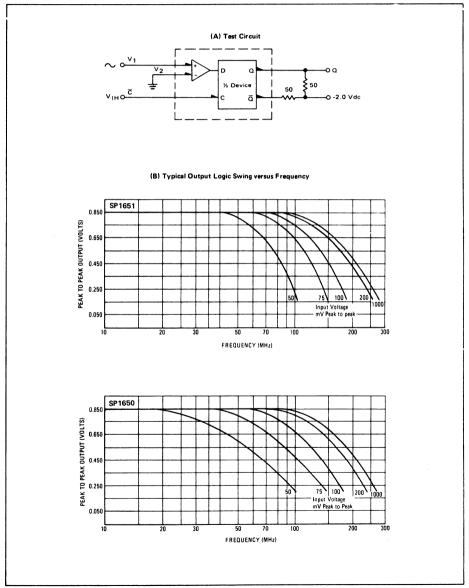

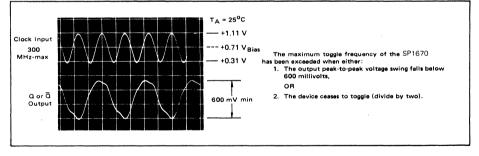

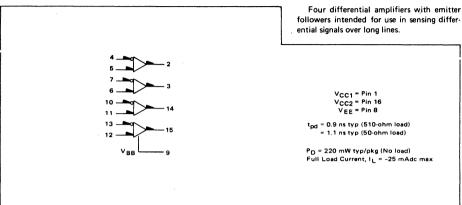

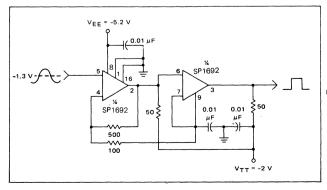

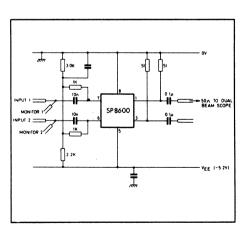

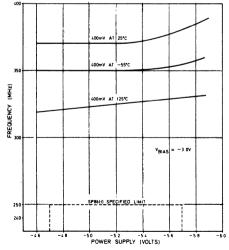

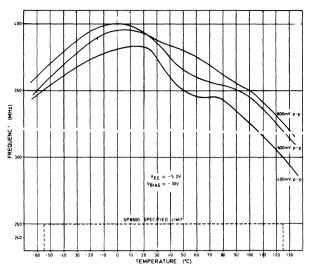

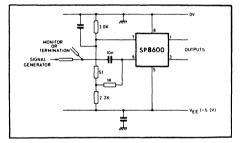

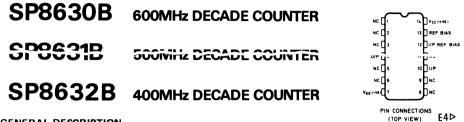

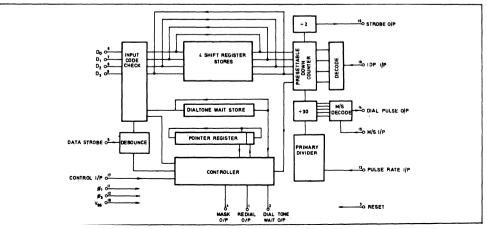

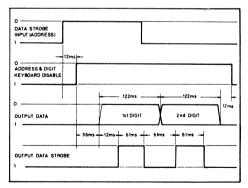

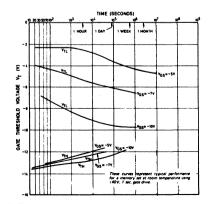

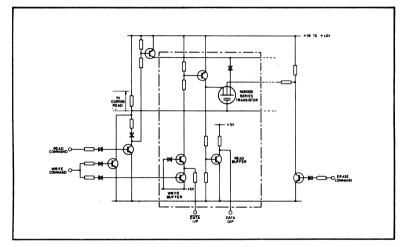

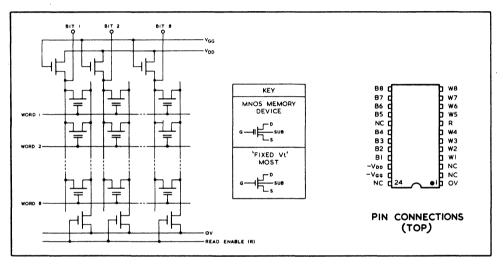

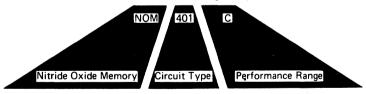

The output capability of each channel is 150 mA for the SP761B and 200 mA for the SP762B. With all five drivers operating at these current levels, a duty cycle of 40% for the SP761B and 33% for the SP762B will allow operation over the temperature range  $0^{\circ}$ C to  $+70^{\circ}$ C.