# N-901

# Interfacing the DP8441 and the 68040

This application notes assumes that the reader is familiar with the modes of operation of the DP8441 DRAM controller and the 68040 microprocessor. The nature of this application note is to give the system designer an idea of a possible memory configuration. After reading this application note, the system designer must do an analysis for his particular application.

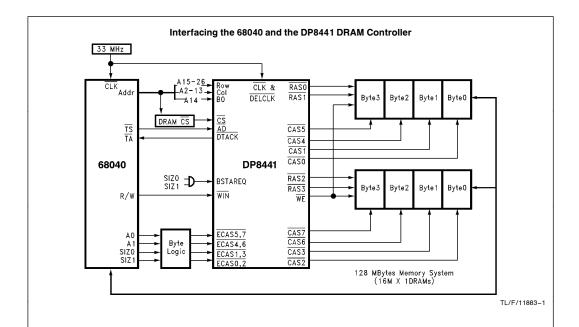

The design's operating frequency is 33 MHz and the design supports page and burst accesses. The design constitutes a complete 128 Megabytes memory system in a 2 bank configuration. The memory array uses 70 ns DRAMs in a 16 Megx1 architecture. Different or more compact memory arrays can be achieved if different DRAMs are used.

The DP8441 performs all housekeeping required by DRAMs. The controller will refresh the memory and it will guarantee precharge times after accesses or refresh cycles. The DP8441 also arbitrates between accesses, refreshes and precharge. The DRAM controller will insert wait states into an access cycle to allow refresh or precharge to take place. The controller will delay a refresh to allow an access in progress to finish.

The DP8441 supports byte, word or double-word writing. This is done through decoding the 68040's A0, A1, SIZ0 and SIZ1 outputs and connect the appropriate  $\overline{\text{BE}}$  (byte enables) to the  $\overline{\text{ECAS}}$  inputs in the DP8441.  $\overline{\text{ECAS}}$  controls the  $\overline{\text{CAS}}$ s to the DRAMs.The DP8441 also supports the 68040 Read-Modify-Write (LOCKED cycle), this is done by connecting the  $\overline{\text{LOCK}}$  output from the 68040 to  $\overline{\text{DISRFSH}}$  input on the DP8441. This guarantees that a refresh will not brake a Read-Modify-Write cycle.

#### RESET AND PROGRAMMING

Resetting the DRAM controller is accomplished by asserting low the RESET input for at least 16 clock cycles. The DP8441 must be programmed before accessing the memory. Programming can be done by writing to an I/O address equal to the programming selection. Programming can also be accomplished during the first memory write. In the latter case the CPU writes to an address equal to the programming selection during the first write cycle after power up.

After  $\overline{\text{ML}}$  negates during the programming cycle, the DP8441 enters a 60 ms initialization period. This period is when the Phase Lock Loop (PLL) locks into place.

The system must wait at least 70 ms before accessing the memory. During this time the DRAM controller performs refreshes to the memory, this makes further "warm up" cycles unnecessary.

#### OPENING ACCESS

A memory access begins when the 68040 outputs a valid address and asserts  $\overline{\text{ADS}}$ . For this design at 33 MHz, the address, the B0 (bank select) and the  $\overline{\text{ADS}}$  inputs meet the set up times required by the DRAM controller. Three address lines are used to do DRAM  $\overline{\text{CS}}$ . The  $\overline{\text{CS}}$  setup time is also met.

The DP8441 will split the address from the CPU and will output the row address to the DRAMs. The appropriate  $\overline{\text{RAS}}$ ,

National Semiconductor Application Note 901 Atilio Canessa June 1993

as decoded by B0, will assert from the next rising clock edge latching the row address into the DRAM. The programmed  $t_{RAH}$  will be guaranteed by the controller before switching the internal multiplexor to the column address. The controller latches the column address into the DRAM after meeting the  $t_{CSC}$ . The  $t_{RAH}$ ,  $t_{CSC}$  and the time when the controller switches the row address to the column address is guaranteed by the on board delay line based on the

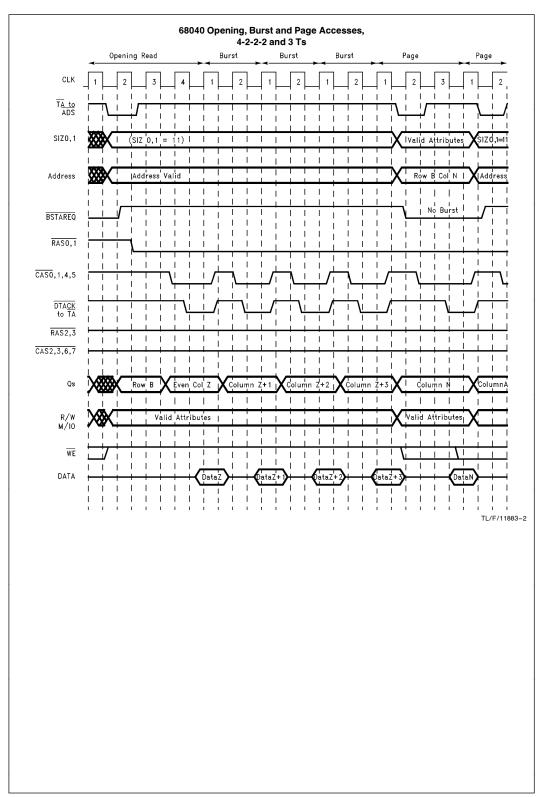

The controller asserts  $\overline{\text{DTACK}}$  after the programmed number of wait states to indicate to the CPU that the access can finish. In this design,  $\overline{\text{DTACK}}$  asserts from the 3rd rising clock edge. The  $\overline{\text{DTACK}}$  setup time required by the CPU is easily met. At the end of the fourth clock the 68040 will either latch the data into its registers in the case of a read cycle, or it will take the data of the bus in the case of a write cycle. For every access,  $\overline{\text{DTACK}}$  asserts for one clock period, and  $\overline{\text{CAS}}$  negates from the same clock edge that  $\overline{\text{DTACK}}$  negates.

#### **PAGE ACCESSES**

Every access finishes when DTACK asserts. In this application note, the DRAM controller is programmed in page mode, thus when DTACK negates, only CAS negate and RAS stays asserted. When the CPU requests a new access (a new address and a new ADS), if this new access is within the same page as the previous access (same row address), a page hit is detected by the on-board page comparator. When there is a page hit, RAS stays asserted and the controller outputs the new column address and asserts CAS from the next rising clock edge. In cases when there is a page miss, the DP8441 negates RAS, meets the programmed number of clock cycles for precharge, and then asserts RAS to latch the new row address into memory. In either case DTACK will assert and negate after the appropriate number of programmed wait states (DATCK for page accesses or for opening accesses).

#### **BURST ACCESSES**

The 68040 indicates that it wants to burst when the attributes SIZ0 and SIZ1 are both 1. The system's glue logic decodes SIZ0 and SIZ1 and generates BSTREQ (a simple AND gate is used). BSTREQ asserted makes the DRAM controller to increment the column address every time \$\overline{\text{DTACK}}\$ negates. The DRAM controller will automatically assert \$\overline{\text{CAS}}\$ to latch the new column address into memory. \$\overline{\text{CAS}}\$ precharge is guaranteed by the on-board delay line, and in this design it is programmed to be 10 ns minimum. The DP8441 will burst for as long as BSTREQ is asserted. Every burst access finishes with the assertion and negation of \$\overline{\text{DTACK}}\$.

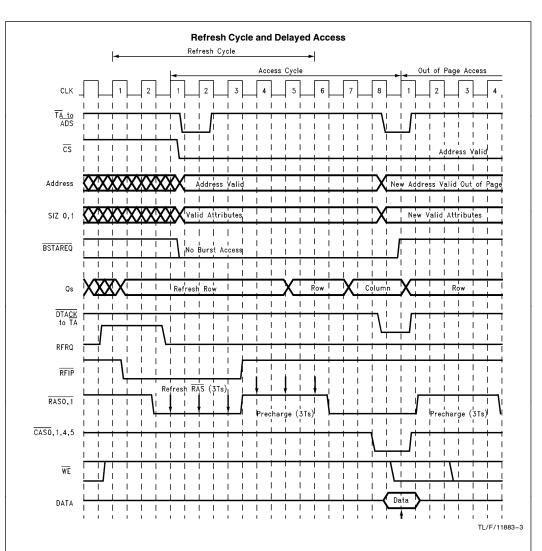

#### REFRESH AND PRECHARGE

The DP844I will request a memory refresh every 15  $\mu$ s. During refresh,  $\overline{RAS}$  will be low for 3 clock periods. The controller will also guarantee precharge of 3 clock periods. These timings are enough for 70 ns DRAMs. If the controller is in the middle of a page mode access ( $\overline{RAS}$  asserted but no

real access may be in progress) the controller will keep track of all missed refresh requests. When there is an access out of page, the DRAM controller will burst refresh the memory the number of refresh requests missed. If the inpage access is idle and there is a sixth refresh request, the DRAM controller will automatically finish the access, meet the precharge time, and burst refresh the memory six times.

# PROGRAMMING BITS

### TABLE I.

| R1, R0<br>0, 1               | RAS Low and Precharge Time<br>3Ts                                                           |

|------------------------------|---------------------------------------------------------------------------------------------|

| R3, R2<br>0, 1               | DTACK during Opening Access Will<br>Assert after RAS<br>2Ts                                 |

| R5, R4<br>0, 1               | DTACK during Burst Access Will<br>Toggle with CAS<br>1T                                     |

| R7, R6<br>0, 1               | DTACK during Page Access Will<br>Assert after CAS<br>1T                                     |

| R8, R9<br>1, 1               | Page Size Select to 4096 for 16 Meg DRAMs                                                   |

| R11, R10<br>0, 1             | Wrap around Size Select 4 (00 01 10 11)                                                     |

| C3, C2, C1, C0<br>0, 1, 0, 0 | Divisor Select for DELCLK to Get<br>Close to 2 MHz<br>15(30/16 = 2)                         |

| C5, C4<br>1, 1               | B0 Is Not Used. Staggered Refresh B1 = 1 → RAS 0,1 CAS 0,1,4,5 B1 = 1 → RAS 2,3 CAS 2,3,6,7 |

# TABLE I. (Continued)

| C6<br>0    | Staggered Refresh Selected                                                  |

|------------|-----------------------------------------------------------------------------|

| C7<br>0    | $t_{RAH} = 10 \text{ ns}$                                                   |

| C8<br>1    | Page Miss Output Selected                                                   |

| C9<br>0    | CAS Precharge Time during Burst<br>1/2T during Read and 1T during Write     |

| C10<br>0   | RAS Only Refresh Selected                                                   |

| C11<br>0   | 15 μs Refresh Period                                                        |

| B0<br>1    | DTACK Rising Edge Increments the Column Counter                             |

| B1         | Page Mode Selected                                                          |

| ECAS0<br>0 | Latch Mode Selected to Be Able to Increment the Column Counter during Burst |

| ECAS1      | Burst Request Select Is Active High                                         |

| ECAS2<br>0 | CAS and DTACK Clock Edge Select Is the Rising Clock Edge                    |

```

TIMINGS FOR THE 68040 AND THE DP8440/41 INTERFACE DRAM CONTROLLER RUNNING AT 33 MHz

(1) Minimum ADS Low Setup Time to CLK High.

1 CLK Period - CLK High to TS Asserted (68040)

30.3 ns - 19 ns

11.3 ns

The DP8440/41 need only 6 ns

(2) Minimum Address Valid Setup Time to CLK High.

1 CLK Period - CLK High to Address Valid (68040)

30.3 ns - 19 ns

The DP8440/41 need only 10 ns

(3) Minimum CS Asserted Setup Time to CLK High.

1 CLK Period - (CLK High to Address Valid + Decoder Delay)

30.3 \text{ ns} - (19 \text{ ns} + 7 \text{ ns})

30.3 ns - 26 ns

4.3 ns

The DP8440/41 need only 4 ns

(4) Wait States through TA during Opening Accesses.

(4a) Access Time from RAS

1 CLK Period + CLK High to RAS Asserted (DP8440/41) + DRAM t<sub>RAC</sub> + Data Setup Time (68040)

30.3 \text{ ns} + 15 \text{ ns} + 70 \text{ ns} + 5 \text{ ns}

120.3 → 4 CLK Periods (121.2 ns)

(4b) Access Time from CAS

1 CLK Period + CLK to CAS Asserted (DP8440/41) + DRAM t_{CAC} + Data Setup Time (68040)

30.3 \text{ ns} + 55 \text{ ns} + 20 \text{ ns} + 5 \text{ ns}

110.3 ns → 4 CLK Periods (121.2 ns)

(4c) Access Time from Column Address Valid

1 CLK Period + CLK High to Column Address Valid (DP8440/41) + DRAM t<sub>AA</sub> + Data Setup Time (68040)

30.3 \text{ ns} + 51 \text{ ns} + 35 \text{ ns} + 5 \text{ ns}

121.3 ns → 4 CLK Periods (121.2 ns)

From 4a, 4b and 4c, DTACK should assert from the 3rd rising CLK edge. Therefore program DTACK during opening accesses

as 2T.

(5) TA Setup Time (68040)

1 CLK Period - \overline{\text{DTACK}} Asserted from CLK High

30.3 ns - 12 ns

The 68040 needs only 10 ns

18.3 ns

(6) /CAS Precharge during Burst Accesses

Program the DP8440/41 for ½T of CAS precharge. It will guarantee a minimum of 10 ns.

(7) Wait States through TA during Burst Accesses.

```

CLK High to CAS Negated + Max CAS Precharge ( $\frac{1}{2}$ T) + DRAM  $t_{CAC}$  + Data Setup Time (68040) 12 ns + 14 ns + 20 ns + 5 ns

41 ns → 2 CLK Periods (60.6 ns), needs 1 Wait State

(8) Wait States through TA during Page Accesses

1 CLK Period - (CLK High to CAS Asserted + DRAM  $t_{CAC}$  + Data Setup) 30.3 ns - (12 ns + 20 ns + 5 ns)

-6.7 ns → 1 Wait State. Page Accesses take 3 CLKs

(9) RAS Low during Refresh

Program the DP8440/41 for 3T of refresh to guarantee 70 ns t<sub>RAS</sub>. Same number of CLKs for precharge.

Note: The timing analysis was done with preliminary AC specs, prior to final characterization of the DP8440/41. The reader is required to check AC timing from the latest DP8440/41 data sheet.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: 1(800) 272-9959 TWX: (910) 339-9240

Livry-Gargan-Str. 10 D-82256 Fürstenfeldbruc Germany Tel: (81-41) 35-0 Teley: 527649

National Semiconductor GmbH Fax: (81-41) 35-1

Japan Ltd Japan Ltd. Sumitomo Chemical Engineering Center Bldg. 7F 1-7-1, Nakase, Mihama-Ku Chiba-City, Ciba Prefecture 261

Fax: (043) 299-2500

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductores Do Brazil Ltda. Do Brazil Ltda.

Rue Deputado Lacorda Franco

120-3A

Sao Paulo-SP

Brazil 05418-000

Tel: (55-11) 212-5066

Telex: 391-1131931 NSBR BR

Fax: (55-11) 212-1181

National Semiconductor (Australia) Pty, Ltd. Building 16 Business Park Drive Monash Business Park Drive Monash Business Park Nottinghill, Melbourne Victoria 3168 Australia Tel: (3) 558-9999 Fax: (3) 558-9998