# Interfacing the DP8420A/21A/22A to the 29000 Utilizing the Burst Access Mode

National Semiconductor Application Note 602 Webster (Rusty) Meier Jr. May 1989

### INTRODUCTION

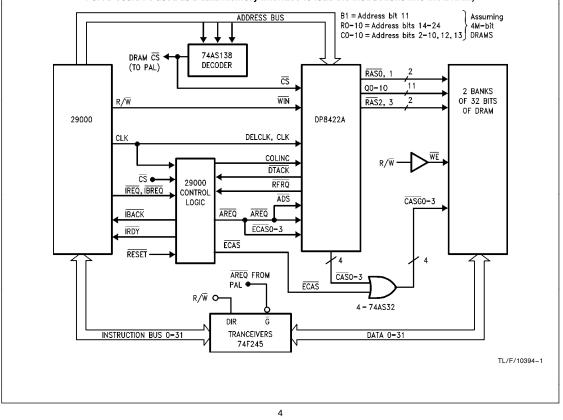

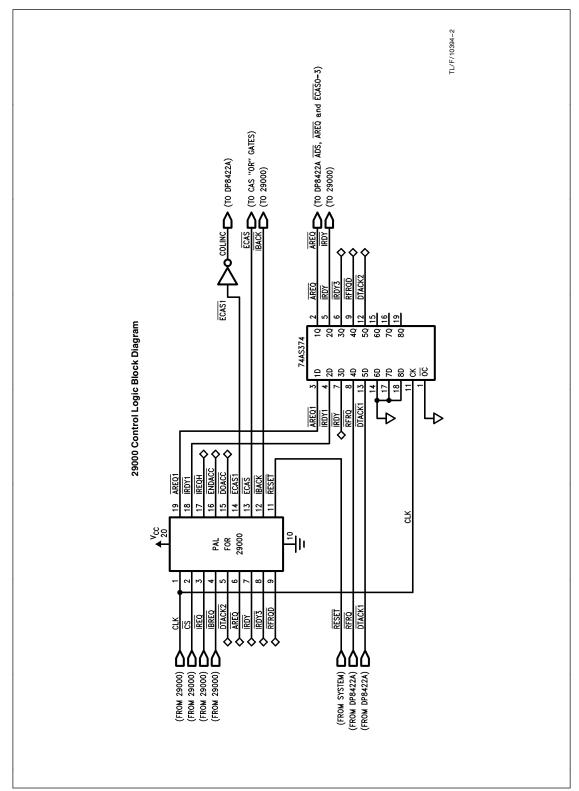

This application note describes how to interface the 29000 microprocessor to the DP8422A DRAM controller (also applicable to DP8420A/21A). The DP8422A supports the 29000 in the burst access mode. It is assumed that the reader is already familiar with 29000 access cycles and the DP8422A modes of operation.

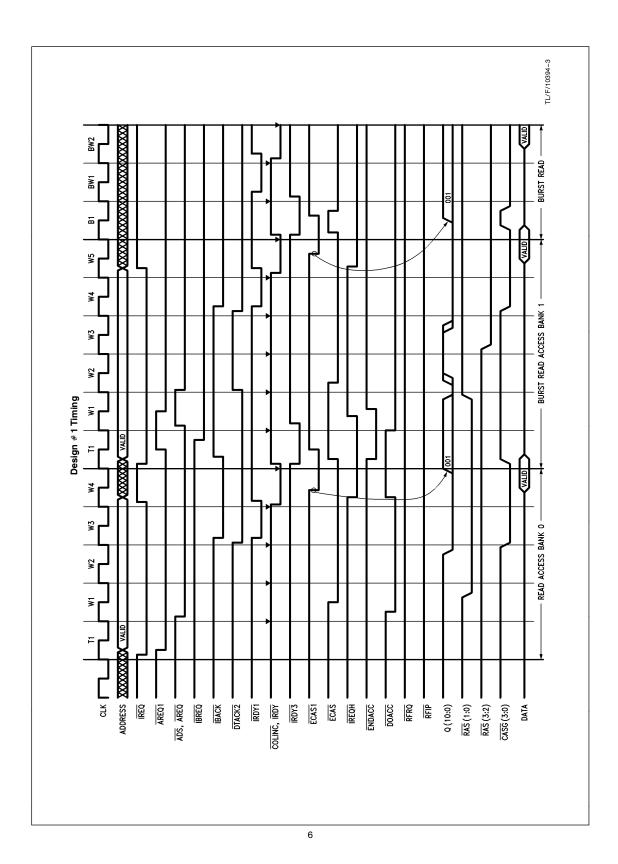

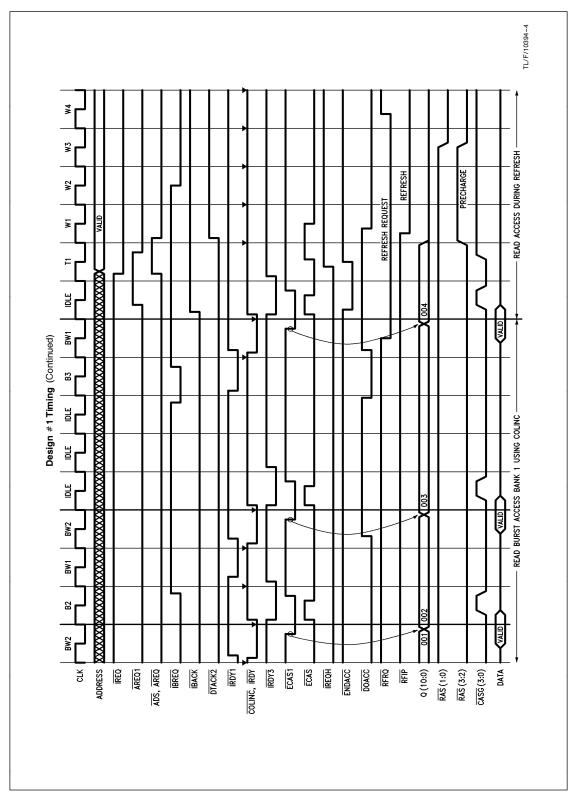

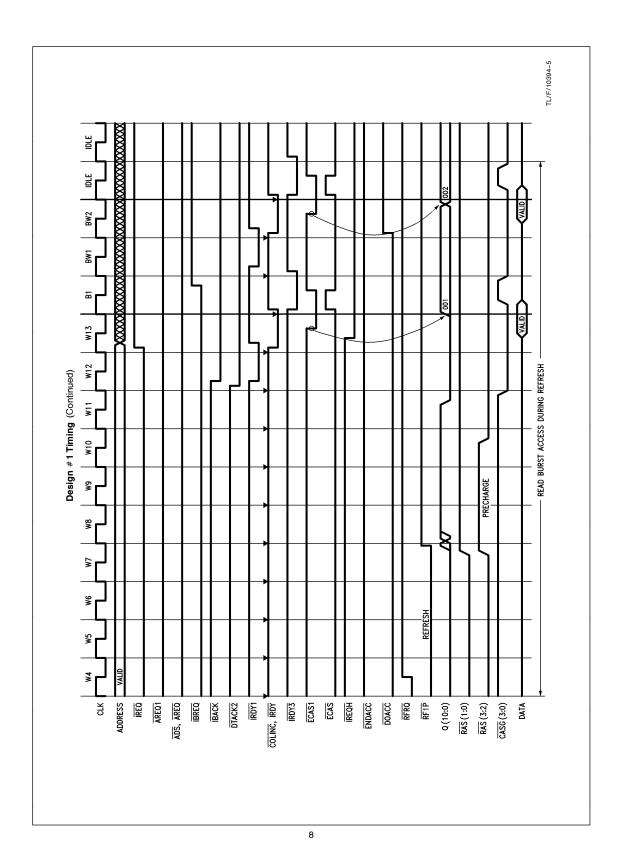

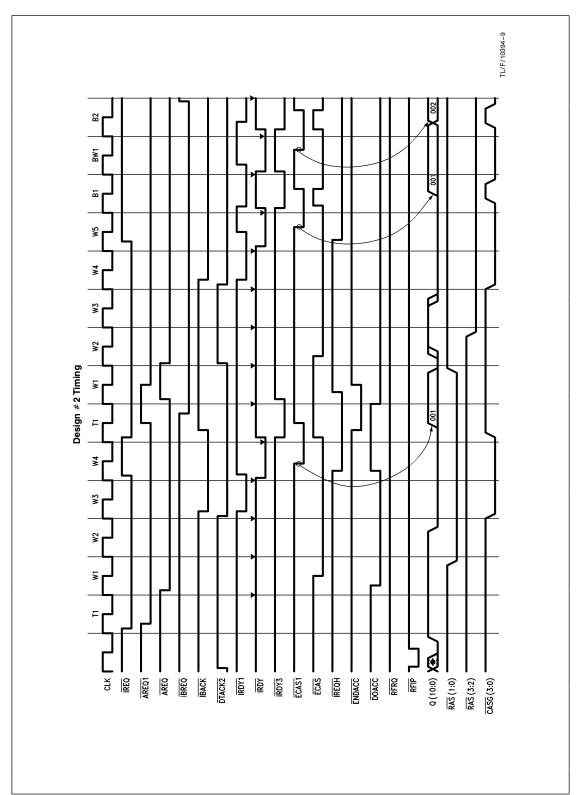

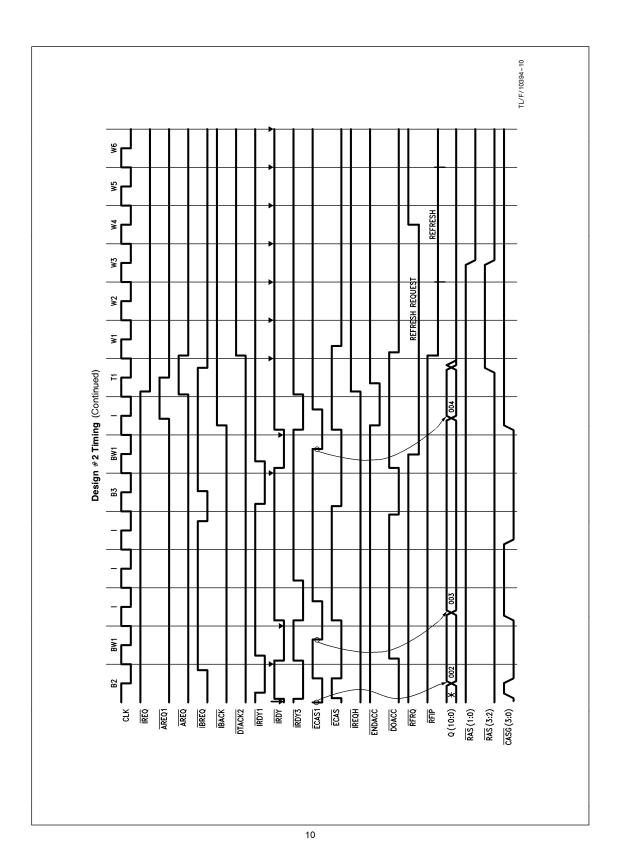

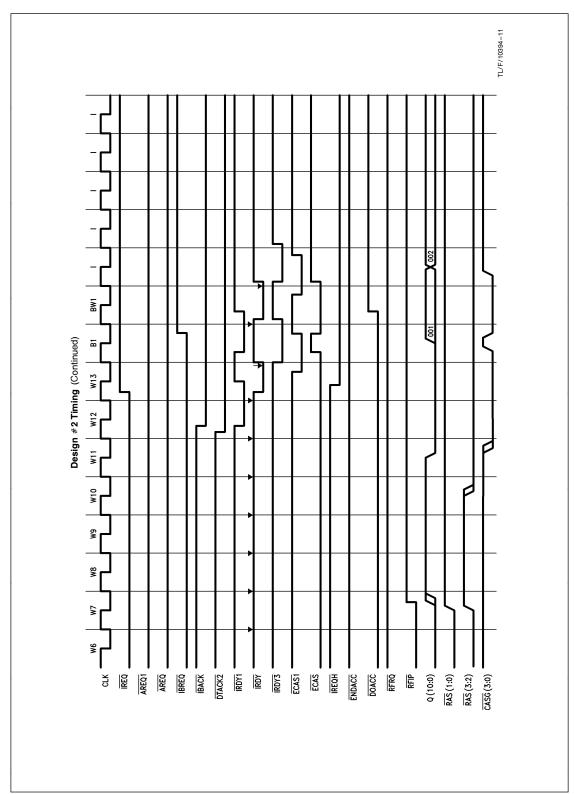

IA. Description of Designs #1 and #2, the 29000 in burst access mode on the instruction bus, allowing operation up to 25 MHz with four wait states in normal accesses and one or two wait states in burst accesses

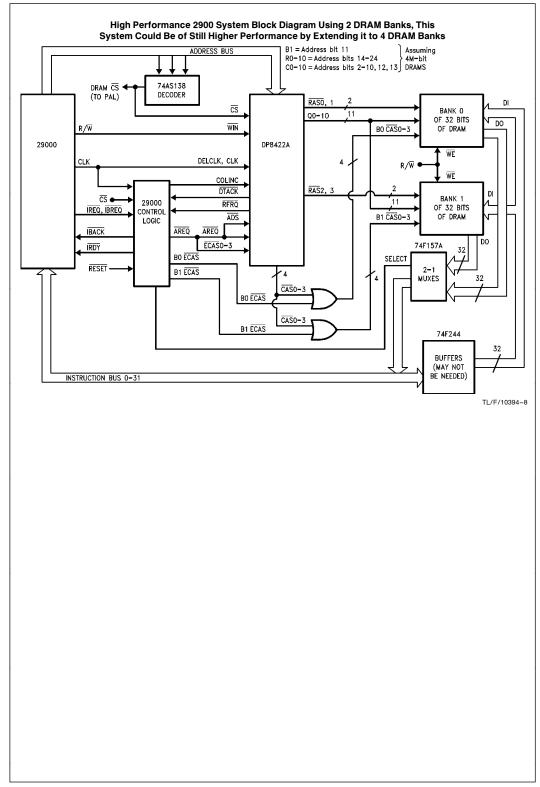

The two designs of this application note consist of the DP8422A DRAM controller, a single PAL® (PAL16L8D), several flip-flops, and several logic gates. These parts interface to the 29000 as shown in the block diagrams. This design accommodates two banks of DRAM, each bank being 32 bits in width, giving a maximum memory capacity of 32 Mbytes (using 4M-bit X 1 DRAMs).

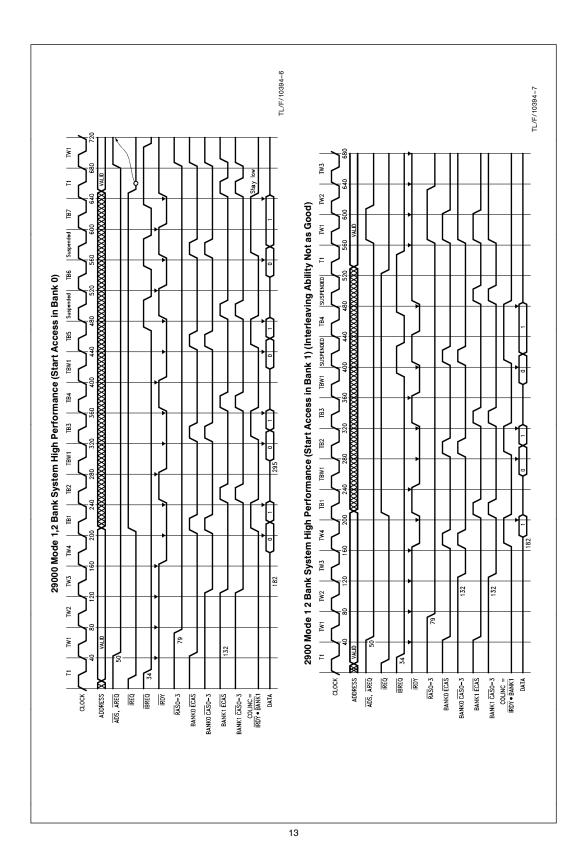

This memory design supports burst accesses by the 29000 to the instruction bus but could also support burst accessing to the data bus given a few minor changes. Design #1 inserts 4 wait states in normal accesses and 2 wait states in burst accesses. Design #2 inserts 4 wait states in normal accesses and 1 wait state in burst accesses. When idle states occur during a burst access the next occurring access will only have one wait state.

This application allows page mode DRAMs to be used by holding RAS low after an access is completed (IRDY low) until either a refresh request or a new access request (IREQ) is generated. If IBREQ (Instruction Burst Request) has transitioned low the next sequential word is accessed from the DRAM via a page mode access. This access involves incrementing the column address (DP8422A COLINC input high) and toggling the CAS outputs via the PAL ECAS output. The instruction burst acknowledge (IBACK) input is driven low except in the case of a refresh request (RFRQ) or a new access (IREQ) being requested.

If the user wants to do dual accessing with the DP8422A DRAM controller, address buffers (74AS244s) must be added to the address, ECAS0-3, LOCK, and WIN inputs.

Note that the DP8422A DRAM controller could be used to allow instruction memory accessing thru Port A. The instruction memory could be loaded thru a data memory interface to Port B.

The logic shown in these applications form a complete 29000 memory sub-system, no other logic is needed. This sub-system automatically takes care of:

- A. arbitration between Port A, and refreshing the DRAM:

- B. the insertion of wait states to the processor (Port A) when needed;

- C. remaining in burst access mode unless a refresh request (RFRQ) or new instruction request is generated;

- D. incrementing the column address during burst mode accesses; and

E. guaranteeing the RAS and CAS low and precharge times. The timing calculations for this design are included in this application note.

When using the DP8420A/21A/22A at or above 20 MHz the user should program three clock periods of precharge. This is because two clock periods of precharge at 20 MHz will only guarantee 77 ns of RAS precharge ( $2 \times 50 \text{ ns} - \text{tD1}$ , parameter #50 "14 ns" - clock (20 MHz) to AREQ high "9 ns").

#### IB. High Performance NO WAIT State 29000 System

A higher performance 29000 system (similar to the ones discussed in this application note) could be designed using the DP8422A by accessing four RAS banks at once, this could allow zero wait state burst accesses. An example of this method using 2 DRAM banks is shown at the end of this application note. If 2 DRAM controllers were used (4 BANKs) burst accesses could execute in zero wait states. The COLINC inputs to the two DRAM controllers would be staggered in time as well as the four ECAS outputs (B0ECAS-B3ECAS) from the 29000 control logic block.

nterfacing the DP8420A/21A/22A to the 29000 Utilizing the Burst Access Mode

**AN-602**

PLAN™ is a trademark of National Semiconductor Corporation. PAL® is a registered trademark of and is used under license from Monolithic Memories, Inc.

© 1995 National Semiconductor Corporation TL/F/10394

RRD-B30M75/Printed in U. S. A

| Programming<br>Bits                                                                                                                                                                                                                 |                                                                                                                                                                          | Description                                                                                                                                                                  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| R0 = 1<br>R1 = 1                                                                                                                                                                                                                    | RAS low four clocks, RAS precharge of three clocks                                                                                                                       |                                                                                                                                                                              |  |  |  |  |

| R2 = 1<br>R3 = 0                                                                                                                                                                                                                    | DTACK will be asserted on the positive edge of CLK following the access RAS                                                                                              |                                                                                                                                                                              |  |  |  |  |

| $ \begin{array}{l} R4 = 0 \\ R5 = 0 \\ \end{array} $                                                                                                                                                                                | No WAIT states during burst accesses                                                                                                                                     |                                                                                                                                                                              |  |  |  |  |

| R6 = X<br>R7 = 1                                                                                                                                                                                                                    | DTACK out                                                                                                                                                                | DTACK output                                                                                                                                                                 |  |  |  |  |

| R8 = 1<br>R9 = X                                                                                                                                                                                                                    | Non-addres                                                                                                                                                               | ss pipelining to support burst accessing                                                                                                                                     |  |  |  |  |

| C0 = X<br>C1 = X<br>C2 = X                                                                                                                                                                                                          | Select based upon the input clock frequency. Example: if the DELCLK frequency is 20 MHz then choose C0,1,2 = 0,0,0 (divide by ten, this will give a frequency of 2 MHz). |                                                                                                                                                                              |  |  |  |  |

| C3 = X                                                                                                                                                                                                                              |                                                                                                                                                                          |                                                                                                                                                                              |  |  |  |  |

| C4 = 0<br>C5 = 0<br>C6 = 1                                                                                                                                                                                                          | $\overline{RAS}$ and $\overline{CAS}$ groups selected by "B1". This mode allows two RAS and four $\overline{CAS}$ outputs to go low during an access.                    |                                                                                                                                                                              |  |  |  |  |

| C7 = 1<br>C8 = 1                                                                                                                                                                                                                    |                                                                                                                                                                          | dress setup time of 0 ns.<br>ss hold time of 15 ns                                                                                                                           |  |  |  |  |

| C9 = 1                                                                                                                                                                                                                              | Delay CAS during write accesses to one clock after RAS transitions low.                                                                                                  |                                                                                                                                                                              |  |  |  |  |

| B0 = 0                                                                                                                                                                                                                              |                                                                                                                                                                          | the address inputs, needed for the burst accessing f the 29000 (COLINC input in particular).                                                                                 |  |  |  |  |

| B1 = 1<br>= Program with low voltage level                                                                                                                                                                                          | Access mo                                                                                                                                                                |                                                                                                                                                                              |  |  |  |  |

| <ul> <li>Program with high voltage level</li> <li>Program with either low voltage level (doi</li> </ul>                                                                                                                             | n't care condition)                                                                                                                                                      |                                                                                                                                                                              |  |  |  |  |

| III. 29000 25 MHz timing calculations for Design #1 and<br>Design #2, with four wait states per normal access and<br>one or two wait states per burst access<br>1. Maximum time to address valid (with respect to 25 MHz<br>clock): |                                                                                                                                                                          | Therefore the tRAC of the DRAM must be 109 ns or lease<br>7. Determining tCAC (CAS access time needed by t<br>DRAM) and tAA (column address access time):                    |  |  |  |  |

|                                                                                                                                                                                                                                     |                                                                                                                                                                          | 200 ns - 40 ns - 9 ns - 6 ns - 7 ns - 82 ns (CLK<br>CAS low) = 56 ns                                                                                                         |  |  |  |  |

| 14 ns (29000 data sheet #6)<br>Maximim time to ADS low (with res<br>9 ns (74AS374 clock to Q, tPHL)                                                                                                                                 |                                                                                                                                                                          | Therefore the tCAC and tAA (access time from the c<br>umn address) of the DRAM must be 56 ns or less. CO<br>MON 100 ns DRAMS WILL MEET THIS tRAC, tAA, AI<br>tCAC PARAMETER. |  |  |  |  |

| 3. Minimum ADS low setup time to CLK high (DP8422-25 needs 25 ns, #400b):                                                                                                                                                           |                                                                                                                                                                          | <ol> <li>Minimum setup of DTACK1 to the 74AS374 ONLY, (ne 2 ns):</li> </ol>                                                                                                  |  |  |  |  |

| 40 ns (one clock period, 25 MHz) - 9 ns (#2) = 31 ns<br>4. Minimum address setup time to ADS low (DP8422-25<br>needs 14 ns, #404):                                                                                                  |                                                                                                                                                                          | 40 ns (one clock period) $-$ 28 ns (DP8422A-25 $\overline{\text{DTAC}}$ delay, #18) = 12 ns                                                                                  |  |  |  |  |

| 40 ns (One clock period, 25 MHz) + 2 ns (minimum 74AS374 clock to Q) $-$ 14 ns (#1) = 28 ns                                                                                                                                         |                                                                                                                                                                          | <ol> <li>Minimum IRDY setup time to IRDY being sampled (12 is needed by the 29000, #9):</li> </ol>                                                                           |  |  |  |  |

| Minimum $\overline{CS}$ setup time to CLKA h<br>5 ns, #401):                                                                                                                                                                        |                                                                                                                                                                          | 40 ns (one clock period) $-$ 9 ns (maximum 74AS37 clock to Q output delay) = 31 ns                                                                                           |  |  |  |  |

| 24 ns (#4) - 9 ns (74AS138 dec                                                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                                                                                              |  |  |  |  |

|                                                                                                                                                                                                                                     | time needed by the                                                                                                                                                       |                                                                                                                                                                              |  |  |  |  |

| DRAM):                                                                                                                                                                                                                              |                                                                                                                                                                          |                                                                                                                                                                              |  |  |  |  |

| 10a. Determining tCAC during a burst access for Design #1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 120 ns (3 clock periods) $-$ 20 ns (one half clock period during which $\overline{CAS}$ is high) $-$ 10 ns (PAL16L8 maximum propagation delay) $-$ 12 ns (74AS32 propagation delay driving $\approx$ 125 pF with damping resistor and other associated delays) $-$ 6 ns (data setup time) $-$ 7 ns (74F245) $=$ 65 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Therefore the tCAC of the DRAM must be $\leq$ 65 ns<br>10b. Determining tCAC during a burst access for Design<br>#2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 80 ns (2 clock periods) $-20$ ns (one half clock period during which $\overline{CAS}$ is high) $-10$ ns (PAL16L8 maximum propagation delay) $-12$ ns (74AS32 propagation delay driving $\approx 125$ pF with damping resistor and other associated delays) $-6$ ns (data setup time) $-7$ ns (74F245) $= 25$ ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Therefore the tCAC of the DRAM must be $\leq$ 25 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11a. Determining tAA during a burst access for Design #1:<br>160 ns (4 clock periods, because $\overline{\text{IRDY}}$ inverted is<br>COLINC) - 39 ns (DP8422A COLINC to Q's valid,<br>#27) = 121 ns $\geq$ tAA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11b. Determining tAA during a burst access for Design #2:<br>120 ns (3 clock periods, because IRDY inverted is<br>COLINC) - 39 ns (DP8422A COLINC to Q's valid,<br>#27) = 81 ns $\geq$ tAA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IV. 29000 PAL equations, Design <i>#</i> 1, 2 wait states dur-<br>ing burst accesses. Written in National Semiconductor<br>PLAN™ format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PAL16L8D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CLK CS IREQ IBREQ DTACK2 AREQ IRDY IRDY3 RFRQD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND RESET IBACK ECAS ECAS I DOACC ENDACC IREQH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND RESET IBACK ECAS ECAS1 DOACC ENDACC IREQH<br>IRDY1 AREQ1 VCC<br>If (VCC) IBACK = AREQ*RFRQD*IREQH*DTACK2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GND RESET IBACK ECAS ECAS1 DOACC ENDACC IREQH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $\begin{array}{l} \label{eq:gnd_reset_iback_ecas} & \mbox{GND_RESET_iback_ecas} & \mbox{Ecas} & \$ |

| $ \begin{array}{l} \label{eq:gnd_reset_iback_ecas} & \mbox{ECAS} \ \m$ |

| $ \begin{array}{l} \label{eq:gnd_reset_iback_ecas} & \mbox{ECAS} \ \m$ |

| $ \begin{array}{l} eq:generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_$        |

| $ \begin{array}{l} \label{eq:generalized_states} & \mbox{GND} \ \mbox{RESET} \ \mbox{IBACK} \ \mbox{ECAS} \ \mb$ |

| $ \begin{array}{l} eq:generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_generalized_$        |

| $ \begin{array}{l} \label{eq:generalized_states} & \mbox{GND} \ \mbox{RESET} \ \mbox{IBACK} \ \mbox{ECAS} \ \mb$ |

| $ \begin{array}{l} eq:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:sphere:spher$        |

| $ \begin{array}{l} \mbox{GND} \ \mbox{RESET} \ \ \mbox{IBACK} \ \ \mbox{ECAS} \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

29000 PAL equations, Design #2, 1 wait state during burst accesses. Written in National Semiconductor PLAN format

#### PAL16L8D

CLK CS IREQ IBREQ DTACK2 AREQ IRDY IRDY3 RFRQD GND RESET IBACK ECAS ECAS1 DOACC ENDACC IREQH IRDY1 AREQ1 VCC

- If (VCC) IBACK = AREQ\*RFRQD\*IREQH\*DTACK2 + AREQ\*RFRQD\*IREQH\*IREQ + IBACK\*IREQH\*RFRQD

- $\begin{array}{l} \mbox{If (VCC)} \ \overline{\mbox{ECAS}} = \overline{\mbox{AREQ}}^* \overline{\mbox{ECAS1}}^* \overline{\mbox{DOACC}}^* \mbox{RESET} \\ + \overline{\mbox{AREQ}}^* \overline{\mbox{DOACC}}^* \mbox{IRDY3}^* \overline{\mbox{CLK}}^* \mbox{RESET} \\ + \overline{\mbox{AREQ}}^* \overline{\mbox{DOACC}}^* \overline{\mbox{CLK}}^* \mbox{RESET} \\ + \overline{\mbox{ECAS}}^* \mbox{ECAS1}^* \mbox{CLK}^* \mbox{RESET} \\ + \overline{\mbox{ECAS}}^* \mbox{CLK}^* \mbox{RESET} \end{array}$

- If (VCC)  $\overline{\text{ECAS}}1 = \overline{\text{IRDY}}*\overline{\text{CLK}}$

- + ECAS1\*CLK

- $\begin{array}{l} \mbox{If (VCC)} \ \overline{\mbox{DOACC}} = \overline{\mbox{AREQ}}^* \mbox{RFRQD}^* \overline{\mbox{IBREQ}}^* \mbox{RESET} \\ + \overline{\mbox{CS}}^* \overline{\mbox{IREQ}}^* \mbox{IREQH}^* \mbox{AREQ}^* \mbox{RESET} \\ + \overline{\mbox{DOACC}}^* \mbox{IRD} \mbox{V}^* \mbox{RESET} \end{array}$

- If (VCC)  $\overline{ENDACC} = \overline{IREQ}*\overline{IREQH}$ +  $\overline{RFRQD}*\overline{IRDY}$ +  $\overline{RFRQD}*\overline{AREQ}*\overline{IREQH}$

- + ENDACC\*AREQ + RESET

- If (VCC)  $\overline{\text{IREQH}} = \overline{\text{AREQ}}^*\text{IREQ} + \overline{\text{IREQH}}^*\overline{\text{AREQ}}^*\text{RESET}$

- $\begin{array}{l} \mbox{If CVCC)} \ \overline{\mbox{IRDY1}} = \overline{\mbox{DTACK2}^* \overline{\mbox{AREQ}^* \mbox{IREQH}}} \\ + \overline{\mbox{AREQ}^* \mbox{IRDY}^* \mbox{IREQH}^* \mbox{CLK}^* \overline{\mbox{DOACC}}} \\ + \overline{\mbox{IRDY1}^* \mbox{IRDY}^* \mbox{AREQ}} \end{array}$

- $\begin{array}{l} \mbox{If (VCC)} \ \overline{\mbox{AREQ1}} = \overline{\mbox{CS}^* \mbox{IREQ}^* \mbox{IRDY}^* \mbox{ENDACC}^* \mbox{RESET} \\ + \overline{\mbox{AREQ1}^* \mbox{ENDACC}^* \mbox{RESET} \\ + \overline{\mbox{AREQ1}^* \mbox{DOACC}^* \mbox{RESET} \end{array}$

#### Key: Reading PAL equations written in PLAN

EXAMPLE EQUATIONS:  $\overline{\text{READ}}$ : = CS\_RD\*ADS1D\* $\overline{\text{CLKA}}$

$+\overline{READ}*\overline{ADS1D}$  $+\overline{READ}*CLKA$

This example reads: the output "READ" will transition low on the next rising "CLK" clock edge (given that one of the following conditions are valid a setup time before "CLK" transitions high);

- 1. the input "CS\_RD" is high AND the input "ADS1D" is high AND the input "CLKA" is low, OR

- 2. the output "READ" is low AND the input "ADS1D" is low, OR

- 3. the output "READ" is low AND the input "CLKA" is high

| What follow outputs: | pplication note PAL and 74AS374 outputs<br>ws is a brief explanation of the PAL and 74AS374                                                                                                                                                                                                                                                                             | DOACC                    | This combinational output of the PAL is used<br>internal to the PAL to keep track of requested<br>accesses, single (IREQ) or burst (IBREQ and<br>IBACK).                                                                                                    |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AREQ1                | This combinational output of the PAL is sampled at the next rising clock edge (74AS374) to provide the $\overline{ADS}$ and $\overline{AREQ}$ outputs that drive the DP8422A DRAM accesses. This output is held low to allow burst accessing until either a new access is requested by the 29000 ( $\overline{IREQ}$ ) or a refresh is requested ( $\overline{OFRQ}$ ). | ECAS1<br>ECAS            | This combinational output of the PAL is used<br>internal to the PAL to allow the ECAS output to<br>have minimum delay following the CLK high and<br>low.<br>This combinational output of the PAL is used to<br>toggle the CAS outputs of the DP8422A during |  |

| IRDY1                | This combinational output of the PAL is sampled at the next rising clock edge (74AS374) to provide the $\overline{IRDY}$ output that terminates each 29000 access.                                                                                                                                                                                                      | IBACK                    | burst accessing.<br>This combinational output of the PAL is used as<br>an input to the 29000 to indicate when the<br>DP8422A is available to support burst access-                                                                                          |  |

| IREQH                | This combinational output of the PAL is used<br>internal to the PAL as an indication of $\overline{IREQ}$<br>having transitioned high. It is useful in determin-<br>ing when the 29000 is terminating a burst ac-<br>cess to request an access to another page                                                                                                          |                          | ing. This output is pulled high during refresh re-<br>quests ( $\overline{RFRQ}$ ) and out of page accesses<br>( $\overline{IREQH} = \overline{IREQ} = Iow$ ).                                                                                              |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                         | AREQ<br>IRDY             | See AREQ1 explanation.<br>See IRDY1 explanation.                                                                                                                                                                                                            |  |

| ENDACC               | (IREQH = IREQ = low).<br>This combinational output of the PAL is used<br>internal to the PAL as an indication of when to<br>terminate a burst, or single, access. It indicates<br>a new page access (IREQ), a refresh request<br>(RFRQ), or a hardware reset (RESET) opera-                                                                                             | IRDY3<br>RFRQD<br>DTACK2 | This output (74AS374) is used as a state input<br>to the PAL. This term is IRDY delayed by one<br>clock period.<br>This clocked output is used to synchronize the<br>DP8422A RFRQ output.<br>This clocked output is generated from the                      |  |

|                      | tion. Accesses are only terminated after IRDY is<br>issued or during idle states when no accesses<br>are pending.                                                                                                                                                                                                                                                       | DTACKZ                   | DP8422A DTACK1 output and is synchronized to the next rising clock edge.                                                                                                                                                                                    |  |

Block Diagram of 29000/DP8422A Design at 25 MHz (Instruction memory interface to Port A, Port B could be used as a data memory interface to load the instructions into the DRAM)

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.  A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| 1 | 0 | National Semiconductor<br>Corporation<br>2900 Semiconductor Drive<br>P.O. Box 58090<br>Santa Clara, CA 95052-8090<br>Tel: 11600) 272-9959 | National Semiconductor<br>GmbH<br>Livry-Gargan-Str. 10<br>D-82256 Fürstenfeldbruck<br>Germany<br>Tel: (81-41) 35-0 | National Semiconductor<br>Japan Ltd.<br>Sumitomo Chemical<br>Engineering Center<br>Bldg. 7F<br>1-7-1. Nakase. Mihama-Ku | National Semiconductor<br>Hong Kong Ltd.<br>13th Floor, Straight Block,<br>Ocean Centre, 5 Canton Rd.<br>Tsimshatsui, Kowloon<br>Hong Kong | National Semiconductores<br>Do Brazil Ltda.<br>Rue Deputado Lacorda Franco<br>120-3A<br>Sao Paulo-SP<br>Brazil 05418-000 | National Semiconductor<br>(Australia) Pty, Ltd.<br>Building 16<br>Business Park Drive<br>Monash Business Park<br>Nottinghill. Melbourne |

|---|---|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|   |   | TWX: (910) 339-9240                                                                                                                       | Telex: 527649<br>Fax: (81-41) 35-1                                                                                 | Chiba-City,<br>Ciba Prefecture 261<br>Tel: (043) 299-2300<br>Fax: (043) 299-2500                                        | Tel: (852) 2737-1600<br>Fax: (852) 2736-9960                                                                                               | Tel: (55-11) 212-5066<br>Telex: 391-1131931 NSBR BR<br>Fax: (55-11) 212-1181                                             | Victoria 3168 Australia<br>Tel: (3) 558-9999<br>Fax: (3) 558-9998                                                                       |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.