# The HPC as a Front-End Processor

#### ABSTRACT

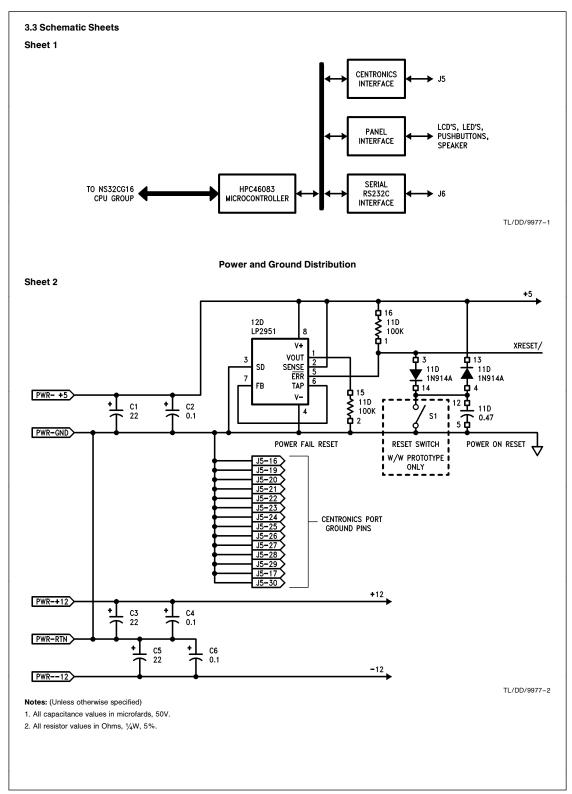

This application note covers the use of the National Semiconductor HPC46083 High-Performance microController as a front-end processor to collect and block data from RS-232 (serial) and Centronics (parallel) ports for a Host CPU (a typical application being an intelligent graphics-oriented printer). This application note builds on Application Note AN-550 (UPI Port); the result being a program that implements a versatile front-end processor for a National NS32CG16 CPU.

## **1.0 INTRODUCTION**

In Application Note AN-550, "A Software Driver for the HPC Universal Peripheral Interface Port", we saw how a National Semiconductor HPC46083 microcontroller can be connected and programmed to perform intelligent peripheral functions for a host CPU; our example being an application connecting an NS32CG16 CPU through the HPC to a typical front panel.

In this application note, we will expand on the hardware and the driver software presented there in order to implement a very useful function for a high-performance microcontroller: that of a front-end processor for data collection. To demonstrate a real-world application for this kind of function, we implement here an intelligent interface to a Centronics-style parallel input port and an RS-232 serial port, typical of a graphics-oriented printer.

# 2.0 THE FRONT-END PROCESSOR FUNCTION

As systems start to support higher data rates, one of the ever-present challenges is to minimize the interrupt processing load on the CPU, which can become intolerable if the CPU must process each character received in a separate interrupt. Since the character transfer task is typically so simple (reading a character from an input port and placing it into a memory buffer), it is often the case that the unavoidable context switch time associated with the interrupt outweighs the time spent processing the input character. In addition, the communication task may not be the CPU's highest priority: for example, in band-style laser printers the CPU must keep up with the paper movement; it can neither rerun an image nor stop the paper. The communication rate therefore suffers; even printers running from a Centronics-style parallel port are typically unable to accept data faster than 4k characters per second.

The traditional technique for overcoming this obstacle is to implement Direct Memory Access (DMA) for the communication ports. This is, however, quite a large investment in hardware, requiring an external DMA controller chip and more sophisticated bus structures to support it. In other words, it may be acceptable for a computer system, but it is overly expensive for an embedded controller application. Also, the response time required of the CPU can still be stringent, especially in implementing flow control to pace the character rate from the external system presenting the data.

The HPC46083 microcontroller, however, allows a much more cost-effective approach to the problem. As a peripheral, it interfaces to the CPU much as any peripheral controller

MICROWIRE/PLUS™ is a trademark of National Semiconductor Corporation.

National Semiconductor Application Note 551 Brian Marley April 1992

The HPC as a Front-End Processo

would. In the application documented here, it buffers up to 128 characters before interrupting the CPU, thus dropping the CPU input interrupt processing frequency by over two orders of magnitude, while allowing a character input rate of over 20 kb/sec.

# 2.1 Data Transfer Technique

The benefit provided by a front-end processor is derived from the efficiency it adds to the process of getting data into the CPU's data buffer; that is, how much of the CPU's processing time gets dedicated to this task.

The efficiency is provided by two means:

- Reduction of interrupt overhead. By interrupting the CPU only once every 100 characters, the overhead per character becomes virtually negligible.

- 2. Elimination of error testing overhead. If the CPU were communicating with a UART directly, it would have to poll for error conditions on each character. In our implementation, there are two interrupt vectors for data transfer: one for good data (which transfers a block of data), and one for bad data (which transfers one character and its error flags). The good data interrupt routine, then, which is invoked almost exclusively, contains a very simple inner loop. After reading the character count from the HPC, all that the CPU needs to do is:

- Move a character from the HPC's OBUF register to the current destination address. No time is wasted polling the HPC status; the hardware synchronization technique described in Application Note AN-550 handles this.

- Increment the destination address. (Checking against buffer limits could be done here, but is more efficiently handled outside the inner loop).

- Decrement the character count and test it; loop if non-zero.

The HPC firmware also supports this technique by guaranteeing that the reporting of character errors (and BREAK conditions) is synchronized with good data, so that the CPU can tell exactly where in the data stream the error occurred.

#### 2.2 Logic Replacement

Front-end processing tasks by no means use up the HPC's capabilities in a system. In our application, the HPC also serves as the CPU's only interrupt controller, allowing a large number of vectors with no additional hardware. It performs additional control tasks such as dynamic RAM refresh request timing, front panel control and real-time clock functions given in Application Note AN-550 with inexpensive interfacing. In a single 4 kbyte program developed in our group, we were also able to add an interface to an inexpensive serial EEPROM device (connected directly to the MI-CROWIRE/PLUS™ port of the HPC) and to a laser-printer engine for non-imaging control functions, and we also implemented a higher-resolution event timing feature. (These are topics for future application notes, however, and are not dealt with here.)

To summarize, then, the HPC not only can provide front-end processing functions, but can pay for itself by replacing other logic in the system.

# 3.0 HARDWARE

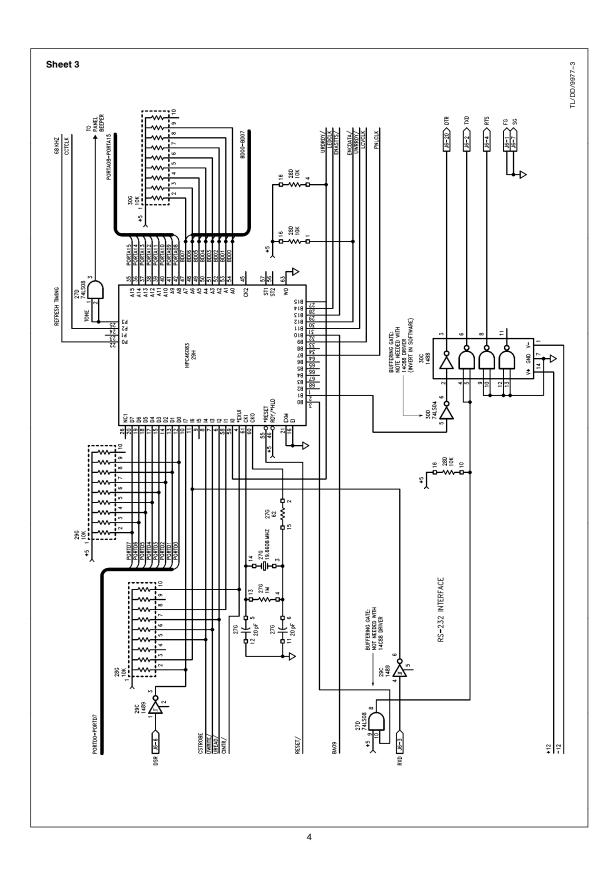

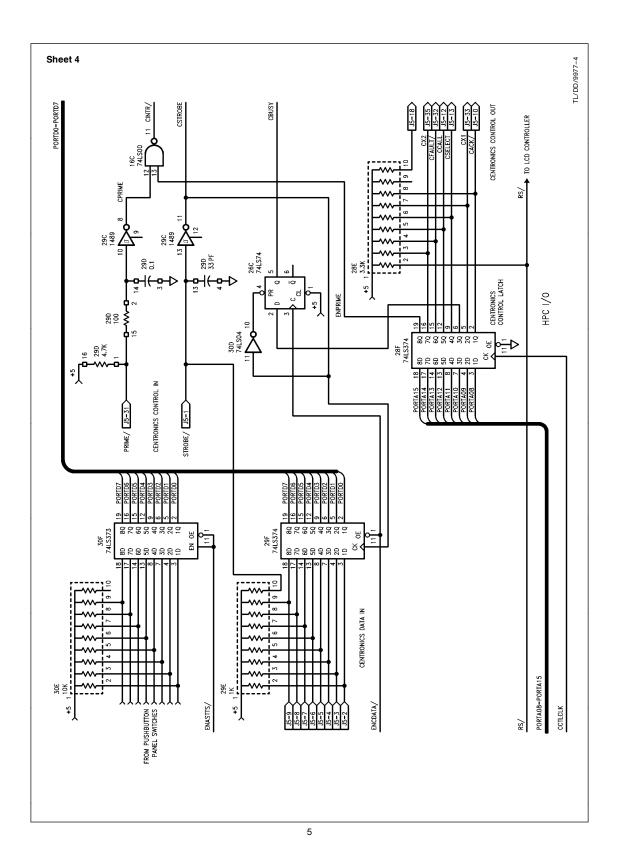

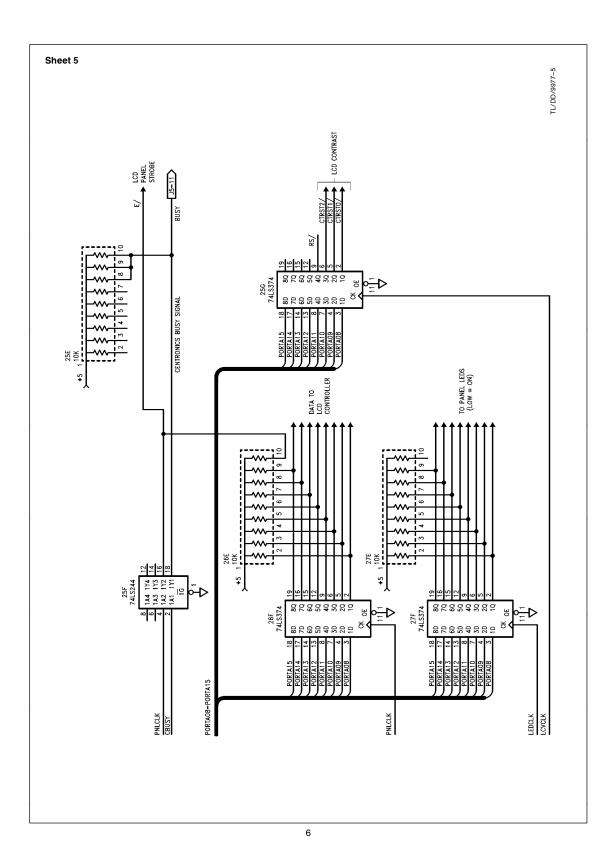

The following sections refer to the schematic pages included. We will discuss here only the portions involving the Centronics Parallel and RS-232 Serial ports. See Application Note AN-550 for details of the other connections shown (the UPI port and front-panel functions).

#### 3.1 The Centronics Parallel Port

The Centronics port was implemented on the connector designated J5. Most of the interface is diagrammed on Sheet 4 of the schematic.

## 3.1.1 Control Inputs

Pin 1 of the J5 connector receives the Data Strobe (STROBE) input, which signals the presence of valid data from the external system. On Sheet 4, in area C5, this signal appears from the connector. It is filtered using a Schmitt trigger (a spare 1488 RS-232 receiver chip), and is then presented to the HPC (Sheet 3) as interrupt signal I4.

Pin 31 is the Input Prime signal (PRIME), which is asserted low by the external system in order to reset the interface. It appears on Sheet 4 in area D5, and is filtered in a similar manner. It is then gated with the signal ENPRIME from the Centronics Control Latch, and the resulting signal is presented to the HPC on pin \*EXUI, which is the External UART Interrupt input. The gating is used to prevent confusion between UART and PRIME interrupts: while the Centronics port is selected, only PRIME causes interrupts, and while the RS-232 port is selected, this gating keeps PRIME interrupts from being asserted.

## 3.1.2 Data Inputs

Eight data bits, from J5 pins 2 through 9, appear in areas B8 and C8 of Sheet 4. They are latched into a 74LS374 latch on the leading edge of the  $\overline{STROBE}$  signal (note the inversion through the Schmitt receiver on  $\overline{STROBE}$ ). The latch is enabled to present data to the HPC's Port D pins by the signal  $\overline{ENCDATA}$ , which comes from HPC pin B12. Note that Port D is also used for inputting pushbutton switch data from a front panel.

#### 3.1.3 Control Outputs

The Centronics control and handshake signals are presented by loading the Centronics Control Latch (Sheet 4, area B4) from the HPC's pins A8 through A15 (Port A Upper) using as a strobe the signal CCTLCLK from HPC pin P2.

Pin 10 of connector J5 is the Centronics Acknowledge (CACK) pulse, which is used to signal the external system that the HPC is ready for the next byte of data. This is one of the two handshake signals used to pace data flow. It is initialized high by the HPC, and is pulsed low when required.

Pin 11 is the Centronics Busy (CBUSY) signal, which is generated by the flip-flop on Sheet 4, area C3. It is set directly by a STROBE pulse, and is also loaded from the Centronics Control Latch whenever the HPC finishes reading a byte of data (rising edge of ENCDATA). This will clear CBUSY under normal conditions, allowing the external system to send another byte of data. Five additional signals, whose functions vary significantly from printer to printer, are presented on connector J5 from the Centronics Control Latch. These are:

Pin 13, which generally indicates that the printer is selected.

Pin 12, which indicates that the printer needs attention (for example, that it is out of paper).

Pin 32, which indicates a more permanent or unusual problem (lamp check or paper jam).

Pins 33 and 35, which vary more widely in use.

These five pins are manipulated by commands from the CPU; the HPC simply presents them as commanded.

## 3.1.4 Other Signals

Pin 18 of the Centronics port connector receives a permanent +5V signal (area B2 of Sheet 4), and a set of other pins (middle of Sheet 2) are connected permanently to ground.

## 3.2 The RS-232 Serial Port

The serial port (on connector J6) makes use of the HPC's on-chip UART and baud rate generator; very little off-chip hardware is required. The entire RS-232 circuit appears on Sheet 3 of the schematic.

This port is implemented in a way typical of printers, and so there are no sophisticated handshaking connections. The interface looks like an RS-232 DTE device: Connector J6 pin 2 is transmitted data (out) and pin 3 is received data (in).

The RS-232 data input appears in area B8 of Sheet 3, as signal RXD. After the RS-232 receiver, it is presented on the HPC's UART input pin (I6). Note that this pin can be monitored directly as a port bit; this enables the HPC to check periodically for the end of a BREAK condition without being subjected to a constant stream of interrupts for null characters.

The Data Set Ready signal (DSR) is received from pin 6 of J6, and presented on HPC pin I7, where it can be monitored by the HPC firmware.

The Request to Send signal (RTS) is a constant high level placed on J6 pin 4.

Transmitted data (TXD) is presented from the HPC's UART output pin (B0), through a buffering gate, to an RS-232 driver, and then out on J6 pin 3. The buffering gate would be unnecessary if the CMOS 14C88 driver were being used, but the gate was a spare and allowed cost savings using the less expensive TTL 1488 chip.

Data Terminal Ready (DTR) is simply presented from a programmable port pin of the HPC (pin B1). It is buffered through a spare inverter, and then presented to RS-232 connector J6 pin 20 through an RS-232 driver. As with the UART output, the buffering would be unnecessary with the 14C88 type of RS-232 driver; however, note that the HPC firmware would have to be modified slightly due to the resulting polarity difference on the pin.

J6 pins 1 (Frame Ground) and 7 (Signal Ground) are, of course, grounded, as shown in this sheet also.

# 4.0 PROTOCOL

The command and interrupt protocol is a superset of that implemented for Application Note AN-550. The two commands SELECT-OENT and SELECT-UART are added to select and initialize each of the communication ports (Centronics or RS-232). The CPU can exercise control over data buffering by the commands FLUSH-BUF, CPU-BUSY, CPU-NOT-BUSY and SET-IFC-BUSY. It can set Centronics port error flags and status using SET-CENT-STS, and it can test for RS-232 status using the TES-UART command. The HPC also allows the CPU to send characters out on the RS-232 port using the SEND-UART command.

New interrupts presented by the HPC are !DATA, which transfers up to 128 bytes of buffered data to the CPU, !PRIME and !UART-STATUS, which inform the CPU of port status changes, and !DATA-ERR, which reports in detail any error ocurring in characters received. The interrupt !ACK-UART is presented to the CPU to acknowledge that the SEND-UART command has been completed.

Note that the command codes for the front panel functions have been changed. Their formats, however, have not changed, nor have their functions, except that the INITIAL-IZE command now performs a disconnection function on the RS-232 and Centronics ports.

#### 4.1 Commands

The first byte (command code) is sent to address FFFC00, and any argument bytes are then written to address FFFE00. The CPU may poll the UPIC register at address FD0000 to determine when the HPC can receive the next byte, or it can simply attempt to write, in which case it will be held in Wait states until the HPC can receive it. Except where noted, the CPU may send commands continuously without waiting for acknowledgement interrupts from previous commands.

00 INITIALIZE

This command has two functions. The first INITIALIZE command after a hardware reset (or RESET-HPC command) enables the IRTC and IBUTTON-DATA interrupts. Both data communcation ports are set to their "Busy" states until a "SELECT" command is sent. The INITIALIZE command may be re-issued by the CPU to de-select both communication ports, and to either start or stop the IRTC interrupts. There is one argument:

**RTC-Interval:** One-byte value. If zero, !RTC interrupts are disabled. Otherwise, the !RTC interrupts occur at the interval specified (in units of 10 ms per count).

01 SELECT-CENT Select the Centronics port and set it ready, using the timing sequence specified by the supplied ACK-Mode argument. Data from the port is enabled, and the !PRIME interrupt is also enabled. Arguments:

## where the Timing field is encoded as: 00 = BUSY falling edge occurs after ACK pulse. 01 = BUSY falling edge occurs during ACK pulse. 10 = BUSY falling edge occurs before ACK pulse. and the L bit, when set, requests Line Mode. It suppresses the removal of BUSY and the occurrence of the ACK pulse when the buffer is passed to the CPU. To fully implement Line Mode, this mode should be used with Pass-Count = 1 and Stop-Count = 1, and the CPU must use the SET-CENT-STS command to acknowledge each character itself. Pass-Count: Number of characters in buffer before the HPC passes them automatically to CPU. One bvte.

ACK-Mode: one byte in the format:

Timing

x x x x L

**Stop-Count:** Number of characters in buffer before HPC tells the external system to stop. One byte.

Note that the buffer is a maximum of 128 bytes in length, in this implementation.

Requires INITIALIZE command first.

02 SELECT-UART Select Serial port and set it ready, according to supplied arguments. Requires INITIALIZE command first. Arguments are:

**Baud:** Baud rate selection. One Byte containing.

- 0 = 300 baud

- 1 = 600 baud

- 2 = 1200 baud

- 3 = 2400 baud

- 4 = 4800 baud

- 5 = 9600 baud

- 6 = 19200 baud

- 7 = 38400 baud

- 8 = 76800 baud

Frame: One byte, selecting character length, parity and number of stop bits.

| Value | Data Bits | Parity | Stop Bits |

|-------|-----------|--------|-----------|

| 0     | 8         | Odd    | 1         |

| 1     | 8         | Even   | 1         |

| 2     | 8         | None   | 1         |

| 3     | 8         | None   | 2         |

| 4     | 7         | Odd    | 1         |

| 5     | 7         | Even   | 1         |

| 6     | 7         | Odd    | 2         |

| 7     | 7         | Even   | 2         |

7

|      |                 | 0      |        | Flow:     One     byte,     bit-encoded     for       handshaking     and     flow     control       modes:     0     XON     DTR     DSR                                         |                 | sending characters. This status is r<br>moved only by performing a SELEC<br>command. Requires INITIALIZ<br>command and SELECT comman                                            |

|------|-----------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 0<br>7          | 0<br>6 | 0<br>5 | 0         XON         DTR         DSR           4         3         2         1         0           DSR:         1         =         the         HPC         disables         the | 08 SET-CENT-STS | first.<br>"Set Centronics Port Status". Load<br>Centronics latch from the supplie<br>argument byte. Argument is eig                                                             |

|      |                 |        |        | UART receiver while the DSR input is inactive.<br>DTR: Polarity of DTR output, and                                                                                                |                 | bits, which must be encoded as fo                                                                                                                                               |

|      |                 |        |        | whether it is used as a flow-control handshake.                                                                                                                                   | ENPRIME CX2 FAU |                                                                                                                                                                                 |

|      |                 |        |        | 00 = Permanently low (negative<br>voltage).<br>01 = Permanently high (positive                                                                                                    |                 | The ACK bit should always be a "1<br>The CPU must use the BUSY bit<br>generate an $\overline{ACK}$ pulse: if the BUS                                                            |

|      |                 |        |        | voltage).<br>10 = Handshaking: low means                                                                                                                                          |                 | bit is zero, the ACK signal will be a<br>tomatically pulsed low, then high, (r<br>gardless of the previous states                                                               |

|      |                 |        |        | ready.<br>11 = Handshaking: high means<br>ready.                                                                                                                                  |                 | BUSY and ACK).<br>Requires INITIALIZE command ar<br>SELECT-CENT command first.                                                                                                  |

|      |                 |        |        | <b>XON:</b> 1 = the HPC performs XON/XOFF flow control.                                                                                                                           | 09 SET-CONTRAST | The single argument is a 3-bit nur<br>ber specifying a contrast level for the                                                                                                   |

|      |                 |        |        | <b>Pass-Count:</b> Number of characters<br>in buffer before the HPC passes<br>them automatically to CPU. One<br>byte.                                                             |                 | LCD panel (0 is least contrast, 7<br>highest contrast). There is no r<br>sponse interrupt. Does not requi<br>INITIALIZE command first.                                          |

|      |                 |        |        | Stop-Count: Number of characters<br>in buffer before HPC tells the exter-                                                                                                         | 0A SEND-LCD     | This writes a string of up to 8 bytes the LCD panel. Arguments are:                                                                                                             |

|      |                 |        |        | nal system to stop. One byte.<br>Note that the buffer is a maximum of<br>128 bytes in length, in this implemen-<br>tation.<br>Requires INITIALIZE command first.                  |                 | <b>flags:</b> A single byte, containing the RS bit associated with each byte data. The first byte's RS value is the least-significant bit of the FLAG byte.                     |

|      | reserve<br>LUSH | ,      |        | No arguments. Flush HPC data com-                                                                                                                                                 |                 | <b>#bytes:</b> The number of bytes to b written to the LCD display.                                                                                                             |

| 04 1 | LUGII           | -001   |        | munication buffer to CPU. Any data<br>in the buffer is immediately sent to                                                                                                        |                 | byte[1]-byte[#bytes]: The da bytes themselves.                                                                                                                                  |

|      |                 |        |        | the CPU (using the !DATA interrupt).<br>This command triggers the !DATA in-<br>terrupt only if the buffer contains at<br>least one byte. Requires INITIALIZE                      |                 | The HPC determines the proper d<br>lay timing required for commar<br>bytes (RS = 0) from their encoding<br>This is either 4.9 ms or 120 $\mu$ s.                                |

| 05 C | CPU-BI          | JSY    |        | command and SELECT command<br>first.<br>No arguments. Indicates that the<br>CPU cannot accept any more data                                                                       |                 | The response from the HPC is the IACK-SEND-LCD interrupt, and the command must not be repeated up the interrupt is received. This contains the interrupt is received.           |

|      |                 |        |        | (the CPU's data buffer is full). This suppresses the !DATA and !DATA-                                                                                                             |                 | mand does not require an INITIA<br>IZE command first.                                                                                                                           |

|      |                 |        |        | ERR interrupts. Requires INITIALIZE<br>command and SELECT command<br>first.                                                                                                       | 0B SEND-LED     | The singe argument is a byte co<br>taining a "1" in each position f<br>which an LED should be lit.                                                                              |

| 06 C | CPU-N           | ЭТ-В   | USY    | No arguments. This undoes a previ-<br>ous CPU-BUSY command, and indi-<br>cates that the CPU can now accept                                                                        |                 | There is no response interrupt, ar<br>this command does not require th<br>INITIALIZE command first.                                                                             |

|      |                 |        |        | more data from the HPC. Requires<br>INITIALIZE command and SELECT<br>command first.                                                                                               | OC BEEP         | No arguments. This beeps the pan<br>for approximately one second. No r<br>sponse interrupt. If a new BEE                                                                        |

| 07 S | SET-IF          | C-BU   | SY     | "Set Interface Busy". No arguments.<br>Commands the HPC to immediately<br>signal the external system to stop                                                                      |                 | command is issued during the bee<br>no error occurs (the buzzer tone<br>extended to one second beyond th<br>most recent command). Does not r<br>quire INITIALIZE command first. |

| 0D SEND-UART                                                                                                                                                                                                             | The single one-byte argument is sent                                                                                                                                                                                                                                                                  | Vector           |                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                          | on the UART port. An acknowledge-<br>ment interrupt !ACK-UART occurs on                                                                                                                                                                                                                               | 00-0F (none)     | (Reserved for CPU internal traps<br>and the NMI interrupt.)                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                          | completion. This command must not<br>be repeated until the interrupt is<br>received. Requires INITIALIZE and<br>SELECT-UART commands first.                                                                                                                                                           | 10 IDATA         | Buffer data is being transferred to<br>CPU. This will happen either auto-<br>matically, at a point defined by the<br>most recent SELECT command,                                                                                                                                                                                               |

| 0E TEST-UART                                                                                                                                                                                                             | Triggers a !UART-STATUS interrupt.<br>This command must not be repeated<br>until the interrupt is received. No ar-<br>guments. Requires INITIALIZE and<br>SELECT-UART commands first.                                                                                                                 |                  | or as the result of a FLUSH-BUF command. It is fol-<br>lowed by a one-byte Length (num-<br>ber of characters: current HPC firmware has a range of 1–128),                                                                                                                                                                                      |

| A5 RESET-HPC                                                                                                                                                                                                             | Resets the HPC if it is written to ad-<br>dress FFFC00. It may be written at<br>any time that the UPI port is ready for<br>input; it will automatically cancel any                                                                                                                                    |                  | then that number of characters.<br>Enabled by SELECT command af-<br>ter at least one INITIALIZE com-<br>mand.                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                          | partially-entered command. The<br>CPU's Maskable Interrupt must be<br>disabled before issuing this com-<br>mand.                                                                                                                                                                                      | 11 IRTC          | Real-Time Clock Interrupt. No<br>data returned. Enabled by INI-<br>TIALIZE command if interval value<br>supplied is non-zero.                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                          | After issuing this command, the CPU<br>should first poll the UPIC register at<br>address FD0000 to see that the HPC<br>has input the command (the least-<br>significant bit [Write Ready] is zero).                                                                                                   |                  | Note: This version of HPC firmware issues<br>a non-fatal IDIAG interrupt if the<br>CPU fails to service each IRTC inter-<br>rupt before the next one becomes<br>pending.                                                                                                                                                                       |

|                                                                                                                                                                                                                          | It must then wait for at least 25 $\mu$ s,                                                                                                                                                                                                                                                            | 12 (reserved)    |                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                          | then read a byte from address FFFE00. The HPC now begins its internal re-initialization. The CPU must wait for at least 80 $\mu$ s to allow the HPC to re-initialize the UPI port.                                                                                                                    | 13 !PRIME        | Centronics INPUT PRIME signal<br>has become active. No data re-<br>turned. Enabled by SELECT-<br>CENT command after at least one<br>INITIALIZE command.                                                                                                                                                                                        |

|                                                                                                                                                                                                                          | Since part of the RESET procedure                                                                                                                                                                                                                                                                     | 14 (reserved)    |                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                          | causes Ports A and B to float briefly                                                                                                                                                                                                                                                                 | 15 (reserved)    |                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                          | (this includes the CPU's Maskable                                                                                                                                                                                                                                                                     | 16 (reserved)    |                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                          | Interrupt input pin), the CPU should                                                                                                                                                                                                                                                                  | 17 IACK-SEND-LCD | This is the response to the SEND-                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                          | keep its maskable interrupt disabled<br>during this time. It also must not en-                                                                                                                                                                                                                        | IT MORECEND-LOD  | LCD command, to acknowledge                                                                                                                                                                                                                                                                                                                    |

| <b>4.2 Interrupts</b>                                                                                                                                                                                                    | ter a command byte during this time<br>because the byte may be lost.                                                                                                                                                                                                                                  |                  | that data has all been written to<br>Panel LCD display. No other data<br>is provided with this interrupt. Al-<br>ways enabled, but occurs only in<br>response to a SEND-LCD com-                                                                                                                                                               |

|                                                                                                                                                                                                                          | vectors for the CPU hardware. The CPU                                                                                                                                                                                                                                                                 |                  | mand.                                                                                                                                                                                                                                                                                                                                          |

| then reads data from<br>provided by the HPC<br>turning from the inter<br>would either hang o<br>may poll the UPIC re<br>when each data byt<br>read from address F<br>until the data is prov<br>Note: All CPU interrupt s | n the HPC at address FFFE00. All data<br>C must be read by the CPU before re-<br>rrupt service routine, otherwise the HPC<br>or generate a false interrupt. The CPU<br>ogister at address FD0000 to determine<br>e is ready, or it may simply attempt to<br>FFE00, and it will be held in Wait states | 18 IBUTTON-DATA  | Pushbutton status has changed:<br>one or more buttons have been ei-<br>ther pressed or released. The new<br>status of the switches is reported<br>in a data byte, encoded as fol-<br>lows:<br>Any pushbutton that is depressed<br>is presented as a "1". All other bit<br>positions, including unused posi-<br>tions, are zeroes. The pushbut- |

|                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                       |                  | tons are debounced before being<br>reported to the CPU. This interrupt<br>is enabled by the first INITIALIZE<br>command after a reset.                                                                                                                                                                                                         |

|                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                       |                  |                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                       |                  |                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                       |                  |                                                                                                                                                                                                                                                                                                                                                |

| 19 !UART-STATUS | interrupt            | tatus has changed. This<br>occurs only while the<br>s selected. A data byte  |               | 5      | Parity Error: Serial Po<br>only.                                                                           |

|-----------------|----------------------|------------------------------------------------------------------------------|---------------|--------|------------------------------------------------------------------------------------------------------------|

|                 |                      | ne UART's new state:                                                         |               | 0      | Framing Error: Seri<br>Port only.                                                                          |

|                 | Bit                  | Condition                                                                    |               | 7 (MSE | B) Data Overrun: Seri                                                                                      |

|                 | 0 (LSB)              | New state of DSR sig-<br>nal. This causes an in-                             |               |        | Port only.                                                                                                 |

|                 |                      | terrupt only if DSR moni-                                                    |               |        | 2, 3 or 4 is set, the community of the set, the community of the set automatical port has been automatical |

|                 |                      | toring was requested in                                                      |               |        | lown by the HPC. The CP                                                                                    |

|                 |                      | the last SELECT-UART command. The UART                                       |               |        | issue a new SELECT con                                                                                     |

|                 |                      | receiver is automatically                                                    |               |        | to re-enable the port.<br>a character is received wi                                                       |

|                 |                      | enabled and disabled by                                                      |               |        | or, all characters appearir                                                                                |

|                 |                      | the HPC, so no CPU ac-<br>tion is required on re-                            |               |        | e it in the buffer are automa                                                                              |

|                 |                      | ceiving this interrupt. If a                                                 |               | ,      | flushed before this interru<br>s. This is done to presen                                                   |

|                 |                      | SELECT-UART com-<br>mand is entered, re-                                     |               | the e  | rror character's position                                                                                  |

|                 |                      | questing DSR monitor-                                                        |               |        | ata stream. If the CPU d to ignore the presence of a                                                       |

|                 |                      | ing, and DSR is inactive,                                                    |               |        | the character may be simp                                                                                  |

|                 |                      | a !UART-STATUS inter-<br>rupt occurs immediately.                            |               |        | ded by the CPU to the da                                                                                   |

|                 | 1                    | This bit is set if a UART                                                    |               | note:  | ly in its data buffer. Pleas<br>If the CPU has issued                                                      |

|                 | 2–7                  | BREAK has just ended.<br>(unused)                                            |               |        | NOT-READY command, th<br>cannot occur, and this inte                                                       |

|                 |                      | the CPU has issued a CPU-NOT-                                                |               |        | vill not be issued until th                                                                                |

|                 |                      | EADY command, this BREAK in-<br>rupt may be seen before the                  |               |        | has occurred.                                                                                              |

|                 | !D.                  | ATA-ERR interrupt that an-                                                   | 1B !ACK-UART  |        | U character has been se<br>e UART, and the UART                                                            |

|                 | (ar                  | unces the start of the BREAK<br>nd its position in the data                  |               |        | for another. No data is r                                                                                  |

|                 |                      | eam).<br>e DSR and UART input (BREAK)                                        |               |        | I with this interrupt. It is a enabled, but occurs only                                                    |

|                 |                      | nals are sampled every 10 ms.                                                |               |        | nse to the SEND-UAF                                                                                        |

| 1A IDATA-ERR    |                      | has been encountered in                                                      |               | comm   | and.                                                                                                       |

|                 |                      | ning from the currently-se-<br>communication port. It is                     | 1C (reserved) | Diama  | - Markenman This inte                                                                                      |

|                 |                      | by the first SELECT com-                                                     | 1D IDIAG      | -      | ostic Interrupt. This inter<br>used to report failure cond                                                 |

|                 |                      | fter the first INITIALIZE<br>Id. Two data bytes are re-                      |               | tions  | and CPU command error                                                                                      |

|                 | turned:              | ,                                                                            |               |        | are five data bytes passe<br>s interrupt:                                                                  |

|                 |                      | One byte containing the<br>or on which the error was                         |               | Sever  | -                                                                                                          |

|                 |                      | his character is NOT                                                         |               | Error  |                                                                                                            |

|                 | placed ir            | n the data buffer).                                                          |               |        | in Error (passed, but co<br>not defined)                                                                   |

|                 | errfgs:<br>error see | Error flags, detailing the<br>en:                                            |               | Currer | nt Command (passed, b<br>nts not defined)                                                                  |

|                 | Bit                  | Error Seen                                                                   |               | Comm   | nand Status (passed, b                                                                                     |

|                 | 0 (LSB)              | (unassigned)                                                                 |               |        | nts not defined)                                                                                           |

|                 | 1                    | (unassigned)                                                                 |               |        | everity byte contains one l<br>ch severity level, as follow                                                |

|                 | 2                    | UART BREAK condition<br>detected. This may be<br>preceded by one or two      | X X           | XF     | X X C N                                                                                                    |

|                 |                      | framing errors.                                                              |               | N (No  | te): least severe. The CF                                                                                  |

|                 | 3                    | Error Overflow: More                                                         |               | misse  | d an event; currently or                                                                                   |

|                 |                      | errors occurred than<br>HPC could report (the                                |               |        | TC interrupt will cause this                                                                               |

|                 |                      | HPC has no FIFO for er-                                                      |               | •      | ommand): medium severit<br>currently implemented. A                                                        |

|                 | 4                    | ror reporting).<br>Buffer Overflow: Flow                                     |               | comm   | and error is now treated a                                                                                 |

|                 | 4                    | control failed to stop the<br>external system, and the<br>buffer overflowed. |               | a FAT  | AL error (below).                                                                                          |

| F (Fatal): highest severity. The<br>HPC has recognized a non-recov-<br>erable error. It must be reset be- |

|-----------------------------------------------------------------------------------------------------------|

|                                                                                                           |

| fore the CPU may re-enable its                                                                            |

| Maskable Interrupt. In this case,                                                                         |

| the remaining data bytes may be                                                                           |

| read by the CPU, but they will all                                                                        |

| contain the value 1D (hexadeci-                                                                           |

| mal). The CPU must issue a RE-                                                                            |

| SET command, or wait for a hard-                                                                          |

| ware reset. See below for the pro-                                                                        |

| cedure for FATAL error recovery.                                                                          |

| The Error Code byte contains, for                                                                         |

| non-FATAL errors, a more specif-                                                                          |

| ic indication of the error condition:                                                                     |

|     |      | •      |         | •   |      | • |

|-----|------|--------|---------|-----|------|---|

| RTC | (Res | servec | l for C | OMM | AND) |   |

|     |      | 1      | 1       | 1   | 1    |   |

RTC = Real-Time Clock overrun: CPU did not acknowledge the RTC interrupt before two had occurred.

The other bits are reserved for details of Command errors, and are not implemented at this time.

The remaining 3 bytes are not yet defined, but are intended to provide details of the HPC's status when an illegal command is received.

Note: Except in the FATAL case, all 5 bytes provided by the HPC *must* be read by the CPU, regardless of the specific cause of the error.

Fatal Error Recovery:

When the HPC signals a !DIAG error with FATAL severity, the CPU may use the following procedure to recover:

- 1. Write the RESET command (A5 hex) to the HPC at address FFFC00.

- By inspecting the UPIC register at address FD0000, wait for the HPC to read the command (the WRRDY bit will go low).

- 3. Wait an additional 25 μs.

4. Read from address FFFE00. This will clear the OBUF register and reset the Read Ready status of the UPI port. The HPC will guarantee that a byte of data is present; it is not necessary to poll the UPIC register. This step is necessary because only a hardware reset will clear the Read Ready indication otherwise (HPC firmware cannot clear it).

- Wait at least 80 μs. This gives the HPC enough time to re-initialize the UPI port.

- 6. After Step 5 has been completed, the CPU may re-enable the Maskable Interrupt and start is suing commands. Since the HPC is still performing initialization, however, the first command may sit in the UPI IBUF register or a few milliseconds before the HPC starts to process it.

# 5.0 SOURCE LISTINGS AND COMMENTARY

#### 5.1 HPC Firmware Guide

This section is intended to provide help in following the flow of the HPC firmware. Discussion of features already documented in Application Note AN-550 are abbreviated here; see that application note for details.

The firmware for the HPC is almost completely interruptdriven. The main program's role is to poll mailboxes that are maintained by the interrupt service routines, and to send an interrupt to the CPU whenever a HPC interrupt routine requests one in its mailbox.

On reset, the HPC firmware begins at the label "start". However, the first routine appearing in ROM is the Fatal Error routine. This is done for ease of breakpointing, to keep this routine at a constant address as changes are made elsewhere in the firmware.

#### 5.1.1 Fatal Error Routine

At the beginning of the ROM is a routine (label "hangup") that is called when a fatal error is detected by the HPC. This routine is identical to that documented in Application Note AN-550.

## 5.1.2 Initialization

At label "start", entered on a Reset signal or by the RESET-HPC command from the CPU, the HPC begins its internal initialization. It loads the PSW register (to select 1 Wait state), and then (at label "srfsh"), it starts the Refresh clock pulses running for the dynamic RAM by initializing Timer T4 and starting it.

At "supi", the UPI port is initialized for transfers between the HPC and the CPU.

At label "sram", all RAM within the HPC is initialized to zero. At "sskint", the stack pointer is initialized to point to the upper bank of on-chip RAM (at address 01C0). The address of the fatal error routine "hangup" is then pushed, so that it will be called if the stack underflows.

At "tminit", the timers T1-T3 are stopped and any interrupts pending from timers T0-T3 are cleared. This step arbitrarily initializes the UART baud rate to 9600, but this selection has no effect.

At "scent", the Centronics port is initialized and set up to appear busy to the external system.

At "suart", the HPC UART is initialized for serial data from the external system. The RS-232 DTR signal is arbitrarily set low, which generally means that the printer is not ready. The state of DTR is not actually valid until the first SELECT-UART command is received, which selects the handshaking mode.

At "sled", the LED control signals are initialized, and all LED indicators are turned off.

At "stmrs", all timers are loaded with their initial values, and timers T5–T7 are stopped and any interrupts pending from them are cleared.

At "slcd", the LCD display is initialized to a default contrast level of 5, then commands are sent to initialize it to 8-bit, 2line mode, with the cursor visible and moving to the right by default. This section calls a subroutine "wrpnl" for each character; the subroutine simply writes the character in the accumulator out to the LCD display and waits for approximately 10 ms.

The program then continues to label "minit", which initializes the variables in the HPC's on-chip RAM to their proper contents.

At label "runsys", the necessary interrupts are enabled (from the timers, and from pin I3, which is the UPI port interrupt from the CPU), and the program exits to the Main Program at label "mainIp". Interrupts from the Centronics and UART ports are not enabled until the appropriate SELECT command is received.

## 5.1.3 Main Program (UPI Port Output to CPU)

The Main Program is the portion of the HPC firmware that runs with interrupts enabled. It consists of a scanning loop at label "mainlp" and a set of subroutines (explained below). It is responsible for interrupting the CPU and passing data to it; the HPC is allowed to write data to the CPU only after interrupting it. Unlike the simpler UPI/Front Panel interface described in Application Note AN-550, this main loop scans two separate variables in on-chip RAM that are set up by interrupt service routines: a word called "alert", and a byte called "bstat" (for "Buffer Status"). Both variables are used to determine whether any conditions exist that should cause an interrupt to the CPU.

The "alert" word contains one bit for each interrupt that the HPC can generate. If a bit is set (by an interrupt service routine), the Main Program jumps to an appropriate subroutine to notify the CPU. The subroutine checks whether the UPI interface's OBUF register is empty, and if not, it waits (by calling the subroutine "rdwait"). It then writes the vector number to the OBUF register. This has the effect of interrupting the CPU (because the pin URDRDY goes low), and the CPU hardware reads the vector from the OBUF register.

If there is more information to give to the CPU, the HPC places it, one byte at a time, into the OBUF register, waiting each time for OBUF to be emptied by the CPU. This technique assumes that the CPU remains in the interrupt service routine until all data has been transferred: if the CPU were to return from interrupt service too early, the next byte of data given to it would cause another interrupt, with an incorrect vector.

(Note, however, that the CPU may be interrupted with a Non-Maskable interrupt from a separate source. This simply inserts a pause into the process of reading data from the HPC. Since the HPC is running its main program at this point, with interrupts still enabled, it will not lose data from its communication port under these circumstances.)

The "bstat" byte represents a special case involving the interrupt !DATA to the CPU. This byte shows the main program whether the data communication buffer (which holds data from the external system) is full enough to send its contents to the CPU. If so, the main program calls the subroutine "snddta", which interrupts the CPU, then sends one data byte containing the number of characters to be transferred (currently as many as 128 are possible), and then the characters themselves.

The CPU may, at any time, demand that the HPC transfer all characters that are within its communication buffer. (This is called a "flush" command, which sets one of the bits of the "alert" word, described above.) The HPC, in response, will empty the buffer to the CPU with a !DATA interrupt, even if only one character is left. If the buffer is completely empty, however, the flush command is ignored.

Subroutines called from the Main Program loop are:

- sndrtc: sends a Real-Time Clock interrupt to the CPU. No data is transferred; only the interrupt vector.

- sndlak: interrupts the CPU to acknowledge that a string of data (from a SEND-LCD command) has been written to the LCD display. No data is transferred for this interrupt.

- sndbtn: interrupts the CPU to inform it that a pushbutton has been pressed or released. A data byte is transferred from variable "swlsnt", which shows the new states of all the pushbuttons.

- sndfsh: performs a Flush operation. If there is data, it jumps to the "snddta" routine to send the contents of the buffer to the CPU. If there is no data, however, this subroutine simply returns without generating an interrupt.

- snddta: sends data from the communication buffer to the CPU. It may be entered for one of three reasons:

- 1. the communication buffer is full enough that it must be sent automatically to the CPU.

- 2. a Flush command has been received from the CPU. (The bit "aflush" in the ALERT word is set.)

- 3. an error has been detected on a character received from the external system. This causes an internal Flush request, so that all good characters are sent to the CPU before the bad character is reported. This case is also different be cause it does not flush the entire buffer, but only up to the point of the error. The limit is held in the variable "fshlim".

Depending on other status of the selected communication port, this subroutine may re-enable communication on the port if it was stopped (for example, if the buffer was too full to accept more data until the "snddta" routine emptied it). This is done at label "sdstp".

sndprm: interrupts the CPU because the INPUT PRIME signal on the Centronics parallel port was activated by the external system. No data is transferred by this interrupt.

sndust: interrupts the CPU to report a change in UART status. This interrupt may also be triggered by the CPU using the TEST-UART command.

- snderr: interrupts the CPU to inform it that a character with an error was received. The character and a byte containing error flags are transferred to the CPU.

- snduak: interrupts the CPU in response to a SEND-UART command, to acknowledge that the requested character has been sent on the UART transmitter, and that it is ready to transmit another character.

- sndiag: interrupts the CPU to inform it of a !DIAG interrupt condition, when it is of NOTE severity. (Other !DIAG conditions are handled at label "hangup".)

# 5.1.4 UPI Port Input from CPU (Interrupt I3)

This interrupt service routine, at label "upiwr", accepts commands from the CPU. Apart from the existence of additional commands, the structure of this routine is identical to that of Application Note AN-550. We document here the labels and functions involved in this larger application.

|              | Cor                                                                                                                                                                                                                                                           | nmand Processing Routines                                                                                                                                                                                            |                                                                                                                               |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| INITIALIZE   | 13 interrupt labels:                                                                                                                                                                                                                                          | State 1 = fcinit                                                                                                                                                                                                     | State 3 = Icinit                                                                                                              |

| SELECT-CENT  | 13 interrupt labels:                                                                                                                                                                                                                                          | State 1 = fcselc                                                                                                                                                                                                     | State 3 = Icselc                                                                                                              |

| SELECT-UART  | 13 interrupt labels:                                                                                                                                                                                                                                          | State 1 = fcselu                                                                                                                                                                                                     | State 3 = Icselu                                                                                                              |

| FLUSH-BUF    | 13 interrupt labels:                                                                                                                                                                                                                                          | State 1 = fcflsh                                                                                                                                                                                                     | State $3 =$ (none)                                                                                                            |

|              | At label "fcflsh", the "alert communication buffer.                                                                                                                                                                                                           | " word bit "aflush" is set, which rec                                                                                                                                                                                | quests that the main program flush the                                                                                        |

| CPU-BUSY     |                                                                                                                                                                                                                                                               | State 1 = fccbsy<br>er status byte ''bstat'' is set to indica<br>HPC. This disables the !DATA inte                                                                                                                   | State $3 =$ (none)<br>ate that the CPU is busy and cannot<br>rrupt.                                                           |

|              |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                      |                                                                                                                               |

| CPU-NOT-BUSY |                                                                                                                                                                                                                                                               | State 1 = fccnby<br>er status byte "bstat" is set to indica<br>ATA interrupt is re-enabled.                                                                                                                          | State $3 = (none)$<br>ate that the CPU is ready to accept more                                                                |

| SET-IFC-BUSY | 13 interrupt labels:                                                                                                                                                                                                                                          | State 1 = fcifby                                                                                                                                                                                                     | State 3 = (none)                                                                                                              |

|              | At label "fcifby", the currer                                                                                                                                                                                                                                 | ntly selected interface is set busy, ir                                                                                                                                                                              | n order to present an error indication.                                                                                       |

| SET-CENT-STS | 13 interrupt labels:                                                                                                                                                                                                                                          | State 1 = fcscst                                                                                                                                                                                                     | State $3 = Icscst$                                                                                                            |

|              | At label "lcscst", the Centr<br>and the Centronics port co                                                                                                                                                                                                    | onics Port status byte ''cps'' is load                                                                                                                                                                               | ded from the value supplied by the CPU these new settings. The subroutine                                                     |

| SET-CONTRAST | l3 interrupt labels:<br>At label ''lcslcv'' (Set LCD                                                                                                                                                                                                          | State $1 = fcslcv$<br>Voltage), the LCD Contrast latch is                                                                                                                                                            | State 3 = Icslcv<br>loaded from the value supplied by the                                                                     |

|              | CPU.                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                      |                                                                                                                               |

| SEND-LCD     | 13 interrupt labels:                                                                                                                                                                                                                                          | State 1 = fcslcd                                                                                                                                                                                                     | State 3 = lcslcd                                                                                                              |