AN991

# Using the Serial Peripheral Interface to Communicate Between Multiple Microcomputers

As the complexity of user applications increases, many designers find themselves needing multiple microprocessors to provide necessary functionality in a circuit. Communication between multiple processors can often be difficult, especially when differing processors are used. A possible solution to this problem is usage of the serial peripheral interface (SPI), an interface intended for communication between integrated circuits on the same printed wire board. The MC68HC05C4 is one of the first single-chip microcomputers to incorporate SPI into hardware. One advantage of the SPI is that it can be provided in software, allowing communication between two microcomputers where one has SPI hardware and one does not. Special interfacing is necessary when using the hardware SPI to communicate with a microcomputer that does not include SPI hardware. This interface can be illustrated with a circuit used to display either temperature or time, that incorporates both a MC68HC05C4 and a MC68705R3. The MC68HC05C4 monitors inputs from a keypad and controls the SPI data exchange, while the MC68705R3 determines temperature by performing an analog-to-digital conversion on inputs from a temperature sensor and controls the LED display. Communication between the microcomputers is handled via SPI, with the MC68HC05C4 handling exchanges in hardware, and the MC68705R3 handling them in software.

Usage of software SPI can be expanded to include circuits where the single-chip implementing the SPI in software controls the data exchange, and those in which neither single-chip has hardware SPI capability. Minor modifications to the SPI code are necessary when data exchanges are controlled by the software.

Debugging designs including multiple processors can often be confusing. Some of the confusion can be alleviated by careful planning of both the physical debugging environment and the order in which software is checked.

### SERIAL PERIPHERAL INTERFACE

Communication between the two processors is handled via the serial peripheral interface (SPI). Every SPI system consists of one master and one or more slaves, where a master is defined as the microcomputer that provides the SPI clock, and a slave is any integrated circuit that receives the SPI clock from the master. It is possible to have a system where more than one IC can be master, but there can only be one master at any given time. In this design, the MC68HC05C4 is the master and the MC68705R3 is the slave. Four basic signals, master-out/slave-in (MOSI), master-in/slave-out (MISO), serial clock (SCK), and slave select (SS), are needed for an SPI. These four signals are provided on the MC68HC05C4 on port D, pins 2-5.

### SIGNALS

The MOSI pin is configured as a data output on the master and a data input on the slave. This pin is used to transfer data serially from the master to a slave, in this case the MC68HC05C4 to the MC68705R3. Data is transferred most significant bit first.

Data transfer from slave to master is carried out across the MISO, master-in/slave-out, line. The MISO pin is configured as an input on the master device and an output on the slave device. As with data transfers across the MOSI line, data is transmitted most significant bit first.

All data transfers are synchronized by the serial clock. One bit of data is transferred every clock pulse, and one byte can be exchanged in eight clock cycles. Since the serial clock is generated by the master, it is an input on the slave. The serial clock is derived from the master's internal processor clock, and clock rate is selected by setting bits 0 and 1 of the serial peripheral control register to choose one of four divide-by values. Values for the MCUs crystal oscillators and the SPI divide-by must be chosen so that the SPI clock is no faster than the internal processor clock on the slave.

The last of the four SPI signals is the slave select (SS). Slave select is an active low signal, and the SS pin is a fixed input which is used to enable a slave to receive data. A master will become a slave when it detects a low level on its SS line. In this design, the MC68HC05C4 is always the master, so its SS line is tied to VDD through a pull-up resistor.

# REGISTERS

Three registers unique to the serial peripheral interface provide control, status, and data storage.

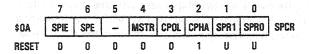

The Serial Peripheral Control Register (SPCR), shown below, provides control for the SPI.

SPIE—Serial Peripheral Interrupt Enable

0 = SPIF interrupts disabled

1 = SPI interrupt if SPIF = 1

SPE-Serial Peripheral System Enable

0 = SPI system off

1 = SPI system on

MSTR-Master Mode Select

0 = Slave mode

1 = Master mode

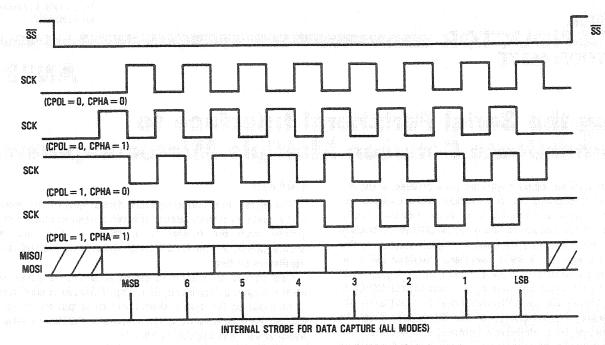

Figure 1. Data Clock Timing Diagram

### CPOL-Clock Polarity

When the clock polarity bit is cleared and data is not being transferred, a steady state low value is produced at the SCK pin of the master device. Conversely, if this bit is set, the SCK pin will idle high. This bit is also used in conjunction with the clock phase control bit to produce the desired clock-data relationship between master and slave. See Figure 1.

### CPHA - Clock Phase

The clock phase bit, in conjunction with the CPOL bit, controls the clock-data relationship between master and slave. The CPOL bit can be thought of as simply inserting an inverter in series with the SCK line. The CPHA bit selects one of two fundamentally different clocking protocols. When CPHA = 0, the shift clock is the OR of SCK with  $\overline{SS}$ . As soon as  $\overline{SS}$  goes low the transaction begins and the first edge on SCK involves the first data sample. When CPHA = 1, the  $\overline{SS}$  pin may be thought of as a simple output enable control. Refer to Figure 1.

## SPR1 and SPR0-SPI Clock Rate Selects

These two serial peripheral rate bits select one of four baud rates (Table 1) to be used as SCK if the device is a master; however, they have no effect in the slave mode.

Table 1. Serial Peripheral

Rate Selection

| SPR1 | SPR0 | Internal Processor<br>Clock Divide By |  |  |

|------|------|---------------------------------------|--|--|

| 0    | 0    | 2                                     |  |  |

| 0    | 1    | 4                                     |  |  |

| 1    | 0    | 16                                    |  |  |

| 1    | 1    | 32                                    |  |  |

Data for the SPI is transmitted and received via the Serial Peripheral Data Register (SPDR). A data transfer is initiated by the master writing to its SPDR. If the master is sending data to a slave, it first loads the data into the SPDR and then transfers it to the slave. When reading data, the data bits are gathered in the SPDR and then the complete byte can be accessed by reading the SPDR.

## **DEMONSTRATION BOARD DESCRIPTION**

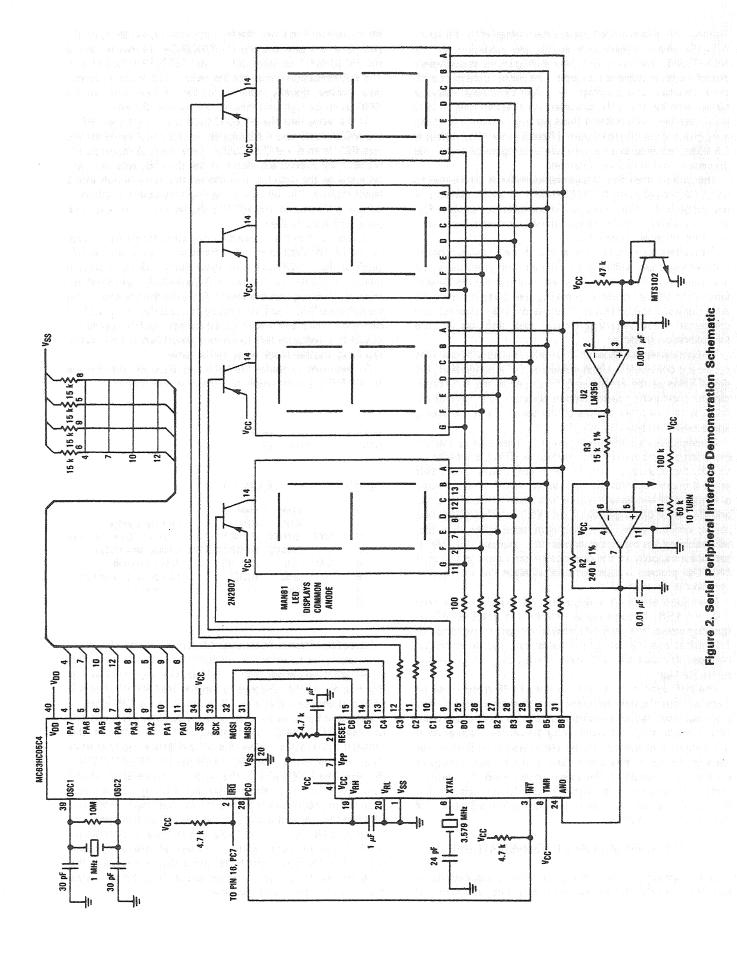

A keypad input from the user is used to choose the output display function. The MC68HC05C4 monitors the keypad, decodes any valid inputs, and sends the data to the MC68705R3. If the user has requested a temperature display, the MC68705R3 sends a binary value of temperature in degrees farenheit to the MC68HC05C4, where the value is converted to a celcius binary coded decimal value and returned to the MC68705R3 to be displayed. The LEDs are common anode displays and are driven directly off of port B on the MC68705R3. If the user desires the circuit to function as a real-time clock, a starting time must be entered and transmitted from the MC68HC05C4 to the MC68705R3. Once the clock has been initialized, the MC68705R3 updates the clock every minute. Clock values are stored in memory, and when the circuit is functioning as a thermometer, the values in memory are updated as required to maintain clock accuracy.

# USING THE A/D CONVERTOR TO MONITOR TEMPERATURE

Temperature monitoring is performed by the Motorola MTS102 silicon temperature sensor and the LM358 Dual Low-Power Operational Amplifier, as shown in the schematic in

Figure 2. Variations in the base-emitter voltage of the Motorola MTS102 silicon temperature sensor are monitored by the MC68705R3, which converts these analog inputs to equivalent digital values in degrees farenheit. The sensor voltage is buffered, inverted, and amplified by a dual differential amplifier before entering the A/D converter. An amplifier gain of 16 is used, resulting in 20-millivolt steps per degree farenheit. Using a VCC of 5 volts, the maximum differential amplifier output is 3.8 volts, resulting in a temperature sensing range from -40 degrees to +140 degrees farenheit.

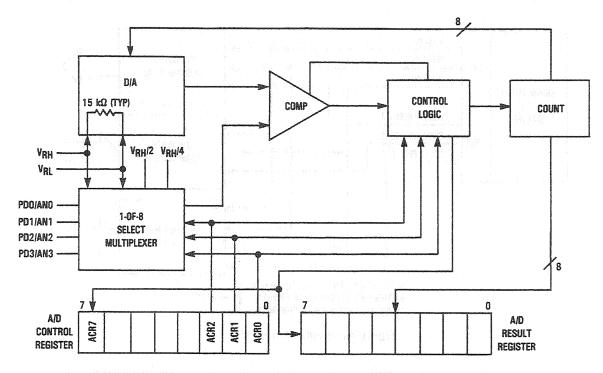

The output from the differential amplifier is connected to the A/D converter on the MC68705R3. A block diagram of the successive approximation A/D converter is shown in Figure 3. Provision is made for four separate external inputs and four internal analog channels.

Two different registers associated with the converter control channel selection, initiate a conversion, and store the result of a completed conversion. Both the external and the internal input channels are chosen by setting the lower 3 bits of the A/D Control Register (ACR). The internal input channels are connected to the VRH/VRL resistor chain and may be used for calibration purposes.

The converter operates continuously, requiring 30 machine cycles per conversion. Upon completion of a conversion, the digital value of the analog input is placed in the A/D result register (ARR) and the conversion complete flag, bit 7 of the ACR, is set. Another sample of the selected input is taken, and a new conversion is started.

Conversions are performed internally in hardware by a simple bisection algorithm. The D/A converter (DAC) is initially set to \$80, the midpoint of the available conversion range. This value is compared with the input value and, if the input value is larger, \$80 becomes the new minimum conversion value and the DAC is once again set to the midpoint of the conversion range, which is now \$C0. If the input value is less than \$80, \$80 becomes the maximum conversion value and the DAC is set to the midpoint of the new conversion range, in this case \$40. This process is repeated until all eight bits of the conversion are determined.

Quantizing errors are reduced to +1/2 LSB, rather than +0, -1 LSB, through usage of a built-in 1/2 LSB offset. Ignoring errors, the transition between 00 and 01 will occur at 1/2 LSB above the voltage reference low, and the transition between \$FE and \$FF will occur 1-1/2 LSBs below voltage reference high.

The A/D convertor returns a value of \$30 when given an input of zero degrees farenheit, so \$30 must be subtracted from the result before converting to celcius. This offset must also be considered when calibrating the sensor. Calibration of the temperature sensor can be performed by adjusting the variable resistor to produce a display of \$00 after a piece of ice has been placed on the temperature sensor for approximately one minute. A 00 display results from a value of \$50 in the ARR, so the variable resistor should be adjusted until this value is reached.

### **COMMUNICATION CONSIDERATIONS**

In this application, an SPI read or write is initiated via an interrupt from the MCU desiring to write data. When any of

the three function keys, display temperature, set time, or display time, are pressed, the MC68HC05C4, as master, sends the MC68705R3 an interrupt on the MC68705R3's INT pin. The MC68HC05C4 writes the key value to its serial peripheral data register, thereby initiating the SPI. It then waits for the SPIF bit to go high and returns to scanning the keypad.

At the same time the MC68HC05C4 is writing to its SPDR, the MC68705R3 sets a bit counter to eight and waits for the first SCK from the MC68HC05C4. After each clock pulse, the MC68705R3 checks the status of the data bit, sets the carry bit equal to the data bit, and rotates the carry bit left into a result register. The bit counter is decremented, compared to zero, and if not zero, the MC68705R3 waits for the next clock pulse and repeats the cycle.

To ensure proper data transfers, the internal processor clock of the MC68705R3 must be sufficiently faster than the SPI clock of the MC68HC05C4 to allow the MC68705R3 time to complete this routine before the MC68HC05C4 can send another bit. This requires the user to first write the code to handle the software SPI, count machine cycles, and then choose MCU oscillator values that allow the additional machine cycles required in a software SPI to be completed before the master can send another clock pulse to the slave.

For example, consider the following piece of code for the MC68705R3, a slave receiving data from the master.

| DATA IN | PORTC pin | 5 |

|---------|-----------|---|

| SCK     | PORTC pin | 4 |

| Cycles |     | Ir    | struction   |                           |

|--------|-----|-------|-------------|---------------------------|

| 2      |     | LDA   | #\$08       |                           |

| 5      |     | STA   | BITCT       | Set bit counter           |

| 10     | NXT | BRSET | 4,PORTC,*   | Wait for clock transition |

| 10     |     | BRSET | 5,PORTC,STR | Check data status         |

| 6      | STR | ROL   | RESULT      | Store in result           |

| 6      |     | DEC   | BITCT       | Check for end of byte     |

| 4      |     | BNE   | NXT         | Get next bit              |

| 43     |     |       |             |                           |

Execution of this code requires 43 machine cycles. The maximum oscillator speed for an MC68705R3 is 1 MHz, requiring an SPI clock no greater than 1/43 MHz. One way of obtaining this rate for the SPI clock is to run the MC68HC05C4 at 0.5 MHz and choose a divide-by 32 to generate the SPI clock.

If the user has selected a temperature display, it is necessary for the MC68705R3, as a slave, to send data to the MC68HC05C4 master. When the MC68705R3 is ready to send data, it interrupts the MC68HC05C4 via the MC68HC05C4's IRQ line. The MC68HC05C4 then writes to its serial peripheral data register to initiate the transfer and shifts in data bits sent from the MC68705R3 until the SPIF bit goes high. While the MC68HC05C4 is writing to its SPDR, the MC68705R3 program is setting a bit counter to 8. When it detects a clock pulse on the SCK pin, the data register is rotated left one bit, placing the MSB in the carry. The MOSI pin is then set equal to the carry bit, the bit counter is decremented and, if it is greater than zero, the process is repeated.

Figure 3. A/D Block Diagram

### ADDITIONAL USES OF SPI

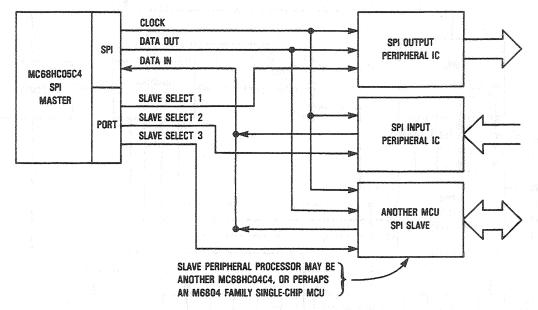

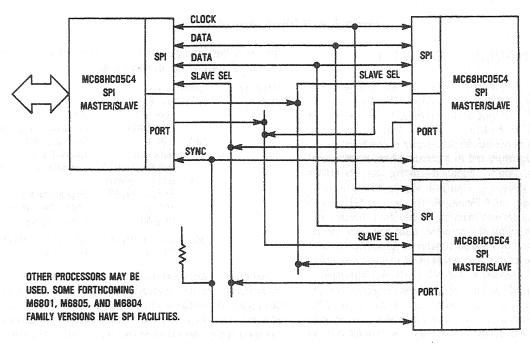

Many variations of this usage of the SPI are possible. The three possibilities are hardware SPI at both master and slave, software SPI at the master and hardware at the slave, and software SPI at both master and slave. Table 1 shows the various MCUs that have SPI implemented in hardware.

SPI is fairly straightforward in a circuit where both master and slave have hardware SPI capability. In this case, the MCUs are connected as shown in Figure 4. Figure 4a illustrates a single master system, and Figure 4b shows a system where either MCU can be system master. When both master and slave have SPI capability in hardware, data transfers can be handled full duplex. For a single master system, both master and slave write the data to be transferred to their respective serial peripheral data registers. A data transfer is initiated when the master writes to its serial peripheral data register. A slave device can shift data at a maximum rate equal to the CPU clock, so clock values must be chosen that allow the slave to transfer data at a rate equal to the master's transfer rate. In a multiple master system, the master must pull the slave's SS line low prior to writing to its serial peripheral data register and initiating the transfer.

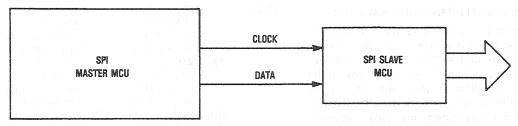

### PROGRAMMING A MASTER FOR SOFTWARE SPI

When the master in an SPI system does not have hardware SPI capabilities, the resulting system is quite different. An SPI system with a master providing the SPI in software is shown in Figure 5. This system only requires two lines between the microcomputers; data and clock. A slave select line can be added for use with multiple slaves. If operated with one data line, the SPI will function half-duplex only. Data is stored in a register, rotated left one bit at a time, and a port pin is set equal to the data bit. The master then provides the serial clock by toggling a different port pin. A bit counter must also be used to count the eight bits in the byte. Bit manipulation instructions are very useful for implementing SPI in software.

One possible software implementation for a write from the master to the slave is shown below.

| DATA OUT | PORT | C pin 0      |                             |  |  |  |

|----------|------|--------------|-----------------------------|--|--|--|

| SCK      | PORT | PORTC pin 1  |                             |  |  |  |

|          |      | LDX #\$08    | Bit counter                 |  |  |  |

|          |      | LDA DATA     | Put data in register A      |  |  |  |

|          | RPT  | ROLA         | Shift a data bit into carry |  |  |  |

|          |      | BCS SET      | Check for a 1               |  |  |  |

|          |      | BCLR 0,PORTC | Set data out line to 0      |  |  |  |

|          | CLK  | BSET 1,PORTC |                             |  |  |  |

|          |      | BCLR 1,PORTC | Toggle clock pin            |  |  |  |

|          |      | DECX         | Check for end of byte       |  |  |  |

|          |      | BNE RPT      | If not, repeat              |  |  |  |

|          | SET  | BSET 0,PORTC | Set data out line to 1      |  |  |  |

|          |      | BRA CLK      | Go to clock                 |  |  |  |

Full duplex operation requires a second data line. One port pin is then devoted to data-out and one to date-in. Data transfer from slave to master is accomplished immediately before the SCK pin is toggled. The state of the data-in pin is tested, and the carry is then set equal to the data-in pin. This value is then rotated in to a result register. The modified code is shown below.

| DATA OUT | PC  | ORTC pin 0          |                             |

|----------|-----|---------------------|-----------------------------|

| SCK      | PC  | ORTC pin 1          |                             |

| DATA IN  | PC  | ORTC pin 2          |                             |

|          |     | LDX #\$08           | Bit counter                 |

|          |     | LDA DATA            | Put data in register A      |

|          |     | BCLR 1,PORTC        | Clear clock pin             |

|          | RPT | ROLA                | Shift a data bit into carry |

|          |     | BCS SET             | Check for a 1               |

|          |     | BCLR 0,PORTC        | Set data out line to 0      |

|          |     | BSET 1,PORTC        | Set clock pin               |

|          | DIN | BRCLR 3, PORTC, CLK | Check state of data         |

|          | CLK | ROL DATAIN          | Rotate input data one bit   |

|          |     | DECX                | Check for end of byte       |

|          |     | BNE RPT             | If not, repeat              |

|          | SET | BSET 0,PORTC        | Set data out line to 1      |

|          |     | BRA DIN             | Go to data input            |

Figure 4a. Single Master SPI

Figure 4b. Multiple Master SPI

Figure 5. Software SPI

### PROGRAMMING A SLAVE FOR SOFTWARE SPI

If the slave in the system is a MCU with hardware SPI capability, the data transfer will happen automatically, one bit per clock pulse. If the slave is a MCU that does not have SPI implemented in hardware, a read requires the following actions. A bit counter is set to eight, the slave polls its SCK pin waiting for a clock transition, once it perceives a clock it checks its data-in pin, sets the carry equal to the data and rotates the carry into a results register. One possible code implementation is shown in the previous timing example.

Converting this to full duplex operation requires the addition of a write from slave to master. The slave rolls a data register to place the data bit to be sent into the carry, and the data-out pin is set equal to the carry. These actions occur prior to the read of data from the master. With these modifications, the code looks as shown below.

| DATA OUT | PORTC pi | n 6         |                           |

|----------|----------|-------------|---------------------------|

| DATA IN  | PORTC pi | n 5         |                           |

| SCK      | PORTC pi | n 4         |                           |

|          | LDA      | #\$08       |                           |

|          | STA      | BITCT       | Set bit counter           |

| AGN      | BRSET    | 4,PORTC,*   | Wait for clock            |

|          | ROL      | RES1        | Shift data to send        |

|          | BCS      | SET1        | Check data status         |

|          | BCLR     | 6,PORTC     | If 0, clear data out      |

|          | BRCLR    | 4,PORTC,*   | Wait for clock transition |

|          | BRSET    | 5,PORTC,STR | Check input data status   |

| STR      | ROL      | RESULT      | Store in result           |

|          | DEC      | ВІТСТ       | Check for end of byte     |

|          | BNE      | AGN         |                           |

### **DEBUGGING TIPS**

Debugging a circuit containing two microcomputers presents various problems not evident when working with a single microcomputer circuit. The first problem is simultaneously providing emulation for both microcomputers. Once emulation capability is arranged, the designer needs to keep track of the progress of each single-chip, and monitor how the actions of one affects the actions of the other.

One of the easiest methods to debug a circuit of this type is to use two emulator stations, complete with separate terminals. Any emulators can be used, but user confusion is reduced if the emulators have similar commands and syntax. Physical separation also helps reduce confusion. It is somewhat easier to keep track of the concurrent operations if one side of the prototype board is devoted to each single-chip and the majority of peripherals they each must interface with, and the emulator for that microcomputer is placed to that side of the printed circuit board.

Before starting simultaneous debugging, it is best to individually debug the code for each microcomputer wherever possible. Once it becomes necessary for the microcomputers to communicate with one another, halt one of the microcomputers anytime they are not actually talking and work with the remaining microcomputer. As the debugging progresses, keep in mind that an error in the function of one single-chip does not necessarily indicate an error in the corresponding code for that single-chip, but rather, the error may have been caused by an incorrect or unintended transmission from the other single-chip.

Although the aforementioned suggestions reduce debugging problems, some will remain. Long periods of debug can result in an obscuring of the separation of the functions of the two programs. It helps to take periodic breaks to get away from the system and clear the thought processes. Expect to occasionally be confused, be willing to retrace sections of code multiple numbers of times, and the debugging will proceed fairly smoothly.

### CONCLUSION

The Serial Peripheral Interface can be used as a tool to innerconnect to MCU with various other MCUs or peripherals, and can be used with any microcomputer. A special case occurs when one, or more, of the MCUs in a circuit do not have SPI capability in hardware. In this case, a simple software routine can be written to perform the SPI. Used in this manner, the SPI eliminates the need for costly, inconvenient parallel expansion buses and Universal Asynchronous Receiver/Transmitters (UARTs) and simplifies the design effort.

```

0003 that if the least of the design of the transfer one will defeat

0005 index at a fine state of the state of t

0006 0000 porta equ

0007 0002 portc equ

0008 0003 portd equ

4 - Popular de Company de Region de Company

0009 0004 ddra equ

0010 0006 ddrc equ

0011 000A spcr equ

0012 000B spsr equ

0013 000C spdr equ

0014 0012 tcr equ

$05 pro skyling of a company of the property o

$0c

$12

0015

0016

0017 00B0

org $b0

0018

0019 00B0

an and one in some the second of the company of the

tmpa rmb 1

0020 00B1

0021 00B2

detr rmb 1

0022 00B3

ctl. ....rmb 1

0023 0084 base rmb 4 0024 0088 lsb rmb 1

0025 0089

msb rmb 1

0026

0027 0020

org

$20

0028

0029

***** KEYPAD LOOKUP TABLE *****

0030

0031 0020

kypd equ

0032

fcb $07

0033 0020 07

0034 0021 04

fcb

fcb

fcb

0035 0022 01

0036 0023 00

$00

$00

$08

$05

$02

$0a disp. temp.

0037 0024 08

0038 0025 05

0039 0026 02

fcb

$0a disp. temp.

0040 0027 DA

fcb

0041 0028 09

fcb

$09

0042 0029 06

fcb

$06

0043 002A 03

fcb

$03

0044 002B 0E

fcb

$0e

set time

0045 002C 0D

fcb

$04

am

0046 002D 0C

fcb

$0c

o m

0047 002E OF

fcb

$0 f

disp. time

0048 002F 0B

fcb

$0b

blank

0049

0050 0100

org $100 program start

0051

0052 0100 9C

start

rso

0053 0101 3F 12

cir ter

mask timer interrupts

0054 0103 AE 7B

ldx #$7ь

0055 0105 BF

02

stx portc

initialize port c

0056 0107 AE 7F

ldx #$7f

0057 0109 BF 0A

stx spcr set spi cont. reg.

0058 010B BF 04

stx ddrc set cO as output

0059 0100 3F 00

clear keypad inputs

cir porta

0060 010F A6 F0

|da #$f0

set up port a

0061 0111 B7 04

sta ddra

a7-a4 out., a0-a3 in

0062 0113 9B

sei

```

```

0064

** check keypad **

3045

3066 0114 CD 01 67

key

jsr keypad

0067 0117 A1 0A

cmp #$Oa

check for disp. temp

0068 0119 27 DE

beq dtmp

0069 011B A1 DE

cmp #$0e

check for set time

0070 011D 27 2B

beg sttm

0071 011F A1 OF

cmp #$Of

check for disp. time

0072 0121 27 06

beg dtmp

0073 0123 A1 0B

cmp #$05

check for disp. sec

0074 0125 27 02

beq dtmp

0075 0127 20 EB

bra key

wait for next input

0076

0077

** display temp **

0078

0079 0129 11 02

dtmp

bolr Opports send interrupt for spi

0080 012B CD 01 59

jsr spiwr send byte

0081 012E A1 0A

cmp #$Oa

check for disp. temp.

0082 0130 27 02

beq cir

0083 0132 20 E0

bra key

0084

0085 0134 9A

clr cli

0086 0135 20 DD

bra key

0087

3088

** set time **

3089 0137 CD 01 67

nudig jsr keypad

0090 013A A1 0A

cmp #$Oa

0091 013C 27 F9

beg nudig

0072 013E A1 0B

cmp #$0b

0093 0140 27 F5

beg nudig look for valid digit

0094 0142 A1 DE

cmp #$0e

0095 0144 27 F1

beg nudig

0076 0146 A1 OF

cmp #$0f

0097 0148 27 ED

beq nudig

0098 014A 11 02

sttm

bolr Opporto send int. for spi

0099 014C CD 01 59

jsr spiwr send value

0100 014F A1 0C

cmp #$0c

check for pm

0101 0151 27 C1

beq key

yes, wait for next input

0102 0153 A1 0D

cmp #$0d

check for am

0103 0155 27 BD

beg key

yes, wait for next input

0104 0157 20 DE

bra nudia

get next time digit

0105

0106

** Spi write subroutine **

0107

0108 0159

5piwr

equ *

0109 0159 B7 GC

sta spdr put data in data reg.

0110 015B OF OB FD

brclr 7,spsr,* wait for end of byte

0111 015E 10 02

bset Opporta

0112 0160 81

spiflg rts

done

0113

3114

** spi read subroutine **

0115

0116 0161

spird

equ *

0117 0161 BF DC

stx spdr initiate transfer

0118 0163 OF OB FD

brcir 7, spsr, * wait for end of byte

5119 0166 81

rdend

rts

3120

```

```

0121

** keypad scanning routine **

0122

0123 0167

keypad equ *

0124

0125

** 32 msec delay **

0126

0127 0167 A6 20

wtip

lda #$20

set up outer loop

0128 0169 B7 B3

sta ct1

counter

Ida #$32 set up inner loop

deca dec. inner loop

D129 D16B A6 32

Otip

0130 0160 4A

inlp

D131 D16E 26 FD

bne inlp when 0;

0132 0170 3A B3

dec ct1

decrement outer loop

0133 0172 26 F7

bne otlp

0134 0174 5F

clrx

set up row counter

check first row

0135 0175 A6 80

|da #$80

0136 0177 B7 00

sta porta

0137 0179 B6 00

Ida porta check for key

nxtr

and #$Of mask upper nibble

cmp #$OO look for zero

bne debnc branch if have a key

asr ports

0138 017B A4 0F

0139 017D A1 00

D140 D17F 26 D9

0141 0181 37 00

asr porta

try next row

D142 D183 5C

incx

decrement row counter

0143 0184 A3 03

cpx #$03

check for zero

0144 0186 23 F1

bls nxtr

test next row

0145 0188 20 DD

inval bra wtlp

no key pressed

0146

0147

** debounce key input **

0148

0149 018A B7 B1

debnc

sta tmpa

save value

0150 018C BF B0

stx rwno save row number

0151 018E A6 FF

lda #$ff set up delay

0152 0190 4A

ioop

deca

0153 0191 26 FD

bne loop

wait

0154 0193 B6 00

lda porta check row again

and #$Of mask upper nibble

0155 0195 A4 OF

0156 0197 B1 B1

cmp tmpa

check for same key

0157 0199 26 CC

bne wtlp

return if invalid

3158

0159

** wait for key release **

0160

0161 019B B6 00

lda porta check value

wtr

0162 019D A4 OF

and #$Of

mask upper nibble

0163 019F A1 00

cmp #$00

look for zero

0164 01A1 26 F8

bne wtr

wait for release

0165

0166

** decade key value **

0167

0168 01A3 B6 B1

ida tmpa restore value

3169 D1A5 5F

cirx

set up column ctr.

0170 01A6 44

isra

shift columns

nxtc

0171 01A7 25 03

bcs col

branch if have column

0172 01A9 5C

incx

J173 D1AA 20 FA

bra nxtc

try next column

0174 D1AC 58

lsix

0175 01AD 58

Islx

x=4*col. no.

txa

0176 01AE 9F

place x in a

0177 01AF BB B0

add rwno

key vu.__

place a in x

key value =4*coi + row

0178 01B1 97

tax

0179 01B2 E6 20

lda kypd,x

convert to decimal

G180 01B4 B7 B1

sta tmpa

0181 C1B6 81

0182

```

```

0183 ***** temperature conversion routine ******

0184

0185

* farenheit value is received from 705r3 via

0186

* spi and received in the a register. the value

0187

* is converted to celcius and the leftmost

* led is blanked.

0188

0189

r3int

0190 01B7

0191 01B7 CD 01 61

0192 01BA B6 0C

sub #$20

bhs conv

0193 01BC AD 20

0194 D1BE 24 D5

0195 0100 40

nega

|d× #$Oa

negate

0196 01C1 AE DA

0197 01C3 BF B6

stx base+2 '-' pattern

0198

*** temperature conversion ***

0199

** a 16-bit multiply by 5 is performed on the

0200

** value received from the r3. this number

0201

0202

** is then divided by 9.

0203

0204 01C5 3F B9

cir msb

clear counters

CONV

0205 01C7 3F B8

cir isb

sta isb

0206 01C9 B7 B8

Isla

0207 01CB 48

multiply by 2

0208 01CC 39 B9

rol msb

load overflow into msb

0209 01CE 48

Isla

multiply by 2

0210 01CF 39 B9

rol msb

load overflow into msb

0211 01D1 BB B8

add isb

a contains value x5

0212 01D3 24 02

bcc div

0213 01D5 3C B9

inc msb

if overflow, inc msb

0214 01D7 3F B2

cir dctr

0215 01D9 B7 B8

sta isb

0216 01DB 98

cic

0217 01DC 3C B2

nxt9 inc dctr

0218 01DE B7 B8

sta isb

0219 01E0 B6 B9

lda msb

0220 D1E2 A2 00

sbc #$00

subtract borrow from msb

0221 01E4 B7 B9

sta msb

0222 01E6 B6 B8

lda Isb

count factors of 9

0223 01E8 AD 09

sub #$09

0224 01EA 24 FD

bcc nxt9

if no borrow, repeat

0225 D1EC 3D B9

if barrow, check for end

tst msb

0226 D1EE 26 EC

bne nxt9

repeat if not end

0227

0228

0229

*** end of divide, add last 9 back in and

0230

*** check remainder for rounding

0231

0232 01F0 AB 09

add #$09

find remainder

cmp #$04 if greater

bhi done than 4, rour

0233 01F2 A1 04

0234 01F4 22 02

than 4, round up

0235 01F6 3A B2

dec dctr

0236 01F8 B6 B2

lda dctr

done

0237

0238 01FA AE 0B

idx #$0b

POS

blank pattern

0239 01FC BF B7

stx base+3 blank most sig. digit

0240

0241

**** convert binary value to bcd value ****

П747

0243

* the x registers begins with the binary value

0244

* and exits with zero. each digit, units, tens

```

```

0245

* and hundreds; is stored separately and checked

0246

* for a value equal to 10.

0247

7248 01FE 97

place a into x

tax

3249 D1FF 4F

cira

1250 0200 3F B5

clear values

clr base+1

1251 0202 3F B6

clr base+2

check for end

if complete, send to r3

3252 0204 5D

st

tstx

1253 0205 27 17

beg send

1254 0207 5A

dec×

decrement hex number

1255 0208 4C

inca

increment decimal number

cmp #$Oa equal to 10?

bne st no, keep going

3256 0209 A1 DA

J257 020B 26 F7

1258 0200 3C B5

inc base+1 increment tens

1259 020F B6 B5

Ida base+1 test for 10

1260 0211 A1 0A

cmp #$0a

if equal, set hundreds

1261 0213 27 03

beg hund

1262 0215 4F

cira

bra st

zero

clear ones

1263 0216 20 EC

count next 10

cir base+1 clear tens

1264 0218 3F B5

hund

)265 021A 3C B6

inc base+2 increment hundreds

1266 021C 20 F7

bra zero

1267

1268

* send all digits to 705r3 via spi

1269

* start by interrupting r3 and then

1270

* sequentially sending four values

1271

1272 021E B7 B4

send

sta base

store ones

1273 0220 B6 B6

lda base+2

1274 0222 27 OB

beq blk

1275 0224 E6 B4

Ida base;x start at base

nxtdg

1276 0226 CD 01 59

jsr spiwr send to r3

1277 0229 5C

incx

1278 022A A3 03

cpx #$03 look for end

1279 022C 26 F6

bne nxtdg if no, next digit

1280 022E 80

rti

1281 022F A6 0B

blk

lda #$Ob

1282 0231 B7 B6

sta base+2

1283 0233 20 EF

bra nxtdg

1284

1285

1286

*** initialize interrupt vectors ***

1287

1288 1FF4

org $1ff4

1289

1290 1FF4 01 00

spivec fdb start

1291 1FF6 01 00

scivec fdb start

1292 1FF8 01 00

tmrvec fdb start

1293 1FFA 01 B7

irquec fdb r3int

1294 1FFC 01 00

swivec fdb start

1295 1FFE 01 00

reset fdb start

```

```

0001

0002

nam r3disp

0003

0004

****** REGISTER DEFINITION *****

0005

0006 0001

portb equ

1

0007 0002

2

portc equ

0008 0005

ddrb

5

equ

0009 0006

ddrc

equ

6

0010 0008

8

tdr

equ

0011 0009

9

ter

equ

0012 000E

14

acr

equ

0013 000F

equ 15

arr

0014

0015

0016 0040

org $40

0017

0018

0019 0040

wrdat rmb 1

0020 0041

timtmp rmb

1

0021 0042

ct rmb 1

0022 0043

ct1

rmb 1

0023 0044

result rmb

1

0024 0045

resi rmb 1

0025 0046

bitct rmb

1

0026 0047

rmb

sec

1

0027 0048

seamnt rmb

0028 0049

P m

rmb

1

0029 004A

base

rmb

4

0030

0031 0080

org $80

0032

0033

**** display look-up table ****

0034

0035 0080

segtab equ *

0036 0080 01

feb %00000001 0

0037 0081 4F

fcb %01001111 1

0038 0082 12

fcb %00010010 2

0039 0083 06

fcb %00000110 3

0040 0084 4C

fcb %01001100 4

0041 0085 24

fcb %00100100 5

0042 0086 20

fcb %00100000 6

0043 0087 OF

fcb %00001111 7

0044 0088 00

f∈b %00000000 8

0045 0089 OC

fcb %00001100 9

0046 008A 7E

fcb %01111110 -

0047 008B 7F

fcb %01111111 blank

0048 008C 7F

fcb %01111111 pm

0049 008D 18

fcb %00011000 p

0050

0051 0090

org $90 program start

0052

0053

*** initialize variables ***

0054

0055 0090

start equ *

0056 0090 A6 07

lda #$07

0057 0092 C7 OF 38

sta $f38

set MOR

0058 0095 A6 FF

Ida #$ff

0059 0097 B7 05

sta ddrb

set up port b as output

0060 0099 B7 08

sta tdr

set timer for prescale of 128

0061 009B B7 4A

sta base

0062 0090 B7 4B

sta base+1

blank time display

```

```

0063 009F B7 4C

sta base+2

0064 00A1 B7 4D

sta base+3

0065 00A3 A6 EF

lda #$ef

7066 00A5 B7 02

sta portcassas set portc to choose msd

1067 00A7 B7 48

sta segmnt

1068 00A9 A6 CF

lda #$cf

1069 DOAB B7 06

sta ddrc

set up c0-3,c6,c7 as outputs

1070 00AD A6 OF

lda #$Of

1071 00AF B7 09

sta tcr

unmask timer interrupt

1072 00B1 3F 41

clr timtmp

start with time disp.

1073 00B3 3F 47

cir sec

set seconds to zero

1074 00B5 3F 49

cir pm

start with am

1075 00B7 A6 3B

lda #$3b

1076 00B9 B7 42

sta ct

set up timing loops

1077 00BB A6 08

lda #$08

1078 00BD B7 43

sta cti

1079 00BF 9A

eli

1080

1081

₩

delay for

1082

1083 00C0 AE FF

Idx #$ff

dlay

1084 00C2 A6 FF

Ida #$ff

1085 00C4 4A

deca

1086 00C5 26 FD

bne dlay+4

1087 00C7 5A

decx

1088 00C8 26 F8

bne dlay+2

1089

1090

temperature measurement *

1091

1092 00CA 3F DE

cir acr

clear conv. complete flag

1093 00CC B6 DE

lda acr

1094 DOCE 2A FC

bpl *-2

1095 0000 B6 OF

lda arr

get result

1096 00D2 A2 30

sbc #$30

adjust so 0 deg =$30

1097 0004 B7 45

store in spi data register

sta res1

1098 00D6 B6 41

lda timtmp

1099 00D8 A1 07

cmp #$07

check for temp, update

1100 00DA 26 E4

bne dlay

1101

1102

***

send temperature value to hc05c4 for

1103

*

conversion into celcius, start by

1104

*

interrupting the hc05c4 and then transmit

1105

*

data via the spi.

1106

1107 00DC 9B

sei

1108 0000 1F 02

bclr 7, ports interrupt hc05c4

1109 000F CD 01 18

jsr spiwr write data to hc05c4

1110 DOEZ AE 04

1dx #$04

1111

112

wait for return data ~ 140 cycles *

113

114 DOE4 A6 DB

Ida #$Ob

115 DOE6 B7 51

sta base+7

116 DOE8 A6 DE

lda #$De

117 ODEA 4A

timlp

deca

118 DOEB 26 FD

bne timle

119

120

*

get decimal values in celcius from

121

hc05c4

122

123 DOED CD 01 01

nxtdg

jsr spird

124 00F0 B6 44

lda result

get value

```

```

0125 00F2 E7 4A

sta base,×

store

0126 00F4 5C

incx

0127 00F5 A3 07

CPX #$07

check for end

0128 00F7 26 F4

bne nxtdg

0129 00F9 9A

cli

0130 00FA 20 C4

bra dlay

0131

** select temperature display **

0132

0133

0134 00FC A6 07

temp | Ida #$07

0135 OOFE B7 41

sta timtmp choose temp. display

0136 0100 80

rti

0137

0138

***** spi routines *****

0139

* the three pins used for the spi are

0140

miso bit 6, portc

0141

*

mosi bit 5, portc

0142

₩

sck bit 4, portc

*

0143

the r3 waits for a high-to-low

0144

transition of the spi clock, which

0145

is provided by the hc05c4 and sent

0146

on portc pin 4. a bit of data is

0147

*

0148

transferred on each high-to-low

0149

፠

transition of the clock.

0150

0151

spi read *

0152

0153 0101

spird equ *

lda #$08

0154 0101 A6 08

sta bitct set bit counter

0155 0103 B7 46

0156 0105 08 02 FD

brset 4, portc, * wait for clock transition

nxt

brset 5, portc, str check data status

0157 0108 0A 02 00

0158

note: the brset command automatically

0159

sets the carry bit to be equal to the

0160

0161

bit under test

0162

0163 010B 39 44

str rol result store in result

0164 0100 A6 02

lda #$02

delay loop

stall deca

0165 010F 4A

0166 0110 26 FD

bne stall

0167 0112 90

nop

dec bitct

0168 0113 3A 46

check for end of byte

0169 0115 26 EE

bne nxt

get next bit

0170 0117 81

rts

0171

0172

*

spi write *

data to be sent is in result at

0173

*

0174

₩

start of write

0175

0176 0118

spiwr equ *

0177 0118 A6 08

lda #$08

sta bitct

rol res1

bcs set1

0178 011A B7 46

set bit counter

0179 011C 39 45

0180 011E 25 12

shift data

aan

check data status

0181 0120 1D 02

bclr 6, portc if 0, clear miso

0182 0122 1E 02

bset 7, portc clear interrupt

0183 0124 19 02

bolr 4, porto

0184 0126 90

nap

0185 0127 9D

timing delay.

nop

0186 0128 08 02 FD tst brset 4, portc, * wait for clock trans.

```

```

0187 012B 3A 46

dec bitct

check for end of byte

0188 012D 26 ED

bne agn

0189 012F 1E 02

bset 7, ports clear interrupt

0190 0131 81

rts

0191

set1 bset 6, portc if 1, set miso bset 7, portc clear interrupt

0192 0132 1C 02

D193 D134 1E D2

0194 0136 18 02

bset 4, portc

0195 0138 20 EE

bra tst

0196

0197

initialization of data read via spi **

**

0198

*

0199

a data read is initiated via an interrupt

*

0200

፠

from the hc05c4. the value received is

*

0201

tested to determine which function is

0202

*

requested and the processor jumps to the

0203

×

proper routine.

0204

*

0205

D206 013A CD 01 01

c4int jsr spird

get value

0207 013D A6 03

lda #$03

0208 013F B7 41

sta timtmp

choose time

0209 0141 B6 44

lda result

0210 0143 A1 0A

cmp #$Da

check for disp temp

0211 0145 27 B5

beq temp

0212 0147 A1 OF

check for display time

cmp #$0f

D213 D149 27 3C

beg rtry

0214 014B A1 0E

cmp #$0e

check for set time

D215 D14D 27 39

beq cirtm

0216 014F A1 0D

cmp #$Od

check for am

D217 D151 27 DC

beq am

cmp #$0b

0218 0153 A1 0B

check for secs

0219 0155 27 6A

beq dsec

D220 0157 A1 0C

check for pm

cmp #$0c

0221 0159 26 39

bne dig

no, set digit

lda #$ff

0222 015B A6 FF

set pm address

0223 015D B7 49

sta pm

0224

0225

check for valid input **

**

0226

D227 D15F B6 4D

lda base+3

am

check tens of hours

0228 0161 27 08

beg blhr

if zero, blank digit

0229 0163 A1 01

cmp #$01

0230 0165 27 46

beq twoc

D231 D167 A1 DB

cmp #$0b

look for blank

0232 0169 26 48

bne blank

if not, blank display

0233 016B A6 0B

lda #$Ob

blhr

0234 016D B7 4D

sta base+3

blank tens of hours

D235 D16F B6 4B

lda base+1

mtn

check tens of minutes

check against 5

D236 D171 A1 D5

cmp #$05

D237 D173 22 3E

bhi blank

if greater, blank display

0238

0239

¥

valid input; set timer counter *

0240

0241 0175 A6 DF

lda #$Of

0242 0177 B7 09

sta tcr

unmask timer interrupt

lda #$43

0243 0179 A6 43

0244 017B B7 42

sta ct

load inner loop counter

0245 017D A6 06

Ida #$06

0246 017F B7 43

sta ct1

load outer loop counter

0247 0181 3F 47

cir sec

clr base+8

0248 0183 3F 52

```

```

0249 0185 3F 53

clr base+9

0250 0187 80

rti

rtry

0251

0252

clear displays *

0253

0254 0188 A6 0B

lda #$Ob

cirtm

0255 018A B7 4A

sta base

0256 018C B7 4B

sta base+1

0257 018E B7 4C

sta base+2

0258 0190 B7 4D

sta base+3

0259 0192 20 F3

bra rtry

0260

0261

0262

input digit *

0263

0264

time setting routine ***

***

0265

time is inputted left to right

*

0266

*

and the end of input is indicated

0267

*

be pressing either the am or pm

0248

*

button. pm is denoted on the

0269

*

display by lighting the decimal

point, counters are set to zero out

0270

*

0271

*

after each second.

0272

0273

0274

0275 0194 9A

dig

cli

0276 0195 B6 4C

Ida base+2

0277 0197 B7 4D

sta base+3

0278 0199 B6 4B

lda base+1

shift data left one

0279 019B B7 4C

sta base+2

digit

0280 019D B6 4A

lda base

0281 019F B7 4B

sta base+1

0282 01A1 B6 44

ida result

enter digit 1

0283 01A3 B7 4A

sta base

0284 01A5 A1 09

cmp #$09

check for valid digit

0285 01A7 22 DE

bhi rtry

0286 01A9 B7 4A

sta base

0287 01AB 20 DA

bra rtry

get next number

0288

0289

*

check if time less than 12 o'clock

0290

*

blank display if not

0291

0292 01AD B6 4C

twoc | ida base+2

check hours units

0293 01AF A1 02

cmp #$02

0294 01B1 23 BC

bls mtn

okay, check tens of min.

0295 01B3 3F 4D

blank clr base+3

0296 01B5 3F 4C

clr base+2

0297 01B7 A6 0D

lda #$Od

0298 01B9 B7 4B

sta base+1

send error message

0299 01BB A6 05

lda #$05

0300 018D B7 4A

sta base

0301 01BF 20 CA

bra rtry

0302

0303

**** seconds display ****

0304

* blank first two leds

0305

*

0306 01C1 B7 41

dsec

sta timtmp

set timtmp to $0b

0307 01C3 B7 55

sta base+$b

blank 1st two leds

0308 01C5 B7 54

sta base+$a

0309 01C7 80

rti

0310

```

```

0311

0312

****

display routine *****

0313

0314

displays are refreshed every

displays are refreshed every msec when a timer interrupt occurs. the

0315

*

0316

፠

most significant digit is displayed

0317

×

first. at the conclusion of each

0318

minute, the time is updated

0319

0320

0321 0108

tmrint equ *

0322

D323 D1C8 99

sec

0324 01C9 BE 41

ldx timtmp

choose time or temp

0325 01CB A6 FF

lda #$ff

blank displays

send to leds

0326 01CD B7 01

sta portb

0327 01CF 36 48

0328 01D1 25 04

ror segmnt

select display

bcs min2

look for restart

0329

0330

0331 0103 A6 F7

lda #$f7

restart with msd

J332 0105 B7 48

sta segmnt

min2 | Ida base,x

J333 01D7 E6 4A

load a with minutes

3334 0109 5A

point to next digit

J335 01DA 02 48 02

brset 1, segmnt, hrs1 check hours units

J336 01DD E6 4A

Ida base, x load a with tens of min.

J337 01DF 5A

hrs1 decx

point to next digit

J338 D1ED D4 48 D2

brset 2, segmnt, hrs2 check tens of hrs.

J339 D1E3 E6 4A

Ida base,x load a with hours units

hrs2

J340 01E5 5A

decx

point to next digit

J341 01E6 06 48 02

brset 3, segmnt, disp display value

J342 D1E9 E6 4A

Ida base,x load a with tens of hrs

J343 01EB A4 OF

disp

and #$Of

mask upper nibble

set x equal to a

display value table

3344 D1ED 97

tax

1345 DIEE EE 80

ldx segtab,x

3346 D1FD BF D1

stx portb enable display drivers

J347 01F2 B6 48

lda segmnt

J348 01F4 B7 02

sta portc enable display

1349

1350

**

count display refreshes. 402 refreshes

3351

*

equals one second. after 402 refreshes,

1352

*

update clock

1353

1354

3355 01F6 A6 10

lda #$10

set timer to interrupt

356 D1F8 B7 D8

sta tdr

after 2048 cycles

3357 D1FA A6 DF

lda #$Of

1358 01FC B7 09

1359 01FE 3A 42

1360 0200 26 08

sta tcr

reset timer interrupt flag

dec ct

decrement inner loop

bne ret

3361 0202 A6 3B

lda #$3b

reset inner loop

1362 0204 B7 42

sta ct

1363 0206 3A 43

dec ct1

decrement outer loop

1364 0208 27 01

beg tmchg

if one sec., to time change

1365 DZDA 8D

ret

1366

1367

time change routine ****

****

1368

*

when 60 seconds are counted,

1369

*

increase minutes by one, if

1370

necessary, blank minutes and increase

*

1371

*

hours. change am/pm if needed.

1372

```

| 0373                               |          |       |                   |                                             |

|------------------------------------|----------|-------|-------------------|---------------------------------------------|

| 0374 020B                          | tmchs    | 6 d n | *                 |                                             |

| 0375 020B 3C 47                    |          |       |                   | increase seconds                            |

| 0376 020D 3C 52                    |          |       | base+8            | inc. secs. units                            |

| 0377 020F B6 52                    |          | Ida   | base+8            |                                             |

| 0378 0211 A1 0A                    |          | cmp   | #\$0a             | look for ten                                |

| 0379 0213 27 38                    |          | beg   | tens              | if yes, inc. tens                           |

| 0380 0215 A6 3C                    | minck    | Ida   | #\$3 <sub>E</sub> | look for a minute                           |

| 0381 0217 B1 47                    |          | C MP  | sec               |                                             |

| 0382 0219 26 54                    |          |       |                   | wait for next second                        |

| 0383 021B 3F 47                    |          | clr   | Sec               |                                             |

| 0384 021D 3F 53                    |          |       | base+9            | zero display                                |

| 0385 021F B6 4A                    |          |       | base              | check min. units                            |

| 0386 0221 A1 09                    |          |       | #\$09             | less than 9?                                |

| 0387 0223 26 20                    |          |       | inm1              | increase                                    |

| 0388 0225 3F 4A                    |          |       | base              | min. units = 0                              |

| 0389 0227 B6 4B                    |          |       | base+1            | check tens of min.                          |

| 0390 0229 A1 05                    |          |       | #\$05             | less than 5?                                |

| 0391 022B 26 1C                    |          |       | inm2              | increase                                    |

| 0392 022D 3F 4B                    |          |       | base+1            | tens of min =0                              |

| 0393 022F B6 4D                    |          |       | base+3            | check tens of hrs.                          |

| 0374 0231 A1 0B                    |          |       | #\$Ob             | look for blank                              |

| 0375 0233 27 1E                    |          |       | hrck              | less than 10:00                             |

| 0376 0235 B6 4C                    |          |       | base+2            | check hrs. units                            |

| 0397 0237 A1 02                    |          |       | #\$02             | less than 2?                                |

| 0398 0239 26 2A                    |          |       | inhr1a            | increase                                    |

| 0399 023B A6 0B                    |          |       | #\$0b             | increase                                    |

| 0400 023D B7 4D                    |          |       | mauo<br>base+3    | : 1.00                                      |

| 0400 0235 B7 45<br>0401 023F A6 D1 |          |       | #\$01             | set time to 1:00                            |

| 0401 0237 A6 01<br>0402 0241 B7 4C |          |       |                   |                                             |

|                                    |          |       | base+2            |                                             |

| 0403 0243 20 2A                    | •4       |       | ret1              | done                                        |

| 0404 0245 3C 4A<br>0405 0247 20 26 | inm1     |       | base              | increase min. units                         |

|                                    |          |       | ret1              | done                                        |

| 0406 0249 3C 4B                    | inm2     |       | base+1            | increase tens of min.                       |

| 0407 024B 20 22                    |          | bra   | ret1              |                                             |

| 0408                               | •        |       |                   |                                             |

| 0409 024D 3F 52                    | tens     |       | base+8            | zero sec. units                             |

| 0410 024F 3C 53                    |          |       | base+9            | inc sec. tens                               |

| 0411 0251 20 C2                    |          | bra   | minck             |                                             |

| 0412                               |          |       | ,                 |                                             |

| 0413                               | *        | Inc   | rease hours       | *                                           |

| 0414                               | <b>.</b> |       |                   |                                             |

| 0415 0253 B6 4C                    | hrck     |       |                   | check hours units                           |

| 0416 0255 A1 09                    |          |       |                   | less than 9?                                |

| 0417 0257 26 08                    |          |       | inhr1             | increase                                    |

| 0418 0259 3F 4C                    |          |       |                   | hours units =0                              |

| 0419 025B 3F 4D                    |          |       | base+3            |                                             |

|                                    |          |       |                   | tens of hours =1                            |

| 0421 025F 20 0E                    |          | bra   | retl              | done se |

| 0422 0261 3C 4C                    | inhr1    | inc   | base+2            | increase hours units                        |

| 0423 0263 20 0A                    |          | bra   | retl              |                                             |

| 0424 0265 3C 4C                    | inhr1a   | inc   | base+2            | increase hours units                        |

| 0425 0267 B6 4C                    |          | lda   | base+2            | check value<br>for 12:00                    |

| 0426 0269 A1 02                    |          | CMP   | #\$02             | for 12:00                                   |

| 0427 026B 26 9D                    |          | bne   | ret               | no, done                                    |

| D428 D26D 33 49                    |          | COM   | PM                | switch pm indicator                         |

| 0429 026F A6 3B                    | ret1     | lda   | Pm<br>#\$3b       |                                             |

| 0430 0271 B7 42                    |          | sta   | ct                | reset inner loop counter                    |

| 0431 0273 A6 08                    |          | lda   | <b>#\$</b> 08     |                                             |

| 0432 0275 B7 43                    |          | sta   | ct1               | reset outer loop counter                    |

| 0433 0277 80                       |          | rti   |                   |                                             |

| <b>0434</b>                        |          |       |                   |                                             |

```

0435

initialize interrupt vectors ***

0436

***

137

.38 DFF8

org $ff8

139

tmrvec fdb tmrint

+40 OFF8 01 C8

41 OFFA 01 3A

intveq fdb c4int

42 DFFC 00 90

swiveg fdb start

.43 OFFE 00 90

reset fdb start

```

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and 🛞 are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

### Literature Distribution Centers:

JSA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

ζ

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

10TOROLA