# MOSTEK 1983

COMPUTER PRODUCTS DATA BOOK

1983 COMPUTER PRODUCTS DATA BOOK

Copyright © 1983 Mostek Corporation (All rights reserved)

Trade Marks Registered ®

Mostek reserves the right to make changes in specifications at any time and without notice. The information furnished by Mostek in this publication is believed to be acurate and reliable. However, no responsibility is assumed by Mostek for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Mostek.

PRINTED IN USA March 1983

# 1983 COMPUTER PRODUCTS DATA BOOK

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | STD Bes Merrocropoter Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RIOX Surres Provident                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 Source and the second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | n 1999 (here and and a loss of the processing for the state of the transmission of the state of     |   |

| and the second sec | 1997 - Contra Calendaria de Contrata de Contra<br>Esta de Contrata de |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Integrated Digital Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

# TABLE OF CONTENTS

| Table of Contents                                                                                                                                                                                                                                                                                                   | I-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

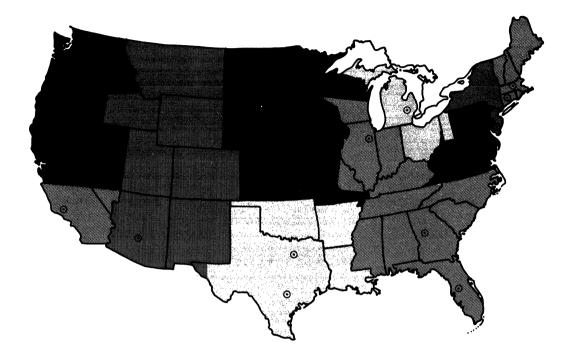

| General Information<br>Mostek - Technology for Today and Tomorrow<br>U.S. and Canadian Sales Offices<br>U.S. and Canadian Representatives.<br>U.S. and Canadian Distributors<br>International Sales Representatives/Distributors<br>International Marketing Offices<br>European Sales Representatives/Distributors. | 11-5<br>11-6<br>11-7<br>11-8<br>11-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

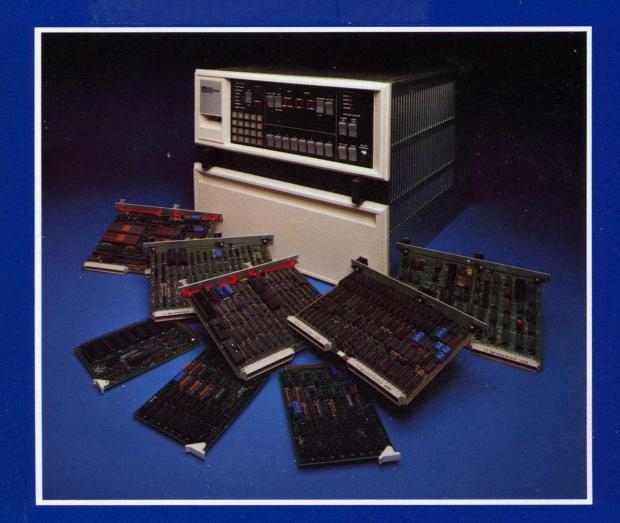

| VMEbus           VME-SBC           VME-SASI           VME-SIO           VME-FDC           VME-DRAM           MMCPU           VME Baseline System                                                                                                                                                                    | -13<br>   -23<br>   -33<br>   -37<br>   -41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| STD-Z80 Bus<br>STD-Z80 Bus Systems                                                                                                                                                                                                                                                                                  | IV-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| STD Bus Microcomputer Systems<br>Matrix 80/OEM .<br>Matrix 010, 100<br>Matrix 200                                                                                                                                                                                                                                   | . IVA-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MDX Series Data Processing<br>MDX-CPU1 and MDX-CPU1A<br>MDX-CPU2A<br>MDX-CPU3<br>MDX-CPU4<br>MDX-Math<br>MD-SBC1                                                                                                                                                                                                    | IVB-7<br>. IVB-15<br>. IVB-21<br>. IVB-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

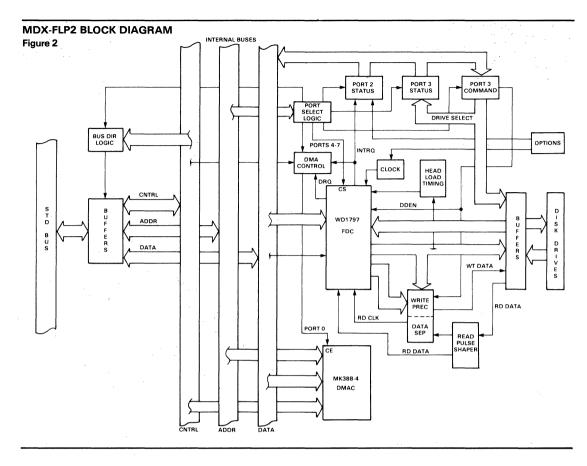

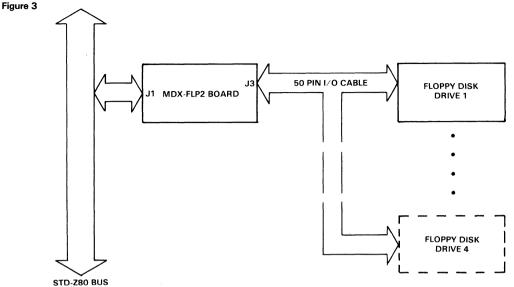

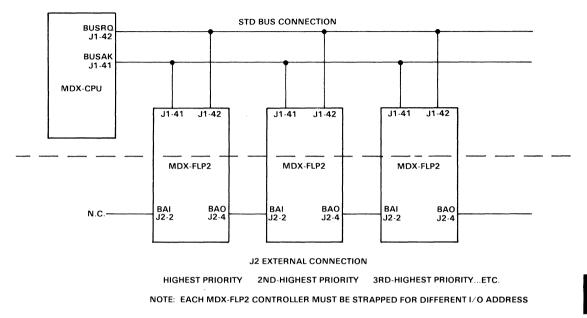

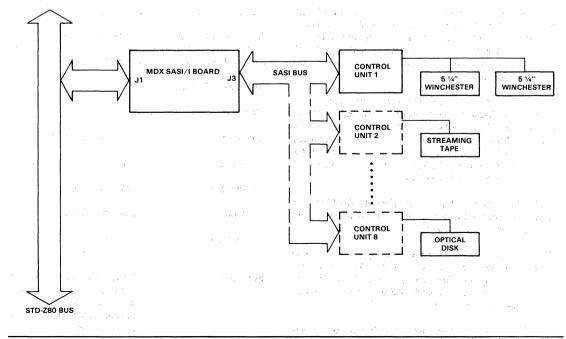

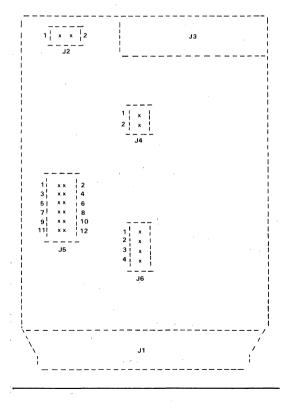

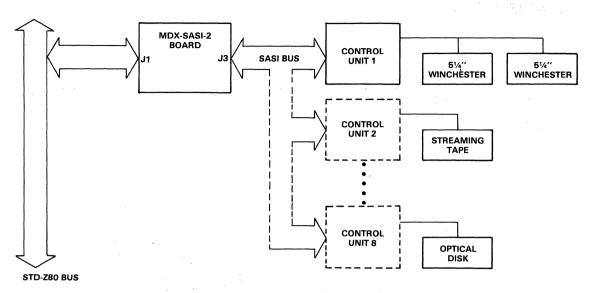

| MDX Series Input/Output<br>MDX Series System Interrupt Units (SIU) Table.<br>MDX-FLP2.<br>MDX-SASI-1.<br>MDX-SASI-2.<br>MDX-488.<br>MDX-ISIO.<br>MDX-SIO2.<br>MDX-SIO2.<br>MDX-4221.<br>MDX-422N.<br>RSCU.<br>RIOC.<br>DIOB1.<br>DIOP.<br>MDX-PIO                                                                   | IVC-3<br>IVC-9<br>. IVC-15<br>. IVC-23<br>. IVC-25<br>. IVC-27<br>. IVC-47<br>. IVC-51<br>. IVC-55<br>. IVC-63<br>. IVC-71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                     | General Information Mostek - Technology for Today and Tomorrow . U.S. and Canadian Sales Offices U.S. and Canadian Distributors International Marketing Offices European Sales Representatives/Distributors International Marketing Offices European Sales Representatives/Distributors VME-SBC VME-SBC VME-SBC VME-SASI VME-SASI VME-PDC VME-PDC VME-PDC STD-Z80 Bus STD-Z80 Bus STD-Z80 Bus Systems STD Bus Microcomputer Systems Matrix 80/OEM Matrix 010, 100 Matrix 200. MDX Series Data Processing MDX-CPU3 MDX-CPU4 MDX-CPU3 MDX-CPU4 MDX-SEC1 MDX Series System Interrupt Units (SIU) Table MDX-SASI-1 MDX-SASI-2 MDX-488 MDX-IP2 MDX-422N MDX-422N MDX-422N MSCU RIOC |

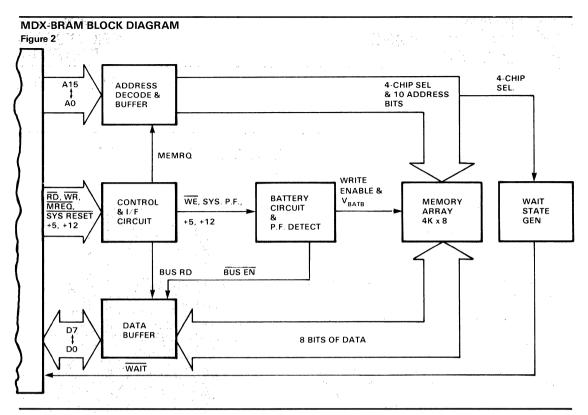

| IVD. | MD Series Memory         .IVD-1           MDX-DRAM         .IVD-1           MDX-EPROM/UART         .IVD-7           MDX-UMC         .IVD-17           MDX-UMC2         .IVD-23           MDX-BRAM         .IVD-29           MDX-RAM 64/128         .IVD-33                                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IVE. | MD Series Special FunctionsMDX-DEBUGIVE-1MDX-INTIVE-7MDX-SC/DIVE-13MDX-PFDIVE-17MDX-BCLKIVE-21                                                                                                                                                                                                                                                                |

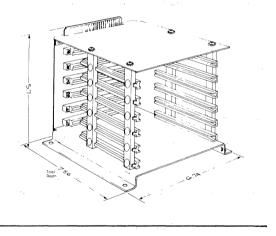

| IVF. | MD Series Accessories           MD-ACC         IVF-1           Matrix 80/OEM Printer Cable         IVF-9           MDX-CPU3/4 Printer Cable         IVF-11           MD-PWR1         IVF-13           MDFRMC12         IVF-15           RMDFSS         IVF-19           Enclosure         IVF-25                                                              |

| V.   | SD Series Data Processing           SDE-Combo.         V-1           OEM-80E.         V-15           DCC-80E         V-19           FLP-80E.         V-25           RAM-80E.         V-29           VDI-80E         V-33                                                                                                                                      |

| VI.  | SDE Series Accessories         SDE-ACC       VI-1         SDE-RMC6       VI-5                                                                                                                                                                                                                                                                                 |

| VII. | Development Systems           Radius         VII-1           AIM 68000         VII-5           AIM Z80BE         VII-11           AIM 7XE         VII-15           EPP-1         VII-19           Matrix 80/SDS         VII-25           EVAL 70         VII-29           PPG 8/16C         VII-33           Development System Ordering Guide         VII-35 |

# VIII. Application Notes

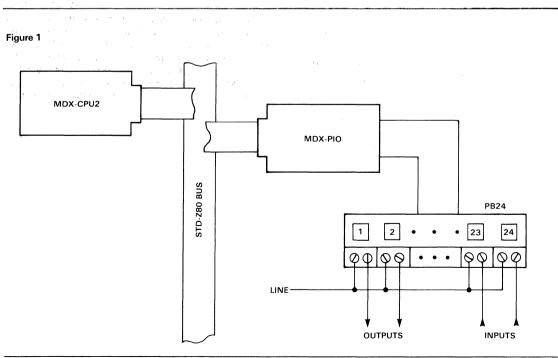

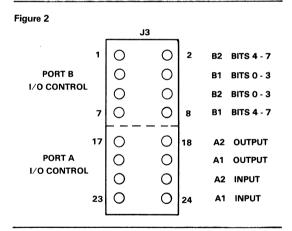

| Interfacing Mostek's MDX-PIO to Opto-22 BP24 App. Note #1                 | VIII-1  |

|---------------------------------------------------------------------------|---------|

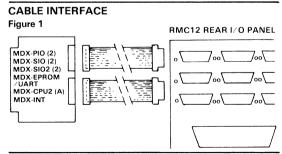

| MD-RMC12/MD-RMC12-50 App. Note #2                                         | VIII-5  |

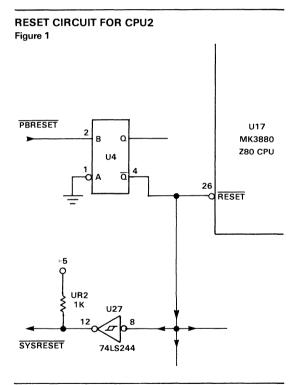

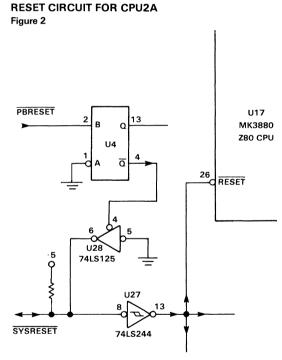

| MDX-CPU2A App. Note #3                                                    | VIII-11 |

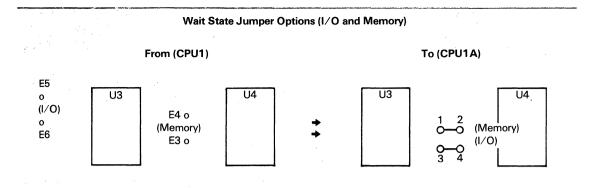

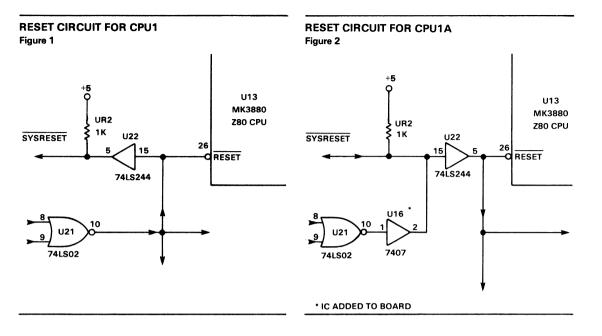

| Reset Circuit for MDX-CPU1A App. Note #4                                  | VIII-13 |

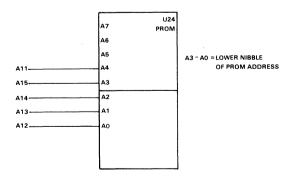

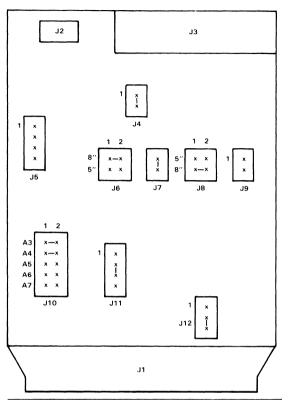

| Customizing MDX-CPU3 PROMs App. Note #5                                   | VIII-17 |

| Upgrading from MDX-FLP1 to MDX-FLP2 App. Note #6                          | VIII-23 |

| MDX-SASI1: The Hard Disk Interface App. Note #7                           | VIII-27 |

| MDX-FLP2 vs. MDX-FLP1: Hardware and Software Issues App. Note #8          | VIII-35 |

| MDX-CPU3/4 I/O Drivers App. Note #10                                      | VIII-39 |

| Pro-Log M900 Universal PROM Programmer with the STD-Z80 Bus App. Note #11 | VIII-55 |

# IX. Software Products

| M/OS-80   | <br> | IX-1  |

|-----------|------|-------|

| MOSGEN    | <br> | IX-5  |

| ASM-68000 | <br> |       |

| Microsoft | <br> |       |

| CRASM     | <br> | IX-11 |

| MOD-LIB   | <br> |       |

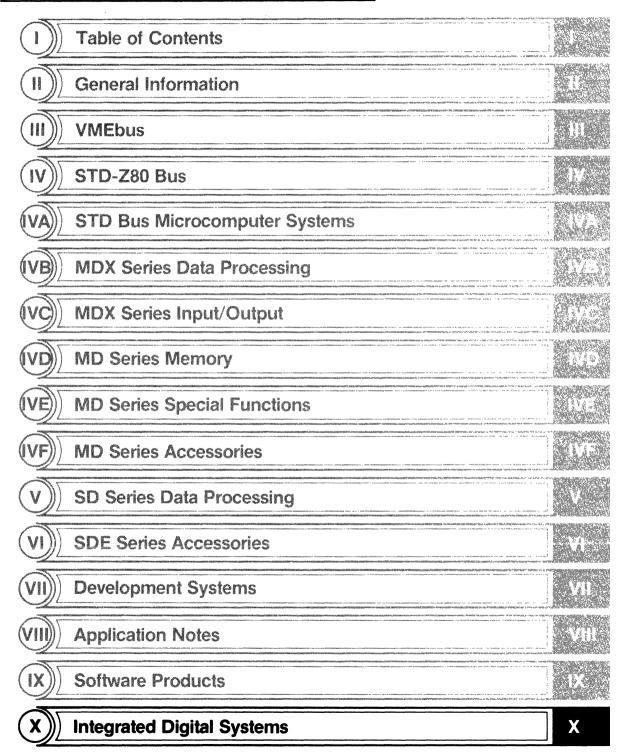

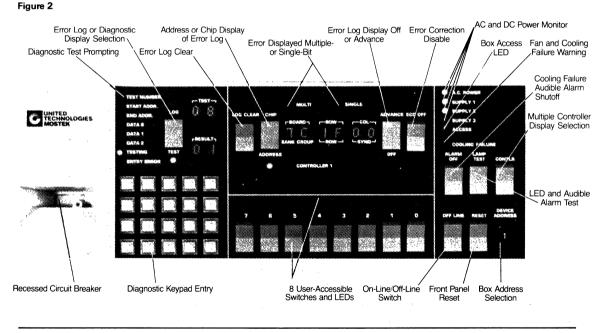

# X. Integrated Digital Systems

| 8200 | <br> | <br> | <br> | ••••• | X-1 |

|------|------|------|------|-------|-----|

. . .

.

# **1983 COMPUTER PRODUCTS DATA BOOK**

| (I) General Information |     |

|-------------------------|-----|

|                         | ML  |

|                         | n s |

|                         |     |

|                         |     |

|                         |     |

|                         |     |

|                         |     |

|                         |     |

|                         |     |

|                         |     |

|                         |     |

|                         |     |

|                         |     |

|                         |     |

# Mostek - Technology For Today And Tomorrow

# TECHNOLOGY

From its beginning, Mostek has been an innovator. From the developments of the 1K dynamic RAM and the single-chip calculator in 1970 to the current 64K dynamic RAM, Mostek technological breakthroughs have proved the benefits and cost-effectiveness of metal oxide semiconductors. Today, Mostek represents one of the industry's most productive bases of MOS/LSI technology, including Direct-Step-on-Wafer processing.

The addition of the Microelectronics Research Center in Colorado Springs adds a new dimension to Mostek circuit design capabilities. Using the latest computer-aided design techniques, center engineers are keeping ahead of the future with new technologies and processes.

# QUALITY

The worth of a product is measured by how well it is designed, manufactured and tested, and by how well it works in your system.

In design, production and testing, the

Mostek goal is meeting specifications the first time on every product. This goal requires a collective discipline from the company as well as individual efforts. Discipline, coupled with very personal pride, has enabled Mostek to build in quality at every level of production.

# **PRODUCTION CAPABILITY**

The commitment to increasing production capability has made Mostek one of the world's largest manufacturers of dynamic RAMs. Mostek capital expenditures as a percentage of sales are one of the highest in the industry, enabling us to provide high volumes of quality state-of-the-art products.

# THE PRODUCTS

# **Memory Products**

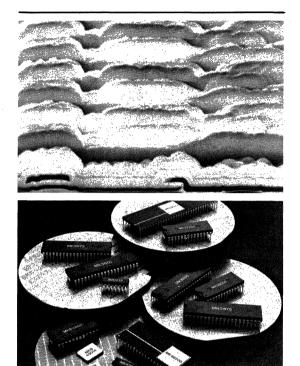

Through innovations in circuit design, wafer processing and production, Mostek has become one of the industry's leading suppliers of dynamic RAMs.

II-1

Examples of Mostek leadership are families of x1 and x8 high-performance static RAMs and our extremely successful 64K ROMs with more codes processed than any other mask-ROM in the industry. Another performance and density milestone is our 256K ROM, the MK38000.

Advanced circuit techniques and design used in our fast MK4564 64K dynamic RAM enhance manufacturability to satisfy the demands of a huge marketplace. This year Mostek introduced a new generation of 64K dynamic RAMs, operating at previously unheard-of speeds and breaking yet another barrier in VLSI technology.

### **Memory Systems**

Taking full advantage of our leadership in memory components technology, Mostek offers a broad line of memory systems products, all with the performance and reliability to match our industry-standard circuits. Mostek offers add-in memory boards for popular DEC, Data General, and Perkin-Elmer minicomputers.

Mostek also offers general-purpose and custom memory boards for special applications.

**Military Products**

An extension of the high quality in fabrication and design inherent in Mostek's product line allows many of our ICs to be made available screened to MIL-STD-883. In addition, select parts are qualified to the rigors of MIL-M-38510 and are processed on our QPL certified lines.

The MKB product line begins with the complete memory products offering, and extends into microprocessors and gate arrays. Leadless Chip Carrier (LCC) packaging and prepared customer SCDs address the particular needs of the military community.

# **Telecommunications Products**

Mostek is a leading supplier of tone dialers, pulse dialers and CODEC devices. As each new generation of telecommunications systems emerges, Mostek is ready with new generation components, including PCM filters, tone decoders, repertory dialers, new integrated tone dialers, and pulse dialers.

These products, many of them using CMOS technology, represent the most modern advancements in telecommunications component design.

# Industrial Products

Mostek's line of Industrial Products offers a high degree of versatility per device. This family of components includes various microprocessor-compatible A/D converters,

a counter/time-base circuit for the division of clock signals, and combined counter/display decoders. A low parts count provides an economical alternative to discrete logic systems.

# **Microcomputer Components**

Mostek's microcomputer components cover the entire spectrum of microcomputer applications.

Our MK68000 16-bit microprocessor family is designed for high-performance, memory-intensive systems.

Our Z80 is today's industry-standard 8-bit microprocessor. The Mostek 3870 family of single-chip microcomputers offers upgrade options in ROM, RAM and I/O—all in the same socket. The MK38P70 EPROM piggyback microcomputer emulates the entire family and is ideal for low-volume applications.

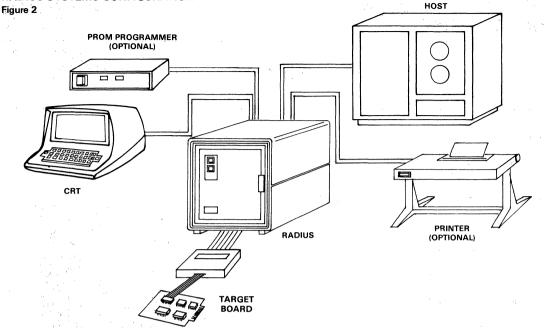

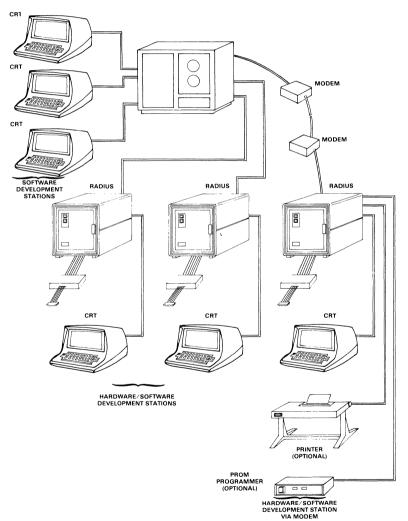

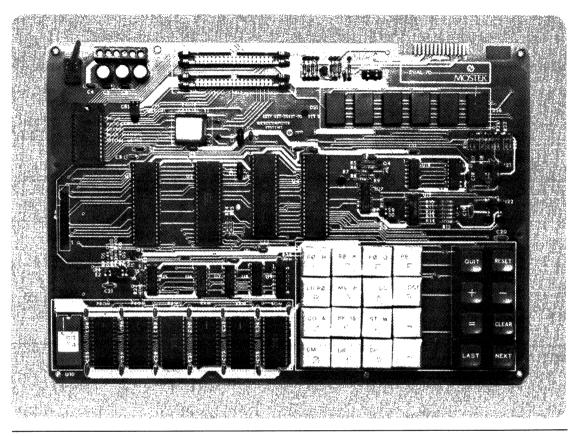

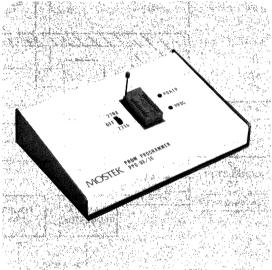

Development systems include the RADIUS<sup>™</sup> remote development station that lets you use your host minicomputer to develop the applications software. The program is then downloaded into the RADIUS which then lets you perform realtime in-circuit emulation and debug. The Mostek MATRIX<sup>™</sup> Development System is a stand-alone hardware and software debug and integration system.

# **Microcomputer Systems**

Mostek is the world's leading manufacturer of Z80-based STD BUS system components. This year Mostek introduced a new line of microsystems using the VMEbus and based on the MK68000.

Computer systems include our MATRIX line, which uses STD BUS cards to let you custom-design your own system.

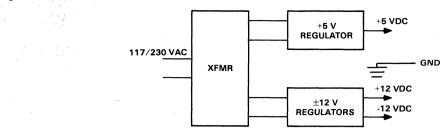

# Semicustom Circuits