# MOSTEK 1982

TELECOMMUNICATIONS DATA BOOK

> REPRESENTED BY CARLSON ELECTRONIC SALES CO. NORTHBROOK EXECUTIVE CTR. 10701 WEST NORTH AVENUE MILWAUKEE, WISCONSIN 53226 414 476-2790

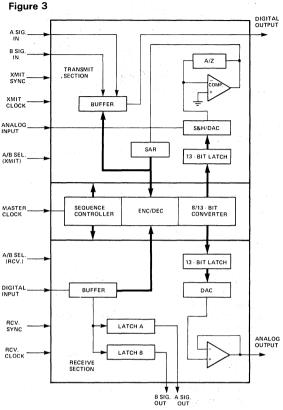

#### Copyright © 1981 Mostek Corporation (All rights reserved)

#### Trade Marks Registered ®

The "PRODUCT PROFILE" designation on a Mostek literature item indicates that the product is not available as of the print date of this document and that the specification goals have not yet been fully established. The PRODUCT PROFILE is an initial disclosure of a new product's features and general information. The information given in the PRODUCT PROFILE is subject to change and is not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in the product at any time and without notice.

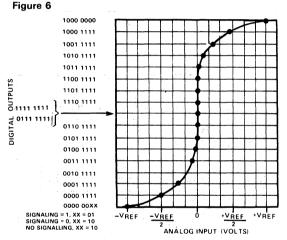

The "TARGET SPECIFICATION" designation on a Mostek data sheet indicates that the product is not yet available. The TARGET SPECIFICATION is an initial disclosure of specification goals for the product. The specifications are subject to change, are based on design goals, and are not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in specifications at any time and without notice.

The "PRELIMINARY" designation on a Mostek data sheet indicates that the product is not characterized. The specifications are subject to change, are based on design goals or preliminary part evaluation, and are not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in specifications at any time and without notice.

The "APPLICATION BRIEF" or "APPLICATION NOTE" designation on a Mostek literature item indicates that the literature item contains information regarding Mostek product features and/or their varied applications. The information given in the APPLICATION BRIEF or APPLICATION NOTE is believed to be accurate and reliable; however, the information is subject to change and is not guaranteed. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek.

Mostek reserves the right to make changes in specifications at any time and without notice. The information furnished by Mostek in this publication is believed to be accurate and reliable. However, no responsibility is assumed by Mostek for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Mostek.

PRINTED IN USA December 1981

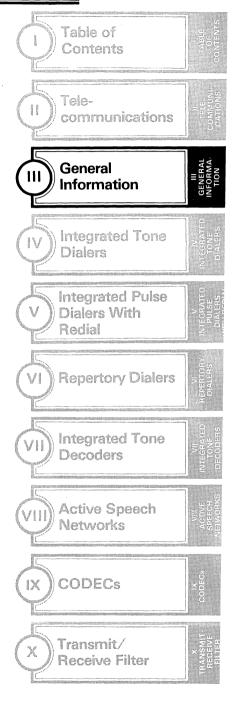

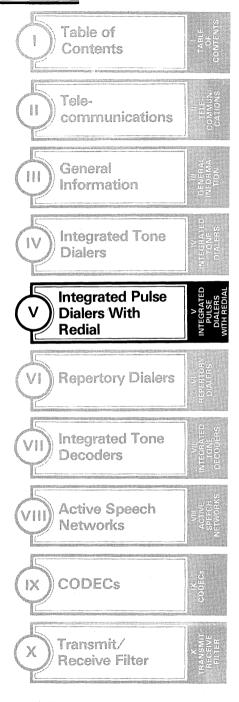

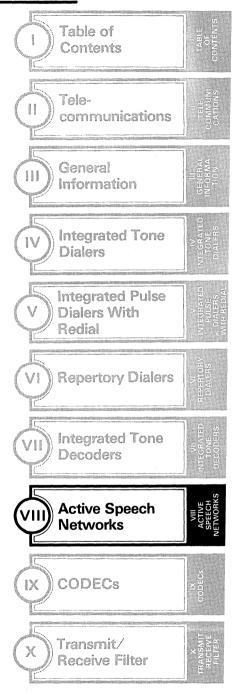

# TABLE OF CONTENTS

| 1 - 1 | able of Contents                                                     |

|-------|----------------------------------------------------------------------|

|       | Functional IndexI-i                                                  |

|       | Numerical Index I-iii                                                |

|       |                                                                      |

| H - ' | Telecommunications                                                   |

|       | Introduction to Telecommunication Products II-i                      |

|       | Telecommunications Terms Application Brief II-iii                    |

|       | Definitions of Data Sheet DesignationsII-vii                         |

|       | Order Information II-ix                                              |

|       | Package Descriptions II-xi                                           |

|       |                                                                      |

| 111 - | General Information                                                  |

|       | Mostek Profile                                                       |

|       | U.S. and Canadian Sales Offices III-v                                |

|       | U.S. and Canadian Representatives III-vi                             |

|       | U.S. and Canadian Distributors III-vii                               |

|       | International Marketing Offices Ill-ix                               |

|       |                                                                      |

| IV -  | Integrated Tone Dialers                                              |

|       | MK5087 Integrated Tone Dialer IV-1                                   |

|       | MK5089 Integrated Tone Dialer                                        |

|       | MK5087/89 Electronic Drive Application BriefIV-13                    |

|       | MK5091 Integrated Tone DialerIV-15                                   |

|       | MK5092 Integrated Tone Dialer IV-21                                  |

|       | MK5094 Integrated Tone Dialer IV-29                                  |

|       | MK5380 Integrated Tone Dialer IV-37                                  |

|       | MK5382 Integrated Tone Dialer With Redial IV-45                      |

|       | Integrated Dialer Comparison - Tone II vs Tone III Application Brief |

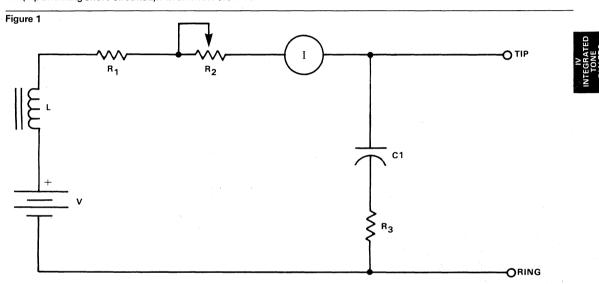

|       | Loop Simulator Application Brief IV-49                               |

|       |                                                                      |

| V -   | Integrated Pulse Dialers with Redial                                 |

|       | MK50981 Integrated Pulse Dialer with Redial V-1                      |

|       | MK50982 Integrated Pulse Dialer with Redial V-7                      |

|       | MK50991 Integrated Pulse Dialer with Redial V-13                     |

|       | MK50992 Integrated Pulse Dialer with Redial V-19                     |

|       | Current Sources Application Brief                                    |

|       | Pulse Dialer Comparison Application Brief V-27                       |

|       |                                                                      |

| VI -  | Repertory Dialers                                                    |

|       | MK5170 Repertory Dialer                                              |

|       | MK5175 Ten-Number Repertory DialerVI-19                              |

| \/11  | Integrated Tana Dagadara                                             |

| VII   | - Integrated Tone Decoders                                           |

|       | MK5102-5 Integrated Tone Receiver                                    |

|       | MK5102-5 DTMF Decoder Application Note                               |

|       | MK5102/S3525A DTMF Receiver System Application Brief                 |

|       | MK5103-5 Integrated Tone Decoder                                     |

|       | DTMF Receiver System Application Brief VII-23                        |

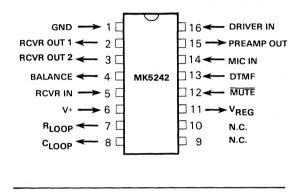

| VIII-1                                                                                                           | MK5242 Active Speech Networks<br>MK5242 Active Speech Network |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

|                                                                                                                  | X - CODECs                                                    |

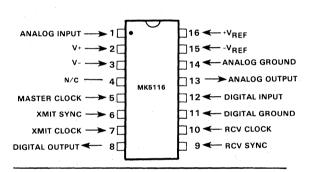

| IX-1                                                                                                             | MK5116 μ-255 Law Companding CODEC                             |

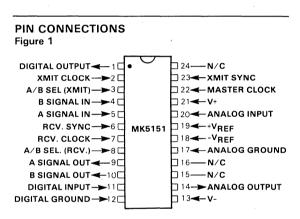

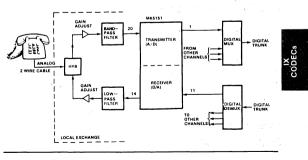

| IX-11                                                                                                            | MK5151 μ-255 Law Companding CODEC                             |

|                                                                                                                  | MK5156 A-Law Companding CODEC                                 |

| IX-33                                                                                                            | MK5316 Companding CODEC with Filters                          |

|                                                                                                                  | Integrated PCM CODEC Technology Update                        |

|                                                                                                                  |                                                               |

| and the second | C - Transmit/Receive Filter                                   |

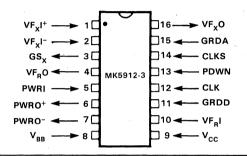

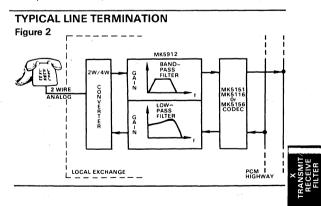

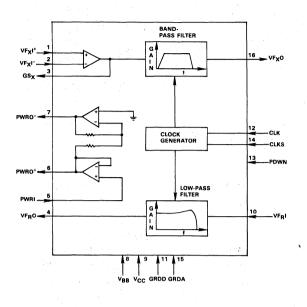

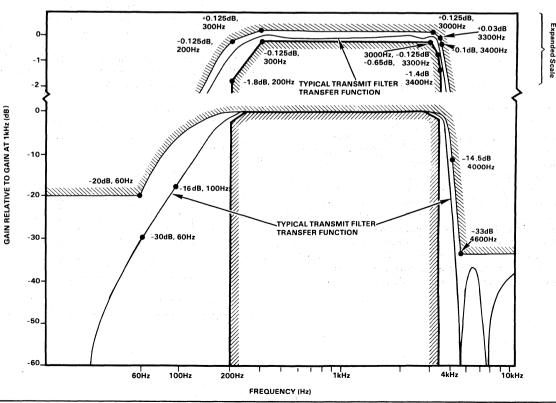

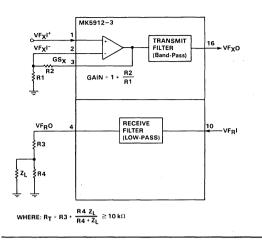

| X-1                                                                                                              | MK5912-3 PCM Transmit/Receive Filter                          |

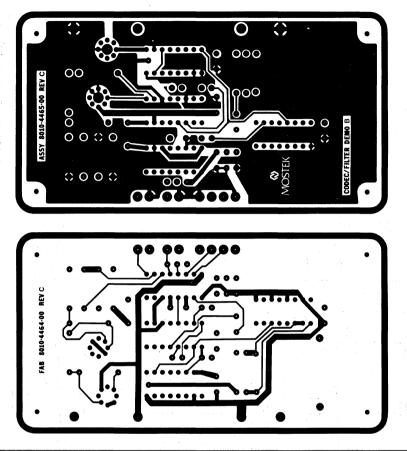

|                                                                                                                  | CODEC/Filter Demo Board Application Brief                     |

## NUMERICAL INDEX

| MK5087        | Integrated Tone Dialer IV-1                                        |

|---------------|--------------------------------------------------------------------|

| MK5087/89     | Electronic Drive Application BriefIV-13                            |

| MK5089        | Integrated Tone Dialer IV-7                                        |

| MK5091        | Integrated Tone Dialer IV-15                                       |

| MK5092        | Integrated Tone Dialer, IV-21                                      |

| MK5094        | Integrated Tone Dialer IV-29                                       |

| MK5102-5      | Integrated Tone Receiver VII-1                                     |

| MK5102-5      | DTMF Decoder Application Note VII-5                                |

| MK5102/S3525A | DTMF Receiver System Application Brief VII-15                      |

| MK5103-5      | Integrated Tone Decoder VII-17                                     |

| MK5116        | μ-255 Law Companding CODEC IX-1                                    |

| MK5151        | $\mu$ -255 Law Companding CODEC                                    |

| MK5156        | A-Law Companding CODEC IX-23                                       |

| MK5170        | Repertory Dialer VI-1                                              |

| MK5175        | Ten-Number Repertory DialerVI-19                                   |

| MK5242        | Active Speech Network VIII-1                                       |

| MK5316        | Companding CODEC with Filters IX-33                                |

| MK5380        | Integrated Tone Dialer IV-37                                       |

| MK5382        | Integrated Tone Dialer with RedialIV-45                            |

| MK5912-3      | PCM Transmit/Receive Filter X-1                                    |

| MK50981       | Integrated Pulse Dialer with Redial V-1                            |

| MK50982       | Integrated Pulse Dialer with Redial V-7                            |

| MK50991       | Integrated Pulse Dialer with Redial V-13                           |

| MK50992       | Integrated Pulse Dialer with Redial V-19                           |

|               | CODEC/Filter Demo Board Application Brief X-11                     |

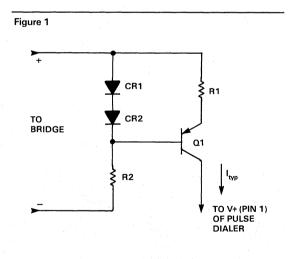

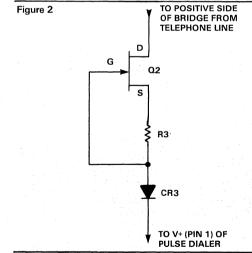

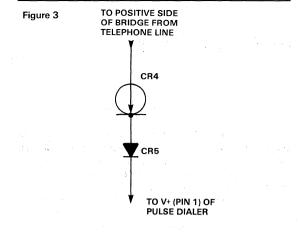

|               | Current Sources Application Brief V-25                             |

|               | DTMF Receiver System Application Brief VII-23                      |

|               | Integrated Dialer Comparison-Tone II vs Tone III Application Brief |

|               | Integrated PCM CODEC Technology UpdateIX-35                        |

|               | Loop Simulator Application BriefIV-49                              |

|               | Pulse Dialer Comparison Application Brief                          |

|               | Telecommunications Terms Application Brief Il-iii                  |

#### **Telecommunications**

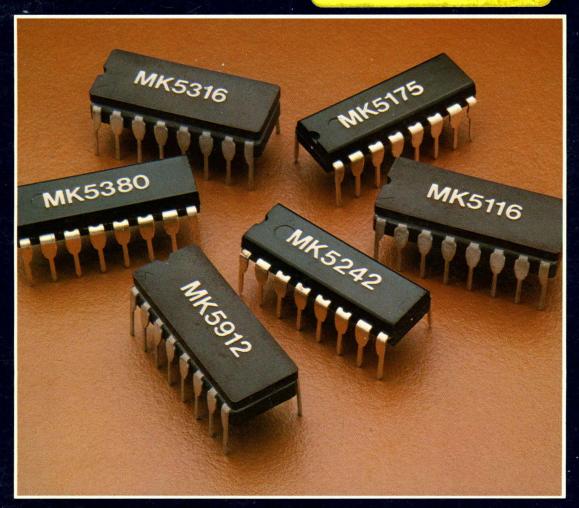

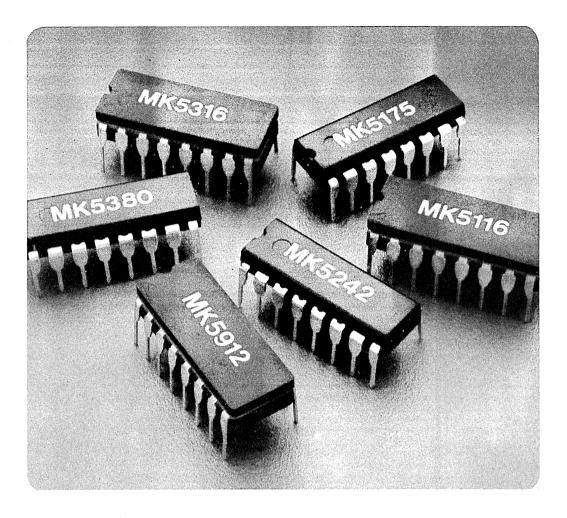

Mostek offers a broad line of telecommunications circuits aimed at cost-effective solutions for large or small systems. At Mostek, you have a choice. Tone dialers, pulse dialers, repertory dialers, tone decoders, CODECs, and PCM filters are available in volume now.

Mostek made its commitment to telecommunications products in 1974, the year we produced our first tone dialer. Since 1974, we have shipped over nine million tone dialers and we have earned our reputation as a dependable source for reliable products. Our extensive testing and quality control procedures all assure reliable systems in the field.

Some excellent examples of Mostek's technological leadership are the recently introduced ten-number repertory dialer and the switched-capacitor PCM filter. In an application where space and power are the most critical parameters, Mostek's CODEC and PCM filter offer industry's lowest power.

II-i

(a) A set of the s

الأمانية معادمة المراكز المراكز المراكز المراكز المعادية ومن المراكز المراكز المراكز المراكز المراكز المراكز ال المراكز المراكز المعادية المراكز المراكز

## APPLICATION BRIEF

# TELECOMMUNICATION PRODUCTS Telecommunications Terms

**BALANCED LINE:** A line or circuit utilizing two identical conductors, each having the same electro-magnetic characteristics with respect to other conductors and ground. A balanced line is preferred in circumstances where minimum noise and crosstalk are desired.

**BALANCING NETWORK:** An arrangement of impedances connected to one branch of hybrid to match the impedance of a line connected to the opposite branch.

**BASEBAND**: The total frequency band occupied by the aggregate of all the information signals used to modulate a carrier (multiplex or radio).

**CARRIER:** A form of communication using waves that can be modulated by changing their amplitude, frequency, or phase so that they can "carry" intelligence. Carrier communication is used as a means of transmitting one or more messages over a single open-wire pair, cable pair, or radio circuit.

**CENTRAL OFFICE (CO):** A place or building where telephone calls are switched or connected, either automatically or manually.

**C-MESSAGE:** A frequency weighting which evaluates the effects of noise corresponding to its annoyance to the "typical" subscriber of standard telephone service. This weighting is also used to evaluate the effects of noise (background and impulse) on voice-grade data services.

**C-NOTCHED:** A frequency weighting similar to C-Message weighting except for the addition of a narrow stopband or notch at 1010 Hz. Used in making noise-withtone measurements.

**CODEC:** A circuit comprised of an encoder and decoder in the same device.

**COMPANDOR:** A compandor is an electronic circuit used in carrier systems to provide better signal-to-noise ratios. The name is a contraction of two—compressor and expandor, which describe the actions of the two types of circuits in the equipment—a speech compressor at the transmitting end and a speech expandor at the receiving end.

**COMPRESSOR:** The part of a compandor that is used to compress the intensity range of signals at the transmitting end of a circuit. It amplifies weak signals and attenuates strong signals.

**CONTROL OFFICE:** The control office is the location designated on the circuit order card as having the responsibility for maintaining the overall circuit. This office is sometimes referred to as the control point. In most cases, this is the office which coordinates all activities on a circuit with the customer.

**CORNER EFFECT**: The rounding off of the attenuation vs. frequency characteristic of a filter at the extremes (or corners) of the passband.

TELE-COMMUNI-CATIONS

**CROSS MODULATION:** A type of intermodulation due to the modulation of the carrier of the desired signal by an undesired signal wave.

**CROSSTALK:** Crosstalk is the presence of unwanted voice currents. It may or may not be intelligible, but it can be heard. There are two general forms of crosstalk, near-end and far-end.

CVSD: Continuously Variable Slope Delta Modulation.

**dBm**: dBm is a transmission level referenced to a specified impedance. For instance, 0 dBm/600  $\Omega$  is a power of 1 milliwatt across a 600  $\Omega$  impedance. (0 dBm = 1 mW) **dBm0**: The power expressed in dBm measured at, or referenced to, a point of zero transmission level.

**dBm0p:** Based upon 1.0 milliwatt at the 0.0 dBm TLP, psophometrically weighted.

**dBrn:** dBrn is used for noise measurement on telephone lines. Reference noise is -90 dBm (0 dBrn).

**dBrnc0**: A C-Message weighted value based upon -90.0 dBmC referenced to a point of zero transmission level ie., 0.0 dBrnc0 = -90.0 dBmC0.

**DELTA MODULATION:** A means of encoding analog signals in control and communication systems. The output of the delta encoder is a single-weighted digital pulse train which may be decoded at the receiving end to reconstruct the original analog signal.

**DESENSITIZATION:** The tendency of a receiver to fail to recognize valid DTMF signals in the presence of such factors as dial tone, pilot signals, or data signals.

**DROP CHANNEL:** This refers to a type of operation where one or more channels of a multichannel system are terminated (dropped) at some point intermediate between the end terminals of the system.

**DROPOUT:** Short interruptions of service where the transmitted signal experiences a sudden large drop in power; often, the signal becomes undetectable. Present standards define a dropout as a decrease in signal level of 12 dB with a duration greater than 10 ms.

**DRY LINE:** A telephone line without battery voltage present.

ECHO: The result of impedance mismatches, hybrid unbalance, and time delay. Depending upon the location of impedance irregularities and the propagation characteristics of a facility, echo may interfere with the talker or listener, or both. The greater out-of-phase the currents are, the greater the interfering effect.

ECHO RETURN LOSS(ERL): Is a weighted average of the return losses at all frequencies between 500 and 2500 Hz.

**ECHO SUPPRESSOR:** Echo Suppressors are used to minimize the effect of echo. They work in such a way as to block the echo return currents. They are voice-operated gates which allow communication one way at a time.

**ENVELOPE DELAY DISTORTION:** Envelope delay is the derivative of the circuit phase shift (in radians) with respect to frequency (radians p r second). The deviation of this derivative at any frequency from the derivative's value at a prescribed frequency (usually 1800 Hz) is called envelope delay distortion (EDD).

**EQUALIZER:** An electrical network in which attenuation (or gain) varies with frequency and is used to provide equalization of a frequency-dependent transmission line.

**EXPANDOR:** A part of a compandor. It is used at the receiving end of a circuit to return the compressed signal to its original form. It amplifies strong signals.

FOUR-WIRE CIRCUIT: A four-wire circuit is considered to be one which terminates at the customer's premises in four wires. Transmission is done over one pair and reception is done over the other pair. The circuit is four-wire throughout and may include repeaters, carrier, or both. When carrier is used, the circuit is sometimes referred to as "equivalent four-wire" since different transmitting frequencies may be superimposed in the same cable pair or open-wire.

**FREQUENCY RESPONSE:** The frequency response of a circuit refers to its overall transmission characteristics. The frequencies to be measured and their limits are shown on the circuit order card.

**FREQUENCY SHIFT:** A fixed offset in each received frequency of a signal relative to the transmitted signal, due to differences in the inserted carrier frequencies in the receivers and transmitters of transmission systems.

**FULL DUPLEX:** Telegraph or signaling circuits arranged for transmission in both directions at the same time.

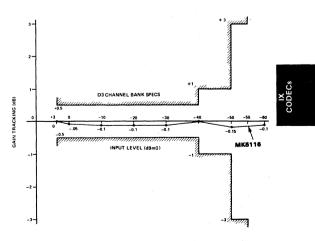

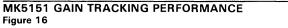

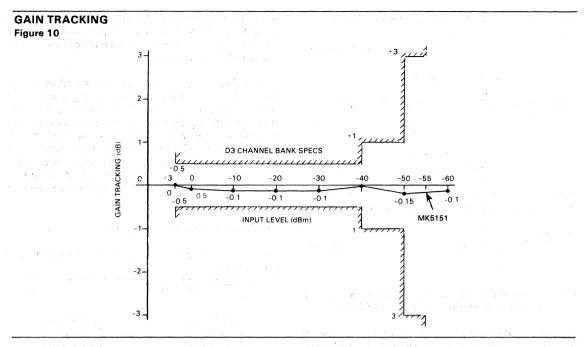

**GAIN TRACKING:** Loss deviation (1000 Hz reference) over the range of levels of interest.

HALF DUPLEX: Transmission in one direction at a time over a single channel. Thus, in a half-duplex telegraph system, information can be transmitted in only one direction at a time.

**HOOKSWITCH**: The switch on the telephone set which is activated by placing the receiver on the hook. The two conditions are defined as off-hook and on-hook conditions, corresponding to busy and idle circuits respectively.

**HYBRID:** A bridge-type circuit or connecting device that combines the function of providing impedance matching between certain circuits and isolation between other circuits. A hybrid is often used to connect four-wire lines to a two-wire line so that in both directions of transmission the four-wire lines are isolated from each other, but are connected to the two-wire line.

**HYBRID COIL:** A hybrid coil is a transformer arrangement used to convert a two-way, two-wire circuit into two separate two-wire circuits (four-wire operation).

**IMPULSE NOISE:** Characterized by large excursions of the total noise waveform which are much higher than the normal peaks of the message circuit noise.

**LOOP RESISTANCE:** The loop resistance of a cable pair is the dc resistance from the telephone office to a distant point. It may include a coil at the far end. If no coil is present, a short must be placed across the tip and ring. Corrections for temperature variations from 68°F must be made to the measured dc resistance in order to determine if the loop resistance is correct.

**LOSS:** End-to-end circuit attenuation usually measured at 1000 Hz.

**MESSAGE CIRCUIT NOISE:** Background noise measured between two balanced lines. Also called "Metallic Noise".

**MODEM:** A single unit of equipment which combines the functions of modulator and demodulator. Connects enduser's equipment with telephone system.

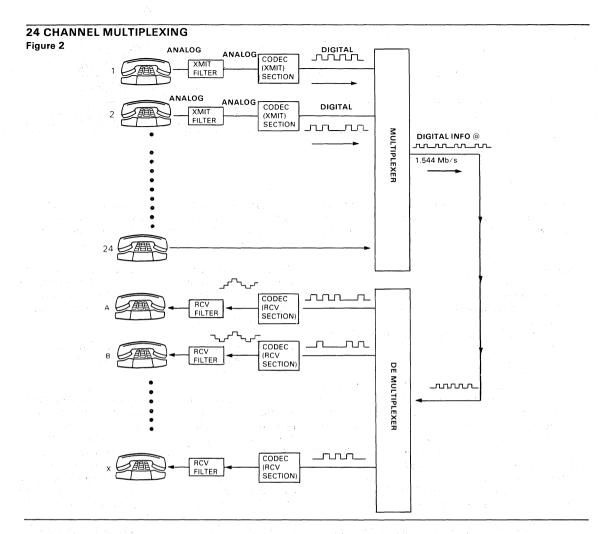

**MULTIPLEX:** A means of transmitting two or more signals over the same medium.

**NET LOSS:** The net loss of a circuit is the transmission loss at 1000 cycles in dB between two locations. The greater the number, the poorer the circuit. It is sometimes referred to as the specified equivalent or the card loss.

**NETWORK:** Network, as generally used, refers to an impedance matching device associated with a hybrid coil or terminating set. It is used to balance the derived two-wire circuit (line) for maximum return loss. Networks are of two broad types—precision and compromise. Networks of this type may be referred to as a balancing net, precision net, comp. net, or net.

**NOISE FIGURE:** The noise figure expresses the amount of noise introduced by a piece of equipment over the basic thermal noise that is present. It represents the relationship of the signal-to-noise ratio at the input of the device to the signal-to-noise ratio at its output.

**NOISE IMMUNITY:** A measure of a DTMF receiver's ability to prevent valid signals from being rejected as noise. It is sometimes specified as the ability of the receiver to operate under conditions of gaussian noise in dBrnC.

**NOISE-TO-GROUND:** A noise measurement where the noise is measured from a balanced line to ground.

**NOISE WEIGHTING:** Noise weighting is used to give the proper interfering effect when noise currents are converted to sound. The weighting networks integrate the noise power over the frequency range by giving each small band of frequencies a weighting proportional to its contribution to the total interfering effect.

**NONLINEAR DISTORTION:** The generation of new signal components not present in the original transmitted signal. This usually happens when the loss on a channel is nonlinear with respect to input level.

PABX: Private Automatic Branch Exchange. Has the same usage as a PBX except that calls within the system are completed automatically by dialing. An attendant at an attendant's board may be required to route and complete incoming calls from the central office. Stations within the system are connected to the central office by dialing directly, or they are made to go through the attendant as company policy dictates.

PBX: Private Branch Exchange. A telephone system located on the premises of a business and requiring an attendant to complete all calls. It is usually owned by the telephone company and is equipped with trunks to a telephone company central office.

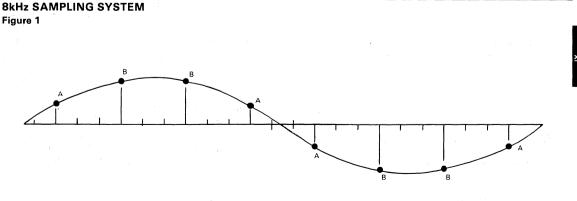

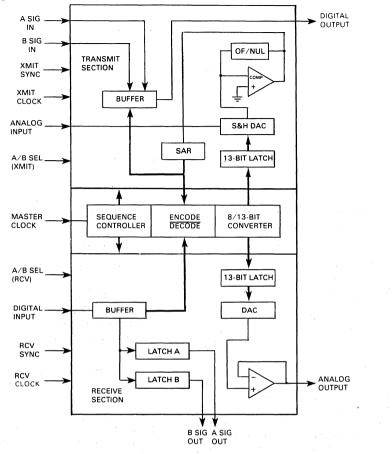

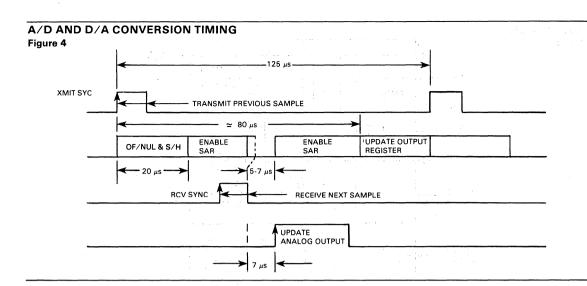

PCM: Pulse-Code Modulation - pulse modulation in which the signal is sampled periodically and each sample is guantized and transmitted as a digital binary code.

PHASE JITTER: The undesired component of a received signal which appears as phase (or frequency) modulation.

PHASE HIT: A sudden change (+ or -) in the received signal phase (or frequency).

PRIVATE LINE CIRCUIT: A private line circuit is a connection between two or more stations for the exclusive use of a customer. It may or may not have access to the nationwide telephone network.

PSOPHOMETRIC-WEIGHTED: A frequency weighting similar to C-Message weighting, which is used as the standard for European telephone system testing.

QUANTIZING NOISE: Signal-correlated noise generally associated with the quantizing error introduced by analogdigital and digital-analog conversions in digital transmission systems.

**REPEATER:** A repeater is an amplifier. Some repeaters use separate amplifiers for each direction of transmission while others use one amplifier for both directions.

REPEATING COIL: A repeating coil is a transformer. There are numerous impedance ratios available to match a variety of telephone cable and equipment impedances. A repeating coil is sometimes called a repeat coil or coil.

RETURN LOSS (R.L.): The return loss of a circuit is a measure of the amount of transmitting current which is transferred to the receiver at the same location due to impedance mismatches. The higher the ratio in dB, the better the return loss. See ERL and SRL.

RINGDOWN SIGNALING: The 90 V at 20 Hz signal used to operate the ringer in a subscriber's telephone set.

RINGER: The signaling bell in a telephone set.

SENSITIVITY: Generally expressed in dBm at a specified impedance (usually 600  $\Omega$ ), sensitivity is a measure of the lowest DTMF signal level that a receiver can detect. It represents an absolute threshold below which detection of a single frequency is not generated.

SHORT: A circuit is said to be "short" when the net loss is less than the limits allow. This may create "singing" (oscillation).

SINGING: Singing means a circuit is oscillating because it has too much gain. It can sing at any frequency, but the effect is worse at those frequencies within the usable band.

SINGING POINT (S.P.): The singing point of a circuit is the threshold at which it goes into oscillation. It is a measure of stability and is a function of return loss. It is measured in dB and the larger the number, the greater the stability.

SINGING RETURN LOSS (SRL): Weighted average of the return losses at all frequencies in a frequency band. There is a low frequency test covering the 200 to 500 Hz band (SRL-LO) and a high frequency test covering the 2500 to 3000 Hz band (SRL-HI).

SKEW: A measure (expressed in percent) of the departure of each individually received signal frequency from its nominal value. A function of component tolerances, aging, environmental conditions, and certain types of transmission-multiplexing equipment, skew is measured at the DTMF receiver.

SLEEVE (S): Sleeve is a term to describe the frame or body portion of a telephone plug or jack. See tip and ring.

SUBSCRIBER'S SUBSET: The telephone instrument on the subscriber's premises.

TALK-OFF: The tendency of a DTMF system to respond falsely to other-than-valid DTMF signals. Talk-off criteria are generally specified very subjectively - sometimes in such broad terms as "good" or "poor".

TERMINATING CONNECTION: A measurement that substitutes the internal resistance of the measuring instrument for the subscriber's subset or other equipment. If the measuring instrument does not have the desired impedance, an external resistor must be placed across the input terminals.

TERMINATING SET: A terminating set is used at the terminals of an equivalent four-wire circuit for converting to two-wire operation. The transformer arrangement is similar to a hybrid coil. The set is sometimes referred to as a four-wire term set or term set.

TIP AND RING: Tip (T) and ring (R) are terms used to identify the two conductors of a circuit. They originate from switchboard terminology pertaining to cord circuits. A fourwire circuit is designated T<sub>1</sub>, T<sub>2</sub> and R<sub>1</sub> and R<sub>2</sub>.

TWIST: The difference (in decibels) between the DTMF high-group and low-group signal levels, mathematically defined as 10 log [(high-group power)/(low-group power)]. Measured at the DTMF receiver, it's a function of both the level difference generated by the signal source and the gain-frequency characteristic of the transmission facility.

TWO-WIRE CIRCUIT: A two-wire circuit is one which terminates at the customer's premises in two wires. It may, however, contain some facilities which are four-wire, such as a repeater or carrier.

VARLEY: A varley (varley loop test) is made with a Wheatstone bridge and is used to detect a difference (unbalance) in the dc resistance of the tip and ring conductors.

WET LINE: A telephone line with battery voltage present.

WHITE NOISE: Random noise whose constant energy per unit bandwidth is independent of the central frequency at the band. The name is taken from the analogous definition of white light.

# levels at other points in the system are referred. The OTLP is usually the transmitting toll switchboard or testboard.

الحيات المحيون المحيون

and an an and a second and a seco A second and a second a s

(1) A state of the set of the

a sense in the set of t A set of the set of

(a) A set of the se

(2) The second secon

a de la companya de l Portes de la companya Portes de la companya de la companya

ZERO TRANSMISSION LEVEL POINT (OTLP): An arbitrary point in a transmission system to which all relative

(a) A set of a set of a sign a sign of a sign of a set of a set

(a) A definition of the second system of the sec

# TELECOMMUNICATION PRODUCTS Definitions of Data Sheet Designations

# PRODUCT PROFILE

A Product Profile is an initial disclosure of a new product's features and general information. A "PRODUCT PROFILE" designation on a Mostek literature item indicates that the product is not yet available and that the specification goals have not yet been fully established. The information given in the Product Profile is subject to change and is not guaranteed. Mostek reserves the right to make changes in the Product Profile at any time and without notice.

## TARGET SPECIFICATION

A Target Specification is an initial disclosure of specification goals for a product. The "TARGET SPECIFICATION" designation on a Mostek data sheet indicates that the product is not yet available. The specifications in the data sheet are subject to change, are based on design goals, and are not guaranteed. Mostek reserves the right to make changes in specifications at any time and without notice.

## PRELIMINARY

A Preliminary data sheet indicates that the specifications in the data sheet are based on design goals or preliminary part evaluation. The "PRELIMINARY" designation on a Mostek data sheet indicates that the product is not characterized. The specifications are subject to change and are not guaranteed. Mostek reserves the right to make changes in specifications at any time and without notice.

A data sheet without any specific designation indicates that the product has been characterized and that the specifications have been verified. The information furnished by Mostek in this data sheet is believed to be accurate and reliable.

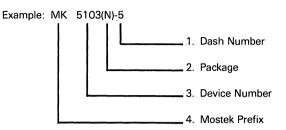

#### ORDER INFORMATION TELECOMMUNICATION PRODUCTS

Factory orders for parts described in this book should include a four-part number as explained below:

1. Dash Number

One or two numerical characters defining specific device performance characteristic.

#### 2. Package

- P Gold side-brazed ceramic DIP

- J CER-DIP

- N Epoxy DIP (Plastic)

- K tin side-brazed ceramic DIP

- T Ceramic DIP with transparent lid

- E Ceramic leadless chip carrier

- 3. Device number

| 1XXX or 1XXXX | - | Shift Register, ROM               |

|---------------|---|-----------------------------------|

| 2XXX or 2XXXX | - | ROM, EPROM                        |

| 3XXX or 3XXXX | - | ROM, EPROM                        |

| 38XX          | - | Microcomputer Components          |

| 4XXX or 4XXXX | - | RAM                               |

| 5XXX or 5XXXX | - | Telecommunications and Industrial |

| 7XXX or 7XXXX | - | Microcomputer Systems             |

4. Mostek Prefix

**MK-Standard Prefix**

MKB-100% 883B screening, with final electrical test at low, room and high-rated temperatures.

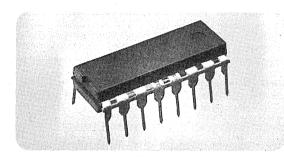

# **Package Descriptions**

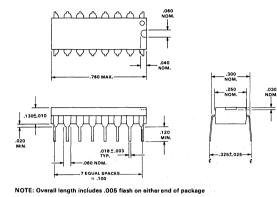

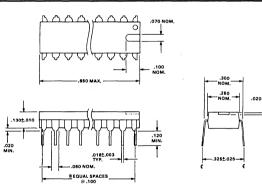

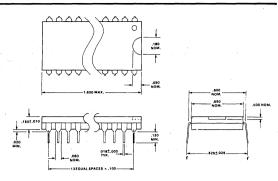

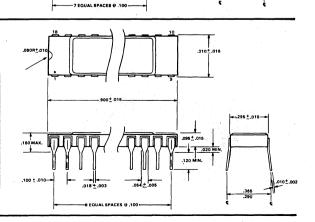

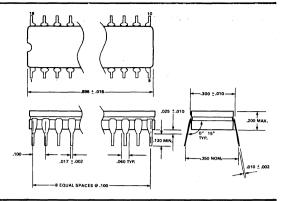

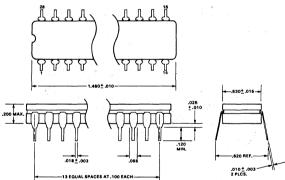

## Plastic Dual-In-Line Package (N) 16-Pin

Plastic Dual-In-Line Package (N) 18-Pin

NOTE: Overall length includes .005 flash on either end of package

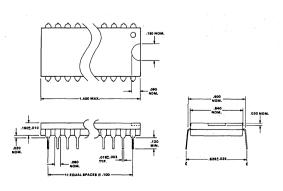

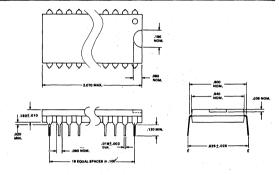

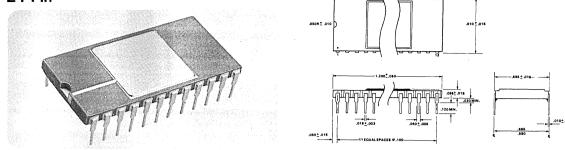

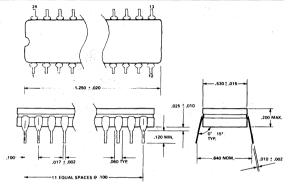

# Plastic Dual-In-Line Package (N) 24-Pin

NOTE: Overall length includes .005 flash on either end of package

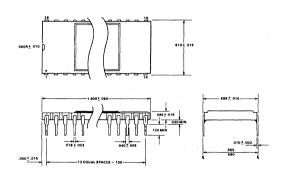

# Plastic Dual-In-Line Package (N) 28-Pin

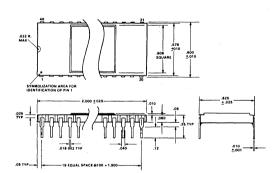

# Plastic Dual-In-Line Package (N) 40-Pin

NOTE: Overall length includes .005 flash on either end of package

.295±.015

NOTE: Overall length includes .005 flash on either end of package

# Side-Braze Ceramic Package (P) 16-Pin

# Side-Braze Ceramic Package (P) 18-Pin

.100 ± .010

# Side-Braze Ceramic Package (P) 24-Pin

# Side-Braze Ceramic Package (P) 28-Pin

# Side-Braze Ceramic Package (P) 40-Pin

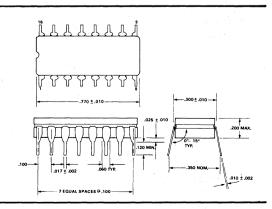

## Cerdip Package (J) 16-Pin

## Cerdip Package (J) 18-Pin

#### Mostek - Technology For Today And Tomorrow

#### TECHNOLOGY

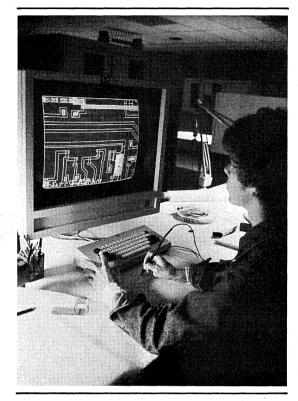

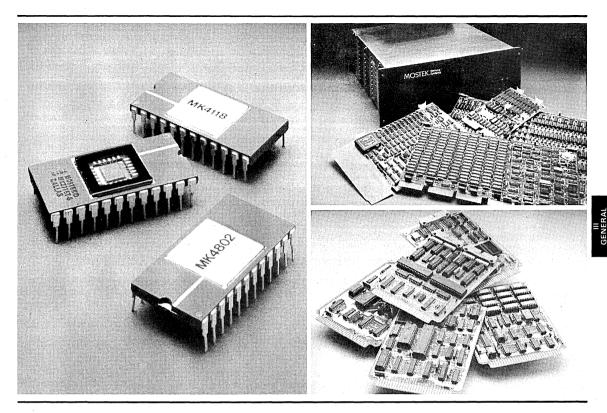

From its beginning, Mostek has been an innovator. From the developments of the 1K dynamic RAM and the single-chip calculator in 1970 to the current 64K dynamic RAM, Mostek technological breakthroughs have proved the benefits and cost-effectiveness of metal oxide semiconductors. Today, Mostek represents one of the industry's most productive bases of MOS/LSI technology, including Direct-Step-on-Wafer processing and ion-implantation techniques.

The addition of the Microelectronics Research Center in Colorado Springs adds a new dimension to Mostek circuit design capabilities. Using the latest computer-aided design techniques, center engineers will be keeping ahead of the future with new technologies and processes.

#### QUALITY

The worth of a product is measured by how well it is designed, manufactured and tested and by how well it works in your

#### system.

In design, production and testing, the Mostek goal is meeting specifications the first time on every product. This goal requires strict discipline from the company and from its individual employees. Discipline, coupled with very personal pride, has enabled Mostek to build in quality at every level of production.

#### **PRODUCTION CAPABILITY**

The commitment to increasing production capability has made Mostek the world's largest manufacturer of dynamic RAMs. We entered the telecommunications market in 1974 with a tone dialer, and have shipped millions of telecom circuits since then. More than two million of our MK3870 single-chip microprocessors are in use throughout the world. To meet the demand, production capability is being constantly increased. Recent construction in Dallas, Ireland and Colorado Springs has added some 50 percent to the Mostek manufacturing capacity.

#### THE PRODUCTS

#### **Telecommunication Products**

Mostek is the leading supplier of tone dialers, pulse dialers, and CODEC devices. As each new generation of telecommunications systems emerges, Mostek is ready with new generation components, including PCM filters, tone decoders, repertory dialers, new integrated tone dialers, and pulse dialers.

These products, many of them using CMOS technology, represent the most modern advancements in telecommunications component design.

#### **Industrial Products**

Mostek's line of Industrial Products offers a high degree of versatility per device. This family of components includes various microprocessor-compatible A/D converters, a counter/time-base circuit for the division of clock signals, and combined counter/display decoders. As a result of the low parts count involved, an economical

alternative to discrete logic systems is provided.

#### Memory Products

Through innovations in both circuit design, wafer processing and production, Mostek has become the industry's leading supplier of memory products.

An example of Mostek leadership is our new BYTEWYDE™ family of static RAMs, ROMs, and EPROMs. All provide high performance, N words x 8-bit organization and common pin configurations to allow easy system upgrades in density and performance. Another important product area is fast static RAMs. With major advances in technology, Mostek static RAMs now feature access times as low as 55 nanoseconds. With high density ROMs and PROMs, static RAMs, dynamic RAMs and pseudostatic RAMs, Mostek now offers one of industry's broadest and most versatile memory product lines.

#### **Microcomputer Components**

Mostek's microcomputer components are designed for a wide range of applications. Our Z80 family is today's industry standard 8-bit microcomputer. The MK3870 family is one of the industry's most popular 8-bit single-chip microcomputers, offering upgrade options in ROM, RAM and I/O, all in the same socket. The 38P7X EPROM versions support and prototype the entire family.

III-ii

#### **Microcomputer Systems**

Complementing the component product line is the powerful MATRIX<sup>TM</sup> microcomputer development system, a Z80based, dual floppy-disk system that is used to develop and debug software and hardware for all Mostek microcomputers.

A software operating system, FLP-80DOS, speeds and eases the design cycle with powerful commands. BASIC, FORTRAN, and PASCAL are also available for use on the MATRIX.

Mostek's MD Series<sup>™</sup> features both stand-alone microcomputer boards and expandable microcomputer boards. The expandable boards are modularized by function, reducing system cost because the designer buys only the specific functional modules his system requires. All MDX boards are STD-Z80 BUS compatible.

#### **Memory Systems**

Taking full advantage of our leadership in memory components technology, Mostek Memory Systems offers a broad line of products, all with the performance and reliability to match our industry-standard circuits. Mostek Memory Systems offers addin memory boards for popular DEC and Data General minicomputers.

Mostek also offers special purpose and custom memory boards for special applications.

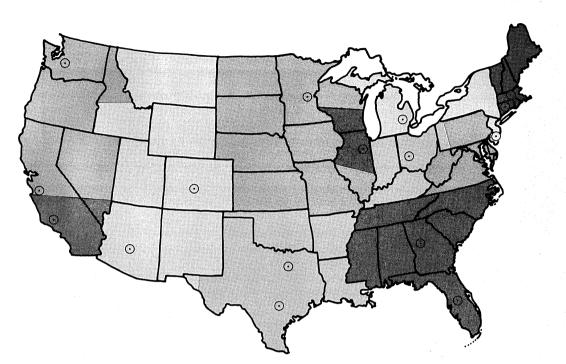

#### **U.S. AND CANADIAN SALES OFFICES**

CORPORATE HEADQUARTERS

Mostek Corporation 1215 W. Crosby Rd. P. O. Box 169 Carrollton, Texas 75006

**REGIONAL OFFICES** Northeastern Area Mostek 49 W. Putnam, 3rd Floor Greenwich, Conn. 06830 203/622-0955 TWX 710-579-2928

Northeast U.S. Mostek Mostek 29 Cummings Park, Suite #426 Woburn, Mass. 01801 617/935-0635 TWX 710-348-0459

Southeastern Area Southeastern Area Mostek 4001B Greentree Executive Campus Route #73 Mariton, New Jersey 08053 609/596-9200 TWX 710-940-0103

Southeast U.S. Mostek 13907 N. Dale Mabry Highway Suite 201 Tampa, Florida 33618 813/962-8338 TWX 810-876-4611

Atlanta Region 2 Exchange Place 2300 Peachford Rd. #2105 Atlanta, GA 30338 404/458-7922 TWX 810-757-4231

Upstate NY Region Mostek 4651 Crossroads Park Dr., Suite 201 Liverpool, NY 13088 315/457-2160 TWX 710-545-0255

Florida Region Mostek 22521 Southwest 66th Ave. Apt. A211 Boca Raton, FL 33433 305/483-2483

Chicago Region Mostek Mostek Two Crossroads of Commerce Suite 360 Rolling Meadows, III. 60008 312/577-9870 TWX 910-291-1207

North Central U.S. Mostek 6101 Green Valley Dr. Bloomington, Mn. 55438 612/831-2322 TWX 910-576-2802 South Central U.S. Mostek 3400 S. Dixie Ave. Suite 101 Kettering, Ohio 45439 513/299-3405 TWX 810-459-1625

Michigan Mostek Orchard Hill Place 21333 Haggerty Road Suite 321 Novi, MI 48050 313/348-8360 TWX 810-242-1471

Central U.S. Mostek 4100 McEwen Road Suite 151 Dallas, Texas 75234 214/386-9340 TWX 910-860-5437

Southwest Region Mostek 4100 McEwen Road Suite 237 Dallas, Texas 75234 214/386-9141 TWX 910-860-5437

Chevy Chase #4 7715 Chevy Chase Dr., Suite 116 Austin, TX 78752 512/458-5226 TWX 910-874-2007

Western Region Northern California Mostek 1762 Technology Drive Suite 126 San Jose, Calif. 95110 408/287-5080 TWX 910-338-7338

Seattle Region Mostek 1107 North East 45th St. Suite 411 Seattle, WA 98105 206/632-0245 TWX 910-444-4030

Southern California Mostek 18004 Skypark Circle Suite 140 Irvine, Calif, 92714 714/549-0397 TWX 910-595-2513

Arizona Region Mostek 2150 East Highland Ave. Suite 101

Suite 101 Phoenix, AZ 85016 602/954-6260 TWX 910-957-4581

Denver Region 3333 Quebec Street, #9090 Denver, CO 80207 303/321-6545 TWX 910-931-2583

#### U.S. AND CANADIAN REPRESENTATIVES

ALABAMA

ALABAMA Beacon Elect. Assoc., Inc.\* 11309 S. Memorial Pkwy. Suite G Huntsville, AL 35803 205/881-5031 TWX 810-726-2136

Conley & Associates, Inc. 3322 Memorial Pkwy., S.W. Suite 17 Suite 17 Huntsville, AL 35801 205/882-0316 TWX 810-726-2159

ARIZONA Summit Sales 7825 E. Redfield Rd. 7825 E. Redfield Rd. Scottsdale, AZ 85260 602/998-4850 TWX 910-950-1283

ARKANSAS Beacon Elect. Assoc., Inc. P.O. Box 5382, Brady Station Little Rock, AK 72215 501/224-5449 TWX 910-722-7310

CALIFORNIA Harvey King, Inc. 8124 Miramar Road San Diego, CA 92126 714/566-5252 TWX 910-335-1231

COLORADO Waugaman Associates\* 4800 Van Gordon Wheat Ridge, CO 80033 303/423-1020 TWX 910-938-0750

CONNECTICUT New England Technical Sales 240 Pomeroy Ave. Meriden, CT 06450 203/237-8827 TWX 710-461-1126

FLORIDA Conley & Associates, Inc.\* P.O. Box 309 235 S. Central Oviedo, FL 32765 305/365-3283 TWX 810-856-3520

Conley & Associates, Inc. 4021 W. Waters Suite 2 Suite 2 Tampa, FL 33614 813/885-7658 TWX 810-876-9136

Conley & Associates, Inc. P.O. Box 700 1612 N.W. 2nd Avenue Boca Raton, FL 33432 305/395-6108 TWX 510-953-7548

GEORGIA Conley & Associates, Inc. 3951 Pleasantdale Road Suite 201 Suite 201 Doraville, GA 30340 404/447-6992 TWX 810-766-0488

ILLINOIS Carlson Electronic Sales\* 600 East Higgins Road Elk Grove Village, IL 60007 312/956-8240 TWX 910-222-1819

INDIANA INDIANA Rich Electronic Marketing\* 599 Industrial Drive Carmel, IN 46032 317/844-8462 TWX 810-260-2631

Rich Electronic Marketing 3448 West Taylor St. Fort Wayne, IN 46804 219/432-5553 TWX 810-332-1404

IOWA Carlson Electronic Sales 204 Collins Rd. NE Cedar Rapids, IA 52402 319/377-6341 TWX 910-222-1819

**REP** Associates 980 Areca Ave. Marion, IA 52302 319/393-0231

KANSAS Rush & West Associates\* 107 N. Chester Street Olathe, KN 66061 913/764-2700 Wichita 316/683-0206 TWX 910-749-6404

KENTUCKY Rich Electronic Marketing 5910 Bardstown Road P. O. Box 91147 Louisville, KY 40291 502/239-2747 TWX 810-535-3757 Arbotek Associates 3600 St. Johns Lane Ellicott City, MD 21043 301/461-1323 TWX 710-862-1874

MARYLAND

MASSACHUSETTS MASSACHUSETTS New England Technical Sales\* 135 Cambridge Street Burlington, MA 01803 617/272-0434 TWX 710-332-0435

MICHIGAN Action Components 21333 Haggerty Road Suite 201 Novi, MI 48050 313/349-3940

MINNESOTA Cahill, Schmitz & Cahill, Inc.\* 315 N. Pierce St. Paul, MN 55104 612/646-7217 TWX 910-563-3737

MISSOURI Rush & West Associates 481 Melanie Meadows Lane Ballwin, MO 63011 314/394-7271

NORTH CAROLINA Conley & Associates, Inc. 4050 Wake Forest Road Suite 102 Raleigh, NC 27609 919/876-9862 TWX 510-928-1829

NEW JERSEY NEW JERSEY Tritek Sales, Inc. 21 E. Euclid Ave. Haddonfield, NJ 08033 609/429-1551 215/627-0149 (Philadelphia Line) TWX 710-896-0881

NEW MEXICO Waugaman Associates P.O. Box 14894 Albuquerque, NM 87111

9004 Menaul NE Suite 7 Albuquerque, NM 87112 505/294-1437 505/294-1437 (Ans. Service)

#### NEW YORK

FRA Inc. EKA Inc. 354 Veterans Memorial Highway Commack, NY 11725 516/543-0510 TWX 510-226-1485 (New Jersey Phone # 800/645-5500, 5501) Precision Sales Corp. 5 Arbustus Ln., MR-97 Binghamton, NY 13901 607/648-3686 607/648-8833

Precision Sales Corp.\* 1 Commerce Blvd. Liverpool, NY 13008 315/451-3480 TWX 710-545-0250 Precision Sales Corp. 3594 Monroe Avenue Pittsford, NY 14534 716/381-2820

Precision Sales Corp. Drake Road Pleasant Valley, NY 12569 914/635-3233

оню OHIO Rich Electronic Marketing 7221 Taylorsville Road Dayton, Ohio 45424 513/237-9422 TWX 810-459-1767

Rich Electronic Marketing 141 E. Aurora Road Northfield, Ohio 44067 216/468-0583 TWX 810-427-9210

OREGON Northwest Marketing Assoc. 9999 S.W. Wilshire St. Suite 124 Portland OR 97225 503/297-2581 TELEX 36-0465 (AMAPORT PTL)

TENNESSEE Conley & Associates, Inc. 1128 Tusculum Blvd. Suite D Greenville, TN 37743 615/639-3139 TWX 810-576-4597

TEXAS

TEXAS Southern States Marketing, Inc.\* P.O. Box 8000 Addison, TX 75001 214/387-2489 TWX 910-860-5138 Southern States Marketing, Inc.

7745 Chevy Chase Suite 219 Austin, TX 78752 512/452-9459

Southern States Marketing, Inc. 9730 Town Park Drive, Suite 105 Houston, Texas 77036 713/988-0991 TWX 910-881-1630

UTAH UTAH Waugaman Associates 2520 S. State Street Suite #159 Salt Lake City, UT 84115 801/467-4263 TWX 910-925-4073

WASHINGTON Northwest Marketing Assoc.\* 12835 Bellevue-Redmond Rd. Suite 203E Bellevue, WA 98005 206/455-5846 TWX 910-443-2445

WISCONSIN Carlson Electronic Sales Northbrook Executive Ctr. 10701 West North Ave. Suite 209 Suite 209 Milwaukee, WI 53226 414/476-2790 TWX 910-222-1819

CANADA CANADA Cantec Representatives Inc.\* 1573 Laperriere Ave. Ottawa, Ontario Canada K1Z 7T3 613/725-3704 TWX 610-562-8967

Cantec Representatives Inc. 33 Galaxy Blvd., Unit 1A (Rexdale) Toronto, Canada M9W 5X6 416/675-2460 TWX 610-492-2655

Cantec Representatives Inc. 3639 Sources Blvd. Suite 116 Suite 116 Dollard Des Ormeaux, Quebec Canada H9B2K4 514/683-6131 TWX 610-422-3985

\*Home Office

#### **U.S. AND CANADIAN DISTRIBUTORS**

#### ARIZONA

CALIFORNIA

Kierulff Electronics 4134 E. Wood St. Phoenix, AZ 85040 602/243-4101 TWX 910/951-1550 Wyle Distribution Group 8155 North 24th Avenue Phoenix, Arizona 85021 602/249-2232 TWX 910/951-4282

CALIFORNIA Bell Industries 1161 N. Fair Oaks Avenue Sunnyvale, CA 94086 408/734-8570 TWX 910/339-9378 Arrow Electronics 521 Weddell Dr. Sunnyvale, CA 94086 408/745-6600 TWX 910/339-9371 Kierulff Electronics 2585 Commerce Way Los Angeles, CA 90040 213/725-0325 TWX 910/580-3106 Kierulff Electronics 8797 Balboa Avenue San Diego, CA 92123 714/278-2112 TWX 910/335-1182 Kierulff Electronics 14101 Franklin Avenue Tustin, CA 92680 714/731-5711 TWX 910/595-2599 Schweber Electronics 17811 Gillette Avenue Irvine, CA 92714 714/556-3880 TWX 910/595-1720 Wx 910/595-1720 Wyle Distribution Group 124 Maryland Street El Segundo, CA 90245 213/322-8100 TWX 910/348-7111 Wyle Distribution Group 9525 Chesapeake Drive San Diego, CA 92123 714/565-9171 TWX 910/335-1590 Wyle Distribution Group 17872 Cowan Ave. Irvine, CA 92714 714/641-1600 TWX 910/348-7111 Wyle Distribution Group 3000 Bowers Ave. Santa Clara, CA 95051 408/727-2500 TWX 910/338-0296

COLORADO Kierulff Electronics 10890 E. 47th Avenue Denver, CO 80239 303/371-6500 TWX 910/932-0169 Wyle Distribution Group 451 E. 124th Ave. Thornton, CO 80241 303/457-9953 TWX 910/936-0770

# CONNECTICUT CONNECTICUT Arrow Electronics 12 Beaumont Rd, Wallingford, CT 06492 203/265-7741 TWX 710/476-0162 Schweber Electronics Finance Drive Commerce Industrial Park Danbury, CT 06810 203/792-3500 TWX 710/456-9405

#### FLORIDA

Arrow Electronics 1001 N.W. 62nd St. Suite 108 Suite 108 Ft. Lauderdale, FL 33309 305/776-7790 TWX 510/955-9456 Arrow Electronics 115 Palm Bay Road, NW Suite 10, Bldg. 200 Palm Bay, FL 32905 305/725-1480 TWX 510-959-6337 Diplomat Southland 2120 Calumet Clearwater, FL 33515 813/443-4514 TWX 810/866-0436 Kierulff Electronics 3247 Tech Drive 3247 Tech Drive St. Petersburg, FL 33702 813/576-1966 TWX 810/863-5625

# GEORGIA Arrow Electronics 2979 Pacific Drive Norcross, GA 30071 404/449-8252 TWX 810/766-0439 Schweber Electronics 303 Research Drive, Suite 210 Norcross, GA 30092 404/449-9170

### ILLINOIS Arrow Electronics 492 Lunt Avenue P. O. Box 94248 Schaumburg, IL 60193 312/893-9420 TWX 910/291-3544 Bell Industries 3422 W. Touhy Avenue Chicago, IL 60645 312/982-9210 TWX 910/223-4519 Kierulff Electronics Nervin Electronics 1536 Lanmeier Elk Grove Village, IL 60007 312/640-0200 TWX 910/222-0351

INDIANA INDIANA Advent Electronics 8446 Moller Indianapolis, IN 46268 317/872-4910 TWX 810/341-3228 Arrow Electronics 2718 Rand Road Indianapolis, IN 46241 317/243-9353 TWX 810/341-3119 Ft. Wayne Electronics 3606 E. Maumee Ft. Wayne, IN 46803 219/423-3422 TWX 810/332-1562 Pioneer Electronics 6408 Castleplace Drive Indianapolis, IN 46250 317/849-7300 TWX 810/260-1794

IOWA Advent Electronics 682 58th Avenue Court South West Cedar Rapids, IA 52404 319/363-0221 TWX 910/525-1337

MASSACHUSETTES Kierulff Electronics 13 Fortune Drive Billerica, MA 01821 617/935-5134 TWX 710/390-1449 Lionex Corporation 1 North Avenue Burlington, MA 01803 617/272-9400 TWX 710/332-1387 Schweber Electronics 25 Wiggins Avenue Bedford, MA 01730 617/275-5100 TWX 710/326-0268 Arrow Electronics Arrow Drive Woburn, MA 01801 617/933-8130 TWX 710/393-6770

## MARYLAND Arrow Electronics 4801 Benson Avenue Baltimore, MD 21227 301/247-5200 TWX 710/236-9005 Pioneer Electronics 9100 Gaither Road Gaithersburg, MD 20760 301/948-0710 TWX 710/828-0545 Schweber Electronics 9218 Gaither Rd. 9218 Gaither Rd. Gaithersburg, MD 20760 301/840-5900 TWX 710/828-9749

MICHIGAN Arrow Electronics 3810 Varsity Drive Ann Arbor, MI 48104 313/971-8220 TWX 810/223-6020 Schweber Electronics 33540 Schoolcraft Road Livonia, MI 48150 313/525-8100 TWX 810/242-2983

## MINNESOTA Arrow Electronics 5251 W. 73rd Street Edina, MN 55435 612/830-1800 TWX 910/576-3125 Kierulff Electronics 5280 W. 74th St. Edina, MN 55435 612/835-4388 TWX 910/576-2721 Industrial Components 5229 Edina Industrial Blvd. Minneapolis, MN 55435 612/831-2666 TWX 910/576-3153

# MISSOURI Arrow Electronics 2380 Schuetz Road St. Louis, MO 63141 314/567-6888 TWX 910/764-0882 Olive Electronics 9910 Page Blvd. St. Louis, MO 63132 314/426-4500 TWX 910/763-0720 Semiconductor Spec 3805 N. Oak Trafficway Kansas City, MO 64116 816/452-3900 TWX 910/771-2114

NEW HAMPSHIRE Arrow Electronics 1 Perimeter Rd. Manchester, NH 03103 603/668-6968 TWX 710/220-1684

NEW JERSEY Arrow Electronics Pleasant Valley Avenue Morrestown, NJ 08057 609/235-1900 TWX 710/897-0829 Arrow Electronics 285 Midland Avenue Saddlebrook, NJ 07662 201/797-5800 TWX 710/988-2206 Kierulff Electronics Kierulff Electronics 3 Edison Place Fairfield, NJ 07006 201/575-6750 TWX 710/734-4372 Schweber Electronics 18 Madison Road Fairfield, NJ 07006 201/227-7880 TWX 710/734-4305

#### **U.S. AND CANADIAN DISTRIBUTORS**

#### NEW MEXICO

NEW YORK

Bell/Century 11728 Linn N.E Albuquerque, NM 87123 505/292-2700 TWX 910/989-0625 Arrow Electronics 2460 Alamo Ave. S.E. Albuquerque, NM 87106 505/243-4566 TWX 910/989-1679

Arrow Electronics 900 Broad Hollow Rd. Farmingdale, L.I., NY 11735 516/694-6800 516/694-6800 TWX 510/224-6494 Arrow Electronics 7705 Mattlage Drive P. O. Box 370 Liverpool, NY 13088 315/652-1000 TWX 710/545-0230 TWX 710/545-0230 Arrow Electronics 3000 S. Winton Road Rochester, NY 14623 716/275-0300 TWX 510/253-4766 Arrow Electronics 20 Oser Ave. Hauppauge, NY 11787 515/231 1000 516/231-1000 TWX 510/227-6623 Lionex Corporation 400 Oser Ave. Hauppauge, NY 11787 516/273-1660 TWX 510/227-1042 Schweber Electronics 2 Twin Line Circle Rochester, NY 14623 716/424-2222 Schweber Electronics Jericho Turnpike Westbury, NY 11590 516/334-7474 TWX 510/222-3660 \*Zeus Components, Inc. 500 Executive Blvd. Elmsford, NY 10523 914/592-4120 TWX 710/567-1248

NORTH CAROLINA Arrow Electronics 938 Burke St. Winston Salem, NC 27102 919/725-8711 TWX 510/931-3169 Hammond Electronics 2923 Pacific Avenue Greensboro, NC 27406 919/275-6391 TWX 510/925-1094

оню Arrow Electronics 7620 McEwen Road Centerville, OH 45459 513/435-5563 TWX 810/459-1611 Arrow Electronics Arrow Electronics 6238 Cochran Road Solon, OH 44139 216/248-3990 TWX 810/427-9409 Schweber Electronics 23880 Commerce Park Road Beachwood, OH 44122 216/464-2970 TWX 810/427-9441 Pioneer Electronics 4800 East 131st Street Cleveland, OH 44105 216/587-3600 TWX 810/422-2211 Pioneer Electronics 4433 Interpoint Blvd. Dayton, OH 45424 513/236-9900 TWX 810/459-1622

OKIAHOMA Quality Components 9934 East 21st South Tulsa, OK 74129 918/664-8812

OREGON Kierulff Electronics 14273 NW Science Park Portland, OR 97229 503/641-9150 TWX 910/467-8753

PENNSYLVANIA Schweber Electronics 101 Rock Road Horsham, PA 19044 215/441-0600 Arrow Electronics 650 Seco Rd. Monroeville, PA 15146 412/856-7000 Pioneer Electronics 560 Alpha Drive Pittsburgh, PA 15238 412/782-2300 TWX 710/795-3122 Pioneer Electronics 261 Gibraltar 261 Gibraltar Horsham, PA 19044 215/674-4000 TWX 510/665-6778

SOUTH CAROLINA Harmond Electronics 1035 Lowndes Hill Rd. Greenville, SC 29602 803/233-4121 TWX 810/281-2233

TEXAS Arrow Electronics 13715 Gamma Road Dallas, TX 75240 214/386-7500 TWX 910/860-5377 TWX 910/860-5377 Quality Components 2427 Rutland Drive Austin, TX 78758 512/835-0220 TWX 910/874-1377 Quality Components 4257 Kellway Circle Addison, TX 75001 214/387-4949 TWX 910/860-5459 Outline Generative Uwx 910/860-5459 Quality Components 6126 Westline Houston, TX 77036 713/772-7100 Schweber Electronics 10625 Richmond, Suite 100 Houston, TX 77042 713/784-3600 TWX 910/881-1109 Arrow Electronics 10700 Corporate Drive Suite 100 Stafford, TX 77477 713/491-4100 TWX 910/880-4439

#### UTAH

Bell/Century 3639 W. 2150 South Salt Lake City, UT 84120 801/972-6969 TWX 910/925-5686 Kierulff Electronics 2121 South 3600 West Salt Lake City, UT 84104 801/973-6913

WASHINGTON WASHINGTON Kierulff Electronics 1005 Andover Park East Tukwila, WA 98188 206/575-4420 TWX 910/444-2034 Wyle Distribution Group 1750 132nd Avenue N.E. Bellevue, Washington 98005 206/453-8300 TWX 910/443-2526

WISCONSIN WISCONSIN Arrow Electronics 434 Rawson Avenue Oak Creek, WI 53154 414/764-6600 TWX 910/262-1193 Kierulff Electronics 2212 E. Moreland Blvd Waukesha, WI 53186 414/784-8160 TWX 910/262-3653

CANADA Preloc Electronics 2767 Thames Gate Drive Mississauga, Ontario Toronto L4T 1G5 416/678-0401 TWX 610/492-8974 Prelco Electronics 480 Port Royal St. W. Montreal 357 P.O. H3L 2B9 514/389-8051 TWX 610/421-3616 Preico Electronics 1770 Woodward Drive Ottawa, Ontario K2C 0P8 613/226-3491 Telex 05-34301 R.A.E. Industrial 3455 Gardner Court Burnaby, B.C. V5G 4J7 604/291-8866 TWX 610/929-3065 Zentronics 141 Catherine Street Ottawa, Ontario K2P 1C3 613/238-6411 Telex 05-33636 Zentronics 1355 Meyerside Drive Mississauga, Ontario (Toronto) L5T 1C9 416/676-9000 Telex 06-983657 Zentronics 2entronics 5010 Rue Pare Montreal, Quebec M4P 1P3 514/735-5361 Telex 05-827535 Zentronics 590 Berry Street St. James, Manitoba (Winnipeg) R2H OR4 204/775-8661 Zentronics 480 "A" Dutton Drive Waterloo, Ontario N2L 4C6 519/884-5700 R.A.E. Industrial 11680 170th St Edmonton, Alberta T5S 1J7 403/451-4001 Telex 03-72653 Zentronics 550 Cambie St. Vancouver, B.C. V6B 2N7 604/688-2533 Telex 04507789 Zentronics 3651 21st Street, N.E. Calgary, Alberta T2E 6T5 403/230-1422 Zentronics 9224 27th Avenue Edmonton, Alberta T6N 1B2 403/463-3014

CANADA

#### INTERNATIONAL MARKETING OFFICES

#### EUROPEAN HEAD OFFICE

Mostek International Av de Tervuren 270-272 Bte 21 B-1150 Brussels/Belgium 02/762.18.80 Telex: 62011

#### FRANCE Mostek France s.a.r.l. 30 Rue du Morvan

SILIC 505 F-94623 Rungis Cedex (1) 687 34.14 Telex: 204049

#### GERMANY PLZ 1-5 Mostek GmbH Friedlandstrasse 1 D-2085 Quickborn (04106) 2077/78 Telex: 213685

PLZ 6-7 Mostek GmbH Schurwaldstrasse 15 D-7303 Neuhausen/Filder (07158) 66.45 Telex: 72.38.86 PLZ 8

Mostek GmbH Zaunkonigstr. 18 D-8012 Ottobrunn (089) 609 1017 Telex: 5216516

ITALY Mostek Italia SRL Via F.D. Guerrazzi 27 I 20145 Milano (02) 318.5337/349.2696 and 34.23.89 Telex: 333601

#### JAPAN

Mostek Japan KK Sanyo Bldg. 3F 1-2-7 Kita-Aoyama Minato-Ku, Tokyo 107 (03) 404-7261 Telex: J23686

SWEDEN Mostek Scandinavia AB Magnusvagen 1/8 tr S-17531 Jarfalla 0758-343 38/343 48/183 30 Telex: 12997 UNITED KINGDOM Mostek U.K. Ltd. Masons House, 1-3 Valley Drive Kingsbury Road London, N.W.9 01-204 9322 Telex: 25940

> II GENERAL INFORMA-TIQN

#### INTERNATIONAL SALES REPRESENTATIVES/DISTRIBUTORS

ARGENTINA Rayo Electronics S.R.L. Belgrano 990, Pisos 6y2 1092 Buenos Aires (38)-1779, 37-9476

Telex - 122153

AUSTRALIA Amtron Tyree Pty.Ltd. 176 Botany Street Waterloo, N.S.W. 2017 (61) 69-89.666 Telex - 25643

AUSTRIA Transistor Vertriebsges, mbH Auhofstrasse 41 A A-1130 Vienna (0222) 82 9451, 83 9404 Telex - 0133738

BRASIL Cosele, Ltd. Rua da Consolacao, 867 Conj. 31 01301 Sao Paulo (55) 11-257.35.35/258.43.25 Telex - 1130869

BELGIUM Sotronic 14 Rue Pere De Deken B-1040 Brussels 02 736.10.07 Telex - 25141

DENMARK Semicap APS Gammel Kongevej 148 DK-1850 Copenhagen 01-22.15.10 Telex - 15987

FINLAND Insele Oy Kumpulantie 1 SF-00520 Helsinki 52 0 735 774 Telex: 122217

FRANCE Copel Rue Fourny, Z.I. B.P. 22, F-78 530 BUC (1) 956 1018 Telex: 69379

Facen 110 Av de Flandre F59290 Wasquehal. Nord (2) 98.92.15

Branch Offices in Chalon/Saone, Lille, Nancy, Rouen, Strasbourg Mecodis 2 Rue Pasteur F-94380 Bonneuil (1) 339.20.20 Telex: 250303

P.E.P. 4 Rue Barthelemy F-92120 Montrouge (1)-735.33.20 Telex: 204 534

Scaib 80 Rue d'Arcueil SILIC 137 F-94523 Rungis Cedex (1)-687.23.12 Telex: 204674

Sorhodis 150-152, Rue A. France F69100 Villeurbanne (78) 850044 Telex: 380181

GERMANY Dr Dohrenberg Bayreuther Strasse 3 D-1000 Berlin 30 (030) 213.80.43 Telex: 0 184860

Neye Enatechnik GmbH Schillerstrasse 14 D-2085 Quickborn (04106) 612-1 Telex: 0 213.590

Branch offices in: Berlin, Hannover, Dusseldorf, Darmstadt, Stuttgart, Munchen

Raffel-Electronic GmbH Lochnerstrasse 1 D-4030 Ratingen 1 (2102) 280.24 Telex: 8585180

Siegfried Ecker Koenigsberger Strasse 2 D-6120 Michelstadt (6061) 2233 Telex: 4191630

Matronic GmbH Lichtenberger Weg 3 D-7400 Tuebingen (7071) 24331 Telex: 7262879

Dema-Electronic GmbH Bluetenstrasse 21 D-8000 Munchen 40 (089) 288018/19 Telex: 05-29345 HONG KONG Cet Limited 1402 Tung Wah Mansion 199-203 Hennessy Road Wanchai, Hong Kong (5)-72.93.76 Telex - 85148

ISRAEL Telsys Ltd. 12, Kehilat Venetsia St. Tel Aviv. Israel 482126/7/8 Telex: 032392

ITALY Comprel s.r.l. V.le Romagna. 1 I-20092 Cinisello B. (MI) (02) 61.20.641/2/3/4/5 Telex: 332484

Branch offices in Bologna, Firenze, Lavagna, Loreto, Padova, Roma, Torino, Vicenza, Bari

Emesa S.P.A. Via L. da Viadana, 9 I-20122 Milano (02) 869.0616 Telex: 335066

Branch offices in Torino, Bologna, Roma

JAPAN Systems Marketing, Inc. 4th Floor, Shindo Blgd. 3:12-5 Uchikanda, Chiyoda-Ku, Tokyo, 100 (81) 3:254.27.51 Telex - 25761

Teijin Advanced Products Corp. 1-1 Uchisaiwai-Cho 2-Chome Chiyoda-Ku Tokyo, 100 (81) 3-506.46.73 Telex - 23548

KOREA Vine Overseas Trading Corp. Room 308 Korea Electric Association Bldg. 11-4 Supyo-Dong Jung-Ku Seoul (82) 2-66-1663 THE NETHERLANDS Nijkerk Elektronika BV Drentestraat 7 NL - 1083 HK Amsterdam (020) 428. 933 Telex: 11625

NEW ZEALAND E.C.S. Div. of Airspares P.O. Box 1048 Airport Palmerston North (77)-047 Telex - 3766

NORWAY Hefro Teknisk A/S Postboks 6596 Rodelokka, Oslo 5 02-38.02.86 Telex: 16205

PORTUGAL Digicontrole LDA Rua Tenente Ferreira Durao 33 R/1 1300 Lisboa 19-688442/652613 Telex: 15084

SINGAPORE Dynamar International, LTD. Suite 526, Cuppage Road Singapore 0922

SOUTH AFRICA Radiokom P.O. Box 56310 Pinegowrie 2123, Transvaal 789-1400 Telex - 8-0838 SA

SPAIN Comelta S.A. Emilio Munoz 41, ESC 1 Planta 1 Nave 2 Madrid-17 01-754 3001/3007 Telex: 42007

SWEDEN Interelko AB, Box 32 S-12221 Enskede 08-13 21 60 Telex: 10 689

Lagercrantz Elektronik AB Box 48 S-19421 Upplands Vasby 0760 861 20 Telex: 11275

SWITZERLAND Memotec AG Einschlagweg, 2 CH-4932 Lotzwil 063-28.11.22 Telex: 68636

TAIWAN Dynamar Taiwan Limited P.O. Box 67-445 2nd Floor, No. 14, Lane 164 Sung Chiang Road Taipei 5418251 Telex - 11064

UNITED KINGDOM Celdis Limited

37-39 Loverock Road Reading Berks RG 31 ED 0734-58.51.71 Telex: 848370

Lock Distribution Ltd. Neville Street Chadderton Oldham Lancashire OL9 6LF 061-652.04.31 Telex: 669971

Pronto Electronic Systems Ltd. 466-478 Cranbrook Road, Gants Hill Ilford Essex 1G2 6LE 01-554 6222 Telex: 895 4213

VSI Electronics (UK) Ltd. Roydondury Industrial Park Horsecroft Rd. Harlow Essex CM19 5BY (0279) 35477 Telex: 81387

Thame Components Ltd. Thame Park Road Thame, Oxon OX9 3XD 084 4213146 Telex: 837917

# **1982 TELECOMMUNICATION PRODUCTS DATA BOOK**

#### FEATURES

- □ Pin-for-pin compatible with MK5085 with improved performance

- □ Direct telephone-line operation with no external power supply

- □ Auxiliary switching functions on chip

- Low standby power

- Minimum external parts count

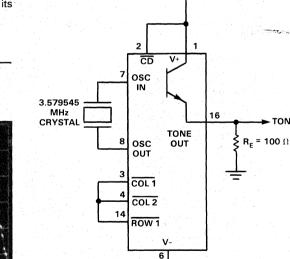

- □ Uses inexpensive 3.579545 MHz television color-burst crystal to provide high-accuracy tones

- On-chip regulation of dual-and single-tone amplitudes

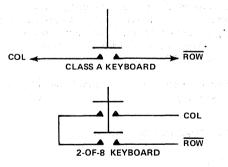

- Uses low-cost calculator-type keyboard (Form A contact) or standard 2-of-8 keyboard

- Multiple key entry pin-selectable to either single tone or no tone

#### DESCRIPTION

The MK5087 is a monolithic integrated circuit fabricated using the complementary-symmetry MOS (CMOS) process. A member of the TONE II\* family of integrated tone dialers. the MK5087 uses an inexpensive crystal reference to provide eight different audio sinusoidal frequencies, which are mixed to provide tones suitable for Dual-Tone-Multi-Frequency (DTMF) telephone dialing.

The MK5087 was designed specifically for integrated tonedialer applications that require the following: wide-supply operation with regulated output, auxiliary switching functions, single-contact keyboard inputs, and Single Tone Inhibit option.

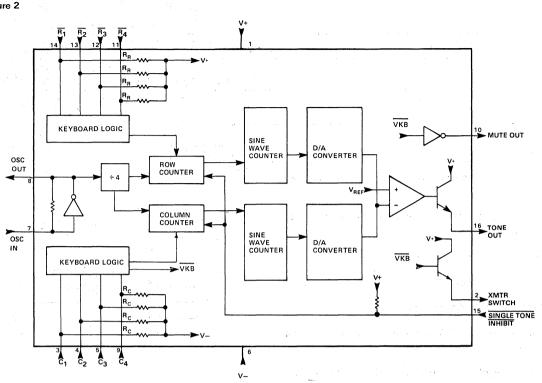

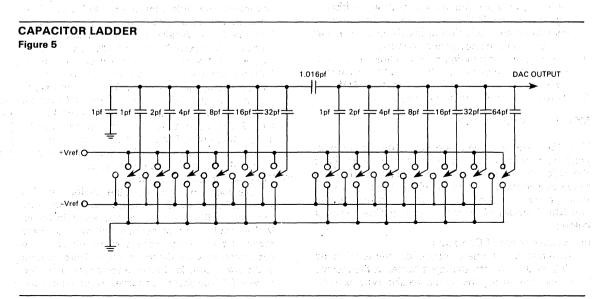

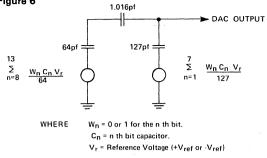

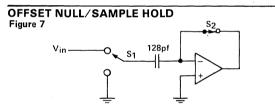

Keyboard entries to the TONE II\* family of integrated tone dialers cause the selection of the proper divide ratio to obtain the required two audio frequencies from the 3.579545 MHz reference oscillator. D-to-A conversion is accomplished on-chip by a conventional R-2R ladder network. The tone output is a stairstep approximation to a

\* Trademark of Mostek Corporation

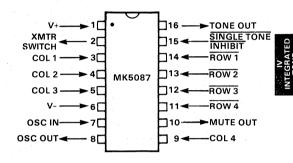

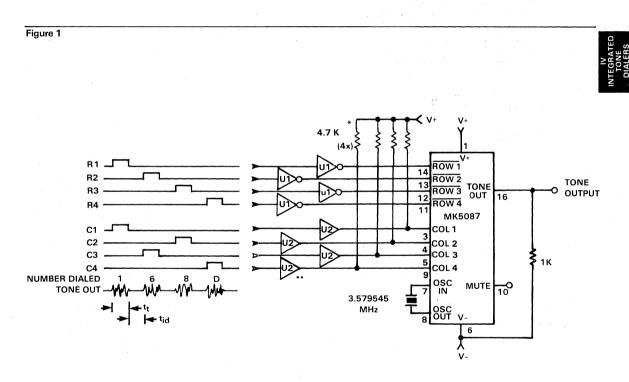

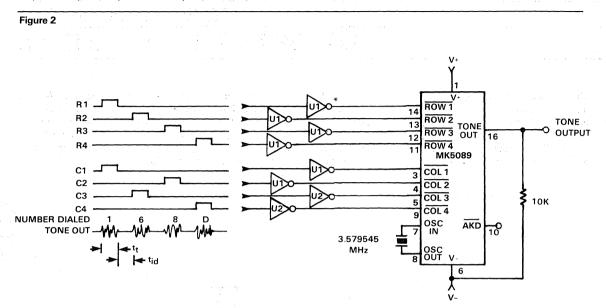

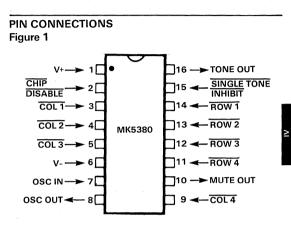

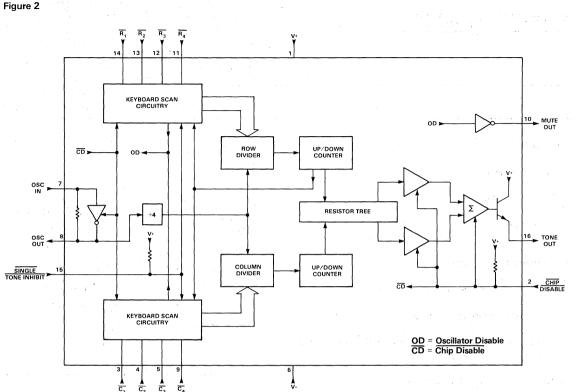

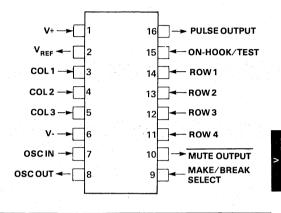

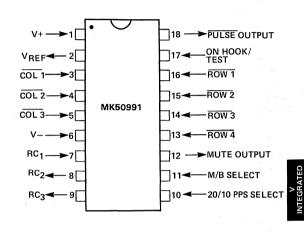

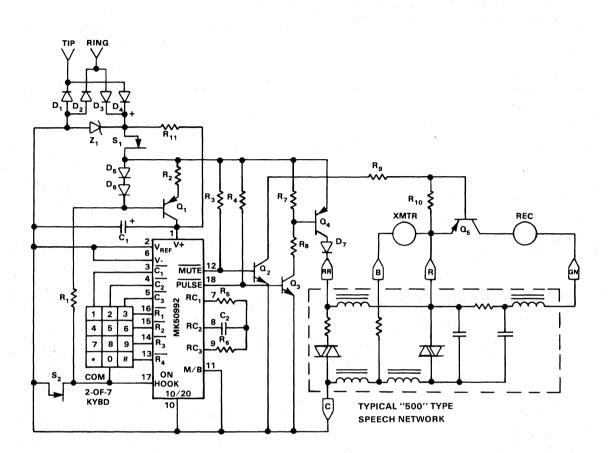

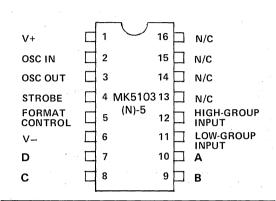

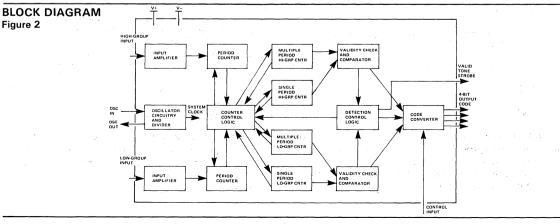

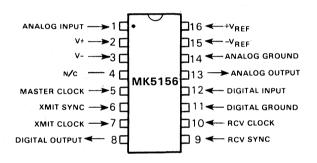

#### **PIN CONNECTIONS** Figure 1

sine wave and requires little or no filtering for low-distortion applications. The same operational amplifier that accomplishes the current-to-voltage transformation necessary for the D-to-A converter also mixes the low and high-group signals. Frequency stability of this type of tone generator is such that no frequency adjustment is needed to meet standard DTMF specifications.

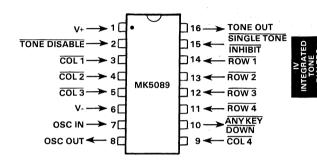

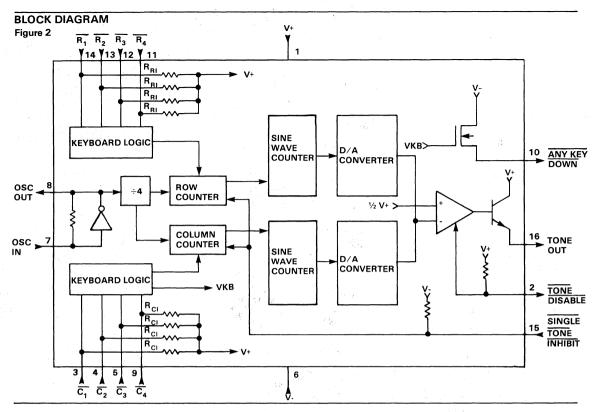

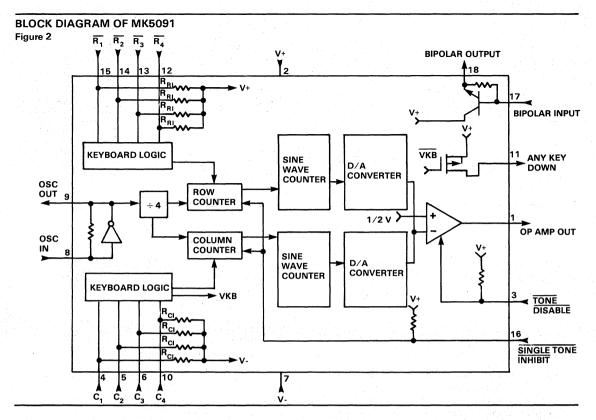

Pin connections are shown in Figure 1 and a block diagram is shown in Figure 2.

## FUNCTIONAL DESCRIPTION

#### V+, Pin 1

Pin 1 is the positive supply pin. The voltage on Pin 1 should be between 3.5 and 10.0 volts, measured relative to V-(Pin 6).

## XMTR SWITCH, Pin 2

Pin 2 is connected to the emitter of an on-chip bipolar transistor whose collector is connected to V+. With no keyboard input this transistor is turned on and pulls Pin 2 up to within V<sub>BF</sub> of the V+ supply. When a keyboard entry is sensed, this output goes open circuit (high impedance). The XMTR Switch output switches regardless of the state of the Single Tone Inhibit input.

#### MK5087 BLOCK DIAGRAM Figure 2

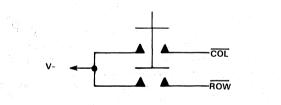

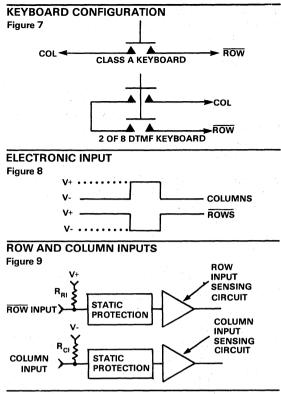

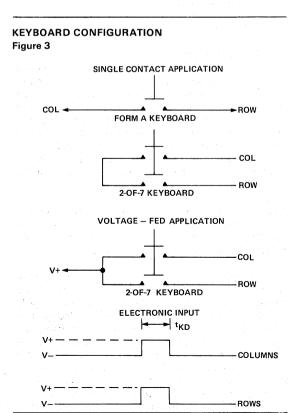

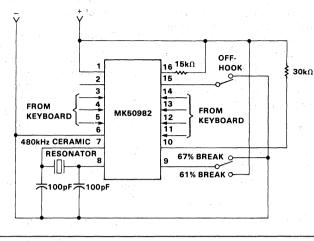

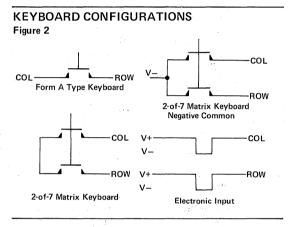

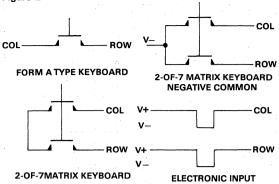

## KEYBOARD CONFIGURATIONS Figure 3

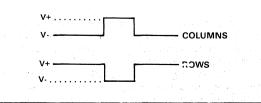

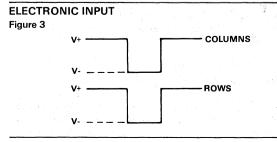

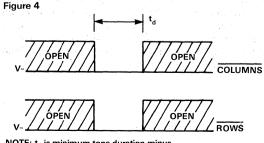

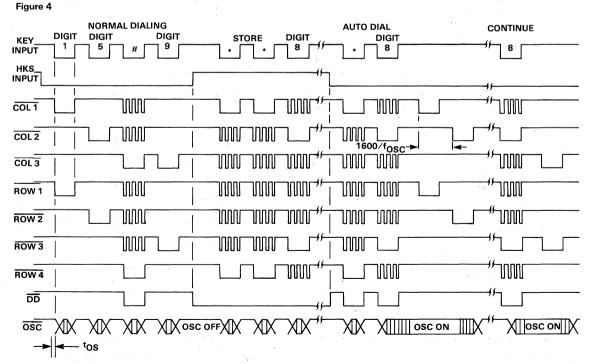

#### ELECTRONIC INPUT Figure 4

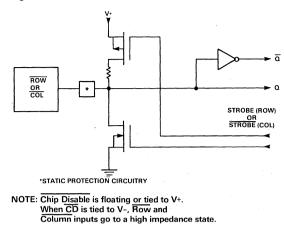

## ROW-COL INPUTS, Pins 3, 4, 5, 9, 11, 12, 13, 14

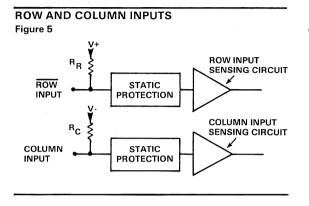

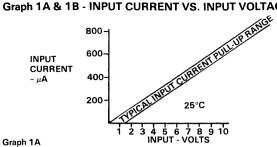

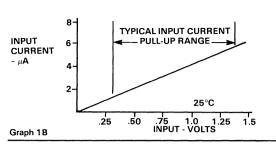

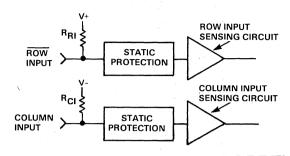

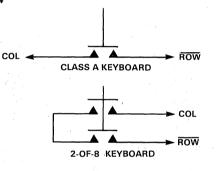

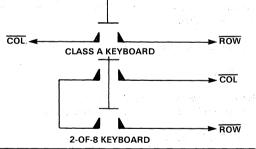

The MK5087 features inputs compatible with the standard 2-of-8 keyboard, the inexpensive single-contact (Form A) keyboard, and electronic input. Figure 3 shows how to connect to the two keyboard types and Figure 4 shows waveforms for electronic input. The inputs are static, i.e. there is no noise generation as occurs with scanned or dynamic inputs.

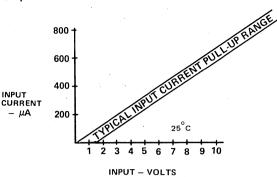

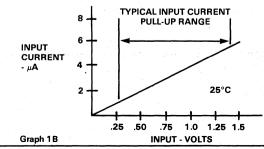

The internal structure of the MK5087 inputs is shown in Figure 5.  $\rm R_{R}$  and  $\rm R_{C}$  pull in opposite directions and hold their associated input sensing circuit turned off. When one or more row or column inputs are tied together, however, the input sensing circuits sense the " $\prime\prime_2$  Level" and deliver a logic signal to the internal circuitry of the MK5087 and cause the proper tone or tones to be generated.

When operating with a keyboard, normal operation is for dual-tone generation when any single button is pushed, and single-tone operation when one or more buttons in the same row or column is pushed. Activation of diagonal buttons will result in no tones being generated.

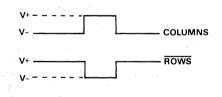

When the inputs to the MK5087 are electronically activated, per Figure 4, input to a single row and column will result in that dual-tone digit's being generated. Input to a

single column will result in that column tone being generated. Input to multiple columns will result in no tone being generated.

Activation of a single row is not sensed by the internal circuitry of the MK5087. If a single-row tone is desired, two columns must be activated along with the desired row.

#### V-, Pin 6

Pin 6 is the power supply return pin and it is the measurement reference for V+ (Pin 1).

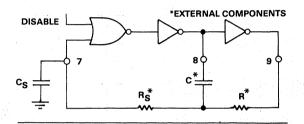

#### OSC IN, Pin 7; OSC OUT, Pin 8

The MK5087 contains an on-board inverter with sufficient loop-gain to provide oscillation when working with a lowcost television color-burst crystal. The inverter's input is Osc In (Pin 7) and output is Osc Out (Pin 8). The circuit is designed to work with a crystal cut to 3.579545 MHz to give the frequencies in Table 1. The oscillator is disabled whenever a keyboard input is not sensed.

Any crystal frequency deviation from 3.579545 MHz will be reflected in the tone output frequency. Most crystals do not vary more than  $\pm$  .02%.

## MUTE OUT, Pin 10

The Mute output is a conventional CMOS gate that pulls to V-with no keyboard input and pulls to the V+ supply when a keyboard entry is sensed. This output is used to control auxiliary switching functions that are required to actuate upon keyboard input. The Mute output switches regardless

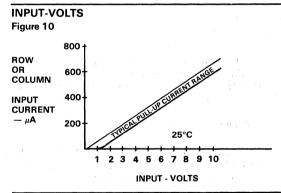

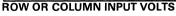

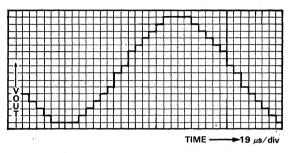

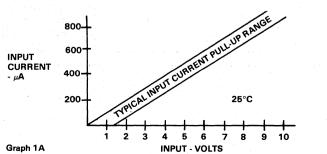

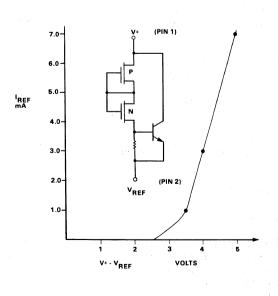

#### INPUT CURRENT VS. INPUT VOLTAGE Graph 1

#### OUTPUT FREQUENCY DEVIATION Table 1

|     |                | Standard DTMF<br>(Hz) | Tone Output<br>Frequency Using<br>3.579545 MHz Crystal | % Deviation<br>From Standard |

|-----|----------------|-----------------------|--------------------------------------------------------|------------------------------|

|     | f <sub>1</sub> | 697                   | 701.3                                                  | +0.62                        |

|     | f2             | 770                   | 771.4                                                  | +0.19 LOW<br>GROUP           |

| ROW | f3             | 852                   | 857.2                                                  | +0.61                        |

|     | f4             | 941                   | 935.1                                                  | -0.63                        |

|     | f <sub>5</sub> | 1209                  | 1215.9                                                 | +0.57                        |

| COL | f <sub>6</sub> | 1336                  | 1331.7                                                 | -0.32 HIGH<br>GROUP          |

|     | f7             | 1477                  | 1471.9                                                 | -0.35                        |

|     | f8             | 1633                  | 1645.0                                                 | +0.73                        |

of the state of the Single Tone Inhibit input.

#### SINGLE TONE INHIBIT, Pin 15

The Single Tone Inhibit input is used to inhibit the generation of other than dual tones. It has a pull-up to the V+ supply and, when left floating or tied to V+, single or dual tones may be generated as described in the paragraph under row-column inputs. When forced to the V- supply, any input situation that would normally result in a single tone will now result in no tone, with all other chip functions operating normally.

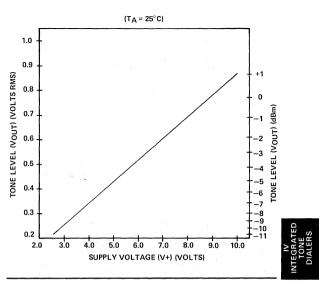

### TONE OUT, Pin 16

The output pin is connected internally in the MK5087 to the emitter of an npn transistor whose collector is tied to V+. The input to this transistor is the on-chip operational amplifier which mixes the row and column tones together.

The level of a dual-tone output is the sum of the levels of a single-row and a single-column output. This level is controlled by an on-chip reference which is not sensitive to variations in the supply voltage.

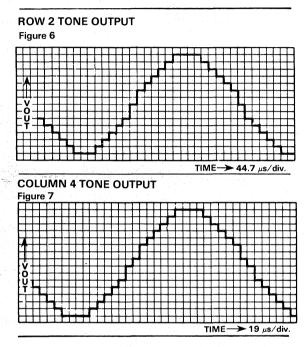

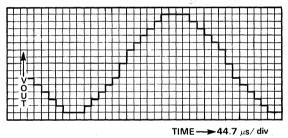

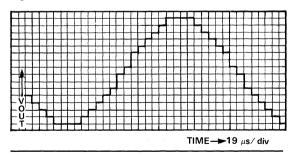

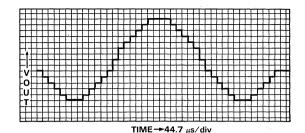

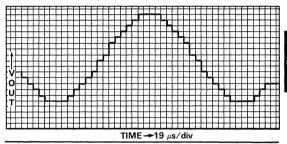

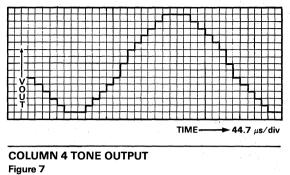

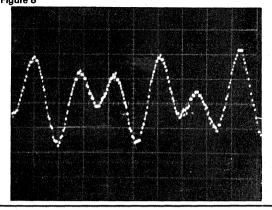

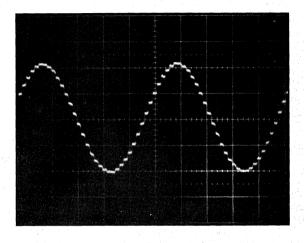

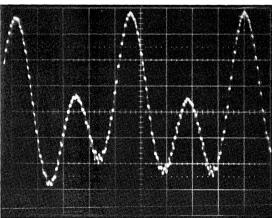

#### **OUTPUT WAVEFORM**

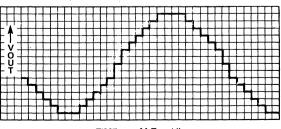

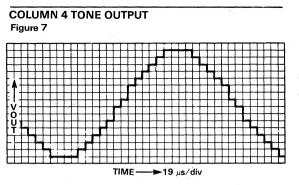

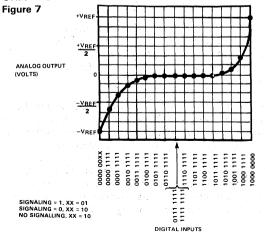

The row and column output waveforms are shown in Figures 6 and 7. These waveforms are digitally-synthesized using on-chip D-to-A converters. Distortion measurement of these unfiltered waveforms will show a typical distortion of 9% or less.

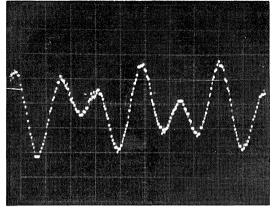

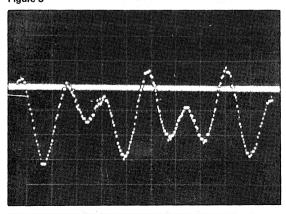

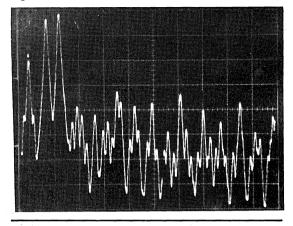

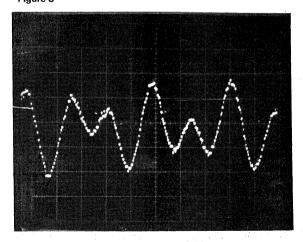

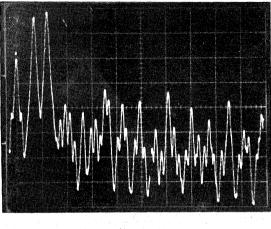

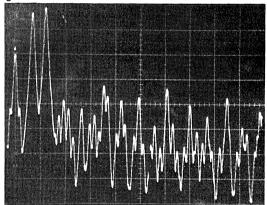

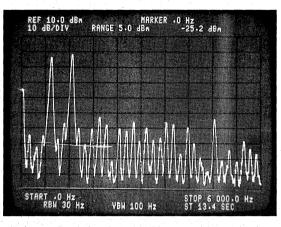

The on-chip operational amplifier of the MK5087 mixes the row and column tones to result in a dual-tone waveform. Spectral analysis of this waveform will show that typically all harmonic and intermodulation distortion components will be -30 dB when referenced to the strongest fundamental (column tone).

A commonly quoted method of dual-tone distortion measurement is the comparison of total power in the unwanted components (i.e. intermodulation and harmonic components) with the total power in the two fundamentals. For the MK5087 dual-tone waveform, THD is -20 dB maximum.

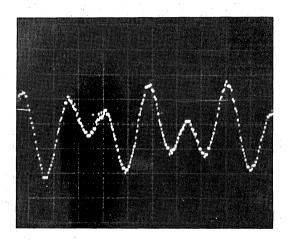

TYPICAL DUAL-TONE WAVEFORM (ROW 1, COL. 1) Figure 8

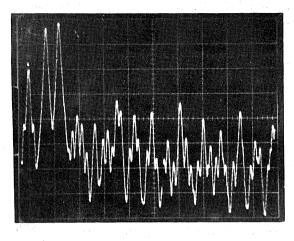

SPECTRAL ANALYSIS OF WAVEFORM IN FIG. 8 (Vert-10 dB/div., Horizontal-1 kHz/div.) Figure 9

A simpler measurement may be made directly from the screen of a spectrum analyzer by relating any component to one of the fundamentals. The MK5087 dual-tone spectrum will show all individual harmonic and IMD components are typically at least –30 dB with respect to the column tone.

Figures 8 and 9 show a typical dual-tone waveform and its spectral analysis.

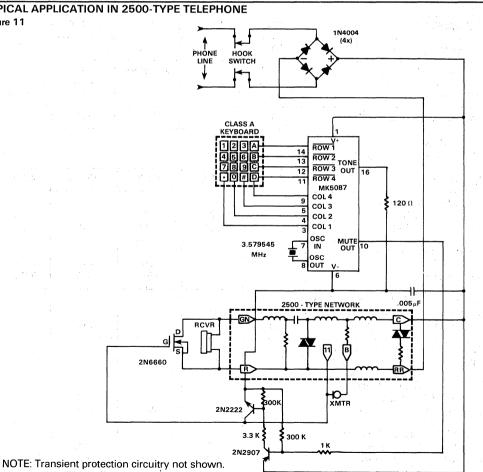

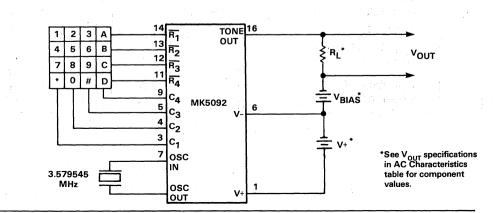

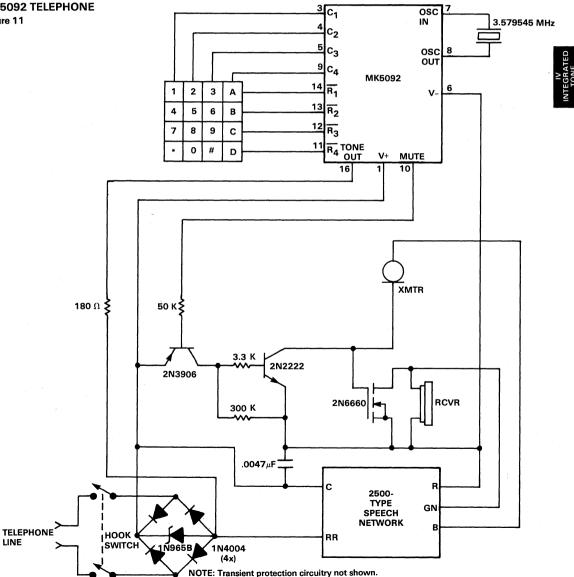

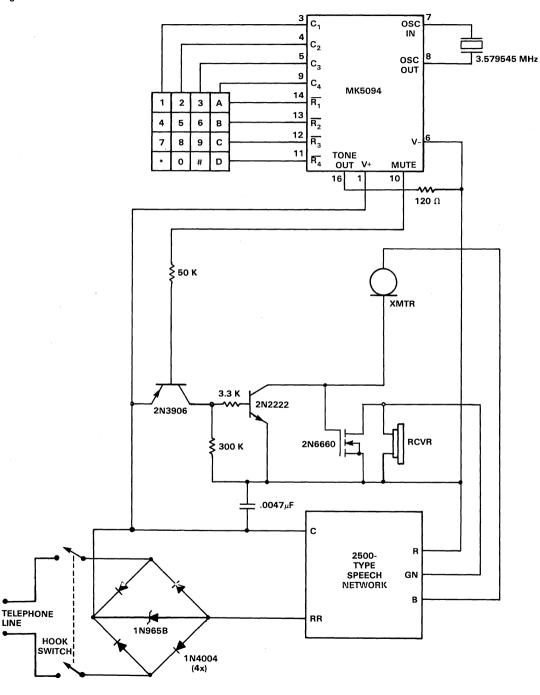

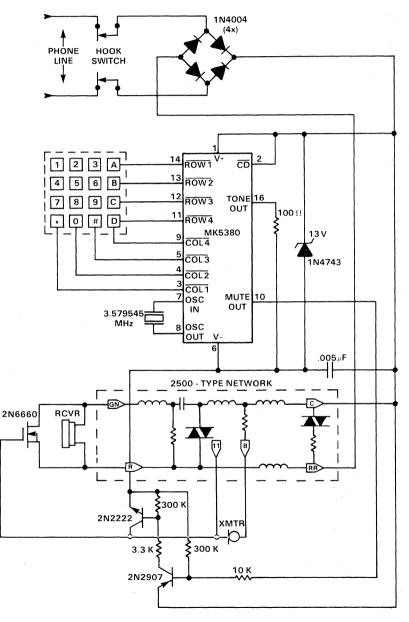

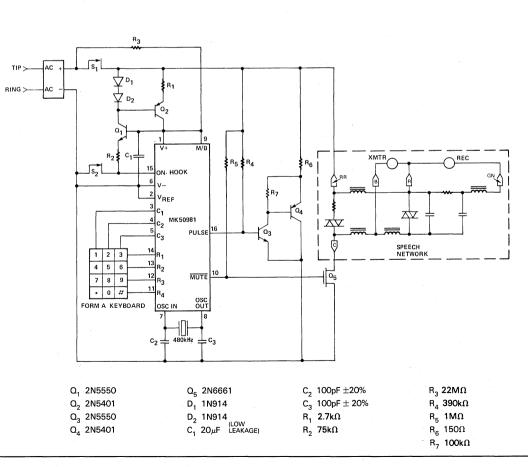

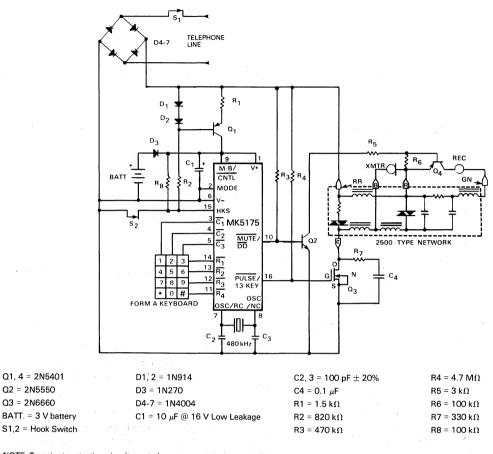

## TYPICAL APPLICATION

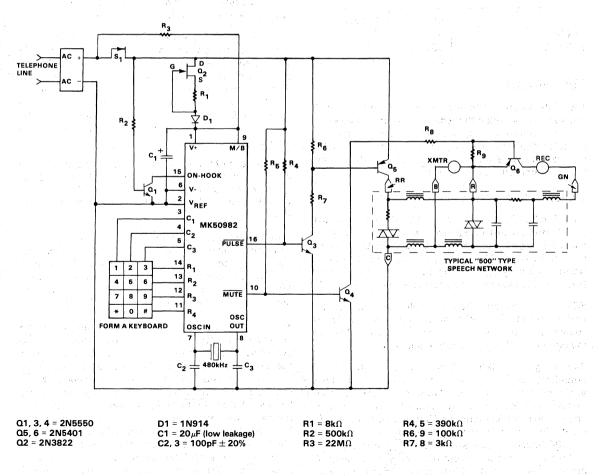

Figure 11 shows an application of the MK5087 in a standard telephone set that uses the standard 2500-type network. The tone levels and loop compensation that result from this application meet the requirements of the U.S. telephone systems.

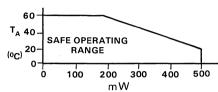

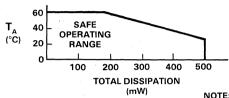

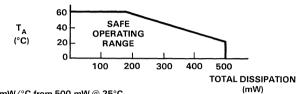

#### **ABSOLUTE MAXIMUM RATINGS\***

| DC Supply Voltage V+                                                                                  |                                                                           |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Any Input Relative to V+                                                                              |                                                                           |

| Any Input Relative to V                                                                               |                                                                           |

| Operating Temperature                                                                                 |                                                                           |

| Storage Temperature                                                                                   | 55°C to +85°C                                                             |

| Maximum Circuit Power Dissipation                                                                     |                                                                           |

| *Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the devic | e. This is a stress rating only and functional operation of the device at |

bees on any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

## **ELECTRICAL CHARACTERISTICS**

DC CHARACTERISTICS

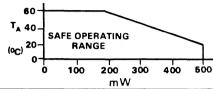

| ( | -30 | C | $\leq$ | Τ <sub>Α</sub> | $\leq$ | 60° | °C) |  |

|---|-----|---|--------|----------------|--------|-----|-----|--|

|---|-----|---|--------|----------------|--------|-----|-----|--|

|                    | ·A = •• •,                    |           |     |           | 1     |       |

|--------------------|-------------------------------|-----------|-----|-----------|-------|-------|

| SYM                | PARAMETER                     | MIN       | ТҮР | МАХ       | UNITS | NOTES |

| V+                 | DC Operating Voltage          | 3.5       |     | 10.0      | v     | 1     |

| V <sub>IL</sub>    | Input Voltage Low - "0"       | . V-      |     | 30% of V+ | V     | 1, 11 |

| V <sub>IH</sub>    | Input Voltage High - "1"      | 70% of V+ |     | V+        | V     | 1, 12 |

| R <sub>IPSTI</sub> | Input Pull-up Resistance, STI | 20        |     | 100       | kΩ    | 3     |

## AC CHARACTERISTICS

$(-30^{\circ}C \le T_{A} \le 60^{\circ}C; 3.0 \text{ V} \le \text{V}+ \le 10.0 \text{ V})$

| SYM              | PARAMETER                                                                                                                                                           | MIN        | ТҮР          | MAX         | UNITS    | NOTES              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|-------------|----------|--------------------|

| I <sub>SSB</sub> | Supply Current-Standby<br>(Pin 6, V+ = $3.5$ V)<br>(Pin 6, V+ = $10.0$ V)                                                                                           |            | 0.25<br>0.50 | 100<br>200  | μΑ<br>μΑ | 2,7<br>2,7         |

| I <sub>SO</sub>  | Supply Current-Operating<br>(V+ = 3.5 V)<br>(V+ = 10.0 V)                                                                                                           | · · ·      | 1.0<br>5.0   | 2.0<br>15.0 | mA<br>mA | 2,6,8,9<br>2,6,8,9 |

| I <sub>онх</sub> | Output Drive, XMTR Switch-No Entry<br>(V+ = $3.5 \text{ V}$ , V <sub>OHX</sub> = $2.5 \text{ V}$ )<br>(V+ = $10.0 \text{ V}$ , V <sub>OHX</sub> = $8.0 \text{ V}$ ) | -15<br>-40 | -25<br>-100  |             | mA<br>mA | ·<br>·             |

| I <sub>OLX</sub> | Output Drive, XMTR Switch-Valid<br>Entry (V+ = 10.0 V, Output = 0.0 V)                                                                                              |            | 0.1          | 10.0        | μΑ       |                    |

| I <sub>ОНМ</sub> | Output Drive, MUTE - Valid Entry<br>(V+ = 3.5 V, V <sub>OH</sub> = 3.0 V)<br>(V+ = 10.0 V, V <sub>OH</sub> = 9.5 V)                                                 |            | 0.5<br>1.0   | 2.0<br>4.0  | mA<br>mA |                    |

| I <sub>OLM</sub> | Output Drive, MUTE - No Entry<br>(V+ = 3.5 V, V <sub>OL</sub> = 0.5 V)<br>(V+ = 10.0 V, V <sub>OL</sub> = 0.5 V)                                                    |            | 0.5<br>1.0   | 2.0<br>4.0  | mA<br>mA |                    |

IV JTEGRATED TONE DIALERS

IV-5

#### AC CHARACTERISTICS (Continued)

| SYM               | PARAMETER                                                                                                                             | MIN        | ТҮР        | MAX        | UNITS          | NOTES          |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|----------------|----------------|

| V <sub>NKD</sub>  | Tone Output-No Key Down                                                                                                               |            |            | -80        | dBm            |                |

| t <sub>RISE</sub> | Tone Output Rise Time                                                                                                                 |            | 3.0        | 5.0        | ms             | 5,9            |

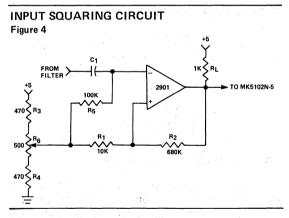

| V <sub>OUT</sub>  | Tone Output Voltage<br>Row Tone ( $R_L = 1K$ , 620 $\Omega$ , 330 $\Omega$ )<br>Col Tone ( $R_L = 1K$ , 620 $\Omega$ , 330 $\Omega$ ) | 317<br>396 | 400<br>500 | 504<br>630 | mVRMS<br>mVRMS | 1,3,6<br>1,3,6 |