# MOSTEK 1980 INDUSTRIAL PRODUCTS DATA BOOK

## 1980 INDUSTRIAL PRODUCTS DATA BOOK

#### Copyright © 1980 Mostek Corporation (All rights reserved)

Trade Marks Registered®

Mostek reserves the right to make changes in specifications at any time and without notice. The information furnished by Mostek in this publication is believed to be accurate and reliable. However, no responsibility is assumed by Mostek for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Mostek.

The "PRELIMINARY" designation on a Mostek data sheet indicates that the product is not characterized. The specifications are subject to change, are based on design goals or preliminary part evaluation, and are not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in specifications at any time and without notice.

PRINTED IN USA April 1980 STD No. 20003

# **1980 INDUSTRIAL PRODUCTS DATA BOOK**

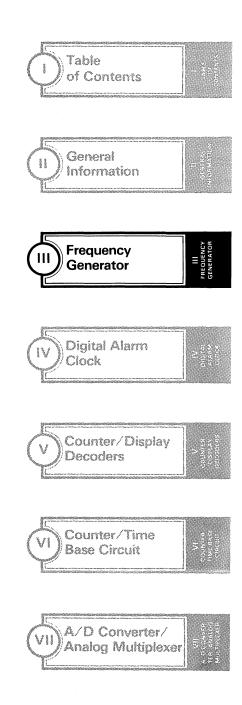

## **TABLE OF CONTENTS**

|       | ible of Contents                                                    |

|-------|---------------------------------------------------------------------|

|       | Functional IndexI-i                                                 |

| I     | Numerical Index                                                     |

|       | ieneral Information                                                 |

|       | Order Information                                                   |

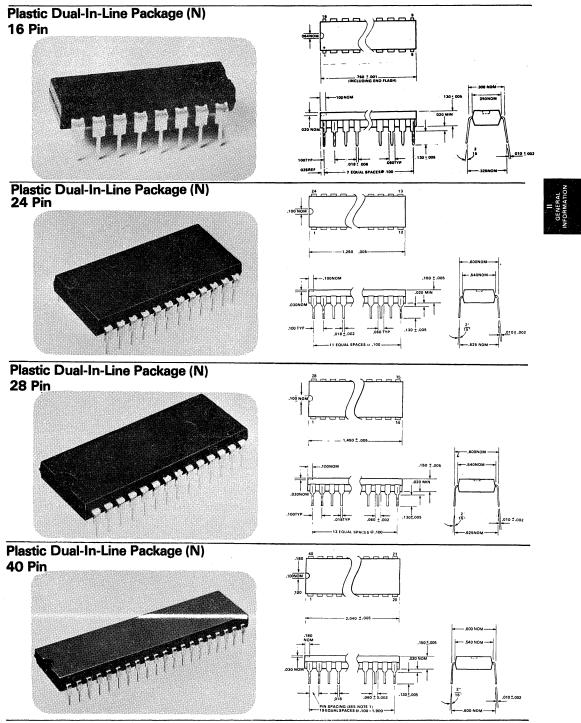

| 1     | Package Description II-iii                                          |

| 1     | Introduction to MostekII-vii                                        |

| 1     | U.S. and Canadian Sales Offices II-ix                               |

| 1     | U.S. and Canadian Representatives II-x                              |

|       | U.S. and Canadian Distributors II-xi                                |

| 1     | International Marketing Offices II-xiii                             |

|       | Frequency Generator                                                 |

| 1     | MK50240/1/2 Top Octave Frequency Generator III-1                    |

|       | Digital Alarm Clock                                                 |

|       | *MK50250 Series MOS Digital Alarm Clock                             |

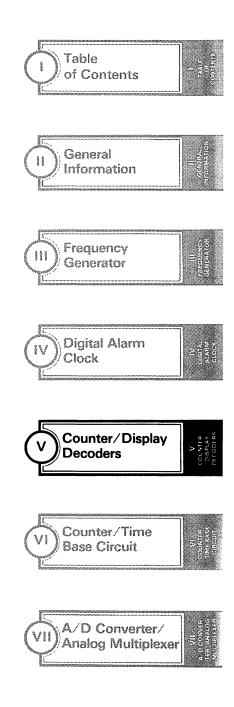

| v - c | Counter/Display Decoders                                            |

| 1     | MK50395/6/7 Six Decade Counter/Display DecoderV-1                   |

| 1     | MK50395/6/7 Application Note                                        |

| I     | MK50398/9 Six Decade Counter/Display Decoder                        |

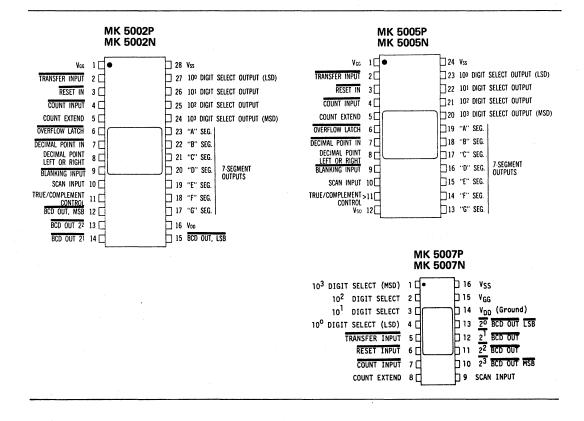

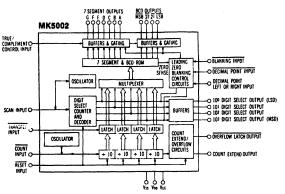

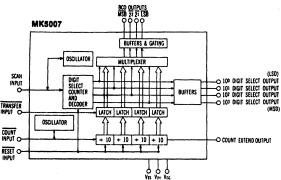

| I     | MK5002/5/7 Four-Digit Counter/Display Decoder                       |

| 1     | MK5002/7 Application Note V-33                                      |

|       | Counter/Time Base Circuit                                           |

| 1     | MK5009 Counter Time-Base Circuit                                    |

| I     | MK5009 Application Note                                             |

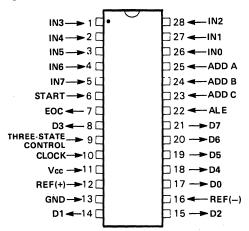

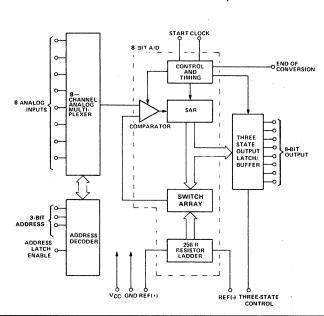

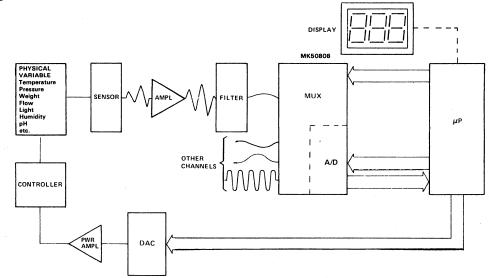

| VII - | A/D Converter/Analog Multiplexer                                    |

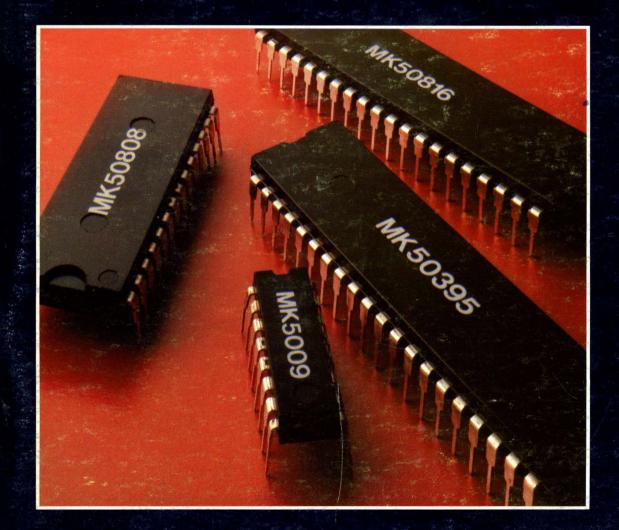

| l     | MK50808 Eight-Bit A/D Converter/8-Channel Analog Multiplexer        |

|       | MK50816 Eight-Bit A/D Converter/16-Channel/Analog Multiplexer VII-9 |

| 4     | *Not Recommended for New Design                                     |

TABLE OF CONTENTS

#### NUMERICAL INDEX

n an an Anna an

MK5002/5/7 MK5002/7 MK5009 MK5009 Top Octave Frequency Generator ...... III-1 MK50240/1/2 \*MK50250 Series Six Decade Counter/Display Decoder ...... V-1 MK50395/6/7 MK50395/6/7 Six Decade Counter/Display Decoder ...... V-23 MK50398/9 Eight-Bit A/D Converter/8-Channel Analog Multiplexer ...... VII-1 MK50808 Eight-Bit A/D Converter/16-Channel/Analog Multiplexer ...... VII-9 MK50816

\*Not Recommended For New Design

# **1980 INDUSTRIAL PRODUCTS DATA BOOK**

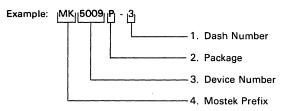

#### **ORDERING INFORMATION**

Factory orders for parts described in this book should include a four-part number as explained below:

1. Dash Number

One or two numerical characters defining specific device performance characteristic.

- 2. Package

- P Gold side-brazed ceramic DIP

- J CER-DIP

- N Epoxy DIP (Plastic)

- K Tin side-brazed ceramic DIP

- T Ceramic DIP with transparent lid

- E Ceramic leadless chip carrier

- 3. Device Number

1XXX or 1XXXX - Shift Register, ROM 2XXX or 2XXXX - ROM, EPROM 3XXX or 3XXXX - ROM, EPROM 38XX - Microcomputer Components 4XXX or 4XXXX - RAM 5XXX or 5XXXX - Counters, Telecommunication and Industrial 7XXX or 7XXXX - Microcomputer Systems

4. Mostek Prefix

**MK-Standard Prefix**

MKB-100% 883B screening, with final electrical test at low, room and high-rated temperatures.

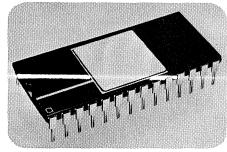

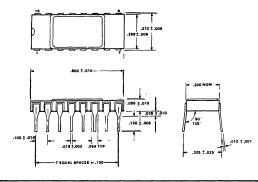

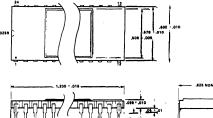

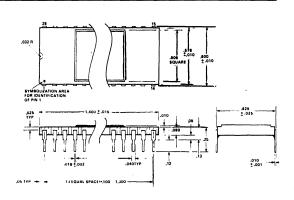

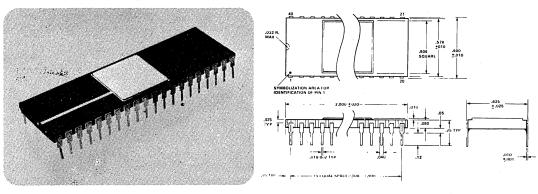

## Ceramic Dual-In-Line Package (P) 16 Pin

## Ceramic Dual-In-Line Package (P) 24 Pin

Ceramic Dual-In-Line Package (P) 40 Pin

II-v

ll-vi

#### TECHNOLOGY

From the beginning, Mostek has been recognized as an innovator. In 1970, Mostek developed the MK4006 1K dynamic RAM and the world's first single-chip calculator circuit, the MK6010. These technical breakthroughs proved the benefits of ionimplantation and cost-effectiveness of MOS. Now, Mostek represents one of the industry's most productive bases of MOS/LSI technology. Each innovation in memories, microcomputers and telecommunications - adds to that technological capability.

#### QUALITY

The worth of a Mostek product is measured by its quality. How well it's designed, manufactured and tested. How well it works in your system.

In design, production and testing, our goal is meeting the spec every time. This goal requires a strict discipline, both from the company and from the individual. This discipline, coupled with a very personal pride, has driven Mostek to build in quality at every level, until every product we take to the market is as well-engineered as can be found in the industry.

#### **PRODUCTION CAPABILITY**

Mostek's commitment to increasing

production capability has made us the world's largest manufacturer of dynamic RAMs. In 1979 we shipped 25 million 4K and 16K dynamic RAMs. We built our first telecommunication tone dialer in 1974; since then, we've shipped over 5 million telecom circuits. The MK3870 single-chip microprocessor is also a large volume product with over two million in application around the world. To meet the demand for our products, production capability must be constantly increased. To accomplish this, Mostek has been in a constant process of expanding and refining our production capabilities.

#### THE PRODUCTS

#### Telecommunications and Industrial Products

Mostek has made a solid commitment to telecommunications with a new generation of products, such as Integrated Pulse Dialers, Tone Dialers, CODECs, monolithic filters, tone receivers, A/D converters and counter time-base circuits.

Since 1974 over five million telecom circuits have been shipped, making Mostek the leading supplier of tone/pulse dialers and CODECs.

#### **Memory Products**

Through innovations in both circuit

ll-vii

design, wafer processing and production, Mostek has become the industry's leading supplier of memory products.

An example of Mostek leadership is our new BYTEWYDE™ family of static RAMs, ROMs, and EPROMs. All provide high performance, N words x 8-bit organization and common pin configurations to allow easy system upgrades in density and performance. Another important product area is fast static RAMs. With major advances in technology, Mostek static RAMs now feature access times as low as 55 nanoseconds. With high density ROMs and PROMs, static RAMs, dynamic RAMs and pseudostatic RAMs, Mostek now offers one of industry's broadest and most versatile memory families.

#### **Microcomputer Components**

Mostek's microcomputer components are designed for a wide range of applications.

Our Z80 family is the highest performance 8-bit microcomputer available today. The MK3870 family is one of the industry's most popular 8-bit single-chip microcomputers, offering upgrade options in ROM, RAM, and I/O, all in the same socket. The MK3874 EPROM version supports and prototypes the entire family.

#### **Microcomputer Systems**

Supporting the entire component product

line is the powerful MATRIX<sup>™</sup> microcomputer development system, a Z80based, dual floppy-disk system that is used to develop and debug software and hardware for all Mostek microcomputers.

A software operating system, FLP-80DOS, speeds and eases the design cycle with powerful commands. BASIC, FORTRAN, and PASCAL are also available for use on the MATRIX.

Mostek's MD Series<sup>™</sup> features both standalone microcomputer boards and expandable microcomputer boards. The expandable boards are modularized by function, reducing system cost because the designer buys only the specific functional modules his system requires. All MDX boards are STD-Z80 BUS compatible.

The STD-Z80 BUS is a multi-sourced motherboard interconnect system designed to handle any MDX card in any card slot.

#### Memory Systems

Taking full advantage of our leadership in memory components technology, Mostek Memory Systems offers a broad line of products, all with the performance and reliability to match our industry-standard circuits. Mostek Memory Systems offers add-in memory boards for popular DEC and Data General minicomputers.

Mostek also offers special purpose and custom memory boards for special applications.

#### J.S. AND CANADIAN SALES OFFICES

CORPORATE HEADQUARTERS Nostek Corporation 1215 W. Crosby Rd. 2. O. Box 169 Carroliton, Texas 75006

REGIONAL OFFICES

Eastern U.S./Canada Vostek 34 W. Putnam, 2nd Floor 3reenwich, Conn. 06830 203/622-0955 WX 710-579-2928

Vortheast U.S. Vostek 29 Cummings Park, Suite #426 Noburn, Mass. 01801 317/935-0635 IWX 710-348-0459

Mid-Atlantic U.S. Mostek East Gate Business Center 125 Gaither Drive, Suite D Mt. Laurel, New Jersey 08054 609/235-4112 TWX 710-897-0723 Southeast U.S. Mostek Exchange Bank Bidg. 1111 N. Westshore Bivd. Suite 414 Tampa, Florida 33607 813/876-1304 TWX 810-876-4611

Central U.S. Mostek 701 E. Irving Park Road Suite 206 Roselle, III. 60172 312/529-3993 TWX 910-291-1207

North Central U.S. Mostek Mostek 6125 Blue Circle Drive, Suite A Minnetonka, Mn. 55343 612/935-4020 TWX 910-576-2802

South Central U.S.

Mostek

228 Byers Road

Suite 105

Miamisburg, Ohio 45342

513/866.3405

TWX 810-473-2976

Michigan Mostek Livonia Pavillion East 29200 Vassar, Suite 520 Livonia, Mich. 48152 313/478-1470 TWX 810-242-2978

Southwest U.S. Southwest U.S. Mostek 4100 McEwen Road Suite 237 Dallas, Texas 75234 214/386-9141 TWX 910-860-5437

Northern California

Northern California Mostek 2025 Gateway Place Suite 268 San Jose, Calif. 95110 408/287-5081 TWX 910-338-7338

Southern California Mostek 17870 Skypark Circle Suite 107 Irvine, Calif. 92714 714/549-0397 TWX 910-595-2513

Rocky Mountains Mostek 8686 N. Central Ave. Suite 126 Phoenix, Ariz. 85020 602/997-7573 TWX 910-957-4581

Northwest Mostek 1107 North East 45th Street Suite 411 Seattle, Wa. 98105 206/632-0245 TWX 910-444-4030

#### **U.S. AND CANADIAN REPRESENTATIVES**

ALABAMA Beacon Elect. Assoc., Inc. 11309 S. Memorial Pkwy. Suite G Huntsville, AL 35803 205/881-5031 TWX 810-726-2136

ARIZONA Summit Sales 7336 E. Shoeman Lane Suite 116E Scottsdale, AZ 85251 602/994-4587 TWX 910-950-1283

ARKANSAS Beacon Elect. Assoc., Inc. P.O. Box 5382, Brady Station Little Rock, AK 72215 501/224-5449 TWX 910-722-7310

**CALIFORNIA** Harvey King, Inc. 8124 Miramar Road San Diego, CA 92126 714/566-5252 TWX 910-335-1231

COLORADO Waugaman Associates 4800 Van Gordon Wheat Ridge, CO 80033 303/423-1020 TWX 910-938-0750

CONNECTICUT New England Technical Sales 240 Pomeroy Ave. Meriden, CT 06450 203/237-8827

FLORIDA Beacon Elect. Assoc., Inc. 6842 N.W. 20th Ave. Ft. Lauderdale, FL 33309 305/971-7320 TWX 510-955-9834

Beacon Elect. Assoc., Inc. 235 Maitland Ave. P. O. Box 1278 Maitland, FL 32751 305/647-3498 TWX 810-853-5038

Beacon Elect. Assoc., Inc. 316 Laurie Melbourne, FL 32935 305/259-0648 TWX 510-950-7251

Beacon Elect. Assoc., Inc. 2280 U.S. Hwy 19 North Suite 163 Clearwater, FL 33515 813/725-4714 TWX 810-866-9739 GEORGIA Beacon Elect. Assoc., Inc.\* 6135 Barfield Rd. Suite 112 Atlanta, GA 30328 404/266-9640 TWX 810-751-3165

ILLINOIS Carlson Electronic Sales\* 600 East Higgins Road Elk Grove Village, IL 60007 312/956-8240 TWX 910-222-1819

INDIANA Rich Electronic Marketing\* 599 Industrial Drive Carmel, IN 46032 317/844-8462 TWX 810-260-2631 Pick Electronic Marketing

Rich Electronic Marketing 3448 West Taylor St. Fort Wayne, IN 46804 219/432-5553 TWX 810-332-1404

IOWA Cahill, Schmitz & Cahill, Inc. 208 Collins Rd. N.E. Suite K Cedar Rapids, IA 52402 319/377-8219 TWX 910-525-1363

Carlson Electronic Sales 204 Collins Rd. N.E. Cedar Rapids, IA 52402 319/377-6341

KANSAS Rush & West Associates\* 107 N. Chester Street Olathe, KN 66061 913/764-2700 TWX 910-749-6404

KENTUCKY Rich Electronic Marketing 5910 Bardstown Road P. O. Box 91147 Louisville, KY 40291 502/239-2747 TWX 810-535-3757

NORTH CAROLINA Beacon Elect. Assoc., Inc. 1207 West Bessemer Ave. Suite 112 Greensboro, NC 27408 919/275-9997 TWX 510-925-1119

Beacon Elect. Assoc., Inc. 3901 Barrett Dr. 3rd Floor Raleigh, NC 27611 919/787-0330

MARYLAND Arbotek Associates 3600 St. Johns Lane Ellicott City, MD 21043 301/461-1323 TWX 710-862-1874

MICHIGAN

MISSOURI

NEW JERSEY

NEW MEXICO Waugaman Associates 9004 Menaul N.E.

Suite 7 P. O. Box 14894 Albuquerque, NM 87112 505/294-1437

MASSACHUSETTS New England Technical Sales\* 135 Cambridge Street Burlington, MA 01803 617/272-0434 TWX 710-332-0435

APJ Associates, Inc. 9880 E. Grand River Ave. Brighton, MI 48116 313/229-6550 TWX 810-242-1510

MINNESOTA Cahill, Schmitz & Cahill, Inc. 315 N. Pierce St. Paul, MN 55104 612/646-7217 TWX 910-563-3737

Rush & West Associates 481 Melanie Meadows Lane Ballwin, MO 63011 314/394-7271

NEW JEHSEY Tritek Sales, Inc. 21E Euclid Ave. Haddonfield, NJ 08033 609/429-1551 215/627-0149 (Philadelphia Line) TWX 710-896-0881

NEW YORK ERA (Engrg. Rep. Assoc.) One DuFont Street Plainview, NY 11803 516/349-1190 TWX 510-221-1849 Precision Sales Corp. 5 Arbustus Ln. MR-97 Binghamton, NY 13901 607/648-3686

Precision Sales Corp.\* 1 Commerce Blvd. Liverpool, NY 13088 315/451-3480 TWX 710-545-0250

Precision Sales Corp. 3594 Monroe Avenue Rochester, NY 14534 716/381-2820

OHIO Rich Electronic Marketing 7221 Taylorsville Road Dayton, Ohio 45424 513/237-9422 TWX 810-459-1767 Rich Electronic Marketing

Rich Electronic Marketing 141 E. Aurora Road Northfield, Ohio 44067 216/468-0583 TWX 810-427-9210 OREGON Northwest Marketing Assoc. 9999 S.W. Wilshire St. Suite 124 Portland OR 97225 503/297-2581 TELEX 36-0465 (AMAPORT PTL)

PENNSYLVANIA CMS Marketing 121A Lorraine Avenue P.O. Box 300 Oreland, PA 19075 215/885-5106 TWX 510-665-0161

TENNESSEE Beacon Elect. Assoc., Inc. 103 Sequoyan Dr. Suite #2 Johnson City, TN 37681 615/282-2421 TWX 810-575-8555

Rich Electronic Marketing 1128 Tusculum Blvd. Suite D Greenville, TN 37743 615/639-3139 TWX 810-576-4597

TEXAS Southern States Marketing, Inc. 14330 Midway Road, Suite 226 Dallas, Texas 75234 214/387-2486 States TWX 910-880-5732 Southern States Marketing, Inc. 9730 Town Park Drive, Suite 104 Houston, Texas 77036 713/988-0991 TVX 910-881-1630 UTAH Waugaman Associates 2520 S. State Street #224 Salt Lake City. UT 84115 801/467-4263 TWX 910-925-4026

WASHINGTON Northwest Marketing Assoc. 12835 Bellevue-Redmond Rd. Suite 2032 Bellevue, WA 98005 206/455-5846 TWX 910-443-2445

WISCONSIN Carlson Electronic Sales Northbrook Executive Ctr. 10701 West North Ave. Suite 209 Milwaukee, WI 53226 414/476-2790 TWX 910-222-1819

CANADA Cantec Representatives Inc.\* 1573 Laperriere Ave. Ottawa, Onterio Canada K12 7T3 613/725-3704 TWX 610-562-8967

Cantec Representatives Inc. 83 Galaxy Blvd., Unit 1A (Rexdale) Toronto, Canada M9W 5X6 416/675-2460 TWX 610-492-2655

#### **U.S. AND CANADIAN DISTRIBUTORS**

ARIZONA Kieruff Electronics 4134 E. Wood St. Phoenix, AZ 85040 602/243-4104 TWX 910/951-1550 Wyle Distribution Group 8155 Nonth 24th Asenue Phoenix, Arizona 85021 602/249-2232 TWX 910/951-4282

CALIPORNIA Brill Folkstries Sunnyvaie. CA 94088 408/734-8570 TWX 910/339-9378 Arrow Electronics 720 Palomes Avenue Sunnyvaie. CA 94084 408/734-8570 TWX 910/339-9371 Kiteruitf Electronics 2585 Commerce Way Los Angeles. CA 90408 408/738-3013 TWX 910/350-3106 Kiteruitf Electronics 716/278-2112 TWX 910/355-1182 Kiteruitf Electronics 716/278-2112 TWX 910/355-1182 Kiteruitf Electronics 1761/278-2112 TWX 910/355-1182 Kiteruitf Electronics 1761/178-5159 Schweber Electronics 1781/16/56-2589 Schweber Electronics 17811/1686-7150 TWX 910/356-1120 TWX 910/356-1120 TWX 910/356-1120 TWX 910/356-1120 TWX 910/356-1120 TWX 910/356-1120 TWX 910/356-1110 TWX 910/358-7111

COLORADO Kierulf Electronics 10690 E. 47th Avenue Denver, CO 80239 303/371-6500 TWX 910/932-0169 Wyle Distribution Group 6777 East 50th Ave. Commerce City, CO 80022 303/287-9611

CONNECTICUT Arrow Electronics 12 Beaumont Rd. Wallingford, CT 06492 203/285-7741 TWX 710/478-0182 Commerce Industrial Park Denbury, CT 06810 203/792-3500 TWX 710/456-9405 FLORIDA Arrow Electronics 1001 N.W. 82nd St. 1001 N.W. 82nd St. 306/776.7780 TWX 510/965-9456 Arrow Electronics 115 Palm Bay Road, N.W. Suite 10 Bids, 200 Palm Bay, FL 32806 306/725.1480-337 Diplomat Southland 2120/Calumet. 33516 Bi3/443-4514 TWX 610/966-0436 Klaruff Electronics 3247 Tech Drive St. Peterburg, FL 33702 813/676-1965

GEORGIA Arrow Electronics 2979 Pacific Ave. Norcross. GA 30071 404./449.8252 TWX 810/786-0439 Schweber Electronics 4126 Pleasantdale Road Atlanta, GA 30340 404./449-9170

LLINOIS Arrow Electronics 492 Lunt Avenue P. O. Box 94248 Schaumburg. II. 60193 312/883-9420 TWX 910/221-3844 Bell Industries 3422 W. Touty Avenue Chicago, II. 60645 312/882-921-3844 Bell Industries IS38 Lammeier Etk Grove Village, II. 60007 312/480-0201 710X 910/222-0351 INDIANA Advant Electronics B446 Moller Indianapolia, IM4288 Moller INX 810/341-3228 FL Wayne Electronics 3006 E. Mennee FL Wayne, IN 48803 3006 E. Mennee FL Wayne, IN 48803 319/423-32422 TWX 810/332-1562 TWX 810/332-1562 317/848-7300 TWX 810/280-1794

IOWA Advent Electronics 682 58th Avenue Court South West Ceder Reptis, IA 52404 319/363-0221 TWX 910/525-1337

NASSACHUSETTES Kierulf Elischonica 13 Fortune Drive Billerica, MA 01821 617/935-5134 TWX 710/3920-1449 Lionex Corporation 1 North Avenue Burlington, MA 01800 617/272-3405 TWX 710/332-1387 TWX 710/326-0268 617/275-100 TWX 710/328-6100 TWX 710/333-6130 TWX 710/333-6770 MARYLAND Arrow Electronics 4901 Benson Avenue Baltimore, MD 21227 301/247-5200 TWX 710/238-9005 Schweber Electronics 9218 Gaithersburg, MD 20760 301/440-5800 TWX 710/828-9749

MICHIGAN Arrow Electronics 3810 Varsity Drive Ann Arbor, MI 48104 313/971-8220 TWX 810/223-6020 Schweber Electronics 33540 Schoolcraft Road Livonia, MI 48150 313/525-8100 TWX 810/242-2983

MINNESOTA Arrow Electronics 5251 W. 73rd Street Edina, MI 55435 612/830-1800 TVX 910/578-9125 Industrial Components 5229 Edina Industrial Bird. Minneapolis, MN 55435 612/831-2666 TVX 910/576-3153 MISSOURI Olive Electronics 9910 Page Bivd. St. Louia, MO 63132 314/426-4500 TWX 910/763-0720 Semiconductor Spec 3805 N. Oak Trafficway Kanses City, MO 64116 816/452-3900 TWX 910/771-2114

NEW HAMPSHIRE Arrow Electronics 1 Perimeter Rd. Manchester, NH 03103 603/668-6968 TWX 710/220-1684

NEW JERSEY Arrow Electronics Pleasant Valley Avenue Morrestown, NJ 08057 609/235-1900 TVX 710/897-0829

1WX 710/95/2625 Arrow Electronics 285 Midland Avenue Sadiebrock, NJ 07682 201/797-5800 YWX 710/988-2208 Kieruff Electronics 3 Edison Piace Feirfield, NJ 07006 201/576-575 201/576-575 Feirfield, NJ 07006 201/227-7880 SENERA. GRMANCA

#### **U.S. AND CANADIAN DISTRIBUTORS**

#### NEW MEXICO Bell Industries 11728 Linn N.E. Albuquerque, NM 87123 505/292-2700 TWX 910/989-0625 Arrow Electronics 2460 Alamo Ave. S.E. Albuquerque, NM 87106 505/243-4566 TWX 910/989-1679

NEW YORK Arrow Electronics 900 Broad Hollow Rd. Farmingdale, LL, NY 11735 516/594-6800 TWX 510/224-6494 Arrow Electronics 7705 Mattage Drive P. 0. Box 370 Liverpool, NY 13088 315/652-1000 TWX 710/545-0230

TWX 710/545-0230 Arrow Electronics 3000 S. Winton Road Rochester, NY 14623 716/275-0300 TWX 510/253-4766 Arrow Electronics 20 Oser Ave. Hauppauge, NY 11787 516/231-1000 TWX 510/227-6623

Lionex Corbergion Lionex Corbergion Lionex Corbergion Life Crossbergherk Drive Woodbury, LL, NY 11797 516/921-4414 TWX 510-221-2196 Schweber Electronics 2 Twin Line Circle Rochester, NY 14623 716/424-2222 Schweber Electronics Jericho Turnpike Westbury, NY 11590 516/334-7474 TWX 510/222-3660

NORTH CAROLINA Arrow Electronics 938 Burks 5t. Winston Salem, NC 27102 919/725-8711 TWX 510/931-3169 Hemmond Electronics 2923 Pacific Avenue Greensboro, NC 27406 919/275-6391 TWX 510/925-1094 OHIO Arrow Electronics 3100 Plainfield Road Kettering, DH 46432 513/253-014 00 Knoll Cruch Drive Reading, OH 45/237 513/761-5432 TWX 810/461-2670 Arrow Electronics 6238 Cochran Road Solon, OH 44139 216/248-3990 Schweber Electronics 6238 Cochran Road Saber State State 218/248-3990 TWX 810/427-9409 Schweber Electronics Basechwood, OH 44122 216/244-3941 Promer/Clevielartenet Clevelingt, OH 44105 215/587-3600 TWX 810/422-2211 Promer/Clevielartenet State St

OREGON Kierulff Electronics 4273 NW Science Park Portland, OR 97227 503/641-9150 TWX 910/467-8753

PENNSYLVANIA Schweber Electronics 101 Rock Road Horsham, PA 19044 215/441-0600 Arrow Electronics 4297 Greensburg Pike Suite 3114 Pittsburg, PA 15221 412/351-4000 Pioneer/Pittsburgh 560 Abha Drive

Pioneer/Pittsburgh 560 Alpha Drive Pittsburgh, PA 15328 412/782-2300 TWX 710/795-3122

SOUTH CAROLINA Hammond Electronics 1035 Lown Des Hill Rd. Greenville, SC 29602 803/233-4121 TWX 810/281-2233 TEXAS Arrow Electronics 13715 Gamma Read P.D. Box 401058 214-386-7500 TWX 910/880-5377 Quality Components 10201 McKalla Suite D Austin, TX 78758 512/835-023 UNIN Stal/874-1377 Duality Components 4303 Alpha Read Vuality Components 4303 Alpha Read 914-287-4549 UNIN Stal/880-5459 UNIN Stal/880-5459 UNIN Stal/880-5459 UNIN Stal/880-5459 UNIN Stal/880-5459 UNIN Stal/881-109

#### UTAH Bell Industries 3639 W. 2150 South Salt Lake City, UT 84120 801/972-5969 TWX 910/925-5686 Kierulff Electronics 3695 W. 1987 South St. Salt Lake City, UT 84104 801/973-6913

WASHINGTON Kierulff Electronics 1005 Andover Park East Tukwila. WA 98188 206/575-4420 TWX 910/444-2034 Wyle Distribution Group 1750 132nd Avenue N.E. Bellevue, Washington 98005 206/453-8300 TWX 910/443-2526

WISCONSIN Arrow Electronics 434 Rawson Avenue Oak Creek, WI 53154 414/764-6600 TWX 910/262-1193 Kierulff Electronics 2212 E. Moreland Blvd. Waukesha, WI 53186 414/784-8160 TWX 910/262-3653

#### CANADA Preico Electronics 2167 Thams and Drive 2167 Thams and Drive 2167 Thams and Drive 2167 Thams and the 2167 The 2000 The 2167 The 2000 The 2167 The 216

2entronics 141 Catherine Street Ottawa, Ontario K2P 1C3 613/238-6411 Telex 05-33636 Zentronics 1355 Meyerside Drive Mississauga, Ontario (fronto) LST 1C9 416/676-9000 Telex 06-983657

Telex 06-983657 Zentronics 5010 Rue Pare Montreal, Quebec M4P 1P3 514/735-5361 Telex 05-827535 Zentronics 550 Berry Street 51. James, Manitoba (Vinnijeg) R2H 0R4 204/775-5861 Zentronics 480A Dutton Drive 480A Dutton Drive 480A Dutton Drive Waterloo, Ontario N2L 426 519/884-5700

ll-xii

#### INTERNATIONAL MARKETING OFFICES

EUROPEAN HEAD OFFICE Mostek Internationa 150 Chaussee de la Hulpe B-1170 Brussels Belaium (32) 2 6606924 Telex - 846 62011 MKBRU B

FRANCE Mostek France S.A.R.L. 30, Rue de Morvan Silic 505 94623 Rungis Cedex (33) 1 6873414 Telex - 842 204049 MKFRANF F

GERMANY Mostek GmbH Talstrasse 172 7024 Filderstadt 1 (Bernhausen) (49) 711 701045 Telex - 841 7255792 MKD

Mostek GmhH Friedlandstrasse 1 2085 Quickborn/Hamburg (49) 40 41062077/2078 Telex - 841 1213685 MKHA D

Mostek GmbH Zaunkoenigstrasse 18 D-8021 Ottobrunn (49) 89 6091017-19 Telex - 841 5216516 MKMU D

ITALY Mostek Italia S.P.A. Via G. da Procida, 10 I-20149 Milano (39) 2 3185337 or 3492696 Telex - 843 333601 MOSTEK I JAPAN Sanyo Bldg 3F 1-2-7 Kita-Aoyama Minato-Ku, Tokyo 107 (81) 3 4047261

Kingsbury Road,

\*Telex 781 23686 J23686 MOSJAOY

London, NW9

(44) 1 2049322

SWEDEN Mostek Scandinavia AB Magnusvagen 1 S-175 31 Jarfalla (46) 758-343-38 Telex - 854 12997 MOSTEK S UNITED KINGDOM Mostek U.K. Ltd. Masons House, 1-3 Valley Drive, Telex - 851 25940 MOSTEK G

#### INTERNATIONAL SALES REPRESENTATIVES/DISTRIBUTORS

ARGENTINA Rayo Electronics S.R.L. Belgrano 990, Pisos 6y2 1092 Buenos Aires (38)-1779, 37-9476 Telex - 122153

AUSTRALIA AUSTRALIA Amtron Tyree Pty.Ltd. 176 Botany Street Waterloo, N.S.W. 2017 (61) 69-89.666 Telex · 25643

AUSTRIA Transistor-Vertriebs GmbH Auhofstrasse 41 A A-1130 Vienna (43) 222-829.45.12 Telex - 13738

BRASIL Cosele, Ltd. Rua da Consolacao, 867 Conj. 31 01301 Sao Paulo (55) 11-257.35.35/258.43.25 Telex - 1130869

BELGIUM Sotronic 14, Rue Pere de Deken B-1040 Brussels (32) 2-736.10.07 Telex - 25141

DENMARK Semicap APS Gammel Kongevej 184.5 DK-1850 Copenhagen (45) 1-22.15.10 Telex - 15987

FINLAND S.W. Instruments Karstulantie 4 B SF-00550 Helsinki 55 (358)-0-73.82.65 Telex - 122411

FRANCE F P. 4, Rue Barthelemy F-92120 Montrouge (33) 1-735.33.20 Telex - 204534

SCAIB 80, Rue d'Arcuil SILIC 137 F-94150 Rungis Cedex (33) 1-687.23.12 Telex - 204674

GERMANY Neye Enatechnik GmbH Schillerstrasse 14 D-2085 Quickborn (49) 4106-61.22.95 Telex - 213.590

**Dr Dohrenberg** Bayreuther Strasse 3 D-1 Berlin 30 (49) 30-213.80.43 Telex - 184860

Raffel-Electronic GmbH Lochnerstrasse 1 D-4030 Ratingen (49) 2102-280.24 Teley . 8585180

Siegfried Ecker Konigsberger Strasse 2 D-6120 Michelstadt (49) 6061-2233 Telex - 4191630

Matronic GmbH Lichtenberger Weg 3 D-7400 Tubingen (49) 7071-24.43.31 Telex - 726 28 79

Dema-Electronic GmbH Blutenstrasse 21 D-8 Munchen 40 (49) 89-288018 Telex - 28345

HONG KONG Cet Limited 1402 Tung Wah Mansion 199-203 Hennessy Road Wanchai, Hong Kong (5)-72.93.76 Telex - 85148

ISRAEL Telsys Limited 54 Jabotinsky Road Ramat-Gan 52462 (972) 73.98.65 72.23.62 Telex - 32392

ITALY Compret S.r.L. Viale Romagna, 1 I-20092 Cinisello Balsamo (39) 2-928.08.09/928.03.45 Telex - 332484

JAPAN Systems Marketing, Inc. 4th Floor, Shindo Bldg. 3-12-5 Uchikanda, Chiyoda-Ku, Tokyo, 100 (81) 3-254.27.51 Telex - 25761

Teijin Advanced Products Corp. 1-1 Uchisaiwai-Cho 2-Chome Chiyoda-Ku Tokyo, 100 (81) 3-506.46.73 Telex - 23548

KOREA Vine Overseas Trading Corp Room 303-Tae Sung Bl 199-1 Jangsa-Dong dg. Jongro-Ku Seoul (26)-1663, 25-9875 Telex - 24154

TH .. NETHERLANDS Niikerk Elektronika 8V Drentestraat 7 1083 HK Amsterd (020.) 428, 933 Telex - 11625

NEW ZEALAND E.C.S. Div. of Airspares P.O. Box 1048 Airport Palmerston North (77)-047 Telex - 3766

NORWAY Hefro Tekniska A/S Postboks 6596 Rodelkka Oslo 5 (47) 2-38.02.86 Telex · 16205

SOUTH AFRICA Radiokom P.O. Box 56310 Pinegowrie 2123, Transva 789-1400 Telex · 8-0838 SA

SWEDEN Interelko AB Strandbergsg. 47 S-11251 Stockholm (46) 8-13.21.60 Telex - 10689

SPAIN Comelta S.A. Cia Electronica Tecnicas Aplicadas Consejo de Ciento, 204 Entlo 3A. Barcelona 11 (34) 3-254.66.07/08 Telex - 51934

SWITZERLAND Memotec AG CH-4932 Lotzwil (41) 63-28.11.22 Telex - 68636 TAIWAN Dynamar Taiwan Limited P.O. Box 67-445 2nd Floor, No. 14, Lane 164 Sung-Chiang Road Taine 5418251 Telex - 11064

UNITED KINGDOM Celdis Limited 37-39 Loverock Road Reading Berks RG 31 ED (44) 734-58.51.71 Telex - 848370

Distronic Limited 50-51 Burnt Mill Elizabeth Way, Harlow Essex CM 202 HU (44) 279-32.497/39.701 Telex - 81387

A.M. Lock Co., Ltd. Neville Street, Chadderton, Oldham, Lancashire (44) 61-652.04.31 Telex - 669971

Pronto Electronic Systems Ltd. 645 High Road, Seven Kings, liford, Essex IG 38 RA (44) 1-599.30.41 Telex - 24507

YUGOSLAVIA Chemcolor Inozemma Zastupstva Proleterskih brigada 37-a 41001 Zagreb (41)-513.911 Telex - 21236

## **1980 INDUSTRIAL PRODUCTS DATA BOOK**

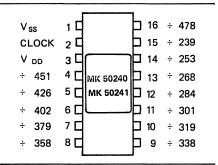

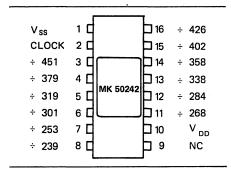

# TOP OCTAVE FREQUENCY GENERATOR MK50240/1/2

#### FEATURES

- □ Single Power Supply

- Broad Supply-Voltage Operating Range

- Low Power Dissipation

- High Output-Drive Capability

- MK 50240 50% Output Duty Cycle

MK 50241 30% Output Duty Cycle

MK 50242 50% Output Duty Cycle

#### DESCRIPTION

The MK 50240 is one of a family of ion-implanted, Pchannel MOS synchronous frequency dividers.

Each output frequency is related to the others by a multiple  $12\sqrt{2}$  providing a full octave plus one note on the equal-tempered scale.

Low threshold-voltage enhancement-mode, as well as depletion-mode devices, are fabricated on the same chip allowing the MK 50240 family to operate from a single, wide-tolerance supply. Depletion-mode technology also allows the entire circuit to operate on less than 600mW of power. The circuits are packaged in 16-pin dual-in-line packages.

RFI emanation and feed-through is minimized by placing the input clock between the VDD and VSs pins. Internally, the layout of the chip isolates the output buffer circuitry from the divisor circuit clock lines. Also, the output buffers limit the minimum rise-time under no load conditions to reduce the RF harmonic content of each output signal.

#### **PIN CONNECTIONS**

#### FUNCTIONAL DIAGRAM

#### ABSOLUTE MAXIMUM RATINGS

| Voltage on any pin relative to VSS + | ⊦0.3V to –20V  |

|--------------------------------------|----------------|

| Operating Temperature (Ambient)      | 0°C to 50°C    |

| Storage Temperature (Ambient)        | -40°C to 100°C |

#### **RECOMMENDED OPERATING CONDITIONS**

(0 ℃ ≤ T A ≤ 50 ℃)

|                 | PARAMETER      | MIN   | ТҮР   | МАХ   | UNITS | FIGURE |

|-----------------|----------------|-------|-------|-------|-------|--------|

| V <sub>ss</sub> | Supply Voltage | 0     |       | 0     | v     |        |

| V <sub>DD</sub> | Supply Voltage | -11.0 | -15.0 | -16.0 |       |        |

#### **ELECTRICAL CHARACTERISTICS**

$(0^{\circ}C \leq T_A \leq 50^{\circ}C; V_{SS} = 0, V_{DD} = -11 \text{ to } -16V \text{ unless otherwise specified})$

|                                    | PARAMETER                                                                  | MIN                   | ТҮР      | MAX             | UNITS | FIGURE              |

|------------------------------------|----------------------------------------------------------------------------|-----------------------|----------|-----------------|-------|---------------------|

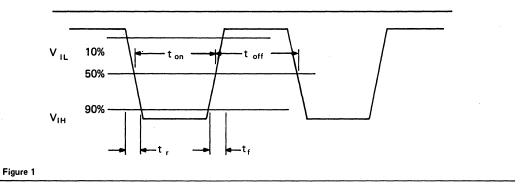

| VIL                                | Input Clock, Low                                                           | 0                     |          | -1.0            | v     | FIG. 1              |

| VIH                                | Input Clock, High                                                          | V <sub>DD</sub> + 1.0 |          | V <sub>DD</sub> | v     |                     |

| f,                                 | Input Clock Frequency                                                      | 100                   | 2000.240 | 2500            | kHz   |                     |

| tr, t <sub>f</sub>                 | Input Clock<br>Rise & Fall Times<br>10% to 90% @ 2.5 MHz                   |                       |          | 30              | nsec  | FIG. 1              |

| t <sub>on</sub> , t <sub>off</sub> | Input Clock<br>On and Off Times<br>@ 2.5 MHz                               |                       | 200      | _               | nsec  | FIG. 1              |

| Cı                                 | Input Capacitance                                                          |                       | 5        | 10              | pF    |                     |

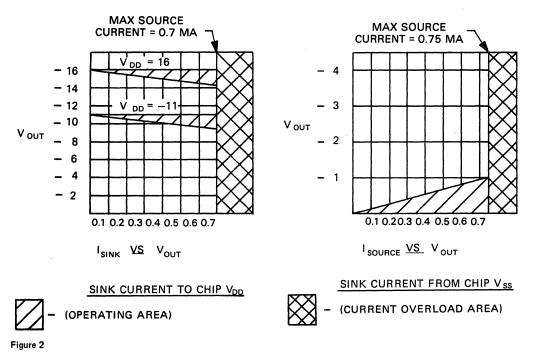

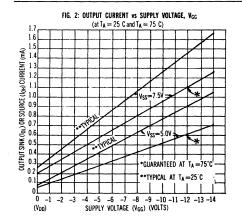

| V <sub>он</sub>                    | Output, High @<br>0.70 mA                                                  | V <sub>DD</sub> + 1.5 |          | V <sub>DD</sub> | V     | FIG. 2              |

| Vol                                | Output, Low @<br>0.75 mA                                                   | V <sub>ss</sub> – 1.0 |          | V <sub>ss</sub> | V     | FIG. 2              |

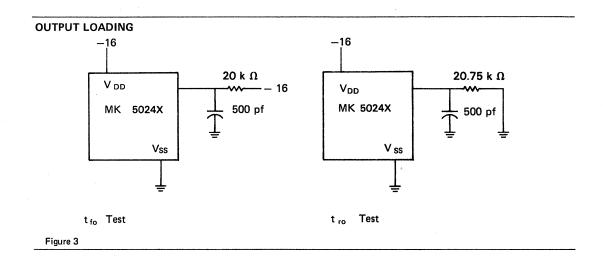

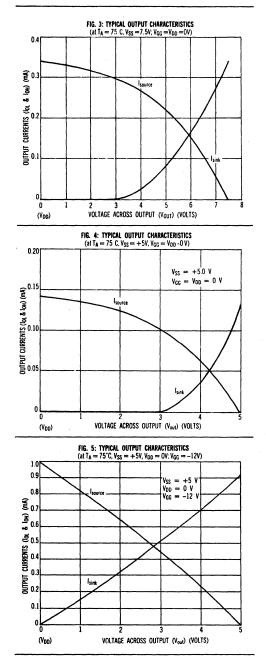

| t <sub>ro</sub> , t <sub>fo</sub>  | Output Rise & Fall<br>Times, 500 pF Load                                   | 250                   |          | 2500            | nsec  | FIG. 3              |

| t <sub>on</sub> , t <sub>off</sub> | Output Duty Cycle<br>MK 50240P & MK<br>50242P<br>MK 50241P<br>(Pin 16 50%) |                       | 50<br>30 |                 | %     |                     |

| I <sub>DD</sub>                    | Supply Current                                                             |                       | 24       | 37              | mA    | outputs<br>unloaded |

#### INPUT CLOCK WAVEFORM

**OUTPUT SIGNAL D. C. LOADING**

HI REQUENCY FNERATOR

## **1980 INDUSTRIAL PRODUCTS DATA BOOK**

#### FEATURES

- □ Single-Voltage Power Supply

- Intensity Control

- Simple Time Setting

- 4-or 6-Digit Display

- □ AM/PM and Activity Indicator

- Selectable Input Frequency and Output Mode MK 50250 — 12 hr/60Hz or 24 hr/50Hz MK 50253 — 12 hr/50Hz or 24 hr/50Hz MK 50254 — 12 hr/60Hz or 24 hr/60Hz

- 24 Hr. Alarm

- Snooze Alarm

#### DESCRIPTION

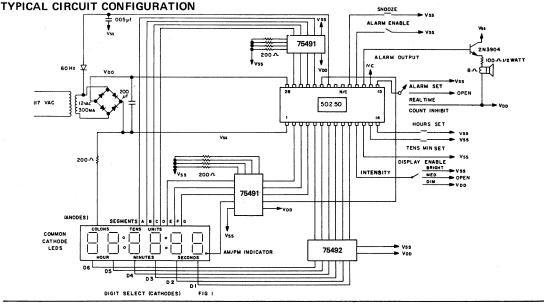

The MK50250 is a versatile MOS/LSI clock circuit manufactured by Mostek using its depletion-mode, ion implantation process and P-channel technology. The circuit can be used to construct a digital alarm clock with the addition of only a simple power supply, display, and standard interfacing components. (See Typical Circuit Configuration). The circuit is compatible with 4- or 6digit seven-segment multiplexed displays. An AM/PM and circuit activity signal is generated by the chip. The alarm operates in a 24-hour mode, which allows the alarm to be disabled and immediately reenabled to activate 24 hours later. The snooze inhibits an activated alarm for 10 minutes.

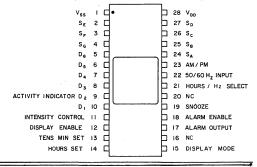

#### **PIN CONNECTIONS**

#### ABSOLUTE MAXIMUM RATINGS OVER OPERATING FREE—AIR TEMPERATURE RANGE

| Voltage on any pin relative to VSS                          | +0.3 to -18.0V    |

|-------------------------------------------------------------|-------------------|

| Output-Voltage Breakdown on any output relative to $V_{SS}$ | –18.0V @ 10 μA    |

| Operating Free-Air Temperature Range                        | 0℃ to 55℃         |

| Storage Temperature Range                                   | .–40°C to + 100°C |

## RECOMMENDED OPERATING CONDITIONS (0 $^{\circ}$ C $\leq$ T $_{A}$ $\,\leq$ 55 $^{\circ}$ C)

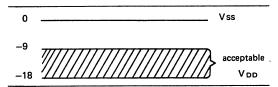

| PARAMETER                                                        | MIN                           | MAX                                          | UNITS          | NOTES |

|------------------------------------------------------------------|-------------------------------|----------------------------------------------|----------------|-------|

| Operating Voltage V <sub>DD</sub><br>Relative to V <sub>SS</sub> | -18.0                         | -9.0                                         | volts          | 9     |

| Input Logic Levels<br>"1" Logic Level<br>"0" Logic Level         | V <sub>ss</sub> -0.3<br>-18.0 | V <sub>ss</sub> +0.3<br>V <sub>DD</sub> +0.5 | volts<br>volts | 1, 2  |

## ELECTRICAL CHARACTERISTICS (9V $\leq$ V $_{ss}$ – V $_{DD} \leq$ 18V, 0 $\,^{\circ}$ C $\leq$ T $_{A}$ $\leq$ 55°C)

| PARAMETER                                                                                                                     | MIN          | MAX         | UNITS                    | NOTES  |

|-------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|--------------------------|--------|

| Output Current<br>S <sub>A</sub> -S <sub>G</sub> , D <sub>6</sub> -D <sub>1</sub> AM/PM<br>"1" Logic Level<br>"0" Logic Level | 0.5          |             | mA                       | 3 4    |

| Alarm Output Current<br>"1" Logic Level<br>"0" Logic Level                                                                    | 0.5<br>—5.0  |             | mA<br>μA                 | 3<br>5 |

| Supply Current, I DD                                                                                                          |              | 10          | mA                       | 8      |

| Input Current<br>Tens Min Set, Hours Set<br>Hours/Hz Select                                                                   | 50<br>5<br>5 | 1000<br>100 | μ <b>Α</b><br>μΑ         | 6      |

| Alarm Enable,Snooze<br>50/60 Hz Input, Display Enable                                                                         | 5<br>—15     | 100<br>200  | μ <b>Α</b><br>μ <b>Α</b> | 7      |

Notes: 1. 50/60 Hz Input has 3 volts of hysteresis for noise protection.

2. "Display Mode" and "Intensity" are three-state inputs which will self-seek third state if left open.

3. Output voltage equal to V<sub>SS</sub>-2.0 volts.

4. Open-drain output.

Output voltage equal to Vob +4.0 volts. For power-up clear, capacitance to Vss must not exceed 20pF. Pull-up device provided on 50/60 Hz input. Outputs open. Pins 16 and 20 may be tied to Vss or left floating. 5. 6. 7. 9.

#### OPERATION

The MK 50250 requires a single power supply with a voltage range from  $9V \le V_{ss} - V_{DD} \le 18$ .

A Three-State Input is one of the features which MOSTEK has employed on the MK 50250 to reduce system expense and simplify operation for the consumer. By switching Display Mode to one of three possible states the mode of operation is as follows:

| Display Mode Input | Mode          |

|--------------------|---------------|

| V <sub>ss</sub>    | Alarm Set     |

| Open               | Real Time     |

| V <sub>pp</sub>    | Count Inhibit |

When in the Alarm Set mode, the alarm time is displayed and may be altered using the time set procedure (see setting). In the Real Time mode, the real time is displayed and may also be altered using the same procedure. Count inhibit halts the counting of the clock. The display shows the halted time and may be altered by the time set procedure.

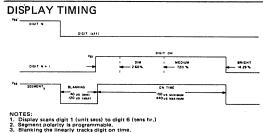

The display outputs of the MK 50250 require the use of seven-segment displays which can be multiplexed. The scanning oscillator is completely internal and requires no external components. As can be seen in the timing diagram, each digit is on 14.29% of the time required to scan all 6 possible digits when the intensity mode switch is on bright.

The Intensity Control Input provides the following degrees of display intensity:

| Intensity Control Input | Mode   | Duty Cycle |

|-------------------------|--------|------------|

| V <sub>ss</sub>         | Bright | 14.29%     |

| Open                    | Medium | 7.20%      |

| V dd                    | Dim    | 2.60%      |

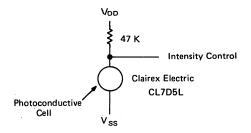

The intensity can be controlled either manually or automatically (see "Automatic Intensity Control" diagram).

The display can be blanked by connecting the Display Enable input to Vbb. Leaving this pin open allows internal pull-up to Vss which enables the display. This feature allows the display to be time shared with other information.

When power is initially applied, both real time and alarm time will be at 12:00:00 midnight in the 12 hr. mode and 00:00:00 in the 24 hr. mode. Time keeping begins when Hrs. Set and Tens Min. set are simultaneously taken to Vss. The units minutes digit can be advanced at a 2 Hz rate by connecting both the Hours Set pin and the Tens Minute Set pin to Vss. This also resets seconds to zero. The Tens Minute digit will advance at a 2 Hz rate when the Tens Minute Set pin is connected to Vss. The hours digit will be advanced by connecting the Hr. Set pin to Vss. The carry from one digit to the next more significant digit does not occur so setting should be performed from the least significant digit to the most significant. Both pins have internal pull-down resistors and can either be left open or tied to VDD when not being used.

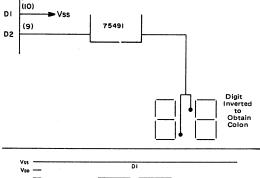

The chip can be used with either a 4- or 6-digit display. If digits D1 and D2 are not used to display seconds and tens of seconds, the user is unable to tell if the circuit is active until the minutes digit changes. In order to more quickly determine clock activity, a colon or other indicator can be flashed at a 1 Hz rate by connecting D1 to Vss. D2 can then be used to drive the colon or activity indicator. The D2 output used in this mode occurs during D4 and D5 time so that the decimal point for digits D4 and D5 can be used as a colon.

#### OPTIONAL ACTIVITY INDICATOR AND TIMING

The AM/PM output operates with an 85% duty cycle at full intensity and conducts to  ${\rm V}_{\rm ss}\,$  for PM indication.

If a "brown out" occurs, the AM/PM indicator will flash at a 1 Hz rate to signify an incorrect display time. This low power indication continues until proper power is restored and the clock is reset.

The Hours/Hz Select input is provided with an internal pulldown resistor to VDD. The options available are as follows:

| Part  | Hours/Hz                       | Mode                             |

|-------|--------------------------------|----------------------------------|

| 50250 | Open or V <sub>DD</sub><br>VSS | 60Hz - 12 Hrs.<br>50Hz - 24 Hrs. |

| 50253 | Open or V <sub>DD</sub><br>VSS | 50Hz - 12 Hrs.<br>50Hz - 24 Hrs. |

| 50254 | Open or V <sub>DD</sub><br>VSS | 60Hz - 12 Hrs.<br>60Hz - 24 Hrs. |

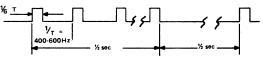

The Alarm Enable pin enables the alarm when connected to Vss. If it is left open, it will disable the alarm due to an internal pull-down resistor to VDD. When alarm occurs it may be disabled and immediately re-enabled and will activate 24 hours later at the alarm time. The output tone will be in the range of 400-600 Hz, and has a 1/6 duty cycle which conducts to Vss 50% of the time at a 1 Hz rate.

The Snooze feature will temporarily turn off an activated alarm signal to allow an additional 10 minutes sleep. Momentarily connecting snooze to Vss will activate the snooze. If left open, an internal pulldown resistor to VDD will maintain the snooze feature inoperative.

#### ALARM OUTPUT

#### AUTOMATIC INTENSITY CONTROL

IV-4

# **1980 INDUSTRIAL PRODUCTS DATA BOOK**

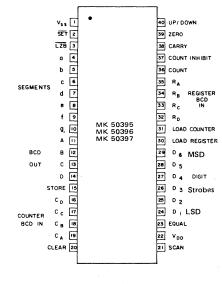

# SIX DECADE COUNTER / DISPLAY DECODER MK50395/6/7

#### FEATURES

- □ Single power supply

- Schmitt Trigger on the count input

Six decades of synchronous up/down

- Six decades of synchronous u counting

- Look-ahead carry or borrow

- Loadable counter

- Loadable compare register with comparator output

- Multiplexed BCD and seven-segment outputs

- Internal scan oscillator

- Direct LED segment drive

- Interfaces directly with CMOS logic

- Leading zero blanking

- MK 50396 programmed to count time: 99 hrs. 59 min. 59 sec.

- MK 50397 programmed to count time: 59 min. 59 sec. 99/100 sec.

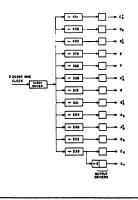

#### DESCRIPTION

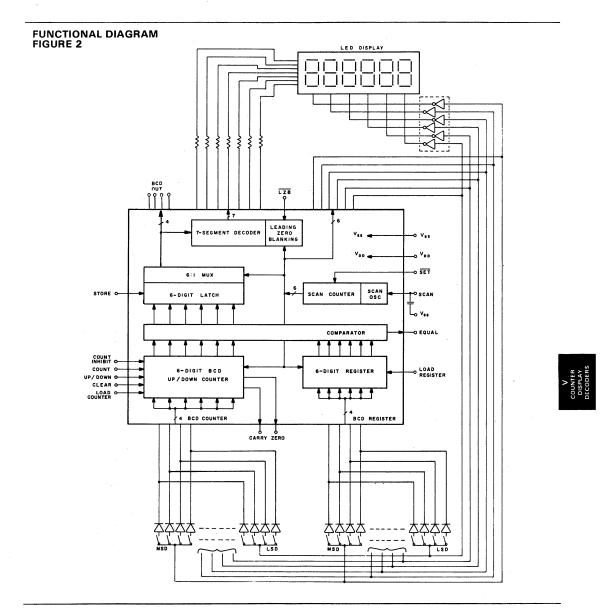

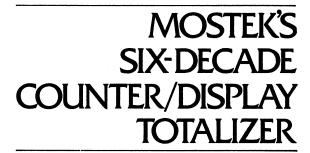

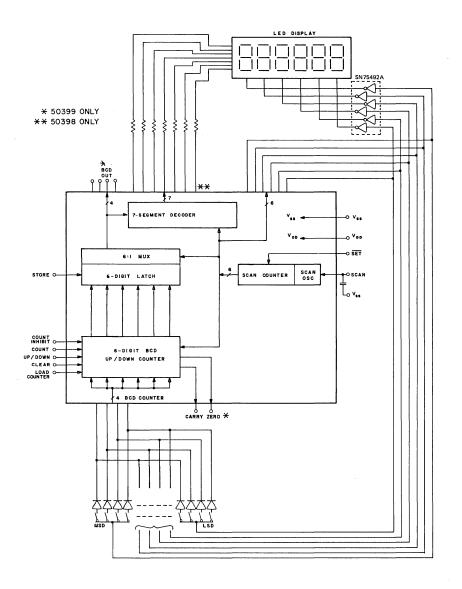

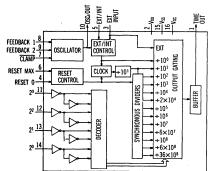

The MK 50395 is an ion-implanted, Pchannel MOS six-decade synchronous up/down counter/display driver with compare register and storage latches. The counter as well as the register can be loaded digit-by-digit with BCD data. The counter has an asynchronous-clear function.

Scanning is controlled by the scan oscillator input which is self-oscillating or can be driven by an external signal. The six-decade register is constantly compared to the state of the six-decade counter and when both the register and the counter have the same content, an EQUAL signal is generated. The contents of the counter can be transferred into the 6-digit latch which is then multiplexed from MSD to LSD in BCD and 7-segment format to the output. The seven-segment decoder incorporates a leading-zero blanking circuit which can be disabled by an external signal. This device is intended to interface directly with the standard CMOS logic families.

The MK 50396 and MK 50397 operate identically to the MK 50395 except that two digits in each were reprogrammed to provide divide by six circuitry instead of divide by ten. The MK 50396 is well suited for industrial timer applications while the MK 50397 is best suited for stop watch or realtime computer clock applications.

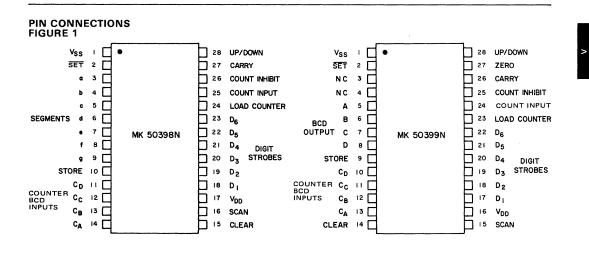

#### PIN CONNECTIONS FIGURE 1

#### V COUNTER DISPLAY DECODERS

#### **OPERATIONS:**

#### SIX-DECADE COUNTER, LATCH

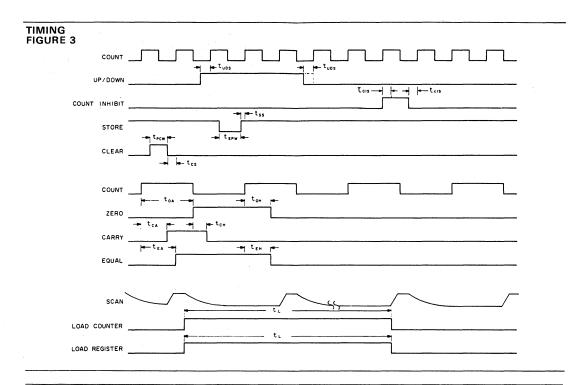

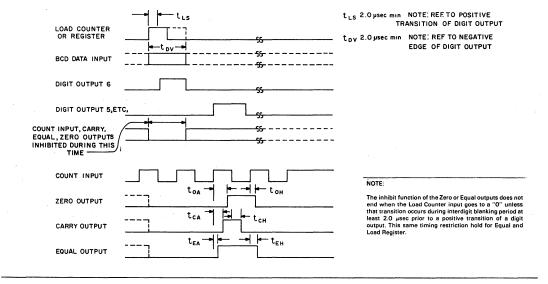

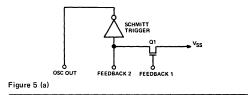

The six-decade counter is synchronously incremented or decremented on the positive edge of the count input signal. A Schmitt trigger on this input provides hysteresis for protection against both a noisy environment and double triggering due to a slow rising edge at the count input.

The count inhibit can be changed in coincidence with the positive transition of the count input; the count input is inhibited when the count inhibit is high.

The counter will increment when the up/down input is high (VSS) and will decrement when the up/down input is low. The up/down input can be changed 0.75  $\mu$ s prior to the positive transition of the count input.

The clear input is asynchronous and will reset all decades to zero when brought high but does not affect the six-digit latch or the scan counter.

As long as the store input is low, data is continuously transferred from the counter to the display. Data in the counter will be latched and displayed when the store input is high. Store can be changed in coincidence with the positive transition of the count input.

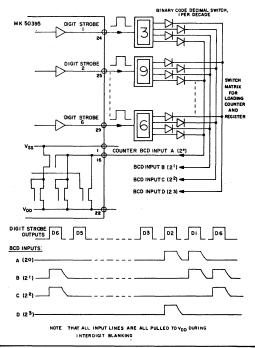

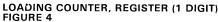

The counter is loaded digit-by-digit corresponding to the digit strobe outputs. BCD thumb wheel switches with four diodes per decade connected between the digit strobe outputs and the BCD inputs is one method to supply BCD data for loading the counter decades.

The load counter pulse must be at VSS 2 microseconds prior to the positive transition of the digit strobe of the digit to be loaded. The load counter pulse may be removed after the positive transition of the digit strobe since the chip internally latches this signal. The BCD data to be loaded must be valid through the negative transition of the digit strobe.

#### INPUTS, OUTPUTS

The seven segment outputs are open drain and capable of sourcing 10mA average current per segment over one digit cycle. Segments are on when at VSs. The Carry, Equal, Zero, BCD and digit strobe outputs are push-pull and are on when at VSs. All inputs except Counter BCD, Register BCD, and SCAN inputs are high-impedance CMOS compatible.

Three basic outputs originate from the counter: Zero output, Equal output, and Carry output. Each output goes high on the positive- (VSS) going edge of the count input under the following conditions:

The Zero output goes high for one count period when all decades contain zero. During a load counter operation the zero output is inhibited.

The Equal output goes high for one count period when the contents of the counter and compare register are equal. The equal output is inhibited by a load counter or load register operation, which lasts until the next interdigit blanking period following a negative transition of Load Counter or Load Register. The Carry output goes high with the leading edge of the count input at the count of 000000 when counting up or at 999999\* when counting down and goes low with the negative going edge of the same count input.

A count frequency of 1 MHz can be achieved if the Equal output, Zero output and Carry output are not used. These outputs do not respond at this frequency due to their output delay, as illustrated on the timing diagram, Figure 3.

#### SIX-DECADE COMPARE REGISTER

The register is loaded identically as described in the load counter paragraph. The register may be loaded independently of the counter. However, the Clear input will not remove the register contents. Contents of the register are not displayed by the BCD or seven-segment outputs.

#### **BCD & SEVEN-SEGMENT OUTPUTS**

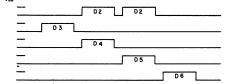

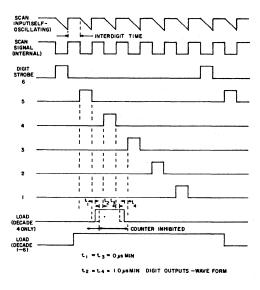

BCD or seven-segment outputs are available. Digit strobes are decoded internally by a divide-by-six Johnson counter. This counter scans from MSD to LSD. By bringing the SET input low, this counter will be forced to the MSD decade count. During this time, the segment outputs are blanked to protect against display burn out.

BCD outputs are valid for MSD when SET is low. Applying Vss to SET allows normal scan to resume. Digit 6 output is active (Vss) until the next scan clock pulse brings up the digit 5 output.

The segment outputs and digit strobes are blanked during the interdigit blanking time. Leading zero blanking affects only the segment outputs. This option is disabled by bringing the LZB input high. Typically, the interdigit blanking time is 5 to 25 microseconds when using the internal scan oscillator.

BCD output data changes at the beginning of the interdigit blanking time. Therefore, the BCD output data is valid when the positive transition of a digit output occurs.

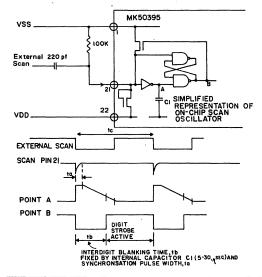

#### SCAN OSCILLATOR

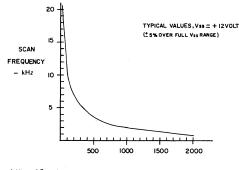

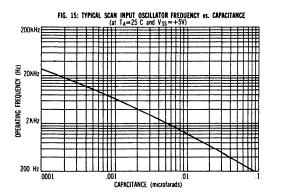

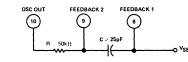

The MK 50395 has an internal scan oscillator. The frequency of the scan oscillator is determined by an external capacitor between VSS or VDD and the scan input. The wave form present on the scan oscillator input is triangular in the self-oscillate mode.

An external oscillator may also be used to drive the scan input.

In the internal drive mode, the interdigit blanking time will be the sum of the negative dwell period of the external oscillator and the normal self-oscillate blanking time (5 - 25  $\mu$ sec). Display brightness can be controlled by the duty cycle of the external scan oscillator.

\*Carry occurs at 99 59 59 for the MK 50396 and 59 59 99 for the MK 50397

Typically, the scan oscillator will oscillate at the following frequencies with these nominal capacitor values from VSS to the Scan input:

| Min   | Max    |        |

|-------|--------|--------|

| 820pF | 1.4kHz | 4.8kHz |

| 470pF | 2.0kHz | 6.8kHz |

| 120pF | 7.0kHz | 20kHz  |

V-3

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage on Any Terminal Relative to V <sub>ss</sub> | . +0.3V to –20V  |

|-----------------------------------------------------|------------------|

| Operating Temperature Range (Ambient).              | . 0° C to +70° C |

| Storage Temperature Range (Ambient).                | 40°C to +100°C   |

#### MAXIMUM OPERATING CONDITIONS

|                 | PARAMETER                                    | MIN | MAX                  | UNITS | NOTES |

|-----------------|----------------------------------------------|-----|----------------------|-------|-------|

| TA              | Operating Temperature                        | 0   | 70                   | °C    |       |

| V <sub>ss</sub> | Supply Voltage (V <sub>DD</sub> = 0V)        | 10  | 15                   | V     |       |

| I <sub>SS</sub> | Supply Current                               |     | 30                   | mA    | 1     |

| B <sub>v</sub>  | Break-Down Voltage<br>(Segment only @ 10 μA) |     | V <sub>ss</sub> - 26 | V     |       |

| PD              | Power Dissipation                            |     | 670                  | mW    | 2     |

$\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} \\ (VDD = 0V, \, VSs = + \, 10.0V \ to \, + \, 15.0V, \, 0^{\circ}C \leqslant Ta \leqslant \ 70^{\circ}C) \end{array}$

Static Operating Conditions

|                 | PARAMETER                                              | MIN                | МАХ             | UNITS    | NOTES  |

|-----------------|--------------------------------------------------------|--------------------|-----------------|----------|--------|

| VIL             | Input Low Voltage, "O"                                 | V <sub>DD</sub>    | 20% of Vss      | V        |        |

| V <sub>iH</sub> | Input High Voltage, "1"                                | V <sub>ss</sub> -1 | V <sub>ss</sub> | V        | 3      |

| V <sub>OL</sub> | Output Voltage "0" @ 30μ A                             |                    | 20% of Vss      | V        | 4      |

| V <sub>он</sub> | Output Voltage "1" @ 1.5 mA                            | 80% of Vss         |                 | V        | 4      |

| I <sub>он</sub> | Output Current "1"<br>digit strobes<br>segment outputs | 3.0<br>10.0        |                 | mA<br>mA | 5<br>6 |

| I SCAN          | Scan Input Pullup Current @ 0V                         |                    | 5.5             | mA       |        |

| I SCAN          | Scan Input Pulldown<br>Current @ 15V                   | 2                  | 40              | μA       |        |

|                 | SET Input Pullup Current @ OV                          | 5                  | 60              | μA       |        |

NOTES:

S: Iss with inputs and outputs open at 0°C 28mA at 25°C and 25mA at 70°C. This does not include segment current. Total power per segment must be limited so as not to exceed power dissipation of package. (θJA = 100°C/Watt) All outputs loaded. MIN Vik from RA RB RC RD CA CB CC CD inputs is Vss ~2.5V. Those inputs have internal pulldown resistors to VoD. This applies to the push-pull CMOS compatible outputs. Does not include digit strobes or segment outputs. For VOUT = Vss ~2.0 volts. Average value over one digit cycle. 1. 2.

3. 4.

5. 6.

### **Dynamic Operating Conditions**

| SYM              | PARAMETER                   | MIN                 | МАХ  | UNITS | NOTES |

|------------------|-----------------------------|---------------------|------|-------|-------|

| f <sub>CI</sub>  | Count Input Frequency       | 0                   | 1.00 | MHz   | 7, 8  |

| f <sub>SI</sub>  | Scan Input Frequency        | 0                   | 20   | kHz   |       |

| t <sub>CPW</sub> | Count Pulse Width           | 400                 |      | ns    | 9     |

| t <sub>SPW</sub> | Store Pulse Width           | 2.0                 |      | μs    |       |

| t <sub>SS</sub>  | Store Setup Time            | 0                   |      | μs    | 10    |

| t <sub>CIS</sub> | Count Inhibit<br>Setup Time | 0                   |      | μs    | 10    |

| t <sub>UDS</sub> | Up/Down Setup<br>Time       | - 0.75              |      | μs    | 10    |

| t <sub>CPW</sub> | Clear Pulse Width           | 2.0                 |      | μs    | 10    |

| t <sub>CS</sub>  | Clear Setup Time            | - 0.5               |      | μs    | 10    |

| t <sub>OA</sub>  | Zero Access Time            |                     | 3.0  | μs    | 10    |

| t <sub>OH</sub>  | Zero Hold Time              |                     | 1.5  | μs    | 10    |

| t <sub>CA</sub>  | Carry Access Time           |                     | 1.5  | μs    | 10    |

| t <sub>CH</sub>  | Carry Hold Time             |                     | 0.9  | μs    | 11    |

| t <sub>EA</sub>  | Equal Access Time           |                     | 2.0  | μs    | 10    |

| t <sub>EH</sub>  | Equal Hold Time             | · · ·               | 1.5  | μs    | 10    |

| t                | Load Time                   | 1/6 f <sub>si</sub> |      |       | 2.    |

NOTES:

Measured at 50% duty cycle.

If Carry, Equal, or Zero outputs are used, the count frequency with be limited by their respective output times.

The count pulse width must be greater than the carry access time when using the carry output.

The positive edge of the count input is the t <sup>-</sup> 0 reference.

Measured from negative edge of count input.

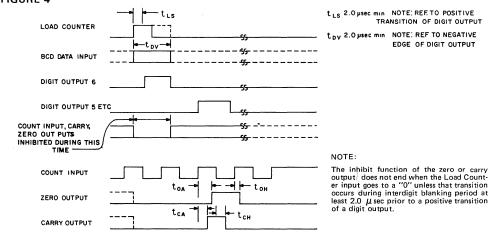

#### LOADING COUNTER, REGISTER (1 DIGIT) FIGURE 4

### Application Information Using Mostek's Six-Decade Counter/Display Totalizer

The MOSTEK MK 50395 has been developed, after careful counter application analysis, as a counting system for most needs. The functional diagram shows that the system consists of six synchronous, up-down decade counters with a data store and an auxiliary storage register that may be compared with the counter value. The circuit is relatively insensitive to power supply variation, and can interface with CMOS logic using power supplies in the 10-to 15-volt range. Counting speeds up to 1.0 MHz are permissable and the circuits are readily cascaded.

Positive logic, i.e., logic 1 is the more positive level, is used in the following description: THE COUNTER

The positive-going edges of a pulse train at the COUNT input (pin 36) are standardized by an internal monostable to a fixed pulse width, thereby giving only a minimum value to the time for which the input pulse must stay high. This pulse is applied synchronously to the six decades and, if the UP/DOWN input is a logic 1, the counters will be incremented. If at logic 0, then the counters will be decremented. At any time, the value in the counter will be set back to zero if the CLEAR COUNTER input goes to a logic 1 for 2  $\mu$ s or longer. This resetting action occurs whether or not there is a counting input pulse train.

In addition to resetting, it is also possible to preset

any desired value into the counter. This is done sequentially, decade-by-decade, under control of the LOAD COUNTER command, in the following manner. If LOAD COUNTER is taken to logic 1 a minimum of 2 microseconds prior to the positive transition of the digit output of the digit being loaded, the chip will latch this command and the BCD data presented the counter will be loaded on the negative to transition of the digit strobe. It is thus possible to load each of the 6 counters individually, if required. While the counter is being loaded, the counting input is inhibited. Internally, the load counter command is synchronized to the scan oscillator. Thus, if load counter is brought to a logic zero in the middle of a digit strobe, the counter will remain inhibited until the next interdigit blanking time. A separate COUNT INHIBIT control is provided to stop the applied count inputs from being accepted while this signal is a logic 1.

The counter section has two control outputs, a CARRY from the most significant decade and a ZERO SIGNAL that indicates when the counter contents are zero. These signals are suppressed during LOAD COUNTER operations to avoid a spurious output being given during a counter presetting operation.

#### COMPARISON AND REGISTER

The six-digit storage register may be preset to any value by bringing the LOAD REGISTER signal to logic 1. The presetting sequence is exactly the same

| UP/DOWN                         | COUNT TIMING                              |  |

|---------------------------------|-------------------------------------------|--|

|                                 | 000000 00000 00000 00000 00000 00000 0000 |  |

| COUNT                           |                                           |  |

| UP/ DOWN                        |                                           |  |

| COUNT INHI                      | BIT                                       |  |

| CARRY                           |                                           |  |

| ZERO                            |                                           |  |

| EQUAL<br>(REGISTER<br>TO 999999 |                                           |  |

| CLEAR                           |                                           |  |

|                                 |                                           |  |

as for the counter. The value on the REGISTER BCD INPUTS is loaded decade-by-decade by the six digit signals in the order "most significant" (digit 6) to "least significant" (digit 1). The outputs of this register are compared continuously with the value currently in the counter. This comparison is made in parallel and not decade-by-decade. When the two values are the same, an EQUAL signal is given. However, during presetting of the counter the CARRY, ZERO and EQUAL signals are inhibited so that no false, intermediate comparison result is given. Since the counter and the register have separate BCD inputs, both may be preset simultaneously if desired. The value held in the register can only be altered by the BCD inputs. The Count Input is not inhibited during load register operations.

#### DIGIT SCANNING AND OUTPUT FUNCTIONS

The digit scan counter is timed from an internal oscillator which may be driven externally from the SCAN input. A capacitor attached from Vss to this pin will determine the scan frequency when external logic drive to this pin is not used. Intenal circuitry gives a fixed delay to the DIGIT OUTPUT signal to ensure that there is a gap between each digit strobe so that a "ghosting" effect in a displayed output due to the storage time of external display driver transistors is eliminated. This is the interdigit blanking time. Typically, this time can range from 3 to 10 microseconds.

#### LOAD COUNTER, REGISTER TIMING

the SET input is used to force the digit strobe counter to the digit 6 position for purposes of synchronizing the counter output. The digit counter outputs are gated by the interdigit blanking period and appear as DIGIT STROBE OUTPUTS. The counter outputs are not directly multiplexed but are buffered by a 6-digit latch controlled by the STORE command. The out-puts of the latch go directly to the output multiplexer. Thus, when the STORE signal is at logic 0, the counter contents are directly available, but as soon as STORE goes to logic 1, the value present as the signal changed is retained and subsequent changes in counter value are ignored. The contents of the store are read out, digit-by-digit - the scan counter again performs this function in the order most-significant to leastsignificant — and appear on BCD OUT pins. The four bits in each BCD digit are encoded simultaneously to seven-segment code and appear as SEGMENTS OUT and can be used to drive a suitable 7-segment display. The SET operation will also turn off these seven outputs, blanking the display, as well as setting the digit counter to digit 6. This is to prevent possible destruction of an LEDtype display when SET is a prolonged signal. Frequently it is required to display only significant numbers, in which case taking the LZB control to a logic 0 will blank the leading zeros in the sevensegment output.

#### **INTERFACING WITH THE MK 50395**

The wide range of power supply, 10.0 - 15.0 volts, makes the counting system particularly suitable for interfacing with CMOS logic.

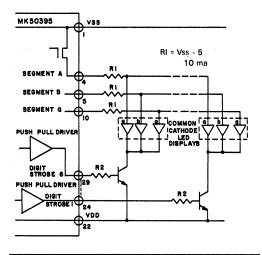

- A. Segment output these transistors can source 10 mA from the Vss supply. There is no internal pull-down to VoD when the transistor is turned off. These transistors are capable of driving small LED displays directly via series resistors.

- B. Digit outputs a push-pull configuration is used here as the most suitable arrangement for driving both external logic and display drivers. These outputs supply 3.0 mA max from  $V_{SS}$  and sink 30  $\mu$ A to  $V_{DD}$ .

When higher-power displays are used, the segment outputs should be buffered by an emitter follower in order to provide the extra current.

The BCD OUTPUTS, EQUAL, ZERO and CARRY are also push-pull. Output drive capabilities are listed in the following table:

| Segment Output<br>(Pins 4-10)       | VOL                                   | VOH<br>V <sub>SS</sub> –3V at 10mA<br>(average over one<br>digit strobe cycle) |

|-------------------------------------|---------------------------------------|--------------------------------------------------------------------------------|

| Digit Outputs<br>(Pins 24-29)       | VDD at no load<br>20% of Vss at 30 μA | V <sub>SS</sub> -2V at 3.0mA                                                   |

| Equal/Zero/Carry<br>(Pins 23,39,38) | VDD at no load<br>20% of Vss at 30 μA | V <sub>SS</sub> –2V at 1.5mA                                                   |

The following inputs, COUNT, STORE, UP/DOWN, COUNT INHIBIT, CLEAR, LZB, LOAD REGISTER have no internal current sources and must therefore be driven from sources that give correct logic 1 and 0

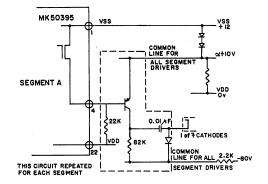

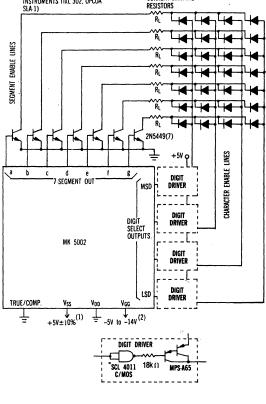

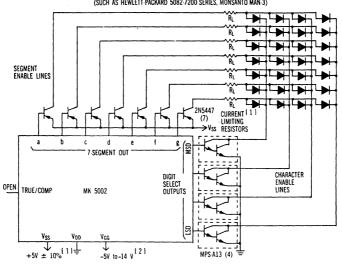

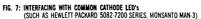

#### SEGMENT DRIVER

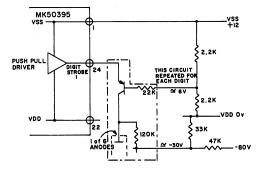

#### **DIGIT DRIVER**

#### DRIVING LED DISPLAYS DIRECTLY

levels - open collector circuits, or switches without pull down resistors for example, may not be used. If any of the above functions are not required then those pins should be tied to the appropriate supply, that is to  $V_{SS}$  for logic 1 and  $V_{DD}$  for logic 0. SET has an internal transistor that pulls the pin to VSS if unconnected thus the driving circuit should be able to sink this current, approximately 60  $\mu$ A, when pulling the input to logic 0. The COUNTER BCD and REGISTER BCD inputs have two internal transistors one static and one switched as a precharge, that pull to VDD. The static current is < 350  $\mu A$  to VDD when the input is taken to VSS, the dynamic current from VSS is 1 mA while the transistor is on. The dynamic precharge ensures that even with the large capacitive loading and leakage current of a switch matrix at these pins, the correct data will be entered at the maximum digit scan frequency.

An example of a switch matrix input illustrates this operation. Six binary-coded-decimal switches are used, one for each decade, the switches being enabled by the corresponding DIGIT STROBE output, with the paralleled switch outputs connected to the COUNTER (or REGISTER) BCD inputs. The DIGIT STROBE outputs are separated by the interdigit blanking time and it is only during this time that the precharge transistors at the BCD inputs are all pulled to logic 0 (V <sub>DD</sub>). After this blanking time, the next DIGIT STROBE output will in its turn switch to logic 1 (only one out of six is ever on) and pull those BCD inputs selected by the switch and diode matrix to logic 1. This value is loaded into the corresponding register or counter stage, i.e. the switch matrix driven by DIGIT STROBE 6 will be loaded into MSD of the

#### **BCD SWITCH MATRIX**

register or counter. As the DIGIT STROBE switches back to logic 0, the next interdigit blanking time begins and the inputs are all pulled back to logic 0 again by the internal precharge. It is possible for the DIGIT STROBE outputs to drive both the switch matrix and a display. If the COUNTER & REGISTER BCD inputs are connected in parallel they may still be driven directly from the DIGIT STROBE outputs.

#### SCAN FREQUENCY VS EXTERNAL CAPACITANCE

Additional Capacitance on Pin 21 (pF)

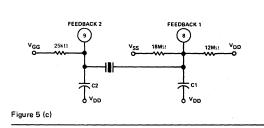

When the scan oscillator is free running, the SCAN input may use an external capacitor to set the scanning frequency to a particular value. The signal seen at the pin is a ramp determined by the capacitance, followed by a period clamped at  $V_{SS}$ . This period clamped at  $V_{SS}$  is determined by the internal oscillator and is the interdigit blanking period. During this time, the DIG-IT STROBE outputs are all turned off. When the SCAN input is driven externally, this fixed interdigit period remains plus the time at which the synchronizing signal is at logic 0. To make the interdigit blanking ing time independent of the external synchronizing signal requires only the addition of a resistor and capacitor as shown on page 50.

Referring to the External Drive To Scan Input drawing on page 50, time a is the interdigit blanking time.

Time b should be greater than  $2\mu$ s—a range of  $2-5\mu$ s is suitable-and time c may be from infinity to  $30\mu$ s. If time c is made too short, then the interdigit blanking circuit never resets itself and will stay at logic 0 and no DIGIT STROBE outputs will appear.

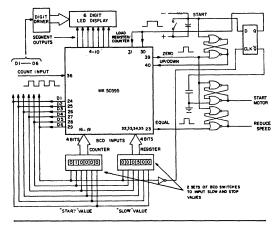

#### TYPICAL MK 50395 APPLICATIONS BATCH CONTROL

In many situations involving the metering of material, whether as a liquid, individual items or revolutions of a spindle, a two-step operation is required for better efficiency. The flow is started at the maximum speed and at a preset point before the end of the operation a signal is required to slow down and eventually stop the equipment. Such applications could be as diverse as filling sacks with cement or controlling the turns on a transformer bobbin. In the system shown on page 50, pressing the start switch allows the input to the D flip-flop to go to logic 1. This is clocked by DIGIT STROBE 6 so that a synchronous signal at least one complete scan counter cycle

#### EXTERNAL DRIVE TO SCAN INPUT

long is obtained. This signal is used as LOAD COUNT-ER and LOAD REGISTER, the two controls being tied in parallel for simultaneous loading. It does not matter how long the load signal is so long as it is at least one scan cycle long and changes synchronously with the scan signal. The two values representing total quantity and "slow-down" quantity are set on the digit switches and these values are loaded at the beginning of each cycle. Once the counter register loading is complete, a start signal is generated to set the equipment in operation. While the train of pulses representing the measured quantity is counted, the UP/DOWN control is in the down mode. Thus with two quantities at, let us say, 10,000 and 500 the counter starts off with 10,000 loaded and counts toward zero. When the counter reaches 500, an EQUAL signal is generated and this sets the signal controlling the brake. After a further 500 pulses, the counter reaches zero, an output on the ZERO pin resets the start flip flop and the equipment is brought to reset awaiting a new start signal. In such an operation the display outputs would probably not be used.

This application can be extended by using the ZERO output to control the UP/DOWN input. The operation is identical but the start signal also sets a latch into the count down state. As ZERO is detected this latch is reset so that the counter mode is now up. Even with a braking facility there may be an "overrun" and the value now held in the counter and displayed is the extra quantity. The operator may now decide if this extra quantity is within the tolerance allowed for the job and to take whatever action is necessary.

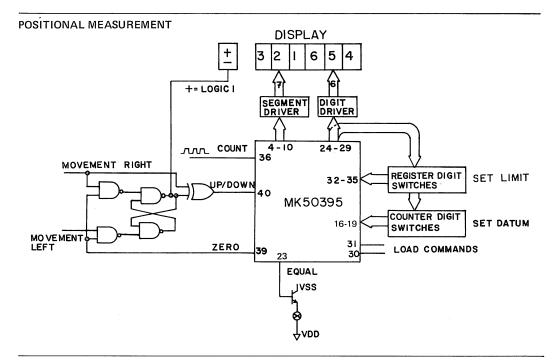

#### POSITIONAL MEASUREMENT

Positional measurement can readily be made using this circuit. The six decades gives considerable ac-

#### BATCH CONTROL

curacy in one package. The two quadrature signals from a graticule-type displacement measurement system must be converted to count impulses and an UP/ DOWN signal. If the measurement zero datum is in the middle of the measurement area then the following counting conditions arise:

| Direction<br>of Movement | Displayed sign<br>+ or —<br>of Datum | Count<br>direction |            |  |

|--------------------------|--------------------------------------|--------------------|------------|--|

| RIGHT                    | -                                    | DOWN               | ZERO DATUM |  |

| RIGHT                    | +                                    | UP                 | CROSSED    |  |

| LEFT                     | +                                    | DOWN               | ZERO DATUM |  |

| LEFT                     | _                                    | UP                 | CROSSED    |  |

|                          |                                      |                    |            |  |

Each time the zero datum is reached and each time the direction of movement is changed, the count direction must be changed. The value displayed thus represents the position either side of the zero datum. The storage register may be used as a means of limiting the travel of the measurement piece. If a value equal to the limit is loaded into the register, the EQUAL output may be used to give a warning that the limit is reached.

It will have been noted from the delay of EQUAL and ZERO to the COUNT edge that ZERO has muchlonger propagation delay than the EQUAL output. In the event that the register is not used, it may be loaded with zeros – by giving a LOAD REGIS-TER command with the BCD inputs as zero – and the EQUAL output then used as zero detect. This has the advantage of increasing the system speed, for, although the counter can accept inputs up to 1.0 MHz, the propagation delay of the outputs is too long to allow a control signal to be changed between clock pulses at this counting rate. In this example, UP/ DOWN has to be controlled, and using the faster out-

put enables a higher counting speed, 600 kHz instead of 300 kHz, to be used if necessary.

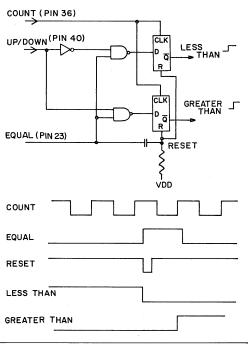

#### **GREATER THAN – LESS THAN DETECTION**

The availability of an EQUAL output facilitates the generation of greater-than and less-than signals. The only requirement is that the circuit is set into the correct initial state. When the counter has the same value as the register, the generation of the "greater/less than" signal depends on the direction of count, i.e. from this EQUAL condition count up gives "greater than" and count down gives "less than". EQUAL is gated with UP and with DOWN and these are connected to the D inputs of two D flip-flops that are both clocked by the counting pulse. As EQUAL is reached, the two flip flops are reset but the next count pulse after the EQUAL condition will set one of the flip flops and thereby provide the appropriate signal.

#### AUTOMATIC STOP

The COUNT INHIBIT input may be used to stop the counter automatically when the EQUAL or ZERO outputs are connected directly to this input. As EQUAL, for example, goes to a logic 1, then further counting is inhibited when this signal is connected directly to COUNT INHIBIT. Since no more count inputs are accepted, the EQUAL value remains and blocks the counting action. The operation of CLEAR, LOAD REGISTER or LOAD COUNTER can be used to start the system counting again.

V-14

V-15

#### SN 7490 TIMING

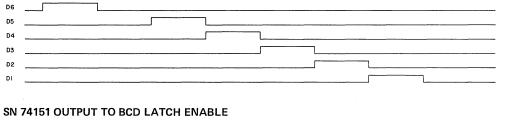

#### SN 74151 LOAD COUNTER PULSE TRAIN OUTPUT

#### MORE APPLICATIONS

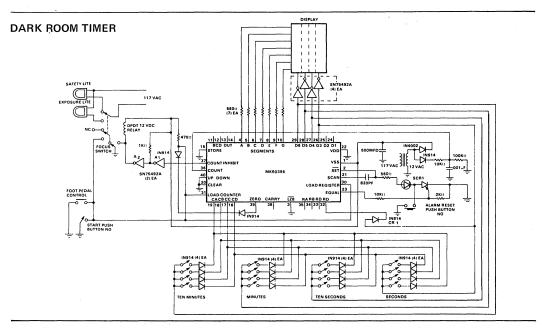

The following applications resulted from an ad contest sponsored by Mostek. These applications represent a cross section of uses for the MK 50395 family and are intended as a guide for applying the counter circuit.

The type of display is left to the user to design into his particular application. The MK 50395 series was designed to allow direct drive of efficient display systems. If the current requirements of a display exceed the specifications of the MK 50395 series, external segment drive circuitry will be required.

Power supply voltage range, wattage, filtering, and decoupling must be observed in all applications. The MK 50395 series was designed to keep power supply restrictions to a minimum.

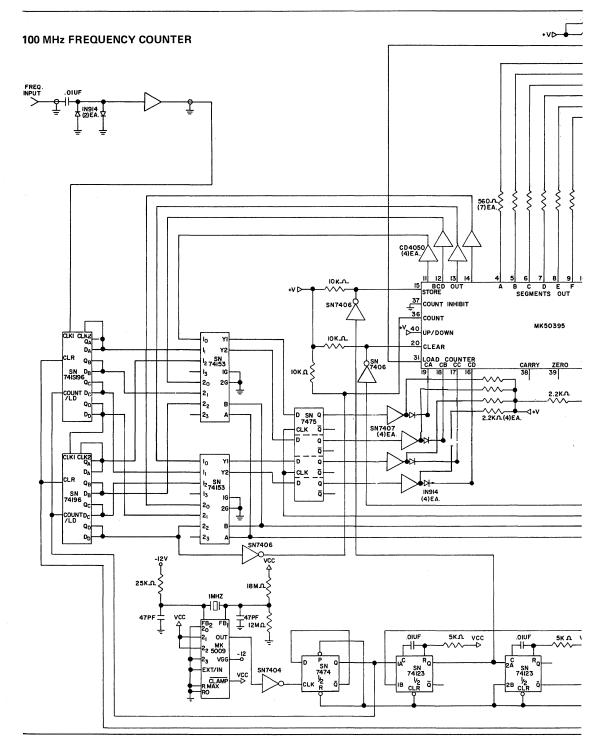

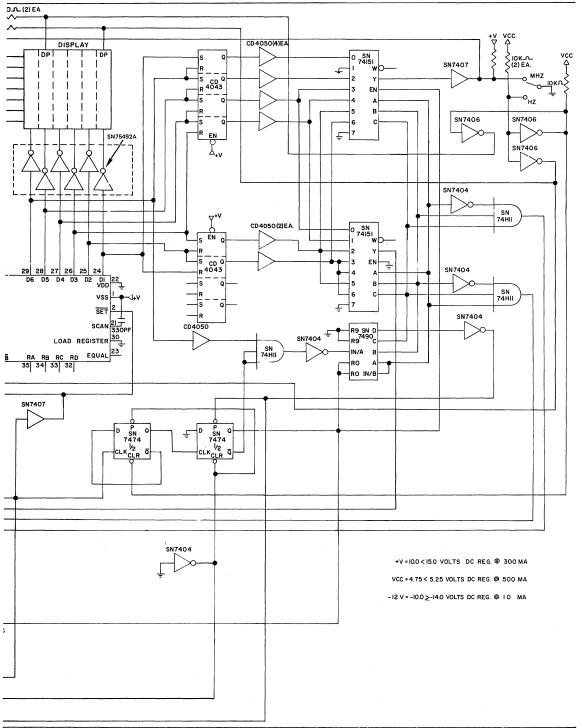

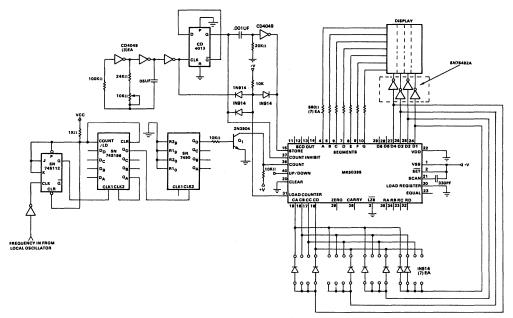

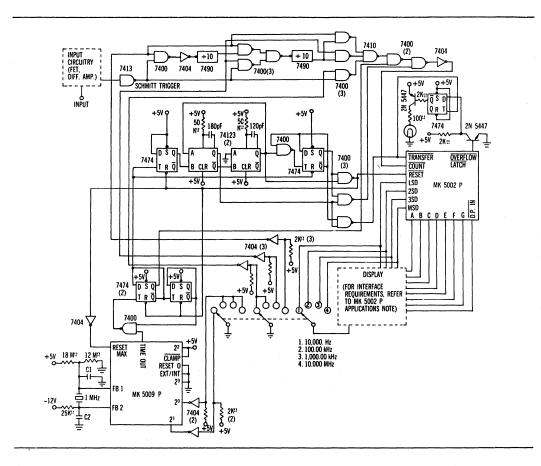

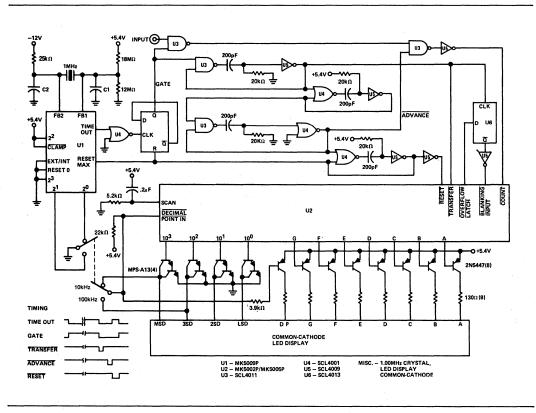

#### **100 MHz FREQUENCY COUNTER**

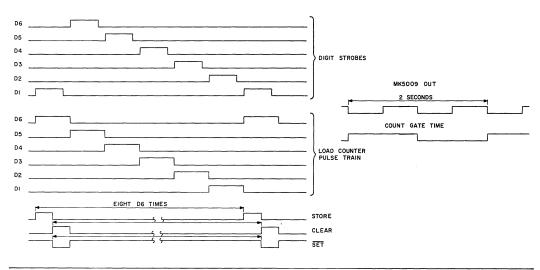

In most counter applications, the problems associated with prescaling result in a loss of resolution, or the need for longer count sample times. This application allows the MK 50395 with some associated circuitry to count at 100 MHz with a one-second gate time achieving one-Hz resolution.

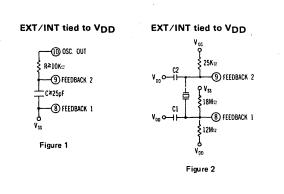

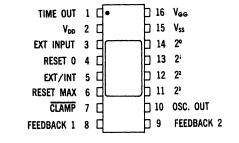

The MK 50395 counts the input frequency after a divide-by-100 using an SN74S196 and an SN74196. Frequency sample time is achieved by a one MHz crystal in conjunction with the MK 5009 time base in the  $\div$  10<sup>6</sup> configuration, followed by a divide-by-

two to give a one-second logic one level. This is applied to the count/load input of the SN74S196 and SN74196 counters. The 10's-of-Hz and one'sof-Hz data is retained in these two counters for later display. Actually, only a count of 99.9999 MHz may be displayed as the MK 50395 would display all zeros and a carry would be generated at the next higher count.

At the end of the one-second sample time, a store is generated and the count data is latched into the display.

A clear counter pulse is generated to ready the MK 50395 for the next data cycle. If the MHz-Hz switch is in the MHz position, the preceeding cycle will again occur at the next gate sample time. Load counter is also disabled in the MHz position.

With the MHz-Hz switch in the Hz position, the first ½ SN7474 is enabled and is clocked at the end of every pulse, which clears the MK 50395. The second SN7474 also changes state, enabling the SN74151 which controls the MK 50395 load counter input, and the Hz cycle begins.

At the end of every clear MK 50395 pulse,  $\overline{\text{SET}}$  is brought low to sync the MK 50395 with the rest of the circuitry.

The MK 50395 loads digit Six with digit Four data into the BCD counter. The digit four data was stored in the SN7475 latch at the previous digit four time.

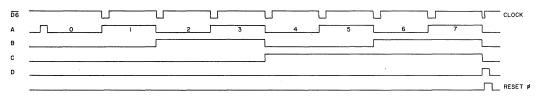

#### TIMING DIAGRAM

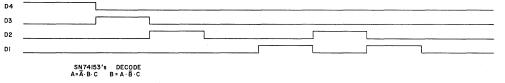

The SN7490 is advanced one count at the digit six time at the start of the sequence.

Latch Digit Four Data, Load Into Counter Digit Six

Latch Digit Three Data, Load Into Counter Digit Five

Latch Digit Two Data, Load Into Counter Digit Four

Latch Digit One Data, Load Into Counter Digit Three

At this time, the output of the SN7490 is decoded to select via the SN74153's first digit two data, then digit one data is selected which at the end of sample time was stored in the SN74196 and SN74S196. So the sequence is continued.

Latch Digit Two Data Load Into Counter Digit Two

Latch Digit One Data Load Into Counter Digit One

At the beginning of the eight count of the SN7490 several things take place. The MK 50395 is furnished with a store pulse to display the shifted data. A clear is applied to the MK 50395 to ready it for a new cycle.

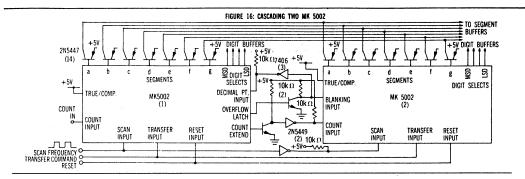

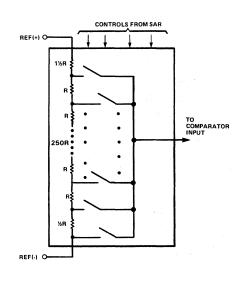

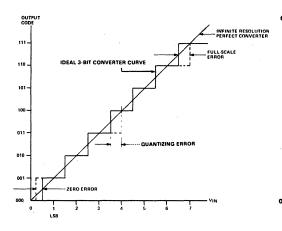

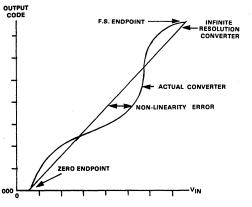

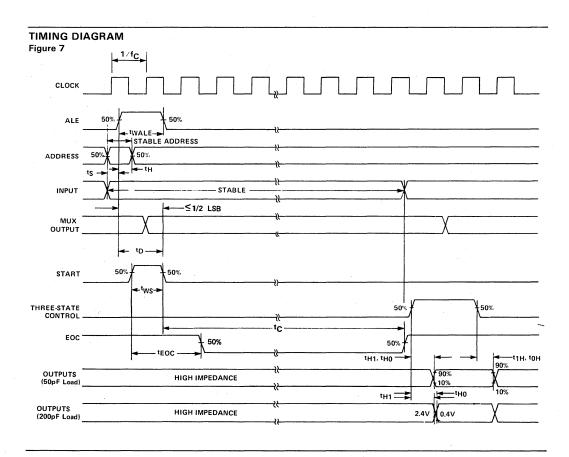

The divide-by-two action of the first  $\frac{1}{2}$  SN7474 allows the second clear clock to have no effect at the second clear pulse. The SN745196 and SN74196 are cleared. The second  $\frac{1}{2}$  SN7474 is preset which disables the load counter SN74151. The SN7490 is reset to zero.